|

ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ AT90USB162 (AT90USB162MU) ąĖąĘ čüąĄą╝ąĄą╣čüčéą▓ą░ AVR USB ą║ąŠą╝ą┐ą░ąĮąĖąĖ Atmel ąĖą╝ąĄąĄčé ą▓ čüą▓ąŠąĄą╝ čüąŠčüčéą░ą▓ąĄ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü USB, ąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüą┐ąĄčåąĖčäąĖą║ą░čåąĖčÄ USB 2.0 ąĮą░ čüą║ąŠčĆąŠčüčéąĖ ą┤ąŠ Full-speed ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ. ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ čĆą░ąĘą┤ąĄą╗ą░ ą┤ą░čéą░čłąĖčéą░ Atmel, ą┐ąŠčüą▓čÅčēąĄąĮąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā USB čŹč鹊ą│ąŠ čćąĖą┐ą░. ąöą░čéą░čłąĖčé Atmel ąĮą░ čćąĖą┐ AT90USB162 (doc7707.pdf) ąĮą░ą┐ąĖčüą░ąĮ ą┤ąŠą▓ąŠą╗čīąĮąŠ ą║ąŠčĆčÅą▓ąŠ, ą┐ąĄčüčéčĆąĖčé ąĮąĄą┤ąŠč湥čéą░ą╝ąĖ ąĖ ąŠą┐ąĄčćą░čéą║ą░ą╝ąĖ. ąÆ ą┐ąĄčĆąĄą▓ąŠą┤ąĄ čÅ ą║ą░ą║ ą╝ąŠą│, ą┐ąŠčüčéą░čĆą░ą╗čüčÅ čŹč鹊 ąĖčüą┐čĆą░ą▓ąĖčéčī.

[19.1 ąÆąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB AT90USB162]

1. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ čüą║ąŠčĆąŠčüčéčī full-speed (high-speed ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ).

2. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ čĆąĄąČąĖą╝ ping-pong (ą▒čāč乥čĆąĖąĘą░čåąĖčÅ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ ą▒ą░ąĮą║ą░), čü ą┐čĆąŠąĘčĆą░čćąĮčŗą╝ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄą╝ ą▒ą░ąĮą║ąŠą▓.

3. 176 ą▒ą░ą╣čé DPRAM (čüą╝. ąĪą╗ąŠą▓ą░čĆąĖą║).

- 1 ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░, ą║ąŠč鹊čĆą░čÅ ą╝ąŠąČąĄčé ąĖą╝ąĄčéčī ą╝ą░ą║čüąĖą╝čāą╝ 64 ą▒ą░ą╣čéą░ (default control endpoint).

- 2 ą║ąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ąĖą╝ąĄčéčī ą╝ą░ą║čüąĖą╝čāą╝ 64 ą▒ą░ą╣čéą░ (ąŠą┤ąĖąĮ ą▒ą░ąĮą║).

- 2 ą║ąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ąĖą╝ąĄčéčī ą╝ą░ą║čüąĖą╝čāą╝ 64 ą▒ą░ą╣čéą░ (ąŠą┤ąĖąĮ ąĖą╗ąĖ ą┤ą▓ą░ ą▒ą░ąĮą║ą░).

ąØą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ AT90USB162 čāą┤ąŠą▒ąĮąŠ čĆąĄą░ą╗ąĖąĘąŠą▓čŗą▓ą░čéčī ąĮąĄčüą╗ąŠąČąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ USB (ą┐čĆąŠą│čĆą░ą╝ą╝ą░č鹊čĆčŗ, čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ą▓ąŠą┤ą░ ąĖ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ, ą║ą╗ą░ą▓ąĖą░čéčāčĆčŗ, ą╝čŗčłąĖ ąĖ čé. ą┐.). ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ čĆąĄąČąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ USB, čĆąĄąČąĖą╝ čģąŠčüčéą░ USB ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ.

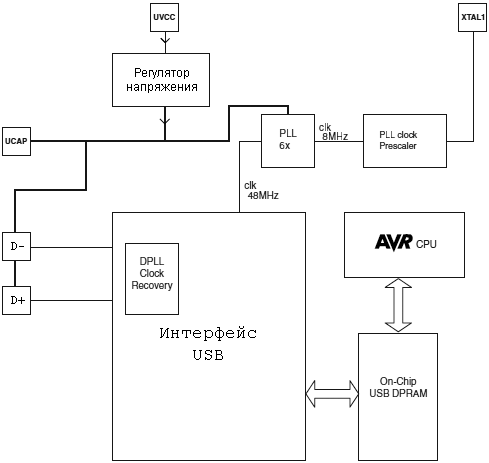

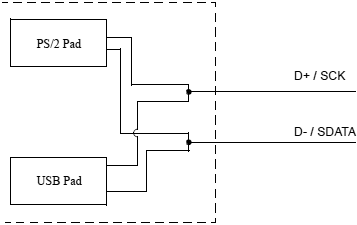

[19.2 ąæą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░]

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą░ą┐ą┐ą░čĆą░čéčāčĆčā ą┤ą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ ą║ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÄ USB ąĖ ą║ ą┐ąŠč鹊ą║čā ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą┐ą░ą┤ą░ąĄčé ą▓ čÅč湥ą╣ą║ąĖ DPRAM.

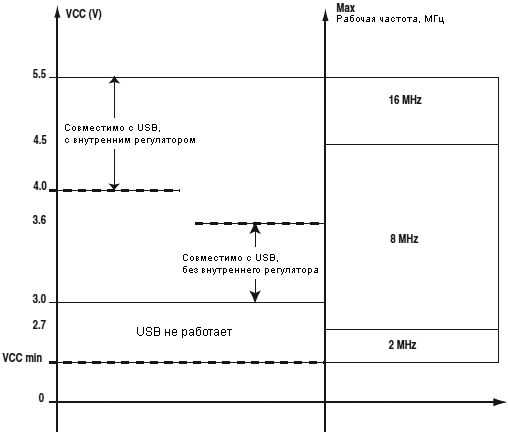

ąöą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░ ąŠą┐ąŠčĆąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ 48 ą£ąōčå ┬▒0.25% (ą┤ą╗čÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü Full-speed), ą║ąŠč鹊čĆą░čÅ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čüąĖčüč鹥ą╝čŗ PLL. PLL ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą▓čŗčüąŠą║čāčÄ čćą░čüč鹊čéčā (48 ą£ąōčå) ą┤ą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ USB ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą▒ąŠą╗ąĄąĄ ąĮąĖąĘą║ąŠą╣ čćą░čüč鹊čéčŗ (ą┐ąŠą╗čāčćą░ąĄą╝ąŠą╣ čü ą┐ąŠą╝ąŠčēčīčÄ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ čĆąĄąĘąŠąĮą░č鹊čĆą░ ąĖą╗ąĖ ą│ąĄąĮąĄčĆą░č鹊čĆą░, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą│ąŠ ąĮą░ ą▓čģąŠą┤ čéą░ą║č鹊ą▓ XTAL1). ąÆąŠąĘą╝ąŠąČąĮčŗ 2 ą▓ą░čĆąĖą░ąĮčéą░ ą┤ą╗čÅ čćą░čüč鹊čéčŗ ą▓ąĮąĄčłąĮąĄą│ąŠ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ čĆąĄąĘąŠąĮą░č鹊čĆą░ (ąĖą╗ąĖ ą│ąĄąĮąĄčĆą░č鹊čĆą░) - 8 ą£ąōčå ąĖą╗ąĖ 16 ą£ąōčå (ą┐čĆąĖ čŹč鹊ą╝ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓čŗą▒ąŠčĆą░ ą┐ąĖčéą░čÄčēąĄą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓ąŠąĘą╝ąŠąČąĮčŗ ą┐čĆąĄą┤ą┐ąŠčćč鹥ąĮąĖčÅ, čüą╝. ą┤ą░ą╗ąĄąĄ čĆąĖčü. 19.2). ąöą╗čÅ ą║ą░č湥čüčéą▓ąĄąĮąĮąŠą╣ čĆą░ą▒ąŠčéčŗ USB ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░ ą▓čŗčüąŠą║ą░čÅ čüčéą░ą▒ąĖą╗čīąĮąŠčüčéčī čćą░čüč鹊čéčŗ ąĖ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┤čĆąŠąČą░ąĮąĖčÅ čäą░ąĘčŗ (ą╝ą░ą╗čŗą╣ ą┤ąČąĖčéč鹥čĆ).

ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ 48 ą£ąōčå ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąĖ ą│ąĄąĮąĄčĆą░čåąĖąĖ čćą░čüč鹊čéčŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖč鹊ą▓ 12 ą£ąōčå ą┤ą╗čÅ Full-speed ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ ą┐ąŠ USB ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ ąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĮą░ ą┐ąŠą╗ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ USB. ąÆąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĄ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ ą▒ą╗ąŠą║ą░ DPLL, ą║ąŠč鹊čĆčŗą╣ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅąĄčé čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ čłąĖąĮčŗ USB ą┐ąŠ ą┤ąČąĖčéč鹥čĆčā.

ą¦č鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čéčĆąĄą▒čāąĄą╝čŗąĄ ą┤ą╗čÅ USB 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ, ąĮąŠąČą║ąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖąĮč鹥čĆč乥ą╣čüą░ USB (D+ ąĖ D-) ą┤ąŠą╗ąČąĮčŗ ą┐ąŠą╗čāčćą░čéčī ą┐ąĖčéą░ąĮąĖąĄ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 3.0 ą┤ąŠ 3.6V. ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ AT90USB82 (AT90USB162) ą╝ąŠąČąĄčé ą┐ąĖčéą░čéčīčüčÅ ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ąŠ 5.5V ą▒ą╗ą░ą│ąŠą┤ą░čĆčÅ ąĮą░ą╗ąĖčćąĖčÄ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ ą▓ ąĮąĄą│ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čĆąĄą│čāą╗čÅč鹊čĆą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 3.3V (ąĄą│ąŠ ą▓čŗčģąŠą┤ ą▓čŗą▓ąĄą┤ąĄąĮ ąĮą░ ąĮąŠąČą║čā 27 UCAP).

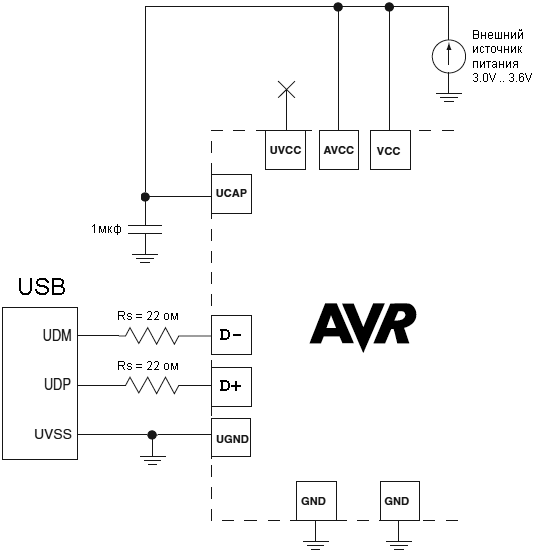

ąĀąĖčü. 19-1. ą×ą▒ąĘąŠčĆąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB.

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą┐ąŠ ą▒ą╗ąŠą║-čüčģąĄą╝ąĄ:

D+, D- ąĮąŠąČą║ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ąĮą░ ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤ą║ą╗čÄčćą░čÄčéčüčÅ čüąĖą│ąĮą░ą╗čīąĮčŗąĄ ą╗ąĖąĮąĖąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ USB.

UCAP ą▓čŗčģąŠą┤ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüčéą░ą▒ąĖą╗ąĖąĘą░č鹊čĆą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 3.3V, ąĮąŠąČą║ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ąĮą░ ą║ąŠč鹊čĆčāčÄ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╣ čäąĖą╗čīčéčĆčāčÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ 1 ą╝ą║ąż.

UVCC ąĮąŠąČą║ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą▓čģąŠą┤ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĖčéą░ąĮąĖčÅ (ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖą╗ąĖ ąŠčé ą┐čĆąŠą▓ąŠą┤ą░ VBUS čłąĖąĮčŗ USB).

DPLL Clock Recovery čüąĖčüč鹥ą╝ą░ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ čéą░ą║č鹊ą▓ ąĖąĘ čüąĖą│ąĮą░ą╗ąŠą▓ čłąĖąĮčŗ USB ąĮą░ ąŠčüąĮąŠą▓ąĄ čåąĖčäčĆąŠą▓ąŠą╣ ążąÉą¤ą¦.

clk 8MHz, clk 48MHz čéą░ą║č鹊ą▓čŗąĄ čćą░čüč鹊čéčŗ.

PLL 6x čüąĖčüč鹥ą╝ą░ čāą╝ąĮąŠąČąĄąĮąĖčÅ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąĮą░ ąŠčüąĮąŠą▓ąĄ ążąÉą¤ą¦ (čāą╝ąĮąŠąČąĄąĮąĖąĄ čćą░čüč鹊čéčŗ ąĮą░ 6).

PLL clock Prescaler ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čī čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, čü ą▓čŗčģąŠą┤ą░ ą║ąŠč鹊čĆąŠą│ąŠ čéą░ą║čéčŗ ą┐ąŠčüčéčāą┐ą░čÄčé ąĮą░ ążąÉą¤ą¦.

AVR CPU ą▓čŗčćąĖčüą╗ąĖč鹥ą╗čīąĮąŠąĄ čÅą┤čĆąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AVR.

On-Chip USB DPRAM ą┤ą▓čāčģą┐ąŠčĆč鹊ą▓ą░čÅ ą┐ą░ą╝čÅčéčī ą┤ą╗čÅ ą▒čāč乥čĆąŠą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ USB.

XTAL1 ąĮąŠąČą║ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą▓čģąŠą┤ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ. ąØą░ ąĮąĄąĄ ą╗ąĖą▒ąŠ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ą▓ą░čĆčå ąĮą░ 8 ąĖą╗ąĖ 16 ą£ąōčå, ą╗ąĖą▒ąŠ ą▓ąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ 8 ąĖą╗ąĖ 16 ą£ąōčå.

[ą×ą▒čēąĖąĄ čāą║ą░ąĘą░ąĮąĖčÅ ą┐ąŠ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÄ]

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ čåąĄą╗ąĄą▓ąŠą╣ čüčģąĄą╝čŗ (ą▓ ą║ąŠč鹊čĆąŠą╣ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ AT90USB162) ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čĆą░ąĘąĮčāčÄ ą░ą┐ą┐ą░čĆą░čéąĮčāčÄ čĆąĄą░ą╗ąĖąĘą░čåąĖčÄ.

ąĀąĖčü. 19-2. ąĀą░ą▒ąŠčćąĖąĄ čĆąĄąČąĖą╝čŗ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą║ą▓ą░čĆčåą░ ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ.

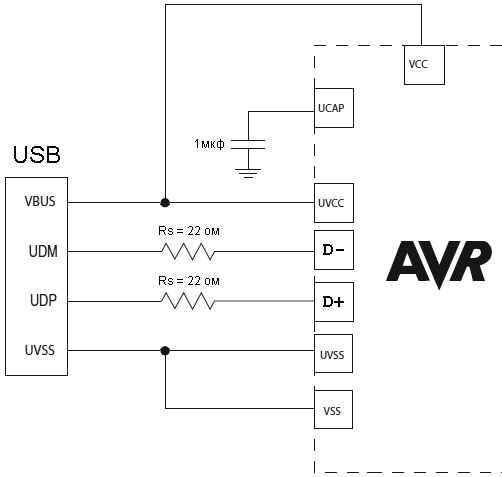

19.3.1 Bus Powered device (čāčüčéčĆąŠą╣čüčéą▓ąŠ USB, ą┐ąĖčéą░ąĄą╝ąŠąĄ ąŠčé čłąĖąĮčŗ USB).

ąĀąĖčü. 19-3.ąóąĖą┐ąĖčćąĮąŠąĄ ą┐ąĖčéą░ąĮąĖąĄ ąŠčé čłąĖąĮčŗ USB, ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĖ 5V I/O.

ąĀąĖčü. 19-4.ąóąĖą┐ąĖčćąĮąŠąĄ ą┐ąĖčéą░ąĮąĖąĄ ąŠčé čłąĖąĮčŗ USB, ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĖ 3V I/O.

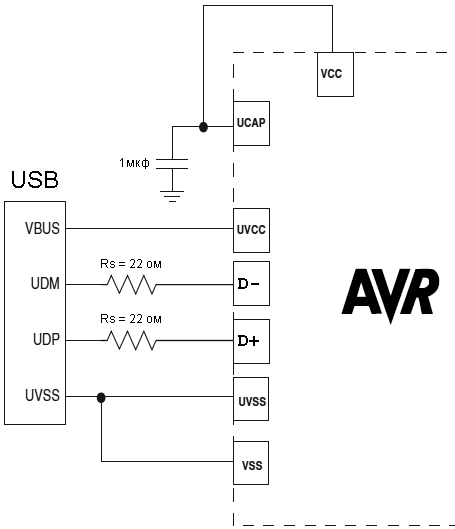

19.3.2 Self Powered device (čāčüčéčĆąŠą╣čüčéą▓ąŠ USB, ą┐ąĖčéą░ąĄą╝ąŠąĄ ąŠčé ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĖčéą░ąĮąĖčÅ, čłąĖąĮą░ USB ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ).

ąĀąĖčü. 19-5.ąóąĖą┐ąĖčćąĮąŠąĄ ą┐ąĖčéą░ąĮąĖąĄ ąŠčé ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░, ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĖ I/O ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 3.4V .. 5.5V.

ąĀąĖčü. 19-6.ąóąĖą┐ąĖčćąĮąŠąĄ ą┐ąĖčéą░ąĮąĖąĄ ąŠčé ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░, ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĖ I/O ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 3.0V .. 3.6V.

19.3.3 ąŻą║ą░ąĘą░ąĮąĖčÅ ą┐ąŠ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĄ

ŌĆó ąĀąĄąĘąĖčüč鹊čĆčŗ, ą▓ą║ą╗čÄčćą░ąĄą╝čŗąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓ čåąĄą┐ąĖ čüąĖą│ąĮą░ą╗ąŠą▓ D+ ąĖ D-, ą┤ąŠą╗ąČąĮčŗ ąĖą╝ąĄčéčī ąĮąŠą╝ąĖąĮą░ą╗ 22 ą×ą╝ (+/- 5%).

ŌĆó ą¤čĆąŠą▓ąŠą┤ąĮąĖą║ąĖ ąĮą░ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░č鹥 ąŠčé čĆą░ąĘčŖąĄą╝ą░ USB (USB type B ąĖą╗ąĖ miniUSB type B [1]) ąĖą╗ąĖ ąŠčé ą╝ąĄčüčéą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ą░ą▒ąĄą╗čÅ USB ą┤ąŠ ąĮąŠąČąĄą║ USB ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą║ąŠčĆąŠčéą║ąĖą╝ąĖ, ąĖ ą┐ąŠą┤čćąĖąĮčÅčéčīčüčÅ ą┐čĆą░ą▓ąĖą╗ą░ą╝ čĆą░ąĘą▓ąŠą┤ą║ąĖ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ (ąĮčāąČąĮčŗ ąŠą┤ąĖąĮą░ą║ąŠą▓ą░čÅ ą┤ą╗ąĖąĮą░, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▒ą╗ąĖąĘą║ąŠąĄ čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĖąĄ ą┤čĆčāą│ ą║ ą┤čĆčāą│čā, ąĮčāąČąĮąŠ ąĖąĘą▒ąĄą│ą░čéčī ą┐ąĄčĆąĄčģąŠą┤ąĮčŗčģ ąŠčéą▓ąĄčĆčüčéąĖą╣).

ŌĆó ą£ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąĘą░čēąĖčéą░ ąŠčé ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ / ESD ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÅ ąĮąŠąČąĄą║ USB ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

ŌĆó ąöą╗čÅ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ ą▓ąĮąĄčłąĮąĖą╣ čäąĖą╗čīčéčĆčāčÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ Ucap ą┤ąŠą╗ąČąĄąĮ ąĖą╝ąĄčéčī ąĄą╝ą║ąŠčüčéčī 1uF (+/- 10%).

ŌĆó ąØą░ čłąĖąĮąĄ VBUS ąŠč湥ąĮčī čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ąĄą╝ą║ąŠčüčéčīčÄ 10uF.

[19.4 ą×čüąĮąŠą▓ąĮčŗąĄ čĆą░ą▒ąŠčćąĖąĄ čĆąĄąČąĖą╝čŗ]

19.4.1 ąÆą▓ąĄą┤ąĄąĮąĖąĄ

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ąĖ ąĄą│ąŠ čĆą░ą▒ąŠčéą░ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čüą▒čĆąŠčüą░, ą║ąŠč鹊čĆčŗą╣ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĖ čüą╗ąĄą┤čāčÄčēąĖčģ čüąŠą▒čŗčéąĖčÅčģ:

- Power on reset (ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖą╣ čüą▒čĆąŠčü ą┐čĆąĖ ą┐ąŠą┤ą░č湥 ą┐ąĖčéą░ąĮąĖčÅ ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ).

- External reset (ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ čüą▒čĆąŠčüą░ ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ).

ŌĆō Watchdog reset (čüą▒čĆąŠčü ą┐čĆąĖ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĖ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░).

- Brown out reset (čüą▒čĆąŠčü ą┐čĆąĖ čāčģąŠą┤ąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĮąĖąČąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą│ąŠ ą┐čĆąĄą┤ąĄą╗ą░ - ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čäčīčĹʹ░ą╝ąĖ).

- debugWIRE reset (čüą▒čĆąŠčü ąŠčé ąĖąĮč鹥čĆč乥ą╣čüą░ ąŠčéą╗ą░ą┤ą║ąĖ debugWIRE).

ąóą░ą║ąČąĄ ą┤ąŠčüčéčāą┐ąĄąĮ ą┐ąŠ ą▓čŗą▒ąŠčĆčā ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ čüą▒čĆąŠčü:

ŌĆō USB End Of Reset (ąŠą║ąŠąĮčćą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ čüą▒čĆąŠčüą░ ą┐ąŠ čłąĖąĮąĄ USB, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čģąŠčüčé USB).

ąÆ čüą╗čāčćą░ąĄ čüą▒čĆąŠčüą░ ą┐ąŠ čłąĖąĮąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ, ąŠą┤ąĮą░ą║ąŠ ąĄą│ąŠ čĆą░ą▒ąŠčéą░ ąĮąĄ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ (čéą░ą║ čćč鹊 ą┤ą╗čÅ čģąŠčüčéą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB ąŠčüčéą░ąĄčéčüčÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝).

19.4.2 Power-on and reset (ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ąĖ čüą▒čĆąŠčü)

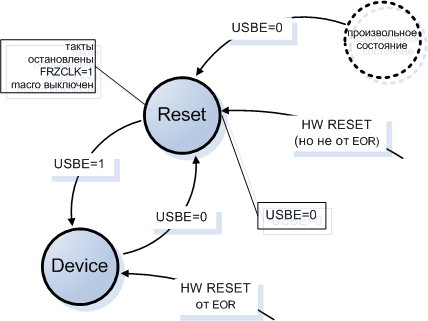

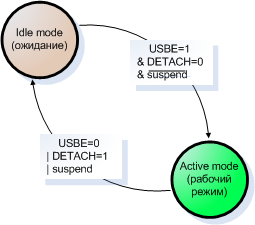

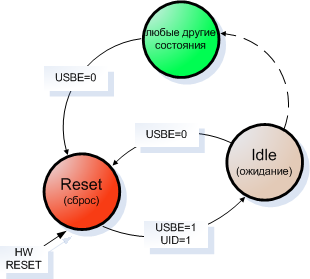

ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╣ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ čĆą░čüą║čĆčŗą▓ą░čÄčéčüčÅ ąŠčüąĮąŠą▓ąĮčŗąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ.

ąĀąĖčü. 19-7. USB controller states ą┐ąŠčüą╗ąĄ reset

ąÜąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░:

ŌĆó USBE ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ,

ŌĆó čéą░ą║čéčŗ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą┤ą╗čÅ čüąĮąĖąČąĄąĮąĖčÅ čŹąĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (FRZCLK=1),

ŌĆó čĆą░ą▒ąŠčéą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB ąĘą░ą┐čĆąĄčēąĄąĮą░,

ŌĆó USB ą▓ čĆąĄąČąĖą╝ąĄ "ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ" (suspend mode),

ŌĆó ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ čāčüčéčĆąŠą╣čüčéą▓ą░ USB - čüą▒čĆąŠčü.

ŌĆó ąæąĖčé DPACC ąĖ ą┐ąŠą╗ąĄ DPADD10:0 ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą║ąŠą┤ąŠą╝ firmware. DPRAM ąĮąĄ ąŠčćąĖčēą░ąĄčéčüčÅ.

ŌĆó ąæąĖčéčŗ SPDCONF ą╝ąŠą│čāčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą║ąŠą┤ąŠą╝ firmware.

ą¤ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ USBE ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ (Device state). ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ ą╗čÄą▒ąŠąĄ ą▓čĆąĄą╝čÅ "ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ" ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ USBE. ążą░ą║čéąĖč湥čüą║ąĖ ąŠčćąĖčüčéą║ą░ USBE ą┤ąĄą╣čüčéą▓čāąĄčé ą║ą░ą║ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čüą▒čĆąŠčü ąĮą░ ą╝ą░ą║čĆąŠčāčĆąŠą▓ąĮąĄ USB.

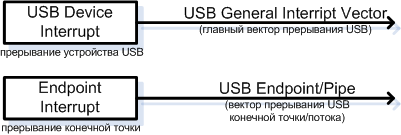

19.4.3 Interrupts (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ)

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā USB ą▓čŗą┤ąĄą╗ąĄąĮąŠ ą┤ą▓ą░ ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

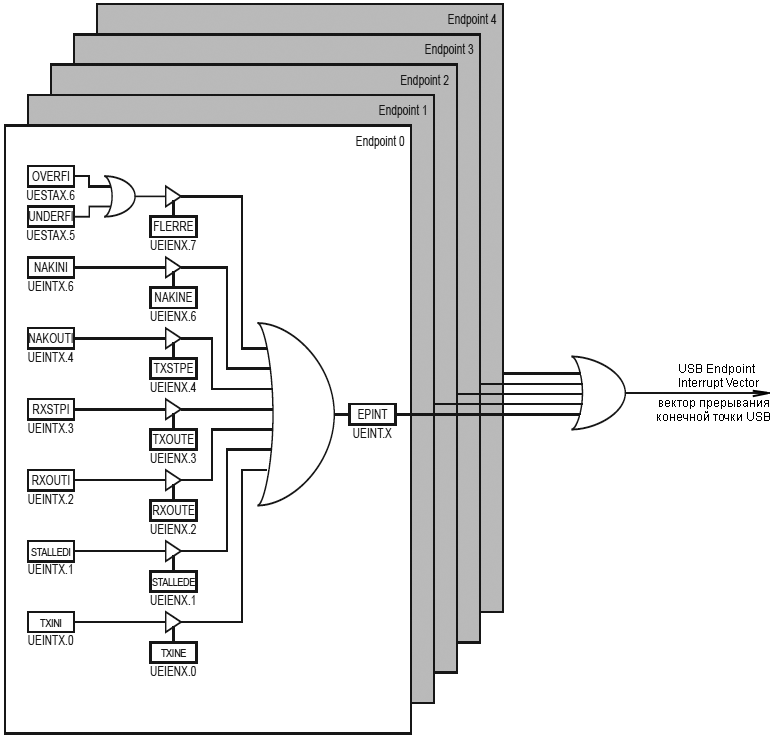

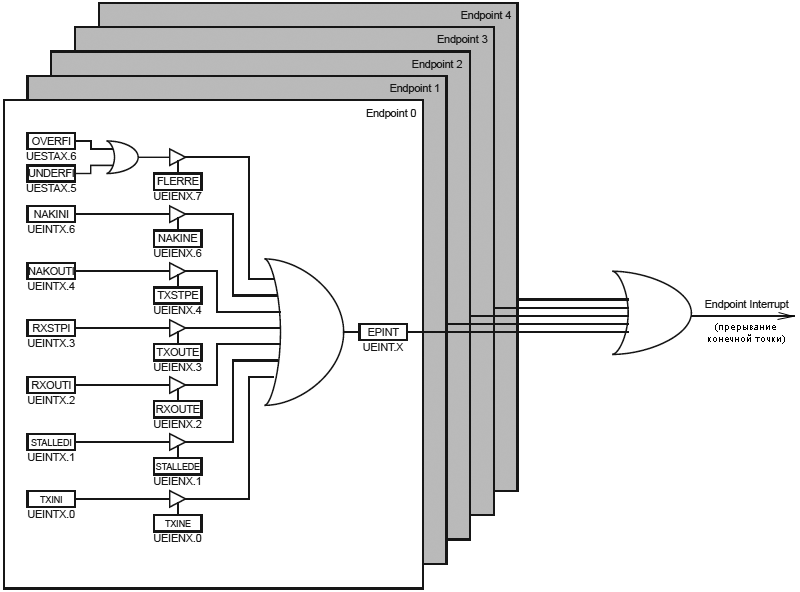

ąĀąĖčü. 19-8. ąĪąĖčüč鹥ą╝ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ USB

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čüčĆą░ą▒ą░čéčŗą▓ą░čÄčé ą┐čĆąĖ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖąĖ čĆą░ąĘą╗ąĖčćąĮčŗčģ čüąŠą▒čŗčéąĖą╣ ą▓ čĆą░ą▒ąŠč鹥 ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB. ąĪ ą┐ąŠą╝ąŠčēčīčÄ ą╝ą░ą║čĆąŠčüąŠą▓ ą╝ąŠąČąĮąŠ ąŠčéą┤ąĄą╗ąĖčéčī ą│ą╗ą░ą▓ąĮčŗąĄ čüąŠą▒čŗčéąĖčÅ (USB General events) ąŠčé čüąŠą▒čŗčéąĖą╣ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ (USB Endpoints events), ą║ąŠč鹊čĆčŗąĄ ąŠčéąĮąŠčüčÅčéčüčÅ ą║ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ ą┤ą░ąĮąĮčŗčģ, čüą▓čÅąĘą░ąĮąĮčŗčģ čü ą║ą░ąČą┤ąŠą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąŠą╣.

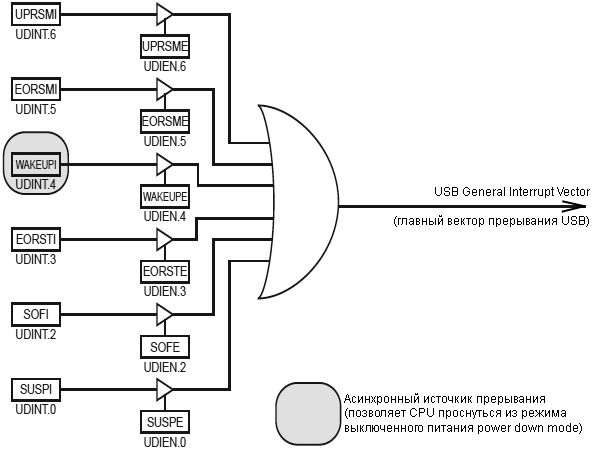

ąĀąĖčü. 19-9. ąśčüč鹊čćąĮąĖą║ąĖ ą┤ą╗čÅ ą│ą╗ą░ą▓ąĮąŠą│ąŠ ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ USB

ąÜą░ąČą┤ąŠąĄ ąĖąĘ čŹčéąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐čĆąĖą▓čÅąĘą░ąĮąŠ ą┐ąŠ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖčÄ ą║ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, čéą░ą║ čćč鹊 ąŠąĮąĖ ą▒čāą┤čāčé čüčĆą░ą▒ą░čéčŗą▓ą░čéčī č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮčŗ čéą░ą║čéčŗ USB (ąŠčćąĖčēąĄąĮ ą▒ąĖčé FRZCLK). ąśčüą║ą╗čÄč湥ąĮąĖąĄ ąĖąĘ čŹč鹊ą│ąŠ ą┐čĆą░ą▓ąĖą╗ą░ - č鹊ą╗čīą║ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ WAKEUP, ą║ąŠč鹊čĆąŠąĄ ą▒čāą┤ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░čéčī ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ ą┤ą░ąĮąĮčŗčģ ą▒čāą┤ąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ (WAKEUP čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą░čüąĖąĮčģčĆąŠąĮąĮąŠ, ąĖ ąĮąĄ ą┐čĆąĖą▓čÅąĘą░ąĮąŠ ą┐ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą║ čéą░ą║čéą░ą╝).

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ WAKEUP ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čĆą░ąĘą▒čāą┤ąĖčéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ, ąĮą░čģąŠą┤čÅčēąĄąĄčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ power-down (菹║ąŠąĮąŠą╝ąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ). ąĀąĄąČąĖą╝ power-down ąŠą▒čŗčćąĮąŠ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┐čĆąĖ ą┐ąĄčĆąĄčģąŠą┤ąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ USB ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (Suspend state).

ąĀąĖčü. 19-10. ąśčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ USB

ąÜą░ąČą┤ą░čÅ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ąĖą╝ąĄąĄčé 8 ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┤ą╗čÅ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ čüą▓čÅąĘą░ąĮčŗ čü čäą╗ą░ą│ą░ą╝ąĖ, ąĖ ą║ą░ąČą┤čŗą╣ ąĖčüč鹊čćąĮąĖą║ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ąĖą╗ąĖ ąĮąĄčé ą┤ą╗čÅ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĄ.

ąĢčüą╗ąĖ ąĮą░ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĄ čĆą░ąĘčĆąĄčłąĄąĮ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ąĖčüč鹊čćąĮąĖą║ ą┤ą╗čÅ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ čüąŠą▒čŗčéąĖąĄ (ąĖą╗ąĖ čüąŠą▒čŗčéąĖčÅ, ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĖčüč鹊čćąĮąĖą║ąŠą▓) ą┐čĆąĖą▓ąĄą┤čāčé ą║ ą┐čĆąĄą║čĆą░čēąĄąĮąĖčÄ čĆą░ą▒ąŠčéčŗ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąĖ ą┐ąĄčĆąĄčģąŠą┤čā ą┐ąŠ ą▓ąĄą║č鹊čĆčā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ (ą║ ą▓čŗąĘąŠą▓čā ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ). ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčüčé ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĖčüč鹊čćąĮąĖą║ čüąŠą▒čŗčéąĖčÅ (ą║ą░ą║ą░čÅ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ą▓čŗąĘą▓ą░ą╗ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ) ą┐čāč鹥ą╝ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ UEINT, ąĖ ą┤ą░ą╗ąĄąĄ ąŠą▒čĆą░ą▒ąŠčéą░čéčī čüąŠą▒čŗčéąĖčÅ ą┐čāč鹥ą╝ ąŠą┐čĆąŠčüą░ čĆą░ąĘą╗ąĖčćąĮčŗčģ čäą╗ą░ą│ąŠą▓ (čćč鹊ą▒čŗ ą▓čŗčÅčüąĮąĖčéčī, ą║ą░ą║ąĖąĄ čüąŠą▒čŗčéąĖčÅ ą▓čŗąĘą▓ą░ą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ).

[19.5 Power modes (čĆąĄąČąĖą╝čŗ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ)]

19.5.1 Idle mode (čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ)

ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čÅą┤čĆąŠ CPU ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ (čéą░ą║čéčŗ ąĮą░ CPU ąĮąĄ ą┐ąŠą┤ą░čÄčéčüčÅ). ąĀąĄąČąĖą╝ Idle ą╝ąŠąČąĄčé ą▒čŗčéčī ą░ą║čéąĖą▓ąĄąĮ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, čĆą░ą▒ąŠčéą░ąĄčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ąĖą╗ąĖ ąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé. CPU ą╝ąŠąČąĄčé ą┐čĆąŠčüąĮčāčéčīčüčÅ (ą▓čŗą╣čéąĖ ąĖąĘ čĆąĄąČąĖą╝ą░ Idle ąĖ ąĮą░čćą░čéčī čĆą░ą▒ąŠčéčā) ą┐ąŠ ą╗čÄą▒ąŠą╝čā ąĖąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ USB.

19.5.2 Power down (ą┐ąĖčéą░ąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąŠ)

ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čĆą░ą▒ąŠčéą░ čéą░ą║č鹊ą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮą░, čćč鹊 ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▓čüąĄ čéą░ą║č鹊ą▓čŗąĄ čćą░čüč鹊čéčŗ (ą║ą░ą║ CPU, čéą░ą║ ąĖ ą┐ąĄčĆąĖč乥čĆąĖąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░). ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ą┐čĆąŠčüąĮąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ WAKEUPI (ąĄą┤ąĖąĮčüčéą▓ąĄąĮąĮąŠąĄ ą░čüąĖąĮčģčĆąŠąĮąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ).

19.5.3 Freeze clock (ąŠčüčéą░ąĮąŠą▓ čéą░ą║č鹊ą▓)

ąÜąŠą┤ firmware ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą╝ąŠąČąĄčé čāą╝ąĄąĮčīčłąĖčéčī 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ FRZCLK, ą║ąŠč鹊čĆčŗą╣ "ąĘą░ą╝ąŠčĆą░ąČąĖą▓ą░ąĄčé" ą│ąĄąĮąĄčĆą░čåąĖčÄ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB. ąÜąŠą│ą┤ą░ ą▒ąĖčé FRZCLK čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą│ąĄąĮąĄčĆą░čåąĖčÅ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB ą┐čĆąĄą║čĆą░čēą░ąĄčéčüčÅ, ąŠą┤ąĮą░ą║ąŠ ą▓ąŠąĘą╝ąŠąČąĄąĮ ą┤ąŠčüčéčāą┐ ą║ čüą╗ąĄą┤čāčÄčēąĖą╝ čĆąĄą│ąĖčüčéčĆą░ą╝:

ŌĆó USBCON,

ŌĆó čĆąĄą│ąĖčüčéčĆčŗ ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ DPRAM (DPADD7:0, UEDATX)

ŌĆó UDCON (detach, ...)

ŌĆó UDINT

ŌĆó UDIEN

ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ą║ąŠą│ą┤ą░ FRZCLK čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą╝ąŠąČąĄčé čüčĆą░ą▒ąŠčéą░čéčī č鹊ą╗čīą║ąŠ ą░čüąĖąĮčģčĆąŠąĮąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ WAKEUPI.

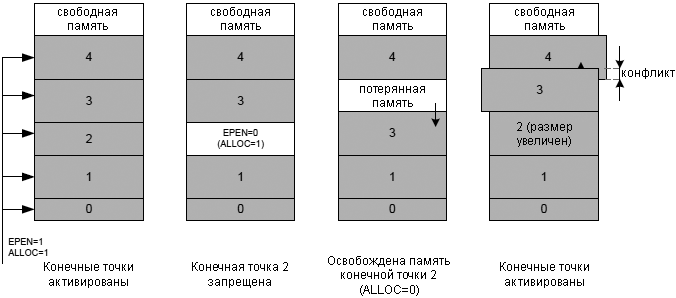

[19.6 Memory management (čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ą░ą╝čÅčéčīčÄ)]

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé č鹊ą╗čīą║ąŠ čüčéčĆąŠą│ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą▓čŗą┤ąĄą╗ąĄąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆąŠąĄ ąŠą┐ąĖčüą░ąĮąŠ ą┤ą░ą╗ąĄąĄ.

ąĀąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ ą┤ą╗čÅ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī č鹊ą╗čīą║ąŠ ą▓ ą┐ąŠčĆčÅą┤ą║ąĄ čāą▓ąĄą╗ąĖč湥ąĮąĖčÅ (ąŠčé endpoint 0 ą┤ąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ endpoint 4). ąóą░ą║ čćč鹊 firmware ą┤ąŠą╗ąČąĮąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą║ąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ č鹊ą╗čīą║ąŠ ą▓ čéą░ą║ąŠą╝ ą┐ąŠčĆčÅą┤ą║ąĄ, ąŠčé 0 ą┤ąŠ 4, ąĖ ąĮąĖą║ą░ą║ ąĖąĮą░č湥.

ąĀąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĖąĄ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ki ąĘą░ą▓ąĄčĆčłąĄąĮąŠ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ALLOC. ąŚą░č鹥ą╝ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ą▓čŗą┤ąĄą╗čÅąĄčé ą┐ą░ą╝čÅčéčī ąĖ ą▓čüčéą░ą▓ą╗čÅąĄčé ąĄčæ ą╝ąĄąČą┤čā ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąŠą╣ ki-1 ąĖ ki+1. ą¤ą░ą╝čÅčéčī ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ čüą┤ą▓ąĖą│ą░ąĄčéčüčÅ ą▓ą▓ąĄčĆčģ (ą▓ čüč鹊čĆąŠąĮčā čāą▓ąĄą╗ąĖč湥ąĮąĖčÅ ą░ą┤čĆąĄčüąŠą▓) ąĖ ą┤ą░ąĮąĮčŗąĄ č鹥čĆčÅčÄčéčüčÅ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ki+2 ąĖ ą┐ą░ą╝čÅčéčī ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ ą▓čŗčłąĄ ąĮąĄ čüą╝ąĄčēą░ąĄčéčüčÅ.

ą×čćąĖčüčéą║ą░ ą▒ąĖčéą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ (Endpoint enable, EPEN) ąĮąĄ ąŠčćąĖčēą░ąĄčé ąĮąĖ ąĄčæ ą▒ąĖčé ALLOC, ąĮąĖ ąĄčæ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ (EPSIZE/PSIZE, EPBK/PBK). ą¦č鹊ą▒čŗ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī ą┐ą░ą╝čÅčéčī ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ, firmware ą┤ąŠą╗ąČąĮąŠ ąŠčćąĖčüčéąĖčéčī ALLOC. ą¤čĆąĖ čŹč鹊ą╝ ą▓čŗą┤ąĄą╗ąĄąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ki+1 čüą╝ąĄčēą░ąĄčéčüčÅ ą▓ąĮąĖąĘ (ą║ ą╝ą╗ą░ą┤čłąĖą╝ ą░ą┤čĆąĄčüą░ą╝). ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ki+2 ąĖ ą┐ą░ą╝čÅčéčī ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ ą▓čŗčłąĄ ąĮąĄ čüą╝ąĄčēą░ąĄčéčüčÅ.

ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╣ čéą░ą▒ą╗ąĖčåąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓čŗą┤ąĄą╗ąĄąĮąĖąĄ ąĖ čĆąĄąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą┐ą░ą╝čÅčéąĖ USB ąĮą░ čéąĖą┐ąĖčćąĮąŠą╝ ą┐čĆąĖą╝ąĄčĆąĄ:

ąóą░ą▒ą╗ąĖčåą░ 19-1. ą¤čĆąŠčåąĄčüčü ą▓čŗą┤ąĄą╗ąĄąĮąĖčÅ ąĖ čĆąĄąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ ą┐ą░ą╝čÅčéąĖ USB ą┤ą╗čÅ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║

ŌĆó ąĪąĮą░čćą░ą╗ą░ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą▓čüąĄ ą║ąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ ąŠčé Endpoint 0 ą┤ąŠ Endpoint 4, ą▓ ą┐ąŠčĆčÅą┤ą║ąĄ ą▓ąŠąĘčĆą░čüčéą░ąĮąĖčÅ. ą¤ą░ą╝čÅčéčī ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ą▒čŗą╗ą░ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮą░ ą▓ DPRAM.

ŌĆó ąŚą░č鹥ą╝ Endpoint 2 ą▒čŗą╗ą░ ąĘą░ą┐čĆąĄčēąĄąĮą░ (EPEN=0), ąŠą┤ąĮą░ą║ąŠ ąĄčæ čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ ą▓čüąĄ ąĄčēąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝.

ŌĆó ą×čćąĖčēąĄąĮ ą▒ąĖčé ALLOC ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ Endpoint 2: ą┐čĆąĖ čŹč鹊ą╝ Endpoint 3 "čüą╝ąĄčüčéąĖą╗ą░čüčī" ą▓ąĮąĖąĘ, Endpoint 4 ąĮąĄ "čüą╝ąĄčüčéąĖą╗ą░čüčī".

ŌĆó ąś ą▓ ąĘą░ą║ą╗čÄč湥ąĮąĖąĄ, firmware čĆąĄčłąĖą╗ąŠ čĆąĄą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī Endpoint 2 ąĮą░ čāą▓ąĄą╗ąĖč湥ąĮąĮčŗą╣ čĆą░ąĘą╝ąĄčĆ. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čĆąĄąĘąĄčĆą▓ąĖčĆčāąĄčé ą┐ą░ą╝čÅčéčī ą┐ąŠčüą╗ąĄ ą┐ą░ą╝čÅčéąĖ endpoint 1 ąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ "čüą┤ą▓ąĖą│ą░ąĄčé" ą┐ą░ą╝čÅčéčī Endpoint 3. ą¤ą░ą╝čÅčéčī ą┤ą╗čÅ Endpoint 4 ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ čüą╝ąĄčēą░ąĄčéčüčÅ, ąĖ ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ą║ąŠąĮčäą╗ąĖą║čé ą┐ą░ą╝čÅčéąĖ, ą┐ąŠč鹊ą╝čā čćč鹊 Endpoint 3 ąĖ 4 ąĖčüą┐ąŠą╗čīąĘčāčÄčé čćą░čüčéąĖčćąĮąŠ ąŠą┤ąĮčā ąĖ čéčā ąČąĄ ą┐ą░ą╝čÅčéčī. ą×ą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ č湥čĆąĄąĘ ą║ąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ 3 ąĖ 4 ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ąĮąĄą╗čīąĘčÅ, čéą░ą║ ą║ą░ą║ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠč鹥ąĮčåąĖą░ą╗čīąĮąŠ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąŠčĆč湥ąĮčŗ.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄąĄ:

ŌĆó ąöą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ Endpoint 0 ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą▒čāą┤čāčé ą┐ąŠč鹥čĆčÅąĮčŗ ą┐čĆąĖ ą░ą║čéąĖą▓ą░čåąĖąĖ ąĖ ą┤ąĄą░ą║čéąĖą▓ą░čåąĖąĖ ą┤čĆčāą│ąĖčģ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║. ąöą░ąĮąĮčŗąĄ Endpoint 0 ą▒čāą┤čāčé ą┐ąŠč鹥čĆčÅąĮčŗ č鹊ą╗čīą║ąŠ ą┐čĆąĖ ąĄčæ ą┤ąĄą░ą║čéąĖą▓ą░čåąĖąĖ.

ŌĆó ąöąĄą░ą║čéąĖą▓ą░čåąĖčÅ ąĖ čĆąĄą░ą║čéąĖą▓ą░čåąĖčÅ ąŠą┤ąĮąŠą╣ ąĖ č鹊ą╣ ąČąĄ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ čü č鹥ą╝ąĖ ąČąĄ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ąĖ ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ "čüą╝ąĄčēąĄąĮąĖčÄ" ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ąĖ ąĮąŠą╝ąĄčĆą░ą╝ąĖ. ąöą╗čÅ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║, ą╗ąĄąČą░čēąĖčģ ą▓čŗčłąĄ, ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé čüąŠčģčĆą░ąĮąĄąĮčŗ.

ŌĆó CFGOK čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą┤ą░ąČąĄ ą▓ čüą╗čāčćą░ąĄ "ą║ąŠąĮčäą╗ąĖą║čéąĮąŠą│ąŠ" ą▓čŗą┤ąĄą╗ąĄąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ.

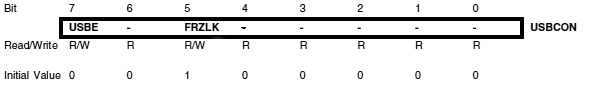

[19.7 PAD suspend (ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ą░ čĆą░ą▒ąŠčéčŗ ąĮąŠąČąĄą║)]

ąĪą╗ąĄą┤čāčÄčēąĖą╣ čĆąĖčüčāąĮąŠą║ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ąĮąŠąČąĄą║ USB ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░:

ŌĆó ąÆ čĆąĄąČąĖą╝ąĄ "idle" (ąŠąČąĖą┤ą░ąĮąĖąĄ) ąĮąŠąČą║ąĖ ą┐ąĄčĆąĄą▓ąŠą┤čÅčéčüčÅ ą▓ čĆąĄąČąĖą╝ ąĮąĖąĘą║ąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (low power consumption mode).

ŌĆó ąÆ "ą░ą║čéąĖą▓ąĮąŠą╝" čĆąĄąČąĖą╝ąĄ ąĮąŠąČą║ąĖ čĆą░ą▒ąŠčéą░čÄčé.

ąĀąĖčü. 19-11. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ ąĮąŠąČąĄą║

ążą╗ą░ą│ SUSPI ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ąĮą░ čłąĖąĮąĄ USB ą▒čŗą╗ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (suspend state). ąŁč鹊čé čäą╗ą░ą│ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ąĮąŠąČą║ąĖ USB ą▓ čĆąĄąČąĖą╝ Idle. ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąŠąČąĖą┤ą░ąĮąĖčÅ (non-idle event) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čäą╗ą░ą│ WAKEUPI ąĖ ą▒čāą┤ąĖčé ą▒čāč乥čĆčŗ ąĮąŠąČąĄą║ USB.

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą║ čĆąĖčüčāąĮą║čā: SUSPI, WAKEUPI - čäą╗ą░ą│ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąŠ čüąŠą▒čŗčéąĖčÅą╝ Suspend, Resume. PAD status - čüąŠčüč鹊čÅąĮąĖąĄ ąĮąŠąČąĄą║ USB ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. Suspend detected = USB pad power down - ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ ąĮąŠąČąĄą║, ą║ąŠą│ą┤ą░ ą▒čŗą╗ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ čüąŠą▒čŗčéąĖąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ čĆą░ą▒ąŠčéčŗ (Suspend). Resume = USB pad wake-up - ą▓ą║ą╗čÄč湥ąĮąĖąĄ ąĮąŠąČąĄą║, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüąŠą▒čŗčéąĖąĄ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ (Resume). Active - ą░ą║čéąĖą▓ąĮčŗą╣ čĆąĄąČąĖą╝ (čāčüčéčĆąŠą╣čüčéą▓ąŠ USB čĆą░ą▒ąŠčéą░ąĄčé). Power Down - čāčüčéčĆąŠą╣čüčéą▓ąŠ USB ą▓čŗą║ą╗čÄč湥ąĮąŠ ąĖ ą╝ą░ą╗ąŠ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄčé.

ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ąĮąŠąČą║ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī čéą░ą║ąČąĄ ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮčŗ ą▓ čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ (idle mode), ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé DETACH. ąØąŠąČą║ąĖ ą▓ąĄčĆąĮčāčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą▓ ą░ą║čéąĖą▓ąĮčŗą╣ čĆąĄąČąĖą╝, ą║ąŠą│ą┤ą░ ą▒ąĖčé DETACH ąŠčćąĖčēą░ąĄčéčüčÅ.

[19.8 D+/D- Read/write (čćč鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī čüąĖą│ąĮą░ą╗ąŠą▓ D+/D-)]

ąŻčĆąŠą▓ąĮąĖ D+ ąĖ D- ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ UPOE. ą¦č鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ąĘą░ą┐ąĖčüą░čéčī ąĘąĮą░č湥ąĮąĖąĄ, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ. ąöą╗čÅ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ą╝ąŠąČąĄčé ą▒čŗčéčī ą║ą░ą║ ąĘą░ą┐čĆąĄčēąĄąĮ, čéą░ą║ ąĖ čĆą░ąĘčĆąĄčłąĄąĮ.

[19.9 ą×ą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓]

19.9.1 USB general registers (ąŠčüąĮąŠą▓ąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ USB)

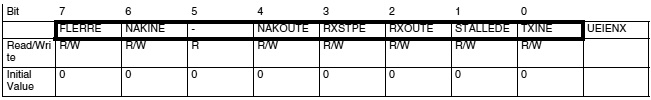

[USBCON]

ŌĆó 7 ŌĆō USBE: USB macro Enable Bit (ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą╝ą░ą║čĆąŠ USB)

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB. ą×čćąĖčüčéąĖč鹥 ą┤ą╗čÅ ąĘą░ą┐čĆąĄčéą░ ąĖ čüą▒čĆąŠčüą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB, ą┤ą╗čÅ ąĘą░ą┐čĆąĄčéą░ čéčĆą░ąĮčüąĖą▓ąĄčĆą░ USB ąĖ ą┤ą╗čÅ ąĘą░ą┐čĆąĄčéą░ čéą░ą║č鹊ą▓čŗčģ ą▓čģąŠą┤ąŠą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB.

ŌĆó 6 ŌĆō ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ąŚąĮą░č湥ąĮąĖąĄ, ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĖąĘ čŹč鹊ą│ąŠ ą▒ąĖčéą░, ą▓čüąĄą│ą┤ą░ ą▒čāą┤ąĄčé 0. ąØąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ą╣č鹥 čŹč鹊čé ą▒ąĖčé.

ŌĆó 5 ŌĆō FRZCLK: Freeze USB Clock Bit (ą▒ąĖčé "ąĘą░ą╝ąŠčĆąŠąĘą║ąĖ" čéą░ą║č鹊ą▓ USB)

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą┤ą╗čÅ ąĘą░ą┐čĆąĄčéą░ čéą░ą║č鹊ą▓čŗčģ ą▓čģąŠą┤ąŠą▓ (ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ŌĆØResume DetectionŌĆØ ą▓čüąĄ ąĄčēąĄ ą░ą║čéąĖą▓ąĮąŠ). ąŁč鹊 čāą╝ąĄąĮčīčłą░ąĄčé 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ. ą×čćąĖčüčéąĖč鹥 ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą║č鹊ą▓čŗčģ ą▓čģąŠą┤ąŠą▓.

ŌĆó 4-0 ŌĆō ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ąŚąĮą░č湥ąĮąĖąĄ, ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĖąĘ čŹčéąĖčģ ą▒ąĖčé, ą▓čüąĄą│ą┤ą░ ą▒čāą┤ąĄčé 0. ąØąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ą╣č鹥 čŹčéąĖ ą▒ąĖčéčŗ.

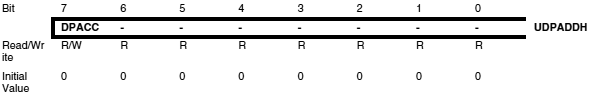

[UDPADDH]

ŌĆó 7 ŌĆō DPACC: DPRAM Direct Access Bit (ą▒ąĖčé ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ DPRAM)

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ ą┐čĆčÅą╝ąŠą│ąŠ čćč鹥ąĮąĖčÅ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ ą┤ą░ąĮąĮčŗčģ ą┤ą▓čāčģą┐ąŠčĆč鹊ą▓ąŠą╣ ą┐ą░ą╝čÅčéąĖ (Dual-Port RAM, DPR) č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆčŗ UEDATX ąĖą╗ąĖ UPDATX. ąĪą╝. čüąĄą║čåąĖčÄ 19.6 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüč鹥ą╣. ą×čćąĖčüčéąĖč鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ ąĖ ą┤ąŠčüčéčāą┐ą░ ą║ DPR č湥čĆąĄąĘ FIFO ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ.

ŌĆó 6-0 ŌĆō ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ąŚąĮą░č湥ąĮąĖąĄ, ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĖąĘ čŹčéąĖčģ ą▒ąĖčé, ą▓čüąĄą│ą┤ą░ ą▒čāą┤ąĄčé 0. ąØąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ą╣č鹥 čŹčéąĖ ą▒ąĖčéčŗ.

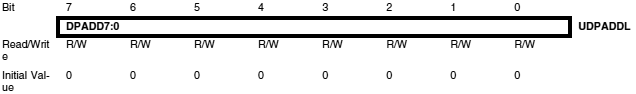

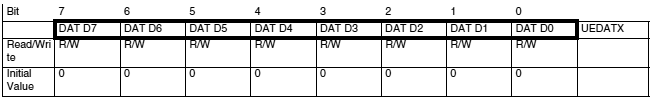

[UDPADDL]

ŌĆó 7-0 ŌĆō DPADD7:0: DPRAM Address Low Byte (ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé ą░ą┤čĆąĄčüą░ DPRAM)

DAPDD7:0 ą╝ą╗ą░ą┤čłą░čÅ ąĘąĮą░čćą░čēą░čÅ čćą░čüčéčī (ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé) ą░ą┤čĆąĄčüą░ DPADD.

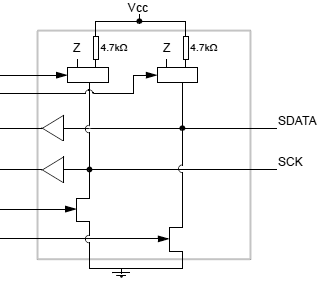

19.9.2 USB/PS2 Software Output Enable register ŌĆō UPOE (čĆąĄą│ąĖčüčéčĆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ USB/PS2)

[UPOE]

ŌĆó Bit 7:6 ŌĆō UPOE[1:0]: USB/PS2 Output enable (čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą▓čŗčģąŠą┤ąŠą▓ USB/PS2)

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹčéąĖ ą▒ąĖčéčŗ, ą║ąŠą│ą┤ą░ ąĮčāąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ąĮčāąČąĮąŠ ąĘą░ą┐čĆąĄčéąĖčéčī ąĖą╗ąĖ čĆą░ąĘčĆąĄčłąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ USB/PS2.

UPOE1 - UPOE0

0 - 0 : ą¤čĆčÅą╝ąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

0 - 1 : ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ.

1 - 0 : ą¤čĆčÅą╝ąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ DP/DM čü čāčĆąŠą▓ąĮčÅą╝ąĖ USB (ąĘąĮą░č湥ąĮąĖčÅ ąĖąĘ ą▒ąĖč鹊ą▓ UPDRV[1:0])

1 - 1 : ą¤čĆčÅą╝ąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ DP/DM čü čāčĆąŠą▓ąĮčÅą╝ąĖ PS/2 (ąĘąĮą░č湥ąĮąĖčÅ ąĖąĘ ą▒ąĖč鹊ą▓ UPDRV[1:0])

ŌĆó Bit 5:4 ŌĆō UPDRV[1:0] : USB/PS2 direct drive values (ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ ą┐čĆčÅą╝ąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ USB/PS2)

ąŚą░ą┐ąĖčłąĖč鹥 ą▓ UPDRV1 ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ D+/SCK čüą╗ąĄą┤čāčÄčēąĄą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ UPOE[1:0].

ąŚą░ą┐ąĖčłąĖč鹥 ą▓ UPDRV0 ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ D-/DATA čüą╗ąĄą┤čāčÄčēąĄą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ UPOE[1:0].

ŌĆó Bit 3 ŌĆō SCKI : SCK Input value (ąĘąĮą░č湥ąĮąĖąĄ ą▓čģąŠą┤ą░ SCK)

ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 1 ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĄčüą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮą░ 1 ąĮą░ SCK (ąĮąŠąČą║ą░ PS/2).

ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 0 ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĄčüą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮą░ 0 ąĮą░ SCK (ąĮąŠąČą║ą░ PS/2).

ŌĆó Bit 2 ŌĆō DATAI : DATA Input value (ąĘąĮą░č湥ąĮąĖąĄ ą▓čģąŠą┤ą░ DATA)

ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 1 ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĄčüą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮą░ 1 ąĮą░ DATA (ąĮąŠąČą║ą░ PS/2).

ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 0 ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĄčüą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮą░ 0 ąĮą░ DATA (ąĮąŠąČą║ą░ PS/2).

ŌĆó Bit 1 ŌĆō DPI : D+ Input value (ą▓čģąŠą┤ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ D+)

ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 1 ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĄčüą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮą░ 1 ąĮą░ D+ (ąĮąŠąČą║ą░ PS/2).

ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 0 ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĄčüą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮą░ 0 ąĮą░ D+ (ąĮąŠąČą║ą░ PS/2).

ŌĆó Bit 0 ŌĆō DMI : D- Input value (ą▓čģąŠą┤ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ D-)

ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 1 ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĄčüą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮą░ 1 ąĮą░ D- (ąĮąŠąČą║ą░ PS/2).

ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 0 ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĄčüą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮą░ 0 ąĮą░ D- (ąĮąŠąČą║ą░ PS/2).

[19.10 USB Software Operating modes (ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗąĄ čĆą░ą▒ąŠčćąĖąĄ čĆąĄąČąĖą╝čŗ USB)]

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆą░ą▒ąŠč湥ą│ąŠ čĆąĄąČąĖą╝ą░ USB, ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ (firmware) ą╝ąŠąČąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčī čüą╗ąĄą┤čāčÄčēąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ:

Power On the USB interface (ą▓ą║ą╗čÄč湥ąĮąĖąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ USB)

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ PLL

ŌĆó ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ PLL

ŌĆó ą¤čĆąŠą▓ąĄčĆą║ą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ąĘą░čģą▓ą░čéą░ ą▓ ą┐ąĄčéą╗ąĄ PLL

ŌĆó ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ USB

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ USB (ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ USB Endpoint 0)

ŌĆó ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ USB (Attach USB device)

Power Off the USB interface (ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ USB)

ŌĆó ą×čéą║ą╗čÄč湥ąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ USB (Detach USB device)

ŌĆó ąŚą░ą┐čĆąĄčé čĆą░ą▒ąŠčéčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ USB

ŌĆó ąĘą░ą┐čĆąĄčé čĆą░ą▒ąŠčéčŗ PLL

Suspending the USB interface (ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ą░ ąĖąĮč鹥čĆč乥ą╣čüą░ USB)

ŌĆó ą×čćąĖčüčéą║ą░ ą▒ąĖčéą░ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (Suspend Bit)

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ąĖ čéą░ą║č鹊ą▓ USB ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (USB suspend clock)

ŌĆó ąŚą░ą┐čĆąĄčé čĆą░ą▒ąŠčéčŗ PLL

ŌĆó ąŻą▒ąĄą┤ąĖčéčīčüčÅ, čćč鹊 čĆą░ąĘčĆąĄčłąĄąĮčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (WAKEUPE) ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ čĆąĄąČąĖą╝ą░ čüąĮą░ (sleep mode)

ŌĆó ą¤ąĄčĆąĄą▓ąŠą┤ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą▓ čĆąĄąČąĖą╝ čüąĮą░ (sleep mode)

Resuming the USB interface (ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ USB)

ŌĆó ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ PLL

ŌĆó ą×ąČąĖą┤ą░ąĮąĖąĄ ąĘą░čģą▓ą░čéą░ ą┐ąĄčéą╗ąĖ PLL

ŌĆó ą×čćąĖčüčéą║ą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ USB ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (USB suspend clock)

ŌĆó ą×čćąĖčüčéą║ą░ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ąĘą░ą┐čāčüą║ą░ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ (Resume information)

[20. USB Device Operating modes (čĆą░ą▒ąŠčćąĖąĄ čĆąĄąČąĖą╝čŗ čāčüčéčĆąŠą╣čüčéą▓ą░ USB)]

[20.1 ąÆą▓ąĄą┤ąĄąĮąĖąĄ]

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čāčüčéčĆąŠą╣čüčéą▓ą░ USB ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┐ąŠą╗ąĮąŠčüą║ąŠčĆąŠčüčéąĮčāčÄ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ (full speed, ą╝ą░ą║čüąĖą╝čāą╝ 12 ą╝ąĄą│ą░ą▒ąĖčé/čüąĄą║). ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (default control endpoint), ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé 4 ą┤čĆčāą│ąĖąĄ ą║ąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ čĆąĄąČąĖą╝ąŠą▓ čĆą░ą▒ąŠčéčŗ control, bulk, interrupt ąĖą╗ąĖ isochronous:

ŌĆó Endpoint 0: ąĖą╝ąĄąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ čĆą░ąĘą╝ąĄčĆ FIFO ą╝ą░ą║čüąĖą╝čāą╝ ą┤ąŠ 64 ą▒ą░ą╣čé, default control endpoint.

ŌĆó Endpoint 1 ąĖ 2: ąĖą╝ąĄąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ čĆą░ąĘą╝ąĄčĆ FIFO ą╝ą░ą║čüąĖą╝čāą╝ ą┤ąŠ 64 ą▒ą░ą╣čé.

ŌĆó Endpoint 3 ąĖ 4: ąĖą╝ąĄąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ čĆą░ąĘą╝ąĄčĆ FIFO ą╝ą░ą║čüąĖą╝čāą╝ ą┤ąŠ 64 ą▒ą░ą╣čé čü čĆąĄąČąĖą╝ąŠą╝ ping-pong.

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąĮą░čćąĖąĮą░ąĄčé čĆą░ą▒ąŠčéčā ą▓ čĆąĄąČąĖą╝ąĄ "idle". ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą▒čāč乥čĆąŠą▓ ąĮąŠąČąĄą║ ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮą░ ą╝ąĖąĮąĖą╝čāą╝ąĄ.

[20.2 Power-on and reset (ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ąĖ čüą▒čĆąŠčü)]

ąĪą╗ąĄą┤čāčÄčēą░čÅ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą│ą╗ą░ą▓ąĮčŗąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB ą┐čĆąĖ ą┐ąŠą┤ą░č湥 ą┐ąĖčéą░ąĮąĖčÅ:

ąĀąĖčü. 20-1. ąĪąŠčüč鹊čÅąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB device ą┐ąŠčüą╗ąĄ reset

ąÆ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (reset state) ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ USB ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

ŌĆó ąóą░ą║čéčŗ macro clock ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą┤ą╗čÅ ą╝ąĖąĮąĖą╝ąĖąĘą░čåąĖąĖ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (FRZCLK čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ).

ŌĆó ąÆąĮčāčéčĆąĄąĮąĮąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ USB device controller - čüą▒čĆąŠčü reset (ą▓čüąĄ čĆąĄą│ąĖčüčéčĆčŗ čüą▒čĆąŠčłąĄąĮčŗ ą▓ čüą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 DETACH čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ).

ŌĆó ąĪą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ ą▒ą░ąĮą║ąĖ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║.

ŌĆó ą¤ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖą╣ čĆąĄąĘąĖčüč鹊čĆ D+ (pull-up) ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ (čĆąĄąČąĖą╝ Detach, ąŠčéą║ą╗čÄč湥ąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ USB ąŠčé čłąĖąĮčŗ).

D+ pull-up ą▒čāą┤ąĄčé ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ ą▒ąĖčé DETACH. Macro ą▒čāą┤ąĄčé ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ "Idle", čü ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╝ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝ 菹ĮąĄčĆą│ąĖąĖ, ąĖ ąĮąĄ ąĮčāąČą┤ą░ąĄčéčüčÅ ą▓ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮąĮąŠą╝ PLL ą┤ą╗čÅ ą▓čģąŠą┤ą░ ą▓ čŹč鹊 čüąŠčüč鹊čÅąĮąĖąĄ.

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čāčüčéčĆąŠą╣čüčéą▓ą░ USB ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ čüą▒čĆąŠčłąĄąĮ ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ USBE.

[20.3 Endpoint reset (čüą▒čĆąŠčü ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ)]

ąÜąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮą░ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ (EPRSTx) ą▓ čĆąĄą│ąĖčüčéčĆąĄ UERST. ąŁč鹊 čüą▒čĆą░čüčŗą▓ą░ąĄčé:

ŌĆó ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą╝ą░čłąĖąĮčā čüąŠčüč鹊čÅąĮąĖą╣ ą┤ą╗čÅ čŹč鹊ą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ,

ŌĆó ąŠčćąĖčēą░čÄčéčüčÅ ą▒ą░ąĮą║ąĖ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ Rx ąĖ Tx, ąĖ ą▓ąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĖčģ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čāą║ą░ąĘą░č鹥ą╗ąĖ,

ŌĆó čĆąĄą│ąĖčüčéčĆčŗ UEINTX, UESTA0X ąĖ UESTA1X ą▓ąŠąĘą▓čĆą░čēą░čÄčéčüčÅ ą▓ čüą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░.

ą¤ąŠą╗ąĄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ (data toggle field) ąŠčüčéą░ąĄčéčüčÅ ąĮąĄąĖąĘą╝ąĄąĮąĄąĮąĮčŗą╝. ąöčĆčāą│ąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ č鹊ąČąĄ ąŠčüčéą░čÄčéčüčÅ ąĮąĄąĖąĘą╝ąĄąĮąĄąĮąĮčŗą╝ąĖ. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ąŠčüčéą░ąĄčéčüčÅ ą░ą║čéąĖą▓ąĮąŠą╣ ąĖ čĆą░ą▒ąŠčéą░ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ą▓čüąĄ ąĄčēąĄ čĆą░ąĘčĆąĄčłąĄąĮą░. ąĪą▒čĆąŠčü ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą▓čÅąĘą░ąĮ ąŠčćąĖčüčéą║ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ data toggle command (ą▒ąĖčé RSTDT) ą▓ ąŠčéą▓ąĄčé ąĮą░ USB-ą║ąŠą╝ą░ąĮą┤čā CLEAR_FEATURE.

[20.4 USB reset (čüą▒čĆąŠčü ą┐ąŠ čłąĖąĮąĄ USB)]

ąÜąŠą│ą┤ą░ ą┤ąĄč鹥ą║čéąĖčĆčāąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄ čüą▒čĆąŠčüą░ ą┐ąŠ čłąĖąĮąĄ USB (čüąŠčüč鹊čÅąĮąĖąĄ SEO čü ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ 100 ą╝ą║čü), ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ:

ŌĆó ąĀą░ą▒ąŠčéą░ ą▓čüąĄčģ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ.

ŌĆó ąÜąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (default control endpoint) ąŠčüčéą░ąĄčéčüčÅ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą╣.

ŌĆó ą×čćąĖčēą░ąĄčéčüčÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ (data toggle) ą┤ą╗čÅ default control endpoint.

ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮą░ čäčāąĮą║čåąĖčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čüą▒čĆąŠčüą░, č鹊 ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüą▒čĆąŠčü čÅą┤čĆą░ CPU AVR ą▒ąĄąĘ ąĘą░ą┐čĆąĄčéą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB (ą║ąŠč鹊čĆčŗą╣ ąŠčüčéą░ąĄčéčüčÅ ą▓ č鹊ą╝ ąČąĄ čüąŠčüč鹊čÅąĮąĖąĖ ą┐ąŠčüą╗ąĄ USB Reset).

[20.5 Endpoint selection (ą▓čŗą▒ąŠčĆ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ)]

ą¤ąĄčĆąĄą┤ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ą╗čÄą▒ąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ CPU čü ą║ąŠąĮąĄčćąĮčŗą╝ąĖ č鹊čćą║ą░ą╝ąĖ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮą░ čüąĮą░čćą░ą╗ą░ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░. ąŁč鹊 ą┤ąĄą╗ą░ąĄčéčüčÅ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖč鹊ą▓ EPNUM2:0 (ą▓ čĆąĄą│ąĖčüčéčĆąĄ UENUM) ą▓ ąĮąŠą╝ąĄčĆ čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠą╣ č湥čĆąĄąĘ CPU ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ.

ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ CPU ą┐ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ firmware ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ čĆą░ąĘą╗ąĖčćąĮčŗą╝ čĆąĄą│ąĖčüčéčĆą░ą╝ ąĖ ą┤ą░ąĮąĮčŗą╝.

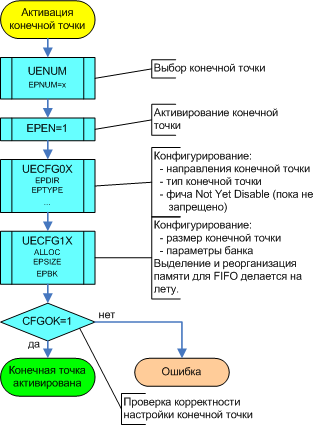

[20.6 Endpoint activation (ą░ą║čéąĖą▓ą░čåąĖčÅ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ)]

ąÜąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ą╝ąŠąČąĄčé ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ reset, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé EPEN. ąöą╗čÅ ą░ą║čéąĖą▓ą░čåąĖąĖ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ čüą╗ąĄą┤čāčÄčēą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣, ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮą░čÅ ąĮą░ čĆąĖčü. 20-2:

ąĀąĖčü. 20-2. Endpoint activation flow

ą¤ąŠą║ą░ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą║ąŠčĆčĆąĄą║čéąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ (ą┐ąŠą║ą░ ą▒ąĖčé CFGOK ąĮąĄ ąŠčćąĖčüčéąĖčéčüčÅ), ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ąĮąĄ ą▒čāą┤ąĄčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░čéčī ą┐ą░ą║ąĄčéčŗ, ą║ąŠč鹊čĆčŗąĄ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ čģąŠčüč鹊ą╝ USB. CFGOK ąĮąĄ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░, ąĄčüą╗ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆ čĆą░ąĘą╝ąĄčĆą░ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ą▒ąŠą╗čīčłąĄ, č湥ą╝ čĆą░ąĘą╝ąĄčĆ DPRAM.

ą×čćąĖčüčéą║ą░ EPEN čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čüą▒čĆąŠčü ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ (čüą╝. čüąĄą║čåąĖčÄ 20.3). ą¤čĆąĖ čŹč鹊ą╝ čéą░ą║ąČąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

ŌĆó ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ (čüąŠčģčĆą░ąĮčÅčÄčé ąĘąĮą░č湥ąĮąĖčÅ EPSIZE, EPBK, ALLOC).

ŌĆó ąĪą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą┐ąŠą╗ąĄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ (data toggle).

ŌĆó ą¤ą░ą╝čÅčéčī DPRAM, čüą▓čÅąĘą░ąĮąĮą░čÅ čü ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąŠą╣, ą▓čüąĄ ąĄčēąĄ ąŠčüčéą░ąĄčéčüčÅ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮąŠą╣.

ąĪą╝. čüąĄą║čåąĖčÄ 19.6, ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüč鹥ą╣ ą┐ąŠ ą┐ąŠą▓ąŠą┤čā ą▓čŗą┤ąĄą╗ąĄąĮąĖčÅ ąĖ čĆąĄąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ ą┐ą░ą╝čÅčéąĖ.

[20.7 Address Setup (ąĮą░čüčéčĆąŠą╣ą║ą░ ą░ą┤čĆąĄčüą░)]

ąÉą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░ USB čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┐čĆąŠč鹊ą║ąŠą╗ąŠą╝ USB čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆó ą¤ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB ąŠčéą▓ąĄčćą░ąĄčé ą┐ąŠ ą░ą┤čĆąĄčüčā 0.

ŌĆó ąźąŠčüčé ąŠčéą┐čĆą░ą▓ą╗čÅąĄčé ą║ąŠą╝ą░ąĮą┤čā SETUP (SET_ADDRESS(addr)),

ŌĆó ąÜąŠą┤ firmware ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ą░ą┤čĆąĄčü ą▓ UADD, ąĮąŠ ą┐ąŠą║ą░ ąŠčüčéą░ą▓ą╗čÅąĄčé ADDEN ąŠčćąĖčēąĄąĮąĮčŗą╝.

ŌĆó ąŻčüčéčĆąŠą╣čüčéą▓ąŠ USB ąŠčéą┐čĆą░ą▓ą╗čÅąĄčé ą║ąŠą╝ą░ąĮą┤čā IN čü 0 ą▒ą░ą╣čéą░ą╝ąĖ (IN 0 Zero Length Packet) ą┤ą╗čÅ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ.

ŌĆó ąś ąĘą░č鹥ą╝ ą║ąŠą┤ firmware ą╝ąŠąČąĄčé čĆą░ąĘčĆąĄčłąĖčéčī ą░ą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░ USB ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ADDEN. ąóąŠą╗čīą║ąŠ ąŠą┤ąĖąĮ ą░ą┤čĆąĄčü, ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝, čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ UADD.

ADDEN ąĖ UADD ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. UADD čüąŠą┤ąĄčƹȹĖčé ą░ą┤čĆąĄčü ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 00h ą┐ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĖą╗ąĖ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ USB.

ADDEN ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ čüą╗čāčćą░čÅčģ:

ŌĆó ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ.

ŌĆó ąÜąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčé ąŠčé čģąŠčüčéą░ čüąĖą│ąĮą░ą╗ USB reset.

ŌĆó ąÜąŠą│ą┤ą░ macro ąĘą░ą┐čĆąĄčēąĄąĮ (ąŠčćąĖčēąĄąĮ ą▒ąĖčé USBE).

ą║ąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé ąŠčćąĖčēąĄąĮ, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą░ą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 00h.

[20.8 ąĪąŠą▒čŗčéąĖčÅ Suspend, Wake-up ąĖ Resume (ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ą░, ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ ąĖ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ)]

ą¤ąŠčüą╗ąĄ 3 ą╝čü ąĮąĄą░ą║čéąĖą▓ąĮąŠčüčéąĖ ąĮą░ čłąĖąĮąĄ USB (čüąŠčüč鹊čÅąĮąĖąĄ J state), ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čäą╗ą░ą│ SUSPI ąĖ ą┐čĆąĖ čŹč鹊ą╝ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ). ąÜąŠą┤ firmware ą╝ąŠąČąĄčé ąĘą░č鹥ą╝ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčé FRZCLK.

CPU čéą░ą║ ąČąĄ ą╝ąŠąČąĄčé, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą░čĆčģąĖč鹥ą║čéčāčĆčŗ firmware, ąĘą░ą┐čĆąĄčéąĖčéčī PLL ąĖ/ąĖą╗ąĖ ą▓ąŠą╣čéąĖ ą▓ idle mode ą┤ą╗čÅ čāą╝ąĄąĮčīčłąĄąĮąĖčÅ čŹąĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (čŹč鹊 čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ą┐ąŠą┤čģąŠą┤ąĖčé ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ USB, ą┐ąĖčéą░ąĄą╝čŗčģ ąŠčé čłąĖąĮčŗ, ąŠčé ą┐čĆąŠą▓ąŠą┤ą░ VBUS).

ąĢčüčéčī ą┤ą▓ą░ čüą┐ąŠčüąŠą▒ą░ ą▓ąŠąĘą▓čĆą░čéą░ ąĖąĘ čĆąĄąČąĖą╝ą░ Suspend:

ŌĆó ą¤ąĄčĆą▓čŗą╣ ą╝ąĄč鹊ą┤ čüąŠčüč鹊ąĖčé ą▓ ąŠčćąĖčüčéą║ąĄ ą▒ąĖčéą░ FRZCLK. ąŁč鹊 ą▓ąŠąĘą╝ąŠąČąĮąŠ, ąĄčüą╗ąĖ CPU ąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ Idle mode.

ŌĆó ąÆč鹊čĆąŠą╣ ą╝ąĄč鹊ą┤, ąĄčüą╗ąĖ CPU ą▓ čĆąĄąČąĖą╝ąĄ idle, čĆą░ąĘčĆąĄčłąĖčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ WAKEUPI (čāčüčéą░ąĮąŠą▓ąĖčéčī WAKEUPE ą┤ąŠ ą▓čģąŠą┤ą░ ą▓ čĆąĄąČąĖą╝ idle). ąŚą░č鹥ą╝, ą║ąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čāą▓ąĖą┤ąĖčé čüąĖą│ąĮą░ą╗ non-idle, čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ WAKEUPI.

ąŚą░č鹥ą╝ firmware ą┤ąŠą╗ąČąĮąŠ ąŠčćąĖčüčéąĖčéčī ą▒ąĖčé FRZCLK ą┤ą╗čÅ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ ą┐ąĄčĆąĄą┤ą░čć.

ąØąĄčé ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ą╝ąĄąČą┤čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ SUSPI ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ WAKEUPI: WAKEUPI čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą┐ą░čéč鹥čĆąĮ non-idle ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ąĮą░ ą┐čĆąŠą▓ąŠą┤ą░čģ ą┤ą░ąĮąĮčŗčģ (D+ ąĖ D-). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ WAKEUPI ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą▓ ą╗čÄą▒ąŠą╝ čüą╗čāčćą░ąĄ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ąĮą░čģąŠą┤ąĖčéčüčÅ ą╗ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ą▓ čĆąĄąČąĖą╝ąĄ suspend ąĖą╗ąĖ ąĮąĄčé. ąÜąŠą│ą┤ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ WAKEUPI čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, č鹊 ąĄčüą╗ąĖ ą▒ąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SUSPI čéą░ą║ąČąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ąŠąĮ ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ.

ąÜąŠą│ą┤ą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SUSPI, ąĄčüą╗ąĖ ą▒ąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ WAKEUPI čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ąŠąĮ ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ.

[20.9 Detach (ąŠčéą║ą╗čÄč湥ąĮąĖąĄ)]

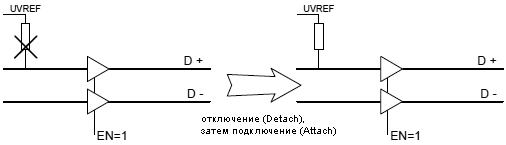

ąĪąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖčéą░ DETACH ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 1. ą£ąŠąČąĮąŠ ąĘą░ąĮąŠą▓ąŠ čüą┤ąĄą╗ą░čéčī 菹Įčāą╝ąĄčĆą░čåąĖčÄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐čĆąŠčüč鹊ą╣ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ąĖ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą╣ ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ DETACH (ą┐čĆąĖ čŹč鹊ą╝ ą┤ąŠą╗ąČąĮąŠ čāčćąĖčéčŗą▓ą░čéčīčüčÅ ą▓čĆąĄą╝čÅ čĆą░ąĘčĆčÅą┤ą░ ą╗ąĖąĮąĖąĖ USB).

ŌĆó ąÜąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čāčüčéčĆąŠą╣čüčéą▓ą░ USB ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ full-speed, čāčüčéą░ąĮąŠą▓ą║ą░ DETACH ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąŠčéą║ą╗čÄč湥ąĮąĖčÄ čĆąĄąĘąĖčüč鹊čĆą░ pull-up ąĮą░ čüąĖą│ąĮą░ą╗čīąĮąŠą╣ ą╗ąĖąĮąĖąĖ D+. ąŚą░č鹥ą╝ ą┐čĆąĖ ąŠčćąĖčüčéą║ąĄ DETACH pull-up čüąĮąŠą▓ą░ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčüčÅ ą║ D+.

ąĀąĖčü. 20-3. Detach (ąŠčéą║ą╗čÄč湥ąĮąĖąĄ) čāčüčéčĆąŠą╣čüčéą▓ą░ USB ą▓ Full-speed:

[20.10 Remote Wake-up (čāą┤ą░ą╗ąĄąĮąĮąŠąĄ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ)]

ąŚą░ą┐čĆąŠčü "Remote Wake-up" (ąĖą╗ąĖ ą║ą░ą║ ąĄą│ąŠ ąĮą░ąĘčŗą▓ą░čÄčé "upstream resume", ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ąŠčé ą░ą┐čüčéčĆąĖą╝) čÅą▓ą╗čÅąĄčéčüčÅ ąĄą┤ąĖąĮčüčéą▓ąĄąĮąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĄą╣, ą║ąŠč鹊čĆą░čÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčéą┐čĆą░ą▓ą╗ąĄąĮą░ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ USB ą┐ąŠ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą╣ ąĖąĮąĖčåąĖą░čéąĖą▓ąĄ (ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ąĖčüą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ čģąŠčüč鹊ą╝). ąØąŠ ą▓ ą╗čÄą▒ąŠą╝ čüą╗čāčćą░ąĄ, čćč鹊ą▒čŗ čüą┤ąĄą╗ą░čéčī čŹč鹊, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ąŠą╗ąČąĮąŠ čüąĮą░čćą░ą╗ą░ ą┐čĆąĖąĮčÅčéčī ąŠčé čģąŠčüčéą░ ąĘą░ą┐čĆąŠčü DEVICE_REMOTE_WAKEUP. ą¤čĆąŠčåąĄą┤čāčĆą░ Remote Wake-up:

ŌĆó ąĪąĮą░čćą░ą╗ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ą┤ąŠą╗ąČąĄąĮ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčī čüąŠčüč鹊čÅąĮąĖąĄ "suspend" ąĮą░ čłąĖąĮąĄ USB: remote wakeup ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé SUSPI.

ŌĆó ąŚą░č鹥ą╝ ą║ąŠą┤ firmware ąĖą╝ąĄąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čāčüčéą░ąĮąŠą▓ąĖčéčī RMWKUP ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą┐ąŠč鹊ą║ą░ "upstream resume". ąŁč鹊 ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą┤ąĄą╗ą░ąĮąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą┐ąŠčüą╗ąĄ 5 ą╝čü ąĮąĄą░ą║čéąĖą▓ąĮąŠčüčéąĖ čłąĖąĮčŗ USB.

ŌĆó ąÜąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąĮą░čćąĮąĄčé ąŠčéą┐čĆą░ą▓ą║čā "upstream resume", čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čäą╗ą░ą│ UPRSMI ąĖ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ). ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ SUSPI, č鹊 ąŠąĮ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ ą░ą┐ą┐ą░čĆą░čéąĮąŠ.

ŌĆó RMWKUP ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ "upstream resume".

ŌĆó ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ, ąĄčüą╗ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┤ąĄč鹥ą║čéąĖčĆčāąĄčé čģąŠčĆąŠčłąĖą╣ čüąĖą│ąĮą░ą╗ "End Of Resume" ąŠčé čģąŠčüčéą░, čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ EORSMI (ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ).

[20.11 STALL request (ąĘą░ą┐čĆąŠčü ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą░ ą┐ąŠ ąŠčłąĖą▒ą║ąĄ)]

ąöą╗čÅ ą║ą░ąČą┤ąŠą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ STALL ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčéčüčÅ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ 3 ą▒ąĖč鹊ą▓:

ŌĆō STALLRQ (enable stall request, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĘą░ą┐čĆąŠčüą░ STALL)

ŌĆō STALLRQC (disable stall request, ąĘą░ą┐čĆąĄčé ąĘą░ą┐čĆąŠčüą░ STALL)

ŌĆō STALLEDI (stall sent interrupt, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčéą┐čĆą░ą▓ą║ąĖ STALL)

ą¦č鹊ą▒čŗ ąŠčéą┐čĆą░ą▓ąĖčéčī STALL handshake ą┐čĆąĖ čüą╗ąĄą┤čāčÄčēąĄą╝ ąĘą░ą┐čĆąŠčüąĄ čģąŠčüčéą░, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé ąĘą░ą┐čĆąŠčüą░ STALLRQ. ąÆčüąĄ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ąĘą░ą┐čĆąŠčüčŗ ą▒čāą┤čāčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░čéčīčüčÅ ąŠčéą▓ąĄč鹊ą╝ STALL, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé STALLRQC.

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ STALLRQC ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčüčéąĖčé ą▒ąĖčé STALLRQ. ąæąĖčé STALLRQ čéą░ą║ąČąĄ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą┐ąŠčüą╗ąĄ ąĄą│ąŠ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĖąĘ firmware. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, firmware ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī čŹč鹊čé ą▒ąĖčé ą║ą░ą║ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣.

ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ STALL handshake, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ USB čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čäą╗ą░ą│ STALLEDI, ąĖ čüčĆą░ą▒ąŠčéą░ąĄčé (ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ) ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ EPINTx.

ą¤čĆąĖčģąŠą┤čÅčēąĖąĄ ą┐ą░ą║ąĄčéčŗ ą▒čāą┤čāčé ąŠčéą▒čĆąŠčłąĄąĮčŗ (ąĮąĄ ą▒čāą┤čāčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ RXOUTI ąĖ RWAL).

ąŚą░č鹥ą╝ čģąŠčüčé ąŠčéą┐čĆą░ą▓ąĖčé ą║ąŠą╝ą░ąĮą┤čā čüą▒čĆąŠčüą░ čüąŠčüč鹊čÅąĮąĖčÅ STALL: firmware ą┐čĆąŠčüč鹊 čāčüčéą░ąĮąŠą▓ąĖčé ą▒ąĖčé STALLRQC ą┤ą╗čÅ čüą▒čĆąŠčüą░ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ.

20.11.1 Special consideration for Control Endpoints (čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ąĘą░ą╝ąĄčćą░ąĮąĖčÅ ą┤ą╗čÅ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ)

ąŚą░ą┐čĆąŠčü SETUP ą▓čüąĄą│ą┤ą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčéčüčÅ ACK. ąĢčüą╗ąĖ ąĘą░ą┐čĆąŠčü STALL čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┤ą╗čÅ Control Endpoint, ąĖ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ąĘą░ą┐čĆąŠčü SETUP, č鹊 ąĘą░ą┐čĆąŠčü SETUP ą┐ąŠą╗čāčćąĖčé ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ACK ąĖ čäą╗ą░ą│ąĖ ąĘą░ą┐čĆąŠčüą░ STALLRQ ąĖ ąŠčéą┐čĆą░ą▓ą║ąĖ STALLEDI ą▒čāą┤čāčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą▒čĆąŠčłąĄąĮčŗ (RXSETUPI čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, TXIN ąŠčćąĖčēąĄąĮ, STALLED ąŠčćąĖčēąĄąĮ, TXINI ąŠčćąĖčēąĄąĮ...).

ąóą░ą║ąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čāą┐čĆąŠčēą░ąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠą╝ 菹Įčāą╝ąĄčĆą░čåąĖąĖ. ąĢčüą╗ąĖ ą║ąŠą╝ą░ąĮą┤ą░ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĖą╗ąĖ čüąŠą┤ąĄčƹȹĖčé ąŠčłąĖą▒ą║čā, č鹊 firmware čāčüčéą░ąĮąŠą▓ąĖčé čäą╗ą░ą│ ąĘą░ą┐čĆąŠčüą░ STALL ąĖ ą╝ąŠąČąĄčé ą▓ąŠąĘą▓čĆą░čéąĖčéčīčüčÅ ą║ ąŠčüąĮąŠą▓ąĮąŠą╣ čĆą░ą▒ąŠč鹥, ąŠąČąĖą┤ą░čÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĘą░ą┐čĆąŠčüą░ SETUP.

ąŁč鹊 čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą¦ą░čüčéąĖ 8 č鹥čüčéą░, ą║ąŠč鹊čĆčŗą╣ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ čüčéą░čéčāčü ą┤ą╗čÅ GET_DESCRIPTOR. ąÜąŠą┤ firmware čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ąĘą░ą┐čĆąŠčü STALL ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ čüčéą░čéčāčüą░. ąÆčüąĄ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čüčéą░čéčāčüčŗ ą▒čāą┤čāčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮčŗ ą▓ STALL, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą┐ąŠą╗čāč湥ąĮ čüą╗ąĄą┤čāčÄčēąĖą╣ ąĘą░ą┐čĆąŠčü SETUP.

20.11.2 STALL handshake and Retry mechanism (ą╝ąĄčģą░ąĮąĖąĘą╝ čĆčāą║ąŠą┐ąŠąČą░čéąĖčÅ STALL ąĖ ą┐ąĄčĆąĄąŠčéą┐čĆą░ą▓ą║ąĖ)

ą£ąĄčģą░ąĮąĖąĘą╝ ą┐ąĄčĆąĄąŠčéą┐čĆą░ą▓ą║ąĖ (Retry) ąĖą╝ąĄąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé ą▓čŗčłąĄ STALL handshake. STALL handshake ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé STALLRQ, ąĖ ąĄčüą╗ąĖ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąĄčĆąĄąŠčéą┐čĆą░ą▓ą║ą░.

[20.12 CONTROL endpoint management (ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖąĄ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ)]

ąŚą░ą┐čĆąŠčü SETUP ą▓čüąĄą│ą┤ą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčéčüčÅ ACK. ąÜąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčé ąĮąŠą▓čŗą╣ ą┐ą░ą║ąĄčé ąĮą░čüčéčĆąŠą╣ą║ąĖ (setup packet), čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RXSTPI (ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ). ą¤čĆąĖ čŹč鹊ą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RXOUTI ąĮąĄ čüčĆą░ą▒ąŠčéą░ąĄčé.

ą¤ąŠą╗čÅ FIFOCON ąĖ RWAL ąĮąĄ ąŠčéąĮąŠčüčÅčéčüčÅ ą║ ą║ąŠąĮąĄčćąĮčŗą╝ č鹊čćą║ą░ą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (CONTROL endpoints). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, firmware ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą▒čāą┤ąĄčé ąĖčģ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ čŹčéąĖčģ ą║ąŠąĮčéčĆąŠą╗čīąĮčŗčģ č鹊č湥ą║. ą¤čĆąĖ čćč鹥ąĮąĖąĖ ąĘąĮą░č湥ąĮąĖąĄ čŹčéąĖčģ ą▒ąĖčé ą▓čüąĄą│ą┤ą░ ą▒čāą┤ąĄčé 0.

CONTROL endpoints ąŠą▒čüą╗čāąČąĖą▓ą░čÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ą▒ąĖčéą░ą╝ąĖ:

ŌĆó RXSTPI čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčé ąĮąŠą▓čŗą╣ ąĘą░ą┐čĆąŠčü SETUP. ą×ąĮ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą║ąŠą┤ąŠą╝ firmware ą┤ą╗čÅ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ą┐ą░ą║ąĄčéą░ ąĖ ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ ą▒ą░ąĮą║ą░ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ.

ŌĆó RXOUTI čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčéčŗ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ OUT. ą×ąĮ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą║ąŠą┤ąŠą╝ firmware ą┤ą╗čÅ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ą┐ą░ą║ąĄčéą░ ąĖ ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ ą▒ą░ąĮą║ą░ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ.

ŌĆó TXINI čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒ą░ąĮą║ ą│ąŠč鹊ą▓ ą┐čĆąĖąĮčÅčéčī ąĮąŠą▓čŗą╣ ą┐ą░ą║ąĄčé IN. ą×ąĮ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą║ąŠą┤ąŠą╝ firmware ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą┐ą░ą║ąĄčéą░ ąĖ ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ ą▒ą░ąĮą║ą░ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ.

CONTROL endpoints ąĮąĄ ą┤ąŠą╗ąČąĮčŗ čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ (ąŠą▒čüą╗čāąČąĖą▓ą░čéčīčüčÅ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝), čŹč鹊 ą┤ąŠą╗ąČąĮąŠ ą┤ąĄą╗ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ą┐čāč鹥ą╝ ąŠą┐čĆąŠčüą░ ą▒ąĖč鹊ą▓ čüčéą░čéčāčüą░.

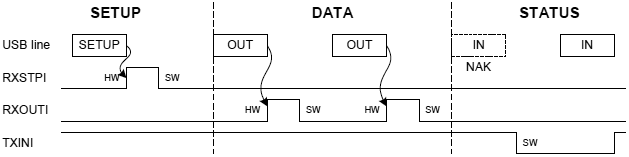

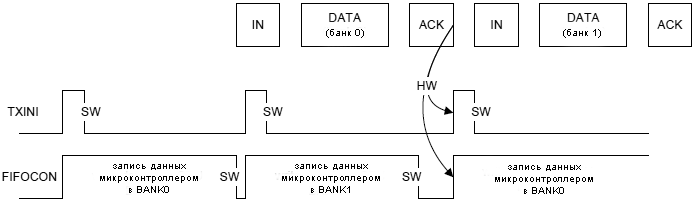

20.12.1 Control Write (ąĘą░ą┐ąĖčüčī ą┐ą░ą║ąĄčéą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ)

ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ čéčĆą░ąĮąĘą░ą║čåąĖčÅ ąĘą░ą┐ąĖčüąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (control write transaction). ąÆąŠ ą▓čĆąĄą╝čÅ čüčéą░ą┤ąĖąĖ čüčéą░čéčāčüą░, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā ąĮąĄąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ąŠčéą┐čĆą░ą▓ą╗čÅčéčī NAK ąĮą░ ą┐ąĄčĆą▓ąŠą╝ č鹊ą║ąĄąĮąĄ IN:

ŌĆó ąĢčüą╗ąĖ firmware ąĘąĮą░ąĄčé č鹊čćąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░, ą║ąŠč鹊čĆąŠąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮąŠ, č鹊 ąŠąĮąŠ ą╝ąŠąČąĄčé ąŠą┐ąĄčĆąĄą┤ąĖčéčī čüčéą░ą┤ąĖčÄ čüčéą░čéčāčüą░ ąĖ ąŠčéą┐čĆą░ą▓ąĖčéčī ZLP (Zero Length Packet, ą┐ą░ą║ąĄčé ąĮčāą╗ąĄą▓ąŠą╣ ą┤ą╗ąĖąĮčŗ) ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ č鹊ą║ąĄąĮą░ IN,

ŌĆó ąĖą╗ąĖ firmware ą╝ąŠąČąĄčé čćąĖčéą░čéčī ą▒ą░ą╣čéčŗ ąĖ ąŠą┐čĆą░čłąĖą▓ą░čéčī NAKINI, ą║ąŠč鹊čĆčŗą╣ ą│ąŠą▓ąŠčĆąĖčé, čćč鹊 ą▓čüąĄ ą▒ą░ą╣čéčŗ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ čģąŠčüč鹊ą╝, ąĖ čéčĆą░ąĮąĘą░ą║čåąĖčÅ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüčéą░čéčāčüą░ (status stage).

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą║ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ: SETUP, DATA, STATUS - čĆą░ąĘą╗ąĖčćąĮčŗąĄ čüčéą░ą┤ąĖąĖ ą┐čĆąŠčåąĄčüčüą░ Control Write (čāą┐čĆą░ą▓ą╗čÅčÄčēą░čÅ ąĘą░ą┐ąĖčüčī). SETUP, OUT, IN - čéąĖą┐čŗ ą┐ą░ą║ąĄč鹊ą▓, ą║ąŠč鹊čĆčŗą╝ąĖ ąŠą▒ą╝ąĄąĮąĖą▓ą░ąĄčéčüčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB ąĖ čģąŠčüčé. USB line - ą║ą░ąĮą░ą╗ čüą▓čÅąĘąĖ USB. RXSTPI, RXOUTI, TXINI - čäą╗ą░ą│ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. NAK - ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ą┐ą░ą║ąĄčéą░. HW - ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ čāčüčéą░ąĮąŠą▓ą║ą░ čäą╗ą░ą│ą░. SW - ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü čäą╗ą░ą│ą░ (ąĖąĘ ą║ąŠą┤ą░ firmware ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░).

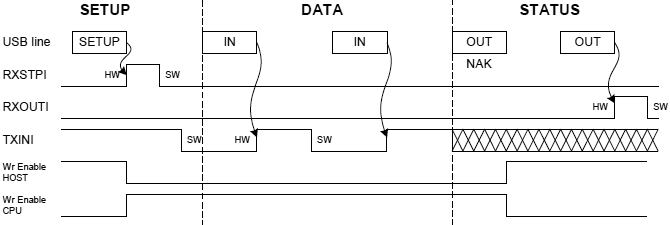

20.12.2 Control Read (čćč鹥ąĮąĖąĄ ą┐ą░ą║ąĄčéą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ)

ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ čéčĆą░ąĮąĘą░ą║čåąĖčÅ čćč鹥ąĮąĖčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (control read transaction). ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮčŗąĄ ąĘą░ą┐čĆąŠčüčŗ ąĘą░ą┐ąĖčüąĖ ąŠčé CPU ąĖ ąŠčé čģąŠčüčéą░ USB:

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą║ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ: SETUP, DATA, STATUS - čĆą░ąĘą╗ąĖčćąĮčŗąĄ čüčéą░ą┤ąĖąĖ ą┐čĆąŠčåąĄčüčüą░ Control Read. SETUP, OUT, IN - čéąĖą┐čŗ ą┐ą░ą║ąĄč鹊ą▓, ą║ąŠč鹊čĆčŗą╝ąĖ ąŠą▒ą╝ąĄąĮąĖą▓ą░ąĄčéčüčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB ąĖ čģąŠčüčé. USB line - ą║ą░ąĮą░ą╗ čüą▓čÅąĘąĖ USB. RXSTPI, RXOUTI, TXINI - čäą╗ą░ą│ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. NAK - ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ą┐ą░ą║ąĄčéą░. HW - ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ čāčüčéą░ąĮąŠą▓ą║ą░ čäą╗ą░ą│ą░. SW - ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü čäą╗ą░ą│ą░ (ąĖąĘ ą║ąŠą┤ą░ firmware ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░). WrEnable HOST - ąĘą░ą┐ąĖčüčī, čĆą░ąĘčĆąĄčłąĄąĮąĮą░čÅ ą┤ą╗čÅ čģąŠčüčéą░. WrEnable CPU - ąĘą░ą┐ąĖčüčī, čĆą░ąĘčĆąĄčłąĄąĮąĮą░čÅ ą┤ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čāčüčéčĆąŠą╣čüčéą▓ą░ USB.

ąØą░ ą┐ąĄčĆą▓čāčÄ ą║ąŠą╝ą░ąĮą┤čā čüčéą░ą┤ąĖąĖ čüčéą░čéčāčüą░ ą▓čüąĄą│ą┤ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ NAK handshake. ąÜąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┤ąĄč鹥ą║čéąĖčĆčāąĄčé čüąŠčüč鹊čÅąĮąĖąĄ čüčéą░čéčāčüą░ (status stage), čüčéąĖčĆą░čÄčéčüčÅ ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ, ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ CPU, ąĖ ąŠčćąĖčüčéą║ą░ TXINI ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░. ąÜąŠą┤ firmware ą┐čĆąŠą▓ąĄčĆčÅąĄčé: ąĘą░ą▓ąĄčĆčłąĄąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░ ąĖą╗ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮ ą┐čĆąĖąĄą╝. The OUT retry ą▓čüąĄą│ą┤ą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčéčüčÅ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠ (ACK). ą¤ąŠą╗čāčćą░ąĄčéčüčÅ ą┐čĆąĖąĄą╝:

- čāčüčéą░ąĮąŠą▓ą║ą░ čäą╗ą░ą│ą░ RXOUTI (ą┐čĆąĖąĮčÅčéčŗ ą┤ą░ąĮąĮčŗąĄ OUT)

- čāčüčéą░ąĮąŠą▓ą║ą░ čäą╗ą░ą│ą░ TXINI (ą┤ą░ąĮąĮčŗąĄ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ, ąĄčüčéčī ą│ąŠč鹊ą▓ąĮąŠčüčéčī ą║ ąĮąŠą▓čŗą╝ ą┤ą░ąĮąĮčŗą╝)

ąÉą╗ą│ąŠčĆąĖčéą╝ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ:

ąŻčüčéą░ąĮąŠą▓ąĖčéčī ą│ąŠč鹊ą▓ąĮąŠčüčéčī ą║ ą┐ąĄčĆąĄą┤ą░č湥 (transmit ready)

ą×ąČąĖą┤ą░ąĮąĖąĄ (ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ OR ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░)

ąĢčüą╗ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮ ą┐čĆąĖąĄą╝, č鹊 ąŠčćąĖčüčéąĖčéčī čäą╗ą░ą│ ąĖ ą▓ąŠąĘą▓čĆą░čéąĖčéčīčüčÅ

ąĢčüą╗ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░, č鹊 ą┐čĆąŠą┤ąŠą╗ąČąĖčéčī

ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąĖąĮčÅč鹊 čüąŠčüč鹊čÅąĮąĖąĄ čüčéą░čéčāčüą░ (status stage), ą║ąŠąĮčéčĆąŠą╗ąĄčĆ USB ąŠąČąĖą┤ą░ąĄčé ąĘą░ą┐čĆąŠčüą░ SETUP. ąŚą░ą┐čĆąŠčü SETUP ąĖą╝ąĄąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé ąĮą░ą┤ ą┤čĆčāą│ąĖą╝ąĖ ąĘą░ą┐čĆąŠčüą░ą╝ąĖ, ąĖ ąŠąĮ ą▒čāą┤ąĄčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠ (ACK). ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą╗čÄą▒ąŠą╣ ą┤čĆčāą│ąŠą╣ čäą╗ą░ą│ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ, ąĖ FIFO ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčé SETUP.

ąÆąØąśą£ąÉąØąśąĢ: čüč湥čéčćąĖą║ ą▒ą░ą╣čé čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčé OUT Zero Length Packet. ąÜąŠą┤ firmware ą┤ąŠą╗ąČąĄąĮ ą┐ąŠąĘą░ą▒ąŠčéąĖčéčīčüčÅ ąŠčé čŹč鹊ą╝.

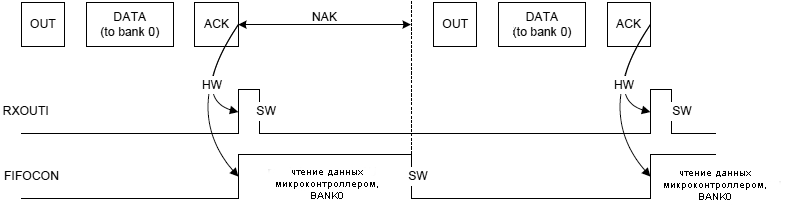

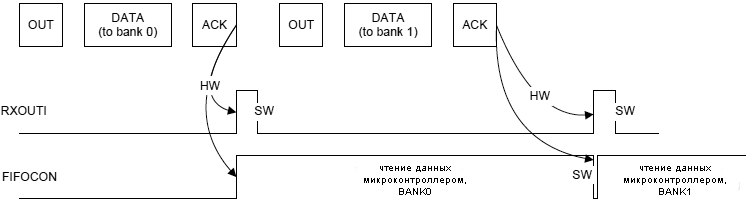

20.13 OUT endpoint management (ą┐ąŠą┤ą┤ąĄčƹȹ║ą░ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ OUT)

ą¤ą░ą║ąĄčéčŗ OUT ąŠčéą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ąŠčé čģąŠčüčéą░ ą║ čāčüčéčĆąŠą╣čüčéą▓čā USB. ąÆčüąĄ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ CPU, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčé ąĖą╗ąĖ ąĮąĄčé ą┐ą░ą║ąĄčé, ą║ąŠą│ą┤ą░ ą▒ą░ąĮą║ ą▒čāą┤ąĄčé ą┐čāčüčé. ą¦č鹊ą▒čŗ čŹč鹊 čĆą░ą▒ąŠčéą░ą╗ąŠ, ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░.

20.13.1.1 ŌĆ£ManualŌĆØ mode (čĆčāčćąĮąŠą╣ čĆąĄąČąĖą╝)

ąÆčüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ č鹥ą║čāčēąĖą╣ ą▒ą░ąĮą║ ąĘą░ą┐ąŠą╗ąĮčÅąĄčéčüčÅ, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą▒ąĖčéčŗ RXOUTI ąĖ FIFOCON. ąŁč鹊 čüąŠą▒čŗčéąĖąĄ ą▓čŗąĘčŗą▓ą░ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ (ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé RXOUTE). ąÜąŠą┤ firmware ą╝ąŠąČąĄčé ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ USB ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ RXOUTI. ąÜąŠą┤ firmware čćąĖčéą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ąĖ ąŠčćąĖčēą░ąĄčé ą▒ąĖčé FIFOCON ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī č鹥ą║čāčēąĖą╣ ą▒ą░ąĮą║. ąĢčüą╗ąĖ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ OUT čüąŠčüčéą░ą▓ą╗ąĄąĮą░ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒ą░ąĮą║ąŠą▓ (ąĖąĘ ą┤ą▓čāčģ), č鹊 ąŠčćąĖčüčéą║ą░ ą▒ąĖčéą░ FIFOCON ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÄ ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ ą▒ą░ąĮą║. ąæąĖčéčŗ RXOUTI ąĖ FIFOCON ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čüąŠ čüčéą░čéčāčüąŠą╝ ąĮąŠą▓ąŠą│ąŠ ą▒ą░ąĮą║ą░.

RXOUTI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čüąĄą│ą┤ą░ ąŠčćąĖčēąĄąĮ ą┐ąĄčĆąĄą┤ ąŠčćąĖčüčéą║ąŠą╣ FIFOCON.

ąæąĖčé RWAL ą▓čüąĄą│ą┤ą░ ąŠčéčĆą░ąČą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ č鹥ą║čāčēąĄą│ąŠ ą▒ą░ąĮą║ą░. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ąĄčüą╗ąĖ firmware ą╝ąŠąČąĄčé čćąĖčéą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą▒ą░ąĮą║ą░, ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą▒ą░ąĮą║ ą┐čāčüčé.

ą¤čĆąĖą╝ąĄčĆ čü 1 ą▒ą░ąĮą║ąŠą╝ ą┤ą░ąĮąĮčŗčģ OUT

ą¤čĆąĖą╝ąĄčĆ čü 2 ą▒ą░ąĮą║ą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ OUT

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą║ čĆąĖčüčāąĮą║ą░ą╝: OUT, DATA, ACK - čüčéą░ą┤ąĖąĖ ą┐čĆąŠčåąĄčüčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (ą┤ą░ąĮąĮčŗąĄ ąŠčé čģąŠčüčéą░, ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ). RXOUTI - čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░. HW - ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ čāčüčéą░ąĮąŠą▓ą║ą░ čäą╗ą░ą│ą░, SW - ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü čäą╗ą░ą│ą░. FIFOCON - ą▒ąĖčé, čāčüčéą░ąĮąŠą▓ą║ą░ ą║ąŠč鹊čĆąŠą│ąŠ ąŠąĘąĮą░čćą░ąĄčé ą┐čĆąĖąĄą╝ ąĮąŠą▓ąŠą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ ą▓ č鹥ą║čāčēąĖą╣ ą▒ą░ąĮą║.

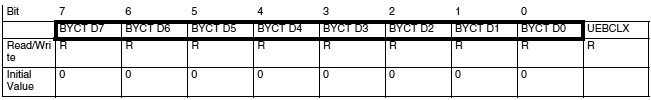

20.13.2 ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ

ąöą░ąĮąĮčŗąĄ čćąĖčéą░čÄčéčüčÅ CPU ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐ąŠčĆčÅą┤ą║ąĄ:

ŌĆó ąÜąŠą│ą┤ą░ ą▒ą░ąĮą║ ąĘą░ą┐ąŠą╗ąĮąĄąĮ čģąŠčüč鹊ą╝, čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (EPINTx), ąĄčüą╗ąĖ čŹč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ (ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ RXOUTE), ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé RXOUTI. CPU ą╝ąŠąČąĄčé čéą░ą║ ąČąĄ ą┐ąŠčüč鹊čÅąĮąĮąŠ ąŠą┐čĆą░čłąĖą▓ą░čéčī čüąŠčüč鹊čÅąĮąĖąĄ RXOUTI ąĖą╗ąĖ FIFOCON, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ.

ŌĆó CPU ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ RXOUTI.

ŌĆó CPU ą╝ąŠąČąĄčé čćąĖčéą░čéčī ąĮąĄą║ąŠč鹊čĆąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé (N) ą▓ č鹥ą║čāčēąĄą╝ ą▒ą░ąĮą║ąĄ (N=BYCT).

ŌĆó CPU ą╝ąŠąČąĄčé čćąĖčéą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘ č鹥ą║čāčēąĄą│ąŠ ą▒ą░ąĮą║ą░ (N čćč鹥ąĮąĖą╣ čĆąĄą│ąĖčüčéčĆą░ UEDATX).

ŌĆó CPU ą╝ąŠąČąĄčé ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī ą▒ą░ąĮą║ ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ FIFOCON, ą║ąŠą│ą┤ą░ ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐čĆąŠčćąĖčéą░ąĮčŗ:

ŌĆó ą┐ąŠčüą╗ąĄ N čćč鹥ąĮąĖą╣ UEDATX,

ŌĆó ą║ą░ą║ č鹊ą╗čīą║ąŠ RWAL ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ ą░ą┐ą┐ą░čĆą░čéąĮąŠ.

ąĢčüą╗ąĖ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčé 2 ą▒ą░ąĮą║ą░, č鹊 ą▓č鹊čĆąŠą╣ ą▒ą░ąĮą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąŠą╗ąĮčÅčéčīčüčÅ čģąŠčüč鹊ą╝, ą┐ąŠą║ą░ ą┐ąĄčĆą▓čŗą╣ č鹥ą║čāčēąĖą╣ ą▒ą░ąĮą║ čćąĖčéą░ąĄčéčüčÅ CPU. ąŚą░č鹥ą╝, ą║ąŠą│ą┤ą░ CPU ąŠčćąĖčēą░ąĄčé FIFOCON, čüą╗ąĄą┤čāčÄčēąĖą╣ ą▒ą░ąĮą║ ą╝ąŠąČąĄčé ą▒čŗčéčī čāąČąĄ ą│ąŠč鹊ą▓ ąĖ č鹊ą│ą┤ą░ RXOUTI čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ.

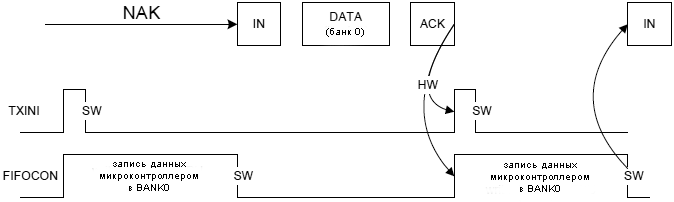

20.14 IN endpoint management (ą┐ąŠą┤ą┤ąĄčƹȹ║ą░ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ IN)

ą¤ą░ą║ąĄčéčŗ IN ąŠčéą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ USB ą▓ čüč鹊čĆąŠąĮčā čģąŠčüčéą░, ą┐ąŠ ąĘą░ą┐čĆąŠčüčā IN request ąŠčé čģąŠčüčéą░. ąÆčüąĄ ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ CPU, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčé ąĖą╗ąĖ ąĮąĄ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčé ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄ ą▒ą░ąĮą║ą░. ą¦č鹊ą▒čŗ čŹč鹊 čĆą░ą▒ąŠčéą░ą╗ąŠ, ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░.

20.14.0.1 ŌĆ£ManualŌĆØ mode (čĆčāčćąĮąŠą╣ čĆąĄąČąĖą╝)

ąæąĖčé TXINI čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ č鹥ą║čāčēąĖą╣ ą▒ą░ąĮą║ čüčéą░ąĮąŠą▓ąĖčéčüčÅ čüą▓ąŠą▒ąŠą┤ąĮčŗą╝. ąŁč鹊 ą▓čŗąĘąŠą▓ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ TXINE. ąÆ č鹊 ąČąĄ čüą░ą╝ąŠąĄ ą▓čĆąĄą╝čÅ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé FIFOCON. CPU ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą▓ FIFO ąĖ ąŠčćąĖčēą░ąĄčé ą▒ąĖčé FIFOCON, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā USB ąŠčéą┐čĆą░ą▓ąĖčéčī ą┤ą░ąĮąĮčŗąĄ. ąĢčüą╗ąĖ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ IN čüąŠčüčéą░ą▓ą╗ąĄąĮą░ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒ą░ąĮą║ąŠą▓ (ąĖąĘ ą┤ą▓čāčģ), č鹊 ąŠčćąĖčüčéą║ą░ FIFOCON čéą░ą║ąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÄ ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ ą▒ą░ąĮą║ ą┤ą░ąĮąĮčŗčģ. ąæąĖčéčŗ TXINI ąĖ FIFOCON ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüčéą░čéčāčüą░ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą▒ą░ąĮą║ą░.

TXINI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čüąĄą│ą┤ą░ ąŠčćąĖčēąĄąĮ ą┐ąĄčĆąĄą┤ ąŠčćąĖčüčéą║ąŠą╣ FIFOCON.

ąæąĖčé RWAL ą▓čüąĄą│ą┤ą░ ąŠčéčĆą░ąČą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ č鹥ą║čāčēąĄą│ąŠ ą▒ą░ąĮą║ą░. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ąĄčüą╗ąĖ firmware ą╝ąŠąČąĄčé ąĘą░ą┐ąĖčüą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒ą░ąĮą║, ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą▒ą░ąĮą║ ąĘą░ą┐ąŠą╗ąĮąĄąĮ.

ą¤čĆąĖą╝ąĄčĆ čü 1 ą▒ą░ąĮą║ąŠą╝ ą┤ą░ąĮąĮčŗčģ IN

ą¤čĆąĖą╝ąĄčĆ čü 2 ą▒ą░ąĮą║ą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ IN

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą║ čĆąĖčüčāąĮą║ą░ą╝: IN, DATA, ACK, NACK - čüčéą░ą┤ąĖąĖ ą┐čĆąŠčåąĄčüčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (ą┤ą░ąĮąĮčŗąĄ ą║ čģąŠčüčéčā, ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ, ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ). TXINI - čäą╗ą░ą│ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░. HW - ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ čāčüčéą░ąĮąŠą▓ą║ą░ čäą╗ą░ą│ą░, SW - ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü čäą╗ą░ą│ą░. FIFOCON - ą▒ąĖčé, čāčüčéą░ąĮąŠą▓ą║ą░ ą║ąŠč鹊čĆąŠą│ąŠ ąŠąĘąĮą░čćą░ąĄčé ą┐čĆąĖąĄą╝ ąĮąŠą▓ąŠą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ ą▓ č鹥ą║čāčēąĖą╣ ą▒ą░ąĮą║.

20.14.1 ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ

ąöą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ CPU ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐ąŠčĆčÅą┤ą║ąĄ:

ŌĆó ąÜąŠą│ą┤ą░ ą▒ą░ąĮą║ ą┐čāčüčé, čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (EPINTx), ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ (ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ TXINE), ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ TXINI. CPU ą╝ąŠąČąĄčé čéą░ą║ąČąĄ ąŠą┐čĆą░čłąĖą▓ą░čéčī TXINI ąĖą╗ąĖ FIFOCON, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ.

ŌĆó CPU ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ TXINI.

ŌĆó CPU ą╝ąŠąČąĄčé ąĘą░ą┐ąĖčüą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ č鹥ą║čāčēąĖą╣ ą▒ą░ąĮą║ (ąĘą░ą┐ąĖčüčÅą╝ąĖ ą▓ čĆąĄą│ąĖčüčéčĆ UEDATX).

ŌĆó CPU ą╝ąŠąČąĄčé ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī ą▒ą░ąĮą║ ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ FIFOCON, ą║ąŠą│ą┤ą░ ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ąĘą░ą┐ąĖčüą░ąĮčŗ:

ŌĆó ą┐ąŠčüą╗ąĄ N ąĘą░ą┐ąĖčüąĄą╣ ą▓ UEDATX

ŌĆó ą║ą░ą║ č鹊ą╗čīą║ąŠ RWAL ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ ą░ą┐ą┐ą░čĆą░čéąĮąŠ.

ąĢčüą╗ąĖ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčé 2 ą▒ą░ąĮą║ą░, č鹊 ą▓č鹊čĆąŠą╣ ą▒ą░ąĮą║ ą╝ąŠąČąĄčé ą▒čŗčéčī čćąĖčéą░čéčīčüčÅ čģąŠčüč鹊ą╝, ą┐ąŠą║ą░ č鹥ą║čāčēąĖą╣ ą┐ąĄčĆą▓čŗą╣ ą▒ą░ąĮą║ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ CPU. ąŚą░č鹥ą╝, ą║ąŠą│ą┤ą░ CPU ąŠčćąĖčüčéąĖčé FIFOCON, čüą╗ąĄą┤čāčÄčēąĖą╣ ą▒ą░ąĮą║ ą╝ąŠąČąĄčé ą▒čŗčéčī čāąČąĄ čüą▓ąŠą▒ąŠą┤ąĮčŗą╝ (ą│ąŠč鹊ą▓čŗą╝ ą┤ą╗čÅ ąĮąŠą▓ąŠą╣ ąĘą░ą┐ąĖčüąĖ ą▓ ąĮąĄą│ąŠ CPU), ąĖ č鹊ą│ą┤ą░ TXINI čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ.

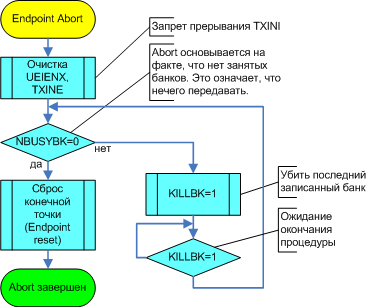

20.14.1.1 Abort

ąĪčéą░ą┤ąĖčÅ "abort" ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮą░ čģąŠčüč鹊ą╝ ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ čüąĖčéčāą░čåąĖčÅčģ:

ŌĆó ąÆ čéčĆą░ąĮąĘą░ą║čåąĖąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (control transaction): ą┐čĆąĖąĮčÅčé ZLP ą┤ą░ąĮąĮčŗčģ OUT ąĮą░ čüčéą░ą┤ąĖąĖ IN.

ŌĆó ąÆ čéčĆą░ąĮąĘą░ą║čåąĖąĖ isochronous IN: ą┐čĆąĖąĮčÅčé ZLP ą┤ą░ąĮąĮčŗčģ OUT ąĮą░ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĄ OUT ąĮą░ čüčéą░ą┤ąĖąĖ IN ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ IN.

ŌĆó ...

ąæąĖčé KILLBK ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, čćč鹊ą▒čŗ "čāą▒ąĖčéčī" ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ "ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╣" ą▒ą░ąĮą║. ąÆąŠčé čüą░ą╝čŗą╣ ą╗čāčćčłąĖą╣ čüą┐ąŠčüąŠą▒ ą▓čŗą┐ąŠą╗ąĮąĖčéčī abort (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣):

ąóą░ą▒ą╗ąĖčåą░ 20-1. Abort flow

[20.15 Isochronous mode (ąĖąĘąŠčģčĆąŠąĮąĮčŗą╣ čĆąĄąČąĖą╝)]

20.15.1 Underflow (ąĮąĄą┤ąŠčüčéą░č鹊čćąĮąŠąĄ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ)

ąĪąŠą▒čŗčéąĖąĄ ąĮąĄą┤ąŠą▒ąŠčĆą░ ą┤ą░ąĮąĮčŗčģ (underflow) ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ čüčéą░ą┤ąĖąĖ IN, ąĄčüą╗ąĖ čģąŠčüčé ą┐ąŠą┐čŗčéą░ą╗čüčÅ ą┐čĆąŠčćąĖčéą░čéčī ą▒ą░ąĮą║, ą║ąŠč鹊čĆčŗą╣ ą┐čāčüčé. ąÆ čŹč鹊ą╣ čüąĖčéčāą░čåąĖąĖ čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ UNDERFI. ąóą░ą║ąČąĄ underflow ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ čüčéą░ą┤ąĖąĖ OUT, ąĄčüą╗ąĖ čģąŠčüčé ąŠčéą┐čĆą░ą▓ąĖą╗ ą┐ą░ą║ąĄčé, ą║ąŠą│ą┤ą░ ą▒ą░ąĮą║ąĖ čāąČąĄ ąĘą░ąĮčÅčéčŗ. ą×ą▒čŗčćąĮąŠ čŹč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąŠč鹊ą╝čā, čćč鹊 CPU ąĮąĄą┤ąŠčüčéą░č鹊čćąĮąŠ ą▒čŗčüčéčĆąŠ ąŠą▒čĆą░ą▒ąŠčéą░ą╗ ą┤ą░ąĮąĮčŗąĄ. ą¤ą░ą║ąĄčé ą▒čāą┤ąĄčé ą┐ąŠč鹥čĆčÅąĮ.

ąØąĄą▓ąŠąĘą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ąŠčłąĖą▒ą║čā underflow ąĮą░ čüčéą░ą┤ąĖąĖ OUT čüąŠ čüč鹊čĆąŠąĮčŗ CPU, ą┐ąŠčüą║ąŠą╗čīą║čā CPU ą┤ąŠą╗ąČąĄąĮ čćąĖčéą░čéčī č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▒ą░ąĮą║ čāąČąĄ ą│ąŠč鹊ą▓ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ą┤ą░ąĮąĮčŗąĄ (RXOUTI=1 ąĖą╗ąĖ RWAL=1)

20.15.2 CRC Error (ąŠčłąĖą▒ą║ą░ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ)

ą×čłąĖą▒ą║ą░ CRC ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ąĮą░ čüčéą░ą┤ąĖąĖ OUT, ąĄčüą╗ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗ ą┐ą╗ąŠčģąŠą╣ ą┐čĆąĖąĮčÅčéčŗą╣ ą┐ą░ą║ąĄčé. ąÆ čŹč鹊ą╣ čüąĖčéčāą░čåąĖąĖ čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ STALLEDI. ąŁč鹊 ąĮąĄ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčé ąŠčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ RXOUTI.

20.16 Overflow (ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ ą▒čāč乥čĆą░)

ąØą░ ą║ąŠąĮąĄčćąĮčŗčģ č鹊čćą║ą░čģ čéąĖą┐ą░ Control, Isochronous, Bulk ąĖą╗ąĖ Interrupt ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĮą░ čüčéą░ą┤ąĖąĖ OUT, ąĄčüą╗ąĖ čģąŠčüčé ą┐ąŠą┐čŗčéą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüą░čéčī ą▓ ą▒ą░ąĮą║, ą║ąŠč鹊čĆčŗą╣ ąŠą║ą░ąČąĄčéčüčÅ čüą╗ąĖčłą║ąŠą╝ ą╝ą░ą╗ąĄąĮčīą║ąĖą╝ ą┤ą╗čÅ ą┐ą░ą║ąĄčéą░. ąÆ čŹč鹊ą╣ čüąĖčéčāą░čåąĖąĖ čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ OVERFI (ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ). ą¤ą░ą║ąĄčé ą▒čāą┤ąĄčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠ (NAK), ąĖ čéą░ą║ąČąĄ čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RXOUTI (ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ). ąæą░ąĮą║ ą▒čāą┤ąĄčé ąĘą░ą┐ąŠą╗ąĮąĄąĮ ą┐ąĄčĆą▓ąŠą╣ čćą░čüčéčīčÄ ą┐ą░ą║ąĄčéą░.

ąØąĄą▓ąŠąĘą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ąŠčłąĖą▒ą║čā overflow ąĮą░ čüčéą░ą┤ąĖąĖ IN čüąŠ čüč鹊čĆąŠąĮčŗ CPU, ą┐ąŠčüą║ąŠą╗čīą║čā CPU ą┤ąŠą╗ąČąĄąĮ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▒ą░ąĮą║ ą│ąŠč鹊ą▓ ą║ ą┐ąŠą╗čāč湥ąĮąĖčÄ ą┤ą░ąĮąĮčŗčģ (TXINI=1 ąĖą╗ąĖ RWAL=1).

[20.17 Interrupts (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ)]

ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓čüąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

ąĀąĖčü. 20-4. USB Device Controller Interrupt System (čüąĖčüč鹥ą╝ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB)

ąŚą┤ąĄčüčī ąĄčüčéčī 2 ą▓ąĖą┤ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣: ąŠą▒čĆą░ą▒ąŠčéą║ą░ (Processing interrupts, ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą║ąŠč鹊čĆčŗąĄ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą║ą░ą║ čćą░čüčéčī ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ) ąĖ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ exception (Exception Interrupts, errors, ąŠčłąĖą▒ą║ąĖ).

Processing interrupts (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ) ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą┐čĆąĖ:

ŌĆó Upstream resume (UPRSMI), ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ą░ą┐čüčéčĆąĖą╝

ŌĆó End of resume (EORSMI), ąŠą║ąŠąĮčćą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ

ŌĆó Wake up (WAKEUPI), ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ

ŌĆó End of reset (Speed Initialization) (EORSTI), ąŠą║ąŠąĮčćą░ąĮąĖąĄ čüą▒čĆąŠčüą░ (ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čüą║ąŠčĆąŠčüčéąĖ)

ŌĆó Start of frame(SOFI, if FNCERR=0), čüąŠą▒čŗčéąĖąĄ ąĮą░čćą░ą╗ą░ čäčĆąĄą╣ą╝ą░

ŌĆó ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ą░ (Suspend) ą┐ąŠčüą╗ąĄ 3 ą╝čü ąĮąĄą░ą║čéąĖą▓ąĮąŠčüčéąĖ (SUSPI).

Exception Interrupts (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąŠčłąĖą▒ą║ąĄ) ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą┐čĆąĖ:

ŌĆó ąŠčłąĖą▒ą║ąĄ CRC ą▓ ąĮąŠą╝ąĄčĆąĄ čäčĆąĄą╣ą╝ą░ SOF (SOFI, FNCERR=1)

ąĀąĖčü. 20-5. USB Device Controller Endpoint Interrupt System (čüąĖčüč鹥ą╝ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB)

Processing interrupts (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ) ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą┐čĆąĖ:

ŌĆó ąōąŠč鹊ą▓ąĮąŠčüčéąĖ ą┐čĆąĖąĮčÅčéčī ą┤ą░ąĮąĮčŗąĄ IN (EPINTx, TXINI=1)

ŌĆó ą¤čĆąĖąĮčÅčé ą┐ą░ą║ąĄčé ą┤ą░ąĮąĮčŗčģ OUT (EPINTx, RXOUTI=1)

ŌĆó ą¤čĆąĖąĮčÅčé ą┐ą░ą║ąĄčé SETUP (EPINTx, RXSTPI=1)

Exception Interrupts (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąŠčłąĖą▒ą║ąĄ) ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą┐čĆąĖ:

ŌĆó Stalled packet (EPINTx, STALLEDI=1), ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ ą┐ąŠ ąŠčłąĖą▒ą║ąĄ ą┐ą░ą║ąĄčé

ŌĆó ą×čłąĖą▒ą║ą░ CRC ąĮą░ OUT ą▓ ąĖąĘąŠčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (EPINTx, STALLEDI=1)

ŌĆó Overflow (EPINTx, OVERFI=1)

ŌĆó Underflow ą▓ ąĖąĘąŠčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (EPINTx, UNDERFI=1)

ŌĆó ą×čéą┐čĆą░ą▓ą╗ąĄąĮ NAK IN (EPINTx, NAKINI=1)

ŌĆó ą×čéą┐čĆą░ą▓ą╗ąĄąĮ NAK OUT (EPINTx, NAKOUTI=1)

[20.18 ąĀąĄą│ąĖčüčéčĆčŗ]

20.18.1 USB device general registers (ąŠčüąĮąŠą▓ąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ čāčüčéčĆąŠą╣čüčéą▓ą░ USB)

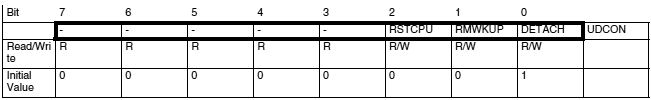

[UDCON]

ŌĆó Bit 2 - RSTCPU - USB Reset CPU, ą▒ąĖčé čüą▒čĆąŠčüą░ CPU

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą▓ 1 ąĖąĘ ą║ąŠą┤ą░ firmware, čćč鹊ą▒čŗ čüą▒čĆąŠčüąĖčéčī CPU ą┐čĆąĖ čüą╗ąĄą┤čāčÄčēąĄą╝ čüąŠą▒čŗčéąĖąĖ USB reset (ą┐čĆąĖ čŹč鹊ą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ąĮąĄ ą▒čāą┤ąĄčé ąĘą░ą┐čĆąĄčēąĄąĮ). ąŚąĮą░č湥ąĮąĖąĄ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ąĮąĄ ą▒čāą┤ąĄčé ąĘą░čéčĆąŠąĮčāč鹊 čüą▒čĆąŠčüąŠą╝ CPU, ą║ąŠč鹊čĆčŗą╣ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄą╝ End Of Reset (ą▒ąĖčé RSTCPU ąŠčüčéą░ąĮąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝). ąŁč鹊čé ą▒ąĖčé čüą▒čĆąŠčłąĄąĮ, ą║ąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ąĘą░ą┐čĆąĄčēąĄąĮ. ąÆ ą┐čĆąŠčéąĖą▓ąĮąŠą╝ čüą╗čāčćą░ąĄ čüą▒čĆąŠčüčīč鹥 čŹč鹊čé ą▒ąĖčé ą▓ 0 ąĖąĘ ą║ąŠą┤ą░ firmware.

ŌĆó Bit 1 - RMWKUP - Remote Wake-up, ą▒ąĖčé čāą┤ą░ą╗ąĄąĮąĮąŠą│ąŠ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ "upstream-resume" čģąŠčüčéčā ą┤ą╗čÅ čāą┤ą░ą╗ąĄąĮąĮąŠą│ąŠ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ. ąæąĖčé SUSPI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī ąŠčéą┐čĆą░ą▓ą║čā remote wake up. ą×čćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąŠčćąĖčüčéą║ą░ ąĖąĘ ą║ąŠą┤ą░ firmware ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░. ąĪą╝. čüąĄą║čåąĖčÄ 20.10 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüč鹥ą╣.

ŌĆó Bit 0 - DETACH - Detach, ą▒ąĖčé ąŠčéą║ą╗čÄč湥ąĮąĖčÅ

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ čäąĖąĘąĖč湥čüą║ąŠą│ąŠ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ą░ USB. ą×čćąĖčüčéąĖč鹥 čŹč鹊čé ą▒ąĖčé, čćč鹊ą▒čŗ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░ąĮąŠą▓ąŠ. ąĪą╝. čüąĄą║čåąĖčÄ 20.9 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüč鹥ą╣.

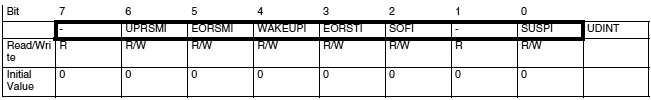

[UDINT]

ŌĆó 7 - ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ąŚąĮą░č湥ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ čćąĖčéą░ąĄčéčüčÅ ąĖąĘ čŹč鹊ą│ąŠ ą▒ąĖčéą░, ą▓čüąĄą│ą┤ą░ 0. ąØąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ą╣č鹥 čŹč鹊čé ą▒ąĖčé.

ŌĆó 6 - UPRSMI - Upstream Resume Interrupt Flag, čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÄ čĆą░ą▒ąŠčéčŗ ąŠčé ą░ą┐čüčéčĆąĖą╝

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ąŠčéą┐čĆą░ą▓ą╗čÅąĄčé čüąĖą│ąĮą░ą╗ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ, čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ "Upstream Resume". ąŁč鹊 ą▓čŗąĘąŠą▓ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ USB, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé UPRSME. ąæąĖčé UPRSMI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą║ąŠą┤ąŠą╝ firmware (ą┐ąĄčĆąĄą┤ čŹčéąĖą╝ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ čéą░ą║čéčŗ USB). ąŻčüčéą░ąĮąŠą▓ą║ą░ UPRSMI ąĖąĘ ą║ąŠą┤ą░ firmware ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ŌĆó 5 - EORSMI - End Of Resume Interrupt Flag, čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ čüąŠą▒čŗčéąĖčÅ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB čģąŠčĆąŠčłąĖą╣ čüąĖą│ąĮą░ą╗ "End Of Resume", ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čģąŠčüč鹊ą╝. ąŁč鹊 ą▓čŗąĘąŠą▓ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ USB, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé EORSME. ąæąĖčé EORSMI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą║ąŠą┤ąŠą╝ firmware (ą┐ąĄčĆąĄą┤ čŹčéąĖą╝ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ čéą░ą║čéčŗ USB). ąŻčüčéą░ąĮąŠą▓ą║ą░ EORSMI ąĖąĘ ą║ąŠą┤ą░ firmware ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ŌĆó 4 - WAKEUPI - Wake-up CPU Interrupt Flag, čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ CPU

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB čĆąĄą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ąŠčéčäąĖą╗čīčéčĆąŠą▓ą░ąĮąĮčŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝ non-idle ąŠčé čüąĖą│ąĮą░ą╗čīąĮčŗčģ ą╗ąĖąĮąĖą╣ USB (čŹč鹊 ąĮąĄ upstream resume). ąŁč鹊 ą▓čŗąĘąŠą▓ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé WAKEUPE. ąæąĖčé WAKEUPI ą┤ąŠą╗ąČąĄąĮ ąŠčćąĖčēą░čéčīčüčÅ ąĖąĘ ą║ąŠą┤ą░ firmware (ą┐ąĄčĆąĄą┤ čŹčéąĖą╝ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ čéą░ą║čéčŗ USB). ąŻčüčéą░ąĮąŠą▓ą║ą░ ąĖąĘ ą║ąŠą┤ą░ firmware ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░. ąöą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüč鹥ą╣ čüą╝. čüąĄą║čåąĖčÄ 20.8.

ŌĆó 3 - EORSTI - End Of Reset Interrupt Flag, čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ čüą▒čĆąŠčüą░ ą┐ąŠ čłąĖąĮąĄ

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ USB ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ čüąĖą│ąĮą░ą╗ "End Of Reset". ąŁč鹊 ą▓čŗąĘąŠą▓ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé EORSTE. ąæąĖčé EORSTI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą║ąŠą┤ąŠą╝ firmware (ą┐ąĄčĆąĄą┤ čŹčéąĖą╝ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ čéą░ą║čéčŗ USB). ąŻčüčéą░ąĮąŠą▓ą║ą░ EORSTI ąĖąĘ ą║ąŠą┤ą░ firmware ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ŌĆó 2 - SOFI - Start Of Frame Interrupt Flag, čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ąĮą░čćą░ą╗ą░ čäčĆąĄą╣ą╝ą░

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ čüąĖą│ąĮą░ą╗ USB "Start Of Frame" PID (SOF), čŹč鹊 čüąŠą▒čŗčéąĖąĄ čüą╗čāčćą░ąĄčéčüčÅ ą║ą░ąČą┤čŗąĄ 1 ą╝čü čü ą▓čŗčüąŠą║ąŠą╣ č鹊čćąĮąŠčüčéčīčÄ. ąÆčŗąĘčŗą▓ą░ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ SOFE.

ŌĆó 1 - ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ŌĆó 0 - SUSPI - Suspend Interrupt Flag, čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą┤ąĄč鹥ą║čéąĖčĆčāąĄčéčüčÅ "ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ą░" čĆą░ą▒ąŠčéčŗ (ą┐čĆąĖ ąŠčéčüčāčéčüčéą▓ąĖąĖ ąŠčé 3 čäčĆąĄą╣ą╝ąŠą▓ ąĖ ą▒ąŠą╗ąĄąĄ: čüąŠčüč鹊čÅąĮąĖąĄ J ą┤ą╗ąĖčéčüčÅ čāąČąĄ 3 ą╝čü). ąŁč鹊 ą▓čŗąĘčŗą▓ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ USB, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ SUSPE. ąæąĖčé SUSPI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą║ąŠą┤ąŠą╝ firmware (ą┐ąĄčĆąĄą┤ čŹčéąĖą╝ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ čéą░ą║čéčŗ USB). ąŻčüčéą░ąĮąŠą▓ą║ą░ SUSPI ąĖąĘ ą║ąŠą┤ą░ firmware ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░. ąĪą╝. čüąĄą║čåąĖčÄ 20.8 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüč鹥ą╣.

ąæąĖčéčŗ čäą╗ą░ą│ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą┤ą░ąČąĄ ą▓ č鹊ą╝ čüą╗čāčćą░ąĄ, ąĄčüą╗ąĖ ąĖčģ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▒ąĖčéčŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ.

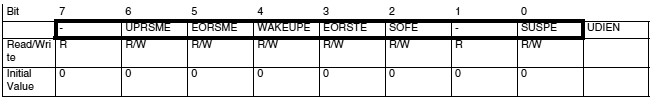

[UDIEN]

ŌĆó 7 - ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ąŚąĮą░č湥ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ čćąĖčéą░ąĄčéčüčÅ ąĖąĘ čŹč鹊ą│ąŠ ą▒ąĖčéą░, ą▓čüąĄą│ą┤ą░ 0. ąØąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ą╣č鹥 čŹč鹊čé ą▒ąĖčé.

ŌĆó 6 - UPRSME - Upstream Resume Interrupt Enable, ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąŠčé ą░ą┐čüčéčĆąĖą╝

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ UPRSMI, čüą▒čĆąŠčüčīč鹥 ą┤ą╗čÅ ąĘą░ą┐čĆąĄčēąĄąĮąĖčÅ čŹč鹊ą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó 5 - EORSME - End Of Resume Interrupt Enable, ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ čüąŠą▒čŗčéąĖčÅ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ.

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ EORSMI, čüą▒čĆąŠčüčīč鹥 ą┤ą╗čÅ ąĘą░ą┐čĆąĄčēąĄąĮąĖčÅ čŹč鹊ą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó 4 - WAKEUPE - Wake-up CPU Interrupt Enable, ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé čüąŠą▒čŗčéąĖčÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ CPU

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ WAKEUPI, čüą▒čĆąŠčüčīč鹥 ą┤ą╗čÅ ąĘą░ą┐čĆąĄčēąĄąĮąĖčÅ čŹč鹊ą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó 3 - EORSTE - End Of Reset Interrupt Enable, ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé čüąŠą▒čŗčéąĖčÅ ąŠą║ąŠąĮčćą░ąĮąĖčÅ čüą▒čĆąŠčüą░ ą┐ąŠ čłąĖąĮąĄ

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ EORSTI, čüą▒čĆąŠčüčīč鹥 ą┤ą╗čÅ ąĘą░ą┐čĆąĄčēąĄąĮąĖčÅ čŹč鹊ą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó 2 - SOFE - Start Of Frame Interrupt Enable, ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé čüąŠą▒čŗčéąĖčÅ ąĮą░čćą░ą╗ą░ čäčĆąĄą╣ą╝ą░

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SOFI, čüą▒čĆąŠčüčīč鹥 ą┤ą╗čÅ ąĘą░ą┐čĆąĄčēąĄąĮąĖčÅ čŹč鹊ą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó 1 - ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ŌĆó 0 - SUSPE - Suspend Interrupt Enable, ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé čüąŠą▒čŗčéąĖčÅ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ.

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SUSPI, čüą▒čĆąŠčüčīč鹥 ą┤ą╗čÅ ąĘą░ą┐čĆąĄčēąĄąĮąĖčÅ čŹč鹊ą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

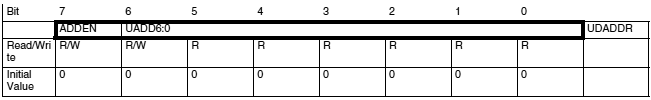

[UDADDR]

ŌĆó 7 - ADDEN - Address Enable Bit, ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą░ą┤čĆąĄčüą░

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą┤ą╗čÅ ą░ą║čéąĖą▓ą░čåąĖąĖ UADD (ą░ą┤čĆąĄčü ą┐ąŠ čłąĖąĮąĄ USB). ą×čćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąŠčćąĖčüčéą║ą░ ąĖąĘ firmware ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░. ąĪą╝. čüąĄą║čåąĖčÄ 20.7 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüč鹥ą╣.

ŌĆó 6-0 - UADD6:0 - ą▒ąĖčéčŗ ą░ą┤čĆąĄčüą░ USB

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą░ą┤čĆąĄčüą░ čāčüčéčĆąŠą╣čüčéą▓ą░. ąŁčéąĖ ą▒ąĖčéčŗ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ąŠčćąĖčēą░čéčīčüčÅ.

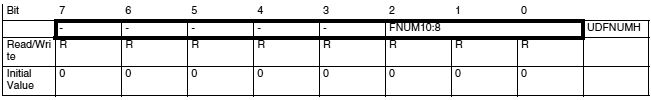

[UDFNUMH]

ŌĆó 7-3 - ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ąŚąĮą░č湥ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ čćąĖčéą░ąĄčéčüčÅ ąĖąĘ čŹčéąĖčģ ą▒ąĖčé, ą▓čüąĄą│ą┤ą░ 0. ąØąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ą╣č鹥 čŹčéąĖ ą▒ąĖčéčŗ.

ŌĆó 2-0 - FNUM10:8 - Frame Number Upper Flag, čäą╗ą░ą│ čüčéą░čĆčłąĖčģ ą▒ąĖčé ąĮąŠą╝ąĄčĆą░ čäčĆąĄą╣ą╝ą░

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ. ąŁčéąĖ ą▒ąĖčéčŗ čüąŠą┤ąĄčƹȹ░čé 3 čüčéą░čĆčłąĖčģ ą▒ąĖčéą░ ąŠčé 11-ą▒ąĖčéąĮąŠą│ąŠ ąĮąŠą╝ąĄčĆą░ čäčĆąĄą╣ą╝ą░. ą×ąĮąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčéčüčÅ ą▓ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝ ą┐čĆąĖąĮčÅč鹊ą╝ ą┐ą░ą║ąĄč鹥 SOF. FNUM ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ, ąĄčüą╗ąĖ ą┐čĆąĖąĮčÅčé ąĖčüą┐ąŠčĆč湥ąĮąĮčŗą╣ SOF.

[UDFNUML]

ŌĆó 7-0 Frame Number Lower Flag, čäą╗ą░ą│ ą╝ą╗ą░ą┤čłąĖčģ ą▒ąĖč鹊ą▓ ąĮąŠą╝ąĄčĆą░ čäčĆąĄą╣ą╝ą░

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ. ąŁčéąĖ ą▒ąĖčéčŗ ąĮąĄčüčāčé ą▓ čüąĄą▒ąĄ 8 ą╝ą╗ą░ą┤čłąĖčģ ą▒ąĖčé ąŠčé 11-ą▒ąĖčéąĮąŠą│ąŠ ąĮąŠą╝ąĄčĆą░ čäčĆąĄą╣ą╝ą░.

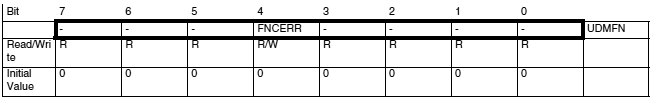

[UDMFN]

ŌĆó 7-5 - ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ąŚąĮą░č湥ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ čćąĖčéą░ąĄčéčüčÅ ąĖąĘ čŹčéąĖčģ ą▒ąĖčé, ą▓čüąĄą│ą┤ą░ 0. ąØąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ą╣č鹥 čŹčéąĖ ą▒ąĖčéčŗ.

ŌĆó 4 - FNCERR - Frame Number CRC Error Flag, ąĮąŠą╝ąĄčĆ čäčĆąĄą╣ą╝ą░ čäą╗ą░ą│ą░ ąŠčłąĖą▒ą║ąĖ CRC

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĄčüą╗ąĖ ą┐čĆąĖąĮčÅčé ąĖčüą┐ąŠčĆč湥ąĮąĮčŗą╣ ąĮąŠą╝ąĄčĆ čäčĆąĄą╣ą╝ą░ ą▓ ą┐ą░ą║ąĄč鹥 ąĮą░čćą░ą╗ą░ čäčĆąĄą╣ą╝ą░. ąŁč鹊čé ą▒ąĖčé ąĖ ą▒ąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SOFI ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ.

ŌĆó 3-0 - ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ąŚąĮą░č湥ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ čćąĖčéą░ąĄčéčüčÅ ąĖąĘ čŹčéąĖčģ ą▒ąĖčé, ą▓čüąĄą│ą┤ą░ 0. ąØąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ą╣č鹥 čŹčéąĖ ą▒ąĖčéčŗ.

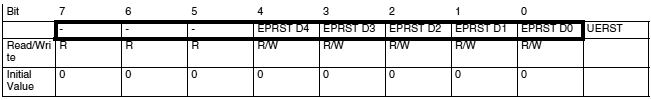

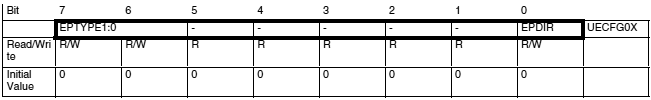

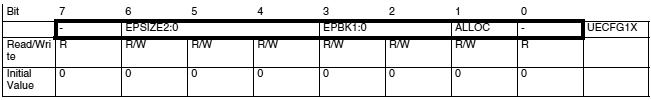

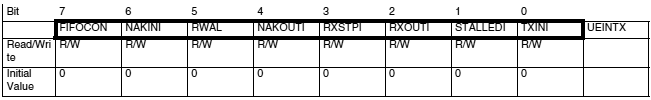

20.18.2 USB device endpoint registers (čĆąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ USB)

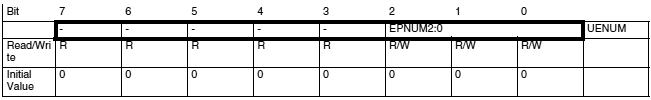

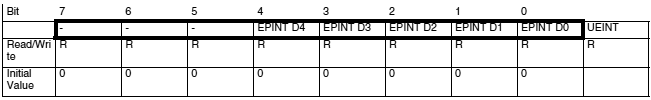

[UENUM]

ŌĆó 7-3 - ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ąŚąĮą░č湥ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ čćąĖčéą░ąĄčéčüčÅ ąĖąĘ čŹčéąĖčģ ą▒ąĖčé, ą▓čüąĄą│ą┤ą░ 0. ąØąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ą╣č鹥 čŹčéąĖ ą▒ąĖčéčŗ.

ŌĆó 2-0 - EPNUM2:0 Endpoint Number, ą▒ąĖčéčŗ ąĮąŠą╝ąĄčĆą░ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ