|

Texas Instruments (ą┤ą░ą╗ąĄąĄ ą┤ą╗čÅ čüąŠą║čĆą░čēąĄąĮąĖčÅ TI) ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ JTAG ą┤ą╗čÅ čüąĖčüč鹥ą╝čŗ ąŠčéą╗ą░ą┤ą║ąĖ (eXtended Development System, XDS), čü čĆą░ąĘąĮčŗą╝ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčÅą╝ąĖ. ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ (ą┐ąĄčĆąĄą▓ąŠą┤ [1]) ąŠą┐ąĖčüą░ąĮčŗ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą┐ąŠ ąĖąĮč鹥ą│čĆą░čåąĖąĖ ą║ąŠąĮąĮąĄą║č鹊čĆą░ XDS ąĮą░ ą┐ą╗ą░čéčā, ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčēąĄą│ąŠ čĆą░ąĘą╗ąĖčćąĮčŗąĄ čäčāąĮą║čåąĖąĖ ąŠčéą╗ą░ą┤ą║ąĖ. ąŁčéą░ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą┐ąŠą╝ąŠąČąĄčé, ąĄčüą╗ąĖ ąÆą░čł ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 菹║čüą┐ąŠčĆčé čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ čÅą┤čĆą░ (core trace) ąĖą╗ąĖ čüąĖčüč鹥ą╝ąĮąŠą╣ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ (system trace) č湥čĆąĄąĘ ąĮąŠąČą║ąĖ EMU, ąĖ ąĮčāąČąĮąŠ čüą┤ąĄą╗ą░čéčī čüą▓ąŠąĄ čåąĄą╗ąĄą▓ąŠąĄ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╝ čü ą┐čĆąŠą┤čāą║čéą░ą╝ąĖ XDS. ąĪą╝. čéą░ą║ąČąĄ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ TRM [2].

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆą░ TRM ąŠąĘąĮą░čćą░ąĄčé Technical Reference Manual.

ąöą╗čÅ ą▓čüąĄčģ ą┐čĆąŠčćąĖčģ čäčāąĮą║čåąĖą╣ ąŠčéą╗ą░ą┤ą║ąĖ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čéąĖą┐ą░ ą┐čĆąŠą┤čāą║čéą░ XDS, ąĘą┤ąĄčüčī ąŠą┐ąĖčüčŗą▓ą░čÄčéčüčÅ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ čåąĄą╗ąĖ ąŠčéą╗ą░ą┤ą║ąĖ. ąĢčüą╗ąĖ čüą╗ąĄą┤ąŠą▓ą░čéčī ąĖą╝, č鹊 ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čü ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠą╝ ą┐čĆąŠą┤čāą║č鹊ą▓ XDS. ąöą░ąČąĄ ą║ąŠą│ą┤ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ XDS ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┤čĆčāą│ąŠą╣ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ ą║ąŠąĮąĮąĄą║č鹊čĆ, ąĖą╝ąĄčÄčéčüčÅ ą░ą┤ą░ą┐č鹥čĆčŗ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ ą╝ąĄąČą┤čā čĆą░ąĘą╗ąĖčćąĮčŗą╝ąĖ 菹╝čāą╗čÅč鹊čĆą░ą╝ąĖ XDS.

ŌĆó JTAG Connectors and Pinout site:ti.com.

ŌĆó JTAG Adapters site:ti.com.

ŌĆó Designing for JTAG Emulation Reference Guide site:ti.com. ąŁč鹊čé ą┤ąŠą║čāą╝ąĄąĮčé ąŠą┐ąĖčüčŗą▓ą░ąĄčé 14-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą║ąŠąĮąĮąĄą║č鹊čĆ JTAG ąĖ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ čåąĄą╗ąĄą▓ąŠą╣ ą┐ą╗ą░č鹥 ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ XDS510 JTAG (ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ ą┤ąŠą║čāą╝ąĄąĮčéą░, čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĖą╝ąĄąĮąĄąĮąŠ ąĖ ą║ ą┤čĆčāą│ąĖą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝, ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ č鹊ą╗čīą║ąŠ ą║ TMS320C6000 DSP).

ŌĆó XDS560 Emulator Technical Reference site:ti.com.

ŌĆó Common Trace Transmission Problems and Solutions site:ti.com. ąŁč鹊čé ą┤ąŠą║čāą╝ąĄąĮčé ą┐ąŠą╝ąŠąČąĄčé čĆąĄčłąĖčéčī ąŠą▒čēąĖąĄ ą┐čĆąŠą▒ą╗ąĄą╝čŗ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ čüąĖą│ąĮą░ą╗ąŠą▓.

ŌĆó Emulation Fundamentals for TI's DSP Solutions site:ti.com.

ąĪčāčēąĄčüčéą▓čāčÄčé čüą╗ąĄą┤čāčÄčēąĖąĄ 菹╝čāą╗čÅč鹊čĆčŗ XDS:

XDS100v1(1) (č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ DSP)

XDS100v2 (ą┤ą╗čÅ čŹč鹊ą│ąŠ 菹╝čāą╗čÅč鹊čĆą░ čüčāčēąĄčüčéą▓čāąĄčé ąŠčéą║čĆčŗčéą░čÅ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÅ - čüčģąĄą╝ą░, ą┐ąĄčćą░čéąĮą░čÅ ą┐ą╗ą░čéą░, ą┐čĆąŠčłąĖą▓ą║ą░ CPLD [8, 9])

XDS100v3 (ą┤ą╗čÅ čŹč鹊ą│ąŠ 菹╝čāą╗čÅč鹊čĆą░ čüčāčēąĄčüčéą▓čāąĄčé ąŠčéą║čĆčŗčéą░čÅ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÅ - čüčģąĄą╝ą░, ą┐ąĄčćą░čéąĮą░čÅ ą┐ą╗ą░čéą░, ą┐čĆąŠčłąĖą▓ą║ą░ CPLD [9])

XDS110(2)

XDS200

XDS510(1, 3)

XDS560(1)

XDS560T(4)

XDS560v2 System Trace

XDS560v2 Pro Trace

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) XDS100v1, XDS510 ąĖ XDS560 čüąĮčÅčéčŗ čü ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░ ąĖ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ.

(2) XDS110 ą┤ąŠčüčéčāą┐ąĄąĮ čéą░ą║ąČąĄ ąĮą░ ąĮąĄą║ąŠč鹊čĆčŗčģ ąŠčéą╗ą░ą┤ąŠčćąĮčŗčģ ą┐ą╗ą░čéą░čģ Simplelink MCU Launchpad: MSP432P401, CC1310, CC2640R2, CC2650, Hercules RM46 ąĖ čé. ą┐., ą░ čéą░ą║ąČąĄ ąĮą░ ąŠą▒ąŠąĖčģ CC1310 ąĖ CC2650 SensorTag.

(3) ąØąĄą║ąŠč鹊čĆčŗąĄ ą╝ąŠą┤ąĄą╗ąĖ XDS510 ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé čāčĆąŠą▓ąĮąĖ 1.8V JTAG. ąĪčāčēąĄčüčéą▓čāčÄčé ą░ą┤ą░ą┐č鹥čĆčŗ, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą╝ąŠą│čāčé ąŠčüčāčēąĄčüčéą▓ąĖčéčī čéčĆą░ąĮčüą╗čÅčåąĖčÄ čāčĆąŠą▓ąĮąĄą╣. ąöą╗čÅ čüą┐ąĄčåąĖčäąĖčćąĮčŗčģ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą┐ąŠ čĆą░ą▒ąŠčćąĖą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅą╝ ąĖ čćą░čüč鹊čéą░ą╝ čüą╝. ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅ.

(4) XDS560T čāčüčéą░čĆąĄą╗.

ąÆ čüą╗ąĄą┤čāčÄčēąĄą╣ čéą░ą▒ą╗ąĖčåąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ ą▓ąĘą░ąĖą╝ąŠčüą▓čÅąĘčī čüąŠ čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╝ąĖ čäčāąĮčåąĖčÅą╝ąĖ ą┤ą╗čÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ čéąĖą┐ąŠą▓ 菹╝čāą╗čÅč鹊čĆąŠą▓ XDS ąĖ ą║ąŠąĮąĮąĄą║č鹊čĆąŠą▓.

| ą£ąŠą┤ąĄą╗čī XDS |

XDS100v1

|

XDS100v2

|

XDS100v3

|

XDS110

|

XDS200

|

XDS510

|

XDS560

|

XDS560 Rev D cable |

XDS560T

|

XDS560v2 System Trace |

XDS560v2

|

| ążčāąĮą║čåąĖčÅ(1) |

| ąóąĖą┐ ą║ąŠąĮąĮąĄą║č鹊čĆą░ |

14-pin TI

20-pin TI |

14-pin TI

20-pin TI

20-pin ARM |

14-pin TI

20-pin TI

20-pin ARM |

20-pin TI |

20-pin TI |

14-pin TI

20-pin TI |

14-pin TI

20-pin TI |

20-pin TI |

60-pin TI |

60-pin MIPI HPST |

60-pin MIPI HPST |

| ąÉą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ(2) |

ąĮąĄčé |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĮąĄčé |

ąĢąĪąóą¼ |

ąĢąĪąóą¼(5) |

ąĢąĪąóą¼(5) |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

| Core Pin Trace(3) |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĢąĪąóą¼ (č鹊ą╗čīą║ąŠ DSP) |

ąĮąĄčé |

ąĮąĄčé |

ąĢąĪąóą¼ |

System Pin

Trace(3) |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

| ą×čéą╗ą░ą┤ą║ą░ SWD + SWO Trace |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

| IEEE1149.7 (cJTAG) |

ąĮąĄčé |

ąĮąĄčé |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

| TVRef |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

| System Reset (nReset) |

ąĢąĪąóą¼(4) |

ąĢąĪąóą¼(4) |

ąĮąĄčé |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼(4) |

ąĢąĪąóą¼(4) |

ąĢąĪąóą¼ |

ąĮąĄčé |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

| Emulation Boot Modes |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

| HS-RTDX |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĢąĪąóą¼ |

ąĢąĪąóą¼ |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąöą╗čÅ ą┐ąŠą╗ąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ čäčāąĮą║čåąĖčÅą╝ ąĖ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╝ čāčĆąŠą▓ąĮčÅą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ čüą╝. ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅ ąĮą░ 菹╝čāą╗čÅč鹊čĆ.

(2) ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ čü čÅą┤čĆą░ą╝ąĖ ARM9 ąĖ ARM11.

(3) ąĢčüą╗ąĖ ąÆą░čł ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čéčĆą░čüčüąĖčĆąŠą▓ą║čā core trace ąĖą╗ąĖ system trace č湥čĆąĄąĘ ąĮąŠąČą║ąĖ EMU, ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, čćč鹊ą▒čŗ čåąĄą╗ąĄą▓ąŠąĄ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čŗą╗ąŠ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠ čü 菹╝čāą╗čÅč鹊čĆą░ą╝ąĖ XDS, čüą┐ąŠčüąŠą▒ąĮčŗą╝ąĖ ą┐ąŠą╗čāčćąĖčéčī ą╗čÄą▒ąŠą╣ čéąĖą┐ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ, čüą╝. čĆąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ TRM [2].

(4) ąŁčéąĖ ąŠčéą╗ą░ą┤čćąĖą║ąĖ ą╝ąŠą│čāčé ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ ą╝ąŠą┤ąĄą╗čÅčģ ą▒čŗčéčī ą┐čĆąŠąĖąĘą▓ąĄą┤ąĄąĮčŗ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą║ąŠąĮąĮąĄą║č鹊čĆą░ą╝ąĖ. ąĢčüą╗ąĖ ąÆą░čł čŹą╝čāą╗čÅč鹊čĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 20-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą║ąŠąĮąĮąĄą║č鹊čĆ čåąŠą║ąŠą╗ąĄą▓ą║ąĖ TI ąĖ/ąĖą╗ąĖ čåąŠą║ąŠą╗ąĄą▓ą║ąĖ ARM [10], č鹊 ąŠąĮ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī čäčāąĮą║čåąĖčÄ čüą▒čĆąŠčüą░ čüąĖčüč鹥ą╝čŗ (System Reset). ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅ.

(5) ąŁčéąĖ ąŠčéą╗ą░ą┤čćąĖą║ąĖ ą╝ąŠą│čāčé ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ ą╝ąŠą┤ąĄą╗čÅčģ ą▒čŗčéčī ą┐čĆąŠąĖąĘą▓ąĄą┤ąĄąĮčŗ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą║ąŠąĮąĮąĄą║č鹊čĆą░ą╝ąĖ. ąĢčüą╗ąĖ ąÆą░čł čŹą╝čāą╗čÅč鹊čĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 20-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą║ąŠąĮąĮąĄą║č鹊čĆ čåąŠą║ąŠą╗ąĄą▓ą║ąĖ TI ąĖ/ąĖą╗ąĖ čåąŠą║ąŠą╗ąĄą▓ą║ąĖ ARM [10], č鹊 ąŠąĮ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī čäčāąĮą║čåąĖčÄ ą░ą┤ą░ą┐čéąĖą▓ąĮąŠą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅ.

[ąÉą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ]

ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ TI ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čÅą┤čĆąŠ ARM, ą║ąŠč鹊čĆąŠąĄ čéčĆąĄą▒čāąĄčé ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą░ą┤ą░ą┐čéąĖą▓ąĮąŠą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ (Adaptive Clocking) ąĮą░ ą▓čŗą▓ąŠą┤ąĄ RTCK ą║ąŠąĮąĮąĄą║č鹊čĆą░ JTAG. ąĪąĖą│ąĮą░ą╗ RTCK ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąŠčéą╗ą░ą┤čćąĖą║ąŠą╝ XDS (ąĄčüą╗ąĖ ąŠąĮ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé Adaptive Clocking), čćč鹊ą▒čŗ čāą┐čĆą░ą▓ą╗čÅčéčī ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖąĄą╝ TCK, ą┐ąŠą║ą░ XDS ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĖčé ą┐ąĄčĆąĄą┐ą░ą┤ RTCK ą▓ ąŠčéą▓ąĄčé ąĮą░ ą┐čĆąĄą┤čŗą┤čāčēąĖą╣ ą┐ąĄčĆąĄą┐ą░ą┤ TCK. ąŚą░ą┤ąĄčƹȹ║ą░ RTCK ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čÅą┤čĆčā ARM čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčī ą▓čģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ JTAG čü čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠą╣ čćą░čüč鹊č鹊ą╣ čéą░ą║č鹊ą▓ čÅą┤čĆą░, čćč鹊 ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąŠą┤čüčéčĆą░ąĖą▓ą░ąĄčé TCK ą┤ą╗čÅ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠą╣ čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ ARM.

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ Adaptive Clocking čü ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąĮąŠąČą║čā RTCK, ą┤ą░ąĄčé ą┐ąŠą▓čŗčłąĄąĮąĮčāčÄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī ąŠčéą╗ą░ą┤ą║ąĖ (čāčüą║ąŠčĆčÅąĄčéčüčÅ ąĘą░ą│čĆčāąĘą║ą░, ą┐ąŠą┤ą┤ąĄčƹȹ║ą░ ą┐ąŠčłą░ą│ąŠą▓ąŠą╣ ąŠčéą╗ą░ą┤ą║ąĖ) ąĖ ą┐ąŠą▓čŗčłą░ąĄčé čüčéą░ą▒ąĖą╗čīąĮąŠčüčéčī čĆą░ą▒ąŠčéčŗ ąŠčéą╗ą░ą┤čćąĖą║ą░.

ąĀąĄąČąĖą╝ą░ ą░ą┤ą░ą┐čéąĖą▓ąĮąŠą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ą┤ą╗čÅ XDS č湥čĆąĄąĘ ąŠčéą╗ą░ą┤čćąĖą║.

ąĢčüą╗ąĖ čā ąÆą░čłąĄą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ TI ąĄčüčéčī ąĮąŠąČą║ą░ RTCK, č鹊 ąŠąĮą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čüąŠąĄą┤ąĖąĮąĄąĮą░ čü čüąĖą│ąĮą░ą╗ąŠą╝ RTCK ą║ąŠąĮąĮąĄą║č鹊čĆą░ XDS, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ čéąĖą┐ą░ čĆą░ąĘčŖąĄą╝ą░ ąĮą░ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╝ čåąĄą╗ąĄą▓ąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ. ąĢčüą╗ąĖ ąÆą░čł čŹą╝čāą╗čÅč鹊čĆ XDS ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą░ą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ, č鹊 ąŠąĮąŠ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮąŠ č湥čĆąĄąĘ IDE (CCS). ąĢčüą╗ąĖ 菹╝čāą╗čÅč鹊čĆ XDS ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą░ą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ, č鹊 ą╝ąŠąČąĄčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ ą░ą┤ą░ą┐č鹥čĆ, čćč鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī ą┐ąŠą╗ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ JTAG. ąÜą░ą║ ą▓ą░čĆąĖą░ąĮčé ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī XDS čü čćą░čüč鹊č鹊ą╣ TCK ą╝ąĄąĮčīčłąĄ 1/8 ąŠčé čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ARM, ąĄčüą╗ąĖ 菹╝čāą╗čÅč鹊čĆ XDS ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą░ą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ.

ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą║ čåąĄą╗ąĄą▓čŗą╝ ą║ą░čĆčéą░ą╝, čĆą░čüčüčćąĖčéą░ąĮąĮčŗą╝ ąĮą░ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ TI, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé RTCK, čüą╝. čĆą░ąĘą┤ąĄą╗ "ąÉą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ".

[ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖąĮč鹥čĆč乥ą╣čüą░ JTAG]

ąÆ ąŠą┐ąĖčüą░ąĮąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ EMU ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą┐ąŠ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĄ Core Trace ąĖ System Trace. ąóą░ą║ąČąĄ čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ čüčéą░ąĮą┤ą░čĆčéą░ IEEE1149.7(cJTAG) [3].

TVRef. ąĪąĖą│ąĮą░ą╗ TVRef (ąĖąĮąŠą│ą┤ą░ ąĮą░ ą║ąŠąĮąĮąĄą║č鹊čĆąĄ ąŠąĮ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ TVDD ąĖą╗ąĖ PD) ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĮą░ ą▓čüąĄčģ ą║ąŠąĮąĮąĄą║č鹊čĆą░čģ, ąĖ ąŠąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čŹą╝čāą╗čÅč鹊čĆąŠą╝ XDS, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĮą░ą╗ąĖčćąĖąĄ ąĖą╗ąĖ ąŠčéčüčāčéčüčéą▓ąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ąĮą░ čåąĄą╗ąĄą▓ąŠą╝ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ, ąĖ čćč鹊ą▒čŗ čāčüčéą░ąĮąŠą▓ąĖčéčī čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēčāčÄ čéčĆą░ąĮčüą╗čÅčåąĖčÄ čāčĆąŠą▓ąĮąĄą╣ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG (1.8V ąĖą╗ąĖ 3.3V), ąĄčüą╗ąĖ čŹč鹊 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 菹╝čāą╗čÅč鹊čĆ XDS (ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗą╝ čāčĆąŠą▓ąĮčÅą╝ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG čüą╝. ą▓ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅ XDS).

TVRef čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐ąŠą┤ą║ą╗čÄčćą░čéčī ą║ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā č湥čĆąĄąĘ č鹊ą║ąŠąŠą│čĆą░ąĮąĖčćąĖą▓ą░čÄčēąĖą╣ čĆąĄąĘąĖčüč鹊čĆ 100 ą×ą╝.

ąĢčüą╗ąĖ čåąĄą┐ąŠčćą║ą░ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čüąŠą┤ąĄčƹȹĖčé čāčüčéčĆąŠą╣čüčéą▓ą░, ą║ąŠč鹊čĆčŗąĄ čéčĆąĄą▒čāčÄčé ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čāčĆąŠą▓ąĮąĄą╣ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ IO (TVRef ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ č鹊ą╗čīą║ąŠ ąĮą░ ąŠą┤ąĖąĮ čāčĆąŠą▓ąĄąĮčī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ), č鹊 ąÆčŗ ą┤ąŠą╗ąČąĮčŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▒čāč乥čĆčŗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čāčĆąŠą▓ąĮąĄą╣, čćč鹊ą▒čŗ ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąŠą┤ąĮąŠą╝čā čāčĆąŠą▓ąĮčÄ čüąĖą│ąĮą░ą╗čŗ JTAG ą▓čüąĄčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą▓ čåąĄą┐ąŠčćą║ąĄ. ąÆčüąĄ čüąĖą│ąĮą░ą╗čŗ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠčüčéčāą┐ą░čÄčé ąĮą░ čĆą░ąĘčŖąĄą╝ XDS, ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąĖą▓ąĄą┤ąĄąĮčŗ ą║ čāčĆąŠą▓ąĮčÄ TVRef.

nRESET. ąĪąĖą│ąĮą░ą╗ nRESET (ą║ąŠč鹊čĆčŗą╣ ąĖąĮąŠą│ą┤ą░ ąĮą░ąĘčŗą▓ą░čÄčé SRST) čŹč鹊 čüąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░ čüąĖčüč鹥ą╝čŗ (System Reset), ąĖ ąŠąĮ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓čüąĄą╝ąĖ čüąŠą▓čĆąĄą╝ąĄąĮąĮčŗą╝ąĖ ąŠčéą╗ą░ą┤čćąĖą║ą░ą╝ąĖ XDS. ąĪąĖą│ąĮą░ą╗ nRESET ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą╝ąĄčģą░ąĮąĖąĘą╝ čāą┤ą░ą╗ąĄąĮąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ą▓čüąĄą╣ čüąĖčüč鹥ą╝čŗ, ąĄčüą╗ąĖ nReset čĆą░ąĘčŖąĄą╝ą░ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ąĮą░ čĆą░ąĘčŖąĄą╝ąĄ ąŠčéą╗ą░ą┤čćąĖą║ą░ ąĖ ą┤ąŠą╗ąČąĄąĮ ąŠą▒čĆą░ąĘąŠą╝ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮ ą▓ ą░ą┐ą┐ą░čĆą░čéčāčĆčā čüą▒čĆąŠčüą░ ą┐ąŠ ą┐ąĖčéą░ąĮąĖčÄ (power-up-reset).

ŌĆó ąöą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ą┐čĆąĖ ąŠčéą╗ą░ą┤ą║ąĄ ą║ąŠą┤ą░ ąĘą░ą│čĆčāąĘą║ąĖ (boot code) čäčāąĮą║čåąĖčÅ Wait in Reset (čüą╝. ą▓čĆąĄąĘą║čā) ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹč鹊čé čüąĖą│ąĮą░ą╗.

ŌĆó ąĪą╝. ą▓čĆąĄąĘą║čā System Reset (Emulation), ą│ą┤ąĄ ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ ąŠą┐ąĖčüą░ąĮąŠ, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹčéčā čäčāąĮą║čåąĖčÄ ą▓ CCS.

ŌĆó ąŁą╝čāą╗čÅč鹊čĆčŗ XDS, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé nRESET, ąŠą▒čŗčćąĮąŠ ą╝ąŠą│čāčé čüą▒čĆąŠčüąĖčéčī č鹊ą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ TI, ą▓ą║ą╗čÄč湥ąĮąĮčŗąĄ ą▓ čåąĄą┐ąŠčćą║čā čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ JTAG.

ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąŠčéą╗ą░ą┤čćąĖą║ XDS, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüąĖą│ąĮą░ą╗ nRESET, ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čüą▒čĆąŠčüąĖčéčī ą▓čüčÄ ą░ą┐ą┐ą░čĆą░čéčāčĆčā ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╣ čüąĖčüč鹥ą╝čŗ, ąĄčüą╗ąĖ čŹč鹊 ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮąŠ ą▓ ąĄčæ ą░ą┐ą┐ą░čĆą░čéčāčĆčā. ąŁč鹊čé čüą▒čĆąŠčü ą▒čāą┤ąĄčé ą░ąĮą░ą╗ąŠą│ąĖč湥ąĮ ą┐ąŠą╗ąĮąŠą╝čā čüą▒čĆąŠčüčā ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (power-up-reset, POR).

nRESET čŹč鹊 ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝ ąŠčé XDS, čéą░ą║ čćč鹊 nRESET ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčé ą║ ą▓ąĄčĆčģąĮąĄą╝čā čāčĆąŠą▓ąĮčÄ čĆąĄąĘąĖčüč鹊čĆąŠą╝ 4.7 ą║ą×ą╝ ą▓ čåąĄą╗ąĄą▓ąŠą╣ čüąĖčüč鹥ą╝ąĄ.

ąĪąĖą│ąĮą░ą╗ nRESET ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ čŹą╝čāą╗čÅč鹊čĆąŠą╝ XDS ą▓ ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0 ą╝ąĖąĮąĖą╝čāą╝ ąĮą░ 500 ą╝ą║čü.

ążčāąĮą║čåąĖčÅ ąŠąČąĖą┤ą░ąĮąĖčÅ ąĮą░ čüą▒čĆąŠčüąĄ (Wait-In-Reset) ą┤ąŠą╗ąČąĮą░ ą┐ąŠą╝ąĄčüčéąĖčéčī ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤ ą║ąŠąĮčéčĆąŠą╗čī ąŠčéą╗ą░ą┤čćąĖą║ą░ ąĮą░ ą┐ąĄčĆą▓ąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą║ąŠč鹊čĆčāčÄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆ. ąŁč鹊 ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠčłą░ą│ąŠą▓ąŠą│ąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą┤ą░, ąĮą░čćąĖąĮą░čÅ čü čüą░ą╝čŗčģ ą┐ąĄčĆą▓čŗčģ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝čŗčģ ą║ąŠą╝ą░ąĮą┤. ążčāąĮą║čåąĖčÅ Wait-In-Reset ąŠč湥ąĮčī ą┐ąŠą╗ąĄąĘąĮą░ ą┤ą╗čÅ ąŠčéą╗ą░ą┤ą║ąĖ čéą░ą║ąŠą│ąŠ ą¤ą×, ą║ą░ą║ ą║ąŠą┤ ąĘą░ą│čĆčāąĘą║ąĖ (boot code) ąĖą╗ąĖ ą║ąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ąĀąĄąČąĖą╝ Wait-In-Reset ąŠą▒čŗčćąĮąŠ ą┤ąĄč鹥ą║čéąĖčĆčāąĄčéčüčÅ ąĮą░ ąŠčüąĮąŠą▓ąĄ čüąŠčüč鹊čÅąĮąĖčÅ ąĮąŠąČąĄą║ EMU0 ąĖ EMU1 ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ, ąĖ ąĖčģ čüąŠčüč鹊čÅąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░čģą▓ą░č湥ąĮąŠ ą▓ąŠ ą▓čĆąĄą╝čÅ čüą▒čĆąŠčüą░ ą┐ąŠ ą┐ąĖčéą░ąĮąĖčÄ. ąöą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ čĆąĄąČąĖą╝ Wait-In-Reset čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ą╝ąŠą┤čāą╗ąĄą╝ ICEPICK [4].

ąöą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓, ąĄčüą╗ąĖ ą┐ą╗ą░čéą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┐čĆą░ą▓ąĖą╗čīąĮčŗąĄ ą║ąŠąĮąĮąĄą║č鹊čĆčŗ JTAG čü čüąĖą│ąĮą░ą╗ąŠą╝ čüą▒čĆąŠčüą░ čüąĖčüč鹥ą╝čŗ, čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗą╝ ąŠčéą╗ą░ą┤čćąĖą║ąŠą╝, č鹊 čäčāąĮą║čåąĖčÅ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┐čĆąĖ čüą▒čĆąŠčüąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąŠčéą╗ą░ą┤čćąĖą║ąŠą╝.

ąØąĄą║ąŠč鹊čĆčŗąĄ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ ąĮą░ čÅą┤čĆąĄ ARM ą▒čŗą╗ąĖ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮčŗ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą┐ąŠą┤ąŠą▒ąĮąŠą│ąŠ ą╝ąĄčģą░ąĮąĖąĘą╝ą░ ą▒ąĄąĘ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ EMU0/EMU1. ąŁč鹊čé ą╝ąĄčģą░ąĮąĖąĘą╝ ą▓ąŠą▓ą╗ąĄą║ą░ąĄčé čāčüčéą░ąĮąŠą▓ą║čā ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą▓ čćąĖą┐ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ ąĘą░čģą▓ą░čéą░ ą▓ąĄą║č鹊čĆą░, čćč鹊ą▒čŗ ą▒čŗą╗ą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮą░ č鹊čćą║ą░ ąŠčüčéą░ąĮąŠą▓ą░ ąĮą░ čüą▒čĆąŠčüąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĘą░č鹥ą╝ ą▓čŗą┤ą░čéčī čüą▒čĆąŠčü ąĖ ąŠą▒čĆą░ą▒ąŠčéą░čéčī čŹčéčā č鹊čćą║čā ąŠčüčéą░ąĮąŠą▓ą░. ąŁč鹊 ą╝ąŠąČąĄčé ąĮąĄ čĆą░ą▒ąŠčéą░čéčī ąĮą░ ą▓čüąĄčģ čÅą┤čĆą░čģ ą┤ą╗čÅ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ.

ąØąĄą║ąŠč鹊čĆčŗąĄ ą║ąŠąĮąĮąĄą║č鹊čĆčŗ JTAG ąĖ 菹╝čāą╗čÅč鹊čĆčŗ (čéą░ą║ąĖąĄ ą║ą░ą║ XDS560 čĆąĄą▓ąĖąĘąĖąĖ D) ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé System Reset. ąÜąŠą│ą┤ą░ čŹč鹊čé čüąĖą│ąĮą░ą╗ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą║ąŠąĮąĮąĄą║č鹊čĆčā JTAG, ą║ąŠč鹊čĆčŗą╣ ąĄą│ąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé čüą▒čĆąŠčüąĖčéčī čåąĄą╗ąĄą▓čāčÄ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝čāčÄ ą┐ą╗ą░čéčā ąĖąĘ ą¤ą× ąŠčéą╗ą░ą┤čćąĖą║ą░.

ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ XDS560 čĆąĄą▓ąĖąĘąĖąĖ D, Code Composer Studio v4 ą╝ąŠąČąĄčé ą┐ąĄčĆąĄą┤ąĄčĆąĮčāčéčī ąĮąŠąČą║čā čüąĖčüč鹥ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ąĮą░ ą┐ąŠą┤čģąŠą┤čÅčēąĄą╝ ą║ąŠąĮąĮąĄą║č鹊čĆąĄ JTAG, čéą░ą║čāčÄ ą║ą░ą║ ąĮąŠąČą║ą░ 20 čĆą░ąĘčŖąĄą╝ą░ Compact TI ąĖą╗ąĖ ąĮąŠąČą║čā 20 ą║ąŠąĮąĮąĄą║č鹊čĆą░ ARM.

[https://processors.wiki.ti.com/images/2/2a/Systemresetimage.jpg]

TDIS. ąĪąĖą│ąĮą░ą╗ TDIS (Target Disconnect) čŹč鹊 čüąĖą│ąĮą░ą╗ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ čåąĄą╗ąĄą▓ąŠą│ąŠ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĖ ąŠąĮ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĮą░ čĆą░ąĘčŖąĄą╝ą░čģ TI. ą×ąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ čåąĄą╗ąĄą▓ąŠą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ ąŠčéą║ą╗čÄč湥ąĮ ąŠčé 菹╝čāą╗čÅč鹊čĆą░ ą┐čāč鹥ą╝ ą░ąĮą░ą╗ąĖąĘą░ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ GND ąŠčé čåąĄą╗ąĄą▓ąŠą╣ ą┐ą╗ą░čéčŗ.

ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čŹą╝čāą╗čÅč鹊čĆ XDS čü čĆą░ąĘčŖąĄą╝ąŠą╝ TI, čüąĖą│ąĮą░ą╗ TDIS ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą╗ąĖ čäąĖąĘąĖč湥čüą║ąĖ ą║ą░ą▒ąĄą╗čī ąŠčéą╗ą░ą┤ą║ąĖ ą║ čåąĄą╗ąĄą▓ąŠą╣ čüąĖčüč鹥ą╝ąĄ. ą×ą▒čŗčćąĮąŠ ą┤ą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą▓ 菹╝čāą╗čÅč鹊čĆąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ pull-up čĆąĄąĘąĖčüč鹊čĆ, ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čÄčēąĖą╣ ą╗ąŠą│. 1 ąĮą░ TDIS, ą║ąŠą│ą┤ą░ ą║ą░ą▒ąĄą╗čī ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ. ą¤čĆąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĖ ą║ą░ą▒ąĄą╗čÅ ą║ ą┐ą╗ą░č鹥 čāčĆąŠą▓ąĄąĮčī TDIS ą┐čĆąŠčüą░ąČąĖą▓ą░ąĄčéčüčÅ ą▓ 0, čćč鹊 ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī 菹╝čāą╗čÅč鹊čĆčā ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĮą░ą╗ąĖčćąĖąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ čåąĄą╗ąĄą▓ąŠą╣ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╣ čüąĖčüč鹥ą╝ąĄ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: pull-down ąĖą╗ąĖ ąŠą│čĆą░ąĮąĖčćąĖą▓ą░čÄčēąĖą╣ č鹊ą║ čĆąĄąĘąĖčüč鹊čĆ ąĮą░ TDIS ąĮąĄ ą▒čāą┤čāčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ ą▓čüąĄčģ ą╝ąŠą┤ąĄą╗čÅčģ 菹╝čāą╗čÅč鹊čĆąŠą▓ XDS. ąÜąŠą│ą┤ą░ TDIS čüąŠąĄą┤ąĖąĮąĄąĮ čü GND ąĮą░ą┐čĆčÅą╝čāčÄ, ąĮąĄą║ąŠč鹊čĆčŗąĄ ą╝ąŠą┤ąĄą╗ąĖ XDS ą▒čāą┤čāčé čüą╗ąĖą▓ą░čéčī č湥čĆąĄąĘ TDIS ąĮąĄą▒ąŠą╗čīčłąŠą╣ č鹊ą║ č湥čĆąĄąĘ pull-up čĆąĄąĘąĖčüč鹊čĆ ą▓ čüčģąĄą╝ąĄ 菹╝čāą╗čÅč鹊čĆą░ XDS. ąĀąĄąĘąĖčüč鹊čĆ pull-down ąĖą╗ąĖ č鹊ą║ąŠąŠą│čĆą░ąĮąĖčćąĖą▓ą░čÄčēąĖą╣ čĆąĄąĘąĖčüč鹊čĆ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ TDIS ąĮą░ čåąĄą╗ąĄą▓ąŠą╣ ą┐ą╗ą░č鹥, ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ č鹊ą╝čā, čćč鹊 XDS ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĖčé ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠąĄ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą▒čāą┤ąĄčé ą▓čŗą┤ą░ąĮą░ ąŠčłąĖą▒ą║ą░ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÅ ą║ą░ą▒ąĄą╗čÅ "cable break far-from itself" [7].

EMU. ąÆčŗą▓ąŠą┤čŗ EMU ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ, ąĖ ąŠąĮąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čäčāąĮą║čåąĖąĖ:

ŌĆó ąĀąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ (Boot Modes).

ŌĆó ąÜčĆąŠčüčü-čéčĆąĖą│ą│ąĄčĆčŗ (Cross Triggers).

ŌĆó ąóčĆą░čüčüąĖčĆąŠą▓ą║ą░ čÅą┤čĆą░ (Core Trace).

ŌĆó ąĪąĖčüč鹥ą╝ąĮą░čÅ čéčĆą░čüčüąĖčĆąŠą▓ą║ą░ (System Trace).

ŌĆó HS-RTDX (high speed RTDX, čāčüčéą░čĆąĄą▓čłąĖą╣ čäčāąĮą║čåąĖąŠąĮą░ą╗).

ąÆ čüą╗čāčćą░ąĄ Boot Modes čüąŠčüč鹊čÅąĮąĖąĄ ąĮąŠąČąĄą║ EMU0/EMU1 čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čŹą╝čāą╗čÅč鹊čĆąŠą╝ XDS. HS-RTDX ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čéčĆą░ąĮčüą┐ąŠčĆčé ą┤ą░ąĮąĮčŗčģ. ąś Core Trace, ąĖ System Trace ą┐ąĄčĆąĄą┤ą░čÄčé ąĖčüč鹊čĆąĖčÄ čüąŠą▒čŗčéąĖą╣ ąĖ ą┤ą░ąĮąĮčŗąĄ ą▓čĆąĄą╝ąĄąĮąĖ ąŠčé čåąĄą╗ąĄą▓ąŠą│ąŠ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▓ 菹╝čāą╗čÅč鹊čĆ XDS. Cross Triggers čŹč鹊 ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ čéčĆąĖą│ą│ąĄčĆčŗ, ą║ąŠč鹊čĆčŗąĄ ą┤ą░čÄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čüąĖčéčāą░čåąĖąĖ, ą║ąŠą│ą┤ą░ čüąŠą▒čŗčéąĖąĄ ą▓ ąŠą┤ąĮąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą┤ąĄą╣čüčéą▓ąĖčÄ ąŠčéą╗ą░ą┤ą║ąĖ ą▓ ą┤čĆčāą│ąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ. ąöą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą║ą░ą║ąĖąĄ ąĮąŠąČą║ąĖ EMU ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ąĖąĘ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮčŗčģ čäčāąĮą║čåąĖą╣, ąŠą▒čĆą░čéąĖč鹥čüčī ą║ ą┤ą░čéą░čłąĖčéčā ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ.

ąÆ čüą╗čāčćą░čÅčģ, ą║ąŠą│ą┤ą░ čā ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▒ąŠą╗čīčłąĄ ąĮąŠąČąĄą║ EMU, č湥ą╝ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé XDS, ą┤ąŠą╗ąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąŠčüąĮąŠą▓ąĮąŠąĄ ą┐čĆą░ą▓ąĖą╗ąŠ - čüąŠąĄą┤ąĖąĮąĖčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čüąĖą│ąĮą░ą╗ąŠą▓ EMU čü ą║ąŠąĮąĮąĄą║č鹊čĆąŠą╝ XDS. ąöą░ąČąĄ ą▓ čüą╗čāčćą░čÅčģ, ą║ąŠą│ą┤ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ XDS ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé č鹊ą╗čīą║ąŠ ą┐ąŠą┤ą╝ąĮąŠąČąĄčüčéą▓ąŠ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéąĖ EMU, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮąŠąĄ čüą┐ąĄčåąĖčäąĖčćąĮčŗą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝, ą║ąŠą╝ą┐ą░ąĮąĖčÅ TI čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčé čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ąĮąŠąČąĄą║ EMU ą╝ąĄąČą┤čā ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ ąĖ čĆą░ąĘčŖąĄą╝ąŠą╝ XDS, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī čü ą┤čĆčāą│ąĖą╝ąĖ 菹╝čāą╗čÅč鹊čĆą░ą╝ąĖ XDS, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ čäčāąĮą║čåąĖąŠąĮą░ą╗.

ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ąŠą┤čéčÅąČą║ą░ pull-up ąĮą░ EMU0 ąĖ EMU1 ąŠą▒čŗčćąĮąŠ čüą╗ą░ą▒ąŠč鹊čćąĮą░čÅ (ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 20 ą║ą×ą╝ .. 30 ą║ą×ą╝) ąĖ ą┐ąŠčŹč鹊ą╝čā čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ąĮąĄčłąĮąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ pull-up ąĮą░ EMU0 ąĖ EMU1. ąĢčüą╗ąĖ ąÆą░čł ą┐čĆąŠčåąĄčüčüąŠčĆ čüąŠą┤ąĄčƹȹĖčé ą▒ąŠą╗čīčłąĄ ąĮąŠąČąĄą║ EMU, č湥ą╝ ąĮą░ 菹╝čāą╗čÅč鹊čĆąĄ, ąĖčģ ąĮąĄ ąĮčāąČąĮąŠ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čéčī čĆąĄąĘąĖčüč鹊čĆą░ą╝ąĖ.

ąĢčüą╗ąĖ ąÆą░čł ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čĆąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ (boot modes) ąĮą░ ąĮąŠąČą║ą░čģ EMU0 ąĖ EMU1, č鹊 čŹčéąĖ čāčĆąŠą▓ąĮąĖ čŹčéąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ POR, čćč鹊ą▒čŗ čāčüčéą░ąĮąŠą▓ąĖčéčī boot mode. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąŠą▒ą░ čüąĖą│ąĮą░ą╗ą░ EMU0 ąĖ EMU1 ą┐ąŠą┤čéčÅąĮčāčéčŗ ą║ ą╗ąŠą│. 1. ąöčĆčāą│ąĖąĄ čĆąĄąČąĖą╝čŗ ąŠą▒čŗčćąĮąŠ ą▓ą║ą╗čÄčćą░čÄčé Boundary Scan ąĖ Wait-In-Reset. ąĪą╝. ą┤ą░čéą░čłąĖčé ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗą╝ čĆąĄąČąĖą╝ą░ą╝ ąĘą░ą│čĆčāąĘą║ąĖ ąĖ čüąŠčüč鹊čÅąĮąĖčÄ ąĮąŠąČąĄą║ EMU, čéčĆąĄą▒čāąĄą╝ąŠą╝čā ą┐čĆąĖ POR ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ boot mode.

ąÆčüąĄ ąĮąŠąČą║ąĖ EMU ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüąĮą░čĆčāąČąĖ ą┐ąŠą┤čéčÅąĮčāčéčŗ ą║ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ ą▓ čüą░ą╝ąŠą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ ąĮąĄčé ą▓čüčéčĆąŠąĄąĮąĮčŗčģ ą▓ąĄčĆčģąĮąĖčģ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓.

ąĢčüą╗ąĖ ąĮą░ 菹╝čāą╗čÅč鹊čĆąĄ XDS ą▒ąŠą╗čīčłąĄ ąĮąŠąČąĄą║ EMU, č湥ą╝ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ, č鹊 ą╝ąŠąČąĮąŠ ąŠčüčéą░ą▓ąĖčéčī ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ąĮąŠąČą║ąĖ EMU ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ.

ą×ą▒čŗčćąĮąŠ ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░čéčī EMU0 ąĖ EMU1, čéą░ą║ ą║ą░ą║ čćą░čüč鹊 čŹčéąĖ čüąĖą│ąĮą░ą╗čŗ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ.

ąĢčüą╗ąĖ ąÆą░čł ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé HS-RTDX, č鹊 čéčĆąĄą▒čāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊ą▒čŗ ą┐ąĄčĆąĄčģąŠą┤čŗ čāčĆąŠą▓ąĮąĄą╣ ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ EMU ą▒čŗą╗ąĖ ą┤ąŠčüčéą░č鹊čćąĮąŠ ą▒čŗčüčéčĆčŗą╝ąĖ, čćč鹊ą▒čŗ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║čĆąŠčüčü-čéčĆąĖą│ą│ąĄčĆąŠą▓.

ŌĆó ąÆčĆąĄą╝čÅ čüą┐ą░ą┤ą░ - ą╝ąĄąĮčīčłąĄ 100 ąĮčü.

ŌĆó ąÆčĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ - ą╝ąĄąĮčīčłąĄ 1 ą╝ą║čü.

ą¦č鹊ą▒čŗ ą▓čŗčćąĖčüą╗ąĖčéčī ą▓čĆąĄą╝čÅ čüą┐ą░ą┤ą░, ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č鹊ą║ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą║ąŠąĮčéą░ą║čéą░ EMU ąŠą┤ąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░, čĆą░ąĘąĮąĖčåčā ą╝ąĄąČą┤čā ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╝ ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╝ čāčĆąŠą▓ąĮčÅą╝ąĖ (ąŠčé VMAX ą┤ąŠ VOL) ąĮąŠąČą║ąĖ EMU, čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠą╣ ą▓ ą╝ą░čüčüąĖą▓ąĄ, ąĖ ąĄą╝ą║ąŠčüčéąĮčāčÄ ąĮą░ą│čĆčāąĘą║čā ą┤ą╗čÅ ą▓čüąĄčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓, ą▓ čüą╗ąĄą┤čāčÄčēąĄą╣ č乊čĆą╝čāą╗ąĄ:

Tfall = (Vdelta x Ci x Ndevices-1) / Io

ąŚą┤ąĄčüčī Vdelta čŹč鹊 VOH(MAX) ŌĆō VOL. ąŚąĮą░č湥ąĮąĖčÅ Io, VOH(MAX), VOL ąĖ Ci ą╝ąŠąČąĮąŠ čāąĘąĮą░čéčī ąĖąĘ ą┤ą░čéą░čłąĖčéą░ ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆ.

ąöą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 č乊čĆą╝čāą╗čā:

tr = 1.5 x (Rpullup x Ndevices x Ci_per_device)

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čŹč鹊 ą▒ą░ąĘąŠą▓ą░čÅ ą║ąŠąĮčüčéą░ąĮčéą░ ą┐ąŠčüč鹊čÅąĮąĮąŠą╣ ą▓čĆąĄą╝ąĄąĮąĖ RC čüčģąĄą╝čŗ, ą│ą┤ąĄ 1.5T čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ ~80% ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░čĆą░čüčéą░ąĮąĖčÅ. ąöą╗čÅ č鹊čćąĮąŠčüčéąĖ, ąĄčüą╗ąĖ ąÆą░čł ą┐čĆąŠčåąĄčüčüąŠčĆ čüąŠą┤ąĄčƹȹĖčé ą▓čüčéčĆąŠąĄąĮąĮčŗąĄ pull-up čĆąĄąĘąĖčüč鹊čĆčŗ ąĮą░ ąĮąŠąČą║ą░čģ EMU (čüą╝. ą┤ą░čéą░čłąĖčé ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆ), č鹊 ąŠą▒čŗčćąĮąŠ ąŠąĮąĖ čüą╗ą░ą▒ąŠč鹊čćąĮčŗąĄ (~ 30 ą║ą×ą╝). ąŁč鹊 ą┤ąŠą╗ąČąĮąŠ čāčćąĖčéčŗą▓ą░čéčīčüčÅ ą┐čĆąĖ čĆą░čüč湥č鹥 Rpullup.

ąöą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé HS-RTDX, čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą▒ąŠą╗ąĄąĄ ąČąĄčüčéą║ąĖąĄ, ą┐ąŠč鹊ą╝čā čćč鹊 ą┐ąĄčĆąĄą┐ą░ą┤čŗ čāčĆąŠą▓ąĮąĄą╣ ąĮą░ ąĮąŠąČą║ą░čģ EMU, ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ, ą╝ąŠą│čāčé ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą║č鹊ą▓ TCK. ąĢčüą╗ąĖ ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĖčéčī čŹčéąĖ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ, č鹊 ąĮčāąČąĮąŠ čüąĮąĖąĘąĖčéčī čćą░čüč鹊čéčā TCK 菹╝čāą╗čÅč鹊čĆą░ XDS ą┤ąŠ ąĘąĮą░č湥ąĮąĖčÅ, ą║ąŠč鹊čĆą░čÅ ąŠą▒ąĄčüą┐ąĄčćąĖčé čéčĆąĄą▒ąŠą▓ą░ąĮąĖąĄ. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ąĖčéčī čćą░čüč鹊čéčā TCK ąĮą░ 10% ąĮąĖąČąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ąĮąĄą║ąŠč鹊čĆčŗą╣ ąĘą░čēąĖčéąĮčŗą╣ ąĘą░ą┐ą░čü ą┤ą╗čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čĆą░ą▒ąŠčćąĖčģ čāčüą╗ąŠą▓ąĖą╣.

ąĀąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ (Boot Modes). ąŻčĆąŠą▓ąĮąĖ čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ, ą║ąŠč鹊čĆčŗąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┤ą╗čÅ čåąĄą╗ąĄą▓ąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĮą░ ąĮąŠąČą║ą░čģ EMU 菹╝čāą╗čÅč鹊čĆ XDS, čüčćąĖčéčŗą▓ą░čÄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ nTRST, ąĖą╗ąĖ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąĀąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ ą╝ąŠą│čāčé čéą░ą║ąČąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ą░ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ Wait-in-Reset. ąØąŠąČą║ąĖ EMU, ą║ąŠč鹊čĆčŗąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čĆąĄąČąĖą╝ąŠą▓ ąĘą░ą│čĆčāąĘą║ąĖ, čéą░ą║ąČąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ čäčāąĮą║čåąĖą╣, ą║ą░ą║ č鹊ą╗čīą║ąŠ ąĘą░ą│čĆčāąĘą║ą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░ ąĖą╗ąĖ čüąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░ čüąĮčÅčé, čéą░ą║ąĖčģ ą║ą░ą║ čéčĆą░čüčüąĖčĆąŠą▓ą║ą░ ąĖą╗ąĖ HS-RTDX.

ąÜčĆąŠčüčü-čéčĆąĖą│ą│ąĄčĆčŗ. ąÜąŠą│ą┤ą░ ąĮąŠąČą║ą░ EMU ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą║čĆąŠčüčü-čéčĆąĖą│ą│ąĄčĆą░ (Cross Trigger), ąĮąĄ ąĮčāąČąĮąŠ ą▓čŗą┤ąĄą╗čÅčéčī ąĮąŠąČą║čā EMU ą║ą░ą║ ą▓čģąŠą┤ąĮąŠą╣ ąĖą╗ąĖ ą▓čŗčģąŠą┤ąĮąŠą╣ čéčĆąĖą│ą│ąĄčĆ, ą┐ąŠčüą║ąŠą╗čīą║čā ąĮąŠąČą║ąĖ EMU ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ. ąĪąŠą▒čŗčéąĖčÅ, ąĘą░ą┐čāčüą║ą░čÄčēąĖąĄ ą▓čŗčģąŠą┤ čéčĆąĖą│ą│ąĄčĆą░ ąĮąŠąČą║ąĖ EMU, ą╝ąŠą│čāčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ąĮą░ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čāčüčéčĆąŠą╣čüčéą▓ą░čģ. ąÆ č鹊 ąČąĄ ą▓čĆąĄą╝čÅ ą▓čüąĄ čŹčéąĖ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ čéą░ą║ąČąĄ ą╝ąŠą│čāčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą┤ą╗čÅ čĆąĄą░ą║čåąĖąĖ ąĮą░ ą▓ą▓ąŠą┤ čéčĆąĖą│ą│ąĄčĆą░ ąĮą░ č鹊ą╣ ąČąĄ čüą░ą╝ąŠą╣ ąĮąŠąČą║ąĄ EMU.

HS-RTDX - čāčüčéą░čĆąĄą▓čłą░čÅ čäčāąĮą║čåąĖčÅ. HS-RTDX ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ ąĮąŠąČą║čā EMU, ąŠą▒čŗčćąĮąŠ č湥čĆąĄąĘ EMU0 ąĖą╗ąĖ EMU1, ąĮą░ čćą░čüč鹊č鹥 JTAG TCK čü ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊č鹊ą╣ 35 ą£ąōčå. ąĢčüą╗ąĖ ąÆą░čł ą┤ąĖąĘą░ą╣ąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ TI, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé HS-RTDX, ąĖ 菹╝čāą╗čÅč鹊čĆ XDS čéą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą║ą░ąĮą░ą╗ąŠą▓ HS-RTDX (XDS560 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé HS-RTDX č湥čĆąĄąĘ EMU0 ąĖ EMU1), č鹊 ą╝ąŠąČąĮąŠ ąĘą░ą┐čāčüčéąĖčéčī HS-RTDX ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čü ą┤ą▓čāą╝čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ. HS-RTDX čéčĆąĄą▒čāąĄčé ąĖąĮč鹥ą│čĆą░čåąĖąĖ čü čåąĄą╗ąĄą▓ąŠą╣ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąŠą╣. ąóą░ą║ąČąĄ čéčĆąĄą▒čāąĄčéčüčÅ čŹą╝čāą╗čÅč鹊čĆ XDS, čéą░ą║ąŠą╣ ą║ą░ą║ XDS560, ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčēąĖą╣ HS-RTDX.

Core Trace ąĖ System Trace. ąóčĆą░čüčüąĖčĆąŠą▓ą║ą░ čÅą┤čĆą░ (Core Trace) ąŠą▒čŗčćąĮąŠ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé, ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝, čéčĆą░čüčüąĖčĆąŠą▓ą║čā čüč湥čéčćąĖą║ą░ ą║ąŠą╝ą░ąĮą┤ (PC) ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĖ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą║čĆąĖčüčéą░ą╗ą╗ą░, ą╝ąŠąČąĄčé čéą░ą║ąČąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčéčī čéčĆą░čüčüąĖčĆąŠą▓ą║čā ą┤ą░ąĮąĮčŗčģ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (data trace) ąĖ čéčĆą░čüčüąĖčĆąŠą▓ą║čā čüąŠą▒čŗčéąĖą╣ (event trace). ąĪąĖčüč鹥ą╝ąĮą░čÅ čéčĆą░čüčüąĖčĆąŠą▓ą║ą░ čŹč鹊 (System Trace) čŹč鹊 ąŠčüąĮąŠą▓ą░ąĮąĮą░čÅ ąĮą░ čüąŠąŠą▒čēąĄąĮąĖčÅčģ č鹥čģąĮąŠą╗ąŠą│ąĖčÅ, ą║ąŠč鹊čĆą░čÅ, ą▒čāą┤čāčćąĖ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą╣, ą╝ąŠąČąĄčé 菹║čüą┐ąŠčĆčéąĖčĆąŠą▓ą░čéčī ąĖąĮčüčéčĆčāą╝ąĄąĮčéčŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗąĄ ą░ą┐ą┐ą░čĆą░čéąĮąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ ąŠčé ą╝ąŠąĮąĖč鹊čĆąŠą▓ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ. ą£ąĮąŠą│ąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ą▓čüčéčĆąŠąĄąĮąĮčŗąĄ ą▒čāč乥čĆčŗ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ (Embedded Trace Buffers, ETB) ą╗ąĖą▒ąŠ ąĖčüą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ, ą╗ąĖą▒ąŠ ą▓ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ čü 菹║čüą┐ąŠčĆč鹊ą╝ ą┤ą░ąĮąĮčŗčģ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ č湥čĆąĄąĘ ąĮąŠąČą║ąĖ EMU ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąÆ čüą╗čāčćą░čÅčģ, ą║ąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖčüą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ETB, ą║ąŠąĮąĮąĄą║č鹊čĆčŗ čü čäčāąĮą║čåąĖąĄą╣ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ (ą╗ąĖą▒ąŠ ąŠčé TI ą╗ąĖą▒ąŠ ąŠčé MIPI 60-ą▓čŗą▓ąŠą┤ąĮčŗąĄ) ąĮąĄ čéčĆąĄą▒čāčÄčéčüčÅ ą┤ą╗čÅ ąĘą░ą╝ąĄąĮčŗ čéčĆą░ą┤ąĖčåąĖąŠąĮąĮčŗčģ 14-ą▓čŗą▓ąŠą┤ąĮčŗčģ ąĖą╗ąĖ 20-ą▓čŗą▓ąŠą┤ąĮčŗčģ ą║ąŠąĮąĮąĄą║č鹊čĆąŠą▓ ąĮą░ ą┐ą╗ą░č鹥, ąĮąŠ ą▒čāč乥čĆčŗ ETB č鹊ą╗čīą║ąŠ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé čāą▓ąĖą┤ąĄčéčī č鹊ą╗čīą║ąŠ ąŠą│čĆą░ąĮąĖč湥ąĮąĮčŗąĄ čüąĮąĖą╝ą║ąĖ ą┤ą░ąĮąĮčŗčģ (ąŠą▒čŗčćąĮąŠ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 4 ą┤ąŠ 32 ą║ąĖą╗ąŠą▒ą░ą╣čé). ą¦č鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą╗ąĖ ąÆą░čł ą┐čĆąŠčåąĄčüčüąŠčĆ čŹą║čüą┐ąŠčĆčé čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ čÅą┤čĆą░ ąĖą╗ąĖ čüąĖčüč鹥ą╝ąĮąŠą╣ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ č湥čĆąĄąĘ ąĮąŠąČą║ąĖ EMU, ąĖ/ąĖą╗ąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą╗ąĖ ąŠą┤ąĖąĮ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒čāč乥čĆąŠą▓ ETB, čüą╝. ą┤ą░čéą░čłąĖčé ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆ. ąöąŠčüč鹊ąĖąĮčüčéą▓ąŠ 菹║čüą┐ąŠčĆčéą░ ą┤ą░ąĮąĮčŗčģ Core Trace ąĖ System Trace č湥čĆąĄąĘ ąĮąŠąČą║ąĖ EMU ą▓ 菹╝čāą╗čÅč鹊čĆ XDS čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ ąĘą░čģą▓ą░čéą░ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ, čéą░ą║ąŠą╣ ą║ą░ą║ XDS560T ąĖą╗ąĖ XDS560v2 System Trace, čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊 ą│ą╗čāą▒ąĖąĮą░ ąĘą░čģą▓ą░čéą░ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ąĮą░ą╝ąĮąŠą│ąŠ ą▒ąŠą╗čīčłąĄ, ąĘą░čģą▓ą░čéčŗą▓ą░čÅ ą▒ąŠą╗čīčłąŠą╣ čĆąĄą│ąĖąŠąĮ ą▓ąĖą┤ąĖą╝ąŠčüčéąĖ, ąĖ ą╝ąŠąČąĮąŠ ą┤ąĄą╗ą░čéčī č鹊čćąĮčŗą╣ ą┐čĆąŠčäą░ą╣ą╗ąĖąĮą│ ąĖ ą░ąĮą░ą╗ąĖąĘ čĆą░ą▒ąŠčéčŗ ą║ąŠą┤ą░.

ąÆ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ TI ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ čŹą║čüą┐ąŠčĆčé čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ čÅą┤čĆą░, ąĖą╗ąĖ ąĄčüą╗ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą║ą░ą║ čéčĆą░čüčüąĖčĆąŠą▓ą║ą░ čÅą┤čĆą░, čéą░ą║ ąĖ čüąĖčüč鹥ą╝ąĮą░čÅ čéčĆą░čüčüąĖčĆąŠą▓ą║ą░, ą┐ąŠčéčĆąĄą▒čāąĄčéčüčÅ ą┐čĆąĖą╝ąĄąĮąĖčéčī 60-ą▓čŗą▓ąŠą┤ąĮčŗą╣ čĆą░ąĘčŖąĄą╝ ą▓ą╝ąĄčüč鹊 čéčĆą░ą┤ąĖčåąĖąŠąĮąĮčŗčģ 14-ą▓čŗą▓ąŠą┤ąĮčŗčģ ąĖą╗ąĖ 20-ą▓čŗą▓ąŠą┤ąĮčŗčģ ą║ąŠąĮąĮąĄą║č鹊čĆąŠą▓ 菹╝čāą╗čÅč鹊čĆą░. ąÆ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé č鹊ą╗čīą║ąŠ 菹║čüą┐ąŠčĆčé ą┤ą░ąĮąĮčŗčģ čüąĖčüč鹥ą╝ąĮąŠą╣ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ, ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ 20-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą║ąŠąĮąĮąĄą║č鹊čĆ čåąŠą║ąŠą╗ąĄą▓ą║ąĖ TI CTI. ąØąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą║ąŠąĮąĮąĄą║č鹊čĆą░, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čüąĖčüč鹥ą╝ą░ ą┤ą╗čÅ core trace ąĖą╗ąĖ system trace, čéčĆąĄą▒čāąĄčéčüčÅ čāčćąĖčéčŗą▓ą░čéčī ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą▓ąŠą┐čĆąŠčüą░ ą┤ąĖąĘą░ą╣ąĮą░, ą▓čŗčģąŠą┤čÅčēąĖąĄ ąĘą░ čĆą░ą╝ą║ąĖ čĆą░čüčüą╝ąŠčéčĆąĄąĮąĖčÅ čŹč鹊ą│ąŠ ą┤ąŠą║čāą╝ąĄąĮčéą░. ą¤čĆąĖ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĄ čüąĖčüč鹥ą╝čŗ čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ čÅą┤čĆą░ ąĖą╗ąĖ čüąĖčüč鹥ą╝ąĮąŠą╣ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čüą╗ąĄą┤ąŠą▓ą░čéčī čāą║ą░ąĘą░ąĮąĖčÅą╝ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ [2].

ąØąĄ ą▓čüąĄ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ XDS, ą║ą░ą▒ąĄą╗ąĄą╣ ąŠčéą╗ą░ą┤ą║ąĖ ąĖ čåąĄą╗ąĄą▓čŗčģ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝čŗčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ą▓čüąĄ čäčāąĮą║čåąĖąĖ 菹╝čāą╗čÅčåąĖąĖ.

[ąÉą┤ą░ą┐č鹥čĆčŗ]

ąÉą┤ą░ą┐č鹥čĆčŗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čåąŠą║ąŠą╗ąĄą▓ąŠą║ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą▒ąŠą╗čīčłąĖąĮčüčéą▓čā 菹╝čāą╗čÅč鹊čĆąŠą▓ XDS ą┐ąŠą┤ą║ą╗čÄčćą░čéčīčüčÅ ą║ ąŠą┤ąĮąŠą╝čā ąĖąĘ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗčģ ą║ąŠąĮąĮąĄą║č鹊čĆąŠą▓ JTAG ąĮą░ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╣ čüąĖčüč鹥ą╝ąĄ. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ąĮąĄą┐ąŠą┤čģąŠą┤čÅčēąĄą│ąŠ ą░ą┤ą░ą┐č鹥čĆą░ ą╝ąŠąČąĄčé ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠ ą┐ąŠą▓ą╗ąĖčÅčéčī ąĮą░ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī ąŠčéą╗ą░ą┤ą║ąĖ.

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ąĖą╝ąĄčÄčéčüčÅ ą░ą┤ą░ą┐č鹥čĆčŗ, čćč鹊ą▒čŗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░čéčī čāčĆąŠą▓ąĮąĖ 3.3V XDS ą║ ą▒ąŠą╗ąĄąĄ ąĮąĖąĘą║ąĖą╝ čāčĆąŠą▓ąĮčÅą╝ ą╗ąŠą│ąĖą║ąĖ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝čŗčģ čüąĖčüč鹥ą╝, čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ ą░ą┤ą░ą┐čéąĖą▓ąĮąŠą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, čéčĆąĄą▒čāąĄą╝ąŠą│ąŠ ą┤ą╗čÅ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░ čÅą┤ąĄčĆ ARM.

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ ą░ą┤ą░ą┐č鹥čĆą░ą╝ ąĖ ą╝ąŠą┤ąĄą╗čÅą╝ JTAG čüą╝. ą▓ čüčéą░čéčīąĄ [5].

ąÜą░ąČą┤čŗą╣ 菹╝čāą╗čÅč鹊čĆ XDS ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą║ąŠąĮąĮąĄą║č鹊čĆ ąĮą░ ą┐ą╗ą░č鹥 ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╣ čüąĖčüč鹥ą╝čŗ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ IEEE 1149.1.

| ą£ąĮąĄą╝. |

ąóąĖą┐ čüąĖą│ąĮą░ą╗ą░ XDS(1) |

ąóąĖą┐ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| TRST |

O |

I |

Test Logic Reset |

ąÜąŠą│ą┤ą░ čŹč鹊čé čüąĖą│ąĮą░ą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ (ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0), ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą▓čüčÅ ą╗ąŠą│ąĖą║ą░ ąŠčéą╗ą░ą┤ą║ąĖ ą▓ą╝ąĄčüč鹥 čü IEEE 1149.1 TAP. |

| TCK |

O |

I |

Text Clock |

ąŁč鹊 čéą░ą║čéčŗ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ ą┐ąŠ čüąŠčüč鹊čÅąĮąĖčÅą╝ ąĖ ą╗ąŠą│ąĖą║ąĄ ą╝ą░čłąĖąĮčŗ čÅč湥ą╣ą║ąĖ IEEE 1149.1 TAP. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą│ąŠ 菹╝čāą╗čÅč鹊čĆą░ XDS, ąĘą┤ąĄčüčī ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą╗ąĖą▒ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠ č乊čĆą╝ąĖčĆčāąĄą╝ą░čÅ čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓, ą╗ąĖą▒ąŠ čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗąĄ ą┐ą░čćą║ąĖ ąĖą╝ą┐čāą╗čīčüąŠą▓, čéčĆąĄą▒čāčÄčēąĖąĄ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ čüąĖą│ąĮą░ą╗ą░ ą▓ąŠąĘą▓čĆą░čéą░ čéą░ą║č鹊ą▓ RTCK(2). |

| TMS |

O |

I |

Test Mode Select |

ąØą░ą┐čĆą░ą▓ą╗čÅąĄčé ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ ą┐ąĄčĆąĄčģąŠą┤ ą┐ąŠ ą╝ą░čłąĖąĮąĄ čüąŠčüč鹊čÅąĮąĖą╣ IEEE 1149.1 TAP. |

| TDI |

O |

I |

Test Data Input |

ąöą░ąĮąĮčŗąĄ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ IEEE 1149.1, ą▓ą▓ąŠą┤ąĖą╝čŗąĄ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆ. |

| TDO |

I |

O |

Test Data Output |

ąöą░ąĮąĮčŗąĄ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ IEEE 1149.1, ą▓čŗą▓ąŠą┤ąĖą╝čŗąĄ ąĖąĘ ą┐čĆąŠčåąĄčüčüąŠčĆą░. |

| RTCK(5) |

I |

O |

Return TCK |

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé XDS ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ JTAG čéą░ą║čéąĖčĆčāčÄčéčüčÅ čü RTCK(3). ąŁą╝čāą╗čÅč鹊čĆ XDS, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą░ą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ, ą╝ąŠąĮąĖč鹊čĆąĖčé RTCK, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą║ąŠą│ą┤ą░ ąĮą░ą┤ąŠ čāą┐čĆą░ą▓ą╗čÅčéčī ą▓čŗą┤ą░č湥ą╣ čéą░ą║č鹊ą▓ TCK. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) I ą▓čģąŠą┤ (Input), O ą▓čŗčģąŠą┤ (output) ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ XDS.

(2) ąĢčüą╗ąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą┐čĆąŠčåąĄčüčüąŠčĆ čü čÅą┤čĆąŠą╝ ARM, č鹊 ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ ą░ą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ (čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ TCK čéčĆąĄą▒čāąĄčé ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ RTCK 菹╝čāą╗čÅč鹊čĆąŠą╝ XDS), čćč鹊ą▒čŗ čćą░čüč鹊čéą░ TCK ą╝ąŠą│ą╗ą░ čāą▓ąĄą╗ąĖčćąĖčéčīčüčÅ čüą▓ąĄčĆčģ 4 ą£ąōčå.

(3) XDS100v1 ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé RTCK, ąĮąŠ TI čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčé čüąŠąĄą┤ąĖąĮąĖčéčī ąĄą│ąŠ ąĮą░ čüąĄą║čåąĖčÄ N, čćč鹊ą▒čŗ čüąŠčģčĆą░ąĮąĖčéčī čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī čü ą┤čĆčāą│ąĖą╝ąĖ 菹╝čāą╗čÅč鹊čĆą░ą╝ąĖ XDS.

(4) ąĢčüą╗ąĖ ąÆą░čł ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĮąŠąČą║čā RTCK, ą┐ąŠą┤ą║ą╗čÄčćąĖč鹥 ąĄčæ ą║ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝čā ą▓čŗą▓ąŠą┤čā ą║ąŠąĮąĮąĄą║č鹊čĆą░ 菹╝čāą╗čÅčåąĖąĖ (čüą╝. ą▓čŗčłąĄ čĆą░ąĘą┤ąĄą╗ "ąÉą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ").

(5) ąÆ ą┤čĆčāą│ąĖčģ ą┤ąŠą║čāą╝ąĄąĮčéą░čģ TI čüąĖą│ąĮą░ą╗ RTCK ą╝ąŠąČąĄčé ąĮą░ąĘčŗą▓ą░čéčīčüčÅ TCK_RET ąĖą╗ąĖ TCLKRTN.

ąÆąŠ ą╝ąĮąŠą│ąĖčģ 菹╝čāą╗čÅč鹊čĆą░čģ XDS ąĮą░ ą║ą░ą▒ąĄą╗ąĄ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╝čā ą┐čĆąŠčåąĄčüčüąŠčĆčā čéą░ą║ąČąĄ ą╝ąŠą│čāčé ą┐čĆąĖčüčāčéčüčéą▓ąŠą▓ą░čéčī čüą╗ąĄą┤čāčÄčēąĖąĄ čüąĖą│ąĮą░ą╗čŗ:

| ą£ąĮąĄą╝. |

ąóąĖą┐ čüąĖą│ąĮą░ą╗ą░ XDS

|

ąóąĖą┐ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| TVRef(2) |

I |

O |

Target Voltage Reference |

ąöąŠą╗ąČąĄąĮ ą▒čŗčéčī čüąŠąĄą┤ąĖąĮąĄąĮ čü ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ąĮą░ čåąĄą╗ąĄą▓ąŠą╝ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ. ą¤čĆąĖ ą░ą║čéąĖą▓ąĮąŠą╝ ą┐ąĖčéą░ąĮąĖąĖ čŹč鹊čé čüąĖą│ąĮą░ą╗ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠą╣ čéčĆą░ąĮčüą╗čÅčåąĖąĄą╣ čāčĆąŠą▓ąĮąĄą╣ ą╗ąŠą│ąĖą║ąĖ JTAG, ąĄčüą╗ąĖ čŹč鹊 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 菹╝čāą╗čÅč鹊čĆ XDS(1). |

| TDIS |

I |

O |

Target Disconnect |

ąŁą╝čāą╗čÅč鹊čĆ XDS, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čŹč鹊čé čüąĖą│ąĮą░ą╗, ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī čĆą░ąĘą╗ąĖčćąĖąĄ ą▓ čüąĖčéčāą░čåąĖčÅčģ, ą║ąŠą│ą┤ą░ ąĮą░ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╣ čüąĖčüč鹥ą╝ąĄ ą▓čŗą║ą╗čÄč湥ąĮąŠ ą┐ąĖčéą░ąĮąĖąĄ, ąĖ ą║ąŠą│ą┤ą░ ą║ą░ą▒ąĄą╗čī ąŠčéą╗ą░ą┤ą║ąĖ čäąĖąĘąĖč湥čüą║ąĖ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ. |

| EMU |

I/O(1) |

Emulation Port |

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĖ ąŠčéą╗ą░ą┤čćąĖą║ą░ XDS, ąĮąŠąČą║ąĖ EMU ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ čäčāąĮą║čåąĖą╣: čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆąĄąČąĖą╝ą░ą╝ąĖ ąĘą░ą│čĆčāąĘą║ąĖ (boot modes), ą║čĆąŠčüčü-čéčĆąĖą│ą│ąĄčĆčŗ (cross triggers), HS-RTDX, Core Trace ąĖ System Trace. ąśąĮč乊čĆą╝ą░čåąĖčÄ ąŠ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĄ čŹčéąĖčģ čäčāąĮą║čåąĖą╣ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ ąĖ ą▓ 菹╝čāą╗čÅč鹊čĆąĄ XDS čüą╝. ą▓ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ. |

| nRESET(5) |

O |

I |

Target Reset |

ąŁč鹊 ąŠą┐čåąĖąŠąĮą░ą╗čīąĮčŗą╣ (ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮčŗą╣) čüąĖą│ąĮą░ą╗, ą║ąŠč鹊čĆčŗą╣ čü ąĖąĮč鹥ą│čĆą░čåąĖąĄą╣ čüąŠ čüčģąĄą╝ąŠą╣ čüą▒čĆąŠčüą░ ą┐ąŠ ą┐ąĖčéą░ąĮąĖčÄ (power-up-reset, POR) ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čāą┤ą░ą╗ąĄąĮąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ąĖąĘ ąŠčéą╗ą░ą┤čćąĖą║ą░ ą▓čüąĄą╣ čåąĄą╗ąĄą▓ąŠą╣ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╣ ą┐ą╗ą░čéčŗ. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ą¦č鹊ą▒čŗ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčéčī čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī 菹╝čāą╗čÅč鹊čĆą░ XDS čü ąĖą╝ąĄčÄčēąĖą╝ąĖčüčÅ ąĮą░ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╣ ą┐ą╗ą░č鹥/ą┐čĆąŠčåąĄčüčüąŠčĆąĄ čéąĖą┐ą░ą╝ąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖ ąĖčģ čāčĆąŠą▓ąĮčÅą╝ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣, ąŠą▒čĆą░čéąĖč鹥čüčī ą║ ą┤ą░čéą░čłąĖčéčā ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ.

(2) ąÆ ą┤čĆčāą│ąĖčģ ą┤ąŠą║čāą╝ąĄąĮčéą░čģ TI čüąĖą│ąĮą░ą╗ TVRef ą╝ąŠąČąĄčé ąĮą░ąĘčŗą▓ą░čéčīčüčÅ ą║ą░ą║ TVD, VREF_DEBUG ąĖ VTRef (čüąĖčüč鹥ą╝ą░ ąĖą╝ąĄąĮąŠą▓ą░ąĮąĖčÅ ą▓ čåąŠą║ąŠą╗ąĄą▓ą║ąĄ ARM).

(3) ąÆ ą┤čĆčāą│ąĖčģ ą┤ąŠą║čāą╝ąĄąĮčéą░čģ TI čüąĖą│ąĮą░ą╗ nRESET ą╝ąŠąČąĄčé ąĮą░ąĘčŗą▓ą░čéčīčüčÅ ą║ą░ą║ nSYSRST ąĖą╗ąĖ nTGTRST.

ąśąĮč乊čĆą╝ą░čåąĖčÄ ąŠ ą║ąŠąĮąĮąĄą║č鹊čĆą░čģ JTAG ąĖ ąĖčģ čåąŠą║ąŠą╗ąĄą▓ą║ąĄ čüą╝. ąĮą░ čüčéčĆą░ąĮąĖčćą║ąĄ [6]. ąĪ ą┐ąŠą╝ąŠčēčīčÄ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąĮą░ čŹč鹊ą╣ čüčéčĆą░ąĮąĖčćą║ąĄ ą┐čĆąŠčēąĄ ą▓čŗą▒čĆą░čéčī čĆą░ąĘčŖąĄą╝/ą║ąŠąĮąĮąĄą║č鹊čĆ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čüąĄą╝ąĄą╣čüčéą▓ą░ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ąĖ ą┐ąŠą╗čāčćąĖčéčī ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠą▒ ąĖą╝ąĄąĮąŠą▓ą░ąĮąĖąĖ 菹╝čāą╗čÅč鹊čĆąŠą▓ ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓.

[ąĀą░ąĘčĆą░ą▒ąŠčéą║ą░ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ čü 菹╝čāą╗čÅč鹊čĆąŠą▓ JTAG]

ąśčüą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ ą▓ą░ąČąĮąŠ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ą▓čŗčüąŠą║ąŠą║ą░č湥čüčéą▓ąĄąĮąĮčŗąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąŠą▓ ą╝ąĄąČą┤čā 菹╝čāą╗čÅč鹊čĆąŠą╝ XDS ąĖ čåąĄą╗ąĄą▓čŗą╝ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝čŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ (čü ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ąĮą░ ą┐ą╗ą░č鹥 čĆą░ąĘčĆą░ą▒ą░čéčŗą▓ą░ąĄą╝ąŠą╣ čüąĖčüč鹥ą╝čŗ). ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ čüą╗čāčćą░čÅčģ ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ čüąŠąĄą┤ąĖąĮąĖčéčī ą▓ ąŠą┤ąĮčā čåąĄą┐ąŠčćą║čā JTAG ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓/ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ąĮą░ ą┐ą╗ą░č鹥, čćč鹊ą▒čŗ ą║ ąĮąĖą╝ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ąŠą▒čĆą░čēą░čéčīčüčÅ č湥čĆąĄąĘ ąŠą┤ąĖąĮ ą║ąŠąĮąĮąĄą║č鹊čĆ, ąĖą╗ąĖ ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ čāčüčéą░ąĮąŠą▓ąĖčéčī ąĮą░ ą┐ą╗ą░č鹥 ą║ąŠąĮąĮąĄą║č鹊čĆ čŹą╝čāą╗čÅč鹊čĆą░ ą┤ą░ą╗čīčłąĄ, č湥ą╝ čŹč鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▒ąĄąĘ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąĖčéčāą░čåąĖąĖ, ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ ą┐čĆąĖą╝ąĄąĮąĖčéčī ą║ąŠčĆčĆąĄą║čéąĮčāčÄ ą▒čāč乥čĆąĖąĘą░čåąĖčÄ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą╝ąĄąČą┤čā ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą┐čĆą░ą▓ąĖą╗čīąĮčāčÄ čĆą░ą▒ąŠčéčā 菹╝čāą╗čÅč鹊čĆą░ XDS ąĖ čåąĄą╗ąĄą▓ąŠą╣ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╣ čüąĖčüč鹥ą╝čŗ.

ąóąĄą║čāčēąĖąĄ 菹╝čāą╗čÅč鹊čĆčŗ XDS čĆą░ą▒ąŠčéą░čÄčé ąĮą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 JTAG ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 10 ą┤ąŠ 50 ą£ąōčå, ąŠą┤ąĮą░ą║ąŠ ą▒čāą┤čāčēąĖąĄ 菹╝čāą╗čÅč鹊čĆčŗ XDS ą▒čāą┤čāčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ ąĄčēąĄ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖčģ čćą░čüč鹊čéą░čģ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī ą┤ąĖąĘą░ą╣ąĮą░ čü ą▒čāą┤čāčēąĖą╝ąĖ 菹╝čāą╗čÅč鹊čĆą░ą╝ąĖ, ą║ąŠą╝ą┐ą░ąĮąĖčÅ TI čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčé čĆą░ąĘčĆą░ą▒ąŠčéą░čéčī ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG ą┤ą╗čÅ čćą░čüč鹊čé 100 ą£ąōčå.

ąóą░ą║ąČąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÄ čü čåąĄą╗ąĄą▓čŗą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ ąĘą░ą▓ąĖčüčÅčé ąŠčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗčģ čäčāąĮą║čåąĖą╣ ąŠčéą╗ą░ą┤ą║ąĖ ą║ą░ą║ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ, čéą░ą║ ąĖ ą▓ 菹╝čāą╗čÅč鹊čĆąĄ XDS. ąöą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ąĖ 菹╝čāą╗čÅč鹊čĆąŠą▓ XDS, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé čéčĆą░čüčüąĖčĆąŠą▓ą║čā čÅą┤čĆą░ (core trace) ąĖą╗ąĖ čüąĖčüč鹥ą╝ąĮčāčÄ čéčĆą░čüčüąĖčĆąŠą▓ą║čā (system trace), čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ą┤ąĖąĘą░ą╣ąĮčā ą┐ą╗ą░čéčŗ ą▒ąŠą╗ąĄąĄ ąČąĄčüčéą║ąĖąĄ, ą┐ąŠč鹊ą╝čā čćč鹊 čŹčéąĖ čäčāąĮą║čåąĖąĖ čĆą░ą▒ąŠčéą░čÄčé ąĮą░ ą┐ąŠą▓čŗčłąĄąĮąĮčŗčģ čćą░čüč鹊čéą░čģ. ąĢčüą╗ąĖ ąÆą░čł ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čéčĆą░čüčüąĖčĆąŠą▓ą║čā čÅą┤čĆą░ ąĖą╗ąĖ čüąĖčüč鹥ą╝ąĮčāčÄ čéčĆą░čüčüąĖčĆąŠą▓ą║čā č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤čŗ EMU, ąŠą▒čĆą░čēą░ą╣č鹥čüčī ą║ čĆąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖčÅą╝ ą┐ąŠ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĄ ą▓ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ [2].

ąÆ čüą╗čāčćą░čÅčģ, ą║ąŠą│ą┤ą░ 菹╝čāą╗čÅč鹊čĆ XDS ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčāčÄ čäčāąĮą║čåąĖčÄ, čéą░ą║čāčÄ ą║ą░ą║ Core Trace ąĖą╗ąĖ System Trace, ąĮąŠ čåąĄą╗ąĄą▓ąŠą╣ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝čŗą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĄčæ, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čéčēą░č鹥ą╗čīąĮąŠ ąŠčåąĄąĮąĖčéčī ą║ąŠą╝ą┐čĆąŠą╝ąĖčüčü ą┤ąĖąĘą░ą╣ąĮą░ čüčģąĄą╝čŗ ąŠčéą╗ą░ą┤ą║ąĖ ąĮą░ ą┐ą╗ą░č鹥, čćč鹊ą▒čŗ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą▓čŗą▒čĆą░čéčī čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī ą║ą░ą║ čü č鹥ą║čāčēąĖą╝ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╝ 菹╝čāą╗čÅč鹊čĆąŠą╝, čéą░ą║ ąĖ čü ą▒ąŠą╗ąĄąĄ čüąŠą▓čĆąĄą╝ąĄąĮąĮčŗą╝ąĖ 菹╝čāą╗čÅč鹊čĆą░ą╝ąĖ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čĆąĄčłąĄąĮąĖčÅ čüą╗ąŠąČąĮčŗčģ ą┐čĆąŠą▒ą╗ąĄą╝ ąŠčéą╗ą░ą┤ą║ąĖ.

[ą×ą┤ąĖąĮ ą┐čĆąŠčåąĄčüčüąŠčĆ, ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ]

ąĢčüą╗ąĖ ąĮąŠąČą║ąĖ EMU ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé čéčĆą░čüčüąĖčĆąŠą▓ą║čā čÅą┤čĆą░ ąĖą╗ąĖ čüąĖčüč鹥ą╝ąĮčāčÄ čéčĆą░čüčüąĖčĆąŠą▓ą║čā, ąĖ ąĄčüą╗ąĖ ą┤ą╗ąĖąĮą░ ą┤ąŠčĆąŠąČąĄą║ ą▓čüąĄčģ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG ąĖ EMU ą╝ąĄąČą┤čā ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ ąĖ čĆą░ąĘčŖąĄą╝ąŠą╝ ąŠčéą╗ą░ą┤ą║ąĖ ą╝ąĄąĮčīčłąĄ 6 ą┤čÄą╣ą╝ąŠą▓ (ą╝ąĄąĮčīčłąĄ 15.24 čüą░ąĮčéąĖą╝ąĄčéčĆąŠą▓), č鹊 ą▒čāč乥čĆąĖąĘą░čåąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG ąĮąĄ ąĮčāąČąĮą░. ąŻą║ą░ąĘą░ąĮąĖčÅ ą┐ąŠ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÄ ąĖ čĆą░ąĘą▓ąŠą┤ą║ąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖą╣, ąĄčüą╗ąĖ ąĮąŠąČą║ąĖ EMU ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé 菹║čüą┐ąŠčĆčé čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ čÅą┤čĆą░ ąĖą╗ąĖ čüąĖčüč鹥ą╝ąĮąŠą╣ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ, čüą╝. ą▓ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ [2].

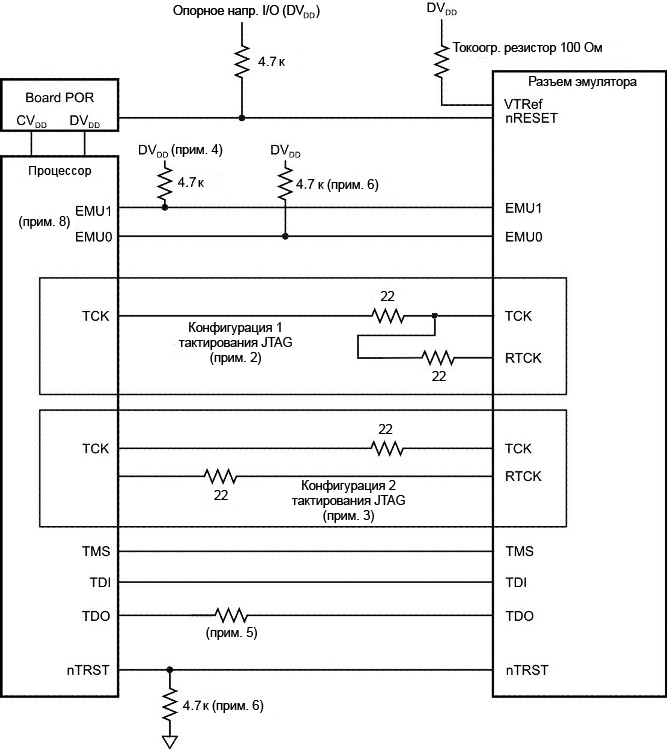

ąØą░ čüčģąĄą╝ąĄ čĆąĖčü. 1 ą┐ąŠą║ą░ąĘą░ąĮčŗ čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ąĮąĄ ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓.

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: čŹčéą░ čüčģąĄą╝ą░ ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé ą┐čĆąĄą┤čŗą┤čāčēąĄą╣ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ TI ą▓ č鹊ą╝ čüą╝čŗčüą╗ąĄ, čćč鹊 č鹥ą┐ąĄčĆčī TI ą┐čĆąĄą┤ą╗ą░ą│ą░ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ čéą░ą║č鹊ą▓ JTAG ąĖ čüąĖą│ąĮą░ą╗ąĄ TDO. ą¤čĆąĖčćąĖąĮą░ čŹč鹊ą│ąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓ č鹊ą╝, čćč鹊 ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ XDS ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą┤čĆą░ą╣ą▓ąĄčĆčŗ čüąĖą│ąĮą░ą╗ąŠą▓ čü ą▒ąŠą╗ąĄąĄ ą║čĆčāčéčŗą╝ąĖ čäčĆąŠąĮčéą░ą╝ąĖ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ąĖ čüą┐ą░ą┤ą░, č湥ą╝ ą┐čĆąĄą┤čŗą┤čāčēąĖąĄ ą▓ąĄčĆčüąĖąĖ 菹╝čāą╗čÅč鹊čĆąŠą▓ XDS, čćč鹊 čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé čłą░ąĮčüčŗ ąŠčéčĆą░ąČąĄąĮąĖą╣ čŹčéąĖčģ ą║čĆąĖčéąĖč湥čüą║ąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓.

ąĀąĖčü. 1. ąĪąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ ą║ąŠąĮąĮąĄą║č鹊čĆą░ 菹╝čāą╗čÅčåąĖąĖ čü ąŠą┤ąĮąĖą╝ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝čŗą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝, čü ąĮąĄą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ JTAG ąĖ EMU(1).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąÆčüąĄ čĆą░čüčüč鹊čÅąĮąĖčÅ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ ąŠčé čŹčéąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ ą┤ąŠ ą┐čĆąŠą▒ąĮąĖą║ą░ ąŠčéą╗ą░ą┤ą║ąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą╝ąĄąĮčīčłąĄ 6 ą┤čÄą╣ą╝ąŠą▓ (15.24 čüą░ąĮčéąĖą╝ąĄčéčĆąŠą▓). ąĢčüą╗ąĖ ąŠčéą╗ą░ą┤čćąĖą║ XDS560v2 ąĖą╗ąĖ XDS ProTrace, č鹊 ą▓ ąĮąĖčģ ąĄčüčéčī ą▓čüčéčĆąŠąĄąĮąĮčŗąĄ ą▒čāč乥čĆčŗ, čāčüąĖą╗ąĖą▓ą░čÄčēąĖąĄ čüąĖą│ąĮą░ą╗čŗ ąĮą░ ą║ą░ą▒ąĄą╗ąĄ, ąĖ ą┤ą╗čÅ čŹč鹊ą│ąŠ čüą╗čāčćą░čÅ ą┤ą╗ąĖąĮą░ čéčĆą░čüčü ą╝ąŠąČąĄčé ą▒čŗčéčī čāą▓ąĄą╗ąĖč湥ąĮą░.

(2) ąĢčüą╗ąĖ ąÆą░čł ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮąĄ ąĖą╝ąĄąĄčé ąĮąŠąČą║ąĖ RTCK, č鹊ą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 Configuration 1. ąöą╗čÅ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą║ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÄ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG ą▓ čŹč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čüą╝. ą┤ą░ą╗ąĄąĄ čüąĄą║čåąĖčÄ "ąóąĄčĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąĄ ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓".

(3) ąĢčüą╗ąĖ ąÆą░čł ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖą╝ąĄąĄčé ąĮąŠąČą║čā RTCK, č鹊 ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 Configuration 2. ąöą╗čÅ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą║ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÄ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG ą▓ čŹč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čüą╝. ą┤ą░ą╗ąĄąĄ čüąĄą║čåąĖčÄ "ąóąĄčĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąĄ ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓".

(4) DVDD čŹč鹊 ąĮąŠąČą║ą░ JTAG/EMU, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčēąĄąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ą╗čÅ čāčĆąŠą▓ąĮčÅ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG.

(5) ąöą╗čÅ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą║ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÄ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG čüą╝. ą┤ą░ą╗ąĄąĄ čüąĄą║čåąĖčÄ "ąóąĄčĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąĄ ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓".

(6) ąóčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąŠą▓ EMU čüą╝. ą▓čŗčłąĄ ą▓ čüąĄą║čåąĖąĖ čü ąŠą┐ąĖčüą░ąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗ąŠą▓ EMU.

(7) ąØą░ čüąĖą│ąĮą░ą╗ąĄ TRST čéčĆąĄą▒čāąĄčéčüčÅ ąĮąĖąČąĮąĖą╣ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖą╣ čĆąĄąĘąĖčüč鹊čĆ (pull-down). ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ čüą╝. ą▓ąŠ ą▓čĆąĄąĘą║ąĄ "ąĪą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ąĘą░ą╝ąĄčćą░ąĮąĖčÅ ą┐ąŠ čüąĖą│ąĮą░ą╗ą░ą╝ JTAG ąĖ nTRST (ą▓ą║ą╗čÄčćą░čÅ TMS ąĖ TDI)".

(8) ąĢčüą╗ąĖ čā ąÆą░čłąĄą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▒ąŠą╗čīčłąĄ ą┤ą▓čāčģ ąĮąŠąČąĄą║ EMU, č鹊 ą▓ąĄčĆąŠčÅčéąĮąŠ, čćč鹊 ąŠąĮ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé core trace ąĖą╗ąĖ system trace (ąĖą╗ąĖ ąŠą▒ąĄ čŹčéąĖčģ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ). ąŁčéąĖ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗąĄ čäčāąĮą║čåąĖąĖ ą┤ąŠą▒ą░ą▓ą╗čÅčÄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ čåąĄą╗ąĄą▓ąŠą╣ ą┐ą╗ą░č鹥 (ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ [2]).

ąĢčüą╗ąĖ ą▓ ąÆą░čłąĄą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ ąĮąĄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ą▓ąĄčĆčģąĮąĖčģ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓ (pull-up) ąĮą░ TMS ąĖ TDI ąĖą╗ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąĮąĖąČąĮąĄą│ąŠ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĄą│ąŠ (pull-down) čĆąĄąĘąĖčüč鹊čĆą░ ąĮą░ TCK, č鹊 čéčĆąĄą▒čāąĄčéčüčÅ čŹčéąĖ čĆąĄąĘąĖčüč鹊čĆčŗ čāčüčéą░ąĮąŠą▓ąĖčéčī ąĮą░ ą┐ą╗ą░č鹥 ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╣ čüąĖčüč鹥ą╝čŗ. ąæąŠą╗čīčłąĖąĮčüčéą▓ąŠ čüąŠą▓čĆąĄą╝ąĄąĮąĮčŗčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ąĖą╝ąĄčÄčé čŹčéąĖ čĆąĄąĘąĖčüč鹊čĆčŗ.

ą¤ąŠčüą║ąŠą╗čīą║čā TDO ąĖ RTCK ą▓čŗčģąŠą┤čŗ, ą▓ąĮąĄčłąĮąĖąĄ pull-up ąĖą╗ąĖ pull-down čĆąĄąĘąĖčüč鹊čĆčŗ ąĮąĄ čéčĆąĄą▒čāčÄčéčüčÅ.

ąæąŠą╗čīčłąĖąĮčüčéą▓ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ TI čéčĆąĄą▒čāčÄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ nTRST ąĖ čüą▒čĆąŠčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░, čćč鹊ą▒čŗ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ą╗čüčÅ ą┐čĆąŠčåąĄčüčüąŠčĆ. ąĪąĖą│ąĮą░ą╗ nTRST ą╝ąŠąČąĄčé ąŠčüčéą░ą▓ą░čéčīčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝, ą║ąŠą│ą┤ą░ čüą▒čĆąŠčü ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┤ąĄą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ, čćč鹊ą▒čŗ ą┐čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠą│ ąĮąŠčĆą╝ą░ą╗čīąĮąŠ čĆą░ą▒ąŠčéą░čéčī. ąöą╗čÅ ą╗čÄą▒čŗčģ ąŠčéą║ą╗ąŠąĮąĄąĮąĖą╣ ąŠčé čŹčéąĖčģ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ čüą╝. ą┤ą░čéą░čłąĖčé ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ. ą¤ąŠčüą║ąŠą╗čīą║čā ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ pull-up ąĖ pull-down ąŠą▒čŗčćąĮąŠ čüą╗ą░ą▒ąŠč鹊čćąĮčŗąĄ (ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 20 ą║ą×ą╝ .. ~30 ą║ą×ą╝), čćč鹊ą▒čŗ čāą▓ąĄą╗ąĖčćąĖčéčī ą┐ąŠą╝ąĄčģąŠąĘą░čēąĖčēąĄąĮąĮąŠčüčéčī, ą║ąŠą│ą┤ą░ ą║ą░ą▒ąĄą╗čī 菹╝čāą╗čÅč鹊čĆą░ XDS ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐čĆąĖą╝ąĄąĮčÅčéčī ą▓ąĮąĄčłąĮąĖą╣ čĆąĄąĘąĖčüč鹊čĆ pull-down, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 1.

ąĢčüą╗ąĖ ąÆčŗ ąĖčüą┐ąŠą╗čīąĘčāąĄč鹥 ąĮąĄ XDS-菹╝čāą╗čÅč鹊čĆ, ą░ ą┤čĆčāą│ąŠą╣ ą░ą┤ą░ą┐č鹥čĆ ą┤ą╗čÅ ą┐ąŠą│čĆą░ąĮąĖčćąĮąŠą│ąŠ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ (Boundary Scan, JTAG-č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖąĄ čüčģąĄą╝čŗ), č鹊 ą┐ąŠčüą║ąŠą╗čīą║čā čüąĖą│ąĮą░ą╗ TRST čŹč鹊 ąŠą┐čåąĖąŠąĮą░ą╗čīąĮą░čÅ čäčāąĮą║čåąĖčÅ ą┐ąŠ čüčéą░ąĮą┤ą░čĆčéčā IEEE 1149.1, ąŠą▒čĆą░čéąĖč鹥čüčī ą║ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅ ąĮą░ ą┐čĆąĄą┤ą╝ąĄčé ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĄ nTRST. ąĢčüą╗ąĖ čŹč鹊 ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ, č鹊 čā ąÆą░čü ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą┤čéčÅąĮčāčéčī ąĮą░ ą┐ą╗ą░č鹥 čüąĖą│ąĮą░ą╗ nTRST ą║ ą╗ąŠą│. 1 (ą▓ ąĮąĄą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī), čćč鹊ą▒čŗ čĆą░ą▒ąŠčéą░ą╗ą░ č鹥čģąĮąŠą╗ąŠą│ąĖčÅ Boundary Scan. ąÆ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ TI ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ pull-down ąĮą░ nTRST, čćč鹊ą▒čŗ čāą┤ąĄčƹȹĖą▓ą░čéčī ą╗ąŠą│ąĖą║čā 菹╝čāą╗čÅčåąĖąĖ ą▓ čüą▒čĆąŠčüąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī čĆą░ą▒ąŠčéčā ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ. ą¦č鹊ą▒čŗ čāąĘąĮą░čéčī, ąĖą╝ąĄąĄčéčüčÅ ą╗ąĖ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ TI ąĮą░ čüąĖą│ąĮą░ą╗ąĄ nTRST ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ąŠą┤čéčÅąČą║ą░ pull-down, ąŠą▒čĆą░čéąĖč鹥čüčī ą║ ąĄą│ąŠ ą┤ą░čéą░čłąĖčéčā.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ čü ąĮąĖąĘą║ąĖą╝ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝ 菹ĮąĄčĆą│ąĖąĖ ą╝ąŠą│čāčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčī čāą╝ąĄąĮčīčłąĄąĮąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą▓ąĮąĄčłąĮąĖčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓ pull-up ąĖą╗ąĖ pull-down, čćč鹊ą▒čŗ čāą╗čāčćčłąĖčéčī ą┐ąŠą╝ąĄčģąŠąĘą░čēąĖčēąĄąĮąĮąŠčüčéčī ąĮą░ ą▓čģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ą░čģ JTAG (TMS, TDI, TCK ąĖ nTRST), ą║ąŠą│ą┤ą░ ą║ą░ą▒ąĄą╗čī 菹╝čāą╗čÅč鹊čĆą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ.

ąóąĄčĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąĄą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓. ąĀąĖčü. 1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ čéą░ą║č鹊ą▓ JTAG.

ŌĆó ąĢčüą╗ąĖ čā ąÆą░čłąĄą│ąŠ čåąĄą╗ąĄą▓ąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĮąĄčé čüąĖą│ąĮą░ą╗ą░ RTCK: čüąŠąĄą┤ąĖąĮąĖč鹥 TCK ąĖ RTCK, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą┤ą╗čÅ JTAG-ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 1 ąĮą░ čĆąĖčü. 1. ąÆąŠąĘą▓čĆą░čé čüąĖą│ąĮą░ą╗ą░ TCK ąĮą░ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ąĮą░ čüąĖą│ąĮą░ą╗ RTCK č湥čĆąĄąĘ čĆą░ąĘčŖąĄą╝ 菹╝čāą╗čÅč鹊čĆą░. ąÆ čŹč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čéčĆąĄą▒čāčÄčéčüčÅ čĆąĄąĘąĖčüč鹊čĆčŗ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ 22 ą×ą╝ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓ TCK ąĖ RTCK, čĆąĄąĘąĖčüč鹊čĆčŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▒ą╗ąĖąĘą║ąŠ ą║ ą║ąŠąĮąĮąĄą║č鹊čĆčā 菹╝čāą╗čÅč鹊čĆą░.

ŌĆó ąĢčüą╗ąĖ čā ąÆą░čłąĄą│ąŠ čåąĄą╗ąĄą▓ąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĄčüčéčī čüąĖą│ąĮą░ą╗ RTCK: čüąŠąĄą┤ąĖąĮąĖč鹥 TCK ąĖ RTCK, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą┤ą╗čÅ JTAG-ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 2 ąĮą░ čĆąĖčü. 1. ąŚą┤ąĄčüčī čüąĖą│ąĮą░ą╗ RTCK ą┐čĆąŠčåąĄčüčüąŠčĆą░ čüąŠąĄą┤ąĖąĮąĄąĮ čü RTCK ąĮą░ ą║ąŠąĮąĮąĄą║č鹊čĆąĄ 菹╝čāą╗čÅč鹊čĆą░. ąóąĄčĆą╝ąĖąĮąĖčĆčāčÄčēąĖą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ čĆąĄąĘąĖčüč鹊čĆ 22 ą×ą╝ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ TCK ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░čüą┐ąŠą╗ąŠąČąĄąĮ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▒ą╗ąĖąĘą║ąŠ ą║ ą║ąŠąĮąĮąĄą║č鹊čĆčā 菹╝čāą╗čÅč鹊čĆą░. ąóąĄčĆą╝ąĖąĮąĖčĆčāčÄčēąĖą╣ čĆąĄąĘąĖčüč鹊čĆ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ RTCK ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░čüą┐ąŠą╗ąŠąČąĄąĮ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▒ą╗ąĖąĘą║ąŠ ą║ ą┐čĆąŠčåąĄčüčüąŠčĆčā. ąÆąĄą╗ąĖčćąĖąĮą░ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĄą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ RTCK ąŠą▒čŗčćąĮąŠ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 22 .. 42 ą×ą╝. ąŁčéą░ ą▓ąĄą╗ąĖčćąĖąĮą░ ą┤ąŠą╗ąČąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī ą▓ąŠą╗ąĮąŠą▓ąŠą╝čā ąĖą╝ą┐ąĄą┤ą░ąĮčüčā ą║ą░ą▒ąĄą╗čÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅ čåąĄą╗ąĄą▓ąŠą╣ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╣ čüąĖčüč鹥ą╝čŗ (ąŠą▒čŗčćąĮąŠ 50 ą×ą╝) ą╝ąĖąĮčāčü ąĖą╝ą┐ąĄą┤ą░ąĮčü ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą▒čāč乥čĆą░ RTCK ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąŁč鹊čé ą▓čŗčģąŠą┤ąĮąŠą╣ ąĖą╝ą┐ąĄą┤ą░ąĮčü ą▒čāč乥čĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąŠą▒čŗčćąĮąŠ ą╝ąŠąČąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┐ąŠ ą╝ąŠą┤ąĄą╗ąĖ IBIS ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąöąŠą║čāą╝ąĄąĮčé [2] TI ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ čüąŠą┤ąĄčƹȹĖčé ąĖąĮčüčéčĆčāą║čåąĖąĖ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĖą╝ą┐ąĄą┤ą░ąĮčüą░ ą▒čāč乥čĆą░ RTCK ąĖąĘ ą╝ąŠą┤ąĄą╗ąĖ IBIS ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ŌĆó ąöą╗čÅ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG, ąĮąĄ ąŠčéąĮąŠčüčÅčēąĖčģčüčÅ ą║ čéą░ą║čéą░ą╝: ąĮą░ ą▓čģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ą░čģ JTAG, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ čÅą▓ą╗čÅčÄčéčüčÅ čéą░ą║čéą░ą╝ąĖ, ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ ąŠą▒čŗčćąĮąŠ ąĮąĄ čéčĆąĄą▒čāčÄčéčüčÅ. ąØą░ ą▓čŗčģąŠą┤ąĮąŠą╝ čüąĖą│ąĮą░ą╗ąĄ JTAG (TDO) č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĖą╣ čĆąĄąĘąĖčüč鹊čĆ ąĮčāąČąĮąŠ ą┐ąŠą╝ąĄčüčéąĖčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▒ą╗ąĖąĘą║ąŠ ą║ ą┐čĆąŠčåąĄčüčüąŠčĆčā. ą¦č鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĮąŠą╝ąĖąĮą░ą╗ čŹč鹊ą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ ą┤ą╗čÅ TDO, čüą╗ąĄą┤čāą╣č鹥 č鹥ą╝ ąČąĄ ąĖąĮčüčéčĆčāą║čåąĖčÅą╝, čćč鹊 ąĖ ą┐čĆąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĖ ąĮąŠą╝ąĖąĮą░ą╗ą░ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĖąĄą│ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ ą┤ą╗čÅ RTCK.

ąŚą░ą╝ąĄčćą░ąĮąĖčÅ ą┐ąŠ 14-ą▓čŗą▓ąŠą┤ąĮąŠą╝čā ą║ąŠąĮąĮąĄą║č鹊čĆčā 菹╝čāą╗čÅč鹊čĆąŠą▓ XDS100/XDS510/XDS560. ąĢčüą╗ąĖ ąÆą░čł ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖą╝ąĄąĄčé ą▒ąŠą╗čīčłąĄ ą┤ą▓čāčģ ąĮąŠąČąĄą║ EMU, č鹊 ą▓čüąĄ ąĄčēąĄ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī 14-ą▓čŗą▓ąŠą┤ąĮčŗą╣ čĆą░ąĘčŖąĄą╝, ąĮąŠ ąĮąĄą╗čīąĘčÅ ą▒čāą┤ąĄčé 菹║čüą┐ąŠčĆčéąĖčĆąŠą▓ą░čéčī čéčĆą░čüčüąĖčĆąŠą▓ą║čā čÅą┤čĆą░ (Core Trace), ąĖ ą▓ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ čüą╗čāčćą░ąĄą▓ ąĮąĄą╗čīąĘčÅ ą▒čāą┤ąĄčé 菹║čüą┐ąŠčĆčéąĖčĆąŠą▓ą░čéčī čüąĖčüč鹥ą╝ąĮčāčÄ čéčĆą░čüčüąĖčĆąŠą▓ą║čā (System Trace), ąĄčüą╗ąĖ ą║ą░ą║ą░čÅ-č鹊 ąĖąĘ čŹčéąĖčģ čéčĆą░čüčüąĖčĆąŠą▓ąŠą║ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝. ąÆ ąŠą▒ąŠąĖčģ čüą╗čāčćą░čÅčģ čéčĆąĄą▒čāąĄčéčüčÅ ą║ąŠąĮąĮąĄą║č鹊čĆ čü ą▒ąŠą╗čīčłąĖą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ ą║ąŠąĮčéą░ą║č鹊ą▓: 60-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą┤ą╗čÅ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ čÅą┤čĆą░ ąĖ 20-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą┤ą╗čÅ čüąĖčüč鹥ą╝ąĮąŠą╣ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ. ąĢčüą╗ąĖ ąÆą░čł ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖą╝ąĄąĄčé č鹊ą╗čīą║ąŠ ąŠą┤ąĮčā ąĮąŠąČą║čā EMU, č鹊 čüąŠąĄą┤ąĖąĮąĖč鹥 ąĄčæ čü ą║ąŠąĮčéą░ą║č鹊ą╝ EMU0 ąĮą░ 14-ą▓čŗą▓ąŠą┤ąĮąŠą╝ čĆą░ąĘčŖąĄą╝ąĄ JTAG. ąÆčüąĄ ąĮąŠąČą║ąĖ EMU ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčéčŗ čüąĮą░čĆčāąČąĖ ą║čĆąŠą╝ąĄ čüą╗čāčćą░ąĄą▓, ą║ąŠą│ą┤ą░ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ ąĄčüčéčī ą┤ąŠčüčéą░č鹊čćąĮą░čÅ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ pull-up ą┐ąŠą┤čéčÅąČą║ą░ ąĮąŠąČąĄą║ EMU.

ąöą╗čÅ ąĮąŠą▓čŗčģ čĆą░ąĘčĆą░ą▒ąŠč鹊ą║ 14-ą▓čŗą▓ąŠą┤ąĮčŗą╣ čĆą░ąĘčŖąĄą╝ ą▒ąŠą╗čīčłąĄ ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ. TI čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī 20-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą║ąŠąĮąĮąĄą║č鹊čĆ CTI čü čåąŠą║ąŠą╗ąĄą▓ą║ąŠą╣ TI čü čłą░ą│ąŠą╝ ą▓čŗą▓ąŠą┤ąŠą▓ 1.27 ą╝ą╝, čā ą║ąŠč鹊čĆąŠą│ąŠ čĆą░ąĘą╝ąĄčĆ ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ą╝ąĄąĮčīčłąĄ 14-ą▓čŗą▓ąŠą┤ąĮąŠą│ąŠ ą║ąŠąĮąĮąĄą║č鹊čĆą░ čü čłą░ą│ąŠą╝ ą▓čŗą▓ąŠą┤ąŠą▓ 2.54 ą╝ą╝.

ąŚą░ą╝ąĄčćą░ąĮąĖčÅ ą┐ąŠ 20-ą▓čŗą▓ąŠą┤ąĮąŠą╝čā ą║ąŠąĮąĮąĄą║č鹊čĆčā XDS560. ąĢčüą╗ąĖ ąÆą░čł ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüąĖčüč鹥ą╝ąĮčāčÄ čéčĆą░čüčüąĖčĆąŠą▓ą║čā (System Trace), č鹊ą│ą┤ą░ ą┤ą╗čÅ ą┐ą╗ą░čéčŗ ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī 20-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą║ąŠąĮąĮąĄą║č鹊čĆ CTI čü čåąŠą║ąŠą╗ąĄą▓ą║ąŠą╣ TI, čüą╝. [2].

ąĢčüą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖą╝ąĄąĄčé ą▒ąŠą╗čīčłąĄ ą┐čÅčéąĖ ąĮąŠąČąĄą║ EMU, č鹊 ąÆčŗ ą▓čüąĄ ąĄčēąĄ ą╝ąŠąČąĄč鹥 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī 20-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą║ąŠąĮąĮąĄą║č鹊čĆ, ąĮąŠ ąĮąĄ ą┐ąŠą╗čāčćąĖčéčüčÅ čŹą║čüą┐ąŠčĆčéąĖčĆąŠą▓ą░čéčī čéčĆą░čüčüąĖčĆąŠą▓ą║čā čÅą┤čĆą░ (Core Trace) ąĄčüą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čŹčéčā čéčĆą░čüčüąĖčĆąŠą▓ą║čā. ąöą╗čÅ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ čÅą┤čĆą░ čéčĆąĄą▒čāąĄčéčüčÅ 60-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą║ąŠąĮąĮąĄą║č鹊čĆ. ąĢčüą╗ąĖ čā ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą╝ąĄąĮčīčłąĄ ą┐čÅčéąĖ ąĮąŠąČąĄą║ EMU, č鹊 čüąŠąĄą┤ąĖąĮąĖč鹥 čŹčéąĖ ąĮąŠąČą║ąĖ, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ, čü ąŠą┤ąĮąŠąĖą╝ąĄąĮąĮčŗą╝ąĖ ąĮąŠąČą║ą░ą╝ąĖ ąĮą░ ą║ąŠąĮąĮąĄą║č鹊čĆąĄ JTAG (EMU0 ą┐čĆąŠčåąĄčüčüąŠčĆą░ čüąŠąĄą┤ąĖąĮąĖč鹥 čü EMU0 ąĮą░ ą║ąŠąĮąĮąĄą║č鹊čĆąĄ, ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ).

ąŚą░ą╝ąĄčćą░ąĮąĖčÅ ą┐ąŠ 20-ą▓čŗą▓ąŠą┤ąĮąŠą╝čā ą║ąŠąĮąĮąĄą║č鹊čĆčā čü čåąŠą║ąŠą╗ąĄą▓ą║ąŠą╣ ARM. ąÆ č鹥čģ čüą╗čāčćą░čÅčģ, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąŠčåąĄčüčüąŠčĆ TI čü čåąŠą║ąŠą╗ąĄą▓ą║ąŠą╣ ARM 20-ą▓čŗą▓ąŠą┤ąĮąŠą│ąŠ ą║ąŠąĮąĮąĄą║č鹊čĆą░ JTAG, ą┤ą╗čÅ ąŠčéą╗ą░ą┤čćąĖą║ą░ XDS ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą░ą┤ą░ą┐č鹥čĆ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čåąŠą║ąŠą╗ąĄą▓ą║ąĖ.

ą¤čĆąĖ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĖ 20-ą▓čŗą▓ąŠą┤ąĮąŠą│ąŠ ą║ąŠąĮąĮąĄą║č鹊čĆą░ ARM čü ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ TI ą┤ą▓ąĄ ąĮąŠąČą║ąĖ čĆą░ąĘčŖąĄą╝ą░ DBGRQ ąĖ DBGACK ąŠčüčéą░čÄčéčüčÅ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ, ą┐ąŠč鹊ą╝čā čćč鹊 čŹčéąĖ čüąĖą│ąĮą░ą╗čŗ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ TI. ąĢčüą╗ąĖ ąÆčŗ ąĖčüą┐ąŠą╗čīąĘčāąĄč鹥 ą░ą┤ą░ą┐č鹥čĆ-ą┐ąĄčĆąĄčģąŠą┤ąĮąĖą║ čü 20-ą▓čŗą▓ąŠą┤ąĮąŠą│ąŠ čĆą░ąĘčŖąĄą╝ą░ ARM ąĮą░ ą║ą░ą▒ąĄą╗čī 菹╝čāą╗čÅč鹊čĆą░ XDS, č鹊 čüąĖą│ąĮą░ą╗ Vsupply ą║ą░ą▒ąĄą╗čÅ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąĮą░ ąĮąĄą║ąŠč鹊čĆčŗčģ ą░ą┤ą░ą┐č鹥čĆąŠą▓ ą▓ ą║ą░č湥čüčéą▓ąĄ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ąĮąŠ XDS ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąĄą│ąŠ ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ č鹊ą║ą░.

20-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą║ąŠąĮąĮąĄą║č鹊čĆ ARM ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĮąŠąČą║ąĖ EMU, čéą░ą║ čćč鹊 ąĮąĄ ą▒čāą┤ąĄčé ą┤ąŠčüčéčāą┐ąĮą░ ą╗čÄą▒ą░čÅ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄą╝ą░čÅ ąŠčéą╗ą░ą┤čćąĖą║ąŠą╝ XDS č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤čŗ EMU (čéą░ą║ą░čÅ ą║ą░ą║ čĆąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ, ąĄčüą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮąĄ čüąŠą┤ąĄčƹȹĖčé ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą┐ąŠą┤čéčÅąČą║ąĖ pull-up ąĮą░ ąĮąŠąČą║ą░čģ EMU, č鹊 čŹčéąĖ ąĮąŠąČą║ąĖ EMU ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčéčŗ čĆąĄąĘąĖčüč鹊čĆą░ą╝ąĖ pulled-up čüąĮą░čĆčāąČąĖ. ąĢčüą╗ąĖ ąĮą░ ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ąŠą╣ ą┐ą╗ą░č鹥 ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ čü čÅą┤čĆą░ą╝ąĖ ARM, čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗąĄ ą▓ ąŠą┤ąĮčā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčāčÄ čåąĄą┐ąŠčćą║čā čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ JTAG, ąĖ ą▓čüąĄ ąÆą░čłąĖ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąĮąŠąČą║ąĖ EMU, č鹊 ą▓čüąĄ ąĄčēąĄ ą╝ąŠąČąĮąŠ čüąŠąĄą┤ąĖąĮąĖčéčī ąĮąŠąČą║ąĖ EMU ą╝ąĄąČą┤čā ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ, čćč鹊ą▒čŗ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī čäčāąĮą║čåąĖąŠąĮą░ą╗ ą║čĆąŠčüčü-čéčĆąĖą│ą│ąĄčĆąŠą▓ (cross triggers), ąĄčüą╗ąĖ čŹč鹊 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ. ąĀąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ (ąĄčüą╗ąĖ čŹč鹊 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝) čéą░ą║ąČąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮčŗ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ č湥čĆąĄąĘ pull-up/pull-down čĆąĄąĘąĖčüč鹊čĆąŠą▓ ąĮą░ ą┐ą╗ą░č鹥, ąĮąŠ ąĮąĄą╗čīąĘčÅ ą▒čāą┤ąĄčé ą┐ąŠą╝ąĄąĮčÅčéčī ąĘąĮą░č湥ąĮąĖąĄ čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ č湥čĆąĄąĘ XDS. ąØąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą▒čāą┤ąĄčé čāą▒ąĄą┤ąĖčéčīčüčÅ, čćč鹊 ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄčģąŠą┤ ą║ ą┐čĆąŠą┤ą░ąČą░ą╝, č鹊 ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą▒čāą┤ąĄčé ą▓čŗą▒čĆą░ąĮ čĆąĄąČąĖą╝ ąĘą░ą│čĆčāąĘą║ąĖ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (ąŠą▒ą░ čüąĖą│ąĮą░ą╗ą░ EMU0 ąĖ EMU1 ą┐ąŠą┤čéčÅąĮčāčéčŗ ą║ ą╗ąŠą│. 1) ą┤ą╗čÅ ą▓čüąĄčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé čĆąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ.

ąöą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ čü čÅą┤čĆą░ą╝ąĖ ARM ąŠą▒čŗčćąĮąŠ čéčĆąĄą▒čāąĄčéčüčÅ ą░ą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ. ąĢčüą╗ąĖ čā ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĄčüčéčī ąĮąŠąČą║ą░ RTCK, č鹊 ąŠąĮą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüąŠąĄą┤ąĖąĮąĄąĮą░ čü čüąĖą│ąĮą░ą╗ąŠą╝ ą║ą░ą▒ąĄą╗čÅ ąŠčéą╗ą░ą┤ą║ąĖ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą║ąŠąĮąĮąĄą║č鹊čĆą░ JTAG. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. čĆą░ąĘą┤ąĄą╗ "ąÉą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ".

ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ąĖ ą┐ąŠč鹥ąĮčåąĖą░ą╗čīąĮčŗčģ ąŠą│čĆą░ąĮąĖč湥ąĮąĖą╣, ąĄčüą╗ąĖ čüąŠąĄą┤ąĖąĮčÅčÄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓, ą║ąŠą│ą┤ą░ čā ąĮąĖčģ čā ą▓čüąĄčģ čÅą┤čĆą░ ARM, čüą╝. čĆą░ąĘą┤ąĄą╗ "ąÉą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ".

ąöą╗čÅ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą┐ąŠ ą┤ąĖąĘą░ą╣ąĮčā 60-ą▓čŗą▓ąŠą┤ąĮąŠą│ąŠ ą║ąŠąĮąĮąĄą║č鹊čĆą░ XDS560T/XDS560v2 System Trace/XDS ProTrace čüą╝. [2].

[ąæčāč乥čĆąĖąĘą░čåąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓]

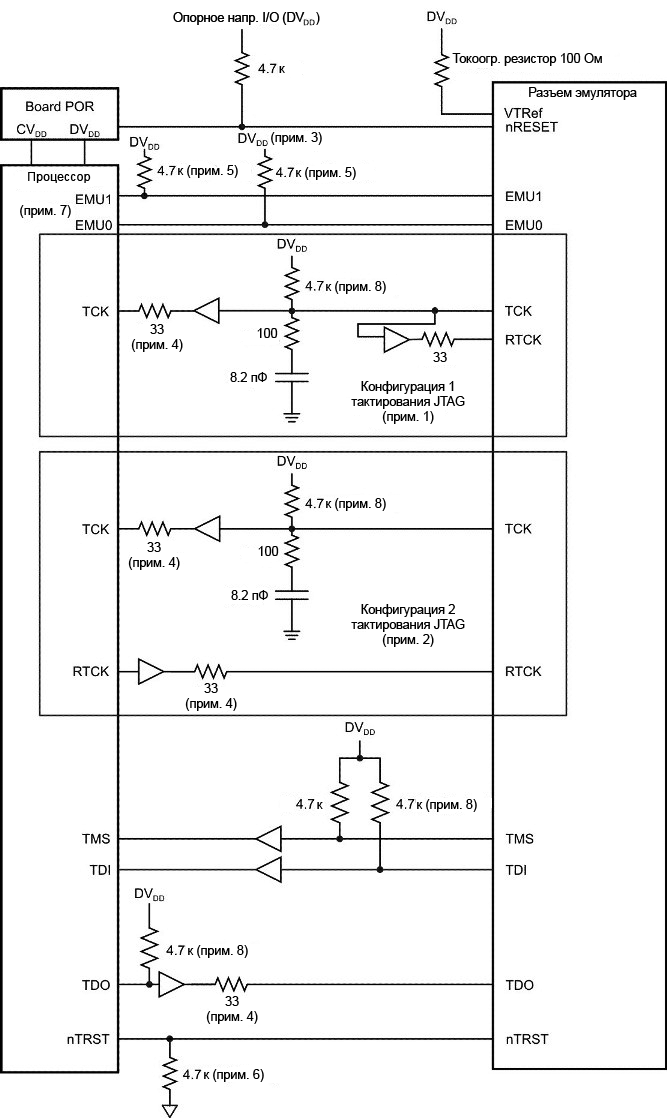

ąĢčüą╗ąĖ čĆą░čüčüč鹊čÅąĮąĖąĄ ą╝ąĄąČą┤čā ąŠčéą╗ą░ą┤čćąĖą║ąŠą╝ ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ ą▒ąŠą╗čīčłąĄ 6 ą┤čÄą╣ą╝ąŠą▓ (15.24 čüą░ąĮčéąĖą╝ąĄčéčĆąŠą▓), č鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čāčüąĖą╗ąĖą▓ą░čéčī čüąĖą│ąĮą░ą╗čŗ JTAG ą▒čāč乥čĆą░ą╝ąĖ, čüą╝. čĆąĖčü. 2. ąöą╗čÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ąĮąĄ JTAG čüąĖą│ąĮą░ą╗ą░ą╝ čüą╝. ą▓čŗčłąĄ čĆą░ąĘą┤ąĄą╗ "ą×ą┤ąĖąĮ ą┐čĆąŠčåąĄčüčüąŠčĆ, ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ".

ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąŠčéą╗ą░ą┤čćąĖą║ XDS560v2 ąĖą╗ąĖ XDS ProTrace, č鹊 ą▓ ąĮąĖčģ čāąČąĄ ą▓čüčéčĆąŠąĄąĮčŗ ą▒čāč乥čĆčŗ, ą┐ąŠčŹč鹊ą╝čā ą┤ą╗ąĖąĮą░ čüąŠąĄą┤ąĖąĮąĄąĮąĖą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ.

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: čĆąĖčü. 2 ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé ą┐čĆąĄą┤čŗą┤čāčēąĄą╣ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ TI č鹥ą╝, čćč鹊 č鹥ą┐ąĄčĆčī čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ ąĮą░ ą▓čģąŠą┤ąĄ ą▒čāč乥čĆą░ TCK ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠąĄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮą░ ą┤čĆčāą│ąĖčģ ą║čĆąĖčéąĖč湥čüą║ąĖčģ čüąĖą│ąĮą░ą╗ą░čģ. ą¤čĆąĖčćąĖąĮą░ čŹč鹊ą│ąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓ č鹊ą╝, čćč鹊 ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ XDS ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą┤čĆą░ą╣ą▓ąĄčĆčŗ čü ą▒ąŠą╗ąĄąĄ ą▒čŗčüčéčĆčŗą╝ąĖ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ąĖ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ, č湥ą╝ čĆą░ąĮčīčłąĄ, čćč鹊 čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ čłą░ąĮčüčŗ ąŠčéčĆą░ąČąĄąĮąĖą╣ čŹčéąĖčģ ą║čĆąĖčéąĖč湥čüą║ąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓.

ąĀąĖčü. 2. ą×ą┤ąĖąĮ ą║ąŠąĮąĮąĄą║č鹊čĆ čŹą╝čāą╗čÅčåąĖąĖ čü ąŠą┤ąĮąĖą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ ąĖ ą▒čāč乥čĆą░ą╝ąĖ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąĢčüą╗ąĖ čā ąÆą░čłąĄą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĮąĄčé ąĮąŠąČą║ąĖ RTCK, č鹊 ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ 1.

(2) ąĢčüą╗ąĖ čā ąÆą░čłąĄą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĄčüčéčī ąĮąŠąČą║ą░ RTCK, č鹊 ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ 2.

(3) DVDD čŹč鹊 ąĮąŠąČą║ą░ JTAG/EMU ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖčÅ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čāčĆąŠą▓ąĮąĄą╣ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░.

(4) ąØąŠą╝ąĖąĮą░ą╗ 33 ą×ą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĄą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ ąĮą░ čŹč鹊ą╣ čüčģąĄą╝ąĄ ą▒čŗą╗ ą▓čŗą▒čĆą░ąĮ ąĮą░ ąŠčüąĮąŠą▓ąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ 74LVC1G32 (ą┤čĆą░ą╣ą▓ąĄčĆą░) ą▓ ą║ą░č湥čüčéą▓ąĄ ąĮąĄ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĄą│ąŠ ą▒čāč乥čĆą░. ąŚąĮą░č湥ąĮąĖąĄ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĖčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĖą╝ąĄąĮčÅąĄą╝ąŠą│ąŠ ą▒čāč乥čĆą░.

(5) ąØąĄąŠą▒čģąŠą┤ąĖą╝čŗ ą▓ąĄčĆčģąĮąĖąĄ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ (pull-up) ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ EMU0 ąĖ EMU1. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ čüą╝. ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ EMU.

(6) ąØą░ čüąĖą│ąĮą░ą╗ąĄ TRST čéčĆąĄą▒čāąĄčéčüčÅ ąĮąĖąČąĮąĖą╣ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖą╣ čĆąĄąĘąĖčüč鹊čĆ (pull-down). ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ JTAG ąĖ čüąĖą│ąĮą░ą╗ą░ nTRST ą▓ąŠ ą▓čĆąĄąĘą║ąĄ "ąĪą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ąĘą░ą╝ąĄčćą░ąĮąĖčÅ ą┐ąŠ čüąĖą│ąĮą░ą╗ą░ą╝ JTAG ąĖ nTRST (ą▓ą║ą╗čÄčćą░čÅ TMS ąĖ TDI)".

(7) ąĢčüą╗ąĖ čā ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▒ąŠą╗čīčłąĄ ą┤ą▓čāčģ ąĮąŠąČąĄą║ EMU, č鹊 čüą║ąŠčĆąĄąĄ ą▓čüąĄą│ąŠ ąŠąĮ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 菹║čüą┐ąŠčĆčé čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ čÅą┤čĆą░ (core trace) ąĖą╗ąĖ čüąĖčüč鹥ą╝ąĮąŠą╣ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ (system trace), ąĖą╗ąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąŠą▒ąĄ čŹčéąĖ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ. ąŁč鹊 ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗąĄ čäčāąĮą║čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĄą┤čŖčÅą▓ą╗čÅčÄčé ą║ ą┐ą╗ą░č鹥 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [2]).

(8) ąÆąĄčĆčģąĮąĖąĄ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖąĄ (pull-up) čĆąĄąĘąĖčüč鹊čĆčŗ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐ąŠčüčéą░ą▓ąĖčéčī ąĮą░ ą▓čüąĄčģ ą▓čģąŠą┤ą░čģ ą▒čāč乥čĆąŠą▓, čćč鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī ą▓ąĄčĆąŠčÅčéąĮąŠčüčéčī ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą┐ąŠą╝ąĄčģ ąĮą░ ą▓čŗčģąŠą┤ą░čģ ą▒čāč乥čĆąŠą▓, ą║ąŠą│ą┤ą░ ą║ą░ą▒ąĄą╗čī XDS ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ.

ąöą╗čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ čü ą▒čāč乥čĆą░ą╝ąĖ (čüą╝. čĆą░ąĘą┤ąĄą╗ "ąöąĖą░ą│čĆą░ą╝ą╝ą░ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG") čüąĖą│ąĮą░ą╗ TDO ą┤ąŠą╗ąČąĄąĮ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮčÅčéčīčüčÅ ąŠą▒čĆą░čéąĮąŠ ąŠčé ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą║ 菹╝čāą╗čÅč鹊čĆčā ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ 1/2 ą┐ąĄčĆąĖąŠą┤ą░ TCK, čéą░ą║ čćč鹊 ąĄčüą╗ąĖ ąÆčŗ ą┐čĆąĖą╝ąĄąĮąĖą╗ąĖ ą▒čāč乥čĆ RTCK ą▓ č鹊ą╝ ąČąĄ ą╝ąĄčüč鹥 ąĮą░ ą┐ą╗ą░č鹥, čćč鹊 ąĖ ą▒čāč乥čĆ TCK, č鹊 ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ąĮąĄ ą▓ą║ą╗čÄčćą░ąĄčé ąĘą░ą┤ąĄčƹȹ║čā TCK, ąĖ ą▓ą║ą╗čÄčćą░ąĄčé č鹊ą╗čīą║ąŠ ąĘą░ą┤ąĄčƹȹ║čā TDO. ąĢčüą╗ąĖ ąÆčŗ ą┐ąĄčĆąĄą┤ą░ąĄč鹥 TCK ąŠą▒čĆą░čéąĮąŠ ą▓ RTCK ąĮą░ ą║ąŠąĮąĮąĄą║č鹊čĆąĄ JTAG ąĖ ąĮąĄ ą▒čāč乥čĆąĖąĘąĖčĆčāąĄč鹥 ąĄą│ąŠ, č鹊 ą┤ąŠą╗ąČąĮčŗ čāč湥čüčéčī ąĘą░ą┤ąĄčƹȹ║čā TCK ą┐ą╗čÄčü ąĘą░ą┤ąĄčƹȹ║čā TDO, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ ąĘą░ą┤ąĄčƹȹ║čā.

[ąØąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ą▓ čåąĄą┐ąŠčćą║ąĄ JTAG]

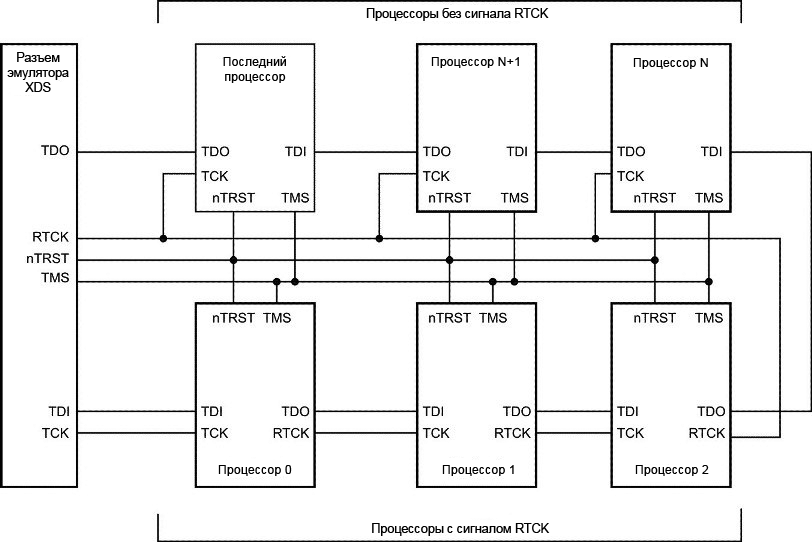

ąĢčüą╗ąĖ ąĮą░ ą┐ą╗ą░č鹥 ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓, čüąŠą▓ą╝ąĄčüčéąĖą╝čŗčģ čüąŠ čüčéą░ąĮą┤ą░čĆč鹊ą╝ JTAG 1149.1, č鹊 ą╝ąŠąČąĮąŠ ą┐čĆąĖą╝ąĄąĮąĖčéčī ąŠą┤ąĖąĮ ą║ąŠąĮąĮąĄą║č鹊čĆ čŹą╝čāą╗čÅč鹊čĆą░, čüąŠąĄą┤ąĖąĮąĖą▓ ą▓čüąĄ čŹčéąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čāčÄ čåąĄą┐ąŠčćą║čā čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ JTAG (scan chain). ąØąŠąČą║ąĖ EMU ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ TI ą┐čĆąĖ čŹč鹊ą╝ čüąŠąĄą┤ąĖąĮčÅčÄčéčüčÅ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 3. ąŁčéą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüą╗ąĄą┤čāčÄčēąĖąĄ čäčāąĮą║čåąĖąĖ, čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄą╝čŗąĄ ą┤ą╗čÅ ąŠčéą╗ą░ą┤ą║ąĖ ą▓ čüąĖčüč鹥ą╝ą░čģ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ:

ŌĆó ąĪąĖąĮčģčĆąŠąĮąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ą║ąŠą┤ą░.

ŌĆó ąōą╗ąŠą▒ą░ą╗čīąĮčŗąĄ č鹊čćą║ąĖ ąŠčüčéą░ąĮąŠą▓ą░.

ŌĆó ąÜčĆąŠčüčü-čéčĆąĖą│ą│ąĄčĆčŗ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ EMU.

ąĀąĖčü. 3. ą×ą┤ąĖąĮ ą║ąŠąĮąĮąĄą║č鹊čĆ čŹą╝čāą╗čÅčåąĖąĖ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ ąĖ ą▒čāč乥čĆą░ą╝ąĖ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąĢčüą╗ąĖ čā ąÆą░čłąĖčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ąĄčüčéčī ąĮąŠąČą║ą░ RTCK, čüą╝. "ąÉą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ".

(2) ąĢčüą╗ąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓ čåąĄą┐ąŠčćą║ąĄ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮą░ čĆą░čüčüč鹊čÅąĮąĖąĖ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ 6 ą┤čÄą╣ą╝ąŠą▓ (15.24 čüą░ąĮčéąĖą╝ąĄčéčĆąŠą▓) ąŠčé ą║ąŠąĮąĮąĄą║č鹊čĆą░ 菹╝čāą╗čÅč鹊čĆą░, č鹊 ą▒čāč乥čĆ ą┤ą╗čÅ TDO ą╝ąŠąČąĄčé ąĮąĄ ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ.

(3) DVDD čŹč鹊 ąĮąŠąČą║ą░ JTAG/EMU ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖčÅ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čāčĆąŠą▓ąĮąĄą╣ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░.

(4) ąŁčéą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé, čćč鹊 ą┐čĆąŠčåąĄčüčüąŠčĆčŗ ąĮą░čģąŠą┤čÅčéčüčÅ ąĮą░ čĆą░čüčüč鹊čÅąĮąĖąĖ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ 6 ą┤čÄą╣ą╝ąŠą▓ (15.24 čüą░ąĮčéąĖą╝ąĄčéčĆąŠą▓) ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░. ą£ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ą▒čāč乥čĆąĖąĘą░čåąĖčÅ TDO ąĖ TDI ą╝ąĄąČą┤čā ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ, ąĄčüą╗ąĖ čĆą░čüčüč鹊čÅąĮąĖąĄ ą╝ąĄąČą┤čā ąĮąĖą╝ąĖ ą┐čĆąĄą▓čŗčłą░ąĄčé 6 ą┤čÄą╣ą╝ąŠą▓.

(5) ąØąŠą╝ąĖąĮą░ą╗ 33 ą×ą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĄą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ ąĮą░ čŹč鹊ą╣ čüčģąĄą╝ąĄ ą▒čŗą╗ ą▓čŗą▒čĆą░ąĮ ąĮą░ ąŠčüąĮąŠą▓ąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ SN74VC1G32 (ą┤čĆą░ą╣ą▓ąĄčĆą░) ą▓ ą║ą░č湥čüčéą▓ąĄ ąĮąĄ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĄą│ąŠ ą▒čāč乥čĆą░. ąŚąĮą░č湥ąĮąĖąĄ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĖčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĖą╝ąĄąĮčÅąĄą╝ąŠą│ąŠ ą▒čāč乥čĆą░.

(6) ąØąĄąŠą▒čģąŠą┤ąĖą╝čŗ ą▓ąĄčĆčģąĮąĖąĄ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ (pull-up) ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ EMU0 ąĖ EMU1. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ čüą╝. ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ EMU.

(7) ąØą░ čüąĖą│ąĮą░ą╗ąĄ TRST čéčĆąĄą▒čāąĄčéčüčÅ ąĮąĖąČąĮąĖą╣ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖą╣ čĆąĄąĘąĖčüč鹊čĆ (pull-down). ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ JTAG ąĖ čüąĖą│ąĮą░ą╗ą░ nTRST ą▓ąŠ ą▓čĆąĄąĘą║ąĄ "ąĪą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ąĘą░ą╝ąĄčćą░ąĮąĖčÅ ą┐ąŠ čüąĖą│ąĮą░ą╗ą░ą╝ JTAG ąĖ nTRST (ą▓ą║ą╗čÄčćą░čÅ TMS ąĖ TDI)".

(8) ąĢčüą╗ąĖ čā ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▒ąŠą╗čīčłąĄ ą┤ą▓čāčģ ąĮąŠąČąĄą║ EMU, č鹊 čüą║ąŠčĆąĄąĄ ą▓čüąĄą│ąŠ ąŠąĮ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 菹║čüą┐ąŠčĆčé čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ čÅą┤čĆą░ (core trace) ąĖą╗ąĖ čüąĖčüč鹥ą╝ąĮąŠą╣ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ (system trace), ąĖą╗ąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąŠą▒ąĄ čŹčéąĖ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ. ąŁč鹊 ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗąĄ čäčāąĮą║čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĄą┤čŖčÅą▓ą╗čÅčÄčé ą║ ą┐ą╗ą░č鹥 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [2]).

(9) ąÆąĄčĆčģąĮąĖąĄ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖąĄ (pull-up) čĆąĄąĘąĖčüč鹊čĆčŗ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐ąŠčüčéą░ą▓ąĖčéčī ąĮą░ ą▓čüąĄčģ ą▓čģąŠą┤ą░čģ ą▒čāč乥čĆąŠą▓, čćč鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī ą▓ąĄčĆąŠčÅčéąĮąŠčüčéčī ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą┐ąŠą╝ąĄčģ ąĮą░ ą▓čŗčģąŠą┤ą░čģ ą▒čāč乥čĆąŠą▓, ą║ąŠą│ą┤ą░ ą║ą░ą▒ąĄą╗čī XDS ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ.

ą×ą▒čŗčćąĮąŠ čéčĆąĄą▒čāąĄčéčüčÅ ą▒čāč乥čĆąĖąĘą░čåąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ TCK, TMS, TDI ąĖ TDO, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ą░ą┤ąĄą║ą▓ą░čéąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čāčĆąŠą▓ąĮčÅą╝ąĖ ą╝ąĄąČą┤čā ą╝ą░čüčüąĖą▓ąŠą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ąĖ 菹╝čāą╗čÅč鹊čĆąŠą╝ XDS. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ, čćč鹊ą▒čŗ TCK, TMS ąĖ TDI ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ą╗ąĖčüčī ą┤čĆą░ą╣ą▓ąĄčĆą░ą╝ąĖ ąĖąĘ ąŠą┤ąĮąŠą│ąŠ ąĖ č鹊ą│ąŠ ąČąĄ čäąĖąĘąĖč湥čüą║ąŠą│ąŠ ą║ąŠčĆą┐čāčüą░, čćč鹊ą▒čŗ ą╗čāčćčłąĄ čāą┐čĆą░ą▓ą╗čÅčéčī čŹčäč乥ą║čéą░ą╝ąĖ ą│ąŠąĮą║ąĖ čüąĖą│ąĮą░ą╗ąŠą▓. ąĢčüą╗ąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓ čåąĄą┐ąŠčćą║ąĄ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮą░ čĆą░čüčüč鹊čÅąĮąĖąĖ ą╝ąĄąĮčīčłąĄ 6 ą┤čÄą╣ą╝ąŠą▓ (15.24 čüą░ąĮčéąĖą╝ąĄčéčĆąŠą▓) ąŠčé ą║ąŠąĮąĮąĄą║č鹊čĆą░ XDS, č鹊 ą▒čāč乥čĆ TDO ą╝ąŠąČąĄčé ąĮąĄ ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ.

ąÆčģąŠą┤čŗ ą▒čāč乥čĆąŠą▓ TMS, TDI ąĖ TCK ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüąĮą░ą▒ąČąĄąĮčŗ ą▓ąĄčĆčģąĮąĖą╝ąĖ (pull-up) ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖą╝ąĖ čĆąĄąĘąĖčüč鹊čĆą░ą╝ąĖ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ ą║ ąŠą┐ąŠčĆąĮąŠą╝čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ DVDD, čćč鹊ą▒čŗ čŹčéąĖ čüąĖą│ąĮą░ą╗čŗ ąĮą░čģąŠą┤ąĖą╗ąĖčüčī ą▓ ą┐čĆą░ą▓ąĖą╗čīąĮčŗčģ čāčĆąŠą▓ąĮčÅčģ, ą║ąŠą│ą┤ą░ ą║ą░ą▒ąĄą╗čī XDS ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ. ąöą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čĆąĄąĘąĖčüč鹊čĆčŗ ąĮąŠą╝ąĖąĮą░ą╗ą░ 4.7 ą║ą×ą╝ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ąŠą╗čīčłąĄ.

ąÆ čüą╗čāčćą░čÅčģ, ą║ąŠą│ą┤ą░ ąÆą░čł ą┤ąĖąĘą░ą╣ąĮ čüąŠą┤ąĄčƹȹĖčé č鹊ą╗čīą║ąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ (ąĮąĄ ą▒ąŠą╗čīčłąĄ 3) ąĮą░ čåąĄą┐ąŠčćą║ąĄ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ, ąĖ čĆą░ąĘą▓ąŠą┤ą║ą░ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG (TCK, TMS, TDO ąĖ TDI) ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą┤ą╗ąĖąĮąŠą╣ ą╝ąĄąĮčīčłąĄ 6 6 ą┤čÄą╣ą╝ąŠą▓ (15.24 čüą░ąĮčéąĖą╝ąĄčéčĆąŠą▓), č鹊 ą▒čāč乥čĆąĖąĘą░čåąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG ą╝ąŠąČąĄčé ąĮąĄ ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ. ąĢčüą╗ąĖ ąÆčŗ čĆąĄčłąĖč鹥, čćč鹊 ą┤ąĖąĘą░ą╣ąĮ ąĮąĄ čéčĆąĄą▒čāąĄčé ą▒čāč乥čĆąŠą▓, č鹊 ą▓čüąĄ ąĄčēąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐čĆąĖą╝ąĄąĮąĖčéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ, ą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čü ąŠą┤ąĮąĖą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ (čüą╝. ą▓čŗčłąĄ čĆą░ąĘą┤ąĄą╗ "ą×ą┤ąĖąĮ ą┐čĆąŠčåąĄčüčüąŠčĆ, ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ").

ąĢčüą╗ąĖ ą┤ąĖąĘą░ą╣ąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąŠą╗čīčłąĄ 3 ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓, č鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐čĆąŠą▓ąĄčüčéąĖ čüąĖą╝čāą╗čÅčåąĖčÄ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą┐čāč鹥ą╣ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ TCK ąĖ TMS. TI ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčé čüąŠąĄą┤ąĖąĮčÅčéčī ą▒ąŠą╗čīčłąĄ 30 čāčüčéčĆąŠą╣čüčéą▓ ą▓ ąŠą┤ąĮčā čåąĄą┐ąŠčćą║čā čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ JTAG.

ąŚą░ą╝ąĄčćą░ąĮąĖčÅ ą┐ąŠ čüąĖą│ąĮą░ą╗ą░ą╝ EMU ą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅčģ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ čüą╝. ą▓ąŠ ą▓čĆąĄąĘą║ąĄ "ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ EMU ą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅčģ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ".

[ąöąĖą░ą│čĆą░ą╝ą╝ą░ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG]

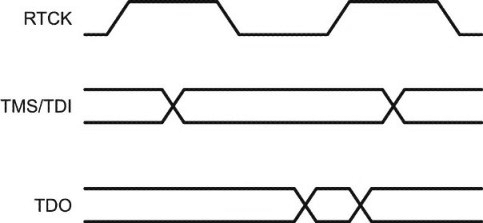

ąĀąĖčü. 4 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▒ą░ąĘąŠą▓čāčÄ ą┤ąĖą░ą│čĆą░ą╝ą╝čā ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą┤čĆčāą│ ą┤čĆčāą│ą░. ą×čüąŠą▒ąĄąĮąĮąŠčüčéčī 菹╝čāą╗čÅč鹊čĆą░ XDS - ąŠąĮ 菹║čüą┐ąŠčĆčéąĖčĆčāąĄčé TMS ąĖ TDI ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ RTCK. TDO ą▓čŗą▓ąŠą┤ąĖčéčüčÅ ąĖąĘ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ TCK, ąĖ čŹč鹊 ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī č鹊ą╗čīą║ąŠ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ 1/2 ą┐ąĄčĆąĖąŠą┤ą░ TCK ą┤ą╗čÅ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ ą┤ąŠ XDS, ą│ą┤ąĄ TDO ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čäčĆąŠąĮč鹥 ąĮą░čĆą░čüčéą░ąĮąĖčÅ RTCK. ą£ąĮąŠą│ąĖąĄ ą╝ąŠą┤ąĄą╗ąĖ XDS ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąŠą┐čåąĖąŠąĮą░ą╗čīąĮčŗą╣ ąĘą░čģą▓ą░čé TDO ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ RTCK, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÅ ą▒ąŠą╗čīčłąĄ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čāčĆąŠą▓ąĮčÅ, ąĮąŠ ą┐ąŠč鹥ąĮčåąĖą░ą╗čīąĮąŠ ą╝ąĄąĮčīčłąĄ ą▓čĆąĄą╝ąĄąĮąĖ čāą┤ąĄčƹȹ░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ ą┐ąŠ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ ą▓čĆąĄą╝ąĄąĮąĖ čüą╝. ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅ XDS.

ąĀąĖčü. 4. ąóą░ą╣ą╝ąĖąĮą│ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG.

[ąÉą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ]

ąĢčüą╗ąĖ ąÆą░čł ą┤ąĖąĘą░ą╣ąĮ čüąŠą┤ąĄčƹȹĖčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ čü čüąĖą│ąĮą░ą╗ą░ą╝ąĖ RTCK, ą║ąŠč鹊čĆčŗąĄ čéčĆąĄą▒čāčÄčé ą░ą┤ą░ą┐čéąĖą▓ąĮąŠą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, č鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą▓čŗą▒čĆą░čéčī ą╗ąĖą▒ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčāčÄ, ą╗ąĖą▒ąŠ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčāčÄ č鹊ą┐ąŠą╗ąŠą│ąĖčÄ. ą¤ą░čĆą░ą╗ą╗ąĄą╗čīąĮą░čÅ č鹊ą┐ąŠą╗ąŠą│ąĖčÅ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą▒ąŠą╗čīčłąĄąĄ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ, č湥ą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮą░čÅ, ąŠą┤ąĮą░ą║ąŠ ąŠąĮą░ ą▒ąŠą╗ąĄąĄ čüą╗ąŠąČąĮą░čÅ ą▓ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ.

ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. ą▓čŗčłąĄ čĆą░ąĘą┤ąĄą╗ "ąÉą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ".

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮą░čÅ č鹊ą┐ąŠą╗ąŠą│ąĖčÅ. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 5, ą▓ čŹč鹊ą╣ č鹊ą┐ąŠą╗ąŠą│ąĖąĖ čüąĖą│ąĮą░ą╗čŗ RTCK ą╝ąĄąČą┤čā ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ ą║ą░čüą║ą░ą┤ąĖčĆčāčÄčéčüčÅ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčāčÄ čåąĄą┐ąŠčćą║čā čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ. ąŁč鹊 ąĘą░čüčéą░ą▓ą╗čÅąĄčé čüą╗ąĄą┤čāčÄčēąĄąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ čåąĄą┐ąŠčćą║ąĄ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčī TCK ąŠčé RTCK ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čåąĄą┐ąŠčćą║ąĄ, čćč鹊 ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┤ą▓ą░ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čüąĖčüč鹥ą╝čā:

ŌĆó RTCK ą┐ąŠčÅą▓ą╗čÅčÄčēąĖą╣čüčÅ ąĮą░ ą║ąŠąĮčéą░ą║č鹥 菹╝čāą╗čÅč鹊čĆą░ XDS ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ ą╝ąĄą┤ą╗ąĄąĮąĮąĄąĄ, č湥ą╝ čüą░ą╝ąŠąĄ ą╝ąĄą┤ą╗ąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ čåąĄą┐ąŠčćą║ąĄ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ.

ŌĆó ąöą░ąČąĄ ąĄčüą╗ąĖ ą▓čüąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čåąĄą┐ąŠčćą║ąĄ čĆą░ą▒ąŠčéą░čÄčé ąĮą░ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠą╣ čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓, ąĘą░ą┤ąĄčĆą║ąČąĖ ą▓ ą╗ąŠą│ąĖą║ąĄ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą▒čāą┤čāčé ąĘą░ą╝ąĄą┤ą╗čÅčéčī ą║ąŠąĮąĄčćąĮčŗą╣ čüąĖą│ąĮą░ą╗ RTCK.

ąĪ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ č鹊ą┐ąŠą╗ąŠą│ąĖąĖ ą▓čüąĄ ąĄčēąĄ ą╝ąŠąČąĮąŠ ą┐čĆąĖą╝ąĄąĮčÅčéčī 菹╝čāą╗čÅč鹊čĆ XDS, ą║ąŠč鹊čĆčŗą╣ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą░ą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ ąÆčŗ čāčüčéą░ąĮąŠą▓ąĖč鹥 čćą░čüč鹊čéčā TCLK ą▓ 8 čĆą░ąĘ ą╝ąĄąĮčīčłąĄ, č湥ą╝ čüą░ą╝ą░čÅ ąĮąĖąĘą║ą░čÅ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ čÅą┤čĆą░ ąĖąĘ ą▓čüąĄčģ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ą▓ čåąĄą┐ąŠčćą║ąĄ.

ąĀąĖčü. 5. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮą░čÅ č鹊ą┐ąŠą╗ąŠą│ąĖčÅ čüąĖą│ąĮą░ą╗ą░ RTCK.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čĆąĖčü. 5 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé č鹊ą╗čīą║ąŠ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ, ąĮąĄ ąŠą▒čĆą░čēą░čÅ ą▓ąĮąĖą╝ą░ąĮąĖąĄ ąĮą░ ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖą╗ąĖ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ą▓čŗčłąĄ čĆą░ąĘą┤ąĄą╗ "ąØąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ą▓ čåąĄą┐ąŠčćą║ąĄ JTAG").

ą¤ą░čĆą░ą╗ą╗ąĄą╗čīąĮą░čÅ č鹊ą┐ąŠą╗ąŠą│ąĖčÅ. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 6, čŹčéą░ č鹊ą┐ąŠą╗ąŠą│ąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮą░, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┤ąĄą│čĆą░ą┤ą░čåąĖąĖ čéą░ą║č鹊ą▓ RTCK ąĖąĘ-ąĘą░ ą║ą░čüą║ą░ą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ RTCK ą╝ąĄąČą┤čā ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ, ą║ą░ą║ čŹč鹊 ą▒čŗą╗ąŠ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ č鹊ą┐ąŠą╗ąŠą│ąĖąĖ. ą¤ą░čĆą░ą╗ą╗ąĄą╗čīąĮą░čÅ č鹊ą┐ąŠą╗ąŠą│ąĖčÅ čéčĆąĄą▒čāąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ ą╗ąŠą│ąĖą║ąĖ CPLD, čćč鹊ą▒čŗ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ąĖąĘą▒ąĖčĆą░č鹥ą╗čīąĮčāčÄ ą╗ąŠą│ąĖą║čā čéą░ą║č鹊ą▓ (clock voting logic). Clock voting logic ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé TCK ą┤ą╗čÅ ą▓čüąĄčģ čāčüčéčĆąŠą╣čüčéą▓ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ, ąĮąŠ ąĘą░č鹥ą╝ ąČą┤ąĄčé ą│ąĄąĮąĄčĆą░čåąĖąĖ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ RTCK ą┤ą╗čÅ XDS, ą┐ąŠą║ą░ ą▓čüąĄ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ ą▓ čåąĄą┐ąŠčćą║ąĄ ąŠčéą▓ąĄčćą░čÄčé čü ąŠąČąĖą┤ą░ąĄą╝čŗą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą╝ RTCK. ąĪ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ č鹊ą┐ąŠą╗ąŠą│ąĖąĄą╣ RTCK ą┤ąŠčģąŠą┤ąĖčé ą┤ąŠ XDS čü ą┐ąŠąĮąĖąČąĄąĮąĮąŠą╣ čćą░čüč鹊č鹊ą╣, ąĘą░ą▓ąĖčüčÅčēąĄą╣ ąŠčé čüą░ą╝ąŠą│ąŠ ą╝ąĄą┤ą╗ąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čåąĄą┐ąŠčćą║ąĄ, ą▓ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą╣ č鹊ą┐ąŠą╗ąŠą│ąĖąĖ čāą┤ą░ąĄčéčüčÅ ąĖąĘą▒ąĄąČą░čéčī čŹč鹊ą╣ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĮąŠą╣ ąĘą░ą┤ąĄčƹȹ║ąĖ RTCK, ą▓čŗąĘą▓ą░ąĮąĮąŠą╣ ą║ą░čüą║ą░ą┤ąĖčĆąŠą▓ą░ąĮąĖąĄą╝.

ą¤čĆąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą╣ č鹊ą┐ąŠą╗ąŠą│ąĖąĖ ą▓čüąĄ ąĄčēąĄ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī XDS, ą║ąŠč鹊čĆčŗą╣ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą░ą┤ą░ą┐čéąĖą▓ąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ, ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čüą╗ąĄą┤čāąĄčé čāčüčéą░ąĮąŠą▓ąĖčéčī čćą░čüč鹊čéčā TCLK ą▓ 8 čĆą░ąĘ ą╝ąĄąĮčīčłąĄ, č湥ą╝ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čüą░ą╝ąŠą│ąŠ ą╝ąĄą┤ą╗ąĄąĮąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▓ čüąĖčüč鹥ą╝ąĄ.