|

ąŻąĮąĖą▓ąĄčĆčüą░ą╗čīąĮčŗą╣ čüąĖąĮčģčĆąŠąĮąĮčŗą╣/ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ čéčĆą░ąĮčüąĖą▓ąĄčĆ (universal synchronous asynchronous receiver transmitter, USART) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą│ąĖą▒ą║ąĖą╣ čüą┐ąŠčüąŠą▒ ą┐ąŠą╗ąĮąŠą┤čāą┐ą╗ąĄą║čüąĮąŠą│ąŠ ąŠą▒ą╝ąĄąĮą░ čü ą▓ąĮąĄčłąĮąĖą╝ ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮąĖąĄą╝, čćč鹊 čéčĆąĄą▒čāčÄčé ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮčŗąĄ čüčéą░ąĮą┤ą░čĆčéčŗ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓ č乊čĆą╝ą░č鹥 NRZ. USART ą╝ąŠąČąĮąŠ ąĮą░čüčéčĆąŠąĖčéčī ąĮą░ čüą║ąŠčĆąŠčüčéčī ąŠą▒ą╝ąĄąĮą░ ą▓ čłąĖčĆąŠą║ąŠą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą▒ą╗ą░ą│ąŠą┤ą░čĆčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┤čĆąŠą▒ąĮąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čüą║ąŠčĆąŠčüčéąĖ (fractional baud rate generator).

ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą▓ ą╗čÄą▒čāčÄ čüč鹊čĆąŠąĮčā ąĖ ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą▓ ąŠą▒ąĄ čüč鹊čĆąŠąĮčŗ ą┐ąŠ ąŠą┤ąĮąŠą╝čā ą┐čĆąŠą▓ąŠą┤čā (half-duplex single wire). ąóą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą┐čĆąŠč鹊ą║ąŠą╗čŗ LIN (local interconnection network), Smartcard Protocol ąĖ IrDA (infrared data association) čüą┐ąĄčåąĖčäąĖą║ą░čåąĖą╣ SIR ENDEC ąĖ ąŠą┐ąĄčĆą░čåąĖąĖ ą╝ąŠą┤ąĄą╝ą░ (CTS/RTS). ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ą╝čāą╗čīčéąĖą┐čĆąŠčåąĄčüčüąŠčĆąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ. ąÆčŗčüąŠą║ą░čÅ čüą║ąŠčĆąŠčüčéčī ąŠą▒ą╝ąĄąĮą░ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣ DMA ą┤ą╗čÅ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒čāč乥čĆąŠą▓.

ŌĆó ą¤ąŠą╗ąĮčŗą╣ ą┤čāą┐ą╗ąĄą║čü, ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ.

ŌĆó ąĪčéą░ąĮą┤ą░čĆčéąĮčŗą╣ č乊čĆą╝ą░čé NRZ (Mark/Space).

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗą╣ ą╝ąĄč鹊ą┤ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ (oversampling) ąĮą░ 16 ąĖą╗ąĖ ąĮą░ 8 ą┤ą╗čÅ ą│ąĖą▒ą║ąŠą│ąŠ ą║ąŠą╝ą┐čĆąŠą╝ąĖčüčüą░ ą╝ąĄąČą┤čā čüą║ąŠčĆąŠčüčéčīčÄ ąĖ ą┤ąŠą┐čāčüą║ąŠą╝ ąĮą░ čćą░čüč鹊čéčā čéą░ą║č鹊ą▓.

ŌĆó ąöčĆąŠą▒ąĮčŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ čüą║ąŠčĆąŠčüčéąĖ (Fractional baud rate generator) čĆąĄą░ą╗ąĖąĘčāąĄčé ąŠą▒čēčāčÄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čāčÄ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čüą║ąŠčĆąŠčüčéčī ąĘą░ą▓ąĖčüąĖčé ąŠčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊čéčŗ APB (čüą╝. ą┤ą░čéą░čłąĖčé).

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ ą┤ą╗ąĖąĮą░ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ (8 ąĖą╗ąĖ 9 ą▒ąĖčé).

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ stop-ą▒ąĖč鹊ą▓ - ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ 1 ąĖą╗ąĖ 2 čüč鹊ą┐-ą▒ąĖčéą░.

ŌĆó ąÆąŠąĘą╝ąŠąČąĮąŠčüčéčī ąŠčéą┐čĆą░ą▓ą║ąĖ LIN Master Synchronous Break ąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ LIN slave break. ąōąĄąĮąĄčĆą░čåąĖčÅ 13-ą▒ąĖčéąĮąŠą│ąŠ break ąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ break 10/11 ą▒ąĖčé, ą║ąŠą│ą┤ą░ USART ą░ą┐ą┐ą░čĆą░čéąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ LIN.

ŌĆó ąóą░ą║č鹊ą▓čŗą╣ ą▓čŗčģąŠą┤ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ŌĆó ąÜąŠą┤ąĄčĆ/ą┤ąĄą║ąŠą┤ąĄčĆ IrDA SIR. ąöą╗čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī 3/16 ą▒ąĖčé.

ŌĆó ąÆąŠąĘą╝ąŠąČąĮąŠčüčéčī 菹╝čāą╗čÅčåąĖąĖ čüą╝ą░čĆčé-ą║ą░čĆčéčŗ:

ŌĆō ąśąĮč鹥čĆč乥ą╣čü Smartcard ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┐čĆąŠč鹊ą║ąŠą╗ čüą╝ą░čĆčé-ą║ą░čĆčé, ą║ą░ą║ čŹč鹊 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą▓ čüčéą░ąĮą┤ą░čĆčéą░čģ ISO 7816-3.

ŌĆō ąöą╗čÅ čĆą░ą▒ąŠčéčŗ Smartcard ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ 0.5, 1.5 stop-ą▒ąĖčé.

ŌĆó ą¤ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┐ąŠ ąŠą┤ąĮąŠą╝čā čüąĖą│ąĮą░ą╗čīąĮąŠą╝čā ą┐čĆąŠą▓ąŠą┤čā (Single-wire half-duplex).

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗą╣ multibuffer-ąŠą▒ą╝ąĄąĮ ą┤ą╗čÅ DMA. ąæą░ą╣čéčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ ą┐ąŠą╝ąĄčēą░čÄčéčüčÅ ą▓ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą▒čāč乥čĆčŗ SRAM.

ŌĆó ą×čéą┤ąĄą╗čīąĮčŗąĄ ą▒ąĖčéčŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░.

ŌĆó ążą╗ą░ą│ąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠą▒ą╝ąĄąĮą░:

ŌĆō ąæčāč乥čĆ ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮ

ŌĆō ąæčāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé

ŌĆō ążą╗ą░ą│ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ

ŌĆó ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ąĄą╝ č湥čéąĮąŠčüčéąĖ:

ŌĆō ą¤ąĄčĆąĄą┤ą░čćą░ parity-ą▒ąĖčéą░

ŌĆō ą¤čĆąŠą▓ąĄčĆą║ą░ č湥čéąĮąŠčüčéąĖ ą▓ ą┐čĆąĖąĮčÅč鹊ą╝ ą▒ą░ą╣č鹥

ŌĆó 4 čäą╗ą░ą│ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ:

ŌĆō Overrun error (ąŠčłąĖą▒ą║ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ)

ŌĆō Noise detection (ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čłčāą╝ą░)

ŌĆō Frame error (ąŠčłąĖą▒ą║ą░ čäčĆąĄą╣ą╝ą░)

ŌĆō Parity error (ąŠčłąĖą▒ą║ą░ č湥čéąĮąŠčüčéąĖ)

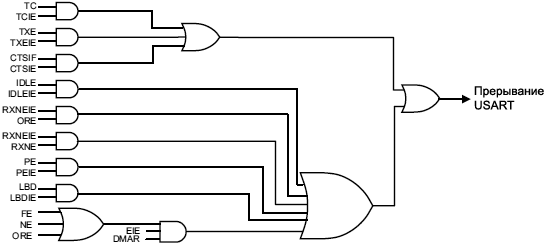

ŌĆó 10 ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü čäą╗ą░ą│ą░ą╝ąĖ:

ŌĆō ąśąĘą╝ąĄąĮąĄąĮąĖąĄ CTS

ŌĆō ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ LIN break

ŌĆō ą¤čāčüčé čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čćąĖ

ŌĆō ąŚą░ą▓ąĄčĆčłąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ

ŌĆō ąĀąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮ

ŌĆō ą¤čĆąĖąĮčÅčé čüąĖą│ąĮą░ą╗ ąŠąČąĖą┤ą░ąĮąĖčÅ ą╗ąĖąĮąĖąĖ (idle line)

ŌĆō ą×čłąĖą▒ą║ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ (Overrun error)

ŌĆō ą×čłąĖą▒ą║ą░ čäčĆąĄą╣ą╝ą░ (Framing error)

ŌĆō ą×čłąĖą▒ą║ą░ ąĖąĘ-ąĘą░ čłčāą╝ą░ (Noise error)

ŌĆō ą×čłąĖą▒ą║ą░ č湥čéąĮąŠčüčéąĖ (Parity error)

ŌĆó ą£čāą╗čīčéąĖą┐čĆąŠčåąĄčüčüąŠčĆąĮčŗą╣ ąŠą▒ą╝ąĄąĮ - ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ ą╝ąŠą╗čćą░ąĮąĖčÅ (mute mode), ąĄčüą╗ąĖ ąĮąĄ ą▒čŗą╗ąŠ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ ą░ą┤čĆąĄčüą░.

ŌĆó ą¤čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ ąĖąĘ čĆąĄąČąĖą╝ą░ ą╝ąŠą╗čćą░ąĮąĖčÅ (Wake up from mute mode) - ąĖąĘ-ąĘą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ idle line ąĖą╗ąĖ address mark.

ŌĆó ąöą▓ą░ čĆąĄąČąĖą╝ą░ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░: ą▒ąĖčé ą░ą┤čĆąĄčüą░ (MSB, 9-ą╣ ą▒ąĖčé), čüąĖą│ąĮą░ą╗ idle line.

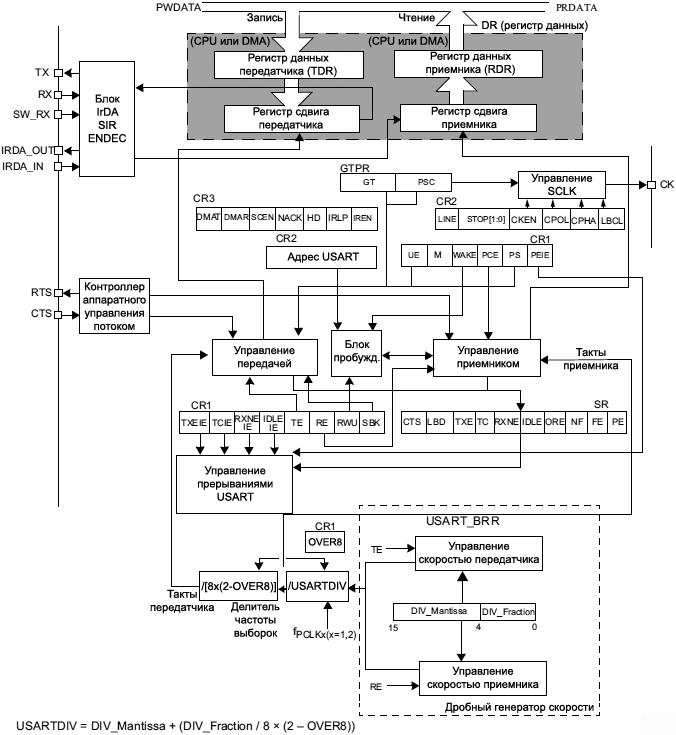

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ USART]

ąśąĮč鹥čĆč乥ą╣čü ąŠą▒čŗčćąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą▓ąĮąĄčłąĮąĖą╝ čüąĖčüč鹥ą╝ą░ą╝ čéčĆąĄą╝čÅ ąĮąŠąČą║ą░ą╝ąĖ (čüą╝. čĆąĖčü. 296). ąøčÄą▒ąŠą╣ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ąŠą▒ą╝ąĄąĮ USART čéčĆąĄą▒čāąĄčé ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą┤ą▓čāčģ čüąĖą│ąĮą░ą╗čīąĮčŗčģ ą▓čŗą▓ąŠą┤ąŠą▓: ą▓čģąŠą┤ąĮčŗąĄ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ (Receive Data In, RX) ąĖ ą▓čŗčģąŠą┤ąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ (Transmit Data Out, TX):

RX: ą▓čģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ. ąśčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ č鹥čģąĮąĖą║ąĖ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ą┤ą╗čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, čćč鹊ą▒čŗ ąŠčéą┤ąĄą╗ąĖčéčī ą┐ąŠą╗ąĄąĘąĮčŗąĄ ą┐čĆąĖčģąŠą┤čÅčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ ąŠčé čłčāą╝ą░.

TX: ą▓čŗčģąŠą┤ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĘą░ą┐čĆąĄčēąĄąĮ, ąĮąŠąČą║ą░ ą▓čŗčģąŠą┤ą░ ą▓ąŠąĘą▓čĆą░čéąĖčé čüą▓ąŠčÄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ ą┐ąŠčĆčéą░ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (GPIO). ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ čĆą░ąĘčĆąĄčłąĄąĮ ąĖ ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ, čāčĆąŠą▓ąĄąĮčī ą▓čŗčģąŠą┤ą░ ąĮąŠąČą║ąĖ TX ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1. ąÆ čĆąĄąČąĖą╝ą░čģ single-wire ąĖ smartcard, čŹč鹊čé ą▓čŗą▓ąŠą┤ I/O ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ (ąĮą░ čāčĆąŠą▓ąĮąĄ USART ą┤ą░ąĮąĮčŗąĄ ąĘą░č鹥ą╝ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ąĮą░ SW_RX).

ą¦ąĄčĆąĄąĘ čŹčéąĖ ą▓čŗą▓ąŠą┤čŗ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ąĖ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ USART ą║ą░ą║ čäčĆąĄą╣ą╝čŗ. ąÆ čŹč鹊ą╝ ą┐čĆąŠčåąĄčüčüąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĄąĄ:

ŌĆó ąĪąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ ą╗ąĖąĮąĖąĖ (Idle Line) ą┤ąŠ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╗ąĖ ą┐čĆąĖąĄą╝ą░.

ŌĆó Start-ą▒ąĖčé.

ŌĆó ąĪą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ (8 ąĖą╗ąĖ 9 ą▒ąĖčé), čüą░ą╝čŗą╣ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé čüą╗ąŠą▓ą░ (LSB) ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝.

ŌĆó 0.5,1, 1.5, 2 Stop-čüč鹊ą┐-ą▒ąĖčé, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖčģ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ čäčĆąĄą╣ą╝ą░.

ŌĆó ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤čĆąŠą▒ąĮčŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ čüą║ąŠčĆąŠčüčéąĖ - čü 12-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ą╝ą░ąĮčéąĖčüčüąŠą╣ ąĖ 4-ą▒ąĖčéąĮąŠą╣ ą┤čĆąŠą▒ąĮąŠą╣ čćą░čüčéčīčÄ.

ŌĆó ąĀąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ (USART_SR).

ŌĆó ąĀąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ (USART_DR).

ŌĆó ąĀąĄą│ąĖčüčéčĆ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čüą║ąŠčĆąŠčüčéąĖ (USART_BRR) čü 12-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ą╝ą░ąĮčéąĖčüčüąŠą╣ ąĖ 4-ą▒ąĖčéąĮąŠą╣ ą┤čĆąŠą▒ąĮąŠą╣ čćą░čüčéčīčÄ.

ŌĆó ąĀąĄą│ąĖčüčéčĆ ąĘą░čēąĖčéąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, Guardtime Register (USART_GTPR) ą▓ čüą╗čāčćą░ąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čĆąĄąČąĖą╝ą░ Smartcard.

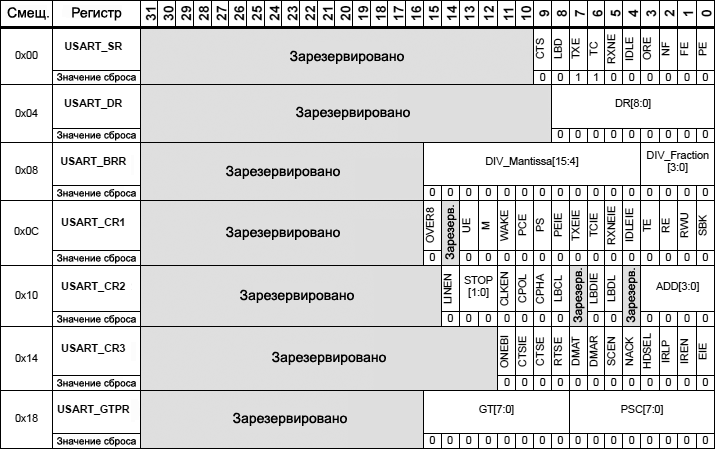

ą×ą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ąĖčģ ą▒ąĖčé čüą╝. ą┤ą░ą╗ąĄąĄ ą▓ąŠ ą▓čĆąĄąĘą║ą░čģ čĆą░ąĘą┤ąĄą╗ą░ "ąĀąĄą│ąĖčüčéčĆčŗ USART".

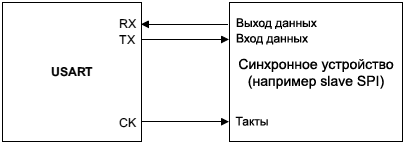

ąöą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ą▓čŗą▓ąŠą┤ čéą░ą║č鹊ą▓:

ŌĆó CK: ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░. ąØą░ čŹč鹊čé ą▓čŗą▓ąŠą┤ ą▓čŗą┤ą░čÄčéčüčÅ čéą░ą║čéčŗ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ čĆąĄąČąĖą╝čā SPI master (ąĮąĄčé čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĮą░ ą▒ąĖčéą░čģ start ąĖ stop, ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą▓čŗą▒ąĖčĆą░ąĄą╝ą░čÅ ąŠą┐čåąĖčÅ ąŠčéą┐čĆą░ą▓ą║ąĖ čéą░ą║č鹊ą▓ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ ąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝ ą▒ąĖč鹥 ą┤ą░ąĮąĮčŗčģ). ą¤ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ąĖ čüąĖąĮčģčĆąŠąĮąĮąŠ ą╝ąŠą│čāčé ą┐čĆąĖąĮąĖą╝ą░čéčīčüčÅ ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ ąĮąŠąČą║čā RX. ąŁč鹊 ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ąĮąĄčłąĮąĖą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, čā ą║ąŠč鹊čĆčŗčģ ąĄčüčéčī čĆąĄą│ąĖčüčéčĆčŗ čüą┤ą▓ąĖą│ą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ ą┤čĆą░ą╣ą▓ąĄčĆčŗ LCD). ążą░ąĘą░ ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ. ąÆ čĆąĄąČąĖą╝ąĄ smartcard CK ą╝ąŠąČąĄčé ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčéčī čéą░ą║čéčŗ ą┤ą╗čÅ čüą╝ą░čĆčé-ą║ą░čĆčéčŗ.

ąÆ čĆąĄąČąĖą╝ąĄ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ąŠą╝ čéčĆąĄą▒čāčÄčéčüčÅ ąĄčēąĄ 2 ą▓čŗą▓ąŠą┤ą░:

ŌĆó CTS: čüąĖą│ąĮą░ą╗ Clear To Send, ą▒ą╗ąŠą║ąĖčĆčāčÄčēąĖą╣ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ č鹥ą║čāčēąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ (ą║ąŠą│ą┤ą░ CTS = 1).

ŌĆó RTS: čüąĖą│ąĮą░ą╗ Request To Send, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖą╣, čćč鹊 USART ą│ąŠč鹊ą▓ ą┐čĆąĖąĮąĖą╝ą░čéčī ą┤ą░ąĮąĮčŗąĄ (ą║ąŠą│ą┤ą░ RTS = 0).

ąĀąĖčü. 296. ąæą╗ąŠą║-čüčģąĄą╝ą░ USART.

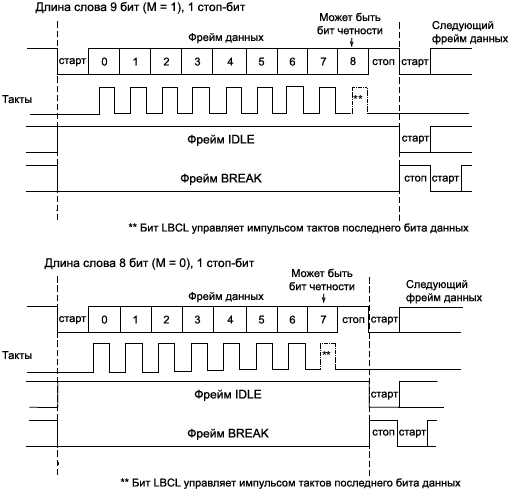

ąĪąĖą╝ą▓ąŠą╗ USART. ąöą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī ą┤ą╗ąĖąĮčā čüą╗ąŠą▓ą░ 8 ąĖą╗ąĖ 9 ą▒ąĖčé ą┐čāč鹥ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖčéą░ M ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1 (čüą╝. čĆąĖčü. 297).

ąØąŠąČą║ą░ TX ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ start-ą▒ąĖčé, ąĖ ą▓ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ stop-ą▒ąĖčé.

Idle. ąĪąĖą╝ą▓ąŠą╗ Idle ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆčāąĄčéčüčÅ ą║ą░ą║ čäčĆąĄą╣ą╝ (ąĖą┤čāčēąĖą╣ ą┐ąŠčüą╗ąĄ start-ą▒ąĖčéą░), ą│ą┤ąĄ ą▓čüąĄ ą▒ąĖčéčŗ čĆą░ą▓ąĮčŗ 1 (ą▓čüąĄ ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ą▓ ą╗ąŠą│. 1, čŹč鹊 čüąŠčüč鹊čÅąĮąĖąĄ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ stop-ą▒ąĖč鹊ą▓).

Break. ąĪąĖą╝ą▓ąŠą╗ Break ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ą▓čüąĄ 0 ą▓ č鹥č湥ąĮąĖąĄ ą▓čüąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ čäčĆąĄą╣ą╝ą░. ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┤ą░ąĮąĮčŗčģ čäčĆąĄą╣ą╝ą░ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ą▓čüčéą░ą▓ą╗čÅąĄčé 1 ąĖą╗ąĖ 2 stop-ą▒ąĖčéą░ (ą╗ąŠą│. 1), čćč鹊ą▒čŗ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčéčī start-ą▒ąĖčé.

ą¤ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝ čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ąŠą▒čēąĖą╝ ą│ąĄąĮąĄčĆą░č鹊čĆąŠą╝ čüą║ąŠčĆąŠčüčéąĖ (baud rate generator). ąóą░ą║čéčŗ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ.

ąĀąĖčü. 297. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą╗ąĖąĮčŗ čüą╗ąŠą▓ą░ (čäčĆąĄą╣ą╝ą░).

ą¤ąĄčĆąĄą┤ą░čéčćąĖą║ ą╝ąŠąČąĄčé ąŠčéą┐čĆą░ą▓ą╗čÅčéčī čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ 8 ąĖą╗ąĖ 9 ą▒ąĖčé, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčéą░ M. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit enable, TE), ą┤ą░ąĮąĮčŗąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓čŗą▓ąŠą┤ąĖčéčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤ TX, ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čéą░ą║č鹊ą▓čŗąĄ ąĖą╝ą┐čāą╗čīčüčŗ ąĮą░ ą▓čŗą▓ąŠą┤ CK.

ą¤ąĄčĆąĄą┤ą░čćą░ čüąĖą╝ą▓ąŠą╗ą░. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ USART ą┤ą░ąĮąĮčŗąĄ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĮą░čĆčāąČčā ąĮą░ ą▓čŗą▓ąŠą┤ TX, ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé (LSB) ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čĆąĄą│ąĖčüčéčĆ USART_DR čüąŠčüč鹊ąĖčé ąĖąĘ ą▒čāč乥čĆą░ (TDR) ą╝ąĄąČą┤čā ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čłąĖąĮąŠą╣ ąĖ čĆąĄą│ąĖčüčéčĆąŠą╝ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (čüą╝. čĆąĖčü. 296).

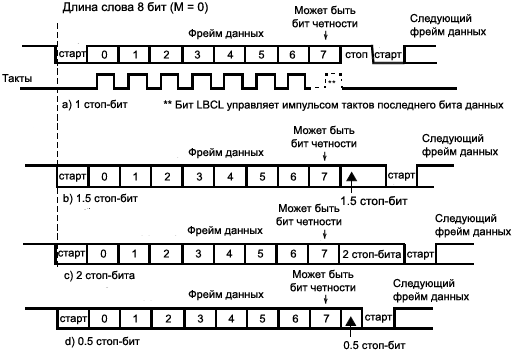

ąÜą░ąČą┤ąŠą╝čā čüąĖą╝ą▓ąŠą╗čā ą┐čĆąĄą┤čłąĄčüčéą▓čāąĄčé start-ą▒ąĖčé čü ą╗ąŠą│. 0 ą▓ č鹥č湥ąĮąĖąĄ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąŠą┤ąĮąŠą│ąŠ ą▒ąĖčéą░. ąĪąĖą╝ą▓ąŠą╗ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ stop-ą▒ąĖčé. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ ą▓ą░čĆąĖą░ąĮčéčŗ ą▓čŗą▒ąŠčĆą░ stop-ą▒ąĖč鹊ą▓: 0.5, 1, 1.5 ąĖ 2 stop-ą▒ąĖčéą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖčé TE ąĮąĄ ą┤ąŠą╗ąČąĄąĮ čüą▒čĆą░čüčŗą▓ą░čéčīčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. ąĪą▒čĆąŠčü ą▒ąĖčéą░ TE ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠą▓čĆąĄą┤ąĖčé ą┤ą░ąĮąĮčŗąĄ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TX, ą┐ąŠč鹊ą╝čā čćč鹊 ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čüč湥čéčćąĖą║ąĖ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čüą║ąŠčĆąŠčüčéąĖ ąŠčüčéą░ąĮąŠą▓čÅčéčüčÅ, ąĖ č鹥ą║čāčēąĖąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐ąŠč鹥čĆčÅąĮčŗ. ą¤ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą▒ąĖčéą░ TE ą▒čāą┤ąĄčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ čäčĆąĄą╣ą╝ idle.

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ stop-ą▒ąĖč鹊ą▓. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ čü ą║ą░ąČą┤čŗą╝ čüąĖą╝ą▓ąŠą╗ąŠą╝ stop-ą▒ąĖč鹊ą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ 2 (USART_CR2), ą▒ąĖčéą░ą╝ąĖ 13:12.

ŌĆó 1 stop-ą▒ąĖčé: čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ ą║ąŠą╗ąĖč湥čüčéą▓ą░ stop-ą▒ąĖč鹊ą▓.

ŌĆó 2 stop-ą▒ąĖčéą░: čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą▒čāą┤ąĄčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čĆąĄąČąĖą╝ą░čģ ąŠą▒čŗčćąĮąŠą│ąŠ USART, single-wire ąĖ čĆąĄąČąĖą╝ąĄ ą╝ąŠą┤ąĄą╝ą░.

ŌĆó 0.5 stop-ą▒ąĖčéą░: ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖ ą┐čĆąĖąĄą╝ąĄ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ Smartcard.

ŌĆó 1.5 stop-ą▒ąĖčéą░: ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ąĖ ą┐čĆąĖąĄą╝ąĄ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ Smartcard.

ążčĆąĄą╣ą╝ idle čéą░ą║ąČąĄ ą▒čāą┤ąĄčé ą▓ą║ą╗čÄčćą░čéčī ą▓ čüąĄą▒čÅ ąĖ stop-ą▒ąĖčéčŗ.

ą¤ąĄčĆąĄą┤ą░čćą░ break ą▒čāą┤ąĄčé čüąŠčüč鹊čÅčéčī ąĖąĘ 10 ą▒ąĖčé ą▓ ą╗ąŠą│. 0, ąĘą░ ą║ąŠč鹊čĆčŗą╝ąĖ ąĖą┤ąĄčé čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ stop-ą▒ąĖčé (ą║ąŠą│ą┤ą░ ą▒ąĖčé M = 0) ąĖ 11 ą▒ąĖčé ą▓ ą╗ąŠą│. 0, ąĘą░ ą║ąŠč鹊čĆčŗą╝ąĖ ąĖą┤ąĄčé čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ stop-ą▒ąĖčé (ą║ąŠą│ą┤ą░ ą▒ąĖčé M = 1). ąØąĄą╗čīąĘčÅ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą╗ąĖąĮąĮčŗąĄ čüąĖą╝ą▓ąŠą╗čŗ break (ą║ąŠą│ą┤ą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ąĮčāą╗ąĄą╣ ą▒ąŠą╗čīčłąĄ 10/11 ą▒ąĖčé).

ąĀąĖčü. 298. ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗąĄ stop-ą▒ąĖčéčŗ.

ą¤čĆąŠčåąĄą┤čāčĆą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░:

1. ąĀą░ąĘčĆąĄčłąĖč鹥 USART ąĘą░ą┐ąĖčüčīčÄ ą▓ 1 ą▒ąĖčéą░ UE čĆąĄą│ąĖčüčéčĆą░ USART_CR1.

2. ąŚą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāą╣č鹥 ą▒ąĖčé M ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┤ą╗ąĖąĮčā čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ.

3. ąŚą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāą╣č鹥 ą║ąŠą╗ąĖč湥čüčéą▓ąŠ stop-ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR2.

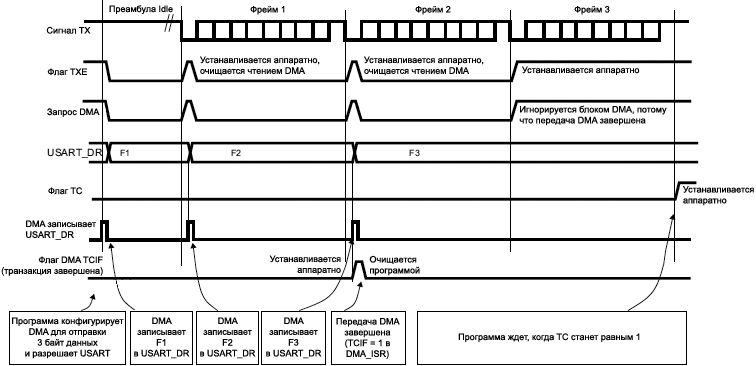

4. ąÆčŗą▒ąĄčĆąĖč鹥 čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ DMA ą┐ąĄčĆąĄą┤ą░čćąĖ (DMAT) ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR3, ąĄčüą╗ąĖ ąĖą╝ąĄčÄčé ą╝ąĄčüč鹊 ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą▒čāč乥čĆą░ą╝ąĖ (Multibuffer Communication). ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 čĆąĄą│ąĖčüčéčĆ DMA, ą║ą░ą║ čāą║ą░ąĘą░ąĮąŠ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ multibuffer communication.

5. ąÆčŗą▒ąĄčĆąĖč鹥 ąČąĄą╗ą░ąĄą╝čāčÄ čüą║ąŠčĆąŠčüčéčī (baud rate), ąĖčüą┐ąŠą╗čīąĘčāčÅ čĆąĄą│ąĖčüčéčĆ USART_BRR.

6. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé TE ą▓ USART_CR1, čćč鹊ą▒čŗ ąŠčéą┐čĆą░ą▓ąĖčéčī idle frame ą▓ ą║ą░č湥čüčéą▓ąĄ ą┐ąĄčĆą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

7. ąŚą░ą┐ąĖčłąĖč鹥 ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą▓ čĆąĄą│ąĖčüčéčĆ USART_DR (čŹč鹊 ąŠčćąĖčüčéąĖčé ą▒ąĖčé TXE). ąÆ čüą╗čāčćą░ąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ą▒čāč乥čĆą░ ą┐ąŠą▓č鹊čĆčÅą╣č鹥 čŹčéčā ąŠą┐ąĄčĆą░čåąĖčÄ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čüąĖą╝ą▓ąŠą╗ą░.

8. ą¤ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ USART_DR ą┐ąŠą┤ąŠąČą┤ąĖč鹥, ą║ąŠą│ą┤ą░ TC čüčéą░ąĮąĄčé čĆą░ą▓ąĮčŗą╝ 1. ąŁč鹊 ą┐ąŠą║ą░ąČąĄčé, čćč鹊 ą▒čŗą╗ą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čäčĆąĄą╣ą╝ą░. ąØą░ą┐čĆąĖą╝ąĄčĆ, čŹč鹊 čéčĆąĄą▒čāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ USART ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ąĖą╗ąĖ ą▓ą▓ąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ Halt, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

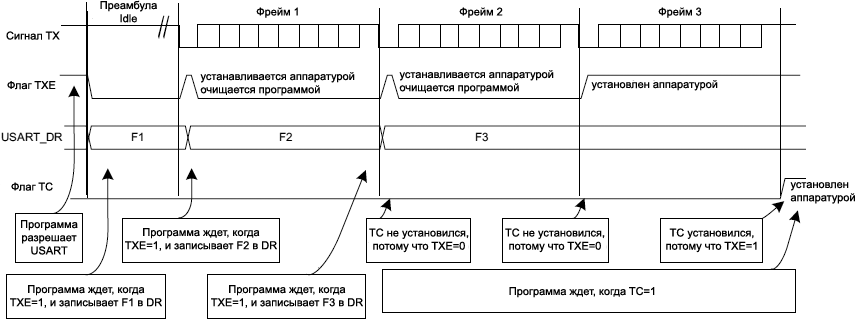

ą×ą┤ąĮąŠą▒ą░ą╣čéąĮčŗą╣ ąŠą▒ą╝ąĄąĮ. ąæąĖčé TXE ą▓čüąĄą│ą┤ą░ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ. TXE čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĖ čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé:

ŌĆó ąöą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮčŗ ąĖąĘ TDR ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąĖ ąĮą░čćą░ą╗ą░čüčī ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ.

ŌĆó ąĀąĄą│ąĖčüčéčĆ TDR ą┐čāčüčé.

ŌĆó ą£ąŠąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ USART_DR ą▒ąĄąĘ čĆąĖčüą║ą░ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüąĖ ą┐čĆąĄą┤čŗą┤čāčēąĖčģ ą┤ą░ąĮąĮčŗčģ.

ąŁč鹊čé čäą╗ą░ą│ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TXEIE.

ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą┤ą░čćą░, ąĖąĮčüčéčĆčāą║čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ USART_DR čüąŠčģčĆą░ąĮčÅąĄčé ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ TDR, ąĖ čŹčéąĖ ą┤ą░ąĮąĮčŗąĄ ąŠčéčéčāą┤ą░ ąĘą░č鹥ą╝ ą║ąŠą┐ąĖčĆčāčÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ą║ąŠą│ą┤ą░ ąĘą░ą║ąŠąĮčćąĖčéčüčÅ č鹥ą║čāčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░.

ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ, ąĖąĮčüčéčĆčāą║čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ USART_DR čüčĆą░ąĘčā ą┐ąŠą╝ąĄčēą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ, ąĖ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé TXE.

ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ čäčĆąĄą╣ą╝ (ą┐ąŠčüą╗ąĄ stop-ą▒ąĖčéą░), ąĖ čāčüčéą░ąĮąŠą▓ąĖą╗čüčÅ ą▒ąĖčé TXE, ą▒ąĖčé TC ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ 1. ąæčāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TCIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1.

ą¤ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆ USART_DR ą▓ą░ąČąĮąŠ ą┐ąŠą┤ąŠąČą┤ą░čéčī ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ TC=1 ą┐ąĄčĆąĄą┤ ąĘą░ą┐čĆąĄč鹊ą╝ USART, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ low-power mode (čüą╝. čĆąĖčü. 299, ą│ą┤ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ TC/TXE ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥).

ąĀąĖčü. 299. ąÜą░ą║ ą▓ąĄą┤čāčé čüąĄą▒čÅ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ą▒ąĖčéčŗ TC ąĖ TXE.

ąæąĖčé TC ąŠčćąĖčēą░ąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ąĖ ąŠą┐ąĄčĆą░čåąĖčÅą╝ąĖ:

1. ą¦č鹥ąĮąĖąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ USART_SR.

2. ąŚą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ USART_DR.

ąĪąĖą╝ą▓ąŠą╗ Break. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ SBK ą┐ąĄčĆąĄą┤ą░ąĄčé čüąĖą╝ą▓ąŠą╗ break (čüąĖą│ąĮą░ą╗ ąŠčüčéą░ąĮąŠą▓ą║ąĖ ą┐ąŠč鹊ą║ą░ ą┤ą░ąĮąĮčŗčģ). ąöą╗ąĖąĮą░ čäčĆąĄą╣ą╝ą░ break (ą║ą░ą║ ąĖ ą┤ą╗ąĖąĮą░ čäčĆąĄą╣ą╝ą░ ą▓čüąĄčģ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ čüąĖą╝ą▓ąŠą╗ąŠą▓) ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▒ąĖčéą░ M (čüą╝. čĆąĖčü. 297).

ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1 ą▒ąĖčé SBK, čüąĖą╝ą▓ąŠą╗ break ą┐ąŠčüčŗą╗ą░ąĄčéčüčÅ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ TX ą┐ąŠčüą╗ąĄ č鹥ą║čāčēąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąĖą╝ą▓ąŠą╗ą░. ąŁč鹊čé ą▒ąĖčé čüą▒čĆąŠčüąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ čüąĖą╝ą▓ąŠą╗ą░ break ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ (ą▓ąŠ ą▓čĆąĄą╝čÅ stop-ą▒ąĖčéą░ čüąĖą╝ą▓ąŠą╗ą░ break). USART ą▓čüčéą░ą▓ą╗čÅąĄčé ą▒ąĖčé ą╗ąŠą│. 1 ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čäčĆąĄą╣ą╝ą░ break, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī čĆą░čüą┐ąŠąĘąĮą░ą▓ą░ąĮąĖąĄ start-ą▒ąĖčéą░ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čäčĆąĄą╣ą╝ą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ čüą▒čĆąŠčüąĖčé ą▒ąĖčé SBK ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ break, č鹊 čüąĖą╝ą▓ąŠą╗ break ąĮąĄ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ. ąöą╗čÅ ą┤ą▓čāčģ čüą╗ąĄą┤čāčÄčēąĖčģ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ break ą▒ąĖčé SBK ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┐ąŠčüą╗ąĄ stop-ą▒ąĖčéą░ ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ break.

ąĪąĖą╝ą▓ąŠą╗ Idle. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ TE ą┐ąŠą▒čāąČą┤ą░ąĄčé USART ąŠčéą┐čĆą░ą▓ąĖčéčī čäčĆąĄą╣ą╝ idle ą┐ąĄčĆąĄą┤ ą┐ąĄčĆą▓čŗą╝ čäčĆąĄą╣ą╝ąŠą╝ ą┤ą░ąĮąĮčŗčģ.

USART ą╝ąŠąČąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčīčÄ 8 ąĖą╗ąĖ 9 ą▒ąĖčé, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▒ąĖčéą░ M ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1.

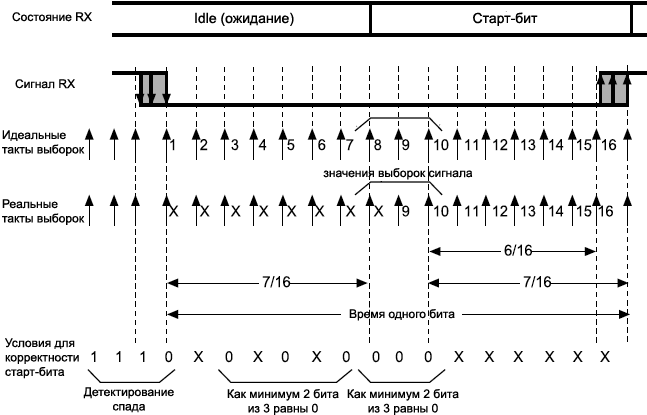

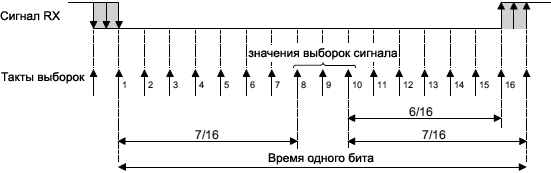

ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ start-ą▒ąĖčéą░. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüčéą░čĆčé-ą▒ąĖčéą░ ąŠą┤ąĖąĮą░ą║ąŠą▓ą░čÅ, ą║ąŠą│ą┤ą░ ą┤ąĄą╗ą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖčÅ čüąĖą│ąĮą░ą╗ą░ (oversampling) čü ą║čĆą░čéąĮąŠčüčéčīčÄ 16 ąĖą╗ąĖ 8.

ąÆ USART start-ą▒ąĖčé ą┤ąĄč鹥ą║čéąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čĆą░čüą┐ąŠąĘąĮą░ąĮą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą▒ąŠčĆąŠą║ čüąĖą│ąĮą░ą╗ą░: 1 1 1 0 X 0 X 0 X 0 0 0 0.

ąĀąĖčü. 300. ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ start-ą▒ąĖčéą░ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ 16 ąĖą╗ąĖ 8.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĮąĄ ąĘą░ą▓ąĄčĆčłąĄąĮą░, č鹊 ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ start-ą▒ąĖčéą░ ą┐čĆąĄą║čĆą░čēą░ąĄčéčüčÅ, ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ą▓ąŠąĘą▓čĆą░čēą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ idle state (ąĮąĖą║ą░ą║ąŠą╣ čäą╗ą░ą│ ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ), ą║ąŠą│ą┤ą░ ąŠąĮ ąŠąČąĖą┤ą░ąĄčé čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░.

ą¤ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąŠ ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄ start-ą▒ąĖčéą░ (čāčüčéą░ąĮąŠą▓ąĖą╗čüčÅ čäą╗ą░ą│ RXNE, ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ RXNEIE=1), ąĄčüą╗ąĖ 3 ą▓čŗą▒ąŠčĆą║ąĖ ą▒ąĖčéą░ čĆą░ą▓ąĮčŗ 0 (ą┐ąĄčĆą▓ą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ąĮą░ 3-ąĄą╝, 5-ąŠą╝ ąĖ 7-ąŠą╝ ą▒ąĖčéą░čģ ąĮą░čģąŠą┤ąĖčé 3 ą▒ąĖčéą░ ą▓ ą╗ąŠą│. 0, ąĖ ą▓č鹊čĆą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ąĮą░ 8-ąŠą╝, 9-ąŠą╝ ąĖ 10-ąŠą╝ ą▒ąĖčéą░čģ čéą░ą║ąČąĄ ąĮą░čģąŠą┤ąĖčé 3 ą▒ąĖčéą░ ą▓ ą╗ąŠą│. 0).

Start-ą▒ąĖčé čüčćąĖčéą░ąĄčéčüčÅ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╝ (čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RXNE, ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ RXNEIE=1), ąŠą┤ąĮą░ą║ąŠ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé NE (noise error, čäą╗ą░ą│ čłčāą╝ą░), ąĄčüą╗ąĖ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ ą▓čŗą▒ąŠčĆąŠą║ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 2 ąĖąĘ 3 ą▓čŗą▒ąŠčĆąŠą║ ą▒ąĖčé čŹč鹊 0 (ą▓čŗą▒ąŠčĆą║ą░ ąĮą░ 3-ąĄą╝, 5-ąŠą╝ ąĖ 7-ąŠą╝ ą▒ąĖčéą░čģ, ąĖ ą▓čŗą▒ąŠčĆą║ą░ ąĮą░ 8-ąŠą╝, 9-ąŠą╝ ąĖ 10-ąŠą╝ ą▒ąĖčéą░čģ). ąĢčüą╗ąĖ čāčüą╗ąŠą▓ąĖąĄ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ, ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüčéą░čĆčéą░ ąŠą▒čĆčŗą▓ą░ąĄčéčüčÅ, ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ą▓ąŠąĘą▓čĆą░čēą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ idle state (ąĮąĖą║ą░ą║ąŠą╣ čäą╗ą░ą│ ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ).

ąĢčüą╗ąĖ ą┤ą╗čÅ ąŠą┤ąĮąŠą╣ ąĖąĘ ą▓čŗą▒ąŠčĆąŠą║ (ą▓čŗą▒ąŠčĆą║ą░ ąĮą░ 3, 5 ąĖ 7 ą▒ąĖčéą░čģ, ąĖą╗ąĖ ą▓čŗą▒ąŠčĆą║ą░ ąĮą░ 8, 9 ąĖ 10 ą▒ąĖčéą░čģ), 2 ąĖąĘ 3 ą▒ąĖč鹊ą▓ ąĮą░ą╣ą┤ąĄąĮčŗ ą▓ 0, č鹊 start-ą▒ąĖčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčéčüčÅ, ąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé čłčāą╝ą░ NE.

ą¤čĆąĖąĄą╝ čüąĖą╝ą▓ąŠą╗ą░. ąØą░ ą┐čĆąĖąĄą╝ąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ ą▓čŗą▓ąŠą┤ RX, ąĮą░čćąĖąĮą░čÅ čü ą▒ąĖčéą░ LSB. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čĆąĄą│ąĖčüčéčĆ USART_DR čüąŠčüč鹊ąĖčé ąĖąĘ ą▒čāč乥čĆą░ (RDR) ą╝ąĄąČą┤čā ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čłąĖąĮąŠą╣ ąĖ čĆąĄą│ąĖčüčéčĆąŠą╝ čüą┤ą▓ąĖą│ą░ ą┐čĆąĖąĄą╝ą░.

ą¤čĆąŠčåąĄą┤čāčĆą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░:

1. ąĀą░ąĘčĆąĄčłąĖč鹥 USART ąĘą░ą┐ąĖčüčīčÄ ą▓ 1 ą▒ąĖčéą░ UE čĆąĄą│ąĖčüčéčĆą░ USART_CR1.

2. ąŚą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāą╣č鹥 ą▒ąĖčé M ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┤ą╗ąĖąĮčā čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ.

3. ąŚą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāą╣č鹥 ą║ąŠą╗ąĖč湥čüčéą▓ąŠ stop-ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR2.

4. ąÆčŗą▒ąĄčĆąĖč鹥 čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ DMA ą┐čĆąĖąĄą╝ą░ (DMAR) ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR3, ąĄčüą╗ąĖ ąĖą╝ąĄčÄčé ą╝ąĄčüč鹊 ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą▒čāč乥čĆą░ą╝ąĖ (Multibuffer Communication). ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 čĆąĄą│ąĖčüčéčĆ DMA, ą║ą░ą║ čāą║ą░ąĘą░ąĮąŠ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ multibuffer communication.

5. ąÆčŗą▒ąĄčĆąĖč鹥 ąČąĄą╗ą░ąĄą╝čāčÄ čüą║ąŠčĆąŠčüčéčī (baud rate), ąĖčüą┐ąŠą╗čīąĘčāčÅ čĆąĄą│ąĖčüčéčĆ USART_BRR.

6. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé RE ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1. ąŁč鹊 čĆą░ąĘčĆąĄčłąĖčé ą┐čĆąĖąĄą╝ąĮąĖą║, ą║ąŠč鹊čĆčŗą╣ ąĮą░čćąĮąĄčé ąĖčüą║ą░čéčī start-ą▒ąĖčé.

ąÜąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčé čüąĖą╝ą▓ąŠą╗:

ŌĆó ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé RXNE. ąŁč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą▓ RDR. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą┐čĆąĖąĮčÅčéčŗ, ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ (ą░ čéą░ą║ąČąĄ čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ąĮąĖą╝ čäą╗ą░ą│ąĖ ąŠčłąĖą▒ąŠą║).

ŌĆó ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé RXNEIE.

ŌĆó ą£ąŠą│čāčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ čäą╗ą░ą│ąĖ ąŠčłąĖą▒ą║ąĖ, ąĄčüą╗ąĖ ąĖą╝ąĄą╗ąĖ ą╝ąĄčüč鹊 (ą▒čŗą╗ąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮčŗ) čüąŠą▒čŗčéąĖčÅ ąŠčłąĖą▒ą║ąĖ čäčĆąĄą╣ą╝ą░ (frame error), čłčāą╝ą░ (noise error) ąĖą╗ąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ (overrun error).

ŌĆó ąÆ čĆąĄąČąĖą╝ąĄ multibuffer ą▒ąĖčé RXNE čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą▒ą░ą╣čéą░, ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ čćč鹥ąĮąĖąĄą╝ DMA ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┤ą░ąĮąĮčŗčģ.

ŌĆó ąÆ čĆąĄąČąĖą╝ąĄ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ą▒čāč乥čĆą░ ąŠčćąĖčüčéą║ą░ ą▒ąĖčéą░ RXNE ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, ą┐čāč鹥ą╝ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ USART_DR. ążą╗ą░ą│ RXNE čéą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ąŠčćąĖčüčéąĖčéčī ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ąĮčāą╗čÅ. ąæąĖčé RXNE ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą┐ąĄčĆąĄą┤ ąŠą║ąŠąĮčćą░ąĮąĖąĄą╝ ą┐čĆąĖąĄą╝ą░ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüąĖą╝ą▓ąŠą╗ą░, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąŠčłąĖą▒ą║ąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ (overrun error).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖčé RE ąĮąĄ ą┤ąŠą╗ąČąĄąĮ čüą▒čĆą░čüčŗą▓ą░čéčīčüčÅ ą┐čĆąĖ ą┐čĆąĖąĄą╝ąĄ ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ ą▒ąĖčé RE ąĘą░ą┐čĆąĄčēąĄąĮ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĖąĄą╝ą░, č鹊 ą┐čĆąĖąĄą╝ č鹥ą║čāčēąĄą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ ą▒čāą┤ąĄčé ąŠą▒ąŠčĆą▓ą░ąĮ.

ąĪąĖą╝ą▓ąŠą╗ Break. ąÜąŠą│ą┤ą░ ą▒čŗą╗ ą┐čĆąĖąĮčÅčé čüąĖą╝ą▓ąŠą╗ break, USART ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé čŹč鹊 ą║ą░ą║ ąŠčłąĖą▒ą║čā čäčĆąĄą╣ą╝ą░ (framing error).

ąĪąĖą╝ą▓ąŠą╗ Idle. ąÜąŠą│ą┤ą░ ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ čäčĆąĄą╣ą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ (idle frame), č鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čéą░ ąČąĄ ą┐čĆąŠčåąĄą┤čāčĆą░, čćč鹊 ąĖ ą┐čĆąĖ ą┐čĆąĖąĄą╝ąĄ čüąĖą╝ą▓ąŠą╗ą░, ą┐ą╗čÄčü ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé IDLEIE.

ą×čłąĖą▒ą║ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ. Overrun error ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčé ąĮąŠą▓čŗą╣ čüąĖą╝ą▓ąŠą╗, ąĮąŠ čäą╗ą░ą│ RXNE ąĮąĄ ą▒čŗą╗ ąŠčćąĖčēąĄąĮ. ąöą░ąĮąĮčŗąĄ ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąĄčĆąĄą╝ąĄčēąĄąĮčŗ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▓ čĆąĄą│ąĖčüčéčĆ RDR, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ ą▒ąĖčé RXNE.

ążą╗ą░ą│ RXNE čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ. ą×čłąĖą▒ą║ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ąĄčüą╗ąĖ čäą╗ą░ą│ RXNE čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčéčŗ čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ąĮąĄ ą▒čŗą╗ ąŠą▒čĆą░ą▒ąŠčéą░ąĮ ą┐čĆąĄą┤čŗą┤čāčēąĖą╣ ąĘą░ą┐čĆąŠčü DMA. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé overrun error:

ŌĆó ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé ORE.

ŌĆó ąóąĄą║čāčēąĄąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ RDR ąĮąĄ č鹥čĆčÅąĄčéčüčÅ. ą¤čĆąĄą┤čŗą┤čāčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠčüčéčāą┐ąĮčŗ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ USART_DR.

ŌĆó ąĀąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮ. ąÆ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ą╗čÄą▒čŗąĄ ą┐čĆąĖąĮčÅčéčŗąĄ ą┐čĆąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐ąŠč鹥čĆčÅąĮčŗ.

ŌĆó ąĪą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ ą╗ąĖą▒ąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé RXNEIE, ą╗ąĖą▒ąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ąŠą▒ą░ ą▒ąĖčéą░ EIE ąĖ DMAR.

ŌĆó ąæąĖčé ORE čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ USART_SR, ąĘą░ ą║ąŠč鹊čĆčŗą╝ čüą╗ąĄą┤čāąĄčé ąŠą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ USART_DR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖčé ORE, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ 菹╗ąĄą╝ąĄąĮčé ą┤ą░ąĮąĮčŗčģ ąĮą░ ą┐čĆąĖąĄą╝ąĄ ą▒čŗą╗ ą┐ąŠč鹥čĆčÅąĮ. ąĢčüčéčī 2 ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ:

ŌĆó ąĢčüą╗ąĖ RXNE=1, č鹊 ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ čüąŠčģčĆą░ąĮąĄąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┐čĆąĖąĄą╝ą░ RDR, ąĖ ąŠąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ.

ŌĆó ąĢčüą╗ąĖ RXNE=0, č鹊 čŹč鹊 ąĘąĮą░čćąĖčé, čćč鹊 ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čāąČąĄ ą▒čŗą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮčŗ, ąĖ ą┐ąŠčŹč鹊ą╝čā ą▓ RDR ąĮąĄč湥ą│ąŠ čüčćąĖčéčŗą▓ą░čéčī. ąŁč鹊čé čüą╗čāčćą░ą╣ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ, ą║ąŠą│ą┤ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖąĘ RDR ą▓ č鹊čé ą╝ąŠą╝ąĄąĮčé, ą║ą░ą║ ąĮąŠą▓čŗąĄ (ąĖ čāąČąĄ ą┐ąŠč鹥čĆčÅąĮąĮčŗąĄ) ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą┐čĆąĖąĮčÅčéčŗ. ąŁč鹊 čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ, ą║ąŠą│ą┤ą░ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĖąĮčÅčéčŗ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čćč鹥ąĮąĖčÅ (ą╝ąĄąČą┤čā ą┤ąŠčüčéčāą┐ąŠą╝ ąĮą░ čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ USART_SR ąĖ ą┤ąŠčüčéčāą┐ąŠą╝ ąĮą░ čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ USART_DR).

ąÆčŗą▒ąŠčĆ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą│ąŠ ą╝ąĄč鹊ą┤ą░ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ. ą¤čĆąĖąĄą╝ąĮąĖą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčé čĆą░ąĘąĮčŗąĄ, ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ č鹥čģąĮąĖą║ąĖ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ (ą║čĆąŠą╝ąĄ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░) ą┤ą╗čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, ą┐čāč鹥ą╝ ąŠčéą┤ąĄą╗ąĄąĮąĖčÅ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗčģ ą┐čĆąĖčģąŠą┤čÅčēąĖčģ ą┤ą░ąĮąĮčŗčģ ąĖ čłčāą╝ą░.

ą£ąĄč鹊ą┤ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą▒ąĖčéą░ OVER8 ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1, ąĖ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī 16 ąĖą╗ąĖ 8 ą║čĆą░čéąĮą░čÅ ą║ čéą░ą║čéą░ą╝ čüą║ąŠčĆąŠčüčéąĖ (čüą╝. čĆąĖčü. 301 ąĖ 302).

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ:

ŌĆó ąÆčŗą▒ąĄčĆąĖč鹥 ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖčÄ ąĮą░ 8 (OVER8=1), čćč鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī čāą▓ąĄą╗ąĖč湥ąĮąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ (ą┤ąŠ fPCLK/8). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ą┤ąŠą┐čāčüą║ ąĮą░ ą┤ąĄą▓ąĖą░čåąĖčÄ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ čüąĮąĖąČą░ąĄčéčüčÅ (čüą╝. ą┤ą░ą╗ąĄąĄ čüąĄą║čåąĖčÄ "ąöąŠą┐čāčüą║ čāčģąŠą┤ą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ USART").

ŌĆó ąÆčŗą▒ąĄčĆąĖč鹥 ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖčÄ ąĮą░ 16 (OVER8=0), čćč鹊ą▒čŗ čāą▓ąĄą╗ąĖčćąĖčéčī ą┤ąŠą┐čāčüą║ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą║ ą┤ąĄą▓ąĖą░čåąĖąĖ čéą░ą║č鹊ą▓. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čüą║ąŠčĆąŠčüčéčī ąŠą│čĆą░ąĮąĖč湥ąĮą░ fPCLK/16.

ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčéą░ ONEBIT ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR3 ą▓čŗą▒ąĖčĆą░ąĄčé ą╝ąĄč鹊ą┤, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┤ą╗čÅ ąŠčåąĄąĮą║ąĖ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░. ąĢčüčéčī 2 ąŠą┐čåąĖąĖ:

ŌĆó ą£ą░ąČąŠčĆąĖčéą░čĆąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ąĖąĘ 3 ąŠą▒čĆą░ąĘčåąŠą▓ čüąĖą│ąĮą░ą╗ą░, ą▓ąĘčÅčéčŗčģ ą┐ąŠ čåąĄąĮčéčĆčā ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠą│ąŠ ą▒ąĖčéą░. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ 3 čŹčéąĖ ą▓čŗą▒ąŠčĆą║ąĖ ąĮąĄ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗąĄ, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé NF.

ŌĆó ą×ą┤ąĮą░ ą▓čŗą▒ąŠčĆą║ą░ ą▓ čåąĄąĮčéčĆąĄ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠą│ąŠ ą▒ąĖčéą░.

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ:

ŌĆō ąÆčŗą▒ąĄčĆąĖč鹥 ą╝ąĄč鹊ą┤ ą╝ą░ąČąŠčĆąĖčéą░čĆąĮąŠčüčéąĖ ąĖąĘ 3 ą▓čŗą▒ąŠčĆąŠą║ (ONEBIT=0) ą║ąŠą│ą┤ą░ čĆą░ą▒ąŠčéą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ ąĘą░čłčāą╝ą╗ąĄąĮąĮąŠą╝ ąŠą║čĆčāąČąĄąĮąĖąĖ, ąĖ ąŠčéą▒čĆą░čüčŗą▓ą░ą╣č鹥 ą┤ą░ąĮąĮčŗąĄ, ą║ąŠą│ą┤ą░ ą▒čŗą╗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ čłčāą╝ (čüą╝. čéą░ą▒ą╗ąĖčåčā 133), ą┐ąŠč鹊ą╝čā čćč鹊 čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą┐ą░čĆą░ąĘąĖčéąĮčŗą╣ ą▓čŗą▒čĆąŠčü ą┐ąŠą╝ąĄčģąĖ.

ŌĆō ąÆčŗą▒ąĄčĆąĖč鹥 ą╝ąĄč鹊ą┤ ąŠą┤ąĖąĮąŠčćąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ (ONEBIT=1) ą║ąŠą│ą┤ą░ ąĮą░ ą╗ąĖąĮąĖąĖ čćąĖčüčéčŗą╣ čüąĖą│ąĮą░ą╗, čćč鹊ą▒čŗ čāą▓ąĄą╗ąĖčćąĖčéčī ą┤ąŠą┐čāčüą║ ąĮą░ ą┤ąĄą▓ąĖą░čåąĖčÄ čéą░ą║č鹊ą▓ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ (čüą╝. ą┤ą░ą╗ąĄąĄ čüąĄą║čåąĖčÄ "ąöąŠą┐čāčüą║ čāčģąŠą┤ą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ USART"). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▒ąĖčé NF ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ.

ąÜąŠą│ą┤ą░ ą▓ąŠ čäčĆąĄą╣ą╝ąĄ ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ čłčāą╝:

ŌĆó ąæąĖčé NF čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ ą▒ąĖčéą░ RXNE.

ŌĆó ąØąĄą┐čĆą░ą▓ąĖą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą╝ąĄčüčéčÅčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▓ čĆąĄą│ąĖčüčéčĆ USART_DR.

ŌĆó ąØąĄ ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ čüą╗čāčćą░ąĄ ąŠą▒ą╝ąĄąĮą░ ą┐ąŠ ąŠą┤ąĮąŠą╝čā ą▒ą░ą╣čéčā. ą×ą┤ąĮą░ą║ąŠ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čü ą▒ąĖč鹊ą╝ RXNE, ą║ąŠč鹊čĆčŗą╣ čüą░ą╝ ą┐ąŠ čüąĄą▒ąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąÆ čüą╗čāčćą░ąĄ multibuffer-ąŠą▒ą╝ąĄąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé ą▓čŗą┤ą░ąĮąŠ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé EIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR3.

ąæąĖčé NF čüą▒čĆąŠčüąĖčéčüčÅ ąŠą┐ąĄčĆą░čåąĖąĄą╣ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ USART_SR, ąĘą░ ą║ąŠč鹊čĆąŠą╣ ąĖą┤ąĄčé ąŠą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ USART_DR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖčÅ ąĮą░ 8 ąĮąĄą┤ąŠčüčéčāą┐ąĮą░ ą▓ čĆąĄąČąĖą╝ą░čģ Smartcard, IrDA ąĖ LIN. ąÆ čŹčéąĖčģ čĆąĄąČąĖą╝ą░čģ ą▒ąĖčé OVER8 ą░ą┐ą┐ą░čĆą░čéąĮąŠ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą▓ 0.

ąĀąĖčü. 301. ąÆčŗą▒ąŠčĆą║ą░ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ 16.

ąĀąĖčü. 302. ąÆčŗą▒ąŠčĆą║ą░ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ 8.

ąóą░ą▒ą╗ąĖčåą░ 133. ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čłčāą╝ą░ ą┤ą╗čÅ čüčćąĖčéčŗą▓ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ.

| ą×čåąĖčäčĆ. ąĘąĮą░č湥ąĮąĖąĄ |

ąĪčéą░čéčāčü NE |

ą¤čĆąĖąĮčÅč鹊ąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░ |

| 000 |

0 |

0 |

| 001 |

1 |

0 |

| 010 |

1 |

0 |

| 011 |

1 |

1 |

| 100 |

1 |

0 |

| 101 |

1 |

1 |

| 110 |

1 |

1 |

| 111 |

0 |

1 |

ą×čłąĖą▒ą║ą░ čäčĆąĄą╣ą╝ą░. Framing error ą┤ąĄč鹥ą║čéąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąĮąĄ ą▒čŗą╗ čĆą░čüą┐ąŠąĘąĮą░ąĮ stop-ą▒ąĖčé ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĖąĄą╝ą░ ą▓ ąŠąČąĖą┤ą░ąĄą╝ąŠą╝ ą┐čĆąŠą╝ąĄąČčāčéą║ąĄ ą▓čĆąĄą╝ąĄąĮąĖ - ą╗ąĖą▒ąŠ ąĖąĘ-ąĘą░ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, ą╗ąĖą▒ąŠ ąĖąĘ-ąĘą░ čćčĆąĄąĘą╝ąĄčĆąĮąŠą│ąŠ čłčāą╝ą░.

ąÜąŠą│ą┤ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮą░ ąŠčłąĖą▒ą║ą░ čäčĆąĄą╣ą╝ą░:

ŌĆó ąæąĖčé FE čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ.

ŌĆó ąØąĄą┐čĆą░ą▓ąĖą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▓ čĆąĄą│ąĖčüčéčĆ USART_DR.

ŌĆó ąÆ čüą╗čāčćą░ąĄ ąŠą┤ąĮąŠą▒ą░ą╣č鹊ą▓ąŠą│ąŠ ąŠą▒ą╝ąĄąĮą░ ąĮąĖą║ą░ą║ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ. ą×ą┤ąĮą░ą║ąŠ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čü ą▒ąĖč鹊ą╝ RXNE, ą║ąŠč鹊čĆčŗą╣ čüą░ą╝ ą┐ąŠ čüąĄą▒ąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąÆ čüą╗čāčćą░ąĄ ą╝ąĮąŠą│ąŠą▒ą░ą╣čéąĮąŠą╣ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ ą▒čāą┤ąĄčé ą▓čŗą┤ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé EIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR3.

ąæąĖčé FE čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ USART_SR, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ąŠą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ USART_DR.

ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗąĄ stop-ą▒ąĖčéčŗ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĖąĄą╝ą░. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ stop-ą▒ąĖčé ą╝ąŠąČąĮąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą▒ąĖčéą░ą╝ąĖ USART_CR2. ąŁč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī 1 ąĖą╗ąĖ 2 ą▒ąĖčéą░ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ, ąĖ 0.5 ąĖą╗ąĖ 1.5 ą▓ čĆąĄąČąĖą╝ąĄ Smartcard.

0.5 stop-ą▒ąĖčéą░ (ą┐čĆąĖąĄą╝ ą▓ čĆąĄąČąĖą╝ąĄ Smartcard): ą┤ą╗čÅ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ ąĮąĄ ą┤ąĄą╗ą░čÄčéčüčÅ ą▓čŗą▒ąŠčĆą║ąĖ. ąÜą░ą║ čüą╗ąĄą┤čüčéą▓ąĖąĄ, ą┐čĆąĖ ą▓čŗą▒ąŠčĆąĄ 0,5 čüč鹊ą┐-ą▒ąĖčéą░ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą▒ąĮą░čĆčāąČąĄąĮą░ ąŠčłąĖą▒ą║ą░ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĮąŠą│ąŠ čäčĆąĄą╣ą╝ą░, ąĖ čüąĖą│ąĮą░ą╗ break ąĮąĄ ą┤ąĄč鹥ą║čéąĖčĆčāąĄčéčüčÅ.

1 stop-ą▒ąĖčé: ą░ąĮą░ą╗ąĖąĘ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ 1 stop-ą▒ąĖčéą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĮą░ 8-ąŠą╣, 9-ąŠą╣ ąĖ 10-ąŠą╣ ą▓čŗą▒ąŠčĆą║ą░čģ.

1.5 stop-ą▒ąĖčéą░ (čĆąĄąČąĖą╝ Smartcard): ą║ąŠą│ą┤ą░ ąĖą┤ąĄčé ą┐ąĄčĆąĄą┤ą░čćą░ ą▓ čĆąĄąČąĖą╝ąĄ smartcard, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠą▓ąĄčĆąĖčéčī, ą║ą░ą║ąĖąĄ ą┤ą░ąĮąĮčŗąĄ ąŠčéą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▒ą╗ąŠą║ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ (ą▒ąĖčé RE=1 ą▓ USART_CR1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ), ąĖ stop-ą▒ąĖčé ą┐čĆąŠą▓ąĄčĆčÅąĄčéčüčÅ ąĮą░ ąĮą░ą╗ąĖčćąĖąĄ ąŠčłąĖą▒ą║ąĖ č湥čéąĮąŠčüčéąĖ ąĮą░ čüą╝ą░čĆčé-ą║ą░čĆč鹥. ąĢčüą╗ąĖ ą▒čŗą╗ąŠ čüąŠą▒čŗčéąĖąĄ ąŠčłąĖą▒ą║ąĖ č湥čéąĮąŠčüčéąĖ, č鹊 čüą╝ą░čĆčé-ą║ą░čĆčéą░ ą┐ąŠą┤čéčÅą│ąĖą▓ą░ąĄčé čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ ą▓ ą╗ąŠą│. 0 ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ (čüąĖą│ąĮą░ą╗ NACK), ą║ąŠč鹊čĆčŗą╣ ąŠą┐ąŠąĘąĮą░ąĄčéčüčÅ ą║ą░ą║ ąŠčłąĖą▒ą║ą░ čäčĆąĄą╣ą╝ą░. ąŚą░č鹥ą╝ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ FE ą▓ą╝ąĄčüč鹥 čü RXNE ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ 1.5 stop-ą▒ąĖčéą░. ąÉąĮą░ą╗ąĖąĘ čāčĆąŠą▓ąĮčÅ ą┤ą╗čÅ 1.5 stop-ą▒ąĖčéą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĮą░ 16-ąŠą╣, 17-ąŠą╣ ąĖ 18-ąŠą╣ ą▓čŗą▒ąŠčĆą║ą░čģ (1 ą┐ąĄčĆąĖąŠą┤ čüą║ąŠčĆąŠčüčéąĖ ą┐ąŠčüą╗ąĄ ąĮą░čćą░ą╗ą░ stop-ą▒ąĖčéą░). ąöą╗čÅ 1.5 stop-ą▒ąĖčéą░ ą╝ąŠąČąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą┤ąĄą║ąŠą╝ą┐ąŠąĘąĖčåąĖčÅ ąĮą░ 2 čćą░čüčéąĖ: ąŠą┤ąĮą░ ąĖąĘ 0.5 ą┐ąĄčĆąĖąŠą┤ą░ čüą║ąŠčĆąŠčüčéąĖ, ą║ąŠą│ą┤ą░ ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ąĘą░ ą║ąŠč鹊čĆąŠą╣ ąĖą┤ąĄčé ą▓čĆąĄą╝čÅ 1 ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ stop-ą▒ąĖčéą░, ą▓ č鹥č湥ąĮąĖąĄ ą║ąŠč鹊čĆąŠą│ąŠ ą┐ąŠčüąĄčĆąĄą┤ąĖąĮąĄ ąĖą┤ąĄčé ą░ąĮą░ą╗ąĖąĘ čüąĖą│ąĮą░ą╗ą░. ąĪą╝. čüąĄą║čåąĖčÄ 30.3.11: Smartcard ą┤ą░čéą░čłąĖčéą░ [1].

2 stop-ą▒ąĖčéą░: ą░ąĮą░ą╗ąĖąĘ ą┤ą╗čÅ 2 čüč鹊ą┐-ą▒ąĖčé ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĮą░ 8-ąŠą╣, 9-ąŠą╣ ąĖ 10-ąŠą╣ ą▓čŗą▒ąŠčĆą║ą░čģ ą┐ąĄčĆą▓ąŠą│ąŠ čüč鹊ą┐-ą▒ąĖčéą░. ąĢčüą╗ąĖ ą▒čŗą╗ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ąŠčłąĖą▒ą║ą░ čäčĆąĄą╣ą╝ą░ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆą▓ąŠą│ąŠ čüč鹊ą┐-ą▒ąĖčéą░, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ čäčĆąĄą╣ą╝ą░. ąÆč鹊čĆąŠą╣ čüč鹊ą┐-ą▒ąĖčé ąĮąĄ ą┐čĆąŠą▓ąĄčĆčÅąĄčéčüčÅ ąĮą░ ą┐čĆąĄą┤ą╝ąĄčé ąŠčłąĖą▒ą║ąĖ čäčĆąĄą╣ą╝ą░. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RXNE ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą┐ąĄčĆą▓ąŠą│ąŠ stop-ą▒ąĖčéą░.

ąöčĆąŠą▒ąĮčŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ čüą║ąŠčĆąŠčüčéąĖ. ąĪą║ąŠčĆąŠčüčéčī ąŠą▒ą╝ąĄąĮą░ (baud rate) ą┤ą╗čÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (ąŠą▒ąŠąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓ RX ąĖ TX) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ Mantissa ąĖ Fraction ą┤ąĄą╗ąĖč鹥ą╗čÅ USARTDIV.

ążąŠčĆą╝čāą╗ą░ 1. čüą║ąŠčĆąŠčüčéčī ą┤ą╗čÅ čüčéą░ąĮą┤ą░čĆčéąĮąŠą│ąŠ USART (ą▓ą║ą╗čÄčćą░čÅ čĆąĄąČąĖą╝ SPI):

fCK

Tx/Rx baud = --------------------------

8 x (2 ŌĆō OVER8) x USARTDIV

ążąŠčĆą╝čāą╗ą░ 2. čüą║ąŠčĆąŠčüčéčī ą┤ą╗čÅ čĆąĄąČąĖą╝ąŠą▓ Smartcard, LIN ąĖ IrDA:

fCK

Tx/Rx baud = -------------

16 x USARTDIV

USARTDIV čŹč鹊 čćąĖčüą╗ąŠ čü čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ąĘą░ą┐čÅč鹊ą╣ ą▒ąĄąĘ ąĘąĮą░ą║ą░, ąĘą░ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_BRR.

ŌĆó ąÜąŠą│ą┤ą░ OVER8=0, ą┤čĆąŠą▒ąĮą░čÅ čćą░čüčéčī ą║ąŠą┤ąĖčĆčāąĄčéčüčÅ 4 ą▒ąĖčéą░ą╝ąĖ, ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ DIV_fraction[3:0] čĆąĄą│ąĖčüčéčĆą░ USART_BRR.

ŌĆó ąÜąŠą│ą┤ą░ OVER8=1, ą┤čĆąŠą▒ąĮą░čÅ čćą░čüčéčī ą║ąŠą┤ąĖčĆčāąĄčéčüčÅ 3 ą▒ąĖčéą░ą╝ąĖ, ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ DIV_fraction[2:0] čĆąĄą│ąĖčüčéčĆą░ USART_BRR, ąĖ ą▒ąĖčé DIV_fraction[3] ą┤ąŠą╗ąČąĄąĮ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ čüą▒čĆąŠčłąĄąĮąĮčŗą╝ ą▓ 0.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čüč湥čéčćąĖą║ąĖ čüą║ąŠčĆąŠčüčéąĖ ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ąĮąŠą▓čŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čüą║ąŠčĆąŠčüčéąĖ ą┐ąŠčüą╗ąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą▓ USART_BRR. ąĪą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, čĆąĄą│ąĖčüčéčĆą░ čüą║ąŠčĆąŠčüčéąĖ ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ąĖąĘą╝ąĄąĮčÅčéčīčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą░ą║čéąĖą▓ąĮąŠą│ąŠ ąŠą▒ą╝ąĄąĮą░.

[ą¤čĆąĖą╝ąĄčĆ 1]

ąĢčüą╗ąĖ DIV_Mantissa = 0d27 ąĖ DIV_Fraction = 0d12 (USART_BRR = 0x1BC), č鹊ą│ą┤ą░

Mantissa (USARTDIV) = 0d27

Fraction (USARTDIV) = 12/16 = 0d0.75

Therefore USARTDIV = 0d27.75

[ą¤čĆąĖą╝ąĄčĆ 2]

ąöą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ USARTDIV = 0d25.62 ą┐ąŠą╗čāčćą░ąĄčéčüčÅ:

DIV_Fraction = 16*0d0.62 = 0d9.92

ąæą╗ąĖąČą░ą╣čłąĄąĄ čĆąĄą░ą╗čīąĮąŠąĄ čćąĖčüą╗ąŠ 0d10 = 0xA

DIV_Mantissa = mantissa (0d25.620) = 0d25 = 0x19

ąóąŠą│ą┤ą░ USART_BRR = 0x19A čüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ USARTDIV = 0d25.625

[ą¤čĆąĖą╝ąĄčĆ 3]

ąöą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ USARTDIV = 0d50.99 ą┐ąŠą╗čāčćą░ąĄčéčüčÅ:

DIV_Fraction = 16*0d0.99 = 0d15.84

ąæą╗ąĖąČą░ą╣čłąĄąĄ čĆąĄą░ą╗čīąĮąŠąĄ čćąĖčüą╗ąŠ 0d16 = 0x10 => ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ DIV_frac[3:0] => ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┤ąŠą▒ą░ą▓ą╗ąĄąĮ ą┐ąĄčĆąĄąĮąŠčü ą║ ą╝ą░ąĮčéąĖčüčüąĄ.

DIV_Mantissa = mantissa (0d50.990 + carry) = 0d51 = 0x33

ąóąŠą│ą┤ą░ USART_BRR = 0x330 hence USARTDIV = 0d51.000

[ą¤čĆąĖą╝ąĄčĆ 1]

ąĢčüą╗ąĖ DIV_Mantissa = 0x27 ąĖ DIV_Fraction[2:0]= 0d6 (USART_BRR = 0x1B6), č鹊ą│ą┤ą░

Mantissa (USARTDIV) = 0d27

Fraction (USARTDIV) = 6/8 = 0d0.75

ą×čéčüčÄą┤ą░ USARTDIV = 0d27.75.

[ą¤čĆąĖą╝ąĄčĆ 2]

ąöą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ USARTDIV = 0d25.62. ąŁč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā:

DIV_Fraction = 8*0d0.62 = 0d4.96

ąæą╗ąĖąČą░ą╣čłąĄąĄ čĆąĄą░ą╗čīąĮąŠąĄ čćąĖčüą╗ąŠ 0d5 = 0x5

DIV_Mantissa = mantissa (0d25.620) = 0d25 = 0x19

ąóąŠą│ą┤ą░ USART_BRR = 0x195 => USARTDIV = 0d25.625.

[ą¤čĆąĖą╝ąĄčĆ 3]

ąöą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ USARTDIV = 0d50.99. ąŁč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā:

DIV_Fraction = 8*0d0.99 = 0d7.92

ąæą╗ąĖąČą░ą╣čłąĄąĄ čĆąĄą░ą╗čīąĮąŠąĄ čćąĖčüą╗ąŠ 0d8 = 0x8 => ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ DIV_frac[2:0] => ą║ ą╝ą░ąĮčéąĖčüčüąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┤ąŠą▒ą░ą▓ą╗ąĄąĮ ą┐ąĄčĆąĄąĮąŠčü.

DIV_Mantissa = mantissa (0d50.990 + ą┐ąĄčĆąĄąĮąŠčü) = 0d51 = 0x33.

ąóąŠą│ą┤ą░ USART_BRR = 0x0330 => USARTDIV = 0d51.000.

ąÆ čéą░ą▒ą╗ąĖčåą░čģ 134 .. 143 ą┤ą░čéą░čłąĖčéą░ [1] ą┐čĆąĖą▓ąĄą┤ąĄąĮčŗ čĆą░čüčüčćąĖčéą░ąĮąĮčŗąĄ ą┐čĆą░ą║čéąĖč湥čüą║ąĖąĄ ą┐ąŠą│čĆąĄčłąĮąŠčüčéąĖ ąĘą░ą┤ą░ąĮąĮčŗčģ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ čüą║ąŠčĆąŠčüč鹥ą╣ ą┤ą╗čÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ čāčüą╗ąŠą▓ąĖą╣ (čćą░čüč鹊čéčŗ čłąĖąĮčŗ PCLK, ą▓ą░čĆąĖą░ąĮčéčŗ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ).

ąöąŠą┐čāčüą║ čāčģąŠą┤ą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ USART. ąÉčüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┐čĆąĖąĄą╝ąĮąĖą║ USART ą║ąŠčĆčĆąĄą║čéąĮąŠ čĆą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ąŠą▒čēą░čÅ ą┤ąĄą▓ąĖą░čåąĖčÅ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ čüąĖčüč鹥ą╝čŗ ą╝ąĄąĮčīčłąĄ, č湥ą╝ ą┤ąŠą┐čāčüą║ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ USART. ą¤čĆąĖčćąĖąĮčŗ, ą║ąŠč鹊čĆčŗąĄ čüą┐ąŠčüąŠą▒čüčéą▓čāčÄčé ąŠą▒čēąĄą╝čā ąŠčéą║ą╗ąŠąĮąĄąĮąĖčÄ:

ŌĆó DTRA: ą┤ąĄą▓ąĖą░čåąĖčÅ ąĖąĘ-ąĘą░ ąŠčłąĖą▒ą║ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (čćč鹊 čéą░ą║ąČąĄ ą▓ą║ą╗čÄčćą░ąĄčé ą┤ąĄą▓ąĖą░čåąĖčÄ ą╗ąŠą║ą░ą╗čīąĮąŠą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░).

ŌĆó DQUANT: ąŠčłąĖą▒ą║ą░ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ čüą║ąŠčĆąŠčüčéąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░.

ŌĆó DREC: ą┤ąĄą▓ąĖą░čåąĖčÅ čćą░čüč鹊čéčŗ ą╗ąŠą║ą░ą╗čīąĮąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čéą░ą║č鹊ą▓ ą┐čĆąĖąĄą╝ąĮąĖą║ą░.

ŌĆó DTCL: ą┤ąĄą▓ąĖą░čåąĖčÅ ąĖąĘ-ąĘą░ ą╗ąĖąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (ąŠą▒čŗčćąĮąŠ ąĖąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ąĖ ą╝ąŠą│čāčé ą┤ą░ą▓ą░čéčī ąĮąĄčüąĖą╝ą╝ąĄčéčĆąĖčćąĮčŗąĄ ą┐ąĄčĆąĄą┐ą░ą┤čŗ 0 -> 1 ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ąĖ 1 -> 0)

DTRA + DQUANT + DREC + DTCL < ą┤ąŠą┐čāčüą║ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ USART

ąöąŠą┐čāčüą║ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ USART ą┤ą╗čÅ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą│ąŠ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ čĆą░ą▓ąĄąĮ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╣ ą┤ąĄą▓ąĖą░čåąĖąĖ ąĖ ąĘą░ą▓ąĖčüąĖčé ąŠčé čüą╗ąĄą┤čāčÄčēąĖčģ ą▓čŗą▒čĆą░ąĮąĮčŗčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓:

ŌĆó ąöą╗ąĖąĮą░ čäčĆąĄą╣ą╝ą░ čüąĖą╝ą▓ąŠą╗ą░ 10 ąĖą╗ąĖ 11 ą▒ąĖčé, čćč鹊 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▒ąĖč鹊ą╝ M ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1.

ŌĆó ą¤ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖčÅ 8 ąĖą╗ąĖ 16, čćč鹊 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▒ąĖč鹊ą╝ OVER8 ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1.

ŌĆó ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĖą╗ąĖ ąĮąĄčé ą┤čĆąŠą▒ąĮą░čÅ čāčüčéą░ąĮąŠą▓ą║ą░ čüą║ąŠčĆąŠčüčéąĖ.

ŌĆó ąśčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ 1 ąĖą╗ąĖ 3 ą▒ąĖčéą░ ą┤ą╗čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą┤ą░ąĮąĮčŗčģ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▒ąĖčéą░ ONEBIT čĆąĄą│ąĖčüčéčĆą░ USART_CR3.

ąóą░ą▒ą╗ąĖčåą░ 144. ąöąŠą┐čāčüą║ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ USART, ą║ąŠą│ą┤ą░ DIV fraction = 0.

ąæąĖčé M

|

OVER8 = 0 |

OVER8 = 1 |

| ONEBIT = 0 |

ONEBIT = 1 |

ONEBIT = 0 |

ONEBIT = 1 |

| 0 |

3.75% |

4.375% |

2.50% |

3.75% |

| 1 |

3.41% |

3.97% |

2.27% |

3.41% |

ąóą░ą▒ą╗ąĖčåą░ 145. ąöąŠą┐čāčüą║ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ USART, ą║ąŠą│ą┤ą░ DIV fraction ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé 0.

ąæąĖčé M

|

OVER8 = 0 |

OVER8 = 1 |

| ONEBIT = 0 |

ONEBIT = 1 |

ONEBIT = 0 |

ONEBIT = 1 |

| 0 |

3.33% |

3.88% |

2% |

3% |

| 1 |

3.03% |

3.53% |

1.82% |

2.73% |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖąĮč乊čĆą╝ą░čåąĖčÅ, čāą║ą░ąĘą░ąĮąĮą░čÅ ą▓ čéą░ą▒ą╗ąĖčåą░čģ 144 ąĖ 145, ą╝ąŠąČąĄčé ąĮąĄąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ąŠčéą╗ąĖčćą░čéčīčüčÅ ą▓ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╝ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗąĄ čäčĆąĄą╣ą╝čŗ č鹊čćąĮąŠ 10-ą▒ąĖčéąĮčŗąĄ ą┐čĆąĖ M=0 (11-ą▒ąĖčéąĮčŗąĄ ą┐čĆąĖ M=1).

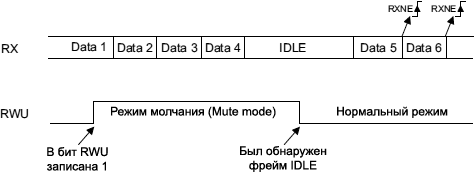

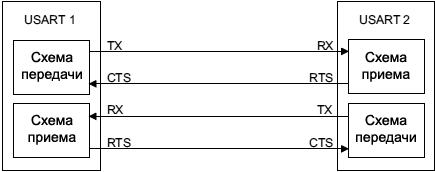

ąĢčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą╝ąĮąŠą│ąŠą┐čĆąŠčåąĄčüčüąŠčĆąĮčŗą╣ ąŠą▒ą╝ąĄąĮ č湥čĆąĄąĘ USART (ąĮąĄčüą║ąŠą╗čīą║ąŠ USART, ąŠą▒čŖąĄą┤ąĖąĮąĄąĮąĮčŗčģ ą▓ čüąĄčéčī). ąØą░ą┐čĆąĖą╝ąĄčĆ, ąŠą┤ąĖąĮ USART ą╝ąŠąČąĄčé ą▒čŗčéčī ą│ą╗ą░ą▓ąĮčŗą╣ (master), ąĄą│ąŠ ą▓čŗčģąŠą┤ TX ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ąŠ ą▓čģąŠą┤čā RX ą┤čĆčāą│ąĖčģ USART. ąöčĆčāą│ąĖąĄ USART čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ (slave), ąĖčģ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▓čŗčģąŠą┤čŗ ą╗ąŠą│ąĖč湥čüą║ąĖ ąŠą▒čŖąĄą┤ąĖąĮąĄąĮčŗ ą┐ąŠ ąś (AND), ąĖ ą▓čüąĄ ą▓ą╝ąĄčüč鹥 ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ąŠ ą▓čģąŠą┤čā RX čāčüčéčĆąŠą╣čüčéą▓ą░ master.

ąÆ ą╝ąĮąŠą│ąŠą┐čĆąŠčåąĄčüčüąŠčĆąĮčŗčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅčģ ąŠą▒ą╝ąĄąĮą░ čćą░čüč鹊 ąČąĄą╗ą░č鹥ą╗čīąĮąŠ, čćč鹊ą▒čŗ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ą┐ąŠą╗čāčćą░č鹥ą╗čī čüąŠąŠą▒čēąĄąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą░ą║čéąĖą▓ąĮąŠ ą┐čĆąĖąĮčÅčéčī ą▓čüąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ čåąĄą╗ąĖą║ąŠą╝, čćč鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī ąŠą▒čĆą░ą▒ąŠčéą║čā ąĖąĘą▒čŗč鹊čćąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą▓čüąĄčģ ą┐čĆąĖąĄą╝ąĮąĖą║ąŠą▓, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ ą░ą┤čĆąĄčüąŠą▓ą░ąĮčŗ.

ąØąĄ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą╝ąĄčēąĄąĮčŗ ą▓ čĆąĄąČąĖą╝ ą╝ąŠą╗čćą░ąĮąĖčÅ (mute mode) čü ą┐ąŠą╝ąŠčēčīčÄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ čäčāąĮą║čåąĖąĖ (muting). ąÆ čĆąĄąČąĖą╝ąĄ ą╝ąŠą╗čćą░ąĮąĖčÅ:

ŌĆó ąØąĖą║ą░ą║ąŠą╣ ąĖąĘ ą▒ąĖč鹊ą▓ čüčéą░čéčāčüą░ ą┐čĆąĖąĄą╝ą░ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ.

ŌĆó ąÆčüąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐čĆąĄčēąĄąĮčŗ.

ŌĆó ąæąĖčé RWU ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1. RWU ą╝ąŠąČąĄčé čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĖą╗ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ čüąĖčéčāą░čåąĖčÅčģ.

USART ą╝ąŠąČąĄčé ą╗ąĖą▒ąŠ ą▓ąŠą╣čéąĖ ą▓ mute mode, ą╗ąĖą▒ąŠ ą▓čŗą╣čéąĖ ąĖąĘ mute mode, ąĖčüą┐ąŠą╗čīąĘčāčÅ ąŠą┤ąĖąĮ ąĖąĘ ą┤ą▓čāčģ ą╝ąĄč鹊ą┤ąŠą▓, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▒ąĖčéą░ WAKE ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1:

ŌĆó ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ ą╗ąĖąĮąĖąĖ (Idle Line), ąĄčüą╗ąĖ čüą▒ąŠ ą▒ąĖčé WAKE.

ŌĆó ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ ą╝ąĄčéą║ąĖ ą░ą┤čĆąĄčüą░ (Address Mark), ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé WAKE.

ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ Idle Line (WAKE=0). USART ą▓ąŠą╣ą┤ąĄčé ą▓ čĆąĄąČąĖą╝ ą╝ąŠą╗čćą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą▓ ą▒ąĖčé RWU ąĘą░ą┐ąĖčüą░ąĮą░ 1. ą×ąĮ ą┐čĆąŠčüąĮąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒čāą┤ąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ čäčĆąĄą╣ą╝ Idle. ąóąŠą│ą┤ą░ ą▒ąĖčé RWU ąŠčćąĖčüčéąĖčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, ąĮąŠ ą▒ąĖčé IDLE ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_SR ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ. ąæąĖčé RWU čéą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ą▓ 0 ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ.

ą¤čĆąĖą╝ąĄčĆ ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą╝ąŠą╗čćą░ąĮąĖčÅ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ Idle ą╗ąĖąĮąĖąĖ ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 303.

ąĀąĖčü. 303. ąĀąĄąČąĖą╝ Mute čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ ąŠąČąĖą┤ą░ąĮąĖčÅ (Idle) ą╗ąĖąĮąĖąĖ.

ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą╝ąĄčéą║ąĖ ą░ą┤čĆąĄčüą░ (WAKE=1). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą▒ą░ą╣čéčŗ čĆą░čüą┐ąŠąĘąĮą░čÄčéčüčÅ ą║ą░ą║ ą░ą┤čĆąĄčüą░, ąĄčüą╗ąĖ čüčéą░čĆčłąĖą╣ ą▒ąĖčé (MSB) čĆą░ą▓ąĄąĮ 1, ąĖąĮą░č湥 ąŠąĮąĖ čüčćąĖčéą░čÄčéčüčÅ ą┤ą░ąĮąĮčŗą╝ąĖ. ąÆ ą▒ą░ą╣č鹥 ą░ą┤čĆąĄčüą░ ą░ą┤čĆąĄčü čåąĄą╗ąĄą▓ąŠą│ąŠ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą┐ąŠą╝ąĄčēą░ąĄčéčüčÅ ą▓ 4 ą╝ą╗ą░ą┤čłąĖčģ ą▒ąĖčéą░ (LSB). ąŁč鹊 4-ą▒ąĖčéąĮąŠąĄ čüą╗ąŠą▓ąŠ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčéčüčÅ ą┐čĆąĖąĄą╝ąĮąĖą║ąŠą╝ čüąŠ čüą▓ąŠąĖą╝ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝, ą║ąŠč鹊čĆčŗą╣ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ ą▒ąĖčéčŗ ADD čĆąĄą│ąĖčüčéčĆą░ USART_CR2.

USART ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ ą╝ąŠą╗čćą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčé čüąĖą╝ą▓ąŠą╗ ą░ą┤čĆąĄčüą░, ą║ąŠč鹊čĆčŗą╣ ąĮąĄ čüąŠąŠčéą▓ą▓ąĄčéčüčéą▓čāąĄčé ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą╝čā ą░ą┤čĆąĄčüčā. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▒ąĖčé RWU čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ. ąöą╗čÅ čŹč鹊ą│ąŠ ą▒ą░ą╣čéą░ ą░ą┤čĆąĄčüą░ čäą╗ą░ą│ RXNE ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ąĖ ąĮąĄ ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ąĮąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĮąĖ ąĘą░ą┐čĆąŠčü ą┐ąĄčĆąĄą┤ą░čćąĖ DMA, ą┐ąŠčüą║ąŠą╗čīą║čā USART ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čĆąĄąČąĖą╝ ą╝ąŠą╗čćą░ąĮąĖčÅ.

USART ą▓čŗą╣ą┤ąĄčé ąĖąĘ čĆąĄąČąĖą╝ą░ ą╝ąŠą╗čćą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčé čüąĖą╝ą▓ąŠą╗ ą░ą┤čĆąĄčüą░, čüąŠą▓ą┐ą░ą┤ą░čÄčēąĖą╣ čü ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝. ąóąŠą│ą┤ą░ ą▒ąĖčé RWU čüą▒čĆąŠčüąĖčéčüčÅ, ąĖ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ą▒ą░ą╣čéčŗ ą▒čāą┤čāčé ąĮąŠčĆą╝ą░ą╗čīąĮąŠ ą┐čĆąĖąĮčÅčéčŗ. ąæąĖčé RXNE čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąĖą╝ą▓ąŠą╗ą░ ą░ą┤čĆąĄčüą░, ą┐ąŠčüą║ąŠą╗čīą║čā ą▒ąĖčé RWU ą▒čŗą╗ čüą▒čĆąŠčłąĄąĮ.

ąæąĖčé RWU čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ 0 ąĖą╗ąĖ 1, ą║ąŠą│ą┤ą░ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĮąĄ čüąŠą┤ąĄčƹȹĖčé ą┤ą░ąĮąĮčŗčģ (RXNE=0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_SR). ąśąĮą░č湥 ą┐ąŠą┐čŗčéą║ą░ ąĘą░ą┐ąĖčüąĖ ą▒čāą┤ąĄčé ą┐čĆąŠąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░ąĮą░.

ą¤čĆąĖą╝ąĄčĆ ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą╝ąŠą╗čćą░ąĮąĖčÅ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąĄčéą║ąĖ ą░ą┤čĆąĄčüą░ ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 304.

ąĀąĖčü. 304. ąĀąĄąČąĖą╝ Mute čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąĄčéą║ąĖ ą░ą┤čĆąĄčüą░.

ą¤čĆąŠą▓ąĄčĆą║ą░ č湥čéąĮąŠčüčéąĖ ą▒ąĖčé (ą│ąĄąĮąĄčĆą░čåąĖčÅ parity-ą▒ąĖčéą░ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ąĖ ą┐čĆąŠą▓ąĄčĆą║ą░ č湥čéąĮąŠčüčéąĖ ąĮą░ ą┐čĆąĖąĄą╝ąĄ) ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ PCE (Parity Control Enable) ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┤ą╗ąĖąĮčŗ čäčĆąĄą╣ą╝ą░, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝ąŠą╣ ą▒ąĖč鹊ą╝ M, ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ č乊čĆą╝ą░čéčŗ čäčĆąĄą╣ą╝ą░ USART ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ 146. ąÆąĖą┤ ą┐čĆąŠą▓ąĄčĆą║ąĖ ąĮą░ č湥čéąĮąŠčüčéčī ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▒ąĖč鹊ą╝ PS (Parity Select) čĆąĄą│ąĖčüčéčĆą░ USART_CR1.

ąóą░ą▒ą╗ąĖčåą░ 146. ążąŠčĆą╝ą░čéčŗ čäčĆąĄą╣ą╝ą░.

| ąæąĖčé M |

ąæąĖčé PCE |

ążčĆąĄą╣ą╝ USART(1) |

| 0 |

0 |

| SB | 8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ | STB | |

| 0 |

1 |

| SB | 7 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ | PB | STB | |

| 1 |

0 |

| SB | 9 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ | STB | |

| 1 |

1 |

| SB | 8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ PB | STB | |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ą╗ąĄą│ąĄąĮą┤ą░ čüą╗ąĄą┤čāčÄčēą░čÅ: SB čüčéą░čĆčé-ą▒ąĖčé, STB čüč鹊ą┐-ą▒ąĖčé, PB: parity-ą▒ąĖčé.

ą¤čĆąŠą▓ąĄčĆą║ą░ ąĮą░ č湥čéąĮąŠčüčéčī. Parity-ą▒ąĖčé ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ čéą░ą║, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī č湥čéąĮčāčÄ čüčāą╝ą╝čā ą▓čüąĄčģ ąĄą┤ąĖąĮąĖč湥ą║ ą▓ąŠ čäčĆąĄą╣ą╝ąĄ ąĖąĘ 7 ąĖą╗ąĖ 8 ą▒ąĖčé (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčéą░ M) ąĖ parity-ą▒ąĖčéą░.

ąØą░ą┐čĆąĖą╝ąĄčĆ: data=00110101; ąĘą┤ąĄčüčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ 4 ą▒ąĖčéą░, ą┐ąŠčŹč鹊ą╝čā ą▒ąĖčé č湥čéąĮąŠčüčéąĖ ą▒čāą┤ąĄčé 0, ąĄčüą╗ąĖ ą▓čŗą▒čĆą░ąĮą░ ą┐čĆąŠą▓ąĄčĆą║ą░ ąĮą░ č湥čéąĮąŠčüčéčī (ą▒ąĖčé PS ą▓ USART_CR1 čĆą░ą▓ąĄąĮ 0).

ą¤čĆąŠą▓ąĄčĆą║ą░ ąĮą░ ąĮąĄč湥čéąĮąŠčüčéčī. ąŚą┤ąĄčüčī ą▓čüąĄ ąĮą░ąŠą▒ąŠčĆąŠčé - parity-ą▒ąĖčé ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ čéą░ą║, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ąĮąĄč湥čéąĮčāčÄ čüčāą╝ą╝čā.

ąØą░ą┐čĆąĖą╝ąĄčĆ: data=00110101; čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ 4 ą▒ąĖčéą░ => ą▒ąĖčé č湥čéąĮąŠčüčéąĖ ą▒čāą┤ąĄčé 1, ąĄčüą╗ąĖ ą▓čŗą▒čĆą░ąĮą░ ą┐čĆąŠą▓ąĄčĆą║ą░ ąĮą░ ąĮąĄč湥čéąĮąŠčüčéčī (ą▒ąĖčé PS ą▓ USART_CR1 čĆą░ą▓ąĄąĮ 1).

ą¤čĆąŠą▓ąĄčĆą║ą░ č湥čéąĮąŠčüčéąĖ ąĮą░ ą┐čĆąĖąĄą╝ąĄ. ąĢčüą╗ąĖ ą┐čĆąŠą▓ąĄčĆą║ą░ ąĮą░ č湥čéąĮąŠčüčéčī/ąĮąĄč湥čéąĮąŠčüčéčī ą┐ąŠą║ą░ąĘą░ą╗ą░ ąŠčłąĖą▒ą║čā ą▓ ą┤ą░ąĮąĮčŗčģ, č鹊 ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_SR čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ PE (Parity Error), ąĖ čüą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüną░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé PEIE (Parity Error Interrupt Enable) ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1. ążą╗ą░ą│ PE ąŠčćąĖčüčéąĖčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ ą┤ąĄą╣čüčéą▓ąĖą╣ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ (čćč鹥ąĮąĖąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüčéą░čéčāčüą░, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐ąĖčüčī čĆąĄą│ąĖčüčéčĆą░ USART_DR).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ čüą╗čāčćą░ąĄ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ą┐ąŠ ą╝ąĄčéą║ąĄ ą░ą┤čĆąĄčüą░ (wakeup address mark): ą▒ąĖčé MSB čāčćąĖčéčŗą▓ą░ąĄčéčüčÅ ą┤ą╗čÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ ą░ą┤čĆąĄčüą░, ąĮąŠ ąĮąĄ ą▒ąĖčé č湥čéąĮąŠčüčéąĖ. ąś ą┐čĆąĖąĄą╝ąĮąĖą║ ąĮąĄ ą┐čĆąŠą▓ąĄčĆčÅąĄčé č湥čéąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ ą░ą┤čĆąĄčüą░ (PE ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ čüą╗čāčćą░ąĄ ąŠčłąĖą▒ą║ąĖ č湥čéąĮąŠčüčéąĖ).

ąōąĄąĮąĄčĆą░čåąĖčÅ ą▒ąĖčéą░ parity ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥. ąĢčüą╗ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé PCE, č鹊 ą▒ąĖčé MSB ą┤ą░ąĮąĮčŗčģ, ąĘą░ą┐ąĖčüą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ, ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ, ąĮąŠ ąŠąĮ ąĖąĘą╝ąĄąĮčÅąĄčéčüčÅ parity-ą▒ąĖč鹊ą╝ (ą┤ą╗čÅ č湥čéąĮąŠčüčéąĖ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ąĄą┤ąĖąĮąĖč湥ą║ ą▓ ą┤ą░ąĮąĮčŗčģ, ąĄčüą╗ąĖ PS=0, ąĖą╗ąĖ ą┤ą╗čÅ ąĮąĄč湥čéąĮąŠčüčéąĖ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ąĄą┤ąĖąĮąĖč湥ą║, ąĄčüą╗ąĖ PS=1).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░, ą║ąŠč鹊čĆą░čÅ ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā, ą╝ąŠąČąĄčé ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░čéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣, ą║ąŠč鹊čĆą░čÅ ąŠčćąĖčüčéąĖčé čäą╗ą░ą│ PE (čćč鹥ąĮąĖąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüčéą░čéčāčüą░ USART, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ąŠą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ ąĮą░ą┤ čĆąĄą│ąĖčüčéčĆąŠą╝ ą┤ą░ąĮąĮčŗčģ USART). ąÜąŠą│ą┤ą░ čĆą░ą▒ąŠčéą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüą░, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, čŹč鹊 ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ č鹊ą╝čā, čćč鹊 čäą╗ą░ą│ PE ą▒čāą┤ąĄčé ąĮąĄąŠąČąĖą┤ą░ąĮąĮąŠ ąŠčćąĖčēąĄąĮ.

ąĀąĄąČąĖą╝ LIN ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ LINEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR2. ąÆ čĆąĄąČąĖą╝ąĄ LIN ą┤ąŠą╗ąČąĮčŗ ą┤ąĄčƹȹ░čéčīčüčÅ čüą▒čĆąŠčłąĄąĮąĮčŗą╝ąĖ čüą╗ąĄą┤čāčÄčēąĖąĄ ą▒ąĖčéčŗ:

ŌĆó STOP[1:0] ąĖ CLKEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR2.

ŌĆó SCEN, HDSEL ąĖ IREN ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR3.

ą¤ąĄčĆąĄą┤ą░čćą░ LIN. ąóą░ ąČąĄ ą┐čĆąŠčåąĄą┤čāčĆą░, ą║ąŠč鹊čĆą░čÅ ą▒čŗą╗ą░ ąŠą┐ąĖčüą░ąĮą░ ą▓čŗčłąĄ ą▓ąŠ ą▓čĆąĄąĘą║ąĄ "ą¤ąĄčĆąĄą┤ą░čéčćąĖą║", ą┐čĆąĖą╝ąĄąĮąĖą╝ą░ ą║ ą┐ąĄčĆąĄą┤ą░č湥 LIN Master, ą║ąŠč鹊čĆą░čÅ čĆą░ą▒ąŠčéą░ąĄčé čéą░ą║ ąČąĄ, ą║ą░ą║ ąĖ ąŠą▒čŗčćąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ USART, čüąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ąŠčéą╗ąĖčćąĖčÅą╝ąĖ:

ŌĆó ąæąĖčé M ąŠčćąĖčēą░ąĄčéčüčÅ, čćč鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą┤ą╗ąĖąĮčā čüą╗ąŠą▓ą░ 8 ą▒ąĖčé.

ŌĆó ą×čüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé LINEN ą┤ą╗čÅ ą▓čģąŠą┤ą░ ą▓ čĆąĄąČąĖą╝ LIN. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ SBK (Send BReak) ąŠčéą┐čĆą░ą▓ąĖčé 13 ąĮčāą╗ąĄą▓čŗčģ ą▒ąĖčé ą▓ ą║ą░č湥čüčéą▓ąĄ čüąĖą╝ą▓ąŠą╗ą░ break. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą▒čāą┤ąĄčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ ą▒ąĖčé 1, čćč鹊ą▒čŗ ą▒čŗą╗ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčī čüą╗ąĄą┤čāčÄčēąĖą╣ start.

ą¤čĆąĖąĄą╝ LIN. ąĪčģąĄą╝ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ break čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ąĮą░ ąĖąĮč鹥čĆč乥ą╣čüąĄ USART, ąĮąŠ ąĄčæ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ LIN ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ąŠą▒čŗčćąĮąŠą│ąŠ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ USART. Break ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą│ą┤ąĄ ąŠąĮ ą┐ąŠčÅą▓ąĖą╗čüčÅ - ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ (Idle) ąĖą╗ąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ čäčĆąĄą╣ą╝ą░.

ąÜąŠą│ą┤ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ čĆą░ąĘčĆąĄčłąĄąĮ (RE=1 in USART_CR1), čüčģąĄą╝ą░ ąŠą┐čĆą░čłąĖą▓ą░ąĄčé ą▓čģąŠą┤ RX ą▓ ąŠąČąĖą┤ą░ąĮąĖąĖ čüąĖą│ąĮą░ą╗ą░ start. ą£ąĄč鹊ą┤ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé čüąĖą│ąĮą░ą╗ą░ start čéą░ą║ąŠą╣ ąČąĄ, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąĖ ą░ąĮą░ą╗ąĖąĘąĄ čüąĖą╝ą▓ąŠą╗ąŠą▓ break ąĖą╗ąĖ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ą▒ąĖčé start, čüčģąĄą╝ą░ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ ą▒ąĖčéčŗ čéą░ą║ ąČąĄ, ą║ą░ą║ ąĖ ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ (ąĮą░ 8-ąŠą╣, 9-ąŠą╣ ąĖ 10-ąŠą╣ ą▓čŗą▒ąŠčĆą║ą░čģ). ąĢčüą╗ąĖ 10 (ą║ąŠą│ą┤ą░ LBDL = 0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR2) ąĖą╗ąĖ 11 (ą║ąŠą│ą┤ą░ LBDL=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR2) ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ą▒ąĖčéčŗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ 0, ąĖ ąĘą░ ą║ąŠč鹊čĆčŗą╝ąĖ čüą╗ąĄą┤čāąĄčé čüąĖą╝ą▓ąŠą╗ čĆą░ąĘą┤ąĄą╗ąĖč鹥ą╗čÅ, č鹊 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé LBD ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_SR. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé LBDIE, č鹊 ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ą¤ąĄčĆąĄą┤ ą┐čĆąŠą▓ąĄčĆą║ąŠą╣ ą║ąŠčĆčĆąĄą║čéąĮąŠčüčéąĖ break ą┐čĆąŠą▓ąĄčĆčÅąĄčéčüčÅ čĆą░ąĘą┤ąĄą╗ąĖč鹥ą╗čī, čéą░ą║ ą║ą░ą║ ąŠąĮ ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čüąĖą│ąĮą░ą╗ RX ą▓ąĄčĆąĮčāą╗čüčÅ ąĮą░ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1.

ąĢčüą╗ąĖ ą▒čŗą╗ą░ ąŠą▒ąĮą░čĆčāąČąĄąĮą░ 1 ą┐ąĄčĆąĄą┤ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖąĄą╝ 10 ąĖą╗ąĖ 11 ą▒ąĖčéą░, čüčģąĄą╝ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ break ąŠčéą╝ąĄąĮčÅąĄčé č鹥ą║čāčēąĄąĄ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ, ąĖ čüąĮąŠą▓ą░ ąĖčēąĄčé ą▒ąĖčé start.

ąĢčüą╗ąĖ čĆąĄąČąĖą╝ LIN ąĘą░ą┐čĆąĄčēąĄąĮ (LINEN=0), ą┐čĆąĖąĄą╝ąĮąĖą║ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé čĆą░ą▒ąŠčéčā ą║ą░ą║ ąŠą▒čŗčćąĮčŗą╣ USART, ą▒ąĄąĘ čāč湥čéą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ break.

ąĢčüą╗ąĖ čĆąĄąČąĖą╝ LIN čĆą░ąĘčĆąĄčłąĄąĮ (LINEN=1), ą║ą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąŠčłąĖą▒ą║ą░ čäčĆąĄą╣ą╝ą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ stop-ą▒ąĖčé ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ 0, čćč鹊 ą▒čāą┤ąĄčé ą▓ čüą╗čāčćą░ąĄ ą╗čÄą▒ąŠą│ąŠ ąŠą▒čĆčŗą▓ą░ čäčĆąĄą╣ą╝ą░, break), ą┐čĆąĖąĄą╝ąĮąĖą║ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą║ąŠą│ą┤ą░ čüčģąĄą╝ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ break ą┐čĆąĖą╝ąĄčé ą╗ąĖą▒ąŠ 1, ąĄčüą╗ąĖ čüą╗ąŠą▓ąŠ break ą▒čŗą╗ąŠ ąĮąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąŠ, ąĖą╗ąĖ čüąĖą╝ą▓ąŠą╗ čĆą░ąĘą┤ąĄą╗ąĖč鹥ą╗čÅ, ąĄčüą╗ąĖ ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ break.

ąĀąĖčü. 305. ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ Break ą▓ čĆąĄąČąĖą╝ąĄ LIN (ą┤ą╗ąĖąĮą░ break 11 ą▒ąĖčé - čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé LBDL).

ąĀąĖčü. 306. ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ break ą▓ čĆąĄąČąĖą╝ąĄ LIN, ąŠčéą╗ąĖčćąĖąĄ ąŠčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ čäčĆąĄą╣ą╝ą░.

ąĪąĖąĮčģčĆąŠąĮąĮčŗą╣ čĆąĄąČąĖą╝ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ 1 ą▒ąĖčéą░ CLKEN čĆąĄą│ąĖčüčéčĆą░ USART_CR2. ąÆ čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠčćąĖčēąĄąĮčŗ čüą╗ąĄą┤čāčÄčēąĖąĄ ą▒ąĖčéčŗ:

ŌĆó ąæąĖčé LINEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR2.

ŌĆó ąæąĖčéčŗ SCEN, HDSEL ąĖ IREN ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR3.

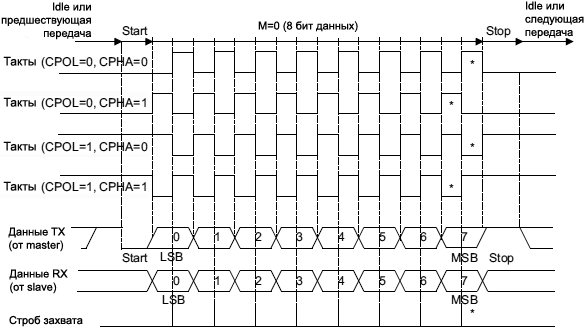

USART ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ čāą┐čĆą░ą▓ą╗čÅčéčī ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╝ čüąĖąĮčģčĆąŠąĮąĮčŗą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ ąŠą▒ą╝ąĄąĮąŠą╝ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ master. ąÆčŗą▓ąŠą┤ CK čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ USART. ąØąĖą║ą░ą║ąĖąĄ čéą░ą║č鹊ą▓čŗąĄ ąĖą╝ą┐čāą╗čīčüčŗ ąĮąĄ ą┐ąŠčüčŗą╗ą░čÄčéčüčÅ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ CK ą▓ąŠ ą▓čĆąĄą╝čÅ ą▒ąĖčéą░ start ąĖ ą▒ąĖčéą░ stop. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčéą░ LBCL ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR2 čéą░ą║č鹊ą▓čŗąĄ ąĖą╝ą┐čāą╗čīčüčŗ ą▒čāą┤čāčé ąĖą╗ąĖ ąĮąĄ ą▒čāą┤čāčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠą│ąŠ ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ (ą╝ą░čĆą║ąĄčĆ ą░ą┤čĆąĄčüą░, address mark). ąæąĖčé CPOL ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR2 ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▓čŗą▒čĆą░čéčī ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓, ąĖ ą▒ąĖčé CPHA ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR2 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą▒čĆą░čéčī čäą░ąĘčā ą▓ąĮąĄčłąĮąĖčģ čéą░ą║č鹊ą▓ (čüą╝. čĆąĖčü. 307, 308 ąĖ 309).

ąĀąĖčü. 307. ą¤čĆąĖą╝ąĄčĆ čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ USART.

ąĀąĖčü. 308. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ čéą░ą║č鹊ą▓ USART (M=0).

* ąæąĖčé LBCL čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ ąĖą╝ą┐čāą╗čīčüąŠą╝ ą┤ą░ąĮąĮčŗčģ.

ąĀąĖčü. 309. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ čéą░ą║č鹊ą▓ USART (M=1).

* ąæąĖčé LBCL čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ ąĖą╝ą┐čāą╗čīčüąŠą╝ ą┤ą░ąĮąĮčŗčģ.

ąĀąĖčü. 310. ąÆčĆąĄą╝čÅ setup/hold ą┤ą░ąĮąĮčŗčģ RX. tSETUP = tHOLD = 1/16 ą▓čĆąĄą╝ąĄąĮąĖ ą▒ąĖčéą░.

ąÆąŠ ą▓čĆąĄą╝čÅ čüąŠčüč鹊čÅąĮąĖčÅ Idle, ą┐čĆąĄą░ą╝ą▒čāą╗čŗ ąĖ ąŠčéą┐čĆą░ą▓ą║ąĖ break ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ CK ąĮąĄ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ.

ąÆ čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ USART čĆą░ą▒ąŠčéą░ąĄčé č鹊čćąĮąŠ čéą░ą║ ąČąĄ, ą║ą░ą║ ą▓ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ. ą×ą┤ąĮą░ą║ąŠ ą▒ąĖčé CK ąĘą░čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮ čü TX (ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĮą░čüčéčĆąŠą╣ą║ą░ą╝ąĖ CPOL ąĖ CPHA), ą┤ą░ąĮąĮčŗąĄ ąĮą░ TX čüąĖąĮčģčĆąŠąĮąĮčŗąĄ.

ąÆ čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąĄą╝ąĮąĖą║ USART čĆą░ą▒ąŠčéą░ąĄčé ąĮąĄ čéą░ą║, ą║ą░ą║ ą▓ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ. ąĢčüą╗ąĖ RE=1, č鹊 ą┤ą░ąĮąĮčŗąĄ ą░ąĮą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĮąŠ čü čüąĖą│ąĮą░ą╗ąŠą╝ CK (ą┐ąŠ čäčĆąŠąĮčéčā ąĖą╗ąĖ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé CPOL ąĖ CPHA), ą▒ąĄąĘ ą║ą░ą║ąŠą╣-ą╗ąĖą▒ąŠ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ. ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ (setup time) ąĖ čāą┤ąĄčƹȹ░ąĮąĖčÅ (hold time) ą┤ąŠą╗ąČąĮąŠ čüąŠą▒ą╗čÄą┤ą░čéčīčüčÅ (ąĘą░ą▓ąĖčüąĖčé ąŠčé baud rate: 1/16 ąŠčé ą▓čĆąĄą╝ąĄąĮąĖ ą▒ąĖčéą░).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓čŗą▓ąŠą┤ CK čĆą░ą▒ąŠčéą░ąĄčé ą▓ą╝ąĄčüč鹥 čü ą▓čŗą▓ąŠą┤ąŠą╝ TX. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čéą░ą║čéčŗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ (TE=1), ąĖ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ (ąĘą░ą┐ąĖčüą░ąĮ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ USART_DR). ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮąĄą▓ąŠąĘą╝ąŠąČąĮąŠ ą┐čĆąĖąĮąĖą╝ą░čéčī čüąĖąĮčģčĆąŠąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒ąĄąĘ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ.

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▒ąĖčé LBCL, CPOL ąĖ CPHA ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮą░, ą║ąŠą│ą┤ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║, ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĘą░ą┐čĆąĄčēąĄąĮčŗ (TE=RE=0), čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą║ąŠčĆčĆąĄą║čéąĮčāčÄ čĆą░ą▒ąŠčéčā ąĖą╝ą┐čāą╗čīčüąŠą▓ čéą░ą║č鹊ą▓. ąŁčéąĖ ą▒ąĖčéčŗ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ąĖąĘą╝ąĄąĮčÅčéčīčüčÅ, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĖą╗ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║.

ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčī ą▒ąĖčéčŗ TE ąĖ RE ąŠą┤ąĮąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĄą╣, čćč鹊ą▒čŗ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ą▓čĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ (setup time) ąĖ čāą┤ąĄčƹȹ░ąĮąĖčÅ (hold time) ą┐čĆąĖąĄą╝ąĮąĖą║ą░.

USART ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé č鹊ą╗čīą║ąŠ čĆąĄąČąĖą╝ master: ąŠąĮ ąĮąĄ ą╝ąŠąČąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī ąĖą╗ąĖ ąŠčéą┐čĆą░ą▓ą╗čÅčéčī ą┤ą░ąĮąĮčŗąĄ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čüąŠ ą▓čģąŠą┤ąŠą╝ čéą░ą║č鹊ą▓ (CK ą▓čüąĄą│ą┤ą░ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗčģąŠą┤).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čäčāąĮą║čåąĖčÅ CK ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Smartcard (čüą╝. ą┤ą░ą╗ąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░).

ąŁč鹊čé čĆąĄąČąĖą╝ (single-wire, half-duplex) ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▓ 1 ą▒ąĖčéą░ HDSEL ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR3. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠčćąĖčēąĄąĮčŗ čüą╗ąĄą┤čāčÄčēąĖąĄ ą▒ąĖčéčŗ:

ŌĆó ąæąĖčéčŗ LINEN ąĖ CLKEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR2.

ŌĆó ąæąĖčéčŗ SCEN ąĖ IREN ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR3.

USART ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖčÅ ąŠą┤ąĮąŠą┐čĆąŠą▓ąŠą┤ąĮąŠą╝čā ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĮąŠą╝čā ą┐čĆąŠč鹊ą║ąŠą╗čā, ą│ą┤ąĄ ą╗ąĖąĮąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ TX ąĖ RX čüąŠąĄą┤ąĖąĮąĄąĮčŗ ą▓ąĮčāčéčĆąĖ ą║čĆąĖčüčéą░ą╗ą╗ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ (čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ HDSEL ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR3).

ąÜą░ą║ č鹊ą╗čīą║ąŠ HDSEL ąĘą░ą┐ąĖčüą░ąĮ ą▓ 1:

ŌĆó ąĪąĖą│ąĮą░ą╗čŗ TX ąĖ RX čüąŠąĄą┤ąĖąĮčÅčÄčéčüčÅ ą▓ąĮčāčéčĆąĖ.

ŌĆó ąÆąĮąĄčłąĮąĖą╣ ą▓čŗą▓ąŠą┤ RX ą▒ąŠą╗čīčłąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

ŌĆó ąÆčŗą▓ąŠą┤ TX ą▓čüąĄą│ą┤ą░ ąŠčüą▓ąŠą▒ąŠąČą┤ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąŠąĮ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓ą▓ąŠą┤/ą▓čŗą▓ąŠą┤ (GPIO) ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ ąĖą╗ąĖ ą┐čĆąĖąĄą╝ą░. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▓ą▓ąŠą┤/ą▓čŗą▓ąŠą┤ TX ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ čéą░ą║, čćč鹊ą▒čŗ ąŠąĮ ą▒čŗą╗ ą▓čŗčüąŠą║ąŠąŠą╝ąĮčŗą╝ ą▓čģąŠą┤ąŠą╝ (ąĖą╗ąĖ ą▓čŗčģąŠą┤ąŠą╝ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝), ą║ąŠą│ą┤ą░ ąŠąĮ ąĮąĄ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ąŠčé USART.

ąÜčĆąŠą╝ąĄ čŹč鹊ą╣ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéąĖ, ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ čéą░ą║ąŠą╣ ąČąĄ, ą║ą░ą║ ą▓ ąŠą▒čŗčćąĮąŠą╝ čĆąĄąČąĖą╝ąĄ USART. ąÜąŠąĮčäą╗ąĖą║čéčŗ ąĮą░ ą╗ąĖąĮąĖąĖ čüą▓čÅąĘąĖ ą┤ąŠą╗ąČąĮčŗ čĆą░ąĘčĆąĄčłą░čéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čåąĄąĮčéčĆą░ą╗ąĖąĘąŠą▓ą░ąĮąĮąŠą│ąŠ ą░čĆą▒ąĖčéčĆą░ čłąĖąĮčŗ). ąÆ čćą░čüčéąĮąŠčüčéąĖ, ą┐ąĄčĆąĄą┤ą░čćą░ ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą▒ą╗ąŠą║ąĖčĆčāąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĖ ą▒čāą┤ąĄčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčīčüčÅ, ą┐ąŠą║ą░ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╝ ą▒ąĖč鹥 TE.

ąĀąĄąČąĖą╝ čüą╝ą░čĆčé-ą║ą░čĆčéčŗ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SCEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR3. ąÆ čĆąĄąČąĖą╝ąĄ čüą╝ą░čĆčé-ą║ą░čĆčéčŗ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ąŠčćąĖčēąĄąĮąĮčŗą╝ąĖ čüą╗ąĄą┤čāčÄčēąĖąĄ ą▒ąĖčéčŗ:

ŌĆó ąæąĖčé LINEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR2.

ŌĆó ąæąĖčéčŗ HDSEL ąĖ IREN ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR3.

ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé CLKEN, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī čéą░ą║čéčŗ ą┤ą╗čÅ čüą╝ą░čĆčé-ą║ą░čĆčéčŗ.

ąśąĮč鹥čĆč乥ą╣čü Smartcard čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░ čüą╝ą░čĆčé-ą║ą░čĆčé, ą║ą░ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ čüčéą░ąĮą┤ą░čĆč鹊ą╝ ISO 7816-3. USART ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆó 8 ą▒ąĖčé ą┐ą╗čÄčü parity: M=1 ąĖ PCE=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR1.

ŌĆó 1.5 stop-ą▒ąĖčéą░ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ąĖ ą┐čĆąĖąĄą╝ąĄ: STOP=11 ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR2.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čéą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī 0.5 stop-ą▒ąĖčéą░ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░, ąĮąŠ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī 1.5 stop-ą▒ąĖčéą░ ąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅą╝ąĖ.

ąĀąĖčü. 311 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆąĖą╝ąĄčĆčŗ, ą║ą░ą║ ą▓čŗą│ą╗čÅą┤ąĖčé čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ čü ąŠčłąĖą▒ą║ąŠą╣ č湥čéąĮąŠčüčéąĖ ąĖ ą▒ąĄąĘ ąŠčłąĖą▒ą║ąĖ č湥čéąĮąŠčüčéąĖ.

ąĀąĖčü. 311. ąÉčüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┐čĆąŠč鹊ą║ąŠą╗ ISO 7816-3.

ąÜąŠą│ą┤ą░ USART ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ čüą╝ą░čĆčé-ą║ą░čĆč鹥, ą▓čŗčģąŠą┤ TX čāą┐čĆą░ą▓ą╗čÅąĄčé ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą╣ ą╗ąĖąĮąĖąĄą╣, ą║ąŠč鹊čĆą░čÅ čéą░ą║ąČąĄ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝ čüą╝ą░čĆčé-ą║ą░čĆčéčŗ. ąØąŠąČą║ą░ TX ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą║ą░ą║ ąŠčéą║čĆčŗčéčŗą╣ čüč鹊ą║. Smartcard čŹč鹊 ąŠą┤ąĮąŠą┐čĆąŠą▓ąŠą┤ąĮčŗą╣, ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĮčŗą╣ ą┐čĆąŠč鹊ą║ąŠą╗ ąŠą▒ą╝ąĄąĮą░.

ŌĆó ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čü ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 1/2 čéą░ą║čéą░ čüą║ąŠčĆąŠčüčéąĖ. ą¤čĆąĖ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĖ ą┐ąŠą╗ąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ąĮą░čćąĮąĄčéčüčÅ čüą┤ą▓ąĖą│ąŠą╝ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ čéą░ą║č鹊ą▓ čüą║ąŠčĆąŠčüčéąĖ. ąÆ čĆąĄąČąĖą╝ąĄ Smartcard čŹčéą░ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ąĘą░ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĮą░ 1/2 čéą░ą║čéą░ čüą║ąŠčĆąŠčüčéąĖ.

ŌĆó ąĢčüą╗ąĖ ą▒čŗą╗ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮą░ ąŠčłąĖą▒ą║ą░ č湥čéąĮąŠčüčéąĖ ąĮą░ ą┐čĆąĖąĄą╝ąĄ čäčĆąĄą╣ą╝ą░, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čü 0.5 ąĖą╗ąĖ 1.5 ą┐ąĄčĆąĖąŠą┤ąŠą╝ stop-ą▒ąĖčéą░, ą╗ąĖąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠą┤čéčÅą│ąĖą▓ą░ąĄčéčüčÅ ą░ ą╗ąŠą│. 0 ąĮą░ ą┐ąĄčĆąĖąŠą┤ čéą░ą║č鹊ą▓ čüą║ąŠčĆąŠčüčéąĖ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ čäčĆąĄą╣ą╝ą░. ąŁč鹊 čüą╗čāąČąĖčé ąĖąĮą┤ąĖą║ą░čåąĖąĄą╣, čćč鹊 ą┤ą░ąĮąĮčŗąĄ čüą╝ą░čĆčé-ą║ą░čĆčéčŗ, ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗąĄ ą▓ USART ąĮąĄ ą▒čŗą╗ąĖ ą║ąŠčĆčĆąĄą║čéąĮąŠ ą┐čĆąĖąĮčÅčéčŗ. ąŁč鹊čé čüąĖą│ąĮą░ą╗ NACK (ą┐ąŠą┤čéčÅą│ąĖą▓ą░ąĮąĖąĄ ą║ ą╗ąŠą│. 0 ą╗ąĖąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ 1 čéą░ą║čé čüą║ąŠčĆąŠčüčéąĖ) ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÄ ąŠčłąĖą▒ą║ąĖ čäčĆąĄą╣ą╝ą░ ąĮą░ čüč鹊čĆąŠąĮąĄ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čü 1.5 stop-ą▒ąĖč鹊ą╝). ą¤čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ąŠą▒čĆą░ą▒ąŠčéą░čéčī čŹčéčā čüąĖčéčāą░čåąĖčÄ ą┐ąŠą▓č鹊čĆąĮąŠą╣ ąŠčéą┐čĆą░ą▓ą║ąŠą╣ ą┤ą░ąĮąĮčŗčģ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┐čĆąŠč鹊ą║ąŠą╗ąŠą╝. ą×čłąĖą▒ą║ą░ č湥čéąĮąŠčüčéąĖ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ą┐čĆąĖąĄą╝ąĮąĖą║ąŠą╝ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ą║ą░ą║ NACK (No ACKnowledge), ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą▒ąĖčé NACK, ąĖąĮą░č湥 NACK ąĮąĄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ.

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ čäą╗ą░ą│ą░ TC ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┤ąĄčƹȹ░ąĮą░ ą┐čāč鹥ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ąĘą░čēąĖčéąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (Guard Time). ą¤čĆąĖ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĖ TC čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą┐čāčüč鹊賹░ąĄčéčüčÅ, ąĖ ą▒ąŠą╗čīčłąĄ ąĮąĄčé ąŠąČąĖą┤ą░čÄčēąĖčģ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĘą░ą┐čĆąŠčüąŠą▓. ąÆ čĆąĄąČąĖą╝ąĄ Smartcard ą┐čāčüč鹊ą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĘą░ą┐čāčüą║ą░ąĄčé čüč湥čéčćąĖą║ ąĘą░čēąĖčéąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ čüč湥čéą░ ą┤ąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ Guard Time. ąÆ č鹥č湥ąĮąĖąĄ ąĘą░čēąĖčéąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ TC ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0. ąÜąŠą│ą┤ą░ čüč湥čéčćąĖą║ ąĘą░čēąĖčéąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ąŠčüčéąĖą│ąĮąĄčé ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ, TC ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ 1.

ŌĆó ąØą░ čüąĮčÅčéąĖąĄ čäą╗ą░ą│ą░ TC čĆąĄąČąĖą╝ čüą╝ą░čĆčé-ą║ą░čĆčéčŗ ąĮąĄ ą▓ą╗ąĖčÅąĄčé.

ŌĆó ąĢčüą╗ąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮą░ ąŠčłąĖą▒ą║ą░ čäčĆąĄą╣ą╝ą░ ąĮą░ čüč鹊čĆąŠąĮąĄ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (ą┐ąŠ čüąĖą│ąĮą░ą╗čā NACK ąŠčé ą┐čĆąĖąĄą╝ąĮąĖą║ą░), NACK ąĮąĄ ą▒čāą┤ąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ start-ą▒ąĖčé ą▒ą╗ąŠą║ąŠą╝ ą┐čĆąĖąĄą╝ą░ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░. ąÆ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┐čĆąŠč鹊ą║ąŠą╗ąŠą╝ ISO, ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą┐čĆąĖąĮčÅč鹊ą│ąŠ NACK ą╝ąŠąČąĄčé ą▒čŗčéčī 1 ąĖą╗ąĖ 2 ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą║č鹊ą▓ čüą║ąŠčĆąŠčüčéąĖ.

ŌĆó ąØą░ čüč鹊čĆąŠąĮąĄ ą┐čĆąĖąĄą╝ąĮąĖą║ą░, ąĄčüą╗ąĖ ą▒čŗą╗ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮą░ ąŠčłąĖą▒ą║ą░ č湥čéąĮąŠčüčéąĖ, ąĖ ą▒čŗą╗ ą┐ąĄčĆąĄą┤ą░ąĮ čüąĖą│ąĮą░ą╗ NACK, č鹊 ąŠąĮ ąĮąĄ ą▒čāą┤ąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ start-ą▒ąĖčé.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čüąĖą╝ą▓ąŠą╗ break ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ Smartcard. ąöą░ąĮąĮčŗąĄ 0x00 čü ąŠčłąĖą▒ą║ąŠą╣ čäčĆąĄą╣ą╝ą░ ą▒čāą┤čāčé ąŠą▒čĆą░ą▒ąŠčéą░ąĮčŗ ą║ą░ą║ ą┤ą░ąĮąĮčŗąĄ, ąĮąĄ ą║ą░ą║ break.

ążčĆąĄą╣ą╝ Idle ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą▒ąĖčé TE. ążčĆąĄą╣ą╝ Idle (ą║ą░ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣) ą▓ ą┐čĆąŠč鹊ą║ąŠą╗ąĄ ISO ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ.

ąĀąĖčü. 312 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ čüąĖą│ąĮą░ą╗ NACK ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ USART. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ USART ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ, ąĖ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ čü 1.5 stop-ą▒ąĖč鹊ą╝. ąæą╗ąŠą║ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ USART čĆą░ąĘčĆąĄčłąĄąĮ, čćč鹊ą▒čŗ ą┐čĆąŠą▓ąĄčĆčÅčéčī čåąĄą╗ąŠčüčéąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ ąĖ čüąĖą│ąĮą░ą╗ NACK.

ąĀąĖčü. 312. ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ č湥čéąĮąŠčüčéąĖ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ 1.5 stop-ą▒ąĖč鹊ą▓.

USART ą╝ąŠąČąĄčé ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī čéą░ą║čéčŗ ą┤ą╗čÅ čüą╝ą░čĆčé-ą║ą░čĆčéčŗ č湥čĆąĄąĘ ą▓čŗčģąŠą┤ CK. ąÆ čĆąĄąČąĖą╝ąĄ čüą╝ą░čĆčéą║ą░čĆčéčŗ CK ąĮąĄ čüą▓čÅąĘą░ąĮ čü ąŠą▒ą╝ąĄąĮąŠą╝ ą┤ą░ąĮąĮčŗą╝ąĖ, ąŠąĮ ą┐čĆąŠčüč鹊 ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā, ą┐ąŠą╗čāč湥ąĮąĮčāčÄ ąĖąĘ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą▓čģąŠą┤ą░ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĖč乥čĆąĖąĖ č湥čĆąĄąĘ 5-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ. ąÜąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ USART_GTPR. ą¦ą░čüč鹊čéą░ CK ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ąŠčé fCK/2 ą┤ąŠ fCK/62, ą│ą┤ąĄ fCK čŹč鹊 čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ ą▓čģąŠą┤ą░ ą┐ąĄčĆąĖč乥čĆąĖąĖ.

ąĀąĄąČąĖą╝ IrDA mode ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ IREN ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR3. ąÆ čĆąĄąČąĖą╝ąĄ IrDA ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ąŠčćąĖčēąĄąĮąĮčŗą╝ąĖ čüą╗ąĄą┤čāčÄčēąĖąĄ ą▒ąĖčéčŗ:

ŌĆó LINEN, STOP ąĖ CLKEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR2.

ŌĆó SCEN ąĖ HDSEL ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_CR3.

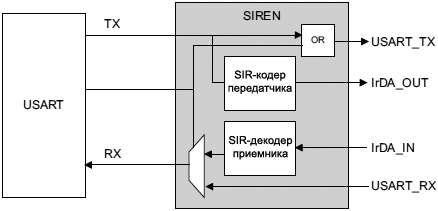

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆą░ SIR ąŠąĘąĮą░čćą░ąĄčé Serial InfraRed, ą░ ENDEC ąŠąĘąĮą░čćą░ąĄčé ENcoder-DECorer.

ążąĖąĘąĖč湥čüą║ąĖą╣ čüą╗ąŠą╣ IrDA SIR ąĘą░ą┤ą░ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüčģąĄą╝čā ą╝ąŠą┤čāą╗čÅčåąĖąĖ čü ą▓ąŠąĘą▓čĆą░č鹊ą╝ ą║ ąĮčāą╗čÄ ąĖ ąĖąĮą▓ąĄčĆčüąĖąĄą╣ RZI (Return to Zero Inverted), ą║ąŠč鹊čĆą░čÅ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ą╗ąŠą│. 0 ą║ą░ą║ ąĖą╝ą┐čāą╗čīčü ąĖąĮčäčĆą░ą║čĆą░čüąĮąŠą│ąŠ ąĖąĘą╗čāč湥ąĮąĖčÅ (čüą╝. čĆąĖčü. 313).

ąĀąĖčü. 313. ąæą╗ąŠą║-čüčģąĄą╝ą░ IrDA SIR ENDEC.

ąÜąŠą┤ąĄčĆ ą┐ąĄčĆąĄą┤ą░čćąĖ SIR ą╝ąŠą┤čāą╗ąĖčĆčāąĄčé ą▓čŗčģąŠą┤ąĮąŠą╣ ą┐ąŠč鹊ą║ ą▒ąĖčé Non Return to Zero (NRZ) ąĖąĘ USART. ąÆčŗčģąŠą┤ąĮąŠą╣ ą┐ąŠč鹊ą║ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĮą░ ą▓ąĮąĄčłąĮąĖą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ ą┤čĆą░ą╣ą▓ąĄčĆ ąĖ ąĖąĮčäčĆą░ą║čĆą░čüąĮčŗą╣ čüą▓ąĄč鹊ą┤ąĖąŠą┤. USART ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┤ą╗čÅ SIR ENDEC č鹊ą╗čīą║ąŠ čüą║ąŠčĆąŠčüčéąĖ ą┤ąŠ 115.2 Kbps. ąÆ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ čłąĖčĆąĖąĮą░ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ ąĘą░ą┤ą░ąĮą░ ą║ą░ą║ 3/16 ąŠčé ą┐ąĄčĆąĖąŠą┤ą░ ą▒ąĖčéą░.

ąöąĄą║ąŠą┤ąĄčĆ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ SIR ą┤ąĄą╝ąŠą┤čāą╗ąĖčĆčāąĄčé ą┐ąŠč鹊ą║ return-to-zero ą▒ąĖčé ąĖąĘ ą┤ąĄč鹥ą║č鹊čĆą░ ąĖąĮčäčĆą░ą║čĆą░čüąĮąŠą│ąŠ ąĖąĘą╗čāč湥ąĮąĖčÅ, ąĖ ą▓čŗą▓ąŠą┤ąĖčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠč鹊ą║ ą▒ąĖčé NRZ ą▓ USART. ąÆčģąŠą┤ ą┤ąĄą║ąŠą┤ąĄčĆą░ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ čĆąĄąČąĖą╝ą░ ąŠąČąĖą┤ą░ąĮąĖčÅ Idle ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1 (čüąŠčüč鹊čÅąĮąĖąĄ marking). ąÜąŠą┤ąĄčĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓čŗą▓ąŠą┤ąĖčé ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčāčÄ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī ąĮą░ ą▓čģąŠą┤ ą┤ąĄą║ąŠą┤ąĄčĆą░. ąæąĖčé start ą┤ąĄč鹥ą║čéąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąĮą░ ą▓čģąŠą┤ąĄ ą┤ąĄą║ąŠą┤ąĄčĆą░ ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ą╗ąŠą│. 0.

ŌĆó IrDA čÅą▓ą╗čÅąĄčéčüčÅ ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĮčŗą╝ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąŠąĮąĮčŗą╝ ą┐čĆąŠč鹊ą║ąŠą╗ąŠą╝. ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĘą░ąĮčÅčé (ąĮą░ą┐čĆąĖą╝ąĄčĆ USART ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą▓ ą║ąŠą┤ąĄčĆ IrDA), č鹊 ą╗čÄą▒čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĮą░ ą╗ąĖąĮąĖąĖ ą┐čĆąĖąĄą╝ą░ IrDA ą▒čāą┤čāčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą┤ąĄą║ąŠą┤ąĄčĆąŠą╝ IrDA, ąĖ ąĄčüą╗ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĘą░ąĮčÅčé (USART ą┐čĆąĖąĮąĖą╝ą░ąĄčé ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ USART), č鹊 ą┤ą░ąĮąĮčŗąĄ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ TX ąĖąĘ USART ą▓ IrDA ąĮąĄ ą▒čāą┤čāčé ą║ąŠą┤ąĖčĆąŠą▓ą░čéčīčüčÅ IrDA. ą¤čĆąĖ ą┐čĆąĖąĄą╝ąĄ ą┤ą░ąĮąĮčŗčģ čüą╗ąĄą┤čāąĄčé ąĖąĘą▒ąĄą│ą░čéčī ą┐ąĄčĆąĄą┤ą░čćąĖ, ą┐ąŠčüą║ąŠą╗čīą║čā ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą▓čĆąĄąČą┤ąĄąĮčŗ.

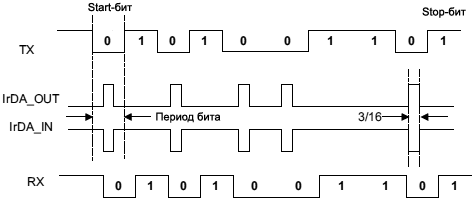

ŌĆó 0 ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą║ą░ą║ ąĖą╝ą┐čāą╗čīčü ą╗ąŠą│. 1, ąĖ 1 ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą║ą░ą║ ą╗ąŠą│. 0. ą©ąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ąĘą░ą┤ą░ąĮą░ ą║ą░ą║ 3/16 ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ ą▒ąĖčéą░ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (čüą╝. čĆąĖčü. 314).

ąĀąĖčü. 314. ą£ąŠą┤čāą╗čÅčåąĖčÅ ą┤ą░ąĮąĮčŗčģ IrDA (3/16) - ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝.

ŌĆó ąöąĄą║ąŠą┤ąĄčĆ SIR ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčé čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╣ čü IrDA ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗą╣ čüąĖą│ąĮą░ą╗ ą▓ ą┐ąŠč鹊ą║ ą▒ąĖčé ą┤ą╗čÅ USART.

ŌĆó ąøąŠą│ąĖą║ą░ ą┐čĆąĖąĄą╝ą░ SIR ą╗ąŠą│ąĖč湥čüą║ąĖ ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆčāąĄčé ą▓čŗčüąŠą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą║ą░ą║ ą╗ąŠą│. 1, ąĖ ąĖą╝ą┐čāą╗čīčüčŗ ą╗ąŠą│. 0 ą║ą░ą║ ą╗ąŠą│. 0.

ŌĆó ąÆčŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą║ąŠą┤ąĄčĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╝ąĄąĄčé ą┐ąŠą╗čÅčĆąĮąŠčüčéčī, ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčāčÄ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┤ąĄą║ąŠą┤ąĄčĆą░. ąÆčŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ SIR ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0 ą┐čĆąĖ čĆąĄąČąĖą╝ąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ (Idle).

ŌĆó ąĪą┐ąĄčåąĖčäąĖą║ą░čåąĖčÅ IrDA čéčĆąĄą▒čāąĄčé ą┐čĆąĖąĄą╝ą░ ąĖą╝ą┐čāą╗čīčüąŠą▓, ą┐čĆąĄą▓čŗčłą░čÄčēąĖčģ 1.41 ą╝ą║čü. ąöąŠą┐čāčüčéąĖą╝ą░čÅ čłąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ. ąøąŠą│ąĖą║ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą┐ąŠą╝ąĄčģ (glitch detection) ąĮą░ čüč鹊čĆąŠąĮąĄ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąŠčéčäąĖą╗čīčéčĆąŠą▓čŗą▓ą░ąĄčé ąĖą╝ą┐čāą╗čīčüčŗ, čłąĖčĆąĖąĮą░ ą║ąŠč鹊čĆčŗčģ ą╝ąĄąĮčīčłąĄ 2 ą┐ąĄčĆąĖąŠą┤ąŠą▓ PSC (PSC čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüą║ąŠčĆąŠčüčéąĖ ąĮąĖąĘą║ąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čŹąĮąĄčĆą│ąĖąĖ IrDA, USART_GTPR). ąśą╝ą┐čāą╗čīčüčŗ čłąĖčĆąĖąĮąŠą╣ ą╝ąĄąĮčīčłąĄ 1 ą┐ąĄčĆąĖąŠą┤ą░ PSC ąŠčéą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ ą▓čüąĄą│ą┤ą░, ąĮąŠ ąĖą╝ą┐čāą╗čīčüčŗ čłąĖčĆąĖąĮąŠą╣ ą▒ąŠą╗čīčłąĄ 1 ą┐ąĄčĆąĖąŠą┤ą┐ą░ ąĖ ą╝ąĄąĮčīčłąĄ 2 ą┐ąĄčĆąĖąŠą┤ąŠą▓ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąĖąĮčÅčéčŗ ąĖą╗ąĖ ąŠčéą▒čĆąŠčłąĄąĮčŗ, ą░ ąĖą╝ą┐čāą╗čīčüčŗ ą▒ąŠą╗čīčłąĄ 2 ą┐ąĄčĆąĖąŠą┤ąŠą▓ ą▒čāą┤čāčé ą┐čĆąĖąĮčÅčéčŗ ą║ą░ą║ ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü. ąÜąŠą┤ąĄčĆ/ą┤ąĄą║ąŠą┤ąĄčĆ IrDA ąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé, ą║ąŠą│ą┤ą░ PSC=0.

ŌĆó ą¤čĆąĖąĄą╝ąĮąĖą║ ą╝ąŠąČąĄčé ąŠą▒ą╝ąĄąĮąĖą▓ą░čéčīčüčÅ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ąŠą╝ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąĮąĖąĘą║ąŠą╣ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝ąŠą╣ ą╝ąŠčēąĮąŠčüčéąĖ.

ŌĆó ąÆ čĆąĄąČąĖą╝ąĄ IrDA, ą┐ąŠą╗ąĄ ą▒ąĖčé STOP čĆąĄą│ąĖčüčéčĆą░ USART_CR2 ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ čüąŠčüč鹊čÅąĮąĖčÅ "1 čüč鹊ą┐-ą▒ąĖčé".

[IrDA ą▓ čĆąĄąČąĖą╝ąĄ ąĮąĖąĘą║ąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ]

ą¤ąĄčĆąĄą┤ą░čéčćąĖą║. ąÆ čĆąĄąČąĖą╝ąĄ ąĮąĖąĘą║ąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (low-power mode) čłąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĮą░ 3/16 ąŠčé ą┐ąĄčĆąĖąŠą┤ą░ ą▒ąĖčéą░. ąÆą╝ąĄčüč鹊 čŹč鹊ą│ąŠ čłąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ą▓ 3 čĆą░ąĘą░ ą┐čĆąĄą▓čŗčłą░ąĄčé ą╝ą░ą╗ąŠą╝ąŠčēąĮčāčÄ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ, ą║ąŠč鹊čĆą░čÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą╝ąĖąĮąĖą╝čāą╝ 1.42 ą£ąōčå. ą×ą▒čŗčćąĮąŠ čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ čüąŠčüčéą░ą▓ą╗čÅąĄčé 1.8432 ą£ąōčå (1.42 ą£ąōčå < PSC < 2.12 ą£ąōčå). ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī čĆąĄąČąĖą╝ą░ ąĮąĖąĘą║ąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą┤ąĄą╗ąĖčé čüąĖčüč鹥ą╝ąĮčāčÄ čćą░čüč鹊čéčā, čćč鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī čŹč鹊ą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ.

ą¤čĆąĖąĄą╝ąĮąĖą║. ą¤čĆąĖąĄą╝ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čŹąĮąĄčĆą│ąĖąĖ ą┐ąŠą┤ąŠą▒ąĄąĮ ą┐čĆąĖąĄą╝čā ą▓ ąŠą▒čŗčćąĮąŠą╝ čĆąĄąČąĖą╝ąĄ. ąöą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą┐ąŠą╝ąĄčģ (glitch detection) USART ą┤ąŠą╗ąČąĄąĮ ąŠčéą▒čĆą░čüčŗą▓ą░čéčī ąĖą╝ą┐čāą╗čīčüčŗ, ą║ąŠč鹊čĆčŗąĄ ą║ąŠčĆąŠč湥 1/PSC. ąöąŠą┐čāčüčéąĖą╝čŗą╣ 0 ą┐čĆąĖąĮąĖą╝ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ąĄą│ąŠ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą▒ąŠą╗čīčłąĄ 2 ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ IrDA ąĮąĖąĘą║ąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (ąĘąĮą░č湥ąĮąĖąĄ PSC ą▓ čĆąĄą│ąĖčüčéčĆąĄ USART_GTPR).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖą╝ą┐čāą╗čīčü čłąĖčĆąĖąĮąŠą╣ ą╝ąĄąĮčīčłąĄ 2 ąĖ ą▒ąŠą╗čīčłąĄ 1 ą┐ąĄčĆąĖąŠą┤ą░ PSC ąŠčéą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ąĮąĄ ą▓čüąĄą│ą┤ą░.

ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ (set up time) ą┤ąŠą╗ąČąĮąŠ čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣. ąöą╗čÅ čäąĖąĘąĖč湥čüą║ąŠą│ąŠ čüą╗ąŠčÅ IrDA čüą┐ąĄčåąĖčäąĖą║ą░čåąĖčÅ ąĘą░ą┤ą░ąĄčé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčāčÄ ąĘą░ą┤ąĄčƹȹ║čā 10 ą╝čü ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░č湥ą╣ ąĖ ą┐čĆąĖąĄą╝ąŠą╝ (IrDA čÅą▓ą╗čÅąĄčéčüčÅ ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĮčŗą╝ ą┐čĆąŠč鹊ą║ąŠą╗ąŠą╝).

[ą¤čĆąŠą┤ąŠą╗ąČąĖč鹥ą╗čīąĮčŗą╣ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ąĮą░ ąŠčüąĮąŠą▓ąĄ DMA]

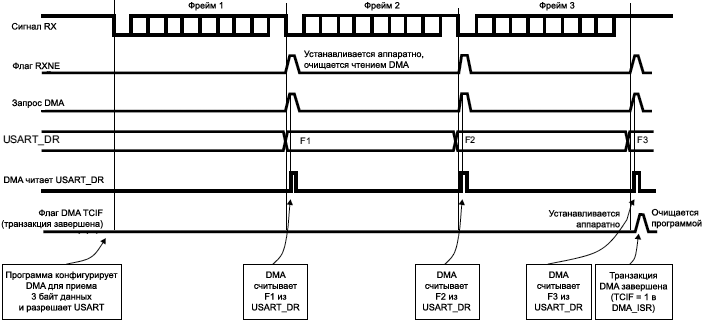

USART ą╝ąŠąČąĄčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčŗą╣ ąŠą▒ą╝ąĄąĮ čü ą┐ąŠą╝ąŠčēčīčÄ DMA. ąŚą░ą┐čĆąŠčüčŗ DMA ą┤ą╗čÅ ą▒čāč乥čĆąŠą▓ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ.