|

ąŻ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI ąĄčüčéčī 2 ąŠčüąĮąŠą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ - ą╗ąĖą▒ąŠ ą┐ąŠą┤ą┤ąĄčƹȹ║ą░ ą┐čĆąŠč鹊ą║ąŠą╗ą░/ąĖąĮč鹥čĆč乥ą╣čüą░ SPI [2], ą╗ąĖą▒ąŠ audio-ą┐čĆąŠč鹊ą║ąŠą╗ą░ I2S. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą▓čŗą▒čĆą░ąĮą░ čäčāąĮą║čåąĖčÅ SPI. ą£ąŠąČąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčī čĆąĄąČąĖą╝ ąĖąĘ SPI ą▓ I2S.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąŠą┐ąĖčüą░ąĮąĖąĄ ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ - ą┐ąĄčĆąĄą▓ąŠą┤ čĆą░ąĘą┤ąĄą╗ą░ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ "28. Serial peripheral interface (SPI)" ąĖąĘ ą┤ą░čéą░čłąĖčéą░ [1]. ąÆčüčÅ ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąŠą▒ SPI ąŠčéąĮąŠčüąĖčéčüčÅ ą║ čüąĄą╝ąĄą╣čüčéą▓čā ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32F4xx, ąĄčüą╗ąĖ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ ąĮąĄčćč鹊 ą┤čĆčāą│ąŠąĄ.

SPI. SPI ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĮčŗą╣ ąĖą╗ąĖ ą┐ąŠą╗ąĮąŠą┤čāą┐ą╗ąĄą║čüąĮčŗą╣, čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą▓ąĮąĄčłąĮąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ. ąŁč鹊čé ąĖąĮč鹥čĆč乥ą╣čü ą╝ąŠąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą╗ąĖą▒ąŠ ą║ą░ą║ ą▓ čĆąĄąČąĖą╝ąĄ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (master), ą╗ąĖą▒ąŠ ą║ą░ą║ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (slave). ąÆ čĆąĄąČąĖą╝ąĄ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI č乊čĆą╝ąĖčĆčāąĄčé ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ (SCK) ą┤ą╗čÅ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čéą░ą║ąČąĄ čĆą░ą▒ąŠčéą░čéčī ą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą│ą╗ą░ą▓ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ąĮą░ čłąĖąĮąĄ (ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ multimaster).

ąÆąŠąĘą╝ąŠąČąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖą╣ SPI ąŠč湥ąĮčī čłąĖčĆąŠą║ąĖą╣, ą▓ą║ą╗čÄčćą░čÅ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčāčÄ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ ąĖą╗ąĖ ąĮą░ą┤ąĄąČąĮčāčÄ čüą▓čÅąĘčī ą╝ąĄąČą┤čā čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, ąĘą░čēąĖčēąĄąĮąĮčāčÄ ą┐čĆąŠą▓ąĄčĆą║ąŠą╣ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ (CRC).

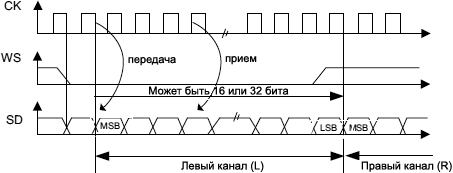

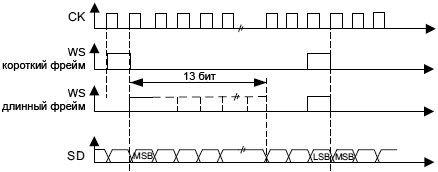

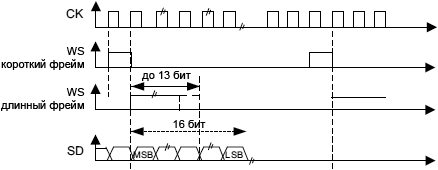

I2S. I2S čŹč鹊 čéą░ą║ąČąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü. ą×ąĮ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą┐ąŠ 4 čĆą░ąĘą╗ąĖčćąĮčŗą╝ čüčéą░ąĮą┤ą░čĆčéą░ą╝, ą▓ą║ą╗čÄčćą░čÅ I2S Philips, čüčéą░ąĮą┤ą░čĆčéčŗ čü ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ MSB ąĖ LSB, ąĖ čüčéą░ąĮą┤ą░čĆčé PCM. ąÆąŠąĘą╝ąŠąČąĮą░ čĆą░ą▒ąŠčéą░ ą║ą░ą║ slave ąĖą╗ąĖ ą║ą░ą║ master-čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ ą┐ąŠą╗ąĮąŠą┤čāą┐ą╗ąĄą║čüąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ 4 ą▓čŗą▓ąŠą┤ąŠą▓) ąĖą╗ąĖ ą▓ ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĄ (ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 3 ą▓čŗą▓ąŠą┤ą░). ą¦ą░čüč鹊čéą░ čéą░ą║č鹊ą▓ ąŠčé master ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮą░ ą┤ą╗čÅ slave-čāčüčéčĆąŠą╣čüčéą▓ą░, ą║ąŠą│ą┤ą░ I2S čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ.

ą¤čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖąĄ: ą┐ąŠčüą║ąŠą╗čīą║čā ąĮąĄą║ąŠč鹊čĆčŗąĄ čüąĖą│ąĮą░ą╗čŗ SPI1 ąĖ SPI3/I2S3 ą╝ąŠą│čāčé ąŠč鹊ą▒čĆą░ąČą░čéčīčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤čŗ čü čäčāąĮą║čåąĖčÅą╝ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ JTAG (SPI1_NSS ąĮą░ JTDI, SPI3_NSS/I2S3_WS ąĮą░ JTDI ąĖ SPI3_SCK/I2S3_CK ąĮą░ JTDO), č鹊 ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ čü čŹčéąĖą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ą╝ąŠąČąĮąŠ ą┐ąŠčüčéčāą┐ąĖčéčī ą▓ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ čüą┐ąŠčüąŠą▒ą░ą╝ąĖ:

ŌĆō ąŠč鹊ą▒čĆą░ąĘąĖčéčī čüąĖą│ąĮą░ą╗čŗ SPI/I2S ąĮą░ ą┤čĆčāą│ąĖąĄ ą▓čŗą▓ąŠą┤čŗ ą║ąŠčĆą┐čāčüą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░

ŌĆō ąĘą░ą┐čĆąĄčéąĖčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ JTAG, ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ąŠčéą╗ą░ą┤ą║ąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą▓ą╝ąĄčüč鹊 ąĮąĄą│ąŠ ąĖąĮč鹥čĆč乥ą╣čü SWD - ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ąĖ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą▓čŗą▓ąŠą┤čŗ, ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮčŗąĄ ą║ą░ą║ ąĮąŠąČą║ąĖ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ SPI, ąĖą╗ąĖ

ŌĆō ąĘą░ą┐čĆąĄčéąĖčéčī ąŠą▒ą░ ąĖąĮč鹥čĆč乥ą╣čüą░ ąŠčéą╗ą░ą┤ą║ąĖ, ąĖ JTAG, ąĖ SWD (ą┐čĆąĖą╝ąĄąĮąĖą╝ąŠ ą┤ą╗čÅ čāąČąĄ ąŠčéą╗ą░ąČąĄąĮąĮčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣).

ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ąĮąŠąČą║ą░ą╝ JTAG/SWD čüą╝. čüąĄą║čåąĖčÄ "8.3.2: I/O pin multiplexer and mapping" ą┤ą░čéą░čłąĖčéą░ [1] (ąĖą╗ąĖ čüąĄą║čåąĖčÄ "ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ąĮąŠąČąĄą║ I/O" čüčéą░čéčīąĖ [4]).

ŌĆó ą¤ąŠą╗ąĮąŠą┤čāą┐ą╗ąĄą║čüąĮą░čÅ čüąĖąĮčģčĆąŠąĮąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąŠ 3 čüąĖą│ąĮą░ą╗čīąĮčŗą╝ ą╗ąĖąĮąĖčÅą╝.

ŌĆó ąĪąĖą╝ą┐ą╗ąĄą║čüąĮą░čÅ čüąĖąĮčģčĆąŠąĮąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąŠ 2 čüąĖą│ąĮą░ą╗čīąĮčŗą╝ ą╗ąĖąĮąĖčÅą╝, čü ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą╣ ą╗ąĖąĮąĖąĄą╣ ąĖą╗ąĖ ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą╣ ą╗ąĖąĮąĖąĄą╣ ą┤ą░ąĮąĮčŗčģ.

ŌĆó ążąŠčĆą╝ą░čé čäčĆąĄą╣ą╝ą░ 8 ąĖą╗ąĖ 16 ą▒ąĖčé.

ŌĆó ąĀą░ą▒ąŠčéą░ ą▓ čĆąĄąČąĖą╝ąĄ master ąĖą╗ąĖ slave.

ŌĆó ąÆąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ čĆąĄąČąĖą╝ą░ Multimaster.

ŌĆó 8 čĆąĄąČąĖą╝ąŠą▓ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ čüą║ąŠčĆąŠčüčéąĖ ą┤ą╗čÅ master (ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ SCK čéą░ą║č鹊ą▓ fPCLK/2).

ŌĆó ą£ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ čĆąĄąČąĖą╝ą░ slave čĆą░ą▓ąĮą░ fPCLK/2 max.

ŌĆó ąŻčüą║ąŠčĆąĄąĮąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą╗čÅ čĆąĄąČąĖą╝ąŠą▓ master ąĖ slave.

ŌĆó ąÉą┐ą┐ą░čĆą░čéąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą▒ąŠčĆą║ą░ą╝ąĖ NSS, ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ, ą┤ąŠčüčéčāą┐ąĮąŠąĄ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ čĆąĄąČąĖą╝ąŠą▓ master ąĖ slave. ąæą╗ą░ą│ąŠą┤ą░čĆčÅ čŹč鹊ą╝čā ą╝ąŠąČąĮąŠ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąĖ ą╝ąĄąĮčÅčéčī čäčāąĮą║čåąĖąŠąĮą░ą╗ master/slave.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī ąĖ čäą░ąĘą░ ą┤ą╗čÅ čéą░ą║č鹊ą▓ (CPOL, CPHA).

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ ą┐ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ čüčéą░čĆčłąĖąĮčüčéą▓ą░ ą▒ąĖčé - ą╗ąĖą▒ąŠ čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ ą▓ą┐ąĄčĆąĄą┤ (MSB-first), ą╗ąĖą▒ąŠ ą╝ą╗ą░ą┤čłąĖą╝ (LSB-first).

ŌĆó ą×čéą┤ąĄą╗čīąĮčŗąĄ čäą╗ą░ą│ąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ŌĆó ążą╗ą░ą│ čüčéą░čéčāčüą░ ąĘą░ąĮčÅč鹊čüčéąĖ čłąĖąĮčŗ (SPI bus busy).

ŌĆó ąĀąĄąČąĖą╝ SPI TI.

ŌĆó ążčāąĮą║čåąĖčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ CRC ą┤ą╗čÅ ąĮą░ą┤ąĄąČąĮąŠą│ąŠ ąŠą▒ą╝ąĄąĮą░:

ŌĆō ąŚąĮą░č湥ąĮąĖąĄ CRC ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą║ą░ą║ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ą░ą╣čé ą▓ čĆąĄąČąĖą╝ąĄ Tx.

ŌĆō ąÉą▓č鹊ą╝ą░čéąĖč湥čüą║ą░čÅ ą┐čĆąŠą▓ąĄčĆą║ą░ CRC ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą▒ą░ą╣čéą░.

ŌĆó ążą╗ą░ą│ąĖ ąŠčłąĖą▒ąŠą║ Master mode fault, overrun ąĖ CRC error, čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó 1-ą▒ą░ą╣čéąĮčŗą╣ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ DMA: ąŠą▒čĆą░ą▒ąŠčéą║ą░ ąĘą░ą┐čĆąŠčüąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ (Tx request ąĖ Rx request).

ŌĆó ą¤ąŠą╗ąĮąŠą┤čāą┐ą╗ąĄą║čüąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ.

ŌĆó ą¤ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĮčŗą╣ ąŠą▒ą╝ąĄąĮ (č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĖą╗ąĖ č鹊ą╗čīą║ąŠ ą┐čĆąĖąĄą╝ąĮąĖą║).

ŌĆó ąĀą░ą▒ąŠčéą░ ą▓ čĆąĄąČąĖą╝ą░čģ master ąĖą╗ąĖ slave.

ŌĆó 8-ą▒ąĖčéąĮčŗą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ ą╗ąĖąĮąĄą╣ąĮčŗą╣ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ, čćč鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī č鹊čćąĮčŗčģ čćą░čüč鹊čé ą▓čŗą▒ąŠčĆąŠą║ ąĘą▓čāą║ą░ (ąŠčé 8 ą║ąōčå ą┤ąŠ 192 ą║ąōčå).

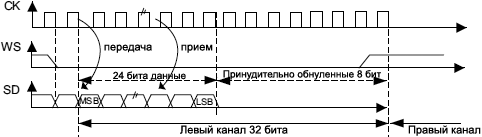

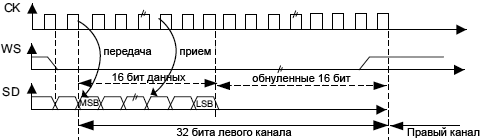

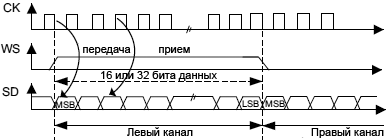

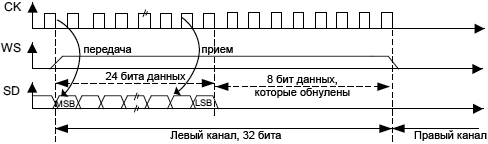

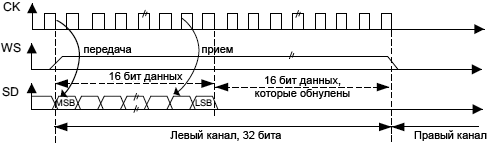

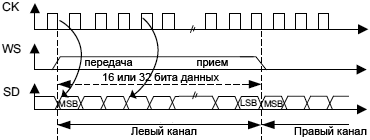

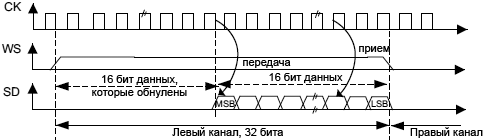

ŌĆó ążąŠčĆą╝ą░čé ą┤ą░ąĮąĮčŗčģ ą╝ąŠąČąĄčé ą▒čŗčéčī 16 ą▒ąĖčé, 24 ą▒ąĖčéą░ ąĖą╗ąĖ 32 ą▒ąĖčéą░.

ŌĆó ążčĆąĄą╣ą╝ ą┐ą░ą║ąĄčéą░, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ą┐ąŠ ą░čāą┤ąĖąŠą║ą░ąĮą░ą╗čā, čäąĖą║čüąĖčĆąŠą▓ą░ąĮ ąĮą░ 16 ą▒ąĖčé (čäčĆąĄą╣ą╝ ą┤ą░ąĮąĮčŗčģ 16 ą▒ąĖčé) ąĖą╗ąĖ ąĮą░ 32 ą▒ąĖčéą░ (čäčĆąĄą╣ą╝ ą┤ą░ąĮąĮčŗčģ 16, 24, 32 ą▒ąĖčéą░).

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ (čāčüč鹊ą╣čćąĖą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ, steady state).

ŌĆó ążą╗ą░ą│ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ (underrun) ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ slave, čäą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ (overrun) ą▓ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąĄą╝ą░ (master ąĖ slave), čäą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ ą║ą░ą┤čĆą░ (Frame Error) ą▓ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (č鹊ą╗čīą║ąŠ slave).

ŌĆó 16-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ čü ąŠą┤ąĮąĖą╝ čĆąĄą│ąĖčüčéčĆąŠą╝ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ ą║ą░ąĮą░ą╗ąŠą▓ (ą╗ąĄą▓čŗą╣ ąĖ ą┐čĆą░ą▓čŗą╣).

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗąĄ ą┐čĆąŠč鹊ą║ąŠą╗čŗ I2S:

ŌĆō I2S Phillps standard

ŌĆō MSB-justified standard (left-justified)

ŌĆō LSB-justified standard (right-justified)

ŌĆō PCM standard (čü ą║ąŠčĆąŠčéą║ąŠą╣ ąĖą╗ąĖ ą┤ą╗ąĖąĮąĮąŠą╣ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĄą╣ čäčĆąĄą╣ą╝ą░ ąĮą░ 16-ą▒ąĖčéąĮąŠą╝ čäčĆąĄą╣ą╝ąĄ ą║ą░ąĮą░ą╗ą░ ąĖą╗ąĖ 16-ą▒ąĖčéąĮąŠą╝ čäčĆąĄą╣ą╝ąĄ ą┤ą░ąĮąĮčŗčģ, čĆą░čüčłąĖčĆąĄąĮąĮąŠą╝ ą┤ąŠ 32-ą▒ąĖčéąĮąŠą│ąŠ čäčĆąĄą╣ą╝ą░ ą║ą░ąĮą░ą╗ą░).

ŌĆó ą¤ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé - čüčéą░čĆčłąĖą╣ ą▒ąĖčé ą▓čüąĄą│ą┤ą░ ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝ (MSB first).

ŌĆó ąÆąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ DMA ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ (ą┤ą░ąĮąĮčŗčģ čłąĖčĆąĖąĮąŠą╣ 16 ą▒ąĖčé).

ŌĆó ą£ąŠąČąĄčé ą▓čŗą▓ąŠą┤ąĖčéčīčüčÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ (master clock) ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ąĮąĄčłąĮąĖą╝ ą░čāą┤ąĖąŠ-ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą╝. ąÜąŠčŹčäčäąĖčåąĖąĄąĮčé čäąĖą║čüąĖčĆąŠą▓ą░ąĮ ąĮą░ 256 x FS (ąĘą┤ąĄčüčī FS čŹč鹊 čćą░čüč鹊čéą░ ą░čāą┤ąĖąŠą▓čŗą▒ąŠčĆąŠą║).

ŌĆó ą×ą▒ą░ ą▓ą░čĆąĖą░ąĮčéą░ I2S (I2S2 ąĖ I2S3) ąĖą╝ąĄčÄčé ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗą╣ ą▒ą╗ąŠą║ PLL (PLLI2S), čćč鹊ą▒čŗ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĄčēąĄ ą▒ąŠą╗ąĄąĄ č鹊čćąĮčāčÄ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā.

ŌĆó ąóą░ą║čéčŗ I2S (I2S2 ąĖ I2S3) ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮčŗ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą┐ąŠčüčéčāą┐ą░čÄčēąĄą│ąŠ ąĮą░ ą▓čŗą▓ąŠą┤ I2S_CKIN.

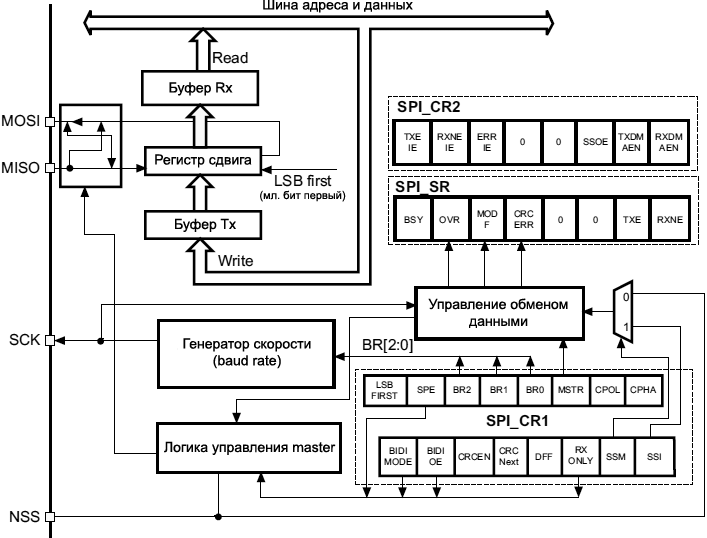

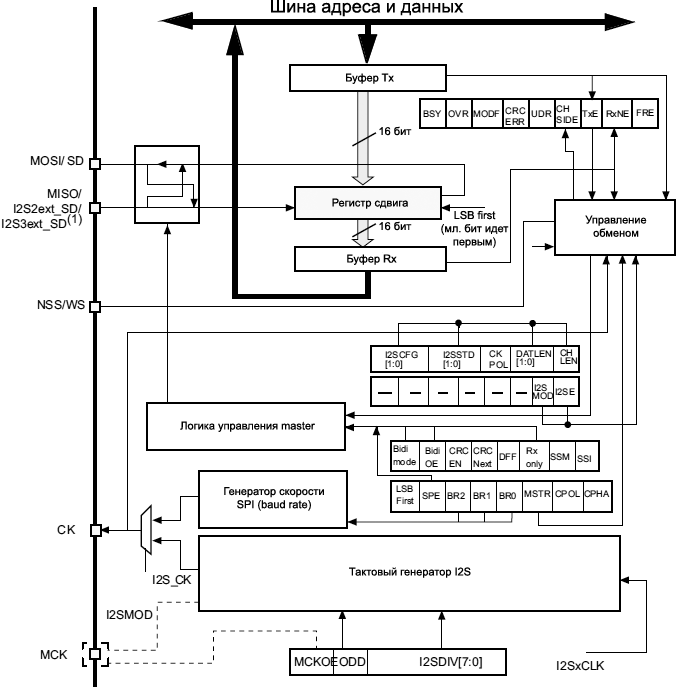

[ą×ą▒čēąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ SPI]

ąĀąĖčü. 246. ąæą╗ąŠą║-čüčģąĄą╝ą░ SPI.

ą×ą▒čŗčćąĮąŠ SPI ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą▓ąĮąĄčłąĮąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ č湥čĆąĄąĘ 4 čüąĖą│ąĮą░ą╗ą░ (ąŠąĮąĖ ąŠč鹊ą▒čĆą░ąČą░čÄčéčüčÅ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗą╝ąĖ čäčāąĮą║čåąĖčÅą╝ąĖ AF ąĮą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ [3, 4]):

MISO: ą┤ą░ąĮąĮčŗąĄ Master In / Slave Out. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ slave ąĖ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ master.

MOSI: Master Out / Slave In, ą┤ą░ąĮąĮčŗąĄ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ master ąĖ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ slave.

SCK: Serial Clock, čéą░ą║č鹊ą▓čŗą╣ ą▓čŗčģąŠą┤ ą┤ą╗čÅ SPI master ąĖ čéą░ą║č鹊ą▓čŗą╣ ą▓čģąŠą┤ ą┤ą╗čÅ SPI slave.

NSS: Node Slave Select. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ąĮąĄąŠą▒čÅąĘą░č鹥ą╗ąĄąĮ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ, ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą║ą░ą║ ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ slave-čāčüčéčĆąŠą╣čüčéą▓ą░. ąĪąĖą│ąĮą░ą╗ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą│ą╗ą░ą▓ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā čłąĖąĮčŗ SPI ą▓čŗą▒čĆą░čéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą║ąŠąĮčäą╗ąĖą║čéą░ ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ ą┤ą░ąĮąĮčŗčģ. ąĪąĖą│ąĮą░ą╗čŗ ą▓čŗą▒ąŠčĆą║ąĖ NSS ąĮą░ ą│ą╗ą░ą▓ąĮąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ ą╝ąŠą│čāčé čéą░ą║ąČąĄ ą▓čŗčĆą░ą▒ą░čéčŗą▓ą░čéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ąĮąŠąČą║ą░ą╝ąĖ GPIO. ąØąŠąČą║ą░ NSS čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ą▓čŗčģąŠą┤, ąĄčüą╗ąĖ čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ (ą▒ąĖč鹊ą╝ SSOE), ąĖ ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ ą▓ ą╗ąŠą│. 0 ą┐čĆąĖ ąŠą▒čĆą░čēąĄąĮąĖąĖ ą║ ą▓ąĮąĄčłąĮąĖą╝ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝, ąĄčüą╗ąĖ SPI čĆą░ą▒ąŠčéą░ąĄčé ą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ master. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▓čüąĄ ąĮąŠąČą║ąĖ NSS čāčüčéčĆąŠą╣čüčéą▓, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą║ čüąĖą│ąĮą░ą╗čā Master NSS, ą▓ąĖą┤čÅčé ą╗ąŠą│. 0 ąĖ čüčéą░ąĮąŠą▓čÅčéčüčÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ ą┐ąŠ ąĮąĖąĘą║ąŠą╝čā čāčĆąŠą▓ąĮčÄ, ą║ąŠą│ą┤ą░ ąŠąĮąĖ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą▓ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą▓čŗą▒ąŠčĆą║ąĖ NSS. ąÜąŠą│ą┤ą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ čĆąĄąČąĖą╝ master, ąĖ NSS ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤ (MSTR=1 ąĖ SSOE=0), ąĖ ąĄčüą╗ąĖ NSS ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0, č鹊 SPI ą▓čģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąŠčéą║ą░ąĘą░ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (master mode fault state): ą▒ąĖčé MSTR ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ, ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, slave mode (čüą╝. ą┤ą░ą╗ąĄąĄ čĆą░ąĘą┤ąĄą╗ "ążą╗ą░ą│ąĖ ąŠčłąĖą▒ąŠą║").

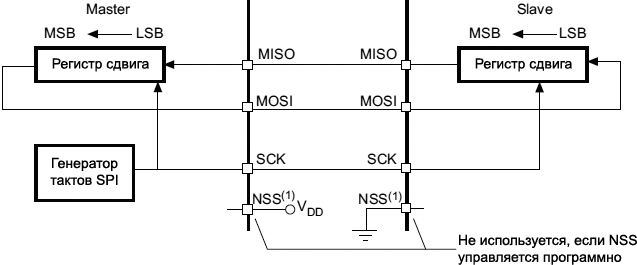

ąæą░ąĘąŠą▓čŗą╣ ą┐čĆąĖą╝ąĄčĆ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖčÅ ą╝ąĄąČą┤čā ąŠą┤ąĮąĖą╝ master ąĖ ąŠą┤ąĮąĖą╝ slave ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 247.

ąĀąĖčü. 247. ą¤čĆąĖą╗ąŠąČąĄąĮąĖąĄ, ą│ą┤ąĄ čüąŠąĄą┤ąĖąĮąĄąĮą░ ąŠą┤ąĖąĮąŠčćąĮą░čÅ ą┐ą░čĆą░ čāčüčéčĆąŠą╣čüčéą▓ master ąĖ slave.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ąĘą┤ąĄčüčī ą▓čŗą▓ąŠą┤ NSS čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čģąŠą┤.

ąÆčüąĄ ąŠą┤ąĮąŠąĖą╝ąĄąĮąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ čüąŠąĄą┤ąĖąĮčÅčÄčéčüčÅ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą╝ąĄąČą┤čā master ąĖ slave, ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓ ą┤ą▓čāčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ MSB ą▓ą┐ąĄčĆąĄą┤).

ą×ą▒ą╝ąĄąĮ ą▓čüąĄą│ą┤ą░ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ čüąŠ čüč鹊čĆąŠąĮčŗ master-čāčüčéčĆąŠą╣čüčéą▓ą░. ąÜąŠą│ą┤ą░ master ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ slave-čāčüčéčĆąŠą╣čüčéą▓čā č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ MOSI, slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ąŠčéą▓ąĄčćą░ąĄčé ą┤ą░ąĮąĮčŗą╝ąĖ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ MISO. ąŁč鹊 ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé ą┐ąŠą╗ąĮąŠą┤čāą┐ą╗ąĄą║čüąĮčŗą╣ ąŠą▒ą╝ąĄąĮ, ąĘą░čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ąŠą┤ąĮąĖą╝ čéą░ą║č鹊ą▓čŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝ SCK (čŹč鹊čé čüąĖą│ąĮą░ą╗ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé master).

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą▒ąŠčĆą║ąŠą╣ NSS. ąæąĖč鹊ą╝ SSM ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮąŠ ą░ą┐ą┐ą░čĆą░čéąĮąŠąĄ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą╝ NSS.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ NSS (SSM = 1). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąŠą▒ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄ SSI ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1. ąÆąĮąĄčłąĮąĖą╣ ą▓čŗą▓ąŠą┤ NSS ąŠčüčéą░ąĄčéčüčÅ čüą▓ąŠą▒ąŠą┤ąĮčŗą╝ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ čäčāąĮą║čåąĖą╣ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ.

ŌĆó ąÉą┐ą┐ą░čĆą░čéąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ NSS (SSM = 0). ąÆąŠąĘą╝ąŠąČąĮčŗ 2 ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čŗčģąŠą┤ą░ NSS (ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ ą▒ąĖč鹊ą╝ SSOE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2):

ŌĆō ąĀą░ąĘčĆąĄčłąĄąĮ ą▓čŗčģąŠą┤ NSS (SSM = 0, SSOE = 1). ąŁčéą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ master. ąĪąĖą│ąĮą░ą╗ NSS ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ master ąĘą░ą┐čāčüą║ą░ąĄčé ąŠą▒ą╝ąĄąĮ, ąĖ NSS čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0 ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ SPI ąĮąĄ ą▒čāą┤ąĄčé ąĘą░ą┐čĆąĄčēąĄąĮ.

ŌĆō ąÆčŗčģąŠą┤ NSS ąĘą░ą┐čĆąĄčēąĄąĮ (SSM = 0, SSOE = 0). ąŁčéą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čĆą░ą▒ąŠčéą░čéčī ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ ą│ą╗ą░ą▓ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ ąĮą░ čłąĖąĮąĄ (multimaster). ąöą╗čÅ čāčüčéčĆąŠą╣čüčéą▓, ąĮą░čüčéčĆąŠąĄąĮąĮčŗčģ ą║ą░ą║ slave, ą▓čŗą▓ąŠą┤ NSS čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą║ą╗ą░čüčüąĖč湥čüą║ąĖą╣ ą▓čģąŠą┤ NSS: ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąĮą░ NSS ą┐ąŠą┤ą░ąĄčéčüčÅ ą╗ąŠą│. 0, ąĖ ąĄą│ąŠ ą▓čŗą▒ąŠčĆą║ą░ čüąĮąĖą╝ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąĮą░ NSS ą┐ąŠą┤ą░ąĮą░ ą╗ąŠą│. 1.

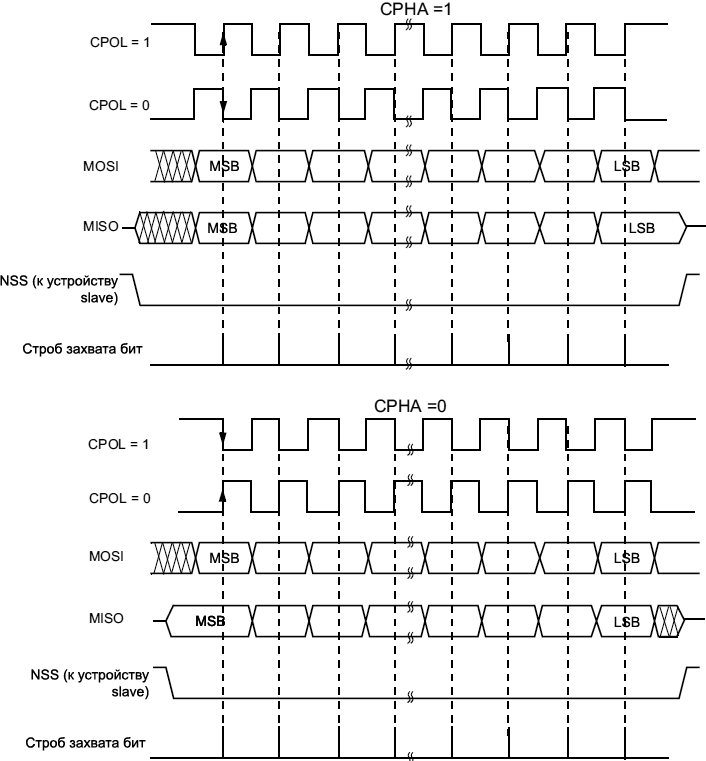

ążą░ąĘą░ ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą╝ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī 4 ą▓ą░čĆąĖą░ąĮčéą░ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖčÅ ą┐ąŠ čłąĖąĮąĄ SPI, ąĖčüą┐ąŠą╗čīąĘčāčÅ ą▒ąĖčéčŗ CPOL ąĖ CPHA ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1. ąæąĖčé CPOL (Clock POLarity, ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓) čāą┐čĆą░ą▓ą╗čÅąĄčé čāčüč鹊ą╣čćąĖą▓čŗą╝ (čé. ąĄ. ąĖčüčģąŠą┤ąĮčŗą╝) čüąŠčüč鹊čÅąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ. ąŁč鹊čé ą▒ąĖčé ą▓ą╗ąĖčÅąĄčé ąĮą░ ąŠą▒ą░ čĆąĄąČąĖą╝ą░, master ąĖ slave. ąĢčüą╗ąĖ CPOL=0, č鹊 ąĮąŠąČą║ą░ SCK ą▓ čĆąĄąČąĖą╝ąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0. ąĢčüą╗ąĖ CPOL=1, č鹊 ąĮąŠąČą║ą░ SCK ą▓ čĆąĄąČąĖą╝ąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1.

ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé CPHA (Clock PHAse, čäą░ąĘą░ čéą░ą║č鹊ą▓), č鹊 ą▓č鹊čĆąŠą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SCK (čüą┐ą░ą┤ ą▓ čüą╗čāčćą░ąĄ CPOL=0, čäčĆąŠąĮčé ą▓ čüą╗čāčćą░ąĄ CPOL=1) čüą╗čāąČąĖčé čüčéčĆąŠą▒ąŠą╝ ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ MSB). ąöą░ąĮąĮčŗąĄ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą┐čĆąĖ ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĖ ą▓č鹊čĆąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čéą░ą║č鹊ą▓. ąĢčüą╗ąĖ CPHA=0, č鹊 čüčéčĆąŠą▒ąŠą╝ čüą╗čāąČąĖčé ą┐ąĄčĆą▓čŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SCK (čüą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ ą┐čĆąĖ CPOL=1, ąĮą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ą┐čĆąĖ CPOL=0). ąöą░ąĮąĮčŗąĄ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą┐čĆąĖ ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĖ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čéą░ą║č鹊ą▓.

ąÜąŠą╝ą▒ąĖąĮą░čåąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčé CPOL ąĖ CPHA ą▓čŗą▒ąĖčĆą░ąĄčé čéą░ą║č鹊ą▓čŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą┤ą╗čÅ ąĘą░čģą▓ą░čéą░ ą┤ą░ąĮąĮčŗčģ.

ąĀąĖčü. 248 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ SPI ą┤ą╗čÅ ą▓čüąĄčģ č湥čéčŗčĆąĄčģ ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ą║ąŠą╝ą▒ąĖąĮą░čåąĖą╣ ą▒ąĖčé CPHA ąĖ CPOL. ąŁčéą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆąŠą▓ą░ąĮą░ ą║ą░ą║ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ čüąĖą│ąĮą░ą╗ąŠą▓ master ąĖą╗ąĖ slave, ą│ą┤ąĄ ą▓čŗą▓ąŠą┤čŗ SCK, MISO, MOSI čüąŠąĄą┤ąĖąĮąĄąĮčŗ ąĮą░ą┐čĆčÅą╝čāčÄ ą╝ąĄąČą┤čā čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ master ąĖ slave. ą¤ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé, ą║ąŠą│ą┤ą░ čüčéą░čĆčłąĖą╣ ą▒ąĖčé (MSB) ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝, ą▓čŗą▒čĆą░ąĮ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (ą▒ąĖčé LSBFIRST=0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1).

ąĀąĖčü. 248. ąöąĖą░ą│čĆą░ą╝ą╝čŗ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą╗čÅ čĆą░ąĘąĮčŗčģ ą▓ą░čĆąĖą░ąĮč鹊ą▓ č乊čĆą╝ą░čéą░ čäčĆąĄą╣ą╝ą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą┐ąŠą╝ąĄąĮčÅčéčī ą▒ąĖčéčŗ CPOL/CPHA, ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮąŠ ą┐čāč鹥ą╝ čüą▒čĆąŠčüą░ ą▒ąĖčéą░ SPE. Master ąĖ slave ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ą▓ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╝ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ. ąĪąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ SCK ą┤ąŠą╗ąČąĮąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1 (ą╗ąŠą│. 1 ąĮą░ SCK ą┐čĆąĖ CPOL=1, ąĖą╗ąĖ ą╗ąŠą│. 0 ąĮą░ SCK ą┐čĆąĖ CPOL=0). ążąŠčĆą╝ą░čé ą┤ą░ąĮąĮčŗčģ čäčĆąĄą╣ą╝ą░ (8 ąĖą╗ąĖ 16 ą▒ąĖčé) ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▒ąĖč鹊ą╝ DFF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1, ąĖ čŹč鹊 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┤ą╗ąĖąĮčā ą┤ą░ąĮąĮčŗčģ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ/ą┐čĆąĖąĄą╝ą░.

ą¤ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé. ążąŠčĆą╝ą░čé čäčĆąĄą╣ą╝ą░ čéą░ą║ąČąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé č鹊ą│ąŠ, ą║ą░ą║ąŠą╣ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝ - čüčéą░čĆčłąĖą╣ (MSB) ąĖą╗ąĖ ą╝ą╗ą░ą┤čłąĖą╣ (LSB). ąŁč鹊 ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčéą░ LSBFIRST ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1.

ąöą╗ąĖąĮą░ čäčĆąĄą╣ą╝ą░. ąŁą╗ąĄą╝ąĄąĮčéą░čĆąĮą░čÅ ą┐ąŠčĆčåąĖčÅ ą┤ą░ąĮąĮčŗčģ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ą░čÅ ą┐ąŠ čłąĖąĮąĄ (čäčĆąĄą╣ą╝, ąĖą╗ąĖ ą║ą░ą┤čĆ), ą╝ąŠąČąĄčé čüąŠčüč鹊čÅčéčī ą╗ąĖą▒ąŠ ąĖąĘ 8, ą╗ąĖą▒ąŠ ąĖąĘ 16 ą▒ąĖčé, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčéą░ DFF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1.

ąÆčŗą▒čĆą░ąĮąĮčŗą╣ č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░ (ą┐ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé ąĖ ą┤ą╗ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ) čĆą░čüą┐čĆąŠčüčéčĆą░ąĮčÅąĄčéčüčÅ ąĮą░ ą┐čĆąĖąĄą╝ ąĖ/ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćčā.

ąÆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ slave ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ čéą░ą║čéčŗ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SCK ąŠčé čāčüčéčĆąŠą╣čüčéą▓ą░ master. ąŚąĮą░č湥ąĮąĖąĄ, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠąĄ ą▒ąĖčéą░ą╝ąĖ BR[2:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1, ąĮąĖą║ą░ą║ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čĆą░ąĘčĆąĄčłąĖčéčī SPI ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ master ąĮą░čćąĮąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗. ąĢčüą╗ąĖ čŹč鹊 ąĮąĄ čüą┤ąĄą╗ą░čéčī, č鹊 ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ. ąĀąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą│ąŠč鹊ą▓ ą┐ąĄčĆąĄą┤ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖąĄą╝ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ ąŠą║ąŠąĮčćą░ąĮąĖąĄą╝ ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčēąĄą│ąŠčüčÅ ąŠą▒ą╝ąĄąĮą░. ąÆą░ąČąĮąŠ, čćč鹊ą▒čŗ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ ą▒čŗą╗ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ čĆą░ąĘčĆąĄčłąĄąĮą░ čĆą░ą▒ąŠčéą░ čāčüčéčĆąŠą╣čüčéą▓ slave ąĖ master.

ąöą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ SPI ą▓ čĆąĄąČąĖą╝ąĄ slave ą▓čŗą┐ąŠą╗ąĮąĖč鹥 čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čłą░ą│ąŠą▓:

1. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░ DFF, čćč鹊ą▒čŗ ą▓čŗą▒čĆą░čéčī 8- ąĖą╗ąĖ 16-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ.

2. ąŚąĮą░č湥ąĮąĖąĄ ą▒ąĖčé CPOL ąĖ CPHA, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąŠą┤ąĖąĮ ąĖąĘ 4 ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ą▓ą░čĆąĖą░ąĮč鹊ą▓ ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖ čéą░ą║č鹊ą▓ (čüą╝. čĆąĖčü. 248). ą¦č鹊ą▒čŗ ą║ąŠčĆčĆąĄą║čéąĮąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ, ą▒ąĖčéčŗ CPOL ąĖ CPHA ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠ čā slave ąĖ čā master. ąŁč鹊čé čłą░ą│ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒ąĖč鹊ą╝ FRF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2 ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čĆąĄąČąĖą╝ TI.

3. ąÆčŗą▒ąĄčĆąĖč鹥 ą┐ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé (MSB-first ąĖą╗ąĖ LSB-first) ą┐čāč鹥ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖčéą░ LSBFIRST ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1. ąŻčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ ą┐ąŠčĆčÅą┤ąŠą║ ą▒ąĖčé ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čéą░ą║ąŠą╣ ąČąĄ, ą║ą░ą║ ąĖ čā čāčüčéčĆąŠą╣čüčéą▓ą░ master. ąŁč鹊čé čłą░ą│ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒ąĖč鹊ą╝ FRF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2 ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čĆąĄąČąĖą╝ TI.

4. ąÆ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╝ čĆąĄąČąĖą╝ąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąŠą╣ ąĮąŠąČą║ą░ NSS ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čüąŠąĄą┤ąĖąĮąĄąĮą░ čü ą╗ąŠą│. 0 ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąŠą╗ąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ čäčĆąĄą╣ą╝ą░. ąÆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ NSS čāčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé SSM ąĖ ąŠčćąĖčüčéąĖč鹥 ą▒ąĖčé SSI ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1. ąŁč鹊čé čłą░ą│ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒ąĖč鹊ą╝ FRF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2 ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čĆąĄąČąĖą╝ TI.

5. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé FRF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2, čćč鹊ą▒čŗ ą▓čŗą▒čĆą░čéčī čĆąĄąČąĖą╝ ą┐čĆąŠč鹊ą║ąŠą╗ą░ TI.

6. ą×čćąĖčüčéąĖč鹥 ą▒ąĖčé MSTR ąĖ čāčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé SPE (ąŠą▒ą░ čŹčéąĖ ą▒ąĖčéą░ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1), čćč鹊ą▒čŗ ąĮą░ąĘąĮą░čćąĖčéčī ą▓čŗą▓ąŠą┤ą░ą╝ SPI ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ.

ąÆ čŹč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĮąŠąČą║ą░ MOSI čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤ ą┤ą░ąĮąĮčŗčģ, ą░ ąĮąŠąČą║ą░ MISO ą║ą░ą║ ą▓čŗčģąŠą┤ ą┤ą░ąĮąĮčŗčģ.

ą¤ąĄčĆąĄą┤ą░čćą░. ą¤ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ą░čÅ ą┐ąŠčĆčåąĖčÅ ą┤ą░ąĮąĮčŗčģ (8 ąĖą╗ąĖ 16 ą▒ąĖčé) ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ ą▒čāč乥čĆ Tx ą▓ąŠ ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░ ąĘą░ą┐ąĖčüąĖ.

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░čćąĖąĮą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠą╗čāčćąĖčé čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ąĖ č鹊ą│ą┤ą░ ąŠąĮąŠ ą▓čŗą▓ąĄą┤ąĄčé čüą▓ąŠą╣ ą┐ąĄčĆą▓čŗą╣ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ (MSB ąĖą╗ąĖ LSB, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▒ąĖčéą░ LSBFIRST) ąĮą░ ąĮąŠąČą║čā MOSI. ą×čüčéą░ą╗čīąĮčŗąĄ ą▒ąĖčéčŗ (7 ą▒ąĖčé ą▓ čüą╗čāčćą░ąĄ 8-čĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ ąĖ 15 ą▓ čüą╗čāčćą░ąĄ 16-čĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ) ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ TXE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_SR ą┐čĆąĖ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĖ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą▒čāč乥čĆą░ Tx ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąĖ ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ TXEIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2.

ą¤čĆąĖąĄą╝. ąöą╗čÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░, ą║ąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą┐čĆąŠčåąĄą┤čāčĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ:

ŌĆó ąöą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą╝ąĄčüčéčÅčéčüčÅ ą▓ ą▒čāč乥čĆ Rx, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RXNE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_SR.

ŌĆó ąæčāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ RXNEIE.

ą¤ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé RXNE, ą║ąŠą┐ąĖčÅ ą┐čĆąĖąĮčÅč鹊ą╣ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą╝ąĄčüčéąĖčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▓ ą▒čāč乥čĆ Rx. ą¤čĆąĖ čüčćąĖčéčŗą▓ą░ąĮąĖąĖ čĆąĄą│ąĖčüčéčĆą░ SPI_DR ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI ą▓ąĄčĆąĮąĄčé čŹč鹊 ą┐čĆąĖąĮčÅč鹊ąĄ ąĘąĮą░č湥ąĮąĖąĄ.

ą×čćąĖčüčéą║ą░ ą▒ąĖčéą░ RXNE ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ SPI_DR.

ą¤čĆąŠč鹊ą║ąŠą╗ SPI TI. ąÆ čĆąĄąČąĖą╝ąĄ slave ąĖąĮč鹥čĆč乥ą╣čü SPI čüąŠą▓ą╝ąĄčüčéąĖą╝ čü ą┐čĆąŠč鹊ą║ąŠą╗ąŠą╝ TI. ąöą╗čÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü čŹčéąĖą╝ ą┐čĆąŠč鹊ą║ąŠą╗ąŠą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé FRF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2.

ą¤ąŠą╗čÅčĆąĮąŠčüčéčī ąĖ čäą░ąĘą░ čéą░ą║č鹊ą▓ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą▓ č乊čĆą╝ą░čé ą┐čĆąŠč鹊ą║ąŠą╗ą░ TI, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĮą░čüčéčĆąŠąĄą║ čĆąĄą│ąĖčüčéčĆą░ SPI_CR1. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ NSS čéą░ą║ąČąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čüą┐ąĄčåąĖčäąĖčćąĮčŗą╝ ą┤ą╗čÅ ą┐čĆąŠč鹊ą║ąŠą╗ą░ TI, čćč鹊 ą┤ąĄą╗ą░ąĄčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ NSS č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆčŗ SPI_CR1 ąĖ SPI_CR2 (čüąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖčé SSM, SSI, SSOE) ą┐čĆąŠąĘčĆą░čćąĮąŠą╣ ą┤ą╗čÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

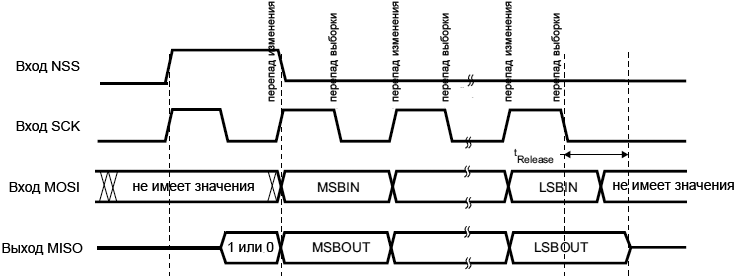

ąÆ čĆąĄąČąĖą╝ąĄ Slave (čĆąĖčü. 249 TI mode - Slave mode, ąŠą┤ąĖąĮąŠčćąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĖ čĆąĖčü. 250 TI mode - Slave mode, ąĮąĄą┐čĆąĄčĆčŗą▓ąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░), ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╝ąŠą╝ąĄąĮč鹊ą╝ ą┐ąĄčĆąĄčģąŠą┤ą░ čüąŠčüč鹊čÅąĮąĖčÅ ą▓čŗą▓ąŠą┤ą░ MISO ą▓ Hi-Z (ąŠčéą║ą╗čÄč湥ąĮąŠ) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ čüą║ąŠčĆąŠčüčéąĖ (SPI baud rate prescaler). ą£ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą╗čÄą▒ą░čÅ čüą║ąŠčĆąŠčüčéčī, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ąŠą▒ąĖčéčīčüčÅ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ ą│ąĖą▒ą║ąŠčüčéąĖ ą┐čĆąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĖ čŹč鹊ą│ąŠ ą╝ąŠą╝ąĄąĮčéą░ ą▓čĆąĄą╝ąĄąĮąĖ. ą×ą┤ąĮą░ą║ąŠ čüą║ąŠčĆąŠčüčéčī ąŠą▒čŗčćąĮąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ SCK ą▓ąĮąĄčłąĮąĄą│ąŠ master. ąÆčĆąĄą╝čÅ ą┤ą╗čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ čüąĖą│ąĮą░ą╗ą░ MISO ą▓ čüąŠčüč鹊čÅąĮąĖąĄ HI-Z (ąŠčüą▓ąŠą▒ąŠąČą┤ąĄąĮąĖąĄ čłąĖąĮčŗ SPI) ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čĆąĄčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖą╣ ąĖ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ čüą║ąŠčĆąŠčüčéąĖ, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą│ąŠ ą▒ąĖčéą░ą╝ąĖ BR[2:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1. ąŁč鹊 ą▓čĆąĄą╝čÅ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

tbaud_rate tbaud_rate

---------- + 4 x tpclk < trelease < ---------- + 6 x tpclk

2 2

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čŹčéą░ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąĮąĄą┤ąŠčüčéčāą┐ąĮą░ ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ Motorola SPI (FRF=0).

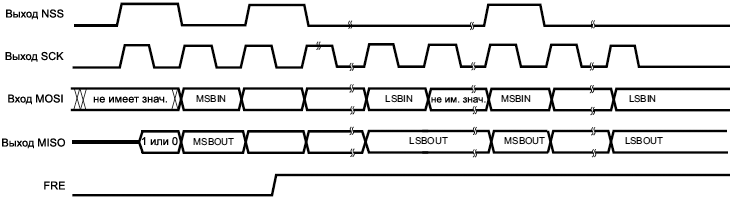

ąĀąĖčü. 249. TI mode - slave mode, ąŠą┤ąĖąĮąŠčćąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░.

ąĀąĖčü. 250. TI mode - slave mode, ąĮąĄą┐čĆąĄčĆčŗą▓ąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░.

ą¦č鹊ą▒čŗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčī ąŠčłąĖą▒ą║ąĖ čäčĆąĄą╣ą╝ą░ TI ą▓ čĆąĄąČąĖą╝ąĄ "č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║" (Slave transmitter only mode) čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ (Error interrupt, ERRIE = 1), SPI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ 2-ą┐čĆąŠą▓ąŠą┤ąĮąŠą╝ ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1 ą▒ąĖčéą░ BIDIMODE ąĖ ą▒ąĖčéą░ BIDIOE ą▓ ą╗ąŠą│. 1. ąÜąŠą│ą┤ą░ BIDIMODE=0, ą▒ąĖčé OVR čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ 1, ą┐ąŠč鹊ą╝čā čćč鹊 čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ąĮąĖą║ąŠą│ą┤ą░ ąĮą░ čüčćąĖčéčŗą▓ą░ąĄčéčüčÅ ąĖ ą▓čüąĄą│ą┤ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ąŠą│ą┤ą░ BIDIMODE=1, ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ąĖ OVR ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ.

ąÆ čĆąĄąČąĖą╝ąĄ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (master) SPI č乊čĆą╝ąĖčĆčāąĄčé čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗. ąöą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ SPI ą▓ čĆąĄąČąĖą╝ąĄ master ą▓čŗą┐ąŠą╗ąĮąĖč鹥 čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čłą░ą│ąŠą▓:

1. ą×ą┐čĆąĄą┤ąĄą╗ąĖč鹥 ą▒ąĖčéą░ą╝ąĖ BR[2:0] čćą░čüč鹊čéčā čéą░ą║č鹊ą▓ SCK (čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ SPI_CR1).

2. ąŚąĮą░č湥ąĮąĖčÅą╝ąĖ ą▒ąĖčé CPOL ąĖ CPHA ą▓čŗą▒ąĄčĆąĖč鹥 ąŠą┤ąĖąĮ ąĖąĘ 4 ą▓ą░čĆąĖą░ąĮč鹊ą▓ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ čéą░ą║č鹊ą▓ ąĖ ą┤ą░ąĮąĮčŗčģ (čüą╝. čĆąĖčü. 248). ąŁč鹊čé čłą░ą│ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮ čĆąĄąČąĖą╝ TI.

3. ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ą▒ąĖčé DFF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1 ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ 8- ąĖą╗ąĖ 16-čĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ č乊čĆą╝ą░čéą░ ą┤ą░ąĮąĮčŗčģ čäčĆąĄą╣ą╝ą░.

4. ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ą▒ąĖčé LSBFIRST ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1 ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ č乊čĆą╝ą░čéą░ čäčĆąĄą╣ą╝ą░. ąŁč鹊čé čłą░ą│ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮ čĆąĄąČąĖą╝ TI.

5. ąĢčüą╗ąĖ ąĮąŠąČą║ą░ NSS čéčĆąĄą▒čāąĄčéčüčÅ ą▓ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą▓čģąŠą┤ą░, č鹊 čüąŠąĄą┤ąĖąĮąĖč鹥 NSS čü čüąĖą│ąĮą░ą╗ąŠą╝ ą▓čŗčüąŠą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą░ą╣čéą░. ąÆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ NSS čāčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčéčŗ SSM ąĖ SSI ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1. ąĢčüą╗ąĖ ąĮąŠąČą║ą░ NSS ąĮčāąČąĮą░ ą║ą░ą║ ą▓čŗčģąŠą┤, č鹊 ąĮčāąČąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī č鹊ą╗čīą║ąŠ ą▒ąĖčé SSOE. ąŁč鹊čé čłą░ą│ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮ čĆąĄąČąĖą╝ TI.

6. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé FRF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2, čćč鹊ą▒čŗ ą▓čŗą▒čĆą░čéčī čĆąĄąČąĖą╝ ą┐čĆąŠč鹊ą║ąŠą╗ą░ TI.

7. ąöąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▒ąĖčéčŗ MSTR ąĖ SPE (ąŠąĮąĖ ąŠčüčéą░ąĮčāčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ąĖ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▓čģąŠą┤ NSS čüąŠąĄą┤ąĖąĮąĄąĮ čü čüąĖą│ąĮą░ą╗ąŠą╝ ą╗ąŠą│. 1).

ąÆ čŹč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĮąŠąČą║ą░ MOSI čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗčģąŠą┤ ą┤ą░ąĮąĮčŗčģ, ąĖ ąĮąŠąČą║ą░ MISO ą║ą░ą║ ą▓čģąŠą┤ ą┤ą░ąĮąĮčŗčģ.

ą¤ąĄčĆąĄą┤ą░čćą░. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░čćąĖąĮą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓ ą▒čāč乥čĆ Tx ąĘą░ą┐ąĖčüą░ąĮ ą▒ą░ą╣čé. ąŁč鹊čé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ (č湥čĆąĄąĘ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ čłąĖąĮčā) ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąĄčĆą▓ąŠą│ąŠ ą▒ąĖčéą░, ąĖ ąĘą░č鹥ą╝ ą▒ąĖčéčŗ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ č湥čĆąĄąĘ MOSI čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ (MSB) ąĖą╗ąĖ ą╝ą╗ą░ą┤čłąĖą╝ąĖ ą▒ąĖč鹊ą╝ (LSB) ą▓ą┐ąĄčĆąĄą┤, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčéą░ LSBFIRST ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ TXE ą▓ ą╝ąŠą╝ąĄąĮčé ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą▒čāč乥čĆą░ Tx ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąĖ ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TXEIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2.

ą¤čĆąĖąĄą╝. ąöą╗čÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ąĘą░ą▓ąĄčĆčłąĄąĮą░:

ŌĆó ąöą░ąĮąĮčŗąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄąĮąŠčüčÅčéčüčÅ ą▓ ą▒čāč乥čĆ RX, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RXNE.

ŌĆó ąæčāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé RXNEIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2.

ąØą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝ čéą░ą║č鹊ą▓ąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ ąĘą░čģą▓ą░čéą░ ą▒ąĖčéą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé RXNE, ąĖ ą║ąŠą┐ąĖčÅ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą▒ą░ą╣čéą░ ą┐ąĄčĆąĄą╝ąĄčüčéąĖčéčüčÅ ą▓ ą▒čāč乥čĆ Rx. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüčćąĖčéčŗą▓ą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ SPI_DR, ą▓ąŠąĘą▓čĆą░čēą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą▒ą░ą╣čéą░ ąĖąĘ ą▒čāč乥čĆą░.

ą×čćąĖčüčéą║ą░ ą▒ąĖčéą░ RXNE ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐čāč鹥ą╝ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ SPI_DR.

ąØąĄą┐čĆąĄčĆčŗą▓ąĮčŗą╣ ą┐ąŠč鹊ą║ ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠčüčéąĖą│ąĮčāčé, ąĄčüą╗ąĖ čüą╗ąĄą┤čāčÄčēą░čÅ ą┐ąŠčĆčåąĖčÅ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒čŗą╗ą░ ą┐ąŠą╝ąĄčēąĄąĮą░ ą▓ ą▒čāč乥čĆ Tx ą▓ ą╝ąŠą╝ąĄąĮčé, ą║ąŠą│ą┤ą░ ąĮą░čćą░ą╗ą░čüčī ą┐ąĄčĆąĄą┤ą░čćą░. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 čäą╗ą░ą│ TXE ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ čüąŠčüč鹊čÅąĮąĖąĖ 1 ą┐ąĄčĆąĄą┤ ą╗čÄą▒ąŠą╣ ąĘą░ą┐ąĖčüčīčÄ ą▓ ą▒čāč乥čĆ Tx.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ master ąŠą▒ą╝ąĄąĮąĖą▓ą░ąĄčéčüčÅ čüąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ SPI, čā ą║ąŠč鹊čĆčŗčģ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąŠčéą╝ąĄąĮąĄąĮą░ ą▓čŗą▒ąŠčĆą║ą░ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ, ąĮąŠąČą║ą░ NSS ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą║ą░ą║ GPIO, ąĖą╗ąĖ ą┤čĆčāą│ąŠą╣ ą▓čŗą▓ąŠą┤ GPIO ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ.

ą¤čĆąŠč鹊ą║ąŠą╗ SPI TI. ąÆ čĆąĄąČąĖą╝ąĄ master ąĖąĮč鹥čĆč乥ą╣čü SPI čüąŠą▓ą╝ąĄčüčéąĖą╝ čü ą┐čĆąŠč鹊ą║ąŠą╗ąŠą╝ TI. ąöą╗čÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü čŹčéąĖą╝ ą┐čĆąŠč鹊ą║ąŠą╗ąŠą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé FRF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2.

ą¤ąŠą╗čÅčĆąĮąŠčüčéčī ąĖ čäą░ąĘą░ čéą░ą║č鹊ą▓ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą▓ č乊čĆą╝ą░čé ą┐čĆąŠč鹊ą║ąŠą╗ą░ TI, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĮą░čüčéčĆąŠąĄą║ čĆąĄą│ąĖčüčéčĆą░ SPI_CR1. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ NSS čéą░ą║ąČąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čüą┐ąĄčåąĖčäąĖčćąĮčŗą╝ ą┤ą╗čÅ ą┐čĆąŠč鹊ą║ąŠą╗ą░ TI, čćč鹊 ą┤ąĄą╗ą░ąĄčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ NSS č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆčŗ SPI_CR1 ąĖ SPI_CR2 (čüąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖčé SSM, SSI, SSOE) ą┐čĆąŠąĘčĆą░čćąĮąŠą╣ ą┤ą╗čÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ąĀąĖčü. 251. TI mode - master mode, ąŠą┤ąĖąĮąŠčćąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░.

ąĀąĖčü. 252. TI mode - master mode, ąĮąĄą┐čĆąĄčĆčŗą▓ąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░.

ąĀąĖčüčāąĮą║ąĖ 251 ąĖ 252 ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé č乊čĆą╝čŗ čüąĖą│ąĮą░ą╗ąŠą▓ SPI master, ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮ čĆąĄąČąĖą╝ TI.

SPI ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąŠą╝ ą▓ ą┤ą▓čāčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ.

ŌĆó 1 čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ąĖ 1 ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ (BIDIMODE = 1).

ŌĆó 1 čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ąĖ 1 ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ (BIDIMODE = 0, č鹊ą╗čīą║ąŠ ą┐čĆąĖąĄą╝ ąĖą╗ąĖ č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čćą░).

ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮą░čÅ ą╗ąĖąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ. ąŁč鹊čé čĆąĄąČąĖą╝ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ BIDIMODE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1. ąĪąĖą│ąĮą░ą╗ SCK ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ čéą░ą║čéčŗ, ąĖ čüąĖą│ąĮą░ą╗ ąĮąŠąČą║ą░ MOSI ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ master, ąĖą╗ąĖ ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮąŠąČą║ą░ MISO ą▓ čĆąĄąČąĖą╝ąĄ slave. ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ (ą▓čģąŠą┤ ąĖą╗ąĖ ą▓čŗčģąŠą┤) ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▒ąĖč鹊ą╝ BIDIOE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1, ą╗ąĖąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗčģąŠą┤, ąĖąĮą░č湥 ą║ą░ą║ ą▓čģąŠą┤.

ą×ą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮą░čÅ ą╗ąĖąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī SPI ą╗ąĖą▒ąŠ č鹊ą╗čīą║ąŠ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā, ą╗ąĖą▒ąŠ č鹊ą╗čīą║ąŠ ąĮą░ ą┐čĆąĖąĄą╝.

ŌĆó ąĀąĄąČąĖą╝ "č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čćą░" (transmit-only) ą┐ąŠą┤ąŠą▒ąĄąĮ čĆąĄąČąĖą╝čā ą┐ąŠą╗ąĮąŠą│ąŠ ą┤čāą┐ą╗ąĄą║čüą░ (BIDIMODE=0, RXONLY=0): ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ č湥čĆąĄąĘ MOSI ą▓ čĆąĄąČąĖą╝ąĄ master ąĖą╗ąĖ č湥čĆąĄąĘ MISO ą▓ čĆąĄąČąĖą╝ąĄ slave). ąØąŠąČą║ą░ ą┐čĆąĖąĄą╝ą░ (MISO ą▓ čĆąĄąČąĖą╝ąĄ master ąĖą╗ąĖ MOSI ą▓ čĆąĄąČąĖą╝ąĄ slave) ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ąŠą▒čŗčćąĮčŗą╣ ą┐ąŠčĆčé ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (GPIO). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÄ ą┐čĆąŠčüč鹊 ąĮčāąČąĮąŠ ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī ą▒čāč乥čĆ Rx (ąĄčüą╗ąĖ ą┐čĆąŠčćąĖčéą░čéčī čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ SPI_DR, č鹊 ą▓ ąĮąĄą╝ ąĮąĄ ą▒čāą┤ąĄčé čüąŠą┤ąĄčƹȹ░čéčīčüčÅ ą┐čĆąĖąĮčÅč鹊ąĄ ąĘąĮą░č湥ąĮąĖąĄ).

ŌĆó ąÆ čĆąĄąČąĖą╝ąĄ "č鹊ą╗čīą║ąŠ ą┐čĆąĖąĄą╝" (receive-only) ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé ąĘą░ą┐čĆąĄčéąĖčéčī čäčāąĮą║čåąĖčÄ ą▓čŗčģąŠą┤ą░ SPI ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ RXONLY ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąŠčüą▓ąŠą▒ąŠąČą┤ą░ąĄčéčüčÅ ąĮąŠąČą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (MOSI ą▓ čĆąĄąČąĖą╝ąĄ master ąĖą╗ąĖ MISO ą▓ čĆąĄąČąĖą╝ąĄ slave), ąĖ ąĄčæ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ čåąĄą╗ąĄą╣.

ąöą╗čÅ čüčéą░čĆčéą░ ąŠą▒ą╝ąĄąĮą░ ą▓ čĆąĄąČąĖą╝ąĄ receive-only čüą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ąĖ čĆą░ąĘčĆąĄčłąĖč鹥 SPI čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆó ąÆ čĆąĄąČąĖą╝ąĄ master ą┐čĆąĖąĄą╝ ąĮą░čćąĮąĄčéčüčÅ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąĖ ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ ą▒ąĖčé SPE. ąĪą▒čĆąŠčü ą▒ąĖčéą░ SPE ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąŠčüčéą░ąĮąŠą▓ąĖčé č鹥ą║čāčēąĖą╣ ą┐čĆąĖąĄą╝. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ čüčćąĖčéčŗą▓ą░čéčī čäą╗ą░ą│ ąĘą░ąĮčÅč鹊čüčéąĖ BSY. ą×ąĮ ą▓čüąĄą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠą▒ą╝ąĄąĮ SPI.

ŌĆó ąÆ čĆąĄąČąĖą╝ąĄ slave ą▒ą╗ąŠą║ SPI ą┐čĆąŠą┤ąŠą╗ąČąĖčé ą┐čĆąĖąĮąĖą╝ą░čéčī, ą┐ąŠą║ą░ ąĮąŠąČą║ą░ NSS ą┐čĆąĖčéčÅąĮčāčéą░ ą║ ą╗ąŠą│. 0 (ąĖą╗ąĖ ą┐ąŠą║ą░ ąŠčćąĖčēąĄąĮ ą▒ąĖčé SSI ą▓ čĆąĄąČąĖą╝ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ NSS), ąĖ ą┐ąŠą║ą░ ą┐ąŠčüčéčāą┐ą░čÄčé čéą░ą║čéčŗ SCK.

[ą¤čĆąŠčåąĄą┤čāčĆčŗ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ]

ąæčāč乥čĆčŗ Rx ąĖ Tx. ą¤čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝ ą▒čāč乥čĆąĄ Rx, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą▒čāč乥čĆ Tx, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ąŠąĮąĖ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ.

ąöąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ą║ čĆąĄą│ąĖčüčéčĆčā SPI_DR ą▓ąŠąĘą▓čĆą░čéąĖčé ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ Rx, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī ą║ SPI_DR čüąŠčģčĆą░ąĮąĖčé ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆ Tx.

Master ą▓ ą┐ąŠą╗ąĮąŠą╝ ą┤čāą┐ą╗ąĄą║čüąĄ (BIDIMODE=0, RXONLY=0). ą¤čĆąŠčåąĄčüčü ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĮą░čćąĖąĮą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_DR (ą▒čāč乥čĆ Tx). ąŚą░č鹥ą╝ ą┤ą░ąĮąĮčŗąĄ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĖąĘ ą▒čāč乥čĆą░ Tx ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąĖ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąĖčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą▓čŗą▓ąŠą┤ č湥čĆąĄąĘ ąĮąŠąČą║čā MOSI. ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗąĄ č湥čĆąĄąĘ ąĮąŠąČą║čā MISO ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąĖ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐čĆąĖąĄą╝ą░ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_DR (ą▒čāč乥čĆ Rx).

ą×ą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ master, č鹊ą╗čīą║ąŠ ą┐čĆąĖąĄą╝ (BIDIMODE=0, RXONLY=1). ą¤čĆąŠčåąĄčüčü ąĮą░čćąĮąĄčéčüčÅ, ą║ą░ą║ č鹊ą╗čīą║ąŠ SPE=1, ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĮą░čćąĮąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ ąĮąŠąČą║čā MISO ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓ą┤ą▓ąĖą│ą░čéčī ąĖąĘ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░. ą¤ąŠčüą╗ąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗąĄ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_DR (ą▒čāč乥čĆ Rx).

ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ master ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ (BIDIMODE=1, BIDIOE=1). ą¤čĆąŠčåąĄčüčü ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░čćąĖąĮą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_DR (ą▒čāč乥čĆ Tx). ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą┤ą░ąĮąĮčŗąĄ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ąĖąĘ ą▒čāč乥čĆą░ Tx ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čü ą┐ąĄčĆąĄą┤ą░č湥ą╣ ą┐ąĄčĆą▓ąŠą│ąŠ ą▒ąĖčéą░. ąÆčüąĄ ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ č湥čĆąĄąĘ ąĮąŠąČą║čā MOSI. ą¤čĆąĖ čŹč鹊ą╝ ąĮąĖą║ą░ą║ąĖąĄ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ.

ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ master ą▓ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąĄą╝ą░ (BIDIMODE=1, BIDIOE=0). ą¤ąŠčĆąŠčåąĄčüčü ąĮą░čćąĖąĮą░ąĄčéčüčÅ, ą║ą░ą║ č鹊ą╗čīą║ąŠ SPE=1 ąĖ BIDIOE=0. ą¤čĆąĖąĮčÅčéčŗąĄ č湥čĆąĄąĘ ąĮąŠąČą║čā MOSI ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąĖ ąĘą░č鹥ą╝ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_DR (ą▒čāč乥čĆ Rx). ą¤ąĄčĆąĄą┤ą░čéčćąĖą║ ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ, ąĖ č湥čĆąĄąĘ ąĮąŠąČą║čā MOSI ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ.

Slave ą▓ ą┐ąŠą╗ąĮąŠą╝ ą┤čāą┐ą╗ąĄą║čüąĄ (BIDIMODE=0, RXONLY=0). ą¤čĆąŠčåąĄčüčü ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąŠ ą╝ąĄčĆąĄ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĮą░ ąĮąŠąČą║čā SCK, ą┤ą░ąĮąĮčŗąĄ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ ąĮąŠąČą║čā MOSI. ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąĘą░ą│čĆčāąČąĄąĮąĮčŗąĄ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆ Tx ą▒čāą┤čāčé ą▓čŗą┤ą▓ąĖą│ą░čéčīčüčÅ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ąĮą░čĆčāąČčā, ą┐ąŠčÅą▓ą╗čÅčÅčüčī ąĮą░ ąĮąŠąČą║ąĄ ą▓čŗčģąŠą┤ą░ MISO. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ SPI_DR (ą▒čāč乥čĆ Tx) ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ SPI master ąĮą░čćąĮąĄčé ą┐čĆąŠčåąĄčüčü ą┐ąĄčĆąĄą┤ą░čćąĖ.

ą×ą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ slave, č鹊ą╗čīą║ąŠ ą┐čĆąĖąĄą╝ (BIDIMODE=0, RXONLY=1). ą¤čĆąŠčåąĄčüčü ąĮą░čćąĖąĮą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ slave ą┐ąŠą╗čāčćą░ąĄčé čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ąĖ ą┐ąĄčĆą▓čŗą╣ ą▒ąĖčé ą┐ąŠčüčéčāą┐ąĖčé ąĮą░ ą▓čģąŠą┤ MOSI. ą¤čĆąĖąĮąĖą╝ą░ąĄą╝čŗąĄ ą▒ąĖčéčŗ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ č湥čĆąĄąĘ ąĮąŠąČą║čā MOSI, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤čāčé ą┐čĆąĖąĮčÅčéčŗ ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ ą▒ąĖčéčŗ. ą¤ąĄčĆąĄą┤ą░čéčćąĖą║ ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ, ąĖ ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ ąĮąŠąČą║čā MISO ąĮąĄ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ.

ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ slave ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 (BIDIMODE=1, BIDIOE=1). ą¤čĆąŠčåąĄčüčü ąĮą░čćąĖąĮą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ slave ą┐ąŠą╗čāčćąĖčé čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓, ą┐ąĄčĆą▓čŗą╣ ą▒ąĖčé ą▓ ą▒čāč乥čĆąĄ Tx ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ MISO. ąŚą░č鹥ą╝ ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ą┐ąŠ čéą░ą║č鹊ą▓čŗą╝ ąĖą╝ą┐čāą╗čīčüą░ą╝ SCK ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ č湥čĆąĄąĘ MISO, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┤ą▓ąĖąĮčāčé ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ SPI_DR (ą▒čāč乥čĆ Tx) ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ SPI master ąĮą░čćąĮąĄčé ą┐čĆąŠčåąĄčüčü ą┐ąĄčĆąĄą┤ą░čćąĖ. ąØąĖą║ą░ą║ąĖąĄ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ.

ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ slave ąĮą░ ą┐čĆąĖąĄą╝ąĄ (BIDIMODE=1, BIDIOE=0). ą¤čĆąŠčåąĄčüčü ąĮą░čćąĖąĮą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ slave ą┐ąŠą╗čāčćąĖčé čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓, ąĖ ą┐ąĄčĆą▓čŗą╣ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗą╣ ą▒ąĖčé ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ąĮą░ ą▓čģąŠą┤ąĄ MOSI. ąÆčüąĄ ą┐ąŠčüčéčāą┐ą░čÄčēąĖąĄ ą┐ąŠ čéą░ą║čéą░ą╝ SCK ą┤ą░ąĮąĮčŗąĄ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ą▓ą┐ą╗ąŠčéčī ą┤ąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ąĖčéą░, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą┤ą░ąĮąĮčŗąĄ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą┐ąĄčĆąĄąĮąŠčüčÅčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_DR (ą▒čāč乥čĆ Rx). ą¤ąĄčĆąĄą┤ą░čéčćąĖą║ ąĮąĄ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ, ąĖ ąĮąĖą║ą░ą║ąĖąĄ ą┤ą░ąĮąĮčŗąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ MISO ąĮąĄ ą┐ąŠčÅą▓ą╗čÅčÄčéčüčÅ.

ą×ą▒čĆą░ą▒ąŠčéą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ. ążą╗ą░ą│ TXE (Tx buffer empty, ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆ Tx ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą┐ąĄčĆąĄąĮąĄčüąĄąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░. ążą░ą║čé čāčüčéą░ąĮąŠą▓ą║ąĖ čŹč鹊ą│ąŠ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą▒čāč乥čĆ Tx ą│ąŠč鹊ą▓ ą║ ąĘą░ą│čĆčāąĘą║ąĄ čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ. ąÆ ą╝ąŠą╝ąĄąĮčé čāčüčéą░ąĮąŠą▓ą║ąĖ TXE ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TXEIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2. ą×čćąĖčüčéą║ą░ ą▒ąĖčéą░ TXE ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_DR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1 čäą╗ą░ą│ą░ TXE ą┐ąĄčĆąĄą┤ ą╗čÄą▒ąŠą╣ ą┐ąŠą┐čŗčéą║ąŠą╣ ąĘą░ą┐ąĖčüąĖ ą▓ ą▒čāč乥čĆ Tx (čĆąĄą│ąĖčüčéčĆ SPI_DR). ąśąĮą░č湥 ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą┐ąĄčĆąĄąĘą░ą┐ąĖčłąĄčé ą┤ą░ąĮąĮčŗąĄ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ąŠąĮąĖ ą▒čŗą╗ąĖ čĆąĄą░ą╗čīąĮąŠ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ.

ążą╗ą░ą│ RXNE (Rx buffer not empty, ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ąĮąĄ ą┐čāčüčé) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝ čéą░ą║č鹊ą▓ąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ ą┐čĆąĖąĄą╝ą░ ą▒ąĖčé, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄąĮąŠčüčÅčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▓ ą▒čāč乥čĆ Rx (čĆąĄą│ąĖčüčéčĆ SPI_DR). ążą░ą║čé čāčüčéą░ąĮąŠą▓ą║ąĖ čŹč鹊ą│ąŠ čäą╗ą░ą│ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą│ąŠč鹊ą▓čŗ ą║ čćč鹥ąĮąĖčÄ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ SPI_DR. ąÆ ą╝ąŠą╝ąĄąĮčé čāčüčéą░ąĮąŠą▓ą║ąĖ čäą╗ą░ą│ą░ RXNE ą╝ąŠąČąĄčé ą▒čŗčéčī čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé RXNEIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2. ą×čćąĖčüčéą║ą░ ą▒ąĖčéą░ RXNE ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐čāč鹥ą╝ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ SPI_DR.

ąöą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čäą╗ą░ą│ BSY ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą┤ą░ąĮąĮčŗčģ, čćč鹊ą▒čŗ ąČą┤ą░čéčī ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ.

ąöčāą┐ą╗ąĄą║čü. ąöą╗čÅ ą┐ąŠą╗ąĮąŠą┤čāą┐ą╗ąĄą║čüąĮąŠą╣ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ ą▓ čĆąĄąČąĖą╝ąĄ master ąĖą╗ąĖ slave (BIDIMODE=0, RXONLY=0) ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ čüą╗ąĄą┤ąŠą▓ą░čéčī čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐čĆąŠčåąĄą┤čāčĆąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ (čüą╝. čĆąĖčü. 253 ąĖ čĆąĖčü. 254):

1. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SPE=1.

2. ąŚą░ą┐ąĖčüčī ą┐ąĄčĆą▓ąŠą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_DR (čŹč鹊 ąŠčćąĖčüčéąĖčé čäą╗ą░ą│ TXE).

3. ą×ąČąĖą┤ą░ąĮąĖąĄ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ TXE=1, ąĖ ąĘą░č鹥ą╝ ąĘą░ą┐ąĖčüčī ą▓č鹊čĆąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮčŗčģ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ąŠąČąĖą┤ą░ąĮąĖąĄ RXNE=1 ąĖ čćč鹥ąĮąĖąĄ SPI_DR, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą┐ąĄčĆą▓čŗą╣ ą┐čĆąĖąĮčÅčéčŗą╣ 菹╗ąĄą╝ąĄąĮčé ą┤ą░ąĮąĮčŗčģ (čćč鹥ąĮąĖąĄ SPI_DR ąŠčćąĖčüčéąĖčé ą▒ąĖčé RXNE). ą©ą░ą│ 3 ą┐ąĄčĆąĄą┤ą░čćąĖ/ą┐čĆąĖąĄą╝ą░ ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą┐čĆąĖąĮčÅč鹊 nŌĆō1 菹╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ą░ąĮąĮčŗčģ.

4. ą×ąČąĖą┤ą░ąĮąĖąĄ RXNE=1, ąĖ ąĘą░č鹥ą╝ čćč鹥ąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┐čĆąĖąĮčÅč鹊ą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ.

5. ą×ąČąĖą┤ą░ąĮąĖąĄ TXE=1, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ąŠąČąĖą┤ą░ąĮąĖąĄ BSY=0 ą┐ąĄčĆąĄą┤ ąĘą░ą┐čĆąĄč鹊ą╝ SPI.

ąŁčéą░ ą┐čĆąŠčåąĄą┤čāčĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čéą░ą║ąČąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ čü ą┐ąŠą╝ąŠčēčīčÄ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗčģ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (ISR), ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┐čāčüą║ą░čÄčéčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé čāčüčéą░ąĮąŠą▓ą║ąĖ čäą╗ą░ą│ą░ RXNE ąĖą╗ąĖ TXE.

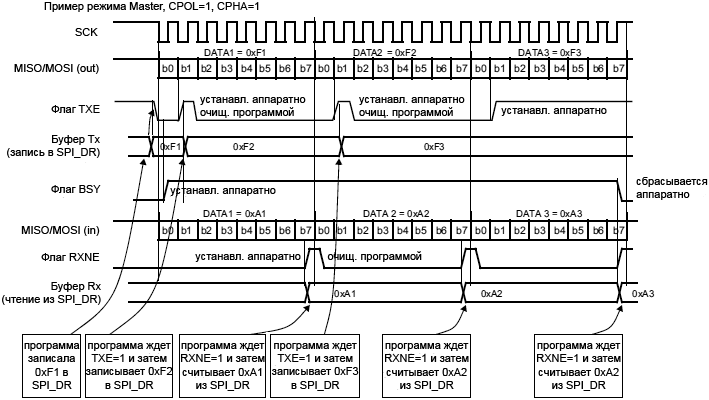

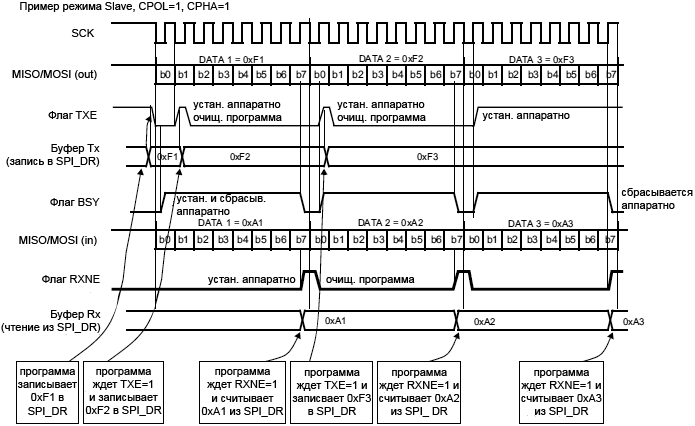

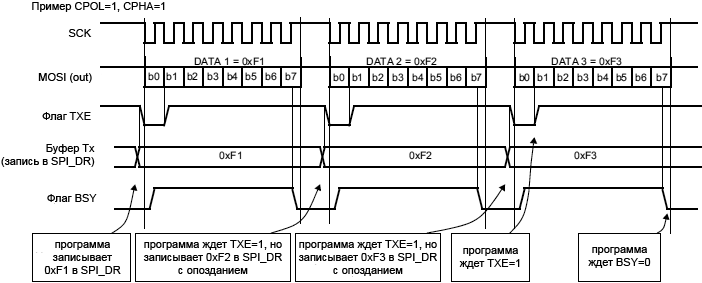

ąĀąĖčü. 253. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ TXE/RXNE/BSY ą▓ čĆąĄąČąĖą╝ąĄ Master / full-duplex (BIDIMODE=0, RXONLY=0), ą▓ čüą╗čāčćą░ąĄ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąĀąĖčü. 254. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ TXE/RXNE/BSY ą▓ čĆąĄąČąĖą╝ąĄ Slave / full-duplex (BIDIMODE=0, RXONLY=0), ą▓ čüą╗čāčćą░ąĄ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ą×ą▒čĆą░ą▒ąŠčéą║ą░ č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čćąĖ (BIDIMODE=0, RXONLY=0). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąŠčåąĄą┤čāčĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čüąŠą║čĆą░čēąĄąĮą░, ąĖ ą▒ąĖčé BSY ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠąČąĖą┤ą░ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (čüą╝. čĆąĖčü. 255 ąĖ 256).

1. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI čāčüčéą░ąĮąŠą▓ą║ąŠą╣ SPE=1.

2. ąŚą░ą┐ąĖčüčī ą┐ąĄčĆą▓ąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_DR (čŹč鹊 ąŠčćąĖčüčéąĖčé TXE).

3. ą×ąČąĖą┤ą░ąĮąĖąĄ TXE=1 ąĖ ąĘą░ą┐ąĖčüčī čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ. ą©ą░ą│ 3 ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ ą║ą░ąČą┤čŗą╣ 菹╗ąĄą╝ąĄąĮčé ą┤ą░ąĮąĮčŗčģ.

4. ą¤ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ ą▓ SPI_DR ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąŠąČąĖą┤ą░ąĮąĖąĄ TXE=1, ąĘą░č鹥ą╝ ąŠąČąĖą┤ą░ąĮąĖąĄ BSY=0, čćč鹊 ą┐ąŠą║ą░ąČąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ.

ąŁčéą░ ą┐čĆąŠčåąĄą┤čāčĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čéą░ą║ąČąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ čü ą┐ąŠą╝ąŠčēčīčÄ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗčģ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (ISR), ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┐čāčüą║ą░čÄčéčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé čāčüčéą░ąĮąŠą▓ą║ąĖ čäą╗ą░ą│ą░ TXE.

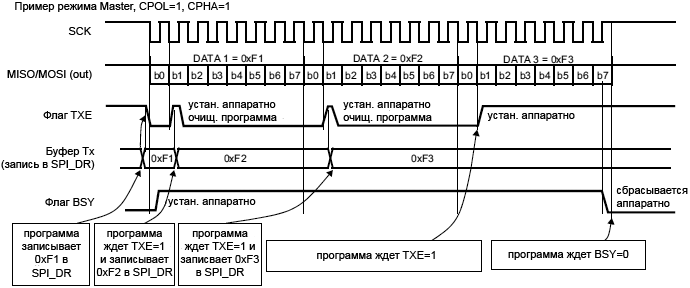

ąĀąĖčü. 255. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ TXE/BSY ą▓ čĆąĄąČąĖą╝ąĄ Master / transmit-only (BIDIMODE=0, RXONLY=0), ą▓ čüą╗čāčćą░ąĄ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąĀąĖčü. 256. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ TXE/BSY ą▓ čĆąĄąČąĖą╝ąĄ Slave / transmit-only (BIDIMODE=0, RXONLY=0), ą▓ čüą╗čāčćą░ąĄ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĄčĆčŗą▓ąĖčüčéčŗčģ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖą╣ čüčāčēąĄčüčéą▓čāąĄčé ąĘą░ą┤ąĄčƹȹ║ą░ 2 ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą║č鹊ą▓ APB ą╝ąĄąČą┤čā ąŠą┐ąĄčĆą░čåąĖąĄą╣ ąĘą░ą┐ąĖčüąĖ ą▓ SPI_DR ąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ BSY. ąÜą░ą║ čüą╗ąĄą┤čüčéą▓ąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ "č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čćą░", ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüąĮą░čćą░ą╗ą░ ą┤ąŠąČą┤ą░čéčīčüčÅ čāčüčéą░ąĮąŠą▓ą║ąĖ TXE, ąĖ ąĘą░č鹥ą╝ ąČą┤ą░čéčī ąŠčćąĖčüčéą║ąĖ BSY ą┐ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą▓čāčģ 菹╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ "č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čćą░", čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ OVR ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_SR, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ čüčćąĖčéčŗą▓ą░čÄčéčüčÅ.

ą×ą▒čĆą░ą▒ąŠčéą║ą░ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠ ąŠą┤ąĮąŠą╝čā čüąĖą│ąĮą░ą╗čā ą┤ą░ąĮąĮčŗčģ (BIDIMODE=1, BIDIOE=1). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąŠčåąĄą┤čāčĆą░ ą┐ąŠą┤ąŠą▒ąĮą░ ą┐čĆąŠčåąĄą┤čāčĆąĄ "č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čćą░" čü č鹥ą╝ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝, čćč鹊 ąŠą▒ą░ ą▒ąĖčéą░ BIDIMODE ąĖ BIDIOE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2 ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą┐ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ SPI.

ą×ą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ą┐čĆąĖąĄą╝ (BIDIMODE=0, RXONLY=1). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüą╗ąĄą┤čāčÄčēą░čÅ čāą┐čĆąŠčēąĄąĮąĮą░čÅ ą┐čĆąŠčåąĄą┤čāčĆą░ (čüą╝. čĆąĖčü. 257):

1. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé RXONLY ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1.

2. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▓ 1 ą▒ąĖčéą░ SPE:

a) ąÆ čĆąĄąČąĖą╝ąĄ master čŹč鹊 ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą░ą║čéąĖą▓ąĖąĘąĖčĆčāąĄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ čéą░ą║č鹊ą▓ SCK, ąĖ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┐čĆąĖąĮąĖą╝ą░čéčīčüčÅ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ SPI ąĮąĄ ą▒čāą┤ąĄčé ąĘą░ą┐čĆąĄčēąĄąĮ (SPE=0).

b) ąÆ čĆąĄąČąĖą╝ąĄ slave ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI master ą┐ąĄčĆąĄą▓ąĄą┤ąĄčé čüąĖą│ąĮą░ą╗ NSS ą▓ ą╗ąŠą│. 0 ąĖ ąĮą░čćąĮąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čéą░ą║čéčŗ SCK.

3. ą×ąČąĖą┤ą░ąĮąĖąĄ RXNE=1, ąĖ ąĘą░č鹥ą╝ čćč鹥ąĮąĖąĄ SPI_DR ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐čĆąĖąĮčÅčéčŗčģ ą┤ą░ąĮąĮčŗčģ (čŹč鹊 ąŠčćąĖčüčéąĖčé ą▒ąĖčé RXNE). ą©ą░ą│ 3 ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą║ą░ąČą┤čŗą╣ 菹╗ąĄą╝ąĄąĮčé ą┤ą░ąĮąĮčŗčģ.

ą×ą┐ąĖčüą░ąĮąĮą░čÅ ą┐čĆąŠčåąĄą┤čāčĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ čü ą┐ąŠą╝ąŠčēčīčÄ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗčģ ą┐čĆąŠčåąĄą┤čāčĆ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ISR) ąĮą░ ą║ą░ąČą┤ąŠą╣ čāčüčéą░ąĮąŠą▓ą║ąĄ čäą╗ą░ą│ą░ RXNE.

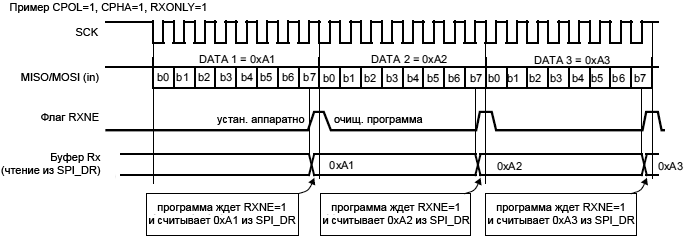

ąĀąĖčü. 257. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ RXNE ą▓ čĆąĄąČąĖą╝ąĄ receive-only (BIDIRMODE=0, RXONLY=1) ą▓ čüą╗čāčćą░ąĄ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ čéčĆąĄą▒čāąĄčéčüčÅ ąĘą░ą┐čĆąĄčé SPI ą┐ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, čüą╗ąĄą┤čāą╣č鹥 ą┐čĆąŠčåąĄą┤čāčĆąĄ, ąŠą┐ąĖčüą░ąĮąĮąŠą╣ ą┤ą░ą╗ąĄąĄ ą▓ čüąĄą║čåąĖąĖ "ąŚą░ą┐čĆąĄčé SPI".

ą¤čĆąĖąĄą╝ ą▓ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (BIDIMODE=1, BIDIOE=0). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąŠčåąĄą┤čāčĆą░ ą┐ąŠą┤ąŠą▒ąĮą░ čĆąĄąČąĖą╝čā "č鹊ą╗čīą║ąŠ ą┐čĆąĖąĄą╝" čü č鹥ą╝ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝, čćč鹊 ą▒ąĖčé BIDIMODE ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖ ą▒ąĖčé BIDIOE ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2 ą┐ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ SPI.

ąØąĄą┐čĆąĄčĆčŗą▓ąĮčŗąĄ ąĖ ą┐čĆąĄčĆčŗą▓ąĖčüčéčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄąČąĖą╝ąĄ master, ąĄčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ čĆą░ą▒ąŠčéą░ąĄčé ą┤ąŠčüčéą░č鹊čćąĮąŠ ą▒čŗčüčéčĆąŠ, čćč鹊ą▒čŗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčī ą║ą░ąČą┤čŗą╣ ą╝ąŠą╝ąĄąĮčé čāčüčéą░ąĮąŠą▓ą║ąĖ čäą╗ą░ą│ą░ TXE (ąĖą╗ąĖ čüą▓ąŠąĄą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ TXE) ąĖ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī čĆąĄą│ąĖčüčéčĆ SPI_DR ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ č鹥ą║čāčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī, č鹊 ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ čüčćąĖčéą░ąĄčéčüčÅ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčŗą╝. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĮąĄčé ą┐ą░čāąĘ ą▓ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ SPI, ąĖ ą▒ąĖčé BSY ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ ą║ą░ąČą┤ąŠą╣ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ.

ąØą░ą┐čĆąŠčéąĖą▓, ąĄčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ čĆą░ą▒ąŠčéą░ąĄčé ąĮąĄą┤ąŠčüčéą░č鹊čćąĮąŠ ą▒čŗčüčéčĆąŠ, č鹊 ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąĄčĆąĄčĆčŗą▓čŗ ą▓ ąŠą▒ą╝ąĄąĮąĄ ą┤ą░ąĮąĮčŗą╝ąĖ. ąóąŠą│ą┤ą░ ą▒ąĖčé BSY ąŠčćąĖčēą░ąĄčéčüčÅ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ (čüą╝. čĆąĖčü. 258).

ąĀąĖčü. 258. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ TXE/BSY ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 (BIDIRMODE=0, RXONLY=0) ą▓ čüą╗čāčćą░ąĄ ą┐čĆąĄčĆčŗą▓ąĖčüč鹊ą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąÆ čĆąĄąČąĖą╝ąĄ master receive-only (RXONLY=1), ąŠą▒ą╝ąĄąĮ ą▓čüąĄą│ą┤ą░ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčŗą╣, ąĖ čäą╗ą░ą│ BSY ą▓čüąĄą│ą┤ą░ čüčćąĖčéčŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ 1.

ąÆ čĆąĄąČąĖą╝ąĄ slave ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠčüčéčī ąŠą▒ą╝ąĄąĮą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čåąĄą╗ąĖą║ąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ master čłąĖąĮčŗ SPI. ąÆ ą╗čÄą▒ąŠą╝ čüą╗čāčćą░ąĄ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ąŠą▒ą╝ąĄąĮ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčŗą╣, čäą╗ą░ą│ BSY ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0 ą╝ąĄąČą┤čā ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥ą╣ ąĮą░ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ą▓čĆąĄą╝ąĄąĮąĖ ą▓ 1 čéą░ą║čé ą┐ąĄčĆąĖąŠą┤ą░ SPI (čüą╝. čĆąĖčü. 256).

ąöą╗čÅ ąĮą░ą┤ąĄąČąĮąŠčüčéąĖ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖą╣ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ ą║ą░ą╗čīą║čāą╗čÅč鹊čĆčŗ CRC, ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĖ ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░. CRC ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╝čā ą┐ąŠą╗ąĖąĮąŠą╝čā, ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą▒ąĖč鹥. ąÆčŗčćąĖčüą╗ąĄąĮąĖąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā ą▓čŗą▒ąŠčĆą║ąĖ ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗą╣ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ CPHA ąĖ CPOL ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ą╗ąŠą║ SPI ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čĆąĄą░ą╗ąĖąĘą░čåąĖčÄ 2 ą▓ąĖą┤ąŠą▓ čüčéą░ąĮą┤ą░čĆč鹊ą▓ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ CRC, čćč鹊 ąĮą░ą┐čĆčÅą╝čāčÄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ č乊čĆą╝ą░čéą░ ą┤ą░ąĮąĮčŗčģ čäčĆąĄą╣ą╝ą░ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ/ąĖą╗ąĖ ą┐čĆąĖąĄą╝ą░: 8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ (CRąĪ8) ąĖ 16 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ (CRC16).

ąÆčŗčćąĖčüą╗ąĄąĮąĖąĄ CRC čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ CRCEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1. ąŁč鹊 ą┤ąĄą╣čüčéą▓ąĖąĄ čüą▒čĆąŠčüąĖčé čĆąĄą│ąĖčüčéčĆčŗ CRC (SPI_RXCRCR ąĖ SPI_TXCRCR). ąÆ čĆąĄąČąĖą╝ą░čģ full-duplex ąĖą╗ąĖ transmit-only, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ (čĆąĄąČąĖą╝ CPU), ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĘą░ą┐ąĖčüą░čéčī ą▒ąĖčé CRCNEXT čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ 菹╗ąĄą╝ąĄąĮčé ą┤ą░ąĮąĮčŗčģ ą▒čŗą╗ ąĘą░ą┐ąĖčüą░ąĮ ą▓ SPI_DR. ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ čŹč鹊ą╣ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ SPI_TXCRCR.

ąÆ čĆąĄąČąĖą╝ąĄ receive-only, ąĖ ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ (čĆąĄąČąĖą╝ CPU), ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĘą░ą┐ąĖčüą░čéčī CRCNEXT ą┐ąŠčüą╗ąĄ ą┐čĆąĄą┤ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┐čĆąĖąĮčÅč鹊ą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ. CRC ą┐čĆąĖąĮąĖą╝ą░ąĄčéčüčÅ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ, ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐čĆąŠą▓ąĄčĆą║ą░ CRC. ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĖ CRC čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ CRCERR ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_SR, ąĄčüą╗ąĖ ą▒čŗą╗ą░ ąŠą▒ąĮą░čĆčāąČąĄąĮą░ ąŠčłąĖą▒ą║ą░ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ.

ąĢčüą╗ąĖ ą▓ ą▒čāč乥čĆąĄ TX ą┐čĆąĖčüčāčéčüčéą▓čāčÄčé ą┤ą░ąĮąĮčŗąĄ, č鹊 ąĘąĮą░č湥ąĮąĖąĄ CRC ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ CRC ą║ą░ą╗čīą║čāą╗čÅč鹊čĆ CRC ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ, ąĖ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ ąŠčüčéą░ąĄčéčüčÅ ąĮąĄąĖąĘą╝ąĄąĮąĮčŗą╝.

ąÜąŠą╝ą╝čāąĮąĖą║ą░čåąĖčÅ SPI čü ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄą╝ CRC ą▓ąŠąĘą╝ąŠąČąĮą░ ą┐čĆąĖ čüąŠą▒ą╗čÄą┤ąĄąĮąĖąĖ čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐čĆąŠčåąĄą┤čāčĆčŗ:

1. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĘąĮą░č湥ąĮąĖą╣ CPOL, CPHA, LSBFirst, BR, SSM, SSI ąĖ MSTR.

2. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąŠą╗ąĖąĮąŠą╝ą░ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_CRCPR.

3. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ CRC čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ CRCEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1. ąŁč鹊 čéą░ą║ąČąĄ ąŠčćąĖčüčéąĖčé čĆąĄą│ąĖčüčéčĆčŗ SPI_RXCRCR ąĖ SPI_TXCRCR.

4. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SPE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1.

5. ąŚą░ą┐čāčü ąŠą▒ą╝ąĄąĮą░, ąĖ ąĄą│ąŠ ą┐čĆąŠą┤ąŠą╗ąČąĄąĮąĖąĄ ą┤ąŠ č鹊ą│ąŠ ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠą║ą░ ą▓čüąĄ ą║čĆąŠą╝ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ąĮčŗ ąĖą╗ąĖ ą┐čĆąĖąĮčÅčéčŗ.

ŌĆō ąÆ čĆąĄąČąĖą╝ąĄ full-duplex ąĖą╗ąĖ transmit-only, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░č湥ą╣ čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ą░, ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒čāč乥čĆ Tx čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé CRCNEXT ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1, ą┐ąŠą║ą░ąĘčŗą▓ą░čÅ č鹥ą╝ čüą░ą╝čŗą╝, čćč鹊 ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮą░ CRC ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ.

ŌĆō ąÆ čĆąĄąČąĖą╝ąĄ receive-only čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé CRCNEXT ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐čĆąĄą┤ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ, čćč鹊ą▒čŗ ą┐ąŠą┤ą│ąŠč鹊ą▓ąĖčéčī SPI ą║ąŠ ą▓čģąŠą┤čā ą▓ čäą░ąĘčā CRC ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐čĆąĖąĄą╝ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ CRC ą▓čŗčćąĖčüą╗ąĄąĮąĖąĄ CRC ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ.

6. ą¤ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ SPI ą▓čģąŠą┤ąĖčé ą▓ čäą░ąĘčā ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąŠą▓ąĄčĆą║ąĖ CRC. ąÆ čĆąĄąČąĖą╝ąĄ full-duplex ąĖą╗ąĖ receive-only ą┐čĆąĖąĮčÅč鹊ąĄ ąĘąĮą░č湥ąĮąĖąĄ CRC čüčĆą░ą▓ąĮąĖą▓ą░ąĄčéčüčÅ čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ SPI_RXCRCR. ąĢčüą╗ąĖ ąĘąĮą░č湥ąĮąĖčÅ ąĮąĄ čüąŠą▓ą┐ą░ą╗ąĖ, č鹊 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ CRCERR ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_SR, ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ERRIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2.

ąÜąŠą│ą┤ą░ SPI čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ slave, ą▒čāą┤čīč鹥 ąŠčüč鹊čĆąŠąČąĮčŗ, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī ą▓čŗčćąĖčüą╗ąĄąĮąĖąĄ CRC č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čéą░ą║čéčŗ čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆąŠą▓ą░ą╗ąĖčüčī, čé. ąĄ. čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čāčüč鹊ą╣čćąĖą▓ąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ. ąĢčüą╗ąĖ čŹč鹊ą│ąŠ ąĮąĄ čüą┤ąĄą╗ą░čéčī, č鹊 ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ ą▓čŗčćąĖčüą╗ąĄąĮąĖąĄ CRC. ążą░ą║čéąĖč湥čüą║ąĖ CRC čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠ ą║ąŠ ą▓čģąŠą┤čā čéą░ą║č鹊ą▓ SCK slave, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé CRCEN, ąĖ ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčéą░ SPE.

ąØą░ ą▓čŗčüąŠą║ąĖčģ čüą║ąŠčĆąŠčüčéčÅčģ ą▒čāą┤čīč鹥 ąŠčüč鹊čĆąŠąČąĮčŗ čü ą┐ąĄčĆąĄą┤ą░č湥ą╣ CRC. ą¤ąŠčüą║ąŠą╗čīą║čā ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ čéą░ą║č鹊ą▓ CPU ąĮą░ čäą░ąĘąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ CRC ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╝, ąĮą░čüą║ąŠą╗čīą║ąŠ čŹč鹊 ą▓ąŠąĘą╝ąŠąČąĮąŠ, ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ą▓čŗąĘčŗą▓ą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗąĄ čäčāąĮą║čåąĖąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ CRC, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąŠčłąĖą▒ąŠą║ ą▓ ą┐čĆąĖąĄą╝ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ ą┤ą░ąĮąĮčŗčģ ąĖ CRC. ążą░ą║čéąĖč湥čüą║ąĖ ą▒ąĖčé CRCNEXT ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą┐ąĄčĆąĄą┤ ąŠą║ąŠąĮčćą░ąĮąĖąĄą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ/ą┐čĆąĖąĄą╝ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ.

ąöą╗čÅ ą▓čŗčüąŠą║ąĖčģ čüą║ąŠčĆąŠčüč鹥ą╣ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čĆąĄąČąĖą╝ DMA, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┤ąĄą│čĆą░ą┤ą░čåąĖąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą║ą░ąĮą░ą╗ą░ SPI ąĖąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ą┤ąŠčüčéčāą┐ CPU čüąĮąĖąČą░ąĄčé ą┐ąŠą╗ąŠčüčā ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ SPI.

ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ą░ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ slave, ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ NSS, č鹊 NSS ąĮčāąČąĮąŠ čāą┤ąĄčƹȹĖą▓ą░čéčī ą▓ ą╗ąŠą│. 0 ą╝ąĄąČą┤čā čäą░ąĘąŠą╣ ą┤ą░ąĮąĮčŗčģ ąĖ čäą░ąĘąŠą╣ CRC.

CRC ąĖ NSS. ąÜąŠą│ą┤ą░ SPI čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ slave čü čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą╣ čäčāąĮą║čåąĖąĄą╣ CRC, ą▓čŗčćąĖčüą╗ąĄąĮąĖąĄ CRC ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ąĮą░ ą▓čŗą▓ąŠą┤ NSS ą┐ąŠą┤ą░ąĮą░ ą╗ąŠą│. 1. ąŁč鹊 ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą▓ čüą╗čāčćą░ąĄ čāčüą╗ąŠą▓ąĖą╣ čĆą░ą▒ąŠčéčŗ ą▓ ąŠą║čĆčāąČąĄąĮąĖąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą│ą╗ą░ą▓ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ SPI (multislave), ą║ąŠą│ą┤ą░ master ąŠą▒ą╝ąĄąĮą░ ąŠą▒čĆą░čēą░ąĄčéčüčÅ ą║ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ ą┐ąŠąŠč湥čĆąĄą┤ąĮąŠ.

ą£ąĄąČą┤čā čüąĮčÅčéąĖąĄą╝ ą▓čŗą▒ąŠčĆą║ąĖ čüąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ (ą╗ąŠą│. 1 ąĮą░ NSS) ąĖ ąĮąŠą▓ąŠą╣ ą▓čŗą▒ąŠčĆą║ąŠą╣ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ (ą╗ąŠą│. 0 ąĮą░ NSS), ąĘąĮą░č湥ąĮąĖąĄ CRC ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮąŠ ąĮą░ ąŠą▒ąŠąĖčģ čüč鹊čĆąŠąĮą░čģ - master ąĖ slave, čćč鹊ą▒čŗ ąĘą░ąĮąŠą▓ąŠ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčī ą┐čĆąŠčåąĄčüčü ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ CRC ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ.

ą¦č鹊ą▒čŗ čüą▒čĆąŠčüąĖčéčī CRC, ą▓čŗą┐ąŠą╗ąĮąĖč鹥 čüą╗ąĄą┤čāčÄčēčāčÄ ą┐čĆąŠčåąĄą┤čāčĆčā:

1. ąŚą░ą┐čĆąĄčéąĖč鹥 SPI (SPE=0).

2. ą×čćąĖčüčéąĖč鹥 ą▒ąĖčé CRCEN.

3. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé CRCEN.

4. ąĀą░ąĘčĆąĄčłąĖč鹥 SPI (SPE=1).

[ążą╗ą░ą│ąĖ čüčéą░čéčāčüą░]

ąĪčāčēąĄčüčéą▓čāąĄčé 4 čäą╗ą░ą│ą░ čüčéą░čéčāčüą░, ąŠą┐čĆą░čłąĖą▓ą░čÅ ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąŠčéčüą╗ąĄąČąĖą▓ą░čéčī čüąŠčüč鹊čÅąĮąĖąĄ čłąĖąĮčŗ SPI.

ąæčāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé (TXE). ąÜąŠą│ą┤ą░ čŹč鹊čé čäą╗ą░ą│ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▒čāč乥čĆ Tx ą┐čāčüčé, ąĖ ą│ąŠč鹊ą▓ ą║ ąĘą░ą┐ąĖčüąĖ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ. ążą╗ą░ą│ TXE ąŠčćąĖčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ SPI_DR.

ąæčāč乥čĆ ą┐čĆąĖąĄą╝ą░ ąĮąĄ ą┐čāčüčé (RXNE). ąÜąŠą│ą┤ą░ čŹč鹊čé čäą╗ą░ą│ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓ ą▒čāč乥čĆąĄ Rx ą┐čĆąĖčüčāčéčüčéą▓čāčÄčé ą┐čĆąĖąĮčÅčéčŗąĄ, ąĮąŠ ąĄčēąĄ ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ. ążą╗ą░ą│ RXNE ąŠčćąĖčēą░ąĄčéčüčÅ čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ SPI_DR.

ąŚą░ąĮčÅč鹊čüčéčī (BSY). ąŁč鹊čé čäą╗ą░ą│ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ (ąĘą░ą┐ąĖčüčī ą▓ čŹč鹊čé ą▒ąĖčé ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░). ążą╗ą░ą│ BSY ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ čüą╗ąŠčÅ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ SPI.

ąÜąŠą│ą┤ą░ BSY=1, čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 SPI ąĘą░ąĮčÅčé ąŠą▒ą╝ąĄąĮąŠą╝. ąĪčāčēąĄčüčéą▓čāąĄčé ąĖčüą║ą╗čÄč湥ąĮąĖąĄ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ master / ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ą┐čĆąĖąĄą╝ (MSTR=1, BDM=1 ąĖ BDOE=0), ą║ąŠą│ą┤ą░ BSY ąŠčüčéą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0 ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĖąĄą╝ą░.

ążą╗ą░ą│ BSY ą┐ąŠą╗ąĄąĘąĄąĮ ą┤ą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠą║ąŠąĮčćą░ąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ, ąĄčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ čģąŠč湥čé ąĘą░ą┐čĆąĄčéąĖčéčī SPI ąĖ ą▓ąŠą╣čéąĖ ą▓ čĆąĄąČąĖą╝ ąŠčüčéą░ąĮąŠą▓ą║ąĖ (Halt mode), ąĖą╗ąĖ ąĘą░ą┐čĆąĄčéąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (ą┤ą╗čÅ čüąĮąĖąČąĄąĮąĖčÅ čŹąĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ). ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ ąĘą░ąĮčÅč鹊čüčéąĖ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖąĘą▒ąĄąČą░čéčī ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ. ąöą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ąĮčāąČąĮąŠ čüčéčĆąŠą│ąŠ čüąŠą▒ą╗čÄą┤ą░čéčī ąŠą┐ąĖčüą░ąĮąĮčāčÄ ąĮąĖąČąĄ ą┐čĆąŠčåąĄą┤čāčĆčā.

ążą╗ą░ą│ BSY čéą░ą║ąČąĄ ą┐ąŠą╗ąĄąĘąĄąĮ, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą║ąŠą╗ą╗ąĖąĘąĖą╣ ąĘą░ą┐ąĖčüąĖ ą▓ čüąĖčüč鹥ą╝ą░čģ multimaster.

ążą╗ą░ą│ BSY čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░, ą║čĆąŠą╝ąĄ čĆąĄąČąĖą╝ą░ master/ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ą┐čĆąĖąĄą╝ (MSTR=1, BDM=1 ąĖ BDOE=0).

ążą╗ą░ą│ BSY ąŠčćąĖčüčéąĖčéčüčÅ:

ŌĆó ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ (ą║čĆąŠą╝ąĄ čĆąĄąČąĖą╝ą░ master, ąĄčüą╗ąĖ ąŠą▒ą╝ąĄąĮ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčŗą╣).

ŌĆó ąÜąŠą│ą┤ą░ SPI ąĘą░ą┐čĆąĄčēąĄąĮ.

ŌĆó ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąŠčłąĖą▒ą║ą░ čĆąĄąČąĖą╝ą░ master (master mode fault, MODF=1).

ąÜąŠą│ą┤ą░ ąŠą▒ą╝ąĄąĮ ą┐čĆąĄčĆčŗą▓ąĖčüčéčŗą╣, čäą╗ą░ą│ BSY ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0 ą╝ąĄąČą┤čā ą║ą░ąČą┤čŗą╝ ąŠą▒ą╝ąĄąĮąŠą╝.

ąÜąŠą│ą┤ą░ ąŠą▒ą╝ąĄąĮ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčŗą╣:

ŌĆó ąÆ čĆąĄąČąĖą╝ąĄ master čäą╗ą░ą│ BSY ą┤ąŠą╗ąČąĄąĮ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ ą╗ąŠą│. 1 ą╝ąĄąČą┤čā ą▓čüąĄą╝ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ.

ŌĆó ąÆ čĆąĄąČąĖą╝ąĄ slave čäą╗ą░ą│ BSY ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. ąĮą░ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ą▓ 1 ą┐ąĄčĆąĖąŠą┤ čéą░ą║č鹊ą▓ SPI ą╝ąĄąČą┤čā ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥ą╣.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 čäą╗ą░ą│ BSY, čćč鹊ą▒čŗ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčī ą║ą░ąČą┤čāčÄ ą┐ąĄčĆąĄą┤ą░čćčā ąĖą╗ąĖ ą┐čĆąĖąĄą╝. ąÆą╝ąĄčüč鹊 čŹč鹊ą│ąŠ ą╗čāčćčłąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čäą╗ą░ą│ąĖ TXE ąĖ RXNE.

[ąŚą░ą┐čĆąĄčé SPI]

ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐čĆąĄčĆčŗą▓ą░ąĄčéčüčÅ, ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé ąŠčüčéą░ąĮąŠą▓ąĖčéčī ąŠą▒ą╝ąĄąĮ ąĘą░ą┐čĆąĄč鹊ą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI. ąŁč鹊 ą┤ąĄą╗ą░ąĄčéčüčÅ ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ SPE.

ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅčģ ąĘą░ą┐čĆąĄčé SPI ąĖ ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ ąŠčüčéą░ąĮąŠą▓ą║ąĖ (Halt mode) ą▓ąŠ ą▓čĆąĄą╝čÅ č鹥ą║čāčēąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ, ąĖ/ąĖą╗ąĖ čäą╗ą░ą│ BSY ą╝ąŠąČąĄčé čüčéą░čéčī ąĮąĄąĮą░ą┤ąĄąČąĮčŗą╝. ą¦č鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐ąŠą┤ąŠą▒ąĮčŗčģ čŹčäč乥ą║č鹊ą▓, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čüąŠą▒ą╗čÄą┤ą░čéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą┐čĆąŠčåąĄą┤čāčĆčā ąĘą░ą┐čĆąĄčéą░ SPI.

ą¤ąŠą╗ąĮčŗą╣ ą┤čāą┐ą╗ąĄą║čü master ąĖą╗ąĖ slave (BIDIMODE=0, RXONLY=0):

1. ą×ąČąĖą┤ą░ąĮąĖąĄ RXNE=1 ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ ą┤ą░ąĮąĮčŗčģ.

2. ą×ąČąĖą┤ą░ąĮąĖąĄ TXE=1.

3. ą×ąČąĖą┤ą░ąĮąĖąĄ BSY=0.4.

ąŚą░ą┐čĆąĄčé SPI (SPE=0) ąĖ, ąĄčüą╗ąĖ čéčĆąĄą▒čāąĄčéčüčÅ, ą▓čģąŠą┤ ą▓ Halt mode (ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé čéą░ą║č鹊ą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░).

ą×ą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ (transmit-only), master ąĖą╗ąĖ slave (BIDIMODE=0, RXONLY=0), ą╗ąĖą▒ąŠ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ (BIDIMODE=1, BIDIOE=1). ą¤ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_DR:

1. ą×ąČąĖą┤ą░ąĮąĖąĄ TXE=1.

2. ą×ąČąĖą┤ą░ąĮąĖąĄ BSY=0.

3. ąŚą░ą┐čĆąĄčé SPI (SPE=0) ąĖ, ąĄčüą╗ąĖ čéčĆąĄą▒čāąĄčéčüčÅ, ą▓čģąŠą┤ ą▓ Halt mode (ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé čéą░ą║č鹊ą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░).

ą×ą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ master receive-only (MSTR=1, BIDIMODE=0, RXONLY=1), ąĖą╗ąĖ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ ą┐čĆąĖąĄą╝ą░ (MSTR=1, BIDIMODE=1, BIDIOE=0). ąŁč鹊ą╝ čüą╗čāčćą░ą╣ ą┤ąŠą╗ąČąĄąĮ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčīčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 SPI ąĮąĄ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ą╗ ąĮąŠą▓čāčÄ ą┐ąĄčĆąĄą┤ą░čćčā. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣ ąĮąĖąČąĄ ą┤ąŠą┐čāčüčéąĖą╝ą░ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ SPI Motorola (FRF=0):

1. ą×ąČąĖą┤ą░ąĮąĖąĄ ą┐čĆąĄą┤ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ RXNE=1 (ą┐čĆąĖąĮčÅčé nŌĆō1 菹╗ąĄą╝ąĄąĮčé ą┤ą░ąĮąĮčŗčģ).

2. ą×ąČąĖą┤ą░ąĮąĖąĄ ą▓ č鹥č湥ąĮąĖąĄ 1 čéą░ą║čéą░ SPI (čü ą┐ąŠą╝ąŠčēčīčÄ ą┐čāčüč鹊ą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čåąĖą║ą╗ą░ ąĘą░ą┤ąĄčƹȹ║ąĖ) ą┐ąĄčĆąĄą┤ ąĘą░ą┐čĆąĄč鹊ą╝ SPI (SPE=0).

3. ąŚą░č鹥ą╝ ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ RXNE=1 ą┐ąĄčĆąĄą┤ ą▓čģąŠą┤ąŠą╝ ą▓ Halt mode (ąĖą╗ąĖ ąĘą░ą┐čĆąĄč鹊ą╝ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░).

ąÜąŠą│ą┤ą░ SPI čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ TI (FRF=1), ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüąŠą▒ą╗čÄą┤ą░čéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą┐čĆąŠčåąĄą┤čāčĆčā, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ ąĮą░ NSS, ą║ąŠą│ą┤ą░ SPI ąĘą░ą┐čĆąĄčēąĄąĮ:

1. ą×ąČąĖą┤ą░ąĮąĖąĄ ą┐čĆąĄą┤ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ RXNE=1 (ą┐čĆąĖąĮčÅčé nŌĆō1 菹╗ąĄą╝ąĄąĮčé ą┤ą░ąĮąĮčŗčģ).

2. ąŚą░ą┐čĆąĄčé SPI (SPE=0) ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ąŠą║ąĮąĄ čäčĆąĄą╣ą╝ą░, čü ą┐ąŠą╝ąŠčēčīčÄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čåąĖą║ą╗ą░:

ŌĆō ą┐ąŠčüą╗ąĄ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 1 ąĖą╝ą┐čāą╗čīčüą░ čéą░ą║č鹊ą▓ SPI,

ŌĆō ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĮą░ ą┐čĆąĖąĄą╝ąĄ ą▓ čĆąĄąČąĖą╝ąĄ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą│ąŠ master (MSTR=1, BDM=1, BDOE=0), čäą╗ą░ą│ BSY čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0 ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čć.

ąÆ čĆąĄąČąĖą╝ąĄ slave receive-only (MSTR=0, BIDIMODE=0, RXONLY=1) ąĖą╗ąĖ ąĮą░ ą┐čĆąĖąĄą╝ąĄ ą▓ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (MSTR=0, BIDIMODE=1, BIDOE=0).

1. ąÆčŗ ą╝ąŠąČąĄč鹥 ąĘą░ą┐čĆąĄčéąĖčéčī SPI (ąĘą░ą┐ąĖčüčīčÄ SPE=0) ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ: č鹥ą║čāčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą▒čāą┤ąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮą░ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ SPI čüčéą░ąĮąĄčé ąĘą░ą┐čĆąĄčēąĄąĮąĮčŗą╝.

2. ąŚą░č鹥ą╝, ąĄčüą╗ąĖ ąÆčŗ čģąŠčéąĖč鹥 ą▓ąŠą╣čéąĖ ą▓ Halt mode, č鹊 ą┤ąŠą╗ąČąĮčŗ čüąĮą░čćą░ą╗ą░ ą┐ąŠą┤ąŠąČą┤ą░čéčī BSY=0 ą┐ąĄčĆąĄą┤ ą▓čģąŠą┤ąŠą╝ ą▓ Halt mode (ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ ąĘą░ą┐čĆąĄč鹊ą╝ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░).

[ą×ą▒ą╝ąĄąĮ SPI čü ą┐ąŠą╝ąŠčēčīčÄ DMA]

ą¦č鹊ą▒čŗ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī čĆą░ą▒ąŠčéčā ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ, ą▓ SPI ą┤ąŠą╗ąČąĮčŗ ą┐ąŠčüčéčāą┐ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čü ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ ąĘą░ą┤ąĄčƹȹ║ąŠą╣. ąóąŠčćąĮąŠ čéą░ą║ ąČąĄ čéčĆąĄą▒čāąĄčéčüčÅ čüą▓ąŠąĄą▓čĆąĄą╝ąĄąĮąĮąŠ čüčćąĖčéčŗą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą▒čāč乥čĆą░ Rx, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ (overrun). ą¦č鹊ą▒čŗ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī čŹčéčā ąĘą░ą┤ą░čćčā ąĖ čĆą░ąĘą│čĆčāąĘąĖčéčī ą┐čĆąŠčåąĄčüčüąŠčĆ ąŠčé ą┤ąĄą╣čüčéą▓ąĖą╣ ą┐ąŠ ąĘą░ą│čĆčāąĘą║ąĄ/čüčćąĖčéčŗą▓ą░ąĮąĖčÄ ą┤ą░ąĮąĮčŗčģ, ą▒ą╗ąŠą║ SPI ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čäčāąĮą║čåąĖčÄ DMA, čĆąĄą░ą╗ąĖąĘčāčÄčēčāčÄ ą┐čĆąŠčüč鹊ą╣ ą┐čĆąŠč鹊ą║ąŠą╗ ąĘą░ą┐čĆąŠčüą░/ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ.

ąöąŠčüčéčāą┐ DMA ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐čĆąŠčüą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR2. ąöąŠą╗ąČąĮčŗ ą▓čŗą┤ą░ą▓ą░čéčīčüčÅ ąŠčéą┤ąĄą╗čīąĮčŗąĄ ąĘą░ą┐čĆąŠčüčŗ ą┤ą╗čÅ ą▒čāč乥čĆąŠą▓ Tx ąĖ Rx (čüą╝. čĆąĖčü. 259 ąĖ 260):

ŌĆó ą¤čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ąĘą░ą┐čĆąŠčü DMA ą▓čŗą┤ą░ąĄčéčüčÅ ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą▒ąĖčé TXE čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1. ąŚą░č鹥ą╝ DMA ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_DR (čŹč鹊 ąŠčćąĖčüčéąĖčé čäą╗ą░ą│ TXE).

ŌĆó ąØą░ ą┐čĆąĖąĄą╝ąĄ ąĘą░ą┐čĆąŠčü DMA ą▓čŗą┤ą░ąĄčéčüčÅ ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą▒ąĖčé RXNE čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1. ąŚą░č鹥ą╝ DMA čüčćąĖčéčŗą▓ą░ąĄčé čĆąĄą│ąĖčüčéčĆ SPI_DR (čŹč鹊 ąŠčćąĖčüčéąĖčé čäą╗ą░ą│ RXNE).

ąÜąŠą│ą┤ą░ SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ, ą╝ąŠąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī č鹊ą╗čīą║ąŠ ą║ą░ąĮą░ą╗ SPI Tx DMA. ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ OVR, ą┐ąŠč鹊ą╝čā čćč鹊 ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą▒čāą┤čāčé čüčćąĖčéčŗą▓ą░čéčīčüčÅ.

ąÜąŠą│ą┤ą░ SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ, ą╝ąŠąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī č鹊ą╗čīą║ąŠ ą║ą░ąĮą░ą╗ SPI Rx DMA.

ąÆ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą║ąŠą│ą┤ą░ DMA ąĘą░ą┐ąĖčüą░ą╗ ą▓čüąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ (čāčüčéą░ąĮąŠą▓ąĖą╗čüčÅ čäą╗ą░ą│ TCIF ą▓ čĆąĄą│ąĖčüčéčĆąĄ DMA_ISR), ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčéčüą╗ąĄąČąĄąĮąŠ čüąŠčüč鹊čÅąĮąĖąĄ čäą╗ą░ą│ą░ BSY, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą┐ąŠą╗ąĮąŠąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ąŠą▒ą╝ąĄąĮą░ SPI. ąŁč鹊 ąĮčāąČąĮąŠ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąĄčĆąĄą┤ ąĘą░ą┐čĆąĄč鹊ą╝ SPI ąĖą╗ąĖ ą▓čģąŠą┤ąŠą╝ ą▓ čĆąĄąČąĖą╝ ąŠčüčéą░ąĮąŠą▓ą║ąĖ (Stop mode). ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąČą┤ą░čéčī TXE=1, ąĖ ąĘą░č鹥ą╝ ąČą┤ą░čéčī BSY=0.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĄčĆčŗą▓ąĖčüčéčŗčģ ąŠą▒ą╝ąĄąĮąŠą▓ čüčāčēąĄčüčéą▓čāąĄčé ąĘą░ą┤ąĄčƹȹ║ą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ 2 čéą░ą║čéą░ APB ą╝ąĄąČą┤čā ąŠą┐ąĄčĆą░čåąĖąĄą╣ ąĘą░ą┐ąĖčüąĖ ą▓ SPI_DR ąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ BSY. ąÜą░ą║ čüą╗ąĄą┤čüčéą▓ąĖąĄ, čüąĮą░čćą░ą╗ą░ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┤ąŠąČą┤ą░čéčīčüčÅ TXE=1, ąĖ ąĘą░č鹥ą╝ ą┤ąŠąČą┤ą░čéčīčüčÅ BSY=0 ą┐ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ ą┤ą░ąĮąĮčŗčģ.

ąĀąĖčü. 259. ą¤ąĄčĆąĄą┤ą░čćą░ čü ą┐ąŠą╝ąŠčēčīčÄ DMA.

ąĀąĖčü. 260. ą¤čĆąĖąĄą╝ čü ą┐ąŠą╝ąŠčēčīčÄ DMA.

DMA čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ CRC. ąÜąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮ ąŠą▒ą╝ąĄąĮ SPI čü čäčāąĮą║čåąĖąĄą╣ CRC ą▓ čĆąĄąČąĖą╝ąĄ DMA, ą┐ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝ CRC ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ąŠą▒ą╝ąĄąĮą░ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▒ąĖčéą░ CRCNEXT. ą¤ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ CRC, CRC ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_DR, čćč鹊ą▒čŗ ąŠčćąĖčüčéąĖčéčī čäą╗ą░ą│ RXNE.

ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą┐ąĄčĆąĄą┤ą░čć ą┤ą░ąĮąĮčŗčģ ąĖ CRC čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ CRCERR ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_SR, ąĄčüą╗ąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą▒ąĮą░čĆčāąČąĖą╗ąŠčüčī ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ (ąĮąĄ čüąŠą▓ą┐ą░ą╗ą░ CRC ąĮą░ ą┐čĆąĖąĄą╝ąĄ).

[ążą╗ą░ą│ąĖ ąŠčłąĖą▒ąŠą║]

Master mode fault (MODF). ą×čéą║ą░ąĘ čĆąĄąČąĖą╝ą░ master ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ master ąŠą▒ąĮą░čĆčāąČąĖą╗ąŠ, čćč鹊 ąĮą░ ąĄą│ąŠ ą▓čģąŠą┤ NSS ą┐ąŠčüčéčāą┐ąĖą╗ ą╗ąŠą│. 0 (ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čĆąĄąČąĖą╝ NSS), ąĖą╗ąĖ ą▒ąĖčé SSI ą▓ ą╗ąŠą│. 0 (ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čĆąĄąČąĖą╝ NSS), ą┐čĆąĖ čŹč鹊ą╝ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé MODF. ą×čéą║ą░ąĘ čĆąĄąČąĖą╝ą░ master ą▓ą╗ąĖčÅąĄčé ąĮą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆó ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé MODF, ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPI, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ERRIE.

ŌĆó ą×čćąĖčüčéąĖčéčüčÅ ą▒ąĖčé SPE. ąŁč鹊 ąĘą░ą▒ą╗ąŠą║ąĖčĆčāąĄčé ą▓čüąĄ ą▓čŗčģąŠą┤čŗ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░, ąĖ ąĘą░ą┐čĆąĄčéąĖčé ąĖąĮč鹥čĆč乥ą╣čü SPI.

ŌĆó ą×čćąĖčüčéąĖčéčüčÅ ą▒ąĖčé MSTR, čŹč鹊 ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą▓ąĄą┤ąĄčé čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ čĆąĄąČąĖą╝ slave.

ąśčüą┐ąŠą╗čīąĘčāą╣č鹥 čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ, čćč鹊ą▒čŗ ąŠčćąĖčüčéąĖčéčī ą▒ąĖčé MODF:

1. ąÆčŗą┐ąŠą╗ąĮąĖč鹥 ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐ąĖčüčī ą║ čĆąĄą│ąĖčüčéčĆčā SPI_SR, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ąĖą╗čüčÅ ą▒ąĖčé MODF.

2. ąÆčŗą┐ąŠą╗ąĮąĖč鹥 ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ SPI_CR1.

ą¦č鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą║ąŠąĮčäą╗ąĖą║č鹊ą▓ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ slave-čāčüčéčĆąŠą╣čüčéą▓ ą▓ čüąĖčüč鹥ą╝ąĄ, čüąŠčüč鹊čÅčēąĄą╣ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ MCU, ąĮąŠąČą║ą░ NSS ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčéą░ ą║ ą╗ąŠą│. 1 ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąŠčåąĄą┤čāčĆčŗ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ MODF. ą¤ąŠčüą╗ąĄ čŹč鹊ą╣ ą┐čĆąŠčåąĄą┤čāčĆčŗ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéčŗ SPE ąĖ MSTR ą╝ąŠą│čāčé ą▒čŗčéčī ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ ąĖčģ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ.

ąÆ čåąĄą╗čÅčģ ą▒ąĄąĘąŠą┐ą░čüąĮąŠčüčéąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ąĮąĄ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčéčŗ SPE ąĖ MSTR, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé MODF.

ąÆ slave-čāčüčéčĆąŠą╣čüčéą▓ąĄ ą▒ąĖčé MODF ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ. ą×ą┤ąĮą░ą║ąŠ ą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ multimaster čāčüčéčĆąŠą╣čüčéą▓ąŠ ą╝ąŠąČąĄčé ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ slave čü čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▒ąĖč鹊ą╝ MODF. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▒ąĖčé MODF ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüąĖčüč鹥ą╝ąŠą╣ ą╝ąŠą│ ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą║ąŠąĮčäą╗ąĖą║čé multimaster. ą£ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ISR, čćč鹊ą▒čŗ ą║ąŠčĆčĆąĄą║čéąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĄ ąĖąĘ čŹč鹊ą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čāč鹥ą╝ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čüą▒čĆąŠčüą░ ąĖą╗ąĖ ą▓ąŠąĘą▓čĆą░čéą░ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ.

ą¤ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ (OVR). ąĪąŠą▒čŗčéąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ master ąŠčéą┐čĆą░ą▓ąĖą╗ ą┤ą░ąĮąĮčŗąĄ, ąĖ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ąŠčćąĖčüčéąĖą╗ąŠ ą▒ąĖčé RXNE, ą║ąŠč鹊čĆčŗą╣ ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐čĆąĄą┤čŗą┤čāčēąĖčģ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ:

ŌĆó ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé OVR, ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ERRIE.

ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮąŠ ąĮąŠą▓čŗą╝ąĖ ą┐čĆąĖąĮčÅčéčŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ, ą┐ąŠą╗čāč湥ąĮąĮčŗą╝ąĖ ąŠčé čāčüčéčĆąŠą╣čüčéą▓ą░ master. ą¦č鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ SPI_DR ą▓ąĄčĆąĮąĄčé čŹčéąĖ ą┤ą░ąĮąĮčŗąĄ. ąÆčüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąŠčłą╗ąĖ ą┤ąŠ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ SPI_DR, ą▒čāą┤čāčé ą┐ąŠč鹥čĆčÅąĮčŗ.

ą×čćąĖčüčéą║ą░ ą▒ąĖčéą░ OVR ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čćč鹥ąĮąĖąĄą╝ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ SPI_DR, čü ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖą╝ čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ SPI_SR.

ą×čłąĖą▒ą║ą░ CRC (CRCERR). ąŁč鹊 čäą╗ą░ą│ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé CRCEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CR1. ążą╗ą░ą│ CRCERR ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_SR čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ąĄčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ, ą┐čĆąĖąĮčÅč鹊ąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüą┤ą▓ąĖą│ą░, ąĮąĄ čüąŠą▓ą┐ą░ą┤ą░ąĄčé čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ SPI_RXCRCR ą┐čĆąĖąĄą╝ąĮąĖą║ą░.

ą×čłąĖą▒ą║ą░ č乊čĆą╝ą░čéą░ čäčĆąĄą╣ą╝ą░ TI (FRE). ą×čłąĖą▒ą║ą░ č乊čĆą╝ą░čéą░ čäčĆąĄą╣ą╝ą░ TI ą┤ąĄč鹥ą║čéąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ąĖą╝ą┐čāą╗čīčü NSS ą▓ąŠ ą▓čĆąĄą╝čÅ č鹥ą║čāčēąĄą│ąŠ ąŠą▒ą╝ąĄąĮą░, ą║ąŠą│ą┤ą░ SPI čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ slave, ąĖ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ą┐čĆąŠč鹊ą║ąŠą╗ą░ TI. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ą░ čŹčéą░ ąŠčłąĖą▒ą║ą░, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ FRE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_SR. SPI ąĮąĄ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čéą░ą║ą░čÅ ąŠčłąĖą▒ą║ą░, ąĖą╝ą┐čāą╗čīčü NSS ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ, ąĖ SPI ąŠąČąĖą┤ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ NSS ą┐ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ąĮąŠą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąöą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą▓čĆąĄąČą┤ąĄąĮčŗ, ą┐ąŠčüą║ąŠą╗čīą║čā ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ą┐ąŠč鹥čĆąĄ 2 ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ.

ążą╗ą░ą│ FRE ąŠčćąĖčēą░ąĄčéčüčÅ čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ SPI_SR. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ERRIE, č鹊 ą┐čĆąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĖ NSS ą▒čāą┤ąĄčé ą▓čŗąĘą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ SPI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ, ą┐ąŠč鹊ą╝čā čćč鹊 čåąĄą╗ąŠčüčéąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ ą▒ąŠą╗čīčłąĄ ąĮąĄ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ, ąĖ ąŠą▒ą╝ąĄąĮ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮ ąĘą░ąĮąŠą▓ąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ master, ą║ąŠą│ą┤ą░ slave SPI čüąĮąŠą▓ą░ ą▒čāą┤ąĄčé čĆą░ąĘčĆąĄčłąĄąĮ.

ąĀąĖčü. 261. ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ č乊čĆą╝ą░čéą░ čäčĆąĄą╣ą╝ą░ čĆąĄąČąĖą╝ą░ TI.

[ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SPI]

ąóą░ą▒ą╗ąĖčåą░ 126. ąŚą░ą┐čĆąŠčüčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ SPI.

| ąĪąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ |

ążą╗ą░ą│ čüąŠą▒čŗčéąĖčÅ |

ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ |

| Transmit buffer empty (ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé) |

TXE |

TXEIE |

| Receive buffer not empty (ą▓ ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░ ąĖą╝ąĄčÄčéčüčÅ ą│ąŠč鹊ą▓čŗąĄ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗąĄ) |

RXNE |

RXNEIE |

| Master Mode fault (čüą▒ąŠą╣ čĆąĄąČąĖą╝ą░ master) |

MODF |

ERRIE |

| Overrun error (ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ) |

OVR |

| CRC error (ąĮąĄčüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ ąĮą░ ą┐čĆąĖąĄą╝ąĄ) |

CRCERR |

| TI frame format error (ąŠčłąĖą▒ą║ą░ čäčĆąĄą╣ą╝ą░ č乊čĆą╝ą░čéą░ ą┐čĆąŠč鹊ą║ąŠą╗ą░ TI) |

FRE |