|

ąŻ ą║ą░ąČą┤ąŠą│ąŠ ąĖąĘ ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (general-purpose I/O port, GPIO) ąĄčüčéčī č湥čéčŗčĆąĄ 32-ą▒ąĖčéąĮčŗčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░ (GPIOx_MODER, GPIOx_OTYPER, GPIOx_OSPEEDR ąĖ GPIOx_PUPDR, ąĘą┤ąĄčüčī x ąĘą░ą╝ąĄąĮčÅąĄčéčüčÅ ą▒čāą║ą▓ąŠą╣ A, B, C, D, E, F, G, H, I, ąĖ čā ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąĄą┤čüčéą░ą▓ąĖč鹥ą╗ąĄą╣ MCU ą┤ą░ąČąĄ ąĄčüčéčī ą┐ąŠčĆčéčŗ GPIOJ ąĖ GPIOK), ą┤ą▓ą░ 32-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░ ą┤ą░ąĮąĮčŗčģ (GPIOx_IDR ąĖ GPIOx_ODR), 32-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čāčüčéą░ąĮąŠą▓ą║ąĖ/čüą▒čĆąŠčüą░ čāčĆąŠą▓ąĮčÅ (GPIOx_BSRR), 32-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (GPIOx_LCKR) ąĖ ą┤ą▓ą░ 32-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ GPIO (GPIOx_AFRH ąĖ GPIOx_AFRL).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ (ą┐ąĄčĆąĄą▓ąŠą┤ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ [1]) ąŠčéąĮąŠčüąĖčéčüčÅ ą║ąŠ ą▓čüąĄą╝čā čüąĄą╝ąĄą╣čüčéą▓čā STM32F4xx, ąĄčüą╗ąĖ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ čćč鹊-č鹊 ą┤čĆčāą│ąŠąĄ.

[ą×čüąĮąŠą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ GPIO]

ŌĆó ąöąŠ 16 čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗčģ ąĮąŠąČąĄą║ I/O.

ŌĆó ąĪąŠčüč鹊čÅąĮąĖčÅ ą▓čŗčģąŠą┤ą░: ą┤ą▓čāčģčéą░ą║čéąĮčŗą╣ ą┤čĆą░ą╣ą▓ąĄčĆ (push-pull) ąĖą╗ąĖ ąŠčéą║čĆčŗčéčŗą╣ čüč鹊ą║ (open drain) čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ą▓ąĄčĆčģąĮąĖčģ (pull-up) ąĖ ąĮąĖąČąĮąĖčģ (pull-down) ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓.

ŌĆó ą¤ąŠčüčéčāą┐ą╗ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ąĮą░ ą▓čŗčģąŠą┤ ą╗ąĖą▒ąŠ ąŠčé čĆąĄą│ąĖčüčéčĆą░ ą┤ą░ąĮąĮčŗčģ ą▓čŗčģąŠą┤ą░ (output data register, GPIOx_ODR), ą╗ąĖą▒ąŠ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮą░čÅ čäčāąĮą║čåąĖčÅ ą▓čŗčģąŠą┤ą░ GPIO).

ŌĆó ąÆčŗą▒ąŠčĆ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ąĮąŠąČą║ąĖ I/O.

ŌĆó ąĪąŠčüč鹊čÅąĮąĖčÅ ą▓čģąŠą┤ą░: ąŠą▒čĆčŗą▓ ąĖą╗ąĖ ą▓čŗčüąŠą║ąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ (floating), ą┐ąŠą┤čéčÅąČą║ą░ ą▓ą▓ąĄčĆčģ (pull-up), ą┐ąŠą┤čéčÅąČą║ą░ ą▓ąĮąĖąĘ (pull-up/down), ą░ąĮą░ą╗ąŠą│ąŠą▓ą░čÅ čäčāąĮą║čåąĖčÅ.

ŌĆó ąÆčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčüčéčāą┐ą░čÄčé ą▓ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ą▓čģąŠą┤ą░ (input data register, GPIOx_IDR), ąĖą╗ąĖ ą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮą░čÅ čäčāąĮą║čåąĖčÅ ą▓čģąŠą┤ą░ GPIO).

ŌĆó ąĀąĄą│ąĖčüčéčĆ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĖ čüą▒čĆąŠčüą░ ą▒ąĖčé (GPIOx_BSRR) ą┤ą╗čÅ ą┐ąŠą▒ąĖčéąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ GPIOx_ODR.

ŌĆó ą£ąĄčģą░ąĮąĖąĘą╝ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (GPIOx_LCKR) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą╝ąŠčĆąŠąĘą║ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ I/O.

ŌĆó ąÉąĮą░ą╗ąŠą│ąŠą▓ą░čÅ čäčāąĮą║čåąĖčÅ.

ŌĆó ąĀąĄą│ąĖčüčéčĆčŗ ą▓čŗą▒ąŠčĆą░ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ (AF) ą▓čģąŠą┤ą░/ą▓čŗčģąŠą┤ą░ (ą┤ąŠ 16 AF ąĮą░ ąĮąŠąČą║čā I/O).

ŌĆó ąÆąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▒čŗčüčéčĆąŠą│ąŠ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ, ą┐ąŠąĘą▓ąŠą╗čÅčÄčēą░čÅ ą╝ąĄąĮčÅčéčī čāčĆąŠą▓ąĄąĮčī ąĘą░ ą║ą░ąČą┤čŗąĄ 2 ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą║č鹊ą▓.

ŌĆó ąōąĖą▒ą║ąŠąĄ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓, ą┐ąŠąĘą▓ąŠą╗čÅčÄčēąĄąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĮąŠąČą║ąĖ I/O ą║ą░ą║ GPIO ąĖą╗ąĖ ą║ą░ą║ ą░ą┐ą┐ą░čĆą░čéąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ GPIO]

ąÜą░ąČą┤čŗą╣ ą▒ąĖčé ą┐ąŠčĆčéą░ GPIO ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ čĆąĄąČąĖą╝ą░čģ:

ŌĆó ą¤ą╗ą░ą▓ą░čÄčēąĖą╣ ą▓čģąŠą┤ (ą▓čŗčüąŠą║ąŠąĄ ą▓čģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ).

ŌĆó ąÆčģąŠą┤ čü ą┐ąŠą┤čéčÅąČą║ąŠą╣ ą║ ą┐ą╗čÄčüčā ą┐ąĖčéą░ąĮąĖčÅ (pull-up).

ŌĆó ąÆčģąŠą┤ čü ą┐ąŠą┤čéčÅąČą║ąŠą╣ ą║ ą╝ąĖąĮčāčüčā ą┐ąĖčéą░ąĮąĖčÅ (pull-down).

ŌĆó ąÉąĮą░ą╗ąŠą│ąŠą▓ą░čÅ čäčāąĮą║čåąĖčÅ.

ŌĆó ąÆčŗčģąŠą┤ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝ (open-drain) čü ą▓ąĄčĆčģąĮąĖą╝ ąĮą░ą│čĆčāąĘąŠčćąĮčŗą╝ čĆąĄąĘąĖčüč鹊čĆąŠą╝ (pull-up) ąĖą╗ąĖ čü čäčāąĮą║čåąĖąĄą╣ ąĮąĖąČąĮąĄą╣ ą┐ąŠą┤čéčÅąČą║ąĖ (pull-down).

ŌĆó ąÆčŗčģąŠą┤ čü ą┤ą▓čāčģčéą░ą║čéąĮčŗą╝ ą┤čĆą░ą╣ą▓ąĄčĆąŠą╝ (push-pull), čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ ą▓ąĄčĆčģąĮąĄą╣ ąĖą╗ąĖ ąĮąĖąČąĮąĄą╣ ą┐ąŠą┤čéčÅąČą║ąĖ.

ŌĆó ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮą░čÅ čäčāąĮą║čåąĖčÅ čü ą┤ą▓čāčģčéą░ą║čéąĮčŗą╝ ą▓čŗčģąŠą┤ąŠą╝ ąĖ čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ ą▓ąĄčĆčģąĮąĄą╣ ąĖą╗ąĖ ąĮąĖąČąĮąĄą╣ ą┐ąŠą┤čéčÅąČą║ąĖ.

ŌĆó ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮą░čÅ čäčāąĮą║čåąĖčÅ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝ ąĖ čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ ą▓ąĄčĆčģąĮąĄą╣ ąĖą╗ąĖ ąĮąĖąČąĮąĄą╣ ą┐ąŠą┤čéčÅąČą║ąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠą┤čĆąŠą▒ąĮčŗąĄ čäąĖąĘąĖč湥čüą║ąĖąĄ ąĖ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąŠčĆčéą░ I/O čüą╗ąĄą┤čāąĄčé ąĖčüą║ą░čéčī ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ą║ąŠąĮą║čĆąĄčéąĮčāčÄ ą╝ąŠą┤ąĄą╗čī ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32.

ąÜą░ąČą┤čŗą╣ ą▓čŗą▓ąŠą┤ ą┐ąŠčĆčéą░ I/O čüą▓ąŠą▒ąŠą┤ąĮąŠ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, ąŠą┤ąĮą░ą║ąŠ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ ą┐ąŠčĆčéą░ I/O ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ą░ą║ ą║ 32-ą▒ąĖčéąĮčŗą╝ čüą╗ąŠą▓ą░ą╝, ą┐ąŠą╗ąŠą▓ąĖąĮą░ą╝ čüą╗ąŠą▓ą░ ąĖą╗ąĖ ą▒ą░ą╣čéą░ą╝. ąØą░ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ GPIOx_BSRR - ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ą░č鹊ą╝ą░čĆąĮčŗą╣ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ/ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÄ ą║ ą╗čÄą▒ąŠą╝čā čĆąĄą│ąĖčüčéčĆčā GPIO. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąŠčéčüčāčéčüčéą▓čāąĄčé čĆąĖčüą║ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąĄąČą┤čā ą┤ąŠčüčéčāą┐ą░ą╝ąĖ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī.

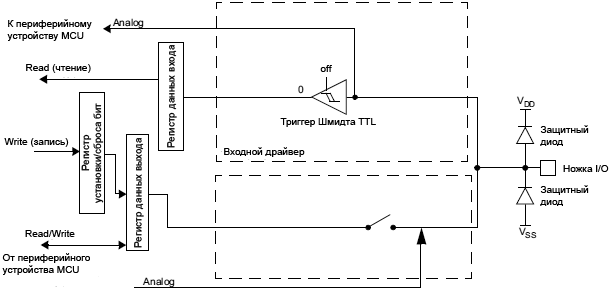

ąØą░ čĆąĖčü. 25 ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą░ąĘąŠą▓ą░čÅ čüčéčĆčāą║čéčāčĆą░ ą▒ąĖčéą░ I/O, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą┤ą░čćąĖ ąĮą░ ą▓čģąŠą┤ čāčĆąŠą▓ąĮčÅ 5V (čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ą░čÅ čäčāąĮą║čåąĖčÅ 5V tolerant ą▓čģąŠą┤ą░ ą┐čĆąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ 3.3V ą┤ą╗čÅ ą┐ąŠčĆč鹊ą▓ I/O). ąÆ čéą░ą▒ą╗ąĖčåąĄ 39 ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮčŗ ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▒ąĖčéą░ ą┐ąŠčĆčéą░.

ąĀąĖčü. 25. ąæą░ąĘąŠą▓ą░čÅ čüčéčĆčāą║čéčāčĆą░ 5V-tolerant ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ I/O.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): VDD_FT ą┐ąŠč鹥ąĮčåąĖą░ą╗ čüą┐ąĄčåąĖčäąĖč湥ąĮ ą┤ą╗čÅ 5V-tolerant I/O ąĖ ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé VDD.

ąóą░ą▒ą╗ąĖčåą░ 35. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▒ąĖčéą░ ą┐ąŠčĆčéą░ (1).

MODER(i)

[1:0] |

OTYPER(i) |

OSPEEDR(i)

[B:A]

|

PUPDR(i)

[1:0]

|

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ I/O |

| 01 |

0 |

SPEED[B:A] |

0 |

0 |

GP-ą▓čŗčģąŠą┤ |

PP |

| 0 |

0 |

1 |

GP-ą▓čŗčģąŠą┤ |

PP+PU |

| 0 |

1 |

0 |

GP-ą▓čŗčģąŠą┤ |

PP+PD |

| 0 |

1 |

1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 1 |

0 |

0 |

GP-ą▓čŗčģąŠą┤ |

OD |

| 1 |

0 |

1 |

GP-ą▓čŗčģąŠą┤ |

OD+PU |

| 1 |

1 |

0 |

GP-ą▓čŗčģąŠą┤ |

OD+PD |

| 1 |

1 |

1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 10 |

0 |

0 |

0 |

AF |

PP |

| 0 |

0 |

1 |

AF |

PP+PU |

| 0 |

1 |

0 |

AF |

PP+PD |

| 0 |

1 |

1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 1 |

0 |

0 |

AF |

OD |

| 1 |

0 |

1 |

AF |

OD+PU |

| 1 |

1 |

0 |

AF |

OD+PD |

| 1 |

1 |

1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 00 |

x |

x |

x |

0 |

0 |

ąÆčģąŠą┤ |

ą¤ą╗ą░ą▓ą░čÄčēąĖą╣ ą▓čģąŠą┤ |

| x |

x |

x |

0 |

1 |

ąÆčģąŠą┤ |

PU |

| x |

x |

x |

1 |

0 |

ąÆčģąŠą┤ |

PD |

| x |

x |

x |

1 |

1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ (ą┐ą╗ą░ą▓ą░čÄčēąĖą╣ ą▓čģąŠą┤) |

| 11 |

x |

x |

x |

0 |

0 |

ąÆčģąŠą┤/ą▓čŗčģąŠą┤ |

Analog |

| x |

x |

x |

0 |

1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| x |

x |

x |

1 |

0 |

| x |

x |

x |

1 |

1 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): GP = general-purpose, PP = push-pull, PU = pull-up, PD = pull-down, OD = open-drain, AF = alternate function.

GPIO. ąÆąŠ ą▓čĆąĄą╝čÅ čüą▒čĆąŠčüą░ ąĖ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą┐ąŠčüą╗ąĄ ąĮąĄą│ąŠ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ ąĮąĄ ą░ą║čéąĖą▓ąĮčŗ, ąĖ ąĮąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ I/O ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ą╗ą░ą▓ą░čÄčēąĄą│ąŠ ą▓čģąŠą┤ą░ čü ą▓čŗčüąŠą║ąĖą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝ (input floating mode).

ąÆčŗą▓ąŠą┤čŗ ą┐ąŠčĆčéą░ ąŠčéą╗ą░ą┤ą║ąĖ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ (AF) pull-up/pull-down:

ŌĆó PA15: ą▓čģąŠą┤ JTDI čü pull-up.

ŌĆó PA14: ą▓čģąŠą┤ JTCK/SWCLK čü pull-down.

ŌĆó PA13: ą▓čģąŠą┤ JTMS/SWDAT čü pull-up.

ŌĆó PB4: ą▓čģąŠą┤ NJTRST čü pull-up.

ŌĆó PB3: ą▓čŗčģąŠą┤ JTDO ą▓ ąŠčéą║ą╗čÄč湥ąĮąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ (floating state).

ąÜąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čŗčģąŠą┤, ąĘą░ą┐ąĖčüą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓ čĆąĄą│ąĖčüčéčĆ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (GPIOx_ODR) ą▓čŗą▓ąŠą┤ąĖčéčüčÅ ąĮą░ ąĮąŠąČą║čā ą┐ąŠčĆčéą░ I/O. ą£ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓čŗčģąŠą┤ąĮąŠą╣ ą┤čĆą░ą╣ą▓ąĄčĆ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ ą▓ čĆąĄąČąĖą╝ąĄ ą┤ą▓čāčģčéą░ą║čéąĮąŠą│ąŠ ą▓čŗčģąŠą┤ą░ (push-pull mode) ąĖą╗ąĖ ą▓ čĆąĄąČąĖą╝ąĄ ąŠčéą║čĆčŗč鹊ą│ąŠ čüč鹊ą║ą░ (open-drain mode, ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĮąĖąČąĮąĄąĄ ą┐ą╗ąĄč湊 N-MOS, ą║ąŠą│ą┤ą░ ąĮą░ ą▓čŗčģąŠą┤ ą▓čŗą▓ąŠą┤ąĖčéčüčÅ ą╗ąŠą│. 0).

ąĀąĄą│ąĖčüčéčĆ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (GPIOx_IDR) ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčé ą▓ čüąĄą▒čÅ ą┤ą░ąĮąĮčŗąĄ, ą┐čĆąĖčüčāčéčüčéą▓čāčÄčēąĖąĄ ąĮą░ ąĮąŠąČą║ąĄ I/O, ąĮą░ ą║ą░ąČą┤ąŠą╝ čéą░ą║č鹥 AHB1.

ąÆčüąĄ ąĮąŠąČą║ąĖ GPIO ąĖą╝ąĄčÄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čüą╗ą░ą▒čŗąĄ čĆąĄąĘąĖčüč鹊čĆčŗ ą┐ąŠą┤čéčÅąČą║ąĖ ą║ ą┐ą╗čÄčüčā ą┐ąĖčéą░ąĮąĖčÅ (pull-up) ąĖ ą║ ąĘąĄą╝ą╗ąĄ (pull-down), ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮčŗ ąĖą╗ąĖ ąĮąĄčé, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ GPIOx_PUPDR.

ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ąĮąŠąČąĄą║ I/O. ąØąŠąČą║ąĖ I/O ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ č湥čĆąĄąĘ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆ, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąŠą┤čüąŠąĄą┤ąĖąĮąĖčéčī ą▓ ą▓čŗą▓ąŠą┤čā I/O č鹊ą╗čīą║ąŠ ąŠą┤ąĮčā ąĖąĘ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ (AF). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą║ąŠąĮčäą╗ąĖą║čéą░ ą╝ąĄąČą┤čā čĆą░ąĘąĮčŗą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, čā ą║ąŠč鹊čĆčŗčģ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąŠą▒čēą░čÅ ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ I/O.

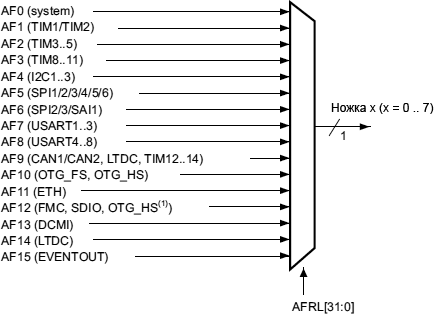

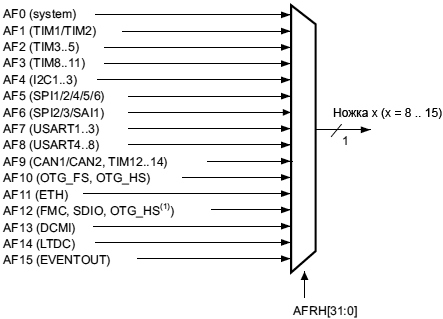

ąŻ ą║ą░ąČą┤ąŠą╣ ąĮąŠąČą║ąĖ I/O ąĄčüčéčī ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆ čü 16 ą▓čģąŠą┤ą░ą╝ąĖ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ (ąŠčé AF0 ą┤ąŠ AF15), ąŠą┤ąĮčā ąĖąĘ ą║ąŠč鹊čĆčŗčģ ą╝ąŠąČąĮąŠ čüą║ąŠąĮčäąĖą│čāąĖčĆąŠą▓ą░čéčī č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆčŗ GPIOx_AFRL (ą┤ą╗čÅ čĆą░ąĘčĆčÅą┤ąŠą▓ ąĮąŠąČąĄą║ ą┐ąŠčĆč鹊ą▓ 0 .. 7) ąĖ GPIOx_AFRH (ą┤ą╗čÅ čĆą░ąĘčĆčÅą┤ąŠą▓ ąĮąŠąČąĄą║ ą┐ąŠčĆč鹊ą▓ 8 .. 15):

ŌĆó ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą▓čüąĄ ąĮąŠąČą║ąĖ I/O ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ čüąĖčüč鹥ą╝ąĮąŠą╣ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ 0 (AF0), SYS.

ŌĆó ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąŠč鹊ą▒čĆą░ąČą░čÄčéčüčÅ ąŠčé AF1 ą┤ąŠ AF13.

ŌĆó Cortex┬«-M4 čü FPU EVENTOUT ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĮą░ AF15.

ąŁčéą░ čüčéčĆčāą║čéčāčĆą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ą┤ą░ą╗ąĄąĄ ąĮą░ čĆąĖčüčāąĮą║ą░čģ 26 ąĖ 27.

ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ čŹč鹊ą╣ ą│ąĖą▒ą║ąŠą╣ ą░čĆčģąĖč鹥ą║čéčāčĆąĄ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖčÅ I/O, ą║ą░ąČą┤ąŠąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĖą╝ąĄąĄčé čüą▓ąŠąĖ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ, ąŠč鹊ą▒čĆą░ąČąĄąĮąĮčŗąĄ ąĮą░ čĆą░ąĘą╗ąĖčćąĮčŗąĄ ąĮąŠąČą║ąĖ I/O, čćč鹊ą▒čŗ ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą┤ąŠčüčéčāą┐ąĮčŗčģ ą▓ ą║ąŠčĆą┐čāčüą░čģ čü ą╝ąĄąĮčīčłąĖą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ ą▓čŗą▓ąŠą┤ąŠą▓.

ąöą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ I/O ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čŗą┐ąŠą╗ąĮąĖč鹥 čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ:

ŌĆó ąĪąĖčüč鹥ą╝ąĮą░čÅ čäčāąĮą║čåąĖčÅ (SYS). ą¤ąŠą┤ą║ą╗čÄčćąĖč鹥 ąĮąŠąČą║čā I/O ą║ AF0 ąĖ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ąĄčæ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╣ čäčāąĮą║čåąĖąĖ:

ŌĆō JTAG/SWD, ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ čüą▒čĆąŠčüą░ čŹčéąĖ ą▓čŗą▓ąŠą┤čŗ ąĮą░ąĘąĮą░čćą░čÄčéčüčÅ ą║ą░ą║ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗąĄ ą┤ą╗čÅ čäčāąĮą║čåąĖąĖ ąŠčéą╗ą░ą┤ą║ąĖ, ąĖ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čģąŠčüč鹊ą╝ ąŠčéą╗ą░ą┤ą║ąĖ (ąĮąŠąČą║ą░ ąĮąĄ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ GPIO).

ŌĆō RTC_REFIN: čŹč鹊čé ą▓čŗą▓ąŠą┤ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ ą▓čģąŠą┤ą░ čü ą▓čŗčüąŠą║ąĖą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝ (input floating mode).

ŌĆō MCO1 ąĖ MCO2: čŹčéąĖ ą▓čŗą▓ąŠą┤čŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą▓ čĆąĄąČąĖą╝ąĄ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ąĘą░ą┐čĆąĄčéąĖčéčī ąĮąĄą║ąŠč鹊čĆčŗąĄ ąĖą╗ąĖ ą▓čüąĄ ąĮąŠąČą║ąĖ JTAG/SWD, ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī ąĖčģ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą║ą░ą║ GPIO (ąŠčüą▓ąŠą▒ąŠąČą┤ąĄąĮąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ ą┐ąŠą┤čüą▓ąĄč湥ąĮčŗ čüąĄčĆčŗą╝ ą▓ čéą░ą▒ą╗ąĖčåąĄ 36).

ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. čüąĄą║čåąĖąĖ Section 7.2.10: Clock-out capability ąĖ Section 6.2.10: Clock-out capability ą┤ą░čéą░čłąĖčéą░ [1].

ąóą░ą▒ą╗ąĖčåą░ 36. ąōąĖą▒ą║ąŠąĄ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ ąŠčéą╗ą░ą┤čćąĖą║ą░ SWJ-DP. "ą×čüą▓ąŠą▒ąŠąČą┤ąĄąĮąŠ" - ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čŹčéąĖ ąĮąŠąČą║ąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čäčāąĮą║čåąĖą╣ ąŠčéą╗ą░ą┤ą║ąĖ ąĖ ą╝ąŠą│čéčā ą▒čŗčéčī ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮčŗ ą║ą░ą║ ą┐ąŠčĆčéčŗ GPIO.

ąöąŠčüčéčāą┐ąĮčŗąĄ ą┐ąŠčĆčéčŗ ąŠčéą╗ą░ą┤ą║ąĖ

|

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ąĮąŠąČąĄą║ SWJ I/O

|

PA13/

JTMS/

SWDIO |

PA14/

JTCK/

SWCLK |

PA15/

JTDI |

PB3/

JTDO |

PB4/

NJTRST |

| ą¤ąŠą╗ąĮčŗą╣ SWJ (JTAG-DP + SW-DP) - čüąŠčüč鹊čÅąĮąĖąĄ čüą▒čĆąŠčüą░ |

x |

x |

x |

x |

x |

| ą¤ąŠą╗ąĮčŗą╣ SWJ (JTAG-DP + SW-DP), ąĮąŠ ą▒ąĄąĘ NJTRST |

x |

x |

x |

x |

ą×čüą▓ąŠą▒. |

| JTAG-DP ąĘą░ą┐čĆąĄčēąĄąĮ ąĖ SW-DP čĆą░ąĘčĆąĄčłąĄąĮ |

x |

x |

ą×čüą▓ąŠą▒ąŠąČą┤ąĄąĮąŠ |

| ąŚą░ą┐čĆąĄčēąĄąĮčŗ ąĖ JTAG-DP, ąĖ SW-DP |

ą×čüą▓ąŠą▒ąŠąČą┤ąĄąĮąŠ |

ŌĆó GPIO. ąĀąĄą│ąĖčüčéčĆąŠą╝ GPIOx_MODER ąĮčāąČąĮą░čÅ ąĮąŠąČą║ą░ I/O ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤ ąĖą╗ąĖ ą▓čŗčģąŠą┤.

ŌĆó AF (ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮą░čÅ čäčāąĮą║čåąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░). ąöą╗čÅ ADC ąĖ DAC čüą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ąĮčāąČąĮčāčÄ ąĮąŠąČą║čā I/O ą║ą░ą║ ą░ąĮą░ą╗ąŠą│ąŠą▓čāčÄ čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄą│ąĖčüčéčĆą░ GPIOx_MODER.

ąöą╗čÅ ą┤čĆčāą│ąĖčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓:

ŌĆō ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ąĮčāąČąĮčāčÄ ąĮąŠąČą║čā I/O ą▓ ą║ą░č湥čüčéą▓ąĄ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄą│ąĖčüčéčĆą░ GPIOx_MODER.

ŌĆō ąÆčŗą▒ąĄčĆąĖč鹥 čéąĖą┐, pull-up/pull-down ąĖ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ GPIOx_OTYPER, GPIOx_PUPDR ąĖ GPIOx_OSPEEDR.

ŌĆō ąĪąŠąĄą┤ąĖąĮąĖč鹥 I/O čü ąĮčāąČąĮąŠą╣ čäčāąĮą║čåąĖąĄą╣ AFx ą▓ čĆąĄą│ąĖčüčéčĆąĄ GPIOx_AFRL ąĖą╗ąĖ GPIOx_AFRH.

ŌĆó EVENTOUT. ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ąĮąŠąČą║čā I/O ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ Cortex┬«-M4 čüąĖą│ąĮą░ą╗ą░ FPU EVENTOUT, ą┐čāč鹥ą╝ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ąĄą│ąŠ ą║ AF15.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: EVENTOUT ąĮąĄ ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĮą░ čüą╗ąĄą┤čāčÄčēąĖąĄ ą┐ąŠčĆčéčŗ I/O: PC13, PC14, PC15, PH0, PH1 ąĖ PI8.

ąĪą╝. čéą░ą▒ą╗ąĖčåčā ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ (Alternate function mapping) ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčāčÄ ą╝ąŠą┤ąĄą╗čī ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą│ą┤ąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ąŠą┐ąĖčüą░ąĮąŠ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ą║ą░ąČą┤ąŠą╣ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ ąĮą░ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčāčÄ čäčāąĮą║čåąĖčÄ. ąöą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32F407 čéą░ą▒ą╗ąĖčåą░ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ą▓ čüčéą░čéčīąĄ [2], ą┤ą╗čÅ STM32F429 čéą░ą▒ą╗ąĖčåą░ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ.

ąöą╗čÅ ąĮąŠąČąĄą║ ąŠčé 0 ą┤ąŠ 7 čĆąĄą│ąĖčüčéčĆ GPIOx_AFRL[31:0] ą▓čŗą▒ąĖčĆą░ąĄčé ą▓čŗą┤ąĄą╗ąĄąĮąĮčāčÄ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčāčÄ čäčāąĮą║čåąĖčÄ:

ąöą╗čÅ ąĮąŠąČąĄą║ ąŠčé 8 ą┤ąŠ 15 čĆąĄą│ąĖčüčéčĆ GPIOx_AFRH[31:0] ą▓čŗą▒ąĖčĆą░ąĄčé ą▓čŗą┤ąĄą╗ąĄąĮąĮčāčÄ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčāčÄ čäčāąĮą║čåąĖčÄ:

ąĀąĖčü. 26. ąÆčŗą▒ąŠčĆ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ STM32F405xx/07xx ąĖ STM32F415xx/17xx.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą▓ FS.

ąöą╗čÅ ąĮąŠąČąĄą║ ąŠčé 0 ą┤ąŠ 7 čĆąĄą│ąĖčüčéčĆ GPIOx_AFRL[31:0] ą▓čŗą▒ąĖčĆą░ąĄčé ą▓čŗą┤ąĄą╗ąĄąĮąĮčāčÄ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčāčÄ čäčāąĮą║čåąĖčÄ:

ąöą╗čÅ ąĮąŠąČąĄą║ ąŠčé 8 ą┤ąŠ 15 čĆąĄą│ąĖčüčéčĆ GPIOx_AFRH[31:0] ą▓čŗą▒ąĖčĆą░ąĄčé ą▓čŗą┤ąĄą╗ąĄąĮąĮčāčÄ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčāčÄ čäčāąĮą║čåąĖčÄ:

ąĀąĖčü. 27. ąÆčŗą▒ąŠčĆ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ STM32F42xxx ąĖ STM32F43xxx.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą▓ FS.

ąĀąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠčĆč鹊ą╝ I/O. ąÜą░ąČą┤čŗą╣ ą┐ąŠčĆčé GPIO čüąĮą░ą▒ąČąĄąĮ 32-čĆą░ąĘčĆčÅą┤ąĮčŗą╝ąĖ, ąŠč鹊ą▒čĆą░ąČąĄąĮąĮčŗą╝ąĖ ąĮą░ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ (GPIOx_MODER, GPIOx_OTYPER, GPIOx_OSPEEDR, GPIOx_PUPDR), ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗą╝ąĖ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ąŠ 16 ąĮąŠąČąĄą║ I/O.

ąĀąĄą│ąĖčüčéčĆ GPIOx_MODER ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ I/O (ą▓ą▓ąŠą┤, ą▓čŗą▓ąŠą┤, AF, ą░ąĮą░ą╗ąŠą│ąŠą▓ą░čÅ čäčāąĮą║čåąĖčÅ). ąĀąĄą│ąĖčüčéčĆčŗ GPIOx_OTYPER ąĖ GPIOx_OSPEEDR ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ čéąĖą┐ą░ ą▓čŗčģąŠą┤ą░ (push-pull ąĖą╗ąĖ open-drain) ąĖ ąĄą│ąŠ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ (ąĮąŠąČą║ąĖ čüą║ąŠčĆąŠčüčéąĖ I/O ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝čā čĆąĄą│ąĖčüčéčĆčā GPIOx_OSPEEDR, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ I/O). ąĀąĄą│ąĖčüčéčĆ GPIOx_PUPDR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą┐ąŠą┤čéčÅąČą║ąĖ pull-up/pull-down ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ I/O.

ąĀąĄą│ąĖčüčéčĆčŗ ą┤ą░ąĮąĮčŗčģ ą┐ąŠčĆčéą░ I/O. ąŻ ą║ą░ąČą┤ąŠą│ąŠ GPIO ąĄčüčéčī ą┤ą▓ą░ 16-ą▒ąĖčéąĮčŗčģ ąŠč鹊ą▒čĆą░ąČąĄąĮąĮčŗčģ ąĮą░ ą┐ą░ą╝čÅčéčī čĆąĄą│ąĖčüčéčĆą░: čĆąĄą│ąĖčüčéčĆčŗ ą▓čģąŠą┤ąĮčŗčģ ąĖ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (GPIOx_IDR ąĖ GPIOx_ODR). ąÆ GPIOx_ODR čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░, ąŠąĮ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ. ąÆčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčĆčéą░ I/O čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┤ą░ąĮąĮčŗčģ ą▓čģąŠą┤ą░ (GPIOx_IDR), čŹč鹊 čĆąĄą│ąĖčüčéčĆ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ą░ąĮąĮčŗčģ čüą╝. ą▓ čüąĄą║čåąĖąĖ 8.4.5: GPIO port input data register (GPIOx_IDR) (x = A..I/J/K) ąĖ čüąĄą║čåąĖąĖ 8.4.6: GPIO port output data register (GPIOx_ODR) (x = A..I/J/K) ą┤ą░čéą░čłąĖčéą░ [1].

ą£ą░ąĮąĖą┐čāą╗čÅčåąĖčÅ čĆą░ąĘčĆčÅą┤ą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ I/O. ąĀąĄą│ąĖčüčéčĆ čāčüčéą░ąĮąŠą▓ą║ąĖ/čüą▒čĆąŠčüą░ ą▒ąĖčéą░ (GPIOx_BSRR) čŹč鹊 32-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ, ą┐ąŠąĘą▓ąŠą╗čÅčÄčēąĖą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ ą░č鹊ą╝ą░čĆąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ąĖ čüą▒čĆąŠčüąĖčéčī ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (GPIOx_ODR). ąŻ čĆąĄą│ąĖčüčéčĆą░ čāčüčéą░ąĮąŠą▓ą║ąĖ/čüą▒čĆąŠčüą░ GPIOx_BSRR ą▒ąĖčé ą▓ 2 čĆą░ąĘą░ ą▒ąŠą╗čīčłąĄ, č湥ą╝ čā čĆąĄą│ąĖčüčéčĆą░ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ GPIOx_ODR.

ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą▒ąĖčéą░ ą▓ GPIOx_ODR čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé 2 ą▒ąĖčéą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ GPIOx_BSRR: BSRR(i) ąĖ BSRR(i+SIZE). ąÜąŠą│ą┤ą░ ą▓ ą▒ąĖčé BSRR(i) ąĘą░ą┐ąĖčüą░ąĮą░ 1, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ODR(i). ąÜąŠą│ą┤ą░ ą▓ ą▒ąĖčé BSRR(i+SIZE) ąĘą░ą┐ąĖčüą░ąĮą░ 1, čüą▒čĆąŠčüąĖčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ODR(i).

ąŚą░ą┐ąĖčüčī 0 ą▓ ą╗čÄą▒ąŠą╣ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ GPIOx_BSRR ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé GPIOx_ODR. ąĢčüą╗ąĖ čüą┤ąĄą╗ą░ąĮą░ ą┐ąŠą┐čŗčéą║ą░ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮčŗčģ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĖ čüą▒čĆąŠčüą░ ą▒ąĖčéą░ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ GPIOx_BSRR, č鹊 ą┤ąĄą╣čüčéą▓ąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĖą╝ąĄąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé.

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ GPIOx_BSRR ą┤ą╗čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖą╣ ąŠčéą┤ąĄą╗čīąĮčŗčģ ą▒ąĖčé ą▓ GPIOx_ODR čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ "ąŠą┤ąĖąĮąŠčćąĮčŗą╣ ą▓čŗčüčéčĆąĄą╗", ą║ąŠč鹊čĆčŗą╣ ąĮąĄ ą▒ą╗ąŠą║ąĖčĆčāąĄčé ą▒ąĖčéčŗ GPIOx_ODR. ąÜ ą▒ąĖčéą░ą╝ GPIOx_ODR ą▓čüąĄą│ą┤ą░ ą╝ąŠąČąĮąŠ ąŠą▒čĆą░čēą░čéčīčüčÅ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ. ąĀąĄą│ąĖčüčéčĆ GPIOx_BSRR ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą┐ąŠčüąŠą▒ ą░č鹊ą╝ą░čĆąĮąŠą│ąŠ ą┐ąŠą▒ąĖčéąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮčŗą╝ąĖ čĆą░ąĘčĆčÅą┤ą░ą╝ąĖ ą┐ąŠčĆčéą░. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ąĘą░ą┐čĆąĄčēą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ GPIOx_ODR ąĮą░ čāčĆąŠą▓ąĮąĄ ą▒ąĖčé: ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░čéčī ąŠą┤ąĖąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ąĘą░ ąŠą┤ąĖąĮ ą░č鹊ą╝ą░čĆąĮčŗą╣ ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī ą┐ąŠ čłąĖąĮąĄ AHB1.

ą£ąĄčģą░ąĮąĖąĘą╝ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ GPIO. ąĢčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąĘą░ą╝ąŠčĆąŠąĘąĖčéčī čĆąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ GPIO čü ą┐ąŠą╝ąŠčēčīčÄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ GPIOx_LCKR. ąŚą░ą╝ąŠčĆą░ąČąĖą▓ą░čÄčéčüčÅ čĆąĄą│ąĖčüčéčĆčŗ GPIOx_MODER, GPIOx_OTYPER, GPIOx_OSPEEDR, GPIOx_PUPDR, GPIOx_AFRL ąĖ GPIOx_AFRH.

ąöą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ GPIOx_LCKR ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą┐ąĖčüąĖ/čćč鹥ąĮąĖčÅ. ąÜąŠą│ą┤ą░ ą┐čĆą░ą▓ąĖą╗čīąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (LOCK sequence) ą┐čĆąĖą╝ąĄąĮąĄąĮą░ ą┤ą╗čÅ ą▒ąĖčéą░ 16 ą▓ čŹč鹊ą╝ čĆąĄą│ąĖčüčéčĆąĄ, ąĘąĮą░č湥ąĮąĖąĄ LCKR[15:0] ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĮąŠąČąĄą║ I/O (ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ ąĘąĮą░č湥ąĮąĖąĄ LCKR[15:0] ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ąĖ). ąÜąŠą│ą┤ą░ LOCK sequence ą┐čĆąĖą╝ąĄąĮąĄąĮą░ ą║ ą▒ąĖčéčā ą┐ąŠčĆčéą░, ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░ ą┐ąŠčĆčéą░ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąŠ ą┤ąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüą▒čĆąŠčüą░ MCU ąĖą╗ąĖ ą┐ąĄčĆąĖč乥čĆąĖąĖ. ąÜą░ąČą┤čŗą╣ ą▒ąĖčé GPIOx_LCKR freezes the corresponding bit in the control registers (GPIOx_MODER, GPIOx_OTYPER, GPIOx_OSPEEDR, GPIOx_PUPDR, GPIOx_AFRL and GPIOx_AFRH).

LOCK sequence ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ č鹊ą╗čīą║ąŠ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ čĆąĄą│ąĖčüčéčĆčā GPIOx_LCKR čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ 32-ą▒ąĖčéąĮčŗčģ čüą╗ąŠą▓, ą┐ąŠč鹊ą╝čā čćč鹊 ą▒ąĖčé 16 čĆąĄą│ąĖčüčéčĆą░ GPIOx_LCKR ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čü ą▒ąĖčéą░ą╝ąĖ [15:0].

ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ ą┐ąŠ čäčāąĮą║čåąĖąĖ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čüą╝. ąĮąĖąČąĄ ą▓ąŠ ą▓čĆąĄąĘą║ąĄ čü ąŠą┐ąĖčüą░ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ GPIOx_LCKR.

AF (ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮą░čÅ čäčāąĮą║čåąĖčÅ I/O). ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮčŗ 2 čĆąĄą│ąĖčüčéčĆą░ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ąŠą┤ąĮąŠą╣ ąĖąĘ 16 ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ ą▓čģąŠą┤ą░/ą▓čŗčģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ąĮąŠąČą║ąĖ I/O. ąĪ ą┐ąŠą╝ąŠčēčīčÄ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ąÆčŗ ą╝ąŠąČąĄč鹥 ą┐ąŠą┤čüąŠąĄą┤ąĖąĮąĖčéčī ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčāčÄ čäčāąĮą║čåąĖčÄ ą║ ą║ą░ą║ąŠą╣-č鹊 ą┤čĆčāą│ąŠą╣ ąĮąŠąČą║ąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą║ą░ą║ č鹊ą│ąŠ čéčĆąĄą▒čāąĄčé ąÆą░čłąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ.

ąŁč鹊 ąĘąĮą░čćąĖčé, čćč鹊 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▓ąŠąĘą╝ąŠąČąĮčŗčģ čäčāąĮą║čåąĖą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤čāčÄ ąĮąŠąČą║čā GPIO čü ą┐ąŠą╝ąŠčēčīčÄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ GPIOx_AFRL ąĖ GPIOx_AFRH. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą▓čŗą▒čĆą░čéčī ąŠą┤ąĮčā ąĖąĘ ą▓ąŠąĘą╝ąŠąČąĮčŗčģ čäčāąĮą║čåąĖą╣ (AF) ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ąĮąŠąČą║ąĖ I/O. ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą░ AF ąŠą▒čēąĖą╣ ą┤ą╗čÅ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ ą▓čģąŠą┤ą░ ąĖ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ ą▓čŗčģąŠą┤ą░, ąŠą┤ąĖąĮ ą║ą░ąĮą░ą╗ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┤ą╗čÅ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ąŠą┤ąĮąŠą╣ ąĮąŠąČą║ąĖ I/O.

ą¦č鹊ą▒čŗ čāąĘąĮą░čéčī, ą║ą░ą║ąĖąĄ čäčāąĮą║čåąĖąĖ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆčāčÄčéčüčÅ ąĮą░ ą║ą░ą║ąŠą╝ ą▓čŗą▓ąŠą┤ąĄ GPIO, čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ą║ąŠąĮą║čĆąĄčéąĮčŗą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čéą░ą▒ą╗ąĖčåčā "Alternate function mapping". ąöą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32F407 čéą░ą▒ą╗ąĖčåą░ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ą▓ čüčéą░čéčīąĄ [2], ą┤ą╗čÅ STM32F429 čéą░ą▒ą╗ąĖčåą░ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ąĮąŠąČą║ąĖ I/O ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮą░ č鹊ą╗čīą║ąŠ ąŠą┤ąĮą░ ąĖąĘ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣.

ąøąĖąĮąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ/ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ. ąŻ ą▓čüąĄčģ ą┐ąŠčĆč鹊ą▓ ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą┤ą░čćąĖ čüąĖą│ąĮą░ą╗ą░ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (external interrupt). ąöą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čŹč鹊ą╣ čäčāąĮą║čåąĖąĖ ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą▓ čĆąĄąČąĖą╝ ą▓čģąŠą┤ą░, čüą╝. čüąĄą║čåąĖąĖ 12.2: External interrupt/event controller (EXTI) ąĖ 12.2.3: Wakeup event management ą▓ ą┤ą░čéą░čłąĖč鹥 [1].

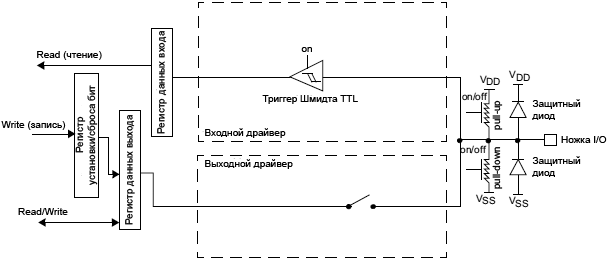

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓ą▓ąŠą┤ą░. ąÜąŠą│ą┤ą░ ą┐ąŠčĆčé I/O ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čģąŠą┤:

ŌĆó ąÆčŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ąĘą░ą┐čĆąĄčēąĄąĮ.

ŌĆó ąÉą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ čéčĆąĖą│ą│ąĄčĆ ą©ą╝ąĖą┤čéą░ ą┐ąŠ ą▓čģąŠą┤čā.

ŌĆó ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĘą░ą┐ąĖčüą░ąĮąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆ GPIOx_PUPDR ą╝ąŠą│čāčé ą▒čŗčéčī ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮčŗ ą▓ąĄčĆčģąĮąĖąĄ (pull-up) ąĖ/ąĖą╗ąĖ ąĮąĖąČąĮąĖąĄ (pull-down) čĆąĄąĘąĖčüč鹊čĆčŗ.

ŌĆó ąöą░ąĮąĮčŗąĄ, ą┐čĆąĖčüčāčéčüčéą▓čāčÄčēąĖąĄ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ I/O ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąĮą░ ą║ą░ąČą┤ąŠą╝ čéą░ą║č鹥 AHB1.

ŌĆó ąöąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčĆč鹊ą▓ I/O.

ąĀąĖčü. 28 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓čģąŠą┤ąĮčāčÄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ ą▒ąĖčéą░ ą┐ąŠčĆčéą░ I/O.

ąĀąĖčü. 28. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čģąŠą┤ą░ ą┤ą╗čÅ čĆąĄąČąĖą╝ąŠą▓ floating, pull-up ąĖ pull-down.

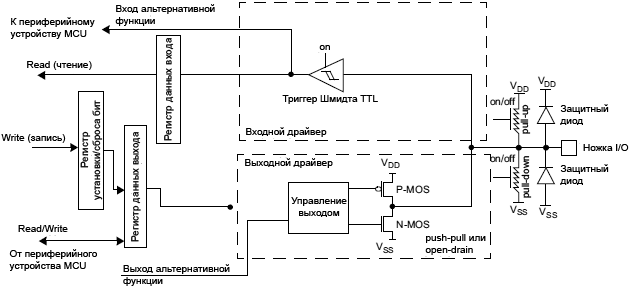

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čŗą▓ąŠą┤ą░. ąÜąŠą│ą┤ą░ ą┐ąŠčĆčé I/O ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čŗčģąŠą┤:

ŌĆó ąÆčŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ čĆą░ąĘčĆąĄčłąĄąĮ:

ŌĆō ąĀąĄąČąĖą╝ ąŠčéą║čĆčŗč鹊ą│ąŠ čüč鹊ą║ą░ (open-drain): ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╣ ą╗ąŠą│. 0 ą▓ čĆąĄą│ąĖčüčéčĆ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą░ą║čéąĖą▓ąĖčĆčāąĄčé (ąŠčéą║čĆčŗą▓ą░ąĄčé) ąĮąĖąČąĮąĄąĄ ą┐ą╗ąĄč湊 ą┤čĆą░ą╣ą▓ąĄčĆą░ N-MOS, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ąĘą░ą┐ąĖčüą░ąĮąĮą░čÅ ą╗ąŠą│. 1 ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ąĮąŠąČą║čā ą┐ąŠčĆčéą░ ą▓ ąŠčéą║ą╗čÄč湥ąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ Hi-Z (ą▓ąĄčĆčģąĮąĄąĄ ą┐ą╗ąĄč湊 ą┤čĆą░ą╣ą▓ąĄčĆą░ P-MOS ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ).

ŌĆō ąĀąĄąČąĖą╝ ą┤ą▓čāčģčéą░ą║čéąĮąŠą│ąŠ ą▓čŗčģąŠą┤ą░ (push-pull): ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╣ ą╗ąŠą│. 0 ą▓ čĆąĄą│ąĖčüčéčĆ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą░ą║čéąĖą▓ąĖčĆčāąĄčé (ąŠčéą║čĆčŗą▓ą░ąĄčé) ąĮąĖąČąĮąĄąĄ ą┐ą╗ąĄč湊 ą┤čĆą░ą╣ą▓ąĄčĆą░ N-MOS, ą▓ąĄčĆčģąĮąĄąĄ ą┐ą╗ąĄč湊 ą┤čĆą░ą╣ą▓ąĄčĆą░ P-MOS ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ. ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ ą╗ąŠą│. 1 ą▓ čĆąĄą│ąĖčüčéčĆ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąŠčéą║ą╗čÄčćą░ąĄčé ąĮąĖąČąĮąĄąĄ ą┐ą╗ąĄč湊 N-MOS ąĖ ąŠčéą║čĆčŗą▓ą░ąĄčé ą▓ąĄčĆčģąĮąĄąĄ ą┐ą╗ąĄč湊 P-MOS, ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ą╗ąŠą│. 1.

ŌĆó ąÉą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ą▓čģąŠą┤ąĮąŠą╣ čéčĆąĖą│ą│ąĄčĆ ą©ą╝ąĖą┤čéą░.

ŌĆó ąÉą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮčŗ ą╗ąĖ čüą╗ą░ą▒čŗąĄ čĆąĄąĘąĖčüč鹊čĆčŗ ą┐ąŠą┤čéčÅąČą║ąĖ (weak pull-up ąĖ pull-down), ąĖą╗ąĖ ąĮąĄčé, ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĘąĮą░č湥ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ GPIOx_PUPDR.

ŌĆó ąöą░ąĮąĮčŗąĄ, ą┐čĆąĖčüčāčéčüčéą▓čāčÄčēąĖąĄ ąĮą░ ąĮąŠąČą║ąĄ I/O, ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąĮą░ ą║ą░ąČą┤ąŠą╝ čéą░ą║č鹥 AHB1.

ŌĆó ąöąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčĆč鹊ą▓ I/O.

ŌĆó ąöąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ą▓ čĆąĄą│ąĖčüčéčĆą░ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą║ą░ąČąĄčé ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ ąĘą░ą┐ąĖčüą░ąĮąĮąŠąĄ ą▓ ąĮąĄą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ.

ąĀąĖčü. 29 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓čŗčģąŠą┤ąĮčāčÄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ ą▒ąĖčéą░ ą┐ąŠčĆčéą░ I/O.

ąĀąĖčü. 29. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čŗčģąŠą┤ą░.

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ AF. ąÜąŠą│ą┤ą░ ąĮą░ ąĮąŠąČą║čā I/O ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮą░čÅ čäčāąĮą║čåąĖčÅ (AF):

ŌĆó ąÆčŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą╗ąĖą▒ąŠ ą║ą░ą║ ąŠčéą║čĆčŗčéčŗą╣ čüč鹊ą║ (open-drain), ą╗ąĖą▒ąŠ ą║ą░ą║ ą┤ą▓čāčģčéą░ą║čéąĮčŗą╣ ą▒čāč乥čĆ (push-pull).

ŌĆó ąØą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą┐ąŠčüčéčāą┐ą░ąĄčé čüąĖą│ąĮą░ą╗ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ ą┤ą░ąĮąĮčŗąĄ ąŠčé ąĮąĄą│ąŠ).

ŌĆó ąÉą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ą▓čģąŠą┤ąĮąŠą╣ čéčĆąĖą│ą│ąĄčĆ ą©ą╝ąĖą┤čéą░.

ŌĆó ąÉą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮčŗ ą╗ąĖ čüą╗ą░ą▒čŗąĄ čĆąĄąĘąĖčüč鹊čĆčŗ ą┐ąŠą┤čéčÅąČą║ąĖ (weak pull-up ąĖ pull-down), ąĖą╗ąĖ ąĮąĄčé, ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĘąĮą░č湥ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ GPIOx_PUPDR.

ŌĆó ąöą░ąĮąĮčŗąĄ, ą┐čĆąĖčüčāčéčüčéą▓čāčÄčēąĖąĄ ąĮą░ ąĮąŠąČą║ąĄ I/O, ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąĮą░ ą║ą░ąČą┤ąŠą╝ čéą░ą║č鹥 AHB1.

ŌĆó ąöąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčĆč鹊ą▓ I/O.

ąĀąĖčü. 30 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ ą▒ąĖčéą░ ą┐ąŠčĆčéą░ I/O.

ąĀąĖčü. 30. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ (AF).

ąÉąĮą░ą╗ąŠą│ąŠą▓ą░čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ. ąÜąŠą│ą┤ą░ ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ I/O ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ą▓ analog-čĆąĄąČąĖą╝ąĄ:

ŌĆó ąÆčŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ąĘą░ą┐čĆąĄčēąĄąĮ.

ŌĆó ąóčĆąĖą│ą│ąĄčĆ ą©ą╝ąĖą┤čéą░ ąĮą░ ą▓čģąŠą┤ąĄ ą┤ąĄą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ, ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čÅ ąĮčāą╗ąĄą▓ąŠąĄ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ č鹊ą║ą░ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ąĮą░ ąĮąŠąČą║ąĄ I/O. ąÆčŗčģąŠą┤ čéčĆąĖą│ą│ąĄčĆą░ ą©ą╝ąĖą┤čéą░ ą┐ąŠą╗čāčćą░ąĄčé ą┐ąŠčüč鹊čÅąĮąĮąŠąĄ ąĮčāą╗ąĄą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ.

ŌĆó ąĪą╗ą░ą▒čŗąĄ čĆąĄąĘąĖčüč鹊čĆčŗ ą┐ąŠą┤čéčÅąČą║ąĖ (weak pull-up ąĖ weak pull-down) ąĘą░ą┐čĆąĄčēąĄąĮčŗ.

ŌĆó ąöąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ą▓ čĆąĄą│ąĖčüčéčĆčā ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┤ą░čüčé ąĘąĮą░č湥ąĮąĖąĄ "0".

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ analog-ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čŗą▓ąŠą┤čŗ I/O č鹥čĆčÅčÄčé čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą┐čĆąĖąĮąĖą╝ą░čéčī ą┐ąŠ ą▓čģąŠą┤čā čāčĆąŠą▓ąĄąĮčī 5V (ąŠąĮąĖ ąĮąĄ čÅą▓ą╗čÅčÄčéčüčÅ 5V tolerant).

ąØą░ čĆąĖčü. 31 ą┐ąŠą║ą░ąĘą░ąĮą░ ą▓čŗčüąŠą║ąŠąŠą╝ąĮą░čÅ, ą░ąĮą░ą╗ąŠą│ąŠą▓ą░čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą▒ąĖčéą░ ą┐ąŠčĆčéą░ I/O.

ąĀąĖčü. 31. Hi-Z analog-ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ.

OSC32_IN/OSC32_OUT ą║ą░ą║ GPIO. ąÆčŗą▓ąŠą┤čŗ LSE-ą│ąĄąĮąĄčĆą░č鹊čĆą░ OSC32_IN ąĖ OSC32_OUT ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ąĮąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ I/O ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ, PC14 ąĖ PC15 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ, ą║ąŠą│ą┤ą░ LSE-ą│ąĄąĮąĄčĆą░č鹊čĆ ą▓čŗą║ą╗čÄč湥ąĮ. ąØąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ PC14 ąĖ PC15 ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą║ą░ą║ ą▓ąĮąĄčłąĮąĖąĄ ą▓čŗą▓ąŠą┤čŗ OSC32_IN ąĖ OSC32_OUT č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ LSE-ą│ąĄąĮąĄčĆą░č鹊čĆ ą▓ą║ą╗čÄč湥ąĮ. ąÆą║ą╗čÄč湥ąĮąĖąĄ ą│ąĄąĮąĄčĆą░č鹊čĆą░ LSE ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ LSEON ą▓ čĆąĄą│ąĖčüčéčĆąĄ RCC_BDCR. ąæąĖčé LSE ąĖą╝ąĄąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé ąĮą░ą┤ čäčāąĮą║čåąĖąĄą╣ GPIO.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čäčāąĮą║čåąĖąŠąĮą░ą╗ PC14/PC15 GPIO č鹥čĆčÅąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┤ąŠą╝ąĄąĮ ą┐ąĖčéą░ąĮąĖčÅ 1.2V ą▓čŗą║ą╗čÄč湥ąĮ (ą║ąŠą│ą┤ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ standby), ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮ ą┤ąŠą╝ąĄąĮ ą┐ąĖčéą░ąĮąĖčÅ VBAT (VDD ą▒ąŠą╗čīčłąĄ ąĮąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ I/O čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ čĆąĄąČąĖą╝ą░ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░.

OSC_IN/OSC_OUT ą║ą░ą║ GPIO. ąÆčŗą▓ąŠą┤čŗ HSE-ą│ąĄąĮąĄčĆą░č鹊čĆą░ OSC_IN ąĖ OSC_OUT ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ąĮąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ I/O ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ, PH0 ąĖ PH1 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ, ą║ąŠą│ą┤ą░ HSE-ą│ąĄąĮąĄčĆą░č鹊čĆ ą▓čŗą║ą╗čÄč湥ąĮ (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ HSE-ą│ąĄąĮąĄčĆą░č鹊čĆ ą▓čŗą║ą╗čÄč湥ąĮ). ąØąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ PH0/PH1 ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą║ą░ą║ ą▓čŗą▓ąŠą┤čŗ HSE-ą│ąĄąĮąĄčĆą░č鹊čĆą░ OSC_IN/OSC_OUT č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ HSE-ą│ąĄąĮąĄčĆą░č鹊čĆ ą▓ą║ą╗čÄč湥ąĮ. ąÆą║ą╗čÄč湥ąĮąĖąĄ HSE-ą│ąĄąĮąĄčĆą░č鹊čĆą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ HSEON ą▓ čĆąĄą│ąĖčüčéčĆąĄ RCC_CR. ążčāąĮą║čåąĖčÅ HSE ąĖą╝ąĄąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé ąĮą░ą┤ čäčāąĮą║čåąĖąĄą╣ GPIO.

ąÆčŗą▒ąŠčĆ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ RTC_AF1 ąĖ RTC_AF2. ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ STM32F4xx ąĖą╝ąĄąĄčé ą┤ą▓ą░ ą▓čŗą▓ąŠą┤ą░ GPIO RTC_AF1 ąĖ RTC_AF2, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüąŠą▒čŗčéąĖčÅ ą▓ąĘą╗ąŠą╝ą░/ą▓ą╝ąĄčłą░č鹥ą╗čīčüčéą▓ą░ (tamper event) ąĖą╗ąĖ čüąŠą▒čŗčéąĖčÅ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ (time stamp event), ąĖą╗ąĖ ą║ą░ą║ ą▓čŗčģąŠą┤čŗ RTC_ALARM ąĖą╗ąĖ RTC_CALIB čćą░čüąŠą▓ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (Real Time Clock, RTC).

RTC_AF1 (PC13) ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĖčģ čåąĄą╗ąĄą╣:

ŌĆó ąÆčŗčģąŠą┤ RTC_ALARM: čŹč鹊čé ą▓čŗčģąŠą┤ ą╝ąŠąČąĄčé ą▒čŗčéčī čüąĖą│ąĮą░ą╗ąŠą╝ RTC Alarm A, RTC Alarm B ąĖą╗ąĖ RTC Wakeup, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▒ąĖčé OSEL[1:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ RTC_CR.

ŌĆó ąÆčŗčģąŠą┤ RTC_CALIB: čŹčéą░ čäčāąĮą║čåąĖčÅ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ COE[23] ą▓ čĆąĄą│ąĖčüčéčĆąĄ RTC_CR.

ŌĆó RTC_TAMP1: ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ ą▓ąĘą╗ąŠą╝ą░ (tamper event).

ŌĆó RTC_TS: ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ (time stamp event).

RTC_AF2 (PI8) ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĖčģ čåąĄą╗ąĄą╣:

ŌĆó RTC_TAMP1: ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ ą▓ąĘą╗ąŠą╝ą░.

ŌĆó RTC_TAMP2: ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ ą▓ąĘą╗ąŠą╝ą░.

ŌĆó RTC_TS: ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ.

ąÆčŗą▒ąŠčĆ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ąĮąŠąČą║ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ RTC_TAFCR čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆó TAMP1INSEL ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░, ą║ą░ą║ą░čÅ ąĮąŠąČą║ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤ RTC_TAMP1 tamper.

ŌĆó TSINSEL ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░, ą║ą░ą║ą░čÅ ąĮąŠąČą║ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤ RTC_TS time stamp.

ŌĆó ALARMOUTTYPE ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░, ą║ą░ą║ čĆą░ą▒ąŠčéą░ąĄčé ą▓čŗčģąŠą┤ RTC_ALARM - ą▓ ą┤ą▓čāčģčéą░ą║čéąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (push-pull) ąĖą╗ąĖ ą║ą░ą║ ąŠčéą║čĆčŗčéčŗą╣ čüč鹊ą║ąŠą╝ (open-drain).

ą£ąĄčģą░ąĮąĖąĘą╝ ą▓čŗčģąŠą┤ą░ čüą╗ąĄą┤čāąĄčé ą┐ąŠčĆčÅą┤ą║čā ą┐čĆąĖąŠčĆąĖč鹥čéą░, ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮąŠą╝čā ą▓ čéą░ą▒ą╗ąĖčåą░čģ 37 ąĖ 38.

ąóą░ą▒ą╗ąĖčåą░ 37. ąØąŠąČą║ą░ RTC_AF1(1).

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ

ąĖ čäčāąĮą║čåąĖčÅ ąĮąŠąČą║ąĖ |

RTC_ALARM

čĆą░ąĘčĆąĄčłąĄąĮąŠ |

RTC_CALIB

čĆą░ąĘčĆąĄčłąĄąĮąŠ |

Tamper

čĆą░ąĘčĆąĄčłąĄąĮąŠ |

Time stamp

čĆą░ąĘčĆąĄčłąĄąĮąŠ |

ąÆčŗą▒ąŠčĆ ąĮąŠąČą║ąĖ

TAMP1INSEL

TAMPER1 |

ąÆčŗą▒ąŠčĆ ąĮąŠąČą║ąĖ

TSINSEL

TIMESTAMP |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ

ALARMOUTTYPE

RTC_ALARM |

| ąÆčŗčģąŠą┤ Alarm, OD |

1 |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

0 |

| ąÆčŗčģąŠą┤ Alarm, PP |

1 |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

1 |

| ąÆčŗčģąŠą┤ Calibration, ąŚąŚ |

0 |

1 |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

| ą¤ą╗ą░ą▓ą░čÄčēąĖą╣ ą▓čģąŠą┤ TAMPER1 |

0 |

0 |

1 |

0 |

0 |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

| ą¤ą╗ą░ą▓ą░čÄčēąĖą╣ ą▓čģąŠą┤ TIMESTAMP ąĖ TAMPER1 |

0 |

0 |

1 |

1 |

0 |

0 |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

| ą¤ą╗ą░ą▓ą░čÄčēąĖą╣ ą▓čģąŠą┤ TIMESTAMP |

0 |

0 |

0 |

1 |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

0 |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

| ąĪčéą░ąĮą┤ą░čĆčéąĮčŗą╣ GPIO |

0 |

0 |

0 |

0 |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): OD ąŠąĘąĮą░čćą░ąĄčé open-drain (ąŠčéą║čĆčŗčéčŗą╣ čüč鹊ą║), PP push-pull (ą┤ą▓čāčģčéą░ą║čéąĮčŗą╣ ą┤čĆą░ą╣ą▓ąĄčĆ).

ąóą░ą▒ą╗ąĖčåą░ 38. ąØąŠąČą║ą░ RTC_AF2.

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ

ąĖ čäčāąĮą║čåąĖčÅ ąĮąŠąČą║ąĖ |

Tamper

čĆą░ąĘčĆąĄčłąĄąĮąŠ |

Time stamp

čĆą░ąĘčĆąĄčłąĄąĮąŠ |

ąÆčŗą▒ąŠčĆ ąĮąŠąČą║ąĖ

TAMP1INSEL

TAMPER1 |

ąÆčŗą▒ąŠčĆ ąĮąŠąČą║ąĖ

TSINSEL

TIMESTAMP |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ

ALARMOUTTYPE

RTC_ALARM |

| ą¤ą╗ą░ą▓ą░čÄčēąĖą╣ ą▓čģąŠą┤ TAMPER1 |

1 |

0 |

1 |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

| ą¤ą╗ą░ą▓ą░čÄčēąĖą╣ ą▓čģąŠą┤ TIMESTAMP ąĖ TAMPER1 |

1 |

1 |

1 |

1 |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

| ą¤ą╗ą░ą▓ą░čÄčēąĖą╣ ą▓čģąŠą┤ TIMESTAMP |

0 |

1 |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

1 |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

| ąĪčéą░ąĮą┤ą░čĆčéąĮčŗą╣ GPIO |

0 |

0 |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąØąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

[ąĀąĄą│ąĖčüčéčĆčŗ GPIO]

ąÆ čŹč鹊ą╣ čüąĄą║čåąĖąĖ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ą┐ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ GPIO. ą×ą▒ąĘąŠčĆąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ąĖčģ ą▒ąĖčé, ą▓ą╝ąĄčüč鹥 čü ą░ą┤čĆąĄčüą░ą╝ąĖ čüą╝ąĄčēąĄąĮąĖčÅ ąĖ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ ą▒ąĖčé ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 39.

ąÜ čĆąĄą│ąĖčüčéčĆą░ą╝ GPIO ą╝ąŠąČąĮąŠ ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ą░ą║ ą║ ą▒ą░ą╣čéą░ą╝ (8 ą▒ąĖčé), ą┐ąŠą╗ąŠą▓ąĖąĮą║ą░ą╝ čüą╗ąŠą▓ (16 ą▒ąĖčé) ąĖą╗ąĖ ą┐ąŠą╗ąĮčŗą╝ čüą╗ąŠą▓ą░ą╝ (32 ą▒ąĖčéą░).

ąÆ ąĖą╝ąĄąĮą░čģ čĆąĄą│ąĖčüčéčĆą░ x čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠą┤ąĮąŠą╣ ąĖąĘ ą▒čāą║ą▓ A..I/J/K. ąĪą╝ąĄčēąĄąĮąĖčÅ ą░ą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆą░ čāą║ą░ąĘą░ąĮčŗ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą░ą▒čüąŠą╗čÄčéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░, ąĘą░ą▓ąĖčüčÅčēąĄą│ąŠ ąŠčé ą▒čāą║ą▓čŗ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32F429 čŹčéąĖ ą░ą┤čĆąĄčüą░ čüą╗ąĄą┤čāčÄčēąĖąĄ (ą┤ą░ąĮąĮčŗąĄ ą▓ąĘčÅčéčŗ ąĖąĘ ąĘą░ą│ąŠą╗ąŠą▓ąŠčćąĮąŠą│ąŠ čäą░ą╣ą╗ą░ stm32f429xx.h ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĖ CMSIS):

#define GPIOA_BASE (AHB1PERIPH_BASE + 0x0000UL)

#define GPIOB_BASE (AHB1PERIPH_BASE + 0x0400UL)

#define GPIOC_BASE (AHB1PERIPH_BASE + 0x0800UL)

#define GPIOD_BASE (AHB1PERIPH_BASE + 0x0C00UL)

#define GPIOE_BASE (AHB1PERIPH_BASE + 0x1000UL)

#define GPIOF_BASE (AHB1PERIPH_BASE + 0x1400UL)

#define GPIOG_BASE (AHB1PERIPH_BASE + 0x1800UL)

#define GPIOH_BASE (AHB1PERIPH_BASE + 0x1C00UL)

#define GPIOI_BASE (AHB1PERIPH_BASE + 0x2000UL)

#define GPIOJ_BASE (AHB1PERIPH_BASE + 0x2400UL)

#define GPIOK_BASE (AHB1PERIPH_BASE + 0x2800UL)

ąŚą┤ąĄčüčī ą║ąŠąĮčüčéą░ąĮčéą░ AHB1PERIPH_BASE čĆą░ą▓ąĮą░ ą░ą┤čĆąĄčüčā (PERIPH_BASE + 0x00020000UL), ąĖą╗ąĖ 0x40020000.

ąÆ ąŠą┐ąĖčüą░ąĮąĖąĖ čäčāąĮą║čåąĖą╣ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ čüąŠą║čĆą░čēąĄąĮąĖčÅ:

read/write (rw) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé čćąĖčéą░čéčī ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī čŹčéąĖ ą▒ąĖčéčŗ.

read-only (r) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé č鹊ą╗čīą║ąŠ čćąĖčéą░čéčī čŹčéąĖ ą▒ąĖčéčŗ.

write-only (w) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą▓ čŹč鹊čé ą▒ąĖčé. ą¦č鹥ąĮąĖąĄ ą▒ąĖčéą░ ą▓ąĄčĆąĮąĄčé ąĘąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░.

Reserved (Res.) ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▒ąĖčé, ąĄą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ąĮą░ ąĘąĮą░č湥ąĮąĖąĖ čüą▒čĆąŠčüą░.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x00

ąŚąĮą░č湥ąĮąĖčÅ čüą▒čĆąŠčüą░:

ŌĆó 0xA8000000 ą┤ą╗čÅ ą┐ąŠčĆčéą░ A

ŌĆó 0x00000280 ą┤ą╗čÅ ą┐ąŠčĆčéą░ B

ŌĆó 0x00000000 ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ ą┐ąŠčĆč鹊ą▓

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

MODER15[1:0]

rw

|

MODER14[1:0]

rw

|

MODER13[1:0]

rw

|

MODER12[1:0]

rw

|

MODER11[1:0]

rw |

MODER10[1:0]

rw |

MODER9[1:0]

rw |

MODER8[1:0]

rw |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

MODER7[1:0]

rw

|

MODER6[1:0]

rw |

MODER5[1:0]

rw |

MODER4[1:0]

rw |

MODER3[1:0]

rw

|

MODER2[1:0]

rw

|

MODER1[1:0]

rw

|

MODER0[1:0]

rw

|

MODERy[1:0]: ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▒ąĖčé ą┐ąŠčĆčéą░ x (y = 0..15). ąŁčéąĖ ą▒ąĖčéčŗ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ I/O.

00: ą▓čģąŠą┤ (ąŠą▒čŗčćąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ)

01: čĆąĄąČąĖą╝ ą▓čŗą▓ąŠą┤ą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ

10: čĆąĄąČąĖą╝ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ

11: ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čĆąĄąČąĖą╝

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x04

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

OT15

rw

|

OT14

rw |

OT13

rw |

OT12

rw |

OT11

rw |

OT10

rw |

OT9

rw |

OT8

rw |

OT7

rw

|

OT6

rw |

OT5

rw

|

OT4

rw |

OT3

rw

|

OT2

rw |

OT1

rw

|

OT0

rw |

ąæąĖčéčŗ 31:16 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

OTy (ą▒ąĖčéčŗ 15:0): ą▒ąĖčéčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░ x (y = 0..15). ąŁčéąĖ ą▒ąĖčéčŗ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī čéąĖą┐ ą▓čŗčģąŠą┤ą░ ą┐ąŠčĆčéą░ I/O.

0: ą┤ą▓čāčģčéą░ą║čéąĮčŗą╣ ą▓čŗčģąŠą┤, push-pull (čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░)

1: ą▓čŗčģąŠą┤ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝, open-drain

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x08

ąŚąĮą░č湥ąĮąĖčÅ čüą▒čĆąŠčüą░:

ŌĆó 0x0C000000 ą┤ą╗čÅ ą┐ąŠčĆčéą░ A

ŌĆó 0x000000C0 ą┤ą╗čÅ ą┐ąŠčĆčéą░ B

ŌĆó 0x00000000 ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ ą┐ąŠčĆč鹊ą▓

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

OSPEEDR15[1:0]

rw

|

OSPEEDR14[1:0]

rw

|

OSPEEDR13[1:0]

rw

|

OSPEEDR12[1:0]

rw

|

OSPEED11[1:0]

rw |

OSPEED10[1:0]

rw |

OSPEED9[1:0]

rw |

OSPEED8[1:0]

rw |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

OSPEED7[1:0]

rw

|

OSPEED6[1:0]

rw |

OSPEED5[1:0]

rw |

OSPEED4[1:0]

rw |

OSPEED3[1:0]

rw

|

OSPEED2[1:0]

rw

|

OSPEED1[1:0]

rw

|

OSPEED0[1:0]

rw

|

OSPEEDRy[1:0]: ą▒ąĖčéčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░ x (y = 0..15). ąŁčéąĖ ą▒ąĖčéčŗ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▓čŗčģąŠą┤ą░.

00: ąĮąĖąĘą║ą░čÅ čüą║ąŠčĆąŠčüčéčī

01: čüčĆąĄą┤ąĮčÅčÅ čüą║ąŠčĆąŠčüčéčī

10: ą▓čŗčüąŠą║ą░čÅ čüą║ąŠčĆąŠčüčéčī

11: ąŠč湥ąĮčī ą▓čŗčüąŠą║ą░čÅ čüą║ąŠčĆąŠčüčéčī

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčé OSPEEDRy ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ VDD ąĖ ą▓ąĮąĄčłąĮąĄą╣ ąĮą░ą│čĆčāąĘą║ąĖ.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x0C

ąŚąĮą░č湥ąĮąĖčÅ čüą▒čĆąŠčüą░:

ŌĆó 0x64000000 ą┤ą╗čÅ ą┐ąŠčĆčéą░ A

ŌĆó 0x00000100 ą┤ą╗čÅ ą┐ąŠčĆčéą░ B

ŌĆó 0x00000000 ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ ą┐ąŠčĆč鹊ą▓

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

PUPDR15[1:0]

rw

|

PUPDR14 [1:0]

rw

|

PUPDR13 [1:0]

rw

|

PUPDR12 [1:0]

rw

|

PUPDR11[1:0]

rw |

PUPDR10[1:0]

rw |

PUPDR9[1:0]

rw |

PUPDR8[1:0]

rw |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

PUPDR7[1:0]

rw

|

PUPDR6[1:0]

rw |

PUPDR5[1:0]

rw |

PUPDR4[1:0]

rw |

PUPDR3[1:0]

rw

|

PUPDR2[1:0]

rw

|

PUPDR1[1:0]

rw

|

PUPDR0[1:0]

rw

|

PUPDRy[1:0]: ą▒ąĖčéčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░ x (y = 0..15). ąŁčéąĖ ą▒ąĖčéčŗ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą▓ąĄčĆčģąĮąĖąĄ (pull-up) ąĖą╗ąĖ ąĮąĖąČąĮąĖąĄ (pull-down) ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ.

00: ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ ąŠčéą║ą╗čÄč湥ąĮčŗ

01: pull-up

10: pull-down

11: ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x10

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x0000XXXX (ąĘą┤ąĄčüčī X ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĘąĮą░č湥ąĮąĖąĄ ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ)

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

IDR15

r

|

IDR14

r |

IDR13

r |

IDR12

r |

IDR11

r |

IDR10

r |

IDR9

r |

IDR8

r |

IDR7

r

|

IDR6

r |

IDR5

r

|

IDR4

r |

IDR3

r

|

IDR2

r |

IDR1

r

|

IDR0

r

|

ąæąĖčéčŗ 31:16 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

IDRy (ą▒ąĖčéčŗ 15:0): ą▓čģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčĆčéą░ (y = 0..15). ąŁčéąĖ ą▒ąĖčéčŗ čĆą░ą▒ąŠčéą░čÄčé č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ, ąĖ ą║ ąĮąĖą╝ ą╝ąŠąČąĮąŠ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą║ą░ą║ ą║ čüą╗ąŠą▓čā (32 ą▒ąĖčéą░). ą¤čĆąŠčćąĖčéą░ąĮąĮąŠąĄ čüą╗ąŠą▓ąŠ čüąŠą┤ąĄčƹȹĖčé ą▓čģąŠą┤ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą┐ąŠčĆčéą░ I/O.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x14

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ODR15

rw

|

ODR14

rw |

ODR13

rw |

ODR12

rw |

ODR11

rw |

ODR10

rw |

ODR9

rw |

ODR8

rw |

ODR7

rw

|

ODR6

rw |

ODR5

rw

|

ODR4

rw |

ODR3

rw

|

ODR2

rw |

ODR1

rw

|

ODR0

rw

|

ąæąĖčéčŗ 31:16 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

ODRy (ą▒ąĖčéčŗ 15:0): ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčĆčéą░ (y = 0..15). ąŁčéąĖ ą▒ąĖčéčŗ ą╝ąŠąČąĮąŠ čüčćąĖčéčŗą▓ą░čéčī ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ą╗čÅ ą░č鹊ą╝ą░čĆąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ąĖ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčé ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čĆąĄą│ąĖčüčéčĆ GPIOx_BSRR (x = A..I/J/K).

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x18

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

BR15

w |

BR14

w |

BR13

w |

BR12

w |

BR11

w |

BR10

w |

BR9

w |

BR8

w |

BR7

w |

BR6

w |

BR5

w |

BR4

w |

BR3

w |

BR2

w |

BR1

w |

BR0

w |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

BS15

w

|

BS14

w |

BS13

w |

BS12

w |

BS11

w |

BS10

w |

BS9

w |

BS8

w |

BS7

w

|

BS6

w |

BS5

w

|

BS4

w |

BS3

w

|

BS2

w |

BS1

w

|

BS0

w

|

BRy (ą▒ąĖčéčŗ 31:16): ą▒ąĖčéčŗ ą┤ą╗čÅ čüą▒čĆąŠčüą░ čĆą░ąĘčĆčÅą┤ąŠą▓ y ą┐ąŠčĆčéą░ x (y = 0..15). ąŁčéąĖ ą▒ąĖčéčŗ čĆą░ą▒ąŠčéą░čÄčé č鹊ą╗čīą║ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī, ąĖ ą║ ąĮąĖą╝ ą╝ąŠąČąĮąŠ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą┤ąŠčüčéčāą┐ ą║ą░ą║ ą║ ą┐ąŠą╗ąĮąŠą╝čā čüą╗ąŠą▓čā (32 ą▒ąĖčéą░), ą┐ąŠą╗ąŠą▓ąĖąĮąĄ čüą╗ąŠą▓ą░ (16 ą▒ąĖčé) ąĖą╗ąĖ ą▒ą░ą╣čéčā (8 ą▒ąĖčé). ą¦č鹥ąĮąĖąĄ čŹčéąĖčģ ą▒ąĖčé ą▓ąŠąĘą▓čĆą░čéąĖčé ąĘąĮą░č湥ąĮąĖąĄ 0x0000.

0: ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ODRx

1: čüą▒čĆąŠčüąĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ODRx

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą▓ ąŠą┤ąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą║ąŠąĮą║čāčĆąĖčĆčāčÄčēąĖąĄ ą▒ąĖčéčŗ BSx ąĖ BRx, č鹊 ą▒ąĖčé BSx ąĖą╝ąĄąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé.

BSy (ą▒ąĖčéčŗ 15:0): ą▒ąĖčéčŗ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čĆą░ąĘčĆčÅą┤ąŠą▓ y ą┐ąŠčĆčéą░ x (y = 0..15). ąŁčéąĖ ą▒ąĖčéčŗ čĆą░ą▒ąŠčéą░čÄčé č鹊ą╗čīą║ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī, ąĖ ą║ ąĮąĖą╝ ą╝ąŠąČąĮąŠ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą┤ąŠčüčéčāą┐ ą║ą░ą║ ą║ ą┐ąŠą╗ąĮąŠą╝čā čüą╗ąŠą▓čā (32 ą▒ąĖčéą░), ą┐ąŠą╗ąŠą▓ąĖąĮąĄ čüą╗ąŠą▓ą░ (16 ą▒ąĖčé) ąĖą╗ąĖ ą▒ą░ą╣čéčā (8 ą▒ąĖčé). ą¦č鹥ąĮąĖąĄ čŹčéąĖčģ ą▒ąĖčé ą▓ąŠąĘą▓čĆą░čéąĖčé ąĘąĮą░č湥ąĮąĖąĄ 0x0000.

0: ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ODRx

1: čāčüčéą░ąĮąŠą▓ąĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ODRx

ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▒ąĖčé ą┐ąŠčĆčéą░, ą║ąŠą│ą┤ą░ ą┐čĆąĖą╝ąĄąĮąĄąĮą░ ą║ąŠčĆčĆąĄą║čéąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą┐ąĖčüąĖ ą║ ą▒ąĖčéčā 16 (LCKK). ąŚąĮą░č湥ąĮąĖąĄ ą▒ąĖčé [15:0] ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ GPIO. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ ąĘąĮą░č湥ąĮąĖąĄ LCKR[15:0] ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą╝ąĄąĮčÅčéčīčüčÅ. ąÜąŠą│ą┤ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (LOCK sequence) ą▒čŗą╗ą░ ą┐čĆąĖą╝ąĄąĮąĄąĮą░ ą║ ą▒ąĖčéčā ą┐ąŠčĆčéą░, ąĘąĮą░č湥ąĮąĖąĄ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ą▒ąŠą╗čīčłąĄ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮąŠ, ą┐ąŠą║ą░ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé čüą╗ąĄą┤čāčÄčēąĖą╣ čüą▒čĆąŠčü MCU ąĖą╗ąĖ ą┐ąĄčĆąĖč乥čĆąĖąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ GPIOx_LCKR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą┐ąĖčüąĖ. ąÆąŠ ą▓čĆąĄą╝čÅ čŹč鹊ą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą║ čĆąĄąČąĖą╝ąĄ ą┐ąŠą╗ąĮąŠą│ąŠ čüą╗ąŠą▓ą░ (32 ą▒ąĖčéą░).

ąÜą░ąČą┤ą░čÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ą░ ą▒ąĖčéą░ ąĘą░ą╝ąŠčĆą░ąČąĖą▓ą░ąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ (čĆąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ).

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x1C

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

LCKK

rw |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

LCK15

rw

|

LCK14

rw |

LCK13

rw |

LCK12

rw |

LCK11

rw |

LCK10

rw |

LCK9

rw |

LCK8

rw |

LCK7

rw

|

LCK6

rw |

LCK5

rw

|

LCK4

rw |

LCK3

rw

|

LCK2

rw |

LCK1

rw

|

LCK0

rw

|

ąÆąŠąĘą╝ąŠąČąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī, ąĮąŠ č鹊ą╗čīą║ąŠ 32-ą▒ąĖčéąĮčŗą╣.

ąæąĖčéčŗ 31:17 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

LCKK (ą▒ąĖčé 16): LoCK Key, ą║ą╗čÄčć ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ. ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ. ąśąĘą╝ąĄąĮąĄąĮ ąŠąĮ ą╝ąŠąČąĄčé ą▒čŗčéčī č鹊ą╗čīą║ąŠ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (lock key write sequence).

0: ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░ ąĮąĄ ą░ą║čéąĖą▓ąĮą░

1: ą░ą║čéąĖą▓ąĮą░ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░. ąĀąĄą│ąĖčüčéčĆ GPIOx_LCKR ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé čüą▒čĆąŠčü MCU ąĖą╗ąĖ čüą▒čĆąŠčü ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

LOCK key write sequence:

WR LCKR[16] = ŌĆś1ŌĆÖ + LCKR[15:0]

WR LCKR[16] = ŌĆś0ŌĆÖ + LCKR[15:0]

WR LCKR[16] = ŌĆś1ŌĆÖ + LCKR[15:0]

RD LCKR

RD LCKR[16] = ŌĆś1ŌĆÖ (čŹčéą░ ąŠą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮą░, ąŠą┤ąĮą░ą║ąŠ ąŠąĮą░ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčé, čćč鹊 ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ą░ ą░ą║čéąĖą▓ąĮą░).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą┐ąĄčĆą░čåąĖąĖ LOCK key write sequence, ąĘąĮą░č湥ąĮąĖąĄ LCK[15:0] ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ąĖąĘą╝ąĄąĮčÅčéčīčüčÅ. ąøčÄą▒ą░čÅ ąŠčłąĖą▒ą║ą░ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ ąŠą▒ąŠčĆą▓ąĄčé (ąŠčéą╝ąĄąĮąĖčé) čāčüčéą░ąĮąŠą▓ą║čā ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą┐ąĄčĆą▓ą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą╗čÄą▒ąŠą│ąŠ ą▒ąĖčéą░ ą┐ąŠčĆčéą░ ą╗čÄą▒ąŠą╣ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ą▒ąĖčéą░ LCKK ą▓čüąĄą│ą┤ą░ ą▓ąŠąĘą▓čĆą░čéąĖčé 1, ą┐ąŠą║ą░ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé čüą╗ąĄą┤čāčÄčēąĖą╣ čüą▒čĆąŠčü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

LCKy (ą▒ąĖčéčŗ 15:0): ą▒ą╗ąŠą║ąĖčĆčāąĄą╝čŗą╣ ą▒ąĖčé y ą┐ąŠčĆčéą░ x (y= 0..15). ąŁčéąĖ ą▒ąĖčéčŗ ą╝ąŠąČąĮąŠ čćąĖčéą░čéčī ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī, ąŠą┤ąĮą░ą║ąŠ ąŠąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą▒ąĖčé LCKK ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0.

0: ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ąŠčĆčéą░ ąĮąĄ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮą░

1: ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ąŠčĆčéą░ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮą░

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x20

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

AFRL7[3:0]

rw

|

AFRL6[3:0]

rw |

AFRL5[3:0]

rw |

AFRL4[3:0]

rw |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

AFRL3[3:0]

rw |

AFRL2[3:0]

rw |

AFRL1[3:0]

rw |

AFRL0[3:0]

rw

|

AFRLy (ą▒ąĖčéčŗ 31:0): ą▓čŗą▒ąŠčĆ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ ą┤ą╗čÅ ą▒ąĖčéą░ y ą┐ąŠčĆčéą░ x (y = 0..7). ąŁčéąĖ ą▒ąĖčéčŗ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ą░, čćč鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčāčÄ čäčāąĮą║čåąĖčÄ I/O.

ąæąĖčéčŗ AFRLy ą▓čŗą▒ąĖčĆą░čÄčé:

0000: AF0 1000: AF8

0001: AF1 1001: AF9

0010: AF2 1010: AF10

0011: AF3 1011: AF11

0100: AF4 1100: AF12

0101: AF5 1101: AF13

0110: AF6 1110: AF14

0111: AF7 1111: AF15

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x24

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

AFRH15[3:0]

rw

|

AFRH14[3:0]

rw |

AFRH13[3:0]

rw |

AFRH12[3:0]

rw |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

AFRH11[3:0]

rw |

AFRH10[3:0]

rw |

AFRH9[3:0]

rw |

AFRH8[3:0]

rw

|

AFRHy (ą▒ąĖčéčŗ 31:0): ą▓čŗą▒ąŠčĆ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĖ ą┤ą╗čÅ ą▒ąĖčéą░ y ą┐ąŠčĆčéą░ x (y = 8..15). ąŁčéąĖ ą▒ąĖčéčŗ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ą░, čćč鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčāčÄ čäčāąĮą║čåąĖčÄ I/O.

ąæąĖčéčŗ AFRLy ą▓čŗą▒ąĖčĆą░čÄčé:

0000: AF0 1000: AF8

0001: AF1 1001: AF9

0010: AF2 1010: AF10

0011: AF3 1011: AF11

0100: AF4 1100: AF12

0101: AF5 1101: AF13

0110: AF6 1110: AF14

0111: AF7 1111: AF15

[ąóą░ą▒ą╗ąĖčåčŗ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ ą┐ąŠčĆč鹊ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32F427xx, STM32F429xx]

ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░) ą▓čüąĄ ąĮąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ GPIOx ąĮą░čüčéčĆąŠąĄąĮčŗ ąĮą░ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčāčÄ čäčāąĮą║čåąĖčÄ AF0. ąóą░ą▒ą╗ąĖčåčā ą▓čüąĄčģ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ, ąŠąĮą░ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ Alternate function mapping.

ąÆąĮąĖą╝ą░ąĮąĖąĄ: čā ąĮąĄą║ąŠč鹊čĆčŗčģ ąĮąŠąČąĄą║ ą┐ąŠčĆč鹊ą▓ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čäčāąĮą║čåąĖąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ čäčāąĮą║čåąĖąĖ ąÉą”ą¤, ą”ąÉą¤, ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ (čüą╝. čüč鹊ą╗ą▒ąĄčå Analog). ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĮąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ PA4 ąĖ PA5 ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32F4xx ą▓čŗą┐ąŠą╗ąĮčÅčÄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čäčāąĮą║čåąĖąĖ ą▓čŗčģąŠą┤ąŠą▓ ą”ąÉą¤ (DAC_OUT1 ąĖ DAC_OUT2).

| ą¤ąŠčĆčé |

AF0 |

AF1 |

AF2 |

AF3 |

AF4 |

AF5 |

AF6 |

AF7 |

| SYS |

TIM1/2 |

TIM3..5 |

TIM8..11 |

I2C3 |

SPI1 |

SPI3/SAI1 |

USART1..2 |

| PA0 |

|

TIM2_CH1/

TIM2_ETR |

TIM5_CH1 |

TIM8_ETR |

|

|

|

USART2_CTS |

| PA1 |

|

TIM2_CH2 |

TIM5_CH2 |

|

|

|

|

USART2_RTS |

| PA2 |

|

TIM2_CH3 |

TIM5_CH3 |

TIM9_CH1 |

|

|

|

USART2_TX |

| PA3 |

|

TIM2_CH4 |

TIM5_CH4 |

TIM9_CH2 |

|

|

|

USART2_RX |

| PA4 |

|

|

|

|

|

SPI1_NSS |

SPI3_NSS/

I2S3_WS |

USART2_CK |

| PA5 |

|

TIM2_CH1/

TIM2_ETR |

|

TIM8_CH1N |

|

SPI1_SCK |

|

|

| PA6 |

|

TIM1_BKIN |

TIM3_CH1 |

TIM8_BKIN |

|

SPI1_MISO |

|

|

| PA7 |

|

TIM1_CH1N |

TIM3_CH2 |

TIM8_CH1N |

|

SPI1_MOSI |

|

|

| PA8 |

MCO1 |

TIM1_CH1 |

|

|

I2C3_SCL |

|

|

USART1_CK |

| PA9 |

|

TIM1_CH2 |

|

|

I2C3_SMBA |

|

|

USART1_TX |

| PA10 |

|

TIM1_CH3 |

|

|

|

|

|

USART1_RX |

| PA11 |

|

TIM1_CH4 |

|

|

|

|

|

USART1_CTS |

| PA12 |

|

TIM1_ETR |

|

|

|

|

|

USART1_RTS |

| PA13 |

JTMS-SWDIO |

|

|

|

|

|

|

|

| PA14 |

JTCK-SWCLK |

|

|

|

|

|

|

|

| PA15 |

JTDI |

TIM2_CH1/

TIM2_ETR |

|

|

|

SPI1_NSS |

SPI3_NSS/

I2S3_WS |

|

| ą¤ąŠčĆčé |

AF8 |

AF9 |

AF10 |

AF11 |

AF12 |

AF13 |

AF14 |

AF15 |

Analog |

| UART4 |

CAN1

TIM13..14 |

OTG_FS/

OTG_HS |

ETH |

OTG_HS |

DCMI |

LCD |

SYS |

| PA0 |

UART4_TX |

|

|

ETH_MII_CRS |

|

|

|

EVENTOUT |

ADC123_IN0

WKUP(1) |

| PA1 |

UART4_RX |

|

|

ETH_MII_RX_CLK

ETH_RMII_REF_CLK |

|

|

|

EVENTOUT |

ADC123_IN1 |

| PA2 |

|

|

|

ETH_MDIO |

|

|

|

EVENTOUT |

ADC123_IN2 |

| PA3 |

|

|

OTG_HS_ULPI_D0 |

ETH _MII_COL |

|

|

LCD_B5 |

EVENTOUT |

ADC123_IN3 |

| PA4 |

|

|

|

|

OTG_HS_SOF |

DCMI_HSYNC |

LCD_VSYNC |

EVENTOUT |

ADC12_IN4

DAC_OUT1 |

| PA5 |

|

|

OTG_HS_ULPI_CK |

|

|

|

|

EVENTOUT |

ADC12_IN5

DAC_OUT2 |

| PA6 |

|

TIM13_CH1 |

|

|

|

DCMI_PIXCK |

LCD_G2 |

EVENTOUT |

ADC12_IN6 |

| PA7 |

|

TIM14_CH1 |

|

ETH_MII_RX_DV

ETH_RMII_CRS_DV |

|

|

|

EVENTOUT |

ADC12_IN7 |

| PA8 |

|

|

OTG_FS_SOF |

|

|

|

LCD_R6 |

EVENTOUT |

|

| PA9 |

|

|

|

|

|

DCMI_D0 |

|

EVENTOUT |

|

| PA10 |

|

|

OTG_FS_ID |

|

|

DCMI_D1 |

|

EVENTOUT |

|

| PA11 |

|

CAN1_RX |

OTG_FS_DM |

|

|

|

LCD_R4 |

EVENTOUT |

|

| PA12 |

|

CAN1_TX |

OTG_FS_DP |

|

|

|

LCD_R5 |

EVENTOUT |

|

| PA13 |

|

|

|

|

|

|

|

EVENTOUT |

|

| PA14 |

|

|

|

|

|

|

|

EVENTOUT |

|

| PA15 |

|

|

|

|

|

|

|

EVENTOUT |

|

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): FT = 5V tolerant (ą▓čģąŠą┤čŗ ą┤ąŠą┐čāčüą║ą░čÄčé čāčĆąŠą▓ąĄąĮčī 5V), ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čüą╗čāčćą░čÅ, ą║ąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĄąĮ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čĆąĄąČąĖą╝ ąĖą╗ąĖ čĆąĄąČąĖą╝ ą│ąĄąĮąĄčĆą░č鹊čĆą░ (ą┤ą╗čÅ PC14, PC15, PH0 ąĖ PH1).

| ą¤ąŠčĆčé |

AF0 |

AF1 |

AF2 |

AF3 |

AF4 |

AF5 |

AF6 |

AF7 |

| SYS |

TIM1/2 |

TIM3..4 |

TIM8/TIM10/TIM11 |

I2C1..2 |

SPI1/SPI2/

I2S2 |

SPI3/I2Sext/

I2S3 |

USART1/USART3/

I2S3ext |

| PB0 |

|

TIM1_CH2N |

TIM3_CH3 |

TIM8_CH2N |

|

|

|

|

| PB1 |

|

TIM1_CH3N |

TIM3_CH4 |

TIM8_CH3N |

|

|

|

|

| PB2 |

BOOT1 |

|

|

|

|

|

|

|

| PB3 |

JTDO/

TRACESWO |

TIM2_CH2 |

|

|

|

SPI1_SCK |

SPI3_SCK

I2S3_CK |

|

| PB4 |

NJTRST |

|

TIM3_CH1 |

|

|

SPI1_MISO |

SPI3_MISO |

I2S3ext_SD |

| PB5 |

|

|

TIM3_CH2 |

|

I2C1_SMBA |

SPI1_MOSI |

SPI3_MOSI

I2S3_SD |

|

| PB6 |

|

|

TIM4_CH1 |

|

I2C1_SCL |

|

|

USART1_TX |

| PB7 |

|

|

TIM4_CH2 |

|

I2C1_SDA |

|

|

USART1_RX |

| PB8 |

|

|

TIM4_CH3 |

TIM10_CH1 |

I2C1_SCL |

|

|

|

| PB9 |

|

|

TIM4_CH4 |

TIM11_CH1 |

I2C1_SDA |

SPI2_NSS

I2S2_WS |

|

|

| PB10 |

|

TIM2_CH3 |

|

|

I2C2_SCL |

SPI2_SCK

I2S2_CK |

|

USART3_TX |

| PB11 |

|

TIM2_CH4 |

|

|

I2C2_SDA |

|

|

USART3_RX |

| PB12 |

|

TIM1_BKIN |

|

|

I2C2_SMBA |

SPI2_NSS

I2S2_WS |

|

USART3_CK |

| PB13 |

|

TIM1_CH1N |

|

|

|

SPI2_SCK

I2S2_CK |

|

USART3_CTS |

| PB14 |

|

TIM1_CH2N |

|

TIM8_CH2N |

|

SPI2_MISO |

I2S2ext_SD |

USART3_RTS |

| PB15 |

RTC_REFIN |

TIM1_CH3N |

|

TIM8_CH3N |

|

SPI2_MOSI

I2S2_SD |

|

|

| ą¤ąŠčĆčé |

AF8 |

AF9 |

AF10 |

AF11 |

AF12 |

AF13 |

AF14 |

AF15 |

Analog |

| - |

CAN1/CAN2/

TIM12/LCD |

OTG_HS |

ETH |

FMC/FSMC/

SDIO/OTG_HS |

DCMI |

LCD |

SYS |

| PB0 |

|

LCD_R3 |

OTG_HS_ULPI_D1 |

ETH_MII_RXD2 |

|

|

|

EVENTOUT |

ADC12_IN8 |

| PB1 |

|

LCD_R6 |

OTG_HS_ULPI_D2 |

ETH_MII_RXD3 |

|

|

|

EVENTOUT |

ADC12_IN9 |

| PB2 |

|

|

|

|

|

|

|

EVENTOUT |

|

| PB3 |

|

|

|

|

|

|

|

EVENTOUT |

|

| PB4 |

|

|

|

|

|

|

|

EVENTOUT |

|

| PB5 |

|

CAN2_RX |

OTG_HS_ULPI_D7 |

ETH_PPS_OUT |

FMC_SDCKE1 |

DCMI_D10 |

|

EVENTOUT |

|

| PB6 |

|

CAN2_TX |

|

|

FMC_SDNE1 |

DCMI_D5 |

|

EVENTOUT |

|

| PB7 |

|

|

|

|

FSMC_NL |

DCMI_VSYNC |

|

EVENTOUT |

|

| PB8 |

|

CAN1_RX |

|

ETH_MII_TXD3 |

SDIO_D4 |

DCMI_D6 |

LCD_B6 |

EVENTOUT |

|

| PB9 |

|

CAN1_TX |

|

|

SDIO_D5 |

DCMI_D7 |

LCD_B7 |

EVENTOUT |

|

| PB10 |

|

|

OTG_HS_ULPI_D3 |

ETH_MII_RX_ER |

|

|

LCD_G4 |

EVENTOUT |

|

| PB11 |

|

|

OTG_HS_ULPI_D4 |

ETH_MII_TX_EN

ETH_RMII_TX_EN |

|

|

LCD_G5 |

EVENTOUT |

|

| PB12 |

|

CAN2_RX |

OTG_HS_ULPI_D5 |

ETH_MII_TXD0

ETH_RMII_TXD0 |

OTG_HS_ID |

|

|

EVENTOUT |

|

| PB13 |

|

CAN2_TX |

OTG_HS_ULPI_D6 |

ETH_MII_TXD1

ETH_RMII_TXD1 |

|

|

|

EVENTOUT |

|

| PB14 |

|

TIM12_CH1 |

|

|

OTG_HS_DM |

|

|

EVENTOUT |

|

| PB15 |

|

TIM12_CH2 |

|

|

OTG_HS_DP |

|

|

EVENTOUT |

|

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĮąŠąČą║ą░ ą║ąŠčĆą┐čāčüą░ ą┐ąŠčĆčéą░ PB2 čüąŠą▓ą╝ąĄčēąĄąĮą░ čü čäčāąĮą║čåąĖąĄą╣ BOOT1, ą▓čŗą▒ąĖčĆą░čÄčēąĄą╣ ą▓ą╝ąĄčüč鹥 čü čäčāąĮą║čåąĖąĄą╣ ą▓čŗą▓ąŠą┤ą░ BOOT0 čĆąĄąČąĖą╝ ąĘą░ą│čĆčāąĘą║ąĖ. ąŻčĆąŠą▓ąĄąĮčī ąĮą░ BOOT1 ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖąĄ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ąĮą░ BOOT0 čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1.

| ą¤ąŠčĆčé |

AF0 |

AF1

|

AF2 |

AF3 |

AF4 |

AF5 |

AF6 |

AF7 |

| SYS |

TIM3 |

TIM8 |

I2C3 |

SPI2/I2S/

I2S2/I2S3ext |

SPI3/I2Sext/

I2S3 |

USART3 |

| PC0 |

|

|

|

|

|

|

|

|

| PC1 |

|

|

|

|

|

|

|

|

| PC2 |

|

|

|

|

|

SPI2_MISO |

I2S2ext_SD |

|

| PC3 |

|

|

|

|

|

SPI2_MOSI

I2S2_SD |

|

|

| PC4 |

|

|

|

|

|

|

|

|

| PC5 |

|

|

|

|

|

|

|

|

| PC6 |

|

|

TIM3_CH1 |

TIM8_CH1 |

|

I2S2_MCK |

|

|

| PC7 |

|

|

TIM3_CH2 |

TIM8_CH2 |

|

|

I2S3_MCK |

|

| PC8 |

|

|

TIM3_CH3 |

TIM8_CH3 |

|

|

|

|

| PC9 |

MCO2 |

|

TIM3_CH4 |

TIM8_CH4 |

I2C3_SDA |

I2S_CKIN |

|

|

| PC10 |

|

|

|

|

|

|

SPI3_SCK

I2S3_CK |

USART3_TX |

| PC11 |

|

|

|

|

|

I2S3ext_SD |

SPI3_MISO |

USART3_RX |

| PC12 |

|

|

|

|

|

|

SPI3_MOSI

I2S3_SD |

USART3_CK |

| PC13 |

|

|

|

|

|

|

|

|

| PC14 |

|

|

|

|

|

|

|

|

| PC15 |

|

|

|

|

|

|

|

|

| ą¤ąŠčĆčé |

AF8 |

AF9

|

AF10 |

AF11 |

AF12 |

AF13 |

AF14 |

AF15 |

Analog |

UART4/5/

USART6 |

OTG_HS |

ETH |

FMC/SDIO |

DCMI |

LCD |

SYS |

| PC0 |

|

|

OTG_HS_ULPI_STP |

|

FMC_SDNWE |

|

|

EVENTOUT |

ADC123_IN10 |

| PC1 |

|

|

|

ETH_MDC |

|

|

|

EVENTOUT |

ADC123_IN11 |

| PC2 |

|

|

OTG_HS_ULPI_DIR |

ETH_MII_TXD2 |

FMC_SDNE0 |

|

|

EVENTOUT |

ADC123_IN12 |

| PC3 |

|

|

OTG_HS_ULPI_NXT |

ETH_MII_TX_CLK |

FMC_SDCKE0 |

|

|

EVENTOUT |

ADC123_IN13 |

| PC4 |

|

|

|

ETH_MII_RXD0

ETH_RMII_RXD0 |

|

|

|

EVENTOUT |

ADC12_IN14 |

| PC5 |

|

|

|

ETH_MII_RXD1

ETH_RMII_RXD1 |

|

|

|

EVENTOUT |

ADC12_IN15 |

| PC6 |

USART6_TX |

|

|

|

SDIO_D6 |

DCMI_D0 |

LCD_HSYNC |

EVENTOUT |

|

| PC7 |

USART6_RX |

|

|

|

SDIO_D7 |

DCMI_D1 |

LCD_G6 |

EVENTOUT |

|

| PC8 |

USART6_CK |

|

|

|

SDIO_D0 |

DCMI_D2 |

|

EVENTOUT |

|

| PC9 |

|

|

|

|

SDIO_D1 |

DCMI_D3 |

|

EVENTOUT |

|

| PC10 |

UART4_TX |

|

|

|

SDIO_D2 |

DCMI_D8 |

LCD_R2 |

EVENTOUT |

|

| PC11 |

UART4_RX |

|

|

|

SDIO_D3 |

DCMI_D4 |

|

EVENTOUT |

|

| PC12 |

UART5_TX |

|

|

|

SDIO_CK |

DCMI_D9 |

|

EVENTOUT |

|

| PC13 |

|

|

|

|

|

|

|

EVENTOUT |

|

| PC14 |

|

|

|

|

|

|

|

EVENTOUT |

|

| PC15 |

|

|

|

|

|

|

|

EVENTOUT |

|

| ą¤ąŠčĆčé |

AF0

|

AF1

|

AF2 |

AF3

|

AF4

|

AF5 |

AF6 |

AF7 |

| TIM3/TIM4 |

SPI2/SPI3 |

SAI1 |

USART2/USART3 |

| PD0 |

|

|

|

|

|

|

|

|

| PD1 |

|

|

|

|

|

|

|

|

| PD2 |

|

|

TIM3_ETR |

|

|

|

|

|

| PD3 |

|

|

|

|

|

SPI2_SCK

I2S2_CK |

|

USART2_CTS |

| PD4 |

|

|

|

|

|

|

|

USART2_RTS |

| PD5 |

|

|

|

|

|

|

|

USART2_TX |

| PD6 |

|

|

|

|

|

SPI3_MOSI

I2S3_SD |

SAI1_SD_A |

USART2_RX |

| PD7 |

|

|

|

|

|

|

|

USART2_CK |

| PD8 |

|

|

|

|

|

|

|

USART3_TX |

| PD9 |

|

|

|

|

|

|

|

USART3_RX |

| PD10 |

|

|

|

|

|

|

|

USART3_CK |

| PD11 |

|

|

|

|

|

|

|

USART3_CTS |

| PD12 |

|

|

TIM4_CH1 |

|

|

|

|

USART3_RTS |

| PD13 |

|

|

TIM4_CH2 |

|

|

|

|

|

| PD14 |

|

|

TIM4_CH3 |

|

|

|

|

|

| PD15 |

|

|

TIM4_CH4 |

|

|

|

|

|

| ą¤ąŠčĆčé |

AF8 |

AF9 |

AF10

|

AF11

|

AF12 |

AF13 |

AF14 |

AF15 |

| UART5 |

CAN1 |

FSMC/SDIO |

DCMI |

LCD |

SYS |

| PD0 |

|

CAN1_RX |

|

|

FSMC_D2 |

|

|

EVENTOUT |

| PD1 |

|

CAN1_TX |

|

|

FSMC_D3 |

|

|

EVENTOUT |

| PD2 |

UART5_RX |

|

|

|

SDIO_CMD |

DCMI_D11 |

|

EVENTOUT |

| PD3 |

|

|

|

|

FSMC_CLK |

DCMI_D5 |

LCD_G7 |

EVENTOUT |

| PD4 |

|

|

|

|

FSMC_NOE |

|

|

EVENTOUT |

| PD5 |

|

|

|

|

FSMC_NWE |

|

|

EVENTOUT |

| PD6 |

|

|

|

|

FSMC_NWAIT |

DCMI_D10 |

LCD_B2 |

EVENTOUT |

| PD7 |

|

|

|

|

FSMC_NE1

FSMC_NCE2 |

|

|

EVENTOUT |

| PD8 |

|

|

|

|

FSMC_D13 |

|

|

EVENTOUT |

| PD9 |

|

|

|

|

FSMC_D14 |

|

|

EVENTOUT |

| PD10 |

|

|

|

|

FSMC_D15 |

|

LCD_B3 |

EVENTOUT |

| PD11 |

|

|

|

|

FSMC_A16 |

|

|

EVENTOUT |

| PD12 |

|

|

|

|

FSMC_A17 |

|

|

EVENTOUT |

| PD13 |

|

|

|

|

FSMC_A18 |

|

|

EVENTOUT |

| PD14 |

|

|

|

|

FSMC_D0 |

|

|

EVENTOUT |

| PD15 |

|

|

|

|

FSMC_D1 |

|

|

EVENTOUT |

| ą¤ąŠčĆčé |

AF0 |

AF1 |

AF2 |

AF3 |

AF4

|

AF5 |

AF6 |

AF7

|

| SYS |

TIM1 |

TIM4 |

TIM9 |

SPI4 |

SAI1 |

| PE0 |

|

|

TIM4_ETR |

|

|

|

|

|

| PE1 |

|

|

|

|

|

|

|

|

| PE2 |

TRACECLK |

|

|