|

ąÆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ STM32F429 ą▓čüčéčĆąŠąĄąĮąŠ 3 ą░ąĮą░ą╗ąŠą│ąŠ-čåąĖčäčĆąŠą▓čŗčģ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ (analog-to-digital converters, ADC). ąÜą░ąČą┤čŗą╣ ADC ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čĆą░ąĘčĆąĄčłą░čÄčēčāčÄ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą┤ąŠ 12 ą▒ąĖčé, ąĖ ą╝ąŠąČąĄčé ąŠčåąĖčäčĆąŠą▓čŗą▓ą░čéčī čüąĖą│ąĮą░ą╗, ą┐ąŠčüčéčāą┐ą░čÄčēąĖą╣ ą┐ąŠ 16 ą▓ąĮąĄčłąĮąĖą╝ ą║ą░ąĮą░ą╗ą░ą╝, ą▓čŗą┐ąŠą╗ąĮčÅčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓ ąŠą┤ąĖąĮąŠčćąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (single-shot mode) ąĖą╗ąĖ čĆąĄąČąĖą╝ąĄ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ (scan mode). ąÆ čĆąĄąČąĖą╝ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮą░ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą│čĆčāą┐ą┐ąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą▓čģąŠą┤ąŠą▓. ąØąĄą┐ąŠąĮčÅčéąĮčŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ ąĪą╗ąŠą▓ą░čĆąĖą║ąĄ [3].

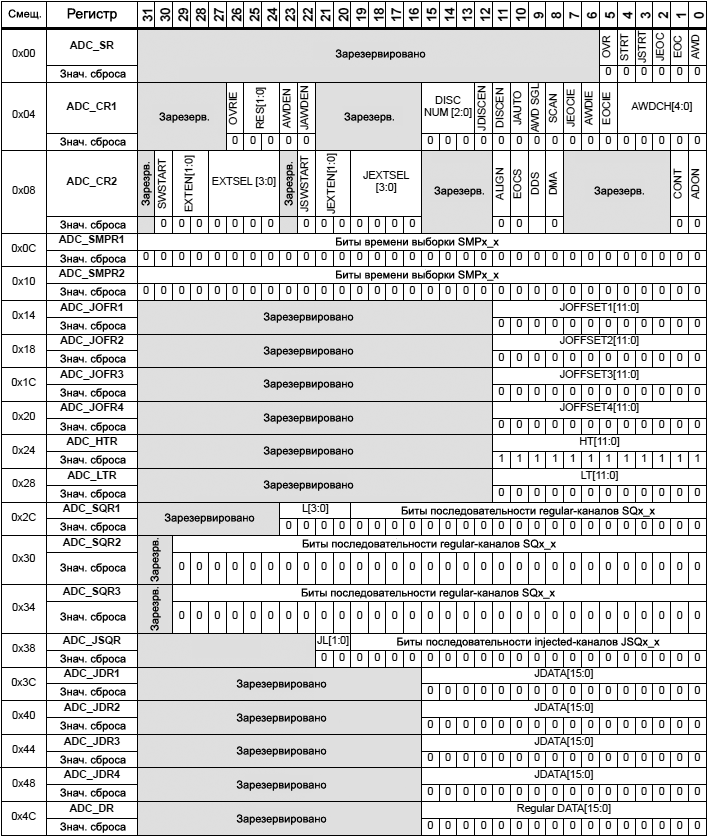

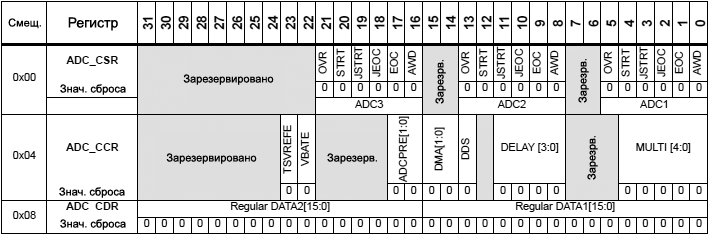

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą╗ąŠą│ąĖč湥čüą║ąĖąĄ čäčāąĮą║čåąĖąĖ, ą▓čüčéčĆąŠąĄąĮąĮčŗąĄ ą▓ ąĖąĮč鹥čĆč乥ą╣čü ADC:

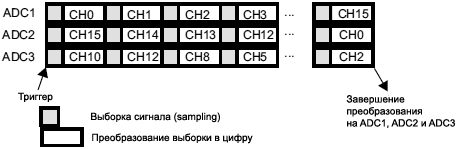

ŌĆó ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮčŗąĄ ą▓čŗą▒ąŠčĆą║ą░ ąĖ čģčĆą░ąĮąĄąĮąĖąĄ (simultaneous sample and hold).

ŌĆó ąÆčŗą▒ąŠčĆą║ą░ ąĖ čģčĆą░ąĮąĄąĮąĖąĄ čü č湥čĆąĄą┤ąŠą▓ą░ąĮąĖąĄą╝ (interleaved sample and hold).

ADC ą╝ąŠąČąĄčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ DMA. ążčāąĮą║čåąĖčÅ analog watchdog ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠč湥ąĮčī č鹊čćąĮąŠ ą╝ąŠąĮąĖč鹊čĆąĖčéčī ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄą╝ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ąŠą┤ąĮąŠą╝, ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ąĖą╗ąĖ ą▓čüąĄčģ ą▓čŗą▒čĆą░ąĮąĮčŗčģ ą║ą░ąĮą░ą╗ą░čģ. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄą╝ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓čŗčģąŠą┤ąĖčé ąĘą░ ą┐čĆąĄą┤ąĄą╗čŗ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą┐ąŠčĆąŠą│ąŠą▓. ąöą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą░ąĮą░ą╗ąŠą│ąŠ-čåąĖčäčĆąŠą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĮą░ ąĮčāąČąĮčāčÄ čćą░čüč鹊čéčā ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ ADC ą┤ąŠą╗ąČąĄąĮ ąĘą░ą┐čāčüą║ą░čéčīčüčÅ ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĖąĘ čéą░ą╣ą╝ąĄčĆąŠą▓ TIM1, TIM2, TIM3, TIM4, TIM5 ąĖą╗ąĖ TIM8.

ąóą░ą▒ą╗ąĖčåą░ 10. ąØčāą╝ąĄčĆą░čåąĖčÅ ąĖ čäčāąĮą║čåąĖąĖ ą▓čŗą▓ąŠą┤ąŠą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32F427xx ąĖ STM32F429xx.

| Pin |

ąśą╝čÅ(1) |

ąóąĖą┐ |

ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮą░čÅ čäčāąĮą║čåąĖčÅ |

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čäčāąĮą║čåąĖąĖ |

| 6 |

VBAT |

S(5) |

|

|

| 13 |

PF3 |

I/O, FT(5) |

FMC_A3, EVENTOUT |

ADC3_IN9 |

| 14 |

PF4 |

I/O, FT(5) |

FMC_A4, EVENTOUT |

ADC3_IN14 |

| 15 |

PF5 |

I/O, FT(5) |

FMC_A5, EVENTOUT |

ADC3_IN15 |

| 16 |

VSS |

S(5)

|

|

|

| 17 |

VDD |

|

|

| 18 |

PF6 |

I/O, FT(5) |

TIM10_CH1, SPI5_NSS, SAI1_SD_B, UART7_Rx, FMC_NIORD, EVENTOUT |

ADC3_IN4 |

| 19 |

PF7 |

I/O, FT(5) |

TIM11_CH1, SPI5_SCK, SAI1_MCLK_B, UART7_Tx, FMC_NREG, EVENTOUT |

ADC3_IN5 |

| 20 |

PF8 |

I/O, FT(5) |

SPI5_MISO, SAI1_SCK_B, TIM13_CH1, FMC_NIOWR, EVENTOUT |

ADC3_IN6 |

| 21 |

PF9 |

I/O, FT(5) |

SPI5_MOSI, SAI1_FS_B, TIM14_CH1, FMC_CD, EVENTOUT |

ADC3_IN7 |

| 22 |

PF10 |

I/O, FT(5) |

FMC_INTR, DCMI_D11, LCD_DE, EVENTOUT |

ADC3_IN8 |

| 26 |

PC0 |

I/O, FT(5) |

OTG_HS_ULPI_STP, FMC_SDNWE, EVENTOUT |

ADC123_IN10 |

| 27 |

PC1 |

I/O, FT(5) |

ETH_MDC, EVENTOUT |

ADC123_IN11 |

| 28 |

PC2 |

I/O, FT(5) |

SPI2_MISO, I2S2ext_SD, OTG_HS_ULPI_DIR, ETH_MII_TXD2, FMC_SDNE0, EVENTOUT |

ADC123_IN12 |

| 29 |

PC3 |

I/O, FT(5) |

SPI2_MOSI/I2S2_SD, OTG_HS_ULPI_NXT, ETH_MII_TX_CLK, FMC_SDCKE0, EVENTOUT |

ADC123_IN13 |

| 30 |

VDD |

S(5)

|

|

|

| 31 |

VSSA |

|

|

| 32 |

VREF+ |

|

|

| 33 |

VDDA |

|

|

| 34 |

PA0-WKUP (PA0) |

I/O, FT(6) |

TIM2_CH1/TIM2_ETR, TIM5_CH1, TIM8_ETR, USART2_CTS, UART4_TX, ETH_MII_CRS, EVENTOUT |

ADC123_IN0/WKUP(5) |

| 35 |

PA1 |

I/O, FT(5) |

TIM2_CH2, TIM5_CH2, USART2_RTS, UART4_RX, ETH_MII_RX_CLK/ETH_RMII_REF_CLK, EVENTOUT |

ADC123_IN1 |

| 36 |

PA2 |

I/O, FT(5) |

TIM2_CH3, TIM5_CH3, TIM9_CH1, USART2_TX, ETH_MDIO, EVENTOUT |

ADC123_IN2 |

| 37 |

PA3 |

I/O, FT(5) |

TIM2_CH4, TIM5_CH4, TIM9_CH2, USART2_RX, OTG_HS_ULPI_D0, ETH_MII_COL, LCD_B5, EVENTOUT |

ADC123_IN3 |

| 38 |

VSS |

S(5)

|

|

|

| 39 |

VDD |

|

|

| 40 |

PA4 |

I/O, TTa(5) |

SPI1_NSS, SPI3_NSS/I2S3_WS, USART2_CK, OTG_HS_SOF, DCMI_HSYNC, LCD_VSYNC, EVENTOUT |

ADC12_IN4/DAC_OUT1 |

| 41 |

PA5 |

I/O, TTa(5) |

TIM2_CH1/TIM2_ETR, TIM8_CH1N, SPI1_SCK, OTG_HS_ULPI_CK, EVENTOUT |

ADC12_IN5/DAC_OUT2 |

| 42 |

PA6 |

I/O, FT(5) |

TIM1_BKIN, TIM3_CH1, TIM8_BKIN, SPI1_MISO, TIM13_CH1, DCMI_PIXCLK, LCD_G2, EVENTOUT |

ADC12_IN6 |

| 43 |

PA7 |

I/O, FT(5) |

TIM1_CH1N, TIM3_CH2, TIM8_CH1N, SPI1_MOSI, TIM14_CH1, ETH_MII_RX_DV/ETH_RMII_CRS_DV, EVENTOUT |

ADC12_IN7 |

| 44 |

PC4 |

I/O, FT(5) |

ETH_MII_RXD0/ETH_RMII_RXD0, EVENTOUT |

ADC12_IN14 |

| 45 |

PC5 |

I/O, FT(5) |

ETH_MII_RXD1/ETH_RMII_RXD1, EVENTOUT |

ADC12_IN15 |

| 46 |

PB0 |

I/O, FT(5) |

TIM1_CH2N, TIM3_CH3, TIM8_CH2N, LCD_R3, OTG_HS_ULPI_D1, ETH_MII_RXD2, EVENTOUT |

ADC12_IN8 |

| 47 |

PB1 |

I/O, FT(5) |

TIM1_CH3N, TIM3_CH4, TIM8_CH3N, LCD_R6, OTG_HS_ULPI_D2, ETH_MII_RXD3, EVENTOUT |

ADC12_IN9 |

| 51 |

VSS |

S(5) |

|

|

| 52 |

VDD |

|

|

| 61 |

VSS |

|

|

| 62 |

VDD |

|

|

| 71 |

VCAP_1 |

|

|

| 72 |

VDD |

|

|

| 83 |

VSS |

|

|

| 84 |

VDD |

|

|

| 94 |

VSS |

|

|

| 95 |

VDD |

|

|

| 106 |

VCAP_2 |

|

|

| 107 |

VSS |

|

|

| 108 |

VDD |

|

|

| 120 |

VSS |

|

|

| 121 |

VDD |

|

|

| 130 |

VSS |

|

|

| 131 |

VDD |

|

|

| 144 |

VDD |

|

|

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1). ąśą╝čÅ ą▓ čŹč鹊ą╣ ą║ąŠą╗ąŠąĮą║ąĄ ąŠą▒ąŠąĘąĮą░čćą░ąĄčé čäčāąĮą║čåąĖčÄ ą▓čŗą▓ąŠą┤ą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, čĆą░ą▒ąŠčéą░čÄčēčāčÄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░. ąöąŠčüčéčāą┐ąĮąŠčüčéčī čäčāąĮą║čåąĖąĖ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą╝ąŠą┤ąĄą╗ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, čüą╝. ąĄą│ąŠ ą┤ą░čéą░čłąĖčé.

(5) FT = 5V tolerant (ą▓čģąŠą┤čŗ ą┤ąŠą┐čāčüą║ą░čÄčé čāčĆąŠą▓ąĄąĮčī 5V), ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čüą╗čāčćą░čÅ, ą║ąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĄąĮ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čĆąĄąČąĖą╝ ąĖą╗ąĖ čĆąĄąČąĖą╝ ą│ąĄąĮąĄčĆą░č鹊čĆą░ (ą┤ą╗čÅ PC14, PC15, PH0 ąĖ PH1). S ąŠą▒ąŠąĘąĮą░čćą░ąĄčé ą▓čŗą▓ąŠą┤ ą┤ą╗čÅ ą┐ąŠą┤ą░čćąĖ ą┐ąĖčéą░ąĮąĖčÅ.

(6) ąĢčüą╗ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▓ ą║ąŠčĆą┐čāčüą░čģ WLCSP143, UFBGA169, UFBGA176, LQFP176 ąĖą╗ąĖ TFBGA216, ąĖ ą▓čŗą▓ąŠą┤ BYPASS_REG čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĮą░ VDD (čĆąĄąČąĖą╝ Regulator OFF/internal reset ON), č鹊 ąĮąŠąČą║ą░ PA0 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüą▒čĆąŠčü Reset (čü ą░ą║čéąĖą▓ąĮčŗą╝ čāčĆąŠą▓ąĮąĄą╝ ą╗ąŠą│. 0).

[ą×ą▒čēąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ADC]

ADC čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐čĆąĖą▒ą╗ąĖąČąĄąĮąĖčÅ (successive approximation). ąŻ ąĮąĄą│ąŠ ą▓čüąĄą│ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠ 19 ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓, ą┐ąŠąĘą▓ąŠą╗čÅčÄčēąĖčģ ąĖąĘą╝ąĄčĆčÅčéčī čüąĖą│ąĮą░ą╗čŗ ąŠčé 16 ą▓ąĮąĄčłąĮąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓, ą┤ą▓čāčģ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ąĖ ąŠčé ą║ą░ąĮą░ą╗ą░ VBAT. ąÉąĮą░ą╗ąŠą│ąŠ-čåąĖčäčĆąŠą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą║ą░ąĮą░ą╗ąŠą▓ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčéčīčüčÅ ą▓ čĆąĄąČąĖą╝ą░čģ single, continuous, scan ąĖą╗ąĖ discontinuous. ąĀąĄąĘčāą╗čīčéą░čé ADC čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ 16-ą▒ąĖčéąĮąŠą╝ čĆąĄą│ąĖčüčéčĆąĄ ą┤ą░ąĮąĮčŗčģ čü ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄą╝ čŹčéąĖčģ ą┤ą░ąĮąĮčŗčģ ą▓ą╗ąĄą▓ąŠ ąĖą╗ąĖ ą▓ą┐čĆą░ą▓ąŠ.

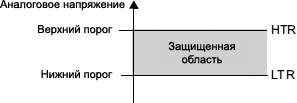

ążčāąĮą║čåąĖčÅ analog watchdog ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÄ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčī čüąĖčéčāą░čåąĖčÄ, ą║ąŠą│ą┤ą░ ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓čŗčģąŠą┤ąĖčé ąĘą░ ą┐čĆąĄą┤ąĄą╗čŗ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖą╗ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐ąŠčĆąŠą│ąŠą▓, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čŗčģ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝.

ą×čüąĮąŠą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ADC:

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī 12, 10, 8 ąĖą╗ąĖ 6 ą▒ąĖčé.

ŌĆó ąōąĄąĮąĄčĆą░čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ąŠą║ąŠąĮčćą░ąĮąĖčÄ injected-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ą░ čéą░ą║ąČąĄ ą▓ čüą╗čāčćą░ąĄ čüąŠą▒čŗčéąĖą╣ analog watchdog ąĖą╗ąĖ overrun.

ŌĆó ąĀąĄąČąĖą╝čŗ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ąĖ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (single ąĖ continuous conversion modes).

ŌĆó ąĀąĄąČąĖą╝ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąŠčé ą║ą░ąĮą░ą╗ą░ 0 ą┤ąŠ ą║ą░ąĮą░ą╗ą░ n.

ŌĆó ąÆčŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ čüąŠ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą║ąŠą│ąĄčĆąĄąĮčéąĮąŠčüčéčīčÄ.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠąĄ ą▓čĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą║ą░ąĮą░ą╗ąĄ.

ŌĆó ą×ą┐čåąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ čü ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ąŠą╣ ą┐ąŠą╗čÅčĆąĮąŠčüčéčīčÄ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣ regular ąĖ injected.

ŌĆó ą¤čĆąĄčĆčŗą▓ąĖčüčéčŗą╣ čĆąĄąČąĖą╝ (discontinuous mode).

ŌĆó ąĀąĄąČąĖą╝ Dual/Triple (ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ, čā ą║ąŠč鹊čĆčŗčģ 2 ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ADC).

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ąŠąĄ čģčĆą░ąĮąĖą╗ąĖčēąĄ ą┤ą░ąĮąĮčŗčģ DMA ą▓ čĆąĄąČąĖą╝ąĄ Dual/Triple ADC.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅą╝ąĖ ą▓ čĆąĄąČąĖą╝ąĄ Dual/Triple interleaved.

ŌĆó ąóąĖą┐čŗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC (čüą╝. [2]).

ŌĆó ąóčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ ą┐ąĖčéą░ąĮąĖčÅ ADC: 2.4V .. 3.6V ąĮą░ ą┐ąŠą╗ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ ąĖ ą┐čĆąĖ čüąĮąĖąČąĄąĮąĖąĖ ą┤ąŠ 1.8V ąĮą░ ą╝ąĄąĮčīčłąĄą╣ čüą║ąŠčĆąŠčüčéąĖ.

ŌĆó ąöąĖą░ą┐ą░ąĘąŠąĮ ą▓čģąŠą┤ąĮčŗčģ čāčĆąŠą▓ąĮąĄą╣ ADC VIN ąŠčé VREFŌĆō ą┤ąŠ VREF+.

ŌĆó ąōąĄąĮąĄčĆą░čåąĖčÅ ąĘą░ą┐čĆąŠčüą░ DMA ą┐čĆąĖ regular ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĖ ą║ą░ąĮą░ą╗ą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓čŗą▓ąŠą┤ VREFŌĆō, ąĄčüą╗ąĖ ąŠąĮ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čéąĖą┐ą░ ą║ąŠčĆą┐čāčüą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░), ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčé ą║ VSSA.

[ąÆą░ąČąĮčŗąĄ ąĘą░ą╝ąĄčćą░ąĮąĖčÅ ą┐ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÄ ąÉą”ą¤ STM32]

1. ąÆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ STM32 ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčé 1 ą┤ąŠ 3 ą▒ą╗ąŠą║ąŠą▓ ADC, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą╝ąŠą┤ąĄą╗ąĖ. ąŻ STM32F4x ąĖčģ čéčĆąĖ: ADC1, ADC2 ąĖ ADC3 (ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ ą┤ą╗čÅ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ ąÉą”ą¤ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆą░ ADCx).

2. ąæą╗ąŠą║ ADCx ą╝ąŠąČąĄčé č湥čĆąĄąĘ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆ ą┐ąŠą┤ą║ą╗čÄčćą░čéčīčüčÅ ą║ ą║ą░ą║ąŠą╝čā-ą╗ąĖą▒ąŠ ą▓čģąŠą┤ąĮąŠą╝čā ą║ą░ąĮą░ą╗čā. ąÆčüąĄą│ąŠ ąĄčüčéčī 16 ą▓ąĮąĄčłąĮąĖčģ ą║ą░ąĮą░ą╗ąŠą▓ ąŠčé IN0 ą┤ąŠ IN15 (ą┤ą╗čÅ čüčüčŗą╗ą║ąĖ ąĮą░ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮčŗą╣ ą║ą░ąĮą░ą╗ ąĘą┤ąĄčüčī ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆą░ INy), ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ ąĮąŠąČą║ą░ą╝ GPIO ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąÜčĆąŠą╝ąĄ čŹčéąĖčģ ą▓ąĮąĄčłąĮąĖčģ ą║ą░ąĮą░ą╗ąŠą▓ ąĄčüčéčī ąĄčēąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ, č湥čĆąĄąĘ ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ąŠą┐čĆą░čłąĖą▓ą░čéčī ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą┤ą░čéčćąĖą║ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ, VREFINT ąĖą╗ąĖ VBAT.

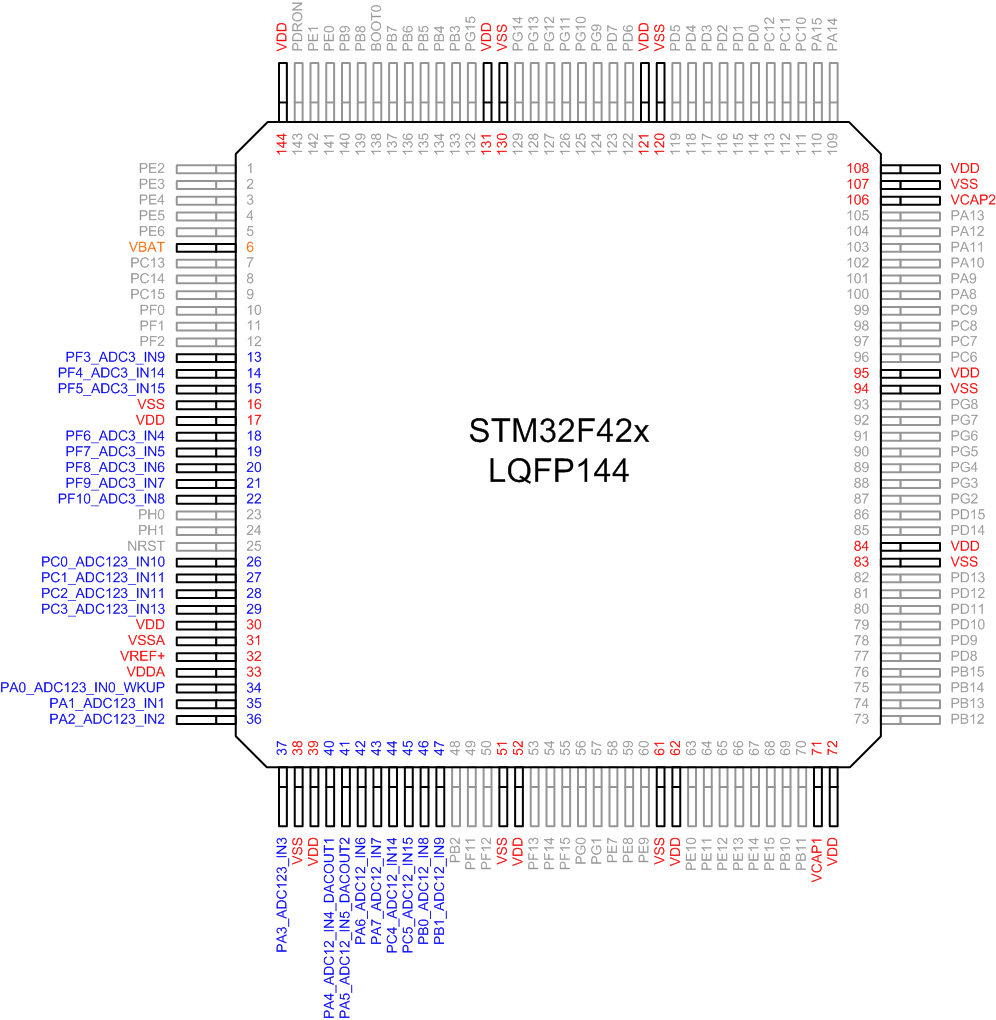

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą║ą░ąČą┤čŗą╣ ą▒ą╗ąŠą║ ADCx ąĖą╝ąĄąĄčé čüą▓ąŠą╣ ąĮą░ą▒ąŠčĆ ą║ą░ąĮą░ą╗ąŠą▓, ą║ ą║ąŠč鹊čĆčŗą╝ ąĄą│ąŠ ą╝ąŠąČąĮąŠ ą┐čĆąĖą▓čÅąĘą░čéčī. ąó. ąĄ. ąĮąĄą╗čīąĘčÅ ą║ ą╗čÄą▒ąŠą╝čā ADCx ą┐čĆąĖą▓čÅąĘą░čéčī ą╗čÄą▒ąŠą╣ ą║ą░ąĮą░ą╗ INy. ą¤ąŠčŹč鹊ą╝čā ąĮąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ GPIO, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĮą░ąĘąĮą░č湥ąĮčŗ ą║ą░ą║ ą▓čģąŠą┤čŗ ADC, ąŠą▒ąŠąĘąĮą░čćą░čÄčéčüčÅ ą┤ąŠą▓ąŠą╗čīąĮąŠ čģąĖčéčĆčŗą╝, ąĮąĄ čüčĆą░ąĘčā ą┐ąŠąĮčÅčéąĮčŗą╝ čüą┐ąŠčüąŠą▒ąŠą╝. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ STM32F4x ą▓ ą║ąŠčĆą┐čāčüąĄ LQFP144 (čüą╝. ą▓čĆąĄąĘą║čā ą▓čŗčłąĄ):

- ADC3_IN4, ADC3_IN5, ADC3_IN6, ADC3_IN7, ADC3_IN8, ADC3_IN9, ADC3_IN14, ADC3_IN15 ąŁčéąĖ ąĖą╝ąĄąĮą░ ąĮąŠąČąĄą║ ąŠąĘąĮą░čćą░čÄčé, čćč鹊 ąŠąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ ą▒ą╗ąŠą║čā ADC3 ą▓ ą║ą░č湥čüčéą▓ąĄ ą║ą░ąĮą░ą╗ąŠą▓ 4 .. 9, 14, 15.

- ADC12_IN4, ADC12_IN5, ADC12_IN6, ADC12_IN7, ADC12_IN8, ADC12_IN9, ADC12_IN14, ADC12_IN15 ąŁčéąĖ ąĖą╝ąĄąĮą░ ąĮąŠąČąĄą║ ąŠąĘąĮą░čćą░čÄčé, čćč鹊 ąŠąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ ą▒ą╗ąŠą║čā ADC1 ąĖą╗ąĖ ADC2 (ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ č鹊ą╗čīą║ąŠ ą║ ąŠą┤ąĮąŠą╝čā ąĖąĘ ąĮąĖčģ, ą┐ąŠ ą▓čŗą▒ąŠčĆčā) ą▓ ą║ą░č湥čüčéą▓ąĄ ą║ą░ąĮą░ą╗ąŠą▓ 4 .. 9, 14, 15.

- ADC123_IN0, ADC123_IN1, ADC123_IN2, ADC123_IN3, ADC123_IN10, ADC123_IN11, ADC123_IN12, ADC123_IN13. ąŁčéąĖ ąĖą╝ąĄąĮą░ ąĮąŠąČąĄą║ ąŠąĘąĮą░čćą░čÄčé, čćč鹊 ąŠąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ ą▒ą╗ąŠą║čā ADC1, ADC2 ąĖą╗ąĖ ADC3 (ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ č鹊ą╗čīą║ąŠ ą║ ąŠą┤ąĮąŠą╝čā ąĖąĘ ąĮąĖčģ, ą┐ąŠ ą▓čŗą▒ąŠčĆčā) ą▓ ą║ą░č湥čüčéą▓ąĄ ą║ą░ąĮą░ą╗ąŠą▓ 0 .. 3, 10 .. 13.

3. ąśą╝ąĄąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VREFINT (čéąĖą┐ąŠą▓ą░čÅ ą▓ąĄą╗ąĖčćąĖąĮą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 1.21V), ąŠą┤ąĮą░ą║ąŠ ą┤ą╗čÅ ąÉą”ą¤ ą▓čüąĄą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ąĮąĄčłąĮąĄąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VREF. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, VREFINT ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ąĄčüą╗ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ č鹊čćąĮąŠ ąĖąĘą╝ąĄčĆčÅčéčī čāčĆąŠą▓ąĄąĮčī čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čģąŠą┤ąĄ ąÉą”ą¤.

ąöą╗čÅ ą▓ąĮąĄčłąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąŠčéą┤ąĄą╗čīąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ VREF- ąĖ VREF+ (ąĖčģ ąĮą░ą╗ąĖčćąĖąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą╝ąŠą┤ąĄą╗ąĖ ąĖ ą║ąŠčĆą┐čāčüą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░). ą×ą┤ąĮą░ą║ąŠ ąĖčģ čāčĆąŠą▓ąĮąĖ ąĖą╝ąĄčÄčé ąČąĄčüčéą║ąĖąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ, ą┐čĆąĖą▓čÅąĘą░ąĮąĮčŗąĄ čüąŠąŠą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą║ GND ąĖ VDD/VDDA (ąŠą▒čŗčćąĮąŠ 3.3V). ą¤ąŠčŹč鹊ą╝čā čĆą░ąĘčĆą░ą▒ąŠčéčćąĖą║ąĖ čćą░čüč鹊 VREF- ąĮą░ą║ąŠčĆąŠčéą║ąŠ ąĘą░ą╝čŗą║ą░čÄčé ąĮą░ GND, ą░ VREF+ čüąŠąĄą┤ąĖąĮčÅčÄčé c VDD (ą▓ ą┐čĆąŠčüč鹥ą╣čłąĄą╝ čüą╗čāčćą░ąĄ ąĮą░ą┐čĆčÅą╝čāčÄ, ą╗ąĖą▒ąŠ ą┐čĆąĖ ąŠčüąŠą▒čŗčģ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅčģ č湥čĆąĄąĘ RC-čåąĄą┐ąŠčćą║čā ąĖą╗ąĖ čäąĖą╗čīčéčĆ). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ, ąĄčüą╗ąĖ VDD čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ čü ąĮąĄą▓čŗčüąŠą║ąŠą╣ č鹊čćąĮąŠčüčéčīčÄ, ąĮąŠ čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąŠą▓čŗčłąĄąĮąĮą░čÅ č鹊čćąĮąŠčüčéčī ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ ą░ą▒čüąŠą╗čÄčéąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ, č鹊 ą┐čĆąĖą╝ąĄąĮčÅčÄčé ą║ą░ą╗ąĖą▒čĆąŠą▓ą║čā VREF ą┐ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ VREFINT čü čāč湥č鹊ą╝ ą║ą░ą╗ąĖą▒čĆąŠą▓ąŠčćąĮčŗčģ ą┤ą░ąĮąĮčŗčģ, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╝ ąĮą░ ąĘą░ą▓ąŠą┤ąĄ. ąŻ STM32F4 čŹč鹊 čÅč湥ą╣ą║ą░ ą┐ą░ą╝čÅčéąĖ ąĖąĘ ą┤ą▓čāčģ ą▒ą░ą╣čé ą┐ąŠ ą░ą┤čĆąĄčüą░ą╝ 0x1FFF7A2A ąĖ 0x1FFF7A2B, ą│ą┤ąĄ ąĘą░ą┐ąĖčüą░ąĮčŗ čüčŗčĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC, čüąĮčÅčéčŗąĄ ą┐čĆąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ čāčüą╗ąŠą▓ąĖčÅčģ. ąĪą╝. ąĮąĖąČąĄ ą▓čĆąĄąĘą║čā "ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ADC", čéą░ą▒ą╗ąĖčåčŗ 83 ąĖ 84.

4. ąÜą░ąĮą░ą╗čŗ ąÉą”ą¤ ą▒čŗą▓ą░čÄčé ą┤ą▓čāčģ čéąĖą┐ąŠą▓: čĆąĄą│čāą╗čÅčĆąĮčŗąĄ (regular) ąĖ ąĖąĮąČąĄą║čéąĖčĆąŠą▓ą░ąĮąĮčŗąĄ (injected). ąØą░ąĘą▓ą░ąĮąĖąĄ "ąĖąĮąČąĄą║čéąĖčĆąŠą▓ą░ąĮąĮčŗą╣" ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĘą░ą┐čāčüą║ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čŹč鹊ą│ąŠ ą║ą░ąĮą░ą╗ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī "ą▓čüčéą░ą▓ą╗ąĄąĮąŠ" ą╝ąĄąČą┤čā ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅą╝ąĖ čĆąĄą│čāą╗čÅčĆąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓, čé. ąĄ. ąŠą▒čĆą░ą▒ąŠčéą║ą░ čĆąĄą│čāą╗čÅčĆąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ ą┐čĆąĖ čŹč鹊ą╝ ą┐čĆąĖąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ. ąśąĮąČąĄą║čéąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą║ą░ąĮą░ą╗čŗ ąŠą┐čĆą░čłąĖą▓ą░čÄčéčüčÅ ą╝ąĄąČą┤čā čĆąĄą│čāą╗čÅčĆąĮčŗą╝ąĖ.

ą×čüąŠą▒ąĄąĮąĮąŠčüčéčī ąĖąĮąČąĄą║čéąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ąĘą░ą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ č鹊ą╝, čćč鹊 čā ąĮąĄą│ąŠ ąĄčüčéčī čüą▓ąŠą╣ ąŠčéą┤ąĄą╗čīąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ą┤ą╗čÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░čéą░. ąóąŠ ąĄčüčéčī ąĄčüą╗ąĖ ą║ą░ąĮą░ą╗čŗ IN0, IN1, IN2, IN3 ąĮą░čüčéčĆąŠąĖčéčī ą║ą░ą║ ąĖąĮąČąĄą║čéąĖčĆąŠą▓ą░ąĮąĮčŗąĄ, č鹊 ąĖčģ čĆąĄąĘčāą╗čīčéą░čéčŗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▒čāą┤čāčé čüąŠčģčĆą░ąĮąĄąĮčŗ ą▓ č湥čéčŗčĆąĄ čĆą░ąĘąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░ (ADCx_JDR1, ADCx_JDR2, ADCx_JDR3, ADCx_JDR4). ąśąĮąČąĄą║čéąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ ą┤ą╗čÅ ADCx ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ č湥čéčŗčĆčæčģ. ąøčÄą▒ąŠą╣ ą┤ąŠčüčéčāą┐ąĮčŗą╣ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ (ą┤ąŠčüčéčāą┐ąĮąŠčüčéčī ąĘą░ą▓ąĖčüąĖčé ąŠčé ą╝ąŠą┤ąĄą╗ąĖ ąĖ ą║ąŠčĆą┐čāčüą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░) ą╝ąŠąČąĮąŠ ąĮą░čüčéčĆąŠąĖčéčī ą║ą░ą║ ąĖąĮąČąĄą║čéąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą║ą░ąĮą░ą╗.

ąĀąĄą│čāą╗čÅčĆąĮčŗąĄ ą║ą░ąĮą░ą╗čŗ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą▓čģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐ąŠąŠč湥čĆąĄą┤ąĮąŠ, čü ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ ą┐ąĄčĆąĖąŠą┤ąĖčćąĮąŠčüčéčīčÄ. ą¤ąŠčŹč鹊ą╝čā ąŠąĮąĖ ąĖ ąĮą░ąĘčŗą▓ą░čÄčéčüčÅ čĆąĄą│čāą╗čÅčĆąĮčŗą╝ąĖ. ąŻ čĆąĄą│čāą╗čÅčĆąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ ąĄčüčéčī č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čĆąĄą│ąĖčüčéčĆ ą┤ą╗čÅ ąĘą░ą▒ąŠčĆą░ čĆąĄąĘčāą╗čīčéą░č鹊ą▓, ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗą╣ ąĮą░ ą▓čüąĄ ą║ą░ąĮą░ą╗čŗ - ADCx_DR. ąóąŠ ąĄčüčéčī ąĄčüą╗ąĖ ą║ą░ąĮą░ą╗čŗ ąĀąÉ0, ąĀąÉ1, ąĀąÉ2, ąĀąÉ3 ąĮą░čüčéčĆąŠąĖčéčī ą║ą░ą║ čĆąĄą│čāą╗čÅčĆąĮčŗąĄ ą┤ą╗čÅ ą║ą░ą║ąŠą│ąŠ-č鹊 ąĖąĘ ADCx, č鹊 čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▒ąŠčéčŗ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüčŗą▓ą░čéčīčüčÅ ą▓ ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ čĆąĄą│ąĖčüčéčĆ, ąĘą░čéąĖčĆą░čÅ ą┐čĆąĄą┤čŗą┤čāčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ. ąó. ąĄ. ąĄčüą╗ąĖ ąĮąĄ čāčüą┐ąĄą╗ąĖ čüą▓ąŠąĄą▓čĆąĄą╝ąĄąĮąĮąŠ ąĘą░ą▒čĆą░čéčī ą┤ą░ąĮąĮčŗąĄ, č鹊 ąŠąĮąĖ ą▒čāą┤čāčé ą┐ąŠč鹥čĆčÅąĮčŗ. ąŁčéčā ą┐čĆąŠą▒ą╗ąĄą╝čā ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čĆąĄčłąĖčéčī čäčāąĮą║čåąĖčÅ DMA.

5. ąśčüą┐ąŠą╗čīąĘčāčÅ čĆąĄąČąĖą╝ čüą┤ą▓ąŠąĄąĮąĮčŗčģ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣, ą╝ąŠąČąĮąŠ ą┐čĆąĄą▓čĆą░čéąĖčéčī ą┤ą▓ą░ ADC ą▓ ąŠą┤ąĖąĮ, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ ąĮą░ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąŠą╣ čüą║ąŠčĆąŠčüčéąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

6. ąĀąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADCx ąĖą╝ąĄąĄčé ą▒ąĄąĘąĘąĮą░ą║ąŠą▓čŗą╣ čéąĖą┐. ąŁč鹊 ąĮąĄ ą▓čüąĄą│ą┤ą░ čāą┤ąŠą▒ąĮąŠ ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ DSP, ą║ąŠč鹊čĆčŗąĄ čćą░čüč鹊 ą┐čĆąĖą╝ąĄąĮčÅčÄčé čćąĖčüą╗ą░ čüąŠ ąĘąĮą░ą║ąŠą╝. ąÆąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░čéą░ ą▓ą╗ąĄą▓ąŠ (ą▓ čüčéą░čĆčłąĖąĄ čĆą░ąĘčĆčÅą┤čŗ) čāą┤ąŠą▒ąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ č乊čĆą╝ą░č鹥 16-ą▒ąĖčéąĮąŠą│ąŠ čćąĖčüą╗ą░ čüąŠ ąĘąĮą░ą║ąŠą╝ (ą┤ą▓ąŠąĖčćąĮąŠąĄ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ, čéąĖą┐ short).

ą¤ąŠą┤čüąĖčüč鹥ą╝ą░ ąÉą”ą¤ STM32 ąĮą░ą╝ąĮąŠą│ąŠ čüą╗ąŠąČąĮąĄąĄ ą▓ čüčĆą░ą▓ąĮąĄąĮąĖąĖ čü čéčĆą░ą┤ąĖčåąĖąŠąĮąĮčŗą╝ąĖ 8-ą▒ąĖčéąĮčŗą╝ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ AVR. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÅ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÅ ąŠą▒čłąĖčĆąĮą░čÅ, ąĖ ą▓ ąĮąĄą╣ ą┤ąŠą▓ąŠą╗čīąĮąŠ čéčĆčāą┤ąĮąŠ čĆą░ąĘąŠą▒čĆą░čéčīčüčÅ. ą”ąĄą╗ąĄčüąŠąŠą▒čĆą░ąĘąĮąŠ ą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą│ąŠč鹊ą▓čŗą╝ąĖ ą┐čĆąĖą╝ąĄčĆą░ą╝ąĖ ą║ąŠą┤ą░, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą▓ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĄ STM32Cube, ąĖ ąĮą░ ąŠčüąĮąŠą▓ąĄ ąĖčģ čüąŠąĘą┤ą░ą▓ą░čéčī čüąŠą▒čüčéą▓ąĄąĮąĮčŗąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ.

ąĀąĖčü. 44. ąæą╗ąŠą║-čüčģąĄą╝ą░ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ADC.

ąóą░ą▒ą╗ąĖčåą░ 65. ąÆčŗą▓ąŠą┤čŗ ADC.

| ąśą╝čÅ |

ąóąĖą┐ čüąĖą│ąĮą░ą╗ą░ |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ |

| VREF+ |

ąÆčģąŠą┤, ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. |

ąĪą░ą╝ąŠąĄ ą▓čŗčüąŠą║ąŠąĄ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ą╗čÅ ADC, 1.8V Ōēż VREF+ Ōēż VDDA |

| VDDA |

ąÆčģąŠą┤, ą┐ą╗čÄčü ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čüčģąĄą╝. |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čüčģąĄą╝, čĆą░ą▓ąĮąŠąĄ VDD, ąĖ:

2.4V Ōēż VDDA Ōēż VDD (3.6V) ą┤ą╗čÅ ą┐ąŠą╗ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ

1.8V Ōēż VDDA Ōēż VDD (3.6V) ą┤ą╗čÅ čüąĮąĖąČąĄąĮąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ |

| VREFŌĆō |

ąÆčģąŠą┤, ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ(1). |

ąĪą░ą╝ąŠąĄ ąĮąĖąČąĮąĄąĄ/ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ADC, VREFŌĆō = VSSA |

| VSSA |

ąÆčģąŠą┤, ą╝ąĖąĮčāčü ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čüčģąĄą╝. |

ąŚąĄą╝ą╗čÅ ą┤ą╗čÅ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ, ą┐ąŠ čāčĆąŠą▓ąĮčÄ ą┐ąŠč鹥ąĮčåąĖą░ą╗ą░ čĆą░ą▓ąĮą░čÅ VSS |

| ADCx_IN[15:0] |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ. |

16 ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą▓čģąŠą┤ąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ąĮą░ ą║ąŠčĆą┐čāčüąĄ LQFP144 ą▓čŗą▓ąŠą┤ą░ VREF- ąĮąĄčé, ąŠąĮ čüąŠąĄą┤ąĖąĮąĄąĮ ą▓ąĮčāčéčĆąĖ ą║čĆąĖčüčéą░ą╗ą╗ą░ čü ą▓čŗą▓ąŠą┤ąŠą╝ VSSA.

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓ą║ą╗čÄč湥ąĮąĖąĄą╝ ąĖ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ADC. ADC ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ ADON ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR2. ąÜąŠą│ą┤ą░ ą▒ąĖčé ADON čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┐ąĄčĆą▓čŗą╣ čĆą░ąĘ, čŹč鹊 ą▓čŗą▓ąŠą┤ąĖčé ADC ąĖąĘ čĆąĄąČąĖą╝ą░ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (Power-down mode).

ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą╗ąĖą▒ąŠ ą▒ąĖčé SWSTART, ą╗ąĖą▒ąŠ ą▒ąĖčé JSWSTART.

ąÆčŗ ą╝ąŠąČąĄč鹥 ąŠčüčéą░ąĮąŠą▓ąĖčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĖ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ ADC ą▓ čĆąĄąČąĖą╝ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (power down mode) ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ ADON. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ADC ą┐ąŠčćčéąĖ ąĮąĄ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄčé č鹊ą║ą░ (č鹊ą╗čīą║ąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą╝ąĖą║čĆąŠą░ą╝ą┐ąĄčĆ).

ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ADC. ąĪčāčēąĄčüčéą▓čāąĄčé ą┤ą▓ąĄ čüčģąĄą╝čŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ:

ŌĆó ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čüčģąĄą╝: ADCCLK, čŹč鹊 ąŠą▒čēąĄąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą╗čÅ ą▓čüąĄčģ ADC. ąŁčéąĖ čéą░ą║čéčŗ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ąĖąĘ čéą░ą║č鹊ą▓ APB2, ą┐ąŠą┤ąĄą╗ąĄąĮąĮčŗčģ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╝ ą┐čĆąĄčüą║ą░ą╗ąĄčĆąŠą╝, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ADC čĆą░ą▒ąŠčéą░čéčī ąĮą░ čćą░čüč鹊čéą░čģ fPCLK2/2, /4, /6 ąĖą╗ąĖ /8. ąĪą╝. ą┤ą░čéą░čłąĖčé ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ čāąĘąĮą░čéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ADCCLK.

ŌĆó ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą╗čÅ čåąĖčäčĆąŠą▓ąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ (ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ ąĮą░ čćč鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī). ąŁčéą░ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čĆą░ą▓ąĮą░ čćą░čüč鹊č鹥 APB2. ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čåąĖčäčĆąŠą▓ąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ/ąĘą░ą┐čĆąĄčēąĄąĮąŠ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ADC č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą┐ąĄčĆąĖč乥čĆąĖąĖ RCC APB2 (RCC_APB2ENR).

ąÆčŗą▒ąŠčĆ ą║ą░ąĮą░ą╗ą░. ąśą╝ąĄąĄčéčüčÅ 16 ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓. ąśčģ ą╝ąŠąČąĮąŠ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░čéčī ą▓ 2 ą│čĆčāą┐ą┐čŗ: regular ąĖ injected. ąōčĆčāą┐ą┐ą░ čüąŠčüč鹊ąĖčé ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ ąĮą░ ą╗čÄą▒ąŠą╝ ą║ą░ąĮą░ą╗ąĄ ąĖ ą▓ ą╗čÄą▒ąŠą╝ ą┐ąŠčĆčÅą┤ą║ąĄ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą╝ąŠąČąĮąŠ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐ąŠčĆčÅą┤ą║ąĄ: ADC_IN3, ADC_IN8, ADC_IN2, ADC_IN2, ADC_IN0, ADC_IN2, ADC_IN2, ADC_IN15.

ŌĆó ąÆ ą│čĆčāą┐ą┐čā regular ą╝ąŠąČąĄčé ą▓čģąŠą┤ąĖčéčī ą┤ąŠ 16 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣. ąÜą░ąĮą░ą╗čŗ regular ąĖ ąĖčģ ą┐ąŠčĆčÅą┤ąŠą║ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ ADC_SQRx. ą×ą▒čēąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣ ą▓ ą│čĆčāą┐ą┐ąĄ regular ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ ą▒ąĖčéčŗ L[3:0] čĆąĄą│ąĖčüčéčĆą░ ADC_SQR1.

ŌĆó ąÆ ą│čĆčāą┐ą┐čā injected ą▓čģąŠą┤ąĖčé ą┤ąŠ 4 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣. ąÜą░ąĮą░ą╗čŗ injected ąĖ ąĖčģ ą┐ąŠčĆčÅą┤ąŠą║ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_JSQR. ą×ą▒čēąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ ą▒ąĖčéčŗ L[1:0] čĆąĄą│ąĖčüčéčĆą░ ADC_JSQR.

ąĢčüą╗ąĖ čĆąĄą│ąĖčüčéčĆčŗ ADC_SQRx ąĖą╗ąĖ ADC_JSQR ą╝ąŠą┤ąĖčäąĖčåąĖčĆčāčÄčéčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, č鹊 č鹥ą║čāčēąĄąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ, ąĖ ą▓ ADC ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ąĮąŠą▓čŗą╣ ąĖą╝ą┐čāą╗čīčü ąĘą░ą┐čāčüą║ą░ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĮąŠą▓ąŠą╣ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą│čĆčāą┐ą┐čŗ.

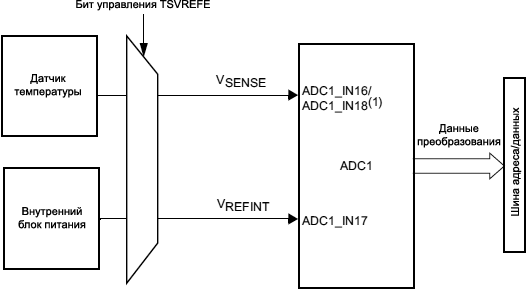

ŌĆó ąÆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ STM32F40x ąĖ STM32F41x ą┤ą░čéčćąĖą║ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ (temperature sensor) ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą▓ąĮčāčéčĆąĖ ą║čĆąĖčüčéą░ą╗ą╗ą░ ą║ ą║ą░ąĮą░ą╗čā ADC1_IN16. ąÆąĮčāčéčĆąĄąĮąĮąĄąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VREFINT ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ą║ ADC1_IN17.

ŌĆó ąÆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ STM32F42x ąĖ STM32F43x ą┤ą░čéčćąĖą║ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą▓ąĮčāčéčĆąĖ ą║čĆąĖčüčéą░ą╗ą╗ą░ ą║ ą║ą░ąĮą░ą╗čā ADC1_IN18, ą║ąŠč鹊čĆčŗą╣ čüąŠą▓ą╝ąĄčēąĄąĮ čü VBAT. ąÆ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ąĖčüč鹊čćąĮąĖą║ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ąŠčé ą┤ą░čéčćąĖą║ą░ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ ąĖą╗ąĖ ąŠčé VBAT. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą┤ą░čéčćąĖą║ą░ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ VBAT, č鹊 ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ č鹊ą╗čīą║ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ VBAT. ąÆąĮčāčéčĆąĄąĮąĮąĄąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VREFINT ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ą║ ADC1_IN17.

ąÜą░ąĮą░ą╗ VBAT (ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ ą║ą░ąĮą░ą╗čā ADC1_IN18) ą╝ąŠąČąĄčé ą▒čŗčéčī čéą░ą║ąČąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮ ą║ą░ą║ ą║ą░ąĮą░ą╗ injected ąĖą╗ąĖ ą║ą░ąĮą░ą╗ regular.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ą░ąĮą░ą╗čŗ ą┤ą░čéčćąĖą║ą░ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ, VREFINT ąĖ VBAT ą┤ąŠčüčéčāą┐ąĮčŗ č鹊ą╗čīą║ąŠ ąĮą░ ą┐ąĄčĆąĖč乥čĆąĖąĖ ADC1.

ąĀąĄąČąĖą╝ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (single conversion mode). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ADC ą┐ąŠčüą╗ąĄ ąĘą░ą┐čāčüą║ą░ ą┤ąĄą╗ą░ąĄčé č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ. ąŁč鹊čé čĆąĄąČąĖą╝ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ čü ą▒ąĖč鹊ą╝ CONT, čĆą░ą▓ąĮčŗą╝ 0, ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓:

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ SWSTART ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR2 (č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ regular).

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ JSWSTART (ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ injected).

ŌĆó ąÆąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ (ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ regular ąĖą╗ąĖ injected).

ąóą░ą▒ą╗ąĖčåą░ 80. ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą┤ą░čéčćąĖą║ą░ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ.

| ąĪąĖą╝ą▓ąŠą╗ |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

MIN |

Typ |

MAX |

ąĢą┤. |

| TL(1) |

ąøąĖąĮąĄą╣ąĮąŠčüčéčī VSENSE ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ |

- |

┬▒1 |

┬▒2 |

┬░C |

| Avg_Slope(1) |

ąĪčĆąĄą┤ąĮąĖą╣ ąĮą░ą║ą╗ąŠąĮ |

- |

2.5 |

|

mV/┬░C |

| V25(1) |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐čĆąĖ 25┬░C |

- |

0.76 |

|

V |

| tSTART(2) |

ąÆčĆąĄą╝čÅ ąĘą░ą┐čāčüą║ą░ |

- |

6 |

10 |

ą╝ą║čü |

| TS_temp(2) |

ąÆčĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ ADC (sampling time) ą┐čĆąĖ čćč鹥ąĮąĖąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ (č鹊čćąĮąŠčüčéčī 1┬░C) |

10 |

- |

- |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąōą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ čĆąĄąĘčāą╗čīčéą░čéą░ą╝ąĖ ąĖčüą┐čŗčéą░ąĮąĖą╣ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║.

(2) ąōą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ ą┤ąĖąĘą░ą╣ąĮąŠą╝.

ąóą░ą▒ą╗ąĖčåą░ 81. ąŚąĮą░č湥ąĮąĖčÅ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ ą┤ą░čéčćąĖą║ą░ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ.

| ąĪąĖą╝ą▓ąŠą╗ |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąÉą┤čĆąĄčü ą┐ą░ą╝čÅčéąĖ |

| TS_CAL1 |

ąĪčŗčĆčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ADC ą┤ą░čéčćąĖą║ą░ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ (TS), čüąĮčÅčéčŗąĄ ą┐čĆąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ 30┬░C, VDDA = 3.3V. |

0x1FFF7A2C - 0x1FFF7A2D |

| TS_CAL2 |

ąĪčŗčĆčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ADC ą┤ą░čéčćąĖą║ą░ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ (TS), čüąĮčÅčéčŗąĄ ą┐čĆąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ 110┬░C, VDDA = 3.3V. |

0x1FFF7A2E - 0x1FFF7A2F |

ąóą░ą▒ą╗ąĖčåą░ 82. ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ VBAT.

| ąĪąĖą╝ą▓ąŠą╗ |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

MIN |

Typ |

MAX |

ąĢą┤. |

| R |

ąĀąĄąĘąĖčüč鹊čĆąĮčŗą╣ ą╝ąŠčüčé ą┤ą╗čÅ VBAT |

- |

50 |

- |

ą║ą×ą╝ |

| Q |

ąÜąŠčŹčäčäąĖčåąĖąĄąĮčé ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ VBAT |

- |

4 |

- |

|

| Er(1) |

ą×čłąĖą▒ą║ą░ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ Q |

-1 |

- |

+1 |

% |

| TS_vbat(2) |

ąÆčĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ ADC, ą║ąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čćč鹥ąĮąĖąĄ VBAT čü č鹊čćąĮąŠčüčéčīčÄ 1 mV |

5 |

- |

- |

ą╝ą║čü |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąōą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ ą┤ąĖąĘą░ą╣ąĮąŠą╝.

(2) ąĪą░ą╝ąŠąĄ ą║ąŠčĆąŠčéą║ąŠąĄ ą▓čĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ąĖč鹥čĆą░čåąĖčÅą╝ąĖ.

ąÜąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░:

ŌĆó ąĢčüą╗ąĖ ą▒čŗą╗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮ ą║ą░ąĮą░ą╗ regular:

ŌĆō ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ 16-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ADC_DR.

ŌĆō ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ EOC (end of conversion, ąŠą║ąŠąĮčćą░ąĮąĖąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ).

ŌĆō ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé EOCIE.

ŌĆó ąĢčüą╗ąĖ ą▒čŗą╗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮ ą║ą░ąĮą░ą╗ injected:

ŌĆō ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ 16-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ADC_JDR1.

ŌĆō ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ JEOC (end of conversion injected, ąŠą║ąŠąĮčćą░ąĮąĖąĄ ąĖąĮąČąĄą║čéąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ).

ŌĆō ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé JEOCIE.

ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ADC ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ.

ąĀąĄąČąĖą╝ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčŗčģ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣ (čüontinuous conversion mode). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ADC ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąĘą░ą┐čāčüčéąĖčé ąĮąŠą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ č鹥ą║čāčēąĄą│ąŠ. ąŁč鹊čé čĆąĄąČąĖą╝ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ čü ą▒ąĖč鹊ą╝ CONT, čĆą░ą▓ąĮčŗą╝ 1, ą╗ąĖą▒ąŠ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░, ą╗ąĖą▒ąŠ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SWSTRT ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR2 (č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ąŠą▓ regular).

ą¤ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (ąĄčüą╗ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ą╗ą░čüčī ą│čĆčāą┐ą┐ą░ ą║ą░ąĮą░ą╗ąŠą▓ regular):

ŌĆō ą¤ąŠčüą╗ąĄą┤ąĮąĖąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ 16-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ADC_DR.

ŌĆō ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ EOC.

ŌĆō ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé EOCIE.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ą░ąĮą░ą╗čŗ injected ąĮąĄ ą╝ąŠą│čāčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓čŗą▓ą░čéčīčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ continuous. ąĢą┤ąĖąĮčüčéą▓ąĄąĮąĮąŠąĄ ąĖčüą║ą╗čÄč湥ąĮąĖąĄ - ą║ąŠą│ą┤ą░ ą║ą░ąĮą░ą╗ injected čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐ąŠčüą╗ąĄ ą║ą░ąĮą░ą╗ąŠą▓ regular ą▓ čĆąĄąČąĖą╝ąĄ continuous (čü ą┐ąŠą╝ąŠčēčīčÄ ą▒ąĖčéą░ JAUTO), čüą╝. čüąĄą║čåąĖčÄ Auto-injection).

ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 45, ą┤ą╗čÅ ADC čéčĆąĄą▒čāąĄčéčüčÅ ą▓čĆąĄą╝čÅ čüčéą░ą▒ąĖą╗ąĖąĘą░čåąĖąĖ tSTAB ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ąŠąĮ čüą╝ąŠąČąĄčé č鹊čćąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ. ą¤ąŠčüą╗ąĄ čüčéą░čĆčéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC ąĖ ą┐ąŠčüą╗ąĄ 15 čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ EOC, ąĖ ą▓ 16-ą▒ąĖčéąĮąŠą╝ čĆąĄą│ąĖčüčéčĆąĄ ą┤ą░ąĮąĮčŗčģ ADC ą┐ąŠčÅą▓ąĖčéčüčÅ čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

ąĀąĖčü. 45. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ čĆą░ą▒ąŠčéčŗ ADC.

Analog watchdog. ąæąĖčé čüčéą░čéčāčüą░ AWD ą┤ą╗čÅ analog watchdog čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ąĄčüą╗ąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄą╝ąŠąĄ ADC, ąŠą║ą░ąČąĄčéčüčÅ ąĮąĖąČąĄ ąĮąĖąČąĮąĄą│ąŠ ą┐ąŠčĆąŠą│ą░ ąĖą╗ąĖ ą▓čŗčłąĄ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ąŠčĆąŠą│ą░. ąŁčéąĖ ą┐ąŠčĆąŠą│ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ ą▓ 12 ą╝ą╗ą░ą┤čłąĖčģ ą▒ąĖčéą░čģ 16-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ADC_HTR ąĖ ADC_LTR. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮąŠ ą▒ąĖč鹊ą╝ AWDIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR1.

ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠčĆąŠą│ą░ ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ, ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą▒ąĖč鹊ą╝ ALIGN ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR2. ąÉąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčéčüčÅ čü ąĮąĖąČąĮąĖą╝ ąĖ ą▓ąĄčĆčģąĮąĖą╝ ą┐ąŠčĆąŠą│ą░ą╝ąĖ ą┐ąĄčĆąĄą┤ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄą╝.

ąĀąĖčü. 46. ąŚą░čēąĖčēąĄąĮąĮą░čÅ ąŠą▒ą╗ą░čüčéčī analog watchdog.

ąóą░ą▒ą╗ąĖčåą░ 66 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ čĆąĄą│ąĖčüčéčĆ ADC_CR1, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī analog watchdog ąĮą░ ąŠą┤ąĮąŠą╝ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąĄ ą║ą░ąĮą░ą╗ąŠą▓.

ąóą░ą▒ą╗ąĖčåą░ 66. ąÆčŗą▒ąŠčĆ ą║ą░ąĮą░ą╗ą░ analog watchdog.

ąÜą░ąĮą░ą╗čŗ, ąĘą░čēąĖčēąĄąĮąĮčŗąĄ Analog Watchdog

|

ąŻą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ ADC_CR1

(x - ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ)

|

| AWDSGL |

AWDEN |

JAWDEN |

| ąØąĄčé ąĘą░čēąĖčéčŗ |

x |

0 |

0 |

| ąÆčüąĄ injected ą║ą░ąĮą░ą╗čŗ |

0 |

0 |

1 |

| ąÆčüąĄ regular ą║ą░ąĮą░ą╗čŗ |

0 |

1 |

0 |

| ąÆčüąĄ regular ąĖ injected ą║ą░ąĮą░ą╗čŗ |

0 |

1 |

1 |

| ą×ą┤ąĖąĮ(1) injected ą║ą░ąĮą░ą╗ |

1 |

0 |

1 |

| ą×ą┤ąĖąĮ(1) regular ą║ą░ąĮą░ą╗ |

1 |

1 |

0 |

| ą×ą┤ąĖąĮ(1) regular ąĖą╗ąĖ injected ą║ą░ąĮą░ą╗ |

1 |

1 |

1 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ AWDCH[4:0].

ąĀąĄąČąĖą╝ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ. ąŁč鹊čé čĆąĄąČąĖą╝ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą│čĆčāą┐ą┐čŗ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą║ą░ąĮą░ą╗ąŠą▓. ąĀąĄąČąĖą╝ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SCAN ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR1. ąÜą░ą║ č鹊ą╗čīą║ąŠ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ADC čüą║ą░ąĮąĖčĆčāąĄčé ą▓čüąĄ ą║ą░ąĮą░ą╗čŗ, ą▓čŗą▒čĆą░ąĮąĮčŗąĄ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ ADC_SQRx (ą┤ą╗čÅ ą║ą░ąĮą░ą╗ąŠą▓ regular) ąĖą╗ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_JSQR (ą┤ą╗čÅ ą║ą░ąĮą░ą╗ąŠą▓ injected). ą×ą┤ąĖąĮąŠčćąĮąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ą│čĆčāą┐ą┐čŗ. ą¤ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╣ ą║ą░ąĮą░ą╗ ą▓ ą│čĆčāą┐ą┐ąĄ. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé CONT, č鹊 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ regular ąĮąĄ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝ ą▓čŗą▒čĆą░ąĮąĮąŠą╝ ą║ą░ąĮą░ą╗ąĄ ą│čĆčāą┐ą┐čŗ, ą▓ą╝ąĄčüč鹊 čŹč鹊ą│ąŠ čüąĮąŠą▓ą░ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĮą░ ą┐ąĄčĆą▓ąŠą╝ ą▓čŗą▒čĆą░ąĮąĮąŠą╝ ą║ą░ąĮą░ą╗ąĄ ą│čĆčāą┐ą┐čŗ.

ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé DMA, č鹊 ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ (direct memory access, DMA) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ą░ąĮąĮčŗčģ, ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗčģ ąĖąĘ ą│čĆčāą┐ą┐čŗ ą║ą░ąĮą░ą╗ąŠą▓ regular (čüąŠčģčĆą░ąĮąĄąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_DR) ą▓ SRAM ą┐ąŠčüą╗ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ regular.

ąÆ čĆąĄą│ąĖčüčéčĆąĄ ADC_SR čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé EOC:

ŌĆó ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą║ą░ąČą┤ąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą│čĆčāą┐ą┐čŗ regular, ąĄčüą╗ąĖ ą▒ąĖčé EOCS čüą▒čĆąŠčłąĄąĮ ą▓ 0.

ŌĆó ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą║ą░ąČą┤ąŠą│ąŠ regular ą║ą░ąĮą░ą╗ą░, ąĄčüą╗ąĖ ą▒ąĖčé EOCS čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1.

ąöą░ąĮąĮčŗąĄ, ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ąĖąĘ injected-ą║ą░ąĮą░ą╗ą░ ą▓čüąĄą│ą┤ą░ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ ADC_JDRx.

[ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĖąĮąČąĄą║čéąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ą║ą░ąĮą░ą╗ą░ą╝ąĖ]

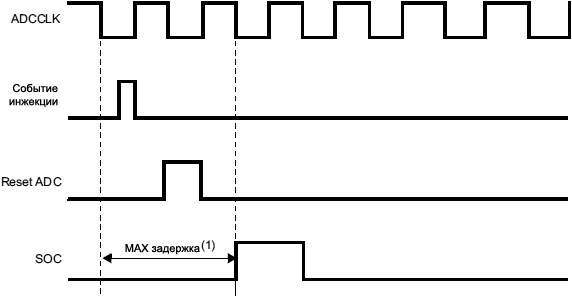

ąśąĮąČąĄą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąŠ čéčĆąĖą│ą│ąĄčĆčā. ąöą╗čÅ triggered injection ą▒ąĖčé JAUTO ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR1 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą▓ 0.

1. ąŚą░ą┐čāčüą║ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą│čĆčāą┐ą┐čŗ ą║ą░ąĮą░ą╗ąŠą▓ regular ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą╗ąĖą▒ąŠ ą▓ąĮąĄčłąĮąĖą╝ čéčĆąĖą│ą│ąĄčĆąŠą╝, ą╗ąĖą▒ąŠ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SWSTART ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR2.

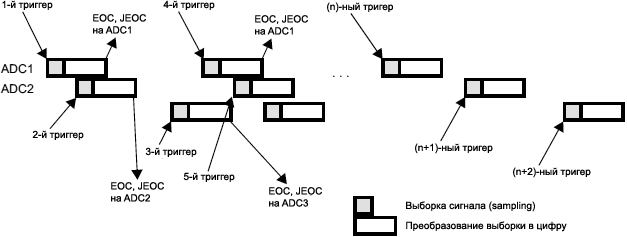

2. ąĢčüą╗ąĖ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ąĮąĄčłąĮąĖą╣ injected-čéčĆąĖą│ą│ąĄčĆ, ąĖą╗ąĖ ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé JSWSTART ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ regular ą│čĆčāą┐ą┐čŗ ą║ą░ąĮą░ą╗ąŠą▓, č鹊 č鹥ą║čāčēąĄąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī injected-ą║ą░ąĮą░ą╗ą░ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠą│ąŠ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ.

3. ąŚą░č鹥ą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ regular ą│čĆčāą┐ą┐čŗ ą║ą░ąĮą░ą╗ąŠą▓ ą▓ąŠąĘąŠą▒ąĮąŠą▓ąĖčéčüčÅ ąŠčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┐čĆąĄčĆą▓ą░ąĮąĮąŠą│ąŠ regular-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąĢčüą╗ąĖ čüąŠą▒čŗčéąĖąĄ regular ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą▓ąŠ ą▓čĆąĄą╝čÅ injected-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, č鹊 injected-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĮąĄ ą┐čĆąĄčĆčŗą▓ą░ąĄčéčüčÅ, ą▓ą╝ąĄčüč鹊 čŹč鹊ą│ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī regular ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ injected. ąĀąĖčü. 47 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēčāčÄ ą┤ąĖą░ą│čĆą░ą╝ą╝čā ą▓čĆąĄą╝ąĄąĮąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ triggered injection ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čāą▒ąĄą┤ąĖčéčīčüčÅ, čćč鹊 ąĖąĮč鹥čĆą▓ą░ą╗ ą╝ąĄąČą┤čā čüąŠą▒čŗčéąĖčÅą╝ąĖ čéčĆąĖą│ą│ąĄčĆą░ ą▒ąŠą╗čīčłąĄ, č湥ą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī injection. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ ą┤ą╗ąĖąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 30 čéą░ą║č鹊ą▓ ADC (čé. ąĄ. 2 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čüąŠ ą▓čĆąĄą╝ąĄąĮąĄą╝ ą▓čŗą▒ąŠčĆą║ąĖ 3 čéą░ą║č鹊ą▓čŗčģ ą┐ąĄčĆąĖąŠą┤ą░), č鹊 ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ą╝ąĄąČą┤čā čéčĆąĖą│ą│ąĄčĆą░ą╝ąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī 31 čéą░ą║čé ADC.

ąĀąĖčü. 47. ąøą░č鹥ąĮčéąĮąŠčüčéčī injected-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą╗ą░č鹥ąĮčéąĮąŠčüčéąĖ ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą▓ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖčģ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░čģ ą┤ą░čéą░čłąĖč鹊ą▓ ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ STM32F4xx.

Auto-injection. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé JAUTO, č鹊 ą║ą░ąĮą░ą╗čŗ ą▓ ą│čĆčāą┐ą┐ąĄ injected ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘčāčÄčéčüčÅ ą┐ąŠčüą╗ąĄ regular-ą│čĆčāą┐ą┐čŗ ą║ą░ąĮą░ą╗ąŠą▓. ąŁč鹊 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┤ąŠ 20 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ ADC_SQRx ąĖ ADC_JSQR.

ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ ą▓ąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ ąĮą░ injected-ą║ą░ąĮą░ą╗ą░čģ.

ąĢčüą╗ąĖ ą▓ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ ą▒ąĖčéčā JAUTO čéą░ą║ąČąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé CONT, č鹊 regular-ą║ą░ąĮą░ą╗čŗ, ąĘą░ ą║ąŠč鹊čĆčŗą╝ąĖ ąĖą┤čāčé injected-ą║ą░ąĮą░ą╗čŗ, ą▒čāą┤čāčé ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓čŗą▓ą░čéčīčüčÅ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĮąĄą▓ąŠąĘą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čĆąĄąČąĖą╝čŗ auto-injected ąĖ discontinuous.

[ą¤čĆąĄčĆčŗą▓ąĖčüčéčŗą╣ (discontinuous) čĆąĄąČąĖą╝]

ąōčĆčāą┐ą┐ą░ regular. ąŁč鹊čé čĆąĄąČąĖą╝ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ DISCEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR1. ąĀąĄąČąĖą╝ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą║ąŠčĆąŠčéą║ąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĖąĘ n ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣ (n Ōēż 8), čŹč鹊 čćą░čüčéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣, ą▓čŗą▒čĆą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ ADC_SQRx. ąŚąĮą░č湥ąĮąĖąĄ n ąĘą░ą┤ą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ą▒ąĖčéčŗ DISCNUM[2:0] čĆąĄą│ąĖčüčéčĆą░ ADC_CR1.

ąÜąŠą│ą┤ą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą▓ąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ, čŹč鹊 ąĘą░ą┐čāčüą║ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ n ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣, ą▓čŗą▒čĆą░ąĮąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ ADC_SQRx, ą┐ąŠą║ą░ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅčéčüčÅ ą▓čüąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ. ą×ą▒čēą░čÅ ą┤ą╗ąĖąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ L[3:0] čĆąĄą│ąĖčüčéčĆą░ ADC_SQR1.

ą¤čĆąĖą╝ąĄčĆ:

ŌĆó n = 3, ą║ą░ąĮą░ą╗čŗ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ 0, 1, 2, 3, 6, 7, 9, 10.

ŌĆó 1-ą╣ čéčĆąĖą│ą│ąĄčĆ: ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī 0, 1, 2. ąĪąŠą▒čŗčéąĖąĄ EOC ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĖ.

ŌĆó 2-ą╣ čéčĆąĖą│ą│ąĄčĆ: ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī 3, 6, 7. ąĪąŠą▒čŗčéąĖąĄ EOC ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĖ.

ŌĆó 3-ą╣ čéčĆąĖą│ą│ąĄčĆ: ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī 9, 10. ąĪąŠą▒čŗčéąĖąĄ EOC ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĖ.

ŌĆó 4-ą╣ čéčĆąĖą│ą│ąĄčĆ: ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī 0, 1, 2. ąĪąŠą▒čŗčéąĖąĄ EOC ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ ą│čĆčāą┐ą┐ą░ regular ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ discontinuous, ą┐čĆąŠą╗ąŠąĮą│ą░čåąĖčÅ ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé. ąÜąŠą│ą┤ą░ ą▓čüąĄ ą┐ąŠą┤ą│čĆčāą┐ą┐čŗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮčŗ, čüą╗ąĄą┤čāčÄčēąĖą╣ čéčĆąĖą│ą│ąĄčĆ ąĘą░ą┐čāčüčéąĖčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆą▓ąŠą╣ ą┐ąŠą┤ą│čĆčāą┐ą┐čŗ. ąÆ ą┐ąŠą║ą░ąĘą░ąĮąĮąŠą╝ ą▓čŗčłąĄ ą┐čĆąĖą╝ąĄčĆąĄ 4-ą╣ čéčĆąĖą│ą│ąĄčĆ ąĘą░ąĮąŠą▓ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčé ą║ą░ąĮą░ą╗čŗ 0, 1 ąĖ 2 ą▓ 1-ą╣ ą┐ąŠą┤ą│čĆčāą┐ą┐ąĄ.

ąōčĆčāą┐ą┐ą░ injected. ąŁč鹊čé čĆąĄąČąĖą╝ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ JDISCEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR1. ąĀąĄąČąĖą╝ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ, ą▓čŗą▒čĆą░ąĮąĮąŠą╣ čĆąĄą│ąĖčüčéčĆąŠą╝ ADC_JSQR, ą║ą░ąĮą░ą╗ ąĘą░ ą║ą░ąĮą░ą╗ąŠą╝, ą┐ąŠčüą╗ąĄ čüąŠą▒čŗčéąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░.

ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüąŠą▒čŗčéąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░, ąŠąĮąŠ ąĘą░ą┐čāčüą║ą░ąĄčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą║ą░ąĮą░ą╗ą░, ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_JSQR, ą┐ąŠą║ą░ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅčéčüčÅ ą▓čüąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ. ą×ą▒čēą░čÅ ą┤ą╗ąĖąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ JL[1:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_JSQR.

ą¤čĆąĖą╝ąĄčĆ:

n = 1, ą║ą░ąĮą░ą╗čŗ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ 1, 2, 3.

ŌĆó 1-ą╣ čéčĆąĖą│ą│ąĄčĆ: ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčéčüčÅ ą║ą░ąĮą░ą╗ 1.

ŌĆó 2-ą╣ čéčĆąĖą│ą│ąĄčĆ: ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčéčüčÅ ą║ą░ąĮą░ą╗ 2.

ŌĆó 3-ą╣ čéčĆąĖą│ą│ąĄčĆ: ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčéčüčÅ ą║ą░ąĮą░ą╗ 3, ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄ JEOC.

ŌĆó 3-ą╣ čéčĆąĖą│ą│ąĄčĆ: ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčéčüčÅ ą║ą░ąĮą░ą╗ 1.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ ą▓čüąĄ injected-ą║ą░ąĮą░ą╗čŗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮčŗ, čüą╗ąĄą┤čāčÄčēąĖą╣ čéčĆąĖą│ą│ąĄčĆ ąĘą░ą┐čāčüčéąĖčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆą▓ąŠą│ąŠ injected-ą║ą░ąĮą░ą╗ą░. ąÆ ą┐ąŠą║ą░ąĘą░ąĮąĮąŠą╝ ą▓čŗčłąĄ ą┐čĆąĖą╝ąĄčĆąĄ 4-ą╣ čéčĆąĖą│ą│ąĄčĆ čüąĮąŠą▓ą░ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčé 1-ą╣ injected ą║ą░ąĮą░ą╗ 1. ąØąĄą▓ąŠąĘą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠą▒ą░ čĆąĄąČąĖą╝ą░ auto-injected ąĖ discontinuous. ąĀąĄąČąĖą╝ discontinuous ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčīčüčÅ ą┤ą╗čÅ regular-ą│čĆčāą┐ą┐čŗ ąĖ injected-ą│čĆčāą┐ą┐čŗ. ąĀąĄąČąĖą╝ discontinuous ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąŠą┤ąĮąŠą╣ ą│čĆčāą┐ą┐čŗ ą║ą░ąĮą░ą╗ąŠą▓.

[ąÆčŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ]

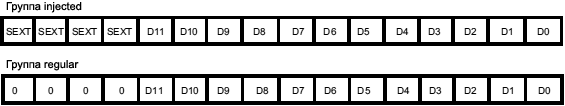

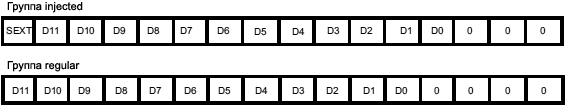

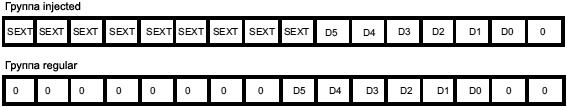

ąæąĖčé ALIGN ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR2 ą▓čŗą▒ąĖčĆą░ąĄčé ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ, čüąŠčģčĆą░ąĮčÅąĄą╝čŗčģ ą┐ąŠčüą╗ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąöą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗčĆą░ą▓ąĮąĄąĮčŗ ą▓ą┐čĆą░ą▓ąŠ ąĖą╗ąĖ ą▓ą╗ąĄą▓ąŠ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčüčāąĮą║ą░čģ 48 ąĖ 49.

ąĀąĖčü. 48. ą¤čĆą░ą▓ąŠąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ 12-ą▒ąĖčéąĮčŗčģ ą┤ą░ąĮąĮčŗčģ.

ąĀąĖčü. 49. ąøąĄą▓ąŠąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ 12-ą▒ąĖčéąĮčŗčģ ą┤ą░ąĮąĮčŗčģ.

ąŚąĮą░č湥ąĮąĖąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąĖąĘ injected ą│čĆčāą┐ą┐čŗ ą║ą░ąĮą░ą╗ąŠą▓ čāą╝ąĄąĮčīčłą░ąĄčéčüčÅ ąĮą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝ąŠąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ čüą╝ąĄčēąĄąĮąĖąĄ, ąĘą░ą┐ąĖčüą░ąĮąĮąŠąĄ ą▓ čĆąĄą│ąĖčüčéčĆčŗ ADC_JOFRx, čćč鹊ą▒čŗ čĆąĄąĘčāą╗čīčéą░čé ą╝ąŠą│ čüčéą░čéčī ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝. ąæąĖčé SEXT ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čĆą░čüčłąĖčĆąĄąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüąŠ ąĘąĮą░ą║ąŠą╝.

ąöą╗čÅ ą║ą░ąĮą░ą╗ąŠą▓ ą▓ ą│čĆčāą┐ą┐ąĄ regular ąĮąĖą║ą░ą║ąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ ąĮąĄ ą▓čŗčćąĖčéą░ąĄčéčüčÅ, ą┐ąŠčŹč鹊ą╝čā ą▓čüąĄą│ą┤ą░ ąĘąĮą░čćą░čēąĖą╝ąĖ ą▒čāą┤čāčé 12 ą▒ąĖčé.

ąĪą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ čüą╗čāčćą░ą╣: ą┐čĆąĖ ą╗ąĄą▓ąŠą╝ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĖ ą┤ą░ąĮąĮčŗąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░čÄčéčüčÅ ąĮą░ ą▒ą░ąĘąĄ ą┐ąŠą╗ąŠą▓ąĖąĮčŗ čüą╗ąŠą▓ą░ (ą▓ 2 ą▒ą░ą╣čéą░čģ), ą║čĆąŠą╝ąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╣ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ 6 ą▒ąĖčé. ąöą╗čÅ 6-ą▒ąĖčéąĮąŠą╣ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░čÄčéčüčÅ ąĮą░ ą▒ą░ąĘąĄ ąŠą┤ąĮąŠą│ąŠ ą▒ą░ą╣čéą░, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 50.

ąĀąĖčü. 50. ąøąĄą▓ąŠąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ 6-ą▒ąĖčéąĮčŗčģ ą┤ą░ąĮąĮčŗčģ.

[ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠąĄ ą▓čĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ ą║ą░ąČą┤ąŠą╝ ą║ą░ąĮą░ą╗ąĄ]

ADC ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčé ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĘą░ ADCCLK čéą░ą║č鹊ą▓, čćč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮąŠ ą▒ąĖčéą░ą╝ąĖ SMP[2:0] čĆąĄą│ąĖčüčéčĆąŠą▓ ADC_SMPR1 ąĖ ADC_SMPR2. ąŻ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčéą╗ąĖčćą░čÄčēąĄąĄčüčÅ ą▓čĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ (sampling time).

ą×ą▒čēąĄąĄ ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

Tconv = ą▓čĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ + 12 čéą░ą║č鹊ą▓

ą¤čĆąĖą╝ąĄčĆ: ą┐čĆąĖ ADCCLK = 30 MHz ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ą▓čŗą▒ąŠčĆą║ąĖ 3 čéą░ą║čéą░, Tconv = 3 + 12 = 15 čéą░ą║č鹊ą▓ = 0.5 ą╝ą║čü ą┐čĆąĖ APB2 ąĮą░ čćą░čüč鹊č鹥 60 ą£ąōčå.

[ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą┐ąŠ ą▓ąĮąĄčłąĮąĄą╝čā čéčĆąĖą│ą│ąĄčĆčā ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéčĆąĖą│ą│ąĄčĆą░]

ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čāčēąĄąĮąŠ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ čüąŠą▒čŗčéąĖčÅ (ąĮą░ą┐čĆąĖą╝ąĄčĆ timer capture, ą╗ąĖąĮąĖčÅ EXTI). ąĢčüą╗ąĖ ą▒čŗčéčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ EXTEN[1:0] (ą┤ą╗čÅ regular-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ) ąĖą╗ąĖ ą▒ąĖčéčŗ JEXTEN[1:0] (ą┤ą╗čÅ injected-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ) ąŠčéą╗ąĖčćą░čÄčéčüčÅ ąŠčé 0b00, č鹊 ą▓ąĮąĄčłąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ čü ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą┐ąŠą╗čÅčĆąĮąŠčüčéčīčÄ ą╝ąŠą│čāčé ąĘą░ą┐čāčüčéąĖčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ. ąóą░ą▒ą╗ąĖčåą░ 67 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ ą╝ąĄąČą┤čā ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ EXTEN[1:0] ąĖ JEXTEN[1:0] ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéčīčÄ čéčĆąĖą│ą│ąĄčĆą░.

ąóą░ą▒ą╗ąĖčåą░ 67. ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ čéčĆąĖą│ą│ąĄčĆą░.

| ąśčüč鹊čćąĮąĖą║ |

EXTEN[1:0] / JEXTEN[1:0] |

| ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čéčĆąĖą│ą│ąĄčĆą░ ąĘą░ą┐čĆąĄčēąĄąĮąŠ |

00 |

| ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ |

01 |

| ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ |

10 |

| ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ ą┐ąŠ čäčĆąŠąĮčéčā, ąĖ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ |

11 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠą╗čÅčĆąĮąŠčüčéčī ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ą╝ąŠąČąĮąŠ ą╝ąĄąĮčÅčéčī ąĮą░ ą╗ąĄčéčā.

ąæąĖčéčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ EXTSEL[3:0] ąĖ JEXTSEL[3:0] ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░, ą║ą░ą║ąŠąĄ ąĖąĘ 16 ą▓ąŠąĘą╝ąŠąČąĮčŗčģ čüąŠą▒čŗčéąĖą╣ ą╝ąŠąČąĄčé ąĘą░ą┐čāčüčéąĖčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą┤ą╗čÅ regular ąĖą╗ąĖ injected ą│čĆčāą┐ą┐čŗ.

ąÆ čéą░ą▒ą╗ąĖčåąĄ 68 ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą▓ąŠąĘą╝ąŠąČąĮčŗą╣ ą▓ąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ ą┤ą╗čÅ regular-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

ąóą░ą▒ą╗ąĖčåą░ 68. ąÆąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ąŠą▓ regular.

| ąśčüč鹊čćąĮąĖą║ čüąŠą▒čŗčéąĖčÅ |

ąóąĖą┐ |

EXTSEL[3:0] |

| TIM1_CH1 |

ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ

ąŠčé čéą░ą╣ą╝ąĄčĆąŠą▓

ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ |

0000 |

| TIM1_CH2 |

0001 |

| TIM1_CH3 |

0010 |

| TIM2_CH2 |

0011 |

| TIM2_CH3 |

0100 |

| TIM2_CH4 |

0101 |

| TIM2_TRGO |

0110 |

| TIM3_CH1 |

0111 |

| TIM3_TRGO |

1000 |

| TIM4_CH4 |

1001 |

| TIM5_CH1 |

1010 |

| TIM5_CH2 |

1011 |

| TIM5_CH3 |

1100 |

| TIM8_CH1 |

1101 |

| TIM8_TRGO |

1110 |

| EXTI line11 |

ąÆąĮąĄčłąĮąĖą╣ ą▓čŗą▓ąŠą┤ |

1111 |

ąÆ čéą░ą▒ą╗ąĖčåąĄ 69 ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą▓ąŠąĘą╝ąŠąČąĮčŗą╣ ą▓ąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ ą┤ą╗čÅ injected-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

| ąśčüč鹊čćąĮąĖą║ čüąŠą▒čŗčéąĖčÅ |

ąóąĖą┐ |

JEXTSEL[3:0] |

| TIM1_CH4 |

ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ

ąŠčé čéą░ą╣ą╝ąĄčĆąŠą▓

ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ |

0000 |

| TIM1_TRGO |

0001 |

| TIM2_CH1 |

0010 |

| TIM2_TRGO |

0011 |

| TIM3_CH2 |

0100 |

| TIM3_CH4 |

0101 |

| TIM4_CH1 |

0110 |

| TIM4_CH2 |

0111 |

| TIM4_CH3 |

1000 |

| TIM4_TRGO |

1001 |

| TIM5_CH4 |

1010 |

| TIM5_TRGO |

1011 |

| TIM8_CH2 |

1100 |

| TIM8_CH3 |

1101 |

| TIM8_CH4 |

1110 |

| EXTI line15 |

ąÆąĮąĄčłąĮąĖą╣ ą▓čŗą▓ąŠą┤ |

1111 |

ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĖąĮąĖčåąĖąĖčĆčāąĄą╝čŗą╣ čéčĆąĖą│ą│ąĄčĆ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SWSTART (ą┤ą╗čÅ regular-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ) ąĖą╗ąĖ ą▒ąĖčéą░ JSWSTART (ą┤ą╗čÅ injected-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ) ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR2.

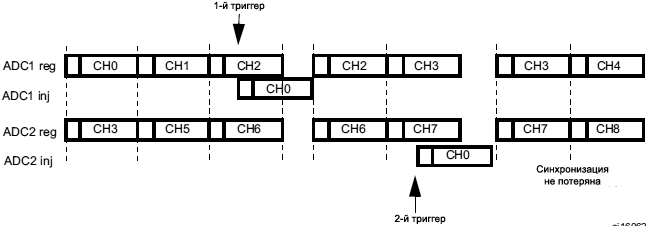

ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą│čĆčāą┐ą┐čŗ regular ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĄčĆą▓ą░ąĮąŠ injected-čéčĆąĖą│ą│ąĄčĆąŠą╝.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓čŗą▒ąŠčĆ čéčĆąĖą│ą│ąĄčĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ ąĮą░ ą╗ąĄčéčā. ą×ą┤ąĮą░ą║ąŠ ą┐čĆąĖ čüą╝ąĄąĮąĄ ą▓čŗą▒ąŠčĆą░ ąĄčüčéčī ąŠą║ąĮąŠ ą▓čĆąĄą╝ąĄąĮąĖ 1 čéą░ą║čé APB, ą▓ č鹥č湥ąĮąĖąĄ ą║ąŠč鹊čĆąŠą│ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čéčĆąĖą│ą│ąĄčĆą░ ąĘą░ą┐čĆąĄčēąĄąĮąŠ. ąŁč鹊 čüą┤ąĄą╗ą░ąĮąŠ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī čüą╗čāčćą░ą╣ąĮąŠą│ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣.

[ąĀąĄąČąĖą╝ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (fast conversion mode)]

ąĢčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čāčüą║ąŠčĆąĖčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą┐čāč鹥ą╝ čāą╝ąĄąĮčīčłąĄąĮąĖąĄ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ (čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ) ADC. ąæąĖčéčŗ RES ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ąĖčé, ą┤ąŠčüčéčāą┐ąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┤ą░ąĮąĮčŗčģ. ą£ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą▓ą░čĆąĖą░ąĮčéą░ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ čüą╗ąĄą┤čāčÄčēąĄąĄ:

12 ą▒ąĖčé: 3 + 12 = 15 čéą░ą║č鹊ą▓ ADCCLK

10 ą▒ąĖčé: 3 + 10 = 13 čéą░ą║č鹊ą▓ ADCCLK

8 ą▒ąĖčé: 3 + 8 = 11 čéą░ą║č鹊ą▓ ADCCLK

6 ą▒ąĖčé: 3 + 6 = 9 čéą░ą║č鹊ą▓ ADCCLK

[ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗą╝ąĖ]

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ DMA. ą¤ąŠčüą║ąŠą╗čīą║čā ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ regular-ą║ą░ąĮą░ą╗ą░ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ ąŠą┤ąĮąŠą╝ čāąĮąĖą║ą░ą╗čīąĮąŠą╝ čĆąĄą│ąĖčüčéčĆąĄ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠą╗ąĄąĘąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī DMA ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ regular-ą║ą░ąĮą░ą╗ą░. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗ąĖčé ąĖąĘą▒ąĄąČą░čéčī ą┐ąŠč鹥čĆąĖ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ čāąČąĄ čüąŠčģčĆą░ąĮąĄąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_DR.

ąÜąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮ čĆąĄąČąĖą╝ DMA (ą▒ąĖčé DMA ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR2 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1), ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ regular-ą║ą░ąĮą░ą╗ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĘą░ą┐čĆąŠčü DMA. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąĄčĆąĄą┤ą░čéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ ADC_DR ą▓ ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ, ą▓čŗą▒čĆą░ąĮąĮąŠąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣.

ąØąĄčüą╝ąŠčéčĆčÅ ąĮą░ čŹč鹊, ą▓ čüą╗čāčćą░ąĄ ą┐ąŠč鹥čĆąĖ ą┤ą░ąĮąĮčŗčģ (ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé OVR ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_SR, ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ OVRIE). ąóąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA ąĘą░ą┐čĆąĄčēą░čÄčéčüčÅ, ąĖ ąĘą░ą┐čĆąŠčüčŗ DMA ą▒ąŠą╗čīčłąĄ ąĮąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ, ąĄčüą╗ąĖ ą┤ąĄą╗ą░ąĄčéčüčÅ ąĘą░ą┐čĆąŠčü DMA, regular-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąŠą▒čĆčŗą▓ą░čÄčéčüčÅ, ąĖ ą┤ą░ą╗čīąĮąĄą╣čłąĖąĄ regular-čéčĆąĖą│ą│ąĄčĆčŗ ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ. ąØąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąŠčćąĖčüčéąĖčéčī čäą╗ą░ą│ OVR ąĖ ą▒ąĖčé DMAEN ą▓ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╝ ą┐ąŠč鹊ą║ąĄ DMA (DMA stream), ąĖ ąĘą░ąĮąŠą▓ąŠ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī ąĖ DMA, ąĖ ADC, čćč鹊ą▒čŗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ąČąĄą╗ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░ą╗ąĖčüčī ą▓ ą┐čĆą░ą▓ąĖą╗čīąĮčāčÄ čÅč湥ą╣ą║čā ą┐ą░ą╝čÅčéąĖ. ąóąŠą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąŠ, ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ čüąĮąŠą▓ą░ čĆą░ąĘčĆąĄčłąĄąĮą░. ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ injected-ą║ą░ąĮą░ą╗ą░ ąĮąĄ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮčŗ ą║ ąŠčłąĖą▒ą║ą░ą╝ overrun.

ąÜąŠą│ą┤ą░ OVR = 1 ą▓ čĆąĄąČąĖą╝ąĄ DMA, ąĘą░ą┐čĆąŠčüčŗ DMA ą▒ą╗ąŠą║ąĖčĆčāčÄčéčüčÅ ą┐ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗčģ ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ, ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗąĄ ą▓ RAM, ą╝ąŠąČąĮąŠ čüčćąĖčéą░čéčī ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╝ąĖ.

ą¤ąŠčüą╗ąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA (ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąĄčĆąĄą┤ą░čć ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ DMA_SxNTR ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA):

ŌĆó ąØąŠą▓čŗąĄ ąĘą░ą┐čĆąŠčüčŗ DMA ąĮąĄ ą▓čŗą┤ą░čÄčéčüčÅ ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA, ąĄčüą╗ąĖ ą▒ąĖčé DDS ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR2 čüą▒čĆąŠčłąĄąĮ ą▓ 0 (čŹč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖąĘą▒ąĄąČą░čéčī ąŠčłąĖą▒ą║ąĖ overrun). ą×ą┤ąĮą░ą║ąŠ ą▒ąĖčé DMA ąĮąĄ ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ. ąÆ ąĮąĄą│ąŠ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ 0, ąĘą░č鹥ą╝ 1 ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ąĮąŠą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ŌĆó ąŚą░ą┐čĆąŠčüčŗ ą╝ąŠą│čāčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčī ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ, ąĄčüą╗ąĖ ą▒ąĖčé DDS čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī DMA ą▓ čĆąĄąČąĖą╝ąĄ ą║ąŠą╗čīčåąĄą▓ąŠą│ąŠ ą▒čāč乥čĆą░ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣.

ąöą╗čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ADC ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ OVR, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ DMA, ą▓čŗą┐ąŠą╗ąĮąĖč鹥 čüą╗ąĄą┤čāčÄčēąĖąĄ čłą░ą│ąĖ:

1. ą¤ąĄčĆąĄąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāą╣č鹥 DMA (ąĮą░čüčéčĆąŠą╣č鹥 ą░ą┤čĆąĄčü ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ąĖ čüč湥čéčćąĖą║ NDTR).

2. ą×čćąĖčüčéąĖč鹥 ą▒ąĖčé OVR ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_SR.

3. ąŚą░ą┐čāčüčéąĖč鹥 ADC (čéčĆąĖą│ą│ąĄčĆ) ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣ ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ DMA. ąĢčüą╗ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ą┤ąŠčüčéą░č鹊čćąĮąŠ ą╝ąĄą┤ą╗ąĄąĮąĮąŠ, č鹊 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą╝ąŠąČąĮąŠ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▒ąĖčé EOCS ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CR2 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čćč鹊ą▒čŗ ą▒ąĖčé čüčéą░čéčāčüą░ EOC čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ą╗čüčÅ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą║ą░ąČą┤ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ąĮąĄ č鹊ą╗čīą║ąŠ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ. ąÜąŠą│ą┤ą░ EOCS = 1, ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ overrun ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ. ą¤ąŠčŹč鹊ą╝čā ą║ą░ąČą┤čŗą╣ čĆą░ąĘ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé EOC čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ąĖ ą╝ąŠąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ADC_DR. ą×ą▒čĆą░ą▒ąŠčéą║ą░ overrun čéą░ ąČąĄ čüą░ą╝ą░čÅ, ą║ą░ą║ ąĖ ą▓ čüąĖčéčāą░čåąĖąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ DMA.

ąöą╗čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ADC ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ OVR, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé EOCS, ą▓čŗą┐ąŠą╗ąĮąĖč鹥 čüą╗ąĄą┤čāčÄčēąĖąĄ čłą░ą│ąĖ:

1. ą×čćąĖčüčéąĖč鹥 ą▒ąĖčé ADC OVR ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_SR.

2. ąÉą║čéąĖą▓ąĖčĆčāą╣č鹥 čéčĆąĖą│ą│ąĄčĆ ADC ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▒ąĄąĘ DMA ąĖ ą▒ąĄąĘ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ overrun. ą£ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗ąĄąĘąĮąŠ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī ADC ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░čéčī ąŠą┤ąĖąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ čćąĖčüą╗ąŠ ą║ą░ąĮą░ą╗ąŠą▓ ą▒ąĄąĘ čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ analog watchdog). ąöą╗čÅ čŹč鹊ą│ąŠ DMA ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ (DMA = 0), ąĖ ą▒ąĖčé EOC ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ č鹊ą╗čīą║ąŠ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ (EOCS = 0). ąÆ čéą░ą║ąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ overrun ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

[Multi ADC]

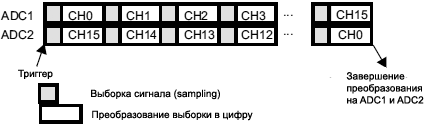

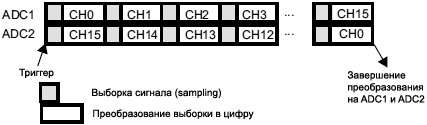

ąÆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ, ą│ą┤ąĄ ą┤ą▓ą░ ADC ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄ, ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čĆąĄąČąĖą╝čŗ Dual (čü ą┤ą▓čāą╝čÅ ADC) ąĖ Triple (čü čéčĆąĄą╝čÅ ADC), čüą╝. čĆąĖčü. 51.

ąĀąĖčü. 51. ąæą╗ąŠą║-čüčģąĄą╝ą░ Multi ADC.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čĆąĖčü. 51:

(1) ąźąŠčéčÅ ą▓ąĮąĄčłąĮąĖąĄ čéčĆąĖą│ą│ąĄčĆčŗ ą┐čĆąĖčüčāčéčüčéą▓čāčÄčé ąĮą░ ADC2 ąĖ ADC3, ąĮą░ čŹč鹊ą╣ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ąŠąĮąĖ ąĮąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ.

(2) ąÆ čĆąĄąČąĖą╝ąĄ Dual ADC ą║ąŠą╝ą┐ąŠąĮąĄąĮčé ADC3 slave ąĮąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮ.

(3) ąÆ čĆąĄąČąĖą╝ąĄ Triple ADC ąŠą▒čēąĖą╣ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ADC (ADC_CDR) čüąŠą┤ąĄčƹȹĖčé regular ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ADC1, ADC2 ąĖ ADC3. ąÆčüąĄ 32 ą▒ąĖčéą░ čĆąĄą│ąĖčüčéčĆą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą▓čŗą▒čĆą░ąĮąĮčŗą╝ ą┐ąŠčĆčÅą┤ą║ąŠą╝ čģčĆą░ąĮąĄąĮąĖčÅ. ąÆ čĆąĄąČąĖą╝ąĄ Dual ADC ąŠą▒čēąĖą╣ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ADC (ADC_CDR) čüąŠą┤ąĄčƹȹĖčé regular ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖ ADC1, ąĖ ADC2. ąśčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓čüąĄ 32 ą▒ąĖčéą░ čĆąĄą│ąĖčüčéčĆą░.

ąÆ čĆąĄąČąĖą╝ąĄ multi ADC ąĘą░ą┐čāčüą║ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ąĖą╗ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠčé ADC1 master ą┤ą╗čÅ slave ADC2 ąĖ ADC3, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ ą▒ąĖčéą░ą╝ąĖ MULTI[4:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CCR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ čĆąĄąČąĖą╝ąĄ multi ADC, ą║ąŠą│ą┤ą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ čéčĆąĖą│ą│ąĄčĆ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ čüąŠą▒čŗčéąĖčÅ, ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī čéčĆąĖą│ą│ąĄčĆ č鹊ą╗čīą║ąŠ ąŠčé master, ąĖ ąĘą░ą┐čĆąĄčéąĖčéčī čéčĆąĖą│ą│ąĄčĆ ąŠčé slave, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī čüą╗čāčćą░ą╣ąĮčŗąĄ čéčĆąĖą│ą│ąĄčĆčŗ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ąĘą░ą┐čāčüčéąĖčéčī ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮčŗąĄ slave-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

ąĀąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ 4 ą▓ąŠąĘą╝ąŠąČąĮčŗčģ čĆąĄąČąĖą╝ą░:

ŌĆó Injected simultaneous mode

ŌĆó Regular simultaneous mode

ŌĆó Interleaved mode

ŌĆó Alternate trigger mode

ąóą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐čĆąĄą┤čŗą┤čāčēąĖąĄ čĆąĄąČąĖą╝čŗ, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗąĄ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ čüą┐ąŠčüąŠą▒ą░ą╝ąĖ:

ŌĆó Injected simultaneous mode + Regular simultaneous mode

ŌĆó Regular simultaneous mode + Alternate trigger mode

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ čĆąĄąČąĖą╝ąĄ multi ADC ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┤ą░ąĮąĮčŗčģ multi-mode (ADC_CDR). ąæąĖčéčŗ čüčéą░čéčāčüą░ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ multi-mode (ADC_CSR).

ąŚą░ą┐čĆąŠčüčŗ DMA ą▓ čĆąĄąČąĖą╝ąĄ Multi ADC. ąÆ čĆąĄąČąĖą╝ąĄ Multi ADC ą▒ą╗ąŠą║ DMA ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ čéčĆąĄčģ čĆą░ąĘą╗ąĖčćąĮčŗčģ čĆąĄąČąĖą╝ą░čģ. ąÆąŠ ą▓čüąĄčģ čüą╗čāčćą░čÅčģ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┐ąŠč鹊ą║ąĖ DMA, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ą║ ADC:

ŌĆō DMA mode 1: ąĮą░ ą║ą░ąČą┤ąŠą╝ ąĘą░ą┐čĆąŠčüąĄ DMA (ą┤ąŠčüčéčāą┐ąĄąĮ ąŠą┤ąĖąĮ 菹╗ąĄą╝ąĄąĮčé ą┤ą░ąĮąĮčŗčģ) ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąŠą╗ąŠą▓ąĖąĮą░ čüą╗ąŠą▓ą░ (2 ą▒ą░ą╣čéą░), ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčēą░čÅ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC.

ąÆ čĆąĄąČąĖą╝ąĄ Triple ADC ą┤ą░ąĮąĮčŗąĄ ADC1 ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ąĮą░ ą┐ąĄčĆą▓ąŠą╝ ąĘą░ą┐čĆąŠčüąĄ, ą┤ą░ąĮąĮčŗąĄ ADC2 ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ąĮą░ ą▓č鹊čĆąŠą╝ ąĘą░ą┐čĆąŠčüąĄ, ąĖ ą┤ą░ąĮąĮčŗąĄ ADC3 ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ąĮą░ čéčĆąĄčéčīąĄą╝ ąĘą░ą┐čĆąŠčüąĄ; ąĘą░č鹥ą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, DMA čüąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ADC1, ąĘą░č鹥ą╝ ą┤ą░ąĮąĮčŗąĄ ADC2, ąĘą░č鹥ą╝ ą┤ą░ąĮąĮčŗąĄ ADC3, ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ. ąĀąĄąČąĖą╝ DMA 1 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ simultaneous triple mode.

ą¤čĆąĖą╝ąĄčĆ:

Regular simultaneous triple mode: ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ 3 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ąĘą░ą┐čĆąŠčüą░ DMA (ą┐ąŠ ąŠą┤ąĮąŠą╝čā ąĮą░ ą║ą░ąČą┤čŗą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗą╣ 菹╗ąĄą╝ąĄąĮčé ą┤ą░ąĮąĮčŗčģ).

1-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[31:0] = ADC1_DR[15:0]

2-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[31:0] = ADC2_DR[15:0]

3-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[31:0] = ADC3_DR[15:0]

4-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[31:0] = ADC1_DR[15:0]

ŌĆō DMA mode 2: ąĮą░ ą║ą░ąČą┤ąŠą╝ ąĘą░ą┐čĆąŠčüąĄ DMA (ą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą▓ą░ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ) 2 ą┐ąŠą╗čāčüą╗ąŠą▓ą░ (2 ą┐ąŠ 2 ą▒ą░ą╣čéą░) ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé ą┤ą▓ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗčģ ADC 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ą║ą░ą║ čüą╗ąŠą▓ąŠ (4 ą▒ą░ą╣čéą░).

ąÆ čĆąĄąČąĖą╝ąĄ Dual ADC, ą┤ą░ąĮąĮčŗąĄ ąŠą▒ąŠąĖčģ ADC2 ąĖ ADC1 ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ąĮą░ ą┐ąĄčĆą▓ąŠą╝ ąĘą░ą┐čĆąŠčüąĄ (ADC2 ą┤ą░ąĮąĮčŗąĄ ąĘą░ąĮąĖą╝ą░čÄčé čüčéą░čĆčłąĄąĄ ą┐ąŠą╗čāčüą╗ąŠą▓ąŠ, ąĖ ą┤ą░ąĮąĮčŗąĄ ADC1 ąĘą░ąĮąĖą╝ą░čÄčé ą╝ą╗ą░ą┤čłąĄąĄ ą┐ąŠą╗čāčüą╗ąŠą▓ąŠ), ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ.

ąÆ čĆąĄąČąĖą╝ąĄ Triple ADC ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ čéčĆąĖ ąĘą░ą┐čĆąŠčüą░ DMA. ąØą░ ą┐ąĄčĆą▓ąŠą╝ ąĘą░ą┐čĆąŠčüąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ ąŠą▒ąŠąĖčģ ADC2 ąĖ ADC1 (ADC2 ą┤ą░ąĮąĮčŗąĄ ąĘą░ąĮąĖą╝ą░čÄčé čüčéą░čĆčłąĄąĄ ą┐ąŠą╗čāčüą╗ąŠą▓ąŠ, ąĖ ą┤ą░ąĮąĮčŗąĄ ADC1 ąĘą░ąĮąĖą╝ą░čÄčé ą╝ą╗ą░ą┤čłąĄąĄ ą┐ąŠą╗čāčüą╗ąŠą▓ąŠ). ąØą░ ą▓č鹊čĆąŠą╝ ąĘą░ą┐čĆąŠčüąĄ ą┐čĆąĄą┤ą░čÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ ąŠą▒ąŠąĖčģ ADC1 ąĖ ADC3 (ADC1 ą┤ą░ąĮąĮčŗąĄ ąĘą░ąĮąĖą╝ą░čÄčé čüčéą░čĆčłąĄąĄ ą┐ąŠą╗čāčüą╗ąŠą▓ąŠ, ąĖ ą┤ą░ąĮąĮčŗąĄ ADC3 ąĘą░ąĮąĖą╝ą░čÄčé ą╝ą╗ą░ą┤čłąĄąĄ ą┐ąŠą╗čāčüą╗ąŠą▓ąŠ). ąØą░ čéčĆąĄčéčīąĄą╝ ąĘą░ą┐čĆąŠčüąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ ąŠą▒ąŠąĖčģ ADC3 ąĖ ADC2 (ADC3 ą┤ą░ąĮąĮčŗąĄ ąĘą░ąĮąĖą╝ą░čÄčé čüčéą░čĆčłąĄąĄ ą┐ąŠą╗čāčüą╗ąŠą▓ąŠ, ąĖ ą┤ą░ąĮąĮčŗąĄ ADC2 ąĘą░ąĮąĖą╝ą░čÄčé ą╝ą╗ą░ą┤čłąĄąĄ ą┐ąŠą╗čāčüą╗ąŠą▓ąŠ), ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ.

DMA mode 2 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ interleaved mode ąĖ ą▓ regular simultaneous mode (č鹊ą╗čīą║ąŠ čĆąĄąČąĖą╝ Dual ADC).

ą¤čĆąĖą╝ąĄčĆ:

a) Interleaved dual mode: ąĘą░ą┐čĆąŠčü DMA ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┤ąŠčüčéčāą┐ąĮčŗ 2 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ:

1-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

2-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

b) Interleaved triple mode: ąĘą░ą┐čĆąŠčü DMA ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┤ąŠčüčéčāą┐ąĮčŗ 2 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ:

1-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

2-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[31:0] = ADC1_DR[15:0] | ADC3_DR[15:0]

3-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[31:0] = ADC3_DR[15:0] | ADC2_DR[15:0]

4-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

ŌĆō DMA mode 3: čŹč鹊čé čĆąĄąČąĖą╝ ą┐ąŠą┤ąŠą▒ąĄąĮ DMA mode 2. ąĢą┤ąĖąĮčüčéą▓ąĄąĮąĮąŠąĄ čĆą░ąĘą╗ąĖčćąĖąĄ čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊 ą▓ ą║ą░ąČą┤ąŠą╝ ąĘą░ą┐čĆąŠčüąĄ DMA (ą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą▓ą░ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ) ą┤ą▓ą░ ą▒ą░ą╣čéą░, ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčēąĖąĄ ą┤ą▓ą░ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ, ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗčģ ADC, ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ ą▓ąĖą┤ąĄ ą┐ąŠą╗čāčüą╗ąŠą▓ą░. ą¤ąŠčĆčÅą┤ąŠą║ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą░ąĮą░ą╗ąŠą│ąĖč湥ąĮ ą┐ąŠčĆčÅą┤ą║čā ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ DMA 2.

DMA mode 3 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ interleaved mode čü čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčÅą╝ąĖ 6 ąĖ 8 ą▒ąĖčé (dual ąĖ triple mode).

ą¤čĆąĖą╝ąĄčĆ:

a) Interleaved dual mode: ąĘą░ą┐čĆąŠčü DMA ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┤ąŠčüčéčāą┐ąĮčŗ 2 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ.

1-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[15:0] = ADC2_DR[7:0] | ADC1_DR[7:0]

2-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[15:0] = ADC2_DR[7:0] | ADC1_DR[7:0]

b) Interleaved triple mode: ąĘą░ą┐čĆąŠčü DMA ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┤ąŠčüčéčāą┐ąĮčŗ 2 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ.

1-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[15:0] = ADC2_DR[7:0] | ADC1_DR[7:0]

2-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[15:0] = ADC1_DR[7:0] | ADC3_DR[7:0]

3-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[15:0] = ADC3_DR[7:0] | ADC2_DR[7:0]

4-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[15:0] = ADC2_DR[7:0] | ADC1_DR[7:0]

ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ overrun: ąĄčüą╗ąĖ ą▒čŗą╗ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ overrun ąĮą░ ąŠą┤ąĮąŠą╝ ąĖąĘ ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮąĮčŗčģ ADC (ADC1 ąĖ ADC2 ą▓ čĆąĄąČąĖą╝ą░čģ dual ąĖ triple, ADC3 č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ triple), ąĘą░ą┐čĆąŠčüčŗ DMA ą▒ąŠą╗čīčłąĄ ąĮąĄ ą▓čŗą┤ą░čÄčéčüčÅ, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ, ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗąĄ ą▓ RAM, ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗ. ą£ąŠąČąĄčé čüą╗čāčćąĖčéčīčüčÅ čéą░ą║, čćč鹊 ą▒ąĖčé EOC, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ąŠą┤ąĮąŠą╝čā ąĖąĘ ADC, ąŠčüčéą░ąĮąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝, ą┐ąŠč鹊ą╝čā čćč鹊 čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ čŹč鹊ą│ąŠ ADC čüąŠą┤ąĄčƹȹĖčé ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ.

Injected simultaneous mode. ąŁč鹊čé čĆąĄąČąĖą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓čŗą▓ą░ąĄčé ąĖąĮąČąĄą║čéąĖčĆąŠą▓ą░ąĮąĮčāčÄ ą│čĆčāą┐ą┐čā ą║ą░ąĮą░ą╗ąŠą▓. ąĪąĖą│ąĮą░ą╗ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ą┐čĆąĖčģąŠą┤ąĖčé ąŠčé ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆą░ ą│čĆčāą┐ą┐čŗ injected ADC1 (ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ JEXTSEL[3:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC1_CR2). Simultaneous trigger ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮ ą┤ą╗čÅ ADC2 ąĖ ADC3.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĮąĄ čüą╗ąĄą┤čāąĄčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓čŗą▓ą░čéčī ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ ą║ą░ąĮą░ą╗ ąĮą░ ą┤ą▓čāčģ/čéčĆąĄčģ ADC (ą┐čĆąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĖ ąŠą┤ąĮąŠą│ąŠ ąĖ č鹊ą│ąŠ ąČąĄ ą║ą░ąĮą░ą╗ą░ ąĮąĄčé ą┐ąĄčĆąĄą║čĆčŗą▓ą░čÄčēąĖčģčüčÅ ą┐ąĄčĆąĖąŠą┤ąŠą▓ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ą┤ą╗čÅ ą┤ą▓čāčģ/čéčĆąĄčģ ADC).

ąÆ simultaneous mode ąŠą┤ąĖąĮ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░čéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ą┤ą╗ąĖąĮąŠą╣, ąĖą╗ąĖ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊ą▒čŗ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą╝ąĄąČą┤čā čéčĆąĖą│ą│ąĄčĆą░ą╝ąĖ ą▒čŗą╗ąĖ ą▒ąŠą╗čīčłąĄ, č湥ą╝ 2 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ (čĆąĄąČąĖą╝ Dual ADC) / 3 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ (čĆąĄąČąĖą╝ Triple ADC). ąśąĮą░č湥 ADC čü ą▒ąŠą╗ąĄąĄ ą║ąŠčĆąŠčéą║ąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ ą╝ąŠąČąĄčé ą┐ąĄčĆąĄąĘą░ą┐čāčüčéąĖčéčīčüčÅ, ą┐ąŠą║ą░ ADC čü ą▒ąŠą╗ąĄąĄ ą┤ą╗ąĖąĮąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ ąĘą░ą▓ąĄčĆčłą░ąĄčé ą┐čĆąĄą┤čŗą┤čāčēąĖąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

Regular ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą╝ąŠąČąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąĮą░ ąŠą┤ąĮąŠą╝ ąĖą╗ąĖ ąĮą░ ą▓čüąĄčģ ADC. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąŠąĮąĖ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ ąĖ ą┐čĆąĄčĆčŗą▓ą░čÄčéčüčÅ ą┐čĆąĖ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖąĖ injected čüąŠą▒čŗčéąĖčÅ. ą×ąĮąĖ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ą▓ ą║ąŠąĮčåąĄ injected-ą│čĆčāą┐ą┐čŗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

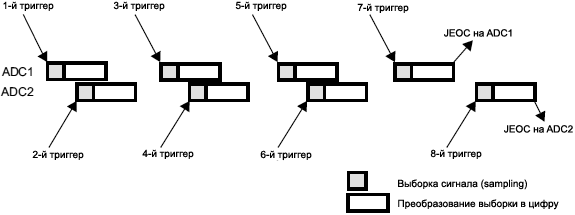

ąĀąĄąČąĖą╝ Dual ADC. ąØą░ čüąŠą▒čŗčéąĖąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC1 ąĖą╗ąĖ ADC2:

ŌĆó ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆčŗ ADC_JDRx ą║ą░ąČą┤ąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ADC.

ŌĆó ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ JEOC (ąĄčüą╗ąĖ čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĮą░ ąŠą┤ąĮąŠą╝ ąĖąĘ ą┤ą▓čāčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ ADC), ą║ąŠą│ą┤ą░ ą▒čŗą╗ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮčŗ injected-ą║ą░ąĮą░ą╗čŗ ADC1/ADC2.

ąĀąĖčü. 52. Injected simultaneous mode ąĮą░ 4 ą║ą░ąĮą░ą╗ą░čģ: dual ADC mode.

ąĀąĄąČąĖą╝ Triple ADC. ąØą░ čüąŠą▒čŗčéąĖąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC1, ADC2 ąĖą╗ąĖ ADC3:

ŌĆó ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ ADC_JDRx ą║ą░ąČą┤ąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ADC.

ŌĆó ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ JEOC (ąĄčüą╗ąĖ čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĮą░ ąŠą┤ąĮąŠą╝ ąĖąĘ čéčĆąĄčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ ADC), ą║ąŠą│ą┤ą░ ą▒čŗą╗ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮčŗ injected-ą║ą░ąĮą░ą╗čŗ ADC1/ADC2/ADC3.

ąĀąĖčü. 53. Injected simultaneous mode ąĮą░ 4 ą║ą░ąĮą░ą╗ą░čģ: triple ADC mode.

[Regular simultaneous mode]

ąŁč鹊čé čĆąĄąČąĖą╝ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮą░ regular ą│čĆčāą┐ą┐ąĄ ą║ą░ąĮą░ą╗ąŠą▓. ąĪąĖą│ąĮą░ą╗ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ą┐ąŠčüčéčāą┐ą░ąĄčé ąĖąĘ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆą░ ą│čĆčāą┐ą┐čŗ regular ADC1 (ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ EXTSEL[3:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC1_CR2). Simultaneous čéčĆąĖą│ą│ąĄčĆ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą┤ą╗čÅ ADC2 ąĖ ADC3.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĮąĄ ą┐čĆąĄąŠą▒čĆą░ąĘčāą╣č鹥 ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ ą║ą░ąĮą░ą╗ ąĮą░ ą┤ą▓čāčģ/čéčĆąĄčģ ADC (ą┐čĆąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĖ ąŠą┤ąĮąŠą│ąŠ ąĖ č鹊ą│ąŠ ąČąĄ ą║ą░ąĮą░ą╗ą░ ąĮąĄčé ą┐ąĄčĆąĄą║čĆčŗą▓ą░čÄčēąĖčģčüčÅ ą┐ąĄčĆąĖąŠą┤ąŠą▓ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ą┤ą╗čÅ ą┤ą▓čāčģ/čéčĆąĄčģ ADC).

ąÆ čĆąĄąČąĖą╝ąĄ regular simultaneous ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░čéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ą┤ą╗ąĖąĮąŠą╣, ąĖą╗ąĖ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊ą▒čŗ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą╝ąĄąČą┤čā čéčĆąĖą│ą│ąĄčĆą░ą╝ąĖ ą▒čŗą╗ąĖ ą▒ąŠą╗čīčłąĄ, č湥ą╝ 2 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ (čĆąĄąČąĖą╝ Dual ADC) / 3 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ (čĆąĄąČąĖą╝ Triple ADC). ąśąĮą░č湥 ADC čü ą▒ąŠą╗ąĄąĄ ą║ąŠčĆąŠčéą║ąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ ą╝ąŠąČąĄčé ą┐ąĄčĆąĄąĘą░ą┐čāčüčéąĖčéčīčüčÅ, ą┐ąŠą║ą░ ADC čü ą▒ąŠą╗ąĄąĄ ą┤ą╗ąĖąĮąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ ąĘą░ą▓ąĄčĆčłą░ąĄčé ą┐čĆąĄą┤čŗą┤čāčēąĖąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

Injected-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮčŗ.

ąĀąĄąČąĖą╝ Dual ADC. ąØą░ čüąŠą▒čŗčéąĖąĖ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC1 ąĖą╗ąĖ ADC2:

ŌĆó ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ 32-ą▒ąĖčéąĮčŗą╣ ąĘą░ą┐čĆąŠčü DMA (ąĄčüą╗ąĖ ą▒ąĖčéčŗ DMA[1:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CCR čĆą░ą▓ąĮčŗ 0b10). ąŁč鹊čé ąĘą░ą┐čĆąŠčü ą┐ąĄčĆąĄą╝ąĄčēą░ąĄčé ą┤ą░ąĮąĮčŗąĄ, ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ADC2, čüąŠčģčĆą░ąĮąĄąĮąĮčŗąĄ ą▓ čüčéą░čĆčłąĄą╝ ą┐ąŠą╗čāčüą╗ąŠą▓ąĄ 32-ą▒ąĖčéąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ADC_CDR, ą▓ SRAM, ąĖ ąĘą░č鹥ą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ADC1, čüąŠčģčĆą░ąĮąĄąĮąĮčŗąĄ ą▓ ą╝ą╗ą░ą┤čłąĄą╝ ą┐ąŠą╗čāčüą╗ąŠą▓ąĄ ADC_CDR, ą▓ SRAM.

ŌĆó ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ EOC (ąĄčüą╗ąĖ čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĮą░ ąŠą┤ąĮąŠą╝ ąĖąĘ ą┤ą▓čāčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ ADC), ą║ąŠą│ą┤ą░ ą▒čŗą╗ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮčŗ ą▓čüąĄ regular ą║ą░ąĮą░ą╗čŗ ADC1/ADC2.

ąĀąĖčü. 54. Regular simultaneous mode ąĮą░ 16 ą║ą░ąĮą░ą╗ą░čģ: dual ADC mode.

ąĀąĄąČąĖą╝ Triple ADC. ąØą░ čüąŠą▒čŗčéąĖąĖ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC1, ADC2 ąĖą╗ąĖ ADC3:

ŌĆó ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čéčĆąĖ 32-ą▒ąĖčéąĮčŗčģ ąĘą░ą┐čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA (ąĄčüą╗ąĖ ą▒ąĖčéčŗ DMA[1:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CCR čĆą░ą▓ąĮčŗ 0b01). ą¤čĆąŠąĖčüčģąŠą┤čÅčé 3 ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖąĘ 32-ą▒ąĖčéąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ADC_CDR ą▓ SRAM: čüąĮą░čćą░ą╗ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ADC1, ąĘą░č鹥ą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ADC2, ąĖ ąĘą░č鹥ą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ADC3. ą¤čĆąŠčåąĄčüčü ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ ą┤ą╗čÅ ą║ą░ąČą┤čŗčģ čéčĆąĄčģ ąĮąŠą▓čŗčģ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣.

ŌĆó ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ EOC (ąĄčüą╗ąĖ čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĮą░ ąŠą┤ąĮąŠą╝ ąĖąĘ čéčĆąĄčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ ADC), ą║ąŠą│ą┤ą░ ą▒čŗą╗ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮčŗ ą▓čüąĄ regular-ą║ą░ąĮą░ą╗čŗ ADC1/ADC2/ADC3.

ąĀąĖčü. 55. Regular simultaneous mode ąĮą░ 16 ą║ą░ąĮą░ą╗ą░čģ: triple ADC mode.

[Interleaved mode]

ąŁč鹊čé čĆąĄąČąĖą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čāčēąĄąĮ č鹊ą╗čīą║ąŠ ąĮą░ ą│čĆčāą┐ą┐ąĄ regular (ąŠą▒čŗčćąĮąŠ ąŠą┤ąĖąĮ ą║ą░ąĮą░ą╗). ąĪąĖą│ąĮą░ą╗ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ą┐ąŠčüčéčāą┐ą░ąĄčé ąĖąĘ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆą░ regular ą║ą░ąĮą░ą╗ą░ ADC1.

ąĀąĄąČąĖą╝ Dual ADC. ą¤ąŠčüą╗ąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

ŌĆó ADC1 čüčéą░čĆčéčāąĄčé ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ.

ŌĆó ADC2 čüčéą░čĆčéčāąĄčé ą┐ąŠčüą╗ąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čéą░ą║č鹊ą▓ ADC.

ą£ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░, ą║ąŠč鹊čĆą░čÅ čĆą░ąĘą┤ąĄą╗čÅąĄčé 2 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ interleaved, ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ DELAY ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CCR. ą×ą┤ąĮą░ą║ąŠ ADC ąĮąĄ ą╝ąŠąČąĄčé ąĘą░ą┐čāčüčéąĖčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗą╣ ADC ą▓čüąĄ ąĄčēąĄ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčé čüą▓ąŠą╣ ą▓čģąŠą┤ (č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ADC ą╝ąŠąČąĄčé ą┤ąĄą╗ą░čéčī ą▓čŗą▒ąŠčĆą║čā ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ą░ą╗ą░ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą▓čĆąĄą╝čÅ). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĘą░ą┤ąĄčƹȹ║ą░ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čĆą░ą▓ąĮąŠą╣ ą▓čĆąĄą╝ąĄąĮąĖ ą▓čŗą▒ąŠčĆą║ąĖ + 2 čéą░ą║čéą░ ADC. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ DELAY = 5 čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ąŠą▓, ąĖ ą▓čŗą▒ąŠčĆą║ą░ ąĘą░ąĮąĖą╝ą░ąĄčé 15 čéą░ą║č鹊ą▓ ąĮą░ ąŠą▒ąŠąĖčģ ADC, č鹊 17 čéą░ą║č鹊ą▓ ą▒čāą┤čāčé čĆą░ąĘą┤ąĄą╗čÅčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC1 ąĖ ADC2.

ąĢčüą╗ąĖ ą▒ąĖčé CONT čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĮą░ ąŠą▒ąŠąĖčģ ADC1 ąĖ ADC2, č鹊 ą▓čŗą▒čĆą░ąĮąĮčŗąĄ regular-ą║ą░ąĮą░ą╗čŗ ąŠą▒ąŠąĖčģ ADC ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓čŗą▓ą░čÄčéčüčÅ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆą▓ą░ąĮą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA), multi-ADC čüąĄą║ą▓ąĄąĮčüąŠčĆ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą┐čāč鹥ą╝ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą│ąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ independent (ą▒ąĖčéčŗ DUAL[4:0] = 00000) ą┐ąĄčĆąĄą┤ ą┐ąŠą▓č鹊čĆąĮčŗą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čĆąĄąČąĖą╝ą░ interleaved.

ą¤ąŠčüą╗ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ EOC, čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ADC2 (ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą▒ąĖč鹊ą╝ EOCIE), ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĘą░ą┐čĆąŠčü 32-ą▒ąĖčéąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA (ąĄčüą╗ąĖ ą▒ąĖčéčŗ DMA[1:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADC_CCR čĆą░ą▓ąĮčŗ 0b10). ąŁč鹊čé ąĘą░ą┐čĆąŠčü čüąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ADC2 ą┤ą░ąĮąĮčŗąĄ, čüąŠčģčĆą░ąĮąĄąĮąĮčŗąĄ ą▓ čüčéą░čĆčłąĄą╣ ą┐ąŠą╗ąŠą▓ąĖąĮąĄ 32-ą▒ąĖčéąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ADC_CDR, ą▓ SRAM, ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ADC1 ą┤ą░ąĮąĮčŗąĄ, čüąŠčģčĆą░ąĮąĄąĮąĮčŗąĄ ą▓ ą╝ą╗ą░ą┤čłąĄą╣ ą┐ąŠą╗ąŠą▓ąĖąĮąĄ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░, ą▓ SRAM.

ąĀąĖčü. 56. Interleaved mode ąĮą░ ą║ą░ąĮą░ą╗ąĄ 1 ą▓ čĆąĄąČąĖą╝ąĄ continuous conversion: dual ADC mode.

ąĀąĄąČąĖą╝ Triple ADC. ą¤ąŠčüą╗ąĄ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░:

ŌĆó ąØąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ čüčéą░čĆčéčāąĄčé ADC1, ąĖ

ŌĆó ADC2 čüčéą░čĆčéčāąĄčé ą┐ąŠčüą╗ąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čéą░ą║č鹊ą▓ ADC,

ŌĆó ADC3 čüčéą░čĆčéčāąĄčé ą┐ąŠčüą╗ąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čéą░ą║č鹊ą▓ ADC ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC2.

ą£ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░, ą║ąŠč鹊čĆą░čÅ čĆą░ąĘą┤ąĄą╗čÅąĄčé 2 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓ interleaved mode ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ DELAY čĆąĄą│ąĖčüčéčĆą░ ADC_CCR. ą×ą┤ąĮą░ą║ąŠ ADC ąĮąĄ ą╝ąŠąČąĄčé ąĘą░ą┐čāčüčéąĖčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗą╣ ADC ą▓čüąĄ ąĄčēąĄ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčé čüą▓ąŠą╣ ą▓čģąŠą┤ (č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ADC ą╝ąŠąČąĄčé ą┤ąĄą╗ą░čéčī ą▓čŗą▒ąŠčĆą║čā ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĘą░ą┤ąĄčƹȹ║ą░ čüčéą░ąĮąŠą▓ąĖčéčüčÅ čĆą░ą▓ąĮąŠą╣ ą▓čĆąĄą╝ąĄąĮąĖ ą▓čŗą▒ąŠčĆą║ąĖ + 2 čéą░ą║čéą░ ADC. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ DELAY = 5 čéą░ą║č鹊ą▓ ąĖ ą▓čŗą▒ąŠčĆą║ą░ ąĘą░ąĮąĖą╝ą░ąĄčé 15 čéą░ą║č鹊ą▓ ąĮą░ čéčĆąĄčģ ADC, č鹊 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĮą░ ADC1, ADC2 ąĖ ADC3 ą▒čāą┤čāčé čĆą░ąĘą┤ąĄą╗čÅčéčīčüčÅ 17 čéą░ą║čéą░ą╝ąĖ).

ąĢčüą╗ąĖ ą▒ąĖčé CONT čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĮą░ ADC1, ADC2 ąĖ ADC3, č鹊 ą▓čŗą▒čĆą░ąĮąĮčŗąĄ regular-ą║ą░ąĮą░ą╗čŗ ą▓čüąĄčģ ADC ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠ ą┐čĆąĄąŠą▒čĆą░ąĘčāčÄčé čüąĖą│ąĮą░ą╗.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆą▓ą░ąĮą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąŠą║ąŠąĮčćą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA), č鹊 čüąĄą║ą▓ąĄąĮčüąŠčĆ multi-ADC ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą┐čāč鹥ą╝ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą│ąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ąĄą│ąŠ ą▓ independent-čĆąĄąČąĖą╝ąĄ (ą▒ąĖčéčŗ DUAL[4:0] = 00000) ą┐ąĄčĆąĄą┤ ą┐ąŠą▓č鹊čĆąĮčŗą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ interleaved-čĆąĄąČąĖą╝ą░.

ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąĘą░ą┐čĆąŠčü DMA ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┤ąŠčüčéčāą┐ąĮąŠ 2 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ (ąĄčüą╗ąĖ ą▒ąĖčéčŗ DMA[1:0] čĆąĄą│ąĖčüčéčĆą░ ADC_CCR čĆą░ą▓ąĮčŗ 0b10). ąŚą░ą┐čĆąŠčü čüąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░ąĄčé ą▓ SRAM ą┐ąĄčĆą▓čŗąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, čüąŠčģčĆą░ąĮąĄąĮąĮčŗąĄ ą▓ ą╝ą╗ą░ą┤čłąĄą╝ ą┐ąŠą╗čāčüą╗ąŠą▓ąĄ 32-ą▒ąĖčéąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ADC_CDR, ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą┤ą░ąĄčé ą▓ SRAM ą▓č鹊čĆčŗąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, čüąŠčģčĆą░ąĮąĄąĮąĮčŗąĄ ą▓ čüčéą░čĆčłąĄą╝ ą┐ąŠą╗čāčüą╗ąŠą▓ąĄ ADC_CDR. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čüą╗ąĄą┤čāčÄčēą░čÅ:

1-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0]

2-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[31:0] = ADC1_DR[15:0] | ADC3_DR[15:0]

3-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[31:0] = ADC3_DR[15:0] | ADC2_DR[15:0]

4-ą╣ ąĘą░ą┐čĆąŠčü: ADC_CDR[31:0] = ADC2_DR[15:0] | ADC1_DR[15:0], ...

ąĀąĖčü. 57. Interleaved mode ąĮą░ 1 ą║ą░ąĮą░ą╗ąĄ ą▓ continuous conversion mode: triple ADC mode.

ąĀąĄąČąĖą╝ alternate trigger. ąŁč鹊čé čĆąĄąČąĖą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čāčēąĄąĮ č鹊ą╗čīą║ąŠ ąĮą░ injected-ą│čĆčāą┐ą┐ąĄ. ąĪąĖą│ąĮą░ą╗ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ą┐čĆąĖčģąŠą┤ąĖčé ąŠčé ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆą░ injected-ą│čĆčāą┐ą┐čŗ ADC1.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: regular ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĮą░ ąŠą┤ąĮąŠą╝ ąĖą╗ąĖ ą▓čüąĄčģ ADC. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ regular ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĮąĄ ąĘą░ą▓ąĖčüčÅčé ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░. ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ regular ą┐čĆąĄčĆčŗą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ADC ą┤ąŠą╗ąČąĄąĮ ą▓čŗą┐ąŠą╗ąĮąĖčéčī injected ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ. ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ regular ą▓ąŠąĘąŠą▒ąĮąŠą▓ąĖčéčüčÅ, ą║ąŠą│ą┤ą░ injected ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ.