|

ąÆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ čüąĄčĆąĖąĖ STM32F4 (ą║ą░ą║ ą▓ą┐čĆąŠč湥ą╝, ąĖ ą╝ąĮąŠą│ąĖčģ ą┤čĆčāą│ąĖčģ čüąĄčĆąĖą╣ STM32) ą▓čüčéčĆąŠąĄąĮčŗ ą┤ą▓ą░ čéą░ą╣ą╝ąĄčĆą░, ą║ąŠč鹊čĆčŗąĄ čāą┤ąŠą▒ąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ ą║ą░č湥čüčéą▓ąĄ čüč鹊čĆąŠąČąĄą▓čŗčģ - ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ (Independent WatchDoG, IWDG [2]) ąĖ ąŠą║ąŠąĮąĮčŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ (Window WatchDoG, WWDG). ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ čĆą░ąĘą┤ąĄą╗ąŠą▓ ą┤ą░čéą░čłąĖčéą░ RM0090. ąÆčüčÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ, ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮą░čÅ ąĮąĖąČąĄ, ąŠčéąĮąŠčüąĖčéčüčÅ ą║ čüąĄą╝ąĄą╣čüčéą▓čā STM32F4xx, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ ąĮąĄčćč鹊 ąĖąĮąŠąĄ. ąÆčüąĄ ąĮąĄą┐ąŠąĮčÅčéąĮčŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ čüčéą░čéčīąĄ-čüą╗ąŠą▓ą░čĆąĖą║ąĄ [3].

ą×ą▒ą░ čüč鹊čĆąŠąČąĄą▓čŗčģ čéą░ą╣ą╝ąĄčĆą░ (IWDG ąĖ WWDG) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÄ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ą▒ąĄąĘąŠą┐ą░čüąĮąŠčüčéąĖ, č鹊čćąĮąŠą│ąŠ ąŠčéčüč湥čéą░ ą▓čĆąĄą╝ąĄąĮąĖ, ą│ąĖą▒ą║ąŠčüčéąĖ ą▓ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ. ąĪč鹊čĆąŠąČąĄą▓čŗąĄ čéą░ą╣ą╝ąĄčĆčŗ ą┐ąŠčüą╗ąĄ ąĖčģ ąĮą░čüčéčĆąŠą╣ą║ąĖ čĆą░ą▒ąŠčéą░čÄčé ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąŠčüąĮąŠą▓ąĮčŗčģ ą┐ąŠč鹊ą║ąŠą▓ ą▓čŗčćąĖčüą╗ąĄąĮąĖą╣ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ, ą┤ą░ą▓ą░čÅ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąŠą▒ąĮą░čĆčāąČąĖą▓ą░čéčī ąĖ čāčüčéčĆą░ąĮčÅčéčī ą┐čĆąŠą▒ą╗ąĄą╝čŗ, ą▓ąŠąĘąĮąĖą║ą░čÄčēąĖąĄ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ (ąĘą░ą▓ąĖčüą░ąĮąĖąĄ, ąĘą░ą┤ąĄčƹȹ║ą░ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ). ąÆ ą┐ąŠą┤ąŠą▒ąĮčŗčģ čüąĖčéčāą░čåąĖčÅčģ čüč湥čéčćąĖą║ čéą░ą╣ą╝ąĄčĆą░ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ čéą░ą╣ą╝ą░čāčéą░, ąĖ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ą╝ąŠąČąĮąŠ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (č鹊ą╗čīą║ąŠ ą┤ą╗čÅ WWDG) ąĖą╗ąĖ čüąĖčüč鹥ą╝ąĮčŗą╣ čüą▒čĆąŠčü.

ąØąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ (IWDG) čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé čüą▓ąŠąĄą│ąŠ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą│ąŠ, ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąĮąĖąĘą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ LSI (Low-Speed Internal clock), ą┐ąŠčŹč鹊ą╝čā IWDG ąŠčüčéą░ąĄčéčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ąŠčéą║ą░ąĘ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąŠčüąĮąŠą▓ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ (HSI ąĖą╗ąĖ HSE). ą¦ą░čüč鹊čéą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠą║ąŠąĮąĮąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (WWDG) ą┐ąŠčüčéčāą┐ą░ąĄčé č湥čĆąĄąĘ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ąŠčé čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ APB1. ą×ą║ąĮąŠ ą▓čĆąĄą╝ąĄąĮąĖ WWDG ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčī ąĮąĄąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ ąĘą░ą┐ą░ąĘą┤čŗą▓ą░ąĮąĖąĄ ąŠčéą║ą╗ąĖą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, ą╗ąĖą▒ąŠ čüą╗ąĖčłą║ąŠą╝ čĆą░ąĮąĮčÄčÄ ą░ą║čéąĖą▓ą░čåąĖčÄ ą┤ąĄą╣čüčéą▓ąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ.

ąĪč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ IWDG ą╗čāčćčłąĄ ą▓čüąĄą│ąŠ ą┐ąŠą┤čģąŠą┤ąĖčé ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣, ą║ąŠč鹊čĆčŗąĄ čéčĆąĄą▒čāčÄčé ą┐ąŠą╗ąĮąŠą╣ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░ ąŠčé ąŠčüąĮąŠą▓ąĮąŠą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ąĖą╝ąĄčÅ ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄą▒ąŠą╗čīčłąĖąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ č鹊čćąĮąŠčüčéąĖ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ čéą░ą╣ą╝ą░čāčéą░. ą×ą║ąŠąĮąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ WWDG ą╗čāčćčłąĄ ą┐ąŠą┤čģąŠą┤ąĖčé ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣, ą║ąŠč鹊čĆčŗąĄ čéčĆąĄą▒čāčÄčé čĆąĄą░ą║čåąĖąĖ ą▓ č鹊čćąĮąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╝ ąŠą║ąĮąĄ ą▓čĆąĄą╝ąĄąĮąĖ.

[ąĪč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ IWDG]

ą×čüąĮąŠą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ IWDG:

ŌĆó ąØąĄąĘą░ą▓ąĖčüąĖą╝ąŠ čĆą░ą▒ąŠčéą░čÄčēąĖą╣ čüč湥čéčćąĖą║, čüčćąĖčéą░čÄčēąĖą╣ ą▓ąĮąĖąĘ

ŌĆó ąóą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ RC-ą│ąĄąĮąĄčĆą░č鹊čĆą░, ą┐ąŠčŹč鹊ą╝čā ąŠčüčéą░ąĄčéčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ ą▓ čĆąĄąČąĖą╝ą░čģ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ Standby ąĖ Stop

ŌĆó ąĪą▒čĆą░čüčŗą▓ą░ąĄčé ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ (ąĄčüą╗ąĖ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ), ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┐čĆąĖ čüč湥č鹥 ą▓ąĮąĖąĘ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ 0x000

ŌĆó Hardware watchdog

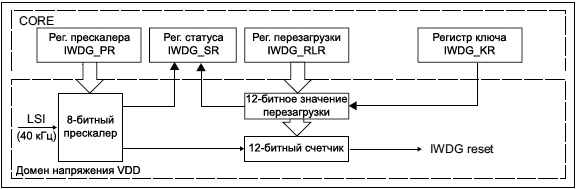

ąØą░ čĆąĖčü. 213 ą┐ąŠą║ą░ąĘą░ąĮčŗ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗąĄ ą▒ą╗ąŠą║ąĖ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ IWDG.

ąĀąĖčü. 213. ąæą╗ąŠą║-čüčģąĄą╝ą░ Independent WatchDoG.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čäčāąĮą║čåąĖčÅ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ą▓ ą┤ąŠą╝ąĄąĮąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ VDD, ą║ąŠč鹊čĆčŗą╣ ąŠčüčéą░ąĄčéčüčÅ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗą╝ ą▓ čĆąĄąČąĖą╝ą░čģ Stop ąĖ Standby.

IWDG ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ 0xCCCC ą▓ čĆąĄą│ąĖčüčéčĆ ą║ą╗čÄčćą░ (IWDG_KR), ą┐čĆąĖ čŹč鹊ą╝ čüč湥čéčćąĖą║ ąĮą░čćąĖąĮą░ąĄčé čüč湥čé ą▓ąĮąĖąĘ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ čüą▒čĆąŠčüą░ 0xFFF. ąÜąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ą║ąŠąĮąĄčćąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ 0x000, ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░ (IWDG reset). ąÆčüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ ą║ą╗čÄčćą░ 0xAAAA ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ IWDG_KR, ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ IWDG_RLR ą┐ąĄčĆąĄąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ čüč湥čéčćąĖą║, čćč鹊 ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčé ąĄą│ąŠ ąŠą▒ąĮčāą╗ąĄąĮąĖąĄ ąĖ ą║ą░ą║ čüą╗ąĄą┤čüčéą▓ąĖąĄ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčé čüą▒čĆąŠčü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

Hardware watchdog. ążčāąĮą║čåąĖčÅ "Hardware watchdog" čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ č湥čĆąĄąĘ ą▒ąĖčéčŗ ąŠą┐čåąĖą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, č鹊ą│ą┤ą░ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čüą▒čĆąŠčü, ąĄčüą╗ąĖ ąĮąĄ ą▒čŗą╗ąŠ čüą▓ąŠąĄą▓čĆąĄą╝ąĄąĮąĮąŠ (ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ čüč湥čéčćąĖą║ąŠą╝ ąĮčāą╗čÅ) ąĘą░ą┐ąĖčüą░ąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ 0xAAAA ą▓ čĆąĄą│ąĖčüčéčĆ ą║ą╗čÄčćą░ IWDG_KR.

ąŚą░čēąĖčēąĄąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝. ąöąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆčŗ IWDG_PR ąĖ IWDG_RLR čüąĮą░ą▒ąČąĄąĮ ąĘą░čēąĖč鹊ą╣, čćč鹊 ą┐ąŠą╝ąŠą│ą░ąĄčé ąĖąĘą▒ąĄąČą░čéčī ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ąŠčłąĖą▒ąŠčćąĮčŗčģ ą┤ąĄą╣čüčéą▓ąĖą╣ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ. ą¦č鹊ą▒čŗ ąĖąĘą╝ąĄąĮąĖčéčī IWDG_PR ąĖ IWDG_RLR, čüąĮą░čćą░ą╗ą░ ąĮą░ą┤ąŠ ąĘą░ą┐ąĖčüą░čéčī ą║ąŠą┤ 0x5555 ą▓ čĆąĄą│ąĖčüčéčĆ ą║ą╗čÄčćą░ IWDG_KR. ąŚą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ ą║ą╗čÄčćą░ ą┤čĆčāą│ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ąŠą▒ąŠčĆą▓ąĄčé ą┐čĆąŠčåąĄą┤čāčĆčā ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ IWDG_PR ąĖ IWDG_RLR, ąĖ ąĘą░čēąĖčéą░ čüąĮąŠą▓ą░ ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ. ąŁč鹊 ą▓ąĄčĆąĮąŠ ąĖ ą┤ą╗čÅ čüą╗čāčćą░čÅ ąŠą┐ąĄčĆą░čåąĖąĖ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ čüč湥čéčćąĖą║ą░ (ąĘą░ą┐ąĖčüčī ą▓ IWDG_KR ąĘąĮą░č湥ąĮąĖčÅ 0xAAAA).

ąśą╝ąĄąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖą╣ čüąŠčüč鹊čÅąĮąĖąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĖą╗ąĖ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ čüč湥čéčćąĖą║ą░.

ąĀąĄąČąĖą╝ ąŠčéą╗ą░ą┤ą║ąĖ. ąÜąŠą│ą┤ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ STM32 ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ ąŠčéą╗ą░ą┤ą║ąĖ (debug mode, ą▓ ą║ąŠč鹊čĆąŠą╝ čÅą┤čĆąŠ Cortex┬«-M4 čüąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ ą▒ą╗ąŠą║ąŠą╝ FPU ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ), IWDG ą▒čāą┤ąĄčé ą╗ąĖą▒ąŠ ą┐čĆąŠą┤ąŠą╗ąČą░čéčī čüą▓ąŠą╣ čüč湥čé, ą╗ąĖą▒ąŠ ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮąŠą│ąŠ ą▒ąĖčéą░ DBG_IWDG_STOP ą▓ ą╝ąŠą┤čāą╗ąĄ DBG. ąöą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. čüąĄą║čåąĖčÄ 38.16.2 "Debug support for timers, watchdog, bxCAN and I2C" čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ [1].

ąóą░ą▒ą╗ąĖčåą░ 107. ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĖąŠą┤ čéą░ą╣ą╝ą░čāčéą░ IWDG ą▓ ą╝ąĖą╗ą╗ąĖčüąĄą║čāąĮą┤ą░čģ, ą║ąŠą│ą┤ą░ LSI čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čćą░čüč鹊č鹥 32 ą║ąōčå(1).

ąöąĄą╗ąĖč鹥ą╗čī

ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ |

PR[2:0] |

Min čéą░ą╣ą╝ą░čāčé (ą╝čü)

RL[11:0]=0x000 |

Max čéą░ą╣ą╝ą░čāčé (ą╝čü)

RL[11:0]=0xFFF |

| /4 |

0 |

0.125 |

512 |

| /8 |

1 |

0.25 |

1024 |

| /16 |

2 |

0.5 |

2048 |

| /32 |

3 |

1 |

4096 |

| /64 |

4 |

2 |

8192 |

| /128 |

5 |

4 |

16384 |

| /256 |

6 |

8 |

32768 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): čāą║ą░ąĘą░ąĮąĮčŗąĄ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓ IWDG 32 ą║ąōčå. ą×ą┤ąĮą░ą║ąŠ čŹčéčā čćą░čüč鹊čéčā ą▓čŗčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ RC-ą│ąĄąĮąĄčĆą░č鹊čĆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ąĖ ą┐ąŠčŹč鹊ą╝čā čćą░čüč鹊čéą░ ą╝ąŠąČąĄčé ąĖąĘą╝ąĄąĮčÅčéčīčüčÅ ąŠčé ą▓ąĮąĄčłąĮąĖčģ čāčüą╗ąŠą▓ąĖą╣ (č鹥ą┐ąĄčĆą░čéčāčĆą░, ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ). ąöą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊č鹥 LSI ąŠą▒čĆą░čéąĖč鹥čüčī ą║ ą┤ą░čéą░čłąĖčéčā ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ.

ąĀąĄą│ąĖčüčéčĆčŗ IWDG. ąÜ čĆąĄą│ąĖčüčéčĆą░ą╝ ą╝ąŠąČąĮąŠ ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ą░ą║ ą║ ą┐ąŠą╗ąŠą▓ąĖąĮą║ą░ą╝ čüą╗ąŠą▓ (16 ą▒ąĖčé) ąĖą╗ąĖ ą║ą░ą║ ą║ ą┐ąŠą╗ąĮčŗą╝ čüą╗ąŠą▓ą░ą╝ (32 ą▒ąĖčéą░). ąĪą╝ąĄčēąĄąĮąĖąĄ čāą║ą░ąĘą░ąĮąŠ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32F429 ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü čĆą░ą▓ąĄąĮ 0x40003000 (čüą╝. ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ IWDG_BASE ą▓ ąĘą░ą│ąŠą╗ąŠą▓ąŠčćąĮąŠą╝ čäą░ą╣ą╗ąĄ stm32f429xx.h ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĖ CMSIS).

ąÆ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖčÅčģ ą▒ąĖčé ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆčŗ r, w, rw, čćč鹊 ąŠąĘąĮą░čćą░ąĄčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

r ą┤ąŠčüčéčāą┐ ą║ ą▒ąĖčéčā ą▓ąŠąĘą╝ąŠąČąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ (Read)

w ą┤ąŠčüčéčāą┐ ą║ ą▒ąĖčéčā ą▓ąŠąĘą╝ąŠąČąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ (Write)

rw ą┤ąŠčüčéčāą┐ ą║ ą▒ąĖčéčā ą▓ąŠąĘą╝ąŠąČąĄąĮ ąĖ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, ąĖ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ.

ąĪą╝ąĄčēąĄąĮąĖąĄ 0x00

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░ 0x00000000 (čüą▒čĆąŠčü ą▓ čĆąĄąČąĖą╝ąĄ Standby)

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

KEY[15:0]

w

|

ąæąĖčéčŗ 31:16 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

KEY[15:0] (ą▒ąĖčéčŗ 15:0) ąĘąĮą░č湥ąĮąĖąĄ ą║ą╗čÄčćą░. ąæąĖčéčŗ čĆą░ą▒ąŠčéą░čÄčé č鹊ą╗čīą║ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī, čüčćąĖčéčŗą▓ą░čÄčéčüčÅ ą║ą░ą║ 0x0000. ąÜąŠą│ą┤ą░ IWDG ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ, ą▓ čŹčéąĖ ą▒ąĖčéčŗ ą┤ąŠą╗ąČąĮčŗ ąĘą░ą┐ąĖčüčŗą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗąĄ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ:

0xAAAA ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ čüą▒čĆąŠčüą░ ą┐ąŠ ąŠą▒ąĮčāą╗ąĄąĮąĖčÄ čüč湥čéčćąĖą║ą░.

0x5555 ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ IWDG_PR ąĖ IWDG_RLR.

0xCCCC ąĘą░ą┐čāčüą║ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░. ąŁčéą░ ąĘą░ą┐ąĖčüčī ąĮčāąČąĮą░ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ąŠą┐čåąĖčÅą╝ąĖ ąĮąĄ ą▓čŗą▒čĆą░ąĮą░ čäčāąĮą║čåąĖčÅ hardware watchdog.

ąĪą╝ąĄčēąĄąĮąĖąĄ 0x04

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░ 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄčĆąĄąĘą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

PR[2:0]

rw |

ąæąĖčéčŗ 31:3 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

PR[2:0] (ą▒ąĖčéčŗ 2:0) ą▓čŗą▒ąŠčĆ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ą┤ą╗čÅ ą┐ąŠą┤ą░čćąĖ čéą░ą║č鹊ą▓ ąĮą░ čüč湥čéčćąĖą║ IWDG. ąŚą░ą┐ąĖčüčī ą▓ čŹčéąĖ ą▒ąĖčéčŗ ąĘą░čēąĖčēąĄąĮą░ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ ą║ą╗čÄčćą░ (čüą╝. ą▓čŗčłąĄ čüąĄą║čåąĖčÄ "ąŚą░čēąĖčēąĄąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝"). ąæąĖčé PVU ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ IWDG_SR ą▓ čüąŠčüč鹊čÅąĮąĖąĖ 0 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓ ą┤ą░ąĮąĮčŗą╣ ą╝ąŠą╝ąĄąĮčé ą╝ąŠąČąĮąŠ ąĖąĘą╝ąĄąĮąĖčéčī ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░.

000: ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ LSI ąĮą░ 4

001: ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ LSI ąĮą░ 8

010: ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ LSI ąĮą░ 16

011: ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ LSI ąĮą░ 32

100: ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ LSI ąĮą░ 64

101: ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ LSI ąĮą░ 128

110: ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ LSI ąĮą░ 256

111: ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ LSI ąĮą░ 256

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ IWDG_PR ą▓ąĄčĆąĮąĄčé ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĖąĘ ą┤ąŠą╝ąĄąĮą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ VDD. ąŁč鹊 ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╝, ąĄčüą╗ąĖ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą░ą║čéąĖą▓ąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▓ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ ąĘąĮą░č湥ąĮąĖąĄ, ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĖąĘ IWDG_PR, ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ čüą▒čĆąŠčłąĄąĮ ą▒ąĖčé PVU ą▓ čĆąĄą│ąĖčüčéčĆąĄ IWDG_SR.

ąĪą╝ąĄčēąĄąĮąĖąĄ 0x08

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░ 0x00000FFF (čüą▒čĆąŠčü ą▓ čĆąĄąČąĖą╝ąĄ Standby)

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄčĆąĄąĘą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

RL[11:0]

rw

|

ąæąĖčéčŗ 31:12 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

RL[11:0] (ą▒ąĖčéčŗ 11:0) ąĘąĮą░č湥ąĮąĖąĄ, ą║ąŠč鹊čĆčŗą╝ ą┐ąĄčĆąĄąĘą░ą│čĆčāąČą░ąĄčéčüčÅ čüč湥čéčćąĖą║ IWDG. ąŚą░ą┐ąĖčüčī ą▓ čŹčéąĖ ą▒ąĖčéčŗ ąĘą░čēąĖčēąĄąĮą░ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ ą║ą╗čÄčćą░ (čüą╝. ą▓čŗčłąĄ čüąĄą║čåąĖčÄ "ąŚą░čēąĖčēąĄąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝"). ąĪč湥čéčćąĖą║ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘąĖčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖąĘ IWDG_RLR, ą║ąŠą│ą┤ą░ ą▓ čĆąĄą│ąĖčüčéčĆ ą║ą╗čÄčćą░ IWDG_KR ą▒čŗą╗ąŠ ąĘą░ą┐ąĖčüą░ąĮąŠ čüą┐ąĄčåąĖą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ 0xAAAA. ąĪč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą▓ąĮąĖąĘ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ IWDG_RLR, ą┐ąŠčŹč鹊ą╝čā ą▓čĆąĄą╝čÅ čéą░ą╣ą╝ą░čāčéą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ IWDG_RLR ąĖ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣, ą┐ąŠą┤ą░ą▓ą░ąĄą╝ąŠą╣ ąĮą░ čüč湥čéčćąĖą║ (ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ IWDG_PR). ąæąĖčé RVU ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ IWDG_SR ą▓ čüąŠčüč鹊čÅąĮąĖąĖ 0 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓ ą┤ą░ąĮąĮčŗą╣ ą╝ąŠą╝ąĄąĮčé ą╝ąŠąČąĮąŠ ąĖąĘą╝ąĄąĮąĖčéčī ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ IWDG_RLR ą▓ąĄčĆąĮąĄčé ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ čüč湥čéčćąĖą║ą░ ąĖąĘ ą┤ąŠą╝ąĄąĮą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ VDD. ąŁč鹊 ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╝, ąĄčüą╗ąĖ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą░ą║čéąĖą▓ąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▓ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ ąĘąĮą░č湥ąĮąĖąĄ, ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĖąĘ IWDG_RLR, ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ čüą▒čĆąŠčłąĄąĮ ą▒ąĖčé RVU ą▓ čĆąĄą│ąĖčüčéčĆąĄ IWDG_SR.

ąĪą╝ąĄčēąĄąĮąĖąĄ 0x0C

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░ 0x00000000 (čüą▒čĆąŠčü ąĮąĄ ą▓ čĆąĄąČąĖą╝ąĄ Standby)

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄčĆąĄąĘą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

RVU

r |

PVU

r

|

ąæąĖčéčŗ 31:2 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

RVU (ą▒ąĖčé 1) Reload Value Update. ąæąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ. ąøąŠą│. 1 ą▓ čŹč鹊ą╝ ą▒ąĖč鹥 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą░ą║čéąĖą▓ąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ (čĆąĄą│ąĖčüčéčĆ IWDG_RLR). ąæąĖčé čüą▒čĆąŠčüąĖčéčüčÅ ą▓ ą╗ąŠą│. 0 ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą▓ ą┤ąŠą╝ąĄąĮąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ VDD (ą▓čĆąĄą╝čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĘą░ąĮąĖą╝ą░ąĄčé ą┤ąŠ 5 čéą░ą║č鹊ą▓ RC-ą│ąĄąĮąĄčĆą░č鹊čĆą░ LSI). ąŚąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ IWDG_RLR ą╝ąŠąČąĮąŠ ąŠą▒ąĮąŠą▓ąĖčéčī č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▒ąĖčé RVU čüą▒čĆąŠčłąĄąĮ ą▓ 0.

PVU (ą▒ąĖčé 0) Prescaler Value Update. ąæąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ. ąøąŠą│. 1 ą▓ čŹč鹊ą╝ ą▒ąĖč鹥 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą░ą║čéąĖą▓ąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ (čĆąĄą│ąĖčüčéčĆ IWDG_PR). ąæąĖčé čüą▒čĆąŠčüąĖčéčüčÅ ą▓ ą╗ąŠą│. 0 ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą▓ ą┤ąŠą╝ąĄąĮąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ VDD (ą▓čĆąĄą╝čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĘą░ąĮąĖą╝ą░ąĄčé ą┤ąŠ 5 čéą░ą║č鹊ą▓ RC-ą│ąĄąĮąĄčĆą░č鹊čĆą░ LSI). ąŚąĮą░č湥ąĮąĖąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ IWDG_PR ą╝ąŠąČąĮąŠ ąŠą▒ąĮąŠą▓ąĖčéčī č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▒ąĖčé PVU čüą▒čĆąŠčłąĄąĮ ą▓ 0.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĘąĮą░č湥ąĮąĖą╣ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĘąĮą░č湥ąĮąĖą╣ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░, č鹊 ą┐ąĄčĆąĄą┤ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄą╝ ąĘąĮą░č湥ąĮąĖčÅ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ ą▓ą░ąČąĮąŠ ą┐ąŠą┤ąŠąČą┤ą░čéčī, ą║ąŠą│ą┤ą░ ą▒ąĖčéčŗ RVU čüą▒čĆąŠčüąĖčéčüčÅ. ą×ą┤ąĮą░ą║ąŠ ą┐ąŠčüą╗ąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĖ/ąĖą╗ąĖ ąĘąĮą░č湥ąĮąĖčÅ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ąČą┤ą░čéčī čüą▒čĆąŠčüą░ RVU ąĖą╗ąĖ PVU ą┐ąĄčĆąĄą┤ ą┐čĆąŠą┤ąŠą╗ąČąĄąĮąĖąĄą╝ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą┤ą░ (ą┤ą░ąČąĄ ą▓ čüą╗čāčćą░ąĄ ą▓čģąŠą┤ą░ ą▓ čĆąĄąČąĖą╝ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čŹąĮąĄčĆą│ąĖąĖ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▒čāą┤ąĄčé čāčćč鹥ąĮą░ ąĖ ą▓čüčéčāą┐ąĖčé ą▓ čüąĖą╗čā).

[ą×ą║ąŠąĮąĮčŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ WWDG]

ą×ą║ąŠąĮąĮčŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ąŠą▒ąĮą░čĆčāąČąĖčéčī ąĮąĄąĘą░ą┐ą╗ą░ąĮąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą▓ čĆąĄą░ą╗čīąĮąŠą╝ ą▓čĆąĄą╝ąĄąĮąĖ. ą×ą▒čŗčćąĮąŠ čéą░ą║ąŠąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĖąĘ-ąĘą░ ą▓ąĮąĄčłąĮąĖčģ ą┐ąŠą╝ąĄčģ ąĖą╗ąĖ ąĮąĄą┐čĆąĄą┤ą▓ąĖą┤ąĄąĮąĮčŗčģ ą╗ąŠą│ąĖč湥čüą║ąĖčģ čāčüą╗ąŠą▓ąĖą╣, čćč鹊 ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ąŠčéą║ą░ąĘčā ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąĪčģąĄą╝ą░ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ WWDG ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüą▒čĆąŠčü MCU ą┐ąŠ ąĖčüč鹥č湥ąĮąĖąĖ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ ą▓čĆąĄą╝ąĄąĮąĖ, ąĄčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮąĄ ąŠą▒ąĮąŠą▓ąĖčé ąĘąĮą░č湥ąĮąĖąĄ čüčćąĖčéą░čÄčēąĄą│ąŠ ą▓ąĮąĖąĘ čüč湥čéčćąĖą║ą░ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą▒ąĖčé T6 ąŠčćąĖčüčéąĖčéčüčÅ. ąĪą▒čĆąŠčü MCU čéą░ą║ąČąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ, ąĄčüą╗ąĖ 7-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ) ąŠą▒ąĮąŠą▓ąĖčéčüčÅ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ąĮąĄčé ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ąŠą║ąĮą░. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ čŹčéąĖ 2 čāčüą╗ąŠą▓ąĖčÅ čüą▒čĆąŠčüą░ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čÄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░ ą▓ čüčéčĆąŠą│ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝, ąŠą│čĆą░ąĮąĖč湥ąĮąĮąŠą╝ ąŠą║ąĮąĄ ą▓čĆąĄą╝ąĄąĮąĖ.

ą×čüąĮąŠą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ WWDG:

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ čüą▓ąŠą▒ąŠą┤ąĮąŠ čüčćąĖčéą░čÄčēąĖą╣ ą▓ąĮąĖąĘ čüč湥čéčćąĖą║

ŌĆó ąĪą▒čĆąŠčü (ąĄčüą╗ąĖ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ), ą║ąŠą│ą┤ą░ čüčćąĖčéą░čÄčēąĖą╣ ą▓ąĮąĖąĘ čüč湥čéčćąĖą║ čüčéą░ąĮąĄčé ą╝ąĄąĮčīčłąĄ 0x40

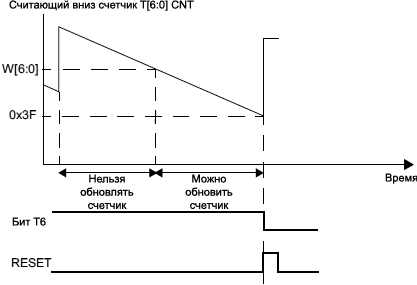

ŌĆó ąĪą▒čĆąŠčü (ąĄčüą╗ąĖ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ), ą║ąŠą│ą┤ą░ čüčćąĖčéą░čÄčēąĖą╣ ą▓ąĮąĖąĘ čüč湥čéčćąĖą║ ą▒čŗą╗ ą┐ąĄčĆąĄąĘą░ą│čĆčāąČąĄąĮ ą▓ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą│ąŠ ąŠą║ąĮą░ (čüą╝. čĆąĖčü. 215)

ŌĆó ąōąĄąĮąĄčĆą░čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ EWI (Early Wakeup Interrupt), ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĖ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ, ą║ąŠą│ą┤ą░ čüčćąĖčéą░čÄčēąĖą╣ ą▓ąĮąĖąĘ čüč湥čéčćąĖą║ čüčéą░ąĮąŠą▓ąĖčéčüčÅ čĆą░ą▓ąĮčŗą╝ 0x40

ąĢčüą╗ąĖ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ (čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé WDGA ą▓ čĆąĄą│ąĖčüčéčĆąĄ WWDG_CR), č鹊 ą▒čāą┤ąĄčé ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮ čüą▒čĆąŠčü, ą║ąŠą│ą┤ą░ 7-ą▒ąĖčéąĮčŗą╣ čüčćąĖčéą░čÄčēąĖą╣ ą▓ąĮąĖąĘ čüč湥čéčćąĖą║ (ą▒ąĖčéčŗ T[6:0] čĆąĄą│ąĖčüčéčĆą░ WWDG_CR) ą┐ąĄčĆąĄą╣ą┤ąĄčé ąŠčé ąĘąĮą░č湥ąĮąĖčÅ 0x40 ą║ ąĘąĮą░č湥ąĮąĖčÄ 0x3F (ą▒ąĖčé T6 ąŠčćąĖčüčéąĖčéčüčÅ). ąĢčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘąĖčé čüč湥čéčćąĖą║, ą║ąŠą│ą┤ą░ ąŠąĮ ą▒ąŠą╗čīčłąĄ ąĘąĮą░č湥ąĮąĖčÅ, čüąŠčģčĆą░ąĮąĄąĮąĮąŠą│ąŠ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ąŠą║ąĮą░, č鹊 čéą░ą║ąČąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüą▒čĆąŠčü.

ąĀąĖčü. 214. ąæą╗ąŠą║-čüčģąĄą╝ą░ ąŠą║ąŠąĮąĮąŠą│ąŠ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ WWDG.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ čüą▓ąŠąĄą│ąŠ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī čĆąĄą│ąĖčüčéčĆ WWDG_CR ą▓ čĆąĄą│čāą╗čÅčĆąĮčŗąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī čüą▒čĆąŠčü MCU. ąŁčéą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą┤ąŠą╗ąČąĮą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą╝ąĄąĮčīčłąĄ, č湥ą╝ ąĘąĮą░č湥ąĮąĖąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ąŠą║ąĮą░. ąŚąĮą░č湥ąĮąĖąĄ, čüąŠčģčĆą░ąĮąĄąĮąĮąŠąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ WWDG_CR, ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ ą╝ąĄąČą┤čā 0xFF ąĖ 0xC0.

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░. ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ą▓čüąĄą│ą┤ą░ ąĘą░ą┐čĆąĄčēąĄąĮ. ą×ąĮ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ WDGA ą▓ čĆąĄą│ąĖčüčéčĆąĄ WWDG_CR, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ, ą║čĆąŠą╝ąĄ ą║ą░ą║ č湥čĆąĄąĘ čüą▒čĆąŠčü.

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüč湥čéčćąĖą║ąŠą╝. ąĪč湥čéčćąĖą║ čüą▓ąŠą▒ąŠą┤ąĮąŠ čüčćąĖčéą░ąĄčé ą▓ąĮąĖąĘ, ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ąĘą░ą┐čĆąĄčēąĄąĮ. ąÜąŠą│ą┤ą░ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ, ą▒ąĖčé T6 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮčŗą╣ čüą▒čĆąŠčü.

ąæąĖčéčŗ T[5:0] čüąŠą┤ąĄčƹȹ░čé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĖąĮą║čĆąĄą╝ąĄąĮč鹊ą▓, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé ąĘą░ą┤ąĄčƹȹ║čā ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ čüą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüą▒čĆąŠčü. ąÆčĆąĄą╝čÅ ą╝ąĄąĮčÅąĄčéčüčÅ ą╝ąĄąČą┤čā ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╝ ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖąĘ-ąĘą░ ąĮąĄąĖąĘą▓ąĄčüčéąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ WWDG_CR (čüą╝. čĆąĖčü. 215). ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ (WWDG_CFR) čüąŠą┤ąĄčƹȹĖčé ą▓ąĄčĆčģąĮąĖą╣ ą┐čĆąĄą┤ąĄą╗ ąŠą║ąĮą░: čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī čüą▒čĆąŠčü, čüč湥čéčćąĖą║ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄąĘą░ą│čĆčāąČąĄąĮ, ą║ąŠą│ą┤ą░ ąĄą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ ą╝ąĄąĮčīčłąĄ, č湥ą╝ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ ąŠą║ąĮą░, ąĖ ą┐čĆąĖ čŹč鹊ą╝ ą▒ąŠą╗čīčłąĄ, č湥ą╝ 0x3F. ąĀąĖčü. 215 ąŠą┐ąĖčüčŗą▓ą░ąĄčé čĆą░ą▒ąŠčéčā ąŠą║ąĮą░ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖčé T6 ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ (ą┤ą╗čÅ čŹč鹊ą│ąŠ ąĮą░ą┤ąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčé WDGA ąĖ ąŠčćąĖčüčéąĖčéčī ą▒ąĖčé T6, ą╗ąĖą▒ąŠ ą┐ąŠą┤ąŠąČą┤ą░čéčī, ą║ąŠą│ą┤ą░ ąŠąĮ čüą░ą╝ ąŠčćąĖčüčéąĖčéčüčÅ).

ążčāąĮą║čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠą║ąŠąĮąĮąŠą│ąŠ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░. ą£ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ The Early Wakeup Interrupt (EWI), ąĄčüą╗ąĖ ą┐ąĄčĆąĄą┤ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ čĆąĄą░ą╗čīąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą║ą░ą║ąĖąĄ-ąĮąĖą▒čāą┤čī ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮčŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ ąŠčćąĖčüčéą║ąĖ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą▓ ą╗ąŠą│). ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ EWI čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ EWI ą▓ čĆąĄą│ąĖčüčéčĆąĄ WWDG_CFR. ąÜąŠą│ą┤ą░ čüčćąĖčéą░čÄčēąĖą╣ ą▓ąĮąĖąĘ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ 0x40, ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ EWI, ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ISR) ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗčģ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ ą┤ąĄą╣čüčéą▓ąĖą╣ (čéą░ą║ąĖčģ ą║ą░ą║ ąĮą░ą┐čĆąĖą╝ąĄčĆ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ąĖą╗ąĖ ąĘą░ą┐ąĖčüčī ą┤ą░ąĮąĮčŗčģ ą▓ ą╗ąŠą│) ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ.

ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ EWI ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ ą┐čĆąŠą▓ąĄčĆą║ąĖ čüąĖčüč鹥ą╝čŗ ąĖ/ąĖą╗ąĖ ą║ąŠčĆčĆąĄą║čéąĮąŠą│ąŠ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ čüąĖčüč鹥ą╝čŗ ą▒ąĄąĘ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüą▒čĆąŠčüą░. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ISR ą┤ąŠą╗ąČąĄąĮ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘąĖčéčī čüč湥čéčćąĖą║ WWDG, čćč鹊ą▒čŗ ąĮąĄ ą┐čĆąŠąĖąĘąŠčłąĄą╗ čüą▒čĆąŠčü WWDG, ąĘą░č鹥ą╝ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ.

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ EWI ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ 0 ą▓ ą▒ąĖčé EWIF čĆąĄą│ąĖčüčéčĆą░ WWDG_SR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ EWI ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą▒čĆą░ą▒ąŠčéą░ąĮąŠ, ąĮą░ą┐čĆąĖą╝ąĄčĆ ąĖąĘ-ąĘą░ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čüąĖčüč鹥ą╝čŗ ą▓ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąŠą┐čĆąĖąŠčĆąĖč鹥čéąĮąŠą╣ ąĘą░ą┤ą░č湥, č鹊 ąĖąĮąŠą│ą┤ą░ ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ čüą▒čĆąŠčü WWDG.

ąÜą░ą║ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĘąĮą░č湥ąĮąĖąĄ čéą░ą╣ą╝ą░čāčéą░ WWDG. ą¤čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖąĄ: ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ WWDG_CR, ą▓čüąĄą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ą╣č鹥 1 ą▓ ą▒ąĖčé T6, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠą│ąŠ čüą▒čĆąŠčüą░.

ąĀąĖčü. 215. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ čĆą░ą▒ąŠčéčŗ ąŠą║ąŠąĮąĮąŠą│ąŠ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░.

ążąŠčĆą╝čāą╗ą░ ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ čéą░ą╣ą╝ą░čāčéą░ WWDG (ą▓ ą╝ąĖą╗ą╗ąĖčüąĄą║čāąĮą┤ą░čģ):

tWWDG = tPCLK1 ├Ś 4096 ├Ś 2WDGTB[1:0] ├Ś (T[5:0] + 1)

ąŚą┤ąĄčüčī:

tWWDG: čéą░ą╣ą╝ą░čāčé WWDG

tPCLK1: ą┐ąĄčĆąĖąŠą┤ APB1, ąĖąĘą╝ąĄčĆąĄąĮąĮčŗą╣ ą▓ ą╝ąĖą╗ą╗ąĖčüąĄą║čāąĮą┤ą░čģ

4096: ąĘąĮą░č湥ąĮąĖąĄ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝čā ą┤ąĄą╗ąĖč鹥ą╗čÄ

ąöą╗čÅ ą┐čĆąĖą╝ąĄčĆą░ ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĖą╝, čćč鹊 čćą░čüč鹊čéą░ APB1 čĆą░ą▓ąĮą░ 24 ą£ąōčå, ą▒ąĖčéčŗ WDGTB[1:0] čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ąĮą░ 3 ąĖ ą▒ąĖčéčŗ T[5:0] čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ąĮą░ 63:

tWWDG = 1 Ōüä 24000 ├Ś 4096 ├Ś 23 ├Ś (63 + 1) = 21.85 ą╝čü

ąóą░ą▒ą╗ąĖčåą░ 109. ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗąĄ ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ čéą░ą╣ą╝ą░čāčéą░ ąĮą░ 30 ą£ąōčå (fPCLK1).

| ą¤čĆąĄčüą║ą░ą╗ąĄčĆ |

WDGTB |

Min čéą░ą╣ą╝ą░čāčé (ą╝ą║čü)

T[5:0]=0x00 |

Max čéą░ą╣ą╝ą░čāčé (ą╝čü)

T[5:0]=0x3F |

| 1 |

0 |

136.53 |

8.74 |

| 2 |

1 |

273.07 |

17.48 |

| 4 |

2 |

546.13 |

34.95 |

| 8 |

3 |

1092.27 |

69.91 |

ąĀąĄąČąĖą╝ ąŠčéą╗ą░ą┤ą║ąĖ. ąÜąŠą│ą┤ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ STM32 ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ ąŠčéą╗ą░ą┤ą║ąĖ (debug mode, čÅą┤čĆąŠ Cortex┬«-M4 čü ą▒ą╗ąŠą║ąŠą╝ FPU ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ), čüč湥čéčćąĖą║ WWDG ą╗ąĖą▒ąŠ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé čüą▓ąŠą╣ čüč湥čé, ą╗ąĖą▒ąŠ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▒ąĖčéą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ DBG_WWDG_STOP ą▓ ą╝ąŠą┤čāą╗ąĄ DBG. ąöą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. čüąĄą║čåąĖčÄ 38.16.2 "Debug support for timers, watchdog, bxCAN and I2C" čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ [1].

ąĀąĄą│ąĖčüčéčĆčŗ WWDG. ąÜ čĆąĄą│ąĖčüčéčĆą░ą╝ ą╝ąŠąČąĮąŠ ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ą░ą║ ą║ ą┐ąŠą╗ąŠą▓ąĖąĮą║ą░ą╝ čüą╗ąŠą▓ (16 ą▒ąĖčé) ąĖą╗ąĖ ą║ą░ą║ ą║ ą┐ąŠą╗ąĮčŗą╝ čüą╗ąŠą▓ą░ą╝ (32 ą▒ąĖčéą░). ąĪą╝ąĄčēąĄąĮąĖąĄ čāą║ą░ąĘą░ąĮąŠ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32F429 ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü čĆą░ą▓ąĄąĮ 0x40002C00 (čüą╝. ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ IWDG_BASE ą▓ ąĘą░ą│ąŠą╗ąŠą▓ąŠčćąĮąŠą╝ čäą░ą╣ą╗ąĄ stm32f429xx.h ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĖ CMSIS).

ąÆ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖčÅčģ ą▒ąĖčé ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆčŗ r, w, rw, rs, rc_w0, čćč鹊 ąŠąĘąĮą░čćą░ąĄčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

r ą┤ąŠčüčéčāą┐ ą║ ą▒ąĖčéčā ą▓ąŠąĘą╝ąŠąČąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ (Read)

w ą┤ąŠčüčéčāą┐ ą║ ą▒ąĖčéčā ą▓ąŠąĘą╝ąŠąČąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ (Write)

rw ą┤ąŠčüčéčāą┐ ą║ ą▒ąĖčéčā ą▓ąŠąĘą╝ąŠąČąĄąĮ ąĖ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, ąĖ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ

rs read/set, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčī čŹč鹊čé ą▒ąĖčé. ąŚą░ą┐ąĖčüčī 0 ą▓ ą▒ąĖčé ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░

rc_w0 read/clear, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī ąĖ čüą▒čĆąŠčüąĖčéčī čŹč鹊čé ą▒ąĖčé. ąŚą░ą┐ąĖčüčī 1 ą▓ ą▒ąĖčé ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░

ąĪą╝ąĄčēąĄąĮąĖąĄ 0x00

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░ 0x0000007F

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄčĆąĄąĘą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

WDGA

rs |

T[6:0]

rw |

ąæąĖčéčŗ 31:8 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

WDGA (ą▒ąĖčé 7) WatchDoG Activation, ą░ą║čéąĖą▓ą░čåąĖčÅ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ ą╗ąŠą│. 1. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, ąĖ ąŠąĮ ą╝ąŠąČąĄčé čüą▒čĆąŠčüąĖčéčīčüčÅ č鹊ą╗čīą║ąŠ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░. ąÜąŠą│ą┤ą░ WDGA = 1, čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čüą▒čĆąŠčü.

0: čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ąĘą░ą┐čĆąĄčēąĄąĮ.

1: čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ.

T[6:0] (ą▒ąĖčéčŗ 6:0) 7-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (ąŠčé čüčéą░čĆčłąĄą│ąŠ ą▒ąĖčéą░ MSB ą║ ą╝ą╗ą░ą┤čłąĄą╝čā ą▒ąĖčéčā LSB). ąŁčéąĖ ą▒ąĖčéčŗ čüąŠą┤ąĄčƹȹ░čé ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░. ą×ąĮ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗąĄ (4096 x 2WDGTB[1:0]) čéą░ą║č鹊ą▓ PCLK1. ąĪą▒čĆąŠčü ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┐ąĄčĆąĄą▓ą░ą╗ąĖą▓ą░ąĄčé ąŠčé ąĘąĮą░č湥ąĮąĖčÅ 0x40 ą║ ąĘąĮą░č湥ąĮąĖčÄ 0x3F (ą║ąŠą│ą┤ą░ ą▒ąĖčé T6 ąŠčćąĖčēą░ąĄčéčüčÅ).

ąĪą╝ąĄčēąĄąĮąĖąĄ 0x04

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░ 0x0000007F

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄčĆąĄąĘą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

EWI

rs |

WDGTB[1:0]

rw |

W[6:0]

rw

|

ąæąĖčéčŗ 31:10 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

EWI (ą▒ąĖčé 9) Early Wakeup Interrupt. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ąĮąĄčé ąĘąĮą░č湥ąĮąĖčÅ 0x40. ąŁč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčćąĖčēą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░.

WDGTB[1:0] (ą▒ąĖčéčŗ 8:7) ą▒ą░ąĘą░ ą▓čĆąĄą╝ąĄąĮąĖ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝ą░čÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆąŠą╝. ą×ąĮą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

00: čćą░čüč鹊čéą░ čüč湥čéčćąĖą║ą░ čĆą░ą▓ąĮą░ (PCLK1 / 4096) / 1

01: čćą░čüč鹊čéą░ čüč湥čéčćąĖą║ą░ čĆą░ą▓ąĮą░ (PCLK1 / 4096) / 2

10: čćą░čüč鹊čéą░ čüč湥čéčćąĖą║ą░ čĆą░ą▓ąĮą░ (PCLK1 / 4096) / 4

11: čćą░čüč鹊čéą░ čüč湥čéčćąĖą║ą░ čĆą░ą▓ąĮą░ (PCLK1 / 4096) / 8

W[6:0] (ą▒ąĖčéčŗ 6:0) 7-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąŠą║ąĮą░ ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠč鹊čĆąŠąĄ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčéčüčÅ čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ čüčćąĖčéą░čÄčēąĄą│ąŠ ą▓ąĮąĖąĘ čüč湥čéčćąĖą║ą░.

ąĪą╝ąĄčēąĄąĮąĖąĄ 0x08

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░ 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąĘą░čĆąĄčĆąĄąĘą▓ąĖčĆąŠą▓ą░ąĮąŠ |

EWIF

rc_w0

|

ąæąĖčéčŗ 31:1 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

EWIF (ą▒ąĖčé 0) Early Wakeup Interrupt Flag. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą┤ąŠčüčéąĖą│ąĮąĄčé 0x40. ąæąĖčé ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 0, ąĘą░ą┐ąĖčüčī ą╗ąŠą│. 1 ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░. ąŁč鹊čé ą▒ąĖčé čéą░ą║ąČąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ąĄčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ ą▒čŗą╗ąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ.

[ąĪčüčŗą╗ą║ąĖ]

1. RM0090 Reference manual STM32F405/415, STM32F407/417, STM32F427/437 and STM32F429/439 advanced Arm®-based 32-bit MCUs site:st.com.

2. STM32 IWDG.

3. STM32: ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆčŗ ąĖ č鹥čĆą╝ąĖąĮčŗ.

4. ąĀčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ą┐ąŠ čüč鹊čĆąŠąČąĄą▓čŗą╝ čéą░ą╣ą╝ąĄčĆą░ą╝ ą┤ą╗čÅ ą▓čüčéčĆą░ąĖą▓ą░ąĄą╝čŗčģ čüąĖčüč鹥ą╝. |