|

ąÉą▒ą▒čĆąĄą▓ąĖą░čéčāčĆą░ IWDG ąŠą▒ąŠąĘąĮą░čćą░ąĄčé Independent Watchdog, čé. ąĄ. "ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ". ąŁč鹊 čüą░ą╝čŗą╣ ąŠą▒čŗčćąĮčŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ, ą║ąŠč鹊čĆčŗą╣ čāąČąĄ ą┤ą░ą▓ąĮąŠ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą▓ąŠ ą▓čüąĄčģ čüąŠą▓čĆąĄą╝ąĄąĮąĮčŗčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ. ąóą░ą╣ą╝ąĄčĆ IWDG ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čüą▒čĆąŠčüą░ čüąĖčüč鹥ą╝čŗ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ąĘą░ą▓ąĖčüą░ąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, ą░ čéą░ą║ąČąĄ ą║ą░ą║ čüą▓ąŠą▒ąŠą┤ąĮąŠ čüčćąĖčéą░čÄčēąĖą╣ ą▓ąĮąĖąĘ 12-ą▒ąĖčéąĮčŗą╣ čüč湥čéčćąĖą║ ą┤ą╗čÅ ąŠčéčüą╗ąĄąČąĖą▓ą░ąĮąĖčÅ čéą░ą╣ą╝ą░čāčéą░ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ (č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░ą┤ąĄčƹȹĄą║).

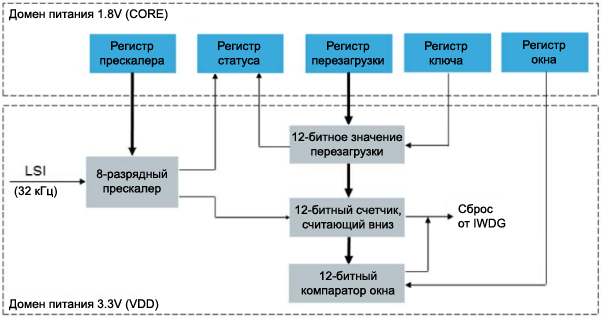

ąĢčüą╗ąĖ IWDG ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ, č鹊 ąĄą│ąŠ ąĮąĄą╗čīąĘčÅ ąĘą░ą┐čĆąĄčéąĖčéčī, ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖ ąŠą▒ąĮąŠą▓ą╗čÅčéčī. IWDG ą┐ąŠą╗čāčćą░ąĄčé čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčé ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠą│ąŠ ąĮąĖąĘą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą│ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ 32 ą║ąōčå (Low-Speed Internal RC generator, LSI), ą┐ąŠčŹč鹊ą╝čā čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ LSI čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ąŠčéą║ą░ąĘą░ą╗ ąŠčüąĮąŠą▓ąĮąŠą╣ čéą░ą║č鹊ą▓čŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ čüąĖčüč鹥ą╝čŗ. ąĪ ą┐ąŠą╝ąŠčēčīčÄ 8-ą▒ąĖčéąĮąŠą│ąŠ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░, ą║ąŠč鹊čĆčŗą╣ ą┤ąĄą╗ąĖčé čćą░čüč鹊čéčā LSI, ą╝ąŠąČąĮąŠ čāą┐čĆą░ą▓ą╗čÅčéčī čćą░čüč鹊č鹊ą╣ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ IWDG. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąŠčüąĮąŠą▓ąĮąŠąĄ ą┤ąŠčüč鹊ąĖąĮčüčéą▓ąŠ IWDG ą▓ č鹊ą╝, čćč鹊 ąŠąĮ čĆą░ą▒ąŠčéą░ąĄčé ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąŠčüąĮąŠą▓ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąóą░ą║ąČąĄ IWDG ą╝ąŠąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą░ą┐ą┐ą░čĆą░čéąĮąŠ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, ąĖčüą┐ąŠą╗čīąĘčāčÅ ą▒ą░ą╣čéčŗ ąŠą┐čåąĖą╣.

ąĀąĄą│ąĖčüčéčĆčŗ IWDG ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ą┤ąŠą╝ąĄąĮąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ čÅą┤čĆą░ (CORE, 1.8V), ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čäčāąĮą║čåąĖąĖ IWDG ą╝ąŠą│čāčé ą▓ą╗ąĖčÅčéčī ąĮą░ ą┤ąŠą╝ąĄąĮ VDD ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ąóą░ą╣ą╝ąĄčĆ IWDG ą╝ąŠąČąĮąŠ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ąĖčéčī ą▓čģąŠą┤ąŠą╝ ą▓ čĆąĄąČąĖą╝ Standby ąĖą╗ąĖ Stop. ą×ą┤ąĮą░ą║ąŠ ą░čĆčģąĖč鹥ą║čéčāčĆą░ IWDG čāčüčéčĆąŠąĄąĮą░ čéą░ą║, čćč鹊 ąŠąĮ ą╝ąŠąČąĮąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖčéčī čĆą░ą▒ąŠčéą░čéčī ą▓ čĆąĄąČąĖą╝ą░čģ Standby ąĖą╗ąĖ Stop.

ąÜąŠą│ą┤ą░ IWDG ąĘą░ą┐čāčēąĄąĮ, ąĄą│ąŠ 12-ą▒ąĖčéąĮčŗą╣ čüč湥čéčćąĖą║ ąĮą░čćąĖąĮą░ąĄčé čüčćąĖčéą░čéčī ą▓ąĮąĖąĘ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ čüą▒čĆąŠčüą░ 0xFFF. ą¦č鹊ą▒čŗ ąŠą▒ąĮąŠą▓ąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ IWDG ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ, ą▓ čĆąĄą│ąĖčüčéčĆ ą║ą╗čÄčćą░ (IWDG_KR) ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ 0x0000AAAA. ąĢčüą╗ąĖ čŹč鹊ą│ąŠ ąĮąĄ čüą┤ąĄą╗ą░čéčī, č鹊 ą▓ ą╝ąŠą╝ąĄąĮčé ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ čüč湥čéčćąĖą║ąŠą╝ IWDG ąĘąĮą░č湥ąĮąĖčÅ 0x000 čüą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüą▒čĆąŠčü čüąĖčüč鹥ą╝čŗ.

ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮą░ ąŠą┐čåąĖčÅ ąŠą║ąĮą░, č鹊 čüč湥čéčćąĖą║ ą┤ąŠą╗ąČąĄąĮ ąŠą▒ąĮąŠą▓ą╗čÅčéčīčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ čŹč鹊ą│ąŠ ąŠą║ąĮą░, ąĖąĮą░č湥 ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮ čüą▒čĆąŠčü.

ąĢčüą╗ąĖ IWDG čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą▒ą░ą╣čéą░ą╝ąĖ ąŠą┐čåąĖą╣, č鹊 ąŠąĮ čüčĆą░ąĘčā ąĮą░čćąĖąĮą░ąĄčé čĆą░ą▒ąŠčéą░čéčī ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ. ąöą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ čüą▒čĆąŠčüą░ čĆąĄą│ąĖčüčéčĆ ą║ą╗čÄčćą░ čü čĆąĄą│čāą╗čÅčĆąĮčŗą╝ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ąĖ ą┤ąŠą╗ąČąĄąĮ ąŠą▒ąĮąŠą▓ą╗čÅčéčīčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ 0x0000AAAA, čćč鹊ą▒čŗ čüč湥čéčćąĖą║ IWDG ąĮąĄ čāčüą┐ąĄą╗ ą┤ąŠčüčćąĖčéą░čéčī ą┤ąŠ 0. ąĢčüą╗ąĖ ąŠą┐čåąĖčÅ ąŠą║ąĮą░ čĆą░ąĘčĆąĄčłąĄąĮą░, č鹊 ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąŠą║ąĮą░.

ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ IWDG:

1. ąĀą░ąĘčĆąĄčłąĖč鹥 IWDG ąĘą░ą┐ąĖčüčīčÄ 0x0000CCCC ą▓ IWDG_KR (čĆąĄą│ąĖčüčéčĆ ą║ą╗čÄčćą░). ąŁč鹊 ąĘą░ą┐čāčüčéąĖčé čüč湥čéčćąĖą║ čéą░ą╣ą╝ąĄčĆą░ IWDG.

2. ąĀą░ąĘčĆąĄčłąĖč鹥 ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆčā ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ 0x00005555 ą▓ IWDG_KR. ąŁč鹊 čüąĮąĖą╝ą░ąĄčé ąĘą░čēąĖčéčā čĆąĄą│ąĖčüčéčĆąŠą▓ IWDG.

3. ąŚą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāą╣č鹥 ą┐čĆąĄčüą║ą░ą╗ąĄčĆ IWDG ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ IWDG_PR.

4. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ IWDG_RLR (čĆąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ).

5. ą¤ąŠą┤ąŠąČą┤ąĖč鹥 ą╝ąŠą╝ąĄąĮčéą░ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ (IWDG_SR = 0x00000000).

6. ąĢčüą╗ąĖ ąĮčāąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī ąŠą┐čåąĖčÄ ąŠą║ąĮą░, č鹊 ąĘą░ą┐ąĖčłąĖč鹥 ąĘąĮą░č湥ąĮąĖąĄ ąŠą║ąĮą░ ą▓ čĆąĄą│ąĖčüčéčĆ IWDG_WINR. ąŁč鹊 ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠą▒ąĮąŠą▓ąĖčé čüč湥čéčćąĖą║ ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖąĘ IWDG_RLR.

7. ąĢčüą╗ąĖ ąŠą┐čåąĖčÅ ąŠą║ąĮą░ čĆą░ąĘčĆąĄčłąĄąĮą░, č鹊 ąŠą▒ąĮąŠą▓ą╗čÅą╣č鹥 čüč湥čéčćąĖą║ ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖąĘ IWDG_RLR ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ 0x0000AAAA ą▓ čĆąĄą│ąĖčüčéčĆ IWDG_KR.

ąśąĮč鹥čĆą▓ą░ą╗ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ IWDT ą╝ąŠąČąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ąŠčé 125 ą╝ą║čü ą┤ąŠ 32.8 čüąĄą║čāąĮą┤. ąÆąĄą╗ąĖčćąĖąĮą░ čéą░ą╣ą╝ą░čāčéą░ IWDG ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ č乊čĆą╝čāą╗ąŠą╣:

t_IWDG(ą╝čü) = t_LSI(ą╝čü) * 4 * 2(IWDG_PW[2:0]) * (IWDG_RLR[11:0]+1)

ąŚą┤ąĄčüčī t_LSI čŹč鹊 ą┐ąĄčĆąĖąŠą┤ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüąŠą▓ LSI, čĆą░ą▓ąĮčŗą╣ 1/32000 = 0.03125 čüąĄą║čāąĮą┤čŗ, ąĖą╗ąĖ 31.25 ą╝čü.

ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą╝ąŠąČąĮąŠ ą┐čĆąŠą▓ąĄčĆąĖčéčī, ą▒čŗą╗ ą╗ąĖ čŹč鹊čé čüą▒čĆąŠčü ą▓čŗąĘą▓ą░ąĮ IWDG, ą┐čāč鹥ą╝ čćč鹥ąĮąĖčÅ čäą╗ą░ą│ą░ IWDGRSTF ą▓ čĆąĄą│ąĖčüčéčĆąĄ RCC_CSR.

ąĪč湥čéčćąĖą║ IWDG ą╝ąŠąČąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī, ą║ąŠą│ą┤ą░ čÅą┤čĆąŠ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ DBG_IWDG_STOP ą▓ ą╝ąŠą┤čāą╗ąĄ DBG. ąÜąŠą│ą┤ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32 ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ ąŠčéą╗ą░ą┤ą║ąĖ (Degug mode), čüč湥čéčćąĖą║ IWDG ą┐čĆąŠą┤ąŠą╗ąČąĖčé ąĮąŠčĆą╝ą░ą╗čīąĮąŠ čüčćąĖčéą░čéčī ą╗ąĖą▒ąŠ ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ - ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▒ąĖčéą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ DBG_IWDG_STOP ą▓ ą╝ąŠą┤čāą╗ąĄ DBG (MCUAPB1).

IWDG ą╝ąŠąČąĄčé čüčćąĖčéą░čéčī (ą▒čŗčéčī ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ) ą▓ čĆą░ą▒ąŠčćąĖčģ čĆąĄąČąĖą╝ą░čģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąĖ ąĄą│ąŠ čĆąĄąČąĖą╝ą░čģ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ą║čĆąŠą╝ąĄ čĆąĄąČąĖą╝ą░ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ Shutdown. ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ą▓ čĆąĄąČąĖą╝ą░čģ Stop0, Stop1, Stop2 ąĖ Standby čüč湥čéčćąĖą║ IWDG ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą╗ąĖą▒ąŠ ą╝ąŠąČąĄčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčī čüč湥čé ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_OPTR.

ąóą░ą▒ą╗ąĖčåą░ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ IWDG ą▓ čĆą░ąĘą╗ąĖčćąĮčŗčģ čĆąĄąČąĖą╝ą░čģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ (ąĄčüą╗ąĖ IWDG ą▒čŗą╗ čĆą░ąĘčĆąĄčłąĄąĮ):

| ąĀąĄąČąĖą╝ STM32 |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ IWDG |

| Run |

ąÉą║čéąĖą▓ąĄąĮ. |

| Sleep |

| Low power run |

| Low-power sleep |

| Stop0, Stop1 |

ąÉą║čéąĖą▓ąĄąĮ, ąĖą╗ąĖ čüč湥čé ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▒ąĖčéą░ IWDG_STOP ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_OPTR. |

| Stop2 |

| Standby |

ąÉą║čéąĖą▓ąĄąĮ, ąĖą╗ąĖ čüč湥čé ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▒ąĖčéą░ IWDG_STDBY ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_OPTR. |

| Shutdown |

ąÆčŗą║ą╗čÄč湥ąĮ. |

[ąĪčüčŗą╗ą║ąĖ]

1. ąĪč鹊čĆąŠąČąĄą▓čŗąĄ čéą░ą╣ą╝ąĄčĆčŗ STM32F4. |