|

ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ STM32F407 ąĖą╝ąĄčÄčé ą▓ąĄčüčīą╝ą░ ąĮąĄą┐čĆąŠčüč鹊ąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüąĖčüč鹥ą╝ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, čéčĆąĄą▒čāčÄčēąĄąĄ ą▓ąĮąĖą╝ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĘčāč湥ąĮąĖčÅ. ąŚą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ ą░ą┐čéąĮąŠčāčéą░ AN3988 "Clock configuration tool for STM32F40xx/41xx/427x/437x microcontrollers" ą║ąŠą╝ą┐ą░ąĮąĖąĖ ST.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖčüčģąŠą┤ąĮąŠą│ąŠ ą║ąŠą┤ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čéą░ą║č鹊ą▓ ą╝ąŠąČąĮąŠ čéą░ą║ąČąĄ ą▓ąŠčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▒ąĄčüą┐ą╗ą░čéąĮčŗą╝ ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░čĆąĖąĄą╝ CubeMX. ąŁč鹊 čāčéąĖą╗ąĖčéą░, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮą░čÅ ą┤ą╗čÅ ą░ą▓č鹊ą╝ą░čéąĖąĘąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čüąŠąĘą┤ą░ąĮąĖčÅ čłą░ą▒ą╗ąŠąĮą░ ą┐čĆąŠąĄą║čéą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ STM32.

ąŁč鹊čé ą░ą┐ąĮąŠčāčé ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ąŠą┐ąĖčüą░ąĮąĖąĄ ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (STSW-STM32091) ą┤ą╗čÅ čüąĄą╝ąĄą╣čüčéą▓ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32F4xx. ąØą░ąĘąĮą░č湥ąĮąĖąĄ čŹč鹊ą│ąŠ ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░ - ą┐ąŠą╝ąŠčćčī ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ą▓ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĖ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, čāčćąĖčéčŗą▓ą░čÅ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐čĆąŠą┤čāą║čéą░, čéą░ą║ąĖąĄ ą║ą░ą║ ą┐ąĖčéą░ąĮąĖąĄ ąĖ čĆąĄąČąĖą╝ ą┤ąŠčüčéčāą┐ą░ ą║ FLASH. ąśąĮčüčéčĆčāą╝ąĄąĮčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ą▓ čäą░ą╣ą╗ąĄ STM32F4xx_Clock_Configuration_VX.Y.Z.xls, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▓ą╝ąĄčüč鹥 čü čŹčéąĖą╝ ą░ą┐ąĮąŠčāč鹊ą╝ [1], ą║ąŠč鹊čĆčŗą╣ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮ čü čüą░ą╣čéą░ www.st.com.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: VX.Y.Z ąŠąĘąĮą░čćą░ąĄčé ąĮąŠą╝ąĄčĆ ą▓ąĄčĆčüąĖąĖ, ąĮą░ą┐čĆąĖą╝ąĄčĆ V1.0.0.

ąöą╗čÅ STM32F4xx ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēą░čÅ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī:

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ (system clock), ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ HCLK ąĖ ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖčÅ FLASH (latency), čé. ąĄ. ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ (wait states) ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čćą░čüč鹊čéčŗ HCLK.

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ čćą░čüč鹊čé PCLK1, PCLK2, TIMCLK (čćą░čüč鹊čéčŗ čéą░ą╣ą╝ąĄčĆą░), USBCLK ąĖ I2SCLK.

ŌĆó ąōąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą│ąŠč鹊ą▓ąŠą│ąŠ ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÄ ą╝ąŠą┤čāą╗čÅ ą║ąŠą┤ą░ system_stm32f4xx.c, ą║ąŠč鹊čĆčŗą╣ čüąŠą┤ąĄčƹȹĖčé ą▓ čüąĄą▒ąĄ ą▓čüąĄ ą▓čŗčłąĄą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮčŗąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ (čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖčüčģąŠą┤ąĮčŗą╣ čäą░ą╣ą╗ čüą╗ąŠčÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ąĄčĆąĖč乥čĆąĖąĖ, STM32F4xx CMSIS Cortex-M4 Device Peripheral Access Layer).

ąÆ čŹč鹊ą╝ ą┤ąŠą║čāą╝ąĄąĮč鹥 čäą░ą╣ą╗ STM32F4xx_Clock_Configuration_VX.Y.Z.xls čāą┐ąŠą╝ąĖąĮą░ąĄčéčüčÅ ą║ą░ą║ "clock tool". ą¤ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī clock tool, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐čĆąŠčćąĖčéą░čéčī čüą┐čĆą░ą▓ąŠčćąĮąŠąĄ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ą┐ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā STM32F4xx (RM0090) [1]. ąŁč鹊čé ą░ą┐ąĮąŠčāčé ąĮąĄ ąĘą░ą╝ąĄąĮčÅąĄčé čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ RM0090.

ą¤čĆąĖą╝. ą┐ąĄčĆąĄą▓ąŠą┤čćąĖą║ą░: ąśą£ąźą× ą╗čāčćčłąĄ čüą┤ąĄą╗ą░čéčī čü č鹊čćąĮąŠčüčéčīčÄ ą┤ąŠ ąĮą░ąŠą▒ąŠčĆąŠčé, ą┐ąŠč鹊ą╝čā čćč鹊 čüčĆą░ąĘčā ąŠą║čāąĮą░čéčīčüčÅ ą▓ ą┤ą░čéą░čłąĖčé RM0090 čüą╗ąĖčłą║ąŠą╝ čüą╗ąŠąČąĮąŠ. ąøčāčćčłąĄ ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ RM0090 ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ.

[ąóčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝čā ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÄ]

ą¦č鹊ą▒čŗ ąĘą░ą┐čāčüčéąĖčéčī clock tool, ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 čüą▓ąĄąČąĖąĄ ą▓ąĄčĆčüąĖąĖ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ Windows, čéą░ą║ąĖąĄ ą║ą░ą║ Windows XP, Vista ąĖą╗ąĖ Windows 7. ąÜąŠą╝ą┐čīčÄč鹥čĆ ą┐čĆąĖ čŹč鹊ą╝ ą┤ąŠą╗ąČąĄąĮ ąĖą╝ąĄčéčī ąŠą▒čŖąĄą╝ ą┐ą░ą╝čÅčéąĖ ąĮąĄ ą╝ąĄąĮąĄąĄ 256 ą╝ąĄą│ą░ą▒ą░ą╣čé RAM. ąŻ ąÆą░čü ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ Microsoft┬« Office, čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą╝ą░ą║čĆąŠčüąŠą▓ ąĖ ą║ąŠąĮčéčĆąŠą╗čŗ ActiveX. ąóą░ą║ąČąĄ čāą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 ąÆčŗ ąĘą░ą│čĆčāąĘąĖą╗ąĖ ą┐ąŠčüą╗ąĄą┤ąĮčÄčÄ ą▓ąĄčĆčüąĖčÄ ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░ clock tool čü čüą░ą╣čéą░ www.st.com.

ąÆąĄčĆčüąĖąĖ Excel┬« 1997-2003, ą║ą░ą║ čĆą░ąĘčĆąĄčłąĖčéčī ą╝ą░ą║čĆąŠčüčŗ ąĖ ActiveX: ą▓čŗą▒ąĄčĆąĖč鹥 ą╝ąĄąĮčÄ Tools -> Macro -> Security -> Low (not recommended).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą║ąŠąĮčéčĆąŠą╗čŗ ActiveX ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮčŗ, č鹊 ą▒čāą┤ąĄčé ąŠč鹊ą▒čĆą░ąČąĄąĮąŠ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ą░čÄčēąĄąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ąŠ č鹊ą╝, čćč鹊 ąÆčŗ čĆą░ąĘčĆąĄčłą░ąĄč鹥 ActiveX. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čüą╗ąĄą┤čāąĄčé ąŠčéą▓ąĄčéąĖčéčī OK, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī ActiveX.

ąÆąĄčĆčüąĖąĖ Excel┬« 2007, ą║ą░ą║ čĆą░ąĘčĆąĄčłąĖčéčī ą╝ą░ą║čĆąŠčüčŗ ąĖ ActiveX: ą║ą╗ąĖą║ąĮąĖč鹥 ąĮą░ ą║ąĮąŠą┐ą║čā Microsoft Office -> Excel options -> Trust Center -> Trust center settings -> Macro settings -> ą▓čŗą▒ąĄčĆąĖč鹥 Enable all macros (not recommended, potentially dangerous code can run). ąŚą░č鹥ą╝ Trust Center -> Trust center settings -> ActiveX settings -> ą▓čŗą▒ąĄčĆąĖč鹥 Enable all controls without restrictions and without prompting (not recommended; potentiality dangerous controls can run). ąÜą╗ąĖą║ąĮąĖč鹥 OK.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĘą░ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĄą╣, ą║ą░ą║ čĆą░ąĘčĆąĄčłąĖčéčī ą╝ą░ą║čĆąŠčüčŗ ąĖ ActiveX controls, ąŠą▒čĆą░čéąĖč鹥čüčī ąĮą░ čüą░ą╣čé Microsoft Office.

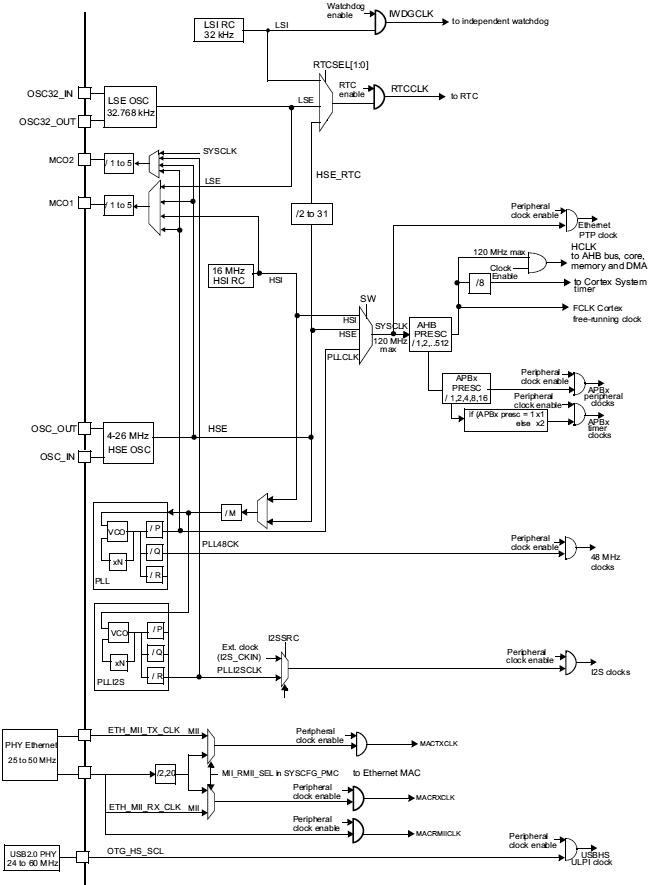

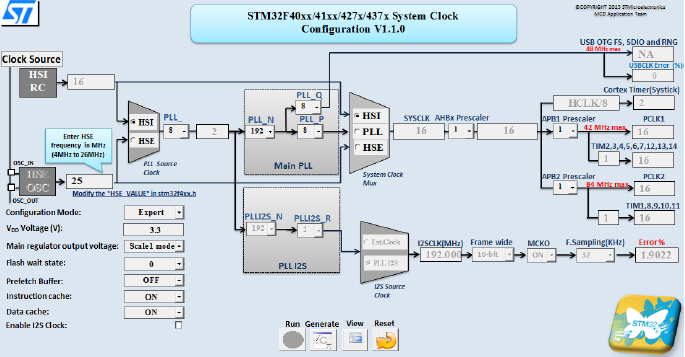

[ąĪčģąĄą╝ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32F4xx]

ąśąĮčüčéčĆčāą╝ąĄąĮčé clock tool čüą┐ąĄčåąĖą░ą╗čīąĮąŠ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ ą┤ą╗čÅ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠą┤čāą╗čÅ ą║ąŠą┤ą░ system_stm32f4xx.c, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ čüąĄą╝ąĄą╣čüčéą▓ą░ STM32F4xx. ążą░ą╣ą╗ ą╝ąŠą┤čāą╗čÅ system_stm32f4xx.c ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą║ą░ą║ čłą░ą▒ą╗ąŠąĮ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĮąŠ ą╗ąĄą│ą║ąŠ ą┐ąŠą┤čüčéčĆąŠąĖčéčī ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ąĮčāąČąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ čüąĖčüč鹥ą╝čŗ ąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮčāąČąĮąŠą╣ ą╗ą░č鹥ąĮčéąĮąŠčüčéąĖ Flash.

ąÆ čŹč鹊ą╣ čüąĄą║čåąĖąĖ ąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čüčģąĄą╝ą░ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ, ą║ąŠč鹊čĆą░čÅ ąĘą░ą▓ąĖčüąĖčé ąŠčé čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą║ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ ą┐ąĖčéą░ąĮąĖčÅ (VDD) ą┐čĆąŠčéąĖą▓ ąĘąĮą░č湥ąĮąĖčÅ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąĖ ą╗ą░č鹥ąĮčéąĮąŠčüčéąĖ Flash ą┐čĆąŠčéąĖą▓ ąĘąĮą░č湥ąĮąĖčÅ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ. ą£ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čéčĆąĖ čĆą░ąĘąĮčŗąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī čüąĖčüč鹥ą╝ąĮčŗąĄ čéą░ą║čéčŗ (SYSCLK):

1. ąóą░ą║čéčŗ ą│ąĄąĮąĄčĆą░č鹊čĆą░ HSI (16 ą£ąōčå).

2. ąóą░ą║čéčŗ ą│ąĄąĮąĄčĆą░č鹊čĆą░ HSE (4..26 ą£ąōčå).

3. ą×čüąĮąŠą▓ąĮą░čÅ ą┐ąĄčéą╗čÅ ążąÉą¤ą¦ (phase-locked loop, PLL) ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ čéą░ą║č鹊ą▓, čü ą│ąĄąĮąĄčĆą░č鹊čĆąŠą╝, čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ą▓ ą┐ąĄčéą╗ąĄ PLL (PLLVCO). ąÆčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ čüąĖčüč鹥ą╝čŗ PLL ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą╝ąĄąČą┤čā 1 ąĖ 2 ą£ąōčå (čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī 2 ą£ąōčå, čćč鹊ą▒čŗ ąŠą│čĆą░ąĮąĖčćąĖčéčī ą┤ąČąĖčéč鹥čĆ PLL). ąÆ PLL čāčćą░čüčéą▓čāčÄčé ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ čāą╝ąĮąŠąČąĄąĮąĖčÅ ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ M, N, P ąĖ Q.

ąÆčüąĄ čéą░ą║č鹊ą▓čŗąĄ čćą░čüč鹊čéčŗ ą┤ą╗čÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąŠąĖąĘą▓ąŠą┤čÅčéčüčÅ ąŠčé čćą░čüč鹊čéčŗ SYSCLK, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝:

1. ąóą░ą║č鹊ą▓čŗąĄ čćą░čüč鹊čéčŗ USB OTG FS clock (48 ą£ąōčå), RNG (48 ą£ąōčå) ąĖ SDIO (48 ą£ąōčå), ą║ąŠč鹊čĆą░čÅ ą┐čĆąĖčģąŠą┤ąĖčé ąŠčé čüą┐ąĄčåąĖą░ą╗čīąĮąŠą│ąŠ ą▓čŗčģąŠą┤ą░ PLL (PLL48CLK).

2. ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ I2S. ą¦č鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī ą▓čŗčüąŠą║ąŠą│ąŠ ą║ą░č湥čüčéą▓ą░ ąĘą▓čāą║ą░, čéą░ą║čéčŗ I2S ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮčŗ ą╗ąĖą▒ąŠ ąŠčé ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ čāąĘą╗ą░ PLL (PLLI2S), ą╗ąĖą▒ąŠ ąŠčé ą▓ąĮąĄčłąĮąĄą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, ą║ąŠč鹊čĆą░čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ ą║ ąĮąŠąČą║ąĄ I2S_CKIN.

ąĀąĖčü. 1. ąĪčģąĄą╝ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ STM32F4xx.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čüčģąĄą╝ąĄ (čüą╝. čéą░ą║ąČąĄ ąĪą╗ąŠą▓ą░čĆąĖą║ [2]):

Ethernet PTP clock čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ Precision time protocol ą┤ą╗čÅ Ethernet.

HSE_RTC čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ RTC (HSE, ą┐ąŠą┤ąĄą╗ąĄąĮąĮą░čÅ ąĮą░ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą│ąŠ ą┤ąĄą╗ąĖč鹥ą╗čÅ).

independent watchdog ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ.

LSE OSC Low Speed External, ą▓ąĮąĄčłąĮąĖą╣ ąĮąĖąĘą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ RC-ą│ąĄąĮąĄčĆą░č鹊čĆ 32.768 ą║ąōčå (ą║ ą║ąŠč鹊čĆąŠą╝čā ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ąŠčéą┤ąĄą╗čīąĮčŗą╣ ąĮąĖąĘą║ąŠčćą░čüč鹊čéąĮčŗą╣ ą║ą▓ą░čĆčåąĄą▓čŗą╣ čĆąĄąĘąŠąĮą░č鹊čĆ).

LSI RC Low Speed Internal, ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąĮąĖąĘą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ RC-ą│ąĄąĮąĄčĆą░č鹊čĆ 32 ą║ąōčå.

MCO1, MCO2 Microcontroller clock output, ą▓čŗčģąŠą┤čŗ čéą░ą║č鹊ą▓ 1 ąĖ 2.

OSC_OUT, OSC_IN ą▓čŗą▓ąŠą┤čŗ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą▓čŗčüąŠą║ąŠčćą░čüč鹊čéąĮąŠą│ąŠ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ čĆąĄąĘąŠąĮą░č鹊čĆą░ (4..26 ą£ąōčå).

Watchdog enable čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ FLASH (wait states, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĄąĄ ą╗ą░č鹥ąĮčéąĮąŠčüčéčī) ąĘą░ą┤ą░ąĄčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čćą░čüč鹊č鹊ą╣ CPU (Cortex-M4), ąĖ ąĮąĄ ąĮą░ą┐čĆčÅą╝čāčÄ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ (VDD), čüą╝. čéą░ą▒ą╗ąĖčåčā 2.

ąóą░ą▒ą╗ąĖčåą░ 2. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓ wait states ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ CPU HCLK, čćą░čüč鹊čéą░ HCLK čāą║ą░ąĘą░ąĮą░ ą▓ ą£ąōčå.

| Wait states WS (LATENCY) |

VDD 2.7V .. 3.6V |

VDD 2.4V .. 2.7V |

VDD 2.1V .. 2.4V |

VDD 1.8V .. 2.1V

Prefetch OFF |

| 0 WS (1 CPU cycle) |

0 < HCLK Ōēż 30 |

0 < HCLK Ōēż 24 |

0 < HCLK Ōēż 22 |

0 < HCLK Ōēż 20 |

| 1 WS (2 CPU cycles) |

30 < HCLK Ōēż 60 |

24 < HCLK Ōēż 48 |

22 < HCLK Ōēż 44 |

20 < HCLK Ōēż 40 |

| 2 WS (3 CPU cycles) |

60 < HCLK Ōēż 90 |

48 < HCLK Ōēż 72 |

44 < HCLK Ōēż 66 |

40 < HCLK Ōēż 60 |

| 3 WS (4 CPU cycles) |

90 < HCLK Ōēż 120 |

72 < HCLK Ōēż 96 |

66 < HCLK Ōēż 88 |

60 < HCLK Ōēż 80 |

| 4 WS (5 CPU cycles) |

120 < HCLK Ōēż 150 |

96 < HCLK Ōēż 120 |

88 < HCLK Ōēż 110 |

80 < HCLK Ōēż 100 |

| 5 WS (6 CPU cycles) |

150 < HCLK Ōēż 168 |

120 < HCLK Ōēż 144 |

110 < HCLK Ōēż 132 |

100 < HCLK Ōēż 120 |

| 6 WS (7 CPU cycles) |

|

144 < HCLK Ōēż 168 |

132 < HCLK Ōēż 154 |

120 < HCLK Ōēż 140 |

| 7 WS (8 CPU cycles) |

|

|

154 < HCLK Ōēż 168 |

140 < HCLK Ōēż 160 |

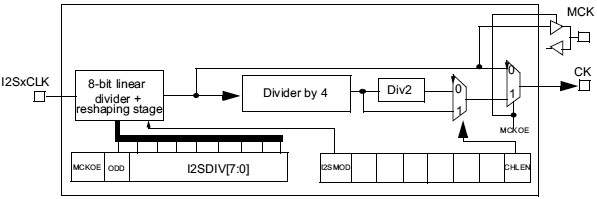

[ąōąĄąĮąĄčĆą░č鹊čĆ čéą░ą║č鹊ą▓ I2S]

ąōąĄąĮąĄčĆą░čåąĖčÅ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ I2S ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĮą░ą╗ąĖčćąĖčÅ čćą░čüč鹊čéčŗ MCLK (čĆą░ąĘčĆąĄčłąĄąĮą░ ąŠąĮą░ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮą░), čłąĖčĆąĖąĮčŗ čäčĆąĄą╣ą╝ą░, ąĖ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╣ čćą░čüč鹊čéčŗ I2S (I2SCLK).

ąĀąĖčü. 2. ąÉčĆčģąĖč鹥ą║čéčāčĆą░ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čéą░ą║č鹊ą▓ I2S.

ą¦ą░čüč鹊čéą░ ą░čāą┤ąĖąŠą▓čŗą▒ąŠčĆąŠą║ ą╝ąŠąČąĄčé ą▒čŗčéčī 192 ą║ąōčå, 96 ą║ąōčå, 48 ą║ąōčå, 44.1 ą║ąōčå, 32 ą║ąōčå, 22.05 ą║ąōčå, 16 ą║ąōčå, 11.025 ą║ąōčå ąĖą╗ąĖ 8 ą║ąōčå. ą¦č鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī ąĮčāąČąĮąŠą╣ čćą░čüč鹊čéčŗ, ą╗ąĖąĮąĄą╣ąĮčŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī (DIV) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą┐ąŠ č乊čĆą╝čāą╗ą░ą╝ ąĮąĖąČąĄ.

ąÜąŠą│ą┤ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ MCLK (čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé MCKOE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_I2SPR):

ŌĆó Fs = I2SxCLK/[(16*2)*((2*I2SDIV)+ODD)*8)] ą║ąŠą│ą┤ą░ čäčĆąĄą╣ą╝ ą║ą░ąĮą░ą╗ą░ čłąĖčĆąĖąĮąŠą╣ 16 ą▒ąĖčé.

ŌĆó Fs = I2SxCLK/[(32*2)*((2*I2SDIV)+ODD)*4)] ą║ąŠą│ą┤ą░ čäčĆąĄą╣ą╝ ą║ą░ąĮą░ą╗ą░ čłąĖčĆąĖąĮąŠą╣ 32 ą▒ąĖčé.

ODD čÅą▓ą╗čÅąĄčéčüčÅ ą╝ąĮąŠąČąĖč鹥ą╗ąĄą╝ ąĮąĄč湥čéąĮąŠčüčéąĖ ą┤ą╗čÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░. ąÜąŠą│ą┤ą░ MCLK ąĘą░ą┐čĆąĄčēąĄąĮą░ (ąŠčćąĖčēąĄąĮ ą▒ąĖčé MCKOE):

ŌĆó FS = I2SxCLK/[(16*2)*((2*I2SDIV)+ODD))] ą║ąŠą│ą┤ą░ čäčĆąĄą╣ą╝ ą║ą░ąĮą░ą╗ą░ čłąĖčĆąĖąĮąŠą╣ 16 ą▒ąĖčé.

ŌĆó FS = I2SxCLK/[(32*2)*((2*I2SDIV)+ODD))] ą║ąŠą│ą┤ą░ čäčĆąĄą╣ą╝ ą║ą░ąĮą░ą╗ą░ čłąĖčĆąĖąĮąŠą╣ 32 ą▒ąĖčé.

ąśąĮčüčéčĆčāą╝ąĄąĮčé clock tool ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ąĮą░ąĖą╗čāčćčłąĄąĄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ PLLI2S_N ąĖ PLLI2S_R čü ą╝ąĖąĮąĖą╝čāą╝ąŠą╝ ąŠčłąĖą▒ąŠą║ ą┤ą╗čÅ čćą░čüč鹊čéčŗ ą▓čŗą▒ąŠčĆąŠą║ ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖčÅ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ I2S (čłąĖčĆąĖąĮą░ čäčĆąĄą╣ą╝ą░, MCKO, sampling frequency).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čäą░ą╣ą╗ąŠą╝ system_stm32f4xx.c ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ č鹊ą╗čīą║ąŠ PLLI2S_N ąĖ PLLI2S_R, čĆąĄą│ąĖčüčéčĆ I2S ąĮąĄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ. ą×čłąĖą▒ą║ą░ čćą░čüč鹊čéčŗ ą▓čŗą▒ąŠčĆąŠą║ (sampling frequency) ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą║ą░ą║ ąĖąĮą┤ąĖą║ą░č鹊čĆ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖčÅ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ I2S, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą▓ ą▓čŗčģąŠą┤ąĮąŠą╝ čäą░ą╣ą╗ąĄ system_stm32f4xx.c.

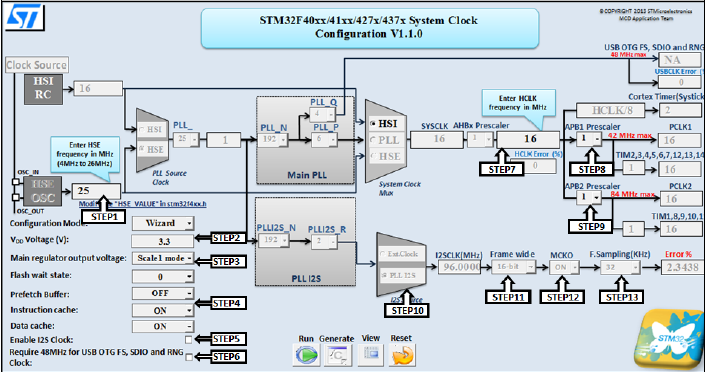

ąśą╝ąĄąĄčéčüčÅ ą┤ą▓ą░ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ clock tool: Wizard ąĖ Expert, čĆąĄąČąĖą╝ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▓ ą╗ąĖčüčé-ą▒ąŠą║čüąĄ Configuration mode.

[ąĀąĄąČąĖą╝ Wizard (ą╝ą░čüč鹥čĆ ą┐ąŠą┤čüą║ą░ąĘąŠą║)]

ąŁč鹊čé čĆąĄąČąĖą╝ (ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ) ą┐čĆąŠą▓ąŠą┤ąĖčé ąÆą░čü č湥čĆąĄąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ čłą░ą│ąĖ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┤ą╗čÅ ą┐čĆąŠčüč鹊ą│ąŠ ąĖ ą▒čŗčüčéčĆąŠą│ąŠ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĮčāąČąĮąŠą╣ čüąĖčüč鹥ą╝ąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé.

ąĀąĖčü. 3. ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą▓ čĆąĄąČąĖą╝ąĄ Wizard.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąĮąŠą┐ą║ą░ View čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąŠčüą╝ąŠčéčĆ xls-čäą░ą╣ą╗ą░ ą▓ ą┐ąŠą╗ąĮčŗą╣ 菹║čĆą░ąĮ (čŹč鹊čé ą┐čĆąŠčüą╝ąŠčéčĆ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ąĖą╗ąĖ ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ). ąÜąĮąŠą┐ą║ą░ Reset čĆą░ąĘčĆąĄčłą░ąĄčé čāčüčéą░ąĮąŠą▓ą║čā ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ.

ąöą░ą╗ąĄąĄ ą▒čāą┤ąĄčé ąŠą┐ąĖčüą░ąĮ ą┐ąŠčłą░ą│ąŠą▓čŗą╣ ą┐čĆąŠčåąĄčüčü ą┐ąŠą╗čāč湥ąĮąĖčÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓ čĆąĄąČąĖą╝ąĄ Wizard.

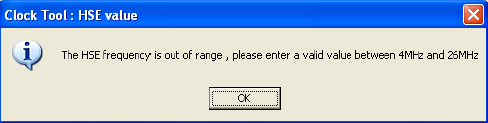

1. ąÜąŠą│ą┤ą░ ą▓ ąÆą░čłąĄą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ HSE (ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ ą▓ąĮąĄčłąĮąĖą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ), čāčüčéą░ąĮąŠą▓ąĖč鹥 ąĄą│ąŠ čćą░čüč鹊čéčā ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 4..26 ą£ąōčå, ąĄčüą╗ąĖ ą┤ą╗čÅ STM32F4xx ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą▓ą░čĆčåąĄą▓čŗą╣ čĆąĄąĘąŠąĮą░č鹊čĆ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą╝ą░ą║čĆąŠąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ HSE_VALUE ą▓ čäą░ą╣ą╗ąĄ stm32f4xx.h ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąŠ ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąĄąĮčÅąĄčé ąĘąĮą░č湥ąĮąĖąĄ ą│ąĄąĮąĄčĆą░č鹊čĆą░ HSE.

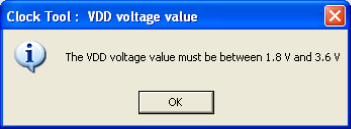

ąĢčüą╗ąĖ ą▓ą▓ąĄą┤ąĄąĮąĮą░čÅ čćą░čüč鹊čéą░ ąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą┤ąŠą┐čāčüčéąĖą╝čŗčģ ą┐čĆąĄą┤ąĄą╗ą░čģ, č鹊 ą▒čāą┤ąĄčé ąŠč鹊ą▒čĆą░ąČąĄąĮąŠ čüąŠąŠą▒čēąĄąĮąĖąĄ ąŠą▒ ąŠčłąĖą▒ą║ąĄ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 4.

ąĀąĖčü. 4. ąŚąĮą░č湥ąĮąĖąĄ čćą░čüč鹊čéčŗ HSE ą▓ąĮąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░.

2. ąÆąĄą┤ąĖč鹥 ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ VDD ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1.8V ą┤ąŠ 3.6V (čüą╝. čĆąĖčü. 3). ąĢčüą╗ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VDD ą▓čŗčģąŠą┤ąĖčé ąĘą░ čŹčéąĖ ą┐čĆąĄą┤ąĄą╗čŗ, č鹊 ą▒čāą┤ąĄčé ąŠč鹊ą▒čĆą░ąČąĄąĮą░ ąŠčłąĖą▒ą║ą░, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 5.

ąĀąĖčü. 5. ąŚąĮą░č湥ąĮąĖąĄ VDD ą▓ąĮąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░.

3. ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čĆąĄą│čāą╗čÅč鹊čĆą░:

ŌĆō ąÆčŗą▒ąĄčĆąĖč鹥 Scale1 mode ąĖąĘ ą╗ąĖčüčé-ą▒ąŠą║čüą░, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā čüąĖčüč鹥ą╝čŗ (fHCLK) 168 ą£ąōčå.

ŌĆō ąÆčŗą▒ąĄčĆąĖč鹥 Scale2 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (fHCLK) 144 ą£ąōčå.

4. ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ą▒čāč乥čĆ Prefetch (ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮą░čÅ ąĘą░ą│čĆčāąĘą║ą░ ą║ąŠą╝ą░ąĮą┤), Instruction Cash (ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤) ąĖ Data cash (ą║čŹčł ą┤ą░ąĮąĮčŗčģ) - ą▓čŗą▒ąĄčĆąĖč鹥 ON ąĖą╗ąĖ OFF ąĖąĘ ą╗ąĖčüčé-ą▒ąŠą║čüą░.

5. ąÆčŗą▒ąĄčĆąĖč鹥 PLLI2S, ąĄčüą╗ąĖ čŹč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ. ąĢčüą╗ąĖ ąĮčāąČąĮąŠ, čĆą░ąĘčĆąĄčłąĖč鹥 čŹč鹊 ąĖ čüą╗ąĄą┤čāą╣č鹥 čłą░ą│ą░ą╝ 9, 10, 11 ąĖ 12. ąśąĮą░č湥 ą┐ąĄčĆąĄą╣ą┤ąĖč鹥 ą║ čłą░ą│čā 5.

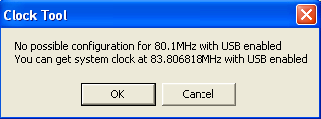

6. ąŻą║ą░ąČąĖč鹥, ąĄčüą╗ąĖ 48 ą£ąōčå ąĮčāąČąĮčŗ ą┤ą╗čÅ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ USB OTG FS, RNG ąĖą╗ąĖ SDIO. ąĢčüą╗ąĖ čŹčéąĖ čäčāąĮą║čåąĖąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗ, čŹč鹊 ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ą┤ą╗čÅ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčēąĖčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ PLL. ąĢčüą╗ąĖ čŹčéąĖ čäčāąĮą║čåąĖąĖ ąĮąĄ ąĮčāąČąĮčŗ, č鹊 ąĮąĄ ą▒čāą┤čāčé ą┤ąŠą▒ą░ą▓ą╗ąĄąĮčŗ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ USB.

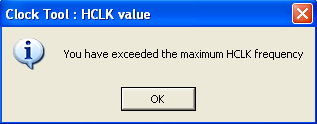

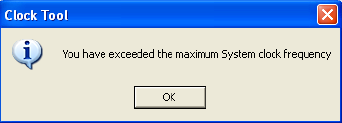

7. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ąĮčāąČąĮčāčÄ čćą░čüč鹊čéčā HCLK. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ HCLK ąĘą░ą▓ąĖčüąĖčé ą║ą░ą║ ąŠčé ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čĆąĄą│čāą╗čÅč鹊čĆą░ (Scale1/Scale2, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ ąĮą░ čłą░ą│ąĄ 4), čéą░ą║ ąĖ ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VDD (čüą╝. čéą░ą▒ą╗ąĖčåčā 2). ąĢčüą╗ąĖ ą▓ą▓ąĄą┤ąĄąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąŠą╗čīčłąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊čéčŗ HCLK, č鹊 ą▒čāą┤ąĄčé ąŠč鹊ą▒čĆą░ąČąĄąĮąŠ čüąŠąŠą▒čēąĄąĮąĖąĄ ąŠą▒ ąŠčłąĖą▒ą║ąĄ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 6.

ąĀąĖčü. 6. ą×čłąĖą▒ą║ą░ čćą░čüč鹊čéčŗ CLK.

8. ąÆčŗą▒ąĄčĆąĖč鹥 ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ PCLK1 ąĖ PCLK2 ąĖąĘ ą╗ąĖčüčé-ą▒ąŠą║čüą░, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī čéčĆąĄą▒čāąĄą╝čŗąĄ čćą░čüč鹊čéčŗ PCLK1 ąĖ PCLK2. ą¦ą░čüč鹊čéčŗ TIMCLK ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čāčüčéą░ąĮąŠą▓ąŠą║ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ PCLK1 ąĖ PCLK2.

9. ą¤čĆąŠčüą╝ąŠčéčĆąĖč鹥 ąĮą░čüčéčĆąŠą╣ą║ąĖ, čüą┤ąĄą╗ą░ąĮąĮčŗąĄ ąĮą░ čłą░ą│ąĄ 8.

10. ąÆčŗą▒ąĄčĆąĖč鹥 ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ I2S. ąśą│ąĮąŠčĆąĖčĆčāą╣č鹥 čłą░ą│ąĖ 10, 11 ąĖ 12, ąĄčüą╗ąĖ ą▓čŗą▒čĆą░ąĮčŗ ą▓ąĮąĄčłąĮąĖąĄ čéą░ą║čéčŗ ą┤ą╗čÅ I2S.

11. ąĢčüą╗ąĖ PLLI2S ą▓čŗą▒čĆą░ąĮ ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą┤ą╗čÅ I2S, ą▓čŗą▒ąĄčĆąĖč鹥 čłąĖčĆąĖąĮčā čäčĆąĄą╣ą╝ą░ (16 ąĖą╗ąĖ 32 ą▒ąĖčéą░).

12. ąŻą║ą░ąČąĖč鹥, ą┤ąŠą╗ąČąĮą░ ą╗ąĖ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░ ą│ą╗ą░ą▓ąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ (master clock, MCLK), ą┤ą╗čÅ č湥ą│ąŠ ą▓čŗą▒ąĄčĆąĖč鹥 ON ąĖą╗ąĖ OFF ą▓ ą╗ąĖčüčé-ą▒ąŠą║čüąĄ.

13. ąÆčŗą▒ąĄčĆąĖč鹥 Fs ąĖąĘ ą╗ąĖčüčé-ą▒ąŠą║čüą░. ąŚąĮą░č湥ąĮąĖąĄ Fs ą╝ąŠąČąĄčé ą▒čŗčéčī 192 ą║ąōčå, 96 ą║ąōčå, 48 ą║ąōčå, 44.1 ą║ąōčå, 32 ą║ąōčå, 22.05 ą║ąōčå, 16 ą║ąōčå, 11.025 ą║ąōčå ąĖ 8 ą║ąōčå.

14. ąÜą╗ąĖą║ąĮąĖč鹥 ąĮą░ ą║ąĮąŠą┐ą║ąĄ RUN.

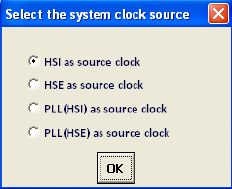

ąĢčüą╗ąĖ ą┐ąŠčéčĆąĄą▒čāąĄčéčüčÅ čüą┤ąĄą╗ą░čéčī ą▓čŗą▒ąŠčĆ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, č鹊 ą┤ą╗čÅ čŹč鹊ą│ąŠ ąŠč鹊ą▒čĆą░ąĘąĖčéčüčÅ ąŠą║ąĮąŠ (čüą╝. čĆąĖčü. 7). ąÆčŗą▒ąĄčĆąĖč鹥 HSE, HSI ąĖą╗ąĖ PLL (ąĖčüč鹊čćąĮąĖą║ąŠą╝ ą┤ą╗čÅ PLL ą╝ąŠąČąĄčé ą▒čŗčéčī HSI ąĖą╗ąĖ HSE).

ąĀąĖčü. 7. ąÆčŗą▒ąŠčĆ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮčŗ čäčāąĮą║čåąĖąĖ USB ąĖ/ąĖą╗ąĖ I2S (ą▓ clock tool čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ č湥ą║ą▒ąŠą║čü) ąĖ ą▓čŗą▒čĆą░ąĮąĮą░čÅ čćą░čüč鹊čéą░ HCLK ąĮąĄ čÅą▓ą╗čÅąĄčéčüčÅ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╣, č鹊 ą▓ ąŠą║ąĮąĄ ąŠč鹊ą▒čĆą░ąĘąĖčéčüčÅ čüąŠąŠą▒čēąĄąĮąĖąĄ ąŠ ą▒ą╗ąĖąČą░ą╣čłąĄą╣ ą▓ąŠąĘą╝ąŠąČąĮąŠą╣ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čćą░čüč鹊č鹥 HCLK (čüą╝. čĆąĖčü. 8).

ąĀąĖčü. 8. ąĪąŠąŠą▒čēąĄąĮąĖąĄ ąŠ č鹊ą╝, čćč鹊 ąĮąĄą╗čīąĘčÅ čāčüčéą░ąĮąŠą▓ąĖčéčī čéčĆąĄą▒čāąĄą╝čāčÄ čćą░čüč鹊čéčā HCLK.

ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 Flash Latency (ą╗ą░č鹥ąĮčéąĮąŠčüčéčī, ą▓čĆąĄą╝čÅ ą┤ąŠčüčéčāą┐ą░ ą║ FLASH): ą┐ąŠčüą╗ąĄ ąĘą░ą┐čāčüą║ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ wait states ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ąĮą░ ą╗čāčćčłąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ (ąĮą░ąĖą╝ąĄąĮčīčłąĄąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠąĄ), ą║ąŠč鹊čĆąŠąĄ ąÆčŗ ą╝ąŠąČąĄč鹥 ąĖąĘą╝ąĄąĮąĖčéčī ąĮą░ ą╗čÄą▒ąŠąĄ ą┤čĆčāą│ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓ čüč鹊čĆąŠąĮčā čāą▓ąĄą╗ąĖč湥ąĮąĖčÅ.

ąØą░ąČą░čéąĖąĄ ą║ąĮąŠą┐ą║ąĖ RUN ąŠč鹊ą▒čĆą░ąĘąĖčé ą┐ąŠą╗ąŠčüčā ą┐čĆąŠą│čĆąĄčüčüą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ.

15. ąØą░ ąĘą░ą▓ąĄčĆčłą░čÄčēąĄą╝ čłą░ą│ąĄ ą║ą╗ąĖą║ąĮąĖč鹥 ąĮą░ ą║ąĮąŠą┐ą║ąĄ Generate, čćč鹊ą▒čŗ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čäą░ą╣ą╗ system_stm32f4xx.c. ąŁč鹊čé čäą░ą╣ą╗ čüą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą▓ č鹊ą╝ ąČąĄ ą╝ąĄčüč鹥 ąĮą░ ą┤ąĖčüą║ąĄ, ą│ą┤ąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ XLS-čäą░ą╣ą╗ clock tool. ą¤čĆąŠčüą╝ąŠčéčĆąĖč鹥 čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čäą░ą╣ą╗, čćč鹊ą▒čŗ ą┐čĆąŠą▓ąĄčĆąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ system clock, SystemCoreClock, ąĘąĮą░č湥ąĮąĖčÅ HCLK, PCLK1, PCLK2, Flash access mode ąĖ ą┤čĆčāą│ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗąĄ ą▓ čäčāąĮą║čåąĖąĖ SetSysClock.

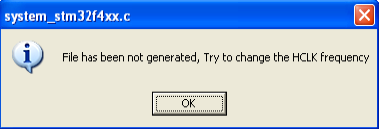

ążą░ą╣ą╗ system_stm32f4xx.c ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┤ąŠą▒ą░ą▓ą╗ąĄąĮ ą║ čĆą░ą▒ąŠč湥ą╝čā ą┐čĆąŠąĄą║čéčā ą┤ą╗čÅ čüąŠą▓ą╝ąĄčüčéąĮąŠą╣ čüą▒ąŠčĆą║ąĖ. ąĢčüą╗ąĖ čäą░ą╣ą╗ ąĮąĄ ą▒čŗą╗ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮ, č鹊 ą▒čāą┤ąĄčé ąŠč鹊ą▒čĆą░ąČąĄąĮąŠ čüąŠąŠą▒čēąĄąĮąĖąĄ ąŠą▒ ąŠčłąĖą▒ą║ąĄ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 9.

ąĀąĖčü. 9. ą×čłąĖą▒ą║ą░ ą│ąĄąĮąĄčĆą░čåąĖąĖ čäą░ą╣ą╗ą░.

[ąĀąĄąČąĖą╝ Expert]

ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąŠ ą▒ąŠą╗čīčłąĄ ą│ąĖą▒ą║ąŠčüčéąĖ ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ, ąŠą┤ąĮą░ą║ąŠ ą║ąŠčĆčĆąĄą║čéąĮąŠčüčéčī ą▓ą▓ąĄą┤ąĄąĮąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĘą░ą▓ąĖčüąĖčé ąŠčé č鹊ą│ąŠ, ąĮą░čüą║ąŠą╗čīą║ąŠ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĄčæ čüąŠčüčéą░ą▓ąĖą╗ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī.

ąĀąĖčü. 10. ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą▓ čĆąĄąČąĖą╝ąĄ 菹║čüą┐ąĄčĆčéą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąĮąŠą┐ą║ą░ View čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąŠčüą╝ąŠčéčĆ xls-čäą░ą╣ą╗ą░ ą▓ ą┐ąŠą╗ąĮčŗą╣ 菹║čĆą░ąĮ (čŹč鹊čé ą┐čĆąŠčüą╝ąŠčéčĆ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ąĖą╗ąĖ ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ). ąÜąĮąŠą┐ą║ą░ Reset čĆą░ąĘčĆąĄčłą░ąĄčé čāčüčéą░ąĮąŠą▓ą║čā ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ.

ąöą░ą╗ąĄąĄ ą▒čāą┤ąĄčé ąŠą┐ąĖčüą░ąĮ ą┐čĆąŠčåąĄčüčü ą┐ąŠą╗čāč湥ąĮąĖčÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓ čĆąĄąČąĖą╝ąĄ Expert.

1. ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 čćą░čüč鹊čéčā SYSCLK čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

a) ąĢčüą╗ąĖ ą▓ ąÆą░čłąĄą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ HSE, č鹊 ąĘą░ą┤ą░ą╣č鹥 ąĘąĮą░č湥ąĮąĖąĄ čćą░čüč鹊čéčŗ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 4..26 ą£ąōčå.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą╝ą░ą║čĆąŠąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ HSE_VALUE ą▓ čäą░ą╣ą╗ąĄ stm32f4xx.h ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąŠ ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąĄąĮčÅąĄčé ąĘąĮą░č湥ąĮąĖąĄ ą│ąĄąĮąĄčĆą░č鹊čĆą░ HSE.

ąĢčüą╗ąĖ ą▓ą▓ąĄą┤ąĄąĮąĮą░čÅ čćą░čüč鹊čéą░ ąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą┤ąŠą┐čāčüčéąĖą╝čŗčģ ą┐čĆąĄą┤ąĄą╗ą░čģ, č鹊 ą▒čāą┤ąĄčé ąŠč鹊ą▒čĆą░ąČąĄąĮąŠ čüąŠąŠą▒čēąĄąĮąĖąĄ ąŠą▒ ąŠčłąĖą▒ą║ąĄ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 4.

b) ąÆą▓ąĄą┤ąĖč鹥 ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ VDD ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1.8V ą┤ąŠ 3.6V (čüą╝. čĆąĖčü. 10).

c) ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čĆąĄą│čāą╗čÅč鹊čĆą░:

ŌĆō ąÆčŗą▒ąĄčĆąĖč鹥 Scale1 mode ąĖąĘ ą╗ąĖčüčé-ą▒ąŠą║čüą░, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā čüąĖčüč鹥ą╝čŗ (fHCLK) 168 ą£ąōčå.

ŌĆō ąÆčŗą▒ąĄčĆąĖč鹥 Scale2 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (fHCLK) 144 ą£ąōčå.

d) ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ąĖčüč鹊čćąĮąĖą║ SYSCLK (PLL, HSE ąĖą╗ąĖ HSI). ąĢčüą╗ąĖ ą▓čŗą▒ąŠčĆ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ąĮąĄą▓ąĄčĆąĄąĮ (čćą░čüč鹊čéą░ HCLK čüą╗ąĖčłą║ąŠą╝ ą▒ąŠą╗čīčłą░čÅ) č鹊 ąŠč鹊ą▒čĆą░ąĘąĖčéčüčÅ čüąŠąŠą▒čēąĄąĮąĖąĄ ąŠą▒ ąŠčłąĖą▒ą║ąĄ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 11.

ąĀąĖčü. 11. ą¤čĆąĄą▓čŗčłąĄąĮąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ.

e) ąĢčüą╗ąĖ ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ SYSCLK ą▓čŗą▒čĆą░ąĮą░ PLL, č鹊 ąĮčāąČąĮąŠ ą▓čŗą▒čĆą░čéčī ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ ą┤ą╗čÅ PLL (HSE ąĖą╗ąĖ HSI).

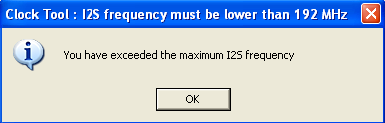

f) ąĢčüą╗ąĖ ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ SYSCLK ą▓čŗą▒čĆą░ąĮą░ PLL, č鹊 čüą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ą│ą╗ą░ą▓ąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ PLL(M), čćč鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī čćą░čüč鹊čéčŗ PLLVCO ą╝ąĄąČą┤čā 0.95 ąĖ 2.1 ą£ąōčå (ąĘą░ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéčÅą╝ąĖ ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čĆą░ąĘą┤ąĄą╗čā "PLL characteristics" ą┤ą░čéą░čłąĖčéą░ STM32F4xx. ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝, č鹊 ąŠč鹊ą▒čĆą░ąĘąĖčéčüčÅ čüąŠąŠą▒čēąĄąĮąĖąĄ ąŠą▒ ąŠčłąĖą▒ą║ąĄ. ąĢčüą╗ąĖ čćą░čüč鹊čéą░ I2S ą▓čŗčłąĄ 192 ą£ąōčå, č鹊 ąŠč鹊ą▒čĆą░ąĘąĖčéčüčÅ čüąŠąŠą▒čēąĄąĮąĖąĄ ąŠą▒ ąŠčłąĖą▒ą║ąĄ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 12.

ąĀąĖčü. 12. ą¦ą░čüč鹊čéą░ I2S ą▓ąĮąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░.

g) ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą┐čĆąĄčüą║ą░ą╗ąĄčĆ HCLK, ąĖčüą┐ąŠą╗čīąĘčāčÅ ą╗ąĖčüčé-ą▒ąŠą║čü AHBPrescaler, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ąČąĄą╗ą░ąĄą╝čāčÄ čćą░čüč鹊čéčā HCLK.

h) ąÆčŗą▒ąĄčĆąĖč鹥 ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ PCLK1 ąĖąĘ ą╗ąĖčüčé-ą▒ąŠą║čüą░, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ąČąĄą╗ą░ąĄą╝čāčÄ čćą░čüč鹊čéčā PCLK1. ą¦ą░čüč鹊čéčŗ TIMCLK ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ PCLK1.

i) ąÆčŗą▒ąĄčĆąĖč鹥 ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ PCLK2 ąĖąĘ ą╗ąĖčüčé-ą▒ąŠą║čüą░, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ąČąĄą╗ą░ąĄą╝čāčÄ čćą░čüč鹊čéčā PCLK2. ą¦ą░čüč鹊čéčŗ TIMCLK ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ PCLK2.

j) ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ą╗ą░č鹥ąĮčéąĮąŠčüčéčī Flash: ą┐ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ HCLK ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ Flash wait states ąĮą░ čüą░ą╝ąŠąĄ ą╗čāčćčłąĄąĄ, ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ. ąÆčŗ ą╝ąŠąČąĄč鹥 ąĖąĘą╝ąĄąĮąĖčéčī čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ ą╗čÄą▒ąŠąĄ ą▓ čüč鹊čĆąŠąĮčā čāą▓ąĄą╗ąĖč湥ąĮąĖčÅ.

k) ąĪą│ąĄąĮąĄčĆąĖčĆčāą╣č鹥 čäą░ą╣ą╗čŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ, ąĮą░ąČą░ą▓ ąĮą░ ą║ąĮąŠą┐ą║čā Generate.

2. ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 čćą░čüč鹊čéčā I2S čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

a) ąĢčüą╗ąĖ ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī PLLI2S, čĆą░ąĘčĆąĄčłąĖč鹥 čŹč鹊 ąĖ čüą╗ąĄą┤čāą╣č鹥 čłą░ą│ą░ą╝ ąĮąĖąČąĄ.

b) ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮ ą▓ąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ I2S, č鹊 čüą╗ąĄą┤čāčÄčēąĖąĄ čłą░ą│ąĖ ą╝ąŠąČąĮąŠ ą┐čĆąŠąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī.

c) ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮąŠ PLLI2S ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą┤ą╗čÅ I2S, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą╝ąĮąŠąČąĖč鹥ą╗čÅ PLLI2S(N).

d) ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮąŠ PLLI2S ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą┤ą╗čÅ I2S, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĖč鹥ą╗čÅ PLLI2S(R).

e) ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮąŠ PLLI2S ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą┤ą╗čÅ I2S, ą▓čŗą▒ąĄčĆąĖč鹥 čłąĖčĆąĖąĮčā čäčĆąĄą╣ą╝ą░ (16 ąĖą╗ąĖ 32 ą▒ąĖčéą░) ąĖ čāą║ą░ąČąĖč鹥, čĆą░ąĘčĆąĄčłąĄąĮą░ ąĖą╗ąĖ ąĮąĄčé ą│ą╗ą░ą▓ąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ MCLK.

f) ąÆčŗą▒ąĄčĆąĖč鹥 Fs ąĖąĘ ą╗ąĖčüčé-ą▒ąŠą║čüą░. ąŚąĮą░č湥ąĮąĖąĄ Fs ą╝ąŠąČąĄčé ą▒čŗčéčī 192 ą║ąōčå, 96 ą║ąōčå, 48 ą║ąōčå, 44.1 ą║ąōčå, 32 ą║ąōčå, 22.05 ą║ąōčå, 16 ą║ąōčå, 11.025 ą║ąōčå ąĖ 8 ą║ąōčå.

3. ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 čéą░ą║čéčŗ čāąĘą╗ąŠą▓ USB OTG FS, RNG ąĖą╗ąĖ SDIO. ąÆčŗą▒ąĄčĆąĖč鹥 ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ PLL(Q) ą┤ą╗čÅ USB OTG FS, SDIO ąĖ RNG.

4. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠąĄ ąĮąĄąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠąĄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ. ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ą▒čāč乥čĆ Prefetch (ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮą░čÅ ąĘą░ą│čĆčāąĘą║ą░ ą║ąŠą╝ą░ąĮą┤), Instruction Cash (ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤) ąĖ Data cash (ą║čŹčł ą┤ą░ąĮąĮčŗčģ).

5. ąĪą│ąĄąĮąĄčĆąĖčĆčāą╣č鹥 čäą░ą╣ą╗ system_stm32f4xx.c, čēąĄą╗ą║ąĮčāą▓ ąĮą░ ą║ąĮąŠą┐ą║čā Generate. ąŁč鹊čé čäą░ą╣ą╗ čüą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą▓ č鹊ą╝ ąČąĄ ą╝ąĄčüč鹥 ąĮą░ ą┤ąĖčüą║ąĄ, ą│ą┤ąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ XLS-čäą░ą╣ą╗ clock tool. ą¤čĆąŠčüą╝ąŠčéčĆąĖč鹥 čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čäą░ą╣ą╗, čćč鹊ą▒čŗ ą┐čĆąŠą▓ąĄčĆąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ system clock, SystemCoreClock, ąĘąĮą░č湥ąĮąĖčÅ HCLK, PCLK1, PCLK2, Flash access mode ąĖ ą┤čĆčāą│ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗąĄ ą▓ čäčāąĮą║čåąĖąĖ SetSysClock. ąöąŠą▒ą░ą▓čīč鹥 čäą░ą╣ą╗ system_stm32f4xx.c ą▓ čüą▓ąŠą╣ ą┐čĆąŠąĄą║čé.

[ąśąĘą▓ąĄčüčéąĮčŗąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ clock tool]

ąŁč鹊čé ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░čĆąĖą╣ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą▓ąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ HSE (HSE bypass).

[ąĪčüčŗą╗ą║ąĖ]

1. 140808STM32F407.zip - ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÅ ą┐ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ STM32F40x/41x, ą┐ąŠ ą┐ą╗ą░č鹥 Olimex STM32-P407, čüčģąĄą╝ą░, ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░.

2. STM32: ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆčŗ ąĖ č鹥čĆą╝ąĖąĮčŗ. |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ

RSS ą╗ąĄąĮčéą░ ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖąĄą▓ čŹč鹊ą╣ ąĘą░ą┐ąĖčüąĖ