|

ąÆ čüčéą░čéčīąĄ ąŠą┐ąĖčüą░ąĮ ą┐ąŠčĆčé SSC ąĖ ą╝ąĄč鹊ą┤čŗ čĆą░ą▒ąŠčéčŗ čü ąĮąĖą╝.

ąĪčĆą░ąĘčā čģąŠčćčā ąĘą░ą╝ąĄčéąĖčéčī, čćč鹊 ą┐ąŠčĆčé SSC - ąĮąĄ ą┐ąŠą┤ą░čĆąŠą║, čā ąĮąĄą│ąŠ ąĄčüčéčī ą│ą╗čÄą║ąĖ (ą║ą░ą║ ąŠą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ errata ą┤ą░čéą░čłąĖčéą░, čéą░ą║ ąĖ ąĮąĄ ąŠą┐ąĖčüą░ąĮąĮčŗąĄ). ąöąŠčüčéčāą┐ąĮčŗčģ ą┐čĆąĖą╝ąĄčĆąŠą▓ ą║ąŠą┤ą░ ąŠč湥ąĮčī ą╝ą░ą╗ąŠ, ąĖ čćč鹊ą▒čŗ čĆą░ąĘąŠą▒čĆą░čéčīčüčÅ, ą║ą░ą║ SSC čĆą░ą▒ąŠčéą░ąĄčé, ą┐čĆąĖą┤ąĄčéčüčÅ ą▓čüąĄ ą┐ąĄčĆąĄą┐čĆąŠą▒ąŠą▓ą░čéčī čüą░ą╝ąŠą╝čā. ąÆąŠąĘą╝ąŠąČąĮąŠ, čŹč鹊čé ą╝ą░č鹥čĆąĖą░ą╗ č湥ą╝-ąĮąĖą▒čāą┤čī ą┐ąŠą╝ąŠąČąĄčé.

ąĪąĮą░čćą░ą╗ą░ ąŠą▒čüčāą┤ąĖą╝ ąĮąĄčüą║ąŠą╗čīą║ąŠ č鹥čĆą╝ąĖąĮąŠą▓, ą║ąŠč鹊čĆčŗąĄ ą▒čāą┤čāčé ą▓čüčéčĆąĄčćą░čéčīčüčÅ ą┤ą░ą╗ąĄąĄ ą▓ čüčéą░čéčīąĄ. ą¤ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░ ą▒ąĖčéčŗ, ą▒ąĖčéčŗ čāą║ą╗ą░ą┤čŗą▓ą░čÄčéčüčÅ ą▓ čüą╗ąŠą▓ą░ (ą▓ čüą╗ąŠą▓ąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī 2..32 ą▒ąĖčéą░, ąĘą░ą┤ą░ąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ DATLEN čĆąĄą│ąĖčüčéčĆą░ SSC_TFMR), čüą╗ąŠą▓ą░ čāą║ą╗ą░ą┤čŗą▓ą░čÄčéčüčÅ ą▓ąŠ čäčĆąĄą╣ą╝čŗ (ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čüą╗ąŠą▓ ą▓ čäčĆąĄą╣ą╝ąĄ ąĘą░ą┤ą░ąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ DATNB čĆąĄą│ąĖčüčéčĆą░ SSC_TFMR). ąÆčüąĄ ąĮą░čüčéčĆąŠąĄčćąĮčŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ čģčĆą░ąĮčÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ ąĖ/ąĖą╗ąĖ ąĮą░ą▒ąŠčĆą░čģ ąĖčģ ą▒ąĖč鹊ą▓ (ą┐ąŠą╗čÅčģ). ąöą░ą╗ąĄąĄ ą┤ą╗čÅ ą┐čĆąŠčüč鹊čéčŗ ąĖą╝čÅ čĆąĄą│ąĖčüčéčĆą░ čü ąĖą╝ąĄąĮąĄą╝ ą┐ąŠą╗čÅ ą▒čāą┤čā čāą║ą░ąĘčŗą▓ą░čéčī ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ č湥čĆąĄąĘ č鹊čćą║čā.

1. SSC čüąŠą┤ąĄčƹȹĖčé ą┐čĆąĖąĄą╝ąĮąĖą║ ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║. ąś ą┐čĆąĖąĄą╝ąĮąĖą║, ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĖą╝ąĄčÄčé ą┐ąŠ 3 čüąĖą│ąĮą░ą╗ą░ - ą┤ą░ąĮąĮčŗąĄ, čéą░ą║čéčŗ ą▒ąĖčé ąĖ čéą░ą║čéčŗ čäčĆąĄą╣ą╝ą░. ą¤ąŠą┤ čäčĆąĄą╣ą╝ąŠą╝ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░čÄčé ą┐ąŠčĆčåąĖčÄ ą▒ąĖčé, ą║ąŠč鹊čĆčāčÄ ą┐ąĄčĆąĄą┤ą░čÄčé ąĘą░ 1 čĆą░ąĘ (ąĘą░ą▓ąĖčüąĖčé ąŠčé ą║ąŠą╗ąĖč湥čüčéą▓ą░ ąĖ ą┤ą╗ąĖąĮčŗ čüą╗ąŠą▓, čé. ąĄ. ąŠčé ą┐ąŠą╗čÅ DATLEN čĆąĄą│ąĖčüčéčĆą░ SSC_TFMR ąĖ ą┐ąŠą╗čÅ DATNB čĆąĄą│ąĖčüčéčĆą░ SSC_TFMR). ąöą╗čÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ čŹčéąĖ čüąĖą│ąĮą░ą╗čŗ ąĮą░ąĘčŗą▓ą░čÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

RD ą▓čģąŠą┤, ą▓ąĮąĄčłąĮąĖąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░

RK ą╝ąŠąČąĄčé ą▒čŗčéčī ą║ą░ą║ ą▓čģąŠą┤ąŠą╝, čéą░ą║ ąĖ ą▓čŗčģąŠą┤ąŠą╝ - čéą░ą║čéčŗ ą▒ąĖčé ą┐čĆąĖąĄą╝ąĮąĖą║ą░

RF ą╝ąŠąČąĄčé ą▒čŗčéčī ą║ą░ą║ ą▓čģąŠą┤ąŠą╝, čéą░ą║ ąĖ ą▓čŗčģąŠą┤ąŠą╝ - čéą░ą║čéčŗ čäčĆąĄą╣ą╝ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ą░

TD ą▓čŗčģąŠą┤, ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░

TK ą╝ąŠąČąĄčé ą▒čŗčéčī ą║ą░ą║ ą▓čģąŠą┤ąŠą╝, čéą░ą║ ąĖ ą▓čŗčģąŠą┤ąŠą╝ - čéą░ą║čéčŗ ą▒ąĖčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░

TF ą╝ąŠąČąĄčé ą▒čŗčéčī ą║ą░ą║ ą▓čģąŠą┤ąŠą╝, čéą░ą║ ąĖ ą▓čŗčģąŠą┤ąŠą╝ - čéą░ą║čéčŗ čäčĆąĄą╣ą╝ą░ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░

ąØąŠąČą║ąĖ SSC čüąŠą▓ą╝ąĄčēąĄąĮčŗ čü ą┐ąŠčĆčéą░ą╝ąĖ ą▓ą▓ąŠą┤ą░ ą▓čŗą▓ąŠą┤ą░ PIO, ą┐ąŠčŹč鹊ą╝čā ą┐ąĄčĆąĄą┤ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ SSC ąĮą░ą┤ąŠ čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī PIO. ąóą░ą║čéąĖčĆčāąĄčéčüčÅ SSC č湥čĆąĄąĘ PMC, ą┐ąŠčŹč鹊ą╝čā ąĮčāąČąĮąŠ čéą░ą║ąČąĄ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĖ ąĄą│ąŠ. ą¤čĆąŠčēąĄ ą▓čüąĄ čŹč鹊 čüą┤ąĄą╗ą░čéčī, ą▓ąŠčüą┐ąŠą╗čīąĘąŠą▓ą░ą▓čłąĖčüčī čüčéą░ąĮą┤ą░čĆčéąĮčŗą╝ąĖ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ą╝ąĖ, ą┐ąŠčüčéą░ą▓ą╗čÅąĄą╝čŗą╝ąĖ ą▓ ą╝ąŠą┤čāą╗ąĄ ssc.c ąŠčé IAR (ą┐čĆąĖą╝ąĄčĆčŗ čüą╝. ą┤ą░ą╗ąĄąĄ).

ąś ą┐čĆąĖąĄą╝ąĮąĖą║, ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ čĆą░ą▒ąŠčéą░čÄčé ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░, ąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą▒čēąĖą╣ ą┤ąĄą╗ąĖč鹥ą╗čī čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ. ąæą╗ą░ą│ąŠą┤ą░čĆčÅ ą│ąĖą▒ą║ąŠčüčéąĖ ą▓ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĖ SSC ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╗ąĄą│ą║ąŠ ą│ąĄąĮąĄčĆąĖčéčī čĆčÅą┤ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ą┐čĆąŠč鹊ą║ąŠą╗ąŠą▓ - I2S, Short Frame Sync, Long Frame Sync.

2. ąśąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠč鹊ą║ą░ ą┤ą░ąĮąĮčŗčģ ą▒ąĖčéčŗ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ąĖ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĮąŠ čü čéą░ą║č鹊ą▓čŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝. ąóą░ą║čéčŗ ą▒ąĖčé ą┤ą╗čÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮčŗ ąĖąĘ:

ŌĆó ą▓ąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ą┐ąŠą┤ą░ąĮąĮčŗą╣ ąĮą░ ąĮąŠąČą║čā RK (ąĮąŠąČą║ą░ RK čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤)

ŌĆó čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░

ŌĆó ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą┤ąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ (ą┤ąĄą╗ąĖčé čćą░čüč鹊čéčā MCK)

ąÉąĮą░ą╗ąŠą│ąĖčćąĮąŠ, čéą░ą║čéčŗ ą▒ąĖčé ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮčŗ ąĖąĘ:

ŌĆó ą▓ąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ą┐ąŠą┤ą░ąĮąĮčŗą╣ ąĮą░ ąĮąŠąČą║čā TK (ąĮąŠąČą║ą░ TK čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤)

ŌĆó čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┐čĆąĖąĄą╝ąĮąĖą║ą░

ŌĆó ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą┤ąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ (ą┤ąĄą╗ąĖčé čćą░čüč鹊čéčā MCK)

ą¤čĆąĖąĄą╝ąĮąĖą║ ą╝ąŠąČąĄčé čéą░ą║ąČąĄ ą▓čŗą▓ąŠą┤ąĖčéčī čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ąĮą░ ąĮąŠąČą║čā RK, ą░ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ - ąĮą░ ąĮąŠąČą║čā TK. ą×ą▒čŗčćąĮąŠ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║, ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗, čģąŠčéčÅ čŹč鹊 ąĖ ąĮąĄąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ.

ąÜąŠą│ą┤ą░ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĖ, č鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čćą░čüč鹊čéą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ MCK, ą┐ąŠą┤ąĄą╗ąĄąĮąĮą░čÅ ąĮą░ 2 ąĖ ą┤ą░ą╗ąĄąĄ ąĮą░ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą│ąŠ ą┤ąĄą╗ąĖč鹥ą╗čÅ. ąś ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░, ąĖ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ čŹč鹊čé ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ąĘą░ą┤ą░ąĄčéčüčÅ ą▓ 12-ą▒ąĖčéąĮąŠą╝ ą┐ąŠą╗ąĄ SSC_CMR.DIV (CMR čĆą░čüčłąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ Clock Mode Register) ąÆ ąĖč鹊ą│ąĄ ą╝ąŠąČąĮąŠ ą│ąĄąĮąĄčĆąĖčéčī čćą░čüč鹊čéčā ąŠčé MCK/2 (SSC_CMR.DIV = 000000000001b) ą┤ąŠ MCK/8190 (SSC_CMR.DIV = 111111111111b). ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ąĮąŠą╗ąĖą║ą░ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čĆą░ą▓ąĮą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĄą┤ąĖąĮąĖčåčŗ (ą╝ąĄą░ąĮą┤čĆ), ąĖ čĆą░ą▓ąĮą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĖąŠą┤ą░ MCK, čāą╝ąĮąŠąČąĄąĮąĮąŠą│ąŠ ąĮą░ SSC_CMR.DIV. ąĢčüą╗ąĖ ą▓ SSC_CMR.DIV ąĘą░ą┐ąĖčüą░ąĮčŗ ąĮčāą╗ąĖ, č鹊 čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą▓ąŠąŠą▒čēąĄ ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ.

3. ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ SSC_TCMR.CKS (TCMR čĆą░čüčłąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ Transmit Clock Mode Register). ąśąĮą▓ąĄčĆčüąĖčÅ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĘą░ą┤ą░ąĄčéčüčÅ ą▓ SSC_TCMR.CKI.

ą¤ąĄčĆąĄą┤ą░čéčćąĖą║ ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čéą░ą║čéčŗ ąĮą░ ąĮąŠąČą║ąĄ TK ą┐ąŠčüč鹊čÅąĮąĮąŠ, ą╗ąĖą▒ąŠ č鹊ą╗čīą║ąŠ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. ąŁč鹊 ąĘą░ą┤ą░ąĄčéčüčÅ ą▓ SSC_TCMR.CKO. ąØąĄą╗čīąĘčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą┐ąŠčüč鹊čÅąĮąĮčāčÄ ą│ąĄąĮąĄčĆą░čåąĖčÄ čéą░ą║č鹊ą▓ ąĖ ą▓čŗą▒čĆą░čéčī ąĮąŠąČą║čā TK ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, SSC_TCMR.CKO == 1 ąĖ SSC_TCMR.CKS == 2) - čŹč鹊 ąĘą░ą╝čŗą║ą░ąĄčé ą▓čģąŠą┤ ąĮą░ ą▓čŗčģąŠą┤ ąĖ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ ą┐ąŠčüą╗ąĄą┤čüčéą▓ąĖčÅą╝.

ąŻ ą╝ąĄąĮčÅ ą┐ąŠč湥ą╝čā-č鹊 čĆąĄąČąĖą╝ čü ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ čüąĖąĮčģčĆąŠąĖą╝ą┐čāą╗čīčüąŠą▓ č鹊ą╗čīą║ąŠ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čĆą░ą▒ąŠčéą░ą╗ ąĮąĄą║ąŠčĆčĆąĄą║čéąĮąŠ (ą┐čĆąŠą▓ąĄčĆčÅą╗ ą┐ąŠ ą┤ą▓čāčģą║ą░ąĮą░ą╗čīąĮąŠą╝čā ąŠčüčåąĖą╗ą╗ąŠą│čĆą░čäčā čüąĖą│ąĮą░ą╗čŗ TK ąĖ TD) - ąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąŠčéą┐čĆą░ą▓ą╗čÅąĄą╝čŗą╣ ą▒ąĖčé ąĮąĄ ą▒čŗą╗ąŠ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāčÄčēąĄą│ąŠ ąĖą╝ą┐čāą╗čīčüą░, ą┐čĆąĖč湥ą╝ ą▓ąĮą░čćą░ą╗ąĄ čüą╗ąŠą▓ą░ ą▒čŗą╗ ąĮąĄąĮčāąČąĮčŗą╣ ą▒ąĖčé. ąøčāčćčłąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐ąŠčüč鹊čÅąĮąĮąŠąĄ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, čéą░ą║ ą║ą░ą║ ąĖąĮą░č湥 ą┐čĆąŠčÅą▓ą╗čÅąĄčéčüčÅ ąĮąĄą┐čĆąĖčÅčéąĮčŗą╣ ą│ą╗čÄą║ ą┐ąŠčĆčéą░ - ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ą▒ąĖčé ąĮąĄ ą┐ąŠą╗čāčćą░ąĄčé čéą░ą║č鹊ą▓ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░. ąÆčŗą│ą╗čÅą┤ąĖčé čŹč鹊 čéą░ą║, ą║ą░ą║ ą▒čāą┤č鹊 čéą░ą║č鹊ą▓ą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ą░ TK ąĮą░ 1 ą▒ąĖčé ąŠą┐ąĄčĆąĄąČą░ąĄčé ą┐ąŠč鹊ą║ ą┤ą░ąĮąĮčŗčģ ąĮą░ ąĮąŠąČą║ąĄ TD, ą┐čĆąĖč湥ą╝ ą┐ąĄčĆą▓čŗą╣ čéą░ą║čé ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą┐čāčüč鹊ą╣ (ąĮąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąĮąĖą║ą░ą║ąŠą╝čā ą┐ąŠą╗ąĄąĘąĮąŠą╝čā ą▒ąĖčéčā), ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé ąĮąĄ ąĖą╝ąĄąĄčé ąĮčāąČąĮąŠą│ąŠ čéą░ą║čéą░. ą×ą▒ąŠą╣čéąĖ čŹč鹊čé ą│ą╗čÄą║ ą╝ąŠąČąĮąŠ ą┤ą▓čāą╝čÅ ą┐čāčéčÅą╝ąĖ - ą╗ąĖą▒ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą│ąĄąĮąĄčĆąĖčĆčāčÅ čéą░ą║čéčŗ ąĮą░ ąĮąŠąČąĄą║ TK, ą╗ąĖą▒ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ čüą║ąŠčĆčĆąĄą║čéąĖčĆąŠą▓ą░čéčī ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ą┐ąŠč鹊ą║ (ą▓čŗą▒čĆą░čéčī čĆąĄąČąĖą╝ čü ąŠą┤ąĮąĖą╝ ą╗ąĖčłąĮąĖą╝ ą▒ąĖč鹊ą╝, ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ, čüą┤ą▓ąĖąĮčāčéčŗąĄ ąĮą░ 1 ą▒ąĖčé ą▓ą╗ąĄą▓ąŠ). ąÆ ą┤ą░čéą░čłąĖč鹥 ą┐čĆąĄą┤ą╗ą░ą│ą░ąĄčéčüčÅ ą┤čĆčāą│ąŠą╣ ą╝ąĄč鹊ą┤, ąĮą░ ą╝ąŠą╣ ą▓ąĘą│ą╗čÅą┤ čüąŠą▓ąĄčĆčłąĄąĮąĮąŠ čāą▒ąŠą│ąĖą╣ - ą┐čĆąĖą╝ąĄąĮąĖčéčī ą┤ą╗čÅ ą║ąŠčĆčĆąĄą║čåąĖąĖ ąĘą░ą┤ąĄčƹȹ║ąĖ čéą░ą║č鹊ą▓ čüą┐ąĄčåąĖą░ą╗čīąĮčāčÄ čüčģąĄą╝čā.

4. ąöą╗čÅ čĆą░ą▒ąŠčéčŗ čü SSC ą┤ąŠčüčéčāą┐ąĮčŗ 2 ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗčģ ą║ą░ąĮą░ą╗ą░ PDC (DMA), čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čüąĖą╗čīąĮąŠ čĆą░ąĘą│čĆčāąĘąĖčéčī ą┐čĆąŠčåąĄčüčüąŠčĆ. ą£ąŠąČąĮąŠ čéą░ą║ąČąĄ ą▓ąŠčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ.

5. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ą╗čÅ ą▒ąĖčé (ąĮąŠąČą║ąĖ TK ąĖ RK) čĆą░ą▓ąĮą░ MCK/2. ąöąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ 12-ą▒ąĖčéąĮčŗą╝ ą┐ąŠą╗ąĄą╝ DIV čĆąĄą│ąĖčüčéčĆą░ SSC_CMR (0..4095), čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ąĄą╗ąĖčéčī čćą░čüč鹊čéčā ą╝ą░ą║čüąĖą╝čāą╝ ąĮą░ 8190. ąÜąŠą│ą┤ą░ ą┐ąŠą╗ąĄ DIV čĆą░ą▓ąĮąŠ 0, č鹊 ą┤ąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ ąĮąĄą░ą║čéąĖą▓ąĄąĮ (čéą░ą║čéčŗ ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą▓ąŠąŠą▒čēąĄ ąĖ ą┐ąŠčĆčé ąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé). ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ MCK=48ą£ąōčå ąĖ ą┐ąŠą╗ąĄ DIV=17, č鹊 čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čüąĖą│ąĮą░ą╗ą░ TK (ąĖą╗ąĖ RK) čüąŠčüčéą░ą▓ąĖčé ą┐čĆąĖą╝ąĄčĆąĮąŠ 1.4ą£ąōčå. ąĢčüą╗ąĖ DIV=1, č鹊 čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čüąŠčüčéą░ą▓ąĖčé 24ą£ąōčå. ą£ąŠąČąĮąŠ ą╝ąĄąĮčÅčéčī ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠą╗čÅ DIV čĆąĄą│ąĖčüčéčĆą░ SSC_CMR ą┐čĆčÅą╝ąŠ ą▓ ą┤ąĄą▒ą░ą│ą│ąĄčĆąĄ IAR (View -> Register -> SSC), čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą╝ąĄąĮčÅąĄčéčüčÅ čüčĆą░ąĘčā - ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ čüč鹊ąĖčé ąĮą░ č鹊čćą║ąĄ ąŠčüčéą░ąĮąŠą▓ą░.

6. ą¤ąĄčĆąĄą┤ą░čéčćąĖą║ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą┤ą▓čāą╝čÅ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ - SSC_TCMR (čĆąĄąČąĖą╝ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ) ąĖ SSC_TFMR (čĆąĄąČąĖą╝ čäčĆąĄą╣ą╝ąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ).

7. ą¤čĆąĖą╝ąĄčĆ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ą┐ąŠčĆčéą░ SSC čā AT91SAM7X256:

#define BOARD_MCK 48000000

/// ą£ą░ą║čĆąŠčü ą▓čŗčćąĖčüą╗čÅąĄčé ą▓ąĄą╗ąĖčćąĖąĮčā ą┐ąŠą╗čÅ STTDLY ą┐ąŠ ą║ąŠą╗ąĖč湥čüčéą▓čā čåąĖą║ą╗ąŠą▓ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄą┤ ą┐ąĄčĆą▓čŗą╝ ą▒ąĖč鹊ą╝

/// ąĮąŠą▓ąŠą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čäčĆąĄą╣ą╝ą░:

#define SSC_STTDLY(bits) (bits << 16)

/// ąÆčŗčćąĖčüą╗čÅąĄčé ą▓ąĄą╗ąĖčćąĖąĮčā ą┐ąŠą╗čÅ PERIOD čĆąĄą│ąĖčüčéčĆą░ Transmit Clock Mode Register

/// ąĖąĮč鹥čĆč乥ą╣čüą░ SSC ą┐ąŠ ąČąĄą╗ą░ąĄą╝ąŠą╣ ą▓ąĄą╗ąĖčćąĖąĮąĄ ą┤ąĄą╗ąĖč鹥ą╗čÅ čéą░ą║č鹊ą▓:

#define SSC_PERIOD(divider) (((divider / 2) - 1) << 24)

/// ąÆčŗčćąĖčüą╗čÅąĄčé ą▓ąĄą╗ąĖčćąĖąĮčā ą┐ąŠą╗čÅ DATLEN čĆąĄą│ąĖčüčéčĆą░ Transmit Frame Mode Register

/// ąĖąĮč鹥čĆč乥ą╣čüą░ SSC ą┐ąŠ ą║ąŠą╗ąĖč湥čüčéą▓čā ą▒ąĖčé ą▓ ąŠą┤ąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĄ:

#define SSC_DATLEN(bits) (bits - 1)

/// ąÆčŗčćąĖčüą╗čÅąĄčé ą▓ąĄą╗ąĖčćąĖąĮčā ą┐ąŠą╗čÅ DATNB čĆąĄą│ąĖčüčéčĆą░ Transmit Frame Mode Register

/// ąĖąĮč鹥čĆč乥ą╣čüą░ SSC ą┐ąŠ ą║ąŠą╗ąĖč湥čüčéą▓čā ą▓čŗą▒ąŠčĆąŠą║ ą▓ ąŠą┤ąĮąŠą╝ čäčĆąĄą╣ą╝ąĄ.

#define SSC_DATNB(samples) ((samples -1) << 8)

/// ąÆčŗčćąĖčüą╗čÅąĄčé ą▓ąĄą╗ąĖčćąĖąĮčā ą┐ąŠą╗čÅ FSLEN ą▓ Transmit Frame Mode Register

/// ąĖąĮč鹥čĆč乥ą╣čüą░ SSC ą┐ąŠ ą║ąŠą╗ąĖč湥čüčéą▓čā čéą░ą║č鹊ą▓čŗčģ ą┐ąĄčĆąĖąŠą┤ąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą║ąŠč鹊čĆčŗąĄ

/// ą┤ąŠą╗ąČąĄąĮ ą┐ąŠą╗čāčćąĖčéčī čüąĖą│ąĮą░ą╗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ (frame sync signal).

#define SSC_FSLEN(periods) ((periods - 1) << 16)

// ą£ą░ą║čĆąŠąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┤ą╗čÅ ąĮąŠąČąĄą║ ą┐ąŠčĆčéą░ SSC

#define PIN_SSC_TF {1 << 21, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_A, PIO_DEFAULT}

#define PIN_SSC_TK {1 << 22, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_A, PIO_DEFAULT}

#define PIN_SSC_TD {1 << 23, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_A, PIO_DEFAULT}

#define PIN_SSC_RD {1 << 24, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_A, PIO_DEFAULT}

#define PIN_SSC_RK {1 << 25, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_A, PIO_DEFAULT}

#define PIN_SSC_RF {1 << 26, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_A, PIO_DEFAULT}

#define PINS_SSC PIN_SSC_TF, PIN_SSC_TK, PIN_SSC_TD, PIN_SSC_RD, PIN_SSC_RK, PIN_SSC_RF

const Pin SSC_pins[] = {PINS_SSC};

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąŠąČąĄą║ ą┐ąŠčĆčéą░ SSC

PIO_Configure(DSP_pins, PIO_LISTSIZE(DSP_pins));

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąŠčĆčéą░ SSC

SSC_Configure(AT91C_BASE_SSC,

AT91C_ID_SSC,

1411200 /* čćą░čüč鹊čéą░ TK ą▒čāą┤ąĄčé 1.4ą£ąōčå*/,

BOARD_MCK/* masterClock */);

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░

SSC_ConfigureTransmitter(AT91C_BASE_SSC,

(AT91C_SSC_CKS_DIV | AT91C_SSC_CKO_DATA_TX | AT91C_SSC_START_FALL_RF |

SSC_STTDLY(1) | SSC_PERIOD(32)),

(SSC_DATLEN(8) | AT91C_SSC_MSBF | SSC_DATNB(1) | SSC_FSLEN(16) |

AT91C_SSC_FSOS_NEGATIVE));

//ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░

SSC_EnableTransmitter(AT91C_BASE_SSC);

8. ą¤ąŠą╗ąĄ START čĆąĄą│ąĖčüčéčĆą░ SSC_TCMR ąĘą░ą┤ą░ąĄčé čāčüą╗ąŠą▓ąĖąĄ ąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (ąŠą▒čŗčćąĮąŠ ą┐ąŠ ąŠą┤ąĮąŠą╝čā ąĖąĘ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ čüąĖą│ąĮą░ą╗ą░ TF). ą×ą▒čŗčćąĮąŠ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čüą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░ TF (SSC_TCMR.START == 4).

9. ą¤ąŠą╗ąĄ PERIOD čĆąĄą│ąĖčüčéčĆą░ SSC_TCMR ąĘą░ą┤ą░ąĄčé ą┐ąĄčĆąĖąŠą┤ čüąĖą│ąĮą░ą╗ą░ TF, ą┐čĆąĖč湥ą╝ čĆą░ą▒ąŠčéą░ąĄčé ąĮąĄ čüąŠą▓čüąĄą╝ čéą░ą║, ą║ą░ą║ čāą║ą░ąĘą░ąĮąŠ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ. ą£ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ą┐čĆąĖ ą║ąŠč鹊čĆąŠą╝ TF ąĄčēąĄ ą│ąĄąĮąĄčĆąĖčéčüčÅ, čĆą░ą▓ąĮąŠ 0x08 (ąĄą┤ąĖąĮąĖčćą║ąĖ čĆą░ą▓ąĮčŗ 1.4 ą╝ą║čü, ąĮąŠą╗ąĖą║ąĖ 11.25 ą╝ą║čü ą┤ą╗čÅ ą┐čĆąĖą╝ąĄčĆą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐. 6 č湥ą╝ ąĮąŠą╗ąĖą║ąĖ). ą¤čĆąĖ čāą▓ąĄą╗ąĖč湥ąĮąĖąĖ PERIOD čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ąĄą┤ąĖąĮąĖčćą║ąĖ. ą¤čĆąĖ ąĘąĮą░č湥ąĮąĖąĖ 0x0F čüąĖą│ąĮą░ą╗ TF - ą╝ąĄą░ąĮą┤čĆ čü ą┐ąĄčĆąĖąŠą┤ąŠą╝ 23 ą╝ą║čü.

ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ąĮą░ čüąĖą│ąĮą░ą╗ TF ą▓ą╗ąĖčÅąĄčé 4-ą▒ąĖčéąĮąŠąĄ ą┐ąŠą╗ąĄ FSLEN čĆąĄą│ąĖčüčéčĆą░ SSC_TFMR. ąŁč鹊 čćąĖčüą╗ąŠ (0..15) ąĘą░ą┤ą░ąĄčé ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī TF ą▓ ą┐ąĄčĆąĖąŠą┤ą░čģ čüąĖąĮčģčĆąŠčüąĖą│ąĮą░ą╗ą░ TK (1..16).

ąóąĖą┐ čüąĖąĮčģčĆąŠčüąĖą│ąĮą░ą╗ą░ TF (ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣, ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü, ąĮąĖąĘą║ąĖą╣, ą▓čŗčüąŠą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī, ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ) ąĘą░ą┤ą░ąĄčéčüčÅ 3-ą▒ąĖčéąĮčŗą╝ ą┐ąŠą╗ąĄą╝ FSOS čĆąĄą│ąĖčüčéčĆą░ SSC_TFMR.

10. 5-ą▒ąĖč鹊ą▓ąŠąĄ ą┐ąŠą╗ąĄ DATLEN čĆąĄą│ąĖčüčéčĆą░ SSC_TFMR ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé ą┤ą╗ąĖąĮčā ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒ąĖčéą░čģ (ą┤ą╗ąĖąĮčā čäčĆąĄą╣ą╝ą░). ą¦ąĖčüą╗ą░ 1..31 (0 ąĘą░ą┐čĆąĄčēąĄąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ) ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčé ą┤ą╗ąĖąĮčā čäčĆąĄą╣ą╝ą░ 2..32 ą▒ąĖčéą░.

11. SSC_TFMR.DATDEF ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĘąĮą░č湥ąĮąĖąĄ ąĮąŠąČą║ąĖ TD ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (0 ąĖą╗ąĖ 1) - ą┤ąŠ ąĖą╗ąĖ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ.

12. SSC_TFMR.MSBF ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąŠčĆčÅą┤ąŠą║ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ąĖčé. ąĢčüą╗ąĖ 0, č鹊 ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝.

13. ąÜą░ą║ ąĖ ą╝ąĮąŠą│ąĖąĄ ą┤čĆčāą│ąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ AT91SAM7X256, SSC ąĖą╝ąĄąĄčé 2 ą║ą░ąĮą░ą╗ą░ PDC. ą×ą┤ąĖąĮ ą║ą░ąĮą░ą╗ ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé ą┐čĆąĖąĄą╝, ą░ ą┤čĆčāą│ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćčā. ąĀąĄą│ąĖčüčéčĆčŗ PDC ąĖą╝ąĄčÄčé čüą╝ąĄčēąĄąĮąĖąĄ 0x100 ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ SSC, čé. ąĄ. ąĮą░čćąĖąĮą░čÄčéčüčÅ čü ą░ą┤čĆąĄčüą░ AT91C_BASE_SSC + 0x100 = 0xFFFD4100.

14. ąŚą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┐čĆąŠčåąĄčüčü ą┐ąĄčĆąĄą┤ą░čćąĖ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ PDC ą┐čĆąŠčüč鹊:

AT91S_SSC *ssc;

ssc = AT91C_BASE_SSC;

ssc->SSC_TPR = (unsigned int) buffer;

ssc->SSC_TCR = length;

ssc->SSC_PTCR = AT91C_PDC_TXTEN;

15. ąöą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠčüčéąĖ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ (ą┐čĆąĖąĄą╝ą░ ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ) ą┤ą░ąĮąĮčŗčģ PDC ąĖą╝ąĄąĄčé 2 ą┐ą░čĆčŗ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░. ąØą░ ą┐čĆąĖą╝ąĄčĆąĄ SSC čŹč鹊 čüą╗ąĄą┤čāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ:

RPR, TPR 32-ą▒ąĖčéąĮčŗąĄ čāą║ą░ąĘą░č鹥ą╗ąĖ ąĮą░ ąĮą░čćą░ą╗ąŠ ą┐ąĄčĆąĄą╝ąĄčēą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ (ąĮą░ ą▒čāč乥čĆ) ą┐čĆąĖąĄą╝ą░, ą┐ąĄčĆąĄą┤ą░čćąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ

RNPR, TNPR 32-ą▒ąĖčéąĮčŗąĄ čāą║ą░ąĘą░č鹥ą╗ąĖ ąĮą░ ąĮą░čćą░ą╗ąŠ čüą╗ąĄą┤čāčÄčēąĖčģ ą┐ąĄčĆąĄą╝ąĄčēą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ (ąĮą░ ą▒čāč乥čĆ) ą┐čĆąĖąĄą╝ą░, ą┐ąĄčĆąĄą┤ą░čćąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ

ąĢčüą╗ąĖ RNPR, TNPR ąĮąĄ čĆą░ą▓ąĮąŠ 0, č鹊 ą┐čĆąĖ ą┤ąŠčüčéąĖąČąĄąĮąĖąĖ ąĮčāą╗čÅ RCR, TCR čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ čĆąĄą│ąĖčüčéčĆčŗ RPR, TPR ą┐ąĄčĆąĄą│čĆčāąČą░čÄčéčüčÅ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ RNPR, TNPR ąĖ RCR, TCR ą┐ąĄčĆąĄą│čĆčāąČą░čÄčéčüčÅ RNCR, TNCR.

RCR, TCR 16-ą▒ąĖčéąĮčŗąĄ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄą╝čŗąĄ čüč湥čéčćąĖą║ąĖ ąĄą┤ąĖąĮąĖčå čāąČąĄ ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (ąĄą┤ąĖąĮąĖčåą░ - ą╗ąĖą▒ąŠ ą▒ą░ą╣čé, ą╗ąĖą▒ąŠ 2, ą╗ąĖą▒ąŠ 4 ą▒ą░ą╣čéą░)

RNCR, TNCR 16-ą▒ąĖčéąĮčŗąĄ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄą╝čŗąĄ čüč湥čéčćąĖą║ąĖ ąĄą┤ąĖąĮąĖčå čāąČąĄ ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (ąĄą┤ąĖąĮąĖčåą░ - ą╗ąĖą▒ąŠ ą▒ą░ą╣čé, ą╗ąĖą▒ąŠ 2, ą╗ąĖą▒ąŠ 4 ą▒ą░ą╣čéą░)

ąĀą░čüčüą╝ąŠčéčĆąĖą╝ čĆą░ą▒ąŠčéčā PDC ąĮą░ ą┐čĆąĖą╝ąĄčĆąĄ ą║ą░ąĮą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąśčéą░ą║, ą░ą╗ą│ąŠčĆąĖčéą╝ čĆą░ą▒ąŠčéčŗ čü ą┤ą▓čāą╝čÅ ą▒čāč乥čĆą░ą╝ąĖ ąĮą░ ą┐čĆąĖą╝ąĄčĆąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ SSC čüą╗ąĄą┤čāčÄčēąĖą╣:

1. ąÆ ą┐ą░ą╝čÅčéąĖ ą▓čŗą┤ąĄą╗čÅčÄčéčüčÅ 2 ą▒čāč乥čĆą░ bufA ąĖ bufB ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ čĆą░ąĘą╝ąĄčĆą░ (ą╝ą░ą║čüąĖą╝čāą╝ ą▓ 65536 ą▒ą░ą╣čé, čéą░ą║ ą║ą░ą║ čüč湥čéčćąĖą║ SSC_TPR 16-ą▒ąĖčéąĮčŗą╣).

2. TPR = bufA;

TCR = sizeof(bufA);

TNPR = bufB;

TNCR = sizeof(bufB);

3. ąØą░čüčéčĆą░ąĖą▓ą░ąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮą░ ENDTX (ąŠą║ąŠąĮčćą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒čāč乥čĆą░ bufA, ą║ąŠą│ą┤ą░ TCR ąŠą▒ąĮčāą╗čÅąĄčéčüčÅ) ąĖ TXBUFE (ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ąĮąĄč湥ą│ąŠ, ąŠą▒ą░ ą▒čāč乥čĆą░ bufA ąĖ bufB ą┐ąĄčĆąĄą┤ą░ąĮčŗ).

4. ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą┤ąĄą╗ą░čéčī čüą╗ąĄą┤čāčÄčēąĄąĄ:

- ąĄčüą╗ąĖ TCR==0, č鹊 ąĘą░ą│čĆčāąČą░ąĄą╝ ą▓ ą▒čāč乥čĆ bufA ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ, ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄą╝ TPR, TCR ą▒čāč乥čĆąŠą╝ bufA (ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ąŠą╗ąČąĮą░ ąĘą░ą┐čāčüčéąĖčéčīčüčÅ ą┐ąŠ ąĮąŠą▓ąŠą╣), ąĘą░č鹥ą╝ ąĘą░ą│čĆčāąČą░ąĄą╝ ą┤ą░ąĮąĮčŗąĄ ą▓ bufB ąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄą╝ TNPR, TNCR ą▒čāč乥čĆąŠą╝ bufB.

- ąĖąĮą░č湥 ąĄčüą╗ąĖ TNCR==0, č鹊 ąĘą░ą│čĆčāąČą░ąĄą╝ ą┤ą░ąĮąĮčŗąĄ ą▓ bufB ąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄą╝ TNPR, TNCR ą▒čāč乥čĆąŠą╝ bufB.

5. ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ąĮąŠąČą║ąĖ SSC ą▓čŗąĘąŠą▓ąŠą╝ PIO_Configure.

6. ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ SSC ą▓čŗąĘąŠą▓ąŠą╝ SSC_Configure (ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ čüą║ąŠčĆąŠčüčéčī čĆą░ą▒ąŠčéčŗ SSC).

7. ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ SSC ą▓čŗąĘąŠą▓ąŠą╝ SSC_ConfigureTransmitter (ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ).

8. ąŚą░ą┐čāčüą║ą░ąĄą╝ ą┐ąĄčĆąĄą┤ą░čćčā č湥čĆąĄąĘ PDC

SSC_CR = AT91C_SSC_TXEN;

ąÆąĮąĖą╝ą░ąĮąĖąĄ! ą×ą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą┤ąŠą╗ąČąĮčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī ą┤čĆčāą│ ą┤čĆčāą│čā čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ ą▓ ą▒ą░ą╣čéą░čģ, č鹊 čćč鹊 ą▓čŗ ą┐ąĖčłąĄč鹥 ą▓ čüč湥čéčćąĖą║ąĖ TCR, TNCR ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ SSC_DATLEN(8), SSC_DATNB(1). ąŚą░ą║ąŠąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖčÅ čéą░ą║ąŠą╣ (ąĘą┤ąĄčüčī DATLEN ąĖ DATNB čŹč鹊 č鹊, čćč鹊 ą┐ąŠą┤čüčéą░ą▓ą╗čÅąĄą╝ ą▓ ą╝ą░ą║čĆąŠčüčŗ SSC_DATLEN() ąĖ SSC_DATNB() čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ):

čĆą░ąĘą╝ąĄčĆ_ą▒čāč乥čĆą░_ą▓_ą▒ą░ą╣čéą░čģ = ąĘąĮą░č湥ąĮąĖąĄ_TCR * (DATLEN/8)

DATNB = DATLEN/8

16. ąÉą╗ą│ąŠčĆąĖčéą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

1. ąØą░čüčéčĆą░ąĖą▓ą░ąĄą╝ ą┐ąŠčĆčé SSC ą║ą░ą║ ąŠą▒čŗčćąĮąŠ, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ č鹊ą│ąŠ, čćč鹊 ąĮąĄ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ:

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ąĮąŠąČą║ąĖ čā SSC

PIO_Configure(DSP_pins, PIO_LISTSIZE(DSP_pins));

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ SSC ąĮą░ čüą║ąŠčĆąŠčüčéčī 1411200 ą▒ąĖčé/čüąĄą║

SSC_Configure(AT91C_BASE_SSC,

AT91C_ID_SSC,

1411200,

BOARD_MCK/*masterClock*/);

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║

// - čéą░ą║čéčŗ ą▒ąĖčé ą│ąĄąĮąĄčĆčÅčéčüčÅ ą▓ąĮčāčéčĆąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąŠą┤ąĄą╗ąĄąĮąĮą░čÅ čćą░čüč鹊čéą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ MCK

// (AT91C_SSC_CKS_DIV)

// - čéą░ą║čéčŗ ą▒ąĖčé ą▓čüąĄą│ą┤ą░, ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠ (AT91C_SSC_CKO_CONTINOUS)

// - čüčéą░čĆčé ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠ čüą┐ą░ą┤čā čüąĖą│ąĮą░ą╗ą░ čäčĆąĄą╣ą╝ą░ TF (AT91C_SSC_START_FALL_RF)

// - ąĘą░ą┤ąĄčƹȹ║ą░ ąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ 0 čéą░ą║čé (SSC_STTDLY(0))

// - ą┐ąŠą╗ąĄ PERIOD ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ 1 (SSC_PERIOD(32)) - ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé

// ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą┐ąĄčĆąĖąŠą┤ą░ čäčĆąĄą╣ą╝ą░

// - ą┤ą╗ąĖąĮą░ ą┐ąŠčüčŗą╗ą║ąĖ 8 ą▒ąĖčé (SSC_DATLEN(8))

// - ą┐ąĄčĆąĄą┤ą░čćą░ ąĖą┤ąĄčé čüčéą░čĆčłąĖą╝ąĖ ą▒ąĖčéą░ą╝ąĖ ą▓ą┐ąĄčĆąĄą┤ (AT91C_SSC_MSBF)

// - ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąŠą┤ąĮąŠ čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ (SSC_DATNB(1))

// - ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čüąĖąĮčģčĆąŠčüąĖą│ąĮą░ą╗ą░ čäčĆąĄą╣ą╝ą░ (ąĮąŠą╗ąĖą║ą░) čĆą░ą▓ąĮą░ 16 čéą░ą║čéą░ą╝ (SSC_FSLEN(16)).

// ąŻ ąĮą░čü čŹč鹊čé čüąĖąĮčģčĆąŠčüąĖą│ąĮą░ą╗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ (FSDEN == 0), ą┐ąŠčŹč鹊ą╝čā FSLEN ą╝ąŠąČąĮąŠ

// ąĘą░ą┤ą░čéčī ą╗čÄą▒ąŠą╣ ą┤ą╗ąĖąĮčŗ.

// - čéąĖą┐ ąĖą╝ą┐čāą╗čīčüą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ - ąĮąŠą╗ąĖą║, ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗąĄ ąĖą╝ą┐čāą╗čīčüčŗ

// (AT91C_SSC_FSOS_NEGATIVE)

SSC_ConfigureTransmitter(AT91C_BASE_SSC,

(AT91C_SSC_CKS_DIV | AT91C_SSC_CKO_CONTINOUS | AT91C_SSC_START_FALL_RF |

SSC_STTDLY(0) | SSC_PERIOD(32)),

(SSC_DATLEN(8) | AT91C_SSC_MSBF | SSC_DATNB(1) | SSC_FSLEN(16) |

AT91C_SSC_FSOS_NEGATIVE));

//ą▓ą║ą╗čÄčćą░ąĄą╝ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║

SSC_EnableTransmitter(AT91C_BASE_SSC);

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ą┐čĆąĖąĄą╝ąĮąĖą║ (ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą▓čģąŠą┤ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĘą░ą╝ą║ąĮčāčé

// ąĮą░ ą▓čŗčģąŠą┤ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░)

// - čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą▒ąĖčé ą▒ąĄčĆąĄčéčüčÅ čüąŠ ą▓čģąŠą┤ą░ RK (AT91C_SSC_CKS_RK)

// - čüčéą░čĆčé ą┐čĆąĖąĄą╝ą░ ą┐ąŠ čüą┐ą░ą┤čā čüąĖą│ąĮą░ą╗ą░ čäčĆąĄą╣ą╝ą░ RF (AT91C_SSC_START_FALL_RF)

// - ąĘą░ą┤ąĄčƹȹ║ą░ ąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ 0 čéą░ą║čé (SSC_STTDLY(0))

// - ą┤ą╗ąĖąĮą░ ą┐ąŠčüčŗą╗ą║ąĖ 8 ą▒ąĖčé (SSC_DATLEN(8))

// - ą┐ąĄčĆąĄą┤ą░čćą░ ąĖą┤ąĄčé čüčéą░čĆčłąĖą╝ąĖ ą▒ąĖčéą░ą╝ąĖ ą▓ą┐ąĄčĆąĄą┤ (AT91C_SSC_MSBF)

// - ą┐čĆąĖąĮąĖą╝ą░ąĄčéčüčÅ ąŠą┤ąĮąŠ čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ (SSC_DATNB(1))

// - ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čüąĖąĮčģčĆąŠčüąĖą│ąĮą░ą╗ą░ čäčĆąĄą╣ą╝ą░ (ąĮąŠą╗ąĖą║ą░) čĆą░ą▓ąĮą░ 16 čéą░ą║čéą░ą╝ (SSC_FSLEN(16)).

// ąŻ ąĮą░čü čŹč鹊čé čüąĖąĮčģčĆąŠčüąĖą│ąĮą░ą╗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ (FSDEN == 0), ą┐ąŠčŹč鹊ą╝čā FSLEN ą╝ąŠąČąĮąŠ

// ąĘą░ą┤ą░čéčī ą╗čÄą▒ąŠą╣ ą┤ą╗ąĖąĮčŗ.

SSC_ConfigureReceiver(AT91C_BASE_SSC,

(AT91C_SSC_CKS_RK | AT91C_SSC_START_FALL_RF | SSC_STTDLY(0)),

(SSC_DATLEN(8) | AT91C_SSC_MSBF | SSC_DATNB(1) | SSC_FSLEN(16)));

//ą▓ą║ą╗čÄčćą░ąĄą╝ ą┐čĆąĖąĄą╝ąĮąĖą║

SSC_EnableReceiver(AT91C_BASE_SSC);

ą¤ąŠčüą╗ąĄ čŹč鹊ą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┤ąĄą╣čüčéą▓ąĖą╣ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ čüčĆą░ąĘčā ąĮą░čćąĖąĮą░ąĄčé ą│ąĄąĮąĄčĆąĖčéčī čüąĖą│ąĮą░ą╗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą▒ąĖčé TK ąĖ čüąĖą│ąĮą░ą╗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ TF. ąØąŠąČą║ą░ ą┤ą░ąĮąĮčŗčģ TD ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ 0.

2. ą¤ąĄčĆąĄą┤ą░ąĄą╝ čäčĆąĄą╣ą╝, čé. ąĄ. čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ (4 ą▒ą░ą╣čéą░ ąĘą░čĆą░ąĘ, ąĄčüą╗ąĖ ą▓čŗą▒čĆą░ą╗ąĖ SSC_DATLEN(32), ąĖ č鹊ą╗čīą║ąŠ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé, ąĄčüą╗ąĖ SSC_DATLEN(8)):

u32 dataword = 0x12345678;

SSC_Write(AT91C_BASE_SSC, dataword);

ą¤ąĄčĆąĄą┤ą░čćą░ čüčĆą░ąĘčā ąČąĄ ąĮą░čćąĖąĮą░ąĄčéčüčÅ, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą▓čŗąĘą▓ą░ąĮą░ SSC_Write (ąĮą░ ąĮąŠąČą║ąĄ TD ą╝ąŠąČąĮąŠ ąĮą░ą▒ą╗čÄą┤ą░čéčī ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ). ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ ą▓čŗąĘąŠą▓ąŠą╝ SSC_Write ą▒čŗą╗ą░ čāąČąĄ ąĘą░ą┐čāčēąĄąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą▓ čåąĖą║ą╗ąĄ ą┐čĆąĄą┤čŗą┤čāčēąĖą╝ ą▓čŗąĘąŠą▓ąŠą╝ SSC_Write), č鹊 ąŠč湥čĆąĄą┤ąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮąĄ ąĮą░čćąĮąĄčéčüčÅ, ą┐ąŠą║ą░ ąĮąĄ ąŠą║ąŠąĮč湥ąĮą░ ą┐čĆąĄą┤čŗą┤čāčēą░čÅ (čéą░ą║ čĆą░ą▒ąŠčéą░ąĄčé SSC_Write - ąŠąĮą░ ąŠą┐čĆą░čłąĖą▓ą░ąĄčé čäą╗ą░ą│ SSC_TXRDY, čüą╝. ssc.c).

ąĢčüą╗ąĖ ą╝čŗ čģąŠčéąĖą╝ čüčĆą░ąĘčā ą┐čĆąĖąĮčÅčéčī ą▒ą░ą╣čé, č鹊 ąĮčāąČąĮąŠ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ą┤ąŠąČą┤ą░čéčīčüčÅ, ą║ąŠą│ą┤ą░ ą▒ą░ą╣čé ą▓čŗą╣ą┤ąĄčé ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ (ąĮą░ą┤ąŠ ą┐čĆąŠą▓ąĄčĆčÅčéčī ąĮąĄ SSC_SR.TXRDY, ą░ SSC_SR.TXEMPTY):

//ąČą┤ąĄą╝, čćč鹊 ą▒ą░ą╣čé čāčüą┐ąĄčłąĮąŠ čāčłąĄą╗

while ((AT91C_BASE_SSC->SSC_SR & AT91C_SSC_TXEMPTY) == 0);

//č鹥ą┐ąĄčĆčī ą┐čĆąĖą╝ąĄą╝ ą▒ą░ą╣čé

u8 RX;

RX = SSC_Read(AT91C_BASE_SSC);

17. ą£ąŠąČąĮąŠ čüąŠąĄą┤ąĖąĮąĖčéčī ą▓čŗčģąŠą┤ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ čüąŠ ą▓čģąŠą┤ąŠą╝ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ čäąĖąĘąĖč湥čüą║ąĖ (TF->RF, TK->RK, TD->RD), ą░ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāčÅ ą▒ąĖčé SSC_RFMR.LOOP. ą×ąĮ ąĘą░ą╝čŗą║ą░ąĄčé ą▓čģąŠą┤čŗ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĮą░ ą▓čŗčģąŠą┤čŗ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (ą▓čüąĄ ą║ą░ą║ ąĖ ąĮą░ą┐ąĖčüą░ąĮąŠ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ TF->RF, TK->RK, TD->RD), ąĮąŠ č鹊ą╗čīą║ąŠ ą▓ąĮčāčéčĆąĖ AT91SAM7X256 - ąĮą░ ąĮąŠąČą║ą░čģ RF, RK, RD čüąĖą│ąĮą░ą╗čŗ ąĮąĄ ą▓ąĖą┤ąĮčŗ, ą░ ąĮą░ TF, TK, TD ąĮą░ą▒ą╗čÄą┤ą░čÄčéčüčÅ. ąØąĄčüą╝ąŠčéčĆčÅ ąĮą░ čŹč鹊, ą┐čĆąĖąĄą╝ąĮąĖą║ čĆą░ą▒ąŠčéą░ąĄčé čéą░ą║, ą║ą░ą║ ą▒čāą┤č鹊 čüąĖą│ąĮą░ą╗čŗ čü ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ą┐čĆąĖčģąŠą┤čÅčé, ą┐čĆąĖč湥ą╝ ąĘą░ą╝čŗą║ą░ąĮąĖąĄ ą▓čŗčģąŠą┤ąŠą▓ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĮą░ ąĘąĄą╝ą╗čÄ ą┐čĆąŠą▓ąŠą┤ą║ą░ą╝ąĖ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ.

18. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, č鹊 ąĮčāąČąĮąŠ ą┐ąĄčĆąĄą┤ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄą╝ SSC ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī AIC.

19. ą¦č鹊 ąŠąĘąĮą░čćą░čÄčé ą▒ąĖčéčŗ čüčéą░čéčāčüą░ SSC:

SSC_SR.TXRDY čĆąĄą│ąĖčüčéčĆ, ą║ąŠč鹊čĆčŗą╣ čüą╗čāąČąĖčé ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą┤ą░ąĮąĮčŗčģ (SSC_THR) ą│ąŠč鹊ą▓ ą║ ą┐čĆąĖąĮčÅčéąĖčÄ ąŠč湥čĆąĄą┤ąĮąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ. ąŁč鹊 ąĮąĄ ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čüą╗ąŠą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ čéčāą┤ą░ ą▒čŗą╗ąŠ ąĘą░ą┐ąĖčüą░ąĮąŠ čĆą░ąĮąĄąĄ, čāąČąĄ čäąĖąĘąĖč湥čüą║ąĖ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąŠ - ą┐čĆąŠčüč鹊 čŹč鹊 čüą╗ąŠą▓ąŠ ą▒ą╗ą░ą│ąŠą┐ąŠą╗čāčćąĮąŠ čāčłą╗ąŠ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąĖ, ąĄčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĮąĄ ąĘą░ą┐čĆąĄčēąĄąĮ, č鹊 čüąĄą╣čćą░čü ąŠčéą┐čĆą░ą▓ąĖčéčüčÅ ąĮą░čĆčāąČčā.

SSC_SR.TXEMPTY čäčĆąĄą╣ą╝, ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╣ ą▓ SSC_THR čāčüą┐ąĄčłąĮąŠ čāčłąĄą╗ ąĮą░čĆčāąČčā, ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą▒ąŠą╗čīčłąĄ ąĮąĄč湥ą│ąŠ.

ąæąĖčé SSC_RFMR.LOOP ąĘą░ą╝čŗą║ą░ąĄčé ą▓čģąŠą┤čŗ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĮą░ ą▓čŗčģąŠą┤čŗ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (ą▓čüąĄ ą║ą░ą║ ąĖ ąĮą░ą┐ąĖčüą░ąĮąŠ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ TF->RF, TK->RK, TD->RD), ąĮąŠ č鹊ą╗čīą║ąŠ ą▓ąĮčāčéčĆąĖ AT91SAM7X256 - ąĮą░ ąĮąŠąČą║ą░čģ RF, RK, RD čüąĖą│ąĮą░ą╗čŗ ąĮąĄ ą▓ąĖą┤ąĮčŗ, ą░ ąĮą░ TF, TK, TD ąĮą░ą▒ą╗čÄą┤ą░čÄčéčüčÅ. ąØąĄčüą╝ąŠčéčĆčÅ ąĮą░ čŹč鹊, ą┐čĆąĖąĄą╝ąĮąĖą║ čĆą░ą▒ąŠčéą░ąĄčé čéą░ą║, ą║ą░ą║ ą▒čāą┤č鹊 čüąĖą│ąĮą░ą╗čŗ čü ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ą┐čĆąĖčģąŠą┤čÅčé.

20. ąØą░ą║ąŠąĮąĄčå-č鹊 čĆą░ąĘąŠą▒čĆą░ą╗čüčÅ, ą┐ąŠč湥ą╝čā ąĮąĄ ą┐ąŠą╗čāčćą░ą╗ąŠčüčī ą┤ąĄą╗ą░čéčī ąĄą┤ąĖąĮąĖčćąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą¤čĆąŠčüč鹊 čÅ ąĮąĄ ą┤ąŠąČąĖą┤ą░ą╗čüčÅ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ - čćąĖčéą░ą╗ čĆąĄą│ąĖčüčéčĆ ą┐čĆąĖąĄą╝ą░ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ čäčĆąĄą╣ą╝ čāčłąĄą╗ (ąĮą░ą┤ąŠ ą▒čŗą╗ąŠ ą┐čĆąŠą▓ąĄčĆčÅčéčī čāčüčéą░ąĮąŠą▓ą║čā čäą╗ą░ąČą║ą░ TXEMPTY, ą░ čÅ ą┐čĆąŠą▓ąĄčĆčÅą╗ TXRDY).

21. ąĀąĄąĘčāą╗čīčéą░čéčŗ ą┐čĆąŠą▓ąĄčĆą║ąĖ čĆą░ą▒ąŠčéčŗ ą┐ąŠčĆčéą░ ą▓ čĆąĄąČąĖą╝ąĄ LOOP:

SSC_xFMR.FSLEN ąĮąĖ ąĮą░ čćč鹊 ąĮąĄ ą▓ą╗ąĖčÅąĄčé, ą┐čĆąŠą▒ąŠą▓ą░ą╗ 0..F

SSC_xCMR.STTDLY ąĮąĖ ąĮą░ čćč鹊 ąĮąĄ ą▓ą╗ąĖčÅąĄčé, čüą░ą╝ąŠąĄ ą│ą╗ą░ą▓ąĮąŠąĄ, čćč鹊ą▒čŗ ą▒čŗą╗ąŠ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝.

SSC_TCMR.PERIOD ąĮąĖ ąĮą░ čćč鹊 ąĮąĄ ą▓ą╗ąĖčÅąĄčé.

22. ą¤čĆąĖą╝ąĄčĆ ąŠčéą┐čĆą░ą▓ą║ąĖ ą▒ą╗ąŠą║ą░ ą┤ą░ąĮąĮčŗčģ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠą│ąŠ čĆą░ąĘą╝ąĄčĆą░ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ PDC (DMA) ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąöą╗čÅ ą┐čĆąŠčüč鹊čéčŗ ą▓ ą┐čĆąĖą╝ąĄčĆąĄ ą┐čĆąĄą┤ą┐ąŠą╗ą░ą│ą░ąĄčéčüčÅ, čćč鹊 ą┤ą░ąĮąĮčŗąĄ ąŠčéą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą▒ą░ą╣čéą░ą╝ąĖ, ą┐ąŠ 8 ą▒ąĖčé ąĮą░ čäčĆąĄą╣ą╝ SSC.

ą¤čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ - ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčüčŗą╗ą░čÄčéčüčÅ ą┐ąŠčĆčåąĖčÅą╝ąĖ ą┐ąŠ 256 ą▒ą░ą╣čé (čŹč鹊 ą┤ą╗čÅ ą┤ąĄą╝ąŠąĮčüčéčĆą░čåąĖąĖ, čéą░ą║ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą▒čŗ ąĖčģ čüčĆą░ąĘčā ąŠčéą┐čĆą░ą▓ąĖčéčī ąŠą┤ąĮąŠą╣ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ PDC). ą¤čĆąĖ čŹč鹊ą╝ ą▓ PDC ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čĆąĄą│ąĖčüčéčĆčŗ SSC_TPR, SSC_TCR (ą┤ą╗čÅ ą┐ąĄčĆą▓ąŠą│ąŠ ą▒čāč乥čĆą░ PDC) ąĖ SSC_TNPR, SSC_TNCR (ą┤ą╗čÅ ą▓č鹊čĆąŠą│ąŠ ą▒čāč乥čĆą░ PDC). ąśčüčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ - ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ ą▓ ą┐ą░ą╝čÅčéąĖ buf (ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ą┐ąĄčĆąĄą┤ą░ąĄą╝) ąĖ čĆą░ąĘą╝ąĄčĆ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒ą░ą╣čéą░čģ len. ąöą╗čÅ čĆą░ą▒ąŠčéčŗ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ 3 ą│ą╗ąŠą▒ą░ą╗čīąĮčŗąĄ ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗąĄ (ą│ą╗ąŠą▒ą░ą╗čīąĮčŗąĄ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą║ ąĮąĖą╝ ą▒čŗą╗ ą┤ąŠčüčéčāą┐ ą║ą░ą║ ąĖąĘ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, čéą░ą║ ąĖ ąĖąĘ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SSC) SSCbytecnt (ąŠčüčéą░ą▓čłą░čÅčüčÅ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą┤ą╗ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒ą░ą╣čéą░čģ), SSCpnt (čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą║ą░ ąĮąĄ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ) ąĖ bSSCsendDone (čäą╗ą░ąČąŠą║, čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāčÄčēąĖą╣ ąŠą▒ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ). ąÜąŠčĆąŠčéą║ąŠ ą░ą╗ą│ąŠčĆąĖčéą╝ čéą░ą║ąŠą╣:

- ąĮą░čüčéčĆą░ąĖą▓ą░ąĄą╝ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ (čüą╝. ą┐čĆąĖą╝ąĄčĆ čĆą░ąĮąĄąĄ) ąĮą░ ąĮčāąČąĮčŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ.

- SSCbytecnt = len, SSCpnt = buf

- ąĘą░ą┐ąĖčģąĖą▓ą░ąĄą╝ ą▓ PDC ą┐ąĄčĆą▓čāčÄ ą┐ąŠčĆčåąĖčÄ ą┤ą░ąĮąĮčŗčģ (ą┐ąĄčĆąĄą┤ą░čćą░ ąĮą░čćąĮąĄčéčüčÅ čüčĆą░ąĘčā, ą║ą░ą║ č鹊ą╗čīą║ąŠ ąĘą░ą│čĆčāąĘąĖčéčüčÅ čĆąĄą│ąĖčüčéčĆ SSC_TPR). ąĢčüą╗ąĖ SSCbytecnt < 256, č鹊 ą▓čŗąĘąŠą▓ SSC_WriteBuffer ą▒čāą┤ąĄčé ąŠą┤ąĮąŠą║čĆą░čéąĮčŗą╝, ąĄčüą╗ąĖ ą▒ąŠą╗čīčłąĄ, č鹊 ą┤ą▓čāčģą║čĆą░čéąĮčŗą╝ (ą▒čāą┤čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┐ąĄčĆą▓čŗą╣ ąĖ ą▓č鹊čĆąŠą╣ ą▒čāč乥čĆčŗ PDC). ąĪ ą║ą░ąČą┤ąŠą╣ ą┐ąŠčĆčåąĖąĄą╣ ą┤ą░ąĮąĮčŗčģ čüč湥čéčćąĖą║ ą┤ą░ąĮąĮčŗčģ SSCbytecnt čāą╝ąĄąĮčīčłą░ąĄčéčüčÅ ąĮą░ čĆą░ąĘą╝ąĄčĆ ą┐ąŠčĆčåąĖąĖ.

- ąŠąČąĖą┤ą░ąĄą╝ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÆčüčÄ ą┤ą░ą╗čīąĮąĄą╣čłčāčÄ ą┐ąŠą┤ą┤ąĄčƹȹ║čā ąĘą░ą│čĆčāąĘąŠą║ ą▒čāč乥čĆąŠą▓ PDC ą▒ąĄčĆąĄčé ąĮą░ čüąĄą▒čÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SSC. ą×ąĮ č鹊čćąĮąŠ čéą░ą║ ąČąĄ ąĘą░ą│čĆčāąČą░ąĄčé ą▒čāč乥čĆčŗ PDC ą┐ąŠčĆčåąĖčÅą╝ąĖ, ą┐ąŠą║ą░ ąĮąĄ ąĘą░ą║ąŠąĮčćą░čéčüčÅ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąÆąŠčé ą▓čŗąČąĖą╝ą║ą░ ąĖąĘ ą║ąŠą┤ą░ (ą┐čĆąŠčåąĄą┤čāčĆčŗ SSC_WriteBuffer, SSC_DisableInterrupts ąĖ ą┐čĆąŠčćąĖąĄ ą▓ąĘčÅčéčŗ ąĖąĘ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĖ ssc.c ąŠčé Atmel):

void ConfigureSSC (void)

{

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ąĮąŠąČą║ąĖ čā SSC

PIO_Configure(DSP_pins, PIO_LISTSIZE(DSP_pins));

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ SSC ąĮą░ čüą║ąŠčĆąŠčüčéčī 1411200 ą▒ąĖčé/čüąĄą║

SSC_Configure(AT91C_BASE_SSC,

AT91C_ID_SSC,

1411200,

BOARD_MCK/*masterClock*/);

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║:

// [TCMR]

// - ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ąŠą┤ąĄą╗ąĄąĮąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░

// (AT91C_SSC_CKS_DIV)

// - čéą░ą║čéčŗ ą▒ąĖčé ą▓čüąĄą│ą┤ą░ (AT91C_SSC_CKO_CONTINOUS)

// - čüčéą░čĆčé ą┐čĆąĖąĄą╝ą░ ą┐ąŠ čüą┐ą░ą┤čā RF (AT91C_SSC_START_FALL_RF)

// - ąĘą░ą┤ąĄčƹȹ║ą░ ąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ 0 čéą░ą║čé (SSC_STTDLY(0))

// - ą┐ąŠą╗ąĄ PERIOD ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ 1 (SSC_PERIOD(32))

// [TFMR]

// - ą┤ą╗ąĖąĮą░ ą┐ąŠčüčŗą╗ą║ąĖ 8 ą▒ąĖčé (SSC_DATLEN(8))

// - ą┐ąĄčĆąĄą┤ą░čćą░ ąĖą┤ąĄčé čüčéą░čĆčłąĖą╝ąĖ ą▒ąĖčéą░ą╝ąĖ ą▓ą┐ąĄčĆąĄą┤ (AT91C_SSC_MSBF)

// - ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąŠą┤ąĮąŠ čüą╗ąŠą▓ąŠ ąĘą░ čäčĆąĄą╣ą╝ (SSC_DATNB(1))

// - ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čüąĖąĮčģčĆąŠčüąĖą│ąĮą░ą╗ą░ čäčĆąĄą╣ą╝ą░ (ąĮąŠą╗ąĖą║ą░) čĆą░ą▓ąĮą░ 16 čéą░ą║čéą░ą╝ (SSC_FSLEN(16))

// - čéąĖą┐ ąĖą╝ą┐čāą╗čīčüą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ TF - ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗąĄ ąĖą╝ą┐čāą╗čīčüčŗ

// (AT91C_SSC_FSOS_NEGATIVE)

// ąöčĆčāą│ąĖąĄ ą▓ą░čĆąĖą░čåąĖąĖ ąŠą┐čåąĖą╣:

// - čéą░ą║čéčŗ ą▒ąĖčé č鹊ą╗čīą║ąŠ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (AT91C_SSC_CKO_DATA_TX) - ąĮąĄ ąĘą░čĆą░ą▒ąŠčéą░ą╗ąŠ

// - ąĘą░ą┤ąĄčƹȹ║ą░ ąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ 1 čéą░ą║čé (SSC_STTDLY(1)) - ąĮčāąČąĮąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčéčī

// čüąĖąĮčģčĆąŠąĮąĮąŠ čü ą┐čĆąĖąĄą╝ąĮąĖą║ąŠą╝

SSC_ConfigureTransmitter(AT91C_BASE_SSC,

(AT91C_SSC_CKS_DIV | AT91C_SSC_CKO_CONTINOUS | AT91C_SSC_START_FALL_RF |

SSC_STTDLY(0) | SSC_PERIOD(32)),

(SSC_DATLEN(8) | AT91C_SSC_MSBF | SSC_DATNB(1) | SSC_FSLEN(16) |

AT91C_SSC_FSOS_NEGATIVE));

//ą▓ą║ą╗čÄčćą░ąĄą╝ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║

SSC_EnableTransmitter(AT91C_BASE_SSC);

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ą┐čĆąĖąĄą╝ąĮąĖą║

SSC_ConfigureReceiver(AT91C_BASE_SSC,

(AT91C_SSC_CKS_RK | AT91C_SSC_START_FALL_RF | SSC_STTDLY(0)),

(SSC_DATLEN(8) | AT91C_SSC_MSBF | SSC_DATNB(1) | SSC_FSLEN(16)));

//ą▓ą║ą╗čÄčćą░ąĄą╝ ą┐čĆąĖąĄą╝ąĮąĖą║

SSC_EnableReceiver(AT91C_BASE_SSC);

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ąĖ čĆą░ąĘčĆąĄčłą░ąĄą╝ SSC interrupt

AIC_ConfigureIT(AT91C_ID_SSC, 0, ISR_Ssc);

AIC_EnableIT(AT91C_ID_SSC);

}

//------------------------------------------------------------------------------

/// Interrupt handler for the SSC. ą¤ąŠčĆčåąĖčÅą╝ąĖ ą┐ąŠ 256 ą▒ą░ą╣čé ąŠčéą┐čĆą░ą▓ą╗čÅąĄčé ą┤ą░ąĮąĮčŗąĄ.

/// ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čäą╗ą░ąČąŠą║ bSSCsendDone, ą║ąŠč鹊čĆčŗą╣ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠą▒ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ.

//------------------------------------------------------------------------------

void ISR_Ssc(void)

{

unsigned int status = AT91C_BASE_SSC->SSC_SR;

unsigned int portion;

// ąöą░ąĮąĮčŗąĄ ąŠčéą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą┐ąŠčĆčåąĖčÅą╝ąĖ ą┐ąŠ 256 ą▒ą░ą╣čé.

// ą×čéą┐čĆą░ą▓ą╗ąĄąĮ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒čāč乥čĆ

if ((status & AT91C_SSC_TXBUFE) != 0)

{

SSC_DisableInterrupts(AT91C_BASE_SSC, AT91C_SSC_ENDTX | AT91C_SSC_TXBUFE);

AT91C_BASE_SSC->SSC_PTCR = AT91C_PDC_TXTDIS;

bSSCsendDone = true;

}

// ą×ą┤ąĖąĮ ą▒čāč乥čĆ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ, ąĖ ąĄčüčéčī ąĄčēąĄ ą▒čāč乥čĆčŗ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ

else if (SSCbytecnt > 0)

{

if (SSCbytecnt <= 256)

{

portion = SSCbytecnt;

}

else

{

portion = 256;

}

SSCbytecnt -= portion;

SSC_WriteBuffer(AT91C_BASE_SSC, (void *) SSCpnt, portion);

SSCpnt += portion;

}

// ą×ą┤ąĖąĮ ą▒čāč乥čĆ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ, ą▒ąŠą╗čīčłąĄ ą▒čāč乥čĆąŠą▓ ąĮąĄčé

else

{

SSC_DisableInterrupts(AT91C_BASE_SSC, AT91C_SSC_ENDTX);

}

}

//------------------------------------------------------------------------------

/// ąÜąŠą┤, ąĘą░ą┐čāčüą║ą░čÄčēąĖą╣ ąŠčéą┐čĆą░ą▓ą║čā ą┤ą░ąĮąĮčŗčģ.

//------------------------------------------------------------------------------

ConfigureSSC();

...

bSSCsendDone = false;

SSCbytecnt = to_allocate;

SSCpnt = dspdata;

// Fill first PDC buffer

if (SSCbytecnt <= 256)

{

portion = SSCbytecnt;

}

else

{

portion = 256;

}

SSCbytecnt -= portion;

SSC_WriteBuffer(AT91C_BASE_SSC, (void *) SSCpnt, portion);

SSCpnt += portion;

// Fill second buffer if necessary

if (SSCbytecnt > 0)

{

if (SSCbytecnt <= 256)

{

portion = SSCbytecnt;

}

else

{

portion = 256;

}

SSCbytecnt -= portion;

SSC_WriteBuffer(AT91C_BASE_SSC, (void *) SSCpnt, portion);

SSCpnt += portion;

}

//ąöą╗čÅ čĆą░ąĘčĆąĄčłąĖą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą┐ąĄčĆąĄą┤ą░čćąĖ

SSC_EnableInterrupts(AT91C_BASE_SSC, AT91C_SSC_TXBUFE | AT91C_SSC_ENDTX);

//ąČą┤ąĄą╝ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ

while (!bSSCsendDone);

ą¤čĆąĖ čĆą░ą▒ąŠč鹥 PDC ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠąČąĮąŠ ąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ąŠąŠą▒čēąĄ, ąĄčüą╗ąĖ ąŠčéą┐čĆą░ą▓ąĖčéčī ą┤ą░ąĮąĮčŗąĄ ąŠą┤ąĮąĖą╝ ą▒ą╗ąŠą║ąŠą╝ ąĘą░čĆą░ąĘ (ąŠą┤ąĮąĖą╝ ą▓čŗąĘąŠą▓ąŠą╝ SSC_WriteBuffer). ąŚą░ą▓ąĄčĆčłąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮčāąČąĮąŠ ą┐čĆąĖ čŹč鹊ą╝ ąŠčéčüą╗ąĄąČąĖą▓ą░čéčī ą┐ąŠ čäą╗ą░ąČą║čā AT91C_BASE_SSC->SSC_SR.TXBUFE - ąŠąĮ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąŠą▒ą░ čüč湥čéčćąĖą║ą░ ą▒čāč乥čĆąŠą▓ PDC (SSC_TCR ąĖ SSC_TNCR) čĆą░ą▓ąĮčŗ ąĮčāą╗čÄ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗąĄ ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗąĄ SSCbytecnt, SSCpnt ąĖ bSSCsendDone ąĮąĄ ąĮčāąČąĮčŗ. ąØąĄą┤ąŠčüčéą░č鹊ą║ čéą░ą║ąŠą│ąŠ ą╝ąĄč鹊ą┤ą░ - ąĮąĄčé ą║ąŠąĮčéčĆąŠą╗čÅ ąĘą░ ą┐čĆąŠčåąĄčüčüąŠą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ.

23. ąĪąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ čüčéą░čĆčéą░ ą┐čĆąĖąĄą╝ą░ čĆą░ą▒ąŠčéą░ąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĮąĄ čéą░ą║, ą║ą░ą║ ąŠąČąĖą┤ą░ą╗ąŠčüčī:

- čüąŠą▒čŗčéąĖąĄ čüčéą░čĆčéą░ ąĮąĄ ąĘą░ą┐čāčüą║ą░ąĄčé ą┐čĆąĖąĄą╝, ą┐čĆąĖąĄą╝ ąĮčāąČąĮąŠ ą▓ą║ą╗čÄčćąĖčéčī ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ čüčéą░čĆčéą░ (ą┐čĆąŠą▓ąĄčĆąĖą▓ čäą╗ą░ąČąŠą║ SSC_CP0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ SSC_SR). ąÆą║ą╗čÄč湥ąĮąĖąĄ ą┐čĆąĖąĄą╝ą░ ąĘą░ą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ č鹊ą╝, čćč鹊 ąĮčāąČąĮąŠ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░čéčī ą┐ąŠą╗ąĄ START ą▓ čĆąĄą│ąĖčüčéčĆąĄ SSC_RCMR, ąĘą░ą╝ąĄąĮąĖą▓ ąĘąĮą░č湥ąĮąĖąĄ AT91C_SSC_START_0 ąĮą░ ąĘąĮą░č湥ąĮąĖąĄ AT91C_SSC_START_FALL_RF.

- čüąŠą▒čŗčéąĖąĄ čüčéą░čĆčéą░ ąĮąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą┐ąŠą║ą░ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą┤ą╗čÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ SSC_RFMR.FSLEN) ą▒čāą┤ąĄčé ą▒ąŠą╗čīčłąĄ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ąĖčé ą▓ąŠ čäčĆąĄą╣ą╝ąĄ (ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ SSC_RFMR.DATLEN). ąóąŠčćąĮąĄąĄ ą│ąŠą▓ąŠčĆčÅ, ąŠčüčéą░ą╗čīąĮčŗąĄ ą┐čĆąĖąĮčÅčéčŗąĄ ą▒ąĖčéčŗ ą▒čāą┤čāčé ąĮčāą╗ąĄą▓čŗąĄ (ąĄčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čüąĖą│ąĮą░ą╗ą░ ą┤ą░ąĮąĮčŗčģ TD ąĮčāą╗ąĄą▓ąŠąĄ, čćč鹊 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ SSC_TFMR.DATDEF).

24. ąÆąĮąĖą╝ą░ąĮąĖąĄ, ąÆąÉą¢ąØą×: ą▓ čĆąĄą│ąĖčüčéčĆčŗ PDC (DMA), ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ/ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ (čŹč鹊 čĆąĄą│ąĖčüčéčĆčŗ SSC_TCR, SSC_TNCR, SSC_RCR, SSC_RNCR) ą┐ąĖčłąĄčéčüčÅ ąĮąĄ ą▓čüąĄą│ą┤ą░ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒ą░ą╣čéą░čģ. ąĢą┤ąĖąĮąĖčåčŗ, ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗąĄ ą▓ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ, ąĘą░ą▓ąĖčüčÅčé ąŠčé ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ąĖčé ą▓ čäčĆąĄą╣ą╝ąĄ (čé. ąĄ. ąŠčé ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠą╗čÅ SSC_TFMR.DATLEN) čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

- ą▒ąĖčé ą▓ąŠ čäčĆąĄą╣ą╝ąĄ 2..8 (DATLEN == 1..7) ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĖčłąĄčéčüčÅ ą▓ ą▒ą░ą╣čéą░čģ

- ą▒ąĖčé ą▓ąŠ čäčĆąĄą╣ą╝ąĄ 9..16 (DATLEN == 8..15) ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĖčłąĄčéčüčÅ ą▓ ą┐ąŠą╗čāčüą╗ąŠą▓ą░čģ (16-ą▒ąĖčéąĮčŗčģ ąĄą┤ąĖąĮąĖčåą░čģ)

- ą▒ąĖčé ą▓ąŠ čäčĆąĄą╣ą╝ąĄ 17..32 (DATLEN == 16..31) ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĖčłąĄčéčüčÅ ą▓ čüą╗ąŠą▓ą░čģ (32-ą▒ąĖčéąĮčŗčģ ąĄą┤ąĖąĮąĖčåą░čģ)

ąÉą┤čĆąĄčü, ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ ą▓ čāą║ą░ąĘą░č鹥ą╗čī PDC (DMA), ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖą╣ ą╝ąĄčüč鹊ą┐ąŠą╗ąŠąČąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ (čŹč鹊 čĆąĄą│ąĖčüčéčĆčŗ SSC_TPR, SSC_TNPR, SSC_RPR, SSC_RNPR), ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ąĮą░ čüą╗ąĄą┤čāčÄčēąĖąĄ ą▓ąĄą╗ąĖčćąĖąĮčŗ:

- ą▒ąĖčé ą▓ąŠ čäčĆąĄą╣ą╝ąĄ 2..8 (DATLEN == 1..7) ąĖąĮą║čĆąĄą╝ąĄąĮčé ą║čĆą░č鹥ąĮ 1 (čü ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥ą╣ čäčĆąĄą╣ą╝ą░ čāą║ą░ąĘą░č鹥ą╗čī ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąĮą░ 1)

- ą▒ąĖčé ą▓ąŠ čäčĆąĄą╣ą╝ąĄ 9..16 (DATLEN == 8..15) ąĖąĮą║čĆąĄą╝ąĄąĮčé ą║čĆą░č鹥ąĮ 2 (čü ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥ą╣ čäčĆąĄą╣ą╝ą░ čāą║ą░ąĘą░č鹥ą╗čī ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąĮą░ 2)

- ą▒ąĖčé ą▓ąŠ čäčĆąĄą╣ą╝ąĄ 17..32 (DATLEN == 16..31) ąĖąĮą║čĆąĄą╝ąĄąĮčé ą║čĆą░č鹥ąĮ 4 (čü ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥ą╣ čäčĆąĄą╣ą╝ą░ čāą║ą░ąĘą░č鹥ą╗čī ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąĮą░ 4)

[ą¤čĆąĖą╝ąĄčĆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ]

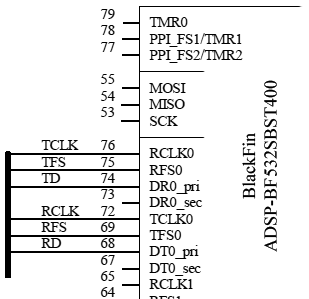

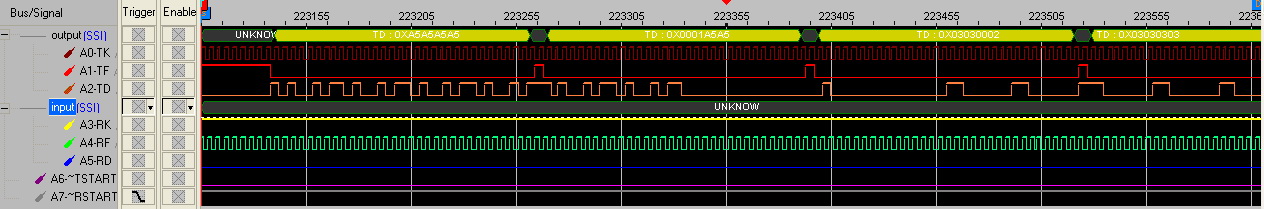

ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą┐ąŠčĆčé SSC ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗čüčÅ ą┤ą╗čÅ čüą▓čÅąĘąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AT91SAM7X256 čü DSP-ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ BlackFin ą║ąŠą╝ą┐ą░ąĮąĖąĖ AnalogDevices ADSP-BF532SBST400. ąÜčĆąŠą╝ąĄ 6 čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐ąŠčĆčéą░ SSC (čüą╝. čüčģąĄą╝čā), ąŠą▒čüą╗čāąČąĖą▓ą░ąĄą╝čŗčģ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ ą┐čĆąŠč鹊ą║ąŠą╗ą░ ąŠą▒ą╝ąĄąĮą░ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮčŗ 2 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ čüąĖą│ąĮą░ą╗ą░ (ąĮą░ čüčģąĄą╝ąĄ ąĮąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ), čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗčģ ąĖ ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄą╝čŗčģ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ. ąŁčéąĖ čüąĖą│ąĮą░ą╗čŗ čāą║ą░ąĘčŗą▓ą░čÄčé ąĮą░ ą╝ąŠą╝ąĄąĮčé ąĮą░čćą░ą╗ą░ ą▒ą╗ąŠą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (ą┐ąĄčĆąĄą┤ą░čćą░ ą▓čüąĄą│ą┤ą░ ąĖą┤ąĄčé ą▒ą╗ąŠą║ą░ą╝ąĖ ą┐ąŠ SSC_BLOCK_LEN ą▒ą░ą╣čé, čĆą░ąĘą╝ąĄčĆ ą▒ą╗ąŠą║ą░ ą║čĆą░č鹥ąĮ 4, ą┐ąŠčüą║ąŠą╗čīą║čā ą▓čŗą▒čĆą░ąĮ čĆą░ąĘą╝ąĄčĆ čäčĆąĄą╣ą╝ą░ 32 ą▒ąĖčéą░).

|

|

ąĪąĖą│ąĮą░ą╗čŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ (TK, RK) ąĖ čäčĆąĄą╣ą╝ąŠą▓ (TF, RF) ąĮą░čüčéčĆąŠąĄąĮčŗ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊 ą┤ąĄą║ąŠą┤ąĖčĆčāčÄčéčüčÅ ą║ą░ą║ čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ (SSI) ą╗ąŠą│ąĖč湥čüą║ąĖą╝ ą░ąĮą░ą╗ąĖąĘą░č鹊čĆąŠą╝ ąÉąÜąśą¤-9103. ąØą░ čĆąĖčüčāąĮą║ąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą▓čŗą┤ą░ąĮąĮą░čÅ ą░ąĮą░ą╗ąĖąĘą░č鹊čĆąŠą╝.

ąöą░ą╗ąĄąĄ ą┐čĆąĖą▓ąŠąČčā ą║čāčüą║ąĖ ą║ąŠą┤ą░, ąĖą╗ą╗čÄčüčéčĆąĖčĆčāčÄčēąĖąĄ čĆą░ą▒ąŠčéčā čü ą┐ąŠčĆč鹊ą╝ SSC ą▓ AT91SAM7X256.

typedef struct _SSC

{

u32 txcnt; // čüą║ąŠą╗čīą║ąŠ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┤ą░čć

u32 rxcnt; // čüą║ąŠą╗čīą║ąŠ ą▒čŗą╗ąŠ čāčüą┐ąĄčłąĮčŗčģ ą┐čĆąĖąĄą╝ąŠą▓

u32 rxcntOK; // čüą║ąŠą╗čīą║ąŠ ą▒čŗą╗ąŠ čāčüą┐ąĄčłąĮčŗčģ ą┐čĆąĖąĄą╝ąŠą▓

u8 header_detected; // čüąĖąĮčģčĆąŠą▒ą░ą╣čéčŗ ąĮą░čćą░ą╗ą░ 0xA5 0xA5 0xA5 0xA5 0xA5 0xA5 ą┐čĆąŠčłą╗ąĖ

u8 tail_detected; // čüąĖąĮčģčĆąŠą▒ą░ą╣čéčŗ ą║ąŠąĮčåą░ 0xE6 0xE6 0xE6 0xE6 0xE6 ą┐čĆąŠčłą╗ąĖ

u8 txdone; // ą┐ąĄčĆąĄą┤ą░čćą░ ąŠą║ąŠąĮč湥ąĮą░, ą╝ąŠąČąĮąŠ ąĘą░ą┐čāčüčéąĖčéčī ąĮąŠą▓čāčÄ ą┐ąĄčĆąĄą┤ą░čćčā

u8 rxdone; // ą┐čĆąĖąĄą╝ ąŠą║ąŠąĮč湥ąĮ, ą╝ąŠąČąĮąŠ čćąĖčéą░čéčī ą▒čāč乥čĆ

u32 errmissheader; // čüč湥čéčćąĖą║ ąĮąĄ ąĮą░ą╣ą┤ąĄąĮąĮčŗčģ ąĘą░ą│ąŠą╗ąŠą▓ą║ąŠą▓

u32 errcrc; // čüč湥čéčćąĖą║ ąŠčłąĖą▒ąŠą║ CRC

u32 errtimeout; // ąŠčłąĖą▒ą║ą░ čéą░ą╣ą╝ą░čāčéą░

u8 pdcbufRX[SSC_BLOCK_LEN]; // ą▒čāč乥čĆ PDC (DMA) ą┐čĆąĖąĄą╝ą░

u8 bufRX [SSC_BLOCK_LEN]; // ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░

u8 pdcbufTX[SSC_BLOCK_LEN]; // ą▒čāč乥čĆ PDC (DMA) ą┐ąĄčĆąĄą┤ą░čćąĖ

u32 rectimeout;

} tSSC;

tSSC vSSC; //ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐čĆąĖąĄą╝ą░ SSC

//ąĖąĮč鹥čĆč乥ą╣čü SSC, čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗą╣ čü ą┐ą╗ą░č鹊ą╣ DSP, čüąĖą│ąĮą░ą╗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čäčĆąĄą╣ą╝ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ TF

#define PIN_SSC_TF {1 << 21, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_A, PIO_DEFAULT | PIO_PULLUP}

//ąĖąĮč鹥čĆč乥ą╣čü SSC, čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗą╣ čü ą┐ą╗ą░č鹊ą╣ DSP, čüąĖą│ąĮą░ą╗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé ą┐ąĄčĆąĄą┤ą░čćąĖ TK

#define PIN_SSC_TK {1 << 22, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_A, PIO_DEFAULT}

//ąĖąĮč鹥čĆč乥ą╣čü SSC, čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗą╣ čü ą┐ą╗ą░č鹊ą╣ DSP, čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čćąĖ TD

#define PIN_SSC_TD {1 << 23, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_A, PIO_DEFAULT}

//ąĖąĮč鹥čĆč乥ą╣čü SSC, čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗą╣ čü ą┐ą╗ą░č鹊ą╣ DSP, čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ą░ RD

#define PIN_SSC_RD {1 << 24, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_A, PIO_DEFAULT}

//ąĖąĮč鹥čĆč乥ą╣čü SSC, čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗą╣ čü ą┐ą╗ą░č鹊ą╣ DSP, čüąĖą│ąĮą░ą╗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé ą┐čĆąĖąĄą╝ą░ RK

#define PIN_SSC_RK {1 << 25, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_A, PIO_DEFAULT}

//ąĖąĮč鹥čĆč乥ą╣čü SSC, čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗą╣ čü ą┐ą╗ą░č鹊ą╣ DSP, čüąĖą│ąĮą░ą╗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čäčĆąĄą╣ą╝ą░ ą┐čĆąĖąĄą╝ą░ RF

#define PIN_SSC_RF {1 << 26, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_A, PIO_DEFAULT}

#define PINS_SSC PIN_SSC_TF, PIN_SSC_TK, PIN_SSC_TD, PIN_SSC_RD, PIN_SSC_RK, PIN_SSC_RF

const Pin SSC_pins[] = {PINS_SSC};

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ąĮąŠąČą║ąĖ čā SSC

PIO_Configure(SSC_pins, PIO_LISTSIZE(SSC_pins));

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ SSC ąĮą░ čüą║ąŠčĆąŠčüčéčī 1411200 ą▒ąĖčé/čüąĄą║

SSC_Configure(AT91C_BASE_SSC,

AT91C_ID_SSC,

1411200/*čüą║ąŠčĆąŠčüčéčī 1411200 ą▒ąĖčé/čüąĄą║*/,

BOARD_MCK/*masterClock==48000000*/);

#define SSC_BIT_PER_FRAME 32

ą¤čĆąŠčåąĄą┤čāčĆą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐ąŠčĆčéą░ SSC ą┤ą╗čÅ AT91SAM7X256:

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║:

SSC_ConfigureTransmitter(AT91C_BASE_SSC,

(AT91C_SSC_CKS_DIV | AT91C_SSC_CKO_CONTINOUS | AT91C_SSC_START_FALL_RF |

SSC_STTDLY(0) | SSC_PERIOD(33) | AT91C_SSC_CKI)/*čĆąĄą│ąĖčüčéčĆ TCMR*/,

(SSC_DATLEN(SSC_BIT_PER_FRAME) | SSC_DATNB(1) | SSC_FSLEN(1) |

AT91C_SSC_FSOS_POSITIVE)/*čĆąĄą│ąĖčüčéčĆ TFMR*/);

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ą┐čĆąĖąĄą╝ąĮąĖą║

SSC_ConfigureReceiver(AT91C_BASE_SSC,

(AT91C_SSC_CKS_RK | AT91C_SSC_START_FALL_RF | SSC_STTDLY(0) | AT91C_SSC_CKI),

(SSC_DATLEN(SSC_BIT_PER_FRAME) | SSC_DATNB(1) | SSC_FSLEN(1)));

ą¤čĆąŠčåąĄą┤čāčĆčŗ ąĘą░ą┐čāčüą║ą░ ąĖ ąŠčüčéą░ąĮąŠą▓ą░ ą┐ąŠčĆčéą░ SSC:

void SSC_EnableTransmitter(AT91S_SSC *ssc)

{

ssc->SSC_CR = AT91C_SSC_TXEN;

}

void SSC_DisableTransmitter(AT91S_SSC *ssc)

{

ssc->SSC_CR = AT91C_SSC_TXDIS;

}

void SSC_EnableReceiver(AT91S_SSC *ssc)

{

ssc->SSC_CR = AT91C_SSC_RXEN;

}

void SSC_DisableReceiver(AT91S_SSC *ssc)

{

ssc->SSC_CR = AT91C_SSC_RXDIS;

}

ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠčĆčéą░ SSC:

//------------------------------------------------------------------------------

/// Interrupt handler for the SSC. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čäą╗ą░ąČąŠą║, ą║ąŠč鹊čĆčŗą╣

/// čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠą▒ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ.

//------------------------------------------------------------------------------

void ISR_Ssc(void)

{

unsigned int status = AT91C_BASE_SSC->SSC_SR;

if ((status & AT91C_SSC_TXBUFE)/* ą▒čāč乥čĆ DMA ą┐čāčüčé */

&& (status & AT91C_SSC_TXENA) /* ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ą▓ą║ą╗čÄč湥ąĮ */)

{

// ą¤ąĄčĆąĄą┤ą░čćą░ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ PDC ąĘą░ą║ąŠąĮč湥ąĮą░

SSC_DisableInterrupts(AT91C_BASE_SSC, AT91C_SSC_ENDTX | AT91C_SSC_TXBUFE);

AT91C_BASE_SSC->SSC_PTCR = AT91C_PDC_TXTDIS;

//ąČą┤ąĄą╝, ą║ąŠą│ą┤ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ čäčĆąĄą╣ą╝ ą▓čŗčüą║ąŠčćąĖčé ąĖąĘ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░

while (!(AT91C_BASE_SSC->SSC_SR & AT91C_SSC_TXEMPTY));

PIO_Set(&outINTarm);

SSC_DisableTransmitter(AT91C_BASE_SSC);

vSSC.txdone = true;

}

if ((status & AT91C_SSC_RXBUFF)/* ą▒čāč乥čĆ DMA ą┐ąŠą╗ąŠąĮ */)

{

if (status & AT91C_SSC_RXENA)/* ą┐čĆąĖąĄą╝ąĮąĖą║ ą▓ą║ą╗čÄč湥ąĮ */

{

// ą¤čĆąĖąĄą╝ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ PDC ąĘą░ą║ąŠąĮč湥ąĮ

SSC_DisableInterrupts(AT91C_BASE_SSC, AT91C_SSC_ENDRX | AT91C_SSC_RXBUFF);

AT91C_BASE_SSC->SSC_PTCR = AT91C_PDC_RXTDIS;

SSC_DisableReceiver(AT91C_BASE_SSC);

vSSC.rxdone = true;

vSSC.rxcnt++;

//LED(1);

}

}

}

ą¤čĆąĖąĄą╝ ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ čĆą░ą▒ąŠčéą░čÄčé čü čāčćą░čüčéąĖąĄą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ PDC (ąĖą╗ąĖ DMA). ą×ą║ąŠąĮčćą░ąĮąĖąĄ ą┐čĆąĖąĄą╝ą░ ąŠčéčüą╗ąĄąČąĖą▓ą░ąĄčéčüčÅ ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ISR_Ssc, ąĖ čéą░ą╝ ąČąĄ ą▓ąĘą▓ąŠą┤ąĖčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čäą╗ą░ą│ vSSC.rxdone. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĖąĄą╝ą░ ąŠčéčüą╗ąĄąČąĖą▓ą░ąĄčéčüčÅ čéą░ą╣ą╝ą░čāčé, ąĖ ąĄčüą╗ąĖ ą┐čĆąĖąĄą╝ ąĮąĄ ąĘą░ą▓ąĄčĆčłąĖą╗čüčÅ ą▓ č鹥č湥ąĮąĖąĄ ąŠąČąĖą┤ą░ąĄą╝ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, č鹊 čĆąĄą│ąĖčüčéčĆąĖčĆčāąĄčéčüčÅ ąŠčłąĖą▒ą║ą░.

ąÆąŠčé čéą░ą║ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ (SSC_BLOCK_LEN - čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ ą▒ą░ą╣čéą░čģ. ąöąĄą╗ąĖčéčüčÅ ąŠąĮ ąĮą░ 4 ą┐ąŠč鹊ą╝čā, čćč鹊 čĆą░ąĘą╝ąĄčĆ čäčĆąĄą╣ą╝ą░ ą▓čŗą▒čĆą░ąĮ 32 ą▒ąĖčéą░):

SSC_WriteBuffer(AT91C_BASE_SSC, (void *) vSSC.pdcbufTX, SSC_BLOCK_LEN/4);

//čĆą░ąĘčĆąĄčłąĖą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą┐ąĄčĆąĄą┤ą░čćąĖ

SSC_EnableInterrupts(AT91C_BASE_SSC, AT91C_SSC_TXBUFE);

//čĆą░ąĘčĆąĄčłą░ąĄą╝ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║

SSC_EnableTransmitter(AT91C_BASE_SSC);

[ąĪčüčŗą╗ą║ąĖ]

1. ąöąĖą░ą│čĆą░ą╝ą╝čŗ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐ąŠčĆčéą░ SSC. |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ

RSS ą╗ąĄąĮčéą░ ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖąĄą▓ čŹč鹊ą╣ ąĘą░ą┐ąĖčüąĖ