|

ąÜąŠąĮčéčĆąŠą╗ąĄčĆ čüą▒čĆąŠčüą░ (Reset Controller, čüąŠą║čĆą░čēąĄąĮąĮąŠ RSTC) ąŠčüąĮąŠą▓ą░ąĮąĮčŗą╣ ąĮą░ čüčģąĄą╝ą░čģ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüą▒čĆąŠčüą░ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ, ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą▓čüąĄ čüą▒čĆąŠčüčŗ čüąĖčüč鹥ą╝čŗ ą▒ąĄąĘ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ ą║ą░ą║ąĖčģ-ą╗ąĖą▒ąŠ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ ą▓ąĮąĄčłąĮąĖčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓. ą×ąĮ ą╝ąŠąČąĄčé čüąŠąŠą▒čēąĖčéčī, ą║ąŠą│ą┤ą░ čüą▒čĆąŠčü ą▒čŗą╗ ą┐čĆąŠąĖąĘą▓ąĄą┤ąĄąĮ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆą░ąĘ, ąĖ ą║ą░ą║ąŠą╣ čŹč鹊 ą▒čŗą╗ čéąĖą┐ čüą▒čĆąŠčüą░.

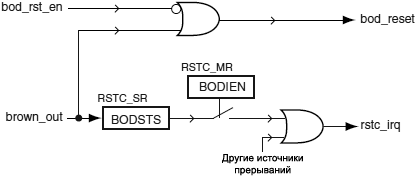

RSTC čéą░ą║ąČąĄ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąĖą╗ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą▓ąĮąĄčłąĮąĖą╣ čüą▒čĆąŠčü, ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ čÅą┤čĆąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąóą░ą║ąČąĄ ą▓ RSTC ąĖą╝ąĄąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮą░čÅ čüąĖčüč鹥ą╝ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąŠą▓ą░ą╗ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ (brownout detection), ą║ąŠč鹊čĆą░čÅ ąĘą░čēąĖčēą░ąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆ ąŠčé ą┐ąŠą┐ą░ą┤ą░ąĮąĖčÅ ą▓ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ.

ąĀąĖčü. 13-1. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čüą▒čĆąŠčüą░.

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ]

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüą▒čĆąŠčüą░ RSTC ą┐ąŠčüčéčĆąŠąĄąĮ ąĖąĘ ą▒ą╗ąŠą║ąŠą▓ NRST Manager, Brownout Manager, Startup Counter ąĖ Reset State Manager. ą×ąĮąĖ čĆą░ą▒ąŠčéą░čÄčé ąŠčé ą╝ąĄą┤ą╗ąĄąĮąĮčŗčģ čéą░ą║č鹊ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (Slow Clock, SLCK) ąĖ ą│ąĄąĮąĄčĆąĖčĆčāčÄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čüąĖą│ąĮą░ą╗čŗ čüą▒čĆąŠčüą░:

proc_nreset: čüąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ą×ąĮ čéą░ą║ąČąĄ čüą▒čĆą░čüčŗą▓ą░ąĄčé čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ (Watchdog Timer).

periph_nreset: ą▓ą╗ąĖčÅąĄčé ąĮą░ ą▓ąĄčüčī ąĮą░ą▒ąŠčĆ ą▓čüčéčĆąŠąĄąĮąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

nrst_out: čāą┐čĆą░ą▓ą╗čÅąĄčé ą▓čŗčģąŠą┤ąĮčŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝ NRST.

ąŁčéąĖ čüąĖą│ąĮą░ą╗čŗ čüą▒čĆąŠčüą░ ą▓čŗčüčéą░ą▓ą╗čÅčÄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ čüą▒čĆąŠčüą░ ą╗ąĖą▒ąŠ ąŠčé ą▓ąĮąĄčłąĮąĖčģ čüąŠą▒čŗčéąĖą╣, ą╗ąĖą▒ąŠ ąŠčé ą┤ąĄą╣čüčéą▓ąĖą╣ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ. Reset State Manager čāą┐čĆą░ą▓ą╗čÅąĄčé ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ čüąĖą│ąĮą░ą╗ąŠą▓ čüą▒čĆąŠčüą░ ąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüąĖą│ąĮą░ą╗ ą┤ą╗čÅ NRST Manager, ą║ąŠą│ą┤ą░ čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗčüčéą░ą▓ąĖčéčī ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ NRST.

NRST Manager ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗ NRST ą▓ č鹥č湥ąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆą░ą▓ąĖą╗čīąĮąŠ čüą▒čĆą░čüčŗą▓ą░čéčī ą▓ąĮąĄčłąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░.

ąĪč湥čéčćąĖą║ ąĘą░ą┐čāčüą║ą░ (startup counter) ąČą┤ąĄčé ą┐ąŠą╗ąĮąŠčåąĄąĮąĮąŠą│ąŠ ąĘą░ą┐čāčüą║ą░ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░. ąŚą░ą┤ąĄčƹȹ║ą░ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┤ą░ąĄčéčüčÅ ą┐ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╝čā ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┐čāčüą║ą░ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĮąŠ čāąĘąĮą░čéčī ą▓ čüąĄą║čåąĖąĖ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ Crystal Oscillator Characteristics (čĆą░ąĘą┤ąĄą╗ Electrical Characteristics) ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ.

NRST Manager. ą£ąĄąĮąĄą┤ąČąĄčĆ NRST ąŠą┐čĆą░čłąĖą▓ą░ąĄčé ą▓čŗą▓ąŠą┤ NRST ą║ą░ą║ ą▓čģąŠą┤ ąĖ čāą┐čĆą░ą▓ą╗čÅąĄčé čŹčéąĖą╝ ą▓čŗčģąŠą┤ąŠą╝, ą┐ąĄčĆąĄą▓ąŠą┤čÅ ąĄą│ąŠ ą▓ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ čŹč鹊ą│ąŠ čéčĆąĄą▒čāąĄčé Reset State Manager. ąĀąĖčü. 13-2 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▒ą╗ąŠą║-čüčģąĄą╝čā NRST Manager.

ąĀąĖčü. 13-2. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą╝ąĄąĮąĄą┤ąČąĄčĆą░ čüąĖą│ąĮą░ą╗ą░ NRST.

ą£ąĄąĮąĄą┤ąČąĄčĆ NRST ąŠą┐čĆą░čłąĖą▓ą░ąĄčé ą▓čŗą▓ąŠą┤ ą║ąŠčĆą┐čāčüą░ NRST ąĮą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 Slow Clock (SLCK). ąÜąŠą│ą┤ą░ ąŠą▒ąĮą░čĆčāąČąĄąĮąŠ, čćč鹊 čāčĆąŠą▓ąĄąĮčī ą┐ąĄčĆąĄčłąĄą╗ ą▓ ą╗ąŠą│. 0, ą┤ą╗čÅ Reset State Manager čüąŠąŠą▒čēą░ąĄčéčüčÅ ąŠ čüąŠą▒čŗčéąĖąĖ User Reset (čüą▒čĆąŠčü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ).

ą×ą┤ąĮą░ą║ąŠ ą╝ąĄąĮąĄą┤ąČąĄčĆ NRST ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ čéą░ą║, čćč鹊ą▒čŗ ąĮąĄ ą▓čŗąĘčŗą▓ą░čéčī čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ čüą▒čĆąŠčüą░, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ąĮąĄčłąĮąĄąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą╝ NRST. ąŚą░ą┐ąĖčüčī ą▒ąĖčéą░ URSTEN ą▓ 0 čĆąĄą│ąĖčüčéčĆą░ RSTC_MR ąĘą░ą┐čĆąĄčēą░ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ User Reset.

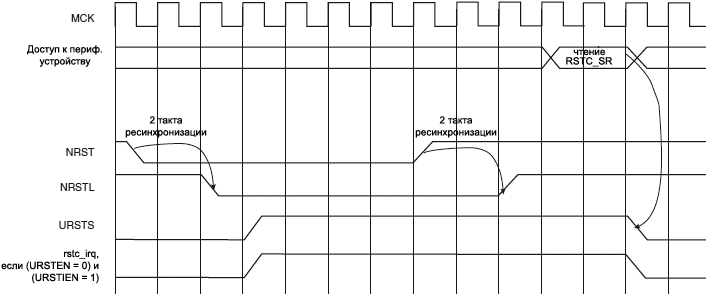

ąøąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ NRST ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą┐čĆąŠčćąĖčéą░ąĮ čćč鹥ąĮąĖąĄą╝ ą▒ąĖčéą░ NRSTL (čüąŠą║čĆą░čēąĄąĮąĖąĄ ąŠčé NRST level) ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSTC_SR. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ čüąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ NRST, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé URSTS ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSTC_SR. ąŁč鹊čé ą▒ąĖčé ąŠčćąĖčēą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čćąĖčéą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ RSTC_SR.

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüą▒čĆąŠčüą░ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ą╝ąĄčüč鹊 ą│ąĄąĮąĄčĆą░čåąĖąĖ čüą▒čĆąŠčüą░. ąöą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą▒ąĖčé URSTIEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSTC_MR ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ 1.

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓ąĮąĄčłąĮąĖą╝ čüą▒čĆąŠčüąŠą╝ NRST. Reset State Manager ą▓čŗčüčéą░ą▓ą╗čÅąĄčé čüąĖą│ąĮą░ą╗ ext_nreset, čćč鹊ą▒čŗ ą▓čŗčüčéą░ą▓ąĖčéčī čāčĆąŠą▓ąĄąĮčī čüą▒čĆąŠčüą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ NRST. ąÜąŠą│ą┤ą░ čŹč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, čüąĖą│ąĮą░ą╗ nrst_out ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. ą╝ąĄąĮąĄą┤ąČąĄčĆąŠą╝ NRST ąĮą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠąĄ ą▓čĆąĄą╝čÅ, ą║ąŠč鹊čĆąŠąĄ ąĘą░ą┤ą░ąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ ą▒ąĖčé ERSTL ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSTC_MR. ąŁčéą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ą░ čüą▒čĆąŠčüą░, ą║ąŠč鹊čĆą░čÅ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ EXTERNAL_RESET_LENGTH, čĆą░ą▓ąĮą░ ą┐ąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖč鹥ą╗čīąĮąŠčüčéąĖ 2(ERSTL+1) čéą░ą║č鹊ą▓ Slow Clock. ąŁč鹊 ą┤ą░ąĄčé ą┐čĆąĖą▒ą╗ąĖąĘąĖč鹥ą╗čīąĮčāčÄ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ą░ čüą▒čĆąŠčü ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 60 ą╝ą║čü ą┤ąŠ 2 čüąĄą║čāąĮą┤. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĘąĮą░č湥ąĮąĖąĄ 0 ą┐ąŠą╗čÅ ERSTL ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ąĖą╝ą┐čāą╗čīčüą░ NRST čĆą░ą▓ąĮąŠą╣ ą┤ą▓čāą╝ čéą░ą║čéą░ą╝.

ąŁčéą░ čäčāąĮą║čåąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā čüą▒čĆąŠčüą░ č乊čĆą╝ąĖčĆąŠą▓ą░čéčī čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ NRST, ą│ą░čĆą░ąĮčéąĖčĆčāčÅ, čćč鹊 čüąĖą│ąĮą░ą╗ NRST ą▒čāą┤ąĄčé ą┐ąŠą┤čéčÅąĮčāčé ą║ ą╗ąŠą│. 0 ąĮą░ ą▓čĆąĄą╝čÅ, ą┤ąŠčüčéą░č鹊čćąĮąŠąĄ ą┤ą╗čÅ čüą▒čĆąŠčüą░ ą▓ąĮąĄčłąĮąĖčģ čāčüčéčĆąŠą╣čüčéą▓, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą┐ąŠč鹥ąĮčåąĖą░ą╗čīąĮąŠ ą┐čĆąĖčüčāčéčüčéą▓ąŠą▓ą░čéčī ą▓ čüąĖčüč鹥ą╝ąĄ ąĖ čüą▒čĆą░čüčŗą▓ą░čéčīčüčÅ ąŠčé čüąĖčüč鹥ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░.

Brownout Manager. ąŁč鹊čé ą▒ą╗ąŠą║ ąĘą░čēąĖčēą░ąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆ ąŠčé ą┐ąŠą┐ą░ą┤ą░ąĮąĖčÅ ą▓ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ, ąĄčüą╗ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą┐čĆąŠčüčÅą┤ąĄčé ąĮąĖąČąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ. ąÜąŠą│ą┤ą░ VDDCORE ą┐ą░ą┤ą░ąĄčé ąĮąĖąČąĄ ą┐ąŠčĆąŠą│ą░ brownout, Brownout Manager ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ brownout-čüą▒čĆąŠčüą░ ą┐čāč鹥ą╝ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ bod_reset.

ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčüčé ą╝ąŠąČąĄčé ąĘą░ą┐čĆąĄčéąĖčéčī brownout reset ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓ ą╗ąŠą│. 0 ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ bod_rst_en, ąĮą░ą┐čĆąĖą╝ąĄčĆ ą┐čāč鹥ą╝ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ čŹąĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ (general-purpose NVM bit), ą║ąŠč鹊čĆčŗą╣ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ąŠ FLASH. ąÜąŠą│ą┤ą░ brownout reset ąĘą░ą┐čĆąĄčēąĄąĮ, čüą▒čĆąŠčü ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ. ąÆą╝ąĄčüč鹊 čŹč鹊ą│ąŠ ąŠ čüąŠą▒čŗčéąĖąĖ ą┐čĆąŠčüą░ą┤ą║ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (brownout detection) čüąŠąŠą▒čēą░ąĄčéčüčÅ ą▓ ą▒ąĖč鹥 BODSTS čĆąĄą│ąĖčüčéčĆą░ RSTC_SR. BODSTS čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ čüčćąĖčéčŗą▓ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ RSTC_SR.

ąæąĖčé BODSTS ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé BODIEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSTC_MR. ąĪ ąĘą░ą▓ąŠą┤ą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ brownout reset ąĘą░ą┐čĆąĄčēąĄąĮ.

ąĀąĖčü. 13-3. Brownout Manager.

[ąĪąŠčüč鹊čÅąĮąĖčÅ čüą▒čĆąŠčüą░]

Reset State Manager ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé čĆą░ąĘąĮčŗąĄ ąĖčüč鹊čćąĮąĖą║ąĖ čüą▒čĆąŠčüą░ ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ čüą▒čĆąŠčüą░. ą×ąĮ čüąŠąŠą▒čēą░ąĄčé ąŠ č鹥ą║čāčēąĄą╝ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ ąĘąĮą░č湥ąĮąĖąĄą╝ ą┐ąŠą╗čÅ RSTTYP ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ (RSTC_SR). ą×ą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą▒ąĖč鹊ą▓ąŠą│ąŠ ą┐ąŠą╗čÅ RSTTYP ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓čŗčģąŠą┤ąĖčé ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ čüą▒čĆąŠčüą░.

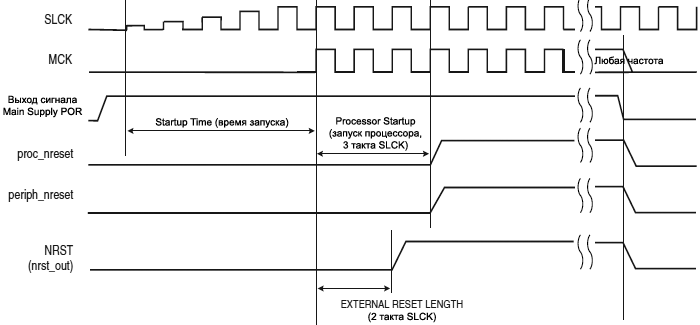

Power-up Reset. ąÜąŠą│ą┤ą░ ą┐ąŠčüčéčāą┐ą░ąĄčé ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ąĮą░ VDDCORE, ą▓čŗčģąŠą┤ čÅč湥ą╣ą║ąĖ Main Supply POR (čüą▒čĆąŠčü ąŠčé ą▓ą║ą╗čÄč湥ąĮąĖčÅ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ) čäąĖą╗čīčéčĆčāąĄčéčüčÅ čüč湥čéčćąĖą║ąŠą╝ ąĘą░ą┐čāčüą║ą░ (start-up counter), ą║ąŠč鹊čĆčŗą╣ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ ą╝ąĄą┤ą╗ąĄąĮąĮčŗčģ čéą░ą║čéą░čģ (Slow Clock, SLCK). ąØą░ąĘąĮą░č湥ąĮąĖąĄ čŹč鹊ą│ąŠ čüč湥čéčćąĖą║ą░ - ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ą│ąĄąĮąĄčĆą░č鹊čĆ Slow Clock ąĘą░čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ą░.

ąÆčĆąĄą╝čÅ ąĘą░ą┐čāčüą║ą░ (startup time), ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 13-4, čü ą┐ąŠą╝ąŠčēčīčÄ ą│ąĄąĮąĄčĆą░č鹊čĆą░ Slow Clock čäąĖą║čüąĖčĆąŠą▓ą░ąĮąŠ ąĘą░ą┤ą░ąĮąŠ ą┤ą╗čÅ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĄąĮąĖčÅ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┐čāčüą║ą░ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░. ą¤ąŠčüą╗ąĄ ąĖčüč鹥č湥ąĮąĖčÅ ą▓čĆąĄą╝ąĄąĮąĖ startup čüąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░ čüąĮąĖą╝ą░ąĄčéčüčÅ, ąĖ ą┐ąŠą╗ąĄ RSTTYP ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSTC_SR čüąŠąŠą▒čēąĖčé ąŠ čüąŠą▒čŗčéąĖąĖ Power-up Reset (čüą▒čĆąŠčü ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ).

ąĀąĖčü. 13-4. Power-up Reset.

ąÜąŠą│ą┤ą░ čÅč湥ą╣ą║ąŠą╣ Main Supply POR ą▒čŗą╗ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ, čćč鹊 VDDCORE ą▓ ąĮąĖąĘą║ąŠą╝ čāčĆąŠą▓ąĮąĄ, čüąĖą│ąĮą░ą╗čŗ čüą▒čĆąŠčüą░ ą▓čŗčüčéą░ą▓ą╗čÅčÄčéčüčÅ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ.

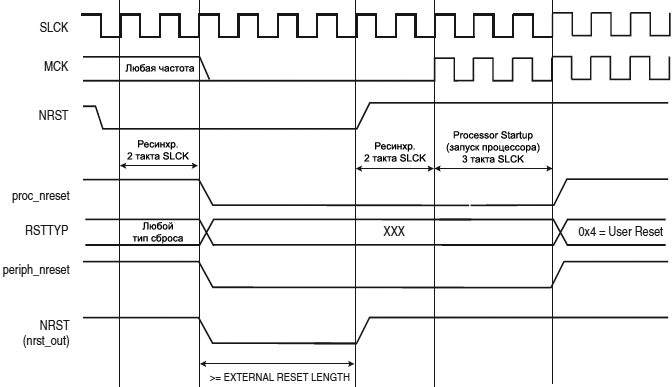

User Reset. ą¤čĆąŠąĖčüčģąŠą┤ąĖčé ą▓čģąŠą┤ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ čüą▒čĆąŠčüą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (User Reset), ą║ąŠą│ą┤ą░ ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ NRST, ąĖ ą▒ąĖčé URSTEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSTC_MR ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1. ąÆčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ NRST čĆąĄčüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ čü čćą░čüč鹊č鹊ą╣ ą╝ąĄą┤ą╗ąĄąĮąĮčŗčģ čéą░ą║č鹊ą▓ SLCK, čćč鹊ą▒čŗ ąĘą░čüčéčĆą░čģąŠą▓ą░čéčī ą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čüąĖčüč鹥ą╝čŗ.

ąÆ čüąŠčüč鹊čÅąĮąĖąĄ User Reset ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ą║ą░ą║ č鹊ą╗čīą║ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą╗ąŠą│. 0 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ NRST. ąÆčŗčüčéą░ą▓ą╗čÅčÄčéčüčÅ čüąĖą│ąĮą░ą╗čŗ čüą▒čĆąŠčüą░ Processor Reset ąĖ Peripheral Reset.

ąśąĘ čüąŠčüč鹊čÅąĮąĖčÅ User Reset ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓čŗčģąŠą┤, ą║ąŠą│ą┤ą░ čāčĆąŠą▓ąĄąĮčī NRST ą┐ąŠą┤ąĮąĖą╝ą░ąĄčéčüčÅ, ą┐ąŠčüą╗ąĄ ą┤ą▓čāčģ čéą░ą║č鹊ą▓ ą▓čĆąĄą╝ąĄąĮąĖ čĆąĄčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ąĖ čéčĆąĄčģ čéą░ą║č鹊ą▓, ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗčģ ą┤ą╗čÅ čüčéą░čĆčéą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąŠ čüąŠčüč鹊čÅąĮąĖąĄ NRST ą▓ ą╗ąŠą│. 1.

ąÜąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ čüąĮąĖą╝ą░ąĄčéčüčÅ, ą┐ąŠą╗ąĄ RSTTYP čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ (RSTC_SR) ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ 0x4, č湥ą╝ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ User Reset.

ą£ąĄąĮąĄą┤ąČąĄčĆ NRST ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 ąĮą░ ą╗ąĖąĮąĖąĖ NRST ą▒čāą┤ąĄčé ą▓čŗčüčéą░ą▓ą╗ąĄąĮ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī čüą▒čĆąŠčüą░ ąĮą░ ą▓čĆąĄą╝čÅ ąĮąĄ ą╝ąĄąĮąĄąĄ EXTERNAL_RESET_LENGTH čéą░ą║č鹊ą▓ Slow Clock, ą║ą░ą║ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą▓ ą┐ąŠą╗ąĄ ERSTL. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ NRST ąĮąĄ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ą╗ąŠą│. 1 ą┐ąŠčüą╗ąĄ EXTERNAL_RESET_LENGTH ąĖąĘ-ąĘą░ ą▓ąĮąĄčłąĮąĄą╣ ą┐ąŠą┤čéčÅąČą║ąĖ ą║ ą╗ąŠą│. 0, č鹊 ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüą▒čĆąŠčü ąŠčüčéą░ąĄčéčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ NRST ąĮąĄ ą┐ąŠą┤ąĮąĖą╝ąĄčéčüčÅ ą║ ą╗ąŠą│. 1.

ąĀąĖčü. 13-5. ąĪąŠčüč鹊čÅąĮąĖąĄ User Reset.

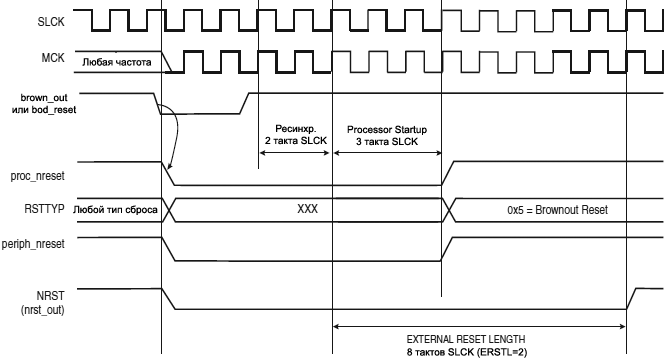

Brownout Reset. ąÜąŠą│ą┤ą░ ą▓čŗčüčéą░ą▓ą╗ąĄąĮ čüąĖą│ąĮą░ą╗ brown_out / bod_reset, č鹊 Reset State Manager ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą▓čģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ Brownout Reset (čüą▒čĆąŠčü ą┐ąŠ ą┐čĆąŠą▓ą░ą╗čā ą┐ąĖčéą░ąĮąĖčÅ). ąÆ čŹč鹊ą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą▓čŗčüčéą░ą▓ą╗čÅčÄčéčüčÅ čüąĖą│ąĮą░ą╗čŗ čüą▒čĆąŠčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĄą│ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą░ čéą░ą║ąČąĄ ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░ NRST.

Brownout Reset ąŠčüčéą░ąĄčéčüčÅ ąĮą░ 3 čéą░ą║čéą░ Slow Clock ą┐ąŠčüą╗ąĄ ąĮą░čĆą░čüčéą░ąĮąĖčÅ brown_out / bod_reset, ą┐ąŠčüą╗ąĄ 2 čéą░ą║č鹊ą▓ čĆąĄčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ. ąóą░ą║ąČąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé čüąĖą│ąĮą░ą╗ ą▓ąĮąĄčłąĮąĄą│ąŠ čüą▒čĆąŠčüą░.

ąÜąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓čŗčģąŠą┤ąĖčé ąĖąĘ čüą▒čĆąŠčüą░, ą┐ąŠą╗ąĄ RSTTYP čĆąĄą│ąĖčüčéčĆą░ RSTC_SR ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ 0x5, ą┐ąŠą║ą░ąĘčŗą▓ą░čÅ č鹥ą╝ čüą░ą╝čŗą╝, čćč鹊 ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ čüą▒čĆąŠčü ą▒čŗą╗ čéąĖą┐ą░ Brownout Reset.

ąĀąĖčü. 13-6. ąĪąŠčüč鹊čÅąĮąĖąĄ Brownout Reset.

Software Reset. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüą▒čĆąŠčüą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą║ąŠą╝ą░ąĮą┤, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą┤ą╗čÅ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖčÅ čĆą░ąĘąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ čüą▒čĆąŠčüą░. ąŁčéąĖ ą║ąŠą╝ą░ąĮą┤čŗ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (RSTC_CR) ą▓ ą╗ąŠą│. 1 čüą╗ąĄą┤čāčÄčēąĖčģ ą▒ąĖčé:

PROCRST: ąĘą░ą┐ąĖčüčī ą▓ čŹč鹊čé ą▒ąĖčé ąĄą┤ąĖąĮąĖčćą║ąĖ čüą▒čĆąŠčüąĖčé ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ.

PERRST: ąĘą░ą┐ąĖčüčīčÄ ą▓ čŹč鹊čé ą▒ąĖčé ąĄą┤ąĖąĮąĖčćą║ąĖ čüą▒čĆąŠčüąĖčé ą▓čüąĄ ą▓čüčéčĆąŠąĄąĮąĮčŗąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, ą▓ą║ą╗čÄčćą░čÅ ą┐ąŠą┤čüąĖčüč鹥ą╝čā ą┐ą░ą╝čÅčéąĖ, ąĖ ą▓ čćą░čüčéąĮąŠčüčéąĖ ą║ąŠą╝ą░ąĮą┤čā Remap. ąĪą▒čĆąŠčü ą┐ąĄčĆąĖč乥čĆąĖąĖ ąŠą▒čŗčćąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ čåąĄą╗čÅčģ ąŠčéą╗ą░ą┤ą║ąĖ.

EXTRST: ąĘą░ą┐ąĖčüčī ą▓ čŹč鹊čé ą▒ąĖčé ąĄą┤ąĖąĮąĖčćą║ąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0 čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ NRST ąĮą░ ą▓čĆąĄą╝čÅ, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą┐ąŠą╗ąĄą╝ ERSTL ą▓ čĆąĄą│ąĖčüčéčĆąĄ čĆąĄąČąĖą╝ą░ (RSTC_MR).

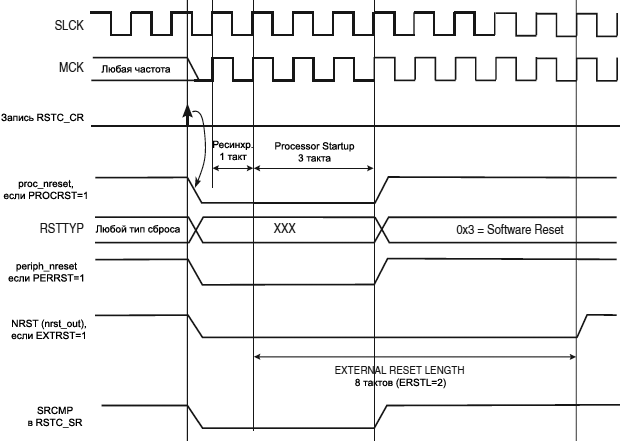

ą¤čĆąŠąĖčüčģąŠą┤ąĖčé ą▓čģąŠą┤ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ (Software Reset), ąĄčüą╗ąĖ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ąĖąĘ čŹčéąĖčģ ą▒ąĖčé ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ. ąÆčüąĄ čŹčéąĖ ą║ąŠą╝ą░ąĮą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ (ą┐ąŠ ąŠčéą┤ąĄą╗čīąĮąŠčüčéąĖ) ąĖą╗ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü ą┤ą╗ąĖčéčüčÅ 3 čéą░ą║čéą░ Slow Clock (SLCK).

ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ čüą▒čĆąŠčüą░ ą▓čŗčüčéą░ą▓ą╗čÅčÄčéčüčÅ, ą║ą░ą║ č鹊ą╗čīą║ąŠ ąŠčüčāčēąĄčüčéą▓ąĖą╗ą░čüčī ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ. ąŁč鹊 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąĮą░ ąŠčüąĮąŠą▓ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 (Master Clock, MCK). ąĪąĖą│ąĮą░ą╗čŗ čüą▒čĆąŠčüą░ čüąĮąĖą╝ą░čÄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓čŗčģąŠą┤ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░, čé. ąĄ. čüąĖąĮčģčĆąŠąĮąĮąŠ čü čüąĖą│ąĮą░ą╗ąŠą╝ ą╝ąĄą┤ą╗ąĄąĮąĮčŗčģ čéą░ą║č鹊ą▓ SLCK.

ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé EXTRST, č鹊 čüąĖą│ąĮą░ą╗ nrst_out ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┐ąŠą╗čÅ ERSTL. ą×ą┤ąĮą░ą║ąŠ čĆąĄąĘčāą╗čīčéąĖčĆčāčÄčēąĖą╣ čüą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ NRST ąĮąĄ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ User Reset.

ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ č鹊ą╗čīą║ąŠ ą▒ąĖčé PROCRST, č鹊 ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüą▒čĆąŠčüą░ čüąŠąŠą▒čēąĖčé ąŠ čüąŠčüč鹊čÅąĮąĖąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ą▓ ą┐ąŠą╗ąĄ RSTTYP čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ Status Register (RSTC_SR). ąöčĆčāą│ąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ Software Resets ąĮąĄ čüąŠąŠą▒čēą░čÄčéčüčÅ ą┐ąŠą╗ąĄą╝ RSTTYP.

ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▒čŗą╗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čģą░čĆą░ą║č鹥čĆ čüą▒čĆąŠčüą░, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé SRCMP (Software Reset Command in Progress) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ (RSTC_SR). ą×ąĮ ąŠčćąĖčüčéąĖčéčüčÅ ą║ą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą▓čŗčģąŠą┤ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░. ąØąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ ą┤čĆčāą│ąĖąĄ ą▓ąĖą┤čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░, ą┐ąŠą║ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé SRCMP, ąĖ ąĘą░ą┐ąĖčüčī ą╗čÄą▒ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆ RSTC_CR ąĮąĄ ą┤ą░čüčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ąĀąĖčü. 13-7. Software Reset.

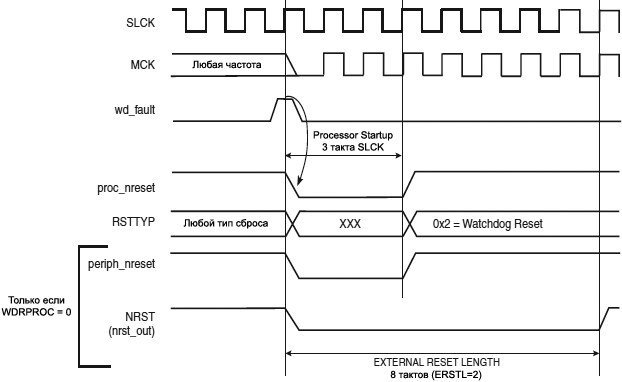

Watchdog Reset. ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą▓čģąŠą┤ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ čüą▒čĆąŠčüą░ Watchdog Reset, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▒čŗčéąĖąĄ ąŠčéą║ą░ąĘą░ ą¤ą×, ąŠą▒ąĮą░čĆčāąČąĄąĮąĮąŠąĄ čüč鹊čĆąŠąČąĄą▓čŗą╝ čéą░ą╣ą╝ąĄčĆąŠą╝ (watchdog fault). ąŁč鹊 čüąŠčüč鹊čÅąĮąĖąĄ ą┤ą╗ąĖčéčüčÅ 3 čéą░ą║čéą░ Slow Clock.

ąÆ čüąŠčüč鹊čÅąĮąĖąĖ Watchdog Reset ą░ą║čéąĖą▓ą░čåąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ čüą▒čĆąŠčüą░ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▒ąĖčéą░ WDRPROC ą▓ čĆąĄą│ąĖčüčéčĆąĄ WDT_MR:

ŌĆó ąĢčüą╗ąĖ WDRPROC = 0, č鹊 ą▒čāą┤čāčé ą▓čŗčüčéą░ą▓ą╗ąĄąĮčŗ čüąĖą│ąĮą░ą╗čŗ čüą▒čĆąŠčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (Processor Reset) ąĖ ą┐ąĄčĆąĖč乥čĆąĖąĖ (Peripheral Reset). ą¤ąŠčÅą▓ąĖčéčüčÅ čéą░ą║ąČąĄ čüąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ NRST, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠą╗čÅ ERSTL. ą×ą┤ąĮą░ą║ąŠ čĆąĄąĘčāą╗čīčéąĖčĆčāčÄčēąĖą╣ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ čüąĖą│ąĮą░ą╗ąĄ NRST ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüąŠčüč鹊čÅąĮąĖčÄ User Reset.

ŌĆó ąĢčüą╗ąĖ WDRPROC = 1, č鹊 ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮ č鹊ą╗čīą║ąŠ čüą▒čĆąŠčü ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ąĪč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ (Watchdog Timer [1]) čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ąŠą╝ proc_nreset. ą¤ąŠčüą║ąŠą╗čīą║čā čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (watchdog fault) ą▓čüąĄą│ą┤ą░ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ čüą▒čĆąŠčüčā ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé WDRSTEN, č鹊 čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ą▓čüąĄą│ą┤ą░ čüą▒čĆąŠčüąĖčéčüčÅ ą┐ąŠčüą╗ąĄ Watchdog Reset, ąĖ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą▒čāą┤ąĄčé čĆą░ąĘčĆąĄčłąĄąĮ čü ą▓čĆąĄą╝ąĄąĮąĄą╝ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ąĮą░ ą╝ą░ą║čüąĖą╝čāą╝.

ąÜąŠą│ą┤ą░ čüą▒čĆąŠčłąĄąĮ ą▒ąĖčé WDRSTEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ WDT_MR, čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (čüąŠą▒čŗčéąĖąĄ watchdog fault) ąĮąĖą║ą░ą║ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą║ąŠąĮčéčĆąŠą╗ąĄčĆ čüą▒čĆąŠčüą░.

ąĀąĖčü. 13-8. Watchdog Reset.

ą¤čĆąĖąŠčĆąĖč鹥čéčŗ čüąŠčüč鹊čÅąĮąĖą╣ čüą▒čĆąŠčüą░. Reset State Manager ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé čĆą░ąĘą╗ąĖčćąĮčŗąĄ ąĖčüč鹊čćąĮąĖą║ąĖ čüą▒čĆąŠčüą░ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐ąŠčĆčÅą┤ą║ąĄ ą┐čĆąĖąŠčĆąĖč鹥čéą░, ą┐čĆąĖąŠčĆąĖč鹥čé ą┐ąŠąĮąĖąČą░ąĄčéčüčÅ ąŠčé ąĮą░čćą░ą╗ą░ ą║ ą║ąŠąĮčåčā čüą┐ąĖčüą║ą░:

ŌĆó Power-up Reset (čüą▒čĆąŠčü ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ).

ŌĆó Brownout Reset (čüą▒čĆąŠčü ą┐čĆąĖ ą┐čĆąŠą┐ą░ą┤ą░ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ).

ŌĆó Watchdog Reset (čüą▒čĆąŠčü ąŠčé čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░).

ŌĆó Software Reset (ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü).

ŌĆó User Reset (ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ąĖą╣ čüą▒čĆąŠčü ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą╗ąŠą│. 0, ą┐ąŠą┤ą░ąĮąĮąŠą│ąŠ ąĮą░ ą▓čŗą▓ąŠą┤ NRST).

ąØąĖąČąĄ ąŠą┐ąĖčüą░ąĮčŗ čćą░čüčéąĮčŗąĄ čüą╗čāčćą░ąĖ:

ŌĆó ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé User Reset:

ŌĆō ąĪąŠą▒čŗčéąĖąĄ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ ąĮąĄ ą╝ąŠąČąĄčé ą▓ąŠąĘąĮąĖą║ąĮčāčéčī, ą┐ąŠč鹊ą╝čā čćč鹊 Watchdog Timer čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ąŠą╝ proc_nreset.

ŌĆō ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü ąĮąĄą▓ąŠąĘą╝ąŠąČąĄąĮ, ą┐ąŠč鹊ą╝čā čćč鹊 ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ą╗čüčÅ čüą▒čĆąŠčü ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ŌĆó ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé Software Reset:

ŌĆō ąĪąŠą▒čŗčéąĖąĄ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ ąĖą╝ąĄąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé ąĮą░ą┤ č鹥ą║čāčēąĖą╝ čüąŠčüč鹊čÅąĮąĖąĄą╝.

ŌĆō ąĪąĖą│ąĮą░ą╗ NRST ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ŌĆó ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé Watchdog Reset:

ŌĆō ąÉą║čéąĖą▓ąĄąĮ čüą▒čĆąŠčü ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą┐ąŠčŹč鹊ą╝čā ąĮąĄą╗čīąĘčÅ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī Software Reset.

ŌĆō ąØąĄą╗čīąĘčÅ ą▓ąŠą╣čéąĖ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ User Reset.

ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čüą▒čĆąŠčüą░. ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ (RSTC_SR) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĖąĮč乊čĆą╝ą░čåąĖąŠąĮąĮčŗčģ ą▒ąĖčé ąĖ ą▒ąĖč鹊ą▓čŗčģ ą┐ąŠą╗ąĄą╣ čüčéą░čéčāčüą░:

RSTTYP. ąŁč鹊 ą┐ąŠą╗ąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čéąĖą┐ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čüą▒čĆąŠčüą░, ą║ą░ą║ čŹč鹊 ą▒čŗą╗ąŠ ąŠą▒čŖčÅčüąĮąĄąĮąŠ čĆą░ąĮąĄąĄ.

SRCMP. ąŁč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ (Software Reset Command), ąĖ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą┐čĆąĄą┤ą┐čĆąĖąĮąĖą╝ą░čéčīčüčÅ ą┤čĆčāą│ąĖąĄ ą┐ąŠą┐čŗčéą║ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░, ą┐ąŠą║ą░ ąĮąĄ ąĘą░ą║ąŠąĮčćąĖčéčüčÅ č鹥ą║čāčēąĖą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü. ąæąĖčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą▒čĆąŠčüąĖčéčüčÅ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ č鹥ą║čāčēąĄą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░.

NRSTL. ąŁč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ NRST, ą║ąŠč鹊čĆčŗą╣ ąŠčåąĄąĮąĖą▓ą░ąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ čäčĆąŠąĮč鹥 čéą░ą║č鹊ą▓ MCK (Master Clock, ąŠčüąĮąŠą▓ąĮą░čÅ čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆą░).

URSTS. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐čĆąĖ ą┐ąĄčĆąĄčģąŠą┤ąĄ čāčĆąŠą▓ąĮčÅ ąŠčé ą╗ąŠą│. 1 ą║ ą╗ąŠą│. 0 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ NRST. ąŁč鹊čé ą┐ąĄčĆąĄčģąŠą┤ čéą░ą║ąČąĄ ą┤ąĄč鹥ą║čéąĖčĆčāąĄčéčüčÅ ąĮą░ čćą░čüč鹊č鹥 ąŠčüąĮąŠą▓ąĮčŗčģ čéą░ą║č鹊ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ MCK (čüą╝. čĆąĖčü. 13-9). ąĢčüą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮ User Reset (URSTEN = 0), ąĖ ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ URSTIEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSTC_MR, č鹊 ą▒ąĖčé URSTS ą▓čŗąĘąŠą▓ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ą¦č鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ RSTC_SR čüą▒čĆąŠčüąĖčé ą▒ąĖčé URSTS ąĖ ąŠčćąĖčüčéąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

BODSTS. ąŁč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠą▒čŗčéąĖąĄ brownout detection, ą║ąŠą│ą┤ą░ brownout reset ąĘą░ą┐čĆąĄčēąĄąĮ (bod_rst_en = 0). ąŁč鹊 ą▓čŗąĘąŠą▓ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ BODIEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSTC_MR. ą¦č鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ RSTC_SR čüą▒čĆąŠčüąĖčé ą▒ąĖčé BODSTS ąĖ ąŠčćąĖčüčéąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

ąĀąĖčü. 13-9. ąĪčéą░čéčāčü ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čüą▒čĆąŠčüą░ ąĖ čüčéą░čéčāčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

[ąĀąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čüą▒čĆąŠčüą░]

ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ WDT čüąŠčüčéą░ą▓ą╗čÅčÄčé čéčĆąĖ 32-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗąĄ ą▓ čéą░ą▒ą╗ąĖčåąĄ 13-1. ąÆ čüč鹊ą╗ą▒čåąĄ "ąĪą╝ąĄčēąĄąĮąĖąĄ" čāą║ą░ąĘą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ AT91C_BASE_RSTC (0xFFFFFD00).

ąóą░ą▒ą╗ąĖčåą░ 13-1. ąÜą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čüą▒čĆąŠčüą░ RSTC.

| ąĪą╝ąĄčēąĄąĮąĖąĄ |

ąĀąĄą│ąĖčüčéčĆ |

ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

ąöąŠčüčéčāą┐(1) |

ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ |

| 0x00 |

Control Register (čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ) |

RSTC_CR |

WO |

- |

| 0x04 |

Status Register (čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ) |

RSTC_SR |

RO |

0x00000000

|

| 0x08 |

Mode Register (čĆąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░) |

RSTC_MR |

RW |

0x00000000 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): WO ąŠąĘąĮą░čćą░ąĄčé č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüčī (Write Only), RW ąŠąĘąĮą░čćą░ąĄčé čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī (Read Write), RO ąŠąĘąĮą░čćą░ąĄčé č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ (Read Only).

Reset Controller Control Register (RSTC_CR)

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| KEY |

- |

- |

- |

- |

- |

- |

-

|

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

EXTRST |

PERRST |

- |

PROCRST |

PROCRST: Processor Reset

0 ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 ąĄčüą╗ąĖ KEY ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╣, č鹊 ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ ą┐čĆąŠčåąĄčüčüąŠčĆ.

PERRST: Peripheral Reset

0 ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 ąĄčüą╗ąĖ KEY ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╣, č鹊 ą▒čāą┤čāčé čüą▒čĆąŠčłąĄąĮčŗ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░.

EXTRST: External Reset

0 ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 ąĄčüą╗ąĖ KEY ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╣, č鹊 ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮ ąĖą╝ą┐čāą╗čīčü ą╗ąŠą│. 0 (čüąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░ ą▓ąĮąĄčłąĮąĖčģ čāčüčéčĆąŠą╣čüčéą▓) ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ą║ąŠčĆą┐čāčüą░ NRST.

KEY: Password

ąĪą┐ąĄčåąĖą░ą╗čīąĮąŠąĄ ąĘą░čēąĖčéąĮąŠąĄ ą┐ąŠą╗ąĄ, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮąŠąĄ ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ čüą╗čāčćą░ą╣ąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ąĮą░ ąĘą░ą┐ąĖčüčī ą║ čĆąĄą│ąĖčüčéčĆčā RSTC_CR. ąÆ ą┐ąŠą╗ąĄ KEY ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ 0xA5. ąŚą░ą┐ąĖčüčī čüčÄą┤ą░ ą╗čÄą▒ąŠą│ąŠ ą┤čĆčāą│ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ąŠčéą╝ąĄąĮąĖčé ąŠą┐ąĄčĆą░čåąĖčÄ ąĘą░ą┐ąĖčüąĖ.

Reset Controller Status Register (RSTC_SR)

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

SRCMP |

NRSTL |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

RSTTYP |

- |

- |

- |

- |

- |

- |

BODSTS |

URSTS |

URSTS: User Reset Status

0 ąĮąĄ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ čāčĆąŠą▓ąĮčÅ 1 -> 0 ąĮą░ NRST čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ RSTC_SR.

1 ą▒čŗą╗ ąŠą▒ąĮą░čĆčāąČąĄąĮ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ą┐ąĄčĆąĄčģąŠą┤ čāčĆąŠą▓ąĮčÅ 1 -> 0 ąĮą░ NRST čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ RSTC_SR.

BODSTS: Brownout Detection Status

0 ąĮąĄ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ 1 -> 0 čüąĖą│ąĮą░ą╗ą░ brownout čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ RSTC_SR.

1 ą▒čŗą╗ ą┐ąĄčĆąĄčģąŠą┤ 1 -> 0 čüąĖą│ąĮą░ą╗ą░ brownout čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ RSTC_SR.

RSTTYP: Reset Type

ąŁč鹊 ą▒ąĖč鹊ą▓ąŠąĄ ą┐ąŠą╗ąĄ čüąŠąŠą▒čēą░ąĄčé ąŠ čéąĖą┐ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čüą▒čĆąŠčüą░. ą¦č鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ RSTC_SR ąĮąĄ čüą▒čĆą░čüčŗą▓ą░ąĄčé čŹč鹊 ą┐ąŠą╗ąĄ.

| RSTTYP |

ąóąĖą┐ čüą▒čĆąŠčüą░ |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ |

| 000 |

Power-up Reset |

ą¤čĆąŠąĖąĘąŠčłą╗ąŠ ąĮą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ VDDCORE. |

| 010 |

Watchdog Reset |

ą¤čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▒čŗčéąĖąĄ ąŠčéą║ą░ąĘą░ ą¤ą× (čüąŠą▒čŗčéąĖąĄ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░) |

| 011 |

Software Reset |

ąĪą▒čĆąŠčü ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą▓čŗąĘą▓ą░ąĮąĮčŗą╣ ą║ąŠą╝ą░ąĮą┤ąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. |

| 100 |

User Reset |

ąæčŗą╗ ąŠą▒ąĮą░čĆčāąČąĄąĮ čüą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ą║ąŠčĆą┐čāčüą░ NRST. |

| 101 |

Brownout Reset |

ą¤čĆąŠąĖąĘąŠčłąĄą╗ čüą▒čĆąŠčü ąĖąĘ-ąĘą░ ą┐čĆąŠčüą░ą┤ą║ąĖ ą┐ąĖčéą░ąĮąĖčÅ. |

NRSTL: NRST Pin Level

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĘą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮąĮąŠąĄ čü čćą░čüč鹊č鹊ą╣ MCK čüąŠčüč鹊čÅąĮąĖąĄ (ą╗ąŠą│. čāčĆąŠą▓ąĄąĮčī) ą▓čŗą▓ąŠą┤ą░ ą║ąŠčĆą┐čāčüą░ NRST.

SRCMP: Software Reset Command in Progress

0 ą▓ ąĮą░čüč鹊čÅčēąĄąĄ ą▓čĆąĄą╝čÅ ą║ąŠąĮčéčĆąŠą╗ąĄčĆ čüą▒čĆąŠčüą░ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą║ąŠą╝ą░ąĮą┤čā ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüą▒čĆąŠčüą░ ą│ąŠč鹊ą▓ ą║ ą┐čĆąĖąĄą╝čā ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ.

1 ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ čüą▒čĆąŠčüą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąŠą┤ąĮą░ ąĖąĘ ą║ąŠą╝ą░ąĮą┤ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░. ąÜąŠąĮčéčĆąŠą╗ąĄčĆ čüą▒čĆąŠčüą░ ąĘą░ąĮčÅčé.

Reset Controller Mode Register (RSTC_MR)

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| KEY |

- |

- |

- |

- |

- |

- |

-

|

BODIEN |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

ERSTL |

- |

- |

- |

URSTIEN |

- |

- |

- |

URSTEN |

URSTEN: User Reset Enable

0 ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ą║ąŠčĆą┐čāčüą░ NRST ąĮąĄ čüą│ąĄąĮąĄčĆąĖčĆčāąĄčé User Reset.

1 ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ą║ąŠčĆą┐čāčüą░ NRST čüą│ąĄąĮąĄčĆąĖčĆčāąĄčé User Reset.

URSTIEN: User Reset Interrupt Enable

0 ą▒ąĖčé USRTS ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSTC_SR, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ ą▓ 1, ąĮąĄ ąŠą║ą░ąČąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░ ąĮą░ čüąĖą│ąĮą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ rstc_irq.

1 ą▒ąĖčé USRTS ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSTC_SR, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ ą▓ 1, ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čāčüčéą░ąĮąŠą▓ą║ąĄ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ rstc_irq, ąĄčüą╗ąĖ URSTEN = 0.

BODIEN: Brownout Detection Interrupt Enable

0 ą▒ąĖčé BODSTS ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSTC_SR, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ ą▓ 1, ąĮąĄ ąŠą║ą░ąČąĄčé ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čüąĖą│ąĮą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ rstc_irq.

1 ą▒ąĖčé BODSTS ą▓ čĆąĄą│ąĖčüčéčĆąĄ RSTC_SR, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ ą▓ 1, ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čāčüčéą░ąĮąŠą▓ą║ąĄ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ rstc_irq.

ERSTL: External Reset Length

ąŁč鹊 ą┐ąŠą╗ąĄ ąĘą░ą┤ą░ąĄčé ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ą░ čüą▒čĆąŠčüą░ ą▓ąĮąĄčłąĮąĖčģ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ą║ąŠčĆą┐čāčüą░ NRST. ąÆčĆąĄą╝čÅ ąĖą╝ą┐čāą╗čīčüą░ čüą▒čĆąŠčüą░ (ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ąĖą╝ą┐čāą╗čīčüą░ ą╗ąŠą│. 0) čĆą░ą▓ąĮąŠ 2(ERSTL+1) čéą░ą║ąŠą▓ Slow Clock. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ą░ čüą▒čĆąŠčüą░ ą▓ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ ąŠčé 60 ╬╝s ą┤ąŠ 2 čüąĄą║čāąĮą┤.

KEY: Password

ąĪą┐ąĄčåąĖą░ą╗čīąĮąŠąĄ ąĘą░čēąĖčéąĮąŠąĄ ą┐ąŠą╗ąĄ, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮąŠąĄ ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ čüą╗čāčćą░ą╣ąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ąĮą░ ąĘą░ą┐ąĖčüčī. ąÆ ą┐ąŠą╗ąĄ KEY ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ 0xA5. ąŚą░ą┐ąĖčüčī čüčÄą┤ą░ ą╗čÄą▒ąŠą│ąŠ ą┤čĆčāą│ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ąŠčéą╝ąĄąĮąĖčé ąŠą┐ąĄčĆą░čåąĖčÄ ąĘą░ą┐ąĖčüąĖ.

[ąĪčüčŗą╗ą║ąĖ]

1. ąĪč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ AT91SAM7X.

2. ąĪč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ (WatchDog, WDT) ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ ARM AT91SAM7X. |