|

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (Embedded Flash Controller, EFC) ą▓čģąŠą┤ąĖčé ą║ą░ą║ čüąŠčüčéą░ą▓ąĮą░čÅ čćą░čüčéčī ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐ą░ą╝čÅčéąĖ (Memory Controller, MC [2]), ąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĖąĮč鹥čĆč乥ą╣čü ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ FLASH č湥čĆąĄąĘ 32-ą▒ąĖčéąĮčāčÄ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ čłąĖąĮčā. ąŁč鹊 čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ Thumb ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą║ąŠą┤ą░ čü čüąĖčüč鹥ą╝ąĮčŗą╝ąĖ 32-ą▒ąĖčéąĮčŗą╝ąĖ ą▒čāč乥čĆą░ą╝ąĖ. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ EFC čéą░ą║ąČąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐ąŠą╗ąĮčŗą╣ ąĮą░ą▒ąŠčĆ ą║ąŠą╝ą░ąĮą┤ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ, ąŠčćąĖčüčéą║ąĖ, ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ąĮą░ ąĘą░ą┐ąĖčüčī ąĖ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ą╗ąŠą║ąŠą▓ ą┐ą░ą╝čÅčéąĖ.

ą¤čĆąŠčåąĄčüčüąŠčĆ AT91SAM7X512 ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮ ą┤ą▓čāą╝čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ EFC: EFC0 ąĖ EFC1, ą║ą░ąČą┤čŗą╣ ąĖčģ ą║ąŠč鹊čĆčŗčģ ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé čüą▓ąŠčÄ ą┐ąŠą╗ąŠą▓ąĖąĮčā ą┐ą░ą╝čÅčéąĖ FLASH. ąŻ EFC1 ąĮąĄ ąĖą╝ąĄąĄčéčüčÅ čäčāąĮą║čåąĖąĖ ą▒ąĖč鹊ą▓ ąĘą░čēąĖčéčŗ (Security bit) ąĖ ą▒ąĖč鹊ą▓ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (GPNVM), ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [3]. ąæąĖčéčŗ Security ąĖ GPNVM ą▓čüčéčĆąŠąĄąĮčŗ č鹊ą╗čīą║ąŠ ą▓ EFC0, ąĖ ąŠąĮąĖ ąŠčéąĮąŠčüčÅčéčüčÅ ą║ ą┤ą▓čāą╝ ą▒ą╗ąŠą║ą░ą╝ ą┐ą░ą╝čÅčéąĖ AT91SAM7X512.

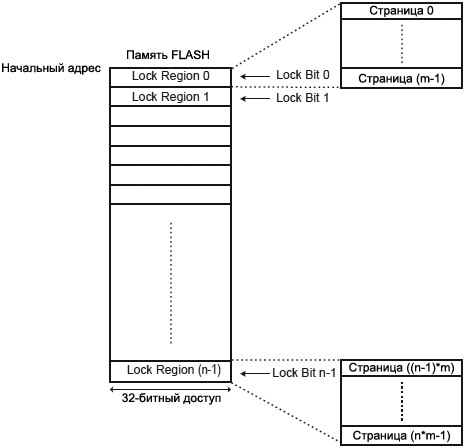

[ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ FLASH]

ąÜ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ FLASH ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐čĆčÅą╝ąŠą╣ ą┤ąŠčüčéčāą┐ č湥čĆąĄąĘ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ 32-ą▒ąĖčéąĮčāčÄ čłąĖąĮčā. ąöąŠčüčéčāą┐ čüąŠčüčéą░ą▓ą╗ąĄąĮ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓:

ŌĆó ą×ą┤ąĖąĮ ą▒ą╗ąŠą║ ą┐ą░ą╝čÅčéąĖ (memory plane) ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮąĮčŗą╣ ą▓ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čüčéčĆą░ąĮąĖčåą░čģ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ čĆą░ąĘą╝ąĄčĆą░.

ŌĆó ąöą▓ą░ 32-ą▒ąĖčéąĮčŗčģ ą▒čāč乥čĆą░ čćč鹥ąĮąĖčÅ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą┤ą╗čÅ ąŠą┐čéąĖą╝ąĖąĘą░čåąĖąĖ čćč鹥ąĮąĖčÅ ą║ąŠą┤ą░ (čüą╝. čüąĄą║čåąĖčÄ "ą×ą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ").

ŌĆó ą×ą┤ąĖąĮ ą▒čāč乥čĆ ąĘą░ą┐ąĖčüąĖ, ąŠą▒čüą╗čāąČąĖą▓ą░čÄčēąĖą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ FLASH. ąĀą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ ąĘą░ą┐ąĖčüąĖ čĆą░ą▓ąĄąĮ čĆą░ąĘą╝ąĄčĆčā čüčéčĆą░ąĮąĖčåčŗ. ąÜ čŹč鹊ą╝čā ą▒čāč乥čĆčā ą▓ąŠąĘą╝ąŠąČąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī, ąĖ ąŠąĮ ą┤ąŠčüčéčāą┐ąĄąĮ ą▓ąŠ ą▓čüąĄą╝ ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ 1 ą╝ąĄą│ą░ą▒ą░ą╣čé, čéą░ą║ čćč鹊 ą║ą░ąČą┤ąŠąĄ čüą╗ąŠą▓ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ ą┐ąŠ čüą▓ąŠąĄą╝čā ą║ąŠąĮąĄčćąĮąŠą╝čā ą░ą┤čĆąĄčüčā (čüą╝. čüąĄą║čåąĖčÄ "ą×ą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ").

ŌĆó ąØąĄčüą║ąŠą╗čīą║ąŠ ą▒ąĖč鹊ą▓ ąĘą░čēąĖčéčŗ, ąĖą╗ąĖ ą▒ąĖč鹊ą▓ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (lock bits) ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąĘą░čēąĖčéčŗ ąŠčé ąŠą┐ąĄčĆą░čåąĖą╣ ąĘą░ą┐ąĖčüąĖ ąĖ ąŠčćąĖčüčéą║ąĖ ąĮą░ čĆąĄą│ąĖąŠąĮą░čģ ą┐ą░ą╝čÅčéąĖ, ą│ą┤ąĄ čŹčéąĖ ą▒ąĖčéčŗ ąĘą░čēąĖčéčŗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ. ąŚą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čĆąĄą│ąĖąŠąĮ čüąŠčüč鹊ąĖčé ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ąĮą░čģąŠą┤čÅčēąĖčģčüčÅ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ čüčéčĆą░ąĮąĖčå, ąĖ ą║ą░ąČą┤čŗą╣ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čĆąĄą│ąĖąŠąĮ ąĖą╝ąĄąĄčé čüą▓ąŠą╣ čüą▓ąŠą╣ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣, čüą▓čÅąĘą░ąĮąĮčŗą╣ čü ąĮąĖą╝ ą▒ąĖčé ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ.

ŌĆó ąØąĄčüą║ąŠą╗čīą║ąŠ 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą▒ąĖčé ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (general-purpose NVM bits, čüąŠą║čĆą░čēąĄąĮąĮąŠ GPNVM). ąÜą░ąČą┤čŗą╣ ąĖčģ čŹčéąĖčģ ą▒ąĖčé čāą┐čĆą░ą▓ą╗čÅąĄčé ąĮąĄą║ąŠč鹊čĆąŠą╣ čäčāąĮą║čåąĖąĄą╣ čćąĖą┐ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čĆą░ąĘą┤ąĄą╗, ą┐ąŠčüą▓čÅčēąĄąĮąĮčŗą╣ ąĮą░ąĘąĮą░č湥ąĮąĖčÄ GPNVM [3].

ą×ą▒čēąĖą╣ čĆą░ąĘą╝ąĄčĆ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ FLASH, čĆą░ąĘą╝ąĄčĆ ąĄčæ čüčéčĆą░ąĮąĖčåčŗ, ąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čĆąĄą│ąĖąŠąĮąŠą▓ ą┐ą░ą╝čÅčéąĖ FLASH ąŠą┐ąĖčüą░ąĮą░ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ARM7.

ąóą░ą▒ą╗ąĖčåą░ 19-1. ąĪą║ąŠą╗čīą║ąŠ ą▒ąĖčé ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (lock bits) ąĖ ą▒ąĖčé ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (GPNVM bits) ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ čüąĄčĆąĖąĖ AT91SAM7X.

| ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé |

AT91SAM7X128 |

AT91SAM7X256 |

AT91SAM7X512 |

| ąĪą║ąŠą╗čīą║ąŠ ą▒ąĖčé GPNVM |

3 |

| ąĪą║ąŠą╗čīą║ąŠ ą▒ąĖčé ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ |

8 |

16 |

32 |

ąĀąĖčü. 19-1. ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ FLASH.

[ą×ą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ]

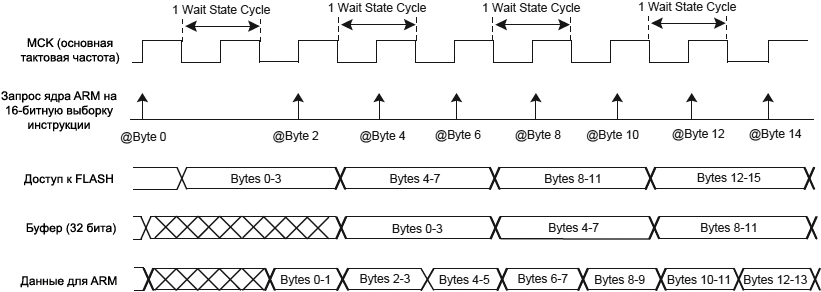

ą×ą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐čĆąŠčåąĄčüčüąŠą╝ čćč鹥ąĮąĖčÅ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐ą░ą╝čÅčéąĖ FLASH. ąĪąĖčüč鹥ą╝ą░ ąĖąĘ 2 x 32-ą▒ąĖčéąĮčŗčģ ą▒čāč乥čĆą░ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮą░ ą▓ ą┐ąŠčĆčÅą┤ą║ąĄ ąĮą░čćą░ą╗ą░ ą┤ąŠčüčéčāą┐ą░ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą░ą┤čĆąĄčüčā ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓č鹊čĆąŠą│ąŠ čćč鹥ąĮąĖčÅ, čćč鹊 čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą║ąŠą│ą┤ą░ ąŠąĮ čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ Thumb (16-ą▒ąĖčéąĮčŗąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ). ąĪą╝. čĆąĖčü. 19-2, 19-3 ąĖ 19-4.

ąŁčéą░ ąŠą┐čéąĖą╝ąĖąĘą░čåąĖčÅ ą║ą░čüą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓čŗą▒ąŠčĆą║ąĖ ą║ąŠą┤ą░, ąĮąŠ ąĮąĄ ąŠą▒čĆą░čēąĄąĮąĖčÅ ą║ ą┤ą░ąĮąĮčŗą╝.

ą×ą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ ą║ą░ą║ čü ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄą╝ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ (wait state), čéą░ą║ ąĖ ą▒ąĄąĘ ąĮąĖčģ. ą£ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą┤ąŠ 3 wait state čü ą┐ąŠą╝ąŠčēčīčÄ ą┐ąŠą╗čÅ FWS (Flash Wait State) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čĆąĄąČąĖą╝ą░ FLASH (Flash Mode Register, MC_FMR), čüą╝. čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēčāčÄ ą▓čĆąĄąĘą║čā ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąśąĮč鹥čĆč乥ą╣čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ EFC". ąĢčüą╗ąĖ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī FWS ą║ą░ą║ 0, č鹊 čŹč鹊 čĆą░ąĘčĆąĄčłą░ąĄčé ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ FLASH ąĘą░ 1 čéą░ą║čé čÅą┤čĆą░, ą▒ąĄąĘ ą┐čĆąŠą┐čāčüą║ą░ ąĮą░ čéą░ą║čéčŗ ąŠąČąĖą┤ą░ąĮąĖčÅ.

ąÜ ą┐ą░ą╝čÅčéąĖ FLASH ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ č湥čĆąĄąĘ 8-, 16- ąĖ 32-ą▒ąĖčéąĮčŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ.

ą¤ąŠčüą║ąŠą╗čīą║čā čĆą░ąĘą╝ąĄčĆ ą▒ą╗ąŠą║ą░ ą┐ą░ą╝čÅčéąĖ FLASH ą╝ąĄąĮčīčłąĄ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░, ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┐ąŠą┤ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī, ą┤ąŠčüčéčāą┐ ą║ FLASH ą┐čĆąĖ ą▓čŗčģąŠą┤ąĄ ąĘą░ ąĄčæ ą│čĆą░ąĮąĖčåčŗ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čü čåąĖą║ą╗ąĖč湥čüą║ąĖą╝ ą▓ąŠąĘą▓čĆą░č鹊ą╝ ą▓ ąĮą░čćą░ą╗ąŠ ąŠą▒ą╗ą░čüčéąĖ FLASH.

ąĀąĖčü. 19-2. ą×ą┐čéąĖą╝ąĖąĘą░čåąĖčÅ čćč鹥ąĮąĖčÅ ą║ąŠą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą▓ čĆąĄąČąĖą╝ąĄ Thumb ą┤ą╗čÅ FWS=0.

ąĀąĖčü. 19-3. ą×ą┐čéąĖą╝ąĖąĘą░čåąĖčÅ čćč鹥ąĮąĖčÅ ą║ąŠą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą▓ čĆąĄąČąĖą╝ąĄ Thumb ą┤ą╗čÅ FWS=1.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ FWS = 1 ą▓ čüą╗čāčćą░ąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čćč鹥ąĮąĖą╣ ą▓čüąĄ ą┤ąŠčüčéčāą┐čŗ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ąĘą░ ąŠą┤ąĖąĮ čéą░ą║čé (ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĄčĆą▓ąŠą│ąŠ čćč鹥ąĮąĖčÅ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ).

ąĀąĖčü. 19-4. ą×ą┐čéąĖą╝ąĖąĘą░čåąĖčÅ čćč鹥ąĮąĖčÅ ą║ąŠą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą▓ čĆąĄąČąĖą╝ąĄ Thumb ą┤ą╗čÅ FWS=3.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ FWS = 2 ąĖą╗ąĖ 3 ą▓ čüą╗čāčćą░ąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čćč鹥ąĮąĖą╣ ą┐ąĄčĆą▓čŗą╣ ą┤ąŠčüčéčāą┐ ą┐ąŠą╗čāčćą░ąĄčé FWS čéą░ą║č鹊ą▓ ąĘą░ą┤ąĄčƹȹ║ąĖ, ą▓č鹊čĆąŠą╣ ą┤ąŠčüčéčāą┐ ąĘą░ąĮąĖą╝ą░ąĄčé ąŠą┤ąĖąĮ čéą░ą║čé, čéčĆąĄčéąĖą╣ ąĘą░ąĮąĖą╝ą░ąĄčé FWS čéą░ą║č鹊ą▓, č湥čéą▓ąĄčĆčéčŗą╣ 1 čéą░ą║čé ąĖ čé. ą┤.

[ą×ą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ]

ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ, ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮą░čÅ ą┤ą╗čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ FLASH, čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮą░ č湥čĆąĄąĘ ą▒čāč乥čĆ ąĘą░čēąĄą╗ą║ąĖ, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ. ą×ą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ čāčćąĖčéčŗą▓ą░čÄčé č鹊ą╗čīą║ąŠ 8 ą╝ą╗ą░ą┤čłąĖčģ ą▒ąĖčé ą░ą┤čĆąĄčüą░, ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą┐čĆąĖ ą▓čŗčģąŠą┤ąĄ ą░ą┤čĆąĄčüą░ ąĘą░ ą┐čĆąĄą┤ąĄą╗čŗ ąŠą▒ą╗ą░čüčéąĖ, ąŠą│čĆą░ąĮąĖč湥ąĮąĮąŠą╣ čŹčéąĖą╝ąĖ 8 ą▒ąĖčéą░ą╝ąĖ, ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čåąĖą║ą╗ąĖč湥čüą║ąĖą╣ ą┐ąĄčĆąĄčģąŠą┤ ąĮą░ ąĮą░čćą░ą╗ąŠ, čćč鹊 ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ 1024 čĆą░ąĘą░ ą┐ąŠ ą▓čüąĄą╝čā ą░ą┤čĆąĄčüąĮąŠą╝čā ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓čā ą▒ą╗ąŠą║ą░ FLASH-ą┐ą░ą╝čÅčéąĖ.

ą×ą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮčŗ ą┐čāč鹥ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ą╗ąŠą║ą░ ąĘą░čēąĖčéčŗ ą┐ą░ą╝čÅčéąĖ (Memory Protection Unit) ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ąŚą░ą┐ąĖčüčī 8-ą▒ąĖčéąĮčŗčģ ąĖ 16-ą▒ąĖčéąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ąŠ FLASH-ą┐ą░ą╝čÅčéčī ąĮąĄ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ, ąĖ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÄ ą┤ą░ąĮąĮčŗčģ.

ą×ą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ąĘą░ ą▓čĆąĄą╝čÅ ą▓ ą║ąŠą╗ąĖč湥čüčéą▓ą░čģ čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ, čĆą░ą▓ąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓čā čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ + 1, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ FWS = 3 (čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ čĆąĄąČąĖą╝ą░ FLASH MC_FMR ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ą▓čĆąĄąĘą║ąĄ).

[ąÜąŠą╝ą░ąĮą┤čŗ FLASH]

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ EFC ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĮą░ą▒ąŠčĆ ą║ąŠą╝ą░ąĮą┤ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą┐ą░ą╝čÅčéąĖ FLASH, ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąŠą╣ ąĖ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąŠą╣ čüąĄą║č鹊čĆąŠą▓, ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąŠą╣, ąĖ ą┐ąŠą╗ąĮąŠą╣ ąŠčćąĖčüčéą║ąŠą╣ FLASH.

ąÜąŠą╝ą░ąĮą┤ą░

|

ąŚąĮą░č湥ąĮąĖąĄ |

ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

| Write page (ąĘą░ą┐ąĖčüčī čüčéčĆą░ąĮąĖčåčŗ) |

0x01 |

WP |

| Set Lock Bit (čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ) |

0x02 |

SLB |

| Write Page and Lock (ąĘą░ą┐ąĖčüčī čüčéčĆą░ąĮąĖčåčŗ ąĖ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ą░) |

0x03 |

WPL |

| Clear Lock Bit (ąŠčćąĖčüčéą║ą░ ą▒ąĖčéą░ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ) |

0x04 |

CLB |

| Erase all (čüč鹥čĆąĄčéčī ą▓čüčÄ FLASH) |

0x08 |

EA |

| Set General-purpose NVM Bit (čāčüčéą░ąĮąŠą▓ąĖčéčī 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ ą▒ąĖčé ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ) |

0x0B |

SGPB |

| Clear General-purpose NVM Bit (čüą▒čĆąŠčüąĖčéčī 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ ą▒ąĖčé ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ) |

0x0D |

CGPB |

| Set Security Bit (čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčé ąĘą░čēąĖčéčŗ) |

0x0F |

SSB |

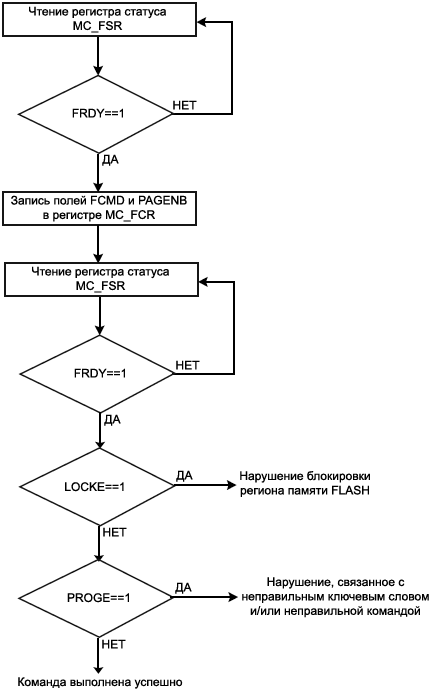

ą¦č鹊ą▒čŗ ąĘą░ą┐čāčüčéąĖčéčī ąŠą┤ąĮčā ąĖąĘ čŹčéąĖčģ ą║ąŠą╝ą░ąĮą┤, ą▓ ą┐ąŠą╗ąĄ FCMD čĆąĄą│ąĖčüčéčĆą░ MC_FCR ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ąĮąŠą╝ąĄčĆ ą║ąŠą╝ą░ąĮą┤čŗ. ąÜą░ą║ č鹊ą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆ MC_FCR ąĘą░ą┐ąĖčüą░ąĮ, čäą╗ą░ą│ FRDY ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ. ąÜą░ą║ č鹊ą╗čīą║ąŠ č鹥ą║čāčēą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮą░, čäą╗ą░ą│ FRDY ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ. ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FMR, č鹊 ą░ą║čéąĖą▓ąĖąĘąĖčĆčāąĄčéčüčÅ ą╗ąĖąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐ą░ą╝čÅčéąĖ (Memory Controller, MC [2]).

ąÆčüąĄ ą║ąŠą╝ą░ąĮą┤čŗ ąĘą░čēąĖčēąĄąĮčŗ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ ą║ą╗čÄč湥ą▓čŗą╝ čüą╗ąŠą▓ąŠą╝ (ą║ą╗čÄčć), ą║ąŠč鹊čĆąŠąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ 8 čüčéą░čĆčłąĖčģ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ MC_FCR.

ąŚą░ą┐ąĖčüčī MC_FCR ą┤ą░ąĮąĮčŗą╝ąĖ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ čüąŠą┤ąĄčƹȹ░čé ą║ąŠčĆčĆąĄą║čéąĮąŠą│ąŠ ą║ą╗čÄčćą░ ąĖ/ąĖą╗ąĖ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ, ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░čÄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░ ąĖ ąĮąĄ ą▓ą╗ąĖčÅčÄčé ąĮą░ ą┐ą╗ąŠčüą║ąŠčüčéčī ą┐ą░ą╝čÅčéąĖ FLASH; ąŠą┤ąĮą░ą║ąŠ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ PROGE ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FSR. ąŁč鹊čé čäą╗ą░ą│ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ MC_FSR.

ąÜąŠą│ą┤ą░ č鹥ą║čāčēą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ąĖą╗ąĖ ąŠčćąĖčēą░ąĄčé čüčéčĆą░ąĮąĖčåčā ą▓ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮąŠą╝ čĆąĄą│ąĖąŠąĮąĄ, ą║ąŠą╝ą░ąĮą┤ą░ ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ ą┐ą░ą╝čÅčéčī FLASH; ąŠą┤ąĮą░ą║ąŠ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé LOCKE ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FSR. ąŁč鹊čé čäą╗ą░ą│ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčüčéąĖčéčüčÅ ą┐čĆąĖ čćč鹥ąĮąĖąĖ čĆąĄą│ąĖčüčéčĆą░ MC_FSR.

ąĀąĖčü. 19-5. ąÉą╗ą│ąŠčĆąĖčéą╝ ąĘą░ą┐čāčüą║ą░ ą║ąŠą╝ą░ąĮą┤čŗ FLASH.

ą¦č鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą┤ąŠą┐čāčüčéąĖą╝čŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ čü ą┐ą░ą╝čÅčéčīčÄ FLASH, ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą║ąŠčĆčĆąĄą║čéąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą┐ąŠą╗ąĄ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą╝ąĖą║čĆąŠčüąĄą║čāąĮą┤ąĮčŗčģ čåąĖą║ą╗ąŠą▓ (Flash Microsecond Cycle Number, FMCN) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čĆąĄąČąĖą╝ą░ FLASH (Flash Mode Register, MC_FMR). ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ą▓čĆąĄąĘą║čā čü ąŠą┐ąĖčüą░ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ MC_FMR.

[ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ FLASH]

ą¤ą░ą╝čÅčéčī FLASH ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ čüčéčĆą░ąĮąĖčåą░ą╝ąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐ąŠą╝ąĄąĮčÅčéčī č鹊ą╗čīą║ąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ą░ą╣čé ąĮą░ čüčéčĆą░ąĮąĖčåąĄ, č鹊 ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ąĮčāąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī ą▓čüčÄ čüčéčĆą░ąĮąĖčåčā čåąĄą╗ąĖą║ąŠą╝ ą▓ąŠ ą▓čĆąĄą╝ąĄąĮąĮčŗą╣ ą▒čāč乥čĆ, ąĘą░ą╝ąĄąĮąĖčéčī ą▓ čŹč鹊ą╝ ą▒čāč乥čĆąĄ ąĮčāąČąĮčŗąĄ ą▒ą░ą╣čéčŗ, ąĖ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ąŠčćąĖčüčéąĖčéčī ąĮčāąČąĮčāčÄ čüčéčĆą░ąĮąĖčåčā ąĖ ąĘą░ą┐ąĖčüą░čéčī ąĄčæ. ąöą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ FLASH ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą║ąŠą╝ą░ąĮą┤.

ąóąĄčģąĮąŠą╗ąŠą│ąĖčÅ FLASH čéčĆąĄą▒čāąĄčé, čćč鹊ą▒čŗ ą┐ąĄčĆąĄą┤ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą▒čŗą╗ą░ ą┐čĆąŠąĖąĘą▓ąĄą┤ąĄąĮą░ ąŠčćąĖčüčéą║ą░ - ą╗ąĖą▒ąŠ ą▓čüąĄą╣ ą┐ą░ą╝čÅčéąĖ FLASH, ą╗ąĖą▒ąŠ ąŠą┤ąĮąŠą╣ čüčéčĆą░ąĮąĖčåčŗ, ą║ąŠč鹊čĆą░čÅ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮą░. ąŚą░ ąŠą┤ąĖąĮ čĆą░ąĘ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮą░ ą▓čüčÅ ą┐ą░ą╝čÅčéčī, ą╗ąĖą▒ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēąĄąĮą░ ąŠą┤ąĮą░ čüčéčĆą░ąĮąĖčåą░ ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ NEBP ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FMR ą┐ąĄčĆąĄą┤ ąĘą░ą┐ąĖčüčīčÄ ą║ąŠą╝ą░ąĮą┤čŗ ą▓ čĆąĄą│ąĖčüčéčĆ MC_FCR.

ą¤čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ NEBP ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FMR čüčéčĆą░ąĮąĖčåą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ąĘą░ ąĮąĄčüą║ąŠą╗čīą║ąŠ čłą░ą│ąŠą▓, ąĄčüą╗ąĖ ąŠąĮą░ ą▒čŗą╗ą░ ą┐ąĄčĆąĄą┤ čŹčéąĖą╝ ąŠčćąĖčēąĄąĮą░ (čüą╝. čĆąĖčü. 19-6).

ąĀąĖčü. 19-6. ą¤čĆąĖą╝ąĄčĆ čćą░čüčéąĖčćąĮąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüčéčĆą░ąĮąĖčåčŗ FLASH.

ąĀąĄąČąĖą╝ čćą░čüčéąĖčćąĮąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ (Partial Programming) čĆą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ čü 32-ą▒ąĖčéąĮčŗą╝ąĖ (ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄą╣ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ) ą│čĆą░ąĮąĖčåą░ą╝ąĖ. ą×ąĮ ąĮąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čü čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčīčÄ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ ą╝ąĄąĮčīčłąĄ 32 ą▒ąĖčéą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, 8 ąĖą╗ąĖ 16 ą▒ąĖčé).

ą¤ąŠčüą╗ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüčéčĆą░ąĮąĖčåą░ (ą▓ąĄčüčī ą▒ą╗ąŠą║ąĖčĆčāąĄą╝čŗą╣ čĆąĄą│ąĖąŠąĮ) ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮą░ ąĮą░ ąĘą░ą┐ąĖčüčī, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ ąĖą╗ąĖ ąŠčćąĖčüčéą║ąĖ. ąæąĖčé ąĘą░čēąĖčéčŗ ą╝ąŠąČąĄčé ą▒čŗčéčī ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┐ąŠčüą╗ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ąŠą╝ą░ąĮą┤čā ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüčéčĆą░ąĮąĖčåčŗ WPL.

ąŚą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝ ą▒čāč乥čĆąĄ-ąĘą░čēąĄą╗ą║ąĄ. ąĀą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░-ąĘą░čēąĄą╗ą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čĆą░ąĘą╝ąĄčĆčā čüčéčĆą░ąĮąĖčåčŗ FLASH. ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▒čāč乥čĆą░-ąĘą░čēąĄą╗ą║ąĖ čåąĖą║ą╗ąĖč湥čüą║ąĖ ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ ą▓ ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ ą┐čĆąĖ ą┐ąĄčĆąĄčüąĄč湥ąĮąĖąĖ ą░ą┤čĆąĄčüą░ č湥čĆąĄąĘ ą│čĆą░ąĮąĖčåčā čüčéčĆą░ąĮąĖčåčŗ FLASH, ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąŠą▓č鹊čĆąŠą▓ čĆą░ą▓ąĮąŠ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čüčéčĆą░ąĮąĖčå ą▓ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ FLASH.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĘą░ą┐ąĖčüčī 8- ąĖ 16-ą▒ąĖčéąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ. ąóą░ą║ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ čü ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝ąŠą╝čā ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÄ ą┤ą░ąĮąĮčŗčģ.

ąöą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ ą▒čāč乥čĆ-ąĘą░čēąĄą╗ą║ąĖ ą┐ąĄčĆąĄą┤ ąĘą░ą┐ąĖčüčīčÄ ą║ąŠą╝ą░ąĮą┤čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ (Flash Command Register, MC_FCR). ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą░ą╗ą│ąŠčĆąĖčéą╝ą░ čüą╗ąĄą┤čāčÄčēą░čÅ:

ŌĆó ąŚą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓čüčÅ čüčéčĆą░ąĮąĖčåą░ ą┐ą░ą╝čÅčéąĖ FLASH ą┐ąŠą╗ąĮąŠčüčéčīčÄ, ą┐ąŠ ą╗čÄą▒ąŠą╝čā ą░ą┤čĆąĄčüčā čüčéčĆą░ąĮąĖčåčŗ, ąĮą░čģąŠą┤čÅčēąĄą╝čāčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ FLASH, čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ 32-ą▒ąĖčéąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░. ą¤čĆąĖ čŹč鹊ą╝ ą▓ čĆąĄą░ą╗čīąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą▒čāč乥čĆ-ąĘą░čēąĄą╗ą║čā.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĘą░ą┐čāčüčéąĖčéčüčÅ, ą║ą░ą║ č鹊ą╗čīą║ąŠ ąĮąŠą╝ąĄčĆ čüčéčĆą░ąĮąĖčåčŗ ąĖ ą║ąŠą╝ą░ąĮą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ MC_FCR. ą¤čĆąĖ čŹč鹊ą╝ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčüčéąĖčéčüčÅ ą▒ąĖčé FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ FLASH (Flash Programming Status Register, MC_FSR).

ŌĆó ąÜąŠą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąŠ, ą▒ąĖčé FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ FLASH (MC_FSR) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ. ąĢčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FMR, č鹊 ą▒čāą┤ąĄčé ą░ą║čéąĖą▓ąĖąĘąĖčĆąŠą▓ą░ąĮą░ ą╗ąĖąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐ą░ą╝čÅčéąĖ MC [2].

ą£ąŠą│čāčé ą▒čŗčéčī ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮčŗ 2 ąŠčłąĖą▒ą║ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FSR ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ:

ŌĆó Programming Error (ąŠčłąĖą▒ą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ): ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ MC_FCR ą▒čŗą╗ąŠ ąĘą░ą┐ąĖčüą░ąĮąŠ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ ą║ą╗čÄč湥ą▓ąŠąĄ čüą╗ąŠą▓ąŠ ąĖą╗ąĖ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝ą░čÅ ą║ąŠą╝ą░ąĮą┤ą░.

ŌĆó Lock Error (ąŠčłąĖą▒ą║ą░, čüą▓čÅąĘą░ąĮąĮą░čÅ čü ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąŠą╣): ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ čüčéčĆą░ąĮąĖčåą░ ą┐ą░ą╝čÅčéąĖ ą┐čĆąĖąĮą░ą┤ą╗ąĄąČąĖčé ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮąŠą╝čā čĆąĄą│ąĖąŠąĮčā FLASH. ą¤ąĄčĆąĄą┤ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ ą┤ą╗čÅ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĖčÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖąŠąĮą░.

[ąÜąŠą╝ą░ąĮą┤ą░ Erase All]

ąÆčüčÅ ą┐ą░ą╝čÅčéčī ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮą░ ą║ąŠą╝ą░ąĮą┤ąŠą╣ Erase All (EA), ąĘą░ą┐ąĖčüą░ąĮąĮąŠą╣ ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ MC_FCR.

ą×ą┐ąĄčĆą░čåąĖčÅ Erase All čĆą░ąĘčĆąĄčłąĄąĮą░ č鹊ą╗čīą║ąŠ ą▓ č鹊ą╝ čüą╗čāčćą░ąĄ, ąĄčüą╗ąĖ ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĮąĖ ąŠą┤ąĖąĮ ą▒ąĖčé ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (lock bit). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ čĆąĄą│ąĖąŠąĮ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮ FLASH, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé LOCKE ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FSR, ąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ ą▒čāą┤ąĄčé ąŠčéą╝ąĄąĮąĄąĮąŠ. ąĢčüą╗ąĖ ą▒čŗą╗ ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1 ą▒ąĖčé LOCKE ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FMR, č鹊 ą▒čāą┤ąĄčé ąĘą░ą┐čāčēąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

ąÜąŠą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąŠ, čāčüčéą░ąĮąŠą▓ąĖčéčīčüčÅ ą▒ąĖčé FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ FLASH (MC_FSR). ąĢčüą╗ąĖ ą▒čŗą╗ąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FMR, č鹊 ą▒čāą┤ąĄčé ą░ą║čéąĖą▓ąĖąĘąĖčĆąŠą▓ą░ąĮą░ ą╗ąĖąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ MC.

ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮčŗ ą┤ą▓ąĄ ąŠčłąĖą▒ą║ąĖ (č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ MC_FSR):

ŌĆó Programming Error (ąŠčłąĖą▒ą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ): ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ MC_FCR ą▒čŗą╗ąŠ ąĘą░ą┐ąĖčüą░ąĮąŠ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ ą║ą╗čÄč湥ą▓ąŠąĄ čüą╗ąŠą▓ąŠ ąĖą╗ąĖ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝ą░čÅ ą║ąŠą╝ą░ąĮą┤ą░.

ŌĆó Lock Error (ąŠčłąĖą▒ą║ą░, čüą▓čÅąĘą░ąĮąĮą░čÅ čü ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąŠą╣): ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ čüčéčĆą░ąĮąĖčåą░ ą┐ą░ą╝čÅčéąĖ ą┐čĆąĖąĮą░ą┤ą╗ąĄąČąĖčé ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮąŠą╝čā čĆąĄą│ąĖąŠąĮčā FLASH. ą¤ąĄčĆąĄą┤ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ ą┤ą╗čÅ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĖčÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖąŠąĮą░.

[ąŚą░čēąĖčéą░ ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖč鹊ą╝ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ]

ąæąĖčéčŗ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (Lock bits) čüą▓čÅąĘą░ąĮčŗ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ čüčéčĆą░ąĮąĖčåą░ą╝ąĖ ąĮą░ ą▓čüąĄą╣ ą┐ą╗ąŠčüą║ąŠčüčéąĖ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ FLASH. ą×ąĮąĖ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ąĘą░ą┤ą░čéčī ą▒ą╗ąŠą║ąĖčĆčāąĄą╝čŗąĄ čĆąĄą│ąĖąŠąĮčŗ ą▓ ą┐ą░ą╝čÅčéąĖ FLASH, ąĘą░čēąĖčēąĄąĮąĮčŗąĄ ąŠčé ąĘą░ą┐ąĖčüąĖ ąĖą╗ąĖ ąŠčćąĖčüčéą║ąĖ.

ą¤ąŠčüą╗ąĄ ą▓čŗčģąŠą┤ą░ čü ąĘą░ą▓ąŠą┤ą░ čćąĖą┐ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćąĖčéčī ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║čā ąĮąĄą║ąŠč鹊čĆčŗčģ čĆąĄą│ąĖąŠąĮąŠą▓ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ FLASH. ąŁčéąĖ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ čĆąĄą│ąĖąŠąĮčŗ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ ą┐čĆąĖą▓čÅąĘą║ąĖ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą║ą░čĆčéčŗ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ FLASH. ąŚą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ čüąĄą║č鹊čĆčŗ ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ ąĖ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤čĆčāą│ąĖą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄą╝ ąĖą╗ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ.

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čüą╗ąĄą┤čāčÄčēą░čÅ:

ŌĆó ąÆ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ MC_FCR ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ čüą╗ąĄą┤čāčÄčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ:

(0x5A << 24) | (lockPageNumber << 8 & PAGEN) | SLB

lockPageNumber čŹč鹊 ąĮąŠą╝ąĄčĆ čüčéčĆą░ąĮąĖčåčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ą╗ąŠą║ąĖčĆčāąĄą╝ąŠą│ąŠ čĆąĄą│ąĖąŠąĮą░.

ŌĆó ąÜąŠą│ą┤ą░ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ (MC_FSR). ąĢčüą╗ąĖ ą▒čŗą╗ąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FMR, č鹊 ą▒čāą┤ąĄčé ą░ą║čéąĖą▓ąĖąĘąĖčĆąŠą▓ą░ąĮą░ ą╗ąĖąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ MC.

ą×čłąĖą▒ą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ, čüą▓čÅąĘą░ąĮąĮą░čÅ čü ąŠčłąĖą▒ąŠčćąĮčŗą╝ ą║ą╗čÄč湥ą▓čŗą╝ čüą╗ąŠą▓ąŠą╝ ąĖ/ąĖą╗ąĖ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝ąŠą╣ ą║ąŠą╝ą░ąĮą┤ąŠą╣, ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╝ąĖ ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ MC_FCR, ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮą░ ą┐ąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠą╝čā čĆąĄą│ąĖčüčéčĆą░ MC_FSR.

ą£ąŠąČąĮąŠ ąŠčćąĖčüčéąĖčéčī ą▒ąĖčéčŗ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ, ą║ąŠč鹊čĆčŗąĄ ą▒čŗą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ čĆą░ąĮąĄąĄ. ąóąŠą│ą┤ą░ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ čĆąĄą│ąĖąŠąĮčŗ ą╝ąŠą│čāčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮčŗ ąĖą╗ąĖ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čüą╗ąĄą┤čāčÄčēą░čÅ:

ŌĆó ąÆ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ MC_FCR ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ čüą╗ąĄą┤čāčÄčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ:

(0x5A << 24) | (lockPageNumber << 8 & PAGEN) | CLB

lockPageNumber čŹč鹊 ąĮąŠą╝ąĄčĆ čüčéčĆą░ąĮąĖčåčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆčāąĄą╝ąŠą│ąŠ čĆąĄą│ąĖąŠąĮą░.

ŌĆó ąÜąŠą│ą┤ą░ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ (MC_FSR). ąĢčüą╗ąĖ ą▒čŗą╗ąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FMR, č鹊 ą▒čāą┤ąĄčé ą░ą║čéąĖą▓ąĖąĘąĖčĆąŠą▓ą░ąĮą░ ą╗ąĖąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ MC.

ą×čłąĖą▒ą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ, čüą▓čÅąĘą░ąĮąĮą░čÅ čü ąŠčłąĖą▒ąŠčćąĮčŗą╝ ą║ą╗čÄč湥ą▓čŗą╝ čüą╗ąŠą▓ąŠą╝ ąĖ/ąĖą╗ąĖ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝ąŠą╣ ą║ąŠą╝ą░ąĮą┤ąŠą╣, ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╝ąĖ ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ MC_FCR, ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮą░ ą┐ąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠą╝čā čĆąĄą│ąĖčüčéčĆą░ MC_FSR.

ąÜąŠą╝ą░ąĮą┤ą░ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé ą▒ąĖčé ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (lock bit) ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1; čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé LOCKSx ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FSR ą▒čāą┤ąĄčé čćąĖčéą░čéčīčüčÅ ą║ą░ą║ 0. ąÜąŠą╝ą░ąĮą┤ą░ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé ą▒ąĖčé ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 0; čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé LOCKSx ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FSR ą▒čāą┤ąĄčé čćąĖčéą░čéčīčüčÅ ą║ą░ą║ 1.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ąŠčüčéčāą┐ ą║ FLASH ą▓ čĆąĄąČąĖą╝ąĄ čćč鹥ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ ą║ąŠą╝ą░ąĮą┤čŗ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖą╗ąĖ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ.

[ąæąĖčéčŗ GPNVM]

ąŁąĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗąĄ ą▒ąĖčéčŗ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (General-purpose NVM, ąĖą╗ąĖ čüąŠą║čĆą░čēąĄąĮąĮąŠ ą▒ąĖčéčŗ GPNVM) ąĮąĄ čüą▓čÅąĘą░ąĮčŗ čü ą┐ą╗ąŠčüą║ąŠčüčéčīčÄ ą┐ą░ą╝čÅčéąĖ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ FLASH. ą×ąĮąĖ čéą░ą║ąČąĄ ąĮąĄ ąŠčéąĮąŠčüčÅčéčüčÅ ą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā EFC1 čćąĖą┐ą░ AT91SAM7X512. ąŁčéąĖ ą▒ąĖčéčŗ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ ą┤ą╗čÅ ąĘą░čēąĖčéčŗ ą┤čĆčāą│ąĖčģ čćą░čüč鹥ą╣ ą║čĆąĖčüčéą░ą╗ą╗ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ą×ąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ (ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮčŗ) ąĖą╗ąĖ ąŠčćąĖčēąĄąĮčŗ ą║ą░ąČą┤čŗą╣ ą┐ąŠ ąŠčéą┤ąĄą╗čīąĮąŠčüčéąĖ. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčé GPNVM čüą╝. ą░ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆ.

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą░ą║čéąĖą▓ąĖąĘą░čåąĖąĖ ą▒ąĖčéą░ GPNVM čüą╗ąĄą┤čāčÄčēą░čÅ:

ŌĆó ąŚą░ą┐čāčüčéąĖč鹥 ą║ąŠą╝ą░ąĮą┤čā čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ GPNVM (Set General Purpose Bit, SGPB) ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ MC_FCR ą║ąŠą╝ą░ąĮą┤čŗ SGPB ąĖ ąĮąŠą╝ąĄčĆą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄą╝ąŠą│ąŠ ą▒ąĖčéą░ GPNVM ą▓ ą┐ąŠą╗ąĄ PAGEN.

ŌĆó ąÜąŠą│ą┤ą░ ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ (MC_FSR). ąĢčüą╗ąĖ ą▒čŗą╗ąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FMR, č鹊 ą▒čāą┤ąĄčé ą░ą║čéąĖą▓ąĖąĘąĖčĆąŠą▓ą░ąĮą░ ą╗ąĖąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ MC.

ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮčŗ ą┤ą▓ąĄ ąŠčłąĖą▒ą║ąĖ (č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ MC_FSR):

ŌĆó Programming Error (ąŠčłąĖą▒ą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ): ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ MC_FCR ą▒čŗą╗ąŠ ąĘą░ą┐ąĖčüą░ąĮąŠ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ ą║ą╗čÄč湥ą▓ąŠąĄ čüą╗ąŠą▓ąŠ ąĖą╗ąĖ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝ą░čÅ ą║ąŠą╝ą░ąĮą┤ą░.

ŌĆó ąĢčüą╗ąĖ ą▒čŗą╗ čāą║ą░ąĘą░ąĮ ąĮąŠą╝ąĄčĆ ą▒ąĖčéą░ GPNVM ą▒ąŠą╗čīčłąĄ, č湥ą╝ ąŠą▒čēąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖč鹊ą▓ GPNVM, č鹊 ą║ąŠą╝ą░ąĮą┤ą░ ąĮąĄ ąŠą║ą░ąČąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ą£ąŠąČąĮąŠ ą┤ąĄą░ą║čéąĖą▓ąĖčĆąŠą▓ą░čéčī ą▒ąĖčé GPNVM, ą║ąŠč鹊čĆčŗą╣ ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čĆą░ąĮąĄąĄ. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąŠčćąĖčüčéą║ąĖ čüą╗ąĄą┤čāčÄčēą░čÅ:

ŌĆó ąŚą░ą┐čāčüčéąĖč鹥 ą║ąŠą╝ą░ąĮą┤čā ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ GPNVM (Clear General-purpose Bit, CGPB) ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ MC_FCR ą║ąŠą╝ą░ąĮą┤čŗ CGPB ąĖ ąĮąŠą╝ąĄčĆą░ ąŠčćąĖčēą░ąĄą╝ąŠą│ąŠ ą▒ąĖčéą░ GPNVM ą▓ ą┐ąŠą╗ąĄ PAGEN.

ŌĆó ąÜąŠą│ą┤ą░ ąŠčćąĖčüčéą║ą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ (MC_FSR). ąĢčüą╗ąĖ ą▒čŗą╗ąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FMR, č鹊 ą▒čāą┤ąĄčé ą░ą║čéąĖą▓ąĖąĘąĖčĆąŠą▓ą░ąĮą░ ą╗ąĖąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ MC.

ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮčŗ ą┤ą▓ąĄ ąŠčłąĖą▒ą║ąĖ (č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ MC_FSR):

ŌĆó Programming Error (ąŠčłąĖą▒ą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ): ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ MC_FCR ą▒čŗą╗ąŠ ąĘą░ą┐ąĖčüą░ąĮąŠ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ ą║ą╗čÄč湥ą▓ąŠąĄ čüą╗ąŠą▓ąŠ ąĖą╗ąĖ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝ą░čÅ ą║ąŠą╝ą░ąĮą┤ą░.

ŌĆó ąĢčüą╗ąĖ ą▒čŗą╗ čāą║ą░ąĘą░ąĮ ąĮąŠą╝ąĄčĆ ą▒ąĖčéą░ GPNVM ą▒ąŠą╗čīčłąĄ, č湥ą╝ ąŠą▒čēąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖč鹊ą▓ GPNVM, č鹊 ą║ąŠą╝ą░ąĮą┤ą░ ąĮąĄ ąŠą║ą░ąČąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ąÜąŠą╝ą░ąĮą┤ą░ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ GPNVM ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé ąĄą│ąŠ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 0; čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé GPNVMx ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FSR ą▒čāą┤ąĄčé čćąĖčéą░čéčīčüčÅ ą║ą░ą║ 0. ąÜąŠą╝ą░ąĮą┤ą░ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ GPNVM ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé ąĄą│ąŠ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1; čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé GPNVMx ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FSR ą▒čāą┤ąĄčé čćąĖčéą░čéčīčüčÅ ą║ą░ą║ 1.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ FLASH ą▓ čĆąĄąČąĖą╝ąĄ čćč鹥ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ą║ąŠą╝ą░ąĮą┤čŗ čāčüčéą░ąĮąŠą▓ą║ąĖ, ąŠčćąĖčüčéą║ąĖ ąĖą╗ąĖ čćč鹥ąĮąĖčÅ ą▒ąĖčé GPNVM.

[ąæąĖčé ąĘą░čēąĖčéčŗ]

ą”ąĄą╗čī ą▒ąĖčéą░ ąĘą░čēąĖčéčŗ (security bit) - ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī ą▓ąĮąĄčłąĮąĖą╣ ą┤ąŠčüčéčāą┐ ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮąĄ (čŹč鹊 ąĮąĄ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā EFC1 čćąĖą┐ą░ AT91SAM7X512). ą¤čĆąĖ čŹč鹊ą╝ ą▒čāą┤čāčé ąĘą░ą┐čĆąĄčēąĄąĮčŗ čäčāąĮą║čåąĖąĖ JTAG, ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ FLASH (Fast Flash Programming) ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ FLASH (Flash Serial Test Interface). ąæčāą┤čāčćąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝, čŹč鹊čé ą▒ąĖčé ą╝ąŠąČąĮąŠ čüą▒čĆąŠčüąĖčéčī č鹊ą╗čīą║ąŠ ą┐čāč鹥ą╝ ą▓ąĮąĄčłąĮąĄą│ąŠ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ąĘą░ą┐čĆąŠčüą░ ERASE ą┤ą╗čÅ ą▓čüąĄą│ąŠ ą║čĆąĖčüčéą░ą╗ą╗ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ ą▓čŗą▓ąŠą┤ ą║ąŠčĆą┐čāčüą░, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÄ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ čäčāąĮą║čåąĖąĄą╣ ERASE, čüą╝. ą┤ą░čéą░čłąĖčé ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆ. ą¤čĆąĖ ą▓čŗą┤ą░č湥 ERASE ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮą░ ą▓čüčÅ ą┐ą░ą╝čÅčéčī FLASH, čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮčŗ ą▓čüąĄ ąĄčæ čĆąĄą│ąĖąŠąĮčŗ ąĖ čüą▒čĆąŠčłąĄąĮčŗ ą▓čüąĄ ą▒ąĖčéčŗ GPNVM ąĖ čüą▒čĆąŠčłąĄąĮ čüą░ą╝ ą▒ąĖčé ąĘą░čēąĖčéčŗ. ąæąĖčé ąĘą░čēąĖčéčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FSR ąŠčćąĖčēą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐čĆąĖ ą▓čŗą┤ą░č湥 ERASE. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą░ą║čéąĖą▓ąĖąĘą░čåąĖąĖ (čāčüčéą░ąĮąŠą▓ą║ąĖ) ą▒ąĖčéą░ ąĘą░čēąĖčéčŗ čüą╗ąĄą┤čāčÄčēą░čÅ:

ŌĆó ąŚą░ą┐čāčüčéąĖč鹥 ą║ąŠą╝ą░ąĮą┤čā čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ ąĘą░čēąĖčéčŗ (Set Security Bit command, SSB) ąĘą░ą┐ąĖčüčīčÄ ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ MC_FCR.

ŌĆó ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ ąĘą░čēąĖčéčŗ ąĘą░ą▓ąĄčĆčłąĄąĮą░, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ (MC_FSR). ąĢčüą╗ąĖ ą▒čŗą╗ąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ FRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FMR, č鹊 ą▒čāą┤ąĄčé ą░ą║čéąĖą▓ąĖąĘąĖčĆąŠą▓ą░ąĮą░ ą╗ąĖąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ MC.

ąÜąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĄąĮ ą▒ąĖčé ąĘą░čēąĖčéčŗ, č鹊 ą▒ąĖčé SECURITY ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_FSR čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ.

[ąśąĮč鹥čĆč乥ą╣čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ EFC]

ąśąĮč鹥čĆč乥ą╣čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ EFC ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮ ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐ą░ą╝čÅčéąĖ MC (čüą╝. [2]). ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüąŠą▓ čĆąĄą│ąĖčüčéčĆąŠą▓ ąŠčéčüčćąĖčéčŗą▓ą░ąĄčéčüčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą░ą┤čĆąĄčüą░ 0xFFFFFF00.

ą¤čĆąŠčåąĄčüčüąŠčĆ AT91SAM7X512 ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮ ą┤ą▓čāą╝čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ EFC: EFC0 ąĖ EFC1. ą¤čĆąĖą▓čÅąĘą║ą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ąŠą║ą░ąĘą░ąĮą░ ą▓ čéą░ą▒ą╗ąĖčåą░čģ ąĮąĖąČąĄ.

ąóą░ą▒ą╗ąĖčåą░ 19-3. ąĀąĄą│ąĖčüčéčĆčŗ EFC0.

| ąĪą╝ąĄčēąĄąĮąĖąĄ |

ąĀąĄą│ąĖčüčéčĆ |

ąśą╝čÅ |

ąöąŠčüčéčāą┐ |

ąĪą▒čĆąŠčü |

| 0x0060 |

MC Flash Mode Register (čĆąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ ą┐ą░ą╝čÅčéąĖ FLASH) |

MC_FMR |

R/W |

0x00000000 |

| 0x0064 |

MC Flash Command Register (čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤) |

MC_FCR |

W |

- |

| 0x0068 |

MC Flash Status Register (čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ FLASH) |

MC_FSR |

R |

- |

| 0x006C |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

- |

- |

- |

ąóą░ą▒ą╗ąĖčåą░ 19-4. ąĀąĄą│ąĖčüčéčĆčŗ EFC1.

| ąĪą╝ąĄčēąĄąĮąĖąĄ |

ąĀąĄą│ąĖčüčéčĆ |

ąśą╝čÅ |

ąöąŠčüčéčāą┐ |

ąĪą▒čĆąŠčü |

| 0x0070 |

MC Flash Mode Register (čĆąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ ą┐ą░ą╝čÅčéąĖ FLASH) |

MC_FMR |

R/W |

0x00000000 |

| 0x0074 |

MC Flash Command Register (čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤) |

MC_FCR |

W |

- |

| 0x0078 |

MC Flash Status Register (čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ FLASH) |

MC_FSR |

R |

- |

| 0x007C |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

- |

- |

-

|

ąĀąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ FLASH (MC Flash Mode Register). ąĀą░ą▒ąŠčéą░ąĄčé ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

- |

- |

- |

FMCN

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| - |

- |

- |

- |

- |

- |

FWS

|

NEBP |

- |

- |

- |

PROGE |

LOCKE |

- |

FRDY |

FRDY: Flash Ready Interrupt Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ FLASH.

0: ą║ąŠą│ą┤ą░ FLASH ą│ąŠč鹊ą▓ą░ ą║ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÄ čüą╗ąĄą┤čāčÄčēąĄą╣ ą║ąŠą╝ą░ąĮą┤čŗ, č鹊 čŹč鹊 ąĮąĄ ą▓čŗąĘąŠą▓ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

1: ą║ąŠą│ą┤ą░ FLASH ą│ąŠč鹊ą▓ą░ ą║ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÄ čüą╗ąĄą┤čāčÄčēąĄą╣ ą║ąŠą╝ą░ąĮą┤čŗ, č鹊 čŹč鹊 ą▓čŗąĘąŠą▓ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

LOCKE: Lock Error Interrupt Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąŠčłąĖą▒ą║ąĄ, čüą▓čÅąĘą░ąĮąĮąŠą╣ čü ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąŠą╣.

0: ąŠčłąĖą▒ą║ą░ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ąĮąĄ ą▓čŗąĘąŠą▓ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

1: ąŠčłąĖą▒ą║ą░ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą▓čŗąĘąŠą▓ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

PROGE: Programming Error Interrupt Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąŠčłąĖą▒ą║ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ.

0: ąŠčłąĖą▒ą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮąĄ ą▓čŗąĘąŠą▓ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

1: ąŠčłąĖą▒ą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗąĘąŠą▓ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

NEBP: No Erase Before Programming, ąĮąĄ ą┤ąĄą╗ą░čéčī ąŠčćąĖčüčéą║čā ą┐ąĄčĆąĄą┤ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝.

0: ą┐ąĄčĆąĄą┤ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ FLASH ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐čĆąŠąĖąĘą▓ąĄą┤ąĄąĮą░ ąĄčæ ąŠčćąĖčüčéą║ą░.

1: ą┐ąĄčĆąĄą┤ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ FLASH ąĮąĄ ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐čĆąŠąĖąĘą▓ąĄą┤ąĄąĮą░ ąĄčæ ąŠčćąĖčüčéą║ą░.

FWS: Flash Wait State, ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ FLASH.

ąŁč鹊 ą┐ąŠą╗ąĄ ąĘą░ą┤ą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ:

| FWS |

ą×ą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ |

ą×ą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ |

| 0 |

1 čéą░ą║čé |

2 čéą░ą║čéą░ |

| 1 |

2 čéą░ą║čéą░ |

3 čéą░ą║čéą░ |

| 2 |

3 čéą░ą║čéą░ |

4 čéą░ą║čéą░ |

| 3 |

4 čéą░ą║čéą░ |

4 čéą░ą║čéą░ |

FMCN: Flash Microsecond Cycle Number, ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓ ąĮą░ ą╝ąĖą║čĆąŠčüąĄą║čāąĮą┤čā.

ą¤ąĄčĆąĄą┤ ąĘą░ą┐ąĖčüčīčÄ čŹąĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą▒ąĖčé (Non Volatile Memory, NVM), čŹč鹊 ąŠčéąĮąŠčüąĖčéčüčÅ ą║ ą▒ąĖčéą░ą╝ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (Lock bits), ą▒ąĖčéą░ą╝ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (General Purpose NVM, GPNVM) ąĖ ą▒ąĖčéčā ąĘą░čēąĖčéčŗ (Security bit), čŹč鹊 ą┐ąŠą╗ąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓ ąŠčüąĮąŠą▓ąĮąŠą╣ čćą░čüč鹊čéčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (Master Clock, MCK), ą┐čĆąĖčģąŠą┤čÅčēąĖčģčüčÅ ąĮą░ ąŠą┤ąĮčā ą╝ąĖą║čĆąŠčüąĄą║čāąĮą┤čā.

ąÜąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ąŠčüčéą░ą╗čīąĮą░čÅ ą┐ą░ą╝čÅčéčī FLASH, čŹč鹊 ą┐ąŠą╗ąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓ MCK ą▓ 1.5 ą╝ąĖą║čĆąŠčüąĄą║čāąĮą┤čŗ. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠą║čĆčāą│ą╗ąĄąĮąŠ ą▓ą▓ąĄčĆčģ ą┤ąŠ ą▒ą╗ąĖąČą░ą╣čłąĄą│ąŠ čåąĄą╗ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ.

ąÆąĮąĖą╝ą░ąĮąĖąĄ: ąĘąĮą░č湥ąĮąĖąĄ 0 čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠč湥ąĮčī ą▒ąŠą╗čīčłąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą║č鹊ą▓ MCK ąĮąĄ ą╝ąĄąĮčīčłąĄ 30 ą╝ąĖą║čĆąŠčüąĄą║čāąĮą┤.

ąÆąĮąĖą╝ą░ąĮąĖąĄ: čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą║ąŠčĆčĆąĄą║čéąĮąŠčüčéčī ąŠą┐ąĄčĆą░čåąĖą╣ čü ą┐ą░ą╝čÅčéčīčÄ FLASH, ą┐ąŠą╗ąĄ FMCN ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ.

ąĀąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ FLASH (MC Flash Command Register). ąĀą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

KEY

|

- |

- |

- |

- |

- |

- |

PAGEN

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

PAGEN

|

- |

- |

- |

- |

FCMD |

FCMD: Flash Command, ą║ąŠą╝ą░ąĮą┤ą░ FLASH.

| FCMD |

ąöąĄą╣čüčéą▓ąĖąĄ |

| 0000 |

ą×čéčüčāčéčüčéą▓ąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ. ąØąĄ ą▓čŗąĘčŗą▓ą░ąĄčé čāčüčéą░ąĮąŠą▓ą║čā čäą╗ą░ą│ą░ čüąŠčüč鹊čÅąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ (Programming Error Status, PROGE) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ FLASH (MC_FSR). |

| 0001 |

Write Page Command (WP), ą║ąŠą╝ą░ąĮą┤ą░ ąĘą░ą┐ąĖčüąĖ čüčéčĆą░ąĮąĖčåčŗ: ąĘą░ą┐čāčüą║ą░ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ, čāą║ą░ąĘą░ąĮąĮąŠą╣ ą▓ ą┐ąŠą╗ąĄ PAGEN. |

| 0010 |

Set Lock Bit Command (SLB), ą║ąŠą╝ą░ąĮą┤ą░ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ: ąĘą░ą┐čāčüą║ą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čĆąĄą│ąĖąŠąĮą░ ą┐ą░ą╝čÅčéąĖ, čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ ą▓ ą┐ąŠą╗ąĄ PAGEN. |

| 0011 |

Write Page and Lock Command (WPL), ą║ąŠą╝ą░ąĮą┤ą░ ąĘą░ą┐ąĖčüąĖ čüčéčĆą░ąĮąĖčåčŗ ąĖ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĄčæ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ: ąĘą░ą┐čāčüą║ą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą┐ąĖčüąĖ čüčéčĆą░ąĮąĖčåčŗ čü ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąŠą╣ ąĮą░ ąĘą░ą┐ąĖčüčī ą┐ąŠčüą╗ąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüčéčĆą░ąĮąĖčåčŗ. |

| 0100 |

Clear Lock Bit Command (CLB), ą║ąŠą╝ą░ąĮą┤ą░ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čüčéčĆą░ąĮąĖčåčŗ: ąĘą░ą┐čāčüą║ą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čĆąĄą│ąĖąŠąĮą░ ą┐ą░ą╝čÅčéąĖ, čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ ą▓ ą┐ąŠą╗ąĄ PAGEN. |

| 1000 |

Erase All Command (EA), ą║ąŠą╝ą░ąĮą┤ą░ ą┐ąŠą╗ąĮąŠą╣ ąŠčćąĖčüčéą║ąĖ: ąĘą░ą┐čāčüą║ą░ąĄčé ąŠčćąĖčüčéą║čā ą▓čüąĄą╣ ą┐ą░ą╝čÅčéąĖ FLASH. ąĢčüą╗ąĖ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĮą░ čüčéčĆą░ąĮąĖčåą░ ą┐ą░ą╝čÅčéąĖ FLASH ą▒čŗą╗ą░ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮą░, č鹊 ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ ąŠčéą╝ąĄąĮčÅąĄčéčüčÅ. |

| 1011 |

Set General-purpose NVM Bit (SGPB), ą║ąŠą╝ą░ąĮą┤ą░ čāčüčéą░ąĮąŠą▓ą║ąĖ 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠą│ąŠ ą▒ąĖčéą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ: ą░ą║čéąĖą▓ąĖąĘąĖčĆčāąĄčé (čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé) ą▒ąĖčé GPNVN, čāą║ą░ąĘą░ąĮąĮčŗą╣ ą┐ąŠ ąĮąŠą╝ąĄčĆčā ą▓ ą┐ąŠą╗ąĄ PAGEN. |

| 1101 |

Clear General Purpose NVM Bit (CGPB), ą║ąŠą╝ą░ąĮą┤ą░ ąŠčćąĖčüčéą║ąĖ 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠą│ąŠ ą▒ąĖčéą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ: ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčé (čüą▒čĆą░čüčŗą▓ą░ąĄčé) ą▒ąĖčé GPNVN, čāą║ą░ąĘą░ąĮąĮčŗą╣ ą┐ąŠ ąĮąŠą╝ąĄčĆčā ą▓ ą┐ąŠą╗ąĄ PAGEN. |

| 1111 |

Set Security Bit Command (SSB), ą║ąŠą╝ą░ąĮą┤ą░ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ ąĘą░čēąĖčéčŗ ą┐ą░ą╝čÅčéąĖ FLASH. |

| ąöčĆčāą│ąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. ąĢčüą╗ąĖ ą▒čāą┤ąĄčé čāą║ą░ąĘą░ąĮąŠ ąŠą┤ąĮąŠ ąĖąĘ čŹčéąĖčģ ąĘąĮą░č湥ąĮąĖą╣, č鹊 ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ (PROGE) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ FLASH (MC_FSR). |

PAGEN: Page Number, ąĮąŠą╝ąĄčĆ čüčéčĆą░ąĮąĖčåčŗ.

| ąÜąŠą╝ą░ąĮą┤ą░ |

ą×ą┐ąĖčüą░ąĮąĖąĄ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ PAGEN |

| ąŚą░ą┐ąĖčüčī čüčéčĆą░ąĮąĖčåčŗ (WP) |

ąŚą░ą┤ą░ąĄčé ąĮąŠą╝ąĄčĆ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝ąŠą╣ čüčéčĆą░ąĮąĖčåčŗ. |

| ąŚą░ą┐ąĖčüčī čüčéčĆą░ąĮąĖčåčŗ čü ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąŠą╣ (WPL). |

ąŚą░ą┤ą░ąĄčé ąĮąŠą╝ąĄčĆ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝ąŠą╣ čüčéčĆą░ąĮąĖčåčŗ ąĖ čüą▓čÅąĘą░ąĮąĮčŗą╣ čü ąĮąĖą╝ ą▒ą╗ąŠą║ąĖčĆčāąĄą╝čŗą╣ čĆąĄą│ąĖąŠąĮ ą┐ą░ą╝čÅčéąĖ. |

| ąÜąŠą╝ą░ąĮą┤ą░ ą┐ąŠą╗ąĮąŠą╣ ąŠčćąĖčüčéą║ąĖ (EA) |

ąöą╗čÅ čŹč鹊ą╣ ą║ąŠą╝ą░ąĮą┤čŗ ą┐ąŠą╗ąĄ PAGEN ąĮąĄ ąĖą╝ąĄąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ. |

| ąÜąŠą╝ą░ąĮą┤čŗ čāčüčéą░ąĮąŠą▓ą║ąĖ/ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (SLB/CLB) |

ąŚą░ą┤ą░ąĄčé ąĮąŠą╝ąĄčĆ čüčéčĆą░ąĮąĖčåčŗ ą▒ą╗ąŠą║ąĖčĆčāąĄą╝ąŠą│ąŠ ąĖą╗ąĖ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆčāąĄą╝ąŠą│ąŠ čĆąĄą│ąĖąŠąĮą░. |

| ąÜąŠą╝ą░ąĮą┤ą░ čāčüčéą░ąĮąŠą▓ą║ąĖ/ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ GPNVM (SGPB/CGPB) |

ąŚą░ą┤ą░ąĄčé ąĮąŠą╝ąĄčĆ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄą╝ąŠą│ąŠ/čüą▒čĆą░čüčŗą▓ą░ąĄą╝ąŠą│ąŠ ą▒ąĖčéą░ GPNVM. |

| ąÜąŠą╝ą░ąĮą┤ą░ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ ąĘą░čēąĖčéčŗ (SSB) |

ąöą╗čÅ čŹč鹊ą╣ ą║ąŠą╝ą░ąĮą┤čŗ ą┐ąŠą╗ąĄ PAGEN ąĮąĄ ąĖą╝ąĄąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ąŠą╝ą░ąĮą┤čŗ, ą▓čüąĄ ąĖą╗ąĖ ąĮąĄą║ąŠč鹊čĆčŗąĄ ąĖąĘ ą▒ąĖč鹊ą▓ PAGEN ą╝ąŠą│čāčé ąĮąĄ ąĖą╝ąĄčéčī ąĘąĮą░č湥ąĮąĖčÅ.

KEY: Write Protection Key, ą║ą╗čÄčć ąĘą░čēąĖčéčŗ ąŠčé ąŠčłąĖą▒ąŠčćąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ.

ąÆ čŹč鹊 ą┐ąŠą╗ąĄ čüą╗ąĄą┤čāąĄčé ąĘą░ą┐ąĖčüą░čéčī ąĘąĮą░č湥ąĮąĖąĄ 0x5A, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ, ąĘą░ą┤ą░ąĮąĮąŠą╣ ą▒ąĖčéą░ą╝ąĖ ą┐ąŠą╗čÅ FCMD. ąĢčüą╗ąĖ ą▓ ą┐ąŠą╗ąĄ KEY ąĘą░ą┐ąĖčüą░ąĮąŠ ą┤čĆčāą│ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, č鹊 ą║ąŠą╝ą░ąĮą┤ą░ ąĘą░ą┐ąĖčüąĖ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąĖ ą┤ąĄą╣čüčéą▓ąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ ą▒čāą┤ąĄčé ąŠčéą╝ąĄąĮąĄąĮąŠ.

ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ FLASH (MC Flash Status Register). ąĀą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

| LOCKS15 |

LOCKS14 |

LOCKS13 |

LOCKS12 |

LOCKS11 |

LOCKS10 |

LOCKS9 |

LOCKS8 |

| 23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| LOCKS7 |

LOCKS6 |

LOCKS5 |

LOCKS4 |

LOCKS3 |

LOCKS2 |

LOCKS1 |

LOCKS0 |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| - |

- |

- |

- |

- |

GPNVM2 |

GPNVM1 |

GPNVM0 |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

SECURITY |

PROGE |

LOCKE |

- |

FRDY |

FRDY: Flash Ready Status, čüąŠčüč鹊čÅąĮąĖąĄ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ FLASH.

0: ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ EFC ąĘą░ąĮčÅčé, ąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą┐ąŠą┤ąŠąČą┤ą░čéčī ąĄą│ąŠ ąŠčüą▓ąŠą▒ąŠąČą┤ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ąĮąŠą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ.

1: ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ EFC ą│ąŠč鹊ą▓ ą║ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÄ ąĮąŠą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ.

LOCKE: Lock Error Status, čüąŠčüč鹊čÅąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ, čüą▓čÅąĘą░ąĮąĮąŠą╣ čü ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąŠą╣.

0: ąĮąĄ ą▒čŗą╗ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĮąŠą│ąŠ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čĆąĄą│ąĖąŠąĮą░ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ MC_FSR.

1: ą▒čŗą╗ą░ ą┐ąŠą┐čŗčéą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĮąŠą│ąŠ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čĆąĄą│ąĖąŠąĮą░ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ MC_FSR.

PROGE: Programming Error Status, čüąŠčüč鹊čÅąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ.

0: ąĮąĄ ąĘą░ą┐ąĖčüąĖ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ ąĖ/ąĖą╗ąĖ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠą│ąŠ ą║ą╗čÄč湥ą▓ąŠą│ąŠ čüą╗ąŠą▓ą░ ą▓ čĆąĄą│ąĖčüčéčĆ MC_FCR.

1: ą▒čŗą╗ą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąĘą░ą┐ąĖčüčī ąĮąĄą┤ąŠą┐čāčüčéąĖą╝ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ ąĖ/ąĖą╗ąĖ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠą│ąŠ ą║ą╗čÄč湥ą▓ąŠą│ąŠ čüą╗ąŠą▓ą░ ą▓ čĆąĄą│ąĖčüčéčĆ MC_FCR.

SECURITY: Security Bit Status, čüąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖčéą░ ąĘą░čēąĖčéčŗ (ąĮąĄ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ EFC1 ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AT91SAM7X512).

0: ą▒ąĖčé ąĘą░čēąĖčéčŗ ąĮąĄą░ą║čéąĖą▓ąĄąĮ.

1: ą▒ąĖčé ąĘą░čēąĖčéčŗ ą░ą║čéąĖą▓ąĄąĮ.

GPNVMx: General-purpose NVM Bit Status, čüąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖčé GPNVM (ąĮąĄ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ EFC1 ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AT91SAM7X512).

0: čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé GPNVM ąĮąĄą░ą║čéąĖą▓ąĄąĮ.

1: čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé GPNVM ą░ą║čéąĖą▓ąĄąĮ.

LOCKSx: Lock Region x Lock Status, čüąŠčüč鹊čÅąĮąĖąĄ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čĆąĄą│ąĖąŠąĮą░ x.

0: čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čĆąĄą│ąĖąŠąĮ ąĮąĄ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮ ąĮą░ ąĘą░ą┐ąĖčüčī.

1: čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čĆąĄą│ąĖąŠąĮ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮ ąĮą░ ąĘą░ą┐ąĖčüčī.

[ąĪčüčŗą╗ą║ąĖ]

1. ARM-based Flash MCU SAM7X512 / SAM7X256 / SAM7X128 DATASHEET site:atmel.com.

2. AT91SAM7 Memory Controller (MC).

3. ARM Atmel čüąĄčĆąĖąĖ AT91SAM7X: ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé GPNVM. |