|

ąÆ Cortex┬«-M7 ą╝ąŠą┤čāą╗čī MPU (Memory Protection Unit, ą▒ą╗ąŠą║ ąĘą░čēąĖčéčŗ ą┐ą░ą╝čÅčéąĖ [2]) ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░čéčī ą░čéčĆąĖą▒čāčéčŗ ą║čŹčłą░ ą┐ąĄčĆą▓ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ (L1) ą┐ąŠ ąŠą▒ą╗ą░čüčéčÅą╝. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą║čŹčłąĄą╝ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐čĆąĖ ą┐ąŠą╝ąŠčēąĖ čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą║čŹčłą░, ąĮąŠ MPU ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī čĆąĄąČąĖą╝ ą║čŹčłą░ ąĖ ą▒čāą┤ąĄčé ą╗ąĖ ą┤ąŠčüčéčāą┐ ąŠą▒ą╗ą░čüčéąĖ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ąĖą╗ąĖ ąĮąĄčé. ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ čüą╗čāčćą░čÅčģ ą║čŹčłąĖčĆčāąĄą╝čŗąĄ čüąĖčüč鹥ą╝čŗ ą┤ąŠą╗ąČąĮčŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā čÅą┤čĆąŠą╝ ąĖ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéčīčÄ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖąĄ čü čüąŠą▓ą╝ąĄčüčéąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ.

ąŚą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ ą░ą┐ąĮąŠčāčéą░ AN4839 [1] (ą░ą▓č鹊čĆ ą┐ąĄčĆąĄą▓ąŠą┤ą░ Marat Galyamov), ą║ąŠč鹊čĆčŗą╣ ąŠą┐ąĖčüčŗą▓ą░ąĄčé ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą║čŹčłą░ L1 ąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆąĖą╝ąĄčĆ, ą║ą░ą║ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą║čŹčłą░ ą▓ čüąĄčĆąĖąĖ STM32F7.

ąöą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ ą▒ą╗ąŠą║ąĄ MPU, ą░ čéą░ą║ąČąĄ ąŠ č鹊ą╝, ą║ą░ą║ čāčüčéą░ąĮąŠą▓ąĖčéčī ą░čéčĆąĖą▒čāčéčŗ ą┐ą░ą╝čÅčéąĖ čüąŠą│ą╗ą░čüąĮąŠ čéąĖą┐čā ą┐ą░ą╝čÅčéąĖ ąĖ ą┐ąŠą╗ąĖčéąĖą║ąĄ ą║čŹčłą░, ąŠą▒čĆą░čéąĖč鹥čüčī ą║ ą┤ąŠą║čāą╝ąĄąĮčéą░ą╝, ą┤ąŠčüčéčāą┐ąĮčŗą╝ ąĮą░ www.st.com:

ŌĆó STM32F7 Series Cortex┬«-M7 processor programming manual (PM0253)

ŌĆó Managing memory protection unit (MPU) in STM32 MCUs (AN4838) [2]

[ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą║čŹčłąĄą╝]

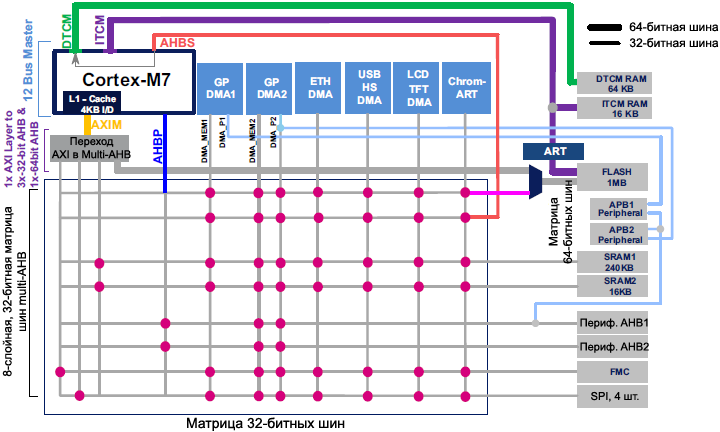

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ čüąĄą╝ąĄą╣čüčéą▓ą░ STM32F7 ą╝ąŠą│čāčé ąĖą╝ąĄčéčī ą║čŹčł L1 ą┤ą╗čÅ ą║ąŠą╝ą░ąĮą┤ ąĖ ą┤ą░ąĮąĮčŗčģ ąŠą▒čŖąĄą╝ąŠą╝ 4 Ką▒ą░ą╣čé, 8 Ką▒ą░ą╣čé ąĖą╗ąĖ 16 Ką▒ą░ą╣čé. ąÜčŹčł L1 čģčĆą░ąĮąĖčé ą┤ą░ąĮąĮčŗąĄ/ą║ąŠą╝ą░ąĮą┤čŗ čĆčÅą┤ąŠą╝ čü CPU ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ CPU ąĮąĄ ąĮčāąČąĮąŠ ą▓čŗą▒ąĖčĆą░čéčī č鹥 ąČąĄ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąĮąĄąŠą┤ąĮąŠą║čĆą░čéąĮąŠ, ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą║ą░ą║ ą▓ ąĮąĄą▒ąŠą╗čīčłąŠą╝ čåąĖą║ą╗ąĄ. ąĀąĖčü. 1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą░čĆčģąĖč鹥ą║čéčāčĆčā čüąĖčüč鹥ą╝čŗ čüąĄčĆąĖąĖ STM32F7.

ąĀąĖčü. 1. ąÉčĆčģąĖč鹥ą║čéčāčĆą░ čüąĖčüč鹥ą╝čŗ čüąĄčĆąĖąĖ STM32F7.

ąöąŠčüčéčāą┐čŗ ą┐ą░ą╝čÅčéąĖ ą║ ą┐ąŠą┤čüąĖčüč鹥ą╝ąĄ ą╝ąŠą│čāčé ąĘą░ąĮąĖą╝ą░čéčī ą╝ąĮąŠąČąĄčüčéą▓ąŠ čåąĖą║ą╗ąŠą▓ (ąŠčüąŠą▒ąĄąĮąĮąŠ ą▓ ąĖąĮč鹥čĆč乥ą╣čüą░čģ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ čü čüąŠčüč鹊čÅąĮąĖčÅą╝ąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čüąŠą▒čŗčéąĖą╣). ąÜčŹčłąĖ ąĮčāąČąĮčŗ, čćč鹊ą▒čŗ čāčüą║ąŠčĆąĖčéčī ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ-ąĘą░ą┐ąĖčüąĖ ą▓ ą┐ą░ą╝čÅčéčī. ąśą┤ąĄčÅ čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊 ąŠą▒ąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░ąĮčŗ, ąĄčüą╗ąĖ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ą╗ąŠą║ą░ą╗čīąĮąŠ (ą▓ ąŠą▒ą╗ą░čüčéąĖ, ą║ąŠč鹊čĆą░čÅ čéčĆąĄą▒čāąĄčé č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čåąĖą║ą╗ ą┤ąŠčüčéčāą┐ą░). ąöąŠčüčéčāą┐ čłąĖąĮčŗ ą║ ą┐ąŠą┤čüąĖčüč鹥ą╝ąĄ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆčŗą╣ ąĘą░ąĮąĖą╝ą░ąĄčé ą▒ąŠą╗ąĄąĄ ąŠą┤ąĮąŠą│ąŠ čåąĖą║ą╗ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ, ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé ą║ąŠąĮą▓ąĄą╣ąĄčĆąĮąŠą│ąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐ąŠč鹊ą║ą░ ą║ąŠą╝ą░ąĮą┤ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ąŠčüčéąĖčćčī ą▓čŗčüąŠą║ąŠą╣ čüą║ąŠčĆąŠčüčéąĖ. ąÜčŹčł ąŠą▒čŗčćąĮąŠ čĆąĄą░ą╗ąĖąĘčāąĄčéčüčÅ ąĮą░ą▒ąŠčĆąŠą╝ čüčéčĆąŠą║, ą│ą┤ąĄ čüčéčĆąŠą║ą░ - ą┐čĆąŠčüč鹊 ą║ąŠčĆąŠčéą║ąĖą╣ čüąĄą│ą╝ąĄąĮčé ą┐ą░ą╝čÅčéąĖ. ą¦ąĖčüą╗ąŠ čüčéčĆąŠą║ ą▓ ąĮą░ą▒ąŠčĆąĄ ąĮą░ąĘčŗą▓ą░čÄčé ąź-ą║ą░ąĮą░ą╗čīąĮąŠą╣ ą░čüčüąŠčåąĖą░čéąĖą▓ąĮąŠčüčéčīčÄ. ąŁč鹊 čüą▓ąŠą╣čüčéą▓ąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ąĮą░ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╝ čāčĆąŠą▓ąĮąĄ.

ą¤čĆąĖ čćč鹥ąĮąĖąĖ ą┐ąŠą╗čāčćą░čÄčé čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĖąĄ ą▓ ą┐ą░ą╝čÅčéąĖ č鹊ą╗čīą║ąŠ ą▓ ą┐ąĄčĆą▓čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┐ąŠą╗čāčćą░čÄčé ą┤ąŠčüčéčāą┐ ą║ čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĖčÄ. ą¤čĆąĖ ąĘą░ą┐ąĖčüąĖ ąĘąĮą░č湥ąĮąĖąĄ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮąŠ čüčĆą░ąĘčā (čüą║ą▓ąŠąĘąĮą░čÅ ąĘą░ą┐ąĖčüčī) ąĖą╗ąĖ ą▒čāą┤ąĄčé čĆą░ąĘą╝ąĄčēąĄąĮąŠ ą▓ ą║čŹčłąĄ ą┤ą╗čÅ ą▒ąŠą╗ąĄąĄ ą┐ąŠąĘą┤ąĮąĄą╣ ąĘą░ą┐ąĖčüąĖ (čĆąĄąČąĖą╝ ąŠą▒čĆą░čéąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ). ąŻ ą║ą░ąČą┤ąŠą│ąŠ čĆąĄąČąĖą╝ą░ ąĄčüčéčī čüą▓ąŠąĖ ą┐ą╗čÄčüčŗ/ą╝ąĖąĮčāčüčŗ ą▓ ąŠčéąĮąŠčłąĄąĮąĖąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčćč鹥ąĮčŗ, čāčćąĖčéčŗą▓ą░čÅ čüą┐ąĄčåąĖčäąĖą║čā ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ.

ąÆ čüą╗čāčćą░ąĄ čü ą┐ą░ą╝čÅčéčīčÄ čü ąŠą▒čĆą░čéąĮąŠą╣ ąĘą░ą┐ąĖčüčīčÄ (write-back, WB), ąĄčüą╗ąĖ čüčéčĆąŠą║ą░ ą║čŹčłą░ ąŠčéą╝ąĄč湥ąĮą░ ą║ą░ą║ "ą│čĆčÅąĘąĮą░čÅ", č鹊 ąĘą░ą┐ąĖčüčī ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ ąĖąĮč鹥čĆč乥ą╣čüąĄ AXIM, ą║ąŠą│ą┤ą░ čüčéčĆąŠą║ą░ ą▓čŗą│čĆčāąČą░ąĄčéčüčÅ. ąÜąŠą│ą┤ą░ "ą│čĆčÅąĘąĮą░čÅ" čüčéčĆąŠą║ą░ ą║čŹčłą░ ą▓čŗą│čĆčāąČąĄąĮą░, ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ ą▒čāč乥čĆ ąĘą░ą┐ąĖčüąĖ ą▓ ąĖąĮč鹥čĆč乥ą╣čü AXIM, ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮ ą▓ čüąĖčüč鹥ą╝čā ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ.

ąÜčŹčł L1 ąĮą░ ą▓čüąĄčģ Cortex┬«-M7 čĆą░ąĘą┤ąĄą╗ąĄąĮ ąĮą░ čüčéčĆąŠą║ąĖ ą┐ąŠ 32 ą▒ą░ą╣čéą░. ąÜą░ąČą┤ą░čÅ čüčéčĆąŠą║ą░ ąĖą╝ąĄąĄčé čé菹│ čü ą░ą┤čĆąĄčüąŠą╝. ąÜčŹčł ą┤ą░ąĮąĮčŗčģ ąĖą╝ąĄąĄčé ą░čüčüąŠčåąĖą░čéąĖą▓ąĮąŠčüčéčī 4 ą║ą░ąĮą░ą╗ą░ (4 čüčéčĆąŠą║ąĖ ą▓ ąĮą░ą▒ąŠčĆąĄ), ą║čŹčł ą║ąŠą╝ą░ąĮą┤ ąĖą╝ąĄąĄčé ą░čüčüąŠčåąĖą░čéąĖą▓ąĮąŠčüčéčī 2 ą║ą░ąĮą░ą╗ą░. ąŁč鹊 ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ą║ąŠą╝ą┐čĆąŠą╝ąĖčüčü, čćč鹊ą▒čŗ ąĮąĄ ą┐čĆąĖčüą▓ą░ąĖą▓ą░čéčī čé菹│ ą║ą░ąČą┤ąŠą╣ čüčéčĆąŠą║ąĄ čü ą░ą┤čĆąĄčüąŠą╝.

ąŻą┤ą░čćąĮąŠąĄ ąŠą▒čĆą░čēąĄąĮąĖąĄ ą▓ ą║čŹčł (cache hit) - ą║ąŠą│ą┤ą░ ą░ą┤čĆąĄčü ą┐ąŠą┐ą░ą┤ą░ąĄčé ą▓ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠąĄ ą╝ąĄčüč鹊 ąĮą░ ą┤ą░ąĮąĮąŠą╝ ąĮą░ą▒ąŠčĆąĄ čüčéčĆąŠą║. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą░ą┐ą┐ą░čĆą░čéąĮčŗąĄ čüčĆąĄą┤čüčéą▓ą░ ą┤ąŠą╗ąČąĮčŗ ą┤ąĄą╗ą░čéčī ą╝ąĄąĮčīčłąĄ ąŠą┐ąĄčĆą░čåąĖą╣ čüčĆą░ą▓ąĮąĄąĮąĖčÅ, čćč鹊ą▒čŗ čāąĘąĮą░čéčī, ą║čŹčłąĖčĆąŠą▓ą░ąĮ ą╗ąĖ ą░ą┤čĆąĄčü. ąĢčüą╗ąĖ ąŠą▒čĆą░čēąĄąĮąĖąĄ čāčüą┐ąĄčłąĮąŠąĄ, č鹊 ąĘąĮą░č湥ąĮąĖąĄ ą║čŹčłą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, ąĖą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ. ąĢčüą╗ąĖ ąŠą▒čĆą░čēąĄąĮąĖąĄ ąĮąĄčāą┤ą░čćąĮąŠąĄ (ą┐čĆąŠą╝ą░čģ, cache miss), č鹊 ą▓čŗą┤ąĄą╗čÅąĄčéčüčÅ ąĮąŠą▓ą░čÅ čüčéčĆąŠą║ą░ ąĖ ą┐čĆąĖčüą▓ą░ąĖą▓ą░ąĄčéčüčÅ čé菹│, ąĖ ą║čŹčł ąĘą░ą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą╗ąĖą▒ąŠ ąŠčé ą┤ąŠčüčéčāą┐ą░ ąĮą░ čćč鹥ąĮąĖąĄ, ą╗ąĖą▒ąŠ ąŠčé ą┤ąŠčüčéčāą┐ą░ ąĮą░ ąĘą░ą┐ąĖčüčī. ąĢčüą╗ąĖ ą▓čüąĄ čüčéčĆąŠą║ąĖ čāąČąĄ ą▓čŗą┤ąĄą╗ąĄąĮčŗ(ąĘą░ą┐ąŠą╗ąĮąĄąĮčŗ), ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą║čŹčł- ą┐ą░ą╝čÅčéąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą┐čĆąŠčåąĄčüčü ąĘą░ą╝ąĄčēąĄąĮąĖčÅ čüčéčĆąŠą║ąĖ, ą▓ ą║ąŠč鹊čĆąŠą╝ ą▓čŗą▒čĆą░ąĮąĮą░čÅ čüčéčĆąŠą║ą░(ąĘą░ą▓ąĖčüąĖčé ąŠčé ą░ą╗ą│ąŠčĆąĖčéą╝ą░ ąĘą░ą╝ąĄčēąĄąĮąĖčÅ) ąŠčćąĖčēą░ąĄčéčüčÅ/ą░ąĮąĮčāą╗ąĖčĆčāąĄčéčüčÅ, ąĖ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄčĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ. ąÜčŹčł ą┤ą░ąĮąĮčŗčģ ąĖ ą║čŹčł ą║ąŠą╝ą░ąĮą┤ čĆąĄą░ą╗ąĖąĘčāčÄčé ą┐čüąĄą▓ą┤ąŠčüą╗čāčćą░ą╣ąĮčŗą╣ ą░ą╗ą│ąŠčĆąĖčéą╝ ąĘą░ą╝ąĄčēąĄąĮąĖčÅ.

ąÜčŹčł L1 ą╝ąŠąČąĄčé čāą▓ąĄą╗ąĖčćąĖčéčī ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ čüąŠč湥čéą░ąĮąĖąĖ čü ąĖąĮč鹥čĆč乥ą╣čüą░ą╝ąĖ ą┐ą░ą╝čÅčéąĖ ąĮą░ čłąĖąĮąĄ AXI. ąØąĄ ąĮčāąČąĮąŠ ą┐čāčéą░čéčī čü ą┐ą░ą╝čÅčéčīčÄ čü ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ Tightly Couple Memory (TCM), ą║ąŠč鹊čĆą░čÅ ąĮąĄ čÅą▓ą╗čÅąĄčéčüčÅ ą║čŹčłąĖčĆčāąĄą╝ąŠą╣. ąøčÄą▒ą░čÅ ąŠą▒čŗčćąĮą░čÅ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ą║čŹčłąĖčĆčāąĄą╝ąŠą╣, ą║ą░ą║ ąŠą┐ąĖčüą░ąĮąŠ ą▓čŗčłąĄ, ąĮąŠ ą╗čāčćčłąĖą╣ čĆąĄąĘčāą╗čīčéą░čé ą▒čāą┤ąĄčé čā ą┐ą░ą╝čÅčéąĖ, ą║ ą║ąŠč鹊čĆąŠą╣ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ č湥čĆąĄąĘ čłąĖąĮčā AXI, čéą░ą║ąĖąĄ ą║ą░ą║: ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ążą╗čŹčł-ą┐ą░ą╝čÅčéčī, ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ SRAM ąĖ ą▓ąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī, čüą▓čÅąĘą░ąĮąĮą░čÅ č湥čĆąĄąĘ ą╝ąŠą┤čāą╗čī FMC ąĖą╗ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ Quad-SPI.

ąĢčüčéčī č湥čéčŗčĆąĄ ąŠčüąĮąŠą▓ąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖąĖ čü ą║čŹčłąĄą╝: ą▓ą║ą╗čÄč湥ąĮąĖąĄ, ąŠčéą║ą╗čÄč湥ąĮąĖąĄ, ąŠčćąĖčüčéą║ą░ ąĖ ą░ąĮąĮčāą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ. ąöą╗čÅ čŹčéąĖčģ ąŠą┐ąĄčĆą░čåąĖą╣ ą┤ąŠčüčéčāą┐ąĮčŗ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ čäčāąĮą║čåąĖąĖ API Cube STM32F7, čćč鹊 čāą╝ąĄąĮčīčłą░ąĄčé ą▓čĆąĄą╝čÅ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ.

[ąöąŠčüčéčāą┐ ą║ ąĮą░čüčéčĆąŠą╣ą║ąĄ ą║čŹčłą░ Cortex┬«-M7 čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ CMSIS]

ążčāąĮą║čåąĖąĖ CMSIS ą║čŹčłą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą▓ čäą░ą╣ą╗ąĄ core_cm7.h ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ ąóą░ą▒ą╗. 1.

ąóą░ą▒ą╗ąĖčåą░ 1. CMSIS čäčāąĮą║čåąĖąĖ ą║čŹčłą░.

| CMSIS čäčāąĮą║čåąĖąĖ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| void SCB_EnableICache (void)

|

ąÉąĮąĮčāą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ ąĘą░č鹥ą╝ ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą║čŹčłą░ ą║ąŠą╝ą░ąĮą┤ |

| void SCB_DisableICache (void)

|

ą×čéą║ą╗čÄč湥ąĮąĖąĄ ą║čŹčłą░ ą║ąŠą╝ą░ąĮą┤ ąĖ ą░ąĮąĮčāą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą▓ ąĮąĄą╝ |

| void SCB_InvalidateICache (void)

|

ąÉąĮąĮčāą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ ą║čŹčłą░ ą║ąŠą╝ą░ąĮą┤ |

| void SCB_EnableDCache (void)

|

ąÉąĮąĮčāą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ ąĘą░č鹥ą╝ ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ |

| void SCB_DisableDCache (void)

|

ą×čéą║ą╗čÄč湥ąĮąĖąĄ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ, ąŠčćąĖčüčéą║ą░ ąĖ ą░ąĮąĮčāą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĄą│ąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ |

| void SCB_InvalidateDCache (void)

|

ąÉąĮąĮčāą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ |

| void SCB_CleanDCache (void)

|

ą×čćąĖčüčéą║ą░ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ |

| void SCB_CleanInvalidateDCache (void)

|

ą×čćąĖčüčéą║ą░ ąĖ ą░ąĮąĮčāą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ |

ą×čćąĖčüčéą║ą░ ą║čŹčłą░: ąŠą┐ąĄčĆą░čåąĖčÅ ąŠą▒čĆą░čéąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ "ą│čĆčÅąĘąĮąŠą╣" čüčéčĆąŠą║ąĖ ą║čŹčłą░ ą▓ ą┐ą░ą╝čÅčéčī (čéą░ą║čāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ ąĖąĮąŠą│ą┤ą░ ąĮą░ąĘčŗą▓ą░čÄčé čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĄą╣ ąĖą╗ąĖ čüą▒čĆąŠčüąŠą╝, flush).

ąÉąĮąĮčāą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ ą║čŹčłą░: ąŠą┐ąĄčĆą░čåąĖčÅ ą┐ąŠą╝ąĄčćą░ąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą║čŹčłą░ ą║ą░ą║ ąĮąĄą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠąĄ (ąŠą▒čŗčćąĮąŠ, čŹč鹊 ąŠą┐ąĄčĆą░čåąĖčÅ čāą┤ą░ą╗ąĄąĮąĖčÅ).

[ąĀą░ą▒ąŠčéą░ čü ą║čŹčłąĄą╝]

ąÆ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ čüą╗čāčćą░ąĄą▓ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║čŹčł ąĮąĄčüą╗ąŠąČąĮąŠ. ąØąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ąŠą▒ą╗ą░čüčéčī ą▓ ą╝ąŠą┤čāą╗ąĄ MPU ąĖ ą▓ą║ą╗čÄčćąĖčéčī ą║čŹčł čü ą┐ąŠą╝ąŠčēčīčÄ čäčāąĮą║čåąĖą╣ CMSIS, čāą║ą░ąĘą░ąĮąĮčŗčģ ąĮąĖąČąĄ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą╝ąŠąČąĮąŠ čüą┤ąĄą╗ą░čéčī ąĮą░čüčéčĆąŠą╣ą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāčÅ ąŠą▒čĆą░čéąĮčāčÄ ąĖą╗ąĖ čüą║ą▓ąŠąĘąĮčāčÄ ąĘą░ą┐ąĖčüčī.

ą×ą▒čĆą░čéąĮą░čÅ ąĘą░ą┐ąĖčüčī (write-back, WB): ą║čŹčł ąĮąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▓ ą┐ą░ą╝čÅčéčī, ą┐ąŠą║ą░ ąĮąĄ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ ąŠčćąĖčüčéą║ąĖ.

ąĪą║ą▓ąŠąĘąĮą░čÅ ąĘą░ą┐ąĖčüčī (write-through, WT): ąĘą░ą┐čāčüą║ą░ąĄčé ąĘą░ą┐ąĖčüčī ą▓ ą┐ą░ą╝čÅčéčī ą║ą░ą║ č鹊ą╗čīą║ąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ čüčéčĆąŠą║čā ą║čŹčłą░. ąŁč鹊 ą▒ąŠą╗ąĄąĄ ą▒ąĄąĘąŠą┐ą░čüąĮąŠ ą┤ą╗čÅ čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ, ąĮąŠ čéčĆąĄą▒čāąĄčé ą▒ąŠą╗čīčłąĄą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ čłąĖąĮąĄ. ąØą░ ą┐čĆą░ą║čéąĖą║ąĄ ąĘą░ą┐ąĖčüčī ą▓ ą┐ą░ą╝čÅčéčī čüą┤ąĄą╗ą░ąĮą░ ą▓ č乊ąĮąŠą▓ąŠą╝ čĆąĄąČąĖą╝ąĄ ąĖ ąĖą╝ąĄąĄčé ąĮąĄą▒ąŠą╗čīčłąŠą╣ čŹčäč乥ą║čé, ąĄčüą╗ąĖ ą║ čŹč鹊ą╝čā ąČąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠą╝čā ą║čŹčłą░ ąĮąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąŠč湥ąĮčī ą▒čŗčüčéčĆčŗą╣ ąĖ ą┐ąŠčüč鹊čÅąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čŹč鹊 ą▓čüąĄą│ą┤ą░ ą║ąŠą╝ą┐čĆąŠą╝ąĖčüčü.

[STM32F7 ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ]

ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą╝ąŠą┤čāą╗čī MPU ąŠčéą║ą╗čÄč湥ąĮ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą║čŹčłą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą║ą░ą║ čéą░ą▒ą╗ąĖčåą░ ą░ą┤čĆąĄčüąŠą▓ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ.

ąóą░ą▒ą╗ąĖčåą░. 2. ą×ą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ, ąŠą▒čēąĖą╣ ą┤ąŠčüčéčāą┐ ąĖ ą┐ąŠą╗ąĖčéąĖą║ąĖ ą║čŹčłą░.

| ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓

|

ą×ą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ

|

ąóąĖą┐ ą┐ą░ą╝čÅčéąĖ

|

ąĪąŠą▓ą╝ąĄčüčéąĮąŠąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ

|

ą¤ąŠą╗ąĖčéąĖą║ą░ ą║čŹčłą░

|

| 0x00000000-0x1FFFFFFF

|

Code |

ą×ą▒čŗčćąĮą░čÅ (Normal) |

ąØąĄčé |

WT |

| 0x20000000-0x3FFFFFFF

|

SRAM |

WBWA |

| 0x40000000-0x5FFFFFFF

|

ą¤ąĄčĆąĖčä. čāčüčéčĆąŠą╣čüčéą▓ą░ |

Device |

ąØąĄčé |

- |

| 0x60000000-0x7FFFFFFF

|

ąÆąĮąĄčłąĮąĄąĄ RAM |

ą×ą▒čŗčćąĮą░čÅ (Normal) |

ąØąĄčé |

WBWA |

| 0x80000000-0x9FFFFFFF

|

WT |

| 0xA0000000-0xBFFFFFFF

|

ąÆąĮąĄčłąĮąĄąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ |

Device |

ąöą░ |

- |

| 0xC0000000-0xDFFFFFFF

|

ąØąĄčé |

| 0xE0000000-0xE00FFFFF

|

ą¦ą░čüčéąĮą░čÅ čłąĖąĮą░ ą┐ąĄčĆąĖčä. čāčüčéčĆąŠą╣čüčéą▓ |

ąĪčéčĆąŠą│ąŠ čāą┐ąŠčĆčÅą┤ąŠč湥ąĮąĮą░čÅ ąĮą░ ą┤ąŠčüčéčāą┐ |

ąØąĄčé |

- |

| 0xE0100000-0xFFFFFFFF

|

ąĪąĖčüč鹥ą╝ą░, ąĘą░ą▓ąĖčüčÅčēą░čÅ ąŠčé ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅ |

Device |

ąØąĄčé |

- |

[ą¤čĆąĖą╝ąĄčĆ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą║čŹčłą░ ąĖ čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ]

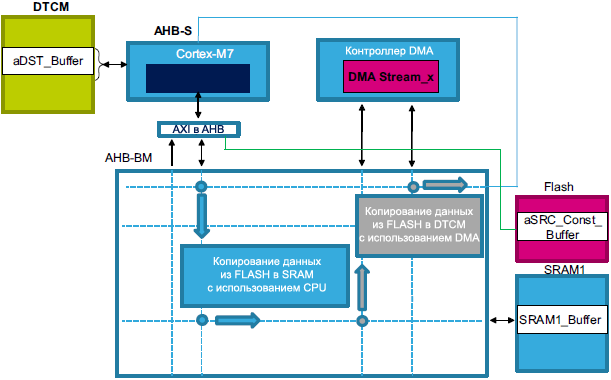

ą”ąĄą╗čī čŹč鹊ą│ąŠ ą┐čĆąĖą╝ąĄčĆą░ čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊ą▒čŗ ąŠąĘąĮą░ą║ąŠą╝ąĖčéčīčüčÅ čü ą║ąŠą│ąĄčĆąĄąĮčéąĮąŠčüčéčīčÄ ą║čŹčł-ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ ARM┬« Cortex┬«-M7.

ąĪąĮą░čćą░ą╗ą░ CPU ą║ąŠą┐ąĖčĆčāąĄčé 128 ą║ąŠąĮčüčéą░ąĮčéąĮčŗčģ ą▒ą░ą╣čé ąĖąĘ ążą╗čŹčł-ą┐ą░ą╝čÅčéąĖ aSRC_Const_Buffer ą▓ąŠ ą▓čĆąĄą╝ąĄąĮąĮčŗą╣ ą▒čāč乥čĆ pBuffer SRAM1.

ąŚą░č鹥ą╝ CPU ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčé ąĖ ą▓ą║ą╗čÄčćą░ąĄčé DMA ą┤ą╗čÅ čüąŠą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čéąĖą┐ą░ ą┐ą░ą╝čÅčéčī- ą┐ą░ą╝čÅčéčī ąĖ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖąĘ SRAM1 pBuffer ą▓ ą▒čāč乥čĆ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ aDST_Buffer, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ ą▓ DTCM RAM.

ąØą░ą║ąŠąĮąĄčå, CPU čüčĆą░ą▓ąĮąĖą▓ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ, ą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ DMA ąĖąĘ aDST_Buffer čü čłą░ą▒ą╗ąŠąĮąŠą╝ ą║ąŠąĮčüčéą░ąĮčé ąĖąĘ ążą╗čŹčł-ą┐ą░ą╝čÅčéąĖ aSRC_Const_Buffer.

ąĀąĖčü. 2 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüčģąĄą╝čā ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ.

ąĀąĖčü. 2. ą¤čāčéąĖ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ.

ą”ąĄą╗čī čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī ą▓ą╗ąĖčÅąĮąĖąĄ ąĮą░ čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā CPU ąĖ DMA ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ ą║čŹčłąĖčĆčāąĄą╝ąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ čü ą░čéčĆąĖą▒čāč鹊ą╝ ąŠą▒čĆą░čéąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ (write-back).

ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░, ą║čŹčł ą┤ą░ąĮąĮčŗčģ ąĖ ą║ąŠą╝ą░ąĮą┤ ąŠčéą║ą╗čÄč湥ąĮ. ąÜąŠą│ą┤ą░ ą║čŹčł ą┤ą░ąĮąĮčŗčģ ąŠčéą║ą╗čÄč湥ąĮ, ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā SRAM1 ąĖ RAM DTCM ą▒čāą┤ąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮą░ čāčüą┐ąĄčłąĮąŠ ą▓ čüčģąĄą╝ąĄ, ąŠą┐ąĖčüą░ąĮąĮąŠą╣ ą▓čŗčłąĄ.

ą¤čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĄąČą┤ąĄ, č湥ą╝ ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ ąŠą┐ąĖčüą░ąĮąĮčŗą╣ čüčåąĄąĮą░čĆąĖą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą▒čāą┤ąĄčé ąŠą▒ąĮą░čĆčāąČąĄąĮąŠ ąĮąĄčüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā ą┤ą░ąĮąĮčŗą╝ąĖ ą▓ aDST_Buffer (čåąĄą╗ąĄą▓ąŠą╣ ą▒čāč乥čĆ DMA ą▓ DTCM) ąĖ aSRC_Const_Buffer (ą▒čāč乥čĆ ąĖčüč鹊čćąĮąĖą║ą░ ą┤ą░ąĮąĮčŗčģ CPU ą▓ąŠ ążą╗čŹčł-ą┐ą░ą╝čÅčéąĖ).

ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą║čŹčłą░ L1 ą▓čüąĄą│ą┤ą░ ąŠčüčéą░ąĄčéčüčÅ ą┐čĆąŠą▒ą╗ąĄą╝ą░, ąĖąĮąŠą│ą┤ą░ ąĮą░ąĘčŗą▓ą░ąĄą╝ą░čÅ ą║ąŠą│ąĄčĆąĄąĮčéąĮąŠčüčéčīčÄ ą║čŹčłą░. ąŁč鹊čé ą▓ąŠą┐čĆąŠčü ą▓ąŠąĘąĮąĖą║ą░ąĄčé, ą║ąŠą│ą┤ą░ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą╝ą░čüč鹥čĆ- čāčüčéčĆąŠą╣čüčéą▓ą░ (CPU, DMA...) ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą┐ą░ą╝čÅčéčī čüąŠą▓ą╝ąĄčüčéąĮąŠ . ąĢčüą╗ąĖ CPU ą┐ąĖčłąĄčé čćč鹊-č鹊 ą▓ ąŠą▒ą╗ą░čüčéčī, čā ą║ąŠč鹊čĆąŠą╣ ąĄčüčéčī ą░čéčĆąĖą▒čāčé ą║čŹčłą░ čü ąŠą▒čĆą░čéąĮąŠą╣ ąĘą░ą┐ąĖčüčīčÄ (ą┐čĆąĖą╝ąĄčĆ SRAM1), čĆąĄąĘčāą╗čīčéą░čé ąĘą░ą┐ąĖčüąĖ ąĮąĄ ą▒čāą┤ąĄčé ą▓ąĖą┤ąĄąĮ ą▓ SRAM, ą┐ąŠčüą║ąŠą╗čīą║čā ą┤ąŠčüčéčāą┐ ą▒čāč乥čĆąĖąĘąŠą▓ą░ąĮ, ąĖ ąĘą░č鹥ą╝, ąĄčüą╗ąĖ DMA čüčćąĖčéą░ąĄčé čéčā ąČąĄ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ, čćč鹊ą▒čŗ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ, č鹊 ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĮąĄ ą▒čāą┤ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī ąŠąČąĖą┤ą░ąĄą╝čŗą╝ ą┤ą░ąĮąĮčŗą╝.

ąĀąĄčłąĄąĮąĖąĄ 1: ą▓čŗą┐ąŠą╗ąĮčÅčéčī ąŠą┐ąĄčĆą░čåąĖčÄ ą┐ąŠ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖčÄ ą║čŹčłą░ ą┐ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ą▓ ą║čŹčłąĖčĆčāąĄą╝čāčÄ ąŠą▒ą╗ą░čüčéčī, ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą▓čŗąĘčŗą▓ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÄ ąŠčćąĖčüčéą║ąĖ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ čäčāąĮą║čåąĖąĄą╣ CMSIS SCB_CleanDCache() (ą▓čüąĄ "ą│čĆčÅąĘąĮčŗąĄ" čüčéčĆąŠą║ąĖ ą▒čāą┤čāčé ąŠą▒čĆą░čéąĮąŠ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ SRAM1).

ąĀąĄčłąĄąĮąĖąĄ 2: ą▓čŗą┐ąŠą╗ąĮčÅčéčī ąŠą┐ąĄčĆą░čåąĖčÄ ą┐ąŠ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖčÄ ą║čŹčłą░, ąĖąĘą╝ąĄąĮčÅčÅ ą░čéčĆąĖą▒čāčéčŗ MPU ą┐ą░ą╝čÅčéąĖ SRAM1 ąŠčé ąŠą▒čĆą░čéąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ(ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ) ą║ ą┐ąŠą╗ąĖčéąĖą║ąĄ čüą║ą▓ąŠąĘąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ.

ąĀąĄčłąĄąĮąĖąĄ 3: ąĖąĘą╝ąĄąĮčÅčÅ ą░čéčĆąĖą▒čāčéčŗ MPU ą┐ą░ą╝čÅčéąĖ SRAM1 ąĖčüą┐ąŠą╗čīąĘčāčÅ ąŠą▒čēąĖąĄ ą░čéčĆąĖą▒čāčéčŗ. ąŁč鹊 ą▒čāą┤ąĄčé ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐čĆąĄą┐čÅčéčüčéą▓ąŠą▓ą░čéčī ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖčÄ SRAM1 ą▓ ą║čŹčłąĄ ą┤ą░ąĮąĮčŗčģ.

ąĀąĄčłąĄąĮąĖąĄ 4: ą▓čŗą┐ąŠą╗ąĮčÅčéčī ąŠą┐ąĄčĆą░čåąĖčÄ ą┐ąŠ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖčÄ ą║čŹčłą░, ą▓čŗąĘčŗą▓ą░čÅ ą┐ąŠą╗ąĖčéąĖą║čā čüą║ą▓ąŠąĘąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ ą┤ą╗čÅ ą▓čüąĄčģ ąŠą┐ąĄčĆą░čåąĖą╣ ąĘą░ą┐ąĖčüąĖ. ąŁč鹊 ą╝ąŠąČąĮąŠ čüą┤ąĄą╗ą░čéčī, ą▓ą║ą╗čÄčćąĖą▓ čüą║ą▓ąŠąĘąĮčāčÄ ąĘą░ą┐ąĖčüčī č湥čĆąĄąĘ čāčüčéą░ąĮąŠą▓ą║čā ą▒ąĖčéą░ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ (D-Cache bit) ą▓ čĆąĄą│ąĖčüčéčĆąĄ CACR.

ąĪąŠą│ą╗ą░čüąŠą▓ą░ąĮąĮąŠčüčéčī (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī) ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā čÅą┤čĆąŠą╝ ąĖ DMA ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ą╝ąĄč鹊ą┤ą░ą╝ąĖ:

1. ąæčāč乥čĆčŗ SRAM1 ą┤ąĄą╗ą░čÄčéčüčÅ ąĮąĄ ą║čŹčłąĖčĆčāąĄą╝čŗą╝ąĖ.

2. ąÆą║ą╗čÄčćą░ąĄčéčüčÅ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒čāč乥čĆąŠą▓ SRAM1 čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ ąŠą▒čĆą░čéąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ, ą┐čĆ čŹč鹊ą╝ čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĮąŠčüčéčī ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ (ąŠčćąĖčüčéą║ą░ ąĖą╗ąĖ ą░ąĮąĮčāą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ).

3. ąśąĘą╝ąĄąĮąĄąĮąĖąĄą╝ ą░čéčĆąĖą▒čāčéą░ ąŠą▒ą╗ą░čüčéąĖ MPU ą▓ SRAM1 ąĮą░ čüąŠą▓ą╝ąĄčüčéąĮčāčÄ ąŠą▒ą╗ą░čüčéčī.

4. ąÆą║ą╗čÄčćą░ąĄčéčüčÅ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒čāč乥čĆąŠą▓ SRAM1 čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ čüą║ą▓ąŠąĘąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ.

ąöčĆčāą│ąŠą╣ čüą╗čāčćą░ą╣ - ą║ąŠą│ą┤ą░ DMA ą┐ąĖčłąĄčé ą▓ SRAM1, ąĖ CPU čüąŠą▒ąĖčĆą░ąĄčéčüčÅ čüčćąĖčéą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘ SRAM1. ą¦č鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā ą║čŹčłąĄą╝ ąĖ SRAM1, ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą░ąĮąĮčāą╗ąĖčĆąŠą▓ą░čéčī ą║čŹčł ą┐ąĄčĆąĄą┤ čćč鹥ąĮąĖąĄą╝ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąĖąĘ SRAM1.

ąŚą░ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĄą╣ ą┐ąŠ ąĮą░čüčéčĆąŠą╣ą║ąĄ ą║čŹčłą░ ąŠą▒čĆą░čéąĖč鹥čüčī ą║ ą┤ąŠą║čāą╝ąĄąĮčéčā (PM0253) STM32F7 Series Cortex┬«-M7 processor programming manual.

[ą¤ąŠą┤čüą║ą░ąĘą║ąĖ ąĖ čüąŠą▓ąĄčéčŗ]

ŌĆó ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ąĮą░ą┤ąŠ ą░ąĮąĮčāą╗ąĖčĆąŠą▓ą░čéčī ą║ą░ąČą┤čŗą╣ ą║čŹčł ą┐ąĄčĆąĄą┤ ąĄą│ąŠ ą▓ą║ą╗čÄč湥ąĮąĖąĄą╝, ą▓ ą┐čĆąŠčéąĖą▓ąĮąŠą╝ čüą╗čāčćą░ąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝.

ŌĆó ą¤čĆąĖ ąŠčéą║ą╗čÄč湥ąĮąĖąĖ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąŠčćąĖčēą░čéčī ąŠą▒ą╗ą░čüčéčī ą║čŹčłą░, čćč鹊ą▒čŗ ą▒čŗčéčī čāą▓ąĄčĆąĄąĮąĮčŗą╝ ą▓ č鹊ą╝, čćč鹊 ą╗čÄą▒čŗąĄ "ą│čĆčÅąĘąĮčŗąĄ" ą┤ą░ąĮąĮčŗąĄ čüą▒čĆąŠčłąĄąĮčŗ ą▓ąŠ ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī.

ŌĆó ą¤ąĄčĆąĄą┤ ą▓ą║ą╗čÄč湥ąĮąĖąĄą╝ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą░ąĮąĮčāą╗ąĖčĆąŠą▓ą░čéčī ąŠą▒ą╗ą░čüčéčī ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ, ąĄčüą╗ąĖ ą▓ąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī ą╝ąŠąČąĄčé ąĖą╝ąĄčéčī ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą┐ąŠčüą║ąŠą╗čīą║čā ą║čŹčł ą▒čŗą╗ ąŠčéą║ą╗čÄč湥ąĮ.

ŌĆó ą¤ąĄčĆąĄą┤ ą▓ą║ą╗čÄč湥ąĮąĖąĄą╝ ą║čŹčłą░ ą║ąŠą╝ą░ąĮą┤ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą░ąĮąĮčāą╗ąĖčĆąŠą▓ą░čéčī ąŠą▒ą╗ą░čüčéčī ą║čŹčłą░ ą║ąŠą╝ą░ąĮą┤ ąĄčüą╗ąĖ ą▓ąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī ą╝ąŠąČąĄčé ąĖą╝ąĄčéčī ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą┐ąŠčüą║ąŠą╗čīą║čā ą║čŹčł ą▒čŗą╗ ąŠčéą║ą╗čÄč湥ąĮ.

ŌĆó ąĢčüą╗ąĖ ą¤ą× ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą║čŹčłąĖčĆčāąĄą╝čāčÄ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ ą┤ą╗čÅ ą▒čāč乥čĆąŠą▓ ą┐čĆąĖąĄą╝ą░/ą┐ąĄčĆąĄą┤ą░čćąĖ DMA, ąŠąĮąŠ ą┤ąŠą╗ąČąĮąŠ ą▓čŗąĘą▓ą░čéčī ąŠčćąĖčüčéą║čā ą║čŹčłą░ ą┐ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ąŠą┐ąĄčĆą░čåąĖą╣ DMA, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮčŗ ą▓ ą┐ąŠą┤čüąĖčüč鹥ą╝ąĄ ą┐ą░ą╝čÅčéąĖ. ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ DMA-ą┐ąĄčĆąĄą┤ą░čćąĖ , ą┐čĆąĖ čćč鹥ąĮąĖąĖ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą┐ąĄčĆąĖč乥čĆąĖąĖ, ą¤ą× ą┤ąŠą╗ąČąĮąŠ ą░ąĮąĮčāą╗ąĖčĆąŠą▓ą░čéčī ą║čŹčł ą┐ąĄčĆąĄą┤ čćč鹥ąĮąĖąĄą╝-DMA ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ.

ŌĆó ąÆčüąĄą│ą┤ą░ ą╗čāčćčłąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĮąĄą║čŹčłąĖčĆąŠą▓ą░ąĮąĮčāčÄ ąŠą▒ą╗ą░čüčéčī ą┤ą╗čÅ ą▒čāč乥čĆąŠą▓ DMA. ą¤ą× ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī MPU ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĮąĄą║čŹčłąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ ą┐ą░ą╝čÅčéąĖ, čćč鹊ą▒čŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ą░ą║ ąŠą▒čēčāčÄ ą┐ą░ą╝čÅčéčī ą╝ąĄąČą┤čā CPU ąĖ DMA.

ŌĆó ąØąĄ ą▓ą║ą╗čÄčćą░ą╣č鹥 ą║čŹčł ą┤ą╗čÅ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆą░čÅ ąĖąĮč鹥ąĮčüąĖą▓ąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ DMA.

ŌĆó ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą░ą║čüąĄą╗ąĄčĆą░č鹊čĆ ART, CPU ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī ą║ąŠą╝ą░ąĮą┤čā ą▓čüąĄą│ąŠ ąĘą░ 1 čéą░ą║čé ąĖąĘ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čäą╗čŹčł-ą┐ą░ą╝čÅčéąĖ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, 0-wait state). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą║čŹčł ą║ąŠą╝ą░ąĮą┤ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮ ą┤ą╗čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čäą╗čŹčł ą┐ą░ą╝čÅčéąĖ.

ŌĆó ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ NOR Flash ąŠą▒čĆą░čéąĮą░čÅ ąĘą░ą┐ąĖčüčī ą▓čŗąĘčŗą▓ą░ąĄčé ą┐čĆąŠą▒ą╗ąĄą╝čŗ, čéą░ą║ ą║ą░ą║ ą║ąŠą╝ą░ąĮą┤čŗ Erase ąĖ Write ąĮąĄ ąŠčéą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą▓ąŠ ą▓ąĮąĄčłąĮčÄčÄ čäą╗čŹčł ą┐ą░ą╝čÅčéčī.

ŌĆó ąĢčüą╗ąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ čÅą▓ą╗čÅąĄčéčüčÅ ąŠą▒čŗčćąĮąŠą╣ ą┐ą░ą╝čÅčéčīčÄ, ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗ąĄąĘąĮčŗą╝ čćč鹥ąĮąĖąĄ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ (D-cache). ą×ą┤ąĮą░ą║ąŠ, ąĄčüą╗ąĖ ą▓ąĮąĄčłąĮąĄąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ čÅą▓ą╗čÅąĄčéčüčÅ ASIC ąĖ/ąĖą╗ąĖ FIFO, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąŠčéą║ą╗čÄčćąĖčéčī ą║čŹčł ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

[ąĪčüčŗą╗ą║ąĖ]

1. AN4839 Level 1 cache on STM32F7 Series site:st.com.

2. AN4838: ą╝ąŠą┤čāą╗čī čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░čēąĖč鹊ą╣ ą┐ą░ą╝čÅčéąĖ STM32. |