|

ąŁč鹊 ą┐ąĄčĆąĄą▓ąŠą┤ ą░ą┐ąĮąŠčāčéą░ AN4838 [1] (ą░ą▓č鹊čĆ ą┐ąĄčĆąĄą▓ąŠą┤ą░ Marat Galyamov), ą║ąŠč鹊čĆčŗą╣ ąŠą┐ąĖčüčŗą▓ą░ąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą╝ąŠą┤čāą╗ąĄą╝ ąĘą░čēąĖčéčŗ ą┐ą░ą╝čÅčéąĖ (memory protection unit, MPU) ą▓ ą░čĆčģąĖč鹥ą║čéčāčĆąĄ STM32. ąæą╗ąŠą║ MPU čÅą▓ą╗čÅąĄčéčüčÅ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮčŗą╝ (ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄą╝čŗą╝) ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą╝ ą┤ą╗čÅ ąĘą░čēąĖčéčŗ ą┐ą░ą╝čÅčéąĖ. ąÆą║ą╗čÄč湥ąĮąĖąĄ ą╝ąŠą┤čāą╗čÅ MPU ą▓ STM32 ą┤ąĄą╗ą░ąĄčé čĆą░ą▒ąŠčéčā ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▒ąŠą╗ąĄąĄ čāčüč鹊ą╣čćąĖą▓ąŠą╣ ąĖ ąĮą░ą┤ąĄąČąĮąŠą╣. MPU ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮ ąĖ ą▓ą║ą╗čÄč湥ąĮ ą┐ąĄčĆąĄą┤ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝. ąĢčüą╗ąĖ ą╝ąŠą┤čāą╗čī MPU ąĮąĄ ą▓ą║ą╗čÄč湥ąĮ, č鹊 ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣ ą▓ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĖ čüąĖčüč鹥ą╝čŗ ą┐ą░ą╝čÅčéąĖ. ąŁč鹊čé ą░ą┐ąĮąŠčāčé ą║ą░čüą░ąĄčéčüčÅ ą▓čüąĄ ą┐čĆąŠą┤čāą║č鹊ą▓ STM32, ą▓ą║ą╗čÄčćą░čÅ Cortex┬«-M0+/M3/M4 ąĖ M7 ą▓ą░čĆąĖą░ąĮčéčŗ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé MPU.

ąŚą░ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĄą╣ ąŠ MPU, ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čüą╗ąĄą┤čāčÄčēąĖą╝ ą┤ąŠą║čāą╝ąĄąĮčéą░ą╝ ąĮą░ čüą░ą╣č鹥 www.st.com:

ŌĆó STM32F7 Series Cortex┬«-M7 processor programming manual (PM0253)

ŌĆó STM32F3 and STM32F4 Series Cortex┬«-M4 programming manual (PM0214)

ŌĆó STM32F10xxx/20xxx/21xxx/L1xxxx Cortex┬«-M3 programming manual (PM0056)

ŌĆó STM32L0 Series Cortex┬«-M0+ programming manual (PM0223)

ąóą░ą▒ą╗ąĖčåą░ 1. ą¤čĆąŠčåąĄčüčüąŠčĆčŗ STM32, ą║ąŠč鹊čĆčŗąĄ ąĖą╝ąĄčÄčé ą▒ą╗ąŠą║ MPU.

ąóąĖą┐

|

ą£ąŠą┤ąĄą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ (čüąĄčĆąĖąĖ) |

| ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ |

STM32F1, STM32F2, STM32F3, STM32F4, STM32F7, STM32L0, STM32L1, STM32L4 |

[ą×ą▒ąĘąŠčĆ čüąĖčüč鹥ą╝čŗ MPU]

MPU ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮ ą┤ą╗čÅ ą┐ąŠą▓čŗčłąĄąĮąĖčÅ čāčüč鹊ą╣čćąĖą▓ąŠčüčéąĖ ąĖ ąĮą░ą┤ąĄąČąĮąŠčüčéąĖ čüąĖčüč鹥ą╝čŗ, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ:

ŌĆó MPU ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ąŠą╝čā ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÄ ąĖąĘą╝ąĄąĮčÅčéčī ą┤ą░ąĮąĮčŗąĄ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą║čĆąĖčéąĖč湥čüą║ąĖą╝ąĖ ąĘą░ą┤ą░čćą░ą╝ąĖ (čéą░ą║ąŠą╣, ą║ą░ą║ čÅą┤čĆąŠ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ).

ŌĆó MPU ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ SRAM ą║ą░ą║ ąĮąĄąĖčüą┐ąŠą╗ąĮčÅąĄą╝čāčÄ ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ ą░čéą░ą║ąĖ ą▓ąĮąĄą┤čĆąĄąĮąĮąŠą│ąŠ ą║ąŠą┤ą░.

ŌĆó MPU ąĖąĘą╝ąĄąĮčÅąĄčé ą░čéčĆąĖą▒čāčéčŗ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ.

MPU ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮ ą┤ą╗čÅ ąĘą░čēąĖčéčŗ 8 ąŠą▒ą╗ą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ. ąÆ čüą▓ąŠčÄ ąŠč湥čĆąĄą┤čī, ąŠąĮąĖ ą╝ąŠą│čāčé ąĖą╝ąĄčéčī 8 ą┐ąŠą┤ąŠą▒ą╗ą░čüč鹥ą╣, ąĄčüą╗ąĖ čĆą░ąĘą╝ąĄčĆ ąŠą▒ą╗ą░čüčéąĖ ąĮąĄ ą╝ąĄąĮąĄąĄ 256 ą▒ą░ą╣čé. ą¤ąŠą┤ąŠą▒ą╗ą░čüčéąĖ ą▓čüąĄą│ą┤ą░ ąĖą╝ąĄčÄčé čĆą░ą▓ąĮčŗą╣ čĆą░ąĘą╝ąĄčĆ, ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓ą║ą╗čÄč湥ąĮčŗ ąĖą╗ąĖ ąŠčéą║ą╗čÄč湥ąĮčŗ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ąĮąŠą╝ąĄčĆą░ ą┐ąŠą┤ąŠą▒ą╗ą░čüčéąĖ. ą¤ąŠčüą║ąŠą╗čīą║čā ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ čĆą░ąĘą╝ąĄčĆ ąŠą▒ą╗ą░čüčéąĖ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┤ą╗ąĖąĮčŗ čüčéčĆąŠą║ąĖ ą║čŹčłą░ (32 ą▒ą░ą╣čéą░), 8 ą┐ąŠą┤ąŠą▒ą╗ą░čüč鹥ą╣ ą┐ąŠ 32 ą▒ą░ą╣čéą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé 256 ą▒ą░ą╣čéą░ą╝.

ą×ą▒ą╗ą░čüčéąĖ ą┐čĆąŠąĮčāą╝ąĄčĆąŠą▓ą░ąĮčŗ ąŠčé 0 ą┤ąŠ 7. ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĄčüčéčī ą┤čĆčāą│ą░čÅ ąŠą▒ą╗ą░čüčéčī, ąĮą░ąĘą▓ą░ąĮąĮą░čÅ ąŠą▒ą╗ą░čüčéčīčÄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, čü ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą╝ -1. ąÆčüąĄ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 0 ą┤ąŠ 7 ąĖą╝ąĄčÄčé ą┐čĆąĖąŠčĆąĖč鹥čé ąĮą░ą┤ ąŠą▒ą╗ą░čüčéčīčÄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ.

ą×ą▒ą╗ą░čüčéąĖ ą╝ąŠą│čāčé ą┐ąĄčĆąĄą║čĆčŗą▓ą░čéčīčüčÅ, ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓ą╗ąŠąČąĄąĮąĮčŗą╝ąĖ. ą×ą▒ą╗ą░čüčéčī 7 ąĖą╝ąĄąĄčé ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé, ąŠą▒ą╗ą░čüčéčī 0 - ąĮąĖąĘą║ąĖą╣, ąĖ čŹč鹊 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐ąĄčĆąĄą║čĆčŗą▓ą░čÄčēąĖčģčüčÅ ąŠą▒ą╗ą░čüč鹥ą╣. ą¤čĆąĖąŠčĆąĖč鹥čéčŗ čäąĖą║čüąĖčĆąŠą▓ą░ąĮčŗ ąĖ ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮčŗ.

ąĀąĖčü. 1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆąĖą╝ąĄčĆ čü 6-čÄ ąŠą▒ą╗ą░čüčéčÅą╝ąĖ. ąŁč鹊čé ą┐čĆąĖą╝ąĄčĆ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ąŠą▒ą╗ą░čüčéčī 4 ą┐ąĄčĆąĄą║čĆčŗą▓ą░ąĄčé ąŠą▒ą╗ą░čüčéąĖ 0 ąĖ 1. ą×ą▒ą╗ą░čüčéčī 5 ą▓ą║ą╗čÄč湥ąĮą░ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą▓ ąŠą▒ą╗ą░čüčéčī 3. ąóą░ą║ ą║ą░ą║ ą┐čĆąĖąŠčĆąĖč鹥čé ąĖą┤ąĄčé ą▓ ą┐ąŠčĆčÅą┤ą║ąĄ ą▓ąŠąĘčĆą░čüčéą░ąĮąĖčÅ, čā ąŠą▒ą╗ą░čüč鹥ą╣ ą┐ąĄčĆąĄą║čĆčŗčéąĖčÅ (ąČąĄą╗čéčŗąĄ) ąĄčüčéčī ą┐čĆąĖąŠčĆąĖč鹥čé ąĮą░ą┤ ą┤čĆčāą│ąĖą╝ąĖ ąŠą▒ą╗ą░čüčéčÅą╝ąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ ąŠą▒ą╗ą░čüčéčī 0 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą║ą░ą║ ą┤ąŠčüčéčāą┐ąĮą░čÅ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ, ą░ ąŠą▒ą╗ą░čüčéčī 4 ąĮą░ąŠą▒ąŠčĆąŠčé, ąĮąĄą┤ąŠčüčéčāą┐ąĮą░čÅ, č鹊 ą░ą┤čĆąĄčü, ą┐ąŠą┐ą░ą┤ą░čÄčēąĖą╣ ą▓ ąĘąŠąĮčā ą┐ąĄčĆąĄą║čĆčŗčéąĖčÅ ąŠą▒ą╗ą░čüč鹥ą╣, ąĮąĄ ą▒čāą┤ąĄčé ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ.

ąĀąĖčü. 1. ą¤čĆąĖą╝ąĄčĆ ą┐ąĄčĆąĄą║čĆčŗčéąĖčÅ ąŠą▒ą╗ą░čüč鹥ą╣.

MPU ąĄą┤ąĖąĮ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░, čćč鹊 ąŠąĘąĮą░čćą░ąĄčé ąŠčéčüčāčéčüčéą▓ąĖąĄ čĆą░ąĘą┤ąĄą╗ąĄąĮąĖčÅ ąŠą▒ą╗ą░čüč鹥ą╣ ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ ąĖ ą║ąŠą╝ą░ąĮą┤.

MPU ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┤čĆčāą│ąĖčģ ą░čéčĆąĖą▒čāč鹊ą▓ ą┐ą░ą╝čÅčéąĖ, čéą░ą║ąĖčģ ą║ą░ą║ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖąĄ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī 菹║čüą┐ąŠčĆčéąĖčĆąŠą▓ą░ąĮčŗ (ą┐čĆąĖą╝ąĄąĮąĄąĮčŗ) ą▓ čüąĖčüč鹥ą╝ąĮąŠą╝ ą▒ą╗ąŠą║ąĄ ą║čŹčł-ą┐ą░ą╝čÅčéąĖ ąĖą╗ąĖ ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ą┐ą░ą╝čÅčéąĖ.

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą║čŹčłąĄą╝ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ ą┐ąŠčüčĆąĄą┤čüčéą▓ąŠą╝ čĆąĄą│ąĖčüčéčĆą░ ą║ąŠą╝ą░ąĮą┤ ą║čŹčłą░, ąĮąŠ MPU ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┐ąŠą╗ąĖčéąĖą║ąĖ ą║čŹčłą░, ąĖ ą▒čāą┤ąĄčé ą╗ąĖ ąŠą▒ą╗ą░čüčéčī ą║čŹčłąĖčĆčāąĄą╝ąŠą╣ ąĖą╗ąĖ ąĮąĄčé. MPU ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāčüčéą░ąĮąŠą▓ąĖčéčī ą░čéčĆąĖą▒čāčéčŗ ą║čŹčłą░ ą┤ą╗čÅ ąŠą▒ą╗ą░čüčéąĖ ą║čŹčłąĄą╝ čāčĆąŠą▓ąĮčÅ L1 (ą┤ąŠčüčéčāą┐ąĮąŠ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čüąĄčĆąĖąĖ STM32F7, čā ą║ąŠč鹊čĆąŠą╣ ąĄčüčéčī ą║čŹčł L1).

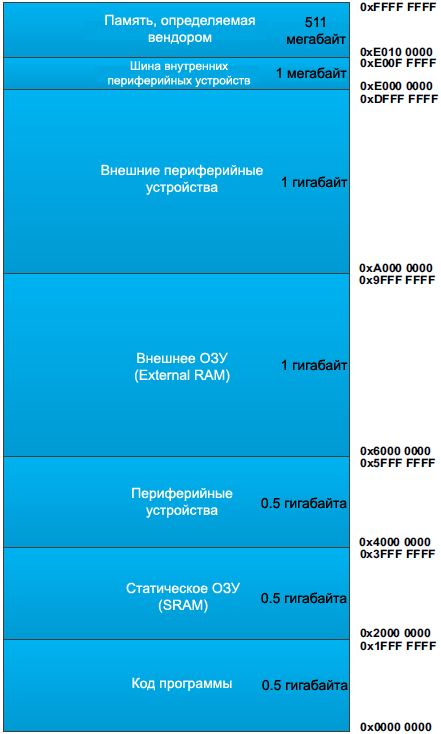

ą£ąŠą┤ąĄą╗čī ą┐ą░ą╝čÅčéąĖ. ąÆ ą░čĆčģąĖč鹥ą║čéčāčĆąĄ STM32 ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖą╝ąĄąĄčé ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčāčÄ ą║ą░čĆčéčā čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆą░čÅ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ąŠ 4 ą│ąĖą│ą░ą▒ą░ą╣čé ą░ą┤čĆąĄčüčāąĄą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ. ąØą░ čĆąĖčü. 2 ą┐ąŠą║ą░ąĘą░ąĮą░ ą║ą░čĆčéą░ čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ.

ąĀąĖčü. 2. ąĀą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

[ąóąĖą┐čŗ ą┐ą░ą╝čÅčéąĖ, čĆąĄą│ąĖčüčéčĆčŗ ąĖ ą░čéčĆąĖą▒čāčéčŗ]

ąÜą░čĆčéą░ čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ ąĖ ąĮą░čüčéčĆąŠą╣ą║ą░ MPU čĆą░ąĘą┤ąĄą╗čÅčÄčé ą║ą░čĆčéčā ąĮą░ ąŠą▒ą╗ą░čüčéąĖ. ąÜą░ąČą┤ą░čÅ ąŠą▒ą╗ą░čüčéčī ąĖą╝ąĄąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ čéąĖą┐ ą┐ą░ą╝čÅčéąĖ ąĖ ąĄčæ ą░čéčĆąĖą▒čāčéčŗ.

ąóąĖą┐čŗ ą┐ą░ą╝čÅčéąĖ. ąĢčüčéčī čéčĆąĖ ąŠą▒čēąĖčģ čéąĖą┐ą░ ą┐ą░ą╝čÅčéąĖ:

ŌĆó ą¤ą░ą╝čÅčéčī Normal: ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą│čĆčāąČą░čéčī ąĖ čģčĆą░ąĮąĖčéčī ą▒ą░ą╣čéčŗ, ą┐ąŠą╗čāčüą╗ąŠą▓ą░ ąĖ čüą╗ąŠą▓ą░, ą║ąŠč鹊čĆčŗąĄ ą▒čāą┤čāčé čŹčäč乥ą║čéąĖą▓ąĮąŠ čĆą░čüą┐ąŠą╗ąŠąČąĄąĮčŗ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ (ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆčā ąĮąĄąĖąĘą▓ąĄčüčéąĮąŠ ąŠ čéąĖą┐ą░čģ ąŠą▒ą╗ą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ). ąöą╗čÅ čŹč鹊ą╣ ąŠą▒ą╗ą░čüčéąĖ ąĘą░ą│čĆčāąĘą║ą░/čģčĆą░ąĮąĄąĮąĖąĄ ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▓ č鹊ą╝ ą┐ąŠčĆčÅą┤ą║ąĄ, ą║ąŠč鹊čĆčŗą╣ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą▓ ąĖčüčģąŠą┤ąĮąŠą╝ ą║ąŠą┤ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ.

ŌĆó ą¤ą░ą╝čÅčéčī Device: ą▓ čŹč鹊ą╝ čĆąĄą│ąĖąŠąĮąĄ ąĘą░ą│čĆčāąĘą║ą░ ąĖ čģčĆą░ąĮąĄąĮąĖąĄ čüąŠą▓ąĄčĆčłą░čÄčéčüčÅ ą▓ čüčéčĆąŠą│ąŠ čāą┐ąŠčĆčÅą┤ąŠč湥ąĮąĮąŠą╝ ą▓ąĖą┤ąĄ. ąŁč鹊 ą┤ąŠą╗ąČąĮąŠ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą│čĆčāąĘą║ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą▓ ąĮą░ą┤ą╗ąĄąČą░čēąĄą╝ ą┐ąŠčĆčÅą┤ą║ąĄ.

ŌĆó ąĪčéčĆąŠą│ąŠ čāą┐ąŠčĆčÅą┤ąŠč湥ąĮąĮą░čÅ ą┐ą░ą╝čÅčéčī: ą▓čüąĄą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ ą┐ąŠčĆčÅą┤ą║ąĄ, ąĮą░ą┐ąĖčüą░ąĮąĮąŠą╝ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ, ąŠąČąĖą┤ą░ąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĘą░ą┐ąĖčüąĖ/čģčĆą░ąĮąĄąĮąĖčÅ (čŹčäč乥ą║čéąĖą▓ąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ čłąĖąĮąĄ) ą┐čĆąĄąČą┤ąĄ, č湥ą╝ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ ąĖąĮčüčéčĆčāą║čåąĖčÄ ą▓ ą┐ąŠč鹊ą║ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. ąŁč鹊 ą╝ąŠąČąĄčé čüąĄčĆčīąĄąĘąĮąŠ čüąĮąĖąĘąĖčéčī ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī.

ąĀąĄą│ąĖčüčéčĆčŗ MPU. ąĀąĄą│ąĖčüčéčĆčŗ MPU čĆą░čüą┐ąŠą╗ąŠąČąĄąĮčŗ ą┐ąŠ ą░ą┤čĆąĄčüčā 0xE000ED90. ąĢčüčéčī 5 ąŠčüąĮąŠą▓ąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ MPU ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆąŠą▓-ą┐čüąĄą▓ą┤ąŠąĮąĖą╝ąŠą▓ (alias registers) ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ąŠą▒ą╗ą░čüčéąĖ. ąĪą╗ąĄą┤čāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ąŠą▒ą╗ą░čüč鹥ą╣ ą▓ MPU:

MPU_TYPE čĆąĄą│ąĖčüčéčĆ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┤ąĄč鹥ą║čåąĖąĖ ąĮą░ą╗ąĖčćąĖčÅ MPU.

MPU_CTRL čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ.

MPU_RNR ąĮąŠą╝ąĄčĆ ąŠą▒ą╗ą░čüčéąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┤ąŠą┐čāčüčéąĖą╝čŗčģ ąŠą┐ąĄčĆą░čåąĖą╣ ą║ ąĮąĄą╣.

MPU_RBAR ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ąŠą▒ą╗ą░čüčéąĖ.

MPU_RASR ą░čéčĆąĖą▒čāčéčŗ ąŠą▒ą╗ą░čüčéąĖ ąĖ čĆą░ąĘą╝ąĄčĆ.

MPU_RBAR_An n-ą╣ ą┐čüąĄą▓ą┤ąŠąĮąĖą╝ MPU_RBAR, ą│ą┤ąĄ n ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1 ą┤ąŠ 3(a).

MPU_RASR_An n-ą╣ ą┐čüąĄą▓ą┤ąŠąĮąĖą╝ MPU_RASR, ą│ą┤ąĄ n ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1 ą┤ąŠ 3(a).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (a): ąÆ Cortex┬«-M0+ čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ąĮąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ.

ąöą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐čĆąŠ čĆąĄą│ąĖčüčéčĆčŗ MPU ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ą╝, ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮčŗą╝ ą▓ąŠ ą▓čĆąĄąĘą║ąĄ "ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą┐čĆąŠ MPU".

ąÉčéčĆąĖą▒čāčéčŗ ą┐ą░ą╝čÅčéąĖ. ąÆ čĆąĄą│ąĖčüčéčĆąĄ ą░čéčĆąĖą▒čāč鹊ą▓ ąĖ čĆą░ąĘą╝ąĄčĆą░ (MPU_RASR) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą▓čüąĄ ą░čéčĆąĖą▒čāčéčŗ ą┐ą░ą╝čÅčéąĖ. ąóą░ą▒ą╗ąĖčåą░ 2 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą║čĆą░čéą║ąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ ą░čéčĆąĖą▒čāč鹊ą▓ ąĖ čĆą░ąĘą╝ąĄčĆą░.

ąóą░ą▒ą╗ąĖčåą░ 2. ąĀąĄą│ąĖčüčéčĆ ą░čéčĆąĖą▒čāč鹊ą▓ ąĖ čĆą░ąĘą╝ąĄčĆą░ ąŠą▒ą╗ą░čüčéąĖ - MPU_RASR.

| Ōä¢ ą▒ąĖčéą░ |

ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 28 |

XN |

Execute never, ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅčéčī. |

| 26:24 |

AP |

Data Access Permission, čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╣ čéąĖą┐ ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄą│ąĖąŠąĮčā (RO, RW ąĖą╗ąĖ ąĮąĄčé ą┤ąŠčüčéčāą┐ą░). |

| 21:19 |

TEX |

Type Extension, čĆą░čüčłąĖčĆąĄąĮąĖąĄ čéąĖą┐ą░. |

| 18 |

S |

Shareable, ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čüąŠą▓ą╝ąĄčüčéąĮąŠą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ. |

| 17 |

C |

Cacheable, ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖčÅ. |

| 16 |

B |

Bufferable, ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▒čāč乥čĆąĖąĘą░čåąĖąĖ. |

| 15:8 |

SRD |

Subregion disable, ąĘą░ą┐čĆąĄčé ą┐ąŠą┤čĆąĄą│ąĖąŠąĮą░. ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąŠą┤čĆąĄą│ąĖąŠąĮą░ 1=ąĘą░ą┐čĆąĄčēąĄąĮąŠ, 0=čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| 5:1 |

SIZE |

ąŻą║ą░ąĘčŗą▓ą░ąĄčé čĆą░ąĘą╝ąĄčĆ čĆąĄą│ąĖąŠąĮą░, ąĘą░čēąĖčēą░ąĄą╝ąŠą│ąŠ MPU. |

XN. ąŁč鹊čé čäą╗ą░ą│ XN čāą┐čĆą░ą▓ą╗čÅąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ą║ąŠą┤ą░. ąÆ čüą╗čāčćą░ąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤ ą▓ ąŠą▒ą╗ą░čüčéąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĮą░ čāčĆąŠą▓ąĮąĄ ą┐čĆąĖą▓ąĖą╗ąĄą│ąĖą╣ ąĖ XN ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī 0. ąśąĮą░č湥 ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮą░ ąŠčłąĖą▒ą║ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą░ą╝čÅčéčīčÄ (MemManage).

AP. ąŁč鹊 ą┐ąŠą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą┤ą░ąĮąĮčŗą╝ (čüą╝. čéą░ą▒ą╗ąĖčåčā 3).

ąóą░ą▒ą╗ąĖčåą░ 3. ą¤čĆą░ą▓ą░ ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄą│ąĖąŠąĮą░ą╝ ą┐ą░ą╝čÅčéąĖ.

| AP[2:0] |

ą¤čĆąĖą▓ąĖą╗ąĄą│ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ |

ąØąĄ ą┐čĆąĖą▓ąĖą╗ąĄą│ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 000 |

ąØąĄčé ą┤ąŠčüčéčāą┐ą░ |

ąØąĄčé ą┤ąŠčüčéčāą┐ą░ |

ąøčÄą▒ą░čÅ ą┐ąŠą┐čŗčéą║ą░ ą┤ąŠčüčéčāą┐ą░ ą▓čŗąĘčŗą▓ą░ąĄčé ąŠčłąĖą▒ą║čā ąĮą░čĆčāčłąĄąĮąĖčÅ ąĘą░čēąĖčéčŗ ą┤ąŠčüčéčāą┐ą░ (permission fault). |

| 001 |

RW (ą┐ąŠą╗ąĮčŗą╣ ą┤ąŠčüčéčāą┐) |

ąØąĄčé ą┤ąŠčüčéčāą┐ą░ |

ąĀą░ąĘčĆąĄčłąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐čĆąĖą▓ąĖą╗ąĄą│ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ. |

| 010 |

RW (ą┐ąŠą╗ąĮčŗą╣ ą┤ąŠčüčéčāą┐) |

RO (č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ) |

ą¤ąŠą┐čŗčéą║ą░ ąĘą░ą┐ąĖčüąĖ ąĮąĄą┐čĆąĖą▓ąĖą╗ąĄą│ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄą╝ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąŠčłąĖą▒ą║ąĄ ąĘą░čēąĖčéčŗ ą┤ąŠčüčéčāą┐ą░ (permission fault). |

| 011 |

RW (ą┐ąŠą╗ąĮčŗą╣ ą┤ąŠčüčéčāą┐) |

RW (ą┐ąŠą╗ąĮčŗą╣ ą┤ąŠčüčéčāą┐) |

ąĀą░ąĘčĆąĄčłąĄąĮ ą┐ąŠą╗ąĮčŗą╣ ą┤ąŠčüčéčāą┐. |

| 100 |

ąØąĄ ą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╣ čĆąĄąĘčāą╗čīčéą░čé |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| 101 |

RO (č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ) |

ąØąĄčé ą┤ąŠčüčéčāą┐ą░ |

ąĀą░ąĘčĆąĄčłąĄąĮąŠ č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ, ąĖ č鹊ą╗čīą║ąŠ ą┐čĆąĖą▓ąĖą╗ąĄą│ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄą╝. |

| 110 |

RO (č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ) |

RO (č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ) |

ąĀą░ąĘčĆąĄčłąĄąĮąŠ č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ. |

| 111 |

S. ą¤ąŠą╗ąĄ S ą┤ą╗čÅ ąŠą▒ą╗ą░čüčéąĖ čüąŠą▓ą╝ąĄčüčéąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ: čüąĖčüč鹥ą╝ą░ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÄ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čłąĖąĮąŠą╣ ą▓ čüąĖčüč鹥ą╝ąĄ čü ą╝ąĮąŠą│ąŠą║čĆą░čéąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čłąĖąĮąŠą╣, ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą┐čĆąŠčåąĄčüčüąŠčĆ čü ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ DMA.

TEX, C, B. ąæąĖčéčŗ TEX, C ąĖ B ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čüą▓ąŠą╣čüčéą▓ ą║čŹčłą░ ąŠą▒ą╗ą░čüčéąĖ ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąĄą│ąŠ čüąŠą▓ą╝ąĄčüčéąĮąŠą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ. ąÆą░čĆąĖą░ąĮčéčŗ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ 4.

ąóą░ą▒ą╗ąĖčåą░ 4. ąĪą▓ąŠą╣čüčéą▓ą░ ą║čŹčłą░ ąĖ ąĄą│ąŠ čüąŠą▓ą╝ąĄčüčéąĮąŠąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ.

| TEX |

C |

B |

ąóąĖą┐ ą┐ą░ą╝čÅčéąĖ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ąĪąŠą▓ą╝ąĄčüčéąĮąŠąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ |

| 000 |

0 |

0 |

Strongly Ordered |

ąĪčéčĆąŠą│ąŠ čāą┐ąŠčĆčÅą┤ąŠč湥ąĮąĮą░čÅ ą┐ą░ą╝čÅčéčī. |

ąöą░ |

| 000 |

0 |

1 |

Device |

ąĪąŠą▓ą╝ąĄčüčéąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ. |

ąöą░ |

| 000 |

1 |

0 |

Normal |

ąĪą║ą▓ąŠąĘąĮą░čÅ ąĘą░ą┐ąĖčüčī (Write through), ąĮąĄčé ą▓čŗą┤ąĄą╗ąĄąĮąĖčÅ ąĮą░ ąĘą░ą┐ąĖčüčī. |

ąæąĖčé S |

| 000 |

1 |

1 |

Normal |

ą×ą▒čĆą░čéąĮą░čÅ ąĘą░ą┐ąĖčüčī (Write-back), ąĮąĄčé ą▓čŗą┤ąĄą╗ąĄąĮąĖčÅ ąĮą░ ąĘą░ą┐ąĖčüčī. |

ąæąĖčé S |

| 001 |

0 |

0 |

Normal |

ąØąĄčé ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖčÅ. |

ąæąĖčé S |

| 001 |

0 |

1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 001 |

1 |

0 |

ąØąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ |

| 001 |

1 |

1 |

Normal |

ą×ą▒čĆą░čéąĮą░čÅ ąĘą░ą┐ąĖčüčī, ąŠą▒čŗčćąĮą░čÅ ąĘą░ą┐ąĖčüčī ąĖ ą▓čŗą┤ąĄą╗ąĄąĮąĖąĄ ąĮą░ čćč鹥ąĮąĖąĄ. |

ąæąĖčé S |

| 010 |

0 |

0 |

Device |

ąŻčüčéčĆąŠą╣čüčéą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ ąĮąĄą╗čīąĘčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüąŠą▓ą╝ąĄčüčéąĮąŠ. |

ąØąĄčé |

| 010 |

0 |

1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

SRD. ąŁč鹊 ą▒ąĖčéčŗ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ ą┐ąŠą┤ąŠą▒ą╗ą░čüčéąĖ, ą║ąŠč鹊čĆčŗąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą▓ą║ą╗čÄč湥ąĮą░ ą╗ąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮą░čÅ ą┐ąŠą┤ąŠą▒ą╗ą░čüčéčī ąĖą╗ąĖ ąĮąĄčé. ą×čéą║ą╗čÄč湥ąĮąĖąĄ ą┐ąŠą┤ąŠą▒ą╗ą░čüčéąĖ ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┤čĆčāą│ą░čÅ ąŠą▒ą╗ą░čüčéčī, ą┐ąĄčĆąĄą║čĆčŗą▓ą░čÄčēą░čÅ ąŠčéą║ą╗čÄč湥ąĮąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąĄą╣ ą▓ą╝ąĄčüč鹊 čŹč鹊ą│ąŠ. ąĢčüą╗ąĖ ąĮąĖą║ą░ą║ą░čÅ ą┤čĆčāą│ą░čÅ ą▓ą║ą╗čÄč湥ąĮąĮą░čÅ ąŠą▒ą╗ą░čüčéčī ąĮąĄ ą┐ąĄčĆąĄą║čĆčŗą▓ą░ąĄčé ąŠčéą║ą╗čÄč湥ąĮąĮčāčÄ ą┐ąŠą┤ąŠą▒ą╗ą░čüčéčī, MPU ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąŠčłąĖą▒ą║čā.

ąöą╗čÅ ą╝ąŠą┤ąĄą╗ąĄą╣ čü čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąĮčŗą╝ ą║čŹčłąĄą╝ (č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čüąĄčĆąĖąĖ STM32F7, čā ą║ąŠč鹊čĆąŠą╣ ąĄčüčéčī ą║čŹčł L1) čüčāčēąĄčüčéą▓čāčÄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą░čéčĆąĖą▒čāčéčŗ ą┐ą░ą╝čÅčéąĖ:

ŌĆó ąÜčŹčłąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ąĖą╗ąĖ ąĮąĄ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĮčŗą╣: ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗąĄ ąŠą▒ą╗ą░čüčéąĖ ą╝ąŠą│čāčé ą▒čŗčéčī čüąŠčģčĆą░ąĮąĄąĮčŗ ą▓ ą║čŹčłąĄ ąĖą╗ąĖ ąĮąĄčé.

ŌĆó ą¤čĆčÅą╝ą░čÅ ąĘą░ą┐ąĖčüčī ą▒ąĄąĘ ą▓čŗą┤ąĄą╗ąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ: ą┐čĆąĖ čāčüą┐ąĄčģąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ą▓ ą║čŹčł ąĖ ąŠčüąĮąŠą▓ąĮčāčÄ ą┐ą░ą╝čÅčéčī, ą┐čĆąĖ ą┐čĆąŠą┐čāčüą║ąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčé ą▒ą╗ąŠą║ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ąĮąĄ ą┐ąĄčĆąĄąĮąŠčüčÅčēąĄą╣ čŹč鹊čé ą▒ą╗ąŠą║ ą▓ ą║čŹčł.

ŌĆó ą×ą▒čĆą░čéąĮą░čÅ ąĘą░ą┐ąĖčüčī ą▒ąĄąĘ ą▓čŗą┤ąĄą╗ąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ: ą┐čĆąĖ čāčüą┐ąĄčģąĄ ą┐ąĖčłąĄčé ą▓ ą║čŹčł "ą│čĆčÅąĘąĮčŗą╣ ą▒ąĖčé" ą┤ą╗čÅ ą▒ą╗ąŠą║ą░,ąŠčüąĮąŠą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī ąĮąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ. ą¤čĆąĖ ą┐čĆąŠą┐čāčüą║ąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčé ą▒ą╗ąŠą║ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ąĮąĄ ą┐ąĄčĆąĄąĮąŠčüčÅčēąĄą╣ čŹč鹊čé ą▒ą╗ąŠą║ ą▓ ą║čŹčł.

ŌĆó ą×ą▒čĆą░čéąĮą░čÅ ąĘą░ą┐ąĖčüčī čü ą▓čŗą┤ąĄą╗ąĄąĮąĖąĄą╝ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ: ą┐čĆąĖ čāčüą┐ąĄčģąĄ ą┐ąĖčłąĄčé ą▓ ą║čŹčł, čü čāčüčéą░ąĮąŠą▓ą║ąŠą╣ "ą│čĆčÅąĘąĮąŠą│ąŠ ą▒ąĖčéą░" ą┤ą╗čÅ ą▒ą╗ąŠą║ą░, ąŠčüąĮąŠą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī ąĮąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ. ą¤čĆąĖ ą┐čĆąŠą┐čāčüą║ąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčé ą▒ą╗ąŠą║ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ąĖ ą┐ąĄčĆąĄąĮąŠčüąĖčé ą▒ą╗ąŠą║ ą▓ ą║čŹčł.

[ąĪčĆą░ą▓ąĮąĄąĮąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ MPU čā čĆą░ąĘą╗ąĖčćąĮčŗčģ ą╝ąŠą┤ąĄą╗ąĄą╣ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓]

ąĢčüčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čĆą░ąĘą╗ąĖčćąĖą╣ ą╝ąĄąČą┤čā čāčĆąŠą▓ąĮčÅą╝ąĖ MPU Cortex┬«-M0+, Cortex┬«-M3/M4 ąĖ Cortex┬«-M7, ą┐ąŠčŹč鹊ą╝čā ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčé ą┤ąŠą╗ąČąĄąĮ ąĘąĮą░čéčī ąŠ ąĮąĖčģ, ąĄčüą╗ąĖ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĖ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ MPU. ąóą░ą▒ą╗ąĖčåą░ 5 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čĆą░ąĘą╗ąĖčćąĖčÅ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ MPU ą╝ąĄąČą┤čā Cortex┬«-M0+, Cortex┬«-M3/M4 ąĖ Cortex┬«-M7.

ąóą░ą▒ą╗ąĖčåą░ 5. ąĪčĆą░ą▓ąĮąĄąĮąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ MPU STM32.

ą¤ą░čĆą░ą╝ąĄčéčĆ

|

ą£ąŠą┤ąĄą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ (čüąĄčĆąĖąĖ)

|

| Cortex®-M0+ |

Cortex®-M3/M4 |

Cortex®-M7 |

| ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čĆąĄą│ąĖąŠąĮąŠą▓ ą┐ą░ą╝čÅčéąĖ |

8 |

| ąŻąĮąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮčŗąĄ čĆąĄą│ąĖąŠąĮčŗ I ąĖ D |

ąöą░ |

| ąÉą┤čĆąĄčü čĆąĄą│ąĖąŠąĮą░ |

ąöą░ |

| ąĀą░ąĘą╝ąĄčĆ čĆąĄą│ąĖąŠąĮą░ |

256 ą▒ą░ą╣čé .. 4 ą│ąĖą│ą░ą▒ą░ą╣čéą░ |

| ąÉčéčĆąĖą▒čāčéčŗ ą┐ą░ą╝čÅčéąĖ čĆąĄą│ąĖąŠąĮą░ |

S, C, B, XN(1) |

TEX, S, C, B, XN |

| ąŻčüčéą░ąĮąŠą▓ą║ą░ čĆą░ąĘčĆąĄčłąĄąĮąĖą╣ ąĮą░ ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖąŠąĮčā ą┐ą░ą╝čÅčéąĖ (AP) |

ąöą░ |

| ąŚą░ą┐čĆąĄčé ą┐ąŠą┤čĆąĄą│ąĖąŠąĮą░ |

8 ą▒ąĖčé |

| ą¤čĆąŠą┐čāčüą║ MPU ą┤ą╗čÅ NMI (ąĮąĄ ą╝ą░čüą║ąĖčĆčāąĄą╝ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ) / Hardfault (ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ ąŠčłąĖą▒ą║ą░) |

ąöą░ |

| ą¤čüąĄą▓ą┤ąŠąĮąĖą╝čŗ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ MPU |

ąØąĄčé |

ąöą░ |

| ąōąĄąĮąĄčĆą░čåąĖčÅ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ ą┐čĆąĖ ąŠčéą║ą░ąĘąĄ (fault exception) |

ąóąŠą╗čīą║ąŠ Hardfault |

Hardfault / MemManage |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1). Cortex┬«-M0+ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąŠą┤ąĖąĮ čāčĆąŠą▓ąĄąĮčī ą┐ąŠą╗ąĖčéąĖą║ąĖ ą║čŹčłą░, ą┐ąŠčŹč鹊ą╝čā ą┐ąŠą╗ąĄ TEX ąĮąĄą┤ąŠčüčéčāą┐ąĮąŠ ą▓ cortex┬«-M0+.

ąóą░ą▒ą╗ąĖčåą░ 6 ąŠą┐ąĖčüčŗą▓ą░ąĄčé ą┐čĆąĖą╝ąĄčĆ ąĮą░čüčéčĆąŠą╣ą║ąĖ MPU čüąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ąŠą▒ą╗ą░čüčéčÅą╝ąĖ ą┐ą░ą╝čÅčéąĖ: ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī SRAM, ążą╗čŹčł-ą┐ą░ą╝čÅčéčī ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą║ą░čĆčéą░ čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąĖą▓ąĖą╗ąĄą│ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą▓ ą║ą░č湥čüčéą▓ąĄ č乊ąĮąŠą▓ąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ, MPU ąĮąĄ ą▓ą║ą╗čÄč湥ąĮ ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ąŠčéą║ą░ąĘą░ HARD ąĖ NMI.

ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī SRAM: 8 Ką▒ą░ą╣čé čüčéą░čéąĖč湥čüą║ąŠą╣ ą┐ą░ą╝čÅčéąĖ (SRAM) ą▒čāą┤čāčé čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ Region0. ąÉčéčĆąĖą▒čāčéčŗ ą┐ą░ą╝čÅčéąĖ: ąŠą▒čēąĄą┤ąŠčüčéčāą┐ąĮą░čÅ ą┐ą░ą╝čÅčéčī, ą┐čĆčÅą╝ą░čÅ ąĘą░ą┐ąĖčüčī ą▒ąĄąĘ ą▓čŗą┤ąĄą╗ąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ, ą┐čĆą░ą▓ą░ ą┐ąŠą╗ąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ąĖ ą▓ą║ą╗čÄč湥ąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░.

ążą╗čŹčł-ą┐ą░ą╝čÅčéčī : ą▓čüčÅ čäą╗čŹčł-ą┐ą░ą╝čÅčéčī ą▒čāą┤ąĄčé čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą║ą░ą║ Region1. ąÉčéčĆąĖą▒čāčéčŗ ą┐ą░ą╝čÅčéąĖ : ąĮąĄ ąŠą▒čēąĄą┤ąŠčüčéčāą┐ąĮą░čÅ ą┐ą░ą╝čÅčéčī, ą┐čĆčÅą╝ą░čÅ ąĘą░ą┐ąĖčüčī ą▒ąĄąĘ ą▓čŗą┤ąĄą╗ąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ, ą┐čĆą░ą▓ą░ ą┐ąŠą╗ąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ąĖ ą▓ą║ą╗čÄč湥ąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░.

ą×ą▒ą╗ą░čüčéčī ą┐ąĄčĆąĖč乥čĆąĖąĖ: ą▒čāą┤ąĄčé čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą║ą░ą║ Region2. ąÉčéčĆąĖą▒čāčéčŗ ą┐ą░ą╝čÅčéąĖ: ąŠą▒čēąĄą┤ąŠčüčéčāą┐ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą┐čĆą░ą▓ą░ ą┐ąŠą╗ąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ąĖ ą▓čŗą║ą╗čÄč湥ąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░.

ąóą░ą▒ą╗ąĖčåą░. 6. ą¤čĆąĖą╝ąĄčĆ ąĮą░čüčéčĆąŠą╣ą║ąĖ MPU.

| ąØą░ąĘąĮą░č湥ąĮąĖąĄ |

ąóąĖą┐ ą┐ą░ą╝čÅčéąĖ |

ąæą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü |

Ōä¢ čĆąĄą│ąĖąŠąĮą░ |

ąĀą░ąĘą╝ąĄčĆ |

ąÉčéčĆąĖą▒čāčéčŗ ą┐ą░ą╝čÅčéąĖ |

| ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ čüčéą░čéąĖč湥čüą║ą░čÅ ą┐ą░ą╝čÅčéčī (SRAM) |

ą×ą▒čŗčćąĮą░čÅ ą┐ą░ą╝čÅčéčī (Normal) |

0x2000 0000 |

Region0 |

8 ą║ą▒ą░ą╣čé |

ąĪąŠą▓ą╝ąĄčüčéąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ą░čÅ, ą║čŹčł čüą║ą▓ąŠąĘąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ, ąĮąĄčé ą▓čŗą┤ąĄą╗ąĄąĮąĖčÅ ąĮą░ ąĘą░ą┐ąĖčüčī

C=1, B = 0, TEX = 0, S=1, SRD = 0, XN= 0, AP = ą┐ąŠą╗ąĮčŗą╣ ą┤ąŠčüčéčāą┐ |

| ą¤ą░ą╝čÅčéčī FLASH |

0x0800 0000 |

Region1 |

1 ą£ą▒ą░ą╣čé |

ąæąĄąĘ čüąŠą▓ą╝ąĄčüčéąĮąŠą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ, ą║čŹčł čüą║ą▓ąŠąĘąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ, ąĮąĄčé ą▓čŗą┤ąĄą╗ąĄąĮąĖčÅ ąĮą░ ąĘą░ą┐ąĖčüčī

C=1, B = 0, TEX = 0, S=0, SRD = 0, XN= 0, AP = ą┐ąŠą╗ąĮčŗą╣ ą┤ąŠčüčéčāą┐ |

| FMC |

0x6000 0000 |

Region2 |

512 ą£ą▒ą░ą╣čé |

ąĪąŠą▓ą╝ąĄčüčéąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ą░čÅ, ą║čŹčł čüą║ą▓ąŠąĘąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ, ąĮąĄčé ą▓čŗą┤ąĄą╗ąĄąĮąĖčÅ ąĮą░ ąĘą░ą┐ąĖčüčī

C=1, B = 0, TEX = 0, S=1, SRD = 0, XN= 0, AP = ą┐ąŠą╗ąĮčŗą╣ ą┤ąŠčüčéčāą┐ |

//ąØą░čüčéčĆąŠą╣ą║ą░ MPU ą┐čĆąĖ ą┐ąŠą╝ąŠčēąĖ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĖ Cube HAL.

void MPU_RegionConfig(void)

{

MPU_Region_InitTypeDef MPU_InitStruct;

/* ąŚą░ą┐čĆąĄčé MPU */

HAL_MPU_Disable();

/* ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čĆąĄą│ąĖąŠąĮą░ RAM ą║ą░ą║ Region 0, čĆą░ąĘą╝ąĄčĆąŠą╝ 8 ą║ąĖą╗ąŠą▒ą░ą╣čé,

čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ (R/W) */

MPU_InitStruct.Enable = MPU_REGION_ENABLE;

MPU_InitStruct.BaseAddress = 0x20000000;

MPU_InitStruct.Size = MPU_REGION_SIZE_8KB;

MPU_InitStruct.AccessPermission = MPU_REGION_FULL_ACCESS;

MPU_InitStruct.IsBufferable = MPU_ACCESS_NOT_BUFFERABLE;

MPU_InitStruct.IsCacheable = MPU_ACCESS_CACHEABLE;

MPU_InitStruct.IsShareable = MPU_ACCESS_SHAREABLE;

MPU_InitStruct.Number = MPU_REGION_NUMBER0;

MPU_InitStruct.TypeExtField = MPU_TEX_LEVEL0;

MPU_InitStruct.SubRegionDisable = 0x00;

MPU_InitStruct.DisableExec = MPU_INSTRUCTION_ACCESS_ENABLE;

HAL_MPU_ConfigRegion(&MPU_InitStruct);

/* ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čĆąĄą│ąĖąŠąĮą░ FLASH ą║ą░ą║ Region 1, čĆą░ąĘą╝ąĄčĆąŠą╝ 1 ą╝ąĄą│ą░ą▒ą░ą╣čé,

čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ (R/W) */

MPU_InitStruct.BaseAddress = 0x08000000;

MPU_InitStruct.Size = MPU_REGION_SIZE_1MB;

MPU_InitStruct.IsShareable = MPU_ACCESS_NOT_SHAREABLE;

MPU_InitStruct.Number = MPU_REGION_NUMBER1;

HAL_MPU_ConfigRegion(&MPU_InitStruct);

/* ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čĆąĄą│ąĖąŠąĮą░ FMC ą║ą░ą║ Region 2, čĆą░ąĘą╝ąĄčĆąŠą╝ 0.5 ą│ąĖą│ą░ą▒ą░ą╣čéą░,

čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ (R/W) */

MPU_InitStruct.BaseAddress = 0x60000000;

MPU_InitStruct.Size = MPU_REGION_SIZE_512MB;

MPU_InitStruct.IsShareable = MPU_ACCESS_SHAREABLE;

MPU_InitStruct.Number = MPU_REGION_NUMBER2;

HAL_MPU_ConfigRegion(&MPU_InitStruct);

/* ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ MPU */

HAL_MPU_Enable(MPU_PRIVILEGED_DEFAULT);

}

[ąŚą░ą║ą╗čÄč湥ąĮąĖąĄ]

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ MPU ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ STM32 ą┤ąĄą╗ą░ąĄčé ąĖčģ čāčüč鹊ą╣čćąĖą▓čŗą╝ąĖ, ąĮą░ą┤ąĄąČąĮčŗą╝ąĖ, ąĖ ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ čüą╗čāčćą░čÅčģ ą▒ąŠą╗ąĄąĄ ą▒ąĄąĘąŠą┐ą░čüąĮčŗą╝ąĖ, ą┐čĆąĄą┐čÅčéčüčéą▓čāčÅ ąĘą░ą┤ą░čćą░ą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┐ąŠą╗čāčćąĖčéčī ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ čüč鹥ą║čā ąĖą╗ąĖ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ, ąĖą╗ąĖ ą┐ąŠą▓čĆąĄą┤ąĖčéčī čüč鹥ą║ ąĖ ą┐ą░ą╝čÅčéčī ą┤ą░ąĮąĮčŗčģ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤čĆčāą│ąĖą╝ąĖ ąĘą░ą┤ą░čćą░ą╝ąĖ.

[ąĪčüčŗą╗ą║ąĖ]

1. AN4838 Managing memory protection unit (MPU) in STM32 MCUs site:www.st.com.

2. AN4839: ą║čŹčł ą┐ąĄčĆą▓ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ STM32F7. |