|

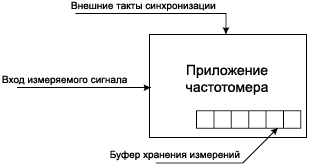

ąóą░ą╣ą╝ąĄčĆ - ąŠč湥ąĮčī ą▓ą░ąČąĮąŠąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ ąĮą░ą▒ąŠčĆąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą╣ą╝ąĄčĆąŠą▓ ąĖ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗčģ ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣ ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé ąŠą┤ąĮąŠą│ąŠ čüąĄą╝ąĄą╣čüčéą▓ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32 ą║ ą┤čĆčāą│ąŠą╝čā, ąŠą┤ąĮą░ą║ąŠ ą▓čüąĄ ąČąĄ čā ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░ čéą░ą╣ą╝ąĄčĆąŠą▓ ąĄčüčéčī ąŠą▒čēąĖąĄ čäčāąĮą║čåąĖąĖ ąĖ čĆą░ą▒ąŠčćąĖąĄ čĆąĄąČąĖą╝čŗ.

ąóą░ą╣ą╝ąĄčĆ STM32 čĆą░ąĘčĆą░ą▒ą░čéčŗą▓ą░ą╗čüčÅ ą║ą░ą║ ą║čĆą░ąĄčāą│ąŠą╗čīąĮčŗą╣ ą║ą░ą╝ąĄąĮčī ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░ ą▓čüčéčĆą░ąĖą▓ą░ąĄą╝čŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣: ąŠąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čüą░ą╝čŗčģ čĆą░ąĘąĮčŗčģ ąĘą░ą┤ą░čć ąŠčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ą▓ąĖą│ą░č鹥ą╗čÅą╝ąĖ ą┤ąŠ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖčģ čüąŠą▒čŗčéąĖą╣ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ. ąĪą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ čéą░ą╣ą╝ąĄčĆą░ ą┤ąŠčüčéčāą┐ąĮčŗ ą▓ąŠ ą▓čüąĄčģ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░čģ STM32, ąĖ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ čéą░ą╣ą╝ąĄčĆą░ą╝ ąŠč湥ąĮčī ą╝ąĮąŠą│ąŠ ąĖąĘ-ąĘą░ ąĖčģ čłąĖčĆąŠą║ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗčģ ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣.

ąØą░ąĘąĮą░č湥ąĮąĖąĄ čŹč鹊ą│ąŠ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ (ą┐ąĄčĆąĄą▓ąŠą┤ [1]) - ą┤ą░čéčī ą┐čĆąŠčüč鹊ąĄ ąĖ čÅčüąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą▒ą░ąĘąŠą▓čŗčģ čäčāąĮą║čåąĖą╣ ąĖ čĆą░ą▒ąŠčćąĖčģ čĆąĄąČąĖą╝ąŠą▓ čéą░ą╣ą╝ąĄčĆąŠą▓ STM32 ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ. ąŁč鹊 čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗąĄ general-purpose čéą░ą╣ą╝ąĄčĆčŗ (čüąŠą║čĆą░čēąĄąĮąĮąŠ GP). ąŁč鹊čé ą┤ąŠą║čāą╝ąĄąĮčé čüąŠą┐čĆąŠą▓ąŠąČą┤ą░ąĄčé čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ čéą░ą╣ą╝ąĄčĆąŠą▓ STM32, ą┤ąŠčüčéčāą┐ąĮčŗčģ ą▓ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ ą┐ąŠ ą║ą░ąČą┤ąŠą╣ ą║ąŠąĮą║čĆąĄčéąĮąŠą╣ čüąĄčĆąĖąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čĆą░čüčłąĖčäčĆąŠą▓ą║čā ąĮąĄą║ąŠč鹊čĆčŗčģ ąĮąĄą┐ąŠąĮčÅčéąĮčŗčģ č鹥čĆą╝ąĖąĮąŠą▓ ąĖ čüąŠą║čĆą░čēąĄąĮąĖą╣ ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą▓ čüčéą░čéčīąĄ [5].

ąŁč鹊čé ą┤ąŠą║čāą╝ąĄąĮčé ą┐ąŠą┤ąĄą╗ąĄąĮ ąĮą░ 2 ąŠčüąĮąŠą▓ąĮčŗąĄ čćą░čüčéąĖ:

ŌĆó ą¤ąĄčĆą▓ą░čÅ čćą░čüčéčī ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ą▒ą░ąĘąŠą▓čŗąĄ čäčāąĮą║čåąĖąĖ čéą░ą╣ą╝ąĄčĆąŠą▓ STM32 ąĖ ą┐čĆąŠčüčéčŗą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ ąŠą▒čŖčÅčüąĮčÅąĄčé ąĮąĄą║ąŠč鹊čĆčŗąĄ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ čäčāąĮą║čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ ąŠą▒čŗčćąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ čéą░ą╣ą╝ąĄčĆąŠą▓.

ŌĆó ąÆ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ čüąĄą║čåąĖčÅčģ čāą┤ąĄą╗ąĄąĮąŠ ą▓ąĮąĖą╝ą░ąĮąĖąĄ ąŠą┐ąĖčüą░ąĮąĖčÄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ čüčåąĄąĮą░čĆąĖąĄą▓ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ STM32. ąŚą┤ąĄčüčī ą▒čāą┤ąĄčé ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąŠ ą▒ąŠą╗ąĄąĄ ą│ą╗čāą▒ąŠą║ąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ąŠčüąĮąŠą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ čéą░ą╣ą╝ąĄčĆą░ STM32, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą┤ą╗čÅ čüąŠąĘą┤ą░ąĮąĖčÅ ą┤ąĄą╝ąŠąĮčüčéčĆą░čåąĖąŠąĮąĮąŠą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąŚą┤ąĄčüčī čéą░ą║ąČąĄ ą▒čāą┤ąĄčé ąŠą┐ąĖčüą░ąĮą░ ą░čĆčģąĖč鹥ą║čéčāčĆą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ąĖčüčģąŠą┤ąĮąŠą│ąŠ ą║ąŠą┤ą░.

ąÆ čŹč鹊ą╝ ą┤ąŠą║čāą╝ąĄąĮč鹥 ąŠą▒čüčāąČą┤ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐čĆąŠčüčéčŗąĄ ą▓ąŠą┐čĆąŠčüčŗ, ąĖ ąĮąĄ ą▒čāą┤čāčé ąĘą░čéčĆąŠąĮčāčéčŗ čéą░ą║ąĖąĄ čüą╗ąŠąČąĮčŗąĄ č鹥ą╝čŗ, ą║ą░ą║ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ą▓ąĖą│ą░č鹥ą╗čÅą╝ąĖ. ąśąĮč乊čĆą╝ą░čåąĖčÅ, ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĮą░čÅ ąĘą┤ąĄčüčī, ą┐čĆąĖą╝ąĄąĮąĖą╝ą░ ą║ čüą╗ąĄą┤čāčÄčēąĖą╝ čüąĄčĆąĖčÅą╝ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32:

STM32F0, STM32F1, STM32F2, STM32F3, STM32F4, STM32F7, STM32L0, STM32L1, STM32L1W, STM32L4.

ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ STM32 ąĖą╝ąĄčÄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ čéą░ą╣ą╝ąĄčĆąŠą▓, ą║ąŠč鹊čĆčŗąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąŠčéčüč湥čéą░ ą▓čĆąĄą╝ąĄąĮąĖ, ą┐ąŠą┤čüč湥čéą░ ąĖą╝ą┐čāą╗čīčüąŠą▓, ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĖ ą┐ąĄčĆąĖąŠą┤ąŠą▓ čüąĖą│ąĮą░ą╗ąŠą▓, ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą©ąśą£, ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▓ąĮąĄčłąĮąĖčģ čāčüčéčĆąŠą╣čüčéą▓. ą×ą┤ąĮą░ą║ąŠ ą▓ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░ 8-ą▒ąĖčéąĮčŗčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓, ą▓ ą║ąŠč鹊čĆčŗčģ ąĄčüčéčī 2/3 čéą░ą╣ą╝ąĄčĆą░ čü ąŠą│čĆą░ąĮąĖč湥ąĮąĮčŗą╝ čäčāąĮą║čåąĖąŠąĮą░ą╗ąŠą╝, čéą░ą╣ą╝ąĄčĆčŗ STM32 ą▓ąĄčüčīą╝ą░ ąĖąĘąŠčēčĆąĄąĮąĮčŗąĄ ąĖ čüą╗ąŠąČąĮčŗąĄ. ąŁč鹊 ąŠą▒čŖčÅčüąĮčÅąĄčé č鹊čé čäą░ą║čé, čćč鹊 ąŠą┐ąĖčüą░ąĮąĖąĄ ą╝ąŠą┤čāą╗ąĄą╣ čéą░ą╣ą╝ąĄčĆąŠą▓ ąĘą░ąĮąĖą╝ą░ąĄčé ą┐čĆąĖą╝ąĄčĆąĮąŠ 25% ą┤ą░čéą░čłąĖčéą░ ą╗čÄą▒ąŠą│ąŠ STM32.

ą¤ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ąĮą░čćą░čéčī čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čéčī čéą░ą╣ą╝ąĄčĆčŗ STM32, čüą╗ąĄą┤čāąĄčé ąĘą░ą╝ąĄčéąĖčéčī, čćč鹊 ąŠąĮąĖ čüą╗ąĖčłą║ąŠą╝ čüą╗ąŠąČąĮčŗ, čćč鹊ą▒čŗ ą▓ ąŠą┤ąĮąŠą╣ čüčéą░čéčīąĄ čĆą░čüčüą╝ąŠčéčĆąĄčéčī ą▓čüąĄ ąĖčģ čäčāąĮą║čåąĖąĖ. ą¤ąŠčŹč鹊ą╝čā ąĘą┤ąĄčüčī ą╝čŗ čĆą░čüčüą╝ąŠčéčĆąĖą╝ ą▒ą░ąĘąŠą▓čŗąĄ ą▓ąŠą┐čĆąŠčüčŗ čĆą░ą▒ąŠčéčŗ čü čéą░ą╣ą╝ąĄčĆą░ą╝ąĖ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗ąĖčé ąĮą░čćą░čéčī ąĖčģ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī. ą¤ąŠą╗ąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąĖčēąĖč鹥 ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ą║ąŠąĮą║čĆąĄčéąĮčāčÄ ą╝ąŠą┤ąĄą╗čī ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

[ąÜą╗ą░čüčüąĖčäąĖą║ą░čåąĖčÅ čéą░ą╣ą╝ąĄčĆąŠą▓ STM32]

ąóą░ą╣ą╝ąĄčĆčŗ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32 ą╝ąŠąČąĮąŠ ą┐ąŠą┤ąĄą╗ąĖčéčī ąĮą░ čüą╗ąĄą┤čāčÄčēąĖąĄ ą║ą░č鹥ą│ąŠčĆąĖąĖ:

ŌĆó ą¤čĆąŠą┤ą▓ąĖąĮčāčéčŗąĄ (Advanced Timers)

ŌĆó ą×ą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (General Purpose Timers, čüąŠą║čĆą░čēąĄąĮąĮąŠ GP)

ŌĆó ąæą░ąĘąŠą▓čŗąĄ (Basic Timers)

ąśąĘ čŹčéąĖčģ čéčĆąĄčģ čéąĖą┐ąŠą▓ čéą░ą╣ą╝ąĄčĆąŠą▓ ą┐ąĄčĆą▓čŗąĄ ą┤ą▓ą░ ą▒čāą┤čāčé ąŠą▒čēąĖą╝ąĖ ą┤ą╗čÅ ą▓čüąĄčģ ą╝ąŠą┤ąĄą╗ąĄą╣ STM32. ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čéčĆąĄčéąĖą╣ čéąĖą┐ ą┤ąŠčüčéčāą┐ąĄąĮ č鹊ą╗čīą║ąŠ ą▓ čüčéą░čĆčłąĖčģ ą╝ąŠą┤ąĄą╗čÅčģ. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą╣ą╝ąĄčĆąŠą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą║ą╗ą░čüčüą░ čéą░ą║ąČąĄ ą╝ąĄąĮčÅąĄčéčüčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĄą╝ą║ąŠčüčéąĖ ąĖą╗ąĖ čĆą░ąĘą╝ąĄčĆą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32. ąØą░ą┐čĆąĖą╝ąĄčĆ, čā STM32F103C8T6 ąĄčüčéčī ąŠą┤ąĖąĮ ą┐čĆąŠą┤ą▓ąĖąĮčāčéčŗą╣ čéą░ą╣ą╝ąĄčĆ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čā STM32F103VET6 ą┤ą▓ą░ ą┐čĆąŠą┤ą▓ąĖąĮčāčéčŗčģ čéą░ą╣ą╝ąĄčĆą░. ąæąĖą▒ą╗ąĖąŠč鹥ą║ą░ STM32CubeMX ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ č鹊ą│ąŠ, ą║ą░ą║ąĖąĄ čéą░ą╣ą╝ąĄčĆčŗ ą┤ąŠčüčéčāą┐ąĮčŗ ą▓ ąĖą╝ąĄčÄčēąĄą╣čüčÅ ą╝ąŠą┤ąĄą╗ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ąĄčüą╗ąĖ ąÆčŗ ąĮąĄ čģąŠčéąĖč鹥 ąĘą░ą▒ą╗čāą┤ąĖčéčīčüčÅ ą▓ ą▒ąŠą╗čīčłąŠą╝ ą╝ą░čüčüąĖą▓ąĄ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ.

ąÆ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮčŗ ąŠčüąĮąŠą▓ąĮčŗąĄ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ čéą░ą╣ą╝ąĄčĆąŠą▓ čĆą░ąĘą╗ąĖčćąĮčŗčģ čéąĖą┐ąŠą▓.

| ąóąĖą┐ čéą░ą╣ą╝ąĄčĆą░ |

ąóą░ą╣ą╝ąĄčĆ |

ąĀą░ąĘčĆ. čüč湥čéčćąĖą║ą░ |

ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüč湥čéą░ |

ąÜąŠčŹčä. ą┐čĆąĄčüą║ą░ą╗. |

DMA |

ąÜą░ąĮą░ą╗čŗ Capt./Comp. |

ąÜąŠą╝ą┐ą╗. ą▓čŗčģąŠą┤čŗ |

| ą¤čĆąŠą┤ą▓ąĖąĮčāčéčŗą╣ |

TIM1, TIM8 |

16 ą▒ąĖčé |

ąÆą▓ąĄčĆčģ, ą▓ąĮąĖąĘ, ą▓ ą┤ą▓čāčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ |

1..65535 |

ąĢčüčéčī |

4 |

ąĢčüčéčī |

| GP |

TIM2, TIM5 |

32 ą▒ąĖčéą░ |

ąØąĄčé |

| TIM3, TIM4 |

16 ą▒ąĖčé |

| TIM9 |

16 ą▒ąĖčé |

ąóąŠą╗čīą║ąŠ ą▓ą▓ąĄčĆčģ |

ąØąĄčé |

2 |

| TIM10, TIM11 |

16 ą▒ąĖčé |

1 |

| TIM12 |

16 ą▒ąĖčé |

2 |

| TIM13, TIM14 |

16 ą▒ąĖčé |

1 |

| ąæą░ąĘąŠą▓čŗą╣ |

TIM6, TIM7 |

16 ą▒ąĖčé |

ąĢčüčéčī |

0 |

General purpose (GP) čéą░ą╣ą╝ąĄčĆčŗ ąĖą╝ąĄčÄčé ą▓čüąĄ čäčāąĮą║čåąĖąĖ čüčéą░ąĮą┤ą░čĆčéąĮąŠą│ąŠ ą╝ąŠą┤čāą╗čÅ čéą░ą╣ą╝ąĄčĆą░-čüč湥čéčćąĖą║ą░, ąŠąĮąĖ ą┐ąŠčćčéąĖ čéą░ą║ąĖąĄ ąČąĄ, ą║ą░ą║ ą▓ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ 8-ą▒ąĖčéąĮčŗčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓. GP-čéą░ą╣ą╝ąĄčĆčŗ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą╗čÄą▒čŗčģ čüą▓čÅąĘą░ąĮąĮčŗčģ čü ąŠčéčüč湥č鹊ą╝ ą▓čĆąĄą╝ąĄąĮąĖ ąĖ ą┐ąŠą┤čüč湥č鹊ą╝ čüąŠą▒čŗčéąĖą╣ čåąĄą╗ąĄą╣, ą▓ č鹊ą╝ čćąĖčüą╗ąĄ ąĖ ą│ąĄąĮąĄčĆą░čåąĖčÅ ą©ąśą£ ąĖ ąĘą░čģą▓ą░čé ąĖą╝ą┐čāą╗čīčüąŠą▓. ą×ą▒čŗčćąĮąŠ ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ STM32 ą▒ąŠą╗čīčłąĄ ą▓čüąĄą│ąŠ ąĖą╝ąĄąĮąĮąŠ čéą░ą╣ą╝ąĄčĆąŠą▓ GP, č湥ą╝ čéą░ą╣ą╝ąĄčĆąŠą▓ ą┤čĆčāą│ąĖčģ ą║ą╗ą░čüčüąŠą▓. ąśąĘčāč湥ąĮąĖąĄ GP-čéą░ą╣ą╝ąĄčĆąŠą▓ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╗čāčćčłąĄ ą┐ąŠąĮčÅčéčī ą▒ą░ąĘąŠą▓čŗąĄ ą║ąŠąĮčåąĄą┐čåąĖąĖ.

ąŻ ą▒ą░ąĘąŠą▓čŗčģ čéą░ą╣ą╝ąĄčĆąŠą▓ ąĮąĄčé ą║ą░ąĮą░ą╗ąŠą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ą┤ą╗čÅ ąĘą░čģą▓ą░čéą░ ą▓čģąŠą┤ąĮčŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ (čüąŠą▒čŗčéąĖą╣) ąĖ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą©ąśą£, ą┐ąŠčŹč鹊ą╝čā čéą░ą║ąĖąĄ čéą░ą╣ą╝ąĄčĆčŗ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čåąĄą╗ąĄą╣ ąŠčéčüč湥čéą░ ą▓čĆąĄą╝ąĄąĮąĖ. ąæą░ąĘąŠą▓čŗąĄ čéą░ą╣ą╝ąĄčĆčŗ ą┤ąŠčüčéčāą┐ąĮčŗ č鹊ą╗čīą║ąŠ ą▓ čüčéą░čĆčłąĖčģ ą╝ąŠą┤ąĄą╗čÅčģ STM32, ąĖ čŹč鹊 čüą░ą╝čŗą╣ ą┐čĆąŠčüč鹊ą╣ ą║ą╗ą░čüčü čéą░ą╣ą╝ąĄčĆąŠą▓.

ą¤čĆąŠą┤ą▓ąĖąĮčāčéčŗąĄ čéą░ą╣ą╝ąĄčĆčŗ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╝ ą┐ąŠčģąŠąČąĖ ąĮą░ GP-čéą░ą╣ą╝ąĄčĆčŗ, ąĮąŠ ąĖą╝ąĄčÄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą┐ąŠ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą©ąśą£, ą░ čéą░ą║ąČąĄ č乊čĆą╝ąĖčĆąŠą▓ą░čéčī čüąĖą│ąĮą░ą╗ č鹊čĆą╝ąŠąČąĄąĮąĖčÅ ąĖ čäą░ąĘčŗ ą©ąśą£ čü "ą╝ąĄčĆčéą▓čŗą╝" ąĖąĮč鹥čĆą▓ą░ą╗ąŠą╝, ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░čÄčēąĖą╝ čüą║ą▓ąŠąĘąĮčŗąĄ č鹊ą║ąĖ čüąĖą╗ąŠą▓ąŠą│ąŠ ą╝ąŠčüčéą░ (dead-time). ąŁčéąĖ čäčāąĮą║čåąĖąĖ ą┐ąŠą╗ąĄąĘąĮčŗ ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣, čüą▓čÅąĘą░ąĮąĮčŗčģ čü čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┤ą▓ąĖą│ą░č鹥ą╗čÅą╝ąĖ, čü čüąĖą╗ąŠą▓čŗą╝ąĖ ąĖąĮą▓ąĄčĆč鹊čĆą░ą╝ąĖ, čüąĖčüč鹥ą╝ą░ą╝ąĖ SMPS ąĖ ą┤čĆčāą│ąĖą╝ąĖ ąĘą░ą┤ą░čćą░ą╝ąĖ, čüą▓čÅąĘą░ąĮąĮčŗą╝ąĖ čü ąĖčüč鹊čćąĮąĖą║ą░ą╝ąĖ ą┐ąĖčéą░ąĮąĖčÅ čŹą╗ąĄą║čéčĆąŠąĮąĖą║ąĖ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą╝ąŠčēąĮąŠčüčéčīčÄ. ąÆ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32 ąĄčüčéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ čéą░ą║ąŠą╣ čéą░ą╣ą╝ąĄčĆ. ąÆ čüčéą░čĆčłąĖčģ ą╝ąŠą┤ąĄą╗čÅčģ STM32, ą┐čĆąŠą┤ą▓ąĖąĮčāčéčŗčģ čéą░ą╣ą╝ąĄčĆąŠą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ą▓ą░.

ąÜą░ąČą┤čŗą╣ čéą░ą╣ą╝ąĄčĆ ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ STM32 ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┤čĆčāą│ąĖčģ, ąĖ ą┐ąŠčŹč鹊ą╝čā ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąĮąĖą║ą░ą║ąĖąĄ ąŠą▒čēąĖąĄ čĆąĄčüčāčĆčüčŗ. ąĢą┤ąĖąĮčüčéą▓ąĄąĮąĮąŠąĄ, čćč鹊 ąŠą▒čēąĄąĄ ą╝ąĄąČą┤čā čéą░ą╣ą╝ąĄčĆą░ą╝ąĖ, čŹč鹊 čéąĖą┐čŗ čĆąĄą│ąĖčüčéčĆąŠą▓, ą┐čĆąĖąĮčåąĖą┐čŗ ąĖą╝ąĄąĮąŠą▓ą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ąŠą▒čēąĖą╣ ą┐čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ. ąĪ ąŠč湥ąĮčī ą╝ą░ą╗čŗą╝ąĖ ąĖčüą║ą╗čÄč湥ąĮąĖčÅą╝ąĖ ą╝ąŠą┤čāą╗ąĖ čéą░ą╣ą╝ąĄčĆąŠą▓ ą▒ąŠą╗ąĄąĄ ąĖą╗ąĖ ą╝ąĄąĮąĄąĄ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗ ą┐ąŠ ą▓čüąĄą╝ čüąĄą╝ąĄą╣čüčéą▓ą░ą╝ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąÆčŗ ąĮąĄ ąĮą░ą╣ą┤ąĄč鹥 ąĘąĮą░čćąĖč鹥ą╗čīąĮčŗčģ čĆą░ąĘą╗ąĖčćąĖą╣ ą▓ ą░ą┐ą┐ą░čĆą░čéčāčĆąĄ čéą░ą╣ą╝ąĄčĆąŠą▓ ą┐čĆąĖ ą╝ąĖą│čĆą░čåąĖąĖ ą┐čĆąŠąĄą║čéą░ čü čüąĄčĆąĖąĖ STM32F1xx ąĮą░ čüąĄčĆąĖčÄ STM32F4xx. ąŁč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī čüąŠą▓čüąĄą╝ ąĮąĄ čéą░ą║ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ - ą┐ąŠčĆč鹊ą▓ GPIO, ADC, ąĖ čé. ą┐.

ąÆ čéą░ą▒ą╗ąĖčåąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ą╗ąĖčćąĖąĄ čéą░ą╣ą╝ąĄčĆąŠą▓ čĆą░ąĘąĮčŗčģ ą║ą╗ą░čüčüąŠą▓ ą▓ čüąĄą╝ąĄą╣čüčéą▓ą░ą╝ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32.

ąóąĖą┐ čéą░ą╣ą╝ąĄčĆą░

|

STM32F0 |

STM32F101, 102, 103, 105, 107 |

STM32F100 |

STM32L1 |

STM32F2, STM32F4 |

STM32F30x, STM32F3x8 |

STM32F37x |

| ą¤čĆąŠą┤ą▓ąĖąĮčāčéčŗą╣ |

TIM1 |

TIM1 |

TIM1 |

- |

TIM1 |

TIM1 |

- |

| - |

TIM8 |

- |

- |

TIM8 |

TIM8 |

- |

| - |

- |

- |

- |

- |

TIM20 |

- |

| GP |

16 ą▒ąĖčé |

- |

TIM2 |

TIM2 |

TIM2 |

- |

TIM2 |

TIM2 |

| TIM3 |

TIM3 |

TIM3 |

TIM3 |

TIM3 |

TIM3 |

TIM |

| - |

TIM4 |

TIM4 |

TIM4 |

TIM4 |

TIM4 |

TIM4 |

| - |

TIM5 |

TIM5 |

- |

- |

- |

TIM5 |

| - |

- |

- |

- |

- |

- |

TIM19 |

| 32 ą▒ąĖčéą░ |

TIM2 |

- |

- |

- |

TIM2 |

TIM2 |

TIM2 |

| - |

- |

- |

- |

TIM5 |

- |

TIM5 |

| ąæą░ąĘąŠą▓čŗą╣ |

TIM6 |

TIM6 |

TIM6 |

TIM6 |

TIM6 |

TIM6 |

TIM6 |

| - |

TIM7 |

TIM7 |

TIM7 |

TIM7 |

TIM7 |

TIM7 |

| - |

- |

- |

- |

- |

- |

TIM18 |

| 1 ą║ą░ąĮą░ą╗ |

- |

TIM10 |

- |

TIM10 |

TIM10 |

- |

- |

| - |

TIM11 |

- |

TIM11 |

TIM11 |

- |

- |

| - |

TIM13 |

TIM13 |

- |

TIM13 |

- |

TIM13 |

| TIM14 |

TIM14 |

TIM14 |

- |

TIM14 |

- |

TIM14 |

| 2 ą║ą░ąĮą░ą╗ą░ |

- |

TIM9 |

- |

TIM9 |

TIM9 |

- |

- |

| - |

TIM12 |

TIM12 |

- |

TIM12 |

- |

TIM12 |

| 1 ą║ą░ąĮą░ą╗ čü ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗą╝ ą▓čŗčģąŠą┤ąŠą╝ |

TIM15 |

- |

TIM15 |

- |

- |

TIM15 |

TIM15 |

| 2 ą║ą░ąĮą░ą╗ą░ čü ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗą╝ ą▓čŗčģąŠą┤ąŠą╝ |

TIM16 |

- |

TIM16 |

- |

- |

TIM16 |

TIM16 |

| TIM17 |

- |

TIM17 |

- |

- |

TIM17 |

TIM17 |

[ą×ą▒ąĘąŠčĆ čéą░ą╣ą╝ąĄčĆąŠą▓]

ą×ą▒čŗčćąĮąŠ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ čéą░ą╣ą╝ąĄčĆąŠą▓ STM32 čüąŠčüč鹊ąĖčé ąĖąĘ 16-ą▒ąĖčéąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░ čü ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ąĘą░ą│čĆčāąĘą║ąŠą╣ ąĖ 16-ą▒ąĖčéąĮąŠą│ąŠ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░. ą¤čĆąĄčüą║ą░ą╗ąĄčĆ ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ ą┤ąĄą╗ąĄąĮąĖąĄ ą┐čĆąĖčģąŠą┤čÅčēąĄą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čüąŠą│ą╗ą░čüąĮąŠ ą┐ąŠčéčĆąĄą▒ąĮąŠčüčéčÅą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ążčāąĮą║čåąĖčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ąĘą░ą│čĆčāąĘą║ąĖ čüč湥čéčćąĖą║ą░ čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠčćčéąĖ čéą░ą║ ąČąĄ, ą║ą░ą║ ą╝čŗ ą┐čĆąĖą▓čŗą║ą╗ąĖ ą▓ąĖą┤ąĄčéčī ą▓ 8-ą▒ąĖčéąĮčŗčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ, čü ąĄą┤ąĖąĮčüčéą▓ąĄąĮąĮčŗą╝ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝. ąÆ 8-ą▒ąĖčéąĮčŗčģ MCU čüčéą░čĆąŠą╣ čłą║ąŠą╗čŗ ąĮą░ą╝ ąĮčāąČąĮąŠ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘąĖčéčī čéą░ą╣ą╝ąĄčĆ ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖą╗ąĖ ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░. ąŁč鹊 ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą▓ čéą░ą╣ą╝ąĄčĆą░čģ STM32, čéą░ą║ ą║ą░ą║ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ.

ąÆ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ą╝ąĮąŠą│ąĖčģ ą┤čĆčāą│ąĖčģ MCU, ą▓ ą║ąŠč鹊čĆčŗčģ čéą░ą╣ą╝ąĄčĆčŗ ąŠą▒čŗčćąĮąŠ čüčćąĖčéą░čÄčé ąĮą░ čāą▓ąĄą╗ąĖč湥ąĮąĖąĄ (ąĮą░ ąĖąĮą║čĆąĄą╝ąĄąĮčé), čéą░ą╣ą╝ąĄčĆčŗ STM32 ą╝ąŠą│čāčé čüčćąĖčéą░čéčī ą▓ą▓ąĄčĆčģ, ą▓ąĮąĖąĘ ąĖą╗ąĖ ą▓ą▓ąĄčĆčģ/ą▓ąĮąĖąĘ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ čüčĆąĄą┤ąĮąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ. ą×ą┤ąĮą░ą║ąŠ ą▓ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ čéčĆą░ą┤ąĖčåąĖąŠąĮąĮąŠ ąĖ ą┐čĆąĄą┤ą┐ąŠčćčéąĖč鹥ą╗čīąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüč湥čé ą▓ą▓ąĄčĆčģ.

ąŚą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ą▒ą░ąĘąŠą▓čŗčģ čéą░ą╣ą╝ąĄčĆąŠą▓, ą▓čüąĄ čéą░ą╣ą╝ąĄčĆčŗ STM32 ąĖą╝ąĄčÄčé 4 ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą║ą░ąĮą░ą╗ą░ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (I/O channels TIMx_CH1 .. TIMx_CH4). ą×ąĮąĖ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆó Input Capture (ąĘą░čģą▓ą░čé ą▓ąĮąĄčłąĮąĖčģ čüąŠą▒čŗčéąĖą╣)

ŌĆó Output Compare, ąĖą╗ąĖ PWM (ą©ąśą£)

ŌĆó One Pulse Mode (čĆąĄąČąĖą╝ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąŠą┤ąĮąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░)

ąóą░ą╣ą╝ąĄčĆčŗ ą╝ąŠą│čāčé čéą░ą║čéąĖčĆąŠą▓ą░čéčīčüčÅ ą╗ąĖą▒ąŠ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ (čéą░ą║č鹊ą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ RC ąĖą╗ąĖ ąŠčé ą│ąĄąĮąĄčĆą░č鹊čĆą░, čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą▓ąĮąĄčłąĮąĖą╝ ą║ą▓ą░čĆčåąĄą╝), ąĖą╗ąĖ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓. ąÆąĮąĄčłąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ:

ŌĆó External Mode 1 (čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ TI1 ąĖ TI2)

ŌĆó External Mode 2 (čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ETR)

ŌĆó Internal Trigger (ITRx)

ąĪąŠą▒čŗčéąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ DMA ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ čüąĖčéčāą░čåąĖčÅčģ:

ŌĆó ą×ą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ: ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąĖ čüč湥č鹥 ą▓ą▓ąĄčĆčģ (overflow) ąĖą╗ąĖ ąŠą▒ąĮčāą╗ąĄąĮąĖąĄ ą┐čĆąĖ čüč湥č鹥 ą▓ąĮąĖąĘ (underflow), ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ čüč湥čéčćąĖą║ą░, ą┤čĆčāą│ąĖąĄ čüąŠą▒čŗčéąĖčÅ.

ŌĆó ąóčĆąĖą│ą│ąĄčĆ: čüčéą░čĆčé čüč湥čéą░, ąŠčüčéą░ąĮąŠą▓ą║ą░ čüč湥čéą░, ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ čüč湥čéčćąĖą║ą░, ą┤čĆčāą│ąĖąĄ čüąŠą▒čŗčéąĖčÅ.

ŌĆó Input Capture / Output Compare.

ŌĆó ąöčĆčāą│ąĖąĄ čüąŠą▒čŗčéąĖčÅ.

ąóą░ą▒ą╗ąĖčåą░ ąĮąĖąČąĄ ą┤ą░ąĄčé ąŠą▒ąĘąŠčĆ ąĮą░ ąŠą▒čēąĖąĄ čäčāąĮą║čåąĖąĖ čéą░ą╣ą╝ąĄčĆąŠą▓ STM32.

ąóąĖą┐ čéą░ą╣ą╝ąĄčĆą░

|

ąĀą░ąĘčĆ. čüč湥čéčćąĖą║ą░

|

ąĪč湥čé

|

DMA

|

ąÜą░ąĮą░ą╗ąŠą▓

|

ążčāąĮą║čå. čüčĆą░ą▓ąĮ.

|

ąĪąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ |

| Master |

Slave |

| ą¤čĆąŠą┤ą▓ąĖąĮčāčéčŗą╣ |

16 ą▒ąĖčé |

ąÆą▓ąĄčĆčģ, ą▓ąĮąĖąĘ ąĖ čü

ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄą╝

ą┐ąŠ čåąĄąĮčéčĆčā |

ąĢčüčéčī |

5 |

3 |

ąĢčüčéčī |

ąĢčüčéčī |

| GP |

16 ą▒ąĖčé, 32 ą▒ąĖčéą░(1) |

ąĢčüčéčī |

4 |

0 |

ąĢčüčéčī |

ąĢčüčéčī |

| ąæą░ąĘąŠą▓čŗą╣ |

16 ą▒ąĖčé |

ąóąŠą╗čīą║ąŠ ą▓ą▓ąĄčĆčģ |

ąĢčüčéčī |

0 |

0 |

ąĢčüčéčī |

- |

| 1 ą║ą░ąĮą░ą╗ |

16 ą▒ąĖčé |

- |

1 |

0 |

ąĢčüčéčī (čüąĖą│ąĮą░ą╗ OC) |

- |

| 2 ą║ą░ąĮą░ą╗ą░ |

16 ą▒ąĖčé |

- |

2 |

0 |

ąĢčüčéčī |

ąĢčüčéčī |

| 1 ą║ą░ąĮą░ą╗ čü ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗą╝ ą▓čŗčģąŠą┤ąŠą╝ |

16 ą▒ąĖčé |

ąĢčüčéčī |

1 |

1 |

ąĢčüčéčī (čüąĖą│ąĮą░ą╗ OC) |

- |

| 2 ą║ą░ąĮą░ą╗ą░ čü ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗą╝ ą▓čŗčģąŠą┤ąŠą╝ |

16 ą▒ąĖčé |

ąĢčüčéčī |

2 |

1 |

ąØąĄčé |

ąØąĄčé |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): TIM2 ąĖ TIM5 čŹč鹊 32-ą▒ąĖčéąĮčŗąĄ čüč湥čéčćąĖą║ąĖ ą▓ čüąĄčĆąĖčÅčģ STM32F2 ąĖ STM32F4, čāčüčéčĆąŠą╣čüčéą▓ą░čģ STM32F303xB, STM32F303xC, STM32F303xD, STM32F303xE ąĖ STM32F3x8.

ąśąĘ ą▓čüąĄą╣ čŹč鹊ą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą▓ąĖą┤ąĮą░ čāąĮąĖą▓ąĄčĆčüą░ą╗čīąĮąŠčüčéčī čéą░ą╣ą╝ąĄčĆąŠą▓ STM32, ąĖ ą┐ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ ąŠąĮąĖ ąĮąĄ ąŠč湥ąĮčī ą┐čĆąŠčüčéčŗ ą┤ą╗čÅ ąŠčüą▓ąŠąĄąĮąĖčÅ ąĮą░čćąĖąĮą░čÄčēąĖą╝ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčéą░ą╝ąĖ.

[ąĀąĄą│ąĖčüčéčĆčŗ čéą░ą╣ą╝ąĄčĆą░]

ą¤ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą╝čŗ ąĮą░čćąĮąĄą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī, čüą╗ąĄą┤čāąĄčé ąŠą▒čĆą░čéąĖčéčī ą▓ąĮąĖą╝ą░ąĮąĖąĄ ąĮą░ ą▓ąŠąĘą╝ąŠąČąĮąŠ ąĮą░ąĖą▒ąŠą╗ąĄąĄ čüą╗ąŠąČąĮčŗą╣ ąĮą░ą▒ąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32, ąŠčéąĮąŠčüčÅčēąĖą╣čüčÅ ą║ ą╝ąŠą┤čāą╗čÅą╝ čéą░ą╣ą╝ąĄčĆą░-čüč湥čéčćąĖą║ą░. ąÆ ą║ąŠąĮą║čĆąĄčéąĮąŠą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ ą▓čüąĄ čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ą╝ąŠą│čāčé ąĮąĄ ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ, ąĖ čćč鹊ą▒čŗ čāą┐čĆąŠčüčéąĖčéčī ąĖčģ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ, ą╝čŗ ą┐čĆąŠčüč鹊 ąŠą▒čüčāą┤ąĖą╝ ąĖčģ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ ąĘą░ą┤ą░čćąĖ. ąØąĄą║ąŠč鹊čĆčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĮčāąČąĮčŗ ą▒čāą┤čāčé ą▓čüąĄą│ą┤ą░, ąŠą┤ąĮą░ą║ąŠ ąĮąĄą║ąŠč鹊čĆčŗąĄ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čéą░ą║ąĖčģ ąĘą░ą┤ą░čć, ą║ą░ą║ input capture / output compare. ąĢčēąĄ ąŠą┤ąĮą░ ą▓ą░ąČąĮą░čÅ ą▓ąĄčēčī, ą║ąŠč鹊čĆčāčÄ čüč鹊ąĖčéčī ąŠčéą╝ąĄčéąĖčéčī - ą▓čüąĄ čĆąĄą│ąĖčüčéčĆčŗ ą▓ čÅą┤čĆąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ARM ąĖą╝ąĄčÄčé čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī 32 ą▒ąĖčéą░, ąĖ ą┤ą╗čÅ ą╝ąŠą┤čāą╗ąĄą╣ čéą░ą╣ą╝ąĄčĆąŠą▓ ąĖ ą╝ąĮąŠą│ąĖčģ ą┤čĆčāą│ąĖčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąĮąŠą│ąĖąĄ ą▒ąĖčéčŗ ą▓ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆą░čģ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ (čé. ąĄ. ąŠąĮąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ, ąĮąŠ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ ą▒čāą┤čāčēąĖčģ ą╝ąŠą┤ąĄą╗čÅčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓). ąŁč鹊 čāą┐čĆąŠčēą░ąĄčé ąŠą▒čĆą░ą▒ąŠčéą║čā ą▒ąĖčé. ą¦č鹊ą▒čŗ ąĄčēąĄ ą▒ąŠą╗čīčłąĄ čāą┐čĆąŠčüčéąĖčéčī ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ, ą▓ čŹč鹊ą╝ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ ą▒čāą┤čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüąŠą▒čüčéą▓ąĄąĮąĮčŗąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĖ čäčāąĮą║čåąĖąĖ, ą┐ąŠą┤ąŠą▒ąĮčŗąĄ č鹥ą╝, čćč鹊 ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĄ SPL ąŠčé ST. ąæąĖą▒ą╗ąĖąŠč鹥ą║ąĖ MikroC čéą░ą║ąČąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą┐ąŠčģąŠąČąĖą╣ ą┐ąŠą┤čģąŠą┤ ą║ ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÄ.

ąØąĖąČąĄ ą▓ čéą░ą▒ą╗ąĖčåąĄ ą║ą░č湥čüčéą▓ąĄ čüą┐čĆą░ą▓ąŠčćąĮąĖą║ą░ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ą║ą░čĆčéą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą╝ąŠą┤čāą╗čÅ čéą░ą╣ą╝ąĄčĆą░.

ą¤čĆąĖ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĄ ą║ąŠą┤ą░ ą┤ą╗čÅ čéą░ą╣ą╝ąĄčĆąŠą▓ čüą╗ąĄą┤čāąĄčé čāčćąĖčéčŗą▓ą░čéčī čüą╗ąĄą┤čāčÄčēąĖąĄ ą╝ąŠą╝ąĄąĮčéčŗ:

ŌĆó ą¤ąĄčĆąĄą┤ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą╝ąŠą┤čāą╗ąĖ čéą░ą╣ą╝ąĄčĆąŠą▓ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüąĮą░čćą░ą╗ą░ čĆą░ąĘčĆąĄčłąĄąĮčŗ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ RCC_APBx_ENR. ąĀą░ą▒ąŠčéą░ ąŠčéą┤ąĄą╗čīąĮčŗčģ čüč湥čéčćąĖą║ąŠą▓, čäčāąĮą║čåąĖą╣ DMA ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▓čüąĄą│ąŠ ąŠčüčéą░ą╗čīąĮąŠą│ąŠ.

ŌĆó ąĪčĆą░ąĘčā ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ą║ą░ąČą┤čŗą╣ ą▒ąĖčé ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32 čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ čüą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ. ąöą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ čéą░ą╣ą╝ąĄčĆą░ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čŹč鹊 ą▓čüąĄ ąĮčāą╗ąĖ, čćč鹊 ąŠąĘąĮą░čćą░ąĄčé ąĘą░ą┐čĆąĄčé ą▓čüąĄčģ čäčāąĮą║čåąĖą╣. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĮąĄ ąĮčāąČąĮąŠ čŹčéąĖ ą▒ąĖčéčŗ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ąŠčćąĖčēą░čéčī ą┐čĆąĖ čüčéą░čĆč鹥 (č鹊čćąĮąŠ čéą░ą║ ąČąĄ ąŠą▒čüč鹊čÅčé ą┤ąĄą╗ą░ ąĖ čü ą╗čÄą▒čŗą╝ ą┤čĆčāą│ąĖą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ STM32). ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ąÆą░ą╝ ąĮčāąČąĮąŠ ą┐ąŠą╝ąĄąĮčÅčéčī ą║ąŠąĄ-čćč鹊 ąĮą░ ą╗ąĄčéčā, č鹊 ą╗čāčćčłąĄ ą▓čüąĄą│ąŠ čüąĮą░čćą░ą╗ą░ čüą▒čĆąŠčüąĖčéčī ą▓čüąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ, čćč鹊ą▒čŗ ąĮąĄ ą┐ąŠą┐ą░čüčéčī ą▓ čüąĖčéčāą░čåąĖčÄ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝ąŠą│ąŠ ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆąŠą▓ ąĖ ąŠą▒čüą╗čāąČąĖą▓ą░čÄčēąĄą│ąŠ ąĖčģ ą║ąŠą┤ą░.

ŌĆó ąóą░ą╣ą╝ąĄčĆčŗ ąĮąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ čćą░čüąŠą▓ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (RTC) ąĖąĘ-ąĘą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ čäą░ą║č鹊čĆąŠą▓, ąĖ ąŠąĮąĖ ąĮąĄ ą▓čüąĄą│ą┤ą░ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé čģčĆą░ąĮąĖčéčī ąĖ ąŠčéčüą╗ąĄąČąĖą▓ą░čéčī č鹊čćąĮąŠąĄ ą▓čĆąĄą╝čÅ. ąĢčüą╗ąĖ č鹊čćąĮąŠčüčéčī ąĮąĄ ąŠč湥ąĮčī ą▓ą░ąČąĮą░, č鹊 čéą░ą╣ą╝ąĄčĆčŗ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ ąŠą▒čŗčćąĮąŠą│ąŠ čüčĆąĄą┤čüčéą▓ą░ ąŠčéčüą╗ąĄąČąĖą▓ą░ąĮąĖčÅ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ. ąæąĄąĘ čüąŠą╝ąĮąĄąĮąĖą╣ čéą░ą╣ą╝ąĄčĆčŗ ą▒ąŠą╗ąĄąĄ č鹊čćąĮčŗ ąĖ čŹčäč乥ą║čéąĖą▓ąĮčŗ, č湥ą╝ čéčāą┐čŗąĄ ą┐čāčüčéčŗąĄ čåąĖą║ą╗čŗ ąĘą░ą┤ąĄčƹȹ║ąĖ, ąĮąŠ ąŠąĮąĖ ąĮąĄ ąŠč湥ąĮčī čģąŠčĆąŠčłąĖ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ą╝ąĄčüč鹊 ą▓čŗą┤ąĄą╗ąĄąĮąĮąŠą╣ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ RTC.

ŌĆó ąÜąŠą│ą┤ą░ ąĮąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ GPIO ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čäčāąĮą║čåąĖą╣ čĆąĄąČąĖą╝ą░ capture/compare, čéčēą░č鹥ą╗čīąĮąŠ ąĖąĘčāčćąĖč鹥, ą║ą░ą║ąĖąĄ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą▓čŗą▓ąŠą┤čŗ I/O, ą┐ąŠč鹊ą╝čā čćč鹊 ąĖąĮąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤čŗ I/O, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü čŹčéąĖą╝ąĖ čäčāąĮą║čåąĖčÅą╝ąĖ, ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ ą║ą░ą║ąŠą╣-č鹊 ą┤čĆčāą│ąŠą╣ čäčāąĮą║čåąĖąĖ. ąśčüą┐ąŠą╗čīąĘčāą╣č鹥 STM32CubeMX, čćč鹊ą▒čŗ ąĮą░ą╣čéąĖ, ą║ą░ą║ąĖąĄ ą▓čŗą▓ąŠą┤čŗ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čü ą║ą░ąČą┤čŗą╝ ą║ąŠąĮą║čĆąĄčéąĮčŗą╝ čéą░ą╣ą╝ąĄčĆąŠą╝.

ŌĆó ą£ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▒ą╗ąŠą║ AFIO ą┤ą╗čÅ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą▓čŗą▓ąŠą┤ąŠą▓ I/O, ą┐ąŠčüą║ąŠą╗čīą║čā capture/compare čŹč鹊 ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ ąŠą▒čŗčćąĮčŗčģ ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ GPIO. ąæą╗ąŠą║ AFIO ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. ąÆčŗą▓ąŠą┤čŗ GPIO ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ AFIO ą┤ą╗čÅ čĆąĄąČąĖą╝ąŠą▓ compare/output.

ŌĆó ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čĆąĄąČąĖą╝ ąĘą░čģą▓ą░čéą░ ą┐ąŠ ą▓čģąŠą┤čā (input capture), ąŠą▒ąĄčüą┐ąĄčćčīč鹥 čāčüą╗ąŠą▓ąĖčÅ, čćč鹊ą▒čŗ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąŠčüčéčāą┐ą░čÄčēąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮąĄ ą┐čĆąĄą▓čŗčüąĖą╗ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ. ąØąĄ ą▓čüąĄ, ąĮąŠ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ ąĮąŠąČąĄą║ ą▓čŗą▓ąŠą┤ąŠą▓ I/O ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą┐ąŠą┤ą░ą▓ą░čéčī ą▓čģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī 5 ą▓ąŠą╗čīčé ą┐čĆąĖ ą┐ąĖčéą░ąĮąĖąĖ ą┐ąŠą┤čüąĖčüč鹥ą╝ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ąŠčé čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ 3.3 ą▓ąŠą╗čīčéą░ (ą┐čĆąŠ čéą░ą║ąĖąĄ ą▓čŗą▓ąŠą┤čŗ ą┐ąŠčĆč鹊ą▓ ą│ąŠą▓ąŠčĆčÅčé, čćč鹊 ąŠąĮąĖ ąŠą▒ą╗ą░ą┤ą░čÄčé čäčāąĮą║čåąĖąĄą╣ "5V tolerant"). ą×ą┤ąĮą░ą║ąŠ ą▓čüąĄ čĆą░ą▓ąĮąŠ ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĮąĄ ą┐čĆąĄą▓čŗčłą░čéčī čāčĆąŠą▓ąĄąĮčī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ VDD, ą║ąŠč鹊čĆčŗą╣ ąŠą▒čŗčćąĮąŠ čüąŠčüčéą░ą▓ą╗čÅąĄčé 3.3V.

ŌĆó ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ čĆąĄąČąĖą╝ą░ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (output compare mode) čāą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 ąĮą░ą│čĆčāąĘą║ą░ ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ čüą▓ąĄč鹊ą┤ąĖąŠą┤ą░ ąĖą╗ąĖ ąŠą┐čéčĆąŠąĮąĮąŠą│ąŠ ąĖąĘąŠą╗čÅč鹊čĆą░ ąĮąĄ ą┐čĆąĖą▓ąŠą┤ąĖą╗ą░ ą║ čüą╗ąĖčłą║ąŠą╝ ą▒ąŠą╗čīčłąŠą╝čā č鹊ą║čā č湥čĆąĄąĘ ą┤čĆą░ą╣ą▓ąĄčĆ ą▓čŗčģąŠą┤ą░. ą×č湥ąĮčī ą▓ą░ąČąĮąŠ, čćč鹊ą▒čŗ č鹊ą║ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąĮąĄ ą┐čĆąĄą▓čŗčłą░ą╗ ą┐čĆąĄą┤ąĄą╗, čāą║ą░ąĘą░ąĮąĮčŗą╣ ą▓ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ. ąĢčüą╗ąĖ ą▓čŗčģąŠą┤ąĮąŠą╣ č鹊ą║ ąĮąĄą┤ąŠčüčéą░č鹊č湥ąĮ, č鹊 ą┐čĆąĖą╝ąĄąĮčÅą╣č鹥 čāčüąĖą╗ąĖą▓ą░čÄčēąĖąĄ čéčĆą░ąĮąĘąĖčüč鹊čĆąĮčŗąĄ ą║ą╗čÄčćąĖ ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą▒čāč乥čĆą░.

ŌĆó ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32 ą┤ąŠą▓ąŠą╗čīąĮąŠ č鹊čćąĮčŗą╣ (čü ą┤ąŠą┐čāčüą║ąŠą╝ 1%), ąŠą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ąĮčāąČąĮą░ ąĮą░ą╝ąĮąŠą│ąŠ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ą░čÅ č鹊čćąĮąŠčüčéčī, č鹊 ą╗čāčćčłąĄ ą▓čüąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ą░ą╗ąĖą▒čĆąŠą▓ą░ąĮąĮčŗąĄ ą▓ąĮąĄčłąĮąĖąĄ ą│ąĄąĮąĄčĆą░č鹊čĆčŗ ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĖąĄ č鹊čćąĮčŗąĄ ą║ą▓ą░čĆčåąĄą▓čŗąĄ čĆąĄąĘąŠąĮą░č鹊čĆčŗ.

ŌĆó ąŻčćąĖčéčŗą▓ą░ą╣č鹥 ą▓ą╗ąĖčÅąĮąĖąĄ ąĮą░ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā ą┐čĆąĄčüą║ą░ą╗ąĄčĆąŠą▓ čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║č鹊ą▓, čāą╝ąĮąŠąČąĖč鹥ą╗ąĄą╣ ąĖ ąĖčüč鹊čćąĮąĖą║ąŠą▓ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ.

ŌĆó ą¤ąŠą╝ąĮąĖč鹥, čćč鹊 ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ą║ čłąĖąĮąĄ APB2, ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čłąĖąĮčŗ APB1 ąŠą│čĆą░ąĮąĖč湥ąĮčŗ ą┐ąŠą╗ąŠą▓ąĖąĮąŠą╣ čŹč鹊ą╣ čüą║ąŠčĆąŠčüčéąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čéą░ą╣ą╝ąĄčĆčŗ APB1 ąĮąĄ ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ č鹊ą╣ ąČąĄ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥, ą║ą░ą║ čéą░ą╣ą╝ąĄčĆčŗ APB2.

ŌĆó ą¤ąŠčüą║ąŠą╗čīą║čā ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ ą║ą░ąČą┤ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĄą│ąŠ čłąĖąĮčŗ APB, č鹊 ąÆčŗ ą┤ąŠą╗ąČąĮčŗ ąĘąĮą░čéčī, ą║ ą║ą░ą║ąŠą╣ čłąĖąĮąĄ APB ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ čéą░ą╣ą╝ąĄčĆ. ąŻčéąĖą╗ąĖčéą░ Timer Calculator ąŠčé MikroElektronika (MikroE) ą┐ąŠąĘą▓ąŠą╗ąĖčé čāčćąĖčéčŗą▓ą░čéčī čŹčéąĖ čäą░ą║č鹊čĆčŗ ą┤ą╗čÅ čĆąĄą░ą╗čīąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąśčüą┐ąŠą╗čīąĘčāą╣č鹥 čĆąĄą┤ą░ą║č鹊čĆ ą┐čĆąŠąĄą║čéą░ STM32CubeMX, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī čüą║ąŠčĆąŠčüčéąĖ čłąĖąĮčŗ APB. ąØąĖąČąĄ ąĮą░ ą║ą░čĆčéąĖąĮą║ąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐čĆąĖą╝ąĄčĆ, ąĘą┤ąĄčüčī čéą░ą╣ą╝ąĄčĆčŗ APB1 ą┐ąŠą╗čāčćą░čÄčé čéą░ą║čéčŗ 36 ą£ąōčå, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čéą░ą╣ą╝ąĄčĆčŗ APB2 čéą░ą║čéąĖčĆčāčÄčéčüčÅ ąŠčé 72 ą£ąōčå.

[ą×čéčüč湥čé ą▓čĆąĄą╝ąĄąĮąĖ]

ą×čéčüč湥čé č鹥ą║čāčēąĄą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ - ąŠčüąĮąŠą▓ąĮąŠą╣ čĆąĄąČąĖą╝ čéą░ą╣ą╝ąĄčĆą░. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ čéą░ą║, čćč鹊ą▒čŗ ąŠąĮ ą▓čŗąĘčŗą▓ą░ą╗ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗąĄ čüąŠą▒čŗčéąĖčÅ čü čĆą░ą▓ąĮčŗą╝ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ąĖ ą▓čĆąĄą╝ąĄąĮąĖ (čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ ą▓čĆąĄą╝ąĄąĮąĮąŠą╣ ą▒ą░ąĘčŗ). ąöą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą╝čŗ ą╝ąŠąČąĄą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą╗čÄą▒ąŠą╣ čéą░ą╣ą╝ąĄčĆ, ąŠą┤ąĮą░ą║ąŠ ą╗čāčćčłąĄ ą▓čüąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĖą╗ąĖ ą▒ą░ąĘąŠą▓čŗą╣ čéą░ą╣ą╝ąĄčĆ (ąĄčüą╗ąĖ ąŠąĮ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé), ąĖą╗ąĖ GP-čéą░ą╣ą╝ąĄčĆ.

ąöą╗čÅ čüąŠąĘą┤ą░ąĮąĖčÅ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ą▓čĆąĄą╝ąĄąĮąĮąŠą╣ ą▒ą░ąĘčŗ čĆą░čåąĖąŠąĮą░ą╗čīąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą╝ąĄč鹊ą┤ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąĪąĮą░čćą░ą╗ą░ ąĮą░ą┤ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčīčüčÅ, ą║ą░ą║ąŠą╣ čéą░ą╣ą╝ąĄčĆ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī, ąĖ ą║ą░ą║ą░čÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čćą░čüč鹊čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čéą░ą╣ą╝ąĄčĆą░. ąŚą░č鹥ą╝ ąĮčāąČąĮąŠ ą▒čāą┤ąĄčé čĆą░čüčüčćąĖčéą░čéčī ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ (PSC), čĆąĄą│ąĖčüčéčĆą░ ą░ą▓č鹊ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ (auto-reload register, ARR) ąĖ čĆąĄą│ąĖčüčéčĆą░ čüč湥čéčćąĖą║ą░ ą┐ąŠą▓č鹊čĆąĄąĮąĖą╣ (repetition counter register, RCR), ąĄčüą╗ąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé. ąĪč湥čéčćąĖą║ąĖ ą┐ąŠą▓č鹊čĆąĄąĮąĖą╣ ą┤ąŠčüčéčāą┐ąĮčŗ č鹊ą╗čīą║ąŠ ą▓ ą┐čĆąŠą┤ą▓ąĖąĮčāčéčŗčģ čéą░ą╣ą╝ąĄčĆą░čģ. ą£ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüą╗ąĄą┤čāčÄčēčāčÄ č乊čĆą╝čāą╗čā ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čćą░čüč鹊čéčŗ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

TIMxCLK

ąĪąŠą▒čŗčéąĖąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ = ----------------

((PSC+1)(ARR+1))

RCR ą▒čāą┤ąĄčé ąĮčāą╗ąĄą▓čŗą╝ ą║čĆąŠą╝ąĄ čüą╗čāčćą░ąĄą▓, ą║ąŠą│ą┤ą░ ąŠąĮ ą┤ąŠčüčéčāą┐ąĄąĮ ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, č鹊ą│ą┤ą░ č乊čĆą╝čāą╗ą░ ą▒čāą┤ąĄčé čüą╗ąĄą┤čāčÄčēąĄą╣:

TIMxCLK

ąĪąŠą▒čŗčéąĖąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ = -----------------------

((PSC+1)(ARR+1)(RCR+1))

ą¦ą░čüč鹊čéą░ čéą░ą║č鹊ą▓ TIMx ąĘą░ą▓ąĖčüąĖčé ąŠčé čćą░čüč鹊čéčŗ čłąĖąĮčŗ APB.

ąÆ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ čĆą░ąĘčĆąĄčłą░čÄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ ąĖ čĆą░ą▒ąŠčéą░ čüą░ą╝ąŠą│ąŠ ą╝ąŠą┤čāą╗čÅ čéą░ą╣ą╝ąĄčĆą░.

ąöą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ čéą░ą╣ą╝ąĄčĆą░ ą▓ ą║ą░č湥čüčéą▓ąĄ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüą╗ąĄą┤čāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ (ą▓ą╝ąĄčüč鹊 x ą┐ąŠą┤čüčéą░ą▓ą╗čÅąĄčéčüčÅ ąĮąŠą╝ąĄčĆ čéą░ą╣ą╝ąĄčĆą░):

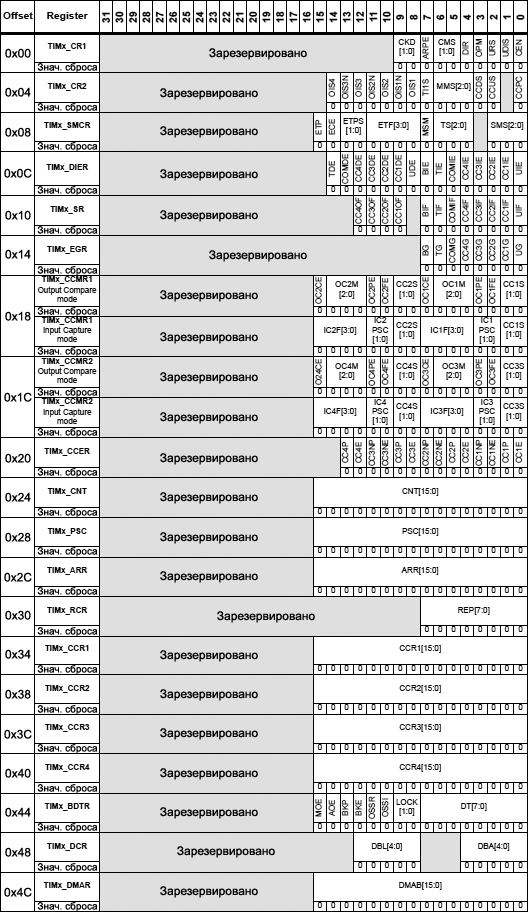

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ 1 (TIMx_CR1), čüą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░ 0x00, ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 0x0000.

| ąĀą░ąĘčĆčÅą┤ |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąæąĖčé |

ąĀąĄąĘąĄčĆą▓ |

CKD[1:0] |

ARPE |

CMS

|

DIR |

OPM |

URS |

UDIS |

CEN |

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

ąĀąĄą│ąĖčüčéčĆ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ DMA/ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (TIMx_DIER), čüą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░ 0x0C, ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 0x0000.

| ąĀą░ąĘčĆčÅą┤ |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąæąĖčé |

ąĀąĄąĘ. |

TDE |

ąĀąĄąĘ. |

CC4DE |

CC3DE |

CC2DE |

CC1DE |

UDE |

ąĀąĄąĘ. |

TIE

|

ąĀąĄąĘ. |

CC4IE |

CC3IE |

CC2IE |

CC1IE |

UIE |

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

ą¤čĆąĄčüą║ą░ą╗ąĄčĆ (TIMx_PSC), čüą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░ 0x28, ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 0x0000.

| ąĀą░ąĘčĆčÅą┤ |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąĀąĄą│ąĖčüčéčĆ |

PSC[15:0] |

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

ąĀąĄą│ąĖčüčéčĆ ą░ą▓č鹊ąĘą░ą│čĆčāąĘą║ąĖ (TIMx_ARR), čüą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░ 0x2C, ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 0x0000.

| ąĀą░ąĘčĆčÅą┤ |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąĀąĄą│ąĖčüčéčĆ |

ARR[15:0] |

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

[ąæą░ąĘąŠą▓čŗąĄ čĆą░ą▒ąŠčćąĖąĄ čĆąĄąČąĖą╝čŗ GP-čéą░ą╣ą╝ąĄčĆąŠą▓]

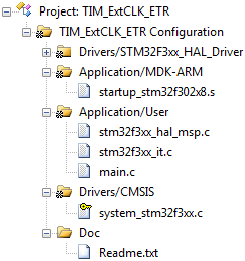

ąÆčüąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ STM32 ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮčŗ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĮąĖą╝ čéą░ą╣ą╝ąĄčĆąŠą╝, ąĖ ą╝ąĮąŠą│ąĖąĄ ąĖąĘ ąĮąĖčģ ąĖą╝ąĄčÄčé ą▓ čüą▓ąŠąĄą╝ čüąŠčüčéą░ą▓ąĄ ą┐ąĄčĆąĖč乥čĆąĖąĖ čéą░ą╣ą╝ąĄčĆčŗ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čéąĖą┐ąŠą▓. ąÆ čŹč鹊ą╝ ą┤ąŠą║čāą╝ąĄąĮč鹥 čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ ąŠą▒čŗčćąĮčŗąĄ čéą░ą╣ą╝ąĄčĆčŗ (general purpose, GP-čéą░ą╣ą╝ąĄčĆčŗ). GP-čéą░ą╣ą╝ąĄčĆčŗ ą╝ąŠąČąĮąŠ ąŠčéą╗ąĖčćąĖčéčī ąŠčé čéą░ą╣ą╝ąĄčĆąŠą▓ ą┤čĆčāą│ąĖčģ čéąĖą┐ąŠą▓ ą┐ąŠ ąĖą╝ąĄąĮąĖ ą▓ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32.

ąÆ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32 GP-čéą░ą╣ą╝ąĄčĆ ąĖą╝ąĄąĮčāąĄčéčüčÅ ą║ą░ą║ "TIMx timer", ą│ą┤ąĄ "x" ą╝ąŠąČąĄčé ą▒čŗčéčī ą╗čÄą▒čŗą╝ čćąĖčüą╗ąŠą╝, ąĖ čŹč鹊 ąĮąĄ ąŠčéčĆą░ąČą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą╣ą╝ąĄčĆąŠą▓, ą▓čüčéčĆąŠąĄąĮąĮčŗčģ ą▓ čŹč鹊čé ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ čüąĄčĆąĖąĖ STM32F100 ąĖą╝ąĄčÄčé ąĮą░ ą▒ąŠčĆčéčā čéą░ą╣ą╝ąĄčĆ TIM17, ąŠą┤ąĮą░ą║ąŠ ąŠą▒čēąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą╣ą╝ąĄčĆąŠą▓ ą▓ čŹč鹊ą╝ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ą╝ąĄąĮčīčłąĄ 17.

ąÆ ąŠčüąĮąŠą▓ąĮąŠą╝ č湥čĆąĄąĘ ą▓čüąĄ čüąĄą╝ąĄą╣čüčéą▓ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32 čüąŠą▒ą╗čÄą┤ą░ąĄčéčüčÅ ą┐čĆąĖąĮčåąĖą┐, čćč鹊 čéą░ą╣ą╝ąĄčĆčŗ čü ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ ąĖą╝ąĄąĮąĄą╝ ąĖą╝ąĄčÄčé ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ ąĮą░ą▒ąŠčĆ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗčģ ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣, ąĮąŠ ąĖąĘ čŹč鹊ą│ąŠ ą┐čĆą░ą▓ąĖą╗ą░ ąĄčüčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĖčüą║ą╗čÄč湥ąĮąĖą╣. ąØą░ą┐čĆąĖą╝ąĄčĆ čéą░ą╣ą╝ąĄčĆ TIM1 ąŠą▒čēąĖą╣ ą▓ąŠ ą▓čüąĄčģ čüąĄčĆąĖčÅčģ STM32F1, STM32F2 ąĖ STM32F4, ąĮąŠ ą┤ą╗čÅ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą│ąŠ čüą╗čāčćą░čÅ čüąĄą╝ąĄą╣čüčéą▓ą░ STM32F30x čéą░ą╣ą╝ąĄčĆ TIM1 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ąŠą╗čīčłąĖą╣ ąĮą░ą▒ąŠčĆ čäčāąĮą║čåąĖą╣, č湥ą╝ čéą░ą╣ą╝ąĄčĆ TIM1 ą▓ ą┤čĆčāą│ąĖčģ čüąĄą╝ąĄą╣čüčéą▓ą░čģ.

GP-čéą░ą╣ą╝ąĄčĆčŗ, ą▓čüčéčĆąŠąĄąĮąĮčŗąĄ ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ STM32, ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čāčÄ ąŠčüąĮąŠą▓ąĮčāčÄ čüčéčĆčāą║čéčāčĆčā; ąŠąĮąĖ ąŠčéą╗ąĖčćą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ čāčĆąŠą▓ąĮąĄą╝ čäčāąĮą║čåąĖą╣, ą▓čüčéčĆąŠąĄąĮąĮčŗčģ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ.

ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čéą░ą╣ą╝ąĄčĆąŠą▓ ą╝ąŠąČąĮąŠ ą║ą╗ą░čüčüąĖčäąĖčåąĖčĆąŠą▓ą░čéčī čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆó ą¤čĆąŠą┤ą▓ąĖąĮčāčéčŗąĄ čéą░ą╣ą╝ąĄčĆčŗ, čéą░ą║ąĖąĄ ą║ą░ą║ TIM1 ąĖ TIM8.

ŌĆó GP-čéą░ą╣ą╝ąĄčĆčŗ, ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ TIM2 ąĖ TIM3.

ŌĆó ąóą░ą╣ą╝ąĄčĆčŗ čü ąŠą▒ą╗ąĄą│č湥ąĮąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣, čéą░ą║ąĖąĄ ą║ą░ą║ TIM9, TIM10, TIM12 ąĖ TIM16.

ŌĆó ąæą░ąĘąŠą▓čŗąĄ čéą░ą╣ą╝ąĄčĆčŗ, čéą░ą║ąĖąĄ ą║ą░ą║ TIM6 ąĖ TIM7.

ąÉą┐ąĮąŠčāčé AN4013 [2] ą┤ą░ąĄčé ą┐ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ čéą░ą╣ą╝ąĄčĆąŠą▓ STM32 ą┐ąŠ ą▓čüąĄą╝ čĆą░ąĘą╗ąĖčćąĮčŗą╝ čüąĄą╝ąĄą╣čüčéą▓ą░ą╝ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32.

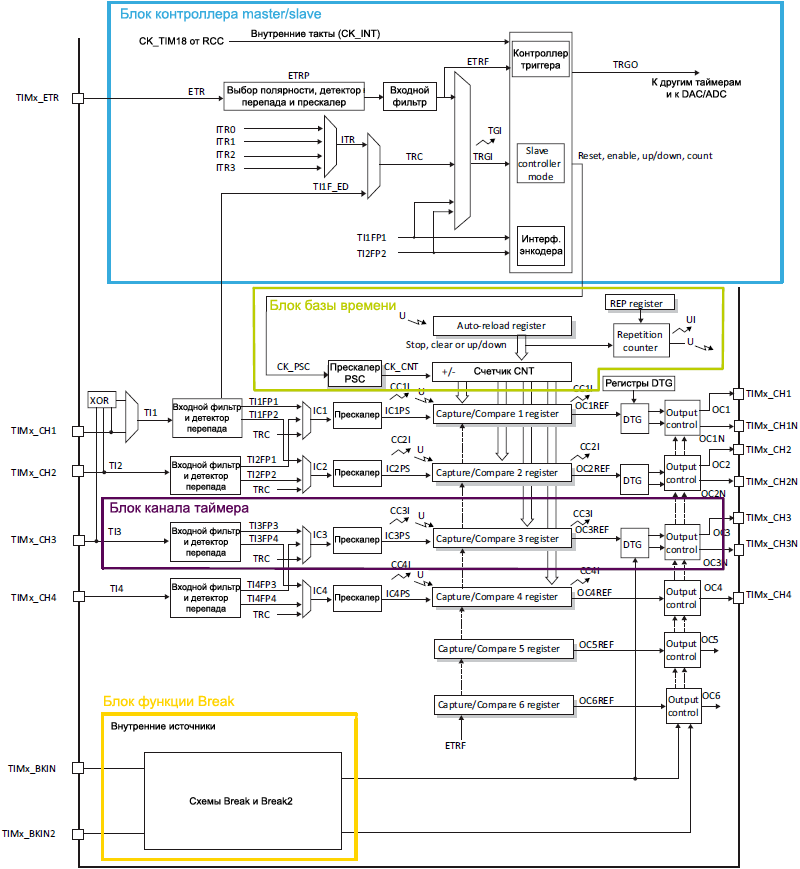

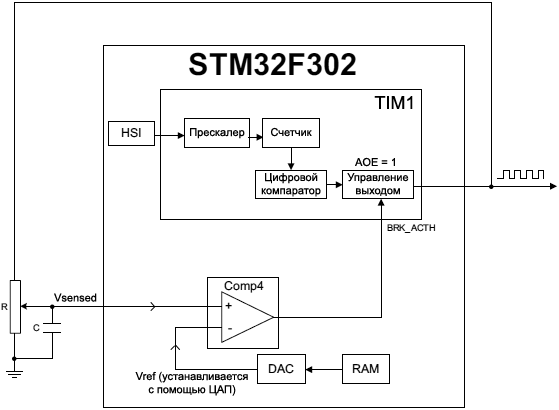

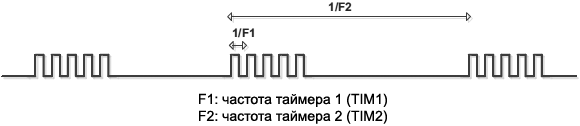

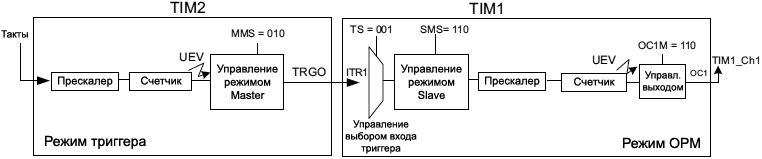

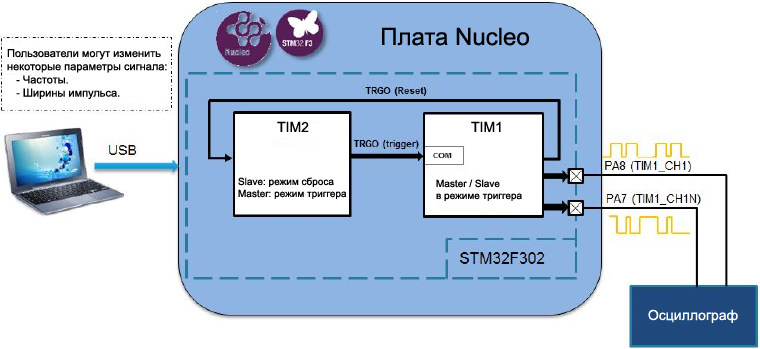

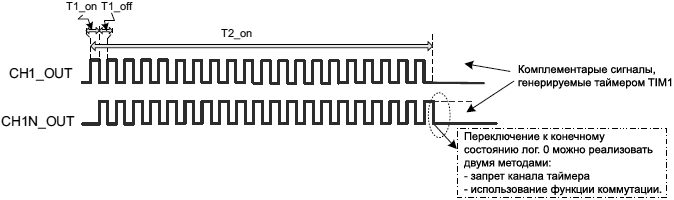

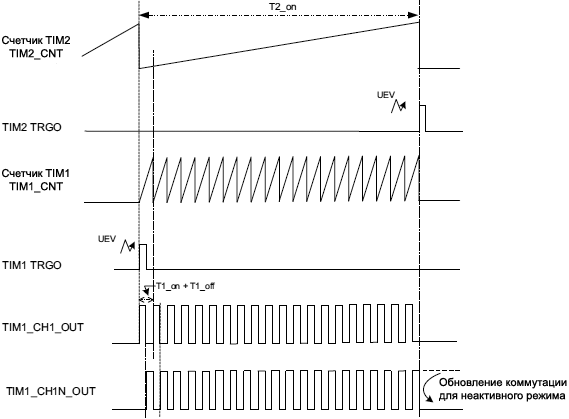

TIM1. ąØą░ čĆąĖčü. 1 ą▒ą╗ąŠą║-čüčģąĄą╝čŗ čéą░ą╣ą╝ąĄčĆą░ TIM1 ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĄą│ąŠ č湥čéčŗčĆąĄ ąŠčüąĮąŠą▓ąĮčŗčģ ą▒ą╗ąŠą║ą░:

1. ąæą╗ąŠą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ master/slave.

2. ąæą╗ąŠą║ ą▒ą░ąĘčŗ ą▓čĆąĄą╝ąĄąĮąĖ.

3. ąæą╗ąŠą║ ą║ą░ąĮą░ą╗ąŠą▓ čéą░ą╣ą╝ąĄčĆą░.

4. ąæą╗ąŠą║ čäčāąĮą║čåąĖąĖ Break.

ąĀąĖčü. 1. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ čéą░ą╣ą╝ąĄčĆą░ TIM1.

ąæą╗ąŠą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ master/slave. ąæą╗ąŠą║ master/slave ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą▒ą╗ąŠą║ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, ąŠčéčüčćąĖčéčŗą▓ą░čÄčēąĖą╣ ąĖą╝ą┐čāą╗čīčüčŗ čéą░ą║č鹊ą▓ (ąĮą░ą┐čĆąĖą╝ąĄčĆ CK_PSC), ą░ čéą░ą║ąČąĄ čüąĖą│ąĮą░ą╗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ čüč湥čéą░. ąŁč鹊čé ą▒ą╗ąŠą║ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╝ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čüąĖą│ąĮą░ą╗čŗ ą┤ą╗čÅ ą▒ą╗ąŠą║ą░ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ.

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ master/slave ą┐čĆąĖą╝ąĄąĮčÅąĄčé ą┐čĆą░ą▓ąĖą╗čīąĮčāčÄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ čüč湥čéą░ ą┤ą╗čÅ ą▒ą╗ąŠą║ą░ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, ąŠčüąĮąŠą▓čŗą▓ą░čÅčüčī ąĮą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ master/slave; ąŠąĮ čéą░ą║ąČąĄ ąŠčåąĄąĮąĖą▓ą░ąĄčé čĆąĄą░ą╗čīąĮčŗą╣ čüčéą░čéčāčü čüč湥čéą░.

ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ čéą░ą╣ą╝ąĄčĆ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ ąŠą┤ąĮąŠą╝ ąĖąĘ čĆąĄąČąĖą╝ąŠą▓ 菹Įą║ąŠą┤ąĄčĆą░ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄąĄ ą▒ąĖč鹊ą▓ąŠąĄ ą┐ąŠą╗ąĄ SMS čĆąĄą│ąĖčüčéčĆą░ TIMx_SMCR, č鹊 čüąĖą│ąĮą░ą╗ ą┐ąŠą┤čüčćąĖčéčŗą▓ą░ąĄą╝čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĖ čüąĖą│ąĮą░ą╗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ čüč湥čéą░ ą▒čāą┤ąĄčé ą▓čŗčćąĖčüą╗čÅčéčīčüčÅ ąĮą░ ąŠčüąĮąŠą▓ąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą▓čģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ čäą░ąĘ 菹Įą║ąŠą┤ąĄčĆą░ TI1FP1 ąĖ TI2FP2.

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ master/slave ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÄ ą╝ąĄąČą┤čā čéą░ą╣ą╝ąĄčĆą░ą╝ąĖ. ąŁč鹊čé ą▒ą╗ąŠą║ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ čüąĖą│ąĮą░ą╗ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ (čüąĖą│ąĮą░ą╗ TRGO) čĆčÅą┤ąŠą╝ čü ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čüąŠą▒čŗčéąĖąĄą╝ čéą░ą╣ą╝ąĄčĆą░. ą×ąĮ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ čéą░ą║ąČąĄ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüč湥čéčćąĖą║ąŠą╝ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą▓ čäčāąĮą║čåąĖąĖ ą▓ąĮąĄčłąĮąĖčģ čüąŠą▒čŗčéąĖą╣ (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čüąŠą▒čŗčéąĖą╣ ą┤čĆčāą│ąĖčģ čéą░ą╣ą╝ąĄčĆąŠą▓ ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓).

ą£ąŠąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ąŠą┤ąĖąĮ slave-čéą░ą╣ą╝ąĄčĆ ą┤ą╗čÅ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ čüą▓ąŠąĄą│ąŠ čüč湥čéčćąĖą║ą░, ą▒ą░ąĘąĖčĆčāčÅčüčī ąĮą░ čüąŠą▒čŗčéąĖčÅčģ master-čéą░ą╣ą╝ąĄčĆą░, čéą░ą║ąĖčģ ą║ą░ą║ ąĄą│ąŠ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ čüąŠą▒čŗčéąĖąĄ master-čéą░ą╣ą╝ąĄčĆą░ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ą▒ą╗ąŠą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ master/slave. ąŁč鹊čé čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą▒ą╗ąŠą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüąĖą│ąĮą░ą╗ ą▓čŗčģąŠą┤ą░ master-čéą░ą╣ą╝ąĄčĆą░ TRGO. ąĪąĖą│ąĮą░ą╗ ą▓čŗčģąŠą┤ą░ master-čéą░ą╣ą╝ąĄčĆą░ TRGO ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ slave-čéą░ą╣ą╝ąĄčĆą░ TRGI. ąæą╗ąŠą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ master/slave slave-čéą░ą╣ą╝ąĄčĆą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ TRGI ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ slave-čéą░ą╣ą╝ąĄčĆą░.

ąØąĄ čā ą▓čüąĄčģ čéą░ą╣ą╝ąĄčĆąŠą▓ STM32 ąĄčüčéčī čäčāąĮą║čåąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ master/slave. ąÆ čéą░ą╣ą╝ąĄčĆąĄ TIM1, ą║ąŠč鹊čĆčŗą╣ ą┤ą░ąĮ ą┤ą╗čÅ ą┐čĆąĖą╝ąĄčĆą░, ą▓čüčéčĆąŠąĄąĮ ą┐ąŠą╗ąĮčŗą╣ čäčāąĮą║čåąĖąŠąĮą░ą╗ master/slave; ą▓ čüčĆą░ą▓ąĮąĄąĮąĖąĖ čü ąĮąĖą╝ ą▒ą░ąĘąŠą▓čŗąĄ čéą░ą╣ą╝ąĄčĆčŗ TIM6 ąĖ TIM7 ąĖą╝ąĄčÄčé čüą░ą╝čŗą╣ ą┐čĆąŠčüč鹊ą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ master/slave. ąŻ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ master/slave čéą░ą╣ą╝ąĄčĆąŠą▓ TIM6 ąĖ TIM7 ąĮąĄčé čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą│ąŠ ą┐ąŠą╗čÅ ą▒ąĖčé.

ąöą╗čÅ čéą░ą╣ą╝ąĄčĆąŠą▓ TIM6 ąĖ TIM7 čüč湥čéčćąĖą║ ą▒ą░ąĘčŗ ą▓čĆąĄą╝ąĄąĮąĖ ą▓čüąĄą│ą┤ą░ čüčćąĖčéą░ąĄčé ą▓ą▓ąĄčĆčģ, ą▒ąĄąĘ čüą▒čĆąŠčüą░ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ ą┐ąŠ ą▓ąĮąĄčłąĮąĖą╝ čüąŠą▒čŗčéąĖčÅą╝. ąØąĄą╗čīąĘčÅ ąĖčģ čéą░ą║čéąĖčĆąŠą▓ą░čéčī ąĮąĖ ąŠčé ą┤čĆčāą│ąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓, ąĮąĖ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čéą░ą║č鹊ą▓.

ąæą╗ąŠą║ ą▒ą░ąĘčŗ ą▓čĆąĄą╝ąĄąĮąĖ. ąæą╗ąŠą║ ą▒ą░ąĘčŗ ą▓čĆąĄą╝ąĄąĮąĖ čüą┤ąĄą╗ą░ąĮ ąĮą░ ąŠčüąĮąŠą▓ąĄ čüč湥čéčćąĖą║ą░ ą▓ą╝ąĄčüč鹥 čü ą║ą░čüą║ą░ą┤ąŠą╝ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĖ čüč湥čéčćąĖą║ąŠą╝ ą┐ąŠą▓č鹊čĆąĄąĮąĖą╣. ąóą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┐ąŠčüčéčāą┐ą░ąĄčé ą▓ ą▒ą╗ąŠą║ ą▒ą░ąĘčŗ ą▓čĆąĄą╝ąĄąĮąĖ, ą┐čĆąŠčģąŠą┤čÅ č湥čĆąĄąĘ ą║ą░čüą║ą░ą┤ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą┤ąŠčüčéąĖčćčī čüč湥čéčćąĖą║ą░ ą▒ą░ąĘčŗ ą▓čĆąĄą╝ąĄąĮąĖ.

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ čéą░ą╣ą╝ąĄčĆą░ TIMx_PSC, čćą░čüč鹊čéą░ čüčćąĖčéą░ąĄą╝čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī čüąĮąĖąČąĄąĮą░ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą┤ąŠčüčéąĖčćčī čüčéą░ą┤ąĖąĖ čüč湥čéčćąĖą║ą░. ąĪąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ čÅą▓ą╗čÅąĄčéčüčÅ čéą░ą║č鹊ą▓čŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝ čüč湥čéą░, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠčüčéčāą┐ą░ąĄčé ąĮą░ ą║ą░čüą║ą░ą┤ čüč湥čéčćąĖą║ą░.

ąĪč湥čéčćąĖą║ čéą░ą╣ą╝ąĄčĆą░ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą┤ą▓čāą╝čÅ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ:

ŌĆó TIMx_CNT, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░.

ŌĆó TIMx_ARR, čüąŠą┤ąĄčƹȹĖčé ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░.

ąÉą▓č鹊ą╝ą░čéąĖč湥čüą║ą░čÅ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ą░ čüč湥čéčćąĖą║ą░ čĆą░ą▒ąŠčéą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝. ąĢčüą╗ąĖ čüč湥čéčćąĖą║ čéą░ą╣ą╝ąĄčĆą░ čüčćąĖčéą░ąĄčé ą▓ą▓ąĄčĆčģ, ąĖ ą┤ąŠčüčéąĖą│ ąĘąĮą░č湥ąĮąĖčÅ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ TIMx_ARR, č鹊 čüč湥čéčćąĖą║ čéą░ą╣ą╝ąĄčĆą░ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ąĖ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąĮąŠą▓čŗą╣ čåąĖą║ą╗ čüč湥čéą░. ąĢčüą╗ąĖ čüč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą▓ąĮąĖąĘ, ąĖ ą┤ąŠčüčéąĖą│ ąĮčāą╗čÅ, č鹊 ą▓ čüč湥čéčćąĖą║ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ TIMx_ARR, ąĖ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąĮąŠą▓čŗą╣ čåąĖą║ą╗ čüč湥čéą░.

ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąĮąŠą▓čŗą╣ čåąĖą║ą╗ čüč湥čéą░, čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé "čüąŠą▒čŗčéąĖąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ" čéą░ą╣ą╝ąĄčĆą░, ą┐ąŠą║ą░ čüč湥čéčćąĖą║ ą┐ąŠą▓č鹊čĆąĄąĮąĖą╣ (repetition counter) čĆą░ą▓ąĄąĮ 0. ąĢčüą╗ąĖ čüč湥čéčćąĖą║ ą┐ąŠą▓č鹊čĆąĄąĮąĖą╣ ąĮąĄ čĆą░ą▓ąĄąĮ 0, č鹊 čüąŠą▒čŗčéąĖąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ąĮąĄ čüčĆą░ą▒ąŠčéą░ąĄčé, ąĮąŠ ą┐ąĄčĆąĄąĘą░ą┐čāčüčéąĖčéčüčÅ ąĮąŠą▓čŗą╣ čåąĖą║ą╗ čüč湥čéą░, ąĖ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čüč湥čéčćąĖą║ą░ ą┐ąŠą▓č鹊čĆąĄąĮąĖą╣ čāą╝ąĄąĮčīčłąĖčéčüčÅ ąĮą░ 1. ąÜąŠą│ą┤ą░ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čüč湥čéčćąĖą║ą░ ą┐ąŠą▓č鹊čĆąĄąĮąĖą╣ ą┤ąŠčüčéąĖą│ąĮąĄčé ąĮčāą╗čÅ, ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé čüąŠą▒čŗčéąĖąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ, ąĖ ą▓ čüč湥čéčćąĖą║ ą┐ąŠą▓č鹊čĆąĄąĮąĖą╣ ąĘą░ą│čĆčāąĘąĖčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ, čüąŠčģčĆą░ąĮąĄąĮąĮąŠąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMx_RCR.

ąØąĄ čā ą▓čüąĄčģ čéą░ą╣ą╝ąĄčĆąŠą▓ STM32 ąĄčüčéčī čüč湥čéčćąĖą║ ą┐ąŠą▓č鹊čĆąĄąĮąĖą╣. ąĢčüą╗ąĖ ąĄą│ąŠ ąĮąĄčé, č鹊 čéą░ą╣ą╝ąĄčĆ ą▓ąĄą┤ąĄčé čüąĄą▒čÅ čéą░ą║, ą║ą░ą║ ąĄčüą╗ąĖ ą▒čŗ čüč湥čéčćąĖą║ ą┐ąŠą▓č鹊čĆąĄąĮąĖą╣ ą▒čŗą╗ ą▓čüąĄą│ą┤ą░ čĆą░ą▓ąĄąĮ 0.

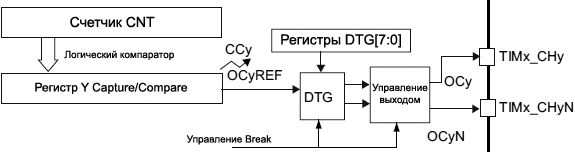

ąæą╗ąŠą║ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░. ąÜą░ąĮą░ą╗čŗ čéą░ą╣ą╝ąĄčĆą░ čŹč鹊 čĆą░ą▒ąŠčćąĖąĄ 菹╗ąĄą╝ąĄąĮčéčŗ čéą░ą╣ą╝ąĄčĆą░, čü ą┐ąŠą╝ąŠčēčīčÄ ąĮąĖčģ čéą░ą╣ą╝ąĄčĆ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓čāąĄčé čü ą▓ąĮąĄčłąĮąĖą╝ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╝ ąŠą║čĆčāąČąĄąĮąĖąĄą╝. ąÆ čåąĄą╗ąŠą╝ ą║ą░ąĮą░ą╗čŗ čéą░ą╣ą╝ąĄčĆą░ ąŠč鹊ą▒čĆą░ąČą░čÄčéčüčÅ ąĮą░ ą▓ąĮąĄčłąĮąĖąĄ ą▓čŗą▓ąŠą┤čŗ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32, čü ąĮąĄą║ąŠč鹊čĆčŗą╝ąĖ ąĖčüą║ą╗čÄč湥ąĮąĖčÅą╝ąĖ, čéą░ą║ąĖą╝ąĖ ą║ą░ą║ ą║ą░ąĮą░ą╗čŗ 5 ąĖ 6 čéą░ą╣ą╝ąĄčĆą░ TIM1 čüąĄą╝ąĄą╣čüčéą▓ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32F30x. ąÜą░ąĮą░ą╗ čéą░ą╣ą╝ąĄčĆą░, ąŠč鹊ą▒čĆą░ąČąĄąĮąĮčŗą╣ ąĮą░ ą▓čŗą▓ąŠą┤ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32, ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą╗ąĖą▒ąŠ ą║ą░ą║ ą▓čģąŠą┤, ą╗ąĖą▒ąŠ ą║ą░ą║ ą▓čŗčģąŠą┤.

ąÜąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čŗčģąŠą┤, ą║ą░ąĮą░ą╗ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓. ą¤ąŠą║ą░ ą║ą░ąĮą░ą╗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ ą▓čŗčģąŠą┤ą░, čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ ą║ą░ąĮą░ą╗ą░ TIMx_CCRy čüčĆą░ą▓ąĮąĖą▓ą░ąĄčéčüčÅ čü čüąŠą┤ąĄčƹȹĖą╝čŗą╝ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░. ąØą░ ąŠčüąĮąŠą▓ąĄ čŹč鹊ą│ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ąĖ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┐ąŠą┤čĆąĄąČąĖą╝ą░ ą▓čŗčģąŠą┤ą░ (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ PWM1 mode ąĖą╗ąĖ Inactive mode), ą║ą░ąĮą░ą╗ čéą░ą╣ą╝ąĄčĆą░ ą╗ąĖą▒ąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé, ą╗ąĖą▒ąŠ čüą▒čĆą░čüčŗą▓ą░ąĄčé čäą╗ą░ą│ OCyREF, ąĖ ąĄą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüčéčāą┐ą░ąĄčé ąĮą░ ą║ą░čüą║ą░ą┤ ą▓čŗčģąŠą┤ą░ ą║ą░ąĮą░ą╗ą░. ąÜą░čüą║ą░ą┤ ą▓čŗčģąŠą┤ą░ ą┐čĆąĖą╝ąĄąĮčÅąĄčé ąĮą░ą▒ąŠčĆ čāč鹊čćąĮčÅčÄčēąĖčģ ąŠą┐ąĄčĆą░čåąĖą╣ ą║ čüąĖą│ąĮą░ą╗čā OCyREF, ą▒ą░ąĘąĖčĆčāčÅčüčī ąĮą░ ąĮą░ą▒ąŠčĆąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ ą║ą░ąĮą░ą╗ą░ ąĖą╗ąĖ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖąĮč鹥čĆą▓ą░ą╗ą░ dead-time, ąĖ ą┤čĆčāą│ąĖčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓).

ąÆčŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą║ą░čüą║ą░ą┤ą░ ą▓čŗčģąŠą┤ą░ ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤čŗ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą║ą░ą║ ąĖčģ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮą░čÅ čäčāąĮą║čåąĖčÅ ą┐ąŠčĆčéą░. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĮąĄą║ąŠč鹊čĆčŗąĄ ą║ą░čüą║ą░ą┤čŗ ą▓čŗčģąŠą┤ą░ ą║ą░ąĮą░ą╗ąŠą▓ čéą░ą╣ą╝ąĄčĆą░, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 2, ą╝ąŠą│čāčé ą▒čŗčéčī ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮčŗ ą║ą░ą║ ą┤ą▓ą░ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗčģ čüąĖą│ąĮą░ą╗ą░ (čŹč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą╗ąĄčćą░ą╝ąĖ čüąĖą╗ąŠą▓ąŠą│ąŠ ą╝ąŠčüčéą░).

ąĀąĖčü. 2. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░, ą║ąŠą│ą┤ą░ ąŠąĮ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąĮą░ ą▓čŗą▓ąŠą┤.

ąŻą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ ą▒ąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ ą┤ą╗čÅ čéą░ą║ąŠą│ąŠ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą║ą░čüą║ą░ą┤ą░ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čÄčé čüčĆąĄą┤čüčéą▓ą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą║ą░ąČą┤ąŠą│ąŠ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┐ąŠ ąŠčéą┤ąĄą╗čīąĮąŠčüčéąĖ (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ/ąĘą░ą┐čĆąĄčéą░ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ ąĖą╗ąĖ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ).

ąÜąŠą│ą┤ą░ ą║ą░ąĮą░ą╗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąĮą░ ą▓čģąŠą┤, ąŠąĮ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąĘą░ą┐ąŠą╝ąĖąĮą░ąĮąĖčÅ ą╝ąĄč鹊ą║ ą▓čĆąĄą╝ąĄąĮąĖ ą▓ ą╝ąŠą╝ąĄąĮčéčŗ ą┐ąĄčĆąĄčģąŠą┤ąŠą▓ čāčĆąŠą▓ąĮčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ - ą╗ąĖą▒ąŠ ą┐ąŠ ąĄą│ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ čāčĆąŠą▓ąĮčÅ, ą╗ąĖą▒ąŠ ą┐ąŠ čüą┐ą░ą┤čā, ą╗ąĖą▒ąŠ ą┐ąŠ ąŠą▒ąŠąĖą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝. ąöą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ čŹč鹊ą╣ čäčāąĮą║čåąĖąĖ ą▓čģąŠą┤ ą║ą░ąĮą░ą╗ą░ ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĮą░ ąŠą┤ąĖąĮ ąĖąĘ ą▓čŗą▓ąŠą┤ąŠą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

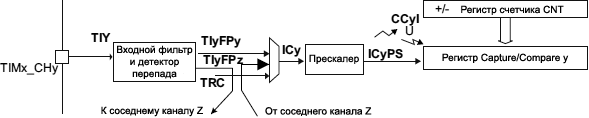

ąØąĄą║ąŠč鹊čĆčŗąĄ ą▓čģąŠą┤čŗ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░ čéą░ą║ąČąĄ ą╝ąŠą│čāčé ąŠč鹊ą▒čĆą░ąČą░čéčīčüčÅ ąĮą░ ąĮąĄą║ąŠč鹊čĆčŗąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ čćąĖą┐ą░, ąĮą░ą┐čĆąĖą╝ąĄčĆ ąĮą░ ą▓čŗčģąŠą┤ ą│ąĄąĮąĄčĆą░č鹊čĆą░ - čü čåąĄą╗čīčÄ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ čćą░čüč鹊čéčŗ. ąØą░ ą▓čģąŠą┤ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░ TIy ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čüčģąĄą╝ąŠą╣ ą║ąŠąĮą┤ąĖčåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░, čćč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 3. ąĪčģąĄą╝ą░ ą║ąŠąĮą┤ąĖčåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ą║ą╗čÄčćą░ąĄčé ą║ą░čüą║ą░ą┤ čäąĖą╗čīčéčĆą░čåąĖąĖ ąĖ ą┤ąĄč鹥ą║č鹊čĆ ą┐ąĄčĆąĄą┐ą░ą┤ą░. ąÜą░čüą║ą░ą┤ čäąĖą╗čīčéčĆą░ ą▓čŗčĆąĄąĘą░ąĄčé ąĖą╝ą┐čāą╗čīčüčŗ, ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ąŠč鹊čĆčŗčģ ą╝ąĄąĮčīčłąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą╣. ąöąĄč鹥ą║č鹊čĆ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą╗ąĖ ąĮą░ ąĮčāąČąĮąŠą╝ ą▓čģąŠą┤ąĄ ą┐ąŠčüą╗ąĄ čäąĖą╗čīčéčĆą░čåąĖąĖ ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ.

ąĀąĖčü. 3. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░, ą║ąŠą│ą┤ą░ ąŠąĮ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąĮą░ ą▓ą▓ąŠą┤.

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą░ą║čéąĖą▓ąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐čāč鹥ą╝ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▒ąĖč鹊ą▓čŗčģ ą┐ąŠą╗ąĄą╣ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMx_CCER. ąĪčģąĄą╝ą░ ą║ąŠąĮą┤ąĖčåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗą▓ąŠą┤ąĖčé ą┤ą▓ą░ čüąĖą│ąĮą░ą╗ą░:

ŌĆó TIyFPy: ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ čéą░ą╣ą╝ąĄčĆą░ TIy, ą║ąŠč鹊čĆčŗą╣ ą▒čŗą╗ ąŠčéčäąĖą╗čīčéčĆąŠą▓ą░ąĮ, ąĖ čā ą║ąŠč鹊čĆąŠą│ąŠ ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░ ŌĆ£yŌĆØ.

ŌĆó TIyFPz: ą▓čüąĄą│ą┤ą░ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░ TIy, ą║ąŠč鹊čĆčŗą╣ ą▒čŗą╗ ąŠčéčäąĖą╗čīčéčĆąŠą▓ą░ąĮ, ąĮąŠ ąĮą░ ą║ąŠč鹊čĆąŠą╝ ą▒čŗą╗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░ ŌĆ£zŌĆØ.

ąĪąĖą│ąĮą░ą╗ TIyFPz ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ąĮą░ ą▓čģąŠą┤ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ą║ą░ąĮą░ą╗ą░ ŌĆ£zŌĆØ, ą│ą┤ąĄ čüąĖą│ąĮą░ą╗ TIzFPy ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ąĮą░ ą▓čģąŠą┤ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ą║ą░ąĮą░ą╗ą░ ŌĆ£yŌĆØ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 3 ą▓čŗčłąĄ. ą¤ąĄčĆąĄą║čĆąĄčüčéąĮąŠąĄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ čäąĖą╗čīčéčĆąŠą▓ą░ąĮąĮčŗčģ ą▓čģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ąŠč湥ąĮčī ą┐ąŠą╗ąĄąĘąĮąŠ ą┤ą╗čÅ čäąĖą║čüą░čåąĖąĖ ą╝ąŠą╝ąĄąĮč鹊ą▓ ą▓čĆąĄą╝ąĄąĮąĖ ą║ą░ą║ ą┤ą╗čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ, čéą░ą║ ąĖ ą┤ą╗čÅ čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ ąŠčåąĄąĮą║ąĖ ą©ąśą£).

ąÜą░ąČą┤čŗą╣ ą║ą░ąĮą░ą╗ čéą░ą╣ą╝ąĄčĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ ąŠą┤ąĖąĮ ąĖąĘ čéčĆąĄčģ ą▓ąŠąĘą╝ąŠąČąĮčŗčģ čĆąĄąČąĖą╝ąŠą▓. ąÜą░ąČą┤čŗą╣ ą▓čģąŠą┤ąĮąŠą╣ čĆąĄąČąĖą╝ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠą┤ąĮąŠą╝čā ąĖąĘ ą▓ąŠąĘą╝ąŠąČąĮčŗčģ čéčĆąĄčģ ą▓čģąŠą┤ąŠą▓ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆą░ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą│ąŠ ą║ ą┐čĆąĄčüą║ą░ą╗ąĄčĆčā ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░. ąæąĖč鹊ą▓ąŠąĄ ą┐ąŠą╗ąĄ CCyS ą▓ą╗ąĖčÅąĄčé ąĮą░ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░, ąĄčüą╗ąĖ ąŠąĮ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ ą▓čŗą▓ąŠą┤ą░ (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ CCyS[1:0] = 00), ąĖą╗ąĖ ąĄčüą╗ąĖ ąŠąĮ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ ąŠą┤ąĮąŠą╝ ąĖąĘ čĆąĄąČąĖą╝ąŠą▓ ą▓ą▓ąŠą┤ą░ (ą║ąŠą│ą┤ą░ ą▒ąĖčéčŗ CCyS[1:0] ąŠčéą╗ąĖčćą░čÄčéčüčÅ ąŠčé 00).

ąóąĄ ąČąĄ čüą░ą╝čŗąĄ čĆąĄą│ąĖčüčéčĆčŗ čéą░ą╣ą╝ąĄčĆą░ TIMx_CCMRn (n ą╝ąŠąČąĄčé ą▒čŗčéčī ą╗čÄą▒čŗą╝ čćąĖčüą╗ąŠą╝, ąĮąŠ ąŠą▒čŗčćąĮąŠ čŹč鹊 1 ąĖą╗ąĖ 2) ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░ąĮą░ą╗ąŠą▓ čéą░ą╣ą╝ąĄčĆą░ ąĮą░ ą▓ą▓ąŠą┤ ąĖą╗ąĖ ą▓čŗą▓ąŠą┤. ąØąĄą║ąŠč鹊čĆčŗąĄ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ ą▒ąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ TIMx_CCMRn ą┐ąŠ-čĆą░ąĘąĮąŠą╝čā ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆčāčÄčéčüčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą║ą░ąĮą░ą╗ą░, čĆąĄąČąĖą╝ąŠą▓ ą▓ą▓ąŠą┤ą░ ąĖą╗ąĖ ą▓čŗą▓ąŠą┤ą░.

ą¤čĆąĄčüą║ą░ą╗ąĄčĆ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ čüąĮąĖąČąĄąĮąĖčÅ čćą░čüč鹊čéčŗ ą░ą║čéąĖą▓ąĮčŗčģ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓, ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąĮą░ ą▓čģąŠą┤ąĄ čéą░ą╣ą╝ąĄčĆą░ TIy. ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą░ą║čéąĖą▓ąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą┐ąĄčĆąĄąĮąŠčüčā čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ ą▓ čĆąĄą│ąĖčüčéčĆ ŌĆ£yŌĆØ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░ TIMx_CCRy.

ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ ŌĆ£yŌĆØ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░ TIMx_CCRy čŹč鹊 ą╝ąĄčéą║ą░ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą░ą║čéąĖą▓ąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ą║ą░ąĮą░ą╗ą░ ŌĆ£yŌĆØ. ąŁč鹊 ą╝ąĄčéą║ą░ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą░ą║čéąĖą▓ąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ąĮą░ ą▓čģąŠą┤ąĄ čéą░ą╣ą╝ąĄčĆą░ TIy, ąĄčüą╗ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ą║ą░ąĮą░ą╗ą░ ŌĆ£yŌĆØ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąĮąĄ čüąĮąĖąČą░čéčī čćą░čüč鹊čéčā ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą║ąŠą│ą┤ą░ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ = 1 ąĖ čüąĖą│ąĮą░ą╗ ą┐čĆąŠčģąŠą┤ąĖčé č湥čĆąĄąĘ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ą▒ąĄąĘ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣, čé. ąĄ. ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ąŠčéą║ą╗čÄč湥ąĮ).

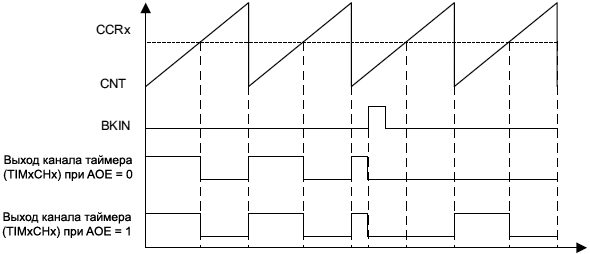

ąæą╗ąŠą║ čäčāąĮą║čåąĖąĖ Break. ążčāąĮą║čåąĖčÅ Break ą▓čüčéčĆąŠąĄąĮą░ č鹊ą╗čīą║ąŠ ą▓ č鹥 čéą░ą╣ą╝ąĄčĆčŗ, čā ą║ąŠč鹊čĆčŗčģ ąĄčüčéčī ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗąĄ ą▓čŗčģąŠą┤čŗ. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, č鹊ą╗čīą║ąŠ č鹥 čéą░ą╣ą╝ąĄčĆčŗ, čā ą║ąŠč鹊čĆčŗčģ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ą║ą░ąĮą░ą╗ čüąĮą░ą▒ąČąĄąĮ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗą╝ąĖ ą▓čŗčģąŠą┤ą░ą╝ąĖ, ąĖą╝ąĄąĄčé čäčāąĮą║čåąĖčÄ Break.

ążčāąĮą║čåąĖčÅ Break ą┤ąĄą╣čüčéą▓čāąĄčé ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╝ ą║ą░čüą║ą░ą┤ąĄ ą║ą░ąĮą░ą╗ąŠą▓ čéą░ą╣ą╝ąĄčĆą░ ą▓ čĆąĄąČąĖą╝ąĄ ą▓čŗą▓ąŠą┤ą░. ąÜą░ą║ č鹊ą╗čīą║ąŠ ąĮą░ ą▓čģąŠą┤ąĄ break ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤, ą▓čŗčģąŠą┤čŗ ą║ą░ąĮą░ą╗ąŠą▓ čéą░ą╣ą╝ąĄčĆą░, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą▓ čĆąĄąČąĖą╝ąĄ ą▓čŗą▓ąŠą┤ą░, ą╗ąĖą▒ąŠ ą▓čŗą║ą╗čÄčćą░čÄčéčüčÅ, ą╗ąĖą▒ąŠ ą┐ąĄčĆąĄą▓ąŠą┤čÅčéčüčÅ ą▓ ą┐čĆąĄą┤ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą▒ąĄąĘąŠą┐ą░čüąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ. ążčāąĮą║čåąĖčÅ Break ąŠą▒čŗčćąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą▒ąĄąĘąŠą┐ą░čüąĮąŠą│ąŠ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ čüąĖą╗ąŠą▓ąŠą│ąŠ ą╝ąŠčüčéą░ ą▓ ąĖąĮą▓ąĄčĆč鹊čĆą░čģ ą▒ą╗ąŠą║ąŠą▓ ą┐ąĖčéą░ąĮąĖčÅ ą▓ čüą╗čāčćą░ąĄ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ ą║ą░ą║ąĖčģ-č鹊 č鹥čģąĮąĖč湥čüą║ąĖčģ ą░ąĮąŠą╝ą░ą╗ąĖą╣ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą┐ąĄčĆąĄą│čĆčāąĘą║ąĖ ą┐ąŠ č鹊ą║čā).

ąÆ ą░ą┐ąĮąŠčāč鹥 AN4277 [3] ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąŠ ą┐ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆą░ą▒ąŠčéčŗ čäčāąĮą║čåąĖąĖ Break ą▓ čĆą░ąĘą╗ąĖčćąĮčŗčģ čüąĄą╝ąĄą╣čüčéą▓ą░čģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32.

[ą¤čĆąĖą╝ąĄčĆčŗ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ]

ąØąĖąČąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮčŗ ą║čāčüą║ąĖ ą║ąŠą┤ą░ ąĮą░ čÅąĘčŗą║ąĄ C, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖąĄ ą▒ą░ąĘąŠą▓čŗąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čéą░ą╣ą╝ąĄčĆą░ STM32.

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▒ą░ąĘčŗ ą▓čĆąĄą╝ąĄąĮąĖ. ąĀąĄą░ą╗ąĖąĘą░čåąĖčÅ č鹊čćąĮąŠą│ąŠ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čåąĖą║ą╗ą░ ąĘą░ą┤ąĄčƹȹ║ąĖ ąĮą░ čéą░ą╣ą╝ąĄčĆąĄ TIM6. ą£ąŠąČąĮąŠ ą┤ą╗čÅ č鹊ą╣ ąČąĄ čåąĄą╗ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą╗čÄą▒ąŠą╣ ą┤čĆčāą│ąŠą╣ čéą░ą╣ą╝ąĄčĆ STM32, ąĮąŠ ą▒čŗą╗ ą▓čŗą▒čĆą░ąĮ TIM6, ą┐ąŠčüą║ąŠą╗čīą║čā ąŠąĮ ąĮąĄ čüą░ą╝čŗą╣ čüą╗ąŠąČąĮčŗą╣. ąöčĆčāą│ąĖąĄ čéą░ą╣ą╝ąĄčĆčŗ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ą▒ąŠą╗ąĄąĄ čüą╗ąŠąČąĮčŗčģ ąĘą░ą┤ą░čć.

#define ANY_DELAY_RQUIRED 0x0FFF

/* ą×čćąĖčüčéą║ą░ čäą╗ą░ą│ą░ čüąŠą▒čŗčéąĖčÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ: */

TIM6->SR = 0

/* ąŻčüčéą░ąĮąŠą▓ą║ą░ čéčĆąĄą▒čāąĄą╝ąŠą╣ ąĘą░ą┤ąĄčƹȹ║ąĖ: */

// ą¤čĆąĄčüą║ą░ą╗ąĄčĆ čéą░ą╣ą╝ąĄčĆą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 0:

// TIM6->PSC = 0;

// ąĢčüą╗ąĖ čéčĆąĄą▒čāąĄčéčüčÅ ą▒ąŠą╗ąĄąĄ ą┤ą╗ąĖąĮąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░, č鹊 čĆąĄą│ąĖčüčéčĆ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░

// ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą┤čĆčāą│ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ:

TIM6->ARR = ANY_DELAY_RQUIRED;

/* ąŚą░ą┐čāčüą║ čüč湥čéą░ čéą░ą╣ą╝ąĄčĆą░ */

TIM6->CR1 |= TIM_CR1_CEN;

/* ą”ąĖą║ą╗ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ čüąŠą▒čŗčéąĖčÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ: */

while (!(TIM6->SR & TIM_SR_UIF));

/* ąóčĆąĄą▒čāąĄą╝ą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą▓čĆąĄą╝ąĄąĮąĖ ąĖčüč鹥ą║ą╗ą░, ą┤ą░ą╗čīčłąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī

ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗą╣ ą║ąŠą┤ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. */

...

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą║ą░ąĮą░ą╗ą░ ąĮą░ ą▓ą▓ąŠą┤.

// ą¤ąĄčĆąĄą╝ąĄąĮąĮą░čÅ ą┤ą╗čÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ

// ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą░ą║čéąĖą▓ąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ąĮą░ ą▓čģąŠą┤ąĄ:

uint32_t TimeStamp;

// ąĪąŠčüč鹊čÅąĮąĖąĄ čüą▒čĆąŠčüą░ čĆąĄą│ąĖčüčéčĆą░ ARR ą┤ą╗čÅ čéą░ą╣ą╝ąĄčĆą░ TIM3 čĆą░ą▓ąĮąŠ

// 0x0000FFFF. ąŁč鹊 ą┤ąŠą╗ąČąĮąŠ ą┐ąŠą┤ąŠą╣čéąĖ ą┤ą╗čÅ ąĮą░čłąĄą│ąŠ ą┐čĆąĖą╝ąĄčĆą░.

// ąĢčüą╗ąĖ ąĮčāąČąĮąŠ ą┐ąŠą╝ąĄąĮčÅčéčī ąĘąĮą░č湥ąĮąĖąĄ ARR, č鹊 čĆą░čüą║ąŠą╝ą╝ąĄąĮčéąĖčĆčāą╣č鹥

// čüą╗ąĄą┤čāčÄčēčāčÄ čüčéčĆąŠą║čā ą║ąŠą┤ą░:

// TIM3->ARR = ANY_VALUE_YOU_WANT;

// ąØą░čüčéčĆąŠą╣ą║ą░ ą║ą░ąĮą░ą╗ą░ 1 čéą░ą╣ą╝ąĄčĆą░ TIM3 ąĮą░ ą▓ą▓ąŠą┤.

// ąæąĖčéčŗ CC1S ą┤ąŠčüčéčāą┐ąĮčŗ ąĮą░ ąĘą░ą┐ąĖčüčī č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą║ą░ąĮą░ą╗ 1 ą▓čŗą║ą╗čÄč湥ąĮ.

// ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą▓čüąĄ ą║ą░ąĮą░ą╗čŗ ą▓čŗą║ą╗čÄč湥ąĮčŗ.

TIM3->CCMR1 |= TIM_CCMR1_CC1S_0;

// ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ 1 čéą░ą╣ą╝ąĄčĆą░ TIM3 ąĖ čüąŠčģčĆą░ąĮąĄąĮąĖąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ

// ą║ą░ąĮą░ą╗ą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░) ą┤ą╗čÅ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ

// ą║ą░ąĮą░ą╗ą░.

TIM3->CCER |= TIM_CCER_CC1E;

// ąĪčéą░čĆčé čüč湥čéą░ čéą░ą╣ą╝ąĄčĆą░:

TIM3->CR1 |= TIM_CR1_CEN;

// ą×čćąĖčüčéą║ą░ čäą╗ą░ą│ą░ čüąŠą▒čŗčéąĖčÅ ąĘą░čģą▓ą░čéą░ (Capture event flag)

// ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1:

TIM3->SR = ~TIM_SR_CC1IF;

// ą”ąĖą║ą╗, ą┐ąŠą║ą░ ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ capture event flag:

while (!(TIM3->SR & TIM_SR_CC1IF));

// ąæčŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤, čüąŠčģčĆą░ąĮąĄąĮąĖąĄ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ:

TimeStamp = TIM3->CCR1;

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą║ą░ąĮą░ą╗ą░ ąĮą░ ą▓čŗą▓ąŠą┤.

// ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ čĆąĄą│ąĖčüčéčĆą░ ARR ą┤ą╗čÅ čéą░ą╣ą╝ąĄčĆą░ TIM3 čĆą░ą▓ąĮąŠ

// 0x0000FFFF. ąŁč鹊 ą┤ąŠą╗ąČąĮąŠ ą┐ąŠą┤ąŠą╣čéąĖ ą┤ą╗čÅ ąĮą░čłąĄą│ąŠ ą┐čĆąĖą╝ąĄčĆą░. ąĢčüą╗ąĖ

// ąĮčāąČąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ą┤čĆčāą│ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, č鹊 čĆą░čüą║ąŠą╝ą╝ąĄąĮčéąĖčĆčāą╣č鹥

// čüą╗ąĄą┤čāčÄčēčāčÄ čüčéčĆąŠą║čā:

// TIM3->ARR = ANY_VALUE_YOU_WANT;

// ąÜą░ąĮą░ą╗ 1 čéą░ą╣ą╝ąĄčĆą░ TIM3 ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąĮą░ ą▓čŗą▓ąŠą┤,

// TIM3->CC1S čĆą░ą▓ąĄąĮ 0.

// ąöą╗čÅ ą▓čŗą▒ąŠčĆą░ čĆąĄąČąĖą╝ą░ ą▓čŗą▓ąŠą┤ą░ ą©ąśą£ PWM2 ą▒ąĖč鹊ą▓ąŠąĄ ą┐ąŠą╗ąĄ OC1M

// čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 111:

TIM3->CCMR1 |= TIM_CCMR1_OC1M_0 | TIM_CCMR1_OC1M_1 | TIM_CCMR1_OC1M_2;

// ąŻčüčéą░ąĮąŠą▓ą║ą░ čüą║ą▓ą░ąČąĮąŠčüčéąĖ 50%:

TIM3->CCR1 = TIM3->ARR / 2;

// ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1 ą▓čŗą║ą╗čÄč湥ąĮą░.

// ą¦č鹊ą▒čŗ ąĖąĘą╝ąĄąĮąĖčéčī čŹč鹊, čĆą░čüą║ąŠą╝ą╝ąĄąĮčéąĖčĆčāą╣č鹥 čüą╗ąĄą┤čāčÄčēčāčÄ čüčéčĆąŠą║čā:

// TIM3->CCMR1 |= TIM_CCMR1_OC1PE;

// ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ 1 čéą░ą╣ą╝ąĄčĆą░ TIM3 ąĖ čüąŠčģčĆą░ąĮąĄąĮąĖąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ

// ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░) ą┤ą╗čÅ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ ą║ą░ąĮą░ą╗ą░:

TIM3->CCER |= TIM_CCER_CC1E;

// ąĪčéą░čĆčé čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░:

TIM3->CR1 |= TIM_CR1_CEN;

[ą¤čĆąŠą┤ą▓ąĖąĮčāčéčŗąĄ čäčāąĮą║čåąĖąĖ čéą░ą╣ą╝ąĄčĆą░ STM32]

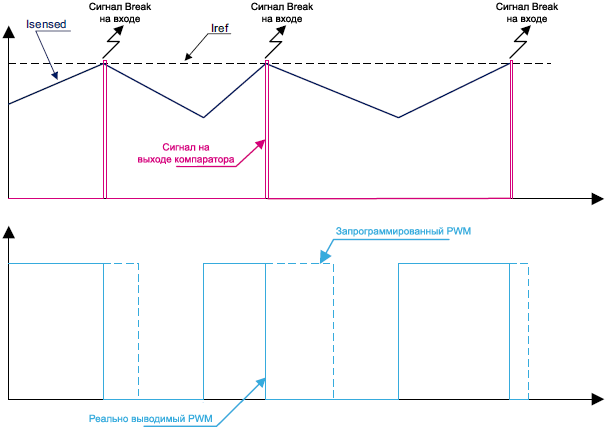

ąÆ čŹč鹊ą╝ čĆą░ąĘą┤ąĄą╗ąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ą┤ąĄčéą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ąĮąĄą║ąŠč鹊čĆčŗčģ ąŠą▒čēąĖčģ čäčāąĮą║čåąĖą╣ čéą░ą╣ą╝ąĄčĆą░, ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą▒čāą┤čāčé ą┤ą░ąĮčŗ ą┐čĆąĖą╝ąĄčĆčŗ.

ąÜą░čüą║ą░ą┤ čäąĖą╗čīčéčĆą░čåąĖąĖ. ąÆčģąŠą┤čŗ čéą░ą╣ą╝ąĄčĆą░ (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ ą▓čģąŠą┤ą░ ETR ąĖą╗ąĖ ą▓čģąŠą┤ąŠą▓ ą║ą░ąĮą░ą╗ąŠą▓) čüąĮą░ą▒ąČąĄąĮčŗ ą║ą░čüą║ą░ą┤ąŠą╝ čäąĖą╗čīčéčĆą░čåąĖąĖ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ąŠčéą▒čĆą░čüčŗą▓ą░ąĮąĖčÅ ą▓ąĮąĄčłąĮąĖčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ čüąĖą│ąĮą░ą╗ą░, ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ąŠč鹊čĆčŗčģ ą╝ąĄąĮčīčłąĄ ąČąĄą╗ą░ąĄą╝ąŠą│ąŠ ą┐ąŠčĆąŠą│ą░.

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čäąĖą╗čīčéčĆčāąĄą╝čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┤ą▓čāčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓:

ŌĆó ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą║ą░čüą║ą░ą┤ą░ čäąĖą╗čīčéčĆą░čåąĖąĖ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą▓čģąŠą┤ą░ čéą░ą╣ą╝ąĄčĆą░. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą║ą░čüą║ą░ą┤ čäąĖą╗čīčéčĆą░čåąĖąĖ ą▓čģąŠą┤ą░ ETR ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ ETF[3:0] čĆąĄą│ąĖčüčéčĆą░ TIMx_SMCR. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą║ą░čüą║ą░ą┤ą░ ą▓čģąŠą┤ąĮąŠą╣ čäąĖą╗čīčéčĆą░čåąĖąĖ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé ą▓čŗą▒ąŠčĆ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą▓čģąŠą┤ąĮčŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓, čāčüčéą░ąĮąŠą▓ą║ąĖ čćą░čüč鹊čéčŗ ą▓čŗą▒ąŠčĆą║ąĖ čéą░ą║č鹊ą▓ ąĖ čāčüčéą░ąĮąŠą▓ą║ąĖ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ ą▓ ąĄą┤ąĖąĮąĖčåą░čģ čéą░ą║č鹊ą▓ čāąČąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą╣ čćą░čüč鹊čéčŗ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

ŌĆó ąÆ čüą╗čāčćą░ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ FDTS ą▓ ą║ą░č湥čüčéą▓ąĄ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąŠčåąĖčäčĆąŠą▓ą║ąĖ, ą║ą░čüą║ą░ą┤ čäąĖą╗čīčéčĆą░čåąĖąĖ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ąĮą░ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝čāčÄ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą┐čĆąŠčģąŠą┤čÅčēąĄą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ ąĘą░ą┐ąĖčüčīčÄ ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą┐ąŠą╗ąĄ ą▒ąĖčé CKD[1:0] čĆąĄą│ąĖčüčéčĆą░ TIMx_CR1. ąóą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ FDTS ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ąĖąĘ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░, ąĖ ą┐ąŠą╗ąĄ ą▒ąĖčé CKD[1:0] čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą╝ąĄąČą┤čā čŹčéąĖą╝ąĖ ą┤ą▓čāą╝čÅ čéą░ą║č鹊ą▓čŗą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ.

ą£ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąŠą┤ąĖąĮ ąĖąĘ ą┤ą▓čāčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ čéą░ą║č鹊ą▓ ą▓ ą║ą░č湥čüčéą▓ąĄ čćą░čüč鹊čéčŗ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ čäąĖą╗čīčéčĆą░čåąĖąĖ, ą╗ąĖą▒ąŠ čüąĖą│ąĮą░ą╗ čéą░ą╣ą╝ąĄčĆą░ FCK_INT, ą╗ąĖą▒ąŠ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ FDTS.

ąĀąĖčü. 4 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆą░ą║čéąĖč湥čüą║ąĖą╣ ą┐čĆąĖą╝ąĄčĆ, ą│ą┤ąĄ ą║ą░čüą║ą░ą┤ čäąĖą╗čīčéčĆą░čåąĖąĖ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čģąŠą┤ą░ čéą░ą╣ą╝ąĄčĆą░ ETR. ąöą╗čÅ čŹč鹊ą│ąŠ ą┤ąĄą╝ąŠąĮčüčéčĆą░čéąĖą▓ąĮąŠą│ąŠ ą┐čĆąĖą╝ąĄčĆą░ ąĮą░čüčéčĆąŠąĄąĮčŗ čüą╗ąĄą┤čāčÄčēąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ:

ŌĆó ą¦ą░čüč鹊čéą░ čéą░ą║č鹊ą▓ čéą░ą╣ą╝ąĄčĆą░ FCK_INT = 1 ą£ąōčå.

ŌĆó CKD [1:0] = 01. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ FDTS ą▓ 2 čĆą░ąĘą░ ą╝ąĄąĮčīčłąĄ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ čüąĖą│ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░: Fdts = Fck_int/2 = 500 ą║ąōčå.

ŌĆó ETF [3:0] = 0100. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▓čŗą▒čĆą░ąĮ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ FDTS ą▓ ą║ą░č湥čüčéą▓ąĄ čćą░čüč鹊čéčŗ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą┤ą╗čÅ čäąĖą╗čīčéčĆą░, ą┐ąŠąĮąĖąČąĄąĮąĮąŠą╣ ą▓ 2 čĆą░ąĘą░. ąóą░ą║ąČąĄ čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ąĖą╝ą┐čāą╗čīčü, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąŠą╣ą┤ąĄčé č湥čĆąĄąĘ čäąĖą╗čīčéčĆ, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą▒čŗčéčī ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī 6 čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ąŠčåąĖčäčĆąŠą▓ą║ąĖ.

ąöą╗čÅ čŹč鹊ą│ąŠ ą┐čĆąĖą╝ąĄčĆą░ ą╗čÄą▒ąŠą╣ ąĖą╝ą┐čāą╗čīčüąĮčŗą╣ čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čģąŠą┤ąĄ čéą░ą╣ą╝ąĄčĆą░ ETR, ą║ąŠč鹊čĆčŗą╣ ą║ąŠčĆąŠč湥 6 x Tsampling = 6 x 1 / 250 ą║ąōčå = 24 ą╝ą║čü, ą▒čāą┤ąĄčé ąŠčéą▒čĆąŠčłąĄąĮ.

ąĀąĖčü. 4. ążąĖą╗čīčéčĆą░čåąĖčÅ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (ETF [3:0]= 0100): FSAMPLING = FDTS/2, N=6.

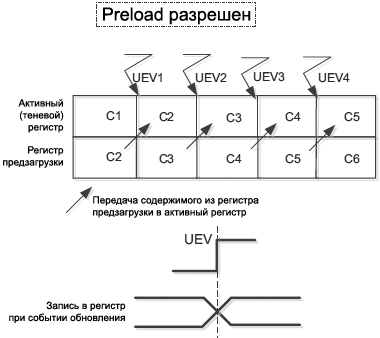

ążčāąĮą║čåąĖčÅ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ čéą░ą╣ą╝ąĄčĆą░. ą¤čĆąĄą┤ąĘą░ą│čĆčāąĘą║ą░ (preload) ą▓ ą║ąŠąĮč鹥ą║čüč鹥 čéą░ą╣ą╝ąĄčĆą░ STM32 ąŠčéąĮąŠčüąĖčéčüčÅ ą║ ą┤čāą▒ą╗ąĖčĆąŠą▓ą░ąĮąĖčÄ ąĮąĄą║ąŠč鹊čĆčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ čéą░ą╣ą╝ąĄčĆą░ ąĖą╗ąĖ ąĮąĄą║ąŠč鹊čĆčŗčģ ą▒ąĖč鹊ą▓čŗčģ ą┐ąŠą╗ąĄą╣ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ąóą░ą║ ą║ą░ą║ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ąĮąĄą║ąŠč鹊čĆčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ čéą░ą╣ą╝ąĄčĆą░ ąĖ ąĮąĄą║ąŠč鹊čĆčŗčģ ą▒ąĖč鹊ą▓čŗčģ ą┐ąŠą╗ąĄą╣ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą▓čŗą▓ąŠą┤ąĖą╝čŗąĄ ąĖąĘ ą║ą░ąĮą░ą╗ąŠą▓ čéą░ą╣ą╝ąĄčĆą░ č乊čĆą╝čŗ čüąĖą│ąĮą░ą╗ą░, ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ ą▒ąĖč鹊ą▓čŗčģ ą┐ąŠą╗ąĄą╣ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī č湥čéą║ąŠ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮąŠ čü čüąŠą▒čŗčéąĖąĄą╝ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ (update event), ą║ąŠč鹊čĆąŠąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĮą░ ąĮą░čćą░ą╗ąĄ ąĮąŠą▓ąŠą│ąŠ čåąĖą║ą╗ą░ čüč湥čéą░. ąŁčéą░ ąČąĄčüčéą║ą░čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ ąĮą░ ą┐čĆą░ą║čéąĖą║ąĄ ąĮąĄ ą▒čŗą╗ą░ ą▒čŗ ą▓ąŠąĘą╝ąŠąČąĮą░, ąĄčüą╗ąĖ ą▒čŗ ąĮąĄ ą▒čŗą╗ąŠ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ čäčāąĮą║čåąĖąĖ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ ą▒ąĖč鹊ą▓čŗčģ ą┐ąŠą╗ąĄą╣.

ąÜąŠą│ą┤ą░ čā čĆąĄą│ąĖčüčéčĆą░ čéą░ą╣ą╝ąĄčĆą░ ąĄčüčéčī čäčāąĮą║čåąĖčÅ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ, č鹊 čüčāčēąĄčüčéą▓čāąĄčé ą┤ą▓ą░ 菹║ąĘąĄą╝ą┐ą╗čÅčĆą░ čĆąĄą│ąĖčüčéčĆąŠą▓ čéą░ą╣ą╝ąĄčĆą░:

ŌĆó ąÉą║čéąĖą▓ąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ (čéą░ą║ąČąĄ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ č鹥ąĮąĄą▓čŗą╝ čĆąĄą│ąĖčüčéčĆąŠą╝): ąĄą│ąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą╗ąŠą│ąĖą║ąŠą╣ čéą░ą╣ą╝ąĄčĆą░ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▓ ą║ą░ąĮą░ą╗ąĄ čéą░ą╣ą╝ąĄčĆą░.

ŌĆó ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ: čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ą┤ąŠčüčéčāą┐ąĄąĮ čüąŠ čüč鹊čĆąŠąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮą░ čäčāąĮą║čåąĖčÅ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čĆąĄą│ąĖčüčéčĆą░.

ąĢčüą╗ąĖ čäčāąĮą║čåąĖčÅ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ ą▓čŗą║ą╗čÄč湥ąĮą░, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 5, č鹊 ą▓čüčéčāą┐ą░čÄčé ą▓ ą┤ąĄą╣čüčéą▓ąĖąĄ ą┤ą▓ąĄ ąŠčüąĮąŠą▓ąĮčŗąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ:

ŌĆó ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ ą║ą░ą║ ąĮąĄ čüčāčēąĄčüčéą▓čāčÄčēąĖą╣.

ŌĆó ąøčÄą▒ą░čÅ ą┐ąŠą┐čŗčéą║ą░ ą┤ąŠčüčéčāą┐ą░ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čĆąĄą│ąĖčüčéčĆ čüąŠ čüč鹊čĆąŠąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąĮą░ą┤ ą░ą║čéąĖą▓ąĮčŗą╝ čĆąĄą│ąĖčüčéčĆąŠą╝.

ąĀąĖčü. 5. ą£ąĄčģą░ąĮąĖąĘą╝ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ čĆąĄą│ąĖčüčéčĆą░ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░ ąĘą░ą┐čĆąĄčēąĄąĮ.

ąĢčüą╗ąĖ čäčāąĮą║čåąĖčÅ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ ą▓ą║ą╗čÄč湥ąĮą░, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 6, č鹊 ą▓čüčéčāą┐ą░čÄčé ą▓ ą┤ąĄą╣čüčéą▓ąĖąĄ ą┤ą▓ąĄ ąŠčüąĮąŠą▓ąĮčŗąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ:

ŌĆó ąøčÄą▒ąŠą╣ ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čĆąĄą│ąĖčüčéčĆ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮą░ą┤ čĆąĄą│ąĖčüčéčĆąŠą╝ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą░ą║čéąĖą▓ąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ąĮąĄ ąĖąĘą╝ąĄąĮčÅąĄčéčüčÅ.

ŌĆó ąÜą░ą║ č鹊ą╗čīą║ąŠ čéą░ą╣ą╝ąĄčĆąŠą╝ čüą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ "update event", čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąĄčĆąĄąĮąŠčüąĖčéčüčÅ ą▓ ą░ą║čéąĖą▓ąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ. ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąČąĄčüčéą║ąŠ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗą╝ čü čüąŠą▒čŗčéąĖąĄą╝ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, čŹč鹊čé ą┐čĆąŠčåąĄčüčü čüčéčĆąŠą│ąŠ čüąĖąĮčģčĆąŠąĮąĄąĮ čü čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ ąĮąŠą▓ąŠą╝ čåąĖą║ą╗ąĄ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą©ąśą£.

ąĀąĖčü. 6. ą£ąĄčģą░ąĮąĖąĘą╝ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ čĆąĄą│ąĖčüčéčĆą░ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░ čĆą░ąĘčĆąĄčłąĄąĮ.

ążčāąĮą║čåąĖčÅ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ ą┤ąŠčüčéčāą┐ąĮą░ ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ ą▒ąĖč鹊ą▓čŗčģ ą┐ąŠą╗ąĄą╣:

ŌĆó Auto-reload timer register (TIMx_ARR).

ŌĆó Timer prescaler register (TIMx_PSC) (ąĄą│ąŠ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ą░ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą║ą╗čÄč湥ąĮą░).

ŌĆó Timer channel registers (TIMx_CCRy).

ŌĆó ąæąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ CCxE ąĖ CCxNE ą▓ čĆąĄą│ąĖčüčéčĆąĄ čéą░ą╣ą╝ąĄčĆą░ TIMx_CCER.

ŌĆó ąæąĖč鹊ą▓ąŠąĄ ą┐ąŠą╗ąĄ OCxM ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čéą░ą╣ą╝ąĄčĆą░ TIMx_CCMRn.

ążčāąĮą║čåąĖčÅ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ą▒ąŠą╗čīčłąŠą╣ ąĖąĮč鹥čĆąĄčü ą┐čĆąĖ ą▓čŗą▓ąŠą┤ąĄ čüąĖą│ąĮą░ą╗ą░ ą©ąśą£ (PWM) ąĮą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝ ą║ą░ąĮą░ą╗ąĄ čéą░ą╣ą╝ąĄčĆą░. ąŻčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ą░ąĮą░ą╗ą░ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą╝ąĄąČą┤čā ąĘąĮą░č湥ąĮąĖąĄą╝ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ ąĖ čĆąĄą│ąĖčüčéčĆąŠą╝ TIMx_CCRy, ą┐ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ ą╗čÄą▒ąŠąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠą╝čā ąĖąĘą╝ąĄąĮąĄąĮąĖčÄ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ čéą░ą╣ą╝ąĄčĆą░. ąÆ čüą╗ąĄą┤čüčéą▓ąĖąĄ čŹč鹊ą│ąŠ ą┐čĆčÅą╝ą░čÅ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ ą║ą░ąĮą░ą╗ą░ ą┐ąŠčüąĄčĆąĄą┤ąĖąĮąĄ ą┐ąĄčĆąĖąŠą┤ą░ PWM ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüą╗čāčćą░ą╣ąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓.

ą¦č鹊ą▒čŗ čĆąĄčłąĖčéčī čŹčéčā ą┐čĆąŠą▒ą╗ąĄą╝čā, ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░ čäčāąĮą║čåąĖčÅ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ ą┤ą╗čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░. ąÜąŠą│ą┤ą░ čäčāąĮą║čåąĖčÅ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ čĆą░ąĘčĆąĄčłąĄąĮą░, ą╗čÄą▒ąŠą╣ ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ ą║ą░ąĮą░ą╗ą░ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą░ą║čéąĖą▓ąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ą║ą░ąĮą░ą╗ą░ ąŠčüčéą░ąĮąĄčéčüčÅ ąĮąĄčéčĆąŠąĮčāčéčŗą╝. ąŁč鹊 čāčüčéčĆą░ąĮąĖčé ą┐ąĄčĆčéčāčĆą▒ą░čåąĖąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ ą©ąśą£.

ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé čüąŠą▒čŗčéąĖąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░, čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą▓ ą░ą║čéąĖą▓ąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ. ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ ą©ąśą£ ą┤ą╗čÅ ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĮąŠą▓ąŠą╣ čüą║ą▓ą░ąČąĮąŠčüčéąĖ ą┐ąĄčĆąĖąŠą┤ą░ ą©ąśą£.

ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čäčāąĮą║čåąĖčÅ ą┐čĆąĄą┤ąĘą░ą│čĆčāąĘą║ąĖ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé ąŠčéčüčāčéčüčéą▓ąĖąĄ ąŠčłąĖą▒ąŠčćąĮčŗčģ ą┐ąĄčĆąĖąŠą┤ąŠą▓ ą©ąśą£ ąĮą░ ą▓čŗčģąŠą┤ąĄ čéą░ą╣ą╝ąĄčĆą░, ą║ąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ čéą░ą╣ą╝ąĄčĆą░ ąĖ ą▒ąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ, ą║ąŠč鹊čĆčŗąĄ ąŠą║ą░ąĘčŗą▓ą░čÄčé ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠąĄ ą▓ą╗ąĖčÅąĮąĖąĄ ąĮą░ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą©ąśą£, ąŠčüąŠą▒ąĄąĮąĮąŠ čŹč鹊 ą▓ą░ąČąĮąŠ ą┐ąŠčüąĄčĆąĄą┤ąĖąĮąĄ ą┐ąĄčĆąĖąŠą┤ą░ čüąĖą│ąĮą░ą╗ą░ ą©ąśą£.

[ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░ STM32 ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░]

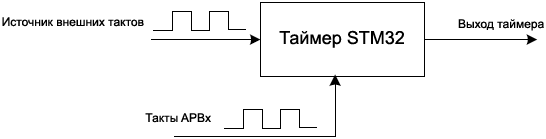

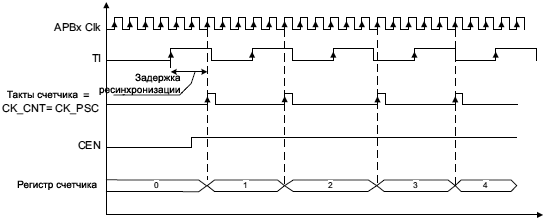

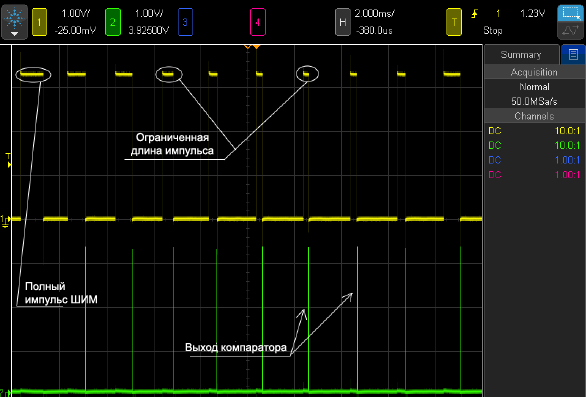

ąóą░ą╣ą╝ąĄčĆ STM32 ą╝ąŠąČąĄčé čéą░ą║čéąĖčĆąŠą▓ą░čéčīčüčÅ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, ąĮąŠ čŹč鹊 ąĮąĄ ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮąĄ ąĮčāąČąĮąŠ čéą░ą║čéąĖčĆąŠą▓ą░čéčī čłąĖąĮčā APB (advanced peripheral bus). ąóą░ą╣ą╝ąĄčĆ STM32, čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮ ą▓ąĮąĄčłąĮąĖą╝ čéą░ą║č鹊ą▓čŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝ čüąŠ čüą▓ąŠąĄą╣ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą╣ čćą░čüč鹊č鹊ą╣ čÅą┤čĆą░ (ą║ąŠč鹊čĆą░čÅ čÅą▓ą╗čÅąĄčéčüčÅ čéą░ą║čéą░ą╝ąĖ APB). ąĀąĄąĘčāą╗čīčéąĖčĆčāčÄčēąĖą╣ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ ą┐ąŠčüčéčāą┐ą░ąĄčé ąĮą░ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ čéą░ą╣ą╝ąĄčĆą░, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠčüą╗ąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĖą┤ąĄčé ąĮą░ čüč湥čéčćąĖą║.

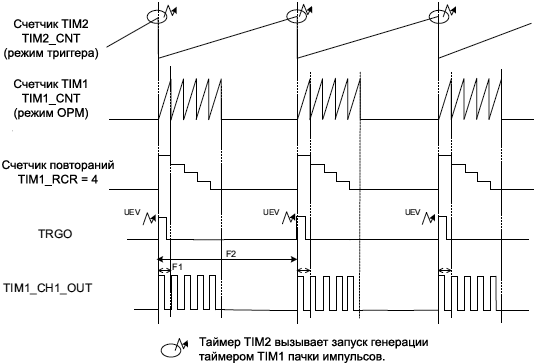

ąóą░ą╣ą╝ąĄčĆ STM32 čéčĆąĄą▒čāąĄčé 2 ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░, čćč鹊ą▒čŗ ą┐ąŠčüč鹊čÅąĮąĮąŠ ąŠą▒ąĮąŠą▓ą╗čÅą╗ą░čüčī ą▓čĆąĄą╝ąĄąĮąĮą░čÅ ą▒ą░ąĘą░ (čüą╝. čĆąĖčü. 7). ą¤ąĄčĆąĖąŠą┤ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ čŹč鹊 ąĄą┤ąĖąĮąĖčåą░ ą▓čĆąĄą╝ąĄąĮąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ą░čÅ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą▒ą░ąĘčŗ ą▓čĆąĄą╝ąĄąĮąĖ čéą░ą╣ą╝ąĄčĆą░.

ąĀąĖčü. 7. ąĪąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ čéą░ą╣ą╝ąĄčĆą░ ą▓ąĮąĄčłąĮąĖą╝ čéą░ą║č鹊ą▓čŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝.

ąĢčüčéčī ą┤ą▓ą░ čüą┐ąŠčüąŠą▒ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ (ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ) čéą░ą╣ą╝ąĄčĆą░ STM32:

ŌĆó ąĀąĄąČąĖą╝ 1 ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ: ą▓ąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┐ąŠčüčéčāą┐ą░ąĄčé ąĮą░ ąŠą┤ąĖąĮ ąĖąĘ ą▓čģąŠą┤ąŠą▓ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░ TIx.

ŌĆó ąĀąĄąČąĖą╝ 2 ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ: ą▓ąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┐ąŠčüčéčāą┐ą░ąĄčé ąĮą░ ą▓čģąŠą┤ ETR (ąĄčüą╗ąĖ čŹč鹊 čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ ą▓ čéą░ą╣ą╝ąĄčĆąĄ ąĖ ą┤ąŠčüčéčāą┐ąĮąŠ).

ąĀąĖčü. 8 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖąĄ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ čŹčéąĖčģ čĆąĄąČąĖą╝ąŠą▓.

ąĀąĖčü. 8. ąĀą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖąĄ čéą░ą║č鹊ą▓ ą┤ą╗čÅ čĆąĄąČąĖą╝ąŠą▓ ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ.

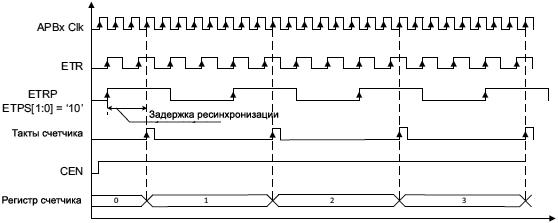

ąæą╗ąŠą║ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ. ą¤ąĄčĆąĄą┤ ą▓ą▓ąĄą┤ąĄąĮąĖąĄą╝ ą▓ čĆąĄąČąĖą╝čŗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čéą░ą╣ą╝ąĄčĆą░ ą▓ąĮąĄčłąĮąĖą╝ čüąĖą│ąĮą░ą╗ąŠą╝ ą▓ą░ąČąĮąŠ čüąĮą░čćą░ą╗ą░ ą┐ąŠą║ą░ąĘą░čéčī ą╝ąĄčģą░ąĮąĖąĘą╝ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąĮčŗą╣ ą▓ čéą░ą╣ą╝ąĄčĆąĄ STM32, ą║ąŠą│ą┤ą░ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ STM32 čĆą░ą▒ąŠčéą░ąĄčé čü ą▓ąĮąĄčłąĮąĖą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ. ąÆąĮąĄčłąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ čŹč鹊 čéą░ą║ąĖąĄ čüąĖą│ąĮą░ą╗čŗ, ą║ąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ ą┐ąŠčüčéčāą┐ą░ąĄčé ąĖąĘą▓ąĮąĄ čéą░ą╣ą╝ąĄčĆą░. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ą╝ąŠąČąĄčé ą▒čŗčéčī ą║ą░ą║ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮ čü čéą░ą║č鹊ą▓čŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝, čéą░ą║ ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╝.

ąóą░ą╣ą╝ąĄčĆ ą┤ąŠą╗ąČąĄąĮ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčī ą▓ąĮąĄčłąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╝ąĖ, ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą┐ąŠą┤čüčéčĆą░ąĖą▓ą░čéčī ą▓čŗčģąŠą┤ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ č乊čĆą╝ąĖčĆčāąĄą╝čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓. ąóą░ą╣ą╝ąĄčĆ čéą░ą║ąČąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą┐ąŠčüąŠą▒ąĄąĮ ąĖąĮč乊čĆą╝ąĖčĆąŠą▓ą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ąŠ ą╝ąĄčéą║ą░čģ ą▓čĆąĄą╝ąĄąĮąĖ, ąĮą░ ą║ąŠč鹊čĆčŗčģ čüąĖą│ąĮą░ą╗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ ą╝ąĄąĮčÅąĄčé čüą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ (ąĮą░ą┐čĆąĖą╝ąĄčĆ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░).

ą¦č鹊ą▒čŗ ąŠą▒čĆą░ą▒ąŠčéą░čéčī ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗, ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ čéą░ą╣ą╝ąĄčĆą░ čüąĮą░čćą░ą╗ą░ ąĮčāąČą┤ą░ąĄčéčüčÅ ą▓ č鹊ą╝, čćč鹊ą▒čŗ ą┐ąĄčĆąĄčüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčī čüą▓ąŠą╣ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓. ąĢą│ąŠ ą╝ąŠąČąĄčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ ą┐ąĄčĆąĄčüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčī ąĮą░ą┐čĆąĖą╝ąĄčĆ čü čéą░ą║č鹊ą▓čŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝ ą╗ąŠą│ąĖą║ąĖ čÅą┤čĆą░ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą┐ąĄčĆąĄą┤ą░čéčī čĆąĄąĘčāą╗čīčéąĖčĆčāčÄčēąĖą╣ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ ą▓ čĆą░ąĘąĮčŗąĄ čüčāą▒ą▒ą╗ąŠą║ąĖ čéą░ą╣ą╝ąĄčĆą░. ąŁč鹊 ą┤ąĄą╣čüčéą▓ąĖąĄ ąĘą░čēąĖčéąĖčé ą╗ąŠą│ąĖą║čā čÅą┤čĆą░ čéą░ą╣ą╝ąĄčĆą░ ąŠčé ą┐čĆąŠą▒ą╗ąĄą╝ ą╝ąĄčéą░čüčéą░ą▒ąĖą╗čīąĮąŠčüčéąĖ.

ąĀąĖčü. 9 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąĖąĮąŠą┐čéąĖč湥čüą║čāčÄ ą┤ąĖą░ą│čĆą░ą╝ą╝čā ą┤ą╗čÅ čüčģąĄą╝čŗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╣ ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą▓ąĮąĄčłąĮąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓, ą┐ąŠčüčéčāą┐ą░čÄčēąĖčģ ąĮą░ ą▓čģąŠą┤čŗ čéą░ą╣ą╝ąĄčĆą░. ąĪčģąĄą╝ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čüąŠčüčéą░ą▓ą╗ąĄąĮą░ ą│ą╗ą░ą▓ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĖąĘ ą┤ą▓čāčģ čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗčģ ą║ą░čüą║ą░ą┤ąŠą╝ D-čéčĆąĖą│ą│ąĄčĆąŠą▓, ą║ąŠč鹊čĆčŗąĄ čéą░ą║čéąĖčĆčāčÄčéčüčÅ čüąĖą│ąĮą░ą╗ąŠą╝ čÅą┤čĆą░ čéą░ą╣ą╝ąĄčĆą░. ąÆąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ ą┐čĆąĖčģąŠą┤ąĖčé ąĮą░ ą▓čģąŠą┤ ą┐ąĄčĆą▓ąŠą│ąŠ ą║ą░čüą║ą░ą┤ą░ D-čéčĆąĖą│ą│ąĄčĆą░, ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą▓č鹊čĆąŠą│ąŠ ą║ą░čüą║ą░ą┤ą░ D-čéčĆąĖą│ą│ąĄčĆą░. ąŁč鹊čé ą▒ą╗ąŠą║ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą▓ą▓ąŠą┤ąĖčé ąĘą░ą┤ąĄčƹȹ║čā ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 2 čéą░ą║čéą░ čÅą┤čĆą░ čéą░ą╣ą╝ąĄčĆą░ ąĖ ą╝ą░ą║čüąĖą╝čāą╝ 3 čéą░ą║čéą░.

ąĀąĖčü. 9. ąæą╗ąŠą║ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ.

ąÆ čéą░ą╣ą╝ąĄčĆąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ŌĆ£ą┐ąĄčĆą▓ąŠąĮą░čćą░ą╗čīąĮą░čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅŌĆØ ąĮą░ ą▓čüąĄčģ ą▓čģąŠą┤ą░čģ, ą║čĆąŠą╝ąĄ ETR, ą│ą┤ąĄ ą┐ąĄčĆą▓čŗą╝ ąĖą┤ąĄčé ą┐čĆąĄčüą║ą░ą╗ąĄčĆ, ą┐ąŠčüą╗ąĄ ąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ ą┐ąĄčĆąĄčüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ.

ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ č乊čĆą╝čāą╗ąŠą╣ ąĮąĖąČąĄ, čćą░čüč鹊čéą░ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓ 3 čĆą░ąĘą░ ą╝ąĄąĮčīčłąĄ, č湥ą╝ čćą░čüč鹊čéą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čÅą┤čĆą░.

FreqTIMCLK Ōēź 3 x Freqinputsignal

ąĀąĄąČąĖą╝ 1 ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ąÜąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ external clock-source mode 1, ą╗čÄą▒ąŠą╣ čüąĖą│ąĮą░ą╗, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮ ąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüąĖą│ąĮą░ą╗ čéą░ą╣ą╝ąĄčĆą░ TRGI, ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čéą░ą║ąČąĄ ą║ą░ą║ čéą░ą║čéčŗ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░. ąĀąĖčü. 8 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ ąĖčüč鹊čćąĮąĖą║ąĖ čéą░ą║č鹊ą▓ ą┤ą╗čÅ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░:

ŌĆó ąÆčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ETRF: čüąĖą│ąĮą░ą╗ ETR ą┐ąŠčüą╗ąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ ąĖ ąĘą░č鹥ą╝ čäąĖą╗čīčéčĆčāąĄčéčüčÅ.

ŌĆó ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čéą░ą╣ą╝ąĄčĆą░ (ą▓čģąŠą┤čŗ ITR).

ŌĆó ąĪąĖą│ąĮą░ą╗ TI1FD, ą║ąŠč鹊čĆčŗą╣ čÅą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝ ą║ą░ąĮą░ą╗ą░ 1 čéą░ą╣ą╝ąĄčĆą░, ąĮąŠ ą║ąŠč鹊čĆčŗąĄ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮčŗ ą║ ąŠą▒ąŠąĖą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ čüąĖą│ąĮą░ą╗ą░ (ą║ą░ąČą┤čŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ąĮą░ ą▓čģąŠą┤ąĄ čéą░ą╣ą╝ąĄčĆą░ 1 ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĖą╝ą┐čāą╗čīčü).

ŌĆó ąÆčģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ TI1FP1 ąĖ TI2FP2 čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāčÄčéčüčÅ, čäąĖą╗čīčéčĆčāčÄčéčüčÅ, ąĘą░č鹥ą╝ ą┐ąŠą┤ą░čÄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ąĮą░ ą┐čĆąĄčüą║ą░ą╗ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą▓čģąŠą┤čŗ čéą░ą╣ą╝ąĄčĆą░ TI1 ąĖ TI2.

ąÆ čŹč鹊ą╣ čüąĄą║čåąĖąĖ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ external clock mode 1, ą║ąŠą│ą┤ą░ ą▓ąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┐ąŠą┤ą░ąĄčéčüčÅ ąĮą░ čéą░ą╣ą╝ąĄčĆ č湥čĆąĄąĘ ąŠą┤ąĖąĮ ąĖąĘ ąĄą│ąŠ ą▓čģąŠą┤ąŠą▓, ą┤čĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ą║ąŠą│ą┤ą░ čéą░ą║čéčŗ ą┐ąŠą┤ą░čÄčéčüčÅ ąĮą░ čéą░ą╣ą╝ąĄčĆ č湥čĆąĄąĘ ą▓čģąŠą┤čŗ ETR, TI1 ąĖą╗ąĖ TI2.

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą▓čģąŠą┤ą░ ETR ą┤ą╗čÅ čéą░ą╣ą╝ąĄčĆą░ čŹč鹊 ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮą░čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┤ą╗čÅ external clock-source mode 2, čéą░ą║ čćč鹊 ą┐ąŠą┤čĆąŠą▒ąĮąŠ ąŠąĮą░ ą▓ čŹč鹊ą╣ čüąĄą║čåąĖąĖ ąĮąĄ ąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ. ąĪąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ čüąŠą┤ąĄčƹȹĖčé ą┐čĆą░ą▓ąĖą╗čīąĮčāčÄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ ą┤ą╗čÅ ą░ą║čéąĖą▓ą░čåąĖąĖ čŹč鹊ą╣ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓čŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ.

ąÆčģąŠą┤čŗ čéą░ą╣ą╝ąĄčĆą░, TI1 ąĖ TI2 ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ąŠą▓ čéą░ą║č鹊ą▓. ąÜąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ external clock mode 1, č鹊ą╗čīą║ąŠ ą▓čģąŠą┤čŗ TI1 ąĖ TI2 ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐ąŠą┤ą░čćąĖ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░ čüč湥čéčćąĖą║ čéą░ą╣ą╝ąĄčĆą░. ąĢčüą╗ąĖ ą▓ čéą░ą╣ą╝ąĄčĆąĄ ąĮąĄ ą▓čüčéčĆąŠąĄąĮąŠ 4 ą║ą░ąĮą░ą╗ą░, ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą▓čģąŠą┤čŗ TI3 ąĖ TI4 ąĮąĄ ą╝ąŠą│čāčé čéą░ą║čéąĖčĆąŠą▓ą░čéčī čéą░ą╣ą╝ąĄčĆ.

ąóą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ą┐ąŠčüčéčāą┐ą░čÄčēąĖą╣ ąĮą░ ą▓čģąŠą┤čŗ čéą░ą╣ą╝ąĄčĆą░ TI1 ąĖą╗ąĖ TI2, čüąĮą░čćą░ą╗ą░ ą║ąŠąĮą┤ąĖčåąĖąŠąĮąĖčĆčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖąĄą╝ ąĮą░ čüč湥čéčćąĖą║. ąÜąŠąĮą┤ąĖčåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓čģąŠą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą║ą░čüą║ą░ą┤ąŠą╝ ą▓ąĮąĄčłąĮąĄą╣ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, ąĘą░č鹥ą╝ čüąĖą│ąĮą░ą╗ ą┐čĆąŠčģąŠą┤ąĖčé č湥čĆąĄąĘ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ąĖ ą║ą░čüą║ą░ą┤ čäąĖą╗čīčéčĆą░čåąĖąĖ.

ąÆčģąŠą┤ąĮąŠą╣ čäąĖą╗čīčéčĆ ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ. ąÜą░ąĮą░ą╗, čüą▓čÅąĘą░ąĮąĮčŗą╣ čü čåąĄą╗ąĄą▓čŗą╝ ą▓čģąŠą┤ąŠą╝ čéą░ą╣ą╝ąĄčĆą░, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čģąŠą┤ąĮąŠą╣; ąĘą░č鹥ą╝ č鹥 ąČąĄ čüą░ą╝čŗąĄ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ ą▒ąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čģąŠą┤ąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░, ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čģąŠą┤ą░ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓.

ąØąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ čéąĖą┐ąŠą▓ą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čģąŠą┤ąŠą▓ TI1 ąĖą╗ąĖ TI2 ą║ą░ą║ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓:

1. ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą║ą░ąĮą░ą╗ą░, čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüąŠ ą▓čģąŠą┤ąŠą╝ čéą░ą╣ą╝ąĄčĆą░, ąĮą░ ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą┤ą░ąĄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗. ąöą░ąČąĄ ą┐čĆąĖ č鹊ą╝, čćč鹊 ą╗čÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé, ą║čĆąŠą╝ąĄ 00, ąĘą░ą┐ąĖčüą░ąĮąĮąŠąĄ ą▓ ą┐ąŠą╗ąĄ capture/compare selection (CCxS), čāčüčéą░ąĮąŠą▓ąĖčé ą║ą░ąĮą░ą╗ čéą░ą╣ą╝ąĄčĆą░ ą▓ čĆąĄąČąĖą╝ ą▓čģąŠą┤ą░, ą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ CCxS = 01.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖč鹊ą▓ąŠąĄ ą┐ąŠą╗ąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čüą▓čÅąĘą░ąĮąĮčŗą╣ čü ąĮąĖą╝ ą║ą░ąĮą░ą╗ čéą░ą╣ą╝ąĄčĆą░ ąĘą░ą┐čĆąĄčēąĄąĮ (ą║ąŠą│ą┤ą░ čüą▒čĆąŠčłąĄąĮąŠ ą▒ąĖč鹊ą▓ąŠąĄ ą┐ąŠą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ/ąĘą░ą┐čĆąĄčéą░ ą┤ą╗čÅ čŹč鹊ą│ąŠ ą║ą░ąĮą░ą╗ą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMx_CCER, CCxE = 0.

2. ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ ą░ą║čéąĖą▓ąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░. ąÆčüčéčĆąŠąĄąĮąĮčŗąĄ čéą░ą╣ą╝ąĄčĆčŗ ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ STM32 ąĖą╝ąĄčÄčé ą▓čģąŠą┤čŗ ą▓čģąŠą┤čŗ, čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮčŗąĄ ą║ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ, ąĮą░čĆą░čüčéą░ąĮąĖčÄ čāčĆąŠą▓ąĮčÅ ąĖą╗ąĖ ą║ ąŠą▒ąŠąĖą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ čüąĄčĆąĖąĖ STM32F2); ą▓ ą┤čĆčāą│ąĖčģ čüąĄą╝ąĄą╣čüčéą▓ą░čģ STM32 ą▓čüčéčĆąŠąĄąĮąĮčŗąĄ čéą░ą╣ą╝ąĄčĆčŗ ąĖą╝ąĄčÄčé ą▓čģąŠą┤čŗ, čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮčŗąĄ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čüą┐ą░ą┤ą░ ąĖą╗ąĖ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ čüąĄčĆąĖąĖ STM32F1). ąĪą┐čĆą░ą▓ąŠčćąĮčŗą╣ ą┤ąŠą║čāą╝ąĄąĮčé čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32 čāą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ ą▒ąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠą╗čÅčĆąĮąŠčüčéčīčÄ. ąÆ ą║ą░č湥čüčéą▓ąĄ ą┐čĆąĖą╝ąĄčĆą░, čćč鹊ą▒čŗ ąĮą░čüčéčĆąŠąĖčéčī ą▓čģąŠą┤ čéą░ą╣ą╝ąĄčĆą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32F30x ąĮą░ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ ąŠą▒ąŠąĖą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝, ą▒ąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ ą┤ą╗čÅ ąĖąĮč鹥čĆąĄčüčāčÄčēąĄą│ąŠ ą║ą░ąĮą░ą╗ą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ CCxP = 1 ąĖ CCxNP = 1.