|

ąæąŠą╗čīčłąĖąĮčüčéą▓ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32 (MCU) čüąĮą░ą▒ąČąĄąĮąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ 12-čĆą░ąĘčĆčÅą┤ąĮčŗą╝ ą”ąÉą¤ (Digital-to-Analog Converter, DAC), ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ čüą║ąŠčĆąŠčüčéąĖ ą┤ąŠ 1 Msps (ą╝ąĄą│ą░čüąĄą╝ą┐ą╗ąŠą▓ ą▓ čüąĄą║čāąĮą┤čā). ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ ą▒čŗą╗ąŠ ą▒čŗ ą┐ąŠą╗ąĄąĘąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ąŠčé DAC ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čĆą░ą▒ąŠčéčŗ ąĮą░ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖčģ čüą║ąŠčĆąŠčüčéčÅčģ. ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ (ą┐ąĄčĆąĄą▓ąŠą┤ ą░ą┐ąĮąŠčāčéą░ AN4566 [1]) čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ ą▓ąŠą┐čĆąŠčüčŗ ą┐ąŠą▓čŗčłąĄąĮąĖčÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ čü ą┐ąŠą╝ąŠčēčīčÄ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ (ą×ąŻ). ą¤čĆąĖą╝ąĄčĆ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čü čćą░čüč鹊č鹊ą╣ ą▓čŗą▒ąŠčĆąŠą║ 5 Msps. ą×ą┐ąĖčüą░ąĮąĖąĄ ą┐čĆąĖą╝ąĄąĮąĖą╝ąŠ ą║ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ čüąĄčĆąĖą╣ STM32F0, STM32F1, STM32F2, STM32F3, STM32F4, STM32F7, STM32G0, STM32G4, STM32H7, STM32L0, STM32L1, STM32L4, STM32L4+, STM32L5.

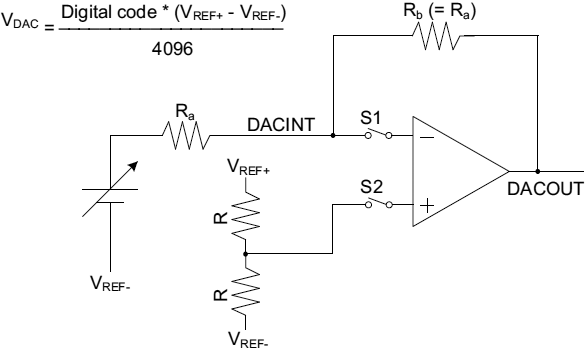

DAC STM32 ą╝ąŠąČąĄčé ą▒čŗčéčī čüą╝ąŠą┤ąĄą╗ąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗą╣ čåąĖčäčĆąŠą▓čŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ ąĖčüč鹊čćąĮąĖą║ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čü ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ ą▓čŗčģąŠą┤ąĮčŗą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 1. ąÆčŗčģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ DAC ą┐ąŠčüč鹊čÅąĮąĮąŠąĄ, ąŠąĮąŠ ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▓čģąŠą┤ąĮąŠą│ąŠ čåąĖčäčĆąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

ąĀąĖčü. 1. ąŁą║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮą░čÅ čüčģąĄą╝ą░ DAC.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąŠą▒čŗčćąĮąŠ VREF+ čĆą░ą▓ąĮąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ ą┐ąĖčéą░ąĮąĖčÅ +3.3V, ą░ VREF- čüąŠąĄą┤ąĖąĮčÅąĄčéčüčÅ ą▓ ąĘąĄą╝ą╗ąĄą╣ GND (čĆą░ą▓ąĮąŠ 0V).

ąÜąŠą│ą┤ą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ DAC ąŠčéą║ą╗čÄč湥ąĮ, DACINT ąĖ DACOUT čüąŠąĄą┤ąĖąĮąĄąĮčŗ č湥čĆąĄąĘ čĆąĄąĘąĖčüč鹊čĆ Rb, ą┐ąŠčŹč鹊ą╝čā ą▓čŗčģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ DAC čĆą░ą▓ąĮąŠ Ra + Rb (Rb = Ra), ąĖ RDAC = 2 * Ra (ą┐čĆąĖ ąŠčéą║ą╗čÄč湥ąĮąĮąŠą╝ ą▒čāč乥čĆąĄ ą║ą╗čÄčćąĖ S1 ąĖ S2 čĆą░ąĘąŠą╝ą║ąĮčāčéčŗ).

ąÜąŠą│ą┤ą░ ą▒čāč乥čĆ čĆą░ąĘčĆąĄčłąĄąĮ, ą×ąŻ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĖą╣ čāčüąĖą╗ąĖč鹥ą╗čī čü ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą╝ čāčüąĖą╗ąĄąĮąĖčÅ Av = -1, ąĖ ą▓čŗčģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą┐ąŠčćčéąĖ čĆą░ą▓ąĮąŠ ąĮčāą╗čÄ ą▒ą╗ą░ą│ąŠą┤ą░čĆčÅ ą┐ąĄčéą╗ąĄ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ čĆą░ąĘčĆąĄčłąĄąĮ. ą×ąĮ ąŠčéą║ą╗čÄčćą░ąĄčéčüčÅ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▓ ą╗ąŠą│. 1 ą▒ąĖčé BOFF1 (ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1) ąĖ BOFF2 (ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1). ą×ą▒ą░ čŹčéąĖčģ ą▒ąĖčéą░ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ DAC_CR (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [2]).

ąĪą║ąŠčĆąŠčüčéąĮčŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ DAC. ąÜąŠą│ą┤ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ DAC čĆą░ąĘčĆąĄčłąĄąĮ ą▒čāč乥čĆ, ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ čŹč鹊ą│ąŠ ą▒čāč乥čĆą░. ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ DAC ą╝ąŠąČąĮąŠ čāąĘąĮą░čéčī č湥čĆąĄąĘ ą┐ą░čĆą░ą╝ąĄčéčĆ Tsettling ąĖą╗ąĖ Update rate ą┤ą░čéą░čłąĖčéą░ ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ STM32.

ąÜąŠą│ą┤ą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ąĘą░ą┐čĆąĄčēąĄąĮ, čüą║ąŠčĆąŠčüčéčī ąĮą░čĆą░čüčéą░ąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĘą░ą▓ąĖčüąĖčé ą┐čĆąŠčüč鹊 ąŠčé ą┐ąŠčüč鹊čÅąĮąĮąŠą╣ ą▓čĆąĄą╝ąĄąĮąĖ RC, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝ąŠą╣ ą▓čŗčģąŠą┤ąĮčŗą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝ DAC RDAC (ą║ąŠč鹊čĆąŠąĄ čĆą░ą▓ąĮąŠ 2*Ra) ąĖ ąĄą╝ą║ąŠčüčéčīčÄ, ą║ąŠč鹊čĆąŠą╣ ąĮą░ą│čĆčāąČąĄąĮą░ ąĮąŠąČą║ą░ ą▓čŗčģąŠą┤ą░ DACOUT.

ąØą░ą┐čĆąĖą╝ąĄčĆ, STM32F407 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą▓čŗčģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą┐čĆąĖ ą▓čŗą║ą╗čÄč湥ąĮąĮąŠą╝ ą▒čāč乥čĆąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ 15 ą║ą×ą╝. ąĢčüą╗ąĖ ą┐čĆąĖąĮčÅčéčī ąĘą░ ą┐ą░čĆą░ąĘąĖčéąĮčāčÄ ąĄą╝ą║ąŠčüčéčī čéąĖą┐ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ 10 ą┐ąż (čŹč鹊 ą▓ą║ą╗čÄčćą░ąĄčé ą┐ą░čĆą░ąĘąĖčéąĮčāčÄ ąĄą╝ą║ąŠčüčéčī ą║ąŠą┐čāčüą░ ąĖ ą║čĆąĖčüčéą░ą╗ą╗ą░ STM32F407 ąĮą░ ąĮąŠąČą║ąĄ DACOUT), č鹊 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ┬▒1 LSB ą║ąŠąĮąĄčćąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ (ą┐ąĄčĆąĄčģąŠą┤ ąŠčé čüą░ą╝ąŠą│ąŠ ą╝ą░ą╗ąŠą│ąŠ ą║ąŠą┤ą░ ą║ čüą░ą╝ąŠą╝čā ą▒ąŠą╗čīčłąŠą╝čā ą║ąŠą┤čā) ą╝čŗ ą┐ąŠą╗čāčćąĖą╝:

1

1 - ---- = 1 - eT/(CR)

2N

ąÆčŗčćąĖčüą╗ąĖą╝ T:

T = CR ┬Ę N ┬Ę ln 2 = 0.693 CR ┬Ę N = 1.8 ą╝ą║čü

ąĪą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ą▓ čŹč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą╝ąĄąĮčīčłąĄ 1.8 ą╝ą║čü (čćč鹊 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮąŠ čćą░čüč鹊č鹥 555 ą║ąōčå).

ąŁč鹊čé ą░ąĮą░ą╗ąĖąĘ ąĮąĄ ą▓ą║ą╗čÄčćą░ąĄčé ą║ą░ą║ąŠą╣-ą╗ąĖą▒ąŠ čŹčäč乥ą║čé čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ čüą░ą╝ąŠą│ąŠ DAC ąĖ ą▓ą╗ąĖčÅąĄąĮąĖąĄ ąĄą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüą░. ą¤čĆąĖ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĖ čŹčéąĖ čäą░ą║č鹊čĆčŗ ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī ąĮąĄą╗čīąĘčÅ, ąŠąĮąĖ čüąĮąĖąČą░čÄčé ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī ą”ąÉą¤.

[ąĀąĄą░ą╗ąĖąĘą░čåąĖčÅ ąĮą░ ą▓ąĮąĄčłąĮąĄą╝ ą×ąŻ]

ąÜą░ą║ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī ą▓čŗčłąĄ, ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ DAC ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ ą▓čŗčģąŠą┤ąĮčŗą╝ ą▒čāč乥čĆąŠą╝, ą║ąŠą│ą┤ą░ ąŠąĮ čĆą░ąĘčĆąĄčłąĄąĮ. ąÜąŠą│ą┤ą░ ą▒čāč乥čĆ ąĘą░ą┐čĆąĄčēąĄąĮ, ą▓čŗčģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ąĖ ąĄą╝ą║ąŠčüčéčī DACOUT (Cp) ą▒čāą┤čāčé ąŠą┐čĆąĄą┤ąĄą╗čÅčéčī ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

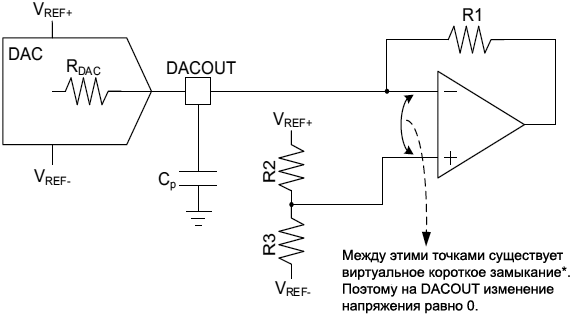

ąĪčāčēąĄčüčéą▓čāąĄčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ, ą▓ ą║ąŠč鹊čĆąŠą╣ ą╝ąŠąČąĮąŠ ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī ąĄą╝ą║ąŠčüčéčī DACOUT. ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ą×ąŻ ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮą▓ąĄčĆčüąĖąĖ ą▓ čåąĄą┐ąĖ DACOUT ą▒čāą┤ąĄčé čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╝, ąĖ čĆą░ą▓ąĮčŗą╝ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┤ąĄą╗ąĖč鹥ą╗čÅ R2R3, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 2.

ąĀąĖčü. 2. DAC čü ą▓ąĮąĄčłąĮąĖą╝ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮčŗą╝ čāčüąĖą╗ąĖč鹥ą╗ąĄą╝ (ą×ąŻ).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ *: čéą░ą║ąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čüčģąĄą╝čŗ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮčŗą╝ čāčüąĖą╗ąĖč鹥ą╗ąĄą╝ ą▓ ą┐čĆąĖčüčāčéčüčéą▓ąĖąĖ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ (R1).

ąÆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠ čüčģąĄą╝ąĄ čĆąĖčü. 2 ą▓ą╗ąĖčÅąĮąĖąĄ ą║ąŠąĮčüčéą░ąĮčéčŗ RC ąĮąĄąĘąĮą░čćąĖč鹥ą╗čīąĮąŠąĄ, ąŠčüąĮąŠą▓ąĮąŠąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąĖąĄ ą┐ąŠ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ čüą║ąŠčĆąŠčüčéčīčÄ ą▓ąĮąĄčłąĮąĄą│ąŠ ą×ąŻ (čāčüąĖą╗ąĄąĮąĖąĄą╝ ą▓ ą┐ąŠą╗ąŠčüąĄ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ąĖ čüą║ąŠčĆąŠčüčéčīčÄ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ) ąĖ čüą║ąŠčĆąŠčüčéčīčÄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čåąĖčäčĆąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ DAC. ą×ą┤ąĮą░ą║ąŠ čŹčéą░ čüčģąĄą╝ą░ ąĖą╝ąĄąĄčé ąĮąĄą║ąŠč鹊čĆčŗąĄ ąĮąĄą┤ąŠčüčéą░čéą║ąĖ. ąĀąĄąĘąĖčüč鹊čĆ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ R1 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░ą▓ąĄąĮ RDAC ą║čĆąĖčüčéą░ą╗ą╗ą░ STM32 (ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī č鹊čćąĮąŠ ą┐ąŠą┤ąŠą▒čĆą░ąĮ), ąĖąĮą░č湥 ą┐ąŠą╗čāčćąĖčéčüčÅ ąŠčłąĖą▒ą║ą░ čāčüąĖą╗ąĄąĮąĖčÅ DAC.

ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ ą▓čüčéčĆąŠąĄąĮąĮčŗąĄ čĆąĄąĘąĖčüč鹊čĆčŗ ą║čĆąĖčüčéą░ą╗ą╗ą░ ąŠą▒čŗčćąĮąŠ ąĖą╝ąĄčÄčé čłąĖčĆąŠą║ąĖą╣ čĆą░ąĘą▒čĆąŠčü ą┐ąŠ čüą▓ąŠąĄą╝čā ą░ą▒čüąŠą╗čÄčéąĮąŠą╝čā ąĘąĮą░č湥ąĮąĖčÄ, ąĖ ąĘąĮą░čćąĖč鹥ą╗čīąĮčŗąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ, ą┐ąŠčŹč鹊ą╝čā ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąŠčéą║ą░ą╗ąĖą▒čĆąŠą▓ą░čéčī ąŠčłąĖą▒ą║čā čāčüąĖą╗ąĄąĮąĖčÅ (čŹč鹊 ąŠą▒čüčāąČą┤ą░ąĄčéčüčÅ ą┤ą░ą╗ąĄąĄ ą▓ čüąĄą║čåąĖąĖ "ąÜą░ą╗ąĖą▒čĆąŠą▓ą║ą░ čāčüąĖą╗ąĄąĮąĖčÅ ą┐ąŠ ą▓čŗčģąŠą┤čā").

ąóą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ąĮąĄčłąĮąĖą╣ ą×ąŻ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą▓č鹊čĆąĖč鹥ą╗čī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą▓ ą▓ąĖą┤ąĄ ąĮąĄ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĄą│ąŠ ą▒čāč乥čĆą░). ąŁč鹊 ąĮąĄąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ą┐ąŠą▓čŗčüąĖčé ą▓čŗčģąŠą┤ąĮčāčÄ ą┐ąŠą╗ąŠčüčā čćą░čüč鹊čé ąĖ čüą║ąŠčĆąŠčüčéčī ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ, ąŠą┤ąĮą░ą║ąŠ ą▓čŗčģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ RDAC ąĖ ą┐ą░čĆą░ąĘąĖčéąĮą░čÅ ąĄą╝ą║ąŠčüčéčī DACOUT ą▒čāą┤čāčé č乊čĆą╝ąĖčĆąŠą▓ą░čéčī RC-čäąĖą╗čīčéčĆ, ąŠą│čĆą░ąĮąĖčćąĖą▓ą░čÄčēąĖą╣ čüą║ąŠčĆąŠčüčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąØąŠ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ą┐ąŠą▓č鹊čĆąĖč鹥ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą×ąŻ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ą░ čāčüąĖą╗ąĄąĮąĖčÅ.

ąĪą║ąŠčĆąŠčüčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čåąĖčäčĆąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ. ąöą░ąĮąĮčŗąĄ STM32 DAC ą┤ąŠą╗ąČąĮčŗ ąĘą░ą┐ąĖčüčŗą▓ą░čéčīčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čģčĆą░ąĮąĄąĮąĖčÅ DHR (čüčāčēąĄčüčéą▓čāąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ čĆą░ąĘąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ DHR: DHR12Rx, DHR12Lx, DHR8Rx, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗąĄ ą┤ą╗čÅ čĆą░ąĘąĮčŗčģ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖą╣ ąĖ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [2]), ą║ąŠč鹊čĆčŗąĄ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄąĮąŠčüčÅčéčüčÅ ą▓ ą▓čŗčģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ DAC (DOR1 ąĖą╗ąĖ DOR2, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ą░ąĮą░ą╗ą░ DAC, čüą╝. [2]) ą┤ą╗čÅ ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

ą×ą▒čŗčćąĮąŠ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ RAM, ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ CPU čü ąĮčāąČąĮąŠą╣ čćą░čüč鹊č鹊ą╣ ą┐ąĄčĆąĄą╝ąĄčēą░ąĄčé čŹčéąĖ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ RAM ą▓ DAC.

ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ DMA [3,4] ąŠą▒čēą░čÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī ą▓čüąĄą╣ čüąĖčüč鹥ą╝čŗ ą┐ąŠą▓čŗčłą░ąĄčéčüčÅ, ą┐ąŠč鹊ą╝čā čćč鹊 čÅą┤čĆąŠ CPU ąŠčüą▓ąŠą▒ąŠąČą┤ą░ąĄčéčüčÅ ąŠčé ą┤ąĄą╣čüčéą▓ąĖą╣ ą┐ąŠ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÄ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą┐ą░ą╝čÅčéąĖ ą▓ DAC (čŹčéąĖą╝ ąĘą░ąĮąĖą╝ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ DMA). ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠąĄ ą▓čĆąĄą╝čÅ CPU ą▓čŗčüą▓ąŠą▒ąŠąČą┤ą░ąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┤čĆčāą│ąĖčģ ąŠą┐ąĄčĆą░čåąĖą╣.

ąŚą░ą┐čāčüą║ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, ą▓ąĮąĄčłąĮąĖą╝ąĖ čéčĆąĖą│ą│ąĄčĆą░ą╝ąĖ ąĖą╗ąĖ ą┐ąŠ čüąĖą│ąĮą░ą╗čā (čéčĆąĖą│ą│ąĄčĆčā) čéą░ą╣ą╝ąĄčĆą░ (čüąŠą▒čŗčéąĖąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ TIM6 ąĖą╗ąĖ TIM7). ąöą╗čÅ ą▓čŗčüąŠą║ąĖčģ čüą║ąŠčĆąŠčüč鹥ą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čéčĆąĖą│ą│ąĄčĆ čéą░ą╣ą╝ąĄčĆą░ ą▓ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ čü DMA.

ąĪą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖąĘ ą┐ą░ą╝čÅčéąĖ ą▓ DAC ąŠą│čĆą░ąĮąĖčćąĖą▓ą░ąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ čäą░ą║č鹊čĆą░ą╝ąĖ, čüčĆąĄą┤ąĖ ą║ąŠč鹊čĆčŗčģ:

ŌĆó ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ APB ąĖą╗ąĖ AHB (čé. ąĄ. čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ DAC).

ŌĆó ąÆčĆąĄą╝čÅ čåąĖą║ą╗ą░ čéčĆą░ąĮąĘą░ą║čåąĖąĖ DMA ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÄ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą┐ą░ą╝čÅčéąĖ ą▓ (ą▓ą║ą╗čÄčćą░ąĄčé ąĘą░ą┤ąĄčƹȹ║čā ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠčé AHB ą┤ąŠ ą╝ąŠčüčéą░ APB).

ŌĆó ąĀą░ą▒ąŠč鹊ą╣ čüą░ą╝ąŠą│ąŠ ą╝ąĄčģą░ąĮąĖąĘą╝ą░ čéčĆąĖą│ą│ąĄčĆą░.

ąöą╗čÅ ą┐čĆąĖą╝ąĄčĆą░, ą║ąŠą│ą┤ą░ DAC ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32F407x čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čłąĖąĮąĄ APB1:

ŌĆó 3 čéą░ą║čéą░ ą┐ąŠčüą╗ąĄ čéčĆąĖą│ą│ąĄčĆą░, ą▓ č鹥č湥ąĮąĖąĄ ą║ąŠč鹊čĆčŗčģ ą┤ą░ąĮąĮčŗąĄ DHR ą┐ąĄčĆąĄą╝ąĄčēą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ DOR.

ŌĆó ąÆ č鹊 ąČąĄ čüą░ą╝ąŠąĄ ą▓čĆąĄą╝čÅ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĘą░ą┐čĆąŠčü DMA ąŠčé DAC.

ŌĆó ą¤ąĄčĆąĄą┤ą░čćą░ DMA ąĘą░ąĮąĖą╝ą░ąĄčé ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 1 čéą░ą║čé čłąĖąĮčŗ APB.

ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čéčĆąĄą▒čāąĄčéčüčÅ 4 čéą░ą║čéą░ čłąĖąĮčŗ APB ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ DOR. ąØą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊č鹥 APB1 42 ą£ąōčå (ą┤ą╗čÅ ST32F407x) ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čüą║ąŠčĆąŠčüčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ 10.5 Msps ą┤ą╗čÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ DAC, ą║ąŠą│ą┤ą░ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čéčĆąĖą│ą│ąĄčĆ čéą░ą╣ą╝ąĄčĆą░ ąĖ DMA. ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ čåąĖą║ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ DMA ą┤ą╗čÅ DAC ąĮąĄ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ ą┤ą╗čÅ ą▓čüąĄčģ ą╝ąŠą┤ąĄą╗ąĄą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32, ą┐ąŠč鹊ą╝čā čćč鹊 čā ąĮąĖčģ ą╝ąŠą│čāčé ąŠčéą╗ąĖčćą░čéčīčüčÅ ą║ą░ą║ čéą░ą║č鹊ą▓čŗąĄ čćą░čüč鹊čéčŗ, čéą░ą║ ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čłąĖąĮčŗ.

ąĀąĄąČąĖą╝ ą┤ą▓ąŠą╣ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ DMA. ąØąĄą║ąŠč鹊čĆčŗąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗ąĖ DAC ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé čĆąĄąČąĖą╝ ą┤ą▓ąŠą╣ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ DMA (DMA double data mode). ąÜąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (Normal mode), ąĘą░ą┐čĆąŠčü DMA ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ č鹊ą╗čīą║ąŠ ą┐ąŠčĆčåąĖčÅą╝ąĖ ą┐ąŠ 8 ąĖą╗ąĖ 12 ą▒ąĖčé (ą▒ą░ą╣čé ąĖą╗ąĖ ą┐ąŠą╗čāčüą╗ąŠą▓ąŠ). ąæą╗ą░ą│ąŠą┤ą░čĆčÅ č鹊ą╝čā, čćč鹊 ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ STM32 ą▓ąĮčāčéčĆąĖ ąĖą╝ąĄčÄčé 32-ą▒ąĖčéąĮčāčÄ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ, čĆąĄąČąĖą╝ DMA double data ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą▓ą░ ą┐ąŠą╗čāčüą╗ąŠą▓ą░ ąĮą░ ąŠą┤ąĮčā ąŠą┐ąĄčĆą░čåąĖčÄ (ą┤ą▓ąĄ 12-ą▒ąĖčéąĮčŗąĄ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ, čćč鹊 ą┤ą░ąĄčé čüąĮąĖąČąĄąĮąĖąĄ ąĘą░ą│čĆčāąĘą║ąĖ čłąĖąĮčŗ ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╝ čĆąĄąČąĖą╝ąŠą╝.

ąÆ čéą░ą▒ą╗ąĖčåąĄ 2 ą┐ąŠą║ą░ąĘą░ąĮčŗ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗąĄ čćą░čüč鹊čéčŗ ą▓čŗą▒ąŠčĆąŠą║ ą┤ą╗čÅ čĆą░ąĘąĮčŗčģ ą╝ąŠą┤ąĄą╗ąĄą╣ MCU STM32.

ąóą░ą▒ą╗ąĖčåą░ 2. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮčŗąĄ čćą░čüč鹊čéčŗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čĆą░ąĘąĮčŗčģ STM32(1).

| MCU |

Max čüą║ąŠčĆąŠčüčéčī

čłąĖąĮčŗ, ą£ąōčå |

Max čćą░čüč鹊čéą░ ą┤ąĖčüą║čĆ.

DAC, Msps |

| STM32F0 čüąĄčĆąĖčÅ |

48 |

4.8 |

| STM32F100xx |

24 |

2.4 |

STM32F101xx

STM32F103xx

STM32F105xx

STM32F107xx |

36 |

4.5 |

| STM32F2 čüąĄčĆąĖčÅ |

30 |

7.5 |

| STM32F3 čüąĄčĆąĖčÅ |

36 |

4.5 |

STM32F40x

STM32F41x |

42 |

10.5 |

| STM32F42x |

45 |

11.25 |

| STM32F7 čüąĄčĆąĖčÅ |

54 |

13.5 |

| STM32G0 čüąĄčĆąĖčÅ |

64 |

8.0 |

| STM32G4 čüąĄčĆąĖčÅ |

150 |

16.67

30(2) |

| STM32H7 čüąĄčĆąĖčÅ |

100 |

18.18 |

| STM32L0 čüąĄčĆąĖčÅ |

32 |

4.0 |

| STM32L1 čüąĄčĆąĖčÅ |

32 |

3.2 |

| STM32L4 čüąĄčĆąĖčÅ |

80 |

10 |

| STM32L4+ čüąĄčĆąĖčÅ |

120 |

12 |

| STM32L5 |

110 |

11 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąŚąĮą░č湥ąĮąĖčÅ, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗąĄ ą▓ čéą░ą▒ą╗ąĖčåąĄ 2, ą▒čŗą╗ąĖ ą┐ąŠą╗čāč湥ąĮčŗ ą▓ ą╗ą░ą▒ąŠčĆą░č鹊čĆąĮčŗčģ čāčüą╗ąŠą▓ąĖčÅčģ ąĮą░ čüč鹥ąĮą┤ąĄ, ą║ąŠą│ą┤ą░ čłąĖąĮą░ STM32 ąĮąĄ ą▒čŗą╗ą░ ąĮą░ą│čĆčāąČąĄąĮą░ ą┤čĆčāą│ąĖą╝ąĖ ąŠą┐ąĄčĆą░čåąĖčÅą╝ąĖ. ą¤ąŠčŹč鹊ą╝čā ą▓ čĆąĄą░ą╗čīąĮčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅą╝ ą╝ąŠąČąĄčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ ą▓ą▓ąĄčüčéąĖ ąĮąĄą║ąŠč鹊čĆąŠąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąĖąĄ ą┐ąŠ čüą║ąŠčĆąŠčüčéąĖ, čćč鹊ą▒čŗ ąŠčüčéą░ą▓ąĖčéčī ąĘą░ą┐ą░čü ą┐ąŠą╗ąŠčüčŗ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ čłąĖąĮčŗ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ ąĮčāąČą┤.

(2) ąĀąĄąČąĖą╝ DMA double data.

ąÜą░ą║ ą╝ąŠąČąĮąŠ čāą▓ąĖą┤ąĄčéčī, ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ą×ąŻ ą╝ąŠąČąĮąŠ ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ą┐ąŠą▓čŗčüąĖčéčī čüą║ąŠčĆąŠčüčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ąĖ ą┐ąŠą╗čāčćąĖčéčī čüą║ąŠčĆąŠčüčéčī ąĮą░ą╝ąĮąŠą│ąŠ ą▒ąŠą╗čīčłčāčÄ, č湥ą╝ ąĘą░čÅą▓ą╗ąĄąĮąĮčŗąĄ 1 Msps (čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐čĆąĖą╝ąĄčĆą░ ą┤ą░ą╗ąĄąĄ).

[ą¤čĆąĖą╝ąĄčĆ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą×ąŻ ą┤ą╗čÅ ą┐ąŠą▓čŗčłąĄąĮąĖčÅ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖčÅ DAC]

ą¤čĆąĖ ą▓čŗą▒ąŠčĆąĄ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ čüą╗ąĄą┤čāąĄčé čāčćąĖčéčŗą▓ą░čéčī čüą╗ąĄą┤čāčÄčēąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ.

ŌĆó ąĪą║ąŠčĆąŠčüčéčī ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ (Slew Rate).

ŌĆó ą¤ąŠą╗ąŠčüą░ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ą┐ąŠ čāčüąĖą╗ąĄąĮąĖčÄ (gain bandwidth, GBW).

ŌĆó ąŻčüąĖą╗ąĄąĮąĖąĄ ą┐čĆąĖ ąŠčéčüčāčéčüčéą▓ąĖąĖ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ.

ŌĆó ąöąĖą░ą┐ą░ąĘąŠąĮ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ.

ŌĆó ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

ŌĆó ąöąĖą░ą┐ą░ąĘąŠąĮ čüąĖąĮčäą░ąĘąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ ą▓čģąŠą┤ąĄ.

ŌĆó ą£ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ čüčéą░ą▒ąĖą╗čīąĮąŠąĄ čāčüąĖą╗ąĄąĮąĖąĄ.

ąÆ čüą╗čāčćą░ąĄ ą┐ąĄčĆąĄčģąŠą┤ą░ ąŠčé čüą░ą╝ąŠą│ąŠ ą╝ą░ą╗ąŠą│ąŠ ą┤ąŠ čüą░ą╝ąŠą│ąŠ ą▒ąŠą╗čīčłąŠą│ąŠ ą║ąŠą┤ą░ ąĮą░ čćą░čüč鹊č鹥 ą▓čŗą▒ąŠčĆąŠą║ 5 Msps ąĖ ąŠą┐ąŠčĆąĮąŠą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ VREF 3.3V, čā ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī slew rate ą▒ąŠą╗čīčłąĄ č湥ą╝ 3.3 ┬Ę 5 ┬Ę 106 = 16.5 V/ą╝ą║čü.

ąĢčüą╗ąĖ STM32 DAC čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ 3.3V, ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ 3.3V ą┤ą╗čÅ ą×ąŻ (čéą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĖ ą┤čĆčāą│ąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, 3.3V ąĘą┤ąĄčüčī ą▓čŗą▒čĆą░ąĮąŠ č鹊ą╗čīą║ąŠ ą▓ ą║ą░č湥čüčéą▓ąĄ ą┐čĆąĖą╝ąĄčĆą░).

ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖą╝ąĄčéčī ą┐ąŠ ą║čĆą░ą╣ąĮąĄą╣ ą╝ąĄčĆąĄ ą┤ą▓čāą║čĆą░čéąĮčŗą╣ ąĘą░ą┐ą░čü ą┐ąŠ čāčüąĖą╗ąĄąĮąĖčÄ ą▓ ą┐ąŠą╗ąŠčüąĄ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü čćą░čüč鹊č鹊ą╣ ą▓čŗą▒ąŠčĆąŠą║ DAC. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ čćą░čüč鹊čéą░ ą▓čŗą▒ąŠčĆąŠą║ 5 Msps, č鹊 GBW ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čłąĖčĆąĄ 10 ą£ąōčå.

ą¦č鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čģąŠčĆąŠčłčāčÄ ą╗ąĖąĮąĄą╣ąĮąŠčüčéčī DAC, čāčüąĖą╗ąĄąĮąĖąĄ ą×ąŻ ą┐čĆąĖ čĆą░ąĘąŠą╝ą║ąĮčāč鹊ą╣ ą┐ąĄčéą╗ąĄ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ 60 dB.

ąĢčüą╗ąĖ ąĮčāąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▒ą╗ąĖąĘą║ąĖą╝ ą║ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ ą┐ąĖčéą░ąĮąĖčÅ, č鹊 ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą×ąŻ ąČąĄą╗ą░č鹥ą╗čīąĮąŠ ą▓čŗą▒čĆą░čéčī rail to rail. ąśąĮą░č湥, ąĄčüą╗ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖą▒ą╗ąĖąĘąĖčéčüčÅ ą║ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ ą┐ąĖčéą░ąĮąĖčÅ ąĖą╗ąĖ ą║ čāčĆąŠą▓ąĮčÄ ąĘąĄą╝ą╗ąĖ, ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąĮą░čüčŗčēąĄąĮąĖąĄ čāčüąĖą╗ąĖč鹥ą╗čÅ, ąĖ ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą▒čāą┤ąĄčé ąĖčüą║ą░ąČąĄąĮ.

ąöą░ąČąĄ ą║ąŠą│ą┤ą░ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ ą▓čģąŠą┤ ą×ąŻ ąĘą░čäąĖą║čüąĖčĆąŠą▓ą░ąĮ ąĮą░ čāčĆąŠą▓ąĮąĄ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐čĆąŠą▓ąĄčĆąĖčéčī ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ čüąĖąĮčäą░ąĘąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, čćč鹊ą▒čŗ ąŠąĮ ą┐ąĄčĆąĄą║čĆčŗą▓ą░ą╗ čü ąĘą░ą┐ą░čüąŠą╝ čāčĆąŠą▓ąĄąĮčī ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

ąśčüą┐ąŠą╗čīąĘčāąĄą╝ąŠąĄ čāčüąĖą╗ąĄąĮąĖąĄ ą×ąŻ ą┐ąŠčĆčÅą┤ą║ą░ -1, ą┐ąŠčŹč鹊ą╝čā ąŠąĮ ą┐čĆąĖ čéą░ą║ąŠą╝ čāčüąĖą╗ąĄąĮąĖąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüčéą░ą▒ąĖą╗ąĄąĮ.

ąĪ čāč湥č鹊ą╝ ą▓čüąĄčģ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮčŗčģ ą▓čŗčłąĄ ą║čĆąĖč鹥čĆąĖąĄą▓ ą┐ąŠą┤ąŠą╣ą┤čāčé ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮčŗąĄ čāčüąĖą╗ąĖč鹥ą╗ąĖ LMH6645/LMH6646/LMH6647 ą║ąŠą╝ą┐ą░ąĮąĖąĖ Texas Instruments:

ŌĆó slew rate: 22 V/ą╝ą║čü;

ŌĆó gain band width: 55 ą£ąōčå;

ŌĆó čāčüąĖą╗ąĄąĮąĖąĄ ą┐čĆąĖ ąŠčéčüčāčéčüčéą▓ąĖąĖ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ: 87 dB;

ŌĆó ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ: 2.5V .. 12 V;

ŌĆó ą┤ąĖą░ą┐ą░ąĘąŠąĮ čüąĖąĮčäą░ąĘąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąŠ ą▓čģąŠą┤čā ąĮą░ 0.3V ą┐čĆąĄą▓čŗčłą░ąĄčé čāčĆąŠą▓ąĮąĖ čłąĖąĮ ą┐ąĖčéą░ąĮąĖčÅ;

ŌĆó ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 20 mV ąĮąĖąČąĄ čāčĆąŠą▓ąĮąĄą╣ ą┐ąĖčéą░ąĮąĖčÅ;

ŌĆó čüčéą░ą▒ąĖą╗čīąĮąŠčüčéčī čāčüąĖą╗ąĄąĮąĖčÅ, ąĮą░čćąĖąĮą░čÅ čü +1.

ąöą╗čÅ čŹč鹊ą│ąŠ ą┐čĆąĖą╝ąĄčĆą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ STM32F407, ąĘą░ą┐ąĖčéą░ąĮąĮčŗą╣ ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 3.3V.

ą¤ąŠą┤ą│ąŠč鹊ą▓ą║ą░ čłą░ą▒ą╗ąŠąĮą░ čüąĖąĮčāčüąŠąĖą┤čŗ. ąÜą░ą║ ą▒čŗą╗ąŠ ąŠą┐ąĖčüą░ąĮąŠ ą▓ ą░ą┐ąĮąŠčāč鹥 AN3126 [3], ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ čłą░ą▒ą╗ąŠąĮą░ čüąĖąĮčāčüąŠąĖą┤čŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤ą│ąŠč鹊ą▓ą╗ąĄąĮčŗ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

2Pi 0xFFF + 1

ySineDigital(x) = (sin(x ┬Ę -----) + 1) ┬Ę (-----------)

ns 2

ą”ąĖčäčĆąŠą▓čŗąĄ ą▓čģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĄąŠą▒čĆą░ąĘčāčÄčéčüčÅ ą▓ ą▓čŗčģąŠą┤ąĮčŗąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą╗ąĖąĮąĄą╣ąĮąŠ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 0 ą┤ąŠ VREF+. ąÉąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ DAC ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

DOR

DACOutput = VREF ┬Ę -------------------------

DAC_MaxDigitalValue + 1

ąÆčŗčćąĖčüą╗ąĖčéčī č乊čĆą╝čā čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą│ąŠ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą╝ąŠąČąĮąŠ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

ySineDigital(x)

ySineAnalog(x) = 3.3V ┬Ę --------------

0xFFF + 1

ąóą░ą▒ą╗ąĖčåą░ ąĘą░čĆą░ąĮąĄąĄ ą┐ąŠą┤ą│ąŠč鹊ą▓ą╗ąĄąĮąĮąŠą╣ č乊čĆą╝čŗ čüąĖą│ąĮą░ą╗ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čüąŠčģčĆą░ąĮąĄąĮą░ ą▓ ą┐ą░ą╝čÅčéčī ąĖ ą┐ąĄčĆąĄą┤ą░ąĮą░ ą▓ DAC č湥čĆąĄąĘ DMA [3,4]. ą¤ąĄčĆąĄą┤ą░čćą░ ą║ą░ąČą┤ąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ DAC ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ č鹥ą╝ ąČąĄ čüą░ą╝čŗą╝ čéą░ą╣ą╝ąĄčĆąŠą╝, ą║ąŠč鹊čĆčŗą╣ ąĘą░ą┐čāčüą║ą░ąĄčé DAC.

ąŻčüčéą░ąĮąŠą▓ą║ą░ čćą░čüč鹊čéčŗ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ą¦č鹊ą▒čŗ čāčüčéą░ąĮąŠą▓ąĖčéčī čćą░čüč鹊čéčā čüąĖąĮčāčüąŠąŠą▒čĆą░ąĘąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ čāčüčéą░ąĮąŠą▓ąĖčéčī čćą░čüč鹊čéčā čéą░ą╣ą╝ąĄčĆą░, ą│ąĄąĮąĄčĆąĖčĆčāčÄčēąĄą│ąŠ čüąĖą│ąĮą░ą╗ čéčĆąĖą│ą│ąĄčĆą░. ą¦ą░čüč鹊čéą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą│ąŠ čüąĖąĮčāčüąŠąŠą▒čĆą░ąĘąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

fSinewave = fTimerTRGO / nS

ąĢčüą╗ąĖ čćą░čüč鹊čéą░ čéčĆąĖą│ą│ąĄčĆą░ TIMx_TRGO čĆą░ą▓ąĮą░ 5 ą£ąōčå (nS = 25), č鹊 čćą░čüč鹊čéą░ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ DAC ą┐ąŠą╗čāčćąĖčéčüčÅ 200 ą║ąōčå.

ą¦č鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī č鹊čćąĮčāčÄ čćą░čüč鹊čéčā ąĮą░ ą▓čŗčģąŠą┤ąĄ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐ąŠą┤čüčéčĆąŠąĖčéčī čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā čüąĖčüč鹥ą╝čŗ ą▓ą╝ąĄčüč鹥 čü čćą░čüč鹊č鹊ą╣ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░, čćč鹊ą▒čŗ čéą░ą╣ą╝ąĄčĆ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ą╗ čüąĖą│ąĮą░ą╗ čéčĆąĖą│ą│ąĄčĆą░ č鹊čćąĮąŠ ąĮą░ čćą░čüč鹊č鹥 5 ą£ąōčå.

ąÆ čüąĖčüč鹥ą╝ąĄ STM32F407 ąĮąĄą║ąŠč鹊čĆčŗąĄ čéą░ą╣ą╝ąĄčĆčŗ ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ čāą┤ą▓ąŠąĄąĮąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 čłąĖąĮčŗ APB1 [5], ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą▓ 2 čĆą░ąĘą░ ą▓čŗčłąĄ, č湥ą╝ ą┐čĆąĖ čĆą░ą▒ąŠč鹥 ąĮą░ čćą░čüč鹊č鹥 APB1. ą×ą┤ąĮą░ą║ąŠ DAC ą┐ąŠą╗čāčćą░ąĄčé čüąĖą│ąĮą░ą╗ čéčĆąĖą│ą│ąĄčĆą░ ąĮą░ čćą░čüč鹊č鹥 APB1, čéą░ą║ čćč鹊 čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī DAC ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą╗čāčćčłąĄ, č湥ą╝ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ APB1.

ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ čéą░ą╣ą╝ąĄčĆ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ąĮą░ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ č湥čĆąĄąĘ ą║ą░ąČą┤čŗąĄ 25 ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓, čĆą░ą▒ąŠčéą░čÅ ąĮą░ čāą┤ą▓ąŠąĄąĮąĮąŠą╣ čćą░čüč鹊č鹥 APB1 (čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé 12.5 ą┐ąĄčĆąĖąŠą┤ą░ą╝ čéą░ą║č鹊ą▓ APB1), č鹊 DAC ą▒čāą┤ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░čéčī ąŠčé čéčĆąĖą│ą│ąĄčĆą░ č鹊 ą┐ąŠčüą╗ąĄ 12 čéą░ą║č鹊ą▓, č鹊 ą┐ąŠčüą╗ąĄ 13 čéą░ą║č鹊ą▓, ą┐ąŠ ąŠč湥čĆąĄą┤ąĖ. ąŁč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┤čĆąŠąČą░ąĮąĖčÄ ą┐ąĄčĆąĖąŠą┤ą░ čćą░čüč鹊čéčŗ ą▓čŗą▒ąŠčĆą║ąĖ.

ąÆ ąĮą░čłąĄą╝ ą┐čĆąĖą╝ąĄčĆąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ čéą░ą║č鹊ą▓:

ŌĆó ąśčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ čüąĖčüč鹥ą╝čŗ = PLL (čćą░čüč鹊čéą░ HSE, ą▓čŗčĆą░ą▒ą░čéčŗą▓ą░ąĄą╝ą░čÅ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ą║ą▓ą░čĆčåą░)

ŌĆó SYSCLK (ąōčå) = 160000000

ŌĆó HCLK (ąōčå) = 160000000

ŌĆó AHB ą┐čĆąĄčüą║ą░ą╗ąĄčĆ = 1

ŌĆó APB1 ą┐čĆąĄčüą║ą░ą╗ąĄčĆ = 4

ŌĆó APB2 ą┐čĆąĄčüą║ą░ą╗ąĄčĆ = 2

ŌĆó ą¦ą░čüč鹊čéą░ HSE (ąōčå) = 8000000

ŌĆó PLL_M = 8

ŌĆó PLL_N = 320

ŌĆó PLL_P = 2

ŌĆó PLL_Q = 7

ąöą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ čéčĆąĖą│ą│ąĄčĆą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čéą░ą╣ą╝ąĄčĆ TIM6.

ąĪ čŹč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣ 80 ą£ąōčå ą▒čāą┤ąĄčé čćą░čüč鹊čéą░ čéą░ą╣ą╝ąĄčĆą░, ą┐ąŠą╗čāčćą░ąĄčéčüčÅ 5 ą£ąōčå čćą░čüč鹊čéą░ čéčĆąĖą│ą│ąĄčĆą░. ą¤čĆąĄčüą║ą░ą╗ąĄčĆ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĮą░ 1 (PSC = 0) ąĖ čüč湥čéčćąĖą║ ą┤ąŠą╗ąČąĄąĮ čüčćąĖčéą░čéčī ą┤ąŠ 16 (CNT = 15).

ąÜą░ą╗ąĖą▒čĆąŠą▓ą║ą░ čüą╝ąĄčēąĄąĮąĖčÅ. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ ą×ąŻ ą▓ą▓ąĄą┤ąĄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čüą╝ąĄčēąĄąĮąĖčÅ, čüčĆąĄą┤ ąĮąĖčģ čüą╝ąĄčēąĄąĮąĖąĄ ą║ą░ą║ čüą░ą╝ąŠą│ąŠ ą×ąŻ, čéą░ą║ ąĖ čüą╝ąĄčēąĄąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą┐ąŠčüčéčāą┐ą░ąĄčé ąŠčé čåąĄą┐ąŠčćą║ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ VREF.

ąöą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüąŠąĄą┤ąĖąĮąĖčéčī ą▓čŗčģąŠą┤ ą×ąŻ čü ąŠą┤ąĮąĖą╝ ąĖąĘ ą┤ąŠčüčéčāą┐ąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ ąÉą”ą¤ (ADC) ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32. ą¤čĆąŠčåąĄą┤čāčĆą░ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ čüą╗ąĄą┤čāčÄčēą░čÅ (čüą╝. čéą░ą▒ą╗ąĖčåčā 3):

1. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▓ čĆąĄą│ąĖčüčéčĆąĄ DOR ą▒ą╗ąŠą║ą░ DAC ąĘąĮą░č湥ąĮąĖąĄ 2047.

2. ąśąĘą╝ąĄčĆčīč鹥 čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗčģąŠą┤ąĄ ą×ąŻ čü ą┐ąŠą╝ąŠčēčīčÄ ADC.

3. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 DAC DOR ą┐ąŠ čĆąĄąĘčāą╗čīčéą░čéčā ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ ADC (ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ 2065).

4. ąĪčĆą░ą▓ąĮąĖč鹥 čĆąĄąĘčāą╗čīčéą░čé čü ADC (ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ 2048, čćč鹊 čüąŠčüčéą░ą▓ąĖčé ą┤ą╗čÅ čüą╝ąĄčēąĄąĮąĖąĄ 1 ą╝ą╗ą░ą┤čłąĖą╣ čĆą░ąĘčĆčÅą┤).

ąóą░ą▒ą╗ąĖčåą░ 3. ą¤čĆąĖą╝ąĄčĆ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ ąĖ ą║ąŠą╝ą┐ąĄąĮčüą░čåąĖąĖ čüą╝ąĄčēąĄąĮąĖčÅ DAC.

| DAC DOR |

ąĀąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC |

| 2047 |

2065 |

| 2065 |

2048 |

ąÜą░ą╗ąĖą▒čĆąŠą▓ą║ą░ čāčüąĖą╗ąĄąĮąĖčÅ ą┐ąŠ ą▓čŗčģąŠą┤čā. ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, čāčüąĖą╗ąĄąĮąĖąĄ ą┐ąŠ ą▓čŗčģąŠą┤čā ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ DAC ąĖ čĆąĄąĘąĖčüč鹊čĆą░ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ ąĮą░ ą▓ąĮąĄčłąĮąĄą╝ ą×ąŻ.

ąÜą░ą╗ąĖą▒čĆąŠą▓ą║ą░ čāčüąĖą╗ąĄąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą▓ąŠ ą▓čĆąĄą╝čÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čćąĖą┐ą░, ąĖ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ ą┐čĆąĖ ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠą╝ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ ą▒ąŠą╗čīčłąĄ č湥ą╝ ąĮą░ 10 ┬░C). ąśąĘą╝ąĄąĮąĄąĮąĖąĄ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ ą╝ąŠąČąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗čÅčéčī ą┐ąŠ ą▓čüčéčĆąŠąĄąĮąĮąŠą╝čā ą▓ čćąĖą┐ STM32 ą┤ą░čéčćąĖą║čā č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ.

ąöą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ čüąŠąĄą┤ąĖąĮąĖč鹥 ą▓čŗčģąŠą┤ ą×ąŻ čü ąŠą┤ąĮąĖą╝ ąĖąĘ ą┤ąŠčüčéčāą┐ąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ ADC ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32. ąöą╗čÅ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ čāčüąĖą╗ąĄąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 čüą╗ąĄą┤čāčÄčēąĖą╣ ą╝ąĄč鹊ą┤ (čüą╝. čéą░ą▒ą╗ąĖčåčā 4):

1. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▓ čĆąĄą│ąĖčüčéčĆąĄ DOR DAC ąĘąĮą░č湥ąĮąĖąĄ 1023.

2. ąśąĘą╝ąĄčĆčīč鹥 čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗčģąŠą┤ąĄ ą×ąŻ čü ą┐ąŠą╝ąŠčēčīčÄ ADC.

3. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▓ čĆąĄą│ąĖčüčéčĆąĄ DOR DAC ąĘąĮą░č湥ąĮąĖąĄ 3071.

4. ąśąĘą╝ąĄčĆčīč鹥 čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗčģąŠą┤ąĄ ą×ąŻ čü ą┐ąŠą╝ąŠčēčīčÄ ADC.

ąóą░ą▒ą╗ąĖčåą░ 4. ą¤čĆąĖą╝ąĄčĆ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ ąĖ ą║ąŠą╝ą┐ąĄąĮčüą░čåąĖąĖ čāčüąĖą╗ąĄąĮąĖčÅ ą┐ąŠ ą▓čŗčģąŠą┤čā DAC.

| DAC DOR |

ąĀąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC |

| 1023 |

3135 |

| 3071 |

983 |

ą¤ąŠ čŹčéąĖą╝ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅą╝ ą╝ąŠąČąĮąŠ ą▓čŗčćąĖčüą╗ąĖčéčī čāčüąĖą╗ąĄąĮąĖąĄ, ą┤ą╗čÅ ąĮą░čłąĄą│ąŠ ą┐čĆąĖą╝ąĄčĆą░ ąŠąĮąŠ čĆą░ą▓ąĮąŠ 1.0508, čüąŠą│ą╗ą░čüąĮąŠ č乊čĆą╝čāą╗ąĄ (3135 - 983) / 2048.

ąŁč鹊čé čĆąĄąĘčāą╗čīčéą░čé ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ č乊čĆą╝čāą╗čŗ YSineDigital(x), ą┐ąŠą║ą░ąĘą░ąĮąĮąŠą╣ ą▓čŗčłąĄ ą▓ čüąĄą║čåąĖąĖ "ą¤ąŠą┤ą│ąŠč鹊ą▓ą║ą░ čłą░ą▒ą╗ąŠąĮą░ čüąĖąĮčāčüąŠąĖą┤čŗ". ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖą╝ąĄčéčī ąĮąĄą║ąŠč鹊čĆčŗą╣ ąĘą░ą┐ą░čü (ąĮą░ą┐čĆąĖą╝ąĄčĆ 100 mV) ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĖąĘ čāčĆąŠą▓ąĮąĄą╣ - ą┤ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ą┤ą╗čÅ ąĘąĄą╝ą╗ąĖ GND. ą”ąĖčäčĆąŠą▓ąŠą╣ ą║ąŠą┤ ą┤ąŠą╗ąČąĄąĮ ą╝ąĄąĮčÅčéčīčüčÅ ą╝ąĄąĮčīčłąĄ č湥ą╝ ąĮą░ 200 mV ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ čŹč鹊ą│ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ.

3.1 2Pi 0xFFF + 1

ySineDigital(x) = -------------- ┬Ę (sin(x ┬Ę -----) + 1) ┬Ę (-----------) + 18

3.3 ┬Ę 1.0508 ns 2

ą¤ąŠ čŹč鹊ą╣ č乊čĆą╝čāą╗ąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮą░ čéą░ą▒ą╗ąĖčåą░ 5.

ąóą░ą▒ą╗ąĖčåą░ 5. ą¤čĆąĖą╝ąĄčĆ čåąĖčäčĆąŠą▓čŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą▓čŗą▒ąŠčĆąŠą║ (čłą░ą▒ą╗ąŠąĮ čüąĖąĮčāčüąŠąĖą┤čŗ).

| ąÆčŗą▒ąŠčĆą║ą░ |

ą”ąĖčäčĆąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ

ą▓čŗą▒ąŠčĆą║ąĖ YSineDigital(x) |

| 0 |

2066 |

| 1 |

2521 |

| 2 |

2948 |

| 3 |

3319 |

| 4 |

3612 |

| 5 |

3807 |

| 6 |

3893 |

| 7 |

3864 |

| 8 |

3723 |

| 9 |

3477 |

| 10 |

3142 |

| 11 |

2740 |

| 12 |

2295 |

| 13 |

1837 |

| 14 |

1392 |

| 15 |

990 |

| 16 |

655 |

| 17 |

409 |

| 18 |

268 |

| 19 |

239 |

| 20 |

325 |

| 21 |

520 |

| 22 |

813 |

| 23 |

1184 |

| 24 |

1611 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮ ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ čåąĖčäčĆąŠą▓ąŠą╝čā ą║ąŠą┤čā, ą┐ąŠč鹊ą╝čā čćč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą×ąŻ ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĄą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ.

[ą¤čĆąĖą╝ąĄčĆ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ]

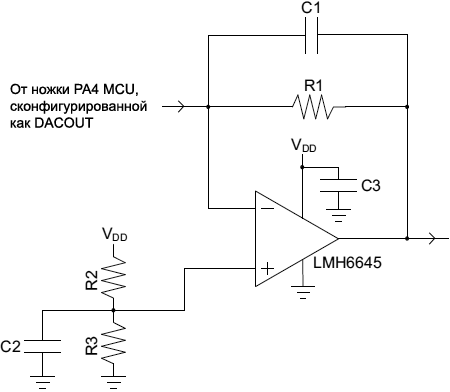

ąĀąĄą░ą╗čīąĮą░čÅ čüčģąĄą╝ą░ ą┤ąŠčĆą░ą▒ąŠčéą║ąĖ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 3, ąĘąĮą░č湥ąĮąĖčÅ ąĄčæ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ 6. R1 ą▓čŗą▒čĆą░ąĮ ą┐ąŠ čéąĖą┐ąŠą▓ąŠą╝čā ąĘąĮą░č湥ąĮąĖčÄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ DAC, čĆą░ą▓ąĮąŠą╝čā 12.5 ą║ą×ą╝ (ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ čéąĖą┐ąŠą▓ MCU STM32 čüą╝. ąĖčģ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą▓ ą┤ą░čéą░čłąĖč鹥). C1 ą┤ąŠą▒ą░ą▓ą╗ąĄąĮ ą▓ąŠ ąĖąĘą▒ąĄąČą░ąĮąĖąĄ ą┐ąĄčĆąĄą│čĆčāąĘą║ąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

ąĀąĖčü. 3. ą¤čĆąĖąĮčåąĖą┐ąĖą░ą╗čīąĮą░čÅ čüčģąĄą╝ą░ ą┤ąŠčĆą░ą▒ąŠčéą║ąĖ DAC.

ąóą░ą▒ą╗ąĖčåą░ 6. ąŚąĮą░č湥ąĮąĖčÅ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓.

| R1 |

12 ą║ą×ą╝ |

| R2 |

10 ą║ą×ą╝ |

| R3 |

| C1 |

5 ą┐ąż |

| C2 |

100 ąĮąż |

| C3 |

ą¤ąŠą║ą░ąĘą░ąĮąĮčŗą╣ ą┐čĆąĖą╝ąĄčĆ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą▒čŗą╗ ą▓čŗą┐ąŠą╗ąĮąĄąĮ ąĮą░ ą┐ą╗ą░č鹥 STM32F4Discovery. ąÆčŗčģąŠą┤ STM32F407 DAC1 ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮą░ ąĮąŠąČą║ąĄ ą┐ąŠčĆčéą░ PA4, ą║ąŠč鹊čĆčŗą╣ ą▓ čüą▓ąŠčÄ ąŠč湥čĆąĄą┤čī čüąŠąĄą┤ąĖąĮąĄąĮ čü ą░čāą┤ąĖąŠą║ąŠą┤ąĄą║ąŠą╝ CS43L22 ąĮą░ ą┐ą╗ą░č鹥 (ąĮąŠąČą║ą░ 40 LRCK ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ U7), ąĖ č湥čĆąĄąĘ čĆąĄąĘąĖčüč鹊čĆ R44 100 ą║ą×ą╝ čüąŠąĄą┤ąĖąĮąĄąĮ čü GND. ą¦č鹊ą▒čŗ čāčüčéčĆą░ąĮąĖčéčī čŹč鹊, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą▓čŗą┐ą░čÅčéčī čĆąĄąĘąĖčüč鹊čĆ R48 (0 ą×ą╝).

ąØą░ čĆąĖčü. 4. ą┐ąŠą║ą░ąĘą░ąĮ čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗčģąŠą┤ąĄ DAC, ą░ ąĮą░ čĆąĖčü. 5 ą┐ąŠą║ą░ąĘą░ąĮ ąĄą│ąŠ čüą┐ąĄą║čéčĆą░ą╗čīąĮčŗą╣ ą░ąĮą░ą╗ąĖąĘ FFT.

ąĀąĖčü. 4. ąÆčŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗.

ąöąĖą░ą┐ą░ąĘąŠąĮ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮąĄ čĆą░ą▓ąĄąĮ 3.1V ąŠčé ą┐ąĖą║ą░ ą┤ąŠ ą┐ąĖą║ą░, čéą░ą║ ą║ą░ą║ ą╝ąŠą╝ąĄąĮčéčŗ ą▓čŗą▒ąŠčĆąŠą║ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ąĮąĄ čüąŠą▓ą┐ą░ą┤ą░čÄčé čü ą┐ąĖą║ąŠą╝ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

ąĀąĖčü. 5. ąĀąĄąĘčāą╗čīčéą░čé ą░ąĮą░ą╗ąĖąĘą░ čüą┐ąĄą║čéčĆą░ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ.

ąÆč鹊čĆą░čÅ ąĖ čéčĆąĄčéčīčÅ ą│ą░čĆą╝ąŠąĮąĖą║ąĖ ąĮą░čģąŠą┤čÅčéčüčÅ ą┐ąŠ čāčĆąŠą▓ąĮčÄ ą┐čĆąĖą▒ą╗ąĖąČąĄąĮčŗ ą║ čłčāą╝čā. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ąĘą░ą╝ąĄčćą░ąĮąĖčÅ:

ŌĆó ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓čŗčüąŠą║ąŠą╣ čćą░čüč鹊čéčŗ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ą╝ąŠąČąĮąŠ čāą╝ąĄąĮčīčłąĖčéčī ą┐ąŠčĆčÅą┤ąŠą║ ą░ąĮčéąĖą░ą╗ąĖą░čüąĖąĮą│ąŠą▓ąŠą│ąŠ čäąĖą╗čīčéčĆą░.

ŌĆó ąĪ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ ADC ą╝ąŠąČąĮąŠ ą║ą░ą╗ąĖą▒čĆąŠą▓ą░čéčī čāčüąĖą╗ąĄąĮąĖąĄ ąĖ ąŠčłąĖą▒ą║čā čüą╝ąĄčēąĄąĮąĖčÅ ą┐ąŠ ą▓čŗčģąŠą┤čā.

[ąĪčüčŗą╗ą║ąĖ]

1. AN4566 Extending the DAC performance of STM32 microcontrollers site:st.com.

2. STM32F4xx: čåąĖčäčĆąŠ-ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī (ą”ąÉą¤).

3. AN3126: č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą░čāą┤ąĖąŠčüąĖą│ąĮą░ą╗ą░ čü ą┐ąŠą╝ąŠčēčīčÄ DAC STM32.

4. STM32: ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA.

5. STM32: čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆąŠą▓ ąŠčé APB1 ąĖ APB2. |