|

ą£ąŠą┤čāą╗čī DAC čŹč鹊 12-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čåąĖčäčĆąŠ-ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī, ą”ąÉą¤ (digital-to-analog converter, DAC). DAC ą╝ąŠąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą▓ 8- ąĖą╗ąĖ 12-ą▒ąĖčéąĮąŠą╝ čĆąĄąČąĖą╝ąĄ, ąĖ čüąŠą▓ą╝ąĄčüčéąĮąŠ čü ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ DMA. ąÆ 12-ą▒ąĖčéąĮąŠą╝ čĆąĄąČąĖą╝ą░ ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗčĆąŠą▓ąĮąĄąĮčŗ ą▓ą╗ąĄą▓ąŠ ąĖą╗ąĖ ą▓ą┐čĆą░ą▓ąŠ. ąŻ DAC ąĄčüčéčī ą┤ą▓ą░ ą▓čŗčģąŠą┤ąĮčŗčģ ą║ą░ąĮą░ą╗ą░, čā ą║ą░ąČą┤ąŠą│ąŠ čüą▓ąŠą╣ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī. ąÆ ą┤ą▓čāčģą║ą░ąĮą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą▒čŗčéčī ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗąĄ ąĖą╗ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮčŗąĄ, ą║ąŠą│ą┤ą░ ąŠą▒ą░ ą║ą░ąĮą░ą╗ą░ ą│čĆčāą┐ą┐ąĖčĆčāčÄčéčüčÅ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ. ąöąŠčüčéčāą┐ąĄąĮ ą▓čģąŠą┤ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VREF+ (ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüąŠą▓ą╝ąĄčüčéąĮąŠ čü ADC), čćč鹊 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╣ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮą░čÅ ąĘą┤ąĄčüčī ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ STM32F4xx, ąĄčüą╗ąĖ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ čćč鹊-č鹊 ą┤čĆčāą│ąŠąĄ (ą┐ąĄčĆąĄą▓ąŠą┤ čĆą░ąĘą┤ąĄą╗ą░ 14 "Digital-to-analog converter" ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ [1]).

ą×čüąĮąŠą▓ąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ DAC:

ŌĆó 2 ą▓čŗčģąŠą┤ąĮčŗčģ ą║ą░ąĮą░ą╗ą░

ŌĆó ąÆ 12-ą▒ąĖčéąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗčĆąŠą▓ąĮąĄąĮčŗ ą▓ą╗ąĄą▓ąŠ ąĖą╗ąĖ ą▓ą┐čĆą░ą▓ąŠ

ŌĆó ąÆąŠąĘą╝ąŠąČąĮąŠčüčéčī čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ

ŌĆó ąōąĄąĮąĄčĆą░čåąĖčÅ čüąĖą│ąĮą░ą╗ą░ čłčāą╝ą░

ŌĆó ąōąĄąĮąĄčĆą░čåąĖčÅ čéčĆąĄčāą│ąŠą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░

ŌĆó 2 ą║ą░ąĮą░ą╗ą░ DAC, ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąĖą╗ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ

ŌĆó ąÆąŠąĘą╝ąŠąČąĮąŠčüčéčī DMA ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░

ŌĆó ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ DMA (DMA underrun)

ŌĆó ąÆąĮąĄčłąĮąĖąĄ čéčĆąĖą│ą│ąĄčĆčŗ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ

ŌĆó ąÆčģąŠą┤ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VREF+

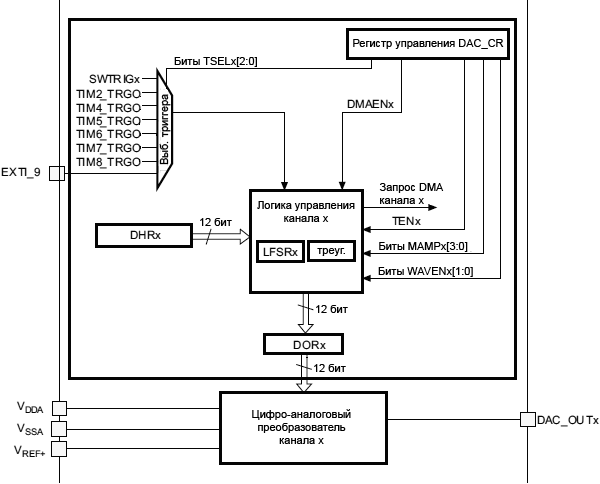

ąĀąĖčü. 64 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▒ą╗ąŠą║-čüčģąĄą╝čā ą║ą░ąĮą░ą╗ą░ DAC, ąĖ ą▓ čéą░ą▒ą╗ąĖčåąĄ 74 ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ąŠą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓.

ąĀąĖčü. 64. ąæą╗ąŠą║ čüčģąĄą╝ą░ ą║ą░ąĮą░ą╗ą░ DAC.

ąóą░ą▒ą╗ąĖčåą░ 74. ąØąŠąČą║ąĖ DAC.

| ąśą╝čÅ |

ąóąĖą┐ čüąĖą│ąĮą░ą╗ą░ |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ |

| VREF+ |

ąÆčģąŠą┤, ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ. |

ą¤ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ DAC, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĄąĄ čüą░ą╝ąŠąĄ ą▓čŗčüąŠą║ąŠąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ą¤čĆąĄą┤ąĄą╗čŗ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 1.8V Ōēż VREF+ Ōēż VDDA. |

| VDDA |

ąÆčģąŠą┤, ą┐ą╗čÄčü ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ. |

|

| VSSA |

ąÆčģąŠą┤, ą░ąĮą░ą╗ąŠą│ąŠą▓ą░čÅ ąĘąĄą╝ą╗čÅ ąĖ ą╝ąĖąĮčāčü ą┐ąĖčéą░ąĮąĖčÅ. |

|

| DAC_OUTx |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗. |

ąÆčŗčģąŠą┤ ą║ą░ąĮą░ą╗ą░ x DAC (x = 1 ąĖą╗ąĖ 2). |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ą░ą║ č鹊ą╗čīą║ąŠ ą║ą░ąĮą░ą╗ x DAC čĆą░ąĘčĆąĄčłąĄąĮ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ąĮąŠąČą║ą░ GPIO (PA4 ąĖą╗ąĖ PA5) ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą▓čŗčģąŠą┤čā ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ (DAC_OUTx, x = 1 ąĖą╗ąĖ 2). ą¦č鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐ą░čĆą░ąĘąĖčéąĮąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, čüąĮą░čćą░ą╗ą░ ą▓čŗą▓ąŠą┤ PA4 ąĖą╗ąĖ PA5 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąĮą░ ą░ąĮą░ą╗ąŠą│ąŠą▓čāčÄ čäčāąĮą║čåąĖčÄ (AIN).

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ DAC]

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║ą░ąĮą░ą╗ą░. ąØą░ ą║ą░ąČą┤čŗą╣ ą║ą░ąĮą░ą╗ DAC ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą░ąĮąŠ ą┐ąĖčéą░ąĮąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ ENx ą▓ čĆąĄą│ąĖčüčéčĆąĄ DAC_CR. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą║ą░ąĮą░ą╗ DAC ą▒čāą┤ąĄčé čĆą░ąĘčĆąĄčłąĄąĮ ą┐ąŠ ąĖčüč鹥č湥ąĮąĖąĖ ąĘą░ą┤ąĄčƹȹ║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┐čāčüą║ą░ (startup time tWAKEUP).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖčé ENx čĆą░ąĘčĆąĄčłą░ąĄčé č鹊ą╗čīą║ąŠ ą╝ą░ą║čĆąŠčÅč湥ą╣ą║čā analog DAC ą║ą░ąĮą░ą╗ą░ x. ąĪą░ą╝ čåąĖčäčĆąŠą▓ąŠą╣ ąĖąĮč鹥čĆč乥ą╣čü ą║ą░ąĮą░ą╗ą░ x DAC čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą▒ąĖčé ENx čüą▒čĆąŠčłąĄąĮ.

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą▒čāč乥čĆą░. ąÆ DAC ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮąŠ 2 ą▓čŗčģąŠą┤ąĮčŗčģ ą▒čāč乥čĆą░, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čāą╝ąĄąĮčīčłąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą╣ ąĮą░ą│čĆčāąĘą║ąŠą╣ ąĮą░ą┐čĆčÅą╝čāčÄ, ą▒ąĄąĘ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ. ąÜą░ąČą┤čŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą║ą░ąĮą░ą╗ą░ DAC ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮ čü ą┐ąŠą╝ąŠčēčīčÄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ BOFFx ą▓ čĆąĄą│ąĖčüčéčĆąĄ DAC_CR.

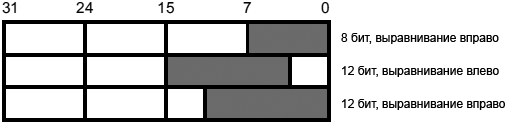

ążąŠčĆą╝ą░čé ą┤ą░ąĮąĮčŗčģ. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░, ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ, ą║ą░ą║ ąŠą┐ąĖčüą░ąĮąŠ ąĮąĖąČąĄ.

ŌĆó ąĪ ąŠą┤ąĮąĖą╝ ą║ą░ąĮą░ą╗ąŠą╝ x (x = 1 ąĖą╗ąĖ 2) DAC ąĄčüčéčī čéčĆąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ:

ŌĆō 8-ą▒ąĖčéąĮąŠąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ą▓ą┐čĆą░ą▓ąŠ: ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąĘą░ą│čĆčāąČą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒ąĖčéčŗ DAC_DHR8Rx [7:0] (čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ ą▒ąĖčéčŗ DHRx[11:4]).

ŌĆō 12-ą▒ąĖčéąĮąŠąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ą▓ą╗ąĄą▓ąŠ: ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąĘą░ą│čĆčāąČą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒ąĖčéčŗ DAC_DHR12Lx [15:4] (čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ ą▒ąĖčéčŗ DHRx[11:0]).

ŌĆō 12-ą▒ąĖčéąĮąŠąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ą▓čĆą░ą▓ąŠ: ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąĘą░ą│čĆčāąČą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒ąĖčéčŗ DAC_DHR12Rx [11:0] (čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ ą▒ąĖčéčŗ DHRx[11:0]).

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĘą░ą│čĆčāąČąĄąĮąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ DAC_DHRyyyx, ą┤ą░ąĮąĮčŗąĄ, ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝, čüą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĖ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ DHRx (data holding register x, čĆąĄą│ąĖčüčéčĆąĄ čģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ). ąŁčéąĖ DHRx čÅą▓ą╗čÅčÄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ąĖ, ąĮąĄ ąŠč鹊ą▒čĆą░ąČą░ąĄą╝čŗą╝ąĖ ąĮą░ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ. ąŚą░č鹥ą╝ čĆąĄą│ąĖčüčéčĆ DHRx ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ DORx ą╗ąĖą▒ąŠ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą╗ąĖą▒ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ čéčĆąĖą│ą│ąĄčĆąŠą╝, ą╗ąĖą▒ąŠ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░.

ąĀąĖčü. 65. ąĀąĄą│ąĖčüčéčĆčŗ ą┤ą░ąĮąĮčŗčģ ą▓ ąŠą┤ąĮąŠą║ą░ąĮą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ DAC.

ŌĆó ąĪ ą┤ą▓čāą╝čÅ ą║ą░ąĮą░ą╗ą░ą╝ąĖ DAC ąĄčüčéčī čéčĆąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ:

ŌĆō 8-ą▒ąĖčéąĮąŠąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ą▓ą┐čĆą░ą▓ąŠ: ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1 DAC ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ ą▒ąĖčéčŗ DAC_DHR8RD [7:0] (čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ ą▒ąĖčéą░čģ DHR1[11:4]), ąĖ ą┤ą░ąĮąĮčŗąĄ ą║ą░ąĮą░ą╗ą░ 2 DAC ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ DAC_DHR8RD [15:8] (čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ ą▒ąĖčéą░čģ DHR2[11:4]).

ŌĆō 12-ą▒ąĖčéąĮąŠąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ą▓ą╗ąĄą▓ąŠ: ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1 DAC ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ ą▒ąĖčéčŗ DAC_DHR12LD [15:4] (čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ ą▒ąĖčéą░čģ DHR1[11:0]) ąĖ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2 DAC ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ ą▒ąĖčéčŗ DAC_DHR12LD [31:20] (čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ ą▒ąĖčéą░čģ DHR2[11:0]).

ŌĆō 12-ą▒ąĖčéąĮąŠąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ą▓ą┐čĆą░ą▓ąŠ: ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1 DAC ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ ą▒ąĖčéčŗ DAC_DHR12RD [11:0] (čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ ą▒ąĖčéą░čģ DHR1[11:0]) ąĖ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2 DAC ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ ą▒ąĖčéčŗ DAC_DHR12LD [27:16] (čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ ą▒ąĖčéą░čģ DHR2[11:0]).

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĘą░ą│čĆčāąČąĄąĮąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ DAC_DHRyyyD, ą┤ą░ąĮąĮčŗąĄ, ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝, čüą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĖ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ DHR1 ąĖ DHR2 (data holding registers, čĆąĄą│ąĖčüčéčĆčŗ čģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ). ąŁčéąĖ čĆąĄą│ąĖčüčéčĆčŗ čÅą▓ą╗čÅčÄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ąĖ, ąĮąĄ ąŠč鹊ą▒čĆą░ąČą░ąĄą╝čŗą╝ąĖ ąĮą░ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ. ąĀąĄą│ąĖčüčéčĆčŗ DHR1 ąĖ DHR2 ąĘą░č鹥ą╝ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆčŗ DOR1 ąĖ DOR2, ą╗ąĖą▒ąŠ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą╗ąĖą▒ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ čéčĆąĖą│ą│ąĄčĆąŠą╝, ą╗ąĖą▒ąŠ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░.

ąĀąĖčü. 66. ąĀąĄą│ąĖčüčéčĆčŗ ą┤ą░ąĮąĮčŗčģ ą▓ ą┤ą▓čāčģą║ą░ąĮą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ DAC.

ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ DAC. DAC_DORx ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ąĮą░ą┐čĆčÅą╝čāčÄ, ąĖ ą╗čÄą▒ą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą▓ ą║ą░ąĮą░ą╗ x DAC ą┤ąŠą╗ąČąĮą░ ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ ąĘą░ą│čĆčāąĘą║ąŠą╣ čĆąĄą│ąĖčüčéčĆą░ DAC_DHRx (ąĘą░ą┐ąĖčüčī ą▓ DAC_DHR8Rx, DAC_DHR12Lx, DAC_DHR12Rx, DAC_DHR8RD, DAC_DHR12LD ąĖą╗ąĖ DAC_DHR12LD).

ąöą░ąĮąĮčŗąĄ, čüąŠčģčĆą░ąĮąĄąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DHRx, ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DORx ą┐ąŠčüą╗ąĄ ąŠą┤ąĮąŠą│ąŠ čéą░ą║čéą░ APB1, ąĄčüą╗ąĖ ąĮąĄ ą▒čŗą╗ ą▓čŗą▒čĆą░ąĮ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ (čüą▒čĆąŠčłąĄąĮ ą▒ąĖčé TENx ą▓ čĆąĄą│ąĖčüčéčĆąĄ DAC_CR). ą×ą┤ąĮą░ą║ąŠ ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ (čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TENx ą▓ čĆąĄą│ąĖčüčéčĆąĄ DAC_CR), ąĖ ąŠąĮ čüčĆą░ą▒ąŠčéą░ą╗, ą┐ąĄčĆąĄą┤ą░čćą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮą░ 3 čéą░ą║čéą░ APB1 ą┐ąŠąĘąČąĄ.

ąÜąŠą│ą┤ą░ DAC_DORx ąĘą░ą│čĆčāąČąĄąĮ čüąŠą┤ąĄčƹȹĖą╝čŗą╝ DAC_DHRx, ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐ąŠčüą╗ąĄ ą▓čĆąĄą╝ąĄąĮąĖ tSETTLING, ą║ąŠč鹊čĆąŠąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ąĮą░ą│čĆčāąĘą║ąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čŗčģąŠą┤ą░.

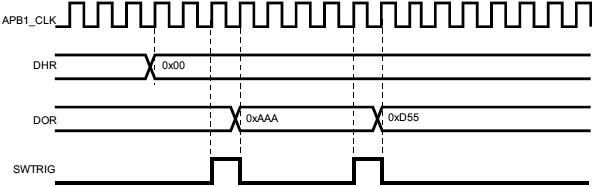

ąĀąĖčü. 67. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čü ąĘą░ą┐čĆąĄčēąĄąĮąĮčŗą╝ čéčĆąĖą│ą│ąĄčĆąŠą╝, TENx = 0.

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ DAC. ą”ąĖčäčĆąŠą▓čŗąĄ ą▓čģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĄąŠą▒čĆą░ąĘčāčÄčéčüčÅ ą▓ ą▓čŗčģąŠą┤ąĮčŗąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą╗ąĖąĮąĄą╣ąĮąŠ, čü čāčĆąŠą▓ąĮčÅą╝ąĖ ą╝ąĄąČą┤čā 0 ąĖ VREF+. ąÉąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čŗčģąŠą┤ąĮčŗąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ ą║ą░ąČą┤ąŠą╣ ąĮąŠąČą║ąĄ ą║ą░ąĮą░ą╗ą░ DAC ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ą▓čŗčĆą░ąČąĄąĮąĖąĄą╝:

DOR

DACoutput = VREF x ------

4096

ąÆčŗą▒ąŠčĆ čéčĆąĖą│ą│ąĄčĆą░ DAC. ąĢčüą╗ąĖ ą▒ąĖčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ TENx čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą╝ąŠąČąĄčé ąĘą░ą┐čāčüčéąĖčéčīčüčÅ ą▓ąĮąĄčłąĮąĖą╝ čéčĆąĖą│ą│ąĄčĆąŠą╝ (ąŠčé čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░, ą▓ąĮąĄčłąĮąĄą╣ ą╗ąĖąĮąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ). ąæąĖčéčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ TSELx[2:0] ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą║ą░ą║ąŠąĄ ąĖąĘ 8 ą▓ąŠąĘą╝ąŠąČąĮčŗčģ čüąŠą▒čŗčéąĖą╣ ą▓čŗąĘąŠą▓ąĄčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ, čćč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 75.

ąóą░ą▒ą╗ąĖčåą░ 75. ąÆąĮąĄčłąĮąĖąĄ čéčĆąĖą│ą│ąĄčĆčŗ.

| ąśčüč鹊čćąĮąĖą║ |

ąóąĖą┐ |

TSEL[2:0] |

| Timer 6 TRGO event |

ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ čüąĖą│ąĮą░ą╗ ąŠčé ą▓čüčéčĆąŠąĄąĮąĮčŗčģ čéą░ą╣ą╝ąĄčĆąŠą▓. |

000 |

| Timer 8 TRGO event |

001 |

| Timer 7 TRGO event |

010 |

| Timer 5 TRGO event |

011 |

| Timer 2 TRGO event |

100 |

| Timer 4 TRGO event |

101 |

| EXTI line9 |

ąÆąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗, ą┐ąŠą┤ą░ą▓ą░ąĄą╝čŗą╣ ąĮą░ ąĮąŠąČą║čā ą║ąŠčĆą┐čāčüą░. |

110 |

| SWTRIG |

ąæąĖčé, čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ (ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ SW). |

111 |

ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ąĖąĮč鹥čĆč乥ą╣čü DAC ą┤ąĄč鹥ą║čéąĖčĆčāąĄčé čäčĆąŠąĮčé ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ TRGO ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░, ąĖą╗ąĖ ąĮą░ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą╗ąĖąĮąĖąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 9, ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ čüąŠčģčĆą░ąĮąĄąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ DAC_DHRx ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DORx. ąĀąĄą│ąĖčüčéčĆ DAC_DORx ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ąĮą░ 3 čéą░ą║čéą░ APB1 ą┐ąŠąĘąČąĄ čüąŠą▒čŗčéąĖčÅ čéčĆąĖą│ą│ąĄčĆą░.

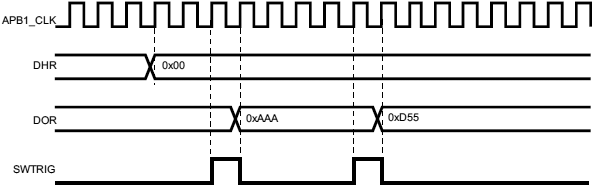

ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ (SW), č鹊 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé SWTRIG. ąæąĖčé SWTRIG čüą▒čĆąŠčüąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ą░ą║ č鹊ą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆ DAC_DORx ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüąŠą┤ąĄčƹȹĖą╝čŗą╝ čĆąĄą│ąĖčüčéčĆą░ DAC_DHRx.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖčéčŗ TSELx[2:0] ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮčŗ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ENx. ąÜąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ, ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ DAC_DHRx ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DORx ą┐čĆąŠąĖčüčģąŠą┤ąĖčé č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ ąŠą┤ąĮąŠą│ąŠ čéą░ą║čéą░ APB1.

[ąŚą░ą┐čĆąŠčü DMA]

ąŻ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ DAC ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī DMA. ąöą▓ą░ ą║ą░ąĮą░ą╗ą░ DMA ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąŠčüąŠą▓ DMA ą║ą░ąĮą░ą╗ąŠą▓ DAC.

ąŚą░ą┐čĆąŠčü DAC DMA ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą▓ąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ (ąĮąŠ ąĮąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ), ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé DMAENx.ąóąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ DAC_DHRx ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DORx.

ąÆ ą┤ą▓čāčģą║ą░ąĮą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ąŠą▒ą░ ą▒ąĖčéą░ DMAENx, ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą┤ą▓ą░ ąĘą░ą┐čĆąŠčüą░ DMA. ąĢčüą╗ąĖ ąĮčāąČąĄąĮ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ąĘą░ą┐čĆąŠčü DMA, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ čāčüčéą░ąĮąŠą▓ąĖčéčī č鹊ą╗čīą║ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé DMAENx. ąóą░ą║ąĖą╝ ą╝ąĄč鹊ą┤ąŠą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé ąŠą▒čüą╗čāąČąĖą▓ą░čéčī ąŠą▒ą░ ą║ą░ąĮą░ą╗ą░ DAC ą▓ ą┤ą▓čāčģą║ą░ąĮą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ, ąĖčüą┐ąŠą╗čīąĘčāčÅ ąŠą┤ąĖąĮ ąĘą░ą┐čĆąŠčü DMA ąĖ čāąĮąĖą║ą░ą╗čīąĮčŗą╣ ą║ą░ąĮą░ą╗ DMA.

DMA underrun. ą¤čĆąĖ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĄ DMA ąĘą░ą┐čĆąŠčü DAC DMA ąĮąĄ čüčéą░ą▓ąĖčéčüčÅ ą▓ ąŠč湥čĆąĄą┤čī: ąĄčüą╗ąĖ ą┐ąŠčüčéčāą┐ąĖą╗ ą▓č鹊čĆąŠą╣ ą▓ąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ąŠ ą┐ąŠą╗čāč湥ąĮąŠ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ąŠčé ą┐ąĄčĆą▓ąŠą│ąŠ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ (ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ą┐ąĄčĆą▓ąŠą│ąŠ ąĘą░ą┐čĆąŠčüą░), č鹊 ąĮąĄ ą▓čŗą┤ą░ąĄčéčüčÅ ąĮąŠą▓čŗą╣ ąĘą░ą┐čĆąŠčü, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ DMAUDRx ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ DMA ą║ą░ąĮą░ą╗ą░ x ą▓ čĆąĄą│ąĖčüčéčĆąĄ DAC_SR, čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāčÅ ąŠ čüąŠą▒čŗčéąĖąĖ ąŠčłąĖą▒ą║ąĖ. ąóąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ DMA ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ, ąĖ ą▒čāą┤čāčēąĖą╣ ąĘą░ą┐čĆąŠčü DMA ąĮąĄ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ. ąÜą░ąĮą░ą╗ x DAC ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓čŗą▓ą░čéčī čüčéą░čĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąŠčćąĖčüčéąĖčéčī čäą╗ą░ą│ DMAUDRx ąĘą░ą┐ąĖčüčīčÄ ą╗ąŠą│. 1, ąŠčćąĖčüčéąĖčéčī ą▒ąĖčé DMAEN ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą┐ąŠč鹊ą║ą░ DMA ąĖ ąĘą░ąĮąŠą▓ąŠ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī ąĖ DMA, ąĖ ą║ą░ąĮą░ą╗ x DAC, čćč鹊ą▒čŗ ą║ąŠčĆčĆąĄą║čéąĮąŠ ą┐ąĄčĆąĄąĘą░ą┐čāčüčéąĖčéčī ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ. ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąĖąĘą╝ąĄąĮąĖčéčī čćą░čüč鹊čéčā čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ čéčĆąĖą│ą│ąĄčĆą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ DAC, ąĖą╗ąĖ ąŠą▒ą╗ąĄą│čćąĖčéčī čĆą░ą▒ąŠčćčāčÄ ąĮą░ą│čĆčāąĘą║čā DMA, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąĮąŠą▓ąŠą╣ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ DMA. ąś ąĮą░ą║ąŠąĮąĄčå, ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ DAC ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ DMA, ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ čéčĆąĖą│ą│ąĄčĆą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ x DAC čéą░ą║ąČąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé DMAUDRIEx ą▓ čĆąĄą│ąĖčüčéčĆąĄ DAC_CR.

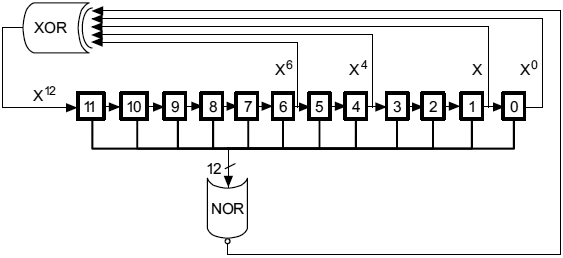

ąöą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čüąĄą▓ą┤ąŠčüą╗čāčćą░ą╣ąĮąŠą│ąŠ čłčāą╝ą░ čü ąĖąĘą╝ąĄąĮčÅčÄčēąĄą╣čüčÅ ą░ą╝ą┐ą╗ąĖčéčāą┤ąŠą╣ ą┤ąŠčüčéčāą┐ąĄąĮ čĆąĄą│ąĖčüčéčĆ LFSR (linear feedback shift register). ąōąĄąĮąĄčĆą░čåąĖčÅ čłčāą╝ą░ DAC ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé WAVEx[1:0] ą▓ čüąŠčüč鹊čÅąĮąĖąĄ 01. ąöą╗čÅ LFSR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ąĘą░ą│čĆčāąČą░ąĄą╝ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ 0xAAA. ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ č湥čĆąĄąĘ 3 čéą░ą║čéą░ APB1 ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ čüąŠą▒čŗčéąĖčÅ čéčĆąĖą│ą│ąĄčĆą░, ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ ą┐ąŠ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╝čā ą▓čŗčćąĖčüą╗ąĖč鹥ą╗čīąĮąŠą╝čā ą░ą╗ą│ąŠčĆąĖčéą╝čā.

ąĀąĖčü. 68. ąÉą╗ą│ąŠčĆąĖčéą╝ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆąĄ DAC LFSR.

ąŚąĮą░č湥ąĮąĖąĄ LFSR, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĄčé ą╝ą░čüą║ąĖčĆąŠą▓ą░čéčīčüčÅ čćą░čüčéąĖčćąĮąŠ ąĖą╗ąĖ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą▒ąĖčéą░ą╝ąĖ MAMPx[3:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ DAC_CR, ą┤ąŠą▒ą░ą▓ą╗čÅąĄčéčüčÅ ą║ čüąŠą┤ąĄčƹȹĖą╝ąŠą╝čā DAC_DHRx ą▒ąĄąĘ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ, ąĖ čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DORx.

ąĢčüą╗ąĖ LFSR ą┐ąŠą╗čāčćąĖčé ąĘąĮą░č湥ąĮąĖąĄ 0x0000, č鹊 ą▓ ąĮąĄą│ąŠ ąĖąĮąČąĄą║čéąĖčĆčāąĄčéčüčÅ 1 (ą╝ąĄčģą░ąĮąĖąĘą╝ antilock-up). ą£ąŠąČąĮąŠ čüą▒čĆąŠčüąĖčéčī ą│ąĄąĮąĄčĆą░čåąĖčÄ čüąĖą│ąĮą░ą╗ą░ LFSR čüą▒čĆąŠčüąŠą╝ ą▒ąĖčé WAVEx[1:0].

ąĀąĖčü. 69. ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ DAC (čĆą░ąĘčĆąĄčłąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ SW) čü ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ čüąĖą│ąĮą░ą╗ą░ LFSR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čéčĆąĖą│ą│ąĄčĆ DAC ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čłčāą╝ą░ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ TENx ą▓ čĆąĄą│ąĖčüčéčĆąĄ DAC_CR.

ą£ąŠąČąĮąŠ ą┤ąŠą▒ą░ą▓ąĖčéčī čéčĆąĄčāą│ąŠą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ ą╝ą░ą╗ąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ ą║ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā ą▓čŗčģąŠą┤ąĮąŠą╝čā čāčĆąŠą▓ąĮčÄ DAC, ąĖą╗ąĖ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą╝ąĄąĮčÅčÄčēąĖą╣čüčÅ čéčĆąĄčāą│ąŠą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗. ąōąĄąĮąĄčĆą░čåąĖčÅ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé WAVEx[1:0] ą▓ čüąŠčüč鹊čÅąĮąĖąĄ 10. ąÉą╝ą┐ą╗ąĖčéčāą┤ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ MAMPx[3:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ DAC_CR. ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąĮą░ 3 čéą░ą║čéą░ APB1 ą┐ąŠąĘąČąĄ ą║ą░ąČą┤ąŠą│ąŠ čüąŠą▒čŗčéąĖčÅ čéčĆąĖą│ą│ąĄčĆą░. ąŚą░č鹥ą╝ čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą┤ąŠą▒ą░ą▓ą╗čÅąĄčéčüčÅ ą▒ąĄąĘ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DAC_DHRx ąĖ ą┐ąŠą╗čāč湥ąĮąĮą░čÅ čüčāą╝ą╝ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DORx. ąĪč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąŠąĮ ą╝ąĄąĮčīčłąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ ą▒ąĖčéą░ą╝ąĖ MAMPx[3:0]. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▒čŗą╗ą░ ą┤ąŠčüčéąĖą│ąĮčāčéą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ ą░ą╝ą┐ą╗ąĖčéčāą┤ą░, čüč湥čéčćąĖą║ ąĮą░čćąĖąĮą░ąĄčé ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ ą▓ąĮąĖąĘ ą┤ąŠ 0, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ąĮą░čćąĮąĄčé čüąĮąŠą▓ą░ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ, ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ.

ąĀąĖčü. 70. ąōąĄąĮąĄčĆą░čåąĖčÅ čéčĆąĄčāą│ąŠą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ DAC.

ą£ąŠąČąĮąŠ čüą▒čĆąŠčüąĖčéčī ą│ąĄąĮąĄčĆą░čåąĖčÄ čéčĆąĄčāą│ąŠą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čüą▒čĆąŠčüąŠą╝ ą▒ąĖčé WAVEx[1:0].

ąĀąĖčü. 71. ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ DAC (čĆą░ąĘčĆąĄčłąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ SW) čü ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ čéčĆąĄčāą│ąŠą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ čéčĆąĖą│ą│ąĄčĆ DAC ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čłčāą╝ą░, ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ TENx ą▓ čĆąĄą│ąĖčüčéčĆąĄ DAC_CR. ąæąĖčéčŗ MAMPx[3:0] ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┐ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ DAC, ąĖąĮą░č湥 ąĖčģ ąĮąĄą╗čīąĘčÅ ą▒čāą┤ąĄčé ąĖąĘą╝ąĄąĮąĖčéčī.

ąöą╗čÅ čŹčäč乥ą║čéąĖą▓ąĮąŠą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐ąŠą╗ąŠčüčŗ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ čłąĖąĮčŗ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ, ą│ą┤ąĄ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąĮčāąČąĮčŗ 2 ą║ą░ąĮą░ą╗ą░ DAC, čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ 3 ą┤ą▓ąŠą╣ąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░: DHR8RD, DHR12RD ąĖ DHR12LD. ąóąŠą│ą┤ą░ čéčĆąĄą▒čāąĄčéčüčÅ čāąĮąĖą║ą░ą╗čīąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝, čćč鹊ą▒čŗ čāą┐čĆą░ą▓ą╗čÅčéčī ąŠą▒ąŠąĖą╝ąĖ ą║ą░ąĮą░ą╗ą░ą╝ąĖ DAC ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ.

ąĪ čŹčéąĖą╝ąĖ ą┤ą▓ąŠą╣ąĮčŗą╝ąĖ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ ąĖ ą┤ą▓čāą╝čÅ ą║ą░ąĮą░ą╗ą░ą╝ąĖ DAC ą┤ąŠčüčéčāą┐ąĮčŗ 11 ą▓ąŠąĘą╝ąŠąČąĮčŗčģ čĆąĄąČąĖą╝ąŠą▓ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąóąĄą╝ ąĮąĄ ą╝ąĄąĮąĄąĄ, ą▓čüąĄ čĆąĄąČąĖą╝čŗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ąŠčéą┤ąĄą╗čīąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ DHRx.

ąØąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ čéčĆąĖą│ą│ąĄčĆ. ą¦č鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī DAC ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣:

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé TEN1 ąĖ TEN2 čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą▓čāčģ čéčĆąĖą│ą│ąĄčĆąŠą▓ ą║ą░ąĮą░ą╗ąŠą▓ DAC.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čĆą░ąĘąĮčŗčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ čéčĆąĖą│ą│ąĄčĆą░ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čĆą░ąĘąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą▓ ą▒ąĖčéą░čģ TSEL1[2:0] ąĖ TSEL2[2:0].

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ ą┤ą▓čāčģą║ą░ąĮą░ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ ąČąĄą╗ą░ąĄą╝čŗą╣ čĆąĄą│ąĖčüčéčĆ DHR (DAC_DHR12RD, DAC_DHR12LD ąĖą╗ąĖ DAC_DHR8RD).

ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 1 DAC, čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ DHR1 ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DOR1 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 2 DAC, čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ DHR2 ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DOR2 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1).

ąØąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ čéčĆąĖą│ą│ąĄčĆ čü ąŠą┤ąĮąĖą╝ LFSR. ą¦č鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī DAC ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣:

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé TEN1 ąĖ TEN2 čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą▓čāčģ čéčĆąĖą│ą│ąĄčĆąŠą▓ ą║ą░ąĮą░ą╗ąŠą▓ DAC.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čĆą░ąĘąĮčŗčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ čéčĆąĖą│ą│ąĄčĆą░ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čĆą░ąĘąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą▓ ą▒ąĖčéą░čģ TSEL1[2:0] ąĖ TSEL2[2:0].

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą▒ąĖčéą░ą╝ąĖ WAVEx[1:0], čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ąĖčģ ą▓ 01, ąĖ čāčüčéą░ąĮąŠą▓ą║ą░ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą╝ą░čüą║ąĖ LFSR ą▓ ą▒ąĖčéą░čģ MAMPx[3:0].

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ ą┤ą░ąĮąĮčŗčģ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą▓ ąČąĄą╗ą░ąĄą╝čŗą╣ čĆąĄą│ąĖčüčéčĆ DHR (DHR12RD, DHR12LD ąĖą╗ąĖ DHR8RD).

ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 1 DAC, čüč湥čéčćąĖą║ LFSR1, čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ą╝ą░čüą║ąŠą╣, ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR1, ąĖ čüčāą╝ą╝ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ DAC_DOR1 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąŚą░č鹥ą╝ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüč湥čéčćąĖą║ LFSR1. ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 2 DAC, čüč湥čéčćąĖą║ LFSR2, čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ą╝ą░čüą║ąŠą╣, ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR2, ąĖ čüčāą╝ą╝ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ DAC_DOR2 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąŚą░č鹥ą╝ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüč湥čéčćąĖą║ LFSR2.

ąØąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ čéčĆąĖą│ą│ąĄčĆ čü čĆą░ąĘąĮčŗą╝ąĖ LFSR. ą¦č鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī DAC ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣:

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé TEN1 ąĖ TEN2 čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą▓čāčģ čéčĆąĖą│ą│ąĄčĆąŠą▓ ą║ą░ąĮą░ą╗ąŠą▓ DAC.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čĆą░ąĘąĮčŗčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ čéčĆąĖą│ą│ąĄčĆą░ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čĆą░ąĘąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą▓ ą▒ąĖčéą░čģ TSEL1[2:0] ąĖ TSEL2[2:0].

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą▒ąĖčéą░ą╝ąĖ WAVEx[1:0], čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ąĖčģ ą▓ 01, ąĖ čāčüčéą░ąĮąŠą▓ą║ą░ čĆą░ąĘąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą╝ą░čüą║ąĖ LFSR ą▓ ą▒ąĖčéą░čģ MAMP1[3:0] ąĖ MAMP2[3:0].

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ ą┤ą░ąĮąĮčŗčģ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą▓ ąČąĄą╗ą░ąĄą╝čŗą╣ čĆąĄą│ąĖčüčéčĆ DHR (DAC_DHR12RD, DAC_DHR12LD ąĖą╗ąĖ DAC_DHR8RD).

ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 1 DAC, čüč湥čéčćąĖą║ LFSR1, čü ą╝ą░čüą║ąŠą╣, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą▓ MAMP1[3:0], ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR1, ąĖ čüčāą╝ą╝ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ DAC_DOR1 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąŚą░č鹥ą╝ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüč湥čéčćąĖą║ LFSR1. ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 2 DAC, čüč湥čéčćąĖą║ LFSR2, čü ą╝ą░čüą║ąŠą╣, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą▓ MAMP2[3:0], ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR2, ąĖ čüčāą╝ą╝ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ DAC_DOR2 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąŚą░č鹥ą╝ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüč湥čéčćąĖą║ LFSR2.

ąØąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ čéčĆąĖą│ą│ąĄčĆ čü ąŠą┤ąĮąĖą╝ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ąŠą╝. ą¦č鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī DAC ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣:

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé TEN1 ąĖ TEN2 čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą▓čāčģ čéčĆąĖą│ą│ąĄčĆąŠą▓ ą║ą░ąĮą░ą╗ąŠą▓ DAC.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čĆą░ąĘąĮčŗčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ čéčĆąĖą│ą│ąĄčĆą░ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čĆą░ąĘąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą▓ ą▒ąĖčéą░čģ TSEL1[2:0] ąĖ TSEL2[2:0].

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą▒ąĖčéą░ą╝ąĖ WAVEx[1:0], ą▓ ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ 1x, čü ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ ą▓ ą▒ąĖčéą░čģ MAMPx[3:0].

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ ą┤ą░ąĮąĮčŗčģ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą▓ ąČąĄą╗ą░ąĄą╝čŗą╣ čĆąĄą│ąĖčüčéčĆ DHR (DAC_DHR12RD, DAC_DHR12LD ąĖą╗ąĖ DAC_DHR8RD).

ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 1 DAC, čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 1 DAC, čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤ąŠą╣ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░, ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR1, ąĖ čüčāą╝ą╝ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ DAC_DOR1 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąŚą░č鹥ą╝ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 1 DAC. ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 2 DAC, čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 2 DAC, čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤ąŠą╣ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░, ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR2, ąĖ čüčāą╝ą╝ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ DAC_DOR2 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąŚą░č鹥ą╝ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 2 DAC.

ąØąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ čéčĆąĖą│ą│ąĄčĆ čü ą┤ą▓čāą╝čÅ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ą╝ąĖ. ą¦č鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī DAC ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣:

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé TEN1 ąĖ TEN2 čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą▓čāčģ čéčĆąĖą│ą│ąĄčĆąŠą▓ ą║ą░ąĮą░ą╗ąŠą▓ DAC.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čĆą░ąĘąĮčŗčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ čéčĆąĖą│ą│ąĄčĆą░ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čĆą░ąĘąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą▓ ą▒ąĖčéą░čģ TSEL1[2:0] ąĖ TSEL2[2:0].

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą▒ąĖčéą░ą╝ąĖ WAVEx[1:0], ą▓ ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ 1x, čü čĆą░ąĘąĮčŗą╝ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╝ąĖ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ ą▓ ą▒ąĖčéą░čģ MAMP1[3:0] ąĖ MAMP2[3:0].

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ ą┤ą░ąĮąĮčŗčģ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą▓ ąČąĄą╗ą░ąĄą╝čŗą╣ čĆąĄą│ąĖčüčéčĆ DHR (DAC_DHR12RD, DAC_DHR12LD ąĖą╗ąĖ DAC_DHR8RD).

ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 1 DAC, čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 1 DAC, čü ą░ą╝ą┐ą╗ąĖčéčāą┤ąŠą╣ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą▒ąĖčéą░ą╝ąĖ MAMP1[3:0], ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR1, ąĖ čüčāą╝ą╝ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ DAC_DOR1 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 2 DAC, čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 2 DAC, čü ą░ą╝ą┐ą╗ąĖčéčāą┤ąŠą╣ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą▒ąĖčéą░ą╝ąĖ MAMP2[3:0], ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR2, ąĖ čüčāą╝ą╝ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ DAC_DOR2 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1).

ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮčŗą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüčéą░čĆčé. ą¦č鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī DAC ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣:

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ ą┤ą░ąĮąĮčŗčģ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą▓ ąČąĄą╗ą░ąĄą╝čŗą╣ čĆąĄą│ąĖčüčéčĆ DHR (DAC_DHR12RD, DAC_DHR12LD ąĖą╗ąĖ DAC_DHR8RD).

ąÆ čŹč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 1 čéą░ą║čé APB1 čĆąĄą│ąĖčüčéčĆčŗ DHR1 ąĖ DHR2 ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆčŗ DAC_DOR1 ąĖ DAC_DOR2.

ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ. ą¦č鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī DAC ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣:

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé TEN1 ąĖ TEN2 čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą▓čāčģ čéčĆąĖą│ą│ąĄčĆąŠą▓ ą║ą░ąĮą░ą╗ąŠą▓ DAC.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéčĆąĖą│ą│ąĄčĆą░ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą▒ąĖčéą░čģ TSEL1[2:0] ąĖ TSEL2[2:0].

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ ą┤ą░ąĮąĮčŗčģ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą▓ ąČąĄą╗ą░ąĄą╝čŗą╣ čĆąĄą│ąĖčüčéčĆ DHR (DAC_DHR12RD, DAC_DHR12LD ąĖą╗ąĖ DAC_DHR8RD).

ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ, čĆąĄą│ąĖčüčéčĆčŗ DHR1 ąĖ DHR2 ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆčŗ DAC_DOR1 ąĖ DAC_DOR2 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1).

ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ čü ąŠą┤ąĮąĖą╝ LFSR. ą¦č鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī DAC ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣:

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé TEN1 ąĖ TEN2 čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą▓čāčģ čéčĆąĖą│ą│ąĄčĆąŠą▓ ą║ą░ąĮą░ą╗ąŠą▓ DAC.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéčĆąĖą│ą│ąĄčĆą░ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą▒ąĖčéą░čģ TSEL1[2:0] ąĖ TSEL2[2:0].

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą▒ąĖčéą░ą╝ąĖ WAVEx[1:0], čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ąĖčģ ą▓ 01, ąĖ čāčüčéą░ąĮąŠą▓ą║ą░ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą╝ą░čüą║ąĖ LFSR ą▓ ą▒ąĖčéą░čģ MAMPx[3:0].

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ DAC ą▓ ąČąĄą╗ą░ąĄą╝čŗą╣ čĆąĄą│ąĖčüčéčĆ DHR (DHR12RD, DHR12LD ąĖą╗ąĖ DHR8RD).

ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ, čüč湥čéčćąĖą║ LFSR1, čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ą╝ą░čüą║ąŠą╣, ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR1, ąĖ čüčāą╝ą╝ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ DAC_DOR1 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąŚą░č鹥ą╝ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüč湥čéčćąĖą║ LFSR1. ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé č鹊 ąČąĄ čüą░ą╝ąŠąĄ ąĖ čü ą║ą░ąĮą░ą╗ąŠą╝ 2: čüč湥čéčćąĖą║ LFSR2, čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ą╝ą░čüą║ąŠą╣, ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR2, ąĖ čüčāą╝ą╝ą░ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮą░ ą▓ DAC_DOR2 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąŚą░č鹥ą╝ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüč湥čéčćąĖą║ LFSR2.

ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ čü čĆą░ąĘąĮčŗą╝ąĖ LFSR. ą¦č鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī DAC ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣:

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé TEN1 ąĖ TEN2 čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą▓čāčģ čéčĆąĖą│ą│ąĄčĆąŠą▓ ą║ą░ąĮą░ą╗ąŠą▓ DAC.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéčĆąĖą│ą│ąĄčĆą░ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą▒ąĖčéą░čģ TSEL1[2:0] ąĖ TSEL2[2:0].

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą▒ąĖčéą░ą╝ąĖ WAVEx[1:0], čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ąĖčģ ą▓ 01, ąĖ čāčüčéą░ąĮąŠą▓ą║ą░ čĆą░ąĘąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą╝ą░čüą║ąĖ LFSR ą▓ ą▒ąĖčéą░čģ MAMP1[3:0] ąĖ MAMP2[3:0].

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ DAC ą▓ ąČąĄą╗ą░ąĄą╝čŗą╣ čĆąĄą│ąĖčüčéčĆ DHR (DHR12RD, DHR12LD ąĖą╗ąĖ DHR8RD).

ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ, čüč湥čéčćąĖą║ LFSR1, čü ą╝ą░čüą║ąŠą╣, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą▒ąĖčéą░ą╝ąĖ MAMP1[3:0], ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR1, ąĖ čüčāą╝ą╝ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ DAC_DOR1 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąŚą░č鹥ą╝ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüč湥čéčćąĖą║ LFSR1. ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ č鹊 ąČąĄ čüą░ą╝ąŠąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąĖ čü ą║ą░ąĮą░ą╗ąŠą╝ 2: čüč湥čéčćąĖą║ LFSR2, čü ą╝ą░čüą║ąŠą╣, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą▒ąĖčéą░ą╝ąĖ MAMP2[3:0], ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR2, ąĖ čüčāą╝ą╝ą░ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮą░ ą▓ DAC_DOR2 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąŚą░č鹥ą╝ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüč湥čéčćąĖą║ LFSR2.

ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ čü ąŠą┤ąĮąĖą╝ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ąŠą╝. ą¦č鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī DAC ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣:

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé TEN1 ąĖ TEN2 čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą▓čāčģ čéčĆąĖą│ą│ąĄčĆąŠą▓ ą║ą░ąĮą░ą╗ąŠą▓ DAC.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéčĆąĖą│ą│ąĄčĆą░ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą▒ąĖčéą░čģ TSEL1[2:0] ąĖ TSEL2[2:0].

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą▒ąĖčéą░ą╝ąĖ WAVEx[1:0], čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ąĖčģ ą▓ 1x, ąĖ čāčüčéą░ąĮąŠą▓ą║ą░ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ ą▒ąĖčéą░ą╝ąĖ MAMPx[3:0].

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ DAC ą▓ ąČąĄą╗ą░ąĄą╝čŗą╣ čĆąĄą│ąĖčüčéčĆ DHR (DHR12RD, DHR12LD ąĖą╗ąĖ DHR8RD).

ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ, čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 1, čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤ąŠą╣, ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR1, ąĖ čüčāą╝ą╝ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ DAC_DOR1 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąŚą░č鹥ą╝ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 1. ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé č鹊 ąČąĄ čüą░ą╝ąŠąĄ ąĖ čü ą║ą░ąĮą░ą╗ąŠą╝ 2: čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 2, čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤ąŠą╣, ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR2, ąĖ čüčāą╝ą╝ą░ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮą░ ą▓ DAC_DOR2 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąŚą░č鹥ą╝ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 2.

ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ čü čĆą░ąĘąĮčŗą╝ąĖ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ą╝ąĖ. ą¦č鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī DAC ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣:

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé TEN1 ąĖ TEN2 čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą▓čāčģ čéčĆąĖą│ą│ąĄčĆąŠą▓ ą║ą░ąĮą░ą╗ąŠą▓ DAC.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéčĆąĖą│ą│ąĄčĆą░ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą▒ąĖčéą░čģ TSEL1[2:0] ąĖ TSEL2[2:0].

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ DAC ą▒ąĖčéą░ą╝ąĖ WAVEx[1:0], čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ąĖčģ ą▓ 1x, ąĖ čāčüčéą░ąĮąŠą▓ą║ą░ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ ą▒ąĖčéą░ą╝ąĖ MAMPx[3:0].

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ DAC ą▓ ąČąĄą╗ą░ąĄą╝čŗą╣ čĆąĄą│ąĖčüčéčĆ DHR (DHR12RD, DHR12LD ąĖą╗ąĖ DHR8RD).

ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé čéčĆąĖą│ą│ąĄčĆ, čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 1, čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤ąŠą╣, ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR1, ąĖ čüčāą╝ą╝ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ DAC_DOR1 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąŚą░č鹥ą╝ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 1. ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé č鹊 ąČąĄ čüą░ą╝ąŠąĄ ąĖ čü ą║ą░ąĮą░ą╗ąŠą╝ 2: čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 2, čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤ąŠą╣, ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā DHR2, ąĖ čüčāą╝ą╝ą░ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮą░ ą▓ DAC_DOR2 (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ 3 čéą░ą║čéą░ APB1). ąŚą░č鹥ą╝ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüč湥čéčćąĖą║ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 2.

[ąĀąĄą│ąĖčüčéčĆčŗ DAC]

ąÜ čĆąĄą│ąĖčüčéčĆą░ą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ DAC ąĮčāąČąĮąŠ ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ą░ą║ ą║ čüą╗ąŠą▓ą░ą╝ (32-ą▒ąĖčéąĮčŗą╣ ą┤ąŠčüčéčāą┐). ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░ čāą║ą░ąĘą░ąĮąŠ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ DAC_BASE (čüą╝. čäą░ą╣ą╗ stm32f429xx.h). ąöą╗čÅ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ DAC ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą░ą┤čĆąĄčüą░ 0x0x40007400 .. 0x400077FF (ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü 0x40007400).

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░ ą▒ąĖčé čā ą▓čüąĄčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĮčāą╗ąĄą▓čŗąĄ (0x00000000).

ąÆ ąŠą┐ąĖčüą░ąĮąĖąĖ čäčāąĮą║čåąĖą╣ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ čüąŠą║čĆą░čēąĄąĮąĖčÅ:

read/write (rw) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé čćąĖčéą░čéčī ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī čŹčéąĖ ą▒ąĖčéčŗ.

read-only (r) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé č鹊ą╗čīą║ąŠ čćąĖčéą░čéčī čŹčéąĖ ą▒ąĖčéčŗ.

write-only (w) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą▓ čŹč鹊čé ą▒ąĖčé. ą¦č鹥ąĮąĖąĄ ą▒ąĖčéą░ ą▓ąĄčĆąĮąĄčé ąĘąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░.

read/clear (rc_w1) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī ą▒ąĖčé, ą░ čéą░ą║ąČąĄ čüą▒čĆąŠčüąĖčéčī ąĄą│ąŠ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüčīčÄ 1. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

read/clear (rc_w0) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī ą▒ąĖčé, ą░ čéą░ą║ąČąĄ čüą▒čĆąŠčüąĖčéčī ąĄą│ąŠ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüčīčÄ 0. ąŚą░ą┐ąĖčüčī 1 ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

read/clear by read (rc_r) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī čŹč鹊čé ą▒ąĖčé. ą¦č鹥ąĮąĖąĄ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą▒čĆąŠčüąĖčé ąĄą│ąŠ ą▓ 0. ąŚą░ą┐ąĖčüčī 0 ą▓ ą▒ąĖčé ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

read/set (rs) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī, ą░ čéą░ą║ąČąĄ čāčüčéą░ąĮąŠą▓ąĖčéčī čŹč鹊čé ą▒ąĖčé. ąŚą░ą┐ąĖčüčī 0 ą▓ ą▒ąĖčé ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

read-only write trigger (rt_w) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī čŹč鹊čé ą▒ąĖčé. ąŚą░ą┐ąĖčüčī 0 ąĖą╗ąĖ 1 ą▓čŗąĘąŠą▓ąĄčé ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ (čéčĆąĖą│ą│ąĄčĆ), ąĮąŠ ąĮąĄ ąŠą║ą░ąČąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░.

toggle (t) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčī čŹč鹊čé ą▒ąĖčé ąĘą░ą┐ąĖčüčīčÄ 1. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

Reserved (Res.) ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▒ąĖčé, ąĄą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ąĮą░ ąĘąĮą░č湥ąĮąĖąĖ čüą▒čĆąŠčüą░.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x00

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

DMAUDRIE2

rw |

DMAEN2

rw |

MAMP2[3:0]

rw |

WAVE2[1:0]

rw |

TSEL2[2:0]

rw |

TEN2

rw |

BOFF2

rw |

EN2

rw |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

DMAUDRIE1

rw |

DMAEN1

rw |

MAMP1[3:0]

rw |

WAVE1[1:0]

rw |

TSEL1[2:0]

rw |

TEN1

rw |

BOFF1

rw |

EN1

rw |

ąæąĖčéčŗ 31:30 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DMAUDRIE2 (ą▒ąĖčé 29): DAC channel2 DMA underrun interrupt enable, ą▒ąĖčé čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ DMA ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2 DAC. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ).

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ.

DMAEN2 (ą▒ąĖčé 28): DAC channel2 DMA enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ DMA ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2 DAC. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣.

0: čĆąĄąČąĖą╝ DMA ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2 DAC ąĘą░ą┐čĆąĄčēąĄąĮ.

1: čĆąĄąČąĖą╝ DMA ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2 DAC čĆą░ąĘčĆąĄčłąĄąĮ.

MAMP2[3:0] (ą▒ąĖčéčŗ 27:24): ą▓čŗą▒ąŠčĆ ą╝ą░čüą║ąĖ/ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ ą║ą░ąĮą░ą╗ą░ 2 DAC. ąŁčéąĖ ą▒ąĖčéčŗ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ ą▓čŗą▒čĆą░čéčī ą╝ą░čüą║čā ą▓ čĆąĄąČąĖą╝ąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ čłčāą╝ą░, ąĖą╗ąĖ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ ą▓ čĆąĄąČąĖą╝ąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░.

0000: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčéą░ 0 LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 1

0001: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [1:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 3

0010: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [2:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 7

0011: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [3:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 15

0100: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [4:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 31

0101: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [5:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 63

0110: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [6:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 127

0111: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [7:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 255

1000: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [8:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 511

1001: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [9:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 1023

1010: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [10:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 2047

>= 1011: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [11:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 4095

WAVE2[1:0] (ą▒ąĖčéčŗ 23:22): čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆąĄąČąĖą╝ą░ ą│ąĄąĮąĄčĆą░čåąĖąĖ čłčāą╝ą░ ąĖą╗ąĖ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 2 DAC. ąŁčéąĖ ą▒ąĖčéčŗ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĖ ąŠčćąĖčēą░čÄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣.

00: ą│ąĄąĮąĄčĆą░čåąĖčÅ čüąĖą│ąĮą░ą╗ą░ ąĘą░ą┐čĆąĄčēąĄąĮą░

01: čĆą░ąĘčĆąĄčłąĄąĮą░ ą│ąĄąĮąĄčĆą░čåąĖčÅ čłčāą╝ą░

1x: čĆą░ąĘčĆąĄčłąĄąĮą░ ą│ąĄąĮąĄčĆą░čåąĖčÅ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▒ąĖčé TEN2 = 1 (čĆą░ąĘčĆąĄčłąĄąĮ čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 2 DAC).

TSEL2[2:0] (ą▒ąĖčéčŗ 21:19): DAC channel2 trigger selection, ą▓čŗą▒ąŠčĆ čéčĆąĖą│ą│ąĄčĆą░ ą║ą░ąĮą░ą╗ą░ 2 DAC. ąŁčéąĖ ą▒ąĖčéčŗ ą▓čŗą▒ąĖčĆą░čÄčé ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ (čéčĆąĖą│ą│ąĄčĆ), ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2 DAC.

000: Timer 6 TRGO event

001: Timer 8 TRGO event

010: Timer 7 TRGO event

011: Timer 5 TRGO event

100: Timer 2 TRGO event

101: Timer 4 TRGO event

110: External line9

111: Software trigger

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▒ąĖčé TEN2 = 1 (čĆą░ąĘčĆąĄčłąĄąĮ čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 2 DAC).

TEN2 (ą▒ąĖčé 18): DAC channel2 trigger enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čéčĆąĖą│ą│ąĄčĆą░ ą║ą░ąĮą░ą╗ą░ 2 DAC. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī/ąĘą░ą┐čĆąĄčéąĖčéčī čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 2 DAC.

0: čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 2 DAC ąĘą░ą┐čĆąĄčēąĄąĮ, ąĖ ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DHRx ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DOR2 čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ ą▓ 1 čéą░ą║čé APB1.

1: čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 2 DAC čĆą░ąĘčĆąĄčłąĄąĮ, ąĖ ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DHRx ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DOR2 čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ ą▓ 3 čéą░ą║čéą░ APB1.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ, ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ DAC_DHRx ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DOR2 ąĘą░ąĮąĖą╝ą░ąĄčé č鹊ą╗čīą║ąŠ 1 čéą░ą║čé APB1.

BOFF2 (ą▒ąĖčé 17): DAC channel2 output buffer disable, ąĘą░ą┐čĆąĄčé ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą▒čāč乥čĆą░ ą║ą░ąĮą░ą╗ą░ 2 DAC. ąŁč鹊čé ą▒ąĖčé ąŠčćąĖčēą░ąĄčéčüčÅ ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī/ąĘą░ą┐čĆąĄčéąĖčéčī ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą║ą░ąĮą░ą╗ą░ 2 DAC.

0: ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą║ą░ąĮą░ą╗ą░ 2 DAC čĆą░ąĘčĆąĄčłąĄąĮ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ).

1: ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą║ą░ąĮą░ą╗ą░ 2 DAC ąĘą░ą┐čĆąĄčēąĄąĮ.

EN2 (ą▒ąĖčé 16): čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ 2 DAC. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī/ąĘą░ą┐čĆąĄčéąĖčéčī ą║ą░ąĮą░ą╗ 2 DAC.

0: ą║ą░ąĮą░ą╗ 2 DAC ąĘą░ą┐čĆąĄčēąĄąĮ.

1: ą║ą░ąĮą░ą╗ 2 DAC čĆą░ąĘčĆąĄčłąĄąĮ.

ąæąĖčéčŗ 15:14 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DMAUDRIE1 (ą▒ąĖčé 13): DAC channel1 DMA underrun interrupt enable, ą▒ąĖčé čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ DMA ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1 DAC. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ).

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ.

DMAEN1 (ą▒ąĖčé 12): DAC channel1 DMA enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ DMA ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1 DAC. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣.

0: čĆąĄąČąĖą╝ DMA ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1 DAC ąĘą░ą┐čĆąĄčēąĄąĮ.

1: čĆąĄąČąĖą╝ DMA ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1 DAC čĆą░ąĘčĆąĄčłąĄąĮ.

MAMP1[3:0] (ą▒ąĖčéčŗ 11:8): ą▓čŗą▒ąŠčĆ ą╝ą░čüą║ąĖ/ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ ą║ą░ąĮą░ą╗ą░ 1 DAC. ąŁčéąĖ ą▒ąĖčéčŗ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ ą▓čŗą▒čĆą░čéčī ą╝ą░čüą║čā ą▓ čĆąĄąČąĖą╝ąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ čłčāą╝ą░, ąĖą╗ąĖ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ ą▓ čĆąĄąČąĖą╝ąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░.

0000: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčéą░ 0 LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 1

0001: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [1:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 3

0010: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [2:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 7

0011: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [3:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 15

0100: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [4:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 31

0101: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [5:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 63

0110: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [6:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 127

0111: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [7:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 255

1000: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [8:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 511

1001: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [9:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 1023

1010: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [10:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 2047

>= 1011: ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé [11:0] LFSR / ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ čĆą░ą▓ąĮą░ 4095

WAVE1[1:0] (ą▒ąĖčéčŗ 7:6): čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆąĄąČąĖą╝ą░ ą│ąĄąĮąĄčĆą░čåąĖąĖ čłčāą╝ą░ ąĖą╗ąĖ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░ ą║ą░ąĮą░ą╗ą░ 1 DAC. ąŁčéąĖ ą▒ąĖčéčŗ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĖ ąŠčćąĖčēą░čÄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣.

00: ą│ąĄąĮąĄčĆą░čåąĖčÅ čüąĖą│ąĮą░ą╗ą░ ąĘą░ą┐čĆąĄčēąĄąĮą░

01: čĆą░ąĘčĆąĄčłąĄąĮą░ ą│ąĄąĮąĄčĆą░čåąĖčÅ čłčāą╝ą░

1x: čĆą░ąĘčĆąĄčłąĄąĮą░ ą│ąĄąĮąĄčĆą░čåąĖčÅ čéčĆąĄčāą│ąŠą╗čīąĮąĖą║ą░

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▒ąĖčé TEN1 = 1 (čĆą░ąĘčĆąĄčłąĄąĮ čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 1 DAC).

TSEL1[2:0] (ą▒ąĖčéčŗ 5:3): DAC channel1 trigger selection, ą▓čŗą▒ąŠčĆ čéčĆąĖą│ą│ąĄčĆą░ ą║ą░ąĮą░ą╗ą░ 1 DAC. ąŁčéąĖ ą▒ąĖčéčŗ ą▓čŗą▒ąĖčĆą░čÄčé ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ (čéčĆąĖą│ą│ąĄčĆ), ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1 DAC.

000: Timer 6 TRGO event

001: Timer 8 TRGO event

010: Timer 7 TRGO event

011: Timer 5 TRGO event

100: Timer 2 TRGO event

101: Timer 4 TRGO event

110: External line9

111: Software trigger

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▒ąĖčé TEN1 = 1 (čĆą░ąĘčĆąĄčłąĄąĮ čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 1 DAC).

TEN1 (ą▒ąĖčé 2): DAC channel1 trigger enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čéčĆąĖą│ą│ąĄčĆą░ ą║ą░ąĮą░ą╗ą░ 1 DAC. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī/ąĘą░ą┐čĆąĄčéąĖčéčī čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 1 DAC.

0: čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 1 DAC ąĘą░ą┐čĆąĄčēąĄąĮ, ąĖ ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DHRx ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DOR1 čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ ą▓ 1 čéą░ą║čé APB1.

1: čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 1 DAC čĆą░ąĘčĆąĄčłąĄąĮ, ąĖ ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DHRx ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DOR1 čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ ą▓ 3 čéą░ą║čéą░ APB1.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ, ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ DAC_DHRx ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DOR1 ąĘą░ąĮąĖą╝ą░ąĄčé č鹊ą╗čīą║ąŠ 1 čéą░ą║čé APB1.

BOFF1 (ą▒ąĖčé 1): DAC channel1 output buffer disable, ąĘą░ą┐čĆąĄčé ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą▒čāč乥čĆą░ ą║ą░ąĮą░ą╗ą░ 1 DAC. ąŁč鹊čé ą▒ąĖčé ąŠčćąĖčēą░ąĄčéčüčÅ ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī/ąĘą░ą┐čĆąĄčéąĖčéčī ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą║ą░ąĮą░ą╗ą░ 1 DAC.

0: ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą║ą░ąĮą░ą╗ą░ 1 DAC čĆą░ąĘčĆąĄčłąĄąĮ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ).

1: ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą║ą░ąĮą░ą╗ą░ 1 DAC ąĘą░ą┐čĆąĄčēąĄąĮ.

EN1 (ą▒ąĖčé 0): čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ 1 DAC. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī/ąĘą░ą┐čĆąĄčéąĖčéčī ą║ą░ąĮą░ą╗ 1 DAC.

0: ą║ą░ąĮą░ą╗ 1 DAC ąĘą░ą┐čĆąĄčēąĄąĮ.

1: ą║ą░ąĮą░ą╗ 1 DAC čĆą░ąĘčĆąĄčłąĄąĮ.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x04

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

SWTRIG2

w |

SWTRIG1

w

|

ąæąĖčéčŗ 31:2 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

SWTRIG2 (ą▒ąĖčé 1): DAC channel2 software trigger, ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 2 DAC. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī/ąĘą░ą┐čĆąĄčéąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ.

0: ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ (SW) ąĘą░ą┐čĆąĄčēąĄąĮ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ).

1: ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ (SW) čĆą░ąĘčĆąĄčłąĄąĮ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čŹč鹊čé ą▒ąĖčé ąŠčćąĖčüčéąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ ą▓ 1 čéą░ą║čé APB1), ą║ą░ą║ č鹊ą╗čīą║ąŠ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ DAC_DHR2 ą▒čŗą╗ąŠ ąĘą░ą│čĆčāąČąĄąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DOR2.

SWTRIG1 (ą▒ąĖčé 0): DAC channel1 software trigger, ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ ą║ą░ąĮą░ą╗ą░ 1 DAC. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī/ąĘą░ą┐čĆąĄčéąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ.

0: ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ (SW) ąĘą░ą┐čĆąĄčēąĄąĮ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ).

1: ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ (SW) čĆą░ąĘčĆąĄčłąĄąĮ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čŹč鹊čé ą▒ąĖčé ąŠčćąĖčüčéąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ (čü ąĘą░ą┤ąĄčƹȹ║ąŠą╣ ą▓ 1 čéą░ą║čé APB1), ą║ą░ą║ č鹊ą╗čīą║ąŠ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ DAC_DHR1 ą▒čŗą╗ąŠ ąĘą░ą│čĆčāąČąĄąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆ DAC_DOR1.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x08

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

DACC1DHR[11:0]

rw

|

ąæąĖčéčŗ 31:12 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DACC1DHR[11:0] (ą▒ąĖčéčŗ 11:0): ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗąĄ ą▓ą┐čĆą░ą▓ąŠ 12-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1 DAC.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x0C

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

DACC1DHR[11:0]

rw

|

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąæąĖčéčŗ 31:16 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DACC1DHR[11:0] (ą▒ąĖčéčŗ 14:4): ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗąĄ ą▓ą╗ąĄą▓ąŠ 12-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1 DAC.

ąæąĖčéčŗ 3:0 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x10

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

DACC1DHR[7:0]

rw

|

ąæąĖčéčŗ 31:8 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DACC1DHR[7:0] (ą▒ąĖčéčŗ 7:0): ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗąĄ ą▓ą┐čĆą░ą▓ąŠ 8-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą║ą░ąĮą░ą╗ą░ 1 DAC.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x14

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

DACC2DHR[11:0]

rw

|

ąæąĖčéčŗ 31:12 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DACC2DHR[11:0] (ą▒ąĖčéčŗ 11:0): ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗąĄ ą▓ą┐čĆą░ą▓ąŠ 12-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2 DAC.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x18

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

DACC2DHR[11:0]

rw

|

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

ąæąĖčéčŗ 31:16 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DACC2DHR[11:0] (ą▒ąĖčéčŗ 14:4): ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗąĄ ą▓ą╗ąĄą▓ąŠ 12-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2 DAC.

ąæąĖčéčŗ 3:0 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x1C

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

DACC2DHR[7:0]

rw

|

ąæąĖčéčŗ 31:8 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DACC2DHR[7:0] (ą▒ąĖčéčŗ 7:0): ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗąĄ ą▓ą┐čĆą░ą▓ąŠ 8-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą║ą░ąĮą░ą╗ą░ 2 DAC.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x20

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

DACC2DHR[11:0]

rw |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

DACC1DHR[11:0]

rw

|

ąæąĖčéčŗ 31:28 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DACC2DHR[11:0] (ą▒ąĖčéčŗ 27:16): DAC channel2 12-bit right-aligned data, ą▓čŗčĆą░ą▓ąĮąĄąĮąĮčŗąĄ ą▓ą┐čĆą░ą▓ąŠ 12-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2 DAC.

ąæąĖčéčŗ 15:12 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DACC1DHR[11:0] (ą▒ąĖčéčŗ 11:0): DAC channel1 12-bit right-aligned data, ą▓čŗčĆą░ą▓ąĮąĄąĮąĮčŗąĄ ą▓ą┐čĆą░ą▓ąŠ 12-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1 DAC.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x24

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

DACC2DHR[11:0]

rw

|

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

DACC1DHR[11:0]

rw

|

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

DACC2DHR[11:0] (ą▒ąĖčéčŗ 31:20): DAC channel2 12-bit left-aligned data, ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗąĄ ą▓ą╗ąĄą▓ąŠ 12-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2 DAC.

ąæąĖčéčŗ 19:16 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DACC1DHR[11:0] (ą▒ąĖčéčŗ 15:4): DAC channel1 12-bit left-aligned data, ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗąĄ ą▓ą╗ąĄą▓ąŠ 12-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1 DAC.

ąæąĖčéčŗ 3:0 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x28

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

DACC2DHR[7:0]

rw

|

DACC1DHR[7:0]

rw

|

ąæąĖčéčŗ 31:16 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DACC2DHR[7:0] (ą▒ąĖčéčŗ 15:8): DAC channel2 8-bit right-aligned data, ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗąĄ ą▓ą┐čĆą░ą▓ąŠ 8-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą║ą░ąĮą░ą╗ą░ 2 DAC.

DACC1DHR[7:0] (ą▒ąĖčéčŗ 7:0): DAC channel1 8-bit right-aligned data, ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗąĄ ą▓ą┐čĆą░ą▓ąŠ 8-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą║ą░ąĮą░ą╗ą░ 1 DAC.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x2C

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

DACC1DOR[11:0]

r

|

ąæąĖčéčŗ 31:12 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DACC1DOR[11:0] (ą▒ąĖčéčŗ 11:0): ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą║ą░ąĮą░ą╗ą░ 1 DAC. ąŁčéąĖ ą▒ąĖčéčŗ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x30

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

DACC2DOR[11:0]

r

|

ąæąĖčéčŗ 31:12 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DACC2DOR[11:0] (ą▒ąĖčéčŗ 11:0): ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą║ą░ąĮą░ą╗ą░ 2 DAC. ąŁčéąĖ ą▒ąĖčéčŗ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x34

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

DMAUDR2

rc_w1 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

DMAUDR1

rc_w1 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąæąĖčéčŗ 31:30 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DMAUDR2 (ą▒ąĖčé 29): DAC channel2 DMA underrun flag, čäą╗ą░ą│ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ DMA ą║ą░ąĮą░ą╗ą░ 2 DAC. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ (ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ ąĮąĄą│ąŠ 1).

0: ąĮąĄ ą▒čŗą╗ąŠ čüąŠą▒čŗčéąĖčÅ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ DMA ąĮą░ ą║ą░ąĮą░ą╗ąĄ 2 DAC.

1: ą▒čŗą╗ąŠ čüąŠą▒čŗčéąĖąĄ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ DMA ąĮą░ ą║ą░ąĮą░ą╗ąĄ 2 DAC. ąÆčŗą▒čĆą░ąĮąĮčŗą╣ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé čéčĆąĖą│ą│ąĄčĆ, čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄą╝ ąĮą░ ą║ą░ąĮą░ą╗ąĄ 2 DAC, čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé čüąŠ čüą╗ąĖčłą║ąŠą╝ ą▓čŗčüąŠą║ąŠą╣ čćą░čüč鹊č鹊ą╣, ą▒ąŠą╗čīčłąĄą╣ č湥ą╝ DMA ą╝ąŠąČąĄčé ąŠą▒čüą╗čāąČąĖčéčī.

ąæąĖčéčŗ 28:14 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DMAUDR1 (ą▒ąĖčé 13): DAC channel1 DMA underrun flag, čäą╗ą░ą│ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ DMA ą║ą░ąĮą░ą╗ą░ 1 DAC. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ (ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ ąĮąĄą│ąŠ 1).

0: ąĮąĄ ą▒čŗą╗ąŠ čüąŠą▒čŗčéąĖčÅ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ DMA ąĮą░ ą║ą░ąĮą░ą╗ąĄ 1 DAC.

1: ą▒čŗą╗ąŠ čüąŠą▒čŗčéąĖąĄ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ DMA ąĮą░ ą║ą░ąĮą░ą╗ąĄ 1 DAC. ąÆčŗą▒čĆą░ąĮąĮčŗą╣ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé čéčĆąĖą│ą│ąĄčĆ, čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄą╝ ąĮą░ ą║ą░ąĮą░ą╗ąĄ 1 DAC, čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé čüąŠ čüą╗ąĖčłą║ąŠą╝ ą▓čŗčüąŠą║ąŠą╣ čćą░čüč鹊č鹊ą╣, ą▒ąŠą╗čīčłąĄą╣ č湥ą╝ DMA ą╝ąŠąČąĄčé ąŠą▒čüą╗čāąČąĖčéčī.

[ą¤čĆąĖą╝ąĄčĆčŗ]

DAC_SignalAny - ą┐čĆąŠąĄą║čé, ąŠčüąĮąŠą▓ą░ ą║ąŠč鹊čĆąŠą│ąŠ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮą░ ą▓ STM32CubeMX čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ FreeRTOS. ą¤čĆąŠčåąĄčüčüąŠčĆ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čćą░čüč鹊č鹥 168 ą£ąōčå, TIM2 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖčüč鹥ą╝ąĮčŗčģ čéąĖą║ąŠą▓ 1 ą╝čü, TIM6 ąĮą░čüčéčĆąŠąĄąĮ ąĮą░ čćą░čüč鹊čéčā čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ 44100 ąōčå (čüą╝. ą╝ą░ą║čĆąŠčü DAC_SAMPLE_RATE). ąöą╗čÅ DAC ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ ąĘą░ą┐čāčüą║ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąÆ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ čüč湥čéčćąĖą║ čäą░ąĘčŗ, ąĖ ą┐ąŠ čéą░ą▒ą╗ąĖčåąĄ čüąĖąĮčāčüą░ ą▒ąĄčĆąĄčéčüčÅ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ DAC (čüą╝. ą║ąŠą┤ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ TIM6_DAC_IRQHandler). ąÜą░ąČą┤čāčÄ čüąĄą║čāąĮą┤čā ą▓ ąĘą░ą┤ą░č湥 StartDefaultTask ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą│ąĄąĮąĄčĆą░čåąĖčÅ ąĮąŠą▓ąŠą╣ čćą░čüč鹊čéčŗ, čćą░čüč鹊čéčŗ ą╝ąĄąĮčÅčÄčéčüčÅ čåąĖą║ą╗ąĖč湥čüą║ąĖ ąŠčé 500 ąōčå ą┤ąŠ 20000 ąōčå čü čłą░ą│ąŠą╝ 500 ąōčå.

DAC_SignalsGeneration - ą┐čĆąŠąĄą║čé ąĖąĘ ą┐čĆąĖą╝ąĄčĆąŠą▓ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĖ STM32Cube_FW_F4_V1.24.0. ąŚą┤ąĄčüčī DAC ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ ą┤ą▓čāčģ čĆąĄąČąĖą╝ą░čģ (čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ąĮą░ąČą░čéąĖąĄą╝ ą║ąĮąŠą┐ą║ąĖ Tamper/Key) - ą╗ąĖą▒ąŠ ą│ąĄąĮąĄčĆą░čåąĖčÅ čéčĆąĄčāą│ąŠą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą╗ąĖą▒ąŠ ą╗ąĄčüčéąĮąĖčćąĮąŠą│ąŠ. ąōąĄąĮąĄčĆą░čåąĖąĄą╣ ą╗ąĄčüčéąĮąĖčćąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čāą┐čĆą░ą▓ą╗čÅąĄčé DMA, ą▒ąĄąĘ čāčćą░čüčéąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. DMA ą┐ąŠčüčŗą╗ą░ąĄčé ą▓ DAC 6 čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ąĖąĘ ą╝ą░čüčüąĖą▓ą░ aEscalator8bit[6], čüą╝ąĄąĮą░ ąĘąĮą░č湥ąĮąĖą╣ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąŠ čéčĆąĖą│ą│ąĄčĆčā čéą░ą╣ą╝ąĄčĆą░ TIM6.

ą¤čĆąĖą╝ąĄčĆčŗ ą╝ąŠąČąĮąŠ čüą║ą░čćą░čéčī ą▓ ą░čĆčģąĖą▓ąĄ [2], ąŠąĮąĖ ą║ąŠą╝ą┐ąĖą╗ąĖčĆąŠą▓ą░ą╗ąĖčüčī ąĖ č鹥čüčéąĖčĆąŠą▓ą░ą╗ąĖčüčī ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ IAR 8.30.

[ąĪčüčŗą╗ą║ąĖ]

1. RM0090 Reference manual STM32F405/415, STM32F407/417, STM32F427/437 and STM32F429/439 advanced Arm®-based 32-bit MCUs site:st.com.

2. 200312STM32F429-DAC-examples.zip - ą┐čĆąĖą╝ąĄčĆčŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ DAC. |