|

ąŁč鹊čé ą┤ąŠą║čāą╝ąĄąĮčé (ą┐ąĄčĆąĄą▓ąŠą┤ čĆą░ąĘą┤ąĄą╗ą░ "Universal serial bus full-speed device interface (USB)" ąĖąĘ ą┤ą░čéą░čłąĖčéą░ [1]) ąŠčéąĮąŠčüąĖčéčüčÅ ą║ ą┐ąĄčĆąĖč乥čĆąĖąĖ USB ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ čüąĄą╝ąĄą╣čüčéą▓ STM32F103xx ąĖ STM32F102xx. ąÆčüąĄ ąĮąĄą┐ąŠąĮčÅčéąĮčŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ąĪą╗ąŠą▓ą░čĆąĖą║ąĄ [4].

ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB čĆąĄą░ą╗ąĖąĘčāąĄčé ąĖąĮč鹥čĆč乥ą╣čü ą╝ąĄąČą┤čā čłąĖąĮąŠą╣ full-speed USB 2.0 ąĖ čłąĖąĮąŠą╣ APB1 ą┐čĆąŠčåąĄčüčüąŠčĆą░. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ čüąĖą│ąĮą░ą╗čŗ USB suspend/resume, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ąŠčüčéą░ąĮąŠą▓ąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ą╗čÅ čüąĮąĖąČąĄąĮąĖčÅ čŹąĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ.

ą×čüąĮąŠą▓ąĮčŗąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗąĄ čäčāąĮą║čåąĖąĖ ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ:

ŌĆó ąĪąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī čüąŠ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĄą╣ USB 2.0 full-speed.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ ąŠčé 1 ą┤ąŠ 8.

ŌĆó ąōąĄąĮąĄčĆą░čåąĖčÅ/ą┐čĆąŠą▓ąĄčĆą║ą░ CRC, ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ NRZI ąĖ bit-stuffing.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ ąĖąĘąŠčģčĆąŠąĮąĮčŗčģ (isochronous) čéčĆą░ąĮąĘą░ą║čåąĖą╣.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ bulk/isochronous.

ŌĆó ą×ą┐ąĄčĆą░čåąĖąĖ USB Suspend/Resume.

ŌĆó ąōąĄąĮąĄčĆą░čåąĖčÅ ąĖą╝ą┐čāą╗čīčüąŠą▓ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┐ąŠ čäčĆąĄą╣ą╝čā (Frame locked clock pulse generation).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ MCU ą║ą╗ą░čüčüąŠą▓ low-density, medium-density, high-density ąĖ XL-density, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ USB ąĖ CAN ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą▒čēčāčÄ ą┐ą░ą╝čÅčéčī SRAM čĆą░ąĘą╝ąĄčĆąŠą╝ 512 ą▒ą░ą╣čé ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░, ą┐ąŠčŹč鹊ą╝čā čŹčéąĖ ąĖąĮč鹥čĆč乥ą╣čüčŗ ąĮąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ (ą║ čŹč鹊ą╣ ąŠą▒čēąĄą╣ RAM ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čŹą║čüą║ą╗čĹʹĖą▓ąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ą░ą║ čüąŠ čüč鹊čĆąŠąĮčŗ CAN, čéą░ą║ ąĖ USB). ą¤ąŠčŹč鹊ą╝čā USB ąĖ CAN ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ ąŠą┤ąĮąŠą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ, ąĮąŠ ąĮąĄ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ.

ąŁč鹊 čāčüą╗ąŠą▓ąĮą░čÅ ą║ą╗ą░čüčüąĖčäąĖą║ą░čåąĖčÅ MCU ąŠčé ą║ąŠą╝ą┐ą░ąĮąĖąĖ ST ą┐ąŠ čĆą░ąĘą╝ąĄčĆčā ą┐ą░ą╝čÅčéąĖ.

Low-density čŹč鹊 MCU STM32F101xx, STM32F102xx ąĖ STM32F103xx, čā ą║ąŠč鹊čĆčŗčģ čĆą░ąĘą╝ąĄčĆ Flash-ą┐ą░ą╝čÅčéąĖ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 16 ą┤ąŠ 32 ą║ąĖą╗ąŠą▒ą░ą╣čé.

Medium-density čŹč鹊 MCU STM32F101xx, STM32F102xx ąĖ STM32F103xx, čā ą║ąŠč鹊čĆčŗčģ čĆą░ąĘą╝ąĄčĆ Flash-ą┐ą░ą╝čÅčéąĖ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 64 ą┤ąŠ 128 ą║ąĖą╗ąŠą▒ą░ą╣čé.

High-density čŹč鹊 MCU STM32F101xx ąĖ STM32F103xx, čā ą║ąŠč鹊čĆčŗčģ čĆą░ąĘą╝ąĄčĆ Flash-ą┐ą░ą╝čÅčéąĖ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 256 ą┤ąŠ 512 ą║ąĖą╗ąŠą▒ą░ą╣čé.

XL-density čŹč鹊 MCU STM32F101xx ąĖ STM32F103xx, čā ą║ąŠč鹊čĆčŗčģ čĆą░ąĘą╝ąĄčĆ Flash-ą┐ą░ą╝čÅčéąĖ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 768 ą┤ąŠ 1 ą╝ąĄą│ą░ą▒ą░ą╣čéą░.

Connectivity line čŹč鹊 MCU STM32F105xx ąĖ STM32F107xx.

ąŚą┤ąĄčüčī xx čŹč鹊 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą▒čāą║ą▓ąĄąĮąĮčŗąĄ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖčÅ, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖčģ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÄ MCU (čéąĖą┐ ą║ąŠčĆą┐čāčüą░, č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĖ čé. ą┐.).

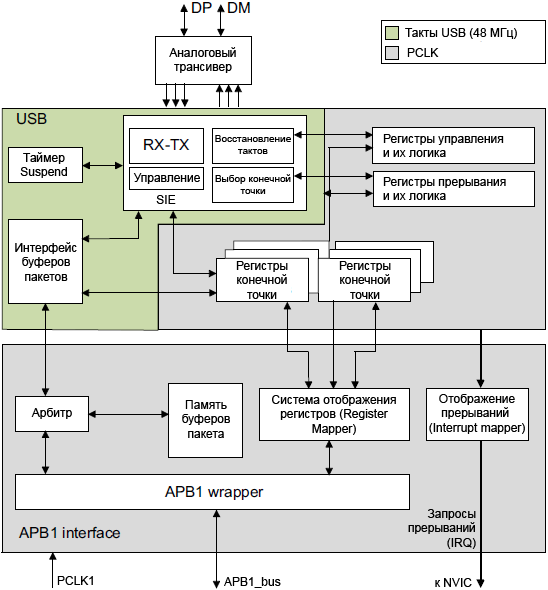

ąØą░ čĆąĖčü. 220 ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░) USB.

ąĀąĖčü. 220. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB ą┤ą╗čÅ MCU čüąĄą╝ąĄą╣čüčéą▓ STM32F103xx ąĖ STM32F102xx.

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé USB-čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą╝ąĄąČą┤čā čģąŠčüč鹊ą╝ PC (čģąŠčüč鹊ą╝ PC ąĮą░ąĘčŗą▓ą░čÄčé ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čłąĖąĮąĄ USB, čŹč鹊 ąŠą▒čŗčćąĮąŠ ą║ąŠą╝ą┐čīčÄč鹥čĆ) ąĖ čäčāąĮą║čåąĖąĄą╣ (čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ USB ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą║ą╗ą░čüčüąŠą▓), čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąĮąŠą╣ ą▓ MCU. ą¤ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā čģąŠčüč鹊ą╝ PC ąĖ čüąĖčüč鹥ą╝ąĮąŠą╣ ą┐ą░ą╝čÅčéčīčÄ MCU ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ č湥čĆąĄąĘ ą▓čŗą┤ąĄą╗ąĄąĮąĮčāčÄ ą▒čāč乥čĆąĮčāčÄ ą┐ą░ą╝čÅčéčī ą┐ą░ą║ąĄčéą░, ą║ ą║ąŠč鹊čĆąŠą╣ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą┐ąŠą╗čāčćą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB. ąĀą░ąĘą╝ąĄčĆ čŹč鹊ą╣ ą▓čŗą┤ąĄą╗ąĄąĮąĮąŠą╣ ą▒čāč乥čĆąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą┤ąŠą╗ąČąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī ą║ąŠą╗ąĖč湥čüčéą▓čā ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╝čā čĆą░ąĘą╝ąĄčĆčā ą┐ą░ą║ąĄčéą░. ąŁčéą░ ą▓čŗą┤ąĄą╗ąĄąĮąĮą░čÅ ą┐ą░ą╝čÅčéčī ąĖą╝ąĄąĄčé čĆą░ąĘą╝ąĄčĆ 512 ą▒ą░ą╣čé, ąĖ ą╝ąŠąČąĄčé ąŠą▒čüą╗čāąČąĖą▓ą░čéčī ą┤ąŠ 16 ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║, ąĖą╗ąĖ ą┤ąŠ 8 ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ USB ą┤ąĄč鹥ą║čéąĖčĆčāąĄčé č鹊ą║ąĄąĮčŗ ą┐ą░ą║ąĄč鹊ą▓, ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā/ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ ąĖ ą┐ą░ą║ąĄčéčŗ čĆčāą║ąŠą┐ąŠąČą░čéąĖčÅ (handshake packet), ą║ą░ą║ č鹊ą│ąŠ čéčĆąĄą▒čāąĄčé čüčéą░ąĮą┤ą░čĆčé USB. ążąŠčĆą╝ą░čéąĖčĆąŠą▓ą░ąĮąĖąĄ čéčĆą░ąĮąĘą░ą║čåąĖą╣ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą▓ą║ą╗čÄčćą░čÅ ą│ąĄąĮąĄčĆą░čåąĖčÄ ąĖ ą┐čĆąŠą▓ąĄčĆą║čā CRC.

ąÜą░ąČą┤ą░čÅ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ čüą▓čÅąĘą░ąĮą░ čü ą▒ą╗ąŠą║ąŠą╝ ąŠą┐ąĖčüą░ąĮąĖčÅ ą▒čāč乥čĆą░ (buffer description block), ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖą╝, ą║ą░ą║ą░čÅ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ ą▓čŗą┤ąĄą╗ąĄąĮą░ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĄ - ąĄčæ ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ąĖ čĆą░ąĘą╝ąĄčĆ, čé. ąĄ. čüą║ąŠą╗čīą║ąŠ ą▒ą░ą╣čé ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮąŠ. ąÜąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ USB ąŠą▒ąĮą░čĆčāąČąĄąĮą░ ą┤ąŠą┐čāčüčéąĖą╝ą░čÅ ą┐ą░čĆą░ čäčāąĮą║čåąĖčÅ/ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░, ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ čéčĆą░ąĮąĘą░ą║čåąĖčÅ ą┤ą░ąĮąĮčŗčģ (ąĄčüą╗ąĖ čŹč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, ąĖ ąĄčüą╗ąĖ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░). ąöą░ąĮąĮčŗąĄ, ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ USB, ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ 16-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ, ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ ą▓čŗą┤ąĄą╗ąĄąĮąĮąŠą╝čā ą▒čāč乥čĆčā. ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮčŗ ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ, č鹊 ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ handshake-ą┐ą░ą║ąĄčé ą┐ąŠ čłąĖąĮąĄ USB, ąĖą╗ąĖ ąŠąČąĖą┤ą░ąĄčéčüčÅ ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄ čéą░ą║ąŠą│ąŠ ą┐ą░ą║ąĄčéą░ - ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ.

ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąŠčéąĮąŠčüčÅčēąĄąĄčüčÅ ą║ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĄ, ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ čüąŠčüč鹊čÅąĮąĖą╣ ąĖ/ąĖą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čĆą░ąĘąĮčŗąĄ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. MCU ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī:

ŌĆó ą×ą▒čüą╗čāąČąĖą▓ą░ąĄą╝čāčÄ ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā.

ŌĆó ąóąĖą┐ ą┐čĆąŠąĖąĘąŠčłąĄą┤čłąĄą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ, ą┐čĆąŠąĖąĘąŠčłą╗ąĖ ą╗ąĖ ąŠčłąĖą▒ą║ąĖ (čéą░ą║ąĖąĄ ą║ą░ą║ ąŠčłąĖą▒ą║ąĖ bit-stuffing, format, CRC, ą┐čĆąŠč鹊ą║ąŠą╗ą░, ąŠčéčüčāčéčüčéą▓ąĖąĄ ACK, over/underrun).

ąöą╗čÅ ąĖąĘąŠčģčĆąŠąĮąĮčŗčģ ąĖ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗčģ bulk-čéčĆą░ąĮąĘą░ą║čåąĖą╣ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮą░čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ą░ ą▓ ą▓ąĖą┤ąĄ ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čüąĄą│ą┤ą░ ąĖą╝ąĄčéčī ą┤ąŠčüčéčāą┐ąĮčŗą╣ ą▒čāč乥čĆ ą┤ą╗čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ MCU ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┤čĆčāą│ąŠą╣ ą▒čāč乥čĆ.

ąÜąŠą│ą┤ą░ čŹč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, ą▒ą╗ąŠą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ čĆąĄąČąĖą╝ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (SUSPEND mode) ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ąóąŠą│ą┤ą░ ąĖąĘą▒ąĄą│ą░ąĄčéčüčÅ ą╗čÄą▒ąŠąĄ čüčéą░čéąĖč湥čüą║ąŠąĄ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ 菹ĮąĄčĆą│ąĖąĖ, ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ USB ąĘą░ą╝ąĄą┤ą╗čÅąĄčéčüčÅ ąĖą╗ąĖ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ. ą¤čĆąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĖ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ąĮą░ ą▓čģąŠą┤ą░čģ USB, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ low-power mode, ą░čüąĖąĮčģčĆąŠąĮąĮąŠ ą▓čŗą▓ąĄą┤ąĄčé čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĖąĘ čüąĮą░. ąÜ čüąĖą│ąĮą░ą╗čā ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ (wakeup line) ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čćč鹊ą▒čŗ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī čüąĖčüč鹥ą╝ąĄ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąĄčĆąĄąĘą░ą┐čāčüčéąĖčéčīčüčÅ čü ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ čéą░ą║č鹊ą▓ ąĖ/ąĖą╗ąĖ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠą│ąŠ ąĘą░ą┐čāčüą║ą░/ąŠčüčéą░ąĮąŠą▓ą║ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ.

[ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ą╗ąŠą║ąŠą▓ USB]

ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB čĆąĄą░ą╗ąĖąĘčāąĄčé ą▓čüąĄ čäčāąĮą║čåąĖąĖ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ USB, ą║ąŠč鹊čĆčŗąĄ ą▓ą║ą╗čÄčćą░čÄčé čüą╗ąĄą┤čāčÄčēąĖąĄ ą▒ą╗ąŠą║ąĖ:

ŌĆó Serial Interface Engine (SIE): čäčāąĮą║čåąĖąĖ ą▓ čŹč鹊ą╝ ą▒ą╗ąŠą║ąĄ ą▓ą║ą╗čÄčćą░čÄčé čĆą░čüą┐ąŠąĘąĮą░ą▓ą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüč鹥ą╣ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, bit-stuffing, ą│ąĄąĮąĄčĆą░čåąĖčÄ ąĖ ą┐čĆąŠą▓ąĄčĆą║čā CRC, ą┐čĆąŠą▓ąĄčĆą║čā ąĖ ą│ąĄąĮąĄčĆą░čåąĖčÄ PID, ą▓čŗčćąĖčüą╗ąĄąĮąĖąĄ handshake. ąŁč鹊 ą┤ąŠą╗ąČąĮąŠ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ąĖąĮč鹥čĆč乥ą╣čü čü čéčĆą░ąĮčüąĖą▓ąĄčĆą░ą╝ąĖ USB ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓ąĖčĆčéčāą░ą╗čīąĮčŗąĄ ą▒čāč乥čĆčŗ, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄą╝čŗąĄ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ ą║ ą╗ąŠą║ą░ą╗čīąĮąŠą╝čā čģčĆą░ąĮąĖą╗ąĖčēčā ą┤ą░ąĮąĮčŗčģ. ąŁč鹊čé ą▒ą╗ąŠą║ čéą░ą║ąČąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗čŗ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čüąŠą▒čŗčéąĖčÅą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖąĖ USB, čéą░ą║ąĖą╝ąĖ ą║ą░ą║ Start of Frame (SOF), USB_Reset, Data errors ąĖ čé. ą┤., ąĖ ą┤ą╗čÅ čüąŠą▒čŗčéąĖą╣, čüą▓čÅąĘą░ąĮąĮčŗčģ čü čüąŠą▒čŗčéąĖčÅą╝ąĖ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╗ąĖ ą║ąŠčĆčĆąĄą║čéąĮąŠą│ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░; čŹčéąĖ čüąĖą│ąĮą░ą╗čŗ ąĘą░č鹥ą╝ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ŌĆó ąóą░ą╣ą╝ąĄčĆ: čŹč鹊čé ą▒ą╗ąŠą║ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĖą╝ą┐čāą╗čīčü, čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄą╝čŗą╣ ą┐ąŠ čüąĖą│ąĮą░ą╗čā ąĮą░čćą░ą╗ą░ čäčĆąĄą╣ą╝ą░ (start-of-frame, SOF), ąĖ ą┤ąĄč鹥ą║čéąĖčĆčāąĄčé ą│ą╗ąŠą▒ą░ą╗čīąĮčāčÄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║čā (global suspend, ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čģąŠčüč鹊ą╝), ą║ąŠą│ą┤ą░ ąĮąĄ ą▒čŗą╗ąŠ čéčĆą░čäąĖą║ą░ ą▓ č鹥č湥ąĮąĖąĄ ą▓čĆąĄą╝ąĄąĮąĖ 3 ą╝čü ąĖ ą▒ąŠą╗ąĄąĄ.

ŌĆó Packet Buffer Interface (ąĖąĮč鹥čĆč乥ą╣čü ą▒čāč乥čĆą░ ą┐ą░ą║ąĄčéą░): čŹč鹊čé ą▒ą╗ąŠą║ čāą┐čĆą░ą▓ą╗čÅąĄčé ą╗ąŠą║ą░ą╗čīąĮąŠą╣ ą┐ą░ą╝čÅčéčīčÄ, ą│ąĖą▒ą║ąŠ čĆąĄą░ą╗ąĖąĘčāčÅ ąĮą░ą▒ąŠčĆ ą▒čāč乥čĆąŠą▓ ą║ą░ą║ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, čéą░ą║ ąĖ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░. ą×ąĮ ą▓čŗą▒ąĖčĆą░ąĄčé ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╣ ą▒čāč乥čĆ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĘą░ą┐čĆąŠčüą░ą╝ąĖ, ą┐čĆąĖčģąŠą┤čÅčēąĖą╝ąĖ ąŠčé SIE, ąĖ čĆą░ąĘą╝ąĄčēą░ąĄčé ąĖčģ ą▓ ą┐ą░ą╝čÅčéąĖ, ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą╣ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ. ą×ąĮ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčé ą░ą┤čĆąĄčü ą┐ąŠčüą╗ąĄ ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖčÅ ą║ą░ąČą┤ąŠą│ąŠ čüą╗ąŠą▓ą░ ąŠą▒ą╝ąĄąĮą░ ą┤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ą░ą║ąĄčéą░, ąŠčéčüą╗ąĄąČąĖą▓ą░čÅ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐čĆąŠčłąĄą┤čłąĖčģ ą▒čāč乥čĆąŠą▓ ąĖ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░čÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ ą▒čāč乥čĆą░ čüą▓ąĄčĆčģ ąĄą│ąŠ ąĄą╝ą║ąŠčüčéąĖ.

ŌĆó ąĀąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║: čā ą║ą░ąČą┤ąŠą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ąĄčüčéčī čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ąĮąĄą╣ čĆąĄą│ąĖčüčéčĆčŗ, ą│ą┤ąĄ čüąŠą┤ąĄčƹȹĖčéčüčÅ čéąĖą┐ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ąĖ ąĄčæ č鹥ą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ. ąöą╗čÅ ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ čü ąŠą┤ąĮąĖą╝ ą▒čāč乥čĆąŠą╝ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą┤ą▓čāčģ čĆą░ąĘąĮčŗčģ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąŠą┤ąĖąĮ čĆąĄą│ąĖčüčéčĆ. ąÆčüąĄą│ąŠ čĆąĄą│ąĖčüčéčĆąŠą▓ 8, čćč鹊 ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ą┤ąŠ 16 ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ čü ąŠą┤ąĮąĖą╝ ą▒čāč乥čĆąŠą╝, ąĖą╗ąĖ ą┤ąŠ 7 ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ čü ą┤ą▓ąŠą╣ąĮčŗą╝ ą▒čāč乥čĆąŠą╝ ą▓ ą╗čÄą▒ąŠą╣ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ 4 ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣ ąĖ 8 ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ čü ąŠą┤ąĮąĖą╝ ą▒čāč乥čĆąŠą╝.

ŌĆó ąĀąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ: čŹč鹊 čĆąĄą│ąĖčüčéčĆčŗ, čüąŠą┤ąĄčƹȹ░čēąĖąĄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ čüąŠčüč鹊čÅąĮąĖąĖ ą▓čüąĄą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ USB, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ ąŠčéčüą╗ąĄąČąĖą▓ą░ąĮąĖčÅ ąĮąĄą║ąŠč鹊čĆčŗčģ čüąŠą▒čŗčéąĖą╣ USB, čéą░ą║ąĖčģ ą║ą░ą║ resume (ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ) ąĖ power-down (ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ).

ŌĆó ąĀąĄą│ąĖčüčéčĆčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣: čüąŠą┤ąĄčƹȹ░čé ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčé čüąŠą▒čŗčéąĖčÅ. ą×ąĮąĖ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĖčćąĖąĮčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖą╗ąĖ ąŠčćąĖčüčéą║ąĖ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąŠąČąĖą┤ą░čÄčēąĄą│ąŠ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ.

ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ą║ čłąĖąĮąĄ APB1 č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü APB1, čüąŠą┤ąĄčƹȹ░čēąĖą╣ čüą╗ąĄą┤čāčÄčēąĖąĄ ą▒ą╗ąŠą║ąĖ:

ŌĆó ą¤ą░ą╝čÅčéčī ą┐ą░ą║ąĄč鹊ą▓ (Packet Memory): čŹč鹊 ą╗ąŠą║ą░ą╗čīąĮą░čÅ ą┐ą░ą╝čÅčéčī, ą│ą┤ąĄ čäąĖąĘąĖč湥čüą║ąĖ čüąŠą┤ąĄčƹȹ░čéčüčÅ ą▒čāč乥čĆčŗ ą┐ą░ą║ąĄč鹊ą▓ (Packet Buffers). ą×ąĮą░ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ ą▒čāč乥čĆą░ ą┐ą░ą║ąĄč鹊ą▓, ą║ąŠč鹊čĆčŗą╣ čüąŠąĘą┤ą░ąĄčé čüčéčĆčāą║čéčāčĆčā ą┤ą░ąĮąĮčŗčģ ąĖ ą║ ą║ąŠč鹊čĆąŠą╝čā ą╝ąŠąČąĮąŠ ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ąĖąĘ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąĀą░ąĘą╝ąĄčĆ Packet Memory čüąŠčüčéą░ą▓ą╗čÅąĄčé 512 ą▒ą░ą╣čé, čćč鹊 čüčéčĆčāą║čéčāčĆąĖčĆąŠą▓ą░ąĮąŠ ą║ą░ą║ 256 čüą╗ąŠą▓ ą┐ąŠ 16 ą▒ąĖčé.

ŌĆó ąÉčĆą▒ąĖčéčĆ: čŹč鹊čé ą▒ą╗ąŠą║ ą┐ąŠą╗čāčćą░ąĄčé ąĘą░ą┐čĆąŠčüčŗ ą║ ą┐ą░ą╝čÅčéąĖ, ą┐ąŠčüčéčāą┐ą░čÄčēąĖąĄ ąŠčé čłąĖąĮčŗ APB1 ąĖ ąŠčé ąĖąĮč鹥čĆč乥ą╣čüą░ USB. ą×ąĮ čĆą░ąĘčĆąĄčłą░ąĄčé ą║ąŠąĮčäą╗ąĖą║čéčŗ ą┤ą░ą▓ą░čÅ ą┐čĆąĖąŠčĆąĖč鹥čé ą┤ąŠčüčéčāą┐ą░ ą║ APB1, ą┐čĆąĖ čŹč鹊ą╝ ą▓čüąĄą│ą┤ą░ čĆąĄąĘąĄčĆą▓ąĖčĆčāąĄčéčüčÅ ą┐ąŠą╗ąŠą▓ąĖąĮą░ ą┐ąŠą╗ąŠčüčŗ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą▓čüąĄčģ čéčĆą░ąĮąĘą░ą║čåąĖą╣ USB. ąŁčéą░ ą▓čĆąĄą╝ąĄąĮąĮą░čÅ ą┤čāą┐ą╗ąĄą║čüąĮą░čÅ čüčģąĄą╝ą░ čĆąĄą░ą╗ąĖąĘčāąĄčé ą▓ąĖčĆčéčāą░ą╗čīąĮčāčÄ ą┤ą▓čāčģą┐ąŠčĆč鹊ą▓čāčÄ SRAM, ą┐ąŠąĘą▓ąŠą╗čÅčÄčēčāčÄ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ USB. ą¤ąŠ čŹč鹊ą╣ čüčģąĄą╝ąĄ čéą░ą║ąČąĄ ą┐ąŠąĘą▓ąŠą╗čÅčÄčéčüčÅ ą╝ąĮąŠą│ąŠčüą╗ąŠą▓ąĮčŗąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ APB1 ą╗čÄą▒ąŠą╣ ą┤ą╗ąĖąĮčŗ.

ŌĆó ąĪąĖčüč鹥ą╝ą░ ą┐čĆąĖą▓čÅąĘą║ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ (Register Mapper): čŹč鹊čé ą▒ą╗ąŠą║ čüąŠą▒ąĖčĆą░ąĄčé čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą▒ą░ą╣č鹊ą▓čŗąĄ ąĖ ą▒ąĖč鹊ą▓čŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ą┐ąĄčĆąĖč乥čĆąĖąĖ USB ą▓ čüčéčĆčāą║čéčāčĆąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ąĮą░ą▒ąŠčĆ 16-ą▒ąĖčéąĮčŗčģ čüą╗ąŠą▓, ą░ą┤čĆąĄčüčāąĄą╝čŗčģ ą┐ąŠ čłąĖąĮąĄ APB1.

ŌĆó APB1 Wrapper: ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĖąĮč鹥čĆč乥ą╣čü ą║ APB1 ą┤ą╗čÅ ą┐ą░ą╝čÅčéąĖ ąĖ čĆąĄą│ąĖčüčéčĆą░. ą×ąĮ čéą░ą║ąČąĄ ąŠč鹊ą▒čĆą░ąČą░ąĄčé ą▓čüąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB ąĮą░ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ APB1.

ŌĆó Interrupt Mapper: čŹč鹊čé ą▒ą╗ąŠą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░, ą║ą░ą║ąĖąĄ ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ čüąŠą▒čŗčéąĖčÅ USB ą╝ąŠą│čāčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĖ ą┐čĆąĖą▓čÅąĘčŗą▓ą░ąĄčé ąĖčģ ą║ čéčĆąĄą╝ čĆą░ąĘąĮčŗą╝ ą╗ąĖąĮąĖčÅą╝ NVIC:

ŌĆō ąĮąĖąĘą║ąŠą┐čĆąĖąŠčĆąĖč鹥čéąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ USB (ą║ą░ąĮą░ą╗ 20): ą▓čŗąĘčŗą▓ą░ąĄčéčüčÅ ą▓čüąĄą╝ąĖ čüąŠą▒čŗčéąĖčÅą╝ąĖ USB (ą║ąŠčĆčĆąĄą║čéąĮą░čÅ čéčĆą░ąĮąĘą░ą║čåąĖčÅ, čüą▒čĆąŠčü USB, ąĖ čé. ą┤.). Firmware ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠą▓ąĄčĆąĖčéčī ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆō ą▓čŗčüąŠą║ąŠą┐čĆąĖąŠčĆąĖč鹥čéąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ USB (ą║ą░ąĮą░ą╗ 19): ą▓čŗąĘčŗą▓ą░ąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄą╝ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ ąĖąĘąŠčģčĆąŠąĮąĮąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ąĖ bulk-čéčĆą░ąĮąĘą░ą║čåąĖąĖ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣, čćč鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī čüą░ą╝čŗčģ ą▓čŗčüąŠą║ąĖčģ ą▓ąŠąĘą╝ąŠąČąĮčŗčģ čüą║ąŠčĆąŠčüč鹥ą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ŌĆō USB wakeup interrupt (ą║ą░ąĮą░ą╗ 42): čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ąŠčé čüąŠą▒čŗčéąĖčÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ (wakeup event) ąĖąĘ čĆąĄąČąĖą╝ą░ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ USB (USB Suspend).

ąÆ čüą╗ąĄą┤čāčÄčēąĖčģ čüąĄą║čåąĖčÅčģ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ čüą┐ąŠčüąŠą▒čŗ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖčÅ ą╝ąĄąČą┤čā ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ USB ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, čćč鹊ą▒čŗ čāą┐čĆąŠčüčéąĖčéčī čĆą░ąĘčĆą░ą▒ąŠčéą║čā firmware ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

[ą×ą▒čēąĄąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ USB]

ąÆ čŹč鹊ą╣ čüąĄą║čåąĖąĖ ąŠą┐ąĖčüą░ąĮčŗ ąŠčüąĮąŠą▓ąĮčŗąĄ ąĘą░ą┤ą░čćąĖ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, čéčĆąĄą▒čāąĄą╝čŗąĄ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ USB-čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠą│ąŠ ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ. ąÜ čŹčéąĖą╝ ą┤ąĄą╣čüčéą▓ąĖčÅą╝ ąŠčéąĮąŠčüčÅčéčüčÅ ąŠą▒čĆą░ą▒ąŠčéą║ą░ ąŠčüąĮąŠą▓ąĮčŗčģ čüąŠą▒čŗčéąĖą╣ USB ąĖ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ čüą╗čāčćą░ąĖ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣ ąĖ ąĖąĘąŠčģčĆąŠąĮąĮčŗąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ąÜčĆąŠą╝ąĄ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░, ą┤ąĄą╣čüčéą▓ąĖąĄ ą▓čüąĄą│ą┤ą░ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ USB, čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗą╝ ąŠą┤ąĮąĖą╝ ąĖąĘ čüąŠą▒čŗčéąĖą╣ USB, ąŠą┐ąĖčüą░ąĮąĮčŗčģ ąĮąĖąČąĄ.

System reset ąĖ power-on reset. ą¤čĆąĖ čüąĖčüč鹥ą╝ąĮąŠą╝ čüą▒čĆąŠčüąĄ ąĖ čüą▒čĆąŠčüąĄ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ą┐ąĄčĆą▓ąŠąĄ, čćč鹊 ą┤ąŠą╗ąČąĮą░ čüą┤ąĄą╗ą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝ą░ - ąĮą░čüčéčĆąŠąĖčéčī ą▓čüąĄ čéčĆąĄą▒čāąĄą╝čŗąĄ čüąĖą│ąĮą░ą╗čŗ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ USB, ąĖ ąĘą░č鹥ą╝ čüąĮčÅčéčī ąĄą│ąŠ čüąĖą│ąĮą░ą╗ reset, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ USB. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓čüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ (čüą╝. ą┤ą░ą╗ąĄąĄ).

ą¤ąĄčĆą▓čŗą╣ čłą░ą│, ą║ąŠč鹊čĆčŗą╣ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąĄą┤ą┐čĆąĖąĮčÅčéčī ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ - ą░ą║čéąĖą▓ą░čåąĖčÅ čéą░ą║č鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ ą╝ą░ą║čĆąŠčÅč湥ą╣ą║ąĖ ąĖ čüąĮčÅčéčī ąĄąĄ čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░, ąĖčüą┐ąŠą╗čīąĘčāčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▒ąĖčéčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╗ąŠą│ąĖą║ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝.

ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą░ąĮą░ą╗ąŠą│ąŠą▓ą░čÅ čćą░čüčéčī čāčüčéčĆąŠą╣čüčéą▓ą░, čüą▓čÅąĘą░ąĮąĮą░čÅ čü čéčĆą░ąĮčüąĖą▓ąĄčĆąŠą╝ USB, ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓ą║ą╗čÄč湥ąĮą░ čü ą┐ąŠą╝ąŠčēčīčÄ ą▒ąĖčéą░ PDWN ą▓ čĆąĄą│ąĖčüčéčĆąĄ CNTR, ą║ąŠč鹊čĆčŗą╣ čéčĆąĄą▒čāąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ. ąŁč鹊čé ą▒ąĖčé ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ą┐ąĖčéą░čÄčé ą┐ąŠčĆčé čéčĆą░ąĮčüąĖą▓ąĄčĆą░. ąŻ čŹč鹊ą╣ čüčģąĄą╝čŗ ąĄčüčéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą▓čĆąĄą╝čÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ (startup time, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝ąŠąĄ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą╝ tSTARTUP ąĖąĘ ą┤ą░čéą░čłąĖčéą░), ą▓ č鹥č湥ąĮąĖąĄ ą║ąŠč鹊čĆąŠą│ąŠ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čéčĆą░ąĮčüąĖą▓ąĄčĆą░ USB ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ. ą¤ąŠčŹč鹊ą╝čā čüą╗ąĄą┤čāąĄčé ą┐ąŠą┤ąŠąČą┤ą░čéčī čŹč鹊 ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ PDWN ą▓ čĆąĄą│ąĖčüčéčĆąĄ CNTR ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ čüąĮčÅčéčī čüąĖą│ąĮą░ą╗ reset čü ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ USB (ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ FRES ą▓ čĆąĄą│ąĖčüčéčĆąĄ CNTR ). ąŚą░č鹥ą╝ ąŠčćąĖčüčéą║ą░ ą▒ąĖčéą░ ISTR ąŠčćąĖčēą░ąĄčé ą╗čÄą▒čŗąĄ čüą╗čāčćą░ą╣ąĮčŗąĄ ąŠąČąĖą┤ą░čÄčēąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą╗čÄą▒ą░čÅ ą┤čĆčāą│ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ ą╝ą░ą║čĆąŠčÅč湥ą╣ą║ąĖ.

ą¤čĆąĖ čüąĖčüč鹥ą╝ąĮąŠą╝ čüą▒čĆąŠčüąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┤ąŠą╗ąČąĄąĮ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī ą▓čüąĄ čéčĆąĄą▒čāąĄą╝čŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĖ čéą░ą▒ą╗ąĖčåčā ąŠą┐ąĖčüą░ąĮąĖčÅ ą▒čāč乥čĆą░ ą┐ą░ą║ąĄčéą░, čćč鹊ą▒čŗ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB ą╝ąŠą│ą╗ąŠ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą┤ą░ąĮąĮčŗčģ. ąÆčüąĄ čĆąĄą│ąĖčüčéčĆčŗ, ąĮąĄ ąŠčéąĮąŠčüčÅčēąĖąĄčüčÅ ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĄ, ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮčŗ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĮčāąČą┤ą░ą╝ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ (ą▓čŗą▒ąŠčĆ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą▓čŗą▒ąŠčĆ ą░ą┤čĆąĄčüą░ ą▒čāč乥čĆąŠą▓ ą┐ą░ą║ąĄčéą░ ąĖ čé. ą┤.). ąŚą░č鹥ą╝ ą┐čĆąŠčåąĄčüčü ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčéčüčÅ ą║ą░ą║ ą┤ą╗čÅ čüą╗čāčćą░čÅ čüą▒čĆąŠčüą░ ą┐ąŠ čłąĖąĮąĄ USB (USB reset).

USB reset (RESET interrupt). ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüąŠą▒čŗčéąĖąĄ čüą▒čĆąŠčüą░ ą┐ąŠ čłąĖąĮąĄ USB, ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ č鹊 ąČąĄ čüą░ą╝ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ, ąŠą┐ąĖčüą░ąĮąĮąŠą╣ ą▓ ą┐čĆąĄą┤čŗą┤čāčēąĖčģ ą░ą▒ąĘą░čåą░čģ: ąŠą▒ą╝ąĄąĮ ąĘą░ą┐čĆąĄčēąĄąĮ, ąĖ ąĘą░ą┐čĆąĄčēąĄąĮčŗ ą▓čüąĄ čĆąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ (ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB ąĮąĄ ą▒čāą┤ąĄčé ąŠčéą▓ąĄčćą░čéčī ąĮą░ ą╗čÄą▒ąŠą╣ ą┐ą░ą║ąĄčé). ąÜą░ą║ ąŠčéą▓ąĄčé ąĮą░ čüąŠą▒čŗčéąĖąĄ USB, ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░ čäčāąĮą║čåąĖčÅ USB, čā ą║ąŠč鹊čĆąŠą╣ USB-ą░ą┤čĆąĄčü 0, čĆąĄą░ą╗ąĖąĘčāčÄčēą░čÅ č鹊ą╗čīą║ąŠ ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (default control endpoint, ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ 0). ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ Enable Function (EF) ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_DADDR ąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĄą╣ čĆąĄą│ąĖčüčéčĆą░ EP0R ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą▒čāč乥čĆąŠą▓ ą┐ą░ą║ąĄčéą░. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐čĆąŠčåąĄčüčüą░ 菹Įčāą╝ąĄčĆą░čåąĖąĖ USB čģąŠčüčé ąĮą░ąĘąĮą░čćą░ąĄčé čāąĮąĖą║ą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü čŹč鹊ą╝čā čāčüčéčĆąŠą╣čüčéą▓čā, ą║ąŠč鹊čĆčŗą╣ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą▒ąĖčéčŗ ADD[6:0] čĆąĄą│ąĖčüčéčĆą░ USB_DADDR, ąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą╗čÄą▒ą░čÅ ą┤čĆčāą│ą░čÅ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░čÅ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░.

ąÜąŠą│ą┤ą░ ą┐čĆąĖąĮčÅč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RESET, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ č鹊, čćč鹊ą▒čŗ čüąĮąŠą▓ą░ čĆą░ąĘčĆąĄčłąĖčéčī default endpoint USB-čäčāąĮą║čåąĖąĖ 0 ą▓ č鹥č湥ąĮąĖąĄ 10 ą╝čü ąŠčé ą║ąŠąĮčåą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čüą▒čĆąŠčüą░, ą║ąŠč鹊čĆą░čÅ ą▓čŗąĘą▓ą░ą╗ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

ąĪčéčĆčāą║čéčāčĆą░ ą▒čāč乥čĆąŠą▓ ą┐ą░ą║ąĄčéą░ ąĖ ąĖčģ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ. ąÜą░ąČą┤ą░čÅ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮą░čÅ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ą╝ąŠąČąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąŠčé čģąŠčüčéą░ ąĖ ą║ čģąŠčüčéčā. ą¤čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ ą▓čŗą┤ąĄą╗ąĄąĮąĮąŠą╝ ą▒čāč乥čĆąĄ ą┐ą░ą╝čÅčéąĖ, ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮąŠą╝ ą┤ą╗čÅ čŹč鹊ą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┤čĆčāą│ąŠą╣ ą▒čāč乥čĆ ą┐ą░ą╝čÅčéąĖ čüąŠą┤ąĄčƹȹĖčé ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖąĘ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ. ąöąŠčüčéčāą┐ ą║ čŹč鹊ą╣ ą┐ą░ą╝čÅčéąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ č湥čĆąĄąĘ ą▒ą╗ąŠą║ ąĖąĮč鹥čĆč乥ą╣čüą░ ą▒čāč乥čĆą░ ą┐ą░ą║ąĄčéą░, ą║ąŠč鹊čĆą░čÅ ą┐ąĄčĆąĄą┤ą░ąĄčé ąĘą░ą┐čĆąŠčü ąĮą░ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ ąĖ ąŠąČąĖą┤ą░ąĄčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąĮą░ ąĮąĄą│ąŠ. ą¤ąŠčüą║ąŠą╗čīą║čā ą║ ą┐ą░ą╝čÅčéąĖ ą▒čāč乥čĆą░ ą┐ą░ą║ąĄčéą░ ą┤ąŠą╗ąČąĄąĮ čéą░ą║ąČąĄ ą┐ąŠą╗čāčćą░čéčī ą┤ąŠčüčéčāą┐ ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ, ą╗ąŠą│ąĖą║ą░ ą░čĆą▒ąĖčéčĆą░ąČą░ čĆą░ąĘčĆąĄčłą░ąĄčé ą║ąŠąĮčäą╗ąĖą║čéčŗ ą┤ąŠčüčéčāą┐ą░, ąĖčüą┐ąŠą╗čīąĘčāčÅ ą┐ąŠą╗ąŠą▓ąĖąĮčā čåąĖą║ą╗ą░ APB1 ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ąĖ ąŠčüčéą░ą╗čīąĮčāčÄ ą┐ąŠą╗ąŠą▓ąĖąĮčā ą┐ąŠą╗ąŠčüčŗ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ čüąŠ čüč鹊čĆąŠąĮčŗ ą┐ąĄčĆąĖč乥čĆąĖąĖ USB. ąóą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ąŠą▒ą░ čŹčéąĖčģ ą░ą│ąĄąĮčéą░ ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī čéą░ą║, ą║ą░ą║ ąĄčüą╗ąĖ ą▒čŗ ą┐ą░ą╝čÅčéčī ą┐ą░ą║ąĄčéą░ ą▒čŗą╗ą░ ą▒čŗ ą┤ą▓čāčģą┐ąŠčĆč鹊ą▓ąŠą╣ SRAM, ąĖ ąĮąĄ ąĮčāąČąĮąŠ ą▒ąĄčüą┐ąŠą║ąŠąĖčéčīčüčÅ ąŠ ą╗čÄą▒ąŠą╝ ą║ąŠąĮčäą╗ąĖą║č鹥, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ąŠą┐ąĄčĆą░čåąĖčÄ čćč鹥ąĮąĖąĄ-ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ-ąĘą░ą┐ąĖčüčī (back-to-back access). ąøąŠą│ąĖą║ą░ ą┐ąĄčĆąĖč乥čĆąĖąĖ USB ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓čŗą┤ąĄą╗ąĄąĮąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ. ą¦ą░čüč鹊čéą░ čŹčéąĖčģ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗčģ čéą░ą║č鹊ą▓ čäąĖą║čüąĖčĆąŠą▓ą░ąĮą░ ąĮą░ 48 ą£ąōčå ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ąĖ čüčéą░ąĮą┤ą░čĆčéą░ USB, ąĖ čŹčéą░ čćą░čüč鹊čéą░ ą╝ąŠąČąĄčé ąŠčéą╗ąĖčćą░čéčīčüčÅ ąŠčé čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╣ ą┤ą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ ą║ čłąĖąĮąĄ APB1. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ čĆą░ąĘąĮčŗąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čéą░ą║č鹊ą▓, ą│ą┤ąĄ čćą░čüč鹊čéą░ APB1 ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗčłąĄ ąĖą╗ąĖ ąĮąĖąČąĄ čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĖč乥čĆąĖąĖ USB.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖąĘ-ąĘą░ čüą║ąŠčĆąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ USB ąĖ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą║ ąĖąĮč鹥čĆč乥ą╣čüčā ą┐ą░ą╝čÅčéąĖ, čćą░čüč鹊čéą░ APB1 ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗčłąĄ 8 ą£ąōčå, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐čĆąŠą▒ą╗ąĄą╝ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ/ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ (overrun/underrun).

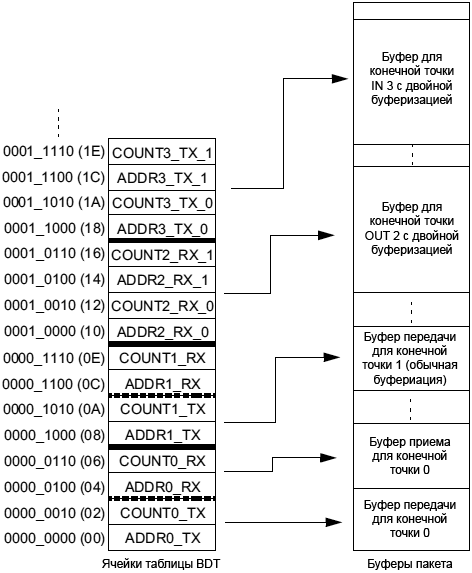

ąÜą░ąČą┤ą░čÅ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ čüą▓čÅąĘą░ąĮą░ čü ą┤ą▓čāą╝čÅ ą▒čāč乥čĆą░ą╝ąĖ ą┐ą░ą║ąĄčéą░ (ąŠą▒čŗčćąĮąŠ ąŠą┤ąĖąĮ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą┤čĆčāą│ąŠą╣ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░). ąæčāč乥čĆčŗ ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░ąĘą╝ąĄčēąĄąĮčŗ ą▓ ą╗čÄą▒ąŠą╝ ą╝ąĄčüč鹥 ą┐ą░ą╝čÅčéąĖ ą┐ą░ą║ąĄč鹊ą▓, ą┐ąŠč鹊ą╝čā čćč鹊 ąĖčģ čĆą░ąĘą╝ąĄčēąĄąĮąĖąĄ ąĖ čĆą░ąĘą╝ąĄčĆ čāą║ą░ąĘčŗą▓ą░čÄčéčüčÅ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąŠą┐ąĖčüą░ąĮąĖčÅ ą▒čāč乥čĆąŠą▓, ą║ąŠč鹊čĆą░čÅ čéą░ą║ąČąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą┐ą░ą╝čÅčéąĖ ą┐ą░ą║ąĄč鹊ą▓ ą┐ąŠ ą░ą┤čĆąĄčüčā, ą║ąŠč鹊čĆčŗą╣ ąĘą░ą┤ą░ąĄčé čĆąĄą│ąĖčüčéčĆ USB_BTABLE. ąÜą░ąČą┤ą░čÅ ąĘą░ą┐ąĖčüčī ą▓ čéą░ą▒ą╗ąĖčåąĄ čüą▓čÅąĘą░ąĮą░ čü čĆąĄą│ąĖčüčéčĆąŠą╝ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ, ąĖ ąŠąĮą░ čüąŠčüč鹊ąĖčé ąĖąĘ č湥čéčŗčĆąĄčģ 16-ą▒ąĖčéąĮčŗčģ čüą╗ąŠą▓ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊 ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü čéą░ą▒ą╗ąĖčåčŗ ą▓čüąĄą│ą┤ą░ ą▓čŗčĆąŠą▓ąĮąĄąĮ ą┐ąŠ 8-ą▒ą░ą╣čéąĮąŠą╣ ą│čĆą░ąĮąĖčåąĄ (čéčĆąĖ ą╝ą╗ą░ą┤čłąĖąĄ ą▒ąĖčéą░ čĆąĄą│ąĖčüčéčĆą░ USB_BTABLE ą▓čüąĄą│ą┤ą░ čĆą░ą▓ąĮčŗ 000). ąŚą░ą┐ąĖčüąĖ ą▓ čéą░ą▒ą╗ąĖčåąĄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ ą▒čāč乥čĆąŠą▓ ąŠą┐ąĖčüą░ąĮčŗ ąĮąĖąČąĄ ą▓ čüąĄą║čåąĖąĖ "ąóą░ą▒ą╗ąĖčåą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ ą▒čāč乥čĆąŠą▓ (BDT)". ąĢčüą╗ąĖ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮą░čÅ, ąĖ ąŠąĮą░ ąĮąĄ ąĖąĘąŠčģčĆąŠąĮąĮą░čÅ ąĖ ąĮąĄ čéąĖą┐ą░ bulk čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣, č鹊 čéčĆąĄą▒čāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ą▒čāč乥čĆ ą┐ą░ą║ąĄčéą░ (ąŠąĮ čüą▓čÅąĘą░ąĮ čü ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ). ąöčĆčāą│ąĖąĄ ą╝ąĄčüčéą░ ą▓ čéą░ą▒ą╗ąĖčåąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ, ą║ąŠč鹊čĆčŗąĄ ąŠčéąĮąŠčüčÅčéčüčÅ ą║ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╗ąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╝ ą║ąŠąĮąĄčćąĮčŗą╝ č鹊čćą║ą░ą╝. ąśąĘąŠčģčĆąŠąĮąĮčŗąĄ ąĖ bulk ą║ąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣ ąĖą╝ąĄčÄčé čüą┐ąĄčåąĖą░ą╗čīąĮčāčÄ ąŠą▒čĆą░ą▒ąŠčéą║čā ą▒čāč乥čĆąŠą▓ ą┐ą░ą║ąĄčéą░ (čüą╝. čüąĄą║čåąĖčÄ "ąśąĘąŠčģčĆąŠąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ" ąĖ čüąĄą║čåąĖčÄ "ąÜąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣" čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ). ąÆąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖąĄ ą╝ąĄąČą┤čā ąĘą░ą┐ąĖčüčÅą╝ąĖ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąŠą┐ąĖčüą░ąĮąĖčÅ ą▒čāč乥čĆąŠą▓ ąĖ ąŠą▒ą╗ą░čüčéčÅą╝ąĖ ą▒čāč乥čĆą░ ą┐ą░ą║ąĄčéą░ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 221.

ąĀąĖčü. 221. ą×ą▒ą╗ą░čüčéąĖ ą▒čāč乥čĆą░ ą┐ą░ą║ąĄčéą░ čü ą┐čĆąĖą╝ąĄčĆą░ą╝ąĖ čÅč湥ąĄą║ čéą░ą▒ą╗ąĖčåčŗ ąŠą┐ąĖčüą░ąĮąĖčÅ ą▒čāč乥čĆąŠą▓.

ąÜą░ąČą┤čŗą╣ ą▒čāč乥čĆ ą┐ą░ą║ąĄčéą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą╗ąĖą▒ąŠ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĖąĄą╝ą░, ą╗ąĖą▒ąŠ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĮą░čćąĖąĮą░čÅ čü ąĮąĖąČąĮąĄą╣ čćą░čüčéąĖ ą▒čāč乥čĆą░. ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą▒čāą┤ąĄčé ą╝ąĄąĮčÅčéčī ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ, čüąŠčüąĄą┤ąĮąĖąĄ čü ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗą╝ąĖ ą▒čāč乥čĆą░ą╝ąĖ ą┐ą░ą╝čÅčéąĖ; ąĄčüą╗ąĖ ą▒čāč乥čĆ ą┐ą░ą║ąĄčéą░ ą▒ąŠą╗čīčłąĄ, č湥ą╝ ą┐čĆąĖąĮčÅčéą░čÅ ą┤ą╗ąĖąĮą░ ą▒čāč乥čĆą░ (čüąŠą▒čŗčéąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▒čāč乥čĆą░, buffer overrun), č鹊 ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą║ąŠą┐ąĖčĆąŠą▓ą░čéčīčüčÅ ą▓ ą┐ą░ą╝čÅčéčī č鹊ą╗čīą║ąŠ ą┤ąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╣ čÅč湥ą╣ą║ąĖ.

ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ. ą¤ąĄčĆą▓čŗą╣ čłą░ą│ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ - ąĘą░ą┐ąĖčüą░čéčī ą┐ąŠą┤čģąŠą┤čÅčēąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆčŗ ADDRn_TX/ADDRn_RX, čćč鹊ą▒čŗ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB ąĮą░čłą╗ąŠ čāąČąĄ ą│ąŠč鹊ą▓čŗąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ, ąĖ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│ą╗ąĖ ą▒čŗčéčī ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮčŗ. ąæąĖčéčŗ EP_TYPE ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_EPnR ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čéąĖą┐ąŠą╝ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ, ąĖąĮąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▒ąĖčé EP_KIND ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠą╣ čäčāąĮą║čåąĖąĖ. ąØą░ čüč鹊čĆąŠąĮąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░ ą▒ąĖčéą░ą╝ąĖ STAT_TX ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_EPnR, ąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮ COUNTn_TX. ąöą╗čÅ ą┐čĆąĖąĄą╝ą░ ą▒ąĖčéčŗ STAT_RX ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░, ąĖ ą▓ COUNTn_RX ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ čĆą░ąĘą╝ąĄčĆ ą▓čŗą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą▒čāč乥čĆą░ čü ą┐ąŠą╝ąŠčēčīčÄ ą┐ąŠą╗ąĄą╣ BL_SIZE ąĖ NUM_BLOCK. ą×ą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ ą║ąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ, ą║čĆąŠą╝ąĄ ąĖąĘąŠčģčĆąŠąĮąĮčŗčģ ąĖ bulk-č鹊č湥ą║ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣, ąĮčāąČą┤ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą▒ąĖčé ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓, čüą▓čÅąĘą░ąĮąĮčŗčģ čü ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čćą░ ąĖ/ąĖą╗ąĖ ą┐čĆąĖąĄą╝ čĆą░ąĘčĆąĄčłąĄąĮčŗ, čĆąĄą│ąĖčüčéčĆ USB_EPnR ąĖ čÅč湥ą╣ą║ąĖ ADDRn_TX/ADDRn_RX, COUNTn_TX/COUNTn_RX (čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ) ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ą┐ąŠčüą║ąŠą╗čīą║čā ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ą╝ąŠąČąĄčé ą┐ąŠą╝ąĄąĮčÅčéčī ąĖčģ ąĘąĮą░č湥ąĮąĖčÅ ąĮą░ ą╗ąĄčéčā. ąÜąŠą│ą┤ą░ ąŠą┐ąĄčĆą░čåąĖčÅ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĘą░ą▓ąĄčĆčłąĄąĮą░, ąŠ č湥ą╝ ąŠą┐ąŠą▓ąĄčēą░ąĄčé čüąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CTR, ą║ ąĮąĖą╝ ą╝ąŠąČąĮąŠ čüąĮąŠą▓ą░ ąŠą▒čĆą░čéąĖčéčīčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĮąŠą▓ąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ.

ą¤ą░ą║ąĄčéčŗ IN (ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ). ąÜąŠą│ą┤ą░ ą┐čĆąĖąĮąĖą╝ą░ąĄčéčüčÅ č鹊ą║ąĄąĮ IN ą▓ ą┐ą░ą║ąĄč鹥, ąĄčüą╗ąĖ ą┐čĆąĖąĮčÅčéčŗą╣ ą░ą┤čĆąĄčü čüąŠą▓ą┐ą░ą┤ą░ąĄčé ąĖ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą┤ąŠą┐čāčüčéąĖą╝ą░čÅ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░, ą┐ąĄčĆąĖč乥čĆąĖčÅ USB ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčé ą┤ąŠčüčéčāą┐ ą║ čüąŠą┤ąĄčƹȹĖą╝ąŠą╝čā čÅč湥ąĄą║ ADDRn_TX ąĖ COUNTn_TX ą▓ąĮčāčéčĆąĖ ąĘą░ą┐ąĖčüąĖ čéą░ą▒ą╗ąĖčåčŗ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▒čāč乥čĆą░, ąŠčéąĮąŠčüčÅčēąĄą╣čüčÅ ą║ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĄ. ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ čŹčéąĖčģ čÅč湥ąĄą║ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ ąĖčģ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ 16-ą▒ąĖčéąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ADDR ąĖ COUNT (ąĮąĄą┤ąŠčüčéčāą┐ąĮčŗąĄ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ). ąÜ ą┐ą░ą╝čÅčéąĖ ą┐ą░ą║ąĄč鹊ą▓ ąŠą▒čĆą░čēą░čÄčéčüčÅ čüąĮąŠą▓ą░ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ą┐ąĄčĆą▓ąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (čüą╝. "ąĪčéčĆčāą║čéčāčĆą░ ą▒čāč乥čĆąŠą▓ ą┐ą░ą║ąĄčéą░ ąĖ ąĖčģ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ"), ąĮ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąŠčéą┐čĆą░ą▓ą║ą░ DATA0 ąĖą╗ąĖ DATA1 PID ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą▒ąĖč鹊ą╝ DTOG_TX čĆąĄą│ąĖčüčéčĆą░ USB_EPnR. ąÜąŠą│ą┤ą░ PID ąĘą░ą▓ąĄčĆčłąĄąĮ, ą┐ąĄčĆą▓čŗą╣ ą▒ą░ą╣čé ąĖąĘ čüą╗ąŠą▓ą░ čćąĖčéą░ąĄčéčüčÅ ąĖąĘ ą┐ą░ą╝čÅčéąĖ ą▒čāč乥čĆą░, ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ ą▓čŗčģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠ čłąĖąĮąĄ USB. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąĄčĆąĄą┤ą░ąĮ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ą░ą╣čé, ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓čŗčćąĖčüą╗ąĄąĮąĮą░čÅ CRC. ąĢčüą╗ąĖ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮą░čÅ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝ą░, ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ handshake-ą┐ą░ą║ąĄčé NAK ąĖą╗ąĖ STALL ą▓ą╝ąĄčüč鹊 ą┐ą░ą║ąĄčéą░ ą┤ą░ąĮąĮčŗčģ, ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą▒ąĖčéą░ą╝ąĖ STAT_TX ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_EPnR.

ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│ąĖčüčéčĆ ADDR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ą╝ąĄčüč鹊 ą▓ ą┐ą░ą╝čÅčéąĖ č鹥ą║čāčēąĄą│ąŠ ą▒čāč乥čĆą░, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ COUNT ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ąŠčüčéą░ą▓čłąĖčģčüčÅ ą▒ą░ą╣čé ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÜą░ąČą┤ąŠąĄ čüą╗ąŠą▓ąŠ, ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĖąĘ ą┐ą░ą╝čÅčéąĖ ą▒čāč乥čĆą░ ą┐ą░ą║ąĄčéą░, ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąŠ čłąĖąĮąĄ USB, ąĮą░čćąĖąĮą░čÅ čü čüą░ą╝ąŠą│ąŠ ą╝ą╗ą░ą┤čłąĄą│ąŠ ąĘąĮą░čćą░čēąĄą│ąŠ ą▒ą░ą╣čéą░. ą¦č鹥ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ą▒čāč乥čĆą░ ą▓ ą┐ą░ą╝čÅčéąĖ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü ą░ą┤čĆąĄčüą░, čāą║ą░ąĘčŗą▓ą░ąĄą╝ąŠą│ąŠ ADDRn_TX ą┤ą╗čÅ COUNTn_TX/2 čüą╗ąŠą▓. ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ą┐ą░ą║ąĄčé čüąŠčüčéą░ą▓ą╗ąĄąĮ ąĖąĘ ąĮąĄč湥čéąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ą░ą╣čé, č鹊 ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮą░ č鹊ą╗čīą║ąŠ ą╝ą╗ą░ą┤čłą░čÅ ą┐ąŠą╗ąŠą▓ąĖąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čüą╗ąŠą▓ą░, ą║ ą║ąŠč鹊čĆąŠą╝čā ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐.

ą¤čĆąĖ ą┐ąŠą╗čāč湥ąĮąĖąĖ ACK-ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ čģąŠčüčéą░ čĆąĄą│ąĖčüčéčĆ USB_EPnR ąŠą▒ąĮąŠą▓ąĖčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝: ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčüčÅ ą▒ąĖčé DTOG_TX, ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ą┤ąĄą╗ą░ąĄčéčüčÅ ąĮąĄą┤ąŠčüčéčāą┐ąĮąŠą╣ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ STAT_TX=10 (NAK) ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé CTR_TX. ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ čüąĮą░čćą░ą╗ą░ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░čéčī ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā, ą║ąŠč鹊čĆą░čÅ ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄčé ą▓ąĮąĖą╝ą░ąĮąĖąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą┐čāč鹥ą╝ ąŠčåąĄąĮą║ąĖ ą▒ąĖčé EP_ID ąĖ DIR ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_ISTR. ą×ą▒čüą╗čāąČąĖą▓ą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ CTR_TX ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ; ąĘą░č鹥ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┐ąŠą┤ą│ąŠčéą░ą▓ą╗ąĖą▓ą░ąĄčé ą┤čĆčāą│ąŠą╣ ą▒čāč乥čĆ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ąŠčéą┐čĆą░ą▓ą╗čÅąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ, ąŠą▒ąĮąŠą▓ą╗čÅąĄčé COUNTn_TX ą▓ čéą░ą▒ą╗ąĖčåąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ ąĮą░ą║ąŠąĮąĄčå čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ STAT_TX ą▓ 11 (VALID), ą┤ą╗čÅ ąĮąŠą▓ąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą¤ąŠą║ą░ ą▒ąĖčéčŗ STAT_TX ą▓ čüąŠčüč鹊čÅąĮąĖąĖ 10 (NAK), ą╗čÄą▒ąŠą╣ IN-ąĘą░ą┐čĆąŠčü, ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮčŗą╣ ą▓ čŹčéčā ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā, ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ąŠčéą║ą░ąĘąŠą╝ NAK, ą┐ąŠą║ą░ąĘčŗą▓ą░čÅ čāčüą╗ąŠą▓ąĖąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ąŠą╝ (flow control): čģąŠčüčé USB ą▒čāą┤ąĄčé ą┐čŗčéą░čéčīčüčÅ ą┐ąŠą▓č鹊čĆąĖčéčī čéčĆą░ąĮąĘą░ą║čåąĖčÄ ą┤ąŠ ąĄčæ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ. ąÆą░ąČąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąŠą┐ąĄčĆą░čåąĖą╣, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗčģ ą▓čŗčłąĄ, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐ąŠč鹥čĆąĖ ąŠą┐ąŠą▓ąĄčēąĄąĮąĖčÅ ą▓č鹊čĆąŠą╣ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą╣ ąĮą░ č鹊ą╣ ąČąĄ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĄ IN čéčĆą░ąĮąĘą░ą║čåąĖąĖ, ą║ąŠč鹊čĆą░čÅ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąŠčüą╗ąĄą┤čāąĄčé ąĘą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CTR.

ą¤ą░ą║ąĄčéčŗ OUT ąĖ SETUP (ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ). ąŁčéąĖ ą┤ą▓ą░ č鹊ą║ąĄąĮą░ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ USB ą▒ąŠą╗ąĄąĄ ąĖą╗ąĖ ą╝ąĄąĮąĄąĄ čéą░ą║ąĖą╝ ąČąĄ ąŠą▒čĆą░ąĘąŠą╝; ąŠčéą╗ąĖčćąĖčÅ ą▓ ąŠą▒čĆą░ą▒ąŠčéą║ąĄ ą┐ą░ą║ąĄč鹊ą▓ SETUP ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐ąŠą║ą░ąĘą░ąĮ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐ą░čĆą░ą│čĆą░č乥, ąŠą┐ąĖčüčŗą▓ą░čÄčēąĄą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (control transfer). ąÜąŠą│ą┤ą░ ą┐čĆąĖąĮąĖą╝ą░ąĄčéčüčÅ OUT/SETUP PID, ąĄčüą╗ąĖ ą░ą┤čĆąĄčü čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü ą┐čĆą░ą▓ąĖą╗čīąĮąŠą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąŠą╣, ą┐ąĄčĆąĖč乥čĆąĖčÅ USB ąŠą▒čĆą░čēą░ąĄčéčüčÅ ą║ čüąŠą┤ąĄčƹȹĖą╝ąŠą╝čā čÅč湥ąĄą║ ADDRn_RX ąĖ COUNTn_RX ą▓ąĮčāčéčĆąĖ ąĘą░ą┐ąĖčüąĖ čéą░ą▒ą╗ąĖčåčŗ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ ą▒čāč乥čĆąŠą▓, ąŠčéąĮąŠčüčÅčēąĄą╣čüčÅ ą║ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĄ. ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ ADDRn_RX čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│ąĖčüčéčĆ ADDR. ąźąŠčéčÅ COUNT čüąĄą╣čćą░čü čüą▒čĆąŠčłąĄąĮ, ąĖ ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖč鹊ą▓čŗčģ ą┐ąŠą╗ąĄą╣ BL_SIZE ąĖ NUM_BLOCK, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖąĘ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ COUNTn_RX, ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ BUF_COUNT, ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ 16-ą▒ąĖčéąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░, ą║ąŠč鹊čĆčŗą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ čüąŠą▒čŗčéąĖčÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▒čāč乥čĆą░ - buffer overrun condition (ą▓čüąĄ čŹčéąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĮąĄą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ). ąæą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┐čĆąĖąĮčÅčéčŗąĄ ą┐ąĄčĆąĖč乥čĆąĖąĄą╣ USB, čāą┐ą░ą║ąŠą▓čŗą▓ą░čÄčéčüčÅ ą▓ čüą╗ąŠą▓ą░ (ą┐ąĄčĆą▓čŗą╣ ą┐čĆąĖąĮčÅčéčŗą╣ ą▒ą░ą╣čé čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ čüą░ą╝čŗą╣ ą╝ą╗ą░ą┤čłąĖą╣ ąĘąĮą░čćą░čēąĖą╣ ą▒ą░ą╣čé) ąĖ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą╝ąĄčēą░čÄčéčüčÅ ą▓ ą▒čāč乥čĆ ą┐ą░ą║ąĄčéą░, ąĮą░čćąĖąĮą░čÅ čü ą░ą┤čĆąĄčüą░, čüąŠą┤ąĄčƹȹ░čēąĄą│ąŠčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ ADDR, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ BUF_COUNT ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ, ąĖ COUNT ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ čü ą║ą░ąČą┤čŗą╝ ą┐čĆąĖąĮčÅčéčŗą╝ ą▒ą░ą╣č鹊ą╝. ąÜąŠą│ą┤ą░ ą▒čāą┤ąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą║ąŠąĮąĄčå ą┐ą░ą║ąĄčéą░ DATA, ą┐čĆąŠą▓ąĄčĆąĄąĮą░ ą║ąŠčĆčĆąĄą║čéąĮąŠčüčéčī ą┐čĆąĖąĮčÅč鹊ą╣ CRC, ąĖ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ąĮąĄčé ąŠčłąĖą▒ąŠą║ ą┐čĆąĖ ą┐čĆąĖąĄą╝ąĄ, ą┐ąĄčĆąĄą┤ą░čÄčēąĄą╝čā čģąŠčüčéčā ąŠą▒čĆą░čéąĮąŠ ąŠčéą┐čĆą░ą▓ąĖčéčüčÅ handshake-ą┐ą░ą║ąĄčé ACK.

ąÆ čüą╗čāčćą░ąĄ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠą╣ CRC ąĖą╗ąĖ ą┤čĆčāą│ąŠą│ąŠ čĆąŠą┤ą░ ąŠčłąĖą▒ąŠą║ (ąĮą░čĆčāčłąĄąĮąĖčÅ bit-stuff, ąŠčłąĖą▒ą║ąĖ čäčĆąĄą╣ą╝ą░ ąĖ čé. ą┤.), ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ ą▓čüąĄ ąĄčēąĄ ą║ąŠą┐ąĖčĆčāčÄčéčüčÅ ą▓ ą┐ą░ą╝čÅčéčī ą▒čāč乥čĆą░ ą┐ą░ą║ąĄčéą░, ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą┤ąŠ č鹊čćą║ąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ, ąŠą┤ąĮą░ą║ąŠ ACK-ą┐ą░ą║ąĄčé ąĮąĄ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé ERR ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_ISTR. ą×ą┤ąĮą░ą║ąŠ ą▓ čéą░ą║ąŠą╝ čüą╗čāčćą░ąĄ ąĘą┤ąĄčüčī ąŠą▒čŗčćąĮąŠ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┤ąĄą╣čüčéą▓ąĖą╣ ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝čŗ: ą┐ąĄčĆąĖč乥čĆąĖčÅ USB ą▓ąŠčüčüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĖąĘ ąŠčłąĖą▒ąŠą║ ą┐čĆąĖąĄą╝ą░ ąĖ ąŠčüčéą░ąĮąĄčéčüčÅ ą│ąŠč鹊ą▓ąŠą╣ ą║ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÄ čüą╗ąĄą┤čāčÄčēąĄą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ąĢčüą╗ąĖ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮą░čÅ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ąĮąĄ ą┤ąŠą┐čāčüčéąĖą╝ą░ (not valid), ą▓ą╝ąĄčüč鹊 ACK ą▒čāą┤ąĄčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ handshake-ą┐ą░ą║ąĄčé NAK ąĖą╗ąĖ STALL, ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą▒ąĖčéą░ą╝ąĖ STAT_RX ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_EPnR ąĖ ąĮąĖą║ą░ą║ąĖąĄ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ ą┐ą░ą╝čÅčéčī ą▒čāč乥čĆąŠą▓ ą┐čĆąĖąĄą╝ą░.

ą»č湥ą╣ą║ąĖ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ, ąĮą░čćąĖąĮą░čÅ čü ą░ą┤čĆąĄčüą░, čüąŠą┤ąĄčƹȹ░čēąĄą│ąŠčüčÅ ą▓ ADDRn_RX ą┤ą╗čÅ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ą░ą╣čé, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą┤ą╗ąĖąĮąĄ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą┐ą░ą║ąĄčéą░ ą┤ą░ąĮąĮčŗčģ, ą▓ą║ą╗čÄčćą░čÅ CRC (čé. ąĄ. ą┤ą╗ąĖąĮą░ ą┐ąŠą╗ąĄąĘąĮąŠą╣ ąĮą░ą│čĆčāąĘą║ąĖ + 2), ąĖą╗ąĖ ą┤ąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą▓čŗą┤ąĄą╗ąĄąĮąĮąŠą╣ čÅč湥ą╣ą║ąĄ ą┐ą░ą╝čÅčéąĖ, ą║ą░ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ BL_SIZE ąĖ NUM_BLOCK, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠčüčéčāą┐ą░čÄčé ą┐ąĄčĆą▓čŗą╝ąĖ. ą¤čĆąĖ čéą░ą║ąŠą╝ čüą┐ąŠčüąŠą▒ąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖčÅ USB ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą▓čŗą╣ą┤ąĄčé ąĘą░ ą┐čĆąĄą┤ąĄą╗čŗ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ, ą▓čŗą┤ąĄą╗ąĄąĮąĮąŠą╣ ą┐ąŠą┤ ą▒čāč乥čĆ. ąĢčüą╗ąĖ ą┤ą╗ąĖąĮą░ ą┐ą░ą║ąĄčéą░ ą┐ąŠą╗ąĄąĘąĮąŠą╣ ąĮą░ą│čĆčāąĘą║ąĖ ą┤ą░ąĮąĮčŗčģ (čĆąĄą░ą╗čīąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ą░ąĮąĮčŗčģ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄą╝) ą▒ąŠą╗čīčłąĄ, č湥ą╝ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗą╣ ą▒čāč乥čĆ, ą┐ąĄčĆąĖč乥čĆąĖčÅ USB ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čüąŠą▒čŗčéąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▒čāč乥čĆą░ (buffer overrun condition). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąŠčéą┐čĆą░ą▓ąĖčéčüčÅ STALL handshake ą▓ą╝ąĄčüč鹊 ąŠą▒čŗčćąĮąŠą│ąŠ ACK, čćč鹊ą▒čŗ ąŠą┐ąŠą▓ąĄčüčéąĖčéčī čģąŠčüčé ąŠ ą┐čĆąŠą▒ą╗ąĄą╝ąĄ, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĖ čéčĆą░ąĮąĘą░ą║čåąĖčÅ čüčćąĖčéą░ąĄčéčüčÅ ąĮąĄčāą┤ą░čćąĮąŠą╣.

ąÜąŠą│ą┤ą░ čéčĆą░ąĮąĘą░ą║čåąĖčÅ ą║ąŠčĆčĆąĄą║čéąĮąŠ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą┐čāč鹥ą╝ ąŠčéą┐čĆą░ą▓ą║ąĖ handshake-ą┐ą░ą║ąĄčéą░ ACK, ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│ąĖčüčéčĆ COUNT ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą▓ čÅč湥ą╣ą║čā COUNTn_RX, ąĮą░čģąŠą┤čÅčēčāčÄčüčÅ ą▓ ąĘą░ą┐ąĖčüąĖ čéą░ą▒ą╗ąĖčåčŗ ąŠą┐ąĖčüą░ąĮąĖčÅ ą▒čāč乥čĆąŠą▓, ąŠčüčéą░ą▓ą╗čÅčÅ ąĮąĄ ąĖąĘą╝ąĄąĮąĄąĮąĮčŗą╝ąĖ ą┐ąŠą╗čÅ BL_SIZE ąĖ NUM_BLOCK, ą║ąŠč鹊čĆčŗąĄ ąŠą▒čŗčćąĮąŠ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčŗą▓ą░čéčī, ąĖ čĆąĄą│ąĖčüčéčĆ USB_EPnR ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝: ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą▒ąĖčé DTOG_RX, ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ą┤ąĄą╗ą░ąĄčéčüčÅ "invalid" ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ STAT_RX = 10 (NAK), ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé CTR_RX. ąĢčüą╗ąĖ čéčĆą░ąĮąĘą░ą║čåąĖčÅ ą▒čŗą╗ą░ ąĮąĄčāą┤ą░čćąĮąŠą╣ ąĖąĘ-ąĘą░ ąŠčłąĖą▒ąŠą║ ąĖą╗ąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▒čāč乥čĆą░, č鹊 ąĮąĖą║ą░ą║ąĖąĄ ąĖąĘ čĆą░ąĮąĄąĄ čāą┐ąŠą╝čÅąĮčāčéčŗčģ ą┤ąĄą╣čüčéą▓ąĖą╣ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ. ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ čüąĮą░čćą░ą╗ą░ ą┤ąŠą╗ąČąĮą░ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░čéčī ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā, ą║ąŠč鹊čĆą░čÅ ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄčé ą▓ąĮąĖą╝ą░ąĮąĖąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą┐čāč鹥ą╝ ąŠčåąĄąĮą║ąĖ ą▒ąĖčé EP_ID ąĖ DIR ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_ISTR. ąĪąŠą▒čŗčéąĖąĄ CTR_RX ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čéą░ą║, čćč鹊 čüąĮą░čćą░ą╗ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čéąĖą┐ čéčĆą░ąĮąĘą░ą║čåąĖąĖ (ą▒ąĖčé SETUP ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_EPnR); ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ ąŠčćąĖčüčéąĖčéčī ą▒ąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▒ąĖčé čäą╗ą░ą│ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ ą┐ąŠą╗čāčćąĖčéčī ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐čĆąĖąĮčÅčéčŗčģ ą▒ą░ą╣čé čćč鹥ąĮąĖąĄą╝ čÅč湥ą╣ą║ąĖ COUNTn_RX ą▓ąĮčāčéčĆąĖ ąĘą░ą┐ąĖčüąĖ čéą░ą▒ą╗ąĖčåčŗ ąŠą┐ąĖčüą░ąĮąĖčÅ ą▒čāč乥čĆąŠą▓, ąŠčéąĮąŠčüčÅčēąĄą╣čüčÅ ą║ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄą╝ąŠą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĄ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąŠą▒čĆą░ą▒ąŠčéą░ąĮčŗ, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčéčŗ STAT_RX ą▓ 11 (Valid) ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_EPnR, č鹥ą╝ čüą░ą╝čŗą╝ čĆą░ąĘčĆąĄčłą░čÅ ą▒čāą┤čāčēąĖąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ą¤ąŠą║ą░ ą▒ąĖčéčŗ STAT_RX čĆą░ą▓ąĮčŗ 10 (NAK), ą╗čÄą▒čŗąĄ ąĘą░ą┐čĆąŠčüčŗ OUT ą║ čŹč鹊ą╣ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĄ ą▒čāą┤čāčé ąŠčéą║ą╗ąŠąĮčÅčéčīčüčÅ ą┐ą░ą║ąĄč鹊ą╝ NAK, ą┐ąŠą║ą░ąĘčŗą▓ą░čÅ čāčüą╗ąŠą▓ąĖąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ąŠą╝: čģąŠčüčé USB ą▒čāą┤ąĄčé ą┤ąĄą╗ą░čéčī ą┐ąŠą▓č鹊čĆąĮčŗąĄ ą┐ąŠą┐čŗčéą║ąĖ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čéčĆą░ąĮąĘą░ą║čåąĖčÄ ą┤ąŠ ąĄčæ čāčüą┐ąĄčłąĮąŠą│ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ. ąÆą░ąČąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąŠą┐ąĄčĆą░čåąĖą╣, čāą┐ąŠą╝čÅąĮčāčéčŗčģ ą▓čŗčłąĄ, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐ąŠč鹥čĆąĖ ąŠą┐ąŠą▓ąĄčēąĄąĮąĖčÅ ą▓č鹊čĆąŠą╣ OUT-čéčĆą░ąĮąĘą░ą║čåąĖąĖ, ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą╣ ą▓ čéčā ąČąĄ čüą░ą╝čāčÄ ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā, ą║ąŠč鹊čĆą░čÅ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ čüą╗ąĄą┤čāąĄčé ąĘą░ čüčĆą░ą▒ąŠčéą░ą▓čłąĖą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ CTR.

ą¤ąĄčĆąĄą┤ą░čćąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ąŻą┐čĆą░ą▓ą╗čÅčÄčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĄą╣ SETUP, ąĘą░ ą║ąŠč鹊čĆąŠą╣ ąĖą┤čāčé 0 ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čüčéą░ą┤ąĖą╣ ą┤ą░ąĮąĮčŗčģ, ą▓čüąĄ ą▓ č鹊ą╝ ąČąĄ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ, ąĘą░ ą║ąŠč鹊čĆčŗą╝ąĖ ąĖą┤ąĄčé čüčéą░ą┤ąĖčÅ čüčéą░čéčāčüą░ (ą┐ąĄčĆąĄą┤ą░čćą░ ąĮčāą╗ąĄą▓ąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ą░ą╣čé ą▓ ąŠą▒čĆą░čéąĮąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ). ąóčĆą░ąĮąĘą░ą║čåąĖąĖ SETUP ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠąĮąĄčćąĮčŗą╝ąĖ č鹊čćą║ą░ą╝ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (control endpoint) ąŠč湥ąĮčī ą┐ąŠčģąŠąČąĄ ąĮą░ ą║ąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ OUT (ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ), ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ č鹊ą│ąŠ, čćč鹊 ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčé DTOG_TX ąĖ DTOG_RX čĆąĄą│ąĖčüčéčĆąŠą▓ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ čāčüčéą░ąĮąŠą▓čÅčéčüčÅ ą▓ 1 ąĖ 0 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą┤ą╗čÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ ąŠą▒ą░ ą┐ąŠą╗čÅ STAT_TX ąĖ STAT_RX čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą▓ 10 (NAK), čćč鹊ą▒čŗ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ čĆąĄčłąĖčéčī, ą┤ąŠą╗ąČąĮčŗ ą╗ąĖ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą▒čŗčéčī IN ąĖą╗ąĖ OUT, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ SETUP. ąŻą┐čĆą░ą▓ą╗čÅčÄčēą░čÅ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ą┤ąŠą╗ąČąĮą░ ą┐čĆąŠą▓ąĄčĆąĖčéčī ą▒ąĖčé SETUP ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_EPnR ąĮą░ ą║ą░ąČą┤ąŠą╝ čüąŠą▒čŗčéąĖąĖ CTR_RX, čćč鹊ą▒čŗ ąŠčéą┤ąĄą╗ąĖčéčī ąŠą▒čŗčćąĮčŗąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ OUT ąŠčé čéčĆą░ąĮąĘą░ą║čåąĖą╣ SETUP. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ USB ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĖ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüčéą░ą┤ąĖą╣ ą┤ą░ąĮąĮčŗčģ ą┐čāč鹥ą╝ ąĖąĮč鹥čĆą┐čĆąĄčéą░čåąĖąĖ ą┤ą░ąĮąĮčŗčģ, ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗčģ ąĮą░ čüčéą░ą┤ąĖąĖ SETUP, ąĖ čéčĆąĄą▒čāąĄčéčüčÅ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ą░ (STALL) čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą▓ čüą╗čāčćą░ąĄ ąŠčłąĖą▒ąŠą║. ą¦č鹊ą▒čŗ čŹč鹊 čüą┤ąĄą╗ą░čéčī, ą▓čüąĄ čüčéą░ą┤ąĖąĖ ą┤ą░ąĮąĮčŗčģ ą┤ąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą▓ ąĮąĄąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ STALL, čéą░ą║ čćč鹊 ąĄčüą╗ąĖ čģąŠčüčé ą┐ąŠą╝ąĄąĮčÅąĄčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ čüą╗ąĖčłą║ąŠą╝ ą▒čŗčüčéčĆąŠ, č鹊 ą┐ąŠą╗čāčćąĖčé STALL ą║ą░ą║ čüąŠčüč鹊čÅąĮąĖąĄ čüčéą░ą┤ąĖąĖ.

ąÜąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąĮčÅčÅ čüčéą░ą┤ąĖčÅ ą┤ą░ąĮąĮčŗčģ, ąŠą▒čĆą░čéąĮąŠąĄ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ NAK ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊 ąĄčüą╗ąĖ čģąŠčüčé ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąŠą╝ąĄąĮčÅąĄčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ (ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čüčéą░ą┤ąĖąĖ čüčéą░čéčāčüą░), ąŠąĮ ąŠčüčéą░ąĮąĄčéčüčÅ ą▓ ąŠąČąĖą┤ą░ąĮąĖąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ąĢčüą╗ąĖ ąŠą┐ąĄčĆą░čåąĖčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī čāčüą┐ąĄčłąĮąŠ, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐ąŠą╝ąĄąĮčÅąĄčé NAK ąĮą░ VALID, ąĖąĮą░č湥 ą▓ STALL. ąÆ č鹊 ąČąĄ ą▓čĆąĄą╝čÅ, ąĄčüą╗ąĖ čüčéą░ą┤ąĖčÅ čüčéą░čéčāčüą░ ą▒čāą┤ąĄčé OUT, č鹊 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé STATUS_OUT (EP_KIND ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_EPnR), čćč鹊ą▒čŗ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ą╗ą░čüčī ąŠčłąĖą▒ą║ą░, ąĄčüą╗ąĖ čéčĆą░ąĮąĘą░ą║čåąĖčÅ čüčéą░čéčāčüą░ ą▓čŗą┐ąŠą╗ąĮąĖą╗ą░čüčī čü ąĮąĄ ąĮčāą╗ąĄą▓čŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ. ąÜąŠą│ą┤ą░ ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčéčüčÅ čéčĆą░ąĮąĘą░ą║čåąĖčÅ čüčéą░čéčāčüą░, ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ąŠčćąĖčēą░ąĄčé ą▒ąĖčé STATUS_OUT bit ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé STAT_RX ą▓ VALID (čćč鹊ą▒čŗ ą┐čĆąĖąĮčÅčéčī ąĮąŠą▓čāčÄ ą║ąŠą╝ą░ąĮą┤čā) ąĖ STAT_TX ą▓ NAK (čćč鹊ą▒čŗ ąŠčéą╗ąŠąČąĖčéčī ą▓ąŠąĘą╝ąŠąČąĮčāčÄ čüčéą░ą┤ąĖčÄ čüčéą░čéčāčüą░ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą╣ ąĮą░čüčéčĆąŠą╣ą║ąĖ, ą▓čŗą┐ąŠą╗ąĮąĄąĮąĮąŠą╣ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ).

ą¤ąŠčüą║ąŠą╗čīą║čā čüą┐ąĄčåąĖčäąĖą║ą░čåąĖčÅ USB čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé, čćč鹊 ąĮą░ ą┐ą░ą║ąĄčé SETUP ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī handshake, ąŠčéą╗ąĖčćą░čÄčēąĄą│ąŠčüčÅ ąŠčé ACK, č鹊 ąĖąĮąŠą│ą┤ą░ ąŠą▒čĆčŗą▓ą░ąĄčéčüčÅ čĆą░ąĮąĄąĄ ą▓čŗą┤ą░ąĮąĮą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ąĮąŠą▓ąŠą╣, ą╗ąŠą│ąĖą║ą░ USB ąĮąĄ ą┤ąŠą╗ąČąĮą░ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĄ ąŠčéą▓ąĄčéąĖčéčī ą┐ą░ą║ąĄč鹊ą╝ NAK ąĖą╗ąĖ STALL ąĮą░ č鹊ą║ąĄąĮ SETUP, ą┐čĆąĖąĮčÅčéčŗą╣ ąŠčé čģąŠčüčéą░.

ąÜąŠą│ą┤ą░ ą▒ąĖčéčŗ STAT_RX čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 01 (STALL) ąĖą╗ąĖ 10 (NAK), ąĖ ą┐čĆąĖąĮčÅčé č鹊ą║ąĄąĮ SETUP, USB ą┐čĆąĖąĮąĖą╝ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ, ą▓čŗą┐ąŠą╗ąĮčÅąĄčé čéčĆąĄą▒čāąĄą╝čŗąĄ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčé ąŠą▒čĆą░čéąĮąŠ ACK handshake. ąĢčüą╗ąĖ čŹčéą░ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ą┐ąŠą╗čāčćąĖą╗ą░ čĆą░ąĮąĄąĄ ą▓čŗą┤ą░ąĮąĮčŗą╣ ąĘą░ą┐čĆąŠčü CTR_RX, ąĮąŠ čŹč鹊 ą┐ąŠą║ą░ ąĮąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄą╝ (ąĮą░ą┐čĆąĖą╝ąĄčĆ ą▒ąĖčé CTR_RX ą▓čüąĄ ąĄčēąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čĆą░ąĮąĄąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĮčŗą╝ ą┐čĆąĖąĄą╝ąŠą╝), č鹊 USB ąŠčéą▒čĆą░čüčŗą▓ą░ąĄčé čéčĆą░ąĮąĘą░ą║čåąĖčÄ SETUP ąĖ ąĮąĄ ąŠčéą▓ąĄčćą░ąĄčé ą╗čÄą▒čŗą╝ handshake-ą┐ą░ą║ąĄč鹊ą╝ ąĮąĄ ąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čüą▓ąŠąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ, čüąĖą╝čāą╗ąĖčĆčāčÅ ąŠčłąĖą▒ą║čā ą┐čĆąĖąĄą╝ą░, ąĖ ą┐čĆąĖąĮčāąČą┤ą░čÅ čģąŠčüčé čüąĮąŠą▓ą░ ąŠčéą┐čĆą░ą▓ąĖčéčī č鹊ą║ąĄąĮ SETUP. ąŁč鹊 ą┤ąĄą╗ą░ąĄčéčüčÅ čü čåąĄą╗čīčÄ ąĖąĘą▒ąĄąČą░čéčī ą┐ąŠč鹥čĆąĖ ąŠą┐ąŠą▓ąĄčēąĄąĮąĖčÅ ąŠ čéčĆą░ąĮąĘą░ą║čåąĖąĖ SETUP, ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą╣ ą▓ čéčā ąČąĄ ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā, ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ čüą╗ąĄą┤čāčÄčēąĄą╣ ąĘą░ čéčĆą░ąĮąĘą░ą║čåąĖąĄą╣, ą║ąŠč鹊čĆą░čÅ ą▓čŗąĘą▓ą░ą╗ą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CTR_RX.

ąÜąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣. ąÆčüąĄ ą┤čĆčāą│ąĖąĄ čéąĖą┐čŗ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗąĄ čüčéą░ąĮą┤ą░čĆč鹊ą╝ USB, ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą╝ąŠą┤ąĄą╗ąĖ čéčĆą░čäąĖą║ą░, ąĖ ąŠą┐ąĖčüčŗą▓ą░čÄčé čéąĖą┐ąŠą▓čŗąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ čĆą░ąĘą╗ąĖčćąĮąŠą│ąŠ ą▓ąĖą┤ą░ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ ą╝ąĄąČą┤čā čģąŠčüč鹊ą╝ ąĖ čäčāąĮą║čåąĖąĄą╣ USB ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▒ąŠą╗čīčłąĖąĄ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ, čéąĖą┐ bulk ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ - ąĮą░ąĖą▒ąŠą╗ąĄąĄ ą┐ąŠą┤čģąŠą┤čÅčēą░čÅ ą╝ąŠą┤ąĄą╗čī. ą¤čĆąĖčćąĖąĮą░ ą▓ č鹊ą╝, čćč鹊 čģąŠčüčé ą┐ą╗ą░ąĮąĖčĆčāąĄčé bulk-čéčĆą░ąĮąĘą░ą║čåąĖąĖ čéą░ą║, čćč鹊ą▒čŗ ąĘą░ą┐ąŠą╗ąĮąĖčéčī ą▓čüčÄ ą┤ąŠčüčéčāą┐ąĮčāčÄ ą┐ąŠą╗ąŠčüčā ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ čäčĆąĄą╣ą╝ą░ čłąĖąĮčŗ, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ čāą▓ąĄą╗ąĖčćąĖą▓ą░čÅ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠą║ą░ čäčāąĮą║čåąĖčÅ USB ą│ąŠč鹊ą▓ą░ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčī ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮčāčÄ ąĄčæ bulk-čéčĆą░ąĮąĘą░ą║čåąĖčÄ. ąĢčüą╗ąĖ čäčāąĮą║čåąĖčÅ USB ą▓čüąĄ ąĄčēąĄ ąĘą░ąĮčÅčéą░ ą┐čĆąĄą┤čŗą┤čāčēąĄą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĄą╣, ą║ąŠą│ą┤ą░ čāąČąĄ ą┐ąŠčüčéčāą┐ą░ąĄčé čüą╗ąĄą┤čāčÄčēą░čÅ, č鹊 ąĮą░ ąĮąĄčæ ą▒čāą┤ąĄčé ą▓čŗą┤ą░ąĮą░ ą▓ ąŠčéą▓ąĄčé NAK handshake, ąĖ čģąŠčüčé PC čüąĮąŠą▓ą░ ą▓čŗą┤ą░čüčé čéčā ąČąĄ čüą░ą╝čāčÄ čéčĆą░ąĮąĘą░ą║čåąĖčÄ, ą┐ąŠą║ą░ USB čäčāąĮą║čåąĖčÅ ąĮąĄ čüčéą░ąĮąĄčé ą│ąŠč鹊ą▓ąŠą╣ ą║ ąĄčæ ąŠą▒čĆą░ą▒ąŠčéą║ąĄ, čüąĮąĖąČą░čÅ čĆąĄą░ą╗čīąĮčāčÄ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖąĘ-ąĘą░ ą┐ąŠą╗ąŠčüčŗ, ąĘą░ąĮąĖą╝ą░ąĄą╝ąŠą╣ ą┐ąŠą▓č鹊čĆąĮčŗą╝ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ čü bulk-ą║ąŠąĮąĄčćąĮčŗą╝ąĖ č鹊čćą║ą░ą╝ąĖ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮą░čÅ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ.

ąÜąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮą░ ą┤ą▓ąŠą╣ąĮą░čÅ ą▒čāč乥čĆąĖąĘą░čåąĖčÅ, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░, ą║ą░ą║ąŠą╣ ą▒čāč乥čĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąĄčĆąĖč乥čĆąĖąĄą╣ USB ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čéčĆąĄą▒čāąĄą╝čŗčģ ą┐ąĄčĆąĄą┤ą░čć ą┤ą░ąĮąĮčŗčģ, ąĖčüą┐ąŠą╗čīąĘčāčÅ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ ą║ą░ą║ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, čéą░ą║ ąĖ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░, čćč鹊ą▒čŗ ąŠą▒čĆą░ą▒ąŠčéą░čéčī ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▒čāč乥čĆąŠą▓ ą┐čĆąĖ ą║ą░ąČą┤ąŠą╣ čāčüą┐ąĄčłąĮąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ, čćč鹊ą▒čŗ ą▓čüąĄą│ą┤ą░ ąĖą╝ąĄčéčī ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮčŗą╣ ą▒čāč乥čĆ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄą╝, ą┐ąŠą║ą░ ą┐ąĄčĆąĖč乥čĆąĖčÅ USB ąĘą░ą┐ąŠą╗ąĮčÅąĄčé ą┤čĆčāą│ąŠą╣ ą▒čāč乥čĆ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą▓ąŠ ą▓čĆąĄą╝čÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ OUT, ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą╣ ąĮą░ ą┐čĆąĖąĄą╝ č湥čĆąĄąĘ bulk-ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣, ą┐ąŠą║ą░ ąŠą┤ąĖąĮ ą▒čāč乥čĆ ąĘą░ą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮąŠą▓čŗą╝ąĖ ą┐čĆąĖčģąŠą┤čÅčēąĖą╝ąĖ č湥čĆąĄąĘ USB ąŠčé čģąŠčüčéą░ ą┤ą░ąĮąĮčŗą╝ąĖ, ą┤čĆčāą│ąŠą╣ ą▒čāč乥čĆ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ (č鹊 ąČąĄ čüą░ą╝ąŠąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čü ą┐ąĄčĆąĄą┤ą░čÄčēąĄą╣ bulk-ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ IN).

ą¤ąŠčüą║ąŠą╗čīą║čā čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄą╝ ą▒čāč乥čĆąŠą▓ čéčĆąĄą▒čāąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓čüąĄčģ č湥čéčŗčĆąĄčģ ąĘą░ą┐ąĖčüąĄą╣ čéą░ą▒ą╗ąĖčåčŗ ąŠą┐ąĖčüą░ąĮąĖčÅ ą▒čāč乥čĆąŠą▓ ą┤ą╗čÅ ą░ą┤čĆąĄčüąŠą▓ ą▒čāč乥čĆąŠą▓ ą▓ ą┐ą░ą╝čÅčéąĖ ąĖ ąĖčģ ą┤ą╗ąĖąĮčŗ, č鹊 čĆąĄą│ąĖčüčéčĆčŗ USB_EPnR, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ bulk-ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣, ą┐čĆąĖčģąŠą┤ąĖčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čåąĄą╗ąĖą║ąŠą╝ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, č鹊ą╗čīą║ąŠ ąŠą┤ąĮą░ ą┐ą░čĆą░ ą▒ąĖčé STAT ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ ąĘąĮą░č湥ąĮąĖąĄ, ąŠčéą╗ąĖčćą░čÄčēąĄąĄčüčÅ ąŠčé 00 (Disabled): STAT_RX, ąĄčüą╗ąĖ čŹč鹊 bulk ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░, ąĖą╗ąĖ STAT_TX, ąĄčüą╗ąĖ čŹč鹊 bulk ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣, čĆą░ąĘčĆąĄčłąĄąĮąĮą░čÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÆ čüą╗čāčćą░ąĄ, ąĄčüą╗ąĖ čéčĆąĄą▒čāčÄčéčüčÅ ą║ąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ bulk čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣ ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ - ąĖ ą┐čĆąĖąĄą╝ą░, ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, č鹊 ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮčŗ ą┤ą▓ą░ čĆąĄą│ąĖčüčéčĆą░ USB_EPnR.

ą¦č鹊ą▒čŗ ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░čéčī čäčāąĮą║čåąĖčÄ ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ ąĖ ą┤ąŠčüčéąĖčćčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠ čłąĖąĮąĄ, ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮą░ čüčéčĆčāą║čéčāčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ąŠą╝ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ, ąŠą┐ąĖčüą░ąĮąĮą░čÅ ą▓ ą┐čĆąĄą┤čŗą┤čāčēąĖčģ čüąĄą║čåąĖčÅčģ, čćč鹊ą▒čŗ ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčī čüčéą░čéčāčü ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ą▓ NAK č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą║ąŠąĮčäą╗ąĖą║čé ąĘą░ ą┤ąŠčüčéčāą┐ ą║ ą▒čāč乥čĆčā ą╝ąĄąČą┤čā ą┐ąĄčĆąĖč乥čĆąĖąĄą╣ USB ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ą▓ą╝ąĄčüč鹊 č鹊ą│ąŠ, čćč鹊ą▒čŗ ą┤ąĄą╗ą░čéčī čŹč鹊 ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą║ą░ąČą┤ąŠą╣ čāčüą┐ąĄčłąĮąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ąæčāč乥čĆ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆčŗą╣ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąĄčĆąĖč乥čĆąĖąĄą╣ USB, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠ ą▒ąĖčéčā DTOG, ąŠčéąĮąŠčüčÅčēąĄą╝čāčüčÅ ą║ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÄ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ: DTOG_RX (ą▒ąĖčé 14 čĆąĄą│ąĖčüčéčĆą░ USB_EPnR) ą┤ą╗čÅ ą┐čĆąĖąĄą╝ąĮąŠą╣ bulk-ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣, ąĖą╗ąĖ DTOG_TX (ą▒ąĖčé 6 čĆąĄą│ąĖčüčéčĆą░ USB_EPnR) ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čÄčēąĄą╣ bulk-ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣. ąöą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ąĮąŠą▓ąŠą╣ čüčģąĄą╝čŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ąŠą╝ ą┐ąĄčĆąĖč乥čĆąĖčÅ USB ą┤ąŠą╗ąČąĮą░ ąĘąĮą░čéčī, ą║ą░ą║ąŠą╣ ą▒čāč乥čĆ ą┐ą░ą║ąĄčéą░ ą▓ ąĮą░čüč鹊čÅčēąĄąĄ ą▓čĆąĄą╝čÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą╗čÄą▒ąŠą│ąŠ ą║ąŠąĮčäą╗ąĖą║čéą░. ą¤ąŠčüą║ąŠą╗čīą║čā ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_EPnR ąĄčüčéčī ą┤ą▓ą░ ą▒ąĖčéą░ DTOG, ąĮąŠ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąĄčĆąĖč乥čĆąĖąĄą╣ USB ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▒čāč乥čĆąŠą▓ (ąĖąĘ-ąĘą░ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠčüčéąĖ, čéčĆąĄą▒čāąĄą╝ąŠą│ąŠ ą┤ą╗čÅ čäčāąĮą║čåąĖąĖ ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ), ą┤čĆčāą│ąŠą╣ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī, ą║ą░ą║ąŠą╣ ą▒čāč乥čĆ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. ąŁč鹊čé ąĮąŠą▓čŗą╣ čäą╗ą░ą│ ą▒čāč乥čĆą░ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ SW_BUF. ąÆ čüą╗ąĄą┤čāčÄčēąĄą╣ čéą░ą▒ą╗ąĖčåąĄ ąŠą▒čŖčÅčüąĮčÅąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ ą╝ąĄąČą┤čā ą▒ąĖčéą░ą╝ąĖ čĆąĄą│ąĖčüčéčĆą░ USB_EPnR ąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅą╝ąĖ DTOG/SW_BUF ą┤ą╗čÅ čüą╗čāčćą░ąĄą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ čā bulk-ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣.

ąóą░ą▒ą╗ąĖčåą░ 169. ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ čäą╗ą░ą│ą░ ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ.

| ążą╗ą░ą│ ą▒čāč乥čĆą░ |

ą¤ąĄčĆąĄą┤ą░čÄčēą░čÅ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ |

ą¤čĆąĖąĮąĖą╝ą░čÄčēą░čÅ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ |

| DTOG |

DTOG_TX (USB_EPnR, ą▒ąĖčé 6) |

DTOG_RX (USB_EPnR, ą▒ąĖčé 14) |

| SW_BUF |

USB_EPnR, ą▒ąĖčé 14 |

USB_EPnR, ą▒ąĖčé 6 |

ąæčāč乥čĆ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆčŗą╣ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąĄčĆąĖč乥čĆąĖąĄą╣ USB, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čäą╗ą░ą│ ą▒čāč乥čĆą░ DTOG, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą▒čāč乥čĆ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆčāąĄčéčüčÅ čäą╗ą░ą│ąŠą╝ SW_BUF. ąÆąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖąĄ ą╝ąĄąČą┤čā ąĘąĮą░č湥ąĮąĖąĄą╝ ą▒čāč乥čĆą░ čäą╗ą░ą│ą░ ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╝ ą▒čāč乥čĆąŠą╝ ą┐ą░ą║ąĄčéą░ č鹊 ąČąĄ čüą░ą╝ąŠąĄ ą▓ ąŠą▒ąŠąĖčģ čüą╗čāčćą░čÅčģ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╣ čéą░ą▒ą╗ąĖčåąĄ.

ąóą░ą▒ą╗ąĖčåą░ 170. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ bulk ą▒čāč乥čĆąŠą▓ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣.

| ąóąĖą┐ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ |

DTOG |

SW_BUF |

ąæčāč乥čĆ ą┐ą░ą║ąĄčéą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┐ąĄčĆąĖč乥čĆąĖąĄą╣ USB |

ąæčāč乥čĆ ą┐ą░ą║ąĄčéą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ |

| IN |

0 |

1 |

ADDRn_TX_0 / COUNTn_TX_0

ąĘą░ą┐ąĖčüąĖ BDT |

ADDRn_TX_1 / COUNTn_TX_1

ąĘą░ą┐ąĖčüąĖ BDT |

| 1 |

0 |

ADDRn_TX_1 / COUNTn_TX_1

ąĘą░ą┐ąĖčüąĖ BDT |

ADDRn_TX_0 / COUNTn_TX_0

ąĘą░ą┐ąĖčüąĖ BDT |

| 0 |

0 |

ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ(1)

|

ADDRn_TX_0 / COUNTn_TX_0

čÅč湥ą╣ą║ąĖ BDT |

| 1 |

1 |

| OUT |

0 |

1 |

ADDRn_RX_0 / COUNTn_RX_0

ąĘą░ą┐ąĖčüąĖ BDT |

ADDRn_RX_1 / COUNTn_RX_1

ąĘą░ą┐ąĖčüąĖ BDT |

| 1 |

0 |

ADDRn_RX_1 / COUNTn_RX_1

ąĘą░ą┐ąĖčüąĖ BDT |

ADDRn_RX_0 / COUNTn_RX_0

ąĘą░ą┐ąĖčüąĖ BDT |

| 0 |

0 |

ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ(1)

|

ADDRn_RX_0 / COUNTn_RX_0

ąĘą░ą┐ąĖčüąĖ BDT |

| 1 |

1 |

ADDRn_RX_1 / COUNTn_RX_1

ąĘą░ą┐ąĖčüąĖ BDT |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ NAK.

ążčāąĮą║čåąĖčÅ ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ ą┤ą╗čÅ bulk ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ:

ŌĆó ąĘą░ą┐ąĖčüčīčÄ ą┐ąŠą╗čÅ ą▒ąĖčé EP_TYPE ą▓ 00 čĆąĄą│ąĖčüčéčĆą░ USB_EPnR, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā ą║ą░ą║ bulk, ąĖ

ŌĆó čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ EP_KIND ą▓ 1 (DBL_BUF) č鹊ą│ąŠ ąČąĄ čĆąĄą│ąĖčüčéčĆą░.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÄ ą▒ąĖčé DTOG ąĖ SW_BUF ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┐ąĄčĆą▓čŗą╝ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╝ ą▒čāč乥čĆąŠą╝; čŹč鹊 čāčćąĖčéčŗą▓ą░ąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮąŠąĄ čüą▓ąŠą╣čüčéą▓ąŠ "č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ", ą║ąŠč鹊čĆąŠąĄ ąĖą╝ąĄčÄčé čŹčéąĖ ą┤ą▓ą░ ą▒ąĖčéą░. ą×ą║ąŠąĮčćą░ąĮąĖąĄ ą┐ąĄčĆą▓ąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ, ą┐čĆąŠąĖąĘąŠčłąĄą┤čłąĄą╣ ą┐ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ DBL_BUF, ą▓čŗąĘčŗą▓ą░ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ąŠą╝ ą┤ą╗čÅ bulk ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣, čćč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čüąĄčģ čéčĆą░ąĮąĘą░ą║čåąĖą╣, ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮčŗčģ čŹč鹊ą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĄ, ą┐ąŠą║ą░ ą▒ąĖčé DBL_BUF ąŠčüčéą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝. ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą║ą░ąČą┤ąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé CTR_RX ąĖą╗ąĖ CTR_TX bit čĆąĄą│ąĖčüčéčĆą░ USB_EPnR ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą│ąŠ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ąÆ č鹊 ąČąĄ ą▓čĆąĄą╝čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé DTOG ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_EPnR ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą┤ąĄą╗ą░čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▒čāč乥čĆąŠą▓ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╝ ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. ąÆ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ąŠą▒čēąĖčģ čéčĆą░ąĮąĘą░ą║čåąĖąĖ, ąĖ ą┐ąĄčĆą▓ąŠą╣ ą┐ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ DBL_BUF, ąĮą░ ą┐ą░čĆčā ą▒ąĖčé STAT ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ, ąĖ ąĖčģ ąĘąĮą░č湥ąĮąĖąĄ ąŠčüčéą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ 11 (Valid). ą×ą┤ąĮą░ą║ąŠ ą║ą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąĖąĮčÅčé ą┐ą░ą║ąĄčé č鹊ą║ąĄąĮą░ ąĮąŠą▓ąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ, ą░ą║čéčāą░ą╗čīąĮčŗą╣ čüčéą░čéčāčü ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ą▒čāą┤ąĄčé ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ 10 (NAK), ą║ąŠą│ą┤ą░ ąŠą▒ąĮą░čĆčāąČąĄąĮ ą║ąŠąĮčäą╗ąĖą║čé ą╝ąĄąČą┤čā ą┐ąĄčĆąĖč乥čĆąĖąĄą╣ USB ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ (čŹč鹊 čüąŠčüč鹊čÅąĮąĖąĄ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆčāąĄčéčüčÅ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ DTOG ąĖ SW_BUF, čüą╝. čéą░ą▒ą╗ąĖčåčā 170). ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ ąŠą▒čĆą░ą▒ąŠčéą║čā ąŠą┐ąŠą▓ąĄčēąĄąĮąĖčÅ ąŠ čüąŠą▒čŗčéąĖąĖ CTR ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ čäą╗ą░ą│ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ ąĘą░ą┐čāčüą║ą░ ą╗čÄą▒ąŠą╣ čéčĆąĄą▒čāąĄą╝ąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĮąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ąÜąŠą│ą┤ą░ ąĘą░ą║ą░ąĮčćąĖą▓ą░ąĄčéčüčÅ čĆą░ą▒ąŠčéą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĮą░ą┤ ą▒čāč乥čĆąŠą╝ ą┐ą░ą║ąĄčéą░, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčé ą▒ąĖčé SW_BUF ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ ąĮąĄą│ąŠ 1, čćč鹊ą▒čŗ ąŠą┐ąŠą▓ąĄčüčéąĖčéčī ą┐ąĄčĆąĖč乥čĆąĖčÄ USB ąŠ ą┤ąŠčüčéčāą┐ąĮąŠčüčéąĖ čŹč鹊ą│ąŠ ą▒čāč乥čĆą░. ąóą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéčĆą░ąĮąĘą░ą║čåąĖą╣ čü NAK ąŠą│čĆą░ąĮąĖčćąĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄą╝, čćč鹊 čüą▓čÅąĘą░ąĮąŠ čüąŠ čüą║ąŠčĆąŠčüčéčīčÄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┤ą░ąĮąĮčŗčģ: ąĄčüą╗ąĖ ą▓čĆąĄą╝čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą║ąŠčĆąŠč湥, č湥ą╝ ą▓čĆąĄą╝čÅ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠąĄ ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą┐ąŠ čłąĖąĮąĄ USB, č鹊 ąĮąĄ ą┐ąŠčéčĆąĄą▒čāčÄčéčüčÅ ą┐ąŠą▓č鹊čĆąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖąĘ-ąĘą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ąŠą╝, ąĖ čĆąĄą░ą╗čīąĮą░čÅ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒čāą┤ąĄčé ąŠą│čĆą░ąĮąĖč湥ąĮą░ č鹊ą╗čīą║ąŠ čģąŠčüč鹊ą╝ PC.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą▓čüąĄą│ą┤ą░ ą╝ąŠąČąĄčé ąŠčéą╝ąĄąĮąĖčéčī čüą┐ąĄčåąĖą░ą╗čīąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝, čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąĮąŠąĄ ą┤ą╗čÅ bulk ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣, ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ čÅą▓ąĮąŠą│ąŠ čüčéą░čéčāčüą░, ąŠčéą╗ąĖčćą░čÄčēąĄą│ąŠčüčÅ ąŠčé 11 (Valid), ą▓ ą┐ą░čĆčā ą▒ąĖčé STAT čĆąĄą│ąĖčüčéčĆą░ USB_EPnR. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┐ąĄčĆąĖč乥čĆąĖčÅ USB ą▒čāą┤ąĄčé ą▓čüąĄą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čüčéą░čéčāčü ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▒čāč乥čĆą░.

ąśąĘąŠčģčĆąŠąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąĪčéą░ąĮą┤ą░čĆčé USB ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┐ąŠą╗ąĮąŠčüą║ąŠčĆąŠčüčéąĮčŗąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, čéčĆąĄą▒čāčÄčēąĖąĄ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ąĖ č鹊čćąĮąŠą╣ čćą░čüč鹊čéčŗ ą│ąĄąĮąĄčĆą░čåąĖąĖ/ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, čéą░ą║ąŠą╣ ą▓ąĖą┤ čéčĆą░čäąĖą║ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą║ą░ą║ "ąĖąĘąŠčģčĆąŠąĮąĮčŗą╣". ąóąĖą┐ąĖčćąĮčŗąĄ ą┐čĆąĖą╝ąĄčĆčŗ čéą░ą║ąĖčģ ą┤ą░ąĮąĮčŗčģ: ą▓čŗą▒ąŠčĆą║ąĖ ąĘą▓čāą║ą░, ą┐ąŠč鹊ą║ąĖ čüąČą░č鹊ą│ąŠ ą▓ąĖą┤ąĄąŠ ąĖ ą╗čÄą▒ąŠą╣ ą▓ąĖą┤ ąŠčåąĖčäčĆąŠą▓ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ, čā ą║ąŠč鹊čĆčŗčģ ąĄčüčéčī ąČąĄčüčéą║ąŠąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąĖąĄ ą┤ą╗čÅ č鹊čćąĮąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą╣ čćą░čüč鹊čéčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÜąŠą│ą┤ą░ ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą║ą░ą║ "ąĖąĘąŠčģčĆąŠąĮąĮą░čÅ" ą▓ąŠ ą▓čĆąĄą╝čÅ čäą░ąĘčŗ 菹Įčāą╝ąĄčĆą░čåąĖąĖ, čģąŠčüčé ą▓čŗą┤ąĄą╗čÅąĄčé ą▓ čäčĆąĄą╣ą╝ąĄ čéčĆąĄą▒čāąĄą╝čāčÄ ą┐ąŠą╗ąŠčüčā ąĖ ą┐ąĄčĆąĄą┤ą░ąĄčé č鹊čćąĮąŠ ąŠą┤ąĖąĮ ą┐ą░ą║ąĄčé IN ąĖą╗ąĖ OUT ą▓ ą║ą░ąČą┤ąŠą╝ čäčĆąĄą╣ą╝ąĄ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ. ąśąĘ-ąĘą░ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą║ ą┐ąŠą╗ąŠčüąĄ ą┤ą╗čÅ ąĖąĘąŠčģčĆąŠąĮąĮąŠą│ąŠ čéčĆą░čäąĖą║ą░ ąĮąĄą▓ąŠąĘą╝ąŠąČąĮčŗ ą┐ąŠą▓č鹊čĆąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠčłąĖą▒ąŠčćąĮčŗčģ čéčĆą░ąĮąĘą░ą║čåąĖą╣; čŹč鹊 ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ č鹊ą╝čā, čćč鹊 čäą░ą║čéąĖč湥čüą║ąĖ ąĖąĘąŠčģčĆąŠąĮąĮčŗąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ąĮąĄ ąĖą╝ąĄčÄčé čäą░ąĘčŗ handshake, ąĖ ąĮąĄ ąŠąČąĖą┤ą░ąĄčéčüčÅ ą┐ą░ą║ąĄčé ACK ąĖą╗ąĖ ąĄą│ąŠ ąŠčéą┐čĆą░ą▓ą║ą░ ą┐ąŠčüą╗ąĄ ą┐ą░ą║ąĄčéą░ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠ č鹊ą╣ ąČąĄ ą┐čĆąĖčćąĖąĮąĄ ąĖąĘąŠčģčĆąŠąĮąĮčŗąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, ąĖ ą▓čüąĄą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčé DATA0 PID ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą╗čÄą▒ąŠą│ąŠ ą┐ą░ą║ąĄčéą░ ą┤ą░ąĮąĮčŗčģ.

ąśąĘąŠčģčĆąŠąĮąĮąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┤ą╗čÅ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé EP_TYPE ą▓ 10 (ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_EPnR). ą¤ąŠčüą║ąŠą╗čīą║čā čäą░ąĘą░ handshake ąŠčéčüčāčéčüčéą▓čāąĄčé, č鹊 ą┤ą╗čÅ ą┐ą░čĆ ą▒ąĖčé STAT_RX/STAT_TX ą╗ąĄą│ą░ą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ č鹊ą╗čīą║ąŠ 00 (Disabled) ąĖ 11 (Valid), ą╗čÄą▒ąŠąĄ ą┤čĆčāą│ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čĆąĄąĘčāą╗čīčéą░čéą░ą╝, ąĮąĄ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╝ čüąŠ čüčéą░ąĮą┤ą░čĆč鹊ą╝ USB. ąśąĘąŠčģčĆąŠąĮąĮčŗąĄ ą║ąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ čĆąĄą░ą╗ąĖąĘčāčÄčé ą┤ą▓ąŠą╣ąĮčāčÄ ą▒čāč乥čĆąĖąĘą░čåąĖčÄ ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ąĖčüą┐ąŠą╗čīąĘčāčÅ ą┐čĆąĖ čŹč鹊ą╝ ąŠą▒ąĄ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ "ą┐ąĄčĆąĄą┤ą░čćąĖ" ąĖ "ą┐čĆąĖąĄą╝ą░", čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▒čāč乥čĆąŠą▓ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ čāčüą┐ąĄčłąĮąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ąŁč鹊 ąŠą▒ąĄčüą┐ąĄčćąĖčé ą▓ ą┤ąŠčüčéčāą┐ąĮąŠčüčéčī ąŠą┤ąĮąŠą│ąŠ ą▒čāč乥čĆą░ ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┐ąĄčĆąĖč乥čĆąĖčÅ USB čĆą░ą▒ąŠčéą░ąĄčé čü ą┤čĆčāą│ąĖą╝ ą▒čāč乥čĆąŠą╝.

ą¤ą░ą╝čÅčéčī ą▒čāč乥čĆą░, ą║ąŠč鹊čĆą░čÅ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąĄčĆąĖč乥čĆąĖąĄą╣ USB, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▒ąĖč鹊ą╝ DTOG, čüą▓čÅąĘą░ąĮąĮčŗą╝ čü ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ (DTOG_RX ą┤ą╗čÅ ą┐čĆąĖąĮąĖą╝ą░čÄčēąĖčģ ąĖąĘąŠčģčĆąŠąĮąĮčŗčģ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║, DTOG_TX ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čÄčēąĖčģ ąĖąĘąŠčģčĆąŠąĮąĮčŗčģ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║, ąŠą▒ą░ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ USB_EPnR), ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 171.

ąóą░ą▒ą╗ąĖčåą░ 171. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ ąĖąĘąŠčģčĆąŠąĮąĮčŗčģ ą▒čāč乥čĆąŠą▓.

| ąóąĖą┐ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ |

DTOG |

ąæčāč乥čĆ ą┐ą░ą║ąĄčéą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┐ąĄčĆąĖč乥čĆąĖąĄą╣ USB |

ąæčāč乥čĆ ą┐ą░ą║ąĄčéą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ |

| IN |

0 |

ADDRn_TX_0 / COUNTn_TX_0

ąĘą░ą┐ąĖčüąĖ BDT |

ADDRn_TX_1 / COUNTn_TX_1

ąĘą░ą┐ąĖčüąĖ BDT |

| 1 |

ADDRn_TX_1 / COUNTn_TX_1

ąĘą░ą┐ąĖčüąĖ BDT |

ADDRn_TX_0 / COUNTn_TX_0

ąĘą░ą┐ąĖčüąĖ BDT |

| OUT |

0 |

ADDRn_RX_0 / COUNTn_RX_0

ąĘą░ą┐ąĖčüąĖ BDT |

ADDRn_RX_1 / COUNTn_RX_1

ąĘą░ą┐ąĖčüąĖ BDT |

| 1 |

ADDRn_RX_1 / COUNTn_RX_1

ąĘą░ą┐ąĖčüąĖ BDT |

ADDRn_RX_0 / COUNTn_RX_0

ąĘą░ą┐ąĖčüąĖ BDT |

ąÜą░ą║ čŹč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĖ čā bulk-ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣, čĆąĄą│ąĖčüčéčĆčŗ USB_EPnR, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ąĖąĘąŠčģčĆąŠąĮąĮčŗčģ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║, ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą│ąŠ ą┐ąŠč鹊ą║ą░ ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ čéčĆąĄą▒čāąĄčéčüčÅ čĆą░ąĘčĆąĄčłąĖčéčī ąĖąĘąŠčģčĆąŠąĮąĮčŗąĄ ą║ąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖą╣ ą┤ą░ąĮąĮčŗčģ - ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, č鹊 ą┤ąŠą╗ąČąĮčŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą▓ą░ čĆąĄą│ąĖčüčéčĆą░ USB_EPnR.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÄ ą▒ąĖčéą░ DTOG ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┐ąĄčĆą▓čŗą╝ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╝ ą▒čāč乥čĆąŠą╝; čŹč鹊 ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čüą┤ąĄą╗ą░ąĮąŠ čü čāč湥č鹊ą╝ čüą▓ąŠą╣čüčéą▓ą░ "č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ", ą║ąŠč鹊čĆąŠąĄ ąĖą╝ąĄčÄčé čŹčéąĖ ą┤ą▓ą░ ą▒ąĖčéą░. ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą║ą░ąČą┤ąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé CTR_RX ąĖą╗ąĖ CTR_TX ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_EPnR ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą╣ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÆ č鹊 ąČąĄ čüą░ą╝ąŠąĄ ą▓čĆąĄą╝čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé DTOG ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_EPnR ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčüčÅ, ą┐ąĄčĆąĄą║ą╗čÄčćą░čÅ ą▒čāč乥čĆ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ. ąØą░ ą┐ą░čĆčā ą▒ąĖčé STAT ąĮąĄ ą┐ąŠą▓ą╗ąĖčÅąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ; ą┐ąŠčüą║ąŠą╗čīą║čā ą┤ą╗čÅ ąĖąĘąŠčģčĆąŠąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čć ąĮąĄą▓ąŠąĘą╝ąŠąČąĮąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ (flow control), čéą░ą║ ą║ą░ą║ čā ąĮąĄčé čäą░ąĘčŗ handshake, ą║ąŠąĮąĄčćąĮą░čÅ č鹊čćą║ą░ ą▓čüąĄą│ą┤ą░ ąŠčüčéą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ 11 (Valid). ąśąĘąŠčģčĆąŠąĮąĮčŗąĄ OUT-čéčĆą░ąĮąĘą░ą║čåąĖąĖ, ą│ą┤ąĄ ąĄčüčéčī ąŠčłąĖą▒ą║ąĖ CRC, ąĖą╗ąĖ čüąĖčéčāą░čåąĖąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▒čāč乥čĆą░ (buffer-overrun condition), ą▓čüąĄą│ą┤ą░ čüčćąĖčéą░čÄčéčüčÅ ą║ąŠčĆčĆąĄą║čéąĮčŗą╝ąĖ čéčĆą░ąĮąĘą░ą║čåąĖčÅą╝ąĖ, ąŠąĮąĖ ą▓čüąĄą│ą┤ą░ ą▓čŗąĘčŗą▓ą░čÄčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ CTR_RX. ą×ą┤ąĮą░ą║ąŠ ąŠčłąĖą▒ą║ąĖ CRC ą▓čüąĄ čĆą░ą▓ąĮąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčé ą▒ąĖčé ERR ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_ISTR, čćč鹊ą▒čŗ ąŠą┐ąŠą▓ąĄčüčéąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝čā ąŠ ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÅčģ ą┤ą░ąĮąĮčŗčģ.

ąĪąŠą▒čŗčéąĖčÅ Suspend/Resume. ąĪčéą░ąĮą┤ą░čĆčé USB ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ąŠąĄ SUSPEND (ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ą░), ą▓ ą║ąŠč鹊čĆąŠą╝ čüčĆąĄą┤ąĮąĖą╣ č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ąŠčé čłąĖąĮčŗ USB ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąĄą▓čŗčłą░čéčī 2.5 ą╝ąÉ. ąŁč鹊 čéčĆąĄą▒ąŠą▓ą░ąĮąĖąĄ čäčāąĮą┤ą░ą╝ąĄąĮčéą░ą╗čīąĮąŠąĄ ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ USB, ą┐ąŠą╗čāčćą░čÄčēąĖčģ ą┐ąĖčéą░ąĮąĖąĄ ąŠčé čłąĖąĮčŗ (bus-powered device), ą┐ąŠčüą║ąŠą╗čīą║čā čāčüčéčĆąŠą╣čüčéą▓ą░ USB čü čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╝ ą┐ąĖčéą░ąĮąĖąĄą╝ (self-powered device) ąĮąĄ čéčĆąĄą▒čāčÄčé č鹊ą║ą░ čłąĖąĮčŗ, ąĖ ą┤ą╗čÅ ąĮąĖčģ ąĮąĄąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ čüąŠą▒ą╗čÄą┤ą░čéčī čŹč鹊 ąŠą│čĆą░ąĮąĖč湥ąĮąĖąĄ. ąÆ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ čģąŠčüčé PC ąŠčéą┐čĆą░ą▓ą╗čÅąĄčé ąŠą┐ąŠą▓ąĄčēąĄąĮąĖąĄ, ą║ąŠą│ą┤ą░ ąĮąĄ ą┐ąŠčüčŗą╗ą░ąĄčé ąĮąĖą║ą░ą║ąŠą╣ čéčĆą░čäąĖą║ ą┐ąŠ čłąĖąĮąĄ USB ą▓ č鹥č湥ąĮąĖąĄ ą▓čĆąĄą╝ąĄąĮąĖ ą▒ąŠą╗čīčłąĄ 3 ą╝čü. ą¤ąŠčüą║ąŠą╗čīą║čā SOF ą┐ą░ą║ąĄčéą░ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąŠčģąŠą┤ąĖčéčī ą║ą░ąČą┤čāčÄ 1 ą╝čü ą▓ąŠ ą▓čĆąĄą╝čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ, ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐čĆąŠą┐ą░ą┤ą░ąĮąĖąĄ 3 čüą╗ąĄą┤čāčÄčēąĖčģ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ą┐ą░ą║ąĄč鹊ą▓ SOF, ąĖ čéčĆą░ą║čéčāąĄčé čŹč鹊 ą║ą░ą║ ąĘą░ą┐čĆąŠčü ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ ąŠčé čģąŠčüčéą░. ąŁč鹊 čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▒ąĖčé SUSP čĆąĄą│ąĖčüčéčĆą░ USB_ISTR ą▓ 1 ąĖ ą▓čŗąĘčŗą▓ą░ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ. ąÜą░ą║ č鹊ą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ąĖą╗ąŠ čüą▓ąŠčÄ čĆą░ą▒ąŠčéčā, ąĄą│ąŠ ąĮąŠčĆą╝ą░ą╗čīąĮą░čÅ čĆą░ą▒ąŠč鹊čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ RESUME (ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ), ą║ąŠč鹊čĆčāčÄ ą╝ąŠąČąĄčé ąĮą░čćą░čéčī čģąŠčüčé PC ąĖą╗ąĖ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą┐ąŠ čüąĖą│ąĮą░ą╗čā ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ąĖą╗ąĖ ą┐ąŠ čüą▓ąŠąĄą╝čā čüąŠą▒čüčéą▓ąĄąĮąĮąŠą╝čā čüąĖą│ąĮą░ą╗čā. ą¤čĆąĖąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB ą▓čüąĄą│ą┤ą░ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čüą┐ąŠčüąŠą▒ąĮąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī RESET ąĮą░ čłąĖąĮąĄ USB, čĆąĄą░ą│ąĖčĆčāčÅ ąĮą░ čŹč鹊 čüąŠą▒čŗčéąĖąĄ ą║ą░ą║ ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ čüąŠą▒čŗčéąĖąĄ čüą▒čĆąŠčüą░ USB (USB reset event).

ąĀąĄą░ą╗čīąĮą░čÅ ą┐čĆąŠčåąĄą┤čāčĆą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ą░čÅ ą┤ą╗čÅ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖąĖ USB, ąĘą░ą▓ąĖčüąĖčé ąŠčé čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ąĄą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ č鹊ą║ą░, ąĖ ą┤ą╗čÅ čüąĮąĖąČąĄąĮąĖčÅ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą╝ąŠą│čāčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ.

ąØąĖąČąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąŠ ą║čĆą░čéą║ąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čéąĖą┐ąŠą▓ąŠą╣ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ, čüč乊ą║čāčüąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ąĮą░ čüą▓čÅąĘą░ąĮąĮčŗčģ čü USB ą░čüą┐ąĄą║čéą░čģ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ąŠčéą▓ąĄčćą░čÄčēąĄą╣ ąĮą░ ąŠą┐ąŠą▓ąĄčēąĄąĮąĖąĄ SUSP ą┐ąĄčĆąĖč乥čĆąĖąĖ USB:

1. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé FSUSP čĆąĄą│ąĖčüčéčĆą░ USB_CNTR ą▓ 1. ąŁč鹊 ą┤ąĄą╣čüčéą▓ąĖąĄ ą░ą║čéąĖą▓ąĖčĆčāąĄčé čĆąĄąČąĖą╝ suspend ą┤ą╗čÅ ą┐ąĄčĆąĖč乥čĆąĖąĖ USB. ąÜą░ą║ č鹊ą╗čīą║ąŠ čĆąĄąČąĖą╝ suspend ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ą╗čüčÅ, ą┐čĆąŠą▓ąĄčĆčīč鹥, čćč鹊 ą┐čĆąĖąĄą╝ mode SOF ąĘą░ą┐čĆąĄčēąĄąĮ, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą▒čāą┤čāčēąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ SUSP, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ, ą║ąŠą│ą┤ą░ USB ą┐čĆąĖąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ.

2. ą×čéą║ą╗čÄčćąĖč鹥 ąĖą╗ąĖ čüąĮąĖąĘčīč鹥 ą╗čÄą▒ąŠąĄ čüčéą░čéąĖč湥čüą║ąŠąĄ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ č鹊ą║ą░ ą▓ ą┤čĆčāą│ąĖčģ ą▒ą╗ąŠą║ą░čģ, ąĮąĄ ąŠčéąĮąŠčüčÅčēąĖčģčüčÅ ą║ USB.

3. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▓ 1 ą▒ąĖčé LP_MODE čĆąĄą│ąĖčüčéčĆą░ USB_CNTR, čćč鹊ą▒čŗ čāčüčéčĆą░ąĮąĖčéčī čüčéą░čéąĖč湥čüą║ąŠąĄ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą╝ąŠčēąĮąŠčüčéąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čéčĆą░ąĮčüąĖą▓ąĄčĆąŠą▓ USB, ąĮąŠ čüąŠčģčĆą░ąĮčÅą╣č鹥 ąĖčģ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ, ą║ąŠą│ą┤ą░ ą▓ąŠąĘą╝ąŠąČąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ resume.

4. ą×ą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą▓čŗą║ą╗čÄčćąĖč鹥 ą▓ąĮąĄčłąĮąĖą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ ąĖ PLL, čćč鹊ą▒čŗ ąŠčüčéą░ąĮąŠą▓ąĖčéčī ą╗čÄą▒čāčÄ ą░ą║čéąĖą▓ąĮąŠčüčéčī ą▓ąĮčāčéčĆąĖ čāčüčéčĆąŠą╣čüčéą▓ą░.

ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé čüąŠą▒čŗčéąĖąĄ USB, ąĄčüą╗ąĖ ą▓čüąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ SUSPEND, ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓ąŠą▓ą╗ąĄč湥ąĮą░ ą┐čĆąŠčåąĄą┤čāčĆą░ RESUME, čćč鹊ą▒čŗ ą▓ąŠčüčüčéą░ąĮąŠą▓ąĖčéčī ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ ą▓ąŠčüčüčéą░ąĮąŠą▓ąĖčéčī ąŠą▒čŗčćąĮąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ USB. ą×čüąŠą▒ąĄąĮąĮąŠąĄ ą▓ąĮąĖą╝ą░ąĮąĖąĄ ąĮčāąČąĮąŠ čāą┤ąĄą╗ąĖčéčī ą│ą░čĆą░ąĮčéąĖąĖ, čćč鹊 čŹč鹊čé ą┐čĆąŠčåąĄčüčü ąĮąĄ ąĘą░ą╣ą╝ąĄčé ą┐ąŠ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą▒ąŠą╗čīčłąĄ 10 ą╝čü, ą║ąŠą│ą┤ą░ čüąŠą▒čŗčéąĖąĄą╝ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ čÅą▓ą╗čÅąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī USB reset (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ čüčéą░ąĮą┤ą░čĆčéą░ USB [2]). ąØą░čćą░ą╗ąŠ resume ąĖą╗ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ USB reset, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĖč乥čĆąĖčÅ USB ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮą░, ą░čüąĖąĮčģčĆąŠąĮąĮąŠ ąŠčćąĖčüčéąĖčé ą▒ąĖčé LP_MODE čĆąĄą│ąĖčüčéčĆą░ USB_CNTR. ąöą░ąČąĄ ąĄčüą╗ąĖ čŹč鹊 čüąŠą▒čŗčéąĖąĄ ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ WKUP, ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ, ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠčéą▓ąĄčé ą┐čĆąŠčåąĄą┤čāčĆąŠą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ ąŠčüč鹊čĆąŠąČąĮąŠ, čćč鹊ą▒čŗ ąĮąĄ ą▓čŗąĘčŗą▓ą░čéčī ą┤ąŠą╗ą│ąŠą╣ ą╗ą░č鹥ąĮčéąĮąŠčüčéąĖ ąĮą░ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║č鹊ą▓. ą¦č鹊ą▒čŗ čüąĮąĖąĘąĖčéčī ą╗ą░č鹥ąĮčéąĮąŠčüčéčī ą┐ąĄčĆąĄą┤ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄą╝ ąĮąŠą╝ąĖąĮą░ą╗čīąĮąŠą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐ąŠą╝ąĄčüčéąĖčéčī ą┐čĆąŠčåąĄą┤čāčĆčā ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ, čćč鹊ą▒čŗ ą║ąŠą┤ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čüčĆą░ąĘčā ąĮą░čćą░ą╗ ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄąĘą░ą┐čāčüčéčÅčéčüčÅ čüąĖčüč鹥ą╝ąĮčŗąĄ čéą░ą║čéčŗ. ą¦č鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī čĆą░ąĘčĆčÅą┤čŗ ESD ąĖą╗ąĖ ą╗čÄą▒čŗąĄ ą┤čĆčāą│ąĖąĄ ą▓ąĖą┤čŗ ą┐ąŠą╝ąĄčģ ąĖąĘ-ąĘą░ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ čüąĖčüč鹥ą╝čŗ (ą▓čŗčģąŠą┤ ąĖąĘ čĆąĄąČąĖą╝ą░ suspend čŹč鹊 ą░čüąĖąĮčģčĆąŠąĮąĮąŠąĄ čüąŠą▒čŗčéąĖąĄ), ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ą┐ąŠą┤čģąŠą┤čÅčēąĖą╣ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čäąĖą╗čīčéčĆ ąĮą░ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąĖąĮąĖąĖ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠą╗ąŠčüą░ čüčĆąĄąĘą░ čäąĖą╗čīčéčĆą░ čüąŠčüčéą░ą▓ą╗čÅąĄčé ąŠą║ąŠą╗ąŠ 70 ąĮčü.

ąĪą┐ąĖčüąŠą║ ą┤ąĄą╣čüčéą▓ąĖą╣ ą┤ą╗čÅ resume-ą┐čĆąŠčåąĄą┤čāčĆčŗ:

1. ą×ą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą▓ą║ą╗čÄčćąĖč鹥 ą▓ąĮąĄčłąĮąĖą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ ąĖ/ąĖą╗ąĖ PLL (ąĄčüą╗ąĖ ąŠąĮąĖ ą▓čŗą║ą╗čÄč湥ąĮčŗ).

2. ą×čćąĖčüčéąĖč鹥 ą▒ąĖčé FSUSP čĆąĄą│ąĖčüčéčĆą░ USB_CNTR.

3. ąĢčüą╗ąĖ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąŠ čüąŠą▒čŗčéąĖąĄ resume, ą▒ąĖčéčŗ RXDP ąĖ RXDM ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_FNR ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┐ąŠ čéą░ą▒ą╗ąĖčåąĄ 172, ą║ąŠč鹊čĆą░čÅ čéą░ą║ąČąĄ ą┐ąĄčĆąĄčćąĖčüą╗čÅąĄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą▓ąŠ ą▓čüąĄčģ čüą╗čāčćą░čÅčģ. ąĢčüą╗ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, ąŠą║ąŠąĮčćą░ąĮąĖąĄ resume ąĖą╗ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ reset ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą┐čāč鹥ą╝ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ čüčéą░čéčāčüą░ ą▓čŗčłąĄčāą┐ąŠą╝čÅąĮčāčéčŗčģ ą▒ąĖčé ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ, ą║ąŠą│ą┤ą░ ąŠąĮąĖ ą┤ąŠčüčéąĖą│ąĮčāčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 10, čćč鹊 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖąĄ čłąĖąĮčŗ USB (Idle bus state). ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ reset čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ 1 ą▒ąĖčé RESET ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_ISTR. ą¤čĆąĖ čŹč鹊ą╝ čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ, ąĖ čŹč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠą▒čĆą░ą▒ąŠčéą░ąĮąŠ ąŠą▒čŗčćąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝.

ąóą░ą▒ą╗ąĖčåą░ 172. ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ resume.

| ąĪąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖčé [RXDP,RXDM] |

Wakeup event (čüąŠą▒čŗčéąĖąĄ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ) |

ąöąĄą╣čüčéą▓ąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠąĄ

ą┤ą╗čÅ resume (ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ) |

| 00 |

Root reset (čüą▒čĆąŠčü) |

ąØąĄčé ą┤ąĄą╣čüčéą▓ąĖą╣ |

| 10 |

None (ąĮąĖč湥ą│ąŠ, čłčāą╝ ąĮą░ čłąĖąĮąĄ) |

ą¤ąĄčĆąĄčģąŠą┤ ąŠą▒čĆą░čéąĮąŠ ą▓ čĆąĄąČąĖą╝ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (Suspend mode) |

| 01 |

Root resume (ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ) |

ąØąĄčé ą┤ąĄą╣čüčéą▓ąĖą╣ |

| 11 |

ąØąĄą┤ąŠą┐čāčüčéąĖą╝ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ (čłčāą╝ ąĮą░ čłąĖąĮąĄ) |

ą¤ąĄčĆąĄčģąŠą┤ ąŠą▒čĆą░čéąĮąŠ ą▓ čĆąĄąČąĖą╝ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (Suspend mode) |

ąŻčüčéčĆąŠą╣čüčéą▓čā ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ ą▓čŗą╣čéąĖ ąĖąĘ čĆąĄąČąĖą╝ą░ suspend ą▓ ąŠčéą▓ąĄčé ąĮą░ ąŠčéą┤ąĄą╗čīąĮčŗąĄ čüąŠą▒čŗčéąĖčÅ, ąĮąĄ ąŠčéąĮąŠčüčÅčēąĖąĄčüčÅ ąĮą░ą┐čĆčÅą╝čāčÄ ą║ ą┐čĆąŠč鹊ą║ąŠą╗čā USB (ąĮą░ą┐čĆąĖą╝ąĄčĆ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄ ą╝čŗčłąĖ ą▓čŗąĘčŗą▓ą░ąĄčé ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ ą▓čüąĄą╣ čüąĖčüč鹥ą╝čŗ). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī resume ą╝ąŠąČąĄčé ąĮą░čćąĖąĮą░čéčīčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▓ 1 ą▒ąĖčéą░ RESUME čĆąĄą│ąĖčüčéčĆą░ USB_CNTR ąĖ čüą▒čĆąŠčüąŠą╝ ąĄą│ąŠ ą▓ 0 ą┐ąŠčüą╗ąĄ ąĖąĮč鹥čĆą▓ą░ą╗ą░ ą╝ąĄąČą┤čā 1 ą╝čü ąĖ 15 ą╝čü (čŹč鹊čé ąĖąĮč鹥čĆą▓ą░ą╗ ą╝ąŠąČąĄčé ąŠčéčüą╗ąĄąČąĖą▓ą░čéčīčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ESOF, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ą║ą░ąČą┤čŗąĄ 1 ą╝čü, ą║ąŠą│ą┤ą░ čéą░ą║čéčŗ čüąĖčüč鹥ą╝čŗ čĆą░ą▒ąŠčéą░čÄčé ąĮą░ ąĮąŠą╝ąĖąĮą░ą╗čīąĮąŠą╣ čćą░čüč鹊č鹥). ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▒ąĖčé RESUME ąŠčćąĖčēąĄąĮ, ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī resume ą▒čāą┤ąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮą░ čģąŠčüč鹊ą╝ PC, ąĖ ąĄą│ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĄ čüąĮąŠą▓ą░ ąŠčéčüą╗ąĄąČąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ RXDP ąĖ RXDM ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_FNR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖčé RESUME ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čüąĄą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąĄčĆąĖč乥čĆąĖčÅ USB ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮą░ ą▓ čĆąĄąČąĖą╝ suspend čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▓ 1 ą▒ąĖčéą░ FSUSP ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_CNTR.

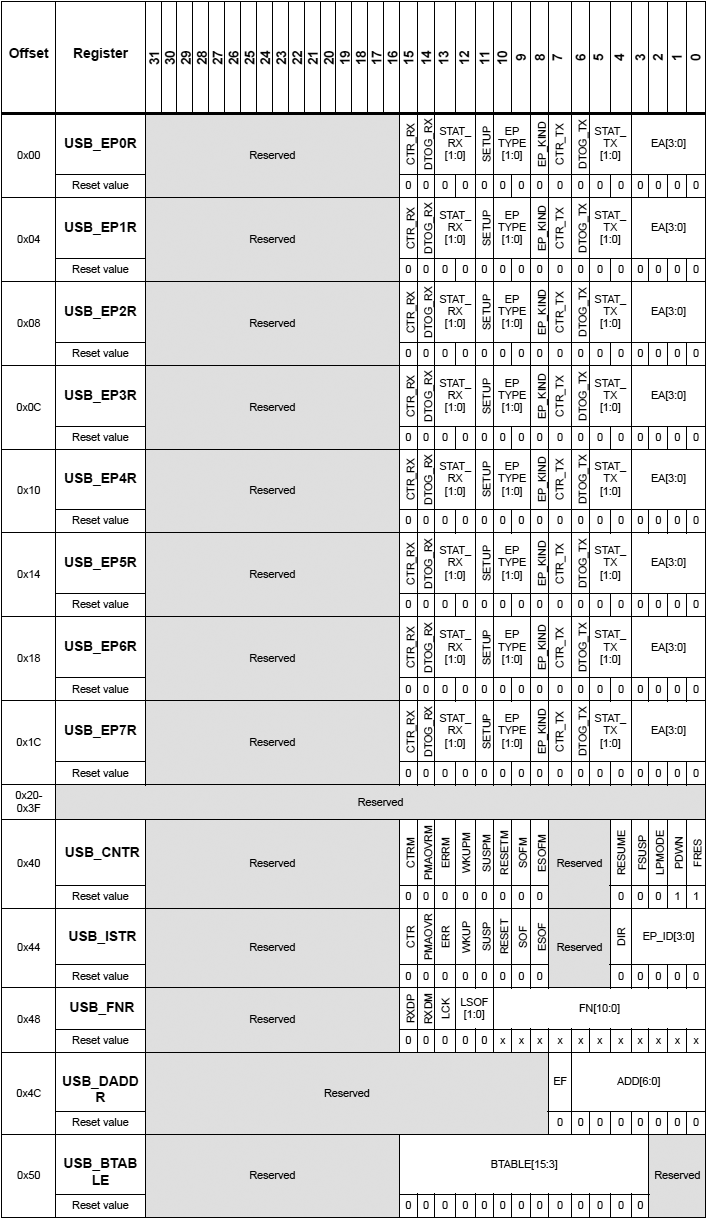

ąĀąĄą│ąĖčüčéčĆčŗ USB. ąĀąĄą│ąĖčüčéčĆčŗ ą┐ąĄčĆąĖč乥čĆąĖąĖ USB ą╝ąŠąČąĮąŠ ą┐ąŠą┤ąĄą╗ąĖčéčī ąĮą░ čüą╗ąĄą┤čāčÄčēąĖąĄ ą│čĆčāą┐ą┐čŗ:

ŌĆó ą×ą▒čēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ: čĆąĄą│ąĖčüčéčĆčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ.

ŌĆó ąĀąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║: ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ąĖ čüčéą░čéčāčü ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ.

ŌĆó ąóą░ą▒ą╗ąĖčåą░ ąŠą┐ąĖčüą░ąĮąĖčÅ ą▒čāč乥čĆąŠą▓ (Buffer Descriptor Table, BDT): ą╝ąĄčüč鹊 ą▓ ą▒čāč乥čĆąĄ ą┐ą░ą║ąĄč鹊ą▓, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠąĄ ą┤ą╗čÅ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ ą▒čāč乥čĆąŠą▓ ą┤ą░ąĮąĮčŗčģ.

ąÆčüąĄ ą░ą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓čŗčĆą░ąČą░čÄčéčüčÅ ą║ą░ą║ čüą╝ąĄčēąĄąĮąĖčÅ ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ ą▒ą░ąĘąŠą▓ąŠą╝čā čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ąĄčĆąĖč乥čĆąĖąĖ USB 0x40005C00, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čÅč湥ąĄą║ BDT, ą║ąŠč鹊čĆą░čÅ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąŠ ą░ą┤čĆąĄčüčā, čāą║ą░ąĘą░ąĮąĮąŠą╝čā ą▓ čĆąĄą│ąĖčüčéčĆąĄ USB_BTABLE. ąśąĘ-ąĘą░ ąŠą▒čēąĄą│ąŠ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ą╝ąŠčüč鹊ą▓ APB1 ąĮą░ ą░ą┤čĆąĄčüą░čåąĖčÄ čüą╗ąŠą▓, ą▓čüąĄ ą░ą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓čŗčĆąŠą▓ąĮąĄąĮčŗ ąĮą░ ą│čĆą░ąĮąĖčåčŗ 32-ą▒ąĖčéąĮčŗčģ čüą╗ąŠą▓, čģąŠčéčÅ čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ą┤ą╗ąĖąĮąŠą╣ 16 ą▒ąĖčé. ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ą░ą┤čĆąĄčüą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čÅč湥ą╣ą║ą░ą╝ąĖ ą▒čāč乥čĆą░ ą┐ą░ą║ąĄč鹊ą▓, ą║ąŠč鹊čĆčŗą╣ čĆą░ąĘą╝ąĄčēą░ąĄčéčüčÅ ąĮą░čćąĖąĮą░čÅ čü ą░ą┤čĆąĄčüą░ 0x40006000.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆčŗ ą┤ą╗čÅ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖčÅ čüą┐ąŠčüąŠą▒ą░ ą┤ąŠčüčéčāą┐ą░ ą║ ą▒ąĖčéą░ą╝ čĆąĄą│ąĖčüčéčĆąŠą▓ (rw, r, w, rc_w1 ąĖ čé. ą┤.). ąĪą╝. ą▓čĆąĄąĘą║čā ąĮąĖąČąĄ.

read/write (rw) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé čćąĖčéą░čéčī ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī čŹčéąĖ ą▒ąĖčéčŗ.

read-only (r) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé č鹊ą╗čīą║ąŠ čćąĖčéą░čéčī čŹčéąĖ ą▒ąĖčéčŗ.