|

SSD1322 čÅą▓ą╗čÅąĄčéčüčÅ ąŠą┤ąĮąŠą║čĆąĖčüčéą░ą╗čīąĮčŗą╝ ą┤čĆą░ą╣ą▓ąĄčĆąŠą╝ CMOS ą┤ą╗čÅ ą┤ąĖčüą┐ą╗ąĄąĄą▓ OLED/PLED (ą╝ą░čéčĆąĖčćąĮčŗą╣ 菹║čĆą░ąĮ ąĮą░ ąŠčüąĮąŠą▓ąĄ ąŠčĆą│ą░ąĮąĖč湥čüą║ąĖčģ/ą┐ąŠą╗ąĖą╝ąĄčĆąĮčŗčģ čüą▓ąĄč鹊ą┤ąĖąŠą┤ąŠą▓), čüąŠą▓ą╝ąĄčēąĄąĮąĮčŗą╝ čü ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝. ą×ąĮ čüąŠčüč鹊ąĖčé ąĖąĘ 480 čüąĄą│ą╝ąĄąĮč鹊ą▓ ąĖ 128 ąŠą▒čēąĖčģ ą╗ąĖąĮąĖą╣. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮą░ ą▓ čĆą░čüč湥č鹥 ąĮą░ ą┐ą░ąĮąĄą╗ąĖ OLED/PLED čü ąŠą▒čēąĖą╝ ą║ą░č鹊ą┤ąŠą╝.

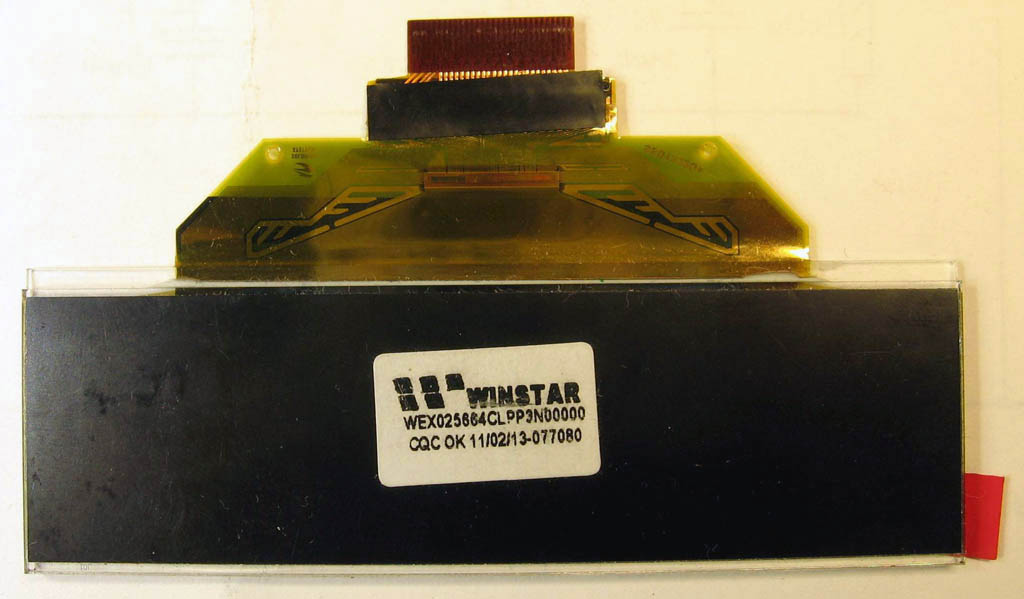

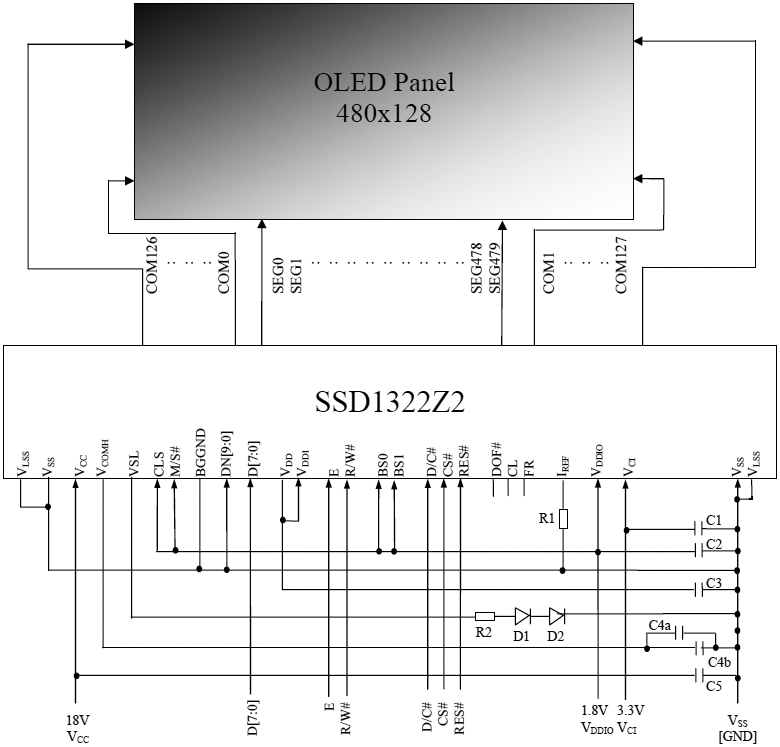

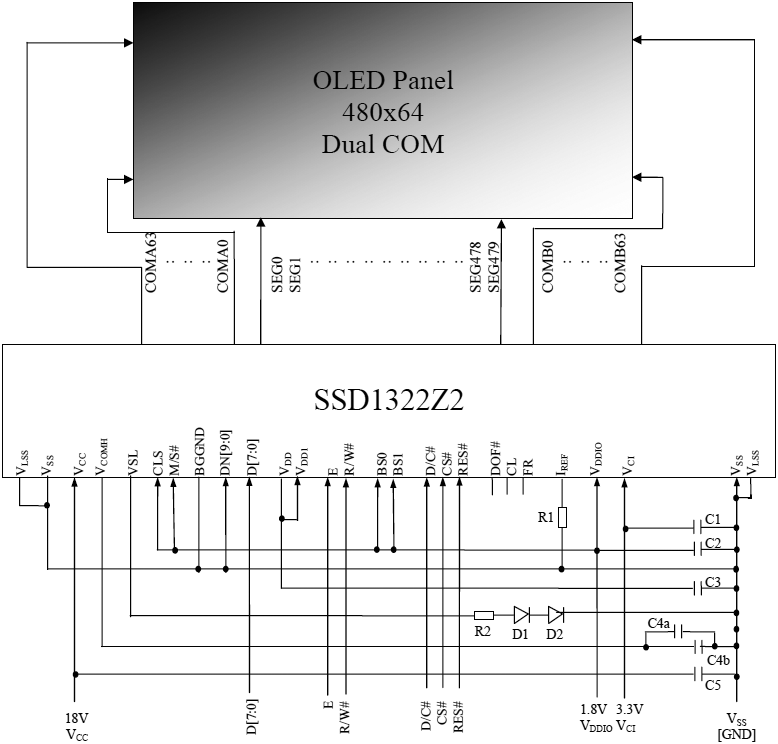

SSD1322 ąŠč鹊ą▒čĆą░ąČą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ąĮą░ą┐čĆčÅą╝čāčÄ ąĖąĘ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ 480 x 128 x 4 ą▒ąĖčé Graphic Display Data RAM (GDDRAM). ąöą░ąĮąĮčŗąĄ ąĖ ą║ąŠą╝ą░ąĮą┤čŗ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ąŠčé čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą│ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü, čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ą░ą┐ą┐ą░čĆą░čéąĮąŠ (ą┤ąŠčüčéčāą┐ąĮčŗ ą▓ą░čĆąĖą░ąĮčéčŗ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ą▓ čüčéąĖą╗ąĄ čłąĖąĮ MCU 6800 ąĖą╗ąĖ 8080, ą░ čéą░ą║ąČąĄ ą▓ą░čĆąĖą░ąĮčéčŗ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ čłąĖąĮčŗ SPI). ą£ąĖą║čĆąŠčüčģąĄą╝ą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆąĄą│čāą╗ąĖčĆąŠą▓ą║ąŠą╣ ą║ąŠąĮčéčĆą░čüčéąĮąŠčüčéąĖ ą▓ 256 čłą░ą│ąŠą▓, ąĖ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ąŠ ą╝ąĮąŠą│ąĖčģ ąĖąĮą┤čāčüčéčĆąĖą░ą╗čīąĮčŗčģ ąĖ ą░ą▓č鹊ą╝ąŠą▒ąĖą╗čīąĮčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ. ąØą░ č乊č鹊 ą┐ąŠą║ą░ąĘą░ąĮ ąĖąĮą┤ąĖą║ą░č鹊čĆ WEX025664CLPP3N00000 ą║ąŠą╝ą┐ą░ąĮąĖąĖ Winstar, ą┐ąŠčüčéčĆąŠąĄąĮąĮčŗą╣ ąĮą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ SSD1322:

[2. ą×čüąĮąŠą▓ąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ SSD1322]

ŌĆó ą£ą░čéčĆąĖčåą░ č鹊č湥ą║ 480 x 128

ŌĆó ąØą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ:

VDD = 2.4V..2.6V (ą┐ąĖčéą░ąĮąĖąĄ čÅą┤čĆą░, ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čĆąĄą│čāą╗čÅč鹊čĆąŠą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąŠčé ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VCI)

VDDIO = 1.65V..VCI (ą╗ąŠą│ąĖč湥čüą║ąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝)

VCI = 2.4V - 3.5V (ąĮąĖąĘą║ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ)

VCC = 10.0V ŌĆō 20.0V (ą┐ąĖčéą░ąĮąĖąĄ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą┐ą░ąĮąĄą╗ąĖ)

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ VCI ą╝ąĄąĮčīčłąĄ č湥ą╝ 2.6V, VDD ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĖčéą░ąĮąĖčÅ.

ŌĆó ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ą┤ą╗čÅ ą╝ą░čéčĆąĖčćąĮąŠą│ąŠ ą┤ąĖčüą┐ą╗ąĄčÅ:

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ą▓čŗč鹥ą║ą░čÄčēąĖą╣ č鹊ą║ čüąĄą│ą╝ąĄąĮčéą░: 300 ┬ĄA

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ą▓č鹥ą║ą░čÄčēąĖą╣ č鹊ą║ ąŠą▒čēąĄą│ąŠ ą▓čŗą▓ąŠą┤ą░: 80 mA

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą║ąŠąĮčéčĆą░čüčéąĮąŠčüčéčīčÄ ąĖ čÅčĆą║ąŠčüčéčīčÄ 256 ą│čĆą░ą┤ą░čåąĖą╣, 16 ą│čĆą░ą┤ą░čåąĖą╣ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ č鹊ą║ąŠą╝

ŌĆó ąöą╗čÅ ą║ą░ąČą┤ąŠą╣ č鹊čćą║ąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ 16 čāčĆąŠą▓ąĮąĄą╣ čüąĄčĆąŠą│ąŠ ą▒ą╗ą░ą│ąŠą┤ą░čĆčÅ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą▒čāč乥čĆąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ 菹║čĆą░ąĮą░ 480 x 128 x 4 ą▒ąĖčé SRAM

ŌĆó ą£ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī čĆą░ąĘąĮčŗąĄ čéąĖą┐čŗ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝:

ą¤ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╣ 8-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ą▓ čüčéąĖą╗ąĄ čłąĖąĮ ą╝ąĖą║čĆąŠą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ 6800 ąĖą╗ąĖ 8080

3/4-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ SPI

ŌĆó ąÆčŗą▒ąĖčĆą░ąĄą╝čŗą╣ čĆąĄąČąĖą╝ ą▓čŗč鹥ą║ą░čÄčēąĄą│ąŠ ąŠą▒čēąĄą│ąŠ č鹊ą║ą░ (Common current sinking):

Dual COM mode

Single COM mode

ŌĆó 8-čĆą░ąĘčĆčÅą┤ąĮą░čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ čéą░ą▒ą╗ąĖčåą░ ą│čĆą░ą┤ą░čåąĖą╣ čüąĄčĆąŠą│ąŠ (Gray Scale Look Up Table)

ŌĆó ąŚą░čēąĖčéą░ ą┐ąŠ ą┐ąĖčéą░ąĮąĖčÄ (High Power Protection)

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ čüą║ąŠčĆąŠčüčéąĖ čüą╝ąĄąĮčŗ čäčĆąĄą╣ą╝ąŠą▓ ąĖ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖčÅ (Frame Rate ąĖ Multiplexing Ratio)

ŌĆó ą¤ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ ą┐čĆąĖą▓čÅąĘą║ą░ čüčéčĆąŠą║ ąĖ čüč鹊ą╗ą▒čåąŠą▓ (Row re-mapping ąĖ Column re-mapping)

ŌĆó ąĀąĄąČąĖą╝ čüąĮą░, ą║ąŠą│ą┤ą░ č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ < 10┬ĄA

ŌĆó ąĀą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ -40┬░C..85┬░C.

ąóą░ą▒ą╗ąĖčåą░ 3-1. ąÆą░čĆąĖą░ąĮčéčŗ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą┤ąŠčüčéčāą┐ąĮčŗąĄ ą┤ą╗čÅ ą┐ąŠčüčéą░ą▓ą║ąĖ.

| Ordering Part Number |

SEG |

COM |

ąóąĖą┐ čāą┐ą░ą║ąŠą▓ą║ąĖ |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ |

| SSD1322Z2 |

480 |

128 |

Gold bump Die |

ŌĆó Min čłą░ą│ SEG: 25┬Ąm

ŌĆó Min čłą░ą│ COM: 35┬Ąm

ŌĆó ąóąŠą╗čēąĖąĮą░: 300┬▒15┬Ąm |

| SSD1322UR1 |

256 |

64 (ą┤ą▓ąŠą╣ąĮąŠą╣ COM) |

COF |

ŌĆó 70mm film, 5 SPH

ŌĆó ąśąĮč鹥čĆč乥ą╣čüčŗ 8-bit 8080/6800/SPI

ŌĆó SEG, COM čłą░ą│ ą▓čŗą▓ąŠą┤ąŠą▓ 0.12mm x 0.999 = 0.11988mm

ŌĆó ąóą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ 128 MUX (ąŠą┤ąĖąĮąŠčćąĮčŗą╣ COM)

ŌĆó ąóąŠą╗čēąĖąĮą░: 457┬▒25┬Ąm |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ą░čĆąĖą░ąĮčé ą┐ąŠčüčéą░ą▓ą║ąĖ SSD1322Z2 ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮč鹥čĆąĄčüąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╣ ąĖąĮą┤ąĖą║ą░č鹊čĆąŠą▓, ą┐ąŠčŹč鹊ą╝čā ąĮąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ č鹊ą╗čīą║ąŠ čåąŠą║ąŠą╗ąĄą▓ą║ą░ ą┤ą╗čÅ ą▓ą░čĆąĖą░ąĮčéą░ SSD1322UR1 (ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą╗ąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. ą┤ą░čéą░čłąĖčé ssd1322.pdf ąĖąĘ ą░čĆčģąĖą▓ą░ [1]).

ąĀąĖčü. 6-1. ą”ąŠą║ąŠą╗ąĄą▓ą║ą░ ąĖąĮč鹥čĆč乥ą╣čüą░ ą▓ą░čĆąĖą░ąĮčéą░ ą┐ąŠčüčéą░ą▓ą║ąĖ SSD1322UR1.

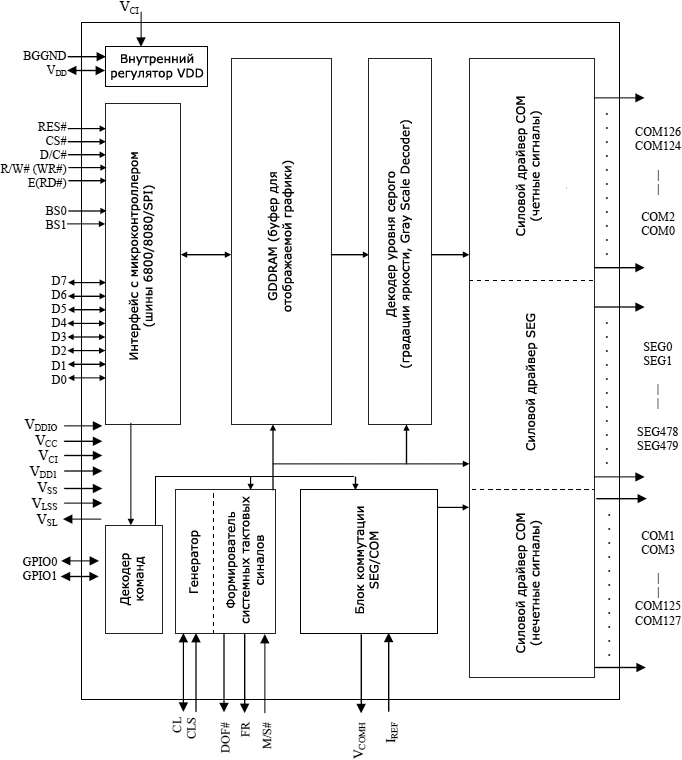

ąĀąĖčü. 4-1. ąæą╗ąŠą║-čüčģąĄą╝ą░ SSD1322.

[7. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓]

ąøąĄą│ąĄąĮą┤ą░ ą┤ą╗čÅ čéąĖą┐ą░ ą▓čŗą▓ąŠą┤ą░:

I ą▓čģąŠą┤

O ą▓čŗčģąŠą┤

IO ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ (input/output)

P ą▓čŗą▓ąŠą┤ ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ

NC ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ

ąóą░ą▒ą╗ąĖčåą░ 7-1. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ SSD1322.

| ą£ąĮąĄą╝. |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| VDD |

P |

ąÆčŗą▓ąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ (ą▓čģąŠą┤ ąĖą╗ąĖ ą▓čŗčģąŠą┤) ą┤ą╗čÅ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą╗ąŠą│ąĖą║ąĖ čÅą┤čĆą░. ą£ąĄąČą┤čā ą▓čŗą▓ąŠą┤ąŠą╝ VDD ąĖ VCC ąĮčāąČąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī čĆą░ąĘą▓čÅąĘčŗą▓ą░čÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čüąĄą║čåąĖčÄ 8.10. |

| VDDIO |

P |

ąÆčŗą▓ąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ (ą▓čģąŠą┤) ą┤ą╗čÅ ą╗ąŠą│ąĖą║ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░. ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé ą╗ąŠą│ąĖč湥čüą║ąĖąĄ čāčĆąŠą▓ąĮąĖ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ. VDDIO ą┤ąŠą╗ąČąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī čāčĆąŠą▓ąĮčÅą╝ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖąĮč鹥čĆč乥ą╣čüą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. |

| VCI |

P |

ąÆčŗą▓ąŠą┤ ąĮąĖąĘą║ąŠą▓ąŠą╗čīčéąĮąŠą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ (ą▓čģąŠą┤). ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ VCI ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čĆą░ą▓ąĮąŠ ąĖą╗ąĖ ą▓čŗčłąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ VDD ąĖ VDDIO. |

| VCC |

P |

ąÆčŗą▓ąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ (ą▓čģąŠą┤) ą┤ą╗čÅ čüąĖą╗ąŠą▓ąŠą╣ ą╗ąŠą│ąĖą║ąĖ ą┐ą░ąĮąĄą╗ąĖ. ąŁč鹊 čüą░ą╝ąŠąĄ ą▓čŗčüąŠą║ąŠąĄ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą┐ąŠą┤ą░ąĄčéčüčÅ ąĮą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ (ąŠą▒čŗčćąĮąŠ +15..18V). |

| VDD1 |

P |

ąÆčŗą▓ąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ (ą▓čģąŠą┤), ą║ąŠč鹊čĆčŗą╣ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ VDD. |

| VSS |

P |

ą×ą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤ (ąĘąĄą╝ą╗čÅ, GND). |

| VLSS |

P |

ą×ą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čüčģąĄą╝. |

| VCOMH |

P |

ąŻčĆąŠą▓ąĄąĮčī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ą╗čÅ ąĮąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ COM. ą£ąĄąČą┤čā VCOMH ąĖ VSS ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ čĆą░ąĘą▓čÅąĘčŗą▓ą░čÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ. |

| BGGND |

P |

ąŁč鹊čé ą▓čŗą▓ąŠą┤ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüąŠąĄą┤ąĖąĮąĄąĮ čü ąŠą▒čēąĖą╝ ą┐čĆąŠą▓ąŠą┤ąŠą╝. |

| GPIO0, GPIO1 |

IO |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ą▒čāą┤čāčēąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ. ąŁčéąĖ ą▓čŗą▓ąŠą┤čŗ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ. |

| VSL |

P |

ą×ą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ą╗čÅ SEG. ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ VSL, ąĄą│ąŠ ąĮčāąČąĮąŠ č湥čĆąĄąĘ čĆąĄąĘąĖčüč鹊čĆ ąĖ ą┤ąĖąŠą┤ čüąŠąĄą┤ąĖąĮąĖčéčī čü ąŠą▒čēąĖą╝ ą┐čĆąŠą▓ąŠą┤ąŠą╝ (ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ ąĘą░ą▓ąĖčüčÅčé ąŠčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ). |

| BS0, BS1 |

I |

ąÆčŗą▓ąŠą┤čŗ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝, ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čüąĄą║čåąĖčÄ 8.1. |

| IREF |

I |

ąŁč鹊čé ą▓čŗą▓ąŠą┤ ąĘą░ą┤ą░ąĄčé ąŠą┐ąŠčĆąĮčŗą╣ č鹊ą║ ą┤ą╗čÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ č鹊ą║ą░ SEG. ą£ąĄąČą┤čā IREF ąĖ VSS ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ čĆąĄąĘąĖčüč鹊čĆ, č湥čĆąĄąĘ ą║ąŠč鹊čĆčŗą╣ č鹥č湥čé č鹊ą║ ą┐ąŠčĆčÅą┤ą║ą░ 10┬ĄA. ąöą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ąĮąŠą╝ąĖąĮą░ą╗ą░ čĆąĄąĘąĖčüč鹊čĆą░ čüą╝. č乊čĆą╝čāą╗čā ą▓ čüąĄą║čåąĖąĖ 8.6. |

| M/S# |

I |

ąŁč鹊čé ą▓čŗą▓ąŠą┤ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ VSS, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā ą║čĆąĖčüčéą░ą╗ą╗ą░. |

| CL |

IO |

ąÆčŗą▓ąŠą┤ ą┤ą╗čÅ čéą░ą║č鹊ą▓. ąÜąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą│ąĄąĮąĄčĆą░čåąĖčÅ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (ąĮą░ CLS ą┐ąŠą┤ą░ąĮą░ ą╗ąŠą│. 1), č鹊 čŹč鹊čé ą▓čŗą▓ąŠą┤ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ąŠą▒čēąĄą╝čā ą┐čĆąŠą▓ąŠą┤čā. ąÜąŠą│ą┤ą░ ąĘą░ą┐čĆąĄčēąĄąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą│ąĄąĮąĄčĆą░čåąĖčÅ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (ąĮą░ CLS ą┐ąŠą┤ą░ąĮ ą╗ąŠą│. 0), č鹊 čŹč鹊 ą▓čģąŠą┤, ąĮą░ ą║ąŠč鹊čĆčŗą╣ ąĮčāąČąĮąŠ ą┐ąŠą┤ą░čéčī ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. |

| CLS |

I |

ąÆčŗą▒ąŠčĆ čüąĖą│ąĮą░ą╗ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ąÜąŠą│ą┤ą░ ąĮą░ čŹč鹊čé ą▓čŗą▓ąŠą┤ ą┐ąŠą┤ą░ąĮą░ ą╗ąŠą│. 1, č鹊 čĆą░ąĘčĆąĄčłąĄąĮą░ čĆą░ą▒ąŠčéą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ (ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝). ąÜąŠą│ą┤ą░ ąĮą░ čŹč鹊čé ą▓čŗą▓ąŠą┤ ą┐ąŠą┤ą░ąĮ ą╗ąŠą│. 0, č鹊 ąĮą░ ą▓čŗą▓ąŠą┤ CL ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą░ąĮ ą▓ąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗. |

| CS# |

I |

ąŁč鹊 ą▓čŗą▓ąŠą┤ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ (chip select), ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā. ą×ą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą▓ąŠąĘą╝ąŠąČąĄąĮ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ ąĮą░ CS# ą┐ąŠą┤ą░ąĮ ą╗ąŠą│. 0. |

| RES# |

I |

ąÆčŗą▓ąŠą┤ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ą░ čüą▒čĆąŠčüą░. ąÜąŠą│ą┤ą░ ąĮą░ ąĮąĄą│ąŠ ą┐ąŠą┤ą░ąĮ ą╗ąŠą│. 0, č鹊 ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąÆąŠ ą▓čĆąĄą╝čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ ąĮą░ ą▓ą▓ąŠą┤ąĄ RES# ą┤ąŠą╗ąČąĄąĮ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1. |

| D/C# |

I |

ąŁč鹊 ą▓čŗą▓ąŠą┤ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠą┤ą░č湥ą╣ ą┤ą░ąĮąĮčŗčģ (ą║ąŠą│ą┤ą░ ą╗ąŠą│. 1) ąĖą╗ąĖ ą║ąŠą╝ą░ąĮą┤čŗ (ą║ąŠą│ą┤ą░ ą╗ąŠą│. 0). |

| R/W# (WR#) |

I |

ąŁč鹊 ą▓čģąŠą┤ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čćč鹥ąĮąĖąĄą╝/ąĘą░ą┐ąĖčüčīčÄ ąĖąĮč鹥čĆč乥ą╣čüą░ čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝.

ąÜąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮ čĆąĄąČąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüą░ 6800, čŹč鹊čé ą▓čŗą▓ąŠą┤ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ (R/W#). ąĀąĄąČąĖą╝ čćč鹥ąĮąĖčÅ ą▓čŗą▒čĆą░ąĮ, ą║ąŠą│ą┤ą░ ąĮą░ čŹč鹊ą╝ ą▓čģąŠą┤ąĄ ą╗ąŠą│. 1, ąĖ čĆąĄąČąĖą╝ ąĘą░ą┐ąĖčüąĖ, ą║ąŠą│ą┤ą░ ą╗ąŠą│. 0.

ąÆ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ 8080 čŹč鹊čé ą▓čģąŠą┤ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čüąĖą│ąĮą░ą╗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (WR#). ąĀąĄąČąĖą╝ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čŹč鹊čé ą▓čģąŠą┤ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0 ąĖ čĆą░ą▒ąŠčéą░ ąĖąĮč鹥čĆč乥ą╣čüą░ čĆą░ąĘčĆąĄčłąĄąĮą░ (CS# čéą░ą║ąČąĄ ą▓ ą╗ąŠą│. 0).

ąÆ čĆąĄąČąĖą╝ąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI čŹč鹊čé ą▓čŗą▓ąŠą┤ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ VSS. |

| E (RD#) |

I |

ąŁč鹊 čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą▓čģąŠą┤ ąĖąĮč鹥čĆč乥ą╣čüą░ čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝.

ąÜąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮ čĆąĄąČąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüą░ 6800, čŹč鹊čé ą▓čŗą▓ąŠą┤ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ (E). ąĀąĄąČąĖą╝ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąĮą░ čŹč鹊ą╝ ą▓čŗą▓ąŠą┤ąĄ ą╗ąŠą│. 1 ąĖ čĆą░ą▒ąŠčéą░ ąĖąĮč鹥čĆč乥ą╣čüą░ čĆą░ąĘčĆąĄčłąĄąĮą░ (CS# == ą╗ąŠą│. 0).

ąÆ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ 8080 čŹč鹊čé ą▓čģąŠą┤ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čüąĖą│ąĮą░ą╗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čćč鹥ąĮąĖčÅ (RD#). ąĀąĄąČąĖą╝ čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čŹč鹊čé ą▓čģąŠą┤ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0 ąĖ čĆą░ą▒ąŠčéą░ ąĖąĮč鹥čĆč乥ą╣čüą░ čĆą░ąĘčĆąĄčłąĄąĮą░ (CS# čéą░ą║ąČąĄ ą▓ ą╗ąŠą│. 0).

ąÆ čĆąĄąČąĖą╝ąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI čŹč鹊čé ą▓čŗą▓ąŠą┤ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ VSS. |

| D7..D0 |

IO |

ąÆ čĆąĄąČąĖą╝ąĄ 8-čĆą░ąĘčĆčÅą┤ąĮčŗčģ čłąĖąĮ čŹč鹊 ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čüą▓čÅąĘąĖ čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝. ąÆ čĆąĄąČąĖą╝ąĄ SPI čüąĖą│ąĮą░ą╗čŗ D7..D3 ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ, ąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ VSS, čüąĖą│ąĮą░ą╗ D2 čéą░ą║ąČąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĖ ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝, ąĖ čüąĖą│ąĮą░ą╗čŗ D1 ąĖ D0 ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čüąĄą║čåąĖąĖ 8.1. |

| DN9..DN0 |

IO |

ąŁčéąĖ ą▓čŗą▓ąŠą┤čŗ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ą▒čāą┤čāčēąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ VSS. |

| FR |

O |

ąŁč鹊čé ą▓čŗą▓ąŠą┤ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĮąĖą║čāą┤ą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ. |

| DOF# |

O |

ąŁč鹊čé ą▓čŗą▓ąŠą┤ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĮąĖą║čāą┤ą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ. |

| SEG479..SEG0 |

O |

ąŁčéąĖ ą▓čŗą▓ąŠą┤čŗ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüąĄą│ą╝ąĄąĮčéą░ą╝ąĖ ą┐ą░ąĮąĄą╗ąĖ OLED. ąÜąŠą│ą┤ą░ ą┐ą░ąĮąĄą╗čī ą▓čŗą║ą╗čÄč湥ąĮą░, č鹊 ąĮą░ čŹčéąĖčģ ą▓čŗą▓ąŠą┤ą░čģ čāčĆąŠą▓ąĄąĮčī VSS. |

| COM127..COM0 |

O |

ąŁčéąĖ ą▓čŗą▓ąŠą┤čŗ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąŠą▒čēąĖą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ą┐ą░ąĮąĄą╗ąĖ OLED. ąÜąŠą│ą┤ą░ ą┐ą░ąĮąĄą╗čī ą▓čŗą║ą╗čÄč湥ąĮą░, č鹊 čŹčéąĖ ą▓čŗą▓ąŠą┤čŗ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą▓čŗčüąŠą║ąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čüąĄčĆčŗą╝ čłčĆąĖčäč鹊ą╝ ą┐ąŠą║ą░ąĘą░ąĮčŗ čüąĖą│ąĮą░ą╗čŗ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ ą▓čŗčģąŠą┤čÅčé ąĮą░ ą▓ąĮąĄčłąĮąĖą╣ ą║ąŠąĮąĮąĄą║č鹊čĆ 30-pin ą║ąŠąĮąĮąĄą║č鹊čĆą░ ą▓ ą▓ą░čĆąĖą░ąĮč鹥 ą┐ąŠčüčéą░ą▓ą║ąĖ SSD1322UR1.

[8. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą▒ą╗ąŠą║ąŠą▓]

8.1. ąÆą░čĆąĖą░ąĮčéčŗ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝.

ąśąĮč鹥čĆč乥ą╣čü čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ čā SSD1322 čüąŠčüč鹊ąĖčé ąĖąĘ 8 ą▓čŗą▓ąŠą┤ąŠą▓ ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ ąĖ 5 ą▓čŗą▓ąŠą┤ąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ąĀąĄąČąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ čāčĆąŠą▓ąĮąĄą╣ ą▓čŗą▓ąŠą┤ąŠą▓ BS0 ąĖ BS1:

| BS[1:0] |

ąóąĖą┐ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ |

| 00 |

4-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ SPI |

| 01 |

3-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ SPI |

| 10 |

8-ą▒ąĖčé ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮą░čÅ čłąĖąĮą░ 8080 |

| 11 |

8-ą▒ąĖčé ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮą░čÅ čłąĖąĮą░ 6800 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: 0 ą║ąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ BSx čüąŠąĄą┤ąĖąĮąĄąĮ čü VSS, 1 ą║ąŠą│ą┤ą░ BSx čüąŠąĄą┤ąĖąĮąĄąĮ čü VDDIO.

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ ą┤ą╗čÅ čĆą░ąĘąĮčŗčģ čĆąĄąČąĖą╝ąŠą▓ ąĖąĮč鹥čĆč乥ą╣čüą░ čüą▓ąĄą┤ąĄąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåčā 8-1.

ąóą░ą▒ą╗ąĖčåą░ 8-1. ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ ąĖąĮč鹥čĆč乥ą╣čüą░ čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą▓ čĆą░ąĘąĮčŗčģ čĆąĄąČąĖą╝ą░čģ.

| ąóąĖą┐ ąĖąĮč鹥čĆč乥ą╣čüą░ |

ąśąĮč鹥čĆč乥ą╣čü ą┤ą░ąĮąĮčŗčģ/ą║ąŠą╝ą░ąĮą┤ |

ąĪąĖą│ąĮą░ą╗čŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ |

| D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

E |

R/W# |

CS# |

D/C# |

RES# |

| 8-ą▒ąĖčé 8080 |

D[7:0] |

RD# |

WR# |

CS# |

D/C# |

RES# |

| 8-ą▒ąĖčé 8080 |

E |

R/W# |

| 3-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ SPI |

ąøąŠą│. 0 |

NC |

MOSI |

SCLK |

ąøąŠą│. 0 |

ąøąŠą│. 0 |

| 4-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ SPI |

D/C# |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą╗ąŠą│. 0 ąŠąĘąĮą░čćą░ąĄčé čüąŠąĄą┤ąĖąĮąĖčéčī čü ąŠą▒čēąĖą╝ ą┐čĆąŠą▓ąŠą┤ąŠą╝ VSS, NC ąŠąĘąĮą░čćą░ąĄčé ąĮąĖą║čāą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ.

ą¤ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čüąŠčüč鹊ąĖčé ąĖąĘ 8 ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ (D[7:0]), ąĖ čüąĖą│ąĮą░ą╗ąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ R/W#, D/C#, E ąĖ CS# (ą▓čģąŠą┤čŗ). ąøąŠą│. 0 ąĮą░ R/W# ą│ąŠą▓ąŠčĆąĖčé ąŠą▒ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ, ąĖ ą╗ąŠą│. 1 ąĮą░ R/W# ąŠą▒ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ. ąøąŠą│. 0 ąĮą░ D/C# ą│ąŠą▓ąŠčĆąĖčé ąŠ čćč鹥ąĮąĖąĖ/ąĘą░ą┐ąĖčüąĖ ą║ąŠą╝ą░ąĮą┤čŗ, ąĖ ą╗ąŠą│. 1 ąŠ čćč鹥ąĮąĖąĖ /ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ. ąÆčģąŠą┤ E ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ CS# ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0. ąöą░ąĮąĮčŗąĄ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ E (ą┐ąĄčĆąĄčģąŠą┤ ąŠčé ą╗ąŠą│. 1 ą║ ą╗ąŠą│. 0).

ąóą░ą▒ą╗ąĖčåą░ 8-2. ąĪąŠčüč鹊čÅąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čłąĖąĮčŗ 6800.

| ążčāąĮą║čåąĖčÅ |

E |

R/W# |

CS# |

D/C# |

| ąŚą░ą┐ąĖčüčī ą║ąŠą╝ą░ąĮą┤čŗ |

H->L |

L |

L |

L |

| ą¦č鹥ąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ |

H->L |

H |

L |

L |

| ąŚą░ą┐ąĖčüčī ą┤ą░ąĮąĮčŗčģ |

H->L |

L |

L |

H |

| ą¦č鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ |

H->L |

H |

L |

H |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

H->L ąŠąĘąĮą░čćą░ąĄčé ą┐ąĄčĆąĄčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ ąŠčé ą╗ąŠą│. 1 ą║ ą╗ąŠą│. 0

H ąŠąĘąĮą░čćą░ąĄčé ą╗ąŠą│. 1

L ąŠąĘąĮą░čćą░ąĄčé ą╗ąŠą│. 0

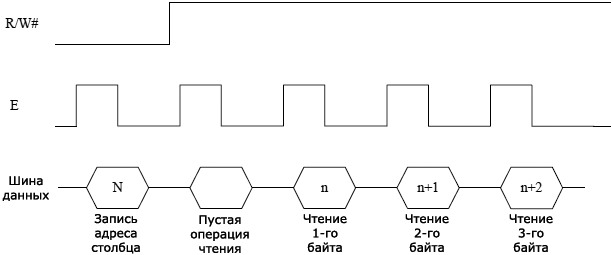

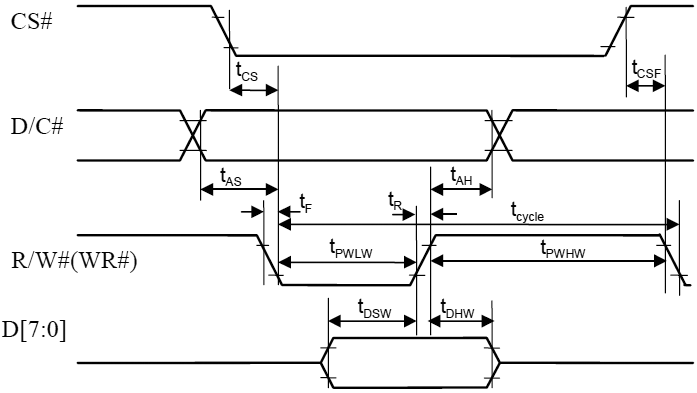

ą¦č鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ čĆą░ą▒ąŠč湥ą╣ čćą░čüč鹊čéčŗ ą▒čāč乥čĆąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ čü čĆą░ą▒ąŠč鹊ą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą▓ąĮčāčéčĆąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮąĄą║ąŠč鹊čĆą░čÅ ą║ąŠąĮą▓ąĄą╣ąĄčĆąĖąĘą░čåąĖčÅ, ą║ąŠč鹊čĆą░čÅ čéčĆąĄą▒čāąĄčé ą▓čüčéą░ą▓ą║ąĖ ą┐čāčüč鹊ą╣ ą║ąŠą╝ą░ąĮą┤čŗ čćč鹥ąĮąĖčÅ ą┐ąĄčĆąĄą┤ ą┐ąĄčĆą▓čŗą╝ ą░ą║čéčāą░ą╗čīąĮčŗą╝ čćč鹥ąĮąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ. ąŁč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 8-1.

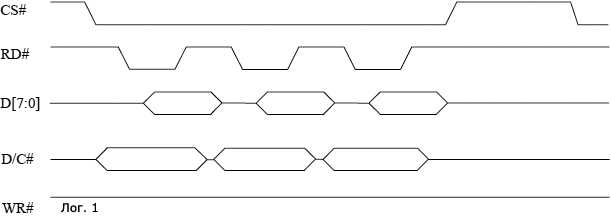

ąĀąĖčü. 8-1. ąÜą░ą║ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠą▒čĆą░čéąĮąŠąĄ čćč鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ: ą▓čüčéą░ą▓ą║ą░ ą┐čāčüč鹊ą╣ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ.

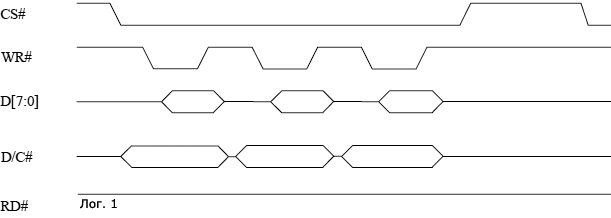

ą¤ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čüąŠčüč鹊ąĖčé ąĖąĘ 8 ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ (D[7:0]), ąĖ čüąĖą│ąĮą░ą╗ąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ RD#, WR#, D/C# ąĖ CS#. ąøąŠą│. 0 ąĮą░ D/C# ą│ąŠą▓ąŠčĆąĖčé ąŠ čćč鹥ąĮąĖąĖ/ąĘą░ą┐ąĖčüąĖ ą║ąŠą╝ą░ąĮą┤čŗ, ąĖ ą╗ąŠą│. 1 ąŠ čćč鹥ąĮąĖąĖ /ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ. ąØą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ RD# čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ, ą║ąŠą│ą┤ą░ CS# ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0. ąØą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ WR# čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ/ą║ąŠą╝ą░ąĮą┤čŗ, ą║ąŠą│ą┤ą░ CS# ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0.

ąĀąĖčü. 8-2. ą¤čĆąĖą╝ąĄčĆ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ 8080.

ąĀąĖčü. 8-3. ą¤čĆąĖą╝ąĄčĆ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ 8080.

ąóą░ą▒ą╗ąĖčåą░ 8-3. ąĪąŠčüč鹊čÅąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čłąĖąĮčŗ 8080.

| ążčāąĮą║čåąĖčÅ |

RD# |

WR# |

CS# |

D/C# |

| ąŚą░ą┐ąĖčüčī ą║ąŠą╝ą░ąĮą┤čŗ |

H |

L->H |

L |

L |

| ą¦č鹥ąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ |

L->H |

H |

L |

L |

| ąŚą░ą┐ąĖčüčī ą┤ą░ąĮąĮčŗčģ |

H |

L->H |

L |

H |

| ą¦č鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ |

L->H |

H |

L |

H |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

L->H ąŠąĘąĮą░čćą░ąĄčé ą┐ąĄčĆąĄčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ ąŠčé ą╗ąŠą│. 0 ą║ ą╗ąŠą│. 1

H ąŠąĘąĮą░čćą░ąĄčé ą╗ąŠą│. 1

L ąŠąĘąĮą░čćą░ąĄčé ą╗ąŠą│. 0

ąĪą╝. čéą░ą║ąČąĄ čĆąĖčü. 13-2 ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ 8080.

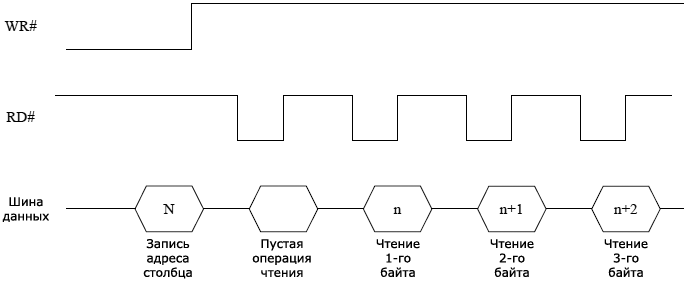

ą¦č鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ čĆą░ą▒ąŠč湥ą╣ čćą░čüč鹊čéčŗ ą▒čāč乥čĆąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ čü čĆą░ą▒ąŠč鹊ą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą▓ąĮčāčéčĆąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮąĄą║ąŠč鹊čĆą░čÅ ą║ąŠąĮą▓ąĄą╣ąĄčĆąĖąĘą░čåąĖčÅ, ą║ąŠč鹊čĆą░čÅ čéčĆąĄą▒čāąĄčé ą▓čüčéą░ą▓ą║ąĖ ą┐čāčüč鹊ą╣ ą║ąŠą╝ą░ąĮą┤čŗ čćč鹥ąĮąĖčÅ ą┐ąĄčĆąĄą┤ ą┐ąĄčĆą▓čŗą╝ ą░ą║čéčāą░ą╗čīąĮčŗą╝ čćč鹥ąĮąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ. ąŁč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 8-4.

ąĀąĖčü. 8-4. ąÜą░ą║ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠą▒čĆą░čéąĮąŠąĄ čćč鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ: ą▓čüčéą░ą▓ą║ą░ ą┐čāčüč鹊ą╣ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ.

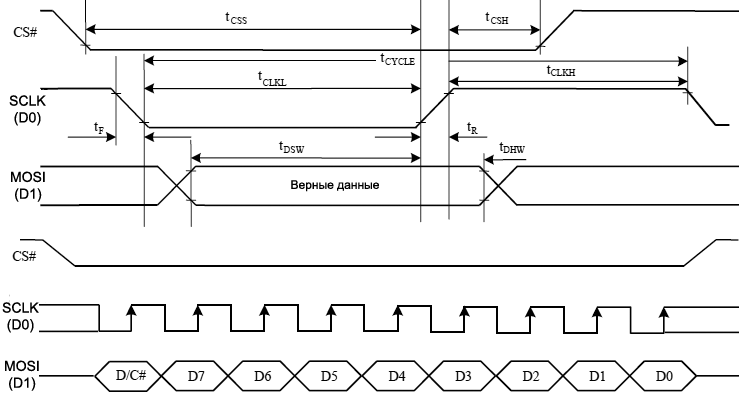

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ 4-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü čüąŠčüč鹊ąĖčé ąĖąĘ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ SCLK, čüąĖą│ąĮą░ą╗ą░ ą┤ą░ąĮąĮčŗčģ SDIN (MOSI), ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓ D/C#, CS#. ąÆ čĆąĄąČąĖą╝ąĄ SPI čüąĖą│ąĮą░ą╗ D0 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ SCLK, D1 ą║ą░ą║ SDIN. ąØąĄąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ čüąĖą│ąĮą░ą╗ D2 ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ ą┐ąŠą┤ą▓ąĄčłąĄąĮąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ (ąĮąĖą║čāą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ), ą░ ąĮąĄąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ čüąĖą│ąĮą░ą╗čŗ D3..D7, E ąĖ R/W# ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ ąŠą▒čēąĄą╝čā ą┐čĆąŠą▓ąŠą┤čā (GND).

ąóą░ą▒ą╗ąĖčåą░ 8-4. ąĀą░ą▒ąŠčéą░ čüąĖą│ąĮą░ą╗ąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ 4-ą┐čĆąŠą▓ąŠą┤ąĮąŠą│ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░.

| ążčāąĮą║čåąĖčÅ |

E (RD#) |

R/W# (WR#) |

CS# |

D/C# |

D0 |

D2 |

| ąŚą░ą┐ąĖčüčī ą║ąŠą╝ą░ąĮą┤čŗ |

VSS |

VSS |

L |

L |

L->H |

NC |

| ąŚą░ą┐ąĖčüčī ą┤ą░ąĮąĮčŗčģ |

VSS |

VSS |

L |

H |

L->H |

NC |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

L->H ąŠąĘąĮą░čćą░ąĄčé ą┐ąĄčĆąĄčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ ąŠčé ą╗ąŠą│. 0 ą║ ą╗ąŠą│. 1

H ąŠąĘąĮą░čćą░ąĄčé ą╗ąŠą│. 1

L ąŠąĘąĮą░čćą░ąĄčé ą╗ąŠą│. 0

VSS čüąŠąĄą┤ąĖąĮąĖčéčī čü ąŠą▒čēąĖą╝ ą┐čĆąŠą▓ąŠą┤ąŠą╝ VSS

NC ąĮąĖą║čāą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ

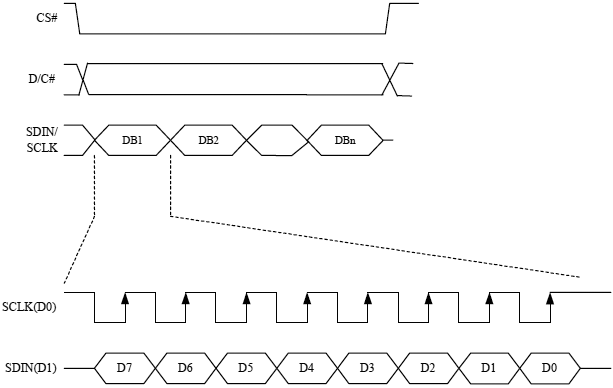

ąŻčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čģąŠą┤ąĄ SDIN (MOSI) ą▓ą┤ą▓ąĖą│ą░ąĄčéčüčÅ ą▓ 8-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ą┐ąŠ ą║ą░ąČą┤ąŠą╝čā čäčĆąŠąĮčéčā (ą┐ąĄčĆąĄčģąŠą┤čā ąŠčé ą╗ąŠą│. 0 ą║ ą╗ąŠą│. 1) čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ SCLK ą▓ ą┐ąŠčĆčÅą┤ą║ąĄ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé D7, D6, ... D0 (čüčéą░čĆčłąĖą╣ ą▒ąĖčé ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝). ąŻčĆąŠą▓ąĄąĮčī D/C# čüčćąĖčéčŗą▓ą░ąĄčéčüčÅ ą┐ąŠ ą║ą░ąČą┤ąŠą╝čā 8-ą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ąĖ ą┤ą░ąĮąĮčŗąĄ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▒čāą┤čāčé ąĘą░ą┐ąĖčüą░ąĮčŗ ą╗ąĖą▒ąŠ ą▓ ą▒čāč乥čĆąĮčāčÄ ą┐ą░ą╝čÅčéčī ą┤ąĖčüą┐ą╗ąĄčÅ (Graphic Display Data RAM, GDDRAM), ą╗ąĖą▒ąŠ ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ ąĮą░ č鹊ą╝ ąČąĄ čüą░ą╝ąŠą╝ čéą░ą║č鹊ą▓ąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ. ąÆ čĆąĄąČąĖą╝ąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┤ąŠą┐čāčüą║ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ.

ąĀąĖčü. 8-5. ą×ą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄąČąĖą╝ąĄ 4-ą┐čĆąŠą▓ąŠą┤ąĮąŠą│ąŠ SPI.

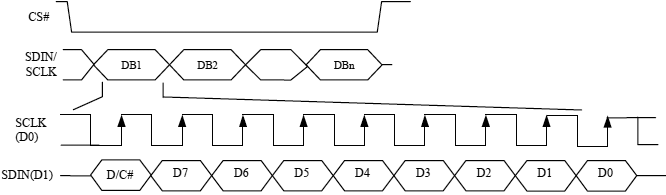

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ 3-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü čüąŠčüč鹊ąĖčé ąĖąĘ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ SCLK, čüąĖą│ąĮą░ą╗ą░ ą┤ą░ąĮąĮčŗčģ SDIN (MOSI), ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ CS#. ąÆ čĆąĄąČąĖą╝ąĄ SPI čüąĖą│ąĮą░ą╗ D0 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ SCLK, D1 ą║ą░ą║ SDIN. ąØąĄąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ čüąĖą│ąĮą░ą╗ D2 ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ ą┐ąŠą┤ą▓ąĄčłąĄąĮąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ (ąĮąĖą║čāą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ), ą░ ąĮąĄąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ čüąĖą│ąĮą░ą╗čŗ D3..D7, E, R/W# ąĖ D/C# ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ ąŠą▒čēąĄą╝čā ą┐čĆąŠą▓ąŠą┤čā (GND). ąÆčüąĄ čĆą░ą▒ąŠčéą░ąĄčé č鹊čćąĮąŠ čéą░ą║ ąČąĄ, ą║ą░ą║ ąĖ ą▓ 4-ą┐čĆąŠą▓ąŠą┤ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ, ąŠčéą╗ąĖčćąĖąĄ č鹊ą╗čīą║ąŠ ą▓ č鹊ą╝, čćč鹊 D/C# ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. ąŚą┤ąĄčüčī ą▓ čåąĄą╗ąŠą╝ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ 9-ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐ąŠčĆčÅą┤ą║ąĄ: ą▒ąĖčé D/C#, ąĘą░č鹥ą╝ D7 ąĖ ą┤ą░ą╗ąĄąĄ ą▒ąĖčéčŗ ąŠčé D6 ą┤ąŠ D0. ąŚąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░ D/C# (ą┐ąĄčĆą▓čŗą╣ ą▒ąĖčé ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ) ą▒čāą┤ąĄčé ąŠą┐čĆąĄą┤ąĄą╗čÅčéčī, ą║ą░ą║ ą▒čāą┤ąĄčé ąŠą▒čĆą░ą▒ąŠčéą░ąĮ ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╣ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą▒ą░ą╣čé: ąĖą╗ąĖ ąŠąĮ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮ ą▓ Display Data RAM (ą║ąŠą│ą┤ą░ D/C# = 1), ąĖą╗ąĖ ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤čŗ (D/C# = 0). ąÆ čĆąĄąČąĖą╝ąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┤ąŠą┐čāčüą║ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ.

ąóą░ą▒ą╗ąĖčåą░ 8-5. ąĀą░ą▒ąŠčéą░ čüąĖą│ąĮą░ą╗ąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ 3-ą┐čĆąŠą▓ąŠą┤ąĮąŠą│ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░.

| ążčāąĮą║čåąĖčÅ |

E (RD#) |

R/W# (WR#) |

CS# |

D/C# |

D0 |

D2 |

| ąŚą░ą┐ąĖčüčī ą║ąŠą╝ą░ąĮą┤čŗ |

VSS |

VSS |

L |

VSS |

L->H |

NC |

| ąŚą░ą┐ąĖčüčī ą┤ą░ąĮąĮčŗčģ |

VSS |

VSS |

L |

VSS |

L->H |

NC |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

L->H ąŠąĘąĮą░čćą░ąĄčé ą┐ąĄčĆąĄčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ ąŠčé ą╗ąŠą│. 0 ą║ ą╗ąŠą│. 1

H ąŠąĘąĮą░čćą░ąĄčé ą╗ąŠą│. 1

L ąŠąĘąĮą░čćą░ąĄčé ą╗ąŠą│. 0

VSS čüąŠąĄą┤ąĖąĮąĖčéčī čü ąŠą▒čēąĖą╝ ą┐čĆąŠą▓ąŠą┤ąŠą╝ VSS

NC ąĮąĖą║čāą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ

ąĀąĖčü. 8-6. ą×ą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄąČąĖą╝ąĄ 3-ą┐čĆąŠą▓ąŠą┤ąĮąŠą│ąŠ SPI.

ąÆą░ąČąĮąŠąĄ ąĘą░ą╝ąĄčćą░ąĮąĖąĄ ą┐ąŠ ą┐ąŠą▓ąŠą┤čā čüąĖą│ąĮą░ą╗ą░ CS#: ąĮąĄčüą╝ąŠčéčĆčÅ ąĮą░ č鹊, čćč鹊 ą╝ąŠąČąĮąŠ čŹč鹊čé čüąĖą│ąĮą░ą╗ ąĮą░ą▓čüąĄą│ą┤ą░ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ ą▓ ą╗ąŠą│. 0, ąĖ ąĖąĮą┤ąĖą║ą░č鹊čĆ ą▒čāą┤ąĄčé ą┐čĆąĖ čŹč鹊ą╝ ą▓ąŠčüą┐čĆąĖąĮąĖą╝ą░čéčī ą║ąŠą╝ą░ąĮą┤čŗ ąĖ ą┤ą░ąĮąĮčŗąĄ, čéą░ą║ąŠą╣ ą▓ą░čĆąĖą░ąĮčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čĆą░ą▒ąŠčéą░ąĄčé ąĮąĄąĮą░ą┤ąĄąČąĮąŠ. ąøčāčćčłąĄ ą▓čüąĄą│ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčī čüąĖą│ąĮą░ą╗ CS# ą▓ ą╗ąŠą│. 0 č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ą▓ ąĖąĮą┤ąĖą║ą░č鹊čĆ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ (ąĖą╗ąĖ ą▒ą╗ąŠą║ą░ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒ą░ą╣čé), ąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčī ąĄą│ąŠ ą▓ ą╗ąŠą│. 1 ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (ą▒ą░ą╣čéą░ ąĖą╗ąĖ ą▒ą╗ąŠą║ą░). ąöąŠą┐čāčüčéąĖą╝ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą▓ąĄčüčī ą▒ą╗ąŠą║ ą┤ą░ąĮąĮčŗčģ (ą┤ą░ąČąĄ ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ 菹║čĆą░ąĮą░ čåąĄą╗ąĖą║ąŠą╝), čāą┤ąĄčƹȹĖą▓ą░čÅ čüąĖą│ąĮą░ą╗ CS# ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0, ąĮąŠ ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ čŹč鹊ą│ąŠ ą▒ą╗ąŠą║ą░ ąĖ ą┐ąŠ ąĄą│ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ CS# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1.

8.2. ąĪčģąĄą╝ą░ čüą▒čĆąŠčüą░.

ąÜąŠą│ą┤ą░ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ RES# ą┐čĆąĖčéčÅąĮčāčé ą║ ą╗ąŠą│. 0, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ SSD1322 ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ą▓ čüą╗ąĄą┤čāčÄčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ:

1. ąöąĖčüą┐ą╗ąĄą╣ ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ

2. ąĀąĄąČąĖą╝ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ 128 MUX

3. ąÆą║ą╗čÄčćą░ąĄčéčüčÅ ąĮąŠčĆą╝ą░ą╗čīąĮą░čÅ ą┐čĆąĖą▓čÅąĘą║ą░ čüąĄą│ą╝ąĄąĮčéą░ ąĖ ą┤ą░ąĮąĮčŗčģ 菹║čĆą░ąĮą░ ą║ ą░ą┤čĆąĄčüčā čüč鹊ą╗ą▒čåą░ ąĖ čüčéčĆąŠą║ąĖ (SEG0 ą┐čĆąĖą▓čÅąĘą░ąĮ ą║ ą░ą┤čĆąĄčüčā 00h, ąĖ COM0 ą┐čĆąĖą▓čÅąĘą░ąĮ ą║ ą░ą┤čĆąĄčüčā 00h)

4. ąØą░čćą░ą╗čīąĮą░čÅ čüčéčĆąŠą║ą░ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĮą░ ą░ą┤čĆąĄčü 0 ą┐ą░ą╝čÅčéąĖ RAM 菹║čĆą░ąĮą░

5. ąĪč湥čéčćąĖą║ ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 0

6. ąØą░ ą▓čŗčģąŠą┤ą░čģ COM čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ

7. ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą║ąŠąĮčéčĆą░čüčéąĮąŠčüčéčīčÄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 7Fh.

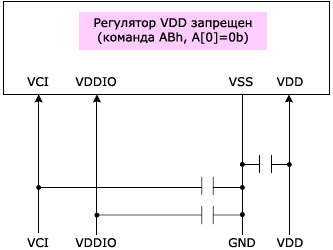

8.3. ąæčāč乥čĆ čŹą║čĆą░ąĮą░ GDDRAM.

8.3.1. ąĪčéčĆčāą║čéčāčĆą░ GDDRAM ą▓ čĆąĄąČąĖą╝ąĄ ą│čĆą░ą┤ą░čåąĖą╣ čüąĄčĆąŠą│ąŠ (Gray Scale mode)

ąóą░ą▒ą╗ąĖčåą░ 8-6 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą║ą░čĆčéčā ą┐ą░ą╝čÅčéąĖ GDDRAM, ą║ąŠą│ą┤ą░ GDDRAM ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ Gray Scale mode. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ 16 čāčĆąŠą▓ąĮąĄą╣ čüąĄčĆąŠą│ąŠ, ąĖ ą┐ąŠą┤ čāčĆąŠą▓ąĄąĮčī čüąĄčĆąŠą│ąŠ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ č鹊čćą║ąĖ ą▓čŗą┤ąĄą╗čÅąĄčéčüčÅ 4 ą▒ąĖčéą░ (ąŠą┤ąĖąĮ ąĮąĖą▒ą▒ą╗). ąØą░ą┐čĆąĖą╝ąĄčĆ D30480[3:0] ą▓ čéą░ą▒ą╗ąĖčåąĄ 8-6 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé č鹊čćą║ąĄ, čĆą░ąĘą╝ąĄčēąĄąĮąĮąŠą╣ ą▓ ą┐ąŠąĘąĖčåąĖąĖ (COM127, SEG2). ąóą░ą║ čćč鹊 čüčéą░čĆčłąĖą╣ ąĖ ą╝ą╗ą░ą┤čłąĖą╣ ąĮąĖą▒ą▒ą╗ D0, D1, D2, ..., D30717, D30718, D30719 ą▓ čéą░ą▒ą╗ąĖčåąĄ 8-6 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé ą▓ GDDRAM ąĮąĖą▒ą▒ą╗čŗ ą┤ą░ąĮąĮčŗčģ 480x128.

ąóą░ą▒ą╗ąĖčåą░ 8-6. GDDRAM ą▓ Gray Scale mode (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░).

-table8-6.png)

8.3.2. ą¤čĆąĖą▓čÅąĘą║ą░ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ ą║ RAM

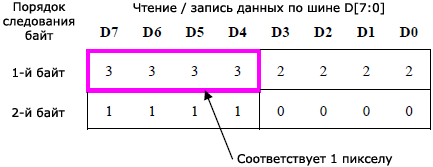

ąØąĖąČąĄ ą▓ čéą░ą▒ą╗ąĖčåąĄ 8-7 ą┐ąŠą║ą░ąĘą░ąĮą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ ą┐ąŠčĆčåąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖąĘ 2 ą▒ą░ą╣čé, ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ąŠč鹊čĆąŠą╣ čüčĆą░ąĘčā ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ 4 ą┐ąĖą║čüąĄą╗ą░ ąĮą░ 菹║čĆą░ąĮąĄ.

Table 8-7. ąÜą░ą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ.

8.4. ąöąĄą║ąŠą┤ąĄčĆ ą║ąŠą╝ą░ąĮą┤.

ąŁč鹊čé ą▒ą╗ąŠą║ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą┤ąŠą╗ąČąĮčŗ ą╗ąĖ ą▓čģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ą┤ą░ąĮąĮčŗąĄ ąĖą╗ąĖ ą║ą░ą║ ą║ąŠą╝ą░ąĮą┤ą░, ąŠčüąĮąŠą▓čŗą▓ą░čÅčüčī ąĮą░ ą▓čģąŠą┤ąĮąŠą╝ čüąĖą│ąĮą░ą╗ąĄ ą▓čŗą▓ąŠą┤ą░ D/C#. ąĢčüą╗ąĖ čāčĆąŠą▓ąĄąĮčī D/C# ą╗ąŠą│. 1, č鹊 ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ Graphic Display Data RAM (GDDRAM). ąĢčüą╗ąĖ ą╗ąŠą│. 0, č鹊 D0..D7 ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆčāčÄčéčüčÅ ą║ą░ą║ ą║ąŠą╝ą░ąĮą┤ą░, ąĖ ąŠąĮą░ ą▒čāą┤ąĄčé ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮą░ ąĖ ąĘą░ą┐ąĖčüą░ąĮą░ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤čŗ.

8.5. ąōąĄąĮąĄčĆą░č鹊čĆ ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ.

ąĀąĖčü. 8-7. ąæą╗ąŠą║ ą│ąĄąĮąĄčĆą░č鹊čĆą░.

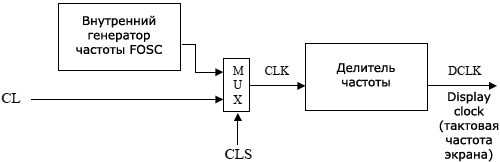

ąØą░ čĆąĖčü. 8-7 ą┐ąŠą║ą░ąĘą░ąĮ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą╝ą░ą╗ąŠą╝ąŠčēąĮčŗą╣ RC-ą│ąĄąĮąĄčĆą░č鹊čĆ. ąĀą░ą▒ąŠčćą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ (CLK) ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮą░ ą╗ąĖą▒ąŠ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░, ą╗ąĖą▒ąŠ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ CL, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ CLS. ąĢčüą╗ąĖ CLS = ą╗ąŠą│. 1, č鹊 ą▓čŗą▒čĆą░ąĮ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ. ąĢčüą╗ąĖ CLS = ą╗ąŠą│. 0, č鹊 ą┤ą╗čÅ CLK ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ CL. ą¦ą░čüč鹊čéą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ą╝ąŠąČąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčīčüčÅ ą║ąŠą╝ą░ąĮą┤ąŠą╣ B3h.

ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ąĖčüą┐ą╗ąĄčÅ (DCLK) ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ą▓čĆąĄą╝ąĄąĮąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ąĖčüą┐ą╗ąĄčÅ (Display Timing Generator) ą▓čŗą▓ąŠą┤ąĖčéčüčÅ ąĖąĘ CLK. ąÜąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ "D" ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ąŠčé 1 ą┤ąŠ 1024 ą║ąŠą╝ą░ąĮą┤ąŠą╣ B3h.

ą¦ą░čüč鹊čéą░ čüą╝ąĄąĮčŗ čäčĆąĄą╣ą╝ąŠą▓ ą┤ąĖčüą┐ą╗ąĄčÅ ą▒čāą┤ąĄčé ąŠą┐čĆąĄą┤ąĄą╗čÅčéčīčüčÅ ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╣ č乊čĆą╝čāą╗ąĄ:

FOSC

FFRM = ---------------

D * K * NMUX

ą│ą┤ąĄ D ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ čéą░ą║č鹊ą▓. ą×ąĮ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ąŠą╣ B3h A[3:0]. ąöąĖą░ą┐ą░ąĘąŠąĮ ą┤ą╗čÅ ą┤ąĄą╗ąĖč鹥ą╗čÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčé 1 ą┤ąŠ 1024.

K ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓ ą┤ąĖčüą┐ą╗ąĄčÅ ąĮą░ čüčéčĆąŠą║čā, ąĘąĮą░č湥ąĮąĖąĄ K ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ K = Phase 1 period + Phase 2 period + X. ąŚą┤ąĄčüčī X = DCLK ą▓ č鹥ą║čāčēąĄą╝ ą┐ąĄčĆąĖąŠą┤ąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ąź ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čĆą░ą▓ąĄąĮ constant + GS15 = 10 +112 = 122. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ K = 9 + 7 + 122 = 138.

NMUX ąĘąĮą░č湥ąĮąĖąĄ čüą║ąŠčĆąŠčüčéąĖ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖčÅ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ąŠą╣ A8h. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 127 (ąĮą░ą┐čĆąĖą╝ąĄčĆ 128MUX).

FOSC čćą░čüč鹊čéą░ ą│ąĄąĮąĄčĆą░č鹊čĆą░. ą×ąĮą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮą░ ą║ąŠą╝ą░ąĮą┤ąŠą╣ B3h A[7:4]. ą¦ąĄą╝ ą▒ąŠą╗čīčłąĄ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░, č鹥ą╝ ą▓čŗčłąĄ ą▒čāą┤ąĄčé čćą░čüč鹊čéą░.

ąĢčüą╗ąĖ čćą░čüč鹊čéą░ čäčĆąĄą╣ą╝ąŠą▓ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ čüą╗ąĖčłą║ąŠą╝ ą╝ą░ą╗ąŠą╣, č鹊 ą╝ąŠąČąĄčé ąĮą░ą▒ą╗čÄą┤ą░čéčīčüčÅ ą╝ąĄčĆčåą░ąĮąĖąĄ 菹║čĆą░ąĮą░. ąĪ ą┤čĆčāą│ąŠą╣ čüč鹊čĆąŠąĮčŗ, čüą╗ąĖčłą║ąŠą╝ ą▓čŗčüąŠą║ą░čÅ čćą░čüč鹊čéą░ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╝čā ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÄ čŹąĮąĄčĆą│ąĖąĖ ą┤ą╗čÅ ą▓čüąĄą╣ čüąĖčüč鹥ą╝čŗ.

8.6. ąæą╗ąŠą║ ą║ąŠą╝ą╝čāčéą░čåąĖąĖ SEG/COM.

ąŁč鹊čé ą▒ą╗ąŠą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖąĘ 菹ĮąĄčĆą│ąĖąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐ąĖčéą░ąĮąĖčÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ čāčĆąŠą▓ąĮąĄą╣ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ąĖ č鹊ą║ąŠą▓ ą┤ą╗čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ.

ŌĆó VCC čÅą▓ą╗čÅąĄčéčüčÅ čüą░ą╝čŗą╝ ą▓čŗčüąŠą║ąĖą╝ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ.

ŌĆó VCOMH čÅą▓ą╗čÅąĄčéčüčÅ ąŠą▒čēąĖą╝ čāčĆąŠą▓ąĮąĄą╝ čüąŠčüč鹊čÅąĮąĖčÅ ąŠčéčüčāčéčüčéą▓ąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ (Common deselected level). ą×ąĮ čĆąĄą│čāą╗ąĖčĆčāąĄčéčüčÅ čüčģąĄą╝ąŠą╣ ą▓ąĮčāčéčĆąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

ŌĆó VLSS čÅą▓ą╗čÅąĄčéčüčÅ ąŠą▒čēąĖą╝ ą┐čĆąŠą▓ąŠą┤ąŠą╝ ą┤ą╗čÅ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čåąĄą┐ąĄą╣ ąĖ č鹊ą║ą░ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą│čĆą░čäąĖč湥čüą║ąŠą╣ ą┐ą░ąĮąĄą╗ąĖ.

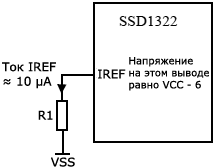

ŌĆó IREF čÅą▓ą╗čÅąĄčéčüčÅ ąŠą┐ąŠčĆąĮčŗą╝ č鹊ą║ąŠą╝ ą┤ą╗čÅ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ č鹊ą║ą░ čüąĄą│ą╝ąĄąĮč鹊ą▓ ISEG. ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī ą╝ąĄąČą┤čā ąŠą┐ąŠčĆąĮčŗą╝ č鹊ą║ąŠą╝ ąĖ č鹊ą║ąŠą╝ čüąĄą│ą╝ąĄąĮčéą░:

ISEG = Contrast / 256 * IREF * scale factor * 2

ąŚą┤ąĄčüčī ą║ąŠąĮčéčĆą░čüčéąĮąŠčüčéčī (0..255) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ąŠą╣ Set Contrast (C1h); čäą░ą║č鹊čĆ ą╝ą░čüčłčéą░ą▒ąĖčĆąŠą▓ą░ąĮąĖčÅ scale factor (1..16) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ąŠą╣ Master Current Control (C7h). ąØą░ą┐čĆąĖą╝ąĄčĆ, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī č鹊ą║ ISEG = 300 ┬ĄA čü ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ ą║ąŠąĮčéčĆą░čüčéąĮąŠčüčéčīčÄ 255, IREF čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąŠą║ąŠą╗ąŠ 10 ┬ĄA. ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄą╝ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐ąŠą┤čģąŠą┤čÅčēąĄą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ ą╝ąĄąČą┤čā ą▓čŗą▓ąŠą┤ąŠą╝ IREF ąĖ ą▓čŗą▓ąŠą┤ąŠą╝ VSS (ąŠą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤), ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 8-8. ąĀąĄą║ąŠą╝ąĄąĮą┤ąŠą▓ą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ IREF = 10 ┬ĄA.

ąĀąĖčü. 8-8. ąŻčüčéą░ąĮąŠą▓ą║ą░ č鹊ą║ą░ IREF čü ą┐ąŠą╝ąŠčēčīčÄ ą▓ąĮąĄčłąĮąĄą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░.

ą¤ąŠčüą║ąŠą╗čīą║čā ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ IREF čĆą░ą▓ąĮąŠ VCC ŌĆō 6V, č鹊 ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ R1 ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą║ą░ą║ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą┤ą╗čÅ IREF = 10 ┬ĄA, VCC = 18V:

R1 = (ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ IREF ŌĆō VSS) / IREF = (18 ŌĆō 6) / 10 ┬ĄA = 1.2 M╬®.

8.7. ąĪąĖą╗ąŠą▓ąŠą╣ ą┤čĆą░ą╣ą▓ąĄčĆ čüąĖą│ąĮą░ą╗ąŠą▓ SEG / COM.

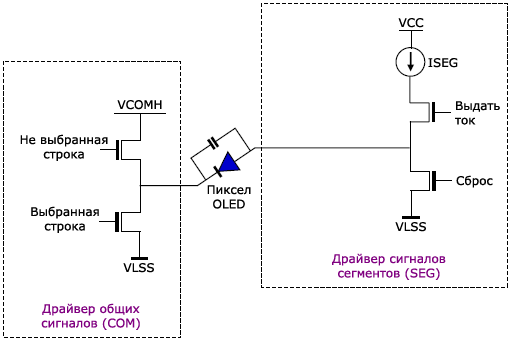

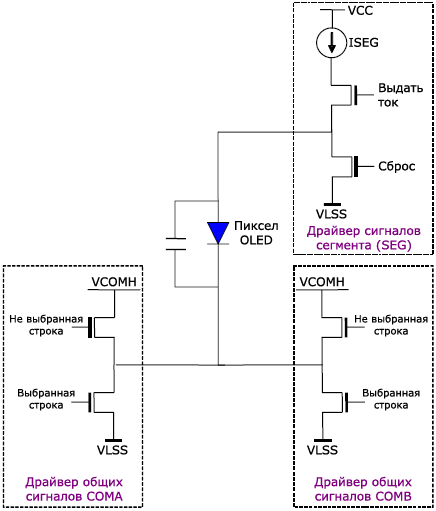

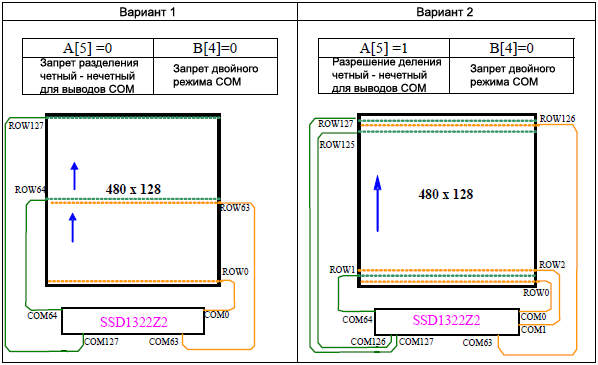

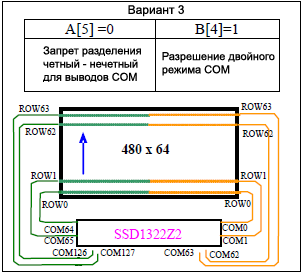

ążąŠčĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą│čĆą░čäąĖč湥čüą║ąŠą│ąŠ ąĖąĘąŠą▒čĆą░ąČąĄąĮąĖčÅ ą▓ ą╝ą░čéčĆąĖčåąĄ č鹊č湥ą║ čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╝čā ą┐čĆąĖąĮčåąĖą┐čā ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą╣ ąĖąĮą┤ąĖą║ą░čåąĖąĖ. ąöčĆą░ą╣ą▓ąĄčĆčŗ čüąĄą│ą╝ąĄąĮčéą░ (SEG) čüąŠčüč鹊čÅčé ąĖąĘ 480 ąĖčüč鹊čćąĮąĖą║ąŠą▓ č鹊ą║ą░ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą░ąĮąĄą╗čīčÄ OLED (čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé čüč鹊ą╗ą▒čåą░ą╝ ą╝ą░čéčĆąĖčåčŗ). ąŻą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ č鹊ą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 0 ą┤ąŠ 300 ┬ĄA čü ą┐ąŠą╝ąŠčēčīčÄ 8 ą▒ąĖčé (256 ą│čĆą░ą┤ą░čåąĖą╣). ąŁč鹊 ą┤ąĄą╗ą░ąĄčé ą║ąŠą╝ą░ąĮą┤ą░ čāčüčéą░ąĮąŠą▓ą║ąĖ ą║ąŠąĮčéčĆą░čüčéąĮąŠčüčéąĖ (C1h). ąöčĆą░ą╣ą▓ąĄčĆčŗ ąŠą▒čēąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ (COM) ą│ąĄąĮąĄčĆąĖčĆčāčÄčé ąĖą╝ą┐čāą╗čīčü čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ (čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé čüčéčĆąŠą║ą░ą╝ ą╝ą░čéčĆąĖčåčŗ). ąæą╗ąŠą║ąŠą▓čŗąĄ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ąĖ č乊čĆą╝čŗ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ SEG ąĖ COM ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮąĖąČąĄ.

ąĀąĖčü. 8-9. ąæą╗ąŠą║ąĖ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ SEG ąĖ COM ą▓ čĆąĄąČąĖą╝ąĄ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ COM (Single COM mode).

ąĀąĖčü. 8-10. ąæą╗ąŠą║ąĖ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ SEG ąĖ COM ą▓ čĆąĄąČąĖą╝ąĄ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ COM (Dual COM mode).

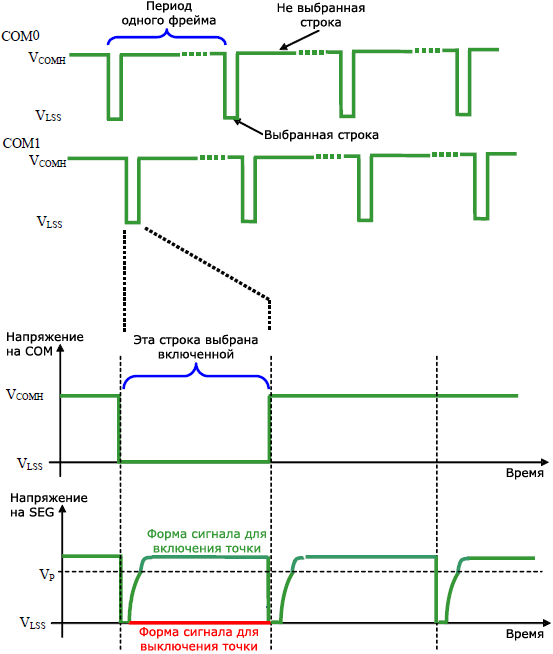

ąĪąĖą│ąĮą░ą╗čŗ ąŠą▒čēąĖčģ ą┐čĆąŠą▓ąŠą┤ąŠą▓ (COM) čüą║ą░ąĮąĖčĆčāčÄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, čüčéčĆąŠą║ą░ ąĘą░ čüčéčĆąŠą║ąŠą╣. ąĢčüą╗ąĖ čüčéčĆąŠą║ą░ ąĮąĄ ą▓čŗą▒čĆą░ąĮą░, č鹊 ą▓čüąĄ ą┐ąĖą║čüąĄą╗čŗ ą▓ čüčéčĆąŠą║ąĄ ą┐ąŠą╗čāčćą░čé ąŠą▒čĆą░čéąĮąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ, čéą░ą║ ą║ą░ą║ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ COM ąĖą╝ąĄąĄčé ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VCOMH, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 8-11.

ąÆ čüą║ą░ąĮąĖčĆčāąĄą╝ąŠą╣ čüčéčĆąŠą║ąĄ ą┐ąĖą║čüąĄą╗čŗ čüčéčĆąŠą║ąĖ ą▒čāą┤čāčé ą▓ą║ą╗čÄč湥ąĮčŗ ąĖą╗ąĖ ą▓čŗą║ą╗čÄč湥ąĮčŗ ą┐čāč鹥ą╝ ąŠčéą┐čĆą░ą▓ą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗą▓ąŠą┤čŗ čüąĄą│ą╝ąĄąĮčéą░ (SEG). ąĢčüą╗ąĖ ą┐ąĖą║čüąĄą╗ ą▓čŗą║ą╗čÄč湥ąĮ, č鹊 č鹊ą║ čüąĄą│ą╝ąĄąĮčéą░ čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ čĆą░ą▓ąĮčŗą╝ 0. ąÜąŠą│ą┤ą░ ą┐ąĖą║čüąĄą╗ ą▓ą║ą╗čÄč湥ąĮ (čüą▓ąĄčéąĖčéčüčÅ), čüąĄą│ą╝ąĄąĮčé ą▓čŗą┤ą░ąĄčé č鹊ą║ ISEG.

ąĀąĖčü. 8-11. ążąŠčĆą╝čŗ čüąĖą│ąĮą░ą╗ąŠą▓ SEG ąĖ COM.

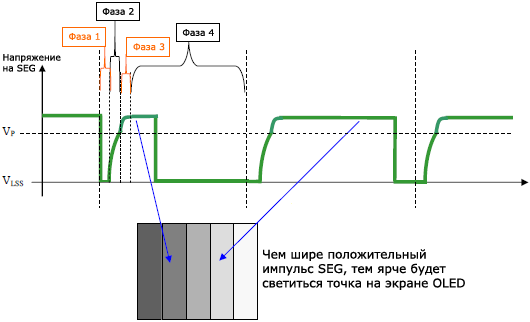

ąŚą┤ąĄčüčī ą┐ąŠą║ą░ąĘą░ąĮčŗ 4 čäą░ąĘčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ č鹊čćą║ą░ą╝ąĖ OLED. ąÆ čäą░ąĘąĄ 1 č鹊čćą║ą░ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą┤čĆą░ą╣ą▓ąĄčĆąŠą╝ SEG ą║ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ VLSS, čćč鹊ą▒čŗ čĆą░ąĘčĆčÅą┤ąĖčéčī ą┐čĆąĄą┤čŗą┤čāčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ, čüąŠčģčĆą░ąĮąĄąĮąĮčŗąĄ ą▓ ą┐ą░čĆą░ąĘąĖčéąĮąŠą╣ ąĄą╝ą║ąŠčüčéąĖ ąĮą░ 菹╗ąĄą║čéčĆąŠą┤ąĄ SEG. ą¤ąĄčĆąĖąŠą┤ čäą░ąĘčŗ 1 ą╝ąŠąČąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą║ąŠą╝ą░ąĮą┤ąŠą╣ B1h A[3:0]. ą¤ą░ąĮąĄą╗čī OLED, čā ą║ąŠč鹊čĆąŠą╣ ą▒ąŠą╗čīčłąĄ ąĄą╝ą║ąŠčüčéčī, čéčĆąĄą▒čāąĄčé čāą▓ąĄą╗ąĖč湥ąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░ ą┤ą╗čÅ čĆą░ąĘčĆčÅą┤ą░.

ąÆ čäą░ąĘąĄ 2 ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮčŗą╣ ąĘą░čĆčÅą┤. ąóąŠčćą║ą░ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VP ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ VLSS. ąÉą╝ą┐ą╗ąĖčéčāą┤ą░ VP ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ą║ąŠą╝ą░ąĮą┤ąŠą╣ BBh. ą¤ąĄčĆąĖąŠą┤ čäą░ąĘčŗ 2 ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą║ąŠą╝ą░ąĮą┤ąŠą╣ B1h A[7:4]. ą¦ąĄą╝ ą▒ąŠą╗čīčłąĄ ąĄą╝ą║ąŠčüčéčī ą┐ąĖą║čüąĄą╗ą░ ą┐ą░ąĮąĄą╗ąĖ OLED, č鹥ą╝ čéčĆąĄą▒čāąĄčéčüčÅ ą▒ąŠą╗čīčłąĄ ą┐ąĄčĆąĖąŠą┤ ąĘą░čĆčÅą┤ą░ ąĄą╝ą║ąŠčüčéąĖ, čćč鹊ą▒čŗ ąŠąĮ ą┤ąŠčüčéąĖą│ ąĮčāąČąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

ąÆ čäą░ąĘąĄ 3 ą┐ąĖą║čüąĄą╗ OLED čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čåąĄą╗ąĄą▓čŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ąĮą░ ą▓č鹊čĆąŠą╣ čäą░ąĘąĄ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą│ąŠ ąĘą░čĆčÅą┤ą░. ąØą░ ą▓č鹊čĆąŠą╝ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ąĄ ą╝ąŠąČąĮąŠ čāą┐čĆą░ą▓ą╗čÅčéčī čüą║ąŠčĆąŠčüčéčīčÄ ą┐čĆąŠčåąĄčüčüą░ ąĘą░čĆčÅą┤ą░. ą¤ąĄčĆąĖąŠą┤ čäą░ąĘčŗ 3 ą╝ąŠąČąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą║ąŠą╝ą░ąĮą┤ąŠą╣ B6h.

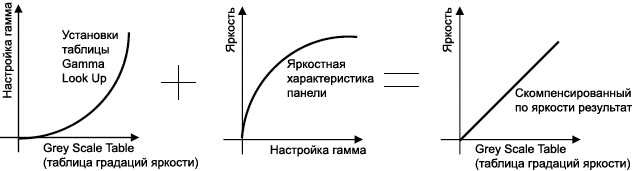

ą¤ąŠčüą╗ąĄą┤ąĮčÅčÅ 4 čäą░ąĘą░ ą▓čŗą┤ą░ąĄčé č鹊ą║ ąĮą░ ąĘą░ąČąĖą│ą░ąĄą╝čŗą╣ ą┐ąĖą║čüąĄą╗. ąśčüč鹊čćąĮąĖą║ č鹊ą║ą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ čüąĄą│ą╝ąĄąĮčéą░ ą┐ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐ąŠčüč鹊čÅąĮąĮčŗą╣ č鹊ą║ ą┤ą╗čÅ ą┐ąĖą║čüąĄą╗ą░. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ čĆąĄą░ą╗ąĖąĘčāąĄčé ą╝ąĄč鹊ą┤ PWM (Pulse Width Modulation, ą┐ąŠ-čĆčāčüčüą║ąĖ ą©ąśą£, čłąĖčĆąŠčéąĮąŠ-ąĖą╝ą┐čāą╗čīčüąĮą░čÅ ą╝ąŠą┤čāą╗čÅčåąĖčÅ) ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą│čĆą░ą┤ą░čåąĖčÅą╝ąĖ čüąĄčĆąŠą│ąŠ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĖą║čüąĄą╗ą░. ąŻčĆąŠą▓ąĄąĮčī čüąĄčĆąŠą│ąŠ (gray scale) ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą│ą░ą╝ą╝ą░ ą║ąŠą╝ą░ąĮą┤ąŠą╣ B8h/B9h. ą¦ąĄą╝ ą▒ąŠą╗čīčłąĄ čāčüčéą░ąĮąŠą▓ą║ą░ ą│ą░ą╝ą╝ą░, č鹥ą╝ ą▒čāą┤ąĄčé čłąĖčĆąĄ ąĖą╝ą┐čāą╗čīčü č鹊ą║ą░, ąĖ č鹥ą╝ ą▒čāą┤ąĄčé čÅčĆč湥 čüą▓ąĄčéąĖčéčīčüčÅ ą┐ąĖą║čüąĄą╗, ąĖ ąĮą░ąŠą▒ąŠčĆąŠčé (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čüąĄą║čåąĖčÄ 8.8). ą¤čĆąĖąĮčåąĖą┐ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čäą░ąĘą░ą╝ąĖ ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čĆąĖčüčāąĮą║ąĄ.

ąĀąĖčü. 8-12: čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą│čĆą░ą┤ą░čåąĖčÅą╝ąĖ čüąĄčĆąŠą│ąŠ (Gray Scale Control) čü ą┐ąŠą╝ąŠčēčīčÄ PWM ąĮą░ čüąĄą│ą╝ąĄąĮč鹥.

ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čäą░ąĘčŗ 4 ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ąŠą▒čĆą░čéąĮąŠ ą║ čäą░ąĘąĄ 1, čćč鹊ą▒čŗ ąŠč鹊ą▒čĆą░ąĘąĖčéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘąŠą▒čĆą░ąČąĄąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĄą╣ čüčéčĆąŠą║ąĖ. ąŁčéąĖ č湥čéčŗčĆąĄčģčäą░ąĘąŠą▓čŗąĄ čåąĖą║ą╗čŗ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą┐ąŠą▓č鹊čĆčÅčÄčéčüčÅ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖąĘąŠą▒čĆą░ąČąĄąĮąĖčÅ ąĮą░ ą┐ą░ąĮąĄą╗ąĖ OLED.

ąöą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čäą░ąĘčŗ 4 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ą░ą╝ąĖ B8h ąĖą╗ąĖ B9h. ąÆ čéą░ą▒ą╗ąĖčåąĄ čāčĆąŠą▓ąĄąĮčī čüąĄčĆąŠą│ąŠ (gray scale) ąĘą░ą┤ą░ąĮ ą┐ąŠ ą╝ąĄč鹊ą┤čā ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮąĖčÅ, čüąŠ čüčüčŗą╗ą║ąŠą╣ ąĮą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ąĖąĘ ą┐čĆąĄą┤čŗą┤čāčēąĄą╣ ąĘą░ą┐ąĖčüąĖ čéą░ą▒ą╗ąĖčåčŗ.

8.8. ąöąĄą║ąŠą┤ąĄčĆ čāčĆąŠą▓ąĮčÅ čüąĄčĆąŠą│ąŠ (Gray Scale Decoder).

ąŁčäč乥ą║čé ą│čĆą░ą┤ą░čåąĖą╣ čüąĄčĆąŠą│ąŠ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ ąĖą╝ą┐čāą╗čīčüą░ č鹊ą║ą░, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ GS0, ą║ąŠą│ą┤ą░ ąĮąĄčé ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░ (čäą░ąĘčŗ 2, 3) čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ č鹊ą║ąŠą╝ (čäą░ąĘą░ 4). ą¤ąĄčĆąĖąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░ą┤ą░ąĄčéčüčÅ ą┐ąŠ čāčüčéą░ąĮąŠą▓ą║ą░ą╝ čłą║ą░ą╗čŗ čüąĄčĆąŠą│ąŠ (0 .. 180). ą¦ąĄą╝ ą▒ąŠą╗čīčłąĄ čāčüčéą░ąĮąŠą▓ą║ą░, č鹥ą╝ čÅčĆč湥 ą▒čāą┤ąĄčé čüą▓ąĄčéąĖčéčīčüčÅ ą┐ąĖą║čüąĄą╗. ąóą░ą▒ą╗ąĖčåą░ čāčĆąŠą▓ąĮčÅ čüąĄčĆąŠą│ąŠ čģčĆą░ąĮąĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čāčĆąŠą▓ąĮąĖ ą│čĆą░ą┤ą░čåąĖąĖ čüąĄčĆąŠą│ąŠ (ą▓čüąĄą│ąŠ 16 čāčĆąŠą▓ąĮąĄą╣, GS0..GS15), ąĘą░ą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ąĖ ą║ąŠą╝ą░ąĮą┤ą░ą╝ąĖ B8h ąĖą╗ąĖ B9h.

ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 8-13, ą┤ą░ąĮąĮčŗąĄ GDDRAM čüąŠčüč鹊čÅčé ąĖąĘ 4 ą▒ąĖčé, ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčēąĖąĄ 16 čāčĆąŠą▓ąĮąĄą╣ ą│čĆą░ą┤ą░čåąĖąĖ čüąĄčĆąŠą│ąŠ ąŠčé GS0 ą┤ąŠ GS15. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĮą░ čćą░čüč鹊čéčā čäčĆąĄą╣ą╝ą░ ą▓ą╗ąĖčÅąĄčé čāčüčéą░ąĮąŠą▓ą║ą░ GS15.

ąóą░ą▒ą╗ąĖčåą░ 8-13. ąÆąĘą░ąĖą╝ąŠčüą▓čÅąĘčī ą╝ąĄąČą┤čā čüąŠą┤ąĄčƹȹĖą╝čŗą╝ GDDRAM ąĖ čüąŠą┤ąĄčƹȹĖą╝čŗą╝ čéą░ą▒ą╗ąĖčåčŗ ą│čĆą░ą┤ą░čåąĖą╣ čüąĄčĆąŠą│ąŠ (Gray Scale table). ąÜąŠą╝ą░ąĮą┤ąŠą╣ B9h čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą╗ąĖąĮąĄą╣ąĮą░čÅ čéą░ą▒ą╗ąĖčåą░ ą│čĆą░ą┤ą░čåąĖą╣ čüąĄčĆąŠą│ąŠ.

| ąöą░ąĮąĮčŗąĄ GDDRAM (4 ą▒ąĖčéą░) |

ąóą░ą▒ą╗ąĖčåą░ ą│čĆą░ą┤ą░čåąĖą╣ čüąĄčĆąŠą│ąŠ |

ąōą░ą╝ą╝ą░-ąĮą░čüčéčĆąŠą╣ą║ą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (ą║ąŠą╝ą░ąĮą┤ą░ B9h) |

| 0000 |

GS0 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ 0 |

| 0001 |

GS1(1) |

ąŻčüčéą░ąĮąŠą▓ą║ą░ 0 |

| 0010 |

GS2 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ 8 |

| 0011 |

GS3 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ 16 |

| ... |

... |

... |

| 1101 |

GS13 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ 96 |

| 1110 |

GS14 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ 104 |

| 1111 |

GS15 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ 112 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ą│čĆą░ą┤ą░čåąĖąĖ čüąĄčĆąŠą│ąŠ GS0 ąĖ GS1 ąĮąĄ ąĖą╝ąĄčÄčé ą▓č鹊čĆąŠą╣ čäą░ąĘčŗ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░ (čäą░ąĘčŗ 3) ąĖ č鹊ą║ą░ čäą░ąĘčŗ (čäą░ąĘčŗ 4), ąŠą┤ąĮą░ą║ąŠ GS1 ąĖą╝ąĄąĄčé ą┐ąĄčĆą▓čāčÄ čäą░ąĘčā ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░ (čäą░ąĘą░ 2).

8.9. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓ą║ą╗čÄč湥ąĮąĖčÅ ąĖ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ.

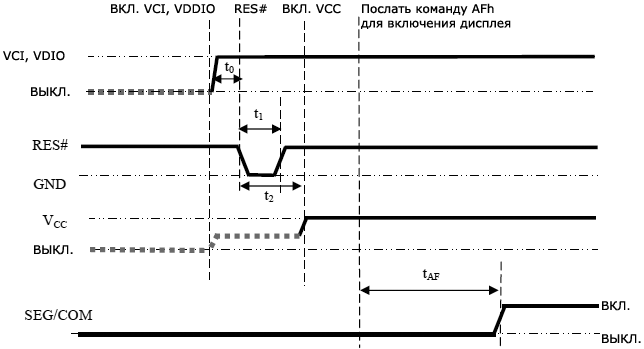

ąĪą╗ąĄą┤čāčÄčēąĖąĄ čĆąĖčüčāąĮą║ąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čĆąĄą║ąŠą╝ąĄąĮą┤ąŠą▓ą░ąĮąĮčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ą╗čÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ąĖ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ SSD1322 (ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 VCI ąĖ VDDIO ąĖą╝ąĄčÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüčéą░ą▒ąĖą╗ąĖąĘą░č鹊čĆ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ą╗čÅ VDD).

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓ą║ą╗čÄč湥ąĮąĖčÅ:

1. ą¤ąŠą┤ą░čéčī ą┐ąĖčéą░ąĮąĖąĄ ąĮą░ VCI, VDDIO.

2. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čüčéą░ąĮąĄčé čüčéą░ą▒ąĖą╗čīąĮčŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ VCI ąĖ VDDIO, ąĮčāąČąĮąŠ ą┐ąŠą┤ąŠąČą┤ą░čéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 1 ą╝čü (t0) ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čüčéą░ą╗ąŠ čüčéą░ą▒ąĖą╗čīąĮčŗą╝. ąŚą░č鹥ą╝ ą▓čŗčüčéą░ą▓ąĖčéčī čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0 RES# ąĮą░ ą▓čĆąĄą╝čÅ ą╝ąĖąĮąĖą╝čāą╝ 100 ą╝ą║čü (t1) (4) ąĖ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ RES# ąĮą░ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1.

3. ą¤ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čŗą▓ąŠą┤ą░ RES# ą▓ ą╗ąŠą│. 0 ąĮčāąČąĮąŠ ą┐ąŠą┤ąŠąČą┤ą░čéčī ą╝ąĖąĮąĖą╝čāą╝ 100 ą╝ą║čü (t2), ąĘą░č鹥ą╝ ą▓ą║ą╗čÄčćąĖčéčī VCC. (1)

4. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ VCC čüčéą░ąĮąĄčé čüčéą░ą▒ąĖą╗čīąĮčŗą╝, ą┐ąŠčüą╗ą░čéčī ą║ąŠą╝ą░ąĮą┤čā AFh ą┤ą╗čÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┤ąĖčüą┐ą╗ąĄčÅ. ąöčĆą░ą╣ą▓ąĄčĆčŗ SEG/COM ą▓ą║ą╗čÄčćą░čéčüčÅ ą┐ąŠčüą╗ąĄ 200 ą╝čü (tAF).

5. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ VCI čüčéą░ąĮąĄčé čüčéą░ą▒ąĖą╗čīąĮčŗą╝, ą┐ąŠą┤ąŠąČą┤ą░čéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 300 ą╝čü, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą╝ąŠąČąĮąŠ ą┐ąŠčüčŗą╗ą░čéčī ą║ąŠą╝ą░ąĮą┤čŗ ąĖ ą┤ą░ąĮąĮčŗąĄ ąĮą░ ąĖąĮą┤ąĖą║ą░č鹊čĆ.

ąĀąĖčü. 8-14. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓ą║ą╗čÄč湥ąĮąĖčÅ SSD1322.

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ:

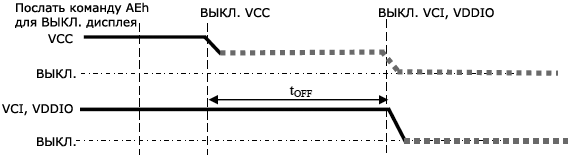

1. ą¤ąŠčüą╗ą░čéčī ą║ąŠą╝ą░ąĮą┤čā AEh ą┤ą╗čÅ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą┤ąĖčüą┐ą╗ąĄčÅ.

2. ąÆčŗą║ą╗čÄčćąĖčéčī ą┐ąĖčéą░ąĮąĖąĄ VCC(1)(2).

3. ą¤ąŠą┤ąŠąČą┤ą░čéčī ą▓čĆąĄą╝čÅ tOFF. ąÆčŗą║ą╗čÄčćąĖčéčī VCI, VDDIO (ąĘą┤ąĄčüčī ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ tOFF=0 ą╝čü(3), čéąĖą┐ąĖčćąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ tOFF=100 ą╝čü).

ąĀąĖčü. 8-15. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ SSD1322.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ą¤ąŠčüą║ąŠą╗čīą║čā čüčģąĄą╝ą░ ąĘą░čēąĖčéčŗ ąŠčé čüčéą░čéąĖč湥čüą║ąŠą│ąŠ 菹╗ąĄą║čéčĆąĖč湥čüčéą▓ą░ (ESD) ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ ą╝ąĄąČą┤čā VCI, VDDIO ąĖ VCC, VCC čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĮąĖąČąĄ VCI ą║ą░ąČą┤čŗą╣ čĆą░ąĘ ą║ąŠą│ą┤ą░ VCI, VDDIO ą▓ą║ą╗čÄč湥ąĮčŗ, ąĖ VCC ą▓čŗą║ą╗čÄč湥ąĮąŠ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą┐čāąĮą║čéąĖčĆąĮąŠą╣ ą╗ąĖąĮąĖąĄą╣ ą┤ą╗čÅ VCC ąĮą░ čĆąĖčü. 8-14 ąĖ čĆąĖčü. 8-15.

(2) ą©ąĖąĮą░ VCC ą┤ąŠą╗ąČąĮą░ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ ą┐ąŠą┤ą▓ąĄčłąĄąĮąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ (ą┐ąĖčéą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ), ą║ąŠą│ą┤ą░ čüąŠčüč鹊čÅąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ "ą▓čŗą║ą╗čÄč湥ąĮąŠ".

(3) VCI, VDDIO ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą▓čŗą║ą╗čÄčćą░čéčīčüčÅ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą▒čāą┤ąĄčé ą▓čŗą║ą╗čÄč湥ąĮąŠ VCC.

(4) ąŚąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▒čāą┤čāčé čüą▒čĆąŠčłąĄąĮčŗ ą┐ąŠčüą╗ąĄ t1.

(5) ąÆčŗą▓ąŠą┤čŗ ą┐ąĖčéą░ąĮąĖčÅ (VDD, VCC) ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąĖčéčÅąĮčāčéčŗ ą║ ąĘąĄą╝ą╗ąĄ ąĮąĖ ą┐čĆąĖ ą║ą░ą║ąĖčģ ąŠą▒čüč鹊čÅč鹥ą╗čīčüčéą▓ą░čģ.

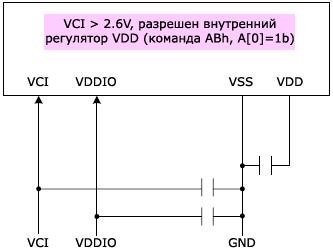

8.10. ą¤ąĖčéą░ąĮąĖąĄ čÅą┤čĆą░ VDD ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│čāą╗čÅč鹊čĆ.

ąŻ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ SSD1322 ąĄčüčéčī ą▓čŗą▓ąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ ą╗ąŠą│ąĖą║ąĖ čÅą┤čĆą░ VDD, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą╗ąĖą▒ąŠ ą┤ą╗čÅ ą┐ąŠą┤ą░čćąĖ ą┐ąĖčéą░ąĮąĖčÅ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░, ą╗ąĖą▒ąŠ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčéčī ą┐ąĖčéą░ąĮąĖąĄ ąĮą░ VDD č湥čĆąĄąĘ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│čāą╗čÅč鹊čĆ ą┐ąĖčéą░ąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąĀą░ą▒ąŠčéą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čĆąĄą│čāą╗čÅč鹊čĆą░ VDD čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ A[0] ą▓ ąĄą┤ąĖąĮąĖčåčā ą║ąŠą╝ą░ąĮą┤ąŠą╣ ABh "Function Selection" (ą▓čŗą▒ąŠčĆ čäčāąĮą║čåąĖąĖ). ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čĆąĄą│čāą╗čÅč鹊čĆą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ VCI ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ 2.6V (VCI ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ą╗čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čĆąĄą│čāą╗čÅč鹊čĆą░ VDD). ąóąĖą┐ąĖčćąĮąŠąĄ čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VDD čĆą░ą▓ąĮąŠ ą┐čĆąĖą╝ąĄčĆąĮąŠ 2.5V.

ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą▒čāą┤ąĄčé ą╗ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ą╗čÅ VDD ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąŠ ą▓ąĮąĄčłąĮąĖą╝ ą┐ąĖčéą░ąĮąĖąĄą╝ ąĖą╗ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čĆąĄą│čāą╗čÅč鹊čĆąŠą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VCI ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓čüąĄą│ą┤ą░ ą▓čŗčłąĄ č湥ą╝ VDD ąĖ VDDIO. ąĪą╗ąĄą┤čāčÄčēą░čÅ ą║ą░čĆčéąĖąĮą║ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüčģąĄą╝čā ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą▓čŗą▓ąŠą┤ą░ VDD čĆąĄą│čāą╗čÅč鹊čĆą░:

ąĀąĖčü. 8-16. ąĪčģąĄą╝ą░ ą┐ąĖčéą░ąĮąĖčÅ ą┤ą╗čÅ čüą╗čāčćą░čÅ, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│čāą╗čÅč鹊čĆ ą┤ą╗čÅ VDD, ąĖ VCI > 2.6V.

ąĀąĖčü. 8-17. ąĪčģąĄą╝ą░ ą┐ąĖčéą░ąĮąĖčÅ ą┤ą╗čÅ čüą╗čāčćą░čÅ, ą║ąŠą│ą┤ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│čāą╗čÅč鹊čĆ ą┤ą╗čÅ VDD ąĘą░ą┐čĆąĄčēąĄąĮ.

[9. ąĪąĖčüč鹥ą╝ą░ ą║ąŠą╝ą░ąĮą┤ SSD1322]

ąóą░ą▒ą╗ąĖčåą░ 9-1. ą×ą▒čēąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤ SSD1322.

| D/C# |

Hex |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

ąÜąŠą╝ą░ąĮą┤ą░ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 0 |

00 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Enable Gray Scale Table |

ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ą▓čŗą┤ą░ąĄčéčüčÅ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā čéą░ą▒ą╗ąĖčåčŗ ą│čĆą░ą┤ą░čåąĖą╣ čÅčĆą║ąŠčüčéąĖ (Gray Scale Table), ą║ąŠč鹊čĆą░čÅ ą▒čŗą╗ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ą║ąŠą╝ą░ąĮą┤ąŠą╣ B8h. |

0

1

1 |

15

A[6:0]

B[6:0] |

0

*

* |

0

A6

B6 |

0

A5

B5 |

1

A4

B4 |

0

A3

B3 |

1

A2

B2 |

0

A1

B1 |

1

A0

B0 |

Set Column Address |

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą░ą┤čĆąĄčüą░ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ąĖ ą║ąŠąĮąĄčćąĮąŠą│ąŠ čüč鹊ą╗ą▒čåą░. A[6:0] ąĘą░ą┤ą░ąĄčé ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ =0), B[6:0] ą║ąŠąĮąĄčćąĮčŗą╣ ą░ą┤čĆąĄčü (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ =119). ąÉą┤čĆąĄčü ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 0 ą┤ąŠ 119. |

| 0 |

5C |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

Write RAM Command |

ąĀą░ąĘčĆąĄčłą░ąĄčé ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā ąĘą░ą┐ąĖčüą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ RAM. |

| 0 |

5D |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

Read RAM Command |

ąĀą░ąĘčĆąĄčłą░ąĄčé ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā ą┐čĆąŠčćąĖčéą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘ RAM. |

0

1

1 |

75

A[6:0]

B[6:0] |

0

*

* |

1

A6

B6 |

1

A5

B5 |

1

A4

B4 |

0

A3

B3 |

1

A2

B2 |

0

A1

B1 |

1

A0

B0 |

Set Row Address |

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą░ą┤čĆąĄčüą░ ąĮą░čćą░ą╗čīąĮąŠą╣ ąĖ ą║ąŠąĮąĄčćąĮąŠą╣ čüčéčĆąŠą║ąĖ. A[6:0] ąĘą░ą┤ą░ąĄčé ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ =0), B[6:0] ą║ąŠąĮąĄčćąĮčŗą╣ ą░ą┤čĆąĄčü (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ =127). ąÉą┤čĆąĄčü ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 0 ą┤ąŠ 127. |

0

1

1 |

A0

A[7:0]

B[4] |

1

0

* |

0

0

* |

1

A5

0 |

0

A4

B4 |

0

0

0 |

0

A2

0 |

0

A1

0 |

0

A0

1 |

Set Re-map and Dual COM Line mode |

A[0]=0b, ąĖąĮą║čĆąĄą╝ąĄąĮčé ą░ą┤čĆąĄčüą░ ą┐ąŠ ą│ąŠčĆąĖąĘąŠąĮčéą░ą╗ąĖ (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░)

A[0]=1b, ąĖąĮą║čĆąĄą╝ąĄąĮčé ą░ą┤čĆąĄčüą░ ą┐ąŠ ą▓ąĄčĆčéąĖą║ą░ą╗ąĖ

A[1]=0b, ąĘą░ą┐čĆąĄčé ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåąŠą▓ (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░)

A[1]=1b, čĆą░ąĘčĆąĄčłąĖčéčī ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåąŠą▓

A[2]=0b, ąĘą░ą┐čĆąĄčé ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖčÅ ąĮąĖą▒ą▒ą╗ąŠą▓ (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░)

A[2]=1b, čĆą░ąĘčĆąĄčłąĖčéčī ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ ąĮąĖą▒ą▒ą╗ąŠą▓

A[4]=0b, čüą║ą░ąĮąĖčĆąŠą▓ą░čéčī ąŠčé COM0 ą┤ąŠ COM[N ŌĆō1] (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░)

A[4]=1b, čüą║ą░ąĮąĖčĆąŠą▓ą░čéčī ąŠčé COM[N-1] ą┤ąŠ COM0, ą│ą┤ąĄ N ąĘą░ą┤ą░ąĄčé ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ (Multiplex ratio)

A[5]=0b, ąĘą░ą┐čĆąĄčé ą┤ąĄą╗ąĄąĮąĖąĄ COM ąĮą░ č湥čéąĮčŗąĄ ąĖ ąĮąĄč湥čéąĮčŗąĄ (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░)

A[5]=1b, čĆą░ąĘčĆąĄčłąĖčéčī ą┤ąĄą╗ąĄąĮąĖąĄ COM ąĮą░ č湥čéąĮčŗąĄ ąĖ ąĮąĄč湥čéąĮčŗąĄ

B[4], čĆą░ąĘčĆąĄčłąĖčéčī (1b) / ąĘą░ą┐čĆąĄčéąĖčéčī (0b, ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░) čĆąĄąČąĖą╝ Dual COM Line

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čüąĄą║čåąĖąĖ 10.1.6 |

0

1 |

A1

A[6:0] |

1

* |

0

A6 |

1

A5 |

0

A4 |

0

A3 |

0

A2 |

0

A1 |

1

A0 |

Set Display Start Line |

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ ąĮą░čćą░ą╗čīąĮąŠą╣ čüčéčĆąŠą║ąĖ RAM ą┤ąĖčüą┐ą╗ąĄčÅ ą▓ ąĘąĮą░č湥ąĮąĖąĄ ąŠčé 0 ą┤ąŠ 127. ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ąĘąĮą░č湥ąĮąĖąĄ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čĆą░ą▓ąĮąŠ 00h. |

0

1 |

A2

A[6:0] |

1

* |

0

A6 |

1

A5 |

0

A4 |

0

A3 |

0

A2 |

1

A1 |

0

A0 |

Set Display Offset |

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▓ąĄčĆčéąĖą║ą░ą╗čīąĮčāčÄ ą┐čĆąŠą║čĆčāčéą║čā COM ą▓ ąĘąĮą░č湥ąĮąĖąĄ ąŠčé 0 ą┤ąŠ 127. ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ 00h. |

| 0 |

A4 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

Set Display Mode |

ą¤ąŠą╗ąĮąŠčüčéčīčÄ ą▓čŗą║ą╗čÄčćą░ąĄčé ą┤ąĖčüą┐ą╗ąĄą╣, ą▓čüąĄ ą┐ąĖą║čüąĄą╗čŗ ą┐ąŠą│ą░čłąĄąĮčŗ (ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čÅčĆą║ąŠčüčéąĖ GS0). |

| 0 |

A5 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

ą¤ąŠą╗ąĮąŠčüčéčīčÄ ą▓ą║ą╗čÄčćą░ąĄčé ą┤ąĖčüą┐ą╗ąĄą╣, ą▓čüąĄ ą┐ąĖą║čüąĄą╗čŗ ąĘą░ą│ąŠčĆą░čÄčéčüčÅ (ą┐ąĄčĆąĄą▓ąŠą┤čÅčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ čÅčĆą║ąŠčüčéąĖ GS15). |

| 0 |

A6 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

ąØąŠčĆą╝ą░ą╗čīąĮą░čÅ čĆą░ą▒ąŠčéą░ (čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░). |

| 0 |

A7 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

ąśąĮą▓ąĄčĆčüąĖčÅ ą┤ąĖčüą┐ą╗ąĄčÅ. |

0

1

1 |

A8

A[6:0]

B[6:0] |

1

0

0 |

0

A6

B6 |

1

A5

B5 |

0

A4

B4 |

1

A3

B3 |

0

A2

B2 |

0

A1

B1 |

0

A0

B0 |

Enable Partial Display |

ąÜąŠą╝ą░ąĮą┤ą░ čĆą░ąĘčĆąĄčłą░ąĄčé čĆąĄąČąĖą╝ čćą░čüčéąĖčćąĮąŠą│ąŠ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ. ą×ą▒ą╗ą░čüčéčī 菹║čĆą░ąĮą░ ą┤ą╗čÅ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ąĘą░ą┤ą░ąĄčéčüčÅ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ąĖ:

A[6:0] ąĮą░čćą░ą╗čīąĮą░čÅ čüčéčĆąŠą║ą░ ąŠč鹊ą▒čĆą░ąČą░ąĄą╝ąŠą╣ ąŠą▒ą╗ą░čüčéąĖ, B[6:0] ą║ąŠąĮąĄčćąĮą░čÅ čüčéčĆąŠą║ą░ ąŠč鹊ą▒čĆą░ąČą░ąĄą╝ąŠą╣ ąŠą▒ą╗ą░čüčéąĖ. ąŚąĮą░č湥ąĮąĖąĄ B[6:0] ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠ A[6:0]. |

| 0 |

A9 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

Exit Partial Display |

ą×čéą╝ąĄąĮą░ čĆąĄąČąĖą╝ą░ čćą░čüčéąĖčćąĮąŠą│ąŠ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ. |

0

1 |

AB

A[0] |

1

0 |

0

0 |

1

0 |

0

0 |

1

0 |

0

0 |

1

0 |

1

A0 |

Function Selection |

A[0]=0b, ą▓čŗą▒čĆą░čéčī ą▓ąĮąĄčłąĮąĄąĄ ą┐ąĖčéą░ąĮąĖąĄ ą┤ą╗čÅ VDD (ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│čāą╗čÅč鹊čĆ ąĘą░ą┐čĆąĄčēąĄąĮ).

A[0]=1b, čĆą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čĆąĄą│čāą╗čÅč鹊čĆą░ ą┤ą╗čÅ VDD (čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░). |

| 0 |

AE |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

Set Sleep mode ON/OFF |

ąĀąĄąČąĖą╝ čüąĮą░ (ą┤ąĖčüą┐ą╗ąĄą╣ ą▓čŗą║ą╗čÄč湥ąĮ). |

| 0 |

AF |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

ąÆčŗą╣čéąĖ ąĖąĘ čĆąĄąČąĖą╝ą░ čüąĮą░ (ą┤ąĖčüą┐ą╗ąĄą╣ čĆą░ą▒ąŠčéą░ąĄčé). |

0

1 |

B1

A[7:0] |

1

A7 |

0

A6 |

1

A5 |

1

A4 |

0

A3 |

0

A2 |

0

A1 |

1

A0 |

Set Phase Length |

A[3:0] ąĘą░ą┤ą░ąĄčé ą┐ąĄčĆąĖąŠą┤ čäą░ąĘčŗ 1 (ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čäą░ąĘčŗ čüą▒čĆąŠčüą░ ąĘą░čĆčÅą┤ą░) ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 5..31 čéą░ą║č鹊ą▓ DCLK.

A[7:4] ąĘą░ą┤ą░ąĄčé ą┐ąĄčĆąĖąŠą┤ čäą░ąĘčŗ 2 (ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čäą░ąĘčŗ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░) ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 3..15 čéą░ą║č鹊ą▓ DCLK.

ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čüąĄą║čåąĖąĖ 10.1.14. |

0

1 |

B3

A[7:0] |

1

A7 |

0

A6 |

1

A5 |

1

A4 |

0

A3 |

0

A2 |

1

A1 |

1

A0 |

Set Front Clock Divider / Oscillator Frequency |

A[3:0] (ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 0) ąĘą░ą┤ą░ąĄčé ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ čćą░čüč鹊čéčŗ ą│ąĄąĮąĄčĆą░č鹊čĆą░ (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čüąĄą║čåąĖčÄ 10.1.15).

A[7:4] (ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 1100b) ąĘą░ą┤ą░ąĄčé čćą░čüč鹊čéčā ą│ąĄąĮąĄčĆą░č鹊čĆą░. ą¦ąĄą╝ ą▒ąŠą╗čīčłąĄ ąĘąĮą░č湥ąĮąĖąĄ, č鹥ą╝ ą▓čŗčłąĄ čćą░čüč鹊čéą░. |

0

1

1 |

B4

A[1:0]

B[7:3] |

1

1

B7 |

0

0

B6 |

1

1

B5 |

1

0

B4 |

0

0

B3 |

1

0

1 |

0

A1

0 |

0

A0

1 |

Display Enhancement A |

A[1:0]=00b: čĆą░ąĘčĆąĄčłąĖčéčī ą▓ąĮąĄčłąĮąĄąĄ VSL

A[1:0]=10b: ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ VSL (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░)

B[7:3]=11111b: čāą╗čāčćčłą░ąĄčé ą║ą░č湥čüčéą▓ąŠ GS ą┤ąĖčüą┐ą╗ąĄčÅ

B[7:3]=10110b: ąŠą▒čŗčćąĮčŗą╣ čĆąĄąČąĖą╝ (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░) |

0

1 |

B5

A[3:0] |

1

* |

0

* |

1

* |

1

* |

0

A3 |

1

A2 |

0

A1 |

1

A0 |

Set GPIO |

ąŻčüčéą░ąĮąŠą▓ąĖčéčī čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čüąĄą║čåąĖąĖ 10.1.17. |

0

1 |

B6

A[3:0] |

1

* |

0

* |

1

* |

1

* |

0

A3 |

1

A2 |

1

A1 |

0

A0 |

Set Second Precharge Period |

A[3:0] čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą▓č鹊čĆąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čüąĄą║čåąĖąĖ 10.1.18. |

0

1

1

..

1

1 |

B8

A1[7:0]

A2[7:0]

..

A14[7:0]

A15[7:0] |

1

A17

A27

..

A147

A157 |

0

A16

A26

..

A146

A156 |

1

A15

A25

..

A145

A155 |

1

A14

A24

..

A144

A154 |

1

A13

A23

..

A143

A153 |

0

A12

A22

..

A142

A152 |

0

A11

A21

..

A141

A151 |

0

A10

A20

..

A140

A150 |

Set Gray Scale Table |

ąĪą╗ąĄą┤čāčÄčēąĖąĄ ąĘą░ ą║ąŠą╝ą░ąĮą┤ąŠą╣ 15 ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé čéą░ą▒ą╗ąĖčåčā ą│čĆą░ą┤ą░čåąĖą╣ čÅčĆą║ąŠčüčéąĖ (Gray Scale, GS) ą┐čāč鹥ą╝ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĖą╝ą┐čāą╗čīčüą░ č鹊ą║ą░ ą▓ ąĄą┤ąĖąĮąĖčåą░čģ DCLK (ą┤ąĖą░ą┐ą░ąĘąŠąĮ 0..180).

ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čüąĄą║čåąĖąĖ 10.1.19. |

| 0 |

B9 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

Select Default Linear Gray Scale table |

ąĪą▒čĆą░čüčŗą▓ą░ąĄčé čéą░ą▒ą╗ąĖčåčā ą│čĆą░ą┤ą░čåąĖą╣ čÅčĆą║ąŠčüčéąĖ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (ą╗ąĖąĮąĄą╣ąĮą░čÅ čéą░ą▒ą╗ąĖčåą░ čü ąĮą░čĆą░čüčéą░ąĮąĖąĄą╝ čÅčĆą║ąŠčüčéąĖ ąŠčé GS0 ą┤ąŠ GS1). ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čüąĄą║čåąĖąĖ 10.1.20. |

0

1 |

BB

A[4:0] |

1

* |

0

* |

1

* |

1

A4 |

1

A3 |

0

A2 |

1

A1 |

1

A0 |

Set Pre-charge voltage |

ąŻčüčéą░ąĮąŠą▓ąĖčéčī čāčĆąŠą▓ąĄąĮčī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░ (čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 17h). ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čüąĄą║čåąĖąĖ 10.1.21. |

0

1 |

BE

A[2:0] |

1

* |

0

* |

1

* |

1

* |

1

0 |

1

A2 |

1

A1 |

0

A0 |

Set VCOMH |

ąŻčüčéą░ąĮąŠą▓ą║ą░ čāčĆąŠą▓ąĮčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ą╗čÅ ąĮąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ COM (ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 04h). ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čüąĄą║čåąĖąĖ 10.1.22. |

0

1 |

C1

A[7:0] |

1

A7 |

1

A6 |

0

A5 |

0

A4 |

0

A3 |

0

A2 |

0

A1 |

1

A0 |

Set Contrast Current |

A[7:0] ąĘą░ą┤ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ č鹊ą║ą░ ą║ąŠąĮčéčĆą░čüčéąĮąŠčüčéąĖ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 0..255. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĘą░ą┤ą░ąĄčéčüčÅ 256 ą│čĆą░ą┤ą░čåąĖą╣ ą┤ą╗čÅ č鹊ą║ą░ ISEG (ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 127). |

0

1 |

C7

A[3:0] |

1

* |

1

* |

0

* |

0

* |

0

A3 |

1

A2 |

1

A1 |

1

A0 |

Master Contrast Current Control |

ąŻą┐čĆą░ą▓ą╗čÅąĄčé čāčĆąŠą▓ąĮąĄą╝ č鹊ą║ą░ ą┤ą╗čÅ ą▓čüąĄčģ čÅčĆą║ąŠčüč鹥ą╣, čéą░ą║ čćč鹊 ąĘą░ą┤ą░ąĄčé ąŠą▒čēąĖą╣ čāčĆąŠą▓ąĄąĮčī ą║ąŠąĮčéčĆą░čüčéąĮąŠčüčéąĖ ą┤ąĖčüą┐ą╗ąĄčÅ. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čüąĄą║čåąĖčÄ 10.1.24. |

0

1 |

CA

A[6:0] |

1

* |

1

A6 |

0

A5 |

0

A4 |

1

A3 |

0

A2 |

1

A1 |

0

A0 |

Set MUX Ratio |

ąŚą░ą┤ą░ąĄčé čĆąĄąČąĖą╝ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčé 16MUX ą┤ąŠ 128MUX, ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čüąĄą║čåąĖčÄ 10.1.25. |

0

1

1 |

D1

A[5:4]

20 |

1

1

0 |

1

0

0 |

0

A5

1 |

1

A4

0 |

0

0

0 |

0

0

0 |

0

1

0 |

1

0

0 |

Display Enhancement B |

A[5:4] = 00b: ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ

A[5:4] = 10b: ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░). |

0

1 |

FD

A[2] |

1

0 |

1

0 |

1

0 |

1

1 |

1

0 |

1

A2 |

0

1 |

1

0 |

Set Command Lock |

A[2] ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĘą░čēąĖčéčā ąĖąĮč鹥čĆč乥ą╣čüą░ ąŠčé ą┤ąŠčüčéčāą┐ą░ čüąŠ čüč鹊čĆąŠąĮčŗ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ (ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 12h). ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čüąĄą║čåąĖąĖ 10.1.27. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: * ąŠąĘąĮą░čćą░ąĄčé ą╗čÄą▒ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ (ą╝ąŠąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ąĖą╗ąĖ 0, ąĖą╗ąĖ 1, čŹč鹊 ąĮąĖ ąĮą░ čćč鹊 ąĮąĄ ą▓ą╗ąĖčÅąĄčé).

[10. ą×ą┐ąĖčüą░ąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤]

ąÜąŠą╝ą░ąĮą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą▒ą╗ąĖčåčŗ ą│čĆą░ą┤ą░čåąĖą╣ čüąĄčĆąŠą│ąŠ (čéą░ą▒ą╗ąĖčåą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ąŠą╣ B8h).

ąÜąŠą╝ą░ąĮą┤ą░ ąĖąĘ čéčĆąĄčģ ą▒ą░ą╣čé ąĘą░ą┤ą░ąĄčé ąĮą░čćą░ą╗čīąĮčŗą╣ ąĖ ą║ąŠąĮąĄčćąĮčŗą╣ ą░ą┤čĆąĄčü RAM ą┤ąĖčüą┐ą╗ąĄčÅ. ąóą░ą║ąČąĄ čŹčéą░ ą║ąŠą╝ą░ąĮą┤ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čāą║ą░ąĘą░č鹥ą╗čī ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░ ąĮą░ ąĮą░čćą░ą╗čīąĮčŗą╣ čüč鹊ą╗ą▒ąĄčå. ąŁč鹊čé čāą║ą░ąĘą░č鹥ą╗čī ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ č鹥ą║čāčēąĄą│ąŠ ą░ą┤čĆąĄčüą░ ą║ą░ą║ ą░ą┤čĆąĄčüą░ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ RAM 菹║čĆą░ąĮą░. ąĢčüą╗ąĖ ą║ąŠą╝ą░ąĮą┤ąŠą╣ A0h čĆą░ąĘčĆąĄčłąĄąĮ čĆąĄąČąĖą╝ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ ą░ą┤čĆąĄčüą░ ą┐ąŠ ą│ąŠčĆąĖąĘąŠąĮčéą░ą╗ąĖ, č鹊 ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ąŠą┤ąĮąŠą│ąŠ čüč鹊ą╗ą▒čåą░ ą┤ą░ąĮąĮčŗčģ čāą║ą░ąĘą░č鹥ą╗čī ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮ čéą░ą║, čćč鹊 ą▒čāą┤ąĄčé čāą║ą░ąĘčŗą▓ą░čéčī ąĮą░ ą░ą┤čĆąĄčü čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüč鹊ą╗ą▒čåą░. ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čāą║ą░ąĘą░č鹥ą╗čī ą░ą┤čĆąĄčüą░ ąĘą░ą▓ąĄčĆčłą░ąĄčé ąŠą┐ąĄčĆą░čåąĖčÄ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝čā čüč鹊ą╗ą▒čåčā ąĖ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ąŠą▒čĆą░čéąĮąŠ ąĮą░ ą┐ąĄčĆą▓čŗą╣ čüč鹊ą╗ą▒ąĄčå, ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮ ą░ą┤čĆąĄčü čüčéčĆąŠą║ąĖ ą┤ą╗čÅ ąŠą▒čĆą░čēąĄąĮąĖčÅ ą║ čüą╗ąĄą┤čāčÄčēąĄą╣ čüčéčĆąŠą║ąĄ.

ą¤ąŠčüą╗ąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čŹč鹊ą╣ ąŠą┤ąĮąŠą▒ą░ą╣čéąĮąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ąĘą░ą┐ąĖčüčŗą▓ą░čéčīčüčÅ ą▓ RAM 菹║čĆą░ąĮą░ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┤ą░ąĮą░ ą┤čĆčāą│ą░čÅ ą║ąŠą╝ą░ąĮą┤ą░. ąŻą║ą░ąĘą░č鹥ą╗čī ą░ą┤čĆąĄčüą░ ą▒čāą┤ąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą┐čĆąĖ ą║ą░ąČą┤ąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ. ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┐ąŠčüą╗ą░ąĮą░ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą┤ą░ąĮąĮčŗąĄ ą▓ RAM 菹║čĆą░ąĮą░.

ą¤ąŠčüą╗ąĄ ą▓ą▓ąŠą┤ą░ čŹč鹊ą╣ ąŠą┤ąĮąŠą▒ą░ą╣č鹊ą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ čćąĖčéą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé čüčćąĖčéčŗą▓ą░čéčīčüčÅ ąĖąĘ RAM 菹║čĆą░ąĮą░ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┤ą░ąĮą░ ą┤čĆčāą│ą░čÅ ą║ąŠą╝ą░ąĮą┤ą░. ąŻą║ą░ąĘą░č鹥ą╗čī ą░ą┤čĆąĄčüą░ ą▒čāą┤ąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą┐čĆąĖ ą║ą░ąČą┤ąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ. ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┐ąŠčüą╗ą░ąĮą░ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ RAM 菹║čĆą░ąĮą░.

ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░čćą░ą╗čīąĮčŗą╣ ąĖ ą║ąŠąĮąĄčćąĮčŗą╣ ą░ą┤čĆąĄčü ą┤ą░ąĮąĮčŗčģ RAM 菹║čĆą░ąĮą░. ąóą░ą║ąČąĄ čŹčéą░ ą║ąŠą╝ą░ąĮą┤ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą░ą┤čĆąĄčü čāą║ą░ąĘą░č鹥ą╗čÅ čüčéčĆąŠą║ąĖ ąĮą░ ą┐ąĄčĆą▓čāčÄ čüčéčĆąŠą║čā. ąŁč鹊čé čāą║ą░ąĘą░č鹥ą╗čī ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ąĘą░ą┤ą░čéčī ą░ą┤čĆąĄčü čüčéčĆąŠą║ąĖ č鹥ą║čāčēąĄą╣ ą┐ąŠąĘąĖčåąĖąĖ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ RAM 菹║čĆą░ąĮą░. ąĢčüą╗ąĖ ą║ąŠą╝ą░ąĮą┤ąŠą╣ A0h čĆą░ąĘčĆąĄčłąĄąĮ čĆąĄąČąĖą╝ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ ą░ą┤čĆąĄčüą░ ą┐ąŠ ą▓ąĄčĆčéąĖą║ą░ą╗ąĖ, č鹊 ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ąŠą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ, čāą║ą░ąĘą░č鹥ą╗čī ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮ ąĮą░ ą░ą┤čĆąĄčü čüą╗ąĄą┤čāčÄčēąĄą╣ čüčéčĆąŠą║ąĖ. ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čāą║ą░ąĘą░č鹥ą╗čī ą░ą┤čĆąĄčüą░ ąĘą░ą▓ąĄčĆčłą░ąĄčé ąŠą┐ąĄčĆą░čåąĖčÄ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ čüčéčĆąŠą║ąĄ, č鹊 ąŠąĮ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĮą░ ą░ą┤čĆąĄčü ą┐ąĄčĆą▓ąŠą╣ čüčéčĆąŠą║ąĖ.

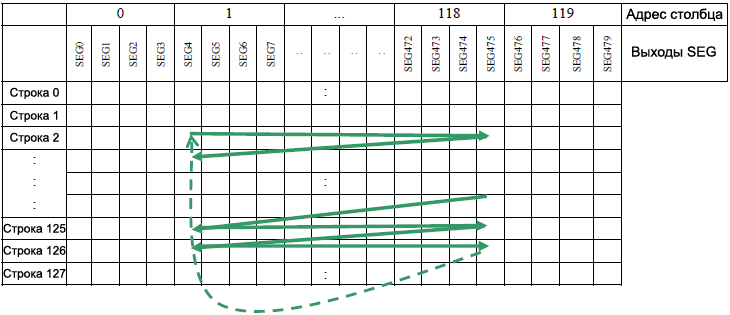

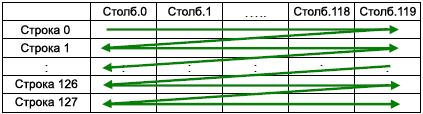

ąØą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ čāą║ą░ąĘą░č鹥ą╗čÅ ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░ ąĖ čüčéčĆąŠą║ąĖ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐čĆąĖą╝ąĄčĆąĄ:

1. ąØą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü čüč鹊ą╗ą▒čåą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1 ąĖ ą║ąŠąĮąĄčćąĮčŗą╣ ą░ą┤čĆąĄčü čüč鹊ą╗ą▒čåą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 118, ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü čüčéčĆąŠą║ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 2 ąĖ ą║ąŠąĮąĄčćąĮčŗą╣ ą░ą┤čĆąĄčü čüčéčĆąŠą║ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 126.

2. ąÜąŠą╝ą░ąĮą┤ąŠą╣ A0h čĆą░ąĘčĆąĄčłąĄąĮąŠ čĆąĄąČąĖą╝ ą│ąŠčĆąĖąĘąŠąĮčéą░ą╗čīąĮąŠą│ąŠ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ ą░ą┤čĆąĄčüą░.

ąĀąĖčü. 10-110-2. ą¤čĆąĖą╝ąĄčĆ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ čāą║ą░ąĘą░č鹥ą╗čÅ ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░ ąĖ čüčéčĆąŠą║ąĖ (Gray Scale Mode).

ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą┤ą░ąĮąĮčŗąĄ RAM ą┤ąŠčüčéčāą┐ąĮčŗ č鹊ą╗čīą║ąŠ ąŠčé čüč鹊ą╗ą▒čåą░ 1 ą┤ąŠ čüč鹊ą╗ą▒čåą░ 118, ąĖ č鹊ą╗čīą║ąŠ ąŠčé čüčéčĆąŠą║ąĖ 1 ą┤ąŠ čüčéčĆąŠą║ąĖ 126. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ čāą║ą░ąĘą░č鹥ą╗čī čüč鹊ą╗ą▒čåą░ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, ą░ čāą║ą░ąĘą░č鹥ą╗čī čüčéčĆąŠą║ąĖ ą▓ 2. ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ 4 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ (čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé čÅčĆą║ąŠčüčéąĖ 1 ą┐ąĖą║čüąĄą╗ą░) ą░ą┤čĆąĄčü čüč鹊ą╗ą▒čåą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāą▓ąĄą╗ąĖčćąĖčéčüčÅ ąĮą░ 1 ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čüą╗ąĄą┤čāčÄčēąĄą╣ čÅč湥ą╣ą║ąĄ RAM ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĄą╣ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ (čüą┐ą╗ąŠčłąĮą░čÅ ą╗ąĖąĮąĖčÅ ąĮą░ čĆąĖčü. 10-110-2). ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čāą║ą░ąĘą░č鹥ą╗čī ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░ ąĘą░ą▓ąĄčĆčłąĖčé ą┤ąŠčüčéčāą┐ ą║ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝čā čüč鹊ą╗ą▒čåčā 118, ąŠąĮ čüą▒čĆąŠčüąĖčéčüčÅ čüąĮąŠą▓ą░ ąĮą░ąĘą░ą┤ ą║ čüč鹊ą╗ą▒čåčā 1, ąĖ ą░ą┤čĆąĄčü čüčéčĆąŠą║ąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāą▓ąĄą╗ąĖčćąĖčéčüčÅ ąĮą░ 1 (čüą┐ą╗ąŠčłąĮą░čÅ ą╗ąĖąĮąĖčÅ ąĮą░ čĆąĖčü. 10-110-2). ąÜąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ čüčéčĆąŠą║ąĄ 126 ąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝čā čüč鹊ą╗ą▒čåčā 118 RAM, ą░ą┤čĆąĄčü čüčéčĆąŠą║ąĖ čüą▒čĆąŠčüąĖčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą║ 2, ąĖ ą░ą┤čĆąĄčü čüč鹊ą╗ą▒čåą░ čüą▒čĆąŠčüąĖčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą║ 1 (ą┐čāąĮą║čéąĖčĆąĮą░čÅ ą╗ąĖąĮąĖčÅ ąĮą░ čĆąĖčü. 10-110-2).

ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ąĖą╝ąĄąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ ąĖ ą║ą░ąČą┤čŗą╣ ąĮą░čüčéčĆąŠąĄčćąĮčŗą╣ ą▒ąĖčé ąŠąĘąĮą░čćą░ąĄčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

ŌĆó Address increment mode (A[0])

ąÜąŠą│ą┤ą░ A[0] čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0, ą┤čĆą░ą╣ą▓ąĄčĆ ąĮą░čüčéčĆąŠąĄąĮ ą▓ čĆąĄąČąĖą╝ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ ą│ąŠčĆąĖąĘąŠąĮčéą░ą╗čīąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░. ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ RAM čāą║ą░ąĘą░č鹥ą╗čī ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ ąĮą░ 1. ąĢčüą╗ąĖ ą░ą┤čĆąĄčü čüč鹊ą╗ą▒čåą░ ą┤ąŠčüčéąĖą│ą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čüč鹊ą╗ą▒čåą░, č鹊 čāą║ą░ąĘą░č鹥ą╗čī ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░ čüą▒čĆąŠčüąĖčéčüčÅ ąĮą░ ą░ą┤čĆąĄčü ąĮą░čćą░ą╗čīąĮąŠą│ąŠ čüč鹊ą╗ą▒čåą░, ąĖ čāą║ą░ąĘą░č鹥ą╗čī ą░ą┤čĆąĄčüą░ čüčéčĆąŠą║ąĖ čāą▓ąĄą╗ąĖčćąĖčéčüčÅ ąĮą░ 1. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┐ąŠ čüčéčĆąŠą║ą░ą╝ ąĖ čüč鹊ą╗ą▒čåą░ą╝ ą┤ą╗čÅ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 10-3.

ąĀąĖčü. 10-3. ą¤ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄ čāą║ą░ąĘą░č鹥ą╗čÅ ą░ą┤čĆąĄčüą░ ą▓ čĆąĄąČąĖą╝ąĄ ą│ąŠčĆąĖąĘąŠąĮčéą░ą╗čīąĮąŠą│ąŠ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ ą░ą┤čĆąĄčüą░.

ąÜąŠą│ą┤ą░ A[0] čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, ą┤čĆą░ą╣ą▓ąĄčĆ ąĮą░čüčéčĆąŠąĄąĮ ą▓ čĆąĄąČąĖą╝ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ ą▓ąĄčĆčéąĖą║ą░ą╗čīąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░. ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ RAM čāą║ą░ąĘą░č鹥ą╗čī ą░ą┤čĆąĄčüą░ čüčéčĆąŠą║ąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ ąĮą░ 1. ąĢčüą╗ąĖ ą░ą┤čĆąĄčü čüčéčĆąŠą║ąĖ ą┤ąŠčüčéąĖą│ą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čüčéčĆąŠą║ąĖ, č鹊 čāą║ą░ąĘą░č鹥ą╗čī ą░ą┤čĆąĄčüą░ čüčéčĆąŠą║ąĖ čüą▒čĆąŠčüąĖčéčüčÅ ąĮą░ ą░ą┤čĆąĄčü ąĮą░čćą░ą╗čīąĮąŠą╣ čüčéčĆąŠą║ąĖ, ąĖ čāą║ą░ąĘą░č鹥ą╗čī ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░ čāą▓ąĄą╗ąĖčćąĖčéčüčÅ ąĮą░ 1. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┐ąŠ čüčéčĆąŠą║ą░ą╝ ąĖ čüč鹊ą╗ą▒čåą░ą╝ ą┤ą╗čÅ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 10-4.

ąĀąĖčü. 10-4. ą¤ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄ čāą║ą░ąĘą░č鹥ą╗čÅ ą░ą┤čĆąĄčüą░ ą▓ čĆąĄąČąĖą╝ąĄ ą▓ąĄčĆčéąĖą║ą░ą╗čīąĮąŠą│ąŠ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ ą░ą┤čĆąĄčüą░.

ŌĆó Column Address Remap (A[1])

ąŁč鹊čé ą▒ąĖčé ą║ąŠą╝ą░ąĮą┤čŗ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé ą│ąĖą▒ą║ąŠčüčéčī čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ čüąĄą│ą╝ąĄąĮčéą░ (SEG) ą▓ ą╝ąŠą┤čāą╗ąĄ OLED, ą║ąŠą│ą┤ą░ čüąĄą│ą╝ąĄąĮčéčŗ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮčŗ čüą╗ąĄą▓ą░ ąĮą░ą┐čĆą░ą▓ąŠ (A[1] = 0) ąĖą╗ąĖ ąĮą░ąŠą▒ąŠčĆąŠčé (A[1] = 1), ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 10-5.

A[1] = 0 (čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░): čüč鹊ą╗ą▒čåčŗ RAM 0 .. 119 ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ SEG0-SEG3 .. SEG476-SEG479

A[1] = 1: čüč鹊ą╗ą▒čåčŗ RAM 0 .. 119 ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ SEG476-SEG479 .. SEG0-SEG3

ŌĆó Nibble Remap (A[2])

A[2] = 0 (čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░): ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ąĮą░ą┐čĆčÅą╝čāčÄ

A[2] = 1: 4 ąĮąĖą▒ą▒ą╗ą░ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ RAM ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮčŗ

ąŁčäč乥ą║čéčŗ ąŠčé čŹč鹊ą│ąŠ ą┐čĆąŠą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆąŠą▓ą░ąĮčŗ ąĮą░ čĆąĖčü. 10-5.

ąĀąĖčü. 10-5. GDDRAM ą▓ čĆąĄąČąĖą╝ąĄ ą│čĆą░ą┤ą░čåąĖą╣ čüąĄčĆąŠą│ąŠ (Gray Scale mode) čü ą▓ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ ąĖ ą▓čŗą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ ą┐čĆąĖą▓čÅąĘąŠą║ Column Address (A[1]) ąĖ Nibble (A[2]).

ŌĆó COM scan direction Remap (A[4])

ąŁč鹊čé ą▒ąĖčé ą║ąŠą╝ą░ąĮą┤čŗ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠą▒čēąĖčģ (COM) čüąĖą│ąĮą░ą╗ąŠą▓, čćč鹊 ą┐ąŠą▓čŗčłą░ąĄčé ą│ąĖą▒ą║ąŠčüčéčī čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╝ą░čéčĆąĖčåąĄą╣. ąĪą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠą▒čēąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą╝ąŠą┤čāą╗čÅ OLED ą╝ąŠąČąĄčé ą▒čŗčéčī ą╗ąĖą▒ąŠ čüą▓ąĄčĆčģčā ą▓ąĮąĖąĘ, ą╗ąĖą▒ąŠ ąĮą░ąŠą▒ąŠčĆąŠčé.

A[1] = 0 (čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░): čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖąĄ čüą▓ąĄčĆčģčā ą▓ąĮąĖąĘ

A[1] = 1: čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖąĄ čüąĮąĖąĘčā ą▓ą▓ąĄčĆčģ

ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čĆą░čüčüčéą░ąĮąŠą▓ą║ąĖ ą▓čŗą▓ąŠą┤ąŠą▓ ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ąĮą░ čĆąĖčü. 10-5.

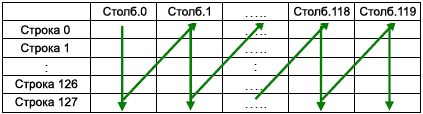

ŌĆó Odd even split of COM pins (A[5])

ąŁč鹊čé ą▒ąĖčé ą║ąŠą╝ą░ąĮą┤čŗ ą╝ąŠąČąĄčé čāčüčéą░ąĮąŠą▓ąĖčéčī č湥čéąĮąŠąĄ/ąĮąĄč湥čéąĮąŠąĄ čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ COM.

A[5] = 0 (čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░): ąĘą░ą┐čĆąĄčé čĆą░ąĘą┤ąĄą╗ąĄąĮąĖčÅ COM ąĮą░ č湥čéąĮčŗąĄ / ąĮąĄč湥čéąĮčŗąĄ, ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ COM ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠąĄ, COM127, COM126...COM65, COM64...SEG479...SEG0...COM0 COM1...COM62, COM63

A[5] = 1: čĆą░ąĘčĆąĄčłąĖčéčī čĆą░ąĘą┤ąĄą╗ąĄąĮąĖąĄ COM ąĮą░ č湥čéąĮčŗąĄ ąĖ ąĮąĄč湥čéąĮčŗąĄ, ąĮčāą╝ąĄčĆą░čåąĖčÅ ą▒čāą┤ąĄčé COM127, COM125...COM3, COM1...SEG479...SEG0...COM0, COM2...COM124, COM126

ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĖčÅ ą▓čŗą▓ąŠą┤ąŠą▓ ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ąĮą░ čĆąĖčü. 10-6.

ŌĆó Set Dual COM mode (B[4])

ąŁč鹊čé ą▒ąĖčé ą║ąŠą╝ą░ąĮą┤čŗ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┤ą▓ąŠą╣ąĮąŠą╣ čĆąĄąČąĖą╝ COM.

B[4] = 0 (čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░): ą┤ą▓ąŠą╣ąĮąŠą╣ čĆąĄąČąĖą╝ ą┤ą╗čÅ COM ąĘą░ą┐čĆąĄčēąĄąĮ, čüą╝. čĆąĖčü. 10-6

B[4] = 1: ą┤ą▓ąŠą╣ąĮąŠą╣ čĆąĄąČąĖą╝ COM čĆą░ąĘčĆąĄčłąĄąĮ, čüą╝. čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ ąĮą░ čĆąĖčü. 10-7

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮ ą┤ą▓ąŠą╣ąĮąŠą╣ čĆąĄąČąĖą╝ COM (B[4]=1), č鹊 čĆąĄąČąĖą╝ "Odd even split of COM pins" ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ (A[5]=0), ąĖ MUX ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čĆą░ą▓ąĮčŗą╝ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ 63 (MUX ? 63).

ąĀąĖčü. 10-6. ąÉą┐ą┐ą░čĆą░čéąĮą░čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ 1 ą▓čŗą▓ąŠą┤ąŠą▓ COM (MUX ratio: 128).

ąĀąĖčü. 10-7. ąÉą┐ą┐ą░čĆą░čéąĮą░čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ 2 ą▓čŗą▓ąŠą┤ąŠą▓ COM (MUX ratio: 64).

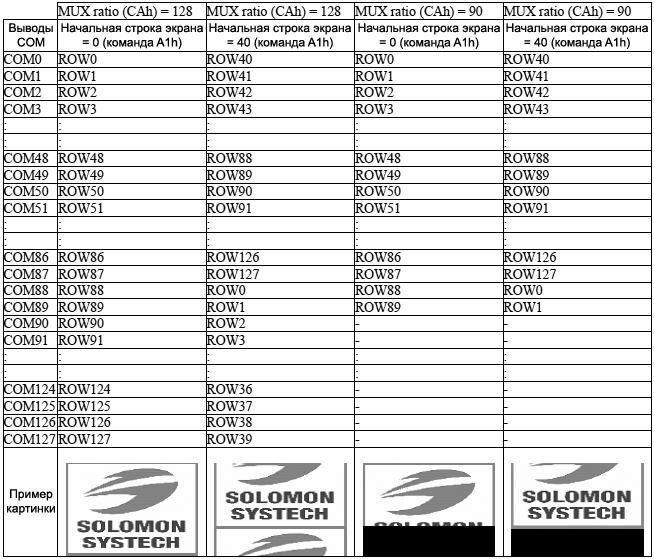

ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čĆąĄą│ąĖčüčéčĆą░ ąĮą░čćą░ą╗čīąĮąŠą╣ čüčéčĆąŠą║ąĖ ą┤ąĖčüą┐ą╗ąĄčÅ (Display Start Line register), čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ąŠč鹊ą▒čĆą░ąČą░ąĄą╝ąŠą│ąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ RAM 菹║čĆą░ąĮą░ ąŠčé 0 ą┤ąŠ 127. ąĀąĖčü. 10-8 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆąĖą╝ąĄčĆ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čŹč鹊ą╣ ą║ąŠą╝ą░ąĮą┤čŗ, ą║ąŠą│ą┤ą░ MUX ratio = 128 ąĖ MUX ratio = 90, ąĖ Display Start Line = 40. ąŚą┤ąĄčüčī "Row" ąŠą▒ąŠąĘąĮą░čćą░ąĄčé ą│čĆą░čäąĖč湥čüą║ąĖąĄ ą┤ą░ąĮąĮčŗąĄ čüčéčĆąŠą║ąĖ RAM 菹║čĆą░ąĮą░.

ąĀąĖčü. 10-8 : ą¤čĆąĖą╝ąĄčĆ Set Display Start Line ą▒ąĄąĘ ą▓ą║ą╗čÄč湥ąĮąĮąŠą│ąŠ Remap.

ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ąĘą░ą┤ą░ąĄčé ą┐čĆąĖą▓čÅąĘą║čā ąĮą░čćą░ą╗čīąĮąŠą╣ čüčéčĆąŠą║ąĖ 菹║čĆą░ąĮą░ - ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 COM0 ąĮą░čćą░ą╗čīąĮą░čÅ čüčéčĆąŠą║ą░ ą┤ąĖčüą┐ą╗ąĄčÅ, ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ ąĮą░čćą░ą╗čīąĮąŠą╣ čüčéčĆąŠą║ąĖ 菹║čĆą░ąĮą░ (display start line register) čĆą░ą▓ąĄąĮ 0 - ą║ ąŠą┤ąĮąŠą╝čā ąĖąĘ COM0-127. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ COM39 ą┐ąŠ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÄ ą║ COM0 ąĮą░ 40 čüčéčĆąŠą║, 7 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ą▓ąŠ ą▓č鹊čĆąŠą╣ ą║ąŠą╝ą░ąĮą┤ąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī 0101000. ąØą░ čĆąĖčüčāąĮą║ąĄ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąĖą╝ąĄčĆ čŹč鹊ą╣ ą║ąŠą╝ą░ąĮą┤čŗ. ąŚą┤ąĄčüčī "Row" ąŠą▒ąŠąĘąĮą░čćą░ąĄčé ą│čĆą░čäąĖč湥čüą║ąĖąĄ ą┤ą░ąĮąĮčŗąĄ čüčéčĆąŠą║ąĖ RAM 菹║čĆą░ąĮą░.

ąĀąĖčü. 10-9. ą¤čĆąĖą╝ąĄčĆ Set Display Offset ą▒ąĄąĘ ą▓ą║ą╗čÄč湥ąĮąĮąŠą│ąŠ Remap.

ąŁč鹊 ąŠą┤ąĮąŠą▒ą░ą╣čéąĮą░čÅ ą║ąŠą╝ą░ąĮą┤ą░, ą║ąŠč鹊čĆą░čÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čĆąĄąČąĖą╝ąŠą▓ Normal Display (ąŠą▒čŗčćąĮčŗą╣ 菹║čĆą░ąĮ), Entire Display ON (菹║čĆą░ąĮ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą▓ą║ą╗čÄč湥ąĮ), Entire Display OFF (菹║čĆą░ąĮ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą┐ąŠą│ą░čłąĄąĮ) ąĖ Inverse Display (ąĖąĮą▓ąĄčĆčüąĮčŗą╣ 菹║čĆą░ąĮ).

ŌĆó Normal Display (A4h)

ąĪą▒čĆąŠčüąĖčéčī ą┐čĆąĄą┤čŗą┤čāčēąĖąĄ čŹčäč乥ą║čéčŗ ąĖ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ ą┤ą░ąĮąĮčŗąĄ ąĮą░ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ čāčĆąŠą▓ąĮąĄ ą│čĆą░ą┤ą░čåąĖą╣ čüąĄčĆąŠą│ąŠ. ąØą░ čĆąĖčü. 10-10 ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąĖą╝ąĄčĆ čĆą░ą▒ąŠčéčŗ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░.

ąĀąĖčü. 10-10. ą¤čĆąĖą╝ąĄčĆ čĆą░ą▒ąŠčéčŗ čĆąĄąČąĖą╝ą░ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ (Normal Display).

ŌĆó Set Entire Display ON (A5h)

ą¤čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą▓čüąĄ č鹊čćą║ąĖ 菹║čĆą░ąĮą░ ą▓ čÅčĆą║ąŠčüčéčī GS15 ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ ą┤ą░ąĮąĮčŗčģ RAM ą▒čāč乥čĆą░ 菹║čĆą░ąĮą░, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 10-11.

ąĀąĖčü. 10-11. ą¤čĆąĖą╝ąĄčĆ ą┤ąĄą╣čüčéą▓ąĖčÅ čĆąĄąČąĖą╝ą░ Entire Display ON.

ŌĆó Set Entire Display OFF (A6h)

ą¤čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą▓čüąĄ č鹊čćą║ąĖ 菹║čĆą░ąĮą░ ą▓ čÅčĆą║ąŠčüčéčī GS0 ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ ą┤ą░ąĮąĮčŗčģ RAM ą▒čāč乥čĆą░ 菹║čĆą░ąĮą░, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 10-12.

ąĀąĖčü. 10-12. ą¤čĆąĖą╝ąĄčĆ Entire Display OFF.

ŌĆó Inverse Display (A7h)

ąŻčĆąŠą▓ąĮąĖ čüąĄčĆąŠą│ąŠ ą┤ą░ąĮąĮčŗčģ ą┤ąĖčüą┐ą╗ąĄčÅ ą┐čĆąĖ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĖ ą▒čāą┤čāčé ą┐ąĄčĆąĄčāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ąĮą░ąŠą▒ąŠčĆąŠčé, čéą░ą║ čćč鹊 GS0 ą▒čāą┤ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī čÅčĆą║ąŠčüčéąĖ GS15, GS1 - GS14 ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ. ąØą░ čĆąĖčü. 10-13 ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąĖą╝ąĄčĆ čĆą░ą▒ąŠčéčŗ ąĖąĮą▓ąĄčĆčüąĖąĖ 菹║čĆą░ąĮą░.

ąĀąĖčü. 10-13. ą¤čĆąĖą╝ąĄčĆ čĆą░ą▒ąŠčéčŗ Inverse Display.

ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ą▓ą║ą╗čÄčćą░ąĄčé ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ čćą░čüčéąĖ 菹║čĆą░ąĮą░. ą×č鹊ą▒čĆą░ąČą░ąĄą╝ą░čÅ ąŠą▒ą╗ą░čüčéčī ąĘą░ą┤ą░ąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ąŠą╣ ąĖąĘ 3 ą▒ą░ą╣čé. ąĀąĖčü. 10-14 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆąĖą╝ąĄčĆ ą▓ą║ą╗čÄč湥ąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ čćą░čüčéąĖ 菹║čĆą░ąĮą░ čü ąĮą░čćą░ą╗čīąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝ čüčéčĆąŠą║ąĖ A[6:0] = 20h ąĖ ą║ąŠąĮąĄčćąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝ čüčéčĆąŠą║ąĖ B[6:0] = 5Fh, ą║ąŠą│ą┤ą░ MUX ratio = 128.

ąĀąĖčü. 10-14. ą¤čĆąĖą╝ąĄčĆ čĆą░ą▒ąŠčéčŗ Partial Mode Display.

ąŁčéą░ ąŠą┤ąĮąŠą▒ą░ą╣čéąĮą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ ą▓čŗą║ą╗čÄčćą░ąĄčé čĆąĄąČąĖą╝ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ čćą░čüčéąĖ 菹║čĆą░ąĮą░ (ąŠčéą╝ąĄąĮčÅąĄčé ą┤ąĄą╣čüčéą▓ąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ A8h).

ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ąĖąĘ 2 ą▒ą░ą╣čé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čĆąĄą│čāą╗čÅč鹊čĆą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ą╗čÅ VDD. ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│čāą╗čÅč鹊čĆ VDD ą▓ą║ą╗čÄč湥ąĮ, ąĄčüą╗ąĖ ą▒ąĖčé A[0] čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, ąĖ ą▓čŗą║ą╗čÄč湥ąĮ (č鹊ą│ą┤ą░ ą┤ąŠą╗ąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ąĮąĄčłąĮąĄąĄ ą┐ąĖčéą░ąĮąĖąĄ ą┤ą╗čÅ VDD), ą║ąŠą│ą┤ą░ A[0] čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0.

ąŁčéą░ ąŠą┤ąĮąŠą▒ą░ą╣čéąĮą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ąĖą╗ąĖ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą┐ą░ąĮąĄą╗ąĖ OLED. ąÜąŠą│ą┤ą░ ą┤ąĖčüą┐ą╗ąĄą╣ ą▓ą║ą╗čÄč湥ąĮ (ą║ąŠą╝ą░ąĮą┤ąŠą╣ AFh), č鹊 ą▓čŗą▒čĆą░ąĮąĮčŗąĄ čüčģąĄą╝čŗ (ą║ąŠą╝ą░ąĮą┤ąŠą╣ Set Master Configuration) ą▒čāą┤čāčé ą▓ą║ą╗čÄč湥ąĮčŗ. ąÜąŠą│ą┤ą░ ą┤ąĖčüą┐ą╗ąĄą╣ ą▓čŗą║ą╗čÄč湥ąĮ (ą║ąŠą╝ą░ąĮą┤ąŠą╣ AEh), č鹊 čŹčéąĖ čüčģąĄą╝čŗ ą▓čŗą║ą╗čÄč湥ąĮčŗ, SEG ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ VSS ąĖ COM ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą▓čŗčüąŠą║ąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ.

ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ąĖąĘ 2 ą▒ą░ą╣čé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┤ą╗ąĖąĮčā čäą░ąĘ 1 ąĖ 2 č乊čĆą╝čŗ čüąĖą│ąĮą░ą╗ą░ SEG ą┤čĆą░ą╣ą▓ąĄčĆą░.

ŌĆó ążą░ąĘą░ 1 (A[3:0]): čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┐ąĄčĆąĖąŠą┤ ąŠčé 5 ą┤ąŠ 31 ą▓ ąĄą┤ąĖąĮąĖčåą░čģ 2 DCLK. ą¤ąŠą▓čŗčłąĄąĮąĮą░čÅ ąĄą╝ą║ąŠčüčéčī ą┐ąĖą║čüąĄą╗ą░ OLED ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčī čāą▓ąĄą╗ąĖč湥ąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░ ą┤ą╗čÅ ą┐ąŠą╗ąĮąŠą│ąŠ čĆą░ąĘčĆčÅą┤ą░ čĆą░ąĮąĄąĄ ąĘą░ą┐ąĖčüą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ.

| A[3:0] |

ą¤ąĄčĆąĖąŠą┤ čäą░ąĘčŗ 1 |

| 0000 |

ąĮąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠ |

| 0001 |

ąĮąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠ |

| 0010 |

5 DCLK |

| 0011 |

7 DCLK |

| 0100 |

9 DCLK

(čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░) |

| .. |

.. |

| 1111 |

32 DCLK |

ŌĆó ążą░ąĘą░ 2 (A[7:4]): čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┐ąĄčĆąĖąŠą┤ ąŠčé 3 ą┤ąŠ 15 ą▓ ąĄą┤ąĖąĮąĖčåą░čģ DCLK. ą¦ąĄą╝ ą▒ąŠą╗čīčłąĄ ąĄą╝ą║ąŠčüčéčī ą┐ąĖą║čüąĄą╗ą░ OLED, č鹥ą╝ ąĮčāąČąĄąĮ ą▒ąŠą╗čīčłąĄ ą┐ąĄčĆąĖąŠą┤ ąĘą░čĆčÅą┤ą░ ą║ čåąĄą╗ąĄą▓ąŠą╝čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ VP.

| A[7:4] |

ą¤ąĄčĆąĖąŠą┤ čäą░ąĘčŗ 1 |

| 0000 |

ąĮąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠ |

| 0001 |

ąĮąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠ |

| 0010 |

ąĮąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠ |

| 0011 |

3 DCLK |

| .. |

.. |

| 0111 |

7 DCLK

(čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░) |

| .. |

.. |

| 1111 |