|

M25P80 čŹč鹊 ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą┐ą░ą╝čÅčéąĖ FLASH ąĮą░ 8 ą╝ąĄą│ą░ą▒ąĖčé (1 ą╝ąĄą│ą░ą▒ą░ą╣čé, 1Mb x 8) čü ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝, čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╝ čü SPI [2]. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą▓čŗčüąŠą║ąŠą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮčŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ ąĮą░ čćą░čüč鹊č鹥 ą┤ąŠ 75 ą£ąōčå.

ą¤ą░ą╝čÅčéčī ą╝ąŠąČąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĘą░ ąŠą┤ąĖąĮ čĆą░ąĘ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ ą▒ą░ą╣čé ąŠčé 1 ą┤ąŠ 256, ąĖčüą┐ąŠą╗čīąĘčāčÅ ą║ąŠą╝ą░ąĮą┤čā PAGE PROGRAM. ą¤ą░ą╝čÅčéčī ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮą░ ą▓ 16 čüąĄą║č鹊čĆąŠą▓, ą║ą░ąČą┤čŗą╣ ąĖąĘ ą║ąŠč鹊čĆčŗčģ čüąŠą┤ąĄčƹȹĖčé 256 čüčéčĆą░ąĮąĖčå. ąÜą░ąČą┤ą░čÅ čüčéčĆą░ąĮąĖčåą░ ąĖą╝ąĄąĄčé čĆą░ąĘą╝ąĄčĆ 256 ą▒ą░ą╣čé. ą¤ą░ą╝čÅčéčī ą╝ąŠąČąĮąŠ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čéčī ą║ą░ą║ 4096 čüčéčĆą░ąĮąĖčå, ąĖą╗ąĖ ą║ą░ą║ 1048576 ą▒ą░ą╣čé. ąÆčüčÅ ą┐ą░ą╝čÅčéčī ą╝ąŠąČąĄčé ą▒čŗčéčī čüč鹥čĆčéą░ ą║ąŠą╝ą░ąĮą┤ąŠą╣ BULK ERASE, ąĖą╗ąĖ ą╝ąŠąČąĮąŠ čüčéąĖčĆą░čéčī ą┐ąŠ ąŠą┤ąĮąŠą╝čā čüąĄą║č鹊čĆčā ą║ąŠą╝ą░ąĮą┤ąŠą╣ SECTOR ERASE.

ąŁč鹊čé ą┤ą░čéą░čłąĖčé (ą┐ąĄčĆąĄą▓ąŠą┤ [1]) ą┐ąŠą┤čĆąŠą▒ąĮąŠ ąŠą┐ąĖčüčŗą▓ą░ąĄčé čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ M25P80, ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąŠ ą║ąŠč鹊čĆąŠą╣ ąŠčüąĮąŠą▓ą░ąĮą░ ąĮą░ č鹥čģą┐čĆąŠčåąĄčüčüąĄ 110 ąĮą╝.

ą×čüąĮąŠą▓ąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ M25P80:

ŌĆó SPI-čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╣ ąĖąĮč鹥čĆč乥ą╣čü, ą┤ą░čÄčēąĖą╣ ą┤ąŠčüčéčāą┐ ą║ 8 ą╝ąĄą│ą░ą▒ąĖčé FLASH-ą┐ą░ą╝čÅčéąĖ ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊č鹥 75 ą£ąōčå.

ŌĆó ą×ą┤ąĮąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 2.7V .. 3.6V.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ (ą▒ą╗ąŠą║ąŠą╝ ą┤ąŠ 256 ą▒ą░ą╣čé) ąĘą░ 0.64 ą╝čü (čéąĖą┐ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ).

ŌĆó ąÆąŠąĘą╝ąŠąČąĮąŠčüčéąĖ čüčéąĖčĆą░ąĮąĖčÅ:

ŌĆō čüčéąĖčĆą░ąĮąĖąĄ čüąĄą║č鹊čĆą░: 512 ą║ąĖą╗ąŠą▒ąĖčé ąĘą░ 0.6 čüąĄą║čāąĮą┤čŗ (čéąĖą┐ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ).

ŌĆō ą┐ąŠą╗ąĮąŠąĄ čüčéąĖčĆą░ąĮąĖąĄ (Bulk Erase): 8 ą╝ąĄą│ą░ą▒ąĖčé ąĘą░ 8 čüąĄą║čāąĮą┤ (čéąĖą┐ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ).

ŌĆó ążčāąĮą║čåąĖčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ: ąĘą░čēąĖčēąĄąĮąĮą░čÅ ąŠą▒ą╗ą░čüčéčī ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą▒ąĖčé BP0, BP1, BP2.

ŌĆó ąĀąĄąČąĖą╝ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (Deep power-down): 1 ą╝ą║ąÉ (čéąĖą┐ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ).

ŌĆó ąŁą╗ąĄą║čéčĆąŠąĮąĮčŗą╣ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ (Electronic signature):

ŌĆō 2-ą▒ą░ą╣čéąĮą░čÅ čüąĖą│ąĮą░čéčāčĆą░ (2014h), čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčÄčēą░čÅ čüčéą░ąĮą┤ą░čĆčéčā JEDEC.

ŌĆō ąŻąĮąĖą║ą░ą╗čīąĮčŗą╣ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ (Unique ID, UID) ąĖąĘ 16 ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĮą░ Common Flash Interface (CFI).

ŌĆō ąÜąŠą╝ą░ąĮą┤ą░ RES, 1-ą▒ą░ą╣čéąĮą░čÅ čüąĖą│ąĮą░čéčāčĆą░ (13h) ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ąŠą▒čĆą░čéąĮąŠą╣ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ.

ŌĆó ąæąŠą╗čīčłąĄ 100000 čåąĖą║ą╗ąŠą▓ ąĘą░ą┐ąĖčüąĖ ąĮą░ čüąĄą║č鹊čĆ.

ŌĆó ąæąŠą╗čīčłąĄ 20 ą╗ąĄčé čüąŠčģčĆą░ąĮąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ.

ŌĆó ąöąŠčüčéčāą┐ąĮčŗ čāčüčéčĆąŠą╣čüčéą▓ą░ ą║ą╗ą░čüčüą░ Automotive.

ŌĆó ąÜąŠčĆą┐čāčüą░ (čüąŠą▓ą╝ąĄčüčéąĖą╝čŗąĄ čü RoHS):

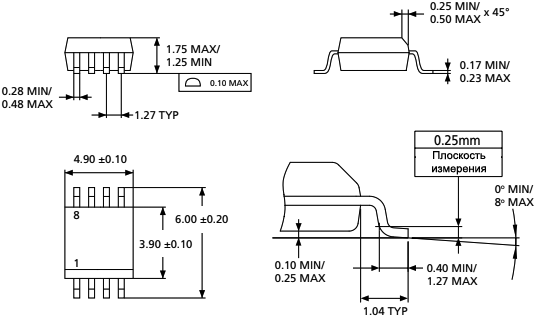

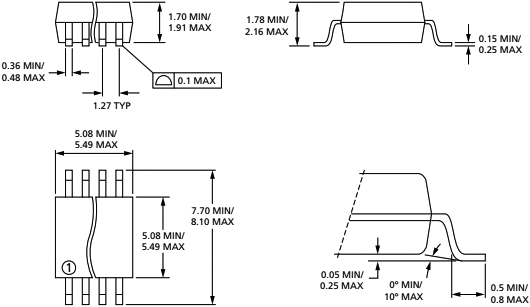

ŌĆō SO8N (MN) čłąĖčĆąĖąĮąŠą╣ 150 mil

ŌĆō SO8W (MW) čłąĖčĆąĖąĮąŠą╣ 208 mil

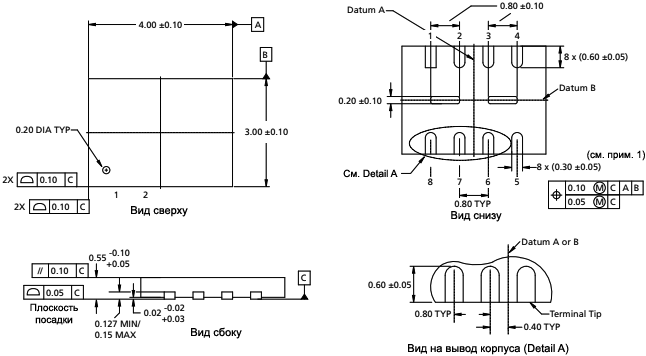

ŌĆō VFDFPN8 (MP) MLP8 6 x 5 ą╝ą╝

ŌĆō UFDFPN8 (MC) MLP8 4 x 3 ą╝ą╝

ąĀąĖčü. 1. ąÆčŗą▓ąŠą┤čŗ (čüąĖą│ąĮą░ą╗čŗ) M25P80.

ąĀąĖčü. 2. ąĀą░čüą┐ąŠą╗ąŠąČąĄąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ ą║ąŠčĆą┐čāčüąŠą▓ SO8, VFQFPN.

ąŻ ą║ąŠčĆą┐čāčüą░ MLP8 ąĮą░ ą┤ąŠąĮčåąĄ ąĄčüčéčī čåąĄąĮčéčĆą░ą╗čīąĮą░čÅ ą║ąŠąĮčéą░ą║čéąĮą░čÅ ą┐ą╗ąŠčēą░ą┤ą║ą░, ą║ąŠč鹊čĆą░čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą║ VSS (ąĘąĄą╝ą╗čÅ, GND), ąĖ ąŠąĮą░ ąĮąĄ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ ąĮąĖ ą║ ą║ą░ą║ąŠą╝čā ą┤čĆčāą│ąŠą╝čā čüąĖą│ąĮą░ą╗čā ąĖą╗ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ.

ąóą░ą▒ą╗ąĖčåą░ 1. ąśą╝ąĄąĮą░ čüąĖą│ąĮą░ą╗ąŠą▓.

| Ōä¢ |

ąĪąĖą│ąĮą░ą╗ |

ążčāąĮą║čåąĖčÅ |

ąØą░ą┐čĆą░ą▓ą╗. |

| 1 |

S# |

Chip Select (ą▓čŗą▒ąŠčĆą║ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ) |

ąÆčģąŠą┤ |

| 2 |

DQ1 |

ąÆčŗčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ |

ąÆčŗčģąŠą┤ |

| 3 |

W# |

ąŚą░čēąĖčéą░ ąŠčé ąĘą░ą┐ąĖčüąĖ ąĖą╗ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ |

ąÆčģąŠą┤ |

| 4 |

VSS |

ąŚąĄą╝ą╗čÅ, GND |

|

| 5 |

DQ0 |

ąÆčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ |

ąÆčģąŠą┤ |

| 6 |

C |

ąóą░ą║č鹊ą▓čŗą╣ ą▓čģąŠą┤ |

ąÆčģąŠą┤ |

| 7 |

HOLD# |

Hold (čüąĖą│ąĮą░ą╗ čāą┤ąĄčƹȹ░ąĮąĖčÅ) |

ąÆčģąŠą┤ |

| 8 |

VCC |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ |

|

ąóą░ą▒ą╗ąĖčåą░ 2. ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓.

| ąĪąĖą│ąĮą░ą╗ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| S# |

ąÆčģąŠą┤ |

Chip select: ą║ąŠą│ą┤ą░ ąĮą░ ą▓čģąŠą┤ąĄ S# ą╗ąŠą│. 1, čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ą▓čŗą▒čĆą░ąĮąŠ, ąĖ ą▓čŗčģąŠą┤ DQ1 ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ ą▓čŗčüąŠą║ąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ. ąÜčĆąŠą╝ąĄ čüąĖčéčāą░čåąĖą╣, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ ąŠą┐ąĄčĆą░čåąĖą╣ PROGRAM, ERASE ąĖą╗ąĖ WRITE STATUS REGISTER, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čāą┤ąĄčé ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čŹąĮąĄčĆą│ąĖąĖ (standby power mode), ąĮąŠ ąĮąĄ ą▓ čĆąĄąČąĖą╝ąĄ ą│ą╗čāą▒ąŠą║ąŠą│ąŠ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ (deep power down mode). ą¤ąĄčĆąĄą▓ąŠą┤ S# ą▓ ą╗ąŠą│. 0 čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā čāčüčéčĆąŠą╣čüčéą▓ą░, ąŠąĮąŠ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ (active power mode). ą¤ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ čüą┐ą░ą┤ ąĮą░ S# čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ą╗čÄą▒ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ. |

| DQ1 |

ąÆčŗčģąŠą┤ |

Serial data: ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ DQ1 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąŠą▒ąĖčéąĮąŠą│ąŠ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░. ąöą░ąĮąĮčŗąĄ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĖąĘ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ čéą░ą║č鹊ą▓ (C), čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ ą▓ą┐ąĄčĆąĄą┤. |

| W#/VPP |

ąÆčģąŠą┤ |

Write protect: čüąĖą│ąĮą░ą╗ W#/VPP ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą┤ą▓ąŠą╣ąĮčāčÄ čäčāąĮą║čåąĖčÄ - ą▓čģąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ ąĖčüč鹊čćąĮąĖą║ ą┐ąĖčéą░ąĮąĖčÅ. ąŁčéąĖ ą┤ą▓ąĄ čäčāąĮą║čåąĖąĖ ą▓čŗą▒ąĖčĆą░čÄčéčüčÅ ą┐ąŠą┤ą░č湥ą╣ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ ą▓čŗą▓ąŠą┤. ąĢčüą╗ąĖ ąĮą░ ą▓čģąŠą┤ąĄ W#/VPP čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 0V .. VCC), č鹊 čŹč鹊čé ą▓čŗą▓ąŠą┤ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą▓čģąŠą┤. ąóąŠą│ą┤ą░ ą▓čģąŠą┤ W# ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čäąĖą║čüą░čåąĖąĖ čĆą░ąĘą╝ąĄčĆą░ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆą░čÅ ąĘą░čēąĖčēąĄąĮą░ ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ (ą║ąŠą╝ą░ąĮą┤čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čüčéąĖčĆą░ąĮąĖčÅ ą┤ą╗čÅ čŹč鹊ą╣ ąŠą▒ą╗ą░čüčéąĖ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ). ąĀą░ąĘą╝ąĄčĆ ąŠą▒ą╗ą░čüčéąĖ ąĘą░ą┤ą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ BP2, BP1 ąĖ BP0 čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ (Status Register). VPP ą┤ąĄą╣čüčéą▓čāąĄčé ą║ą░ą║ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ ą┐ąĖčéą░ąĮąĖčÅ, ąĄčüą╗ąĖ ą┐ąŠą┤ą░ąĮąĮąŠąĄ ąĮą░ ąĮąĄą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ VPPH, ą║ą░ą║ čŹč鹊 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ AC Measurement Conditions. ąśąĘą▒ąĄą│ą░ą╣č鹥 ą┐ąŠą┤ą░čćąĖ VPPH ąĮą░ ą▓čŗą▓ąŠą┤ W#/VPP ą┐čĆąĖ čĆą░ą▒ąŠč鹥 BULK ERASE. |

| VSS |

ąŚąĄą╝ą╗čÅ |

Ground: ąŠą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤ ą▓čüąĄčģ čüąĖą│ąĮą░ą╗ąŠą▓, ą╝ąĖąĮčāčü ą┐ąĖčéą░ąĮąĖčÅ. |

| DQ0 |

ąÆčģąŠą┤ |

Serial data: ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ DQ0 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝čā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą║ąŠą╝ą░ąĮą┤, ą░ą┤čĆąĄčüąŠą▓ ąĖ ą┤ą░ąĮąĮčŗčģ. ąŚąĮą░č湥ąĮąĖčÅ ąĮą░ ą▓čģąŠą┤ąĄ DQ0 ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ (C), ą┤ą░ąĮąĮčŗąĄ ą┐ąŠą┤ą░čÄčéčüčÅ čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ ą▓ą┐ąĄčĆąĄą┤. |

| C |

ąÆčģąŠą┤ |

Clock: ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ C ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čéą░ą║čéąĖčĆčāčÄčēąĖąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░. ąÜąŠą╝ą░ąĮą┤čŗ, ą░ą┤čĆąĄčüą░ ąĖą╗ąĖ ą┤ą░ąĮąĮčŗąĄ, ą┐ąŠą┤ą░ą▓ą░ąĄą╝čŗąĄ č湥čĆąĄąĘ ą▓čģąŠą┤ DQ0, ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čéą░ą║č鹊ą▓ C. ąöą░ąĮąĮčŗąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ DQ1 ą╝ąĄąĮčÅčÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ čéą░ą║č鹊ą▓ C. |

| HOLD# |

ąÆčģąŠą┤ |

Hold: čüąĖą│ąĮą░ą╗ HOLD# ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąŠčüčéą░ąĮąŠą▓ą║ąĖ ąĮą░ ą┐ą░čāąĘčā ą╗čÄą▒čŗčģ ąŠą▒ą╝ąĄąĮąŠą▓ ą┤ą░ąĮąĮčŗą╝ąĖ čü čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą▒ąĄąĘ čüąĮčÅčéąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ čü ąĮąĄą│ąŠ (čüąŠčüč鹊čÅąĮąĖąĄ čāą┤ąĄčƹȹ░ąĮąĖčÅ). ąÆąŠ ą▓čĆąĄą╝čÅ čüąŠčüč鹊čÅąĮąĖčÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą▓čŗčģąŠą┤ DQ1 ąŠčéą║ą╗čÄčćą░ąĄčéčüčÅ (High-Z). DQ0 ąĖ C čüčéą░ąĮąŠą▓čÅčéčüčÅ ąĮąĄ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮčŗą╝ąĖ ą║ ą┐ąŠą┤ą░č湥 ąĮą░ ąĮąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓. ą¦č鹊ą▒čŗ ąĘą░ą┐čāčüčéąĖčéčī čüąŠčüč鹊čÅąĮąĖąĄ čāą┤ąĄčƹȹ░ąĮąĖčÅ, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮąŠ (S# == 0). |

| VCC |

ą¤ąĖčéą░ąĮąĖąĄ |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ą░. |

[ąĀąĄąČąĖą╝čŗ SPI]

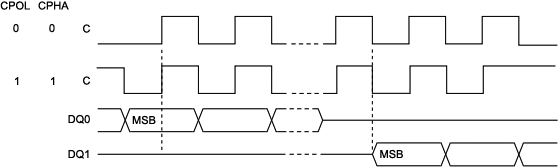

ą£ąĖą║čĆąŠčüčģąĄą╝čŗ M25P80 ą╝ąŠą│čāčé čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ čü ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ SPI, čĆą░ą▒ąŠčéą░čÄčēąĖą╝ ą▓ ąŠą┤ąĮąŠą╝ ąĖąĘ ą┤ą▓čāčģ čĆąĄąČąĖą╝ąŠą▓ SPI [2]:

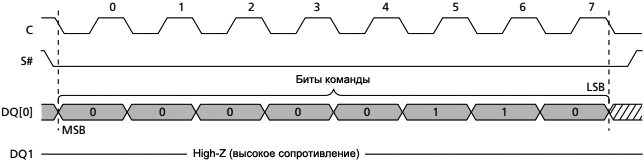

ŌĆó CPOL = 0, CPHA = 0 (SPI mode 0)

ŌĆó CPOL = 1, CPHA = 1 (SPI mode 3)

ąöą╗čÅ čŹčéąĖčģ ą┤ą▓čāčģ čĆąĄąČąĖą╝ąŠą▓ ą▓čģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓čüąĄą│ą┤ą░ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čéą░ą║č鹊ą▓ (C), ąĖ ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ čéą░ą║č鹊ą▓. ąĀą░ąĘą╗ąĖčćąĖčÅ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗą╝ąĖ čĆąĄąČąĖą╝ą░ą╝ąĖ ą▓ ąĮą░čćą░ą╗čīąĮąŠą╝ čāčĆąŠą▓ąĮąĄ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓, ą║ąŠą│ą┤ą░ ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ ąĖ ąĮąĄ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ:

ŌĆó C ąŠčüčéą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0 (CPOL = 0, CPHA = 0)

ŌĆó C ąŠčüčéą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 1 (CPOL = 1, CPHA = 1)

ąĀąĖčü. 3. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗąĄ čĆąĄąČąĖą╝čŗ SPI.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: CPOL čüąŠą║čĆą░čēąĄąĮąĖąĄ ąŠčé Clock POLarity (ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓), CPHA Clock PHAse (čäą░ąĘą░ čéą░ą║č鹊ą▓), MSB Most Significant Bit (čüčéą░čĆčłąĖą╣ ąĘąĮą░čćą░čēąĖą╣ ą▒ąĖčé). ąĪąŠč湥čéą░ąĮąĖąĄ CPOL/CPHA 00 ąŠąĘąĮą░čćą░ąĄčé ą▓čŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ SPI 0, ą░ čüąŠč湥čéą░ąĮąĖąĄ 11 ą▓čŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ SPI 3.

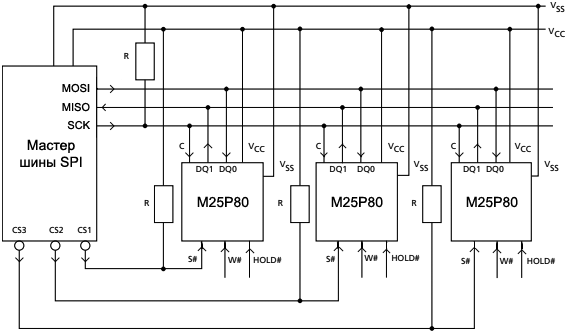

ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ąĮą░ čłąĖąĮąĄ SPI ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ą░ą║čéąĖą▓ąĮčŗą╝ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĖ ąŠą┤ąĖąĮ ą╝ą░čüč鹥čĆ SPI (ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ, MCU), č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčé ą▓čŗčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ DQ1, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ (ąĄčüą╗ąĖ ąŠąĮąĖ čéą░ą║ąČąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ č鹊ą╣ ąČąĄ čłąĖąĮąĄ) ą┤ąĄčƹȹ░čé čüą▓ąŠąĖ ą▓čŗčģąŠą┤čŗ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą▓čŗčüąŠą║ąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ (High-Z). ąØąĖąČąĄ ąĮą░ čĆąĖčü. 4 ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąĖą╝ąĄčĆ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ MCU čéčĆąĄčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą┐ą░ą╝čÅčéąĖ.

ąĀąĖčü. 4. ą£ą░čüč鹥čĆ čłąĖąĮčŗ SPI ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ąĪąĖą│ąĮą░ą╗čŗ WRITE PROTECT (W#) ąĖ HOLD# ą┤ąŠą╗ąČąĮčŗ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1 ąĖą╗ąĖ ą╗ąŠą│. 0 čüąŠą│ą╗ą░čüąĮąŠ ąĖčģ ąĮą░ąĘąĮą░č湥ąĮąĖčÄ.

2. ąĀąĄąĘąĖčüč鹊čĆčŗ (R) ą│ą░čĆą░ąĮčéąĖčĆčāčÄčé, čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ ąĮąĄ ą▓čŗą▒čĆą░ąĮąŠ, ąĄčüą╗ąĖ ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ąŠčüčéą░ą▓ą╗čÅąĄčé čüąĖą│ąĮą░ą╗ S# ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą▓čŗčüąŠą║ąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ (High-Z).

3. ą£ą░čüč鹥čĆ čłąĖąĮčŗ ą╝ąŠąČąĄčé ą▓ąŠą╣čéąĖ ą▓ čéą░ą║ąŠą╣ čĆąĄąČąĖą╝, ą║ąŠą│ą┤ą░ ą▓čüąĄ ąĄą│ąŠ ą┐ąŠčĆčéčŗ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐ąĄčĆąĄčłą╗ąĖ ą▓ ąŠčéą║ą╗čÄč湥ąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ (High-Z); ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłąĄą╗ čüą▒čĆąŠčü ą╝ą░čüč鹥čĆą░ čłąĖąĮčŗ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ C ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą▓ąĮąĄčłąĮąĄą╝čā ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĄą╝čā ą║ ą╗ąŠą│. 0 čĆąĄąĘąĖčüč鹊čĆčā (pulldown), ą║ąŠą│ą┤ą░ ą▓čüąĄ čüąĖą│ąĮą░ą╗čŗ ą╝ą░čüč鹥čĆą░ ą┐ąĄčĆąĄčłą╗ąĖ ą▓ High-Z, S# ą┐čĆąĖ čŹč鹊ą╝ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčé ą║ ą╗ąŠą│. 1. ąŁč鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 S# ąĖ C ąĮąĄ ą▒čāą┤čāčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1, ąĖ ą▒čāą┤ąĄčé čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĄąĮąŠ čāčüą╗ąŠą▓ąĖąĄ tSHCH.

4. ąóąĖą┐ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ R čüąŠčüčéą░ą▓ą╗čÅąĄčé 100 ą║ą×ą╝, ąĄčüą╗ąĖ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░čéčī ą┐ąŠčüč鹊čÅąĮąĮčāčÄ ą▓čĆąĄą╝ąĄąĮąĖ R * Cp (Cp = ą┐ą░čĆą░ąĘąĖčéąĮą░čÅ ąĄą╝ą║ąŠčüčéčī čłąĖąĮčŗ) ą║ąŠčĆąŠč湥 č湥ą╝ ą▓čĆąĄą╝čÅ, ąĮą░ ą║ąŠč鹊čĆąŠąĄ ą╝ą░čüč鹥čĆ ąŠčüčéą░ą▓ą╗čÅąĄčé čłąĖąĮčā SPI ą▓ čüąŠčüč鹊čÅąĮąĖąĖ High-Z.

5. ą¤čĆąĖą╝ąĄčĆ: ą┐čĆąĖ Cp = 50 ą┐ąż (R * Cp = 5 ą╝ą║čü), ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ąĮąĄ ąŠčüčéą░ą▓ą╗čÅąĄčé čüąĖą│ąĮą░ą╗čŗ SPI ą▓ čüąŠčüč鹊čÅąĮąĖąĖ High-Z ąĮą░ ą▓čĆąĄą╝čÅ ą╝ąĄąĮčīčłąĄ 5 ą╝ą║čü.

[ąĀą░ą▒ąŠčćąĖąĄ čĆąĄąČąĖą╝čŗ]

Page Programming. ąöą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠą┤ąĮąŠą│ąŠ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ čéčĆąĄą▒čāąĄčéčüčÅ ą┤ą▓ąĄ ą║ąŠą╝ą░ąĮą┤čŗ: WRITE ENABLE, ą║ąŠč鹊čĆą░čÅ ąĘą░ąĮąĖą╝ą░ąĄčé 1 ą▒ą░ą╣čé, ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī PAGE PROGRAM, čüąŠčüč鹊čÅčēą░čÅ ąĖąĘ 4 ą▒ą░ą╣čé ą┐ą╗čÄčü ą┤ą░ąĮąĮčŗąĄ. ąŚą░ čŹčéąĖą╝ čüą╗ąĄą┤čāąĄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ PROGRAM ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ tPP. ą¦č鹊ą▒čŗ čĆą░čüą┐čĆąĄą┤ąĄą╗ąĖčéčī čŹčéčā ąĮą░ą│čĆčāąĘą║čā, ą║ąŠą╝ą░ąĮą┤ą░ PAGE PROGRAM ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī čüčĆą░ąĘčā ą┤ąŠ 256 ą▒ą░ą╣čé (ą┐ąŠą╝ąĄąĮčÅčéčī ą▓ ąĮąĖčģ ąĄą┤ąĖąĮąĖčćą║ąĖ ąĮą░ ąĮąŠą╗ąĖą║ąĖ), ąĄčüą╗ąĖ ąŠąĮąĖ ą╗ąĄąČą░čé ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą░ą┤čĆąĄčüą░čģ ąĮą░ ąŠą┤ąĮąŠą╣ ąĖ č鹊ą╣ ąČąĄ čüčéčĆą░ąĮąĖčåąĄ ą┐ą░ą╝čÅčéąĖ. ąöą╗čÅ ąŠą┐čéąĖą╝ąĖąĘą░čåąĖąĖ ą▓čĆąĄą╝ąĄąĮąĮčŗčģ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī PAGE PROGRAM ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čüąĄčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ąĖą┤čāčēąĖčģ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ą▒ą░ą╣čé ą▓ ąŠą┤ąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ, ą▓ą╝ąĄčüč鹊 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüč鹥ą╣ PAGE PROGRAM, ą║ą░ąČą┤ą░čÅ ąĖąĘ ą║ąŠč鹊čĆčŗčģ čüąŠą┤ąĄčƹȹĖčé č鹊ą╗čīą║ąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ą░ą╣čé.

Sector Erase, Bulk Erase. ąÜąŠą╝ą░ąĮą┤ą░ PAGE PROGRAM ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čüą▒čĆąŠčüąĖčéčī ą▒ąĖčéčŗ ą▓ ą▒ą░ą╣čéą░čģ čü 1 ąĮą░ 0. ą¤ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ čŹč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī čüą┤ąĄą╗ą░ąĮąŠ, ą▓čüąĄ ą▒ą░ą╣čéčŗ ą┐ą░ą╝čÅčéąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠčćąĖčēąĄąĮčŗ, čé. ąĄ. ą▓čüąĄ ą▒ąĖčéčŗ ą▓ ąĮąĖčģ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĄą┤ąĖąĮąĖčåą░ą╝ąĖ (ą║ą░ąČą┤čŗą╣ ą▒ą░ą╣čé ąĮą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝ąŠą╣ čüčéčĆą░ąĮąĖčåąĄ čĆą░ą▓ąĄąĮ FFh). ąŁč鹊 ą┤ąŠčüčéąĖą│ą░ąĄčéčüčÅ ą▓ ąŠą┤ąĖąĮ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą║ąŠą╝ą░ąĮą┤ąŠą╣ SECTOR ERASE, ąĖą╗ąĖ ą┐ąŠ ą▓čüąĄą╣ ą┐ą░ą╝čÅčéąĖ ą║ąŠą╝ą░ąĮą┤ąŠą╣ BULK ERASE. ąŁčéąĖ ąŠą┐ąĄčĆą░čåąĖąĖ ąĮą░čćąĖąĮą░čÄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čåąĖą║ą╗ąŠą╝ ERASE ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ tSE ąĖą╗ąĖ tBE čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ą¤ąĄčĆąĄą┤ ą║ąŠą╝ą░ąĮą┤ąŠą╣ ERASE ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┤ą░ąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ WRITE ENABLE.

ą×ą┐čĆąŠčü ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą┐ąĄčĆą░čåąĖą╣ ąĘą░ą┐ąĖčüąĖ, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖą╗ąĖ čüčéąĖčĆą░ąĮąĖčÅ. ą£ąŠąČąĮąŠ čāčüą║ąŠčĆąĖčéčī ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĖčģ ąŠą┐ąĄčĆą░čåąĖą╣, ąĮąĄ ą┤ąŠąČąĖą┤ą░čÅčüčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╣ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ ąĘą░ą┤ąĄčƹȹ║ąĖ ąŠą┐ąĄčĆą░čåąĖą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ (ą▓čĆąĄą╝ąĄąĮą░ tW, tPP, tSE ąĖą╗ąĖ tBE):

ŌĆó WRITE STATUS REGISTER

ŌĆó PROGRAM

ŌĆó ERASE (SECTOR ERASE, BULK ERASE)

ąöą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ąĄčüčéčī ą▒ąĖčé, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖą╣ ą░ą║čéąĖą▓ąĮąŠčüčéčī ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ (write in progress, WIP), ą║ąŠč鹊čĆčŗą╣ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ (Status Register). ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĮąŠ ąŠą┐čĆą░čłąĖą▓ą░čéčī, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą╝ąŠą╝ąĄąĮčé, ą║ąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī ąŠą┐ąĄčĆą░čåąĖčÅ WRITE, PROGRAM ąĖą╗ąĖ ERASE.

Active Power, Standby Power ąĖ Deep Power-Down. ąÜąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ (S#) ą▓ ą╗ąŠą│. 0, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓čŗą▒čĆą░ąĮąŠ, ąĖ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą░ą║čéąĖą▓ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (ACTIVE POWER). ąÜąŠą│ą┤ą░ ąĮą░ ą╗ąŠą│ 1, čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ą▓čŗą▒čĆą░ąĮąŠ ąĮąŠ ą▒čāą┤ąĄčé ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ACTIVE POWER ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ąĘą░ą▓ąĄčĆčłą░čéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čåąĖą║ą╗čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ (PROGRAM, ERASE, WRITE STATUS REGISTER). ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čĆąĄąČąĖą╝ STANDBY POWER, č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą┐ą░ą┤ą░ąĄčé ą┤ąŠ ICC1.

ąÆ čĆąĄąČąĖą╝ ą│ą╗čāą▒ąŠą║ąŠą│ąŠ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (DEEP POWER-DOWN) čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓čģąŠą┤ąĖčé ą┐ąŠ ą║ąŠą╝ą░ąĮą┤ąĄ DEEP POWER-DOWN, č鹊ą│ą┤ą░ č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą┐ą░ą┤ą░ąĄčé ą┤ąŠ ICC2. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ ąŠčüčéą░ąĄčéčüčÅ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ RELEASE FROM DEEP POWER-DOWN. ąÆ čĆąĄąČąĖą╝ąĄ DEEP POWER-DOWN čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĖą│ąĮąŠčĆąĖčĆčāąĄčé ą▓čüąĄ ą║ąŠą╝ą░ąĮą┤čŗ WRITE, PROGRAM ąĖ ERASE. ąŁč鹊 ą┤ą░ąĄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ ą╝ąĄčģą░ąĮąĖąĘą╝ ąĘą░čēąĖčéčŗ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ ą┐ą░ą╝čÅčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, ą║ąŠą│ą┤ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮąĄ ą░ą║čéąĖą▓ąĮąŠ: ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą┐čĆąĄą┤ąŠčģčĆą░ąĮąĄąĮąĖąĄ ąŠčé ąĮąĄą┐čĆąĄą┤ąĮą░ą╝ąĄčĆąĄąĮąĮčŗčģ ą║ąŠą╝ą░ąĮą┤ WRITE, PROGRAM ąĖą╗ąĖ ERASE operations. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ DEEP POWER DOWN.

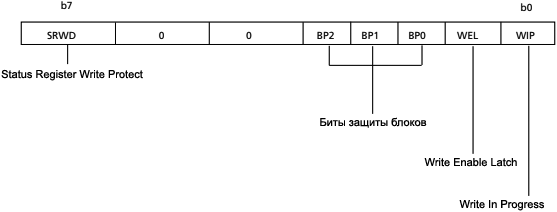

Status Register. ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ (status register) čüąŠą┤ąĄčƹȹĖčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ąĖčé čüąŠčüč鹊čÅąĮąĖčÅ ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ ą▒ąĖčé, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī ąĖą╗ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčī (ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ) čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╝ąĖ ą║ąŠą╝ą░ąĮą┤ą░ą╝ąĖ. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ ą║ąŠą╝ą░ąĮą┤čŗ READ STATUS REGISTER.

ąŚą░čēąĖčéą░ ą┤ą░ąĮąĮčŗčģ čü ą┐ąŠą╝ąŠčēčīčÄ ą┐čĆąŠč鹊ą║ąŠą╗ą░. ąŁąĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝ą░čÅ ą┐ą░ą╝čÅčéčī ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ čāčüą╗ąŠą▓ąĖčÅčģ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé čüąŠą┤ąĄčƹȹ░čéčī čćčĆąĄąĘą╝ąĄčĆąĮčŗą╣ čłčāą╝. ąĪą╗ąĄą┤čāčÄčēąĖąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą╝ąŠą│čāčé ąĘą░čēąĖčéąĖčéčī ą┤ą░ąĮąĮčŗąĄ ą▓ čéą░ą║ąŠą╝ ąĘą░čłčāą╝ą╗ąĄąĮąĮąŠą╝ ąŠą║čĆčāąČąĄąĮąĖąĖ.

ąĪą▒čĆąŠčü ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čéą░ą╣ą╝ąĄčĆ (tPUW) ą╝ąŠą│čāčé ąĘą░čēąĖčéąĖčéčī ąŠčé ąĮąĄą┐čĆąĄą┤ąĮą░ą╝ąĄčĆąĄąĮąĮčŗčģ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ ą┐ąĖčéą░ąĮąĖąĄ ą▓čŗčłą╗ąŠ ąĘą░ ą┐čĆąĄą┤ąĄą╗čŗ čĆą░ą▒ąŠčćąĖčģ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖą╣.

ąÜąŠą╝ą░ąĮą┤čŗ PROGRAM, ERASE ąĖ WRITE STATUS REGISTER ą┐čĆąŠą▓ąĄčĆčÅčÄčéčüčÅ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ąŠąĮąĖ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĖčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░ 8.

ąÆčüąĄą╝ ą║ąŠą╝ą░ąĮą┤ą░ą╝, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą┤ąĖčäąĖčåąĖčĆčāčÄčé ą┤ą░ąĮąĮčŗąĄ, ą┤ąŠą╗ąČąĮą░ ą┐čĆąĄą┤čłąĄčüčéą▓ąŠą▓ą░čéčī ą║ąŠą╝ą░ąĮą┤ą░ WRITE ENABLE ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ ąĘą░čēąĄą╗ą║ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (write enable latch, WEL).

ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ čäčāąĮą║čåąĖąĖ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čŹąĮąĄčĆą│ąĖąĖ, čĆąĄąČąĖą╝ DEEP POWER-DOWN čĆą░čüčłąĖčĆčÅąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčāčÄ ąĘą░čēąĖčéčā ą┤ą░ąĮąĮčŗčģ, ą┐ąŠčüą║ąŠą╗čīą║čā ą▓čüąĄ ą║ąŠą╝ą░ąĮą┤čŗ PROGRAM ąĖ ERASE ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ.

ą¤čĆąŠą│čĆą░ą╝ą╝ąĮą░čÅ ąĘą░čēąĖčéą░ ą┤ą░ąĮąĮčŗčģ. ą¤ą░ą╝čÅčéčī ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą║ą░ą║ read-only (č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ) čü ą┐ąŠą╝ąŠčēčīčÄ ą▒ąĖčé ąĘą░čēąĖčéčŗ ą▒ą╗ąŠą║ąŠą▓ (BP2, BP1, BP0), ąĮą░čģąŠą┤čÅčēąĖčģčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ, čćč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 3.

ąóą░ą▒ą╗ąĖčåą░ 3. ąĀą░ąĘą╝ąĄčĆčŗ ąĘą░čēąĖčēąĄąĮąĮčŗčģ ąŠčé ąĘą░ą┐ąĖčüąĖ ąŠą▒ą╗ą░čüč鹥ą╣ ą┤ą░ąĮąĮčŗčģ.

| ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ Status Register |

ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą┐ą░ą╝čÅčéąĖ |

| BP2 |

BP1 |

BP0 |

ąŚą░čēąĖčēąĄąĮąĮą░čÅ ąŠą▒ą╗ą░čüčéčī |

ąØąĄ ąĘą░čēąĖčēąĄąĮąĮą░čÅ ąŠą▒ą╗ą░čüčéčī |

| 0 |

0 |

0 |

ąĮąĄčé |

ąÆčüąĄ čüąĄą║č鹊čĆčŗ (0 .. 15) |

| 0 |

0 |

1 |

ąĪčéą░čĆčłą░čÅ 16-čÅ čćą░čüčéčī ą┐ą░ą╝čÅčéąĖ (čüąĄą║č鹊čĆ 15) |

ą£ą╗ą░ą┤čłąĖąĄ 15/16 čćą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ (čüąĄą║č鹊čĆčŗ 0 .. 14) |

| 0 |

1 |

0 |

ąĪčéą░čĆčłą░čÅ 8-čÅ čćą░čüčéčī ą┐ą░ą╝čÅčéąĖ (čüąĄą║č鹊čĆčŗ 14 .. 15) |

ą£ą╗ą░ą┤čłąĖąĄ 7/8 čćą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ (čüąĄą║č鹊čĆčŗ 0 .. 13) |

| 0 |

1 |

1 |

ąĪčéą░čĆčłą░čÅ 4-čÅ čćą░čüčéčī ą┐ą░ą╝čÅčéąĖ (čüąĄą║č鹊čĆčŗ 12 .. 15) |

ą£ą╗ą░ą┤čłąĖąĄ 3/4 čćą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ (čüąĄą║č鹊čĆčŗ 0 .. 11) |

| 1 |

0 |

0 |

ąĪčéą░čĆčłą░čÅ ą┐ąŠą╗ąŠą▓ąĖąĮą░ (čüąĄą║č鹊čĆčŗ 8 .. 15) |

ą£ą╗ą░ą┤čłą░čÅ ą┐ąŠą╗ąŠą▓ąĖąĮą░ ą┐ą░ą╝čÅčéąĖ (čüąĄą║č鹊čĆčŗ 0 .. 7) |

| 1 |

0 |

1 |

ąÆčüąĄ čüąĄą║č鹊čĆčŗ (0 .. 15) |

ąĮąĄčé |

| 1 |

1 |

0 |

| 1 |

1 |

1 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: 0 0 0 = ąĮąĄ ąĘą░čēąĖčēąĄąĮąĮą░čÅ ąŠą▒ą╗ą░čüčéčī (čüąĄą║č鹊čĆčŗ): čāčüčéčĆąŠą╣čüčéą▓ąŠ ą│ąŠč鹊ą▓ąŠ ą┐čĆąĖąĮčÅčéčī ą║ąŠą╝ą░ąĮą┤čā BULK ERASE, č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▓čüąĄ ą▒ąĖčéčŗ ąĘą░čēąĖčéčŗ ą▒ą╗ąŠą║ąŠą▓ (BP2, BP1, BP0) ąŠą▒ąĮčāą╗ąĄąĮčŗ.

ąÉą┐ą┐ą░čĆą░čéąĮą░čÅ ąĘą░čēąĖčéą░ ą┤ą░ąĮąĮčŗčģ. ą¤čāč鹥ą╝ ą┐ąŠą┤ą░čćąĖ ą╗ąŠą│. 0 ąĮą░ ą▓čŗą▓ąŠą┤ W# ą╝ąŠąČąĮąŠ ąĘą░čēąĖčéąĖčéčī čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą┐ą░ą╝čÅčéąĖ ąŠčé ąĘą░ą┐ąĖčüąĖ. ąŁč鹊 ąĘą░ą╝ąŠčĆą░ąČąĖą▓ą░ąĄčé čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ "č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ" (read-only). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąĘą░čēąĖčēąĄąĮčŗ ąŠčé ą┤ąŠčüčéčāą┐ą░ ą▒ąĖčéčŗ ąĘą░čēąĖčéčŗ ą▒ą╗ąŠą║ąŠą▓ (BPx) ąĖ ą▒ąĖčé ąĘą░ą┐čĆąĄčéą░ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ (Status Register Write Disable, SRWD).

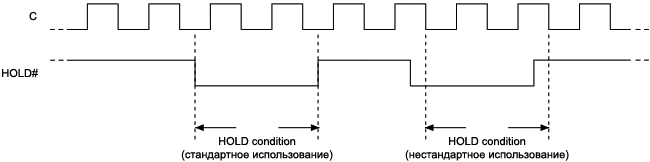

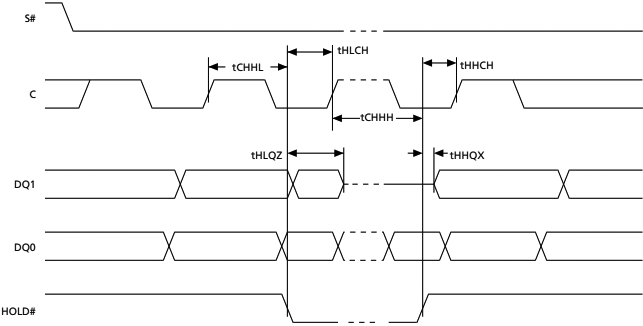

Hold Condition (čüąŠčüč鹊čÅąĮąĖąĄ čāą┤ąĄčƹȹ░ąĮąĖčÅ). ąĪąĖą│ąĮą░ą╗ HOLD# ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąŠčüčéą░ąĮąŠą▓ą║ąĖ ąĮą░ ą┐ą░čāąĘčā ą╗čÄą▒ąŠą│ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąŠą▒ą╝ąĄąĮą░ čü čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą▒ąĄąĘ čüą▒čĆąŠčüą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ą×ą┤ąĮą░ą║ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ čŹč鹊ą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▓ ą╗ąŠą│. 0 ąĮąĄ ą┐čĆąĄčĆčŗą▓ą░ąĄčé ą╗čÄą▒ąŠą╣ ąĘą░ą┐čāčēąĄąĮąĮčŗą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ WRITE STATUS REGISTER, PROGRAM ąĖą╗ąĖ ERASE.

ą¦č鹊ą▒čŗ ą▓ąŠą╣čéąĖ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ čāą┤ąĄčƹȹ░ąĮąĖčÅ, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮąŠ ą┐ąŠą┤ą░č湥ą╣ ą╗ąŠą│. 0 ąĮą░ ą▓čŗą▓ąŠą┤ S#. ąĪąŠčüč鹊čÅąĮąĖąĄ čāą┤ąĄčƹȹ░ąĮąĖčÅ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ HOLD#, ąĄčüą╗ąĖ čŹč鹊 čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü čāčĆąŠą▓ąĮąĄą╝ ą╗ąŠą│. 0 ąĮą░ čüąĖą│ąĮą░ą╗ąĄ čéą░ą║č鹊ą▓ (C). ąĪąŠčüč鹊čÅąĮąĖąĄ čāą┤ąĄčƹȹ░ąĮąĖčÅ ąĘą░ą║ą░ąĮčćąĖą▓ą░ąĄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ HOLD#, ąĄčüą╗ąĖ čŹč鹊 čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü čāčĆąŠą▓ąĮąĄą╝ ą╗ąŠą│. 0 ąĮą░ čüąĖą│ąĮą░ą╗ąĄ čéą░ą║č鹊ą▓ (C). ąĢčüą╗ąĖ čüą┐ą░ą┤ HOLD# ąĮąĄ čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü ą╗ąŠą│. 0 ąĮą░ C, č鹊 čüąŠčüč鹊čÅąĮąĖąĄ čāą┤ąĄčƹȹ░ąĮąĖčÅ čüčéą░čĆčéčāąĄčé čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąĄčĆąĄčģąŠą┤ą░ ą▓ ą╗ąŠą│. 0 čüąĖą│ąĮą░ą╗ą░ C. ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ čäčĆąŠąĮčé ąĮą░čĆą░čüčéą░ąĮąĖčÅ HOLD# ąĮąĄ čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü ą╗ąŠą│. 0 ąĮą░ C, č鹊 čüąŠčüč鹊čÅąĮąĖąĄ čāą┤ąĄčƹȹ░ąĮąĖčÅ ąĘą░ą║ą░ąĮčćąĖą▓ą░ąĄčéčüčÅ ą┐čĆąĖ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐ąĄčĆąĄčģąŠą┤ąĄ ą▓ 0 čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ C.

ąĀąĖčü. 5. ąÉą║čéąĖą▓ą░čåąĖčÅ Hold Condition.

ąÆąŠ ą▓čĆąĄą╝čÅ čüąŠčüč鹊čÅąĮąĖčÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ DQ1 ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą▓čŗčüąŠą║ąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ, ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ čĆąĄą░ą│ąĖčĆčāąĄčé ąĮą░ čüąĖą│ąĮą░ą╗čŗ DQ0 ąĖ C. ą×ą▒čŗčćąĮąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąŠčüčéą░ąĄčéčüčÅ ą▓čŗą▒čĆą░ąĮąĮčŗą╝ (S# = 0) ą▓ąŠ ą▓čĆąĄą╝čÅ hold condition. ąŁč鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 čüąŠčüč鹊čÅąĮąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą╗ąŠą│ąĖą║ąĖ ąŠčüčéą░ąĮąĄčéčüčÅ ąĮąĄ ąĖąĘą╝ąĄąĮąĄąĮąĮčŗą╝ ą▓ ą╝ąŠą╝ąĄąĮčé ą▓čģąŠą┤ą░ ą▓ hold condition. ąĢčüą╗ąĖ S# ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ hold condition, ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą╗ąŠą│ąĖą║ą░ čāčüčéčĆąŠą╣čüčéą▓ą░ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ. ąöą╗čÅ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ čü čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ HOLD# ą▓ ą╗ąŠą│. 1 ąĖ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ S# ą▓ ą╗ąŠą│. 0. ąŁč鹊 ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčé ąŠčé č鹊ą│ąŠ, čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ąŠą▒čĆą░čéąĮąŠ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ hold condition.

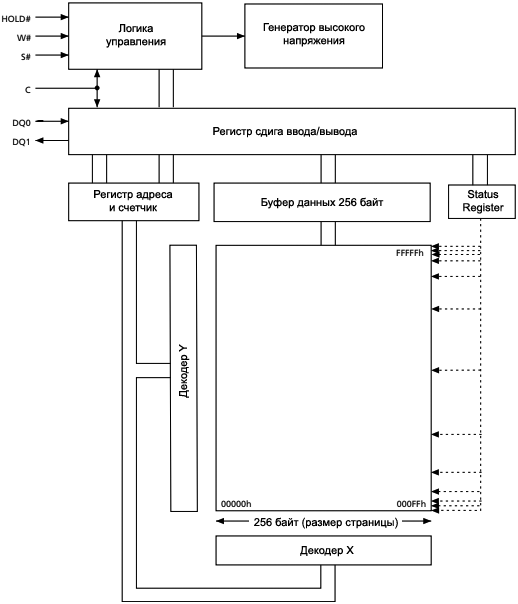

[ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ąĖ ą║ą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ]

ąÜą░ąČą┤ą░čÅ čüčéčĆą░ąĮąĖčåą░ ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ; ą▒ąĖčéčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ ąĖčģ ąĖąĘ 1 ą▓ 0. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ ą╝ąŠąČąĮąŠ čüčéąĖčĆą░čéčī ą┐ąŠ čüąĄą║č鹊čĆą░ą╝ ąĖą╗ąĖ čåąĄą╗ąĖą║ąŠą╝, ąĮąŠ ąĮąĄ čüčéčĆą░ąĮąĖčåą░ą╝ąĖ ąĖ ąĮąĄ ą▒ą░ą╣čéą░ą╝ąĖ; ą▒ąĖčéčŗ čüčéąĖčĆą░čÄčéčüčÅ, ą┐ąĄčĆąĄčģąŠą┤čÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ 1. ąÆčüčÅ ą┐ą░ą╝čÅčéčī 8 ą╝ąĄą│ą░ą▒ąĖčé čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆó 1048576 ą▒ą░ą╣čé (ą▓ ą║ą░ąČą┤ąŠą╝ ą▒ą░ą╣č鹥 8 ą▒ąĖčé)

ŌĆó 16 čüąĄą║č鹊čĆąŠą▓ (512 ą║ąĖą╗ąŠą▒ąĖčé, ąĖą╗ąĖ 65 ą║ąĖą╗ąŠą▒ą░ą╣čé ą▓ ą║ą░ąČą┤ąŠą╝ čüąĄą║č鹊čĆąĄ)

ŌĆó 4096 čüčéčĆą░ąĮąĖčå (256 ą▒ą░ą╣čé ą▓ ą║ą░ąČą┤ąŠą╣ čüčéčĆą░ąĮąĖčåąĄ)

ąĀąĖčü. 6. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą┐ą░ą╝čÅčéąĖ M25P80.

ąóą░ą▒ą╗ąĖčåą░ 4. ąĪąĄą║č鹊čĆčŗ ąŠčé 15 ą┤ąŠ 0.

| ąĪąĄą║č鹊čĆ |

ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ |

| ąØą░čćą░ą╗ąŠ |

ąÜąŠąĮąĄčå |

| 15 |

000F 0000 |

000F FFFF |

| 14 |

000E 0000 |

000E FFFF |

| 13 |

000D 0000 |

000D FFFF |

| 12 |

000C 0000 |

000C FFFF |

| 11 |

000B 0000 |

000B FFFF |

| 10 |

000A 0000 |

000A FFFF |

| 9 |

0009 0000 |

0009 FFFF |

| 8 |

0008 0000 |

0008 FFFF |

| 7 |

0007 0000 |

0007 FFFF |

| 6 |

0006 0000 |

0006 FFFF |

| 5 |

0005 0000 |

0005 FFFF |

| 4 |

0004 0000 |

0004 FFFF |

| 3 |

0003 0000 |

0003 FFFF |

| 2 |

0002 0000 |

0002 FFFF |

| 1 |

0001 0000 |

0001 FFFF |

| 0 |

0000 0000 |

0000 FFFF |

[ą×ą▒ąĘąŠčĆ čüąĖčüč鹥ą╝čŗ ą║ąŠą╝ą░ąĮą┤]

ąÆčüąĄ ą║ąŠą╝ą░ąĮą┤čŗ, ą░ą┤čĆąĄčüą░ ąĖ ą┤ą░ąĮąĮčŗąĄ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĖ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĖąĘ ąĮąĄą│ąŠ čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ (most significant bit, MSB) ą▓ą┐ąĄčĆąĄą┤.

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą▓čģąŠą┤čŗ ą┤ą░ąĮąĮčŗčģ DQ0 ąĖ DQ1 ą░ąĮą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ ą┐ąŠ ą┐ąĄčĆą▓ąŠą╝čā čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ (C) ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ (S#) ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 0. ąŚą░č鹥ą╝ 1 ą▒ą░ą╣čé ą║ąŠą┤ą░ ą║ąŠą╝ą░ąĮą┤čŗ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ą┤ą▓ąĖąĮčāčé ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ ą▓ą┐ąĄčĆąĄą┤, ąĮą░ DQ0 ąĖ DQ1, ą║ą░ąČą┤čŗą╣ ą▒ąĖčé ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čéą░ą║č鹊ą▓ C.

ąÜą░ąČą┤ą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą║ąŠą╝ą░ąĮą┤čŗ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąŠą┤ąĮąŠą▒ą░ą╣čéąĮčŗą╝ ą║ąŠą┤ąŠą╝ ą║ąŠą╝ą░ąĮą┤čŗ. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ąŠą╝ą░ąĮą┤čŗ, ąĘą░ čŹčéąĖą╝ ą║ąŠą┤ąŠą╝ ą║ąŠą╝ą░ąĮą┤čŗ ą╝ąŠąČąĄčé ąĖą┤čéąĖ ą░ą┤čĆąĄčü ąĖą╗ąĖ ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ, ąĖą╗ąĖ ą░ą┤čĆąĄčü ąĖ ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ, ąĖą╗ąĖ ąĮąĄ ą▒čāą┤čāčé ąĖą┤čéąĖ ąĮąĖ ą░ą┤čĆąĄčü, ąĮąĖ ą┤ą░ąĮąĮčŗąĄ. ąöą╗čÅ čüą╗ąĄą┤čāčÄčēąĖčģ ą║ąŠą╝ą░ąĮą┤ ąĘą░ ą▓ą▓ąŠą┤ąŠą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą║ąŠą╝ą░ąĮą┤ čüą╗ąĄą┤čāąĄčé ą▓čŗą▓ąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ. ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ S# ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 1 ą┐ąŠčüą╗ąĄ ą╗čÄą▒ąŠą│ąŠ ą▒ąĖčéą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▓čŗą▓ąŠą┤ą░.

ŌĆó READ DATA BYTES (READ, čćč鹥ąĮąĖąĄ)

ŌĆó READ DATA BYTES at HIGHER SPEED (čćč鹥ąĮąĖąĄ ąĮą░ ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ)

ŌĆó READ STATUS REGISTER (čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ)

ŌĆó READ IDENTIFICATION (čćč鹥ąĮąĖąĄ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąŠąĮąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ)

ŌĆó RELEASE from DEEP POWER-DOWN (ą▓čŗčģąŠą┤ ąĖąĘ čĆąĄąČąĖą╝ą░ ą│ą╗čāą▒ąŠą║ąŠą│ąŠ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ)

ąöą╗čÅ čüą╗ąĄą┤čāčÄčēąĖčģ ą║ąŠą╝ą░ąĮą┤ čüąĖą│ąĮą░ą╗ S# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄčé ą▓ ą╗ąŠą│. 1 čüčĆą░ąĘčā ąĮą░ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą▒ą░ą╣čéą░. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąŠčüą╗ąĄ ą┤ąĄą╗čÅčēąĄą│ąŠčüčÅ ą▒ąĄąĘ ąŠčüčéą░čéą║ą░ ąĮą░ 8 ą║ąŠą╗ąĖč湥čüčéą▓ą░ čéą░ą║č鹊ą▓, ą┐čĆąŠčłąĄą┤čłąĖčģ ą┐čĆąĖ S# ą▓ ą╗ąŠą│. 0, S# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 1. ąśąĮą░č湥 ą║ąŠą╝ą░ąĮą┤ą░ ą▒čāą┤ąĄčé ąŠčéą▒čĆąŠčłąĄąĮą░ ąĖ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮą░.

ŌĆó PAGE PROGRAM

ŌĆó SECTOR ERASE

ŌĆó BULK ERASE

ŌĆó WRITE STATUS REGISTER

ŌĆó WRITE ENABLE

ŌĆó WRITE DISABLE

ąÆčüąĄ ą┐ąŠą┐čŗčéą║ąĖ ą┤ąŠčüčéčāą┐ą░ ą║ ą╝ą░čüčüąĖą▓čā ą┐ą░ą╝čÅčéąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░ ą║ąŠą╝ą░ąĮą┤čŗ WRITE STATUS REGISTER, čåąĖą║ą╗ą░ ą║ąŠą╝ą░ąĮą┤čŗ PROGRAM, ąĖą╗ąĖ čåąĖą║ą╗ą░ ą║ąŠą╝ą░ąĮą┤čŗ ERASE. ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ čŹč鹊ą╣ ą║ąŠą╝ą░ąĮą┤čŗ ąĮąŠčĆą╝ą░ą╗čīąĮąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖčéčüčÅ ą┤ąŠ čüą▓ąŠąĄą│ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ.

ąóą░ą▒ą╗ąĖčåą░ 5. ąÜąŠą┤čŗ čüąĖčüč鹥ą╝čŗ ą║ąŠą╝ą░ąĮą┤.

| ąÜąŠą╝ą░ąĮą┤ą░ |

ąÜąŠą┤ |

ąæą░ą╣čé

|

| ąÉą┤čĆąĄčü |

Dummy |

ąöą░ąĮąĮčŗąĄ |

| WRITE ENABLE |

06h |

0 |

0 |

0 |

| WRITE DISABLE |

04h |

0 |

0 |

0 |

| READ IDENTIFICATION |

9Fh |

0 |

0 |

1 .. 20 |

| 9Eh |

| READ STATUS REGISTER |

05h |

0 |

0 |

1 .. Ōł× |

| WRITE STATUS REGISTER |

01h |

0 |

0 |

1 |

| READ DATA BYTES |

03h |

3 |

0 |

1 .. Ōł× |

| READ DATA BYTES at HIGHER SPEED |

0Bh |

3 |

1 |

1 .. Ōł× |

| PAGE PROGRAM |

02h |

3 |

0 |

1 .. 256 |

| SECTOR ERASE |

D8h |

3 |

0 |

0 |

| BULK ERASE |

C7h |

0 |

0 |

0 |

| DEEP POWER-DOWN |

B9h |

0 |

0 |

0 |

| RELEASE from DEEP POWER-DOWN |

ABh |

0 |

0 |

1 .. Ōł× |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: Dummy čŹč鹊 ą┐čāčüčéčŗąĄ ą▒ą░ą╣čéčŗ, ą║ąŠč鹊čĆčŗąĄ ąĮčāąČąĮčŗ ą┤ą╗čÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą╝ą░čłąĖąĮčŗ čüąŠčüč鹊čÅąĮąĖą╣.

ąÜąŠą╝ą░ąĮą┤ą░ WRITE ENABLE čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▒ąĖčé ąĘą░čēąĄą╗ą║ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (write enable latch, WEL). ąæąĖčé WEL ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┐ąĄčĆąĄą┤ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ą║ą░ąČą┤ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ PROGRAM, ERASE ąĖ WRITE. ąÜąŠą╝ą░ąĮą┤ą░ WRITE ENABLE ą▓ą▓ąŠą┤ąĖčéčüčÅ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą▓ąŠą┤ą░ ą▓ ą╗ąŠą│. 0 čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ S#. ą¤ąŠčüčŗą╗ą░ąĄčéčüčÅ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ, ąĖ ąĘą░č鹥ą╝ čüąĖą│ąĮą░ą╗ S# ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą▓ ą╗ąŠą│. 1.

ąĀąĖčü. 7. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ WRITE ENABLE.

ąøąĄą│ąĄąĮą┤ą░:

|

ąæąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖčÅ (DonŌĆÖt Care) |

ąÜąŠą╝ą░ąĮą┤ą░ WRITE DISABLE čüą▒čĆą░čüčŗą▓ą░ąĄčé ą▒ąĖčé ąĘą░čēąĄą╗ą║ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (write enable latch, WEL). ąÜąŠą╝ą░ąĮą┤ą░ WRITE DISABLE ą▓ą▓ąŠą┤ąĖčéčüčÅ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ S# ą▓ ą╗ąŠą│. 0, ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą┐ąŠčüčŗą╗ą░ąĄčéčüčÅ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ, ąĖ ąĘą░č鹥ą╝ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ S# ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą▓ ą╗ąŠą│. 1.

ąÜčĆąŠą╝ąĄ WRITE DISABLE, ą▒ąĖčé WEL ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ čüąĖčéčāą░čåąĖčÅčģ:

ŌĆó Power-up (ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ)

ŌĆó ąŚą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą╗čÄą▒ąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ čüčéąĖčĆą░ąĮąĖčÅ ERASE, PROGRAM ąĖ WRITE STATUS REGISTER

ąĀąĖčü. 8. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ WRITE DISABLE.

ąøąĄą│ąĄąĮą┤ą░:

|

ąæąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖčÅ (DonŌĆÖt Care) |

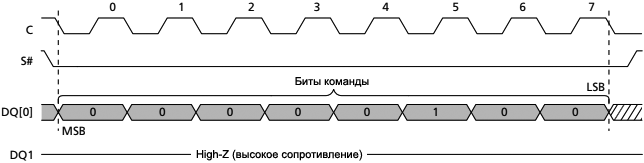

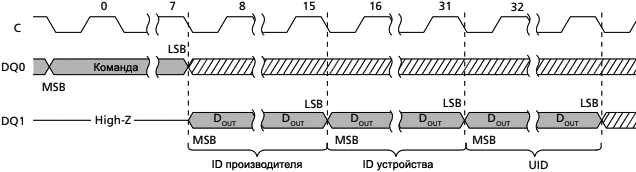

ąÜąŠą╝ą░ąĮą┤ą░ READ IDENTIFICATION čćąĖčéą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąŠąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░:

ŌĆó ąśą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅ (1 ą▒ą░ą╣čé): čŹč鹊čé ID ąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĄą╣ JEDEC.

ŌĆó ąśą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ čāčüčéčĆąŠą╣čüčéą▓ą░ (2 ą▒ą░ą╣čéą░): čŹč鹊čé ID ąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╝ čāčüčéčĆąŠą╣čüčéą▓ą░; ą┐ąĄčĆą▓čŗą╣ ą▒ą░ą╣čé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čéąĖą┐ ą┐ą░ą╝čÅčéąĖ, ąĖ ą▓č鹊čĆąŠą╣ ąĄą╝ą║ąŠčüčéčī ą┐ą░ą╝čÅčéąĖ čāčüčéčĆąŠą╣čüčéą▓ą░.

ŌĆó ąŻąĮąĖą║ą░ą╗čīąĮčŗą╣ ą║ąŠą┤ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ (Unique ID, UID), 17 ą▒ą░ą╣čé, 16 ąĖąĘ ą║ąŠč鹊čĆčŗčģ ą┤ąŠčüčéčāą┐ąĮąŠ ą┐ąŠ ąĘą░ą┐čĆąŠčüčā ą┐ąŠą║čāą┐ą░č鹥ą╗čÅ: ą┐ąĄčĆą▓čŗą╣ ą▒ą░ą╣čé čüąŠą┤ąĄčƹȹĖčé ą┤ą╗ąĖąĮčā ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ ą┤ą░ąĮąĮčŗčģ, ąŠčüčéą░ą╗čīąĮčŗąĄ 16 ą▒ą░ą╣čé čüąŠą┤ąĄčƹȹ░čé ąĮą░čüčéčĆą░ąĖą▓ą░ąĄą╝čŗąĄ ąĘą░ą▓ąŠą┤čüą║ąĖąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (Customized Factory Data, CFD).

ąóą░ą▒ą╗ąĖčåą░ 6. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą▓ąŠą┤ąĖą╝čŗčģ ą┤ą░ąĮąĮčŗčģ ą║ąŠą╝ą░ąĮą┤čŗ READ IDENTIFICATION.

| ąśą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅ |

ąśą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ čāčüčéčĆąŠą╣čüčéą▓ą░

|

UID |

| ąóąĖą┐ ą┐ą░ą╝čÅčéąĖ |

ąĢą╝ą║ąŠčüčéčī ą┐ą░ą╝čÅčéąĖ |

ąöą╗ąĖąĮą░ CFD |

ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ CFD |

| 20h |

20h |

14h |

10h |

16 ą▒ą░ą╣čé |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ą░ą╣čéčŗ CFD ą┤ąŠčüčéčāą┐ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ą┐ąŠ ąĘą░ą┐čĆąŠčüčā ą┤ą░ąĮąĮčŗą╝ąĖ ą┐ąŠą║čāą┐ą░č鹥ą╗čÅ. ąĢčüą╗ąĖ ą┐ąŠą║čāą┐ą░č鹥ą╗čī ąĮąĄ čüą┤ąĄą╗ą░ą╗ ą┤ą╗čÅ čŹč鹊ą│ąŠ ąĘą░ą┐čĆąŠčü, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ čüąŠ ą▓čüąĄą╝ąĖ CFD-ą▒ą░ą╣čéą░ą╝ąĖ, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ąĮčāą╗čÅą╝ąĖ. ąŻčüčéčĆąŠą╣čüčéą▓ą░ čü ą╝ą░čĆą║ąĖčĆąŠą▓ą║ąŠą╣ ą▓ąĄčĆčģąĮąĄą╣ čćą░čüčéąĖ ą║ąŠčĆą┐čāčüą░ ą│ąŠą┤ą░ ąĖ ąĮąĄą┤ąĄą╗ąĖ ą▒ąŠą╗čīčłąĄ č湥ą╝ "06/2015", ąĖ čüąŠą▒čĆą░ąĮąĮčŗąĄ ą▓ ą║ąŠčĆą┐čāčüąĄ UFDFPN8 4 x 3 ą╝ą╝, ąĖą╝ąĄčÄčé ąŠą▒ą╗ą░čüčéčī CFD ą║ąŠčĆą┐čāčüą░, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčāčÄ čü UID. ąöą╗čÅ ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ąĄčĆčģąĮąĄą╣ ą╝ą░čĆą║ąĖčĆąŠą▓ą║ąĖ ą║ąŠą┤ąŠą▓ ą│ąŠą┤ą░ ąĖ ąĮąĄą┤ąĄą╗ąĖ (ąĮąĄą┤ąĄą╗čÅ čüą▒ąŠčĆą║ąĖ), čüą╝. TN-12-24 "Serial Flash Memory Device Marking for the M25P/PE/PX, M45PE, and N25Q Product Families" ąĮą░ čüą░ą╣č鹥 micron.com.

ąĀąĖčü. 9. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ READ IDENTIFICATION.

ąøąĄą│ąĄąĮą┤ą░:

|

ąæąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖčÅ (DonŌĆÖt Care) |

ąÜąŠą╝ą░ąĮą┤ą░ READ IDENTIFICATION ąĮąĄ ą┤ąĄą║ąŠą┤ąĖčĆčāąĄčéčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░ ERASE ąĖą╗ąĖ PROGRAM, ąĖ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ čŹč鹊ą│ąŠ čåąĖą║ą╗ą░. ąÜąŠą╝ą░ąĮą┤ą░ READ IDENTIFICATION ąĮąĄ ą┤ąŠą╗ąČąĮą░ ą▓čŗą┤ą░ą▓ą░čéčīčüčÅ, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą│ą╗čāą▒ąŠą║ąŠą│ąŠ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ (DEEP POWER-DOWN).

ąĪąĮą░čćą░ą╗ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ S# ą▓ ą╗ąŠą│. 0. ąŚą░č鹥ą╝ 8-ą▒ąĖčéąĮčŗą╣ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤ ą▓ą┤ą▓ąĖą│ą░ąĄčéčüčÅ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą┤ą░ąĮąĮčŗąĄ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ č湥čĆąĄąĘ DQ1 čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝: 24-ą▒ąĖčéąĮčŗą╣ ą║ąŠą┤ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ čāčüčéčĆąŠą╣čüčéą▓ą░, 8-ą▒ąĖčéąĮą░čÅ ą┤ą╗ąĖąĮą░ CFD, 16 ą▒ą░ą╣čé čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ CFD. ąÜą░ąČą┤čŗą╣ ą▒ąĖčé ą▓čŗą┤ą▓ąĖą│ą░ąĄčéčüčÅ ąĮą░čĆčāąČčā ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ C.

ąÜąŠą╝ą░ąĮą┤ą░ READ IDENTIFICATION ą┐čĆąĄčĆčŗą▓ą░ąĄčéčüčÅ ą┐čāč鹥ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ą░ ą▓čŗą▒ąŠčĆą║ąĖ S# ą▓ ą╗ąŠą│. 1 ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ S# ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 1, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ (STANDBY POWER mode), ąĖ ąČą┤ąĄčé ą┐ąŠą┤ą░čćąĖ ą▓čŗą▒ąŠčĆą║ąĖ, čćč鹊ą▒čŗ ą┐čĆąĖąĮčÅčéčī, ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░čéčī ąĖ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┤čĆčāą│ąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ.

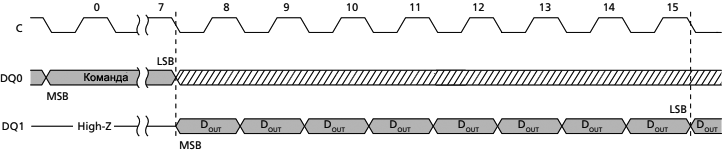

ąÜąŠą╝ą░ąĮą┤ą░ READ STATUS REGISTER ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąŠčćąĖčéą░čéčī čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ. ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé, ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ PROGRAM, ERASE ąĖą╗ąĖ WRITE STATUS REGISTER. ąÜąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ čŹčéąĖ čåąĖą║ą╗čŗ, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐čĆąŠą▓ąĄčĆąĖčéčī ą▒ąĖčé write in progress (WIP) ą┐ąĄčĆąĄą┤ ąŠčéą┐čĆą░ą▓ą║ąŠą╣ ąĮąŠą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ. ąŁč鹊 čéą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ą┤ąĄą╗ą░čéčī ą┐čāč鹥ą╝ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ.

ąĀąĖčü. 10. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ READ STATUS REGISTER.

ąøąĄą│ąĄąĮą┤ą░:

|

ąæąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖčÅ (DonŌĆÖt Care) |

ąĀąĖčü. 11. ążąŠčĆą╝ą░čé Status Register.

WIP. ąæąĖčé ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ (write in progress, WIP) ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ąĘą░ąĮčÅčéą░ ą╗ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą┐ą░ą╝čÅčéąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čåąĖą║ą╗ąŠą╝ WRITE STATUS REGISTER, PROGRAM ąĖą╗ąĖ ERASE. ąÜąŠą│ą┤ą░ ą▒ąĖčé WIP čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗; ą║ąŠą│ą┤ą░ WIP čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0, ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ (ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą│ąŠč鹊ą▓ą░ ą║ ą┐čĆąĖąĄą╝čā, ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÄ ąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÄ ą╗čÄą▒ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ).

WEL. ąæąĖčé ąĘą░čēąĄą╗ą║ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (write enable latch, WEL) ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ąĘą░čēąĄą╗ą║ąĖ, čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ ąĘą░ą┐ąĖčüčī. ąÜąŠą│ą┤ą░ ą▒ąĖčé WEL čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ąĘą░čēąĄą╗ą║ą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ; ą║ąŠą│ą┤ą░ ą▒ąĖčé WEL čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0, ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ąĘą░čēąĄą╗ą║ą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ čüą▒čĆąŠčłąĄąĮą░, ąĖ ąĮąĄ ą▒čāą┤čāčé ą┐čĆąĖąĮąĖą╝ą░čéčīčüčÅ ą║ąŠą╝ą░ąĮą┤čŗ WRITE STATUS REGISTER, PROGRAM ąĖą╗ąĖ ERASE.

ąæąĖčéčŗ ąĘą░čēąĖčéčŗ ą▒ą╗ąŠą║ąŠą▓. ąŁčéąĖ ą▒ąĖčéčŗ 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗ. ą×ąĮąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé čĆą░ąĘą╝ąĄčĆ ąĘą░čēąĖčēąĄąĮąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ, ą║ąŠč鹊čĆčāčÄ ąĮąĄą╗čīąĘčÅ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░čéčī ąĖ čüč鹥čĆąĄčéčī ą║ąŠą╝ą░ąĮą┤ą░ą╝ąĖ PROGRAM ąĖ ERASE. ąæąĖčéčŗ ąĘą░čēąĖčéčŗ ą▒ą╗ąŠą║ąŠą▓ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ąŠą╣ WRITE STATUS REGISTER.

ąÜąŠą│ą┤ą░ ąŠą┤ąĖąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄ ą▒ąĖčé ąĘą░čēąĖčéčŗ ą▒ą╗ąŠą║ąŠą▓ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ, ą║ą░ą║ čŹč鹊 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 3 "ąĀą░ąĘą╝ąĄčĆčŗ ąĘą░čēąĖčēąĄąĮąĮčŗčģ ąŠčé ąĘą░ą┐ąĖčüąĖ ąŠą▒ą╗ą░čüč鹥ą╣ ą┤ą░ąĮąĮčŗčģ", čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĘą░čēąĖčēąĄąĮąĮąŠą╣ ąŠčé ą┤ąĄą╣čüčéą▓ąĖčÅ ą║ąŠą╝ą░ąĮą┤ PAGE PROGRAM ąĖ SECTOR ERASE. ąæąĖčéčŗ ąĘą░čēąĖčéčŗ ą▒ą╗ąŠą║ąŠą▓ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ, čćč鹊ą▒čŗ ą┐čĆąĖą╝ąĄąĮąĖčéčī ą░ą┐ą┐ą░čĆą░čéąĮčāčÄ ąĘą░čēąĖčéčā ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ąŠą▒ą╗ą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ. ąÜąŠą╝ą░ąĮą┤ą░ BULK ERASE ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▓čüąĄ ą▒ąĖčéčŗ ąĘą░čēąĖčéčŗ ą▒ą╗ąŠą║ąŠą▓ ąŠą▒ąĮčāą╗ąĄąĮčŗ.

SRWD. ąŁąĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ ą▒ąĖčé status register write disable (SRWD) čĆą░ą▒ąŠčéą░ąĄčé ą▓ą╝ąĄčüč鹥 čü čüąĖą│ąĮą░ą╗ąŠą╝ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ (W#/VPP). ąÜąŠą│ą┤ą░ ą▒ąĖčé SRWD čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, ąĖ ą▓čŗą▓ąŠą┤ W#/VPP ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 0, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ (hardware protected mode). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗąĄ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ (SRWD ąĖ ą▒ąĖčéčŗ ąĘą░čēąĖčéčŗ ą▒ą╗ąŠą║ąŠą▓) čüčéą░ąĮąŠą▓čÅčéčüčÅ ą┤ąŠčüčéčāą┐ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, ąĖ ą║ąŠą╝ą░ąĮą┤ą░ WRITE STATUS REGISTER ą▒ąŠą╗čīčłąĄ ąĮąĄ čüą╝ąŠąČąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ.

ąÜąŠą╝ą░ąĮą┤ą░ WRITE STATUS REGISTER ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┐ąĖčüą░čéčī ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ. ą¤ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĖąĮčÅčéą░ ą║ąŠą╝ą░ąĮą┤ą░ WRITE STATUS REGISTER, ąĮčāąČąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą║ąŠą╝ą░ąĮą┤čā WRITE ENABLE. ą¤ąŠčüą╗ąĄ ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤čŗ WRITE ENABLE čāčüčéčĆąŠą╣čüčéą▓ąŠ čāčüčéą░ąĮąŠą▓ąĖčé ą▒ąĖčé ąĘą░čēąĄą╗ą║ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (WEL) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ.

ąÜąŠą╝ą░ąĮą┤ą░ WRITE STATUS REGISTER ą▓ą▓ąŠą┤ąĖčéčüčÅ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮčŗą╝ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ ą▓čŗą▒ąŠčĆą║ąĖ S# ą▓ ą╗ąŠą│. 0, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĮą░ ą▓čģąŠą┤ DQ0 ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ ąĖ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ. ąÜąŠą╝ą░ąĮą┤ą░ WRITE STATUS REGISTER ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą▒ąĖčéčŗ b6, b5, b4, b1 ąĖ b0 čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ. ąæąĖčéčŗ b6, b5 ąĖ b4 ą▓čüąĄą│ą┤ą░ čćąĖčéą░čÄčéčüčÅ ą║ą░ą║ "0". ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ S# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 1 ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅčé ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ čŹč鹊 čāčüą╗ąŠą▓ąĖąĄ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ, ą║ąŠą╝ą░ąĮą┤ą░ WRITE STATUS REGISTER ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ.

ąĀąĖčü. 12. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ WRITE STATUS REGISTER.

ąÜąŠą│ą┤ą░ S# ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1, ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ WRITE STATUS REGISTER, ąĄą│ąŠ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čüąŠčüčéą░ą▓ą╗čÅąĄčé tW. ąÜąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ WRITE STATUS REGISTER, čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą▓čüąĄ ąĄčēąĄ ą┤ąŠčüčéčāą┐ąĄąĮ ąĮą░ čćč鹥ąĮąĖąĄ, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą┐čĆąŠą▓ąĄčĆąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░ write in progress (WIP). ąæąĖčé WIP čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ 1 ą▓ąŠ ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░ WRITE STATUS REGISTER, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ 0, ą║ąŠą│ą┤ą░ čŹč鹊čé čåąĖą║ą╗ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ. ąóą░ą║ąČąĄ ą║ąŠą│ą┤ą░ čŹč鹊čé čåąĖą║ą╗ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ, čüą▒čĆąŠčüąĖčéčüčÅ ą▒ąĖčé WEL.

ąÜąŠą╝ą░ąĮą┤ą░ WRITE STATUS REGISTER ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ą┐ąŠą╝ąĄąĮčÅčéčī ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčé ąĘą░čēąĖčéčŗ ą▒ą╗ąŠą║ąŠą▓ (BP2, BP1, BP0). ąŻčüčéą░ąĮąŠą▓ą║ą░ čŹčéąĖčģ ą▒ąĖčé ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čĆą░ąĘą╝ąĄčĆ ąŠą▒ą╗ą░čüčéąĖ, ą║ąŠč鹊čĆą░čÅ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ ą║ą░ą║ ąŠą▒ą╗ą░čüčéčī č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ (čüą╝. čéą░ą▒ą╗ąĖčåčā 3 ą▓čŗčłąĄ).

ąÜąŠą╝ą░ąĮą┤ą░ WRITE STATUS REGISTER čéą░ą║ąČąĄ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāčüčéą░ąĮąŠą▓ąĖčéčī ąĖ čüą▒čĆąŠčüąĖčéčī ą▒ąĖčé status register write disable (SRWD) ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗ąŠą╝ write protect (W#/VPP). ąæąĖčé SRWD ąĖ čüąĖą│ąĮą░ą╗ W#/VPP ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą┐ąŠą╝ąĄčüčéąĖčéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ąĘą░čēąĖčēąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ (hardware protected mode, HPM). ąÜąŠą╝ą░ąĮą┤ą░ WRITE STATUS REGISTER ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ HPM. ą×ą┐čåąĖąĖ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čĆąĄąČąĖą╝ąŠą▓ ąĘą░čēąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ 7.

ąóą░ą▒ą╗ąĖčåą░ 7. ąĀąĄąČąĖą╝čŗ Status Register Protection.

W#/VPP

|

SRWD |

Protection Mode (PM) |

ąŚą░čēąĖčéą░ Status Register |

ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą┐ą░ą╝čÅčéąĖ |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ |

| ąŚą░čēąĖčēąĄąĮąĮą░čÅ ąŠą▒ą╗ą░čüčéčī |

ąØąĄ ąĘą░čēąĖčēąĄąĮąĮą░čÅ ąŠą▒ą╗ą░čüčéčī |

| 1 |

0 |

Software protected mode (SPM) |

ą¤čĆąŠą│čĆą░ą╝ą╝ąĮą░čÅ |

ąÜąŠą╝ą░ąĮą┤čŗ ąĮąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ |

ąÜąŠą╝ą░ąĮą┤čŗ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ |

1, 2, 3 |

| 0 |

0 |

| 1 |

1 |

| 0 |

1 |

Hardware protected mode (SPM) |

ąÉą┐ą┐ą░čĆą░čéąĮą░čÅ |

3, 4, 5 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮą░čÅ ąĘą░čēąĖčéą░: čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ (čé. ąĄ. ą╝ąŠąČąĮąŠ ąĖąĘą╝ąĄąĮąĖčéčī ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčé SRWD, BP2, BP1 ąĖ BP0), ąĄčüą╗ąĖ ą║ąŠą╝ą░ąĮą┤ą░ WRITE ENABLE čāčüčéą░ąĮąŠą▓ąĖą╗ą░ ą▒ąĖčé WEL.

2. ąÜąŠą╝ą░ąĮą┤čŗ PAGE PROGRAM, SECTOR ERASE ąĖ BULK ERASE ąĮąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ.

3. ąÜąŠą╝ą░ąĮą┤čŗ PAGE PROGRAM ąĖ SECTOR ERASE ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąĖąĮčÅčéčŗ.

4. ąÉą┐ą┐ą░čĆą░čéąĮą░čÅ ąĘą░čēąĖčéą░: ą▓ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ąĮąĄą╗čīąĘčÅ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī (ą▒ąĖčéčŗ SRWD, BP2, BP1 ąĖ BP0 ąĖąĘą╝ąĄąĮąĖčéčī ąĮąĄą╗čīąĘčÅ).

5. ąÜąŠą╝ą░ąĮą┤čŗ PAGE PROGRAM, SECTOR ERASE ąĖ BULK ERASE ąĮąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ.

ąÜąŠą│ą┤ą░ ą▒ąĖčé SRWD čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ čĆą░ą▓ąĄąĮ 0 (ąĄą│ąŠ ąĮą░čćą░ą╗čīąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ čü ąĘą░ą▓ąŠą┤ą░), ą╝ąŠąČąĮąŠ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą▓ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą▒ąĖčé WEL ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čĆą░ąĮąĄąĄ ą▓čŗą┤ą░ąĮąĮąŠą╣ ą║ąŠą╝ą░ąĮą┤ąŠą╣ WRITE ENABLE, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą▓ ą║ą░ą║ąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ąĮą░čģąŠą┤ąĖčéčüčÅ čüąĖą│ąĮą░ą╗ W#/VPP, ą▓ ą╗ąŠą│. 1 ąĖą╗ąĖ ą▓ ą╗ąŠą│. 0. ąÜąŠą│ą┤ą░ ą▒ąĖčé SRWD čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, ąĮčāąČąĮąŠ čĆą░čüčüą╝ąŠčéčĆąĄčéčī ą┤ą▓ą░ čüą╗čāčćą░čÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ W#/VPP:

ŌĆó ąĢčüą╗ąĖ ąĮą░ W#/VPP ą╗ąŠą│. 1, č鹊 ą╝ąŠąČąĮąŠ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą▓ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ, ą║ąŠą│ą┤ą░ čĆą░ąĮąĄąĄ ą▒ąĖčé WEL ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą║ąŠą╝ą░ąĮą┤ąŠą╣ WRITE ENABLE.

ŌĆó ąĢčüą╗ąĖ ąĮą░ W#/VPP ą╗ąŠą│. 0, č鹊 ąĮąĄą╗čīąĘčÅ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą▓ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą▒ąĖčé WEL ą▒čŗą╗ čĆą░ąĮąĄąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą║ąŠą╝ą░ąĮą┤ąŠą╣ WRITE ENABLE. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąŠą┐čŗčéą║ąĖ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą▒čāą┤čāčé ąŠčéą║ą╗ąŠąĮčÅčéčīčüčÅ. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ąĘą░čēąĖčēąĄąĮčŗ ąŠčé ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ ą▓čüąĄ ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ąĘą░čēąĖčēąĄąĮąĮčŗčģ ąŠą▒ą╗ą░čüčéčÅčģ (ąĮą░čģąŠą┤čÅčéčüčÅ ą┐ąŠą┤ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ ąĘą░čēąĖč鹊ą╣ SPM). ąŚą░čēąĖčēąĄąĮąĮą░čÅ ąŠą▒ą╗ą░čüčéčī SPM ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čüąŠčüč鹊čÅąĮąĖąĄą╝ ą▒ąĖčé ąĘą░čēąĖčéčŗ ą▒ą╗ąŠą║ąŠą▓ (BP2, BP1, BP0), ą║ąŠč鹊čĆčŗąĄ čéą░ą║ąČąĄ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ąĘą░čēąĖčēąĄąĮčŗ ąŠčé ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ.

ąØąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čŹčéąĖčģ ą┤ą▓čāčģ čüąŠą▒čŗčéąĖą╣, ą╝ąŠąČąĮąŠ ą▓ąŠą╣čéąĖ ą▓ ąĘą░čēąĖčéčā HPM ąŠą┤ąĮąĖą╝ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ čüą┐ąŠčüąŠą▒ąŠą▓:

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ SRWD čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą▓ąŠą┤ą░ čüąĖą│ąĮą░ą╗ą░ W#/VPP ą▓ ą╗ąŠą│. 0.

ŌĆó ą¤ąĄčĆąĄą▓ąŠą┤ čüąĖą│ąĮą░ą╗ą░ W#/VPP ą▓ ą╗ąŠą│. 0 ą┐ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ SRWD čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ.

ąĢą┤ąĖąĮčüčéą▓ąĄąĮąĮčŗą╣ čüą┐ąŠčüąŠą▒ ą▓čŗčģąŠą┤ą░ ąĖąĘ HPM - ą┐ąŠą┤čéčÅąĮčāčéčī čüąĖą│ąĮą░ą╗ W#/VPP ą║ ą╗ąŠą│. 1. ąĢčüą╗ąĖ W#/VPP ą┐ąŠčüč鹊čÅąĮąĮąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1, č鹊 ąĘą░čēąĖčéą░ HPM ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮą░. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┤ąŠčüčéčāą┐ąĮą░ č鹊ą╗čīą║ąŠ ąĘą░čēąĖčéą░ SPM, ąĖčüą┐ąŠą╗čīąĘčāčÄčēą░čÅ ą▒ąĖčéčŗ ąĘą░čēąĖčéčŗ ą▒ą╗ąŠą║ąŠą▓ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ (BP2, BP1, BP0).

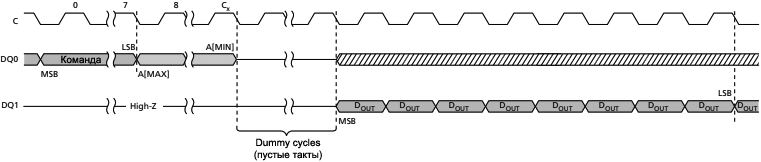

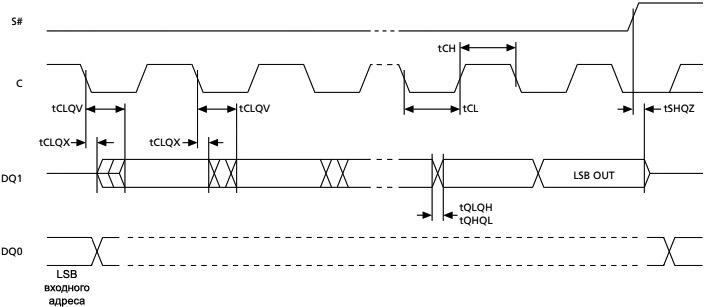

ąöą╗čÅ čćč鹥ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüąĮą░čćą░ą╗ą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ S# ą▓ ą╗ąŠą│. 0. ą¤ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ READ DATA BYTES, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé 3-ą▒ą░ą╣čéąĮčŗą╣ ą░ą┤čĆąĄčü (A23-A0), ą║ą░ąČą┤čŗą╣ ą▒ąĖčé ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ ąĮą░ ą▓čģąŠą┤ąĄ DQ0 ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ C. ąŚą░č鹥ą╝ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą┐ąŠ ąĘą░ą┤ą░ąĮąĮąŠą╝čā ą░ą┤čĆąĄčüčā ą▓čŗą▓ąŠą┤ąĖčéčüčÅ č湥čĆąĄąĘ ą▓čŗčģąŠą┤ DQ1, ą║ą░ąČą┤čŗą╣ ą▒ąĖčé ą▓čŗą┤ą▓ąĖą│ą░ąĄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā čéą░ą║č鹊ą▓ C ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊č鹥 fR.

ą¤ąĄčĆą▓čŗą╣ ą▒ą░ą╣čé ą╝ąŠąČąĄčé ą▒čŗčéčī ą░ą┤čĆąĄčüąŠą▓ą░ąĮ ą▓ ą╗čÄą▒ąŠą╣ čÅč湥ą╣ą║ąĄ. ąÉą┤čĆąĄčü ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ ą┐čĆąĖ ą║ą░ąČą┤ąŠą╝ ą▓čŗą┤ą▓ąĖąĮčāč鹊ą╝ ą▒ą░ą╣č鹥. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą║ąŠą╝ą░ąĮą┤ąŠą╣ READ DATA BYTES ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮą░ ą▓čüčÅ ą┐ą░ą╝čÅčéčī. ąÜąŠą│ą┤ą░ ą▒čŗą╗ ą┤ąŠčüčéąĖą│ąĮčāčé čüą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ ą░ą┤čĆąĄčü, ą░ą┤čĆąĄčü ą▓ąŠąĘą▓čĆą░čéąĖčéčüčÅ ą║ 000000h, ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čćč鹥ąĮąĖčÅ ą╝ąŠąČąĄčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčīčüčÅ ą▒ąĄčüą║ąŠąĮąĄčćąĮąŠ.

ąÜąŠą╝ą░ąĮą┤ą░ READ DATA BYTES ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ ą▓čŗą▒ąŠčĆą║ąĖ S# ą▓ ą╗ąŠą│. 1. ąĪąĖą│ąĮą░ą╗ S# ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 1 ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ. ąøčÄą▒ą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ READ DATA BYTES, ą▓čŗą┤ą░ąĮąĮą░čÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░ ERASE, PROGRAM ąĖą╗ąĖ WRITE, ą▒čāą┤ąĄčé ąŠčéą▒čĆąŠčłąĄąĮą░ ą▒ąĄąĘ ą║ą░ą║ąŠą│ąŠ-ą╗ąĖą▒ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čåąĖą║ą╗ ą║ąŠą╝ą░ąĮą┤čŗ ąĘą░ą┐ąĖčüąĖ/čüčéąĖčĆą░ąĮąĖčÅ.

ąĀąĖčü. 13. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ READ DATA BYTES.

ąøąĄą│ąĄąĮą┤ą░:

|

ąæąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖčÅ (DonŌĆÖt Care) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: Cx = 7 + (A[MAX] + 1).

ąŻčüčéčĆąŠą╣čüčéą▓ąŠ čüąĮą░čćą░ą╗ą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ S# ą▓ ą╗ąŠą│. 0. ąŚą░č鹥ą╝ č湥čĆąĄąĘ ą▓čģąŠą┤ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ DQ0 ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ READ DATA BYTES at HIGHER SPEED, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé 3-ą▒ą░ą╣čéąĮčŗą╣ ą░ą┤čĆąĄčü (A23 .. A0) ąĖ ą┐čāčüč鹊ą╣ (dummy) ą▒ą░ą╣čé. ąÜą░ąČą┤čŗą╣ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ą▒ąĖčé ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ čéą░ą║č鹊ą▓ C. ąŚą░č鹥ą╝ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą┐ą░ą╝čÅčéąĖ ą┐ąŠ ąĘą░ą┤ą░ąĮąĮąŠą╝čā ą░ą┤čĆąĄčüčā ą▓čŗą┤ą▓ąĖą│ą░ąĄčéčüčÅ č湥čĆąĄąĘ ą▓čŗčģąŠą┤ DQ1 čü ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊č鹊ą╣ fC, ą▓ąŠ ą▓čĆąĄą╝čÅ čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ C.

ą¤ąĄčĆą▓čŗą╣ ą▒ą░ą╣čé ą╝ąŠąČąĄčé ą▒čŗčéčī ą░ą┤čĆąĄčüąŠą▓ą░ąĮ ą▓ ą╗čÄą▒ąŠą╣ čÅč湥ą╣ą║ąĄ. ąÉą┤čĆąĄčü ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ ą┐čĆąĖ ą║ą░ąČą┤ąŠą╝ ą▓čŗą┤ą▓ąĖąĮčāč鹊ą╝ ą▒ą░ą╣č鹥. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą║ąŠą╝ą░ąĮą┤ąŠą╣ READ DATA BYTES at HIGHER SPEED ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮą░ ą▓čüčÅ ą┐ą░ą╝čÅčéčī. ąÜąŠą│ą┤ą░ ą▒čŗą╗ ą┤ąŠčüčéąĖą│ąĮčāčé čüą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ ą░ą┤čĆąĄčü, ą░ą┤čĆąĄčü ą▓ąŠąĘą▓čĆą░čéąĖčéčüčÅ ą║ 000000h, ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čćč鹥ąĮąĖčÅ ą╝ąŠąČąĄčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčīčüčÅ ą▒ąĄčüą║ąŠąĮąĄčćąĮąŠ.

ąÜąŠą╝ą░ąĮą┤ą░ READ DATA BYTES at HIGHER SPEED ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ ą▓čŗą▒ąŠčĆą║ąĖ S# ą▓ ą╗ąŠą│. 1. ąĪąĖą│ąĮą░ą╗ S# ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 1 ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ. ąøčÄą▒ą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ READ DATA BYTES at HIGHER SPEED, ą▓čŗą┤ą░ąĮąĮą░čÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░ ERASE, PROGRAM ąĖą╗ąĖ WRITE, ą▒čāą┤ąĄčé ąŠčéą▒čĆąŠčłąĄąĮą░ ą▒ąĄąĘ ą║ą░ą║ąŠą│ąŠ-ą╗ąĖą▒ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čåąĖą║ą╗ ą║ąŠą╝ą░ąĮą┤čŗ ąĘą░ą┐ąĖčüąĖ/čüčéąĖčĆą░ąĮąĖčÅ.

ąĀąĖčü. 14. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ READ DATA BYTES at HIGHER SPEED.

ąøąĄą│ąĄąĮą┤ą░:

|

ąæąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖčÅ (DonŌĆÖt Care) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: Cx = 7 + (A[MAX] + 1).

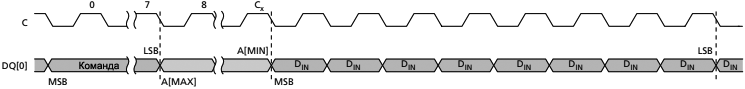

ąÜąŠą╝ą░ąĮą┤ą░ PAGE PROGRAM ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą▒ą░ą╣čéčŗ ą▓ ą┐ą░ą╝čÅčéąĖ, čćč鹊 ąŠąĘąĮą░čćą░ąĄčé ą┐ąĄčĆąĄą▓ąŠą┤ ą▒ąĖč鹊ą▓ ąĖąĘ 1 ą▓ 0. ą¤ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĖąĮčÅčéą░ ą║ąŠą╝ą░ąĮą┤ą░ PAGE PROGRAM, ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ WRITE ENABLE. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ą░ ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ WRITE ENABLE, čāčüčéčĆąŠą╣čüčéą▓ąŠ čāčüčéą░ąĮąŠą▓ąĖčé ą▒ąĖčé ąĘą░čēąĄą╗ą║ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (WEL) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ.

ąÜąŠą╝ą░ąĮą┤ą░ PAGE PROGRAM ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ S# ą▓ ą╗ąŠą│. 0, ąĘą░č鹥ą╝ č湥čĆąĄąĘ ą▓čģąŠą┤ DG0 ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤čāčé čéčĆąĖ ą▒ą░ą╣čéą░ ą░ą┤čĆąĄčüą░, ąĖ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ.

ąĢčüą╗ąĖ ąĮąĄ ą▓čüąĄ čüą░ą╝čŗąĄ ą╝ą╗ą░ą┤čłąĖąĄ ą▒ąĖčéčŗ ą░ą┤čĆąĄčüą░ (A7-A0) čĆą░ą▓ąĮčŗ ąĮčāą╗čÄ, č鹊 ą▓čüąĄ ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ą▒čāą┤čāčé ą╗ąĄąČą░čéčī ąĘą░ ą┐čĆąĄą┤ąĄą╗ą░ą╝ąĖ č鹥ą║čāčēąĄą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ čüčéčĆą░ąĮąĖčåčŗ, ą┐ąĄčĆąĄčüą║ąŠčćą░čé ąĮą░ ąĮą░čćą░ą╗ąŠ č鹊ą╣ ąČąĄ čüčéčĆą░ąĮąĖčåčŗ, čé. ąĄ. ą║ąŠą│ą┤ą░ ą▓čüąĄ ą╝ą╗ą░ą┤čłąĖąĄ ą▒ąĖčéčŗ ą░ą┤čĆąĄčüą░ (A7-A0) čüčéą░ąĮčāčé ąĮčāą╗čÅą╝ąĖ. ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ S# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ ą╗ąŠą│. 0 ą▓ č鹥č湥ąĮąĖąĄ ą▓čüąĄą╣ čŹč鹊ą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąĢčüą╗ąĖ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą▒ąŠą╗čīčłąĄ 256 ą▒ą░ą╣čé, č鹊 čĆą░ąĮąĄąĄ ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗąĄ ą▒ą░ą╣čéčŗ ą▒čāą┤čāčé ąŠčéą▒čĆąŠčłąĄąĮčŗ, ą│ą░čĆą░ąĮčéąĖčĆčāčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ 256 ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĮą░ čéčā ąČąĄ čüčéčĆą░ąĮąĖčåčā. ąĢčüą╗ąĖ ąČąĄ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą╝ąĄąĮčīčłąĄ 256 ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, č鹊 ąŠąĮąĖ ą▒čāą┤čāčé ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ąĮą░čćąĖąĮą░čÅ čü čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░, ąŠčüčéą░ą╗čīąĮčŗąĄ ą▒ą░ą╣čéčŗ ąĮą░ č鹊ą╣ ąČąĄ čüčéčĆą░ąĮąĖčåąĄ ąŠčüčéą░ąĮčāčéčüčÅ ą▒ąĄąĘ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ.

ąöą╗čÅ ąŠą┐čéąĖą╝ąĖąĘą░čåąĖąĖ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ąŠą╝ą░ąĮą┤čā PAGE PROGRAM ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čüąĄčģ čüąŠčüąĄą┤ąĮąĖčģ ą▒ą░ą╣čé čüčéčĆą░ąĮąĖčåčŗ ą▓ ąŠą┤ąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▓ą╝ąĄčüč鹊 č鹊ą│ąŠ, čćč鹊ą▒čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąŠą┤ąĮčā ąĖ čéčā ąČąĄ čüčéčĆą░ąĮąĖčåčā ą┐ąŠ ą║čāčüą║ą░ą╝, ąĖčüą┐ąŠą╗čīąĘčāčÅ ą┤ą╗čÅ ąĮąĄčæ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüč鹥ą╣ ą║ąŠą╝ą░ąĮą┤čŗ PAGE PROGRAM, ą▓ ą║ą░ąČą┤ąŠą╣ ąĖąĘ ą║ąŠč鹊čĆčŗčģ čüąŠą┤ąĄčƹȹĖčéčüčÅ č鹊ą╗čīą║ąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ą░ą╣čé.

ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ S# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 1 ą┐ąŠčüą╗ąĄ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čéą░ą║č鹊ą▓, ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗čÅčēąĄą│ąŠčüčÅ ąĮą░ 8, ąĖąĮą░č湥 ą║ąŠą╝ą░ąĮą┤ą░ PAGE PROGRAM ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░.

ąÜą░ą║ č鹊ą╗čīą║ąŠ S# ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ą╗ąŠą│. 1, ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ PAGE PROGRAM ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ tPP. ąÆąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čåąĖą║ą╗ą░ PAGE PROGRAM čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ, čćč鹊ą▒čŗ ą┐čĆąŠą▓ąĄčĆąĖčéčī ą▒ąĖčé write in progress (WIP). ąæąĖčé WIP ą▓ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ, ąĖ ą▓ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ čåąĖą║ą╗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłąĖą╗čüčÅ. ą¦ąĄčĆąĄąĘ ąĮąĄą║ąŠč鹊čĆąŠąĄ ąĮąĄ čāą║ą░ąĘą░ąĮąĮąŠąĄ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čåąĖą║ą╗ą░ čüą▒čĆąŠčüąĖčéčüčÅ ą▒ąĖčé WEL.

ąÜąŠą╝ą░ąĮą┤ą░ PAGE PROGRAM ąĮąĄ ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ, ąĄčüą╗ąĖ ąŠąĮą░ ą▒čāą┤ąĄčé ąĮą░čåąĄą╗ąĄąĮą░ ąĮą░ čüčéčĆą░ąĮąĖčåčā ą┐ą░ą╝čÅčéąĖ, ąĘą░čēąĖčēąĄąĮąĮčāčÄ ą▒ąĖčéą░ą╝ąĖ BP2, BP1 ąĖ BP0.

ąĀąĖčü. 15. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ PAGE PROGRAM.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: Cx = 7 + (A[MAX] + 1).

ąÜąŠą╝ą░ąĮą┤ą░ SECTOR ERASE čāčüčéą░ąĮąŠą▓ąĖčé ą▓ ąĄą┤ąĖąĮąĖčćą║ąĖ (FFh) ą▓čüąĄ ą▒ąĖčéčŗ ą▓ ą▓čŗą▒čĆą░ąĮąĮąŠą╝ čüąĄą║č鹊čĆąĄ. ą¤ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĖąĮčÅčéą░ ą║ąŠą╝ą░ąĮą┤ą░ SECTOR ERASE, ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ WRITE ENABLE. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ą░ ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ WRITE ENABLE, čāčüčéčĆąŠą╣čüčéą▓ąŠ čāčüčéą░ąĮąŠą▓ąĖčé ą▒ąĖčé ąĘą░čēąĄą╗ą║ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (WEL) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ.

ą¦č鹊ą▒čŗ ą▓ąŠą╣čéąĖ ą▓ ą║ąŠą╝ą░ąĮą┤čā SECTOR ERASE, čüąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0 ą▓čŗą▒ąŠčĆą║ą░ S#, ąĘą░č鹥ą╝ č湥čĆąĄąĘ DQ0 ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ ąĖ 3 ą▒ą░ą╣čéą░ ą░ą┤čĆąĄčüą░. ąøčÄą▒ąŠą╣ ą░ą┤čĆąĄčü ą▓ąĮčāčéčĆąĖ čüąĄą║č鹊čĆą░ čÅą▓ą╗čÅąĄčéčüčÅ ą┤ąŠą┐čāčüčéąĖą╝čŗą╝ ą░ą┤čĆąĄčüąŠą╝ ą┤ą╗čÅ ą║ąŠą╝ą░ąĮą┤čŗ SECTOR ERASE. ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ S# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ ą╗ąŠą│. 0 ą▓ č鹥č湥ąĮąĖąĄ ą▓čüąĄą╣ čŹč鹊ą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ą░ą╣čé ą░ą┤čĆąĄčüą░ ą▒čŗą╗ ą┐ąĄčĆąĄą┤ą░ąĮ, ą▓čŗą▒ąŠčĆą║ą░ S# ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮą░ ą▓ ą╗ąŠą│. 1. ąśąĮą░č湥 ą║ąŠą╝ą░ąĮą┤ą░ SECTOR ERASE ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░. ąÜą░ą║ č鹊ą╗čīą║ąŠ čüąĖą│ąĮą░ą╗ S# ą┐ąĄčĆąĄčłąĄą╗ ą▓ ą╗ąŠą│. 1, ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ SECTOR ERASE ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ tSE. ąÆąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čåąĖą║ą╗ą░ SECTOR ERASE čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ, čćč鹊ą▒čŗ ą┐čĆąŠą▓ąĄčĆąĖčéčī ą▒ąĖčé write in progress (WIP). ąæąĖčé WIP ą▓ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ, ąĖ ą▓ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ čåąĖą║ą╗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłąĖą╗čüčÅ. ą¦ąĄčĆąĄąĘ ąĮąĄą║ąŠč鹊čĆąŠąĄ ąĮąĄ čāą║ą░ąĘą░ąĮąĮąŠąĄ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čåąĖą║ą╗ą░ čüą▒čĆąŠčüąĖčéčüčÅ ą▒ąĖčé WEL.

ąÜąŠą╝ą░ąĮą┤ą░ SECTOR ERASE ąĮąĄ ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ, ąĄčüą╗ąĖ ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄą╝čŗą╣ ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ čüąĄą║č鹊čĆ ąĘą░čēąĖčēąĄąĮ ąŠčé ąĘą░ą┐ąĖčüąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĖą╗ąĖ ą░ą┐ą┐ą░čĆą░čéąĮąŠ.

ąĀąĖčü. 16. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ SECTOR ERASE.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: Cx = 7 + (A[MAX] + 1).

ąÜąŠą╝ą░ąĮą┤ąĄ BULK ERASE čāčüčéą░ąĮąŠą▓ąĖčé ą▓čüąĄ ą▒ąĖčéčŗ ą▓ ąĄą┤ąĖąĮąĖčćą║ąĖ (FFh). ą¤ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą║ąŠą╝ą░ąĮą┤ą░ BULK ERASE, ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ WRITE ENABLE. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ą░ ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ WRITE ENABLE, čāčüčéčĆąŠą╣čüčéą▓ąŠ čāčüčéą░ąĮąŠą▓ąĖčé ą▒ąĖčé ąĘą░čēąĄą╗ą║ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (WEL) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ.

ą¤ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ą║ąŠą╝ą░ąĮą┤čŗ BULK ERASE čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ S# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 0, ąĘą░č鹥ą╝ č湥čĆąĄąĘ ą▓čģąŠą┤ DQ0 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠčüą╗ą░ąĮ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ. ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ S# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ ą╗ąŠą│. 0 ą▓ č鹥č湥ąĮąĖąĄ ą▓čüąĄą╣ čŹč鹊ą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąĄčĆąĄą┤ą░ąĮčŗ ą▓čüąĄ 8 ą▒ąĖčé ą║ąŠą╝ą░ąĮą┤čŗ, čüąĖą│ąĮą░ą╗ S# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 1, ąĖąĮą░č湥 ą║ąŠą╝ą░ąĮą┤ą░ BULK ERASE ąĮąĄ ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ. ąÜą░ą║ č鹊ą╗čīą║ąŠ čüąĖą│ąĮą░ą╗ S# ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 1, ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą░ą▓č鹊ąĮąŠą╝ąĮčŗą╣ čåąĖą║ą╗ BULK ERASE, ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ąŠč鹊čĆąŠą│ąŠ čüąŠčüčéą░ą▓ą╗čÅąĄčé tBE. ąÜąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ čåąĖą║ą╗ BULK ERASE, čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ, čćč鹊ą▒čŗ ą┐čĆąŠą▓ąĄčĆąĖčéčī ą▒ąĖčé write in progress (WIP). ąæąĖčé WIP ą▓ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ ąŠčćąĖčüčéą║ąĖ, ąĖ ą▓ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ čåąĖą║ą╗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłąĖą╗čüčÅ. ą¦ąĄčĆąĄąĘ ąĮąĄą║ąŠč鹊čĆąŠąĄ ąĮąĄ čāą║ą░ąĘą░ąĮąĮąŠąĄ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čåąĖą║ą╗ą░ čüą▒čĆąŠčüąĖčéčüčÅ ą▒ąĖčé WEL.

ąÜąŠą╝ą░ąĮą┤ą░ BULK ERASE ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ č鹊ą╝ čüą╗čāčćą░ąĄ, ąĄčüą╗ąĖ ą▓čüąĄ ą▒ąĖčéčŗ ąĘą░čēąĖčéčŗ ą▒ą╗ąŠą║ąŠą▓ (BP2, BP1, BP0) čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 0. ąÜąŠą╝ą░ąĮą┤ą░ BULK ERASE ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ, ąĄčüą╗ąĖ ąŠą┤ąĖąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čüąĄą║č鹊čĆąŠą▓ ąĘą░čēąĖčēąĄąĮčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ.

ąĀąĖčü. 17. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ BULK ERASE.

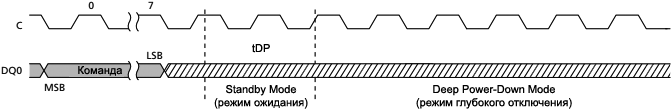

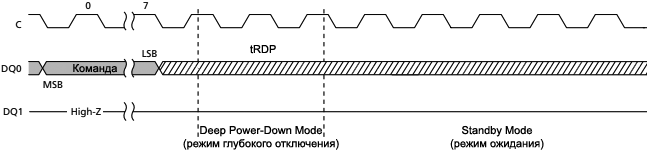

ąóąŠą╗čīą║ąŠ čü ą┐ąŠą╝ąŠčēčīčÄ ą║ąŠą╝ą░ąĮą┤čŗ DEEP POWER-DOWN ą╝ąŠąČąĮąŠ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ, ą║ąŠą│ą┤ą░ ąŠąĮąŠ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄčé ą╝ąĖąĮąĖą╝čāą╝ č鹊ą║ą░ - čĆąĄąČąĖą╝ ą│ą╗čāą▒ąŠą║ąŠą│ąŠ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ (DEEP POWER-DOWN). ąÜąŠą╝ą░ąĮą┤ą░ DEEP POWER-DOWN čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ą╝ąĄčģą░ąĮąĖąĘą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ ąĘą░čēąĖčéčŗ, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ą░ą║čéąĖą▓ąĮąŠ, ą┐ąŠč鹊ą╝čā čćč鹊 ą▓ čĆąĄąČąĖą╝ąĄ DEEP POWER-DOWN ąĖą│ąĮąŠčĆąĖčĆčāąĄčé ą▓čüąĄ ą║ąŠą╝ą░ąĮą┤čŗ WRITE, PROGRAM ąĖ ERASE.

ą¤ąĄčĆąĄą▓ąŠą┤ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ S# ą▓ ą╗ąŠą│. 1 ąŠčéą╝ąĄąĮčÅąĄčé ą▓čŗą▒ąŠčĆ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ąĄą│ąŠ ą▓ čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ (STANDBY POWER mode), ąĄčüą╗ąĖ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ąŠą┐ąĄčĆą░čåąĖčÅ. ąÜą░ą║ č鹊ą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čĆąĄąČąĖą╝ STANDBY POWER, ą╝ąŠąČąĮąŠ ą▓ąŠą╣čéąĖ ą▓ čĆąĄąČąĖą╝ DEEP POWER-DOWN ą┐čāč鹥ą╝ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤čŗ DEEP POWER-DOWN, ą▒ą╗ą░ą│ąŠą┤ą░čĆčÅ č湥ą╝čā čüąĮąĖąĘąĖčéčüčÅ ą┤ąŠ ą╝ąĖąĮąĖą╝čāą╝ą░ č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ąŠčé ICC1 ą┤ąŠ ICC2.

ąöą╗čÅ ą▓čŗą▓ąŠą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖąĘ čĆąĄąČąĖą╝ą░ DEEP POWER-DOWN ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ RELEASE from DEEP POWER-DOWN. ąöčĆčāą│ąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą▓čŗą┤ą░ą▓ą░čéčīčüčÅ, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ DEEP POWER-DOWN. ąĀąĄąČąĖą╝ DEEP POWER-DOWN ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐čĆąĖ ą▓čŗą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ. ą¤čĆąĖ ą┐ąŠą┤ą░č湥 ą┐ąĖčéą░ąĮąĖčÅ ąĮą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąŠąĮąŠ ą▓čüąĄą│ą┤ą░ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čĆąĄąČąĖą╝ STANDBY POWER.

ąÜąŠą╝ą░ąĮą┤čā DEEP POWER-DOWN ą╝ąŠąČąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐čāč鹥ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ą░ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ S# ą▓ ą╗ąŠą│. 0, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ č湥čĆąĄąĘ ą▓čģąŠą┤ DQ0 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ. ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ S# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ ą╗ąŠą│. 0 ą▓ č鹥č湥ąĮąĖąĄ ą▓čüąĄą╣ čŹč鹊ą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ S# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 1 ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ 8 ą▒ąĖčé ą║ąŠą╝ą░ąĮą┤čŗ, ąĖąĮą░č湥 ą║ąŠą╝ą░ąĮą┤ą░ DEEP POWER-DOWN ąĮąĄ ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą║ąŠą╝ą░ąĮą┤ą░ S# ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮą░ ą▓ ą╗ąŠą│. 1, čéčĆąĄą▒čāąĄčéčüčÅ ąĘą░ą┤ąĄčƹȹ║ą░ tDP ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čāą╝ąĄąĮčīčłąĖčéčüčÅ ą┤ąŠ ICC2, ąĖ čüčéą░ąĮąĄčé ą░ą║čéąĖą▓ąĮčŗą╝ čĆąĄąČąĖą╝ DEEP POWER-DOWN.

ąøčÄą▒ą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ DEEP POWER-DOWN, ą▓čŗą┤ą░ąĮąĮą░čÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░ ERASE, PROGRAM ąĖą╗ąĖ WRITE, ą▒čāą┤ąĄčé ąŠčéą▒čĆąŠčłąĄąĮą░ ą▒ąĄąĘ ą║ą░ą║ąŠą│ąŠ-ą╗ąĖą▒ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░.

ąĀąĖčü. 18. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ DEEP POWER-DOWN.

ąøąĄą│ąĄąĮą┤ą░:

|

ąæąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖčÅ (DonŌĆÖt Care) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: Cx = 7 + (A[MAX] + 1).

ąÜą░ą║ č鹊ą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ąŠčłą╗ąŠ ą▓ čĆąĄąČąĖą╝ DEEP POWER-DOWN, ąŠąĮąŠ ą▒čāą┤ąĄčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī ą▓čüąĄ ą║ąŠą╝ą░ąĮą┤čŗ ą║čĆąŠą╝ąĄ ą║ąŠą╝ą░ąĮą┤ RELEASE from DEEP POWER-DOWN ąĖ READ ELECTRONIC SIGNATURE. ąÆčŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą╗čÄą▒ąŠą╣ ąĖąĘ čŹčéąĖčģ ą║ąŠą╝ą░ąĮą┤ ą▓čŗą▓ąĄą┤ąĄčé čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĖąĘ čĆąĄąČąĖą╝ą░ DEEP POWER-DOWN.

ąÜąŠą╝ą░ąĮą┤čā RELEASE from DEEP POWER-DOWN ą╝ąŠąČąĮąŠ ąĘą░ą┐čāčüčéąĖčéčī ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ S# ą▓ ą╗ąŠą│. 0, ąĘą░ ą║ąŠč鹊čĆčŗą╝ č湥čĆąĄąĘ DQ0 ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ. ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ S# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ ą╗ąŠą│. 0 ą▓ č鹥č湥ąĮąĖąĄ ą▓čüąĄą╣ čŹč鹊ą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąÜąŠą╝ą░ąĮą┤ą░ RELEASE from DEEP POWER-DOWN ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ S# ą▓ ą╗ąŠą│. 1. ą×čéą┐čĆą░ą▓ą║ą░ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ čéą░ą║č鹊ą▓ C, ą║ąŠą│ą┤ą░ ą▓čŗą▒ąŠčĆą║ą░ S# ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0, ą┐čĆąĖąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 ą║ąŠą╝ą░ąĮą┤ą░ RELEASE from DEEP POWER-DOWN ą▒čāą┤ąĄčé ąŠčéą▒čĆąŠčłąĄąĮą░ ąĖ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ S# ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 1, č湥čĆąĄąĘ ąĘą░ą┤ąĄčƹȹ║čā tRES čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čĆąĄąČąĖą╝ STANDBY. S# ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ ą╗ąŠą│. 1 ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą▓ č鹥č湥ąĮąĖąĄ čŹč鹊ą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ ą▓čĆąĄą╝ąĄąĮąĖ. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čāą┤ąĄčé ąČą┤ą░čéčī ą▓čŗą▒ąŠčĆą║ąĖ, ąĖ ą╝ąŠąČąĄčé ą┐čĆąĖąĮčÅčéčī, ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░čéčī ąĖ ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą║ąŠą╝ą░ąĮą┤čŗ.

ąøčÄą▒ą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ RELEASE from DEEP POWER-DOWN, ą▓čŗą┤ą░ąĮąĮą░čÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░ ERASE, PROGRAM ąĖą╗ąĖ WRITE, ąŠčéą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą▒ąĄąĘ ą║ą░ą║ąŠą│ąŠ-ą╗ąĖą▒ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗.

ąĀąĖčü. 19. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ RELEASE from DEEP POWER-DOWN.

ąøąĄą│ąĄąĮą┤ą░:

|

ąæąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖčÅ (DonŌĆÖt Care) |

ąÜą░ą║ č鹊ą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ąŠčłą╗ąŠ ą▓ čĆąĄąČąĖą╝ DEEP POWER-DOWN, ąŠąĮąŠ ą▒čāą┤ąĄčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī ą▓čüąĄ ą║ąŠą╝ą░ąĮą┤čŗ ą║čĆąŠą╝ąĄ ą║ąŠą╝ą░ąĮą┤ RELEASE from DEEP POWER-DOWN ąĖ READ ELECTRONIC SIGNATURE. ąÆčŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą╗čÄą▒ąŠą╣ ąĖąĘ čŹčéąĖčģ ą║ąŠą╝ą░ąĮą┤ ą▓čŗą▓ąĄą┤ąĄčé čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĖąĘ čĆąĄąČąĖą╝ą░ DEEP POWER-DOWN.

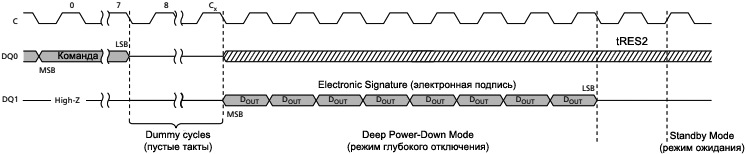

ąÜąŠą╝ą░ąĮą┤čā READ ELECTRONIC SIGNATURE ą╝ąŠąČąĮąŠ ą▓ą▓ąĄčüčéąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ S#, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ č湥čĆąĄąĘ ą▓čģąŠą┤ DQ0 ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ ąĖ 3 ą┐čāčüčéčŗčģ ą▒ą░ą╣čéą░ (dummy bytes). ą¤čĆąĖ čŹč鹊ą╝ ą║ą░ąČą┤čŗą╣ ą▓ą▓ąŠą┤ąĖą╝čŗą╣ ą▒ąĖčé ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ čäčĆąŠąĮč鹊ą╝ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ čéą░ą║č鹊ą▓ C. 8-ą▒ąĖčéąĮą░čÅ čŹą╗ąĄą║čéčĆąŠąĮąĮą░čÅ ą┐ąŠą┤ą┐ąĖčüčī ą▓čŗą┤ą▓ąĖą│ą░ąĄčéčüčÅ č湥čĆąĄąĘ ą▓čŗčģąŠą┤ DQ1 ą┐ąŠ čüą┐ą░ą┤ą░ą╝ čāčĆąŠą▓ąĮčÅ čéą░ą║č鹊ą▓ C; čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ S# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ ą╗ąŠą│. 0 ą▓ č鹥č湥ąĮąĖąĄ ą▓čüąĄą╣ čŹč鹊ą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čćč鹥ąĮąĖčÅ čŹą╗ąĄą║čéčĆąŠąĮąĮąŠą╣ ą┐ąŠą┤ą┐ąĖčüąĖ. ą×ą┤ąĮą░ą║ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ S# ą▓ ą╗ąŠą│. 1 ą┐ąŠčüą╗ąĄ ą║ąŠą┤ą░ ą║ąŠą╝ą░ąĮą┤čŗ, ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą▒čāą┤ąĄčé ą▓čŗą▓ąĄą┤ąĄąĮą░ 8-ą▒ąĖčéąĮą░čÅ čŹą╗ąĄą║čéčĆąŠąĮąĮą░čÅ ą┐ąŠą┤ą┐ąĖčüčī, ą▓čüąĄ ąĄčēąĄ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮąŠ ą▓ čĆąĄąČąĖą╝ STANDBY.

ąŚą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čüąĖčéčāą░čåąĖą╣, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ ERASE, PROGRAM ąĖą╗ąĖ WRITE STATUS REGISTER, ą║ąŠą╝ą░ąĮą┤ą░ READ ELECTRONIC SIGNATURE ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ąŠčüčéčāą┐ ą║ 8-ą▒ąĖčéąĮąŠą╣ 菹╗ąĄą║čéčĆąŠąĮąĮąŠą╣ ą┐ąŠą┤ą┐ąĖčüąĖ čāčüčéčĆąŠą╣čüčéą▓ą░, ąĖ čŹčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┤ą░ąĮą░ ą┤ą░ąČąĄ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ą▓ąŠčłą╗ąŠ ą▓ čĆąĄąČąĖą╝ DEEP POWER-DOWN. ąÜąŠą╝ą░ąĮą┤ą░ READ ELECTRONIC SIGNATURE ąĮąĄ ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĄąĮ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ ERASE, PROGRAM ąĖą╗ąĖ WRITE STATUS REGISTER, ą▒ąĄąĘ ą║ą░ą║ąŠą│ąŠ-ą╗ąĖą▒ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čŹč鹊čé ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗.

ąÜąŠą╝ą░ąĮą┤ą░ READ ELECTRONIC SIGNATURE ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ S# ą▓ ą╗ąŠą│. 1 ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ 菹╗ąĄą║čéčĆąŠąĮąĮą░čÅ ą┐ąŠą┤ą┐ąĖčüčī ą▒čāą┤ąĄčé ą┐čĆąŠčćąĖčéą░ąĮą░ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 1 čĆą░ąĘ. ą×čéą┐čĆą░ą▓ą║ą░ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ čéą░ą║č鹊ą▓ C, ą║ąŠą│ą┤ą░ ą▓čŗą▒ąŠčĆą║ą░ S# ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0, ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą┐ąŠą▓č鹊čĆčÅčÄčēąĄą╝čāčüčÅ ą▓čŗą▓ąŠą┤čā 菹╗ąĄą║čéčĆąŠąĮąĮąŠą╣ ą┐ąŠą┤ą┐ąĖčüąĖ.

ąĢčüą╗ąĖ ą▓čŗą▒ąŠčĆą║ą░ S# ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1, čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čĆąĄąČąĖą╝ STANDBY, ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĮąĄąĄ ąĮąĄ ąĮą░čģąŠą┤ąĖą╗ąŠčüčī ą▓ čĆąĄąČąĖą╝ąĄ DEEP POWER-DOWN. ąĢčüą╗ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ čĆą░ąĮąĄąĄ ą▒čŗą╗ąŠ ą▓ čĆąĄąČąĖą╝ąĄ DEEP POWER-DOWN, ą┐ąĄčĆąĄčģąŠą┤ ą▓ čĆąĄąČąĖą╝ STANDBY ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé č湥čĆąĄąĘ ąĘą░ą┤ąĄčƹȹ║čā, ąŠą┐ąĖčüą░ąĮąĮčāčÄ ąĘą┤ąĄčüčī. ąÜą░ą║ č鹊ą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čĆąĄąČąĖą╝ STANDBY, ąŠąĮąŠ ą▒čāą┤ąĄčé ąŠąČąĖą┤ą░čéčī ą▓čŗą▒ąŠčĆą║čā ąĖ ą╝ąŠąČąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī, ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░čéčī ąĖ ą▓čŗą┐ąŠą╗ąĮčÅčéčī ąĖąĮčüčéčĆčāą║čåąĖąĖ.

ŌĆó ąĢčüą╗ąĖ S# ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1 ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą┐čĆąŠčćąĖčéą░ąĮą░ 菹╗ąĄą║čéčĆąŠąĮąĮą░čÅ ą┐ąŠą┤ą┐ąĖčüčī, ą┐ąĄčĆąĄčģąŠą┤ ą▓ čĆąĄąČąĖą╝ STANDBY ąĘą░ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĮą░ ą▓čĆąĄą╝čÅ tRES1, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą║ąŠą╝ą░ąĮą┤čŗ RELEASE from DEEP POWER-DOWN. ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ S# ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ ą╗ąŠą│. 1 ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą▓čĆąĄą╝čÅ tRES1(max).

ŌĆó ąĢčüą╗ąĖ S# ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1 ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąŠčćąĖčéą░ąĮą░ 菹╗ąĄą║čéčĆąŠąĮąĮą░čÅ ą┐ąŠą┤ą┐ąĖčüčī, ą┐ąĄčĆąĄčģąŠą┤ ą▓ čĆąĄąČąĖą╝ STANDBY ą▒čāą┤ąĄčé ąĘą░ą┤ąĄčƹȹ░ąĮ ąĮą░ ą▓čĆąĄą╝čÅ tRES2. ąÆčŗą▒ąŠčĆą║ą░ S# ą┤ąŠą╗ąČąĮą░ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1 ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąĮą░ ą▓čĆąĄą╝čÅ tRES2(max).

ąĀąĖčü. 20. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ READ ELECTRONIC SIGNATURE.

ąøąĄą│ąĄąĮą┤ą░:

|

ąæąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖčÅ (DonŌĆÖt Care) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: Cx = 7 + (A[MAX] + 1).

[ąÆą║ą╗čÄč湥ąĮąĖąĄ/ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ ąĖ čĆą░ąĘą▓čÅąĘą║ą░ ą┐ąĖčéą░ąĮąĖčÅ]

ąÆ ą╝ąŠą╝ąĄąĮčé ą▓ą║ą╗čÄč湥ąĮąĖčÅ ąĖ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮąŠ; čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ (S#) ą┤ąŠą╗ąČąĄąĮ čüą╗ąĄą┤ąŠą▓ą░čéčī ąĘą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ąĮą░ VCC, ą┐ąŠą║ą░ VCC ąĮąĄ ą┤ąŠčüčéąĖą│ąĮąĄčé ą║ąŠčĆčĆąĄą║čéąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ:

ŌĆó VCC, ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ, ąĖ ąĘą░č鹥ą╝ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĘą░ą┤ąĄčƹȹ║ą░ tVSL.

ŌĆó VSS ą┐čĆąĖ ą▓čŗą║ą╗čÄč湥ąĮąĖąĖ.

ąæąĄąĘąŠą┐ą░čüąĮą░čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ąŠą║ą░ąĘą░ąĮą░ ą▓ čüąĄą║čåąĖąĖ čü ąŠą┐ąĖčüą░ąĮąĖąĄą╝ čĆąĄąČąĖą╝ąŠą▓ SPI.

ą¦č鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖ ąĮąĄą┐čĆąĄą┤ąĮą░ą╝ąĄčĆąĄąĮąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖą╣ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ, ą▓ čāčüčéčĆąŠą╣čüčéą▓ąĄ ąĄčüčéčī čüčģąĄą╝ą░ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüą▒čĆąŠčüą░ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ (power-on-reset, POR). ąøąŠą│ąĖą║ą░ ą▓ąĮčāčéčĆąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ čāą┤ąĄčƹȹĖą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ čüą▒čĆąŠčüą░, ą┐ąŠą║ą░ VCC ą╝ąĄąĮčīčłąĄ VWI, ą┐ąŠčĆąŠą│ąŠą▓ąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ POR ŌĆō ą▓čüąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐čĆąĄčēąĄąĮčŗ, ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ąŠčéą▓ąĄčćą░ąĄčé ąĮą░ ą╗čÄą▒čāčÄ ąĖąĮčüčéčĆčāą║čåąĖčÄ. ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĖą│ąĮąŠčĆąĖčĆčāąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą┐ąŠą║ą░ ąĮąĄ ąĖčüč鹥č湥čé ąĘą░ą┤ąĄčƹȹ║ą░ ą▓čĆąĄą╝ąĄąĮąĖ tPUW ą┐ąŠčüą╗ąĄ ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ VCC ą▓ąŠąĘčĆą░čüč鹥čé ą▓čŗčłąĄ ą┐ąŠčĆąŠą│ą░ VWI:

ŌĆó WRITE ENABLE

ŌĆó PAGE PROGRAM

ŌĆó SECTOR ERASE

ŌĆó BULK ERASE

ŌĆó WRITE STATUS REGISTER

ą×ą┤ąĮą░ą║ąŠ ą║ąŠčĆčĆąĄą║čéąĮą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮąĄ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ, ąĄčüą╗ąĖ ą▓ č鹥č湥ąĮąĖąĄ čŹč鹊ą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ VCC ą▓čüąĄ ąĄčēąĄ ąĮąĖąČąĄ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VCC. ąØąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠčüą╗ą░ąĮčŗ ąĖąĮčüčéčĆčāą║čåąĖąĖ WRITE STATUS REGISTER, PROGRAM ąĖą╗ąĖ ERASE, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ čāčüą╗ąŠą▓ąĖčÅ:

ŌĆó ą¤čĆąŠčłą╗ąŠ ą▓čĆąĄą╝čÅ tPUW ą┐ąŠčüą╗ąĄ ąĮą░čĆą░čüčéą░ąĮąĖčÅ VCC č湥čĆąĄąĘ ą┐ąŠčĆąŠą│ VWI.

ŌĆó ą¤čĆąŠčłą╗ąŠ ą▓čĆąĄą╝čÅ tVSL ą┐ąŠčüą╗ąĄ ąĮą░čĆą░čüčéą░ąĮąĖčÅ VCC ą▓čŗčłąĄ čüą▓ąŠąĄą│ąŠ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ.

ąĢčüą╗ąĖ ą┐čĆąŠčłą╗ąŠ ą▓čĆąĄą╝čÅ tVSL ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ VCC ą▓čŗčĆąŠčüą╗ąŠ ą▓čŗčłąĄ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮąŠ ą┤ą╗čÅ ąĖąĮčüčéčĆčāą║čåąĖą╣ READ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ąĘą░ą┤ąĄčƹȹ║ą░ tPUW ą▓čüąĄ ąĄčēąĄ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĘą░ą║ąŠąĮčćąĖą╗ą░čüčī. VPPH ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐ąŠą┤ą░ąĮąŠ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ VCC čüčéą░ą▒ąĖą╗čīąĮąŠ, ąĖ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ą╝ąĄąČą┤čā is VCCmin ąĖ VCCmax.

ąĀąĖčü. 21. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ.

ą¤ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ čüąŠčüč鹊čÅąĮąĖąĖ:

ŌĆó ąĀąĄąČąĖą╝ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ Standby (čŹč鹊 ąĮąĄ čĆąĄąČąĖą╝ deep power-down)

ŌĆó ąæąĖčé ąĘą░čēąĄą╗ą║ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (Write Enable Latch, WEL) čüą▒čĆąŠčłąĄąĮ

ŌĆó ąæąĖčé ą┐čĆąŠčåąĄčüčüą░ ąĘą░ą┐ąĖčüąĖ (Write In Progress, WIP) čüą▒čĆąŠčłąĄąĮ

ŌĆó ąæąĖčé ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ąĘą░ą┐ąĖčüąĖ (Write lock bit) = 0

ŌĆó Lock down bit = 0

ąöąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąĄą┤ą┐čĆąĖąĮčÅčéčŗ ąŠą▒čŗčćąĮčŗąĄ ą╝ąĄč鹊ą┤čŗ ą┤ą╗čÅ čĆą░ąĘą▓čÅąĘą║ąĖ čåąĄą┐ąĖ ą┐ąĖčéą░ąĮąĖčÅ, čćč鹊ą▒čŗ čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆąŠą▓ą░čéčī čāčĆąŠą▓ąĄąĮčī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VCC. ąØą░ ą║ą░ąČą┤ąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ ą╗ąĖąĮąĖčÅ VCC ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąŠčéčäąĖą╗čīčéčĆąŠą▓ą░ąĮą░ ą┐ąŠą┤čģąŠą┤čÅčēąĖą╝ ą║ąĄčĆą░ą╝ąĖč湥čüą║ąĖą╝ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą╝, čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĮčŗą╝ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▒ą╗ąĖąĘą║ąŠ ą║ ą▓čŗą▓ąŠą┤ą░ą╝ ą┐ąĖčéą░ąĮąĖčÅ ą║ąŠčĆą┐čāčüą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ; ąŠą▒čŗčćąĮąŠ čéą░ą║ąŠą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ąĖą╝ąĄąĄčé ąĄą╝ą║ąŠčüčéčī ą┐ąŠčĆčÅą┤ą║ą░ 100 ąĮąż (0.1 ą╝ą║ąż).

ą¤čĆąĖ ą▓čŗą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ VCC ą┐ą░ą┤ą░ąĄčé ąĮąĖąČąĄ ą┐ąŠčĆąŠą│ą░ VWI ą┤ą╗čÅ čĆą░ą▒ąŠč湥ą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ POR, ą▓čüąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐čĆąĄčēą░čÄčéčüčÅ, ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ąŠčéą▓ąĄčćą░ąĄčé ąĮąĖ ąĮą░ ą║ą░ą║čāčÄ ąĖąĮčüčéčĆčāą║čåąĖčÄ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░ WRITE, PROGRAM ąĖą╗ąĖ ERASE, č鹊 ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖąĄ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┤ą░ąĮąĮčŗčģ.

ąóą░ą▒ą╗ąĖčåą░ 8. ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ą┐ąŠčĆąŠą│ VWI.

| ąĪąĖą╝ą▓ąŠą╗ |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

MIN |

MAX |

ąĢą┤. |

| tVSL |

ą×čé VCCmin ą┤ąŠ S# = 0 |

10 |

- |

ą╝ą║čü |

| tPUW |

ąŚą░ą┤ąĄčƹȹ║ą░ ą┤ąŠ ąĘą░ą┐ąĖčüąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ |

1.0 |

10 |

ą╝čü |

| VWI |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĘą░ą┐čĆąĄčéą░ ąĘą░ą┐ąĖčüąĖ |

1.0 |

2.1 |

V |

ąĢčüą╗ąĖ ąĖčüč鹥ą║ą╗ąŠ ą▓čĆąĄą╝čÅ tVSL ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ VCC ą▓ąŠąĘčĆąŠčüą╗ąŠ ą▓čŗčłąĄ VCCmin, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮąŠ ą┤ą╗čÅ ąĖąĮčüčéčĆčāą║čåąĖą╣ READ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ąĄčēąĄ ąĮąĄ ą┐čĆąŠčłą╗ą░ ą┐ąŠą╗ąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ąĖąĮč鹥čĆą▓ą░ą╗ą░ tPUW.

VPPH ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐ąŠą┤ą░ąĮąŠ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ VCC čüčéą░ą╗ąŠ čüčéą░ą▒ąĖą╗čīąĮčŗą╝ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą╝ąĄąČą┤čā VCCmin ąĖ VCCmax.

ą¤čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖąĄ: ą┐čĆąĄą▓čŗčłąĄąĮąĖąĄ ą░ą▒čüąŠą╗čÄčéąĮčŗčģ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄąŠą▒čĆą░čéąĖą╝ąŠą╝čā ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÄ čāčüčéčĆąŠą╣čüčéą▓ą░. ąŁčéąĖ čüčéčĆąĄčüčüąŠą▓čŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┤ą░ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čĆąĄą╣čéąĖąĮą│ą░, ąĖ čĆą░ą▒ąŠčéą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čéą░ą║ąĖčģ ą┐čĆąĄą┤ąĄą╗čīąĮčŗčģ čāčüą╗ąŠą▓ąĖčÅčģ ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ. ąĀą░ą▒ąŠčéą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čāčüą╗ąŠą▓ąĖčÅčģ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą╝ąŠąČąĄčé ą┐ąŠą▓ą╗ąĖčÅčéčī ąĮą░ ąĮą░ą┤ąĄąČąĮąŠčüčéčī čāčüčéčĆąŠą╣čüčéą▓ą░.

ąóą░ą▒ą╗ąĖčåą░ 9. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮčŗąĄ ą░ą▒čüąŠą╗čÄčéąĮčŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ.

| ąĪąĖą╝ą▓ąŠą╗ |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

MIN |

MAX |

ąĢą┤. |

ą¤čĆąĖą╝. |

| TSTG |

ąóąĄą╝ą┐ąĄčĆą░čéčāčĆą░ čģčĆą░ąĮąĄąĮąĖčÅ |

-65 |

150 |

┬░C |

|

| TLEAD |

ąóąĄą╝ą┐ąĄčĆą░čéčāčĆą░ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ą░ą╣ą║ąĖ |

- |

čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ |

┬░C |

1 |

| VIO |

ąÆčģąŠą┤ąĮąŠąĄ ąĖ ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ (ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ) |

-0.6 |

VCC+0.6 |

V |

2 |

| VCC |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ |

ŌĆō0.6 |

4.0 |

V |

|

| VESD |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ 菹╗ąĄą║čéčĆąŠčüčéą░čéąĖč湥čüą║ąŠą│ąŠ čĆą░ąĘčĆčÅą┤ą░ (Electrostatic Discharge, ESD), ą╝ąŠą┤ąĄą╗čī č鹥ą╗ą░ č湥ą╗ąŠą▓ąĄą║ą░ (Human Body model) |

-2000 |

2000 |

V |

3 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ą¤ą░čĆą░ą╝ąĄčéčĆ TLEAD čüąŠą▓ą╝ąĄčüčéąĖą╝ čüąŠ čüčéą░ąĮą┤ą░čĆčéą░ą╝ąĖ JEDEC Std J-STD-020C (ą┤ą╗čÅ ą╝ą░ą╗ąŠą│ąŠ ą║ąŠčĆą┐čāčüą░, čüą▒ąŠčĆą║ą░ Sn-Pb ąĖą╗ąĖ Pb), čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĄą╣ Micron RoHS 7191395 ąĖ ąĄą▓čĆąŠą┐ąĄą╣čüą║ąŠą╣ ą┤ąĖčĆąĄą║čéąĖą▓ąŠą╣ "Restrictions on Hazardous Substances" (RoHS) 2002/95/EU.

2. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗčģ ą┐čĆąŠčåąĄčüčüąŠą▓ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą┤ąŠčüčéąĖą│ą░čéčī -2V ąĮą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ąĮąĄ ą▒ąŠą╗ąĄąĄ 20 ąĮčü; ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą╝ąŠąČąĄčé ą┤ąŠčüčéąĖą│ą░čéčī VCC + 2V ąĮą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ąĮąĄ ą▒ąŠą╗ąĄąĄ 20 ąĮčü.

3. ą¤ą░čĆą░ą╝ąĄčéčĆ VESD: JEDEC Std JESD22-A114A (C1 = 100 ą┐ąż, R1 = 1500 ╬®, R2 = 500 ╬®).

ąóą░ą▒ą╗ąĖčåą░ 10. ąĀą░ą▒ąŠčćąĖąĄ čāčüą╗ąŠą▓ąĖčÅ.

| ąĪąĖą╝ą▓ąŠą╗ |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

MIN |

MAX |

ąĢą┤. |

ą¤čĆąĖą╝. |

| VCC |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ |

2.7 |

3.6 |

V |

|

| TA |

ąóąĄą╝ą┐ąĄčĆą░čéčāčĆą░ ąŠą║čĆčāąČą░čÄčēąĄą│ąŠ ą▓ąŠąĘą┤čāčģą░ (grade 6) |

-40 |

85 |

┬░C |

1 |

| TA |

ąóąĄą╝ą┐ąĄčĆą░čéčāčĆą░ ąŠą║čĆčāąČą░čÄčēąĄą│ąŠ ą▓ąŠąĘą┤čāčģą░ (grade 3) |

-40 |

125 |

┬░C |

2 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. Autograde 6 ąĖ čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (grade 6) ą┐čĆąŠą▓ąĄčĆčÅčÄčéčüčÅ ą┐čĆąĖ 85 ┬░C. Autograde 6 ąŠčéą▓ąĄčćą░čÄčé čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ ą▓čŗčüąŠą║ąŠą╣ ąĮą░ą┤ąĄąČąĮąŠčüčéąĖ, čćč鹊 ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąŠ č鹥čüčéą░ą╝ąĖ.

2. Autograde 3 ą┐čĆąŠą▓ąĄčĆčÅčÄčéčüčÅ ą┤ą╗čÅ 125 ┬░C.

ąóą░ą▒ą╗ąĖčåą░ 11. ąźčĆą░ąĮąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ąĖ ąĖąĘąĮąŠčüąŠčüč鹊ą╣ą║ąŠčüčéčī.

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąŻčüą╗ąŠą▓ąĖčÅ |

MIN |

MAX |

ąĢą┤. |

| ą”ąĖą║ą╗ąŠą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ/čüčéąĖčĆą░ąĮąĖąĄ |

Grade 6, grade 3, autograde 6 |

100000 |

- |

ą”ąĖą║ą╗ąŠą▓ ąĮą░ ą▒ą╗ąŠą║ |

| ąĪčĆąŠą║ čģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ |

ą¤čĆąĖ 55┬░C |

20 |

- |

ąøąĄčé |

ąóą░ą▒ą╗ąĖčåą░ 12. ąĪą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā (DC Current).

| ąĪąĖą╝ą▓ąŠą╗ |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

MIN |

MAX |

ąĢą┤. |

| ILI |

ąóąŠą║ čāč鹥čćą║ąĖ ą┐ąŠ ą▓čģąŠą┤čā |

- |

- |

┬▒2 |

ą╝ą║ąÉ |

| ILO |

ąóąŠą║ čāč鹥čćą║ąĖ ą┐ąŠ ą▓čŗčģąŠą┤čā |

- |

- |

┬▒2 |

| ICC1 |

ąóąŠą║ ąČą┤čāčēąĄą│ąŠ čĆąĄąČąĖą╝ą░ (Standby, grade 6) |

S# = VCC, VIN = VSS ąĖą╗ąĖ VCC |

- |

50 |

| ICC1 |

ąóąŠą║ ąČą┤čāčēąĄą│ąŠ čĆąĄąČąĖą╝ą░ (Standby, grade 3) |

- |

100 |

| ICC2 |

ąóąŠą║ čĆąĄąČąĖą╝ą░ ą│ą╗čāą▒ąŠą║ąŠą│ąŠ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ (Deep power-down, grade 6) |

S# = VCC, VIN = VSS ąĖą╗ąĖ VCC |

- |

10 |

| ICC2 |

ąóąŠą║ čĆąĄąČąĖą╝ą░ ą│ą╗čāą▒ąŠą║ąŠą│ąŠ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ (Deep power-down current, grade 3) |

- |

100 |

| ICC3 |

ąĀą░ą▒ąŠčćąĖą╣ č鹊ą║ (READ) |