|

ą¤ąĄčĆąĄą▓ąŠą┤ ą┤ą░čéą░čłąĖčéą░ Sanyo ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čā LC72131, LC72131M.

[ą×ą▒ąĘąŠčĆ]

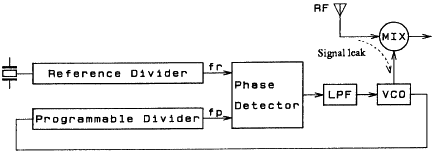

ą£ąĖą║čĆąŠčüčģąĄą╝čŗ LC72131 ąĖ LC72131M čÅą▓ą╗čÅčÄčéčüčÅ čüąĖąĮč鹥ąĘą░č鹊čĆą░ą╝ąĖ čćą░čüč鹊čéčŗ čü ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄą╝ PLL (Phase Locked Loop, ążąÉą¤ą¦, ążąÉąĘąŠą▓ą░čÅ ą¤ąŠą┤čüčéčĆąŠą╣ą║ą░ ą¦ą░čüč鹊čéčŗ) ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ čéčÄąĮąĄčĆą░čģ ą┐ąĄčĆąĄąĮąŠčüąĮčŗčģ ą╝ą░ą│ąĮąĖč鹊ą╗ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ąŠą▓. ąĪ ą┐ąŠą╝ąŠčēčīčÄ čŹčéąĖčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą╗ąĄą│ą║ąŠ čĆąĄą░ą╗ąĖąĘčāčÄčéčüčÅ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓čāčÄčēąĖąĄ čéčÄąĮąĄčĆčŗ AM/FM.

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ]

1. ąÆčŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ą┤ąĄą╗ąĖč鹥ą╗ąĖ:

- FMIN ą┤ą╗čÅ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ 10..160 ą£ąōčå (ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ "ą│ą╗ąŠčéą░č鹥ą╗čī ąĖą╝ą┐čāą╗čīčüąŠą▓" pulse swallower čü ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗ąĄą╝ ąĮą░ 2).

- AMIN ą┤ą╗čÅ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ 2..40 ą£ąōčå (ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ pulse swallower, ą▒ąĄąĘ ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čÅ ąĮą░ 2 ąĖ ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąĄą╗ąĄąĮąĖčÅ čćą░čüč鹊čéčŗ).

- AMIN ą┤ą╗čÅ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ 0.5..10 ą£ąōčå (ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┐čĆčÅą╝ąŠąĄ ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ).

2. IF čüč湥čéčćąĖą║ (čćą░čüč鹊č鹊ą╝ąĄčĆ) - IFIN 0.4..12 ą£ąōčå čćą░čüč鹊č鹊ą╝ąĄčĆ AM/FM.

3. 12 ą▓čŗą▒ąĖčĆą░ąĄą╝čŗčģ ąŠą┐ąŠčĆąĮčŗčģ čćą░čüč鹊čé (ą┐čĆąĖ čćą░čüč鹊č鹥 ą║ą▓ą░čĆčåą░ 4.5 ąĖą╗ąĖ 7.2 ą£ąōčå) 1, 3, 5, 9, 10, 3.125, 6.25, 12.5, 15, 25, 50 ąĖ 100 ą║ąōčå. ąŚąĮą░č湥ąĮąĖąĄ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ ą╗ąĖą▒ąŠ čĆą░ą▓ąĮąŠ, ą╗ąĖą▒ąŠ ą▓ ą┤ą▓ą░ čĆą░ąĘą░ ą╝ąĄąĮčīčłąĄ čłą░ą│ą░ ą┐ąĄčĆąĄčüčéčĆąŠą╣ą║ąĖ čüąĖąĮč鹥ąĘą░č鹊čĆą░ ą┐ąŠ čćą░čüč鹊č鹥 (ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čÅ ąĮą░ 2).

4. ąÜąŠą╝ą┐ą░čĆą░č鹊čĆ čäą░ąĘčŗ.

- čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą╝ąĄčĆčéą▓ąŠą╣ ąĘąŠąĮąŠą╣.

- čāąĘąĄą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ.

- čāąĘąĄą╗ ąŠčćąĖčüčéą║ąĖ ą┤ąĄą░ą┤ą╗ąŠą║ą░.

5. ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ MOS-čéčĆą░ąĮąĘąĖčüč鹊čĆ ą┤ą╗čÅ ą┐ąŠčüčéčĆąŠąĄąĮąĖčÅ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čäąĖą╗čīčéčĆą░ ąĮąĖąČąĮąĖčģ čćą░čüč鹊čé.

6. ą¤ąŠčĆčéčŗ ą▓ą▓ąŠą┤ą░-ą▓čŗą▓ąŠą┤ą░ (I/O).

- 4 ą┐ąŠčĆčéą░, čĆą░ą▒ąŠčéą░čÄčēąĖčģ č鹊ą╗čīą║ąŠ ąĮą░ ą▓čŗą▓ąŠą┤.

- 2 ą┐ąŠčĆčéą░, čĆą░ą▒ąŠčéą░čÄčēąĖčģ ą╗ąĖą▒ąŠ ąĮą░ ą▓čŗą▓ąŠą┤, ą╗ąĖą▒ąŠ ąĮą░ ą▓ą▓ąŠą┤ (ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą▓ąŠą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ IOC1, IOC2 ą▓ čĆąĄąČąĖą╝ąĄ IN2).

- ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓čŗą▓ąŠą┤, ą┐čĆąĖą▓čÅąĘą░ąĮąĮčŗą╣ ą║ čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓.

7. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą▓ą▓ąŠą┤/ą▓čŗą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ - ą┐čĆąĖ ąŠą▒ą╝ąĄąĮąĄ ą┤ą░ąĮąĮčŗą╝ąĖ čü čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ č乊čĆą╝ą░čé CCB.

8. ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ 4.5..5.5 ą▓ąŠą╗čīčé, čĆą░ą▒ąŠčćą░čÅ č鹥ą╝ą┐ąĄčĆą░čéčāčĆą░ -40..85 oC.

9. ąÜąŠčĆą┐čāčüą░ DIP22S ąĖ MFP20.

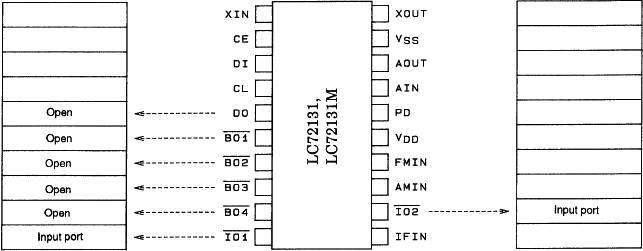

[ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓]

ąĖą╝čÅ

|

Ōä¢ ąĮąŠąČą║ąĖ

(MFP20)

|

čéąĖą┐

|

ąŠą┐ąĖčüą░ąĮąĖąĄ |

ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ |

XIN

XOUT |

1(1)

22(20) |

Xtal OSC |

ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą║ą▓ą░čĆčåą░

4.5 ąĖą╗ąĖ 7.2 ą£ąōčå |

|

| FMIN |

16(14) |

ą▓čģąŠą┤ ą┤ą╗čÅ čćą░čüč鹊čéčŗ ąŠčé ą│ąĄč鹥čĆąŠą┤ąĖąĮą░ |

1. ąÆčģąŠą┤ FMIN čĆą░ą▒ąŠčéą░ąĄčé, ą║ąŠą│ą┤ą░ ą▒ąĖčé DVS ą▓ąŠ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ čĆą░ą▓ąĄąĮ 1

2. ąöąĖą░ą┐ą░ąĘąŠąĮ čćą░čüč鹊čé ą▓čģąŠą┤ą░ FMIN 10..160 ą£ąōčå

3. ąÆčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą┐čĆąŠčģąŠą┤ąĖčé č湥čĆąĄąĘ ą┤ąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ ąĮą░ 2 ąĖ ą┤ą░ą╗ąĄąĄ ą┐čĆąŠčģąŠą┤ąĖčé ąĮą░ čüč湥čéčćąĖą║, ą┐čĆąŠą┐čāčüą║ą░čÄčēąĖą╣ ąĖą╝ą┐čāą╗čīčüčŗ (swallow counter)

4. ąöąĄą╗ąĖč鹥ą╗čī ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 272..65535. ąØąŠ ą┐ąŠčüą║ąŠą╗čīą║čā ąĮą░ ą▓čģąŠą┤ąĄ ąĄčēąĄ čüč鹊ąĖčé ą┤ąĄą╗ąĖč鹥ą╗čī ąĮą░ 2, č鹊 ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ čāą┤ą▓ą░ąĖą▓ą░ąĄčéčüčÅ |

|

| AMIN |

15(13) |

ą▓čģąŠą┤ ą┤ą╗čÅ čćą░čüč鹊čéčŗ ąŠčé ą│ąĄč鹥čĆąŠą┤ąĖąĮą░ |

1. ąÆčģąŠą┤ AMIN čĆą░ą▒ąŠčéą░ąĄčé, ą║ąŠą│ą┤ą░ ą▒ąĖčé DVS ą▓ąŠ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ čĆą░ą▓ąĄąĮ 0

2. ąÜąŠą│ą┤ą░ ą▓čģąŠą┤ąĮąŠą╣ ą▒ąĖčé SNS čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, č鹊 ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą▓čģąŠą┤ąĮčŗčģ čćą░čüč鹊čé 2..40 ą£ą│čå, čüąĖą│ąĮą░ą╗ ą┐čĆąŠčģąŠą┤ąĖčé ą┐čĆčÅą╝ąŠ ąĮą░ čüč湥čéčćąĖą║ ą┐čĆąŠą┐čāčüą║ą░ ąĖą╝ą┐čāą╗čīčüąŠą▓ (swallow counter), ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī 272..65535

3. ąÜąŠą│ą┤ą░ ą▓čģąŠą┤ąĮąŠą╣ ą▒ąĖčé SNS čüą▒čĆąŠčłąĄąĮ ą▓ 0, ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą▓čģąŠą┤ąĮčŗčģ čćą░čüč鹊čé 0.5..10 ą£ąōčå, čüąĖą│ąĮą░ą╗ ą┐ąŠčüčéčāą┐ą░ąĄčé ą┐čĆčÅą╝ąŠ ąĮą░ 12-ą▒ąĖčéąĮčŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ, ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 4..4095 |

|

| CE |

3(2) |

čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║čĆąĖčüčéą░ą╗ą╗ą░ |

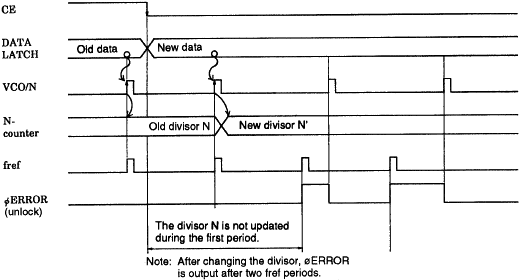

ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹčéčā ąĮąŠąČą║čā ą▓ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ ąĮčāąČąĮąŠ ą▓ą▓ąĄčüčéąĖ (DI) ąĖą╗ąĖ ą▓čŗą▓ąĄčüčéąĖ (DO) ą┤ą░ąĮąĮčŗąĄ |

|

| CL |

5(4) |

čéą░ą║čéčŗ |

ąóą░ą║čéčŗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┤ą╗čÅ ą▓ą▓ąŠą┤ą░ (DI) ąĖ ą▓čŗą▓ąŠą┤ą░ (DO) ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ |

|

| DI |

4(3) |

ą▓čģąŠą┤ ą┤ą░ąĮąĮčŗčģ |

ąÆčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ąŠčé čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą│ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą▓ LC72131 |

|

| DO |

6(5) |

ą▓čŗčģąŠą┤ ą┤ą░ąĮąĮčŗčģ |

ąÆčŗčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ąŠčé LC72131 ą▓ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ |

|

| VDD |

17(15) |

ą┐ąĖčéą░ąĮąĖąĄ |

ąØąŠąČą║ą░ ą┤ą╗čÅ ą┐ąŠą┤ą░čćąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ (VDD = 4.5 .. 5.5 ą▓ąŠą╗čīčé). ąÜąŠą│ą┤ą░ ą┐ąŠą┤ą░ąĄčéčüčÅ ą┐ąĖčéą░ąĮąĖąĄ, č鹊 ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čāąĘąĄą╗ čüą▒čĆąŠčüą░ LC72131 |

|

| VSS |

21(19) |

ąĘąĄą╝ą╗čÅ |

ą×ą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤ ąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ą▓čŗą▓ąŠą┤ ą┤ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ LC72131 |

|

~BO1

~BO2

~BO3

~BO4 |

7(6)

8(7)

9(8)

10(9) |

ą▓čŗčģąŠą┤ąĮąŠą╣ ą┐ąŠčĆčé |

1. ą¤ąŠčĆčéčŗ, čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗąĄ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░

2. ąĪąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčĆč鹊ą▓ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ ~BO1..~BO4 ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (0 - čĆą░ąĘąŠą╝ą║ąĮčāč鹊, 1 - ą╗ąŠą│. 0).

3. ąØą░ ąĮąŠąČą║čā ~BO1 ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▓ąĄą┤ąĄąĮ čüąĖą│ąĮą░ą╗ 8 ąōčå, ą┤ą╗čÅ čŹč鹊ą│ąŠ ą▒ąĖčé TBC ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1.

4. ą×čüąŠą▒ąŠąĄ ą▓ąĮąĖą╝ą░ąĮąĖąĄ ąĮčāąČąĮąŠ čāą┤ąĄą╗čÅčéčī ą▓čŗčģąŠą┤čā ~BO1, čéą░ą║ ą║ą░ą║ čā ąĮąĄčæ ą▓čŗčģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą▒ąŠą╗čīčłąĄ, č湥ą╝ čā ~BO2..~BO4.

5. ą¤čĆąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ą▓čüąĄ ą┐ąŠčĆčéčŗ ~BO1..~BO4 čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ "čĆą░ąĘąŠą╝ą║ąĮčāč鹊". |

|

~IO1

~IO2 |

11(10)

13(12) |

I/O ą┐ąŠčĆčé |

1. ąØąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ I/O, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ ą▓ą▓ąŠą┤ ąĖ ąĮą░ ą▓čŗą▓ąŠą┤ (ą┐ąŠ ą▓čŗą▒ąŠčĆčā).

2. ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ (ą▓čģąŠą┤ ąĖą╗ąĖ ą▓čŗčģąŠą┤) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ IOC1 ąĖ IOC2 (0 - ą▓čģąŠą┤ąĮąŠą╣ ą┐ąŠčĆčé, 1 - ą▓čŗčģąŠą┤ąĮąŠą╣).

3. ąÆ čüą╗čāčćą░ąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐ąŠčĆč鹊ą▓ ą║ą░ą║ ą▓čģąŠą┤ąŠą▓ ąĖčģ čüąŠčüč鹊čÅąĮąĖąĄ ą╝ąŠąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī č湥čĆąĄąĘ ąĮąŠąČą║čā DO (0 - ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī, 1 - ą▓čŗčüąŠą║ąĖą╣).

4. ąÆ čüą╗čāčćą░ąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐ąŠčĆč鹊ą▓ ą║ą░ą║ ą▓čŗčģąŠą┤ąŠą▓ ąĖčģ čüąŠčüč鹊čÅąĮąĖąĄ ą╝ąŠąČąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ IO1 ąĖ IO2 (0 - čĆą░ąĘąŠą╝ą║ąĮčāč鹊, 1 - ą╗ąŠą│. 0).

5. ą¤ąŠčüą╗ąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ čŹčéąĖ ąĮąŠąČą║ąĖ čĆą░ą▒ąŠčéą░čÄčé ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą║ą░ą║ ą▓čģąŠą┤čŗ. |

|

| PD |

18(16) |

ą▓čŗčģąŠą┤ ąĮą░ą║ą░čćą║ąĖ ąĘą░čĆčÅą┤ą░ (charge pump) |

ąÆčŗčģąŠą┤ ąĮą░ą║ą░čćą║ąĖ ąĘą░čĆčÅą┤ą░ PLL. ąÜąŠą│ą┤ą░ čćą░čüč鹊čéą░ ąŠčé ą│ąĄč鹥čĆąŠą┤ąĖąĮą░, ą▓čŗčĆą░ą▒ą░čéčŗą▓ą░ąĄą╝ą░čÅ ąŠčé ą▓čģąŠą┤ą░ FMIN ąĖ AMIN ą┐čāč鹥ą╝ ą┤ąĄą╗ąĄąĮąĖčÅ ąĮą░ N, ą▒ąŠą╗čīčłąĄ č湥ą╝ ąŠą┐ąŠčĆąĮą░čÅ čćą░čüč鹊čéą░, č鹊 ąĮą░ ą▓čŗčģąŠą┤ąĄ PD ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ą╗ąŠą│. 1. ąÉąĮą░ą╗ąŠą│ąĖčćąĮąŠ, ąĄčüą╗ąĖ ą▓čŗčĆą░ą▒ą░čéčŗą▓ą░ąĄą╝ą░čÅ ąŠčé ą│ąĄč鹥čĆąŠą┤ąĖąĮą░ čćą░čüč鹊čéą░ ą╝ąĄąĮčīčłąĄ ąŠą┐ąŠčĆąĮąŠą╣, č鹊 ąĮą░ PD ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ą╗ąŠą│. 0. ą¤čĆąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ čćą░čüč鹊čé ąĮąŠąČą║ą░ PD ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ ąŠčéą║ą╗čÄč湥ąĮąĮąŠąĄ (ą▓čŗčüąŠą║ąŠąĖą╝ą┐ąĄą┤ą░ąĮčüąĮąŠąĄ) čüąŠčüč鹊čÅąĮąĖąĄ. |

|

AIN

AOUT |

19(17)

20(18) |

čāčüąĖą╗ąĖč鹥ą╗čīąĮčŗą╣ LPF (Low Pass Filter) čéčĆą░ąĮąĘąĖčüč鹊čĆ |

n-ą║ą░ąĮą░ą╗čīąĮčŗą╣ MOS čéčĆą░ąĮąĘąĖčüč鹊čĆ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┤ą╗čÅ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čäąĖą╗čīčéčĆą░ ąĮąĖąĘą║ąĖčģ čćą░čüč鹊čé PLL |

|

| IFIN |

12(11) |

ą▓čģąŠą┤ čüč湥čéčćąĖą║ą░ čćą░čüč鹊čéčŗ IF (ą▓čģąŠą┤ čćą░čüč鹊č鹊ą╝ąĄčĆą░) |

1. ą£ąŠąČąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī čćą░čüč鹊čéčā ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 0.4 .. 12 ą£ąōčå.

2. ąÆčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĮą░ čüč湥čéčćąĖą║ IF.

3. ąĀąĄąĘčāą╗čīčéą░čé čüč湥čéą░ ą▓čŗą▓ąŠą┤ąĖčéčüčÅ čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ ą▓ą┐ąĄčĆąĄą┤ (MSB ą▒ąĖčé ą┐ąĄčĆą▓čŗą╣) čü ą┐ąŠą╝ąŠčēčīčÄ ą▓čŗą▓ąŠą┤ą░ DO.

4. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ 4 ą┐ąĄčĆąĖąŠą┤ą░ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ: 4, 8, 32 ąĖ 64 ą╝čü. |

|

[ą£ąĄč鹊ą┤čŗ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ]

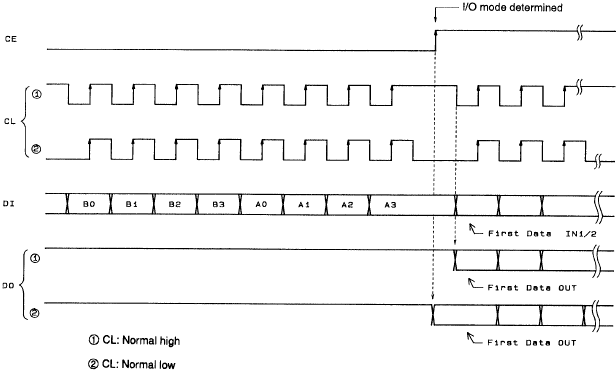

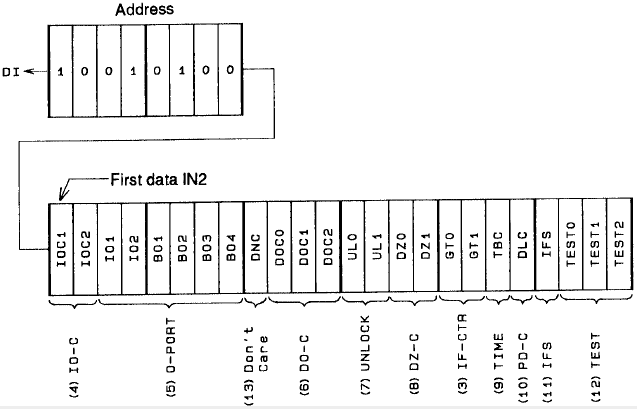

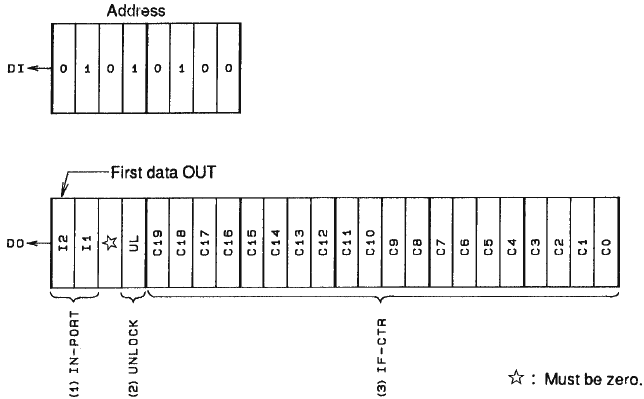

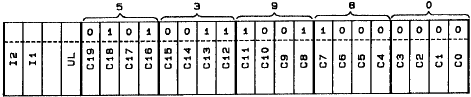

ą×ą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ LC72131 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąŠ ą┐čĆąŠč鹊ą║ąŠą╗čā Sanyo CCB (computer control bus), ąĖą╗ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮą░čÅ čłąĖąĮą░ ą░čāą┤ąĖąŠ LSI. ąÆčüąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 3 čĆąĄąČąĖą╝ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ - IN1 (ą░ą┤čĆąĄčü 0x82), IN2 (ą░ą┤čĆąĄčü 0x92), OUT (ą░ą┤čĆąĄčü 0xA2). ąÉą┤čĆąĄčü ąĘą░ą┤ą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ B0..B3, A0..A3.

|

ąĀąĄąČąĖą╝ I/O

|

ąÉą┤čĆąĄčü

|

ążčāąĮą║čåąĖčÅ

|

|

B0

|

B1

|

B2

|

B3

|

A0

|

A1

|

A2

|

A3

|

| IN1 (82h) |

0

|

0

|

0

|

1

|

0

|

1

|

0

|

0

|

- čĆąĄąČąĖą╝ ą▓ą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą▓ą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ)

- ą▓ą▓ąŠą┤ąĖčéčüčÅ 24 ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ

- čüą╝. čüčéčĆčāą║čéčāčĆčā DI Control Data (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą▓ą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ) ą┤ą╗čÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠą╣ čĆą░čüčłąĖčäčĆąŠą▓ą║ąĖ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ

|

| IN2 (92h) |

1

|

0

|

0

|

1

|

0

|

1

|

0

|

0

|

- čĆąĄąČąĖą╝ ą▓ą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą▓ą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ)

- ą▓ą▓ąŠą┤ąĖčéčüčÅ 24 ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ

- čüą╝. čüčéčĆčāą║čéčāčĆčā DI Control Data (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą▓ą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ) ą┤ą╗čÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠą╣ čĆą░čüčłąĖčäčĆąŠą▓ą║ąĖ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ |

| OUT (A2h) |

0

|

1

|

0

|

1

|

0

|

1

|

0

|

0

|

- čĆąĄąČąĖą╝ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą▓čŗą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ)

- ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▓čŗą▓ąŠą┤ąĖą╝čŗčģ ą▒ąĖčé čĆą░ą▓ąĮąŠ ą║ąŠą╗ąĖč湥čüčéą▓čā čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓

- čüą╝. čüčéčĆčāą║čéčāčĆčā DO Control Data (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą▓čŗą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ) ą┤ą╗čÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠą╣ čĆą░čüčłąĖčäčĆąŠą▓ą║ąĖ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ |

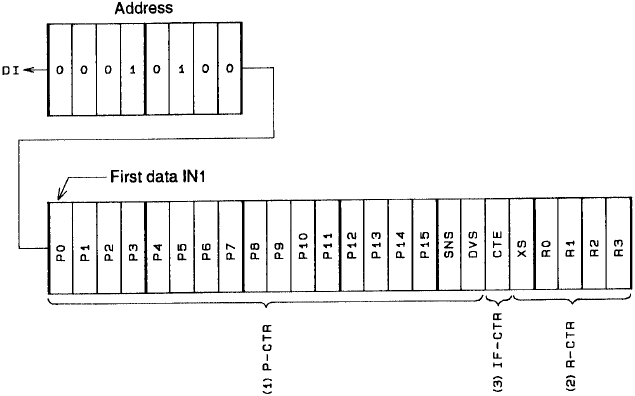

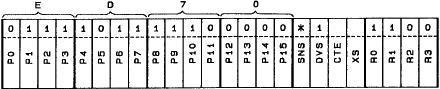

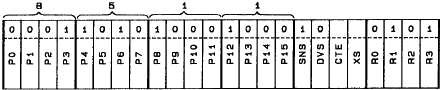

[ąĪčéčĆčāą║čéčāčĆą░ DI Control Data (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą▓ą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ)]

čĆąĄąČąĖą╝ IN1

čĆąĄąČąĖą╝ IN2

[ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ DI]

1. ąöą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą│ąŠ ą┤ąĄą╗ąĖč鹥ą╗čÅ P0..P15, ą▒ąĖčéčŗ DVS, SNS.

ąæąĖčéčŗ P0..P15 ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĄąĮąĖčÅ ą┤ąĄą╗ąĖč鹥ą╗čÅ čćą░čüč鹊čéčŗ. ąæąĖčé P15 čÅą▓ą╗čÅąĄčéčüčÅ čüčéą░čĆčłąĖą╝ (MSB). ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą╝ą╗ą░ą┤čłąĖčģ ą▒ąĖčé (LSB) ąĘą░ą▓ąĖčüąĖčé ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčé DVS ąĖ SNS (* ąĘą▓ąĄąĘą┤ąŠčćą║ą░ ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖčéą░ ąĮąĄ ąĖą│čĆą░ąĄčé čĆąŠą╗ąĖ).

DVS

|

SNS

|

LSB

|

ąÜąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ (N)

|

ąöąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ

|

| 1 |

* |

P0 |

272..65535 |

ąŻą┤ą▓ąŠąĄąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ P0..P15 |

| 0 |

1 |

P0 |

272..65535 |

ąŚąĮą░č湥ąĮąĖąĄ P0..P15 |

| 0 |

0 |

P4 |

4..4095 |

ąŚąĮą░č湥ąĮąĖąĄ P4..P15 |

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: čüąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖčé P0..P3 ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą╝ą╗ą░ą┤čłąĖą╝ ą▒ąĖč鹊ą╝ (LSB) čÅą▓ą╗čÅąĄčéčüčÅ ą▒ąĖčé P4.

ąÜčĆąŠą╝ąĄ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ, ą▒ąĖčéčŗ DVS ąĖ SNS ą▓ą╗ąĖčÅčÄčé ąĮą░ ą▓čŗą▒ąŠčĆ ą▓čģąŠą┤ą░ ą┤ąĄą╗ąĖč鹥ą╗čÅ čćą░čüč鹊čéčŗ (AMIN ąĖą╗ąĖ FMIN) ąĖ čĆą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ čćą░čüč鹊čé.

DVS

|

SNS

|

ą▓čģąŠą┤ ą┤ąĄą╗ąĖč鹥ą╗čÅ čćą░čüč鹊čéčŗ

|

čĆą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ čćą░čüč鹊čé |

| 1 |

* |

FMIN |

10..160 ą£ąōčå |

| 0 |

1 |

AMIN |

2..40 ą£ąōčå |

| 0 |

0 |

AMIN |

0.5..10 ą£ąōčå |

2. ąöąĄą╗ąĖč鹥ą╗čī ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ, ą▒ąĖčéčŗ R0..R3. ąæąĖčé ą▓čŗą▒ąŠčĆą░ čćą░čüč鹊čéčŗ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ čĆąĄąĘąŠąĮą░č鹊čĆą░ XS.

ąÆ ą▒ąĖčéčŗ R0..R3 ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ (fref). ą×ą┐ąŠčĆąĮą░čÅ čćą░čüč鹊čéą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čłą░ą│ ą┐ąĄčĆąĄčüčéčĆąŠą╣ą║ąĖ čüąĖąĮč鹥ąĘą░č鹊čĆą░ čćą░čüč鹊čéčŗ. ąó. ąĄ., ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ ą╝ą░ą│ąĮąĖč鹊ą╗čŗ RX-ES20 ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ FM (87.5..108 ą£ąōčå) ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ fref = 25 ą║ąōčå, čćč鹊 ąŠąĘąĮą░čćą░ąĄčé čłą░ą│ ą┐ąĄčĆąĄčüčéčĆąŠą╣ą║ąĖ čćą░čüč鹊čéčŗ 50 ą║ąōčå (čéą░ą║ ą║ą░ą║ ą▓ą║ą╗čÄč湥ąĮ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čī ąĮą░ 2), ą░ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ AM (522..1629 ą║ąōčå) ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ fref = 9 ą║ąōčå, čćč鹊 ąŠąĘąĮą░čćą░ąĄčé čłą░ą│ ą┐ąĄčĆąĄčüčéčĆąŠą╣ą║ąĖ čćą░čüč鹊čéčŗ 9 ą║ąōčå.

R3

|

R2

|

R1

|

R0

|

ą×ą┐ąŠčĆąĮą░čÅ čćą░čüč鹊čéą░ (ą║ąōčå)

|

| 0 |

0 |

0 |

0 |

100 |

| 0 |

0 |

0 |

1 |

50 |

| 0 |

0 |

1 |

0 |

25 |

| 0 |

0 |

1 |

1 |

25 |

| 0 |

1 |

0 |

0 |

12.5 |

| 0 |

1 |

0 |

1 |

6.25 |

| 0 |

1 |

1 |

0 |

3.125 |

| 0 |

1 |

1 |

1 |

3.125 |

| 1 |

0 |

0 |

0 |

10 |

| 1 |

0 |

0 |

1 |

9 |

| 1 |

0 |

1 |

0 |

5 |

| 1 |

0 |

1 |

1 |

1 |

| 1 |

1 |

0 |

0 |

3 |

| 1 |

1 |

0 |

1 |

15 |

| 1 |

1 |

1 |

0 |

ąĘą░ą┐čĆąĄčé PLL, ąŠčüčéą░ąĮąŠą▓ Xtal OSC |

| 1 |

1 |

1 |

1 |

ąĘą░ą┐čĆąĄčé PLL |

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ:ąĘą░ą┐čĆąĄčé PLL ą▒ą╗ąŠą║ąĖčĆčāąĄčé ą┤ąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ ąĖ čüč湥čéčćąĖą║ IF (čćą░čüč鹊č鹊ą╝ąĄčĆ), ą┐čĆąĖ čŹč鹊ą╝ ąĮąŠąČą║ąĖ FMIN, AMIN, IFIN čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą▓ pull-down čüąŠčüč鹊čÅąĮąĖąĄ (ą┐ąŠą┤čéčÅąČą║ą░ ą║ ąĘąĄą╝ą╗ąĄ), ąĖ ąĮąŠąČą║ą░ ąĮą░ą║ą░čćą║ąĖ ąĘą░čĆčÅą┤ą░ čäą░ąĘąŠą▓ąŠą│ąŠ ą┤ąĄč鹥ą║č鹊čĆą░ PD ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčüąŠą║ąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ (ąŠčéą║ą╗čÄč湥ąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ).

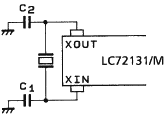

ąæąĖčé XS ą▓čŗą▒ąĖčĆą░ąĄčé čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ čĆąĄąĘąŠąĮą░č鹊čĆą░. ąĢčüą╗ąĖ XS=0, č鹊 ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ą▓ą░čĆčå ąĮą░ 4.5 ą£ąōčå, ą░ ąĄčüą╗ąĖ XS=1, č鹊 ąĮčāąČąĄąĮ ą║ą▓ą░čĆčå ąĮą░ 7.2 ą£ąōčå. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą▓čŗą▒čĆą░ąĮą░ čćą░čüč鹊čéą░ ą║ą▓ą░čĆčåą░ 7.2 ą£ąōčå.

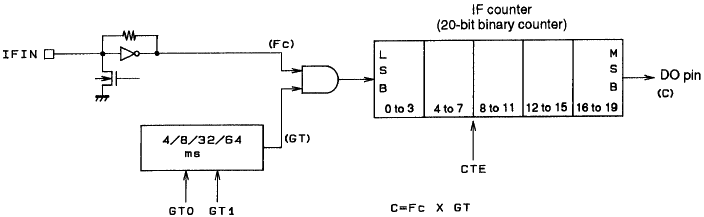

3. ąöą░ąĮąĮčŗąĄ ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ ąĖ ąĘą░ą┐čāčüą║ą░ čćą░čüč鹊č鹊ą╝ąĄčĆą░ IF - ą▒ąĖčéčŗ CTE, GT0, GT1. ąĪą╝. čéą░ą║ąČąĄ IFS.

ąæąĖčé CTE ąĮčāąČąĄąĮ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ čćą░čüč鹊č鹊ą╝ąĄčĆą░. ąĢčüą╗ąĖ CTE=1, č鹊 čüč湥čéčćąĖą║ čćą░čüč鹊č鹊ą╝ąĄčĆą░ ąĘą░ą┐čāčüą║ą░ąĄčé čüč湥čé, ąĄčüą╗ąĖ CTE=0, č鹊 čüč湥čéčćąĖą║ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ.

ąæąĖčéčŗ GT0 ąĖ GT1 ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé ą┐ąĄčĆąĖąŠą┤ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░ IF.

GT1

|

GT0 |

ąÆčĆąĄą╝čÅ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ, ą╝čü

|

ąÆčĆąĄą╝čÅ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą╝čü

|

| 0 |

0 |

4 |

3..4 |

| 0 |

1 |

8 |

3..4 |

| 1 |

0 |

32 |

7..8 |

| 1 |

1 |

64 |

7..8 |

ąöą╗čÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. "ąĪčéčĆčāą║čéčāčĆą░ čüč湥čéčćąĖą║ą░ IF".

4. ąĀąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ~IO1 ąĖ ~IO2, ą▒ąĖčéčŗ IOC1 ąĖ IOC2.

ąŚą░ą┐ąĖčüčī ą▓ čŹčéąĖ ą▒ąĖčéčŗ 0 ą┐ąĄčĆąĄą║ą╗čÄčćą░čÄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą┐ąŠčĆčé ą▓ čĆąĄąČąĖą╝ ą▓ą▓ąŠą┤ą░, ąĘą░ą┐ąĖčüčī 1 - ą▓ čĆąĄąČąĖą╝ ą▓čŗą▓ąŠą┤ą░. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, ą┐ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ čŹčéąĖ ą┐ąŠčĆčéčŗ čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ ą▓čģąŠą┤čŗ.

5. ąöą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą▓čŗčģąŠą┤ąĮčŗčģ ą┐ąŠčĆč鹊ą▓, ą▒ąĖčéčŗ BO1..BO4, IO1, IO2. ąĪą╝. čéą░ą║ąČąĄ IOC1, IOC2.

ąÆ čŹčéąĖčģ ą▒ąĖčéą░čģ čüąŠą┤ąĄčƹȹ░čéčüčÅ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┐ąŠčĆčéą░. ąĢčüą╗ąĖ ą▓ ą▒ąĖčé ąĘą░ą┐ąĖčüą░ąĮ 0, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▓čŗčģąŠą┤ ą┐ąŠčĆčéą░ čĆą░ąĘąŠą╝ą║ąĮčāčé (ą║ą╗čÄčć ąĮąĄ ą┐čĆąŠą▓ąŠą┤ąĖčé č鹊ą║), ą░ ąĄčüą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮ 1, ąĮąŠ ąĮą░ ą▓čŗčģąŠą┤ąĄ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī (ą║ą╗čÄčć ą┐čĆąŠą▓ąŠą┤ąĖčé č鹊ą║). ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, ą┐ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą▓ čŹčéąĖ ą▒ąĖčéčŗ ąĘą░ą┐ąĖčüą░ąĮ 0 (ą▓čüąĄ ą▓čŗčģąŠą┤ąĮčŗąĄ ą║ą╗čÄčćąĖ ą▓ čĆą░ąĘąŠą╝ą║ąĮčāč鹊ą╝ čüąŠčüč鹊čÅąĮąĖąĖ).

6. ąæąĖčéčŗ DOC0, DOC1, DOC2 ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄą╝ ą▓čŗą▓ąŠą┤ą░ DO. ąĪą╝. čéą░ą║ąČąĄ UL0, UL1, CTE, IOC1, IOC2.

DOC2

|

DOC1

|

DOC0

|

čüąŠčüč鹊čÅąĮąĖąĄ ąĮąŠąČą║ąĖ DO

|

| 0 |

0 |

0 |

čĆą░ąĘąŠą╝ą║ąĮčāč鹊 |

| 0 |

0 |

1 |

ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ čüąŠčüč鹊čÅąĮąĖąĄ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (unlock state) |

| 0 |

1 |

0 |

end-UC - ą┐čĆąŠą▓ąĄčĆą║ą░ ąŠą║ąŠąĮčćą░ąĮąĖčÅ čüč湥čéą░ čüč湥čéčćąĖą║ą░ IF (čćą░čüč鹊č鹊ą╝ąĄčĆ) |

| 0 |

1 |

1 |

čĆą░ąĘąŠą╝ą║ąĮčāč鹊 |

| 1 |

0 |

0 |

čĆą░ąĘąŠą╝ą║ąĮčāč鹊 |

| 1 |

0 |

1 |

čüąŠčüč鹊čÅąĮąĖąĄ ąĮąŠąČą║ąĖ ~IO1. ą¤ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ čĆą░ąĘąŠą╝ą║ąĮčāč鹊, ąĄčüą╗ąĖ ąĮąŠąČą║ą░ ~IO1 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗčģąŠą┤ąĮąŠą╣ ą┐ąŠčĆčé. |

| 1 |

1 |

0 |

čüąŠčüč鹊čÅąĮąĖąĄ ąĮąŠąČą║ąĖ ~IO2. ą¤ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ čĆą░ąĘąŠą╝ą║ąĮčāč鹊, ąĄčüą╗ąĖ ąĮąŠąČą║ą░ ~IO2 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗčģąŠą┤ąĮąŠą╣ ą┐ąŠčĆčé. |

| 1 |

1 |

1 |

čĆą░ąĘąŠą╝ą║ąĮčāč鹊 |

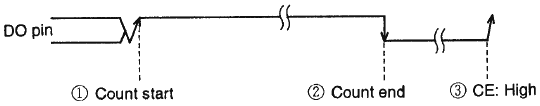

ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé čüąĖą│ąĮą░ą╗ end-UC (ą┐čĆąŠą▓ąĄčĆą║ą░ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čüč湥čéą░ čüč湥čéčćąĖą║ą░ IF ą▓ čćą░čüč鹊č鹊ą╝ąĄčĆąĄ):

(1) ą║ąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ end-UC čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖ čüč湥čéčćąĖą║ IF ąĮą░čćą░ą╗ čüč湥čé (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ ą▒ąĖčéą░ CTE ąĖąĘ 0 ą▓ 1), ąĮąŠąČą║ą░ DO ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ čĆą░ąĘąŠą╝ą║ąĮčāč鹊.

(2) ą║ąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮčŗą╣ čüč湥čé čüč湥čéčćąĖą║ą░ IF, ąĮąŠąČą║ą░ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 0, ą┐ąŠą║ą░ąĘčŗą▓ą░čÅ čŹčéąĖą╝, čćč鹊 ą┐čĆąŠčåąĄčüčü čüč湥čéą░ ąĘą░ą▓ąĄčĆčłąĄąĮ.

(3) ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ą▓ąŠą┤ą░-ą▓čŗą▓ąŠą┤ą░ (ąĮąŠąČą║ą░ CE ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1) ąĮąŠąČą║ą░ DO ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ čĆą░ąĘąŠą╝ą║ąĮčāč鹊.

ąÆąĮąĖą╝ą░ąĮąĖąĄ! ąĪąŠčüč鹊čÅąĮąĖąĄ ąĮąŠąČą║ąĖ DO ą▒čāą┤ąĄčé čĆą░ąĘąŠą╝ą║ąĮčāč鹊 ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓ą▓ąŠą┤ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (ą▓ čĆąĄąČąĖą╝ą░čģ IN1 ąĖą╗ąĖ IN2 ą┐čĆąĖ čüąŠčüč鹊čÅąĮąĖąĖ CE ą▓ ą╗ąŠą│. 1), ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ ą┤ą░ąĮąĮčŗčģ DOC0..DOC2. ąóą░ą║ąČąĄ ąĮąŠąČą║ą░ DO ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ (čĆąĄąČąĖą╝ OUT ą┐čĆąĖ čüąŠčüč鹊čÅąĮąĖąĖ CE ą▓ ą╗ąŠą│. 1) ą▒čāą┤ąĄčé ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčéčī ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĄą╣ ą┐ąŠ ąĮąŠąČą║ąĄ CL, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ ą┤ą░ąĮąĮčŗčģ DOC0..DOC2.

7. ąöą░ąĮąĮčŗąĄ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ (unlock detection) UL0, UL1. ąĪą╝. čéą░ą║ąČąĄ DOC0, DOC1, DOC2.

ąŁčéąĖ ą▒ąĖčéčŗ ą▓čŗą▒ąĖčĆą░čÄčé ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ čäą░ąĘčŗ (fiE) ą┤ą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ ąĘą░čģą▓ą░čéą░ PLL. ążą░ąĘąŠą▓ą░čÅ ąŠčłąĖą▒ą║ą░ čüą▓čŗčłąĄ čāą║ą░ąĘą░ąĮąĮąŠą╣ čłąĖčĆąĖąĮčŗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ ą║ą░ą║ čüąŠčüč鹊čÅąĮąĖąĄ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ.

UL1

|

UL0

|

čłąĖčĆąĖąĮą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ fiE

|

ą▓čŗčģąŠą┤ ą┤ąĄč鹥ą║č鹊čĆą░

|

| 0 |

0 |

ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ |

čĆą░ąĘąŠą╝ą║ąĮčāč鹊 |

| 0 |

1 |

0 |

fiE ą▓čŗą▓ąŠą┤ąĖčéčüčÅ ąĮą░ą┐čĆčÅą╝čāčÄ |

| 1 |

0 |

+- 0.55 ą╝ą║čü |

fiE čĆą░čüčłąĖčĆčÅąĄčéčüčÅ ąĮą░ 1..2 ą╝čü |

| 1 |

1 |

+- 1.11 ą╝ą║čü |

fiE čĆą░čüčłąĖčĆčÅąĄčéčüčÅ ąĮą░ 1..2 ą╝čü |

ąÆ čüąŠčüč鹊čÅąĮąĖąĖ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ąĮąŠąČą║ą░ DO ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0 ąĖ ą▒ąĖčé UL ą▓ ą┐ąŠč鹊ą║ąĄ ą▓čŗą▓ąŠą┤ąĖą╝čŗčģ ą┤ą░ąĮąĮčŗčģ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0.

8. ąŻą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ čäą░ąĘčŗ - ą▒ąĖčéčŗ DZ0, DZ1.

ąŁčéąĖ ą▒ąĖčéčŗ čāą┐čĆą░ą▓ą╗čÅčÄčé ą╝ąĄčĆčéą▓ąŠą╣ ąĘąŠąĮąŠą╣ čäą░ąĘąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░.

| DZ1 |

DZ0 |

ąĀąĄąČąĖą╝ ą┤ą╗čÅ ą╝ąĄčĆčéą▓ąŠą╣ ąĘąŠąĮčŗ

|

| 0 |

0 |

DZA |

| 0 |

1 |

DZB |

| 1 |

0 |

DZC |

| 1 |

1 |

DZD |

ą©ąĖčĆąĖąĮą░ ą╝ąĄčĆčéą▓ąŠą╣ ąĘąŠąĮčŗ DZA < DZB < DZC < DZD

9. ąÆčŗą▓ąŠą┤ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ 8 ąōčå - ą▒ąĖčé TBC (Time Base Clock). ąĪą╝. čéą░ą║ąČąĄ BO1.

ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčé TBC ą▓ ą╗ąŠą│. 1, č鹊 ąĮą░ ą▓čŗčģąŠą┤ąĄ ~BO1 ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ čüąĖą│ąĮą░ą╗ 8 ąōčå (čćą░čüč鹊čéą░ ą▓čŗčĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ ąŠčé ą║ą▓ą░čĆčåą░) čü ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą╝ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ 40%. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖčéą░ BO1 ąĮąĄ ąĖą│čĆą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ.

10. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗčģąŠą┤ąŠą╝ ąĮą░ą║ą░čćą║ąĖ ąĘą░čĆčÅą┤ą░ PD - ą▒ąĖčé DLC (DeadLock Clean).

ąĢčüą╗ąĖ DLC=0, č鹊 ą▓čŗčģąŠą┤ ąĮą░ą║ą░čćą║ąĖ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ąŠą▒čŗčćąĮąŠ, ąĄčüą╗ąĖ DLC=1, č鹊 ąĮą░ ą▓čŗčģąŠą┤ąĄ ą╗ąŠą│. 0. ąĢčüą╗ąĖ ą▓ąŠąĘąĮąĖą║ą░ąĄčé ą╝ąĄčĆčéą▓ą░čÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ą░ (deadlock), ąĮą░ą┐čĆąĖą╝ąĄčĆ ą┐ąŠ ą┐čĆąĖčćąĖąĮąĄ ą┐ąŠąĮąĖąČąĄąĮąĖčÅ ą┤ąŠ ąĮčāą╗čÅ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VCO (Vtune) ąĖ ąŠčüčéą░ąĮąŠą▓ą║ąĖ ą│ąĄąĮąĄčĆą░č鹊čĆą░ VCO, deadlock ą╝ąŠąČąĄčé ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą┐čāč鹥ą╝ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ą░ ą▓čŗčģąŠą┤ą░ ąĮą░ą║ą░čćą║ąĖ ąĘą░čĆčÅą┤ą░ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĖ čāčüčéą░ąĮąŠą▓ą║ąĖ Vtune ąĮą░ čāčĆąŠą▓ąĄąĮčī VCC (čŹč鹊 čāąĘąĄą╗ ąŠčćąĖčüčéą║ąĖ deadlock).

11. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüč湥čéčćąĖą║ąŠą╝ IF (čćą░čüč鹊č鹊ą╝ąĄčĆ) - ą▒ąĖčé IFS.

ąÆ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ čŹč鹊čé ą▒ąĖčé ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčī IFS ą▓ 0, č鹊 čüąĖčüč鹥ą╝ą░ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ čāą╝ąĄąĮčīčłąĄąĮąĖčÅ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ, ąĖ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī čüąĮąĖąČą░ąĄčéčüčÅ čü 10 ą┤ąŠ 300 mVrms. ąĪą╝. ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ "IF Counter Operation".

12. ąóąĄčüč鹊ą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ LSI - ą▒ąĖčéčŗ TEST0..TEST3.

ąÆčüąĄ ą▒ąĖčéčŗ TEST0..TEST3 ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 0. ąŁčéąĖ ą▒ąĖčéčŗ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓ 0 ą┐ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ.

13. ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą▒ąĖčé DNC, ąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 0.

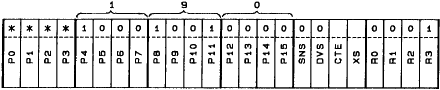

[ąĪčéčĆčāą║čéčāčĆą░ DO Output Data (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą▓čŗą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ)]

čĆąĄąČąĖą╝ OUT

1. ąöą░ąĮąĮčŗąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ - ą▒ąĖčéčŗ I1, I2. ąĪą╝. čéą░ą║ąČąĄ IOC1, IOC2.

ąĪąŠčüč鹊čÅąĮąĖąĄ čŹčéąĖčģ ą▒ąĖčé ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ čü čüąŠčüč鹊čÅąĮąĖčÅ ąĮąŠąČąĄą║ IO1 ąĖ IO2 ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░. ąÆąĄą╗ąĖčćąĖąĮčŗ ą▒ąĖčé I1 ąĖ I2 ą┐ąŠą▓č鹊čĆčÅčÄčé čüąŠčüč鹊čÅąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ąĮąŠąČą║ą░čģ ą┐ąŠčĆč鹊ą▓ ~IO1 ąĖ ~IO2, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ ą║ą░ą║ ąŠąĮąĖ ąĮą░čüčéčĆąŠąĄąĮčŗ - ąĮą░ ą▓čģąŠą┤ ąĖą╗ąĖ ąĮą░ ą▓čŗčģąŠą┤.

2. ąöą░ąĮąĮčŗąĄ ąŠ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĖąĖ PLL - ą▒ąĖčé UL (PLL unlock). ąĪą╝. čéą░ą║ąČąĄ UL0, UL1.

ąĢčüą╗ąĖ UL=0, č鹊 ąŠąĘąĮą░čćą░ąĄčé čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąŠ, ąĄčüą╗ąĖ UL=1, č鹊 ąĘąĮą░čćąĖčé ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąŠ ąĖą╗ąĖ ą░ą║čéąĖą▓ąĄąĮ čĆąĄąČąĖą╝ ąŠčüčéą░ąĮąŠą▓ą║ąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ.

3. ąöą▓ąŠąĖčćąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čüąŠ čüč湥čéčćąĖą║ą░ IF (čćą░čüč鹊č鹊ą╝ąĄčĆ) - ą▒ąĖčéčŗ C19..C0. ąĪą╝. čéą░ą║ąČąĄ CTE, GT0, GT1.

ąŁčéąĖ 20 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ čü ą▓čŗčģąŠą┤ą░ čüč湥čéčćąĖą║ą░ IF. ąĪ19 čüčéą░čĆčłąĖą╣ ą▒ąĖčé (MSB), ąĪ0 ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé (LSB).

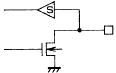

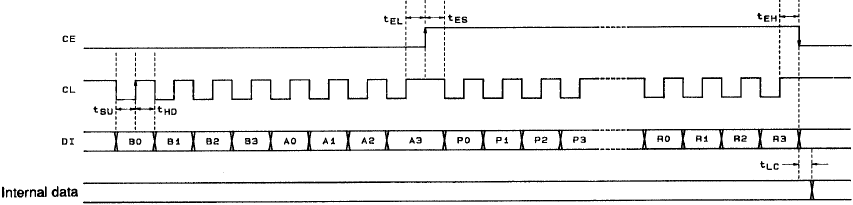

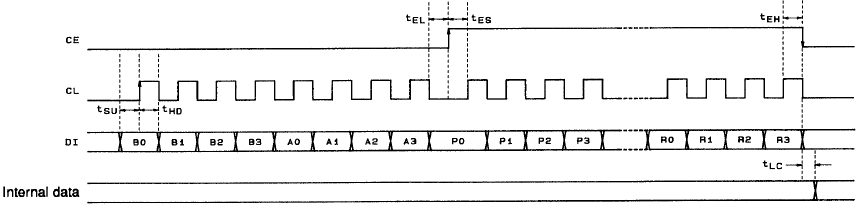

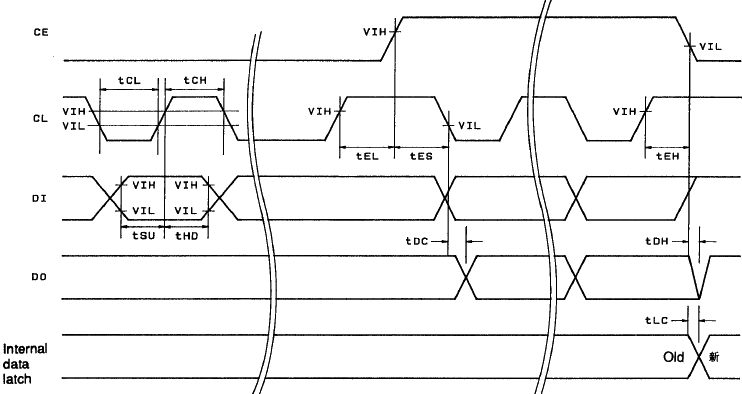

[ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą▓ą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ (IN1/IN2) tSU, tHD, tEL, tES, tEH >= 0.75 ą╝ą║čü, tLC < = 0.75 ą╝ą║čü]

CL ą▓ ąĖčüčģąŠą┤ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1

CL ą▓ ąĖčüčģąŠą┤ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0

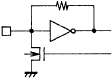

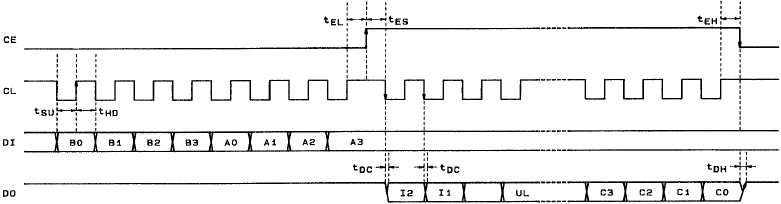

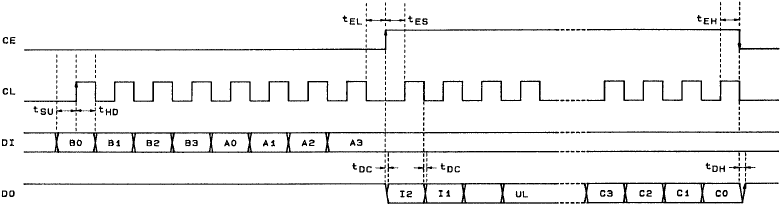

[ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą▓čŗą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ (OUT) tSU, tHD, tEL, tES, tEH >= 0.75 ą╝ą║čü, tDC, tDH < = 0.35 ą╝ą║čü]

CL ą▓ ąĖčüčģąŠą┤ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1

CL ą▓ ąĖčüčģąŠą┤ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠčüą║ąŠą╗čīą║čā ąĮąŠąČą║ą░ DO čÅą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝ ąĮą░ n-ą║ą░ąĮą░ą╗čīąĮąŠą╝ ą┐ąŠą╗ąĄą▓ąŠą╝ čéčĆą░ąĮąĘąĖčüč鹊čĆąĄ, ą▓čĆąĄą╝čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ (tDC ąĖ tDH) ą▒čāą┤čāčé ąŠčéą╗ąĖčćą░čéčīčüčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ ąĮąŠą╝ąĖąĮą░ą╗ą░ pull-up čĆąĄąĘąĖčüč鹊čĆą░ ąĖ ą┐ą░čĆą░ąĘąĖčéąĮąŠą╣ ąĄą╝ą║ąŠčüčéąĖ ą┤ąŠčĆąŠąČąĄą║ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ.

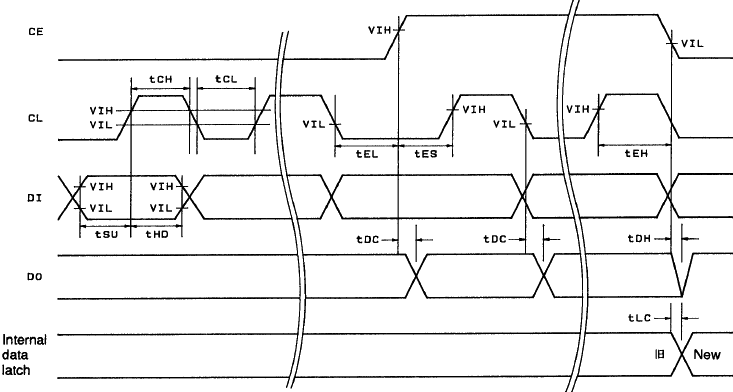

[ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ]

ąÜąŠą│ą┤ą░ CL ą▓ ą┐ą░čāąĘą░čģ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0

ąÜąŠą│ą┤ą░ CL ą▓ ą┐ą░čāąĘą░čģ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1

ą¤ą░čĆą░ą╝ąĄčéčĆ

|

ąĪąĖą╝ą▓ąŠą╗

|

ąØąŠąČą║ąĖ

|

ąŻčüą╗ąŠą▓ąĖčÅ

|

MIN

|

ąĮąŠčĆą╝

|

MAX

|

ąĄą┤ąĖąĮąĖčåčŗ

|

| ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┤ą░ąĮąĮčŗčģ |

tSU |

DI, CL |

|

0.75 |

|

|

ą╝ą║čü |

| ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ |

tHD |

DI, CL |

|

0.75 |

|

|

ą╝ą║čü |

| ąÆčĆąĄą╝čÅ čéą░ą║čéą░ ąĮą░ ą╗ąŠą│. 0 |

tCL |

CL |

|

0.75 |

|

|

ą╝ą║čü |

| ąÆčĆąĄą╝čÅ čéą░ą║čéą░ ąĮą░ ą╗ąŠą│. 1 |

tCH |

CL |

|

0.75 |

|

|

ą╝ą║čü |

| ąÆčĆąĄą╝čÅ ąŠąČąĖą┤ą░ąĮąĖčÅ CE |

tEL |

CE, CL |

|

0.75 |

|

|

ą╝ą║čü

|

| ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ CE |

tES |

CE, CL |

|

0.75 |

|

|

ą╝ą║čü |

| ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ CE |

tEH |

CE, CL |

|

0.75 |

|

|

ą╝ą║čü |

| ąÆčĆąĄą╝čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ąĘą░čēąĄą╗ą║ąĖ |

tLC |

|

|

|

|

0.75 |

ą╝ą║čü |

| ąÆčĆąĄą╝čÅ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ |

tDC |

DO, CL |

ą£ąŠąČąĄčé ą╝ąĄąĮčÅčéčīčüčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓ąĄą╗ąĖčćąĖąĮčŗ pull-up čĆąĄąĘąĖčüč鹊čĆą░ ąĖ ąĄą╝ą║ąŠčüčéąĖ PCB ą╝ąŠąĮčéą░ąČą░. |

|

|

0.35 |

ą╝ą║čü |

| tDH |

DO, CE |

[ąĪčéčĆčāą║čéčāčĆą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą│ąŠ ą┤ąĄą╗ąĖč鹥ą╗čÅ]

DVS

|

SNS

|

ą▓čģąŠą┤ |

ą┤ąĄą╗ąĖč鹥ą╗čī

|

ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮčŗą╣

ą║ąŠčŹčä. ą┤ąĄą╗ąĄąĮąĖčÅ N

|

ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą▓čģ. čćą░čüč鹊čé

ą£ąōčå

|

| 1 |

* |

FMIN |

272..65535 |

čāą┤ą▓ąŠąĄąĮąĮą░čÅ ą▓ąĄą╗ąĖčćąĖąĮą░ ą┤ąĄą╗ąĖč鹥ą╗čÅ |

10..160 |

| 0 |

1 |

AMIN |

272..65535 |

ą▓ąĄą╗ąĖčćąĖąĮą░ ą┤ąĄą╗ąĖč鹥ą╗čÅ |

2..40 |

| 0 |

0 |

AMIN |

4..4095 |

ą▓ąĄą╗ąĖčćąĖąĮą░ ą┤ąĄą╗ąĖč鹥ą╗čÅ |

0.5..10 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: * - čüąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖčéą░ SNS ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ.

[ą¤čĆąĖą╝ąĄčĆčŗ čĆą░čüč湥čéą░ ą┤ąĄą╗ąĖč鹥ą╗čÅ]

1. ąöąĖą░ą┐ą░ąĘąŠąĮ FM, čłą░ą│ ą┐ąĄčĆąĄčüčéčĆąŠą╣ą║ąĖ 50 ą║ąōčå (DVS=1,SNS=*, ą▓čģąŠą┤ FMIN). ą¦ą░čüč鹊čéą░ ą┐čĆąĖąĄą╝ą░ FM RF = 90 ą£ąōčå (IF= +10.7 ą£ąōčå), čćą░čüč鹊čéą░ ą│ąĄč鹥čĆąŠą┤ąĖąĮą░ FM VCO = 100.7 ą£ąōčå, PLL fref = 25 ą║ąōčå (R0=1, R1=1, R2=0, R3=0).

ąÜąŠčŹčäčäąĖčåąĖąĄąĮčé, ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗą╣ ą▓ P0..P15 čĆą░ą▓ąĄąĮ (ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą┤ąĄą╗ąĖą╝ ąĮą░ 2, čéą░ą║ ą║ą░ą║ čĆą░ą▒ąŠčéą░ąĄčé ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī ąĮą░ 2):

FM VCO / (fref * 2) = 100700 / (25*2) = 2014 (07DEh).

2. ąöąĖą░ą┐ą░ąĘąŠąĮ SW (ą║ąŠčĆąŠčéą║ąĖąĄ ą▓ąŠą╗ąĮčŗ), čłą░ą│ ą┐ąĄčĆąĄčüčéčĆąŠą╣ą║ąĖ 5 ą║ąōčå (DVS=0, SNS=1, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AMIN, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ ą▓ čĆąĄąČąĖą╝ąĄ ą▓čŗčüąŠą║ąĖčģ čćą░čüč鹊čé). ą¦ą░čüč鹊čéą░ ą┐čĆąĖąĄą╝ą░ SW RF = 21.75 ą£ąōčå (IF= +450 ą║ąōčå), čćą░čüč鹊čéą░ ą│ąĄč鹥čĆąŠą┤ąĖąĮą░ SW VCO = 22.20 ą£ąōčå, PLL fref = 5 ą║ąōčå (R0=0, R1=1, R2=0, R3=1).

ąÜąŠčŹčäčäąĖčåąĖąĄąĮčé, ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗą╣ ą▓ P0..P15 čĆą░ą▓ąĄąĮ:

SW VCO / fref = 22200 / 5 = 4440 (1158h).

3. ąöąĖą░ą┐ą░ąĘąŠąĮ MW (čüčĆąĄą┤ąĮąĖąĄ ą▓ąŠą╗ąĮčŗ), čłą░ą│ ą┐ąĄčĆąĄčüčéčĆąŠą╣ą║ąĖ 10 ą║ąōčå (DVS=0, SNS=0, ą▓čŗą▒čĆą░ąĮ AMIN, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąĮąĖąĘą║ąĖčģ čćą░čüč鹊čé). ą¦ą░čüč鹊čéą░ ą┐čĆąĖąĄą╝ą░ MW RF = 1000 ą║ąōčå (IF= +450 ą║ąōčå), čćą░čüč鹊čéą░ ą│ąĄč鹥čĆąŠą┤ąĖąĮą░ MW VCO = 1450 ą║ąōčå.

ąÜąŠčŹčäčäąĖčåąĖąĄąĮčé, ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗą╣ ą▓ P0..P15 čĆą░ą▓ąĄąĮ:

MW VCO / fref = 1450 / 10 = 145 (091h).

[ąĪčéčĆčāą║čéčāčĆą░ čćą░čüč鹊č鹊ą╝ąĄčĆą░ (IF Counter)]

ą¦ą░čüč鹊č鹊ą╝ąĄčĆ, ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ LC72131, ąŠčüąĮąŠą▓ą░ąĮ ąĮą░ 20-ą▒ąĖčéąĮąŠą╝ ą┤ą▓ąŠąĖčćąĮąŠą╝ čüč湥čéčćąĖą║ąĄ IF. ąĀąĄąĘčāą╗čīčéą░čé ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ (čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čüč湥čéčćąĖą║ą░) ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ č湥čĆąĄąĘ ąĮąŠąČą║čā DO.

GT1

|

GT2

|

ą▓čĆąĄą╝čÅ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ

|

ą┐ąĄčĆąĖąŠą┤ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ (GT), ą╝čü

|

ą▓čĆąĄą╝čÅ ąŠąČąĖą┤ą░ąĮąĖčÅ (twu), ą╝čü |

| 0 |

0 |

4 |

3..4 |

| 0 |

1 |

8 |

3..4 |

| 1 |

0 |

32 |

7..8 |

| 1 |

1 |

64 |

7..8 |

ą¦ą░čüč鹊čéą░ ąĮą░ ą▓čģąŠą┤ąĄ IF (Fc) ąĖąĘą╝ąĄčĆčÅąĄčéčüčÅ ą┐čāč鹥ą╝ ą┐ąŠą┤čüč湥čéą░ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ąĖą╝ą┐čāą╗čīčüąŠą▓ (C), ą┐ąŠą┤čüčćąĖčéą░ąĮąĮčŗčģ čüč湥čéčćąĖą║ąŠą╝ IF ąĘą░ ą▓čŗą▒čĆą░ąĮąĮčŗą╣ ą┐ąĄčĆąĖąŠą┤ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ (GT).

ąĪ

Fc = ----

GT

[ą¤čĆąĖą╝ąĄčĆčŗ čĆą░čüč湥čéą░ čćą░čüč鹊čéčŗ ą┐ąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠą╝čā čüč湥čéčćąĖą║ą░]

1. ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĖąŠą┤ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ (GT) 32 ą╝čü, čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čüč湥čéčćąĖą║ą░ (C) čĆą░ą▓ąĮąŠ 342400 (53980 hex):

IF čćą░čüč鹊čéą░ (Fc) = 342400 / 32 ą╝čü = 10.7 ą£ąōčå

2. ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĖąŠą┤ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ (GT) 8 ą╝čü, čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čüč湥čéčćąĖą║ą░ (C) čĆą░ą▓ąĮąŠ 3600 (E10 hex):

IF čćą░čüč鹊čéą░ (Fc) = 3600 / 8 ą╝čü = 450 ą║ąōčå

[ąĀą░ą▒ąŠčéą░ čćą░čüč鹊č鹊ą╝ąĄčĆą░ (IF Counter Operation)]

ą¤ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ čüč湥čéčćąĖą║ą░ IF ąĄą│ąŠ ąĮčāąČąĮąŠ ąĘą░čĆą░ąĮąĄąĄ čüą▒čĆąŠčüąĖčéčī, čāčüčéą░ąĮąŠą▓ąĖą▓ ą▒ąĖčé CTE ą▓ 0. ąæąĖčé CTE ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ ą┐ąŠč鹊ą║ąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (čĆąĄąČąĖą╝ IN1). ąĪč湥čéčćąĖą║ IF ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┐čĆąĖ čāčüčéą░ąĮąŠą▓ą║ąĄ ą▒ąĖčéą░ CTE ą▓ 1. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ LC72131, ą║ąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ CE ą┐ą░ą┤ą░ąĄčé ąŠčé ą╗ąŠą│. 1 ą┤ąŠ ą╗ąŠą│. 0. ąśąĘą╝ąĄčĆčÅąĄą╝čŗą╣ čüąĖą│ąĮą░ą╗ IF ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą░ąĮ ąĮą░ ąĮąŠąČą║čā IFIN ą▓ ą┐ąĄčĆąĖąŠą┤ ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąĄąČą┤čā čüą┐ą░ą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ CE ą▓ 0 ąĖ čüą░ą╝ąŠąĄ ą┐ąŠąĘą┤ąĮąĄąĄ ą▓ ą╝ąŠą╝ąĄąĮčé ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą▓čĆąĄą╝ąĄąĮąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ (čüą╝. čéą░ą▒ą╗ąĖčåčā ą▒ąĖčé GT1, GT0). ąöą░ą╗ąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ IF ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮąŠ ą┐ąŠčüą╗ąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ GT, ą┐čĆąĖ čŹč鹊ą╝ ą▒ąĖčé CTE ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗčüčéą░ą▓ą╗ąĄąĮ ą▓ 1 (ąĖąĮą░č湥 čüč湥čéčćąĖą║ IF čüą▒čĆąŠčüąĖčéčüčÅ).

ąÆąĮąĖą╝ą░ąĮąĖąĄ! ą¤čĆąĖ čĆą░ą▒ąŠč鹥 čüč湥čéčćąĖą║ą░ IF čćą░čüč鹊č鹊ą╝ąĄčĆą░ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąŠą▓ąĄčĆčÅčéčī čüąŠčüč鹊čÅąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ ąŠčé čĆą░ą┤ąĖąŠčüčéą░ąĮčåąĖąĖ (IF-IC SD, station detect), ąĖ č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĮą░ą╗ąĖčćąĖčÅ čüąĖą│ąĮą░ą╗ą░ SD ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┤ąŠą╗ąČąĄąĮ ą▓ą║ą╗čÄčćąĖčéčī ą▓čŗčģąŠą┤ ą▒čāč乥čĆą░ čüąĖą│ąĮą░ą╗ą░ IF ąĖ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąŠą┐ąĄčĆą░čåąĖčÄ ą┐ąŠą┤čüč湥čéą░ čüąĖą│ąĮą░ą╗ą░ IF. ąóąĄčģąĮąĖą║ą░ ą░ą▓č鹊ą┐ąŠąĖčüą║ą░ čĆą░ą┤ąĖąŠčüčéą░ąĮčåąĖą╣, ą║ąŠč鹊čĆą░čÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčé č鹊ą╗čīą║ąŠ čüč湥čéčćąĖą║ IF, ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ, čéą░ą║ ą║ą░ą║ ą▓ąŠąĘą╝ąŠąČąĮą░ čāč鹥čćą║ą░ ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ ą▒čāč乥čĆą░ IF, ąĖąĘ-ąĘą░ č湥ą│ąŠ ą▓ąŠąĘą╝ąŠąČąĄąĮ ąŠčłąĖą▒ąŠčćąĮčŗą╣ ąŠčüčéą░ąĮąŠą▓ ą┐čĆąŠčåąĄčüčüą░ ą░ą▓č鹊ą┐ąŠąĖčüą║ą░ ąĮą░ ą╝ąĄčüč鹥, ą│ą┤ąĄ ąĮąĄčé čüčéą░ąĮčåąĖąĖ.

ąĪčéą░ąĮą┤ą░čĆčéąĮą░čÅ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ą▓čģąŠą┤ą░ IFIN (čćą░čüč鹊čéčŗ f ą▓ ą£ąōčå):

| ą▒ąĖčé IFS |

0.4 < = f < = 0.5 |

0.5 < = f < = 8 |

8 <= f < = 12 |

| 1: ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ |

40 mVrms

(0.1..3 mVrms) |

40 mVrms |

40 mVrms

(1..10 mVrms) |

| 0: čĆąĄąČąĖą╝ čāą╝ąĄąĮčīčłąĄąĮąĖčÅ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ |

70 mVrms

(10..15 mVrms) |

70 mVrms |

70 mVrms

(30..40 mVrms) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ąĄą╗ąĖčćąĖąĮčŗ ą▓ čüą║ąŠą▒ą║ą░čģ - ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮčŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą▓ ą║ą░č湥čüčéą▓ąĄ ąŠą▒čĆą░ąĘčåą░.

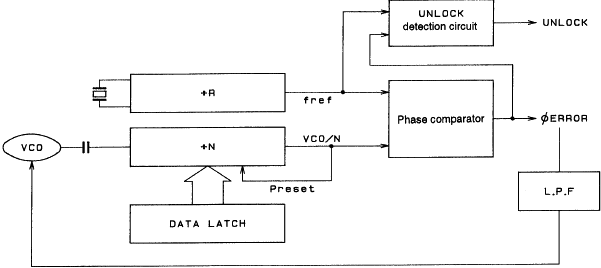

[ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ]

ąĪąŠčüč鹊čÅąĮąĖąĄ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čćą░čüč鹊čéčŗ ą│ąĄč鹥čĆąŠą┤ąĖąĮą░ ąĖ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĖąŠą┤ą░ (interval) ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ (fref). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čéčĆąĄą▒čāąĄčé ą▓čĆąĄą╝čÅ ą▒ą×ą╗čīčłąĄąĄ, č湥ą╝ ą┐ąĄčĆąĖąŠą┤ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ. ą×ą┤ąĮą░ą║ąŠ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąŠčüą╗ąĄ čüą╝ąĄąĮčŗ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĄąĮąĖčÅ N (čćą░čüč鹊čéčŗ) ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ ą┐ąŠčüą╗ąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą┤ą▓čāčģ ą┐ąĄčĆąĖąŠą┤ąŠą▓ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ. ąØą░ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ ą┐čĆąŠčåąĄčüčüą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ.

ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ čćą░čüč鹊čéą░ fref 1 ą║ąōčå, čé. ąĄ. ą┐ąĄčĆąĖąŠą┤ čĆą░ą▓ąĄąĮ 1 ą╝čü, č鹊 ą┐ąŠčüą╗ąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĄąĮąĖčÅ N ąĮčāąČąĮąŠ ąČą┤ą░čéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 2 ą╝čü ą┐ąĄčĆąĄą┤ ą┐čĆąŠą▓ąĄčĆą║ąŠą╣ čüąŠčüč鹊čÅąĮąĖčÅ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ.

ąØą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąŠčåąĄčüčü čĆą░ą▒ąŠčéčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖąĄ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ.

ąÆ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ LC72131 ą▓ąŠąĘą╝ąŠąČąĄąĮ ą▓čŗą▓ąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą▓ ą┐ąŠč鹊ą║ąĄ ą▓čŗą▓ąŠą┤ąĖą╝čŗčģ ą┤ą░ąĮąĮčŗčģ, čŹč鹊 čüąŠčüč鹊čÅąĮąĖąĄ ąĘą░ą┐ąŠą╝ąĖąĮą░ąĄčéčüčÅ ą▓ ą▒ąĖč鹥 UL. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▒čŗčéąĖąĄ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, č鹊 ąŠąĮąŠ ąĘą░ą┐ąŠą╝ąĖąĮą░ąĄčéčüčÅ ą▓ ą▒ąĖč鹥 UL ąĖ ąĮąĄ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ ą▓ą▓ąŠą┤ą░ ąĖą╗ąĖ ą▓čŗą▓ąŠą┤ą░. ąØą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą╝ąĄčüč鹊 ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ ą▓ č鹊čćą║ąĄ (1). ąźąŠčéčÅ čćą░čüč鹊čéą░ ą│ąĄč鹥čĆąŠą┤ąĖąĮą░ VCO čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆąŠą▓ą░ą╗ą░čüčī (locked, ą┐čĆąŠąĖąĘąŠčłąĄą╗ ąĘą░čģą▓ą░čé PLL, ąĖą╗ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ), ą┐ąŠčüą║ąŠą╗čīą║čā ąĮąĄ ą▒čŗą╗ąŠ ąŠą┐ąĄčĆą░čåąĖąĖ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ čü č鹥čģ ą┐ąŠčĆ, ą║ą░ą║ ą┐ąŠą╝ąĄąĮčÅą╗čüčÅ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ N, č鹊 čüąŠčüč鹊čÅąĮąĖąĄ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┐ąŠą║ą░ ąĘą░ą┐ąŠą╝ąĮąĖą╗ąŠčüčī ą▓ ą▒ąĖč鹥 UL. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ą┤ą░ąČąĄ ąĄčüą╗ąĖ čćą░čüč鹊čéą░ čāąČąĄ ąĘą░čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆąŠą▓ą░ą╗ą░čüčī, čüąĖčüč鹥ą╝ą░ ą┤ą╗čÅ ą╝ąĖą║čĆąŠą┐čĆąŠčåąĄčüčüąŠčĆą░ ąŠčüčéą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą┤ąĄčüčéą░ą▒ąĖą╗ąĖąĘą░čåąĖąĖ (čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ).

ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąĄčĆą▓ąŠąĄ čćč鹥ąĮąĖąĄ ą▓ č鹊čćą║ąĄ (1), ą║ąŠč鹊čĆąŠąĄ ą▒čŗą╗ąŠ čüčĆą░ąĘčā ąĘą░ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄą╝ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĄąĮąĖčÅ N, ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐čĆąŠąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░ąĮąŠ. ąÆč鹊čĆąŠąĄ čćč鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą▓ č鹊čćą║ąĄ (2) ą┐ąŠą║ą░ąČąĄčé ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąŠ čüąŠčüč鹊čÅąĮąĖąĖ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čüąĖčüč鹥ą╝čŗ PLL. ąØą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╣ ą░ą╗ą│ąŠčĆąĖčéą╝ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ ąĘą░čģą▓ą░čéą░ PLL.

ąÆąŠąĘą╝ąŠąČąĄąĮ ą┐čĆčÅą╝ąŠą╣ ą▓čŗą▓ąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ąĮą░ ąĮąŠąČą║čā DO (ą┐čāč鹥ą╝ ąĮą░čüčéčĆąŠą╣ą║ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ ą▒ąĖč鹊ą▓ DOC0..DOC2). ąĢčüą╗ąĖ čüąŠčüč鹊čÅąĮąĖąĄ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą▓čŗą▓ąŠą┤ąĖčéčüčÅ ąĮą░ ąĮąŠąČą║čā DO (ą╗ąŠą│. 1 - ąĘą░čģą▓ą░čé ą┐čĆąŠąĖąĘąŠčłąĄą╗, ą╗ąŠą│. 0 - čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ), č鹊 ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠąĄ čćč鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ, ąŠą┐ąĖčüą░ąĮąĮąŠąĄ ą▓ ą░ą╗ą│ąŠčĆąĖčéą╝ąĄ ą▓čŗčłąĄ. ą¤ąŠčüą╗ąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĄąĮąĖčÅ N čüąŠčüč鹊čÅąĮąĖąĄ ąĘą░čģą▓ą░čéą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠą▓ąĄčĆąĄąĮąŠ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┤ą▓čāčģ ą┐ąĄčĆąĖąŠą┤ąŠą▓ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ.

[ąŻą║ą░ąĘą░ąĮąĖčÅ ą┐ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÄ ą▓čŗčģąŠą┤ą░ čüčéą░ą▒ąĖą╗čīąĮąŠą╣ čćą░čüč鹊čéčŗ 8 ąōčå]

ą£ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čāčēąĄąĮąŠ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čćą░čüč鹊čéčŗ 8 ąōčå ąĮą░ ąĮąŠąČą║ąĄ ~BO1 čü ą┐ąŠą╝ąŠčēčīčÄ ą▒ąĖčéą░ TBC. ą¤čĆąĖ čŹč鹊ą╝ ąĮą░ ąĮąŠąČą║ąĄ ~BO1 ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ pull-up čĆąĄąĘąĖčüč鹊čĆ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 100 ą║ą×ą╝. ąŁč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ čāčģčāą┤čłąĄąĮąĖčÅ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ čüąĖą│ąĮą░ą╗/čłčāą╝ (C/N) ą│ąĄč鹥čĆąŠą┤ąĖąĮą░ VCO, ą║ąŠą│ą┤ą░ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ čäąĖą╗čīčéčĆ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ (čäąĖą╗čīčéčĆ ąĮąĖąĘą║ąŠą╣ čćą░čüč鹊čéčŗ), ąŠčüąĮąŠą▓ą░ąĮąĮčŗą╣ ąĮą░ ą▓čüčéčĆąŠąĄąĮąĮąŠą╝ čéčĆą░ąĮąĘąĖčüč鹊čĆąĄ. ą¤ąŠčüą║ąŠą╗čīą║čā ą▓čŗą▓ąŠą┤ čćą░čüč鹊čéčŗ 8 ąōčå ąĖ čäąĖą╗čīčéčĆ ąĮąĖąĘą║ąŠą╣ čćą░čüč鹊čéčŗ ąĖą╝ąĄčÄčé ąŠą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤ ąĘąĄą╝ą╗ąĖ ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, č鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī č鹊ą║ ąŠčé ą▓čŗčģąŠą┤ą░ čćą░čüč鹊čéčŗ 8 ąōčå ąĖ čāčüčéčĆą░ąĮąĖčéčī ąĄą│ąŠ ą▓ą╗ąĖčÅąĮąĖąĄ ąĮą░ čĆą░ą▒ąŠčéčā čäąĖą╗čīčéčĆą░ ąĮąĖąĘą║ąŠą╣ čćą░čüč鹊čéčŗ. ąóą░ą║ąČąĄ ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ ą┤čĆąĄą▒ąĄąĘą│ą░ ą╝čŗ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝ ą┐čĆąĖą╝ąĄąĮąĖčéčī čéčĆąĖą│ą│ąĄčĆ ą©ą╝ąĖčéčéą░ ąĮą░ ą▓čģąŠą┤ąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą┐čĆąĖąĮąĖą╝ą░čÄčēąĄą╝ čüąĖą│ąĮą░ą╗ čćą░čüč鹊čéčŗ 8 ąōčå.

[ąŻą║ą░ąĘą░ąĮąĖčÅ ą┐ąŠ ą╝ąĄčĆčéą▓ąŠą╣ ąĘąŠąĮąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ čäą░ąĘčŗ]

DZ1

|

DZ0

|

ąĀąĄąČąĖą╝ ą╝ąĄčĆčéą▓ąŠą╣ ąĘąŠąĮčŗ |

ąŻąĘąĄą╗ ąĮą░ą║ą░čćą║ąĖ ąĘą░čĆčÅą┤ą░

(ą▓čŗą▓ąŠą┤ PD, charge pump)

|

ą£ąĄčĆčéą▓ą░čÅ ąĘąŠąĮą░

|

| 0 |

0 |

DZA |

ON/ON |

-- 0 čüąĄą║ |

| 0 |

1 |

DZB |

ON/ON |

- 0 čüąĄą║ |

| 1 |

0 |

DZC |

OFF/OFF |

+ 0 čüąĄą║ |

| 1 |

1 |

DZD |

OFF/OFF |

++ 0 čüąĄą║ |

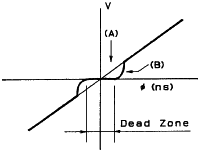

ą¤ąŠčüą║ąŠą╗čīą║čā ąĖą╝ą┐čāą╗čīčüčŗ ą║ąŠčĆčĆąĄą║čåąĖąĖ ą▓čüąĄ čĆą░ą▓ąĮąŠ ą┐čĆąĖčüčāčéčüčéą▓čāčÄčé ąĮą░ ą▓čŗčģąŠą┤ąĄ ąĮą░ą║ą░čćą║ąĖ ąĘą░čĆčÅą┤ą░ PD (ą║ąŠą│ą┤ą░ čüčģąĄą╝ą░ ąĮą░ą║ą░čćą║ąĖ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ON/ON), ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ąĘą░čģą▓ą░čé ąĖ čüčéą░ą▒ąĖą╗ąĖąĘą░čåąĖčÅ PLL, č鹊 ą┐ąĄčéą╗čÅ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ ą╝ąŠąČąĄčé ą╗ąĄą│ą║ąŠ ą┐ąŠč鹥čĆčÅčéčī čüčéą░ą▒ąĖą╗čīąĮąŠčüčéčī. ąÆ čŹč鹊ą╝ ą╝ąĄčüč鹥 ąĮčāąČąĮąŠ ą┐čĆąĄą┤ą┐čĆąĖąĮčÅčéčī čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ą╝ąĄčĆčŗ, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čüčģąĄą╝ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ą░.

ąÆ čüąŠčüč鹊čÅąĮąĖąĖ ON/ON ą╝ąŠą│čāčé ą▒čŗčéčī čüą╗ąĄą┤čāčÄčēąĖąĄ ą┐čĆąŠą▒ą╗ąĄą╝čŗ:

- side band generation (ąĮąĄ čüą╝ąŠą│ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ čŹč鹊čé č鹥čĆą╝ąĖąĮ. ąÆąŠąĘą╝ąŠąČąĮąŠ ąĖą╝ąĄąĄčéčüčÅ ą▓ ą▓ąĖą┤čā ą│ąĄąĮąĄčĆą░čåąĖčÅ ą┐ąŠ čüąŠčüąĄą┤ąĮąĄą╝čā ą║ą░ąĮą░ą╗čā ąĖą╗ąĖ ą▓ čĆą░ą▒ąŠč湥ą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ) ąĖąĘ-ąĘą░ čāč鹥čćą║ąĖ čćą░čüč鹊čéčŗ.

- side band generation ąĖąĘ-ąĘą░ ąŠą│ąĖą▒ą░čÄčēąĄą╣ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą║ąŠčĆčĆąĄą║čåąĖąĖ ąĖ čāč鹥čćą║ąĖ ąĮąĖąĘą║ąŠą╣ čćą░čüč鹊čéčŗ.

ąĪčģąĄą╝čŗ, ą▓ ą║ąŠč鹊čĆčŗčģ ąĄčüčéčī ą╝ąĄčĆčéą▓ą░čÅ ąĘąŠąĮą░ (OFF/OFF), ąĖą╝ąĄčÄčé čģąŠčĆąŠčłčāčÄ čüčéą░ą▒ąĖą╗čīąĮąŠčüčéčī ą┐ąĄčéą╗ąĖ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ PLL, ąĮąŠ čā ąĮąĖčģ čéčĆčāą┤ąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą▓čŗčüąŠą║ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ąŠčéąĮąŠčłąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗/čłčāą╝ (C/N). ąĪ ą┤čĆčāą│ąŠą╣ čüč鹊čĆąŠąĮčŗ, čģąŠčéčÅ ą┐čĆąŠčüč鹊 ą┐ąŠą╗čāčćąĖčéčī ą▓čŗčüąŠą║ąŠąĄ ąŠčéąĮąŠčłąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗/čłčāą╝ ą┤ą╗čÅ čüčģąĄą╝ ą▒ąĄąĘ ą╝ąĄčĆčéą▓ąŠą╣ ąĘąŠąĮčŗ, čā ąĮąĖčģ čéčĆčāą┤ąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą▓čŗčüąŠą║čāčÄ čüčéą░ą▒ąĖą╗čīąĮąŠčüčéčī ą┐ąĄčéą╗ąĖ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ PLL. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą╝ąŠąČąĄčé ą▒čŗčéčī čŹčäč乥ą║čéąĖą▓ąĮčŗą╝ ą▓čŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ DZA ąĖą╗ąĖ DZB, ą║ąŠč鹊čĆčŗą╣ ąĮąĄ ąĖą╝ąĄąĄčé ą╝ąĄčĆčéą▓ąŠą╣ ąĘąŠąĮčŗ, ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ, čéčĆąĄą▒čāčÄčēąĖčģ ąĮą░ FM čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗/čłčāą╝ čüą▓čŗčłąĄ 90..100 dB, ąĖą╗ąĖ ą▓ ą║ąŠč鹊čĆčŗčģ ąČąĄą╗ą░č鹥ą╗čīąĮąŠ čāą▓ąĄą╗ąĖčćąĖčéčī ą│čĆą░ąĮąĖčåčā ąĮąĄčüčāčēąĄą╣ AM čüč鹥čĆąĄąŠ. ąÆ ą┤čĆčāą│ąŠą╝ čüą╗čāčćą░ąĄ ą╝čŗ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝ ą▓čŗą▒čĆą░čéčī DZC ąĖą╗ąĖ DZD (čĆąĄąČąĖą╝čŗ čü ą╝ąĄčĆčéą▓ąŠą╣ ąĘąŠąĮąŠą╣) - ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ čéčĆąĄą▒čāčÄčé ą▓čŗčüąŠą║ąŠąĄ FM čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ čłčāą╝ ąĖ ą▓ ą║ąŠč鹊čĆčŗčģ ą╗ąĖą▒ąŠ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ AM čüč鹥čĆąĄąŠ, ą╗ąĖą▒ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠčüčéąĖą│ąĮčāčéą░ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░čÅ ą│čĆą░ąĮąĖčåą░ ąĮąĄčüčāčēąĄą╣ AM čüč鹥čĆąĄąŠ.

ą£ąĄčĆčéą▓ą░čÅ ąĘąŠąĮą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┐ąĖčüą░ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝. ąÜąŠą╝ą┐ą░čĆą░č鹊čĆ čäą░ąĘčŗ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčé čćą░čüč鹊čéčā fp (ą▓čŗčģąŠą┤ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą│ąŠ ą┤ąĄą╗ąĖč鹥ą╗čÅ) ąĖ ąŠą┐ąŠčĆąĮčāčÄ čćą░čüč鹊čéčā fr, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčüčāąĮą║ąĄ 4. ąźąŠčéčÅ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ čüčģąĄą╝čŗ (čüą╝. čĆąĖčüčāąĮąŠą║ 5) čéą░ą║ąŠą▓čŗ, čćč鹊 ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮąŠ čĆą░ąĘąĮąŠčüčéąĖ čäą░ąĘ (ą╗ąĖąĮąĖčÅ A), ąĄčüčéčī ąŠą▒ą╗ą░čüčéčī (ąĮą░ąĘčŗą▓ą░ąĄą╝ą░čÅ ą╝ąĄčĆčéą▓ąŠą╣ ąĘąŠąĮąŠą╣), ą▓ ą║ąŠč鹊čĆąŠą╣ ąĮąĄą▓ąŠąĘą╝ąŠąČąĮąŠ čüčĆą░ą▓ąĮąĖčéčī ą╝ą░ą╗čāčÄ čĆą░ąĘąĮąŠčüčéčī čäą░ąĘčŗ ą▓ čĆąĄą░ą╗čīąĮąŠą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ, ą┐ąŠčüą║ąŠą╗čīą║čā ąĖą╝ąĄčÄčéčüčÅ ąĘą░ą┤ąĄčƹȹ║ąĖ, čłčāą╝čŗ ąĖ ą┤čĆčāą│ąĖąĄ čäą░ą║č鹊čĆčŗ (ą╗ąĖąĮąĖčÅ B). ąÆąĄą╗ąĖčćąĖąĮą░ ą╝ąĄčĆčéą▓ąŠą╣ ąĘąŠąĮčŗ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą║ą░ą║ ą╝ąŠąČąĮąŠ ą╝ąĄąĮčīčłąĄ ą┤ą╗čÅ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ čü ą▓čŗčüąŠą║ąĖą╝ ąŠčéąĮąŠčłąĄąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗/čłčāą╝.

ą×ą┤ąĮą░ą║ąŠ ą▓ ą░ą┐ą┐ą░čĆą░čéčāčĆąĄ čłąĖčĆąŠą║ąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┐ąŠą▓čŗčłąĄąĮąĮą░čÅ ą╝ąĄčĆčéą▓ą░čÅ ąĘąŠąĮą░, ą┐ąŠčüą║ąŠą╗čīą║čā ąŠąĮą░ čāą┐čĆąŠčēą░ąĄčé čĆąĄą░ą╗ąĖąĘą░čåąĖčÄ čüčģąĄą╝čŗ. ąŁč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąŠč鹊ą╝čā, čćč鹊 ą▓ąŠąĘą╝ąŠąČąĮą░ čāč鹥čćą║ą░ čĆą░ą┤ąĖąŠčüąĖą│ąĮą░ą╗ą░ ąŠčé čüą╝ąĄčüąĖč鹥ą╗čÅ ą▓ ą│ąĄč鹥čĆąŠą┤ąĖąĮ VCO ąĖ ą╝ąŠą┤čāą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ ą│ąĄč鹥čĆąŠą┤ąĖąĮą░ VCO, ą║ąŠą│ą┤ą░ ą┐čĆąĖčģąŠą┤ąĖčé čüąĖą│ąĮą░ą╗ čüą╗ąĖčłą║ąŠą╝ ą▓čŗčüąŠą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ. ąÜąŠą│ą┤ą░ ą╝ąĄčĆčéą▓ą░čÅ ąĘąŠąĮą░ čāąĘą║ą░čÅ, čüčģąĄą╝ą░ ą▓čŗą▓ąŠą┤ąĖčé ąĖą╝ą┐čāą╗čīčüčŗ ą║ąŠčĆčĆąĄą║čåąĖąĖ ąĖ čŹč鹊čé ą▓čŗą▓ąŠą┤ ą╝ąŠąČąĄčé ą╝ąŠą┤čāą╗ąĖčĆąŠą▓ą░čéčī ą│ąĄč鹥čĆąŠą┤ąĖąĮ VCO ąĖ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą▒ąĖąĄąĮąĖčÅ čĆą░ą┤ąĖąŠčćą░čüč鹊čéčŗ.

|

|

| ąĀąĖčü. 4 |

ąĀąĖčü. 5 |

[ąŻą║ą░ąĘą░ąĮąĖčÅ ą┐ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÄ ą▓čŗą▓ąŠą┤ąŠą▓ FMIN, AMIN, IFIN]

ąĀą░ąĘą▓čÅąĘčŗą▓ą░čÄčēąĖąĄ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čĆą░ąĘą╝ąĄčēąĄąĮčŗ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ą╗ąĖąČąĄ ą║ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ąĮąŠąČą║ą░ą╝. ą¢ąĄą╗ą░č鹥ą╗čīąĮą░ ąĄą╝ą║ąŠčüčéčī ą┐ąŠčĆčÅą┤ą║ą░ 100 ą┐ąż. ąÆ čćą░čüčéąĮąŠčüčéąĖ, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĄą╝ą║ąŠčüčéčī 1000 ą┐ąż ąĖ ą▓čŗčłąĄ ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ IF (čćą░čüč鹊č鹊ą╝ąĄčĆ), ą▓čĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čāčĆąŠą▓ąĮčÅ čüą╝ąĄčēąĄąĮąĖčÅ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ ąĖ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ąĮąĄą║ąŠčĆčĆąĄą║čéąĮčŗą╣ ą┐ąŠą┤čüč湥čé, čüą▓čÅąĘą░ąĮąĮčŗą╣ čü ą▓čĆąĄą╝ąĄąĮąĄą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ.

[ąŻą║ą░ąĘą░ąĮąĖčÅ ą┐ąŠ ąĖąĘą╝ąĄčĆąĄąĮąĖčÄ čćą░čüč鹊čéčŗ (čüč湥čé ą┐ąŠ IF)]

ąÆą╝ąĄčüč鹥 čü ą▓čĆąĄą╝ąĄąĮąĄą╝ čüč湥čéą░ IF ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüąĖą│ąĮą░ą╗ SD (ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ čĆą░ą┤ąĖąŠčüčéą░ąĮčåąĖąĖ). ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┤ąŠą╗ąČąĄąĮ ą░ąĮą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī ą┐čĆąĖčüčāčéčüčéą▓ąĖąĄ čüąĖą│ąĮą░ą╗ą░ IF-IC SD (ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüčéą░ąĮčåąĖąĖ) ąĖ ą▓ą║ą╗čÄčćą░čéčī ą▒čāč乥čĆ čüč湥čéčćąĖą║ą░ IF č鹊ą╗čīą║ąŠ ą▓ č鹊ą╝ čüą╗čāčćą░ąĄ, ąĄčüą╗ąĖ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé čüąĖą│ąĮą░ą╗ SD. ąĪčģąĄą╝čŗ, ą▓ ą║ąŠč鹊čĆčŗčģ ą░ą▓č鹊ą┐ąŠąĖčüą║ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ č鹊ą╗čīą║ąŠ ą┐ąŠą┤čüč湥č鹊ą╝ IF ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāčÄčéčüčÅ, ą┐ąŠčüą║ąŠą╗čīą║čā ąŠąĮąĖ ą╝ąŠą│čāčé ąŠčüčéą░ąĮąŠą▓ąĖčéčīčüčÅ ą▓ č鹊čćą║ąĄ ą▒ąĄąĘ čüąĖą│ąĮą░ą╗ą░ ąĖąĘ-ąĘą░ čāč鹥čćą║ąĖ ą▓čŗčģąŠą┤ą░ ąŠčé ą▒čāč乥čĆą░ čüč湥čéčćąĖą║ą░ IF.

[ąóąĄčģąĮąĖą║ą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ąĮąŠąČą║ąĖ DO]

ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÄ ą▓čŗą▓ąŠą┤ą░ DO ą║ą░ą║ ą▓čŗčģąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ, ą▓čŗą▓ąŠą┤ DO ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čüč湥čéą░ čüč湥čéčćąĖą║ą░ IF ąĖ ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ.

[ąÆčŗą▓ąŠą┤čŗ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ]

ąöąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą╝ąĄąČą┤čā ą▓čŗą▓ąŠą┤ą░ą╝ąĖ VDD ąĖ VSS ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 2000 ą┐čä ą┤ą╗čÅ čāčüčéčĆą░ąĮąĄąĮąĖčÅ čłčāą╝ą░. ąÜąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą╝ąĄčēąĄąĮ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ą╗ąĖąČąĄ ą║ ą▓čŗą▓ąŠą┤ą░ą╝ VDD ąĖ VSS.

[ąĪąŠčüč鹊čÅąĮąĖąĄ ąĮąŠąČąĄą║ ą┐ąŠčüą╗ąĄ čüą┐čĆąŠčüą░ ą┐čĆąĖ ą┐ąŠą┤ą░č湥 ą┐ąĖčéą░ąĮąĖčÅ]

[ą¤čĆąĖą╝ąĄčĆ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ (ą║ąŠčĆą┐čāčü MFP20)]

[Absolute Maximum Ratings ą┐čĆąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ 25 oC, VSS 0 V]

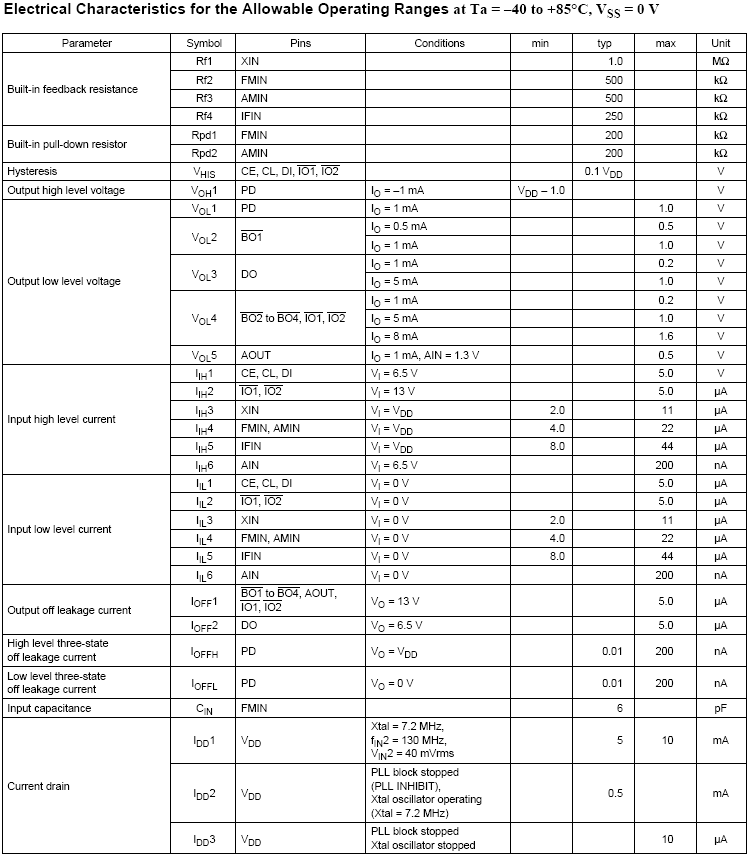

[Allowable Operating Rates ą┐čĆąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ -40..+85 oC, VSS 0 V]

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ: * čĆąĄą║ąŠą╝ąĄąĮą┤ąŠą▓ą░ąĮąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ CI ą┤ą╗čÅ ą║ą▓ą░čĆčåąĄą▓ - CI < = 120 ąŠą╝ (ą┤ą╗čÅ ą║ą▓ą░čĆčåąĄą▓ 4.5 ą£ąōčå) CI < = 70 ąŠą╝ (ą┤ą╗čÅ ą║ą▓ą░čĆčåąĄą▓ 7.2 ą£ąōčå).

ą¤čĆąĖą╝ąĄčĆ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ ą║ą▓ą░čĆčåą░:

ą¤čĆąĖą╝ąĄąĮąĄąĮąĮčŗą╣ ą║ą▓ą░čĆčåąĄą▓čŗą╣ čĆąĄąĘąŠąĮą░č鹊čĆ - HC-49/U (ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čī Kinseki Ltd.), CL = 12 ą┐čä, C1 = C2 = 15 ą┐ąż.

[ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą┤ą╗čÅ Allowable Operating Rates ą┐čĆąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ -40..+85 oC, VSS 0 V]

[ąĪčüčŗą╗ą║ąĖ]

1. AVR-USB-MEGA16: čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą┤ąĖąŠčéčĆą░ą║č鹊ą╝ ą╝ą░ą│ąĮąĖč鹊ą╗čŗ RX-ES20 ąŠčé ą║ąŠą╝ą┐čīčÄč鹥čĆą░.

2. GitHub - RodLophus/SanyoCCB: Arduino library for Sanyo CCB Bus site:github.com. |