|

IR2214/IR22141 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠą▒ąŠą╣ ą┤čĆą░ą╣ą▓ąĄčĆ ąĘą░čéą▓ąŠčĆąŠą▓ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠą╗čāą╝ąŠčüč鹊ą╝ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ ąĖą╝ą┐čāą╗čīčüąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą┐ąĖčéą░ąĮąĖčÅ. ąÆčŗčüąŠą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą┤čĆą░ą╣ą▓ąĄčĆą░ (2A ą▓čŗč鹥ą║ą░čÄčēąĖą╣ č鹊ą║, 3A ą▓č鹥ą║ą░čÄčēąĖą╣) ąĖ ąĮąĖąĘą║ąĖą╣ č鹊ą║ ą┐ąŠą║ąŠčÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č鹥čģąĮąĖą║čā ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ (bootstrap supply) ą▓ čüąĖčüč鹥ą╝ą░čģ čüčĆąĄą┤ąĮąĄą╣ ą╝ąŠčēąĮąŠčüčéąĖ. ąÆ ą┤čĆą░ą╣ą▓ąĄčĆąĄ IR2214/IR22141 čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ą┐ąŠą╗ąĮą░čÅ ąĘą░čēąĖčéą░ ąŠčé ą║ąŠčĆąŠčéą║ąŠą│ąŠ ąĘą░ą╝čŗą║ą░ąĮąĖčÅ (ąÜąŚ), ąŠčüąĮąŠą▓ą░ąĮąĮą░čÅ ąĮą░ ąŠą▒ąĮą░čĆčāąČąĄąĮąĖąĖ ą▓čŗčģąŠą┤ą░ čüąĖą╗ąŠą▓ąŠą│ąŠ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ. IR2214/IR22141 čāą┐čĆą░ą▓ą╗čÅąĄčé ą▓čüąĄą╝ąĖ ą▓ąĖą┤ą░ą╝ąĖ ąŠčéą║ą░ąĘą░ ą┐ąŠą╗čāą╝ąŠčüčéą░, ą╝čÅą│ą║ąŠ ą▓čŗą║ą╗čÄčćą░čÅ ą▓čŗčłąĄą┤čłąĖą╣ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ čéčĆą░ąĮąĘąĖčüč鹊čĆ č湥čĆąĄąĘ ą▓čŗą┤ąĄą╗ąĄąĮąĮčāčÄ ąĮąŠąČą║čā ą╝čÅą│ą║ąŠą│ąŠ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (ą▓čŗą▓ąŠą┤ soft shut down, SSD), ąĘą░čēąĖčēą░čÅ čüąĖą╗ąŠą▓ąŠą╣ ą╝ąŠčüčé ąŠčé ą┐ąĄčĆąĄąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ąĖ čüąĮąĖąČą░čÅ ą│ąĄąĮąĄčĆą░čåąĖčÄ ą┐ąŠą╝ąĄčģ. ąÆ ą╝ąĮąŠą│ąŠčäą░ąĘąĮąŠą╣ čüąĖčüč鹥ą╝ąĄ ą┤čĆą░ą╣ą▓ąĄčĆčŗ IR2214/IR22141 ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčé ąŠą▒ą╝ąĄąĮ č湥čĆąĄąĘ ą▓čŗą┤ąĄą╗ąĄąĮąĮčāčÄ ą╗ąŠą║ą░ą╗čīąĮčāčÄ čåąĄą┐čī (čüąĖą│ąĮą░ą╗čŗ ~SY_FLT ąĖ ~FAULT/SD), čćč鹊ą▒čŗ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ čāą┐čĆą░ą▓ą╗čÅčéčī ą║ąŠčĆąŠčéą║ąĖą╝ąĖ ąĘą░ą╝čŗą║ą░ąĮąĖčÅą╝ąĖ čäą░ąĘčŗ ąĮą░ čäą░ąĘčā. ąĪąĖčüč鹥ą╝ąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą╝ąŠąČąĄčé ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą▓čŗą║ą╗čÄčćąĖčéčī ą╝ąĖą║čĆąŠčüčģąĄą╝čā ąĖą╗ąĖ ą┐čĆąŠčćąĖčéą░čéčī čüąŠčüč鹊čÅąĮąĖąĄ ąŠčéą║ą░ąĘą░ (fault state) č湥čĆąĄąĘ 3.3V čüąŠą▓ą╝ąĄčüčéąĖą╝čāčÄ ąĮąŠąČą║čā CMOS I/O (~FAULT/SD). ą¦č鹊ą▒čŗ čāą▓ąĄą╗ąĖčćąĖčéčī ąĘą░čēąĖčēąĄąĮąĮąŠčüčéčī čüąĖą│ą░ą╗ą░ ąŠčé ą┐ąŠą╝ąĄčģ ą┐ąŠ čłąĖąĮąĄ ą┐ąĖčéą░ąĮąĖčÅ (DC-bus), ąĘąĄą╝ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüąĖą╗ąŠą▓ą░čÅ ąĘąĄą╝ą╗čÅ ąĖą╝ąĄčÄčé ąŠčéą┤ąĄą╗čīąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖąĘą╝ąĄčĆčÅčéčī č鹊ą║ 菹╝ąĖčéč鹥čĆą░ ąĮą░ ąĮąĖąČąĮąĄą╣ ą┐ąŠą╗ąŠą▓ąĖąĮąĄ ą┐ąŠą╗čāą╝ąŠčüčéą░. ąĪąĖčéčāą░čåąĖąĖ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ.

ą×čüąĮąŠą▓ąĮčŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ IR2214/IR22141:

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąŚąĮą░č湥ąĮąĖąĄ |

| VOFFSET |

1200V max |

| ąóąĖą┐ąŠą▓čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ č鹊ą║ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ IO+/- |

2.0A / 3.0A |

| VOUT |

10.4V - 20V |

| ąśąĮč鹥čĆą▓ą░ą╗ čĆąĄą│čāą╗ąĖčĆąŠą▓ą║ąĖ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (max) |

75 ąĮčü |

| ąóąĖą┐ąŠą▓ąŠą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ |

330 ąĮčü |

| ąóąĖą┐ąŠą▓ąŠąĄ ą▓čĆąĄą╝čÅ ą│ą░čłąĄąĮąĖčÅ ą┐čĆąĖ ą▓čŗčģąŠą┤ąĄ čüąĖą╗ąŠą▓čŗčģ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ |

3 ą╝ą║čü |

| ąóąĖą┐ąŠą▓ąŠą╣ ą┐ąŠčĆąŠą│ ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ DSH, DSL |

8.0V |

| ąóąĖą┐ąŠą▓ąŠąĄ ą▓čĆąĄą╝čÅ ą╝čÅą│ą║ąŠą│ąŠ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ |

9.6 ą╝ą║čü |

| ąÜąŠčĆą┐čāčü ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ |

SSOP24 |

ą×čüąĮąŠą▓ąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ IR2214/IR22141:

ŌĆó ą¤ą╗ą░ą▓ą░čÄčēąĖą╣ ą║ą░ąĮą░ą╗ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą▓čŗą┤ąĄčƹȹĖą▓ą░ąĄčé ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ąŠ +1200V

ŌĆó ąÆčŗą║ą╗čÄč湥ąĮąĖąĄ ą┐čĆąĖ ą┐ąĄčĆąĄą│čĆčāąĘą║ąĄ ą┐ąŠ č鹊ą║čā

ŌĆó ąĪąĖą│ąĮą░ą╗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, čćč鹊ą▒čŗ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčī ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ čü ą┤čĆčāą│ąĖą╝ąĖ čäą░ąĘą░ą╝ąĖ

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮą░čÅ čüčģąĄą╝ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ čüąĖą╗ąŠą▓ąŠą│ąŠ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ

ŌĆó ąöą▓čāčģą║ą░čüą║ą░ą┤ąĮčŗą╣ ą▓čŗčģąŠą┤ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ di/dt

ŌĆó ą×čéą┤ąĄą╗čīąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ ą▓čŗčģąŠą┤ąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ pull-up/pull-down

ŌĆó ąÆčŗčģąŠą┤čŗ čü ą┐ąŠą┤ą▒ąŠčĆąŠą╝ ąĘą░ą┤ąĄčƹȹ║ąĖ

ŌĆó ąæą╗ąŠą║ąĖčĆąŠą▓ą║ą░ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (UV lockout) čü ą┐ąŠą╗ąŠčüąŠą╣ ą│ąĖčüč鹥čĆąĄąĘąĖčüą░

ąŻą┐čĆąŠčēąĄąĮąĮą░čÅ čüčģąĄą╝ą░ čéąĖą┐ąŠą▓ąŠą│ąŠ ą▓ą║ą╗čÄč湥ąĮąĖčÅ:

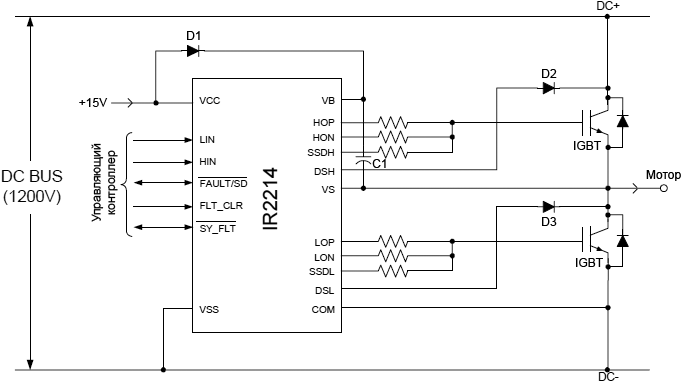

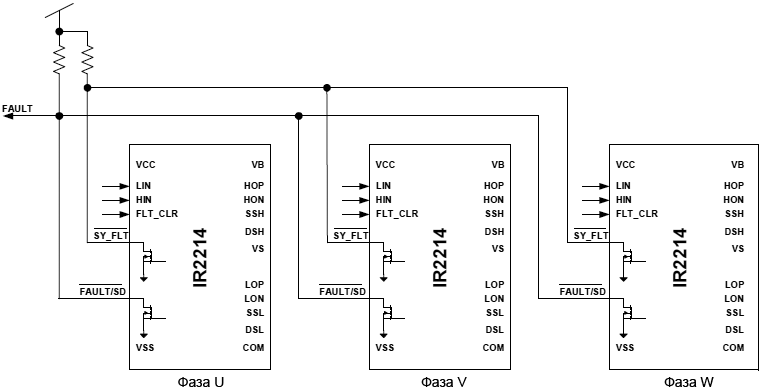

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: D1ąĪ1 čåąĄą┐ąŠčćą║ą░ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ ą┤ą╗čÅ čüąŠąĘą┤ą░ąĮąĖčÅ "ą┐ą╗ą░ą▓ą░čÄčēąĄą│ąŠ" ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░, D2 ąĖ D3 ą┤ąĖąŠą┤čŗ čüąĖčüč鹥ą╝čŗ ąŠą▒ąĮą░čĆčāąČąĄąĮąĖčÅ ą▓čŗčģąŠą┤ą░ čüąĖą╗ąŠą▓čŗčģ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓ IGBT ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ.

ą¤čĆąĄą┤ąĄą╗čīąĮčŗąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ čŹą║čüą┐ą╗čāą░čéą░čåąĖąŠąĮąĮčŗčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓:

| ąĪąĖą╝ą▓. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

min |

MAX |

ąĢą┤. |

| VS |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ čüą╝ąĄčēąĄąĮąĖąĄ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ |

VB - 25 |

VB + 0.3 |

V |

| VB |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ą░ą▓ą░čÄčēąĄą│ąŠ ą┐ą╗ąĄčćą░ |

-0.3 |

1225 |

| VHO |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ą░ą▓ą░čÄčēąĄą│ąŠ ą┐ą╗ąĄčćą░ (HOP, HON ąĖ SSDH) |

VS - 0.3 |

VB + 0.3 |

| VCC |

ążąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ąĖ ą╗ąŠą│ąĖą║ąĖ |

-0.3 |

25 |

| COM |

ąĪąĖą╗ąŠą▓ą░čÅ ąĘąĄą╝ą╗čÅ |

VCC - 25 |

VCC + 0.3 |

| VLO |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ (LOP, LON ąĖ SSDL) |

VCOM - 0.3 |

| VIN |

ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│ąĖą║ąĖ (HIN, LIN ąĖ FLT_CLR) |

-0.3 |

| VFLT |

ąÆčģąŠą┤ąĮąŠąĄ/ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ FAULT (~FAULT/SD ąĖ ~SY_FLT) |

-0.3 |

| VDSH |

ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ DS ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ |

VB - 25 |

VB + 0.3 |

| VDSL |

ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ DS ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ |

VCC - 25 |

VCC + 0.3 |

| dVs/dt |

ąöąŠą┐čāčüčéąĖą╝ą░čÅ čüą║ąŠčĆąŠčüčéčī ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čüą╝ąĄčēąĄąĮąĖčÅ |

- |

50 |

V/ąĮčü |

| PD |

ą£ąŠčēąĮąŠčüčéčī čĆą░čüčüąĄąĖą▓ą░ąĮąĖčÅ ą║ąŠčĆą┐čāčüą░ @ TA Ōēż +25┬░C |

- |

1.5 |

ąÆčé |

| RthJA |

ąóąĄą╝ą┐ąĄčĆą░čéčāčĆąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą╝ąĄąČą┤čā ą║čĆąĖčüčéą░ą╗ą╗ąŠą╝ ąĖ ąŠą║čĆčāąČą░čÄčēąĄą╣ čüčĆąĄą┤ąŠą╣ |

- |

65 |

┬░C/ąÆčé |

| TJ |

ąóąĄą╝ą┐ąĄčĆą░čéčāčĆą░ ą║čĆąĖčüčéą░ą╗ą╗ą░ |

- |

+150 |

┬░C |

| TS |

ąóąĄą╝ą┐ąĄčĆą░čéčāčĆą░ čģčĆą░ąĮąĄąĮąĖčÅ |

-55 |

+150 |

| TL |

ąóąĄą╝ą┐ąĄčĆą░čéčāčĆą░ ą┐ą░ą╣ą║ąĖ (ą▓ č鹥č湥ąĮąĖąĄ 10 čüąĄą║čāąĮą┤) |

- |

+300 |

ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝čŗąĄ čĆą░ą▒ąŠčćąĖąĄ čāčüą╗ąŠą▓ąĖčÅ. ąÆčüąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ čāą║ą░ąĘą░ąĮčŗ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ VSS. ąĀąĄą╣čéąĖąĮą│ čüą╝ąĄčēąĄąĮąĖčÅ VS č鹥čüčéąĖčĆąŠą▓ą░ą╗ąĖčüčī čüąŠ ą▓čüąĄą╝ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅą╝ąĖ ą┐ąĖčéą░ąĮąĖčÅ, čüą╝ąĄčēąĄąĮąĮčŗą╝ąĖ ąĮą░ 15V.

| ąĪąĖą╝ą▓. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

min |

MAX |

ąĢą┤. |

| VS |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ čüą╝ąĄčēąĄąĮąĖąĄ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░(2) |

ąĪą╝. (2) |

1200 |

V |

| VB |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ą░ą▓ą░čÄčēąĄą│ąŠ ą┐ą╗ąĄčćą░(1) |

VS + 11.5 |

VS + 20 |

| VHO |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ą░ą▓ą░čÄčēąĄą│ąŠ ą┐ą╗ąĄčćą░ (HOP, HON ąĖ SSDH) |

VS |

VS + 20 |

| VCC |

ążąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ąĖ ą╗ąŠą│ąĖą║ąĖ(1) |

11.5 |

20 |

| COM |

ąĪąĖą╗ąŠą▓ą░čÅ ąĘąĄą╝ą╗čÅ |

-5 |

5 |

| VLO |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ (LOP, LON ąĖ SSDL) |

VCOM |

VCC |

| VIN |

ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│ąĖą║ąĖ (HIN, LIN ąĖ FLT_CLR) |

0 |

VCC |

| VFLT |

ąÆčģąŠą┤ąĮąŠąĄ/ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ FAULT (~FAULT/SD ąĖ ~SY_FLT) |

0 |

VCC |

| VDSH |

ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ DS ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ |

VB - 20 |

VB |

| VDSL |

ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ DS ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ |

VCC - 20 |

VCC |

| TA |

ąóąĄą╝ą┐ąĄčĆą░čéčāčĆą░ ąŠą║čĆčāąČą░čÄčēąĄą╣ čüčĆąĄą┤čŗ |

-40 |

+125 |

┬░C |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąÆ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čüčģąĄą╝čŗ čĆą░ą▒ąŠč鹊čüą┐ąŠčüąŠą▒ąĮčŗ ą┐čĆąĖ ą▒ąŠą╗ąĄąĄ ąĮąĖąĘą║ąĖčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅčģ ą┐ąĖčéą░ąĮąĖčÅ, č湥ą╝ čāą║ą░ąĘą░ąĮčŗ, ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ą░ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (UV lockout) ąĘą░ą┐čĆąĄčéąĖčé ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤čĆą░ą╣ą▓ąĄčĆčŗ, ąĄčüą╗ąĖ ąĮąĄ ą┤ąŠčüčéąĖą│ąĮčāčéčŗ ą┐ąŠčĆąŠą│ąĖ UV.

(2) ąøąŠą│ąĖą║ą░ čĆą░ą▒ąŠč鹊čüą┐ąŠčüąŠą▒ąĮą░ ą┤ą╗čÅ VS ąŠčé VSS - 5V ą┤ąŠ VSS + 1200V. ąøąŠą│ąĖč湥čüą║ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ, čāą┤ąĄčƹȹĖą▓ą░ąĄą╝ąŠąĄ ą┤ą╗čÅ VS, ąŠčé VSS - 5V ą┤ąŠ VSS - VBS (čüą╝. Design Tip DT97-3 ą┤ą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ).

ąĪčéą░čéąĖč湥čüą║ąĖąĄ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ. VCC = 15V, VSS = COM = 0V, VS = 0 .. 1200V ąĖ TA = 25oC, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ ąĮąĄčćč鹊 ąŠą▒čĆą░čéąĮąŠąĄ.

ąØąŠąČą║ąĖ: VCC, VSS, VB, VS.

| ąĪąĖą╝ą▓. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

min |

typ |

MAX |

ąĢą┤. |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

| VCCUV+ |

ą¤ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆąŠą│ ąĘą░čēąĖčéčŗ ąŠčé čüąĮąĖąČąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ VCC |

9.3 |

10.2 |

11.4 |

V |

|

| VCCUV- |

ą×čéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆąŠą│ ąĘą░čēąĖčéčŗ ąŠčé čüąĮąĖąČąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ VCC |

8.7 |

9.3 |

10.3 |

|

| VCCUVH |

ąōąĖčüč鹥čĆąĄąĘąĖčü ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą┐čĆąĖ čüąĮąĖąČąĄąĮąĖąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ VCC |

- |

0.9 |

- |

|

| VBSUV+ |

ą¤ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆąŠą│ ąĘą░čēąĖčéčŗ ąŠčé čüąĮąĖąČąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ (VB - VS) |

9.3 |

10.2 |

11.4 |

VS = 0V, VS = 1200V |

| VBSUV- |

ą×čéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆąŠą│ ąĘą░čēąĖčéčŗ ąŠčé čüąĮąĖąČąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ (VB-VS) |

8.7 |

9.3 |

10.3 |

| VBSUVH |

ąōąĖčüč鹥čĆąĄąĘąĖčü ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą┐čĆąĖ čüąĮąĖąČąĄąĮąĖąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ (VB - VS) |

- |

0.9 |

- |

|

| ILK |

ąóąŠą║ čāč鹥čćą║ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ čüą╝ąĄčēąĄąĮąĖčÅ |

- |

- |

50 |

╬╝A |

VB = VS = 1200V |

| IQBS |

ąóąŠą║ ą┐ąŠą║ąŠčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ VBS |

- |

400 |

800 |

VIN = 0V ąĖą╗ąĖ 3.3V (ą▒ąĄąĘ ąĮą░ą│čĆčāąĘą║ąĖ) |

| IQCC |

ąóąŠą║ ą┐ąŠą║ąŠčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ VCC |

- |

0.7 |

2.5 |

mA |

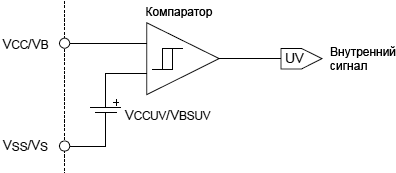

ąĀąĖčü. 1. ąĪčģąĄą╝ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (UV lockout).

ąØąŠąČą║ąĖ: HIN, LIN, FLTCLR, ~FAULT/SD, ~SY_FLT.

| ąĪąĖą╝ą▓. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

min |

typ |

MAX |

ąĢą┤. |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

| VIH |

ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 1 |

2.0 |

- |

- |

V |

VCC = VCCUV- .. 20V |

| VIL |

ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 0 |

- |

- |

0.8 |

| VIHSS |

ąōąĖčüč鹥čĆąĄąĘąĖčü ą▓čģąŠą┤ąĮčŗčģ ą╗ąŠą│ąĖč湥čüą║ąĖčģ čāčĆąŠą▓ąĮąĄą╣ |

0.2 |

0.4 |

- |

| IIN+ |

ąÆčģąŠą┤ąĮąŠą╣ č鹊ą║ čüą╝ąĄčēąĄąĮąĖčÅ ą╗ąŠą│. 1 |

- |

370 |

- |

╬╝A |

VIN = 3.3V |

| IIN- |

ąÆčģąŠą┤ąĮąŠą╣ č鹊ą║ čüą╝ąĄčēąĄąĮąĖčÅ ą╗ąŠą│. 0 |

-1 |

- |

0 |

VIN = 0V |

| RON,FLT |

ąĪąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ąŠčéą║čĆčŗč鹊ą│ąŠ čüč鹊ą║ą░ ~FAULT/SD |

- |

60 |

- |

ą×ą╝ |

|

| RON,SY |

ąĪąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ąŠčéą║čĆčŗč鹊ą│ąŠ čüč鹊ą║ą░ ~SY_FLT |

- |

60 |

- |

P Ōēż 7 ą╝ą║čü |

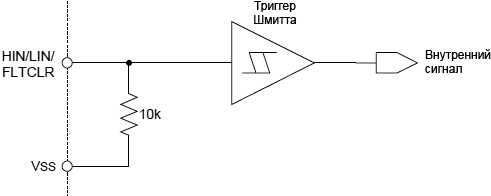

ąĀąĖčü. 2. ąĪčģąĄą╝ą░ HIN, LIN and FLTCLR.

ąĀąĖčü. 3. ąĪčģąĄą╝ą░ ~FAULT/SD ąĖ ~SY_FLT.

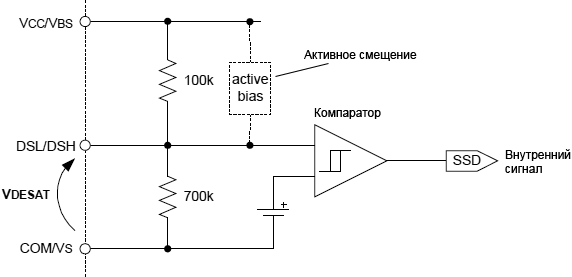

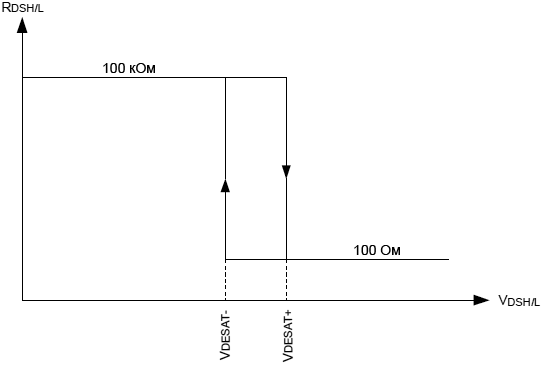

ąØąŠąČą║ąĖ: DSL, DSH. ąÉą║čéąĖą▓ąĮąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé č鹊ą╗čīą║ąŠ ą▓ IR22141. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ VDESAT, IDS ąĖ IDSB ą┐ąŠą║ą░ąĘą░ąĮčŗ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ COM, ąĖ ą┤ą╗čÅ DSL ąĖ DSH ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ VS.

| ąĪąĖą╝ą▓. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

min |

typ |

MAX |

ąĢą┤. |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

| VDESAT+ |

ąÆąĄčĆčģąĮąĄąĄ ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąŠčĆąŠą│ą░ čüąĖą│ąĮą░ą╗ą░ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ |

7.2 |

8.0 |

8.8 |

V |

ąĪą╝. čĆąĖčü. 16, 4 |

| VDESAT- |

ąÆąĄčĆčģąĮąĄąĄ ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąŠčĆąŠą│ą░ čüąĖą│ąĮą░ą╗ą░ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ |

6.3 |

7.0 |

7.7 |

| VIHSS |

ąōąĖčüč鹥čĆąĄąĘąĖčü ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ |

- |

1.0 |

- |

| IDS+ |

ąÆčģąŠą┤ąĮąŠą╣ č鹊ą║ čüą╝ąĄčēąĄąĮąĖčÅ ą▓čŗčüąŠą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ DSH ąĖą╗ąĖ DSL |

- |

21 |

- |

╬╝A |

VDESAT = VCC ąĖą╗ąĖ VBS |

| IDS- |

ąÆčģąŠą┤ąĮąŠą╣ č鹊ą║ čüą╝ąĄčēąĄąĮąĖčÅ ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ DSH ąĖą╗ąĖ DSL |

- |

-160 |

- |

VDESAT = 0V |

| IDSB |

ąÆčģąŠą┤ąĮąŠą╣ č鹊ą║ čüą╝ąĄčēąĄąĮąĖčÅ DSH ąĖą╗ąĖ DSL (č鹊ą╗čīą║ąŠ ą┤ą╗čÅ IR22141) |

- |

-20 |

- |

mA |

VDESAT = (VCC ąĖą╗ąĖ VBS) - 2V |

ąĀąĖčü. 4. ąĪčģąĄą╝ą░ DSH ąĖ DSL.

ąØąŠąČą║ąĖ: HOP, LOP.

| ąĪąĖą╝ą▓. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

min |

typ |

MAX |

ąĢą┤. |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

| VOH |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓čŗčüąŠą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ, VB ŌĆō VHOP ąĖą╗ąĖ VCC ŌĆō VLOP |

- |

20 |

100 |

mV |

IO = 1 mA |

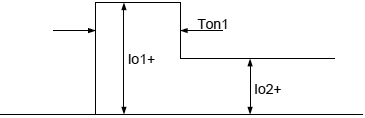

| IO1+ |

ąÆčŗčģąŠą┤ąĮąŠą╣ ąĖą╝ą┐čāą╗čīčüąĮčŗą╣ č鹊ą║ ą║ąŠčĆąŠčéą║ąŠą│ąŠ ąĘą░ą╝čŗą║ą░ąĮąĖčÅ ą▓čŗčüąŠą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ą┐ąĄčĆą▓ąŠą│ąŠ ą║ą░čüą║ą░ą┤ą░ |

- |

2 |

- |

A |

VHOP/LOP = 0V, HIN ąĖą╗ąĖ LIN = 1, PW Ōēż 200 ąĮčü, čĆąĄąĘąĖčüčéąĖą▓ąĮą░čÅ ąĮą░ą│čĆčāąĘą║ą░, čüą╝. čĆąĖčü. 8 |

| IO2+ |

ąÆčŗčģąŠą┤ąĮąŠą╣ ąĖą╝ą┐čāą╗čīčüąĮčŗą╣ č鹊ą║ ą║ąŠčĆąŠčéą║ąŠą│ąŠ ąĘą░ą╝čŗą║ą░ąĮąĖčÅ ą▓čŗčüąŠą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ą▓č鹊čĆąŠą│ąŠ ą║ą░čüą║ą░ą┤ą░ |

- |

1 |

- |

VHOP/LOP = 0V, HIN ąĖą╗ąĖ LIN = 1, 400 ąĮčü Ōēż PW Ōēż 10 ą╝ą║čü, čĆąĄąĘąĖčüčéąĖą▓ąĮą░čÅ ąĮą░ą│čĆčāąĘą║ą░, čüą╝. čĆąĖčü. 8 |

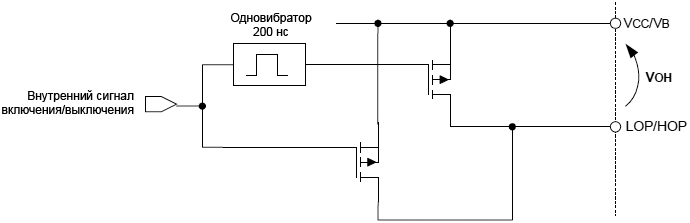

ąĀąĖčü. 5. ąĪčģąĄą╝ą░ HOP ąĖ LOP.

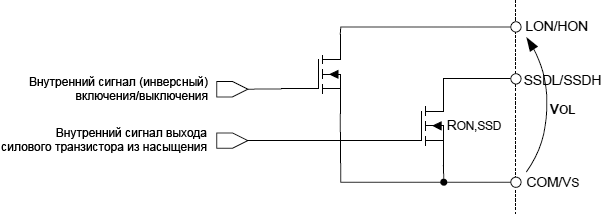

ąØąŠąČą║ąĖ: HON, LON, SSDH, SSDL.

| ąĪąĖą╝ą▓. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

min |

typ |

MAX |

ąĢą┤. |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

| VOL |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ, VHON ąĖą╗ąĖ VLON |

- |

2.3 |

15 |

mV |

IO = 1 mA |

| RON,SSD |

ąĪąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą▓ą║ą╗čÄč湥ąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ Soft ShutDown (SSD) |

- |

90 |

- |

ą×ą╝ |

PW Ōēż 7 ą╝ą║čü |

| IO- |

ąÆčŗčģąŠą┤ąĮąŠą╣ ąĖą╝ą┐čāą╗čīčüąĮčŗą╣ č鹊ą║ ą║ąŠčĆąŠčéą║ąŠą│ąŠ ąĘą░ą╝čŗą║ą░ąĮąĖčÅ ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ |

- |

3 |

- |

A |

VHOP/LOP = 15V, HIN ąĖą╗ąĖ LIN = 0, PW Ōēż 10 ą╝ą║čü |

ąĀąĖčü. 6: ąĪčģąĄą╝ą░ HON, LON, SSDH ąĖ SSDL.

ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā (AC). VCC = VBS = 15V, VS = VSS ąĖ TA = 25┬░C, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ čćč鹊-č鹊 ą┤čĆčāą│ąŠąĄ.

| ąĪąĖą╝ą▓. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

min |

typ |

MAX |

ąĢą┤. |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

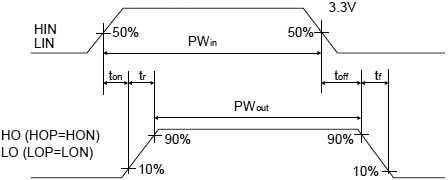

| ton |

ąŚą░ą┤ąĄčƹȹ║ą░ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ |

220 |

440 |

660 |

ąĮčü |

VIN = 0 ąĖą╗ąĖ 1, VS = 0 .. 1200V, HOP ąĘą░ą╝ą║ąĮčāčé ąĮą░ HON, LOP ąĘą░ą╝ą║ąĮčāčé ąĮą░ LON, čĆąĖčü. 7, 10 |

| toff |

ąŚą░ą┤ąĄčƹȹ║ą░ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ |

| tr |

ąÆčĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ (CLOAD=1nF) |

- |

24 |

- |

| tf |

ąÆčĆąĄą╝čÅ čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (CLOAD=1nF) |

- |

7 |

- |

| ton1 |

ąÆčĆąĄą╝čÅ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĄčĆą▓ąŠą│ąŠ ą║ą░čüą║ą░ą┤ą░ |

120 |

200 |

280 |

ąĀąĖčü. 8 |

| tDESAT1 |

ąŚą░ą┤ąĄčƹȹ║ą░ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ SSD ąŠčé DSH ą┤ąŠ HO, ą║ąŠą│ą┤ą░ HO ą▓ą║ą╗čÄč湥ąĮ |

2000 |

3300 |

4600 |

VHIN = 1, VDESAT = 15V, čĆąĖčü. 10 |

| tDESAT2 |

ąŚą░ą┤ąĄčƹȹ║ą░ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ SSD ąŠčé DSH ą┤ąŠ HO ą┐ąŠčüą╗ąĄ ą│ą░čłąĄąĮąĖčÅ |

1050 |

- |

- |

| tDESAT3 |

ąŚą░ą┤ąĄčƹȹ║ą░ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ SSD ąŠčé DSL ą┤ąŠ LO, ą║ąŠą│ą┤ą░ LO ą▓ą║ą╗čÄč湥ąĮ |

2000 |

3300 |

4600 |

VLIN = 1, VDESAT = 15V, čĆąĖčü. 10 |

| tDESAT4 |

ąŚą░ą┤ąĄčƹȹ║ą░ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ SSD ąŠčé DSH ą┤ąŠ HO ą┐ąŠčüą╗ąĄ ą│ą░čłąĄąĮąĖčÅ |

1050 |

- |

- |

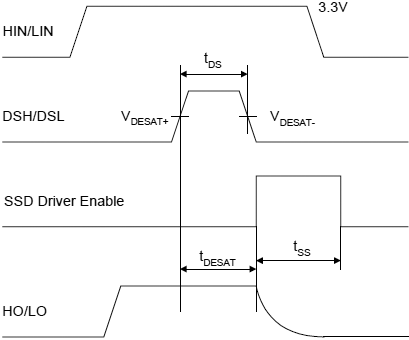

| tDS |

ą£ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ čłąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ SSD ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ čüąĖą╗ąŠą▓ąŠą│ąŠ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ |

1000 |

- |

- |

ąĀąĖčü. 9 |

| tSS |

ą¤ąĄčĆąĖąŠą┤ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ SSD |

5700 |

9600 |

13500 |

CL = TBD ą╝ą║ąż, VDS = 15V, čĆąĖčü. 9 |

| tSY_FLT,DESAT1 |

ąÆčĆąĄą╝čÅ ąĘą░ą┤ąĄčƹȹ║ąĖ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ ąŠčé DSH ą║ SY_FLT ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ HO |

- |

3600 |

- |

VHIN = 1, VDESAT = 15V, čĆąĖčü. 10 |

| tSY_FLT,DESAT2 |

ąÆčĆąĄą╝čÅ ąĘą░ą┤ąĄčƹȹ║ąĖ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ ąŠčé DSH ą║ SY_FLT ą┐ąŠčüą╗ąĄ ą│ą░čłąĄąĮąĖčÅ |

1300 |

- |

- |

| tSY_FLT,DESAT3 |

ąÆčĆąĄą╝čÅ ąĘą░ą┤ąĄčƹȹ║ąĖ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ ąŠčé DSL ą║ SY_FLT ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ LO |

- |

3050 |

- |

VLIN = 1, VDESAT = 15V, čĆąĖčü. 10 |

| tSY_FLT,DESAT4 |

ąÆčĆąĄą╝čÅ ąĘą░ą┤ąĄčƹȹ║ąĖ čĆą░čüčéčĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ ąŠčé DSL ą║ SY_FLT ą┐ąŠčüą╗ąĄ ą│ą░čłąĄąĮąĖčÅ |

1050 |

- |

- |

| tBL |

ąÆčĆąĄą╝čÅ ą│ą░čłąĄąĮąĖčÅ DS ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ |

- |

3000 |

- |

VHIN = VLIN = 1, VDESAT = 15V, čĆąĖčü. 10 |

| ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ/ąĘą░ą┤ąĄčƹȹ║ąĖ |

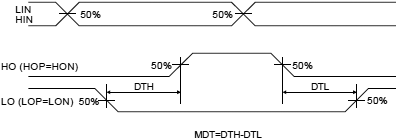

| DT |

Dead-time (ą╝ąĄčĆčéą▓ąŠąĄ ą▓čĆąĄą╝čÅ) |

- |

330 |

- |

ąĮčü |

ąĀąĖčü. 11 |

| MDT |

ąĪąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ Dead-time, MDT = DTH - DTL |

- |

- |

75 |

ąÆąĮąĄčłąĮąĄąĄ DT = 0 ąĮčü, čĆąĖčü. 11 |

| PDM |

ąĪąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ, Max(ton, toff) - Min(ton, toff) |

- |

- |

75 |

ąÆąĮąĄčłąĮąĄąĄ DT > 500 ąĮčü, čĆąĖčü. 7 |

ąĀąĖčü. 7. ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ.

ąĀąĖčü. 8. ąÆčŗčģąŠą┤ąĮąŠą╣ ą▓čŗč鹥ą║ą░čÄčēąĖą╣ č鹊ą║.

ąĀąĖčü. 9. ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ą╝čÅą│ą║ąŠą│ąŠ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ.

ąĀąĖčü. 10. ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ą▓čŗčģąŠą┤ą░ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ (Desat Timing).

ąĀąĖčü. 11. ąÆąĮčāčéčĆąĄąĮąĮąĄąĄ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (Dead-Time).

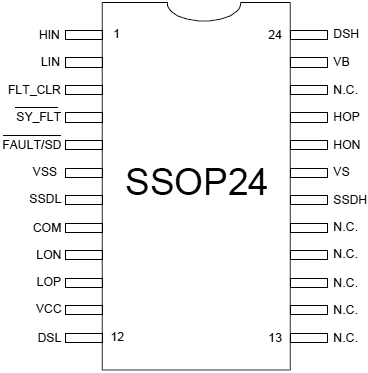

[ą”ąŠą║ąŠą╗ąĄą▓ą║ą░]

24-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą║ąŠčĆą┐čāčü SSOP - IR2214SS, ą▓ąĖą┤ čüą▓ąĄčĆčģčā:

| ąĪąĖą╝ą▓ąŠą╗ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| VCC |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ (+11.5V .. +20V) |

| VSS |

ąŚąĄą╝ą╗čÅ ą╗ąŠą│ąĖą║ąĖ, ą╝ąĖąĮčāčü ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ |

| HIN |

ąøąŠą│ąĖč湥čüą║ąĖą╣ ą▓čģąŠą┤ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąŠą╝ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ (HOP/HON) |

| LIN |

ąøąŠą│ąĖč湥čüą║ąĖą╣ ą▓čģąŠą┤ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąŠą╝ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ (LOP/LON) |

| ~FAULT/SD |

ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ą▓čŗą▓ąŠą┤ (čĆą░ą▒ąŠčéą░ąĄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąĖ ą║ą░ą║ ą▓čģąŠą┤, ąĖ ą║ą░ą║ ą▓čŗčģąŠą┤), ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. ąĪą╝. čĆąĖčü. 17, 18 ąĖ 15. ąÆ ą║ą░č湥čüčéą▓ąĄ ą▓čŗčģąŠą┤ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ (fault condition). ąÆ ą║ą░č湥čüčéą▓ąĄ ą▓čģąŠą┤ą░ ą▓čŗą║ą╗čÄčćą░ąĄčé ą▓čŗčģąŠą┤čŗ ą┤čĆą░ą╣ą▓ąĄčĆą░ ąĘą░čéą▓ąŠčĆąŠą▓, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čāčĆąŠą▓ąĮąĄą╣ ąĮą░ ą▓čģąŠą┤ą░čģ HIN/LIN. |

| ~SY_FLT |

ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ą▓čŗą▓ąŠą┤ (čĆą░ą▒ąŠčéą░ąĄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąĖ ą║ą░ą║ ą▓čģąŠą┤, ąĖ ą║ą░ą║ ą▓čŗčģąŠą┤), ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. ąĪą╝. čĆąĖčü. 17, 18 ąĖ 15. ąÆ ą║ą░č湥čüčéą▓ąĄ ą▓čŗčģąŠą┤ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ SSD (Soft ShutDown, ą╝čÅą│ą║ąŠąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ). ąÆ ą║ą░č湥čüčéą▓ąĄ ą▓čģąŠą┤ą░ čüąĖą│ąĮą░ą╗ ą░ą║čéąĖą▓ąĮąŠą│ąŠ ą╗ąŠą│. 0 ąĘą░ą╝ąŠčĆą░ąČąĖą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ąŠą▒ąŠąĖčģ ą▓čŗčģąŠą┤ąŠą▓. |

| FLT_CLR |

ąÆčģąŠą┤ ąŠčćąĖčüčéą║ąĖ čüąŠčüč鹊čÅąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ (fault clear) čü ą░ą║čéąĖą▓ąĮčŗą╝ čāčĆąŠą▓ąĮąĄą╝ ą╗ąŠą│. 1 (čüą╝. čĆąĖčü. 17). |

| LOP |

ąÆčŗčģąŠą┤ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą┤ą╗čÅ ą▓čŗč鹥ą║ą░čÄčēąĄą│ąŠ č鹊ą║ą░ (ąŠčéą║čĆčŗčéąĖąĄ čüąĖą╗ąŠą▓ąŠą│ąŠ čéčĆą░ąĮąĘąĖčüč鹊čĆą░) |

| LON |

ąÆčŗčģąŠą┤ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą┤ą╗čÅ ą▓č鹥ą║ą░čÄčēąĄą│ąŠ č鹊ą║ą░ (ąĘą░ą║čĆčŗčéąĖąĄ čüąĖą╗ąŠą▓ąŠą│ąŠ čéčĆą░ąĮąĘąĖčüč鹊čĆą░) |

| DSL |

ąÆčģąŠą┤ ą┤ąĄč鹥ą║č鹊čĆą░ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ IGBT |

| SSDL |

ą£čÅą│ą║ąŠąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ |

| COM |

ąÆąŠąĘą▓čĆą░čé č鹊ą║ą░ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ |

| VB |

ą¤ą╗ą░ą▓ą░čÄčēąĄąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ ąĘą░čéą▓ąŠčĆą░ (ą▓čŗčĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čåąĄą┐ąŠčćą║ąŠą╣ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ) |

| HOP |

ąÆčŗčģąŠą┤ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą┤ą╗čÅ ą▓čŗč鹥ą║ą░čÄčēąĄą│ąŠ č鹊ą║ą░ (ąŠčéą║čĆčŗčéąĖąĄ čüąĖą╗ąŠą▓ąŠą│ąŠ čéčĆą░ąĮąĘąĖčüč鹊čĆą░) |

| HON |

ąÆčŗčģąŠą┤ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą┤ą╗čÅ ą▓č鹥ą║ą░čÄčēąĄą│ąŠ č鹊ą║ą░ (ąĘą░ą║čĆčŗčéąĖąĄ čüąĖą╗ąŠą▓ąŠą│ąŠ čéčĆą░ąĮąĘąĖčüč鹊čĆą░) |

| DSH |

ąÆčģąŠą┤ ą┤ąĄč鹥ą║č鹊čĆą░ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ IGBT |

| SSDH |

ą£čÅą│ą║ąŠąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ |

| VS |

ąÆąŠąĘą▓čĆą░čé ą┐ą╗ą░ą▓ą░čÄčēąĄą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ |

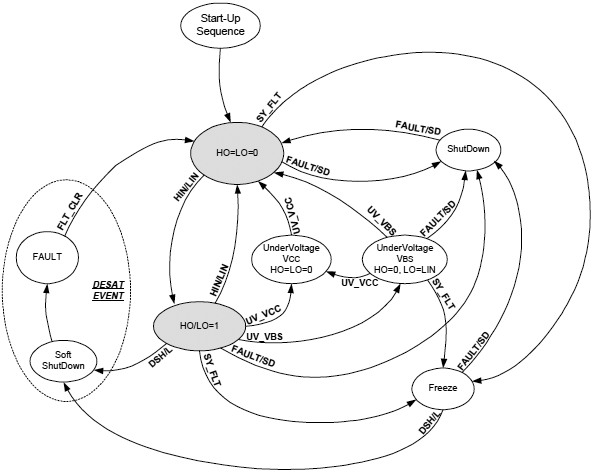

ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░:

ąöąĖą░ą│čĆą░ą╝ą╝ą░ čüąŠčüč鹊čÅąĮąĖą╣:

| ąĪčéą░ą▒ąĖą╗čīąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ |

ąÆčĆąĄą╝ąĄąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ |

ąĪąĖčüč鹥ą╝ąĮčŗąĄ ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗąĄ |

- FAULT

- HO = LO = 0 (ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ)

- HO/LO = 1 (ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ)

- UNDERVOLTAGE VCC (UV, ą┐ąŠąĮąĖąČąĄąĮąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░)

- SHUTDOWN (SD, ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ)

- UNDERVOLTAGE VBS (ą┐ąŠąĮąĖąČąĄąĮąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░. ąŻ čŹč鹊ą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą╝ąĖąĮčāčü ą┐ą╗ą░ą▓ą░čÄčēąĖą╣, ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VBS ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąŠčé ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ)

- FREEZE |

- SOFT SHUTDOWN

- START UP SEQUENCE

|

- FLT_CLR

- HIN/LIN

- UV_VCC

- UV_VBS

- DSH/DSL

- SY_FLT

- FAULT/SD |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąśąĘą╝ąĄąĮąĄąĮąĖąĄ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░, ą┐ąŠą╝ąĄč湥ąĮąĮąŠą│ąŠ ąĮą░ ą╗ąĖąĮąĖąĖ čüčéčĆąĄą╗ą║ąĖ (čüąĖčüč鹥ą╝ąĮą░čÅ ą┐ąĄčĆąĄą╝ąĄąĮąĮą░čÅ) ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐ąĄčĆąĄčģąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ.

(2) ą¤čĆąĖ ą▓čŗčģąŠą┤ąĄ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ UNDERVOLTAGE VBS čüąĖą│ąĮą░ą╗ HO čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1 č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ąĮą░ HIN ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ.

[ąóą░ą▒ą╗ąĖčåą░ ą╗ąŠą│ąĖą║ąĖ IR2214]

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓

ąĪąŠčüč鹊čÅąĮąĖąĄ

HO/LO |

HOP/LOP |

HON/LON |

SSDH/SSDL |

| 0 |

HiZ |

0 |

HiZ |

| 1 |

1 |

HiZ |

HiZ |

| SSD |

HiZ |

HiZ |

0 |

| LO/HO |

ąĪąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčģąŠą┤ąŠą▓ čüą╗ąĄą┤čāąĄčé ąĘą░ ą▓čģąŠą┤ą░ą╝ąĖ (in=1 -> out=1, in=0 -> out=0) |

| LOn-1/HOn-1 |

ąÆčŗčģąŠą┤čŗ čüąŠčģčĆą░ąĮčÅčÄčé ą┐čĆąĄą┤čŗą┤čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ (freeze) |

| |

ąÆčģąŠą┤čŗ

|

ąÆčģąŠą┤čŗ/ą▓čŗčģąŠą┤čŗ |

UnderVoltage

ą┤ą░: V < ą┐ąŠčĆąŠą│ą░ UV

ąĮąĄčé: V > ą┐ąŠčĆąŠą│ą░ UV

X: ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąÆčŗčģąŠą┤čŗ |

| ą×ą┐ąĄčĆą░čåąĖčÅ |

HOP/LOP |

HON/LON |

SSDH/SSDL |

SY_FLT

SSD: desat (ą▓čŗčģ.)

HOLD: freezing (ą▓čģ.) |

FAULT/SD

SD: shutdown (ą▓čģ.)

FAULT: ą┤ąĖą░ą│ąĮ. (ą▓čŗčģ.) |

VCC |

VBS |

HO |

LO |

| Shut Down |

X |

X |

X |

X |

0 (SD) |

X |

X |

0 |

0 |

| Fault Clear |

HIN |

LIN |

_ŌåæŌĆŠ |

ą¤čĆąĖą╝. (1) |

_ŌåæŌĆŠ (FAULT) |

ąĮąĄčé |

ąĮąĄčé |

HO |

LO |

| ąØąŠčĆą╝ą░ą╗čīąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ |

1 |

0 |

0 |

1 |

1 |

ąĮąĄčé |

ąĮąĄčé |

1 |

0 |

| 0 |

1 |

0 |

0 |

1 |

| 0 |

0 |

0 |

0 |

0 |

| ą¤čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖąĄ čüą║ą▓ąŠąĘąĮąŠą│ąŠ č鹊ą║ą░ |

1 |

1 |

0 |

1 |

1 |

ąĮąĄčé |

ąĮąĄčé |

0 |

0 |

| Soft Shut Down (ą▓čģąŠą┤ ą▓ SSD) |

1 |

0 |

0 |

ŌĆŠŌåō_ (SSD) |

1 |

ąĮąĄčé |

ąĮąĄčé |

SSD |

0 |

| 0 |

1 |

0 |

SSD |

| Soft Shut Down (ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ SSD) |

X |

X |

0 |

_ŌåæŌĆŠ (SSD) |

ŌĆŠŌåō_ (FAULT) |

ąĮąĄčé |

ąĮąĄčé |

0 |

0 |

| 0 |

0 |

| Freeze |

X |

X |

X |

0 (HOLD) |

1 |

ąĮąĄčé |

ąĮąĄčé |

HOn-1 |

LOn-1 |

| Under Voltage |

X |

LIN |

X |

1 |

1 |

ąĮąĄčé |

ą┤ą░ |

0 |

LO |

| X |

0 (FAULT) |

ą┤ą░ |

X |

0 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ~SY_FLT ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą▒čĆąŠčüąĖčéčüčÅ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čüąŠą▒čŗčéąĖčÅ SSD, ąĖ FLT_CLR ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ. ą¦č鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą║ąŠąĮčäą╗ąĖą║čéą░ FLT_CLR čü ą┐čĆąŠčåąĄą┤čāčĆąŠą╣ SSD, FLT_CLR ąĮąĄ ą┤ąŠą╗ąČąĄąĮ čĆą░ą▒ąŠčéą░čéčī, ą║ąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĄąĮ ~SY_FLT.

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ]

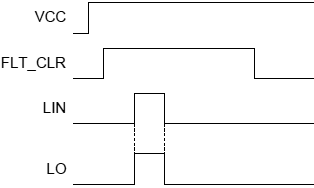

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą┐čāčüą║ą░ (Start-up). ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą┐čāčüą║ą░ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (power supply start-up), čćč鹊ą▒čŗ čāą┤ąĄčƹȹ░čéčī ąĮąŠąČą║čā FLT_CLR ą▓ ą░ą║čéąĖą▓ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ, ą┐ąŠą║ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĮąĄ ąĘą░čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆčāčÄčéčüčÅ ąĮą░ ą║ąŠčĆčĆąĄą║čéąĮčŗčģ čāčĆąŠą▓ąĮčÅčģ. ąŁč鹊 ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčé ą│ąĄąĮąĄčĆą░čåąĖčÄ čüą╗čāčćą░ą╣ąĮčŗčģ ą┤ąĖą░ą│ąĮąŠčüčéąĖč湥čüą║ąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓. ąÆčüąĄ čäčāąĮą║čåąĖąĖ ąĘą░čēąĖčéčŗ čĆą░ą▒ąŠčéą░čÄčé ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ FLT_CLR, ąĖ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčģąŠą┤ą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ ąŠčéčĆą░ąČą░ąĄčé ą▓čģąŠą┤ąĮčŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ.

ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą┐ąŠą╗ąŠą│ąĖčÅ ą▓ąŠą╗čīč鹊ą▒ą░ą▓ą║ąĖ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą┐ą╗ą░ą▓ą░čÄčēąĄą│ąŠ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą┐čāčüą║ą░ (čüą╝. čéą░ą║ąČąĄ čĆąĖčü. 12):

1. ąŻčüčéą░ąĮąŠą▓ąĖčéčī VCC.

2. ąŻčüčéą░ąĮąŠą▓ąĖčéčī ąĮąŠąČą║čā FLT_CLR ą▓ ą╗ąŠą│. 1.

3. ąŻčüčéą░ąĮąŠą▓ąĖčéčī ąĮąŠąČą║čā LIN ą▓ ą╗ąŠą│. 1 ąĖ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī ąĘą░čĆčÅą┤ąĖčéčīčüčÅ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčā ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ.

4. ą¤ąĄčĆąĄą▓ąĄčüčéąĖ LIN ą▓ ą╗ąŠą│. 0.

5. ą¤ąĄčĆąĄą▓ąĄčüčéąĖ FLT_CLR ą▓ ą╗ąŠą│. 0.

ąĀąĖčü. 12. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą┐čāčüą║ą░.

ąóčĆąĄą▒čāąĄčéčüčÅ ąĖą╝ą┐čāą╗čīčü LIN ąĖ FLT-CLR ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ ą╝ąĖąĮąĖą╝čāą╝ 15 ą╝ą║čü.

ąØąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝. ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ start-up, ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠą╗ąĮąŠčüčéčīčÄ čĆą░ą▒ąŠč鹊čüą┐ąŠčüąŠą▒ąĮąŠą╣ (čüąĄčĆčŗąĄ ąŠą▓ą░ą╗čŗ ą▓ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ čüąŠčüč鹊čÅąĮąĖą╣).

ąĪąĖą│ąĮą░ą╗čŗ HIN ąĖ LIN ą┐ąŠą▒čāąČą┤ą░čÄčé ą▓čŗčģąŠą┤čŗ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą╗ąŠą│ąĖą║ą░ ą┐čĆąŠą▓ąĄčĆčÅąĄčé ą▓čģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ, ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░čÅ čüąŠą▒čŗčéąĖčÅ čüą║ą▓ąŠąĘąĮąŠą│ąŠ č鹊ą║ą░ (shoot-through), čü ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (DeadTime, DT).

ąÆčŗą║ą╗čÄč湥ąĮąĖąĄ (Shut Down). ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüąĖčüč鹥ą╝čŗ ą╝ąŠąČąĄčé ą░čüąĖąĮčģčĆąŠąĮąĮąŠ ą▓čŗą┤ą░čéčī ą║ąŠą╝ą░ąĮą┤čā ąČąĄčüčéą║ąŠą│ąŠ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (Hard ShutDown, HSD) č湥čĆąĄąĘ ąĮąŠąČą║čā ~FAULT/SD, čüąŠą▓ą╝ąĄčüčéąĖą╝čāčÄ čü čāčĆąŠą▓ąĮčÅą╝ąĖ ą╗ąŠą│ąĖą║ąĖ 3.3V CMOS. ąŁč鹊 čüąŠą▒čŗčéąĖąĄ ąĮąĄ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ.

ąÆ ą╝ąĮąŠą│ąŠčäą░ąĘąĮąŠą╣ čüąĖčüč鹥ą╝ąĄ čüąĖą│ąĮą░ą╗čŗ ~FAULT/SD ąŠą▒čŖąĄą┤ąĖąĮčÅčÄčéčüčÅ ą╗ąŠą│ąĖą║ąŠą╣ ąśąøąś, čćč鹊ą▒čŗ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąĖą╗ąĖ ąŠą┤ąĖąĮ ąĖąĘ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ ąĘą░čéą▓ąŠčĆąŠą▓ ą╝ąŠą│ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠąĄ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ ą┤čĆčāą│ąĖčģ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ č湥čĆąĄąĘ ąŠą┤ąĮčā ąĖ čéčā ąČąĄ ąĮąŠąČą║čā.

[ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąŠčéą║ą░ąĘą░ą╝ąĖ (Fault Management)]

IR2214 ą╝ąŠąČąĄčé ąŠą▒čüą╗čāąČąĖą▓ą░čéčī ą║ą░ą║ ąŠčéą║ą░ąĘčŗ ą┐ąĖčéą░ąĮąĖčÅ - čüąŠą▒čŗčéąĖčÅ čüąĮąĖąČąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ ąŠą▒ąŠąĖčģ ą┐ą╗ąĄčćą░čģ, ąĮąĖąČąĮąĄą╝ ąĖ ą▓ąĄčĆčģąĮąĄą╝ (Undervoltage), čéą░ą║ ąĖ ąŠčéą║ą░ąĘ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ąŠą▒ąŠąĖčģ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓.

Undervoltage (UV). ążčāąĮą║čåąĖčÅ ąĘą░čēąĖčéčŗ ąŠčé ą┐ąŠąĮąĖąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą┤čĆą░ą╣ą▓ąĄčĆą░ ąĘą░ą┐čĆąĄčēą░ąĄčé ą▓čŗčģąŠą┤ąĮąŠą╣ ą║ą░čüą║ą░ą┤ ą┤čĆą░ą╣ą▓ąĄčĆą░, čćč鹊ą▒čŗ čüąĖą╗ąŠą▓ąŠą╣ ą╝ąŠčüčé ąĮąĄ čāą┐čĆą░ą▓ą╗čÅą╗čüčÅ čüą╗ąĖčłą║ąŠą╝ ąĮąĖąĘą║ąĖą╝ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅą╝ąĖ.

ą×ą▒ą░ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓, ąĮąĖąČąĮąĄąĄ ą┐ą╗ąĄč湊 (ą║ąŠč鹊čĆąŠąĄ ą┐ąĖčéą░ąĄčéčüčÅ ąŠčé VCC) ąĖ ą┐ą╗ą░ą▓ą░čÄčēąĄąĄ ą▓ąĄčĆčģąĮąĄąĄ (ą║ąŠč鹊čĆąŠąĄ ą┐ąĖčéą░ąĄčéčüčÅ ąŠčé VBS, ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ), čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠą╣ čäčāąĮą║čåąĖąĄą╣ ąĘą░čēąĖčéčŗ ąŠčé čüąĮąĖąČąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

UV-čüąŠą▒čŗčéąĖąĄ ąĮą░ VCC (ą║ąŠą│ą┤ą░ VCC < UVVCC-) ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗ ą┤ąĖą░ą│ąĮąŠčüčéąĖą║ąĖ ą┐čāč鹥ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ą░ ąĮąŠąČą║ąĖ ~FAULT/SD ą▓ ą╗ąŠą│. 0 (čüą╝. čüąĄą║čåąĖčÄ ~FAULT/SD ąĖ čĆąĖčü. 14). ąŁč鹊 čüąŠą▒čŗčéąĖąĄ ąĘą░ą┐čĆąĄčēą░ąĄčé ąŠą▒ą░ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ - ąĮąĖąČąĮąĄąĄ ąĖ ą┐ą╗ą░ą▓ą░čÄčēąĄąĄ ą▓ąĄčĆčģąĮąĄąĄ, ąĖ čüąĖą│ąĮą░ą╗ ą┤ąĖą░ą│ąĮąŠčüčéąĖą║ąĖ čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą┤ąŠ č鹥čģ ą┐ąŠčĆ ą┐ąŠą║ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮąĄ ą▓ąŠčüčüčéą░ąĮąŠą▓ąĖčéčüčÅ. ąŁč鹊 čüąŠą▒čŗčéąĖąĄ ąŠčéą║ą░ąĘą░ ąĮąĄ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ, ąĖ ąĮąŠąČą║ą░ ~FAULT/SD ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1 ą║ą░ą║ č鹊ą╗čīą║ąŠ VCC čüčéą░ąĮąĄčé ą▓čŗčłąĄ UVVCC+.

UV-čüąŠą▒čŗčéąĖąĄ ąĮą░ VBS ąĘą░ą┐čĆąĄčéąĖčé č鹊ą╗čīą║ąŠ ą▓ąĄčĆčģąĮąĖą╣ ą┐ą╗ą░ą▓ą░čÄčēąĖą╣ ą┤čĆą░ą╣ą▓ąĄčĆ. Undervoltage ąĮą░ VBS ąĮąĄ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčé ą░ą║čéąĖą▓ą░čåąĖčÄ ą▓čŗčģąŠą┤ą░ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░, ąĖ ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗čŗ ą┤ąĖą░ą│ąĮąŠčüčéąĖą║ąĖ. UV-čüąŠą▒čŗčéąĖąĄ VBS (VBS < UVVBS-) ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčé ą▓čŗčģąŠą┤ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 0. ąöą╗čÅ ą▓ąŠąĘą▓čĆą░čéą░ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ VBS ą┤ąŠą╗ąČąĮąŠ čüąĮąŠą▓ą░ čāčüčéą░ąĮąŠą▓ąĖčéčīčüčÅ ąĮą░ čāčĆąŠą▓ąĄąĮčī ą▓čŗčłąĄ UVVBS+. ą¦č鹊ą▒čŗ ą▓ą║ą╗čÄčćąĖčéčī ą┐ą╗ą░ą▓ą░čÄčēąĖą╣ ą┤čĆą░ą╣ą▓ąĄčĆ, čüąĖą│ąĮą░ą╗ HIN ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ąĮąŠą▓ąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1 (čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ąĮą░ HIN).

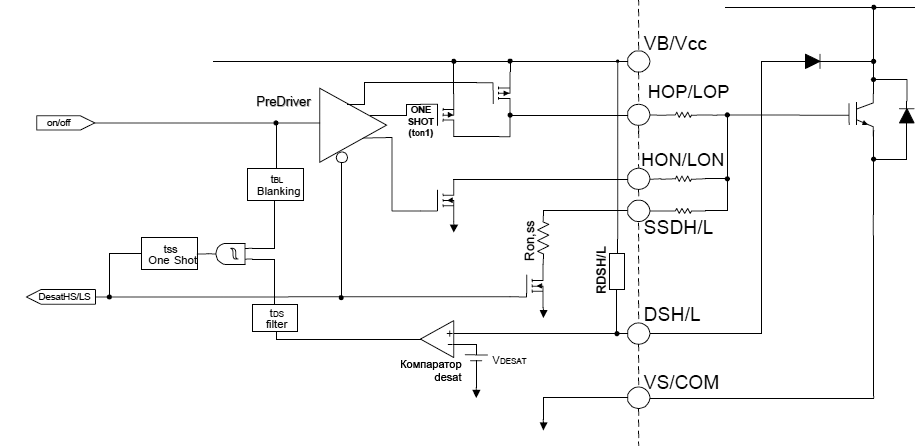

ąÆčŗčģąŠą┤ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ čüąĖą╗ąŠą▓čŗčģ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓. ą×čéą║ą░ąĘ čüąĖą╗ąŠą▓ąŠą│ąŠ ą┐ąŠą╗čāą╝ąŠčüčéą░ ą╝ąŠą│čāčé ą▓čŗąĘą▓ą░čéčī čĆą░ąĘąĮčŗąĄ čüą╗čāčćą░ąĖ, ąĮą░ą┐čĆąĖą╝ąĄčĆ ą║ąŠčĆąŠčéą║ąŠąĄ ąĘą░ą╝čŗą║ą░ąĮąĖąĄ čäą░ąĘčŗ ąĖą╗ąĖ ą┐ąĄčĆąĄą│čĆčāąĘą║ą░ ą▓čŗčģąŠą┤ą░. ąÆąŠ ą▓čüąĄčģ čŹčéąĖčģ čüą╗čāčćą░čÅčģ č湥čĆąĄąĘ čüąĖą╗ąŠą▓čŗąĄ čéčĆą░ąĮąĘąĖčüč鹊čĆčŗ IGBT, ą║ąŠč鹊čĆčŗą╝ąĖ čāą┐čĆą░ą▓ą╗čÅąĄčé ą┤čĆą░ą╣ą▓ąĄčĆ, čĆąĄąĘą║ąŠ ą▓čŗčĆą░čüčéą░ąĄčé č鹊ą║.

ąĪąĖčüč鹥ą╝ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčéą║ą░ąĘąŠą▓ IR2214 ą╝ąŠąĮąĖč鹊čĆąĖčé ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╝ąĄąČą┤čā ą║ąŠą╗ą╗ąĄą║č鹊čĆąŠą╝ ąĖ 菹╝ąĖčéč鹥čĆąŠą╝ (VCE) čüąĖą╗ąŠą▓ąŠą│ąŠ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ IGBT čü ą┐ąŠą╝ąŠčēčīčÄ ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓čŗčüąŠą║ąŠą▓ąŠą╗čīčéąĮąŠą│ąŠ ą┤ąĖąŠą┤ą░. ąĪą╗ąĖčłą║ąŠą╝ ą▒ąŠą╗čīčłąŠą╣ č鹊ą║ č湥čĆąĄąĘ čéčĆą░ąĮąĘąĖčüč鹊čĆ IGBT ą╝ąŠąČąĄčé ą▓čŗą▓ąĄčüčéąĖ ąĄą│ąŠ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ, č鹊ą│ą┤ą░ VCE čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ.

ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą▓čŗčģąŠą┤ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ, č鹊ą║ č湥čĆąĄąĘ čüąĖą╗ąŠą▓ąŠą╣ čéčĆą░ąĮąĘąĖčüč鹊čĆ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ 10 ą▒ąŠą╗čīčłąĄ ąĮąŠą╝ąĖąĮą░ą╗čīąĮąŠą│ąŠ č鹊ą║ą░. ąÆčüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čéčĆą░ąĮąĘąĖčüč鹊čĆ ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ, čŹč鹊čé ą▓čŗčüąŠą║ąĖą╣ č鹊ą║ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓ čüąĖą╗ąŠą▓ąŠą╝ ą║ą░čüą║ą░ą┤ąĄ, ą║ąŠč鹊čĆčŗą╣ ąĮčāąČąĮąŠ čüą│ą╗ą░ą┤ąĖčéčī, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąĮąĄąŠą▒čĆą░čéąĖą╝čŗčģ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖą╣ (ąĖąĘ-ąĘą░ ą┐ąĄčĆąĄąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝, ą▓čŗąĘą▓ą░ąĮąĮčŗą╝ ą▓čŗą▒čĆąŠčüąŠą╝ ąŁąöąĪ čüą░ą╝ąŠąĖąĮą┤čāą║čåąĖąĖ). ąöčĆą░ą╣ą▓ąĄčĆ ąĘą░čéą▓ąŠčĆą░ IR2214 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗą╝ąĖ ą┐čĆąŠčåąĄčüčüą░ą╝ąĖ ą┐čāč鹥ą╝ ą┐ą╗ą░ą▓ąĮąŠą│ąŠ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą▓čŗčłąĄą┤čłąĄą│ąŠ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ čü ą┐ąŠą╝ąŠčēčīčÄ ą░ą║čéąĖą▓ą░čåąĖąĖ ąĮąŠąČą║ąĖ SSD čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ąŠą╣ čäčāąĮą║čåąĖąĄą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐ą╗ą░ą▓ąĮąŠą│ąŠ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (Soft ShutDown sequence, SSD).

ążčāąĮą║čåąĖčÅ DSH/L ąĮą░ čĆąĖčü. 13 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüčéčĆčāą║čéčāčĆčā ą┤ąĄč鹥ą║č鹊čĆą░ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ąĖ ą▒ą╗ąŠą║ą░ ą┐ą╗ą░ą▓ąĮąŠą│ąŠ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ. ąŁčéą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čŗčģąŠą┤ąŠą▓ ąŠą┤ąĖąĮą░ą║ąŠą▓ą░ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ ą┐ą╗ąĄčć, ąĖ ąĮąĖąČąĮąĄą│ąŠ, ąĖ ą┐ą╗ą░ą▓ą░čÄčēąĄą│ąŠ ą▓ąĄčĆčģąĮąĄą│ąŠ.

ąĀąĖčü. 13. ąÆčŗčģąŠą┤ąĮąŠą╣ ą║ą░čüą║ą░ą┤ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░.

ąÆąĮąĄčłąĮąĖą╣ ą▓čŗčüąŠą║ąŠą▓ąŠą╗čīčéąĮčŗą╣ ą┤ąĖąŠą┤ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą┤ąĄč鹥ą║č鹊čĆą░ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ąĖą╝ąĄčéčī ą┤ąŠą┐čāčüčéąĖą╝ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ BV > 1200V ąĖ ąĮąĖąĘą║čāčÄ ą┐ą░čĆą░ąĘąĖčéąĮčāčÄ ąĄą╝ą║ąŠčüčéčī (čćč鹊ą▒čŗ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖąĄ ą┐ąŠą╝ąĄčģ ąĖ ąĘą░ą┤ąĄčƹȹ║ąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ). ąöąĖąŠą┤ čüą╝ąĄčēą░ąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ pull-up čĆąĄąĘąĖčüč鹊čĆąŠą╝ RDSH/L (菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮąŠ ą┤ą╗čÅ VCC/IDS-, ąĖą╗ąĖ VBS/IDS- ą┤ą╗čÅ IR2214), ąĖą╗ąĖ čü ą┐ąŠą╝ąŠčēčīčÄ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ čüčģąĄą╝čŗ (čüą╝. čüąĄą║čåąĖčÄ čü ąŠą┐ąĖčüą░ąĮąĖąĄą╝ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čüą╝ąĄčēąĄąĮąĖčÅ ą┤ą╗čÅ IR22141). ąÜąŠą│ą┤ą░ VCE čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ, ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ąĮąŠąČą║ąĄ DSH/L čéą░ą║ąČąĄ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ. ąæčāą┤čāčćąĖ čüą╝ąĄčēąĄąĮąĮčŗą╝ ą▓ąĮčāčéčĆąĖ ą║ ą╗ąŠą║ą░ą╗čīąĮąŠą╝čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ ą┐ąĖčéą░ąĮąĖčÅ, ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ DSH/L ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čäąĖą║čüąĖčĆčāąĄčéčüčÅ. ąÜąŠą│ą┤ą░ DSH/L ą┐čĆąĄą▓čŗčüąĖčé ą┐ąŠčĆąŠą│ VDESAT+, čüčĆą░ą▒ąŠčéą░ąĄčé ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ (čüą╝. čĆąĖčü. 13). ąÆčŗčģąŠą┤ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ čäąĖą╗čīčéčĆčāąĄčéčüčÅ, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąŠčłąĖą▒ąŠčćąĮąŠą│ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗąĘą▓ą░ąĮąŠ ąĖąĮą┤čāčåąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ čüąĮą░čĆčāąČąĖ ąĖą╝ą┐čāą╗čīčüą░ą╝ąĖ; ąĖą╝ą┐čāą╗čīčüčŗ ą║ąŠčĆąŠč湥, č湥ą╝ tDS, ą▒čāą┤čāčé ąŠčéčäąĖą╗čīčéčĆąŠą▓ą░ąĮčŗ. ą¦č鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąŠčłąĖą▒ąŠčćąĮąŠą│ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąŠčéą║čĆčŗą▓ą░ąĄčéčüčÅ IGBT, čüčģąĄą╝ą░ ą┤ąĄč鹥ą║č鹊čĆą░ ą┤ąĄčüą░čéčāčĆą░čåąĖąĖ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ąŠą╝ ą│ą░čłąĄąĮąĖčÅ (čüą╝. ą▒ą╗ąŠą║ tBL Blanking ąĮą░ čĆąĖčü. 13). ąŁč鹊 ą▓čĆąĄą╝čÅ ąŠčåąĄąĮąŠčćąĮąŠ ą▓čŗą▒čĆą░ąĮąŠ ą┐ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą▓ą║ą╗čÄč湥ąĮąĖčÅ IGBT, ąĖ ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐čĆąĄą▓čŗčłąĄąĮąŠ, čćč鹊 ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčéčüčÅ ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╝ ą▓čŗą▒ąŠčĆąŠą╝ ąĘąĮą░č湥ąĮąĖčÅ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ąĘą░čéą▓ąŠčĆą░. ąÜąŠą│ą┤ą░ IGBT ąĮąĄ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĮą░čüčŗčēąĄąĮ ą┐ąŠčüą╗ąĄ ąĖąĮč鹥čĆą▓ą░ą╗ą░ tBL, ą┤ąĄč鹥ą║čéąĖčĆčāąĄčéčüčÅ ą▓čŗčģąŠą┤ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ąĖ ą┤čĆą░ą╣ą▓ąĄčĆ ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ.

ą¤čĆą░ą▓ąĖą╗čīąĮąŠ čüč乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ąĖąĮąĖčåąĖąĖčĆčāčÄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą╝čÅą│ą║ąŠą│ąŠ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (Soft ShutDown, SSD). ąÆąŠ ą▓čĆąĄą╝čÅ SSD ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤čĆą░ą╣ą▓ąĄčĆčŗ ą┐ąĄčĆąĄčģąŠą┤čÅčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčüąŠą║ąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ, ąĖ ą░ą║čéąĖą▓ąĖčĆčāčÄčéčüčÅ čĆąĄąĘąĖčüč鹊čĆčŗ SSD pull-down (ą┐ąŠą┤čéčÅąČą║ą░ ą▓ąĮąĖąĘ), čćč鹊ą▒čŗ ą▓čŗą║ą╗čÄčćąĖčéčī IGBT č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ SSDH/L. ąÆčŗčģąŠą┤ ~SY_FLT (ą░ą║čéąĖą▓ąĮčŗą╣ ą╗ąŠą│. 0, čüą╝. čĆąĖčü. 14) čüąŠąŠą▒čēą░ąĄčé ąŠ čüąŠčüč鹊čÅąĮąĖąĖ IR2214 ą▓čüąĄ ą▓čĆąĄą╝čÅ, ą┐ąŠą║ą░ ą┤ąĄą╣čüčéą▓čāąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī SSD (tSS). ąÜą░ą║ č鹊ą╗čīą║ąŠ SSD ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ, SYS_FLT ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1, ąĖ IR2214 ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗ ąŠčéą║ą░ąĘą░ FAULT (čüą╝. čüąĄą║čåąĖčÄ ~FAULT/SD) ą░ą║čéąĖą▓ą░čåąĖąĄą╣ ąĮąŠąČą║ąĖ ~FAULT/SD. ąŁč鹊 ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗ ąČąĄčüčéą║ąŠą│ąŠ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (hard shut down) ą┤ą╗čÅ ą▓čŗčģąŠą┤ąŠą▓ ąŠą▒ąŠąĖčģ ą┐ą╗ąĄčć ą┤čĆą░ą╣ą▓ąĄčĆą░, ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ (HO = LO = ą╗ąŠą│. 0). ąÜą░ąČą┤čŗą╣ ą┤čĆą░ą╣ą▓ąĄčĆ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0, ą┐ąŠą║ą░ ąŠčłąĖą▒ą║ą░ ąĮąĄ ąŠčćąĖčüčéąĖčéčüčÅ (čüą╝. FLT_CLR).

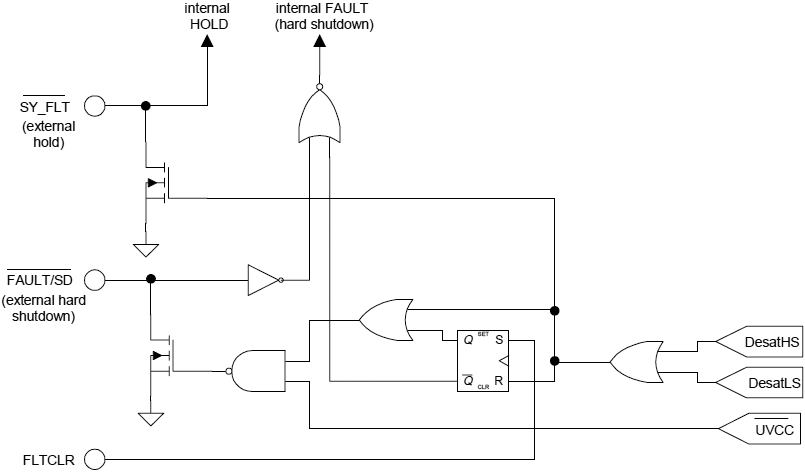

ąĀąĖčü. 14 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüčģąĄą╝čā ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ąŠčéą║ą░ąĘąŠą▓. ąØą░ čüčģąĄą╝ąĄ DesatHS ąĖ DesatLS ąŠą▒ąŠąĘąĮą░čćą░čÄčé ą┤ą▓ą░ čüąĖą│ąĮą░ą╗ą░, ą┐čĆąĖčģąŠą┤čÅčēąĖąĄ ąŠčé ą▓čŗčģąŠą┤ąĮčŗčģ ą║ą░čüą║ą░ą┤ąŠą▓ (čüą╝. čĆąĖčü. 13).

ąĀąĖčü. 14. ąĪčģąĄą╝ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąŠčéą║ą░ąĘą░ą╝ąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: internal hold čŹč鹊 ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüąĖą│ąĮą░ą╗ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą▓čŗčģąŠą┤ąŠą▓, internal FAULT (hard shutdown) čŹč鹊 ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüąĖą│ąĮą░ą╗ ąŠčéą║ą░ąĘą░ čü ąČąĄčüčéą║ąĖą╝ (ą╝ą│ąĮąŠą▓ąĄąĮąĮčŗą╝) ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝, external hold ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą▓čŗčģąŠą┤ąŠą▓, external hard shutdown ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ ąČąĄčüčéą║ąŠą│ąŠ (ą╝ą│ąĮąŠą▓ąĄąĮąĮąŠą│ąŠ) ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ, DesatHS ąĖ DesatLS čŹč鹊 čüąĖą│ąĮą░ą╗čŗ ąŠčé čüčģąĄą╝čŗ ąŠą▒ąĮą░čĆčāąČąĄąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ čüąĖą╗ąŠą▓ąŠą│ąŠ ą┐ąŠą╗čāą╝ąŠčüčéą░ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ.

ąĪą╗ąĄą┤čāąĄčé ąŠčéą╝ąĄčéąĖčéčī, čćč鹊 ą▓ąŠ ą▓čĆąĄą╝čÅ Soft ShutDown, ąŠą▒ą░ čāąĘą╗ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĮąĖąČąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (Under Voltage fault) ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (external Shut Down, SD) ą╝ą░čüą║ąĖčĆčāčÄčéčüčÅ ą┤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÅ SSD. ąŚą░čēąĖčéą░ ąŠčé ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ čĆą░ą▒ąŠčéą░ąĄčé ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ č湥čĆąĄąĘ ą┤čĆčāą│ąŠą╣ ą▓čŗą▓ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, ąĖ ąŠčéą║ą╗čÄčćą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą▓čŗą║ą╗čÄč湥ąĮąŠ ą▓čŗčģąŠą┤ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ.

ą×ą▒čĆą░ą▒ąŠčéą║ą░ ąŠčéą║ą░ąĘąŠą▓ ą▓ ą╝ąĮąŠą│ąŠčäą░ąĘąĮčŗčģ čüąĖčüč鹥ą╝ą░čģ. ąĪ čüąĖčüč鹥ą╝ąĄ, ą│ą┤ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą▓ą░ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ ąĘą░čéą▓ąŠčĆą░ ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ IR2214, ąŠąĮąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüąŠąĄą┤ąĖąĮąĄąĮčŗ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 15.

ąĀąĖčü. 15. ą¤čĆąĖą╝ąĄąĮąĄąĮąĖąĄ IR2214 ą▓ čéčĆąĄčģčäą░ąĘąĮąŠą╣ čüąĖčüč鹥ą╝ąĄ.

~SY_FLT. ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ ąĮąŠąČą║ąĖ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čÄčé ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖąĄ ą▓ąĮčāčéčĆąĖ čüąĖčüč鹥ą╝čŗ č湥čĆąĄąĘ ą╗ąŠą║ą░ą╗čīąĮčŗąĄ čåąĄą┐ąĖ. ąÉą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī - ą╗ąŠą│. 0.

ą£ąĖą║čĆąŠčüčģąĄą╝ą░, ą║ąŠč鹊čĆą░čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗ą░ ą▓čŗčģąŠą┤ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ IGBT, ą░ą║čéąĖą▓ąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗ ~SY_FLT, ą║ąŠč鹊čĆčŗą╣ ąĘą░č鹥ą╝ čüčćąĖčéčŗą▓ą░ąĄčéčüčÅ ą┤čĆčāą│ąĖą╝ąĖ ą┤čĆą░ą╣ą▓ąĄčĆą░ą╝ąĖ ąĘą░čéą▓ąŠčĆąŠą▓. ąÜąŠą│ą┤ą░ SYS_FLT ą░ą║čéąĖą▓ąĄąĮ, ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ ą┤čĆą░ą╣ą▓ąĄčĆčŗ čāą┤ąĄčƹȹĖą▓ą░čÄčé čüą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčģąŠą┤ąŠą▓ ą▓čŗą║ą╗čÄč湥ąĮąĮčŗą╝, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čüąĖą│ąĮą░ą╗ąŠą▓ ąĮą░ ą▓čģąŠą┤ą░čģ (HIN, LIN), ą║ąŠč鹊čĆčŗąĄ ą┐ąŠčüčéčāą┐ą░čÄčé ąŠčé čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą│ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ (freeze state, čüąŠčüč鹊čÅąĮąĖąĄ ąĘą░ą╝ąŠčĆąŠąĘą║ąĖ).

ąŁčéą░ čäčāąĮą║čåąĖčÅ ą▓ čćą░čüčéąĮąŠčüčéąĖ ą▓ą░ąČąĮą░ ą┐čĆąĖ ąĘą░ą╝čŗą║ą░ąĮąĖąĖ ą╝ąĄąČą┤čā čäą░ąĘą░ą╝ąĖ, ą║ąŠą│ą┤ą░ č鹊ą║ č鹥č湥čé č湥čĆąĄąĘ ą┤ą▓ą░ IGBT, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą║ čĆą░ąĘąĮčŗą╝ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓. ążą░ą║čéąĖč湥čüą║ąĖ, ą║ąŠą│ą┤ą░ ąŠą┤ąĖąĮ čéčĆą░ąĮąĘąĖčüč鹊čĆ ą┐čĆąŠčģąŠą┤ąĖčé ą┐čĆąŠčåąĄčüčü ą╝čÅą│ą║ąŠą│ąŠ ą▓ą║ą╗čÄč湥ąĮąĖčÅ, ąĮą░ ą▓č鹊čĆąŠą╝ čéčĆą░ąĮąĘąĖčüč鹊čĆąĄ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮą░ čüąĖčéčāą░čåąĖčÅ ąČąĄčüčéą║ąŠą│ąŠ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ, čćč鹊ą▒čŗ čüąŠčģčĆą░ąĮčÅą╗čüčÅ ą┐čĆąŠčåąĄčüčü ą╝čÅą│ą║ąŠą│ąŠ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ SSD.

ąÆ čüąŠčüč鹊čÅąĮąĖąĖ ąĘą░ą╝ąŠčĆąŠąĘą║ąĖ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗąĄ ą┤čĆą░ą╣ą▓ąĄčĆčŗ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĮąĄą░ą║čéąĖą▓ąĮčŗ, ą┐ąŠč鹊ą╝čā čćč鹊 čäčāąĮą║čåąĖčÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ą▓čüąĄ ąĄčēąĄ ą┐ąŠą╗čāčćą░ąĄčé čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé. ą×ą▒ą╝ąĄąĮ ~SY_FLT čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ ą┤ą╗čÅ čüąŠąĘą┤ą░ąĮąĖčÅ ą╗ąŠą║ą░ą╗čīąĮąŠą╣ čüąĄčéąĖ ą╝ąĄąČą┤čā ą┤čĆą░ą╣ą▓ąĄčĆą░ą╝ąĖ. ąØąĄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ čüąŠąĄą┤ąĖąĮčÅčéčī ~SY_FLT čü ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝.

~FAULT/SD. ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ąĮąŠąČąĄą║ ~FAULT/SD ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčé ąŠą▒ą╝ąĄąĮ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ąĖ čü ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ čüąĖčüč鹥ą╝čŗ. ąÉą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0.

ąÜąŠą│ą┤ą░ ąĮą░ ~FAULT/SD ą╗ąŠą│. 0, čŹč鹊 ą┤ą░ąĄčé ą║ąŠą╝ą░ąĮą┤čā ą▓čŗčģąŠą┤ą░ą╝ ąĮą░ ąČąĄčüčéą║ąŠąĄ ąŠčéą║ą╗čÄč湥ąĮąĖąĄ. ąóčĆąĖ čüąŠą▒čŗčéąĖčÅ ą╝ąŠą│čāčé ą┐ąĄčĆąĄą▓ąĄčüčéąĖ ~FAULT/SD ą▓ ą╗ąŠą│. 0:

1. ąĪąŠą▒čŗčéąĖąĄ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ: ąĮąŠąČą║ą░ FAULT\SD ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ ąĮą░ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčü SSD ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ, ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčé čŹč鹊 čüąŠčüč鹊čÅąĮąĖąĄ č鹊ą╗čīą║ąŠ čüąĖą│ąĮą░ą╗ FLT_CLR.

2. ąĪąĮąĖąČąĄąĮąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VCC (čüąŠą▒čŗčéąĖąĄ UV): ąĮąŠąČą║ą░ FAULT\SD ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0 ąĖ čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0 ąĖ čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ čŹč鹊ą╝ čüąŠčüč鹊čÅąĮąĖąĖ, ą┐ąŠą║ą░ ą░ą║čéąĖą▓ąĮą░ čüąĖčéčāą░čåąĖčÅ ąĮąĄą┤ąŠčüčéą░č鹊čćąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (čŹč鹊 čüąŠčüč鹊čÅąĮąĖąĄ ąĮąĄ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ).

3. ąÜąŠą│ą┤ą░ ~FAULT/SD ą┐čĆąĖčéčÅą│ąĖą▓ą░ąĄčéčüčÅ ą║ ą╗ąŠą│. 0 čüąĮą░čĆčāąČąĖ čüąĖą│ąĮą░ą╗ąŠą╝ ą╗ąĖą▒ąŠ ąŠčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą╗ąĖą▒ąŠ ąŠčé ą┤čĆčāą│ąŠą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ IR2214. ąŁč鹊 čüąŠą▒čŗčéąĖąĄ ąĮąĄ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ, ą┐ąŠčŹč鹊ą╝čā FLT_CLR ąĮąĄ ą╝ąŠąČąĄčé ąĄą│ąŠ ąĘą░ą┐čĆąĄčéąĖčéčī. ąóąŠą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ~FAULT/SD ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ą╗ąŠą│. 1, ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝.

[ąÉą║čéąĖą▓ąĮąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ]

ąĪ čåąĄą╗čīčÄ ąŠą▒ąĮą░čĆčāąČąĄąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ čüąĖą╗ąŠą▓ąŠą│ąŠ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĄą│ąŠ ą║ąŠą╗ą╗ąĄą║č鹊čĆą░ ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ č湥čĆąĄąĘ ą▓ąĮąĄčłąĮąĖą╣ ą▓čŗčüąŠą║ąŠą▓ąŠą╗čīčéąĮčŗą╣ ą┤ąĖąŠą┤. ąŁč鹊čé ą┤ąĖąŠą┤ ąĮąŠčĆą╝ą░ą╗čīąĮąŠ čüą╝ąĄčēąĄąĮ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ pull-up čĆąĄąĘąĖčüč鹊čĆąŠą╝, čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗą╝ čü ą╗ąĖąĮąĖąĄą╣ ą╗ąŠą║ą░ą╗čīąĮąŠą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ (VB ąĖą╗ąĖ VCC). ąÜąŠą│ą┤ą░ čéčĆą░ąĮąĘąĖčüč鹊čĆ "ąŠčéą║čĆčŗčé", ą┤ąĖąŠą┤ ą┐čĆąŠą┐čāčüą║ą░ąĄčé č鹊ą║, ąĖ čüąĖą╗ą░ č鹊ą║ą░ ą▓ čüčģąĄą╝ąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ pull-up čĆąĄąĘąĖčüč鹊čĆą░.

ąÆ čüčģąĄą╝ąĄ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ č鹊ą║ čüą╝ąĄčēąĄąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ą╝ąŠąČąĄčé ą┐ąŠą▓ą╗ąĖčÅčéčī ąĮą░ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ (čüą╝. čĆąĖčü. 19). ążą░ą║čéąĖč湥čüą║ąĖ, čüą╗ąĖčłą║ąŠą╝ ą╝ą░ą╗ąĄąĮčīą║ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄąĘąĖčüč鹊čĆą░ pull-up ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ą▒ąŠą╗čīčłąŠą╝čā č鹊ą║čā, ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ čĆą░ąĘčĆčÅąČą░čÄčēąĄą╝čā ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ čéąĖą┐ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄąĘąĖčüč鹊čĆą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ pull-up ą▓čŗą▒čĆą░ąĮąŠ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 100 ą║ą×ą╝.

ąÆ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ąĮąŠąČąĄą║ DSH/DSL ąŠč湥ąĮčī ąĮąĖąĘą║ąŠąĄ, ą║ąŠą│ą┤ą░ čéčĆą░ąĮąĘąĖčüč鹊čĆ ąŠčéą║čĆčŗčé (ą╝ą░ą╗ąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ čåąĄą┐ąĖ č湥čĆąĄąĘ ą▓ąĮąĄčłąĮąĖą╣ ą┤ąĖąŠą┤ ą┤ąŠ čüąĖą╗ąŠą▓ąŠą│ąŠ čéčĆą░ąĮąĘąĖčüč鹊čĆą░), ą┐čĆąĖ ąĘą░ą║čĆčŗč鹊ą╝ čéčĆą░ąĮąĘąĖčüč鹊čĆąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ąĄčĆčģąĮąĖą╝ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖą╝ čĆąĄąĘąĖčüč鹊čĆąŠą╝ (pull-up). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čāčĆąŠą▓ąĮčÅ, ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░ąĄą╝ąŠąĄ ą║ čüąĖą╗ąŠą▓ąŠą╝čā čéčĆą░ąĮąĘąĖčüč鹊čĆčā ą┐čĆąĖ ą║ąŠą╝ą╝čāčéą░čåąĖąĖ ąĮą░ ą▓čŗčģąŠą┤ąĄ, ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠą╝čā č鹊ą║čā, ąĖąĮąČąĄą║čéąĖčĆčāąĄą╝čā č湥čĆąĄąĘ ą┐ą░čĆą░ąĘąĖčéąĮčāčÄ ąĄą╝ą║ąŠčüčéčī ą┤ąĖąŠą┤ą░ ą▓ ąĮąŠąČą║čā ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ (DSH/L). ąŁč鹊čé ąĮą░ą▓ąŠą┤ąĖą╝čŗą╣ čłčāą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī ą╗ąĄą│ą║ąŠ čāčüčéčĆą░ąĮąĄąĮ ą░ą║čéąĖą▓ąĮčŗą╝ čüą╝ąĄčēąĄąĮąĖąĄą╝ ą┤ąĖąŠą┤ą░ (Active Bias).

ąĪčéčĆčāą║čéčāčĆą░ Active Bias ąĖą╝ąĄąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą▓ąĄčĆčüąĖąĖ IR22141 ą▓čŗą▓ąŠą┤ąŠą▓ DSH/L. ąØą░ ąĮąŠąČą║ą░čģ DSH/L ąĄčüčéčī ą░ą║čéąĖą▓ąĮčŗą╣ pull-up ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ VB/VCC, ąĖ pull-down ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ VS/COM. ąĪą┐ąĄčåąĖą░ą╗čīąĮą░čÅ čüčģąĄą╝ą░ čüąŠąĘą┤ą░ąĮąĖčÅ čüą╝ąĄčēąĄąĮąĖčÅ čāą╝ąĄąĮčīčłą░ąĄčé ąĖą╝ą┐ąĄą┤ą░ąĮčü ąĮąŠąČą║ąĖ DSH/L, ą║ąŠą│ą┤ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐čĆąĄą▓čŗčłą░ąĄčé ą┐ąŠčĆąŠą│ VDESAT (čüą╝. čĆąĖčü. 16). ąŁč鹊 ąĮąĖąĘą║ąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą┐ąŠą╝ąŠą│ą░ąĄčé ą▓ čāčüčéčĆą░ąĮąĄąĮąĖąĖ čłčāą╝ą░, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ąŠčé č鹊ą║ą░ č湥čĆąĄąĘ ą┐ą░čĆą░ąĘąĖčéąĮčāčÄ ąĄą╝ą║ąŠčüčéčī. ąÜąŠą│ą┤ą░ čüąĖą╗ąŠą▓ąŠą╣ čéčĆą░ąĮąĘąĖčüč鹊čĆ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąŠčéą║čĆčŗčé, ą┤ąĖąŠą┤ ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ čüą╝ąĄčēąĄąĮąĮčŗą╝ ą▓ ą┐čĆčÅą╝ąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ, ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ąĮąŠąČą║ąĄ DSH/DSL čāą╝ąĄąĮčīčłą░ąĄčéčüčÅ. ąÆ čŹč鹊ą╣ č鹊čćą║ąĄ čüčģąĄą╝ą░ čüą╝ąĄčēąĄąĮąĖčÅ ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ, čćč鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī č鹊ą║ čüą╝ąĄčēąĄąĮąĖčÅ ą┤ąĖąŠą┤ą░, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 16.

ąĀąĖčü. 16. RDSH/RDSL Active Biasing (čĆą░ą▒ąŠčéą░ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čüą╝ąĄčēąĄąĮąĖčÅ).

[ąÆčŗčģąŠą┤ąĮąŠą╣ ą║ą░čüą║ą░ą┤]

ąĪčéčĆčāą║čéčāčĆą░ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą║ą░čüą║ą░ą┤ą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 13. ą×ąĮą░ čüąŠčüč鹊ąĖčé ąĖąĘ ą┤ą▓čāčģ ą║ą░čüą║ą░ą┤ąŠą▓ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ąĖ ąŠą┤ąĮąŠą│ąŠ ą║ą░čüą║ą░ą┤ą░ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ. ąÜąŠą│ą┤ą░ ą┤čĆą░ą╣ą▓ąĄčĆ ąŠčéą║čĆčŗą▓ą░ąĄčé IGBT (čüą╝. čĆąĖčü. 8), ą┐ąĄčĆą▓čŗą╣ ą║ą░čüą║ą░ą┤ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ą║ą░čüą║ą░ą┤ ąŠčüčéą░ąĄčéčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ č鹊ą╗čīą║ąŠ ąŠą│čĆą░ąĮąĖč湥ąĮąĮąŠąĄ ą▓čĆąĄą╝čÅ (ton1). ąŁčéą░ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéčī čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠčüčéčī čüąĖą╗ąŠą▓čŗčģ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓, čāčüą║ąŠčĆčÅčÅ ąĖčģ ąĮą░čüčŗčēąĄąĮąĖąĄ ąŠčéą║čĆčŗčéąĖąĄ, ą┐ąŠč鹊ą╝čā čćč鹊 ąĄą╝ą║ąŠčüčéčī ąĘą░čéą▓ąŠčĆą░ ąĘą░čĆčÅąČą░ąĄčéčüčÅ ą▒čŗčüčéčĆąĄąĄ.

ą¤čĆąĖ ą▓čŗą║ą╗čÄč湥ąĮąĖąĖ ąŠą┤ąĖąĮ n-ą║ą░ąĮą░ą╗čīąĮčŗą╣ čéčĆą░ąĮąĘąĖčüč鹊čĆ ąĘą░ą╝čŗą║ą░ąĄčé ąĮą░ čüąĄą▒čÅ č鹊ą║ ą┤ąŠ 3A (IO-), ąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čåąĄą┐ąŠčćą║čā ąĮąĖąĘą║ąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ, ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░čÅ čüą░ą╝ąŠą▓ą║ą╗čÄč湥ąĮąĖąĄ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ ąĖąĘ-ąĘą░ ą┐ą░čĆą░ąĘąĖčéąĮąŠą╣ ąĄą╝ą║ąŠčüčéąĖ ą£ąĖą╗ą╗ąĄčĆą░ ą▓ čüąĖą╗ąŠą▓ąŠą╝ ą║ą╗čÄč湥.

[ą×ą┐ąĖčüą░ąĮąĖąĄ ą╗ąŠą│ąĖą║ąĖ ą┤ąĖą░ą│čĆą░ą╝ą╝ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ]

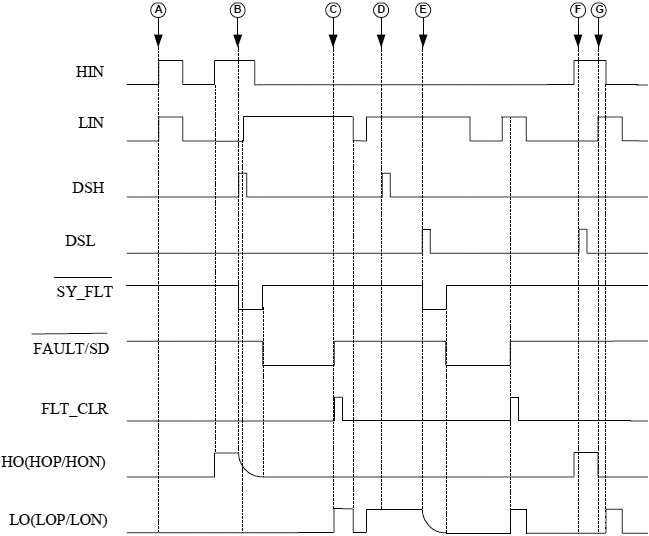

ąĀąĖčü. 17 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąĖą│ąĮą░ą╗čŗ ~SY_FLT ąĖ ~FAULT/SD ą║ą░ą║ ą▓čŗčģąŠą┤čŗ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čĆąĖčü. 18 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĖčģ ą║ą░ą║ ą▓čģąŠą┤čŗ.

ąĀąĖčü. 17. ąóą░ą╣ą╝ąĖąĮą│ąĖ I/O, ą║ąŠą│ą┤ą░ ~SY_FLT ąĖ ~FAULT/SD čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ ą▓čŗčģąŠą┤čŗ.

ąŚą░ą╝ąĄčćą░ąĮąĖčÅ ą┐ąŠ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ą▓čĆąĄą╝ąĄąĮąĖ čĆąĖčü. 17:

A. ąÜąŠą│ą┤ą░ ą▓čģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┤ą░čÄčé ą▓ą║ą╗čÄč湥ąĮąĖąĄ, ą▓čŗčģąŠą┤čŗ ą▓čŗą║ą╗čÄčćą░čÄčéčüčÅ (ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖąĄ čüą║ą▓ąŠąĘąĮąŠą│ąŠ č鹊ą║ą░ čüąĖą╗ąŠą▓čŗčģ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓).

B. ąĪąĖą│ąĮą░ą╗ HO ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ, ąĖ ą▓ąĄčĆčģąĮąĄąĄ ą┐ą╗ąĄč湊 ą▓čŗčģąŠą┤ąĖčé ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ, HO ą┐ą╗ą░ą▓ąĮąŠ ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ~SY_FLT ąŠčüčéą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0. ąÜąŠą│ą┤ą░ ~SY_FLT ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1, ~FAULT/SD ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0. ąÆąŠ ą▓čĆąĄą╝čÅ SSD, ąĄčüą╗ąĖ LIN ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1, LO ąĮąĄ ąĖąĘą╝ąĄąĮčÅąĄčéčüčÅ (ąĘą░ą╝ąŠčĆą░ąČąĖą▓ą░ąĄčéčüčÅ).

C. ąÜąŠą│ą┤ą░ ~FAULT/SD ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0 (čüą╝. čüąĄą║čåąĖčÄ ~FAULT/SD), čüąĖą│ąĮą░ą╗ FLT_CLR ą╝ąŠąČąĄčé ąĘą░ą┐čĆąĄčéąĖčéčī čŹč鹊, ąĖ ą▓čŗčģąŠą┤čŗ ą┐ąĄčĆąĄą╣ą┤čāčé ąŠą▒čĆą░čéąĮąŠ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čģąŠą┤ąŠą▓.

D. DSH ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1, ąŠą┤ąĮą░ą║ąŠ čŹč鹊 ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąŠ, ą┐ąŠč鹊ą╝čā čćč鹊 HO ą▓čŗą║ą╗čÄč湥ąĮ.

E. ąĪąĖą│ąĮą░ą╗ LO ą▓ą║ą╗čÄčćąĖą╗čüčÅ, ąĖ ąĮąĖąČąĮąĄąĄ ą┐ą╗ąĄč湊 IGBT ą▓čŗčłą╗ąŠ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ, ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ čéą░ą║ąŠąĄ ąČąĄ, ą║ą░ą║ ąŠą┐ąĖčüą░ąĮąŠ ą┐čĆąŠ č鹊čćą║čā B.

F. DSL ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1, ąŠą┤ąĮą░ą║ąŠ čŹč鹊 ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąŠ, ą┐ąŠč鹊ą╝čā čćč鹊 LO ą▓čŗą║ą╗čÄč湥ąĮ.

G. ąÜą░ą║ ą▓ č鹊čćą║ąĄ A (ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖąĄ čüą║ą▓ąŠąĘąĮąŠą│ąŠ č鹊ą║ą░ čüąĖą╗ąŠą▓čŗčģ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓).

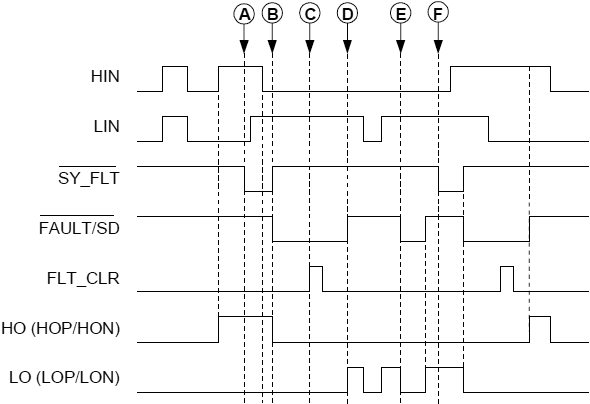

ąĀąĖčü. 18. ąøąŠą│ąĖą║ą░ I/O, ą║ąŠą│ą┤ą░ ~SY_FLT ąĖ ~FAULT/SD čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ ą▓čģąŠą┤čŗ.

ąŚą░ą╝ąĄčćą░ąĮąĖčÅ ą┐ąŠ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ą▓čĆąĄą╝ąĄąĮąĖ čĆąĖčü. 18:

A. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (hold state), ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĖąĘą╝ąĄąĮąĄąĮąĖą╣ ąĮą░ ą▓čģąŠą┤ą░čģ. ąĪąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą▓čŗąĘą▓ą░ąĮąŠ ą┐ąŠą┤čéčÅąČą║ąŠą╣ ~SY_FLT ą║ ą╗ąŠą│. 0 ą▓ąĮąĄčłąĮąĖą╝ čüąĖą│ąĮą░ą╗ąŠą╝.

B. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ č湥čĆąĄąĘ hard shutdown ą┐ąŠ ą║ąŠą╝ą░ąĮą┤ąĄ čüąĮą░čĆčāąČąĖ. A - B ąŠą┤ąĖąĮą░ą║ąŠą▓ą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī, ą║ąŠč鹊čĆą░čÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤čĆčāą│ąŠą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ IR2214 ą▓ ą┐čĆąŠčåąĄą┤čāčĆąĄ SSD.

C. ąĪąĖą│ąĮą░ą╗ ~FAULT/SD, ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮąĮčŗą╣ ą▓ ą╗ąŠą│. 0 čüąĮą░čĆčāąČąĖ (čüąŠčüč鹊čÅąĮąĖąĄ shutdown), ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ č湥čĆąĄąĘ FLT_CLR (čüą╝. čüąĄą║čåąĖčÄ ~FAULT/SD).

D. ~FAULT/SD ą▓ąŠąĘą▓čĆą░čēą░ąĄčéčüčÅ ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ, ąĖ ą▓čŗčģąŠą┤čŗ ą┐ąĄčĆąĄčģąŠą┤čÅčé ąŠą▒čĆą░čéąĮąŠ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čģąŠą┤ąŠą▓.

E. ąĪąĖą│ąĮą░ą╗ ~FAULT/SD, ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮąĮčŗą╣ ą▓ ą╗ąŠą│. 0 čüąĮą░čĆčāąČąĖ: ą▓čŗčģąŠą┤čŗ ą▓čŗą║ą╗čÄčćą░čÄčéčüčÅ č湥čĆąĄąĘ hard shutdown (ą║ą░ą║ ą▓ č鹊čćą║ąĄ B).

F. ąÜą░ą║ ą▓ č鹊čćą║ą░čģ A ąĖ B, ąŠą┤ąĮą░ą║ąŠ ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░.

[ą¤ąĖčéą░ąĮąĖąĄ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ]

ą×čé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VBS ą┐ąĖčéą░ąĄčéčüčÅ ą▓ąĄčĆčģąĮąĄąĄ ą┐ą╗ąĄč湊 ą┤čĆą░ą╣ą▓ąĄčĆą░ IR2214. ąŁč鹊 ą┐ąĖčéą░ąĮąĖąĄ ąŠčĆą│ą░ąĮąĖąĘąŠą▓čŗą▓ą░ąĄčéčüčÅ ą┐ąŠą▓ąĄčĆčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VS, ąĖ ą┐ąŠčŹč鹊ą╝čā ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐ą╗ą░ą▓ą░čÄčēąĖą╝.

ąÆ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ IR2214 ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ VBS ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ (bootstrap). ąÆąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ą░ č乊čĆą╝ąĖčĆčāąĄčéčüčÅ ą┤ąĖąŠą┤ąŠą╝ ąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą╝, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 19.

ąĀąĖčü. 19. ąĪčģąĄą╝ą░ ą┐ąĖčéą░ąĮąĖčÅ ąŠčé ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ.

ąöąŠčüč鹊ąĖąĮčüčéą▓ąŠ čŹč鹊ą│ąŠ ą╝ąĄč鹊ą┤ą░ - ąŠąĮ ą┐čĆąŠčüč鹊ą╣ ąĖ ąĮąĄą┤ąŠčĆąŠą│ąŠą╣, ąĮąŠ ąĖą╝ąĄąĄčé ąĮąĄą║ąŠč鹊čĆčŗąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ą┐ąŠ čüą║ą▓ą░ąČąĮąŠčüčéąĖ ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ą▓ą║ą╗čÄč湥ąĮąĖčÅ, ą┐ąŠčüą║ąŠą╗čīą║čā ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąŠą▒ąĮąŠą▓ą╗čÅčéčī ąĘą░čĆčÅą┤ ą▓ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąĄ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ. ą¤čĆą░ą▓ąĖą╗čīąĮčŗą╣ ą▓čŗą▒ąŠčĆ čŹč鹊ą│ąŠ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ čĆą░ą┤ąĖą║ą░ą╗čīąĮąŠ čüąĮąĖąČą░ąĄčé čŹčéąĖ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ.

ąÆąĄą╗ąĖčćąĖąĮą░ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ. ą¦č鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĮąŠą╝ąĖąĮą░ą╗ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░, čüąĮą░čćą░ą╗ą░ ąĮą░ą┤ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą┐ą░ą┤ąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (╬öVBS), ą┐čĆąĖ ą║ąŠč鹊čĆąŠą╝ ąĄčüčéčī ąĄčēąĄ ąĄčüčéčī ą│ą░čĆą░ąĮčéąĖčÅ ąŠčéą║čĆčŗą▓ą░ąĮąĖčÅ ą▓ąĄčĆčģąĮąĄą│ąŠ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ IGBT.

ąĢčüą╗ąĖ VGEmin čŹč鹊 ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĘą░čéą▓ąŠčĆ-菹╝ąĖčéč鹥čĆ, ą║ąŠč鹊čĆąŠąĄ ą╝čŗ ą┤ąŠą╗ąČąĮčŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī č鹊 ą┐ą░ą┤ąĄąĮąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī:

╬öVBS Ōēż VCC - VF - VGEmin - VCEon

ą┐čĆąĖ čāčüą╗ąŠą▓ąĖąĖ:

VGEmin > VBSUV-

ąŚą┤ąĄčüčī VCC čŹč鹊 ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, VF ą┐čĆčÅą╝ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą┤ąĖąŠą┤ąĄ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ, VCEon ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ 菹╝ąĖčéč鹥čĆ-ą║ąŠą╗ą╗ąĄą║č鹊čĆ čüąĖą╗ąŠą▓ąŠą│ąŠ IGBT ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░, ąĖ VBSUV- ą┐ąŠčĆąŠą│ąŠą▓ąŠąĄ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░.

ąóąĄą┐ąĄčĆčī ą╝čŗ ą┤ąŠą╗ąČąĮčŗ čĆą░čüčüą╝ąŠčéčĆąĄčéčī čäą░ą║č鹊čĆčŗ, ą▓ą╗ąĖčÅčÄčēąĖąĄ ąĮą░ čüąĮąĖąČąĄąĮąĖąĄ VBS:

- ąóčĆąĄą▒čāąĄą╝čŗą╣ ą┤ą╗čÅ ąŠčéą║čĆčŗčéąĖčÅ IGBT ąĘą░čĆčÅą┤ ąĘą░čéą▓ąŠčĆą░ (QG).

- ąóąŠą║ čāč鹥čćą║ąĖ ąĘą░čéą▓ąŠčĆ-ąĖčüč鹊ą║ (菹╝ąĖčéč鹥čĆ) IGBT (ILK_GE).

- ąóąŠą║ ą┐ąŠą║ąŠčÅ ą┐ą╗ą░ą▓ą░čÄčēąĄą│ąŠ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ (IQBS).

- ąóąŠą║ čāč鹥čćą║ąĖ ą┐ą╗ą░ą▓ą░čÄčēąĄą│ąŠ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ (ILK).

- ąóąŠą║ čāč鹥čćą║ąĖ ą┤ąĖąŠą┤ą░ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ (ILK_DIODE).

- ąĪą╝ąĄčēąĄąĮąĖąĄ ą┤ąĖąŠą┤ą░ ą┤ąĄč鹥ą║č鹊čĆą░ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ą┐čĆąĖ ąŠčéą║čĆčŗčéąĖąĖ (IDS-).

- ąŚą░čĆčÅą┤, ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗą╣ ą┤ą╗čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čüčģąĄą╝ čüą┤ą▓ąĖą│ą░ čāčĆąŠą▓ąĮčÅ (QLS); čéąĖą┐ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ 20 nC.

- ąóąŠą║ čāč鹥čćą║ąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ (ILK_CAP).

- ąÆčĆąĄą╝čÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą▓ąĄčĆčģąĮąĄą│ąŠ čüąĖą╗ąŠą▓ąŠą│ąŠ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ (THON).

ILK_CAP ąĖą╝ąĄąĄčé čüą╝čŗčüą╗ čāčćąĖčéčŗą▓ą░čéčī č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čŹą╗ąĄą║čéčĆąŠą╗ąĖčéąĖč湥čüą║ąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ, ąĖ čü ą┤čĆčāą│ąĖą╝ąĖ čéąĖą┐ą░ą╝ąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą▓ čŹč鹊čé ą┐ą░čĆą░ą╝ąĄčéčĆ ą╝ąŠąČąĮąŠ ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī. ąØą░čüč鹊čÅč鹥ą╗čīąĮąŠ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ą║ąĄčĆą░ą╝ąĖč湥čüą║ąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ čü ąĮąĖąĘą║ąĖą╝ ESR, čé. ąĄ. čü ąĮąĖąĘą║ąĖą╝ 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮčŗą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝ (ą▓ čüą╗čāčćą░ąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čŹą╗ąĄą║čéčĆąŠą╗ąĖčéąĖč湥čüą║ąŠą│ąŠ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ąĄą╝čā ą║ąĄčĆą░ą╝ąĖč湥čüą║ąŠą│ąŠ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ čü ąĮąĖąĘą║ąĖą╝ ESR ą╝ąŠąČąĄčé ą▒čŗčéčī čŹčäč乥ą║čéąĖą▓ąĮčŗą╝ čĆąĄčłąĄąĮąĖąĄą╝).

ąóąŠą│ą┤ą░ ą╝čŗ ąĖą╝ąĄąĄą╝ čüą╗ąĄą┤čāčÄčēąĄąĄ:

QTOT = QG + QLS + (ILK_GE + IQBS + ILK + ILK_DIODE + ILK_CAP + IDS-) * THON

ą£ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ ąĄą╝ą║ąŠčüčéčī ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ:

QTOT

CBOOTmin = ------

ΔVBS

ąÆ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐čĆąĖą╝ąĄčĆąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 25A @ 125C IGBT (IRGP30B120KD):

ŌĆó IQBS = 800 ╬╝A (čüą╝. čüčéą░čéąĖč湥čüą║ąĖąĄ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ);

ŌĆó ILK = 50 ╬╝A (čüą╝. čüčéą░čéąĖč湥čüą║ąĖąĄ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ);

ŌĆó QLS = 20 nC;

ŌĆó QG = 160 nC (ą┤ą░čéą░čłąĖčé IRGP30B120KD);

ŌĆó ILK_GE = 100 nA (ą┤ą░čéą░čłąĖčé IRGP30B120KD);

ŌĆó ILK_DIODE = 100 ╬╝A (čü ą▓čĆąĄą╝ąĄąĮąĄą╝ ąŠą▒čĆą░čéąĮąŠą│ąŠ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ < 100 ąĮčü);

ŌĆó ILK_CAP = 0 (ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ ą▓ čüą╗čāčćą░ąĄ ą║ąĄčĆą░ą╝ąĖč湥čüą║ąŠą│ąŠ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░);

ŌĆó IDS- = 150 ╬╝A (čüą╝. čüčéą░čéąĖč湥čüą║ąĖąĄ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ);

ŌĆó THON = 100 ╬╝s.

ąÉ čéą░ą║ąČąĄ:

ŌĆó VCC = 15V

ŌĆó VF = 1V

ŌĆó VCEonmax = 3.1V

ŌĆó VGEmin = 10.5V

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ą░ą┤ąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ╬öVBS:

╬öVBS Ōēż VCC - VF - VGEmin - VCEon = 15V - 1V - 10.5V - 3.1V = 0.4V

ąóąŠą│ą┤ą░ ąĄą╝ą║ąŠčüčéčī ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ:

290nC

CBOOT = ------- = 725 ąĮąż

0.4V

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓čŗčłąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, čćč鹊 ą▒čŗą╗ąŠ ą▓čŗą▒čĆą░ąĮąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VCC 15V. ąØąĄą║ąŠč鹊čĆčŗąĄ IGBT ą╝ąŠą│čāčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčī ą▒ąŠą╗čīčłąĄą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, čćč鹊ą▒čŗ ą║ąŠčĆčĆąĄą║čéąĮąŠ čĆą░ą▒ąŠčéą░ą╗ą░ č鹥čģąĮąĖą║ą░ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ. ąóą░ą║ąČąĄ ą▓ ą┐ąŠą║ą░ąĘą░ąĮąĮčŗčģ ą▓čŗčłąĄ č乊čĆą╝čāą╗ą░čģ ąĮčāąČąĮąŠ čāčćąĖčéčŗą▓ą░čéčī ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ VCC.

[ąØąĄą║ąŠč鹊čĆčŗąĄ ą▓ą░ąČąĮčŗąĄ ąĘą░ą╝ąĄčćą░ąĮąĖčÅ]

ą¤čāą╗čīčüą░čåąĖąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąĪčāčēąĄčüčéą▓čāąĄčé čéčĆąĖ čĆą░ąĘąĮčŗčģ čüą╗čāčćą░čÅ, ą║ąŠą│ą┤ą░ čüčģąĄą╝ą░ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐čĆąŠą▓ąŠą┤čÅčēąĄą╣ (čüą╝. čĆąĖčü. 19):

ŌĆó ILOAD < 0; č鹊ą║ ąĮą░ą│čĆčāąĘą║ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ IGBT čü čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ VCEon

VBS = VCC - VF - VCEon

ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┐ąŠą╗čāčćąĖčéčüčÅ čüą░ą╝ąŠąĄ ąĮąĖąĘą║ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ VBS. ąŁč鹊 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüą░ą╝čŗą╣ čģčāą┤čłąĖą╣ čüą╗čāčćą░ą╣ ą┤ą╗čÅ ąĄą╝ą║ąŠčüčéąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ. ąÜąŠą│ą┤ą░ IGBT ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ, čāąĘąĄą╗ VS ą┐ąŠą┤ąĮąĖą╝ą░ąĄčéčüčÅ č鹊ą║ąŠą╝ ąĮą░ą│čĆčāąĘą║ąĖ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ą┤ąĖąŠą┤ čüą▓ąŠą▒ąŠą┤ąĮąŠą│ąŠ čģąŠą┤ą░ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ąĮąĄ ą▒čāą┤ąĄčé čüą╝ąĄčēąĄąĮ ą▓ ą┐čĆčÅą╝ąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ.

ŌĆó ILOAD = 0; IGBT ąĮąĄ ąĮą░ą│čĆčāąČąĄąĮ, čģąŠčéčÅ ąŠčéą║čĆčŗčé, ąĖ VCE ą╝ąŠąČąĮąŠ ąĮąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čéčī.

VBS = VCC - VF

ŌĆó ILOAD > 0; č鹊ą║ ąĮą░ą│čĆčāąĘą║ąĖ č鹥č湥čé č湥čĆąĄąĘ ą┤ąĖąŠą┤ čüą▓ąŠą▒ąŠą┤ąĮąŠą│ąŠ čģąŠą┤ą░.

VBS = VCC - VF + VFP

ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą╝čŗ ąĖą╝ąĄąĄą╝ čüą░ą╝ąŠąĄ ą▓čŗčüąŠą║ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ VBS. ą¤čĆąĖ ąŠčéą║čĆčŗčéąĖąĖ IGBT ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░, ILOAD ą▓č鹥ą║ą░ąĄčé ą▓ ąĮąĄą│ąŠ, ąĖ VS ą┐ąŠą┤čéčÅą│ąĖą▓ą░ąĄčéčüčÅ ą▓ą▓ąĄčĆčģ.

ąöą╗čÅ čāą╝ąĄąĮčīčłąĄąĮąĖčÅ čĆąĖčüą║ą░ čüąĮąĖąČąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (undervoltage, UV), ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čüą╗čāčćą░čÅ ILOAD < 0.

ąĀąĄąĘąĖčüč鹊čĆ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ. ąĀąĄąĘąĖčüč鹊čĆ (Rboot) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ čü ą┤ąĖąŠą┤ąŠą╝ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ (čüą╝. čĆąĖčü. 19), čćč鹊ą▒čŗ ąŠą│čĆą░ąĮąĖčćąĖčéčī č鹊ą║, ą║ąŠą│ą┤ą░ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ ą▓ ąĮą░čćą░ą╗čīąĮąŠą╣ čüčéą░ą┤ąĖąĖ ąĘą░čĆčÅą┤ą║ąĖ. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą▒čĆą░čéčī čŹč鹊čé čĆąĄąĘąĖčüč鹊čĆ ąĮąĄ ą▒ąŠą╗čīčłąĄ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą×ą╝ (ąŠą▒čŗčćąĮąŠ ą▓čŗą▒ąĖčĆą░čÄčé 5 ą×ą╝, ą╝ą░ą║čüąĖą╝čāą╝ ą╝ąŠąČąĮąŠ ą▓ąĘčÅčéčī 10 ą×ą╝), čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐ąŠą▓čŗčłąĄąĮąĖčÅ ą┐ąŠčüč鹊čÅąĮąĮąŠą╣ ą▓čĆąĄą╝ąĄąĮąĖ VBS. ą£ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ąĘą░čĆčÅą┤ą║ąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ ąĖą╗ąĖ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĄą│ąŠ ąĘą░čĆčÅą┤ą░ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐čĆąŠą▓ąĄčĆąĄąĮąŠ ą┐ąŠ čŹč鹊ą╣ ą┐ąŠčüč鹊čÅąĮąĮąŠą╣ ą▓čĆąĄą╝ąĄąĮąĖ.

ąÜąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ. ąöą╗čÅ čĆą░ąĘčĆą░ą▒ąŠč鹊ą║ čü ą▓čŗčüąŠą║ąĖą╝ THON, ą│ą┤ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čŹą╗ąĄą║čéčĆąŠą╗ąĖčéąĖč湥čüą║ąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čāčćąĖčéčŗą▓ą░čéčī ąĄą│ąŠ ESR. ąŁč鹊 ą┐ą░čĆą░ąĘąĖčéąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ č乊čĆą╝ąĖčĆčāąĄčé ą┤ąĄą╗ąĖč鹥ą╗čī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓ą╝ąĄčüč鹥 čü Rboot, ą│ąĄąĮąĄčĆąĖčĆčāčÅ čłą░ą│ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ VBS ąĮą░ ą┐ąĄčĆą▓ąŠą╝ ąĘą░čĆčÅą┤ąĄ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ. ą©ą░ą│ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ čüą║ąŠčĆąŠčüčéčī ąĮą░čĆą░čüčéą░ąĮąĖčÅ (dVBS/dt) ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠą│čĆą░ąĮąĖč湥ąĮčŗ. ąÆ ą║ą░č湥čüčéą▓ąĄ ąŠą▒čēąĄą│ąŠ ą┐čĆą░ą▓ąĖą╗ą░ ESR ą┤ąŠą╗ąČąĮąŠ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčéčī čüą╗ąĄą┤čāčÄčēąĄą╝čā ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÄ:

ESR

----------- * VCC Ōēż 3V

ESR + RBOOT

ą¤ą░čĆą░ą╗ą╗ąĄą╗čīąĮą░čÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅ ą║ąĄčĆą░ą╝ąĖč湥čüą║ąŠą│ąŠ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą╝ą░ą╗ąŠą╣ ąĄą╝ą║ąŠčüčéąĖ ąĖ 菹╗ąĄą║čéčĆąŠą╗ąĖčéąĖč湥čüą║ąŠą│ąŠ ą▒ąŠą╗čīčłąŠą╣ ąĄą╝ą║ąŠčüčéąĖ ąŠą▒čŗčćąĮąŠ ą╗čāčćčłąĖą╣ ą║ąŠą╝ą┐čĆąŠą╝ąĖčüčü. ąÜąĄčĆą░ą╝ąĖč湥čüą║ąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą┤ąĄą╣čüčéą▓čāąĄčé ą║ą░ą║ ą▒čŗčüčéčĆąŠąĄ čüčĆąĄą┤čüčéą▓ąŠ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąĘą░čĆčÅą┤ą░ ąĘą░čéą▓ąŠčĆą░, ąĖ ąŠą│čĆą░ąĮąĖčćąĖą▓ą░ąĄčé dVBS/dt ą┐čāč鹥ą╝ čāą╝ąĄąĮčīčłąĄąĮąĖčÅ čŹą║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ 菹╗ąĄą║čéčĆąŠą╗ąĖčéąĖč湥čüą║ąĖą╣ čāą┤ąĄčƹȹĖą▓ą░ąĄčé ą┐ą░ą┤ąĄąĮąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VBS ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąČąĄą╗ą░ąĄą╝ąŠą│ąŠ ╬öVBS.

ąöąĖąŠą┤ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ. ąŁč鹊čé ą┤ąĖąŠą┤ ą┤ąŠą╗ąČąĄąĮ ąĖą╝ąĄčéčī ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ BV > 1200V, ąĖ ą╝ą░ą╗ąŠąĄ ą▓čĆąĄą╝čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ (trr < 100 ąĮčü), čćč鹊ą▒čŗ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĘą░čĆčÅą┤ą░, ą▓ąŠąĘą▓čĆą░čēą░ąĄą╝ąŠą│ąŠ ąŠą▒čĆą░čéąĮąŠ ąŠčé ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ ąĮą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ VCC.

[ąĪąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ąĘą░čéą▓ąŠčĆąŠą▓]

ąĪą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ čüąĖą╗ąŠą▓čŗčģ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓ ą╝ąŠąČąĄčé čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╝ ą▓čŗą▒ąŠčĆąŠą╝ ąĮąŠą╝ąĖąĮą░ą╗ąŠą▓ čĆąĄąĘąĖčüč鹊čĆąŠą▓, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖčģ č鹊ą║ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ąĖ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ, ą┐ąŠą┤ą░ą▓ą░ąĄą╝čŗą╣ ąĮą░ ąĘą░čéą▓ąŠčĆ. ąØąĖąČąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ ąĮąĄą║ąŠč鹊čĆčŗąĄ ą▒ą░ąĘąŠą▓čŗąĄ ą┐čĆą░ą▓ąĖą╗ą░ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ąĮąŠą╝ąĖąĮą░ą╗ą░ čŹčéąĖčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ąČąĄą╗ą░ąĄą╝ąŠąĄ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ąĖ čüą║ąŠčĆąŠčüčéčī, čü ą┐ąŠą╝ąŠčēčīčÄ ą▓ą▓ąĄą┤ąĄąĮąĖčÅ čŹą║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮąŠą│ąŠ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ą┤čĆą░ą╣ą▓ąĄčĆą░ ąĘą░čéą▓ąŠčĆą░ (RDRp ąĖ RDRn).

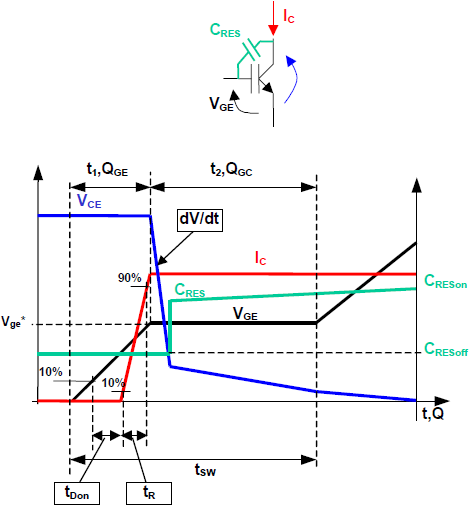

ąÆ ą┐čĆąĖą╝ąĄčĆą░čģ ą▓čüąĄ ą▓čĆąĄą╝čÅ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čüąĖą╗ąŠą▓čŗąĄ čéčĆą░ąĮąĘąĖčüč鹊čĆčŗ IGBT. ąĀąĖčü. 20 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąŠą╝ąĄąĮą║ą╗ą░čéčāčĆčā, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čāčÄ ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ ą┐ą░čĆą░ą│čĆą░čäą░čģ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ Vge* ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ą╗ą░č鹊, Qgc ąĖ Qge ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ąĘą░čĆčÅą┤ ąĘą░čéą▓ąŠčĆ-ą║ąŠą╗ą╗ąĄą║č鹊čĆ ąĖ ąĘą░čéą▓ąŠčĆ-菹╝ąĖčéč鹥čĆ.

ąĀąĖčü. 20. ąØąŠą╝ąĄąĮą║ą╗ą░čéčāčĆą░ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓ IGBT.

ąĀąĄąĘąĖčüč鹊čĆ ą┤ą╗čÅ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ąŠčéą║čĆčŗą▓ą░čÄčēąĄą│ąŠ č鹊ą║ą░ ąĘą░čéą▓ąŠčĆą░. ą¤čĆąĖą╝ąĄąĮąĖč鹥ą╗čīąĮąŠ ą║ ą▓ąŠą┐čĆąŠčüą░ą╝, ą▓ą║ą╗čÄč湥ąĮąĮčŗą╝ ąĮąĖąČąĄ ą▓ čĆą░čüč湥čé, ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ tsw ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą║ą░ą║ ą▓čĆąĄą╝čÅ, ąĘą░čéčĆą░čćąĖą▓ą░ąĄą╝ąŠąĄ ąĮą░ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ ą║ąŠąĮčåą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ą╗ą░č鹊 (ą┤ą╗čÅ ąĘą░čéą▓ąŠčĆą░ IGBT ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ąŠą▒čēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ Qgc + Qge). ą¦č鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ąČąĄą╗ą░ąĄą╝ąŠąĄ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ, ąĮąŠą╝ąĖąĮą░ą╗ čĆąĄąĘąĖčüč鹊čĆą░ ąĘą░čéą▓ąŠčĆą░ ą╝ąŠąČąĄčé ąĮą░čćąĖąĮą░čéčīčüčÅ ąŠčé Qge ąĖ Qgc, VCC, Vge* (čüą╝. čĆąĖčü. 21):

Qgc + Qge

Iavg = -------------

tSW

ąĖ

VCC - Vge*

RTOT = -------------

Iavg

ąĀąĖčü. 21. ąØąŠą╝ąĖąĮą░ą╗ RGon.

ą│ą┤ąĄ RTOT = RDRp + RGon

RGon = čĆąĄąĘąĖčüč鹊čĆ ąĘą░čéą▓ąŠčĆą░ ąĮą░ ąŠčéą║čĆčŗą▓ą░ąĮąĖąĄ čéčĆą░ąĮąĘąĖčüč鹊čĆą░.

RDRp = 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą┤čĆą░ą╣ą▓ąĄčĆą░.

ąÜąŠą│ą┤ą░ RGon > 7 ą×ą╝, RDRp ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ č乊čĆą╝čāą╗ąŠą╣:

ąŚą┤ąĄčüčī IO1+, IO2+ ąĖ ton1 ą▓ąĘčÅčéčŗ ąĖąĘ ą┤ą░čéą░čłąĖčéą░ IR2214.

ąóą░ą▒ą╗ąĖčåą░ 1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ čĆąĄąĘąĖčüč鹊čĆą░ ąĘą░čéą▓ąŠčĆą░ ą┤ą╗čÅ ą┤ą▓čāčģ čćą░čüč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ IGBT (ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ čüą┤ąĄą╗ą░ąĮčŗ ąĮą░ ąŠčüąĮąŠą▓ąĄ čéąĖą┐ąĖčćąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ąĖąĘ ą┤ą░čéą░čłąĖčéą░ ąĖ ą┐čĆąĄą┤ą┐ąŠą╗ą░ą│ą░ąĄą╝ąŠą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ VCC = 15V).

ąóą░ą▒ą╗ąĖčåą░ 1. ąŚąĮą░č湥ąĮąĖčÅ RGon, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖąĄ tsw.

| ąóčĆą░ąĮąĘąĖčüč鹊čĆ IGBT |

Qge, nC |

Qgc, nC |

Vge*, V |

tSW, ąĮčü |

Iavg, A |

RTOT, ą×ą╝ |

RGon ŌåÆ čüčéą░ąĮą┤.

ą║ąŠą╝ą╝ąĄčĆč湥čüą║ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ |

tSW, ąĮčü |

| IRGP30B120K(D) |

19 |

82 |

9 |

400 |

0.25 |

24 |

RTOT - RDRp = 12.7 ą×ą╝ ŌåÆ 10 ą×ą╝ |

ŌåÆ 420 |

| IRG4PH30K(D) |

10 |

20 |

9 |

200 |

0.15 |

40 |

RTOT - RDRp = 32.5 ą×ą╝ ŌåÆ 33 ą×ą╝ |

ŌåÆ 202 |

ąØą░ą║ą╗ąŠąĮ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąĀąĄąĘąĖčüč鹊čĆ ąĘą░čéą▓ąŠčĆą░ ąĮą░ ą▓ą║ą╗čÄč湥ąĮąĖąĄ RGon ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĮą░ą║ą╗ąŠąĮąŠą╝ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (dVOUT/dt).

ąźąŠčéčÅ ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĖąĘą╝ąĄąĮčÅąĄčéčüčÅ ą┐ąŠ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠą╝čā ąĘą░ą║ąŠąĮčā, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ąĮą░ą║ą╗ąŠąĮ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą░ą┐ą┐čĆąŠą║čüąĖą╝ąĖčĆąŠą▓ą░ąĮ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

dVOUT Iavg

----- = -------

dt CRESoff

ą¤ąŠą┤čüčéą░ą▓ąĖą╝ Iavg:

VCC - Vge*

RTOT = ------------------

dVOUT

CRESoff * -----

dt

ąÆ ą║ą░č湥čüčéą▓ąĄ ą┐čĆąĖą╝ąĄčĆą░ čéą░ą▒ą╗ąĖčåą░ 2 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čĆą░ąĘą╝ąĄčĆčŗ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ąĘą░čéą▓ąŠčĆą░, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī dVOUT/dt = 5V/ąĮčü, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą▓ą░ ą┐ąŠą┐čāą╗čÅčĆąĮčŗčģ IGBT, čü čéąĖą┐ąŠą▓čŗą╝ąĖ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ąĖąĘ ą┤ą░čéą░čłąĖčéą░ ąĖ VCC = 15V.

ąóą░ą▒ą╗ąĖčåą░ 2. ąŚąĮą░č湥ąĮąĖčÅ RGon, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖąĄ dVOUT/dt.

| ąóčĆą░ąĮąĘąĖčüč鹊čĆ IGBT |

Qge, nC |

Qgc, nC |

Vge*, V |

CRESoff, ą┐ąż |

RTOT, ą×ą╝ |

RGon ŌåÆ čüčéą░ąĮą┤.

ą║ąŠą╝ą╝ąĄčĆč湥čüą║ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ |

dVOUT/dt |

| IRGP30B120K(D) |

19 |

82 |

9 |

85 |

14 |

RTOT - RDRp = 6.5 ą×ą╝ ŌåÆ 8.2 ą×ą╝ |

ŌåÆ 4.5 V/ąĮčü |

| IRG4PH30K(D) |

10 |

20 |

9 |

14 |

85 |

RTOT - RDRp = 78 ą×ą╝ ŌåÆ 82 ą×ą╝ |

ŌåÆ 5 V/ąĮčü |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓čĆąĄą╝čÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą╝ąĄąĮčīčłąĄ tBL, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮąŠą│ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ąĖ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ čüčģąĄą╝čŗ ą┐ą╗ą░ą▓ąĮąŠą│ąŠ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ SSD.

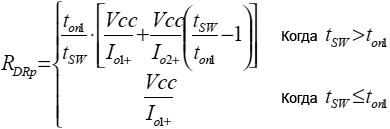

ąĀąĄąĘąĖčüč鹊čĆ ą┤ą╗čÅ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ąĘą░ą║čĆčŗą▓ą░čÄčēąĄą│ąŠ č鹊ą║ą░ ąĘą░čéą▓ąŠčĆą░. ąĪą░ą╝čŗą╣ čģčāą┤čłąĖą╣ čüą╗čāčćą░ą╣ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą▓čŗą║ą╗čÄčćą░čÄčēąĄą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ RGoff - ą║ąŠą│ą┤ą░ ą║ąŠą╗ą╗ąĄą║č鹊čĆ IGBT ą▓ ą▓čŗą║ą╗čÄč湥ąĮąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╝ąĖ čüąŠą▒čŗčéąĖčÅą╝ąĖ (ąĮą░ą┐čĆąĖą╝ąĄčĆ ą▓ą║ą╗čÄč湥ąĮąĖąĄą╝ IGBT ą┤čĆčāą│ąŠą│ąŠ ą┐ą╗ąĄčćą░).

ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ dV/dt ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą┐ą░čĆą░ąĘąĖčéąĮąŠą╝čā č鹊ą║čā č湥čĆąĄąĘ CRESoff, ą║ąŠč鹊čĆčŗą╣ ą▓č鹥ą║ą░ąĄčé ą▓ RGoff ąĖ RDRn (čüą╝. čĆąĖčü. 22).

ąĢčüą╗ąĖ ą┐ą░ą┤ąĄąĮąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ ąĘą░čéą▓ąŠčĆąĄ ą┐čĆąĄą▓čŗčüąĖčé ą┐ąŠčĆąŠą│ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ IGBT, č鹊 ąŠąĮ ą╝ąŠąČąĄčé ąŠčéą║čĆčŗčéčīčüčÅ čüą░ą╝ąŠčüč鹊čÅč鹥ą╗čīąĮąŠ, čćč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą▒ąŠą╗čīčłąĖą╝ ą║ąŠą╗ąĄą▒ą░ąĮąĖčÅą╝ ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝čā čüą║ą▓ąŠąĘąĮąŠą╝čā č鹊ą║čā.

ąĀąĖčü. 22. ąØąŠą╝ąĖąĮą░ą╗ RGoff: čåąĄą┐čī ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖčÅ č鹊ą║ą░, ą║ąŠą│ą┤ą░ ąĮąĖąČąĮąĄąĄ ą┐ą╗ąĄč湊 ą▓čŗą║ą╗čÄč湥ąĮąŠ, ąĖ ą▓ą║ą╗čÄč湥ąĮąŠ ą▓ąĄčĆčģąĮąĄąĄ ą┐ą╗ąĄč湊.

ą¤ąŠą╗čāčćą░čÄčéčüčÅ ą▓čŗčĆą░ąČąĄąĮąĖčÅ:

dVOUT

Vth Ōēź (RGoff + RDRn) * I = (RGoff + RDRn) * CRESoff -------

dt

ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▓čŗčĆą░ąČąĄąĮąĖą╣:

Vth

RGoff Ōēż ------------------ - RDRn

dV

CRESoff * ----

dt

ąÜąŠą│ą┤ą░ RGoff > 4 ą×ą╝, RDRn čģąŠčĆąŠčłąŠ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠ VCC/IO- (IO- ą▓ąĘčÅč鹊 ąĖąĘ ą┤ą░čéą░čłąĖčéą░ IR2214).

ąÆ ą║ą░č湥čüčéą▓ąĄ ą┐čĆąĖą╝ąĄčĆą░ čéą░ą▒ą╗ąĖčåą░ 3 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé RGoff ą┤ą╗čÅ ą┤ą▓čāčģ ą┐ąŠą┐čāą╗čÅčĆąĮčŗčģ IGBT ą┤ą╗čÅ dVOUT/dt = 5 V/ąĮčü.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠą║ą░ąĘą░ąĮąĮčŗąĄ ą▓čŗčłąĄ č乊čĆą╝čāą╗čŗ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮčŗ ą▓ ą║ą░č湥čüčéą▓ąĄ ą┐čĆąĖą▒ą╗ąĖąČąĄąĮąĮąŠą│ąŠ čüą┐ąŠčüąŠą▒ą░ ą▓čŗą▒ąŠčĆą░ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ čĆąĄąĘąĖčüč鹊čĆąŠą▓ ąĘą░čéą▓ąŠčĆą░. ąæąŠą╗ąĄąĄ č鹊čćąĮąŠąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ąĮąŠą╝ąĖąĮą░ą╗ąŠą▓ ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčī ą║ą░č湥čüčéą▓ąĄąĮąĮąŠą│ąŠ ą╝ąŠą┤ąĄą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čāč湥čéą░ ą┐ą░čĆą░ąĘąĖčéąĮąŠą╣ ąĄą╝ą║ąŠčüčéąĖ čĆą░ąĘą▓ąŠą┤ą║ąĖ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ.

ąóą░ą▒ą╗ąĖčåą░ 3. ąÆčŗą▒ąŠčĆ RGoff.

| ąóčĆą░ąĮąĘąĖčüč鹊čĆ IGBT |

Vth (ą╝ąĖąĮąĖą╝čāą╝), V |

CRESoff, ą┐ąż |

RGoff, ą×ą╝ |

| IRGP30B120K(D) |

4 |

85 |

RGoff Ōēż 4 |

| IRG4PH30K(D) |

3 |

14 |

RGoff Ōēż 35 |

[ąĀąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ ą┐ąŠ čĆą░ąĘą▓ąŠą┤ą║ąĄ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ]

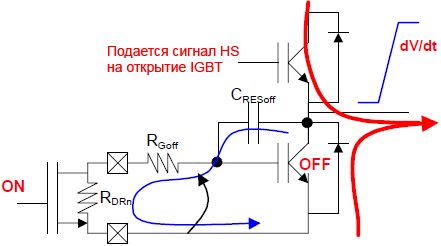

ąśąĮč鹥čĆą▓ą░ą╗ ą╝ąĄąČą┤čā čåąĄą┐čÅą╝ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ H ąĖ L. ą”ąŠą║ąŠą╗ąĄą▓ą║ą░ IR2214 ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé čĆą░čüčüč鹊čÅąĮąĖąĄ ą╝ąĄąČą┤čā ą┐ą╗ą░ą▓ą░čÄčēąĖą╝ ą┐ą╗ąĄč湊ą╝ (ąŠčé DC- ą┤ąŠ DC+) ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ čü ąĮąĖąĘą║ąĖą╝ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅą╝ąĖ. ąØą░čüč鹊čÅč鹥ą╗čīąĮąŠ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čĆą░ąĘą╝ąĄčēą░čéčī ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ, čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗąĄ čü ą┐ą╗ą░ą▓ą░čÄčēąĄą╣ čüąĄą║čåąĖąĄą╣ čüčģąĄą╝čŗ, ąĮą░ ą▓čŗčüąŠą║ąŠą▓ąŠą╗čīčéąĮąŠą╣ čüč鹊čĆąŠąĮąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (čüč鹊čĆąŠąĮą░ VB, VS), čĆą░ąĘą╝ąĄčēą░čÅ ą┐čĆąĖ čŹč鹊ą╝ ą┤čĆčāą│ąĖąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ ąĮą░ ą┤čĆčāą│ąŠą╣ čüč鹊čĆąŠąĮąĄ.

ąŚą░ą╗ąĖą▓ą║ą░ ą╝ąĄą┤ąĖ ąĘąĄą╝ą╗ąĖ. Ground plane ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ąĮą░čģąŠą┤ąĖčéčüčÅ ą┐ąŠą┤ ą▓čŗčüąŠą║ąŠą▓ąŠą╗čīčéąĮčŗą╝ąĖ ą┐ą╗ą░ą▓ą░čÄčēąĖą╝ąĖ čåąĄą┐čÅą╝ąĖ ąĖą╗ąĖ čĆčÅą┤ąŠą╝ čü ąĮąĖą╝ąĖ, čćč鹊ą▒čŗ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖąĄ ą┐ąŠą╝ąĄčģ.

ą¤ąĄčéą╗ąĖ č鹊ą║ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░čéą▓ąŠčĆąŠą╝. ą”ąĄą┐ąĖ č鹊ą║ą░ ą▓ąĄą┤čāčé čüąĄą▒čÅ ą║ą░ą║ ą░ąĮč鹥ąĮąĮą░, ąĖ ą╝ąŠą│čāčé ą┐čĆąĖąĮąĖą╝ą░čéčī ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī 菹╗ąĄą║čéčĆąŠą╝ą░ą│ąĮąĖčéąĮčŗąĄ ą┐ąŠą╝ąĄčģąĖ. ą¦č鹊ą▒čŗ čüąĮąĖąĘąĖčéčī čŹčéąĖ ą┐ąŠą╝ąĄčģąĖ ąĖ čāą╗čāčćčłąĖčéčī ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ čüąĖą╗ąŠą▓čŗčģ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓, ą┤ą╗ąĖąĮą░ čåąĄą┐ąĄą╣ č鹊ą║ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░čéą▓ąŠčĆą░ą╝ąĖ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ čüąĮąĖąČąĄąĮą░. ąĀąĖčü. 23 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čåąĄą┐ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░čéą▓ąŠčĆą░ą╝ąĖ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčć.

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ č鹊ą║ ą▓ ą▓čŗčģąŠą┤ąĮčāčÄ čåąĄą┐čī ą┤čĆą░ą╣ą▓ąĄčĆą░ ą╝ąŠąČąĄčé ąĖąĮąČąĄą║čéąĖčĆąŠą▓ą░čéčīčüčÅ č湥čĆąĄąĘ ą┐ą░čĆą░ąĘąĖčéąĮčāčÄ ąĄą╝ą║ąŠčüčéčī ą║ąŠą╗ą╗ąĄą║č鹊čĆ-ąĘą░čéą▓ąŠčĆ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ IGBT. ą¤ą░čĆą░ąĘąĖčéąĮą░čÅ ąĖąĮą┤čāą║čéąĖą▓ąĮąŠčüčéčī čåąĄą┐ąĖ ąĘą░čéą▓ąŠčĆą░ čüą┐ąŠčüąŠą▒čüčéą▓čāąĄčé čĆą░ąĘą▓ąĖčéąĖčÄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĘą░čéą▓ąŠčĆ-菹╝ąĖčéč鹥čĆ, čāą▓ąĄą╗ąĖčćąĖą▓ą░čÅ ą▓ąĄčĆąŠčÅčéąĮąŠčüčéčī čŹčäč乥ą║čéą░ čüą░ą╝ąŠčüč鹊čÅč鹥ą╗čīąĮąŠą│ąŠ ąŠčéą║čĆčŗčéąĖčÅ IGBT. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ ąĮą░čüč鹊čÅč鹥ą╗čīąĮąŠ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čĆą░ąĘą╝ąĄčēą░čéčī čĆąĄąĘąĖčüč鹊čĆčŗ ąĘą░čéą▓ąŠčĆą░ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ą╗ąĖąČąĄ ą┤čĆčāą│ ą║ ą┤čĆčāą│čā ąĖ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ąŠą▒ą╗ą░čüčéčī ą┐ąĄčéą╗ąĖ č鹊ą║ą░ (čüą╝. čĆąĖčü. 23).

ąĀąĖčü. 23. ą¤ąĄčéą╗čÅ č鹊ą║ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░čéą▓ąŠčĆąŠą╝.

ąÜąŠąĮą┤ąĄąĮčüą░č鹊čĆčŗ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. ąÆčŗčģąŠą┤ąĮčŗąĄ ą║ą░čüą║ą░ą┤čŗ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ IR2214 ą╝ąŠą│čāčé ą▒čŗčüčéčĆąŠ ąŠčéą║čĆčŗčéčī IGBT ą▓čŗčģąŠą┤ąĮčŗą╝ č鹊ą║ąŠą╝ ą┤ąŠ 2A. ąæą╗ąŠą║ąĖčĆčāčÄčēąĖąĄ ą┐čāą╗čīčüą░čåąĖąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čĆą░ąĘą╝ąĄčēąĄąĮčŗ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ą╗ąĖąČąĄ ą║ ą▓čŗą▓ąŠą┤ą░ą╝ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (VCC ąĖ VSS ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ, čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čü ąĘąĄą╝ą╗ąĄą╣, VB ąĖ VS ą┤ą╗čÅ ą┐ą╗ą░ą▓ą░čÄčēąĄą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ), čćč鹊ą▒čŗ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ą┐ą░čĆą░ąĘąĖčéąĮčŗąĄ ąĖąĮą┤čāą║čéąĖą▓ąĮąŠčüčéčī/ąĄą╝ą║ąŠčüčéčī čåąĄą┐ąĄą╣ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą┐čāą╗čīčüą░čåąĖą╣.

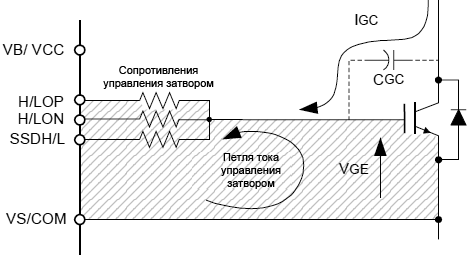

ą¤čĆąĖą╝ąĄčĆ čĆą░ąĘą▓ąŠą┤ą║ąĖ ąĖ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ. ąĀąĖčü. 24 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠą┤ąĖąĮ ąĖąĘ ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ą▓ą░čĆąĖą░ąĮč鹊ą▓ čĆą░ąĘą▓ąŠą┤ą║ąĖ ąĮą░ čéčĆąĄčģčüą╗ąŠą╣ąĮąŠą╣ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░č鹥. ąŁč鹊čé ą┐čĆąĖą╝ąĄčĆ čāčćąĖčéčŗą▓ą░ąĄčé ą▓čüąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮčŗąĄ ą▓čŗčłąĄ čĆąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ. ąĀą░ąĘą╝ąĄčēąĄąĮąĖąĄ ąĖ čĆą░ąĘą▓ąŠą┤ą║ą░ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą▓ ą┐ąŠ ą┐ąĖčéą░ąĮąĖčÄ ąĖ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ąĘą░čéą▓ąŠčĆą░ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆčāčÄčé ą┐čāčéąĖ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ č鹊ą║ą░. ąöąĖąŠą┤ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ čĆą░ąĘą╝ąĄčēąĄąĮ ą┐ąŠą┤ ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣, čćč鹊ą▒čŗ ą║ą░č鹊ą┤ ą┤ąĖąŠą┤ą░ ą▒čŗą╗ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ą╗ąĖąČąĄ ą║ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčā ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ, ąĖ ą░ąĮąŠą┤ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą┤ą░ą╗čīčłąĄ ąŠčé ą▓čŗčüąŠą║ąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĖ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ą╗ąĖąČąĄ ą║ VCC.

ąĀąĖčü. 24. ą¤čĆąĖą╝ąĄčĆ čĆą░ąĘą▓ąŠą┤ą║ąĖ ą▓ąĄčĆčģąĮąĄą╣ (a), ąĮąĖąČąĮąĄą╣ (b) čüč鹊čĆąŠąĮčŗ ą┐ą╗ą░čéčŗ ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüą╗ąŠčÅ ąĘą░ą╗ąĖą▓ą║ąĖ (c).

ąĪąĄą║čåąĖčÅ ą▓ąŠą╗čīčéą┤ąŠą▒ą░ą▓ą║ąĖ: R1, C1, D1. ąŚą░čéą▓ąŠčĆ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░: R2, R3, R4. ąöąĖąŠą┤ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ą╗ąĄčćą░: D2. ąØąĖąČąĮąĄąĄ ą┐ąĖčéą░ąĮąĖąĄ: C2. ąŚą░čéą▓ąŠčĆ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░: R5, R6, R7. ąöąĖąŠą┤ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĮą░čüčŗčēąĄąĮąĖčÅ ąĮąĖąČąĮąĄą│ąŠ ą┐ą╗ąĄčćą░: D3.

[ąĪčüčŗą╗ą║ąĖ]

1. IR2214/IR22141 HALF-BRIDGE GATE DRIVER IC site:irf.com. |