|

[ąĪčāčēąĄčüčéą▓čāčÄčēąĖąĄ ąĘą░ą│čĆčāąĘąŠčćąĮčŗąĄ ą║ą░ą▒ąĄą╗ąĖ Lattice]

ąÆ ąĮą░čüč鹊čÅčēąĄąĄ ą▓čĆąĄą╝čÅ čäąĖčĆą╝ą░ Lattice Semiconductor ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čüą▓ąŠąĖčģ čāčüčéčĆąŠą╣čüčéą▓ ą┐čĆąĄą┤ą╗ą░ą│ą░ąĄčé ą┤ą▓ą░ ą▓ąĖą┤ą░ ąĘą░ą│čĆčāąĘąŠčćąĮčŗčģ ą║ą░ą▒ąĄą╗ąĄą╣ [1]:

| ąØą░ąĖą╝ąĄąĮąŠą▓ą░ąĮąĖąĄ |

PC ąĖąĮč鹥čĆč乥ą╣čü |

ą”ąĄąĮą░ ą▓ Digikey |

ą”ąĄąĮą░ ą▓ ąĀąŠčüčüąĖąĖ |

| HW-USBN-2A |

USB 2.0 |

162$ [2] |

9000 .. 22000čĆ. |

| HW-DLN-3C |

LPT |

71$ [3] |

3500 .. 7500čĆ. |

ą¤čĆąĖ čŹč鹊ą╝ LPT ą║ą░ą▒ąĄą╗čī ąĮąĄčāą┤ąŠą▒ąĄąĮ, ąĘą░ą│čĆčāąĘą║ą░ ą┐ąŠ ąĮąĄą╝čā ą╝ąĄą┤ą╗ąĄąĮąĮą░čÅ, ąŠąĮ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ąĖ ą▓ąĄčĆčüąĖčÅą╝ąĖ MICO32 System, ąĖ čĆą░ąĘčŖčæą╝ ą║ ąĮąĄą╝čā ąŠą▒čŗčćąĮąŠ ąŠčéčüčāčéčüčéą▓čāąĄčé ąĮą░ ąĮąŠą▓čŗčģ ą║ąŠą╝ą┐čīčÄč鹥čĆą░čģ. ąÆ čüąĖą╗čā ą╝ą░ą╗ąŠą╣ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮčæąĮąĮąŠčüčéąĖ ą║ąĖčéą░ą╣čåčŗ ąĮąĄ ąŠčüąŠą▒ąŠ čüą┐ąĄčłą░čé ą║ą╗ąŠąĮąĖčĆąŠą▓ą░čéčī ą║ą░ą▒ąĄą╗ąĖ ą┤ą╗čÅ FPGA Lattice.

ą×čüąĮąŠą▓čā čüčģąĄą╝čŗ HW-USBN-2A [2] čüąŠčüčéą░ą▓ą╗čÅčÄčé čćąĖą┐ FT2232H, ąŠčéą▓ąĄčćą░čÄčēąĖą╣ ąĘą░ USB čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ, ąĖ čéčĆą░ąĮčüą╗čÅč鹊čĆčŗ čāčĆąŠą▓ąĮąĄą╣, ą║ąŠč鹊čĆčŗąĄ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čÄčé čĆą░ą▒ąŠčéčā ą┐čĆąĖ čāčĆąŠą▓ąĮčÅčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ JTAG ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 1.2V .. 5V. ą¤čĆąŠčüč鹊čéą░ čüčģąĄą╝čŗ ąĖ ąŠčéčüčāčéčüčéą▓ąĖąĄ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ąĘą░čēąĖčéčŗ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą║ą╗ąŠąĮąĖčĆąŠą▓ą░čéčī HW-USBN-2A ąĮą░ ąŠčüąĮąŠą▓ąĄ ą│ąŠč鹊ą▓čŗčģ ą┐ą╗ą░čé čéąĖą┐ą░ FT2232H Board [4] ąĖą╗ąĖ FT2232H Mini Module, ą┐čĆąŠčüč鹊 ą┐čĆąĖčüąŠąĄą┤ąĖąĮąĖą▓ JTAG čĆą░ąĘčŖčæą╝ ą║ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ąĮąŠąČą║ą░ą╝ FT2232H.

ąóą░ą║ąŠąĄ čĆąĄčłąĄąĮąĖąĄ ąĖą╝ąĄąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ ą┐čĆąĄąĖą╝čāčēąĄčüčéą▓ą░:

- ą×č湥ąĮčī ąĮąĖąĘą║ą░čÅ čüč鹊ąĖą╝ąŠčüčéčī ąĖ ą╗ąĄą│ą║ąŠą┤ąŠčüčéčāą┐ąĮąŠčüčéčī.

- ąÆąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą╗ąĮąŠčåąĄąĮąĮąŠ čĆą░ą▒ąŠčéą░čéčī č鹥ą╝ ąČąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ąĖ čü FPGA Xilinx.

- ą£ąĄąĮčīčłąĄąĄ ą▓čĆąĄą╝čÅ ąĘą░ą┤ąĄčƹȹ║ąĖ čüąĖą│ąĮą░ą╗ą░ ąĘą░ čüčćčæčé ąŠčéčüčāčéčüčéą▓ąĖčÅ čéčĆą░ąĮčüą╗čÅč鹊čĆąŠą▓ čāčĆąŠą▓ąĮčÅ ą▓ ąĘą░ą│čĆčāąĘąŠčćąĮąŠą╝ ą║ą░ą▒ąĄą╗ąĄ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ąŠčüčéąĖčćčī ą▒ąŠą╗čīčłąĄą╣ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ (ą┤ąŠ 30 ą╝ąĄą│ą░ą▒ąĖčé), ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ą░ą▒ąĄą╗čī ą▓ ą║ą░č湥čüčéą▓ąĄ ąŠčéą╗ą░ą┤ąŠčćąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░.

ąĢčüčéčī ąĖ ąĮąĄą┤ąŠčüčéą░čéą║ąĖ:

- ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ JTAG ą╝ąŠąČąĄčé ą▒čŗčéčī č鹊ą╗čīą║ąŠ 3.3V.

- ąØąĄą▓ąŠąĘą╝ąŠąČąĮąŠ čłčéą░čéąĮčŗą╝ąĖ čüčĆąĄą┤čüčéą▓ą░ą╝ąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčī ą▓čŗčģąŠą┤čŗ ąĘą░ą│čĆčāąĘąŠčćąĮąŠą│ąŠ ą║ą░ą▒ąĄą╗čÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčüąŠą║ąŠą│ąŠ ąĖą╝ą┐ąĄą┤ą░ąĮčüą░ (ąŠčéą║ą╗čÄčćą░čéčī, ą┐čĆąŠčēąĄ ą│ąŠą▓ąŠčĆčÅ).

[ąśąĘą│ąŠč鹊ą▓ą╗ąĄąĮąĖąĄ čüą░ą╝ąŠą┤ąĄą╗čīąĮąŠą│ąŠ ąĘą░ą│čĆčāąĘąŠčćąĮąŠą│ąŠ ą║ą░ą▒ąĄą╗čÅ]

ąÆ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą║ ąĘą░ą│čĆčāąĘąŠčćąĮčŗą╝ ą║ą░ą▒ąĄą╗čÅą╝ Lattice [5] ąŠą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▓ą░čĆąĖą░ąĮč鹊ą▓ čåąŠą║ąŠą╗ąĄą▓ą║ąĖ JTAG. ą» ąĖčüą┐ąŠą╗čīąĘčāčÄ čüčéą░ąĮą┤ą░čĆčéąĮčāčÄ čåąŠą║ąŠą╗ąĄą▓ą║čā čü čĆą░ąĘčŖčæą╝ąŠą╝ 5x2. ąŁč鹊čé čĆą░ąĘčŖčæą╝ čüą╗ąĄą┤čāąĄčé ą┐čĆąĖčüąŠąĄą┤ąĖąĮąĖčéčī ą║ FT2232H Board čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ąóą░ą▒ą╗ąĖčåą░ 1. ą”ąŠą║ąŠą╗ąĄą▓ą║ą░ JTAG ąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą║ ą┐ą╗ą░č鹥 FT2232H Board.

| JTAG |

FT2232H Board |

| ąĪąĖą│ąĮą░ą╗ JTAG |

ąÜąŠąĮčéą░ą║čé ą║ąŠąĮąĮąĄą║č鹊čĆą░ |

ąÜąŠąĮčéą░ą║čé ąĮą░ ą┐ą╗ą░č鹥 |

| TCK |

1 |

ADBUS0 |

| GND |

2 |

GND |

| TMS |

3 |

ADBUS3 |

| GND |

4 |

GND |

| TDI |

5 |

ADBUS1 |

| VCC |

6 |

ąĮąĄ ą┐ąŠą┤ą║ą╗čÄčćą░čéčī |

| TDO |

7 |

ADBUS2 |

| GND |

8 |

GND |

| TRST |

9 |

ADBUS7 |

| ISPEN |

10 |

ADBUS4 |

ąöą░ąĮąĮą░čÅ čüčģąĄą╝ą░ ąŠą▒ą╗ą░ą┤ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖą╝ ąĮąĄą┤ąŠčüčéą░čéą║ąŠą╝: ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ 3.3 ą▓ąŠą╗čīčéą░ ąĮą░ ą▓čŗčģąŠą┤ąĮčŗčģ ąĮąŠąČą║ą░čģ FT2232H ą▒čāą┤ąĄčé ą┐ąŠčÅą▓ą╗čÅčéčīčüčÅ ą┐čĆąĖ čĆą░ą▒ąŠčéą░čÄčēąĄą╝ USB čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ąĘą░ą┐čāčüą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ą░č鹊čĆą░, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĮą░ą╗ąĖčćąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĮą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ ą┐ą╗ą░č鹥. ąöą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ čéą░ą║ąŠą╣ čĆąĄąČąĖą╝ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝ ąĖ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā ą║ąŠčĆąŠčéą║ąŠą│ąŠ ąĘą░ą╝čŗą║ą░ąĮąĖčÅ č湥čĆąĄąĘ ą▓čŗčģąŠą┤ąĮąŠą╣ ą┤čĆą░ą╣ą▓ąĄčĆ FT2232H ąĖ ąĘą░čēąĖčéąĮčŗą╣ ą┤ąĖąŠą┤ ąĮą░ ą▓čģąŠą┤ąĄ, ąĖ ą┤ą░ąČąĄ ą║ čéąĖčĆąĖčüč鹊čĆąĮąŠą╝čā ąĘą░čēčæą╗ą║ąĖą▓ą░ąĮąĖčÄ. ąźąŠčéčÅ čÅ ąĖ ąĮąĄ ąĘąĮą░ą║ąŠą╝ čü FPGA ąĖą╗ąĖ ą╗ąŠą│ąĖč湥čüą║ąĖą╝ąĖ ą▒čāč乥čĆą░ą╝ąĖ, čéą░čÅčēąĖą╝ąĖ ą┐ąŠą┤ąŠą▒ąĮčāčÄ ąŠą┐ą░čüąĮąŠčüčéčī(ą░ ą▓ąŠčé SPI ADC, ąĮą░ą┐čĆąĖą╝ąĄčĆ, čéą░ą║ąĖąĄ ą▓čüčéčĆąĄčćą░čÄčéčüčÅ), ąĮąŠ ą▓čüčæ ąČąĄ ą┐čĆąĄą┤ą┐ąŠčćčæą╗ čĆą░ąĘą▓ąĄčüčéąĖ ą┐ąĖčéą░ąĮąĖąĄ čéą░ą║, čćč鹊ą▒čŗ ąĖčüą║ą╗čÄčćąĖčéčī čŹčéčā čüąĖčéčāą░čåąĖčÄ. ą¤ąŠčéčĆąĄą▒ąŠą▓ą░ą╗ąŠčüčī ą┐ąĄčĆąĄčĆąĄąĘą░čéčī ą┤ą▓ąĄ ą┤ąŠčĆąŠąČą║ąĖ ąĮą░ FT2232H Board ąĖ ą┐ąŠą┤ą░ą▓ą░čéčī 3.3V ąĮąĄ čü USB, ą░ čü ą║ąŠąĮčéą░ą║čéą░ VCC ąĮą░ čĆą░ąĘčŖčæą╝ąĄ JTAG. ąØą░ čüčģąĄą╝ąĄ ą║čĆą░čüąĮčŗą╝ ą┐ąŠą║ą░ąĘą░ąĮą░ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ čåąĄą┐ąĄą╣ ą┐ąĖčéą░ąĮąĖčÅ ą┐ą╗ą░čéčŗ FT2232H Board. ąØą░ č乊č鹊 ą║čĆą░čüąĮčŗą╝ ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą│ą┤ąĄ ą┐ąĄčĆąĄčĆąĄąĘą░ąĮčŗ ą┤ąŠčĆąŠąČą║ąĖ. ą¤ąŠą╝ąĖą╝ąŠ ą┐ąĖčéą░ąĮąĖčÅ, ąŠčéčĆąĄąĘą░ąĮčŗ ąŠčé ACBUS5-ACBUS6 ą▒ąŠą║ąŠą▓čŗąĄ ą▓čŗą▓ąŠą┤čŗ čĆą░ąĘčŖčæą╝ą░, čćč鹊ą▒čŗ ąĮąĄ ą║ąŠčĆąŠčéąĖą╗ąĖ. ąÆ ą┐ąĖčéą░ąĮąĖąĖ ą▓čŗą▓ąŠą┤čŗ IC3.VOUT ąĖ JP3.2 ąŠčéčĆąĄąĘą░ąĮčŗ ąŠčé čłąĖąĮčŗ 3.3V, ąĖ ąŠą▒čŖąĄą┤ąĖąĮąĄąĮčŗ ą▓ VCCINT, ą▓ą╝ąĄčüč鹥 čü C2. JTAG ą║ąŠąĮčéą░ą║čé VCC ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ąŠčéčĆąĄąĘą░ąĮąĮąŠą╣ čłąĖąĮąĄ 3.3V.

ą¦č鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą╗ąĄą│ą║ąŠ ą┐ąŠą┤ą║ą╗čÄčćą░čéčī ą║ FT2232H Board ą║ą░ą▒ąĄą╗ąĖ čü čĆą░ąĘąĮąŠą╣ čåąŠą║ąŠą╗ąĄą▓ą║ąŠą╣, čÅ čāčüčéą░ąĮąŠą▓ąĖą╗ ąĮą░ ą▒ąŠą║ąŠą▓ąŠą╝ ą┐ąŠą╗ąĄ čü ąŠčéą▓ąĄčĆčüčéąĖčÅą╝ąĖ čāą│ą╗ąŠą▓ąŠą╣ čĆą░ąĘčŖčæą╝ 2x5, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąŠą▓ąŠą┤ą║ą░ą╝ąĖ ą┐ąŠą┤ą┐ą░čÅą╗ ą║ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą▒ąŠą║ąŠą▓čŗą╝ ą▓čŗą▓ąŠą┤ą░ą╝ ąĮą░ ą┐ą╗ą░č鹥. ąÆ čŹč鹊čé čĆą░ąĘčŖčæą╝ ą▓čüčéą░ą▓ą╗čÅąĄčéčüčÅ ą┐ą╗ąŠčüą║ąĖą╣ ą┤ąĄčüčÅčéąĖąČąĖą╗čīąĮčŗą╣ ą║ą░ą▒ąĄą╗čī čü ą┤ą▓čāą╝čÅ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ąĖ čĆą░ąĘčŖčæą╝ą░ą╝ąĖ 2x5 ąĮą░ ą║ąŠąĮčåą░čģ, čü ą┤čĆčāą│ąŠą╣ čüč鹊čĆąŠąĮčŗ ą║ą░ą▒ąĄą╗čī ą▓čüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▓ čĆą░ąĘčŖčæą╝ ąĮą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ ą┐ą╗ą░č鹥, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╣ čåąŠą║ąŠą╗ąĄą▓ą║ąĄ, ąŠą┐ąĖčüą░ąĮąĮąŠą╣ ą▓čŗčłąĄ ą▓ čéą░ą▒ą╗ąĖčåąĄ 1.

UPD1405117. ąöą╗čÅ čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĖčÅ čāčĆąŠą▓ąĮąĄą╣ čüąĖą│ąĮą░ą╗ąŠą▓ ą╝ąŠąČąĮąŠ čéą░ą║ąČąĄ ą┐čĆąĖą╝ąĄąĮąĖčéčī ąĘą░čēąĖčéąĮčŗąĄ č鹊ą║ąŠąŠą│čĆą░ąĮąĖčćąĖą▓ą░čÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓ ą║ą░ąČą┤čŗą╣ čüąĖą│ąĮą░ą╗ JTAG čüčéą░ą▓čÅčéčüčÅ čĆąĄąĘąĖčüč鹊čĆčŗ 50..100 ąŠą╝. ąóąŠą│ą┤ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ čüčģąĄą╝čŗ ą╝ąŠąČąĄčé ą▒čŗčéčī ą╗čÄą▒čŗą╝, ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąŠčĆč鹊ą▓ FT2232H ą╝ąŠąČąĮąŠ čüą┤ąĄą╗ą░čéčī 3.3V. ąóąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ąĄą╗čŗą▓ą░čéčī čüčģąĄą╝čā ą┐ąĖčéą░ąĮąĖčÅ ąĮą░ ą┐ą╗ą░č鹥 FT2232H Board ąĮąĄ ą┐ąŠčéčĆąĄą▒čāąĄčéčüčÅ, ąĖ ąĮąĄ ą┐čĆąĖą┤ąĄčéčüčÅ čĆąĄąĘą░čéčī ą┤ąŠčĆąŠąČą║ąĖ.

ąóčāčé ąĄčēčæ ąĖąĮč鹥čĆąĄčüąĮąĄąĄ ą┐ąŠą╗čāčćąĖą╗ąŠčüčī: čÅ ą▓ąĮą░čćą░ą╗ąĄ ą┐ąŠčĆąĄąĘą░ą╗ ą┐ąĖčéą░ąĮąĖąĄ, ą░ ą┐ąŠč鹊ą╝ ą▓ąĮąĖą╝ą░č鹥ą╗čīąĮąŠ ą┐čĆąŠčüą╝ąŠčéčĆąĄą╗ ą┤ą░čéą░čłąĖčéčŗ ąĖ ą▓čŗčÅčüąĮąĖą╗ąŠčüčī, čćč鹊 ą┐ąĖčéą░ąĮąĖąĄ ą╝ąŠąČąĮąŠ ąĖ ąĮąĄ čĆąĄąĘą░čéčī, ą░ ą┐čĆąŠčüč鹊 ąĮąĄ ą┐ąŠą┤ą║ą╗čÄčćą░čéčī JTAG VCC. ąöą╗čÅ ą▓čüąĄčģ ą╝ąĖą║čĆąŠčüčģąĄą╝, ą║ąŠč鹊čĆčŗąĄ ą╝čŗ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ č湥čĆąĄąĘ JTAG, 3.3 ą▓ąŠą╗čīčéą░ ą┐ąŠ ą▓čģąŠą┤čā - čŹč鹊 ą┤ąŠą┐čāčüčéąĖą╝ąŠąĄ ąĮąŠą╝ąĖąĮą░ą╗čīąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ. ąöą░ąČąĄ čĆąĄąĘąĖčüč鹊čĆčŗ ąĮąĄ ąĮčāąČąĮčŗ. ąĪąĄą╣čćą░čü čÅ ą▒čŗ ąĮąĄ čüčéą░ą╗ ą┐ąĄčĆąĄą┤ąĄą╗čŗą▓ą░čéčī ą┐ąĖčéą░ąĮąĖąĄ. ą¤čĆąŠą▒ą╗ąĄą╝ą░ ą▓ č鹊ą╝, čćč鹊 ąĮą░ č乊čéą║ą░čģ čā ą╝ąĄąĮčÅ ą▓ą░čĆąĖą░ąĮčé čü ą┐ąŠčĆąĄąĘą░ąĮąĮčŗą╝:). ąźąŠčéčÅ čü ą┐ąŠčĆąĄąĘą░ąĮąĮčŗą╝ ą▓čüčæ-čéą░ą║ąĖ ą▒ąĄąĘąŠą┐ą░čüąĮąĄąĄ.

ąś ąĄčēčæ, čćč鹊 ą║ą░čüą░ąĄčéčüčÅ čĆąĄąĘąĖčüč鹊čĆąŠą▓, ą▓ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ąĮąĄą║ąŠč鹊čĆčŗčģ, FT2232 - čŹč鹊 čåąĖą▓ąĖą╗ąĖąĘąŠą▓ą░ąĮąĮą░čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ąĖ ąĖą╝ąĄąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčāčÄ čĆąĄą│čāą╗ąĖčĆąŠą▓ą║čā č鹊ą║ą░ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓, ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ č鹊ą║ ąĮą░čüčéčĆąŠąĄąĮ ąĮą░ 4 ą╝ąÉ, čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą▓čŗčģąŠą┤ąŠą▓ ą┐čĆąĖ čŹč鹊ą╝ ą┐ąŠčĆčÅą┤ą║ą░ 50 ą×ą╝, čćč鹊 ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé čģąŠčĆąŠčłčāčÄ Signal Integrity ąĖ ą▒ąĄąĘ čĆąĄąĘąĖčüč鹊čĆąŠą▓.

[ąŻčüčéą░ąĮąŠą▓ą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ]

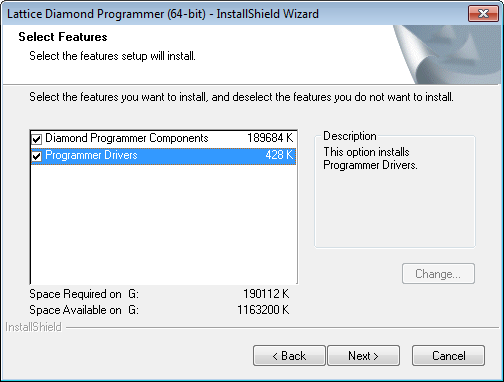

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čüą░ą╝ąŠą┤ąĄą╗čīąĮąŠą│ąŠ ąĘą░ą│čĆčāąĘąŠčćąĮąŠą│ąŠ ą║ą░ą▒ąĄą╗čÅ ąĮąĖč湥ą╝ ąĮąĄ ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé čĆąŠą┤ąĮąŠą│ąŠ čäąĖčĆą╝ąĄąĮąĮąŠą│ąŠ. ąöčĆą░ą╣ą▓ąĄčĆ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ą╝ąĄčüč鹥 čü IDE Lattice Diamond [5], ą╗ąĖą▒ąŠ čü Lattice Diamond Programmer [7], ąĄčüą╗ąĖ ą┐čĆąĖ čāčüčéą░ąĮąŠą▓ą║ąĄ ąĮąĄ čüąĮąĖą╝ą░čéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčāčÄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą│ą░ą╗ąŠčćą║čā "Programmer Drivers".

ą¤ąŠčüą╗ąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ą░ ą║ USB ą┤čĆą░ą╣ą▓ąĄčĆčŗ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ. ą¤čĆąĖ ą┐ąŠą╝ąŠčēąĖ čāčéąĖą╗ąĖčéčŗ FT_Prog ą╝ąŠąČąĮąŠ ąĖąĘą╝ąĄąĮąĖčéčī ąĮą░ąĘą▓ą░ąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, ą║ąŠč鹊čĆąŠąĄ ą▒čāą┤ąĄčé ą▓čŗčüą▓ąĄčćąĖą▓ą░čéčīčüčÅ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ą░č鹊čĆąĄ, ąĖ čüąĄčĆąĖą╣ąĮčŗą╣ ąĮąŠą╝ąĄčĆ, ąŠą┤ąĮą░ą║ąŠ ą▓čüčæ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ąĖ čü čćąĖčüč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣ ą┐ąŠ-čāą╝ąŠą╗čćą░ąĮąĖčÄ.

[ą¤čĆąĖą╝ąĄčĆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ FPGA]

ąŚą┤ąĄčüčī ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąĖą╝ąĄčĆ ąĘą░ą│čĆčāąĘą║ąĖ ą┐čĆąŠčłąĖą▓ą║ąĖ FPGA LFE2M50E čü ą┐ąŠą╝ąŠčēčīčÄ Lattice Standalone Programmer č湥čĆąĄąĘ ą║ą░ą▒ąĄą╗čī ąĮą░ FT2232 Board.

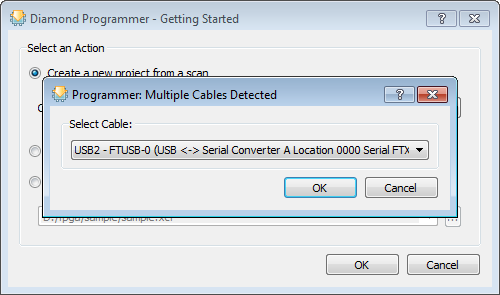

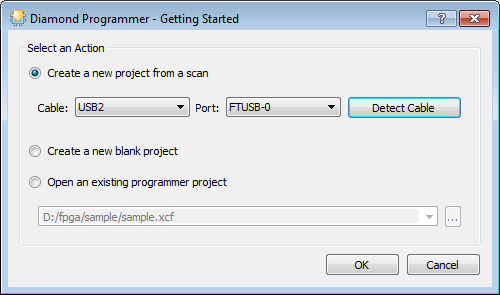

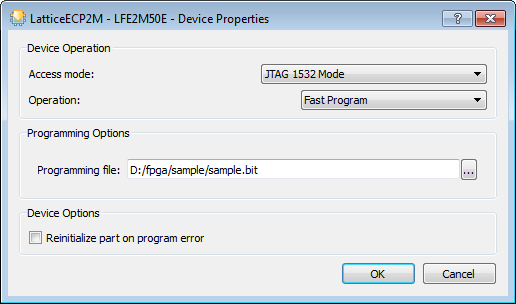

ą¤ąŠčüą╗ąĄ ąĘą░ą┐čāčüą║ą░ Diamond Programmer ą┐ąŠčÅą▓ąĖčéčüčÅ ą┤ąĖą░ą╗ąŠą│ąŠą▓ąŠąĄ ąŠą║ąĮąŠ čü ą┐čĆąĄą┤ą╗ąŠąČąĄąĮąĖąĄą╝ ą▓čŗą▒čĆą░čéčī ąĖą╗ąĖ ą┐čĆąŠą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčī ąĘą░ą│čĆčāąĘąŠčćąĮčŗą╣ ą║ą░ą▒ąĄą╗čī:

ą¤ąŠčüą╗ąĄ ąĮą░ąČą░čéąĖčÅ ąĮą░ ą║ąĮąŠą┐ą║čā "Detect Cable", ą▓čŗą▒ąĄčĆąĖč鹥 ą┐ąĄčĆą▓ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĖąĘ ą▓čŗą┐ą░ą┤ą░čÄčēąĄą│ąŠ čüą┐ąĖčüą║ą░:

ąöą░ą╗ąĄąĄ ąĮą░ąČą╝ąĖč鹥 "OK".

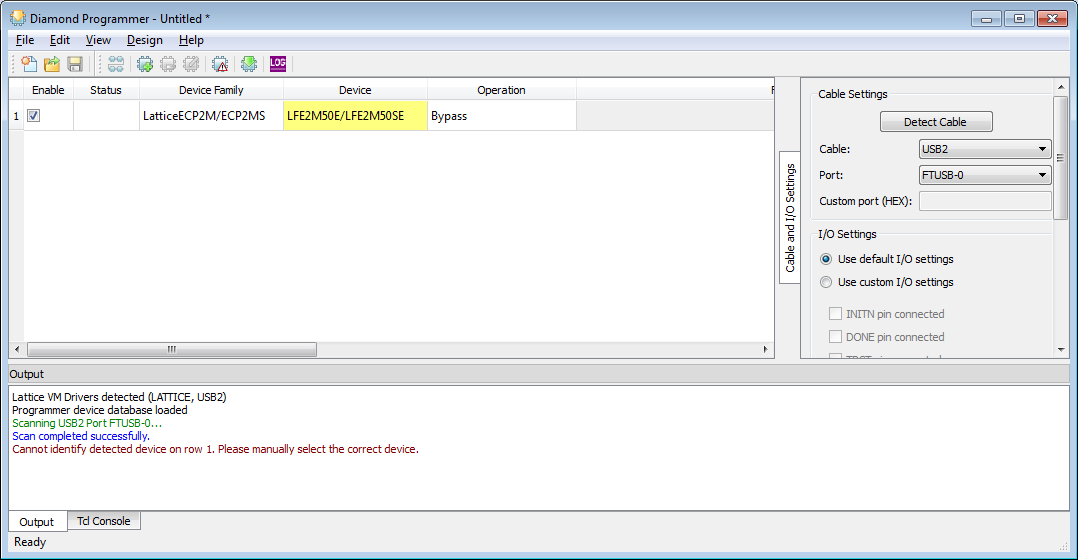

ą¤ąŠčüą╗ąĄ ą┐ą░čĆčŗ čüąĄą║čāąĮą┤ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčéą║čĆąŠąĄčéčüčÅ ą│ą╗ą░ą▓ąĮąŠąĄ ąŠą║ąĮąŠ čüąŠ čüą┐ąĖčüą║ąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ (ąŠąĮąŠ čā ą╝ąĄąĮčÅ ąŠą┤ąĮąŠ) ą▓ čåąĄą┐ąŠčćą║ąĄ JTAG. ąóąĄą┐ąĄčĆčī č鹥ą┐ąĄčĆčī ąĮčāąČąĮąŠ čāč鹊čćąĮąĖčéčī čéąĖą┐ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ FPGA (ą▓čŗą┤ąĄą╗ąĄąĮąŠ ąČąĄą╗čéčŗą╝) ąĮą░ LFE2M50E, ąĖ ą▓čŗą▒čĆą░čéčī ąŠą┐ąĄčĆą░čåąĖčÄ Fast Program ąĖ čäą░ą╣ą╗ čü ą┐čĆąŠčłąĖą▓ą║ąŠą╣.

ą×ą║ąĮąŠ ą▓čŗą▒ąŠčĆą░ ąŠą┐ąĄčĆą░čåąĖąĖ, čĆąĄąČąĖą╝ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čäą░ą╣ą╗ą░ ą┐čĆąŠčłąĖą▓ą║ąĖ:

ążą░ą╣ą╗ ą┐čĆąŠčłąĖą▓ą║ąĖ ąĖ ąŠą┐ąĄčĆą░čåąĖčÅ ą▓čŗą▒čĆą░ąĮčŗ:

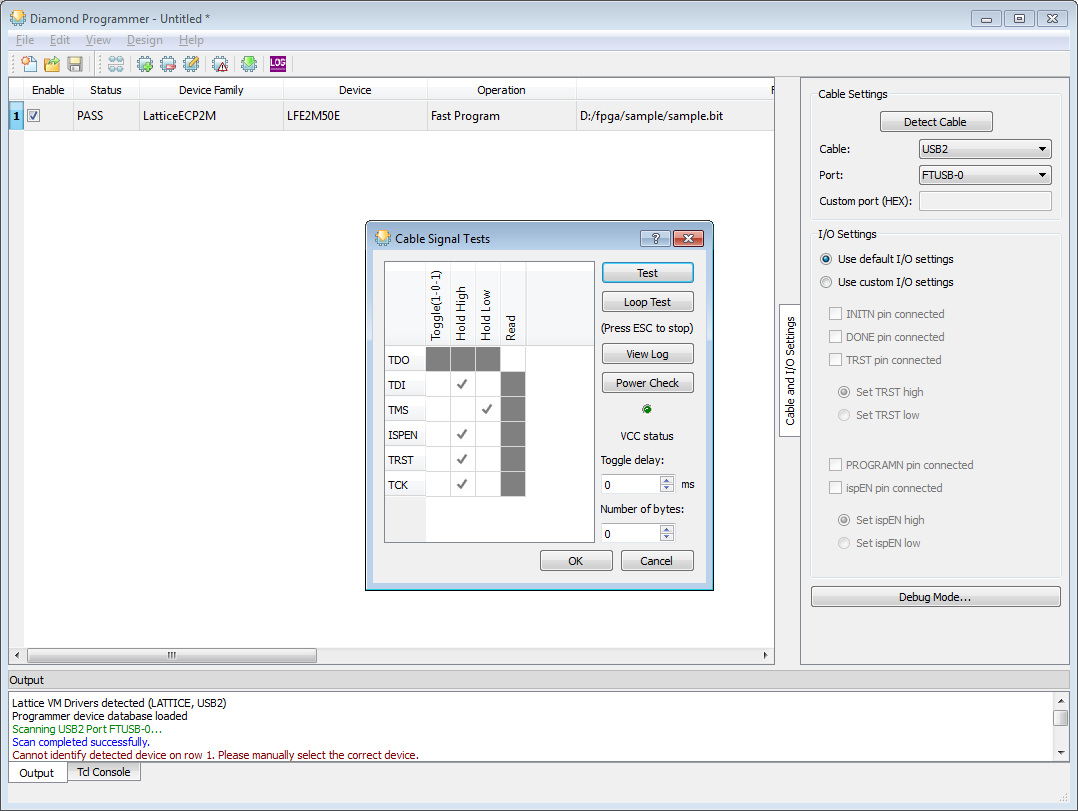

ąØą░ąČą╝ąĖč鹥 ąĮą░ ą║ąĮąŠą┐ą║čā "Program", ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ąĮą░čćąĮąĄčéčüčÅ ąĘą░ą╗ąĖą▓ą║ą░ ą┐čĆąŠčłąĖą▓ą║ąĖ ą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮąŠąĄ ą×ąŚąŻ FPGA.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ FPGA (ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ąĮąĄą║ąŠč鹊čĆčŗčģ ą╝ąŠą┤ąĄą╗ąĄą╣ Actel) ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čüąĄą│ą┤ą░ čģčĆą░ąĮąĖą╗ą░čüčī ą▓ ą×ąŚąŻ, ąĖ ą┤ąŠą╗ąČąĮą░ ąĘą░ą│čĆčāąČą░čéčīčüčÅ ąĖąĘ ą¤ąŚąŻ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░. ą¤ąŚąŻ ąĖąĮąŠą│ą┤ą░ ą▒čŗą▓ą░ąĄčé ą▓ č鹊ą╝ ąČąĄ ą║čĆąĖčüčéą░ą╗ą╗ąĄ, ąĮąŠ ąŠą▒čŗčćąĮąŠ ą▓ąĮąĄčłąĮąĄąĄ. ąóą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ąĘą░ą│čĆčāąĘąĖčéčī ą×ąŚąŻ ą┐čĆčÅą╝ąŠ č湥čĆąĄąĘ JTAG.

ą¤čĆąĖą╝ąĄčĆąĮąŠ č湥čĆąĄąĘ 4 čüąĄą║čāąĮą┤čŗ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ:

[Debug Mode]

ą×čéą╗ą░ą┤ąŠčćąĮčŗą╣ čĆąĄąČąĖą╝ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ąĮą░ąČą░čéąĖąĄą╝ ąĮą░ ą║ąĮąŠą┐ą║čā "Debug mode..." (čüą┐čĆą░ą▓ą░ ą┐ąŠą┤ ą┐ą░ąĮąĄą╗čīčÄ IO settings). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą╝ąŠąČąĮąŠ ą▓čĆčāčćąĮčāčÄ čāą┐čĆą░ą▓ą╗čÅčéčī čāčĆąŠą▓ąĮčÅą╝ąĖ ą▓čüąĄčģ čüąĖą│ąĮą░ą╗ąŠą▓ JTAG, čćč鹊 ą┐ąŠą╗ąĄąĘąĮąŠ ą┤ą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ ą┐čĆą░ą▓ąĖą╗čīąĮąŠčüčéąĖ čüą▒ąŠčĆą║ąĖ. ąöą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čāčĆąŠą▓ąĮčÅą╝ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą│ą░ą╗ąŠčćą║ą░ą╝ąĖ(ą▓ ą║ąŠą╗ąŠąĮą║ą░čģ Hold High ąĖą╗ąĖ Hold Low) ą▓čŗčüčéą░ą▓ąĖčéčī čāčĆąŠą▓ąĮąĖ ą▓čüąĄčģ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖ ąĮą░ąČą░čéčī ąĮą░ ą║ąĮąŠą┐ą║čā "Test". ą¤čĆąĖą╝ąĄčĆąĮąŠ č湥čĆąĄąĘ 2 čüąĄą║čāąĮą┤čŗ ą┐ąŠčüą╗ąĄ ąĮą░ąČą░čéąĖčÅ ąĮą░ Test ąĮąŠą▓čŗąĄ čāčĆąŠą▓ąĮąĖ ą▒čāą┤čāčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ąĮą░ ą▓čüąĄčģ ą▓čŗčģąŠą┤ą░čģ. ą¤čĆąĖ čŹč鹊ą╝ ąĮą░ ą╗ąĖąĮąĖąĖ TRST ą┐ąŠčüč鹊čÅąĮąĮčŗą╣ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčī, ąŠąĮ ąŠą┐čāčüą║ą░ąĄčéčüčÅ ą▓ąĮąĖąĘ ą╗ąĖčłčī ąĮą░ ą┤ąŠą╗čÄ čüąĄą║čāąĮą┤čŗ, čćč鹊, ąŠą┤ąĮą░ą║ąŠ, ąĘą░ą╝ąĄčéąĮąŠ ą┤ą░ąČąĄ ąĮą░ čåąĖčäčĆąŠą▓ąŠą╝ ą╝čāą╗čīčéąĖą╝ąĄčéčĆąĄ.

[ąĪčüčŗą╗ą║ąĖ]

1. Lattice Programming Cables for PC site:latticesemi.com.

2. HW-USBN-2A site:digikey.com.

3. HW-DLN-3C site:digikey.com.

4. FT2232H Board - ą╝ą░ą║ąĄčéąĮą░čÅ ą┐ą╗ą░čéą░ ąĮą░ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╝ čćąĖą┐ąĄ ą╝ąŠčüčéą░ USB čäąĖčĆą╝čŗ FTDI.

5. ispDOWNLOAD Cables user guide site:latticesemi.com.

6. Lattice Diamond Software site:latticesemi.com.

7. Programmer and Deployment Tool - Lattice Diamond Programmer site:latticesemi.com. |