|

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ AT45DB161B čŹč鹊 FLASH-ą┐ą░ą╝čÅčéčī čü ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ SPI, čĆą░ą▒ąŠčéą░čÄčēą░čÅ ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 3.3V, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮą░čÅ ą┤ą╗čÅ čģčĆą░ąĮąĄąĮąĖčÅ ą┐čĆąŠčłąĖą▓ąŠą║ firmware ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ DSP, ą╝ąĖą║čĆąŠčüčģąĄą╝ ą╗ąŠą│ąĖą║ąĖ FPGA, ąĘą░ą┐ąĖčüąĖ čåąĖčäčĆąŠą▓ąŠą│ąŠ ąĘą▓čāą║ą░ [4] ąĖ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ čåąĄą╗ąĄą╣ ą║ą░ą║ 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ čģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ čüčĆąĄą┤ąĮąĄą│ąŠ čĆą░ąĘą╝ąĄčĆą░.

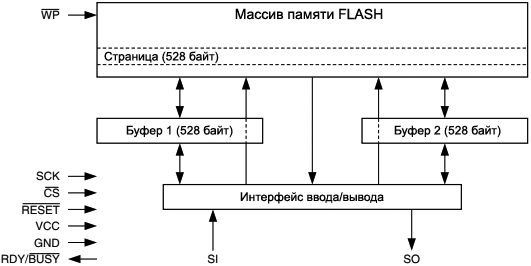

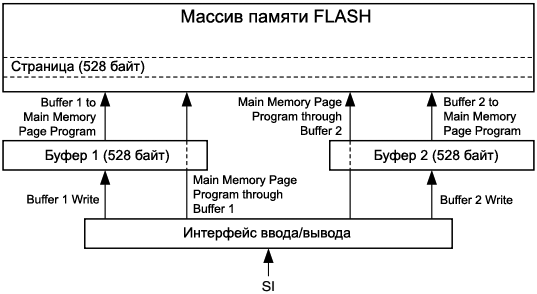

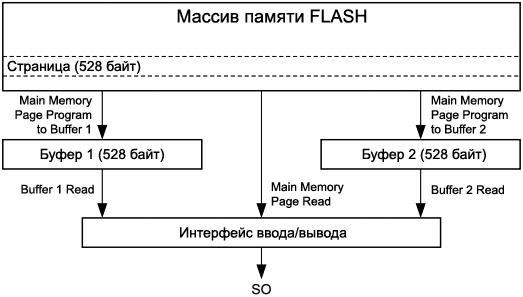

17301504 ą▒ąĖčé ą┐ą░ą╝čÅčéąĖ AT45DB161B ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮčŗ ą▓ 4096 čüčéčĆą░ąĮąĖčå ą┐ąŠ 528 ą▒ą░ą╣čé ą║ą░ąČą┤ą░čÅ. ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ ąŠčüąĮąŠą▓ąĮąŠą╣ 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ, ą▓ AT45DB161B čéą░ą║ąČąĄ ąĄčüčéčī ą┤ą▓ą░ SRAM-ą▒čāč乥čĆą░ ą┐ąŠ 528 ą▒ą░ą╣čé ą║ą░ąČą┤čŗą╣. ąŁčéąĖ ą▒čāč乥čĆčŗ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░čéčī ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčŗą╣ ą┐ąŠč鹊ą║ ą┤ą░ąĮąĮčŗčģ (ą┤ą▓ąŠą╣ąĮą░čÅ ą▒čāč乥čĆąĖąĘą░čåąĖčÅ) ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ąĖ čćč鹥ąĮąĖčÅ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą┐ąŠą║ą░ ąĖą┤ąĄčé ąĘą░ą┐ąĖčüčī čüčéčĆą░ąĮąĖčåčŗ ą▓ ąŠčüąĮąŠą▓ąĮčāčÄ ą┐ą░ą╝čÅčéčī ąĖąĘ ą┐ąĄčĆą▓ąŠą│ąŠ ą▒čāč乥čĆą░, ą┤čĆčāą│ąŠą╣ ą▒čāč乥čĆ ąĮą░ą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┤ą░ąĮąĮčŗą╝ąĖ č湥čĆąĄąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü). ąæąĖčé 菹╝čāą╗čÅčåąĖąĖ EEPROM (ą▒ąĖčé ąĖą╗ąĖ ą▒ą░ą╣čé) ą╗ąĄą│ą║ąŠ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čéčĆąĄčģčüčéčāą┐ąĄąĮčćą░č鹊ą╣ ąŠą┐ąĄčĆą░čåąĖąĄą╣ Read-Modify-Write. ąÆ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ąŠą▒čŗčćąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą┐ą░ą╝čÅčéąĖ FLASH, ą┤ąŠčüčéčāą┐ ą║ ą║ąŠč鹊čĆčŗą╝ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą║ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮčŗą╝ čÅč湥ą╣ą║ą░ą╝ č湥čĆąĄąĘ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü, ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ DataFlash ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü SPI ą┤ą╗čÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ čüą▓ąŠąĖą╝ ą┤ą░ąĮąĮčŗą╝. DataFlash ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé SPI mode 0 ąĖ SPI mode 3. ąŁč鹊čé ą┐čĆąŠčüč鹊ą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü čāą┐čĆąŠčēą░ąĄčé ą░ą┐ą┐ą░čĆą░čéčāčĆčā, ą┐ąŠą▓čŗčłą░ąĄčé ąĮą░ą┤ąĄąČąĮąŠčüčéčī čüąĖčüč鹥ą╝čŗ, čüąĮąĖąČą░ąĄčé ą┐ąŠą╝ąĄčģąĖ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗčģ ą┐čĆąŠčåąĄčüčüąŠą▓ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖą╣ ą╗ąŠą│ąĖč湥čüą║ąĖčģ čāčĆąŠą▓ąĮąĄą╣, čāą╝ąĄąĮčīčłą░ąĄčé čĆą░ąĘą╝ąĄčĆčŗ ą║ąŠčĆą┐čāčüąŠą▓ ąĖ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ AT45DB161B ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ą║ąŠą╝ą╝ąĄčĆč湥čüą║ąĖčģ ąĖ ąĖąĮą┤čāčüčéčĆąĖą░ą╗čīąĮčŗčģ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖą╣, ą│ą┤ąĄ ą▓ą░ąČąĮčŗ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ąĮąĖąĘą║ąŠą╝čā ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÄ čŹąĮąĄčĆą│ąĖąĖ ąĖ ą║ąŠą╝ą┐ą░ą║čéąĮąŠčüčéąĖ.

ą×čüąĮąŠą▓ąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąĖ čäčāąĮą║čåąĖąĖ AT45DB161B:

ŌĆó ą£ąŠąČąĄčé ą┐ąŠą╗čāčćą░čéčī ą┐ąĖčéą░ąĮąĖąĄ ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 2.5V .. 3.6V ąĖą╗ąĖ 2.7V .. 3.6V.

ŌĆó ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ čüąŠ čüčéą░ąĮą┤ą░čĆčéąĮčŗą╝ SPI [3].

ŌĆó ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┤ąŠ 20 ą£ąōčå.

ŌĆó ąĀą░ą▒ąŠčéą░ąĄčé ąĮą░ ąŠčüąĮąŠą▓ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüčéčĆą░ąĮąĖčå:

ŌĆō ą×ą┤ąĖąĮ čåąĖą║ą╗ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ (Erase ąĖ Program).

ŌĆō 4096 čüčéčĆą░ąĮąĖčå (ą┐ąŠ 528 ą▒ą░ą╣čé ąĮą░ čüčéčĆą░ąĮąĖčåčā) ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą▒ą╗ąŠčćąĮčŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ąŠčćąĖčüčéą║ąĖ ąĖ ąŠą┐ąĄčĆą░čåąĖąĖ ąŠčćąĖčüčéą║ąĖ čüčéčĆą░ąĮąĖčå.

ŌĆó ąöą▓ą░ ą▒čāč乥čĆą░ SRAM, ą║ą░ąČą┤čŗą╣ ą┐ąŠ 528-ą▒ą░ą╣čé, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠą╗čāčćą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčüąĮąŠą▓ąĮąŠą╣ 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ ą▓čüąĄą│ąŠ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ (Continuous Read Capability), čćč鹊 ąĖą┤ąĄą░ą╗čīąĮąŠ ą┐ąŠą┤čģąŠą┤ąĖčé ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ čü ąĘą░č鹥ąĮąĄąĮąĖąĄą╝ ą┐ą░ą╝čÅčéąĖ ą║ąŠą┤ą░.

ŌĆó ąØąĖąĘą║ąŠąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ:

ŌĆō 4 ą╝ąÉ ą▓ čĆąĄąČąĖą╝ąĄ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ.

ŌĆō 2 ą╝ą║ąÉ čéąĖą┐ąĖčćąĮčŗą╣ č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą▓ ąČą┤čāčēąĄą╝ čĆąĄąČąĖą╝ąĄ (CMOS Standby Current).

ŌĆó ąÉą┐ą┐ą░čĆą░čéąĮą░čÅ čäčāąĮą║čåąĖčÅ ąĘą░čēąĖčéčŗ ą┤ą░ąĮąĮčŗčģ.

ŌĆó 100% čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī čü AT45DB161.

ŌĆó ąÆčģąŠą┤čŗ, ą┤ąŠą┐čāčüą║ą░čÄčēąĖąĄ ą▓čģąŠą┤ąĮčŗąĄ čāčĆąŠą▓ąĮąĖ 5V (5V-tolerant Inputs): ą▓čŗą▓ąŠą┤čŗ SI, SCK, ~CS, ~RESET ąĖ ~WP.

ŌĆó ąöąŠčüčéčāą┐ąĮčŗ ą▓ą░čĆąĖą░ąĮčéčŗ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┤ą╗čÅ ą║ąŠą╝ą╝ąĄčĆč湥čüą║ąĖčģ ąĖ ąĖąĮą┤čāčüčéčĆąĖą░ą╗čīąĮčŗčģ ą┤ąĖą░ą┐ą░ąĘąŠąĮąŠą▓ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ.

ŌĆó ąĢčüčéčī 菹║ąŠą╗ąŠą│ąĖčćąĮčŗąĄ ą▓ą░čĆąĖą░ąĮčéčŗ ą║ąŠčĆą┐čāčüąŠą▓ (Green Pb/Halide-free).

ą¦č鹊ą▒čŗ čāą┐čĆąŠčüčéąĖčéčī ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓ čüąĖčüč鹥ą╝ąĄ (ą┐čĆąĖąĮčåąĖą┐ ISP), AT45DB161B čüą┐čĆąŠąĄą║čéąĖčĆąŠą▓ą░ąĮą░ čéą░ą║, čćč鹊 ąĮąĄ čéčĆąĄą▒čāąĄčé ą┤ą╗čÅ čŹč鹊ą│ąŠ ąŠčéą┤ąĄą╗čīąĮčŗčģ ą▓čŗčüąŠą║ąĖčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ čĆą░ą▒ąŠčéą░ąĄčé ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 2.5V .. 3.6V ąĖą╗ąĖ 2.7V .. 3.6V, ą║ą░ą║ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, čéą░ą║ ąĖ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ. ąĀą░ą▒ąŠčéą░ AT45DB161B čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą▓čģąŠą┤ąŠą╝ chip select (~CS), ąĖ ą║ ąĄčæ ą┤ą░ąĮąĮčŗą╝ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą┐ąŠ 3-ą┐čĆąŠą▓ąŠą┤ąĮąŠą╝čā ąĖąĮč鹥čĆč乥ą╣čüčā, čüąŠčüč鹊čÅčēąĄą╝čā ąĖąĘ ą▓čģąŠą┤ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (Serial Input, SI), ą▓čŗčģąŠą┤ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (Serial Output, SO) ąĖ čüąĖą│ąĮą░ą╗ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ (Serial Clock, SCK).

ąÆčüąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čåąĖą║ą╗čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čéą░ą║čéąĖčĆčāčÄčéčüčÅ ą░ą▓č鹊ąĮąŠą╝ąĮąŠ, ą┐ąĄčĆąĄą┤ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ąŠčéą┤ąĄą╗čīąĮčŗą╣ čåąĖą║ą╗ ąŠčćąĖčüčéą║ąĖ.

ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ čü ąĘą░ą▓ąŠą┤ą░ (čĆą░ąĮąĄąĄ Atmel, č鹥ą┐ąĄčĆčī Microchip), čüą░ą╝ą░čÅ čüčéą░čĆčłą░čÅ čüčéčĆą░ąĮąĖčåą░ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄ ąŠčćąĖčēąĄąĮą░. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ čüčéčĆą░ąĮąĖčåąĄ ąĮąĄ ą▓čüąĄ ą▒ą░ą╣čéčŗ ą╝ąŠą│čāčé čüąŠą┤ąĄčƹȹ░čéčī ąĘąĮą░č湥ąĮąĖčÅ FFH.

[ąÆčŗą▓ąŠą┤čŗ ąĖ čåąŠą║ąŠą╗ąĄą▓ą║ą░]

| ąÆčŗą▓ąŠą┤ |

ążčāąĮą║čåąĖčÅ |

| ~CS |

ąÆčŗą▒ąŠčĆą║ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (Chip Select) |

| SCK |

ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé (Serial Clock) |

| SI |

ąÆčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (Serial Input) |

| SO |

ąÆčŗčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (Serial Output) |

| ~WP |

ąÆčŗą▓ąŠą┤ ą┤ą╗čÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ąĘą░ą┐čĆąĄčéą░ ąĘą░ą┐ąĖčüąĖ (Hardware Page Write Protect) |

| ~RESET |

ąĪą▒čĆąŠčü |

| RDY/~BUSY |

ąĪąĖą│ąĮą░ą╗ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ/ąĘą░ąĮčÅč鹊čüčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (Ready/Busy) |

ąÆą░čĆąĖą░ąĮčéčŗ čåąŠą║ąŠą╗ąĄą▓ą║ąĖ ą║ąŠčĆą┐čāčüąŠą▓:

ąæą╗ąŠą║-čüčģąĄą╝ą░ AT45DB161B:

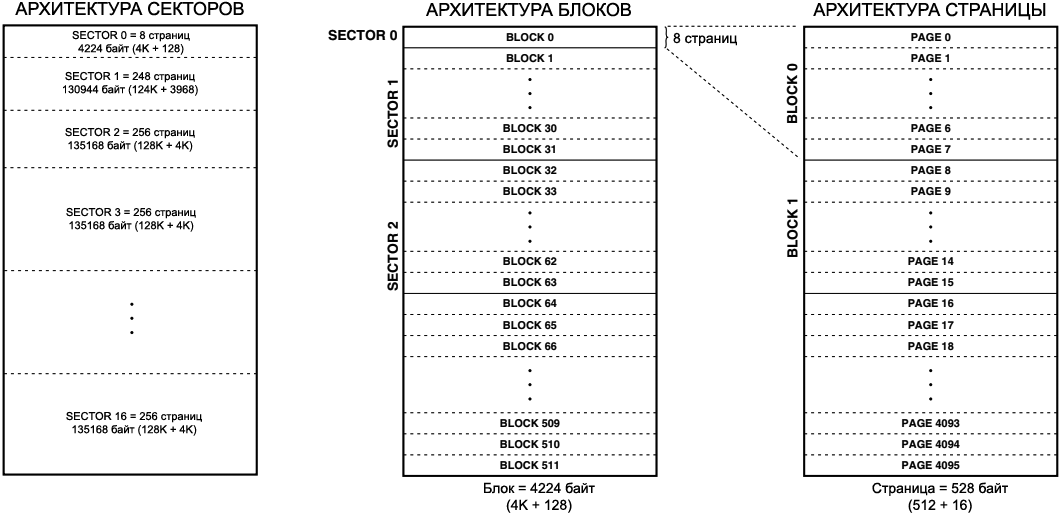

ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ. ąöą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ąŠą┐čéąĖą╝ą░ą╗čīąĮąŠą╣ ą│ąĖą▒ą║ąŠčüčéąĖ ą╝ą░čüčüąĖą▓ ą┐ą░ą╝čÅčéąĖ AT45DB161B ą┐ąŠą┤ąĄą╗ąĄąĮ ąĮą░ 3 čāčĆąŠą▓ąĮčÅ ą│čĆą░ąĮčāą╗čÅčĆąĮąŠčüčéąĖ, ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÅ čüąĄą║č鹊čĆčŗ, ą▒ą╗ąŠą║ąĖ ąĖ čüčéčĆą░ąĮąĖčåčŗ. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą┐ą░ą╝čÅčéąĖ, ą┐ąŠą║ą░ąĘą░ąĮąĮą░čÅ ąĮąĖąČąĄ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ, čüąŠą┤ąĄčƹȹĖčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ąĄ čüčéą░ąĮąĖčå ąĮą░ čüąĄą║č鹊čĆ ąĖ ą▒ą╗ąŠą║. ąÆčüąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ DataFlash ą┐čĆąŠąĖčüčģąŠą┤čÅčé ąĮą░ ąŠčüąĮąŠą▓ąĄ čüčéčĆą░ąĮąĖčå (čüčéčĆą░ąĮąĖčåą░ ąĘą░ čüčéčĆą░ąĮąĖčåąĄą╣); ąŠą┤ąĮą░ą║ąŠ ąŠą┐čéąĖą╝ą░ą╗čīąĮčŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ąŠčćąĖčüčéą║ąĖ ą╝ąŠą│čāčé ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ ąĮą░ čāčĆąŠą▓ąĮąĄ ą▒ą╗ąŠą║ą░ ąĖą╗ąĖ čüčéčĆą░ąĮąĖčåčŗ.

ą¤čĆąĖą╝. ą┐ąĄčĆąĄą▓ąŠą┤čćąĖą║ą░: ąĮąĄ ą┐ąŠąĮčÅą╗, čćč鹊 ąĘąĮą░čćąĖčé "ąÉčĆčģąĖč鹥ą║čéčāčĆą░ čüąĄą║č鹊čĆąŠą▓", ąĖ ą║ą░ą║ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ čüąĄą║č鹊čĆą░. ąöąĄą╗ąŠ ą▓ č鹊ą╝, čćč鹊 ą┤ą░ą╗ąĄąĄ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ ą║ąŠą╝ą░ąĮą┤, ą║ąŠč鹊čĆčŗąĄ ą▓čŗą┐ąŠą╗ąĮčÅčÄčé ąĘą░ą┐ąĖčüčī ąĖą╝ąĄąĮąĮąŠ čüąĄą║č鹊čĆą░, ąĄčüčéčī č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüčī čüčéčĆą░ąĮąĖčåčŗ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čĆą░ąĘą╝ąĄčĆą░ 528 ą▒ą░ą╣čé. ąĪčéąĖčĆą░čéčī čéą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ą╗ąĖą▒ąŠ ą┐ąŠ ąŠą┤ąĮąŠą╣ čüčéčĆą░ąĮąĖčåąĄ, ą╗ąĖą▒ąŠ ą▒ą╗ąŠą║ąŠą╝ ą┐ąŠ 8 čüčéčĆą░ąĮąĖčå. ą×čéą║čāą┤ą░ ą▓ąĘčÅą╗ąĖčüčī čüąĄą║č鹊čĆčŗ?..

[ąĀą░ą▒ąŠčéą░ AT45DB161B]

ąĀą░ą▒ąŠčéą░ čāčüčéčĆąŠą╣čüčéą▓ą░ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖčÅą╝ąĖ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (čģąŠčüčé, ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čłąĖąĮąĄ SPI). ąĪą┐ąĖčüąŠą║ ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖ čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ąĮąĖą╝ąĖ ą║ąŠą┤čŗ ąŠą┐ąĄčĆą░čåąĖą╣ (opcode) čüąŠą┤ąĄčƹȹ░čéčüčÅ ą▓ čéą░ą▒ą╗ąĖčåą░čģ 1 .. 4. ąöąŠą┐čāčüčéąĖą╝ą░čÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čüąŠ čüą┐ą░ą┤ą░ ą╗ąŠą│. čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ ~CS, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ 8-ą▒ąĖčéąĮčŗą╣ opcode, ąĖ ą┤ą░ą╗ąĄąĄ ąĖą┤ąĄčé ąĖąĮč乊čĆą╝ą░čåąĖčÅ, ą░ą┤čĆąĄčüčāčÄčēą░čÅ ąČąĄą╗ą░ąĄą╝čŗą╣ ą▒čāč乥čĆ ąĖą╗ąĖ čÅč湥ą╣ą║čā ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ. ąÜąŠą│ą┤ą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą╗ąŠą│. 1, ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SCK čāą┐čĆą░ą▓ą╗čÅąĄčé ąĘą░ą│čĆčāąĘą║ąŠą╣ ą▒ąĖčé opcode ąĖ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą╣ ą░ą┤čĆąĄčüąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ SI (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą▓čģąŠą┤). ąÆčüąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą░ą┤čĆąĄčüą░ ąĖ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ (most significant bit, MSB) ą▓ą┐ąĄčĆąĄą┤.

ąÉą┤čĆąĄčüą░čåąĖčÅ ą▒čāč乥čĆą░, ą║ą░ą║ ąŠąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ čŹč鹊ą╝ ą┤ą░čéą░čłąĖč鹥, ąĖčüą┐ąŠą╗čīąĘčāąĄčé č鹥čĆą╝ąĖąĮąŠą╗ąŠą│ąĖčÄ BFA9 - BFA0, čćč鹊ą▒čŗ ąŠą▒ąŠąĘąĮą░čćąĖčéčī 10 ą▒ąĖčé ą░ą┤čĆąĄčüą░, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĄą│ąŠ ą░ą┤čĆąĄčü ą▒ą░ą╣čéą░ ą▓ ą▒čāč乥čĆąĄ. ąÉą┤čĆąĄčüą░čåąĖčÅ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčé č鹥čĆą╝ąĖąĮąŠą╗ąŠą│ąĖčÄ PA11 - PA0 ąĖ BA9 - BA0, ą│ą┤ąĄ PA11 - PA0 ąŠą▒ąŠąĘąĮą░čćą░čÄčé 12 ą▒ąĖčé ą░ą┤čĆąĄčüą░ ą┤ą╗čÅ ą░ą┤čĆąĄčüą░ čüčéčĆą░ąĮąĖčåčŗ, ąĖ BA9 - BA0 ąŠą▒ąŠąĘąĮą░čćą░čÄčé 10 ą▒ąĖčé ą░ą┤čĆąĄčüą░, čéčĆąĄą▒čāąĄą╝čŗąĄ ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĖčÅ ąĮą░ ą▒ą░ą╣čé ą▓ąĮčāčéčĆąĖ čüčéčĆą░ąĮąĖčåčŗ.

[ąÜąŠą╝ą░ąĮą┤čŗ čćč鹥ąĮąĖčÅ]

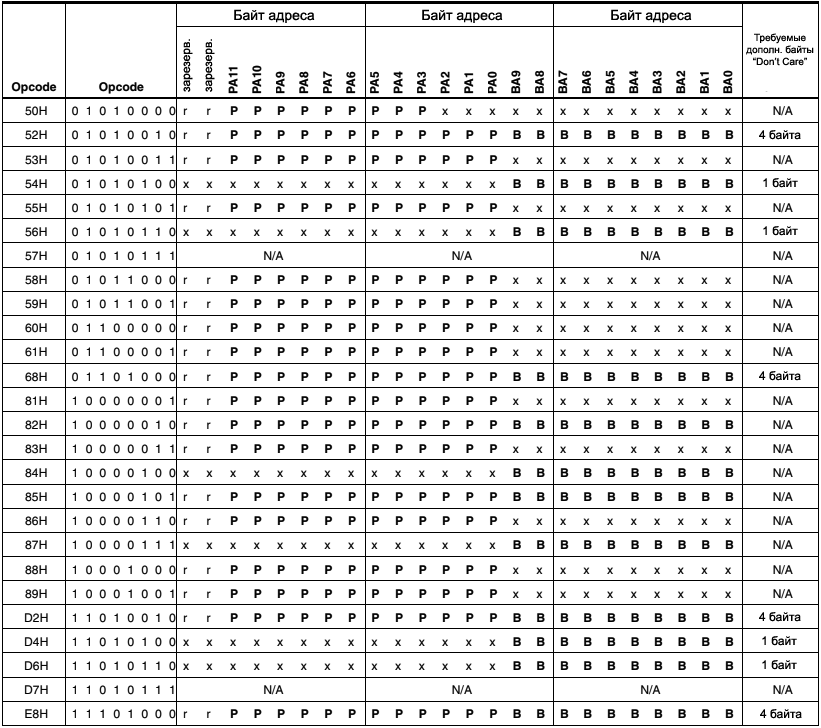

ą¤čāč鹥ą╝ čāą║ą░ąĘą░ąĮąĖčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ opcode, ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖąĘ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ąĖą╗ąĖ ąĖąĘ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą┤ą▓čāčģ ą▒čāč乥čĆąŠą▓ ą┤ą░ąĮąĮčŗčģ. DataFlash ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┤ą▓ą░ čĆąĄąČąĖą╝ą░ čćč鹥ąĮąĖčÅ ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ čüąĖą│ąĮą░ą╗čā SCK. ą×čéą╗ąĖčćąĖčÅ ą╝ąĄąČą┤čā čŹčéąĖą╝ąĖ čĆąĄąČąĖą╝ą░ą╝ąĖ ąŠčéąĮąŠčüčÅčéčüčÅ ą║ ąĮąĄą░ą║čéąĖą▓ąĮąŠą╝čā čüąŠčüč鹊čÅąĮąĖčÄ SCK, ą░ čéą░ą║ąČąĄ ą┐ąŠ ą║ą░ą║ąŠą╝čā čåąĖą║ą╗čā čéą░ą║č鹊ą▓ ą┤ą░ąĮąĮčŗąĄ ąĮą░čćąĮčāčé ą┐ąŠčüčéčāą┐ą░čéčī ąĮą░ ą▓čŗčģąŠą┤. ąŁčéąĖ ą┤ą▓ąĄ ą║ą░č鹥ą│ąŠčĆąĖąĖ, čüąŠčüč鹊čÅčēąĖąĄ ąĖąĘ č湥čéčŗčĆąĄčģ čĆąĄąČąĖą╝ąŠą▓ čĆą░ą▒ąŠčéčŗ, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ ą║ą░ą║ Inactive Clock Polarity Low (ąĮąĄą░ą║čéąĖą▓ąĮą░čÅ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ ą▓ ą╗ąŠą│. 0) ąĖą╗ąĖ Inactive Clock Polarity High (ąĮąĄą░ą║čéąĖą▓ąĮą░čÅ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ ą▓ ą╗ąŠą│. 1) ąĖ čĆąĄąČąĖą╝ąŠą▓ 0 ąĖ 3 ąĖąĮč鹥čĆč乥ą╣čüą░ SPI. ą×čéą┤ąĄą╗čīąĮčŗą╣ opcode (čüą╝. čéą░ą▒ą╗ąĖčåčā 1 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą╗ąĮąŠą│ąŠ čüą┐ąĖčüą║ą░) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą║ą░č鹥ą│ąŠčĆąĖąĖ čćč鹥ąĮąĖčÅ. ąĪą╝. ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ "ą¤ąŠą┤čĆąŠą▒ąĮčŗąĄ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ąĮą░ čāčĆąŠą▓ąĮąĄ ą▒ąĖčé" ą▓ąŠ ą▓čĆąĄąĘą║ąĄ "ąöąĖą░ą│čĆą░ą╝ą╝čŗ čüąĖą│ąĮą░ą╗ąŠą▓" ą┤ą░ą╗ąĄąĄ ą┤ą╗čÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠą│ąŠ ąŠą┐ąĖčüą░ąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüč鹥ą╣ čåąĖą║ą╗ąŠą▓ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čĆąĄąČąĖą╝ą░.

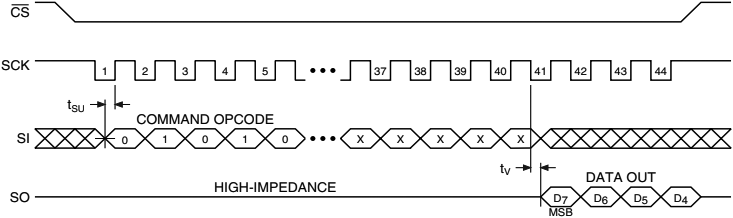

CONTINUOUS ARRAY READ: ą┐čāč鹥ą╝ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖčÅ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╝ ą╝ą░čüčüąĖą▓ąĄ ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ąŠą╝ą░ąĮą┤ą░ Continuous Array Read ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠą│ąŠ ą┐ąŠč鹊ą║ą░ ą┤ą░ąĮąĮčŗčģ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░, čü ą┐čĆąŠčüčéčŗą╝ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓; ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąĖą╗ąĖ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čüąĖą│ąĮą░ą╗čŗ. ąÆ DataFlash ą┤ą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ąĄčüčéčī ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüč湥čéčćąĖą║ ą░ą┤čĆąĄčüą░, ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ čåąĖą║ą╗ąĄ čéą░ą║č鹊ą▓, ą┐ąŠąĘą▓ąŠą╗čÅčÅ ą▓čŗą┐ąŠą╗ąĮčÅčéčī ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠąĄ čćč鹥ąĮąĖąĄ ą▒ąĄąĘ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüč鹥ą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ. ąöą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ opcode 68H ąĖą╗ąĖ E8H ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ąĘą░ čŹčéąĖą╝ opcode ą┤ąŠą╗ąČąĄąĮ ąĖą┤čéąĖ 24-ą▒ąĖčéąĮčŗą╣ ą░ą┤čĆąĄčü ąĖ 32 ąĮąĖč湥ą│ąŠ ąĮąĄ ąĘąĮą░čćą░čēąĖčģ ą▒ąĖčéą░ (donŌĆÖt care bits). ą¤ąĄčĆą▓čŗąĄ ą┤ą▓ą░ ą▒ąĖčéą░ 24-ą▒ąĖčéąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą░ą┤čĆąĄčüą░ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ čĆą░čüčłąĖčĆąĄąĮąĖčÅ ą▓ ą▒čāą┤čāčēąĄą╝ ąĖ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ąŠą▒čĆą░čéąĮąŠą╣ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ DataFlash ą▒ąŠą╗čīčłąĄą╣ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄą╣ ąĄą╝ą║ąŠčüčéąĖ (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ "Command Sequence for Read/Write Operations"). ąĪą╗ąĄą┤čāčÄčēąĖąĄ 12 ą▒ąĖčé ą░ą┤čĆąĄčüą░ (PA11 - PA0) ąĘą░ą┤ą░čÄčé čüčéčĆą░ąĮąĖčåčā ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆą░čÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮą░, ąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ 10 ą▒ąĖčé (BA9 - BA0) ąĘą░ą┤ą░čÄčé ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ą▒ą░ą╣čéą░ ąĮą░ čŹč鹊ą╣ čüčéčĆą░ąĮąĖčåąĄ. 32 donŌĆÖt care ą▒ąĖčéą░, ą║ąŠč鹊čĆčŗąĄ ąĖą┤čāčé ąĘą░ 24 ą▒ąĖčéą░ą╝ąĖ ą░ą┤čĆąĄčüą░, ąĮčāąČąĮčŗ ą┤ą╗čÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ. ą¤ąŠčüą╗ąĄ čŹčéąĖčģ 32 donŌĆÖt care ą▒ąĖčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čéą░ą║č鹊ą▓čŗąĄ ąĖą╝ą┐čāą╗čīčüčŗ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SCK ą┐čĆąĖą▓ąĄą┤čāčé ą║ ą▓čŗą▓ąŠą┤čā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ SO (serial output).

ąŻčĆąŠą▓ąĄąĮčī ąĮą░ ~CS ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ ą╗ąŠą│. 0 ą▓ąŠ ą▓čĆąĄą╝čÅ ąĘą░ą│čĆčāąĘą║ąĖ opcode, ą▒ąĖčé ą░ą┤čĆąĄčüą░, ą▒ąĖčé donŌĆÖt care ąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ čćč鹥ąĮąĖčÅ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ ą┤ąŠčüčéąĖą│ąĮčāčé ą║ąŠąĮąĄčå čüčéčĆą░ąĮąĖčåčŗ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą┐čĆąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĖ ąŠą┐ąĄčĆą░čåąĖąĖ Continuous Array Read, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖčé čćč鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ čü ąĮą░čćą░ą╗ą░ čüą╗ąĄą┤čāčÄčēąĄą╣ čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ ą▒ąĄąĘ ąĘą░ą┤ąĄčƹȹĄą║ ą┐čĆąĖ ą┐ąĄčĆąĄčüąĄč湥ąĮąĖąĖ ą│čĆą░ąĮąĖčåčŗ čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ (ą▓ ą╝ąŠą╝ąĄąĮčé ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čüčéčĆą░ąĮąĖčåčŗ ąĖ ąĮą░čćą░ą╗ąĄ čüą╗ąĄą┤čāčÄčēąĄą╣). ąÜąŠą│ą┤ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé ą▓ ą│ą╗ą░ą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠčćąĖčéą░ąĮ, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖčé čćč鹥ąĮąĖąĄ čü ąĮą░čćą░ą╗ą░ ą┐ąĄčĆą▓ąŠą╣ čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ. ą¤čĆąĖ čŹč鹊ą╝ čéą░ą║ąČąĄ ąĮąĄ ą▒čāą┤ąĄčé ąĮąĖą║ą░ą║ąŠą╣ ąĘą░ą┤ąĄčƹȹ║ąĖ ą┐čĆąĖ ą┐ąĄčĆąĄčģąŠą┤ąĄ ąŠčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ąĖčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ čüčéčĆą░ąĮąĖčåčŗ ą║ ą┐ąĄčĆą▓ąŠą╝čā ą▒ąĖčéčā ą┐ąĄčĆą▓ąŠą╣ čüčéčĆą░ąĮąĖčåčŗ.

ą¤ąĄčĆąĄčģąŠą┤ ąŠčé ą╗ąŠą│. 0 ą║ ą╗ąŠą│. 1 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS ą┐čĆąĄą║čĆą░čéąĖčé ąŠą┐ąĄčĆą░čåąĖčÄ čćč鹥ąĮąĖčÅ ąĖ ą┐ąĄčĆąĄą▓ąĄą┤ąĄčé ą▓čŗą▓ąŠą┤ SO ą▓ čéčĆąĄčéčīąĄ (ąŠčéą║ą╗čÄč湥ąĮąĮąŠąĄ) čüąŠčüč鹊čÅąĮąĖąĄ. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ SCK, ą┤ąŠą┐čāčüčéąĖą╝ą░čÅ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖąĖ Continuous Array Read, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą╝ fCAR. ą×ą┐ąĄčĆą░čåąĖčÅ Continuous Array Read ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą▒čāč乥čĆą░ ą┤ą░ąĮąĮčŗčģ, ąŠčüčéą░ą▓ą╗čÅčÅ ąĮąĄąĖąĘą╝ąĄąĮąĮčŗą╝ ąĖčģ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ.

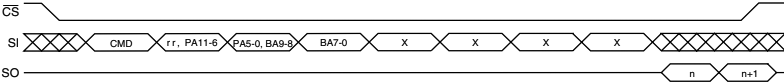

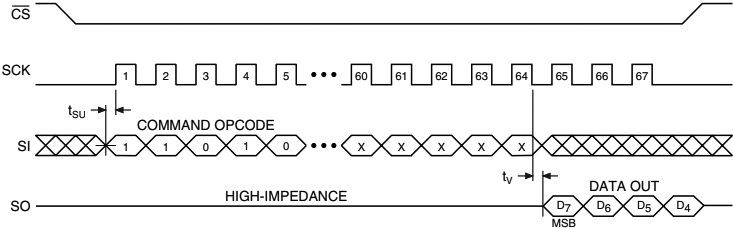

MAIN MEMORY PAGE READ: ą║ąŠą╝ą░ąĮą┤ą░ Main Memory Page Read ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čćąĖčéą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ąĖąĘ ąŠą┤ąĮąŠą╣ ąĖąĘ 4096 čüčéčĆą░ąĮąĖčå ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ą┐čĆąŠą┐čāčüą║ą░čÅ ąŠą▒ą░ ą▒čāč乥čĆą░ ą┤ą░ąĮąĮčŗčģ ąĖ ąŠčüčéą░ą▓ą╗čÅčÅ ąĖčģ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▒ąĄąĘ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ. ą¦č鹊ą▒čŗ ąĮą░čćą░čéčī čćč鹥ąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ, opcode 52H ąĖą╗ąĖ D2H ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ąĘą░ ą║ąŠč鹊čĆąŠą╝ ą┤ąŠą╗ąČąĄąĮ ąĖą┤čéąĖ 24 ą▒ąĖčéą░ ą░ą┤čĆąĄčüą░ ąĖ 32 ą▒ąĖčéą░ donŌĆÖt care. ąÜą░ą║ ąĖ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖąĖ Continuous Array Read, ą┐ąĄčĆą▓čŗąĄ 2 ą▒ąĖčéą░ 24-ą▒ąĖčéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, čüą╗ąĄą┤čāčÄčēąĖąĄ 12 ą▒ąĖčé ą░ą┤čĆąĄčüą░ (PA11 - PA0) ąĘą░ą┤ą░čÄčé ą░ą┤čĆąĄčü čüčéčĆą░ąĮąĖčåčŗ, ąĖ čüą╗ąĄą┤čāčÄčēąĖąĄ 10 ą▒ąĖčé ą░ą┤čĆąĄčüą░ (BA9 - BA0) ąĘą░ą┤ą░čÄčé ąĮą░čćą░ą╗čīąĮčŗą╣ ą▒ą░ą╣čé ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ čŹč鹊ą╣ čüčéčĆą░ąĮąĖčåčŗ. 32 ą▒ąĖčéą░ donŌĆÖt care, ą║ąŠč鹊čĆčŗąĄ ąĖą┤čāčé ąĘą░ 24 ą▒ąĖčéą░ą╝ąĖ ą░ą┤čĆąĄčüą░, ą┐ąŠčüčŗą╗ą░čÄčéčüčÅ ą┤ą╗čÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ. ą¤ąŠčüą╗ąĄ 32 ą▒ąĖčé donŌĆÖt care ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ąĖą╝ą┐čāą╗čīčüčŗ SCK ą┐čĆąĖą▓ąĄą┤čāčé ą║ ą▓čŗą▓ąŠą┤čā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ SO. ąŻčĆąŠą▓ąĄąĮčī ~CS ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ ą╗ąŠą│. 0 ą▓ąŠ ą▓čĆąĄą╝čÅ ąĘą░ą│čĆčāąĘą║ąĖ opcode, ą▒ąĖčé ą░ą┤čĆąĄčüą░, ą▒ąĖčé donŌĆÖt care ąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ čćč鹥ąĮąĖčÅ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ ą▒čāą┤ąĄčé ą┤ąŠčüčéąĖą│ąĮčāčé ą║ąŠąĮąĄčå čüčéčĆą░ąĮąĖčåčŗ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą┐čĆąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĖ ą║ąŠą╝ą░ąĮą┤čŗ Main Memory Page Read, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖčé čćč鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ č鹊ą╣ ąČąĄ čüą░ą╝ąŠą╣ čüčéčĆą░ąĮąĖčåčŗ ąŠčé ąĄčæ ąĮą░čćą░ą╗ą░. ą¤ąĄčĆąĄčģąŠą┤ čāčĆąŠą▓ąĮčÅ ą╗ąŠą│. 0 -> ą╗ąŠą│. 1 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ą▓čŗą▒ąŠčĆą║ąĖ ~CS ą┐čĆąĄčĆą▓ąĄčé ąŠą┐ąĄčĆą░čåąĖčÄ čćč鹥ąĮąĖčÅ ąĖ ą┐ąĄčĆąĄą▓ąĄą┤ąĄčé ą▓čŗą▓ąŠą┤ SO ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčüąŠą║ąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ (tri-state, čéčĆąĄčéčīąĄ, ąĖą╗ąĖ ąŠčéą║ą╗čÄč湥ąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ).

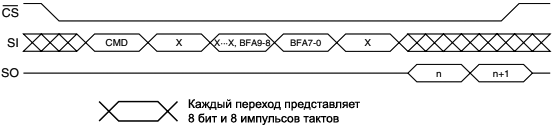

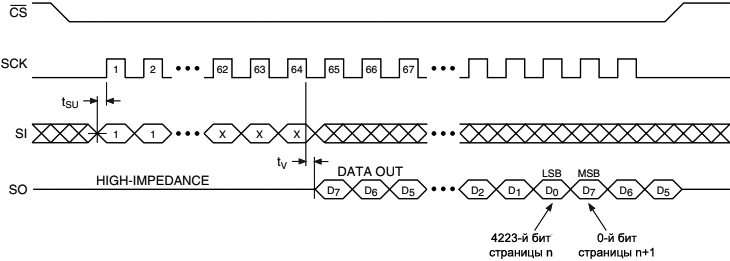

BUFFER READ: ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖąĘ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą┤ą▓čāčģ ą▒čāč乥čĆąŠą▓, ą┤ą╗čÅ č湥ą│ąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čĆą░ąĘąĮčŗąĄ opcode, čāą║ą░ąĘčŗą▓ą░čÄčēąĖąĄ ąĖąĘ ą║ą░ą║ąŠą│ąŠ ą▒čāč乥čĆą░ čćąĖčéą░čéčī. Opcode 54H ąĖą╗ąĖ D4H ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖąĘ ą▒čāč乥čĆą░ 1, ąĖ opcode 56H ąĖą╗ąĖ D6H ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖąĘ ą▒čāč乥čĆą░ 2. ą¦č鹊ą▒čŗ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąŠą┐ąĄčĆą░čåąĖčÄ Buffer Read, ąĘą░ 8 ą▒ąĖčéą░ą╝ąĖ opcode ą┤ąŠą╗ąČąĮčŗ ąĖą┤čéąĖ 14 ą▒ąĖčé donŌĆÖt care, 10 ą▒ąĖčé ą░ą┤čĆąĄčüą░ ąĖ 8 ą▒ąĖčé donŌĆÖt care. ą¤ąŠčüą║ąŠą╗čīą║čā čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ 528 ą▒ą░ą╣čé, č鹊 ąĮčāąČąĮčŗ 10 ą▒ąĖčé ą░ą┤čĆąĄčüą░ (BFA9 - BFA0) ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĖčÅ ą┐ąĄčĆą▓ąŠą│ąŠ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒čāč乥čĆąĄ. ąŻčĆąŠą▓ąĄąĮčī ~CS ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ ą╗ąŠą│. 0 ą▓ąŠ ą▓čĆąĄą╝čÅ ąĘą░ą│čĆčāąĘą║ąĖ opcode, ą▒ąĖčé ą░ą┤čĆąĄčüą░, ą▒ąĖčé donŌĆÖt care ąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ čćč鹥ąĮąĖčÅ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ ą┤ąŠčüčéąĖą│ąĮčāčé ą║ąŠąĮąĄčå ą▒čāč乥čĆą░, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖčé ą▓čŗą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąŠčé ąĄą│ąŠ ąĮą░čćą░ą╗ą░. ą┐čĆąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĖ ą║ąŠą╝ą░ąĮą┤čŗ Main Memory Page Read, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖčé čćč鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ č鹊ą╣ ąČąĄ čüą░ą╝ąŠą╣ čüčéčĆą░ąĮąĖčåčŗ ąŠčé ąĄčæ ąĮą░čćą░ą╗ą░. ą¤ąĄčĆąĄčģąŠą┤ čāčĆąŠą▓ąĮčÅ ą╗ąŠą│. 0 -> ą╗ąŠą│. 1 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ą▓čŗą▒ąŠčĆą║ąĖ ~CS ą┐čĆąĄčĆą▓ąĄčé ąŠą┐ąĄčĆą░čåąĖčÄ čćč鹥ąĮąĖčÅ ąĖ ą┐ąĄčĆąĄą▓ąĄą┤ąĄčé ą▓čŗą▓ąŠą┤ SO ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčüąŠą║ąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ (tri-state, čéčĆąĄčéčīąĄ, ąĖą╗ąĖ ąŠčéą║ą╗čÄč湥ąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ).

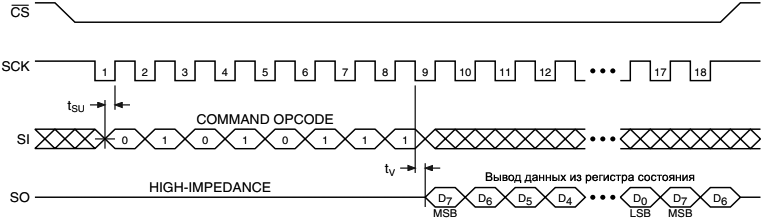

STATUS REGISTER READ: čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ (status register) ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ, ąĘą░ąĮčÅč鹊 ą╗ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ (Ready/Busy status), čĆąĄąĘčāą╗čīčéą░čé ąŠą┐ąĄčĆą░čåąĖąĖ čüčĆą░ą▓ąĮąĄąĮąĖčÅ čüčéčĆą░ąĮąĖčåčŗ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ąĖ ą▒čāč乥čĆą░ (Main Memory Page to Buffer Compare), ąĖą╗ąĖ čćč鹊ą▒čŗ čāąĘąĮą░čéčī ą┐ą╗ąŠčéąĮąŠčüčéčī čāčüčéčĆąŠą╣čüčéą▓ą░. ąöą╗čÅ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠčüą╗ą░ąĮ ą║ąŠą┤ ąŠą┐ąĄčĆą░čåąĖąĖ 57H ąĖą╗ąĖ D7H. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ ą▓ą┤ą▓ąĖąĮčāčé ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé opcode, ąĮą░ čüą╗ąĄą┤čāčÄčēąĖčģ 8 čåąĖą║ą╗ą░čģ čéą░ą║č鹊ą▓ SCK č湥čĆąĄąĘ ą▓čŗčģąŠą┤ SO ą▒čāą┤čāčé ą▓čŗą┤ą▓ąĖąĮčāčéčŗ 8 ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ, ąĮą░čćąĖąĮą░čÅ čüąŠ čüčéą░čĆčłąĄą│ąŠ ą▒ąĖčéą░ (MSB, ą▒ąĖčé 7). 5 čüą░ą╝čŗčģ čüčéą░čĆčłąĖčģ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ čüąŠą┤ąĄčƹȹ░čé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠą▒ čāčüčéčĆąŠą╣čüčéą▓ąĄ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ąŠčüčéą░ą╗čīąĮčŗąĄ 2 ą╝ą╗ą░ą┤čłąĖčģ ą▒ąĖčéą░ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ą▒čāą┤čāčēąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ, ąĖ ąĖčģ ąĘąĮą░č湥ąĮąĖčÅ ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé 0 čĆąĄą│ąĖčüčéčĆą░ čüčéą░čéčāčüą░ ą▒čŗą╗ ą▓čŗą┤ą▓ąĖąĮčāčé, ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ ąĮą░čćąĮąĄčé čåąĖą║ą╗ąĖč湥čüą║ąĖ ą┐ąŠą▓č鹊čĆčÅčéčīčüčÅ, ąĮą░čćąĖąĮą░čÅ čü ą▒ąĖčéą░ 7 (ą┐ąŠą║ą░ ~CS ąŠčüčéą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0 ąĖ ą┐ąŠą║ą░ ą┐ąŠčüčéčāą┐ą░čÄčé ąĖą╝ą┐čāą╗čīčüčŗ čéą░ą║č鹊ą▓ SCK). ąöą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąŠčüč鹊čÅąĮąĮąŠ ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ, ą┐ąŠčŹč鹊ą╝čā ą║ą░ąČą┤ą░čÅ ą┐ąŠą▓č鹊čĆčÅčÄčēą░čÅčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┤ą░čćąĖ ą▒ąĖčé ą╝ąŠąČąĄčé čüąŠą┤ąĄčƹȹ░čéčī ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ.

ążąŠčĆą╝ą░čé čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ:

| ąæąĖčé 7 |

ąæąĖčé 6 |

ąæąĖčé 5 |

ąæąĖčé 4 |

ąæąĖčé 3 |

ąæąĖčé 2 |

ąæąĖčé 1 |

ąæąĖčé 0 |

| RDY/~BUSY |

COMP |

1 |

0 |

1 |

1 |

x |

x |

ą¤čĆąĖą╝. ą┐ąĄčĆąĄą▓ąŠą┤čćąĖą║ą░: čüą║ąŠčĆąĄąĄ ą▓čüąĄą│ąŠ ąĘą┤ąĄčüčī ą▓ č乊čĆą╝ą░č鹥 čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ ą┤ąŠą┐čāčēąĄąĮą░ ąŠčłąĖą▒ą║ą░. ąÉą┐ąĮąŠčāčé "Using AtmelŌĆÖs Serial DataFlash" (AN-4, Atmel_2001_doc0842.pdf) ą┤ą░ąĄčé ą┤čĆčāą│čāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ, čüą╝. čéą░ą▒ą╗ąĖčåčŗ 4 ąĖ 5 čŹč鹊ą│ąŠ ą░ą┐ąĮąŠčāčéą░:

ąóą░ą▒ą╗ąĖčåą░ 4. ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ.

| ąæąĖčé 7 |

ąæąĖčé 6 |

ąæąĖčé 5 |

ąæąĖčé 4 |

ąæąĖčé 3 |

ąæąĖčé 2 |

ąæąĖčé 1 |

ąæąĖčé 0 |

| RDY/~BUSY |

COMP |

ąÜąŠą┤ ą┐ą╗ąŠčéąĮąŠčüčéąĖ (ąĄą╝ą║ąŠčüčéąĖ) čāčüčéčĆąŠą╣čüčéą▓ą░ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ą▒čāą┤čāčēąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ |

ąóą░ą▒ą╗ąĖčåą░ 5. ąÜąŠą┤čŗ ą┐ą╗ąŠčéąĮąŠčüčéąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ DataFlash.

| ąæąĖčé 5 |

ąæąĖčé 4 |

ąæąĖčé 3 |

ą¤ą╗ąŠčéąĮąŠčüčéčī čāčüčéčĆąŠą╣čüčéą▓ą░ |

| 0 |

0 |

0 |

512 ą║ąĖą╗ąŠą▒ąĖčé (64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░) |

| 0 |

0 |

1 |

1 ą╝ąĄą│ą░ą▒ąĖčé (128 ą║ąĖą╗ąŠą▒ą░ą╣čé) |

| 0 |

1 |

0 |

2 ą╝ąĄą│ą░ą▒ąĖčéą░ (256 ą║ąĖą╗ąŠą▒ą░ą╣čé) |

| 0 |

1 |

1 |

4 ą╝ąĄą│ą░ą▒ąĖčéą░ (512 ą║ąĖą╗ąŠą▒ą░ą╣čé) |

| 1 |

0 |

0 |

8 ą╝ąĄą│ą░ą▒ąĖčé (1 ą╝ąĄą│ą░ą▒ą░ą╣čé) |

| 1 |

0 |

1 |

16 ą╝ąĄą│ą░ą▒ąĖčé (2 ą╝ąĄą│ą░ą▒ą░ą╣čéą░) |

| 1 |

1 |

0 |

32 ą╝ąĄą│ą░ą▒ąĖčéą░ (4 ą╝ąĄą│ą░ą▒ą░ą╣čéą░) |

| 1 |

1 |

1 |

64 ą╝ąĄą│ą░ą▒ąĖčéą░ (8 ą╝ąĄą│ą░ą▒ą░ą╣čé) |

RDY/~BUSY. ąĪąŠčüč鹊čÅąĮąĖąĄ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ/ąĘą░ąĮčÅč鹊čüčéąĖ (Ready/Busy, RDY/~BUSY) ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą▒ąĖč鹊ą╝ 7 čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ. ąĢčüą╗ąĖ ą▒ąĖčé 7 čĆą░ą▓ąĄąĮ 1, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ąĘą░ąĮčÅč鹊 ą║ą░ą║ąŠą╣-ą╗ąĖą▒ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ąŠą┐ąĄčĆą░čåąĖąĄą╣, ąĖ ą│ąŠč鹊ą▓ąŠ ą║ ą┐čĆąĖąĄą╝čā ąĮąŠą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ. ąĢčüą╗ąĖ ą▒ąĖčé 7 čĆą░ą▓ąĄąĮ 0, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ č湥ą╝-č鹊 ąĘą░ąĮčÅč鹊. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ą┐ąŠčüč鹊čÅąĮąĮąŠ ąŠą┐čĆą░čłąĖą▓ą░čéčī ą▒ąĖčé 7 čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ, ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÅ ą▓čŗą┤ą░čćčā čéą░ą║č鹊ą▓ SCK ąĮą░ ąĮąĖąĘą║ąŠą╝ čāčĆąŠą▓ąĮąĄ, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą▓čŗą▓ąĄą┤ąĄąĮ ą▒ąĖčé 7. ąæąĖčé čüąŠčüč鹊čÅąĮąĖčÅ 7 ą▒čāą┤ąĄčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčī ą▓čŗą▓ąŠą┤ąĖčéčīčüčÅ ąĮą░ SO, ąĖ ą║ą░ą║ č鹊ą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ, čüąŠčüč鹊čÅąĮąĖąĄ SO ą┐ąŠą╝ąĄąĮčÅąĄčéčüčÅ čü 0 ąĮą░ 1. ąÆčüąĄą│ąŠ 8 ąŠą┐ąĄčĆą░čåąĖą╣ ą╝ąŠą│čāčé ą┐ąĄčĆąĄą▓ąĄčüčéąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ ąĘą░ąĮčÅč鹊ąĄ čüąŠčüč鹊čÅąĮąĖąĄ: Main Memory Page to Buffer Transfer, Main Memory Page to Buffer Compare, Buffer to Main Memory Page Program with Built-in Erase, Buffer to Main Memory Page Program without Built-in Erase, Page Erase, Block Erase, Main Memory Page Program ąĖ Auto Page Rewrite.

COMP. ąĀąĄąĘčāą╗čīčéą░čé čüą░ą╝ąŠą╣ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąŠą┐ąĄčĆą░čåąĖąĖ Main Memory Page to Buffer Compare ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ čüąŠčüč鹊čÅąĮąĖąĄą╝ ą▒ąĖčéą░ 6 čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ. ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čĆą░ą▓ąĄąĮ 0, č鹊 ą┤ą░ąĮąĮčŗąĄ ą▓ čüčéčĆą░ąĮąĖčåąĄ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ čüąŠą▓ą┐ą░ą┤ą░čÄčé čü ą┤ą░ąĮąĮčŗą╝ąĖ ą▒čāč乥čĆą░. ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé 6 čĆą░ą▓ąĄąĮ 1, č鹊 ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ąĮą░ čüčéčĆą░ąĮąĖčåąĄ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ąĮąĄ čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü ą┤ą░ąĮąĮčŗą╝ąĖ ą▓ ą▒čāč乥čĆąĄ.

ą¤ą╗ąŠčéąĮąŠčüčéčī čāčüčéčĆąŠą╣čüčéą▓ą░ ąĘą░ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮą░ ą▒ąĖčéą░ą╝ąĖ 5, 4, 3 ąĖ 2 čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ. ąöą╗čÅ AT45DB161B čŹčéąĖ ą▒ąĖčéčŗ ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖąĄ 1, 0, 1 ąĖ 1 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąöąĄčüčÅčéąĖčćąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čŹčéąĖčģ č湥čéčŗčĆąĄčģ ą▒ąĖčé ąĮąĄ čĆą░ą▓ąĮąŠ ą┐ą╗ąŠčéąĮąŠčüčéąĖ čāčüčéčĆąŠą╣čüčéą▓ą░, ąŠąĮąĖ ą┐čĆąŠčüč鹊 ą║ąŠą┤ąĖčĆčāčÄčé čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą▓ą░čĆąĖą░ąĮčéčŗ ą┐ą╗ąŠčéąĮąŠčüčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ Serial DataFlash (č湥čéčŗčĆąĄ ą▒ąĖčéą░ ą╝ąŠą│čāčé ąĘą░ą║ąŠą┤ąĖčĆąŠą▓ą░čéčī 16 čĆą░ąĘąĮčŗčģ ą▓ą░čĆąĖą░ąĮč鹊ą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ ą┐ą╗ąŠčéąĮąŠčüčéąĖ).

[ąÜąŠą╝ą░ąĮą┤čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ ąŠčćąĖčüčéą║ąĖ]

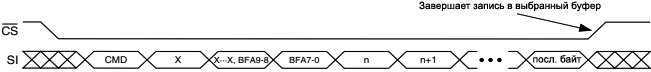

BUFFER WRITE: ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓ą┤ą▓ąĖąĮčāčéčŗ ą▓ ą▓čŗą▓ąŠą┤ SI, čćč鹊ą▒čŗ ąĘą░č鹥ą╝ ą┐ąŠą┐ą░čüčéčī ą╗ąĖą▒ąŠ ą▓ ą▒čāč乥čĆ 1, ą╗ąĖą▒ąŠ ą▓ ą▒čāč乥čĆ 2. ą¦č鹊ą▒čŗ ąĘą░ą│čĆčāąĘąĖčéčī ą┤ą░ąĮąĮčŗąĄ ą▓ ą╗čÄą▒ąŠą╣ ąĖąĘ čŹčéąĖčģ ą▒čāč乥čĆąŠą▓, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠčüą╗ą░ąĮ 8-ą▒ąĖčéąĮčŗą╣ opcode 84H ą┤ą╗čÅ ą▒čāč乥čĆą░ 1 ąĖą╗ąĖ 87H ą┤ą╗čÅ ą▒čāč乥čĆą░ 2, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą┤ąŠą╗ąČąĮčŗ ąĖą┤čéąĖ 14 ą▒ąĖčé donŌĆÖt care, ąĖ ąĘą░č鹥ą╝ 10 ą▒ąĖčé ą░ą┤čĆąĄčüą░ (BFA9 - BFA0). 10 ą▒ąĖčé ą░ą┤čĆąĄčüą░ ąĘą░ą┤ą░čÄčé, ą║ą░ą║ąŠą╣ ąĖąĘ ą▒ą░ą╣čé ą▒čāč乥čĆą░ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüčŗą▓ą░čéčīčüčÅ. ąŚą░ ą▒ąĖčéą░ą╝ąĖ ą░ą┤čĆąĄčüą░ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ ą┤ąŠčüčéąĖą│ąĮčāčé ą║ąŠąĮąĄčå ą▒čāč乥čĆą░, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čāą┤ąĄčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčī čåąĖą║ą╗ąĖč湥čüą║ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąŠčé ąĮą░čćą░ą╗ą░ ą▒čāč乥čĆą░. ąöą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčī ąĘą░ą│čĆčāąČą░čéčīčüčÅ ą▓ ą▒ą░ą╣čéčŗ ą▒čāč乥čĆą░, ą┐ąŠą║ą░ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄčģąŠą┤ 0 -> 1 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS.

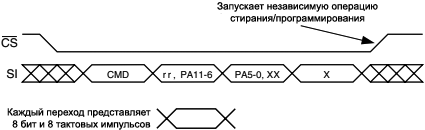

BUFFER TO MAIN MEMORY PAGE PROGRAM WITH BUILT-IN ERASE: ą┤ą░ąĮąĮčŗąĄ, ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆ 1 ąĖą╗ąĖ ą▒čāč乥čĆ 2, ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ą▓ ąŠčüąĮąŠą▓ąĮčāčÄ ą┐ą░ą╝čÅčéčī čāčüčéčĆąŠą╣čüčéą▓ą░. ą¦č鹊ą▒čŗ ąĘą░ą┐čāčüčéąĖčéčī čŹčéčā ąŠą┐ąĄčĆą░čåąĖčÄ, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠčüą╗ą░ąĮ 8-ą▒ąĖčéąĮčŗą╣ opcode 83H ą┤ą╗čÅ ą▒čāč乥čĆą░ 1 ąĖą╗ąĖ 86H ą┤ą╗čÅ ą▒čāč乥čĆą░ 2, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą┤ąŠą╗ąČąĮčŗ ąĖą┤čéąĖ 2 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą▒ąĖčéą░, 12 ą▒ąĖčé ą░ą┤čĆąĄčüą░ (PA11 - PA0), čāą║ą░ąĘčŗą▓ą░čÄčēąĖąĄ čüčéčĆą░ąĮąĖčåčā, ą║ąŠč鹊čĆą░čÅ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮą░, ąĖ 10 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą▒ąĖčé donŌĆÖt care. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄčģąŠą┤ 0 -> 1 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS, čāčüčéčĆąŠą╣čüčéą▓ąŠ čüąĮą░čćą░ą╗ą░ ąŠčćąĖčüčéąĖčé ą▓čŗą▒čĆą░ąĮąĮčāčÄ čüčéčĆą░ąĮąĖčåčā ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ąĖ ąĘą░č鹥ą╝ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé ąĄčæ ą┤ą░ąĮąĮčŗą╝ąĖ ąĖąĘ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą▒čāč乥čĆą░. ą×ą▒ąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ąŠčćąĖčüčéą║ąĖ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ą▓ąĮčāčéčĆąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ąĖ ą┤ąŠą╗ąČąĮčŗ ąĘą░ąĮąĖą╝ą░čéčī ą┐ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĮąĄ ą▒ąŠą╗ąĄąĄ tEP. ąÆ č鹥č湥ąĮąĖąĄ čŹč鹊ą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ ą▒ąĖč鹥 7 ą▒čāą┤ąĄčé ą┐ąŠą║ą░ąĘčŗą▓ą░čéčī ąĘą░ąĮčÅč鹊čüčéčī čāčüčéčĆąŠą╣čüčéą▓ą░.

BUFFER TO MAIN MEMORY PAGE PROGRAM WITHOUT BUILT-IN ERASE: čĆą░ąĮąĄąĄ ąŠčćąĖčēąĄąĮąĮą░čÅ čüčéčĆą░ąĮąĖčåą░ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ čüąŠą┤ąĄčƹȹĖą╝čŗą╝ ą╗ąĖą▒ąŠ ą▒čāč乥čĆą░ 1, ą╗ąĖą▒ąŠ ą▒čāč乥čĆą░ 2. ą¦č鹊ą▒čŗ ąĘą░ą┐čāčüčéąĖčéčī čŹčéčā ąŠą┐ąĄčĆą░čåąĖčÄ, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠčüą╗ą░ąĮ 8-ą▒ąĖčéąĮčŗą╣ opcode, 88H ą┤ą╗čÅ ą▒čāč乥čĆą░ 1 ąĖą╗ąĖ 89H ą┤ą╗čÅ ą▒čāč乥čĆą░ 2, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą┤ąŠą╗ąČąĮčŗ ąĖą┤čéąĖ 2 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą▒ąĖčéą░, 12 ą▒ąĖčé ą░ą┤čĆąĄčüą░ (PA11 - PA0), ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┤ą░čÄčé čüčéčĆą░ąĮąĖčåčā ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆą░čÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮą░, ąĖ ąĘą░č鹥ą╝ 10 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą▒ąĖčé donŌĆÖt care. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄčģąŠą┤ 0 -> 1 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS, čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé ą▓čŗą▒čĆą░ąĮąĮčāčÄ čüčéčĆą░ąĮąĖčåčā ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ čüąŠą┤ąĄčƹȹĖą╝čŗą╝ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą▒čāč乥čĆą░. ąöą╗čÅ čŹč鹊ą│ąŠ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, čćč鹊ą▒čŗ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ čŹčéą░ čüčéčĆą░ąĮąĖčåą░ ą▒čŗą╗ą░ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ čüč鹥čĆčéą░. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ąĖ ąĘą░ą╣ą╝ąĄčé ą┐ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĮąĄ ą▒ąŠą╗ąĄąĄ tP. ąÆ č鹥č湥ąĮąĖąĄ čŹč鹊ą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ ą▒ąĖč鹥 7 ą▒čāą┤ąĄčé ą┐ąŠą║ą░ąĘčŗą▓ą░čéčī ąĘą░ąĮčÅč鹊čüčéčī čāčüčéčĆąŠą╣čüčéą▓ą░.

ąĪą╗ąĄą┤čāčÄčēąĖąĄ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ąŠą┐ąĄčĆą░čåąĖąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĄąĘ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąŠčćąĖčüčéą║ąĖ čüčéčĆą░ąĮąĖčåčŗ ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāčÄčéčüčÅ. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▒ąĖčé ą▓ ą▒ą░ą╣čéą░čģ ąĮą░ čüčéčĆą░ąĮąĖčåąĄ čü "1" ą▓ "0" ą▓ č鹥č湥ąĮąĖąĄ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ąŠą┐ąĄčĆą░čåąĖą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĄąĘ ąŠčćąĖčüčéą║ąĖ čŹč鹊ą╣ čüčéčĆą░ąĮąĖčåčŗ ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ. ąÆąĄčĆąŠčÅčéąĮąŠ, čŹč鹊 čćčĆąĄą▓ą░č鹊 čüąĮąĖąČąĄąĮąĖąĄą╝ čĆąĄčüčāčĆčüą░ čåąĖą║ą╗ąŠą▓ ąĘą░ą┐ąĖčüąĖ DataFlash (ą┐čĆąĖą╝. ą┐ąĄčĆąĄą▓ąŠą┤čćąĖą║ą░).

PAGE ERASE: ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ąŠą╝ą░ąĮą┤ą░ ąŠčćąĖčüčéą║ąĖ čüčéčĆą░ąĮąĖčåčŗ (Page Erase) ą┤ą╗čÅ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠą╣ ąŠčćąĖčüčéą║ąĖ ą╗čÄą▒ąŠą╣ ąĖąĘ čüčéčĆą░ąĮąĖčå ąŠčüąĮąŠą▓ąĮąŠą│ąŠ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠąĘą┤ąĮąĄąĄ ąĘą░ą┐čāčüčéąĖčéčī ą║ąŠą╝ą░ąĮą┤čā Buffer to Main Memory Page Program without Built-in Erase (čŹč鹊 čāčüą║ąŠčĆčÅąĄčé ą┐čĆąŠčåąĄčüčü ąĘą░ą┐ąĖčüąĖ čüčéčĆą░ąĮąĖčåčŗ). ą¦č鹊ą▒čŗ ą▓čŗą┐ąŠą╗ąĮąĖčéčī Page Erase ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮ opcode 81H, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤čāčé 2 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą▒ąĖčéą░, 12 ą▒ąĖčé ą░ą┤čĆąĄčüą░ (PA11 - PA0) ąĖ 10 ą▒ąĖčé donŌĆÖt care. 12 ą▒ąĖčé ą░ą┤čĆąĄčüą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĖčÅ, ą║ą░ą║ą░čÅ čüčéčĆą░ąĮąĖčåą░ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąŠčćąĖčēąĄąĮą░. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄčģąŠą┤ 0 -> 1 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS, čāčüčéčĆąŠą╣čüčéą▓ąŠ čüąŠčéčĆąĄčé ą▓čŗą▒čĆą░ąĮąĮčāčÄ čüčéčĆą░ąĮąĖčåčā čéą░ą║, čćč鹊 ą▓ąŠ ą▓čüąĄčģ ąĄčæ ą▒ąĖčéą░čģ ą▒čāą┤čāčé ąĄą┤ąĖąĮąĖčåčŗ (ą▓čüąĄ ą▒ą░ą╣čéčŗ čĆą░ą▓ąĮčŗ FFh). ą×ą┐ąĄčĆą░čåąĖčÅ ąŠčćąĖčüčéą║ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą▒ąĄąĘ ą▓ąĮąĄčłąĮąĄą│ąŠ čāčćą░čüčéąĖčÅ, ąĖ ą┐ąŠ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą╝ąŠąČąĄčé ąĘą░ąĮąĖą╝ą░čéčī ą▓čĆąĄą╝čÅ ąĮąĄ ą▒ąŠą╗ąĄąĄ tPE. ąÆ č鹥č湥ąĮąĖąĄ čŹč鹊ą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą▒čāą┤ąĄčé ą┐ąŠą║ą░ąĘčŗą▓ą░čéčī, čćč鹊 ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ąĘą░ąĮčÅčéą░.

BLOCK ERASE: ą▒ą╗ąŠą║ ąĖąĘ 8 čüčéčĆą░ąĮąĖčå ą╝ąŠąČąĄčé ą▒čŗčéčī čüč鹥čĆčé ąŠą┤ąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĄą╣ Block Erase, čćč鹊ą▒čŗ čü ą┐ąŠą╝ąŠčēčīčÄ ą║ąŠą╝ą░ąĮą┤čŗ Buffer to Main Memory Page Program without Built-in Erase ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ čāą╝ąĄąĮčīčłąĖčéčī ą▓čĆąĄą╝čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ. ą¦č鹊ą▒čŗ ą▓čŗą┐ąŠą╗ąĮąĖčéčī Block Erase, ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮčāąČąĮąŠ ą┐ąĄčĆąĄą┤ą░čéčī opcode 50H, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą┤ąŠą╗ąČąĮčŗ ąĖą┤čéąĖ 2 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą▒ąĖčéą░, 9 ą▒ąĖčé ą░ą┤čĆąĄčüą░ (PA11 - PA3) ąĖ 13 ą▒ąĖčé donŌĆÖt care. 9 ą▒ąĖčé ą░ą┤čĆąĄčüą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĖčÅ, ą║ą░ą║ąŠą╣ ą▒ą╗ąŠą║ ąĖąĘ 8 čüčéčĆą░ąĮąĖčå ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüč鹥čĆčé. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄčģąŠą┤ 0 -> 1 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS, čāčüčéčĆąŠą╣čüčéą▓ąŠ čüąŠčéčĆąĄčé ą▓čŗą▒čĆą░ąĮąĮčŗą╣ ą▒ą╗ąŠą║, ąĘą░ą┐ąŠą╗ąĮąĖą▓ ąĄą│ąŠ ąĄą┤ąĖąĮąĖčåą░ą╝ąĖ. ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ąŠą┐ąĄčĆą░čåąĖąĖ ąŠčćąĖčüčéą║ąĖ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą▓ąĮčāčéčĆąĖ čāčüčéčĆąŠą╣čüčéą▓ą░, ąĖ ą▓čüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ąĮąĖą╝ą░ąĄčé ą┐ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĮąĄ ą▒ąŠą╗čīčłąĄ tBE. ąÆ č鹥č湥ąĮąĖąĄ čŹč鹊ą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą▒čāą┤ąĄčé ą┐ąŠą║ą░ąĘčŗą▓ą░čéčī, čćč鹊 ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ąĘą░ąĮčÅčéą░.

ąÉą┤čĆąĄčüą░čåąĖčÅ ą║ąŠą╝ą░ąĮą┤čŗ Block Erase:

| PA11 |

PA10 |

PA9 |

PA8 |

PA7 |

PA6 |

PA5 |

PA4 |

PA3 |

PA2 |

PA1 |

PA0 |

ąæą╗ąŠą║ |

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

X |

X |

X |

0 |

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

X |

X |

X |

1 |

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

X |

X |

X |

2 |

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

X |

X |

X |

3 |

| ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

| ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

| ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

| 1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

X |

X |

X |

508 |

| 1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

X |

X |

X |

509 |

| 1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

X |

X |

X |

510 |

| 1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

X |

X |

X |

511 |

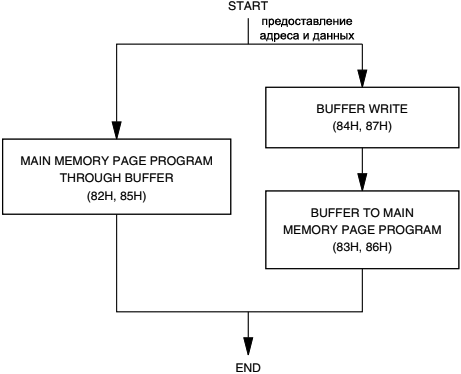

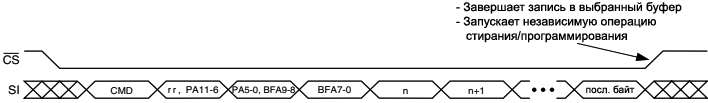

MAIN MEMORY PAGE PROGRAM THROUGH BUFFER: čŹčéą░ ąŠą┐ąĄčĆą░čåąĖčÅ čÅą▓ą╗čÅąĄčéčüčÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĄą╣ ąŠą┐ąĄčĆą░čåąĖą╣ Buffer Write ąĖ Buffer to Main Memory Page Program with Built-in Erase. ąöą░ąĮąĮčŗąĄ čüąĮą░čćą░ą╗ą░ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ ą▒čāč乥čĆ 1 ąĖą╗ąĖ ą▒čāč乥čĆ 2 č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ SI, ąĖ ąĘą░č鹥ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ ą▓ čāą║ą░ąĘą░ąĮąĮčāčÄ čüčéčĆą░ąĮąĖčåčā ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ. ąöą╗čÅ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ 8-ą▒ąĖčéąĮčŗą╣ ą║ąŠą┤ ąŠą┐ąĄčĆą░čåąĖąĖ 82H ą┤ą╗čÅ ą▒čāč乥čĆą░ 1 ąĖą╗ąĖ 85H ą┤ą╗čÅ ą▒čāč乥čĆą░ 2, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤čāčé 2 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą▒ąĖčéą░ ąĖ 22 ą▒ąĖčéą░ ą░ą┤čĆąĄčüą░. ąśąĘ ą▒ąĖčé ą░ą┤čĆąĄčüą░ 12 čüčéą░čĆčłąĖčģ ą▒ąĖčé (PA11 - PA0) ą▓čŗą▒ąĖčĆą░čÄčé čüčéčĆą░ąĮąĖčåčā ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ą║čāą┤ą░ ą▒čāą┤čāčé ąĘą░ą┐ąĖčüčŗą▓ą░čéčīčüčÅ ą┤ą░ąĮąĮčŗąĄ, ąĖ ąŠčüčéą░ą╗čīąĮčŗąĄ 10 ą╝ą╗ą░ą┤čłąĖčģ ą▒ąĖčé (BFA9 - BFA0) ą▓čŗą▒ąĖčĆą░čÄčé ą┐ąĄčĆą▓čŗą╣ ą▒ą░ą╣čé ą▓ ą▒čāč乥čĆąĄ, ą║čāą┤ą░ ą▒čāą┤čāčé ąĘą░ą┐ąĖčüą░ąĮčŗ ą┤ą░ąĮąĮčŗąĄ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▓čüąĄ ą▒ąĖčéčŗ ą░ą┤čĆąĄčüą░ ą▒čāą┤čāčé ą▓ą┤ą▓ąĖąĮčāčéčŗ, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čāą┤ąĄčé ą▓ą┤ą▓ąĖą│ą░čéčī ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ SI, ąĖ čüąŠčģčĆą░ąĮčÅčéčī ąĖčģ ą▓ ąŠą┤ąĖąĮ ąĖąĘ ą▓čŗą▒čĆą░ąĮąĮčŗčģ ą▒čāč乥čĆąŠą▓ ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ ą┤ąŠčüčéąĖą│ąĮčāčé ą║ąŠąĮąĄčå ą▒čāč乥čĆą░, č鹊 ąĘą░ą┐ąĖčüčī ą▒čāą┤ąĄčé ą┐ąĄčĆąĄčüą║ą░ą║ąĖą▓ą░čéčī ą▓ ąĮą░čćą░ą╗ąŠ ą▒čāč乥čĆą░. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄčģąŠą┤ 0 -> 1 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS, čāčüčéčĆąŠą╣čüčéą▓ąŠ čüąĮą░čćą░ą╗ą░ čüąŠčéčĆąĄčé ą▓čŗą▒čĆą░ąĮąĮčāčÄ čüčéčĆą░ąĮąĖčåčā (ą┐čĆąĖ ąŠčćąĖčüčéą║ąĄ ą▓čüąĄ ą▒ą░ą╣čéčŗ čüčéčĆą░ąĮąĖčåčŗ ąĘą░ą┐ąŠą╗ąĮčÅčÄčéčüčÅ ąĄą┤ąĖąĮąĖčćą║ą░ą╝ąĖ), ą░ ą┐ąŠč鹊ą╝ ąĘą░ą┐ąĖčłąĄčé ą▓ ąĮąĄčæ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą▒čāč乥čĆą░, ą║čāą┤ą░ č鹊ą╗čīą║ąŠ čćč鹊 ą▒čŗą╗ąĖ ą┐ąŠą╝ąĄčēąĄąĮčŗ ą┤ą░ąĮąĮčŗąĄ. ą×ą▒ąĄ ąŠą┐ąĄčĆą░čåąĖąĖ čüčéąĖčĆą░ąĮąĖčÅ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüčéčĆą░ąĮąĖčåčŗ ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčéčüčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ, ąĖ čŹčéąĖ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą╣ą╝čāčé ą▓čĆąĄą╝čÅ ąĮąĄ ą▒ąŠą╗ąĄąĄ tEP. ąÆ č鹥č湥ąĮąĖąĄ čŹč鹊ą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą▒čāą┤ąĄčé ą┐ąŠą║ą░ąĘčŗą▓ą░čéčī, čćč鹊 ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ąĘą░ąĮčÅčéą░.

[ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ]

MAIN MEMORY PAGE TO BUFFER TRANSFER: ą┤ą░ąĮąĮčŗąĄ čüčéčĆą░ąĮąĖčåčŗ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą╝ąĄčēąĄąĮčŗ ą▓ ąŠą┤ąĖąĮ ąĖąĘ ą▒čāč乥čĆąŠą▓ 1 ąĖą╗ąĖ 2. ąöą╗čÅ ąĘą░ą┐čāčüą║ą░ čŹč鹊ą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ 8-ą▒ąĖčéąĮčŗą╣ opcode 53H ą┤ą╗čÅ ą▒čāč乥čĆą░ 1 ąĖ 55H ą┤ą╗čÅ ą▒čāč乥čĆą░ 2, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą┤ąŠą╗ąČąĮčŗ ąĖą┤čéąĖ ą┤ą▓ą░ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą▒ąĖčéą░, 12 ą▒ąĖčé ą░ą┤čĆąĄčüą░ (PA11 - PA0), ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┤ą░čÄčé čüčéčĆą░ąĮąĖčåčā ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ąŠčéą║čāą┤ą░ ą▒čāą┤čāčé ą║ąŠą┐ąĖčĆąŠą▓ą░čéčīčüčÅ ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆ, ąĖ ą┤ą░ą╗ąĄąĄ ąĖą┤čāčé 10 ą▒ąĖčé donŌĆÖt care. ąŻčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą▓čŗą▓ąŠą┤ čéą░ą║č鹊ą▓ SCK ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ opcode, ą▒ąĖčé ą░ą┤čĆąĄčüą░ ąĖ ą▒ąĖčé donŌĆÖt care ąĖąĘ ą▓čŗą▓ąŠą┤ą░ SI. ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ čüčéčĆą░ąĮąĖčåčŗ ąĖąĘ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą▓ ą▒čāč乥čĆ ąĮą░čćąĮąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS ą┐ąĄčĆąĄą╣ą┤ąĄčé ąĖąĘ 0 ąĮą░ čāčĆąŠą▓ąĄąĮčī 1. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ (tXFR) ą╝ąŠąČąĮąŠ čćąĖčéą░čéčī čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ąĘą░ą▓ąĄčĆčłąĄąĮąŠ ą╗ąĖ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄ ąĖą╗ąĖ ąĄčēąĄ ąĮąĄčé.

MAIN MEMORY PAGE TO BUFFER COMPARE: ą┤ą░ąĮąĮčŗąĄ čüčéčĆą░ąĮąĖčåčŗ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī čüčĆą░ą▓ąĮąĄąĮčŗ čü ą┤ą░ąĮąĮčŗą╝ąĖ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą▒čāč乥čĆąŠą▓, 1 ąĖą╗ąĖ 2. ąöą╗čÅ ąĖąĮąĖčåąĖą░čåąĖąĖ čŹč鹊ą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ąĮčāąČąĮąŠ ą┐ąĄčĆąĄą┤ą░čéčī 8-ą▒ąĖčéąĮčŗą╣ opcode 60H ą┤ą╗čÅ ą▒čāč乥čĆą░ 1 ąĖ 61H ą┤ą╗čÅ ą▒čāč乥čĆą░ 2, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą┤ąŠą╗ąČąĮčŗ ąĖą┤čéąĖ 24 ą▒ąĖčéą░ ą░ą┤čĆąĄčüą░, čüčéą░čĆčłąĖąĄ ąĖąĘ ąĮąĖčģ ą┤ą▓ą░ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą▒ąĖčéą░, ą┤ą░ą╗ąĄąĄ 12 ą▒ąĖčé ą░ą┤čĆąĄčüą░ (PA11 - PA0), ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┤ą░čÄčé čüčéčĆą░ąĮąĖčåčā ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ. ąöą░ąĮąĮčŗąĄ čŹč鹊ą╣ čüčéčĆą░ąĮąĖčåčŗ ą▒čāą┤čāčé čüčĆą░ą▓ąĮąĖą▓ą░čéčīčüčÅ čü ą▒čāč乥čĆąŠą╝. ąŚą░ ą▒ąĖčéą░ą╝ąĖ ą░ą┤čĆąĄčüą░ ą┤ąŠą╗ąČąĮčŗ ąĖą┤čéąĖ 10 ą▒ąĖčé donŌĆÖt care. ąŻčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ čéą░ą║čéčŗ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SCK ą▓ą┤ą▓ąĖą│ą░čÄčé opcode, ą▒ąĖčéčŗ ą░ą┤čĆąĄčüą░, ą▒ąĖčéčŗ donŌĆÖt care ąĖąĘ ą▓čŗą▓ąŠą┤ą░ SI. ą¤ąĄčĆąĄčģąŠą┤ 0 - 1 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS ąĘą░ą┐čāčüą║ą░čÄčé ąŠą┐ąĄčĆą░čåąĖčÄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ 528 ą▒ą░ą╣čé ą▓čŗą▒čĆą░ąĮąĮąŠą╣ čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ čü 528 ą▒ą░ą╣čéą░ą╝ąĖ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą▒čāč乥čĆą░. ąÆąŠ ą▓čĆąĄą╝čÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (tXFR), čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąŠą║ą░ąČąĄčé, čćč鹊 ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ąĘą░ąĮčÅčéą░. ą¤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ ąŠą┐ąĄčĆą░čåąĖąĖ ą▒ąĖčé 6 čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ ąŠą▒ąĮąŠą▓ąĖčéčüčÅ, ą┐ąŠą║ą░ąĘčŗą▓ą░čÅ čĆąĄąĘčāą╗čīčéą░čé čüčĆą░ą▓ąĮąĄąĮąĖčÅ.

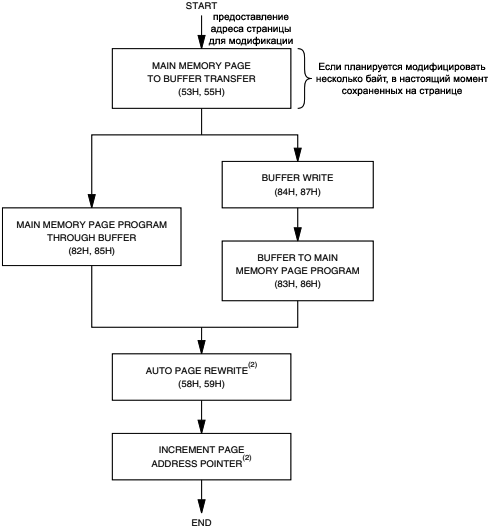

AUTO PAGE REWRITE: čŹč鹊čé čĆąĄąČąĖą╝ čéčĆąĄą▒čāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ą░ą╣čé ąĮą░ čüčéčĆą░ąĮąĖčåąĄ, ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ čüčéčĆą░ąĮąĖčå ą┤ą░ąĮąĮčŗčģ ą▒čŗą╗ąĖ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮčŗ čüą╗čāčćą░ą╣ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝. ąŁč鹊čé čĆąĄąČąĖą╝ ą┤ą░ąĄčé ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÄ ą┤ą▓čāčģ ąŠą┐ąĄčĆą░čåąĖą╣: Main Memory Page to Buffer Transfer ąĖ Buffer to Main Memory Page Program with Built-in Erase. ąĪčéčĆą░ąĮąĖčåą░ ą┤ą░ąĮąĮčŗčģ čüąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĖąĘ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą▓ ą▒čāč乥čĆ 1 ąĖą╗ąĖ ą▒čāč乥čĆ 2, ąĖ ąĘą░č鹥ą╝ č鹥 ąČąĄ čüą░ą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ (ąĖąĘ ą▒čāč乥čĆą░ 1 ąĖą╗ąĖ ą▒čāč乥čĆą░ 2) ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą▓ čüą▓ąŠčÄ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮčāčÄ čüčéčĆą░ąĮąĖčåčā ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ. ąöą╗čÅ ąĘą░ą┐čāčüą║ą░ ąŠą┐ąĄčĆą░čåąĖąĖ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠčüą╗ą░ąĮ 8-ą▒ąĖčéąĮčŗą╣ opcode 58H ą┤ą╗čÅ ą▒čāč乥čĆą░ 1 ąĖą╗ąĖ 59H ą┤ą╗čÅ ą▒čāč乥čĆą░ 2, ąĘą░č鹥ą╝ ą┤ąŠą╗ąČąĮčŗ ąĖą┤čéąĖ 2 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą▒ąĖčéą░, ą┤ą░ą╗ąĄąĄ 12 ą▒ąĖčé ą░ą┤čĆąĄčüą░ (PA11 - PA0), ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┤ą░čÄčé ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čāčÄ čüčéčĆą░ąĮąĖčåčā ą┐ą░ą╝čÅčéąĖ, ąĖ 10 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą▒ąĖčé donŌĆÖt care. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄčģąŠą┤ 0 -> 1 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS, čāčüčéčĆąŠą╣čüčéą▓ąŠ čüąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čüčé ą┤ą░ąĮąĮčŗąĄ ąĖąĘ čüčéčĆą░ąĮąĖčåčŗ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą▓ ą▒čāč乥čĆ, ąĖ ąĘą░č鹥ą╝ ąŠą▒čĆą░čéąĮąŠ ą┐ąĄčĆąĄąĘą░ą┐ąĖčłąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čŹč鹊ą│ąŠ ą▒čāč乥čĆą░ ąŠą▒čĆą░čéąĮąŠ ą▓ čéčā ąČąĄ čüą░ą╝čāčÄ čüčéčĆą░ąĮąĖčåčā ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ. ąŁčéą░ ąŠą┐ąĄčĆą░čåąĖčÅ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, ąĖ ąĘą░ąĮąĖą╝ą░ąĄčé ą▓čĆąĄą╝čÅ ąĮąĄ ą▒ąŠą╗ąĄąĄ tEP. ąÆ č鹥č湥ąĮąĖąĄ čŹč鹊ą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą▒čāą┤ąĄčé ą┐ąŠą║ą░ąĘčŗą▓ą░čéčī, čćč鹊 ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ąĘą░ąĮčÅčéą░.

ąĢčüą╗ąĖ čüąĄą║č鹊čĆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ąĖą╗ąĖ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, čüčéčĆą░ąĮąĖčåą░ ąĘą░ čüčéčĆą░ąĮąĖčåąĄą╣, č鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐čĆąĖą╝ąĄąĮčÅčéčī ą░ą╗ą│ąŠčĆąĖčéą╝, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗą╣ ąĮą░ čĆąĖčü. 1. ąśąĮą░č湥, ąĄčüą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ą░ą╣čé ąĮą░ čüčéčĆą░ąĮąĖčåąĄ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ čüčéčĆą░ąĮąĖčå čüą╗čāčćą░ą╣ąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą▓ čüąĄą║č鹊čĆąĄ, č鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐čĆąĖą╝ąĄąĮčÅčéčī ą░ą╗ą│ąŠčĆąĖčéą╝ ąĮą░ čĆąĖčü. 2. ąÜą░ąČą┤ą░čÅ čüčéčĆą░ąĮąĖčåą░ ą▓ čüąĄą║č鹊čĆąĄ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮą░ / ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮą░ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ čĆą░ąĘ ąĘą░ ą║ą░ąČą┤čāčÄ ąĖąĘ 10000 ą║čāą╝čāą╗čÅčéąĖą▓ąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖą╣ čüčéąĖčĆą░ąĮąĖčÅ/ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ čŹč鹊ą╝ čüąĄą║č鹊čĆąĄ.

ąĀąĖčü. 1. ąÉą╗ą│ąŠčĆąĖčéą╝ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čüąĄą│ąŠ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ąŁč鹊čé čéąĖą┐ ą░ą╗ą│ąŠčĆąĖčéą╝ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣, ą▓ ą║ąŠč鹊čĆčŗčģ ą▓ąĄčüčī ą╝ą░čüčüąĖą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, čü ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ čüčéčĆą░ąĮąĖčåą░ ąĘą░ čüčéčĆą░ąĮąĖčåąĄą╣.

2. ąĪčéčĆą░ąĮąĖčåą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮą░ ą╗ąĖą▒ąŠ ąŠą┐ąĄčĆą░čåąĖąĄą╣ Main Memory Page Program ąĖą╗ąĖ Buffer Write, ąĘą░ ą║ąŠč鹊čĆąŠą╣ ąĖą┤ąĄčé ąŠą┐ąĄčĆą░čåąĖčÅ Buffer to Main Memory Page Program.

3. ąÉą╗ą│ąŠčĆąĖčéą╝, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗą╣ ą▓čŗčłąĄ, ą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆčāąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠą┤ąĮąŠą╣ čüčéčĆą░ąĮąĖčåčŗ. ąŁč鹊čé ą░ą╗ą│ąŠčĆąĖčéą╝ ą▒čāą┤ąĄčé ą┐ąŠą▓č鹊čĆąĄąĮ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ čüčéčĆą░ąĮąĖčåčŗ ą▓ąŠ ą▓čüąĄą╝ ą╝ą░čüčüąĖą▓ąĄ ą┐ą░ą╝čÅčéąĖ.

ąĀąĖčü. 2. ąÉą╗ą│ąŠčĆąĖčéą╝ ą┤ą╗čÅ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠ-čüą╗čāčćą░ą╣ąĮąŠą╣ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ ą┤ą░ąĮąĮčŗčģ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ą¦č鹊ą▒čŗ čüą▒ąĄčĆąĄčćčī čåąĄą╗ąŠčüčéąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ, ą║ą░ąČą┤ą░čÅ čüčéčĆą░ąĮąĖčåą░ ą▓ čüąĄą║č鹊čĆąĄ DataFlash ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮą░ / ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮą░ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ čĆą░ąĘ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ąĖąĘ 10000 ą║čāą╝čāą╗čÅčéąĖą▓ąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖą╣ čüčéąĖčĆą░ąĮąĖčÅ / ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ.

2. ąöąŠą╗ąČąĄąĮ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ čāą║ą░ąĘą░č鹥ą╗čī ą░ą┤čĆąĄčüą░ čüčéčĆą░ąĮąĖčåčŗ (Page Address Pointer), čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī, ą║ą░ą║ą░čÅ čüčéčĆą░ąĮąĖčåą░ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ. ąÜąŠą╝ą░ąĮą┤ą░ Auto Page Rewrite ą┤ąŠą╗ąČąĮą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą░ą┤čĆąĄčü, ąĘą░ą┤ą░ąĮąĮčŗą╣ Page Address Pointer.

3. ąöčĆčāą│ąĖąĄ ą░ą╗ą│ąŠčĆąĖčéą╝čŗ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüąĖ ą┐ąŠčĆčåąĖą╣ ą╝ą░čüčüąĖą▓ą░ Flash. ą¤čĆąĖą╗ąŠąČąĄąĮąĖčÅ čü ąĮąĖąĘą║ąĖą╝ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝ ą╝ąŠą│čāčé ą▓čŗą▒čĆą░čéčī ą░ą╗ą│ąŠčĆąĖčéą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą┐ąŠą║ą░ ąĮą░ą║ąŠą┐čÅčéčüčÅ 10000 ą║čāą╝čāą╗čÅčéąĖą▓ąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖą╣ čüčéąĖčĆą░ąĮąĖčÅ / ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčīčÄ ą▓čüąĄčģ čüčéčĆą░ąĮąĖčå ą▓ čüąĄą║č鹊čĆąĄ. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ ą░ą┐ąĮąŠčāč鹥 AN-4 [2].

ąÉą┤čĆąĄčüą░čåąĖčÅ čüąĄą║č鹊čĆąŠą▓:

| PA11 |

PA10 |

PA9 |

PA8 |

PA7 |

PA6 |

PA5 |

PA4 |

PA3 |

ąæą╗ąŠą║ |

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

0 |

0 |

x |

x |

x |

x |

x |

1 |

| 0 |

0 |

0 |

1 |

x |

x |

x |

x |

x |

2 |

| 0 |

0 |

1 |

0 |

x |

x |

x |

x |

x |

3 |

| ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

| ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

| ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

ŌĆó |

| 1 |

1 |

0 |

0 |

x |

x |

x |

x |

x |

13 |

| 1 |

1 |

0 |

1 |

x |

x |

x |

x |

x |

14 |

| 1 |

1 |

1 |

0 |

x |

x |

x |

x |

x |

15 |

| 1 |

1 |

1 |

1 |

x |

x |

x |

x |

x |

16 |

[ą×ą▒ąĘąŠčĆ čĆą░ą▒ąŠčćąĖčģ čĆąĄąČąĖą╝ąŠą▓]

ąĀąĄąČąĖą╝čŗ ą╝ąŠąČąĮąŠ čĆą░ąĘą┤ąĄą╗ąĖčéčī ąĮą░ ą┤ą▓ąĄ ą│čĆčāą┐ą┐čŗ ŌĆō čĆąĄąČąĖą╝čŗ, ą║ąŠč鹊čĆčŗąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą╝ą░čüčüąĖą▓ ą┐ą░ą╝čÅčéąĖ Flash (ąōčĆčāą┐ą┐ą░ A) ąĖ čĆąĄąČąĖą╝čŗ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą╝ą░čüčüąĖą▓ ą┐ą░ą╝čÅčéąĖ Flash (ąōčĆčāą┐ą┐ą░ B).

ąōčĆčāą┐ą┐ą░ A čüąŠčüč鹊ąĖčé ąĖąĘ ąŠą┐ąĄčĆą░čåąĖą╣:

1. Main Memory Page Read (čćč鹥ąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ).

2. Main Memory Page to Buffer 1 (ąĖą╗ąĖ 2) Transfer (ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ ą▓ ąŠą┤ąĖąĮ ąĖąĘ ą▒čāč乥čĆąŠą▓).

3. Main Memory Page to Buffer 1 (or 2) Compare (čüčĆą░ą▓ąĮąĄąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ ąĖ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą▒čāč乥čĆąŠą▓).

4. Buffer 1 (ąĖą╗ąĖ 2) to Main Memory Page Program with Built-in Erase (ąĘą░ą┐ąĖčüčī ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą▒čāč乥čĆąŠą▓ ą▓ čüčéčĆą░ąĮąĖčåčā čü ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮčŗą╝ čüčéąĖčĆą░ąĮąĖąĄą╝ čŹč鹊ą╣ čüčéčĆą░ąĮąĖčåčŗ).

5. Buffer 1 (ąĖą╗ąĖ 2) to Main Memory Page Program without Built-in Erase (ąĘą░ą┐ąĖčüčī ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą▒čāč乥čĆąŠą▓ ą▓ čüčéčĆą░ąĮąĖčåčā ą▒ąĄąĘ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą│ąŠ čüčéąĖčĆą░ąĮąĖčÅ čŹč鹊ą╣ čüčéčĆą░ąĮąĖčåčŗ).

6. Page Erase (čüčéąĖčĆą░ąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ).

7. Block Erase (čüčéąĖčĆą░ąĮąĖąĄ ą▒ą╗ąŠą║ą░).

8. Main Memory Page Program through Buffer (ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ č湥čĆąĄąĘ ą▒čāč乥čĆ čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ).

9. Auto Page Rewrite (ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ą░čÅ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčī čüčéčĆą░ąĮąĖčåčŗ).

ąōčĆčāą┐ą┐ą░ B čüąŠčüč鹊ąĖčé ąĖąĘ ąŠą┐ąĄčĆą░čåąĖą╣:

1. Buffer 1 (ąĖą╗ąĖ 2) Read (čćč鹥ąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą▒čāč乥čĆąŠą▓).

2. Buffer 1 (ąĖą╗ąĖ 2) Write (ąĘą░ą┐ąĖčüčī ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą▒čāč乥čĆąŠą▓).

3. Status Register Read (čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ).

ąĢčüą╗ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ ąĖąĘ ą│čĆčāą┐ą┐čŗ A (ąŠą┐ąĄčĆą░čåąĖčÅ ąĄčēąĄ ąĮąĄ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĘą░ą▓ąĄčĆčłąĄąĮą░), č鹊 ą┤čĆčāą│ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ ą│čĆčāą┐ą┐čŗ A ąĮąĄ ą┤ąŠą╗ąČąĮą░ ąĘą░ą┐čāčüą║ą░čéčīčüčÅ. ą×ą┤ąĮą░ą║ąŠ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ ąĖąĘ ą│čĆčāą┐ą┐čŗ A ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čāčēąĄąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąĖąĘ ą│čĆčāą┐ą┐čŗ B.

ąŁč鹊 ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī Serial DataFlash ą▓ąĖčĆčéčāą░ą╗čīąĮąŠ ą┐čĆąĖąĮčÅčéčī ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčŗą╣ ą┐ąŠč鹊ą║ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠą║ą░ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ ą▓ ąŠčüąĮąŠą▓ąĮčāčÄ ą┐ą░ą╝čÅčéčī ąĖąĘ ą▒čāč乥čĆą░ 1, ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ąĘą░ą│čĆčāąČą░čéčīčüčÅ ą▓ ą▒čāč乥čĆ 2 (ąĖą╗ąĖ ąĮą░ąŠą▒ąŠčĆąŠčé). ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ą░ą┐ąĮąŠčāčé AN-4 [2].

[ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓]

SERIAL INPUT (SI): ą▓čŗą▓ąŠą┤ SI čĆą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ą║ą░ą║ ą▓čģąŠą┤, ąĖ ąĮą░ ąĮąĄą│ąŠ ą┐ąŠčüčéčāą┐ą░čÄčé ą┤ą░ąĮąĮčŗąĄ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ (opcode, ą░ą┤čĆąĄčüą░, ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ ą╝ą░čüčüąĖą▓ą░ ą┤ą░ąĮąĮčŗčģ ąĖą╗ąĖ ą▒čāč乥čĆą░).

SERIAL OUTPUT (SO): ą▓čŗą▓ąŠą┤ SO čĆą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ą║ą░ą║ ą▓čŗčģąŠą┤, ąĖ ąŠąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░.

SERIAL CLOCK (SCK): ą▓čŗą▓ąŠą┤ SCK čĆą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ą║ą░ą║ ą▓čģąŠą┤, ąĖ ąŠąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ąŠą╝ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠčüčéčāą┐ą░čÄčēąĖčģ ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝čā DataFlash ąĖ ąĖąĘ ąĮąĄčæ. ąöą░ąĮąĮčŗąĄ ą▓čüąĄą│ą┤ą░ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ SCK, ąĖ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ SCK.

CHIP SELECT (~CS): ą▓čģąŠą┤ ą▓čŗą▒ąŠčĆą║ąĖ. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ DataFlash ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ (čé. ąĄ. čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čĆą░ą▒ąŠčéą░ ąĄčæ ąĖąĮč鹥čĆč乥ą╣čüą░), ą║ąŠą│ą┤ą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS ą╗ąŠą│. 0. ąÜąŠą│ą┤ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ąĮąĄ ą▓čŗą▒čĆą░ąĮą░, ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ č湥čĆąĄąĘ ą▓čģąŠą┤ SI, ąĖ ą▓čŗą▓ąŠą┤ SO ąŠčüčéą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą▓čŗčüąŠą║ąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ (čéčĆąĄčéčīąĄ, ąŠčéą║ą╗čÄč湥ąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ). ą¤ąĄčĆąĄčģąŠą┤ 1 -> 0 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS čéčĆąĄą▒čāąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ąŠą┐ąĄčĆą░čåąĖąĖ, ąĖ ą┐ąĄčĆąĄčģąŠą┤ 0 -> 1 čéčĆąĄą▒čāąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ.

WRITE PROTECT: ą▓čģąŠą┤ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ. ąĢčüą╗ąĖ ąĮą░ ą▓čģąŠą┤ąĄ ~WP čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0, č鹊 ą┐ąĄčĆą▓čŗąĄ 256 čüčéčĆą░ąĮąĖčå ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮčŗ. ąØąĄčé ą┤čĆčāą│ąŠą│ąŠ čüą┐ąŠčüąŠą▒ą░ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī čŹčéąĖ ą┐ąĄčĆą▓čŗąĄ 256 čüčéčĆą░ąĮąĖčå, ą║čĆąŠą╝ąĄ ą║ą░ą║ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ ~WP ą▓ ą╗ąŠą│. 1 ąĖ ąĘą░č鹥ą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čĆą░ąĮąĄąĄ ąŠą┐ąĖčüą░ąĮąĮčŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ. ąĢčüą╗ąĖ čŹč鹊čé ą▓čŗą▓ąŠą┤ ąĖ ąĄą│ąŠ čäčāąĮą║čåąĖčÅ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, č鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐ąŠą┤čéčÅąĮčāčéčī čüąĮą░čĆčāąČąĖ ~WP ą║ čāčĆąŠą▓ąĮčÄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ (ą┐ąŠą┤ą░čéčī ą╗ąŠą│. 1).

RESET: ą▓čģąŠą┤ čüą▒čĆąŠčüą░. ąØąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čģąŠą┤ąĄ čüą▒čĆąŠčüą░ (~RESET) ą┐čĆąĄčĆą▓ąĄčé ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝čāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, ąĖ čüą▒čĆąŠčüąĖčé ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą╝ą░čłąĖąĮčā čüąŠčüč鹊čÅąĮąĖčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ (idle state). ąŻčüčéčĆąŠą╣čüčéą▓ąŠ ąŠčüčéą░ąĮąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░, ą┐ąŠą║ą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~RESET ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą╗ąŠą│. 0. ąØąŠčĆą╝ą░ą╗čīąĮą░čÅ čĆą░ą▒ąŠčéą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠą┤ąŠą╗ąČąĄąĮą░, ą║ąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤ ~RESET ą▓ąĄčĆąĮąĄčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą║ ą╗ąŠą│. 1. ąÆ čāčüčéčĆąŠą╣čüčéą▓ąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čüčģąĄą╝ą░ čüą▒čĆąŠčüą░, ą▒ą╗ą░ą│ąŠą┤ą░čĆčÅ č湥ą╝čā ąĮąĄčé ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ą┐ąŠą┤ą░čćčā čüąĖą│ąĮą░ą╗ą░ čüą▒čĆąŠčü. ąĢčüą╗ąĖ ą▓čŗą▓ąŠą┤ ~RESET ąĖ ąĄą│ąŠ čäčāąĮą║čåąĖčÅ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, č鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čüąĮą░čĆčāąČąĖ ą┐ąŠą┤čéčÅąĮčāčéčī čāčĆąŠą▓ąĄąĮčī ą▓čŗą▓ąŠą┤ą░ ~RESET ą║ ą╗ąŠą│. 1.

READY/~BUSY: čŹč鹊 ą▓čŗčģąŠą┤ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝, ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄčģąŠą┤ąĖčéčī ą▓ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░ąĮčÅč鹊 ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ąŠą┐ąĄčĆą░čåąĖąĄą╣. ąŁč鹊čé ą▓čŗą▓ąŠą┤ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1, ąĄčüą╗ąĖ ąŠąĮ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą▓ąĄčĆčģąĮąĄą╝čā ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĄą╝čā čĆąĄąĘąĖčüč鹊čĆčā 1 ą║ą×ą╝ (pull-up). ąŻčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ READY/~BUSY ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ ąĮą░čćąĮąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ, čüčĆą░ą▓ąĮąĄąĮąĖčÅ, ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā čüčéčĆą░ąĮąĖčåąĄą╣ ą┐ą░ą╝čÅčéąĖ ąĖ ą▒čāč乥čĆąŠą╝. ąĪąŠčüč鹊čÅąĮąĖąĄ ąĘą░ąĮčÅč鹊čüčéąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą║ ą╝ą░čüčüąĖą▓čā ą┐ą░ą╝čÅčéąĖ Flash ąĖ ą║ ąŠą┤ąĮąŠą╝čā ąĖąĘ ą▒čāč乥čĆąŠą▓ ąĮąĄą╗čīąĘčÅ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐; ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ ą▓ ą┤čĆčāą│ąŠą╣ ą▒čāč乥čĆ ą┐čĆąĖ čŹč鹊ą╝ ą▓čüąĄ ąĄčēąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ.

ąĪąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ąĖą╗ąĖ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. ąÜąŠą│ą┤ą░ ąĮą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠą┤ą░ąĮąŠ ą┐ąĖčéą░ąĮąĖąĄ, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ čüą▒čĆąŠčüą░, ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ SPI Mode 3. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą▓čŗą▓ąŠą┤ SO ą▒čāą┤ąĄčé ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą▓čŗčüąŠą║ąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ, ąĖ ą┐ąĄčĆąĄčģąŠą┤ ąŠčé ą╗ąŠą│. 1 ą║ ą╗ąŠą│. 0 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS ą┐ąŠčéčĆąĄą▒čāąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ. ąĀąĄąČąĖą╝ SPI ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąŠ ą║ą░ąČą┤ąŠą╝čā čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ ~CS ą┐čāč鹥ą╝ ąŠą┐čĆąŠčüą░ ąĮąĄ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ čéą░ą║č鹊ą▓. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąŠą┤ą░ąĮąŠ ą┐ąĖčéą░ąĮąĖąĄ, ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VCC ą┤ąŠčüčéąĖą│ą╗ąŠ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąŠ ą┤ą░čéą░čłąĖčéčā, čüąĖčüč鹥ą╝ą░ ą┤ąŠą╗ąČąĮą░ ą┐ąŠą┤ąŠąČą┤ą░čéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 20 ą╝čü ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čāčēąĄąĮ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ.

ąóą░ą▒ą╗ąĖčåą░ 1. ąÜąŠą╝ą░ąĮą┤čŗ čćč鹥ąĮąĖčÅ.

| ąÜąŠą╝ą░ąĮą┤ą░ |

ąĀąĄąČąĖą╝ SCK |

Opcode |

| Continuous Array Read |

ICP L/H(1) |

68h |

| ąĀąĄąČąĖą╝ SPI 0 ąĖą╗ąĖ 3 |

E8h |

| Main Memory Page Read |

ICP L/H |

52h |

| ąĀąĄąČąĖą╝ SPI 0 ąĖą╗ąĖ 3 |

D2h |

| Buffer 1 Read |

ICP L/H |

54h |

| ąĀąĄąČąĖą╝ SPI 0 ąĖą╗ąĖ 3 |

D4h |

| Buffer 2 Read |

ICP L/H |

56h |

| ąĀąĄąČąĖą╝ SPI 0 ąĖą╗ąĖ 3 |

D6h |

| Status Register Read |

ICP L/H |

57h |

| ąĀąĄąČąĖą╝ SPI 0 ąĖą╗ąĖ 3 |

D7h |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ICP L/H ąŠąĘąĮą░čćą░ąĄčé "Inactive Clock Polarity Low or High", čé. ąĄ. ą┐ąŠą╗čÅčĆąĮąŠčüčéčī ąĮąĄ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ čéą░ą║č鹊ą▓ ą╝ąŠąČąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī ą╗ąŠą│. 0 ąĖą╗ąĖ ą╗ąŠą│. 1.

ąóą░ą▒ą╗ąĖčåą░ 2. ąÜąŠą╝ą░ąĮą┤čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čüčéąĖčĆą░ąĮąĖčÅ.

| ąÜąŠą╝ą░ąĮą┤ą░ |

ąĀąĄąČąĖą╝ SCK |

Opcode |

| Buffer 1 Write |

ą╗čÄą▒ąŠą╣ |

84h |

| Buffer 2 Write |

87h |

| Buffer 1 to Main Memory Page Program with Built-in Erase |

83h |

| Buffer 2 to Main Memory Page Program with Built-in Erase |

86h |

| Buffer 1 to Main Memory Page Program without Built-in Erase |

88h |

| Buffer 2 to Main Memory Page Program without Built-in Erase |

89h |

| Page Erase |

81h |

| Block Erase |

50h |

| Main Memory Page Program through Buffer 1 |

82h |

| Main Memory Page Program through Buffer 2 |

85h |

ąóą░ą▒ą╗ąĖčåą░ 3. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ.

| ąÜąŠą╝ą░ąĮą┤ą░ |

ąĀąĄąČąĖą╝ SCK |

Opcode |

| Main Memory Page to Buffer 1 Transfer |

ą╗čÄą▒ąŠą╣ |

53h |

| Main Memory Page to Buffer 2 Transfer |

55h |

| Main Memory Page to Buffer 1 Compare |

60h |

| Main Memory Page to Buffer 2 Compare |

61h |

| Auto Page Rewrite through Buffer 1 |

58h |

| Auto Page Rewrite through Buffer 2 |

59h |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ čéą░ą▒ą╗ąĖčåą░čģ 2 ąĖ 3 čĆąĄąČąĖą╝ SCK ąŠą▒ąŠąĘąĮą░č湥ąĮ ą║ą░ą║ "ą╗čÄą▒ąŠą╣", čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠą┤ąĮąŠą╝čā ąĖąĘ č湥čéčŗčĆąĄčģ čĆąĄąČąĖą╝ąŠą▓ čĆą░ą▒ąŠčéčŗ SPI (Inactive Clock Polarity Low, Inactive Clock Polarity High, SPI Mode 0 ąĖą╗ąĖ SPI Mode 3).

ąóą░ą▒ą╗ąĖčåą░ 4. ą¤ąŠą┤čĆąŠą▒ąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą░ą┤čĆąĄčüą░čåąĖąĖ ąĮą░ čāčĆąŠą▓ąĮąĄ ą▒ąĖčé.

ąŻčüą╗ąŠą▓ąĮčŗąĄ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖčÅ ą▓ čéą░ą▒ą╗ąĖčåąĄ 4:

r = ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▒ąĖčé.

P = ą▒ąĖčé ą░ą┤čĆąĄčüą░ čüčéčĆą░ąĮąĖčåčŗ.

B = ą▒ąĖčé ą░ą┤čĆąĄčüą░ ą▒ą░ą╣čéą░ ąĖą╗ąĖ ą▒čāč乥čĆą░.

x = ą▒ąĖčé DonŌĆÖt Care (ąĄą│ąŠ čāčĆąŠą▓ąĄąĮčī ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ).

N/A = ąĮąĄą┤ąŠčüčéčāą┐ąĮąŠ, ąĮąĄ čüčāčēąĄčüčéą▓čāąĄčé.

[ą¤čĆąĄą┤ąĄą╗čīąĮčŗąĄ ą░ą▒čüąŠą╗čÄčéąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ]

ŌĆó ąĀą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ (ą┐ąŠą┤ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝) -55┬░C .. +125┬░C.

ŌĆó ąóąĄą╝ą┐ąĄčĆą░čéčāčĆą░ čģčĆą░ąĮąĄąĮąĖčÅ -65┬░C .. +150┬░C.

ŌĆó ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ą╗čÅ ą▓čüąĄčģ ą▓čŗą▓ąŠą┤ąŠą▓ (ą▓ą║ą╗čÄčćą░čÅ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ NC) ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ GND -0.6V .. +6.25V.

ŌĆó ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čüąĄčģ ą▓čŗčģąŠą┤ą░čģ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ GND -0.6V .. (VCC + 0.6V).

[ąĀą░ą▒ąŠčćąĖąĄ čāčüą╗ąŠą▓ąĖčÅ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā]

ą¤ą░čĆą░ą╝ąĄčéčĆ

|

AT45DB161B

(ą▓ąĄčĆčüąĖčÅ 2.5V) |

AT45DB161B |

| ąĀą░ą▒ąŠčćą░čÅ č鹥ą╝ą┐ąĄčĆą░čéčāčĆą░ (ą║ąŠčĆą┐čāčüą░) |

ąÜąŠą╝ą╝ąĄčĆč湥čüą║ąŠąĄ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ |

0┬░C .. +70┬░C |

0┬░C .. +70┬░C |

| ąśąĮą┤čāčüčéčĆąĖą░ą╗čīąĮąŠąĄ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ |

- |

-40┬░C .. +70┬░C |

| ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ VCC(1) |

2.5V .. 3.6V |

2.7V .. 3.6V |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ą┐ąŠčüą╗ąĄ ą┐ąŠą┤ą░čćąĖ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ąĮą░čĆą░čüčéą░ąĮąĖčÅ VCC ą┤ąŠ čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ą┐ąŠ čŹč鹊ą╝čā ą┤ą░čéą░čłąĖčéčā, ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠą╣čéąĖ 20 ą╝čü ąĘą░ą┤ąĄčƹȹ║ąĖ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą╝ąŠąČąĮąŠ ą┐ąĄčĆąĄčģąŠą┤ąĖčéčī ą▓ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝.

[ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ č鹊ą║ą░]

| ąĪąĖą╝ą▓. |

ą¤ą░čĆą░ą╝ąĄčéčĆ

|

ąŻčüą╗ąŠą▓ąĖčÅ |

Min |

Typ |

Max |

ąĢą┤. |

| ISB |

ąóąŠą║ čüąŠčüč鹊čÅąĮąĖčÅ ąŠąČąĖą┤ą░ąĮąĖčÅ |

~CS, ~RESET, ~WP = VCC, ą▓čüąĄ ą▓čģąŠą┤čŗ ąĮą░ čāčĆąŠą▓ąĮčÅčģ CMOS |

|

2 |

10 |

ą╝ą║ąÉ |

| ICC1(1) |

ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą▓ ą░ą║čéąĖą▓ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ, ąŠą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ |

f = 20 ą£ąōčå; IOUT = 0 ą╝ąÉ;

VCC = 3.6V |

|

4 |

10 |

ą╝ąÉ |

| ICC2 |

ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą▓ ą░ą║čéąĖą▓ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ, ąŠą┐ąĄčĆą░čåąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ, ąŠčćąĖčüčéą║ąĖ

|

VCC = 3.6V |

|

15 |

35 |

ą╝ąÉ |

| ILI |

ąóąŠą║ ąĮą░ą│čĆčāąĘą║ąĖ ą▓čģąŠą┤ą░ |

VIN = čāčĆąŠą▓ąĮąĖ CMOS |

|

|

1 |

ą╝ą║ąÉ |

| ILO |

ąóąŠą║ čāč鹥čćą║ąĖ ą▓čŗčģąŠą┤ą░ |

|

|

|

1 |

ą╝ą║ąÉ |

| VIL |

ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 0 |

|

|

|

0.6 |

V |

| VIH |

ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 1 |

|

2.0 |

|

|

V |

| VOL |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 0 |

IOL = 1.6 ą╝ąÉ; VCC = 2.7V |

|

|

0.4 |

V |

| VOH |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 1 |

IOH = -100 ą╝ą║ąÉ |

VCC - 0.2V |

|

|

V |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ICC1 ą▓ąŠ ą▓čĆąĄą╝čÅ čćč鹥ąĮąĖčÅ ą▒čāč乥čĆą░ čüąŠčüčéą░ą▓ąĖčé 20 ą╝ąÉ ą╝ą░ą║čüąĖą╝čāą╝.

[ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą│ąŠ č鹊ą║ą░]

ąĪąĖą╝ą▓.

|

ą¤ą░čĆą░ą╝ąĄčéčĆ

|

AT45DB161B

(ą▓ąĄčĆčüąĖčÅ 2.5V) |

AT45DB161B

|

ąĢą┤.

|

| ą£in |

Max |

Min |

Max |

| fSCK |

ą¦ą░čüč鹊čéą░ SCK |

|

15 |

|

20 |

ą£ąōčå |

| fCAR |

ą¦ą░čüč鹊čéą░ SCK ą┤ą╗čÅ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ ą╝ą░čüčüąĖą▓ą░ |

|

15 |

|

20 |

ą£ąōčå |

| tWH |

ąÆčĆąĄą╝čÅ ą╗ąŠą│. 1 ą┤ą╗čÅ SCK |

30 |

|

22 |

|

ąĮčü |

| tWL |

ąÆčĆąĄą╝čÅ ą╗ąŠą│. 0 ą┤ą╗čÅ SCK |

30 |

|

22 |

|

ąĮčü |

| tCS |

ą£ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ~CS |

250 |

|

250 |

|

ąĮčü |

| tCSS |

ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ~CS |

250 |

|

250 |

|

ąĮčü |

| tCSH |

ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ~CS |

250 |

|

250 |

|

ąĮčü |

| tCSB |

ąÆčĆąĄą╝čÅ ą╝ąĄąČą┤čā ~CS=1 ą┤ąŠ RDY/~BUSY=0 |

|

200 |

|

200 |

ąĮčü |

| tSU |

ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ |

10 |

|

5 |

|

ąĮčü |

| tH |

ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ |

15 |

|

10 |

|

ąĮčü |

| tHO |

ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ |

0 |

|

0 |

|

ąĮčü |

| tDIS |

ąÆčĆąĄą╝čÅ ąĘą░ą┐čĆąĄčéą░ ą▓čŗčģąŠą┤ą░ |

|

20 |

|

18 |

ąĮčü |

| tV |

ąöą░ąĮąĮčŗąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗ |

|

25 |

|

20 |

ąĮčü |

| tXFR |

ąÆčĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ ą▒čāč乥čĆ / čüčĆą░ą▓ąĮąĄąĮąĖčÅ čüčéčĆą░ąĮąĖčåčŗ |

|

300 |

|

250 |

ą╝ą║čü |

| tEP |

ąÆčĆąĄą╝čÅ ąŠčćąĖčüčéą║ąĖ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüčéčĆą░ąĮąĖčåčŗ |

|

20 |

|

20 |

ą╝čü |

| tP |

ąÆčĆąĄą╝čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüčéčĆą░ąĮąĖčåčŗ |

|

14 |

|

14 |

ą╝čü |

| tPE |

ąÆčĆąĄą╝čÅ ąŠčćąĖčüčéą║ąĖ čüčéčĆą░ąĮąĖčåčŗ |

|

8 |

|

8 |

ą╝čü |

| tBE |

ąÆčĆąĄą╝čÅ ąŠčćąĖčüčéą║ąĖ ą▒ą╗ąŠą║ą░ |

|

12 |

|

12 |

ą╝čü |

| tRST |

ąÆčĆąĄą╝čÅ ąĖą╝ą┐čāą╗čīčüą░ ~RESET |

10 |

|

10 |

|

ą╝ą║čü |

| tREC |

ąÆčĆąĄą╝čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ~RESET |

|

1 |

|

1 |

ą╝ą║čü |

[ąÆčģąŠą┤ąĮčŗąĄ č鹥čüč鹊ą▓čŗąĄ čüąĖą│ąĮą░ą╗čŗ ąĖ čāčĆąŠą▓ąĮąĖ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ]

tR, tF < 3 ąĮčü (10% .. 90%)

[ąØą░ą│čĆčāąĘą║ą░ ą▓čŗčģąŠą┤ą░ ą┐čĆąĖ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖąĖ]

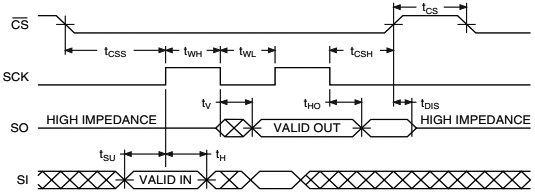

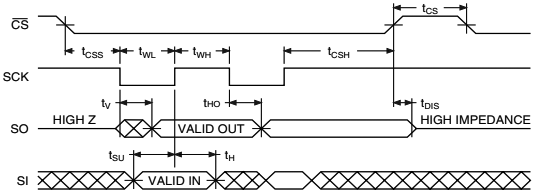

ąØąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą┤ą▓ąĄ čĆą░ąĘąĮčŗąĄ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ. ąöąĖą░ą│čĆą░ą╝ą╝ą░ 1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąĖą│ąĮą░ą╗ SCK ą▓ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ ~CS ą╝ąĄąĮčÅąĄčé čāčĆąŠą▓ąĄąĮčī 1 -> 0, ąĖ ąöąĖą░ą│čĆą░ą╝ą╝ą░ 2 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąĖą│ąĮą░ą╗ SCK ą▓ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ ~CS ą╝ąĄąĮčÅąĄčé čāčĆąŠą▓ąĄąĮčī 1 -> 0. ą×ą▒ąĄ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ą┤ąŠą┐čāčüčéąĖą╝čŗąĄ ą▓ą░čĆąĖą░ąĮčéčŗ čüąĖą│ąĮą░ą╗ąŠą▓. ąÆčĆąĄą╝ąĄąĮą░ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĖ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ą░ SI ąĖąĘą╝ąĄčĆčÅčÄčéčüčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ 0 -> 1 čüąĖą│ąĮą░ą╗ą░ SCK.

ąöąĖą░ą│čĆą░ą╝ą╝ą░ 1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠč鹊čĆčŗąĄ čéą░ą║ąČąĄ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗ čü SPI Mode 0, ąĖ ąöąĖą░ą│čĆą░ą╝ą╝ą░ 2 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ, čüąŠą▓ą╝ąĄčüčéąĖą╝čŗąĄ čü SPI Mode 3.

ąöąĖą░ą│čĆą░ą╝ą╝ą░ 1 ŌĆō ąĮąĄ ą░ą║čéąĖą▓ąĮą░čÅ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ 0 ąĖ SPI Mode 0:

ąöąĖą░ą│čĆą░ą╝ą╝ą░ 2 ŌĆō ąĮąĄ ą░ą║čéąĖą▓ąĮą░čÅ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ 1 ąĖ SPI Mode 3:

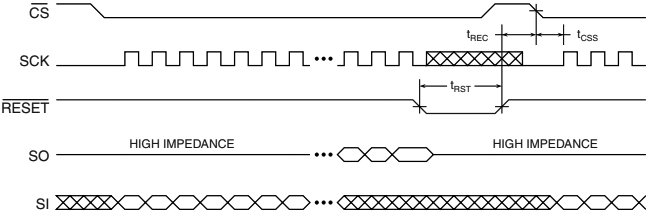

ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ čüą▒čĆąŠčüą░ (ą┐ąŠą║ą░ąĘą░ąĮ ą▓ą░čĆąĖą░ąĮčé ąĮąĄ ą░ą║čéąĖą▓ąĮąŠą╣ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ čéą░ą║č鹊ą▓ 0):

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čüąĖą│ąĮą░ą╗ ~CS ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1 ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ čüąĮąĖą╝ą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ ~RESET. HIGH Z ąĖ HIGH IMPEDANCE ąŠąĘąĮą░čćą░ąĄčé ą▓čŗčüąŠą║ąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ, VALID IN ą┤ąŠą┐čāčüčéąĖą╝čŗąĄ ą▓čģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, VALID OUT ą┤ąŠą┐čāčüčéąĖą╝čŗąĄ ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ.

ąÜąŠą╝ą░ąĮą┤ąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ (ą║čĆąŠą╝ąĄ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ Status Register Read):

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. "r" ąŠą▒ąŠąĘąĮą░čćą░ąĄčé ą▒ąĖčéčŗ, ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą▒ąŠą╗ąĄąĄ ąĄą╝ą║ąĖčģ čāčüčéčĆąŠą╣čüčéą▓.

2. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ, čćč鹊ą▒čŗ "r" ą▒čŗą╗ąĖ ą╗ąŠą│ąĖč湥čüą║ąĖą╝ąĖ ąĮčāą╗čÅą╝ąĖ ą┤ą╗čÅ ą┐ą╗ąŠčéąĮąŠčüč鹥ą╣ 16 ą╝ąĄą│ą░ą▒ąĖčé ąĖ ą╝ąĄąĮąĄąĄ ąĄą╝ą║ąĖčģ čāčüčéčĆąŠą╣čüčéą▓.

3. ąöą╗čÅ ą┐ą╗ąŠčéąĮąŠčüč鹥ą╣ ą▒ąŠą╗čīčłąĄ 16 ą╝ąĄą│ą░ą▒ąĖčé, ą▒ąĖčéčŗ "r" čüčéą░ąĮąŠą▓čÅčéčüčÅ čüčéą░čĆčłąĖą╝ąĖ ą▒ąĖčéą░ą╝ąĖ ą░ą┤čĆąĄčüą░ čüčéčĆą░ąĮąĖčåčŗ ą┤ą╗čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ąĄą╝ą║ąŠčüč鹥ą╣.

4. MSB ąŠąĘąĮą░čćą░ąĄčé čüą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ ą▒ąĖčé (Most Significant Bit), LSB čüą░ą╝čŗą╣ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé (Least Significant Bit).

[ą×ą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ]

ąĪą╗ąĄą┤čāčÄčēą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ ąĖ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą┤ąŠčüčéčāą┐ąĮčŗąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ.

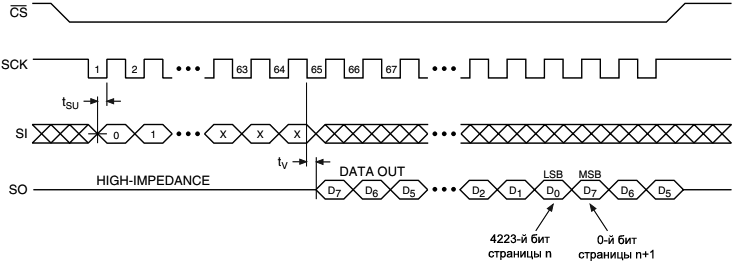

ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ č湥čĆąĄąĘ ą▒čāč乥čĆčŗ:

ąŚą░ą┐ąĖčüčī ą▒čāč乥čĆą░:

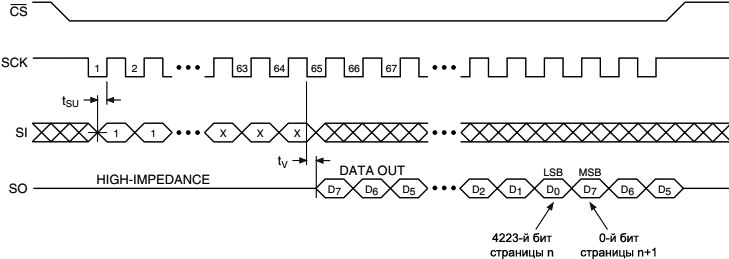

ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒čāč乥čĆą░ ą▓ čüčéčĆą░ąĮąĖčåčā ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą▒čāč乥čĆą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ ą▓ čüčéčĆą░ąĮąĖčåčā FLASH):

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: n čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą┐ąĄčĆą▓ąŠą╝čā ą▒ą░ą╣čéčā, n+1 ą▓č鹊čĆąŠą╝čā ą▒ą░ą╣čéčā ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ. "ąØąĄąĘą░ą▓ąĖčüąĖą╝ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ" ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▓čüąĄ ą┐čĆąŠčåąĄčüčüčŗ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ą┐ąŠ čüą░ą╝ąŠčüč鹊čÅč鹥ą╗čīąĮąŠ č乊čĆą╝ąĖčĆčāąĄą╝ąŠą╝čā čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÄ ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ.

[ą×ą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ]

ąĪą╗ąĄą┤čāčÄčēą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ ąĖ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą┤ąŠčüčéčāą┐ąĮčŗąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čćč鹥ąĮąĖčÅ.

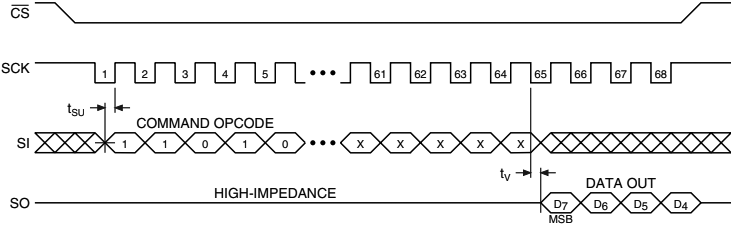

ą¦č鹥ąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ:

ą¤ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄ ąĖąĘ čüčéčĆą░ąĮąĖčåčŗ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą▓ ą▒čāč乥čĆ (ą┤ą░ąĮąĮčŗąĄ ąĖąĘ čüčéčĆą░ąĮąĖčåčŗ FLASH čüčćąĖčéčŗą▓ą░čÄčéčüčÅ ą▓ ą▒čāč乥čĆ):

ą¦č鹥ąĮąĖąĄ ą▒čāč乥čĆą░:

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: n čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą┐ąĄčĆą▓ąŠą╝čā ą▒ą░ą╣čéčā, n+1 ą▓č鹊čĆąŠą╝čā ą▒ą░ą╣čéčā ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ.

[ą¤ąŠą┤čĆąŠą▒ąĮčŗąĄ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ąĮą░ čāčĆąŠą▓ąĮąĄ ą▒ąĖčé - ą┐ąŠą╗čÅčĆąĮąŠčüčéčī ąĮąĄ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ čéą░ą║č鹊ą▓ 0]

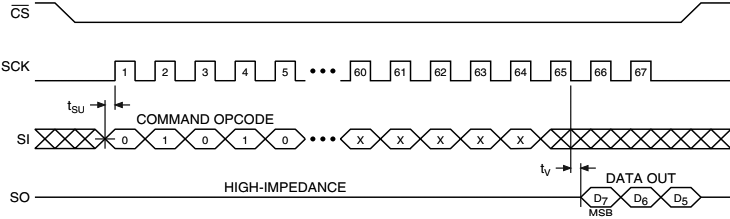

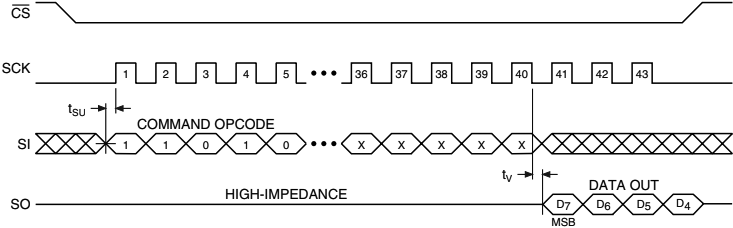

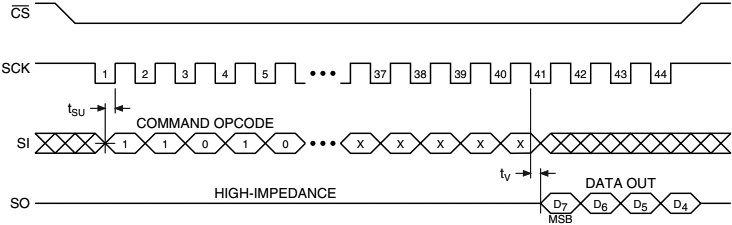

Continuous Array Read (ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠąĄ čćč鹥ąĮąĖąĄ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ, opcode 68H):

Main Memory Page Read (čćč鹥ąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, opcode 52H):

Buffer Read (čćč鹥ąĮąĖąĄ ą▒čāč乥čĆą░, opcode 54H ąĖą╗ąĖ 56H):

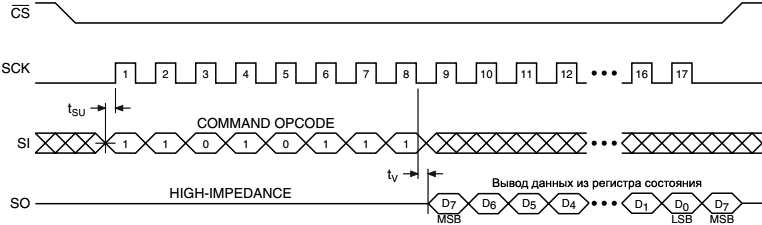

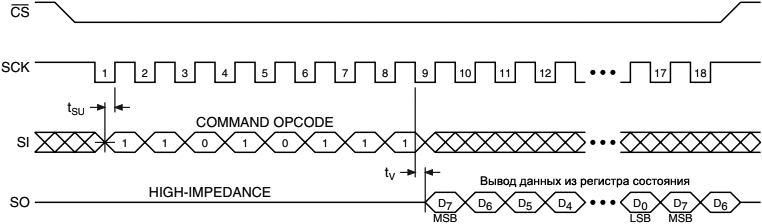

Status Register Read (čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ, opcode 57H):

[ą¤ąŠą┤čĆąŠą▒ąĮčŗąĄ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ąĮą░ čāčĆąŠą▓ąĮąĄ ą▒ąĖčé - ą┐ąŠą╗čÅčĆąĮąŠčüčéčī ąĮąĄ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ čéą░ą║č鹊ą▓ 1]

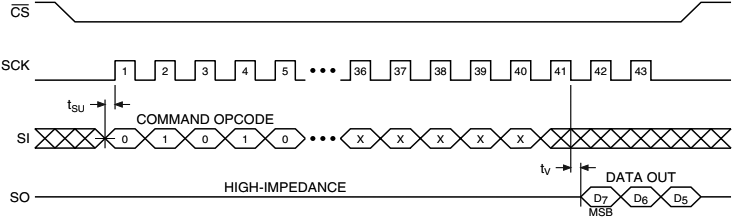

Continuous Array Read (ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠąĄ čćč鹥ąĮąĖąĄ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ, opcode 68H):

Main Memory Page Read (čćč鹥ąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, opcode 52H):

Buffer Read (čćč鹥ąĮąĖąĄ ą▒čāč乥čĆą░, opcode 54H ąĖą╗ąĖ 56H):

Status Register Read (čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ, opcode 57H):

[ą¤ąŠą┤čĆąŠą▒ąĮčŗąĄ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ąĮą░ čāčĆąŠą▓ąĮąĄ ą▒ąĖčé - SPI Mode 0]

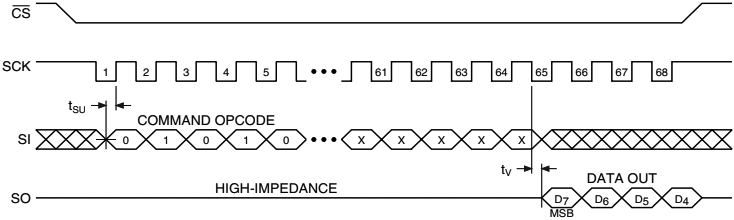

Continuous Array Read (ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠąĄ čćč鹥ąĮąĖąĄ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ, opcode E8H):

Main Memory Page Read (čćč鹥ąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, opcode D2H):

Buffer Read (čćč鹥ąĮąĖąĄ ą▒čāč乥čĆą░, opcode D4H ąĖą╗ąĖ D6H):

Status Register Read (čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ, opcode D7H):

[ą¤ąŠą┤čĆąŠą▒ąĮčŗąĄ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ąĮą░ čāčĆąŠą▓ąĮąĄ ą▒ąĖčé - SPI Mode 3]

Continuous Array Read (ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠąĄ čćč鹥ąĮąĖąĄ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ, opcode E8H):

Main Memory Page Read (čćč鹥ąĮąĖąĄ čüčéčĆą░ąĮąĖčåčŗ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, opcode D2H):

Buffer Read (čćč鹥ąĮąĖąĄ ą▒čāč乥čĆą░, opcode D4H ąĖą╗ąĖ D6H):

Status Register Read (čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ, opcode D7H):

fSCK

(ą£ąōčå)

|

ICC (ą╝ąÉ)

|

ąÜąŠą┤ ą┤ą╗čÅ ą┐ąŠą║čāą┐ą║ąĖ

|

ąÜąŠčĆą┐čāčü

|

ąĀą░ą▒ąŠčćąĖąĄ čāčüą╗ąŠą▓ąĖčÅ

|

| Active |

Standby |

| 15 |

10 |

0.01 |

AT45DB161B-CC-2.5

AT45DB161B-CNC-2.5

AT45DB161B-RC-2.5

AT45DB161B-TC-2.5 |

24C1

8CN3

28R

28T |

ąÜąŠą╝ą╝ąĄčĆč湥čüą║ąŠąĄ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ

(0┬░C .. 70┬░C)

2.5V .. 3.6V |

| 20 |

10 |

0.01 |

AT45DB161B-CC

AT45DB161B-CNC

AT45DB161B-RC

AT45DB161B-TC |

24C1

8CN3

28R

28T |

ąÜąŠą╝ą╝ąĄčĆč湥čüą║ąŠąĄ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ

(0┬░C .. 70┬░C) |

| 20 |

10 |

0.01 |

AT45DB161B-CI

AT45DB161B-CNI

AT45DB161B-RI

AT45DB161B-TI |

24C1

8CN3

28R

28T |

ąśąĮą┤čāčüčéčĆąĖą░ą╗čīąĮąŠąĄ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ

(-40┬░C .. 85┬░C) |

"ąŚąĄą╗ąĄąĮčŗąĄ" ą▓ąĄčĆčüąĖąĖ ą║ąŠčĆą┐čāčüąŠą▓ (Pb/Halide-free):

fSCK

(ą£ąōčå)

|

ICC (ą╝ąÉ)

|

ąÜąŠą┤ ą┤ą╗čÅ ą┐ąŠą║čāą┐ą║ąĖ

|

ąÜąŠčĆą┐čāčü

|

ąĀą░ą▒ąŠčćąĖąĄ čāčüą╗ąŠą▓ąĖčÅ

|

| Active |

Standby |

| 20 |

10 |

0.01 |

AT45DB161B-CNU

AT45DB161B-RU

AT45DB161B-TU |

8CN3

28R

28T |

ąśąĮą┤čāčüčéčĆąĖą░ą╗čīąĮąŠąĄ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ

(-40┬░C .. 85┬░C) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: "ąĘąĄą╗ąĄąĮčŗąĄ" ą║ąŠčĆą┐čāčüą░ čéą░ą║ąČąĄ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčÄčé čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ lead-free.

ąóąĖą┐ ą║ąŠčĆą┐čāčüą░

|

| 24C1 |

24-ball (ą╝ą░čüčüąĖą▓ čłą░čĆąĖą║ąŠą▓ 5 x 5), Plastic Chip-scale Ball Grid Array (CBGA) |

| 8CN3 |

8-ą║ąŠąĮčéą░ą║čéąĮčŗą╣ (6 x 8 ą╝ą╝) Chip Array Small Outline No Lead Package (CASON8) |

| 28R |

28-ą▓čŗą▓ąŠą┤ąĮčŗą╣, čłąĖčĆąĖąĮą░ 0.330", Plastic Gull Wing Small Outline Package (SOIC28) |

| 28T |

28-ą▓čŗą▓ąŠą┤ąĮčŗą╣, Plastic Thin Small Outline Package (TSOP28) |

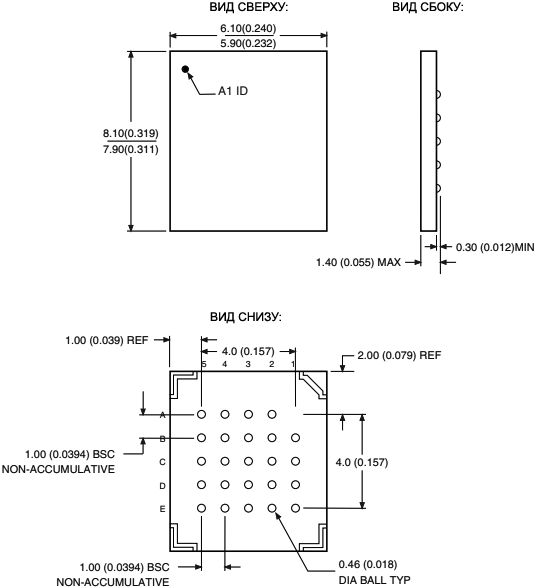

[24C1 ŌĆō CBGA]

ąĀą░ąĘą╝ąĄčĆčŗ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓ ą╝ąĖą╗ą╗ąĖą╝ąĄčéčĆą░čģ (ą▓ čüą║ąŠą▒ą║ą░čģ ą▓ ą┤čÄą╣ą╝ą░čģ). ąÜąŠąĮčéčĆąŠą╗čīąĮčŗąĄ čĆą░ąĘą╝ąĄčĆčŗ ą▓ ą╝ąĖą╗ą╗ąĖą╝ąĄčéčĆą░čģ.

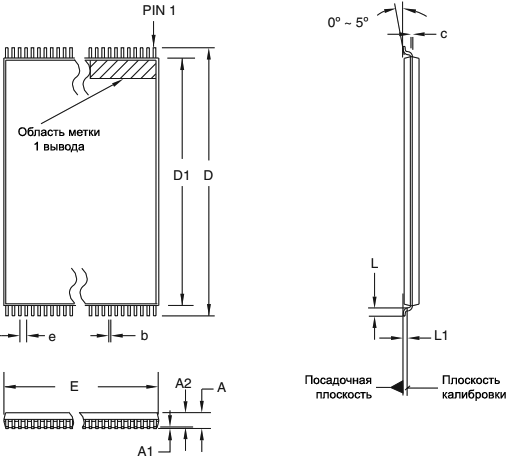

[8CN3 ŌĆō CASON8]

ą×ą▒čēąĖąĄ čĆą░ąĘą╝ąĄčĆčŗ (ą▓ ą╝ąĖą╗ą╗ąĖą╝ąĄčéčĆą░čģ):

| ąĪąĖą╝ą▓ąŠą╗ |

MIN |

NOM |

MAX |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ |

| A |

|

|

1.0 |

|

| A1 |

0.17 |

0.21 |

0.25 |

|

| b |

0.41 TYP |

4 |

| D |

7.90 |

8.00 |

8.10 |

|

| E |

5.90 |

6.00 |

6.10 |

|

| e |

1.27 BSC |

|

| e1 |

1.095 REF |

|

| L |

0.67 TYP |

4 |

| L1 |

0.92 |

0.97 |

1.02 |

4 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ąÆčüąĄ čĆą░ąĘą╝ąĄčĆčŗ ąĖ ą┤ąŠą┐čāčüą║ąĖ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčÄčé čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ ASME Y 14.5M, 1994.

2. ążąĖąĮąĖčłąĮąŠąĄ ą┐ąŠą║čĆčŗčéąĖąĄ ą║ąŠčĆą┐čāčüą░ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī EDM Charmille #24-27.

3. ąöąŠą┐čāčüą║ąĖ čüą╗ąĄą┤čāčÄčēąĖąĄ, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ čćč鹊-č鹊 ą┤čĆčāą│ąŠąĄ: ą┤ąĄčüčÅčéąĖčćąĮčŗąĄ ┬▒0.05, čāą│ą╗ąŠą▓čŗąĄ ┬▒2┬░.

4. ąĀą░ąĘą╝ąĄčĆčŗ ą╝ąĄčéą░ą╗ą╗ąĖč湥čüą║ąŠą╣ ą║ąŠąĮčéą░ą║čéąĮąŠą╣ ą┐ą╗ąŠčēą░ą┤ą║ąĖ.

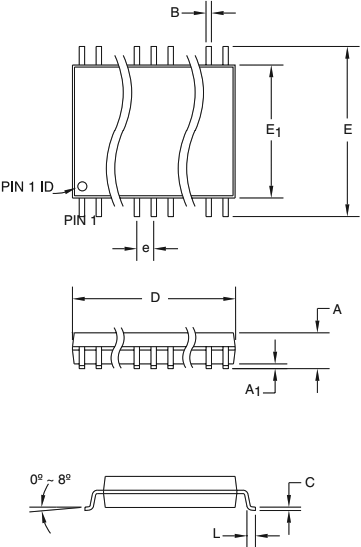

[28R ŌĆō SOIC28]

ą×ą▒čēąĖąĄ čĆą░ąĘą╝ąĄčĆčŗ (ą▓ ą╝ąĖą╗ą╗ąĖą╝ąĄčéčĆą░čģ):

| ąĪąĖą╝ą▓ąŠą╗ |

MIN |

NOM |

MAX |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ |

| A |

2.39 |

- |

2.79 |

|

| A1 |

0.050 |

- |

0.356 |

|

| D |

18.00 |

- |

18.50 |

1 |

| E |

11.70 |

- |

12.50 |

|

| E1 |

8.59 |

- |

8.79 |

1 |

| B |

0.356 |

- |

0.508 |

|

| C |

0.203 |

- |

0.305 |

|

| L |

0.94 |

- |

1.27 |

|

| e |

1.27 TYP |

|

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1: čĆą░ąĘą╝ąĄčĆčŗ D ąĖ E1 ąĮąĄ ą▓ą║ą╗čÄčćą░čÄčé č乊čĆą╝ąŠą▓ą║čā (mold Flash) ąĖą╗ąĖ ą▓čŗčüčéčāą┐. ą×ąĮąĖ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą┐čĆąĄą▓čŗčłą░čéčī 0.25 ą╝ą╝ (0.010").

[28T ŌĆō TSOP28]

ą×ą▒čēąĖąĄ čĆą░ąĘą╝ąĄčĆčŗ (ą▓ ą╝ąĖą╗ą╗ąĖą╝ąĄčéčĆą░čģ):

| ąĪąĖą╝ą▓ąŠą╗ |

MIN |

NOM |

MAX |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ |

| A |

- |

- |

1.20 |

|

| A1 |

0.05 |

- |

0.15 |

|

| A2 |

0.90 |

1.00 |

1.05 |

|

| D |

13.20 |

13.40 |

13.60 |

|

| D1 |

11.70 |

11.80 |

11.90 |

2 |

| E |

7.90 |

8.00 |

8.10 |

2 |

| L |

0.50 |

0.60 |

0.70 |

|

| L1 |

0.25 BASIC |

|

| b |

0.17 |

0.22 |

0.27 |

|

| c |

0.10 |

- |

0.21 |

|

| e |

0.55 BASIC |

|

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ąŁč鹊čé ą║ąŠčĆą┐čāčü čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅąĄčé čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ JEDEC reference MO-183.

2. ąĀą░ąĘą╝ąĄčĆčŗ D1 ąĖ E ąĮąĄ čāčćąĖčéčŗą▓ą░čÄčé č乊čĆą╝ąŠą▓ąŠčćąĮčŗą╣ ą▓čŗčüčéčāą┐. ąöąŠą┐čāčüčéąĖą╝čŗą╣ ą▓čŗčüčéčāą┐ E čüąŠčüčéą░ą▓ą╗čÅąĄčé 0.15 ą╝ą╝ ąĮąĄ čüč鹊čĆąŠąĮčā ąĖ ą┤ą╗čÅ D1 čüąŠčüčéą░ą▓ą╗čÅąĄčé 0.25 ą╝ą╝ ąĮą░ čüč鹊čĆąŠąĮčā.

3. ąÜąŠą┐ą╗ą░ąĮą░čĆąĮąŠčüčéčī ą▓čŗą▓ąŠą┤ąŠą▓ 0.10 ą╝ą╝ ą╝ą░ą║čüąĖą╝čāą╝.

[ąĪčüčŗą╗ą║ąĖ]

1. AT45DB161B DataFlash site:microchip.com.

2. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ Atmel Serial DataFlash.

3. ąśąĮč鹥čĆč乥ą╣čü SPI.

4. AVR335: čåąĖčäčĆąŠą▓ąŠą╣ čĆąĄą║ąŠčĆą┤ąĄčĆ ąĘą▓čāą║ą░ ąĮą░ AVR ąĖ DataFlash. |