|

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ AT24C64D Serial EEPROM ąŠą▒ą╗ą░ą┤ą░ąĄčé ąĄą╝ą║ąŠčüčéčīčÄ 65536 ą▒ąĖčé, čŹčéą░ ą┐ą░ą╝čÅčéčī ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮą░ ą║ą░ą║ 8192 čüą╗ąŠą▓ ą┐ąŠ 8 ą▒ąĖčé (8 ą║ąĖą╗ąŠą▒ą░ą╣čé). ąÜ ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ I2C ą╝ąŠąČąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą┤ąŠ 8 čāčüčéčĆąŠą╣čüčéą▓ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ, ąĖčüą┐ąŠą╗čīąĘčāčÅ ą▓čŗą▓ąŠą┤čŗ ą░ą┤čĆąĄčüą░čåąĖąĖ A2, A1, A0 (ąĮąĄ ąĮą░ ą▓čüąĄčģ ą║ąŠčĆą┐čāčüą░čģ ąĄčüčéčī čŹčéąĖ ą▓čŗą▓ąŠą┤čŗ). ąŻčüčéčĆąŠą╣čüčéą▓ąŠ ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ąŠ ą╝ąĮąŠą│ąĖčģ ąĖąĮą┤čāčüčéčĆąĖą░ą╗čīąĮčŗčģ ąĖ ą║ąŠą╝ą╝ąĄčĆč湥čüą║ąĖčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ, ą│ą┤ąĄ ą▓ą░ąČąĮčŗ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą┐ąŠ ąĮąĖąĘą║ąŠą╝čā 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÄ ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąĮąĖąĘą║ąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ ą┐ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▓ 8-ą▓čŗą▓ąŠą┤ąĮčŗčģ ą║ąŠčĆą┐čāčüą░čģ JEDEC SOIC, 8-ą▓čŗą▓ąŠą┤ąĮčŗčģ TSSOP, 8-ą║ąŠąĮčéą░ą║čéąĮčŗčģ UDFN, XDFN, 8-čłą░čĆąĖą║ąŠą▓čŗčģ VFBGA, 4-čłą░čĆąĖą║ąŠą▓čŗčģ ąĖ 6-čłą░čĆąĖą║ąŠą▓čŗčģ WLCSP. ą£ąĖą║čĆąŠčüčģąĄą╝čŗ ą▓ąŠ ą▓čüąĄčģ čéąĖą┐ą░čģ ą║ąŠčĆą┐čāčüąŠą▓ ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą┐ąĖčéą░čÄčēąĖčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ąŠčé 1.7V ą┤ąŠ 5.5V.

ą×čüąĮąŠą▓ąĮčŗąĄ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ AT24C64D:

ŌĆó ą©ąĖčĆąŠą║ąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ, ąŠčé čüą░ą╝čŗčģ ąĮąĖąĘą║ąĖčģ ą┤ąŠ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ (VCC = 1.7V .. 5.5V).

ŌĆó ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÅ 8192 x 8 (64 ą║ąĖą╗ąŠą▒ąĖčé).

ŌĆó I2C-čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü (2-Wire, TWI) čü ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╝ ą┐čĆąŠč鹊ą║ąŠą╗ąŠą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ:

ŌĆō čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ čĆąĄąČąĖą╝ čü čćą░čüč鹊č鹊ą╣ čéą░ą║č鹊ą▓ 100 ą║ąōčå (VCC = 1.7V .. 5.5V).

ŌĆō ą▒čŗčüčéčĆčŗą╣ čāčüą║ąŠčĆąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ (Fast mode) čü čćą░čüč鹊č鹊ą╣ čéą░ą║č鹊ą▓ 400 ą║ąōčå (VCC = 1.7V .. 5.5V).

- ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ čāčüą║ąŠčĆąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ (Fast Mode Plus, FM+) čü čćą░čüč鹊č鹊ą╣ čéą░ą║č鹊ą▓ 1 ą£ąōčå (VCC = 2.5V .. 5.5V).

ŌĆó ąöą╗čÅ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ čłčāą╝ą░ ąĮą░ ą▓čģąŠą┤ą░čģ ą┐čĆąĖą╝ąĄąĮąĄąĮ čéčĆąĖą│ą│ąĄčĆ ą©ą╝ąĖčéčéą░.

ŌĆó ąśą╝ąĄąĄčéčüčÅ ą▓čŗą▓ąŠą┤ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ (Write Protect, WP).

ŌĆó ąĪčéčĆą░ąĮąĖčćąĮčŗą╣ čĆąĄąČąĖą╝ ąĘą░ą┐ąĖčüąĖ (32-byte Page Write Mode), ą┐ąŠąĘą▓ąŠą╗čÅčÄčēąĖą╣ čćą░čüčéąĖčćąĮčāčÄ ąĘą░ą┐ąĖčüčī čüčéčĆą░ąĮąĖčåčŗ.

ŌĆó ąĀąĄąČąĖą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ ąĖ čĆąĄąČąĖą╝ čćč鹥ąĮąĖčÅ ą┐ąŠ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠą╝čā ą░ą┤čĆąĄčüčā.

ŌĆó ąÉą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖą╣ čåąĖą║ą╗ ąĘą░ą┐ąĖčüąĖ, čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąĮčŗą╣ ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ 5 ą╝čü).

ŌĆó ąŚą░čēąĖčéą░ ąŠčé čüčéą░čéąĖč湥čüą║ąŠą│ąŠ 菹╗ąĄą║čéčĆąĖč湥čüčéą▓ą░ (ESD Protection) > 4000V.

ŌĆó ąÆčŗčüąŠą║ą░čÅ ąĮą░ą┤ąĄąČąĮąŠčüčéčī čģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ:

ŌĆō ąĖąĘąĮąŠčüąŠčüč鹊ą╣ą║ąŠčüčéčī ą║ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüąĖ 1000000 čåąĖą║ą╗ąŠą▓.

ŌĆō čüąŠčģčĆą░ąĮąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ 100 ą╗ąĄčé.

ŌĆó ą×ą┐čåąĖąĖ ą┐ąŠčüčéą░ą▓ą║ąĖ "ąĘąĄą╗ąĄąĮčŗčģ" ą║ąŠčĆą┐čāčüąŠą▓ (Lead-free/Halide-free/RoHS compliant).

ŌĆó AT24C64D ą┐ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▓ čüč鹥čĆč鹊ą╝ čüąŠčüč鹊čÅąĮąĖąĖ, ą║ąŠą│ą┤ą░ ą▓čüčÅ ą┐ą░ą╝čÅčéčī EEPROM ąĘą░ą┐ąŠą╗ąĮąĄąĮą░ ąĄą┤ąĖąĮąĖčåą░ą╝ąĖ (ą▓čüąĄ čÅč湥ą╣ą║ąĖ čüąŠą┤ąĄčƹȹ░čé ąĘąĮą░č湥ąĮąĖąĄ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ FFh).

ą¤čĆąĖą╝ąĄčĆ čüąĖčüč鹥ą╝čŗ, ą│ą┤ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą╝ąĖą║čĆąŠčüčģąĄą╝ AT24XXX (slave, ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░), ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą║ ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ I2C:

ąÆąĖą┤čŗ ą║ąŠčĆą┐čāčüąŠą▓ AT24C64D, ą▓ąĖą┤ čüą▓ąĄčĆčģčā:

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą║ąŠčĆą┐čāčüąŠą▓ 4-ball ąĖ 6-ball WLCSP ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čĆą░ąĘą┤ąĄą╗čā "ąÉą┤čĆąĄčüą░čåąĖčÅ" ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ čāčüčéą░ąĮąŠą▓ą║ąĄ ą▒ąĖčé ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ A2, A1, A0.

ąóą░ą▒ą╗ąĖčåą░ 2-1. ąóą░ą▒ą╗ąĖčåą░ čåąŠą║ąŠą╗ąĄą▓ą║ąĖ ą║ąŠčĆą┐čāčüąŠą▓.

| ąśą╝čÅ |

SOIC8

TSSOP8 |

UDFN8(1),

XDFN8 |

8-ball

VFBGA |

4-ball

WLCSP(2) |

6-ball

WLCSP(2) |

ążčāąĮą║čåąĖčÅ |

| A0(3) |

1 |

1 |

1 |

- |

- |

ąÉą┐ą┐ą░čĆą░čéąĮčŗą╣ ą░ą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░ I2C |

| A1(3) |

2 |

2 |

2 |

- |

- |

| A2(3) |

3 |

3 |

3 |

- |

B3 |

| GND |

4 |

4 |

4 |

A2 |

B2 |

ąŚąĄą╝ą╗čÅ, ąŠą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤ |

| SDA |

5 |

5 |

5 |

B2 |

B1 |

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ |

| SCL |

6 |

6 |

6 |

B1 |

A1 |

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ čéą░ą║čéčŗ |

| WP(3) |

7 |

7 |

7 |

- |

A2 |

ąŚą░čēąĖčéą░ ąŠčé ąĘą░ą┐ąĖčüąĖ |

| VCC |

8 |

8 |

8 |

A1 |

A3 |

+ ą┐ąĖčéą░ąĮąĖčÅ |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ąØąĖąČąĮčÅčÅ ą╝ąĄčéą░ą╗ą╗ąĖč湥čüą║ą░čÅ ą║ąŠąĮčéą░ą║čéąĮą░čÅ ą┐ą╗ąŠčēą░ą┤ą║ą░ (exposed pad) ą║ąŠčĆą┐čāčüą░ UDFN ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ ą║ GND, ąĖą╗ąĖ ąŠčüčéą░ą▓ą╗ąĄąĮą░ ą▒ąĄąĘ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ.

2. ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą║ąŠčĆą┐čāčüąŠą▓ 4-ball ąĖ 6-ball WLCSP ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čĆą░ąĘą┤ąĄą╗čā "ąÉą┤čĆąĄčüą░čåąĖčÅ" ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ čāčüčéą░ąĮąŠą▓ą║ąĄ ą▒ąĖčé ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ A2, A1, A0.

3. ąĢčüą╗ąĖ ąĮą░ ą▓čŗą▓ąŠą┤ WP ąĮąĄ ą┐ąŠą┤ą░ąĮ ąĮąĖą║ą░ą║ąŠą╣ ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ (ąŠąĮ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ), č鹊 ąĄą│ąŠ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┐ąŠą┤čéčÅą│ąĖą▓ą░ąĄčéčüčÅ ą║ GND ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, čé. ąĄ. ąĘą░ą┐ąĖčüčī čĆą░ąĘčĆąĄčłąĄąĮą░. ąŁč鹊čé ą╝ąĄčģą░ąĮąĖąĘą╝ ą┐ąŠą┤čéčÅąČą║ąĖ čüą┤ąĄą╗ą░ąĮ ą┤ąŠą▓ąŠą╗čīąĮąŠ čüąĖą╗čīąĮčŗą╝, čćč鹊ą▒čŗ ąŠąĮ čģąŠčĆąŠčłąŠ čĆą░ą▒ąŠčéą░ą╗ ą▓ čłąĖčĆąŠą║ąŠą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ čĆą░ąĘą╗ąĖčćąĮčŗčģ čĆą░ą▒ąŠčćąĖčģ čāčüą╗ąŠą▓ąĖą╣. ąÜą░ą║ č鹊ą╗čīą║ąŠ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ WP čüą╝ąĄčēą░ąĄčéčüčÅ ą▓čŗčłąĄ ą┐ąŠčĆąŠą│ąŠą▓ąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ą╗čÅ ą▓čģąŠą┤ą░ ą▒čāč乥čĆą░ CMOS (~0.5 x VCC), ą╝ąĄčģą░ąĮąĖąĘą╝ ą┐ąŠą┤čéčÅąČą║ąĖ ąŠčüą▓ąŠą▒ąŠąČą┤ą░ąĄčéčüčÅ. Microchip čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčé ą┐ąŠ ą╝ąĄčĆąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą┐ąŠą┤ą║ą╗čÄčćą░čéčī ą▓čģąŠą┤ WP ą▓ ąĖąĘą▓ąĄčüčéąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ (čü čāčĆąŠą▓ąĮąĄą╝ VCC ąĖą╗ąĖ GND). ą¤ąŠčüą║ąŠą╗čīą║čā čā ą║ąŠčĆą┐čāčüąŠą▓ WLCSP ąĮąĄčé ą▓čŗą▓ąŠą┤ą░ WP, ą┤ą╗čÅ ąĮąĖčģ čäčāąĮą║čåąĖčÅ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ ąĮąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ.

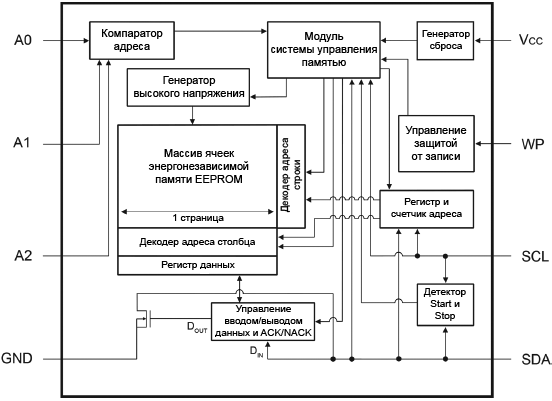

ąæą╗ąŠą║-čüčģąĄą╝ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ AT24C64D:

GND. ąÆčŗą▓ąŠą┤ ąĘąĄą╝ą╗ąĖ, ąŠą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤ ą┤ą╗čÅ ą▓čüąĄčģ čüąĖą│ąĮą░ą╗ąŠą▓, ą╝ąĖąĮčāčü ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ.

A0, A1, A2. ąÉą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ čłąĖąĮąĄ I2C. ąŁčéąĖ ą▓čŗą▓ąŠą┤čŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąČąĄčüčéą║ąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą╗ąĖą▒ąŠ ą║ GND, ą╗ąĖą▒ąŠ ą║ VCC, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī čü ą┤čĆčāą│ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ AT24C, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ ą║ ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą░ą┤čĆąĄčüąŠą▓ą░čéčī ą┤ąŠ 8 čĆą░ąĘąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗčģ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ SCL ąĖ SDA. ąĢčüą╗ąĖ ą▓čŗą▓ąŠą┤čŗ A0, A1, A2 ąŠčüčéą░ą▓ąĖčéčī ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ, č鹊 ąŠąĮąĖ ą┐ąŠą╗čāčćą░čé ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ąŠą┤čéčÅąČą║čā ą║ čāčĆąŠą▓ąĮčÄ GND. ą×ą┤ąĮą░ą║ąŠ ą▓ čéą░ą║ąŠą╝ čüą╗čāčćą░ąĄ ą▓ąŠąĘą╝ąŠąČąĮą░ ąĄą╝ą║ąŠčüčéąĮą░čÅ ąĮą░ą▓ąŠą┤ą║ą░ ą┐ąŠą╝ąĄčģ ąĮą░ čŹčéąĖ ą▓čŗą▓ąŠą┤čŗ, ą┐ąŠčŹč鹊ą╝čā Microchip ą▓čüąĄą│ą┤ą░ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčé ą┐ąŠą┤ą║ą╗čÄčćą░čéčī čŹčéąĖ ą░ą┤čĆąĄčüąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ ą▓ ąĖąĘą▓ąĄčüčéąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ. ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą┤ą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą▓ąĮąĄčłąĮąĖčģ ą▓ąĄčĆčģąĮąĖčģ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓ (pull-up) ąĖčģ ąĮąŠą╝ąĖąĮą░ą╗ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī 10 ą║ą×ą╝ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ.

SDA. ąÆčŗą▓ąŠą┤ SDA ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ąĖąĘ-čüąĄą▒čÅ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ, ą▓čŗčģąŠą┤ ą║ąŠč鹊čĆąŠą│ąŠ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ąĮą░ ą║ą╗čÄč湥 čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ SDA ą┤ąŠą╗ąČąĄąĮ ąĖą╝ąĄčéčī ą▓ąĮąĄčłąĮčÄčÄ ą┐ąŠą┤čéčÅąČą║čā ą║ VCC čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄąĘąĖčüč鹊čĆą░ ąĮąŠą╝ąĖąĮą░ą╗ąŠą╝ ąĮąĄ ą▒ąŠą╗čīčłąĄ 10 ą║ą×ą╝. ąóą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ čĆąĄą░ą╗ąĖąĘčāąĄčéčüčÅ čüčģąĄą╝ą░ ą┐čĆąŠą▓ąŠą┤ąĮąŠą│ąŠ ąśąøąś čü ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╝ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄą╝ (ą┐ąŠčćčéąĖ) ą╗čÄą▒ąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čāčüčéčĆąŠą╣čüčéą▓, čā ą║ąŠč鹊čĆčŗčģ ą▓čŗčģąŠą┤čŗ č鹊ąČąĄ ąĖą╝ąĄčÄčé ąŠčéą║čĆčŗčéčŗą╣ čüč鹊ą║ (ąĖą╗ąĖ ąŠčéą║čĆčŗčéčŗą╣ ą║ąŠą╗ą╗ąĄą║č鹊čĆ).

SCL. ąÆčģąŠą┤, č湥čĆąĄąĘ ą║ąŠč鹊čĆčŗą╣ ąĮą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠą┤ą░ąĄčéčüčÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░, ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą║ąŠč鹊čĆąŠą╣ ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ SDA ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ. ąæąĖčéčŗ ą║ąŠą╝ą░ąĮą┤ ąĖ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠčüčéčāą┐ą░čÄčēąĖčģ ąĮą░ ą▓čŗą▓ąŠą┤ SDA, ą▓čüąĄą│ą┤ą░ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ SCL, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓čŗą▓ąŠą┤čÅčéčüčÅ ąĮą░čĆčāąČčā č湥čĆąĄąĘ č鹊čé ąČąĄ ą▓čŗą▓ąŠą┤ SDA ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ SCL. ąÜąŠą│ą┤ą░ čłąĖąĮą░ I2C ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ, čüąĖą│ąĮą░ą╗ SCL ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąĖčéčÅąĮčāčé ą║ ą╗ąŠą│. 1 ą╗ąĖą▒ąŠ ą▓ąĮąĄčłąĮąĖą╝ ą▓čŗčģąŠą┤ąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ą░čüč鹥čĆą░ čłąĖąĮčŗ, ą╗ąĖą▒ąŠ ą┐ąŠą┤čéčÅąĮčāčé ą║ ą╗ąŠą│. 1 ą▓ąĮąĄčłąĮąĖą╝ ą▓ąĄčĆčģąĮąĖą╝ čĆąĄąĘąĖčüč鹊čĆąŠą╝ pull-up.

WP. ąŁč鹊 ą▓čģąŠą┤ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ (Write Protect). ąÜąŠą│ą┤ą░ ąŠąĮ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ GND, čĆą░ąĘčĆąĄčłą░čÄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ. ąÜąŠą│ą┤ą░ WP ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ VCC, ą▓čüąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ą▓ ą╗čÄą▒čāčÄ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ ąĘą░ą┐čĆąĄčēąĄąĮčŗ. ąĢčüą╗ąĖ čŹč鹊čé ą▓čŗą▓ąŠą┤ ąŠčüčéą░ą▓ąĖčéčī ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝, č鹊 ąŠąĮ ą▒čāą┤ąĄčé ą┐ąŠą┤čéčÅąĮčāčé ą║ čāčĆąŠą▓ąĮčÄ GND ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ. ą×ą┤ąĮą░ą║ąŠ ą▓ čéą░ą║ąŠą╝ čüą╗čāčćą░ąĄ ą▓ąŠąĘą╝ąŠąČąĮą░ ąĄą╝ą║ąŠčüčéąĮą░čÅ ąĮą░ą▓ąŠą┤ą║ą░ ą┐ąŠą╝ąĄčģ ąĮą░ WP, ą┐ąŠčŹč鹊ą╝čā Microchip ą▓čüąĄą│ą┤ą░ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčé ą┐ąŠą┤ą║ą╗čÄčćą░čéčī čŹč鹊čé ą▓čģąŠą┤ ą║ ąĖąĘą▓ąĄčüčéąĮąŠą╝čā čāčĆąŠą▓ąĮčÄ. ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą┤ą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą▓ąĮąĄčłąĮąĖčģ ą▓ąĄčĆčģąĮąĖčģ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓ (pull-up) ąĖčģ ąĮąŠą╝ąĖąĮą░ą╗ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī 10 ą║ą×ą╝ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ.

VCC. ą¤ąĖčéą░ąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░. ąĪą╗ąĄą┤čāąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą▓ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąĖ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ąŠčéčüčāčéčüčéą▓ąĖąĄ ą┐ąŠą╝ąĄčģ, ąĖąĮą░č湥 菹║čüą┐ą╗čāą░čéą░čåąĖčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąŠčłąĖą▒ą║ą░ą╝ ąĖ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ čĆąĄąĘčāą╗čīčéą░čéą░ą╝.

[ąÉą▒čüąŠą╗čÄčéąĮčŗąĄ ą┐čĆąĄą┤ąĄą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ]

ąĀą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ -55┬░C .. +125┬░C

ąöąĖą░ą┐ą░ąĘąŠąĮ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ čģčĆą░ąĮąĄąĮąĖčÅ -65┬░C .. +150┬░C

VCC 6.25V

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą╗čÄą▒ąŠą╝ ą▓čŗą▓ąŠą┤ąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ GND -1.0V .. +7.0V

ą¤ąŠčüč鹊čÅąĮąĮčŗą╣ (DC) ą▓čŗčģąŠą┤ąĮąŠą╣ č鹊ą║ 5.0 mA

ESD ąĘą░čēąĖčéą░ >4 kV

[ąĀą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ DC ąĖ AC]

ąóą░ą▒ą╗ąĖčåą░ 4-1. ąĀą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ.

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąöąĖą░ą┐ą░ąĘąŠąĮ ąĘąĮą░č湥ąĮąĖą╣ |

| ąóąĄą╝ą┐ąĄčĆą░čéčāčĆą░ ą║ąŠčĆą┐čāčüą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (ąĖąĮą┤čāčüčéčĆąĖą░ą╗čīąĮąŠąĄ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ) |

-40┬░C .. +85┬░C |

| ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ VCC (ą║ą╗ą░čüčü ą╝ąĖą║čĆąŠčüčģąĄą╝ čü ąĮąĖąĘą║ąĖą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ, Low Voltage Grade) |

1.7V .. 5.5V |

ąóą░ą▒ą╗ąĖčåą░ 4-2. ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ DC.

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

Sym |

MIN |

nom(1) |

MAX |

ąĢą┤. |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

| ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ |

VCC1 |

- |

- |

5.5 |

V |

|

| ą¤ąŠčéčĆąĄą▒ą╗čÅąĄą╝čŗą╣ č鹊ą║ |

ICC1 |

- |

0.4 |

1.0 |

mA |

VCC = 5.0V, čćč鹥ąĮąĖąĄ ąĮą░ 400 ą║ąōčå |

| ICC2 |

- |

2.0 |

3.0 |

mA |

VCC = 5.0V, ąĘą░ą┐ąĖčüčī ąĮą░ 400 ą║ąōčå |

| ąóąŠą║ čĆąĄąČąĖą╝ą░ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (Standby) |

ISB1 |

- |

- |

1 |

╬╝A |

VCC = 1.7V, VIN = VCC ąĖą╗ąĖ GND |

| - |

- |

6 |

╬╝A |

VCC = 5.0V, VIN = VCC ąĖą╗ąĖ GND |

| ąÆčģąŠą┤ąĮąŠą╣ č鹊ą║ čāč鹥čćą║ąĖ |

ILI |

- |

0.10 |

3.0 |

╬╝A |

VIN = VCC ąĖą╗ąĖ GND; VCC = 5.0V |

| ąÆčŗčģąŠą┤ąĮąŠą╣ č鹊ą║ čāč鹥čćą║ąĖ |

ILO |

- |

0.05 |

3.0 |

╬╝A |

VOUT = VCC ąĖą╗ąĖ GND; VCC = 5.0V |

| ąÆčģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0 |

VIL |

-0.6 |

- |

VCC x 0.3 |

V |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (2) |

| ąÆčģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1 |

VIH |

VCC x 0.7 |

- |

VCC + 0.5 |

V |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (2) |

| ąÆčŗčģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0 |

VOL1 |

- |

- |

0.2 |

V |

VCC = 1.7V, IOL = 0.15 mA |

| ąÆčŗčģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0 |

VOL2 |

- |

- |

0.4 |

V |

VCC = 3.0V, IOL = 2.1 mA |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąóąĖą┐ąŠą▓čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ čāą║ą░ąĘą░ąĮčŗ ą┐čĆąĖ TA = +25┬░C, ąĄčüą╗ąĖ ąĮąĄ ąŠčéą╝ąĄč湥ąĮąŠ čćč鹊-č鹊 ą┤čĆčāą│ąŠąĄ.

(2) ąŁč鹊čé ą┐ą░čĆą░ą╝ąĄčéčĆ čģą░čĆą░ą║č鹥čĆąĖąĘąŠą▓ą░ąĮ, ąŠą┤ąĮą░ą║ąŠ ąĮąĄ ą▒čŗą╗ ąĮą░ 100% ą┐čĆąŠą▓ąĄčĆąĄąĮ ą┐čĆąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąĄ.

[ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ AC]

ąóą░ą▒ą╗ąĖčåą░ 4-3. ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą│ąŠ č鹊ą║ą░ AC(1).

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

Sym |

Fast Mode |

Fast Mode Plus |

ąĢą┤. |

| VCC = 1.7V .. 2.5V |

VCC = 2.5V .. 5.0V |

| MIN |

MAX |

MIN |

MAX |

| ą¦ą░čüč鹊čéą░ čéą░ą║č鹊ą▓ SCL |

fSCL |

- |

400 |

- |

1000 |

ą║ąōčå |

| ąśąĮč鹥čĆą▓ą░ą╗ ą╗ąŠą│. 0 SCL |

tLOW |

1300 |

- |

500 |

- |

ąĮčü |

| ąśąĮč鹥čĆą▓ą░ą╗ ą╗ąŠą│. 1 SCL |

tHIGH |

600 |

- |

400 |

- |

ąĮčü |

| ąśąĮč鹥čĆą▓ą░ą╗ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ čłčāą╝ą░(2) |

tI |

- |

100 |

- |

50 |

ąĮčü |

| ąśąĮč鹥čĆą▓ą░ą╗ ą╝ąĄąČą┤čā SCL=0 ą┤ąŠ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗčģ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ |

tAA |

50 |

900 |

50 |

450 |

ąĮčü |

| ąÆčĆąĄą╝čÅ čüą▓ąŠą▒ąŠą┤ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ čłąĖąĮčŗ ą╝ąĄąČą┤čā Stop ąĖ Start(2) |

tBUF |

1300 |

- |

500 |

- |

ąĮčü |

| ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ čłąĖąĮčŗ (Start Hold Time) |

tHD.STA |

600 |

- |

250 |

- |

ąĮčü |

| ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čüąŠčüč鹊čÅąĮąĖčÅ čüčéą░čĆčéą░ (Start SetŌĆæup Time) |

tSU.STA |

600 |

- |

250 |

- |

ąĮčü |

| ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (Data In Hold Time) |

tHD.DAT |

0 |

- |

0 |

- |

ąĮčü |

| ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čüąŠčüč鹊čÅąĮąĖčÅ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (Data In SetŌĆæup Time) |

tSU.DAT |

100 |

- |

100 |

- |

ąĮčü |

| ąÆčĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čģąŠą┤ąĄ(2) |

tR |

- |

300 |

- |

300 |

ąĮčü |

| ąÆčĆąĄą╝čÅ čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čģąŠą┤ąĄ(2) |

tF |

- |

300 |

- |

100 |

ąĮčü |

| ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čüč鹊ą┐ (Stop Set-up Time) |

tSU.STO |

600 |

- |

250 |

- |

ąĮčü |

| ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (Data Out Hold Time) |

tDH |

50 |

- |

50 |

- |

ąĮčü |

| ąÆčĆąĄą╝čÅ čåąĖą║ą╗ą░ ąĘą░ą┐ąĖčüąĖ |

tWR |

- |

5 |

- |

5 |

ą╝čü |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąŻčüą╗ąŠą▓ąĖčÅ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ AC:

- RPUP (ą▓ąĄčĆčģąĮąĖą╣ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖą╣ čĆąĄąĘąĖčüč鹊čĆ, pull-up ą╝ąĄąČą┤čā SDA ąĖ VCC): 1.3 k╬® (1000 ą║ąōčå), 4 k╬® (400 ą║ąōčå), 10 k╬® (100 ą║ąōčå).

- ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓čģąŠą┤ąĮčŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓: 0.3 VCC .. 0.7 VCC

- ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ąĖ čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čģąŠą┤ąĄ: Ōēż 50 ąĮčü.

- ą×ą┐ąŠčĆąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī, ąŠčé ą║ąŠč鹊čĆąŠą│ąŠ ąŠčéčüčćąĖčéčŗą▓ą░ą╗ąĖčüčī ą▓čģąŠą┤ąĮčŗąĄ ąĖ ą▓čŗčģąŠą┤ąĮčŗąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ: 0.5 VCC.

(2) ąŁč鹊čé ą┐ą░čĆą░ą╝ąĄčéčĆ čāą║ą░ąĘą░ąĮ ą║ą░ą║ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░, ąĖ ąŠąĮ ąĮąĄ ą▒čŗą╗ ą┐čĆąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮ ąĮą░ 100%.

ąĀąĖčü. 4-1. ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ čłąĖąĮčŗ.

[ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ]

ąóčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ą▓ą║ą╗čÄč湥ąĮąĖčÄ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐čĆąĖ čüą▒čĆąŠčüąĄ. ąÆąŠ ą▓čĆąĄą╝čÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ čāčĆąŠą▓ąĄąĮčī VCC, ą┐ąŠą┤ą░ąĮąĮčŗą╣ ąĮą░ AT24C64D, ą┤ąŠą╗ąČąĄąĮ ą╝ąŠąĮąŠč鹊ąĮąĮąŠ ą▓ąŠąĘčĆą░čüčéą░čéčī ąŠčé GND ą┤ąŠ čüą▓ąŠąĄą│ąŠ ąĮąŠą╝ąĖąĮą░ą╗čīąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ, čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 4-1, čüąŠ čüą║ąŠčĆąŠčüčéčīčÄ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ąĮąĄ ą▒čŗčüčéčĆąĄąĄ č湥ą╝ 0.1 V/ą╝ą║čü.

ąĪą▒čĆąŠčü čāčüčéčĆąŠą╣čüčéą▓ą░. ą¦č鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī ąĮąĄą┐čĆąĄą┤ąĮą░ą╝ąĄčĆąĄąĮąĮčŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ąĖą╗ąĖ ą┤čĆčāą│ąĖąĄ čüą╗čāčćą░ą╣ąĮčŗąĄ čüąŠą▒čŗčéąĖčÅ ą┐čĆąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, ą▓ čāčüčéčĆąŠą╣čüčéą▓ąĄ AT24C64D ąĖą╝ąĄąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čüčģąĄą╝ą░ čüą▒čĆąŠčüą░ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ Power-on Reset (POR). ą¤čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ą▒čāą┤ąĄčé ąŠčéą▓ąĄčćą░čéčī ąĮąĖ ąĮą░ ą║ą░ą║ąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ, ą┐ąŠą║ą░ čāčĆąŠą▓ąĄąĮčī VCC ąĮąĄ ą┐ąĄčĆąĄčüąĄč湥čé ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą┐ąŠčĆąŠą│ čüą▒čĆąŠčüą░ (VPOR), ą║ąŠč鹊čĆčŗą╣ ą▓čŗą▓ąĄą┤ąĄčé čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ Reset ąĖ ą┐ąĄčĆąĄą▓ąĄą┤ąĄčé ą▓ čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ (Standby mode).

ąĀą░ąĘčĆą░ą▒ąŠčéčćąĖą║ čüąĖčüč鹥ą╝čŗ ą┤ąŠą╗ąČąĄąĮ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ą▒čāą┤čāčé ąŠčéą┐čĆą░ą▓ą╗čÅčéčīčüčÅ ą║ąŠą╝ą░ąĮą┤čŗ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ čāčĆąŠą▓ąĄąĮčī VCC ąĮąĄ ąĘą░čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ąĮą░ ąĘąĮą░č湥ąĮąĖąĖ, ą▒ąŠą╗čīčłąĄą╝ ąĖą╗ąĖ čĆą░ą▓ąĮąŠą╝ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╝čā čāčĆąŠą▓ąĮčÄ VCC. ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ą║ą░ą║ č鹊ą╗čīą║ąŠ VCC čüčéą░ąĮąĄčé ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮčŗą╝ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╝čā čāčĆąŠą▓ąĮčÄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VCC, ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ą┤ąŠą╗ąČąĄąĮ ą┐ąŠą┤ąŠąČą┤ą░čéčī ą▓ č鹥č湥ąĮąĖąĄ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąĖąĮč鹥čĆą▓ą░ą╗ą░ ą▓čĆąĄą╝ąĄąĮąĖ tPUP ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą▒čāą┤ąĄčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮą░ ą┐ąĄčĆą▓ą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ. ąĪą╝. čéą░ą▒ą╗ąĖčåčā 4-4, ą│ą┤ąĄ čāą║ą░ąĘą░ąĮčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ.

ąóą░ą▒ą╗ąĖčåą░ 4-4. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ąĖ čāčüą╗ąŠą▓ąĖčÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ(1).

| Sym |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

MIN |

MAX |

ąĢą┤. |

| tPUP |

ąØąĄąŠą▒čģąŠą┤ąĖą╝čŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąŠčüą╗ąĄ čüčéą░ą▒ąĖą╗ąĖąĘą░čåąĖąĖ čāčĆąŠą▓ąĮčÅ VCC ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą╝ąŠąČąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī ą║ąŠą╝ą░ąĮą┤čŗ |

100 |

- |

ą╝ą║čü |

| VPOR |

ą¤ąŠčĆąŠą│ąŠą▓ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓čŗčģąŠą┤ą░ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ čüą▒čĆąŠčüą░ |

- |

1.5 |

V |

| tPOFF |

ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ą▓čĆąĄą╝ąĄąĮąĖ ą┐čĆąĖ VCC = 0V ą╝ąĄąČą┤čā ą▓ą║ą╗čÄč湥ąĮąĖčÅą╝ąĖ ą┐ąĖčéą░ąĮąĖčÅ. |

500 |

- |

ą╝čü |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): čŹčéąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┤ą░ąĮčŗ č鹊ą╗čīą║ąŠ ą║ą░ą║ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░, ąŠą┤ąĮą░ą║ąŠ ąŠąĮąĖ ąĮąĄ ą▒čŗą╗ąĖ ąĮą░ 100% ą┐čĆąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮčŗ ą▓ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąĄ.

ąĢčüą╗ąĖ ą▓ čüąĖčüč鹥ą╝ąĄ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▒čŗčéąĖąĄ, ą║ąŠą│ą┤ą░ ą┐ąŠą┤ą░ą▓ą░ąĄą╝čŗą╣ ąĮą░ AT24C64D čāčĆąŠą▓ąĄąĮčī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VCC ą┐ą░ą┤ą░ąĄčé ąĮąĖąČąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ VPOR, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐čĆąŠą▓ąĄčüčéąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐ąŠą╗ąĮąŠą│ąŠ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą┐čāč鹥ą╝ ą┐ąĄčĆą▓ąŠąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ą░ čāčĆąŠą▓ąĮčÅ VCC ą║ GND, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗą┤ąĄčƹȹ░ąĮ ąĖąĮč鹥čĆą▓ą░ą╗ tPOFF, ąĖ ąĘą░č鹥ą╝ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĮą░čćą░čéą░ ąĮąŠą▓ą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, čüąŠą▓ą╝ąĄčüčéąĖą╝ą░čÅ čü čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ąĖ, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ąĖ ą▓ čŹč鹊ą╣ čüąĄą║čåąĖąĖ.

[ą¤ą░čĆą░ąĘąĖčéąĮčŗąĄ ąĄą╝ą║ąŠčüčéąĖ]

ąóą░ą▒ą╗ąĖčåą░ 4-5. ąĢą╝ą║ąŠčüčéąĖ ą▓čŗą▓ąŠą┤ąŠą▓(1).

| Sym |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

MAX |

ąĢą┤. |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

| CI/O |

ąĢą╝ą║ąŠčüčéčī ą▓čģąŠą┤ą░/ą▓čŗčģąŠą┤ą░ (SDA) |

8 |

ą┐ąż |

VI/O = 0V |

| CIN |

ąĢą╝ą║ąŠčüčéčī ą▓čģąŠą┤ą░ (A2, A1, A0 ąĖ SCL) |

6 |

ą┐ąż |

VI/O = 0V |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): čŹčéąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┤ą░ąĮčŗ č鹊ą╗čīą║ąŠ ą║ą░ą║ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░, ąŠą┤ąĮą░ą║ąŠ ąŠąĮąĖ ąĮąĄ ą▒čŗą╗ąĖ ąĮą░ 100% ą┐čĆąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮčŗ ą▓ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąĄ.

[ą¤čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī čÅč湥ąĄą║ ą┐ą░ą╝čÅčéąĖ EEPROM]

ąóą░ą▒ą╗ąĖčåą░ 4-6. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ čÅč湥ąĄą║ ą┐ą░ą╝čÅčéąĖ EEPROM.

| ą×ą┐ąĄčĆą░čåąĖčÅ |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

MIN |

MAX |

ąĢą┤ąĖąĮąĖčåčŗ |

ąśąĘąĮąŠčüąŠčüč鹊ą╣ą║ąŠčüčéčī ąĘą░ą┐ąĖčüąĖ(1)

|

TA = 25┬░C, VCC = 3.3V, čĆąĄąČąĖą╝ ąĘą░ą┐ąĖčüąĖ čüčéčĆą░ąĮąĖčåčŗ |

1000000 |

- |

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓ ąĘą░ą┐ąĖčüąĖ |

| ąĪčĆąŠą║ čģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ(1) |

TA = 55┬░C |

100 |

- |

ąøąĄčé |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): čŹčéąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┐ąŠą╗čāč湥ąĮąĖčÅ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ ąĖ ąŠčåąĄąĮą║ąĖ ą║ą░č湥čüčéą▓ą░.

[ąĀą░ą▒ąŠčéą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ]

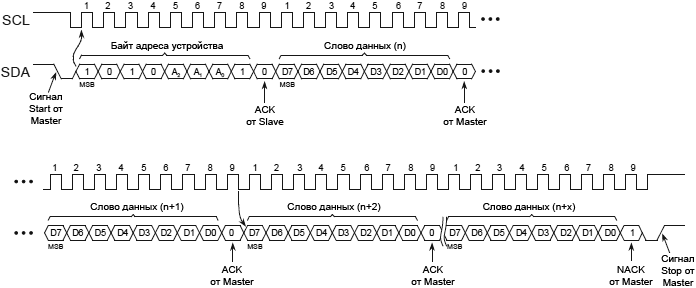

AT24C64D čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ (slave) čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čłąĖąĮąĄ I2C, ąŠą▒ą╝ąĄąĮąĖą▓ą░čÅčüčī ą┤ą░ąĮąĮčŗą╝ąĖ čü ą│ą╗ą░ą▓ąĮčŗą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝, čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╝ ą╝ą░čüč鹥čĆąŠą╝ čłąĖąĮčŗ (bus master). ą£ą░čüč鹥čĆ ąĖąĮąĖčåąĖąĖčĆčāąĄčé ąĖ čāą┐čĆą░ą▓ą╗čÅąĄčé ą▓čüąĄą╝ąĖ ąŠą┐ąĄčĆą░čåąĖčÅą╝ąĖ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ, ąŠčüčāčēąĄčüčéą▓ą╗čÅčÅ ąŠą▒ą╝ąĄąĮ čü ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ ą║ čłąĖąĮąĄ. ąś ą╝ą░čüč鹥čĆ, ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠą│čāčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą┐ąŠ čłąĖąĮąĄ ą▓ ą╗čÄą▒ąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ.

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü čłąĖąĮčŗ čüąŠčüč鹊ąĖčé č鹊ą╗čīą║ąŠ ąĖąĘ ą┤ą▓čāčģ čüąĖą│ąĮą░ą╗ąŠą▓: Serial Clock (SCL) ąĖ Serial Data (SDA). ąÆčŗą▓ąŠą┤ SCL ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ čéą░ą║č鹊ą▓ ąŠčé ą╝ą░čüč鹥čĆą░ (čŹč鹊 ą▓čģąŠą┤), ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ą▓čŗą▓ąŠą┤ SDA ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ą║ąŠą╝ą░ąĮą┤ ąĖ ą┤ą░ąĮąĮčŗčģ ąŠčé ą╝ą░čüč鹥čĆą░, ą░ čéą░ą║ąČąĄ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą┤ą░ąĮąĮčŗčģ ąŠą▒čĆą░čéąĮąŠ ą║ ą╝ą░čüč鹥čĆčā. ąöą░ąĮąĮčŗąĄ, ą┐ąŠčüčéčāą┐ą░čÄčēąĖąĄ ą▓ AT24C64D, ą▓čüąĄą│ą┤ą░ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ čāčĆąŠą▓ąĮčÅ SCL, ąĖ ą▓čüąĄą│ą┤ą░ ą▓čŗą▓ąŠą┤čÅčéčüčÅ ąĖąĘ AT24C64D ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ SCL. ąØą░ ąŠą▒ąŠąĖčģ čüąĖą│ąĮą░ą╗ą░čģ SCL ąĖ SDA ąĖą╝ąĄąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮą░čÅ čüąĖčüč鹥ą╝ą░ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ/čäąĖą╗čīčéčĆą░čåąĖąĖ ą┐ąŠą╝ąĄčģ ąĮą░ čéčĆąĖą│ą│ąĄčĆą░čģ ą©ą╝ąĖčéčéą░.

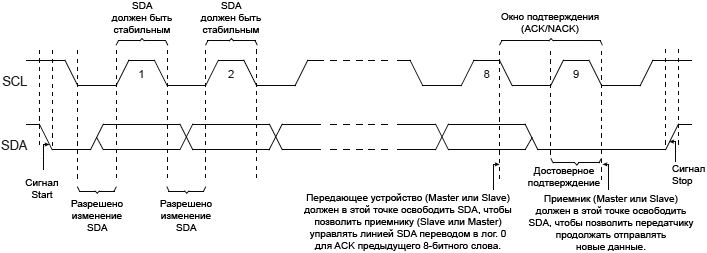

ąśąĮč乊čĆą╝ą░čåąĖčÅ ą║ąŠą╝ą░ąĮą┤ ąĖ ą┤ą░ąĮąĮčŗčģ ą▓čüąĄą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ čüą░ą╝čŗą╝ čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ (Most Significant Bit, MSB) ą▓ą┐ąĄčĆąĄą┤. ąÆąŠ ą▓čĆąĄą╝čÅ ąŠą▒ą╝ąĄąĮą░ ą┐ąŠ čłąĖąĮąĄ ąŠą┤ąĖąĮ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ čéą░ą║č鹥 SCL, ąĖ ą┐ąŠčüą╗ąĄ ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖčÅ 8 ą▒ąĖčé (ąŠą┤ąĮąŠą│ąŠ ą▒ą░ą╣čéą░) ą┐čĆąĖąĮąĖą╝ą░čÄčēąĄąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ąŠą╗ąČąĮąŠ ąŠčéą▓ąĄčéąĖčéčī ą╗ąĖą▒ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╝ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄą╝ (Acknowledge, ACK), ą╗ąĖą▒ąŠ ąŠčéčüčāčéčüčéą▓ąĖąĄą╝ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ (No-Acknowledge, NACK) ą▓ąŠ ą▓čĆąĄą╝čÅ ą┤ąĄą▓čÅč鹊ą│ąŠ čéą░ą║čéą░ SCK (čéą░ą║čé ACK/NACK), čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą╝ą░čüč鹥čĆąŠą╝. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┤ą╗čÅ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ąŠą┤ąĮąŠ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ čéčĆąĄą▒čāąĄčéčüčÅ 9 čéą░ą║č鹊ą▓. ąÆ ąŠą┐ąĄčĆą░čåąĖčÅčģ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ ąĮąĄčé ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ čéą░ą║č鹊ą▓, ą┐ąŠčŹč鹊ą╝čā ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĮąĖą║ą░ą║ąĖčģ ąĮą░čĆčāčłąĄąĮąĖą╣ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ ą▓ ą┐ąŠč鹊ą║ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą░ą╣čéą░ ąĖ ą▒ąĖč鹊ą▓ ACK ąĖą╗ąĖ NACK.

ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖą╣ ą┤ą░ąĮąĮčŗčģ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SDA ą╝ąŠąČąĄčé ą╝ąĄąĮčÅčéčī čüą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčĆąŠą▓ąĄąĮčī SCL ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0, ąĖ ą┤ą░ąĮąĮčŗąĄ ąĮą░ SDA ą┤ąŠą╗ąČąĮčŗ ąŠčüčéą░ą▓ą░čéčīčüčÅ čüčéą░ą▒ąĖą╗čīąĮčŗą╝ąĖ, ą║ąŠą│ą┤ą░ ąĮą░ SCL ą╗ąŠą│. 1. ąĢčüą╗ąĖ ą┤ą░ąĮąĮčŗąĄ ąĮą░ SDA ą╝ąĄąĮčÅčÄčé čāčĆąŠą▓ąĄąĮčī, ą║ąŠą│ą┤ą░ SCL ą▓ ą╗ąŠą│. 1, č鹊 čŹč鹊čé čäą░ą║čé ąŠą▒ąŠąĘąĮą░čćą░ąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ čüąŠą▒čŗčéąĖčÅ čüčéą░čĆčéą░ ąĖą╗ąĖ ąŠčüčéą░ąĮąŠą▓ą░ (čüąĖą│ąĮą░ą╗ Start ąĖą╗ąĖ čüąĖą│ąĮą░ą╗ Stop). ąĪąĖą│ąĮą░ą╗čŗ Start ąĖ Stop ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąĖąĮąĖčåąĖą░čåąĖąĖ ąĖą╗ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą▓čüąĄčģ ąŠą▒ą╝ąĄąĮąŠą▓ ą┤ą░ąĮąĮčŗą╝ąĖ ą╝ąĄąČą┤čā ą╝ą░čüč鹥čĆąŠą╝ ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ą┐ąĄčĆąĄčüčŗą╗ą░ąĄą╝čŗčģ ą╝ąĄąČą┤čā Start ąĖ Stop, ąĮąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąŠ ąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą╝ą░čüč鹥čĆąŠą╝ čłąĖąĮčŗ. ą¦č鹊ą▒čŗ čłąĖąĮą░ I2C ąĮą░čģąŠą┤ąĖą╗ą░čüčī ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ, ąĮą░ ąŠą▒ąŠąĖčģ ą▓čŗą▓ąŠą┤ą░čģ SCL ąĖ SDA ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1.

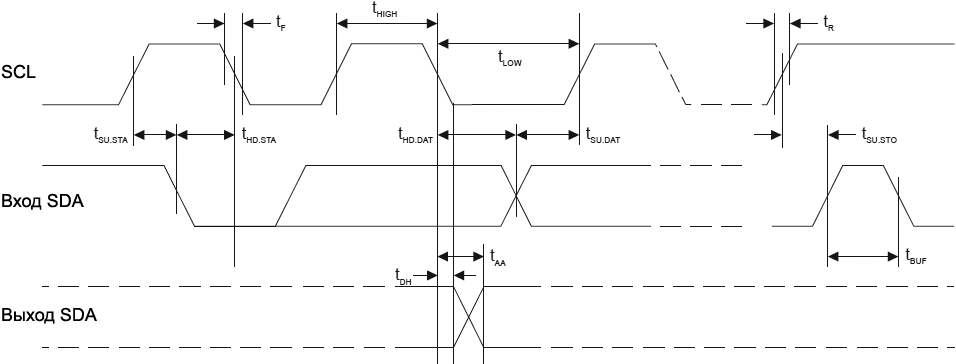

ąóčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅą╝ čāčĆąŠą▓ąĮčÅ ą┤ą░ąĮąĮčŗčģ ąĖ čéą░ą║č鹊ą▓. ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ą▓čŗą▓ąŠą┤ SDA ąĖą╝ąĄąĄčé ą┤čĆą░ą╣ą▓ąĄčĆ ą▓čŗčģąŠą┤ą░ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝, ąĖ ą┐ąŠčŹč鹊ą╝čā ą┤ąŠą╗ąČąĄąĮ ąĖą╝ąĄčéčī ą┐ąŠą┤čéčÅąČą║čā ą║ ą╗ąŠą│. 1 čü ą┐ąŠą╝ąŠčēčīčÄ ą▓ąĮąĄčłąĮąĄą│ąŠ pull-up čĆąĄąĘąĖčüč鹊čĆą░. ąÆčģąŠą┤ SCL ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą║ ą╗ąŠą│. 1 ą╗ąĖą▒ąŠ ą▓ąĮąĄčłąĮąĖą╝ ą▓čŗčģąŠą┤ąŠą╝, ą╗ąĖą▒ąŠ ą▓ąĮąĄčłąĮąĖą╝ pull-up čĆąĄąĘąĖčüč鹊čĆąŠą╝ (ąŠą▒čŗčćąĮąŠ ą┤ą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą▓čüąĄą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ pull-up čĆąĄąĘąĖčüč鹊čĆ, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ą╗ąŠą│. 1 ą▓ ą╝ąŠą╝ąĄąĮčéčŗ ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠą│ą┤ą░ ą╝ą░čüč鹥čĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ąŠčéą║ą╗čÄč湥ąĮąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ). ąÆąĘą░ąĖą╝ąŠčüą▓čÅąĘčī ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą│ąŠ č鹊ą║ą░ (AC timing parameters) čüąĖą│ąĮą░ą╗ąŠą▓ SCL ąĖ SDA ą┤ą╗čÅ AT24C64D ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 4-1 (čüą╝. ą▓čĆąĄąĘą║čā "ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ"). ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ AC ąĖ ąĖčģ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ąŠą▒ąŠąĘąĮą░č湥ąĮčŗ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ AC".

Start ąĖ Stop. ąĪąŠą▒čŗčéąĖąĄ Start ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐ąĄčĆąĄčģąŠą┤ 1 -> 0 ąĮą░ SDA, ą║ąŠą│ą┤ą░ ąĮą░ SCL čüčéą░ą▒ąĖą╗čīąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1, ąĖ čŹč鹊 čüąŠą▒čŗčéąĖąĄ ą▓čŗą▓ąŠą┤ąĖčé čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĖąĘ čĆąĄąČąĖą╝ą░ ąŠąČąĖą┤ą░ąĮąĖčÅ (Standby mode). ąĪąĖą│ąĮą░ą╗ Start ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą╝ą░čüč鹥čĆ, ąĖ ąŠąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčé Start ą┤ą╗čÅ ąĖąĮąĖčåąĖą░čåąĖąĖ ą╗čÄą▒ąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ; čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą║ą░ąČą┤ą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ ą┤ąŠą╗ąČąĮą░ ąĮą░čćąĖąĮą░čéčīčüčÅ čü čüąŠą▒čŗčéąĖčÅ/čüąĖą│ąĮą░ą╗ą░ Start. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą╝ąŠąĮąĖč鹊čĆąĖčé ą▓čŗą▓ąŠą┤čŗ SDA ąĖ SCL ąĮą░ ą┐čĆąĄą┤ą╝ąĄčé ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ Start ąĖ ąĮąĄ ąŠčéą▓ąĄčćą░ąĄčé, ą┐ąŠą║ą░ Start ąĮąĄ ą▒čāą┤ąĄčé ąŠą▒ąĮą░čĆčāąČąĄąĮ (čüą╝. čĆąĖčü. 5-1).

ąĪąŠą▒čŗčéąĖąĄ Stop ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐ąĄčĆąĄčģąŠą┤ 0 -> ąĮą░ SDA, ą║ąŠą│ą┤ą░ ąĮą░ SCL čüčéą░ą▒ąĖą╗čīąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1. ą£ą░čüč鹥čĆ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī Stop ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, ą┐ąĄčĆąĄą▓ąŠą┤čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čā AT24C64D ą▓ čĆąĄąČąĖą╝ Standby. ą£ą░čüč鹥čĆ ą╝ąŠąČąĄčé čéą░ą║ąČąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐ąŠą▓č鹊čĆąĮčŗą╣ čüąĖą│ąĮą░ą╗ Start ą▓ą╝ąĄčüč鹊 čüąĖą│ąĮą░ą╗ą░ Stop, čćč鹊ą▒čŗ ąĘą░ą▓ąĄčĆčłąĖčéčī č鹥ą║čāčēčāčÄ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ, ąĄčüą╗ąĖ ą╝ą░čüč鹥čĆčā ąĮčāąČąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┤čĆčāą│čāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ (čüą╝. čĆąĖčü. 5-1).

ACK ąĖ NACK. ą¤ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą║ą░ąČą┤ąŠą│ąŠ ą▒ą░ą╣čéą░ ą┐čĆąĖąĮąĖą╝ą░čÄčēąĄąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ąŠą╗ąČąĮąŠ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčéčī ą╝ą░čüč鹥čĆčā, čćč鹊 ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą▒čŗą╗ čāčüą┐ąĄčłąĮąŠ ą┐čĆąĖąĮčÅčé, čü ą┐ąŠą╝ąŠčēčīčÄ čüąĖą│ąĮą░ą╗ą░ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ Acknowledge (ACK). ą¤čĆąŠčģąŠąČą┤ąĄąĮąĖąĄ ACK ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝, ą║ąŠą│ą┤ą░ ąŠąĮąŠ ąŠčüą▓ąŠą▒ąŠąČą┤ą░ąĄčé ą╗ąĖąĮąĖčÄ SDA ąĮą░ čüą┐ą░ą┤ąĄ ą▓ąŠčüčīą╝ąŠą│ąŠ čéą░ą║čéą░, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮąĖą╝ą░čÄčēąĄąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąŠčéą▓ąĄčéąĖčé ą╗ąŠą│ąĖč湥čüą║ąĖą╝ ąĮčāą╗ąĄą╝ ą▓ č鹥č湥ąĮąĖąĄ ą▓čüąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ ą╗ąŠą│. 1 ą┤ąĄą▓čÅč鹊ą│ąŠ čéą░ą║čéą░ SCK.

ąÜąŠą│ą┤ą░ AT24C64D ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓čā ą╝ą░čüč鹥čĆ, ą╝ą░čüč鹥čĆ ą╝ąŠąČąĄčé ą┐ąŠą║ą░ąĘą░čéčī, čćč鹊 ąŠąĮ ąĘą░ą▓ąĄčĆčłąĖą╗ ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ ąĖ čģąŠč湥čé ąĘą░ą▓ąĄčĆčłąĖčéčī ąŠą┐ąĄčĆą░čåąĖčÄ ą┐čāč鹥ą╝ ą▓čŗą┤ą░čćąĖ ą╗ąŠą│. 1 ą▓ą╝ąĄčüč鹊 ą╗ąŠą│. 0 ąĮą░ ą┤ąĄą▓čÅč鹊ą╝ čéą░ą║č鹥. ąŁč鹊 ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╝ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄą╝ No-Acknowledge (NACK), ąĖ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčéčüčÅ ąŠčéą┐čĆą░ą▓ą║ąŠą╣ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą╝ą░čüč鹥čĆ ą╗ąŠą│. 1 ą▓ąŠ ą▓čĆąĄą╝čÅ ą┤ąĄą▓čÅč鹊ą│ąŠ čéą░ą║čéą░ SCK, ą▓ čŹč鹊ą╝ ą╝ąĄčüč鹥 AT24C64D ąŠčüą▓ąŠą▒ąŠą┤ąĖčé ą╗ąĖąĮąĖčÄ SDA, čćč鹊ą▒čŗ ą╝ą░čüč鹥čĆ ą╝ąŠą│ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čüąĖą│ąĮą░ą╗ Stop.

ą¤ąĄčĆąĄą┤ą░čÄčēąĄąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą║ąŠč鹊čĆčŗą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī ą╗ąĖą▒ąŠ ą╝ą░čüč鹥čĆ čłąĖąĮčŗ, ą╗ąĖą▒ąŠ Serial EEPROM, ą┤ąŠą╗ąČąĮąŠ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī ą╗ąĖąĮąĖčÄ SDA ąĮą░ čüą┐ą░ą┤ąĄ čāčĆąŠą▓ąĮčÅ ą┤ąĄą▓čÅč鹊ą│ąŠ čéą░ą║čéą░, čćč鹊ą▒čŗ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī ą┐čĆąĖąĮąĖą╝ą░čÄčēąĄą╝čā čāčüčéčĆąŠą╣čüčéą▓čā ą┐ąŠą┤čéčÅąĮčāčéčī čāčĆąŠą▓ąĄąĮčī SDA ą║ ą╗ąŠą│. 0 ą┤ą╗čÅ ą▓čŗą┤ą░čćąĖ ACK ąĮą░ ą┐čĆąĄą┤čŗą┤čāčēąĄąĄ 8-ą▒ąĖčéąĮąŠąĄ čüą╗ąŠą▓ąŠ. ą¤čĆąĖ čŹč鹊ą╝ ą┐čĆąĖąĮąĖą╝ą░čÄčēąĄąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ąŠą╗ąČąĮąŠ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī SDA ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┤ąĄą▓čÅč鹊ą│ąŠ čéą░ą║čéą░ SCK, čćč鹊ą▒čŗ ą┐ąĄčĆąĄą┤ą░čÄčēąĄąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖą╗ąŠ ą┐ąŠčüčŗą╗ą░čéčī ą┤ą░ąĮąĮčŗąĄ. ąÆčüąĄ ą▓čŗčłąĄą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮčŗąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ą┐čĆąŠč鹊ą║ąŠą╗čā čłąĖąĮčŗ ąĖą╗ą╗čÄčüčéčĆąĖčĆčāčÄčéčüčÅ ąĮą░ čĆąĖčü. 5-1.

ąĀąĖčü. 5-1. ąĪąĖą│ąĮą░ą╗ Start, ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, čüąĖą│ąĮą░ą╗ Stop ąĖ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ACK.

ąĀąĄąČąĖą╝ Standby. ąÆ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ AT24C64D čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ čĆąĄąČąĖą╝ ąĮąĖąĘą║ąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (Standby mode), ą║ąŠč鹊čĆčŗą╣ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠą┤ąĮąŠ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ čüąŠą▒čŗčéąĖą╣:

ŌĆó ąÆčŗą┐ąŠą╗ąĮąĄąĮą░ ą┤ąŠą┐čāčüčéąĖą╝ą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ (čüą╝. "ąóčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ą▓ą║ą╗čÄč湥ąĮąĖčÄ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐čĆąĖ čüą▒čĆąŠčüąĄ" ą▓ąŠ ą▓čĆąĄąĘą║ąĄ "ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ").

ŌĆó ą¤čĆąĖąĮčÅčé čüąĖą│ąĮą░ą╗ Stop, ąĄčüą╗ąĖ ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ ąĮą░čćą░ą╗čüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ ąĘą░ą┐ąĖčüąĖ (čüą╝. "ą×ą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ").

ŌĆó ą£ąŠą╝ąĄąĮčé ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░ ąĘą░ą┐ąĖčüąĖ (čüą╝. "ą×ą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ").

ŌĆó ąØąĄčüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ čéąĖą┐ą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖą╗ąĖ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ (čüą╝. "ąÉą┤čĆąĄčüą░čåąĖčÅ").

ŌĆó ą£ą░čüč鹥čĆ čłąĖąĮčŗ ąĮąĄ ąŠčéą▓ąĄčéąĖą╗ čüąĖą│ąĮą░ą╗ąŠą╝ ACK ąĮą░ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ ąĖąĘ AT24C64D ą┤ą░ąĮąĮčŗąĄ, ą╝ąĄčüč鹊 čŹč鹊ą│ąŠ ą╝ą░čüč鹥čĆ ąŠčéą▓ąĄčéąĖą╗ čüąĖą│ąĮą░ą╗ąŠą╝ NACK (čüą╝. "ą×ą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ").

ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü. ą¤ąŠčüą╗ąĄ ąŠą▒čĆčŗą▓ą░ ą▓ ą┐čĆąŠč鹊ą║ąŠą╗ąĄ, ą┐čĆąŠą┐ą░ą┤ą░ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĖą╗ąĖ čüą▒čĆąŠčüą░ čüąĖčüč鹥ą╝čŗ ą╗čÄą▒ąŠąĄ I2C-čāčüčéčĆąŠą╣čüčéą▓ąŠ ą╝ąŠąČąĮąŠ čüą▒čĆąŠčüąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┐čāč鹥ą╝ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ SCL, ą┐ąŠą║ą░ čüąĖą│ąĮą░ą╗ SDA ąĮąĄ ą▒čāą┤ąĄčé ąŠčüą▓ąŠą▒ąŠąČą┤ąĄąĮ ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ EEPROM, ąĖ ąŠąĮ ąĮąĄ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ą╗ąŠą│. 1. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ SDA ą▒čāą┤ąĄčé ąŠčüą▓ąŠą▒ąŠąČą┤ąĄąĮ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ EEPROM, ą▒čāą┤ąĄčé ą▓ą░čĆčīąĖčĆąŠą▓ą░čéčīčüčÅ, ąŠą┤ąĮą░ą║ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ąĘą░ąĮąĖą╝ą░čéčī ą▒ąŠą╗čīčłąĄ 9 ą┐čāčüčéčŗčģ (dummy) čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī, ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░čćą░čé ąĮąŠą▓čŗą╣ ą┐čĆąŠč鹊ą║ąŠą╗ ąŠą▒ą╝ąĄąĮą░ ą┐čāč鹥ą╝ ąŠčéą┐čĆą░ą▓ą║ąĖ čüąĖą│ąĮą░ą╗ą░ Start. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ čĆąĖčü. 5-2.

ąĀąĖčü. 5-2. Software Reset.

ąĢčüą╗ąĖ AT24C64D ą▓čüąĄ ąĄčēąĄ ąĮąĄ ąŠčéą▓ąĄčćą░ąĄčé ąĖą╗ąĖ čāą┤ąĄčƹȹĖą▓ą░ąĄčé ą╗ąĖąĮąĖčÄ SDA, ąĮčāąČąĮąŠ ą▓čŗą║ą╗čÄčćąĖčéčī ąĖ čüąĮąŠą▓ą░ ą▓ą║ą╗čÄčćąĖčéčī ą┐ąĖčéą░ąĮąĖąĄ, čćč鹊ą▒čŗ čüą▒čĆąŠčüąĖčéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ (čüą╝. "ąóčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ą▓ą║ą╗čÄč湥ąĮąĖčÄ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐čĆąĖ čüą▒čĆąŠčüąĄ").

[ąÉą┤čĆąĄčüą░čåąĖčÅ]

AT24C64D ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮąŠ ą▓ąĮčāčéčĆąĖ ą║ą░ą║ 256 čüčéčĆą░ąĮąĖčå, ą║ą░ąČą┤ą░čÅ ąĄą╝ą║ąŠčüčéčīčÄ ą┐ąŠ 32 ą▒ą░ą╣čéą░.

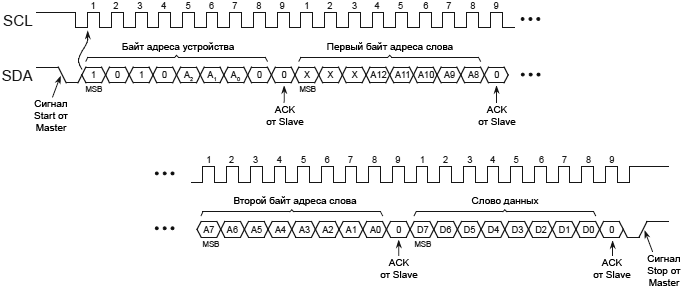

ąöąŠčüčéčāą┐ ą║ čāčüčéčĆąŠą╣čüčéą▓čā čéčĆąĄą▒čāąĄčé 8-ą▒ąĖčéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ čāčüčéčĆąŠą╣čüčéą▓ą░, ą┐ąĄčĆąĄą┤ą░ąĮąĮąŠą│ąŠ ą┐ąŠčüą╗ąĄ čüąĖą│ąĮą░ą╗ą░ Start, ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čĆą░ą▒ąŠčéą░ čü čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ąĮą░ čćč鹥ąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐ąĖčüčī. ą¤ąŠčüą║ąŠą╗čīą║čā ąĮą░ čłąĖąĮąĄ ą╝ąŠąČąĄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐čĆąĖčüčāčéčüčéą▓ąŠą▓ą░čéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓, ą║ą░ąČą┤ąŠąĄ ąĖąĘ ąĮąĖčģ ą┤ąŠą╗ąČąĮąŠ ąĖą╝ąĄčéčī čüą▓ąŠą╣ čāąĮąĖą║ą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü, čćč鹊ą▒čŗ ą╝ą░čüč鹥čĆ ą╝ąŠą│ ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ ą║ą░ąČą┤ąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā ąŠčéą┤ąĄą╗čīąĮąŠ.

4 čüą░ą╝čŗčģ čüčéą░čĆčłąĖčģ ą▒ąĖčéą░ ą░ą┤čĆąĄčüą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čéąĖą┐ čāčüčéčĆąŠą╣čüčéą▓ą░. ąöą╗čÅ AT24C64D čéčĆąĄą▒čāąĄčéčüčÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ čéąĖą┐ą░ čāčüčéčĆąŠą╣čüčéą▓ą░ 1010 (Ah), ą║ąŠč鹊čĆčŗą╣ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą▒ąĖčéą░čģ 7 .. 4 ą▒ą░ą╣čéą░ ą░ą┤čĆąĄčüą░ (čéą░ą▒ą╗ąĖčåą░ 6-1).

ąŚą░ 4 ą▒ąĖčéą░ą╝ąĖ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ čéąĖą┐ą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖą┤čāčé ą▒ąĖčéčŗ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ A0, A1 ąĖ A2. ąŁčéąĖ ą▒ąĖčéčŗ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čĆą░čüčłąĖčĆąĄąĮąĖčÅ ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ąŠą▒čŖąĄą╝ą░ ą┐ą░ą╝čÅčéąĖ ą┐čāč鹥ą╝ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čāčüčéčĆąŠą╣čüčéą▓ Serial EEPROM (ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ą┤ąŠ 8 čāčüčéčĆąŠą╣čüčéą▓). ąÉą┐ą┐ą░čĆą░čéąĮčŗą╣ ą░ą┤čĆąĄčü ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĘą░ą▓ąĖčüąĖčé ąŠ ą╗ąŠą│ąĖč湥čüą║ąĖčģ čāčĆąŠą▓ąĮąĄą╣, ą┐čĆąĖčüčāčéčüčéą▓čāčÄčēąĖčģ ąĮą░ ą░ą┤čĆąĄčüąĮčŗčģ ą▓čŗą▓ąŠą┤ą░čģ A0, A1 ąĖ A2. ąØą░ ą▓čŗą▓ąŠą┤ą░čģ A0, A1 ąĖ A2 ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ AT24C64D čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ čüčģąĄą╝ą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ą┐ąŠą┤čéčÅąČą║ąĖ čāčĆąŠą▓ąĮčÅ ą║ ą╗ąŠą│. 0, ąĄčüą╗ąĖ ą▓čŗą▓ąŠą┤ A0, A1 ąĖ A2 ąŠčüčéą░ą▓ą╗ąĄąĮ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝.

ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą║ąŠčĆą┐čāčüą░ 6-ball WLCSP ą▓čŗą▓ąŠą┤čŗ A1 ąĖ A0 ąĮąĄą┤ąŠčüčéčāą┐ąĮčŗ ąĖ ą┐ąŠą┤čéčÅąĮčāčéčŗ ą║ ą╗ąŠą│. 0 ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ; čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐čĆąĖ ąŠą▒ą╝ąĄąĮąĄ čü ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ ą▓ čéą░ą║ąŠą╝ ą║ąŠčĆą┐čāčüąĄ ą▒ąĖčéčŗ A1 ąĖ A0 ą▓ ą░ą┤čĆąĄčüąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓čüąĄą│ą┤ą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĮčāą╗čÅą╝ąĖ (čüą╝. čéą░ą▒ą╗ąĖčåčā 6-1).

ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą║ąŠčĆą┐čāčüą░ 4-ball WLCSP ą▓čŗą▓ąŠą┤čŗ A2, A1 ąĖ A0 ąĮąĄą┤ąŠčüčéčāą┐ąĮčŗ ąĖ ą┐ąŠą┤čéčÅąĮčāčéčŗ ą║ ą╗ąŠą│. 0 ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ; čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐čĆąĖ ąŠą▒ą╝ąĄąĮąĄ čü ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ ą▓ čéą░ą║ąŠą╝ ą║ąŠčĆą┐čāčüąĄ ą▒ąĖčéčŗ A2, A1 ąĖ A0 ą▓ ą░ą┤čĆąĄčüąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓čüąĄą│ą┤ą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĮčāą╗čÅą╝ąĖ (čüą╝. čéą░ą▒ą╗ąĖčåčā 6-1).

ąŚą░čēąĖčéą░ ą┤ą░ąĮąĮčŗčģ. ąŻ AT24C64D ąĄčüčéčī ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ čüčģąĄą╝ą░ ąĘą░čēąĖčéčŗ ą┤ą░ąĮąĮčŗčģ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ąĘą░čēąĖčéąĖčéčī ąŠčé ąĘą░ą┐ąĖčüąĖ ą▓čüčÄ ą┐ą░ą╝čÅčéčī ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, ą║ąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤ WP ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ VCC. ąŻ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą▓ ą║ąŠčĆą┐čāčüąĄ 4-ball WLCSP ąĮąĄčé ą▓čŗą▓ąŠą┤ą░ WP, ą┐ąŠčŹč鹊ą╝čā č鹊ą╗čīą║ąŠ ą▓ čéą░ą║ąŠą╝ ą║ąŠčĆą┐čāčüąĄ ąĘą░čēąĖčéą░ ąŠčé ąĘą░ą┐ąĖčüąĖ ąŠčéčüčāčéčüčéą▓čāąĄčé.

[ą×ą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ]

ąÆčüąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ AT24C64D ąĮą░čćąĖąĮą░čÄčéčüčÅ čü ąŠčéą┐čĆą░ą▓ą║ąĖ ą╝ą░čüč鹥čĆąŠą╝ čüąĖą│ąĮą░ą╗ą░ Start, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą░ą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░ čü ą╝ą╗ą░ą┤čłąĖą╝ ą▒ąĖč鹊ą╝ R/W, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▓ ą╗ąŠą│. 0, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ąĖą┤čāčé ą▒ą░ą╣čéčŗ ą░ą┤čĆąĄčüą░ čüą╗ąŠą▓ą░. ąŚąĮą░č湥ąĮąĖčÅ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗčģ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ą▒ą░ą╣čé ą░ą┤čĆąĄčüą░ čüą╗ąŠą▓ą░.

ąŚą░ą┐ąĖčüčī ą▒ą░ą╣čéą░ (Byte Write). AT24C64D ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĘą░ą┐ąĖčüčī ąŠą┤ąĮąŠą│ąŠ ą▒ą░ą╣čéą░ (8-ą▒ąĖčéąĮąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ). ąÆčŗą▒ąŠčĆ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ ą▓ AT24C64D čéčĆąĄą▒čāąĄčé 13-ą▒ąĖčéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ čüą╗ąŠą▓ą░.

ą¤ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ą▒ą░ą╣čé ą░ą┤čĆąĄčüą░ čüą╗ąŠą▓ą░, ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ EEPROM ąŠčéą┐čĆą░ą▓ąĖčé ACK. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čāą┤ąĄčé ą│ąŠč鹊ą▓ąŠ ą║ ą┐čĆąĖąĄą╝čā ą┐ąĄčĆą▓ąŠą│ąŠ 8-ą▒ąĖčéąĮąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ 8-ą▒ąĖčéąĮąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ EEPROM ąŠčéą▓ąĄčéąĖčé čüąĖą│ąĮą░ą╗ąŠą╝ ACK. ąØą░ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą╝ ą╝ą░čüč鹥čĆąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ EEPROM ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĘą░ą▓ąĄčĆčłąĄąĮą░ čüąĖą│ąĮą░ą╗ąŠą╝ Stop. ąÆ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ EEPROM ą▓ąŠą╣ą┤ąĄčé ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ ąĘą░ą┐ąĖčüąĖ, ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčīčüčÅ ą▓ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ ą▓čĆąĄą╝ąĄąĮąĖ tWR, čćč鹊ą▒čŗ čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ ą╝ąŠą│ą╗ąŠ ąĘą░ą┐ąĖčüą░čéčīčüčÅ ą▓ 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝čāčÄ ą┐ą░ą╝čÅčéčī EEPROM. ąÆąŠ ą▓čĆąĄą╝čÅ čŹč鹊ą│ąŠ čåąĖą║ą╗ą░ ąĘą░ą┐ąĖčüąĖ ą▓čüąĄ ą▓čģąŠą┤čŗ ąĘą░ą┐čĆąĄčēą░čÄčéčüčÅ, ąĖ EEPROM ąĮąĄ ą▒čāą┤ąĄčé ąŠčéą▓ąĄčćą░čéčī ą┐ąŠ čłąĖąĮąĄ, ą┐ąŠą║ą░ ąĮąĄ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ąĘą░ą┐ąĖčüčī.

ąĀąĖčü. 7-1. ąŚą░ą┐ąĖčüčī ą▒ą░ą╣čéą░.

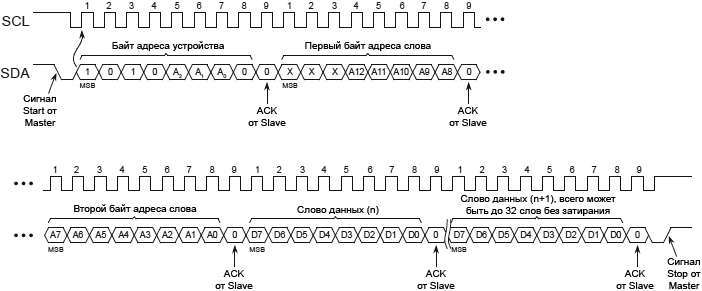

ąŚą░ą┐ąĖčüčī čüčéčĆą░ąĮąĖčåčŗ (Page Write). ą×ą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ čüčéčĆą░ąĮąĖčåčŗ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┐ąĖčüą░čéčī ąĘą░ ąŠą┤ąĖąĮ čĆą░ąĘ ą┤ąŠ 32 ą▒ą░ą╣čé, ą║ąŠą│ą┤ą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčéčüčÅ ą▓čüąĄ ą▒ą░ą╣čéčŗ ą▓ ąŠą┤ąĮąŠą╣ čüčéčĆąŠą║ąĄ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ (ą┐ąŠ ą░ą┤čĆąĄčüą░ą╝, čā ą║ąŠč鹊čĆčŗčģ ą▓čüąĄ ą▒ąĖčéčŗ A12 .. A5 ąŠą┤ąĖąĮą░ą║ąŠą▓čŗąĄ). ąóą░ą║ąČąĄ čĆą░ąĘčĆąĄčłąĄąĮą░ čćą░čüčéąĖčćąĮą░čÅ ąĘą░ą┐ąĖčüčī čüčéčĆą░ąĮąĖčåčŗ, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą╝ąĄąĮčīčłąĄ 32 ą▒ą░ą╣čé.

ąŚą░ą┐ąĖčüčī čüčéčĆą░ąĮąĖčåčŗ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čéą░ą║ ąČąĄ, ą║ą░ą║ ąĘą░ą┐ąĖčüčī ą▒ą░ą╣čéą░, ąĮąŠ ą╝ą░čüč鹥čĆ ąĮąĄ ą┐ąŠčüčŗą╗ą░ąĄčé čüąĖą│ąĮą░ą╗ Stop ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ ą┐ąĄčĆąĄą┤ą░ąĮ ą┐ąĄčĆą▓čŗą╣ ą▒ą░ą╣čé ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ. ąÆą╝ąĄčüč鹊 čŹč鹊ą│ąŠ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ EEPROM ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčé ACK ą┐čĆąĖąĄą╝ ą┐ąĄčĆą▓ąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ, ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ą╝ąŠąČąĄčé ą┐čĆąŠą┤ąŠą╗ąČąĖčéčī ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ąŠ 31 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ čüą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ. EEPROM ąŠčéą▓ąĄčéąĖčé ACK ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▓čüąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░ąĮčŗ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ą┤ąŠą╗ąČąĄąĮ ą┐ąĄčĆąĄą┤ą░čéčī čüąĖą│ąĮą░ą╗ Stop (čĆąĖčü. 7-2), ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ąĮą░čćąĮąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ ąĘą░ą┐ąĖčüąĖ.

ą¤čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ą║ą░ąČą┤ąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ ą╝ą╗ą░ą┤čłąĖąĄ 5 ą▒ąĖčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüč湥čéčćąĖą║ą░ ą░ą┤čĆąĄčüą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāčÄčéčüčÅ. ąĪčéą░čĆčłąĖąĄ ą▒ąĖčéčŗ ą┐čĆąĖ čŹč鹊ą╝ ąŠčüčéą░čÄčéčüčÅ ąĮąĄąĖąĘą╝ąĄąĮąĮčŗą╝ąĖ, ąĖ čģčĆą░ąĮčÅčé ą▓ čüąĄą▒ąĄ ą╝ąĄčüč鹊 čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĖčÅ čüčéčĆąŠą║ąĖ čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ.

ą×ą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ čüčéčĆą░ąĮąĖčåčŗ ą▓čüąĄą│ą┤ą░ ąŠą│čĆą░ąĮąĖč湥ąĮčŗ ą┐ąŠ ąŠą▒čŖąĄą╝čā čĆą░ąĘą╝ąĄčĆąŠą╝ ąŠą┤ąĮąŠą╣ čäąĖąĘąĖč湥čüą║ąŠą╣ čüčéčĆą░ąĮąĖčåčŗ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, čüą║ąŠą╗čīą║ąŠ čĆąĄą░ą╗čīąĮąŠ ą▒čŗą╗ąŠ ąĘą░ą┐ąĖčüą░ąĮąŠ ą▒ą░ą╣čé. ąÜąŠą│ą┤ą░ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄą╝čŗą╣ ą░ą┤čĆąĄčü ą┤ąŠčüčéąĖą│ą░ąĄčé ą│čĆą░ąĮąĖčåčŗ čüčéčĆą░ąĮąĖčåčŗ, čüč湥čéčćąĖą║ ą░ą┤čĆąĄčüą░ ą┐ąĄčĆąĄčüą║ą░ą║ąĖą▓ą░ąĄčé ąĮą░ ąĮą░čćą░ą╗ąŠ čäąĖąĘąĖč湥čüą║ąŠą╣ čüčéčĆą░ąĮąĖčåčŗ. ąóąĄą╝ ąĮąĄ ą╝ąĄąĮąĄąĄ čüą╗ąĄą┤čāąĄčé ąĖąĘą▒ąĄą│ą░čéčī čéą░ą║ąĖčģ čüąĖčéčāą░čåąĖą╣, ą┐ąŠč鹊ą╝čā čćč鹊 ą╝ąŠą│čāčé ą▒čŗčéčī ąĮąĄ čāą╝čŗčłą╗ąĄąĮąĮąŠ ąĖąĘą╝ąĄąĮąĄąĮčŗ čĆą░ąĮąĄąĄ ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ąĮą░ čŹčéčā čüčéčĆą░ąĮąĖčåčā ą┤ą░ąĮąĮčŗąĄ.

ąĀąĖčü. 7-2. ąŚą░ą┐ąĖčüčī čüčéčĆą░ąĮąĖčåčŗ.

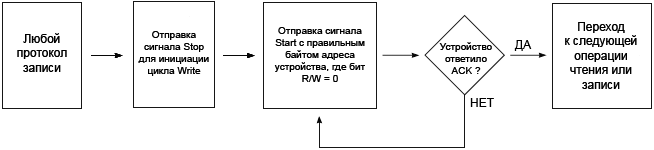

ą×ą┐čĆąŠčü ACK. ą£ąŠąČąĄčé ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąŠą┐čĆąŠčüą░ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (Acknowledge Polling), čćč鹊ą▒čŗ ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ą▓čĆąĄą╝čÅ ąŠą┐ąĄčĆą░čåąĖą╣ ąĘą░ą┐ąĖčüąĖ ąĖ ąĮąĄ ąČą┤ą░čéčī čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠąĄ, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą▓ ą┤ą░čéą░čłąĖč鹥 ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░ ąĘą░ą┐ąĖčüąĖ (tWR). ąŁč鹊čé ą╝ąĄč鹊ą┤ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÄ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ čāąĘąĮą░čéčī ąŠ ą╝ąŠą╝ąĄąĮč鹥, ą║ąŠą│ą┤ą░ Serial EEPROM ąĘą░ą▓ąĄčĆčłąĖą╗ą░ čåąĖą║ą╗ ąĘą░ą┐ąĖčüąĖ, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ąĘą░ą┐čāčüčéąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĘą░ą┐čāčüčéąĖą╗čüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ ąĘą░ą┐ąĖčüąĖ, ą╝ąŠąČąĮąŠ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░čéčī čåąĖą║ą╗ąĖč湥čüą║ąĖąĄ ą▓čŗąĘąŠą▓čŗ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ Acknowledge Polling. ąÆčŗąĘąŠą▓čŗ Acknowledge Polling ą┐čĆąĖą▓ąŠą┤čÅčé ą║ ą┐ąŠą▓č鹊čĆčÅčÄčēąĖą╝čüčÅ ąŠčéą┐čĆą░ą▓ą║ą░ą╝ čüąĖą│ąĮą░ą╗ą░ Start, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╣ ą░ą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░, ą│ą┤ąĄ ą▒ąĖčé R/W čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 0. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ąŠčéą▓ąĄčéąĖčé čüąĖą│ąĮą░ą╗ąŠą╝ ACK, ą┐ąŠą║ą░ ą▓čüąĄ ąĄčēąĄ ąĖą┤ąĄčé čåąĖą║ą╗ ąĘą░ą┐ąĖčüąĖ. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ ąĘą░ą┐ąĖčüąĖ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ, EEPROM ąŠčéą▓ąĄčéąĖčé ACK, čćč鹊 ą┐ąŠąĘą▓ąŠą╗ąĖčé ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąĮą░čćą░čéčī čüą╗ąĄą┤čāčÄčēčāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ. ąØą░ čĆąĖčüčāąĮą║ąĄ 7-3 ą┐ąŠą║ą░ąĘą░ąĮ ą░ą╗ą│ąŠčĆąĖčéą╝, ąĖą╗ą╗čÄčüčéčĆąĖčĆčāčÄčēąĖą╣ čŹčéčā č鹥čģąĮąĖą║čā.

ąĀąĖčü. 7-3. ąÉą╗ą│ąŠčĆąĖčéą╝ ąŠą┐čĆąŠčüą░ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ (Acknowledge Polling).

ąÆčĆąĄą╝čÅ čåąĖą║ą╗ą░ ąĘą░ą┐ąĖčüąĖ. ąöą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čåąĖą║ą╗ą░ ąĘą░ą┐ąĖčüąĖ (tWR) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą║ą░ą║ ą▓čĆąĄą╝čÅ ąŠčé ą╝ąŠą╝ąĄąĮčéą░ čüąĖą│ąĮą░ą╗ą░ Stop, ą║ąŠą│ą┤ą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ, ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ ą▓ ąŠčéą▓ąĄčé ąĮą░ čüąĖą│ąĮą░ą╗ Start čü ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝ AT24C64D ąŠčéą▓ąĄčéąĖčé čüąĖą│ąĮą░ą╗ąŠą╝ ACK.

ąØą░ čĆąĖčü. 7-4 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ čŹč鹊ą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ. ąÆąŠ ą▓čĆąĄą╝čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą╗čÄą▒čŗąĄ ą┐ąŠą┐čŗčéą║ąĖ ąŠą▒čĆą░čēąĄąĮąĖčÅ ą║ čāčüčéčĆąŠą╣čüčéą▓čā ąĮą░ čćč鹥ąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐ąĖčüčī ąĮąĄ ą▒čāą┤čāčé ąŠą▒čĆą░ą▒ąŠčéą░ąĮčŗ.

ąĀąĖčü. 7-4. ąóą░ą╣ą╝ąĖąĮą│ čåąĖą║ą╗ą░ ąĘą░ą┐ąĖčüąĖ.

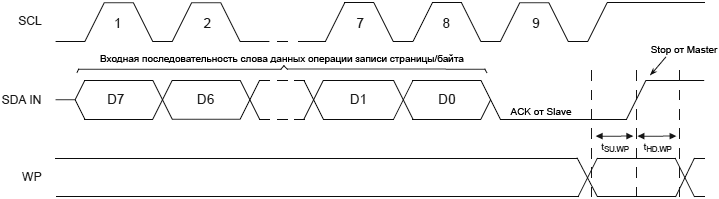

ąŚą░čēąĖčéą░ ąŠčé ąĘą░ą┐ąĖčüąĖ. ąÆ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ AT24C64D čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ ąĘą░čēąĖčéą░ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆą░čÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┐čĆąĄčéąĖčéčī ąĘą░ą┐ąĖčüčī ą▓ąŠ ą▓čüąĄą╝ ą╝ą░čüčüąĖą▓ąĄ ą┐ą░ą╝čÅčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, ą║ąŠą│ą┤ą░ ąĮą░ ą▓čŗą▓ąŠą┤ WP ą┐ąŠą┤ą░ąĮąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VCC (ąĖą╗ąĖ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī VIH, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą╗ąŠą│. 1). ąÜąŠą│ą┤ą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ WP ą╗ąŠą│. 0, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ WP ąŠčüčéą░ą▓ą╗ąĄąĮ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝, ąĘą░čēąĖčéą░ ąŠčé ąĘą░ą┐ąĖčüąĖ ąĮąĄ ą┤ąĄą╣čüčéą▓čāąĄčé. ą£ąĖą║čĆąŠčüčģąĄą╝čŗ ą▓ ą║ąŠčĆą┐čāčüąĄ 4-ball WLCSP ąĮąĄ ąĖą╝ąĄčÄčé čäčāąĮą║čåąĖąĖ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ.

ąĪąŠčüč鹊čÅąĮąĖąĄ ąĮąŠąČą║ąĖ WP ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé čüąĖą│ąĮą░ą╗ą░ Stop ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ ąĘą░ą┐ąĖčüąĖ ą▒ą░ą╣čéą░ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ čüčéčĆą░ąĮąĖčåčŗ, ą┐ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░ ąĘą░ą┐ąĖčüąĖ. ąśąĘą╝ąĄąĮąĄąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą▓čŗą▓ąŠą┤ą░ WP ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ čüąĖą│ąĮą░ą╗ Stop, ąĮąĄ ąĖąĘą╝ąĄąĮąĖčé ąĖą╗ąĖ ąĮąĄ ą┐čĆąĄčĆą▓ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĘą░ą┐čāčēąĄąĮąĮąŠą│ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░ ąĘą░ą┐ąĖčüąĖ. ąĪąŠčüč鹊čÅąĮąĖąĄ ą▓čŗą▓ąŠą┤ą░ WP ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╝ ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ čüąŠ čüą▓čÅąĘą░ąĮąĮčŗą╝ ą▓čĆąĄą╝ąĄąĮąĄą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ (Write-Protect Setup, tSU:WP) ąĖ čāą┤ąĄčƹȹ░ąĮąĖčÅ (Write-Protect Hold, tHD:WP), ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 7-5 ąĮąĖąČąĄ. ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ WP čŹč鹊 ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠą│ą┤ą░ čüąŠčüč鹊čÅąĮąĖąĄ WP ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čüčéą░ą▒ąĖą╗čīąĮčŗą╝ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą▒čāą┤ąĄčé ą▓čŗą┤ą░ąĮ čüąĖą│ąĮą░ą╗ Stop. ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ WP čŹč鹊 ą▓čĆąĄą╝čÅ, ą▓ č鹥č湥ąĮąĖąĄ ą║ąŠč鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĄąĮčī WP ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüčéą░ą▒ąĖą╗čīąĮčŗą╝ ą┐ąŠčüą╗ąĄ ą▓čŗą┤ą░čćąĖ čüąĖą│ąĮą░ą╗ą░ Stop.

ąĀąĖčü. 7-5. ąóą░ą╣ą╝ąĖąĮą│ Write-Protect Setup ąĖ Write-Protect Hold.

ąĢčüą╗ąĖ čüą┤ąĄą╗ą░ąĮą░ ą┐ąŠą┐čŗčéą║ą░ ąĘą░ą┐ąĖčüąĖ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čüąĖą│ąĮą░ą╗ WP, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčé (ACK) ą░ą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ, ąĮąŠ ąĮąĄ ąĘą░ą┐ąĖčłąĄčé ąĖčģ ą▓ 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝čāčÄ ą┐ą░ą╝čÅčéčī ą┐ąŠčüą╗ąĄ ą▓čŗą┤ą░čćąĖ čüąĖą│ąĮą░ą╗ą░ Stop, ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüčéą░ąĮąĄčé ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą│ąŠč鹊ą▓čŗą╝ ą║ ąĮąŠą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤ąĄ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ.

[ą×ą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ]

ą×ą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ čéą░ą║ ąČąĄ, ą║ą░ą║ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ čü č鹥ą╝ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝, čćč鹊 ą▒ąĖčé Read/Write ą▓ ą▒ą░ą╣č鹥 ą░ą┤čĆąĄčüą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ ą╗ąŠą│. 1. ąĪčāčēąĄčüčéą▓čāąĄčé 3 ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ:

ŌĆó Current Address Read (čćč鹥ąĮąĖąĄ ą┐ąŠ č鹥ą║čāčēąĄą╝čā ą░ą┤čĆąĄčüčā)

ŌĆó Random Address Read (čćč鹥ąĮąĖąĄ ą┐ąŠ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠą╝čā ą░ą┤čĆąĄčüčā)

ŌĆó Sequential Read (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠąĄ čćč鹥ąĮąĖąĄ)

Current Address Read. ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ čüč湥čéčćąĖą║ ą░ą┤čĆąĄčüą░ čüą╗ąŠą▓ą░ čģčĆą░ąĮąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą░ą┤čĆąĄčü, ą┐ąŠ ą║ąŠč鹊čĆąŠą╝čā ąŠčüčāčēąĄčüčéą▓ą╗čÅą╗čüčÅ ą┤ąŠčüčéčāą┐ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ, čāą▓ąĄą╗ąĖč湥ąĮąĮčŗą╣ ąĮą░ 1. ąŁč鹊čé ą░ą┤čĆąĄčü ąŠčüčéą░ąĄčéčüčÅ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╝ ą╝ąĄąČą┤čā ąŠą┐ąĄčĆą░čåąĖčÅą╝ąĖ, ą┐ąŠą║ą░ ą┤ą╗čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ VCC. ąÉą┤čĆąĄčü ą┐ąĄčĆąĄą▓ą░ą╗ąĖą▓ą░ąĄčé ąĮą░ ą┐ąĄčĆą▓čŗą╣ ą▒ą░ą╣čé ą┐ąĄčĆą▓ąŠą╣ čüčéčĆą░ąĮąĖčåčŗ ą┐ąŠčüą╗ąĄ čćč鹥ąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ą░ą╣čéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ čüčéčĆą░ąĮąĖčåčŗ.

ą×ą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ ą┐ąŠ č鹥ą║čāčēąĄą╝čā ą░ą┤čĆąĄčüčā ą▓čŗą▓ąĄą┤ąĄčé ą┤ą░ąĮąĮčŗąĄ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝čā čüč湥čéčćąĖą║čā ą░ą┤čĆąĄčüą░ čüą╗ąŠą▓ą░. ąŁčéą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ čüąĖą│ąĮą░ą╗ąŠą╝ Start, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╣ ą░ą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░ čü ą▒ąĖč鹊ą╝ R/W, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▓ ą╗ąŠą│. 1. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čāą┤ąĄčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░čéčī ACK čŹčéčā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī, ąĖ čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ č鹥ą║čāčēąĄą╝čā ą░ą┤čĆąĄčüčā ą▒čāą┤ąĄčé ą▓čŗą▓ąŠą┤ąĖčéčīčüčÅ č湥čĆąĄąĘ ą╗ąĖąĮąĖčÄ SDA. ąÆčüąĄ čéąĖą┐čŗ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ ą▒čāą┤čāčé ą┐čĆąĄčĆčŗą▓ą░čéčīčüčÅ, ąĄčüą╗ąĖ ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ąĮąĄ ąŠčéą▓ąĄčéąĖčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄą╝ ACK (čé. ąĄ. ąŠčéą▓ąĄčéąĖčé čüąĖą│ąĮą░ą╗ąŠą╝ NACK) ąĮą░ ą┤ąĄą▓čÅč鹊ą╝ ąĖą╝ą┐čāą╗čīčüąĄ čéą░ą║č鹊ą▓ SCL. ą¤ąŠčüą╗ąĄ ąŠčéą▓ąĄčéą░ NACK ą╝ą░čüč鹥čĆ ą╝ąŠąČąĄčé ą┐ąŠčüą╗ą░čéčī čüąĖą│ąĮą░ą╗ Stop ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąŠč鹊ą║ąŠą╗ą░, ąĖą╗ąĖ ą╝ąŠąČąĄčé ąŠčéą┐čĆą░ą▓ąĖčéčī čüąĖą│ąĮą░ą╗ Start ą┤ą╗čÅ ąĮą░čćą░ą╗ą░ čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ.

ąĀąĖčü. 8-1. Current Address Read.

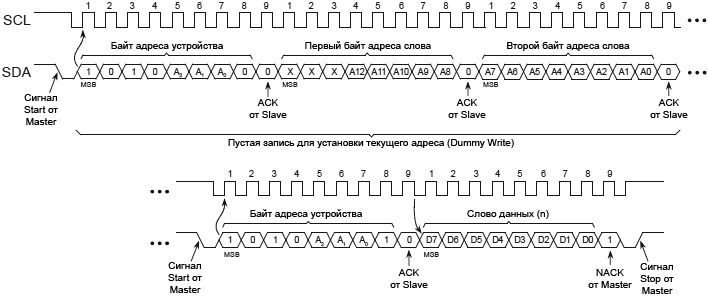

Random Read. ą¤čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠąĄ čćč鹥ąĮąĖąĄ (random read) ąĮą░čćąĖąĮą░ąĄčéčüčÅ čéą░ą║ ąČąĄ, ą║ą░ą║ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▒ą░ą╣čéą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ąĘą░ą│čĆčāąĘą║čā ąĮąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ. ąŁč鹊 ąĖąĘą▓ąĄčüčéąĮąŠ ą║ą░ą║ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čāčüč鹊ą╣ ąĘą░ą┐ąĖčüąĖ (dummy write); ąŠą┤ąĮą░ą║ąŠ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ čüąĖą│ąĮą░ą╗ Stop ąĘą░ą┐ąĖčüąĖ ą▒ą░ą╣čéą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠą┐čāčēąĄąĮčŗ, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī ą▓čģąŠą┤ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗ ąĘą░ą┐ąĖčüąĖ. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą░ą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ą░ą┤čĆąĄčü čüą╗ąŠą▓ą░ ą▓ą┤ą▓ąĖąĮčāčéčŗ ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝čā EEPROM ąĖ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮčŗ ąĄą╣, ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ą┤ąŠą╗ąČąĄąĮ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┤čĆčāą│ąŠą╣ čüąĖą│ąĮą░ą╗ Start. ąóąĄą┐ąĄčĆčī ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąŠą┐ąĄčĆą░čåąĖčÄ čćč鹥ąĮąĖčÅ ą┐ąŠ č鹥ą║čāčēąĄą╝čā ą░ą┤čĆąĄčüčā ąŠčéą┐čĆą░ą▓ą║ąŠą╣ čüąĖą│ąĮą░ą╗ą░ Start, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░ čü ą▒ąĖč鹊ą╝ R/W, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▓ 1. EEPROM ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčé ACK ą░ą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓čŗą┤ą▓ąĖąĮąĄčé čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ ą╗ąĖąĮąĖčÄ SDA. ąÆčüąĄ čéąĖą┐čŗ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ ą▒čāą┤čāčé ąĘą░ą▓ąĄčĆčłąĄąĮčŗ, ąĄčüą╗ąĖ ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ąĮąĄ ąŠčéą▓ąĄčéąĖčé čüąĖą│ąĮą░ą╗ąŠą╝ ACK (ą▓čŗą┤ą░čüčé NACK) ą▓ąŠ ą▓čĆąĄą╝čÅ ą┤ąĄą▓čÅč鹊ą│ąŠ čéą░ą║čéą░ SCK. ą¤ąŠčüą╗ąĄ ąŠčéą▓ąĄčéą░ NACK ą╝ą░čüč鹥čĆ ą╝ąŠąČąĄčé ąŠčéą┐čĆą░ą▓ąĖčéčī čüąĖą│ąĮą░ą╗ Stop ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąŠč鹊ą║ąŠą╗ą░, ąĖą╗ąĖ ą╝ąŠąČąĄčé ąŠčéą┐čĆą░ą▓ąĖčéčī Start ą┤ą╗čÅ ąĮą░čćą░ą╗ą░ čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ.

ąĀąĖčü. 8-2. Random Read.

Sequential Read. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠąĄ čćč鹥ąĮąĖąĄ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą╗ąĖą▒ąŠ ąŠą┐ąĄčĆą░čåąĖąĄą╣ čćč鹥ąĮąĖčÅ ą┐ąŠ č鹥ą║čāčēąĄą╝čā ą░ą┤čĆąĄčüčā (current address read), ą╗ąĖą▒ąŠ ąŠą┐ąĄčĆą░čåąĖąĄą╣ čćč鹥ąĮąĖčÅ ą┐ąŠ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠą╝čā ą░ą┤čĆąĄčüčā (random read). ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą╝ą░čüč鹥čĆ ą┐čĆąĖą╝ąĄčĆ čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ, ąŠąĮ ą┐ąĄčĆąĄą┤ą░čüčé čüąĖą│ąĮą░ą╗ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ (ACK). ą¤ąŠą║ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ EEPROM ą┐čĆąĖąĮąĖą╝ą░ąĄčé ACK, ąŠąĮą░ ą▒čāą┤ąĄčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčī ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčī čüą╗ąŠą▓ąŠ ą░ą┤čĆąĄčüą░ ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓čŗą┤ą▓ąĖą│ą░čéčī čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ ą▒čāą┤ąĄčé ą┤ąŠčüčéąĖą│ąĮčāčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ą┐ą░ą╝čÅčéąĖ, ą░ą┤čĆąĄčü čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą▓ą░ą╗ąĖčé ą▓ 0, ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠąĄ čćč鹥ąĮąĖąĄ ą┐čĆąŠą┤ąŠą╗ąČąĖčéčüčÅ ąŠčé ąĮą░čćą░ą╗ą░ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ. ąÆčüąĄ čéąĖą┐čŗ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłą░čéčüčÅ ą╝ą░čüč鹥čĆąŠą╝ čłąĖąĮčŗ, ą║ąŠą│ą┤ą░ ąŠąĮ ąŠčéą▓ąĄčéąĖčé čüąĖą│ąĮą░ą╗ąŠą╝ NACK ąĮą░ ą┤ąĄą▓čÅč鹊ą╝ čéą░ą║č鹥. ą¤ąŠčüą╗ąĄ ąŠčéą▓ąĄčéą░ NACK ą╝ą░čüč鹥čĆ ą╝ąŠąČąĄčé ąŠčéą┐čĆą░ą▓ąĖčéčī čüąĖą│ąĮą░ą╗ Stop ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąŠč鹊ą║ąŠą╗ą░, ąĖą╗ąĖ ą╝ąŠąČąĄčé ąŠčéą┐čĆą░ą▓ąĖčéčī Start ą┤ą╗čÅ ąĮą░čćą░ą╗ą░ čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ.

ąĀąĖčü. 8-3. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠąĄ čćč鹥ąĮąĖąĄ (Sequential Read).

[ąĪčüčŗą╗ą║ąĖ]

1. AT24C64D: I2C-Compatible (2-Wire) Serial EEPROM 64-Kbit (8,192 x 8) site:microchip.com. |