|

ą£ąĖą║čĆąŠčüčģąĄą╝čŗ ADG714/ADG715 čŹč鹊 菹╗ąĄą║čéčĆąŠąĮąĮčŗąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ 8-ą║ą░ąĮą░ą╗čīąĮčŗąĄ ą║ą╗čÄčćąĖ ąĮą░ ąĘą░ą╝čŗą║ą░ąĮąĖąĄ čü ą┤ą▓čāą╝čÅ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ čüąŠčüč鹊čÅąĮąĖčÅą╝ąĖ (single-pole, single-throw, SPST), čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗąĄ č湥čĆąĄąĘ 2-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ (I2C, ADG715) ąĖą╗ąĖ 3-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ (SPI/QSPI/MICROWIRE, ADG714) ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü. ąøąŠą│ąĖą║ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ąĖ ą║ą╗čÄčćąĖ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ ą┐ąŠ č鹥čģąĮąŠą╗ąŠą│ąĖąĖ CMOS. ąĪąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ąŠčéą║čĆčŗč鹊ą│ąŠ ą║ą╗čÄčćą░ ą╝ą░ą╗ąŠ ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ą╝ąĄąČą┤čā ą║ą░ąĮą░ą╗ą░ą╝ąĖ, ąĖ ąĖą╝ąĄąĄčé ą┐ą╗ąŠčüą║čāčÄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║čā ą▓ąŠ ą▓čüąĄą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ čĆą░ą▒ąŠčćąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓. ąÜą░ąČą┤čŗą╣ ą║ą╗čÄčć ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠ čģąŠčĆąŠčłąŠ ą┐čĆąŠą▓ąŠą┤ąĖčé č鹊ą║ ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ, ąĖ ą┤ąĖą░ą┐ą░ąĘąŠąĮ čāčĆąŠą▓ąĮąĄą╣ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ ą┐ąĖčéą░ąĮąĖčÅ. ąÜą░ąČą┤čŗą╣ ą▒ąĖčé čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą│ąŠ ą▒ą░ą╣čé, ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝ąŠą│ąŠ ą▓ čŹčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą║ą╗čÄč湥ą╣ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ (ą║ą░ąČą┤ąŠą╝čā ąĖąĘ 8 ą║ą░ąĮą░ą╗ąŠą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠą┤ąĖąĮ ąĖąĘ 8 ą▒ąĖčé ą▒ą░ą╣čéą░).

ADG714 ąĖčüą┐ąŠą╗čīąĘčāąĄčé 3-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü, čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╣ čü ą┐ąŠą┐čāą╗čÅčĆąĮčŗą╝ąĖ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮčŗą╝ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ą╝ąĖ SPI [2], QSPIŌäó, MICROWIREŌäó ąĖ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠą╝ ąĖą╝ąĄčÄčēąĖą╝ąĖčüčÅ ąĮą░ čĆčŗąĮą║ąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ DSP. ąÆčŗčģąŠą┤ DOUT čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čüąŠąĄą┤ąĖąĮąĖčéčī ą▓ ąŠą┤ąĮčā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčāčÄ čåąĄą┐ąŠčćą║čā ą▒ąŠą╗čīčłąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą╝ąĖą║čĆąŠčüčģąĄą╝ ADG714.

ADG715 ąĖčüą┐ąŠą╗čīąĘčāąĄčé 2-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü, čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╣ čüąŠ čüčéą░ąĮą┤ą░čĆčéąĮčŗą╝ I2C. ąÆ ADG715 ąĖą╝ąĄąĄčéčüčÅ 4 ąČąĄčüčéą║ąŠ ąĘą░čłąĖčéčŗčģ ą░ą┤čĆąĄčüą░, ą▓čŗą▒ąĖčĆą░ąĄą╝čŗąĄ ą┤ą▓čāą╝čÅ ą▓ąĮąĄčłąĮąĖą╝ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ (A0 ąĖ A1). ąŁč鹊 ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ čü ą┐ąŠą╝ąŠčēčīčÄ 2 ą╝ą╗ą░ą┤čłąĖčģ ą▒ąĖčé 7-ą▒ąĖčéąĮąŠą│ąŠ slave-ą░ą┤čĆąĄčüą░ ą▓čŗą▒čĆą░čéčī ąŠą┤ąĮčā ąĖąĘ 4 ą╝ąĖą║čĆąŠčüčģąĄą╝, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą║ ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ I2C. ąÜ ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ I2C ą╝ąŠąČąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą╝ą░ą║čüąĖą╝čāą╝ 4 ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ADG714.

ą¤čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ čŹčéąĖčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą▓čüąĄ ąĖčģ ą║ą╗čÄčćąĖ čĆą░ąĘąŠą╝ą║ąĮčāčéčŗ, ąĖ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čĆąĄą│ąĖčüčéčĆą░čģ čüąŠą┤ąĄčƹȹ░čéčüčÅ ąĮčāą╗ąĖ ą▓ąŠ ą▓čüąĄčģ čĆą░ąĘčĆčÅą┤ą░čģ. ą£ą░ą╗ąŠąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ąĖ čĆą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ąŠčé 2.7V ą┤ąŠ 5.5V ą┤ąĄą╗ą░čÄčé ADG714/ADG715 ąĖą┤ąĄą░ą╗čīąĮąŠ ą┐ąŠą┤čģąŠą┤čÅčēąĖą╝ąĖ ą┤ą╗čÅ ą╝ąĮąŠą│ąĖčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣. ąŁčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą╝ąŠąČąĮąŠ čéą░ą║ąČąĄ ąĘą░ą┐ąĖčéą░čéčī ąŠčé ą┤ą▓čāčģą┐ąŠą╗čÅčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ┬▒2.5V.

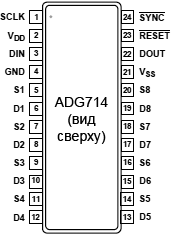

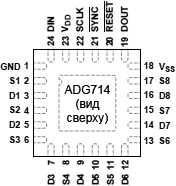

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ ADG714 ą┤ąŠčüčéčāą┐ąĮą░ ą▓ 24-ą▓čŗą▓ąŠą┤ąĮčŗčģ ą║ąŠčĆą┐čāčüą░čģ TSSOP ąĖ LFCSP, ą░ ADG715 ą▓ 24-ą▓čŗą▓ąŠą┤ąĮčŗčģ ą║ąŠčĆą┐čāčüą░čģ TSSOP.

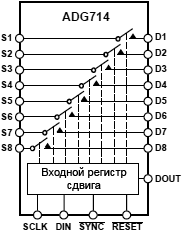

ąĀąĖčü. 1. ąæą╗ąŠą║-čüčģąĄą╝ą░ ADG714.

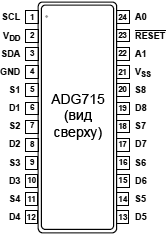

ąĀąĖčü. 2. ąæą╗ąŠą║-čüčģąĄą╝ą░ ADG715.

[ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ]

ąĀąĖčü. 3. 3-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü (SPI) ADG714.

ąĀąĖčü. 4. 2-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü (I2ąĪ) ADG715.

[ą”ąŠą║ąŠą╗ąĄą▓ą║ą░ ąĖ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ ADG714]

ąĀąĖčü. 5. ąÜąŠčĆą┐čāčü TSSOP24 ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ADG714 (ą▓ąĖą┤ čüą▓ąĄčĆčģčā).

ąĀąĖčü. 6. ąÜąŠčĆą┐čāčü LFCSP24 ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ADG714 (ą▓ąĖą┤ čüą▓ąĄčĆčģčā).

ąóą░ą▒ą╗ąĖčåą░ 8. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ ADG714.

| ą£ąĮąĄą╝. |

TSSOP |

LFCSP |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| SCLK |

1 |

22 |

ąÆčģąŠą┤ čéą░ą║č鹊ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░. ąöą░ąĮąĮčŗąĄ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ č湥čĆąĄąĘ DIN ą▓ąŠ ą▓čģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąŠ čüą┐ą░ą┤ą░ą╝ čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ ADG714 ą╝ąŠąČąĄčé ą┐čĆąĖąĮčÅčéčī čćą░čüč鹊čéčā čéą░ą║č鹊ą▓ ą┤ąŠ 30 ą£ąōčå. |

| VDD |

2 |

23 |

ą¤ą╗čÄčü ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ. |

| DIN |

3 |

24 |

ąÆčģąŠą┤ ą┤ą░ąĮąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░. ąöą░ąĮąĮčŗąĄ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ąŠ ą▓čģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čģąŠą┤ąĄ čéą░ą║č鹊ą▓ SCLK. |

| GND |

4 |

1 |

ą×ą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤, ą╝ąĖąĮčāčü ą┐ąĖčéą░ąĮąĖčÅ (ąĘąĄą╝ą╗čÅ). |

| Sx |

5, 7, 9, 11, 14, 16, 18, 20 |

2, 4, 6, 8, 11, 13, 15, 17 |

ąśčüč鹊ą║ CMOS-ą║ą╗čÄčćą░ (Source). ąŁčéą░ ąĮąŠąČą║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą║ą░ą║ ą▓čģąŠą┤ąŠą╝, čéą░ą║ ąĖ ą▓čŗčģąŠą┤ąŠą╝ (ą║ą╗čÄčć ą┐čĆąŠą▓ąŠą┤ąĖčé č鹊ą║ ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ). |

| Dx |

6, 8, 10, 12, 13, 15, 17, 19 |

3, 5, 7, 9, 10, 12, 14, 16 |

ąĪč鹊ą║ CMOS-ą║ą╗čÄčćą░ (Drain). ąŁčéą░ ąĮąŠąČą║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą║ą░ą║ ą▓čģąŠą┤ąŠą╝, čéą░ą║ ąĖ ą▓čŗčģąŠą┤ąŠą╝ (ą║ą╗čÄčć ą┐čĆąŠą▓ąŠą┤ąĖčé č鹊ą║ ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ). |

| VSS |

21 |

18 |

ą×čéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠą╗čÄčü ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ. ąöą╗čÅ ąŠą┤ąĮąŠą┐ąŠą╗čÅčĆąĮąŠą│ąŠ ą▓ą║ą╗čÄč湥ąĮąĖčÅ čŹčéą░ ąĮąŠąČą║ą░ čüąŠąĄą┤ąĖąĮčÅąĄčéčüčÅ čü GND. |

| DOUT |

22 |

19 |

ąÆčŗčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ąĪ ą┐ąŠą╝ąŠčēčīčÄ čŹč鹊ą│ąŠ ą▓čŗą▓ąŠą┤ą░ ą╝ąŠąČąĮąŠ čüąŠąĄą┤ąĖąĮąĖčéčī ą▓ čåąĄą┐ąŠčćą║čā ąĮąĄčüą║ąŠą╗čīą║ąŠ ą╝ąĖą║čĆąŠčüčģąĄą╝, ąĖ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ąĖčģ ą║ ąŠą┤ąĮąŠą╝čā ąĖąĮč鹥čĆč乥ą╣čüčā SPI ą╝ą░čüč鹥čĆą░. ąöą░ąĮąĮčŗąĄ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĮą░ čŹč鹊čé ą▓čŗčģąŠą┤ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ čéą░ą║č鹊ą▓ SCLK. DOUT ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮ ą║ą░ą║ ą▓čŗčģąŠą┤ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝, ą┐ąŠčŹč鹊ą╝čā ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą╗ąŠą│ąĖč湥čüą║ąĖčģ čāčĆąŠą▓ąĮąĄą╣ ą║ ąĮąĄą╝čā ąĮčāąČąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą▓ąĄčĆčģąĮąĖą╣ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖą╣ čĆąĄąĘąĖčüč鹊čĆ (pull-up). |

| /RESET |

23 |

20 |

ąÆčģąŠą┤ čüą▒čĆąŠčüą░ čü ą░ą║čéąĖą▓ąĮčŗą╝ čāčĆąŠą▓ąĮąĄą╝ ą╗ąŠą│. 0. ą¤ąŠčÅą▓ą╗ąĄąĮąĖąĄ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąŠčćąĖčēą░ąĄčé ą▓čģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ ąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą▓čüąĄ ą║ą╗čÄčćąĖ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ "ą▓čŗą║ą╗čÄč湥ąĮąŠ" (OFF). |

| /SYNC |

24 |

21 |

ąÆčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ čü ą░ą║čéąĖą▓ąĮčŗą╝ čāčĆąŠą▓ąĮąĄą╝ ą╗ąŠą│. 0. ąŁčéą░ ąĮąŠąČą║ą░ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ ą║ą░ą┤čĆą░ ą┤ą╗čÅ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ /SYNC ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0, čŹč鹊 ą▓ą║ą╗čÄčćą░ąĄčé ą┐ąĖčéą░ąĮąĖąĄ ą▒čāč乥čĆąŠą▓ SCLK ąĖ DIN, ąĖ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čĆą░ą▒ąŠčéą░ ą▓čģąŠą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░. ąöą░ąĮąĮčŗąĄ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ č湥čĆąĄąĘ ąĮąŠąČą║čā DIN ą┐ąŠ čüą┐ą░ą┤ą░ą╝ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čģąŠą┤ąĄ čéą░ą║č鹊ą▓ SCLK. ą¤ąĄčĆąĄą▓ąŠą┤ /SYNC ą▓ ą╗ąŠą│. 1 ąŠą▒ąĮąŠą▓ą╗čÅąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą║ą╗čÄč湥ą╣. |

| EP |

- |

EP |

Exposed Pad, ą╝ą░čüčüąĖą▓ąĮą░čÅ ą║ąŠąĮčéą░ą║čéąĮą░čÅ ą┐ą╗ąŠčēą░ą┤ą║ą░ ąĮą░ ą┤ąŠąĮčåąĄ ą║ąŠčĆą┐čāčüą░ LFCSP24. ąŁč鹊čé ą▓čŗą▓ąŠą┤ čüąŠąĄą┤ąĖąĮąĄąĮ ą▓ąĮčāčéčĆąĖ ą║ąŠčĆą┐čāčüą░ čü čüčāą▒čüčéčĆą░č鹊ą╝ ą║čĆąĖčüčéą░ą╗ą╗ą░. ąØą░ ą┐ą╗ą░č鹥 EP ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čüąŠąĄą┤ąĖąĮąĄąĮą░ čü VSS. |

[ą”ąŠą║ąŠą╗ąĄą▓ą║ą░ ąĖ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ ADG715]

ąĀąĖčü. 7. ąÜąŠčĆą┐čāčü TSSOP24 ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ADG715 (ą▓ąĖą┤ čüą▓ąĄčĆčģčā).

ąóą░ą▒ą╗ąĖčåą░ 10. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ ADG715.

| ą£ąĮąĄą╝. |

TSSOP |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| SCL |

1 |

ąÆčģąŠą┤ čéą░ą║č鹊ą▓ I2C (Serial Clock Line). ąŁčéą░ ąĮąŠąČą║ą░ ą▓ą╝ąĄčüč鹥 čü SDA ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ 8-ą▒ąĖčéąĮąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░. ą¦ą░čüč鹊čéą░ čéą░ą║č鹊ą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠ 400 ą║ąōčå. |

| VDD |

2 |

ą¤ą╗čÄčü ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ. |

| SDA |

3 |

ąÆčģąŠą┤/ą▓čŗčģąŠą┤ ą┤ą░ąĮąĮčŗčģ I2C (Serial Data Line). ąŁčéą░ ąĮąŠąČą║ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüąŠą▓ą╝ąĄčüčéąĮąŠ čü SCL, čćč鹊ą▒čŗ ą▓ą┤ą▓ąĖą│ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ąŠ ą▓čģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ (ąĖą╗ąĖ ą▓čŗą┤ą▓ąĖą│ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ąĮąĄą│ąŠ ą┐čĆąĖ čćč鹥ąĮąĖąĖ). SDA čŹč鹊 ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ą▓čŗą▓ąŠą┤ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝, ąĖ čéčĆąĄą▒čāąĄčé ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ ąĮąĄą╝čā ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĄą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ (pull-up). |

| GND |

4 |

ą×ą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤, ą╝ąĖąĮčāčü ą┐ąĖčéą░ąĮąĖčÅ (ąĘąĄą╝ą╗čÅ). |

| Sx |

5, 7, 9, 11, 14, 16, 18, 20 |

ąśčüč鹊ą║ CMOS-ą║ą╗čÄčćą░ (Source). ąŁčéą░ ąĮąŠąČą║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą║ą░ą║ ą▓čģąŠą┤ąŠą╝, čéą░ą║ ąĖ ą▓čŗčģąŠą┤ąŠą╝ (ą║ą╗čÄčć ą┐čĆąŠą▓ąŠą┤ąĖčé č鹊ą║ ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ). |

| Dx |

6, 8, 10, 12, 13, 15, 17, 19 |

ąĪč鹊ą║ CMOS-ą║ą╗čÄčćą░ (Drain). ąŁčéą░ ąĮąŠąČą║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą║ą░ą║ ą▓čģąŠą┤ąŠą╝, čéą░ą║ ąĖ ą▓čŗčģąŠą┤ąŠą╝ (ą║ą╗čÄčć ą┐čĆąŠą▓ąŠą┤ąĖčé č鹊ą║ ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ). |

| VSS |

21 |

ą×čéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠą╗čÄčü ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ. ąöą╗čÅ ąŠą┤ąĮąŠą┐ąŠą╗čÅčĆąĮąŠą│ąŠ ą▓ą║ą╗čÄč湥ąĮąĖčÅ čŹčéą░ ąĮąŠąČą║ą░ čüąŠąĄą┤ąĖąĮčÅąĄčéčüčÅ čü GND. |

| A1 |

22 |

ąÆčģąŠą┤ ą░ą┤čĆąĄčüą░, ąĘą░ą┤ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ ą▓č鹊čĆąŠą│ąŠ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą▒ąĖčéą░ 7-ą▒ąĖčéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ I2C. |

| /RESET |

23 |

ąÆčģąŠą┤ čüą▒čĆąŠčüą░ čü ą░ą║čéąĖą▓ąĮčŗą╝ čāčĆąŠą▓ąĮąĄą╝ ą╗ąŠą│. 0. ą¤ąŠčÅą▓ą╗ąĄąĮąĖąĄ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąŠčćąĖčēą░ąĄčé ą▓čģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ ąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą▓čüąĄ ą║ą╗čÄčćąĖ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ "ą▓čŗą║ą╗čÄč湥ąĮąŠ" (OFF). |

| A0 |

24 |

ąÆčģąŠą┤ ą░ą┤čĆąĄčüą░, ąĘą░ą┤ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆą▓ąŠą│ąŠ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą▒ąĖčéą░ 7-ą▒ąĖčéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ I2C. |

[ą×ą┐ąĖčüą░ąĮąĖąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ADG714/ADG715]

ADG714 ąĖ ADG715 čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą┐ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╝čā ąĖąĮč鹥čĆč乥ą╣čüčā (SPI ąĖ I2C čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ), č湥čĆąĄąĘ ą║ąŠč鹊čĆčŗą╣ ą▓ ąĮąĖčģ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą▒ą░ą╣čé. ąÜą░ąČą┤čŗą╣ čĆą░ąĘčĆčÅą┤ čŹč鹊ą│ąŠ ą▒ą░ą╣čéą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čüąŠčüč鹊čÅąĮąĖčÄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ SPST-ą║ą╗čÄčćą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ. ąĢčüą╗ąĖ ą▒ąĖčé ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą║ą░ąĮą░ą╗ ą║ą╗čÄčćą░ ą┐čĆąŠą▓ąŠą┤ąĖčé č鹊ą║ (čüąŠčüč鹊čÅąĮąĖąĄ ON, ą║ą░ąĮą░ą╗ ą║ą╗čÄčćą░ ąŠčéą║čĆčŗčé), ąĄčüą╗ąĖ ąČąĄ 0, č鹊 ą║ą╗čÄčć č鹊ą║ ąĮąĄ ą┐čĆąŠą▓ąŠą┤ąĖčé (čüąŠčüč鹊čÅąĮąĖąĄ OFF, ą║ą░ąĮą░ą╗ ą║ą╗čÄčćą░ ąĘą░ą║čĆčŗčé). ąÜą░ąČą┤čŗą╣ ą║ą╗čÄčć ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ąŠčéą┤ąĄą╗čīąĮčŗą╝ ą▒ąĖč鹊ą╝, ą┐ąŠčŹč鹊ą╝čā ą║ą░ąĮą░ą╗čŗ ą║ą╗čÄč湥ą╣ ą╝ąŠą│čāčé ą▒čŗčéčī ąŠčéą║čĆčŗčéčŗ ąĖą╗ąĖ ąĘą░ą║čĆčŗčéčŗ ą▓ ą╗čÄą▒čŗčģ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅčģ.

ąÜąŠą│ą┤ą░ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐ąŠą╝ąĄąĮčÅčéčī čüąŠčüč鹊čÅąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą║ą╗čÄč湥ą╣, ą▓ąŠ ą▓čģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ąĮąŠą▓ąŠąĄ 8-ą▒ąĖčéąĮąŠąĄ čüą╗ąŠą▓ąŠ. ąØąĄą║ąŠč鹊čĆčŗąĄ ąĖąĘ ą▒ąĖčé čŹč鹊ą│ąŠ čüą╗ąŠą▓ą░ ą╝ąŠą│čāčé ąĖą╝ąĄčéčī č鹊 ąČąĄ čüąŠčüč鹊čÅąĮąĖąĄ, čćč鹊 ąĖ ą▓ ą┐čĆąĄą┤čŗą┤čāčēąĄą╣ ąĘą░ą┐ąĖčüąĖ, ą┐ąŠč鹊ą╝čā čćč鹊 čüąŠčüč鹊čÅąĮąĖąĄ ąĮąĄą║ąŠč鹊čĆčŗčģ ą║ą╗čÄč湥ą╣ ą╝ąĄąĮčÅčéčī ąĮąĄ ąĮą░ą┤ąŠ. ąöą╗čÅ ą╝ąĖąĮąĖą╝ąĖąĘą░čåąĖąĖ ą╗ąĖčłąĮąĖčģ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖą╣ čüąŠčüč鹊čÅąĮąĖčÅ ą║ą╗čÄč湥ą╣, ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčé ą┐čĆąĄą┤čŗą┤čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ ąĖ ąĮąŠą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ, ąĖ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčé č鹊ą╗čīą║ąŠ č鹥 ą║ą╗čÄčćąĖ, čüąŠčüč鹊čÅąĮąĖąĄ ą║ąŠč鹊čĆčŗčģ ą┤ąŠą╗ąČąĮąŠ ąĖąĘą╝ąĄąĮąĖčéčīčüčÅ. ąÜąŠą│ą┤ą░ ą║ą╗čÄčć čāąČąĄ ąĘą░ą╝ą║ąĮčāčé, ąĖ ą▓ ąĮąŠą▓ąŠą╝ ąĘą░ą┐ąĖčüą░ąĮąĮąŠą╝ čüą╗ąŠą▓ąĄ ąŠąĮ č鹊ąČąĄ ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ąĘą░ą╝ą║ąĮčāčéčŗą╝, čŹč鹊 ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆčāąĄčé ą║ąŠą╝ą╝čāčéą░čåąĖąŠąĮąĮčŗąĄ ą┐ąŠą╝ąĄčģąĖ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ ą║ą╗čÄčćą░.

POWER-ON RESET. ą¤čĆąĖ ą┐ąŠą┤ą░č湥 ą┐ąĖčéą░ąĮąĖčÅ ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čā ą▓čüąĄ ą║ą╗čÄčćąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąŠą╗čāčćą░čÄčé čüąŠčüč鹊čÅąĮąĖąĄ "ą▓čŗą║ą╗čÄč湥ąĮąŠ" (OFF), ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│ąĖčüčéčĆ ąĘą░ą┐ąŠą╗ąĮąĄąĮ ąĮčāą╗čÅą╝ąĖ, ąĖ ąŠčüčéą░ąĄčéčüčÅ ą▓ čéą░ą║ąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ, ą┐ąŠą║ą░ ą▓ ąĮąĄą│ąŠ ąĮąĄ ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮą░ ą║ąŠčĆčĆąĄą║čéąĮą░čÅ ąĘą░ą┐ąĖčüčī ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ.

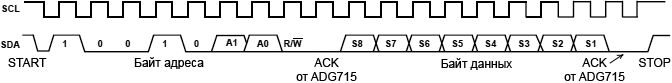

SPI. ąŁčéąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ čüąĮą░ą▒ąČąĄąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ADG714. ąÆ ąĮąĄą╝ ąĖą╝ąĄąĄčéčüčÅ 3 čüąĖą│ąĮą░ą╗ą░: /SYNC, SCLK ąĖ DIN. ąŁč鹊 ąĖąĮč鹥čĆč乥ą╣čü čüąŠą▓ą╝ąĄčüčéąĖą╝ čü ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮčŗą╝ąĖ čüčéą░ąĮą┤ą░čĆčéą░ą╝ąĖ SPI, QSPI ąĖ MICROWIRE. ąØą░ čĆąĖčü. 3 ą┐ąŠą║ą░ąĘą░ąĮą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ čéąĖą┐ąŠą▓ąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ.

ąöą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ 8-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ č湥čĆąĄąĘ ąĮąŠąČą║čā DIN, ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗ąŠą▓ /SYNC ąĖ SCLK. ąöą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą╗čÄą▒čŗą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ ą▒ąĖčé, ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ 8. ąÆ ą║ą░ąČą┤ąŠą╝ čüą╗čāčćą░ąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüą┤ą▓ąĖą│ą░ ąŠčüčéą░čÄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ 8 ąĘą░ą┐ąĖčüą░ąĮąĮčŗčģ ą▒ąĖčé.

ąÜąŠą│ą┤ą░ /SYNC ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0, čĆą░ą▒ąŠčéą░ ą▓čģąŠą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ. ąöą░ąĮąĮčŗąĄ čü ąĮąŠąČą║ąĖ DIN ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čģąŠą┤ąĄ SCLK. ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, ą║ą░ąČą┤čŗą╣ ą▒ąĖčé ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝ąŠą│ąŠ 8-ą▒ąĖčéąĮąŠą│ąŠ čüą╗ąŠą▓ą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠą┤ąĮąŠą╝čā ąĖąĘ 8 ą║ą╗čÄč湥ą╣. ąĀąĖčü. 24 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▓čģąŠą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░. ąöą░ąĮąĮčŗąĄ ą┐ąŠčÅą▓ą╗čÅčÄčéčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ DOUT ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čģąŠą┤ąĄ SCLK, čćč鹊 ą┤ąĄą╗ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮčŗą╝ ą║ą░čüą║ą░ą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčāčÄ čåąĄą┐ąŠčćą║čā, ą┐čĆąĖ čŹč鹊ą╝ ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ ą╝ąĖą║čĆąŠčüčģąĄą╝čā ąĘą░ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĮą░ 8 ą▒ąĖčé. ąÜąŠą│ą┤ą░ ą▓čüąĄ 8 ą▒ąĖčé ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, čüąĖą│ąĮą░ą╗ /SYNC čüąĮąŠą▓ą░ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1. ąÜą╗čÄčćąĖ ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ąĮąŠą▓ąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣, ąĖ ą▓čģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ. ąÜąŠą│ą┤ą░ /SYNC čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 1, ą▓čģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ ąĘą░ą┐čĆąĄčēąĄąĮ, ąĖ ąĮąĖą║ą░ą║ąĖąĄ ą┤ą░ąĮąĮčŗąĄ ąĖą╗ąĖ čłčāą╝ ąĮą░ DIN ąĮąĖą║ą░ą║ ąĮąĄ ą▓ą╗ąĖčÅčÄčé ąĮą░ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░.

ąĀąĖčü. 24. ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▓čģąŠą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░.

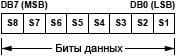

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: MSB ąŠąĘąĮą░čćą░ąĄčé čüčéą░čĆčłąĖą╣ ą▒ąĖčé (Most Significant Bit), LSB ąŠąĘąĮą░čćą░ąĄčé ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé (Least Significant Bit).

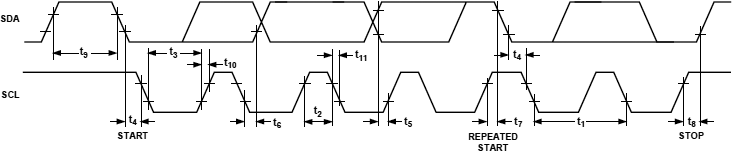

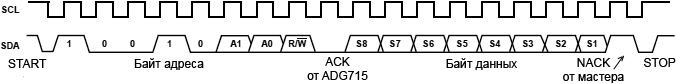

I2C. ąŁčéąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ čüąĮą░ą▒ąČąĄąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ADG715. ąÆ ąĮąĄą╝ ąĖą╝ąĄąĄčéčüčÅ 2 čüąĖą│ąĮą░ą╗ą░: SDA ąĖ SCK. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ ADG715 ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ čłąĖąĮąĄ I2C ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ (slave) čāčüčéčĆąŠą╣čüčéą▓ąŠ, ąĖ ą░ą┤čĆąĄčüčāąĄčéčüčÅ ą┐ąŠ 7-ą▒ąĖčéąĮąŠą╝čā slave-ą░ą┤čĆąĄčüčā. ą¤ąĄčĆą▓čŗąĄ 5 čüčéą░čĆčłąĖčģ ą▒ąĖčé ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī 10010, ąŠčüčéą░ą╗čīąĮčŗąĄ ą┤ą▓ą░ ą╝ą╗ą░ą┤čłąĖčģ ą▒ąĖčéą░ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ čüąŠčüč鹊čÅąĮąĖąĄą╝ ąĮąŠąČąĄą║ ą░ą┤čĆąĄčüą░ A0 ąĖ A1. ąØą░ čĆąĖčü. 4 ą┐ąŠą║ą░ąĘą░ąĮą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ čéąĖą┐ąŠą▓ąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ.

2-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐čĆąŠč鹊ą║ąŠą╗ I2C čĆą░ą▒ąŠčéą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

1. ą£ą░čüč鹥čĆ čłąĖąĮčŗ (ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ I2C) ąĖąĮąĖčåąĖąĖčĆčāąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą╝ START, ą║ąŠč鹊čĆčŗą╣ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą║ą░ą║ ą┐ąĄčĆąĄčģąŠą┤ 1 -> 0 ąĮą░ ą╗ąĖąĮąĖąĖ SDA, ą║ąŠą│ą┤ą░ ąĮą░ SCL ą╗ąŠą│. 1. ąöą░ą╗ąĄąĄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▒ą░ą╣čé ą░ą┤čĆąĄčüą░, čüąŠčüč鹊čÅčēąĖą╣ ąĖąĘ 7 ą▒ąĖčé slave-ą░ą┤čĆąĄčüą░, ą║ąŠč鹊čĆčŗą╣ ąĘą░ą▓ąĄčĆčłą░ąĄčé ą▒ąĖčé R/W (čüąŠčüč鹊čÅąĮąĖąĄ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąŠą┐ąĄčĆą░čåąĖčÄ - ą▒čāą┤čāčé ą┤ą░ąĮąĮčŗąĄ čüčćąĖčéčŗą▓ą░čéčīčüčÅ čüąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖą╗ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčīčüčÅ ą▓ ąĮąĄą│ąŠ).

Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą░ą┤čĆąĄčü ą║ąŠč鹊čĆąŠą│ąŠ čüąŠą▓ą┐ą░ą╗ čü ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗą╝ ą┐ąŠ čłąĖąĮąĄ, ą┐ąŠą┤čéčÅą│ąĖą▓ą░ąĄčé ą║ ą╗ąŠą│. 0 čüąĖą│ąĮą░ą╗ SDA ą▓ąŠ ą▓čĆąĄą╝čÅ 9-ą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ (čŹč鹊 ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆčāąĄčéčüčÅ ą╝ą░čüč鹥čĆąŠą╝ ą║ą░ą║ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ, ACK-ą▒ąĖčé). ąØą░ čŹč鹊ą╣ čüčéą░ą┤ąĖąĖ ąŠą▒ą╝ąĄąĮą░ ą▓čüąĄ ą┤čĆčāą│ąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ čłąĖąĮąĄ, ą║čĆąŠą╝ąĄ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą│ąŠ, ąŠčüčéą░čÄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ, ąĖ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąČą┤ąĄčé ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüąŠą▓ čéą░ą║ąŠą▓ ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ąĖą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖąĘ ąĮąĄą│ąŠ. ąĢčüą╗ąĖ ą▒ąĖčé R/W čĆą░ą▓ąĄąĮ 1, č鹊 ą╝ą░čüč鹥čĆ čüčćąĖčéčŗą▓ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ąĖąĘ slave-čāčüčéčĆąŠą╣čüčéą▓ą░. ąĢčüą╗ąĖ ą▒ąĖčé R/W čĆą░ą▓ąĄąĮ 0, č鹊 ą╝ą░čüč鹥čĆ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą▓ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ.

2. ąöą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┐ąŠ čłąĖąĮąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ ąĖąĘ 9 čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ (8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą▒ąĖčé ACK). ą¤ąĄčĆąĄčģąŠą┤čŗ čāčĆąŠą▓ąĮčÅ ąĮą░ ąĮąŠąČą║ąĄ SDA ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī ą▓ąŠ ą▓čĆąĄą╝čÅ čāčĆąŠą▓ąĮčÅ ą╗ąŠą│. 0 ą┐ąĄčĆąĖąŠą┤ą░ SCL, ąĖ čāčĆąŠą▓ąĄąĮčī ąĮą░ SDA ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ čüčéą░ą▒ąĖą╗čīąĮčŗą╝ ą▓ąŠ ą▓čĆąĄą╝čÅ ą╗ąŠą│. 1 ąĮą░ čéą░ą║čéą░čģ SCL.

3. ąÜąŠą│ą┤ą░ ą▓čüąĄ ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ, ą╝ą░čüč鹥čĆ ą▓čŗą┤ą░ąĄčé čüąĖą│ąĮą░ą╗ STOP. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą║ą░ą║ ą┐ąĄčĆąĄčģąŠą┤ 0 -> 1 ąĮą░ ąĮąŠąČą║ąĄ SDA, ą║ąŠą│ą┤ą░ ąĮą░ ą▓čģąŠą┤ąĄ SCL ą╗ąŠą│. 1. ąÆ čĆąĄąČąĖą╝ąĄ ąĘą░ą┐ąĖčüąĖ ą╝ą░čüč鹥čĆ ą┐ąŠą┤čéčÅą│ąĖą▓ą░ąĄčé ąĮąŠąČą║čā SDA ą║ ą╗ąŠą│. 1 ą▓ąŠ ą▓čĆąĄą╝čÅ 9-ą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░, čćč鹊ą▒čŗ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čüąĖą│ąĮą░ą╗ STOP. ąÆ čĆąĄąČąĖą╝ąĄ čćč鹥ąĮąĖčÅ ą╝ą░čüč鹥čĆ ą▓čŗą┤ą░ąĄčé ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ (NACK) ą┤ą╗čÅ 9-ą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░, ąĖ čāčĆąŠą▓ąĄąĮčī SDA ąŠčüčéą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 1. ą£ą░čüč鹥čĆ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ąĮąŠąČą║čā SDA ą▓ ą╗ąŠą│. 1 ą┐ąĄčĆąĄą┤ ą┤ąĄą▓čÅčéčŗą╝ čéą░ą║č鹊ą▓čŗą╝ ąĖą╝ą┐čāą╗čīčüąŠą╝, ąĖ ąĘą░č鹥ą╝ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ąĮą░ SDA ą╗ąŠą│. 1 ą┐ąŠ ą▓čĆąĄą╝čÅ ą┤ąĄčüčÅč鹊ą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░, čćč鹊ą▒čŗ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ą╗čüčÅ STOP.

ąĪą╝. čĆąĖčü. 25 ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ ADG715.

ą¤ąŠą▓č鹊čĆąĄąĮąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ą│ąĖą▒ą║ąŠčüčéčī ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą╝ą░čéčĆąĖčåčŗ ą║ą╗čÄč湥ą╣ ąĮąĄčüą║ąŠą╗čīą║ąŠ čĆą░ąĘ ą┐ąŠčüą╗ąĄ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ ADG715. ąÆąŠ ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░ ąĘą░ą┐ąĖčüąĖ ą║ą░ąČą┤čŗą╣ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąŠą▒ąĮąŠą▓ą╗čÅąĄčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ ą║ą╗čÄč湥ą╣. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą╝ą░čéčĆąĖčåą░ ą║ą╗čÄč湥ą╣ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčé čüą▓ąŠą╣ ą░ą┤čĆąĄčü ąĖ ą┐čĆąĖą╝ąĄčé ąŠą┤ąĖąĮ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ą║ą╗čÄčćąĖ ąŠą▒ąĮąŠą▓čÅčé čüą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čŹčéąĖą╝ ą▒ą░ą╣č鹊ą╝. ąĢčüą╗ąĖ ą┤čĆčāą│ąŠą╣ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą▒čŗą╗ ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╝ą░čéčĆąĖčåčā ą║ą╗čÄč湥ą╣, ą║ąŠą│ą┤ą░ ąŠąĮą░ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą░ą┤čĆąĄčüą░čåąĖąĖ, č鹊 čŹč鹊čé ą▒ą░ą╣čé čéą░ą║ąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÄ čüąŠčüč鹊čÅąĮąĖčÅ ą║ą╗čÄč湥ą╣. ąóą░ą║ąČąĄ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ ą┐ąŠą▓č鹊čĆąĄąĮąĖąĄ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ ą╝ą░čéčĆąĖčåčŗ ą║ą╗čÄč湥ą╣.

ąĀąĖčü. 25. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą┐ąĖčüąĖ ADG715.

ąÆčģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░. ąÆčģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ 8-ą▒ąĖčéąĮčŗą╣, ąĮą░ čĆąĖčü. 24 ą┐ąŠą║ą░ąĘą░ąĮąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░. ąöą░ąĮąĮčŗąĄ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝čā ą║ą░ą║ 8-ą▒ąĖčéąĮąŠąĄ čüą╗ąŠą▓ąŠ ą┐ąŠ čéą░ą║čéą░ą╝ čüąĖą│ąĮą░ą╗ą░ SCL. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ čŹč鹊ą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 4. 8-ą▒ąĖčéąĮąŠąĄ čüą╗ąŠą▓ąŠ čüąŠčüč鹊ąĖčé ąĖąĘ 8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ, ą║ą░ąČą┤čŗą╣ ą▒ąĖčé čŹč鹊ą│ąŠ čüą╗ąŠą▓ą░ čāą┐čĆą░ą▓ą╗čÅąĄčé ąŠą┤ąĮąĖą╝ ą║ą╗čÄč湊ą╝. ąĪčéą░čĆčłąĖą╣ ą▒ąĖčé MSB (ą▒ąĖčé 7) ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝.

ą×ą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ I2C. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĘą░ą┐ąĖčüčī ą▓ ADG715, ą╝ą░čüč鹥čĆ ąĮą░čćąĖąĮą░ąĄčé čü ą▒ą░ą╣čéą░ ą░ą┤čĆąĄčüą░ ąĖ ą▒ąĖčéą░ R/W=0, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčé čüąĖą│ąĮą░ą╗ąŠą╝ ACK (ą┐ąŠą┤čéčÅą│ąĖą▓ą░ąĮąĖąĄą╝ SDA ą║ ą╗ąŠą│. 0) čüą▓ąŠčÄ ą│ąŠč鹊ą▓ąĮąŠčüčéčī ą║ ą┐čĆąĖąĄą╝čā ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ. ąŚą░ čŹčéąĖą╝ ą░ą┤čĆąĄčüąŠą╝ ąĖą┤ąĄčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ. ą×ą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 25.

ą×ą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ I2C. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čćč鹥ąĮąĖąĄ ąĖąĘ ADG715, ą╝ą░čüč鹥čĆ ąĮą░čćąĖąĮą░ąĄčé čü ą▒ą░ą╣čéą░ ą░ą┤čĆąĄčüą░ ąĖ ą▒ąĖčéą░ R/W=1, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčé čüąĖą│ąĮą░ą╗ąŠą╝ ACK (ą┐ąŠą┤čéčÅą│ąĖą▓ą░ąĮąĖąĄą╝ SDA ą║ ą╗ąŠą│. 0) čüą▓ąŠčÄ ą│ąŠč鹊ą▓ąĮąŠčüčéčī ą║ ą┐ąĄčĆąĄą┤ą░č湥 ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ. ąöą░ą╗ąĄąĄ ą┐ąŠ čéą░ą║čéą░ą╝ SCK ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą▓čŗą┤ą▓ąĖą│ą░ąĄčéčüčÅ ąĖąĘ ą▓čģąŠą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░. ąĘą░ą┐ąĖčüąĖ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 25. ą×ą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 26.

ąĀąĖčü. 26. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čćč鹥ąĮąĖčÅ ADG715.

[ąśąĮč乊čĆą╝ą░čåąĖčÅ ą┐ąŠ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÄ]

I2C, ąĮąĄčüą║ąŠą╗čīą║ąŠ ADG715 ąĮą░ čłąĖąĮąĄ I2C. ąØą░ čĆąĖčü. 27 ą┐ąŠą║ą░ąĘą░ąĮčŗ 4 ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ADG715, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ą║ ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ I2C, čŹč鹊 ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą╝ąĖą║čĆąŠčüčģąĄą╝, ą┤ąŠą┐čāčüčéąĖą╝ąŠąĄ ą┤ą╗čÅ ąŠą┤ąĮąŠą╣ čłąĖąĮčŗ. ąŻ ą║ą░ąČą┤ąŠą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ADG715 ąĮą░čüčéčĆąŠąĄąĮ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü, ą┐ąŠč鹊ą╝čā čćč鹊 ąĮą░ ąĮąŠąČą║ąĖ A0 ąĖ A1 ą┐ąŠą┤ą░ąĮčŗ čĆą░ąĘąĮčŗąĄ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ čāčĆąŠą▓ąĮąĄą╣ (00, 01, 10 ąĖ 11). ąŁčéąĖ čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą░ą┤čĆąĄčüą░ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ ą║ą░ąČą┤čāčÄ ą╝ąĖą║čĆąŠčüčģąĄą╝čā ą┐ąŠ ąŠčéą┤ąĄą╗čīąĮąŠčüčéąĖ.

ąĀąĖčü. 27. ąØąĄčüą║ąŠą╗čīą║ąŠ ADG715 ąĮą░ ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ I2C.

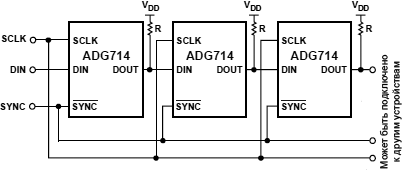

SPI, čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą▓ čåąĄą┐ąŠčćą║čā ADG714. ąØąĄčüą║ąŠą╗čīą║ąŠ ą╝ąĖą║čĆąŠčüčģąĄą╝ ADG714 ą╝ąŠąČąĮąŠ čüąŠąĄą┤ąĖąĮąĖčéčī ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčāčÄ čåąĄą┐ąŠčćą║čā, čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą▓čŗčģąŠą┤ą░ DOUT. ąĀąĖčü. 28 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čéąĖą┐ąŠą▓čāčÄ čĆąĄą░ą╗ąĖąĘą░čåąĖčÄ čéą░ą║ąŠą╣ čüčģąĄą╝čŗ. ąÆčģąŠą┤čŗ /SYNC ą▓čüąĄčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ čüąŠąĄą┤ąĖąĮąĄąĮčŗ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ. ąÜąŠą│ą┤ą░ /SYNC ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą╝ą░čüč鹥čĆąŠą╝ čłąĖąĮčŗ SPI ą▓ ą╗ąŠą│. 0, ą▓čģąŠą┤ąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ čüą┤ą▓ąĖą│ą░ ą▓čüąĄčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ čĆą░ąĘčĆąĄčłąĄąĮčŗ, ąĖ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ ąĮąĖčģ č湥čĆąĄąĘ DIN ąĖ ą┐čĆąŠčģąŠą┤čÅčé č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ą┐ąŠą┐ą░ą┤ą░čÅ ąĮą░ DOUT. ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░, /SYNC ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą╝ą░čüč鹥čĆąŠą╝ ą▓ ą╗ąŠą│. 1, ąĖ ą▓čüąĄ ą║ą╗čÄčćąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąŠ ą┐čĆą░ą║čéąĖč湥čüą║ąĖ ą╗čÄą▒ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čĆąĄą│ąĖčüčéčĆąŠą▓ čüą┤ą▓ąĖą│ą░/ą╝ąĖą║čĆąŠčüčģąĄą╝ ADG714.

ąÆą║ą╗čÄč湥ąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ. ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ CMOS-čāčüčéčĆąŠą╣čüčéą▓ (ą║ąŠč鹊čĆčŗą╝ąĖ čÅą▓ą╗čÅčÄčéčüčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ADG714/ADG715) ą▓ą░ąČąĮąŠ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą┐čĆą░ą▓ąĖą╗čīąĮčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐ąŠą┤ą░čćąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ ąĖ čāčĆąŠą▓ąĮąĄą╣ ąĮą░ ą▓čģąŠą┤čŗ ąĖ ą▓čŗčģąŠą┤čŗ. ąØąĄą┐čĆą░ą▓ąĖą╗čīąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐ąŠą┤ą░čćąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ č鹊ą╝čā, čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠą┐ą░ą┤ąĄčé ą▓ čāčüą╗ąŠą▓ąĖčÅ, ą▓čŗčģąŠą┤čÅčēąĖąĄ ąĘą░ ą┐čĆąĄą┤ąĄą╗čŗ ą░ą▒čüąŠą╗čÄčéąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝čŗčģ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣, ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮčŗčģ ą▓ čéą░ą▒ą╗ąĖčåąĄ 6 ą┤ą░čéą░čłąĖčéą░ [1]. ąØą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ čåąĖčäčĆąŠą▓čŗčģ ąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą▓čģąŠą┤ą░čģ ą▓čüąĄą│ą┤ą░ ą┤ąŠą╗ąČąĮčŗ ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░čéčīčüčÅ ą┐ąŠčüą╗ąĄ ą┐ąŠą┤ą░čćąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą║ąŠčĆčĆąĄą║čéąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ. ąÆ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ čü ą┤ą▓čāą┐ąŠą╗čÅčĆąĮčŗą╝ ą┐ąĖčéą░ąĮąĖąĄą╝, ąĄčüą╗ąĖ ąĮą░ čåąĖčäčĆąŠą▓čŗąĄ ąĖą╗ąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čģąŠą┤čŗ ą┐ąŠą┤ą░ąĄčéčüčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ VDD ąĖ VSS, č鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą▓ąĮąĄčłąĮąĖąĄ ą┤ąĖąŠą┤čŗ ą©ąŠčéčéą║ąĖ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ą║ čŹčéąĖą╝ ą▓čģąŠą┤ą░ą╝ ąĖ čłąĖąĮą░ą╝ VSS ąĖ GND, ą│ą░čĆą░ąĮčéąĖčĆčāčÄčēąĖąĄ ą║ąŠčĆčĆąĄą║čéąĮčāčÄ ą┐ąŠą┤ą░čćčā ą┐ąĖčéą░ąĮąĖčÅ. ąöą╗čÅ ąŠą┤ąĮąŠą┐ąŠą╗čÅčĆąĮąŠą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ VSS ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čüąŠąĄą┤ąĖąĮąĄąĮąŠ čü GND ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ą╗ąĖąČąĄ ą║ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝.

ąĀąĖčü. 28. ąØąĄčüą║ąŠą╗čīą║ąŠ ADG714 ąĮą░ ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ SPI.

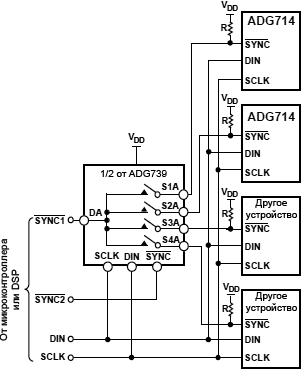

ąØąĄčüą║ąŠą╗čīą║ąŠ ADG714 ą▓ą╝ąĄčüč鹥 čü ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆąŠą╝ ADG739. ąØą░ čĆąĖčü. 29 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ čü ą┐ąŠą╝ąŠčēčīčÄ ADG739 ąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ /SYNC1 ąĮą░ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą╝ąĖą║čĆąŠčüčģąĄą╝ ADG714. ąÆčüąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ąŠą┤ąĮąĖą╝ąĖ ąĖ č鹥ą╝ąĖ ąČąĄ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ ąĖ čéą░ą║č鹊ą▓. ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓čŗą▒ąŠčĆą║čā /SYNC, ą┐čĆąĖčłąĄą┤čłčāčÄ ąŠčé čüąĖą│ąĮą░ą╗ą░ /SYNC1, ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćąĖčéčī č鹊ą╗čīą║ąŠ ąŠą┤ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ADG714. ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆ ADG739 čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą┐ąŠ č鹊ą╣ ąČąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ čłąĖąĮąĄ SPI, ąĮąŠ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ąŠčéą┤ąĄą╗čīąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąŠą╣ /SYNC2. ąóą░ą║ą░čÅ čüčģąĄą╝ą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ ąŠą▒čĆą░čēąĄąĮąĖčÅ ą║ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ ADG714. ąĢčüą╗ąĖ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠčé ąŠą┤ąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ /SYNC1 ą░ą┤čĆąĄčüąŠą▓ą░ąĮąŠ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ADG714, č鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮą░ ą┤čĆčāą│ą░čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆą░ ADG738, čā ą║ąŠč鹊čĆąŠą╣ 8 ą║ą░ąĮą░ą╗ąŠą▓.

ąĀąĖčü. 29. ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮą░čÅ ą░ą┤čĆąĄčüą░čåąĖčÅ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čāčüčéčĆąŠą╣čüčéą▓ ADG714 čü ą┐ąŠą╝ąŠčēčīčÄ ADG739.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čåąĖčäčĆąŠą▓čŗąĄ čüąĖą│ąĮą░ą╗čŗ ą┤ą░ąĮąĮčŗčģ ąĖ čéą░ą║č鹊ą▓ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐ąŠą┤ą░čÄčéčüčÅ ąĮą░ ą▓čüąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą║ą╗čÄč湥ą╣ ADG714. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ą┐ąĄčĆąĄą║čĆąĄčüčéąĮčŗąĄ ą┐ąŠą╝ąĄčģąĖ, ąĮą░ą▓ąŠą┤ąĖą╝čŗąĄ ąŠčé čŹčéąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓ ąĮą░ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą║ą╗čÄčćąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ ADG714.

[ąĪčüčŗą╗ą║ąĖ]

1. ADG714/ADG715 Serially Controlled, Octal SPST Switches site:analog.com.

2. ąśąĮč鹥čĆč乥ą╣čü SPI. |