|

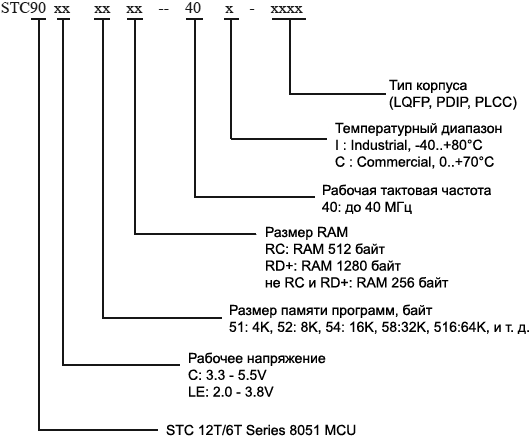

ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ STC90C51RC/RD+, ą║ąŠč鹊čĆčŗąĄ ą▓čŗą┐čāčüą║ą░ąĄčé ą║ąŠą╝ą┐ą░ąĮąĖčÅ STC MCU Limited [1], čŹč鹊 8-ą▒ąĖčéąĮčŗą╣ ąŠą┤ąĮąŠą║čĆąĖčüčéą░ą╗čīąĮčŗą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ, ą┐ąŠą╗ąĮąŠčüčéčīčÄ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╣ ą┐ąŠ čüąĖčüč鹥ą╝ąĄ ą║ąŠą╝ą░ąĮą┤ čü ąĖąĮą┤čāčüčéčĆąĖą░ą╗čīąĮčŗą╝ čüčéą░ąĮą┤ą░čĆč鹊ą╝ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ čüąĄą╝ąĄą╣čüčéą▓ą░ 8051. STC90C51RC/RD+ ąĖą╝ąĄčÄčé ą┤ąŠ 64K ą▒ą░ą╣čé ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ flash ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ą║ąŠč鹊čĆą░čÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüąŠą▓ą╝ąĄčüčéąĮąŠ čü ą║ąŠą┤ąŠą╝ ISP (In-System-Programming, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓ čüąĖčüč鹥ą╝ąĄ. ąóąĄčģąĮąŠą╗ąŠą│ąĖčÅ ISP ąĖ IAP (In-Application-Programming, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖąĘ ą║ąŠą┤ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, čé. ąĄ. čüą░ą╝ąŠą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ąŠą▒ąĮąŠą▓ą╗čÅčéčī ą┐čĆąŠą│čĆą░ą╝ą╝čā ąĖ ą┤ą░ąĮąĮčŗąĄ ą┐čĆčÅą╝ąŠ ą▓ čüąĖčüč鹥ą╝ąĄ. ISP ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ąĘą░ą│čĆčāąČą░čéčī ą║ąŠą┤ ą▒ąĄąĘ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ąĖąĘą▓ą╗ąĄą║ą░čéčī ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąĖąĘ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ąĖąĘą┤ąĄą╗ąĖčÅ; IAP ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą╝ąŠąČąĄčé ąĘą░ą┐ąĖčüčŗą▓ą░čéčī 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ ą┐ą░ą╝čÅčéąĖ Flash ą┐čĆčÅą╝ąŠ ąĖąĘ čĆą░ą▒ąŠčéą░čÄčēąĄą╣ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąśą╝ąĄąĄčéčüčÅ 1280 ą▒ą░ą╣čé ąĖą╗ąĖ 512 ą▒ą░ą╣čé ąĮą░čģąŠą┤čÅčēąĄą╣čüčÅ ąĮą░ ą║čĆąĖčüčéą░ą╗ą╗ąĄ ą┐ą░ą╝čÅčéąĖ RAM, čćč鹊 ą┤ąŠčüčéą░č鹊čćąĮąŠ ą┤ą╗čÅ čłąĖčĆąŠą║ąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąŠčåąĄčüčüąŠčĆ MCU, čćč鹊ą▒čŗ ąŠąĮ čĆą░ą▒ąŠčéą░ą╗ ąĮą░ čüą║ąŠčĆąŠčüčéąĖ 12 čéą░ą║č鹊ą▓ ąĮą░ ąŠą┤ąĖąĮ ą╝ą░čłąĖąĮąĮčŗą╣ čåąĖą║ą╗, ą┤ą░ą▓ą░čÅ čéą░ą║ąŠąĄ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ, čćč鹊 ąĖ čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ MCU 80C51, ąĖą╗ąĖ 6 čéą░ą║č鹊ą▓ ąĮą░ ą╝ą░čłąĖąĮąĮčŗą╣ čåąĖą║ą╗, čāą┤ą▓ą░ąĖą▓ą░čÅ č鹥ą╝ čüą░ą╝čŗą╝ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī. STC90C51RC/RD+ čüąŠčģčĆą░ąĮčÅąĄčé ą▓čüąĄ ą░ą┐ą┐ą░čĆą░čéąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ čüčéą░ąĮą┤ą░čĆčéąĮąŠą│ąŠ 80C51 (čŹčéąĖą╝ čüąĄčĆąĖčÅ STC90xx ąŠč湥ąĮčī ą┐ąŠčģąŠąČą░ ąĮą░ čüąĄčĆąĖčÄ STC89xx, čüą╝. ą┐čĆąĄą┤čŗą┤čāčēčāčÄ ą▓čĆąĄąĘą║čā). ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ MCU čüąĄčĆąĖąĖ STC90xx ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆčé ą▓ą▓ąŠą┤ą░ ą▓čŗą▓ąŠą┤ą░ P4 (ą┐ąŠčĆčé GPIO), Timer2, 8-ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü 4 čāčĆąŠą▓ąĮčÅą╝ąĖ ą┐čĆąĖąŠčĆąĖč鹥čéą░, ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą║ą▓ą░čĆčåąĄą▓čŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ ąĖ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠ čĆą░ąĘčĆąĄčłą░ąĄą╝čŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ (Watchdog Timer, WDT).

ąĪą┐ąĖčüąŠą║ ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣ čüąĄčĆąĖąĖ STC90xx:

ŌĆó ąŻą╗čāčćčłąĄąĮąĮąŠąĄ čÅą┤čĆąŠ 80C51, ą║ąŠč鹊čĆąŠąĄ ą┐ąŠ ą▓čŗą▒ąŠčĆčā ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ čüą║ąŠčĆąŠčüčéąĖ 6T (6 čéą░ą║č鹊ą▓ ąĮą░ ą╝ą░čłąĖąĮąĮčŗą╣ čåąĖą║ą╗, čāčüą║ąŠčĆąĄąĮąĖąĄ ą▓ 2 čĆą░ąĘą░) ąĖą╗ąĖ 12T (12 čéą░ą║č鹊ą▓ ąĮą░ ą╝ą░čłąĖąĮąĮčŗą╣ čåąĖą║ą╗, ą║ą░ą║ ąĮą░ čüčéą░čĆąŠą╣ ą░čĆčģąĖč鹥ą║čéčāčĆąĄ MCS51).

ŌĆó ąĀą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ: 3.3..5.5V (čüąĄčĆąĖčÅ STC90C51RC/RD+) ąĖą╗ąĖ 2.0..3.6V (čüąĄčĆąĖčÅ STC90LE51RC/RD+).

ŌĆó ąĀą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé: 0..80 ą£ąōčå (čĆąĄąČąĖą╝ 12T) ąĖą╗ąĖ 0..40 ą£ąōčå (čĆąĄąČąĖą╝ 6T).

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮą░čÅ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą┐ą░ą╝čÅčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ FLASH čĆą░ąĘą╝ąĄčĆąŠą╝ 4K/8K/13K/16K/32K/40K/48K/56K/61K, čü ą│ąĖą▒ą║ąŠą╣ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ISP/IAP (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą╝ąŠą┤ąĄą╗ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░).

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮą░čÅ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą┐ą░ą╝čÅčéčī ą×ąŚąŻ čĆą░ąĘą╝ąĄčĆąŠą╝ 256/512/1280 ą▒ą░ą╣čé.

ŌĆó ą£ąŠąČąĮąŠ ą░ą┤čĆąĄčüąŠą▓ą░čéčī ą┤ąŠ 64K ą▒ą░ą╣čé ą▓ąĮąĄčłąĮąĄą╣ RAM.

ŌĆó ą£ąŠąČąĮąŠ ą░ą┤čĆąĄčüąŠą▓ą░čéčī ą┤ąŠ 64K ą▒ą░ą╣čé ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ.

ŌĆó ąöą▓ą░ čāą║ą░ąĘą░č鹥ą╗čÅ (DPTR) ą┤ą╗čÅ čāčüą║ąŠčĆąĄąĮąĖčÅ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ.

ŌĆó ąóčĆąĖ 16-ą▒ąĖčéąĮčŗčģ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░. Timer 2 ą╝ąŠąČąĄčé čüčćąĖčéą░čéčī ą▓ą▓ąĄčĆčģ ąĖ ą▓ąĮąĖąĘ, čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ ą▓čŗą▓ąŠą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ čćą░čüč鹊čéčŗ ąĮą░ ąĮąŠąČą║ąĄ ą┐ąŠčĆčéą░ P1.0.

ŌĆó 8 ą░ą┤čĆąĄčüąŠą▓ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čü 4 čāčĆąŠą▓ąĮčÅą╝ąĖ ą┐čĆąĖąŠčĆąĖč鹥čéą░.

ŌĆó ąŻą╗čāčćčłąĄąĮąĮčŗą╣ UART čü ą░ą┐ą┐ą░čĆą░čéąĮčŗą╝ čĆą░čüą┐ąŠąĘąĮą░ą▓ą░ąĮąĖąĄą╝ ą░ą┤čĆąĄčüą░, čäčāąĮą║čåąĖąĄą╣ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ čäčĆąĄą╣ą╝ą░ ąĖ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╝ ą│ąĄąĮąĄčĆą░č鹊čĆąŠą╝ čüą║ąŠčĆąŠčüčéąĖ.

ŌĆó ą×ą┤ąĖąĮ 15-ą▒ąĖčéąĮčŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ čü 8-ą▒ąĖčéąĮčŗą╝ ą┐čĆąĄčüą║ą░ą╗ąĄčĆąŠą╝ (čü čäčāąĮą║čåąĖąĄą╣ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ).

ŌĆó ąśąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆ čüą▒čĆąŠčüą░ MAX810.

ŌĆó ąóčĆąĖ čĆąĄąČąĖą╝ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖąĄą╝: normal mode (ąŠą▒čŗčćąĮčŗą╣ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝), idle mode (čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ), power-down mode (čĆąĄąČąĖą╝ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ).

ŌĆó ąØąĖąĘą║ą░čÅ ą│ąĄąĮąĄčĆą░čåąĖčÅ ą┐ąŠą╝ąĄčģ (EMI): ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąĘą░ą┐čĆąĄčéą░ ą│ąĄąĮąĄčĆą░čåąĖąĖ ALE.

ŌĆó ąśąĘ čĆąĄąČąĖą╝ą░ power down ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą╝ąŠąČąĮąŠ čĆą░ąĘą▒čāą┤ąĖčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ INT0 (ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ P3.2), INT1 (ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ P3.3), T0 (ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ P3.4), T1 (ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ P3.5), RXD (ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ P3.0), INT2 (ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ P4.3), INT3 (ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ P4.2).

ŌĆó ą£ą░ą║čüąĖą╝čāą╝ ą┤ąŠčüčéčāą┐ąĮąŠ ą┤ąŠ 39 ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗčģ ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (GPIO), ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čéąĖą┐ą░ ą║ąŠčĆą┐čāčüą░.

ŌĆó ąśą╝ąĄąĄčéčüčÅ č湥čéčŗčĆąĄ 8-ą▒ąĖčéąĮčŗčģ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ ą┐ąŠčĆčéą░; ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ 4-ą▒ąĖčéąĮčŗą╣ ą┐ąŠčĆčé P4 ą┤ąŠčüčéčāą┐ąĄąĮ ą▓ ą║ąŠčĆą┐čāčüą░čģ PLCC-44 ąĖ LQFP-44.

ŌĆó ąĀą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ: -40..+85┬░C (ąĖąĮą┤čāčüčéčĆąĖą░ą╗čīąĮąŠąĄ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ) / 0..75┬░C (ą║ąŠą╝ą╝ąĄčĆč湥čüą║ąŠąĄ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ).

ŌĆó ąóąĖą┐čŗ ą║ąŠčĆą┐čāčüąŠą▓: LQFP-44, PDIP-40, PLCC-44.

ąĪąĄčĆąĖčÅ STC90xx ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé čüąĄčĆąĖąĖ STC89xx ą▓ ąŠčüąĮąŠą▓ąĮąŠą╝ čüą╗ąĄą┤čāčÄčēąĖą╝: ą┐ąŠą▓čŗčłąĄąĮąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░, ą▒ąŠą╗čīčłąĄ ą▓ą░čĆąĖą░ąĮč鹊ą▓ ą▓čŗą▒ąŠčĆą░ ą┐ąŠ ąŠą▒čŖąĄą╝čā ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ. ąĪąĄčĆąĖčÅ STC90xx ą╝ąŠąČąĄčé ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĘą░ą╝ąĄčéąĖčéčī ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ STC89xx, ą║ą░ą║ ą┐ąŠ ą┤ą▓ąŠąĖčćąĮąŠą╝čā ą║ąŠą┤čā, čéą░ą║ ąĖ ą┐ąŠ čåąŠą║ąŠą╗ąĄą▓ą║ąĄ ą║ąŠčĆą┐čāčüą░.

[ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÅ]

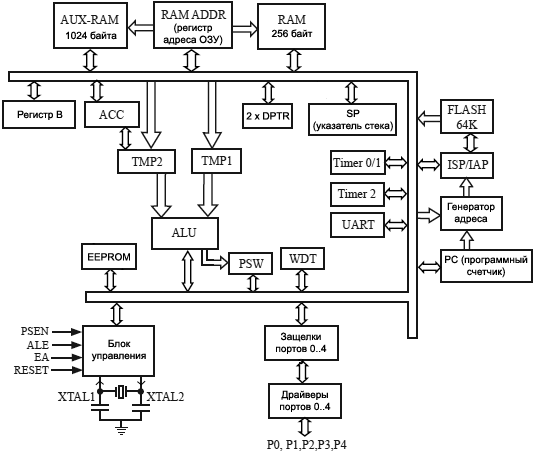

ą»ą┤čĆąŠ CPU čüąĄčĆąĖąĖ STC90xx ą┐ąŠą╗ąĮąŠčüčéčīčÄ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠ čüąŠ čüčéą░ąĮą┤ą░čĆčéąĮčŗą╝ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ 8051, čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ ą▓čüąĄčģ ą╝ąĮąĄą╝ąŠąĮąĖą║ ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖ čüąŠčģčĆą░ąĮąĄąĮąĖąĄą╝ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ ą┐ąŠ ą┤ą▓ąŠąĖčćąĮąŠą╝čā ą║ąŠą┤čā. ąĪąĄčĆąĖčÅ STC90xx ą╝ąŠąČąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą║ąŠą┤ ą▓ 2 čĆą░ąĘą░ ą▒čŗčüčéčĆąĄąĄ, č湥ą╝ čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ 8051 (čĆąĄąČąĖą╝ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ 6T) ąĖą╗ąĖ čü ąŠą▒čŗčćąĮąŠą╣ čüą║ąŠčĆąŠčüčéčīčÄ (čĆąĄąČąĖą╝ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ 12T). ąŻą╗čāčćčłąĄąĮąĖąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąŠčéą┤ąĄą╗čīąĮčŗčģ ą┐čĆąŠą│čĆą░ą╝ą╝ ąĘą░ą▓ąĖčüąĖčé ąŠčé čĆąĄą░ą╗čīąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ąĖąĮčüčéčĆčāą║čåąĖą╣.

ąĀąĖčü. 1. ąæą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ STC90xx.

[ąóą░ą▒ą╗ąĖčåą░ ą▓čŗą▒ąŠčĆą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STC90xx ą┐ąŠ ąŠą▒čēąĖą╝ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝]

ąóąĖą┐

|

VCC, V

|

Max čćą░čüč鹊čéą░, ą£ąōčå |

FLASH,

ą▒ą░ą╣čé

|

SRAM,

ą▒ą░ą╣čé

|

TIMER

|

UART

|

DPTR

|

EEPROM,

ą▒ą░ą╣čé

|

| 5V |

3V |

| ąĪąĄčĆąĖčÅ STC90C/LE51 |

| STC90C51 |

3.3-5.5 |

80 |

|

4K |

256 |

3 |

1 |

2 |

- |

| STC90C52 |

3.3-5.5 |

80 |

|

8K |

256 |

3 |

1 |

2 |

- |

| STC90LE51 |

2.0-3.6 |

|

80 |

4K |

256 |

3 |

1 |

2 |

- |

| STC90LE52 |

2.0-3.6 |

|

80 |

8K |

256 |

3 |

1 |

2 |

- |

| ąĪąĄčĆąĖčÅ STC90C/LE51RC |

| STC90C51RC |

3.3-5.5 |

80 |

|

4K |

512 |

3 |

1 |

2 |

4K |

| STC90C52RC |

3.3-5.5 |

80 |

|

8K |

512 |

3 |

1 |

2 |

4K |

| STC90C53RC |

3.3-5.5 |

80 |

|

13K |

512 |

3 |

1 |

2 |

- |

| STC90C12RC |

3.3-5.5 |

80 |

|

12K |

512 |

3 |

1 |

2 |

1K |

| STC90LE51RC |

2.0-3.6 |

|

80 |

4K |

512 |

3 |

1 |

2 |

4K |

| STC90LE52RC |

2.0-3.6 |

|

80 |

8K |

512 |

3 |

1 |

2 |

4K |

| STC90LE53RC |

2.0-3.6 |

|

80 |

13K |

512 |

3 |

1 |

2 |

- |

| STC90LE12RC |

2.0-3.6 |

|

80 |

12K |

512 |

3 |

1 |

2 |

1K |

| ąĪąĄčĆąĖčÅ STC90C/LE51RD+ |

| STC90C54RD+ |

3.3-5.5 |

80 |

|

16K |

1280 |

3 |

1 |

2 |

45K |

| STC90C58RD+ |

3.3-5.5 |

80 |

|

32K |

1280 |

3 |

1 |

2 |

29K |

| STC90C510RD+ |

3.3-5.5 |

80 |

|

40K |

1280 |

3 |

1 |

2 |

21K |

| STC90C512RD+ |

3.3-5.5 |

80 |

|

48K |

1280 |

3 |

1 |

2 |

13K |

| STC90C514RD+ |

3.3-5.5 |

80 |

|

56K |

1280 |

3 |

1 |

2 |

5K |

| STC90C516RD+ |

3.3-5.5 |

80 |

|

61K |

1280 |

3 |

1 |

2 |

- |

| STC90LE54RD+ |

2.0-3.6 |

|

80 |

16K |

1280 |

3 |

1 |

2 |

45K |

| STC90LE58RD+ |

2.0-3.6 |

|

80 |

32K |

1280 |

3 |

1 |

2 |

29K |

| STC90LE510RD+ |

2.0-3.6 |

|

80 |

40K |

1280 |

3 |

1 |

2 |

21K |

| STC90LE512RD+ |

2.0-3.6 |

|

80 |

48K |

1280 |

3 |

1 |

2 |

13K |

| STC90LE514RD+ |

2.0-3.6 |

|

80 |

56K |

1280 |

3 |

1 |

2 |

5K |

| STC90LE516RD+ |

2.0-3.6 |

|

80 |

61K |

1280 |

3 |

1 |

2 |

- |

ąŻ ą▓čüąĄčģ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮčŗčģ ą▓ čéą░ą▒ą╗ąĖčåąĄ ą╝ąŠą┤ąĄą╗ąĄą╣ ąĖą╝ąĄąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąĮąĖąČąĄąĮąĖčÄ VCC ąĮąĖąČąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ (INT Low VCC), 8 ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ ą▓ąĮąĄčłąĮąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü 4 čāčĆąŠą▓ąĮčÅą╝ąĖ ą┐čĆąĖąŠčĆąĖč鹥čéą░, 4 ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą▓čŗą▓ąŠą┤ąĖčéčī MCU ąĖąĘ čĆąĄąČąĖą╝ą░ čüąĮą░ (power down mode), čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ (WDT).

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą░ą┐ą┐ą░čĆą░čéąĮčŗąĄ čäčāąĮą║čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ: PCA, PWM, D/A, ADC, ąĮą░čüčéčĆąŠą╣ą║ą░ ąĮąĖąČąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠčĆąŠą│ą░ ą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ ą┤ą╗čÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ.

ą¤ąŠą▓čŗčłąĄąĮąĮą░čÅ čŹčäč乥ą║čéąĖą▓ąĮąŠčüčéčī STC90xx ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮą░ č鹊ą╣ ąČąĄ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 ąĖ ą▓ ą▒ąŠą╗ąĄąĄ čłąĖčĆąŠą║ąŠą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą▓ąŠąĘą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą▓ 2 čĆą░ąĘą░ ą▓čŗčłąĄ, čüąŠčģčĆą░ąĮčÅčÅ ą┐čĆąĖ čŹč鹊ą╝ ąĮąĖąĘą║ąŠąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ąĖ ą┐ąŠą╗ąĮčāčÄ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī ą┐ąŠ čüąĖčüč鹥ą╝ąĄ ą║ąŠą╝ą░ąĮą┤ čü čéčĆą░ą┤ąĖčåąĖąŠąĮąĮčŗą╝ čĆąĄąČąĖą╝ąŠą╝ 12 čéą░ą║č鹊ą▓ ąĮą░ ą╝ą░čłąĖąĮąĮčŗą╣ čåąĖą║ą╗. ąĢčüą╗ąĖ MCU ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┤ą▓ąŠą╣ąĮąŠąĄ čāčüą║ąŠčĆąĄąĮąĖąĄ, ą▓ąĮąĄčłąĮčÅčÅ čćą░čüč鹊čéą░ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░ 2, čćč鹊ą▒čŗ čüąĮąĖąĘąĖčéčī čćą░čüč鹊čéčā ąĖ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ. ąÆ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą▓ą░čĆąĖą░ąĮčéčŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ STC90xx.

| ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ |

ąÆąĮąĄčłąĮčÅčÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ |

ą×ą▒čŗčćąĮą░čÅ čüą║ąŠčĆąŠčüčéčī (ą║ą░ą║ čā čüčéą░ąĮą┤ą░čĆčéąĮąŠą│ąŠ 8052) |

ąĀąĄą░ą╗čīąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čÅą┤čĆą░ |

ąŻą┤ą▓ąŠąĄąĮąĮą░čÅ čüą║ąŠčĆąŠčüčéčī |

ąĀąĄą░ą╗čīąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čÅą┤čĆą░ |

ążčāąĮą║čåąĖąĖ IAP/ISP |

| 4.5V - 5.5V |

0 - 44 ą£ąōčå |

0 - 44 ą£ąōčå |

0 - 20 ą£ąōčå |

0 - 80 ą£ąōčå |

0 - 40 ą£ąōčå |

read, program, erase |

| 3.8V - 5.5V |

0 - 33 ą£ąōčå |

0 - 33 ą£ąōčå |

0 - 16.5 ą£ąōčå |

0 - 66 ą£ąōčå |

0 - 33 ą£ąōčå |

read, program, erase |

| 3.6V - 5.5V |

0 - 24 ą£ąōčå |

0 - 24 ą£ąōčå |

0 - 12 ą£ąōčå |

0 - 48 ą£ąōčå |

0 - 24 ą£ąōčå |

read, program, erase |

| 3.4V - 5.5V |

0 - 20 ą£ąōčå |

0 - 20 ą£ąōčå |

0 - 10 ą£ąōčå |

0 - 40 ą£ąōčå |

0 - 20 ą£ąōčå |

č鹊ą╗čīą║ąŠ read |

ąØąĖąĘą║ąŠą▓ąŠą╗čīčéąĮčŗąĄ ą╝ąŠą┤ąĄą╗ąĖ STC90LE51RC/RD+ čĆą░ą▒ąŠčéą░čÄčé ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ 2.0-3.6V. ąÜąŠą│ą┤ą░ čĆą░ą▒ąŠč湥ąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮą░ čāčĆąŠą▓ąĮąĄ ą┐čĆąĖą▒ą╗ąĖąĘąĖč鹥ą╗čīąĮąŠ 1.9-2.3V, č鹊 čäčāąĮą║čåąĖąĖ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ ISP/IAP ąĮąĄ čĆą░ą▒ąŠčéą░čÄčé.

[ą”ąŠą║ąŠą╗ąĄą▓ą║ą░, ąŠą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓]

| ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

PDIP40 |

QFP44 |

PLCC44 |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| P0.0 - P0.7 |

39..32 |

37..30 |

43..36 |

Port0, 8-ą▒ąĖčéąĮčŗą╣ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ą┐ąŠčĆčé ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (GPIO) čüąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ąĖ čĆąĄąĘąĖčüč鹊čĆą░ą╝ąĖ pull-up. ąŁč鹊čé ą┐ąŠčĆčé čéą░ą║ąČąĄ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮ čü ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ čäčāąĮą║čåąĖąĄą╣ ą▓čŗą▓ąŠą┤ą░ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą▒ą░ą╣čéą░ čłąĖąĮčŗ ą░ą┤čĆąĄčüą░ (A7..A0) ąĖ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ (D7..D0), ą║ąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ ąĖ ą┤ą░ąĮąĮčŗčģ. |

| P1.0 - P1.7 |

1..8 |

40..44,

1..3 |

2..9 |

Port1, 8-ą▒ąĖčéąĮčŗą╣ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ą┐ąŠčĆčé ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (GPIO) čüąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ąĖ čĆąĄąĘąĖčüč鹊čĆą░ą╝ąĖ pull-up. ąÜąŠą│ą┤ą░ ą▓ Port1 ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ąĄą┤ąĖąĮąĖčćą║ąĖ, ą╝ąŠčēąĮą░čÅ ą┐ąŠą┤čéčÅąČą║ą░ pull-up ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ ą┤čĆą░ą╣ą▓ąĄčĆą░ą╝ąĖ CMOS č鹊ą╗čīą║ąŠ ąĮą░ 2 ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, ąĖ ąĘą░č鹥ą╝ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ čüą╗ą░ą▒ą░čÅ ą┐ąŠą┤čéčÅąČą║ą░ pull-up čĆąĄąĘąĖčüč鹊čĆą░ą╝ąĖ, ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÅ čāčĆąŠą▓ąĄąĮčī ą▓čŗą▓ąŠą┤ą░ ą┐ąŠčĆčéą░ ą║ ą╗ąŠą│. 1. P1.0 čéą░ą║ąČąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ąĖčüč鹊čćąĮąĖą║ čüąĖą│ąĮą░ą╗ą░ čüąŠą▒čŗčéąĖčÅ ą┤ą╗čÅ Timer2, ąĖą╗ąĖ ą▓čŗą▓ąŠą┤ąĖčé ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ Timer2. P1.1 čéą░ą║ąČąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ąŠą┤ąĖąĮ ąĖąĘ ąĖčüč鹊čćąĮąĖą║ąŠą▓ čüąĖą│ąĮą░ą╗ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░čģą▓ą░č鹊ą╝ ą┤ą╗čÅ Timer2. |

| P1.0/T2 |

1 |

40 |

2 |

| P1.1/T2EX |

2 |

41 |

3 |

| P2.0 - P2.7 |

21..28 |

18..25 |

24..31 |

Port2, 8-ą▒ąĖčéąĮčŗą╣ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ą┐ąŠčĆčé ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░, čüąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ąĖ čĆąĄąĘąĖčüč鹊čĆą░ą╝ąĖ pull-up. ąÜčĆąŠą╝ąĄ GPIO, čŹč鹊čé ą┐ąŠčĆčé ąĖą╝ąĄąĄčé ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆčāąĄą╝čāčÄ ą░ą┐ą┐ą░čĆą░čéąĮčāčÄ čäčāąĮą║čåąĖčÄ ą▓čŗą▓ąŠą┤ą░ čüčéą░čĆčłąĄą│ąŠ ą▒ą░ą╣čéą░ ą░ą┤čĆąĄčüą░ (A15..A8), ą║ąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ ąĖ ą┤ą░ąĮąĮčŗčģ. |

| P3.0/RXD |

10 |

5 |

11 |

Port3, 8-ą▒ąĖčéąĮčŗą╣ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ą┐ąŠčĆčé ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░, čüąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ąĖ čĆąĄąĘąĖčüč鹊čĆą░ą╝ąĖ weak pull-up. ąÜąŠą│ą┤ą░ ą▓ Port3 ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ąĄą┤ąĖąĮąĖčćą║ąĖ, ą╝ąŠčēąĮą░čÅ ą┐ąŠą┤čéčÅąČą║ą░ pull-up ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ ą┤čĆą░ą╣ą▓ąĄčĆą░ą╝ąĖ CMOS č鹊ą╗čīą║ąŠ ąĮą░ 2 ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, ąĖ ąĘą░č鹥ą╝ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ čüą╗ą░ą▒ą░čÅ ą┐ąŠą┤čéčÅąČą║ą░ pull-up čĆąĄąĘąĖčüč鹊čĆą░ą╝ąĖ, ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÅ čāčĆąŠą▓ąĄąĮčī ą▓čŗą▓ąŠą┤ą░ ą┐ąŠčĆčéą░ ą║ ą╗ąŠą│. 1. Port3 čéą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą╝ąĮąŠąČąĄčüčéą▓ąŠ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ čäčāąĮą║čåąĖą╣. ąØąŠąČą║ąĖ P3.0 ąĖ P3.1 čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ ą▓čģąŠą┤ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĖ ą▓čŗčģąŠą┤ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ą┤ą╗čÅ UART. P3.2 ąĖ P3.3 čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ ąĖčüč鹊čćąĮąĖą║ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ /INT0 ąĖ /INT1. P3.4 ąĖ P3.5 čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ ąĖčüč鹊čćąĮąĖą║ąĖ čüąŠą▒čŗčéąĖą╣ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ ą┤ą╗čÅ Timer0 ąĖ Timer1. P3.6 čéą░ą║ąČąĄ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čüąĖą│ąĮą░ą╗ ąĘą░ą┐ąĖčüąĖ /WR, ą░ą║čéąĖą▓ąĖąĘąĖčĆčāąĄą╝čŗą╣ ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. P3.7 čĆą░ą▒ąŠčéą░ąĄčé čéą░ą║ąČąĄ ą║ą░ą║ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čüąĖą│ąĮą░ą╗ čćč鹥ąĮąĖčÅ /RD, ą░ą║čéąĖą▓ąĖąĘąĖčĆčāąĄą╝čŗą╣ ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. |

| P3.1/TXD |

11 |

7 |

13 |

| P3.2/INT0 |

12 |

8 |

14 |

| P3.3/INT1 |

13 |

9 |

15 |

| P3.4/T0 |

14 |

10 |

16 |

| P3.5/T1 |

15 |

11 |

17 |

| P3.6/WR |

16 |

12 |

18 |

| P3.7/RD |

17 |

13 |

19 |

| P4.0 |

|

17 |

23 |

Port4, čĆą░čüčłąĖčĆąĄąĮąĮčŗą╣ ą┐ąŠčĆčé ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░, ą║ąŠč鹊čĆčŗą╣ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ Port1. Port4 ą┤ąŠčüčéčāą┐ąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą▓ą░čĆąĖą░ąĮč鹊ą▓ ą║ąŠčĆą┐čāčüąŠą▓ LQFP44, PLCC44. P4.2 ąĖ P4.3 čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ ąĖčüč鹊čćąĮąĖą║ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ /INT3 ąĖ /INT2. |

| P4.1 |

|

28 |

34 |

| P4.2/INT3 |

|

39 |

1 |

| P4.3/INT2 |

|

6 |

12 |

| P4.4/PSEN |

29 |

26 |

32 |

ą¤ąŠčĆčé GPIO P4.4. ąĪčéčĆąŠą▒ čćč鹥ąĮąĖčÅ ą┤ą╗čÅ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. |

| P4.5/ALE |

30 |

27 |

33 |

ą¤ąŠčĆčé GPIO P4.5. ąÆčŗčģąŠą┤ąĮąŠą╣ ąĖą╝ą┐čāą╗čīčü ą┤ą╗čÅ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĮąĖčÅ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą▒ą░ą╣čéą░ ą░ą┤čĆąĄčüą░ ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. |

| P4.6/EA |

31 |

29 |

35 |

ą¤ąŠčĆčé GPIO P4.6. ąØąŠąČą║ą░ /EA ą┤ąŠą╗ąČąĮą░ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ ą╗ąŠą│. 0, čćč鹊ą▒čŗ MCU ą▒čĆą░ą╗ąŠ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗą╣ ą║ąŠą┤ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą▓ą╝ąĄčüč鹊 ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣. ąØą░ čŹč鹊ą╝ ą▓čŗą▓ąŠą┤ąĄ ąĖą╝ąĄąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ čĆąĄąĘąĖčüč鹊čĆ pull-up. |

| RST |

9 |

4 |

10 |

ąĪąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░ RESET. ąøąŠą│. 1 ąĮą░ čŹč鹊ą╝ ą▓čŗą▓ąŠą┤ąĄ ą▓ č鹥č湥ąĮąĖąĄ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 2 ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüą▒čĆąŠčüčā čāčüčéčĆąŠą╣čüčéą▓ą░. |

| XTAL1 |

19 |

15 |

21 |

ąÆčŗą▓ąŠą┤ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ čĆąĄąĘąŠąĮą░č鹊čĆą░, ą▓čģąŠą┤ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░. ą£ąŠąČąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░. |

| XTAL2 |

18 |

14 |

20 |

ąÆčŗą▓ąŠą┤ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ čĆąĄąĘąŠąĮą░č鹊čĆą░, ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĖą╣ ą▓čŗčģąŠą┤ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░. ąŁč鹊čé ą▓čŗą▓ąŠą┤ ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ čéą░ą║č鹊ą▓. |

| VCC |

40 |

38 |

44 |

ą¤ą╗čÄčü ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. |

| GND |

20 |

16 |

22 |

ą£ąĖąĮčāčü ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, ąŠą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤ ą┤ą╗čÅ ą▓čüąĄčģ čüąĖą│ąĮą░ą╗ąŠą▓, ąĘąĄą╝ą╗čÅ. |

ąÜčĆąŠą╝ąĄ 44-ą▓čŗą▓ąŠą┤ąĮčŗčģ ą║ąŠčĆą┐čāčüąŠą▓ LQFP-44 ąĖ PLCC-44 čüąĄčĆąĖčÅ STC90C51RC/RD+ ąĖą╝ąĄąĄčé čéą░ą║ąČąĄ 44-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą║ąŠčĆą┐čāčü PQFP, ą┐čĆąĖč湥ą╝ ą║ąŠčĆą┐čāčüą░ PLCC-44 ąĖ PQFP-44 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ. ą¤čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čī ą┐ąŠč湥ą╝čā-č鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ąŠčĆą┐čāčüą░ LQFP-44.

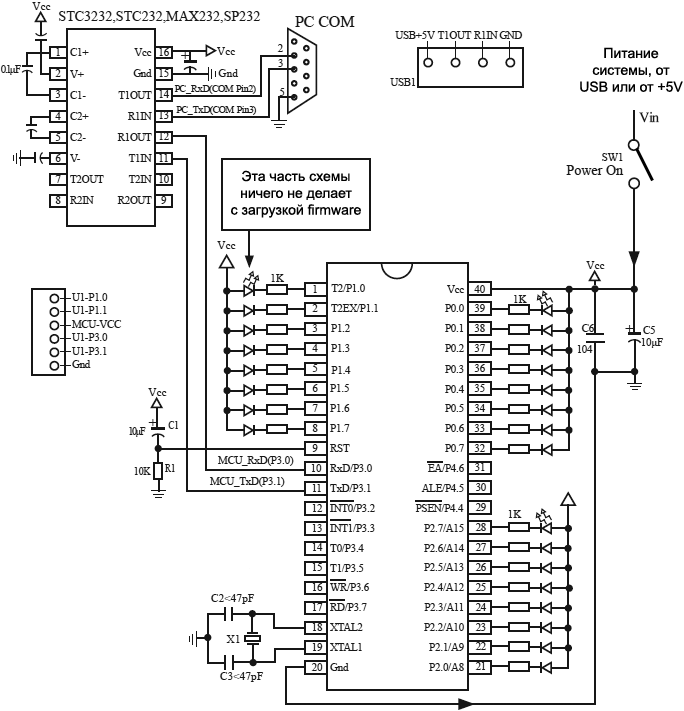

ą¤čĆąĖčćąĖąĮčŗ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STC: ąĮąĖąČąĄ čüč鹊ąĖą╝ąŠčüčéčī ąĖ ą┐ąŠą▓čŗčłąĄąĮąĮą░čÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī. ąÆčüąĄ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąĄčĆąĄąĮąĄčüąĄąĮąŠ ąĮą░ ąĮąŠą▓čŗą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┤ą░ąČąĄ ą▒ąĄąĘ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ čüąĖčüč鹥ą╝čŗ. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĖ ą╝ąŠą│čāčé ąĘą░ą│čĆčāąĘąĖčéčī čüą▓ąŠą╣ ą║ąŠą┤ (ą▓ ą┤ą▓ąŠąĖčćąĮąŠą╝ č乊čĆą╝ą░č鹥 BIN ąĖą╗ąĖ HEX-č乊čĆą╝ą░č鹥) ą▓ ą┐ą░ą╝čÅčéčī ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STC MCU čü ą┐ąŠą╝ąŠčēčīčÄ ą│ąŠč鹊ą▓ąŠą╣ čāčéąĖą╗ąĖčéčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ (Writer / Programmer tool ŌĆö STC-ISP.exe).

ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī Flash ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮą░ ą▒ąŠą╗ąĄąĄ č湥ą╝ 100 čéčŗčüčÅčć čĆą░ąĘ.

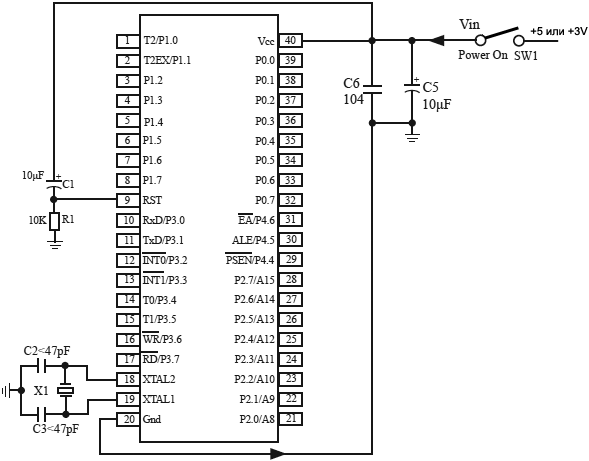

[ą£ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ čĆą░ą▒ąŠčćą░čÅ čüčģąĄą╝ą░ ą┤ą╗čÅ STC90C51RC/RD+]

ąÆčŗą▒ąŠčĆ ąĄą╝ą║ąŠčüčéąĖ C2 ąĖ C3 ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čćą░čüč鹊čéčŗ ą║ą▓ą░čĆčåą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ. ąĢą╝ą║ąŠčüčéčī ą║ą░ąČą┤ąŠą│ąŠ ąĖąĘ čŹčéąĖčģ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą▓ ą┐ąŠ ąŠčéą┤ąĄą╗čīąĮąŠčüčéąĖ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮą░ čĆą░ą▓ąĮąŠą╣ ąĄą╝ą║ąŠčüčéąĖ, čāą║ą░ąĘą░ąĮąĮąŠą╣ ą▓ čüč鹊ą╗ą▒čåąĄ "C".

ąóą░ą▒ą╗ąĖčåą░ 1. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝ą░čÅ ąĄą╝ą║ąŠčüčéčī ą║ąŠčĆčĆąĄą║čéąĖčĆčāčÄčēąĖčģ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą▓ ąĮą░ ąĮąŠąČą║ą░čģ XTAL1, XTAL2.

| ą¦ą░čüč鹊čéą░ ą║ą▓ą░čĆčåą░ X1, ą£ąōčå |

C |

| 4 |

100 |

| 6 |

47..100 |

| 12..25 |

47 |

ąöą╗čÅ ą▓ąĮąĄčłąĮąĄą╣ RC-čåąĄą┐ąĖ čüą▒čĆąŠčüą░ ąŠą▒čŗčćąĮąŠ ą▓čŗą▒ąĖčĆą░čÄčé ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ C1 ąĄą╝ą║ąŠčüčéčīčÄ 10 ą╝ą║čä ąĖ čĆąĄąĘąĖčüč鹊čĆ R1 10 ą║ą×ą╝. ąŻ ą▓ąĄčĆčüąĖąĖ HD ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ RC/RD+ ąĮąŠąČą║ą░ RESET ąĖą╝ąĄąĄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ pull-down čĆąĄąĘąĖčüč鹊čĆ ąĮąŠą╝ąĖąĮą░ą╗ąŠą╝ 45..100 ą║ą×ą╝.

ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą▓čŗą▓ąŠą┤ P4.6/EA čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ GPIO, ąĖ ąĄčæ ą╝ąŠąČąĮąŠ ąŠčüčéą░ą▓ąĖčéčī ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą╣, ąĄčüą╗ąĖ ąŠąĮą░ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. ąØąŠąČą║ą░ P4.5/ALE ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čüąĖą│ąĮą░ą╗ ALE (Address Latch Enable, čüąĖą│ąĮą░ą╗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░čēąĄą╗ą║ąĖ ą░ą┤čĆąĄčüą░), ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĮąŠ ą┐ąĄčĆąĄąĮą░čüčéčĆąŠąĖčéčī ąĮą░ čĆą░ą▒ąŠčéčā ą║ą░ą║ ąĮąŠąČą║ąĖ GPIO P4.5 čü ą┐ąŠą╝ąŠčēčīčÄ čāčéąĖą╗ąĖčéčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ STC-ISP.exe (čüą╝. [2]). ąØąŠąČą║ą░ P4.4/PSEN ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐ąŠčĆčé GPIO, ąĖ ąĄčæ ą╝ąŠąČąĮąŠ ąŠčüčéą░ą▓ąĖčéčī ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą╣, ąĄčüą╗ąĖ ąŠąĮą░ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

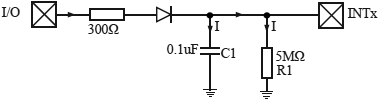

[ąĪčģąĄą╝ą░ ą┤ą╗čÅ STC90C51RC/RD+ čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ ISP]

ąØąŠą╝ąĖąĮą░ą╗čŗ ą║ąŠčĆčĆąĄą║čéąĖčĆčāčÄčēąĖčģ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą▓ C2, C3 čāą║ą░ąĘčŗą▓ą░čÄčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą▓čŗą▒čĆą░ąĮąĮąŠą╣ čĆą░ą▒ąŠč湥ą╣ čćą░čüč鹊č鹊ą╣ ą┐ąŠ čéą░ą▒ą╗ąĖčåąĄ 1. ąĢčüą╗ąĖ čĆą░ą▒ąŠčćą░čÅ čćą░čüč鹊čéą░ ą┐čĆąĄą▓čŗčłą░ąĄčé 33 ą£ąōčå, č鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ąĮąĄčłąĮąĖą╣ ą░ą║čéąĖą▓ąĮčŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ, ą▓čŗčģąŠą┤ ą║ąŠč鹊čĆąŠą│ąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ąĮąŠąČą║ąĄ XTAL1. ąÆ čüą╗čāčćą░ąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ą║ąŠčĆčĆąĄą║čéąĖčĆčāčÄčēąĖąĄ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčŗ C2, C3 ąĮąĄ ąĮčāąČąĮčŗ.

ąöą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ UART P3.0/P3.1, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ č湥čĆąĄąĘ ą░ą┤ą░ą┐č鹥čĆ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čāčĆąŠą▓ąĮąĄą╣ ą║ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╝čā ąĖąĮč鹥čĆč乥ą╣čüčā RS-232, ąĖą╗ąĖ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╝čā ą┐ąĄčĆąĄčģąŠą┤ąĮąĖčćą║čā USB-UART čü čāčĆąŠą▓ąĮčÅą╝ąĖ TTL []. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčé čāčéąĖą╗ąĖčéą░ STC-ISP.exe. ąśą╝ąĄčÅ ą▓čüąĄą│ąŠ 4 čüąĖą│ąĮą░ą╗ą░ Gnd/P3.1/P3.0/Vcc ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ čéą░ą║ąŠą╝čā ą┐čĆąŠą│čĆą░ą╝ą╝ą░č鹊čĆčā, ą╝ąŠąČąĮąŠ ąŠą▒ąĮąŠą▓ą╗čÅčéčī ą┐čĆąŠą│čĆą░ą╝ą╝čā, ąĮąĄ ąĖąĘą▓ą╗ąĄą║ą░čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąĖąĘ čüąĖčüč鹥ą╝čŗ. ą¤čĆąĖą╝ąĄąĮčÅčÄčé čéą░ą║ąČąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠ 6 ą┐čĆąŠą▓ąŠą┤ą░ą╝ Gnd/P3.1/P3.0/Vcc/P1.1/P1.0. ąĢčüą╗ąĖ čā ąÆą░čü ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī 7 čüąĖą│ąĮą░ą╗čīąĮčŗčģ ą╗ąĖąĮąĖą╣ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ Gnd/P3.1/P3.0/Vcc/P1.1/P1.0/Reset, č鹊 ą╝ąŠąČąĮąŠ ą┐čĆąĖą╝ąĄąĮčÅčéčī čüą┐ąĄčåąĖą░ą╗čīąĮčāčÄ ąŠčéą┤ąĄą╗čīąĮčāčÄ ą┐ą╗ą░čéčā ąĘą░ą│čĆčāąĘą║ąĖ, "offline download board" (ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą║ąŠą╝ą┐čīčÄč鹥čĆą░).

ąóąĄąŠčĆąĖčÅ ąĖ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ą┐ąŠ ISP-ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÄ ąĖąĘą╗ąŠąČąĄąĮčŗ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "STC90 Series MCU Development / Programming Tools Help".

[ąĀą░ąĘą╝ąĄčĆčŗ ą║ąŠčĆą┐čāčüąŠą▓]

ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ čüąĄčĆąĖąĖ STC90xx ą▓čŗą┐čāčüą║ą░čÄčéčüčÅ ą▓ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ą║ąŠčĆą┐čāčüą░čģ LQFP-44, PDIP-40, PLCC-44, čüąŠčģčĆą░ąĮčÅčÅ čåąŠą║ąŠą╗ąĄą▓ą║čā čéčĆą░ą┤ąĖčåąĖąŠąĮąĮčŗčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ čüąĄą╝ąĄą╣čüčéą▓ą░ MCS51. ąĀą░ąĘą╝ąĄčĆčŗ ą║ąŠčĆą┐čāčüąŠą▓ čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥 STC90C51RC-en.pdf [2].

[ą¤čĆąĖąĮčåąĖą┐ ąĮą░ąĖą╝ąĄąĮąŠą▓ą░ąĮąĖčÅ čéąĖą┐ąŠą▓ STC90C51RC/RD+]

ąŻą╝ąĄąĮčīčłąĄąĮąĖąĄ ąĖąĘą╗čāč湥ąĮąĖčÅ ą┐ąŠą╝ąĄčģ. ąöą╗čÅ čüąĮąĖąČąĄąĮąĖčÅ čĆą░ą┤ąĖąŠą┐ąŠą╝ąĄčģ ą╝ąŠąČąĮąŠ ą▓čŗą║ą╗čÄčćąĖčéčī čüąĖą│ąĮą░ą╗ ALE ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą▒ąĖčéą░ ALEOFF ą▓ čĆąĄą│ąĖčüčéčĆąĄ AUXR (ą┐ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ AUXR ąĖ ąĄą│ąŠ ą▒ąĖčé čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥 STC90C51RC-en.pdf [2]).

ąóą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ą▓ 2 čĆą░ąĘą░ čüąĮąĖąĘąĖčéčī čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā ąĖ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčīčüčÅ ąĮą░ čĆąĄąČąĖą╝ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ 6T, ą║ąŠą│ą┤ą░ ąĮą░ ąŠą┤ąĖąĮ ą╝ą░čłąĖąĮąĮčŗą╣ čåąĖą║ą╗ CPU ą┐čĆąĖčģąŠą┤ąĖčéčüčÅ ąĮąĄ 12 čéą░ą║č鹊ą▓ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ, ą░ 6 čéą░ą║č鹊ą▓. ą¤čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī CPU ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ čüąĮąĖąĘąĖčéčüčÅ. ąĀąĄąČąĖą╝ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ 6T/12T ą╝ąŠąČąĮąŠ ą┐ąŠą╝ąĄąĮčÅčéčī ą┐čĆąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĖ ąŠą┐čåąĖą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čü ą┐ąŠą╝ąŠčēčīčÄ čāčéąĖą╗ąĖčéčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ STC-ISP Writter/Programmer [2]. ąĢčüą╗ąĖ čćą░čüč鹊čéą░ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ą╝ąĄąĮčīčłąĄ 12 ą£ąōčå, č鹊 čéą░ą║ąČąĄ ą╝ąŠąČąĮąŠ čüąĮąĖąĘąĖčéčī čāčüąĖą╗ąĄąĮąĖąĄ ą│ąĄąĮąĄčĆą░č鹊čĆą░, ą┐čĆąĖ čŹč鹊ą╝ čāčĆąŠą▓ąĄąĮčī ą┐ąŠą╝ąĄčģ ąĖ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝čŗą╣ č鹊ą║ čéą░ą║ąČąĄ čāą╝ąĄąĮčīčłą░čéčüčÅ.

[ąĀąĄąČąĖą╝čŗ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖąĄą╝]

ąÆčüąĄą│ąŠ ąĄčüčéčī 3 čĆąĄąČąĖą╝ą░, ą▓ ą║ąŠč鹊čĆčŗčģ ą╝ąŠąČąĄčé ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ: ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝, čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ (Idle mode, ąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ) ąĖ čĆąĄąČąĖą╝ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (Power-down mode). ąÆ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ čĆą░ą▒ąŠčéčŗ č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą╝ąŠąČąĄčé ą╝ąĄąĮčÅčéčīčüčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 4..7 ą╝ąÉ, ą▓ čĆąĄąČąĖą╝ąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ č鹊ą║ čüąŠčüčéą░ą▓ąĖčé 2 ą╝ąÉ (ą┐ąŠčŹč鹊ą╝čā ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹč鹊čé čĆąĄąČąĖą╝ ą┐čĆą░ą║čéąĖč湥čüą║ąĖ ąĮąĄ ąĖą╝ąĄąĄčé čüą╝čŗčüą╗ą░), ąĖ ą▓ čĆąĄąČąĖą╝ąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čüąŠčüčéą░ą▓ąĖčé ą╝ąĄąĮąĄąĄ 0.1 ą╝ą║ąÉ. ąśąĘ čĆąĄąČąĖą╝ą░ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą╝ąŠąČąĮąŠ ą▓čŗą▓ąĄčüčéąĖ ą▓ąĮąĄčłąĮąĖą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ (ą┐čĆąĖ čŹč鹊ą╝ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąŠą┤ąŠą╗ąČąĖčéčüčÅ ą┐ąŠčüą╗ąĄ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ) ąĖą╗ąĖ čüąĖą│ąĮą░ą╗ąŠą╝ čüą▒čĆąŠčüą░ (ąĮą░čćąĮąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ čü ą░ą┤čĆąĄčüą░ 0).

ą¤ąĄčĆąĄčģąŠą┤ ą▓ čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ ąĖ čĆąĄąČąĖą╝ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ IDL ąĖ PD čĆąĄą│ąĖčüčéčĆą░ PCON.

ąśą╝ąĄąĄčéčüčÅ 2 čĆąĄąČąĖą╝ą░ 菹║ąŠąĮąŠą╝ąĖąĄą╣ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (power saving modes), ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÅ čĆąĄą│ąĖčüčéčĆ PCON.

PCON

| ąæąĖčé |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

SMOD |

SMOD0 |

- |

POF |

GF1 |

GF0 |

PD |

IDL |

SMOD. ąÆčŗą▒ąŠčĆ ą┤ą▓ąŠą╣ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ UART ą┤ą╗čÅ čĆąĄąČąĖą╝ąŠą▓ UART 1, 2 ąĖą╗ąĖ 3. 0: ąŠą▒čŗčćąĮą░čÅ čüą║ąŠčĆąŠčüčéčī (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ), 1: ą┤ą▓ąŠą╣ąĮą░čÅ čüą║ąŠčĆąŠčüčéčī.

SMOD0. ąæąĖčé SM0/FE ą▓čŗą▒ąŠčĆą░ ą┤ą╗čÅ SCON.7. ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 SCON.7 ąĮąŠčüąĖčé čäčāąĮą║čåąĖčÄ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ čäčĆąĄą╣ą╝ą░ (Frame Error). ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé ąŠčćąĖčēąĄąĮ, č鹊 SCON.7 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ąŠą┤ąĖąĮ ąĖąĘ ą▒ąĖčé ą▓čŗą▒ąŠčĆą░ čĆąĄąČąĖą╝ą░ UART.

B5. ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮ.

POF. Power-On flag, čäą╗ą░ą│ ą▓ą║ą╗čÄč湥ąĮąĖčÅ. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┤ąĄą╣čüčéą▓ąĖąĄą╝ ą▓ą║ą╗čÄč湥ąĮąĖčÅ (power-off-on), ąĖ ąĄą│ąŠ ą╝ąŠąČąĮąŠ ąŠčćąĖčüčéąĖčéčī č鹊ą╗čīą║ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ.

GF1. General-purposed flag 1, čäą╗ą░ą│ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ.

GF0. General-purposed flag 0, čäą╗ą░ą│ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ.

PD: Power-Down bit, ą▒ąĖčé ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ.

IDL: Idle mode bit, ą▒ąĖčé čĆąĄąČąĖą╝ą░ ąŠąČąĖą┤ą░ąĮąĖčÅ.

Idle Mode (čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ). ąśąĮčüčéčĆčāą║čåąĖčÅ, ą║ąŠč鹊čĆą░čÅ čāčüčéą░ąĮąŠą▓ąĖčé ą▒ąĖčé IDL (PCON.0) ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 ąŠąĮą░ ą▒čāą┤ąĄčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣, ą║ąŠč鹊čĆą░čÅ ą▒čŗą╗ą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą┐ąĄčĆąĄą┤ ą▓čģąŠą┤ąŠą╝ ą▓ idle mode. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčéą║ą╗čÄčćą░ąĄčéčüčÅ ąŠčé čÅą┤čĆą░ CPU, ąĮąŠ ąĮąĄ ąŠčé čäčāąĮą║čåąĖą╣ ą▒ą╗ąŠą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, čéą░ą╣ą╝ąĄčĆąŠą▓, WDT ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░. ąĪčéą░čéčāčü CPU ą┐ąŠą╗ąĮąŠčüčéčīčÄ čüąŠčģčĆą░ąĮčÅąĄčé čüą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ: čāą║ą░ąĘą░č鹥ą╗čī čüč鹥ą║ą░ (Stack Pointer, SP), čüč湥čéčćąĖą║ ąĖąĮčüčéčĆčāą║čåąĖą╣ (Program Counter, PC), čüą╗ąŠą▓ąŠ čüąŠčüč鹊čÅąĮąĖčÅ (Program Status Word, PSW), ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ (Accumulator, A) ąĖ ą┤čĆčāą│ąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ ą▒čāą┤čāčé čģčĆą░ąĮąĖčéčī čüą▓ąŠąĖ ą┤ą░ąĮąĮčŗąĄ ą▓ąŠ ą▓čĆąĄą╝čÅ čĆąĄąČąĖą╝ą░ ąŠąČąĖą┤ą░ąĮąĖčÅ. ąØąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ ą▒čāą┤čāčé čāą┤ąĄčƹȹĖą▓ą░čéčī čüą▓ąŠąĄ ą╗ąŠą│ąĖč湥čüą║ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ, ą║ą░ą║ąŠąĄ ąŠąĮąĖ ąĖą╝ąĄą╗ąĖ ą▓ ą╝ąŠą╝ąĄąĮčé ą░ą║čéąĖą▓ą░čåąĖąĖ čĆąĄąČąĖą╝ą░ ąŠąČąĖą┤ą░ąĮąĖčÅ. ąØą░ ąĮąŠąČą║ą░čģ ALE ąĖ PSEN čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą╗ąŠą│. 1. Idle mode ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čĆą░ą▒ąŠčéą░čéčī, čéą░ą║ čćč鹊 ąŠąĮąĖ ą╝ąŠą│čāčé čĆą░ąĘą▒čāą┤ąĖčéčī CPU, ą║ąŠą│ą┤ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. Timer 0, Timer 1, Timer 2 ąĖ UART ą▒čāą┤čāčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčī čüą▓ąŠčÄ čĆą░ą▒ąŠčéčā ą▓ čĆąĄąČąĖą╝ąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ.

ąĢčüčéčī ą┤ą▓ą░ čüą┐ąŠčüąŠą▒ą░ ą┐čĆąĄčĆą▓ą░čéčī čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ. ąÆąŠ-ą┐ąĄčĆą▓čŗčģ, ą░ą║čéąĖą▓ą░čåąĖčÅ ą╗čÄą▒ąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 ą▒čāą┤ąĄčé ą░ą┐ą┐ą░čĆą░čéąĮąŠ ąŠčćąĖčēąĄąĮ ą▒ąĖčé IDL, ąĘą░ą▓ąĄčĆčłą░čÅ č鹥ą╝ čüą░ą╝čŗą╝ ą┤ąĄą╣čüčéą▓ąĖąĄ idle mode. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé ąŠą▒čĆą░ą▒ąŠčéą░ąĮąŠ, ąĖ ąĖąĮčüčéčĆčāą║čåąĖčÅ RETI ąĮą░ ą▓čŗčģąŠą┤ąĄ ąĖąĘ ISR ą┐čĆąŠą┤ąŠą╗ąČąĖčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ čüąŠ čüą╗ąĄą┤čāčÄčēąĄą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ąĮą░čģąŠą┤čÅčēąĄą╣čüčÅ ą┐ąŠčüą╗ąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą║ąŠč鹊čĆą░čÅ ą▓ą▓ąĄą╗ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓ čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ.

ąæąĖčéčŗ čäą╗ą░ą│ąŠą▓ (GFO ąĖ GF1) ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ, čćč鹊ą▒čŗ ąĖčüą║čāčüčüčéą▓ąĄąĮąĮąŠ ą┐ąŠą║ą░ąĘą░čéčī, ą▒čŗą╗ąŠ ą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą▒čŗčćąĮąŠą╣ čĆą░ą▒ąŠčéčŗ ąĖą╗ąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ čĆąĄąČąĖą╝ą░ ąŠąČąĖą┤ą░ąĮąĖčÅ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ ąĖąĮčüčéčĆčāą║čåąĖčÅ, ą░ą║čéąĖą▓ąĖčĆčāčÄčēą░čÅ idle mode, čāčüčéą░ąĮąŠą▓ąĖą╗ą░ ąŠą┤ąĖąĮ ąĖą╗ąĖ ąŠą▒ą░ čŹčéąĖčģ čäą╗ą░ą│ą░ ą▓ą╝ąĄčüč鹥 čü ą▒ąĖč鹊ą╝ IDL (ąŠą┐ąĄčĆą░čåąĖąĄą╣ OR ąĮą░ą┤ čĆąĄą│ąĖčüčéčĆąŠą╝ PCON). ąóąŠą│ą┤ą░ ąĄčüą╗ąĖ ą▓čŗčģąŠą┤ ąĖąĘ idle mode ą▒čŗą╗ ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝, č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą╝ąŠąČąĄčé ąĘą░ą╝ąĄčéąĖčéčī čŹč鹊čé čäą░ą║čé, ą░ąĮą░ą╗ąĖąĘąĖčĆčāčÅ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čäą╗ą░ą│ąŠą▓ GF0 ąĖ GF1.

ąÆąŠ-ą▓č鹊čĆčŗčģ, ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▒čāą┤ąĄčé ą▓čŗąĘą▓ą░ąĮąŠ ą┐ąŠą┤čéčÅą│ąĖą▓ą░ąĮąĖąĄą╝ ąĮąŠąČą║ąĖ čüą▒čĆąŠčüą░ RESET ą║ ą╗ąŠą│. 1, ą▓čŗąĘčŗą▓ą░čÅ ą│ąĄąĮąĄčĆą░čåąĖčÄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čüą▒čĆąŠčüą░. ą¤ąŠčüą║ąŠą╗čīą║čā čéą░ą║č鹊ą▓čŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ ą▓čüąĄ ąĄčēąĄ čĆą░ą▒ąŠčéą░ąĄčé, ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čüą▒čĆąŠčü ą┤ąŠą╗ąČąĄąĮ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ ą░ą║čéąĖą▓ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ č鹊ą╗čīą║ąŠ ąĮą░ 2 čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ą░, čćč鹊ą▒čŗ čüą▒čĆąŠčü ą▒čŗą╗ ąĘą░ą▓ąĄčĆčłąĄąĮ.

Power Down (PD) Mode. ąśąĮčüčéčĆčāą║čåąĖčÅ, ą║ąŠč鹊čĆą░čÅ čāčüčéą░ąĮąŠą▓ąĖčé ą▒ąĖčé PD (PCON.1), ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 čŹč鹊 ą▒čāą┤ąĄčé ą┐ąŠčüą╗ąĄą┤ąĮčÅčÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĮą░čÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ ą┐ąĄčĆąĄą┤ ą▓čģąŠą┤ąŠą╝ ą▓ čĆąĄąČąĖą╝ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (Power-Down mode). ąÆ Power-Down mode, ą▒čāą┤čāčé ą▓čŗą║ą╗čÄč湥ąĮčŗ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ ąĖ ą┐ą░ą╝čÅčéčī FLASH, čćč鹊ą▒čŗ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ 菹ĮąĄčĆą│ąĖąĖ. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐ąŠčéčĆąĄą▒ą╗čÅčéčī č鹊ą║ ą▒čāą┤ąĄčé č鹊ą╗čīą║ąŠ čüčģąĄą╝ą░ ą▓ą║ą╗čÄč湥ąĮąĖčÅ (power-on circuit). ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ RAM ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (Special Finction Register, SFR) čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ.

ąĢčüčéčī č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čüą┐ąŠčüąŠą▒ čĆą░ąĘą▒čāą┤ąĖčéčī ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ, čćč鹊ą▒čŗ ą▓čŗą▓ąĄčüčéąĖ ąĄą│ąŠ ąĖąĘ power-down mode - ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čüą▒čĆąŠčü (ąĮąŠąČą║ą░ RESET) ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (/INT0../INT3, ą▓čŗą▓ąŠą┤ RXD, ą▓čŗą▓ąŠą┤čŗ T0, T1). ąÜąŠą│ą┤ą░ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ ą▒čŗą╗ąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ ąĮąŠąČą║ąŠą╣ čüą▒čĆąŠčüą░ RESET, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąŠą┤ąŠą╗ąČąĖčé čüą▓ąŠąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ čü ą░ą┤čĆąĄčüą░ 0000h.

ąæčāą┤čīč鹥 ą▓ąĮąĖą╝ą░č鹥ą╗čīąĮčŗ ą║ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÄ ąĖą╝ą┐čāą╗čīčüą░ čüą▒čĆąŠčüą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ RESET - ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą░ą║čéąĖą▓ąĄąĮ (ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1) ąĮą░ ą▓čĆąĄą╝čÅ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 10 ą╝čü, čćč鹊ą▒čŗ čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ ą╝ąŠą│ą╗ą░ ąĘą░čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆąŠą▓ą░čéčīčüčÅ. ąĢčüą╗ąĖ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ąŠčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąŠąČąĄą║ GPIO, č鹊 CPU ą▓ąŠąĘąŠą▒ąĮąŠą▓ąĖčé čüą▓ąŠčÄ čĆą░ą▒ąŠčéčā čü ą┐ąĄčĆąĄčģąŠą┤ą░ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (interrupt service routine, ISR). ą¤ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ą║ąŠą┤ą░ ISR ą┐ąŠą┤ą░čćą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąĮą░ CPU ą▒ą╗ąŠą║ąĖčĆčāąĄčéčüčÅ, ą┐ąŠą║ą░ ąĮąĄ ą┐čĆąŠą╣ą┤ąĄčé 32768 čéą░ą║č鹊ą▓, čćč鹊ą▒čŗ ąĖčüą║ą╗čÄčćąĖčéčī ą┐ąŠą┤ą░čćčā ąĮąĄčüčéą░ą▒ąĖą╗čīąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąĮą░ čÅą┤čĆąŠ. ą¦č鹊ą▒čŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ąĮąŠąČą║ąĖ GPIO, ą┤ąŠ ą▓čģąŠą┤ą░ ą▓ čĆąĄąČąĖą╝ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┤ąŠą╗ąČąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ čĆąĄą│ąĖčüčéčĆą░čģ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĘą░ ąĖąĮčüčéčĆčāą║čåąĖąĄą╣, ą║ąŠč鹊čĆą░čÅ ą▓čŗą║ą╗čÄčćą░ąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆ (čŹč鹊 čéą░ ąĖąĮčüčéčĆčāą║čåąĖčÅ, ą║ąŠč鹊čĆą░čÅ ą▓ą▓ąŠą┤ąĖčé ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓ power-down čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ PD), ą┤ąŠą╗ąČąĮą░ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ NOP, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ ąŠčé ąĮąŠąČą║ąĖ GPIO. ąÜąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ čĆąĄąČąĖą╝ Power-down ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ, ą┐ąĄčĆąĖąŠą┤ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ąĖčĆčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čüčģąĄą╝ąŠą╣ ąĘą░ą┤ąĄčƹȹ║ąĖ. ą¤ąŠ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā ąĮą░ ąĮąŠąČą║ąĄ, ą│ąĄąĮąĄčĆąĖčĆčāčÄčēąĄą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą│ąĄąĮąĄčĆą░č鹊čĆ, ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čéą░ą╣ą╝ąĄčĆ čüčģąĄą╝čŗ ąĘą░ą┤ąĄčƹȹ║ąĖ ąĮą░čćąĖąĮą░ąĄčé čüč湥čé. ą¤ąŠą┤ą░čćą░ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čéą░ą║č鹊ą▓ ąĮą░ čÅą┤čĆąŠ ą┐ąŠ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą▓čŗčćąĖčüą╗ąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüą░ CPU čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čéą░ą╣ą╝ąĄčĆ ąĘą░ą┤ąĄčƹȹ║ąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĖčéčüčÅ. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą╣ą╝ą░čāčéą░ ąĮą░čćąĮąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ ą║ąŠą┤ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ISR. ą¦č鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī ą┐ąŠą▓č鹊čĆąĮąŠąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą┤ ISR ą┐ąĄčĆąĄą┤ čüą▓ąŠąĖą╝ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄą╝ ą┤ąŠą╗ąČąĄąĮ ąĘą░ą┐čĆąĄčéąĖčéčī čŹč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąØąŠąČą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ ą╗ąŠą│. 0, ą┐ąŠą║ą░ ąĮąĄ ąĖčüč鹥č湥čé čéą░ą╣ą╝ą░čāčé ąĘą░ą┐čāčüą║ą░ čÅą┤čĆą░ ąĖ ąĮąĄ ąĮą░čćąĮąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ ISR. ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąĮąĄ ą┤ąŠą╗ąČąĮą░ ą┐čŗčéą░čéčīčüčÅ ą▓ąŠą╣čéąĖ (ąĖą╗ąĖ ą┐ąŠą▓č鹊čĆąĮąŠ ą▓ąŠą╣čéąĖ) ą▓ power-down mode ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 4 ą╝ą║čü ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ąŠą┤ąĮąŠ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ čüąŠą▒čŗčéąĖą╣: ąĮą░čćą░ą╗ąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą┤ą░ (ą┐ąŠčüą╗ąĄ ą╗čÄą▒ąŠą│ąŠ čéąĖą┐ą░ čüą▒čĆąŠčüą░) ąĖą╗ąĖ ą▓čŗčģąŠą┤ ąĖąĘ power-down mode.

ą¤čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░, ą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆčāčÄčēąĖąĄ ą▓čŗčģąŠą┤ ąĖąĘ power-down mode ą┐ąŠ ą▓ąĮąĄčłąĮąĄą╝čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ ąĮą░ čÅąĘčŗą║ą░čģ C ąĖ ą░čüčüąĄą╝ą▒ą╗ąĄčĆą░ čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥 STC90C51RC-en.pdf [2].

ąĢčüą╗ąĖ ąĮąĄčé ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ MCU, č鹊 ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐čĆąĖą╝ąĄąĮąĖčéčī čüą╗ąĄą┤čāčÄčēčāčÄ čüčģąĄą╝čā:

ąÜą░ą║ čŹčéą░ čüčģąĄą╝ą░ čĆą░ą▒ąŠčéą░ąĄčé, ą┐čĆąŠčåąĄčüčü ą┐ąŠ čłą░ą│ą░ą╝:

1. ą¤ąŠčĆčé ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ čĆąĄąĘąĖčüč鹊čĆčā 300 ąŠą╝, čüąĮą░čćą░ą╗ą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą║ą░ą║ ą┤ą▓čāčģčéą░ą║čéąĮčŗą╣ ą▓čŗčģąŠą┤ čü ą╝ąŠčēąĮąŠą╣ ą▓ąĄčĆčģąĮąĄą╣ ąĮą░ą│čĆčāąĘą║ąŠą╣ (push-pull output, strong pull-up).

2. ąŚą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą╗ąŠą│. 1 ą▓ čŹč鹊čé ą┐ąŠčĆčé, ąĖ č湥čĆąĄąĘ ą┤ąĖąŠą┤ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ C1 ą▒čŗčüčéčĆąŠ ąĘą░čĆčÅąČą░ąĄčéčüčÅ ą┤ąŠ ą▓čŗčüąŠą║ąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

3. ąŚą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ 0 ą▓ ą┐ąŠčĆčé, ąĖ čüčĆą░ąĘčā ąČąĄ MCU ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ power-down.

4. ą¤ąŠą║ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüą┐ąĖčé, C1 ą╝ąĄą┤ą╗ąĄąĮąĮąŠ čĆą░ąĘčĆčÅąČą░ąĄčéčüčÅ č湥čĆąĄąĘ čĆąĄąĘąĖčüč鹊čĆ R1. ąÜąŠą│ą┤ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ C1 čüčéą░ąĮąĄčé ą╝ąĄąĮčīčłąĄ 0.8V, ą▓čŗą▓ąŠą┤ INTx čüą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓čŗą▓ąĄą┤ąĄčé MCU ąĖąĘ čĆąĄąČąĖą╝ą░ čüąĮą░.

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüą▒čĆąŠčüąŠą╝, čĆą░ą▒ąŠčéą░ ą▓čŗą▓ąŠą┤ą░ RESET, čüą▒čĆąŠčü ą┐ąŠ ą▓ą║ą╗čÄč湥ąĮąĖčÄ ą┐ąĖčéą░ąĮąĖčÅ (Power-On Reset, POR), ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü, ąŠą┐ąĖčüą░ąĮąĖąĄ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ MAX810, ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ PCON, ąŠą┐ąĖčüą░ąĮąĖąĄ čĆą░ą▒ąŠčéčŗ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (Watch-Dog-Timer, WDT), ą┐čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ čü WDT, čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥 STC90C51RC-en.pdf [2].

[ąśčüč鹊čćąĮąĖą║ąĖ čüą▒čĆąŠčüą░]

ąŻ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ čüąĄčĆąĖąĖ STC90xx ąĖą╝ąĄąĄčéčüčÅ 4 ąĖčüč鹊čćąĮąĖą║ą░, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüą▒čĆąŠčü. ąŁč鹊 ąĮąŠąČą║ą░ ą▓čŗą▓ąŠą┤ą░ RST, ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü (software reset), ą▓čüčéčĆąŠąĄąĮąĮą░čÅ čüčģąĄą╝ą░ čüą▒čĆąŠčüą░ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (power-on-reset) ąĖ čüą▒čĆąŠčü ąŠčé čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (Watch-Dog-Timer, WDT).

ąØąŠąČą║ą░ čüą▒čĆąŠčüą░ RST. ąÆčŗą▓ąŠą┤ RST ą╝ąŠąČąĄčé ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ čüą▒čĆąŠčüąĖčéčī MCU ą┐ąŠ ąĮą░ą╗ąĖčćąĖčÄ ąĖą╝ą┐čāą╗čīčüą░ ą╗ąŠą│. 1 ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░. ąØą░ ą▓čģąŠą┤ąĄ RST ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé čéčĆąĖą│ą│ąĄčĆ ą©ą╝ąĖčéčéą░. ą¤ąŠčÅą▓ą╗ąĄąĮąĖąĄ ąĮą░ ąĮąŠąČą║ąĄ RST ąĖą╝ą┐čāą╗čīčüą░ ą╗ąŠą│. 1 ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 24 čéą░ą║čéą░ + 10 ą╝ą║čü ą┐čĆąĖą▓ąĄą┤čāčé ą║ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüą▒čĆąŠčüą░. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čāčĆąŠą▓ąĄąĮčī ąĮą░ ąĮąŠąČą║ąĄ RST ą▓ąĄčĆąĮąĄčéčüčÅ ą║ ą╗ąŠą│. 0, MCU ąĘą░ą▓ąĄčĆčłąĖčé čüąŠčüč鹊čÅąĮąĖąĄ čüą▒čĆąŠčüą░ ąĖ ąĮą░čćąĮąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ čü ą░ą┤čĆąĄčüą░ 0.

Software RESET. ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ ą▒ąĖčé SWRST čĆąĄą│ąĖčüčéčĆą░ ISP_CONTR ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░. ąæąĖčé SWBS č鹊ą│ąŠ ąČąĄ čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄą╝ ąŠą▒ą╗ą░čüčéąĖ ąĘą░ą┐čāčüą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░:

;Software reset ąĖąĘ ąŠą▒ą╗ą░čüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (appliction program, AP)

; ąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ąĮą░ ąŠą▒ą╗ą░čüčéčī AP ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ:

MOV ISP_CONTR, #00100000B ;SWBS = 0 (ą▓čŗą▒ąŠčĆ ąŠą▒ą╗ą░čüčéąĖ AP), SWRST = 1 (Software reset)

;Software reset ąĖąĘ ąŠą▒ą╗ą░čüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą╝ąŠąĮąĖč鹊čĆą░ ą▓ąĮčāčéčĆąĖčüčģąĄą╝ąĮąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ

; (ąŠą▒ą╗ą░čüčéąĖ ISP) ąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ąĮą░ ąŠą▒ą╗ą░čüčéčī AP ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ:

MOV ISP_CONTR, 00100000B ;SWBS = 0 (ą▓čŗą▒ąŠčĆ ąŠą▒ą╗ą░čüčéąĖ AP), SWRST = 1 (Software reset)

;Software reset ąĖąĘ ąŠą▒ą╗ą░čüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (appliction program, AP)

; ąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ąĮą░ ąŠą▒ą╗ą░čüčéčī ISP ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ:

MOV ISP_CONTR, 01100000B ;SWBS = 1 (ą▓čŗą▒ąŠčĆ ąŠą▒ą╗ą░čüčéąĖ ISP), SWRST = 1 (Software reset)

;Software reset ąĖąĘ ąŠą▒ą╗ą░čüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą╝ąŠąĮąĖč鹊čĆą░ ą▓ąĮčāčéčĆąĖčüčģąĄą╝ąĮąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ

; (ąŠą▒ą╗ą░čüčéąĖ ISP) ąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ąĮą░ ąŠą▒ą╗ą░čüčéčī ISP ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ:

MOV ISP_CONTR, 01100000B ;SWBS = 1 (ą▓čŗą▒ąŠčĆ ąŠą▒ą╗ą░čüčéąĖ ISP), SWRST = 1 (Software reset)

Software reset čüą▒čĆą░čüčŗą▓ą░ąĄčé ą▓čüčÄ čüąĖčüč鹥ą╝čŗ čåąĄą╗ąĖą║ąŠą╝, ą▓čüąĄ čĆąĄą│ąĖčüčéčĆčŗ SFR ąĖ ą┐ąŠčĆčéčŗ GPIO ą▓ąĄčĆąĮčāčéčüčÅ ą▓ čüą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ.

Power-On Reset (POR). ąÜąŠą│ą┤ą░ VCC čüąĮąĖąČą░ąĄčéčüčÅ ąĮąĖąČąĄ ą┐ąŠčĆąŠą│ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüą▒ąŠčÅ ą┐ąĖčéą░ąĮąĖčÅ čüčģąĄą╝čŗ POR, ą▓čüčÅ ą╗ąŠą│ąĖą║ą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮą░. ąÜąŠą│ą┤ą░ VCC ą▓ąĄčĆąĮąĄčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą║ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝čā čāčĆąŠą▓ąĮčÄ, ą▓čŗčģąŠą┤ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüą▒čĆąŠčüą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąŠčüą╗ąĄ 2048 čéą░ą║č鹊ą▓ (ą┤ą╗čÅ ą▓ąĄčĆčüąĖąĖ HD) ąĖą╗ąĖ 32768 čéą░ą║č鹊ą▓ (ą┤ą╗čÅ ą▓ąĄčĆčüąĖąĖ 90C).

ążą╗ą░ą│ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ Power-On Flag, POF/PCON.4, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, čćč鹊ą▒čŗ čüąŠąŠą▒čēąĖčéčī ąŠ čüąŠą▒čŗčéąĖąĖ čüąĮąĖąČąĄąĮąĖčÅ VCC ąĮąĖąČąĄ ą┐ąŠčĆąŠą│ą░ čüąĖčüč鹥ą╝čŗ POR. ąŁč鹊čé čäą╗ą░ą│ ą┐ąŠą╝ąŠą│ą░ąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ą┐čĆąŠą▓ąĄčĆąĖčéčī, ą▒čŗą╗ ą╗ąĖ ąĘą░ą┐čāčüą║ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ ąŠčé ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, ąĖą╗ąĖ ąŠčé ą▓čŗą▓ąŠą┤ą░ RST, ąĖą╗ąĖ ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░, ąĖą╗ąĖ ąŠčé čüą▒čĆąŠčüą░ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░. ąæąĖčé POF ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ.

Watch-Dog-Timer. ąĪą▒čĆąŠčü MCU ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ čéą░ą║ąČąĄ ąĖ ąŠčé čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░, ąĄčüą╗ąĖ ąĄą│ąŠ čĆą░ą▒ąŠčéą░ ą▒čŗą╗ą░ čĆą░ąĘčĆąĄčłąĄąĮą░. ąĪč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ WDT_CONTR, ąĖ ąĄą│ąŠ čĆą░ą▒ąŠčéą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠ. ąĢčüą╗ąĖ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ, č鹊 ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąĄą│ąŠ čĆąĄą│čāą╗čÅčĆąĮąŠ čüą▒čĆą░čüčŗą▓ą░čéčī, čćč鹊ą▒čŗ ąĮąĄ ą┐čĆąŠąĖąĘąŠčłąĄą╗ čüą▒čĆąŠčü čüąĖčüč鹥ą╝čŗ. ąĪč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ą╝ąŠąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĖą╗ąĖ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ ąŠą┐čåąĖą╣ čü ą┐ąŠą╝ąŠčēčīčÄ čāčéąĖą╗ąĖčéčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ STC-ISP Writter/Programmer. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ čüą╝. ą┤ą░čéą░čłąĖčé STC90C51RC-en.pdf [2].

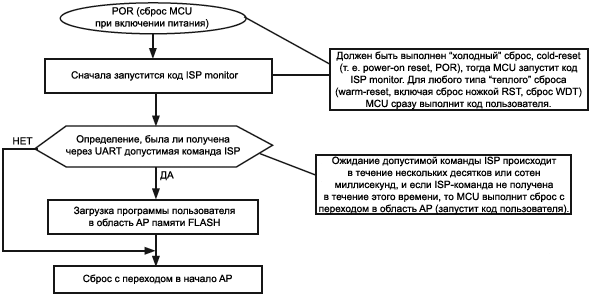

Warm Boot, Cold Boot Reset. MCU ą╝ąŠąČąĄčé ąŠčüčāčēąĄčüčéą▓ąĖčéčī čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čāčÄ "č鹥ą┐ą╗čāčÄ" (Warm Boot) ąĖ čģąŠą╗ąŠą┤ąĮčāčÄ (Cold Boot) ąĘą░ą│čĆčāąĘą║čā, čüą╝. čéą░ą▒ą╗ąĖčåčā.

| ąóąĖą┐ čüą▒čĆąŠčüą░ |

ąśčüč鹊čćąĮąĖą║ čüą▒čĆąŠčüą░ |

ąĀąĄąĘčāą╗čīčéą░čé |

| Warm boot |

ąĪč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ (WDT) |

ąĪą▒čĆąŠčü čüąĖčüč鹥ą╝čŗ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐ąĄčĆąĄčģąŠą┤čā ą║

ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÄ ą║ąŠą┤ą░ AP ą┐ąŠ ą░ą┤čĆąĄčüčā 0000h,

ąĖ ąĮą░čćąĮąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░

ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. |

| ąØąŠąČą║ą░ čüą▒čĆąŠčüą░ (RST) |

| 20H -> ISP_CONTR |

| 60H -> ISP_CONTR |

ąĪą▒čĆąŠčü čüąĖčüč鹥ą╝čŗ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐ąĄčĆąĄčģąŠą┤čā ą║

ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÄ ą║ąŠą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą╝ąŠąĮąĖč鹊čĆą░ ISP,

ąĖ ąĄčüą╗ąĖ ąĮąĄ ą▒čāą┤ąĄčé ąŠą▒ąĮą░čĆčāąČąĄąĮą░ ą╗ąĄą│ąĖčéąĖą╝ąĮą░čÅ

ą║ąŠą╝ą░ąĮą┤ą░ ISP, č鹊 ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖą╣

ą┐ąĄčĆąĄčģąŠą┤ ą║ ą║ąŠą┤čā ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ AP. |

| Cold boot |

Power On (ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ) |

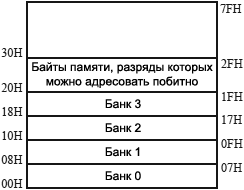

[ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą┐ą░ą╝čÅčéąĖ]

ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ (ą┤ą░ą╗ąĄąĄ čüąŠą║čĆą░čēąĄąĮąĮąŠ MCU) čüąĄčĆąĖąĖ STC89xx ąĖą╝ąĄčÄčé čĆą░ąĘą┤ąĄą╗čīąĮčŗąĄ ą░ą┤čĆąĄčüąĮčŗąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ ą┤ą╗čÅ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ (Program Memory) ąĖ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ (Data Memory), čŹč鹊 čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ą░čÅ ąōą░čĆą▓ą░čĆą┤čüą║ą░čÅ ą░čĆčģąĖč鹥ą║čéčāčĆą░ (čüą╝. ąÆąĖą║ąĖą┐ąĄą┤ąĖčÄ).

ąĀą░ąĘą╗ąĖčćą░čÄčé čĆą░ąĘą┤ąĄą╗čīąĮčŗąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ (Program memory) ąĖ ą┐ą░ą╝čÅčéčī ą┤ą░ąĮąĮčŗčģ. ąŻ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STC90C54RD+ ąĖą╝ąĄąĄčéčüčÅ 256 ą▒ą░ą╣čé ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ąŠą┐ąĄčĆą░čéąĖą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (scratch-pad RAM) ąĖ 1024 ą▒ą░ą╣čé ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ čĆą░čüčłąĖčĆąĄąĮąĮąŠą╣ ąŠą┐ąĄčĆą░čéąĖą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (expanded RAM, XRAM). ąŻ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STC90C51RC ąĖą╝ąĄąĄčéčüčÅ 256 ą▒ą░ą╣čé ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ scratch-pad RAM ąĖ 256 ą▒ą░ą╣čé ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ expanded RAM (XRAM). ąŻ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STC90C51 ąĖą╝ąĄąĄčéčüčÅ č鹊ą╗čīą║ąŠ 256 ą▒ą░ą╣čé ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ scratch-pad RAM. ąóą░ą║ąČąĄ ą┤ą╗čÅ čüąĄčĆąĖąĖ STC90C51RC/RD+ ąĄčüčéčī ą┤ąŠčüčéčāą┐ ą║ 64K ą▒ą░ą╣čé ą▓ąĮąĄčłąĮąĄą╣ čĆą░čüčłąĖčĆąĄąĮąĮąŠą╣ ąŠą┐ąĄčĆą░čéąĖą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (external expanded RAM).

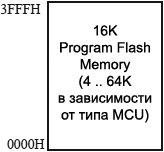

Program memory. ąŁč鹊 ą┐ą░ą╝čÅčéčī, ą▓ ą║ąŠč鹊čĆąŠą╣ čģčĆą░ąĮčÅčéčüčÅ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝čŗąĄ čÅą┤čĆąŠą╝ CPU ąĖąĮčüčéčĆčāą║čåąĖąĖ (ą▓ ą░čĆčģąĖč鹥ą║čéčāčĆąĄ MCS51 čéą░ą║ąČąĄ ą▓ čŹč鹊ą╣ ą┐ą░ą╝čÅčéąĖ ą╝ąŠą│čāčé čģčĆą░ąĮąĖčéčīčüčÅ čéą░ą▒ą╗ąĖčćąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖ čéą░ą▒ą╗ąĖčåčŗ ą┐ąĄčĆąĄčģąŠą┤ąŠą▓). ą£ąŠąČąĮąŠ ą░ą┤čĆąĄčüąŠą▓ą░čéčī ą┤ąŠ 64K ą▒ą░ą╣čé ą┐ą░ą╝čÅčéąĖ flash ą┤ą╗čÅ čģčĆą░ąĮąĖą╗ąĖčēą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąĖ čģčĆą░ąĮąĖą╗ąĖčēą░ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ MCU čüąĄčĆąĖąĖ STC90xx. ąÆčüčéčĆąŠąĄąĮąĮą░čÅ ą┐ą░ą╝čÅčéčī flash ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘą╝ąĄčĆąŠą╝ 4K/8K/13K/16K/32K/40K/48K/56K/62K ą▒ą░ą╣čé, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą╝ąŠą┤ąĄą╗ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąöąĖąĘą░ą╣ąĮ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅą╝ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą┐ą░ą╝čÅčéčī ą║ą░ą║ 3 ąŠčéą┤ąĄą╗čīąĮčŗąĄ čĆą░ąĘą┤ąĄą╗ą░ ą▒ą░ąĮą║ąŠą▓. ą×ąĮąĖ ąĮą░ąĘčŗą▓ą░čÄčéčüčÅ čĆąĄą│ąĖąŠąĮąŠą╝ AP (application program), čĆąĄą│ąĖąŠąĮąŠą╝ IAP (In-Application-Program) ąĖ čĆąĄą│ąĖąŠąĮąŠą╝ ąĘą░ą│čĆčāąĘą║ąĖ ISP (In-System-Program boot). ąĀąĄą│ąĖąŠąĮ AP čŹč鹊 ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ, ą│ą┤ąĄ čĆą░ąĘą╝ąĄčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. ąĀąĄą│ąĖąŠąĮ IAP (In-Application-Program) čŹč鹊 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝ą░čÅ ą┐ą░ą╝čÅčéčī ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆą░čÅ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ ą▓ą░ąČąĮčŗčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ AP. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, čäčāąĮą║čåąĖąŠąĮą░ą╗ IAP čüąĄčĆąĖąĖ STC90xx ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čćąĖčéą░čéčī ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī čüą▓ąŠąĖ ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖąŠąĮąĄ ą┤ą░ąĮąĮčŗčģ flash, čćč鹊 ąĖąĘą▒ą░ą▓ą╗čÅąĄčé ąŠčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī EEPROM. ąĀąĄą│ąĖąŠąĮ ISP boot čŹč鹊 ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čĆą░ąĘą╝ąĄčüčéąĖčéčī čüą┐ąĄčåąĖą░ą╗čīąĮčāčÄ ą┐čĆąŠą│čĆą░ą╝ą╝čā, ą║ąŠč鹊čĆčāčÄ ą╝čŗ ąĮą░ąĘčŗą▓ą░ąĄą╝ ą║ąŠą┤ąŠą╝ čüą░ą╝ąŠą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ (ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ISP). ąÆąĮčāčéčĆąĖ čĆąĄą│ąĖąŠąĮą░ ISP ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé čéą░ą║ąČąĄ čĆą░ąĘčĆąĄčłąĖčéčī ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī ą▓ ą╝ą░ą╗ąĄąĮčīą║ąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ ą┤ą╗čÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ. ą×ą▒čŗčćąĮąŠ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ISP - ąĘą░ą┐ąŠą╗ąĮąĖčéčī čĆąĄą│ąĖąŠąĮ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ AP, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ą░ą┐ą│čĆąĄą╣ą┤ ą║ąŠą┤ą░ ą▒ąĄąĘ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ąĖąĘą▓ą╗ąĄą║ą░čéčī ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖąĘ čüąĖčüč鹥ą╝čŗ.

ąĪąĄčĆąĖčÅ MCU STC90xx ąĖą╝ąĄąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮčāčÄ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ (čćč鹊-č鹊 ą┐ąŠčģąŠąČąĄąĄ ąĮą░ čäčīčÄąĘčŗ AVR). ąÉą┐ą┐ą░čĆą░čéčāčĆą░ MCU ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčé čŹčéčā ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą▓ ą╝ąŠą╝ąĄąĮčé ą▓ą║ą╗čÄč湥ąĮąĖčÅ (power-up), ąĖ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĮąĄą╣ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą░ą┐ą┐ą░čĆą░čéąĮčāčÄ ąĘą░čēąĖčéčā ą┐ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÄ ą┤ąŠčüčéčāą┐ąŠą╝ ą▓ čĆąĄą│ąĖąŠąĮčŗ ą┐ą░ą╝čÅčéąĖ - ą┐ąŠ ą┐čĆąĄą┤ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ ą║čĆąĖč鹥čĆąĖčÅą╝, ąĘą░ą┤ą░ąĮąĮčŗą╝ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ). ąÜčĆąĖč鹥čĆąĖąĖ čüąŠčüč鹊čÅčé ą▓ č鹊ą╝, čćč鹊 čĆą░ąĘčĆąĄčłąĄąĮ ąĖą╗ąĖ ąĮąĄčé ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖąŠąĮčā AP č鹊ą╗čīą║ąŠ ąĖąĘ čĆąĄą│ąĖąŠąĮą░ ISP, ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖąŠąĮčā IAP ąĖąĘ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ISP ąĖ AP, ąĖ ąĘą░ą┐čĆąĄčēąĄąĮ ą╗ąĖ ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖąŠąĮčā ISP ąĖąĘ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ AP ąĖ ąĖąĘ čüą░ą╝ąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ISP. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮą░ ą┐ą░ą╝čÅčéčī ą┤ą░ąĮąĮčŗčģ FLASH ISP ("ISP data flash is enabled"), č鹊 ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ISP ą╝ąŠąČąĄčé čćąĖčéą░čéčī/ąĘą░ą┐ąĖčüčŗą▓ą░čéčī čŹčéčā ąŠą▒ą╗ą░čüčéčī. ąÜąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮčŗąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓ ISP-IAP SFR, ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓čŗčģąŠą┤ ąĘą░ ą┐čĆąĄą┤ąĄą╗čŗ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ("out-of-space"), ąĖ MCU čüąĄčĆąĖąĖ STC90xx ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą▓čŗčłąĄčāą║ą░ąĘą░ąĮąĮčŗą╝ąĖ ą║čĆąĖč鹥čĆąĖčÅą╝ąĖ ąĖą│ąĮąŠčĆąĖčĆčāąĄčé ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čāčÄ ą║ąŠą╝ą░ąĮą┤čā.

ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ CPU ąĮą░čćąĖąĮą░ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ čü ą░ą┤čĆąĄčüą░ 0000H Program Memory, ą│ą┤ąĄ ą┤ąŠą╗ąČąĄąĮ ąĮą░čćąĖąĮą░čéčīčüčÅ ą║ąŠą┤ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (ą▓ąĄą║č鹊čĆ čüą▒čĆąŠčüą░). ąöą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą║ąŠą┤ ISR ą┤ąŠą╗ąČąĄąĮ čĆą░ąĘą╝ąĄčēą░čéčīčüčÅ ą▓ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ ą┐ąŠ čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╝ ą░ą┤čĆąĄčüą░ą╝, ą║ąŠč鹊čĆčŗąĄ ąĮą░ąĘčŗą▓ą░čÄčé ą▓ąĄą║č鹊čĆą░ą╝ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąÆąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ą╝ą╗ą░ą┤čłąĖčģ ą░ą┤čĆąĄčüą░čģ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝, čüčĆą░ąĘčā ąĘą░ ą▓ąĄą║č鹊čĆąŠą╝ čüą▒čĆąŠčüą░. ąÜą░ąČą┤ąŠą╝čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ ąĮą░ąĘąĮą░č湥ąĮ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą░ą┤čĆąĄčü ą▓ąĄą║č鹊čĆą░ ą▓ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, č鹊 CPU ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą║ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÄ ą║ąŠą┤ą░ ą┐ąŠ ą▓ąĄą║č鹊čĆčā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą┐čĆąĖąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ (ąĖą╗ąĖ ą╝ąĄąĮąĄąĄ ą┐čĆąĖąŠčĆąĖč鹥čéąĮąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ). ąØą░ą┐čĆąĖą╝ąĄčĆ, ą▓ąĄą║č鹊čĆ External Interrupt 0 ąĮą░ąĘąĮą░č湥ąĮ ąĮą░ ą░ą┤čĆąĄčü 0003H. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ External Interrupt 0, č鹊 ąĄą│ąŠ ISR ą┤ąŠą╗ąČąĄąĮ ąĮą░čćąĖąĮą░čéčīčüčÅ čü ą░ą┤čĆąĄčüą░ 0003H (ąŠą▒čŗčćąĮąŠ ą▓ čŹč鹊ą╝ ą╝ąĄčüč鹥 ąĮą░čģąŠą┤ąĖčéčüčÅ ą║ąŠą╝ą░ąĮą┤ą░ ą▒ąĄąĘčāčüą╗ąŠą▓ąĮąŠą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ AJMP ąĖą╗ąĖ LJMP). ąĢčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, č鹊 ą╝ąĄčüč鹊 ą┐ąŠą┤ ą║ąŠą┤ ąĄą│ąŠ ą▓ąĄą║č鹊čĆą░ čüą▓ąŠą▒ąŠą┤ąĮą░ ą║ą░ą║ ąŠą▒čŗčćąĮą░čÅ ą┐ą░ą╝čÅčéčī ą┐čĆąŠą│čĆą░ą╝ą╝.

ą»č湥ą╣ą║ąĖ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĖą┤čāčé ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ čü ąĖąĮč鹥čĆą▓ą░ą╗ąŠą╝ 8 ą▒ą░ą╣čé: 0003H ą▓ąĄą║č鹊čĆ ą┤ą╗čÅ External Interrupt 0, 000BH ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ Timer 0, 0013H ą┤ą╗čÅ External Interrupt 1, 001BH ą┤ą╗čÅ Timer 1, ąĖ čé. ą┤. ąĢčüą╗ąĖ ISR ą┤ąŠčüčéą░č鹊čćąĮąŠ ą║ąŠčĆąŠčéą║ąĖą╣, č鹊 ąŠąĮ ą╝ąŠąČąĄčé čāą╗ąŠąČąĖčéčīčüčÅ ą▓ čŹč鹊ą╝ 8-ą▒ą░ą╣čéąĮąŠą╝ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ. ąæąŠą╗ąĄąĄ ą┤ą╗ąĖąĮąĮčŗąĄ ISR ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĖąĮčüčéčĆčāą║čåąĖčÄ ą┐ąĄčĆąĄčģąŠą┤ą░ (AJMP ąĖą╗ąĖ LJMP) ą┤ą╗čÅ ą┐čĆąŠą┐čāčüą║ą░ čüą╗ąĄą┤čāčÄčēąĖčģ ąĮą░ ąĮąĄą╣ čÅč湥ąĄą║ ą┤čĆčāą│ąĖčģ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ąĄčüą╗ąĖ čŹčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ.

ąØąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą┤ą╗čÅ ą┐čĆąĖą╝ąĄčĆą░ čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STC90C54RD+.

|

| ą¤ą░ą╝čÅčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ STC90C54RD+ |

| ąóąĖą┐ |

Program Memory |

| STC90C/LE51 |

0000H~0FFFH (4K) |

| STC90C/LE52 |

0000H~1FFFH (8K) |

| STC90C/LE51RC |

0000H~0FFFH (4K) |

| STC90C/LE52RC |

0000H~1FFFH (8K) |

| STC90C/LE53RC |

0000H~33FFH (13K) |

| STC90C/LE12RC |

0000H~2FFFH (12K) |

| STC90C/LE54RD+ |

0000H~3FFFH (16K) |

| STC90C/LE58RD+ |

0000H~7FFFH (32K) |

| STC90C/LE510RD+ |

0000H~9FFFH (40K) |

| STC90C/LE512RD+ |

0000H~BFFFH (48K) |

| STC90C/LE514RD+ |

0000H~DFFFH (56K) |

| STC90C/LE516RD+ |

0000H~FFFFH (64K) |

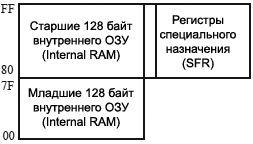

Data Memory. ąŁč鹊 ą┐ą░ą╝čÅčéčī, ą│ą┤ąĄ ą╝ąŠą│čāčé čĆą░ąĘą╝ąĄčēą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ą┤ą░ąĮąĮčŗąĄ. ąĢčüčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čĆą░ąĘąĮąŠą▓ąĖą┤ąĮąŠčüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ.

On-chip Scratch-Pad RAM. ąóąŠčćąĮąŠ čéą░ą║ ąČąĄ, ą║ą░ą║ ąĖ čā ąŠą▒čŗčćąĮąŠą│ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ 8051, čā MCU čüąĄčĆąĖąĖ STC90xx ąĖą╝ąĄąĄčéčüčÅ 256 ą▒ą░ą╣čé čüą▓ąĄčĆčģą▒čŗčüčéčĆąŠą╣ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ (SRAM), ą▓ ą║ąŠč鹊čĆčāčÄ ą▓čģąŠą┤ąĖčé ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ąĖąĘ 128 ą▒ą░ą╣čé SFR. ą£ą╗ą░ą┤čłąĖąĄ 128 ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ąŠčüčéčāą┐ąĮčŗ ą║ą░ą║ č湥čĆąĄąĘ ą┐čĆčÅą╝čāčÄ, čéą░ą║ ąĖ č湥čĆąĄąĘ ą║ąŠčüą▓ąĄąĮąĮčāčÄ ą░ą┤čĆąĄčüą░čåąĖąĖ. ąĪčéą░čĆčłąĖąĄ 128 ą▒ą░ą╣čé ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ ąĖ 128 ą▒ą░ą╣čé SFR ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą▒čēąĄąĄ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ. ąÜ čŹčéąĖą╝ čüčéą░čĆčłąĖą╝ 128 ą▒ą░ą╣čéą░ą╝ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ čü ą┐ąŠą╝ąŠčēčīčÄ ą║ąŠčüą▓ąĄąĮąĮąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ. ąÜ čüčéą░čĆčłąĖą╝ 128 ą▒ą░ą╣čéą░ą╝ SFR ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ č湥čĆąĄąĘ ą┐čĆčÅą╝čāčÄ ą░ą┤čĆąĄčüą░čåąĖčÄ.

|

| On-chip Scratch-Pad RAM |

ą£ą╗ą░ą┤čłąĖąĄ 32 ą▒ą░ą╣čéą░ (čü ą░ą┤čĆąĄčüą░ą╝ąĖ 00H..1FH) ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ čüą│čĆčāą┐ą┐ąĖčĆąŠą▓ą░ąĮčŗ ą▓ 4 ą▒ą░ąĮą║ą░ ą┐ąŠ 8 čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓ ą║ą░ąČą┤ąŠą╝. ąśąĮčüčéčĆčāą║čåąĖąĖ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąŠą▒čĆą░čēą░čÄčéčüčÅ ą║ čŹčéąĖą╝ 8 čĆąĄą│ąĖčüčéčĆą░ą╝ ą║ą░ą║ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ R0..R7. ąæąĖčéčŗ RS0 ąĖ RS1 čĆąĄą│ąĖčüčéčĆą░ PSW (čüą╝. čüąĄą║čåąĖčÄ "ąĀąĄą│ąĖčüčéčĆčŗ SFR ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ RAM") ą▓čŗą▒ąĖčĆą░čÄčé, ą║ą░ą║ąŠą╣ ąĖąĘ čŹčéąĖčģ ą▒ą░ąĮą║ąŠą▓ čüąĄą╣čćą░čü ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. ąśąĮčüčéčĆčāą║čåąĖąĖ, ąĖčüą┐ąŠą╗čīąĘčāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓čāčÄ ą░ą┤čĆąĄčüą░čåąĖčÄ, ą▒čāą┤čāčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą▒ą░ąĮą║ą░. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▒ąŠą╗ąĄąĄ čŹčäč乥ą║čéąĖą▓ąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą║ąŠą┤ą░, ą┐ąŠčüą║ąŠą╗čīą║čā ąĖąĮčüčéčĆčāą║čåąĖąĖ čü čĆąĄą│ąĖčüčéčĆąŠą▓ąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĄą╣ ą║ąŠčĆąŠč湥, č湥ą╝ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ąĖčüą┐ąŠą╗čīąĘčāčÄčēąĖąĄ ą┐čĆčÅą╝čāčÄ ą░ą┤čĆąĄčüą░čåąĖčÄ.

|

| ą£ą╗ą░ą┤čłąĖąĄ 128 ą▒ą░ą╣čé Internal SRAM |

ąĪą╗ąĄą┤čāčÄčēąĖąĄ 16 ą▒ą░ą╣čé (20H..2FH) ąĘą░ ą▒ą░ąĮą║ą░ą╝ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ č乊čĆą╝ąĖčĆčāčÄčé ą▒ą╗ąŠą║ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆčāčÄ ą╝ąŠąČąĮąŠ (čü ą┐ąŠą╝ąŠčēčīčÄ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ ąĖąĮčüčéčĆčāą║čåąĖą╣) ą░ą┤čĆąĄčüąŠą▓ą░čéčī ą║ą░ą║ ąŠčéą┤ąĄą╗čīąĮčŗąĄ ą▒ąĖčéčŗ (čäą╗ą░ą│ąĖ). ąØą░ą▒ąŠčĆ ąĖąĮčüčéčĆčāą║čåąĖą╣ 80C51 ą▓ą║ą╗čÄčćą░ąĄčé ą▓ čüąĄą▒čÅ čłąĖčĆąŠą║ąĖą╣ ąĮą░ą▒ąŠčĆ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą┤ą╗čÅ ą╝ą░ąĮąĖą┐čāą╗čÅčåąĖąĖ ąŠą┤ąĮąĖą╝ ą▒ąĖč鹊ą╝, ąĖ 128 ą▒ąĖčé ą▓ čŹč鹊ą╣ ąŠą▒ą╗ą░čüčéąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąĮą░ą┐čĆčÅą╝čāčÄ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮčŗ čŹčéąĖą╝ąĖ ąĖąĮčüčéčĆčāą║čåąĖčÅą╝ąĖ. ąÉą┤čĆąĄčüą░ ą▒ąĖčé ą▓ čŹč鹊ą╣ ąŠą▒ą╗ą░čüčéąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 00H..7FH.

ąÜ ą╝ą╗ą░ą┤čłąĖą╝ 128 ą▒ą░ą╣čéą░ą╝ ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą╗ąĖą▒ąŠ ą┐čĆčÅą╝ąŠą╣, ą╗ąĖą▒ąŠ ą║ąŠčüą▓ąĄąĮąĮąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĄą╣, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą║ čüčéą░čĆčłąĖą╝ 128 ą▒ą░ą╣čéą░ą╝ ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą║ąŠčüą▓ąĄąĮąĮąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĄą╣. ąĀąĄą│ąĖčüčéčĆčŗ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (SFR) ą▓ą║ą╗čÄčćą░čÄčé ąĘą░čēąĄą╗ą║ąĖ ą┐ąŠčĆč鹊ą▓, čĆąĄą│ąĖčüčéčĆčŗ čéą░ą╣ą╝ąĄčĆąŠą▓, čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ąĖ čé. ą┤. ąÜ čŹčéąĖą╝ čĆąĄą│ąĖčüčéčĆą░ą╝ ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┐čĆčÅą╝ąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĄą╣. 16 ą░ą┤čĆąĄčüąŠą▓ ą▓ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ SFR ą╝ąŠą│čāčé ą▒čŗčéčī ą░ą┤čĆąĄčüąŠą▓ą░ąĮčŗ ąĖ ą║ą░ą║ ą▒ą░ą╣čéčŗ, ąĖ ą║ą░ą║ ą▒ąĖčéčŗ. SFR, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą░ą┤čĆąĄčüąŠą▓ą░ąĮčŗ ą║ą░ą║ ą▒ąĖčéčŗ, ąĖą╝ąĄčÄčé ą░ą┤čĆąĄčüą░, ąĘą░ą║ą░ąĮčćąĖą▓ą░čÄčēąĖąĄčüčÅ ąĮą░ 0H ąĖą╗ąĖ 8H.

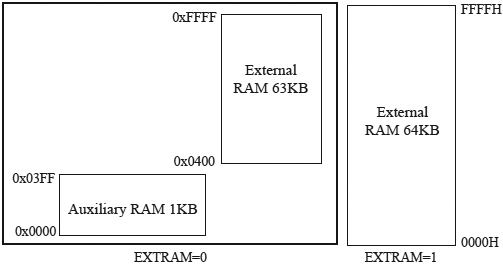

Auxiliary RAM. ąśą╝ąĄąĄčéčüčÅ 1024 ą▒ą░ą╣čé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą│ąŠ ą×ąŚąŻ ą┤ą░ąĮąĮčŗčģ (data RAM) ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ čüąĄčĆąĖąĖ STC90C54RD+ (ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ 256 ą▒ą░ą╣čé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą│ąŠ data RAM ą┤ąŠčüčéčāą┐ąĮąŠ ąĮą░ STC90C51RC). ąÜ čŹč鹊ą╣ ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ąĖąĮčüčéčĆčāą║čåąĖčÅą╝ąĖ MOVX @Ri ąĖą╗ąĖ MOVX @DPTR. ąŻą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą▒ąĖčé EXTRAM ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ AUXR.1 (čüą╝. ąĮąĖąČąĄ čüąĄą║čåąĖčÄ "ąĀąĄą│ąĖčüčéčĆčŗ SFR ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ RAM") ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ ą║ąŠąĮčéčĆąŠą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ auxiliary RAM. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą┤ąŠčüčéčāą┐ ą║ auxiliary RAM ąĘą░ą┐čĆąĄčēąĄąĮ. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé ąŠčćąĖčēąĄąĮ (EXTRAM=0), č鹊 auxiliary RAM čÅą▓ą╗čÅąĄčéčüčÅ čåąĄą╗čīčÄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ą░ą┤čĆąĄčüąŠą▓ 0x0000 .. 0x03FF, ąĖ ą║ ąĮąĄą╝čā ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ č湥čĆąĄąĘ ąĖąĮčüčéčĆčāą║čåąĖčÄ ą║ąŠčüą▓ąĄąĮąĮąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ MOVX @Ri ąĖ MOVX @DPTR. ąĢčüą╗ąĖ EXTRAM=0 ąĖ čåąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü ą▒ąŠą╗čīčłąĄ 0x03FF, č鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠąĄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ąĮą░ ą┤ąŠčüčéčāą┐ ą║ ą▓ąĮąĄčłąĮąĄą╣ RAM. ąÜąŠą│ą┤ą░ EXTRAM=0, č鹊 ą┐čĆąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ MOVX @Ri čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ DPH (čŹč鹊 čüčéą░čĆčłą░čÅ ą┐ąŠą╗ąŠą▓ąĖąĮą░ 16-ą▒ąĖčéąĮąŠą│ąŠ DPTR) ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ.

|

| Auxiliary RAM STC90C54RD+ |

ąöą╗čÅ ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆą░ KEIL-C51 ą┐čĆąĖčüą▓ą░ąĖą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗčģ, čĆą░ąĘą╝ąĄčēąĄąĮąĮčŗčģ ą▓ Auxiliary RAM, ą┤ąŠą╗ąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ pdata ąĖą╗ąĖ xdata. ą¤ąŠčüą╗ąĄ ą║ąŠą╝ą┐ąĖą╗čÅčåąĖąĖ ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗąĄ, ą┤ąĄą║ą╗ą░čĆąĖčĆąŠą▓ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ pdata ąĖ xdata, ą▒čāą┤čāčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ąŠčéąĮąŠčüąĖčéčīčüčÅ ą║ ą┐ą░ą╝čÅčéąĖ, ą║ ą║ąŠč鹊čĆąŠą╣ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ č湥čĆąĄąĘ MOVX @Ri (ą┤ą╗čÅ pdata) ąĖ MOVX @DPTR (ą┤ą╗čÅ xdata). ąóą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ą╝ąŠąČąĮąŠ ą║ąŠčĆčĆąĄą║čéąĮąŠ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ MCU.

External RAM. ąśą╝ąĄąĄčéčüčÅ 64K ą▒ą░ą╣čé ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░, ą║ ą║ąŠč鹊čĆąŠą╝čā ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ą░ą║ ą║ ą▓ąĮąĄčłąĮąĄą╝čā ą×ąŚąŻ ą┤ą░ąĮąĮčŗčģ (external data RAM). ąśąĮč鹥čĆč乥ą╣čü ą┤ąŠčüčéčāą┐ą░ čéą░ą║ąŠą╣ ąČąĄ, ą║ą░ą║ ąĖ čā čüčéą░ąĮą┤ą░čĆčéąĮąŠą│ąŠ 8051 - ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąĮąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ P2, P0, čüąĖą│ąĮą░ą╗ ALE, ąĖ ąĮąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ P3.6 ąĖ P3.7 ą┐ąŠą╗čāčćą░čÄčé ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčāčÄ čäčāąĮą║čåąĖčÄ čüąĖą│ąĮą░ą╗ąŠą▓ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ external data RAM. ąöą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ ą▒ąĖčé EXTRAM ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1. ąöąŠčüčéčāą┐ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ą╗ąĖą▒ąŠ ą┐ąŠ 16-ą▒ąĖčéąĮąŠą╝čā ą░ą┤čĆąĄčüčā (ąĖąĮčüčéčĆčāą║čåąĖąĄą╣ MOVX @DPTR), ąĖą╗ąĖ ą┐ąŠ 8-ą▒ąĖčéąĮąŠą╝čā ą░ą┤čĆąĄčüčā (ąĖąĮčüčéčĆčāą║čåąĖąĄą╣ MOVX @Ri). 8-ą▒ąĖčéąĮčŗą╣ ą░ą┤čĆąĄčü čćą░čüč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ąŠą▒čŖąĄą┤ąĖąĮąĄąĮąĖąĖ čü ąŠą┤ąĮąŠą╣ ąĮąŠąČą║ąŠą╣ ą┐ąŠčĆčéą░ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĖą╝ ąĖčģ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ ą┤ą╗čÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ čüčéčĆą░ąĮąĖčćąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ RAM. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 8-ą▒ąĖčéąĮčŗą╣ ą░ą┤čĆąĄčü, č鹊 Port 2 SFR čüąŠčģčĆą░ąĮčÅąĄčé čüą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▓ąŠ ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░ ą┤ąŠčüčéčāą┐ą░ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. ąŁč鹊 čāą┐čĆąŠčēą░ąĄčé čüčéčĆą░ąĮąĖčćąĮčŗą╣ ą┤ąŠčüčéčāą┐. 16-ą▒ąĖčéąĮčŗąĄ ą░ą┤čĆąĄčüą░ čćą░čüč鹊 ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ 64K ą▒ą░ą╣čé ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ.

|

| External RAM |

[ąĀąĄą│ąĖčüčéčĆčŗ SFR ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ RAM]

ąØąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮąĄą║ąŠč鹊čĆčŗąĄ SFR, ą║ąŠč鹊čĆčŗąĄ ąĖą╝ąĄčÄčé ąŠčéąĮąŠčłąĄąĮąĖąĄ ą║ RAM.

ąöą╗čÅ ą▒čŗčüčéčĆąŠą│ąŠ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ čüąĄčĆąĖčÅ STC89xx ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 2 čāą║ą░ąĘą░č鹥ą╗čÅ ą┤ą░ąĮąĮčŗčģ. ą×ąĮąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą▒čēąĖą╣ ą░ą┤čĆąĄčü SFR, ąĖ ą╝ąŠą│čāčé ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ ą▒ąĖč鹊ą╝ DPS (AUXR1.0).

PSW. ąŁč鹊 čüą╗ąŠą▓ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, (Program Status Word, čüąŠą║čĆą░čēąĄąĮąĮąŠ PSW).

| ąæąĖčé |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

CY |

AC |

F0 |

RS1 |

RS0 |

OV |

F1 |

P

|

CY: Carry (čäą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ, ąĖą╗ąĖ ą┐ąĄčĆąĄąĮąŠčüą░).

AC: Auxilliary Carry Flag (čäą╗ą░ą│ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄąĮąŠčüą░, ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą╗čÅ BCD-ąŠą┐ąĄčĆą░čåąĖą╣; BCD čĆą░čüčłąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ Binary Coded Decimal).

F0: Flag 0 (ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ą╗čÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą║ą░ą║ čäą╗ą░ą│ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ).

RS1: Register bank select control bit 1 (ą▒ąĖčé 1 ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą▒ą░ąĮą║ą░ čĆąĄą│ąĖčüčéčĆąŠą▓).

RS0: Register bank select control bit 0 (ą▒ąĖčé 0 ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą▒ą░ąĮą║ą░ čĆąĄą│ąĖčüčéčĆąŠą▓).

OV: Overflow (čäą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ).

F1: Flag 1. ążą╗ą░ą│, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čŗą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝.

P: Parity (čäą╗ą░ą│ č湥čéąĮąŠčüčéąĖ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░).

ąĀąĄą│ąĖčüčéčĆ AUXR.

| ąæąĖčé |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

- |

- |

- |

- |

- |

- |

EXTRAM |

ALEOFF |

B7..B3: čŹčéąĖ ą▒ąĖčéčŗ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ.

EXTRAM: ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝čā/ą▓ąĮąĄčłąĮąĄą╝čā ą×ąŚąŻ (Internal/External RAM access).

0: ą┤ą╗čÅ čüąĄčĆąĖą╣ RD+ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮą░čÅ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ auxiliary RAM, ąĖ ąŠąĮą░ čĆą░ąĘą╝ąĄčēąĄąĮą░ ą┐ąŠ ą░ą┤čĆąĄčüą░ą╝ 0x0000 .. 0x03FF. ąś ąĄčüą╗ąĖ ą░ą┤čĆąĄčü ą┐čĆąĄą▓čŗčłą░ąĄčé 0x03FF, č鹊 ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą░ą┤čĆąĄčüčāąĄčéčüčÅ ą▓ąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī (external RAM), ąĮą░čģąŠą┤čÅčēą░čÅčüčÅ ą▓ąĮąĄ ą║čĆąĖčüčéą░ą╗ą╗ą░ MCU. ąöą╗čÅ čüąĄčĆąĖą╣ RC čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮą░čÅ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ auxiliary RAM, ąĖ ąŠąĮą░ čĆą░ąĘą╝ąĄčēąĄąĮą░ ą┐ąŠ ą░ą┤čĆąĄčüą░ą╝ 00H .. FFH. ąś ąĄčüą╗ąĖ ą░ą┤čĆąĄčü ą┐čĆąĄą▓čŗčłą░ąĄčé FFH, č鹊 ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą░ą┤čĆąĄčüčāąĄčéčüčÅ ą▓ąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī (external RAM), ąĮą░čģąŠą┤čÅčēą░čÅčüčÅ ą▓ąĮąĄ ą║čĆąĖčüčéą░ą╗ą╗ą░ MCU. 1: ą▓čüčéčĆąŠąĄąĮąĮą░čÅ ą▓ čćąĖą┐ auxiliary RAM ą▓čüąĄą│ą┤ą░ ąĘą░ą┐čĆąĄčēąĄąĮą░.

ALEOFF: ąĘą░ą┐čĆąĄčé/čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ ALE.

0: ALE ą▓čŗą┤ą░ąĄčéčüčÅ čü ą┐ąŠčüč鹊čÅąĮąĮąŠą╣ čćą░čüč鹊č鹊ą╣, čĆą░ą▓ąĮąŠą╣ 1/3 ąŠčé čüąĖčüč鹥ą╝ąĮąŠą╣ (SYSclk) ą▓ čĆąĄąČąĖą╝ąĄ 6T, ąĖ 1/6 ąŠčé SYSclk ą▓ čĆąĄąČąĖą╝ąĄ 12T. 1: ALE ą░ą║čéąĖą▓ąĄąĮ č鹊ą╗čīą║ąŠ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĖąĮčüčéčĆčāą║čåąĖąĖ MOVX ąĖą╗ąĖ MOVC.

ąĀąĄą│ąĖčüčéčĆ AUXR1.

| ąæąĖčé |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

- |

- |

- |

- |

GF2 |

- |

- |

DPS

|

GF2: čäą╗ą░ą│ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čŗą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝. ąĢą│ąŠ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┐ąŠ ą╗čÄą▒ąŠą╝čā ąĮą░ąĘąĮą░č湥ąĮąĖčÄ.

DPS: ą▒ąĖčé ą▓čŗą▒ąŠčĆą░ čĆąĄą│ąĖčüčéčĆąŠą▓ DPTR. ąĢčüą╗ąĖ 0, č鹊 ą▓čŗą▒čĆą░ąĮ DPTR0 (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ); ąĄčüą╗ąĖ 1, č鹊 ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓čŗą▒čĆą░ąĮ ą▓č鹊čĆąĖčćąĮčŗą╣ DPTR (DPTR1).

ąöąĄą╝ąŠąĮčüčéčĆą░čåąĖąŠąĮąĮčŗą╣ ą║ąŠą┤ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čĆą░čüčłąĖčĆąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥 STC89C51RC-en.pdf [2].

SP: Stack Pointer.

ąŻą║ą░ąĘą░č鹥ą╗čī čüč鹥ą║ą░ SP ąĖą╝ąĄąĄčé čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī 8 ą▒ąĖčé, ąĖ ąŠąĮ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ čģčĆą░ąĮąĄąĮąĖčÅ č鹥ą║čāčēąĄą│ąŠ ą░ą┤čĆąĄčüą░ čüąŠčģčĆą░ąĮąĄąĮąĮčŗčģ ą▓ čüč鹥ą║ąĄ ąĘąĮą░č湥ąĮąĖą╣ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░. SP ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé čüąŠčģčĆą░ąĮąĄąĮčŗ ą▓ čüč鹥ą║ąĄ ąĖąĮčüčéčĆčāą║čåąĖčÅą╝ąĖ PUSH ąĖ CALL. ąĪč鹥ą║ ą╝ąŠąČąĄčé čĆą░ąĘą╝ąĄčēą░čéčīčüčÅ ą▓ ą╗čÄą▒ąŠą╝ ą╝ąĄčüč鹥 ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ RAM. ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ SP ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 07H, ąĖ čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čüč鹥ą║ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü čÅč湥ą╣ą║ąĖ 08H, ą║ąŠč鹊čĆą░čÅ čéą░ą║ąČąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą┐ąĄčĆą▓ąŠą╝čā čĆąĄą│ąĖčüčéčĆčā (R0) ą▒ą░ąĮą║ą░ čĆąĄą│ąĖčüčéčĆąŠą▓ 1. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ ą▒ą░ąĮą║ą░ čĆąĄą│ąĖčüčéčĆąŠą▓, č鹊 SP ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮ ą▓ ą┤čĆčāą│ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ ą│ą╗čāą▒ąĖąĮą░ čüč鹥ą║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠ 256 ą▒ą░ą╣čé.

[ąĀąĄą│ąĖčüčéčĆčŗ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (SFR)]

ą×ą┐ąĖčüą░ąĮąĖąĄ SFR ąĖ ąĖčģ ą░ą┤čĆąĄčüą░ čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥 STC90C51RC-en.pdf [2].

[ą¤ąŠčĆčéčŗ GPIO]

ąÆčüąĄ ą┐ąŠčĆčéčŗ ą▓ą▓ąŠą┤ą░ ą▓čŗą▓ąŠą┤ą░ GPIO (ą▓ą║ą╗čÄčćą░čÅ P4) ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ ą▓ ąŠą┤ąĖąĮ ąĖąĘ čéčĆąĄčģ čĆąĄąČąĖą╝ąŠą▓: ą┐čüąĄą▓ąŠą┤ąŠ-ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ (quasi-bidirectional, čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ čĆąĄąČąĖą╝ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┐ąŠčĆčéą░ 8051), č鹊ą╗čīą║ąŠ ą▓čģąŠą┤ (input-only, ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ ąĖą╝ąĄąĄčé ą▓čŗčüąŠą║ąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ) ąĖą╗ąĖ ą▓čŗčģąŠą┤ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝. P1, P2, P3 ąĖ P4 ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░) ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ quasi-bidirectional (č鹊čćąĮąŠ čéą░ą║ ąČąĄ, ą║ą░ą║ ąĖ ą┐ąŠčĆčéčŗ čüčéą░ąĮą┤ą░čĆčéąĮąŠą│ąŠ 8051), ą▓ č鹊 ąČąĄ ą▓čĆąĄą╝čÅ P0 ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĮą░čģąŠą┤ąĖčéčüčÅ čĆąĄąČąĖą╝ąĄ ą▓čŗčģąŠą┤ą░ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝. ąÜąŠą│ą┤ą░ P0 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░čüčłąĖčĆąĄąĮąĖčÅ čłąĖąĮčŗ (ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé ą░ą┤čĆąĄčüą░ A7..A0 ąĖ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ D7..D0), čĆąĄąĘąĖčüč鹊čĆčŗ pull-up ą┤ąŠą▒ą░ą▓ą╗čÅčéčī ąĮąĄ ąĮčāąČąĮąŠ. ą×ą┤ąĮą░ą║ąŠ ą║ąŠą│ą┤ą░ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ P0 ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ą░ą║ ą┐ąŠčĆčéčŗ GPIO, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą▓ąĮąĄčłąĮąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ pull-up (ą▓ąĄčĆčģąĮąĖąĄ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ) ąĮąŠą╝ąĖąĮą░ą╗ąŠą╝ 4.7-10K. ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ ąĮąŠąČąĄą║ ą┐ąŠčĆč鹊ą▓ čüąĄčĆąĖąĖ STC90xx čüąŠą▓ą┐ą░ą┤ą░čÄčé čü ą░ąĮą░ą╗ąŠą│ąĖčćąĮčŗą╝ąĖ čĆąĄąČąĖą╝ą░ą╝ąĖ čüąĄčĆąĖąĖ STC89xx (čüą╝. ą┐čĆąĄą┤čŗą┤čāčēčāčÄ ą▓čĆąĄąĘą║čā).

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ č鹊ą║, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠą│čāčé ą║ąŠą╝ą╝čāčéąĖčĆąŠą▓ą░čéčī čüč鹊ą║ąĖ ąĮąŠąČąĄą║ P0 ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STC90C51RC/RD+ ą┤ą╗čÅ 5V ą▓ąĄčĆčüąĖą╣ čüąŠčüčéą░ą▓ą╗čÅąĄčé 12 ą╝ąÉ, ąĖ ą▓čŗą▓ąŠą┤čŗ ą┤čĆčāą│ąĖčģ ą┐ąŠčĆč鹊ą▓ ą╝ąŠą│čāčé ą║ąŠą╝ą╝čāčéąĖčĆąŠą▓ą░čéčī č鹊ą║ ą┤ąŠ 6 ą╝ąÉ.

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ č鹊ą║, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠą│čāčé ą║ąŠą╝ą╝čāčéąĖčĆąŠą▓ą░čéčī čüč鹊ą║ąĖ ąĮąŠąČąĄą║ P0 ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STC90LE51RC/RD+ ą┤ą╗čÅ 3V ą▓ąĄčĆčüąĖą╣ čüąŠčüčéą░ą▓ą╗čÅąĄčé 8 ą╝ąÉ, ąĖ ą▓čŗą▓ąŠą┤čŗ ą┤čĆčāą│ąĖčģ ą┐ąŠčĆč鹊ą▓ ą╝ąŠą│čāčé ą║ąŠą╝ą╝čāčéąĖčĆąŠą▓ą░čéčī č鹊ą║ ą┤ąŠ 4 ą╝ąÉ.

ą×ą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ SFR ą┤ą╗čÅ ą┐ąŠčĆč鹊ą▓ GPIO, ąŠą┐ąĖčüą░ąĮąĖąĄ ąĖčģ čĆąĄąČąĖą╝ąŠą▓, ą┐čĆąĖą╝ąĄčĆčŗ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ, ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░ čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥 STC90C51RC-en.pdf [2].

[ąĪąĖčüč鹥ą╝ą░ ą║ąŠą╝ą░ąĮą┤]

ąĀąĄąČąĖą╝čŗ ą░ą┤čĆąĄčüą░čåąĖąĖ čÅą▓ą╗čÅčÄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ čćą░čüčéčīčÄ ąĮą░ą▒ąŠčĆą░ ą║ąŠą╝ą░ąĮą┤ ą║ą░ąČą┤ąŠą╣ ą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą╣ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ. ą×ąĮąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé čĆą░ąĘą╗ąĖčćąĮčŗą╝ąĖ čüą┐ąŠčüąŠą▒ą░ą╝ąĖ ąĖčüč鹊čćąĮąĖą║ ąĖ/ąĖą╗ąĖ ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąĖčéčāą░čåąĖąĖ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ. ąÆ ą░čĆčģąĖč鹥ą║čéčāčĆąĄ 8051 ąĖą╝ąĄąĄčéčüčÅ 5 čĆąĄąČąĖą╝ąŠą▓ ą░ą┤čĆąĄčüą░čåąĖąĖ: ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮą░čÅ (Immediate), ą┐čĆčÅą╝ą░čÅ (Direct), ą║ąŠčüą▓ąĄąĮąĮą░čÅ (Indirect), čĆąĄą│ąĖčüčéčĆąŠą▓ą░čÅ (Register), ąĖąĮą┤ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮą░čÅ (Indexed).

Immediate Constant (IMM). ąÉą┤čĆąĄčü čāą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ ąĘąĮą░č湥ąĮąĖąĄ ą║ąŠąĮčüčéą░ąĮčéčŗ, ą║ąŠč鹊čĆą░čÅ čüą╗ąĄą┤čāąĄčé čüčĆą░ąĘčā ąĘą░ ą╝ąĮąĄą╝ąŠąĮąĖą║ąŠą╣ ą║ąŠą┤ą░ ąŠą┐ąĄčĆą░čåąĖąĖ, ąĮą░ą┐čĆąĖą╝ąĄčĆ:

ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ąĘą░ą│čĆčāąČą░ąĄčé ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ čłąĄčüčéąĮą░ą┤čåą░č鹥čĆąĖčćąĮąŠą╣ ą║ąŠąĮčüčéą░ąĮč鹊ą╣ 70h. ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ čćąĖčüą╗ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī čāą║ą░ąĘą░ąĮąŠ ą▓ ą┤ąĄčüčÅčéąĖčćąĮąŠą╣ č乊čĆą╝ąĄ ą║ą░ą║ 112.

Direct (DIR). ąÆ ą┐čĆčÅą╝ąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ ąŠą┐ąĄčĆą░ąĮą┤ čāą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ 8-ą▒ąĖčéąĮąŠą╝ ą┐ąŠą╗ąĄ ą░ą┤čĆąĄčüą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ. ąóą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ą╝ąŠąČąĮąŠ ą░ą┤čĆąĄčüąŠą▓ą░čéčī č鹊ą╗čīą║ąŠ 128 ą╝ą╗ą░ą┤čłąĖčģ ą▒ą░ą╣čé ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ąŠą┐ąĄčĆą░čéąĖą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ (internal data RAM), ąĖ čĆąĄą│ąĖčüčéčĆčŗ SFR ą╝ąŠą│čāčé ą▒čŗčéčī čéą░ą║ąČąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ą┐čĆčÅą╝ąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĄą╣.

Indirect (IND). ąÆ ą║ąŠčüą▓ąĄąĮąĮąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ ąĖąĮčüčéčĆčāą║čåąĖčÅ čāą║ą░ąĘčŗą▓ą░ąĄčé čĆąĄą│ąĖčüčéčĆ, ą║ąŠč鹊čĆčŗą╣ čüąŠą┤ąĄčƹȹĖčé ą░ą┤čĆąĄčü ąŠą┐ąĄčĆą░ąĮą┤ą░. ąóą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī ą░ą┤čĆąĄčüąŠą▓ą░ąĮą░ ą║ą░ą║ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ, čéą░ą║ ąĖ ą▓ąĮąĄčłąĮčÅčÅ ąŠą┐ąĄčĆą░čéąĖą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī (internal RAM, external RAM).

ąÉą┤čĆąĄčüąĮčŗą╝ąĖ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ ą┤ą╗čÅ 8-ą▒ąĖčéąĮąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ ą╝ąŠą│čāčé ą▒čŗčéčī R0 ąĖą╗ąĖ R1 ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą▒ą░ąĮą║ą░, ąĖą╗ąĖ čāą║ą░ąĘą░č鹥ą╗čī čüč鹥ą║ą░ SP. ąöą╗čÅ 16-ą▒ąĖčéąĮąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ ą░ą┤čĆąĄčüąĮčŗą╝ čĆąĄą│ąĖčüčéčĆąŠą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆąĄą│ąĖčüčéčĆ DPTR.

Register (REG). ąÜ čĆąĄą│ąĖčüčéčĆą░ą╝ ą▒ą░ąĮą║ą░ (ą║ą░ąČą┤čŗą╣ ą▒ą░ąĮą║ čüąŠą┤ąĄčƹȹĖčé čĆąĄą│ąĖčüčéčĆčŗ R0..R7) ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ąĖ ąĖąĮčüčéčĆčāą║čåąĖčÅą╝ąĖ, ą▓ ą║ąŠą┤ąĄ ą║ąŠč鹊čĆčŗčģ 3 ą▒ąĖčéą░ą╝ąĖ ąĘą░ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮ ąĮčāąČąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ą▒ą░ąĮą║ą░. ąÉą┤čĆąĄčüą░čåąĖčÅ čéą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ čüą░ą╝ą░čÅ čŹčäč乥ą║čéąĖą▓ąĮą░čÅ, ą┐ąŠč鹊ą╝čā čćč鹊 čüąŠčüč鹊ąĖčé ąĖąĘ 1 ą▒ą░ą╣čéą░, ąĖ ąĮąĄ čéčĆąĄą▒čāąĄčé ą┤ą╗čÅ čüąĄą▒čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą│ąŠ ą▒ą░ą╣čéą░ ą┤ą╗čÅ ą░ą┤čĆąĄčüą░. ą¤čĆąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĖ čŹč鹊ą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ ąŠą┤ąĮąŠą╝čā čĆąĄą│ąĖčüčéčĆąŠą▓ R0..R7 ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą▒ą░ąĮą║ą░.

ąØąĄą║ąŠč鹊čĆčŗąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ čüą┐ąĄčåąĖčäąĖčćąĮčŗ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░. ąØą░ą┐čĆąĖą╝ąĄčĆ ąĮąĄą║ąŠč鹊čĆčŗąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą▓čüąĄą│ą┤ą░ čĆą░ą▒ąŠčéą░čÄčé č鹊ą╗čīą║ąŠ čü ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąŠą╝, ąĖą╗ąĖ č鹊ą╗čīą║ąŠ čü čāą║ą░ąĘą░č鹥ą╗ąĄą╝ ą┤ą░ąĮąĮčŗčģ DPTR ąĖ čé. ą┐. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ą▓ čéą░ą║ąĖčģ ąĖąĮčüčéčĆčāą║čåąĖčÅčģ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ą▒ą░ą╣čé, ą▓čüčÅ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░čÅ ą░ą┤čĆąĄčüąĮą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ čāąČąĄ čüąŠą┤ąĄčƹȹĖčéčüčÅ ą▓ čüą░ą╝ąŠą╝ ą║ąŠą┤ąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ.

Index (IDX). ąśąĮą┤ąĄą║čüąĮčāčÄ ą░ą┤čĆąĄčüą░čåąĖčÄ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝, ąĖ č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ. ąŁč鹊čé čĆąĄąČąĖą╝ ą░ą┤čĆąĄčüą░čåąĖąĖ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ čéą░ą▒ą╗ąĖčå ą┤ą░ąĮąĮčŗčģ (look-up tables), ąĮą░čģąŠą┤čÅčēąĖčģčüčÅ ą▓ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝. 16-ą▒ąĖčéąĮčŗą╣ ą▒ą░ąĘąŠą▓čŗą╣ čĆąĄą│ąĖčüčéčĆ (ą▓ ą║ą░č湥čüčéą▓ąĄ ą║ąŠč鹊čĆąŠą│ąŠ ą╝ąŠąČąĄčé čüą╗čāąČąĖčéčī ą╗ąĖą▒ąŠ DPTR, ą╗ąĖą▒ąŠ PC) čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü čéą░ą▒ą╗ąĖčåčŗ, ąĖ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĖčÅ ąĮą░ ąĮčāąČąĮčŗą╣ ąŠą▒čŖąĄą║čé ą▓ čéą░ą▒ą╗ąĖčåąĄ.

ąöčĆčāą│ąŠą╣ čéąĖą┐ ąĖąĮą┤ąĄą║čüąĮąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ąĖąĮčüčéčĆčāą║čåąĖąĖ čāčüą╗ąŠą▓ąĮąŠą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ (conditional jump). ąÆ čéą░ą║ąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą░ą┤čĆąĄčü ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą║ą░ą║ čüčāą╝ą╝ą░ ą░ą┤čĆąĄčüą░, ąĮą░čģąŠą┤čÅčēąĄą│ąŠčüčÅ ą▓ čāą║ą░ąĘą░č鹥ą╗ąĄ ą▒ą░ąĘčŗ ąĖ ą░ą┤čĆąĄčüą░, ąĮą░čģąŠą┤čÅčēąĄą│ąŠčüčÅ ą▓ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąĄ.

ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čüąĖčüč鹥ą╝čŗ ą║ąŠą╝ą░ąĮą┤ čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥 STC90C51RC-en.pdf [2].

[ąĪąĖčüč鹥ą╝ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣]

ąĪąĄčĆąĖčÅ STC90C51RC/RD+ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 8 ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čü 4 čāčĆąŠą▓ąĮčÅą╝ąĖ ą┐čĆąĖąŠčĆąĖč鹥čéą░. ą¤čĆąĖč湥ą╝ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąŠą▒čĆą░ą▒ąŠčéą║ą░ ą▓ą╗ąŠąČąĄąĮąĮčŗčģ ą┤čĆčāą│ ą▓ ą┤čĆčāą│ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, čćč鹊 ąĮąĄčćą░čüč鹊 ą▓čüčéčĆąĄčćą░ąĄčéčüčÅ ą┤ą░ąČąĄ ą▓ čüąŠą▓čĆąĄą╝ąĄąĮąĮčŗčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ. 8 ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čŹč鹊 external interrupt 0 (ą▓ąĮąĄčłąĮąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ INT0), ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé Timer0, external interrupt 1 (ą▓ąĮąĄčłąĮąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ INT1), ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé Timer1, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░ (UART), ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé Timer2, external interrupt 2 (ą▓ąĮąĄčłąĮąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ INT2) ąĖ external interrupt 3 (ą▓ąĮąĄčłąĮąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ INT3). ąÜą░ąČą┤čŗą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖą▓čÅąĘą░ąĮ ą║ ąŠą┤ąĮąŠą╝čā ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ čäą╗ą░ą│ą░ą╝ ąĘą░ą┐čĆąŠčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĮą░čģąŠą┤čÅčēąĖčģčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ SFR. ąóą░ą║ąČąĄ ą║ą░ąČą┤čŗą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖą▓čÅąĘą░ąĮ ą║ čüą▓ąŠąĄą╝čā ą▓ąĄą║č鹊čĆčā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĮą░čģąŠą┤čÅčēąĄą╝čāčüčÅ ą▓ čéą░ą▒ą╗ąĖčåąĄ ą▓ąĄą║č鹊čĆąŠą▓, ą▓ ąĮą░čćą░ą╗ąĄ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝. ąÜą░ąČą┤ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮąŠ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ąĖą╗ąĖ ąŠčćąĖčüčéą║ąŠą╣ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą▒ąĖčéą░ ą▓ SFR-čĆąĄą│ąĖčüčéčĆą░čģ IE ąĖ XICON. ą×ą┤ąĮą░ą║ąŠ, čćč鹊ą▒čŗ čüąĖčüč鹥ą╝ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čĆą░ą▒ąŠčéą░ą╗ą░, ąĄčæ ąĮčāąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ EA (IE.7) ą▓ ą╗ąŠą│. 1, ąĖąĮą░č湥 ąŠčéą┤ąĄą╗čīąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ ą▒čāą┤čāčé čĆą░čüą┐ąŠąĘąĮą░ą▓ą░čéčīčüčÅ ąĖ ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ. ąĪą▒čĆąŠčü ą▒ąĖčéą░ EA ą▓ ą╗ąŠą│. 0 ąĘą░ą┐čĆąĄčēą░ąĄčé ą▓čüąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĖčģ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčŗčģ ąĮą░čüčéčĆąŠąĄą║.

ąĢčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░, č鹊 ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮ ąĘą░ą┐čĆąŠčü ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ ąĘą░ą┐čĆąŠčüą░ ą┤ą╗čÅ čŹč鹊ą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ č鹥ą║čāčēąĄą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ, CPU ą░ą┐ą┐ą░čĆą░čéąĮąŠ čüą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą▓čŗąĘąŠą▓ LCALL ą┐ąŠ ąĘą░čĆą░ąĮąĄąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝čā ą░ą┤čĆąĄčüčā (ą▓ąĄą║č鹊čĆčā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ), čćč鹊 ą▓čŗąĘąŠą▓ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (interrupt service routine, ISR). ąÜą░ąČą┤čŗą╣ ISR ą┤ąŠą╗ąČąĄąĮ ąĘą░ą▓ąĄčĆčłąĖčéčīčüčÅ ąĖąĮčüčéčĆčāą║čåąĖąĄą╣ RETI, ą║ąŠč鹊čĆą░čÅ ą▓ąĄčĆąĮąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą║ čüą╗ąĄą┤čāčÄčēąĄą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ąĮą░ ą║ąŠč鹊čĆąŠą╣ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą▒čŗą╗ąŠ ą┐čĆąĄčĆą▓ą░ąĮąŠ, ąĄčüą╗ąĖ ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ąĮąŠą▓ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąĢčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮčŗ, č鹊 čäą╗ą░ą│ ąŠąČąĖą┤ą░čÄčēąĄą│ąŠ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▒čāą┤ąĄčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░ąĮ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąŠą┤ąŠą╗ąČąĖčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ ą║ąŠą┤ą░ (ąĮąĄ ISR). ążą╗ą░ą│ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1 ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, čĆą░ąĘčĆąĄčłąĄąĮčŗ ąĖą╗ąĖ ąĮąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.