|

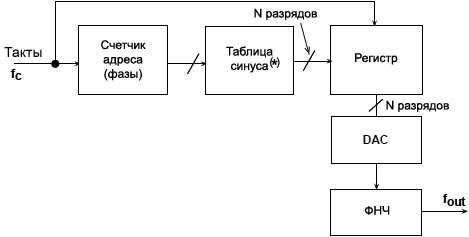

ąÆ čüąĖčüč鹥ą╝ą░čģ ąĖąĘą╝ąĄčĆąĄąĮąĖą╣ ąĖ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖą╣ čłąĖčĆąŠą║ąŠ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą╝ąĄč鹊ą┤ ą┐čĆčÅą╝ąŠą│ąŠ čüąĖąĮč鹥ąĘą░ ą╝ąĮąŠą│ąŠčćą░čüč鹊čéąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ąŠčüąĮąŠą▓ąĄ ąŠą┤ąĮąŠą╣ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ, čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ ą╝ąĄč鹊ą┤ Direct Digital Synthesis (DDS). ąæą░ąĘąŠą▓ą░čÅ ą░čĆčģąĖč鹥ą║čéčāčĆą░ DDS ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 1. ąÆ čŹč鹊ą╣ čāą┐čĆąŠčēąĄąĮąĮąŠą╣ ą╝ąŠą┤ąĄą╗ąĖ čüčéą░ą▒ąĖą╗čīąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čāą┐čĆą░ą▓ą╗čÅąĄčé ą░ą┤čĆąĄčüąŠą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮąŠą╣ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ (PROM), ą▓ ą║ąŠč鹊čĆąŠą╣ čüąŠčģčĆą░ąĮąĄąĮąŠ čåąĄą╗ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąĄčĆąĖąŠą┤ąŠą▓ ąŠą┤ąĮąŠą│ąŠ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ (ą▓ ą┐čĆąĄą┤ąĄą╗čīąĮąŠą╝ čüą╗čāčćą░ąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čüąŠčģčĆą░ąĮąĄąĮą░ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮą░čÅ č乊čĆą╝ą░ čüąĖą│ąĮą░ą╗ą░, ą║ąŠč鹊čĆą░čÅ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖ ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ čü ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ čüč湥čéčćąĖą║ą░ ą░ą┤čĆąĄčüą░). ą¤ąŠ ą╝ąĄčĆąĄ č鹊ą│ąŠ, ą║ą░ą║ čüč湥čéčćąĖą║ ą┐ąŠ čłą░ą│ą░ą╝ ą╝ąĄąĮčÅąĄčé čüą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ, čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą║ą░ąČą┤ąŠą╣ čÅč湥ą╣ą║ąĖ ą┐ą░ą╝čÅčéąĖ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ DAC, ą║ąŠč鹊čĆčŗą╣ ą▓ čüą▓ąŠčÄ ąŠč湥čĆąĄą┤čī ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĮą░ čüą▓ąŠąĄą╝ ą▓čŗčģąŠą┤ąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗. ąĪą┐ąĄą║čéčĆą░ą╗čīąĮą░čÅ čćąĖčüč鹊čéą░ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą│ą╗ą░ą▓ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ąĖ DAC. ążą░ąĘąŠą▓čŗą╣ čłčāą╝ ą│ą╗ą░ą▓ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą║ą░č湥čüčéą▓ą░ ąŠą┐ąŠčĆąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĘą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ ą┤ą░čéą░čłąĖčéą░ MT-085 [1]. ąÆčüąĄ ąĮąĄą┐ąŠąĮčÅčéąĮčŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ ąĪą╗ąŠą▓ą░čĆąĖą║ąĄ [2].

ąĀąĖčü. 1. ąæą░ąĘąŠą▓ą░čÅ čüčģąĄą╝ą░ čüąĖčüč鹥ą╝čŗ DDS.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (*): čéą░ą▒ą╗ąĖčåą░ čüąĖąĮčāčüą░ čüąŠą┤ąĄčƹȹĖčé ą┤ą░ąĮąĮčŗąĄ č乊čĆą╝čŗ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ čåąĄą╗ąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ fc (ąŠą▒čŗčćąĮąŠ čŹč鹊 ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čĆą░ą▓ąĮąŠ čüč鹥ą┐ąĄąĮąĖ čćąĖčüą╗ą░ 2).

ą¤ąŠčüą║ąŠą╗čīą║čā čüąĖčüč鹥ą╝ą░ DDS ą┤ąĖčüą║čĆąĄčéąĮą░čÅ (čüąĖą│ąĮą░ą╗ ą▓ ąĮąĄą╣ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮ ą▓ ą┤ąĖčüą║čĆąĄčéąĮčŗčģ ąĖąĮč鹥čĆą▓ą░ą╗ą░čģ ą▓čĆąĄą╝ąĄąĮąĖ čåąĖčäčĆąŠą▓čŗą╝ąĖ ą▓čŗą▒ąŠčĆą║ą░ą╝ąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ), ą┐čĆąĖ ąĄčæ ą┐čĆąŠąĄą║čéąĖčĆąŠą▓ą░ąĮąĖąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčćč鹥ąĮčŗ ą▓čüąĄ ą┐čĆąŠą▒ą╗ąĄą╝čŗ č鹊čćąĮąŠčüčéąĖ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░: čłčāą╝ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ (quantization noise), ąŠčéčĆą░ąČąĄąĮąĖąĄ čüą┐ąĄą║čéčĆą░ (aliasing), čäąĖą╗čīčéčĆą░čåąĖčÅ ąĖ čé. ą┤. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą│ą░čĆą╝ąŠąĮąĖą║ąĖ ąĮąĄą▓čŗčüąŠą║ąŠą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ DAC čüą▓ąŠčĆą░čćąĖą▓ą░čÄčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą▓ ą┐ąŠą╗ąŠčüčā čćą░čüč鹊čé ąØą░ą╣ą║ą▓ąĖčüčéą░, ą┤ąĄą╗ą░čÅ ąĮąĄą▓ąŠąĘą╝ąŠąČąĮąŠą╣ ąĖčģ čäąĖą╗čīčéčĆą░čåąĖčÄ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą│ą░čĆą╝ąŠąĮąĖą║ąĖ ą▓čŗčüčłąĄą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ čüąĖąĮč鹥ąĘą░č鹊čĆąŠą▓ ąĮą░ ąŠčüąĮąŠą▓ąĄ PLL ą╝ąŠą│čāčé ą▒čŗčéčī ąŠčéčäąĖą╗čīčéčĆąŠą▓ą░ąĮčŗ. ąĢčüčéčī ąĖ ą┤čĆčāą│ąĖąĄ čüąŠąŠą▒čĆą░ąČąĄąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ą▒čāą┤čāčé ą║čĆą░čéą║ąŠ čĆą░čüčüą╝ąŠčéčĆąĄąĮčŗ ą┤ą░ą╗ąĄąĄ.

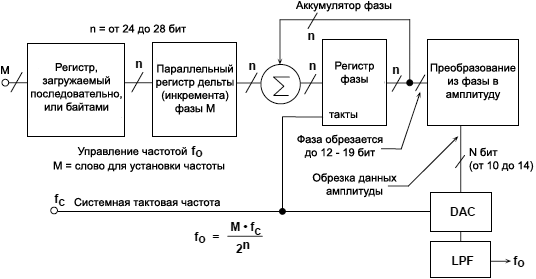

ążčāąĮą┤ą░ą╝ąĄąĮčéą░ą╗čīąĮą░čÅ ą┐čĆąŠą▒ą╗ąĄą╝ą░ čéą░ą║ąŠą╣ ą┐čĆąŠčüč鹊ą╣ čüąĖčüč鹥ą╝čŗ DDS, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 1, čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊 č乊čĆą╝ąĖčĆčāąĄą╝ą░čÅ ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ DDS ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮą░ č鹊ą╗čīą║ąŠ ą╗ąĖčłčī ąĖąĘą╝ąĄąĮąĄąĮąĖąĄą╝ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ, ą╗ąĖą▒ąŠ č湥čĆąĄąĘ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ PROM, čćč鹊 ą┤ąĄą╗ą░ąĄčé čüąĖčüč鹥ą╝čā ą┤ąŠą▓ąŠą╗čīąĮąŠ ąĮąĄ ą│ąĖą▒ą║ąŠą╣. ą¤čĆą░ą║čéąĖč湥čüą║ą░čÅ čüąĖčüč鹥ą╝ą░ DDS čĆąĄą░ą╗ąĖąĘčāąĄčé čŹčéčā ą▒ą░ąĘąŠą▓čāčÄ čäčāąĮą║čåąĖčÄ ą▒ąŠą╗ąĄąĄ ą│ąĖą▒ą║ąĖą╝ ąĖ čŹčäč乥ą║čéąĖą▓ąĮčŗą╝ čüą┐ąŠčüąŠą▒ąŠą╝ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ąŠą│ąŠ čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠą│ąŠ čåąĖčäčĆąŠą▓čŗą╝ ą║ąŠą┤ąŠą╝ ą│ąĄąĮąĄčĆą░č鹊čĆą░, Numerically Controlled Oscillator (NCO). ąæą╗ąŠą║-čüčģąĄą╝ą░ čéą░ą║ąŠą╣ čüąĖčüč鹥ą╝čŗ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 2.

ąĀąĖčü. 2. ąōąĖą▒ą║ą░čÅ čüąĖčüč鹥ą╝ą░ DDS.

ąĪąĄčĆą┤čåąĄą╝ čüąĖčüč鹥ą╝čŗ ąĮą░ čĆąĖčü. 2 čÅą▓ą╗čÅąĄčéčüčÅ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ čäą░ąĘčŗ, čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą║ąŠč鹊čĆąŠą│ąŠ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ čü ą║ą░ąČą┤čŗą╝ ą┐ąĄčĆąĖąŠą┤ąŠą╝ čéą░ą║č鹊ą▓. ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ čäą░ąĘčŗ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ, čåąĖčäčĆąŠą▓ąŠą╣ ą║ąŠą┤ M, čüąŠčģčĆą░ąĮąĄąĮąĮčŗą╣ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ čäą░ąĘčŗ (delta phase register) ą┤ąŠą▒ą░ą▓ą╗čÅąĄčéčüčÅ ą║ čåąĖčäčĆąŠą▓ąŠą╝čā ą║ąŠą┤čā ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░ čäą░ąĘčŗ. ą¤čĆąĄą┤ą┐ąŠą╗ąŠąČąĖą╝, čćč鹊 čćąĖčüą╗ąŠ ą▓ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ čäą░ąĘčŗ čĆą░ą▓ąĮąŠ 00...01, ąĖ ąĮą░čćą░ą╗čīąĮąŠąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░ čäą░ąĘčŗ 00...00. ąÉą║ą║čāą╝čāą╗čÅč鹊čĆ čäą░ąĘčŗ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ/ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ąĮą░ 00...01 čü ą║ą░ąČą┤čŗą╝ ą┐ąĄčĆąĖąŠą┤ąŠą╝ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ. ąĢčüą╗ąĖ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ čäą░ąĘčŗ 32-čĆą░ąĘčĆčÅą┤čŗą╣, čéčĆąĄą▒čāąĄčéčüčÅ 232 (čüą▓čŗčłąĄ 4 ą╝ąĖą╗ą╗ąĖą░čĆą┤ąŠą▓) čéą░ą║č鹊ą▓, čćč鹊ą▒čŗ ąĘąĮą░č湥ąĮąĖąĄ ą▓ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąĄ čäą░ąĘčŗ ą▓ąĄčĆąĮčāą╗ąŠčüčī ąŠą▒čĆą░čéąĮąŠ ą║ 00...00, ąĖ čåąĖą║ą╗ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ ą┐ąŠą▓č鹊čĆąĖčéčüčÅ.

ą×ą▒čĆąĄąĘą░ąĮąĮąŠąĄ ą┐ąŠ čĆą░ąĘčĆčÅą┤ą░ą╝ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░ čäą░ąĘčŗ čāą┐čĆą░ą▓ą╗čÅąĄčé ą░ą┤čĆąĄčüąŠą╝ čéą░ą▒ą╗ąĖčåčŗ čüąĖąĮčāčüą░ (ąĖą╗ąĖ ą║ąŠčüąĖąĮčāčüą░). ąÜą░ąČą┤čŗą╣ ą░ą┤čĆąĄčü ą▓ čŹč鹊ą╣ čéą░ą▒ą╗ąĖčåąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé č鹊čćą║ąĄ čäą░ąĘčŗ ą┐ąĄčĆąĖąŠą┤ą░ čüąĖąĮčāčüą░ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 0┬░ ą┤ąŠ 360┬░. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čéą░ą▒ą╗ąĖčåą░ čüąĖąĮčāčüą░ čüąŠą┤ąĄčƹȹĖčé čåąĖčäčĆąŠą▓čāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠą▒ ą░ą╝ą┐ą╗ąĖčéčāą┤ąĄ ą┐ąŠą╗ąĮąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ čüąĖąĮčāčüąŠąĖą┤čŗ. ąÆ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą┤ą╗čÅ čŹą║ąŠąĮąŠą╝ąĖąĖ ą┐ą░ą╝čÅčéąĖ čéčĆąĄą▒čāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą┤ą╗čÅ 90┬░ čäą░ąĘčŗ ą┐ąĄčĆąĖąŠą┤ą░, ą┐ąŠčüą║ąŠą╗čīą║čā ą┤ą░ąĮąĮčŗąĄ ąŠ č鹊ą╝, ą║ą░ą║ą░čÅ čćą░čüčéčī ąĖąĘ 4 čćą░čüč鹥ą╣ ą┐ąĄčĆąĖąŠą┤ą░ č乊čĆą╝ąĖčĆčāąĄčéčüčÅ, čüąŠą┤ąĄčƹȹĖčéčüčÅ ą▓ 2 čüčéą░čĆčłąĖčģ ą▒ą░ą╣čéą░čģ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░ čäą░ąĘčŗ. ą¤ąŠą╗čāčćą░ąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēą░čÅ čåąĄą┐ąŠčćą║ą░: čéą░ą▒ą╗ąĖčåą░ čüąĖąĮčāčüą░ ąŠč鹊ą▒čĆą░ąČą░ąĄčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ čäą░ąĘąĄ ąĮą░ čüą╗ąŠą▓ąŠ čåąĖčäčĆąŠą▓ąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ, ą║ąŠč鹊čĆąŠąĄ ą▓ čüą▓ąŠčÄ ąŠč湥čĆąĄą┤čī ą┐ąŠą┤ą░ąĄčéčüčÅ ąĮą░ DAC. ąōčĆą░čäąĖč湥čüą║ąĖ čŹč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąŠ ą║ą░ą║ "čäą░ąĘąŠą▓ąŠąĄ ą║ąŠą╗ąĄčüąŠ", čüą╝. čĆąĖčü. 3.

ąĀąĖčü. 3. ą”ąĖą║ą╗ąĖč湥čüą║ąŠąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čåąĖčäčĆąŠą▓ąŠą╣ čäą░ąĘčŗ čü čłą░ą│ąŠą╝ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ M.

ąĀą░čüčüą╝ąŠčéčĆąĖą╝ čüą╗čāčćą░ą╣ ą┤ą╗čÅ n = 32 ąĖ M = 1. ąÉą║ą║čāą╝čāą╗čÅč鹊čĆ čäą░ąĘčŗ ą┐čĆąŠą╣ą┤ąĄčé ą┐ąŠ čłą░ą│ą░ą╝ ą▓čüąĄ 232 ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ą▓čŗčģąŠą┤ąĮčŗčģ čüąŠčüč鹊čÅąĮąĖą╣, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĖčéčüčÅ ąĖ ąĮą░čćąĮąĄčé čüč湥čé čüąĮą░čćą░ą╗ą░. ą¦ą░čüč鹊čéą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čĆą░ą▓ąĮą░ čćą░čüč鹊č鹥 ą▓čģąŠą┤ąĮčŗčģ čéą░ą║č鹊ą▓, ą┐ąŠą┤ąĄą╗ąĄąĮąĮąŠą╣ ąĮą░ 232. ąĢčüą╗ąĖ M=2, č鹊 čĆąĄą│ąĖčüčéčĆ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░ čäą░ąĘčŗ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĖčéčüčÅ ą▓ 2 čĆą░ąĘą░ ą▒čŗčüčéčĆąĄąĄ, ąĖ ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ čāą┤ą▓ąŠąĖčéčüčÅ. ąŁč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą▒ąŠą▒čēąĄąĮąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝.

ąöą╗čÅ n-čĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░ čäą░ąĘčŗ (ą▓ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ DDS-čüąĖčüč鹥ą╝ n ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 24 ą┤ąŠ 32) čüčāčēąĄčüčéą▓čāąĄčé 2n ą▓ąŠąĘą╝ąŠąČąĮčŗčģ č鹊č湥ą║ čäą░ąĘčŗ. ą”ąĖčäčĆąŠą▓ąŠąĄ čüą╗ąŠą▓ąŠ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ čäą░ąĘčŗ M ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ą▓ąĄą╗ąĖčćąĖąĮčā, ąĮą░ ą║ąŠč鹊čĆčāčÄ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ čäą░ąĘčŗ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą┐ąĄčĆąĖąŠą┤ąĄ ą▓čģąŠą┤ąĮčŗčģ čéą░ą║č鹊ą▓. ąĢčüą╗ąĖ fc čŹč鹊 čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ DDS, č鹊 čćą░čüč鹊čéą░ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖąĮč鹥ąĘąĖčĆčāąĄą╝ąŠą│ąŠ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▒čāą┤ąĄčé čĆą░ą▓ąĮą░:

fo = (M * fc) / 2n

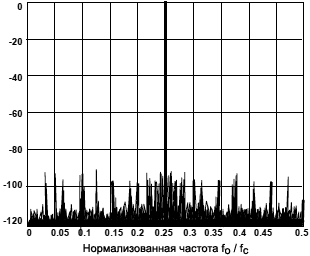

ąŁč鹊 ą▓čŗčĆą░ąČąĄąĮąĖąĄ ąĖąĘą▓ąĄčüčéąĮąŠ ą║ą░ą║ č乊čĆą╝čāą╗ą░ čéą░ą╣ą╝ąĖąĮą│ą░ DDS. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čćą░čüč鹊čéąĮą░čÅ čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī (č鹊čćąĮąŠčüčéčī čāčüčéą░ąĮąŠą▓ą║ąĖ čüąĖąĮč鹥ąĘąĖčĆčāąĄą╝ąŠą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ) čĆą░ą▓ąĮą░ fc/2n. ąöą╗čÅ n = 32 čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čüą▓čŗčłąĄ ąŠą┤ąĮąŠą╣ ą╝ąĖą╗ą╗ąĖą░čĆą┤ąĮąŠą╣! ąÆ ą┐čĆą░ą║čéąĖč湥čüą║ąŠą╣ čüąĖčüč鹥ą╝ąĄ DDS ą▓čüąĄ ą▒ąĖčéčŗ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░ čäą░ąĘčŗ ąĮąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ čéą░ą▒ą╗ąĖčåčā čüąĖąĮčāčüą░, ą░ ąŠą▒čĆąĄąĘą░čÄčéčüčÅ, ąĖ ą▓ ą║ą░č湥čüčéą▓ąĄ ą░ą┤čĆąĄčüą░ ą┤ą╗čÅ čéą░ą▒ą╗ąĖčåčŗ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čüčéą░čĆčłąĖčģ ą▒ąĖčé (ąŠą▒čŗčćąĮąŠ ąŠčé 13 ą┤ąŠ 15). ąŁč鹊 čüąĮąĖąČą░ąĄčé čĆą░ąĘą╝ąĄčĆ čéą░ą▒ą╗ąĖčåčŗ čüąĖąĮčāčüą░, ąĖ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ čĆą░ąĘčĆąĄčłą░čÄčēčāčÄ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą┐ąŠ čćą░čüč鹊č鹥. ą×ą▒čĆąĄąĘą║ą░ ą▒ąĖčé čüč湥čéčćąĖą║ą░ čäą░ąĘčŗ č鹊ą╗čīą║ąŠ ą╗ąĖčłčī ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé ąĮąĄą▒ąŠą╗čīčłąŠąĄ (ąĮąŠ čāčćąĖčéčŗą▓ą░ąĄą╝ąŠąĄ) ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čäą░ąĘąŠą▓ąŠą│ąŠ čłčāą╝ą░ ą▓ čüąĖąĮč鹥ąĘąĖčĆčāąĄą╝čŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ (čüą╝. čĆąĖčü. 4).

ąĀąĖčü. 4. ąĀą░čüčüčćąĖčéą░ąĮąĮčŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čüą┐ąĄą║čéčĆ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé 90 dB SFDR ą┤ą╗čÅ 15-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ąŠą▒čĆąĄąĘą║ąĖ čüč湥čéčćąĖą║ą░ čäą░ąĘčŗ.

ąĀą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī DAC ąŠą▒čŗčćąĮąŠ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąĮą░ 2 .. 4 ą▒ąĖčéą░ ą╝ąĄąĮčīčłąĄ čłąĖčĆąĖąĮčŗ čéą░ą▒ą╗ąĖčåčŗ čüąĖąĮčāčüą░. ąöą░ąČąĄ čüą░ą╝čŗą╣ ą╗čāčćčłąĖą╣ N-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ DAC ą┤ąŠą▒ą░ą▓ąĖčé ą║ ą▓čŗčģąŠą┤čā čłčāą╝ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ. ąĀąĖčü. 4 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓čŗčćąĖčüą╗ąĄąĮąĮčŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čüą┐ąĄą║čéčĆ ą┤ą╗čÅ 32-ą▒ąĖčéąĮąŠą│ąŠ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░ čäą░ąĘčŗ, čā ą║ąŠč鹊čĆąŠą│ąŠ ą┤ą╗čÅ ą░ą┤čĆąĄčüą░ čéą░ą▒ą╗ąĖčåčŗ čüąĖąĮčāčüą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ 15 čüčéą░čĆčłąĖčģ čĆą░ąĘčĆčÅą┤ąŠą▓. ąŚąĮą░č湥ąĮąĖąĄ ą£ ą▒čŗą╗ąŠ ą▓čŗą▒čĆą░ąĮąŠ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊ą▒čŗ ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ ą▒čŗą╗ą░ čüą╗ąĄą│ą║ą░ čüą╝ąĄčēąĄąĮą░ ąŠčé 0,25 čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čłčāą╝ ąĖąĘ-ąĘą░ ąŠą▒čĆąĄąĘą║ąĖ čäą░ąĘčŗ ąĖ ąŠą│čĆą░ąĮąĖč湥ąĮąĮąŠą╣ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ DAC ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ąĮą░ čāčĆąŠą▓ąĮąĄ 90 dB ąĮąĖąČąĄ ą┐ąŠą╗ąĮąŠą╣ čłą║ą░ą╗čŗ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąŁč鹊čé ą┐ą░čĆą░ą╝ąĄčéčĆ ąĮą░ą╝ąĮąŠą│ąŠ ą┐čĆąĄą▓ąŠčüčģąŠą┤ąĖčé ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī ą╗čÄą▒ąŠą│ąŠ ą║ąŠą╝ą╝ąĄčĆč湥čüą║ąĖ ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ 12-čĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ DAC ąĖ čÅą▓ą╗čÅąĄčéčüčÅ ą░ą┤ąĄą║ą▓ą░čéąĮčŗą╝ ą┤ą╗čÅ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣.

ą×ą┐ąĖčüą░ąĮąĮą░čÅ ą▓čŗčłąĄ ą▒ą░ąĘąŠą▓ą░čÅ čüąĖčüč鹥ą╝ą░ DDS ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ąŠč湥ąĮčī ą│ąĖą▒ą║ąŠą╣ ąĖ ąŠą▒ą╗ą░ą┤ą░ąĄčé ą▓čŗčüąŠą║ąŠą╣ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ. ą¦ą░čüč鹊čéą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮą░ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ, ą▒ąĄąĘ čĆą░ąĘčĆčŗą▓ą░ čäą░ąĘčŗ, ą┐čāč鹥ą╝ ą┐čĆąŠčüč鹊ą│ąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ M-čĆąĄą│ąĖčüčéčĆą░. ą×ą┤ąĮą░ą║ąŠ ą┐čĆą░ą║čéąĖč湥čüą║ąĖąĄ DDS-čüąĖčüč鹥ą╝čŗ čéčĆąĄą▒čāčÄčé ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą│čĆčāąĘą║ąĖ (ą┐ąŠą▒ąĖčéąĮąŠ, ąĖą╗ąĖ ą┐ąŠ ą▒ą░ą╣čéą░ą╝, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░) ą┤ą░ąĮąĮčŗčģ ąĮąŠą▓ąŠą│ąŠ čüą╗ąŠą▓ą░ čćą░čüč鹊čéčŗ ą▓ čüą▓ąŠą╣ ą▒čāč乥čĆąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▒čāč乥čĆąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą┐ąĄčĆąĄąĮąŠčüąĖčéčüčÅ ą▓ M-čĆąĄą│ąĖčüčéčĆ. ąŁč鹊 ą┤ąĄą╗ą░ąĄčéčüčÅ ą┤ą╗čÅ čāą╝ąĄąĮčīčłąĄąĮąĖčÅ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▓ąĮąĄčłąĮąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ DDS. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĮąŠą▓ąŠąĄ čüą╗ąŠą▓ąŠ ąĘą░ą│čĆčāąČąĄąĮąŠ ą▓ ą▒čāč乥čĆąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ, čüčéčĆąŠą▒ ą┤ą╗čÅ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ čäą░ąĘčŗ ą┐ąŠą╝ąĄąĮčÅąĄčé ą▓čüąĄ ąĄą│ąŠ ą▒ąĖčéčŗ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. ąóčĆąĄą▒čāąĄą╝ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ą▒čāč乥čĆąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ čäą░ąĘčŗ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ čüą║ąŠčĆąŠčüčéčī, čü ą║ąŠč鹊čĆąŠą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮą░ ą▓čŗčģąŠą┤ąĮą░čÅ čüąĖąĮč鹥ąĘąĖčĆčāąĄą╝ą░čÅ čćą░čüč鹊čéą░.

[ą×čéčĆą░ąČąĄąĮąĖąĄ čüą┐ąĄą║čéčĆą░ ą▓ DDS-čüąĖčüč鹥ą╝ą░čģ (ą░ą╗ąĖą░čüąĖąĮą│)]

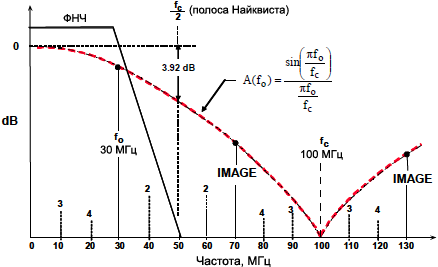

ąĪčāčēąĄčüčéą▓čāąĄčé ąŠą┤ąĮąŠ ą▓ą░ąČąĮąŠąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąĖąĄ ą┤ą╗čÅ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ čüąĖąĮč鹥ąĘąĖčĆčāąĄą╝čŗčģ ą▓čŗčģąŠą┤ąĮčŗčģ čćą░čüč鹊čé, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮčŗ ą┐čĆąŠčüč鹊ą╣ čüąĖčüč鹥ą╝ąŠą╣ DDS. ąóąĄąŠčĆąĄą╝ą░ ąØą░ą╣ą║ą▓ąĖčüčéą░ (Nyquist Criteria) ą│ą╗ą░čüąĖčé, čćč鹊 čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ (čćą░čüč鹊čéą░ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ, ąĖą╗ąĖ čćą░čüč鹊čéą░ ą▓čŗą▒ąŠčĆąŠą║, sample rate) ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą▓ 2 čĆą░ąĘą░ ą▓čŗčłąĄ ą▓čŗčģąŠą┤ąĮąŠą╣ č乊čĆą╝ąĖčĆčāąĄą╝ąŠą╣ čćą░čüč鹊čéčŗ. ąĀąĖčü. 5 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓čŗčģąŠą┤ DAC ą▓ čüąĖčüč鹥ą╝ąĄ DDS, ą║ąŠą│ą┤ą░ ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ 30 ą£ąōčå, ąĖ čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ 100 ą£ąōčå. ąÉąĮčéąĖ-ą░ą╗ąĖą░čüąĖąĮą│ąŠą▓čŗą╣ čäąĖą╗čīčéčĆ ą┤ąŠą╗ąČąĄąĮ čüč鹊čÅčéčī ąĮą░ ą▓čŗčģąŠą┤ąĄ DAC, čćč鹊ą▒čŗ ąŠčüą╗ą░ą▒ąĖčéčī ąĮąĖąČąĮčÄčÄ čćą░čüč鹊čéčā ąŠą▒čĆą░ąĘą░ (100 - 30 = 70 ą£ąōčå), ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 5.

ąĀąĖčü. 5. ąŁčäč乥ą║čé ą░ą╗ąĖą░čüąĖąĮą│ą░ ą▓ čüąĖčüč鹥ą╝ąĄ DDS.

ąĪą╗ąĄą┤čāąĄčé ąŠčéą╝ąĄčéąĖčéčī, čćč鹊 ą░ą╝ą┐ą╗ąĖčéčāą┤ąĮčŗą╣ ąŠčéą║ą╗ąĖą║ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą”ąÉą¤ (ą┐ąĄčĆąĄą┤ čäąĖą╗čīčéčĆą░čåąĖąĄą╣) čüą╗ąĄą┤čāąĄčé ąĘą░ sin (x)/x ąŠčéą║ą╗ąĖą║ąŠą╝, čü ąĮčāą╗čÅą╝ąĖ ąĮą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 ąĖ ą║čĆą░čéąĮčŗą╝ąĖ ąĄą╣ čćą░čüč鹊čéą░čģ. ą¤ąŠą╗ąĮąŠąĄ ą▓čŗčĆą░ąČąĄąĮąĖąĄ ą┤ą╗čÅ ąĮąŠčĆą╝ą░ą╗ąĖąĘąŠą▓ą░ąĮąĮąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤ąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ A(fo), ą│ą┤ąĄ fo čŹč鹊 ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░, fc čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓:

A(fo) = sin(pi*fo/fc) / (pi*fo/fc)

ąŁč鹊čé čüą┐ą░ą┤ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąŠč鹊ą╝čā, čćč鹊 ą▓čŗčģąŠą┤ DAC čŹč鹊 ąĮąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĮčāą╗ąĄą▓ąŠą╣ čłąĖčĆąĖąĮčŗ (ą║ą░ą║ ąĮą░ ąĖą┤ąĄą░ą╗čīąĮąŠą╝ čĆąĄčüąĄą╝ą┐ą╗ąĄčĆąĄ), ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čĆčÅą╝ąŠčāą│ąŠą╗čīąĮčŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓, čłąĖčĆąĖąĮą░ ą║ąŠč鹊čĆčŗčģ ąŠą▒čĆą░čéąĮąŠ ą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮą░ čüą║ąŠčĆąŠčüčéąĖ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ. ąÉą╝ą┐ą╗ąĖčéčāą┤ą░ ąŠčéą║ą╗ąĖą║ą░ sin (x)/x čüąĮąĖąČą░ąĄčéčüčÅ ąĮą░ 3.92 dB ąĮą░ čćą░čüč鹊č鹥 ąØą░ą╣ą║ą▓ąĖčüčéą░ (1/2 čüą║ąŠčĆąŠčüčéąĖ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ DAC). ąØą░ ą┐čĆą░ą║čéąĖą║ąĄ ą┐ąĄčĆąĄą┤ą░č鹊čćąĮą░čÅ čäčāąĮą║čåąĖčÅ ą░ąĮčéąĖ-ą░ą╗ąĖą░čüąĖąĮą│ąŠą▓ąŠą│ąŠ čäąĖą╗čīčéčĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮą░ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊ą▒čŗ čüą║ąŠą╝ą┐ąĄąĮčüąĖčĆąŠą▓ą░čéčī čüą┐ą░ą┤ sin(x)/x, ąĖ ąŠą▒čēą░čÅ čćą░čüč鹊čéąĮą░čÅ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ čüąĖčüč鹥ą╝čŗ ą┐ąŠą╗čāčćąĖą╗ą░čüčī ą┐ą╗ąŠčüą║ąŠą╣ ą▓ą┐ą╗ąŠčéčī ą┤ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ DAC (ąŠą▒čŗčćąĮąŠ 1/3 ąŠčé čćą░čüč鹊čéčŗ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ).

ąöčĆčāą│ąŠą╣ ą▓ą░ąČąĮčŗą╣ ą╝ąŠą╝ąĄąĮčé, ą║ąŠč鹊čĆčŗą╣ čüą╗ąĄą┤čāąĄčé čāč湥čüčéčī - ą▓ ąŠčéą╗ąĖčćąĖąĖ čüąĖčüč鹥ą╝ čüąĖąĮč鹥ąĘą░ čćą░čüč鹊čé ąĮą░ ąŠčüąĮąŠą▓ąĄ PLL, ą▓ąĄčĆčģąĮąĖąĄ ą│ą░čĆą╝ąŠąĮąĖą║ąĖ ąŠčüąĮąŠą▓ąĮąŠą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ ą▓ čüąĖčüč鹥ą╝ąĄ DDS ąĘą░ą▓ąŠčĆą░čćąĖą▓ą░čÄčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą▓ čĆą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĖąĘ-ąĘą░ čŹčäč乥ą║čéą░ ą░ą╗ąĖą░čüąĖąĮą│ą░. ąŁčéąĖ ą│ą░čĆą╝ąŠąĮąĖą║ąĖ ąĮąĄą╗čīąĘčÅ čāčüčéčĆą░ąĮąĖčéčī ą░ąĮčéąĖ-ą░ą╗ąĖą░čüąĖąĮą│ąŠą▓čŗą╝ čäąĖą╗čīčéčĆąŠą╝. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ 100 ą£ąōčå, ąĖ ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ 30 ą£ąōčå, ą▓č鹊čĆą░čÅ ą│ą░čĆą╝ąŠąĮąĖą║ą░ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┐ąŠčÅą▓ąĖčéčüčÅ ąĮąĄ č鹊ą╗čīą║ąŠ ąĮą░ čćą░čüč鹊č鹥 60 ą£ąōčå (ą▓čŗčłąĄ čĆą░ą▒ąŠč湥ą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░), ąĮąŠ čéą░ą║ąČąĄ ąĖ ąĮą░ čćą░čüč鹊č鹥 100 ŌĆō 60 = 40 ą£ąōčå (ą║ąŠą╝ą┐ąŠąĮąĄąĮčé ą░ą╗ąĖą░čüąĖąĮą│ą░). ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ čéčĆąĄčéčīčÅ ą│ą░čĆą╝ąŠąĮąĖą║ą░ (90 ą£ąōčå) čüąŠąĘą┤ą░čüčé ą▓ čĆą░ą▒ąŠč湥ą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą┐ą░čĆą░ąĘąĖčéąĮčŗą╣ čüąĖą│ąĮą░ą╗ 100 ŌĆō 90 = 10 ą£ąōčå, ąĖ 4-čÅ ą│ą░čĆą╝ąŠąĮąĖą║ą░ čüąŠąĘą┤ą░čüčé ą┐ąŠą╝ąĄčģčā 120 ŌĆō 100 ą£ąōčå = 20 ą£ąōčå. ąōą░čĆą╝ąŠąĮąĖą║ąĖ ą▓čŗčüčłąĄą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ čéą░ą║ąČąĄ ą┐ąŠą┐ą░ą┤ą░čÄčé ą▓ ą┐ąŠą╗ąŠčüčā čćą░čüč鹊čé ąØą░ą╣ą║ą▓ąĖčüčéą░ (ąŠčé DC ą┤ąŠ fc/2). ą¤ąŠą╗ąŠąČąĄąĮąĖąĄ ą┐ąĄčĆą▓čŗčģ č湥čéčŗčĆąĄčģ ą│ą░čĆą╝ąŠąĮąĖą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 5.

[DDS ą▓ ą║ą░č湥čüčéą▓ąĄ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čéą░ą║č鹊ą▓ ADC]

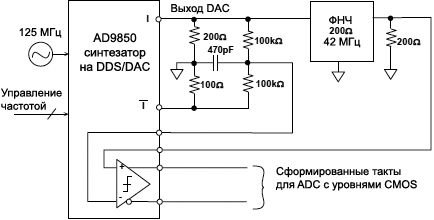

DDS-čüąĖčüč鹥ą╝čŗ, čéą░ą║ąĖąĄ ą║ą░ą║ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ AD9850, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ąĘą░ą╝ąĄčćą░č鹥ą╗čīąĮčŗą╣ čüą┐ąŠčüąŠą▒ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ ADC, ąŠčüąŠą▒ąĄąĮąĮąŠ ą║ąŠą│ą┤ą░ čćą░čüč鹊čéą░ ą▓čŗą▒ąŠčĆąŠą║ ADC ą┤ąŠą╗ąČąĮą░ čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ąĖ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░čéčīčüčÅ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ (čüą╝. čĆąĖčü. 6). ąóąŠą║ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ DAC IOUT ą┐ąŠą┤ą░ąĄčé čüąĖą│ąĮą░ą╗ ąĮą░ ążąØą¦ 200 ą×ą╝ čü čćą░čüč鹊č鹊ą╣ čüčĆąĄąĘą░ 42 ą£ąōčå, čā ą║ąŠč鹊čĆąŠą│ąŠ ąĖ ą▓čģąŠą┤, ąĖ ą▓čŗčģąŠą┤ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮ, čüąŠąĘą┤ą░ą▓ą░čÅ čŹą║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮčāčÄ ąĮą░ą│čĆčāąĘą║čā 100 ą×ą╝. ążąĖą╗čīčéčĆ čāą┤ą░ą╗čÅąĄčé ą┐ą░čĆą░ąĘąĖčéąĮčŗąĄ čćą░čüč鹊čéąĮčŗąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ čüą▓čŗčłąĄ 42 ą£ąōčå. ążąĖą╗čīčéčĆąŠą▓ą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ ą┐ąŠą┤ą░ąĄčéčüčÅ ąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ AD9850. ąÜąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗą╣ ą▓čŗčģąŠą┤ DAC čéą░ą║ąČąĄ ąĮą░ą│čĆčāąČąĄąĮ ąĮą░ 100 ą×ą╝. ąÆčŗčģąŠą┤ąĮąŠą╣ ą┤ąĄą╗ąĖč鹥ą╗čī ąĖąĘ čĆąĄąĘąĖčüč鹊čĆąŠą▓ 100 ą║ą×ą╝, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą╝ąĄąČą┤čā ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗą╝ąĖ ą▓čŗčģąŠą┤ą░ą╝ąĖ DAC, ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ą╗čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░.

ąĀąĖčü. 6. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čüąĖčüč鹥ą╝čŗ DDS ą▓ ą║ą░č湥čüčéą▓ąĄ ą┤čĆą░ą╣ą▓ąĄčĆą░ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ADC.

ąØą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą┐ąĄčĆąĄą┐ą░ą┤čŗ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ąĖ čüą┐ą░ą┤ą░ ąĖą╝ąĄčÄčé ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī 2 ąĮčü, ą│ąĄąĮąĄčĆąĖčĆčāčÅ TTL/CMOS čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╣ ą┐čĆčÅą╝ąŠčāą│ąŠą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗. ąöąČąĖčéč鹥čĆ RMS ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ čüąŠčüčéą░ą▓ą╗čÅąĄčé ąĮąĄ ą▒ąŠą╗ąĄąĄ 20 ą┐čü. ąØą░ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗąĄ ą▓čŗčģąŠą┤čŗ čüąĖą│ąĮą░ą╗ą░, ąĄčüą╗ąĖ čŹč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ.

ąĪčģąĄą╝ą░, ą┐ąŠą║ą░ąĘą░ąĮąĮą░čÅ ąĮą░ čĆąĖčü. 6, ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠą▒čēąĖą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ ą┤ąČąĖčéč鹥čĆ RMS ąĮą░ čāčĆąŠą▓ąĮąĄ 50 ą┐čü ą┤ą╗čÅ čéą░ą║č鹊ą▓ 40 MSPS ADC, ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ čāčģčāą┤čłąĄąĮąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ SNR ą┤ąŠą╗ąČąĮąŠ čāčćąĖčéčŗą▓ą░čéčīčüčÅ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ čü čłąĖčĆąŠą║ąĖą╝ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąĖą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąŠą╝.

[ąÉą╝ą┐ą╗ąĖčéčāą┤ąĮą░čÅ ą╝ąŠą┤čāą╗čÅčåąĖčÅ ą▓ čüąĖčüč鹥ą╝ąĄ DDS]

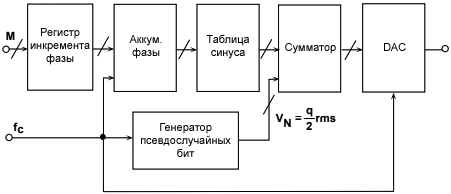

ąÉą╝ą┐ą╗ąĖčéčāą┤ąĮą░čÅ ą╝ąŠą┤čāą╗čÅčåąĖčÅ ą▓ DDS ą╝ąŠąČąĄčé ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ą┐čāč鹥ą╝ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ čåąĖčäčĆąŠą▓ąŠą│ąŠ čāą╝ąĮąŠąČąĖč鹥ą╗čÅ ą╝ąĄąČą┤čā čéą░ą▒ą╗ąĖčåąĄą╣ čüąĖąĮčāčüą░ ąĖ ą▓čģąŠą┤ąŠą╝ DAC, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 7.

ąĀąĖčü. 7. ąÉą╝ą┐ą╗ąĖčéčāą┤ąĮą░čÅ ą╝ąŠą┤čāą╗čÅčåąĖčÅ ą▓ DDS-čüąĖčüč鹥ą╝ąĄ.

ąöčĆčāą│ąŠą╣ ą╝ąĄč鹊ą┤ - ą┐ąŠą┤ą░ą▓ą░čéčī ą╝ąŠą┤čāą╗ąĖčĆčāčÄčēąĖą╣ čüąĖą│ąĮą░ą╗ ąĮą░ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ DAC. ąÆ čüą╗čāčćą░ąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ AD9850 ą┐ąŠą╗ąŠčüą░ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ čāčüąĖą╗ąĖč鹥ą╗čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čüąŠčüčéą░ą▓ą╗čÅąĄčé ą┐čĆąĖą▒ą╗ąĖąĘąĖč鹥ą╗čīąĮąŠ 1 ą£ąōčå. ąŁč鹊čé čüą┐ąŠčüąŠą▒ ą┐ąŠą┤čģąŠą┤ąĖčé ą┤ą╗čÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĮąĄą▒ąŠą╗čīčłąĖčģ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ, ą┐ąŠą║ą░ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ąĮąĄ ą┐čĆąĄą▓čŗčüąĖčé ą┐ą░čĆą░ą╝ąĄčéčĆ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ +1V.

[ąöąĖąĮą░ą╝ąĖč湥čüą║ąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ DDS, čüą▓ąŠą▒ąŠą┤ąĮčŗą╣ ąŠčé ąĖčüą║ą░ąČąĄąĮąĖą╣ (SFDR)]

ąÆąŠ ą╝ąĮąŠą│ąĖčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ DDS ą│ą╗ą░ą▓ąĮčŗą╝ čéčĆąĄą▒ąŠą▓ą░ąĮąĖąĄą╝ čÅą▓ą╗čÅąĄčéčüčÅ čćąĖčüč鹊čéą░ čüą┐ąĄą║čéčĆą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ DAC (Spurious-Free Dynamic Range, SFDR). ąÜ čüąŠąČą░ą╗ąĄąĮąĖčÄ ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ, ą┐čĆąĄą┤čüą║ą░ąĘą░ąĮąĖąĄ ąĖ ą░ąĮą░ą╗ąĖąĘ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą▓ čŹč鹊ą╝ ą║ąŠąĮč鹥ą║čüč鹥 čüą╗ąŠąČąĄąĮ ąĖąĘ-ąĘą░ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▓ą╗ąĖčÅčÄčēąĖčģ ą┤čĆčāą│ ąĮą░ ą┤čĆčāą│ą░ čäą░ą║č鹊čĆąŠą▓.

ąÆ čüąĖčüč鹥ą╝ąĄ DDS ą┤ą░ąČąĄ ąĖą┤ąĄą░ą╗čīąĮčŗą╣ N-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ DAC ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą│ą░čĆą╝ąŠąĮąĖą║ąĖ. ąÉą╝ą┐ą╗ąĖčéčāą┤ą░ čŹčéąĖčģ ą│ą░čĆą╝ąŠąĮąĖą║ čüąĖą╗čīąĮąŠ ąĘą░ą▓ąĖčüąĖčé ąŠčé ąŠčéąĮąŠčłąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ ą║ čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓. ą¤čĆąĖčćąĖąĮą░ ą▓ č鹊ą╝, čćč鹊 čüą┐ąĄą║čéčĆą░ą╗čīąĮą░čÅ ą┐ą╗ąŠčéąĮąŠčüčéčī čłčāą╝ą░ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ DAC ą╝ąĄąĮčÅąĄčéčüčÅ ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ čŹč鹊ą│ąŠ čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ, ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ č鹥ąŠčĆąĄčéąĖč湥čüą║ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ RMS čłčāą╝ą░ ąŠčüčéą░ąĄčéčüčÅ čĆą░ą▓ąĮčŗą╝ q/ŌłÜ12 (ąĘą┤ąĄčüčī q ą▓ąĄčü ą╝ą╗ą░ą┤čłąĄą│ąŠ čĆą░ąĘčĆčÅą┤ą░). ą¤čĆąĄą┤ą┐ąŠą╗ąŠąČąĄąĮąĖąĄ ąŠ č鹊ą╝, čćč鹊 ą▓ čüąĖčüč鹥ą╝ąĄ DDS čłčāą╝ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ čÅą▓ą╗čÅąĄčéčüčÅ ą▒ąĄą╗čŗą╝ čłčāą╝ąŠą╝, ąĖ čćč鹊 čāčĆąŠą▓ąĄąĮčī čłčāą╝ą░ čĆą░ą▓ąĮąŠą╝ąĄčĆąĮąŠ čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮ ą┐ąŠ čüą┐ąĄą║čéčĆčā ą▓ ą┐ąŠą╗ąŠčüąĄ čćą░čüč鹊čé ąØą░ą╣ą║ą▓ąĖčüčéą░, ąĮąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ, ąŠą┤ąĮą░ą║ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮą░čÅ ą║ąŠčĆčĆąĄą╗čÅčåąĖčÅ čü ą▒ąĄą╗čŗą╝ čłčāą╝ąŠą╝ ą▓čüąĄ ąĄčēąĄ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ DAC čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ č鹊čćąĮąŠ ą║ą░ą║ čćąĖčüą╗ąŠ, ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗čÅčēąĄąĄ čćą░čüč鹊čéčā čéą░ą║č鹊ą▓, č鹊 čłčāą╝ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ ą▒čāą┤ąĄčé čüą║ąŠąĮčåąĄąĮčéčĆąĖčĆąŠą▓ą░ąĮ ąĮą░ ąĘąĮą░č湥ąĮąĖčÅčģ ą│ą░čĆą╝ąŠąĮąĖą║ ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ, čé. ąĄ. čłčāą╝ ąĖ ąĄą│ąŠ čüą┐ąĄą║čéčĆ čüąĖą╗čīąĮąŠ ąĘą░ą▓ąĖčüąĖčé ąŠčé čüąĖą│ąĮą░ą╗ą░. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ ąĮąĄčüą║ąŠą╗čīą║ąŠ čüą╝ąĄčēąĄąĮą░ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮąŠą│ąŠ ą┤ąĄą╗ąĖč鹥ą╗čÅ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, č鹊 čłčāą╝ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąŠą╗ąĄąĄ čüą╗čāčćą░ą╣ąĮčŗą╝, čāą╗čāčćčłą░čÅ čŹčäč乥ą║čéąĖą▓ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ SFDR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ čüąĖčüč鹥ą╝ą░čģ, ąŠčüąĮąŠą▓ą░ąĮąĮčŗčģ ą░ąĮ ADC, ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĄąĮąĖąĄ ąŠ ą▒ąĄą╗ąŠą╝ čłčāą╝ąĄ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ ą▒ąŠą╗ąĄąĄ ą┐čĆąĖą▒ą╗ąĖąČąĄąĮąŠ ą║ ąĖčüčéąĖąĮąĮąŠčüčéąĖ, ą┐ąŠčüą║ąŠą╗čīą║čā ADC ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé ąĮąĄą║ąŠč鹊čĆąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čłčāą╝ą░ ą║ čüąĖą│ąĮą░ą╗čā, ą║ąŠč鹊čĆčŗą╣ ąĖą╝ąĄąĄčé č鹥ąĮą┤ąĄąĮčåąĖčÄ ą║ ą┤ąĖąĘąĄčĆąĖąĮą│čā (čüą│ą╗ą░ąČąĖą▓ą░ąĮąĖčÄ), ąĖą╗ąĖ čĆą░ąĮą┤ąŠą╝ąĖąĘą░čåąĖąĖ ąŠčłąĖą▒ą║ąĖ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ.

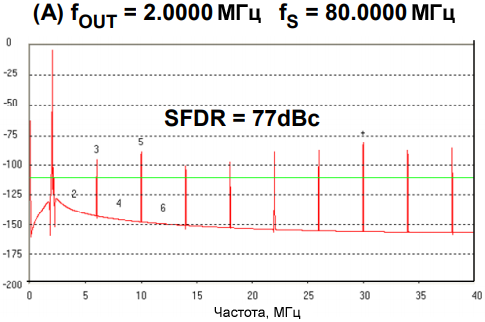

ąŁč鹊 ąĖą╗ą╗čÄčüčéčĆąĖčĆčāąĄčéčüčÅ ąĮą░ čĆąĖčü. 8, ąĘą┤ąĄčüčī ą▓čŗčćąĖčüą╗ąĄąĮąŠ 4096-č鹊č湥čćąĮąŠąĄ (4k) FFT ą┐ąŠ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╝ čåąĖčäčĆąŠą▓čŗą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ą┤ą░ąĮąĮčŗą╝ ąŠčé ąĖą┤ąĄą░ą╗čīąĮąŠą│ąŠ 12-čĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ DAC. ąÆ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ čüą╗ąĄą▓ą░ (A) čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą╝ąĄąČą┤čā čćą░čüč鹊č鹊ą╣ čéą░ą║č鹊ą▓ ąĖ ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊č鹊ą╣ č鹊čćąĮąŠ 40, ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćą░ąĄčéčüčÅ SFDR ąŠą║ąŠą╗ąŠ 77 dBc. ąØą░ ą┐čĆą░ą▓ąŠą╣ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ ąĮąĄą╝ąĮąŠą│ąŠ čüą╝ąĄčēąĄąĮą░, ąĖ čŹčäč乥ą║čéąĖą▓ąĮčŗą╣ SFDR čāą╗čāčćčłąĖą╗čüčÅ ą┤ąŠ 94 dBc. ąÆ čŹč鹊ą╝ ąĖą┤ąĄą░ą╗čīąĮąŠą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą╝čŗ ąĮą░ą▒ą╗čÄą┤ą░ąĄą╝ čāą╗čāčćčłąĄąĮąĖąĄ ą┐ąŠą║ą░ąĘą░č鹥ą╗čÅ ąĖčüą║ą░ąČąĄąĮąĖą╣ ąĮą░ čåąĄą╗čŗčģ 17 dB ą┐čĆąĖ ąĮąĄą▒ąŠą╗čīčłąŠą╝ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ čćą░čüč鹊čé.

ąĀąĖčü. 8. ąöąĄą╝ąŠąĮčüčéčĆą░čåąĖčÅ ą▓ą╗ąĖčÅąĮąĖčÅ čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ fc/fo ąĮą░ SFDR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ąĖąĘą╝ąĄčĆąĄąĮąĖą╣ ą┤ą╗čÅ čĆąĖčü. 8 čüą╗ąĄą┤čāčÄčēąĖąĄ. ąĀą░ąĘą╝ąĄčĆ FFT: 8192 č鹊čćą║ąĖ, č鹥ąŠčĆąĄčéąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĖčüą║ą░ąČąĄąĮąĖą╣ (SNR) 12-ą▒ąĖčéąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ DAC 74 dB, čāčüąĖą╗ąĄąĮąĖąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ FFT 36 dB, čāčĆąŠą▓ąĄąĮčī čłčāą╝ą░ FFT 110 dBFS.

ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čüą░ą╝ąŠąĄ ą╗čāčćčłąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ SFDR ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮąŠ čéčēą░č鹥ą╗čīąĮčŗą╝ ą▓čŗą▒ąŠčĆąŠą╝ čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ ąĖ ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ (ąĖčģ čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ). ą×ą┤ąĮą░ą║ąŠ ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ čŹč鹊 ą▒čŗą▓ą░ąĄčé ąĮąĄą▓ąŠąĘą╝ąŠąČąĮąŠ. ąÆ čüąĖčüč鹥ą╝ą░čģ ąĮą░ ąŠčüąĮąŠą▓ąĄ ADC ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄ ąĮąĄą▒ąŠą╗čīčłąŠą│ąŠ čüą╗čāčćą░ą╣ąĮąŠą│ąŠ čłčāą╝ą░ ąĮą░ ą▓čģąŠą┤ čĆą░ąĮą┤ąŠą╝ąĖąĘąĖčĆčāąĄčé ąŠčłąĖą▒ą║ąĖ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ ąĖ čüąĮąĖąČą░ąĄčé čŹč鹊čé čŹčäč乥ą║čé. ąóąŠą│ąŠ ąČąĄ čüą░ą╝ąŠą│ąŠ ą╝ąŠąČąĮąŠ ą┤ąŠčüčéąĖčćčī ą▓ čüąĖčüč鹥ą╝ąĄ DDS, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 9 (čüą╝. [3, 4, 5]). ąÜ čüą╗ąŠą▓čā ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ čüąĖąĮčāčüą░ DDS ąĮą░ ą▓čģąŠą┤ąĄ DAC ą┤ąŠą▒ą░ą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ą┐čüąĄą▓ą┤ąŠčüą╗čāčćą░ą╣ąĮąŠą│ąŠ čłčāą╝ą░ čü ą░ą╝ą┐ą╗ąĖčéčāą┤ąŠą╣ 1/2 ą╝ą╗ą░ą┤čłąĄą│ąŠ čĆą░ąĘčĆčÅą┤ą░. ąŁč鹊 čĆąĄą░ą╗ąĖąĘčāąĄčé čĆą░ąĮą┤ąŠą╝ąĖąĘą░čåąĖčÄ čåąĄąĮąŠą╣ ąĮąĄą▒ąŠą╗čīčłąŠą│ąŠ čāą▓ąĄą╗ąĖč湥ąĮąĖčÅ ąŠą▒čēąĄą│ąŠ čāčĆąŠą▓ąĮčÅ čłčāą╝ą░. ą×ą┤ąĮą░ą║ąŠ ą▓ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ DDS ą╝ąŠąČąĮąŠ ą┤ąŠčüčéą░č鹊čćąĮąŠ ą│ąĖą▒ą║ąŠ ą╝ąĄąĮčÅčéčī čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ čćą░čüč鹊čé fc/fo, čćč鹊ą▒čŗ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąŠą╗čāčćąĖčéčī čāą╗čāčćčłąĄąĮąĖąĄ SFDR, ą▒ą╗ą░ą│ąŠą┤ą░čĆčÅ č湥ą╝čā čéą░ą║ąŠą╣ ą┐čüąĄą▓ą┤ąŠčüą╗čāčćą░ą╣ąĮčŗą╣ ą┤ąĖąĘąĄčĆąĖąĮą│ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ.

ąĀąĖčü. 9. ąśąĮąČąĄą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čåąĖčäčĆąŠą▓ąŠą│ąŠ ą┤ąĖąĘąĄčĆąĖąĮą│ą░ ą▓ čüąĖčüč鹥ą╝ąĄ DDS, čćč鹊ą▒čŗ čüą┤ąĄą╗ą░čéčī ąŠčłąĖą▒ą║čā ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ čüą╗čāčćą░ą╣ąĮąŠą╣ ąĖ ą┐ąŠą▓čŗčüąĖčéčī SFDR.

ąÜąŠą╝ą┐ą░ąĮąĖčÅ Analog Device ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąŠąĮą╗ą░ą╣ąĮ-čāčéąĖą╗ąĖčéčā ADIsimDDS [6]. ąŁč鹊 ąĖąĮč鹥čĆą░ą║čéąĖą▓ąĮčŗą╣ ąĖąĮčüčéčĆčāą╝ąĄąĮčé, ą┐ąŠą╝ąŠą│ą░čÄčēąĖą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ą▓čŗą▒čĆą░čéčī ą╝ąĖą║čĆąŠčüčģąĄą╝čā DDS ąĖ ąŠčåąĄąĮąĖčéčī ąĄčæ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗą╝ čāčüą╗ąŠą▓ąĖčÅą╝ 菹║čüą┐ą╗čāą░čéą░čåąĖąĖ. ąśąĮčüčéčĆčāą╝ąĄąĮčé ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą╝ą░č鹥ą╝ą░čéąĖč湥čüą║ąĖąĄ č乊čĆą╝čāą╗čŗ ą┤ą╗čÅ ą░ą┐ą┐čĆąŠą║čüąĖą╝ą░čåąĖąĖ ąŠą▒čēąĖčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, ąĖ ąŠąĮ ąĮąĄ ą┐čĆąŠčüčćąĖčéčŗą▓ą░ąĄčé ą▓čüąĄ ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ąŠčłąĖą▒ąŠą║. ąó. ąĄ. čŹč鹊čé ąĖąĮčüčéčĆčāą╝ąĄąĮčé ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ą║ą░ą║ ą┐ąŠą┤čüą║ą░ąĘą║ą░ ą▓ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĄ, ąĖ ąŠąĮ ąĮąĄ ąĘą░ą╝ąĄąĮčÅąĄčé č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖąĄ čäąĖąĘąĖč湥čüą║ąŠą│ąŠ ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮąĖčÅ.

[ąĪčüčŗą╗ą║ąĖ]

1. MT-085 Fundamentals of Direct Digital Synthesis (DDS) site:analog.com.

2. DSP: čüą╗ąŠą▓ą░čĆąĖą║.

3. Richard J. Kerr and Lindsay A. Weaver, "Pseudorandom Dither for Frequency Synthesis Noise," U.S. Patent 4,901,265, filed December 14, 1987, issued February 13, 1990.

4. Henry T. Nicholas, III and Henry Samueli, "An Analysis of the Output Spectrum of Direct Digital Frequency Synthesizers in the Presence of Phase-Accumulator Truncation," IEEE 41st Annual Frequency Control Symposium Digest of Papers, 1987, pp. 495-502, IEEE Publication No. CH2427-3/87/0000-495.

5. Henry T. Nicholas, III and Henry Samueli, "The optimization of direct digital frequency synthesizer performance in the presence of finite word length effects" IEEE 42nd Annual Frequency Control Symposium, 1988.

6. ADIsimDDS (Direct Digital Synthesis) site:analog.com. |