|

ąŚą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ ąŠą┐ąĖčüą░ąĮąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI ąĖąĘ ą┤ą░čéą░čłąĖč鹊ą▓ [1, 2].

[29. Serial Peripheral Interface (SPI)]

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čüą░ (serial peripheral interface, SPI) čÅą▓ą╗čÅąĄčéčüčÅ čüčéą░ąĮą┤ą░čĆčéąĮčŗą╝ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮčŗą╝ ą║ą░ąĮą░ą╗ąŠą╝ čüą▓čÅąĘąĖ, ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčēąĖą╝ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą╝ąĮąŠą│ąĖą╝ąĖ SPI-čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ. ąæą░ąĘąŠą▓ąŠąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI čÅą▓ą╗čÅąĄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĮčŗą╝, 4-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ čü 2 ą▓čŗą▓ąŠą┤ą░ą╝ąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ (ą▓čģąŠą┤ ąĖ ą▓čŗčģąŠą┤), 1 ą▓čŗą▓ąŠą┤ ą▓čŗą▒ąŠčĆą░ čāčüčéčĆąŠą╣čüčéą▓ą░, ąĖ ąĄčēąĄ 1 ą▓čŗą▓ąŠą┤ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗčģ čéą░ą║č鹊ą▓ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ. 2 ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ąŠčüčāčēąĄčüčéą▓ąĖčéčī ą┐ąŠą╗ąĮąŠ-ą┤čāą┐ą╗ąĄą║čüąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąŠ ą┐ąĄčĆąĄą┤ą░č湥 ą┐čĆąĖ ąŠą▒ą╝ąĄąĮąĄ čü ą┤čĆčāą│ąĖą╝ąĖ SPI-čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ. ąöą▓ą░ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ (ąŠą┐čåąĖąŠąĮą░ą╗čīąĮčŗčģ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮčŗ ą┤ą╗čÅ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ SPI ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ čĆą░ą▒ąŠčéčŗ quad SPI. ąóą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ čéą░ą║ąĖąĄ čĆą░čüčłąĖčĆąĄąĮąĮčŗąĄ čĆąĄąČąĖą╝čŗ, ą║ą░ą║ flow control (čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ ą┤ą░ąĮąĮčŗčģ), fast mode (ą▒čŗčüčéčĆčŗą╣ čĆąĄąČąĖą╝), čĆąĄąČąĖą╝ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (dual-I/O mode, DIOM). ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą┐čĆčÅą╝ąŠą╣ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čüą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ čü ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╝ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖąĄą╝ čü ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝. ąĪ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗą╝ąĖ ąŠą┐čåąĖčÅą╝ąĖ ą┐ąŠčĆčéčŗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą┐čĆąŠąĘčĆą░čćąĮąŠąĄ ą░ą┐ą┐ą░čĆą░čéąĮąŠąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ čü ą┤čĆčāą│ąĖą╝ąĖ SPI-čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ą▓ čĆąĄąČąĖą╝ąĄ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (master mode), ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (slave mode), ąĖ ą▓ čĆąĄąČąĖą╝ąĄ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą╝ą░čüč鹥čĆą░ą╝ąĖ (multimaster). ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI ą▓ą║ą╗čÄčćą░ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čāčÄ čüą║ąŠčĆąŠčüčéčī ąŠą▒ą╝ąĄąĮą░, ą┐ąŠą┤čüčéčĆąŠą╣ą║čā čäą░ąĘčŗ ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ čéą░ą║č鹊ą▓. ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ ąŠą║čĆčāąČąĄąĮąĖąĖ multimaster, čĆą░ą▒ąŠčéą░čÅ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┤čĆčāą│ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, ą┤ąĄą╣čüčéą▓čāčÅ ą╗ąĖą▒ąŠ ą║ą░ą║ čāčüčéčĆąŠą╣čüčéą▓ąŠ master, ą╗ąĖą▒ąŠ ą║ą░ą║ čāčüčéčĆąŠą╣čüčéą▓ąŠ slave. ąÆ ąŠą║čĆčāąČąĄąĮąĖąĖ multimaster, ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓čŗčģąŠą┤čŗ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą║ąŠąĮčäą╗ąĖą║č鹊ą▓ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▓čŗčģąŠą┤ąŠą▓ ąĮą░ čłąĖąĮąĄ, čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗčģ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ. ążčāąĮą║čåąĖčÅ flow control čĆą░ąĘčĆąĄčłą░ąĄčé ą╝ąĄą┤ą╗ąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ čĆą░ą▒ąŠčéą░čéčī čü ą▒čŗčüčéčĆčŗą╝ąĖ master-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÅ ą▓čŗą▓ąŠą┤ SPI ready, ą║ąŠč鹊čĆčŗą╣ ą│ąĖą▒ą║ąŠ čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ.

[ąÆąŠąĘą╝ąŠąČąĮąŠčüčéąĖ SPI]

ą£ąŠą┤čāą╗čī SPI ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čäčāąĮą║čåąĖąĖ:

ŌĆó ą¤ąŠą╗ąĮąŠą┤čāą┐ą╗ąĄą║čüąĮčŗą╣, čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü.

ŌĆó ąĀą░ąĘą╝ąĄčĆ čüą╗ąŠą▓ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī 8, 16 ąĖ 32 ą▒ąĖčéą░.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ čüą║ąŠčĆąŠčüčéčī ą▒ąĖčé (baud rate), čäą░ąĘą░ čéą░ą║č鹊ą▓ ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą▓ąĮčāčéčĆąĖ čäčĆąĄą╣ą╝ą░.

ŌĆó ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ (Flow control).

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ čĆąĄąČąĖą╝ąŠą▓ Fast ąĖ DIOM.

ŌĆó ąĀąĄąČąĖą╝čŗ Quad (čüč湥čéą▓ąĄčĆąĄąĮąĮčŗą╣) ąĖ memory-mapped (ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ąĮą░ ą┐ą░ą╝čÅčéčī), ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗąĄ č鹊ą╗čīą║ąŠ SPI2.

ŌĆó ąØąĄąĘą░ą▓ąĖčüąĖą╝čŗąĄ ą║ą░ąĮą░ą╗čŗ DMA ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ŌĆó ą¤ą░ą║ąĄčéąĮčŗą╣ čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ (Burst transfer mode) ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ąŠą▓ ąĘą░ą┐ąĖčüąĖ ąĮąĄ DMA.

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ SPI]

ąĀąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░. ąÆ čüčāčēąĮąŠčüčéąĖ SPI čŹč鹊 čüą┤ą▓ąĖą│ąŠą▓čŗą╣ čĆąĄą│ąĖčüčéčĆ, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĄčé ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ą▓ ą┤čĆčāą│ąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄčé ąĖąĘ ąĮąĖčģ ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ. ąÆąŠ ą▓čĆąĄą╝čÅ ąŠą▒ą╝ąĄąĮą░ SPI ą┤ą░ąĮąĮčŗąĄ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ) ąĖ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ). ąĪąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčé čüą┤ą▓ąĖą│ ąĖ ąŠčåąĖčäčĆąŠą▓ą║čā čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą┤ą▓čāčģ ą╗ąĖąĮčÅčģ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ (ą▓čŗčģąŠą┤ ąĖ ą▓čģąŠą┤).

ążčāąĮą║čåąĖąŠąĮą░ą╗ ą│ą╗ą░ą▓ąĮąŠą│ąŠ (master) ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ (slave) čāčüčéčĆąŠą╣čüčéą▓ą░. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąŠą┤ąĮą░ čüąĖčüč鹥ą╝ą░ SPI ą┤ąĄą╣čüčéą▓čāąĄčé ą║ą░ą║ master ą║ą░ąĮą░ą╗ą░ čüą▓čÅąĘąĖ, ą║ąŠč鹊čĆčŗą╣ čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠč鹊ą║ąŠą╝ ą┤ą░ąĮąĮčŗčģ. ąöčĆčāą│ą░čÅ čüąĖčüč鹥ą╝ą░ ą┤ąĄą╣čüčéą▓čāąĄčé ą║ą░ą║ slave, ą║ąŠč鹊čĆą░čÅ ą▓ą┤ą▓ąĖą│ą░ąĄčé ąĖ ą▓čŗą┤ą▓ąĖą│ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą┐ąŠ čéą░ą║čéą░ą╝ čüąĖčüč鹥ą╝čŗ master. ąĀą░ąĘąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠą│čāčé ą▒čĆą░čéčī ąĮą░ čüąĄą▒čÅ čĆąŠą╗čī master, ąŠą┤ąĮą░ą║ąŠ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ąĮą░ čłąĖąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ master, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓ą┤ą▓ąĖą│ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (čĆąĄąČąĖą╝ čłąĖčĆąŠą║ąŠą▓ąĄčēą░ąĮąĖčÅ, broadcast). ąóą░ą║ąČąĄ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ slave ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠąČąĄčé čāą┐čĆą░ą▓ą╗čÅčéčī ą▓čŗčģąŠą┤ąŠą╝, ą┐ąŠą┤ą░ą▓ą░čÅ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ą░ master. ąŁč鹊 ą┐čĆą░ą▓ąĖą╗ąŠ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐čĆąĖą╝ąĄąĮąĄąĮąŠ ą▓ čĆąĄąČąĖą╝ąĄ broadcast. ąØąĄčüą║ąŠą╗čīą║ąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮčŗ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ, ąĮąŠ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠą╝čā slave čĆą░ąĘčĆąĄčłąĄąĮąŠ ąŠčéą┐čĆą░ą▓ą╗čÅčéčī ą┤ą░ąĮąĮčŗąĄ ąŠą▒čĆą░čéąĮąŠ čāčüčéčĆąŠą╣čüčéą▓čā master.

ąĀą░čüčłąĖčĆąĄąĮąĮčŗąĄ čĆą░ą▒ąŠčćąĖąĄ čĆąĄąČąĖą╝čŗ. SPI ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ čéą░ą║ąĖąĄ čĆąĄąČąĖą╝čŗ, ą║ą░ą║ fast mode, DIOM ąĖ Quad-SPI. ąóą░ą║ąČąĄ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ čüąŠ čüč鹊čĆąŠąĮčŗ slave-čāčüčéčĆąŠą╣čüčéą▓ą░. ąÆ čĆąĄąČąĖą╝ąĄ fast ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą░ąĮą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ ąĮą░ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ čéą░ą║čéą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ą╝ąĄčüč鹊 čüčéą░ąĮą┤ą░čĆčéąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą┐čĆąĖąĄą╝ą░ (ą▓ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄą┐ą░ą┤ čéą░ą║čéą░ ą┐čĆąĖąĄą╝ą░ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĄąĮ ą┐ąĄčĆąĄą┐ą░ą┤čā ą┐ąĄčĆąĄą┤ą░čćąĖ), čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠčüčāčēąĄčüčéą▓ąĖčéčī ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ full-cycle path (ąĮą░čüą║ąŠą╗čīą║ąŠ čÅ ą┐ąŠąĮčÅą╗, ą╝ąŠąČąĮąŠ ą┐čĆąĖąĮąĖą╝ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą┐ąŠ ąŠą▒ąŠąĖą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ čéą░ą║č鹊ą▓). ąÆ čĆąĄąČąĖą╝ąĄ DIOM, ąŠą▒ą░ čüąĖą│ąĮą░ą╗ą░ MOSI ąĖ MISO ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤čŗ ąĖą╗ąĖ ą║ą░ą║ ą▓čŗčģąŠą┤čŗ, ąĖ 2 ą▒ąĖčéą░ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĖą╗ąĖ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ ą┐čĆąĖąĄą╝ą░ ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÆ čĆąĄąČąĖą╝ąĄ Quad-SPI ą▓čüąĄ ą▓čŗą▓ąŠą┤čŗ SPI_D3:0 ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤ ąĖą╗ąĖ ą║ą░ą║ ą▓čŗčģąŠą┤, ąĖ 4 ą▒ąĖčéą░ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĖą╗ąĖ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ ą┐čĆąĖąĄą╝ą░ ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąæąŠą╗ąĄąĄ ą╝ąĄą┤ą╗ąĄąĮąĮąŠąĄ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ą╝ąŠąČąĄčé čāą┐čĆą░ą▓ą╗čÅčéčī ą┐ąŠč鹊ą║ąŠą╝, ą┐čĆąĖąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÅ čüą╗ąĖčłą║ąŠą╝ ą▒čŗčüčéčĆąŠąĄ master-čāčüčéčĆąŠą╣čüčéą▓ąŠ, čü ą┐ąŠą╝ąŠčēčīčÄ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ (SPI0_RDY).

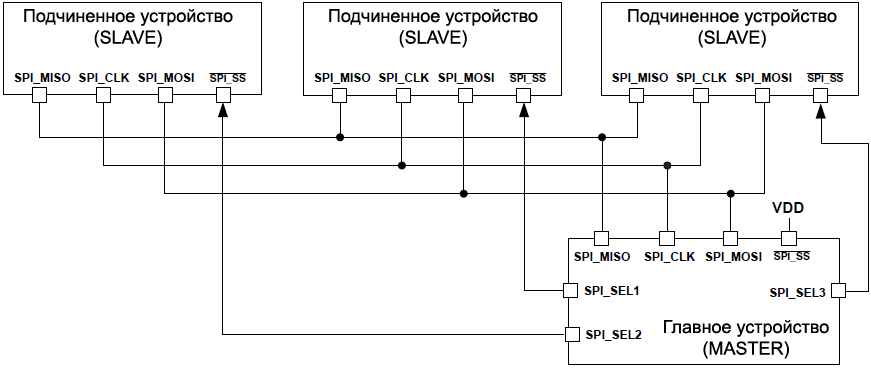

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ ąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čāčüčéčĆąŠą╣čüčéą▓ master. SPI ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ čĆą░ą▒ąŠč湥ą╝ ąŠą║čĆčāąČąĄąĮąĖąĖ, ą│ą┤ąĄ ąĖą╝ąĄąĄčéčüčÅ ą║ą░ą║ 1 master, čéą░ą║ ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ master (čāčüą╗ąŠą▓ąĖčÅ čĆą░ą▒ąŠčéčŗ multi-master). ąĪąĖą│ąĮą░ą╗čŗ SPI_MOSI, SPI_MISO ąĖ SPI_CLK čüąŠąĄą┤ąĖąĮčÅčÄčéčüčÅ čā ą▓čüąĄčģ čāčüčéčĆąŠą╣čüčéą▓ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą▓ ą╗čÄą▒ąŠą╣ ąĖąĘ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣. ą¤ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝ SPI ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąĖą╗ąĖ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĮą░čüčéčĆąŠąĄą║ čĆąĄą│ąĖčüčéčĆąŠą▓ SPI_RXCTL ąĖ SPI_TXCTL. ąÆ čĆąĄąČąĖą╝ąĄ čłąĖčĆąŠą║ąŠą▓ąĄčēą░ąĮąĖčÅ (broadcast), ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ slaves ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ą┐čĆąĖąĄą╝, ąĮąŠ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ąŠą╗ąČąĮąŠ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄą┤ą░č湥, čāą┐čĆą░ą▓ą╗čÅčÅ čüą▓ąŠąĄą╣ ą╗ąĖąĮąĖąĄą╣ SPI_MISO.

[ąĪą┐ąĖčüąŠą║ SPI-čĆąĄą│ąĖčüčéčĆąŠą▓ ADSP-BF70x]

ąóą░ą▒ą╗ąĖčåą░ 29-1. ąĀąĄą│ąĖčüčéčĆčŗ SPI ADSP-BF70x.

| ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| SPI_CLK |

Clock Rate Register (čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čćą░čüč鹊ą╣ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ čéą░ą║č鹊ą▓) |

| SPI_CTL |

Control Register (čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ) |

| SPI_DLY |

Delay Register (čĆąĄą│ąĖčüčéčĆ ąĘą░ą┤ąĄčƹȹ║ąĖ) |

| SPI_ILAT |

Masked Interrupt Condition Register (čĆąĄą│ąĖčüčéčĆ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ čüąŠą▒čŗčéąĖą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ) |

| SPI_ILAT_CLR |

Masked Interrupt Clear Register (čĆąĄą│ąĖčüčéčĆ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčćąĖčüčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣) |

| SPI_IMSK |

Interrupt Mask Register (čĆąĄą│ąĖčüčéčĆ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣) |

| SPI_IMSK_CLR |

Interrupt Mask Clear Register (čĆąĄą│ąĖčüčéčĆ ą╝ą░čüą║ąĖ ąŠčćąĖčüčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣) |

| SPI_IMSK_SET |

Interrupt Mask Set Register (čĆąĄą│ąĖčüčéčĆ ą╝ą░čüą║ąĖ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣) |

| SPI_MMRDH |

Memory Mapped Read Header (ąĘą░ą│ąŠą╗ąŠą▓ąŠą║ ą┐čĆąĖą▓čÅąĘą░ąĮąĮąŠą│ąŠ ą║ ą┐ą░ą╝čÅčéąĖ čćč鹥ąĮąĖčÅ) |

| SPI_MMTOP |

SPI Memory Top Address (ą▓ąĄčĆčģąĮąĖą╣ ą░ą┤čĆąĄčü ą┐ą░ą╝čÅčéąĖ SPI) |

| SPI_RFIFO |

Receive FIFO Data Register (čĆąĄą│ąĖčüčéčĆ FIFO ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ą░) |

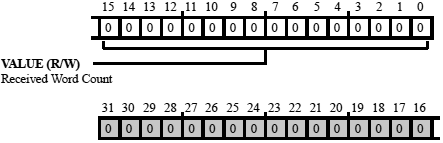

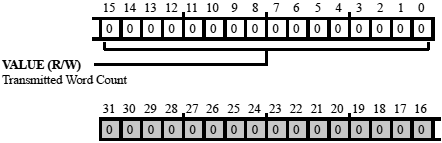

| SPI_RWC |

Received Word Count Register (čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą┐čĆąĖąĮčÅčéčŗčģ čüą╗ąŠą▓) |

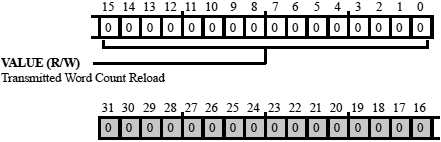

| SPI_RWCR |

Received Word Count Reload Register (čĆąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ čüč湥čéčćąĖą║ą░ ą┐čĆąĖąĮčÅčéčŗčģ čüą╗ąŠą▓) |

| SPI_RXCTL |

Receive Control Register (čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ąŠą╝) |

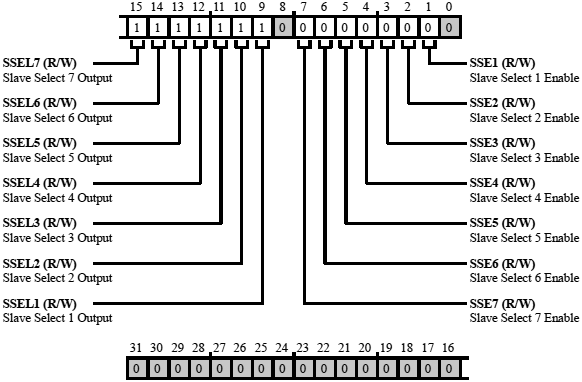

| SPI_SLVSEL |

Slave Select Register (čĆąĄą│ąĖčüčéčĆ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░) |

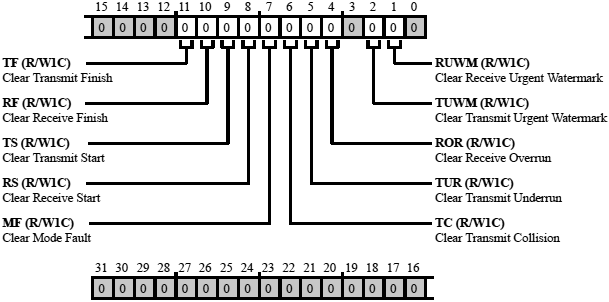

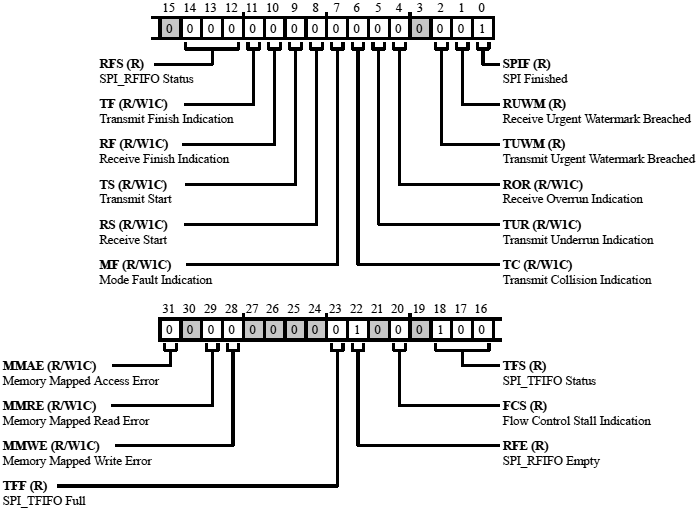

| SPI_STAT |

Status Register (čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ) |

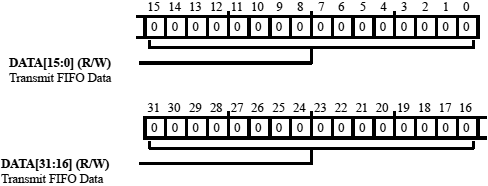

| SPI_TFIFO |

Transmit FIFO Data Register (čĆąĄą│ąĖčüčéčĆ FIFO ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čćąĖ) |

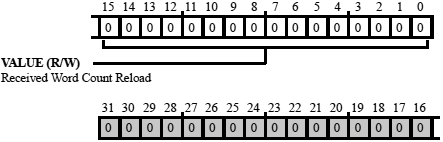

| SPI_TWC |

Transmitted Word Count Register (čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ čüą╗ąŠą▓) |

| SPI_TWCR |

Transmitted Word Count Reload Register (čĆąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ čüč湥čéčćąĖą║ą░ ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗčģ čüą╗ąŠą▓) |

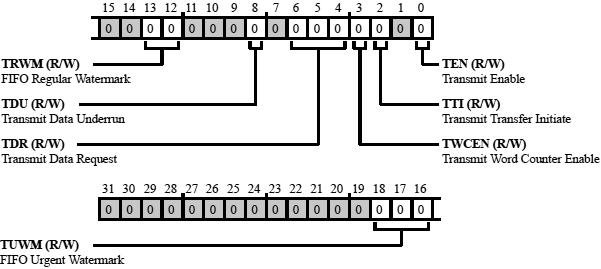

| SPI_TXCTL |

Transmit Control Register (čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░č湥ą╣) |

ąóą░ą▒ą╗ąĖčåą░ 29-2. ąĪą┐ąĖčüąŠą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ SPI ADSP-BF70x.

| Interrupt ID |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ą¦čāą▓čüčéą▓. |

ąÜą░ąĮą░ą╗ DMA |

| 36 |

SPI0_ERR |

SPI0 Error (ąŠčłąĖą▒ą║ą░ SPI0) |

čāčĆąŠą▓ąĄąĮčī |

|

| 37 |

SPI0_STAT |

SPI0 Status (čüąŠčüč鹊čÅąĮąĖąĄ SPI0) |

čāčĆąŠą▓ąĄąĮčī |

|

| 38 |

SPI0_TXDMA |

SPI0 TX DMA Channel (ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA SPI0) |

čāčĆąŠą▓ąĄąĮčī |

4 |

| 39 |

SPI0_RXDMA |

SPI0 RX DMA Channel (ą║ą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ DMA SPI0) |

čāčĆąŠą▓ąĄąĮčī |

5 |

| 40 |

SPI1_ERR |

SPI1 Error (ąŠčłąĖą▒ą║ą░ SPI1) |

čāčĆąŠą▓ąĄąĮčī |

|

| 41 |

SPI1_STAT |

SPI1 Status (čüąŠčüč鹊čÅąĮąĖąĄ SPI1) |

čāčĆąŠą▓ąĄąĮčī |

|

| 42 |

SPI1_TXDMA |

SPI1 TX DMA Channel (ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA SPI1) |

čāčĆąŠą▓ąĄąĮčī |

6 |

| 43 |

SPI1_RXDMA |

SPI1 RX DMA Channel (ą║ą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ DMA SPI1) |

čāčĆąŠą▓ąĄąĮčī |

7 |

| 44 |

SPI2_ERR |

SPI2 Error (ąŠčłąĖą▒ą║ą░ SPI2) |

čāčĆąŠą▓ąĄąĮčī |

|

| 45 |

SPI2_STAT |

SPI2 Status (čüąŠčüč鹊čÅąĮąĖąĄ SPI2) |

čāčĆąŠą▓ąĄąĮčī |

|

| 46 |

SPI2_TXDMA |

SPI1 TX DMA Channel (ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA SPI1) |

čāčĆąŠą▓ąĄąĮčī |

8 |

| 47 |

SPI2_RXDMA |

SPI1 RX DMA Channel (ą║ą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ DMA SPI1) |

čāčĆąŠą▓ąĄąĮčī |

9 |

ąóą░ą▒ą╗ąĖčåą░ 29-3. ąĪą┐ąĖčüąŠą║ čéčĆąĖą│ą│ąĄčĆąŠą▓ ADSP-BF70x SPI master-čāčüčéčĆąŠą╣čüčéą▓.

| Trigger ID |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ą¦čāą▓čüčéą▓. |

| 18 |

SPI0_TXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐ąĄčĆąĄą┤ą░čćąĖ SPI0 |

ą┐ąĄčĆąĄą┐ą░ą┤ |

| 19 |

SPI0_RXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐čĆąĖąĄą╝ą░ SPI0 |

ą┐ąĄčĆąĄą┐ą░ą┤ |

| 20 |

SPI1_TXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐ąĄčĆąĄą┤ą░čćąĖ SPI1 |

ą┐ąĄčĆąĄą┐ą░ą┤ |

| 21 |

SPI1_RXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐čĆąĖąĄą╝ą░ SPI1 |

ą┐ąĄčĆąĄą┐ą░ą┤ |

| 22 |

SPI2_TXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐ąĄčĆąĄą┤ą░čćąĖ SPI2 |

ą┐ąĄčĆąĄą┐ą░ą┤ |

| 23 |

SPI2_RXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐čĆąĖąĄą╝ą░ SPI2 |

ą┐ąĄčĆąĄą┐ą░ą┤ |

ąóą░ą▒ą╗ąĖčåą░ 29-4. ąĪą┐ąĖčüąŠą║ čéčĆąĖą│ą│ąĄčĆąŠą▓ ADSP-BF70x SPI slave-čāčüčéčĆąŠą╣čüčéą▓.

| Trigger ID |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ą¦čāą▓čüčéą▓. |

| 28 |

SPI0_TXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐ąĄčĆąĄą┤ą░čćąĖ SPI0 |

ąĖą╝ą┐čāą╗čīčü |

| 29 |

SPI0_RXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐čĆąĖąĄą╝ą░ SPI0 |

ąĖą╝ą┐čāą╗čīčü |

| 30 |

SPI1_TXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐ąĄčĆąĄą┤ą░čćąĖ SPI1 |

ąĖą╝ą┐čāą╗čīčü |

| 31 |

SPI1_RXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐čĆąĖąĄą╝ą░ SPI1 |

ąĖą╝ą┐čāą╗čīčü |

| 32 |

SPI2_TXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐ąĄčĆąĄą┤ą░čćąĖ SPI2 |

ąĖą╝ą┐čāą╗čīčü |

| 33 |

SPI2_RXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐čĆąĖąĄą╝ą░ SPI2 |

ąĖą╝ą┐čāą╗čīčü |

ąóą░ą▒ą╗ąĖčåą░ 29-5. ąĪą┐ąĖčüąŠą║ ą║ą░ąĮą░ą╗ąŠą▓ DMA ąĖąĮč鹥čĆč乥ą╣čüą░ SPI ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF70x.

| DMA ID |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| DMA4 |

SPI0_TXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐ąĄčĆąĄą┤ą░čćąĖ SPI0 |

| DMA5 |

SPI0_RXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐čĆąĖąĄą╝ą░ SPI0 |

| DMA6 |

SPI1_TXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐ąĄčĆąĄą┤ą░čćąĖ SPI1 |

| DMA7 |

SPI1_RXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐čĆąĖąĄą╝ą░ SPI1 |

| DMA8 |

SPI2_TXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐ąĄčĆąĄą┤ą░čćąĖ SPI2 |

| DMA9 |

SPI2_RXDMA |

ąÜą░ąĮą░ą╗ DMA ą┐čĆąĖąĄą╝ą░ SPI2 |

[ąæą╗ąŠą║-čüčģąĄą╝ą░ SPI]

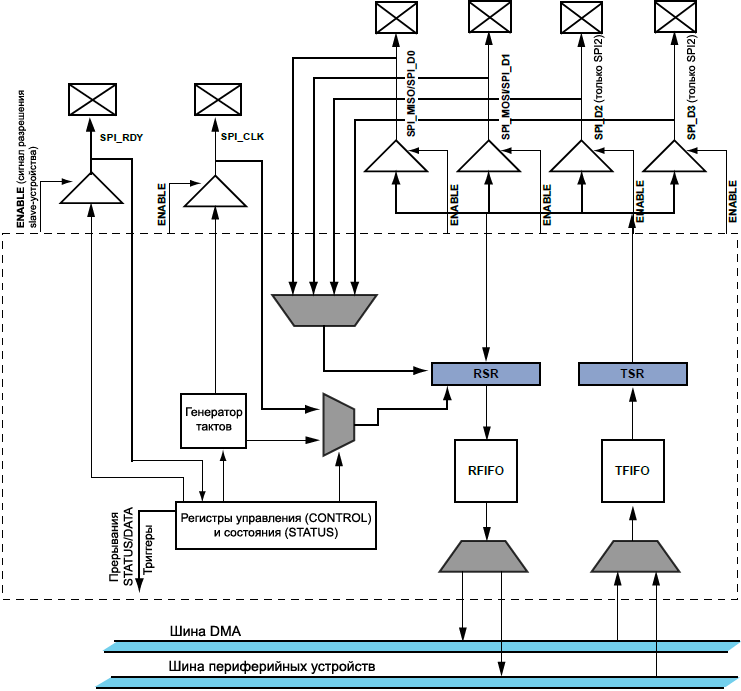

ąæą╗ąŠą║-čüčģąĄą╝ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ SPI ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠčéą┤ąĄą╗čīąĮčŗąĄ ą▒ą╗ąŠą║ąĖ ą╝ąŠą┤čāą╗čÅ SPI. ą£ąŠą┤čāą╗čī ą▓ą║ą╗čÄčćą░ąĄčé ą▓ čüąĄą▒čÅ 3 ąŠčüąĮąŠą▓ąĮčŗąĄ čćą░čüčéąĖ:

ŌĆó ą»ą┤čĆąŠ SPI, čüąŠą┤ąĄčƹȹ░čēąĄąĄ čĆąĄą│ąĖčüčéčĆčŗ ą┤ą░ąĮąĮčŗčģ FIFO ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ąĮąĖą╝ąĖ čĆąĄą│ąĖčüčéčĆčŗ čüą┤ą▓ąĖą│ą░.

ŌĆó ąæą╗ąŠą║ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, čüąŠą┤ąĄčƹȹ░čēąĖąĄ čüąĖąĮčģčĆąŠąĮąĖąĘą░č鹊čĆ ąĖ ą╗ąŠą│ąĖą║čā ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ąŠą╝ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ ą║ąŠąĮą▓ąĄą╣ąĄčĆčŗ.

ŌĆó ąæą╗ąŠą║ čĆąĄą│ąĖčüčéčĆąŠą▓.

ąĀąĖčü. 29-1. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ SPI, Quad Mode (čüč湥čéą▓ąĄčĆąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝).

ą¤čĆąŠč鹊ą║ąŠą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą£ąŠą┤čāą╗čī SPI čĆąĄą░ą╗ąĖąĘčāąĄčé 2 ą║ą░ąĮą░ą╗ą░, ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ (ą┐ąŠčćčéąĖ) - ą║ą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ ąĖ ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÆčŗą┤ąĄą╗ąĄąĮąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ SPI_RXCTL ąĖ SPI_TXCTL čĆą░ąĘą┤ąĄą╗čīąĮąŠ čāą┐čĆą░ą▓ą╗čÅčÄčé čŹčéąĖą╝ąĖ ą║ą░ąĮą░ą╗ą░ą╝ąĖ. ąŚą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čĆąĄąČąĖą╝ąŠą▓ dual ąĖ quad, SPI ą╝ąŠąČąĄčé čĆą░ąĘčĆąĄčłąĖčéčī ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čŹčéąĖčģ ąŠą▒ąŠąĖčģ ą║ą░ąĮą░ą╗ąŠą▓ ą┤ą╗čÅ ą┤čāą┐ą╗ąĄą║čüąĮąŠą│ąŠ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ.

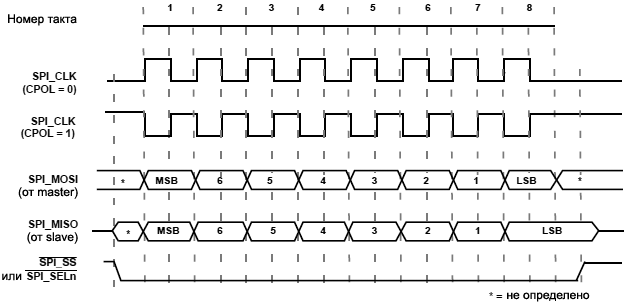

ą¤čĆąŠč鹊ą║ąŠą╗ SPI ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 4 čĆą░ąĘąĮčŗčģ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ čĆą░ą▒ąŠčéčŗ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čéą░ą║č鹊ą▓, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖąĄ ąĖčģ čäą░ąĘčā ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ ą┤ą░ąĮąĮčŗą╝. ąŁčéąĖ 4 ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ ą▓čŗą▒ąĖčĆą░čÄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ SPI_CTL.CPOL and SPI_CTL.CPHA (ą┐ąŠą┤ąŠą▒ąĮčŗąĄ ąŠą┐čåąĖąĖ ąĖą╝ąĄčÄčéčüčÅ ą┐čĆą░ą║čéąĖč湥čüą║ąĖ ą╗čÄą▒ąŠą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ, ąĖą╝ąĄčÄčēąĖą╣ ąĮą░ ą▒ąŠčĆčéčā ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü SPI).

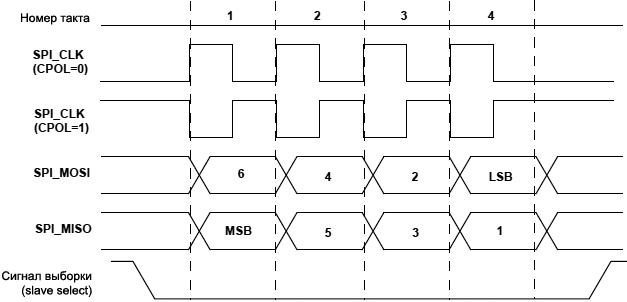

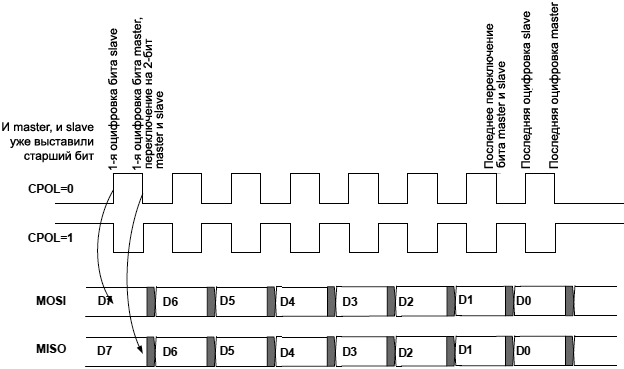

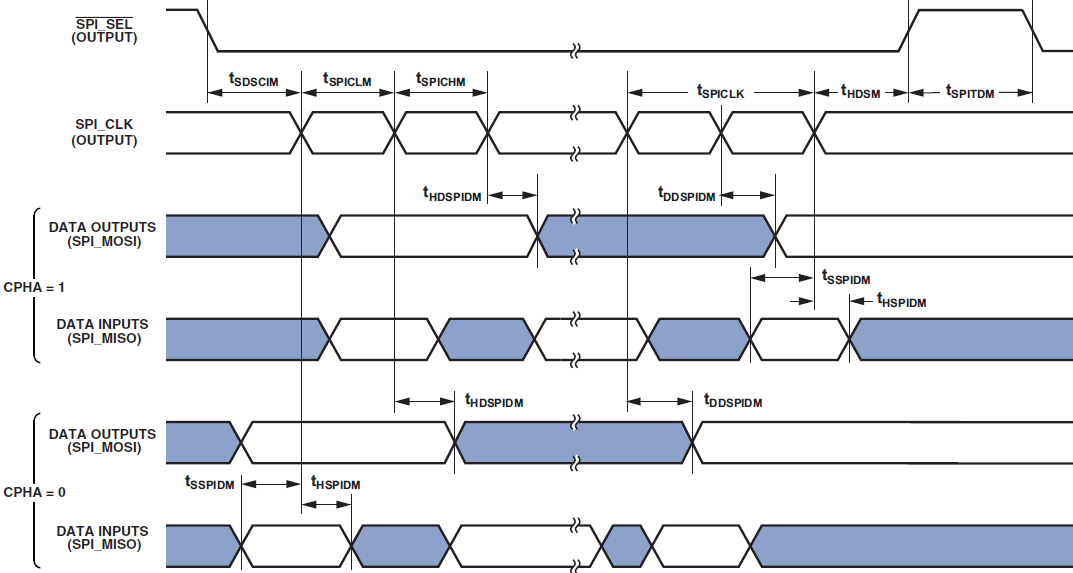

ąĀąĖčüčāąĮą║ąĖ 29-2, 29-3 čü ąŠą┐ąĖčüą░ąĮąĖąĄą╝ ą┐čĆąŠč鹊ą║ąŠą╗ą░ ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ą░ąĮąĮčŗčģ ą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆčāčÄčé 2 ą▒ą░ąĘąŠą▓čŗčģ č乊čĆą╝ą░čéą░, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čŗąĄ ą▒ąĖč鹊ą╝ CPHA (ą▒ąĖčé čäą░ąĘčŗ čéą░ą║č鹊ą▓). ą¤ąŠą║ą░ąĘą░ąĮčŗ 2 ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą╗čÅ SPI_CLK, ąŠą┤ąĮą░ ą┤ą╗čÅ SPI_CTL.CPOL=0, ąĖ ą┤čĆčāą│ą░čÅ ą┤ą╗čÅ SPI_CTL.CPOL=1. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ master ąĖą╗ąĖ slave, ą┐ąŠčüą║ąŠą╗čīą║čā čüąĖą│ąĮą░ą╗čŗ SPI_CLK, SPI_MISO ąĖ SPI_MOSI ąĮą░ą┐čĆčÅą╝čāčÄ čüąŠąĄą┤ąĖąĮčÅčÄčé master ąĖ slave. ąĪąĖą│ąĮą░ą╗ SPI_MISO čÅą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝ ą┤ą╗čÅ slave (ą┐ąŠ ąĮąĄą╝čā slave ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ), ąĖ čüąĖą│ąĮą░ą╗ SPI_MOSI čÅą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝ master (ą┐ąŠ ąĮąĄą╝čā master ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ). Master ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗ SPI_CLK. ąĪąĖą│ąĮą░ą╗ ~SPI_SS čÅą▓ą╗čÅąĄčéčüčÅ ą▓čŗą▒ąŠčĆą║ąŠą╣ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ą║ąŠč鹊čĆčŗą╣ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą│ą╗ą░ą▓ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ (ą┤ą╗čÅ slave čŹč鹊 ą▓čģąŠą┤, ą┤ą╗čÅ master čŹč鹊 ą▓čŗčģąŠą┤). ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé ą┐ąĄčĆąĄą┤ą░čćčā 8-ą▒ąĖčéąĮąŠą│ąŠ čäčĆąĄą╣ą╝ą░ (SPI_CTL.SIZE=0), ą║ąŠą│ą┤ą░ čüčéą░čĆčłąĖą╣ ą▒ąĖčé (MSB) ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝ (SPI_CTL.LSBF=0). ąĀą░ąĘčĆąĄčłąĄąĮą░ ą╗čÄą▒ą░čÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅ ą▒ąĖč鹊ą▓ SPI_CTL.SIZE ąĖ SPI_CTL.LSBF. ąØą░ą┐čĆąĖą╝ąĄčĆ, 16-ą▒ąĖčéąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą╝ą╗ą░ą┤čłąĖą╝ ą▒ąĖč鹊ą╝ (LSB) ą▓ą┐ąĄčĆąĄą┤ čÅą▓ą╗čÅąĄčéčüčÅ ą┤čĆčāą│ąŠą╣ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣.

ą¤ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ ąĖ čäą░ąĘą░ čéą░ą║č鹊ą▓ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĖą┤ąĄąĮčéąĖčćąĮąŠ ąĮą░čüčéčĆąŠąĄąĮčŗ ąĮą░ čüč鹊čĆąŠąĮąĄ master-čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ąĮą░ čüč鹊čĆąŠąĮąĄ slave-čāčüčéčĆąŠą╣čüčéą▓ą░, ą▓ąŠą▓ą╗ąĄč湥ąĮąĮčŗčģ ą▓ ą╗ąĖąĮą║ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ. ążąŠčĆą╝ą░čé ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠčé master ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ, čćč鹊ą▒čŗ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčéčī čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ čĆą░ąĘąĮčŗčģ slave-čāčüčéčĆąŠą╣čüčéą▓.

ą£ąŠą┤čāą╗čī SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčé SPI_CTL.ASSEL čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą║ą░ą║ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čüąĖą│ąĮą░ą╗ SPI_SEL[n] - ą░ą┐ą┐ą░čĆą░čéąĮąŠ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ. ąÜąŠą│ą┤ą░ SPI_CTL.ASSEL=1, čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ slave ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī, ą║ą░ą║ čŹč鹊 ąĘą░ą┤ą░ąĮąŠ ą┐ąŠą╗ąĄą╝ SPI_CTL.SELST ą╝ąĄąČą┤čā ą║ą░ąČą┤ąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥ą╣. ąĀąĄą░ą╗čīąĮąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ SPI_SEL[n] čéą░ą║ąČąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗčģ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_DLY. ąøąŠą│ąĖą║ą░ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ SPI ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāą┐čĆą░ą▓ą╗čÅąĄčé čŹčéąĖą╝ čäčāąĮą║čåąĖąŠąĮą░ą╗ąŠą╝. ąÜąŠą│ą┤ą░ SPI_CTL.ASSEL=0, SPI_SEL[n] ą╝ąŠąČąĄčé ą╗ąĖą▒ąŠ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ ą╝ąĄąČą┤čā čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ, ą╗ąĖą▒ąŠ ą╝ąŠą│čāčé ą▒čŗčéčī ąĮąĄ ą░ą║čéąĖą▓ąĮčŗą╝ąĖ. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ čāą┐čĆą░ą▓ą╗čÅčéčī čŹč鹊ą╣ ą░ą║čéąĖą▓ąĮąŠčüčéčīčÄ ą┐čāč鹥ą╝ ą╝ą░ąĮąĖą┐čāą╗čÅčåąĖąĖ čüąŠą┤ąĄčƹȹĖą╝čŗą╝ čĆąĄą│ąĖčüčéčĆą░ SPI_SLVSEL.

ą¤ą░čĆą░ čĆąĖčüčāąĮą║ąŠą▓ čü ąŠą┐ąĖčüą░ąĮąĖąĄą╝ ą┐čĆąŠč鹊ą║ąŠą╗ą░ SPI ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüą╗čāčćą░ą╣, ą║ąŠą│ą┤ą░ SPI_CTL.ASSEL = 1, ąĖ čüąĖą│ąĮą░ą╗ SPI_SEL[n] ąĮąĄą░ą║čéąĖą▓ąĄąĮ ą╝ąĄąČą┤čā čäčĆąĄą╣ą╝ą░ą╝ąĖ. ąĢčüą╗ąĖ ASSEL = 0, č鹊 ą╗ąĖąĮąĖčÅthe SPI_SEL[n] ą╝ąŠąČąĄčé ąŠčüčéą░ą▓ą░čéčīčüčÅ ą░ą║čéąĖą▓ąĮąŠą╣ ą╝ąĄąČą┤čā čäčĆąĄą╣ą╝ą░ą╝ąĖ; ąŠą┤ąĮą░ą║ąŠ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąĄčĆą▓čŗą╣ ą▒ąĖčé, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ SPI_CLK.

ąĀąĖčü. 29-2. ą¤čĆąŠč鹊ą║ąŠą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI ą┤ą╗čÅ CPHA=0.

ąĀąĖčü. 29-3. ą¤čĆąŠč鹊ą║ąŠą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI ą┤ą╗čÅ CPHA=1.

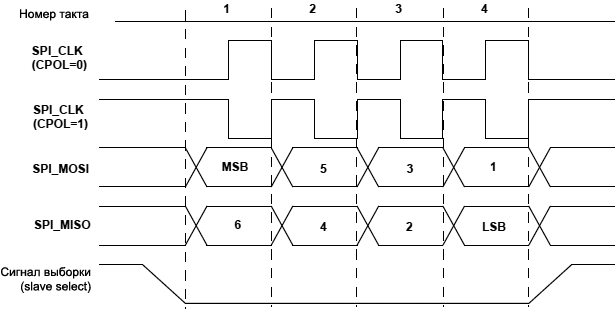

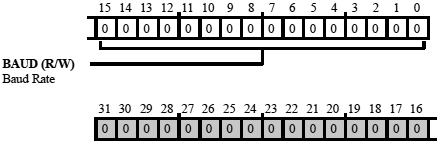

ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ. ąĪąĖą│ąĮą░ą╗ SPI_CLK čŹč鹊 čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗąĄ čéą░ą║čéčŗ, ą║ąŠč鹊čĆčŗąĄ ą░ą║čéąĖą▓ąĮčŗ č鹊ą╗čīą║ąŠ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čć ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ. ąÆ ąŠą▒čŗčćąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (normal mode) ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą░ą║čéąĖą▓ąĮčŗčģ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ čĆą░ą▓ąĮąŠ ą║ąŠą╗ąĖč湥čüčéą▓čā ą▒ąĖčé, ą║ąŠč鹊čĆčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ąĖą╗ąĖ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ. ąÆ čĆąĄąČąĖą╝ąĄ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (dual-I/O mode) ą┐ąŠą╗ąŠą▓ąĖąĮą░ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čéą░ą║č鹊ą▓ č乊čĆą╝ąĖčĆčāąĄčéčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╗ąĖ ą┐čĆąĖąĄą╝ą░, ąĖ ą▓ čüč湥čéą▓ąĄčĆąĄąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (quad-SPI mode) ąŠą┤ąĮą░ č湥čéą▓ąĄčĆčéą░čÅ. ą¦ą░čüč鹊čéą░ čéą░ą║č鹊ą▓ ą╝ąŠąČąĄčé čéą░ą║ąŠą╣ ąČąĄ, ą║ą░ą║ ąĖ čćą░čüč鹊čéą░ SCLK0, ąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ąŠą▒ą░ ą┤ąĄą╗ąĖč鹥ą╗čÅ SCLK0 - č湥čéąĮčŗą╣ ąĖ ąĮąĄč湥čéąĮčŗą╣.

ąöą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ master SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ SPI_CLK ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ ą┤ą╗čÅ slave-čāčüčéčĆąŠą╣čüčéą▓.

ąÜąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ master, čüąĖą│ąĮą░ą╗ SPI_CLK čÅą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝. ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ, ą║ąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ SPI ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ, SPI_CLK čÅą▓ą╗čÅąĄčéčüčÅ ą▓čģąŠą┤ąĮčŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝. Slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖą│ąĮąŠčĆąĖčĆčāčÄčé čéą░ą║čé SPI, ą║ąŠą│ą┤ą░ ąĖčģ ą▓čģąŠą┤ ą▓čŗą▒ąŠčĆą║ąĖ (slave select) ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ. SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüąĖą│ąĮą░ą╗ SPI_CLK ą┤ą╗čÅ ą▓čŗą┤ą▓ąĖą│ą░ąĮąĖčÅ ąĮą░čĆčāąČčā ąĖ ą▓ą┤ą▓ąĖą│ą░ąĮąĖčÅ ą▓ąĮčāčéčĆčī ą┤ą░ąĮąĮčŗčģ, ą┐ąŠčÅą▓ą╗čÅčÄčēąĖčģčüčÅ ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ SPI_MISO ąĖ SPI_MOSI. ąöą░ąĮąĮčŗąĄ ą▓čüąĄą│ą┤ą░ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ą┐ąŠ ąŠą┤ąĮąŠą╝čā ąĖąĘ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ čéą░ą║č鹊ą▓ (čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤), ąĖ ą░ąĮą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ ąĮą░ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ čéą░ą║č鹊ą▓ (čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą▓čŗą▒ąŠčĆą║ąĖ, sampling edge). ą¤ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ ąĖ čäą░ąĘą░ čéą░ą║č鹊ą▓ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą┤ą░ąĮąĮčŗčģ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ SPI_CTL, ąĖ čŹč鹊 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé č乊čĆą╝ą░čé ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čäčĆąĄą╣ą╝ą░.

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĘą░ą┤ąĄčƹȹ║ą░ą╝ąĖ ą╝ąĄąČą┤čā čäčĆąĄą╣ą╝ą░ą╝ąĖ. ąöąĖą░ą│čĆą░ą╝ą╝ą░ SPI ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ąĘą░ą┤ąĄčƹȹ║ą░ą╝ąĖ Lead ąĖ Lag (ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗąĄ ąŠčé SPI_CTL.CPHA čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčé SPI_DLY.LEADX and SPI_DLY.LAGX). ąØą░ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ SPI čü čŹčéąĖą╝ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ąĖ. SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčéčŗ SPI_DLY.LAGX ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą╝ ą╝ąĄąČą┤čā ą░ą║čéąĖą▓ą░čåąĖąĄą╣ čüąĖą│ąĮą░ą╗ą░ slave select (~SPI_SS) ąĖ ą┐ąĄčĆą▓čŗą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą╝ SPI_CLK. ąóą░ą║ąČąĄ SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčé SPI_DLY.LEADX ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą╝ ą╝ąĄąČą┤čā ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą╝ SPI_CLK ąĖ ą┤ąĄą░ą║čéąĖą▓ą░čåąĖąĄą╣ čüąĖą│ąĮą░ą╗ą░ ~SPI_SS.

ąśąĮč鹥čĆą▓ą░ą╗čŗ lead ąĖ lag ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░čüčłąĖčĆąĄąĮčŗ ąĮą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī 1 SPI_CLK ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ čü čāč湥č鹊ą╝ ąŠą│čĆą░ąĮąĖč湥ąĮąĖą╣ ą┐ąŠ ą▓čĆąĄą╝ąĄąĮąĖ čüąŠ čüč鹊čĆąŠąĮčŗ slave-čāčüčéčĆąŠą╣čüčéą▓ą░.

ąĀąĖčü. 29-4. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ Lead ąĖ Lag (ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗąĄ ąŠčé čāčüčéą░ąĮąŠą▓ą║ąĖ SPI_CTL.CPHA).

ąĀąĖčü. 29-5 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą┐čĆąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĖ SPI_DLY.STOP (ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĮą░čüčéčĆąŠą╣ą║ąĖ SPI_CTL.CPHA). ą£ąŠą┤čāą╗čī SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé čŹč鹊čé ąĖąĮč鹥čĆą▓ą░ą╗ ą┤ą╗čÅ ą▓čüčéą░ą▓ą║ąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ąĘą░ą┤ąĄčƹȹĄą║ ą┐ąĄčĆąĖąŠą┤ą░ SPI_CLK ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ. ąĪąĖą│ąĮą░ą╗ ~SPI_SS ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ąĮą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī, čāą║ą░ąĘą░ąĮąĮčāčÄ ą▒ąĖč鹊ą▓čŗą╝ ą┐ąŠą╗ąĄą╝ SPI_DLY.STOP, ą┐čĆąĖ čŹč鹊ą╝ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą▒ąĖčé SPI_CTL.SELST ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą┤ą╗čÅ ą┤ąĄą░ą║čéąĖą▓ą░čåąĖąĖ ą▓čŗą▒ąŠčĆą║ąĖ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ.

ąĢčüą╗ąĖ SPI_DLY.STOP bit=0, č鹊 master čĆą░ą▒ąŠčéą░ąĄčé ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠ (continuous mode). ąŁč鹊čé čĆąĄąČąĖą╝ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠą╝čā čüčéą░čĆčéčā ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓č鹊čĆąŠą│ąŠ čüą╗ąŠą▓ą░ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ čüą╗ąŠą▓ąŠ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłą░čÄčēąĄą│ąŠ ą▒ąĖčéą░ ą┐ąĄčĆą▓ąŠą│ąŠ čüą╗ąŠą▓ą░. ąÆąŠ ą▓čĆąĄą╝čÅ čĆą░ą▒ąŠčéčŗ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ čüąĖą│ąĮą░ą╗ slave select ą░ą║čéąĖą▓ąĄąĮ ą┐ąŠčüč鹊čÅąĮąĮąŠ.

ąĀąĖčü. 29-5. ąśąĮč鹥čĆą▓ą░ą╗čŗ SPI čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ SPI_DLY.STOP (ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗąĄ ąŠčé čāčüčéą░ąĮąŠą▓ą║ąĖ SPI_CTL.CPHA).

ąÜąŠą│ą┤ą░ SPI_DLY.STOP bit=0, ąĖ ąĮą░čćą░ą╗čīąĮčŗąĄ čāčüą╗ąŠą▓ąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ, ąĖąĮč鹥čĆč乥ą╣čü ą┐ąĄčĆąĄčģąŠą┤ąĖčé ąĮą░ ą┐ą░čāąĘčā ą┐ąĄčĆąĄą┤ čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐ąĄčĆąĄą┤ą░č湥ą╣. ąÆąŠ ą▓čĆąĄą╝čÅ čŹč鹊ą╣ ą┐ą░čāąĘčŗ SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčé SPI_CTL.SELST, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗą▓ąŠą┤ą░ slave select. SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčéčŗ SPI_DLY.LEADX ąĖ SPI_DLY.LAGX, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĖąĮč鹥čĆą▓ą░ą╗ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ąĖ SPI_CLK ąĖ čüąĖą│ąĮą░ą╗ąŠą╝ ą▓čŗą▒ąŠčĆą║ąĖ slave select.

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ (Flow Control). ąÆ čĆąĄąČąĖą╝ąĄ master čāčüčéčĆąŠą╣čüčéą▓ąŠ slave ą┤ąŠą╗ąČąĮąŠ čāą┐čĆą░ą▓ą╗čÅčéčī ą▓čŗą▓ąŠą┤ąŠą╝ SPI_RDY. ąŁč鹊čé ą▓čŗą▓ąŠą┤ čā master čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤. Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ąĄą░ą║čéąĖą▓ąĖčĆąŠą▓ą░čéčī čüąĖą│ąĮą░ą╗ SPI_RDY, čćč鹊ą▒čŗ ąŠčüčéą░ąĮąŠą▓ąĖčéčī master-čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ą╗čÅ ąĖąĮąĖčåąĖą░čåąĖąĖ ą╗čÄą▒ąŠą╣ ąĮąŠą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąĢčüą╗ąĖ SPI_RDY ą┤ąĄą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ ą┐ąŠčüąĄčĆąĄą┤ąĖąĮąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ, č鹊 č鹥ą║čāčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčéčüčÅ, ąĖ čüą╗ąĄą┤čāčÄčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮąĄ ąĮą░čćąĖąĮą░ąĄčéčüčÅ, ą┐ąŠą║ą░ slave ąĮąĄ ą░ą║čéąĖą▓ąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗ SPI_RDY. ąÆčüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ slave ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčé SPI_RDY ąĖ ą┐čĆąĖąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé master-čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ SPI master ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ, ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé SPI_STAT.FCS. ąÜąŠą│ą┤ą░ slave ą░ą║čéąĖą▓ąĖčĆčāąĄčé SPI_RDY, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ SPI master ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗čÅąĄčé čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ, ąĖ ą▒ąĖčé SPI_STAT.FCS ąŠčćąĖčēą░ąĄčéčüčÅ.

ąÆ čĆąĄąČąĖą╝ąĄ slave ą▓čŗą▓ąŠą┤ SPI_RDY čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą╗ąĖą▒ąŠ ą┐ąŠ ą║ą░ąĮą░ą╗čā TX, ą╗ąĖą▒ąŠ RX. SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčé SPI_CTL.FCCH ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čŹč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣. ąĢčüą╗ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ TX, č鹊 ą║ą░ą║ č鹊ą╗čīą║ąŠ čüčéą░čéčāčü SPI_TFIFO ą┐čĆąĖą▒ą╗ąĖąČą░ąĄčéčüčÅ ą║ čüąŠą▒čŗčéąĖčÄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ (empty condition), čüąĖą│ąĮą░ą╗ SPI_RDY ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ. ąĢčüą╗ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą┐ąŠ ą║ą░ąĮą░ą╗čā RX, č鹊 ą║ą░ą║ č鹊ą╗čīą║ąŠ čüčéą░čéčāčü SPI_RFIFO ą┐čĆąĖą▒ą╗ąĖąČą░ąĄčéčüčÅ ą║ čüąŠą▒čŗčéąĖčÄ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ (full condition), čüąĖą│ąĮą░ą╗ SPI_RDY ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ. SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčéčŗ SPI_CTL.FCWM ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖąĄą╝ FIFO čü čāčćą░čüčéąĖąĄą╝ čüąĖą│ąĮą░ą╗ą░ ą┤ąĄą░ą║čéąĖą▓ą░čåąĖąĖ SPI_RDY. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ ą▓ čĆąĄąČąĖą╝ąĄ slave ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąŠčüąĮąŠą▓ą░ąĮąŠ ąĮą░ čüąŠčüč鹊čÅąĮąĖąĖ FIFO, ąĖ ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé čüč湥čéčćąĖą║ąŠą▓ čüą╗ąŠą▓. ąĀąĖčüčāąĮąŠą║ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ąŠą╝ master-čāčüčéčĆąŠą╣čüčéą▓ą░ SPI Flow ąĖą╗ą╗čÄčüčéčĆąĖčĆčāąĄčé čŹčéąĖ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ.

ąĀąĖčü. 29-6. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ SPI ą▓ čĆąĄąČąĖą╝ąĄ master.

ąĀą░ą▒ąŠčéą░ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (Slave Select). ąĢčüą╗ąĖ SPI čĆą░ą▒ąŠčéą░ąĄčé ą▓ slave mode čüąĖą│ąĮą░ą╗ ~SPI_SS ą┤ąĄą╣čüčéą▓čāąĄčé ą║ą░ą║ ą▓čģąŠą┤ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (slave select). ąÜąŠą│ą┤ą░ SPI čĆą░ąĘčĆąĄčłąĄąĮ ą║ą░ą║ master, ~SPI_SS ą╝ąŠąČąĄčé ąŠą▒čüą╗čāąČąĖą▓ą░čéčī čäčāąĮą║čåąĖčÄ ą▓čģąŠą┤ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ ą▓ čāčüą╗ąŠą▓ąĖčÅčģ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ multi-master. ąæąĖčé SPI_CTL.PSSE čĆą░ąĘčĆąĄčłą░ąĄčé čŹčéčā čäčāąĮą║čåąĖčÄ. ąÜąŠą│ą┤ą░ SPI_CTL.PSSE=1, ą▓čģąŠą┤ ~SPI_SS čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤ ąŠčłąĖą▒ą║ąĖ čĆąĄąČąĖą╝ą░ master. ąśąĮą░č湥 ~SPI_SS ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ.

ąĪąĖą│ąĮą░ą╗ ~SPI_SS ąĖą╝ąĄąĄčé ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. Master ą░ą║čéąĖą▓ąĖčĆčāąĄčé čŹč鹊čé čüąĖą│ąĮą░ą╗ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī čüąĮčÅčé ąĖą╗ąĖ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ. ąÜąŠą│ą┤ą░ ~SPI_SS ą┤ąĄą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ, SPI_CLK ąĖ ą▓čģąŠą┤čŗ ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ, ą▓čŗčģąŠą┤čŗ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čéčĆąĄčéčīąĄą╝ čüąŠčüč鹊čÅąĮąĖąĖ.

ąæąĖčéčŗ ą▓čŗą▒ąŠčĆą║ąĖ (SPI_SLVSEL.SSE1 .. SPI_SLVSEL.SSEL7) ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓ čāčüą╗ąŠą▓ąĖčÅčģ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ ąĖą╝ąĄąĄčéčüčÅ 8 čāčüčéčĆąŠą╣čüčéą▓ SPI ą▓ čüąĖčüč鹥ą╝ąĄ, ą▓ą║ą╗čÄčćą░čÅ master, č鹊 ą┐čĆąŠčåąĄčüčüąŠčĆ master ą╝ąŠąČąĄčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī čéčĆą░ąĮąĘą░ą║čåąĖąĖ čĆąĄąČąĖą╝ą░ SPI čüąŠ ą▓čüąĄą╝ąĖ čüąĄą╝čīčÄ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ. ąŁčéąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čéčĆąĄą▒čāčÄčé č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ master.

ąöą╗čÅ ą┐čĆąĖą╝ąĄčĆą░ ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĖą╝, čćč鹊 ą┐čĆąŠčåąĄčüčüąŠčĆ SPI čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ master. ąæąĖčéčŗ SPI_SLVSEL.SSE1 .. SPI_SLVSEL.SSEL7 ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą╝ąŠą│čāčé ą▒čŗčéčī čüąŠąĄą┤ąĖąĮąĄąĮčŗ čü ą▓čŗą▓ąŠą┤ą░ą╝ąĖ ą▓čŗą▒ąŠčĆą║ąĖ slave select ą║ą░ąČą┤ąŠą│ąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ą░. ąÆ čŹč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ, ą▒ąĖčéčŗ slave select ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čéčĆąĄą╝čÅ čüą┐ąŠčüąŠą▒ą░ą╝ąĖ. ąÆ ą▓ą░čĆąĖą░ąĮčéą░čģ 1 ąĖ 2, ą┐čĆąŠčåąĄčüčüąŠčĆ čÅą▓ą╗čÅąĄčéčüčÅ master-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝, ąĖ 7 ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ąĖą╗ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ čü SPI-ąĖąĮč鹥čĆč乥ą╣čüą░ą╝ąĖ čÅą▓ą╗čÅčÄčéčüčÅ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ. ą¤čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠąČąĄčé čüą┤ąĄą╗ą░čéčī ąŠą┤ąĮąŠ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ:

1. ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą╗čÅ ą▓čüąĄčģ 7 ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ SPI ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓ čĆąĄąČąĖą╝ąĄ broadcast. ąŚą┤ąĄčüčī ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮčŗ ą▓čüąĄ ą▒ąĖčéčŗ slave select.

2. ą¤čĆąĖąĄą╝ ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ čü ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖąĄą╝ č鹊ą╗čīą║ąŠ čü ąŠą┤ąĮąĖą╝ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ.

3. ąĢčüą╗ąĖ ą▓čüąĄ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ čéą░ą║ąČąĄ čÅą▓ą╗čÅčÄčéčüčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ, č鹊 ąĘą░ą┐čĆą░čłąĖą▓ą░čÄčēąĖą╣ ą╝ąŠąČąĄčé ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą┐čĆąĖąĮąĖą╝ą░čéčī ą┤ą░ąĮąĮčŗąĄ č鹊ą╗čīą║ąŠ ąŠčé ąŠą┤ąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (čŹčéą░ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ SPI_CTL.EMISO ą▓ čłąĄčüčéąĖ ą┤čĆčāą│ąĖčģ slave-ą┐čĆąŠčåąĄčüčüąŠčĆą░čģ). ąŚą░ą┐čĆą░čłąĖą▓ą░čÄčēąĖą╣ ą╝ąŠąČąĄčé čłąĖčĆąŠą║ąŠą▓ąĄčēą░č鹥ą╗čīąĮąŠ čĆą░čüčüčŗą╗ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĮą░ ą▓čüąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. ążčāąĮą║čåąĖčÅ EMISO ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠčüčéčāą┐ąĮą░ ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┤čĆčāą│ąĖčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐čĆąĖą╝ąĄąĮčÅčéčī čäčāąĮą║čåąĖčÄ EMISO čü ą╗čÄą▒čŗą╝ ą┤čĆčāą│ąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ SPI, ą║ąŠč鹊čĆąŠąĄ ąĖą╝ąĄąĄčé čéą░ą║čāčÄ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī.

ąĀąĖčü. 29-7. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ąŠą┤ąĖąĮ master, ąĮąĄčüą║ąŠą╗čīą║ąŠ slave.

ąØą░čćą░ą╗ąŠ ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ą░ąĮąĮčŗčģ SPI ą▒ąĄąĘ DMA. ąĪčéą░čĆčé ąĖ čäąĖąĮąĖčł non-DMA SPI ąĘą░ą▓ąĖčüąĖčé ąŠčé čüą╗ąĄą┤čāčÄčēąĖčģ čāčüčéą░ąĮąŠą▓ąŠą║:

1. ąÜą░ą║ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ - ą║ą░ą║ master ąĖą╗ąĖ ą║ą░ą║ slave.

2. ąĪąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖčéą░ SPI_CTL.ASSEL, ą║ąŠč鹊čĆčŗą╣ ą▓čŗą▒ąĖčĆą░ąĄčé ą╝ąĄąČą┤čā ą░ą┐ą┐ą░čĆą░čéąĮčŗą╝ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ SPI_SLVSEL.

ąÜąŠą│ą┤ą░ SPI_CTL.CPHA=0, čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčī ą▓ ą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčģąŠą┤čŗ slave select. ą×ą┤ąĮą░ą║ąŠ čüąĖą│ąĮą░ą╗ SPI_CLK ąŠčüčéą░ąĄčéčüčÅ ąĮąĄą░ą║čéąĖą▓ąĮčŗą╝ ą┤ą╗čÅ ą┐ąĄčĆą▓ąŠą╣ ą┐ąŠą╗ąŠą▓ąĖąĮčŗ čåąĖą║ą╗ą░ SPI_CLK. ąöą╗čÅ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ čü SPI_CTL.CPHA=0 ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą║ą░ą║ č鹊ą╗čīą║ąŠ ~SPI_SS ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0.

ąÜąŠą│ą┤ą░ SPI_CTL.CPHA=1, ą┐ąĄčĆąĄą┤ą░čćą░ čüčéą░čĆčéčāąĄčé čü ą┐ąĄčĆą▓čŗą╝ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą╝ SPI_CLK ą┤ą╗čÅ ąŠą▒ąŠąĖčģ čāčüčéčĆąŠą╣čüčéą▓ - slave ąĖ master. ąöą╗čÅ master-čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąŠąĮ ąŠčéą┐čĆą░ą▓ąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ ą┤ą░ąĮąĮčŗąĄ ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐čĆąĖą╝ąĄčé ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ. ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą╗čÅ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ąĘą░ą║ą░ąĮčćąĖą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą▓čŗą▒ąŠčĆą║ąĖ (sampling edge) čüąĖą│ąĮą░ą╗ą░ SPI_CLK. ąĢčüą╗ąĖ SPI_CTL.ASSEL=0, ą░ą┐ą┐ą░čĆą░čéčāčĆą░ čüąŠčģčĆą░ąĮčÅąĄčé čäčāąĮą║čåąĖčÄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ~SPI_SS ą╝ąĄąČą┤čā čäčĆąĄą╣ą╝ą░ą╝ąĖ. ąĢčüą╗ąĖ SPI_CTL.ASSEL=1, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ čāą┐čĆą░ą▓ą╗čÅąĄčé čüąĖą│ąĮą░ą╗ąŠą╝ ~SPI_SS, č鹊 ą╝ąŠąČąĮąŠ čāą┤ąĄčƹȹĖą▓ą░čéčī čŹč鹊čé čüąĖą│ąĮą░ą╗ ą░ą║čéąĖą▓ąĮčŗą╝ ą╝ąĄąČą┤čā čäčĆąĄą╣ą╝ą░ą╝ąĖ.

ąæąĖčé SPI_STAT.RFE ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ąŠą│ą┤ą░ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ, ą┐ąŠą║ą░ąĘčŗą▓ą░čÅ, čćč鹊 SPI_RFIFO ąĮąĄ ą┐čāčüčé. ąæąĖčé SPI_STAT.TFF ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ąŠą│ą┤ą░ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ąŠąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī, ą┐ąŠą║ą░ąĘčŗą▓ą░čÅ, čćč鹊 SPI_TFIFO ąĮąĄ ąĘą░ą┐ąŠą╗ąĮąĄąĮ. ą×ą║ąŠąĮčćą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą┤ąĮąŠą│ąŠ čüą╗ąŠą▓ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ ąŠčćąĖčēą░ąĄčéčüčÅ ą▒ąĖčé SPI_STAT.RFE. ąĪčéą░čéčāčü ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ąĮąŠą▓ąŠąĄ čüą╗ąŠą▓ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĖąĮčÅč鹊 ąĖ ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ FIFO ą┐čĆąĖąĄą╝ą░. ąæąĖčé SPI_STAT.RFE ąŠčüčéą░ąĄčéčüčÅ ąŠčćąĖčēąĄąĮąĮčŗą╝, ą┐ąŠą║ą░ ą▓ FIFO ą┐čĆąĖąĄą╝ą░ ąĖą╝ąĄčÄčéčüčÅ ą┤ąŠą┐čāčüčéąĖą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ.

ą¦č鹊ą▒čŗ čüąŠčģčĆą░ąĮąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčāčÄ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī čü ą┤čĆčāą│ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ SPI, ą▒ąĖčé SPI_STAT.SPIF čéą░ą║ąČąĄ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ą╗čÅ ąŠą┐čĆąŠčüą░. ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé čüą╗ąĄą│ą║ą░ ąŠčéą╗ąĖčćą░čéčīčüčÅ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄą╝ ąŠčé ą┤čĆčāą│ąĖčģ ą┤ąŠčüčéčāą┐ąĮčŗčģ ą║ąŠą╝ą╝ąĄčĆč湥čüą║ąĖčģ čāčüčéčĆąŠą╣čüčéą▓.

ąÆ čĆąĄąČąĖą╝ąĄ master čü ąŠčćąĖčēąĄąĮąĮčŗą╝ ą▒ąĖč鹊ą╝ SPI_CTL.ASSEL ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą▓čĆčāčćąĮčāčÄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čéčĆąĄą▒čāąĄą╝čŗą╣ čüąĖą│ąĮą░ą╗ slave select ą┐ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ą¤ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓čüąĄčģ ą┤ą░ąĮąĮčŗčģ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ąŠą▒čŗčćąĮąŠ ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗ slave select.

ąÜąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮčŗ čüč湥čéčćąĖą║ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ čüą╗ąŠą▓ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ SPI_TXCTL ąĖą╗ąĖ SPI_RXCTL, SPI ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čäąĖąĮąĖčłą░ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŁč鹊 ą┐ąŠą┤ą░ąĄčé čüąĖą│ąĮą░ą╗ ąŠą▒ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą▓čüąĄčģ ą┐ąĄčĆąĄą┤ą░čć, čüą▓čÅąĘą░ąĮąĮčŗą╣ čü čŹč鹊ą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĄą╣.

ąĀą░ą▒ąŠčéą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ąĄąĘ DMA. ąĀą░ą▒ąŠčéą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ ąĮąĄ-DMA čĆąĄąČąĖą╝ąĄ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ č湥čĆąĄąĘ ą▒ąĖčé SPI_TXCTL.TEN. ąŁč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąŠą┐ąĄčĆą░čåąĖąĖ ą┐čĆąĖąĄą╝ą░, ąĖ ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ąŠąČąĄčé čüčéą░čéčī ąĖąĮąĖčåąĖąĖčĆčāčÄčēąĖą╝ ą║ą░ąĮą░ą╗ąŠą╝ ąĮą░ ąŠčüąĮąŠą▓ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ SPI_TXCTL.TTI.

ąØąĄą┤ąŠą│čĆčāąĘą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (underrun) ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąĮąĄą▓ąŠąĘą╝ąŠąČąĮą░, ą┐ąŠčüą║ąŠą╗čīą║čā ąĮąĄčé ąĖąĮąĖčåąĖą░čåąĖąĖ ąĮąŠą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą┐ąŠą║ą░ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ FIFO ąĮąĄ ą┐čāčüčé (ą▓ čüą╗čāčćą░ąĄ SPI_TXCTL.TTI=1). ą¤ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ (overflow) ą┐čĆąĖąĄą╝ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ąĮąŠą▓ąŠą│ąŠ čäčĆąĄą╣ą╝ą░ ąĘą░ą╝ąĄąĮčÅčÄčé ą┐čĆąĄą┤čŗą┤čāčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮąŠą╝ FIFO ą┐čĆąĖąĄą╝ą░. ąŁč鹊 čüąŠą▒čŗčéąĖąĄ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ, ąĄčüą╗ąĖ SPI_TXCTL.TTI=1, ąĖ čĆą░ąĘčĆąĄčłąĄąĮ ą║ą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ ą▓ čĆąĄąČąĖą╝ąĄ ąĮąĄ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĖčÅ.

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPI čüčĆą░ą▒ąŠčéą░ąĄčé, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ čĆą░ąĘčĆąĄčłąĄąĮ ąĖ ą▒čāč乥čĆ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮąĄ ą┐ąŠą╗ąŠąĮ. SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé čāčüčéą░ąĮąŠą▓ą║čā ą▒ąĖčéą░ SPI_TXCTL.TDR ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čćą░čüč鹊č鹊ą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąĀą░ą▒ąŠčéą░ ą┐čĆąĖąĄą╝ą░ ą▒ąĄąĘ DMA. ą¤čĆąĖąĄą╝ ą▓ čĆąĄąČąĖą╝ąĄ ą▒ąĄąĘ DMA čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ č湥čĆąĄąĘ ą▒ąĖčé SPI_RXCTL.REN. ąŁč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čĆą░ą▒ąŠčéčŗ ą┐čĆąĖąĄą╝ą░, ąĖ ą║ą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĖąĮąĖčåąĖąĖčĆčāčÄčēąĖą╝ ąĮą░ ą▒ą░ąĘąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ SPI_RXCTL.RTI.

ą¤ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąĖąĄą╝ą░ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąĮąĄą▓ąŠąĘą╝ąŠąČąĮąŠ, ą┐ąŠčüą║ąŠą╗čīą║čā ąĮąŠą▓ą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮąĄ ąĮą░čćąĮąĄčéčüčÅ, ą┐ąŠą║ą░ ą▒čāč乥čĆ FIFO ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮ (ą▓ čüą╗čāčćą░ąĄ SPI_RXCTL.RTI=1). ąØąĄą┤ąŠą│čĆčāąĘą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit underrun) ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ (ą▒ąĖčé SPI_TXCTL.TDU), ą║ąŠą│ą┤ą░ ąĮąĄčé ą┤ąŠą┐čāčüčéąĖą╝čŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_TFIFO, ą║ąŠą│ą┤ą░ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░. ąóą░ą║ąŠąĄ čüąŠą▒čŗčéąĖąĄ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ, ąĄčüą╗ąĖ SPI_RXCTL.RTI=1, ąĖ čĆą░ąĘčĆąĄčłąĄąĮ ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ čü ąĮąĄ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ąĖčüč鹊čćąĮąĖą║ąŠą╝ ą┤ą░ąĮąĮčŗčģ.

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖąĄą╝ą░ SPI čüčĆą░ą▒ąŠčéą░ąĄčé, ą║ą░ą║ č鹊ą╗čīą║ąŠ čĆą░ąĘčĆąĄčłąĄąĮ ą║ą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ ąĖ ą┤ą░ąĮąĮčŗąĄ ąŠąČąĖą┤ą░čÄčé čćč鹥ąĮąĖčÅ. SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé čāčüčéą░ąĮąŠą▓ą║čā ą▒ąĖčéą░ SPI_RXCTL.RDR ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čćą░čüč鹊č鹊ą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąÆ čĆąĄąČąĖą╝ąĄ dual I/O ą▓čŗą▓ąŠą┤čŗ SPI_MISO ąĖ SPI_MOSI ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ ąŠą┤ąĮąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ, čü čāą┤ą▓ąŠąĄąĮąĮąŠą╣ ą┐ąŠą╗ąŠčüąŠą╣. SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčé SPI_CTL.SOSI ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┐ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ. ąÜąŠą│ą┤ą░ ą▒ąĖčé SPI_CTL.SOSI čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠčüčŗą╗ą░ąĄčé ą┐ąĄčĆą▓čŗą╣ ą▒ąĖčé ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SPI_MOSI, ąĖ ą▓č鹊čĆąŠą╣ ą▒ąĖčé ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SPI_MISO. ąĢčüą╗ąĖ ą▒ąĖčé SPI_CTL.SOSI ąŠčćąĖčēąĄąĮ, ą┐ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąŠą▒čĆą░čéąĮčŗą╝. ą¤ąŠčüą║ąŠą╗čīą║čā dual I/O mode ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąŠą▒ą░ ą▓čŗą▓ąŠą┤ą░ čüčĆą░ąĘčā ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╗ąĖ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ, č鹊 čĆą░ąĘčĆąĄčłąĄąĮ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ą║ą░ąĮą░ą╗ (ą╗ąĖą▒ąŠ č鹊ą╗čīą║ąŠ ą┐čĆąĖąĄą╝, ą╗ąĖą▒ąŠ č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čćą░), ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ SPI_RDY ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ. ąØą░ ą│ąĄąĮąĄčĆą░čåąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čĆąĄąČąĖą╝ dual I/O ąĮąĄ ą▓ą╗ąĖčÅąĄčé, ąŠą┤ąĮą░ą║ąŠ ą┐čĆąŠą╝ąĄąČčāč鹊ą║ ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąĄąČą┤čā čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ čāą╝ąĄąĮčīčłą░ąĄčéčüčÅ, ą┐ąŠčüą║ąŠą╗čīą║čā ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čäčĆąĄą╣ą╝ą░ čāą╝ąĄąĮčīčłą░ąĄčéčüčÅ ą▓ 2 čĆą░ąĘą░.

ąĀąĖčü. 29-8. ą¤čĆąŠč鹊ą║ąŠą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ Dual I/O Mode ą┤ą╗čÅ CPHA=0, SOSI=1, čäčĆąĄą╣ą╝ 8 ą▒ąĖčé, LSBF=0.

ąĀąĖčü. 29-9.ą¤čĆąŠč鹊ą║ąŠą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ Dual I/O Mode ą┤ą╗čÅ CPHA=1, SOSI=0, čäčĆąĄą╣ą╝ 8 ą▒ąĖčé, LSBF=0.

ąÆ čĆąĄąČąĖą╝ąĄ SPI ą▓čŗą▓ąŠą┤čŗ SPI_MISO ąĖ SPI_MOSI ą▓ą╝ąĄčüč鹥 čü ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╝ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ SPI_D2 ąĖ SPI_D3 čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ ąŠą┤ąĮąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ. SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčé SPI_CTL.SOSI ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┐ąŠčĆčÅą┤ąŠą║ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ ą▒ąĖčé ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ. ąÜąŠą│ą┤ą░ ą▒ąĖčé SPI_CTL.SOSI čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąĄčĆąĄą┤ą░ąĄčé:

ŌĆó ą¤ąĄčĆą▓čŗą╣ ą▒ąĖčé ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SPI_MOSI.

ŌĆó ąÆč鹊čĆąŠą╣ ą▒ąĖčé ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SPI_MISO.

ŌĆó ąóčĆąĄčéąĖą╣ ą▒ąĖčé ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SPI_D2.

ŌĆó ą¦ąĄčéą▓ąĄčĆčéčŗą╣ ą▒ąĖčé ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SPI_D3.

ąÜąŠą│ą┤ą░ ą▒ąĖčé SPI_CTL.SOSI ąŠčćąĖčēąĄąĮ, ą┐ąŠčĆčÅą┤ąŠą║ ą╝ąĄąĮčÅąĄčéčüčÅ ąĮą░ ąŠą▒čĆą░čéąĮčŗą╣. ą¤ąŠčüą║ąŠą╗čīą║čā quad SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓čüąĄ 4 ą▓čŗą▓ąŠą┤ą░ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╗ąĖ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ, č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ą║ą░ąĮą░ą╗ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ - ą╗ąĖą▒ąŠ ą┐ąĄčĆąĄą┤ą░čćą░, ą╗ąĖą▒ąŠ ą┐čĆąĖąĄą╝. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ ą▓čŗą▓ąŠą┤ąŠą╝ SPI_RDY. ąØą░ ą│ąĄąĮąĄčĆą░čåąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆąĄąČąĖą╝ quad SPI ąĮąĄ ą▓ą╗ąĖčÅąĄčé.

ą¤ąĄčĆąĄčģąŠą┤ ą║ čĆąĄąČąĖą╝čā quad SPI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ, ą║ąŠą│ą┤ą░ SPI ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ "ą╝ąŠą╗čćą░ąĮąĖčÅ".

ąĀąĖčü. 29-10. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ Quad Mode ą┤ą╗čÅ CPHA=0, SOSI=1, 16-ą▒ąĖčéąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░, LSBF=0.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: SPI ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé quad SPI 8-ą▒ąĖčéąĮčāčÄ ą┐ąĄčĆąĄą┤ą░čćčā ą▓ čĆąĄąČąĖą╝ąĄ continuous čāčüčéčĆąŠą╣čüčéą▓ą░ slave, čü čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄą╝ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé SCLK:SPI_CLK ą╝ąĄąĮčīčłąĄ 1:2. ą£ąĖąĮąĖą╝čāą╝ 2 čåąĖą║ą╗ą░ 2 SCLK čéčĆąĄą▒čāąĄčéčüčÅ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ ą▓ 8-ą▒ąĖčéąĮąŠą╝ quad SPI slave mode, čü čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄą╝ SCLK:SPI_CLK ą╝ąĄąĮčīčłąĄ 1:2.

ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüą┤ą▓ąŠąĄąĮąĮčŗą╣ (dual) ąĖą╗ąĖ čüč湥čéą▓ąĄčĆąĄąĮąĮčŗą╣ (quad) čĆąĄąČąĖą╝ I/O ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ čü čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ flash, ą▒ąĖčéčŗ SPI_CTL.CPHA ąĖ SPI_CTL.CPOL=1. ąŁč鹊 ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖąĘą▒ąĄą│ą░ąĄčé ą║ąŠąĮčäą╗ąĖą║čéą░ ąĮą░ čłąĖąĮąĄ ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ, ą┐ąŠč鹊ą╝čā čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ flash ąĮą░čćąĖąĮą░ąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą▒ąĖčéčŗ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąŠčüą╗ąĄ ą┐čāčüčéčŗčģ čåąĖą║ą╗ąŠą▓ ą▓ ąĘą░ą│ąŠą╗ąŠą▓ą║ąĄ čćč鹥ąĮąĖčÅ.

ąæčŗčüčéčĆčŗą╣ čĆąĄąČąĖą╝ (fast mode) ą┐ąŠą┤ąŠą▒ąĄąĮ ąŠą▒čŗčćąĮąŠą╝čā čĆąĄąČąĖą╝čā (normal mode) čĆą░ą▒ąŠčéčŗ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥. ąÜąŠą│ą┤ą░ ąĖą┤ąĄčé ą┐čĆąĖąĄą╝, ą┤ą░ąĮąĮčŗąĄ ą░ąĮą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā ą┐ąĄčĆąĄą┤ą░čćąĖ, ą┐ąŠąĘą▓ąŠą╗čÅčÅ ą┐ąŠą╗ąĮčŗą╣ čåąĖą║ą╗ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ ą▓ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ ą┐čĆąĖąĄą╝ą░. ąŁč鹊čé čĆąĄąČąĖą╝ ą┤ąŠą┐čāčüčéąĖą╝ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ą░ master. ąÜąŠą│ą┤ą░ SPI čĆą░ą▒ąŠčéą░ąĄčé ą▓ fast mode, čāčüčéčĆąŠą╣čüčéą▓ąŠ slave ą▓čŗą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ąŠą┤ąĮąŠą│ąŠ ą┐ąŠą╗ąĮąŠą│ąŠ čéą░ą║čéą░.

ąĀąĖčü. 29-11. ą¤čĆąŠč鹊ą║ąŠą╗ SPI ą▓ Fast Mode ą┤ą╗čÅ SPI_CTL.CPHA=0.

ąĀąĖčü. 29-12. ą¤čĆąŠč鹊ą║ąŠą╗ SPI ą▓ Fast Mode ą┤ą╗čÅ SPI_CTL.CPHA=1.

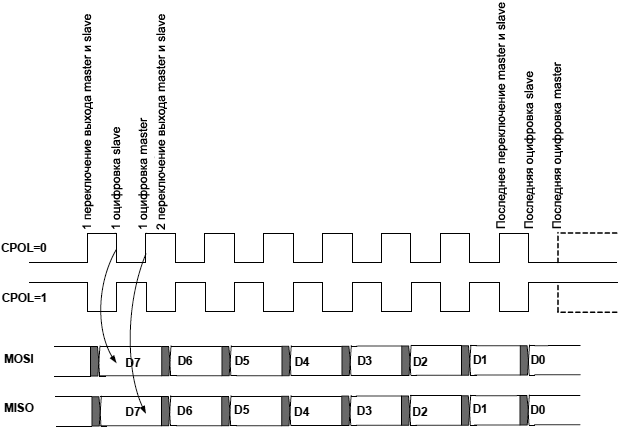

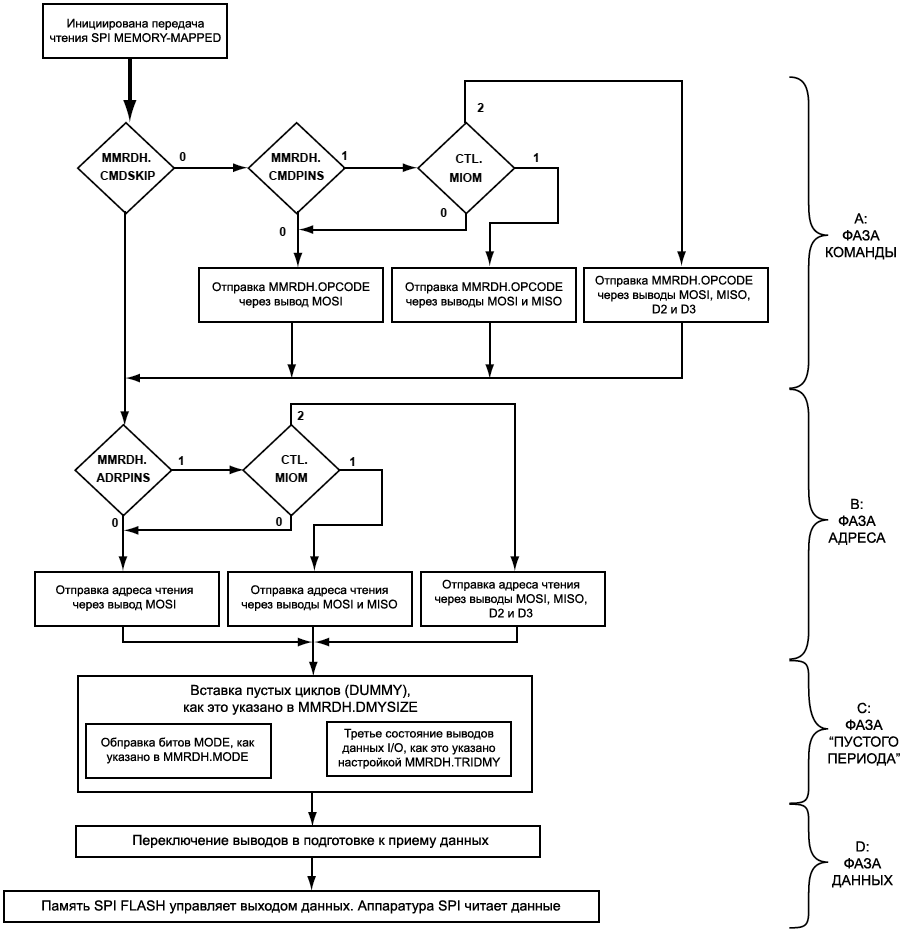

ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčéčüčÅ ą┐čĆčÅą╝čŗąĄ, ąŠč鹊ą▒čĆą░ąČąĄąĮąĮčŗąĄ ąĮą░ ą┐ą░ą╝čÅčéčī ą┤ąŠčüčéčāą┐čŗ čćč鹥ąĮąĖčÅ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ SPI, čćč鹊 čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SPI_CTL.MMSE. ąŁč鹊čé čĆąĄąČąĖą╝ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆčÅą╝ąŠąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖąĘ ą┐ą░ą╝čÅčéąĖ SPI ą▒ąĄąĘ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ąĮąĖąĘą║ąŠčāčĆąŠą▓ąĮąĄą▓ąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░, čéą░ą║ ą║ą░ą║ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ą▒ąĄčĆąĄčé ąĮą░ čüąĄą▒čÅ ą▓čüčÄ ąĮą░ą│čĆčāąĘą║čā ą┐ąŠ čŹč鹊ą╣ ąĘą░ą┤ą░č湥 (čé. ąĄ. ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ čćč鹥ąĮąĖčÅ, ąŠą▒čĆą░ą▒ąŠčéą║ą░ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▓čŗą▓ąŠą┤ąŠą▓ ąĖ ą┐čĆąĖąĄą╝ čĆą░ąĘą╝ąĄčĆąŠą▓ ą┤ą░ąĮąĮčŗčģ). SPI ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗąĄ ąŠą┐čåąĖąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ ą┐čĆąĖą▓čÅąĘą║ąĖ ą║ ą┐ą░ą╝čÅčéąĖ (memory-mapped read header register, SPI_MMRDH), čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī čü čłąĖčĆąŠą║ąĖą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ ą┐ą░ą╝čÅčéąĖ SPI.

ąÆ čĆąĄąČąĖą╝ąĄ ą▒ąĄąĘ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ąĮą░ ą┐ą░ą╝čÅčéčī (non-memory-mapped mode) ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ ąĖ čéčĆąĄą▒čāąĄą╝čŗčģ ą┐čāčüčéčŗčģ čüą╗ąŠą▓ ą┤ą╗čÅ ąŠčéą▓ąĄčéą░ čćč鹥ąĮąĖčÅ (read response), ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą▓čüąĄ čŹč鹊 ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ SPI čĆą░ą▒ąŠčéą░ąĄčé ą▓ memory-mapped mode. ą¤ą░ą╝čÅčéčī čāčüčéčĆąŠą╣čüčéą▓ą░ SPI ą┤ąŠčüčéčāą┐ąĮą░ ąĮą░ą┐čĆčÅą╝čāčÄ č湥čĆąĄąĘ čćč鹥ąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ ąĘą░ą┤ą░ąĮąĮąŠą│ąŠ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░. ąöąŠčüčéčāą┐čŗ ąĮą░ čćč鹥ąĮąĖąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą║ ą║ąŠą┤čā ąĖą╗ąĖ ą║ ą┤ą░ąĮąĮčŗą╝ ą▓ čĆąĄąČąĖą╝ąĄ čÅą┤čĆą░ ąĖą╗ąĖ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ DMA ą┐ąŠ ą┐ą░ą╝čÅčéąĖ (memory DMA, MDMA). ąŁč鹊čé ą┤ąŠčüčéčāą┐ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┐čāčüą║ą░čéčī ą║ąŠą┤ ąĮą░ą┐čĆčÅą╝čāčÄ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ ą┐ą░ą╝čÅčéąĖ SPI (čĆąĄą░ą╗čīąĮčŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ eXecute-In-Place, čé. ąĄ. ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆčÅą╝ąŠ ą┐ąŠ ą╝ąĄčüčéčā), ąĖ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čŹč鹊ą╣ ą┐ą░ą╝čÅčéąĖ SPI ą╝ąŠąČąĄčé ą▒čŗčéčī ą║čŹčłąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ą┐ąŠą▓čŗčłąĄąĮąĖčÅ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖčÅ. ąØąĄ čéčĆąĄą▒čāąĄčéčüčÅ ąŠą▒čĆą░čēąĄąĮąĖąĄ ąĮąĖ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ ą▒čāč乥čĆą░ ą┤ą░ąĮąĮčŗčģ SPI, ąĮąĖ ąŠą┐čĆąŠčü ą▒ąĖč鹊ą▓ čüąŠčüč鹊čÅąĮąĖčÅ SPI; ąŠą┤ąĮą░ą║ąŠ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĮąĖ ąŠą┐ąĄčĆą░čåąĖąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ DMA, ąĮąĖ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą▓ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ SPI.

ąóą░ą▒ą╗ąĖčåą░ čéąĖą┐ąŠą▓ ąŠą┐ąĄčĆą░čåąĖą╣ 29-6 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüčĆą░ą▓ąĮąĄąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖą╣ ą▓ čĆąĄąČąĖą╝ą░čģ non-memory-mapped ąĖ memory-mapped, ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗčģ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ SPI.

ąóą░ą▒ą╗ąĖčåą░ 29-6. ąóąĖą┐čŗ ąŠą┐ąĄčĆą░čåąĖą╣.

| ą×ą┐ąĄčĆą░čåąĖčÅ SPI |

Non-Memory-Mapped Mode |

Memory-Mapped Mode |

| Core data write: ąĘą░ą┐ąĖčüčī ą┤ą░ąĮąĮčŗčģ čÅą┤čĆąŠą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░. |

ąöąÉ |

ąĮąĄčé |

| Core data read: čćč鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ čÅą┤čĆąŠą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░. |

ąöąÉ |

ąöąÉ |

| Code fetch: Execute-In-Place (XIP). ąÆčŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ ąĮą░ą┐čĆčÅą╝čāčÄ ąĖąĘ ą┐ą░ą╝čÅčéąĖ SPI. |

ąĮąĄčé |

ąöąÉ |

| ąöąŠčüčéčāą┐čŗ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ SPI Peripheral DMA. |

ąöąÉ |

ąĮąĄčé |

| ąöąŠčüčéčāą┐čŗ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┤čĆčāą│ąĖą╝ąĖ ą║ą░ąĮą░ą╗ą░ą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖąĖ DMA. |

ąĮąĄčé |

ąĮąĄčé |

| MDMA read: čćč鹥ąĮąĖąĄ DMA ą┐ąŠ ą┐ą░ą╝čÅčéąĖ. |

ąĮąĄčé |

ąöąÉ |

| MDMA write: ąĘą░ą┐ąĖčüčī DMA ą┐ąŠ ą┐ą░ą╝čÅčéąĖ. |

ąĮąĄčé |

ąĮąĄčé |

[ą×ą┐ąĖčüą░ąĮąĖąĄ čĆą░ą▒ąŠčéčŗ Memory-Mapped SPI]

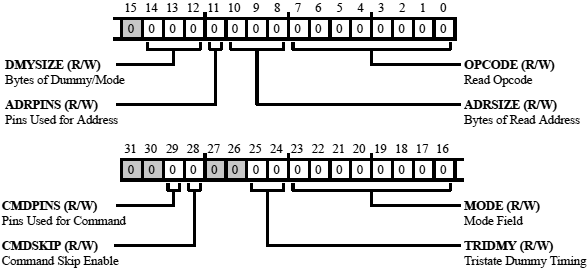

ąĀąĄąČąĖą╝ ą┐čĆąĖą▓čÅąĘą║ąĖ ą║ ą░ą┤čĆąĄčüąĮąŠą╝čā ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓čā ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (Memory-mapped mode) čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SPI_CTL.MMSE. ąÜąŠą│ą┤ą░ čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ, SPI (ąĄčüą╗ąĖ ą│ąŠč鹊ą▓) ą┐čĆąĖąĮąĖą╝ą░ąĄčé ąĘą░ą┐čĆąŠčüčŗ čćč鹥ąĮąĖčÅ č湥čĆąĄąĘ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗą╣ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ slave-ąĖąĮč鹥čĆč乥ą╣čü. ą¤ąŠą┤čüąĖčüč鹥ą╝ą░ ą┐ą░ą╝čÅčéąĖ master-čāčüčéčĆąŠą╣čüčéą▓ą░ čāą┐čĆą░ą▓ą╗čÅąĄčé čŹčéąĖą╝ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ č湥čĆąĄąĘ čäą░ą▒čĆąĖą║čā SCB.

ąÆ čéąĖą┐ąŠą▓ąŠą╝ čüčåąĄąĮą░čĆąĖąĖ ą┐ąŠą┤čüąĖčüč鹥ą╝ą░ ą┐ą░ą╝čÅčéąĖ master-čāčüčéčĆąŠą╣čüčéą▓ą░ čćąĖčéą░ąĄčé ąĘą░ą┐čĆąŠčüčŗ ą┤ą╗čÅ čäą░ą▒čĆąĖą║ąĖ, ąĖ čäą░ą▒čĆąĖą║ą░ ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗čÅąĄčé čŹčéąĖ ąĘą░ą┐čĆąŠčüčŗ ą▓ slave-ą┐ąŠčĆčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ master ąŠą┐ąĖčüčŗą▓ą░ąĄčé ą┤ąŠčüčéčāą┐ čćč鹥ąĮąĖčÅ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ąĮąĄą║ąŠč鹊čĆąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓, čéą░ą║ąĖčģ ą║ą░ą║ ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü, čĆą░ąĘą╝ąĄčĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ čéąĖą┐ą░ ą┐ą░ą║ąĄčéą░ (burst type). SPI ąŠčéą▓ąĄčćą░ąĄčé ąĮą░ čŹč鹊čé ąĘą░ą┐čĆąŠčü čćč鹥ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąŠąĮ ą│ąŠč鹊ą▓ ą║ ąĮąŠą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥. ą×ąĮ ąĘą░ą│čĆčāąČą░ąĄčé ą║ąŠą┤ ąŠą┐ąĄčĆą░čåąĖąĖ (opcode), čāą║ą░ąĘą░ąĮąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ą░ą┤čĆąĄčüą░ ąĖ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą▒ą░ą╣čé čĆąĄąČąĖą╝ą░ ą▓ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ. ą£ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖą╣ SPI ąĮą░čćąĮąĄčé čĆą░ą▒ąŠčéčā, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮčŗ ąŠą▒ą░ ą║ą░ąĮą░ą╗ą░, ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ SPI:

ŌĆó čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ąĖąĮąĖčåąĖą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (SPI_TXCTL.TTI=1), ąĖ

ŌĆó ąŠčćąĖčēąĄąĮ ą▒ąĖčé ąĖąĮąĖčåąĖą░čåąĖąĖ ą┐čĆąĖąĄą╝ą░ (SPI_RXCTL.RTI=0).

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čćč鹥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ SPI ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü ą░ą║čéąĖą▓ą░čåąĖąĖ ą▓čŗą▒ąŠčĆą║ąĖ SPI_SEL1. ąĢčüą╗ąĖ ą╝ą░čłąĖąĮą░ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ SPI ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░, ąŠąĮą░ ąČą┤ąĄčé ą║ąŠą╝ą░ąĮą┤čŗ. ąóąŠą│ą┤ą░ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ SPI ą┐ąŠčüčŗą╗ą░ąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮčāčÄ 8-ą▒ąĖčéąĮčāčÄ ą║ąŠą╝ą░ąĮą┤čā čćč鹥ąĮąĖčÅ (ą║ąŠč鹊čĆą░čÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą┐čĆąŠą┐čāčēąĄąĮą░), ąĘą░ ą║ąŠč鹊čĆąŠą╣ ąĖą┤ąĄčé ą░ą┤čĆąĄčü čćč鹥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ SPI. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą▓čüčéą░ą▓ą╗čÅąĄčéčüčÅ čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ ą┐čāčüč鹊ą╣ ą┐ąĄčĆąĖąŠą┤ (dummy period) ą▓ ą║ąŠč鹊čĆąŠą╝ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▒ą░ą╣čé čĆąĄąČąĖą╝ą░ (mode byte), ąĖ ą▓čŗą▓ąŠą┤čŗ čāą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą▓ čéčĆąĄčéčīąĄą╝ čüąŠčüč鹊čÅąĮąĖąĖ ąĮą░ ą▓čĆąĄą╝čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čāčüč鹊ą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░.

ąŚąÉą£ąĢą¦ąÉąØąśąĢ: čŹč鹊čé ąĘą░ą│ąŠą╗ąŠą▓ąŠą║ čćč鹥ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤čŗ čüčéą░ąĮą┤ą░čĆčéąĮąŠą│ąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░ SPI (SPI_CLK, SPI_MOSI, SPI_MISO, SPI_SEL1) ąĖą╗ąĖ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤čŗ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░ SPI (SPI_CLK, SPI_MOSI, SPI_MISO, SPI_D2, SPI_D3, SPI_SEL1), ąĮą░ ąŠčüąĮąŠą▓ąĄ ąĮą░čüčéčĆąŠąĄą║ ą▒ąĖčé SPI_MMRDH.CMDPINS, SPI_MMRDH.ADRPINS ąĖ SPI_CTL.MIOM. ąŻčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ SPI ąŠą▒čŗčćąĮąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąŠą▒ą╝ąĄąĮ ą▓ čĆąĄąČąĖą╝ąĄ MSB-first (čüčéą░čĆčłąĖą╣ ą▒ąĖčé ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝). ąÆ dual mode SPI ąŠą▒čŗčćąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčé SPI_MISO ą║ą░ą║ IO1, ąĖ SPI_MOSI ą║ą░ą║ IO0. ąÆ quad mode SPI ąŠą▒čŗčćąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčé SPI_D3 ą║ą░ą║ IO3, SPI_D2 ą║ą░ą║ IO2, SPI_MISO ą║ą░ą║ IO1 ąĖ SPI_MOSI ą║ą░ą║ IO0.

ąÜąŠą│ą┤ą░ ą▓čüąĄ ąĮąŠąČą║ąĖ I/O ą┤ą░ąĮąĮčŗčģ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čéčĆąĄčéčīąĄą╝ čüąŠčüč鹊čÅąĮąĖąĖ, SPI ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé čéą░ą║čéąĖčĆąŠą▓ą░čéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ SPI, ą║ąŠč鹊čĆąŠąĄ ą▓čŗą▓ąŠą┤ąĖ ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą╝čā ą╝ąĄčüčéčā, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤čāčé ą┐čĆąĖąĮčÅčéčŗ ą▓čüąĄ ą▒ą░ą╣čéčŗ. ąÉą┐ą┐ą░čĆą░čéčāčĆą░ SPI čćąĖčéą░ąĄčé ą┤ą░ąĮąĮčŗąĄ čéą░ą║, ą║ą░ą║ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ ą▒ąĖčéą░ SPI_CTL.MIOM. ą¤čĆąĖ ą┐čĆąĖąĄą╝ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ą░ą╣čéą░ SPI ąŠą▒čŗčćąĮąŠ ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčé ą▓čŗą▓ąŠą┤ SPI_SEL1, čćč鹊ą▒čŗ ą┐ąŠą┤ą│ąŠč鹊ą▓ąĖčéčī čüą╗ąĄą┤čāčÄčēąĖą╣ ąĘą░ą┐čĆąŠčłąĄąĮąĮčŗą╣ ąĘą░ą│ąŠą╗ąŠą▓ąŠą║ čćč鹥ąĮąĖčÅ.

ąÜąŠą┤ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ opcode ą║ąŠąĮčüąĖčüč鹥ąĮč鹥ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÄ ą╝ąĮąŠąČąĄčüčéą▓ąĄąĮąĮąŠą│ąŠ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░, ąĖ čćč鹊 ą┐ą░čĆą░ą╝ąĄčéčĆčŗ, čāą║ą░ąĘą░ąĮąĮčŗąĄ ą▓ memory-mapped čĆąĄą│ąĖčüčéčĆąĄ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ čćč鹥ąĮąĖčÅ ą║ąŠąĮčüąĖčüč鹥ąĮčéąĮčŗ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ąŠčüčéčāą┐ą░ čćč鹥ąĮąĖčÅ flash.

ąØą░ čĆąĖčü. 29-13 ą┐ąŠą║ą░ąĘą░ąĮą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ąŠą┐ąĄčĆą░čåąĖą╣ čü čĆąĄą│ąĖčüčéčĆąŠą╝ SPI Memory-Mapped, ą║ą░ą║ ą┐ąŠą╗čÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_MMRDH ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé ąĘą░ą│ąŠą╗ąŠą▓ąŠą║ čćč鹥ąĮąĖčÅ ą┐čĆąĖ ąĖąĮąĖčåąĖą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čć ą▓ čĆąĄąČąĖą╝ąĄ memory-mapped.

ąĀąĖčü. 29-13. ą¤ąŠč鹊ą║ ąŠą┐ąĄčĆą░čåąĖą╣ čĆąĄą│ąĖčüčéčĆąŠą▓ čĆąĄąČąĖą╝ą░ SPI Memory-Mapped.

[ąÉčĆčģąĖč鹥ą║čéčāčĆąĮčŗąĄ ą║ąŠąĮčåąĄą┐čåąĖąĖ č鹥čģąĮąŠą╗ąŠą│ąĖąĖ Memory-Mapped]

ąÆ čĆąĄąČąĖą╝ąĄ memory-mapped SPI ą┐čĆąĖąĮąĖą╝ą░ąĄčé ąĘą░ą┐čĆąŠčüčŗ čćč鹥ąĮąĖčÅ č湥čĆąĄąĘ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗą╣ ą┤ą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ slave-ąĖąĮč鹥čĆč乥ą╣čü. SPI (ąĄčüą╗ąĖ ąŠąĮ ą│ąŠč鹊ą▓) ą┐čĆąĖąĮąĖą╝ą░ąĄčé čŹčéąĖ ąĘą░ą┐čĆąŠčüčŗ ąĖ ąĮą░čćąĖąĮą░ąĄčé ą┐čĆąŠčåąĄčüčü čüą▒ąŠčĆą║ąĖ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ čćč鹥ąĮąĖčÅ, ąŠčüąĮąŠą▓čŗą▓ą░čÅčüčī ąĮą░ ą░čéčĆąĖą▒čāčéą░čģ, ąŠą┐ąĖčüą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_MMRDH ąĖ ąĘą░ą┐čĆąŠčüąĄ ą┐ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čłąĖąĮąĄ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ čćč鹥ąĮąĖčÅ, ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąĄčĆąĖąŠą┤ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░, ąĖ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čĆą░ą▒ąŠčéą░ ą┐čĆąĖąĄą╝ąĮąĖą║ą░. SPI ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé čéą░ą║čéąĖčĆąŠą▓ą░čéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ SPI, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤čāčé ą┐čĆąĖąĮčÅčéčŗ ąŠčé ąĮąĄą│ąŠ ą▓čüąĄ ą▒ą░ą╣čéčŗ.

ąÉą┐ą┐ą░čĆą░čéčāčĆą░ SPI memory-mapped ą┐ąŠą┤čģąŠą┤ąĖčé ą║ čĆą░ąĘą╗ąĖčćąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ ą┐ą░ą╝čÅčéąĖ čü čĆą░ąĘąĮčŗą╝ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ. ąÆąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą▓ą║ą╗čÄčćą░čÄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą▒ąĖčéčŗ čĆąĄąČąĖą╝ą░, ąĮą░čüčéčĆą░ąĖą▓ą░ąĄą╝čŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ą┐čāčüč鹊ą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░, čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čéčĆąĄčéčīąĖą╝ čüąŠčüč鹊čÅąĮąĖąĄą╝, ą║ą░ą║ čŹč鹊 čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_MMRDH.

ąØą░ čĆąĖčü. 29-14 ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąŠč鹊ą║ąŠą╗ Memory-Mapped ą┤ą╗čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ SPI, ąĮą░čģąŠą┤čÅčēąĄą│ąŠčüčÅ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ.

ąĀąĖčü. 29-14. ą¤čĆąŠč鹊ą║ąŠą╗ Memory-Mapped ąĖąĮč鹥čĆč乥ą╣čüą░ SPI.

ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčüčāąĮą║ąĄ, ą┐ąŠą╗ąĄ ą║ąŠą╝ą░ąĮą┤čŗ COMMAND (SPI_MMRDH.OPCODE) ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐čĆąĖ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖąĖ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ SPI_SEL[n]. ą¤ą░ą╝čÅčéčī SPI ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆčāąĄčé čŹč鹊 8-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą║ą░ą║ ą║ąŠą╝ą░ąĮą┤čā čćč鹥ąĮąĖčÅ. ąĀą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą╗čÄą▒ąŠą╣ 8-ą▒ąĖčéąĮčŗą╣ ą║ąŠą┤ ąŠą┐ąĄčĆą░čåąĖąĖ (opcode), ą║ąŠč鹊čĆčŗą╣ ą┐ąŠ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ ą▓čĆąĄą╝ąĄąĮąĖ čüąŠą▓ą╝ąĄčüčéąĖą╝ čü SPI ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĖ čĆą░čüčüčćąĖčéą░ąĮ ąĮą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮčāčÄ ą░ą┐ą┐ą░čĆą░čéčāčĆčā memory-mapped, čćą░čēąĄ ą▓čüąĄą│ąŠ ąŠąĮ ą▒čāą┤ąĄčé:

ŌĆó Standard Read, čüčéą░ąĮą┤ą░čĆčéąĮąŠąĄ čćč鹥ąĮąĖąĄ (0x03)

ŌĆó Fast Read, ą▒čŗčüčéčĆąŠąĄ čćč鹥ąĮąĖąĄ (0x0B)

ŌĆó Fast Read Dual Output, ą▒čŗčüčéčĆąŠąĄ čćč鹥ąĮąĖąĄ čü ą┤ą▓ąŠą╣ąĮčŗą╝ ą▓čŗčģąŠą┤ąŠą╝ (0x3B)

ŌĆó Fast Read Dual I/O, ą▒čŗčüčéčĆąŠąĄ čćč鹥ąĮąĖąĄ čü ą┤ą▓ąŠą╣ąĮčŗą╝ ą▓ą▓ąŠą┤ąŠą╝/ą▓čŗą▓ąŠą┤ąŠą╝ (0x6B)

ŌĆó Fast Read Quad Output, ą▒čŗčüčéčĆąŠąĄ čćč鹥ąĮąĖąĄ čüąŠ čüč湥čéą▓ąĄčĆąĄąĮąĮčŗą╝ ą▓čŗčģąŠą┤ąŠą╝ (0xBB)

ŌĆó Fast Read Quad I/O, ą▒čŗčüčéčĆąŠąĄ čćč鹥ąĮąĖąĄ čüąŠ čüč湥čéą▓ąĄčĆąĄąĮąĮčŗą╝ ą▓ą▓ąŠą┤ąŠą╝/ą▓čŗą▓ąŠą┤ąŠą╝ (0xEB)

ŌĆó Word Read Quad I/O, čćč鹥ąĮąĖąĄ čüą╗ąŠą▓ą░ čüąŠ čüč湥čéą▓ąĄčĆąĄąĮąĮčŗą╝ ą▓ą▓ąŠą┤ąŠą╝/ą▓čŗą▓ąŠą┤ąŠą╝ (0xE7)

ŌĆó Octal Word Read Quad I/O, ą▓ąŠčüčīą╝ąĄčĆąĖčćąĮąŠąĄ čćč鹥ąĮąĖąĄ čüą╗ąŠą▓ą░ čüąŠ čüč湥čéą▓ąĄčĆąĄąĮąĮčŗą╝ ą▓ą▓ąŠą┤ąŠą╝/ą▓čŗą▓ąŠą┤ąŠą╝ (0xE3)

ąŚąÉą£ąĢą¦ąÉąØąśąĢ: ą░ą┐ą┐ą░čĆą░čéčāčĆą░ SPI ąĮąĄ ą┐čĆąŠą▓ąĄčĆčÅąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą┐ąŠą╗čÅ SPI_MMRDH.OPCODE ą┐ąĄčĆąĄą┤ ą┐ąĄčĆąĄą┤ą░č湥ą╣.

DMYSIZE (ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐čāčüčéčŗčģ ą▒ą░ą╣čé). ąÜąŠą│ą┤ą░ ąĖą┤ąĄčé čĆą░ą▒ąŠčéą░ ąĮą░ ą▓čŗčüąŠą║ąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 ą▓ čĆąĄąČąĖą╝ą░čģ multi-IO, ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ čāčüčéčĆąŠą╣čüčéą▓ flash čéčĆąĄą▒čāčÄčé ąĮąĄą║ąŠč鹊čĆąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐čāčüčéčŗčģ čéą░ą║č鹊ą▓ ą┐ąŠčüą╗ąĄ ą▒ąĖč鹊ą▓ ą░ą┤čĆąĄčüą░. ąŁčéąĖ ą┐čāčüčéčŗąĄ čéą░ą║čéčŗ (dummy clock cycles) ą┤ą░čÄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čüčģąĄą╝ą░ą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░. ąŁčéąĖ ą▒ąĖčéčŗ ąĘą░ą┤ą░čÄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé, ąŠčéą┤ąĄą╗čÅčÄčēąĖčģ ą┐ąĄčĆąĄą┤ą░čćčā ą░ą┤čĆąĄčüą░ ąĖ ą▓ąŠąĘą▓čĆą░čēą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ čćč鹥ąĮąĖčÅ.

ąóčĆąĄą▒čāąĄą╝ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ dummy cycles ą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘąĮčŗčģ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╣, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ čćč鹥ąĮąĖčÅ ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ąŠčüčéčāą┐ą░ SPI. ąÉą┐ą┐ą░čĆą░čéčāčĆą░ SPI ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī dummy cycles ą▓ ą▒ą░ą╣čéą░čģ čü ą┐ąŠą╝ąŠčēčīčÄ ą┐ąŠą╗čÅ SPI_MMRDH.DMYSIZE, ąĘąĮą░č湥ąĮąĖąĄ ą║ąŠč鹊čĆąŠą│ąŠ čÅą▓ą╗čÅąĄčéčüčÅ čäčāąĮą║čåąĖąĄą╣ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▓čŗą▓ąŠą┤ąŠą▓, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą░ą┤čĆąĄčüą░ (SPI_MMRDH.ADRPINS), ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 29-7.

ąóą░ą▒ą╗ąĖčåą░ 29-7. ąÆčŗą▓ąŠą┤čŗ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą░ą┤čĆąĄčüą░ (ADRPINS).

| |

ą¤čāčüčéčŗąĄ čéą░ą║č鹊ą▓čŗąĄ čåąĖą║ą╗čŗ |

| SPI_MMRDH.DMYSIZE |

(SPI_MMRDH.ADRPINS=0, SPI_CTL.MIOM=x) Dummy-ą▒ą░ą╣čéčŗ, ą┐čĆąŠčģąŠą┤čÅčēąĖąĄ č湥čĆąĄąĘ 1 ą▓čŗą▓ąŠą┤ |

(SPI_MMRDH.ADRPINS=1, SPI_CTL.MIOM=1) Dummy-ą▒ą░ą╣čéčŗ, ą┐čĆąŠčģąŠą┤čÅčēąĖąĄ č湥čĆąĄąĘ 2 ą▓čŗą▓ąŠą┤ą░ |

(SPI_MMRDH.ADRPINS=1, MIOM=2) Dummy-ą▒ą░ą╣čéčŗ, ą┐čĆąŠčģąŠą┤čÅčēąĖąĄ č湥čĆąĄąĘ 4 ą▓čŗą▓ąŠą┤ą░ |

| 000 |

0 |

0 |

0 |

| 001 |

8 |

4 |

2 |

| 010 |

16 |

8 |

4 |

| 011 |

24 |

12 |

6 |

| 100 |

32 |

16 |

8 |

| 101 |

40 |

20 |

10 |

| 110 |

48 |

24 |

12 |

| 111 |

56 |

28 |

14 |

ąŁč鹊čé ą┐ąĄčĆąĖąŠą┤ ą┐čāčüč鹊ą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąĄčĆąĄą┤ą░čéčī ą▒ąĖčéčŗ čĆąĄąČąĖą╝ą░, ą┐ąĄčĆąĄą╣čéąĖ ą▓čŗą▓ąŠą┤ą░ą╝ ą▓ čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ, ąĖ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčīčüčÅ ą▓čŗą▓ąŠą┤ą░ą╝ ą║ ą┐ąŠą┤ą│ąŠč鹊ą▓ą║ąĄ ą║ ą┐čĆąĖąĄą╝čā ą┤ą░ąĮąĮčŗčģ.

[Memory-Mapped ą┤ąŠčüčéčāą┐ čćč鹥ąĮąĖčÅ]

ąÉą┐ą┐ą░čĆą░čéčāčĆą░ SPI ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĮą░ąĖą▒ąŠą╗ąĄąĄ čćą░čüč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ.

ŌĆó 2 čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ čćč鹥ąĮąĖčÅ SPI (čćč鹥ąĮąĖąĄ ąĖ ą▒čŗčüčéčĆąŠąĄ čćč鹥ąĮąĖąĄ), ą║ąŠč鹊čĆčŗąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ SPI_MOSI ąĖ SPI_MISO ą▓ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ ą▓čŗą▓ąŠą┤ą░ą╝ SPI_SEL[n] ąĖ SPI_CLK.

ŌĆó 4 čĆą░čüčłąĖčĆąĄąĮąĮčŗčģ čćč鹥ąĮąĖčÅ SPI čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (extended SPI multiple I/O reads): dual output, quad output, dual I/O ąĖ quad I/O.

ąóą░ą▒ą╗ąĖčåą░ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ SPI 29-8 ąĖ čĆąĖčüčāąĮą║ąĖ 29-15 .. 29.19 ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čéąĖą┐čŗ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāą╣č鹥 ą║ą░ąČą┤čāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ čćč鹥ąĮąĖčÅ čüą┐ąŠčüąŠą▒ąŠą╝, ą║ąŠč鹊čĆčŗą╣ čüąŠą▓ą╝ąĄčüčéąĖą╝ čü ąŠą┐ąĖčüą░ąĮąĖąĄą╝ ą▓ ą┤ą░čéą░čłąĖč鹥 ąĖą╝ąĄčÄčēąĄą╣čüčÅ SPI flash.

ąóą░ą▒ą╗ąĖčåą░ 29-8. ą×ą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ SPI.

| ą×ą┐ąĄčĆą░čåąĖčÅ |

ąÜąŠą╝ą░ąĮą┤ą░ čćč鹥ąĮąĖčÅ (opcode) |

CMDPIN |

ADRPIN |

DMYSIZE |

ąóčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ |

Multiple I/O Mode |

ąÆčŗą▓ąŠą┤čŗ ą┤ą░ąĮąĮčŗčģ |

| Read |

0x03 |

1 |

1 |

0 |

ąĮąĄčé |

ąĮąĄčé |

1 |

| Fast Read |

0x0B |

1 |

1 |

ąĮąĄ 0 |

ąöąÉ |

ąĮąĄčé |

1 |

| Dual Output Read |

0x3B |

1 |

1 |

ąĮąĄ 0 |

ąöąÉ |

ąöąÉ (IO0-1) |

2 |

| Quad Output Read |

0x6B |

1 |

1 |

ąĮąĄ 0 |

ą┤ą░ |

ąöąÉ (IO0-3) |

4 |

| Dual Output Read |

0xBB |

1, 2 |

2 |

ąĮąĄ 0 |

ąöąÉ |

ąöąÉ (IO0-1) |

2 |

| Quad Output Read |

0xEB |

1, 4 |

4 |

ąĮąĄ 0 |

ą┤ą░ |

ąöąÉ (IO0-3) |

4 |

ąØąĄą║ąŠč鹊čĆčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ čéą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąŠą┐ąĄčĆą░čåąĖąĖ čüą╗ąŠą▓ą░ quad I/O read (0xE7) ąĖ octal quad I/O read (0xE3). ąŁčéąĖ ąŠą┐ąĄčĆą░čåąĖąĖ čéčĆąĄą▒čāčÄčé ą╝ąĄąĮčīčłąĄ čéą░ą║č鹊ą▓ dummy, č湥ą╝ ąŠą▒čŗčćąĮčŗąĄ čüč湥čéą▓ąĄčĆąĄąĮąĮčŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ čćč鹥ąĮąĖčÅ (normal quad I/O read).

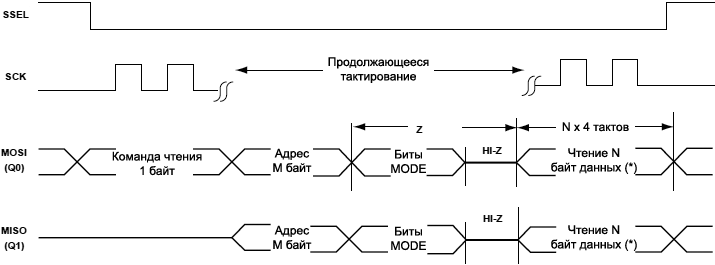

ąĀąĖčü. 29-15. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī SPI Flash Fast Read.

M = 1, 2, 3, 4 (ą▒ą░ą╣čéčŗ ą░ą┤čĆąĄčüą░)

N = 4, 8, 16, 32 (ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ čćč鹥ąĮąĖčÅ)

Z = 0, 8, 16, 24, ..., 56 (čåąĖą║ą╗čŗ ą┤ą╗čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čłąĖąĮčŗ)

* = 1 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ąĮą░ 1 ą┐ąĄčĆąĖąŠą┤ąĄ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄčüčŗą╗ą░ąĄčéčüčÅ č湥čĆąĄąĘ MISO

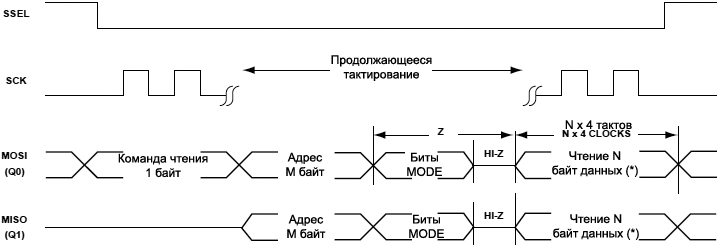

ąĀąĖčü. 29-16. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī SPI Flash Fast Read (Dual Output).

M = 1, 2, 3, 4 (ą▒ą░ą╣čéčŗ ą░ą┤čĆąĄčüą░)

N = 4, 8, 16, 32 (ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ čćč鹥ąĮąĖčÅ)

Z = 0, 4, 12, ..., 28 (čåąĖą║ą╗čŗ ą┤ą╗čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čłąĖąĮčŗ)

* = 2 ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ ąĮą░ 1 ą┐ąĄčĆąĖąŠą┤ąĄ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄčüčŗą╗ą░ąĄčéčüčÅ č湥čĆąĄąĘ ą▓čŗčģąŠą┤čŗ [1:0]

ąĀąĖčü. 29-17. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī SPI Flash Fast Read (Dual I/O).

M = 1, 2, 3, 4 (ą▒ą░ą╣čéčŗ ą░ą┤čĆąĄčüą░)

N = 4, 8, 16, 32 (ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ čćč鹥ąĮąĖčÅ)

Z = 0, 4, 12, ..., 28 (čåąĖą║ą╗čŗ ą┤ą╗čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čłąĖąĮčŗ)

* = 2 ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ ąĮą░ 1 ą┐ąĄčĆąĖąŠą┤ąĄ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄčüčŗą╗ą░ąĄčéčüčÅ č湥čĆąĄąĘ ą▓čŗčģąŠą┤čŗ [1:0]

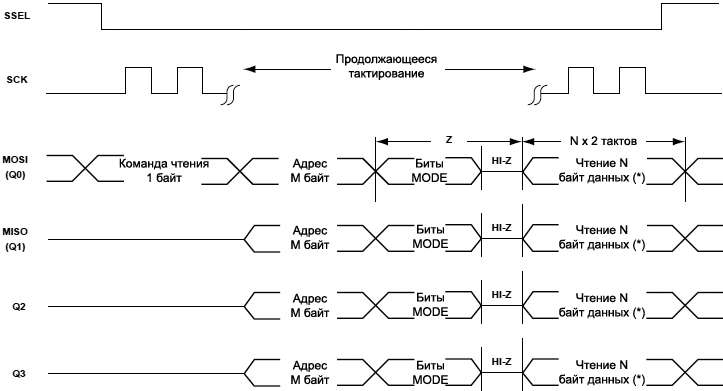

ąĀąĖčü. 29-18. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī SPI Flash Quad Output Read.

M = 1, 2, 3, 4 (ą▒ą░ą╣čéčŗ ą░ą┤čĆąĄčüą░)

N = 4, 8, 16, 32 (ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ čćč鹥ąĮąĖčÅ)

Z = 0, 2, 4, ..., 14 (čåąĖą║ą╗čŗ ą┤ą╗čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čłąĖąĮčŗ)

* = 4 ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ ąĮą░ 1 ą┐ąĄčĆąĖąŠą┤ąĄ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄčüčŗą╗ą░ąĄčéčüčÅ č湥čĆąĄąĘ ą▓čŗčģąŠą┤čŗ [3:0]

ąĀąĖčü. 29-19. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī SPI Flash Quad I/O Read.

M = 1, 2, 3, 4 (ą▒ą░ą╣čéčŗ ą░ą┤čĆąĄčüą░)

N = 4, 8, 16, 32 (ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ čćč鹥ąĮąĖčÅ)

Z = 0, 2, 4, ..., 14 (čåąĖą║ą╗čŗ ą┤ą╗čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čłąĖąĮčŗ)

* = 4 ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ ąĮą░ 1 ą┐ąĄčĆąĖąŠą┤ąĄ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄčüčŗą╗ą░ąĄčéčüčÅ č湥čĆąĄąĘ ą▓čŗčģąŠą┤čŗ [3:0]

ą¦č鹥ąĮąĖčÅ SPI memory-mapped ą╝ąŠą│čāčé ą▒čŗčéčī čüą┤ąĄą╗ą░ąĮčŗ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ čÅą┤čĆą░ ą┐čāč鹥ą╝ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą│ąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄą│ąĖąŠąĮą░ ą║ą░ą║ ą║čŹčłąĖčĆčāąĄą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ ą▒ąĄąĘ ą┐čĆąŠą┐čāčüą║ą░ (without bypass, ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ ą┐ąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÄ ą║čŹčłą░). ąØą░ čĆąĖčüčāąĮą║ą░čģ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ čćč鹥ąĮąĖčÅ (N) ąŠčüąĮąŠą▓ą░ąĮąŠ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝:

ŌĆó ąöą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ čÅą┤čĆąŠą╝ (ą║ąŠą│ą┤ą░ čĆą░ą▒ąŠčéą░ąĄčé čĆąĄąČąĖą╝ XIP); ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĘą░ą▓ąĖčüąĖčé ąŠčé čĆą░ąĘą╝ąĄčĆą░ čüčéčĆąŠą║ąĖ ą║čŹčłą░.

ŌĆó ąöą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą░ąĮąĮčŗčģ čÅą┤čĆąŠą╝ (data read), ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą▓čŗą▒ąŠčĆą║ąĖ ąĘą░ą▓ąĖčüąĖčé ąŠčé čĆą░ąĘą╝ąĄčĆą░ čüčéčĆąŠą║ąĖ ą║čŹčłą░.

ąźąŠčéčÅ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ čĆą░ąĘą╝ąĄčĆ ą┐ąĄčĆąĄąĮąŠčüą░ čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ memory-mapped čüąŠčüčéą░ą▓ą╗čÅąĄčé 4 ą▒ą░ą╣čéą░, ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą▓čŗą▒čĆą░čéčī 1 ą▒ą░ą╣čé ąĖą╗ąĖ 2 ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ąŠąĮąŠ ą╝ąŠąČąĄčé ą▓čŗą▒čĆą░čéčī unsigned char ąĖą╗ąĖ short ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ąŠą┤ą░ C). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┤ą╗čÅ čÅą┤čĆą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčéčüčÅ č鹊ą╗čīą║ąŠ čéčĆąĄą▒čāąĄą╝čŗąĄ ą▒ą░ą╣čéčŗ, ąĖ ą┤čĆčāą│ąĖąĄ ą▒ą░ą╣čéčŗ ą║čŹčłąĖčĆčāčÄčéčüčÅ.

ąÆčüčéčĆąŠąĄąĮąĮą░čÅ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą┐ąŠą┤čüąĖčüč鹥ą╝ą░ ą┐ą░ą╝čÅčéąĖ master ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ą┤ą╗čÅ ą┐ą░ą║ąĄčéą░ (burst) ąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ SPI ą▓čŗą┤ą░ąĄčé čŹč鹊čé ą░ą┤čĆąĄčü ą║ą░ą║ čćą░čüčéčī ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ čćč鹥ąĮąĖčÅ (read header). ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü ą▓čŗčĆąŠą▓ąĮąĄąĮ ą┐ąŠ N ą▒ą░ą╣čéą░ą╝. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ čćč鹥ąĮąĖčÅ 30-ą│ąŠ ą▒ą░ą╣čéą░ ąĖąĘ ą┐ą░ą╝čÅčéąĖ SPI čéąĖą┐ąĖčćąĮčŗą╣ ą░ą┤čĆąĄčü ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ:

ŌĆó 28 (0x0000_001C) ą┤ą╗čÅ 32-ą▒ąĖčéąĮąŠą╣ čüčéčĆąŠą║ąĖ ą║čŹčłą░

ŌĆó 24 (0x0000_0018) ą┤ą╗čÅ 64-ą▒ąĖčéąĮąŠą╣ čüčéčĆąŠą║ąĖ ą║čŹčłą░

ŌĆó 16 (0x0000_0010) ą┤ą╗čÅ 128-ą▒ąĖčéąĮąŠą╣ čüčéčĆąŠą║ąĖ ą║čŹčłą░

ŌĆó 0 (0x0000_0000) ą┤ą╗čÅ 256-ą▒ąĖčéąĮąŠą╣ čüčéčĆąŠą║ąĖ ą║čŹčłą░

ąöą░ąĮąĮčŗąĄ čćč鹥ąĮąĖčÅ ą▓ąŠąĘą▓čĆą░čēą░čÄčéčüčÅ ą▓ ą┐ąŠą┤čüąĖčüč鹥ą╝čā ą┐ą░ą╝čÅčéąĖ ą▓ ą┐ąŠčĆčÅą┤ą║ąĄ, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮąŠą╝ ą┐ą░ą╝čÅčéčīčÄ SPI. ąŚą┤ąĄčüčī ą╝ąŠąČąĄčé ą▒čŗčéčī čāčćąĖčéčŗą▓ą░ąĄą╝ą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą┤ą╗čÅ ąŠąČąĖą┤ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄą╝čŗčģ ą┤ą╗čÅ master.

ŌĆó ąöą╗čÅ čćč鹥ąĮąĖą╣ MDMA ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čćąĖčéą░ąĄą╝čŗčģ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ (N) ą▓čüąĄą│ą┤ą░ čĆą░ą▓ąĮąŠ 4 ą▒ą░ą╣čéą░ą╝. ą¦č鹥ąĮąĖąĄ MDMA ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé čāčüčéą░ąĮąŠą▓ą║ąĖ ą║čŹčłą░. ąöą╗čÅ čćč鹥ąĮąĖą╣ MDMA ą┐čĆąĄą┤ąĄą╗ ą┐ąŠą╗čÅ DMA_CFG.MSIZE 1, 2 ąĖą╗ąĖ 4 ą▒ą░ą╣čéą░. ąÉą┤čĆąĄčü, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮčŗą╣ ą┐ąŠą┤čüąĖčüč鹥ą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ master ą┤ą╗čÅ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ SPI, ą▓čüąĄą│ą┤ą░ ą▓čŗčĆąŠą▓ąĮąĄąĮ ąĮą░ 4 ą▒ą░ą╣čéą░.

[ążčāąĮą║čåąĖąĖ ą▓čŗčüąŠą║ąŠą│ąŠ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖčÅ čćč鹥ąĮąĖčÅ Memory-Mapped]

ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ ą░ą▓č鹊ą╝ą░čéąĖąĘą░čåąĖąĖ ą┤ąŠčüčéčāą┐ąŠą▓ čćč鹥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ SPI, ą░ą┐ą┐ą░čĆą░čéčāčĆą░ memory-mapped čéą░ą║ąČąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĮąĄą║ąŠč鹊čĆčŗąĄ čäčāąĮą║čåąĖąĖ ą┤ą╗čÅ čāą╗čāčćčłąĄąĮąĖčÅ ą▓čŗą▒ąŠčĆąŠą║ ąĖąĘ ą┐ą░ą╝čÅčéąĖ SPI ąĖ ą┐ąŠą▓čŗčłąĄąĮąĖčÅ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖčÅ čüąĖčüč鹥ą╝čŗ. ąŁčéąĖ čäčāąĮą║čåąĖąĖ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ ą▓ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ čüąĄą║čåąĖčÅčģ.

Execute-In-Place (XIP, č鹊ą╗čīą║ąŠ ą┤ą╗čÅ SPI2). ąóąĄčģąĮąŠą╗ąŠą│ąĖčÅ Execute-In-Place, čćą░čēąĄ ąĖąĘą▓ąĄčüčéąĮą░čÅ ą║ą░ą║ XIP, ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ ą║ąŠą┤ ą┐čĆčÅą╝ąŠ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI flash ą▓ą╝ąĄčüč鹊 č鹊ą│ąŠ, čćč鹊ą▒čŗ ąĘą░ą│čĆčāąĘąĖčéčī ą║ąŠą┤ ąĖ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąĄą│ąŠ ąĖąĘ RAM. XIP, čéą░ą║ąČąĄ ąĖąĘą▓ąĄčüčéąĮčŗą╣ ą║ą░ą║ čĆąĄąČąĖą╝ Command Skip, čÅą▓ą╗čÅąĄčéčüčÅ ąŠą▒čēąĖą╝ ą┐ąŠąĮčÅčéąĖąĄą╝, ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĖą╝ąĄąĮąĄąĮ čéą░ą║ąČąĄ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą░ąĮąĮčŗčģ.

ąĢčüčéčī čĆą░ąĘą╗ąĖčćąĖąĄ ą╝ąĄąČą┤čā čĆąĄąČąĖą╝ąŠą╝ XIP ąĖ čüčéą░ąĮą┤ą░čĆčéąĮčŗą╝ čĆąĄąČąĖą╝ąŠą╝. ąÆ čĆąĄąČąĖą╝ąĄ XIP ą┐ąŠčüą╗ąĄ ą▓čŗą▒ąŠčĆą║ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ SPI (CS#=LOW), čŹč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ ąĮąĄ ą┤ąĄą║ąŠą┤ąĖčĆčāąĄčé ą┐ąĄčĆą▓čŗą╣ ą▓čģąŠą┤ąĮąŠą╣ ą▒ą░ą╣čé ą║ą░ą║ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ. ąÆą╝ąĄčüč鹊 čŹč鹊ą│ąŠ ąŠąĮąŠ ąŠąČąĖą┤ą░ąĄčé, čćč鹊 read header ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ąĮą░čćąĮąĄčéčüčÅ čü ą▒ą░ą╣č鹊ą▓ ą░ą┤čĆąĄčüą░. ąÆ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┐ą░ą╝čÅčéčī ą┤ąĄą║ąŠą┤ąĖčĆčāąĄčé ą┐ąĄčĆą▓čŗą╣ ą▓čģąŠą┤ąĮąŠą╣ ą▒ą░ą╣čé ą║ą░ą║ ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ.

ąĀąĄąČąĖą╝ XIP ą┤čĆą░ą╝ą░čéąĖč湥čüą║ąĖ čüąĮąĖąČą░ąĄčé ą▓čĆąĄą╝čÅ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣, ą║ąŠč鹊čĆčŗąĄ čéčĆąĄą▒čāčÄčé ą▒čŗčüčéčĆąŠą│ąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą┤ą░ ą▒ąĄąĘ ąĘą░č鹥ąĮąĄąĮąĖčÅ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ ą┐ą░ą╝čÅčéąĖ ą▓ RAM. ąÉą┐ą┐ą░čĆą░čéčāčĆą░ SPI memory-mapped ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą▒ąĖčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SPI_MMRDH.CMDSKIP ą┤ą╗čÅ ą┐čĆąŠą┐čāčüą║ą░ ą║ąŠą╝ą░ąĮą┤čŗ ąĖąĘ read header.

ąØąĄą║ąŠč鹊čĆčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ SPI čéčĆąĄą▒čāčÄčé ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čüą▓ąŠąĄą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ XIP, ąĖčüą┐ąŠą╗čīąĘčāčÅ ąĮąĄ memory-mapped čĆąĄąČąĖą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░ SPI. ą×ą▒čŗčćąĮąŠ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĖąŠą┤ą░ ą┐čāčüčéčŗčģ čåąĖą║ą╗ąŠą▓ (dummy cycle period) ą▒ąĖčéčŗ čĆąĄąČąĖą╝ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ XIP ąĖ ą┐ąŠą╗ąĄ SPI_MMRDH.MODE ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝. ą£ąŠąČąĄčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ dummy memory mapped ą┤ąŠčüčéčāą┐ ą┐ąĄčĆąĄą┤ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SPI_MMRDH.CMDSKIP, čćč鹊ą▒čŗ čāčüčéą░ąĮąŠą▓ąĖčéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ SPI ą▓ čĆąĄąČąĖą╝ Command Skip.

ąöą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ č鹊ą╝, ą║ą░ą║ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ SPI ą▓ čĆąĄąČąĖą╝ XIP, ąŠą▒čĆą░čéąĖč鹥čüčī ą║ ą┤ą░čéą░čłąĖčéčā čŹč鹊ą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

[ąæąĖčéčŗ čüčéą░čéčāčüą░ ąŠčłąĖą▒ą║ąĖ čĆąĄąČąĖą╝ą░ Memory-Mapped]

ąÉą┐ą┐ą░čĆą░čéčāčĆą░ SPI memory-mapped ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą▒ąĖčéčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_STAT ą┤ą╗čÅ čüąŠąŠą▒čēąĄąĮąĖčÅ ąŠą▒ ąŠčłąĖą▒ą║ą░čģ. ąŁčéąĖ ą▒ąĖčéčŗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠą┐ąŠą▓ąĄčēąĄąĮąĖčÅ, ąĖ ąĖčģ čüąŠčüč鹊čÅąĮąĖąĄ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ąŠą┐ąĄčĆą░čåąĖąĖ SPI. ąŁčéąĖ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗąĄ "ą╗ąĖą┐ą║ąĖąĄ" (sticky), ąĖčģ ąŠčćąĖčēą░ąĄčé ąŠą┐ąĄčĆą░čåąĖčÅ W1C (write-1-to-clear, ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ 1 ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ).

ŌĆó Memory-Mapped Write Error (SPI_STAT.MMWE). ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ (=1), ąĄčüą╗ąĖ čüą┤ąĄą╗ą░ąĮą░ ą┐ąŠą┐čŗčéą║ą░ ąĘą░ą┐ąĖčüą░čéčī ą▓ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ, ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ą┤ą╗čÅ ą┐ą░ą╝čÅčéąĖ memory-mapped SPI. ąÉą┐ą┐ą░čĆą░čéčāčĆą░ SPI memory-mapped ąĮą░ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą░ą▓č鹊ą╝ą░čéąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ąĘą░ą┐ąĖčüąĖ ą▓ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ SPI.

ŌĆó Memory-Mapped Read Error (SPI_STAT.MMRE). ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ (=1), ąĄčüą╗ąĖ čüą┤ąĄą╗ą░ąĮą░ ą┐ąŠą┐čŗčéą║ą░ čćč鹥ąĮąĖčÅ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░, ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┤ą╗čÅ ą┐ą░ą╝čÅčéąĖ memory-mapped SPI, ą║ąŠą│ą┤ą░ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ ąĘą░ą┐čĆąĄčēąĄąĮąŠ (SPI_CTL.MMSE=0).

ŌĆó Memory-Mapped Access Error (SPI_STAT.MMAE). ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ (=1), ąĄčüą╗ąĖ ą▒čŗą╗ą░ čüą┤ąĄą╗ą░ąĮą░ ą┐ąŠą┐čŗčéą║ą░ ą┤ąŠčüčéčāą┐ą░ ą║ ą╗ąĖą▒ąŠ TX, ą╗ąĖą▒ąŠ RX FIFO, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮ ą┤ąŠčüčéčāą┐ memory-mapped ą║ ą┐ą░ą╝čÅčéąĖ SPI. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▒ą╗ąŠą║ąĖčĆčāčÄčéčüčÅ ą┐ąŠą┐čŗčéą║ąĖ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖčÅ čü čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ SPI č湥čĆąĄąĘ čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ą╝ąĄč鹊ą┤čŗ, ąĖ čäą░ą▒čĆąĖą║ą░ ą┐čĆąĖąĄą╝ą░ ąŠčéą▓ąĄčéąĖčé ąŠčłąĖą▒ą║ąŠą╣. ąĪčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ą╝ąĄč鹊ą┤čŗ ą▓ą║ą╗čÄčćą░čÄčé ą╗čÄą▒čŗąĄ ą╝ąĄč鹊ą┤čŗ ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ ą▒čāč乥čĆą░ą╝ FIFO TX b RX FIFO, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčéą║čāą┤ą░ čŹč鹊čé ą┤ąŠčüčéčāą┐ ą┐čĆąŠąĖąĘąŠčłąĄą╗ - ąŠčé DMA ąĖą╗ąĖ ąŠčé MMR ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ŌĆó Memory-Mapped Write Error Mask (SPI_CTL.MMWEM). ąŁč鹊čé ą▒ąĖčé čāą║ą░ąĘčŗą▓ą░ąĄčé, ą▒čŗą╗ ą╗ąĖ čäą░ą▒čĆąĖą║ąĄ ą▓ąŠąĘą▓čĆą░čēąĄąĮ ąŠčéą▓ąĄčé ąŠčłąĖą▒ą║ąĖ ąĮą░ ą┐ąŠą┐čŗčéą║čā ąĘą░ą┐ąĖčüąĖ ą▓ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ, ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ą┤ą╗čÅ čćč鹥ąĮąĖą╣ memory-mapped ą┐ą░ą╝čÅčéąĖ SPI. ąØąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą▒čŗą╗ ą╗ąĖ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮ ąŠčéą▓ąĄčé ąŠčłąĖą▒ą║ąĖ ąĘą░ą┐ąĖčüąĖ čü ą┐ąŠą╝ąŠčēčīčÄ čŹč鹊ą│ąŠ ą▒ąĖčéą░, ą▓čüąĄ čĆą░ą▓ąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ sticky-ą▒ąĖčé ąŠą┐ąŠą▓ąĄčēąĄąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ ąĘą░ą┐ąĖčüąĖ memory-mapped (SPI_STAT.MMWE).

ąŚąÉą£ąĢą¦ąÉąØąśąĢ: ą▓ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ą┤čĆčāą│ąĖčģ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ SPI_STAT čŹčéąĖ ą▒ąĖčéčŗ ąŠčłąĖą▒ą║ąĖ čĆąĄąČąĖą╝ą░ memory-mapped ąĮąĄ ąĖą╝ąĄčÄčé čüą▓čÅąĘą░ąĮąĮčŗčģ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆą░čģ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ SPI (SPI_IMSK) ąĖ čüąŠą▒čŗčéąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SPI (SPI_ILAT).

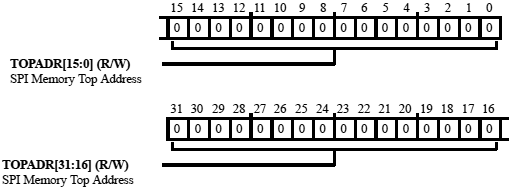

ąĀąĄą│ąĖčüčéčĆ ą▓ąĄčĆčģąĮąĄą╣ ą│čĆą░ąĮąĖčåčŗ (memory-mapped top register, SPI_MMTOP) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, čćč鹊ą▒čŗ ąĘą░ą┤ą░čéčī ą▓ąĄčĆčģąĮąĖą╣ ą┐čĆąĄą┤ąĄą╗ ą░ą┤čĆąĄčüą░ ą┐ą░ą╝čÅčéąĖ SPI. Memory-mapped ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ SPI ą┐ąŠ ą░ą┤čĆąĄčüčā, čĆą░ą▓ąĮąŠą╝čā ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄą╝čā čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ, čüčćąĖčéą░ąĄčéčüčÅ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗą╝. ąóą░ą║ąŠą╣ ą┤ąŠčüčéčāą┐ ą▒ą╗ąŠą║ąĖčĆčāąĄčéčüčÅ ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąŠčéą▓ąĄčé ąŠčłąĖą▒ą║ąĖ čłąĖąĮčŗ.

ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ą┐ąŠą╗ąĄąĘąĄąĮ ą┤ą╗čÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą┤ąŠčüčéčāą┐ą░ ą║ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗą╝ ą░ą┤čĆąĄčüą░ą╝ ą┐ą░ą╝čÅčéąĖ SPI. ąØąĄą║ąŠč鹊čĆčŗąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĖ ą┐ą░ą╝čÅčéąĖ SPI ąĮąĄ č湥čéą║ąŠ ąĘą░ą┤ą░čÄčé (ą▒ąĄąĘ ą│ą░čĆą░ąĮčéąĖąĖ) ą┐čĆąĄą▓čŗčłąĄąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčé ą░ą┤čĆąĄčüą░, čćč鹊ą▒čŗ čéą░ą║ąŠą╣ ą░ą┤čĆąĄčü ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░ą╗čüčÅ, čéą░ą║ čćč鹊 ąĄčüčéčī ąŠą┐ą░čüąĮąŠčüčéčī ą┐ąĄčĆąĄčüą║ąŠą║ą░ ą┤ąŠčüčéčāą┐ą░ ą▓ ąĮą░čćą░ą╗ąŠ ą┐ą░ą╝čÅčéąĖ ą┐čĆąĖ ą┐čĆąĄą▓čŗčłąĄąĮąĖąĖ ąĘąĮą░č湥ąĮąĖčÅ ą░ą┤čĆąĄčüą░.

[ąĀčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ą┐ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÄ Memory-Mapped]

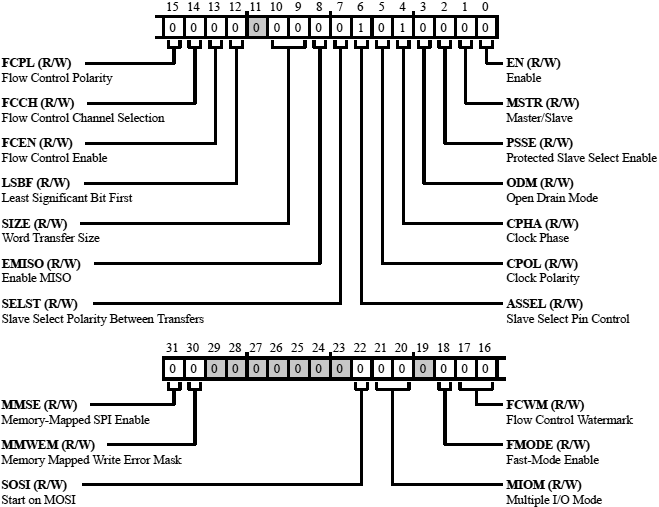

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ SPI_CTL.MMSE čĆą░ąĘčĆąĄčłą░ąĄčé čĆąĄąČąĖą╝ SPI memory-mapped. ąÜąŠą│ą┤ą░ čŹč鹊čé čĆąĄąČąĖą╝ čĆą░ąĘčĆąĄčłąĄąĮ, ąĖąĮč鹥čĆč乥ą╣čü SPI ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą┤ą╗čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖčÅ čü čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ąĖ ą┐ą░ą╝čÅčéąĖ SPI, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čāčüčéą░ąĮąŠą▓ąŠą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ą▒ąĖčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ąÆ čüą╗ąĄą┤čāčÄčēąĖčģ čéą░ą▒ą╗ąĖčåą░čģ ą┐ąŠą║ą░ąĘą░ąĮčŗ čéąĖą┐ąĖčćąĮčŗąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ SPI ą▓ čĆąĄąČąĖą╝ąĄ memory-mapped:

ąóą░ą▒ą╗ąĖčåą░ 29-9. ąĀąĄą│ąĖčüčéčĆ SPI Control (čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SPI_CTL).

| ąæąĖčéčŗ |

ąóąĖą┐ąĖčćąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ |

| SPI_CTL.MSTR |

1 |

Master mode enable (čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆąĄąČąĖą╝ą░ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░) |

|

| SPI_CTL.PSSE |

0 |

Protected slave select enable (ąĘą░čēąĖčēąĄąĮąĮąŠąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░) |

|

| SPI_CTL.ODM |

0 |

Open-drain mode enable (čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą▓čŗčģąŠą┤ąŠą▓ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝) |

|

| SPI_CTL.CPHA, SPI_CTL.CPOL |

00 ąĖą╗ąĖ 11 |

ąĀąĄąČąĖą╝ ąŠą▒ą╝ąĄąĮą░ SPI (č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░) |

ąŚą░ą▓ąĖčüąĖčé ąŠčé ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ FLASH, ąŠą▒čŗčćąĮąŠ SPI flash ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé mode-0 (CPHA=CPOL=0) ąĖ mode-3 (CPHA=CPOL=1). |

| SPI_CTL.ASSEL |

1 |

ąÉą┐ą┐ą░čĆą░čéąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą▒ąŠčĆą║ąŠą╣ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ |

|

| SPI_CTL.SELST |

1 |

ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą▓čŗą▒ąŠčĆą║ąĖ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ |

|

| SPI_CTL.EMISO |

1 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą▓čŗą▓ąŠą┤ą░ MISO |

|

| SPI_CTL.SIZE |

2 |

32-ą▒ąĖčéąĮčŗą╣ čĆą░ąĘą╝ąĄčĆ ą┐ąĄčĆąĄą┤ą░čćąĖ |

|

| SPI_CTL.LSBF |

0 |

ąĀąĄąČąĖą╝, ą║ąŠą│ą┤ą░ čüčéą░čĆčłąĖą╣ ą▒ąĖčé (MSB) ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝ |

ąŚą░ą▓ąĖčüąĖčé ąŠčé ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, ąĮąŠ ąŠą▒čŗčćąĮąŠ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ SPI ą▓ąĄą┤ąĄčé ąŠą▒ą╝ąĄąĮ, ą║ąŠą│ą┤ą░ čüčéą░čĆčłąĖą╣ ą▒ąĖčé ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝. |

| SPI_CTL.FCEN, SPI_CTL.FCCH, SPI_CTL.FCPL, SPI_CTL.FCWM |

0 |

ąæąĖčéčŗ, ąŠčéąĮąŠčüčÅčēąĖąĄčüčÅ ą║ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╝čā čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÄ ą┐ąŠč鹊ą║ąŠą╝ (flow control) |

|

| SPI_CTL.FMODE |

1 |

FAST mode enable (čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą▒čŗčüčéčĆąŠą│ąŠ čĆąĄąČąĖą╝ą░) |

ą×ą▒čŗčćąĮąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 1 ą┤ą╗čÅ čéą░ą╣ą╝ąĖąĮą│ą░ ą┐ąŠą╗ąĮąŠą│ąŠ čåąĖą║ą╗ą░, 0 č鹊ą╗čīą║ąŠ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ ąĮąĖąĘą║ąŠą╣ čüą║ąŠčĆąŠčüčéąĖ. |

| SPI_CTL.SOSI |

0 |

SPI_MOSI čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗą▓ąŠą┤ IO0. |

|

ąóą░ą▒ą╗ąĖčåą░ 29-10. ąĀąĄą│ąĖčüčéčĆ SPI Receive Control (čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ąŠą╝).

| ąæąĖčéčŗ |

ąóąĖą┐ąĖčćąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| SPI_RXCTL.REN |

1 |

Receive channel enable (čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ ą┐čĆąĖąĄą╝ą░) |

| SPI_RXCTL.RTI |

0 |

Receive transfer initiation disable (ąĘą░ą┐čĆąĄčé ąĖąĮąĖčåąĖą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ ą║ą░ąĮą░ą╗ąĄ ą┐čĆąĖąĄą╝ą░) |

| SPI_RXCTL.RWCEN |

0 |

Receive word counter disable (ąĘą░ą┐čĆąĄčé čüč湥čéčćąĖą║ą░ čüą╗ąŠą▓ ą┐čĆąĖąĄą╝ą░) |

| SPI_RXCTL.RDR |

0 |

Receive data request disable (ąĘą░ą┐čĆąĄčé ąĘą░ą┐čĆąŠčüą░ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ą░) |

| SPI_RXCTL.RDO |

0 |

ą×čéą▒čĆą░čüčŗą▓ą░čéčī ą▓čģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, ąĄčüą╗ąĖ ą▒čāč乥čĆ RFIFO ąĘą░ą┐ąŠą╗ąĮąĄąĮ |

| SPI_RXCTL.RRWM |

0 |

Receive FIFO regular watermark (ąŠą▒čŗčćąĮą░čÅ ą│čĆą░ąĮąĖčåą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▒čāč乥čĆą░ FIFO ą┐čĆąĖąĄą╝ą░) |

| SPI_RXCTL.RUWM |

0 |

Receive FIFO urgent watermark disable (ąĘą░ą┐čĆąĄčé čüčĆąŠčćąĮąŠą╣ ą│čĆą░ąĮąĖčåčŗ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▒čāč乥čĆą░ FIFO ą┐čĆąĖąĄą╝ą░) |

ąóą░ą▒ą╗ąĖčåą░ 29-11. ąĀąĄą│ąĖčüčéčĆ SPI Transmit Control (čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░č湥ą╣).

| ąæąĖčéčŗ |

ąóąĖą┐ąĖčćąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| SPI_TXCTL.TEN |

1 |

Transmit channel enable (čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ) |

| SPI_TXCTL.TTI |

1 |

Transmit transfer initiation disable (ąĘą░ą┐čĆąĄčé ąĖąĮąĖčåąĖą░čåąĖąĖ ąĮą░ ą║ą░ąĮą░ą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ) |

| SPI_TXCTL.TWCEN |

0 |

Transmit word counter disable (ąĘą░ą┐čĆąĄčé čüč湥čéčćąĖą║ą░ čüą╗ąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ) |

| SPI_TXCTL.TDR |

0 |

Transmit data request disable (ąĘą░ą┐čĆąĄčé ąĘą░ą┐čĆąŠčüą░ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čćąĖ) |

| SPI_TXCTL.TDU |

0 |

ą×čéą┐čĆą░ą▓ą║ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čüą╗ąŠą▓ą░, ą║ąŠą│ą┤ą░ TFIFO ą┐čāčüčé |

| SPI_TXCTL.TRWM |

0 |

Transmit FIFO regular watermark (ąŠą▒čŗčćąĮą░čÅ ą│čĆą░ąĮąĖčåą░ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ) |

| SPI_TXCTL.TUWM |

0 |

Transmit FIFO urgent watermark disable (ąĘą░ą┐čĆąĄčé čüčĆąŠčćąĮąŠą╣ ą│čĆą░ąĮąĖčåčŗ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ) |

ąóą░ą▒ą╗ąĖčåą░ 29-12. ąĀąĄą│ąĖčüčéčĆ SPI DLY Control (čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░ą┤ąĄčƹȹ║ą░ą╝ąĖ).

| ąæąĖčéčŗ |

ąóąĖą┐ąĖčćąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ* |

| SPI_DLY.LAGX |

1 |

Extended LAG timing (ąĖąĮč鹥čĆą▓ą░ą╗ ą▓čĆąĄą╝ąĄąĮąĖ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ LAG) |

|

| SPI_DLY.LEADX |

1 |

Extended LEAD timing (ąĖąĮč鹥čĆą▓ą░ą╗ ą▓čĆąĄą╝ąĄąĮąĖ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ LEAD) |

|

| SPI_DLY.STOP |

3 |

ąæąĖčé STOP ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ |

ą£ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 1 ą┤ą╗čÅ ą┐ąŠąĮąĖąČąĄąĮąĮčŗčģ čćą░čüč鹊čé SPI. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ *: čüą╝. ą┤ą░čéą░čłąĖčé ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ SPI Flash ą┤ą╗čÅ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ą▓čŗą▒ąŠčĆą║ąĖ CS (ąĮą░ą┐čĆąĖą╝ąĄčĆ SSEL).