|

ąÆ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ Blackfin ADSP-BF538 ąĄčüčéčī 3 čĆą░ąĘąĮąŠą▓ąĖą┤ąĮąŠčüčéąĖ čāčüčéčĆąŠą╣čüčéą▓, ą║ąŠč鹊čĆčŗąĄ ąŠčéąĮąŠčüčÅčéčüčÅ ą║ ąŠčéčüč湥čéčā čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (ą┐čĆąĖą▓čÅąĘą░ąĮąĮąŠą│ąŠ ą║ ą╗ąĖą▒ąŠ ą║ čćą░čüč鹊č鹥 čÅą┤čĆą░, ą╗ąĖą▒ąŠ ą║ čćą░čüč鹊č鹥 čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ). ąŁč鹊 čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ (WatchDog Timer), čüč湥čéčćąĖą║ čéą░ą║č鹊ą▓ čÅą┤čĆą░ (core timer) ąĖ ąŠą▒čŗčćąĮčŗąĄ čéą░ą╣ą╝ąĄčĆčŗ (čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ čéą░ą╣ą╝ąĄčĆčŗ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ, general-purpose programmable timer). ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ čĆą░ąĘą┤ąĄą╗ą░ "Timers" ąĖąĘ ą┤ą░čéą░čłąĖčéą░ [1]. ąÆčüąĄ ąĮąĄą┐ąŠąĮčÅčéąĮčŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąĪą╗ąŠą▓ą░čĆąĖą║", ą▓ ą║ąŠąĮčåąĄ čüčéą░čéčīąĖ.

ąĪč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ [2] ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ (ąĖą╗ąĖ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ) ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĄčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĘą░ą▓ąĖčüą╗ą░.

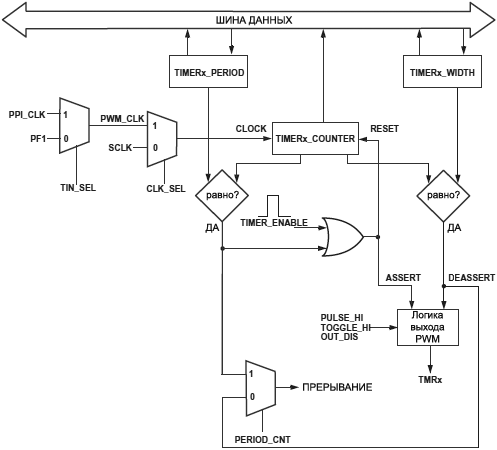

ą×ą▒čŗčćąĮčŗąĄ čéą░ą╣ą╝ąĄčĆčŗ (ąĖčģ 3 čłčéčāą║ąĖ) ą╝ąŠą│čāčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░, čćč鹊ą▒čŗ čüąŠąĘą┤ą░čéčī ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖąĄ čüąŠą▒čŗčéąĖčÅ ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, ąĖą╗ąĖ ą╝ąŠą│čāčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čéą░ą║č鹊ą▓čŗąĄ čćą░čüč鹊čéčŗ ą┤ą╗čÅ čŹą╗ąĄą║čéčĆąŠąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ąĖą╗ąĖ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐ąŠą┤čüč湥čéą░ ą▓ąĮąĄčłąĮąĖčģ ąĖą╝ą┐čāą╗čīčüąŠą▓. ą×ą▒čŗčćąĮčŗąĄ čéą░ą╣ą╝ąĄčĆčŗ ąĖą╝ąĄčÄčé ą▓ąĮąĄčłąĮąĖą╣ ą▓čŗą▓ąŠą┤ ąĮą░ ą║ąŠčĆą┐čāčüąĄ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą╗ąĖą▒ąŠ ą║ą░ą║ ą╝ąŠą┤čāą╗čÅč鹊čĆ ą©ąśą£ (PWM), ą╗ąĖą▒ąŠ ą║ą░ą║ ą▓čŗčģąŠą┤ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą╣ čćą░čüč鹊čéčŗ, ą╗ąĖą▒ąŠ ą║ą░ą║ ą▓čģąŠą┤ ą┤ą╗čÅ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ čéą░ą╣ą╝ąĄčĆą░, ą╗ąĖą▒ąŠ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą╝ąĄčģą░ąĮąĖąĘą╝ą░ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĖ ą┐ąĄčĆąĖąŠą┤ą░ ą▓ąĮąĄčłąĮąĖčģ čüąŠą▒čŗčéąĖą╣. ąŁčéąĖ čéą░ą╣ą╝ąĄčĆčŗ ą╝ąŠą│čāčé čéą░ą║čéąĖčĆąŠą▓ą░čéčīčüčÅ ą╗ąĖą▒ąŠ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą┐ąŠą┤ą░ąĮąĮąŠą│ąŠ ąĮą░ ą▓čŗą▓ąŠą┤ PF1 (TACLK), ą╗ąĖą▒ąŠ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą┐ąŠą┤ą░ąĮąĮąŠą│ąŠ ąĮą░ ą▓čŗą▓ąŠą┤ PPI_CLK (TMRCLK), ą╗ąĖą▒ąŠ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ SCLK. ą×ą▒čŗčćąĮčŗąĄ čéą░ą╣ą╝ąĄčĆčŗ čéą░ą║ąČąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čäčāąĮą║čåąĖąĖ ą░ą▓č鹊ą┤ąĄč鹥ą║čéą░ čüą║ąŠčĆąŠčüčéąĖ UART0 - ąĖąĘą╝ąĄčĆčÅčÄčéčüčÅ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą┐ąŠč鹊ą║ą░ ą┤ą░ąĮąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░.

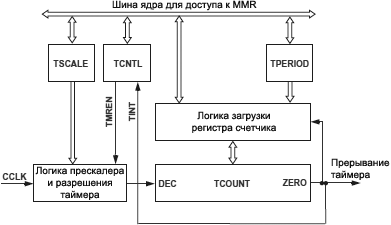

ąĪč湥čéčćąĖą║ čéą░ą║č鹊ą▓ čÅą┤čĆą░ čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé čćą░čüč鹊čéčŗ čÅą┤čĆą░ CCLK, ąĖ ąŠąĮ ąŠą▒čŗčćąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ čéąĖą║ąĖ čüąĖčüč鹥ą╝čŗ - ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ, ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą╝ąĄąČą┤čā ąĘą░ą┤ą░čćą░ą╝ąĖ.

[ąóą░ą╣ą╝ąĄčĆčŗ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (General-Purpose Timers)]

ąÆ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ ADSP-BF538 ąĖą╝ąĄčÄčéčüčÅ 3 čéą░ą╣ą╝ąĄčĆą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (ą┤ą░ą╗ąĄąĄ ą┐čĆąŠčüč鹊 čéą░ą╣ą╝ąĄčĆ), ą║ą░ąČą┤čŗą╣ ąĖąĘ ą║ąŠč鹊čĆčŗčģ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ ąŠą┤ąĖąĮ ąĖąĘ 3 čĆąĄąČąĖą╝ąŠą▓:

ŌĆó ąĀąĄąČąĖą╝ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą©ąśą£ (Pulse-width modulation, PWM_OUT).

ŌĆó ąĀąĄąČąĖą╝ ą┐ąŠą┤čüč湥čéą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĖą╝ą┐čāą╗čīčüą░ ąĖ ąĘą░čģą▓ą░čéą░ (WDTH_CAP).

ŌĆó ąĀąĄąČąĖą╝ ą┐ąŠą┤čüč湥čéą░ ą▓ąĮąĄčłąĮąĖčģ čüąŠą▒čŗčéąĖą╣ (External event, EXT_CLK).

ąÆ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓ąĮąĄčłąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ čéą░ą╣ą╝ąĄčĆąŠą▓.

| ąĪąĖą│ąĮą░ą╗ |

ąóąĖą┐ |

ą©ą░čĆąĖą║ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| TMR2 |

I/O |

K2 |

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆąĄąČąĖą╝ą░ čéą░ą╣ą╝ąĄčĆą░ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ ą▓čŗčģąŠą┤ (ą│ąĄąĮąĄčĆą░čåąĖčÅ ą©ąśą£, čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé) ąĖą╗ąĖ ą║ą░ą║ ą▓čģąŠą┤ (ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĖ ą┐ąĄčĆąĖąŠą┤ą░ ąĖą╝ą┐čāą╗čīčüąŠą▓, ą┐ąŠą┤čüč湥čé ą▓ąĮąĄčłąĮąĖčģ čüąŠą▒čŗčéąĖą╣). |

| TMR1 |

L2 |

| TMR0 |

M2 |

| PF1 |

I |

E1 |

ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗą╣ čéą░ą║č鹊ą▓čŗą╣ ą▓čģąŠą┤ ą┤ą╗čÅ čüč湥čéčćąĖą║ąŠą▓ čéą░ą╣ą╝ąĄčĆąŠą▓ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ. |

| PPI_CLK |

I |

A4 |

ąÆąĮąĄčłąĮčÅčÅ ąŠą┐ąŠčĆąĮą░čÅ čćą░čüč鹊čéą░ ą┤ą╗čÅ čéą░ą╣ą╝ąĄčĆąŠą▓. |

ąŻ ą║ą░ąČą┤ąŠą│ąŠ ąĖąĘ čéą░ą╣ą╝ąĄčĆąŠą▓ ąĄčüčéčī ąŠą┤ąĖąĮ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗą╣ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ ą▓čŗą▓ąŠą┤ ą║ąŠčĆą┐čāčüą░, TMRx. ąŁč鹊čé ą▓čŗą▓ąŠą┤ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą╗ąĖą▒ąŠ ą║ą░ą║ ą▓čŗčģąŠą┤ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT, ą╗ąĖą▒ąŠ ą║ą░ą║ ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ą░čģ WDTH_CAP ąĖ EXT_CLK. ąöą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ čŹčéąĖčģ čäčāąĮą║čåąĖą╣ ą║ą░ąČą┤čŗą╣ čéą░ą╣ą╝ąĄčĆ ąĖą╝ąĄąĄčé ą┐ąŠ 4 čĆąĄą│ąĖčüčéčĆą░ MMR.

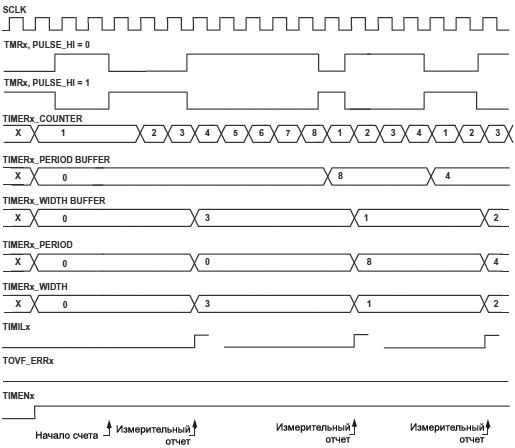

ąĀąĖčü. 16-1. ąæą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ čéą░ą╣ą╝ąĄčĆą░.

ąÆąŠčé ą┐ąŠą╗ąĮčŗą╣ čüą┐ąĖčüąŠą║ čĆąĄą│ąĖčüčéčĆąŠą▓ čéą░ą╣ą╝ąĄčĆą░:

ŌĆó ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ (TIMERx_CONFIG).

ŌĆó ąĪč湥čéčćąĖą║ čéą░ą╣ą╝ąĄčĆą░ (TIMERx_COUNTER).

ŌĆó ą¤ąĄčĆąĖąŠą┤ čéą░ą╣ą╝ąĄčĆą░ (TIMERx_PERIOD).

ŌĆó ą©ąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ čéą░ą╣ą╝ąĄčĆą░ (TIMERx_WIDTH).

ąöą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ čüč湥čéą░ ąĖ č鹊čćąĮąŠčüčéąĖ čüą╗ąĄą┤čāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ čüą┤ąĄą╗ą░ąĮčŗ 32-ą▒ąĖčéąĮčŗą╝ąĖ (čüą╝. čĆąĖčü. 16-1): TIMERx_COUNTER, TIMERx_PERIOD ąĖ TIMERx_WIDTH.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ą╝ąĄčüč鹊 x ą┐ąŠą┤čüčéą░ą▓ą╗čÅąĄčéčüčÅ čćąĖčüą╗ąŠ 0, 1 ąĖą╗ąĖ 2 - ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░.

ąÜąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą┤ą╗čÅ č鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (ąŠąĮą░ ąČąĄ čćą░čüč鹊čéą░ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ SCLK). ą¤čĆąĄą┤ą┐ąŠą╗ąŠąČąĖą╝, čćč鹊 SCLK = 133 ą£ąōčå, č鹊ą│ą┤ą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĖąŠą┤ ą┤ą╗čÅ čüč湥čéą░ čéą░ą╣ą╝ąĄčĆą░ čüąŠčüčéą░ą▓ąĖčé ((2^32-1) / 133 MHz) = 32.2 čüąĄą║čāąĮą┤čŗ.

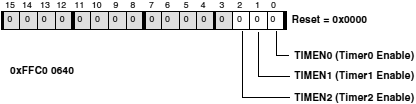

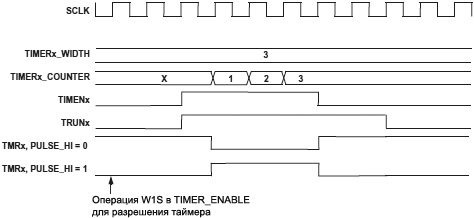

ąĀąĄą│ąĖčüčéčĆ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆąŠą▓ (TIMER_ENABLE) ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ą▓čüąĄčģ 3 čéą░ą╣ą╝ąĄčĆąŠą▓ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. ąÆ čĆąĄą│ąĖčüčéčĆąĄ čüąŠą┤ąĄčƹȹĖčéčüčÅ 3 ą▒ąĖčéą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, čĆą░ą▒ąŠčéą░čÄčēąĖąĄ ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā "write-1-to-set" (ąĘą░ą┐ąĖčüą░čéčī ą╗ąŠą│. 1 ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ), ą┐ąŠ ąŠą┤ąĮąŠą╝čā ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░. ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ, čĆąĄą│ąĖčüčéčĆ ąĘą░ą┐čĆąĄčēąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆąŠą▓ (TIMER_DISABLE) čüąŠą┤ąĄčƹȹĖčé 3 ą▒ąĖčéą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čéąĖą┐ą░ "write-1-to-clear", ą║ąŠč鹊čĆčŗą╝ąĖ ą╝ąŠąČąĮąŠ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąĘą░ą┐čĆąĄčéąĖčéčī ą▓čüąĄ 3 čéą░ą╣ą╝ąĄčĆą░. ą×ą▒ą░ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆą░ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī č鹥ą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆąŠą▓: ą╗ąŠą│. 1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ. ąóą░ą╣ą╝ąĄčĆ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┐ąŠ ąĖčüč鹥č湥ąĮąĖąĖ 3 čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ąŠą▓ SCLK ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TIMENx. ąÆčüąĄ ąĮąĄąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▒ąĖčéčŗ čćąĖčéą░čÄčéčüčÅ ą║ą░ą║ 0.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆąŠą▓, ą┐ąŠą╝ąĄč湥ąĮąĮčŗąĄ ąĮą░ čĆąĖčüčāąĮą║ą░čģ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝, ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ.

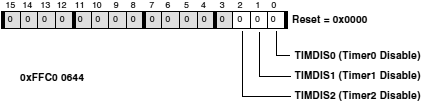

ąĀąĖčü. 16-2. ąĀąĄą│ąĖčüčéčĆ TIMER_ENABLE.

TIMEN2, TIMEN1, TIMEN0. ąĀąĄą│ąĖčüčéčĆ TIMER_DISABLE čüąŠą┤ąĄčƹȹĖčé 3 ą▒ąĖčéą░ ąĘą░ą┐čĆąĄčéą░ čéą░ą╣ą╝ąĄčĆąŠą▓, čĆą░ą▒ąŠčéą░čÄčēąĖąĄ ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā W1C ("write-1-to-clear", čé. ąĄ. ąĘą░ą┐ąĖčüą░čéčī ą╗ąŠą│. 1 ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ). ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 1 ąĘą░ą┐čĆąĄčēą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čéą░ą╣ą╝ąĄčĆ, ąĘą░ą┐ąĖčüčī ą╗ąŠą│. 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ. ąÜą░ąČą┤čŗą╣ ąĖąĘ ą▒ąĖč鹊ą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ, ąĖą╗ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓ ą╗čÄą▒ąŠą╣ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ. ą¦č鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ TIMER_DISABLE ą▓ąŠąĘą▓čĆą░čéąĖčé č鹊čé ąČąĄ čĆąĄąĘčāą╗čīčéą░čé, čćč鹊 ąĖ čćč鹥ąĮąĖąĄ TIMER_ENABLE: ą╗ąŠą│. 1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ. ąÆčüąĄ ąĮąĄąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▒ąĖčéčŗ čćąĖčéą░čÄčéčüčÅ ą║ą░ą║ 0.

ąĀąĖčü. 16-3. ąĀąĄą│ąĖčüčéčĆ TIMER_DISABLE.

TIMDIS2, TIMDIS1, TIMDIS0. ąÆ čĆąĄąČąĖą╝ąĄ PWM_OUT ąĘą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ TIMER_DISABLE ąĮąĄ ąŠčüčéą░ąĮąŠą▓ąĖčé ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čéą░ą╣ą╝ąĄčĆ. ąÆą╝ąĄčüč鹊 čŹč鹊ą│ąŠ čéą░ą╣ą╝ąĄčĆ ą┐čĆąŠą┤ąŠą╗ąČąĖčé čüč湥čé, ąĖ ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ č鹥ą║čāčēąĄą│ąŠ č乊čĆą╝ąĖčĆčāąĄą╝ąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ (ąĄčüą╗ąĖ PERIOD_CNT = 1) ąĖą╗ąĖ ąĖą╝ą┐čāą╗čīčüą░ (ąĄčüą╗ąĖ PERIOD_CNT = 0). ąĢčüą╗ąĖ ąĮčāąČąĮąŠ, ą┐čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠąČąĄčé ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ąŠčüčéą░ąĮąŠą▓ąĖčéčī čéą░ą╣ą╝ąĄčĆ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT ą┐čāč鹥ą╝ ą┐ąĄčĆą▓ąŠąĮą░čćą░ą╗čīąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ ą╗ąŠą│. 1 ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé TIMER_DISABLE, ąĖ ąĘą░č鹥ą╝ ąĘą░ą┐ąĖčüčīčÄ ą╗ąŠą│. 1 ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé TRUNx čĆąĄą│ąĖčüčéčĆą░ TIMER_STATUS. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "ą×čüčéą░ąĮąŠą▓ą║ą░ čéą░ą╣ą╝ąĄčĆą░ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT".

ąÆ čĆąĄąČąĖą╝ą░čģ WDTH_CAP ąĖ EXT_CLK ąĘą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ ą▒ąĖčéčŗ TIMER_DISABLE ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąŠčüčéą░ąĮąŠą▓ąĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čéą░ą╣ą╝ąĄčĆ.

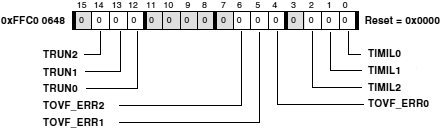

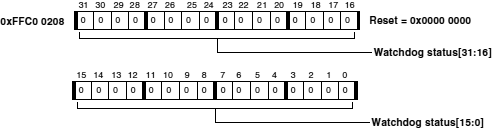

ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ (TIMER_STATUS) ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą▓čüąĄčģ 3 čéą░ą╣ą╝ąĄčĆąŠą▓, ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ čüčéą░čéčāčüą░ ą▓čüąĄčģ 3 čéą░ą╣ą╝ąĄčĆąŠą▓ ąĘą░ ąŠą┤ąĮčā ąŠą┐ąĄčĆą░čåąĖčÄ čćč鹥ąĮąĖčÅ (čüą╝. čĆąĖčü. 16-4). ąæąĖčéčŗ čüčéą░čéčāčüą░ čÅą▓ą╗čÅčÄčéčüčÅ "ą╗ąĖą┐ą║ąĖą╝ąĖ" (sticky), ąĖ čĆą░ą▒ąŠčéą░čÄčé ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā W1C ("Write 1 Clear", ąĘą░ą┐ąĖčüčī 1 ąŠčćąĖčēą░ąĄčé ą▒ąĖčé). ąæąĖčéčŗ TRUNx ą╝ąŠą│čāčé ąŠčćąĖčüčéąĖčéčīčüčÅ čüą░ą╝ąŠčüč鹊čÅč鹥ą╗čīąĮąŠ, čćč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT mode ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĖąŠą┤ą░. ą¤čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ čĆąĄą│ąĖčüčéčĆčā čüąŠčüč鹊čÅąĮąĖčÅ ąĮą░ čćč鹥ąĮąĖąĄ ą▓čüąĄ ąĮąĄąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▒ąĖčéčŗ čćąĖčéą░čÄčéčüčÅ ą║ą░ą║ 0.

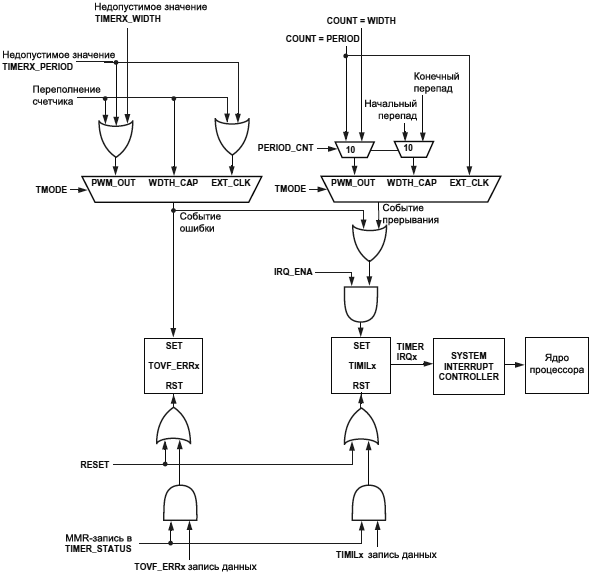

ąÜą░ąČą┤čŗą╣ čéą░ą╣ą╝ąĄčĆ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čāąĮąĖą║ą░ą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ ąĘą░ą┐čĆąŠčüą░ ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąŠą┐čāčüą║ą░ąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą▒ąĖč鹊ą╝ IRQ_ENA ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMERx_CONFIG. ą×ą▒čēąĖą╣ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ TIMER_STATUS ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčé čŹčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čéą░ą║ čćč鹊 ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▒ąĄąĘ čüčüčŗą╗ą║ąĖ ąĮą░ čāąĮąĖą║ą░ą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą▓ čüą╗čāčćą░ąĄ, ąĄčüą╗ąĖ ą▓čüąĄ 3 čéą░ą╣ą╝ąĄčĆą░ ąĮą░ąĘąĮą░č湥ąĮčŗ ąĮą░ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ ą┐čĆąĖąŠčĆąĖč鹥čé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ). ąæąĖčéčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čÅą▓ą╗čÅčÄčéčüčÅ "ą╗ąĖą┐ą║ąĖą╝ąĖ", ąĖ ą┤ąŠą╗ąČąĮčŗ ąŠčćąĖčēą░čéčīčüčÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąŠą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (interrupt service routine, ISR), čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ ą▒čŗą╗ąŠ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąŠ ąĘą░ąĮąŠą▓ąŠ.

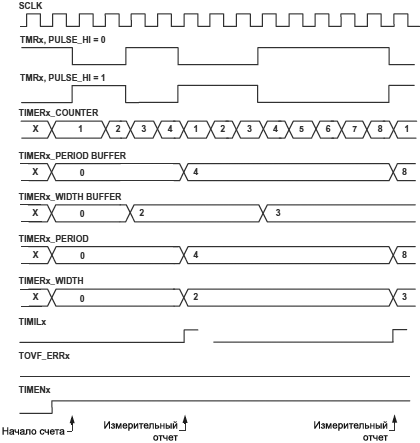

ąæąĖčéčŗ TIMILx čĆą░ą▒ąŠčéą░čÄčé ą▓ą╝ąĄčüč鹥 čü ą▒ąĖč鹊ą╝ IRQ_ENA čĆąĄą│ąĖčüčéčĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ TIMERx_CONFIG, ą┐ąŠą║ą░ąĘčŗą▓ą░čÅ ąĘą░ą┐čĆąŠčüčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąĢčüą╗ąĖ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čāčüą╗ąŠą▓ąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖą╗ąĖ ąŠčłąĖą▒ą║ą░ ąĖ ą▒ąĖčé IRQ_ENA čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą▒ąĖčé TIMILx čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĖ ą▒čāą┤ąĄčé ą▓čŗčüčéą░ą▓ą╗ąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┤ą╗čÅ čÅą┤čĆą░. ąŁč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąŠ čüąĖčüč鹥ą╝ąĮčŗą╝ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (system interrupt controller, SIC). ąĢčüą╗ąĖ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖą╗ąĖ ąŠčłąĖą▒ą║ą░, ąĖ ą▒ąĖčé IRQ_ENA ąŠčćąĖčēąĄąĮ, č鹊 ą▒ąĖčé TIMILx ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗčüčéą░ą▓ą╗ąĄąĮąŠ. ąĢčüą╗ąĖ ą▒ąĖčé TIMILx čāąČąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖ ą▓ ą▒ąĖčé IRQ_ENA ąĘą░ą┐ąĖčüą░ąĮ 0, č鹊 ą▒ąĖčéčŗ TIMILx ąŠčüčéą░ąĮčāčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ąĖ, ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčüčéą░ąĮąĄčéčüčÅ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĮčŗą╝. ąĪą╝. čĆąĖčü. 16-24.

ąĀąĖčü. 16-4. ąĀąĄą│ąĖčüčéčĆ TIMER_STATUS.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆąŠą▓, ą┐ąŠą╝ąĄč湥ąĮąĮčŗąĄ ąĮą░ čĆąĖčüčāąĮą║ąĄ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝, ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ.

TRUN2, TRUN1, TRUN0. ąŁč鹊 ą▒ąĖčéčŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ Slave Enable, čĆą░ą▒ąŠčéą░čÄčēąĖąĄ ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā W1C. ąŚą░ą┐ąĖčüčī 1 ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąŠčüčéą░ąĮąŠą▓ąĖčé čéą░ą╣ą╝ąĄčĆ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT.

TOVF_ERR2, TOVF_ERR1, TOVF_ERR0. ąŁč鹊 ą▒ąĖčéčŗ ąŠčłąĖą▒ą║ąĖ, čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāčÄčēąĖąĄ ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ (Timer Counter Overflow), čĆą░ą▒ąŠčéą░čÄčēąĖąĄ ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā W1C. ąæąĖčé čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ ąĖą╗ąĖ ąŠ čüąŠą▒čŗčéąĖąĖ ąŠčłąĖą▒ą║ąĖ.

TIMIL2, TIMIL1, TIMIL0. ąŁč鹊 čäą╗ą░ą│ąĖ, čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāčÄčēąĖąĄ ąŠ ąĘą░ą┐čĆąŠčüąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░, ąĄčüą╗ąĖ ą▒ąĖčé IRQ_ENA čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ. ąóą░ą║ąČąĄ čĆą░ą▒ąŠčéą░čÄčé ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā W1C.

ą¤čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖč鹊ą▓ TRUNx ąŠčéčĆą░ąČą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ timer slave enable ą▓ąŠ ą▓čüąĄčģ čĆąĄąČąĖą╝ą░čģ ŌĆö čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗąĄ TRUNx ą│ąŠą▓ąŠčĆčÅčé ąŠ č鹊ą╝, čćč鹊 čĆąĄąČąĖą╝ ąĘą░ą┐čāčēąĄąĮ, ąĖ ąŠčćąĖčēąĄąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ TRUNx ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝. ąÆ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čćč鹥ąĮąĖąĄ ą▒ąĖč鹊ą▓ TIMENx ąĖą╗ąĖ TIMDISx ą▒ąĖčéčŗ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ TIMER_ENABLE ąĖ TIMER_DISABLE ąŠčéčĆą░ąČą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░ - čĆą░ąĘčĆąĄčłąĄąĮ ąŠąĮ ąĖą╗ąĖ ąĮąĄčé, ą▒ąĖčéčŗ TRUNx ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé, čüčćąĖčéą░ąĄčé čéą░ą╣ą╝ąĄčĆ ąĖą╗ąĖ ąĮąĄčé. ąÆ čĆąĄąČąĖą╝ą░čģ WDTH_CAP ąĖ EXT_CLK čćč鹥ąĮąĖąĄ ąĖąĘ TIMENx ąĖ TRUNx ą▓čüąĄą│ą┤ą░ ą▓ąŠąĘą▓čĆą░čéčÅčé ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ.

ą×ą┐ąĄčĆą░čåąĖčÅ W1C ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ TIMER_DISABLE ąĘą░ą┐čĆąĄčēą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čéą░ą╣ą╝ąĄčĆ ą▓ąŠ ą▓čüąĄčģ čĆąĄąČąĖą╝ą░čģ. ąÆ čĆąĄąČąĖą╝ąĄ PWM_OUT ąĘą░ą┐čĆąĄčēąĄąĮąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé čüčćąĖčéą░čéčī, ą┐ąŠą║ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗą╣ ą┐ąĄčĆąĖąŠą┤ (PERIOD_CNT = 1) ąĖą╗ąĖ ąĖą╝ą┐čāą╗čīčü (PERIOD_CNT = 0) ąĮąĄ ą▒čāą┤ąĄčé čüč乊čĆą╝ąĖčĆąŠą▓ą░ąĮ ą┤ąŠ ą║ąŠąĮčåą░. ąÆąŠ ą▓čĆąĄą╝čÅ čŹč鹊ą│ąŠ ąĘą░ą▓ąĄčĆčłą░čÄčēąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ TIMENx čćąĖčéą░ąĄčéčüčÅ ą║ą░ą║ 0, ąĮąŠ ą▒ąĖčé TRUNx ą▓čüąĄ ąĄčēąĄ čćąĖčéą░ąĄčéčüčÅ ą║ą░ą║ 1. (čüą╝. čĆąĖčü. 16-10). ąóąŠą╗čīą║ąŠ ą▓ čŹč鹊ą╝ čüąŠčüč鹊čÅąĮąĖąĖ TRUNx čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖč鹊ą╝ W1C. ąÆąŠ ą▓čĆąĄą╝čÅ čŹč鹊ą│ąŠ ąĘą░ą▓ąĄčĆčłą░čÄčēąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ ą┐ąĄčĆąĖąŠą┤ą░ čü ąĘą░ą┐čĆąĄčēąĄąĮąĮčŗą╝ čéą░ą╣ą╝ąĄčĆąŠą╝ ąĘą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ TRUNx ąŠčćąĖčüčéąĖčé TRUNx ąĖ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąŠčüčéą░ąĮąŠą▓ąĖčé čéą░ą╣ą╝ąĄčĆ ą▒ąĄąĘ ąŠąČąĖą┤ą░ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čüč湥čéą░ č鹥ą║čāčēąĄą│ąŠ čåąĖą║ą╗ą░ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░ ąĖą╗ąĖ ąĖą╝ą┐čāą╗čīčüą░.

ąŚą░ą┐ąĖčüčī ą▓ ą▒ąĖčéčŗ TRUNx ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░ ą▓ ą┤čĆčāą│ąĖčģ čĆąĄąČąĖą╝ą░čģ, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮ. ąŚą░ą┐ąĖčüčī ą▒ąĖč鹊ą▓ TRUNx ą▓ 1 ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT ąĮąĄ ą┤ą░ąĄčé čŹčäč乥ą║čéą░ ąĮą░ čéą░ą╣ą╝ąĄčĆąĄ, ą║ąŠč鹊čĆčŗą╣ ąĮąĄ ą▒čŗą╗ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ąĘą░ą┐čĆąĄčēąĄąĮ.

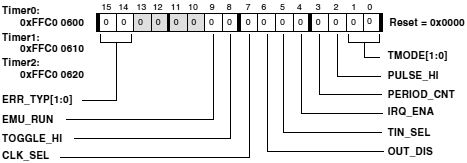

ąĀą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ čāą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ąĄą│ąŠ čĆąĄą│ąĖčüčéčĆąŠą╝ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ (timer configuration register, TIMERx_CONFIG), ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 16-5. ąĀąĄą│ąĖčüčéčĆ TIMERx_CONFIG ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ ąĮąĄ čüčćąĖčéą░ąĄčé. ą¤ąŠčüą╗ąĄ ąĘą░ą┐čĆąĄčéą░ čéą░ą╣ą╝ąĄčĆą░ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT čāą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 čéą░ą╣ą╝ąĄčĆ ąĮą░ čüą░ą╝ąŠą╝ ą┤ąĄą╗ąĄ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ ąĄą│ąŠ ą▒ąĖčéą░ TRUNx ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMER_STATUS, ą┐ąĄčĆąĄą┤ ą┐ąŠą┐čŗčéą║ąŠą╣ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī TIMERx_CONFIG. ąĀąĄą│ąĖčüčéčĆčŗ TIMERx_CONFIG ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ą▓ ą╗čÄą▒ąŠąĄ ą▓čĆąĄą╝čÅ. ą¤ąŠą╗ąĄ ERR_TYP čĆą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ. ą×ąĮąŠ ąŠčćąĖčēą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ. ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ TOVF_ERRx, ą┐ąŠą╗ąĄ ERR_TYP[1:0] ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą║ąŠą┤ąŠą╝, ą║ąŠč鹊čĆčŗą╣ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆčāąĄčé ą║ąŠą┤ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ąŠčłąĖą▒ą║ąĖ. ąŁč鹊 ąĘąĮą░č湥ąĮąĖąĄ čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą┤ąŠ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĄą╣ ąŠčłąĖą▒ą║ąĖ ąĖą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░. ą×ą▒ąĘąŠčĆ čāčüą╗ąŠą▓ąĖą╣ ąŠčłąĖą▒ą║ąĖ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåąĄ 16-1. ąĀąĄą│ąĖčüčéčĆ TIMERx_CONFIG čéą░ą║ąČąĄ čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄą╝ ą▓čŗą▓ąŠą┤ą░ TMRx, ą║ąŠč鹊čĆčŗą╣ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT (TMODE = 01), ą║ąŠą│ą┤ą░ ąŠčćąĖčēąĄąĮ ą▒ąĖčé OUT_DIS.

ąĀąĖčü. 16-5. ąĀąĄą│ąĖčüčéčĆčŗ TIMERx_CONFIG.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆąŠą▓, ą┐ąŠą╝ąĄč湥ąĮąĮčŗąĄ ąĮą░ čĆąĖčüčāąĮą║ąĄ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝, ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ.

ERR_TYP[0:1]. ąæąĖčéčŗ čéąĖą┐ą░ ąŠčłąĖą▒ą║ąĖ, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗąĄ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ. 00: ąĮąĄčé ąŠčłąĖą▒ą║ąĖ, 01: ąŠčłąĖą▒ą║ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░, 10: ąŠčłąĖą▒ą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ą┐ąĄčĆąĖąŠą┤ą░, 11: ąŠčłąĖą▒ą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░.

EMU_RUN. ąæąĖčé ą▓čŗą▒ąŠčĆą░ ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ ą┐čĆąĖ čĆą░ą▒ąŠč鹥 ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▓ čĆąĄąČąĖą╝ąĄ 菹╝čāą╗čÅčåąĖąĖ (ąŠčéą╗ą░ą┤ą║ąĖ). ąĢčüą╗ąĖ 0, č鹊 ą▓ čĆąĄąČąĖą╝ąĄ 菹╝čāą╗čÅčåąĖąĖ čéą░ą╣ą╝ąĄčĆ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čüč湥čé (čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ). ąĢčüą╗ąĖ 1, č鹊 ą▓ čĆąĄąČąĖą╝ąĄ 菹╝čāą╗čÅčåąĖąĖ čéą░ą╣ą╝ąĄčĆ ąĮąĄ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čüč湥čé.

TOGGLE_HI. ąæąĖčé ą▓čŗą▒ąŠčĆą░ čĆąĄąČąĖą╝ą░ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ PULSE_HI čĆąĄąČąĖą╝ą░ PWM_OUT. ąĢčüą╗ąĖ 0, č鹊 čŹčäč乥ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ PULSE_HI ą▒čāą┤ąĄčé ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╝. ąĢčüą╗ąĖ 1, č鹊 čŹčäč乥ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ PULSE_HI ą╝ąĄąĮčÅąĄčéčüčÅ čü ą║ą░ąČą┤čŗą╝ ą┐ąĄčĆąĖąŠą┤ąŠą╝.

CLK_SEL. ąæąĖčé ą▓čŗą▒ąŠčĆą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░. 0: ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ SCLK, 1: ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓čŗą▓ąŠą┤ PWM_CLK.

OUT_DIS. ąæąĖčé ąĘą░ą┐čĆąĄčéą░ ą▓čŗčģąŠą┤ą░. 0: ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT ą▓čŗčģąŠą┤ čéą░ą╣ą╝ąĄčĆą░ čĆą░ąĘčĆąĄčłąĄąĮ, 1: ąĘą░ą┐čĆąĄčēąĄąĮ.

TIN_SEL. ąæąĖčé ą▓čŗą▒ąŠčĆą░ ą▓čģąŠą┤ą░ čéą░ą╣ą╝ąĄčĆą░. 0: ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ čü ą▓čŗą▓ąŠą┤ą░ TMRx ąĖą╗ąĖ PF1, 1: ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ UART RX ąĖą╗ąĖ PPI_CLK.

IRQ_ENA. ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐čĆąŠčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Interrupt Request Enable). 0: ąĘą░ą┐čĆąŠčü ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮ, 1: čĆą░ąĘčĆąĄčłąĄąĮ.

PERIOD_CNT. ąæąĖčé ą▓čŗą▒ąŠčĆą░ ąŠą║ąŠąĮčćą░ąĮąĖčÅ čüč湥čéą░. 0: čüč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą┤ąŠ ą║ąŠąĮčåą░ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░. 1: čüč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą┤ąŠ ą║ąŠąĮčåą░ ą┐ąĄčĆąĖąŠą┤ą░ ąĖą╝ą┐čāą╗čīčüą░, čŹč鹊čé ą▓ą░čĆąĖą░ąĮčé ą▓ čĆąĄąČąĖą╝ąĄ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ PWM (ą©ąśą£) ą┐ąŠąĘą▓ąŠą╗čÅąĄčé č乊čĆą╝ąĖčĆąŠą▓ą░čéčī ąĮą░ ą▓čŗčģąŠą┤ąĄ TMRx ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčāčÄ čćą░čüč鹊čéčā ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą▒ąĄąĘ ą▓čüčÅą║ąŠą│ąŠ ą▓ą╝ąĄčłą░č鹥ą╗čīčüčéą▓ą░ čÅą┤čĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

PULSE_HI. ąæąĖčé ą▓čŗą▒ąŠčĆą░ ą░ą║čéąĖą▓ąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ąĖą╝ą┐čāą╗čīčüą░. ąĢčüą╗ąĖ PULSE_HI=0: ą░ą║čéąĖą▓ąĮčŗą╣ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü, čéą░ą╣ą╝ąĄčĆ ąĮą░čćąĖąĮą░ąĄčé ą┐ąĄčĆąĖąŠą┤ čüč湥čéą░ čü TMRx=0, ąĖ ąĘą░ą║ą░ąĮčćąĖą▓ą░ąĄčé ą┐ąĄčĆąĖąŠą┤ čüč湥čéą░ čü TMRx=1. 1: ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣. ąĢčüą╗ąĖ PULSE_HI=1: ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü, čéą░ą╣ą╝ąĄčĆ ąĮą░čćąĖąĮą░ąĄčé ą┐ąĄčĆąĖąŠą┤ čüč湥čéą░ čü TMRx=1, ąĖ ąĘą░ą║ą░ąĮčćąĖą▓ą░ąĄčé ą┐ąĄčĆąĖąŠą┤ čüč湥čéą░ čü TMRx=0.

TMODE[1:0]. ąæąĖčéčŗ ą▓čŗą▒ąŠčĆą░ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░. 00: čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ (čéą░ą╣ą╝ąĄčĆ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ), 01: čĆąĄąČąĖą╝ PWM_OUT, 10: čĆąĄąČąĖą╝ WDTH_CAP, 11: čĆąĄąČąĖą╝ EXT_CLK.

ąŁčéąĖ čĆąĄą│ąĖčüčéčĆčŗ, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗąĄ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, čüąŠą┤ąĄčƹȹ░čé ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░, ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ ąĘą░ą┐čĆąĄčēąĄąĮ (čüą╝. čĆąĖčü. 16-6). ąÜąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ, čĆąĄą│ąĖčüčéčĆ TIMERx_COUNTER čĆąĄąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā, ąŠčüąĮąŠą▓ą░ąĮąĮąŠą╝čā ąĮą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĖ čĆąĄąČąĖą╝ąĄ. ąĀąĄą│ąĖčüčéčĆ TIMERx_COUNTER ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ (ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, čüčćąĖčéą░ąĄčé čéą░ą╣ą╝ąĄčĆ ąĖą╗ąĖ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ), ąĖ čćč鹥ąĮąĖąĄ ą▓ąĄčĆąĮąĄčé ą║ąŠą│ąĄčĆąĄąĮčéąĮąŠąĄ 32-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ ąĖąĮą║čĆąĄą╝ąĄąĮčé čüč湥čéčćąĖą║ą░ ą╝ąŠąČąĄčé čéą░ą║čéąĖčĆąŠą▓ą░čéčīčüčÅ ąŠčé 4 čĆą░ąĘąĮčŗčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓: SCLK, ą▓čŗą▓ąŠą┤ą░ TMRx, ą▓čŗą▓ąŠą┤ GPIO-ą┐ąŠčĆčéą░ PF1, ąĖą╗ąĖ čéą░ą║čéčŗ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░ PPI_CLK.

ąÜąŠą│ą┤ą░ ą║ čÅą┤čĆčā ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ čüąŠ čüč鹊čĆąŠąĮčŗ ą▓ąĮąĄčłąĮąĄą│ąŠ 菹╝čāą╗čÅč鹊čĆą░-ąŠčéą╗ą░ą┤čćąĖą║ą░ (č湥čĆąĄąĘ JTAG), ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ TIMERx_COUNTER čéą░ą║ąČąĄ ą┐čĆąĖąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čüč湥čé ą▓ąŠ ą▓čĆąĄą╝čÅ ą┤ąŠčüčéčāą┐ą░ 菹╝čāą╗čÅčåąĖąĖ, čćč鹊ą▒čŗ ąŠčüčéą░ą▓ą░čéčīčüčÅ čüąĖąĮčģčĆąŠąĮąĮčŗą╝ čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄą╝. ąæčāą┤čāčćąĖ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝, čüč湥čéčćąĖą║ ąĮąĄ ą┤ąŠčüčéąĖą│ą░ąĄčé ą┐čĆąĄą┤ąĄą╗ąŠą▓ čüč湥čéą░ ŌĆö ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TMRx ą┐ąŠą╗čāčćą░ąĄčéčüčÅ "čĆą░čüčéčÅąĮčāčéčŗą╝"; ą▓ čĆąĄąČąĖą╝ąĄ WDTH_CAP ąĖąĘą╝ąĄčĆąĄąĮąĮčŗąĄ ą▓ąĄą╗ąĖčćąĖąĮčŗ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüč鹥ą╣ ąŠą║ą░ąĘčŗą▓ą░čÄčéčüčÅ ąĮąĄą║ąŠčĆčĆąĄą║čéąĮčŗą╝ąĖ; ą▓ čĆąĄąČąĖą╝ąĄ EXT_CLK ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠą┐čāčēąĄąĮčŗ čüąŠą▒čŗčéąĖčÅ ą┐ąŠ ą▓čģąŠą┤čā ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TMRx. ąÆčüąĄ ą┤čĆčāą│ąĖąĄ čäčāąĮą║čåąĖąĖ čéą░ą╣ą╝ąĄčĆą░, čéą░ą║ąĖąĄ ą║ą░ą║ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī čĆąĄą│ąĖčüčéčĆąŠą▓, čĆą░ąĮąĄąĄ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ąĄčüą╗ąĖ ąŠąĮąĖ ąĮąĄ ą▒čŗą╗ąĖ ąŠčćąĖčēąĄąĮčŗ), ąĖ ąĘą░ą│čĆčāąĘą║ą░ TIMERx_PERIOD ąĖ TIMERx_WIDTH ą▓ čĆąĄąČąĖą╝ąĄ WDTH_CAP ąŠčüčéą░čÄčéčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ąĖ ą┐čĆąĖ ąŠčüčéą░ąĮąŠą▓ą║ąĄ ą▓ąŠ ą▓čĆąĄą╝čÅ čŹą╝čāą╗čÅčåąĖąĖ.

ąØąĄą║ąŠč鹊čĆčŗąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą╝ąŠą│čāčé čéčĆąĄą▒ąŠą▓ą░čéčī ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ą┐čĆąŠą┤ąŠą╗ąČąĄąĮąĖčÅ čüč湥čéą░ čéą░ą╣ą╝ąĄčĆą░ ą┐čĆąĖ ąŠčüčéą░ąĮąŠą▓ą║ąĄ čÅą┤čĆą░ ąĖąĘ-ąĘą░ ąŠčéą╗ą░ą┤ą║ąĖ. ąóą░ą║ąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą▒čāą┤ąĄčé čĆą░ąĘčĆąĄčłąĄąĮąŠ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ EMU_RUN ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMERx_CONFIG.

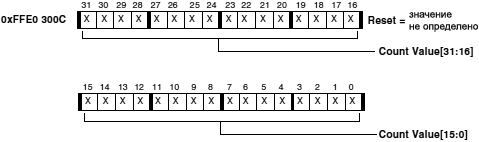

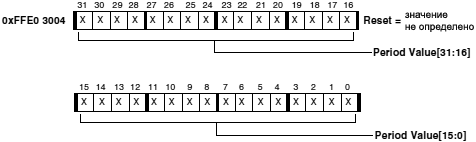

ąĀąĖčü. 16-6. ąĀąĄą│ąĖčüčéčĆčŗ TIMERx_COUNTER.

Timer Counter[31:0]. ąĀąĄą│ąĖčüčéčĆ, ąŠčéčĆą░ąČą░čÄčēąĖą╣ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░.

ąÜąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ ąĖ čüčćąĖčéą░ąĄčé, ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ąĮąŠą▓čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĖąŠą┤ą░ TIMERx_PERIOD ąĖ čĆąĄą│ąĖčüčéčĆ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ TIMERx_WIDTH, čŹčéąĖ ąĘą░ą┐ąĖčüąĖ ą▒čāč乥čĆąĖąĘčāčÄčéčüčÅ ąĖ ąĮąĄ ąŠą▒ąĮąŠą▓ą╗čÅčÄčé čĆąĄą│ąĖčüčéčĆčŗ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą┤ąŠčüčéąĖą│ąĮčāčé ą║ąŠąĮąĄčå č鹥ą║čāčēąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ (ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ čĆą░ą▓ąĄąĮ čĆąĄą│ąĖčüčéčĆčā TIMERx_PERIOD).

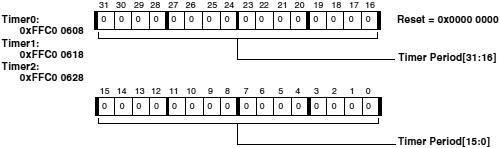

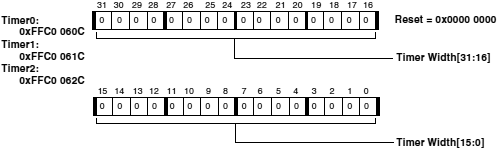

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ TIMERx_PERIOD ąĖ TIMERx_WIDTH (čüą╝. čĆąĖčüčāąĮą║ąĖ 16-7 ąĖ Figure 16-8) ą╝ąĄąĮčÅąĄčéčüčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░:

ŌĆó ąÆ čĆąĄąČąĖą╝ąĄ ą©ąśą£ (PWM_OUT) ąĘąĮą░č湥ąĮąĖčÅ ąŠą▒ąŠąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓, TIMERx_PERIOD ąĖ TIMERx_WIDTH, ą╝ąŠą│čāčé ą▒čŗčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮčŗ "ąĮą░ ą╗ąĄčéčā", čéą░ą║ čćč鹊 čĆąĄą│ąĖčüčéčĆčŗ ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą╣ą╝ąĄčĆą░ ąĖ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ čéą░ą╣ą╝ąĄčĆą░ (čüą║ą▓ą░ąČąĮąŠčüčéčī, duty cycle) ąĖąĘą╝ąĄąĮčÅčÄčéčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ.

ŌĆó ąÆ čĆąĄąČąĖą╝ąĄ ąĘą░čģą▓ą░čéą░ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ ąĖ ą┐ąĄčĆąĖąŠą┤ą░ (WDTH_CAP), ą▒čāč乥čĆąĖąĘąŠą▓ą░ąĮąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą╣ą╝ąĄčĆą░ ąĖ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ čéą░ą╣ą╝ąĄčĆą░ ąĘą░čģą▓ą░čéčŗą▓ą░čÄčéčüčÅ ą▓ ą┐ąŠą┤čģąŠą┤čÅčēąĄąĄ ą▓čĆąĄą╝čÅ. ąóąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆčŗ TIMERx_PERIOD ąĖ TIMERx_WIDTH ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąĖąĘ čüą▓ąŠąĖčģ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą▒čāč乥čĆąŠą▓. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąŠą▒ą░ čĆąĄą│ąĖčüčéčĆą░ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

ŌĆó ąÆ čĆąĄąČąĖą╝ąĄ ąĘą░čģą▓ą░čéą░ čüąŠą▒čŗčéąĖčÅ (EXT_CLK), čĆąĄą│ąĖčüčéčĆ TIMERx_PERIOD ą╝ąŠąČąĮąŠ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī, ąĖ ąŠąĮ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮ "ąĮą░ ą╗ąĄčéčā". ąĀąĄą│ąĖčüčéčĆ TIMERx_WIDTH ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

ąĢčüą╗ąĖ ąĮąŠą▓čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĮąĄ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ TIMERx_PERIOD ąĖą╗ąĖ TIMERx_WIDTH, č鹊 ąĘą░ąĮąŠą▓ąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąĘąĮą░č湥ąĮąĖčÅ ąĖąĘ ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░. ąŚą░ą┐ąĖčüąĖ ą▓ 32-ą▒ąĖčéąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ TIMERx_PERIOD ąĖ TIMERx_WIDTH čÅą▓ą╗čÅčÄčéčüčÅ ą░č鹊ą╝ą░čĆąĮčŗą╝ąĖ; ąĮąĄą▓ąŠąĘą╝ąŠąČąĮą░ čüąĖčéčāą░čåąĖčÅ, ą║ąŠą│ą┤ą░ čüčéą░čĆčłąĄąĄ čüą╗ąŠą▓ąŠ ąĘą░ą┐ąĖčüą░ąĮąŠ ą▒ąĄąĘ ąĘą░ą┐ąĖčüąĖ ą╝ą╗ą░ą┤čłąĄą│ąŠ čüą╗ąŠą▓ą░.

ąŚąĮą░č湥ąĮąĖčÅ, ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆčŗ TIMERx_PERIOD ąĖą╗ąĖ TIMERx_WIDTH, ą▓čüąĄą│ą┤ą░ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ ą▒čāč乥čĆąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ. ą¦č鹥ąĮąĖčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ TIMERx_PERIOD ąĖą╗ąĖ TIMERx_WIDTH ą▓čüąĄą│ą┤ą░ ą▓ąĄčĆąĮčāčé č鹥ą║čāčēąĄąĄ, ą░ą║čéąĖą▓ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĖąŠą┤ą░ ąĖą╗ąĖ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░. ąŚą░ą┐ąĖčüą░ąĮąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĮąĄ ą▒čāą┤čāčé ą┐čĆąŠčćąĖčéą░ąĮčŗ ąŠą▒čĆą░čéąĮąŠ, ą┐ąŠą║ą░ ąŠąĮąĖ ąĮąĄ čüčéą░ąĮčāčé ą░ą║čéąĖą▓ąĮčŗą╝ąĖ. ąÜąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ, ąŠąĮąĖ ąĮąĄ čüčéą░ąĮčāčé ą░ą║čéąĖą▓ąĮčŗą╝ąĖ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤čāčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮčŗ čĆąĄą│ąĖčüčéčĆčŗ TIMERx_PERIOD ąĖ TIMERx_WIDTH ąĖąĘ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą▒čāč乥čĆąŠą▓ ą▓ ą╝ąŠą╝ąĄąĮčé ąŠą║ąŠąĮčćą░ąĮąĖčÅ č鹥ą║čāčēąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ (čüą╝. čĆąĖčü. 16-1).

ąÜąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ ąĘą░ą┐čĆąĄčēąĄąĮ, ąĘą░ą┐ąĖčüąĖ ą▓ ą▒čāč乥čĆąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą║ąŠą┐ąĖčĆčāčÄčéčüčÅ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ TIMERx_PERIOD ąĖą╗ąĖ TIMERx_WIDTH, čéą░ą║ čćč鹊 ąŠąĮąĖ ą▒čāą┤čāčé ą│ąŠč鹊ą▓čŗ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ ą┐ąĄčĆą▓čŗą╣ ą┐ąĄčĆąĖąŠą┤ čéą░ą╣ą╝ąĄčĆą░. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖą╣ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ TIMERx_PERIOD ąĖ/ąĖą╗ąĖ TIMERx_WIDTH ą▓ ą┐ąŠčĆčÅą┤ą║ąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ čāčüčéą░ąĮąŠą▓ąŠą║ ą┤ą╗čÅ ą║ą░ąČą┤čŗčģ ą┐ąĄčĆą▓čŗčģ 3 ą┐ąĄčĆąĖąŠą┤ąŠą▓ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ, ą┐čĆąŠčåąĄą┤čāčĆą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čüą╗ąĄą┤čāčÄčēąĄą╣:

1. ąŚą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāą╣č鹥 ą┐ąĄčĆą▓čŗą╣ ąĮą░ą▒ąŠčĆ ąĘąĮą░č湥ąĮąĖą╣ čĆąĄą│ąĖčüčéčĆąŠą▓.

2. ąĀą░ąĘčĆąĄčłąĖč鹥 čéą░ą╣ą╝ąĄčĆ.

3. ąØąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāą╣č鹥 ą▓č鹊čĆąŠą╣ ąĮą░ą▒ąŠčĆ ąĘąĮą░č湥ąĮąĖą╣ čĆąĄą│ąĖčüčéčĆąŠą▓.

4. ą¤ąŠą┤ąŠąČą┤ąĖč鹥 ą┐ąĄčĆą▓ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░.

5. ąŚą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāą╣č鹥 čéčĆąĄčéąĖą╣ ąĮą░ą▒ąŠčĆ ąĘąĮą░č湥ąĮąĖą╣ čĆąĄą│ąĖčüčéčĆąŠą▓.

ąÜą░ąČą┤ą░čÅ ąĮąŠą▓ą░čÅ čāčüčéą░ąĮąŠą▓ą║ą░ ą▒čāą┤ąĄčé č鹊ą│ą┤ą░ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░.

ąÆ čĆąĄąČąĖą╝ąĄ PWM_OUT čü ąŠč湥ąĮčī ą╝ą░ą╗čŗą╝ąĖ ą┐ąĄčĆąĖąŠą┤ą░ą╝ąĖ (ą╝ąĄąĮčīčłąĄ č湥ą╝ 10 ąŠčéčüč湥č鹊ą▓), ą╝ąŠąČąĄčé ąĮąĄ čģą▓ą░čéąĖčéčī ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ąŠą▒ąŠąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ TIMERx_PERIOD ąĖ TIMERx_WIDTH ą╝ąĄąČą┤čā ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄą╝ ąĖąĘ ą▒čāč乥čĆąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓. ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą┐ąĄčĆąĖąŠą┤ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠą┤ąĮąŠ čüčéą░čĆąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĖ ąŠą┤ąĮąŠ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ. ą¦č鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī ąŠčłąĖą▒ą║ąĖ, čćč鹊 čłąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ą▒čāą┤ąĄčé >= ą┐ąĄčĆąĖąŠą┤ą░, ąĘą░ą┐ąĖčüčŗą▓ą░ą╣č鹥 čĆąĄą│ąĖčüčéčĆ TIMERx_WIDTH ą┐ąĄčĆąĄą┤ čĆąĄą│ąĖčüčéčĆąŠą╝ TIMERx_PERIOD, ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖčÅ čāą╝ąĄąĮčīčłą░čÄčéčüčÅ, ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░ą╣č鹥 čĆąĄą│ąĖčüčéčĆ TIMERx_PERIOD ą┐ąĄčĆąĄą┤ čĆąĄą│ąĖčüčéčĆąŠą╝ TIMERx_WIDTH, ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖčÅ čāą▓ąĄą╗ąĖčćąĖą▓ą░čÄčéčüčÅ.

ąĀąĖčü. 16-7. ąĀąĄą│ąĖčüčéčĆčŗ TIMERx_PERIOD.

Timer Period[31:0]. ąĀąĄą│ąĖčüčéčĆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą╣ą╝ąĄčĆą░.

ąĀąĖčü. 16-8. ąĀąĄą│ąĖčüčéčĆčŗ TIMERx_WIDTH.

Timer Width[31:0]. ąĀąĄą│ąĖčüčéčĆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ čéą░ą╣ą╝ąĄčĆą░.

[ąÜą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čéą░ą╣ą╝ąĄčĆčŗ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ]

ą¦č鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī ąŠčéą┤ąĄą╗čīąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ, čāčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé TIMEN čéą░ą╣ą╝ąĄčĆą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMER_ENABLE. ą¦č鹊ą▒čŗ ąĘą░ą┐čĆąĄčéąĖčéčī ąŠčéą┤ąĄą╗čīąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ, čāčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé TIMDIS ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMER_DISABLE. ą¦č鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī ą▓čüąĄ 3 čéą░ą╣ą╝ąĄčĆą░ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ, čāčüčéą░ąĮąŠą▓ąĖč鹥 ą▓čüąĄ 3 ą▒ąĖčéą░ TIMEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMER_ENABLE.

ą¤ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ čéą░ą╣ą╝ąĄčĆą░ ą▓čüąĄą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāą╣č鹥 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čéą░ą╣ą╝ąĄčĆą░ (TIMERx_CONFIG). ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░, ą┐ąŠą╗čÅčĆąĮąŠčüčéčī ą▓čŗą▓ąŠą┤ą░ TMRx ąĖ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░. ąØąĄ ą╝ąĄąĮčÅą╣č鹥 čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝, ą┐ąŠą║ą░ čéą░ą╣ą╝ąĄčĆ čüčćąĖčéą░ąĄčé.

ą¤čĆąĖą╝ąĄčĆčŗ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĖ ąĘą░ą┐čĆąĄčēąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆąŠą▓ ąĖą╝ąĄčÄčéčüčÅ ąĮą░ čĆąĖčüčāąĮą║ą░čģ 16-9, 16-10 ąĖ 16-11.

ąÜąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆčŗ ąĘą░ą┐čĆąĄčēąĄąĮčŗ, čĆąĄą│ąĖčüčéčĆčŗ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ čüąŠą┤ąĄčƹȹ░čé čüą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ; ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ ąĘą░ąĮąŠą▓ąŠ čĆą░ąĘčĆąĄčłąĄąĮ, čüč湥čéčćąĖą║ čéą░ą╣ą╝ąĄčĆą░ ąĘą░ąĮąŠą▓ąŠ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ąĮą░ ąŠčüąĮąŠą▓ąĄ čĆą░ą▒ąŠč湥ą│ąŠ čĆąĄąČąĖą╝ą░. ąĀąĄą│ąĖčüčéčĆčŗ čüč湥čéčćąĖą║ąŠą▓ čéą░ą╣ą╝ąĄčĆą░ čĆą░ą▒ąŠčéą░čÄčé č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ąĮąĄ ą╝ąŠąČąĄčé ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░čéčī ąĖą╗ąĖ ą┐čĆąĄą┤čāčüčéą░ąĮąŠą▓ąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąĮą░ą┐čĆčÅą╝čāčÄ.

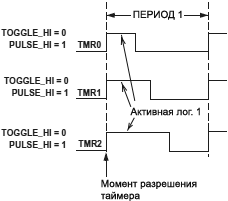

ąĀąĖčü. 16-9. ą¤čĆąĖą╝ąĄčĆ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ (PWM_OUT MODE, PERIOD_CNT = 1).

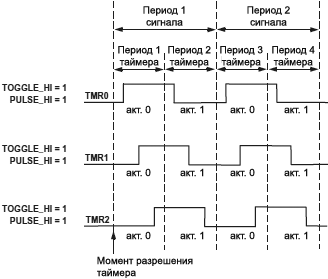

ąĀąĖčü. 16-10. ą¤čĆąĖą╝ąĄčĆ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┐čĆąĄčēąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ (PWM_OUT MODE, PERIOD_CNT = 1).

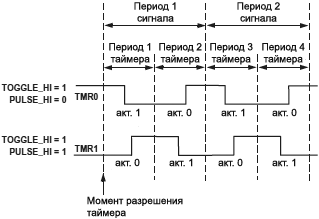

ąĀąĖčü. 16-11. ą¤čĆąĖą╝ąĄčĆ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĖ ą░ą▓č鹊ąĘą░ą┐čĆąĄčēąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ (PWM_OUT MODE, PERIOD_CNT = 0).

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą┐ąŠą╗čÅ TMODE ą▓ ąĘąĮą░č湥ąĮąĖąĄ 01 ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čéą░ą╣ą╝ąĄčĆą░ (TIMERx_CONFIG) čĆą░ąĘčĆąĄčłą░ąĄčé čĆąĄąČąĖą╝ PWM_OUT. ąÆ čĆąĄąČąĖą╝ąĄ PWM_OUT ą▓čŗą▓ąŠą┤ TMRx čéą░ą╣ą╝ąĄčĆą░ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝. ąÆčŗčģąŠą┤ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ OUT_DIS ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čéą░ą╣ą╝ąĄčĆą░.

ąÆ čĆąĄąČąĖą╝ąĄ PWM_OUT ą▒ąĖčéčŗ PULSE_HI, PERIOD_CNT, IRQ_ENA, OUT_DIS, CLK_SEL, EMU_RUN ąĖ TOGGLE_HI čĆą░ąĘčĆąĄčłą░čÄčé ąŠčĆč鹊ą│ąŠąĮą░ą╗čīąĮčāčÄ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī. ą×ąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ ąĖą╗ąĖ ą▓ ą╗čÄą▒ąŠą╣ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ, čģąŠčéčÅ ąĮąĄą║ąŠč鹊čĆčŗąĄ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ čÅą▓ą╗čÅčÄčéčüčÅ ą▒ąĄčüą┐ąŠą╗ąĄąĘąĮčŗą╝ąĖ (čéą░ą║ąĖąĄ ą║ą░ą║ TOGGLE_HI = 1 čü OUT_DIS = 1 ąĖą╗ąĖ PERIOD_CNT = 0), čüą╝. čĆąĖčü. 16-12.

ąÜą░ą║ č鹊ą╗čīą║ąŠ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ, čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ čüčéą░čĆč鹊ą▓čŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝. ąĢčüą╗ąĖ CLK_SEL = 0, č鹊 čüč湥čéčćąĖą║ čéą░ą╣ą╝ąĄčĆą░ ąĮą░čćąĮąĄčé čüč湥čé čü 0x1. ąĢčüą╗ąĖ CLK_SEL = 1, čüč湥čéčćąĖą║ čüą▒čĆąŠčüąĖčéčüčÅ ą▓ 0x0 ą║ą░ą║ ą▓ čĆąĄąČąĖą╝ąĄ EXT_CLK. ąĪč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą▓ą▓ąĄčĆčģ ą┤ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMERx_PERIOD. ąöą╗čÅ ą╗čÄą▒ąŠą╣ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ CLK_SEL, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ čéą░ą╣ą╝ąĄčĆą░ čĆą░ą▓ąĄąĮ ą┐ąĄčĆąĖąŠą┤čā čéą░ą╣ą╝ąĄčĆą░, čüč湥čéčćąĖą║ čéą░ą╣ą╝ąĄčĆą░ čüą▒čĆąŠčüąĖčéčüčÅ ą▓ 0x1 ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čéą░ą║č鹥.

ąĀąĖčü. 16-12. ąÉą╗ą│ąŠčĆąĖčéą╝ čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT.

ąÆ čĆąĄąČąĖą╝ąĄ PWM_OUT ą▒ąĖčé PERIOD_CNT čāą┐čĆą░ą▓ą╗čÅąĄčé, ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą╗ąĖ čéą░ą╣ą╝ąĄčĆ ąŠą┤ąĖąĮ ąĖą╝ą┐čāą╗čīčü ąĖą╗ąĖ ą╝ąĮąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüąŠą▓. ąÜąŠą│ą┤ą░ PERIOD_CNT ąŠčćąĖčēąĄąĮ (čĆąĄąČąĖą╝ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ PWM_OUT), čéą░ą╣ą╝ąĄčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčé čĆąĄą│ąĖčüčéčĆ TIMERx_WIDTH, ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąŠą┤ąĖąĮ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ąĖ ąŠą┤ąĖąĮ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤, ąĘą░č鹥ą╝ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ) ąĖ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ. ąÜąŠą│ą┤ą░ PERIOD_CNT čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ (čĆąĄąČąĖą╝ ą┐čĆąŠą┤ąŠą╗ąČą░čÄčēąĖčģčüčÅ ąĖą╝ą┐čāą╗čīčüąŠą▓ PWM_OUT), čéą░ą╣ą╝ąĄčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąŠą▒ą░ čĆąĄą│ąĖčüčéčĆą░ TIMERx_PERIOD ąĖ TIMERx_WIDTH ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐ąŠą▓č鹊čĆčÅčÄčēąĖąĄčüčÅ (ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠ ą╝ąŠą┤čāą╗ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ) ą┐ąĄčĆąĖąŠą┤čŗ čüąĖą│ąĮą░ą╗ą░. ąóą░ą╣ą╝ąĄčĆ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ) ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ ąĖ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čéą░ą╣ą╝ąĄčĆ ą▒čāą┤ąĄčé ąĘą░ą┐čĆąĄčēąĄąĮ. ąŻčüčéą░ąĮąŠą▓ą║ą░ PERIOD_CNT = 0 ąĘą░ą┤ą░ąĄčé čüč湥čé ą┤ąŠ ą║ąŠąĮčåą░ čłąĖčĆąĖąĮčŗ; čāčüčéą░ąĮąŠą▓ą║ą░ PERIOD_CNT = 1 ąĘą░ą┤ą░ąĄčé čüč湥čé ą┤ąŠ ą║ąŠąĮčåą░ ą┐ąĄčĆąĖąŠą┤ą░.

ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ čĆąĄąČąĖą╝ą░čģ čĆąĄą│ąĖčüčéčĆčŗ TIMERx_PERIOD ąĖ TIMERx_WIDTH čĆą░ą▒ąŠčéą░čÄčé č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ. ąŻą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 ą┐ąŠą╗ąĄ TMODE čĆąĄą│ąĖčüčéčĆą░ TIMERx_CONFIG čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ ąĘąĮą░č湥ąĮąĖąĄ b#01 ą┐ąĄčĆąĄą┤ ąĘą░ą┐ąĖčüčīčÄ ą▓ čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ.

ąŚą░ą┐čĆąĄčé ą▓čŗčģąŠą┤ą░ ą©ąśą£ (Output Pad Disable). ąÆčŗčģąŠą┤ąĮą░čÅ ąĮąŠąČą║ą░ ą©ąśą£ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮą░ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ OUT_DIS ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čéą░ą╣ą╝ąĄčĆą░. ąóąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤ TMRx ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čéčĆąĄčéčīąĄ (ąŠčéą║ą╗čÄč湥ąĮąĮąŠąĄ) čüąŠčüč鹊čÅąĮąĖąĄ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čāčüčéą░ąĮąŠą▓ą║ąĖ PULSE_HI ąĖ TOGGLE_HI. ąŁč鹊 ą╝ąŠąČąĄčé čāą╝ąĄąĮčīčłąĖčéčī 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ, ą║ąŠą│ą┤ą░ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

ąōąĄąĮąĄčĆą░čåąĖčÅ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ (Single Pulse Generation). ąĢčüą╗ąĖ ąŠčćąĖčēąĄąĮ ą▒ąĖčé PERIOD_CNT, čĆąĄąČąĖą╝ PWM_OUT ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąŠą┤ąĖąĮąŠčćąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TMRx. ąŁč鹊čé čĆąĄąČąĖą╝ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čéą░ą║ąČąĄ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ č鹊čćąĮąŠą╣ ąĘą░ą┤ąĄčƹȹ║ąĖ. ą©ąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ąĘą░ą┤ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ TIMERx_WIDTH, ąĖ čĆąĄą│ąĖčüčéčĆ TIMERx_PERIOD ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ąĖą╝ą┐čāą╗čīčüą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé ąĘą░čēąĄą╗ą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ TIMILx, ąĖ čéą░ą╣ą╝ąĄčĆ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ. ąĢčüą╗ąĖ ą▒ąĖčé PULSE_HI čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TMRx ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü. ąĢčüą╗ąĖ PULSE_HI ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą░ą║čéąĖą▓ąĮčŗą╣ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü.

ąōąĄąĮąĄčĆą░čåąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ čü ą┐ąŠą╝ąŠčēčīčÄ ą©ąśą£ (Pulse-Width Modulation Waveform Generation). ąĢčüą╗ąĖ ą▒ąĖčé PERIOD_CNT čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čéą░ą║čéąĖčĆčāąĄą╝čŗą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĄ čéą░ą╣ą╝ąĄčĆ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆčÅą╝ąŠčāą│ąŠą╗čīąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ čü č湥čéą║ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ ą┐ąĄčĆąĖąŠą┤ąŠą╝ ąĖ čüą║ą▓ą░ąČąĮąŠčüčéčīčÄ. ąŁč鹊čé čĆąĄąČąĖą╝ čéą░ą║ąČąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓ čĆąĄą░ą╗čīąĮąŠą╝ ą▓čĆąĄą╝ąĄąĮąĖ.

32-ą▒ąĖčéąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ (TIMERx_PERIOD) ąĖ (TIMERx_WIDTH) ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ ą┐ąĄčĆąĖąŠą┤ą░ čüč湥čéą░ čéą░ą╣ą╝ąĄčĆą░ ąĖ čłąĖčĆąĖąĮąŠą╣ ąĖą╝ą┐čāą╗čīčüą░ čü ą╝ąŠą┤čāą╗ąĖčĆąŠą▓ą░ąĮąĮąŠą╣ čłąĖčĆąĖąĮąŠą╣ ąĖą╝ą┐čāą╗čīčüą░.

ąÜąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ, ą▓čŗą▓ąŠą┤ TMRx ą┐čĆąĖčéčÅą│ąĖą▓ą░ąĄčéčüčÅ ą║ 0 ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ čéą░ą╣ą╝ąĄčĆą░ čüčéą░ąĮąŠą▓ąĖčéčüčÅ čĆą░ą▓ąĮčŗą╝ čĆąĄą│ąĖčüčéčĆčā TIMERx_WIDTH, ąĖ ą▓čŗą▓ąŠą┤ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ 1, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĖąŠą┤ ąĖčüč鹥č湥čé (ąĖą╗ąĖ ą║ąŠą│ą┤ą░ čüčéą░čĆčéčāąĄčé čéą░ą╣ą╝ąĄčĆ).

ą¦č鹊ą▒čŗ čāą┐čĆą░ą▓ą╗čÅčéčī ą┐ąŠą╗čÅčĆąĮąŠčüčéčīčÄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čŗą▓ąŠą┤ą░ TMRx, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▒ąĖčé PULSE_HI ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ TIMERx_CONFIG. ąöą╗čÅ ąĮąĖąĘą║ąŠą│ąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄą╝ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąŠčćąĖčüčéąĖč鹥 čŹč鹊čé ą▒ąĖčé. ąöą╗čÅ ą▓čŗčüąŠą║ąŠą│ąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄą╝ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ čāčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé. ąÜąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT ąĘą░ą┐čĆąĄčēąĄąĮ, ą▓čŗą▓ąŠą┤ TMRx ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ.

ąĢčüą╗ąĖ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ, č鹊 ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░. ISR ą┤ąŠą╗ąČąĄąĮ ąŠčćąĖčüčéąĖčéčī ą▒ąĖčé ąĘą░čēąĄą╗ą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (TIMILx) ąĖ ą╝ąŠąČąĄčé ąĖąĘą╝ąĄąĮąĖčéčī ąĘąĮą░č湥ąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░ ąĖ/ąĖą╗ąĖ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░. ąÆ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ ą©ąśą£ (pulse-width modulation, PWM) ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ąŠą▒ąĮąŠą▓ą╗čÅčéčī ąĘąĮą░č湥ąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░ ąĖ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ ą▓ąŠ ą▓čĆąĄą╝čÅ čüč湥čéą░ čéą░ą╣ą╝ąĄčĆą░. ąÜąŠą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąŠą▒ąĮąŠą▓ą╗čÅąĄčé čĆąĄą│ąĖčüčéčĆčŗ ą┐ąĄčĆąĖąŠą┤ą░ ąĖą╗ąĖ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░, ąĮąŠą▓čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ čāą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░ ąŠą║ąŠąĮčćą░ąĮąĖčÅ č鹥ą║čāčēąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ąĮąŠą▓čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░ ąĖ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ čüčéą░ąĮąŠą▓čÅčéčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ąĖ. ąØąŠą▓čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ TIMERx_PERIOD ąĖ TIMERx_WIDTH ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čüčéą░čĆčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ. ąØąŠą▓čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ čüčéą░ąĮąŠą▓ąĖčéčüčÅ čĆą░ą▓ąĮčŗą╝ č鹥ą║čāčēąĄą╝čā ąĘąĮą░č湥ąĮąĖčÄ ą┐ąĄčĆąĖąŠą┤ą░. ą¦č鹥ąĮąĖčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ TIMERx_PERIOD ąĖ TIMERx_WIDTH ą▓ąŠąĘą▓čĆą░čéčÅčé čüčéą░čĆčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ, ą┐ąŠą║ą░ ąĮąĄ ąĖčüč鹥č湥čé č鹥ą║čāčēąĖą╣ ą┐ąĄčĆąĖąŠą┤.

ąæąĖčé čüąŠčüč鹊čÅąĮąĖčÅ TOVF_ERRx ąŠą▒ąŠąĘąĮą░čćą░ąĄčé čüąŠą▒čŗčéąĖąĄ ąŠčłąĖą▒ą║ąĖ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT. ąæąĖčé TOVF_ERRx čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ąĄčüą╗ąĖ ą┐čĆąĖ ąĘą░ą┐čāčüą║ąĄ TIMERx_PERIOD = 0 ąĖą╗ąĖ TIMERx_PERIOD = 1, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮčÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░. ąæąĖčé čéą░ą║ąČąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮčÅąĄčéčüčÅ, ąĄčüą╗ąĖ čĆąĄą│ąĖčüčéčĆ TIMERx_WIDTH ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĄąĮ čĆąĄą│ąĖčüčéčĆčā TIMERx_PERIOD. ąæąĖčéčŗ ERR_TYP čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé TOVF_ERRx.

ąöą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊čéčŗ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ą▓čŗčģąŠą┤ą░ TMRx čāčüčéą░ąĮąŠą▓ąĖč鹥 ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĖąŠą┤ą░ 2 ąĖ čłąĖčĆąĖąĮčā ąĖą╝ą┐čāą╗čīčüą░ ą▓ 1. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 TMRx ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ čü ą║ą░ąČą┤čŗą╝ čéą░ą║č鹊ą╝ SCLK, čüą║ą▓ą░ąČąĮąŠčüčéčī ąĖą╝ą┐čāą╗čīčüąŠą▓ (duty cycle) čüąŠčüčéą░ą▓ąĖčé 50%. ą¤ąĄčĆąĖąŠą┤ ą╝ąŠąČąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĮą░ ą╗čÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąŠčé 2 ą┤ąŠ (2^32 ŌĆō 1) ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ. ą©ąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1 ą┤ąŠ (ą┐ąĄčĆąĖąŠą┤ ŌĆō 1) ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ. ąÜąŠą│ą┤ą░ PERIOD_CNT = 0, čłąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ą▓ ą╗čÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąŠčé 1 ą┤ąŠ (2^32 ŌĆō 1) ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ.

ąźąŠčéčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ čüąŠąŠą▒čēąĖčé ąŠą▒ ąŠčłąĖą▒ą║ąĄ, ąĄčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ TIMERx_WIDTH čüčéą░ąĮąĄčé čĆą░ą▓ąĮčŗą╝ ąĘąĮą░č湥ąĮąĖčÄ TIMERx_PERIOD, čŹč鹊 ą▓čüąĄ čĆą░ą▓ąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą©ąśą£ čüąŠ čüą║ą▓ą░ąČąĮąŠčüčéčīčÄ čåąĖą║ą╗ą░ 100%. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ą┐čĆąŠčüč鹊 ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī čäą╗ą░ą│ąĖ TOVL_ERRx. ąŚąĮą░č湥ąĮąĖčÅ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ ą▒ąŠą╗čīčłąĄ č湥ą╝ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĖąŠą┤ą░ ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāčÄčéčüčÅ. ąóąŠčćąĮąŠ čéą░ą║ ąČąĄ TIMERx_WIDTH = 0 ąĮąĄ ą┤ąŠą┐čāčüčéąĖą╝ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ. ąĪą║ą▓ą░ąČąĮąŠčüčéąĖ 0% ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ.

ą×čüčéą░ąĮąŠą▓ą║ą░ čéą░ą╣ą╝ąĄčĆą░ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT. ąÆąŠ ą▓čüąĄčģ ą▓ą░čĆąĖą░ąĮčéą░čģ čĆąĄąČąĖą╝ą░ PWM_OUT, čéą░ą╣ą╝ąĄčĆ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ąŠą┐ąĄčĆą░čåąĖčÄ ąĘą░ą┐čĆąĄčéą░ (W1C ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ TIMER_DISABLE) ą║ą░ą║ čāčüą╗ąŠą▓ąĖąĄ "ąĘą░ą┐čĆąŠčüą░ ąĮą░ ąŠčüčéą░ąĮąŠą▓ą║čā". ąÜąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ ąĘą░ą┐čĆąĄčēąĄąĮ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT, ąŠąĮ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą▓ąĄčĆčłąĖčé č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ č鹥ą║čāčēąĄą╣ č乊čĆą╝čŗ čüąĖą│ąĮą░ą╗ą░ ąĖ ą║ąŠčĆčĆąĄą║čéąĮąŠ ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ. ąŁč鹊 ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčé ąŠą▒čĆąĄąĘą║čā č鹥ą║čāčēąĄą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ ąĖ ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮčŗąĄ č乊čĆą╝čŗ čüąĖą│ąĮą░ą╗ą░ ą©ąśą£ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TMRx. ą¤čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ ąŠčüčéą░ąĮąŠą▓ąĖą╗ čüč湥čé, ą┐čāč鹥ą╝ ąŠą┐čĆąŠčüą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ TRUNx ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMER_STATUS, ą║ąŠą│ą┤ą░ ąŠąĮ čüčéą░ą╗ čĆą░ą▓ąĄąĮ 0, ąĖą╗ąĖ ąŠąČąĖą┤ą░ąĮąĖąĄą╝ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ąĄčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮčŗ). ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čéą░ą╣ą╝ąĄčĆ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆąĄą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ (ą▓ čĆąĄą│ąĖčüčéčĆ TIMERx_CONFIG ąĮąĄą╗čīąĘčÅ ąĘą░ą┐ąĖčüą░čéčī ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ), ą┐ąŠą║ą░ čéą░ą╣ą╝ąĄčĆ ąĮąĄ ąŠčüčéą░ąĮąŠą▓ąĖčé čüč湥čé, ąĖ TRUNx ąĮąĄ ą▒čāą┤ąĄčé čćąĖčéą░čéčīčüčÅ ą║ą░ą║ 0.

ąÆ čĆąĄąČąĖą╝ąĄ PWM_OUT čü ąŠą┤ąĖąĮąŠčćąĮčŗą╝ ąĖą╝ą┐čāą╗čīčüąŠą╝ (PERIOD_CNT = 0), ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ąĘą░ą┐ąĖčüą░čéčī čĆąĄą│ąĖčüčéčĆ TIMER_DISABLE ą┤ą╗čÅ ąŠčüčéą░ąĮąŠą▓ą║ąĖ čéą░ą╣ą╝ąĄčĆą░. ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ąĖą╝ą┐čāą╗čīčüą░ čéą░ą╣ą╝ąĄčĆ ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMER_ENABLE (ąĖ ą║ąŠąĮąĄčćąĮąŠ TIMER_DISABLE) ąŠčćąĖčüčéąĖčéčüčÅ, ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé TRUNx čéą░ą║ąČąĄ ąŠčćąĖčüčéąĖčéčüčÅ, čüą╝. čĆąĖčü. 16-11. ą¦č鹊ą▒čŗ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĖą╝ą┐čāą╗čīčüąŠą▓, ąĘą░ą┐ąĖčłąĖč鹥 1 ą▓ čĆąĄą│ąĖčüčéčĆ TIMER_ENABLE, ąČą┤ąĖč鹥 ąŠčüčéą░ąĮąŠą▓ą║ąĖ čéą░ą╣ą╝ąĄčĆą░, ąĘą░č鹥ą╝ ąĘą░ą┐ąĖčłąĖč鹥 ą┤čĆčāą│čāčÄ 1 ą▓ čĆąĄą│ąĖčüčéčĆ TIMER_ENABLE.

ąĢčüą╗ąĖ čŹč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, ą┐čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠąČąĄčé ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮčāčÄ ąŠčüčéą░ąĮąŠą▓ą║čā čéą░ą╣ą╝ąĄčĆą░ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT. ą¦č鹊ą▒čŗ čüą┤ąĄą╗ą░čéčī čŹč鹊, ąĮčāąČąĮąŠ čüąĮą░čćą░ą╗ą░ ąĘą░ą┐ąĖčüą░čéčī 1 ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ TIMER_DISABLE, ąĖ ąĘą░č鹥ą╝ ąĘą░ą┐ąĖčüą░čéčī 1 ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé TRUNx čĆąĄą│ąĖčüčéčĆą░ TIMER_STATUS. ąŁč鹊 ąŠčüčéą░ąĮąŠą▓ąĖčé čéą░ą╣ą╝ąĄčĆ ą▓ ą╗čÄą▒ąŠą╝ čüą╗čāčćą░ąĄ - ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą▒čŗą╗ąŠ ą╗ąĖ ąŠąČąĖą┤ą░ąĮąĖąĄ ą║ąŠąĮčåą░ č鹥ą║čāčēąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ (PERIOD_CNT = 1) ąĖą╗ąĖ ą║ąŠąĮčåą░ č鹥ą║čāčēąĄą╣ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ (PERIOD_CNT = 0). ąŁčéą░ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ, čćč鹊ą▒čŗ ą▓ąĄčĆąĮčāčéčī ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗čī ąĮą░ą┤ čéą░ą╣ą╝ąĄčĆąŠą╝ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ.

ąśčüą┐ąŠą╗čīąĘčāą╣č鹥 čŹčéčā ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čü ąŠčüč鹊čĆąŠąČąĮąŠčüčéčīčÄ, ą┐ąŠč鹊ą╝čā čćč鹊 ąŠąĮą░ ą╝ąŠąČąĄčé ąĮą░čĆčāčłąĖčéčī č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ ą©ąśą£, ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą│ąŠ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TMRx.

ąÆ čĆąĄąČąĖą╝ąĄ ą┐čĆąŠą┤ąŠą╗ąČąĄąĮąĖčÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖą╝ą┐čāą╗čīčüąŠą▓ PWM_OUT (PERIOD_CNT = 1) ą║ą░ąČą┤čŗą╣ čéą░ą╣ą╝ąĄčĆ ąŠą┐čĆą░čłąĖą▓ą░ąĄčé ą▒ąĖčé TIMENx ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░. ąóą░ą╣ą╝ąĄčĆ ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ čćąĖčüč鹊, ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░, ą║ąŠą│ą┤ą░ TIMENx ąŠą║ą░ąČąĄčéčüčÅ ą▓ ą╗ąŠą│. 0. ąŁč鹊 ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé (ą┐čĆąĖ ąĘą░ą┐čĆąĄčēąĄąĮąĖąĖ ą╗čÄą▒čŗčģ W1C ą▓ TRUNx), čćč鹊 čéą░ą╣ą╝ąĄčĆ, ą║ąŠč鹊čĆčŗą╣ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ąĖ ąĘą░č鹥ą╝ ąĘą░ąĮąŠą▓ąŠ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ ąŠą║ąŠąĮčćą░ąĮąĖąĄą╝ č鹥ą║čāčēąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░, ą┐čĆąŠą┤ąŠą╗ąČąĖčé čüč湥čé, ąĄčüą╗ąĖ ąĮąĖč湥ą│ąŠ ąĮąĄ čüą╗čāčćąĖčéčüčÅ. ą×ą▒čŗčćąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąĘą░ą┐čĆąĄčéąĖčéčī čéą░ą╣ą╝ąĄčĆ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT ąĖ ąĘą░č鹥ą╝ ąČą┤ą░čéčī, ą┐ąŠą║ą░ ąŠąĮ čüą░ą╝ ąĮąĄ ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ. ąóą░ą╣ą╝ąĄčĆ ą▓čüąĄą│ą┤ą░ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆą▓ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░, ą║ąŠą│ą┤ą░ PERIOD_CNT = 0.

PWM_OUT, čéą░ą║čéąĖčĆčāąĄą╝čŗą╣ ą▓ąĮąĄčłąĮąĄ. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čéą░ą╣ą╝ąĄčĆ čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čćą░čüč鹊čéčŗ čłąĖąĮčŗ SCLK. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé CLK_SEL ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ (TIMERx_CONFIG), č鹊 čéą░ą╣ą╝ąĄčĆ čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PWM_CLK. ąĪąĖą│ąĮą░ą╗ PWM_CLK ąĮąŠčĆą╝ą░ą╗čīąĮąŠ čÅą▓ą╗čÅąĄčéčüčÅ ą▓čģąŠą┤ąŠą╝, čüąŠą▓ą╝ąĄčēąĄąĮąĮčŗą╝ čü ą▓čŗą▓ąŠą┤ąŠą╝ ą┐ąŠčĆčéą░ PF1, ąŠą┤ąĮą░ą║ąŠ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćą░čéčī čüąĖą│ąĮą░ą╗ ąŠčé ą▓čŗą▓ąŠą┤ą░ PPI_CLK, ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆčŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ čü PPI. ąĀą░ąĘą╗ąĖčćąĮčŗąĄ čéą░ą╣ą╝ąĄčĆčŗ ą╝ąŠą│čāčé ą┐ąŠą╗čāčćą░čéčī čĆą░ąĘą╗ąĖčćąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ąŠčé čüą▓ąŠąĖčģ ą▓čģąŠą┤ąŠą▓ PWM_CLK, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĮą░čüčéčĆąŠąĄąĮąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. ąÜą░ą║ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▒ąĖč鹊ą╝ PERIOD_CNT, čĆąĄąČąĖą╝ PWM_OUT ą╗ąĖą▒ąŠ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗ ą©ąśą£, ą╗ąĖą▒ąŠ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąŠą┤ąĖąĮąŠčćąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü čłąĖčĆąĖąĮąŠą╣, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝ąŠą╣ čĆąĄą│ąĖčüčéčĆąŠą╝ TIMERx_WIDTH.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ CLK_SEL, čüč湥čéčćąĖą║ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą▓ 0x0 ą┐čĆąĖ čüčéą░čĆč鹥 ąĖ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą┐ąŠ ą║ą░ąČą┤ąŠą╝čā čäčĆąŠąĮčéčā PWM_CLK. ą¤ąĄčĆąĄčģąŠą┤čŗ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TMRx ą┐čĆąŠąĖčüčģąŠą┤čÅčé ą┐ąŠ čäčĆąŠąĮčéą░ą╝ PWM_CLK. ąØąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čüą┐ąŠčüąŠą▒ą░ ą▓čŗą▒čĆą░čéčī čüą┐ą░ą┤čŗ čüąĖą│ąĮą░ą╗ą░ PWM_CLK. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą▒ąĖčé PULSE_HI čāą┐čĆą░ą▓ą╗čÅąĄčé č鹊ą╗čīą║ąŠ ą┐ąŠą╗čÅčĆąĮąŠčüčéčīčÄ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓.

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ąĮąĄą╝ąĮąŠą│ąŠ ą┐ąĄčĆąĄą┤ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą╝ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TMRx (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā SCLK, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┐ąĄčĆąĄčģąŠą┤čŗ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ą┐ąŠąĘąČąĄ, ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā čäčĆąŠąĮčéą░ PWM_CLK). ą£ąŠąČąĮąŠ ą▓čüąĄ ąĄčēąĄ ą▒ąĄąĘąŠą┐ą░čüąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĮąŠą▓čŗą╣ ą┐ąĄčĆąĖąŠą┤ ąĖ čłąĖčĆąĖąĮčā ąĖą╝ą┐čāą╗čīčüą░, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąĄčĆąĖąŠą┤ ąĖčüč鹥č湥čé, čüč湥čéčćąĖą║ ą┐ąĄčĆąĄą▓ą░ą╗ąĖą▓ą░ąĄčé č湥čĆąĄąĘ ąĘąĮą░č湥ąĮąĖąĄ 0x1.

ążąŠčĆą╝ą░ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ PWM_CLK ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą┤ąŠą╗ąČąĮą░ ąĖą╝ąĄčéčī čüą║ą▓ą░ąČąĮąŠčüčéčī 50%, ąŠą┤ąĮą░ą║ąŠ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠ ą▓čĆąĄą╝čÅ ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ PWM_CLK ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĮąĄ ą╝ąĄąĮąĄąĄ ąŠą┤ąĮąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ SCLK, ąĖ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ą▓čŗčüąŠą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ PWM_CLK ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĮąĄ ą╝ąĄąĮąĄąĄ ąŠą┤ąĮąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ SCLK. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ PWM_CLK ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗčłąĄ SCLK/2.

ąÆčŗą▓ąŠą┤ PF1 ą╝ąŠąČąĄčé čéą░ą║čéąĖčĆąŠą▓ą░čéčī čéą░ą╣ą╝ąĄčĆ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ PF1 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤. ąÜąŠą│ą┤ą░ ą╗čÄą▒ąŠą╣ čéą░ą╣ą╝ąĄčĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ PWM_OUT čü CLK_SEL = 1 ąĖ TIN_SEL = 0, č鹊 ą▒ąĖčé PF1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ FIO_DIR ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ ąĖ PF1 ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čģąŠą┤ąŠą╝.

ążąŠčĆą╝ą░ čüąĖą│ąĮą░ą╗ą░ čĆąĄąČąĖą╝ą░ PWM_OUT čü PERIOD_CNT = 1 ąŠą▒čŗčćąĮąŠ ąĖą╝ąĄąĄčé čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ą▓čĆąĄą╝čÅ ą╗ąŠą│. 1 ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠąĄ (č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ TIMERx_WIDTH) ą▓čĆąĄą╝čÅ ą╗ąŠą│. 0. ąÜąŠą│ą┤ą░ 2 čéą░ą╣ą╝ąĄčĆą░ čüčćąĖčéą░čÄčé čüąĖąĮčģčĆąŠąĮąĮąŠ čü ąŠą┤ąĮąĖą╝ ąĖ č鹥ą╝ ąČąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą┐ąĄčĆąĖąŠą┤ąŠą╝, ąĖą╝ą┐čāą╗čīčüčŗ ą▓čŗčĆąŠą▓ąĮąĄąĮčŗ ą┐ąŠ čäčĆąŠąĮčéčā čāčüčéą░ąĮąŠą▓ą║ąĖ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 16-13.

ąĀąĄąČąĖą╝ TOGGLE_HI čĆą░ąĘčĆąĄčłą░ąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čĆąĄą╝ąĄąĮąĄą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą╗ąŠą│. 1 ąĖ ą╗ąŠą│. 0 ą┤ą╗čÅ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ążą░ąĘą░ ą╝ąĄąČą┤čā čäčĆąŠąĮč鹊ą╝ ą┤ą▓čāčģ ą▓čŗčģąŠą┤ąŠą▓ čéą░ą╣ą╝ąĄčĆą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ. ąŁčäč乥ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖčéą░ PULSE_HI ą╝ąĄąĮčÅąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ ą┐ąĄčĆąĖąŠą┤. ąĪą╝ąĄąČąĮčŗąĄ ą░ą║čéąĖą▓ąĮčŗąĄ ąĖą╝ą┐čāą╗čīčüčŗ ą╗ąŠą│. 0 ąĖ ą╗ąŠą│. 1, ą▓ąĘčÅčéčŗąĄ ą▓ą╝ąĄčüč鹥, čüąŠčüčéą░ą▓ą╗čÅčÄčé ą┤ą▓ąĄ ą┐ąŠą╗ąŠą▓ąĖąĮčŗ čüąĖą│ąĮą░ą╗ą░ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠą╣ (ąŠą┤ąĮą░ą║ąŠ ą┐čĆčÅą╝ąŠčāą│ąŠą╗čīąĮąŠą╣) č乊čĆą╝čŗ. ąŁčäč乥ą║čéąĖą▓ąĮą░čÅ č乊čĆą╝ą░ čüąĖą│ąĮą░ą╗ą░ ąŠčüčéą░ąĄčéčüčÅ ą░ą║čéąĖą▓ąĮąŠą╣ ą▓ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ PULSE_HI čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖ ą░ą║čéąĖą▓ąĮąŠą╣ ą▓ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ PULSE_HI ąŠčćąĖčēąĄąĮ. ąŚąĮą░č湥ąĮąĖąĄ TOGGLE_HI ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░ ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čüą╗čāčćą░čÅ, ą║ąŠą│ą┤ą░ PWM_OUT ąĖ PERIOD_CNT = 1.

ąÆ čĆąĄąČąĖą╝ąĄ TOGGLE_HI, ą║ąŠą│ą┤ą░ PULSE_HI čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą░ą║čéąĖą▓ąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü ą╗ąŠą│. 0 ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą▓ ą┐ąĄčĆą▓ąŠą╝, čéčĆąĄčéčīąĄą╝, ąĖ ą▓ąŠ ą▓čüąĄčģ ąĮąĄč湥čéąĮčŗčģ ą┐ąĄčĆąĖąŠą┤ą░čģ, ąĖ ą░ą║čéąĖą▓ąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü ą╗ąŠą│. 1 ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą▓ąŠ ą▓č鹊čĆąŠą╝, č湥čéą▓ąĄčĆč鹊ą╝ ąĖ ą▓čüąĄčģ č湥čéąĮčŗčģ ą┐ąĄčĆąĖąŠą┤ą░čģ. ąÜąŠą│ą┤ą░ PULSE_HI ąŠčćąĖčēąĄąĮ, ą░ą║čéąĖą▓ąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü ą╗ąŠą│. 1 ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą▓ ą┐ąĄčĆą▓ąŠą╝, čéčĆąĄčéčīąĄą╝ ąĖ ą▓čüąĄčģ ąĮąĄč湥čéąĮčŗčģ ą┐ąĄčĆąĖąŠą┤ą░čģ, ąĖ ą░ą║čéąĖą▓ąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü ą╗ąŠą│. 0 ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą▓ąŠ ą▓č鹊čĆąŠą╝, č湥čéą▓ąĄčĆč鹊ą╝ ąĖ ą▓čüąĄčģ č湥čéąĮčŗčģ ą┐ąĄčĆąĖąŠą┤ą░čģ.

ąĀąĖčü. 16-13. ąóą░ą╣ą╝ąĄčĆčŗ čü ąĖą╝ą┐čāą╗čīčüą░ą╝ąĖ, ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗą╝ąĖ ą┐ąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā.

ąĪąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 0 ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ąŠą┤ąĮąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čüąŠčüč鹊čÅąĮąĖčÄ ą╗ąŠą│. 1 ąĮą░ ąĮą░čćą░ą╗ąĄ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░, čéą░ą║ čćč鹊 ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą╝ąĄąĮčÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐čĆąĖ Count = Pulse Width (ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ čĆą░ą▓ąĮąŠ čłąĖčĆąĖąĮąĄ ąĖą╝ą┐čāą╗čīčüą░). ąÜąŠąĮąĄčćąĮčŗą╣ čĆąĄąĘčāą╗čīčéą░čé - ąĖą╝ą┐čāą╗čīčü ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ ą║ą░ąČą┤čŗąĄ 2 ą┐ąĄčĆąĖąŠą┤ą░ čüč湥čéčćąĖą║ą░, ąĖ čåąĄąĮčéčĆąĖčĆčāąĄčéčüčÅ ą▓ąŠą║čĆčāą│ ą║ąŠąĮčåą░ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ (ąĖą╗ąĖ ąĮą░čćą░ą╗ą░ ą▓č鹊čĆąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░).

ąØą░ čĆąĖčü. 16-14 ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąĖą╝ąĄčĆ 3 čéą░ą╣ą╝ąĄčĆąŠą▓, čüčćąĖčéą░čÄčēąĖčģ čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ ą┐ąĄčĆąĖąŠą┤ą░. ąÜąŠą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮąĄ ą╝ąĄąĮčÅąĄčé ąĮą░čüčéčĆąŠą╣ą║ąĖ PWM ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ, čüą║ą▓ą░ąČąĮąŠčüčéčī ą▒čāą┤ąĄčé 50%. ąŚąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ TIMERx_WIDTH čāą┐čĆą░ą▓ą╗čÅčÄčé čäą░ąĘąŠą╣ ą╝ąĄąČą┤čā čüąĖą│ąĮą░ą╗ą░ą╝ąĖ.

ąĀąĖčü. 16-14. ąóčĆąĖ čéą░ą╣ą╝ąĄčĆą░ čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą┐ąĄčĆąĖąŠą┤ąŠą╝.

ąÉąĮą░ą╗ąŠą│ąĖčćąĮąŠ, 2 čéą░ą╣ą╝ąĄčĆą░ ą╝ąŠą│čāčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĮąĄ ą┐ąĄčĆąĄą║čĆčŗą▓ą░čÄčēąĖąĄčüčÅ čéą░ą║čéčŗ, ą┐čāč鹥ą╝ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ čåąĄąĮčéčĆąŠą▓ ąĖą╝ą┐čāą╗čīčüąŠą▓ čü ąĖąĮą▓ąĄčĆčüąĖąĄą╣ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą╗čÅ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ čéą░ą╣ą╝ąĄčĆąŠą▓ (čüą╝. čĆąĖčü. 16-15).

ąĀąĖčü. 16-15. ąöą▓ą░ čéą░ą╣ą╝ąĄčĆą░ čü ąĮąĄ ą┐ąĄčĆąĄą║čĆčŗą▓ą░čÄčēąĖą╝ąĖčüčÅ čéą░ą║čéą░ą╝ąĖ.

ąÜąŠą│ą┤ą░ TOGGLE_HI = 0, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąŠą▒ąĮąŠą▓ą╗čÅąĄčé čĆąĄą│ąĖčüčéčĆčŗ TIMERx_PERIOD ąĖ TIMERx_WIDTH ąŠą┤ąĖąĮ čĆą░ąĘ ąĮą░ ą┐ąĄčĆąĖąŠą┤ čüąĖą│ąĮą░ą╗ą░. ąÜąŠą│ą┤ą░ TOGGLE_HI = 1, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąŠą▒ąĮąŠą▓ą╗čÅąĄčé čĆąĄą│ąĖčüčéčĆčŗ TIMERx_PERIOD ąĖ TIMERx_WIDTH ą┤ą▓ą░ąČą┤čŗ ąĮą░ ą┐ąĄčĆąĖąŠą┤ čüąĖą│ąĮą░ą╗ą░, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą┐ąŠą╗ąŠą▓ąĖąĮąĮąŠą╣ ą┤ą╗ąĖąĮčŗ. ąÆ ąĮąĄč湥čéąĮčŗčģ ą┐ąĄčĆąĖąŠą┤ą░čģ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗčģ ą┐ąŠ čåąĄąĮčéčĆčā ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĮčāąČąĮą░ ąĘą░ą┐ąĖčüčī (Period ŌĆō Width) ą▓ą╝ąĄčüč鹊 Width ą▓ čĆąĄą│ąĖčüčéčĆ TIMERx_WIDTH.

ąØą░ą┐čĆąĖą╝ąĄčĆ, ą║ąŠą│ą┤ą░ TOGGLE_HI = 0, ą▓ ą┐čüąĄą▓ą┤ąŠą║ąŠą┤ąĄ čŹč鹊 ą▒čāą┤ąĄčé ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī čéą░ą║:

int period, width;

for (;;)

{

period = generate_period(...);

width = generate_width(...);

waitfor (interrupt);

write(TIMERx_PERIOD, period);

write(TIMERx_WIDTH, width);

}

ąóąŠą│ą┤ą░ ą┐čĆąĖ TOGGLE_HI = 1 ą┐čüąĄą▓ą┤ąŠą║ąŠą┤ ą▒čŗą╗ ą▒čŗ čéą░ą║ąĖą╝:

int period, width;

int per1, per2, wid1, wid2;

for (;;)

{

period = generate_period(...);

width = generate_width(...);

per1 = period/2;

wid1 = width/2;

per2 = period/2;

wid2 = width/2;

waitfor (interrupt);

write(TIMERx_PERIOD, per1);

write(TIMERx_WIDTH, per1 - wid1);

waitfor (interrupt);

write(TIMERx_PERIOD, per2);

write(TIMERx_WIDTH, wid2);

}

ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ, ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗąĄ ąĖą╝ą┐čāą╗čīčüčŗ ąĮąĄ ąĮčāąČą┤ą░čÄčéčüčÅ ą▓ č鹊ą╝, čćč鹊ą▒čŗ ą▒čŗčéčī čüąĖą╝ą╝ąĄčéčĆąĖčćąĮčŗą╝ąĖ (ą┐ąĄčĆąĄą╝ąĄąĮąĮą░čÅ wid1 ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čĆą░ą▓ąĮą░ wid2). ą¤ąĄčĆąĖąŠą┤ ą╝ąŠąČąĄčé ąĖą╝ąĄčéčī čüą╝ąĄčēąĄąĮąĖąĄ ą┤ą╗čÅ ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ čäą░ąĘčŗ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ (ą┐ąĄčĆąĄą╝ąĄąĮąĮą░čÅ per1 ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čĆą░ą▓ąĮąŠą╣ per2).

ąæąĖčé timer slave enable (ą▒ąĖčé TRUNx ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMER_STATUS) ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ č湥čéąĮčŗčģ ą┐ąĄčĆąĖąŠą┤ąŠą▓ čĆąĄąČąĖą╝ą░ TOGGLE_HI. ąÜąŠą│ą┤ą░ TIMER_DISABLE ąĘą░ą┐ąĖčüą░ąĮ ą▓ 1, č鹥ą║čāčēą░čÅ ą┐ą░čĆą░ ą┐ąĄčĆąĖąŠą┤ąŠą▓ čüč湥čéčćąĖą║ą░ (ąŠą┤ąĖąĮ ą┐ąĄčĆąĖąŠą┤ čüąĖą│ąĮą░ą╗ą░) ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ ąĘą░ą┐čĆąĄč鹊ą╝ čéą░ą╣ą╝ąĄčĆą░.

ąÜą░ą║ ąĖ ą┐čĆąĖ TOGGLE_HI = 0, ą▒čāą┤ąĄčé čüąŠąŠą▒čēąĄąĮąĖąĄ ąŠą▒ ąŠčłąĖą▒ą║ą░čģ ąĄčüą╗ąĖ: TIMERx_WIDTH >= TIMERx_PERIOD, TIMERx_PERIOD = 0, ąĖą╗ąĖ TIMERx_PERIOD = 1.

ąÆ čĆąĄąČąĖą╝ąĄ WDTH_CAP ą▓čŗą▓ąŠą┤ TMRx čÅą▓ą╗čÅąĄčéčüčÅ ą▓čģąŠą┤ąŠą╝ (čüą╝. čĆąĖčü. 16-16). ąóą░ą╣ą╝ąĄčĆ, čéą░ą║čéąĖčĆčāąĄą╝čŗą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čćą░čüč鹊č鹊ą╣ čłąĖąĮčŗ, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░ ąĖ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐ąŠčüčéčāą┐ą░čÄčēąĄą│ąŠ ąĮą░ TMRx ą┐čĆčÅą╝ąŠčāą│ąŠą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą┐ąŠą╗čÅ TMODE ą▓ ąĘąĮą░č湥ąĮąĖąĄ b#10 čĆąĄą│ąĖčüčéčĆą░ TIMERx_CONFIG čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░.

ąÜąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ ą▓ čĆąĄąČąĖą╝ąĄ WDTH_CAP, čéą░ą╣ą╝ąĄčĆ čüą▒čĆą░čüčŗą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMERx_COUNTER ąĮą░ 0x00000001, ąĖ ąĮąĄ čüčéą░čĆčéčāąĄčé, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ąĮą░čćą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TMRx.

ąĀąĖčü. 16-16. ąÉą╗ą│ąŠčĆąĖčéą╝ čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░ ą▓ čĆąĄąČąĖą╝ąĄ WDTH_CAP.

ąÜąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ ą┤ąĄč鹥ą║čéąĖčĆčāąĄčé ą┐ąĄčĆą▓čŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤, ąŠąĮ ąĮą░čćąĖąĮą░ąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ. ąÜąŠą│ą┤ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ąĘą░ą▓ąĄčĆčłą░čÄčēąĖą╣ ą┐ąĄčĆąĄą┐ą░ą┤, čéą░ą╣ą╝ąĄčĆ ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčé č鹥ą║čāčēąĄąĄ 32-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ TIMERx_COUNTER ą▓ čĆąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ čłąĖčĆąĖąĮčŗ. ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╝ ąĮą░čćą░ą╗čīąĮąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ čéą░ą╣ą╝ąĄčĆ ą┐ąĄčĆąĄą┤ą░ąĄčé č鹥ą║čāčēąĄąĄ 32-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ TIMERx_COUNTER ą▓ čĆąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┐ąĄčĆąĖąŠą┤ą░. ąĀąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ čüąĮąŠą▓ą░ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 0x00000001, ąĖ čéą░ą╣ą╝ąĄčĆ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé čüč湥čé ąĖ ąĘą░čģą▓ą░čé, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ąĘą░ą┐čĆąĄčēąĄąĮ.

ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ąĖąĘą╝ąĄčĆąĖčéčī ą║ą░ą║ čłąĖčĆąĖąĮčā ąĖą╝ą┐čāą╗čīčüą░, čéą░ą║ ąĖ ą┐ąĄčĆąĖąŠą┤ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ą¦č鹊ą▒čŗ čāą┐čĆą░ą▓ą╗čÅčéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄą╝ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ąĖ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TMRx, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖą╗ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą▒ąĖčé PULSE_HI ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMERx_CONFIG. ąĢčüą╗ąĖ ą▒ąĖčé PULSE_HI = 0, č鹊 ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ (ą┐ąĄčĆąĄčģąŠą┤ 1 -> 0), čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčéčüčÅ ą▓ ą▒čāč乥čĆ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ čāčĆąŠą▓ąĮčÅ (0 -> 1), ąĖ ą┐ąĄčĆąĖąŠą┤ ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčéčüčÅ ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╝čā čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ. ąÜąŠą│ą┤ą░ PULSE_HI = 1, č鹊 ą▓čüąĄ ąĮą░ąŠą▒ąŠčĆąŠčé: ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ čāčĆąŠą▓ąĮčÅ (ą┐ąĄčĆąĄčģąŠą┤ 0 -> 1), čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčéčüčÅ ą▓ ą▒čāč乥čĆ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ (1 -> 0), ąĖ ą┐ąĄčĆąĖąŠą┤ ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčéčüčÅ ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╝čā ąĮą░čĆą░čüčéą░ąĮąĖčÄ čāčĆąŠą▓ąĮčÅ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▒ąĖčé PULSE_HI ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMERx_CONFIG čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠą╗čÅčĆąĮąŠčüčéčīčÄ ą▓čģąŠą┤ą░ TMRx.

ąÆ čĆąĄąČąĖą╝ąĄ WDTH_CAP ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓ąŠąĘąĮąĖą║ą░čÄčé čüčĆą░ąĘčā 3 čüą╗ąĄą┤čāčÄčēąĖąĄ čüąŠą▒čŗčéąĖčÅ ąĮą░ ąŠą┤ąĮąŠą╝ ąĖąĘ čéą░ą╣ą╝ąĄčĆąŠą▓:

1. ąĀąĄą│ąĖčüčéčĆ TIMERx_PERIOD ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ ą▒čāč乥čĆą░ ą┐ąĄčĆąĖąŠą┤ą░.

2. ąĀąĄą│ąĖčüčéčĆ TIMERx_WIDTH ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ ą▒čāč乥čĆą░ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░.

3. ąæąĖčé ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (TIMILx) ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ (ąĄčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ), ąĮąŠ ąĮąĄ ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąŠčłąĖą▒ą║čā.

ąæąĖčé PERIOD_CNT ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMERx_CONFIG čāą┐čĆą░ą▓ą╗čÅąĄčé ą╝ąŠą╝ąĄąĮč鹊ą╝ ą▓čĆąĄą╝ąĄąĮąĖ, ą▓ ą║ąŠč鹊čĆąŠą╝ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮ čŹč鹊čé ąĮą░ą▒ąŠčĆ čéčĆą░ąĮąĘą░ą║čåąĖą╣. ąÆąĘčÅčéčŗąĄ ą▓ą╝ąĄčüč鹥, čŹčéąĖ čéčĆąĖ čüąŠą▒čŗčéąĖčÅ ąĮą░ąĘčŗą▓ą░čÄčéčüčÅ ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮčŗą╝ ąŠčéč湥č鹊ą╝ (measurement report). ąæąĖčé ąŠčłąĖą▒ą║ąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ (TOVF_ERRx) ąĮąĄ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▓ ą╝ąŠą╝ąĄąĮčé ąĮą░čüčéčāą┐ą╗ąĄąĮąĖčÅ ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮąŠą│ąŠ ąŠčéč湥čéą░. ąśąĘą╝ąĄčĆąĖč鹥ą╗čīąĮčŗą╣ ąŠčéč湥čé ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüą░ą╝ąŠąĄ ą▒ąŠą╗čīčłąĄąĄ 1 čĆą░ąĘ ąĘą░ 1 ą┐ąĄčĆąĖąŠą┤ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ ą▓čüąĄą│ą┤ą░ ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆčŗ ą▒čāč乥čĆą░ čłąĖčĆąĖąĮčŗ ąĖ ą┐ąĄčĆąĖąŠą┤ą░ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą▓ ą╝ąŠą╝ąĄąĮčé ąĘą░ą▓ąĄčĆčłą░čÄčēąĄą│ąŠ ąĖ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ąĮąŠ čŹčéąĖ ąĘąĮą░č湥ąĮąĖąĄ ąĮąĄą▓ąĖą┤ąĖą╝čŗ čüąŠ čüč鹊čĆąŠąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ. ąÆčŗą▒ąŠčĆą║ąĖ čüąŠą▒čŗčéąĖčÅ ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮąŠą│ąŠ ąŠčéč湥čéą░ ą┐ąŠą┐ą░ą┤ą░čÄčé ą▓ ą▓ąĖą┤ąĖą╝čŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĖ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░, čćč鹊 čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ąĮąŠą▓čŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ TIMERx_PERIOD ą╝ TIMERx_WIDTH. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ PERIOD_CNT, ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮčŗą╣ ąŠčéč湥čé ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čĆąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┐ąĄčĆąĖąŠą┤ą░ ąĘą░čģą▓ą░čéąĖčé čüą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ (ą▓ ą╝ąŠą╝ąĄąĮčé ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čüąĖą│ąĮą░ą╗ą░). ąÜąŠą│ą┤ą░ PERIOD_CNT čüą▒čĆąŠčłąĄąĮ, ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮčŗą╣ ąŠčéč湥čé ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čĆąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ ąĘą░čģą▓ą░čéąĖčé čüą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ (ą▓ ą╝ąŠą╝ąĄąĮčé ą║ąŠąĮąĄčćąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čüąĖą│ąĮą░ą╗ą░).

ąĢčüą╗ąĖ ą▒ąĖčé PERIOD_CNT čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ąĮą░čćą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ (čüą╝. čĆąĖčü. 16-17), č鹊 čĆąĄą│ąĖčüčéčĆčŗ TIMERx_PERIOD ąĖ TIMERx_WIDTH čüąŠąŠą▒čēą░čé ąŠ ą┐ąĄčĆąĖąŠą┤ąĄ ąĖą╝ą┐čāą╗čīčüą░ ąĖ čłąĖčĆąĖąĮąĄ ąĖą╝ą┐čāą╗čīčüą░, ąĘą░ą╝ąĄčĆąĄąĮąĮčŗąĄ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░. ąĢčüą╗ąĖ ą▒ąĖčé PERIOD_CNT čüą▒čĆąŠčłąĄąĮ, ąĖ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ąĘą░ą▓ąĄčĆčłą░čÄčēąĖą╣ ą┐ąĄčĆąĄą┐ą░ą┤ (čüą╝. čĆąĖčü. 16-18), č鹊 čĆąĄą│ąĖčüčéčĆ TIMERx_WIDTH čüąŠąŠą▒čēą░ąĄčé ąŠ čłąĖčĆąĖąĮąĄ ąĖą╝ą┐čāą╗čīčüą░, ąĖąĘą╝ąĄčĆąĄąĮąĮąŠą╣ čüčĆą░ąĘčā ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ąĖą╝ą┐čāą╗čīčüą░, ąŠą┤ąĮą░ą║ąŠ čĆąĄą│ąĖčüčéčĆ TIMERx_PERIOD čüąŠąŠą▒čēą░ąĄčé ąŠ ą┐ąĄčĆąĖąŠą┤ąĄ ąĖą╝ą┐čāą╗čīčüą░, ąĖąĘą╝ąĄčĆąĄąĮąĮąŠą╝ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░.

ąĢčüą╗ąĖ ą▒ąĖčé PERIOD_CNT ąŠčćąĖčēąĄąĮ, ąĖ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą┐ąĄčĆą▓čŗą╣ ąĘą░ą▓ąĄčĆčłą░čÄčēąĖą╣ ą┐ąĄčĆąĄą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░, č鹊 ą┐ąĄčĆą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĖąŠą┤ą░ ą┐ąŠą║ą░ ąĮąĄ ą▒čŗą╗ąŠ ąĖąĘą╝ąĄčĆąĄąĮąŠ ą┐čĆąĖ ą┐ąĄčĆą▓ąŠą╝ ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮąŠą╝ ąŠčéč湥č鹥, čéą░ą║ čćč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĖąŠą┤ą░ ąĮąĄ ą▒čāą┤ąĄčé ą▓ąĄčĆąĮčŗą╝. ą¦č鹥ąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ TIMERx_PERIOD ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▓ąĄčĆąĮąĄčé 0, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 16-18. ą¦č鹊ą▒čŗ ąĖąĘą╝ąĄčĆąĖčéčī čłąĖčĆąĖąĮčā ąĖą╝ą┐čāą╗čīčüą░ čüąĖą│ąĮą░ą╗ą░, čā ą║ąŠč鹊čĆąŠą│ąŠ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ąĮą░čćą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ąĖ ąŠą┤ąĖąĮ ąĘą░ą▓ąĄčĆčłą░čÄčēąĖą╣ ą┐ąĄčĆąĄą┐ą░ą┤, čāčüčéą░ąĮąŠą▓ąĖč鹥 PERIOD_CNT = 0. ąĢčüą╗ąĖ ąČąĄ ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▒čāą┤ąĄčé PERIOD_CNT = 1, č鹊 ąĮąĄ ą▒čāą┤ąĄčé ąĘą░čģą▓ą░č湥ąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĖąŠą┤ą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą▒čāč乥čĆą░ ą┐ąĄčĆąĖąŠą┤ą░. ąÆą╝ąĄčüč鹊 čŹč鹊ą│ąŠ ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüąŠąŠą▒čēąĄąĮąĖčÅ ąŠą▒ ąŠčłąĖą▒ą║ąĄ (ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ), ą║ąŠą│ą┤ą░ ą┤ąĖą░ą┐ą░ąĘąŠąĮ čüč湥čéčćąĖą║ą░ ą▒čāą┤ąĄčé ą┐čĆąĄą▓čŗčłąĄąĮ, ąĖ ąŠąĮ ą┐ąĄčĆąĄą▓ą░ą╗ąĖčé č湥čĆąĄąĘ čüą▓ąŠąĄ ą┐čĆąĄą┤ąĄą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąŠą▒ą░ čĆąĄą│ąĖčüčéčĆą░ TIMERx_WIDTH ąĖ TIMERx_PERIOD ą▒čāą┤čāčé čćąĖčéą░čéčīčüčÅ ą║ą░ą║ 0 (ą┐ąŠč鹊ą╝čā čćč鹊 ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮčŗą╣ ąŠčéč湥čé ą┤ą╗čÅ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░čģą▓ą░č湥ąĮąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ ą▒čāč乥čĆą░ čłąĖčĆąĖąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ TIMERx_WIDTH). ąĪą╝. ą┐ąĄčĆą▓ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮą░ čĆąĖčü. 16-19.

ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čĆąĄąČąĖą╝ čü PERIOD_CNT = 0, ąŠą┐ąĖčüą░ąĮąĮčŗą╣ čĆą░ąĮąĄąĄ ą┤ą╗čÅ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ čłąĖčĆąĖąĮčŗ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĘą░ą┐čĆąĄčéąĖčéčī čéą░ą╣ą╝ąĄčĆ ą┐ąŠčüą╗ąĄ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗą╝ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ąĖąĮč鹥čĆą▓ą░ą╗ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ. ąĢčüą╗ąĖ čŹč鹊 ąĮčāąČąĮąŠ, čéą░ą╣ą╝ąĄčĆ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ąĮąŠą▓ąŠ čĆą░ąĘčĆąĄčłąĄąĮ ą┐ąŠą┤čģąŠą┤čÅčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą┤ą╗čÅ ą┐ąŠą┤ą│ąŠč鹊ą▓ą║ąĖ ą┤čĆčāą│ąŠą│ąŠ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ. ąŁčéą░ ą┐čĆąŠčåąĄą┤čāčĆą░ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčé čéą░ą╣ą╝ąĄčĆ ąŠčé ą┐čĆąŠą┤ąŠą╗ąČąĄąĮąĖčÅ čüą▓ąŠą▒ąŠą┤ąĮąŠą│ąŠ čüč湥čéą░ ą┐ąŠčüą╗ąĄ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ čłąĖčĆąĖąĮčŗ, ąĖ ąŠčé čäąĖą║čüąĖčĆčāąĄą╝čŗčģ ąŠčłąĖą▒ąŠą║, ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗčģ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░.

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░ (ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ) ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ, ąĄčüą╗ąĖ čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ ą┐ąĄčĆąĄą▓ą░ą╗ąĖą▓ą░ąĄčé ąĘą░ ąĘąĮą░č湥ąĮąĖąĄ 0xFFFFFFFF ąĖ čüčéą░ąĮąŠą▓ąĖčéčüčÅ 0 ą┐čĆąĖ ąŠčéčüčāčéčüčéą▓ąĖąĖ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąÆ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé TOVF_ERRx ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMER_STATUS ąĖ ą▒ąĖčéčŗ ERR_TYP ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMERx_CONFIG, čćč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ čüč湥čéčćąĖą║ą░, ą┐ąŠč鹊ą╝čā čćč鹊 ą┐ąĄčĆąĖąŠą┤ ąŠą║ą░ąĘą░ą╗čüčÅ ą▒ąŠą╗čīčłąĄ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ čüč湥čéčćąĖą║ą░. ąŁčéą░ čüąĖčéčāą░čåąĖčÅ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ąŠčéč湥č鹊ą╝ ąŠą▒ ąŠčłąĖą▒ą║ąĄ. ąÜąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ WDTH_CAP, č鹊 ą╗ąĖą▒ąŠ ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąŠčłąĖą▒ą║ą░ (ąŠčéč湥čé ąŠą▒ ąŠčłąĖą▒ą║ąĄ), ą╗ąĖą▒ąŠ ą│ąŠč鹊ą▓ąŠ ąĮąŠą▓ąŠąĄ ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ (ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮčŗą╣ ąŠčéč湥čé), ąĮąŠ ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠą▒ą░ čŹčéąĖ čüąŠą▒čŗčéąĖčÅ. ąĀąĄą│ąĖčüčéčĆčŗ TIMERx_PERIOD ąĖ TIMERx_WIDTH ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ, ą║ąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠ čüąĄą▒ąĄ ąŠčéč湥čé ąŠą▒ ąŠčłąĖą▒ą║ąĄ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ čüą╝. ąĮą░ čĆąĖčü. 16-19 ąĖ 16-20.

ąĀąĖčü. 16-17. ą¤čĆąĖą╝ąĄčĆ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ąĘą░čģą▓ą░čéą░ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĖąŠą┤ą░ (Period Capture Measurement Report Timing, čĆąĄąČąĖą╝ WDTH_CAP, PERIOD_CNT = 1).

ąĀąĖčü. 16-18. ą¤čĆąĖą╝ąĄčĆ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ąĘą░čģą▓ą░čéą░ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ (Width Capture Measurement Report Timing, čĆąĄąČąĖą╝ WDTH_CAP, PERIOD_CNT = 0).

ąĀąĖčü. 16-19. ą¤čĆąĖą╝ąĄčĆ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ąĘą░čģą▓ą░čéą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░, ąĘą░ ą║ąŠč鹊čĆčŗą╝ čüą╗ąĄą┤čāąĄčé ą┐ąĄčĆąĖąŠą┤ (Period Overflow Followed by Period Capture, čĆąĄąČąĖą╝ WDTH_CAP, PERIOD_CNT = 1).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ ąĮą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░čģ čĆąĖčü. 16-17, 16-18 ąĖ 16-19 ąĮąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąŠąĮąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ąĖ TMRx ąĖ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅą╝ąĖ ą▒čāč乥čĆąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░.

ą×ą▒ą░ ą▒ąĖčéą░ TIMILx ąĖ TOVF_ERRx čÅą▓ą╗čÅčÄčéčüčÅ sticky-ą▒ąĖčéą░ą╝ąĖ, ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ čÅą▓ąĮąŠ ąŠčćąĖčēą░ąĄčé ąĖčģ. ąĢčüą╗ąĖ čéą░ą╣ą╝ąĄčĆ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĖą╗čüčÅ ąĖ PERIOD_CNT = 1, č鹊 ąĮąĄ ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ąĮąĖ čĆąĄą│ąĖčüčéčĆ TIMERx_PERIOD, ąĮąĖ čĆąĄą│ąĖčüčéčĆ TIMERx_WIDTH. ąĢčüą╗ąĖ čéą░ą╣ą╝ąĄčĆ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĖą╗čüčÅ ąĖ PERIOD_CNT = 0, č鹊 čĆąĄą│ąĖčüčéčĆčŗ TIMERx_PERIOD ąĖ TIMERx_WIDTH ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ąĘą░ą▓ąĄčĆčłą░čÄčēąĖą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ąĮą░ ą┐čĆąĄą┤čŗą┤čāčēąĄą╝ ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮąŠą╝ ąŠčéč湥č鹥.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ą┐ąŠą┤čüčćąĖčéą░čéčī ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čü ąŠčéč湥č鹊ą╝ ąŠą▒ ąŠčłąĖą▒ą║ąĄ ą╝ąĄąČą┤čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ čü ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮčŗą╝ ąŠčéč湥č鹊ą╝, čćč鹊ą▒čŗ ąĖąĘą╝ąĄčĆąĖčéčī ą┐ąĄčĆąĖąŠą┤čŗ čüąĖą│ąĮą░ą╗ą░, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗čīčłąĄ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ čüč湥čéą░ 0xFFFFFFFF. ąÜą░ąČą┤čŗą╣ ąŠčéč湥čé ąŠą▒ ąŠčłąĖą▒ą║ąĄ ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé ą┐ąŠą╗ąĮčŗąĄ 2^32 ąŠčéčüč湥č鹊ą▓ SCLK ą║ ąŠą▒čēąĄą╝čā ą┐ąĄčĆąĖąŠą┤čā, ąĮąŠ čłąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ąĮąĄąŠą┤ąĮąŠąĘąĮą░čćąĮą░. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĮą░ čĆąĖčü. 16-19 ą┐ąĄčĆąĖąŠą┤ 0x100000004 (ą▒ąŠą╗čīčłąĄ 0xFFFFFFFF), ąŠą┤ąĮą░ą║ąŠ čłąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ą╝ąŠą│ą╗ą░ ą▒čŗ ą▒čŗčéčī ą╗ąĖą▒ąŠ 0x000000002, ą╗ąĖą▒ąŠ 0x100000002.

ążąŠčĆą╝ą░ čüąĖą│ąĮą░ą╗ą░, ą┐ąŠčüčéčāą┐ą░čÄčēąĄą│ąŠ ąĮą░ ą▓čŗą▓ąŠą┤ TMRx, ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą┤ąŠą╗ąČąĮą░ ąĖą╝ąĄčéčī čüą║ą▓ą░ąČąĮąŠčüčéčī 50%, ąŠą┤ąĮą░ą║ąŠ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ą╗ąŠą│. 0 ą┤ą╗čÅ TMRx čüąŠčüčéą░ą▓ą╗čÅąĄčé 1 ą┐ąĄčĆąĖąŠą┤ SCLK, ąĖ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ą╗ąŠą│. 1 ą┤ą╗čÅ TMRx čéą░ą║ąČąĄ čüąŠčüčéą░ą▓ą╗čÅąĄčé 1 ą┐ąĄčĆąĖąŠą┤ SCLK. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▓čģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ čüąĖą│ąĮą░ą╗ą░ ąĮą░ TMRx ąĮąĄ ą╝ąŠąČąĄčé ą┐čĆąĄą▓čŗčłą░čéčī SCLK/2 ą┐čĆąĖ 50% čüą║ą▓ą░ąČąĮąŠčüčéąĖ. ąĪ čéą░ą║ąĖą╝ąĖ čāčüą╗ąŠą▓ąĖčÅą╝ąĖ čéą░ą╣ą╝ąĄčĆ ą▓ čĆąĄąČąĖą╝ąĄ WDTH_CAP ąĖąĘą╝ąĄčĆąĖą╗ ą▒čŗ ą┐ąĄčĆąĖąŠą┤ = 2 ąĖ čłąĖčĆąĖąĮčā ąĖą╝ą┐čāą╗čīčüą░ = 1.

ąĀąĖčü. 16-20. ą¤čĆąĖą╝ąĄčĆ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ąĘą░čģą▓ą░čéą░ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░, ąĘą░ ą║ąŠč鹊čĆčŗą╝ čüą╗ąĄą┤čāąĄčé ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐ąĄčĆąĖąŠą┤ą░ (Width Capture Followed by Period Overflow, čĆąĄąČąĖą╝ WDTH_CAP, PERIOD_CNT = 0).

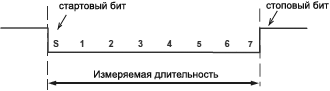

ąøčÄą▒ąŠą╣ ąĖąĘ čéčĆąĄčģ čéą░ą╣ą╝ąĄčĆąŠą▓ ą╝ąŠąČąĄčé ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ą░ą▓č鹊ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüą║ąŠčĆąŠčüčéąĖ ąĮą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ UART0 (universal asynchronous receiver/transmitter). ąæąĖčé ą▓čŗą▒ąŠčĆą░ ą▓čģąŠą┤ą░ čéą░ą╣ą╝ąĄčĆą░ (TIN_SEL) ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMERx_CONFIG ą╝ąŠąČąĄčé ą┐ąŠą▒čāą┤ąĖčéčī čéą░ą╣ą╝ąĄčĆ ą┤ąĄą╗ą░čéčī ą▓čŗą▒ąŠčĆą║ąĖ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ UART0 (ą▓čŗą▓ąŠą┤ RX0) ą▓ą╝ąĄčüč鹊 čüąĖą│ąĮą░ą╗ą░ TMRx, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮ čĆąĄąČąĖą╝ WDTH_CAP.

ąØąĄ čĆą░ąĘčĆąĄčłą░ą╣č鹥 UART0, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮąŠ ą░ą▓č鹊ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüą║ąŠčĆąŠčüčéąĖ.

ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī čłąĖčĆąĖąĮčā ąĖą╝ą┐čāą╗čīčüą░ ą▓ ą┐ąŠč鹊ą║ąĄ ą▒ąĖčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ą▒ą░ąĘą░ ą▓čĆąĄą╝ąĄąĮąĖ ą▓čŗą▒ąŠčĆą║ąĖ čéą░ą╣ą╝ąĄčĆąŠą▓ čüąĖąĮčģčĆąŠąĮąĮą░ čü čĆą░ą▒ąŠč鹊ą╣ UART0 ŌĆö ą▓čüąĄ čéą░ą║čéčŗ ą┐ąŠą╗čāčćą░čÄčéčüčÅ ąŠčé čüąĖčüč鹥ą╝čŗ PLL ŌĆö ąĖąĘą╝ąĄčĆąĄąĮąĮą░čÅ čłąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ą┤ąĄą╗ąĖč鹥ą╗čÅ ą▓ čüąĖčüč鹥ą╝ąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ čüą║ąŠčĆąŠčüčéąĖ ą┐ąŠčĆčéą░ UART0 (čĆąĄą│ąĖčüčéčĆ baud rate divider).

DIVISOR = ((TIMERx_WIDTH) / (16 x ą║ąŠą╗ąĖč湥čüčéą▓ąŠ_ąĘą░čģą▓ą░č湥ąĮąĮčŗčģ_ą▒ąĖčé_UART0))

ą¦č鹊ą▒čŗ čāą▓ąĄą╗ąĖčćąĖčéčī ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąŠčéčüč湥č鹊ą▓ čéą░ą╣ą╝ąĄčĆą░, ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą┐ąŠą▓čŗčüąĖčéčī čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĖ ąĘą░čģą▓ą░č鹥 čüąĖą│ąĮą░ą╗ą░, ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖąĘą╝ąĄčĆčÅčéčī čłąĖčĆąĖąĮčā ąŠą┤ąĮąŠą│ąŠ ą▒ąĖčéą░, ą╗čāčćčłąĄ ą▓čüąĄą│ąŠ ąĖąĘą╝ąĄčĆąĖčéčī ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ąĖčé ą▓ąŠ čäčĆąĄą╣ą╝ąĄ UART. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ čüąĖą╝ą▓ąŠą╗ NULL (ą║ąŠą┤ ASCII 0x00) ąŠą▒čŗčćąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą░ą▓č鹊ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüą║ąŠčĆąŠčüčéąĖ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 16-21.

ąĀąĖčü. 16-21. ąÉą▓č鹊ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ čüą║ąŠčĆąŠčüčéąĖ ąĮą░ čüąĖą╝ą▓ąŠą╗ąĄ 0x00.

ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ą┐čĆąĖą╝ąĄčĆ ąĖą╝ą┐čāą╗čīčüą░ čäčĆąĄą╣ą╝ą░ ąĮą░ čĆąĖčü. 16-21 čüąŠčüč鹊ąĖčé ąĖąĘ 8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ąĖ 1 čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ąĖčéą░, č鹊 ą▓ č乊čĆą╝čāą╗čā ą┐ąŠą┤čüčéą░ą▓ą╗čÅąĄčéčüčÅ 9 ą▒ąĖčé:

DIVISOR = TIMERx_WIDTH/(16 x 9)

ąĀąĄą░ą╗čīąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ RX ą┐ąŠčĆčéą░ UART0 ąĖą╝ąĄčÄčé ą░čüąĖą╝ą╝ąĄčéčĆąĖčćąĮčŗąĄ ą┐ąĄčĆąĄą┐ą░ą┤čŗ čüą┐ą░ą┤ą░ ąĖ čäčĆąŠąĮčéą░, ąĖ ą╗ąŠą│ąĖč湥čüą║ąĖąĄ čāčĆąŠą▓ąĮąĖ ąĮąĄ č鹊čćąĮąŠ ą┐ąŠą┐ą░ą┤ą░čÄčé ą▓ čüąĄčĆąĄą┤ąĖąĮčā ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ą▓čģąŠą┤ąĮčŗčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣. ąØą░ ą▓čŗčüąŠą║ąĖčģ čüą║ąŠčĆąŠčüčéčÅčģ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüą║ąŠčĆąŠčüč鹥ą╣ ąĮą░ ą▒ą░ąĘąĄ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ ą╝ąŠąČąĄčé ą┤ą░čéčī ąĮąĄ ą░ą┤ąĄą║ą▓ą░čéąĮčŗą╣ čĆąĄąĘčāą╗čīčéą░čé ą▒ąĄąĘ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą│ąŠ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ čāą╗čāčćčłąĄąĮąĖčÅ č乊čĆą╝čŗ čüąĖą│ąĮą░ą╗ą░. ąśąĘą╝ąĄčĆąĄąĮąĖąĄ ą┐ąĄčĆąĖąŠą┤ą░ čüąĖą│ąĮą░ą╗ą░ ą▓ą╝ąĄčüč鹊 ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ čĆąĄčłą░ąĄčé čŹčéčā ą┐čĆąŠą▒ą╗ąĄą╝čā, čéą░ą║ čćč鹊 čŹč鹊 ąĮą░čüč鹊čÅč鹥ą╗čīąĮąŠ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝čŗą╣ ą┐čĆąĖąĮčåąĖą┐ ą░ą▓č鹊ą┤ąĄč鹥ą║čéą░ čüą║ąŠčĆąŠčüčéąĖ.

ąØą░ą┐čĆąĖą╝ąĄčĆ, ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĘą░čĆą░ąĮąĄąĄ ąŠą▒čāčüą╗ąŠą▓ą╗ąĄąĮąĮčŗą╣ čüąĖą╝ą▓ąŠą╗ ASCII '@' (ą║ąŠą┤ 40h) ą┐čĆąĖ ą░ą▓č鹊ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĖ čü ąĖąĘą╝ąĄčĆąĄąĮąĖąĄą╝ ą┐ąĄčĆąĖąŠą┤ą░ čüąĖą│ąĮą░ą╗ą░ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ čüą┐ą░ą┤ą░ą╝ąĖ. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 16-22, ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ ą┐ąĄčĆąĖąŠą┤ą░ ą╝ąĄąČą┤čā čüą┐ą░ą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ąĖčéą░ ąĖ čüą┐ą░ą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ ą┐ąŠčüą╗ąĄ ą▒ąĖčéą░ 6. ą¤ąŠčüą║ąŠą╗čīą║čā čŹč鹊čé ą┐ąĄčĆąĖąŠą┤ ąĮą░ą║čĆčŗą▓ą░ąĄčé 8 ą▒ąĖčé, ą▓ č乊čĆą╝čāą╗čā ą┐ąŠą┤čüčéą░ą▓ą╗čÅąĄčéčüčÅ čćąĖčüą╗ąŠ 8:

DIVISOR = TIMERx_PERIOD/(16 x 8)

ąĀąĖčü. 16-22. ąÉą▓č鹊ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ čüą║ąŠčĆąŠčüčéąĖ ąĮą░ čüąĖą╝ą▓ąŠą╗ąĄ 0x40.

ąÆ čĆąĄąČąĖą╝ąĄ EXT_CLK čéą░ą║ąČąĄ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤ (čüą╝. čĆąĖčü. 16-23). ąóą░ą╣ą╝ąĄčĆ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čüč湥čéčćąĖą║, čéą░ą║čéąĖčĆčāąĄą╝čŗą╣ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╝ ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMERx_COUNTER ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą╗ąĖą┤ąĖčĆčāčÄčēąĖčģ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą┐ąŠą╗čÅ TMODE čĆąĄą│ąĖčüčéčĆą░ TIMERx_CONFIG ą▓ ąĘąĮą░č湥ąĮąĖąĄ b#11 čĆą░ąĘčĆąĄčłą░ąĄčé čŹč鹊čé čĆąĄąČąĖą╝. ąĀąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĖąŠą┤ą░ TIMERx_PERIOD ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▓ąĮąĄčłąĮąĖčģ ąŠčéčüč湥č鹊ą▓.

ążąŠčĆą╝ą░ čüąĖą│ąĮą░ą╗ą░, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠčüčéčāą┐ą░ąĄčé ąĮą░ ą▓čŗą▓ąŠą┤ TMRx, ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čü 50% čüą║ą▓ą░ąČąĮąŠčüčéčīčÄ, ąŠą┤ąĮą░ą║ąŠ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ą╗ąŠą│. 0 ą┤ą╗čÅ TMRx čüąŠčüčéą░ą▓ą╗čÅąĄčé 1 ą┐ąĄčĆąĖąŠą┤ SCLK, ąĖ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ą╗ąŠą│. 1 ą┤ą╗čÅ TMRx čéą░ą║ąČąĄ čüąŠčüčéą░ą▓ą╗čÅąĄčé 1 ą┐ąĄčĆąĖąŠą┤ SCLK. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▓čģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ čüąĖą│ąĮą░ą╗ą░ ąĮą░ TMRx ąĮąĄ ą╝ąŠąČąĄčé ą┐čĆąĄą▓čŗčłą░čéčī SCLK/2 ą┐čĆąĖ 50% čüą║ą▓ą░ąČąĮąŠčüčéąĖ.

ą¤ąĄčĆąĖąŠą┤ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ ą╗čÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąŠčé 1 ą┤ąŠ (2^32 ŌĆō 1) ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ.

ąĀąĖčü. 16-23. ąÉą╗ą│ąŠčĆąĖčéą╝ čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░ ą▓ čĆąĄąČąĖą╝ąĄ EXT_CLK.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ, čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čüą▒čĆą░čüčŗą▓ą░ąĄčé čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 0x0, ąĖ ąĘą░č鹥ą╝ čéą░ą╣ą╝ąĄčĆ ąŠąČąĖą┤ą░ąĄčé ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ ą╗ąĖą┤ąĖčĆčāčÄčēąĄą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TMRx. ą¤ąŠčüčéčāą┐ą╗ąĄąĮąĖąĄ čŹč鹊ą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéčā čĆąĄą│ąĖčüčéčĆą░ čüč湥čéčćąĖą║ą░, čéą░ą║ čćč鹊 ąĄą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ čüčéą░ąĮąŠą▓ąĖčéčüčÅ čĆą░ą▓ąĮčŗą╝ 0x1. ąÜą░ąČą┤ąŠąĄ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄąĄ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖąĄ ą╗ąĖą┤ąĖčĆčāčÄčēąĄą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą▒čāą┤ąĄčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčī ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčī čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░. ą¤ąŠčüą╗ąĄ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ čüč湥čéčćąĖą║ąŠą╝ ąĘąĮą░č湥ąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé TIMILx, ąĖ ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą╗ąĖą┤ąĖčĆčāčÄčēąĖą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘąĖčé čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ąĘąĮą░č湥ąĮąĖąĄą╝ 0x1. ąóą░ą╣ą╝ąĄčĆ ą┐čĆąŠą┤ąŠą╗ąČąĖčé ą┐ąŠą┤čüčćąĖčéčŗą▓ą░čéčī ą┐ąŠčüčéčāą┐ą░čÄčēąĖąĄ ą╗ąĖą┤ąĖčĆčāčÄčēąĖąĄ ąĖą╝ą┐čāą╗čīčüčŗ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ąĘą░ą┐čĆąĄčēąĄąĮ. ąæąĖčé PULSE_HI ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąŠą╗čÅčĆąĮąŠčüčéčī ą╗ąĖą┤ąĖčĆčāčÄčēąĄą│ąŠ ąĖą╝ą┐čāą╗čīčüą░: čŹč鹊 ą▒čāą┤ąĄčé ąĮą░čĆą░čüčéą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ (PULSE_HI čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) ąĖą╗ąĖ čüą┐ą░ą┤ (PULSE_HI ąŠčćąĖčēąĄąĮ).

ąæąĖčéčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ TIN_SEL ąĖ PERIOD_CNT ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░čÄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ. ąæąĖčéčŗ TOVF_ERRx ąĖ ERR_TYP čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ, ąĄčüą╗ąĖ čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą┐ąĄčĆąĄą▓ą░ą╗ąĖą▓ą░ąĄčé č湥čĆąĄąĘ 0xFFFFFFFF ąĖ čüčéą░ąĮąŠą▓ąĖčéčüčÅ čĆą░ą▓ąĮčŗą╝ 0, ąĖą╗ąĖ ąĄčüą╗ąĖ ą┐čĆąĖ čüčéą░čĆč鹥 ą┐ąĄčĆąĖąŠą┤ = 0, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą┐ąĄčĆąĄą▓ą░ą╗ąĖą▓ą░ąĄčé č湥čĆąĄąĘ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┐ąĄčĆąĖąŠą┤ (ąŠčé Count = Period ą┤ąŠ Count = 0x1). ąĀąĄą│ąĖčüčéčĆ TIMERx_WIDTH ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

ąöąŠ 2 čéą░ą╣ą╝ąĄčĆąŠą▓ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ ąŠčüąĮąŠą▓ąĮčŗčģ čĆąĄąČąĖą╝ąŠą▓ PPI. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆąŠą▓ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čü PPI, ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čĆą░ąĘą┤ąĄą╗čā "Frame Synchronization in GP Modes" ą┤ą░čéą░čłąĖčéą░ [1] (čćą░čüčéčī ą┤ą░čéą░čłąĖčéą░, ą│ą┤ąĄ ąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ PPI).

[ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ]

ąÜą░ąČą┤čŗą╣ ąĖąĘ čéčĆąĄčģ čéą░ą╣ą╝ąĄčĆąŠą▓ ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąŠą┤ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąóčĆąĖ čĆąĄąĘčāą╗čīčéąĖčĆčāčÄčēąĖčģ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą║ ą▒ą╗ąŠą║čā ą║ąŠąĮčéčĆąŠą╗ąĄčĆąŠą▓ čüąĖčüč鹥ą╝ąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┤ą╗čÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ ą┐čĆąĖąŠčĆąĖč鹥ąĘą░čåąĖąĖ ąĖ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ. ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ (TIMER_STATUS) ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░, čćč鹊ą▒čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą╝ąŠą│ą╗ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŁčéąĖ ą▒ąĖčéčŗ čĆą░ą▒ąŠčéą░čÄčé ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā W1C, ąĖ ąŠąĮąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠčćąĖčēąĄąĮčŗ ą┤ąŠ RTI, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗčüčéą░ą▓ą╗ąĄąĮąŠ ą┐ąŠą▓č鹊čĆąĮąŠ.

ą¦č鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī ą│ąĄąĮąĄčĆą░čåąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čāčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé IRQ_ENA ąĖ ą┤ąĄą╝ą░čüą║ąĖčĆčāą╣č鹥 ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čüąĖčüč鹥ą╝čŗ (system interrupt mask register, SIC_IMASKx). ą¦č鹊ą▒čŗ ąŠą┐čĆą░čłąĖą▓ą░čéčī ą▒ąĖčé TIMILx ą▒ąĄąĘ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čāčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé IRQ_ENA, ąĮąŠ ąŠčüčéą░ą▓čīč鹥 ą┐čĆąĖ čŹč鹊ą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĮčŗą╝. ąĢčüą╗ąĖ čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ IRQ_ENA, ąĘą░ą┐čĆąŠčüčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéą░ą║ąČąĄ ą▒čāą┤čāčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą┐čĆąĖ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖąĖ čüąŠą▒čŗčéąĖą╣ ąŠčłąĖą▒ą║ąĖ. ąĪą╝. čĆąĖčü. 16-24.

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ čüąĖčüč鹥ą╝ąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čĆą░ąĘčĆąĄčłą░čÄčé ą│ąĖą▒ą║čāčÄ ąŠą▒čĆą░ą▒ąŠčéą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąÆčüąĄ čéą░ą╣ą╝ąĄčĆčŗ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠą▒čēąĖą╣ ą║ą░ąĮą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĖą╗ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐ąŠ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠą╝čā ą║ą░ąĮą░ą╗čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░. ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ąŠą┤ąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čéą░ą╣ą╝ąĄčĆąŠą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ISR) ą┤ąŠą╗ąČąĄąĮ čĆą░ąĘą╗ąĖčćą░čéčī ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ - ą║ą░ą║ąŠą╣ čéą░ą╣ą╝ąĄčĆ ąĄą│ąŠ ą▓čŗąĘą▓ą░ą╗. ąÆ čĆąĄąČąĖą╝ąĄ PWM ąĮąĄčüą║ąŠą╗čīą║ąŠ čéą░ą╣ą╝ąĄčĆąŠą▓ ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī čü ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ ąĮą░čüčéčĆąŠąĄąĮąĮčŗą╝ ą┐ąĄčĆąĖąŠą┤ąŠą╝, ąĖ ą╝ąŠą│čāčé ą▓čŗą┤ą░ą▓ą░čéčī čüą▓ąŠąĖ ąĘą░ą┐čĆąŠčüčŗ ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ISR ą╝ąŠąČąĄčé ąŠčćąĖčüčéąĖčéčī ą▓čüąĄ ą▒ąĖčéčŗ ąĘą░čēąĄą╗ą║ąĖ TIMILx ąĘą░ ąŠą┤ąĖąĮ čĆą░ąĘ, ąĄčüą╗ąĖ ąĘą░ą┐ąĖčłąĄčé 0x07 ą▓ čĆąĄą│ąĖčüčéčĆ TIMER_STATUS.