|

ąÆ 103 ąĮąŠą╝ąĄčĆąĄ ąČčāčĆąĮą░ą╗ą░ ą║ą╗čāą▒ą░ Benelux QRP (čüąĄąĮčéčÅą▒čĆčī 2002) ą▒čŗą╗ą░ čüčéą░čéčīčÅ Ton PA0KLT [2] ąŠ čüąĖčüč鹥ą╝ąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ QRP. ąÆ čüąĖčüč鹥ą╝ąĄ čĆą░ą▒ąŠčéą░ąĄčé DDS-ą│ąĄč鹥čĆąŠą┤ąĖąĮ ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ! ąöąŠčüč鹊ąĖąĮčüčéą▓ąŠ čŹč鹊ą│ąŠ čĆąĄčłąĄąĮąĖčÅ - ąĮąĄ ąĮčāąČąĮąŠ ą┐ąŠą║čāą┐ą░čéčī ą┤ąŠčĆąŠą│ąŠą╣ čćąĖą┐ DDS, ąĮąĄ ąĮčāąČąĮąŠ ą┐ą░čÅčéčī ąĄą│ąŠ č鹊ąĮą║ąĖąĄ ą▓čŗą▓ąŠą┤čŗ ą║ąŠčĆą┐čāčüą░ SMD. ąÆčüčÄ čĆą░ą▒ąŠčéčā ą┐ąŠ čüąĖąĮč鹥ąĘčā čćą░čüč鹊čéčŗ ą│ąĄč鹥čĆąŠą┤ąĖąĮą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą╝ą░ą╗ąĄąĮčīą║ąĖą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ. ą×ąĮ ą┤ą░ąČąĄ ąŠą┐čĆą░čłąĖą▓ą░ąĄčé ą┐ąŠą▓ąŠčĆąŠčéąĮčŗą╣ 菹Įą║ąŠą┤ąĄčĆ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ čćą░čüč鹊čéčŗ! ą×ą┤ąĮą░ą║ąŠ, ą║ą░ą║ ąĖ čü ąŠą▒čŗčćąĮąŠą╣ čüąĖčüč鹥ą╝ąŠą╣ DDS, čéčĆąĄą▒čāąĄčéčüčÅ ąĄčēąĄ ąŠą┤ąĮąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ čćą░čüč鹊čéčŗ (ąĘą┤ąĄčüčī ąĖ ą┤ą░ą╗ąĄąĄ ą┐ąĄčĆąĄą▓ąŠą┤ čüčéą░čéčīąĖ [1]).

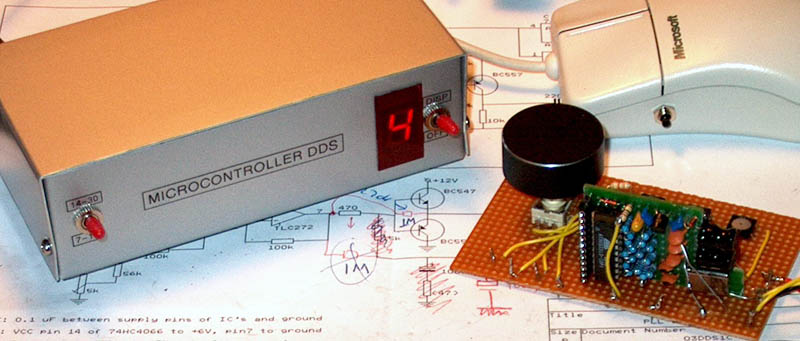

ąÆ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĄ PA2OHH ą┐čĆąĖą╝ąĄąĮąĄąĮą░ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮą░čÅ čüąĖčüč鹥ą╝ą░ ąĖąĮą┤ąĖą║ą░čåąĖąĖ čćą░čüč鹊čéčŗ ąĮą░ ąŠą┤ąĮąŠčĆą░ąĘčĆčÅą┤ąĮąŠą╝ 7-čüąĄą│ą╝ąĄąĮčéąĮąŠą╝ ąĖąĮą┤ąĖą║ą░č鹊čĆąĄ. ąÆ ąŠą┤ąĮąŠą╝ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ąŠą▒čŖąĄą┤ąĖąĮąĄąĮčŗ čäčāąĮą║čåąĖąĖ DDS, ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ čćą░čüč鹊čéčŗ ąĖ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ąĮąŠą┐ąŠą║ ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ čćą░čüč鹊čéčŗ.

ą¤ąŠą┤ą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠą╝ąĄčģ ą▓ ą▓čŗčģąŠą┤ąĮąŠą╝ čüąĖą│ąĮą░ą╗ąĄ DDS. ąöą╗čÅ čćą░čüč鹊čéąĮąŠą│ąŠ čüąĖąĮč鹥ąĘą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗čüčÅ 7-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ DAC ąĮą░ čĆąĄąĘąĖčüč鹊čĆą░čģ ąĮą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 923 ą║ąōčå. ąóą░ą║ą░čÅ čüąĖčüč鹥ą╝ą░ čüąĖąĮč鹥ąĘą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ ąĖą╝ąĄąĄčé čüąĖą│ąĮą░ą╗čŗ ą┐ąŠą╝ąĄčģ. ą×ą┤ąĮą░ą║ąŠ ąŠąĮąĖ čŹčäč乥ą║čéąĖą▓ąĮąŠ ą┐ąŠą┤ą░ą▓ą╗čÅčÄčéčüčÅ čäąĖą╗čīčéčĆąŠą╝ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ PLL! ąĢčüą╗ąĖ ą║ą░ą║ąĖąĄ-č鹊 ą┐ąŠą╝ąĄčģąĖ ąŠčüčéą░čÄčéčüčÅ, č鹊 ąŠąĮąĖ čüą╗ą░ą▒čŗąĄ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąĘą▓čāą║ąŠą▓čŗčģ čćą░čüč鹊čé. ąæąŠą╗čīčłąŠąĄ ą┤ąŠčüč鹊ąĖąĮčüčéą▓ąŠ ą▓ č鹊ą╝, čćč鹊 čŹčéąĖ ą┐ąŠą╝ąĄčģąĖ ąĮąĄ ą┐ąŠą┐ą░ą┤ą░čÄčé ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┐čĆąĖąĄą╝ą░ ą║ą░ą║ ą┐ą░čĆą░ąĘąĖčéąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ, čćč鹊 ą▒čŗą▓ą░ąĄčé ą▓ čüą╗čāčćą░ąĄ "ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣" čüąĖčüč鹥ą╝čŗ DDS ą▒ąĄąĘ PLL. ąś ą┐ąŠą╝ąĄčģąĖ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĖčüč湥ąĘą░čÄčé, ą║ąŠą│ą┤ą░ čćą░čüč鹊čéą░ RF ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ čüąŠ čüą╝ąĄčēąĄąĮąĖąĄą╝ ą▓ą▓ąĄčĆčģ ąĖą╗ąĖ ą▓ąĮąĖąĘ č鹊ą╗čīą║ąŠ ąĮą░ 15 .. 30 ąōčå.

ąĀą░ą▒ąŠčéą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąĪąĄčĆą┤čåąĄą╝ DDS čüą╗čāąČąĖčé ą┐čĆąŠčüč鹊ą╣ ąĖ ą┤ąĄčłąĄą▓čŗą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ AT90S1200. ą¦ą░čüč鹊čéą░ ą║ą▓ą░čĆčåą░ 11999.55 ą║ąōčå, čéą░ą║ čćč鹊 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą▓ą░čĆčå ąĮą░ 12 ą£ąōčå. DDS čāą┐čĆą░ą▓ą╗čÅąĄčé VCO, čĆą░ą▒ąŠčéą░čÄčēąĖą╝ ąĮą░ čćą░čüč鹊č鹥 ąŠčé 6 ą┤ąŠ 30 ą£ąōčå. ą¦ą░čüč鹊čéą░ čŹč鹊ą│ąŠ VCO ą┤ąĄą╗ąĖčéčüčÅ ąĮą░ 128, ąĖ ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčéčüčÅ DDS čü ą┐ąŠą╝ąŠčēčīčÄ čüčģąĄą╝čŗ čäą░ąĘąŠą▓ąŠą╣ ą░ą▓č鹊ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ čćą░čüč鹊čéčŗ (PLL). ąöąĖą░ą┐ą░ąĘąŠąĮ ą│ąĄąĮąĄčĆą░č鹊čĆą░ DDS čüąŠčüčéą░ą▓ą╗čÅąĄčé 46875 .. 234375 ąōčå.

ą×ą┤ąĖąĮ čåąĖą║ą╗ ą┐čĆąŠą║čĆčāčéą║ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ DDS čüąŠčüčéą░ą▓ą╗čÅąĄčé 13 ą╝ą░čłąĖąĮąĮčŗčģ čéą░ą║č鹊ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆą░, čćč鹊 ą┤ą░ąĄčé čćą░čüč鹊čéčā čéą░ą║č鹊ą▓ čüąĖąĮč鹥ąĘą░ DDS 11999.55 / 13 = 923.04 ą║ąōčå. ążąŠčĆą╝ą░ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ čéčĆąĄčāą│ąŠą╗čīąĮą░čÅ, ą░ ąĮąĄ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮą░čÅ. ą¤čĆąŠčüč鹥ą╣čłąĖą╣ 7-ą▒ąĖčéąĮčŗą╣ DAC ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮ ąĮą░ ąĮąŠąČą║ą░čģ ą┐ąŠčĆčéą░ PD6..PD0 ąĮą░ ąŠčüąĮąŠą▓ąĄ čåąĄą┐ąŠčćą║ąĖ čĆąĄąĘąĖčüč鹊čĆąŠą▓.

LC ążąØą¦ ąĖą╝ąĄąĄčé čćą░čüč鹊čéčā čüčĆąĄąĘą░ 200 ą║ąōčå. ąÆąŠąĘą╝ąŠąČąĮąŠ, čćč鹊 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ čüąĄą║čåąĖčÅ čäąĖą╗čīčéčĆą░ ą╝ąŠąČąĄčé ąĮąĄą╝ąĮąŠą│ąŠ čāą╗čāčćčłąĖčéčī ą┐ą░čĆą░ą╝ąĄčéčĆčŗ čäąĖą╗čīčéčĆą░čåąĖąĖ, ą┐ąŠč鹊ą╝čā čćč鹊 čćą░čüč鹊čéą░ čüčĆąĄąĘą░ ą┤ąŠą▓ąŠą╗čīąĮąŠ ą▓čŗčüąŠą║ą░ ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü ą┐ąŠą╗ąŠą▓ąĖąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ DDS 923 ą║ąōčå. ą¤ąŠčĆčéčŗ PB1, PB4, PB5, PB6 ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤čŗ ą┤ą╗čÅ ąŠą┐čĆąŠčüą░ ą║ąĮąŠą┐ąŠą║. LED-ą┤ąĖčüą┐ą╗ąĄą╣ ąŠčéą║ą╗čÄčćą░ąĄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ BC557. ąóčĆą░ąĮąĘąĖčüč鹊čĆ ąŠčéą║čĆčŗą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄčģąŠą┤čÅčé ą▓ ą╗ąŠą│. 0 čāčĆąŠą▓ąĮąĖ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐ąŠčĆčéą░ PB2 ąĖą╗ąĖ PB3. ąóčĆčÄą║ ąĘą░ą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ č鹊ą╝, čćč鹊 čüąĄą│ą╝ąĄąĮčéčŗ B ąĖ C 7-čüąĄą│ą╝ąĄąĮčéąĮąŠą│ąŠ LED-ąĖąĮą┤ąĖą║ą░č鹊čĆą░ ą▓čüąĄą│ą┤ą░ čüą▓ąĄčéčÅčéčüčÅ, ą║ąŠą│ą┤ą░ ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ą╗čÄą▒ą░čÅ ąĖąĘ čåąĖčäčĆ. ąÆą╝ąĄčüč鹊 č鹊ą║ąŠąŠą│čĆą░ąĮąĖčćąĖą▓ą░čÄčēąĄą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ ąĮą░ ą║ą░ąČą┤čŗą╣ čüąĄą│ą╝ąĄąĮčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čĆąĄąĘąĖčüč鹊čĆ. ąÆčŗ ą▓ąŠąĘą╝ąŠąČąĮąŠ ąĘą░ą╝ąĄčéąĖč鹥, čćč鹊 čÅčĆą║ąŠčüčéčī ą▒čāą┤ąĄčé ą╝ąĄąĮčÅčéčīčüčÅ, ą║ąŠą│ą┤ą░ ą╝ąĄąĮčÅąĄčéčüčÅ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĘą░ąČąČąĄąĮąĮčŗčģ čüąĄą│ą╝ąĄąĮč鹊ą▓ (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąŠč鹊ą▒čĆą░ąČą░ąĄą╝ąŠą╣ čåąĖčäčĆčŗ). ąśą£ąźą× ąĮą░ ą┐čĆą░ą║čéąĖą║ąĄ čŹč鹊 ąĮąĄ ąŠč湥ąĮčī ą║čĆąĖčéąĖčćąĮąŠ.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 LED-ąĖąĮą┤ąĖą║ą░č鹊čĆ ą┐ąŠą╗čāčćą░ąĄčé ą┐ąĖčéą░ąĮąĖąĄ ąŠčé +12V, čćč鹊ą▒čŗ ąĮąĄ čüąŠąĘą┤ą░ą▓ą░čéčī ą┐ąŠą╝ąĄčģąĖ ąĮą░ čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆąŠą▓ą░ąĮąĮąŠą╝ ąĖčüč鹊čćąĮąĖą║ąĄ ą┐ąĖčéą░ąĮąĖčÅ 5V ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

ąŚą░ą┐čĆąĄčēąĄąĮąĖąĄ PLL. ąØąŠąČą║ą░ ą┐ąŠčĆčéą░ PB0 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą┐čĆąĄčéą░ PLL ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░čģ AVR, ą║ąŠą│ą┤ą░ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čüąĮąĖąČą░ąĄčéčüčÅ ą┤ąŠ 1/8 x 923 ą║ąōčå. ąØą░ čéą░ą║ąĖčģ ąĮąĖąĘą║ąĖčģ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čéą░čģ, ą║ąŠč鹊čĆčŗąĄ ą╝ąĄąĮčīčłąĄ 1/4 ąŠčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊čéčŗ DDS, ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą▓čŗčģąŠą┤ DDS ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ąĖčüą║ą░ąČąĄąĮ. ąæąĄąĘ ąĘą░ą┐čĆąĄčéą░ PLL (č鹊ą╗čīą║ąŠ 255 ą╝ą║čü) ą▓ąŠ ą▓čĆąĄą╝čÅ čŹčéąĖčģ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ ąÆčŗ ą╝ąŠąČąĄč鹥 čāčüą╗čŗčłą░čéčī ą│čĆąŠą╝ą║ąĖą╣ čēąĄą╗č湊ą║.

ąØą░čüčéčĆąŠą╣ą║ą░ DDS. ąØą░čüčéčĆąŠą╣ą║ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čéčĆąĄą╝čÅ ą║ąĮąŠą┐ą║ą░ą╝ąĖ ąĮą░ čüčéą░čĆąŠą╣ 3-ą║ąĮąŠą┐ąŠčćąĮąŠą╣ ą╝čŗčłąĖ (ą▓ ąĮąĄą╣ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąĮąŠą┐ą║ąĖ). ąöą▓ąĄ ą║ąĮąŠą┐ą║ąĖ ąĮą░čüčéčĆą░ąĖą▓ą░čÄčé čćą░čüč鹊čéčā ą▓ą▓ąĄčĆčģ ąĖą╗ąĖ ą▓ąĮąĖąĘ, čéčĆąĄčéčīčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ čüą║ąŠčĆąŠčüčéąĖ ąĮą░čüčéčĆąŠą╣ą║ąĖ. ąĢčüčéčī 6 čüą║ąŠčĆąŠčüč鹥ą╣ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą║ąŠąĮąĄčćąĮąŠą│ąŠ VCO (ą║ąŠč鹊čĆčŗą╣ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čćą░čüč鹊č鹥, ą▓ 128 čĆą░ąĘ ą▓čŗčłąĄ čćą░čüč鹊čéčŗ DDS): 15.625 ąōčå, 31.25 ąōčå, 62.5 ąōčå, 1 ą║ąōčå, 10 ą║ąōčå ąĖ 100 ą║ąōčå. ąØą░ąČą░čéąĖąĄ ą║ąĮąŠą┐ą║ąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ čüą║ąŠčĆąŠčüčéąĖ čü ąŠą┤ąĮąŠą╣ ąĖąĘ ą║ąĮąŠą┐ąŠą║ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą╝ąĄąĮčÅčÄčé čüą║ąŠčĆąŠčüčéčī, ą║ąŠč鹊čĆą░čÅ ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĮą░ ąĖąĮą┤ąĖą║ą░č鹊čĆąĄ. ąÜąŠą│ą┤ą░ ąĮą░ąČąĖą╝ą░čÄčéčüčÅ ą║ąĮąŠą┐ą║ąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čćą░čüč鹊čéčŗ ą▓ą▓ąĄčĆčģ ąĖą╗ąĖ ą▓ąĮąĖąĘ, DDS čĆą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ čćą░čüčéčī ą▓čĆąĄą╝ąĄąĮąĖ, ąĮą░ 1/8 ąŠčé ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ 923 ą║ąōčå. ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĮąŠ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ čåąĖčäčĆ čćą░čüč鹊čéčŗ. ąĢčüčéčī ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ čéčāą╝ą▒ą╗ąĄčĆ, ąŠčéą║ą╗čÄčćą░čÄčēąĖą╣ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ čćą░čüč鹊čéčŗ ąĖ ą║ąĮąŠą┐ą║ąĖ, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą┐ąŠą╗čāčćąĖčéčī čüą░ą╝čŗą╣ čćąĖčüčéčŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ RF-čüąĖą│ąĮą░ą╗.

ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ čćą░čüč鹊čéčŗ. ąöą╗čÅ ąĮąĖąČąĮąĖčģ čüą║ąŠčĆąŠčüč鹥ą╣ ąĮą░čüčéčĆąŠą╣ą║ąĖ ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ čćą░čüčéąĖ ą║ąĖą╗ąŠą│ąĄčĆčå čćą░čüč鹊čéčŗ. ąÜąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮą░ čüą║ąŠčĆąŠčüčéčī ąĮą░čüčéčĆąŠą╣ą║ąĖ 10 ą║ąōčå ąĖą╗ąĖ 100 ą║ąōčå, ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ ą▓ ą£ąōčå + 100 ą║ąōčå.

ąØąĖąČąĄ ąĮą░ ą┐čĆąĖą╝ąĄčĆąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ą▓čüąĄ čĆą░ą▒ąŠčéą░ąĄčé.

ąöą╗čÅ čćą░čüč鹊čéčŗ 21.345 ą£ąōčå ąĖ čüą║ąŠčĆąŠčüčéąĖ ąĮą░čüčéčĆąŠą╣ą║ąĖ 10 ą║ąōčå ąĖ 100 ą║ąōčå ą░ą╗ą│ąŠčĆąĖčéą╝ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ čćą░čüč鹊čéčŗ čüą╗ąĄą┤čāčÄčēąĖą╣:

ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ čåąĖčäčĆčŗ "2" ą▓ č鹥č湥ąĮąĖąĄ 0.5 čüąĄą║čāąĮą┤.

ąÆčŗą║ą╗čÄč湥ąĮąĖąĄ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ąĮą░ 0.1 čüąĄą║čāąĮą┤čŗ.

ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ čåąĖčäčĆčŗ "1" ą▓ č鹥č湥ąĮąĖąĄ 0.3 čüąĄą║čāąĮą┤čŗ.

ąÆčŗą║ą╗čÄč湥ąĮąĖąĄ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ąĮą░ 0.1 čüąĄą║čāąĮą┤čŗ.

ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ čåąĖčäčĆčŗ "3" ą▓ č鹥č湥ąĮąĖąĄ 0.3 čüąĄą║čāąĮą┤čŗ.

ąŚą░č鹥ą╝ ą┤ąĖčüą┐ą╗ąĄą╣ ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ ąĮą░ 5 čüąĄą║čāąĮą┤, ąĖ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ.

ąöą╗čÅ čćą░čüč鹊čéčŗ 21.345 ą£ąōčå ąĖ ąĮąĖąČąĮąĖčģ čüą║ąŠčĆąŠčüč鹥ą╣ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą░ą╗ą│ąŠčĆąĖčéą╝ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ čćą░čüč鹊čéčŗ čüą╗ąĄą┤čāčÄčēąĖą╣:

ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ čåąĖčäčĆčŗ "3" ą▓ č鹥č湥ąĮąĖąĄ 0.5 čüąĄą║čāąĮą┤čŗ.

ąÆčŗą║ą╗čÄč湥ąĮąĖąĄ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ąĮą░ 0.1 čüąĄą║čāąĮą┤čŗ.

ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ čåąĖčäčĆčŗ "4" ą▓ č鹥č湥ąĮąĖąĄ 0.3 čüąĄą║čāąĮą┤čŗ.

ąÆčŗą║ą╗čÄč湥ąĮąĖąĄ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ąĮą░ 0.1 čüąĄą║čāąĮą┤čŗ.

ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ čåąĖčäčĆčŗ "5" ą▓ č鹥č湥ąĮąĖąĄ 0.3 čüąĄą║čāąĮą┤čŗ.

ąŚą░č鹥ą╝ ą┤ąĖčüą┐ą╗ąĄą╣ ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ ąĮą░ 5 čüąĄą║čāąĮą┤, ąĖ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ.

ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ ąĮą░ 5 čüąĄą║čāąĮą┤, ąĮąŠ ą▓ą║ą╗čÄčćąĖčéčüčÅ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čāą┤ąĄčé ąŠą┐čāčēąĄąĮą░ ąŠą┤ąĮą░ ąĖąĘ ą║ąĮąŠą┐ąŠą║ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čćą░čüč鹊čéčŗ ą▓ą▓ąĄčĆčģ/ą▓ąĮąĖąĘ. ą¤ąĄčĆą▓ą░čÅ čåąĖčäčĆą░ ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĮąĄą╝ąĮąŠą│ąŠ ą┤ąŠą╗čīčłąĄ, č湥ą╝ ą┤čĆčāą│ąĖąĄ, čćč鹊 ą┤ą░ąĄčé ą▒ąŠą╗ąĄąĄ čāą┤ąŠą▒ąĮąŠąĄ čüčćąĖčéčŗą▓ą░ąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ čćą░čüč鹊čéčŗ. ąÜąŠą│ą┤ą░ ąĮą░ąČą░čéą░ ą║ąĮąŠą┐ą║ą░ čüą║ąŠčĆąŠčüčéąĖ ąĮą░čüčéčĆąŠą╣ą║ąĖ, ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ č鹥ą║čāčēą░čÅ čüą║ąŠčĆąŠčüčéčī (ąŠčé 1 ą┤ąŠ 6). ąØą░ąČą░čéąĖąĄ ą║ąĮąŠą┐ąŠą║ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▓ą▓ąĄčĆčģ/ą▓ąĮąĖąĘ ą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą╝ąĄąĮčÅąĄčé čüą║ąŠčĆąŠčüčéčī ąĮą░čüčéčĆąŠą╣ą║ąĖ (0.5 čüąĄą║čāąĮą┤ ąĮą░ 1 čłą░ą│).

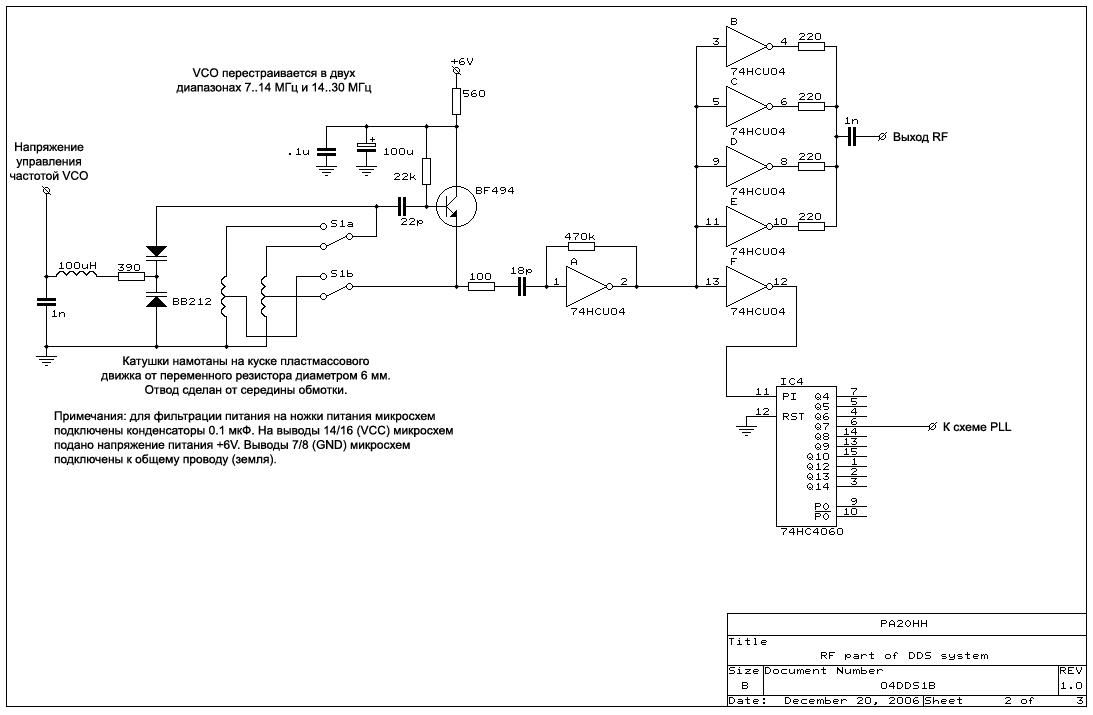

[VCO]

ąōąĄąĮąĄčĆą░č鹊čĆ VCO čüąŠą▒čĆą░ąĮ ąĮą░ ąŠą┤ąĮąŠą╝ čéčĆą░ąĮąĘąĖčüč鹊čĆąĄ ąĖ čüąĮą░ą▒ąČąĄąĮ ą▓čŗčģąŠą┤ąĮčŗą╝ ą┤čĆą░ą╣ą▓ąĄčĆąŠą╝ ąĖ čüč湥čéčćąĖą║ąŠą╝/ą┤ąĄą╗ąĖč鹥ą╗ąĄą╝ ąĮą░ 128. ą¤ąĄčĆąĄą║ą╗čÄčćą░č鹥ą╗čī S1 ą▓čŗą▒ąĖčĆą░ąĄčé ąŠą┤ąĖąĮ ąĖąĘ ą┤ą▓čāčģ ą┤ąĖą░ą┐ą░ąĘąŠąĮąŠą▓ čćą░čüč鹊čé. ąÆ ą║ą░č湥čüčéą▓ąĄ ą▒čāč乥čĆą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 74HCU04 (ą▓ąŠąĘą╝ąŠąČąĮąŠ, čćč鹊 ą▒čāą┤ąĄčé čéą░ą║ąČąĄ čĆą░ą▒ąŠčéą░čéčī ąĖ 74HC04), ąĖ čüč湥čéčćąĖą║ 74HC4060 ą┤ąĄą╗ąĖčé čćą░čüč鹊čéčā VCO ąĮą░ 128. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ą┐čĆąĖčģąŠą┤ąĖčé ąĮą░ čüčģąĄą╝čā PLL.

[PLL]

ą¤ąĄčĆą▓čŗą╣ ą▓ą░čĆąĖą░ąĮčé čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ PLL ąĖą╝ąĄą╗ čüąĖčüč鹥ą╝čā ą▓čŗą▒ąŠčĆą║ąĖ, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ą▒čŗčüčéčĆčāčÄ ą┐ąĄčéą╗čÄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ VCO (ą▓ą░čĆąĖą░ąĮčé čüčéą░čĆąŠą╣ ą▓ąĄčĆčüąĖąĖ ą╝ąŠąČąĮąŠ ą┐ąŠčüą╝ąŠčéčĆąĄčéčī ą┐ąŠ čüčüčŗą╗ą║ąĄ http://www.qsl.net/pa2ohh/03dds1.htm). ą×ą┤ąĮą░ą║ąŠ ą▒čŗčüčéčĆą░čÅ ą┐ąĄčéą╗čÅ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ, ąĮą░ą╝ ąĮčāąČąĮąŠ čüą┐ąĄčåąĖą░ą╗čīąĮą░čÅ ą┐ąĄčéą╗čÅ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ ą┤ą╗čÅ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą░čĆą░ąĘąĖčéąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓. ąöą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą╗čāčćčłąĄ ą┐ąŠą┤čģąŠą┤ąĖčé ąŠą▒čŗčćąĮą░čÅ čüčģąĄą╝ą░ ą┤ąĄč鹥ą║č鹊čĆą░ čćą░čüč鹊čéčŗ/čäą░ąĘčŗ ąĮą░ ąŠčüąĮąŠą▓ąĄ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ ąĘą░čĆčÅą┤ą░, ąĖ čā ąĮąĄčæ ąĮąĄčé ąĮąĄą┤ąŠčüčéą░čéą║ą░ ąĘą░čģą▓ą░čéą░ čćą░čüč鹊čéčŗ ąĮą░ ą│ą░čĆą╝ąŠąĮąĖą║ą░čģ. ąŁč鹊 ą╝ąŠąČąĄčé čéą░ą║ąČąĄ čĆą░ą▒ąŠčéą░čéčī ąĖ ąĮą░ ą╝ąĮąŠą│ąŠ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖčģ čćą░čüč鹊čéą░čģ DDS, č湥ą╝ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ąĮą░čłąĄą╣ čüąĖčüč鹥ą╝ąĄ. ąØą░ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąŠą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊č鹥 DDS ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čāčüą║ąŠčĆąĄąĮąĮčŗą╣ čåąĖą║ą╗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, ąĮą░ ą║ąŠč鹊čĆąŠą╝ ą╝ąĄąĮčīčłąĄ čüąĖą│ąĮą░ą╗čŗ ą┐ąŠą╝ąĄčģ.

ą¦ą░čüč鹊čéąĮąŠ-čäą░ąĘąŠą▓čŗą╣ ą┤ąĄč鹥ą║č鹊čĆ čüąŠą▒čĆą░ąĮ ąĮą░ RS-čéčĆąĖą│ą│ąĄčĆą░čģ. ąæčŗą╗ą░ ąĖą┤ąĄčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą╝ąĖą║čĆąŠčüčģąĄą╝čā čäą░ąĘąŠą▓ąŠą│ąŠ ą┤ąĄč鹥ą║č鹊čĆą░ 74HCT9046, ąĮąŠ ąŠąĮą░ ą▒ąŠą╗čīčłąĄ ąĮąĄą┤ąŠčüčéčāą┐ąĮą░. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 čĆąĄčłąĄąĮąĖąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ą┤ąĄč鹥ą║č鹊čĆ ąĮą░ ąŠą▒čŗčćąĮčŗčģ, čłąĖčĆąŠą║ąŠ ą┤ąŠčüčéčāą┐ąĮčŗčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░čģ. ąöčĆčāą│ąŠąĄ ą┤ąŠčüč鹊ąĖąĮčüčéą▓ąŠ čéą░ą║ąŠą│ąŠ čĆąĄčłąĄąĮąĖčÅ - ąĄčüčéčī ą┤ąŠčüčéčāą┐ ą║ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ą╝, ą║ąŠč鹊čĆčŗąĄ ąŠą▒čŗčćąĮąŠ ąĮąĄą┤ąŠčüčéčāą┐ąĮčŗ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą╝ąŠąČąĮąŠ ąĘą░ą┐čĆąĄčéąĖčéčī čüčģąĄą╝čā ąĮą░ą║ą░čćą║ąĖ ąĘą░čĆčÅą┤ą░ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░čģ, ą║ąŠą│ą┤ą░ ąĖčüą║ą░ąČą░ąĄčéčüčÅ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ DDS.

ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé čüčģąĄą╝ą░ PLL. ąØą░ čéčĆąĄčģ čéčĆą░ąĮąĘąĖčüč鹊čĆą░čģ Q1, Q2 ąĖ Q3 čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ. ąæą░ąĘą░ Q2 ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ ą║ čüčĆąĄą┤ąĮąĄą╝čā ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ čüčģąĄą╝čŗ DDS (čāčüčĆąĄą┤ąĮčÅąĄčéčüčÅ čĆąĄąĘąĖčüč鹊čĆąŠą╝ 10 ą║ą×ą╝ ąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą╝ 0.1 ą╝ą║ąż).

ą¤čĆčÅą╝ąŠčāą│ąŠą╗čīąĮčŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą┐čĆąĖčģąŠą┤ąĖčé ąĮą░ čéą░ą║č鹊ą▓čŗą╣ ą▓čģąŠą┤ D-čéčĆąĖą│ą│ąĄčĆą░ U1A. ąĢą│ąŠ ą▓čģąŠą┤čŗ čüąĮą░ą▒ąČąĄąĮčŗ čüčģąĄą╝ąŠą╣ ą│ąĖčüč鹥čĆąĄąĘąĖčüą░, ą┐ąŠčŹč鹊ą╝čā ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąŠą┤ą░ą▓ą░čéčī čüčéčĆąŠą│ąŠ ą┐čĆčÅą╝ąŠčāą│ąŠą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗. ąĪąĖą│ąĮą░ą╗ ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ VCO (ą┐ąŠą┤ąĄą╗ąĄąĮąĮąŠą╣ ąĮą░ 128) ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ čéą░ą║č鹊ą▓ąŠą╝čā ą▓čģąŠą┤čā ą▓č鹊čĆąŠą│ąŠ D-čéčĆąĖą│ą│ąĄčĆą░ U1B. ąÜąŠą│ą┤ą░ ąĮą░ ąŠą▒ąŠąĖčģ ą▓čŗčģąŠą┤ą░čģ D-čéčĆąĖą│ą│ąĄčĆąŠą▓ ąĮą░čģąŠą┤ąĖčéčüčÅ ą╗ąŠą│. 1, ąŠąĮąĖ čüą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ čüčģąĄą╝ąŠą╣ ą╝ąŠąĮčéą░ąČąĮąŠą│ąŠ "ąś", čüąŠą▒čĆą░ąĮąĮąŠą╣ ąĮą░ ą┤ąĖąŠą┤ą░čģ 1N4148.

ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłąĄą╗ "ąĘą░čģą▓ą░čé" čćą░čüč鹊čéčŗ (čé. ąĄ. ą║ąŠą│ą┤ą░ ą│ąĄąĮąĄčĆą░č鹊čĆ VCO ąĖ DDS čĆą░ą▒ąŠčéą░čÄčé čüąĖąĮčģčĆąŠąĮąĮąŠ), D-čéčĆąĖą│ą│ąĄčĆčŗ ąĖ čüčģąĄą╝ą░ ą╝ąŠąĮčéą░ąČąĮąŠą│ąŠ "ąś" čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ čäą░ąĘąŠą▓čŗą╣ ą┤ąĄč鹥ą║č鹊čĆ, ą░ ą║ąŠą│ą┤ą░ ąĘą░čģą▓ą░čéą░ čćą░čüč鹊čéčŗ ąĮąĄčé, ąŠąĮąĖ čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ čćą░čüč鹊čéąĮčŗą╣ ą┤ąĄč鹥ą║č鹊čĆ.

ąÆčŗčģąŠą┤čŗ čéčĆąĖą│ą│ąĄčĆąŠą▓ čāą┐čĆą░ą▓ą╗čÅčÄčé ą┤ą▓čāą╝čÅ ąĖčüč鹊čćąĮąĖą║ą░ą╝ąĖ č鹊ą║ą░ Q5 ąĖ Q6, ą║ąŠč鹊čĆčŗąĄ ąĘą░čĆčÅąČą░čÄčé ąĮą░ą║ąŠą┐ąĖč鹥ą╗čīąĮčŗą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ 0.1 ą╝ą║ąż. ąśčüč鹊čćąĮąĖą║ąĖ č鹊ą║ą░ ą▓ą╝ąĄčüč鹥 čü čŹčéąĖą╝ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą╝ čéą░ą║ąČąĄ čŹčäč乥ą║čéąĖą▓ąĮąŠ ą┐ąŠą┤ą░ą▓ą╗čÅčÄčé ą▓čüąĄ čüąĖą│ąĮą░ą╗čŗ ą┐ąŠą╝ąĄčģ. ąóąŠą║ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čĆąĄąĘąĖčüč鹊čĆą░ą╝ąĖ 8.2 ą║ą×ą╝. ą¤ą░ą┤ąĄąĮąĖąĄ ąĮą░ čŹčéąĖčģ čĆąĄąĘąĖčüč鹊čĆą░čģ čüąŠčüčéą░ą▓ą╗čÅąĄčé 1V, ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ą╗čÅ VCO ą╝ąĄąĮčÅąĄčéčüčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą┐čĆąĖą▒ą╗ąĖąĘąĖč鹥ą╗čīąĮąŠ ąŠčé 1.5V ą┤ąŠ 10.5V.

ążąĖą╗čīčéčĆ ą┐ąĄčéą╗ąĖ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ PLL čüąŠą▒čĆą░ąĮ ąĮą░ ą┤ą▓čāčģ čéčĆą░ąĮąĘąĖčüč鹊čĆą░čģ Q7 ąĖ Q8, ą║ąŠč鹊čĆčŗąĄ ąĘą░ą▒ąŠčéčÅčéčüčÅ ąŠ ą┐čĆąŠčåąĄą┤čāčĆąĄ ą▒čŗčüčéčĆąŠą│ąŠ ąĘą░čģą▓ą░čéą░, ą║ąŠą│ą┤ą░ VCO čüą╗ąĖčłą║ąŠą╝ ą┤ą░ą╗ąĄą║ąŠ ąŠčéčüčéčĆąŠąĄąĮ ąŠčé čĆą░ą▒ąŠč湥ą╣ čćą░čüč鹊čéčŗ.

Q9 ąĖ Q10 čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ čüčģąĄą╝ą░ ąĘą░ą┐čĆąĄčéą░ ąĮą░ą║ąŠą┐ąĖč鹥ą╗čīąĮąŠą╣ ąĄą╝ą║ąŠčüčéąĖ. PLL ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ąĖ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ą╝ąĖ, ą║ąŠą│ą┤ą░ ą▓čŗčģąŠą┤ DDS ą┐čĆąĄčĆčŗą▓ą░ąĄčéčüčÅ.

[ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ą╗čÅ AT90S1200]

ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ 11999.55 ą║ąōčå. ą×ą┤ąĮą░ ą┐čĆąŠą║čĆčāčéą║ą░ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ DDS ąĘą░ąĮąĖą╝ą░ąĄčé 13 ą╝ą░čłąĖąĮąĮčŗčģ čåąĖą║ą╗ąŠą▓ AVR, čćč鹊 ą┤ą░ąĄčé čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā 923.04225 ą║ąōčå. ąĀąĄą│ąĖčüčéčĆ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░ DDS (DDS Accumulator Register) ąĖą╝ąĄąĄčé ą┤ą╗ąĖąĮčā 4 ą▒ą░ą╣čéą░: 256*256*256*256 = 4294967296. ąĪą╗ąŠą▓ąŠ ąĮą░čüčéčĆąŠą╣ą║ąĖ čćą░čüč鹊čéčŗ (Frequency Tuning Word) čéą░ą║ąČąĄ čüąŠčüč鹊ąĖčé ąĖąĘ 4 ą▒ą░ą╣čé.

ąÆčŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ DDS čĆą░ą▓ąĮą░ (923.04225 kHz * Frequency Tuning Word) / 4294967296, čćą░čüč鹊čéą░ PLL ą▓ 128 čĆą░ąĘ ą▓čŗčłąĄ. ąŚąĮą░č湥ąĮąĖąĄ Frequency Tuning Word ą╝ąĄąĮčÅąĄčéčüčÅ ą║ąĮąŠą┐ą║ą░ą╝ąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čćą░čüč鹊čéčŗ ą▓ą▓ąĄčĆčģ/ą▓ąĮąĖąĘ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ Frequency Tuning Word ąĮą░ 36352 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąĖąĘą╝ąĄąĮąĄąĮąĖčÄ č鹊čćąĮąŠ ąĮą░ 1 ą║ąōčå. ą¦ąĖčüą╗ąŠ 36352 čĆą░ą▓ąĮąŠ 64x568. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čüą░ą╝čŗą╣ ą╝ą░ą╗čŗą╣ čłą░ą│ ą┐ąĄčĆąĄčüčéčĆąŠą╣ą║ąĖ 568, čćč鹊 ą┤ą░ąĄčé ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čćą░čüč鹊čéčŗ ąĮą░ 15.625 ąōčå.

ąĢčüą╗ąĖ ąĖąĘą╝ąĄąĮąĄąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ Frequency Tuning Word, čåąĖčäčĆčŗ ą┤ąĖčüą┐ą╗ąĄčÅ čéą░ą║ąČąĄ ąĖąĘą╝ąĄąĮčÅčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝. ąöą╗čÅ ą║ą░ąČą┤ąŠą╣ ąĖąĘ čåąĖčäčĆ čćą░čüč鹊čéčŗ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ ą┐ąŠ ąŠą┤ąĮąŠą╝čā čĆąĄą│ąĖčüčéčĆčā. ą×ą┤ąĮą░ą║ąŠ čüą░ą╝čŗą╣ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé čéą░ą║ąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą╝ąĄąĮčÅąĄčéčüčÅ ąĮąĄ ąŠčé 0 ą┤ąŠ 9, ą░ ąŠčé 0 ą┤ąŠ 64. ąĢčüą╗ąĖ ą┐čĆąĖ ą┐ąĄčĆąĄčüčéčĆąŠą╣ą║ąĄ čćą░čüč鹊čéčŗ ą▓ą▓ąĄčĆčģ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé ą┐čĆąĄą▓čŗčüąĖčé 63, ąĖą╗ąĖ ą┐čĆąĖ ą┐ąĄčĆąĄčüčéčĆąŠą╣ą║ąĄ čćą░čüč鹊čéčŗ ą▓ąĮąĖąĘ ąŠąĮ čĆą░ą▓ąĄąĮ 0, č鹊 ą▓čüąĄ ą┤čĆčāą│ąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ąĄčüčÅčéąĖčćąĮčŗčģ čåąĖčäčĆ ąĖąĘą╝ąĄąĮčÅčéčüčÅ. ąóą░ą║ąŠą╣ ą╝ąĄč鹊ą┤ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čåąĖčäčĆ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą▓čüąĄ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąŠčéčĆą░ą▒ą░čéčŗą▓ą░ą╗ąĖ ąĘą░ čüčéčĆąŠą│ąŠ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą╝ą░čłąĖąĮąĮčŗčģ čéą░ą║č鹊ą▓ AVR, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, čćč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé. ąĢčüą╗ąĖ ąĮą░ąČą░čéą░ ą║ąĮąŠą┐ą║ą░, č鹊 čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ DDS ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ąĮą░ 1/8 ąŠčé čüą▓ąŠąĄą╣ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ 923 ą║ąōčå, ąĖ Frequency Tuning Word čāą╝ąĮąŠąČą░ąĄčéčüčÅ ąĮą░ 8. ą×ą┤ąĮą░ą║ąŠ ą▒čŗą╗ąŠ ąŠč湥ąĮčī čéčĆčāą┤ąĮąŠ č鹊čćąĮąŠ čāč湥čüčéčī ą▓čüąĄ ą╝ą░čłąĖąĮąĮčŗąĄ čéą░ą║čéčŗ, čéą░ą║ čćč鹊 ą░ą▓č鹊čĆ ą┐čĆąŠą▓ąĄą╗ ą╝ąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ čĆčāčćąĮąŠą╣ ą║ąŠčĆčĆąĄą║čåąĖąĄą╣ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ čéą░ą║č鹊ą▓ ąĘą░čĆčÅą┤ą░ ąĮą░ą║ąŠą┐ąĖč鹥ą╗čīąĮąŠą│ąŠ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ (ą┐čĆą░ą▓ą║ąŠą╣ ą║ąŠą┤ą░ ąĖ ą▓čüčéą░ą▓ą║ąŠą╣ ą║ąŠą╝ą░ąĮą┤ NOP), ąĖąĘą╝ąĄčĆčÅčÅ ąĖčģ čü ą┐ąŠą╝ąŠčēčīčÄ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░čäą░ ąĖ ą┐čĆąŠčüą╗čāčłąĖą▓ą░čÅ ą║ą░č湥čüčéą▓ąŠ ą┐čĆąĖąĄą╝ą░ čŹčäąĖčĆą░.

ąĪą╝ąĄčēąĄąĮąĖąĄ čćą░čüč鹊čéčŗ (čāčćąĖčéčŗą▓ą░čÄčēąĄąĄ čćą░čüč鹊čéčā ą¤ą¦) ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ Frequency Tuning Word ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ąĄčüčÅčéąĖčćąĮčŗčģ čåąĖčäčĆ. ą¤ąŠ čüčüčŗą╗ą║ąĄ [3] ą╝ąŠąČąĮąŠ ąĘą░ą│čĆčāąĘąĖčéčī ą░čĆčģąĖą▓ 04dds1soft.zip, ą│ą┤ąĄ ąĮą░čģąŠą┤čÅčéčüčÅ ą╝ąŠą┤čāą╗ąĖ ąĖčüčģąŠą┤ąĮąŠą│ąŠ ą║ąŠą┤ą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆą░ (čäą░ą╣ą╗čŗ .ASM), ą║ąŠč鹊čĆčŗąĄ ąĮčāąČąĮčŗ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ AT90S1200.

[ą¤ąŠą╗čāč湥ąĮąĮčŗąĄ čĆąĄąĘčāą╗čīčéą░čéčŗ]

VFO ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 5 .. 5.5 ą£ąōčå ą┤ą╗čÅ TS520. ą¤ąŠąĘąČąĄ ą▒čŗą╗ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮ čéčāą╝ą▒ą╗ąĄčĆ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ 120 ą┐ąż ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą▓ą░čĆąĖą║ą░ą┐čā VC, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą┐ąŠą╗čāčćąĖčéčī ą┐ąĄčĆąĄą║čĆčŗčéąĖąĄ ą┐ąŠ čćą░čüč鹊čéą░ą╝ 5 .. 5.5 ą£ąōčå. ąÉą▓č鹊čĆ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗ čŹč鹊čé VFO čüąŠą▓ą╝ąĄčüčéąĮąŠ čüąŠ čüčéą░čĆčŗą╝ čéčĆą░ąĮčüąĖą▓ąĄčĆąŠą╝ TS520SE, ąĖ čüčéą░ą▒ąĖą╗čīąĮąŠčüčéčī čćą░čüč鹊čéčŗ ą┐ąŠą╗čāčćąĖą╗ą░čüčī ą╗čāčćčłąĄ, č湥ą╝ čā ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ VFO, ą┤ąŠčüčéą░č鹊čćąĮą░čÅ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ PSK31.

VFO ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą┐čĆčÅą╝ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. DDS PLL ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗čüčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ VFO ą┤ą╗čÅ ą┐čĆąŠčüč鹊ą│ąŠ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą┐čĆčÅą╝ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗą╣ ą▒čŗą╗ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ąĘą▓čāą║ąŠą▓ąŠą╣ ą║ą░čĆč鹥 ą║ąŠą╝ą┐čīčÄč鹥čĆą░ PC. ąĪčéą░ą▒ąĖą╗čīąĮąŠčüčéčī čćą░čüč鹊čéčŗ ą▒čŗą╗ą░ ąŠč湥ąĮčī čģąŠčĆąŠčłąĄą╣ ą┤ą╗čÅ ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ čåąĖčäčĆąŠą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ čü ą┐ąŠą╝ąŠčēčīčÄ čüą▓ąŠą▒ąŠą┤ąĮąŠ ą┤ąŠčüčéčāą┐ąĮčŗčģ ą┐čĆąŠą│čĆą░ą╝ą╝. ą¤čĆąĖ ąĘą░ą┐čĆąĄč鹥 PLL ą▓ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░čģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą║ąŠą│ą┤ą░ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čüąĮąĖąČą░ą╗ą░čüčī, čüąĖčüč鹥ą╝ą░ PLL ą╝ąŠą│ą╗ą░ čĆą░ą▒ąŠčéą░čéčī ąĮą░ ą▓čŗčüąŠą║ąĖčģ ą▓čŗčģąŠą┤ąĮčŗčģ čćą░čüč鹊čéą░čģ DDS ą▒ąĄąĘ ąĮą░čĆčāčłąĄąĮąĖčÅ ą║ą░č湥čüčéą▓ą░. ą¤čĆąĖ čŹč鹊ą╝ ą▓ ąĘą▓čāą║ąŠą▓ąŠą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą╝ą░ą╗ąŠ ą┐ąŠą╝ąĄčģ. ąĢčüą╗ąĖ ą┐ąŠą╝ąĄčģąĖ ąĖ ą┐ąŠčÅą▓ą╗čÅčÄčéčüčÅ, č鹊 ą┐čĆąĖ ąŠčéčüčéčĆąŠą╣ą║ąĄ ąĮą░ 30 ąōčå ą▓ą▓ąĄčĆčģ ąĖą╗ąĖ ą▓ąĮąĖąĘ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĖčüč湥ąĘą░čÄčé.

[ą×čåąĄąĮą║ą░ ą║ą░č湥čüčéą▓ą░ čüą┐ąĄą║čéčĆą░]

|

|

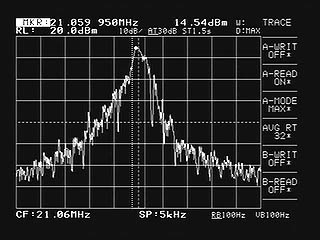

| ąĪąĖą│ąĮą░ą╗ RF ą▒ąĄąĘ ąĘą░ą┐čĆąĄčéą░ PLL ą▓ąŠ ą▓čĆąĄą╝čÅ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝, ą║ąŠą│ą┤ą░ DDS čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ 1/8 ąŠčé ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ. |

ąĪąĖą│ąĮą░ą╗ RF čü ąĘą░ą┐čĆąĄč鹊ą╝ PLL ąĮą░ 255 ą╝ą║čü. |

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą▓ ą║ą░č湥čüčéą▓ąĄ DDS ąŠč湥ąĮčī ąĖąĮč鹥čĆąĄčüąĮą░čÅ ąĖą┤ąĄčÅ, čģąŠčĆąŠčłą░čÅ ą┤ą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ 菹║čüą┐ąĄčĆąĖą╝ąĄąĮč鹊ą▓ ą▓ ą▒čāą┤čāčēąĄą╝.

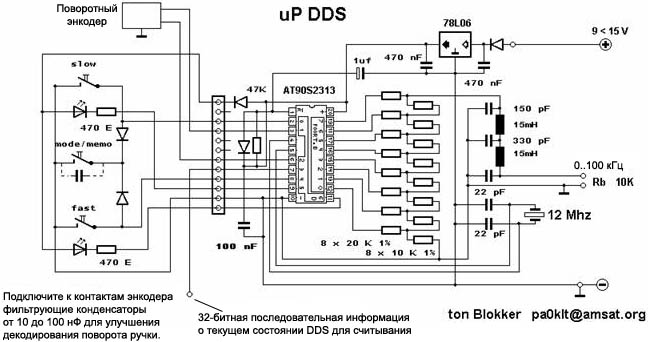

[DDS ąŠčé PA0KLT]

ą×čĆąĖą│ąĖąĮą░ą╗čīąĮą░čÅ čĆą░ąĘčĆą░ą▒ąŠčéą║ą░ DDS [2] ąŠčé Ton PA0KLT (PA0KLT@amsat.org) ąĖą╝ąĄą╗ą░ 8-ą▒ąĖčéąĮčŗą╣ DAC ąĖ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮčŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗, čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą▒čŗą╗ą░ ą▓čŗčłąĄ, ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗ą░čüčī ą┤čĆčāą│ą░čÅ čüąĖčüč鹥ą╝ą░ PLL. ąÆą╝ąĄčüč鹊 čéčĆąĄčģ ą║ąĮąŠą┐ąŠą║ ąĮą░čüčéčĆąŠą╣ą║ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅą╗ą░čüčī čāą┤ąŠą▒ąĮčŗą╝ ą┐ąŠą▓ąŠčĆąŠčéąĮčŗą╝ 菹Įą║ąŠą┤ąĄčĆąŠą╝, ąĖ ą▒čŗą╗ą░ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čāčüčéą░ąĮąŠą▓ą║ąĖ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊čéčŗ, ąĖą╝ąĄą╗ą░čüčī ą┐ą░ą╝čÅčéčī čćą░čüč鹊čé, ąĖ čüą║ąŠčĆąŠčüčéčī ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ą╗ą░čüčī. ąÆ ą║ą░č湥čüčéą▓ąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DDS ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗čüčÅ AT90S2313, ą║ąŠč鹊čĆčŗą╣ ąĖą╝ąĄąĄčé ą▒ąŠą╗čīčłąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣, č湥ą╝ AT90S1200.

ąöčĆčāą│ąŠąĄ ą┤ąŠčüč鹊ąĖąĮčüčéą▓ąŠ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ PA0KLT ą▓ č鹊ą╝, čćč鹊 ąĄą│ąŠ DDS čĆą░ą▒ąŠčéą░ą╗ ąĮą░ ą┐ąŠą╗ąŠą▓ąĖąĮąĄ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, ąĖ ąĮąĄ ą▒čŗą╗ąŠ čüąĮąĖąČąĄąĮąĖčÅ čćą░čüč鹊čéčŗ ą▓ 8 čĆą░ąĘ ą▓ąŠ ą▓čĆąĄą╝čÅ čĆą░ą▒ąŠčéčŗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝.

ąÜ čüąŠąČą░ą╗ąĄąĮąĖčÄ, ąĖčüčģąŠą┤ąĮąŠą│ąŠ ą║ąŠą┤ą░ čüą▓ąŠąĄą│ąŠ ą┐čĆąŠąĄą║čéą░ PA0KLT ąĮąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖą╗, ą┤ąŠčüčéčāą┐ąĮą░ č鹊ą╗čīą║ąŠ ą┐čĆąŠčłąĖą▓ą║ą░ ą▓ HEX-č乊čĆą╝ą░č鹥 (čüą╝. [3]).

[ąĪą╗ąŠą▓ą░čĆąĖą║]

DAC Digital to Analog Converter, čåąĖčäčĆąŠ-ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī (ą”ąÉą¤).

LED Light Emitting Diode, čüą▓ąĄč鹊ą┤ąĖąŠą┤. ąÆ ą┤ą░ąĮąĮąŠą╝ čüą╗čāčćą░ąĄ č鹥čĆą╝ąĖąĮ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ čåąĖčäčĆąŠą▓ąŠą╝čā čüą▓ąĄč鹊ą┤ąĖąŠą┤ąĮąŠą╝čā 7-čüąĄą│ą╝ąĄąĮčéąĮąŠą╝čā ąĖąĮą┤ąĖą║ą░č鹊čĆčā.

PLL Phase-Locked Loop, čäą░ąĘąŠą▓ą░čÅ ą░ą▓č鹊ą┐ąŠą┤čüčéčĆąŠą╣ą║ą░ čćą░čüč鹊čéčŗ.

QRP ą╗čÄą▒ąĖč鹥ą╗čīčüą║ą░čÅ čĆą░ą┤ąĖąŠčüą▓čÅąĘčī ąĮą░ ą╝ą░ą╗ąŠą╣ ą╝ąŠčēąĮąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ąÆąĖą║ąĖą┐ąĄą┤ąĖčÄ).

RF Radio Frequency, čĆą░ą┤ąĖąŠčćą░čüč鹊čéą░.

VCO Voltage Controlled Oscillator, ą│ąĄąĮąĄčĆą░č鹊čĆ, čćą░čüč鹊čéą░ ą║ąŠč鹊čĆąŠą│ąŠ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝.

[ąĪčüčŗą╗ą║ąĖ]

1. EXPERIMENTAL DIRECT DIGITAL SYNTHESIS BASED ON A MICROCONTROLLER AND PHASE LOCKED LOOP site:qsl.net.

2. QRP-AFSTEMSYSTEEM met microcontroller als DDS door PAÆKLT site:pa0klt.nl.

3. 180615DDS-AVR.zip - ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮą░čÅ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÅ, ą┐čĆąŠčłąĖą▓ą║ąĖ ąĖ ąĖčüčģąŠą┤ąĮčŗą╣ ą║ąŠą┤ (ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ ąĄčüčéčī č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐čĆąŠąĄą║čéą░ PA2OHH). |