|

ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ čéčĆąĄą▒čāąĄčé čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą▒ąŠą╗čīčłąĖčģ ąĘą░ą┤ąĄčƹȹĄą║ ą┐ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, čĆą░ąĘčĆą░ą▒ąŠčéčćąĖą║ ą╝ąŠąČąĄčé ą▓čŗą▒čĆą░čéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▓ą░čĆąĖą░ąĮč鹊ą▓ čĆąĄčłąĄąĮąĖčÅ čŹč鹊ą╣ ąĘą░ą┤ą░čćąĖ.

ą×ą┤ąĮąŠ ąĖąĘ čĆąĄčłąĄąĮąĖą╣ čüąŠčüč鹊ąĖčé ą▓ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AVR ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░. ą¤ąŠčüą║ąŠą╗čīą║čā ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī čéą░ą╣ą╝ąĄčĆą░ ąŠą▒čŗčćąĮąŠ ąĮąĄ ą┐čĆąĄą▓čŗčłą░ąĄčé 16 ą▒ąĖčé (ąĖąĮąŠą│ą┤ą░ 24 ą▒ąĖčéą░), č鹊 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ą╗ąĖąĮąĮčŗčģ ąĘą░ą┤ąĄčƹȹĄą║ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čćą░čüč鹊čéčŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ąØą░ą┐čĆąĖą╝ąĄčĆ, 24-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ ąĮą░ čćą░čüč鹊č鹥 1 ą£ąōčå, ą╝ąŠąČąĄčé ą┤ą░čéčī ąĘą░ą┤ąĄčƹȹ║čā č鹊ą╗čīą║ąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┤ąĄčüčÅčéą║ąŠą▓ čüąĄą║čāąĮą┤. ąöą╗čÅ ą╝ąĮąŠą│ąĖčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ čŹč鹊ą│ąŠ ą╝ąŠąČąĄčé ąŠą║ą░ąĘą░čéčīčüčÅ ąĮąĄą┤ąŠčüčéą░č鹊čćąĮčŗą╝.

ąöčĆčāą│ąŠąĄ čĆąĄčłąĄąĮąĖąĄ - ą┐ąŠą┤čüč湥čé ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖą╣ čéą░ą╣ą╝ąĄčĆą░. ą×ą┤ąĮą░ą║ąŠ čŹč鹊 čāčüą╗ąŠąČąĮčÅąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ, ąĖ ąĮąĄ ą┤ą░ąĄčé čÅą┤čĆčā ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ąĮąĖąĘą║ąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠąČąĖą┤ą░ąĮąĖąĄ ąĖčüč鹥č湥ąĮąĖčÅ ąĘą░ą┤ąĄčƹȹ║ąĖ.

ąóčĆąĄčéčīąĄ čĆąĄčłąĄąĮąĖąĄ - ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░čéčī ą▓ąĮąĄčłąĮąĖą╣ ąĮąĖąĘą║ąŠčćą░čüč鹊čéąĮčŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ. ąöą╗čÅ čŹč鹊ą│ąŠ čéą░ą╣ą╝ąĄčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ąĮą░ ą┐ąŠą┤čüč湥čé ą▓ąĮąĄčłąĮąĖčģ čüąŠą▒čŗčéąĖą╣, ąĖ ąĮą░ ąĄą│ąŠ čüčćąĖčéą░čÄčēąĖą╣ (čéą░ą║č鹊ą▓čŗą╣) ą▓čģąŠą┤ ą┐ąŠą┤ą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ ąĮąĖąĘą║ąŠą╣ čćą░čüč鹊čéčŗ. ąóą░ą║ąŠą╣ čüą┐ąŠčüąŠą▒ ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┤ąŠčüčéą░č鹊čćąĮąŠ ą┤ą╗ąĖč鹥ą╗čīąĮčŗąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ. ą×ą┤ąĮą░ą║ąŠ čüč鹊ąĖą╝ąŠčüčéčī ąĖ ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ čüą╗ąŠąČąĮąŠčüčéčī čüąĖčüč鹥ą╝čŗ ą▓ąŠąĘčĆą░čüčéą░čÄčé, čéą░ą║ ą║ą░ą║ ąĮčāąČąĮąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčī ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ 菹╗ąĄą║čéčĆąŠąĮąĮčŗąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ.

ąŚą┤ąĄčüčī ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąŠ čĆąĄčłąĄąĮąĖčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┤ą╗ąĖąĮąĮčŗčģ ąĘą░ą┤ąĄčƹȹĄą║ ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ čüąĄčĆąĖąĖ AVR AT90 (AT90S2313, AT90S4414 ąĖ AT90S8515). ąśčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗąĄ čéą░ą╣ą╝ąĄčĆčŗ ą▒ąĄąĘ čāčćą░čüčéąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čÅą┤čĆčā ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĘą░ą┤ąĄčƹȹ║ąĖ. ą¤ąŠčüą║ąŠą╗čīą║čā čéą░ą╣ą╝ąĄčĆčŗ čéą░ą║čéąĖčĆčāčÄčéčüčÅ ąŠčé čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ, č鹊 ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą║ą░ą║ąĖčģ-č鹊 ą▓ąĮąĄčłąĮąĖčģ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓. ąöą╗čÅ čāą▓ąĄą╗ąĖč湥ąĮąĖčÅ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┤ąĄčƹȹ║ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░čüą║ą░ą┤ąĮąŠąĄ ą▓ą║ą╗čÄč湥ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆąŠą▓ AVR.

ąÆą╝ąĄčüč鹥 čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąŠč湥ąĮčī ą▒ąŠą╗čīčłąĖčģ ą▓čĆąĄą╝ąĄąĮąĮčŗčģ ąĘą░ą┤ąĄčƹȹĄą║ čŹčéą░ čĆąĄą░ą╗ąĖąĘą░čåąĖčÅ čüąŠč湥čéą░ąĄčé ą▓čŗčüąŠą║čāčÄ čüą║ąŠčĆąŠčüčéčī čüąĖčüč鹥ą╝čŗ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ čüąŠ čüą║ąŠčĆąŠčüčéčīčÄ 20 Mips, ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĘą░ą┤ąĄčƹȹ║ąĖ ą┤ą╗ąĖąĮąŠą╣ ą┤ąŠ ą┐ąŠą╗čāčćą░čüą░.

ąÆąŠčé čüą┐ąĖčüąŠą║ ą┐čĆąĖą╝ąĄčĆąĮčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣, ą│ą┤ąĄ ą╝ąŠą│čāčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ ą┤ą╗ąĖąĮąĮčŗąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ:

ŌĆó ąóą░ą╣ą╝ą░čāčéčŗ ą▓ ąĖąĮč鹥čĆč乥ą╣čüąĄ ą╝ąĄąČą┤čā č湥ą╗ąŠą▓ąĄą║ąŠą╝ ąĖ ą╝ą░čłąĖąĮąŠą╣

ŌĆó ąśąĘą╝ąĄčĆąĄąĮąĖčÅ ą▓ ąŠą║čĆčāąČą░čÄčēąĄą╣ čüčĆąĄą┤ąĄ (čāčĆąŠą▓ąĄąĮčī ąĘą▓čāą║ą░, ąĘą░ą│čĆčÅąĘąĮąĄąĮąĖąĄ)

ŌĆó ąĀąĄą│čāą╗ąĖčĆąŠą▓ą║ą░ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠą╝

ą¤čĆąĖą╝. ą┐ąĄčĆąĄą▓ąŠą┤čćąĖą║ą░: ąĮą░ čüą░ą╝ąŠą╝ ą┤ąĄą╗ąĄ ą┐čĆąĄą┤ą╗ąŠąČąĄąĮąĮąŠąĄ čĆąĄčłąĄąĮąĖąĄ ąĖą╝ąĄąĄčé ą┤ąŠą▓ąŠą╗čīąĮąŠ ąŠą│čĆą░ąĮąĖč湥ąĮąĮąŠąĄ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄ - ąŠąĮąŠ čģąŠčĆąŠčłąŠ ą┐ąŠą┤čģąŠą┤ąĖčé č鹊ą╗čīą║ąŠ ą┤ą╗čÅ č鹥čģ čüą╗čāčćą░ąĄą▓, ą║ąŠą│ą┤ą░ ąŠčé čüąĖčüč鹥ą╝čŗ čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąŠąĮąĖąČąĄąĮąĮąŠąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ, ąĖ ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ čéą░ą╣ą╝ąĄčĆčŗ/čüč湥čéčćąĖą║ąĖ ąĮąĄą│ą┤ąĄ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮčŗ. ąöą╗čÅ č鹥čģ čüą╗čāčćą░ąĄą▓, ą║ąŠą│ą┤ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąĮąĄ ą▓čģąŠą┤ąĖčé čĆąĄąČąĖą╝ čüąĮą░, ą┐čĆąĄą┤ą╗ąŠąČąĄąĮąĮąŠąĄ čĆąĄčłąĄąĮąĖąĄ ą▒ąĄčüą┐ąŠą╗ąĄąĘąĮąŠ, ą┐ąŠč鹊ą╝čā čćč鹊 ąĘą░ą┤ąĄčƹȹ║ąĖ ą╗čÄą▒ąŠą╣ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ 菹╗ąĄą╝ąĄąĮčéą░čĆąĮąŠ čĆąĄą░ą╗ąĖąĘčāčÄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ ąŠą▒čŗčćąĮčŗčģ čüč湥čéčćąĖą║ąŠą▓.

[ąóą░ą╣ą╝ąĄčĆčŗ/čüč湥čéčćąĖą║ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ AVR]

ąöą░ą╗ąĄąĄ ą▒čāą┤čāčé ą║ąŠčĆąŠčéą║ąŠ čĆą░čüčüą╝ąŠčéčĆąĄąĮčŗ čéą░ą╣ą╝ąĄčĆčŗ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓ AVR. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠąČą░ą╗čāą╣čüčéą░ ąŠą▒čĆą░čēą░ą╣č鹥čüčī ą║ ą┤ą░čéą░čłąĖčéčā "AVR Enhanced RISC Microcontroller Data Book".

ąóą░ą╣ą╝ąĄčĆčŗ/čüč湥čéčćąĖą║ąĖ. ąĪąĄčĆąĖčÅ AT90 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé 2 čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ (T/C) ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ, ąŠą┤ąĖąĮ 8-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ T/C, ąĖ ąŠą┤ąĖąĮ 16-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ T/C. ąóą░ą╣ą╝ąĄčĆčŗ/čüč湥čéčćąĖą║ąĖ ąĖą╝ąĄčÄčé ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčŗą╣ ą▓čŗą▒ąŠčĆ ą┐ąŠą┤ąĄą╗ąĄąĮąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĖ č鹊ą│ąŠ ąČąĄ 10-ą▒ąĖčéąĮąŠą│ąŠ ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čÅ (ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░). ą×ą▒ą░ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ ą╝ąŠą│čāčé ą╗ąĖą▒ąŠ čéą░ą║čéąĖčĆąŠą▓ą░čéčīčüčÅ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą▒ą░ąĘąŠą▓ąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, ąĖą╗ąĖ čĆą░ą▒ąŠčéą░čéčī ą║ą░ čüč湥čéčćąĖą║ ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĮą░ ą▓ąĮąĄčłąĮąĄą╝ ą▓čŗą▓ąŠą┤ąĄ.

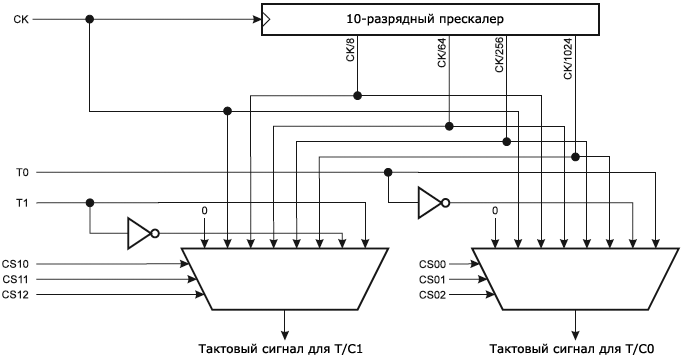

ą¤čĆąĄčüą║ą░ą╗ąĄčĆ ą┤ą╗čÅ T/C. ąØą░ čĆąĖčü. 1 ą┐ąŠą║ą░ąĘą░ąĮą░ čüčģąĄą╝ą░ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ą┤ą╗čÅ T/C. ąĢčüčéčī 4 čĆą░ąĘą╗ąĖčćąĮčŗčģ ą▓ą░čĆąĖą░ąĮčéą░ ą▓čŗą▒ąŠčĆą░ ą┐ąŠą┤ąĄą╗ąĄąĮąĮąŠą╣ čüč湥čéčćąĖą║ąŠą╝ čćą░čüč鹊čéčŗ: CK/8, CK/64, CK/256 ąĖ CK/1024, ą│ą┤ąĄ CK čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą│ąĄąĮąĄčĆą░č鹊čĆą░. ąöą╗čÅ ą┤ą▓čāčģ čéą░ą╣ą╝ąĄčĆąŠą▓/čüč湥čéčćąĖą║ąŠą▓ ąĄčēąĄ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮčŗ ą║ ą▓ą░čĆąĖą░ąĮčéą░ą╝ ą▓čŗą▒ąŠčĆ CK, ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĖ ąŠčüčéą░ąĮąŠą▓ą║ą░ čéą░ą╣ą╝ąĄčĆą░.

ąĀąĖčü. 1. ą¤čĆąĄčüą║ą░ą╗ąĄčĆ ą┤ą╗čÅ čéą░ą╣ą╝ąĄčĆąŠą▓/čüč湥čéčćąĖą║ąŠą▓.

[8-Bit Timer/Counter0]

ąØą░ čĆąĖčü. 2 ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ Timer/Counter0.

ąĀąĖčü. 2. ąæą╗ąŠą║-čüčģąĄą╝ą░ T/C0.

ąöą╗čÅ 8-čĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ Timer/Counter0 ą╝ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčé CK, ą┐ąŠą┤ąĄą╗ąĄąĮąĮąŠą╣ (č湥čĆąĄąĘ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ) CK, ąĖą╗ąĖ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓čģąŠą┤ą░. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ čéą░ą╣ą╝ąĄčĆ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą║ą░ą║ čāą║ą░ąĘą░ąĮąŠ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ Timer/Counter0 Control Register (TCCR0) [2]. ążą╗ą░ą│ąĖ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ Timer/Counter Interrupt Flag Register (TIFR). ąŻą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čäą╗ą░ą│ąĖ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ Timer/Counter0 Control Register (TCCR0). ąØą░čüčéčĆąŠą╣ą║ąĖ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ/ąĘą░ą┐čĆąĄčéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ Timer/Counter0 ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ Timer/Counter Interrupt Mask Register (TIMSK).

ąÜąŠą│ą┤ą░ Timer/Counter0 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓čģąŠą┤ą░, ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ čü čćą░čüč鹊č鹊ą╣ čéą░ą║č鹊ą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čÅą┤čĆą░ (čüąĖčüč鹥ą╝ąĮčŗą╝ąĖ čéą░ą║čéą░ą╝ąĖ) CK. ą¦č鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą║ąŠčĆčĆąĄą║čéąĮčāčÄ ą▓čŗą▒ąŠčĆą║čā ą▓ąĮąĄčłąĮąĖčģ čéą░ą║č鹊ą▓, ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ą╝ąĖ čāčĆąŠą▓ąĮčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĮąŠą╝čā ąĖąĮč鹥čĆą▓ą░ą╗čā ą┐ąĄčĆąĖąŠą┤ą░ CK. ąÆąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ čéą░ą╣ą╝ąĄčĆą░ ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ čāčĆąŠą▓ąĮčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ CK.

[16-Bit Timer/Counter1]

ąØą░ čĆąĖčü. 3 ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ Timer/Counter1.

ąĀąĖčü. 3. ąæą╗ąŠą║-čüčģąĄą╝ą░ T/C1.

ąöą╗čÅ 16-bit Timer/Counter1 ą╝ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčé CK, ą┐ąŠą┤ąĄą╗ąĄąĮąĮąŠą╣ (č湥čĆąĄąĘ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ) CK, ąĖą╗ąĖ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓čģąŠą┤ą░. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ čéą░ą╣ą╝ąĄčĆ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą║ą░ą║ čāą║ą░ąĘą░ąĮąŠ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ Timer/Counter1 Control Registers (TCCR1A ąĖ TCCR1B). ąĀą░ąĘą╗ąĖčćąĮčŗąĄ čäą╗ą░ą│ąĖ čüąŠčüč鹊čÅąĮąĖčÅ (overflow, compare match ąĖ capture event) ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čüąĖą│ąĮą░ą╗čŗ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ TCCR1A ąĖ TCCR1B. ąØą░čüčéčĆąŠą╣ą║ąĖ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ/ąĘą░ą┐čĆąĄčéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ Timer/Counter1 ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ Timer/Counter Interrupt Mask Register (TIMSK).

ąÜąŠą│ą┤ą░ Timer/Counter1 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓čģąŠą┤ą░, ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ čü čćą░čüč鹊č鹊ą╣ čéą░ą║č鹊ą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čÅą┤čĆą░ (čüąĖčüč鹥ą╝ąĮčŗą╝ąĖ čéą░ą║čéą░ą╝ąĖ) CK. ą¦č鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą║ąŠčĆčĆąĄą║čéąĮčāčÄ ą▓čŗą▒ąŠčĆą║čā ą▓ąĮąĄčłąĮąĖčģ čéą░ą║č鹊ą▓, ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ą╝ąĖ čāčĆąŠą▓ąĮčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĮąŠą╝čā ąĖąĮč鹥čĆą▓ą░ą╗čā ą┐ąĄčĆąĖąŠą┤ą░ CK. ąÆąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ čéą░ą╣ą╝ąĄčĆą░ ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ čāčĆąŠą▓ąĮčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ CK.

16-ą▒ąĖčéąĮčŗą╣ Timer/Counter1 čüąŠč湥čéą░ąĄčé ą║ą░ą║ ą▓čŗčüąŠą║čāčÄ čĆą░ąĘčĆąĄčłą░čÄčēčāčÄ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī (ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą▓čŗčüąŠą║čāčÄ č鹊čćąĮąŠčüčéčī), čéą░ą║ ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▓čŗą▒ąŠčĆą░ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą▓ ą┤ąĄą╗ąĄąĮąĖčÅ ą▓čģąŠą┤ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ. ąÆčŗą▒ąŠčĆ ą▓čŗčüąŠą║ąŠą│ąŠ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĄąĮąĖčÅ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą┤ąĄą╗ą░ąĄčé Timer/Counter1 ą┐ąŠą╗ąĄąĘąĮčŗą╝ ą┤ą╗čÅ ąĮąĖąĘą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗčģ čäčāąĮą║čåąĖą╣ ąĖą╗ąĖ ą┤ą╗čÅ č鹊čćąĮąŠą╣ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ąĮąĄčćą░čüč鹊 ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝čŗčģ ą┤ąĄą╣čüčéą▓ąĖą╣.

Timer/Counter1 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 2 čäčāąĮą║čåąĖąĖ čüčĆą░ą▓ąĮąĄąĮąĖčÅ Output Compare čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆąŠą▓ Output Compare Register 1 A ąĖ B (OCR1A ąĖ OCR1B) ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ čüč湥čéčćąĖą║ą░ Timer/Counter1. ążčāąĮą║čåąĖąĖ Output Compare ą▓ą║ą╗čÄčćą░čÄčé ąŠą┐čåąĖąŠąĮą░ą╗čīąĮčāčÄ ąŠčćąĖčüčéą║čā čüč湥čéčćąĖą║ą░ ą┐čĆąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ (compare match), ąĖ ą┤ąĄą╣čüčéą▓ąĖčÅ ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ąŠą▓ Output Compare ą┤ą╗čÅ ąŠą▒ąŠąĖčģ čüčĆą░ą▓ąĮąĄąĮąĖą╣ (compare match A ąĖ B).

[ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ]

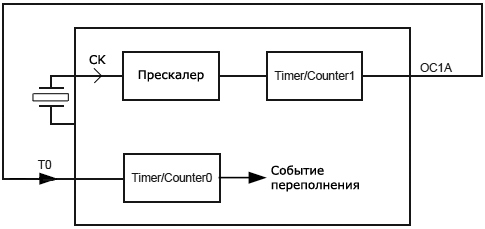

ą¦č鹊ą▒čŗ ą┐čĆąŠąĖąĘą▓ąĄčüčéąĖ ą┤ą╗ąĖąĮąĮčāčÄ ąĘą░ą┤ąĄčƹȹ║čā ąŠčé ą▒čŗčüčéčĆąŠą╣ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ CK, ą║ą░čüą║ą░ą┤ąĖčĆčāčÄčéčüčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ąĖ ą┤ą▓ą░ ą▓čüčéčĆąŠąĄąĮąĮčŗčģ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 4.

ąĀąĖčü. 4. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AVR ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┤ą╗ąĖąĮąĮčŗčģ ąĘą░ą┤ąĄčƹȹĄą║.

Timer/Counter1 ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ čéą░ą╣ą╝ąĄčĆ. ą×ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą┤ą╗čÅ ą┤ąĄą╗ąĄąĮąĖčÅ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ čü ąĘą░ą┤ą░ąĮąĮčŗą╝ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą╝, ąĖ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčé ą▓čŗą▓ąŠą┤ OC1A ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ, ąĘą░ą┐ąĖčüą░ąĮąĮąŠą│ąŠ ą▓ čĆąĄą│ąĖčüčéčĆ čüčĆą░ą▓ąĮąĄąĮąĖčÅ output compare (OCR1AH-OCR1AL). ąÜąŠą│ą┤ą░ ą▓čŗčģąŠą┤ OC1A ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ, čĆąĄą│ąĖčüčéčĆ Timer/Counter1 (TCNT1H-TCNT1L) ą┐ąĄčĆąĄąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĮčāą╗ąĄą▓čŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝, ąĖ ąĮą░čćąĖąĮą░ąĄčé čüč湥čé čüąĮą░čćą░ą╗ą░.

ą¤ąŠčüą║ąŠą╗čīą║čā ą┐ąĄčĆąĄą║ą╗čÄčćą░čÄčēąĖą╣čüčÅ ą▓čŗčģąŠą┤ąĮąŠą╣ ą┐ąŠčĆčé OC1A ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ąŠ ą▓čģąŠą┤čā T0 čüč湥čéčćąĖą║ą░, č鹊 čćą░čüč鹊čéą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ OC1A ą╝ąŠąČąĄčé čüąŠąĘą┤ą░ą▓ą░čéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą╗čÅ Timer/Counter0. ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ čüč湥čéčćąĖą║, ąĖ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą┐ąŠ ą║ą░ąČą┤ąŠą╝čā ąĮą░čĆą░čüčéą░čÄčēąĄą╝čā čäčĆąŠąĮčéčā ąĮą░ ą▓čģąŠą┤ąĄ T0. ąóąŠą│ą┤ą░ Timer/Counter0 ą┐ąĄčĆąĄą┐ąŠą╗ąĮčÅąĄčéčüčÅ, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čäą╗ą░ą│ ą▓ TIFR, ąĖ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąŁč鹊čé ą╝ąŠą╝ąĄąĮčé ą│ąŠą▓ąŠčĆąĖčé ąŠ č鹊ą╝, čćč鹊 ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ąĖčüč鹥ą║ą╗ą░.

ąĪą░ą╝ą░čÅ ą▒ąŠą╗čīčłą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗčćąĖčüą╗ąĄąĮą░ ą┐čĆąĖ čüą╗ąĄą┤čāčÄčēąĖčģ čāčüą╗ąŠą▓ąĖčÅčģ:

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ą┤ą╗čÅ Timer1: 1024

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą┤ą╗čÅ Timer1: 65536

ą¤ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ OC1A ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ąĮą░ 2

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą┤ą╗čÅ Counter0: 256.

ąöą╗čÅ ąŠą▒čēąĄą│ąŠ čüą╗čāčćą░čÅ ą▓ąĄą╗ąĖčćąĖąĮą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ ąĘą░ą┤ąĄčƹȹ║ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗčćąĖčüą╗ąĄąĮą░ ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╣ č乊čĆą╝čāą╗ąĄ:

T = 2 / CK * T1P * OCR1A * (256 ŌĆō TCNT0)

ą│ą┤ąĄ:

CK = čüąĖčüč鹥ą╝ąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░

T1P = ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░, ąĘą░ą┤ą░ąĮąĮčŗ ą▓ TCCR1B (ą╝ąŠąČąĄčé ą▒čŗčéčī ą╗ąĖą▒ąŠ 8, ą╗ąĖą▒ąŠ 64, ą╗ąĖą▒ąŠ 256, ą╗ąĖą▒ąŠ 1024).

ąŁčéą░ ą║ąŠčĆąŠčéą║ą░čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī čéą░ą╣ą╝ąĄčĆčŗ/čüč湥čéčćąĖą║ąĖ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ąĘą░ą┤ąĄčƹȹ║ąĖ ąĮą░ 1 čćą░čü ą┐čĆąĖ čĆą░ą▒ąŠč鹥 ąŠčé čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ CK = 1 ą£ąōčå (ą▓čŗčćąĖčüą╗ąĖč鹥ą╗čīąĮą░čÅ ą╝ąŠčēąĮąŠčüčéčī ą░ąĮą░ą╗ąŠą│ąĖčćąĮą░ 80C51). ąÆąŠ ą▓čĆąĄą╝čÅ čäą░ąĘčŗ ąĘą░ą┐čāčüą║ą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ čéą░ą╣ą╝ąĄčĆčŗ/čüč湥čéčćąĖą║ąĖ ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąŚą░č鹥ą╝ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ čüąĮą░ (idle mode). ą¤ąŠčüą╗ąĄ ąĖčüč鹥č湥ąĮąĖąĖ čćą░čüą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąŁč鹊 čüąŠą▒čŗčéąĖąĄ čĆą░ąĘą▒čāą┤ąĖčé čÅą┤čĆąŠ, ą║ąŠč鹊čĆąŠąĄ ąĘą░ą┐čāčüčéąĖčé ą▓čŗą▒čĆą░ąĮąĮčāčÄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüč鹊ą╝ ąĘą░ą┤ą░čćčā. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą┤ą╗čÅ ą┐čĆąŠčüč鹊čéčŗ č鹊ą╗čīą║ąŠ ą╗ąĖčłčī ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ąĮąŠąČą║ą░ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┐ąŠčĆčéą░ (PA0). ąÜąŠą│ą┤ą░ čŹčéą░ ąĘą░ą┤ą░čćą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░, čÅą┤čĆąŠ čüąĮąŠą▓ą░ ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ čüąĮą░. ąŁč鹊čé čåąĖą║ą╗ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčéčüčÅ ą▒ąĄčüą║ąŠąĮąĄčćąĮąŠ. ąØąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐čĆąŠą║ąŠą╝ą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ąĖčüčģąŠą┤ąĮčŗą╣ ą║ąŠą┤.

; ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą║ąŠąĮčüčéą░ąĮčé ----------------------------------------

.EQU PORTA = $1B

.EQU DDRA = $1A

.EQU DDRD = $11

.EQU TCCR1A = $2F

.EQU OCR1AH = $2B

.EQU OCR1AL = $2A

.EQU MCUCR = $35

.EQU TIMSK = $39

.EQU TCCR0 = $33

.EQU TCCR1B = $2E

.EQU TCNT1L = $2C

.EQU TCNT1H = $2D

.EQU TCNT0 = $32

.EQU SREG = $3F

.EQU SPH = $3E

.EQU SPL = $3D

; ąÆąĄą║č鹊čĆčŗ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ -----------------------------

.ORG $0000

rjmp start

reti ; ąŠą▒čĆą░ą▒ąŠčéą║ą░ INT0 (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ)

reti ; ąŠą▒čĆą░ą▒ąŠčéą║ą░ INT1 (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ)

reti ; ąŠą▒čĆą░ą▒ąŠčéą║ą░ T/C1 (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ)

reti ; ąŠą▒čĆą░ą▒ąŠčéą║ą░ T/C1 compare match A (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ)

reti ; ąŠą▒čĆą░ą▒ąŠčéą║ą░ T/C1 compare match B (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ)

reti ; ąŠą▒čĆą░ą▒ąŠčéą║ą░ T/C1 overflow (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ)

reti ; ąŠą▒čĆą░ą▒ąŠčéą║ą░ T/C0 overflow

reti ; ąŠą▒čĆą░ą▒ąŠčéą║ą░ SPI transfer complete (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ)

reti ; ąŠą▒čĆą░ą▒ąŠčéą║ą░ ą┐čĆąĖąĄą╝ą░ UART (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ)

reti ; ąŠą▒čĆą░ą▒ąŠčéą║ą░ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░ UART (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ)

reti ; ąŠą▒čĆą░ą▒ąŠčéą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ UART (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ)

reti ; ąŠą▒čĆą░ą▒ąŠčéą║ą░ čüąŠą▒čŗčéąĖčÅ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ)

; ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ --------------------------

start:

ldi r17, $01 ; ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ čĆąĄą│ąĖčüčéčĆą░

ldi r16, $01 ; PORTA0 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗčģąŠą┤

out DDRA, r16

ldi r16, $01 ; ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ čāą║ą░ąĘą░č鹥ą╗čÅ čüč鹥ą║ą░ ..

out SPH, r16 ; .. ąĮą░ 0x100

ldi r16, $00

out SPL, r16

ldi r16, $20 ; OC1A čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗčģąŠą┤

out DDRD, r16

ldi r16, $40 ; TCCR1A ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ąĮą░ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ..

out TCCR1A, r16 ; .. OC1A ąĮą░ ą║ą░ąČą┤ąŠą╝ čüąŠą▒čŗčéąĖąĖ compare match

ldi r16, $6D ; ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ output compare ..

out OCR1AH, r16 ; .. ąĮą░ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ..

ldi r16, $DD ; .. 28125

out OCR1AL, r16

ldi r16, $20 ; ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄąČąĖą╝ą░ čüąĮą░

out MCUCR, r16

ldi r16, $02 ; ąĀą░ąĘčĆąĄčłąĖčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ T/C0

out TIMSK, r16

ldi r16, $80 ; ą×ą▒čēąĄąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣

out SREG, r16

; ąæąĄčüą║ąŠąĮąĄčćąĮčŗą╣ čåąĖą║ą╗ ----------------------------------------------

loop:

rcall main ; ąÆčŗąĘąŠą▓ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ

ldi r16, $06 ; ą¤ąĄčĆąĄąĘą░ą│čĆčāąĘąĖčéčī čüč湥čéčćąĖą║ 0 ą┤ą╗čÅ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░

out TCNT0, r16 ; .. ą┤ąĄą╗ąĄąĮąĖčÅ 250

ldi r16, $06 ; ąŚą░ą┐čāčüą║ čüč湥čéčćąĖą║ą░ 0 ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ąŠčé čćą░čüč鹊čéčŗ ..

out TCCR0, r16 ; .. ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓čŗą▓ąŠą┤ą░ T0

ldi r16, $00 ; ąĪą▒čĆąŠčü ąĘąĮą░č湥ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ 1

out TCNT1H, r16

ldi r16, $00

out TCNT1L, r16

ldi R16, $0C ; ąŚą░ą┐čāčüą║ čéą░ą╣ą╝ąĄčĆą░ 1 ą┤ą╗čÅ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĄąĮąĖčÅ ..

out TCCR1B, r16 ; .. 256

sleep ; ąŚą░ą┐čāčüą║ ąŠąČąĖą┤ą░ąĮąĖčÅ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ąĘą░ą┤ąĄčƹȹ║ąĖ

ldi r16, $00 ; ą×čüčéą░ąĮąŠą▓ čéą░ą╣ą╝ąĄčĆą░ 1

out TCCR1B, r16

ldi r16, $00 ; ą×čüčéą░ąĮąŠą▓ čéą░ą╣ą╝ąĄčĆą░ 0

out TCCR0, r16

rjmp loop

; ą×čüąĮąŠą▓ąĮą░čÅ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ----------------------------------------

; ą×ąĮą░ ą▓čüąĄą│ąŠ ą╗ąĖčłčī ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčé ą▓čŗą▓ąŠą┤ PORTA0

main:

in r16, PORTA

eor r16, r17

out PORTA, r16

ret

[ąĪčüčŗą╗ą║ąĖ]

1. AVR133: Long Delay Generation Using the AVR Microcontroller site:atmel.com.

2. AVR130: ąĮą░čüčéčĆąŠą╣ą║ą░ ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆąŠą▓ AVR. |