|

ąÆ ą░ą┐ąĮąŠčāč鹥 AVR131 čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ ą▓ąŠą┐čĆąŠčüčŗ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ čü ą┐ąŠą╝ąŠčēčīčÄ PWM, ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗąĄ čĆąĄąČąĖą╝čŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░. ąÉą▒ą▒čĆąĄą▓ąĖą░čéčāčĆą░ PWM ąŠąĘąĮą░čćą░ąĄčé Pulse Width Modulation (ą©ąĖčĆąŠčéąĮąŠ-ąśą╝ą┐čāą╗čīčüąĮą░čÅ ą£ąŠą┤čāą╗čÅčåąĖčÅ, ą©ąśą£). ąóą░ą║ąŠą╣ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ą╝ąŠą┤čāą╗čÅč鹊čĆ ąĖą╝ąĄąĄčéčüčÅ ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ AVR. ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮčŗ ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą▒čŗčüčéčĆąŠą╣ ą©ąśą£ (fast PWM, high-speed PWM) ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ATtiny26. ąÆ ą╝ą░ą╗ąĄąĮčīą║ąŠą╝ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ATtiny15 č鹊ąČąĄ ąĄčüčéčī čéą░ą╣ą╝ąĄčĆ čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ PWM.

ąĀąĄąČąĖą╝ fast PWM ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖą╝ą┐čāą╗čīčüąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čü ąĖąĘą╝ąĄąĮčÅąĄą╝ąŠą╣ čüą║ą▓ą░ąČąĮąŠčüčéčīčÄ ąĮą░ ąĮąŠąČą║ąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ OC1A (ą▓čŗčģąŠą┤ąĮąŠą╣ ą┐ąŠčĆčé PB1). ąöą╗čÅ čüą│ą╗ą░ąČąĖą▓ą░ąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĖ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąŠą│ąĖą▒ą░čÄčēąĄą╣ čüąĖą│ąĮą░ą╗ą░ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čäąĖą╗čīčéčĆ (ążąØą¦). ąóą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ą╝ąŠąČąĮąŠ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĘą▓čāą║ąĖ ą║ ą┐čĆąĖą╝ąĄčĆčā, čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą╣ č乊čĆą╝čŗ.

ąöąŠčüč鹊ąĖąĮčüčéą▓ąŠ high-speed PWM čüąŠčüč鹊ąĖčé ą▓ čāą▓ąĄą╗ąĖč湥ąĮąĮąŠą╣ ą┐ąŠą╗ąŠčüąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą│ąŠ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ąĖ čāą┐čĆąŠčēąĄąĮąĖąĖ ążąØą¦ ąĘą░ čüč湥čé ą▓čŗčüąŠą║ąŠą╣ čćą░čüč鹊čéčŗ PWM - ą╝ąŠąČąĮąŠ ą┐čĆąĖą╝ąĄąĮąĖčéčī čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčŗ ążąØą¦ ą╝ąĄąĮčīčłąĄą│ąŠ ąĮąŠą╝ąĖąĮą░ą╗ą░ ąĖ ą╝ąĄąĮčīčłąĄą│ąŠ čĆą░ąĘą╝ąĄčĆą░.

[ąØąĄą╝ąĮąŠą│ąŠ č鹥ąŠčĆąĖąĖ: ą║ą░ą║ čŹč鹊 čĆą░ą▒ąŠčéą░ąĄčé]

PWM ą▓ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ čü ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╝ čäąĖą╗čīčéčĆąŠą╝ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ čüąĖąĮč鹥ąĘąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą▓čŗčģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓, čé. ąĄ. ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čåąĖčäčĆąŠ-ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī (Digital-Analog Converter, DAC). ąĪąĖą│ąĮą░ą╗ ą▓ ą▓ąĖą┤ąĄ čåąĖčäčĆąŠą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ 0 ąĖ 1 ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĮą░ ą▒ą░ąĘąĄ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ čćą░čüč鹊čéčŗ ąĖ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ čüą║ą▓ą░ąČąĮąŠčüčéąĖ (čé. ąĄ. čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ 0 ąĖ 1 ą╝ąĄąĮčÅąĄčéčüčÅ). ąĢčüą╗ąĖ ąĮčāąČąĮąŠ čāą▓ąĄą╗ąĖčćąĖčéčī čāčĆąŠą▓ąĄąĮčī ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ, č鹊 ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą╗ąŠą│. 1 čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ, ą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą╗ąŠą│. 0 čāą╝ąĄąĮčīčłą░ąĄčéčüčÅ, ąĖ ąĮą░ąŠą▒ąŠčĆąŠčé.

ąŻčüčĆąĄą┤ąĮąĄąĮąĖąĄ čåąĖčäčĆąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĘą░ ąŠą┤ąĖąĮ ą┐ąĄčĆąĖąŠą┤ (čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ążąØą¦) ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗. ąØą░ą┐čĆąĖą╝ąĄčĆ, čüą║ą▓ą░ąČąĮąŠčüčéčī 50% (ą║ąŠą│ą┤ą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī 0 čĆą░ą▓ąĮą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ 1) ą┤ą░ąĄčé ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ čü ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ą▓ ą┐ąŠą╗ąŠą▓ąĖąĮčā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, čüą║ą▓ą░ąČąĮąŠčüčéčī 75% ą┤ą░ąĄčé čüąĖą│ąĮą░ą╗ čü ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ 75% ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. ą¤čĆąĖą╝ąĄčĆčŗ čäąĖą╗čīčéčĆąŠą▓ą░ąĮąĮčŗčģ ą▓čŗčģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓ ą║ąŠąĮčåąĄ čŹč鹊ą│ąŠ ą┤ąŠą║čāą╝ąĄąĮčéą░.

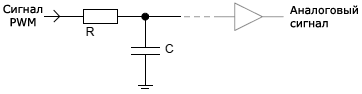

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ążąØą¦, ą║ ą┐čĆąĖą╝ąĄčĆčā, ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠčüčéčĆąŠąĄąĮ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą┐ą░čüčüąĖą▓ąĮąŠą│ąŠ RC-čäąĖą╗čīčéčĆą░. ążąĖą╗čīčéčĆ čāą┤ą░ą╗čÅąĄčé ą▓čŗčüąŠą║čāčÄ ą▒ą░ąĘąŠą▓čāčÄ čćą░čüč鹊čéčŗ ąĖ ąŠčüčéą░ą▓ą╗čÅąĄčé ąĮą░ ą▓čŗčģąŠą┤ąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗. ą¦ą░čüč鹊čéą░ čüčĆąĄąĘą░ čäąĖą╗čīčéčĆą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮą░ ą┤ąŠčüčéą░č鹊čćąĮąŠ ą▓čŗčüąŠą║ąŠą╣, čćč鹊ą▒čŗ ąĮąĄ ą▓ą╗ąĖčÅčéčī ąĮą░ ąĖąĮč鹥čĆąĄčüčāčÄčēąĖą╣ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗. ąÆ č鹊 ąČąĄ čüą░ą╝ąŠąĄ ą▓čĆąĄą╝čÅ čćą░čüč鹊čéą░ čüčĆąĄąĘą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ąĮąĖąĘą║ąŠą╣, čćč鹊ą▒čŗ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ą┐čāą╗čīčüą░čåąĖąĖ ąŠčé ą▒ą░ąĘąŠą▓ąŠą╣ čćą░čüč鹊čéčŗ PWM.

ąĀąĖčü. 1. ą¤čĆąŠčüč鹥ą╣čłąĖą╣ ążąØą¦ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░.

ąĢčüą╗ąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąĖčģąŠą┤ąĖčéčī ąĮą░ ąĮąĖąĘą║ąŠąŠą╝ąĮčāčÄ ąĮą░ą│čĆčāąĘą║čā, č鹊 ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüąĖą╗ąĄąĮ ą▒čāč乥čĆąĮčŗą╝ čāčüąĖą╗ąĖč鹥ą╗ąĄą╝ čü ą▓čŗčüąŠą║ąĖą╝ ą▓čģąŠą┤ąĮčŗą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝, ą▓ą║ą╗čÄč湥ąĮąĮčŗą╝ ą╝ąĄąČą┤čā ą▓čŗčģąŠą┤ąŠą╝ čäąĖą╗čīčéčĆą░ ąĖ ą┐ąŠčéčĆąĄą▒ąĖč鹥ą╗ąĄą╝ čüąĖą│ąĮą░ą╗ą░. ąŁč鹊 ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčé ą┐ą░ą┤ąĄąĮąĖąĄ čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ ąĖ čāą╗čāčćčłąĖčé čĆą░ą▒ąŠčéčā čäąĖą╗čīčéčĆą░.

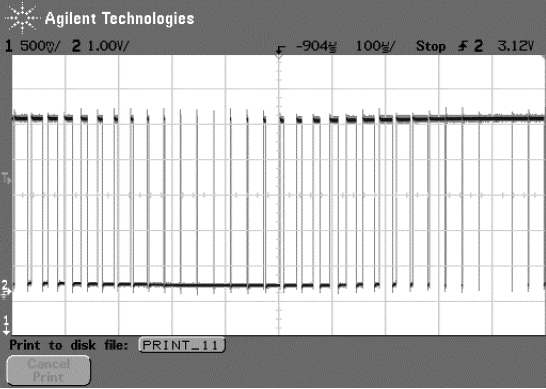

ą¤čĆąĖą╝ąĄčĆ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝čŗ čĆąĄą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ PWM, čā ą║ąŠč鹊čĆąŠą│ąŠ ą╝ąĄąĮčÅąĄčéčüčÅ čüą║ą▓ą░ąČąĮąŠčüčéčī, ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 2.

ąĀąĖčü. 2. ąÆčŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ PWM čü ąĖąĘą╝ąĄąĮčÅąĄą╝ąŠą╣ čüą║ą▓ą░ąČąĮąŠčüčéčīčÄ.

ąÆ AVR čéą░ą╣ą╝ąĄčĆčŗ/čüč湥čéčćąĖą║ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ PWM. ą¦č鹊ą▒čŗ ą┐ąŠą╝ąĄąĮčÅčéčī ą▒ą░ąĘąŠą▓čāčÄ čćą░čüč鹊čéčā PWM, ą╝ąĄąĮčÅčÄčé čćą░čüč鹊čéčā čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ ąĖ ą▓ąĄčĆčģąĮąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čüč湥čéčćąĖą║ą░. ą¦ąĄą╝ ą▓čŗčłąĄ čćą░čüč鹊čéą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, ąĖ/ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ ą▓ąĄčĆčģąĮąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čüč湥čéą░, č鹥ą╝ ą▒čāą┤ąĄčé ą▓čŗčłąĄ ą▒ą░ąĘąŠą▓ą░čÅ čćą░čüč鹊čéą░ PWM, ąĖą╗ąĖ čćą░čüč鹊čéą░ čüąŠą▒čŗčéąĖą╣ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░. ąĪ ą┐ąŠą╗ąĮčŗą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ (ą▓ąĄčĆčģąĮąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ 255) ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ ą▒ą░ąĘąŠą▓ą░čÅ čćą░čüč鹊čéą░ PWM čüąŠčüčéą░ą▓ąĖčé 250 ą║ąōčå. ąŻą▓ąĄą╗ąĖč湥ąĮąĖąĄ ą▒ą░ąĘąŠą▓ąŠą╣ čćą░čüč鹊čéčŗ ą▓čŗčłąĄ čŹč鹊ą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą╝ąŠąČąĄčé ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī ąĘą░ čüč湥čé čāą╝ąĄąĮčīčłąĄąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ, ą┐ąŠčüą║ąŠą╗čīą║čā ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą▒ąŠą╗ąĄąĄ ą│čĆčāą▒čŗą╣ čłą░ą│ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 0% ą┤ąŠ 100% čüą║ą▓ą░ąČąĮąŠčüčéąĖ. ąśąĘą╝ąĄąĮąĄąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (Output Compare Registers, OCR) ą╝ąĄąĮčÅąĄčé čüą║ą▓ą░ąČąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ą░ PWM.

ąŻą▓ąĄą╗ąĖč湥ąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ OCR čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé čüą║ą▓ą░ąČąĮąŠčüčéčī. ąÆčŗčģąŠą┤ PWM čĆą░ą▓ąĄąĮ 1, ą┐ąŠą║ą░ čüč湥čéčćąĖą║ ąĮąĄ ą┤ąŠčüčéąĖą│ ąĄčēąĄ ąĘąĮą░č湥ąĮąĖčÅ OCR, ąĖ čĆą░ą▓ąĄąĮ 0, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┐ąĄčĆąĄą▓ą░ą╗ąĖą╗ ąĘą░ ąĘąĮą░č湥ąĮąĖąĄ OCR ąĖ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé čüčćąĖčéą░čéčī ą┤ąŠ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ. ąŁč鹊čé čĆąĄąČąĖą╝ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą©ąśą£ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ Fast-PWM mode (ą▒čŗčüčéčĆčŗą╣ čĆąĄąČąĖą╝ PWM), ąĖą╗ąĖ high-speed PWM (ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ PWM).

ąĀąĖčü. 3. ąŚąĮą░č湥ąĮąĖčÅ čüč湥čéčćąĖą║ą░ ąĖ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ PWM.

ąÜąŠą│ą┤ą░ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ high-speed PWM, čĆą░ąĘą╝ąĄčĆ čłą░ą│ą░ ą╝ąĄąČą┤čā ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╝ąĖ čāčĆąŠą▓ąĮčÅą╝ąĖ ąĘą░ą▓ąĖčüąĖčé ąŠčé čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ PWM. ą¦ąĄą╝ ą▓čŗčłąĄ ą▒ą░ąĘąŠą▓ą░čÅ čćą░čüč鹊čéą░, č鹥ą╝ ąĄčæ ą┐čĆąŠčēąĄ ąŠčéčäąĖą╗čīčéčĆąŠą▓ą░čéčī ąĮą░ ą▓čŗčģąŠą┤ąĄ, ąĖ ą┐ąŠą╗čāčćąĖčéčī čüąĖą│ąĮą░ą╗ čü ą╝ąĄąĮčīčłąĖą╝ąĖ ą┐čāą╗čīčüą░čåąĖčÅą╝ąĖ. ąÆčŗą▒ąŠčĆ ą╝ąĄąČą┤čā čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ ąĖ ą▒ą░ąĘąŠą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ čÅą▓ą╗čÅąĄčéčüčÅ ą║ąŠą╝ą┐čĆąŠą╝ąĖčüčüąŠą╝ ą┐čĆąĖ čüąŠąĘą┤ą░ąĮąĖąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ.

[ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ]

ąÆčŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ čéą░ą╣ą╝ąĄčĆ ą╝ąŠąČąĄčé čéą░ą║ąČąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▓čŗčüąŠą║ąŠčćą░čüč鹊čéąĮčŗčģ čåąĖčäčĆąŠą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čåąĖčäčĆąŠą▓čŗčģ čāąĘą╗ąŠą▓ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▓ąĄčĆčģąĮąĖą╣ ą┐čĆąĄą┤ąĄą╗ čüč湥čéą░ čüč湥čéčćąĖą║ą░ ą▓ ą╝ą░ą╗ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, č鹊 ą┤ąŠčüčéčāą┐ąĮą░ ą│ąĄąĮąĄčĆą░čåąĖčÅ ą▒ąŠą╗čīčłąĖčģ čćą░čüč鹊čé.

ąĪą░ą╝ą░čÅ ą▒ąŠą╗čīčłą░čÅ ą▓ąŠąĘą╝ąŠąČąĮą░čÅ čćą░čüč鹊čéą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ ATtiny26 čüąŠčüčéą░ą▓ą╗čÅąĄčé 64 ą£ąōčå (ą┐čĆąĖ ąŠčéą║ą╗čÄč湥ąĮąĮąŠą╝ ą┐čĆąĄčüą║ą╗ąĄčĆąĄ). ąĪ ą▒ą░ąĘąŠą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ PWM 16 ą£ąōčå PWM (ą▓ąĄčĆčģąĮąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéą░ 3) ąĘąĮą░č湥ąĮąĖąĄ OCR ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 0, 1 (čüą║ą▓ą░ąČąĮąŠčüčéčī 25%), 2 (čüą║ą▓ą░ąČąĮąŠčüčéčī 50%, čüą╝. A ąĮą░ čĆąĖčü. 4) ąĖą╗ąĖ 3 (čüą║ą▓ą░ąČąĮąŠčüčéčī 100%). ąŁč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐ąŠąĮąĖąČąĄąĮąĖąĄ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ą░ čüč湥čéą░ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé ą▒ą░ąĘąŠą▓čāčÄ čćą░čüč鹊čéčā PWM, ąĮąŠ čüąĮąĖąČą░ąĄčé čéą░ą║ąČąĄ čĆą░ąĘčĆąĄčłą░čÄčēčāčÄ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī PWM.

ą¦č鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ, ą┐ąŠą╗čāčćą░ąĄą╝ąŠą╣ ąŠčé čéą░ą╣ą╝ąĄčĆą░, ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čāčēąĄąĮ ąĮąĄ ą▓ čĆąĄąČąĖą╝ąĄ PWM. ą×ą▒ąĄ ą▓ąĄą╗ąĖčćąĖąĮčŗ, ąĖ OCR ąĖ ą▓ąĄčĆčģąĮąĖą╣ ą┐čĆąĄą┤ąĄą╗ čüč湥čéą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 0. ąóąŠą│ą┤ą░ čüč湥čéčćąĖą║ ąĘą░čüčéčĆąĄą▓ą░ąĄčé ąĮą░ ąĘąĮą░č湥ąĮąĖąĖ 0. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą┤ąĄą╣čüčéą▓ąĖčÅ Output Compare Match ąĮą░ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓čŗčģąŠą┤ą░ (toggle output) čüą┤ąĄą╗ą░ąĄčé čćą░čüč鹊čéčā ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ čü ą║ą░ąČą┤čŗą╝ čéąĖą║ąŠą╝ čéą░ą║č鹊ą▓, ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćąĖčéčüčÅ čüąĖą│ąĮą░ą╗ čü čćą░čüč鹊č鹊ą╣ 32 ą£ąōčå(B ąĮą░ čĆąĖčü. 4).

ąĀąĖčü. 4. ąÆčŗčüąŠą║ąŠčćą░čüč鹊čéąĮčŗą╣ čåąĖčäčĆąŠą▓ąŠą╣ ą▓čŗčģąŠą┤.

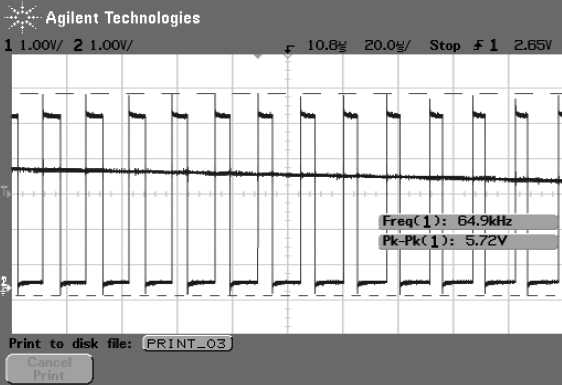

ąØą░ čĆąĖčü. 5 ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ ąĖąĘ ą▓čŗčģąŠą┤ą░ high-speed PWM.

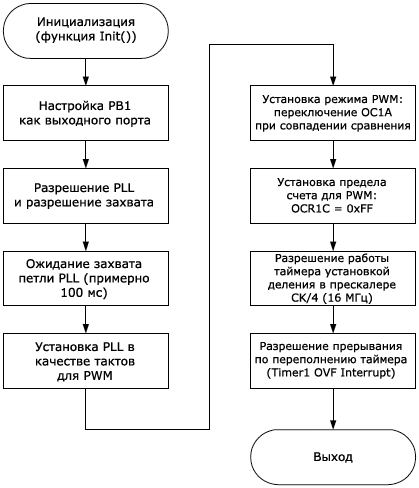

ąÜąŠą┤ čüąŠčüč鹊ąĖčé ąĖąĘ 3 čćą░čüč鹥ą╣: ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ, ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ Timer1 (overflow ISR) čåąĖą║ą╗ čü čāčģąŠą┤ąŠą╝ ą▓ čĆąĄąČąĖą╝ čüąĮą░. ąĀąĄą░ą╗ąĖąĘą░čåąĖčÅ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé ąĮą░ą╗ąĖčćąĖąĄ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ čüąĖčüč鹥ą╝čŗ 8 ą£ąōčå.

ąĀąĖčü. 5. ąōą╗ą░ą▓ąĮčŗą╣ čåąĖą║ą╗ ą┐čĆąĖą╝ąĄčĆą░ ą║ąŠą┤ą░ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ. ą¦č鹊ą▒čŗ ąĘą░čĆą░ą▒ąŠčéą░ą╗ ą▓čŗčģąŠą┤ ąŠčé PWM, ąĮąŠąČą║ą░ Output Compare Timer1 (OC1A) ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮą░ ą║ą░ą║ ą▓čŗčģąŠą┤ąĮąŠą╣ ą┐ąŠčĆčé.

ąöą░ą╗ąĄąĄ ąĮčāąČąĮąŠ ąĮą░čüčéčĆąŠąĖčéčī čéą░ą╣ą╝ąĄčĆ: ą┐ąŠą┤ą│ąŠčéą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖčüč鹊čćąĮąĖą║ ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ ŌĆō ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ PLL, ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čüąĖčüč鹥ą╝ąĮą░čÅ čćą░čüč鹊čéą░ (čŹč鹊 čéčĆąĄą▒čāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ). ąöą╗čÅ čüčéą░ą▒ąĖą╗ąĖąĘą░čåąĖąĖ PLL ąĮčāąČąĮąŠ ą┐čĆąĖą╝ąĄčĆąĮąŠ 100 ą╝čü, ą┐ąŠčŹč鹊ą╝čā ą┐ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ ą║ąŠą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠąČąĖą┤ą░ąĮąĖąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ čüčéą░ą▒ąĖą╗ąĖąĘą░čåąĖąĖ PLL čü ąŠą┐čĆąŠčüąŠą╝ čäą╗ą░ą│ą░ ąĘą░čģą▓ą░čéą░ PLL (PLL lock flag). ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ąĘą░čģą▓ą░čé PLL, ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąĮčāąČąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ą╗čÅ čéą░ą╣ą╝ąĄčĆą░.

ąŚą░č鹥ą╝ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čĆąĄąČąĖą╝ PWM, čćč鹊ą▒čŗ ą▓čŗą▓ąŠą┤ OC1A ą┐ąĄčĆąĄą║ą╗čÄčćą░ą╗čüčÅ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (compare match), ąĖ ą▓ąĄčĆčģąĮąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéą░ čéą░ą╣ą╝ąĄčĆą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 0xFF. ąÆąĄčĆčģąĮąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéą░ ą▓ą╗ąĖčÅąĄčé ąĮą░ čĆą░ąĘčĆąĄčłą░čÄčēčāčÄ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī (č鹊čćąĮąŠčüčéčī) PWM ąĖ ąĮą░ ąĄčæ ą▓ąĄčĆčģąĮčÄčÄ čćą░čüč鹊čéčā ŌĆō č湥ą╝ ą▓čŗčłąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéą░, č鹥ą╝ ą▓čŗčłąĄ č鹊čćąĮąŠčüčéčī (čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī), ąĮąŠ ą╝ąĄąĮčīčłąĄ ą▒ą░ąĘąŠą▓ą░čÅ čćą░čüč鹊čéą░ PWM. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ ą▓ąĄą╗ąĖčćąĖąĮą░ ą┤ą╗čÅ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ čüč湥čéą░.

ąóąĄą┐ąĄčĆčī čéą░ą╣ą╝ąĄčĆ ą│ąŠč鹊ą▓ ą║ čĆą░ą▒ąŠč鹥, ąĖ čāčüčéą░ąĮąŠą▓ą║ą░ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĘą░ą┐čāčüą║ą░ąĄčé čéą░ą╣ą╝ąĄčĆ. ą¤ąŠčüą╗ąĄą┤ąĮąĖą╝ čłą░ą│ąŠą╝ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čĆą░ą▒ąŠčéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÄ (Overflow interrupt).

ąĀąĖčü. 6. ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ Init, ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖ Timer1 ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ čĆąĄąČąĖą╝ąĄ Fast PWM.

;--------------------------------------------------------

; main.asm

;

; ą×ą┐ąĖčüą░ąĮąĖąĄ: ą┐čĆąĖą╝ąĄčĆ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ fast PWM ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ

; ATtiny26 ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

;---------------------------------------------------------

.include "tn26def.inc"

;ąØą░čćą░ą╗ąŠ čéą░ą▒ą╗ąĖčåčŗ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąÆąĄą║č鹊čĆ čüą▒čĆąŠčüą░:

rjmp init

; ąÆąĄą║č鹊čĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ timer1 output compare match A:

.org OC1Aaddr

rjmp OC1A_isr

;ą×čüąĮąŠą▓ąĮąŠą╣ ą║ąŠą┤:

init:

ldi r16, RAMEND ; ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ čāą║ą░ąĘą░č鹥ą╗čÅ čüč鹥ą║ą░

out SP, r16

ldi r16, 0x10 ; ąŚą░ą│čĆčāąĘą║ą░ ą▒ą░ą╣čéą░ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ ą│ąĄąĮąĄčĆą░č鹊čĆą░

out EEAR, r16

ldi r16, (1 << EERE)

out EECR, r16

in r16, EEDR

out OSCCAL, r16

ldi r16, (1 << PB1) ; ąØą░čüčéčĆąŠą╣ą║ą░ PB1 ą║ą░ą║ ą▓čŗčģąŠą┤ą░

out DDRB, r16

ldi r16, (1 << PLLE) ; ąĀą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā PLL

out PLLCSR, r16

waitPLL:

in r16, PLLCSR ; ą×ąČąĖą┤ą░ąĮąĖąĄ ąĘą░čģą▓ą░čéą░ PLL (ą┐čĆąĖą╝ąĄčĆąĮąŠ 100 ą╝čü)

sbrs r16, PLOCK

rjmp waitPLL

in r16, PLLCSR ; ąŻčüčéą░ąĮąŠą▓ą║ą░ PLL ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░

ldi r17, (1 << PCKE) ; čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ PWM

or r16, r17

out PLLCSR, r16

ldi r16, (1 << COM1A0) | (1 << PWM1A) ; ąŻčüčéą░ąĮąŠą▓ą║ą░ čĆąĄąČąĖą╝ą░ PWM:

; ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ OC1A ą┐čĆąĖ čüčĆą░ą▓ąĮąĄąĮąĖąĖ

out TCCR1A, r16 ; ąĀą░ąĘčĆąĄčłąĖčéčī PWM

ldi r16, 0xFF ; ąŻčüčéą░ąĮąŠą▓ą║ą░ ą┐ąĄčĆąĄą┤ąĄą╗ą░ čüč湥čéą░ ą┤ą╗čÅ PWM: OCR1C = 0xFF

out OCR1C, r16

ldi r16, (1 << CS11) | (1 << CS10) | (1 << CTC1)

out TCCR1B, r16 ; ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ PWM

; č湥čĆąĄąĘ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ čü čćą░čüč鹊č鹊ą╣ CK/4 (16 ą£ąōčå)

ldi r16, (1 << OCIE1A) ; ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ Timer1 OVF

out TIMSK, r16

clr r17

clr r18

sei ; ąĀą░ąĘčĆąĄčłąĖčéčī ą│ą╗ąŠą▒ą░ą╗čīąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ

ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Interrupt Service Routine, ISR). ąÜąŠą│ą┤ą░ čüč湥čéčćąĖą║ čéą░ą╣ą╝ąĄčĆą░ ą┤ąŠčüčéąĖą│ą░ąĄčé čüą▓ąŠąĄą│ąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą│ąŠ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ OCR1C (0xFF), ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÄ (Timer1 Overflow ISR). ąŁč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé č湥čĆąĄąĘ ą┐ąŠčüč鹊čÅąĮąĮčŗąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ, ą┐ąŠč鹊ą╝čā čćč鹊 OCR1C ąĮąĄ ą╝ąĄąĮčÅąĄčéčüčÅ. ąŁč鹊čé ąĖąĮč鹥čĆą▓ą░ą╗ čÅą▓ą╗čÅąĄčéčüčÅ ą┐ąĄčĆąĖąŠą┤ąŠą╝ ą▒ą░ąĘąŠą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ fast PWM.

ąÆ ą║ąŠą┤ąĄ Timer1 Overflow ISR ą┤ąĄą╗ą░ąĄčéčüčÅ ą┐čĆąŠčüą╝ąŠčéčĆ čéą░ą▒ą╗ąĖčåčŗ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąĪ ą║ą░ąČą┤čŗą╝ ą┐čĆąŠčüą╝ąŠčéčĆąŠą╝ ąĖąĮą┤ąĄą║čü čéą░ą▒ą╗ąĖčåčŗ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ ąĮą░ 1, čéą░ą║ čćč鹊 ą▒čāą┤ąĄčé ą▓ąĘčÅč鹊 ąĖąĘ čéą░ą▒ą╗ąĖčåčŗ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ. ąŚąĮą░č湥ąĮąĖąĄ ąĖąĘ čéą░ą▒ą╗ąĖčåčŗ čüąĖąĮčāčüą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ OCR1A. ąóą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ čłąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ PWM ą╝ąŠą┤čāą╗ąĖčĆčāąĄčéčüčÅ ą┐ąŠ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą╝čā ąĘą░ą║ąŠąĮčā. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čĆąĄą│ąĖčüčéčĆ OCR1A ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮ, ąĖ čäąĖą║čüą░čåąĖčÅ ą▒čāč乥čĆą░ ą▓ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ OCR1A ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐čĆąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ čéą░ą╣ą╝ąĄčĆą░.

ąÆčŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ąĮąĖą╝ą░ąĄčé 13 čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ąŠą▓ čÅą┤čĆą░. ąÆčŗąĘąŠą▓ ąĖ ą▓ąŠąĘą▓čĆą░čé ą┤ąŠą▒ą░ą▓ą╗čÅčÄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ, ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą▓čüąĄą│ąŠ 21 čéą░ą║čé čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ čÅą┤čĆą░. ą¤ąŠčüą║ąŠą╗čīą║čā Timer1 8-čĆą░ąĘčĆčÅą┤ąĮčŗą╣, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą║ą░ąČą┤čŗą╣ 256/(PWM_clock/system_clock) čåąĖą║ą╗. ą¤čĆąĖą╝ąĄčĆ čĆą░čüčüčćąĖčéą░ąĮ ąĮą░ čĆą░ą▒ąŠčéčā ąŠčé čćą░čüč鹊čéčŗ 8 ą£ąōčå ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ RC-ą│ąĄąĮąĄčĆą░č鹊čĆą░. ąĢčüą╗ąĖ ą▓čŗą▒čĆą░čéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ čćą░čüč鹊čé čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ PWM 64 ą£ąōčå, č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Timer1 Overflow ą▒čāą┤ąĄčé ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī ą║ą░ąČą┤čŗąĄ 32 čåąĖą║ą╗ą░ čÅą┤čĆą░.

ąźąŠčéčÅ ą╝ąŠąČąĮąŠ ąĘą░ą┐čāčüčéąĖčéčī PWM čü ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊č鹊ą╣ 64 ą£ąōčå, ą▓ čŹč鹊ą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ ą▓čŗą▒čĆą░ąĮą░ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ PWM, ą┐ąŠą┤ąĄą╗ąĄąĮąĮą░čÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆąŠą╝ ąĮą░ 4, čé. ąĄ. 16 ą£ąōčå - ą┤ą╗čÅ ąĖą╗ą╗čÄčüčéčĆą░čåąĖąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░.

ąĀąĖčü. 7. ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ Timer1.

OC1A_isr:

ldi ZH, high(sine_table*2) ; ąŻčüčéą░ąĮąŠą▓ą║ą░ Z ąĮą░ ąĮą░čćą░ą╗ąŠ čéą░ą▒ą╗ąĖčåčŗ

ldi ZL, low(sine_table*2) ; čüąĖąĮčāčüą░ sine_table

add ZL, r17 ; ąöąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄ čüą╝ąĄčēąĄąĮąĖčÅ ą║ Z ąĖąĘ r18:r17

adc ZH, r18

lpm ; ąŚą░ą│čĆčāąĘą║ą░ ąĘąĮą░č湥ąĮąĖčÅ ąĖąĘ sine_table ą▓ OCR1A

out OCR1A, r0

inc r17

reti

sine_table:

.db 128,131,134,137,140,144,147,150,153,156,159,162,165,168,171,174

.db 177,179,182,185,188,191,193,196,199,201,204,206,209,211,213,216

.db 218,220,222,224,226,228,230,232,234,235,237,239,240,241,243,244

.db 245,246,248,249,250,250,251,252,253,253,254,254,254,254,254,254

.db 254,254,254,254,254,254,254,253,253,252,251,250,250,249,248,246

.db 245,244,243,241,240,239,237,235,234,232,230,228,226,224,222,220

.db 218,216,213,211,209,206,204,201,199,196,193,191,188,185,182,179

.db 177,174,171,168,165,162,159,156,153,150,147,144,140,137,134,131

.db 128,125,122,119,116,112,109,106,103,100,97,94,91,88,85,82

.db 79,77,74,71,68,65,63,60,57,55,52,50,47,45,43,40

.db 38,36,34,32,30,28,26,24,22,21,19,17,16,15,13,12

.db 11,10,8,7,6,6,5,4,3,3,2,2,2,1,1,1

.db 1,1,1,1,2,2,2,3,3,4,5,6,6,7,8,10

.db 11,12,13,15,16,17,19,21,22,24,26,28,30,32,34,36

.db 38,40,43,45,47,50,52,55,57,60,63,65,68,71,74,77

.db 79,82,85,88,91,94,97,100,103,106,109,112,116,119,122,125

ą×ąČąĖą┤ą░ąĮąĖąĄ (Idle). ąĀąĄąČąĖą╝ čüąĮą░ (sleep mode) Idle ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą▓ąŠą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čĆąĄąČąĖą╝ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠąČąĖą┤ą░ąĮąĖąĄ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ą¤ąŠčüą╗ąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüąĮąŠą▓ą░ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ čüąĮą░.

idle:

ldi r16, (1 << SE) ; ąĀą░ąĘčĆąĄčłąĖčéčī ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ čüąĮą░

out MCUCR, r16

sleep

rjmp idle

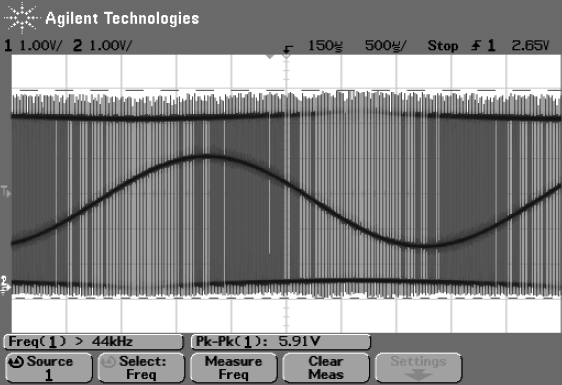

ą×čüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝čŗ. ąØą░ čüą║čĆąĖąĮčłąŠčéą░čģ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą┐čĆąĖą╝ąĄčĆčŗ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, č乊čĆą╝ąĖčĆčāąĄą╝ąŠą│ąŠ PWM ąĮą░ ATtiny26. ą×čüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝čŗ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą▓čŗą▓ąŠą┤ą░ OC1A, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčé čłąĖčĆąŠčéąĮąŠ-ąĖą╝ą┐čāą╗čīčüąĮčŗą╣ ą╝ąŠą┤čāą╗ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗, ąĖ ą▓ą╝ąĄčüč鹥 čü ąĮąĖą╝ ąŠčéčäąĖą╗čīčéčĆąŠą▓ą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ PWM. ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąŠčüč鹊ą╣ RC-čäąĖą╗čīčéčĆ ą┤ą╗čÅ čüą│ą╗ą░ąČąĖą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ PWM ąĖ ą┐čĆąĄą▓čĆą░čēąĄąĮąĖčÅ ąĄą│ąŠ ą▓ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ ŌĆō ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗, čā ą║ąŠč鹊čĆąŠą│ąŠ ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ ąĘą░ą▓ąĖčüąĖčé ąŠčé čüą║ą▓ą░ąČąĮąŠčüčéąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ PWM. ąÆ RC-čäąĖą╗čīčéčĆčŗ čüč鹊čÅčé ąĮąŠą╝ąĖąĮą░ą╗čŗ R = 10 ą║ą×ą╝ C = 100 nF, ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 č湥ą│ąŠ čćą░čüč鹊čéą░ čüčĆąĄąĘą░ čäąĖą╗čīčéčĆą░ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ 1 ą║ąōčå, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĮąĖąĘą║ąŠą╣ čćą░čüč鹊č鹥 čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąŠčģąŠą┤ąĖčéčī č湥čĆąĄąĘ čäąĖą╗čīčéčĆ, ą┐čĆąĖ čŹč鹊ą╝ čāčüą┐ąĄčłąĮąŠ ą┐ąŠą┤ą░ą▓ą╗čÅąĄčéčüčÅ ą▓čŗčüąŠą║ą░čÅ ą▒ą░ąĘąŠą▓ą░čÅ čćą░čüč鹊čéą░ PWM.

ąĀąĖčü. 8. ąÆčŗčģąŠą┤ OC1A ŌĆō čäąĖą╗čīčéčĆąŠą▓ą░ąĮąĮčŗą╣ ąĖ ą▒ąĄąĘ čäąĖą╗čīčéčĆą░.

ąĀąĖčü. 9. ąÆčŗčģąŠą┤ OC1A ŌĆō čäąĖą╗čīčéčĆąŠą▓ą░ąĮąĮčŗą╣ ąĖ ą▒ąĄąĘ čäąĖą╗čīčéčĆą░ (čü čĆą░čüčéčÅąČą║ąŠą╣ ą┐ąŠ ąŠčüąĖ ą▓čĆąĄą╝ąĄąĮąĖ).

[ąĪčüčŗą╗ą║ąĖ]

1. AVR131: Using the AVRŌĆÖs High-speed PWM site:atmel.com. |