|

ąÉą┐ą┐ą░čĆą░čéąĮčŗą╣ ą▒ą╗ąŠą║ 16-čĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ 1 (ą┤ą░ą╗ąĄąĄ ą┤ą╗čÅ čüąŠą║čĆą░čēąĄąĮąĖčÅ TC1) ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ č鹊čćąĮąŠ čĆą░ą▒ąŠčéą░čéčī ą▓ čĆąĄą░ą╗čīąĮąŠą╝ ą▓čĆąĄą╝ąĄąĮąĖ (ąŠčéčüą╗ąĄąČąĖą▓ą░čéčī čüąŠą▒čŗčéąĖčÅ), ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĘą▓čāą║ ąĖ ąĖąĘą╝ąĄčĆčÅčéčī ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĖą╝ą┐čāą╗čīčüąŠą▓.

ą×čüąĮąŠą▓ąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ TC1:

ŌĆó ą¦ąĄčüčéąĮčŗą╣ 16-ą▒ąĖčéąĮčŗą╣ ą┤ąĖąĘą░ą╣ąĮ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ąŠąĮ ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą░ą┐ą┐ą░čĆą░čéąĮąŠ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī 16-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ą©ąśą£).

ŌĆó ąöą▓ą░ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ čāąĘą╗ą░ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (Output Compare Units).

ŌĆó ąĀąĄą│ąĖčüčéčĆčŗ čüčĆą░ą▓ąĮąĄąĮąĖčÅ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣ (Double Buffered Output Compare Registers).

ŌĆó ą×ą┤ąĖąĮ čāąĘąĄą╗ ąĘą░čģą▓ą░čéą░ ą┐ąŠ ą▓čģąŠą┤čā (Input Capture Unit).

ŌĆó ąæą╗ąŠą║ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ čłčāą╝ą░ ąĮą░ ą▓čģąŠą┤ąĄ ąĘą░čģą▓ą░čéą░ (Input Capture Noise Canceler).

ŌĆó ąÉą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖą╣ čüą▒čĆąŠčü čéą░ą╣ą╝ąĄčĆą░ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ ąĘą░čģą▓ą░čéą░, Clear Timer on Compare Match (Auto Reload, ą░ą▓č鹊ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ą░).

ŌĆó ą£ąŠą┤čāą╗čÅč鹊čĆ ą©ąśą£ ą▒ąĄąĘ ą┤čĆąŠąČą░ąĮąĖčÅ čäčĆąŠąĮč鹊ą▓, čü ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ čäą░ąĘąŠą╣ (Glitch-free, Phase Correct Pulse Width Modulator, PWM).

ŌĆó ąśąĘą╝ąĄąĮčÅąĄą╝čŗą╣ ą┐ąĄčĆąĖąŠą┤ ą©ąśą£.

ŌĆó ąōąĄąĮąĄčĆą░č鹊čĆ čćą░čüč鹊čé.

ŌĆó ąĪč湥čéčćąĖą║ ą▓ąĮąĄčłąĮąĖčģ čüąŠą▒čŗčéąĖą╣ (External Event Counter).

ŌĆó 4 ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (TOV1, OCF1A, OCF1B ąĖ ICF1).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ čŹč鹊ą╝ ąŠą┐ąĖčüą░ąĮąĖąĖ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ ąĖą╝ąĄąĮ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ą▒ąĖčé ąĮą░ą┐ąĖčüą░ąĮčŗ ą▓ ąŠą▒čēąĄą╣ č乊čĆą╝ąĄ. ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ ą╝ąĄčüčéą░čģ n ą▓ ąĮąĖąČąĮąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ ąĘą░ą╝ąĄąĮčÅąĄčéčüčÅ ąĮąŠą╝ąĄčĆąŠą╝ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░. ąÆ čćą░čüčéąĮąŠčüčéąĖ, ą▓ čŹč鹊ą╝ č鹥ą║čüč鹥 n ą┐ąŠčćčéąĖ ą▓čüąĄą│ą┤ą░ ąĘą░ą╝ąĄąĮčÅąĄčéčüčÅ ąĮą░ 1, čćč鹊 ąŠąĘąĮą░čćą░ąĄčé Timer/Counter 1, ąĖą╗ąĖ TC1 (ą▓ąŠ ą▓čĆąĄąĘą║ąĄ ą┐čĆąŠ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ą▒čāą║ą▓ą░ n ąŠčüčéą░ą▓ą╗ąĄąĮą░, ą┐ąŠč鹊ą╝čā čćč鹊 ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą┐ąŠ ą┐čĆąĄčüą║ą░ą╗ąĄčĆčā ąŠčéąĮąŠčüąĖčéčüčÅ ą║ ąŠą▒ąŠąĖą╝ čéą░ą╣ą╝ąĄčĆą░ą╝ 0 ąĖ 1, ą┐ąŠčŹč鹊ą╝čā ą▒čāą║ą▓ą░ n ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą╝ąĄąĮąĄąĮą░ ąĮą░ 0 ąĖą╗ąĖ 1). ąæčāą║ą▓ą░ x ą▓ ąĮąĖąČąĮąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ čćą░čüč鹊 ąĘą░ą╝ąĄąĮčÅąĄčé ąŠą▒ąŠąĘąĮą░č湥ąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ Output Compare. ą×ą┤ąĮą░ą║ąŠ ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ąĖą╝ąĄąĮ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ą▒ąĖčé ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ čüą╗ąĄą┤čāąĄčé ą┐čĆąĖą▓ąŠą┤ąĖčéčī ą┐ąŠą╗ąĮąŠąĄ ąĖą╝čÅ, ąĮą░ą┐čĆąĖą╝ąĄčĆ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ąĘąĮą░č湥ąĮąĖčÄ čüč湥čéčćąĖą║ą░ TC1 čüą╗ąĄą┤čāąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĖą╝čÅ čĆąĄą│ąĖčüčéčĆą░ TCNT1, ąĖ čé. ą┐.

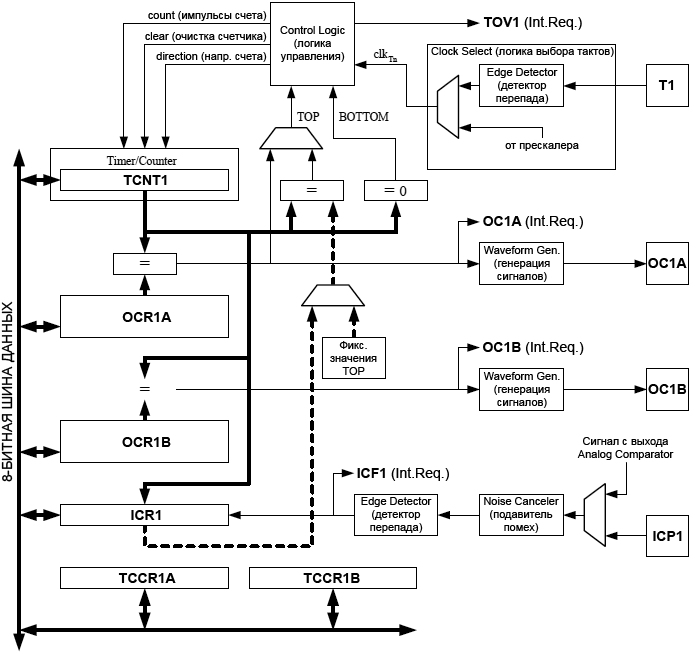

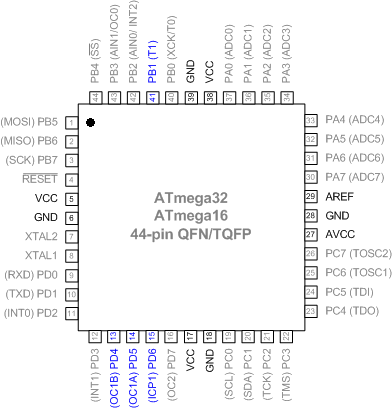

ąŻą┐čĆąŠčēąĄąĮąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ TC1 ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčüčāąĮą║ąĄ 19-1. ąĀąĄą░ą╗čīąĮąŠąĄ čĆą░ąĘą╝ąĄčēąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ ąĮą░ ą▓ąĮąĄčłąĮąĖčģ ą▓čŗą▓ąŠą┤ą░čģ čüą╝. ą▓ąŠ ą▓čĆąĄąĘą║ąĄ ąĮąĖąČąĄ. ąóą░ą║ąČąĄ čüą╝. čĆą░ąĘą┤ąĄą╗čŗ ą┤ą░čéą░čłąĖčéą░ [1]: "Pin Configurations", "Alternate Functions of Port B", "Alternate Functions of Port D".

ąĀąĖčü. 19-1. ąæą╗ąŠą║-čüčģąĄą╝ą░ 16-bit Timer/Counter 1.

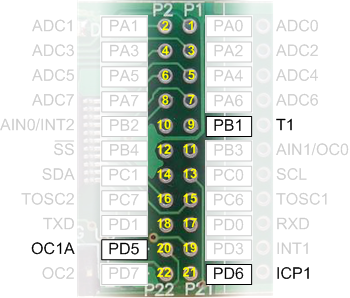

[ąÜąŠčĆą┐čāčü TQFP44]

[ąÆčŗą▓ąŠą┤čŗ ą╝ą░ą║ąĄčéąĮąŠą╣ ą┐ą╗ą░čéčŗ AVR-USB-MEGA16]

| ąÜąŠąĮčéą░ą║čé ą┐ą╗ą░čéčŗ |

ąśą╝čÅ ą┐ąŠčĆčéą░ |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣ |

| P9 |

PB1 |

T1 - čŹčéą░ ąĮąŠąČą║ą░ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ čéą░ą║č鹊ą▓čŗą╣ ą▓čģąŠą┤ ą┤ą╗čÅ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ 1 (Timer/Counter1 External Counter Input). ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čüčéą░čéčīčÄ [4]. |

| P20 |

PD5 |

OC1A - čüąĖą│ąĮą░ą╗ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ A čéą░ą╣ą╝ąĄčĆą░ 1 (Timer/Counter1 Output Compare A Match Output). |

| P21 |

PD6 |

ICP1, ą▓čģąŠą┤ ą┤ą╗čÅ ąĘą░čģą▓ą░čéą░ ą▓ąĮąĄčłąĮąĖčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ (Timer/Counter1 Input Capture Pin). ą£ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüč鹥ą╣ čüąĖą│ąĮą░ą╗ą░ čü ą┐ąŠą╝ąŠčēčīčÄ čéą░ą╣ą╝ąĄčĆą░ 1. |

ąØąŠąČą║ą░ PD4, ą║ ą║ąŠč鹊čĆąŠą╣ ą┐čĆąĖą▓čÅąĘą░ąĮ čüąĖą│ąĮą░ą╗ OC1B, ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮ ąĮą░ čüąĖą│ąĮą░ą╗ USB D-, ąĮąŠ ąĄą│ąŠ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī, ąĄčüą╗ąĖ USB ąĮąĄ ąĮčāąČąĄąĮ.

ąÆ čéą░ą▒ą╗ąĖčåą░čģ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ čäčāąĮą║čåąĖąĖ ąĮąŠąČąĄą║ ą┐ąŠčĆč鹊ą▓ GPIO, ą║ąŠč鹊čĆčŗąĄ ąĖą╝ąĄčÄčé ąŠčéąĮąŠčłąĄąĮąĖąĄ ą║ čĆą░ą▒ąŠč鹥 TC1.

[ą¤ąŠčĆčé PB]

| ą¤ąŠčĆčé |

ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ |

| PB1 |

T1, ą▓ąĮąĄčłąĮąĖą╣ ą▓čģąŠą┤ ą┤ą╗čÅ ą┐ąŠą┤ą░čćąĖ čéą░ą║č鹊ą▓ ąĮą░ čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ 1 (Timer/Counter1 External Counter Input). |

[ą¤ąŠčĆčéčŗ PD]

| ą¤ąŠčĆčé |

ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ |

| PD4 |

OC1B, ą▓čŗčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ ąŠ čüąŠą▒čŗčéąĖąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ 1 čü ąĘą░ą┤ą░ąĮąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ ą║ą░ąĮą░ą╗ą░ B (Timer/Counter1 Output Compare B Match Output). |

| PD5 |

OC1A, ą▓čŗčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ ąŠ čüąŠą▒čŗčéąĖąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ 1 čü ąĘą░ą┤ą░ąĮąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ ą║ą░ąĮą░ą╗ą░ A (Timer/Counter1 Output Compare A Match Output). |

| PD6 |

ICP1, ą▓čģąŠą┤ ąĘą░čģą▓ą░čéą░ ąĘąĮą░č湥ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ ą┐ąŠ ą▓ąĮąĄčłąĮąĄą╝čā čüąŠą▒čŗčéąĖčÄ (Timer/Counter1 Input Capture Pin). |

ą×čüąŠą▒ąĄąĮąĮąŠčüčéąĖ čĆąĄą│ąĖčüčéčĆąŠą▓. ąĀąĄą│ąĖčüčéčĆčŗ Timer/Counter (TCNT1), Output Compare Registers (OCR1A, OCR1B) ąĖ Input Capture Register (ICR1) čÅą▓ą╗čÅčÄčéčüčÅ 16-čĆą░ąĘčĆčÅą┤ąĮčŗą╝ąĖ. ą¤ąŠčŹč鹊ą╝čā ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ąĮąĖą╝ čüą╗ąĄą┤čāąĄčé ą┐čĆąĖą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą┐čĆąŠčåąĄą┤čāčĆčŗ (ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ AVR 8-čĆą░ąĘčĆčÅą┤ąĮčŗą╣). ąŁčéąĖ ą┐čĆąŠčåąĄą┤čāčĆčŗ ąŠą┐ąĖčüą░ąĮčŗ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ ą┤ą░čéą░čłąĖčéą░ "Accessing 16-bit Registers" (čéą░ą║ąČąĄ čüą╝. [2]). ąĀąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ TC1 (Timer/Counter Control Registers TCCR1A ąĖ TCCR1B) 8-čĆą░ąĘčĆčÅą┤ąĮčŗąĄ, čéą░ą║ čćč鹊 ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ąĮąĖą╝ čüąŠ čüč鹊čĆąŠąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ CPU ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ ąŠą│čĆą░ąĮąĖč湥ąĮąĖą╣. ąĪąĖą│ąĮą░ą╗čŗ ąĘą░ą┐čĆąŠčüąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Interrupt requests, čćč鹊 ąĮą░ čĆąĖčü. 19-1 ą┐ąŠą║ą░ąĘą░ąĮčŗ čüąŠą║čĆą░čēąĄąĮąĖčÅą╝ąĖ Int.Req.) ąŠč鹊ą▒čĆą░ąČą░čÄčéčüčÅ ąĮą░ čäą╗ą░ą│ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ Timer Interrupt Flag Register (TIFR). ąÆčüąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ TC1 ą╝ą░čüą║ąĖčĆčāčÄčéčüčÅ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ ą▓ ą▒ąĖčéą░ą╝ąĖ čĆąĄą│ąĖčüčéčĆą░ Timer Interrupt Mask Register (TIMSK). ąØą░ čĆąĖčüčāąĮą║ąĄ TIFR ąĖ TIMSK ąĮąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ, ą┐ąŠč鹊ą╝čā čćč鹊 čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ čéą░ą║ąČąĄ čüą▓čÅąĘą░ąĮčŗ ąĖ čü ą┤čĆčāą│ąĖą╝ąĖ čéą░ą╣ą╝ąĄčĆą░ą╝ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

TC1 ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćą░čéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄ, č湥čĆąĄąĘ ą┤ąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ (prescaler), ąĖą╗ąĖ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ T1. ąøąŠą│ąĖą║ą░ ą▓čŗą▒ąŠčĆą░ čéą░ą║č鹊ą▓ (Clock Select) čāą┐čĆą░ą▓ą╗čÅąĄčé, ą║ą░ą║ąŠą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓, ąĖ ą║ą░ą║ąŠą╣ ąĄą│ąŠ ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ (ąĖą╗ąĖ ą┤ąĄą║čĆąĄą╝ąĄąĮčéą░) ąĘąĮą░č湥ąĮąĖčÅ čüč湥čéčćąĖą║ą░ TC1. ąĪč湥čéčćąĖą║ ąĮąĄ ą░ą║čéąĖą▓ąĄąĮ, ą║ąŠą│ą┤ą░ ąĮąĄ ą▓čŗą▒čĆą░ąĮ ąĖčüč鹊čćąĮąĖą║ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ąÆčŗčģąŠą┤ ą╗ąŠą│ąĖą║ąĖ ą▓čŗą▒ąŠčĆą░ čéą░ą║č鹊ą▓ ąŠą▒ąŠąĘąĮą░čćą░ąĄčéčüčÅ ą║ą░ą║ čéą░ą║čéčŗ čéą░ą╣ą╝ąĄčĆą░ TC1 (čüąĖą│ąĮą░ą╗ clkT1).

ąĀąĄą│ąĖčüčéčĆčŗ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣ (Output Compare Registers, OCR1A, OCR1B) ą┐ąŠčüč鹊čÅąĮąĮąŠ čüčĆą░ą▓ąĮąĖą▓ą░čÄčéčüčÅ čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ čüč湥čéčćąĖą║ą░ TC1 (čĆąĄą│ąĖčüčéčĆ Timer/Counter, TCNT1). ąĀąĄąĘčāą╗čīčéą░čé čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ ą©ąśą£ ąĖą╗ąĖ ą┤ą╗čÅ ąĖąĘą╝ąĄąĮčÅąĄą╝ąŠą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ ąĮą░ ąĮąŠąČą║ą░čģ Output Compare Pin (OC1A, OC1B), ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. "ąŻąĘą╗čŗ Output Compare" ąĮąĖąČąĄ. ą¤čĆąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄ Compare Match, ą║ąŠč鹊čĆąŠąĄ čāčüčéą░ąĮąŠą▓ąĖčé čäą╗ą░ą│ Compare Match Flag (OCF1A, OCF1B), ąĖ čŹč鹊 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĘą░ą┐čĆąŠčüą░ ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Output Compare.

ąĀąĄą│ąĖčüčéčĆ ąĘą░čģą▓ą░čéą░ (Input Capture Register, ICR1) ą╝ąŠąČąĄčé ąĘą░čģą▓ą░čéčŗą▓ą░čéčī ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (TCNT1) ą┐ąŠ ą▓ąĮąĄčłąĮąĄą╝čā čüąŠą▒čŗčéąĖčÄ, ą║ąŠč鹊čĆąŠąĄ ą▓ąŠąĘąĮąĖą║ą░ąĄčé (čŹč鹊 ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ) ą╗ąĖą▒ąŠ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ Input Capture Pin (ICP1), ąĖą╗ąĖ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ Analog Comparator (čüą╝. čĆą░ąĘą┤ąĄą╗ "Analog Comparator" ą┤ą░čéą░čłąĖčéą░ [1]). ąØą░ ą▓čģąŠą┤ąĄ ą▒ą╗ąŠą║ą░ Input Capture ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ čåąĖčäčĆąŠą▓ąŠą╣ čāąĘąĄą╗ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠą╝ąĄčģ (Noise Canceler), čćč鹊ą▒čŗ čüąĮąĖąĘąĖčéčī čłą░ąĮčüčŗ čüą╗čāčćą░ą╣ąĮąŠą│ąŠ ąĘą░čģą▓ą░čéą░ ą║ąŠčĆąŠčéą║ąĖčģ ąĖą╝ą┐čāą╗čīčüąŠą▓.

ąŚąĮą░č湥ąĮąĖąĄ TOP, ąĖą╗ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░, ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ čĆąĄąČąĖą╝ą░čģ čĆą░ą▒ąŠčéčŗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą╗ąĖą▒ąŠ čĆąĄą│ąĖčüčéčĆąŠą╝ OCR1A, ą╗ąĖą▒ąŠ čĆąĄą│ąĖčüčéčĆąŠą╝ ICR1, ą╗ąĖą▒ąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ ąŠą┤ąĮąŠ ąĖąĘ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ (čüą╝. čéą░ą▒ą╗ąĖčåčā 19-1). ąÜąŠą│ą┤ą░ ą▓ čĆąĄąČąĖą╝ąĄ ą©ąśą£ (PWM) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ OCR1A ą▓ ą║ą░č湥čüčéą▓ąĄ ąĘąĮą░č湥ąĮąĖčÅ TOP, čĆąĄą│ąĖčüčéčĆ OCR1A ąĮąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▓čŗčģąŠą┤ą░ ą©ąśą£. ą×ą┤ąĮą░ą║ąŠ ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĘąĮą░č湥ąĮąĖąĄ TOP ą┐ąŠą╗čāčćąĖčé ą┤ą▓ąŠą╣ąĮčāčÄ ą▒čāč乥čĆąĖąĘą░čåąĖčÄ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą╝ąĄąĮčÅčéčī ąĘąĮą░č湥ąĮąĖąĄ TOP ą▓ čĆąĄąČąĖą╝ąĄ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (run time). ąĢčüą╗ąĖ čéčĆąĄą▒čāąĄčéčüčÅ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ TOP, čĆąĄą│ąĖčüčéčĆ ICR1 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ą░, ąŠčüą▓ąŠą▒ąŠąČą┤ą░čÅ OCR1A ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓čŗčģąŠą┤ą░ ą©ąśą£.

ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ. ąÆ čŹč鹊ą╝ ąŠą┐ąĖčüą░ąĮąĖąĖ čćą░čüč鹊 ą▒čāą┤čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ:

ąóą░ą▒ą╗ąĖčåą░ 19-1. ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą║ąŠąĮčüčéą░ąĮčé.

| BOTTOM |

ąĪč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ BOTTOM, ą║ąŠą│ą┤ą░ ąŠąĮ čüčéą░ąĮąŠą▓ąĖčéčüčÅ čĆą░ą▓ąĮčŗą╝ 0x0000. |

| MAX |

ąĪč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ MAX, ą║ąŠą│ą┤ą░ ąŠąĮ čüčéą░ąĮąŠą▓ąĖčéčüčÅ čĆą░ą▓ąĮčŗą╝ 0xFFFF (ą▓ ą┤ąĄčüčÅčéąĖčćąĮąŠą╣ č乊čĆą╝ąĄ 65535). |

| TOP |

ąĪč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé TOP, ą║ąŠą│ą┤ą░ ąŠąĮ čüčéą░ąĮąŠą▓ąĖčéčüčÅ čĆą░ą▓ąĮčŗą╝ čüą░ą╝ąŠą╝čā ą▒ąŠą╗čīčłąŠą╝čā ąĘąĮą░č湥ąĮąĖčÄ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čüč湥čéą░. ąŚąĮą░č湥ąĮąĖąĄ TOP ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░ąĘąĮą░č湥ąĮąŠ ą▓ ąŠą┤ąĮąŠ ąĖąĘ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣: 0x00FF, 0x01FF ąĖą╗ąĖ 0x03FF, ąĖą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ TOP ą╝ąŠąČąĄčé ą▒čŗčéčī čüąŠčģčĆą░ąĮąĄąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆąĄ OCR1A ąĖą╗ąĖ ICR1. ą¤čĆąĖčüą▓ą░ąĖą▓ą░ąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ TOP ąĘą░ą▓ąĖčüąĖčé ąŠčé čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ. |

ąĪąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī. 16-bit Timer/Counter ą▒čŗą╗ ąŠą▒ąĮąŠą▓ą╗ąĄąĮ ąĖ čāą╗čāčćčłąĄąĮ ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü ą┐čĆąĄą┤čŗą┤čāčēąĖą╝ąĖ ą▓ąĄčĆčüąĖčÅą╝ąĖ 16-bit AVR Timer/Counter. ąĪąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī ą┐ąŠą╗ąĮąŠčüčéčīčÄ čüąŠą▒ą╗čÄą┤ą░ąĄčéčüčÅ ą▓ ą║ąŠąĮč鹥ą║čüč鹥 čüą╗ąĄą┤čāčÄčēąĄą│ąŠ:

ŌĆó ąÆčüąĄ čĆąĄą│ąĖčüčéčĆčŗ 16-bit Timer/Counter ąŠčéąĮąŠčüčÅčéčüčÅ ą║ ą░ą┤čĆąĄčüąĮąŠą╝čā ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓čā čĆąĄą│ąĖčüčéčĆąŠą▓ I/O, ą▓ą║ą╗čÄčćą░čÅ čĆąĄą│ąĖčüčéčĆčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čéą░ą╣ą╝ąĄčĆą░ (Timer Interrupt Registers).

ŌĆó ą¤ąŠą╗ąŠąČąĄąĮąĖąĄ ą▒ąĖčé ą▓ąĮčāčéčĆąĖ ą▓čüąĄčģ čĆąĄą│ąĖčüčéčĆąŠą▓ 16-bit Timer/Counter, ą▓ą║ą╗čÄčćą░čÅ čĆąĄą│ąĖčüčéčĆčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čéą░ą╣ą╝ąĄčĆą░.

ŌĆó ąÆąĄą║č鹊čĆčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąŻ čüą╗ąĄą┤čāčÄčēąĖčģ ą▒ąĖčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠą╝ąĄąĮčÅą╗ąĖčüčī ąĖą╝ąĄąĮą░, ąŠą┤ąĮą░ą║ąŠ čā ąĮąĖčģ čüąŠčģčĆą░ąĮąĖą╗čüčÅ čäčāąĮą║čåąĖąŠąĮą░ą╗ ąĖ čĆą░ąĘą╝ąĄčēąĄąĮąĖąĄ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ:

ŌĆó ąśą╝čÅ PWM10 ąĖąĘą╝ąĄąĮąĄąĮąŠ ąĮą░ WGM10.

ŌĆó PWM11 ąĖąĘą╝ąĄąĮąĄąĮąŠ ąĮą░ WGM11.

ŌĆó CTC1 ąĖąĘą╝ąĄąĮąĄąĮąŠ ąĮą░ WGM12.

ąöąŠą▒ą░ą▓ą╗ąĄąĮčŗ čüą╗ąĄą┤čāčÄčēąĖąĄ ą▒ąĖčéčŗ ą▓ čĆąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ:

ŌĆó FOC1A ąĖ FOC1B ą┤ąŠą▒ą░ą▓ą╗ąĄąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ TCCR1A.

ŌĆó WGM13 ą┤ąŠą▒ą░ą▓ą╗ąĄąĮ ą▓ čĆąĄą│ąĖčüčéčĆ TCCR1B.

16-bit Timer/Counter ąĖą╝ąĄąĄčé čāą╗čāčćčłąĄąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ čüą╗čāčćą░čÅčģ ą▓ą╗ąĖčÅčÄčé ąĮą░ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī.

[ąśčüč鹊čćąĮąĖą║ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ]

ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, TC1 ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćą░čéčī čéą░ą║čéčŗ ą╗ąĖą▒ąŠ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ, ą╗ąĖą▒ąŠ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░. ąøąŠą│ąĖą║ą░ ą▓čŗą▒ąŠčĆą░ čéą░ą║č鹊ą▓ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ CS12..CS10, ą║ąŠč鹊čĆčŗąĄ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ Timer/Counter Control Register B (TCCR1B). ą¦ą░čüč鹊čéą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ąĄą╗ąĄąĮą░ ą┐čĆąĄčüą║ą░ą╗ąĄčĆąŠą╝, čüą╝. ą▓čĆąĄąĘą║čā ąĮąĖąČąĄ.

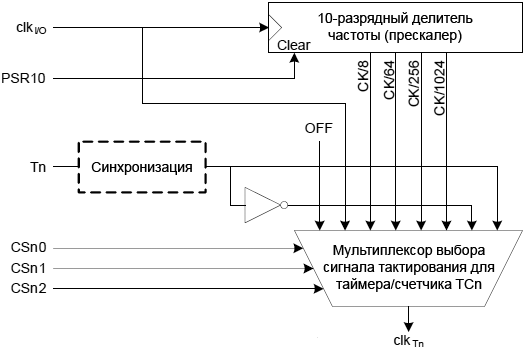

ąóą░ą╣ą╝ąĄčĆčŗ Timer/Counter1 ąĖ Timer/Counter0 (TC1 ąĖ TC0) ąĖą╝ąĄčÄčé ąŠą▒čēąĖą╣ ą╝ąŠą┤čāą╗čī ą┤ąĄą╗ąĖč鹥ą╗čÅ (prescaler module), ąŠą┤ąĮą░ą║ąŠ čŹčéąĖ čéą░ą╣ą╝ąĄčĆčŗ/čüč湥čéčćąĖą║ąĖ ą╝ąŠą│čāčé ąĖą╝ąĄčéčī čĆą░ąĘąĮčŗąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ. ą×ą┐ąĖčüą░ąĮąĖąĄ ąĮąĖąČąĄ ą┐čĆąĖą╝ąĄąĮąĖą╝ąŠ ą║ ąŠą▒ąŠąĖą╝ čéą░ą╣ą╝ąĄčĆą░ą╝/čüč湥čéčćąĖą║ą░ą╝ TC1 ąĖ TC0.

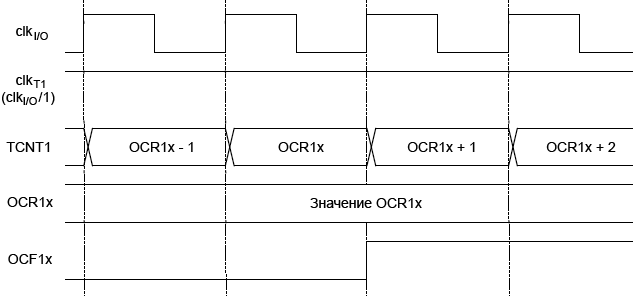

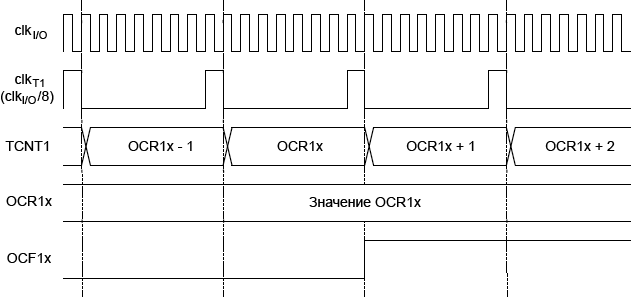

ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓. ąóą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ ą╝ąŠąČąĄčé čéą░ą║čéąĖčĆąŠą▓ą░čéčīčüčÅ ąĮą░ą┐čĆčÅą╝čāčÄ ąŠčé čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ CSn2:0 = 1). ąŁč鹊 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą░ą╝čŗą╣ ą▒čŗčüčéčĆčŗą╣ čüč湥čé, ą┐ąŠčüą║ąŠą╗čīą║čā čüč湥čéčćąĖą║ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čćą░čüč鹊č鹥 čÅą┤čĆą░ ąĖ ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (fCLK_I/O). ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ąŠą┤ąĖąĮ ąĖąĘ ą▓čŗčģąŠą┤ąŠą▓ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░, ą│ą┤ąĄ čćą░čüč鹊čéą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą╗ąĖą▒ąŠ fCLK_I/O/8, fCLK_I/O/64, fCLK_I/O/256 ąĖą╗ąĖ fCLK_I/O/1024.

ąĪą▒čĆąŠčü ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░. ą¤čĆąĄčüą║ą░ą╗ąĄčĆ ą▓čüąĄą│ą┤ą░ čĆą░ą▒ąŠčéą░ąĄčé (čé. ąĄ. ąĄą│ąŠ čĆą░ą▒ąŠčéą░ ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą╗ąŠą│ąĖą║ąĖ ą▓čŗą▒ąŠčĆą░ čéą░ą║č鹊ą▓ čéą░ą╣ą╝ąĄčĆąŠą▓/čüč湥čéčćąĖą║ąŠą▓), ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüąŠą▓ą╝ąĄčüčéąĮąŠ TC1 ąĖ TC0. ą¤ąŠčüą║ąŠą╗čīą║čā ąĮą░ čüą░ą╝ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ą╗ąŠą│ąĖą║ą░ ą▓čŗą▒ąŠčĆą░ čéą░ą║č鹊ą▓, ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĮąĄčÅą▓ąĮąŠ ą▓ą╗ąĖčÅąĄčé ąĮą░ čüąĖčéčāą░čåąĖąĖ, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čćą░čüč鹊čéčŗ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░. ą×ą┤ąĖąĮ ąĖąĘ ą┐čĆąĖą╝ąĄčĆąŠą▓ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖčÅ čéą░ą║ąĖčģ ą░čĆč鹥čäą░ą║č鹊ą▓, ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ ąĖ čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ (6 > CSn2:0 > 1). ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║č鹊ą▓ ąŠčé ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮ, ą┤ąŠ ą┐ąĄčĆą▓ąŠą│ąŠ ą╝ąŠą╝ąĄąĮčéą░ čüč湥čéą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1 ą┤ąŠ N+1 čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ąŠą▓, ą│ą┤ąĄ N čĆą░ą▓ąĮąŠ ą▓čŗą▒čĆą░ąĮąĮąŠą╝čā ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčā ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ (8, 64, 256 ąĖą╗ąĖ 1024).

ąĢčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čüą▒čĆąŠčüąĖčéčī ą┐čĆąĄčüą║ą░ą╗ąĄčĆ, čćč鹊ą▒čŗ ąĘą░čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčī čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ čü čģąŠą┤ąŠą╝ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. ą×ą┤ąĮą░ą║ąŠ ą┐čĆąĖ čŹč鹊ą╝ čüą╗ąĄą┤čāąĄčé ąĖą╝ąĄčéčī ą▓ ą▓ąĖą┤čā, čćč鹊 č鹊čé ąČąĄ čüą░ą╝čŗą╣ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąĖ ą┤čĆčāą│ąĖą╝ čéą░ą╣ą╝ąĄčĆąŠą╝/čüč湥čéčćąĖą║ąŠą╝. ąĪą▒čĆąŠčü ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ą┐ąŠą▓ą╗ąĖčÅąĄčé ąĮą░ ą┐ąĄčĆąĖąŠą┤ ą▓čüąĄčģ čéą░ą╣ą╝ąĄčĆąŠą▓/čüč湥čéčćąĖą║ąŠą▓, ą║ąŠč鹊čĆčŗąĄ ą║ ąĮąĄą╝čā ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ.

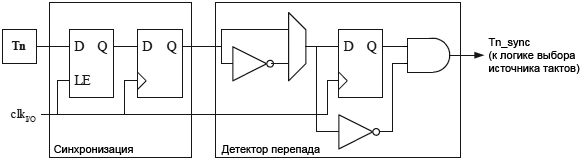

ąÆąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓. ąÆąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ ą▓čŗą▓ąŠą┤čā T1/T0, ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆąŠą▓/čüč湥čéčćąĖą║ąŠą▓ TC1 ąĖ TC0 (čüąĖą│ąĮą░ą╗čŗ clkT1 ąĖ clkT0). ąÆčŗą▓ąŠą┤ T1/T0 ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ čéą░ą║č鹥 čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą╗ąŠą│ąĖą║ąŠą╣ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓čŗą▓ąŠą┤ą░. ąĪąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗą╣ (ąŠčåąĖčäčĆąŠą▓ą░ąĮąĮčŗą╣) ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĮą░ ą┤ąĄč鹥ą║č鹊čĆ ą┐ąĄčĆąĄą┐ą░ą┤ą░. ąØą░ čĆąĖčü. 18-1 ą┐ąŠą║ą░ąĘą░ąĮą░ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ ą╗ąŠą│ąĖą║ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ąĖ ą┤ąĄč鹥ą║č鹊čĆą░ ą┐ąĄčĆąĄą┐ą░ą┤ą░ T1/T0. ąĀąĄą│ąĖčüčéčĆčŗ čéą░ą║čéąĖčĆčāčÄčéčüčÅ ą┐ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ (clkI/O). ąŚą░čēąĄą╗ą║ą░ ą┐čĆąŠąĘčĆą░čćąĮą░ ą▓ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ ą╗ąŠą│. 1 čüąĖą│ąĮą░ą╗ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║č鹊ą▓.

ąöąĄč鹥ą║č鹊čĆ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĖą╝ą┐čāą╗čīčü clkT1/clkT0 ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ (CSn2:0 = 7) ąĖą╗ąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ (CSn2:0 = 6) ą┐ąĄčĆąĄą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ, ą║ąŠč鹊čĆčŗą╣ ąŠąĮ ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗.

ąĀąĖčü. 18-1. ąøąŠą│ąĖą║ą░ ąŠčåąĖčäčĆąŠą▓ą║ąĖ (ą▓čŗą▒ąŠčĆą║ąĖ čāčĆąŠą▓ąĮčÅ) ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ T1/T0.

ąøąŠą│ąĖą║ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ąĖ ą┤ąĄč鹥ą║č鹊čĆą░ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą▓ą▓ąŠą┤ąĖčé ąĘą░ą┤ąĄčƹȹ║čā ąŠčé 2.5 ą┤ąŠ 3.5 čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║čéą░ ą╝ąĄąČą┤čā čüąĖą│ąĮą░ą╗ąŠą╝ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ T1/T0 ąĖ ą╝ąŠą╝ąĄąĮč鹊ą╝ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░.

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖ ąĘą░ą┐čĆąĄčé ą▓čģąŠą┤ą░ čéą░ą║č鹊ą▓ ą┤ąŠą╗ąČąĮčŗ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčīčüčÅ, ą║ąŠą│ą┤ą░ čāčĆąŠą▓ąĄąĮčī T1/T0 čüčéą░ą▒ąĖą╗ąĄąĮ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą▓ č鹥č湥ąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║č鹊ą▓, ąĖąĮą░č湥 ąĄčüčéčī čĆąĖčüą║ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąŠčłąĖą▒ąŠčćąĮąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ čüč湥čéą░ ą┤ą╗čÅ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░.

ąÜą░ąČą┤ą░čÅ ą┐ąŠą╗ąŠą▓ąĖąĮą░ ą┐ąĄčĆąĖąŠą┤ą░ ą┐ąŠčüčéčāą┐ą░čÄčēąĄą╣ ą▓ąĮąĄčłąĮąĄą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┤ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║č鹊ą▓, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą║ąŠčĆčĆąĄą║čéąĮčāčÄ ąŠčåąĖčäčĆąŠą▓ą║čā T1/T0. ąÆąĮąĄčłąĮčÅčÅ čćą░čüč鹊čéą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░ąĮąĮąŠ ąĮąĖąČąĄ ą┐ąŠą╗ąŠą▓ąĖąĮčŗ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ (fExtClk < fclk_I/O/2) ą┐čĆąĖ čüą║ą▓ą░ąČąĮąŠčüčéąĖ 50%. ą¤ąŠčüą║ąŠą╗čīą║čā ą┤ąĄč鹥ą║č鹊čĆ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąŠčåąĖčäčĆąŠą▓ą║čā čāčĆąŠą▓ąĮčÅ, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░, ą║ąŠč鹊čĆčāčÄ ąŠąĮ ą╝ąŠąČąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčī, čĆą░ą▓ąĮą░ ą┐ąŠą╗ąŠą▓ąĖąĮąĄ čćą░čüč鹊čéčŗ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ (ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü č鹥ąŠčĆąĄą╝ąŠą╣ ąØą░ą╣ą║ą▓ąĖčüčéą░). ą×ą┤ąĮą░ą║ąŠ ąĖąĘ-ąĘą░ ą▓ą░čĆąĖą░čåąĖąĖ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ ąĖ čüą║ą▓ą░ąČąĮąŠčüčéąĖ, ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖą╝ąŠą╣ ą│ąĄąĮąĄčĆą░č鹊čĆąŠą╝ (ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┤ąŠą┐čāčüą║ą░ą╝ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ą║ą▓ą░čĆčåą░, ą║ąĄčĆą░ą╝ąĖč湥čüą║ąŠą│ąŠ čĆąĄąĘąŠąĮą░č鹊čĆą░, ąĄą╝ą║ąŠčüčéčīčÄ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą▓, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą║ ą▓čŗą▓ąŠą┤ą░ą╝ XTAL1 ąĖ XTAL2, č鹥ą╝ą┐ąĄčĆą░čéčāčĆąŠą╣ ąŠą║čĆčāąČą░čÄčēąĄą╣ čüčĆąĄą┤čŗ ąĖ ą┤čĆčāą│ąĖą╝ąĖ čäą░ą║č鹊čĆą░ą╝ąĖ), čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąŠą│čĆą░ąĮąĖčćąĖčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ čćą░čüč鹊čéčā ą▓ąĮąĄčłąĮąĖčģ čéą░ą║č鹊ą▓, čćč鹊ą▒čŗ ąŠąĮą░ ą▒čŗą╗ą░ ą╝ąĄąĮčīčłąĄ fclk_I/O/2.5.

ąÆąĮąĄčłąĮčÅčÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ąĄą╗ąĄąĮą░ ą┐čĆąĄčüą║ą░ą╗ąĄčĆąŠą╝.

ąĀąĖčü. 18-2. ą¤čĆąĄčüą║ą░ą╗ąĄčĆ ą┤ą╗čÅ Timer/Counter1 ąĖ Timer/Counter0. ąøąŠą│ąĖą║ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ąĮąŠąČąĄą║ ą▓čģąŠą┤ąŠą▓ (T1/T0) ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčüčāąĮą║ąĄ 18-1.

ąĀąĄą│ąĖčüčéčĆčŗ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░. ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ ą░čüčüąĄą╝ą▒ą╗ąĄčĆą░ IN ąĖ OUT, ąŠčéąĮąŠčüčÅčēąĖąĄčüčÅ ą║ I/O, ą┤ąŠą╗ąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ I/O 0x00 .. 0x3F. ąÜąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆčŗ ą░ą┤čĆąĄčüčāčÄčéčüčÅ č湥čĆąĄąĘ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą┤ą░ąĮąĮčŗčģ ąĖąĮčüčéčĆčāą║čåąĖčÅą╝ąĖ LD ąĖ ST, ą║ čŹčéąĖą╝ ą░ą┤čĆąĄčüą░ą╝ ąĮčāąČąĮąŠ ą┤ąŠą▒ą░ą▓ąĖčéčī 0x20.

SFIOR ŌĆō Special Function IO Register, čüą╝ąĄčēąĄąĮąĖąĄ 0x30 ą▓ ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ I/O, čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 0. ąÜąŠą│ą┤ą░ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ą░ą┤čĆąĄčüčāąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ą░ą╝ąĖ LD ąĖ ST, ą░ą┤čĆąĄčü čüą╝ąĄčēąĄąĮąĖčÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ 0x50.

| ąĀą░ąĘčĆčÅą┤ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

| |

- |

- |

- |

- |

- |

- |

- |

PSR10 |

SFIOR |

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

|

|

|

|

|

|

|

R/W |

|

| ąĪą▒čĆąŠčü |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

PSR10 (ą▒ąĖčé 0): Prescaler Reset Timer/Counter1 ąĖ Timer/Counter0

ąÜąŠą│ą┤ą░ ą▓ čŹč鹊čé ą▒ąĖčé ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą╗ąŠą│. 1, č鹊 ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ ąŠą▒čēąĖą╣ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ą┤ą╗čÅ TC1 ąĖ TC0. ąŁč鹊čé ą▒ąĖčé ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą┐ąŠčüą╗ąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ čüą▒čĆąŠčüą░. ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 0 ą▓ čŹč鹊čé ą▒ąĖčé ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 TC1 ąĖ TC0 ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ, ą┐ąŠčŹč鹊ą╝čā ąĄčüą╗ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮą░ ąŠą▒ąŠąĖčģ čŹčéąĖčģ čéą░ą╣ą╝ąĄčĆą░čģ, č鹊 čüą▒čĆąŠčü ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ą┐ąŠą▓ą╗ąĖčÅąĄčé ąĮą░ ąĮąĖčģ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ, ąĖ ą▓čŗąĘąŠą▓ąĄčé ą┐ąŠą▓ą╗ąĖčÅąĄčé ąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĖąĘ čüč湥čéą░. ąæąĖčé PSR10 ą▓čüąĄą│ą┤ą░ čćąĖčéą░ąĄčéčüčÅ ą║ą░ą║ 0.

[ąŻąĘąĄą╗ čüč湥čéčćąĖą║ą░]

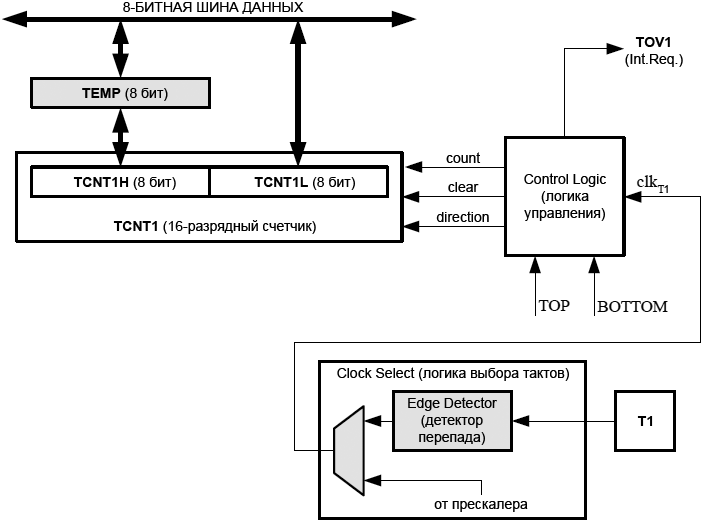

ą×čüąĮąŠą▓ąĮą░čÅ čćą░čüčéčī 16-bit Timer/Counter čŹč鹊 ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ 16-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čüč湥čéčćąĖą║, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé čüčćąĖčéą░čéčī ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ. ąØą░ čĆąĖčü. 19-2 ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ čüč湥čéčćąĖą║ą░ ąĖ ąĄą│ąŠ ąŠą║čĆčāąČąĄąĮąĖčÅ.

ąĀąĖčü. 19-2. ąæą╗ąŠą║-čüčģąĄą╝ą░ Counter Unit.

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓:

count ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčé ąĖą╗ąĖ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčé ąĮą░ ąĄą┤ąĖąĮąĖčåčā TCNT1.

direction ą▓čŗą▒ąĖčĆą░ąĄčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüč湥čéą░ (ąĖąĮą║čĆąĄą╝ąĄąĮčé ąĖą╗ąĖ ą┤ąĄą║čĆąĄą╝ąĄąĮčé).

clear ąŠčćąĖčēą░ąĄčé TCNT1 (čüą▒čĆą░čüčŗą▓ą░ąĄčé ą▓ 0 ą▓čüąĄ ąĄą│ąŠ ą▒ąĖčéčŗ).

clkT1 čéą░ą║čéčŗ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░.

TOP čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé, čćč鹊 TCNT1 ą┤ąŠčüčéąĖą│ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ.

BOTTOM čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé, čćč鹊 TCNT1 ą┤ąŠčüčéąĖą│ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ (ąĮčāą╗čÅ).

16-ą▒ąĖčéąĮčŗą╣ čüč湥čéčćąĖą║ ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĮą░ ą┤ą▓ąĄ 8-ą▒ąĖčéąĮčŗąĄ čÅč湥ą╣ą║ąĖ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ I/O: čüčéą░čĆčłą░čÅ ą┐ąŠą╗ąŠą▓ąĖąĮą░ čüč湥čéčćąĖą║ą░ (TCNT1H) ąĖ ą╝ą╗ą░ą┤čłą░čÅ ą┐ąŠą╗ąŠą▓ąĖąĮą░ čüč湥čéčćąĖą║ą░ (TCNT1L). ąÜ čĆąĄą│ąĖčüčéčĆčā TCNT1H ą┐čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠąČąĄčé ąŠą▒čĆą░čéąĖčéčīčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠčüą▓ąĄąĮąĮąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĄą╣ (indirect access). ąÜąŠą│ą┤ą░ CPU ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčé ą┤ąŠčüčéčāą┐ ą║ TCNT1H čÅč湥ą╣ą║ąĄ I/O, č鹊 ąĮą░ čüą░ą╝ąŠą╝ ą┤ąĄą╗ąĄ CPU ą┐ąŠą╗čāčćą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ ą▓čĆąĄą╝ąĄąĮąĮąŠą╝čā čĆąĄą│ąĖčüčéčĆčā čüčéą░čĆčłąĄą│ąŠ ą▒ą░ą╣čéą░ (TEMP). ąŁč鹊čé ą▓čĆąĄą╝ąĄąĮąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ TCNT1H, ą║ąŠą│ą┤ą░ čćąĖčéą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ TCNT1L, ąĖ TCNT1H ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖąĘ ą▓čĆąĄą╝ąĄąĮąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ TCNT1L. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆčā čćąĖčéą░čéčī ąĖą╗ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą▓ąĄčüčī 16-ą▒ąĖčéąĮčŗą╣ čüč湥čéčćąĖą║ čåąĄą╗ąĖą║ąŠą╝ ąĘą░ 1 čéą░ą║čé č湥čĆąĄąĘ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ 8-ą▒ąĖčéąĮčāčÄ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [2]).

ąÆą░ąČąĮąŠ ąŠčéą╝ąĄčéąĖčéčī, čćč鹊 ąĄčüčéčī čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ čüą╗čāčćą░ąĖ, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ TCNT1 ą┐čĆąĖ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠą╝ čüč湥č鹥 ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ čĆąĄąĘčāą╗čīčéą░čéą░ą╝. ąŁčéąĖ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ čüą╗čāčćą░ąĖ ąŠą┐ąĖčüą░ąĮčŗ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ čüąĄą║čåąĖčÅčģ, ą│ą┤ąĄ čŹč鹊 ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖąĄ.

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ čüč湥čéčćąĖą║ ąŠčćąĖčēą░ąĄčéčüčÅ, ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąĖą╗ąĖ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░ (clkT1). ąĪąĖą│ąĮą░ą╗ clkT1 ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ąĖąĘ ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖą╗ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░, ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą▒ąĖčéą░ą╝ąĖ CS12:0). ąÜąŠą│ą┤ą░ ąĮąĖ ąŠą┤ąĖąĮ ąĖąĘ ąĖčüč鹊čćąĮąĖą║ąŠą▓ čéą░ą║č鹊ą▓ ąĮąĄ ą▓čŗą▒čĆą░ąĮ (CS12:0 = 0), čéą░ą╣ą╝ąĄčĆ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ. ą×ą┤ąĮą░ą║ąŠ ą║ ąĘąĮą░č湥ąĮąĖčÄ čüč湥čéčćąĖą║ą░ TCNT1 ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ čüąŠ čüč鹊čĆąŠąĮčŗ CPU, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé clkT1 ąĖą╗ąĖ ąĮąĄčé. ą×ą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ CPU ąŠčéą╝ąĄąĮčÅčÄčé (čé. ąĄ. ąĘą░ą┐ąĖčüčī ąĖą╝ąĄąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé) ą▓čüąĄ ąŠčćąĖčüčéą║ąĖ čüč湥čéčćąĖą║ą░ ąĖą╗ąĖ ąŠą┐ąĄčĆą░čåąĖąĖ čüč湥čéą░.

ąÆ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čüč湥čéą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé Waveform Generation (WGM13:0), ąĮą░čģąŠą┤čÅčēąĖčģčüčÅ ą▓ Timer/Counter Control Register A ąĖ B (TCCR1A ąĖ TCCR1B). ąśą╝ąĄąĄčéčüčÅ čüčéčĆąŠą│ą░čÅ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéčī ą╝ąĄąČą┤čā ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄą╝ (čüč湥č鹊ą╝) čüč湥čéčćąĖą║ą░ ąĖ č乊čĆą╝ą░ą╝ąĖ čüąĖą│ąĮą░ą╗ą░, ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗą╝ąĖ ąĮą░ ą▓čŗčģąŠą┤ą░čģ Output Compare (OC1x). ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčÅą╝ čüč湥čéą░ ąĖ č乊čĆą╝ą░ą╝ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ čüą╝. "ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ".

ążą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ Timer/Counter Overflow (TOV1) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą▓čŗą▒čĆą░ąĮąĮčŗą╝ ą▒ąĖčéą░ą╝ąĖ WGM13:0 čĆąĄąČąĖą╝ąŠą╝ čĆą░ą▒ąŠčéčŗ. TOV1 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CPU.

[ąŻąĘąĄą╗ Input Capture]

ąÆ čéą░ą╣ą╝ąĄčĆąĄ/čüč湥čéčćąĖą║ąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ čāąĘąĄą╗ ąĘą░čģą▓ą░čéą░ ą┐ąŠ ą▓čģąŠą┤ąĮąŠą╝čā čüąĖą│ąĮą░ą╗čā (Input Capture), ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ąĘą░čģą▓ą░čéčŗą▓ą░čéčī ą▓ąĮąĄčłąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ ąĖ ą┐čĆąĖą▓čÅąĘčŗą▓ą░čéčī ą║ ąĮąĖą╝ ą╝ąĄčéą║ąĖ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ. ąĪąŠą▒čŗčéąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą┐ąŠčüčéčāą┐ą░čéčī ąĮą░ ą▓čŗą▓ąŠą┤ ICP1 ąĖą╗ąĖ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ąĮą░ ą▒ą╗ąŠą║ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ (Analog Comparator). ąŁčéąĖ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ čćą░čüč鹊čéčŗ, čüą║ą▓ą░ąČąĮąŠčüčéąĖ ąĖ ą┤čĆčāą│ąĖčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ čüąĖą│ąĮą░ą╗ą░, ą║ąŠč鹊čĆčŗą╣ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąŠą▒čŗčéąĖčÅ ąĘą░čģą▓ą░čéą░. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čüąŠąĘą┤ą░ąĮąĖčÅ ą╗ąŠą│ą░ čüąŠą▒čŗčéąĖą╣.

Input Capture ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 19-3. ąØą░ čŹč鹊ą╣ ą▒ą╗ąŠą║ čüčģąĄą╝ąĄ 菹╗ąĄą╝ąĄąĮčéčŗ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ čÅą▓ą╗čÅčÄčéčüčÅ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ čćą░čüčéčÅą╝ąĖ čāąĘą╗ą░ Input Capture, ą┐ąŠą║ą░ąĘą░ąĮčŗ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝.

ąĀąĖčü. 19-3. ąæą╗ąŠą║ čüčģąĄą╝ą░ Input Capture Unit.

ąÜąŠą│ą┤ą░ ą╝ąĄąĮčÅąĄčéčüčÅ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī (čŹč鹊 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čÅą▓ą╗čÅąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄą╝) ąĮą░ ą▓čŗą▓ąŠą┤ąĄ Input Capture Pin (ICP1), ąĖą╗ąĖ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ Analog Comparator Output (ACO), č鹊 čŹč鹊 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ, ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄą╝ąŠąĄ ą┤ąĄč鹥ą║č鹊čĆąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░, ą▓čŗąĘąŠą▓ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ąĘą░čģą▓ą░čéą░ (capture). ą¤čĆąĖ ąĘą░čģą▓ą░č鹥 16-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (TCNT1) ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ Input Capture Register (ICR1). ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ Input Capture Flag (ICF1) ąĮą░ č鹊ą╝ ąČąĄ čüąĖčüč鹥ą╝ąĮąŠą╝ čéą░ą║č鹥, ąĮą░ ą║ąŠč鹊čĆąŠą╝ ąĘąĮą░č湥ąĮąĖąĄ TCNT1 ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ ICR1. ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░čģą▓ą░čéą░ (TICIE1 = 1), č鹊 čäą╗ą░ą│ Input Capture ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Input Capture. ążą╗ą░ą│ ICF1 ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą▒čĆąŠčüąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ čäą╗ą░ą│ ICF1 ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą╗ąŠą│. 1 ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēčāčÄ ą┐ąŠąĘąĖčåąĖčÄ ą▒ąĖčéą░ I/O čäą╗ą░ą│ą░ ICF1.

ą¦č鹥ąĮąĖąĄ 16-ą▒ąĖčéąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ Input Capture Register (ICR1) ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čüąĮą░čćą░ą╗ą░ čćč鹥ąĮąĖąĄą╝ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą▒ą░ą╣čéą░ (ICR1L), ąĖ ąĘą░č鹥ą╝ čüčéą░čĆčłąĄą│ąŠ ą▒ą░ą╣čéą░ (ICR1H). ąÜąŠą│ą┤ą░ čćąĖčéą░ąĄčéčüčÅ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé, čüčéą░čĆčłąĖą╣ ą┐čĆąĖ čŹč鹊ą╝ ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ ą▓ąŠ ą▓čĆąĄą╝ąĄąĮąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čüčéą░čĆčłąĄą│ąŠ ą▒ą░ą╣čéą░ (TEMP). ąÜąŠą│ą┤ą░ CPU čćąĖčéą░ąĄčé čÅč湥ą╣ą║čā I/O ICR1H, č鹊 ąĮą░ čüą░ą╝ąŠą╝ ą┤ąĄą╗ąĄ ąŠąĮ čćąĖčéą░ąĄčé čĆąĄą│ąĖčüčéčĆ TEMP [2].

ąĀąĄą│ąĖčüčéčĆ ICR1 ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čĆąĄąČąĖą╝ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ (Waveform Generation mode) ąĖčüą┐ąŠą╗čīąĘčāąĄčé čĆąĄą│ąĖčüčéčĆ ICR1 ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ TOP čüč湥čéčćąĖą║ą░ (čüą╝. čéą░ą▒ą╗ąĖčåčā 19-1). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▒ąĖčéčŗ Waveform Generation mode (WGMn3:0) ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ąĘąĮą░č湥ąĮąĖąĄ TOP ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆ ICR1. ąÜąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ ICR1, čüąĮą░čćą░ą╗ą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮą░ čüčéą░čĆčłąĖą╝ ą▒ą░ą╣č鹊ą╝ I/O čÅč湥ą╣ą║ą░ ICR1H, ąĘą░č鹥ą╝ ąĘą░ą┐ąĖčüą░ąĮ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé ą▓ ICR1L [2].

ąśčüč鹊čćąĮąĖą║ čüąĖą│ąĮą░ą╗ą░ Input Capture. ą×čüąĮąŠą▓ąĮčŗą╝ čéčĆąĖą│ą│ąĄčĆąŠą╝ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą▒ą╗ąŠą║ą░ Input Capture čéą░ą╣ą╝ąĄčĆą░ TC1 čüą╗čāąČąĖčé ą▓čģąŠą┤ Input Capture Pin (ICP1). TC1 ą╝ąŠąČąĄčé ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ą┤ą╗čÅ Input Capture ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓čŗčģąŠą┤ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ (Analog Comparator Output, čüąĖą│ąĮą░ą╗ ACO). Analog Comparator ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą║ą░ą║ ąĖčüč鹊čćąĮąĖą║ čéčĆąĖą│ą│ąĄčĆą░ ąĘą░čģą▓ą░čéą░ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ Analog Comparator Input Capture (ACIC) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆąŠą╝ Analog Comparator Control and Status Register (ACSR). ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéčĆąĖą│ą│ąĄčĆą░ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ą╗ąŠąČąĮąŠą╝čā ąŠą┤ąĖąĮąŠčćąĮąŠą╝čā čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÄ čäčāąĮą║čåąĖąĖ ąĘą░čģą▓ą░čéą░. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čäą╗ą░ą│ ICF1 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą┐ąŠčüą╗ąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░ ąĘą░čģą▓ą░čéą░.

ą×ą▒ą░ ą▓čģąŠą┤ą░, ąĖ Input Capture Pin (ICP1), ąĖ Analog Comparator Output (ACO) ąŠčåąĖčäčĆąŠą▓čŗą▓ą░čÄčéčüčÅ č鹊ą╣ ąČąĄ čüą░ą╝ąŠą╣ č鹥čģąĮąĖą║ąŠą╣, čćč鹊 ąĖ ą▓čŗą▓ąŠą┤ T1 (čüą╝. čĆąĖčü. 18-1). ąöąĄč鹥ą║č鹊čĆ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čéą░ą║ąČąĄ ą░ąĮą░ą╗ąŠą│ąĖčćąĮčŗą╣. ą×ą┤ąĮą░ą║ąŠ ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮ noise canceler, ą┐ąĄčĆąĄą┤ ą┤ąĄč鹥ą║č鹊čĆąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą▓čüčéą░ą▓ą╗čÅąĄčéčüčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ą╗ąŠą│ąĖą║ą░, ą║ąŠč鹊čĆą░čÅ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé ąĘą░ą┤ąĄčƹȹ║čā ąĮą░ 4 čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║čéą░. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā ą▓čģąŠą┤ąĮąŠą╣ noise canceler ąĖ ą┤ąĄč鹥ą║č鹊čĆ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą▓čüąĄą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮčŗ, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čüą╗čāčćą░ąĄą▓, ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ čĆąĄąČąĖą╝ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ (Waveform Generation mode), ą▓ ą║ąŠč鹊čĆąŠą╝ ICR1 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ TOP.

Input Capture ą╝ąŠąČąĄčé čüčĆą░ą▒ąŠčéą░čéčī ą┐ąŠą┤ ą┤ąĄą╣čüčéą▓ąĖąĄą╝ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, ąĄčüą╗ąĖ ąŠąĮą░ čāą┐čĆą░ą▓ą╗čÅąĄčé ąĮąŠąČą║ąŠą╣ ą┐ąŠčĆčéą░ GPIO čüąĖą│ąĮą░ą╗ą░ ICP1, ąĮą░čüčéčĆąŠąĄąĮąĮąŠą│ąŠ ą║ą░ą║ ą▓čŗčģąŠą┤.

Noise Canceler. ąŻąĘąĄą╗ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠą╝ąĄčģ (noise canceler) čāą╗čāčćčłą░ąĄčé ą┐ąŠą╝ąĄčģąŠąĘą░čēąĖčēąĄąĮąĮąŠčüčéčī ą┐čāč鹥ą╝ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ čüčģąĄą╝čŗ čåąĖčäčĆąŠą▓ąŠą╣ čäąĖą╗čīčéčĆą░čåąĖąĖ. ąÆčģąŠą┤ noise canceler ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ 4 čĆą░ąĘą░, ąĖ ą║ąŠą│ą┤ą░ ą▓čüąĄ 4 ą▓čŗą▒ąŠčĆą║ąĖ ąŠą║ą░ąĘčŗą▓ą░čÄčéčüčÅ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ąĖ, č鹊 čŹč鹊čé ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĮą░ ą▓čģąŠą┤ ą┤ąĄč鹥ą║č鹊čĆą░ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą║ą░ą║ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╣.

Noise canceler čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ Input Capture Noise Canceler (ICNC1) ą▓ čĆąĄą│ąĖčüčéčĆąĄ Timer/Counter Control Register B (TCCR1B). ąĢčüą╗ąĖ noise canceler čĆą░ąĘčĆąĄčłąĄąĮ, č鹊 čŹč鹊 ą▓ą▓ąŠą┤ąĖčé ąĘą░ą┤ąĄčƹȹ║čā ąĖąĘ 4 čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║č鹊ą▓ ąŠčé ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čāčĆąŠą▓ąĮčÅ čüąŠą▒čŗčéąĖčÅ ą┤ąŠ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ICR1. Noise canceler ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüąĖčüč鹥ą╝ąĮčāčÄ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā, ą┐ąŠčŹč鹊ą╝čā ąĮą░ ąĮąĄą│ąŠ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░čüčéčĆąŠą╣ą║ą░ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░.

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čāąĘą╗ą░ Input Capture. ą×čüąĮąŠą▓ąĮą░čÅ čüą╗ąŠąČąĮąŠčüčéčī ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ čäčāąĮą║čåąĖąĖ Input Capture - ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ą┤ąŠčüčéą░č鹊čćąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą▓čģąŠą┤ąĮčŗčģ čüąŠą▒čŗčéąĖą╣. ąÆčĆąĄą╝čÅ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ čüąŠčüąĄą┤ąĮąĖą╝ąĖ čüąŠą▒čŗčéąĖčÅą╝ąĖ čÅą▓ą╗čÅąĄčéčüčÅ ą║čĆąĖčéąĖčćąĮčŗą╝, ąĘą░ čŹč鹊 ą▓čĆąĄą╝čÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ čāčüą┐ąĄčéčī ąŠą▒čĆą░ą▒ąŠčéą░čéčī čäą░ą║čé čüąŠą▒čŗčéąĖčÅ. ąĢčüą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮąĄ ą┐čĆąŠčćąĖčéą░ą╗ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ąĮąĄ čāčüą┐ąĄą╗ ą┐čĆąŠčćąĖčéą░čéčī) ąĘąĮą░č湥ąĮąĖąĄ ąĘą░čģą▓ą░čéą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ICR1 ą┤ąŠ ąĮą░čüčéčāą┐ą╗ąĄąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüąŠą▒čŗčéąĖčÅ, č鹊 ICR1 ą▒čāą┤ąĄčé ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮ ąĮąŠą▓čŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ čüč湥čéčćąĖą║ą░. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čĆąĄąĘčāą╗čīčéą░čé ąĘą░čģą▓ą░čéą░ ą▒čāą┤ąĄčé ąĮąĄą║ąŠčĆčĆąĄą║č鹥ąĮ.

ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Input Capture, ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆ ICR1 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą║ą░ą║ ą╝ąŠąČąĮąŠ čĆą░ąĮčīčłąĄ, ąĮą░čüą║ąŠą╗čīą║ąŠ čŹč鹊 ą▓ąŠąĘą╝ąŠąČąĮąŠ. ąöą░ąČąĄ ąĮąĄčüą╝ąŠčéčĆčÅ ąĮą░ č鹊, čćč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Input Capture ąĖą╝ąĄąĄčé ą┤ąŠą▓ąŠą╗čīąĮąŠ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ čĆąĄą░ą║čåąĖąĖ ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓, ą║ąŠč鹊čĆąŠąĄ čéčĆą░čéąĖčéčüčÅ ąĘą░ą┐čĆąŠčüą░ą╝ąĖ ąĮą░ ą┤čĆčāą│ąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąĪą╗ąĄą┤čāąĄčé ą┐ąŠą╝ąĮąĖčéčī, čćč鹊 ą░ą║čéąĖą▓ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ AVR čü ąĮąĖąĘą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĄčĆą▓ą░ąĮąŠ, ąĄčüą╗ąĖ ą▓čŗč鹥čüąĮąĄąĮąĖąĄ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą▓ čŹč鹊ą╝ ąĮąĖąĘą║ąŠą┐čĆąĖąŠčĆąĖč鹥čéąĮąŠą╝ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (čüą╝. "ą× ą┐čĆąĖąŠčĆąĖč鹥čéą░čģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ AVR" ą▓ [3]).

ąØąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čāąĘą╗ą░ Input Capture ą▓ ą╗čÄą▒ąŠą╝ čĆąĄąČąĖą╝ąĄ, ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ TOP (čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī) ą░ą║čéąĖą▓ąĮąŠ ą╝ąĄąĮčÅąĄčéčüčÅ ą▓ ą┐čĆąŠčåąĄčüčüąĄ čĆą░ą▒ąŠčéčŗ.

ąśąĘą╝ąĄčĆąĄąĮąĖąĄ čüą║ą▓ą░ąČąĮąŠčüčéąĖ čüąĖą│ąĮą░ą╗ą░ čéčĆąĄą▒čāąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ąĘą░čģą▓ą░čéą░ ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░. ąśąĘą╝ąĄąĮąĄąĮąĖąĄ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čüą┤ąĄą╗ą░ąĮąŠ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ą╗ąĖąČąĄ ą║ ą╝ąŠą╝ąĄąĮčéčā ąŠą║ąŠąĮčćą░ąĮąĖčÅ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ICR1. ą¤ąŠčüą╗ąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čäą╗ą░ą│ Input Capture Flag (ICF1) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ (ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĄą│ąŠ I/O ą┐ąŠąĘąĖčåąĖčÄ ąĄą┤ąĖąĮąĖčåčŗ). ąöą╗čÅ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ č鹊ą╗čīą║ąŠ čćą░čüč鹊čéčŗ ąŠčćąĖčüčéą║ą░ čäą╗ą░ą│ą░ ICF1 ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ (ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ).

[ąŻąĘą╗čŗ Output Compare]

16-ą▒ąĖčéąĮčŗą╣ čåąĖčäčĆąŠą▓ąŠą╣ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčé TCNT1 čü čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ Output Compare (OCR1x). ąĢčüą╗ąĖ TCNT1 čüčéą░ąĮąŠą▓ąĖčéčüčÅ čĆą░ą▓ąĮčŗą╝ OCR1x, ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ. ąĪąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ čāčüčéą░ąĮąŠą▓ąĖčé čäą╗ą░ą│ Output Compare Flag (OCF1x) ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░. ąĢčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮąŠ (OCIE1x = 1), č鹊 čäą╗ą░ą│ Output Compare ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Output Compare. ążą╗ą░ą│ OCF1x ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ čäą╗ą░ą│ OCF1x ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĘą░ą┐ąĖčüčīčÄ ą╗ąŠą│. 1 ą▓ ąĄą│ąŠ I/O ą┐ąŠąĘąĖčåąĖčÄ ą▒ąĖčéą░. ąōąĄąĮąĄčĆą░č鹊čĆ čüąĖą│ąĮą░ą╗ą░ (waveform generator) ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüąĖą│ąĮą░ą╗ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▓čŗčģąŠą┤ą░ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ čĆąĄąČąĖą╝ąŠą╝ ą▒ąĖčéą░ą╝ąĖ Waveform Generation mode (WGM13:0) ąĖ ą▒ąĖčéą░ą╝ąĖ Compare Output mode (COM1x1, COM1x0). ąĪąĖą│ąĮą░ą╗čŗ TOP ąĖ BOTTOM ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▒ą╗ąŠą║ąŠą╝ waveform generator ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ čüą╗čāčćą░ąĄą▓ ą┐čĆąĄą┤ąĄą╗čīąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ čüč湥čéčćąĖą║ą░ ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ čĆąĄąČąĖą╝ą░čģ čĆą░ą▒ąŠčéčŗ (čüą╝. "ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ").

ąĪą┐ąĄčåąĖą░ą╗čīąĮą░čÅ čäčāąĮą║čåąĖčÅ ą▒ą╗ąŠą║ą░ Output Compare A ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┤ą╗čÅ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ ąĘąĮą░č湥ąĮąĖąĄ TOP (čé. ąĄ. čĆą░ąĘčĆąĄčłą░čÄčēčāčÄ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī čüč湥čéą░). ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ čüč湥čéčćąĖą║ą░, ąĘąĮą░č湥ąĮąĖąĄ TOP ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĖąŠą┤ą░ čüąĖą│ąĮą░ą╗ą░, ą║ąŠč鹊čĆčŗą╣ čüąĖąĮč鹥ąĘąĖčĆčāąĄčé waveform generator.

ąØą░ čĆąĖčü. 19-4 ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ čāąĘą╗ą░ Output Compare. ą£ą░ą╗ąĄąĮčīą║ą░čÅ ą▒čāą║ą▓ą░ x čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠą┤ąĮąŠą╝čā ąĖąĘ ą▒ą╗ąŠą║ąŠą▓ čüčĆą░ą▓ąĮąĄąĮąĖčÅ Output Compare (A/B). ąŁą╗ąĄą╝ąĄąĮčéčŗ ą▒ą╗ąŠą║-čüčģąĄą╝čŗ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ čÅą▓ą╗čÅčÄčéčüčÅ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ čćą░čüčéčīčÄ čāąĘą╗ą░ Output Compare, ąŠą▒ąŠąĘąĮą░č湥ąĮčŗ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝.

ąĀąĖčü. 19-4. ąæą╗ąŠą║-čüčģąĄą╝ą░ Output Compare Unit.

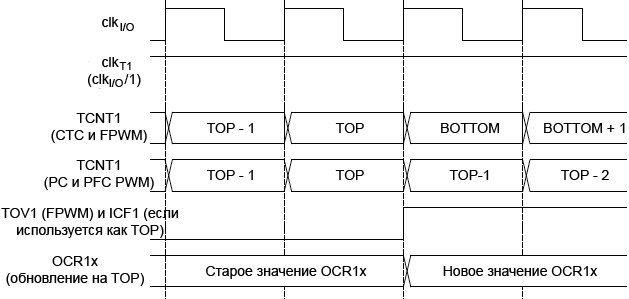

ąĀąĄą│ąĖčüčéčĆ OCR1x ą┐čĆąĖą╝ąĄąĮčÅąĄčé ą┤ą▓ąŠą╣ąĮčāčÄ ą▒čāč乥čĆąĖąĘą░čåąĖčÄ, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąŠą┤ąĖąĮ ąĖąĘ 12 čĆąĄąČąĖą╝ąŠą▓ ą©ąśą£ (Pulse Width Modulation, PWM). ąöą╗čÅ čĆąĄąČąĖą╝ąŠą▓ čĆą░ą▒ąŠčéčŗ Normal ąĖ Clear Timer on Compare (CTC) ą┤ą▓ąŠą╣ąĮą░čÅ ą▒čāč乥čĆąĖąĘą░čåąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮą░. ąöą▓ąŠą╣ąĮą░čÅ ą▒čāč乥čĆąĖąĘą░čåąĖčÅ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ čüčĆą░ą▓ąĮąĄąĮąĖčÅ OCR1x ąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čüč湥čéą░ TOP ąĖą╗ąĖ BOTTOM. ąŁčéą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčé ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄ ąĮąĄčüąĖą╝ą╝ąĄčéčĆąĖčćąĮčŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą©ąśą£, ą│ąĄąĮąĄčĆąĖčĆčāčÅ čćąĖčüčéčŗą╣, čüą▓ąŠą▒ąŠą┤ąĮčŗą╣ ąŠčé ą┐ą░čĆą░ąĘąĖčéąĮčŗčģ ą▓čŗą▒čĆąŠčüąŠą▓ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗.

ąöąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆčā OCR1x ą╝ąŠąČąĄčé ą┐ąŠą║ą░ąĘą░čéčīčüčÅ čüą╗ąŠąČąĮčŗą╝, ąŠą┤ąĮą░ą║ąŠ čŹč鹊 ąĮąĄ čéą░ą║. ąÜąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┤ą▓ąŠą╣ąĮą░čÅ ą▒čāč乥čĆąĖąĘą░čåąĖčÅ, čÅą┤čĆąŠ CPU ą┐ąŠą╗čāčćą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆčā ą▒čāč乥čĆą░ OCR1x, ąĖ ąĄčüą╗ąĖ ą┤ą▓ąŠą╣ąĮą░čÅ ą▒čāč乥čĆąĖąĘą░čåąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮą░, č鹊 ą┤ąŠčüčéčāą┐ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆčā OCR1x ąĮą░ą┐čĆčÅą╝čāčÄ, ą▒ąĄąĘ ą▒čāč乥čĆą░. ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ OCR1x (čĆąĄą│ąĖčüčéčĆą░ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ąĖą╗ąĖ ąĄą│ąŠ ą▒čāč乥čĆą░) ą╝ąĄąĮčÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąŠą┐ąĄčĆą░čåąĖąĄą╣ ąĘą░ą┐ąĖčüąĖ (čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ ąĮąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčé čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą║ą░ą║ ąŠąĮ čŹč鹊 ą┤ąĄą╗ą░ąĄčé čü čĆąĄą│ąĖčüčéčĆąŠą╝ TCNT1 ąĖ ICR1). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, OCR1x ąĮąĄ čćąĖčéą░ąĄčéčüčÅ č湥čĆąĄąĘ ą▓čĆąĄą╝ąĄąĮąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čüčéą░čĆčłąĄą│ąŠ ą▒ą░ą╣čéą░ (TEMP). ą×ą┤ąĮą░ą║ąŠ čģąŠčĆąŠčłąĄą╣ ą┐čĆą░ą║čéąĖą║ąŠą╣ ąŠčüčéą░ąĄčéčüčÅ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠąĄ čćč鹥ąĮąĖąĄ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą▒ą░ą╣čéą░ ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ ą┤čĆčāą│ąĖą╝ 16-ą▒ąĖčéąĮčŗą╝ čĆąĄą│ąĖčüčéčĆą░ą╝. ąŚą░ą┐ąĖčüčī čĆąĄą│ąĖčüčéčĆąŠą▓ OCR1x ą┤ąŠą╗ąČąĮą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčīčüčÅ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ TEMP, ą┐ąŠčüą║ąŠą╗čīą║čā ą▓čüąĄ 16-ą▒ąĖčé ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąĖ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠ. ąĪąĮą░čćą░ą╗ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čüčéą░čĆčłąĖą╣ ą▒ą░čéą╣ (OCR1xH). ąÜąŠą│ą┤ą░ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ąĘą░ą┐ąĖčüą░ąĮ ą▓ čÅč湥ą╣ą║čā I/O, čĆąĄą│ąĖčüčéčĆ TEMP ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ čŹčéąĖą╝ ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝. ąóąŠą│ą┤ą░ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé (OCR1xL), ąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ čŹč鹊ą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ą▓ č鹊ą╝ ąČąĄ čüą░ą╝ąŠą╝ čüąĖčüč鹥ą╝ąĮąŠą╝ čéą░ą║č鹥 čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ą▒čāą┤ąĄčé čüą║ąŠą┐ąĖčĆąŠą▓ą░ąĮ ą▓ čüčéą░čĆčłąĖąĄ 8 ą▒ą░ą╣čé ą╗ąĖą▒ąŠ čĆąĄą│ąĖčüčéčĆą░ OCR1x, ą╗ąĖą▒ąŠ ąĄą│ąŠ ą▒čāč乥čĆą░. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ ąŠą┐ąĄčĆą░čåąĖąĖ čü 16-ą▒ąĖčéąĮčŗą╝ąĖ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ čüą╝. [2].

Force Output Compare. ąÆ čĆąĄąČąĖą╝ą░čģ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░, ąĮąĄ ąŠčéąĮąŠčüčÅčēąĖčģčüčÅ ą║ ą©ąśą£ (non-PWM Waveform Generation modes), ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ąĘą░ą┐čāčüčéąĖčéčī čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ čåąĖčäčĆąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ąĘą░ą┐ąĖčüčīčÄ ą╗ąŠą│. 1 ą▓ ą▒ąĖčé Force Output Compare (FOC1x). Forcing Compare Match ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčé čäą╗ą░ą│ OCF1x ąĖ ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĄ ąĖą╗ąĖ ąŠčćąĖčüčéą║ąĄ čéą░ą╣ą╝ąĄčĆą░, ąŠą┤ąĮą░ą║ąŠ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ OC1x ąŠą▒ąĮąŠą▓ąĖčéčüčÅ, ą║ą░ą║ ąĄčüą╗ąĖ ą▒čŗ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čĆąĄą░ą╗čīąĮąŠąĄ čüąŠą▒čŗčéąĖąĄ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ Compare Match (ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▒ąĖčé COM1x1, COM1x0 ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą║ą░ą║ ąĖąĘą╝ąĄąĮąĖčéčüčÅ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ OC1x: ąŠąĮ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, čüą▒čĆąŠčüąĖčéčüčÅ ąĖą╗ąĖ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčüčÅ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ).

ąæą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĖąĄ Compare Match ąĘą░ą┐ąĖčüčīčÄ ą▓ TCNT1. ąÆčüąĄ ąĘą░ą┐ąĖčüąĖ čüąŠ čüč鹊čĆąŠąĮčŗ CPU ą▓ čĆąĄą│ąĖčüčéčĆ TCNT1 ą▒čāą┤čāčé ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░čéčī ą╗čÄą▒čŗąĄ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ Compare Match, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤čāčé ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░, ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ. ąŁčéą░ čäčāąĮą║čåąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī OCR1x ą▓ č鹊 ąČąĄ čüą░ą╝ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, čćč鹊 ąĖ TCNT1, ą▒ąĄąĘ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░.

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ Output Compare Unit. ą¤ąŠčüą║ąŠą╗čīą║čā ąĘą░ą┐ąĖčüčī TCNT1 ą▓ ą╗čÄą▒ąŠą╝ čĆąĄąČąĖą╝ąĄ čĆą░ą▒ąŠčéčŗ ąĘą░ą▒ą╗ąŠą║ąĖčĆčāąĄčé ą▓čüąĄ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ compare match ąĮą░ ąŠą┤ąĖąĮ čéą░ą║čé čéą░ą╣ą╝ąĄčĆą░, ąĄčüčéčī čĆąĖčüą║ąĖ ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ TCNT1, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą╗čÄą▒ąŠą╣ ąĖąĘ ą║ą░ąĮą░ą╗ąŠą▓ Output Compare, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, čĆą░ą▒ąŠčéą░ąĄčé čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║, ąĖą╗ąĖ ąĮąĄčé. ąĢčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ, ąĘą░ą┐ąĖčüą░ąĮąĮąŠąĄ ą▓ TCNT1, čĆą░ą▓ąĮąŠ ąĘąĮą░č湥ąĮąĖčÄ OCR1x, č鹊 Compare Match ą▒čāą┤ąĄčé ą┐ąŠč鹥čĆčÅąĮąŠ, ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 č湥ą│ąŠ ą┐ąŠą╗čāčćąĖčéčüčÅ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗. ąØąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ą╣č鹥 TCNT1 čĆą░ą▓ąĮčŗą╝ ąĘąĮą░č湥ąĮąĖčÄ TOP ą▓ čĆąĄąČąĖą╝ą░čģ ą©ąśą£ (PWM) čü ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗą╝ąĖ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ TOP. Compare Match ą┤ą╗čÅ TOP ą▒čāą┤ąĄčé ą┐čĆąŠąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░ąĮąŠ, ąĖ čüč湥čéčćąĖą║ ą┐čĆąŠą┤ąŠą╗ąČąĖčé čüč湥čé ą┤ąŠ ąĘąĮą░č湥ąĮąĖčÅ 0xFFFF. ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĮąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ą╣č鹥 ąĘąĮą░č湥ąĮąĖąĄ TCNT1, čĆą░ą▓ąĮčŗą╝ BOTTOM, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą▓ąĮąĖąĘ.

ąØą░čüčéčĆąŠą╣ą║ą░ OC1x ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą┐ąĄčĆąĄą┤ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čĆąĄą│ąĖčüčéčĆą░ Data Direction Register (DDR), čćč鹊ą▒čŗ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ čĆą░ą▒ąŠčéą░ą╗ą░ ą║ą░ą║ ą▓čŗčģąŠą┤. ąĪą░ą╝čŗą╣ ą┐čĆąŠčüč鹊ą╣ čüą┐ąŠčüąŠą▒ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĘąĮą░č湥ąĮąĖčÅ OC1x - ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▒ąĖčéčŗ čüčéčĆąŠą▒ą░ Force Output Compare (FOCnx) ą▓ čĆąĄąČąĖą╝ąĄ Normal. ąĀąĄą│ąĖčüčéčĆ OC1x čüąŠčģčĆą░ąĮčÅąĄčé čüą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ ą╝ąĄąĮčÅčÄčéčüčÅ čĆąĄąČąĖą╝čŗ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ (Waveform Generation modes).

ąæčāą┤čīč鹥 ą▓ąĮąĖą╝ą░č鹥ą╗čīąĮčŗ, ą▒ąĖčéčŗ COM1x1, COM1x0 ąĮąĄ ąĖą╝ąĄčÄčé ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ ą▓ą╝ąĄčüč鹥 čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ čüčĆą░ą▓ąĮąĄąĮąĖčÅ. ąśąĘą╝ąĄąĮąĄąĮąĖąĄ ą▒ąĖčé COM1x1, COM1x0 ą▓čüčéčāą┐ą░čÄčé ą▓ čüąĖą╗čā ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ.

[ąÆčŗčģąŠą┤ Compare Match]

ąæąĖčéčŗ čĆąĄąČąĖą╝ą░ Compare Output (COM1x1, COM1x0) ą▓čŗą┐ąŠą╗ąĮčÅčÄčé 2 čäčāąĮą║čåąĖąĖ. ąōąĄąĮąĄčĆą░č鹊čĆ čüąĖą│ąĮą░ą╗ąŠą▓ (waveform generator) ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčéčŗ COM1x1, COM1x0 ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ Output Compare (OC1x) ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čüąŠą▒čŗčéąĖąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ Compare Match. ąÆč鹊čĆą░čÅ čäčāąĮą║čåąĖčÅ ą▒ąĖčé COM1x1, COM1x0 čŹč鹊 čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ąŠą╝ čüąĖą│ąĮą░ą╗ą░ ą▓čŗčģąŠą┤ą░ ą▓čŗą▓ąŠą┤ą░ OC1x. ąĀąĖčü. 19-5 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čāą┐čĆąŠčēąĄąĮąĮčāčÄ čüčģąĄą╝čā ą╗ąŠą│ąĖą║ąĖ, ąĮą░ ą║ąŠč鹊čĆčāčÄ ą▓ą╗ąĖčÅčÄčé ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▒ąĖčé COM1x1, COM1x0. ąĀąĄą│ąĖčüčéčĆčŗ I/O, ą▒ąĖčéčŗ I/O ąĖ ą▓ąĮąĄčłąĮąĖąĄ ą▓čŗą▓ąŠą┤čŗ I/O ąĮą░ čŹč鹊ą╝ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąČąĖčĆąĮčŗą╝ čłčĆąĖčäč鹊ą╝. ą¤ąŠą║ą░ąĘą░ąĮčŗ č鹊ą╗čīą║ąŠ č鹥 čćą░čüčéąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ GPIO (čĆąĄą│ąĖčüčéčĆčŗ DDR ąĖ PORT), ąĮą░ ą║ąŠč鹊čĆčŗąĄ ą▓ą╗ąĖčÅčÄčé ą▒ąĖčéčŗ COM1x1, COM1x0. ąÜąŠą│ą┤ą░ čüčüčŗą╗ą░čÄčéčüčÅ ąĮą░ čüąŠčüč鹊čÅąĮąĖąĄ OC1x, ąĖą╝ąĄąĄčéčüčÅ ą▓ ą▓ąĖą┤čā ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ OC1x, ą░ ąĮąĄ ą▓čŗą▓ąŠą┤ą░ OC1x. ąĢčüą╗ąĖ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüą▒čĆąŠčü čüąĖčüč鹥ą╝čŗ (System Reset), č鹊 čĆąĄą│ąĖčüčéčĆ OC1x čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą▓ 0.

ąĀąĖčü. 19-5. ąĪčģąĄą╝ą░ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ Compare Match.

ążčāąĮą║čåąĖčÅ GPIO ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ (ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čåąĖčäčĆąŠą▓ąŠą╣ ą▓ą▓ąŠą┤/ą▓čŗą▓ąŠą┤) ąŠčéą╝ąĄąĮčÅąĄčéčüčÅ čäčāąĮą║čåąĖąĄą╣ Output Compare (OC1x) ą│ąĄąĮąĄčĆą░č鹊čĆą░ čüąĖą│ąĮą░ą╗ąŠą▓ (waveform generator), ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą╗čÄą▒ąŠą╣ ąĖąĘ ą▒ąĖčé COM1x1, COM1x0. ą×ą┤ąĮą░ą║ąŠ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ OC1x (ą▓čģąŠą┤ ąĖą╗ąĖ ą▓čŗčģąŠą┤) ą▓čüąĄ ąĄčēąĄ ą║ąŠąĮčéčĆąŠą╗ąĖčĆčāąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą▒ąĖč鹊ą╝ čĆąĄą│ąĖčüčéčĆą░ DDR. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ čéčĆąĄą▒čāąĄčéčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ OC1x č乊čĆą╝ąĖčĆąŠą▓ą░čéčī ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čĆą░ąĘčĆčÅą┤ čĆąĄą│ąĖčüčéčĆą░ DDR (DDR_OC1x) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖąĮą░č湥 ąĘąĮą░č湥ąĮąĖąĄ OC1x ąĮąĄ ą┐ąŠčÅą▓ąĖčéčüčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐ąŠčĆčéą░. ążčāąĮą║čåąĖčÅ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠčĆčéą░ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╝ ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé Waveform Generation mode, ąĮąŠ ąĄčüčéčī ąĮąĄą║ąŠč鹊čĆčŗąĄ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ. ąŚą░ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéčÅą╝ąĖ ąŠą▒čĆą░čēą░ą╣č鹥čüčī ą║ čéą░ą▒ą╗ąĖčåą░ą╝ 19-2, 19-3 ąĖ 19-4.

ąöąĖąĘą░ą╣ąĮ ą╗ąŠą│ąĖą║ąĖ ą▓čŗą▓ąŠą┤ą░ Output Compare ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÄ čüąŠčüč鹊čÅąĮąĖčÅ OC1x ą┐ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ čĆą░ą▒ąŠčéčŗ ą▓čŗčģąŠą┤ą░. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĮąĄą║ąŠč鹊čĆčŗąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▒ąĖčé COM1x1, 0 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ čĆąĄąČąĖą╝ąŠą▓ čĆą░ą▒ąŠčéčŗ (čüą╝. ąĮąĖąČąĄ ą▓ąŠ ą▓čĆąĄąĘą║ą░čģ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓).

ąæąĖčéčŗ COM1x1, COM1x0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░čÄčé ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čāąĘąĄą╗ Input Capture.

Compare Output Mode ąĖ ą│ąĄąĮąĄčĆą░čåąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓. ąōąĄąĮąĄčĆą░č鹊čĆ čüąĖą│ąĮą░ą╗ąŠą▓ (waveform generator) ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčéčŗ COM1x1, COM1x0 ą┐ąŠ-čĆą░ąĘąĮąŠą╝čā ą▓ čĆąĄąČąĖą╝ą░čģ Normal, CTC ąĖ PWM. ąöą╗čÅ ą▓čüąĄčģ čĆąĄąČąĖą╝ąŠą▓ ąĮą░čüčéčĆąŠą╣ą║ą░ COM1x1, COM1x0 = 0 ą│ąŠą▓ąŠčĆąĖčé ą│ąĄąĮąĄčĆą░č鹊čĆčā čüąĖą│ąĮą░ą╗ąŠą▓, čćč鹊 ąĮąĄ ąĮčāąČąĮąŠ ą▓čŗą┐ąŠą╗ąĮčÅčéčī ąĮąĖą║ą░ą║ąĖčģ ą┤ąĄą╣čüčéą▓ąĖą╣ čü čĆąĄą│ąĖčüčéčĆąŠą╝ OC1x ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čüąŠą▒čŗčéąĖąĖ Compare Match. ąöą╗čÅ ą┤ąĄą╣čüčéą▓ąĖą╣, čüą▓čÅąĘą░ąĮąĮčŗčģ čü ą▓čŗą▓ąŠą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (compare output) ą▓ čĆąĄąČąĖą╝ą░čģ ąĮąĄ ą©ąśą£ (non-PWM modes) čüą╝. čéą░ą▒ą╗ąĖčåčā 19-2. ąöą╗čÅ čĆąĄąČąĖą╝ą░ ą▒čŗčüčéčĆąŠą│ąŠ ą©ąśą£ (fast PWM mode) čüą╝. čéą░ą▒ą╗ąĖčåčā 19-3, ąĖ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ą©ąśą£ čü ą║ąŠčĆčĆąĄą║čéąĮčŗą╝ąĖ čćą░čüč鹊č鹊ą╣ ąĖ čäą░ąĘąŠą╣ (čĆąĄąČąĖą╝ phase correct PWM ąĖ čĆąĄąČąĖą╝ phase and frequency correct PWM) čüą╝. čéą░ą▒ą╗ąĖčåčā 19-4.

ąśąĘą╝ąĄąĮąĄąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčé COM1x1, COM1x0 ą┤ą░čüčé čŹčäč乥ą║čé ąĮą░ ą┐ąĄčĆą▓ąŠą╝ Compare Match ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čŹčéąĖ ą▒ąĖčéčŗ ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ. ąöą╗čÅ čĆąĄąČąĖą╝ąŠą▓ ąĮąĄ ą©ąśą£ (non-PWM modes) ą┤ąĄą╣čüčéą▓ąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐čĆąĖą╝ąĄąĮąĄąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą▒ąĖčé čüčéčĆąŠą▒ą░ FOC1x.

ąĀąĄąČąĖą╝ ą▒čŗčüčéčĆąŠą│ąŠ ą©ąśą£ (fast PWM mode) ą▒ąŠą╗čīčłąĄ ą▓čüąĄą│ąŠ ą┐ąŠą┤čģąŠą┤ąĖčé ą┤ą╗čÅ čüąĖąĮč鹥ąĘą░ čüąĖą│ąĮą░ą╗ąŠą▓ ąĘą▓čāą║ąŠą▓čŗčģ čćą░čüč鹊čé. ąĀąĄąČąĖą╝čŗ čü ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ čäą░ąĘąŠą╣ (phase correct PWM ąĖ phase and frequency correct PWM) ą┐ąŠą┤ąŠą╣ą┤čāčé č鹊ą╗čīą║ąŠ ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąĖąĘą╝ąĄąĮčÅčÄčēąĖčģčüčÅ ąĖą╗ąĖ čüčéą░čéąĖčćąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ - ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā ąĮą░čüčéčĆąŠąĖą╗ ąĖ ąĘą░ą▒čŗą╗, ą▒ąĄąĘ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĮą░ ą╗ąĄčéčā ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ą¤čĆąĖčćąĖąĮą░ ą▓ č鹊ą╝, čćč鹊 ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čŹčéąĖčģ čĆąĄąČąĖą╝ąŠą▓ (ą┐ąŠ čäą╗ą░ą│čā ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĖą╗ąĖ čäą╗ą░ą│čā čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ) ą▓ ą┐čĆąĄą┤ąĄą╗čīąĮčŗčģ ąĘąĮą░č湥ąĮąĖčÅčģ čĆąĄą│čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčüčéą░ąĄčéčüčÅ čüą╗ąĖčłą║ąŠą╝ ą╝ą░ą╗ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░ ą┐čĆąŠą▓ąĄą┤ąĄąĮąĖąĄ ą║ą░ą║ąĖčģ-ą╗ąĖą▒ąŠ čüąĄčĆčīąĄąĘąĮčŗčģ ą▓čŗčćąĖčüą╗ąĄąĮąĖą╣.

[ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ]

ąĀąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ (čé. ąĄ. ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ ąĖ ą▓čŗą▓ąŠą┤ąŠą▓ Output Compare) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĄą╣ ąĮą░čüčéčĆąŠąĄą║ ą▒ąĖčé Waveform Generation mode (WGM13:0) ąĖ Compare Output mode (COM1x1, COM1x0). ąæąĖčéčŗ Compare Output mode ąĮąĖą║ą░ą║ ąĮąĄ ą▓ą╗ąĖčÅčÄčé ąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čüč湥čéą░, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą▒ąĖčéčŗ Waveform Generation mode ąĮą░ čŹč鹊 ą▓ą╗ąĖčÅčÄčé. ąæąĖčéčŗ COM1x1, COM1x0 čāą┐čĆą░ą▓ą╗čÅčÄčé, ą┤ąŠą╗ąČąĄąĮ ą╗ąĖ ą▒čŗčéčī ą▓čŗčģąŠą┤ ą©ąśą£ ą┐čĆąŠąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮ ąĖą╗ąĖ ąĮąĄčé (inverted PWM ąĖą╗ąĖ non-inverted PWM). ąöą╗čÅ ąĮąĄ ą©ąśą£ čĆąĄąČąĖą╝ąŠą▓ (non-PWM modes) ą▒ąĖčéčŗ COM1x1, COM1x0 ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą║ą░ą║ ą▒čāą┤ąĄčé ąĖąĘą╝ąĄąĮčÅčéčī čüą▓ąŠą╣ čāčĆąŠą▓ąĄąĮčī OC1x ąĮą░ čüąŠą▒čŗčéąĖčÅčģ Compare Match: čāčüčéą░ąĮąŠą▓ą║ą░, ąŠčćąĖčüčéą║ą░ ąĖą╗ąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ (čüą╝. ą┐čĆąĄą┤čŗą┤čāčēčāčÄ ą│ą╗ą░ą▓čā "ąÆčŗčģąŠą┤ Compare Match").

ą¤ąŠą┤čĆąŠą▒ąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ čü ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ą╝ąĖ ą▓čĆąĄą╝ąĄąĮąĖ čüą╝. ą│ą╗ą░ą▓čā "ąöąĖą░ą│čĆą░ą╝ą╝čŗ čüąĖą│ąĮą░ą╗ąŠą▓ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░".

Normal Mode. ąĪą░ą╝čŗą╣ ą┐čĆąŠčüč鹊ą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ čŹč鹊 čĆąĄąČąĖą╝ Normal (WGM13:0 = 0). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čüč湥čéčćąĖą║ ą▓čüąĄą│ą┤ą░ čüčćąĖčéą░ąĄčé ą▓ą▓ąĄčĆčģ (ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ), ąĖ ąŠčćąĖčüčéą║ą░ čüč湥čéčćąĖą║ą░ ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé. ąĪč湥čéčćąĖą║ ą┐čĆąŠčüč鹊 ą┐ąĄčĆąĄą▓ą░ą╗ąĖą▓ą░ąĄčé č湥čĆąĄąĘ čüą▓ąŠąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ 16-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ (MAX = 0xFFFF), ąĖ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ąĄčé čüč湥čé čüąŠ ąĘąĮą░č湥ąĮąĖčÅ BOTTOM (0x0000). ąÆ čĆąĄąČąĖą╝ąĄ Normal čäą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ Timer/Counter Overflow Flag (TOV1) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĮą░ č鹊ą╝ ąČąĄ čüą░ą╝ąŠą╝ čéą░ą╣č鹥 čéą░ą╣ą╝ąĄčĆą░, ąĮą░ ą║ąŠč鹊čĆąŠą╝ čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ TCNT1 čüčéą░ąĮąĄčé ąĮčāą╗ąĄą╝. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čäą╗ą░ą│ TOV1 ą▓ąĄą┤ąĄčé čüąĄą▒čÅ ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ 17-ą│ąŠ ą▒ąĖčéą░ čüč湥čéčćąĖą║ą░, ą║čĆąŠą╝ąĄ čüą╗čāčćą░ąĄą▓, ąĄčüą╗ąĖ ąŠąĮ č鹊ą╗čīą║ąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĖ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ąĮąĄ ąŠčćąĖčēąĄąĮ. ą×ą┤ąĮą░ą║ąŠ ą▓ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ čäą╗ą░ą│ TOV1 ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░čéčīčüčÅ, ąĖ ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī čéą░ą╣ą╝ąĄčĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čāą▓ąĄą╗ąĖč湥ąĮą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ. ąÆ čĆąĄąČąĖą╝ąĄ Normal ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ čüą╗čāčćą░ąĄą▓, čéčĆąĄą▒čāčÄčēąĖčģ čāč湥čéą░, ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ.

ąæą╗ąŠą║ Input Capture ą▓ čĆąĄąČąĖą╝ąĄ Normal ą┐čĆąŠčüčé ą▓ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ. ą×ą┤ąĮą░ą║ąŠ čĆą░čüčüą╝ąŠčéčĆąĖč鹥 čüąĖčéčāą░čåąĖąĖ, ą║ąŠą│ą┤ą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ąĖąĘą╝ąĄčĆčÅąĄą╝čŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ą▓čĆąĄą╝ąĄąĮąĖ ą┐čĆąĄą▓čŗčłą░ąĄčé čĆą░ąĘčĆąĄčłą░čÄčēčāčÄ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī čüč湥čéčćąĖą║ą░. ąĢčüą╗ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ ą╝ąĄąČą┤čā čüąŠą▒čŗčéąĖčÅą╝ąĖ čüą╗ąĖčłą║ąŠą╝ ą▒ąŠą╗čīčłąŠą╣, č鹊 čüą╗ąĄą┤čāąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ, ąĖą╗ąĖ ąĮčāąČąĮąŠ ąĮą░čüčéčĆąŠąĖčéčī ą┐čĆąĄčüą║ą░ą╗ąĄčĆ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊ą▒čŗ ąĖąĘą╝ąĄąĮąĖčéčī čĆą░ąĘčĆąĄčłą░čÄčēčāčÄ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą▒ą╗ąŠą║ą░ ąĘą░čģą▓ą░čéą░.

ąæą╗ąŠą║ąĖ Output Compare ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ ąĮąĄą║ąŠč鹊čĆąŠąĄ ąĘą░ą┤ą░ąĮąĮąŠąĄ ą▓čĆąĄą╝čÅ. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ Output Compare ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓ čĆąĄąČąĖą╝ąĄ Normal ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ, ą┐ąŠčüą║ąŠą╗čīą║čā čŹč鹊 ą▒čāą┤ąĄčé ąĘą░ąĮąĖą╝ą░čéčī čüą╗ąĖčłą║ąŠą╝ ą╝ąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü ą┤čĆčāą│ąĖą╝ąĖ čĆąĄąČąĖą╝ą░ą╝ąĖ.

Clear Timer on Compare Match (CTC) Mode. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ (ąŠčćąĖčüčéą║ą░ čéą░ą╣ą╝ąĄčĆą░ ą┐čĆąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ čüčĆą░ą▓ąĮąĄąĮąĖčÅ, WGM13:0 = 4 ąĖą╗ąĖ 12), čĆąĄą│ąĖčüčéčĆ OCR1A ąĖą╗ąĖ ICR1 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą╝ą░ąĮąĖą┐čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ čüč湥čéčćąĖą║ą░. ąÆ čĆąĄąČąĖą╝ąĄ CTC čüč湥čéčćąĖą║ ąŠčćąĖčēą░ąĄčéčüčÅ (čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą▓ 0), ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (TCNT1) čüąŠą▓ą┐ą░ą┤ą░ąĄčé ą╗ąĖą▒ąŠ čü OCR1A (WGM13:0 = 4), ą╗ąĖą▒ąŠ čü ICR1 (WGM13:0 = 12). OCR1A ąĖą╗ąĖ ICR1 ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé ą▓ąĄčĆčģąĮąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čüč湥čéčćąĖą║ą░, ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĄą│ąŠ čĆą░ąĘčĆąĄčłą░čÄčēčāčÄ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī. ąŁč鹊čé čĆąĄąČąĖą╝ ą┤ą░ąĄčé ą▒ąŠą╗čīčłąĄ ą║ąŠąĮčéčĆąŠą╗čÅ ąĮą░ą┤ ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊č鹊ą╣ Compare Match. ą×ąĮ čéą░ą║ąČąĄ čāą┐čĆąŠčēą░ąĄčé ąŠą┐ąĄčĆą░čåąĖčÄ ą┐ąŠą┤čüč湥čéą░ ą▓ąĮąĄčłąĮąĖčģ čüąŠą▒čŗčéąĖą╣.

ąØą░ čĆąĖčü. 19-6 ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ čĆą░ą▒ąŠčéčŗ ą▓ čĆąĄąČąĖą╝ąĄ CTC. ąŚąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (TCNT1) čĆą░čüč鹥čé, ą┐ąŠą║ą░ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ Compare Match čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ ą╗ąĖą▒ąŠ OCR1A, ą╗ąĖą▒ąŠ ICR1, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ čüč湥čéčćąĖą║ (TCNT1) ąŠčćąĖčēą░ąĄčéčüčÅ.

ąĀąĖčü. 19-6. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ čĆą░ą▒ąŠčéčŗ CTC Mode.

ą£ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ TOP, ą┐čāč鹥ą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čäą╗ą░ą│ą░ OCF1A ąĖą╗ąĖ ICF1, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹊ą│ąŠ, ą║ą░ą║ąŠą╣ čĆąĄą│ąĖčüčéčĆ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗čüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ TOP. ąĢčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ, č鹊 ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ISR) ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ TOP. ą×ą┤ąĮą░ą║ąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ TOP ąĮą░ ąĘąĮą░č湥ąĮąĖąĄ, ą▒ą╗ąĖąĘą║ąŠąĄ ą║ BOTTOM,

ąÜąŠą│ą┤ą░ čüč湥čéčćąĖą║ čĆą░ą▒ąŠčéą░ąĄčé ą▒ąĄąĘ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĖą╗ąĖ čü ą╝ą░ą╗čŗą╝ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą╝ ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ (čé. ąĄ. čéą░ą║čéąĖčĆčāąĄčéčüčÅ ą▓čŗčüąŠą║ąŠą╣ čćą░čüč鹊č鹊ą╣), čüą╗ąĄą┤čāąĄčé ąŠą▒čĆą░čéąĖčéčī ą▓ąĮąĖą╝ą░ąĮąĖąĄ ąĮą░ č鹊, čćč鹊 čĆąĄąČąĖą╝ CTC ąĮąĄ ąĖą╝ąĄąĄčé čäčāąĮą║čåąĖąĖ ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ. ą¤ąŠčŹč鹊ą╝čā ąĄčüą╗ąĖ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą▒čŗą╗ąŠ ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ OCR1A ąĖą╗ąĖ ICR1, ą╝ąĄąĮčīčłąĄ, č湥ą╝ č鹥ą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ TCNT1, č鹊 čüč湥čéčćąĖą║ ą┐čĆąŠą┐čāčüčéąĖčé Compare Match. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą┐čĆąŠą┐čāčüą║ą░ čüč湥čéčćąĖą║ ą┐čĆąŠą┤ąŠą╗ąČąĖčé čüč湥čé ą┤ąŠ čüą▓ąŠąĄą│ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ 16-ą▒ąĖčéąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ (0xFFFF) ąĖ ą┐ąĄčĆąĄą▓ą░ą╗ąĖčé ą▓ 0x0000 ą┐ąĄčĆąĄą┤ č鹥ą╝ ą║ą░ą║ ą▓ąŠąĘąĮąĖą║ąĮąĄčé Compare Match. ąÆąŠ ą╝ąĮąŠą│ąĖčģ čüą╗čāčćą░čÅčģ čéą░ą║ąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮčŗą╝. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąŠą╣ ą▒čāą┤ąĄčé čĆąĄąČąĖą╝ fast PWM čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ OCR1A ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ TOP (WGM13:0 = 15), ą┐ąŠčüą║ąŠą╗čīą║čā ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ OCR1A ą┐ąŠą╗čāčćąĖčé ą┤ą▓ąŠą╣ąĮčāčÄ ą▒čāč乥čĆąĖąĘą░čåąĖčÄ.

ąöą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ ą▓ čĆąĄąČąĖą╝ąĄ CTC ą▓čŗčģąŠą┤ OC1A ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĮą░ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ čüą▓ąŠąĄą│ąŠ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ Compare Match ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖč鹊ą▓ Compare Output mode ą▓ čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ (toggle mode COM1A1:0 = 1). ąŚąĮą░č湥ąĮąĖąĄ OC1A ąĮąĄ ą┐ąŠčÅą▓ąĖčéčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ą┐ąŠčĆčéą░, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čüąĖą│ąĮą░ą╗čā OC1A, ą┐ąŠą║ą░ čŹč鹊čé ą┐ąŠčĆčé ąĮąĄ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą║ą░ą║ ą▓čŗčģąŠą┤ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ čĆąĄą│ąĖčüčéčĆą░ DDR (DDR_OC1A = 1). ą£ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ fOCnA ą┐ąŠą╗čāčćąĖčéčüčÅ čĆą░ą▓ąĮąŠą╣ fclk_I/O/2, ą║ąŠą│ą┤ą░ OCR1A čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0 (0x0000). ą¦ą░čüč鹊čéą░ ą▓čŗčģąŠą┤ą░ fOCnA ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

fclk_I/O

fOC1A = -------------------

2 ┬Ę N ┬Ę (1 + OCR1A)

N ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ (1, 8, 64, 256 ąĖą╗ąĖ 1024).

ąÜą░ą║ ąĖ ą▓ čĆąĄąČąĖą╝ąĄ Normal, čäą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ TOV1 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĮą░ č鹊ą╝ ąČąĄ čüą░ą╝ąŠą╝ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░, ąĮą░ ą║ąŠč鹊čĆąŠą╝ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą┐ąĄčĆąĄą╣ą┤ąĄčé ąŠčé MAX ą║ 0x0000.

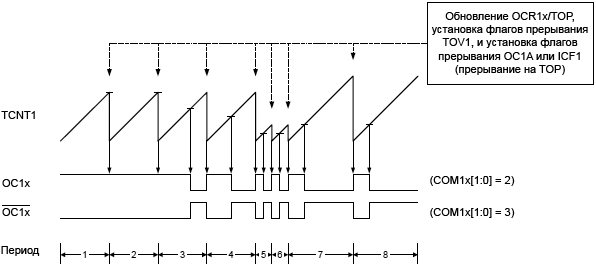

Fast PWM Mode. ąĀąĄąČąĖą╝ ą▒čŗčüčéčĆąŠą╣ ą©ąśą£ (fast Pulse Width Modulation, ąĖą╗ąĖ fast PWM mode, WGM13:0 = 5, 6, 7, 14 ąĖą╗ąĖ 15) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąŠą┐čåąĖčÄ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą©ąśą£ ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╣ čćą░čüč鹊čéčŗ. Fast PWM ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé ą┤čĆčāą│ąĖčģ ąŠą┐čåąĖą╣ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą©ąśą£ čüą▓ąŠąĖą╝ ąŠą┤ąĮąŠčéą░ą║čéąĮčŗą╝ ą┐čĆąĖąĮčåąĖą┐ąŠą╝ čĆą░ą▒ąŠčéčŗ. ąĪč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ąŠčé BOTTOM ą┤ąŠ TOP, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ čüąŠ ąĘąĮą░č湥ąĮąĖčÅ BOTTOM. ąÆ čĆąĄąČąĖą╝ąĄ ąĮąĄ ąĖąĮą▓ąĄčĆčüąĮąŠą│ąŠ ą▓čŗą▓ąŠą┤ą░ ą┐čĆąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (noninverting Compare Output mode) ą▓čŗčģąŠą┤ Output Compare (OC1x) ąŠčćąĖčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ Compare Match ą╝ąĄąČą┤čā TCNT1 ąĖ OCR1x, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĮą░ ąĘąĮą░č湥ąĮąĖąĖ BOTTOM. ąÆ čĆąĄąČąĖą╝ąĄ ąĖąĮą▓ąĄčĆčüąĖąĖ (inverting Compare Output mode) ą▓čüąĄ ąĮą░ąŠą▒ąŠčĆąŠčé, ą▓čŗčģąŠą┤ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐čĆąĖ Compare Match, ąĖ čüą▒čĆąŠčüąĖčéčüčÅ ąĮą░ BOTTOM. ąśąĘ-ąĘą░ ąŠą┤ąĮąŠčéą░ą║čéąĮąŠą│ąŠ ą┐čĆąĖąĮčåąĖą┐ą░ čĆą░ą▒ąŠčéčŗ čćą░čüč鹊čéą░ ą©ąśą£ ą▓ čĆąĄąČąĖą╝ąĄ fast PWM ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ 2 čĆą░ąĘą░ ą▓čŗčłąĄ, č湥ą╝ ą▓ čĆąĄąČąĖą╝ą░čģ phase correct PWM ąĖ phase and frequency correct PWM, ą║ąŠč鹊čĆčŗąĄ čĆą░ą▒ąŠčéą░čÄčé ą┐ąŠ ą┤ą▓čāčģčéą░ą║čéąĮąŠą╝čā ą┐čĆąĖąĮčåąĖą┐čā. ąŁčéą░ ą▓čŗčüąŠą║ą░čÅ čćą░čüč鹊čéą░ ą┤ąĄą╗ą░ąĄčé čĆąĄąČąĖą╝ fast PWM čģąŠčĆąŠčłąŠ ą┐ąŠą┤čģąŠą┤čÅčēąĖą╝ ą┤ą╗čÅ čĆąĄą│čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠčēąĮąŠčüčéąĖ, ą▓čŗą┐čĆčÅą╝ą╗ąĄąĮąĖčÅ č鹊ą║ą░ ąĖ ąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ ą”ąÉą¤ (DAC). ąÆčŗčüąŠą║ą░čÅ čćą░čüč鹊čéą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąĖą╝ąĄąĮčÅčéčī ą▓ąĮąĄčłąĮąĖąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ (ąĖąĮą┤čāą║čéąĖą▓ąĮąŠčüčéąĖ, ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčŗ) ą╝ą░ą╗čŗčģ čĆą░ąĘą╝ąĄčĆąŠą▓, čāą╝ąĄąĮčīčłą░čÅ ąŠą▒čēčāčÄ čüč鹊ąĖą╝ąŠčüčéčī čüąĖčüč鹥ą╝čŗ.

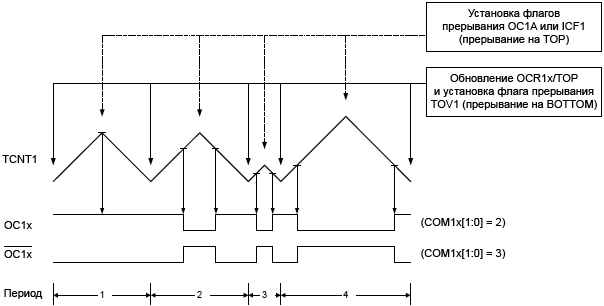

ąĀą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī fast PWM ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░čäąĖą║čüąĖčĆąŠą▓ą░ąĮą░ ąĮą░ 8, 9 ąĖą╗ąĖ 10 ą▒ąĖčéą░čģ, ąĖą╗ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą╗ąĖą▒ąŠ ICR1, ą╗ąĖą▒ąŠ OCR1A. ą£ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ ą┤ąŠą┐čāčüčéąĖą╝ą░čÅ čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī čüąŠčüčéą░ą▓ą╗čÅąĄčé 2 ą▒ąĖčéą░ (ICR1 ąĖą╗ąĖ OCR1A ą▓ ąĘąĮą░č湥ąĮąĖąĖ 0x0003), ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ 16 ą▒ąĖčé (ICR1 ąĖą╗ąĖ OCR1A ą▓ ąĘąĮą░č湥ąĮąĖąĖ MAX). ąĀą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą©ąśą£ ą▓ ą▒ąĖčéą░čģ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

log(TOP+1)

RFPWM = -------------

log(2)

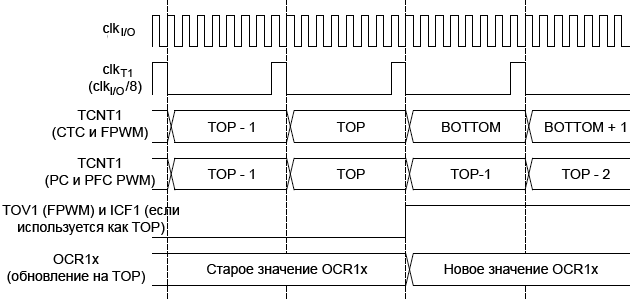

ąÆ čĆąĄąČąĖą╝ąĄ fast PWM čüč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ, ą┐ąŠą║ą░ ąĄą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ ąĮąĄ ą┤ąŠčüčéąĖą│ąĮąĄčé ąŠą┤ąĮąŠą│ąŠ ąĖąĘ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ 0x00FF, 0x01FF ąĖą╗ąĖ 0x03FF (WGM13:0 = 5, 6 ąĖą╗ąĖ 7), ąĘąĮą░č湥ąĮąĖčÅ ą▓ ICR1 (WGM13:0 = 14), ąĖą╗ąĖ ąĘąĮą░č湥ąĮąĖčÅ ą▓ OCR1A (WGM13:0 = 15). ąŚą░č鹥ą╝ čüč湥čéčćąĖą║ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░. ąöąĖą░ą│čĆą░ą╝ą╝ą░ čĆąĄąČąĖą╝ą░ fast PWM ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 19-7 ąĮąĖąČąĄ. ąŚą┤ąĄčüčī ą┐ąŠą║ą░ąĘą░ąĮ čĆąĄąČąĖą╝ fast PWM, ą║ąŠą│ą┤ą░ OCR1A ąĖą╗ąĖ ICR1 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ TOP. ąŚąĮą░č湥ąĮąĖąĄ TCNT1 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ ą│ąĖčüč鹊ą│čĆą░ą╝ą╝ąĄ, čćč鹊ą▒čŗ ą┐čĆąŠąĖą╗ą╗čÄčüčéčĆąĖčĆąŠą▓ą░čéčī ąĄą│ąŠ ąŠą┤ąĮąŠčéą░ą║čéąĮčŗą╣ ą┐čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ. ąŁčéą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą▓ą║ą╗čÄčćą░ąĄčé ąĮąĄ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ (non-inverted PWM) ąĖ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ (inverted PWM) ą▓čŗčģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą©ąśą£. ą£ą░ą╗ąĄąĮčīą║ąĖąĄ ą│ąŠčĆąĖąĘąŠąĮčéą░ą╗čīąĮčŗąĄ č湥čĆč鹊čćą║ąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ ą╝ąĄąČą┤čā ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ OCR1x ąĖ TCNT1. ążą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ OC1x čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé Compare Match.

ąĀąĖčü. 19-7. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ Fast PWM Mode.

ążą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░ TOV1 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé TOP. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ OCF1A ąĖą╗ąĖ ICF1 ąĮą░ č鹊ą╝ ąČąĄ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░, ąĮą░ ą║ą░ą║ąŠą╝ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ TOV1, ą║ąŠą│ą┤ą░ ą╗ąĖą▒ąŠ OCR1A, ą╗ąĖą▒ąŠ ICR1 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ TOP. ąĢčüą╗ąĖ ąŠą┤ąĮąŠ ąĖąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čĆą░ąĘčĆąĄčłąĄąĮąŠ, ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ TOP ąĖ ąĘąĮą░č湥ąĮąĖčÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ.

ąÜąŠą│ą┤ą░ ą╝ąĄąĮčÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ TOP, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ TOP ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠ ąĘąĮą░č湥ąĮąĖčÄ ą▓čüąĄčģ čĆąĄą│ąĖčüčéčĆąŠą▓ čüčĆą░ą▓ąĮąĄąĮąĖčÅ. ąĢčüą╗ąĖ TOP ą╝ąĄąĮčīčłąĄ, č湥ą╝ ą╗čÄą▒ąŠą╣ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ Compare, č鹊 čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ Compare Match ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐čĆąĖ čüč湥č鹥 ą╝ąĄąČą┤čā TCNT1 ąĖ OCR1x. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ TOP, č鹊 ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▒ąĖčéčŗ ą╝ą░čüą║ąĖčĆčāčÄčéčüčÅ ąĮčāą╗čÅą╝ąĖ, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą╗čÄą▒ąŠą╣ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ OCR1x (čé. ąĄ. ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ TOP čāčüą╗ąŠą▓ąĖąĄ TOP >= OCR1x ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ).

ą¤čĆąŠčåąĄą┤čāčĆą░ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ICR1 ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ OCR1A, ą║ąŠą│ą┤ą░ ąŠąĮąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ TOP. ąĀąĄą│ąĖčüčéčĆ ICR1 ąĮąĄ ąĖą╝ąĄąĄčé ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĄčüą╗ąĖ ICR1 ą╝ąĄąĮčÅąĄčéčüčÅ ąĮą░ ą╝ą░ą╗ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ čĆą░ą▒ąŠčéą░ąĄčé ą▒ąĄąĘ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĖą╗ąĖ čü ą╝ą░ą╗čŗą╝ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą╝ ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░, č鹊 ąĄčüčéčī čĆąĖčüą║, čćč鹊 ąĮąŠą▓ąŠąĄ ąĘą░ą┐ąĖčüą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ICR1 ąŠą║ą░ąČąĄčéčüčÅ ą╝ąĄąĮčīčłąĄ č鹥ą║čāčēąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ TCNT1. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 čüč湥čéčćąĖą║ ą┐čĆąŠą┐čāčüčéąĖčé Compare Match ąĮą░ čŹč鹊ą╝ ąĘąĮą░č湥ąĮąĖąĖ TOP, ą┐čĆąŠą┤ąŠą╗ąČą░čÅ čüč湥čé ą┤ąŠ ąĘąĮą░č湥ąĮąĖčÅ MAX (0xFFFF) ąĖ ą▓ąĄčĆąĮąĄčéčüčÅ ą║ ąĮą░čćą░ą╗čīąĮąŠą╝čā ąĘąĮą░č湥ąĮąĖčÄ 0x0000 ą┐ąĄčĆąĄą┤ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖąĄą╝ Compare Match. ą×ą┤ąĮą░ą║ąŠ čĆąĄą│ąĖčüčéčĆ OCR1A ąĖą╝ąĄąĄčé ą┤ą▓ąŠą╣ąĮčāčÄ ą▒čāč乥čĆąĖąĘą░čåąĖčÄ. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▒ąĄąĘąŠą┐ą░čüąĮąŠ ąĘą░ą┐ąĖčüą░čéčī I/O čÅč湥ą╣ą║čā OCR1A ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ. ąÜąŠą│ą┤ą░ I/O čÅč湥ą╣ą║ą░ OCRnA ąĘą░ą┐ąĖčüą░ąĮą░, ąĘą░ą┐ąĖčüą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒čāą┤ąĄčé ą┐ąŠą╝ąĄčēąĄąĮąŠ ą▓ ą▒čāč乥čĆąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ OCR1A. ąŚą░č鹥ą╝ čĆąĄą│ąĖčüčéčĆ OCR1A Compare ą▒čāą┤ąĄčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮ ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖąĘ ą▒čāč乥čĆąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ TCNT1 čüąŠą▓ą┐ą░ą┤ąĄčé čü TOP. ą×ą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąĮą░ č鹊ą╝ ąČąĄ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░, ąĮą░ ą║ą░ą║ąŠą╝ ąŠčćąĖčüčéąĖčéčüčÅ TCNT1 ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ TOV1.

ąĀąĄą│ąĖčüčéčĆ ICR1 ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ TOP čģąŠčĆąŠčłąŠ čĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ TOP (čé. ąĄ. ą║ąŠą│ą┤ą░ ICR1 ą┐ąŠčüč鹊čÅąĮąĮąŠ ąĖ ąĮąĄ ą╝ąĄąĮčÅąĄčéčüčÅ). ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ICR1 čĆąĄą│ąĖčüčéčĆ OCR1A čüą▓ąŠą▒ąŠą┤ąĄąĮ ą┤ą╗čÅ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ ą▓ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĖ ą©ąśą£-čüąĖą│ąĮą░ą╗ą░ ąĮą░ OC1A. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ą▒ą░ąĘąŠą▓ą░čÅ čćą░čüč鹊čéą░ ą©ąśą£ ą░ą║čéąĖą▓ąĮąŠ ą╝ąĄąĮčÅąĄčéčüčÅ (ą┐čāč鹥ą╝ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ TOP), č鹊 ąŠč湥ą▓ąĖą┤ąĮąŠ, čćč鹊 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ OCR1A ą▓ ą║ą░č湥čüčéą▓ąĄ TOP ąĮą░ą╝ąĮąŠą│ąŠ ą▒ąŠą╗ąĄąĄ ą╗čāčćčłąĖą╣ ą▓čŗą▒ąŠčĆ, ą┐ąŠč鹊ą╝čā čćč鹊 OCR1A ąĖą╝ąĄąĄčé ą┤ą▓ąŠą╣ąĮčāčÄ ą▒čāč乥čĆąĖąĘą░čåąĖčÄ.

ąÆ čĆąĄąČąĖą╝ąĄ fast PWM čāąĘą╗čŗ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čüąĖą│ąĮą░ą╗čŗ ą©ąśą£ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ OC1x. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖč鹊ą▓ COM1x1, COM1x0 ą▓ ąĘąĮą░č湥ąĮąĖąĄ 2 ą▒čāą┤ąĄčé ą┤ą░ą▓ą░čéčī ąĮąĄ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ ą©ąśą£ (non-inverted PWM), ąĖ ą┐čĆąĖ čāčüčéą░ąĮąŠą▓ą║ąĄ COM1x1, COM1x0 ą▓ ąĘąĮą░č湥ąĮąĖąĄ 3 ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ ą©ąśą£ (inverted PWM), čüą╝. čéą░ą▒ą╗ąĖčåčā 19-3. ąĪąĖą│ąĮą░ą╗ OC1x ą┐ąŠčÅą▓ąĖčéčüčÅ ąĮą░ ąĮąŠąČą║ąĄ ą┐ąŠčĆčéą░ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ ąĄą│ąŠ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ąĮą░čüčéčĆąŠąĄąĮąŠ čĆąĄą│ąĖčüčéčĆąŠą╝ DDR ą║ą░ą║ ą▓čŗčģąŠą┤ (ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ąĄą┤ąĖąĮąĖčåčā čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé DDR_OC1x). ąĪąĖą│ąĮą░ą╗čŗ ą©ąśą£ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ (ąĖą╗ąĖ ąŠčćąĖčüčéą║ąŠą╣) OC1x ą┐čĆąĖ Compare Match (čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ) ą╝ąĄąČą┤čā OCR1x ąĖ TCNT1, ąĖ ąŠčćąĖčüčéą║ąŠą╣ (ąĖą╗ąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣) OC1x ąĮą░ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░, ą║ąŠą│ą┤ą░ ąĄą│ąŠ čüč湥čéčćąĖą║ ąŠčćąĖčēą░ąĄčéčüčÅ (ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą╝ąĄąĮčÅąĄčé čüą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąŠčé TOP ą║ BOTTOM).

ą¦ą░čüč鹊čéą░ ą©ąśą£ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗčćąĖčüą╗ąĄąĮą░ ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╣ č乊čĆą╝čāą╗ąĄ:

fclk_I/O

fOC1xPWM = -------------

N ┬Ę (1 + TOP)

N ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ (1, 8, 64, 256 ąĖą╗ąĖ 1024).

ą¤čĆąĄą┤ąĄą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ OCR1x ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ čüą╗čāčćą░ąĖ, ą║ąŠą│ą┤ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą©ąśą£ ą▓ čĆąĄąČąĖą╝ąĄ fast PWM. ąĢčüą╗ąĖ OCR1x čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čĆą░ą▓ąĮčŗą╝ BOTTOM (0x0000), č鹊 ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐ąŠą╗čāčćą░čéčüčÅ ą║ąŠčĆąŠčéą║ąĖąĄ ą┐ąĖą║ąĖ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ TOP+1 čéą░ą║čéą░ čéą░ą╣ą╝ąĄčĆą░. ąŻčüčéą░ąĮąŠą▓ą║ą░ OCR1x čĆą░ą▓ąĮčŗą╝ TOP ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā čāčĆąŠą▓ąĮčÄ ą╗ąŠą│. 1 ąĖą╗ąĖ ą╗ąŠą│. 0 (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ/ąĖąĮą▓ąĄčĆčüąĖąĖ OC1x, čćč鹊 čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ COM1x1, COM1x0).

ąōąĄąĮąĄčĆą░čåąĖčÅ čćą░čüč鹊čéčŗ ą┐čĆčÅą╝ąŠčāą│ąŠą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (čüąŠ čüą║ą▓ą░ąČąĮąŠčüčéčīčÄ 50%) ą▓ čĆąĄąČąĖą╝ąĄ fast PWM ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮą░ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ OC1A ą▓ čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ Compare Match (COM1A1:0 = 1). ąŁč鹊 ą┐čĆąĖą╝ąĄąĮąĖą╝ąŠ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ OCR1A ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ TOP (WGM13:0 = 15). ąōąĄąĮąĄčĆąĖčĆčāąĄą╝čŗą╣ čüąĖą│ąĮą░ą╗ ą▒čāą┤ąĄčé ąĖą╝ąĄčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ čćą░čüč鹊čéčā fOC1A = fclk_I/O/2, ą║ąŠą│ą┤ą░ OCR1A čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ąĮąŠą╗čī (0x0000). ąŁčéą░ čäčāąĮą║čåąĖčÅ ą┐ąŠą┤ąŠą▒ąĮą░ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÄ OC1A ąĮą░ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ CTC, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ č鹊ą│ąŠ, čćč鹊 ą▓ čĆąĄąČąĖą╝ąĄ fast PWM čĆą░ąĘčĆąĄčłąĄąĮą░ čäčāąĮą║čåąĖčÅ ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ ą▓ čāąĘą╗ąĄ Output Compare.

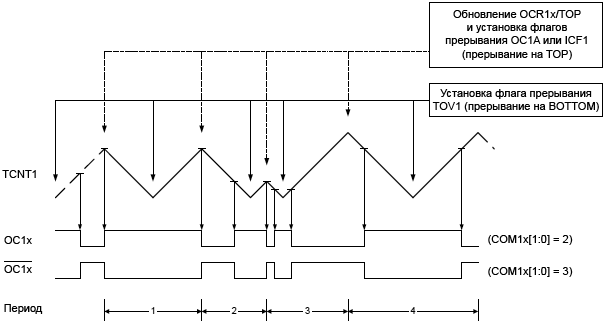

Phase Correct PWM Mode. ąĀąĄąČąĖą╝ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą©ąśą£ čü ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ čäą░ąĘąŠą╣ (phase correct PWM mode, WGM13:0 = 1, 2, 3, 10 ąĖą╗ąĖ 11) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąŠą┐čåąĖčÄ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą║ą░č湥čüčéą▓ąĄąĮąĮąŠą│ąŠ ą©ąśą£ čü ą▓čŗčüąŠą║ąŠą╣ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ. ąĀąĄąČąĖą╝ phase correct PWM, ą║ą░ą║ ąĖ čĆąĄąČąĖą╝ phase and frequency correct PWM, ąŠčüąĮąŠą▓ą░ąĮ ąĮą░ ą┤ą▓čāčģčéą░ą║čéąĮąŠą╝ ą┐čĆąĖąĮčåąĖą┐ąĄ čĆą░ą▒ąŠčéčŗ. ąĪč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé čüąĮą░čćą░ą╗ą░ ąŠčé BOTTOM (0x0000) ą┤ąŠ TOP, ąĖ ąĘą░č鹥ą╝ ąŠą▒čĆą░čéąĮąŠ ąŠčé TOP ą┤ąŠ BOTTOM. ąÆ ąĮąĄ ąĖąĮą▓ąĄčĆčüąĮąŠą╝ (non-inverting Compare Output) čĆąĄąČąĖą╝ąĄ ą▓čŗčģąŠą┤ Output Compare (OC1x) ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ Compare Match ą╝ąĄąČą┤čā TCNT1 ąĖ OCR1x, ą║ąŠą│ą┤ą░ ąĖą┤ąĄčé čüč湥čé ą▓ą▓ąĄčĆčģ, ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐čĆąĖ Compare Match, ą║ąŠą│ą┤ą░ ąĖą┤ąĄčé čüč湥čé ą▓ąĮąĖąĘ. ąÆ ąĖąĮą▓ąĄčĆčüąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą▓čüąĄ ąĮą░ąŠą▒ąŠčĆąŠčé. ąöą▓čāčģčéą░ą║čéąĮčŗą╣ ą┐čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ ą┐ąŠąĮąĖąČą░ąĄčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ čĆą░ą▒ąŠčćčāčÄ čćą░čüč鹊čéčā ą©ąśą£ ą▓ą┤ą▓ąŠąĄ ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü ąŠą┤ąĮąŠčéą░ą║čéąĮčŗą╝ ą┐čĆąĖąĮčåąĖą┐ąŠą╝. ą×ą┤ąĮą░ą║ąŠ ąĖąĘ-ąĘą░ čüąĖą╝ą╝ąĄčéčĆąĖčćąĮąŠčüčéąĖ čüč湥čéą░ ą▓ ą┤ą▓čāčģčéą░ą║čéąĮčŗčģ čĆąĄąČąĖą╝ą░čģ ą©ąśą£ čŹčéąĖ čĆąĄąČąĖą╝čŗ ą╗čāčćčłąĄ ą▓čüąĄą│ąŠ ą┐ąŠą┤čģąŠą┤čÅčé ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╝ąŠč鹊čĆą░ą╝ąĖ.

ąĀą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą©ąśą£ ą▓ čĆąĄąČąĖą╝ąĄ phase correct PWM ą╝ąŠąČąĄčé ą▒čŗčéčī čäąĖą║čüąĖčĆąŠą▓ą░ąĮą░ ąĮą░ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ 8, 9 ąĖą╗ąĖ 10 ą▒ąĖčé, ąĖą╗ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ ICR1 ąĖą╗ąĖ OCR1A. ą£ąĖąĮąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ą░čÅ čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī 2 čĆą░ąĘčĆčÅą┤ą░ (ICR1 ąĖą╗ąĖ OCR1A ą▓ ąĘąĮą░č湥ąĮąĖąĖ 0x0003), ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī 16 čĆą░ąĘčĆčÅą┤ąŠą▓ (ICR1 ąĖą╗ąĖ OCR1A ą▓ ąĘąĮą░č湥ąĮąĖąĖ MAX). ąĀą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą©ąśą£ ą▓ ą▒ąĖčéą░čģ č鹊ą│ą┤ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░čüčüčćąĖčéą░ąĮą░ ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╣ č乊čĆą╝čāą╗ąĄ:

log(TOP+1)

RPCPWM = -------------

log(2)

ąÆ čĆąĄąČąĖą╝ąĄ phase correct PWM čüč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ą┤ąŠčüčéąĖą│ąĮąĄčé ąŠą┤ąĮąŠą│ąŠ ąĖąĘ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ 0x00FF, 0x01FF ąĖą╗ąĖ 0x03FF (WGM13:0 = 1, 2 ąĖą╗ąĖ 3), ąĘąĮą░č湥ąĮąĖčÅ ICR1 (WGM13:0 = 10) ąĖą╗ąĖ ąĘąĮą░č湥ąĮąĖčÅ OCR1A (WGM13:0 = 11). ą¤ąŠ ą┤ąŠčüčéąĖąČąĄąĮąĖąĖ TOP čüč湥čéčćąĖą║ ą╝ąĄąĮčÅąĄčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüč湥čéą░. ąŚąĮą░č湥ąĮąĖąĄ TCNT1 ą▒čāą┤ąĄčé čĆą░ą▓ąĮąŠ TOP ą▓ č鹥č湥ąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ čéą░ą║čéą░ čéą░ą╣ą╝ąĄčĆą░. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ phase correct PWM ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 19-8. ąŁč鹊čé čĆąĖčüčāąĮąŠą║ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čĆąĄąČąĖą╝ phase correct PWM, ą║ąŠą│ą┤ą░ OCR1A ąĖą╗ąĖ ICR1 ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ TOP. ąŚąĮą░č湥ąĮąĖąĄ TCNT1 ąĮą░ čŹč鹊ą╣ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą║ą░ą║ ą│ąĖčüč鹊ą│čĆą░ą╝ą╝ą░ ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖą╗ą╗čÄčüčéčĆą░čåąĖąĖ ą┤ą▓čāčģčéą░ą║čéąĮąŠą│ąŠ ą┐čĆąĖąĮčåąĖą┐ą░ čĆą░ą▒ąŠčéčŗ. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓ą║ą╗čÄčćą░ąĄčé ąĮąĄ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ ąĖ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ ą▓čŗčģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą©ąśą£. ą£ą░ą╗ąĄąĮčīą║ąĖąĄ ą│ąŠčĆąĖąĘąŠąĮčéą░ą╗čīąĮčŗąĄ č湥čĆč鹊čćą║ąĖ ąĮą░ čüą║ą╗ąŠąĮą░čģ ą│ąĖčüč鹊ą│čĆą░ą╝ą╝čŗ ąŠą▒ąŠąĘąĮą░čćą░čÄčé ąĘąĮą░č湥ąĮąĖčÅ TCNT1, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤čÅčé čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ ą╝ąĄąČą┤čā OCR1x ąĖ TCNT1. ążą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ OCF1x čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé Compare Match.

ąĀąĖčü. 19-8. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ Phase Correct PWM Mode.

ążą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ TOV1 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ąĮąĄčé BOTTOM. ąÜąŠą│ą┤ą░ ą╗ąĖą▒ąŠ OCR1A, ą╗ąĖą▒ąŠ ICR1 ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ TOP, čäą╗ą░ą│ąĖ OC1A ąĖą╗ąĖ ICF1 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ čāčüčéą░ąĮąŠą▓čÅčéčüčÅ ąĮą░ č鹊ą╝ ąČąĄ čüą░ą╝ąŠą╝ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░, ąĮą░ ą║ą░ą║ąŠą╝ čĆąĄą│ąĖčüčéčĆčŗ OCR1x ąŠą▒ąĮąŠą▓čÅčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖąĘ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ ą▒čāč乥čĆą░ (ąĮą░ TOP). ążą╗ą░ą│ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ TOP ąĖą╗ąĖ BOTTOM.

ąÜąŠą│ą┤ą░ ą╝ąĄąĮčÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ TOP, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ TOP ąŠą║ą░ąČąĄčéčüčÅ ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠ ąĘąĮą░č湥ąĮąĖčÄ ą▓čüąĄčģ čĆąĄą│ąĖčüčéčĆąŠą▓ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (Compare Registers). ąĢčüą╗ąĖ TOP ą▒čāą┤ąĄčé ą╝ąĄąĮčīčłąĄ, č湥ą╝ ą╗čÄą▒ąŠą╣ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ čüčĆą░ą▓ąĮąĄąĮąĖčÅ, č鹊 Compare Match ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą╝ąĄąČą┤čā TCNT1 ąĖ OCR1x. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ TOP, č鹊 ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ čĆąĄą│ąĖčüčéčĆčŗ OCR1x, ąĖčģ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▒ąĖčéčŗ ą╝ą░čüą║ąĖčĆčāčÄčéčüčÅ ąĮčāą╗čÅą╝ąĖ. ąÜą░ą║ ąĖą╗ą╗čÄčüčéčĆąĖčĆčāąĄčé čéčĆąĄčéąĖą╣ ą┐ąĄčĆąĖąŠą┤ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ čĆąĖčü. 19-8, ą░ą║čéąĖą▓ąĮąŠąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ TOP, ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ Phase Correct, ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄčüąĖą╝ą╝ąĄčéčĆąĖčćąĮąŠą╝čā ą▓čŗčģąŠą┤ąĮąŠą╝čā čüąĖą│ąĮą░ą╗čā. ą¤čĆąĖčćąĖąĮčā čŹč鹊ą│ąŠ ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą▓ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ OCR1x. ą¤ąŠčüą║ąŠą╗čīą║čā ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ OCR1x ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĮą░ TOP, ą┐ąĄčĆąĖąŠą┤ PWM ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąĖ ąĘą░ą║ą░ąĮčćąĖą▓ą░ąĄčéčüčÅ ąĮą░ TOP. ąŁč鹊 ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé, čćč鹊 ą┤ą╗ąĖąĮą░ ą┐ą░ą┤ą░čÄčēąĄą│ąŠ čüą║ą╗ąŠąĮą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐čĆąĄą┤čŗą┤čāčēąĖą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ TOP, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┤ą╗ąĖąĮą░ čüą║ą╗ąŠąĮą░ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąĮąŠą▓čŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ TOP. ąÜąŠą│ą┤ą░ čŹčéąĖ ą┤ą▓ą░ ąĘąĮą░č湥ąĮąĖčÅ čĆą░ąĘą╗ąĖčćą░čÄčéčüčÅ ą┤ą╗čÅ ą┤ą▓čāčģ čüą║ą╗ąŠąĮąŠą▓, ą┤ą▓ą░ ąĮą░ą║ą╗ąŠąĮą░ ą┐ąĄčĆąĖąŠą┤ą░ ą▒čāą┤čāčé ąŠčéą╗ąĖčćą░čéčīčüčÅ ą┐ąŠ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ. ąŁčéą░ čĆą░ąĘąĮąĖčåą░ ą▓ ą┤ą╗ąĖąĮąĄ ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąĮąĄčüąĖą╝ą╝ąĄčéčĆąĖčćąĮąŠą╝čā ą▓čŗčģąŠą┤ąĮąŠą╝čā čüąĖą│ąĮą░ą╗čā.

ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čĆąĄąČąĖą╝ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ čäą░ąĘčŗ ąĖ čćą░čüč鹊čéčŗ (Phase and Frequency Correct mode) ą▓ą╝ąĄčüč鹊 čĆąĄąČąĖą╝ą░ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ čäą░ąĘčŗ (Phase Correct mode), ą║ąŠą│ą┤ą░ ą╝ąĄąĮčÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ TOP ą▓ ą┐čĆąŠčåąĄčüčüąĄ čüč湥čéą░ čéą░ą╣ą╝ąĄčĆą░ čüč湥čéčćąĖą║ą░. ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüčéą░čéąĖč湥čüą║ąŠąĄ TOP (čé. ąĄ. ąĮąĄ ąĖąĘą╝ąĄąĮčÅčÄčēąĄąĄčüčÅ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĄą┤ąĄą╗ą░ čüč湥čéą░), č鹊 ą┐čĆą░ą║čéąĖč湥čüą║ąĖ ąĮąĄčé ąĮąĖą║ą░ą║ąŠą╣ čĆą░ąĘąĮąĖčåčŗ ą▓ čĆą░ą▒ąŠč鹥 čŹčéąĖčģ ą┤ą▓čāčģ čĆąĄąČąĖą╝ąŠą▓.

ąÆ čĆąĄąČąĖą╝ąĄ phase correct PWM čāąĘą╗čŗ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ čüąĖą│ąĮą░ą╗ąŠą▓ ą©ąśą£ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ OC1x. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé COM1x1, COM1x0 ą▓ ąĘąĮą░č湥ąĮąĖąĄ 2 ą┤ą░čüčé ąĮąĄ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ ą©ąśą£ (non-inverted PWM), ąĖ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ ą©ąśą£ (inverted PWM) ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ COM1x1, COM1x0 ą▓ ąĘąĮą░č湥ąĮąĖąĄ 3 (čüą╝. čéą░ą▒ą╗ąĖčåčā 19-4). ąĪąĖą│ąĮą░ą╗ OC1x ą┐ąŠčÅą▓ąĖčéčüčÅ ąĮą░ ąĮąŠąČą║ąĄ ą┐ąŠčĆčéą░ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ ąĄą│ąŠ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ąĮą░čüčéčĆąŠąĄąĮąŠ čĆąĄą│ąĖčüčéčĆąŠą╝ DDR ą║ą░ą║ ą▓čŗčģąŠą┤ (ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ąĄą┤ąĖąĮąĖčåčā čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé DDR_OC1x). ąĪąĖą│ąĮą░ą╗ ą©ąśą£ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ (ąĖą╗ąĖ ąŠčćąĖčüčéą║ąŠą╣) OC1x ąĮą░ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ Compare Match ą╝ąĄąČą┤čā OCR1x ąĖ TCNT1, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą▓ą▓ąĄčĆčģ, ąĖ ąŠčćąĖčēą░ąĄčé (ąĖą╗ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé) OC1x ąĮą░ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ Compare Match ą╝ąĄąČą┤čā OCR1x ąĖ TCNT1, ą║ąŠą│ą┤ą░ čüčćąĖčéčćąĖą║ čüčćąĖčéą░ąĄčé ą▓ąĮąĖąĘ. ą¦ą░čüč鹊čéą░ ą©ąśą£ ąĮą░ ą▓čŗčģąŠą┤ąĄ, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ phase correct PWM, ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗčćąĖčüą╗ąĄąĮą░ ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╣ č乊čĆą╝čāą╗ąĄ:

fclk_I/O

fOC1xPCPWM = -------------

2 ┬Ę N ┬Ę TOP

N ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ (1, 8, 64, 256 ąĖą╗ąĖ 1024).

ą¤čĆąĄą┤ąĄą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ OCR1x ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ čüą╗čāčćą░ąĖ, ą║ąŠą│ą┤ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą©ąśą£ ą▓ čĆąĄąČąĖą╝ąĄ phase correct PWM. ąĢčüą╗ąĖ OCR1x čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ čĆą░ą▓ąĮčŗą╝ BOTTOM, č鹊 ąĮą░ ą▓čŗčģąŠą┤ąĄ ą▒čāą┤ąĄčé ą┐ąŠčüč鹊čÅąĮąĮčŗą╣ ą╗ąŠą│. 0, ąĖ ąĄčüą╗ąĖ OCR1x čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ čĆą░ą▓ąĮčŗą╝ ąĘąĮą░č湥ąĮąĖčÄ TOP č鹊 ąĮą░ ą▓čŗčģąŠą┤ąĄ ą▒čāą┤ąĄčé ą┐ąŠčüč鹊čÅąĮąĮąŠ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ ą©ąśą£ ąĮąĄ ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮ (non-inverted PWM). ąöą╗čÅ ąĖąĮą▓ąĄčĆčüąĮąŠą│ąŠ ą©ąśą£ čŹčéąĖ ą▓čŗčģąŠą┤ąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠą╝ąĄąĮčÅčÄčéčüčÅ ąĮą░ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗąĄ.

ąĢčüą╗ąĖ OCR1A ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ TOP (WGM13:0 = 11), ąĖ COM1A1:0 = 1, č鹊 ą▓čŗčģąŠą┤ OC1A ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ čüąŠ čüą║ą▓ą░ąČąĮąŠčüčéčīčÄ 50%.