|

ąĪąĖčüč鹥ą╝ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖąĄą╝ (Power Management) ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AT90USB162 (ąĖ AT90USB82) ąĖą╝ąĄąĄčé 5 čĆąĄąČąĖą╝ąŠą▓ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (ąĖą╗ąĖ čĆąĄąČąĖą╝ąŠą▓ čüąĮą░, Sleep Modes) - Idle, Power-save, Power-down, Standby ąĖ Extended Standby. ą×ąĮąĖ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą║ąŠą┤čā firmware ą▓čŗą║ą╗čÄčćą░čéčī ąĮąĄąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą╝ąŠą┤čāą╗ąĖ MCU, čćč鹊 菹║ąŠąĮąŠą╝ąĖčé ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝čāčÄ čŹąĮąĄčĆą│ąĖčÄ. ąĀąĄąČąĖą╝čŗ čüąĮą░ ąĖ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ čüą▓čÅąĘą░ąĮčŗ čü čĆą░ą▒ąŠč鹊ą╣ ą╝ąĮąŠą│ąĖčģ čāąĘą╗ąŠą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ (ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ čäčīčĹʹŠą▓, ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝/ąĘą░ą┐čĆąĄč鹊ą╝ ąŠčéą┤ąĄą╗čīąĮčŗčģ ą╝ąŠą┤čāą╗ąĄą╣ čÅą┤čĆą░ ąĖ ą┐ąĄčĆąĖč乥čĆąĖąĖ), ą┐ąŠčŹč鹊ą╝čā ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┤ą╗čÅ ąĘą░čüčŗą┐ą░ąĮąĖčÅ ąĖ ą▓čŗčģąŠą┤ą░ ąĖąĘ čüąĮą░ čÅą▓ą╗čÅąĄčéčüčÅ ąĮąĄą┐čĆąŠčüč鹊ą╣ ąĘą░ą┤ą░č湥ą╣.

ąĪčéą░čéčīčÅ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠą▒ąŠą╣ ą┤ąŠčĆą░ą▒ąŠčéą░ąĮąĮčŗą╣ ą┐ąĄčĆąĄą▓ąŠą┤ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠą│ąŠ ą┤ą░čéą░čłąĖčéą░ Atmel ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ AT90USB162. ąØąĄą║ąŠč鹊čĆčŗąĄ čüąĄą║čåąĖąĖ ą┤ą░čéą░čłąĖčéą░ (ą║ąŠč鹊čĆčŗąĄ ąĖą╝ąĄčÄčé čüą╗ą░ą▒ąŠąĄ ąŠčéąĮąŠčłąĄąĮąĖąĄ ą║ čĆąĄąČąĖą╝ą░ą╝ čüąĮą░) ą▓ čüčéą░čéčīąĄ čāą┐ąŠą╝čÅąĮčāčéčŗ, ąĮąŠ ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮčŗ.

[ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖąĄą╝ ąĖ čĆąĄąČąĖą╝čŗ čüąĮą░ (Power Management and Sleep Modes)]

ąÆčüąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ čüąĄą╝ąĄą╣čüčéą▓ą░ AVR (ATtiny, ATmega) ąĖą╝ąĄąĄčé ą┐ąŠčģąŠąČąĖąĄ čĆąĄąČąĖą╝čŗ čüąĮą░, č鹥 ąČąĄ čüą░ą╝čŗąĄ čĆąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖąĄą╝ ąĖ ą░ąĮą░ą╗ąŠą│ąĖčćąĮčŗąĄ čüą┐ąŠčüąŠą▒čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄąČąĖą╝ąŠą▓ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ. ą×čéą╗ąĖčćą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ąĮąĄąĘąĮą░čćąĖč鹥ą╗čīąĮčŗąĄ ą┤ąĄčéą░ą╗ąĖ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čüąŠ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĄą╣ ą║ąŠąĮą║čĆąĄčéąĮąŠą╣ ą╝ąŠą┤ąĄą╗ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąóą░ą║ čćč鹊 čŹč鹊 čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ąĘčÅč鹊 ąĘą░ ąŠčüąĮąŠą▓čā ą┐čĆąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĖ čĆąĄąČąĖą╝ąŠą▓ čüąĮą░ ą╗čÄą▒čŗčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ AVR ą║ąŠą╝ą┐ą░ąĮąĖąĖ Atmel.

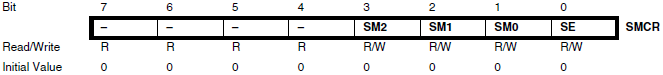

ą¤ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĖą╗ąĖ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓čģąŠą┤ąĖčé ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ (Active mode, ąĖą╗ąĖ non-Idle). ąÆčüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ čĆąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ (ą░ ąĖčģ 5) čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ ą║ą░ą║ čĆąĄąČąĖą╝čŗ čüąĮą░. ąØą░ čüą░ą╝ąŠą╝ ą┤ąĄą╗ąĄ ąĮąĄą║ąŠč鹊čĆčŗąĄ čĆąĄąČąĖą╝čŗ čüąĮą░ ą┤ą╗čÅ AT90USB162 čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠ čüąŠą▓ą┐ą░ą┤ą░čÄčé, čéą░ą║ čćč鹊 čĆąĄą░ą╗čīąĮąŠ ąĄčüčéčī č鹊ą╗čīą║ąŠ 3 čĆą░ąĘą╗ąĖčćąĮčŗčģ ą┐ąŠ čäčāąĮą║čåąĖąŠąĮą░ą╗čā čĆąĄąČąĖą╝ą░ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ - Idle, Power-down, Standby. ąĀąĄąČąĖą╝čŗ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą▓ą║ą╗čÄčćą░čÄčéčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čĆąĄąČąĖą╝ą░ą╝ąĖ Sleep (Sleep Mode Control Register ŌĆō SMCR). ąØąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ SMCR.

Sleep Mode Control Register ŌĆō SMCR

ą¦č鹊ą▒čŗ ą▓ąŠą╣čéąĖ ą▓ ą╗čÄą▒ąŠą╣ ąĖąĘ 5 čĆąĄąČąĖą╝ąŠą▓ Sleep, ąĮčāąČąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SMCR čāčüčéą░ąĮąŠą▓ąĖčéčī ą▓ ą╗ąŠą│. 1 ą▒ąĖčé SE, ą▓čŗą▒čĆą░čéčī ą▒ąĖčéą░ą╝ąĖ SM2, SM1, SM0 ąĮčāąČąĮčŗą╣ čĆąĄąČąĖą╝ ąĖ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąĖąĮčüčéčĆčāą║čåąĖčÄ SLEEP. ąÆ čéą░ą▒ą╗ąĖčåąĄ 8-1 ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ čĆą░ąĘą╗ąĖčćąĮčŗąĄ čĆąĄąČąĖą╝čŗ Sleep ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ąĖą╝ ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖč鹊ą▓ SMx. ąŚąĄą╗ąĄąĮčŗą╝ čåą▓ąĄč鹊ą╝ ą▓čŗą┤ąĄą╗ąĄąĮčŗ čĆąĄą░ą╗čīąĮąŠ čüčāčēąĄčüčéą▓čāčÄčēąĖąĄ ą┤ą╗čÅ AT90USB162 čĆąĄąČąĖą╝čŗ.

ąóą░ą▒ą╗ąĖčåą░ 8-1. ąÆčŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ čüąĮą░.

| SM2 |

SM1 |

SM0 |

ąÆčŗą▒čĆą░ąĮąĮčŗą╣ čĆąĄąČąĖą╝ čüąĮą░ |

| 0 |

0 |

0 |

Idle |

| 0 |

0 |

1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 0 |

1 |

0 |

Power-down |

| 0 |

1 |

1 |

Power-save |

| 1 |

0 |

0 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 1 |

0 |

1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 1 |

1 |

0 |

Standby(1) |

| 1 |

1 |

1 |

Extended Standby(1) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): čĆąĄąČąĖą╝čŗ Standby čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č鹊ą╗čīą║ąŠ čüąŠą▓ą╝ąĄčüčéąĮąŠ čü ą▓ąĮąĄčłąĮąĖą╝ąĖ ą║ą▓ą░čĆčåą░ą╝ąĖ ąĖą╗ąĖ čĆąĄąĘąŠąĮą░č鹊čĆą░ą╝ąĖ.

[Idle Mode]

ąÜąŠą│ą┤ą░ ą▒ąĖčéčŗ SM2..0 ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ 000, ą▒ąĖčé SE čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ SLEEP ą▓ą▓ąŠą┤ąĖčé MCU ą▓ čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ (Idle). ąĀąĄąČąĖą╝ Idle ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čĆą░ą▒ąŠčéčā čÅą┤čĆą░ CPU, ąĮąŠ ą┐čĆąĖ čŹč鹊ą╝ ąŠčüčéą░ąĄčéčüčÅ čĆą░ą▒ąŠčéą░čéčī ą×ąŚąŻ (SRAM), čéą░ą╣ą╝ąĄčĆčŗ/čüč湥čéčćąĖą║ąĖ (Timer/Counters), ą┐ąŠčĆčéčŗ SPI, ą┐ąŠčĆčé USB, USART, ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ, Watchdog ąĖ čüąĖčüč鹥ą╝ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (interrupt system). ą¤čĆąĖ čŹč鹊ą╝ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ clkCPU ąĖ clkFLASH, ąĮąŠ ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ čéą░ą║č鹊ą▓čŗąĄ čüąĖą│ąĮą░ą╗čŗ ą┐čĆąŠą┤ąŠą╗ąČą░čÄčé čĆą░ą▒ąŠčéą░čéčī.

ąĀąĄąČąĖą╝ Idle ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā ą▓ąĄčĆąĮčāčéčīčüčÅ ąŠą▒čĆą░čéąĮąŠ ą▓ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ (non-Idle) ą┐ąŠ čüąŠą▒čŗčéąĖčÄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą║ą░ą║ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ - ąĮą░ą┐čĆąĖą╝ąĄčĆ, ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą▓čģąŠą┤ąĮąŠą│ąŠ ą┐ąŠčĆčéą░ GPIO), čéą░ą║ ąĖ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ - ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÄ čéą░ą╣ą╝ąĄčĆą░, ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ USART ąĖą╗ąĖ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ USB (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ SOFI, WAKEUPI ąĖ ą┐čĆąŠčć.). ąĢčüą╗ąĖ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░, č鹊 ąŠąĮ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą║ą╗čÄč湥ąĮ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ ACD ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆąŠą╝ (Analog Comparator Control and Status Register ŌĆō ACSR) - čŹč鹊 čāą╝ąĄąĮčīčłąĖčé 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ Idle.

[Power-down Mode]

ąÜąŠą│ą┤ą░ ą▒ąĖčéčŗ SM2..0 ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 010, ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ SLEEP ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé MCU ą▓ čĆąĄąČąĖą╝ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (Power-down mode). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ, ąĮąŠ ą▓ąĮąĄčłąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, 2-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü (2-wire Serial Interface) ąĖ Watchdog ą┐čĆąŠą┤ąŠą╗ąČą░čÄčé čĆą░ą▒ąŠčéą░čéčī (ąĄčüą╗ąĖ ąŠąĮąĖ čĆą░ąĘčĆąĄčłąĄąĮčŗ). ąĀą░ąĘą▒čāą┤ąĖčéčī MCU (čé. ąĄ. ą┐ąĄčĆąĄą▓ąĄčüčéąĖ ąĄą│ąŠ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝, non-Idle) ą╝ąŠą│čāčé č鹊ą╗čīą║ąŠ ą▓ąĮąĄčłąĮąĖą╣ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čüą▒čĆąŠčü (External Reset), čüą▒čĆąŠčü ąŠčé čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (Watchdog Reset), čüą▒čĆąŠčü ąŠčé ąĮąĄą║ąŠąĮą┤ąĖčåąĖąŠąĮąĮąŠą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ (Brown-out Reset), čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░ 2-ą┐čĆąŠą▓ąŠą┤ąĮąŠą│ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ (2-wire Serial Interface), ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüą╝ąĄąĮčŗ ą▓ąĮąĄčłąĮąĄą│ąŠ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ ąĮąŠąČą║ą░čģ GPIO (external level interrupt) INT7:4 ąĖ INT3:0, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüą╝ąĄąĮąĄ čüąŠčüč鹊čÅąĮąĖčÅ ąĮąŠąČą║ąĖ ąĖą╗ąĖ ą┐ąŠ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╝čā čüąŠą▒čŗčéąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé USB (č鹊ą╗čīą║ąŠ WAKEUPI). ąŁč鹊čé čĆąĄąČąĖą╝ čüąĮą░ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▓čüąĄ ąŠčüąĮąŠą▓ąĮčŗąĄ čéą░ą║č鹊ą▓čŗąĄ čćą░čüč鹊čéčŗ, ąĖ čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā č鹊ą╗čīą║ąŠ ą░čüąĖąĮčģčĆąŠąĮąĮčŗčģ ą╝ąŠą┤čāą╗ąĄą╣.

ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüą╝ąĄąĮąĄ čāčĆąŠą▓ąĮčÅ (level triggered interrupt) ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ čĆąĄąČąĖą╝ą░ Power-down, čŹč鹊čé ąĖąĘą╝ąĄąĮąĄąĮąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą┤ąŠą╗ąČąĄąĮ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ąĮąĄą║ąŠč鹊čĆąŠąĄ ą▓čĆąĄą╝čÅ, čćč鹊ą▒čŗ MCU ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠ ą╝ąŠą│ ą┐čĆąŠčüąĮčāčéčīčüčÅ. ąŚą░ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéčÅą╝ąĖ ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čüąĄą║čåąĖąĖ ąÆąĮąĄčłąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (External Interrupts).

ą¤čĆąĖ ą▓čŗčģąŠą┤ąĄ ąĖąĘ čüąĮą░ ąĄčüčéčī čéą░ą║ąČąĄ ąĮąĄą║ąŠč鹊čĆą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ąŠčé čüąŠą▒čŗčéąĖčÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ą┤ąŠ ą░ą║čéąĖą▓ą░čåąĖąĖ čĆąĄą░ą╗čīąĮąŠą│ąŠ čĆą░ą▒ąŠč湥ą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ (non-Idle). ąŁčéą░ ąĘą░ą┤ąĄčƹȹ║ą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąĄčĆąĄąĘą░ą┐čāčüčéąĖčéčīčüčÅ ąĖ čüčéą░čéčī čüčéą░ą▒ąĖą╗čīąĮčŗą╝ąĖ čéą░ą║č鹊ą▓čŗą╝ ąĖą╝ą┐čāą╗čīčüą░ą╝, ą║ąŠč鹊čĆčŗąĄ ą▒čŗą╗ąĖ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ. ąŁč鹊čé ą┐ąĄčĆąĖąŠą┤ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ č鹥ą╝ąĖ ąČąĄ čüą░ą╝čŗą╝ąĖ ą▒ąĖčéą░ą╝ąĖ čäčīčĹʹŠą▓ ą▓čŗą▒ąŠčĆą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (CKSEL Fuses), ą║ąŠč鹊čĆčŗąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé čéą░ą╣ą╝ą░čāčé čüą▒čĆąŠčüą░ (Reset Time-out period), ą║ą░ą║ ąŠą┐ąĖčüą░ąĮąŠ ą▓ čüąĄą║čåąĖąĖ ąśčüč鹊čćąĮąĖą║ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ (Clock Sources) ą┤ą░čéą░čłąĖčéą░ (ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ čüąĄą║čåąĖčÅ Clock Sources ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░). ąśčüč鹊čćąĮąĖą║ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░ą┤ą░čÄčéčüčÅ čäčīčĹʹ░ą╝ąĖ CKSEL3..0.

[Power-save Mode]

ąÜąŠą│ą┤ą░ ą▒ąĖčéčŗ SM2..0 ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 011, ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ SLEEP ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé MCU ą▓ čĆąĄąČąĖą╝ 菹║ąŠąĮąŠą╝ąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (Power-save mode). ąŁč鹊čé čĆąĄąČąĖą╝ ąĖą┤ąĄąĮčéąĖč湥ąĮ čĆąĄąČąĖą╝čā Power-down. ą×ąĮ ą▓čŗą┤ąĄą╗ąĄąĮ ą║ą░ą║ ąŠčéą┤ąĄą╗čīąĮčŗą╣ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü ą▒ąŠą╗ąĄąĄ ą╝ąŠčēąĮčŗą╝ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ.

[Standby Mode]

ąÜąŠą│ą┤ą░ ą▒ąĖčéčŗ SM2..0 ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 110, ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ SLEEP ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé MCU ą▓ čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ (Standby mode). ąŁč鹊čé čĆąĄąČąĖą╝ ąĖą┤ąĄąĮčéąĖč湥ąĮ čĆąĄąČąĖą╝čā Power-save, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ č鹊ą│ąŠ, čćč鹊 ą│ąĄąĮąĄčĆą░č鹊čĆ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé čĆą░ą▒ąŠčéą░čéčī. ąæą╗ą░ą│ąŠą┤ą░čĆčÅ čŹč鹊ą╝čā ą▓čŗčģąŠą┤ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠč湥ąĮčī ą▒čŗčüčéčĆąŠ, ą▓čüąĄą│ąŠ ąĘą░ 6 ą┐ąĄčĆąĖąŠą┤ąŠą▓ čćą░čüč鹊čéčŗ ą│ąĄąĮąĄčĆą░č鹊čĆą░.

[Extended Standby Mode]

ąÜąŠą│ą┤ą░ ą▒ąĖčéčŗ SM2..0 ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 111, ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ SLEEP ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé MCU ą▓ čĆą░čüčłąĖčĆąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ (Extended Standby mode). ąŁč鹊čé čĆąĄąČąĖą╝ ąĖą┤ąĄąĮčéąĖč湥ąĮ čĆąĄąČąĖą╝čā Power-save, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ č鹊ą│ąŠ, čćč鹊 ą│ąĄąĮąĄčĆą░č鹊čĆ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé čĆą░ą▒ąŠčéą░čéčī. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čĆąĄąČąĖą╝ Extended Standby Mode čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠ čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü čĆąĄąČąĖą╝ąŠą╝ Standby Mode, ąĖ ą▓čŗą┤ąĄą╗ąĄąĮ ą▓ ąŠčéą┤ąĄą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ č鹊ą╗čīą║ąŠ ą▓ čåąĄą╗čÅčģ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ.

[ą×čéą╗ąĖčćąĖčÅ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ čĆąĄąČąĖą╝ąŠą▓ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ]

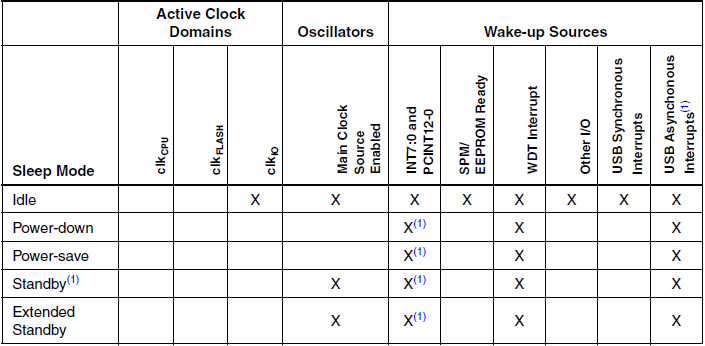

ąŚą┤ąĄčüčī ą▒čāą┤čāčé čĆą░čüčüą╝ąŠčéčĆąĄąĮčŗ č鹊ą╗čīą║ąŠ č鹥 čĆąĄąČąĖą╝čŗ, ą║ąŠč鹊čĆčŗąĄ čĆąĄą░ą╗čīąĮąŠ ąŠčéą╗ąĖčćą░čÄčéčüčÅ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ - Idle, Power-down, Standby. ąÆ čéą░ą▒ą╗ąĖčåą░čģ čüą▓ąĄą┤ąĄąĮčŗ ąŠčéą╗ąĖčćąĖčÅ ą┐ąŠ ą░ą║čéąĖą▓ąĮčŗą╝ čéą░ą║č鹊ą▓čŗą╝ ą┤ąŠą╝ąĄąĮą░ą╝ (Active Clock Domains), ą░ą║čéąĖą▓ąĮąŠčüčéąĖ čéą░ą║č鹊ą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ (čĆą░ą▒ąŠčéą░ąĄčé ą╗ąĖ ą│ą╗ą░ą▓ąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓), ąĖčüč鹊čćąĮąĖą║ą░ą╝ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ (Wake-up Sources).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č鹊ą╗čīą║ąŠ čü ą▓ąĮąĄčłąĮąĖą╝ ą║ą▓ą░čĆčåąĄą╝ ąĖą╗ąĖ čĆąĄąĘąŠąĮą░č鹊čĆąŠą╝ ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ. ąöą╗čÅ INT7:4 čĆą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čāčĆąŠą▓ąĮčÄ (level interrupt). ąöą╗čÅ ą░čüąĖąĮčģčĆąŠąĮąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ USB čĆą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ WAKEUPI.

[ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝ (Power Reduction Register)]

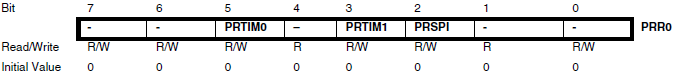

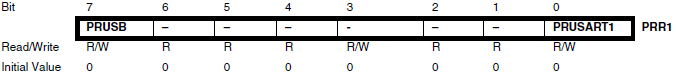

ąĀąĄą│ąĖčüčéčĆ Power Reduction Register, PRR (ąĮą░ čüą░ą╝ąŠą╝ ą┤ąĄą╗ąĄ čŹč鹊 ą┤ą▓ą░ čĆąĄą│ąĖčüčéčĆą░ PRR0 ąĖ PRR1), ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą╝ąĄč鹊ą┤ ą┤ą╗čÅ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠą╣ ąŠčüčéą░ąĮąŠą▓ą║ąĖ čéą░ą║č鹊ą▓ ą┤ą╗čÅ čĆą░ąĘą╗ąĖčćąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāą╝ąĄąĮčīčłą░čéčī 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ. ą¤čĆąĖ ąŠčéą║ą╗čÄč湥ąĮąĖąĖ čéą░ą║č鹊ą▓ č鹥ą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĘą░ą╝ąŠčĆą░ąČąĖą▓ą░ąĄčéčüčÅ, ąĖ ąĄą│ąŠ I/O čĆąĄą│ąĖčüčéčĆčŗ ąĮąĄ ą╝ąŠą│čāčé čćąĖčéą░čéčīčüčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčīčüčÅ. ąĀąĄčüčāčĆčüčŗ, ąĘą░ąĮčÅčéčŗąĄ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĄą╣ ąŠčüčéą░čÄčéčüčÅ ąĘą░ąĮčÅčéčŗą╝ąĖ, čüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ čüą╗čāčćą░ąĄą▓ ą┐ąĄčĆąĄą┤ ąŠčéą║ą╗čÄč湥ąĮąĖąĄą╝ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĖč乥čĆąĖčÄ čüč鹊ąĖčé ąĘą░ą┐čĆąĄčéąĖčéčī. ą¤čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą│ąŠ ą╝ąŠą┤čāą╗čÅ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ PRR, čćč鹊 ą▓ą║ą╗čÄčćą░ąĄčé čéą░ą║čéčŗ ąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą╝ąŠą┤čāą╗čī ą▓ č鹊 ąČąĄ čüąŠčüč鹊čÅąĮąĖąĄ, ą▓ ą║ąŠč鹊čĆąŠą╝ ąŠąĮ ą▒čŗą╗ ą┤ąŠ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ.

ąÆčŗą║ą╗čÄč湥ąĮąĖąĄ ą╝ąŠą┤čāą╗ąĄą╣ čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ą░čģ Active (non-Idle) ąĖ Idle, ąĖ čŹč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ čüąĮąĖąĘąĖčéčī 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ. ąØą░ čĆąĖčüčāąĮą║ą░čģ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ąŠčéą┤ąĄą╗čīąĮčŗčģ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆąŠą▓ PRR0 ąĖ PRR1. ą¦ąĄčĆč鹊čćą║ą░ą╝ąĖ ą┐ąŠą╝ąĄč湥ąĮčŗ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ) ą▒ąĖčéčŗ.

Power Reduction Register 0 - PRR0

PRTIM0: Power Reduction Timer/Counter0

ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ čŹč鹊čé ą▒ąĖčé ą▓čŗą║ą╗čÄčćą░ąĄčé čĆą░ą▒ąŠčéčā ą╝ąŠą┤čāą╗čÅ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ 0 (Timer/Counter0). ąÜąŠą│ą┤ą░ Timer/Counter0 čĆą░ąĘčĆąĄčłąĄąĮ, č鹊 ąŠąĮ ą┐čĆąŠą┤ąŠą╗ąČąĖčé čĆą░ą▒ąŠčéčā čü č鹊ą│ąŠ ą╝ąĄčüčéą░, ą│ą┤ąĄ ą▒čŗą╗ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ.

PRTIM1: Power Reduction Timer/Counter1

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ PRTIM0, č鹊ą╗čīą║ąŠ ą┤ą╗čÅ Timer/Counter1.

PRSPI: Power Reduction Serial Peripheral Interface

ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ čŹč鹊čé ą▒ąĖčé ą▓čŗą║ą╗čÄčćą░ąĄčé čĆą░ą▒ąŠčéčā ą╝ąŠą┤čāą╗čÅ Serial Peripheral Interface (SPI), čéą░ą║ ą║ą░ą║ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĄą│ąŠ ąŠčéą║ą╗čÄčćą░ąĄčéčüčÅ. ąÜąŠą│ą┤ą░ SPI ą┐čĆąŠą▒čāąČą┤ą░ąĄčéčüčÅ čüąĮąŠą▓ą░, č鹊 ą┤ą╗čÅ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ čĆą░ą▒ąŠčéčŗ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░ ą┐ąŠą▓č鹊čĆąĮą░čÅ ą┐ąĄčĆąĄąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ SPI.

Power Reduction Register 1 - PRR1

PRUSB: Power Reduction USB

ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ čŹč鹊čé ą▒ąĖčé ą▓čŗą║ą╗čÄčćą░ąĄčé USB ą┐čāč鹥ą╝ ąŠčüčéą░ąĮąŠą▓ą║ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čŹč鹊ą│ąŠ ą╝ąŠą┤čāą╗čÅ. ąÜąŠą│ą┤ą░ USB ą┐čĆąŠą▒čāąČą┤ą░ąĄčéčüčÅ čüąĮąŠą▓ą░, č鹊 ą┤ą╗čÅ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ čĆą░ą▒ąŠčéčŗ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░ ą┐ąŠą▓č鹊čĆąĮą░čÅ ą┐ąĄčĆąĄąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ USB.

PRUSART1: Power Reduction USART1

ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ čŹč鹊čé ą▒ąĖčé ą▓čŗą║ą╗čÄčćą░ąĄčé USART1 ą┐čāč鹥ą╝ ąŠčüčéą░ąĮąŠą▓ą║ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čŹč鹊ą│ąŠ ą╝ąŠą┤čāą╗čÅ. ąÜąŠą│ą┤ą░ USART1 ą┐čĆąŠą▒čāąČą┤ą░ąĄčéčüčÅ čüąĮąŠą▓ą░, č鹊 ą┤ą╗čÅ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ čĆą░ą▒ąŠčéčŗ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░ ą┐ąŠą▓č鹊čĆąĮą░čÅ ą┐ąĄčĆąĄąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ USART1.

[ą¦č鹊 ąĮčāąČąĮąŠ čāčćąĖčéčŗą▓ą░čéčī ą┤ą╗čÅ ą╝ąĖąĮąĖą╝ąĖąĘą░čåąĖąĖ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ]

ąöą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ čüąĖčüč鹥ą╝čŗ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ AVR, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĖą╝ąĄčéčī ą▓ ą▓ąĖą┤čā ąĮąĄą║ąŠč鹊čĆčŗąĄ ąŠčüąŠą▒čŗąĄ ą╝ąŠą╝ąĄąĮčéčŗ - ą║ą░ą║ąĖąĄ ą╝ąŠą┤čāą╗ąĖ AVR ą▓čŗą║ą╗čÄčćą░čéčī ąĖ ą║ą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝. ąÆ ąŠą▒čēąĄą╝ čüą╗čāčćą░ąĄ ą▓čüąĄą│ą┤ą░ ąČąĄą╗ą░č鹥ą╗čīąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čĆąĄąČąĖą╝čŗ čüąĮą░ ą┐ąŠ ą╝ą░ą║čüąĖą╝čāą╝čā, ąĖ čĆąĄąČąĖą╝ čüąĮą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ čéą░ą║, čćč鹊ą▒čŗ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅą╗ąĖčüčī č鹊ą╗čīą║ąŠ ą░ą▒čüąŠą╗čÄčéąĮąŠ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą┐ąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÄ čāčüčéčĆąŠą╣čüčéą▓ą░. ąÆčüąĄ čäčāąĮą║čåąĖąĖ ąĖ ą╝ąŠą┤čāą╗ąĖ, ąĮąĄąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé, ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮčŗ. ąØąĄą║ąŠč鹊čĆčŗąĄ ą╝ąŠą┤čāą╗ąĖ AVR čéčĆąĄą▒čāčÄčé ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ čĆą░čüčüą╝ąŠčéčĆąĄąĮąĖčÅ ą▓ ą┐ą╗ą░ąĮąĄ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ ąĮą░ąĖą╝ąĄąĮčīčłąĄą│ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ.

Analog Comparator

ą¤čĆąĖ ą▓čģąŠą┤ąĄ ą▓ čĆąĄąČąĖą╝ Idle ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ, ąĄčüą╗ąĖ ąŠąĮ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. ąÆąŠ ą▓čüąĄčģ ąŠčüčéą░ą╗čīąĮčŗčģ čĆąĄąČąĖą╝ą░čģ čüąĮą░ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ. ą×ą┤ąĮą░ą║ąŠ, ąĄčüą╗ąĖ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ą▒čŗą╗ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ąĮą░ ą▓čģąŠą┤ąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (Internal Voltage Reference), č鹊 ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ ą▓čĆčāčćąĮčāčÄ ą▓ąŠ ą▓čüąĄčģ čĆąĄąČąĖą╝ą░čģ čüąĮą░. ąśąĮą░č湥, ąĄčüą╗ąĖ čŹč鹊ą│ąŠ ąĮąĄ ą┤ąĄą╗ą░čéčī, č鹊 ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐čĆąŠą┤ąŠą╗ąČąĖčé čĆą░ą▒ąŠčéčā, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĖą╗ąĖ ąĮąĄčé čĆąĄąČąĖą╝ čüąĮą░. ąöą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą▓čŗčÅčüąĮąĖčéčī ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░, ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čüąĄą║čåąĖąĖ ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ (Analog Comparator).

Brown-out Detector

ąĢčüą╗ąĖ ą┤ąĄč鹥ą║č鹊čĆ ąĮąĄą║ąŠąĮą┤ąĖčåąĖąĖ ą▓ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (Brown-out Detector) ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ firmware, č鹊 čŹč鹊čé ą╝ąŠą┤čāą╗čī ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗą║ą╗čÄč湥ąĮ. ąĢčüą╗ąĖ ąČąĄ Brown-out Detector čĆą░ąĘčĆąĄčłąĄąĮ čäčīčĹʹ░ą╝ąĖ BODLEVEL, č鹊 ąŠąĮ ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī ąĖ ą▓ąŠ ą▓čüąĄčģ čĆąĄąČąĖą╝ą░čģ čüąĮą░, ąĖ čüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ą▓čüąĄą│ą┤ą░ ą▒čāą┤ąĄčé ą┐ąŠčéčĆąĄą▒ą╗čÅčéčī 菹ĮąĄčĆą│ąĖčÄ. ąÆ čĆąĄąČąĖą╝ą░čģ ą│ą╗čāą▒ąŠą║ąŠą│ąŠ čüąĮą░ čŹč鹊 ąŠą║ą░ąČąĄčé ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠąĄ ą▓ą╗ąĖčÅąĮąĖąĄ ąĮą░ ąŠą▒čēąĄąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ. ą¦č鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą┐ąŠą┤čĆąŠą▒ąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ čĆą░ą▒ąŠč鹥 Brown-out Detector ąĖ ąĄą│ąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÄ čäčīčĹʹ░ą╝ąĖ, ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čüąĄą║čåąĖąĖ ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąĄą║ąŠąĮą┤ąĖčåąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (Brown-out Detection) ą┤ą░čéą░čłąĖčéą░.

Internal Voltage Reference

ąśčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (Internal Voltage Reference) ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čĆą░ąĘčĆąĄčłąĄąĮ, ą║ąŠą│ą┤ą░ ąŠąĮ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ Brown-out Detector, ąĖą╗ąĖ ą┤ą╗čÅ Analog Comparator. ąĢčüą╗ąĖ čŹčéąĖ ą┤ą▓ą░ ą╝ąŠą┤čāą╗čÅ ą▒čāą┤čāčé ąĘą░ą┐čĆąĄčēąĄąĮčŗ, ą║ą░ą║ ąŠą┐ąĖčüą░ąĮąŠ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ čüąĄą║čåąĖčÅčģ, č鹊 Internal Voltage Reference ą▒čāą┤ąĄčé čéą░ą║ąČąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą┐čĆąĄčēąĄąĮ, ąĖ ąĮąĄ ą▒čāą┤ąĄčé ą┐ąŠčéčĆąĄą▒ą╗čÅčéčī 菹ĮąĄčĆą│ąĖčÄ. ą¤ąĄčĆąĄą┤ ą▓ą║ą╗čÄč湥ąĮąĖąĄą╝ ąĘą░ąĮąŠą▓ąŠ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ čüąĮąŠą▓ą░ čĆą░ąĘčĆąĄčłąĖčéčī ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, ą┐ąĄčĆąĄą┤ č鹥ą╝ ą║ą░ą║ ąĄą│ąŠ ą▓čŗčģąŠą┤ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ. ąŚą░ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéčÅą╝ąĖ ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čüąĄą║čåąĖąĖ ąśčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (Internal Voltage Reference) ą┤ą░čéą░čłąĖčéą░.

Watchdog Timer

ąĢčüą╗ąĖ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ firmware ąĮąĄ ąĮčāąČąĄąĮ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ (Watchdog Timer), č鹊 čŹč鹊čé ą╝ąŠą┤čāą╗čī ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗą║ą╗čÄč湥ąĮ. ąĢčüą╗ąĖ ąČąĄ Watchdog Timer čĆą░ąĘčĆąĄčłąĄąĮ, č鹊 ąŠąĮ ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ąŠ ą▓čüąĄčģ čĆąĄąČąĖą╝ą░čģ čüąĮą░ ąĖ čüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▒čāą┤ąĄčé ą┐ąŠčéčĆąĄą▒ą╗čÅčéčī 菹ĮąĄčĆą│ąĖčÄ. ąÆ čĆąĄąČąĖą╝ą░čģ ą│ą╗čāą▒ąŠą║ąŠą│ąŠ čüąĮą░ čŹč鹊 ąŠą║ą░ąČąĄčé ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠąĄ ą▓ą╗ąĖčÅąĮąĖąĄ ąĮą░ ąŠą▒čēąĄąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ. ąŚą░ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéčÅą╝ąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čüąĄą║čåąĖąĖ ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Interrupts) ą┤ą░čéą░čłąĖčéą░.

Port Pins

ąÜąŠą│ą┤ą░ čćąĖą┐ ą▓ąŠčłąĄą╗ ą▓ čĆąĄąČąĖą╝ čüąĮą░, ą▓čüąĄ ą┐ąŠčĆčéčŗ ąĮąŠąČąĄą║ (Port Pins) ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ąĮą░ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ. ąØą░ąĖą▒ąŠą╗ąĄąĄ ą▓ą░ąČąĮąŠ čāą▒ąĄą┤ąĖčéčīčüčÅ, čćč鹊 ąĮąĄčé ąĮąŠąČąĄą║, ą║ąŠč鹊čĆčŗąĄ ą▓čŗą┤ą░čÄčé č鹊ą║ ąĮą░ ą░ą║čéąĖą▓ąĮčāčÄ ąĮą░ą│čĆčāąĘą║čā (resistive loads). ąÆ č鹥čģ čĆąĄąČąĖą╝ą░čģ čüąĮą░, ą│ą┤ąĄ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą▓ą▓ąŠą┤ą░ ą▓čŗą▓ąŠą┤ą░ I/O (clkI/O) ąĘą░ą┐čĆąĄčēąĄąĮą░, ą▓čģąŠą┤ąĮčŗąĄ ą▒čāč乥čĆčŗ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▒čāą┤čāčé čéą░ą║ąČąĄ ąĘą░ą┐čĆąĄčēąĄąĮčŗ. ąŁčéąĖą╝ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ, čćč鹊 ąĮąĄ ą▒čāą┤ąĄčé ą┐ąŠčéčĆąĄą▒ą╗čÅčéčīčüčÅ ą╝ąŠčēąĮąŠčüčéčī ą▓čģąŠą┤ąĮčŗą╝ąĖ ą▒čāč乥čĆą░ą╝ąĖ, ą║ąŠą│ą┤ą░ ąŠąĮąĖ ąĮąĄ ąĮčāąČąĮčŗ. ąØąŠ ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ čüą╗čāčćą░čÅčģ ąĮčāąČąĮąŠ ąŠčéčüą╗ąĄąČąĖą▓ą░čéčī čüąŠą▒čŗčéąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ, ąĖ č鹊ą│ą┤ą░ čŹčéąĖ ą▒čāč乥čĆčŗ ąĮčāąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī. ąŚą░ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéčÅą╝ąĖ, ą║ą░ą║ąĖąĄ ąĮąŠąČą║ąĖ ą▒čāą┤čāčé čĆą░ąĘčĆąĄčłąĄąĮčŗ, ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čüąĄą║čåąĖąĖ ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čåąĖčäčĆąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░ ąĖ čĆąĄąČąĖą╝čŗ čüąĮą░ (Digital Input Enable and Sleep Modes) ą┤ą░čéą░čłąĖčéą░. ąĢčüą╗ąĖ ą▓čģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ čĆą░ąĘčĆąĄčłąĄąĮ, ąĖ ą▓čģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī (ą▓čģąŠą┤ąĮąŠą╣ ą▓čŗą▓ąŠą┤ ą┐ąŠčĆčéą░) ąŠčüčéą░ą╗čüčÅ ą▓ ą┐ąŠą┤ą▓ąĄčłąĄąĮąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ąĖą╗ąĖ ąĖą╝ąĄąĄčé ą▓čģąŠą┤ąĮąŠąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ čāčĆąŠą▓ąĮąĄ VCC/2, č鹊 ą▓čģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą▒čāą┤ąĄčé ą┐ąŠčéčĆąĄą▒ą╗čÅčéčī ąĖąĘą╗ąĖčłąĮčÄčÄ ą╝ąŠčēąĮąŠčüčéčī.

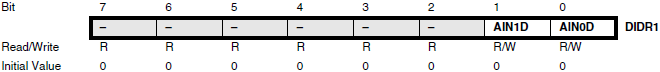

ąöą╗čÅ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą▓čģąŠą┤ąĮčŗčģ ąĮąŠąČąĄą║ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą▓čģąŠą┤čŗ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░), ą▓čģąŠą┤ąĮąŠą╣ čåąĖčäčĆąŠą▓ąŠą╣ ą▒čāč乥čĆ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čüąĄą│ą┤ą░ ąĘą░ą┐čĆąĄčēąĄąĮ. ąÆčģąŠą┤ąĮąŠą╣ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čāčĆąŠą▓ąĄąĮčī ąŠą║ąŠą╗ąŠ VCC/2 ąĮą░ ąĮąŠąČą║ąĄ ą▓čģąŠą┤ą░ ą▓čŗąĘąŠą▓ąĄčé ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠąĄ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ č鹊ą║ą░ ą┤ą░ąČąĄ ą▓ čĆąĄąČąĖą╝ąĄ Active. ą”ąĖčäčĆąŠą▓čŗąĄ ą▓čģąŠą┤ąĮčŗąĄ ą▒čāč乥čĆčŗ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮčŗ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ Digital Input Disable Registers (DIDR1). ąŚą░ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéčÅą╝ąĖ ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čüąĄą║čåąĖąĖ ąĀąĄą│ąĖčüčéčĆ ąĘą░ą┐čĆąĄčéą░ ą▓čģąŠą┤ąĮčŗčģ ą┐ąŠčĆč鹊ą▓ (Digital Input Disable Register 1 ŌĆō DIDR1) ą┤ą░čéą░čłąĖčéą░.

On-chip Debug System

ąÆčüčéčĆąŠąĄąĮąĮą░čÅ ą▓ čćąĖą┐ čüąĖčüč鹥ą╝ą░ ąŠčéą╗ą░ą┤ą║ąĖ (On-chip Debug System) čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čäčīčĹʹŠą╝ OCDEN (ą┤ą╗čÅ čćąĖą┐ą░ AT90USB162 čŹč鹊 čäčīčÄąĘ DWEN), ąĖ ą┐čĆąĖ ą▓čģąŠą┤ąĄ ą▓ čĆąĄąČąĖą╝ čüąĮą░ ą│ą╗ą░ą▓ąĮčŗą╣ čéą░ą║č鹊ą▓čŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ (main clock source) ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé čĆą░ą▒ąŠčéą░čéčī, čćč鹊 čüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓čŗąĘčŗą▓ą░ąĄčé ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą╝ąŠčēąĮąŠčüčéąĖ. ąÆ čĆąĄąČąĖą╝ą░čģ ą│ą╗čāą▒ąŠą║ąŠą│ąŠ čüąĮą░ čŹč鹊 ąŠą║ą░ąČąĄčé ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠąĄ ą▓ą╗ąĖčÅąĮąĖąĄ ąĮą░ ąŠą▒čēąĄąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ.

[ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Interrupts)]

ąŁčéą░ čüąĄą║čåąĖčÅ ąŠą┐ąĖčüčŗą▓ą░ąĄčé čüą┐ąĄčåąĖčäąĖą║čā, čüą▓čÅąĘą░ąĮąĮčāčÄ čü ąŠą▒čĆą░ą▒ąŠčéą║ąŠą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┤ą╗čÅ AVR ą║čĆąĖčüčéą░ą╗ą╗ąŠą▓ AT90USB82 (ąĖ AT90USB162). ą×ą▒čēąĖąĄ ą▓ąŠą┐čĆąŠčüčŗ, ą║ą░čüą░čÄčēąĖąĄčüčÅ čüą▒čĆąŠčüą░ ąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, čüą╝. ą▓ čüąĄą║čåąĖąĖ ąĪą▒čĆąŠčü ąĖ ąŠą▒čĆą░ą▒ąŠčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Reset and Interrupt Handling) ą┤ą░čéą░čłąĖčéą░. ąÆ čéą░ą▒ą╗ąĖčåąĄ 10.1 ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓čüąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓ąĄą║č鹊čĆčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ čüą▒čĆąŠčüą░.

ąóą░ą▒ą╗ąĖčåą░ 10-1. ąÆąĄą║č鹊čĆą░ (ą░ą┤čĆąĄčüą░) čüą▒čĆąŠčüą░ ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

| Ōä¢ |

ąÉą┤čĆąĄčü(2) |

ąśčüč鹊čćąĮąĖą║ |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ |

| 1 |

$0000(1) |

RESET |

ąĪą▒čĆąŠčü ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓čŗą▓ąŠą┤ą░ čüą▒čĆąŠčüą░, ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ, ąŠčé ąĮąĄą║ąŠąĮą┤ąĖčåąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (BOD), čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░, čüą▒čĆąŠčüą░ ą┐ąŠ čłąĖąĮąĄ USB, ąĖ čüą▒čĆąŠčüą░ ąŠčé ąŠčéą╗ą░ą┤ąŠčćąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ debugWIRE AVR. |

| 2 |

$0002 |

INT0 |

External Interrupt Request 0 |

| 3 |

$0004 |

INT1 |

External Interrupt Request 1 |

| 4 |

$0006 |

INT2 |

External Interrupt Request 2 |

| 5 |

$0008 |

INT3 |

External Interrupt Request 3 |

| 6 |

$000A |

INT4 |

External Interrupt Request 4 |

| 7 |

$000C |

INT5 |

External Interrupt Request 5 |

| 8 |

$000E |

INT6 |

External Interrupt Request 6 |

| 9 |

$0010 |

INT7 |

External Interrupt Request 7 |

| 10 |

$0012 |

PCINT0 |

Pin Change Interrupt Request 0 |

| 11 |

$0014 |

PCINT1 |

Pin Change Interrupt Request 1 |

| 12 |

$0016 |

USB General |

ą×čüąĮąŠą▓ąĮąŠą╣ ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ USB |

| 13 |

$0018 |

USB Endpoint |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ USB |

| 14 |

$001A |

WDT |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé čéą░ą╣ą╝ą░čāčéą░ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (Watchdog Time-out Interrupt) |

| 15 |

$001C |

TIMER1 CAPT |

Timer/Counter1 Capture Event |

| 16 |

$001E |

TIMER1 COMPA |

Timer/Counter1 Compare Match A |

| 17 |

$0020 |

TIMER1 COMPB |

Timer/Counter1 Compare Match B |

| 18 |

$0022 |

TIMER1 COMPC |

Timer/Counter1 Compare Match C |

| 19 |

$0024 |

TIMER1 OVF |

Timer/Counter1 Overflow |

| 20 |

$0026 |

TIMER0 COMPA |

Timer/Counter0 Compare Match A |

| 21 |

$0028 |

TIMER0 COMPB |

Timer/Counter0 Compare Match B |

| 22 |

$002A |

TIMER0 OVF |

Timer/Counter0 Overflow |

| 23 |

$002C |

SPI, STC |

SPI Serial Transfer Complete |

| 24 |

$002E |

USART1 RX |

USART1 Rx Complete |

| 25 |

$0030 |

USART1 UDRE |

USART1 Data Register Empty |

| 26 |

$0032 |

USART1TX |

USART1 Tx Complete |

| 27 |

$0034 |

ANALOG COMP |

Analog Comparator |

| 28 |

$0036 |

EE READY |

EEPROM Ready |

| 29 |

$0038 |

SPM READY |

Store Program Memory Ready |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čéą░ą▒ą╗ąĖčåąĄ 10-1:

(1) ąÜąŠą│ą┤ą░ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ čäčīčÄąĘ BOOTRST, ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ąĖą╗ąĖ čüą▒čĆąŠčüąĄ čüą┤ąĄą╗ą░ąĄčé ą▒ąĄąĘčāčüą╗ąŠą▓ąĮčŗą╣ ą┐ąĄčĆąĄčģąŠą┤ ą┐ąŠ ą░ą┤čĆąĄčüčā ą▒čāčéą╗ąŠą░ą┤ąĄčĆą░ (Boot Loader), ąĘą░ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéčÅą╝ąĖ ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čüąĄą║čåąĖąĖ ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ (Memory Programming) ą┤ą░čéą░čłąĖčéą░ (ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ čüąĄą║čåąĖčÅ Memory Programming ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░).

(2) ąÜąŠą│ą┤ą░ IVSEL ą▓ čĆąĄą│ąĖčüčéčĆąĄ MCUCR čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▒čāą┤čāčé ą┐ąĄčĆąĄąĮąĄčüąĄąĮčŗ ąĮą░ ąĮą░čćą░ą╗ąŠ čüąĄą║čåąĖąĖ ą▒čāčéą╗ąŠą░ą┤ąĄčĆą░ (Boot Flash Section). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą░ą┤čĆąĄčü ą║ą░ąČą┤ąŠą│ąŠ ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▒čāą┤ąĄčé čĆą░ą▓ąĄąĮ ą░ą┤čĆąĄčüčā ąĖąĘ čéą░ą▒ą╗ąĖčåąĄ ą┐ą╗čÄčü ą░ą┤čĆąĄčü ąĮą░čćą░ą╗ą░ čüąĄą║čåąĖąĖ ą▒čāčéą╗ąŠą░ą┤ąĄčĆą░. ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ą▓ąĄčĆčüąĖąĖ ą║čĆąĖčüčéą░ą╗ą╗ą░ 8K/16K, čĆą░ąĘą╝ąĄčĆ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖą┤ąĄąĮčéąĖč湥ąĮ (ąĖ ąĘą░ąĮąĖą╝ą░ąĄčé 2 čüą╗ąŠą▓ą░) ą║ą░ą║ ą┤ą╗čÅ 8K, čéą░ą║ ąĖ ą┤ą╗čÅ 16K ą▓ąĄčĆčüąĖąĖ.

ąÆ čéą░ą▒ą╗ąĖčåąĄ 10-2 ą┐ąŠą║ą░ąĘą░ąĮąŠ čĆą░ąĘą╝ąĄčēąĄąĮąĖąĄ ą▓ąĄą║č鹊čĆąŠą▓ čüą▒čĆąŠčüą░ ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą║ąŠą╝ą▒ąĖąĮą░čåąĖą╣ čāčüčéą░ąĮąŠą▓ąŠą║ BOOTRST ąĖ IVSEL. ąĢčüą╗ąĖ ą║ąŠą┤ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ (firmware) ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ čĆą░ąĘčĆąĄčłą░ąĄčé ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, č鹊 ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ, ąĖ ą▓ čŹč鹊 ą╝ąĄčüč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╝ąĄčēąĄąĮ ąŠą▒čŗčćąĮčŗą╣ ą┤ą▓ąŠąĖčćąĮčŗą╣ ą║ąŠą┤ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. ąŁč鹊 čéą░ą║ąČąĄ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ čüą╗čāčćą░čÄ, ą║ąŠą│ą┤ą░ ą▓ąĄą║č鹊čĆ čüą▒čĆąŠčüą░ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąĄą║čåąĖąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ (Application section) ą┐čĆąĖ ąĮą░ą╗ąĖčćąĖąĖ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ čüąĄą║čåąĖąĖ ą▒čāčéą╗ąŠą░ą┤ąĄčĆą░ (Boot section), ąĖ ąĮą░ąŠą▒ąŠčĆąŠčé.

ąóą░ą▒ą╗ąĖčåą░ 10-2. ąĀą░ąĘą╝ąĄčēąĄąĮąĖąĄ ą▓ąĄą║č鹊čĆąŠą▓ čüą▒čĆąŠčüą░ ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (1).

| BOOTRST |

IVSEL |

ąÉą┤čĆąĄčü čüą▒čĆąŠčüą░ |

ąÆąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĖ čüčéą░čĆč鹊ą▓čŗą╣ ą░ą┤čĆąĄčü |

| 1 |

0 |

0x0000 |

0x0002 |

| 1 |

1 |

0x0000 |

Boot Reset Address + 0x0002 |

| 0 |

0 |

Boot Reset Address |

0x0002 |

| 0 |

1 |

Boot Reset Address |

Boot Reset Address + 0x0002 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ą░ą┤čĆąĄčüą░ ą▓ąĄą║č鹊čĆąŠą▓ čüą▒čĆąŠčüą░ (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓ąĄčĆčüąĖąĖ ą║čĆąĖčüčéą░ą╗ą╗ą░ 8K/16K ąĖ čäčīčĹʹŠą▓) ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ 23-8 ą┤ą░čéą░čłąĖčéą░. ąöą╗čÅ čäčīčĹʹ░ BOOTRST "1" ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čäčīčÄąĘ ąĮąĄ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ, ąĖ "0" ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čäčīčÄąĘ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ. Boot Reset Address ąĘą░ą┤ą░ąĄčéčüčÅ ą▓ąĄčĆčüąĖąĄą╣ ą║čĆąĖčüčéą░ą╗ą╗ą░ (AT90USB82 ąĖą╗ąĖ AT90USB162) ąĖ čüąŠčüč鹊čÅąĮąĖąĄą╝ čäčīčĹʹŠą▓ BOOTSZ1 ąĖ BOOTSZ0.

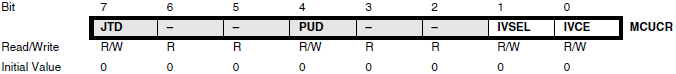

ąĀąĄą│ąĖčüčéčĆ MCUCR ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ čĆą░ąĘą╝ąĄčēąĄąĮąĖąĄ čéą░ą▒ą╗ąĖčåčŗ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

IVSEL: Interrupt Vector Select

ąÜąŠą│ą┤ą░ ą▒ąĖčé IVSEL ąŠčćąĖčēąĄąĮ (čüą▒čĆąŠčłąĄąĮ ą▓ 0), ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąŠą╝ąĄčēąĄąĮčŗ ą▓ ąĮą░čćą░ą╗ąŠ ą┐ą░ą╝čÅčéąĖ FLASH. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ (čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1), ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąĄčĆąĄą╝ąĄčēą░čÄčéčüčÅ ąĮą░ ąĮą░čćą░ą╗ąŠ čüąĄą║čåąĖąĖ ąĘą░ą│čĆčāąĘą║ąĖ (Boot Loader section) ą┐ą░ą╝čÅčéąĖ FLASH. ąĀąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą░ą┤čĆąĄčüą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čäčīčĹʹ░ą╝ąĖ BOOTSZ. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čüąĄą║čåąĖąĖ ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ (Memory Programming) ą┤ą░čéą░čłąĖčéą░ (ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ čüąĄą║čåąĖčÅ Memory Programming ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░). ą¦č鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮčŗčģ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣ ą▓ ą┐ąŠą╗ąŠąČąĄąĮąĖąĖ čéą░ą▒ą╗ąĖčåčŗ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą┤ą╗čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▒ąĖčéą░ IVSEL ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┐čĆąĖą╝ąĄąĮąĄąĮą░ čüą┐ąĄčåąĖą░ą╗čīąĮą░čÅ ą┐čĆąŠčåąĄą┤čāčĆą░ ąĘą░ą┐ąĖčüąĖ:

a. ąØčāąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ą▒ąĖčé Interrupt Vector Change Enable (IVCE) ą▓ 1.

b. ąÆ č鹥č湥ąĮąĖąĄ 4 čåąĖą║ą╗ąŠą▓ čéą░ą║č鹊ą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ąĮčāąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī čéčĆąĄą▒čāąĄą╝ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓ IVSEL, ą┐čĆąĖ čŹč鹊ą╝ ą▓ IVCE ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ 0.

ąÜąŠą│ą┤ą░ čŹčéą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░, č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▒čāą┤čāčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą┐čĆąĄčēąĄąĮčŗ. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąĄčēą░čÄčéčüčÅ ą▓ čåąĖą║ą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ IVCE, ąĖ ąŠčüčéą░čÄčéčüčÅ ąĘą░ą┐čĆąĄčēąĄąĮąĮčŗą╝ąĖ ą┐ąŠčüą╗ąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą║ąŠč鹊čĆą░čÅ čüą╗ąĄą┤čāąĄčé ąĘą░ ąĘą░ą┐ąĖčüčīčÄ ą▓ IVSEL. ąĢčüą╗ąĖ IVSEL ąĮąĄ ąĘą░ą┐ąĖčüą░ąĮ, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčüčéą░čÄčéčüčÅ ąĘą░ą┐čĆąĄčēąĄąĮąĮčŗą╝ąĖ ąĮą░ 4 čåąĖą║ą╗ą░. ąĪąĖčüč鹥ą╝ą░ ą░ą▓č鹊ąĘą░ą┐čĆąĄčéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą▒ąĖčé I čĆąĄą│ąĖčüčéčĆą░ čüčéą░čéčāčüą░ (Status Register).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čĆą░ąĘą╝ąĄčēąĄąĮčŗ ą▓ čüąĄą║čåąĖąĖ ą▒čāčéą╗ąŠą░ą┤ąĄčĆą░ ąĖ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▒ąĖčé ąĘą░čēąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ (Boot Lock) BLB02, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮčŗ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ ą▓ čüąĄą║čåąĖąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ (Application section). ąĢčüą╗ąĖ ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░ąĘą╝ąĄčēąĄąĮčŗ ą▓ čüąĄą║čåąĖąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ (Application section) ąĖ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▒ąĖčé ąĘą░čēąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ (Boot Lock) BLB12, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▒čāą┤čāčé ąĘą░ą┐čĆąĄčēąĄąĮčŗ ą┐čĆąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĖ ą║ąŠą┤ą░ ą▓ čüąĄą║čåąĖąĖ ą▒čāčéą╗ąŠą░ą┤ąĄčĆą░ (Boot Loader section). ąŚą░ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéčÅą╝ąĖ ą┐ąŠ ą▒ąĖčéą░ą╝ ąĘą░čēąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ (Boot Lock) ąŠą▒čĆą░čēą░ą╣č鹥čüčī ą║ čüąĄą║čåąĖąĖ ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ (Memory Programming) ą┤ą░čéą░čłąĖčéą░ (ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ čüąĄą║čåąĖčÅ Memory Programming ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░).

IVCE: Interrupt Vector Change Enable

ąæąĖčé IVCE ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ 1, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą▒čŗ ąĖąĘą╝ąĄąĮąĖčéčī ą▒ąĖčé IVSEL. IVCE ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą▓ č鹥č湥ąĮąĖąĄ 4 čåąĖą║ą╗ąŠą▓ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĘą░ą┐ąĖčüą░ąĮ ą▒ąĖčé IVSEL. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ IVCE ąĘą░ą┐čĆąĄčéąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ą░ą║ ą▒čŗą╗ąŠ ąŠą┐ąĖčüą░ąĮąŠ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ ą▒ąĖčéą░ IVSEL. ąØąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▒ąĖčéą░ IVSEL.

;[ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ]

; Move_interrupts:

; Enable change of Interrupt Vectors

ldi r16, (1<<IVCE)

out MCUCR, r16

; Move interrupts to Boot Flash section

ldi r16, (1<<IVSEL)

out MCUCR, r16

ret

//[ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ C]

void Move_interrupts(void)

{

/* Enable change of Interrupt Vectors */

MCUCR = (1<<IVCE);

/* Move interrupts to Boot Flash section */

MCUCR = (1<<IVSEL);

}

[ąĪą▒čĆąŠčü ąĖ ąŠą▒čĆą░ą▒ąŠčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Reset and Interrupt Handling)]

ąÆ ą░čĆčģąĖč鹥ą║čéčāčĆąĄ AVR ąĘą░ą╗ąŠąČąĄąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŁčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą▓ąĄą║č鹊čĆ čüą▒čĆąŠčüą░ (Reset Vector) ąĖą╝ąĄčÄčé ą║ą░ąČą┤čŗą╣ ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü (ą▓ąĄą║č鹊čĆ) ą▓ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝. ąÆčüąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ ąĮą░ąĘąĮą░č湥ąĮčŗ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčŗąĄ čĆą░ąĘčĆąĄčłą░čÄčēąĖąĄ ą▒ąĖčéčŗ, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ą╗ąŠą│. 1 ą▓ą╝ąĄčüč鹥 čü ąŠą▒čēąĖą╝ ą▒ąĖč鹊ą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Global Interrupt Enable bit, ą▒ąĖčé I) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ (Status Register, SREG), čćč鹊ą▒čŗ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čŗą╗ąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą▒čŗčéčī ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą┐čĆąĄčēąĄąĮčŗ, ą║ąŠą│ą┤ą░ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ą▒ąĖčéčŗ ąĘą░čēąĖčéčŗ (Boot Lock) BLB02 ąĖą╗ąĖ BLB12. ąŁčéą░ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé ąĘą░čēąĖčēąĄąĮąĮąŠčüčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ firmware. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čüąĄą║čåąĖąĖ ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ (Memory Programming) ą┤ą░čéą░čłąĖčéą░ (ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ čüąĄą║čåąĖčÅ Memory Programming ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░).

ąĪą░ą╝čŗąĄ ą╝ą╗ą░ą┤čłąĖąĄ ą░ą┤čĆąĄčüą░ ą▓ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĮą░ąĘąĮą░č湥ąĮčŗ ą┐ąŠą┤ čĆą░ąĘą╝ąĄčēąĄąĮąĖąĄ ą▓ąĄą║č鹊čĆąŠą▓ (ą░ą┤čĆąĄčüąŠą▓) čüą▒čĆąŠčüą░ ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Reset and Interrupt Vectors). ą¤ąŠą╗ąĮčŗą╣ čüą┐ąĖčüąŠą║ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą▓ čüąĄą║čåąĖąĖ ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Interrupts) ą┤ą░čéą░čłąĖčéą░. ąĪą┐ąĖčüąŠą║ (čéą░ą▒ą╗ąĖčåą░ 10-1) čéą░ą║ąČąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗąĄ čāčĆąŠą▓ąĮąĖ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą▓ąĄą║č鹊čĆ ą║ąŠč鹊čĆčŗčģ ąĖą╝ąĄčÄčé ąĮą░ąĖą╝ąĄąĮčīčłąĖą╣ ą░ą┤čĆąĄčü, ąŠą▒ą╗ą░ą┤ą░čÄčé ąĮą░ąĖą▓čŗčüčłąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝. RESET (čüą▒čĆąŠčü) ąĖą╝ąĄąĄčé čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé, čüą╗ąĄą┤čāčÄčēąĖą╣ ąĘą░ ąĮąĖą╝ ąĖą┤ąĄčé INT0 - ą▓ąĮąĄčłąĮąĖą╣ ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 0 (External Interrupt Request 0). ąÆąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąĄčĆąĄąĮąĄčüąĄąĮčŗ ą▓ čüąĄą║čåąĖčÄ ą▒čāčéą╗ąŠą░ą┤ąĄčĆą░ (Boot Flash section) ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ IVSEL ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ (MCU Control Register, MCUCR). ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąĖą╝ąĄąĄčéčüčÅ ą▓ čüąĄą║čåąĖąĖ ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Interrupts) ą┤ą░čéą░čłąĖčéą░. ąÆąĄą║č鹊čĆ čüą▒čĆąŠčüą░ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄąĮąĄčüąĄąĮ ą▓ ąĮą░čćą░ą╗ąŠ čüąĄą║čåąĖąĖ ą▒čāčéą╗ąŠą░ą┤ąĄčĆą░ ą┐čāč鹥ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čäčīčĹʹ░ BOOTRST, čüą╝. čüąĄą║čåąĖčÄ ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ (Memory Programming) ą┤ą░čéą░čłąĖčéą░ (ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ čüąĄą║čåąĖčÅ Memory Programming ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░).

ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ čäą╗ą░ą│ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Global Interrupt Enable I-bit) ą▓ čĆąĄą│ąĖčüčéčĆąĄ SREG, ąĖ ą▓čüąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąĄčēą░čÄčéčüčÅ. ąÜąŠą┤ firmware ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą╝ąŠąČąĄčé ąĘą░ą┐ąĖčüą░čéčī ą▓ ą▒ąĖčé I ą╗ąŠą│. 1, č湥ą╝ ą╝ąŠąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī ą▓ą╗ąŠąČąĄąĮąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą▓čüąĄ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą┐čĆąĄčĆą▓ą░čéčī č鹥ą║čāčēąĖą╣ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąæąĖčé I ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ ą▓ąŠąĘą▓čĆą░čéą░ ąĖąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ RETI.

ąśą╝ąĄąĄčéčüčÅ ą┤ą▓ą░ ą▒ą░ąĘąŠą▓čŗčģ čéąĖą┐ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ą¤ąĄčĆą▓čŗą╣ čéąĖą┐ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐ąŠ čüąŠą▒čŗčéąĖčÄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą│ąŠ čäą╗ą░ą│ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąöą╗čÅ čŹč鹊ą│ąŠ čéąĖą┐ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüč湥čéčćąĖą║ ą┐ąĄčĆąĄąĮąŠčüąĖčéčüčÅ ąĮą░ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮčŗą╣ ą▓ąĄą║č鹊čĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü čåąĄą╗čīčÄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĖ ą┐čĆąĖ čŹč鹊ą╝ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ąŠčćąĖčēą░ąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čäą╗ą░ą│. ążą╗ą░ą│ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą▒čŗčéčī čéą░ą║ąČąĄ ąŠčćąĖčēąĄąĮčŗ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ ąĮąĖčģ ą╗ąŠą│. 1. ąĢčüą╗ąĖ čāčüą╗ąŠą▓ąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ, ą║ąŠą│ą┤ą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčćąĖčēąĄąĮ, č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé, ąĮąŠ čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĖ čŹčéąĖą╝ čüąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé ąĘą░ą┐ąŠą╝ąĮąĄąĮąŠ, ą┐ąŠą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ ą▒čāą┤ąĄčé čĆą░ąĘčĆąĄčłąĄąĮąŠ, ąĖą╗ąĖ čäą╗ą░ą│ ąĮąĄ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ. ą¤ąŠčģąŠąČąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą║ąŠą│ą┤ą░ ąŠą▒čēąĖą╣ čäą╗ą░ą│ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (ą▒ąĖčé I čĆąĄą│ąĖčüčéčĆą░ SREG) čüą▒čĆąŠčłąĄąĮ, č鹊 ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓čŗąĘčŗą▓ą░čéčīčüčÅ ąĮąĄ ą▒čāą┤čāčé, ąĮąŠ čäą╗ą░ą│ąĖ čüąŠą▒čŗčéąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▒čāą┤čāčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčīčüčÅ ąĖ ą▒čāą┤čāčé ąĘą░ą┐ąŠą╝ąĖąĮą░čéčī čüąŠą▒čŗčéąĖčÅ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖčÅ čāčüą╗ąŠą▓ąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ I ąĖ čĆą░ąĘčĆąĄčłąĄąĮčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▒čāą┤čāčé ą▓čŗąĘčŗą▓ą░čéčīčüčÅ ą▓ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ą┐ąŠčĆčÅą┤ą║ąĄ.

ąÆč鹊čĆąŠą╣ čéąĖą┐ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▒čāą┤ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░čéčī čéą░ą║ ą┤ąŠą╗ą│ąŠ, ą║ą░ą║ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé čāčüą╗ąŠą▓ąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŁčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ąĖą╝ąĄčÄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čäą╗ą░ą│ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąĢčüą╗ąĖ čāčüą╗ąŠą▓ąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖčüč湥ąĘą╗ąŠ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čŗą╗ąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ, č鹊 ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ.

ąÜąŠą│ą┤ą░ AVR ą▓čŗčģąŠą┤ąĖčé ąĖąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąŠąĮ ą▓čüąĄą│ą┤ą░ ą▓ąŠąĘą▓čĆą░čēą░ąĄčéčüčÅ ą║ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ąŠą┤ąĮčā ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą┐ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ą╗čÄą▒ąŠą│ąŠ ąŠąČąĖą┤ą░čÄčēąĄą│ąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅbackground-color: #fafad2;ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 čĆąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ SREG ąĮąĄ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐čĆąĖ ą▓čģąŠą┤ąĄ ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĖ ąĮąĄ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗čÅąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐čĆąĖ ą▓čŗčģąŠą┤ąĄ ąĖąĘ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąÆčüąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ ą┐ąŠ čüąŠčģčĆą░ąĮąĄąĮąĖčÄ ąĖ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÄ SREG ą┤ąŠą╗ąČąĄąĮ ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą║ąŠą┤ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ CLI ą┤ą╗čÅ ąĘą░ą┐čĆąĄčéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą▓čüąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▒čāą┤čāčé ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąĘą░ą┐čĆąĄčēąĄąĮčŗ. ąØąĖ ąŠą┤ąĮąŠą│ąŠ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ ą┐ąŠčüą╗ąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĖąĮčüčéčĆčāą║čåąĖąĖ CLI, ą┤ą░ąČąĄ ąĄčüą╗ąĖ čüąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ąŠąĘąĮąĖą║ą╗ąŠ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čü ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ CLI. ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ čŹč鹊 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąĖąĘą▒ąĄąČą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ ą▓ EEPROM.

;[ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ]

in r16, SREG ; čüąŠčģčĆą░ąĮąĄąĮąĖąĄ SREG

cli ; ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣

sbi EECR, EEMPE ; ąĘą░ą┐čāčüą║ ąĘą░ą┐ąĖčüąĖ ą▓ EEPROM

sbi EECR, EEPE

out SREG, r16 ; ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĄ SREG (I-bit)

//[ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ C]

char cSREG;

cSREG = SREG; /* čüąŠčģčĆą░ąĮąĄąĮąĖąĄ SREG */

/* ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ č鹥č湥ąĮąĖąĄ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┐ąĖčüąĖ */

__disable_interrupt();

EECR |= (1<<EEMPE); /* ąĘą░ą┐čāčüą║ ąĘą░ą┐ąĖčüąĖ ą▓ EEPROM */

EECR |= (1<<EEPE);

SREG = cSREG; /* ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĄ SREG (I-bit) */

ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ SEI ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, č鹊 ąĖąĮčüčéčĆčāą║čåąĖčÅ, čüą╗ąĄą┤čāčÄčēą░čÅ ąĘą░ SEI ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ ą┐ąĄčĆąĄą┤ ą╗čÄą▒čŗą╝ ąŠąČąĖą┤ą░čÄčēąĖą╝ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąŠą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ ą┐čĆąĖą╝ąĄčĆąĄ ąĮąĖąČąĄ.

;[ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ]

sei ; čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ I, ąŠą▒čēąĄąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣

sleep ; ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ čüąĮą░ ą▓ ąŠąČąĖą┤ą░ąĮąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ

; ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ čüąĮą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą┤ ą╗čÄą▒čŗą╝ ąŠąČąĖą┤ą░čÄčēąĖą╝

; ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ (ąĖą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ).

//[ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ C]

__enable_interrupt(); /* čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ I, Global Interrupt Enable */

__sleep(); /* ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ čüąĮą░ ą▓ ąŠąČąĖą┤ą░ąĮąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ */

/* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ čüąĮą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą┤ ą▓čŗąĘąŠą▓ąŠą╝ ą╗čÄą▒ąŠą│ąŠ ąŠąČąĖą┤ą░čÄčēąĄą│ąŠ

ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ąĖą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣). */

ąÆčĆąĄą╝čÅ čĆąĄą░ą│ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮą░ čüąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ

ą×čéą▓ąĄčé ąĮą░ čüąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ą║ąŠą┤ą░ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┤ą╗čÅ ą▓čüąĄčģ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ AVR ąĘą░ąĮąĖą╝ą░ąĄčé ą┐ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąĖąĮąĖą╝čāą╝ 5 čåąĖą║ą╗ąŠą▓ čéą░ą║č鹊ą▓. ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ 5 ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▒čāą┤ąĄčé ąĘą░ą┐čāčēąĄąĮ ąĮą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ ą░ą┤čĆąĄčü ą▓ąĄą║č鹊čĆą░ ą┤ą╗čÅ ą┤ąĄą╣čüčéą▓čāčÄčēąĄą│ąŠ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąÆąŠ ą▓čĆąĄą╝čÅ čŹčéąĖčģ 5 čéą░ą║č鹊ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüč湥čéčćąĖą║ ą░ą┤čĆąĄčüą░ ą┐čĆąŠčéą░ą╗ą║ąĖą▓ą░ąĄčéčüčÅ ą▓ čüč鹥ą║. ąÆąĄą║č鹊čĆ ąŠą▒čŗčćąĮąŠ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠą▒ąŠą╣ ą║ąŠą╝ą░ąĮą┤čā ą▒ąĄąĘčāčüą╗ąŠą▓ąĮąŠą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ ąĮą░ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĖ čŹč鹊čé ą┐ąĄčĆąĄčģąŠą┤ ąĘą░ąĮąĖą╝ą░ąĄčé ąĄčēąĄ 3 čåąĖą║ą╗ą░ čéą░ą║č鹊ą▓. ąĢčüą╗ąĖ čāčüą╗ąŠą▓ąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ąĘą░ąĮąĖą╝ą░čÄčēąĄą╣ ąĮąĄčüą║ąŠą╗čīą║ąŠ čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ąŠą▓, č鹊 čŹčéą░ ąĖąĮčüčéčĆčāą║čåąĖčÅ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą┤ąŠ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąĢčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą▓ ą╝ąŠą╝ąĄąĮčé, ą║ąŠą│ą┤ą░ MCU ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ čüąĮą░, č鹊 ą▓čĆąĄą╝čÅ čĆąĄą░ą║čåąĖąĖ ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ ąĮą░ 5 ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓. ąŁč鹊 čāą▓ąĄą╗ąĖč湥ąĮąĖąĄ ą┤ąŠą▒ą░ą▓ą╗čÅąĄčéčüčÅ ą║ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┐čāčüą║ą░ ąĖąĘ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ čüąĮą░.

ąÆąŠąĘą▓čĆą░čé ąĖąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ąĮąĖą╝ą░ąĄčé 3 čåąĖą║ą╗ą░ čéą░ą║č鹊ą▓. ąÆąŠ ą▓čĆąĄą╝čÅ čŹčéąĖčģ 3 ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ čüč湥čéčćąĖą║ ą║ąŠą╝ą░ąĮą┤ (3 ą▒ą░ą╣čéą░) ąĖąĘą▓ą╗ąĄą║ą░ąĄčéčüčÅ ąĖąĘ čüč鹥ą║ą░, čāą║ą░ąĘą░č鹥ą╗čī čüč鹥ą║ą░ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ ąĮą░ 3, ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé I čĆąĄą│ąĖčüčéčĆą░ SREG.

[ąÆąĮąĄčłąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (External Interrupts)]

ąÆąĮąĄčłąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čüčĆą░ą▒ą░čéčŗą▓ą░čÄčé ąŠčé ąĮąŠąČąĄą║ INT7:0 ąĖą╗ąĖ ąŠčé ą╗čÄą▒ąŠą╣ ąĖąĘ ąĮąŠąČąĄą║ PCINT12..0. ąØčāąČąĮąŠ ąĘą░ą╝ąĄčéąĖčéčī, čćč鹊 ąĄčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮčŗ, č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░čéčī ą┤ą╗čÅ INT7:0 ąĖą╗ąĖ PCINT12..0 ą┤ą░ąČąĄ ąĄčüą╗ąĖ čŹčéąĖ ąĮąŠąČą║ąĖ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ ą▓čŗčģąŠą┤čŗ. ąŁčéą░ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéčī ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (software interrupt).

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖčÄ ąĮąŠąČą║ąĖ (Pin change interrupt) PCI0 ą▒čāą┤ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░čéčī, ąĄčüą╗ąĖ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą╗čÄą▒ą░čÅ ąĖąĘ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ ąĮąŠąČąĄą║ PCINT7:0. ąĀąĄą│ąĖčüčéčĆ PCMSK0 čāą┐čĆą░ą▓ą╗čÅąĄčé, ą║ą░ą║ą░čÅ ąĮąŠąČą║ą░ ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗą▓ąŠą┤ą░ ą┐ąŠčĆčéą░. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Pin change interrupt PCI1 čüčĆą░ą▒ąŠčéą░ąĄčé, ąĄčüą╗ąĖ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą╗čÄą▒ą░čÅ ąĖąĘ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ ąĮąŠąČąĄą║ PCINT12:8. ąĀąĄą│ąĖčüčéčĆ PCMSK1 čāą┐čĆą░ą▓ą╗čÅąĄčé, ą║ą░ą║ą░čÅ ąĮąŠąČą║ą░ ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗą▓ąŠą┤ą░ ą┐ąŠčĆčéą░. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ Pin change ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ PCINT12..0 ą┤ąĄč鹥ą║čéąĖčĆčāčÄčéčüčÅ ą░čüąĖąĮčģčĆąŠąĮąĮąŠ (čé. ąĄ. ąĮąĄ ąĮčāąČąĮą░ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░, čćč鹊ą▒čŗ čüčĆą░ą▒ąŠčéą░ą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ). ąĪą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, čŹčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąĖąĘ ą│ą╗čāą▒ąŠą║ąŠą│ąŠ čüąĮą░ (čé. ąĄ. ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąĖ ą┤čĆčāą│ąĖąĄ čĆąĄąČąĖą╝čŗ čüąĮą░, ąŠčéą╗ąĖčćąĮčŗąĄ ąŠčé Idle).

ąÆąĮąĄčłąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé čüčĆą░ą▒ąŠčéą░čéčī ą┐ąŠ čüą┐ą░ą┤čā ąĖą╗ąĖ čäčĆąŠąĮčéčā ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ, ąĖą╗ąĖ ą┐ąŠ ąĮąĖąĘą║ąŠą╝čā čāčĆąŠą▓ąĮčÄ. ąŁč鹊 ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ąĮąĄčłąĮąĖą╝ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ (External Interrupt Control Registers) - EICRA (INT3:0) ąĖ EICRB (INT7:4). ąÜąŠą│ą┤ą░ ą▓ąĮąĄčłąĮąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ, ąĖ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą║ą░ą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čāčĆąŠą▓ąĮčÄ (level triggered), č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░čéčī č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ ąĮąŠąČą║ą░ čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĮą░ čāčĆąŠą▓ąĮąĄ ą╗ąŠą│. 0. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 čĆą░čüą┐ąŠąĘąĮą░ą▓ą░ąĮąĖąĄ ąĖ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖčÄ čāčĆąŠą▓ąĮčÅ INT7:4 čéčĆąĄą▒čāąĄčé ąĮą░ą╗ąĖčćąĖčÅ čéą░ą║č鹊ą▓ ąĮą░ ą┐ąŠčĆčéą░čģ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ I/O, ą║ą░ą║ ąŠą┐ąĖčüą░ąĮąŠ ą▓ čüąĄą║čåąĖąĖ ąĪąĖčüč鹥ą╝ąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ąĖ ąŠą┐čåąĖąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ (System Clock and Clock Options) ą┤ą░čéą░čłąĖčéą░ (ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ čüąĄą║čåąĖčÅ System Clock and Clock Options ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░). ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąĮąĖąĘą║ąŠą╝čā čāčĆąŠą▓ąĮčÄ ąĖ ą┐ąŠ čüčĆąĄąĘčā INT3:0 ą┤ąĄč鹥ą║čéąĖčĆčāčÄčéčüčÅ ą░čüąĖąĮčģčĆąŠąĮąĮąŠ. ąĪą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, čŹčéąĖ ąĮąŠąČą║ąĖ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąĖąĘ čĆąĄąČąĖą╝ąŠą▓ čüąĮą░, ąŠčéą╗ąĖčćą░čÄčēąĖčģčüčÅ ąŠčé Idle. ąóą░ą║čéčŗ ą┤ą╗čÅ I/O ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą▓ąŠ ą▓čüąĄčģ čĆąĄąČąĖą╝ą░čģ čüąĮą░, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čĆąĄąČąĖą╝ą░ čüąĮą░ Idle.

ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĄčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čāčĆąŠą▓ąĮčÄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ąĖąĘ čĆąĄąČąĖą╝ą░ čüąĮą░ Power-down, čéčĆąĄą▒čāąĄą╝čŗą╣ čāčĆąŠą▓ąĄąĮčī ą┤ąŠą╗ąČąĄąĮ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą┤ąŠ ą┐ąŠą╗ąĮąŠą│ąŠ ą▓čŗčģąŠą┤ą░ MCU, čćč鹊ą▒čŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüčĆą░ą▒ąŠčéą░ą╗ąŠ. ąĢčüą╗ąĖ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĖčüč湥ąĘąĮąĄčé ą┤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┐čāčüą║ą░ (Start-up Time), č鹊 ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąŠčüąĮąĄčéčüčÅ, ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ čüčĆą░ą▒ąŠčéą░ąĄčé. ąÆčĆąĄą╝čÅ ąĘą░ą┐čāčüą║ą░ ąĘą░ą┤ą░ąĄčéčüčÅ čäčīčĹʹ░ą╝ąĖ SUT ąĖ CKSEL, ą║ą░ą║ ąŠą┐ąĖčüą░ąĮąŠ ą▓ čüąĄą║čåąĖąĖ ąĪąĖčüč鹥ą╝ąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ąĖ ąŠą┐čåąĖąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ (System Clock and Clock Options) ą┤ą░čéą░čłąĖčéą░.

External Interrupt Control Register A ŌĆō EICRA

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ąĮąĄčłąĮąĖą╝ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ EICRA ąĖ ąĄą│ąŠ ą▒ąĖčéčŗ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ čĆąĖčüčāąĮą║ąĄ.

ISC31, ISC30, ISC21, ISC20, ISC11, ISC10, ISC01, ISC00: External Interrupt 3..0 Sense Control Bits

ąÆąĮąĄčłąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 3..0 ą░ą║čéąĖą▓ąĖąĘąĖčĆčāčÄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╝ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ INT3:0, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ I čĆąĄą│ąĖčüčéčĆą░ SREG ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ą╝ą░čüą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ čĆąĄą│ąĖčüčéčĆąĄ EIMSK. ąŻčĆąŠą▓ąĄąĮčī ąĖ ą┐ąĄčĆąĄą┐ą░ą┤čŗ ąĮą░ ą▓ąĮąĄčłąĮąĖčģ ąĮąŠąČą║ą░čģ ą░ą║čéąĖą▓ąĖąĘąĖčĆčāčÄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 12-1. ą¤ąĄčĆąĄą┐ą░ą┤čŗ ąĮą░ INT3..INT0 ą┤ąĄč鹥ą║čéąĖčĆčāčÄčéčüčÅ ą░čüąĖąĮčģčĆąŠąĮąĮąŠ (čé. ąĄ. ą┤ą╗čÅ čŹč鹊ą│ąŠ ąĮąĄ ąĮčāąČąĮąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ I/O). ąśą╝ą┐čāą╗čīčüčŗ ąĮą░ INT3:0 ą┤ą╗ąĖąĮąĮąĄąĄ, č湥ą╝ 50 ąĮčü (tINT, ą╝ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ ą┤ą╗ąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ą┤ą╗čÅ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ) ą▓čŗąĘąŠą▓čāčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąæąŠą╗ąĄąĄ ą║ąŠčĆąŠčéą║ąĖąĄ ąĖą╝ą┐čāą╗čīčüčŗ ąĮąĄ ą▒čāą┤čāčé ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░ąĮąĮąŠ ą▓čŗąĘčŗą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąĮąĖąĘą║ąŠą╝čā čāčĆąŠą▓ąĮčÄ (low level interrupt), č鹊 ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┤ąŠą╗ąČąĄąĮ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą┤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ č鹥ą║čāčēąĄą╣ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝ąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ, čćč鹊ą▒čŗ ą╝ąŠą│ą╗ąŠ čüčĆą░ą▒ąŠčéą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąĢčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąĮąĖąĘą║ąŠą╝čā čāčĆąŠą▓ąĮčÄ čĆą░ąĘčĆąĄčłąĄąĮąŠ, č鹊 ąŠąĮąŠ ą▒čāą┤ąĄčé ą▓čŗąĘą▓ą░čéčī ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ č鹥č湥ąĮąĖąĄ ą▓čüąĄą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, ą┐ąŠą║ą░ ąĮąŠąČą║ą░ čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĮą░ ąĮąĖąĘą║ąŠą╝ ą╗ąŠą│ąĖč湥čüą║ąŠą╝ čāčĆąŠą▓ąĮąĄ. ąÜąŠą│ą┤ą░ ąĖąĘą╝ąĄąĮčÅąĄčéčüčÅ ą╗čÄą▒ąŠą╣ ąĖąĘ ą▒ąĖč鹊ą▓ ISCn, č鹊 ą╝ąŠąČąĄčé čüčĆą░ą▒ąŠčéą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čüąĮą░čćą░ą╗ą░ ąĘą░ą┐čĆąĄčéąĖčéčī INTn ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ EIMSK, ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą╝ąŠąČąĮąŠ ą╝ąĄąĮčÅčéčī čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ISCn. ąś ąĮą░ą║ąŠąĮąĄčå, čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ INTn ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą╗ąŠą│. 1 ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé čäą╗ą░ą│ą░ (INTFn) čĆąĄą│ąĖčüčéčĆą░ EIFR ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé ąĘą░ąĮąŠą▓ąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ.

ąóą░ą▒ą╗ąĖčåą░ 12-1. Interrupt Sense Control(1).

| ISCn1 |

ISCn0 |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 0 |

0 |

ąØąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ INTn ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. |

| 0 |

1 |

ąøčÄą▒ąŠą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ INTn ą░čüąĖąĮčģčĆąŠąĮąĮąŠ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. |

| 1 |

0 |

ąĪą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ INTn ą░čüąĖąĮčģčĆąŠąĮąĮąŠ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. |

| 1 |

1 |

ąØą░čĆą░čüčéą░ąĮąĖąĄ (čäčĆąŠąĮčé)background-color: #fafad2;čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ INTn ą░čüąĖąĮčģčĆąŠąĮąĮąŠ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): n = 3, 2, 1 ąĖą╗ąĖ 0. ąÜąŠą│ą┤ą░ ą╝ąĄąĮčÅčÄčé ą▒ąĖčéčŗ ISCn1/ISCn0, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮčŗ ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ EIMSK. ąśąĮą░č湥 ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ čŹčéąĖčģ ą▒ąĖčé ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

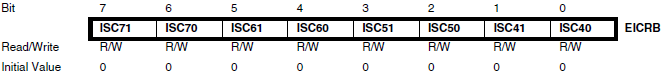

External Interrupt Control Register B ŌĆō EICRB

ISC71, ISC70, ISC61, ISC60, ISC51, ISC50, ISC41, ISC40: External Interrupt 7..4 Sense Control Bits

ąÆąĮąĄčłąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 7..4 ą░ą║čéąĖą▓ąĖąĘąĖčĆčāčÄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╝ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ INT7:4, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ I čĆąĄą│ąĖčüčéčĆą░ SREG ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ą╝ą░čüą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ čĆąĄą│ąĖčüčéčĆąĄ EIMSK. ąŻčĆąŠą▓ąĄąĮčī ąĖ ą┐ąĄčĆąĄą┐ą░ą┤čŗ ąĮą░ ą▓ąĮąĄčłąĮąĖčģ ąĮąŠąČą║ą░čģ ą░ą║čéąĖą▓ąĖąĘąĖčĆčāčÄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 12-3. ąŚąĮą░č湥ąĮąĖąĄ ąĮą░ ąĮąŠąČą║ą░čģ INT7:4 ąĘą░ą┐ąŠą╝ąĖąĮą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓. ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüčĆąĄąĘčā (edge) ąĖą╗ąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÄ (toggle), č鹊 ąĖą╝ą┐čāą╗čīčüčŗ ą┤ą╗ąĖąĮąĮąĄąĄ ąŠą┤ąĮąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą║č鹊ą▓ ą▒čāą┤čāčé ą▓čŗąĘčŗą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąæąŠą╗ąĄąĄ ą║ąŠčĆąŠčéą║ąĖąĄ ąĖą╝ą┐čāą╗čīčüčŗ ąĮąĄ ą▒čāą┤čāčé ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░ąĮąĮąŠ ą▓čŗąĘčŗą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ą¤ąŠą╝ąĮąĖč鹥 ąŠ č鹊ą╝, čćč鹊 čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ CPU ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĖąČąĄ, č湥ą╝ čćą░čüč鹊čéą░ XTAL, ąĄčüą╗ąĖ čĆą░ą▒ąŠčéą░ąĄčé ą┤ąĄą╗ąĖč鹥ą╗čī čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ. ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąĮąĖąĘą║ąŠą╝čā čāčĆąŠą▓ąĮčÄ (low level interrupt), č鹊 ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┤ąŠą╗ąČąĄąĮ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą┤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ č鹥ą║čāčēąĄą╣ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝ąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ, čćč鹊ą▒čŗ ą╝ąŠą│ą╗ąŠ čüčĆą░ą▒ąŠčéą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąĢčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąĮąĖąĘą║ąŠą╝čā čāčĆąŠą▓ąĮčÄ čĆą░ąĘčĆąĄčłąĄąĮąŠ, č鹊 ąŠąĮąŠ ą▒čāą┤ąĄčé ą▓čŗąĘą▓ą░čéčī ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ č鹥č湥ąĮąĖąĄ ą▓čüąĄą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, ą┐ąŠą║ą░ ąĮąŠąČą║ą░ čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĮą░ ąĮąĖąĘą║ąŠą╝ ą╗ąŠą│ąĖč湥čüą║ąŠą╝ čāčĆąŠą▓ąĮąĄ.

Table 12-3. Interrupt Sense Control(1)

| ISCn1 |

ISCn0 |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 0 |

0 |

ąØąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ INTn ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. |

| 0 |

1 |

ąøčÄą▒ąŠą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ INTn ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. |

| 1 |

0 |

ąĪą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ ą▓čŗą▒ąŠčĆą║ą░ą╝ąĖ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ INTn ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. |

| 1 |

1 |

ąØą░čĆą░čüčéą░ąĮąĖąĄ (čäčĆąŠąĮčé)background-color: #fafad2;čāčĆąŠą▓ąĮčÅ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ ą▓čŗą▒ąŠčĆą║ą░ą╝ąĖ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ INTn ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): n = 7, 6, 5 ąĖą╗ąĖ 4. ąÜąŠą│ą┤ą░ ą╝ąĄąĮčÅčÄčé ą▒ąĖčéčŗ ISCn1/ISCn0, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮčŗ ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ EIMSK. ąśąĮą░č湥 ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ čŹčéąĖčģ ą▒ąĖčé ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

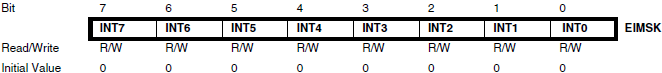

External Interrupt Mask Register ŌĆō EIMSK

INT7..INT0: External Interrupt Request 7-0 Enable

ąÜąŠą│ą┤ą░ ą╗čÄą▒ąŠą╣ ąĖąĘ ą▒ąĖčé INT7..INT0 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé I ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ (SREG), č鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ ą▓ąĮąĄčłąĮąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ąĮąŠąČą║ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąĀąĄą│ąĖčüčéčĆčŗ EICRA ąĖ EICRB ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą║ą░ą║ąŠą╣ čéąĖą┐ ą░ą║čéąĖą▓ąĖąĘąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ (ąĮą░čĆą░čüčéą░ąĮąĖąĄ ąĖą╗ąĖ čüą┐ą░ą┤, ąĖą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čāčĆąŠą▓ąĮčÄ). ąÉą║čéąĖą▓ąĮąŠčüčéčī ąĮą░ čŹčéąĖčģ ąĮąŠąČą║ą░čģ ą▓čŗąĘąŠą▓čāčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ąŠąĮąĖ ąĮą░čüčéčĆąŠąĄąĮčŗ ą║ą░ą║ ą▓čŗčģąŠą┤čŗ. ąŁč鹊 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą┐ąŠčüąŠą▒ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

External Interrupt Flag Register ŌĆō EIFR

INTF7..INTF0: External Interrupt Flags 7-0

ąÜąŠą│ą┤ą░ čüčĆąĄąĘ (edge) ąĖą╗ąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ą▓čŗąĘčŗą▓ą░ąĄčé ąĘą░ą┐čĆąŠčü ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ INT7:0, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 1 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čäą╗ą░ą│ INTF7:0. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1 ą▒ąĖčé I ą▓ čĆąĄą│ąĖčüčéčĆąĄ SREG, ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ INT7:0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ EIMSK, č鹊 MCU ą┐čĆąŠąĖąĘą▓ąĄą┤ąĄčé ą┐ąĄčĆąĄčģąŠą┤ ą┐ąŠ ą▓ąĄą║č鹊čĆčā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ążą╗ą░ą│ ąŠčćąĖčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐čĆąŠčåąĄą┤čāčĆą░ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ). ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗą╣ čüą┐ąŠčüąŠą▒ ąŠčćąĖčüčéą║ąĖ čäą╗ą░ą│ą░ - ąĘą░ą┐ąĖčüčī ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1. ąŁčéąĖ čäą╗ą░ą│ąĖ ą▓čüąĄą│ą┤ą░ ąŠčćąĖčēą░čÄčéčüčÅ, ą║ąŠą│ą┤ą░ INT7:0 čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čāčĆąŠą▓ąĮčÄ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ čüąĮą░ čü ąĘą░ą┐čĆąĄčēąĄąĮąĮčŗą╝ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ INT3:0, ą▓čģąŠą┤ąĮčŗąĄ ą▒čāč乥čĆčŗ čŹčéąĖčģ ąĮąŠąČąĄą║ ą▒čāą┤čāčé ąĘą░ą┐čĆąĄčēąĄąĮčŗ. ąŁč鹊 ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ č鹊ą╝čā, čćč鹊 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą╗ąŠą│ąĖą║ąĖ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čüąĖą│ąĮą░ą╗ą░čģ ą┐čĆąĖą▓ąĄą┤čāčé ą║ čāčüčéą░ąĮąŠą▓ą║ąĄ čäą╗ą░ą│ąŠą▓ INTF3:0. ąöą╗čÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüč鹥ą╣ čüą╝. čüąĄą║čåąĖčÄbackground-color: #fafad2;ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čåąĖčäčĆąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░ ąĖ čĆąĄąČąĖą╝čŗ čüąĮą░ (Digital Input Enable and Sleep Modes).

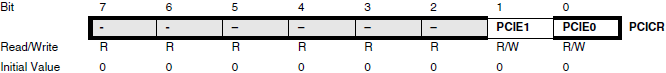

Pin Change Interrupt Control Register - PCICR

PCIE1, PCIE0: Pin Change Interrupt Enable 1-0

ąÜąŠą│ą┤ą░ ą▒ąĖčéčŗ PCIE1, PCIE0 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ ą╗ąŠą│. 1, ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1 ą▒ąĖčé I ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ (SREG), č鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüą╝ąĄąĮąĄ čāčĆąŠą▓ąĮčÅ 1/0 (Pin Change interrupt). ąøčÄą▒ąŠąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ąĮą░ ą╗čÄą▒ąŠą╝ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą╝ ą▓čģąŠą┤ąĄ PCINT12..8/7..0 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ. ą¤čĆąĖ čŹč鹊ą╝ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą▓čŗąĘąŠą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ąĘą░ą┐čĆąŠčüą░ ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĖ ą┐ąĄčĆąĄčģąŠą┤ ą┐ąŠ ą▓ąĄą║č鹊čĆčā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ PCI1/0. ąÆčŗą▓ąŠą┤čŗ PCINT12..8/7..0 čĆą░ąĘčĆąĄčłą░čÄčéčüčÅ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆčŗ PCMSK1 ąĖ PCMSK0.

Pin Change Interrupt Flag Register ŌĆō PCIFR

PCIF1, PCIF0: Pin Change Interrupt Flag 1-0

ąÜąŠą│ą┤ą░ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ ą╗čÄą▒ąŠą╝ ąĖąĘ ą▓čŗą▓ąŠą┤ąŠą▓ PCINT12..8/7..0 ą▓čŗąĘčŗą▓ą░ąĄčé ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, č鹊 čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 1 čäą╗ą░ą│ PCIF1/0. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé I ą▓ SREG ąĖ ą▒ąĖčé PCIE1/0 ą▓ PCICR, MCU ą┐čĆąŠąĖąĘą▓ąĄą┤ąĄčé ą┐ąĄčĆąĄčģąŠą┤ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▓ąĄą║č鹊čĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ążą╗ą░ą│ ąŠčćąĖčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐čĆąŠčåąĄą┤čāčĆą░ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗą╣ čüą┐ąŠčüąŠą▒ ąŠčćąĖčüčéą║ąĖ čäą╗ą░ą│ą░ - ąĘą░ą┐ąĖčüčī ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1.

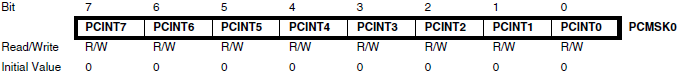

Pin Change Mask Register 0 ŌĆō PCMSK0

PCINT7..0: Pin Change Enable Mask 7..0

ąÜą░ąČą┤čŗą╣ ąĖąĘ ą▒ąĖč鹊ą▓ PCINT7..0 ą▓čŗą▒ąĖčĆą░ąĄčé, čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĖą╗ąĖ ąĮąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüą╝ąĄąĮąĄ čāčĆąŠą▓ąĮčÅ (pin change interrupt) ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ I/O ąĮąŠąČą║ąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąĢčüą╗ąĖ ą╗čÄą▒ąŠą╣ ąĖąĘ ą▒ąĖč鹊ą▓ PCINT7..0 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĖ ą▒ąĖčé PCIE0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ PCICR čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 pin change interrupt čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ąĮąŠąČą║ąĄ ą┐ąŠčĆčéą░ I/O. ąĢčüą╗ąĖ PCINT7..0 ąŠčćąĖčēąĄąĮ, č鹊 ąĘą░ą┐čĆąĄčēąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ pin change ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ ą▓čŗą▓ąŠą┤ąĄ I/O.

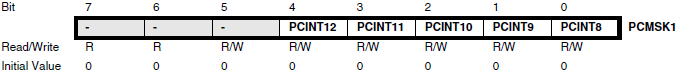

Pin Change Mask Register 1ŌĆō PCMSK1

PCINT12..8: Pin Change Enable Mask 12..8

ąÜą░ąČą┤čŗą╣ ąĖąĘ ą▒ąĖč鹊ą▓ PCINT12..8 ą▓čŗą▒ąĖčĆą░ąĄčé, čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĖą╗ąĖ ąĮąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüą╝ąĄąĮąĄ čāčĆąŠą▓ąĮčÅ (pin change interrupt) ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ I/O ąĮąŠąČą║ąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąĢčüą╗ąĖ ą╗čÄą▒ąŠą╣ ąĖąĘ ą▒ąĖč鹊ą▓ PCINT12..8 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĖ ą▒ąĖčé PCIE1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ PCICR čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 pin change interrupt čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ąĮąŠąČą║ąĄ ą┐ąŠčĆčéą░ I/O. ąĢčüą╗ąĖ PCINT12..8 ąŠčćąĖčēąĄąĮ, č鹊 ąĘą░ą┐čĆąĄčēąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ pin change ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ ą▓čŗą▓ąŠą┤ąĄ I/O.

[ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ (Analog Comparator)]

ąÆ čŹč鹊ą╝ čüąĄą║čåąĖąĖ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ąĮą░ ą┐čĆąĄą┤ą╝ąĄčé ą┐ąŠąĮąĖąČąĄąĮąĖčÅ čŹąĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆąŠą╝ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüčéą░čéčāčüą░ ACSR.

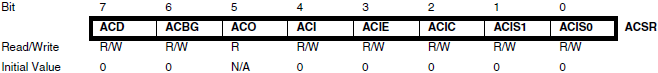

Analog Comparator Control and Status Register ŌĆō ACSR

ACD: Analog Comparator Disable

ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1, ą┐ąĖčéą░ąĮąĖąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ. ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗čÄą▒ąŠąĄ ą▓čĆąĄą╝čÅ ą┤ą╗čÅ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░, čćč鹊 čāą╝ąĄąĮčīčłą░ąĄčé 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ą░čģ Active ąĖ Idle. ąÜąŠą│ą┤ą░ ąĖąĘą╝ąĄąĮčÅąĄčéčüčÅ ą▒ąĖčé ACD, ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ ACIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ ACSR. ąśąĮą░č湥 ą╝ąŠąČąĄčé čüčĆą░ą▒ąŠčéą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░, ą║ąŠą│ą┤ą░ ą╝ąĄąĮčÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░ ACD.

ACBG: Analog Comparator Bandgap Select

ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĮą░ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą▓čģąŠą┤ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą▓ą╝ąĄčüč鹊 ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓čģąŠą┤ą░ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ąĖčüč鹊čćąĮąĖą║ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé ąŠčćąĖčēąĄąĮ, AIN0 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą▓čģąŠą┤ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čüąĄą║čåąĖąĖ ąśčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (Internal Voltage Reference) ą┤ą░čéą░čłąĖčéą░.

ACO: Analog Comparator Output

ąÆčŗčģąŠą┤ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮ ąĖ ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą▒ąĖčéčā ACO. ąĪąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčé ąĘą░ą┤ąĄčƹȹ║čā ą▓ 1-2 čåąĖą║ą╗ą░ čéą░ą║č鹊ą▓.

ACI: Analog Comparator Interrupt Flag

ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą▓čŗčģąŠą┤ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą▓čŗąĘčŗą▓ą░ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą║ą░ą║ ąĘą░ą┤ą░ąĮąŠ ą▒ąĖčéą░ą╝ąĖ ACIS1 ąĖ ACIS0 (čüą╝. čéą░ą▒ą╗ąĖčåčā 22-1). ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ, ąĄčüą╗ąĖ ą▒ąĖčé ACIE čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĖ ą▒ąĖčé I čĆąĄą│ąĖčüčéčĆą░ SREG čéą░ą║ąČąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ. ąæąĖčé ACI ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą║ąŠą┤ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ą▒ąĖčé ACI ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ąĘą░ą┐ąĖčüčīčÄ ą╗ąŠą│. 1 ą▓ čŹč鹊čé čäą╗ą░ą│.

ACIE: Analog Comparator Interrupt Enable

ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1, ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé I čĆąĄą│ąĖčüčéčĆą░ SREG, č鹊 ą░ą║čéąĖą▓ąĖąĘąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. ąÜąŠą│ą┤ą░ ACIE ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 0, čŹč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

ACIC: Analog Comparator Input Capture Enable

ąÜąŠą│ą┤ą░ ą▒ąĖčé ACIC čĆą░ą▓ąĄąĮ ą╗ąŠą│. 1, č鹊 ąŠąĮ čĆą░ąĘčĆąĄčłą░ąĄčé čäčāąĮą║čåąĖčÄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ąĘą░čģą▓ą░čéą░ ą┐ąŠ ą▓čģąŠą┤čā ą▓ Timer/Counter1 ąŠčé ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▓čŗčģąŠą┤ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą╗ąŠą│ąĖą║ąĄ ąĘą░čģą▓ą░čéą░ ą┐ąŠ ą▓čģąŠą┤čā, č湥ą╝ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčéčüčÅ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖąĄ čłčāą╝ą░ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆąŠą╝ ąĖ ą▓čŗą▒ąŠčĆ čüčĆąĄąĘą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░čģą▓ą░čéą░ ą┐ąŠ ą▓čģąŠą┤čā Timer/Counter1. ąÜąŠą│ą┤ą░ ą▒ąĖčé ACIC čĆą░ą▓ąĄąĮ ą╗ąŠą│. 0, č鹊 ąĮąĄčé čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą╝ąĄąČą┤čā ą▓čŗčģąŠą┤ąŠą╝ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ąĖ čäčāąĮą║čåąĖąĄą╣ ąĘą░čģą▓ą░čéą░ ą┐ąŠ ą▓čģąŠą┤čā. ąöą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ą┐ąĄčĆąĄą║ą╗čÄčćą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ą▓čģąŠą┤ąĮąŠą╝čā ąĘą░čģą▓ą░čéčā Timer/Counter1, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ICIE1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ TIMSK1.

ACIS1, ACIS0: Analog Comparator Interrupt Mode Select

ąŁčéąĖ ą▒ąĖčéčŗ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą║ą░ą║ąĖąĄ čüąŠą▒čŗčéąĖčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą▒čāą┤čāčé ą▓čŗąĘčŗą▓ą░čéčī čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. ąĀą░ąĘą╗ąĖčćąĮčŗąĄ ą▓ą░čĆąĖą░ąĮčéčŗ čāčüčéą░ąĮąŠą▓ąŠą║ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ 22-1.

ąóą░ą▒ą╗ąĖčåą░ 22-1. ąŻčüčéą░ąĮąŠą▓ą║ąĖ ACIS1/ACIS0

| ACIS1 |

ACIS0 |

ąĀąĄąČąĖą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ |

| 0 |

0 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ąĮą░ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĖ ą▓čŗčģąŠą┤ą░. |

| 0 |

1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 1 |

0 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ąĮą░ čüą┐ą░ą┤ąĄ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ. |

| 1 |

1 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ąĮą░ čäčĆąŠąĮč鹥 čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ. |

ąÜąŠą│ą┤ą░ ąĮčāąČąĮąŠ ą┐ąŠą╝ąĄąĮčÅčéčī ą▒ąĖčéčŗ ACIS1/ACIS0, č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮąŠ ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ ACIE. ąśąĮą░č湥 ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ čŹčéąĖčģ ą▒ąĖčé.

[ąĀąĄą│ąĖčüčéčĆ ąĘą░ą┐čĆąĄčéą░ ą▓čģąŠą┤ąĮčŗčģ ą┐ąŠčĆč鹊ą▓ (Digital Input Disable Register 1 ŌĆō DIDR1)]

AIN1D, AIN0D: AIN1, AIN0 Digital Input Disable

ąÜąŠą│ą┤ą░ čŹčéąĖ ą▒ąĖčéčŗ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ą╗ąŠą│. 1, čåąĖčäčĆąŠą▓čŗąĄ ą▓čģąŠą┤ąĮčŗąĄ ą▒čāč乥čĆčŗ ą┤ą╗čÅ ąĮąŠąČąĄą║ AIN1/0 ąĘą░ą┐čĆąĄčēąĄąĮčŗ. ąĪąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čĆąĄą│ąĖčüčéčĆ PIN ą▒čāą┤ąĄčé ą▓čüąĄą│ą┤ą░ čćąĖčéą░čéčīčüčÅ ą║ą░ą║ 0, ąĄčüą╗ąĖ čŹčéąĖ ą▒ąĖčéčŗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ. ąÜąŠą│ą┤ą░ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ ą║ ą▓čŗą▓ąŠą┤ą░ą╝ AIN1/0 ąĖ čåąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ ąŠčé čŹčéąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ ąĮąĄ ąĮčāąČąĄąĮ, č鹊 čŹčéąĖ ą▒ąĖčéčŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ą╗ąŠą│. 1 ą┤ą╗čÅ čāą╝ąĄąĮčīčłąĄąĮąĖčÅ čŹąĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ąŠčé čåąĖčäčĆąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ ą▒čāč乥čĆą░.

[ąśčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (Internal Voltage Reference)]

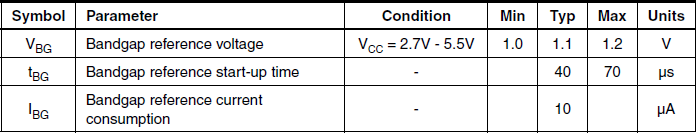

ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ AT90USB82/162 ąĖą╝ąĄąĄčé ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (internal bandgap reference). ąŁč鹊čé ąĖčüč鹊čćąĮąĖą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┤ąĄč鹥ą║č鹊čĆą░ ąĮąĄą║ąŠąĮą┤ąĖčåąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (Brown-out Detection, BOD) ąĖ ą║ą░ą║ ąĖčüč鹊čćąĮąĖą║ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░.

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ąĖą╝ąĄąĄčé ą▓čĆąĄą╝čÅ ąĘą░ą┐čāčüą║ą░, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĄčé ą┐ąŠą▓ą╗ąĖčÅčéčī ąĮą░ ą╝ąĄč鹊ą┤ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąÆčĆąĄą╝čÅ ąĘą░ą┐čāčüą║ą░ čāą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 9-4. ą¦č鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ, ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮąĄ ą▓čüąĄą│ą┤ą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ą║ą╗čÄč湥ąĮ. ąÆą║ą╗čÄč湥ąĮ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ čüą╗čāčćą░čÅčģ:

1. ąÜąŠą│ą┤ą░ BOD čĆą░ąĘčĆąĄčłąĄąĮ (č湥čĆąĄąĘ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čäčīčĹʹŠą▓ BODLEVEL [2..0]).

2. ąÜąŠą│ą┤ą░ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╝čā ą║ąŠą╝ą┐ą░čĆą░č鹊čĆčā (č湥čĆąĄąĘ čāčüčéą░ąĮąŠą▓ą║čā ą▒ąĖčéą░ ACBG ą▓ čĆąĄą│ąĖčüčéčĆąĄ ACSR).

ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ BOD ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮ, ą┐ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ ACBG ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą▓čüąĄą│ą┤ą░ ą┤ąŠą╗ąČąĄąĮ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī ąĖčüč鹊čćąĮąĖą║čā ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĘą░ą┐čāčüčéąĖčéčīčüčÅ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ąĮą░čćąĮąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓čŗčģąŠą┤ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. ąöą╗čÅ čüąĮąĖąČąĄąĮąĖčÅ čŹąĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ Power-down, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ąĖąĘą▒ąĄąČą░čéčī čŹčéąĖčģ čéčĆąĄčģ ą▓čŗčłąĄą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮčŗčģ čāčüą╗ąŠą▓ąĖą╣, čćč鹊ą▒čŗ čāą┤ąŠčüč鹊ą▓ąĄčĆąĖčéčīčüčÅ, čćč鹊 ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▒čāą┤ąĄčé ą▓čŗą║ą╗čÄč湥ąĮ ą┐ąĄčĆąĄą┤ ą▓čģąŠą┤ąŠą╝ ą▓ čĆąĄąČąĖą╝ Power-down.

ąóą░ą▒ą╗ąĖčåą░ 9-4. ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

[ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čåąĖčäčĆąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░ ąĖ čĆąĄąČąĖą╝čŗ čüąĮą░ (Digital Input Enable and Sleep Modes)]

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĖčéčÅąĮčāčé ą║ ąĘąĄą╝ą╗ąĄ ąĮą░ ą▓čģąŠą┤ąĄ čéčĆąĖą│ą│ąĄčĆą░ ą©ą╝ąĖčéčéą░ (čüą╝. čĆąĖčüčāąĮąŠą║).

ąĪąĖą│ąĮą░ą╗, ą┐ąŠą╝ąĄč湥ąĮąĮčŗą╣ ąĮą░ čĆąĖčüčāąĮą║ąĄ ą║ą░ą║ SLEEP, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ čüąĮą░ MCU ą▓ čĆąĄąČąĖą╝ą░čģ Power-down, Power-save ąĖ Standby, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą▓čŗčüąŠą║ąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ąĄčüą╗ąĖ ąĮąĄą║ąŠč鹊čĆčŗąĄ ą▓čģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ąŠčüčéą░ą╗ąĖčüčī ą▓ ą┐ąŠą┤ą▓ąĄčłąĄąĮąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ, ąĖą╗ąĖ ąĖą╝ąĄčÄčé ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąŠą║ąŠą╗ąŠ VCC/2.

ąĪąĖą│ąĮą░ą╗ SLEEP ąĘą░ą┐čĆąĄčēą░ąĄčé čĆą░ą▒ąŠčéčā ą┤ą╗čÅ ąĮąŠąČąĄą║ ą┐ąŠčĆč鹊ą▓ ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓ąĮąĄčłąĮąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąĢčüą╗ąĖ ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮ ąĘą░ą┐čĆąŠčü ąĮą░ ą▓ąĮąĄčłąĮąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┤ą╗čÅ ą║ą░ą║ąŠą╣-č鹊 ąĮąŠąČą║ąĖ, č鹊 ą┤ą╗čÅ čŹč鹊ą╣ ąĮąŠąČą║ąĖ čüąĖą│ąĮą░ą╗ SLEEP čÅą▓ą╗čÅąĄčéčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ (čé. ąĄ. ąĘą░ą┐čĆąĄčēą░ąĄčé čĆą░ą▒ąŠčéčā čŹč鹊ą╣ ąĮąŠąČą║ąĖ ą║ą░ą║ ą▓čģąŠą┤ą░). ąĪąĖą│ąĮą░ą╗ SLEEP čéą░ą║ąČąĄ ąŠčéą╝ąĄąĮčÅąĄčé čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą┤čĆčāą│ąĖąĄ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ ą┐ąŠčĆč鹊ą▓, ą║ąŠč鹊čĆčŗąĄ ąŠą┐ąĖčüą░ąĮčŗ ą▓ čüąĄą║čåąĖąĖ ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ ą┐ąŠčĆč鹊ą▓ (Alternate Port Functions) ą┤ą░čéą░čłąĖčéą░ (ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ čüąĄą║čåąĖčÅ Alternate Port Functions ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░).

ąĢčüą╗ąĖ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ ą▓čŗčüąŠą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī (ą╗ąŠą│. 1) ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮą░ ąĮąŠąČą║ąĄ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą║ą░ą║ "ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čäčĆąŠąĮčéčā, čüą┐ą░ą┤čā ąĖą╗ąĖ ą┐ąŠ ą╗čÄą▒ąŠą╣ čüą╝ąĄąĮąĄ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ" (Interrupt on Rising Edge, Falling Edge, or Any Logic Change on Pin), ąĖ ą┐čĆąĖ čŹč鹊ą╝ ą▓ąĮąĄčłąĮąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąØąĢ čĆą░ąĘčĆąĄčłąĄąĮąŠ, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čäą╗ą░ą│ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (External Interrupt Flag) ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĖ ą▓čŗąĘąŠą▓ąĄčé ą┐čĆąŠčüčŗą┐ą░ąĮąĖąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąĖąĘ ą▓čŗčłąĄčāą┐ąŠą╝čÅąĮčāčéčŗčģ čĆąĄąČąĖą╝ąŠą▓ čüąĮą░, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąĘą░ą┐čĆąŠčłąĄąĮąĮąŠąĄ čüąŠą▒čŗčéąĖąĄ ąĘą░čģą▓ą░čéą░ ąĮą░ ą▓čģąŠą┤ą░čģ ą▓ čŹčéąĖčģ čĆąĄąČąĖą╝ą░čģ.

ąĢčüą╗ąĖ ąĮąĄą║ąŠč鹊čĆčŗąĄ ąĮąŠąČą║ąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čāą┤ąŠčüč鹊ą▓ąĄčĆąĖčéčīčüčÅ, čćč鹊 ąĮą░ ąĮąĖčģ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ąĘą░ą┤ą░ąĮąĮčŗą╣ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī. ąöą░ąČąĄ ąĄčüą╗ąĖ čåąĖčäčĆąŠą▓čŗąĄ ą▓čģąŠą┤čŗ ąĘą░ą┐čĆąĄčēąĄąĮčŗ ą▓ čĆąĄąČąĖą╝ą░čģ ą│ą╗čāą▒ąŠą║ąŠą│ąŠ čüąĮą░, ą║ą░ą║ ą▒čŗą╗ąŠ ąŠą┐ąĖčüą░ąĮąŠ čĆą░ąĮąĄąĄ, ąĮą░ą╗ąĖčćąĖčÅ "ą┐ą╗ą░ą▓ą░čÄčēąĖčģ" ą▓čģąŠą┤ąŠą▓ ąĮčāąČąĮąŠ ąĖąĘą▒ąĄą│ą░čéčī ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ čüąĮąĖąĘąĖčéčī ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ č鹊ą║ą░ ą▓ąŠ ą▓čüąĄčģ ą┤čĆčāą│ąĖčģ čĆąĄąČąĖą╝ą░čģ, ą│ą┤ąĄ čåąĖčäčĆąŠą▓čŗąĄ ą▓čģąŠą┤čŗ čĆą░ąĘčĆąĄčłąĄąĮčŗ (Reset, čĆąĄąČąĖą╝ Active ąĖ čĆąĄąČąĖą╝ Idle).

ąĪą░ą╝čŗą╣ ą┐čĆąŠčüč鹊ą╣ ą╝ąĄč鹊ą┤ čāą▒ąĄą┤ąĖčéčīčüčÅ ą▓ č鹊ą╝, čćč鹊 ąĮą░ ąĮąĄąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĮąŠą╣ ąĮąŠąČą║ąĄ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ąĘą░ą┤ą░ąĮąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī - čĆą░ąĘčĆąĄčłąĖčéčī ą┤ą╗čÅ ąĮąĄčæ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąĮą░ą│čĆčāąĘąŠčćąĮčŗą╣ čĆąĄąĘąĖčüč鹊čĆ (internal pull-up). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĮčāąČąĮąŠ ą┐ąŠą╝ąĮąĖčéčī, čćč鹊 pull-up ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ą┐čĆąĖ čüą▒čĆąŠčüąĄ. ąĢčüą╗ąĖ ą▓ą░ąČąĮąŠ ąĮąĖąĘą║ąŠąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (Reset), č鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ąĮąĄčłąĮąĖą╣ pull-up ąĖą╗ąĖ pull-down čĆąĄąĘąĖčüč鹊čĆ. ą¤čĆčÅą╝ąŠąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ąĮąĄąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ąĮąŠąČąĄą║ ą║ VCC ąĖą╗ąĖ GND ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ, ą┐ąŠčüą║ąŠą╗čīą║čā ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī čćčĆąĄąĘą╝ąĄčĆąĮčŗą╣ č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ąĄčüą╗ąĖ čüą╗čāčćą░ą╣ąĮąŠ čŹčéąĖ ąĮąŠąČą║ąĖ ą▒čāą┤čāčé ąĮą░čüčéčĆąŠąĄąĮčŗ ą║ą░ą║ ą▓čŗčģąŠą┤čŗ.

[ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąĄą║ąŠąĮą┤ąĖčåąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (Brown-out Detection)]

ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ AT90USB82/162 ąĖą╝ąĄąĄčé ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čāąĘąĄą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░č湥čüčéą▓ą░ ą┐ąĖčéą░čÄčēąĄą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (On-chip Brown-out Detection, BOD), ą┤ą╗čÅ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ čāčĆąŠą▓ąĮčÅ VCC ą▓ąŠ ą▓čĆąĄą╝čÅ čĆą░ą▒ąŠčéčŗ. ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐čāč鹥ą╝ čüčĆą░ą▓ąĮąĄąĮąĖčÅ VCC čü čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą┐ąŠčĆąŠą│ąŠą╝ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ. ąŁč鹊čé ą┐ąŠčĆąŠą│ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ą┐čāč鹥ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čäčīčĹʹŠą▓ BODLEVEL (čüą╝. čéą░ą▒ą╗ąĖčåčā 9-2 ą┤ą░čéą░čłąĖčéą░). ąöą╗čÅ čāą╝ąĄąĮčīčłąĄąĮąĖčÅ čŹąĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ BOD ąĮčāąČąĮąŠ ą▓čŗą║ą╗čÄčćąĖčéčī, ą┤ą╗čÅ č湥ą│ąŠ ą▓čüąĄ ą▒ąĖčéčŗ BODLEVEL 2..0 ą┤ąŠą╗ąČąĮčŗ ąŠčüčéą░čéčīčüčÅ ąĮąĄ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ (ą▓ čüąŠčüč鹊čÅąĮąĖąĖ 111).

[ą¤čĆąĖą╝ąĄčĆ ą┐čĆą░ą║čéąĖč湥čüą║ąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄąČąĖą╝ąŠą▓ čüąĮą░]

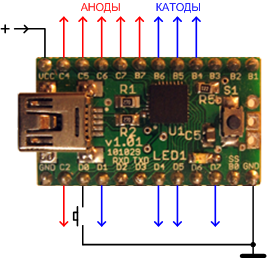

ąŚą░ą┤ą░čćą░: čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ AT90USB162 ą┐ąĖčéą░ąĄčéčüčÅ ąŠčé ą▒ą░čéą░čĆąĄą╣ą║ąĖ, ąĖą╝ąĄąĄčé ą║ąĮąŠą┐ą║čā ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüą▓ąĄč鹊ą┤ąĖąŠą┤ąĮčŗą╣ ą╝ą░čéčĆąĖčćąĮčŗą╣ ąĖąĮą┤ąĖą║ą░č鹊čĆ ąÉąøąĪ340ąÉ1. ąÆ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆą░ą▒ąŠč湥ą╝ čĆąĄąČąĖą╝ąĄ (Active mode) ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčé ą┐ąŠčĆčéčŗ ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖą╝ą▓ąŠą╗ą░ ąĮą░ ąĖąĮą┤ąĖą║ą░č鹊čĆąĄ (ą┤ąĖąĮą░ą╝ąĖč湥čüą║ą░čÅ ąĖąĮą┤ąĖą║ą░čåąĖčÅ) ąĖ ąŠą┐čĆą░čłąĖą▓ą░ąĄčé ą║ąĮąŠą┐ą║čā. ąØą░ąČą░čéąĖąĄ ą║ąĮąŠą┐ą║ąĖ ąĘą░ą╝čŗą║ą░ąĄčé ąĮąŠąČą║čā ą┐ąŠčĆčéą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąĮą░ ąĘąĄą╝ą╗čÄ, GND. ąĢčüą╗ąĖ čŹčéą░ ą║ąĮąŠą┐ą║ą░ ąĮąĄ ą▒čŗą╗ą░ ąĮą░ąČą░čéą░ ą▓ č鹥č湥ąĮąĖąĄ 10 čüąĄą║čāąĮą┤, č鹊 ąĮčāąČąĮąŠ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ čĆąĄąČąĖą╝ 菹║ąŠąĮąŠą╝ąĖąĖ 菹ĮąĄčĆą│ąĖąĖ (Power-down mode). ą¤čĆąĖ čŹč鹊ą╝ ą▓čüąĄ čćč鹊 č鹊ą╗čīą║ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠ, ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓čŗą║ą╗čÄč湥ąĮąŠ. ąĢčüą╗ąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ąĮą░ąČą░ą╗ ąĮą░ ą║ąĮąŠą┐ą║čā, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠčüąĮčāčéčīčüčÅ ąĖ ą▓ąŠąĘąŠą▒ąĮąŠą▓ąĖčéčī čĆą░ą▒ąŠčéčā čü ąĮčāąČąĮąŠą│ąŠ ą╝ąĄčüčéą░.

ąØą░ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ čāą┐čĆąŠčēąĄąĮąĮą░čÅ čüčģąĄą╝ą░ čāčüčéčĆąŠą╣čüčéą▓ą░, čüąŠą▒čĆą░ąĮąĮąŠą│ąŠ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą╝ą░ą║ąĄčéąĮąŠą╣ ą┐ą╗ą░čéčŗ AVR-USB162MU [1]. ąÜčĆą░čüąĮčŗą╝ąĖ ąĖ čüąĖąĮąĖą╝ąĖ ą┐čĆąŠą▓ąŠą┤ą░ą╝ąĖ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą░ąĮąŠą┤ąŠą▓ ąĖ ą║ą░č鹊ą┤ąŠą▓ ąĖąĮą┤ąĖą║ą░č鹊čĆą░ ąÉąøąĪ340ąÉ1 (ą▓čŗčģąŠą┤čŗ). ąĢą┤ąĖąĮčüčéą▓ąĄąĮąĮčŗą╣ ą▓čģąŠą┤ - ą║ąĮąŠą┐ą║ą░, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮą░čÅ ą║ ą┐ąŠčĆčéčā PD0 (INT0). ąóąĄą┐ąĄčĆčī čĆą░čüčüą╝ąŠčéčĆąĖą╝ ą▓čüąĄ ą╝ąŠą╝ąĄąĮčéčŗ, ą║ąŠč鹊čĆčŗąĄ ąĮčāąČąĮąŠ čĆą░čüčüą╝ąŠčéčĆąĄčéčī, čćč鹊ą▒čŗ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ąĮą░čłčā ąĘą░ą┤ą░čćčā. ąśčéą░ą║, ą┐čĆąŠčåąĄčüčü ą┐ąŠ čłą░ą│ą░ą╝.

1. ąØčāąČąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčīčüčÅ čü čĆąĄąČąĖą╝ąŠą╝ čüąĮą░, ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī. ą¤ąŠčüą║ąŠą╗čīą║čā ąĮą░čłą░ ą│ą╗ą░ą▓ąĮą░čÅ čåąĄą╗čī - ą╝ąĖąĮąĖą╝čāą╝ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, č鹊 ąŠč湥ą▓ąĖą┤ąĮąŠ, čćč鹊 čŹč鹊 ą▒čāą┤ąĄčé čĆąĄąČąĖą╝ Power-down. ąöą╗čÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ąĖąĘ Power-down ą▒čāą┤ąĄą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą░čüąĖąĮčģčĆąŠąĮąĮąŠąĄ ąŠčéčüą╗ąĄąČąĖą▓ą░ąĮąĖąĄ čüą┐ą░ą┤ą░ ą╗ąŠą│. čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čģąŠą┤ąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ INT0 (ą┐ąŠčĆčé PD0 ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AT90USB162). ąØą░ąČą░čéąĖąĄ ąĮą░ ą║ąĮąŠą┐ą║čā ą║ą░ą║ čĆą░ąĘ ą▒čāą┤ąĄčé ą▓čŗąĘčŗą▓ą░čéčī čéą░ą║ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĮąĄąĘą░ą▓ąĖčüčÅčēąĄąĄ ąŠčé čĆą░ą▒ąŠčéčŗ čéą░ą║č鹊ą▓čŗčģ ą│ąĄąĮąĄčĆą░č鹊čĆąŠą▓ (čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ I/O ą▓ čĆąĄąČąĖą╝ąĄ Power-down ą▓čŗą║ą╗čÄč湥ąĮąŠ).