|

ąóą░ą║ąĖą╝ čéą░ą╣ą╝ąĄčĆąŠą╝/čüč湥čéčćąĖą║ąŠą╝ čüąĮą░ą▒ąČąĄąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ čüąĄą╝ąĄą╣čüčéą▓ą░ ATmega. ąŚą┤ąĄčüčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮą░ čćą░čüčéčī ą┤ą░čéą░čłąĖčéą░ ATmega32U4, ą┐ąŠčüą▓čÅčēąĄąĮąĮą░čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝čā čāčüčéčĆąŠą╣čüčéą▓čā ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÄ Timer/Counter4.

ąŻ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ 4 (Timer/Counter4) ąĄčüčéčī čüą╗ąĄą┤čāčÄčēąĖąĄ čäčāąĮą║čåąĖąĖ ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ:

ŌĆó ąóąŠčćąĮąŠčüčéčī ą┤ąŠ 10 ą▒ąĖčé.

ŌĆó ąóčĆąĖ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą▒ą╗ąŠą║ą░ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▓čŗčģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ (Output Compare Units).

ŌĆó ąĪą▒čĆąŠčü čéą░ą╣ą╝ąĄčĆą░ ą┐čĆąĖ (Auto Reload) čüąŠą▒čŗčéąĖąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ (Compare Match).

ŌĆó ąóąŠčćąĮą░čÅ ą│ąĄąĮąĄčĆą░čåąĖčÅ čćą░čüč鹊čéčŗ čüąĖą│ąĮą░ą╗ą░ ą©ąśą£ (PWM) ą▒ąĄąĘ ą┤čĆąŠąČą░ąĮąĖčÅ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ ąĖ čäą░ąĘčŗ (Glitch Free, Phase and Frequency Correct Pulse Width Modulator).

ŌĆó ąĀą░čüčłąĖčĆąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą©ąśą£ (Enhanced PWM mode): ąŠą┤ąĖąĮ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ą▒ąĖčé č鹊čćąĮąŠčüčéąĖ, ąĮąĄ ą▓ą╗ąĖčÅčÄčēąĖą╣ ąĮą░ ą▓čŗčģąŠą┤ąĮčāčÄ čćą░čüč鹊čéčā.

ŌĆó ą¤ąĄčĆąĄą╝ąĄąĮąĮčŗą╣ ą┐ąĄčĆąĖąŠą┤ PWM.

ŌĆó ąØąĄąĘą░ą▓ąĖčüąĖą╝čŗąĄ ą│ąĄąĮąĄčĆą░č鹊čĆčŗ "ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ" (Dead Time Generator) ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĖąĘ ą║ą░ąĮą░ą╗ąŠą▓ PWM.

ŌĆó ąĪąĖąĮčģčĆąŠąĮąĮąŠąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ PWM.

ŌĆó ą¤čÅčéčī ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (TOV4, OCF4A, OCF4B, OCF4D, FPF4).

ŌĆó ąÆčŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ (High Speed Asynchronous) ąĖ čüąĖąĮčģčĆąŠąĮąĮčŗą╣ (Synchronous) čĆąĄąČąĖą╝čŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ.

ŌĆó ą×čéą┤ąĄą╗čīąĮčŗą╣ ą▒ą╗ąŠą║ ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čÅ (Prescaler Unit).

Timer/Counter4 čÅą▓ą╗čÅąĄčéčüčÅ ą╝ąŠą┤čāą╗ąĄą╝ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ, čü čéčĆąĄą╝čÅ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╝ąĖ ą▒ą╗ąŠą║ą░ą╝ąĖ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ąĖ čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ PWM.

ąÆ ą║ąŠąĮč鹥ą║čüč鹥 ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ Timer/Counter4 ąŠą▒ą╗ą░ą┤ą░ąĄčé ą▓čŗčüąŠą║ąŠą╣ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ ąĖ č鹊čćąĮąŠčüčéčīčÄ, ąŠčüą▓ąŠą▒ąŠąČą┤ą░čÅ čÅą┤čĆąŠ ąŠčé ą╗ąĖčłąĮąĖčģ ą▓čŗčćąĖčüą╗ąĄąĮąĖą╣. ąĢą│ąŠ čéčĆąĖ ą╝ąŠą┤čāą╗čÅč鹊čĆą░ PWM ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čéą░ą║č鹊ą▓čŗąĄ čćą░čüč鹊čéčŗ ą┤ąŠ 64 ą£ąōčå. ąÆ čĆąĄąČąĖą╝ PWM ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéčĆąĄčģ ąŠčéą┤ąĄą╗čīąĮčŗčģ čüąĖą│ąĮą░ą╗ą░ PWM, ą▓čŗčģąŠą┤čŗ ą║ąŠč鹊čĆčŗčģ čĆą░ą▒ąŠčéą░čÄčé ą▓ čĆąĄąČąĖą╝ą░čģ ą▒ąĄąĘ ą┐ąĄčĆąĄą║čĆčŗčéąĖčÅ (non-overlapping), ą▒ąĄąĘ ąĖąĮą▓ąĄčĆčüąĖąĖ (non-inverted) ąĖ čü ąĖąĮą▓ąĄčĆčüąĖąĄą╣ (inverted). ąĀą░čüčłąĖčĆąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ PWM ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ąŠą▒ąĖčéčīčüčÅ ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╣ č鹊čćąĮąŠčüčéąĖ čü čüąŠčģčĆą░ąĮąĄąĮąĖąĄą╝ čćą░čüč鹊čéčŗ čéą░ą║ąŠą╣ ąČąĄ, ą║ą░ą║ ąĖ ą▓ ąŠą▒čŗčćąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (PWM 8-ą▒ąĖčéąĮąŠą╣ č鹊čćąĮąŠčüčéąĖ ą▓ čĆą░čüčłąĖčĆąĄąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą▓čŗą┤ą░ąĄčé čéčā ąČąĄ čćą░čüč鹊čéčā čüąĖą│ąĮą░ą╗ą░, čćč鹊 ąĖ PWM 7-ą▒ąĖčéąĮąŠą╣ č鹊čćąĮąŠčüčéąĖ ą▓ ąŠą▒čŗčćąĮąŠą╝ čĆąĄąČąĖą╝ąĄ). ążčāąĮą║čåąĖčÅ ąĘą░čģą▓ą░čéą░ (lock feature) ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▒ąĄąĘąŠą┐ą░čüąĮąŠ ąŠą▒ąĮąŠą▓ą╗čÅčéčī čĆąĄą│ąĖčüčéčĆčŗ PWM.

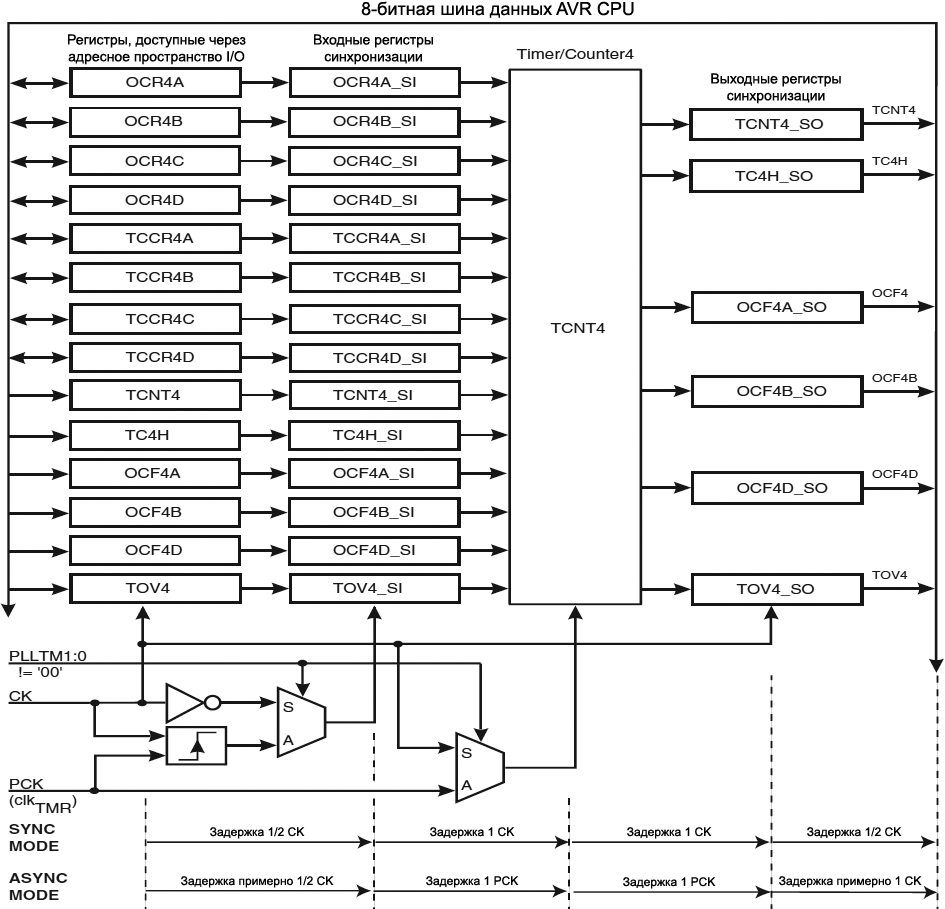

ąŻą┐čĆąŠčēąĄąĮąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ Timer/Counter4 ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 15-1. ąĀąĄą░ą╗čīąĮą░čÅ ą┐čĆąĖą▓čÅąĘą║ą░ ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ ą▓čŗą▓ąŠą┤ąŠą▓ PWM ą║ ąĮąŠąČą║ą░ą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "Pinout" ą┤ą░čéą░čłąĖčéą░ (čüą╝. ą▓čĆąĄąĘą║čā ą┤ą╗čÅ ą║ąŠčĆą┐čāčüą░ TQFP44 ATmega32U4).

ąĀąĖčü. 15-1. ąæą╗ąŠą║-čüčģąĄą╝ą░ Timer/Counter4.

ąĪą║ąŠčĆąŠčüčéčī. Timer/Counter4 ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊č鹥 64MHz. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ąĮąĖąČąĄ 4V, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čāą╝ąĄąĮčīčłąĖčéčī ą▓čģąŠą┤ąĮčāčÄ čćą░čüč鹊čéčā, ą┐ąŠč鹊ą╝čā čćč鹊 Timer/Counter4 ąĮą░ ąĮąĖąĘą║ąĖčģ čāčĆąŠą▓ąĮčÅčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ čĆą░ą▒ąŠčéą░ąĄčé ąĮąĄą┤ąŠčüčéą░č鹊čćąĮąŠ ą▒čŗčüčéčĆąŠ.

ąóąŠčćąĮąŠčüčéčī. Timer/Counter4 ąĖą╝ąĄąĄčé čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī 10 ą▒ąĖčé, ąĮąŠ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ 8-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║. ąĀąĄą│ąĖčüčéčĆčŗ Timer/Counter4 8-ą▒ąĖčéąĮčŗąĄ, ąĖ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüčéą░čĆčłąĖčģ 2-ą▒ąĖčé ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┐čĆąŠą╝ąĄąČčāč鹊čćąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ (High Byte Register, TC4H), ą║ąŠč鹊čĆčŗą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą▓čĆąĄą╝ąĄąĮąĮčŗą╣ ą▒čāč乥čĆ. ąæą╗ą░ą│ąŠą┤ą░čĆčÅ čŹč鹊ą╝čā ą▒čāč乥čĆčā ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī 10-ą▒ąĖčéąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ Timer/Counter4 č湥čĆąĄąĘ 8-ą▒ąĖčéąĮčāčÄ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ AVR CPU, ąĄčüą╗ąĖ čéčĆąĄą▒čāąĄčéčüčÅ 10-ą▒ąĖčéąĮą░čÅ č鹊čćąĮąŠčüčéčī. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ ą┤ą▓ą░ čüčéą░čĆčłąĖčģ ą▒ąĖčéą░ 10-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ čĆą░ą▓ąĮčŗ 0, č鹊 Timer/Counter4 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ 8-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║. ąÜąŠą│ą┤ą░ čüčćąĖčéčŗą▓ą░ąĄčéčüčÅ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé ą╗čÄą▒ąŠą│ąŠ 10-ą▒ąĖčéąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░, ą┤ą▓ą░ ąĄą│ąŠ čüčéą░čĆčłąĖčģ ą▒ąĖčéą░ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ TC4H, ąĖ ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé, ą┤ą▓ą░ čüčéą░čĆčłąĖčģ ą▒ąĖčéą░ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▒ąĄčĆčāčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ TC4H. ąöą╗čÅ čéą░ą║ąŠą│ąŠ 10-ą▒ąĖčéąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ čéčĆąĄą▒čāąĄčéčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣, čćč鹊 ąŠą┐ąĖčüą░ąĮąŠ ąĮąĖąČąĄ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąÜą░ą║ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮ ą┤ąŠčüčéčāą┐ ą║ 10-ą▒ąĖčéąĮčŗą╝ čĆąĄą│ąĖčüčéčĆą░ą╝".

ąĀą░čüčłąĖčĆąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ ą©ąśą£ (Enhanced PWM mode) ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ąŠą▒ą░ą▓ąĖčéčī ąŠą┤ąĖąĮ ą▒ąĖčé čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čüčĆą░ą▓ąĮąĄąĮąĖčÅ A/B/D, ą┐čĆąĖ čŹč鹊ą╝ ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ ąŠčüčéą░ąĄčéčüčÅ ąĖą┤ąĄąĮčéąĖčćąĮąŠą╣ ąŠą▒čŗčćąĮąŠą╝čā čĆąĄąČąĖą╝čā ą©ąśą£ (Normal PWM mode). ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čĆąĄą│ąĖčüčéčĆ TC4H čüąŠą┤ąĄčƹȹĖčé ąŠą┤ąĖąĮ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ą▒ąĖčé, ą║ąŠč鹊čĆčŗą╣ ąĖą│čĆą░ąĄčé čĆąŠą╗čī čüčéą░čĆčłąĄą│ąŠ ą▓ 11-čĆą░ąĘčĆčÅą┤ąĮąŠą╝ čĆą░čüčłąĖčĆąĄąĮąĮąŠą╝ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĖ PWM. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čüąĄą║čåąĖčÄ "Enhanced Compare/PWM mode".

ąĀąĄą│ąĖčüčéčĆčŗ. ąĀąĄą│ąĖčüčéčĆ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ (TCNT4) ąĖ čĆąĄą│ąĖčüčéčĆčŗ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (Output Compare Registers, OCR4A, OCR4B, OCR4C ąĖ OCR4D) čŹč鹊 8-ą▒ąĖčéąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ, ą║ąŠč鹊čĆčŗąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ą░ą║ ąĖčüč鹊čćąĮąĖą║ąĖ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ čüčĆą░ą▓ąĮąĄąĮąĖčÅ TCNT4 čü čüąŠą┤ąĄčƹȹĖą╝čŗą╝ OCR4A, OCR4B, OCR4C ąĖ OCR4D. ąĀąĄą│ąĖčüčéčĆčŗ OCR4A, OCR4B ąĖ OCR4D ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé čĆą░ą▒ąŠčéčā ą▓čŗą▓ąŠą┤ąŠą▓ OC4A, OC4B ąĖ OC4D, ąĖ ąŠąĮąĖ ą╝ąŠą│čāčé čéą░ą║ąČąĄ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ (compare match interrupts). ąĀąĄą│ąĖčüčéčĆ OCR4C čģčĆą░ąĮąĖčé ą▓ąĄčĆčģąĮąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéą░ čéą░ą╣ą╝ąĄčĆą░ čüč湥čéčćąĖą║ą░ (čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ TOP), čé. ąĄ. čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ čåąĖą║ą╗ą░ PWM. ąĀąĄą│ąĖčüčéčĆ čüčéą░čĆčłąĄą│ąŠ ą▒ą░ą╣čéą░ (TC4H) čÅą▓ą╗čÅąĄčéčüčÅ 2-ą▒ąĖčéąĮčŗą╝ čĆąĄą│ąĖčüčéčĆąŠą╝, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╝ ą║ą░ą║ ąŠą▒čēąĖą╣ ą▓čĆąĄą╝ąĄąĮąĮčŗą╣ ą▒čāč乥čĆ ą┤ą╗čÅ čüčéą░čĆčłąĖčģ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆąŠą▓ Timer/Counter4, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 10-čĆą░ąĘčĆčÅą┤ąĮą░čÅ č鹊čćąĮąŠčüčéčī.

ąĪąĖą│ąĮą░ą╗čŗ ąĘą░ą┐čĆąŠčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ TOV4, čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ OCF4A, OCF4B, OCF4D ąĖ ąĘą░čēąĖčéą░ ąŠčé čüą▒ąŠąĄą▓ FPF4) ą┤ąŠčüčéčāą┐ąĮčŗ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ čäą╗ą░ą│ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Timer Interrupt Flag Register, TIFR4) ąĖ Timer/Counter4 Control Register D (TCCR4D). ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ ą╝ą░čüą║ąĖčĆčāčÄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄą│ąĖčüčéčĆą░ Timer Interrupt Mask (TIMSK4) ąĖ ą▒ąĖčéą░ FPIE4 ą▓ čĆąĄą│ąĖčüčéčĆąĄ Timer/Counter4 Control Register D (TCCR4D).

ąĪąĖą│ąĮą░ą╗čŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ TCCR4A, TCCR4B, TCCR4C, TCCR4D ąĖ TCCR4E.

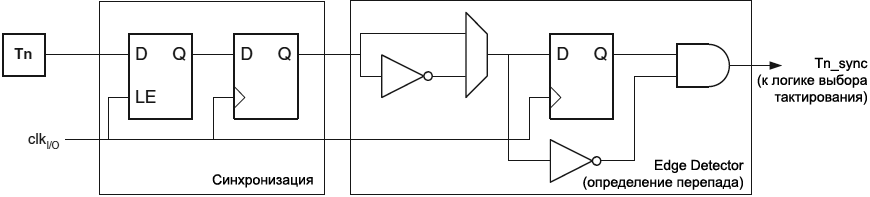

ąĪąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ. ąÆ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ Timer/Counter4 ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé CPU čĆą░ą▒ąŠčéą░čéčī ąŠčé ą╗čÄą▒ąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ čĆą░ą▒ąŠčéą░ąĄčé ąŠčé ą▒čŗčüčéčĆąŠą╣ čćą░čüč鹊čéčŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (fast peripheral clock, PCK), ą║ąŠč鹊čĆą░čÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠ 64 ą£ąōčå. ąŁč鹊 čüčéą░ą╗ąŠ ą▓ąŠąĘą╝ąŠąČąĮčŗą╝ ą┐ąŠč鹊ą╝čā, čćč鹊 ąĄčüčéčī ą│čĆą░ąĮąĖčåą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą╝ąĄąČą┤čā ą┤ąŠą╝ąĄąĮąŠą╝ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ CPU ąĖ ą┤ąŠą╝ąĄąĮąŠą╝ PCK. ąØą░ čĆąĖčü. 15-2 ą┐ąŠą║ą░ąĘą░ąĮ ą▒ą╗ąŠą║ čĆąĄą│ąĖčüčéčĆąŠą▓ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ Timer/Counter 4, ąĖ ąŠą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ąĘą░ą┤ąĄčƹȹ║ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą╝ąĄąČą┤čā čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĮą░ čŹč鹊ą╝ čĆąĖčüčāąĮą║ąĄ ąĮąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖčÅ ą▓čüąĄčģ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé.

ąĀąĖčü. 15-2. ąæą╗ąŠą║-čüčģąĄą╝ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ Timer/Counter4.

ąŚąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ Timer/Counter4 ą┐čĆąŠčģąŠą┤čÅčé č湥čĆąĄąĘ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ ą▓ą▓ąŠą┤čÅčé ąĘą░ą┤ąĄčƹȹ║čā ą▓čģąŠą┤ąĮąŠą╣ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ąĮąŠą▓čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą▓čüčéčāą┐čÅčé ą▓ čüąĖą╗čā ąĖ ą┐ąŠą▓ą╗ąĖčÅčÄčé ąĮą░ čĆą░ą▒ąŠčéčā čüč湥čéčćąĖą║ą░. ąĀąĄą│ąĖčüčéčĆčŗ TCCR4A, TCCR4B, TCCR4C, TCCR4D, OCR4A, OCR4B, OCR4C ąĖ OCR4D ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ą┐ąŠčüą╗ąĄ čüą▓ąŠąĄą╣ ąĘą░ą┐ąĖčüąĖ. ą×ą▒čĆą░čéąĮąŠąĄ čćč鹥ąĮąĖąĄ ąĘą░ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ TCNT4, TC4H ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ čäą╗ą░ą│ąŠą▓ (OCF4A, OCF4B, OCF4D ąĖ TOV4), ą┐ąŠč鹊ą╝čā čćč鹊 ąĖą╝ąĄąĄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ ą╝ąĄąČą┤čā ą▓čģąŠą┤ąŠą╝ ąĖ ą▓čŗčģąŠą┤ąŠą╝.

ąĪąĖčüč鹥ą╝ąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą╝ąĄąĮčīčłąĄ ą┐ąŠą╗ąŠą▓ąĖąĮčŗ čćą░čüč鹊čéčŗ PCK, ą┐ąŠč鹊ą╝čā čćč鹊 ą╝ąĄčģą░ąĮąĖąĘą╝ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ Timer/Counter4 ąĮčāąČą┤ą░ąĄčéčüčÅ ą▓ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą┤ą▓čāčģ ą┐ąĄčĆąĄą┐ą░ą┤ą░čģ PCK, ą║ąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║č鹊ą▓ ą▓ ą╗ąŠą│. 1. ąĢčüą╗ąĖ čüąĖčüč鹥ą╝ąĮą░čÅ čćą░čüč鹊čéą░ čüą╗ąĖčłą║ąŠą╝ ą▓čŗčüąŠą║ą░, ąĄčüčéčī čĆąĖčüą║ ą┐ąŠč鹥čĆąĖ ą┤ą░ąĮąĮčŗčģ ąĖą╗ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ ąĘąĮą░č湥ąĮąĖą╣.

ąóąĄčĆą╝ąĖąĮąŠą╗ąŠą│ąĖčÅ. ą£ąĮąŠą│ąĖąĄ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ąĖčģ ą▒ąĖčé ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ąŠą▒čēąĄą╣ č乊čĆą╝ąĄ. ąæčāą║ą▓ą░ "n" ą▓ ąĮąĖąČąĮąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ ąĘą░ą╝ąĄąĮčÅąĄčéčüčÅ ąĮąŠą╝ąĄčĆąŠą╝ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ (ą┤ą╗čÅ Timer/Counter 4 ą▒čāą║ą▓ą░ n ąĘą░ą╝ąĄąĮčÅąĄčéčüčÅ ąĮą░ 4). ąæčāą║ą▓ą░ "x" ą▓ ąĮąĖąČąĮąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ ąĘą░ą╝ąĄąĮčÅąĄčé ą▒čāą║ą▓ąĄąĮąĮčŗą╣ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ą▒ą╗ąŠą║ą░ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (ą▒čāą║ą▓čŗ A, B, C, D ą▒ą╗ąŠą║ą░ Output Compare). ą×ą┤ąĮą░ą║ąŠ ą║ąŠą│ą┤ą░ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąĖą╝ąĄąĮą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ą▒ąĖčé, ą┤ąŠą╗ąČąĮą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąĮąĄ ąŠą▒čēą░čÅ, ą░ ą┐ąŠą╗ąĮą░čÅ č乊čĆą╝ą░. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čüč湥čéčćąĖą║čā čéą░ą╣ą╝ąĄčĆą░ ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī TCNT4, ąĖ čé. ą┐.

ąóą░ą║ąČąĄ ą▓ čéą░ą▒ą╗ąĖčåą░čģ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ:

BOTTOM ąĪč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ, ą║ąŠą│ą┤ą░ čüčéą░ąĮąŠą▓ąĖčéčüčÅ čĆą░ą▓ąĮčŗą╝ 0.

MAX ą£ą░ą║čüąĖą╝čāą╝. ąĪč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą▓ ąĮąĄą╝ ąĮą░čģąŠą┤ąĖčéčüčÅ čćąĖčüą╗ąŠ 0x3FF (ą┤ąĄčüčÅčéąĖčćąĮąŠąĄ 1023).

TOP ąÆąĄčĆčģąĮąĖą╣ ą┐čĆąĄą┤ąĄą╗. ąĪč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé čŹč鹊ą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ (ąŠąĮąŠ čģčĆą░ąĮąĖčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ OCR1C), ą║ą░ą║ ą┐čĆąĄą┤ąĄą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čüč湥čéą░. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ąĖą╗ąĖ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ) ąĘąĮą░č湥ąĮąĖąĄ TOP čĆą░ą▓ąĮąŠ 0x0FF.

[ąæą╗ąŠą║ čüč湥čéčćąĖą║ą░]

ą×čüąĮąŠą▓ąĮą░čÅ čćą░čüčéčī Timer/Counter4 - ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ čüč湥čéčćąĖą║, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé čüčćąĖčéą░čéčī ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ. ąØą░ čĆąĖčü. 15-3 ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ čüč湥čéčćąĖą║ą░ ąĖ ąĄą│ąŠ ąŠą║čĆčāąČąĄąĮąĖąĄ.

ąĀąĖčü. 15-3. ąæą╗ąŠą║ čüč湥čéčćąĖą║ą░.

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ (čŹč鹊 ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ):

count: čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ ąĖą╗ąĖ ą┤ąĄą║čĆąĄą╝ąĄąĮčéą░ TCNT4.

direction: ą▓čŗą▒ąŠčĆ ą╝ąĄąČą┤čā ąĖąĮą║čĆąĄą╝ąĄąĮč鹊ą╝ ąĖ ą┤ąĄą║čĆąĄą╝ąĄąĮč鹊ą╝.

clear: čüą▒čĆąŠčü TCNT4 (čāčüčéą░ąĮąŠą▓ą║ą░ ą▓čüąĄčģ ąĄą│ąŠ ą▒ąĖčé ą▓ 0).

clkTn: čéą░ą║čéčŗ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░, ą┤ą░ą╗ąĄąĄ ą┐ąŠ č鹥ą║čüčéčā čŹč鹊 clkT4.

top: čüąĖą│ąĮą░ą╗ ąŠ č鹊ą╝, čćč鹊 TCNT4 ą┤ąŠčüčéąĖą│ ą┐čĆąĄą┤ąĄą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ.

bottom: čüąĖą│ąĮą░ą╗ ąŠ č鹊ą╝, čćč鹊 TCNT4 ą┤ąŠčüčéąĖą│ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ (0).

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ čüč湥čéčćąĖą║ ąŠčćąĖčēą░ąĄčéčüčÅ, ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąĖą╗ąĖ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ čéą░ą║č鹥 (čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ clkT4). ąóą░ą║čéčŗ čéą░ą╣ą╝ąĄčĆą░ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ąŠčé čüąĖąĮčģčĆąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ ąĖą╗ąĖ ąŠčé čéą░ą║č鹊ą▓ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ ążąÉą¤ą¦ (asynchronous PLL). ąŁč鹊 ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ ą▓čŗą▒ąŠčĆą░ čéą░ą║č鹊ą▓ CS43..CS40 ąĖ ą▒ąĖčéą░ą╝ąĖ ą┐ąŠčüčé-ą┤ąĄą╗ąĖč鹥ą╗čÅ ążąÉą¤ą¦ (PLL Postscaler for High Speed Timer, PLLTM1:0). ąÜąŠą│ą┤ą░ ąĮąĄ ą▓čŗą▒čĆą░ąĮ ąĖčüč鹊čćąĮąĖą║ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ (CS43..CS40 = 0000), čéą░ą╣ą╝ąĄčĆ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ. ą×ą┤ąĮą░ą║ąŠ ą║ ąĘąĮą░č湥ąĮąĖčÄ čüč湥čéčćąĖą║čā TCNT4 ą╝ąŠąČąĮąŠ ąŠą▒čĆą░čēą░čéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ clkT4, ąĖą╗ąĖ ąĮąĄčé. ąŚą░ą┐ąĖčüčī čüąŠ čüč鹊čĆąŠąĮčŗ čÅą┤čĆą░ CPU ąŠčéą╝ąĄąĮčÅąĄčé (čé. ąĄ. ąĖą╝ąĄąĄčé ą▓čŗčüčłąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé) ą▓čüąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ąŠčćąĖčüčéą║ąĖ ąĖą╗ąĖ čüč湥čéą░.

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čüč湥čéą░ Timer/Counter4 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé WGM40 ąĖ PWM4x (PWM4A, PWM4B, PWM4D), ą║ąŠč鹊čĆčŗąĄ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ TCCR4A, TCCR4C ąĖ TCCR4D. ąæąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ą┐ąŠ čĆąĄąČąĖą╝ą░ą╝ čüč湥čéą░ ąĖ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ čüą╝. čĆą░ąĘą┤ąĄą╗ "ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ". ążą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ čüč湥čéčćąĖą║ą░ (Timer/Counter Overflow TOV4) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆąĄąČąĖą╝ą░, ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą▒ąĖčéą░ą╝ąĖ PWM4x ąĖ WGM40. ążą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ CPU.

ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ čüč湥čéčćąĖą║ą░ ą▓ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ. ą¦č鹊ą▒čŗ ą┐ąŠą╝ąĄąĮčÅčéčī čĆąĄąČąĖą╝ Timer/Counter4 ąĮą░ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣, čüą╗ąĄą┤čāą╣č鹥 ą┐čĆąŠčåąĄą┤čāčĆąĄ:

1. ąĀą░ąĘčĆąĄčłąĖč鹥 PLL.

2. ą¤ąŠą┤ąŠąČą┤ąĖč鹥 100 ą╝ą║čü, čćč鹊ą▒čŗ PLL ąĘą░čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆąŠą▓ą░ą╗ą░čüčī.

3. ą×ą┐čĆą░čłąĖą▓ą░ą╣č鹥 ą▒ąĖčé PLOCK, ą┐ąŠą║ą░ ąŠąĮ ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ.

4. ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 ą▒ąĖčéčŗ PLLTM1:0 čĆąĄą│ąĖčüčéčĆą░ PLLFRQ, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ (čŹčéąĖ ą▒ąĖčéčŗ ą┤ąŠą╗ąČąĮčŗ ą┐ąŠą╗čāčćąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ, ąŠčéą╗ąĖčćą░čÄčēąĄąĄčüčÅ ąŠčé 00).

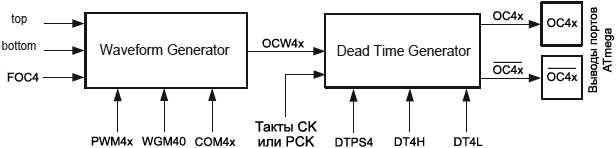

ąæą╗ąŠą║ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (Output Compare Unit). ą”ąĖčäčĆąŠą▓ąŠą╣ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčé TCNT4 čü čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ OCR4A, OCR4B, OCR4C ąĖ OCR4D. ąÆčüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ TCNT4 čüčĆą░ą▓ąĮčÅąĄčéčüčÅ čü ąŠą┤ąĮąĖą╝ ąĖąĘ ąĮąĖčģ, ąĮą░čüčéčāą┐ą░ąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮąŠąĄ čüąŠą▒čŗčéąĖąĄ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ. ąŁč鹊 čüąŠą▒čŗčéąĖąĄ čāčüčéą░ąĮąŠą▓ąĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čäą╗ą░ą│ (Output Compare Flag, OCF4A, OCF4B ąĖą╗ąĖ OCF4D) ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░. ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, č鹊 Output Compare Flag čüą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Output Compare. Output Compare Flag ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčüčéąĖčéčüčÅ ą┐čĆąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĖ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ čŹč鹊čé čäą╗ą░ą│ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ąĘą░ą┐ąĖčüčīčÄ ą╗ąŠą│. 1 ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēčāčÄ ą┐ąŠąĘąĖčåąĖčÄ ą▒ąĖčéą░. ąōąĄąĮąĄčĆą░č鹊čĆ čüąĖą│ąĮą░ą╗ąŠą▓ (Waveform Generator) ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüąĖą│ąĮą░ą╗ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▓čŗčģąŠą┤ą░ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ čĆą░ą▒ąŠčćąĖą╝ čĆąĄąČąĖą╝ąŠą╝. ąŁčéą░ ąĮą░čüčéčĆąŠą╣ą║ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ PWM4x, WGM40 ąĖ Compare Output COM4x1:0 (COM4A1:0, COM4B1:0, COM4D1:0). ąĪąĖą│ąĮą░ą╗čŗ top ąĖ bottom ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ Waveform Generator ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ čüą╗čāčćą░ąĄą▓ ą┐čĆąĄą┤ąĄą╗čīąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ čĆą░ą▒ąŠčćąĖčģ čĆąĄąČąĖą╝ą░čģ (čüą╝. "ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ"). ąØą░ čĆąĖčü. 15-4 ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ Output Compare unit.

ąĀąĖčü. 15-4. ąæą╗ąŠą║ čüčĆą░ą▓ąĮąĄąĮąĖčÅ, Output Compare Unit.

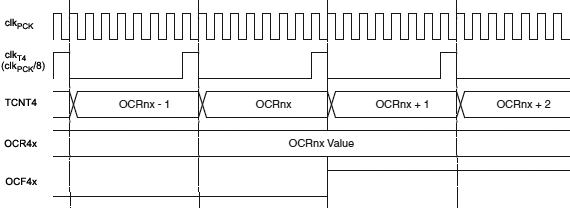

ąĀąĄą│ąĖčüčéčĆčŗ OCR4x ąĖą╝ąĄčÄčé ą┤ą▓ąŠą╣ąĮčāčÄ ą▒čāč乥čĆąĖąĘą░čåąĖčÄ, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓ čĆąĄąČąĖą╝ą░čģ ą©ąśą£ (Pulse Width Modulation, PWM). ąöą╗čÅ ąŠą▒čŗčćąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ (normal mode) ą┤ą▓ąŠą╣ąĮą░čÅ ą▒čāč乥čĆąĖąĘą░čåąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮą░. ąöą▓ąŠą╣ąĮą░čÅ ą▒čāč乥čĆąĖąĘą░čåąĖčÅ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ čüčĆą░ą▓ąĮąĄąĮąĖčÅ OCR4x ą┤ą╗čÅ ąĘąĮą░č湥ąĮąĖą╣ top ąĖą╗ąĖ bottom ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čüč湥čéą░. ąŁčéą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčé ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄ ą║čĆąĖą▓čŗčģ, ąĮąĄ čüąĖą╝ą╝ąĄčéčĆąĖčćąĮčŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą©ąśą£, ą┤ąĄą╗ą░čÅ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ čüą▓ąŠą▒ąŠą┤ąĮčŗą╝ ąŠčé ą▓čŗą▒čĆąŠčüąŠą▓ ąĖ ą│ą╗čÄą║ąŠą▓. ąŁč鹊 ą┐ąŠčÅčüąĮčÅąĄčéčüčÅ čĆąĖčüčāąĮą║ąŠą╝ 15-5. ąÆ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ ą╝ąĄąČą┤čā ąĘą░ą┐ąĖčüčīčÄ ąĖ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄą╝ čćč鹥ąĮąĖąĄ ąĖąĘ OCR4A, OCR4B, OCR4C ąĖą╗ąĖ OCR4D ą▓ąĄčĆąĮąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▓čĆąĄą╝ąĄąĮąĮąŠą╣ čÅč湥ą╣ą║ąĖ. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 č鹊ą╗čīą║ąŠ čćč鹊 ąĘą░ą┐ąĖčüą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓čüąĄą│ą┤ą░ ą▒čāą┤ąĄčé ą┐čĆąŠčćąĖčéą░ąĮąŠ ąĖąĘ OCR4A, OCR4B, OCR4C ąĖą╗ąĖ OCR4D.

ąĀąĖčü. 15-5. ąŁčäč乥ą║čéčŗ ąŠčé ąĮąĄčüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ąĘą░čģą▓ą░čéą░ OCR.

Force Output Compare. ąÆ čĆąĄąČąĖą╝ą░čģ ą│ąĄąĮąĄčĆą░čåąĖąĖ, ąĮąĄ ąŠčéąĮąŠčüčÅčēąĖčģčüčÅ ą║ PWM, ą╝ąŠąČąĮąŠ ąĘą░čüčéą░ą▓ąĖčéčī ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čüąŠą▒čŗčéąĖąĄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ ą╗ąŠą│. 1 ą▒ąĖčéą░ Force Output Compare (FOC4x). Forcing Compare Match ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčé čäą╗ą░ą│ OCF4x ąĖ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ą░/ąŠčćąĖčüčéą║ą░ čéą░ą╣ą╝ąĄčĆą░, ąĮąŠ Waveform Output (OCW4x) ą▒čāą┤ąĄčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮ, ą║ą░ą║ ąĄčüą╗ąĖ ą▒čŗ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čĆąĄą░ą╗čīąĮąŠąĄ čüąŠą▒čŗčéąĖąĄ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ Compare Match. ąØą░čüčéčĆąŠą╣ą║ą░ ą▒ąĖčé COM4x1:0 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ą░ą║ ą▒čāą┤ąĄčé ą╝ąĄąĮčÅčéčīčüčÅ Waveform Output (OCW4x) - čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčīčüčÅ, ąŠčćąĖčēą░čéčīčüčÅ ąĖą╗ąĖ ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ.

ąæą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĖąĄ Compare Match ąĘą░ą┐ąĖčüčīčÄ TCNT4. ąÆčüąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ TCNT4 čüąŠ čüč鹊čĆąŠąĮčŗ čÅą┤čĆą░ CPU ąĘą░ą▒ą╗ąŠą║ąĖčĆčāąĄčé ą╗čÄą▒ąŠąĄ čüąŠą▒čŗčéąĖąĄ Compare Match, ą║ąŠč鹊čĆąŠąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░, ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ. ąŁčéą░ čäčāąĮą║čåąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī OCR4x ą▓ č鹊 ąČąĄ čüą░ą╝ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, čćč鹊 ąĖ TCNT4 ą▒ąĄąĘ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░.

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą▒ą╗ąŠą║ą░ Output Compare. ą¤ąŠčüą║ąŠą╗čīą║čā ąĘą░ą┐ąĖčüčī TCNT4 ą▓ ą╗čÄą▒ąŠą╝ čĆąĄąČąĖą╝ąĄ čĆą░ą▒ąŠčéčŗ ąĘą░ą▒ą╗ąŠą║ąĖčĆčāąĄčé ą▓čüąĄ čüąŠą▒čŗčéąĖčÅ Compare Match ąĮą░ ąŠą┤ąĖąĮ čéą░ą║čé čéą░ą╣ą╝ąĄčĆą░, ąĄčüčéčī čĆąĖčüą║ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ TCNT4 ą▓ąŠ ą▓čĆąĄą╝čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▒ą╗ąŠą║ą░ Output Compare, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, čĆą░ą▒ąŠčéą░ąĄčé čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║, ąĖą╗ąĖ ąĮąĄčé. ąĢčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ, ąĘą░ą┐ąĖčüą░ąĮąĮąŠąĄ ą▓ TCNT4, čĆą░ą▓ąĮąŠ ąĘąĮą░č湥ąĮąĖčÄ OCR4x, č鹊 čüąŠą▒čŗčéąĖąĄ Compare Match ą▒čāą┤ąĄčé ą┐čĆąŠą┐čāčēąĄąĮąŠ, ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćąĖčéčüčÅ ąĮąĄ ą║ąŠčĆčĆąĄą║čéąĮą░čÅ ą│ąĄąĮąĄčĆą░čåąĖčÅ č乊čĆą╝čŗ čüąĖą│ąĮą░ą╗ą░. ą¤ąŠčŹč鹊ą╝čā ąĮąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ą╣č鹥 ą▓ TCNT4 ąĘąĮą░č湥ąĮąĖąĄ, čĆą░ą▓ąĮąŠąĄ BOTTOM, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą▓ąĮąĖąĘ.

ąØą░čüčéčĆąŠą╣ą║čā č乊čĆą╝čŗ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (Waveform Output, OCW4x) ąĮčāąČąĮąŠ ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą┐ąĄčĆąĄą┤ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čĆąĄą│ąĖčüčéčĆą░ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ą▓čŗą▓ąŠą┤ą░ ą┐ąŠčĆčéą░ ąĮą░ ą▓čŗčģąŠą┤ (Data Direction Register, DDRx). ąĪą░ą╝čŗą╣ ą┐čĆąŠčüč鹊ą╣ čüą┐ąŠčüąŠą▒ čāčüčéą░ąĮąŠą▓ąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ OCW4x - ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▒ąĖčéčŗ čüčéčĆąŠą▒ą░ Force Output Compare (FOC4x) ą▓ ąŠą▒čŗčćąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (Normal mode). OC4x čüąŠčģčĆą░ąĮąĖčé čüą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą░ąČąĄ ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ čĆąĄąČąĖą╝ąŠą▓ ą│ąĄąĮąĄčĆą░čåąĖąĖ.

ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą▒ąĖčéčŗ COM4x1:0 ąĮąĄ ąĖą╝ąĄčÄčé ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ ą▓ą╝ąĄčüč鹥 čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ čüčĆą░ą▓ąĮąĄąĮąĖčÅ. ąśąĘą╝ąĄąĮąĄąĮąĖąĄ ą▒ąĖčé COM4x1:0 ą▓čüčéčāą┐ąĖčé ą▓ čüąĖą╗čā ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ.

ąĪ čéą░ą╣ą╝ąĄčĆąŠą╝ Timer/Counter4 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą│ąĄąĮąĄčĆą░č鹊čĆ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (Dead Time Generator), ą┐ąŠąĘą▓ąŠą╗čÅčÄčēąĖą╣ ą▒ąĄąĘąŠą┐ą░čüąĮąŠ ą┐ąŠą┤ą░ą▓ą░čéčī čüąĖą│ąĮą░ą╗ PWM ąĮą░ ą┐ą░čĆčā ą▓čŗčģąŠą┤ąĮčŗčģ ą║ą╗čÄč湥ą╣ čüąĖą╗ąŠą▓ąŠą│ąŠ ą╝ąŠčüčéą░. Dead Time Generator čŹč鹊 ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą▒ą╗ąŠą║, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą▓čüčéą░ą▓ą║ąĖ ą╝ąĄčĆčéą▓čŗčģ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ (ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▒ąĄąĘ ą┐ąĄčĆąĄą║čĆčŗčéąĖčÅ, ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čÄčēąĖčģ ąŠčéčüčāčéčüčéą▓ąĖąĄ čüą║ą▓ąŠąĘąĮčŗčģ č鹊ą║ąŠą▓) ąĮą░ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗčģ ą┐ą░čĆą░čģ ą▓čŗčģąŠą┤ąŠą▓ Timer/Counter4 (OC4x ąĖ ~OC4x), ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮ čĆąĄąČąĖą╝ PWM, ąĖ ą▒ąĖčéčŗ COM4x1:0 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 01. ą×ą▒čēąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ: Waveform Generator ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗčģąŠą┤ąĄ (Waveform Output, OCW4x), ąĖ Dead Time Generator ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĮąĄ ą┐ąĄčĆąĄą║čĆčŗą▓ą░čÄčēčāčÄčüčÅ ą┐ą░čĆčā čüąĖą│ąĮą░ą╗ąŠą▓ PWM ąĮą░ Waveform Output. ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąŠ čéčĆąĖ Dead Time ą│ąĄąĮąĄčĆą░č鹊čĆą░, ą┐ąŠ ąŠą┤ąĮąŠą╝čā ąĮą░ ą║ą░ąČą┤čŗą╣ ą▓čŗčģąŠą┤ PWM. ą£ąĄčĆčéą▓ąŠąĄ ą▓čĆąĄą╝čÅ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ ą▓čŗčģąŠą┤ąŠą▓ PWM.

ąĀąĖčü. 15-6. ąæą╗ąŠą║ čüčĆą░ą▓ąĮąĄąĮąĖčÅ, Output Compare Unit.

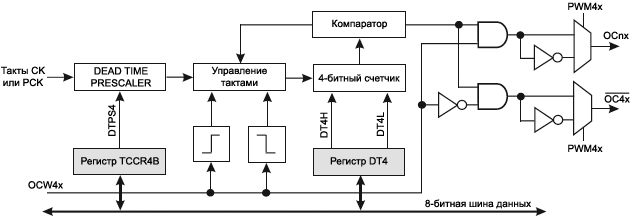

ąōąĄąĮąĄčĆą░čåąĖčÅ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąŠčüąĮąŠą▓ą░ąĮą░ ąĮą░ 4-čĆą░ąĘčĆčÅą┤ąĮąŠą╝ čüčćąĖčéą░čÄčēąĄą╝ ą▓ąĮąĖąĘ čüč湥čéčćąĖą║ąĄ, čćč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 15-7. ąśą╝ąĄąĄčéčüčÅ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗą╣ ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čī ąĮą░ ą▓čģąŠą┤ąĄ Dead Time Generator, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą┤ąĄą╗ąĖčéčī čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā Timer/Counter4 (PCK ąĖą╗ąĖ CK) ąĮą░ 1, 2, 4 ąĖą╗ąĖ 8. ąŁč鹊 ą┤ą░ąĄčé ą▒ąŠą╗čīčłąŠą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ čĆąĄą│čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą│ąŠ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ. ą¤čĆąĄčüą║ą░ą╗ąĄčĆ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą┤ą▓čāą╝čÅ ą▒ąĖčéą░ą╝ąĖ DTPS41..40. ąŁč鹊čé ą▒ą╗ąŠą║ čéą░ą║ąČąĄ ąĖą╝ąĄąĄčé ą┤ąĄč鹥ą║č鹊čĆ čäčĆąŠąĮčéą░ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ ąĖ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čüą┐ą░ą┤ą░, čćč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐ąĄčĆąĖąŠą┤ą░ ąŠčéčüč湥čéą░ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐ąĄčĆąĄą┐ą░ą┤ą░ OC4x ąĖą╗ąĖ ~OC4x ąĘą░ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ, ą┐ąŠą║ą░ čüč湥čéčćąĖą║ ąĮąĄ ą┤ąŠčüčćąĖčéą░ąĄčé ą┤ąŠ ąĮčāą╗čÅ. ąÜąŠą╝ą┐ą░čĆą░č鹊čĆ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčé čüč湥čéčćąĖą║ čü ąĮčāą╗ąĄą╝ ąĖ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▓čüčéą░ą▓ą║čā ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ąŠčüčćąĖčéą░ą╗ ą┤ąŠ ąĮčāą╗čÅ. ąŁč鹊čé čüč湥čéčćąĖą║ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ 4-ą▒ąĖčéąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ DT4H ąĖą╗ąĖ DT4L ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ DT4, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐ąĄčĆąĄą┐ą░ą┤ą░ ąĮą░ Waveform Output (OCW4x), ą║ąŠą│ą┤ą░ ą▓čüčéą░ą▓ą╗čÅąĄčéčüčÅ ąĖąĮč鹥čĆą▓ą░ą╗ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ. ąÆčŗčģąŠą┤ Output Compare ąĘą░ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĮą░ 1 čéą░ą║čé čéą░ą╣ą╝ąĄčĆą░ ą╝ąĖąĮąĖą╝čāą╝ ąŠčé ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ ąĮą░ Waveform Output, ą║ąŠą│ą┤ą░ Dead Time ąĮą░čüčéčĆąŠąĄąĮąŠ ą▓ 0. ąÆčŗčģąŠą┤čŗ OC4x ąĖ ~OC4x ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčéčüčÅ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé PWM Inversion Mode (PWM4X). ąŁč鹊 čéą░ą║ąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 ąĮą░ ąŠą▒ąŠąĖčģ ą▓čŗčģąŠą┤ą░čģ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą╗ąŠą│. 1 ą▓ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ.

ąĀąĖčü. 15-7. Dead Time Generator.

ąöą╗ąĖąĮą░ ą┐ąĄčĆąĖąŠą┤ą░ čüč湥čéą░ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ą┐čāč鹥ą╝ ą▓čŗą▒ąŠčĆą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ dead time prescaler ą▒ąĖčéą░ą╝ąĖ DTPS41:40 ąĖ ą▓čŗą▒ąŠčĆąŠą╝ ąĘąĮą░č湥ąĮąĖčÅ dead time ą▓ čĆąĄą│ąĖčüčéčĆąĄ DT4. ąĀąĄą│ąĖčüčéčĆ DT4 čüąŠčüč鹊ąĖčé ąĖąĘ ą┤ą▓čāčģ 4-ą▒ąĖčéąĮčŗčģ ą┐ąŠą╗ąĄą╣ DT4H ąĖ DT4L, ą║ąŠč鹊čĆčŗąĄ čāą┐čĆą░ą▓ą╗čÅčÄčé ą┐ąĄčĆąĖąŠą┤ą░ą╝ąĖ dead time ą▓čŗčģąŠą┤ąŠą▓ PWM ą┐ąŠ ąŠčéą┤ąĄą╗čīąĮąŠčüčéąĖ ą▓ ąĄą┤ąĖąĮąĖčåą░čģ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ čéą░ą║č鹊ą▓ čüč湥čéčćąĖą║ą░ ą│ąĄąĮąĄčĆą░č鹊čĆą░ dead time. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čäčĆąŠąĮčé ąĮą░čĆą░čüčéą░ąĮąĖčÅ OC4x ąĖ ~OC4x ą╝ąŠąČąĄčé ąĖą╝ąĄčéčī čĆą░ąĘąĮčŗąĄ ą┐ąĄčĆąĖąŠą┤čŗ dead time: tnon-overlap/rising edge ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ 4 ą▒ąĖčéą░ą╝ąĖ DT4H, ąĖ tnon-overlap/falling ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ 4 ą▒ąĖčéą░ą╝ąĖ DT4L.

ąĀąĖčü. 15-8. ąÜąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮą░čÅ ą▓čŗčģąŠą┤ąĮą░čÅ ą┐ą░čĆą░, COM4x1:0 = 1.

[Compare Match Output Unit]

ąæąĖčéčŗ Compare Output Mode (COM4x1:0) ąĖą╝ąĄčÄčé ą┤ą▓ąĄ čäčāąĮą║čåąĖąĖ. Waveform Generator ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčéčŗ COM4x1:0 ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ąĖą╗ąĖ ąĮąĄ ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą▓čŗą▓ąŠą┤ą░ čüąĖą│ąĮą░ą╗ą░ Waveform Output (OCW4x) ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čüąŠą▒čŗčéąĖąĖ Compare Match. ąóą░ą║ąČąĄ ą▒ąĖčéčŗ COM4x1:0 čāą┐čĆą░ą▓ą╗čÅčÄčé ą▓čŗą▓ąŠą┤ą░ą╝ąĖ ąĮąŠąČąĄą║ OC4x ąĖ ~OC4x. ąĀąĖčü. 15-9 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čāą┐čĆąŠčēąĄąĮąĮčāčÄ čüčģąĄą╝čā ą╗ąŠą│ąĖą║ąĖ, ąĮą░ ą║ąŠč鹊čĆčāčÄ ą▓ą╗ąĖčÅąĄčé ąĮą░čüčéčĆąŠą╣ą║ą░ ą▒ąĖčé COM4x1:0. ąĀąĄą│ąĖčüčéčĆčŗ I/O, ą▒ąĖčéčŗ I/O ąĖ ą▓čŗą▓ąŠą┤čŗ I/O ąĮą░ čŹč鹊ą╝ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąČąĖčĆąĮčŗą╝ čłčĆąĖčäč鹊ą╝. ą¤ąŠą║ą░ąĘą░ąĮčŗ č鹊ą╗čīą║ąŠ č鹥 čćą░čüčéąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ GPIO (DDR ąĖ PORT), ąĮą░ ą║ąŠč鹊čĆčŗąĄ ą▓ą╗ąĖčÅčÄčé ą▒ąĖčéčŗ COM4x1:0.

ąĀąĖčü. 15-9. ąĪčģąĄą╝ą░ Compare Match Output Unit.

ąÆ ąŠą▒čŗčćąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (Normal Mode, ąĮąĄ-PWM) Dead Time Generator ąĘą░ą┐čĆąĄčēąĄąĮ, ąĖ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ čüąĖąĮčģčĆąŠąĮąĖąĘą░č鹊čĆą░: Output Compare (OC4x) ąĘą░ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąŠčé Waveform Output (OCW4x) ąĮą░ ąŠą┤ąĖąĮ čéą░ą║čé čéą░ą╣ą╝ąĄčĆą░. ąÆ č鹊 ąČąĄ ą▓čĆąĄą╝čÅ ą▓ čĆąĄąČąĖą╝ą░čģ Fast PWM ąĖ Phase and Frequency Correct PWM, ą║ąŠą│ą┤ą░ ą▒ąĖčéčŗ COM4x1:0 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 01, ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ąĮąĄ ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ąĖ ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▓čŗą▓ąŠą┤ Output Compare, ąĖ ą▓ čüąĖą│ąĮą░ą╗čŗ OC4x ąĖ ~OC4x ą▓čüčéą░ą▓ą╗čÅąĄčéčüčÅ ą╝ąĄčĆčéą▓ąŠąĄ ą▓čĆąĄą╝čÅ, ą║ąŠč鹊čĆąŠąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī čĆąĄąČąĖą╝ąŠą▓ PWM ą┐ąŠą┤ąŠą▒ąĮą░ Normal mode, ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮą░ ą╗čÄą▒ą░čÅ ą┤čĆčāą│ą░čÅ ąĮą░čüčéčĆąŠą╣ą║ą░ ą▒ąĖčé COM4x1:0. ąØą░ čüąŠčüč鹊čÅąĮąĖąĄ OC4x ą▓ą╗ąĖčÅąĄčé ą┐čĆąĄąĖą╝čāčēąĄčüčéą▓ąĄąĮąĮąŠ Dead Time Generator. ąĢčüą╗ąĖ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüąĖčüč鹥ą╝ąĮčŗą╣ čüą▒čĆąŠčü, č鹊 OC4x čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą▓ 0.

ążčāąĮą║čåąĖčÅ ąĮąŠąČą║ąĖ GPIO ąŠčéą╝ąĄąĮčÅąĄčéčüčÅ čäčāąĮą║čåąĖąĄą╣ Output Compare (OC4x / ~OC4x) ąŠčé Dead Time Generator, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą╗čÄą▒ąŠą╣ ąĖąĘ ą▒ąĖčé COM4x1:0. ą×ą┤ąĮą░ą║ąŠ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ą▓čŗą▓ąŠą┤ą░ OC4x (ą▓čģąŠą┤ ąĖą╗ąĖ ą▓čŗčģąŠą┤) ą▓čüąĄ ąĄčēąĄ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ DDR ą▓čŗą▓ąŠą┤ą░ ą┐ąŠčĆčéą░. ąæąĖčé čĆąĄą│ąĖčüčéčĆą░ DDR ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ąŠą▓ OC4x ąĖ ~OC4x (DDR_OC4x ąĖ ~DDR_OC4x) ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ąĘąĮą░č湥ąĮąĖčÅ OC4x ąĖ ~OC4x ą┐ąŠčÅą▓čÅčéčüčÅ ąĮą░ ą▓ą▓ąŠą┤ą░čģ čćąĖą┐ą░. ążčāąĮą║čåąĖčÅ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠčĆčéą░ ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé čĆąĄąČąĖą╝ą░ Output Compare.

ąöąĖąĘą░ą╣ąĮ ą╗ąŠą│ąĖą║ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ Output Compare ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ąĄą╗ą░čéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÄ čüąŠčüč鹊čÅąĮąĖčÅ OC4x ą┐ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ ą▓čŗčģąŠą┤ą░. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĮąĄą║ąŠč鹊čĆčŗąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▒ąĖčé COM4x1:0 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ čĆąĄąČąĖą╝ąŠą▓ čĆą░ą▒ąŠčéčŗ. ąöą╗čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čŗą▓ąŠą┤ąŠą▓ Output Compare ąŠą▒čĆą░čēą░ą╣č鹥čüčī ą║ čéą░ą▒ą╗ąĖčåą░ą╝ 15-1, 15-2, 15-3 ąĖ 15-4.

Compare Output Mode ąĖ Waveform Generation. Waveform Generator ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčéčŗ COM4x1:0 ą┐ąŠ-čĆą░ąĘąĮąŠą╝čā ą▓ čĆąĄąČąĖą╝ąĄ Normal ąĖ čĆąĄąČąĖą╝ą░čģ PWM. ąöą╗čÅ ą▓čüąĄčģ čĆąĄąČąĖą╝ąŠą▓ čāčüčéą░ąĮąŠą▓ą║ą░ COM4x1:0 = 0 ą│ąŠą▓ąŠčĆąĖčé ą┤ą╗čÅ Waveform Generator ąĮąĄ ą┐čĆąĄą┤ą┐čĆąĖąĮąĖą╝ą░čéčī ąĮąĖą║ą░ą║ąĖčģ ą┤ąĄą╣čüčéą▓ąĖą╣ čü ą▓čŗčģąŠą┤ąŠą╝ OCW4x ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čüąŠą▒čŗčéąĖąĖ Compare Match. ąöą╗čÅ ą┤ąĄą╣čüčéą▓ąĖą╣ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐čĆąĖ čüčĆą░ą▓ąĮąĄąĮąĖąĖ ą┤ą╗čÅ ąĮąĄ-PWM čĆąĄąČąĖą╝ąŠą▓ ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čéą░ą▒ą╗ąĖčåąĄ 15-5. ąöą╗čÅ Fast PWM mode čüą╝. čéą░ą▒ą╗ąĖčåčā 15-6, ąĖ ą┤ą╗čÅ Phase ąĖ Frequency Correct PWM čüą╝. čéą░ą▒ą╗ąĖčåčā 15-7. ąśąĘą╝ąĄąĮąĄąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčé COM4x1:0 ą▒čāą┤ąĄčé ąĖą╝ąĄčéčī čŹčäč乥ą║čé ąĮą░ ą┐ąĄčĆą▓ąŠą╝ čüąŠą▒čŗčéąĖąĖ Compare Match ą┐ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ čŹčéąĖčģ ą▒ąĖčé. ąöą╗čÅ čĆąĄąČąĖą╝ąŠą▓ ąĮąĄ-PWM, ą┤ąĄą╣čüčéą▓ąĖąĄ ą╝ąŠąČąĮąŠ ąĘą░ą┤ą░čéčī ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ čü ą┐ąŠą╝ąŠčēčīčÄ ą▒ąĖčé čüčéčĆąŠą▒ą░ FOC4x.

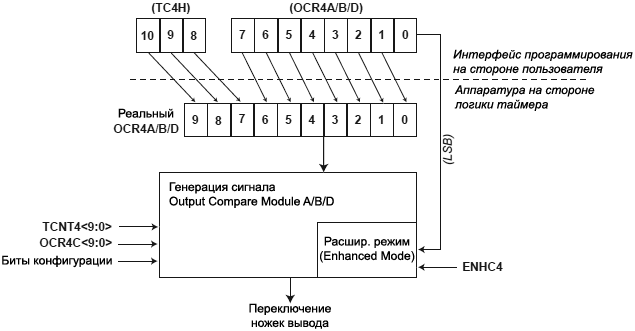

Enhanced Compare/PWM. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ENHC4 ą▓ čĆąĄą│ąĖčüčéčĆąĄ TCCR4E, čĆą░ąĘčĆąĄčłąĄąĮ čĆą░čüčłąĖčĆąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ čüčĆą░ą▓ąĮąĄąĮąĖčÅ/ą©ąśą£ (Enhanced Compare/PWM mode). ąŁč鹊čé čĆąĄąČąĖą╝ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ąŠą▒ą░ą▓ąĖčéčī ąŠą┤ąĖąĮ ą▒ąĖčé č鹊čćąĮąŠčüčéąĖ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ Output Compare OCR4A, OCR4B ąĖ OCR4D. ąóą░ą║ ąČąĄ,ą║ą░ą║ čŹč鹊 ą▒čŗą╗ąŠ ąŠą┐ąĖčüą░ąĮąŠ ą▓čŗčłąĄ, čüąŠą▒čŗčéąĖąĄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ ąŠą┤ąĖąĮ ąĖąĘ čéčĆąĄčģ čĆąĄą│ąĖčüčéčĆąŠą▓ Output Compare (OCR4A/B/D) čüąŠą▓ą┐ą░ą┤ąĄčé čü TCNT4 (10-ą▒ąĖčéąĮąŠąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ). ąÆ ą▒ą░ąĘąŠą▓ąŠą╝ čĆąĄąČąĖą╝ąĄ PWM čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╣ ą▓čŗčģąŠą┤ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčüčÅ ąĮą░ čüąŠą▒čŗčéąĖąĖ Compare Match. ąÆ čĆąĄąČąĖą╝ąĄ Enhanced Compare/PWM ą▓ą▓ąĄą┤ąĄąĮ ą▒ąĖčé, ą║ąŠč鹊čĆčŗą╣ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ąĮą░ ą║ą░ą║ąŠą╝ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝ čéą░ą║č鹊ą▓ąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ čĆąĄą░ą╗čīąĮąŠ ą▒čāą┤ąĄčé čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖčÅ ąŠ čüąŠą▒čŗčéąĖąĖ Compare Match. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▓čŗčģąŠą┤ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčüčÅ ąĮą░ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╝ čéą░ą║č鹊ą▓ąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ (ą║ą░ą║ ą▓ Normal mode), ąĄčüą╗ąĖ LSB čĆąĄą│ąĖčüčéčĆą░ OCR4A/B/D ą▓ ąĘąĮą░č湥ąĮąĖąĖ 0, ąĖą╗ąĖ ąĮą░ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠą╝ (čüą╗ąĄą┤čāčÄčēąĄą╝) ą┐ąĄčĆąĄą┐ą░ą┤ąĄ, ąĄčüą╗ąĖ čŹč鹊čé LSB ą▓ ąĘąĮą░č湥ąĮąĖąĖ 1.

ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ąĘą░ą╝ąĄčéąĖčé, čćč鹊 čā čĆąĄąČąĖą╝ąŠą▓ Normal ąĖ Enhanced PWM ąŠą┤ąĖąĮą░ą║ąŠą▓ą░čÅ ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī PWM ą▒čāą┤ąĄčé ą╗čāčćčłąĄ ą▓ čüą╗čāčćą░ąĄ Enhanced PWM.

ąŚą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆčŗ Output Compare OCR4A/B/D ąĖą╗ąĖ ąĖčģ čćč鹥ąĮąĖąĄ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠ ą▓ ąŠą▒ąŠąĖčģ čĆąĄąČąĖą╝ą░čģ. ąÆ Enhanced mode ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┐čĆąŠčüč鹊 ą┤ąŠą╗ąČąĄąĮ čāčćąĖčéčŗą▓ą░čéčī, čćč鹊 čĆąĄą│ąĖčüčéčĆ TC4H ą╝ąŠąČąĄčé čüąŠą┤ąĄčƹȹ░čéčī ą┤ąŠ 3-ą▒ąĖčé (ąĖ ąĖą╝ąĄčéčī č鹊 ąČąĄ čüą░ą╝ąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐čĆąĖ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ, ą║ą░ą║ ąĖ ą▓ 2-čĆą░ąĘčĆčÅą┤ąĮąŠą╝ ą▓ą░čĆąĖą░ąĮč鹥 čĆą░ą▒ąŠčéčŗ). ąŁč鹊 ą║ą░čüą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆąŠą▓ OCR4A, OCR4B ąĖ OCR4D. ąÜąŠąĮąĄčćąĮąŠ, ą▓ čĆąĄą│ąĖčüčéčĆąĄ OCR4C ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ą▒ąĖčé č鹊čćąĮąŠčüčéąĖ, ąĖ ąŠąĮ ąŠčüčéą░ąĄčéčüčÅ ą▓ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ, ą║ąŠč鹊čĆą░čÅ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąĄčĆąĖąŠą┤ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

ąĀąĖčü. 15-10. ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ ą▓ Enhanced Mode.

ąĀąĖčü. 15-10 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čĆąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ OCR4A/B/D čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąĘąĮą░č湥ąĮąĖčÄ, ąĘą░ą│čĆčāąČąĄąĮąĮąŠą╝čā ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝, čüą┤ą▓ąĖąĮčāč鹊ą╝čā ą▓ą┐čĆą░ą▓ąŠ, čćč鹊ą▒čŗ ą┐ąŠą╝ąĄčüčéąĖčéčī ą╝ą╗ą░ą┤čłąĖą╣ ąĘąĮą░čćą░čēąĖą╣ ą▒ąĖčé ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą▓ ą╝ąŠą┤čāą╗čī ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░.

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠčüčéąĖąČąĖą╝ąŠąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ 11 ą▒ąĖčé, ąĮąŠ ą╝ąŠąČąĮąŠ čāą║ą░ąĘą░čéčī ą╗čÄą▒ąŠąĄ ą┤čĆčāą│ąŠąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ. ąØą░ą┐čĆąĖą╝ąĄčĆ, 8-ą▒ąĖčéąĮąŠąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą╝ąŠąČąĮąŠ ą▒čāą┤ąĄčé ą┐ąŠą╗čāčćąĖčéčī ąĮą░ č鹊ą╣ ąČąĄ čćą░čüč鹊č鹥, čćč鹊 ąĖ ą▓ Normal PWM čü 7-ą▒ąĖčéąĮčŗą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝.

ą¤čĆąĖą╝ąĄčĆ:

- PLL Postcaler output = 64 ą£ąōčå, ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ą┤ą╗čÅ Timer/Counter4 ąĮąĄ ą░ą║čéąĖą▓ąĄąĮ.

- ąŻčüčéą░ąĮąŠą▓ą║ą░ OCR4C = 0x7F ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé č鹥ąŠčĆąĄčéąĖč湥čüą║ąŠąĄ ą┐ąŠą╗ąĮąŠąĄ 7-ą▒ąĖčéąĮąŠąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čü ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊č鹊ą╣ 500 ą║ąōčå.

- ąŻčüčéą░ąĮąŠą▓ą║ą░ OCR4A = 0x85 (= b10000101) ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čĆąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ "Compare A" 0x42 (b01000010), ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čüą║ą▓ą░ąČąĮąŠčüčéčī (51.95%), ąĖ ą╝ąŠąČąĮąŠ čü ą┐čĆąŠą╝ąĄąČčāč鹊čćąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ ą╝ąĄąČą┤čā ą┐ąĄčĆąĖąŠą┤ą░ą╝ąĖ ą┐ąŠą╗čāčćąĖčéčī čüą║ą▓ą░ąČąĮąŠčüčéčī ą┤ą╗čÅ ąĘąĮą░č湥ąĮąĖą╣ čüčĆą░ą▓ąĮąĄąĮąĖčÅ 0x42 ąĖ 0x43 (51.56%, 52.34%).

[ąĪąĖąĮčģčĆąŠąĮąĮąŠąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ]

ą¦č鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąĮąĄ čüąĖąĮčģčĆąŠąĮąĮčŗčģ ąĖ ąĮąĄ ą║ąŠą│ąĄčĆąĄąĮčéąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą▓ čåąĖą║ą╗ąĄ, ąĄčüą╗ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüąĖąĮčģčĆąŠąĮąĮąŠąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąŠą┤ąĮąŠą│ąŠ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ąĘąĮą░č湥ąĮąĖą╣ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ, čü ą┐ąŠą╝ąŠčēčīčÄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čéą░ą╣ą╝ąĄčĆą░ ą▓čüąĄ ąĘąĮą░č湥ąĮąĖčÅ ą╝ąŠąČąĮąŠ ąŠą▒ąĮąŠą▓ąĖčéčī ą▓ ąŠą┤ąĖąĮ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ čåąĖą║ą╗ą░ PWM. ąØąŠą▓čŗą╣ ąĮą░ą▒ąŠčĆ ąĘąĮą░č湥ąĮąĖą╣ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, ąĖ ąĖčģ čŹčäč乥ą║čéąĖą▓ąĮąŠąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣.

ąĀąĖčü. 15-11. ążčāąĮą║čåąĖčÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (Lock Feature) ąĖ čüąĖąĮčģčĆąŠąĮąĮąŠąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ.

ąÆ ąŠą▒čŗčćąĮąŠą╝ čĆąĄąČąĖą╝ąĄ čĆą░ą▒ąŠčéčŗ ą║ą░ąČą┤ą░čÅ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą▓čüčéčāą┐ą░ąĄčé ą▓ ą┤ąĄą╣čüčéą▓ąĖąĄ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ č鹥ą║čāčēąĄą│ąŠ čåąĖą║ą╗ą░. ąØąŠ ąĮąĄą║ąŠč鹊čĆčŗąĄ čüą╗čāčćą░ąĖ čéčĆąĄą▒čāčÄčé čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą▓čāčģ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čĆąĄą│ąĖčüčéčĆąŠą▓ čüčĆą░ą▓ąĮąĄąĮąĖčÅ, ąĖ čŹč鹊 ąĮąĄ ą▓čüąĄą│ą┤ą░ ą▓ąŠąĘą╝ąŠąČąĮąŠ, ąŠčüąŠą▒ąĄąĮąĮąŠ ąĮą░ ą▓čŗčüąŠą║ąĖčģ čćą░čüč鹊čéą░čģ PWM. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąĄčĆąĖąŠą┤ąŠą▓ PWM ą╝ąŠą│čāčé ą┐ąŠą╗čāčćąĖčéčī ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ.

ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ čäčāąĮą║čåąĖąĖ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (TLOCK4=1) ąĘąĮą░č湥ąĮąĖčÅ, ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆčŗ čüčĆą░ą▓ąĮąĄąĮąĖčÅ, ąĮąĄ ą▓čüčéčāą┐ą░čÄčé ą▓ čüąĖą╗čā ąĖ ą▓čĆąĄą╝ąĄąĮąĮąŠ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ ą▒čāč乥čĆčŗ. ąÜąŠą│ą┤ą░ ąŠčüą▓ąŠą▒ąŠąČą┤ą░ąĄčéčüčÅ ą▒ąĖčé TLOCK4, ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ, ąĖ ąĮąŠą▓čŗą╣ ąĮą░ą▒ąŠčĆ ąĘąĮą░č湥ąĮąĖą╣ ą▒čāą┤ąĄčé ąĘą░ą│čĆčāąČąĄąĮ ą▓ąŠ ą▓čüąĄ ąĖąĘą╝ąĄąĮąĄąĮąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ č鹥ą║čāčēąĄą│ąŠ čéą░ą║čéą░ PWM.

ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ TCCR4E ŌĆō Timer/Counter4 Control Register E.

[ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ]

ąĀąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ, čé. ąĄ. ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ ąĖ ą▓čŗą▓ąŠą┤ąŠą▓ Output Compare, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ čĆąĄąČąĖą╝ą░ Waveform Generation (ą▒ąĖčéčŗ PWM4x ąĖ WGM40) ąĖ čĆąĄąČąĖą╝ą░ Compare Output (ą▒ąĖčéčŗ COM4x1:0). ąæąĖčéčŗ čĆąĄąČąĖą╝ą░ Compare Output ąĮąĄ ą▓ą╗ąĖčÅčÄčé ąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čüč湥čéą░, ą░ ą▒ąĖčéčŗ čĆąĄąČąĖą╝ą░ Waveform Generation ą▓ą╗ąĖčÅčÄčé. ąæąĖčéčŗ COM4x1:0 čāą┐čĆą░ą▓ą╗čÅčÄčé, ą┤ąŠą╗ąČąĮčŗ ą╗ąĖ ą▓čŗčģąŠą┤čŗ PWM ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čüąĖą│ąĮą░ą╗ čü ąĖąĮą▓ąĄčĆčüąĖąĄą╣, ą▒ąĄąĘ ąĖąĮą▓ąĄčĆčüąĖąĖ ąĖą╗ąĖ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮąŠ. ąöą╗čÅ ąĮąĄ-PWM čĆąĄąČąĖą╝ąŠą▓ ą▒ąĖčéčŗ COM4x1:0 čāą┐čĆą░ą▓ą╗čÅčÄčé, ą┤ąŠą╗ąČąĮčŗ ą╗ąĖ ą▓čŗčģąŠą┤čŗ ąĮą░ čüąŠą▒čŗčéąĖąĖ Compare Match čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčīčüčÅ, čüą▒čĆą░čüčŗą▓ą░čéčīčüčÅ ąĖą╗ąĖ ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ.

Normal Mode. ąŁč鹊 čüą░ą╝čŗą╣ ą┐čĆąŠčüč鹊ą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ, PWM4x = 0. ąĪč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ąŠčé BOTTOM (ąŠčé 0) ą┤ąŠ TOP (ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ OCR4C), ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ąĘą░ąĮąŠą▓ąŠ ąŠčé BOTTOM. ąĀąĄą│ąĖčüčéčĆ OCR4C ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĘąĮą░č湥ąĮąĖąĄ TOP ą┤ą╗čÅ čüč湥čéčćąĖą║ą░, ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĄą│ąŠ čĆą░ąĘčĆąĄčłą░čÄčēčāčÄ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, ąĖ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāą┐čĆą░ą▓ą╗čÅčéčī čćą░čüč鹊č鹊ą╣ ą▓čŗčģąŠą┤ą░ Compare Match. ąÆ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ Compare Output čüąĖą│ąĮą░ą╗ Waveform Output (OCW4x) ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ (Compare Match) ąĘąĮą░č湥ąĮąĖą╣ TCNT4 ąĖ OCR4x. ąÆ ąĮąĄ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĄą╝ čĆąĄąČąĖą╝ąĄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą▓čŗčģąŠą┤ Waveform Output ąŠčćąĖčēą░ąĄčéčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé Compare Match. ąś ąĮą░ąŠą▒ąŠčĆąŠčé, ą▓ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĄą╝ čĆąĄąČąĖą╝ąĄ ą▓čŗčģąŠą┤ Waveform čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé Compare Match.

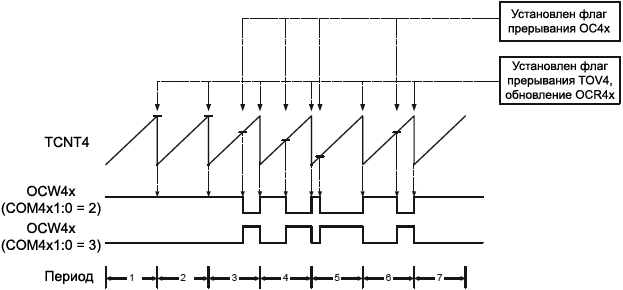

ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ Normal mode ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 15-12. ąŚąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (čĆąĄą│ąĖčüčéčĆ TCNT4), ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ ą│ąĖčüč鹊ą│čĆą░ą╝ą╝ąĄ, ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ čüč湥čéčćąĖą║ąŠą╝ ąĘąĮą░č湥ąĮąĖčÅ TOP, ąĘą░č鹥ą╝ čüč湥čéčćąĖą║ ąŠčćąĖčēą░ąĄčéčüčÅ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čéą░ą║č鹥. ąØą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ Waveform Output (OCW4x) ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą┐čĆąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ čüčĆą░ą▓ąĮąĄąĮąĖčÅ. ą£ą░ą╗ąĄąĮčīą║ą░čÅ ą│ąŠčĆąĖąĘąŠąĮčéą░ą╗čīąĮą░čÅ ą╗ąĖąĮąĖčÅ ą┐ąŠą╝ąĄčćą░ąĄčé ą╝ąŠą╝ąĄąĮčéčŗ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ TCNT4 čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ OCR4x.

ąĀąĖčü. 15-12. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ Normal Mode.

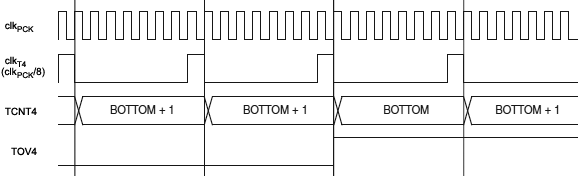

ążą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ Timer/Counter Overflow (TOV4) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ č鹊ą╝ ąČąĄ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░, ą║ąŠą│ą┤ą░ TCNT4 ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ 0. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čäą╗ą░ą│ TOV4 ą▓ąĄą┤ąĄčé čüąĄą▒čÅ ą║ą░ą║ 11-ą╣ ą▒ąĖčé, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ č鹊ą│ąŠ, čćč鹊 ąŠąĮ č鹊ą╗čīą║ąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ąĮąŠ ąĮąĄ ąŠčćąĖčēą░ąĄčéčüčÅ. ą×ą┤ąĮą░ą║ąŠ ą▓ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ čü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░, ą║ąŠč鹊čĆąŠąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčé čäą╗ą░ą│ TOV4, čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī čéą░ą╣ą╝ąĄčĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ čāą▓ąĄą╗ąĖč湥ąĮą░. ąÆ čĆąĄąČąĖą╝ąĄ Normal ąĮąĄčé ą║ą░ą║ąĖčģ-č鹊 čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ čüą╗čāčćą░ąĄą▓, ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ.

ąæą╗ąŠą║ Output Compare ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ ąĮąĄą║ąŠč鹊čĆčŗą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ Output Compare ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓ čĆąĄąČąĖą╝ąĄ Normal ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ, ą┐ąŠčüą║ąŠą╗čīą║čā čŹč鹊 ąĘą░ą╣ą╝ąĄčé ą▒ąŠą╗čīčłąĄ ą▓čĆąĄą╝ąĄąĮąĖ CPU, č湥ą╝ ą▓ ą┤čĆčāą│ąĖčģ čĆąĄąČąĖą╝ą░čģ. ąöą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ ą▓čŗčģąŠą┤ OCW4x ą╝ąŠąČąĮąŠ ąĮą░čüčéčĆąŠąĖčéčī ąĮą░ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ čüą▓ąŠąĄą│ąŠ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ čüąŠą▒čŗčéąĖąĖ Compare Match, čćč鹊 ą┤ąĄą╗ą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé čĆąĄąČąĖą╝ą░ Compare Output ą▓ ąĘąĮą░č湥ąĮąĖąĄ COM4x1:0 = 1. ąŚąĮą░č湥ąĮąĖąĄ OC4x ąĮąĄ ą▒čāą┤ąĄčé ą▓ąĖą┤ąĮąŠ ąĮą░ ąĮąŠąČą║ąĄ ą┐ąŠčĆčéą░, ą┐ąŠą║ą░ ąŠąĮ ąĮąĄ ąĮą░čüčéčĆąŠąĄąĮ ąĮą░ čĆą░ą▒ąŠčéčā ą║ą░ą║ ą▓čŗčģąŠą┤. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ fOC4x = fclkT4/4 ą┐ąŠą╗čāčćąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ OCR4C čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 0. ą¦ą░čüč鹊čéą░ čüąĖą│ąĮą░ą╗ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

fclkT4

fOC4x = -----------------

2 ┬Ę (1 + OCR4C)

ąĀą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čüą║ąŠą╗čīą║ąŠ ą▒ąĖčé čéčĆąĄą▒čāąĄčéčüčÅ, čćč鹊ą▒čŗ ą▓čŗčĆą░ąĘąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ OCR4C. ąŁč鹊 ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

ResolutionPWM = log2(OCR4C + 1)

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čŗą▓ąŠą┤ą░ Output Compare ą▓ čĆąĄąČąĖą╝ąĄ Normal Mode ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ.

ąóą░ą▒ą╗ąĖčåą░ 15-1. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čŗą▓ąŠą┤ąŠą▓ Output Compare ą▓ Normal Mode.

| COM4x1 |

COM4x0 |

ąÆčŗą▓. ~OC4x |

ąÆčŗą▓. OC4x |

| 0 |

0 |

ą×čéą║ą╗čÄč湥ąĮ |

ą×čéą║ą╗čÄč湥ąĮ |

| 0 |

1 |

ą×čéą║ą╗čÄč湥ąĮ |

OC4x |

| 1 |

0 |

ą×čéą║ą╗čÄč湥ąĮ |

OC4x |

| 1 |

1 |

ą×čéą║ą╗čÄč湥ąĮ |

OC4x |

Fast PWM Mode. ąĀąĄąČąĖą╝ ą▒čŗčüčéčĆąŠą│ąŠ ą©ąśą£, ąĖą╗ąĖ Fast PWM mode (PWM4x = 1 ąĖ WGM40 = 0) ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ ą▓čŗčüąŠą║ąŠčćą░čüč鹊čéąĮąŠą│ąŠ ą©ąśą£. Fast PWM ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé ą┤čĆčāą│ąŠą╣ ąŠą┐čåąĖąĖ PWM č鹥ą╝, čćč鹊 čüč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé č鹊ą╗čīą║ąŠ ą▓ ą┐ąĄčĆąĄą┤. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ čüč湥čéčćąĖą║ą░ ąĖą╝ąĄąĄčé č乊čĆą╝čā ą┐ąĖą╗čŗ, ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ ąŠą┤ąĮąŠčüą║ą░čéąĮčŗą╣ ą©ąśą£ (Single Slope PWM). ąĪč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ąŠčé BOTTOM ą┤ąŠ TOP (TOP ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ OCR4C), ąĘą░č鹥ą╝ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ąŠčé BOTTOM. ąÆ ąĮąĄ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĄą╝ čĆąĄąČąĖą╝ąĄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (noninverting Compare Output) ą▓čŗčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ Waveform Output (OCW4x) ąŠčćąĖčēą░ąĄčéčüčÅ ąĮą░ čüąŠą▒čŗčéąĖąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ (Compare Match) ąĘąĮą░č湥ąĮąĖčÅ TCNT4 ąĖ OCR4x, ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĮą░ BOTTOM. ąÆ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĄą╝ čĆąĄąČąĖą╝ąĄ ą▓čüąĄ ąĮą░ąŠą▒ąŠčĆąŠčé, Waveform Output čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĮą░ Compare Match, ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ąĮą░ BOTTOM. ąÆ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮąŠą╝ čĆąĄąČąĖą╝ąĄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (complementary Compare Output) ą▓čŗčģąŠą┤ Waveform ąŠčćąĖčēą░ąĄčéčüčÅ ąĮą░ Compare Match ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĮą░ BOTTOM.

ąśąĘ-ąĘą░ ąŠą┤ąĮąŠčüą║ą░čéąĮąŠą│ąŠ ą┐čĆąĖąĮčåąĖą┐ą░ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░ Fast PWM ą╝ąŠąČąĄčé ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčī ą▓čŗčģąŠą┤ ą▓ 2 čĆą░ąĘą░ ą▒čŗčüčéčĆąĄąĄ, č湥ą╝ čĆąĄąČąĖą╝ Phase and Frequency Correct PWM, ą║ąŠč鹊čĆčŗą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┤ą▓čāčģčüą║ą░čéąĮčŗą╣ ą┐čĆąĖąĮčåąĖą┐. ą¤ąŠčŹč鹊ą╝čā čĆąĄąČąĖą╝ Fast PWM čģąŠčĆąŠčłąŠ ą┐ąŠą┤čģąŠą┤ąĖčé ą┤ą╗čÅ čĆąĄą│čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠčēąĮąŠčüčéąĖ, ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ ą▓čŗą┐čĆčÅą╝ąĖč鹥ą╗ąĄą╣, DAC. ąÆčŗčüąŠą║ą░čÅ čćą░čüč鹊čéą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąĖą╝ąĄąĮąĖčéčī ą╝ąĄą╗ą║ąĖąĄ ą▓ąĮąĄčłąĮąĖąĄ ą┐ą░čüčüąĖą▓ąĮčŗąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ (ą║ą░čéčāčłą║ąĖ, ąĄą╝ą║ąŠčüčéąĖ), čćč鹊 čāą╝ąĄąĮčīčłą░ąĄčé ąŠą▒čēčāčÄ čüč鹊ąĖą╝ąŠčüčéčī čüąĖčüč鹥ą╝čŗ.

ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ Fast PWM ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 15-13. ąĪč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ ąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄčé čü TOP. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ čüč湥čéčćąĖą║ ąŠčćąĖčēą░ąĄčéčüčÅ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░. ąŚąĮą░č湥ąĮąĖąĄ TCNT4 ąĮą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą║ą░ą║ ą│ąĖčüč鹊ą│čĆą░ą╝ą╝ą░, ąĖą╗ą╗čÄčüčéčĆąĖčĆčāčÄčēą░čÅ ąŠą┤ąĮąŠčüą║ą░čéąĮčŗą╣ ą┐čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ. ąØą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ čéą░ą║ąČąĄ ą┐ąŠą║ą░ąĘą░ąĮ čüąĖą│ąĮą░ą╗ Waveform Output ą▓ čĆąĄąČąĖą╝ą░čģ non-inverted ąĖ inverted Compare Output. ą£ą░ą╗ąĄąĮčīą║ą░čÅ ą│ąŠčĆąĖąĘąŠąĮčéą░ą╗čīąĮą░čÅ ą╗ąĖąĮąĖčÅ ą┐ąŠą╝ąĄčćą░ąĄčé ą╝ąŠą╝ąĄąĮčéčŗ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ TCNT4 čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ OCR4x.

ąĀąĖčü. 15-13. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ Fast PWM Mode.

ążą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ Timer/Counter Overflow (TOV4) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ąĮąĄčé ąĘąĮą░č湥ąĮąĖčÅ TOP. ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, č鹊 ąŠąĮąŠ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ. ąÆ čĆąĄąČąĖą╝ąĄ Fast PWM ą▒ą╗ąŠą║ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠčüčāčēąĄčüčéą▓ąĖčéčī ą│ąĄąĮąĄčĆą░čåąĖčÄ ąĖą╝ą┐čāą╗čīčüąŠą▓ PWM ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ OC4x. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé COM4x1:0 ą▓ ąĘąĮą░č湥ąĮąĖąĄ 10 ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĮąĄ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ PWM, ąĖ čāčüčéą░ąĮąŠą▓ą║ą░ ąĖčģ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 11 ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĖąĮą▓ąĄčĆčüąĮčŗą╣ PWM. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé COM4x1:0 ą▓ 01 čĆą░ąĘčĆąĄčłąĖčé ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮąŠąĄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓čŗčģąŠą┤ąŠą▓ OC4x ąĖ ~OC4x. ąĀąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ ąĮąĄ ą▒čāą┤ąĄčé ą▓ąĖą┤ąĖą╝ąŠ ąĮą░ ąĮąŠąČą║ą░čģ ą┐ąŠčĆč鹊ą▓, ą┐ąŠą║ą░ ąŠąĮąĖ ąĮąĄ ą▒čāą┤čāčé ąĮą░čüčéčĆąŠąĄąĮčŗ ą▓ čĆąĄąČąĖą╝ ą▓čŗčģąŠą┤ą░. PWM ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ (ąĖą╗ąĖ ąŠčćąĖčüčéą║ąŠą╣) čüąĖą│ąĮą░ą╗ą░ Waveform Output (OCW4x) ą▓ ą╝ąŠą╝ąĄąĮčéčŗ Compare Match, ą║ąŠą│ą┤ą░ čüąŠą▓ą┐ą░ą┤ą░čÄčé ąĘąĮą░č湥ąĮąĖčÅ OCR4x ąĖ TCNT4, ąĖ ąŠčćąĖčüčéą║ąŠą╣ (ąĖą╗ąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣) Waveform Output ąĮą░ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ąŠčćąĖčēą░ąĄčéčüčÅ (ą┐ąĄčĆąĄčģąŠą┤ąĖčé ąŠčé ąĘąĮą░č湥ąĮąĖčÅ TOP ą║ BOTTOM).

ą¦ą░čüč鹊čéą░ PWM ąĮą░ ą▓čŗčģąŠą┤ąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗčćąĖčüą╗ąĄąĮą░ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

fclkT4

fOC4xPWM = -------

N

ą¤ąĄčĆąĄą╝ąĄąĮąĮą░čÅ N ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čłą░ą│ąŠą▓ ą▓ ąŠą┤ąĮąŠčüą║ą░čéąĮąŠą╝ ą┐ąĄčĆąĖąŠą┤ąĄ čüč湥čéą░. ąŚąĮą░č湥ąĮąĖąĄ N čĆą░ą▓ąĮąŠ ą╗čÄą▒ąŠą╝čā ąĘąĮą░č湥ąĮąĖčÄ TOP.

ąÜčĆą░ą╣ąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ OCR4C ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ čüą╗čāčćą░ąĖ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą©ąśą£ ą▓ čĆąĄąČąĖą╝ąĄ Fast PWM. ąĢčüą╗ąĖ OCR4C čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ čĆą░ą▓ąĮčŗą╝ BOTTOM (čé. ąĄ. ą▓ 0), ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐ąŠą╗čāčćą░čéčüčÅ ą║ąŠčĆąŠčéą║ąĖąĄ ąĖą│ąŠą╗ą║ąĖ ąĮą░ ą║ą░ąČą┤ąŠą╝ MAX+1 čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░. ąŻčüčéą░ąĮąŠą▓ą║ą░ OCR4C ą▓ ąĘąĮą░č湥ąĮąĖąĄ MAX ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā čāčĆąŠą▓ąĮčÄ ą╗ąŠą│. 1 ąĖą╗ąĖ ą╗ąŠą│. 0 ąĮą░ ą▓čŗčģąŠą┤ąĄ (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ ą▓čŗčģąŠą┤ą░, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╣ ą▒ąĖčéą░ą╝ąĖ COM4x1:0).

ą¦ą░čüč鹊čéą░ (čüąŠ čüą║ą▓ą░ąČąĮąŠčüčéčīčÄ 50%) ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▓ čĆąĄąČąĖą╝ąĄ Fast PWM ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠčüčéąĖą│ąĮčāčéą░ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ Waveform Output (OCW4x) ąĮą░ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ čüą▓ąŠąĄą│ąŠ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗą╣ ąĮą░ ą║ą░ąČą┤ąŠą╝ čüąŠą▒čŗčéąĖąĖ Compare Match (čāčüčéą░ąĮąŠą▓ą║ą░ COM4x1:0 = 1). ą¤čĆąĖ čŹč鹊ą╝ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ ą┐ąŠą╗čāčćąĖčéčüčÅ fOC4 = fclkT4/4, ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ OCR4C čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 3.

ążčāąĮą║čåąĖčÅ ą┐ąŠčĆč鹊ą▓ GPIO ąŠčéą╝ąĄąĮčÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ Output Compare (OC4x / ~OC4x) ąĖąĘ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (čüą╝. ą▓čŗčłąĄ ą▓čĆąĄąĘą║čā "Dead Time Generator") ąĄčüą╗ąĖ ą╗čÄą▒ąŠą╣ ąĖąĘ ą▒ąĖčé COM4x1:0 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ DDR ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ąŠą▓ OC4X ąĖ ~OC4X ąĮą░čüčéčĆąŠąĄąĮčŗ ąĮą░ ą▓čŗą▓ąŠą┤. ąĢčüą╗ąĖ ą▒ąĖčéčŗ COM4x1:0 čüą▒čĆąŠčłąĄąĮčŗ, čĆąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ ą▒čāą┤ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī čĆąĄą│ąĖčüčéčĆčā PORT. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čŗą▓ąŠą┤ąŠą▓ Output Compare ąŠą┐ąĖčüą░ąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ.

ąóą░ą▒ą╗ąĖčåą░ 15-2. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĮąŠąČąĄą║ Output Compare ą▓ čĆąĄąČąĖą╝ąĄ Fast PWM.

| COM4x1 |

COM4x0 |

ąÆčŗą▓. ~OC4x |

ąÆčŗą▓. OC4x |

| 0 |

0 |

ą×čéą║ą╗čÄč湥ąĮ |

ą×čéą║ą╗čÄč湥ąĮ |

| 0 |

1 |

~OC4x |

OC4x |

| 1 |

0 |

ą×čéą║ą╗čÄč湥ąĮ |

OC4x |

| 1 |

1 |

ą×čéą║ą╗čÄč湥ąĮ |

OC4x |

Phase and Frequency Correct PWM Mode. ąĀąĄąČąĖą╝ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ čćą░čüč鹊čéčŗ ąĖ čäą░ąĘčŗ ą©ąśą£ (Phase and Frequency Correct PWM Mode, PWM4x = 1 ąĖ WGM40 = 1) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąŠą┐čåąĖčÄ č鹊čćąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą╝ ą©ąśą£, ąŠčüąĮąŠą▓ą░ąĮąĮčāčÄ ąĮą░ ą┤ą▓čāčģčüą║ą░čéąĮąŠą╝ ą┐čĆąĖąĮčåąĖą┐ąĄ. ąĪč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą▓ą▓ąĄčĆčģ ąŠčé BOTTOM ą┤ąŠ TOP (TOP čéčĆą░ą┤ąĖčåąĖąŠąĮąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ OCR4C) ąĖ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ čüčćąĖčéą░ąĄčé ą▓ąĮąĖąĘ, ąŠą▒čĆą░čéąĮąŠ ąŠčé TOP ą┤ąŠ BOTTOM. ąÆ čĆąĄąČąĖą╝ąĄ ą▒ąĄąĘ ąĖąĮą▓ąĄčĆčüąĖąĖ (non-inverting Compare Output Mode) ąĖ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (complimentary Compare Output Mode) ą▓čŗčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ Waveform Output (OCW4x) ąŠčćąĖčēą░ąĄčéčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ (Compare Match) ąĘąĮą░č湥ąĮąĖčÅ TCNT4 ąĖ OCR4x ą┐čĆąĖ čüč湥č鹥 ą▓ą▓ąĄčĆčģ, ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĮą░ Compare Match ą┐čĆąĖ čüč湥č鹥 ą▓ąĮąĖąĘ. ąÆ ąĖąĮą▓ąĄčĆčüąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą▓čüąĄ ąĮą░ąŠą▒ąŠčĆąŠčé. ąŁč鹊 čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ ą┤ą▓čāčģčüą║ą░čéąĮčŗą╣ ą©ąśą£ (Dual Slope PWM). ąöą▓čāčģčüą║ą░čéąĮčŗą╣ ą┐čĆąĖąĮčåąĖą┐ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą©ąśą£ ąĖą╝ąĄąĄčé čćą░čüč鹊čéčā ą▓ 2 čĆą░ąĘą░ ąĮąĖąČąĄ, č湥ą╝ čā ąŠą┤ąĮąŠčüą║ą░čéąĮąŠą│ąŠ ą┐čĆąĖąĮčåąĖą┐ą░. ą×ą┤ąĮą░ą║ąŠ ąĖąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ą┐ąŠą╗čāčćą░čÄčēąĖą╣čüčÅ čüąĖą│ąĮą░ą╗ ąŠčüąŠą▒ąĄąĮąĮąŠ čćąĖčüčéčŗą╣ ąĖ čüąĖą╝ą╝ąĄčéčĆąĖčćąĮčŗą╣, ą┐čĆąĖąĮčåąĖą┐ ą┤ą▓čāčģčüą║ą░čéąĮąŠą│ąŠ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą©ąśą£ ąĮą░čģąŠą┤ąĖčé ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╝ąŠč鹊čĆąŠą╝.

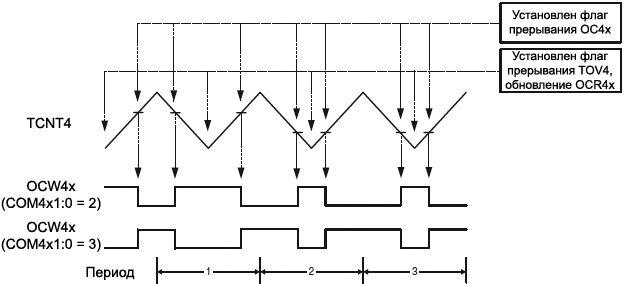

ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ čĆąĄąČąĖą╝ą░ Phase and Frequency Correct PWM ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 15-14 ą│ą┤ąĄ ąĘąĮą░č湥ąĮąĖąĄ TCNT4 ąŠą▒ąŠąĘąĮą░č湥ąĮąŠ ą║ą░ą║ ą│ąĖčüč鹊ą│čĆą░ą╝ą╝ą░, ąĖą╗ą╗čÄčüčéčĆąĖčĆčāčÄčēą░čÅ ą┤ą▓čāčģčüą║ą░čéąĮčŗą╣ ą┐čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ (čüąŠ čüč湥č鹊ą╝ ą▓ą▓ąĄčĆčģ ąĖ ą▓ąĮąĖąĘ). ąĪąĮą░čćą░ą╗ą░ čüč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ TOP. ąÜąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ TOP, ąŠąĮ ą╝ąĄąĮčÅąĄčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüč湥čéą░ ąĖ čüčćąĖčéą░ąĄčé ą▓ąĮąĖąĘ. ąŚąĮą░č湥ąĮąĖąĄ TCNT4 ą▒čāą┤ąĄčé čĆą░ą▓ąĮąŠ TOP ą▓ č鹥č湥ąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ čéą░ą║čéą░ čéą░ą╣ą╝ąĄčĆą░. ąØą░ čŹč鹊ą╣ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ čéą░ą║ąČąĄ ą┐ąŠą║ą░ąĘą░ąĮ čüąĖą│ąĮą░ą╗ Waveform Output (OCW4x) ą▓ ąĮąĄ ąĖąĮą▓ąĄčĆčüąĮąŠą╝ ąĖ ąĖąĮą▓ąĄčĆčüąĮąŠą╝ Compare Output Mode. ą£ą░ą╗ąĄąĮčīą║ąĖąĄ ą│ąŠčĆąĖąĘąŠąĮčéą░ą╗čīąĮčŗąĄ ą╗ąĖąĮąĖąĖ ą┐ąŠą╝ąĄčćą░čÄčé ą╝ąŠą╝ąĄąĮčéčŗ, ą║ąŠą│ą┤ą░ TCNT4 čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü OCR4x.

ąĀąĖčü. 15-14. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ Phase and Frequency Correct PWM Mode.

ążą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ Timer/Counter Overflow (TOV4) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ąĮąĄčé ąĘąĮą░č湥ąĮąĖčÅ BOTTOM. ążą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ BOTTOM.

ąÆ čĆąĄąČąĖą╝ąĄ Phase and Frequency Correct PWM ą▒ą╗ąŠą║ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĖą╝ą┐čāą╗čīčüčŗ ą©ąśą£ ąĮą░ ą▓čŗčģąŠą┤ą░čģ OC4x čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé COM4x1:0 ą▓ 01 ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĮąĄ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ PWM (ą©ąśą£), ąĖ čāčüčéą░ąĮąŠą▓ą║ą░ ą▓ 11 ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĖąĮą▓ąĄčĆčüąĮčŗą╣ ą©ąśą£. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé COM4A1:0 ą▓ ąĘąĮą░č湥ąĮąĖąĄ 01 čĆą░ąĘčĆąĄčłąĖčé čĆąĄąČąĖą╝ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮąŠą│ąŠ ą▓čŗčģąŠą┤ą░ (complementary Compare Output), ą║ąŠą│ą┤ą░ ą▒čāą┤čāčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ąĮąĄ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ OC4x ąĖ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ ~OC4x čüąĖą│ąĮą░ą╗čŗ. ąĀąĄą░ą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠčÅą▓čÅčéčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ ąĮąŠąČąĄą║ ą┐ąŠčĆčéą░, ą║ąŠą│ą┤ą░ ąŠąĮąĖ ą▒čāą┤čāčé ąĮą░čüčéčĆąŠąĄąĮčŗ ą║ą░ą║ ą▓čŗčģąŠą┤ (čĆąĄą│ąĖčüčéčĆąŠą╝ DDR). ąśą╝ą┐čāą╗čīčüčŗ PWM ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ąŠčćąĖčüčéą║ąŠą╣ (ąĖą╗ąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣) čüąĖą│ąĮą░ą╗ą░ Waveform Output (OCW4x) ą▓ ą╝ąŠą╝ąĄąĮčéčŗ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ (Compare Match) ąĘąĮą░č湥ąĮąĖą╣ OCR4x ąĖ TCNT4, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą▓ą▓ąĄčĆčģ, ąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ (ąĖą╗ąĖ ąŠčćąĖčüčéą║ąŠą╣) Waveform Output ą▓ ą╝ąŠą╝ąĄąĮčéčŗ Compare Match, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą▓ąĮąĖąĘ. ą¦ą░čüč鹊čéą░ ą©ąśą£ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą▓ čĆąĄąČąĖą╝ąĄ Phase and Frequency Correct PWM ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗčćąĖčüą╗ąĄąĮą░ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

fclkT4

fOC4xPCPWM = -------

N

ą¤ąĄčĆąĄą╝ąĄąĮąĮą░čÅ N ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čłą░ą│ąŠą▓ ą▓ ą┐ąŠą╗ąŠą▓ąĖąĮąĄ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ čåąĖą║ą╗ą░. ąŚąĮą░č湥ąĮąĖąĄ N čĆą░ą▓ąĮąŠ TOP. ąÜčĆą░ą╣ąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ OCR4C ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ čüą╗čāčćą░ąĖ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą©ąśą£ ą▓ čĆąĄąČąĖą╝ąĄ Phase and Frequency Correct PWM. ąĢčüą╗ąĖ OCR4C čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čĆą░ą▓ąĮčŗą╝ BOTTOM (čé. ąĄ. ą▓ 0), ąĮą░ ą▓čŗčģąŠą┤ąĄ ą▒čāą┤ąĄčé ą┐ąŠčüč鹊čÅąĮąĮčŗą╣ ą╗ąŠą│. 0, ąĖ ąĄčüą╗ąĖ OCR4C čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ MAX, ąĮą░ ą▓čŗčģąŠą┤ąĄ ą▒čāą┤ąĄčé ą┐ąŠčüč鹊čÅąĮąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĄąĮ ąĮąĄ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ čĆąĄąČąĖą╝ PWM. ąöą╗čÅ ąĖąĮą▓ąĄčĆčüąĮąŠą│ąŠ PWM ą▓čŗčģąŠą┤ ą┐ąŠą╝ąĄąĮčÅąĄčé čüą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ąĮą░ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠąĄ.

ążčāąĮą║čåąĖčÅ GPIO ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčé čāčĆąŠą▓ąĮąĖ Output Compare (OC4x / ~OC4x) čüąĖą│ąĮą░ą╗ąŠą╝ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (čüą╝. ą▓čŗčłąĄ ą▓čĆąĄąĘą║čā "Dead Time Generator"), ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą╗čÄą▒ąŠą╣ ąĖąĘ ą▒ąĖčé COM4x1:0, ąĖ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ DDR ą┤ą╗čÅ ąĮąŠąČąĄą║ OC4X ąĖ ~OC4X ąĮą░čüčéčĆąŠąĄąĮčŗ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ čŹčéąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ ąĮą░ ą▓čŗčģąŠą┤. ąĢčüą╗ąĖ ą▒ąĖčéčŗ COM4x1:0 čüą▒čĆąŠčłąĄąĮčŗ, čĆąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ ąĮąŠąČąĄą║ ą┐ąŠčĆčéą░ ą▒čāą┤ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī ąĘąĮą░č湥ąĮąĖčÅą╝ čĆąĄą│ąĖčüčéčĆą░ PORT. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čŗą▓ąŠą┤ąŠą▓ Output Compare ąŠą┐ąĖčüą░ąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ.

ąóą░ą▒ą╗ąĖčåą░ 15-3. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĮąŠąČąĄą║ Output Compare ą▓ čĆąĄąČąĖą╝ąĄ Phase and Frequency Correct PWM.

| COM4x1 |

COM4x0 |

ąÆčŗą▓. ~OC4x |

ąÆčŗą▓. OC4x |

| 0 |

0 |

ą×čéą║ą╗čÄč湥ąĮ |

ą×čéą║ą╗čÄč湥ąĮ |

| 0 |

1 |

~OC4x |

OC4x |

| 1 |

0 |

ą×čéą║ą╗čÄč湥ąĮ |

OC4x |

| 1 |

1 |

ą×čéą║ą╗čÄč湥ąĮ |

OC4x |

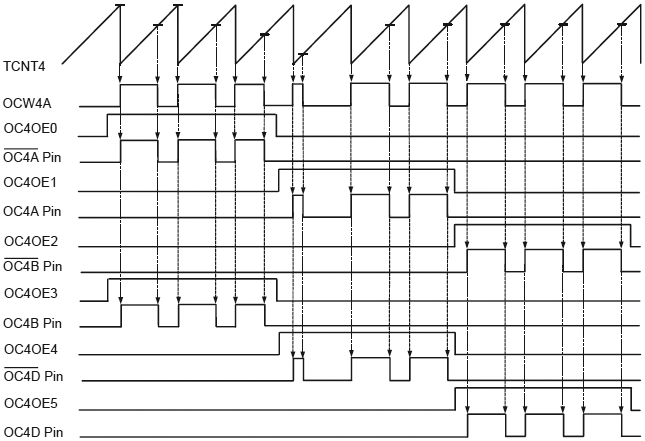

ąĀąĄąČąĖą╝ PWM6. ąŁč鹊čé čĆąĄąČąĖą╝ ą©ąśą£ (PWM4A = 1, WGM41 = 1 ąĖ WGM40 = x) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąŠą┐čåąĖčÄ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čü ą┐ąŠą╝ąŠčēčīčÄ ą©ąśą£ ą▒ąĄčüą║ąŠą╗ą╗ąĄą║č鹊čĆąĮčŗą╝ąĖ ą┤ą▓ąĖą│ą░č鹥ą╗čÅą╝ąĖ ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ č鹊ą║ą░ (Brushless DC, BLDC). ąÆ čĆąĄąČąĖą╝ąĄ PWM6 čĆąĄą│ąĖčüčéčĆ OCR4A čāą┐čĆą░ą▓ą╗čÅąĄčé ą▓čüąĄą╝ąĖ čłąĄčüčéčīčÄ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ Output Compare, čéą░ą║ čćč鹊 ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ Waveform Output (OCW4A) ąŠčé Waveform Generator ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą▓čüąĄčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ čüąĖą│ąĮą░ą╗ą░ ą©ąśą£. ąĀąĄąČąĖą╝ PWM6 čéą░ą║ąČąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čĆąĄą│ąĖčüčéčĆ Output Compare Override Enable (OC4OE), ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠą│ąŠ ąĘą░ą┐čĆąĄčéą░ ąĖą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĮąŠąČąĄą║ Output Compare. ąĢčüą╗ąĖ ą▒ąĖčé Output Compare Override Enable ąŠčćąĖčēąĄąĮ, č鹊 čĆąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ ąĮąŠąČąĄą║ ą▒čāą┤ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī čĆąĄą│ąĖčüčéčĆčā PORT.

ąĀąĄąČąĖą╝ PWM6 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ą▓ą░ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ, ąŠą┤ąĮąŠčüą║ą░čéąĮčŗą╣ ąĖ ąĖ ą┤ą▓čāčģčüą║ą░čéąĮčŗą╣. ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮ ąŠą┤ąĮąŠčüą║ą░čéąĮčŗą╣ čĆąĄąČąĖą╝ (ą▒ąĖčé WGM40 čüą▒čĆąŠčłąĄąĮ ą▓ 0), čüč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ąŠčé BOTTOM ą┤ąŠ TOP (TOP ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ OCR4C), ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ BOTTOM, ą║ą░ą║ čŹč鹊 čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ Fast PWM. ąśą╝ą┐čāą╗čīčüčŗ ą©ąśą£ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ (ąĖą╗ąĖ ąŠčćąĖčüčéą║ąŠą╣) Waveform Output (OCW4A) ą▓ ą╝ąŠą╝ąĄąĮčéčŗ Compare Match, ą║ąŠą│ą┤ą░ čüąŠą▓ą┐ą░ą┤ą░čÄčé ąĘąĮą░č湥ąĮąĖčÅ OCR4A ąĖ TCNT4, ąĖ ąŠčćąĖčüčéą║ąŠą╣ (ąĖą╗ąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣) Waveform Output ąĮą░ čåąĖą║ą╗ąĄ čéą░ą╣ą╝ąĄčĆą░, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ąŠčćąĖčēąĄąĮ (ą┐ąŠą╝ąĄąĮčÅą╗ čüą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąŠčé TOP ąĮą░ BOTTOM). ążą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ Timer/Counter Overflow (TOV4) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ TOP ąĖ, ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąŠąĮąŠ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ OCR4A.

ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮ ą┤ą▓čāčģčüą║ą░čéąĮčŗą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ (ą▒ąĖčé WGM40 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1), č鹊 čüč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ąŠčé BOTTOM ą┤ąŠ TOP (TOP ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ OCR4C), ąĘą░č鹥ą╝ čüčćąĖčéą░ąĄčé ąŠčé TOP ą┤ąŠ BOTTOM č鹊čćąĮąŠ čéą░ą║ ąČąĄ, ą║ą░ą║ ą▓ čĆąĄąČąĖą╝ąĄ Phase and Frequency Correct PWM. ąśą╝ą┐čāą╗čīčüčŗ ą©ąśą£ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ (ąĖą╗ąĖ ąŠčćąĖčüčéą║ąŠą╣) Waveform Output (OCW4A) ą▓ ą╝ąŠą╝ąĄąĮčéčŗ Compare Match (ą║ąŠą│ą┤ą░ čüąŠą▓ą┐ą░ą┤ą░čÄčé ąĘąĮą░č湥ąĮąĖčÅ OCR4A ąĖ TCNT4) ą┐čĆąĖ čüč湥č鹥 ą▓ą▓ąĄčĆčģ, ąĖ ąŠčćąĖčüčéą║ąŠą╣ (ąĖą╗ąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣) Waveform Output ąĮą░ Compare Match ą┐čĆąĖ čüč湥č鹥 ą▓ąĮąĖąĘ. ążą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ Timer/Counter Overflow (TOV4) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ BOTTOM ąĖ, ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąŠąĮąŠ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ OCR4A.

ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ ąŠą┤ąĮąŠčüą║ą░čéąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ PWM6 (WGM41 = 0), ą║ąŠą│ą┤ą░ ą▒ąĖčéčŗ COM4A1:0 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 10, ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 15-15. ąĪč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ ą┤ąŠčüčéąĖą│ąĮąĄčé ąĘąĮą░č湥ąĮąĖčÅ TOP. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ čüč湥čéčćąĖą║ ąŠčćąĖčēą░ąĄčéčüčÅ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čéą░ą║č鹥 čéą░ą╣ą╝ąĄčĆą░. ąŚąĮą░č湥ąĮąĖąĄ TCNT4 ąĮą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą║ą░ą║ ą│ąĖčüč鹊ą│čĆą░ą╝ą╝ą░, ąĖą╗ą╗čÄčüčéčĆąĖčĆčāčÄčēą░čÅ ąŠą┤ąĮąŠčüą║ą░čéąĮčŗą╣ ą┐čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ. ąØą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ čéą░ą║ąČąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓čŗą▓ąŠą┤čŗ OC4A ąĖ ~OC4A, ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▒ąĖčéčŗ Output Compare Override Enable (OC4OE1..OC4OE0).

ąĀąĖčü. 15-15. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ ąŠą┤ąĮąŠčüą║ą░čéąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ PWM6.

ążčāąĮą║čåąĖčÅ GPIO ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčé čāčĆąŠą▓ąĮąĖ Output Compare (OC4x / ~OC4x) čüąĖą│ąĮą░ą╗ąŠą╝ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ą╝ąĄčĆčéą▓ąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (čüą╝. ą▓čŗčłąĄ ą▓čĆąĄąĘą║čā "Dead Time Generator"), ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą╗čÄą▒ąŠą╣ ąĖąĘ ą▒ąĖčé COM4x1:0, ąĖ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ DDR ą┤ą╗čÅ ąĮąŠąČąĄą║ OC4X ąĖ ~OC4X ąĮą░čüčéčĆąŠąĄąĮčŗ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ čŹčéąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ ąĮą░ ą▓čŗčģąŠą┤. ąÆčŗą▓ąŠą┤čŗ Output Compare ą╝ąŠą│čāčé ą▒čŗčéčī čéą░ą║ąČąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮčŗ ą▒ąĖčéą░ą╝ąĖ Output Compare Override Enable OC4OE5..OC4OE0. ąĢčüą╗ąĖ ą▒ąĖčé Override Enable ąŠčćąĖčēąĄąĮ, č鹊 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ą┐ąŠčÅą▓ąĖčéčüčÅ čĆąĄą░ą╗čīąĮąŠąĄ ą╗ąŠą│ąĖč湥čüą║ąŠąĄ ąĘąĮą░č湥ąĮąĖčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ PORT, ąĖ ąĄčüą╗ąĖ ą▒ąĖčé Override Enable čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 čŹč鹊 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ Output Compare ą║ ą▓čŗą▓ąŠą┤čā ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čŗą▓ąŠą┤ąŠą▓ Output Compare ąŠą┐ąĖčüą░ąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ.

ąóą░ą▒ą╗ąĖčåą░ 15-3. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĮąŠąČąĄą║ Output Compare ą▓ čĆąĄąČąĖą╝ąĄ PWM6.

| COM4A1 |

COM4A0 |

~OC4A (PC6) |

OC4A (PC7) |

| 0 |

0 |

ą×čéą║ą╗čÄč湥ąĮ |

ą×čéą║ą╗čÄč湥ąĮ |

| 0 |

1 |

~OC4A ┬Ę OC4OE0 |

OC4A ┬Ę OC4OE1 |

| 1 |

0 |

OC4A ┬Ę OC4OE0 |

OC4A ┬Ę OC4OE1 |

| 1 |

1 |

OC4A ┬Ę OC4OE0 |

OC4A ┬Ę OC4OE1 |

| COM4B1 |

COM4B0 |

~OC4B (PB5) |

OC4B (PB6) |

| 0 |

0 |

ą×čéą║ą╗čÄč湥ąĮ |

ą×čéą║ą╗čÄč湥ąĮ |

| 0 |

1 |

~OC4A ┬Ę OC4OE2 |

OC4A ┬Ę OC4OE3 |

| 1 |

0 |

OC4A ┬Ę OC4OE2 |

OC4A ┬Ę OC4OE3 |

| 1 |

1 |

OC4A ┬Ę OC4OE2 |

OC4A ┬Ę OC4OE3 |

| COM4D1 |

COM4D0 |

~OC4D (PD6) |

OC4A (PD7) |

| 0 |

0 |

ą×čéą║ą╗čÄč湥ąĮ |

ą×čéą║ą╗čÄč湥ąĮ |

| 0 |

1 |

~OC4A ┬Ę OC4OE4 |

OC4A ┬Ę OC4OE5 |

| 1 |

0 |

OC4A ┬Ę OC4OE4 |

OC4A ┬Ę OC4OE5 |

| 1 |

1 |

OC4A ┬Ę OC4OE4 |

OC4A ┬Ę OC4OE5 |

[ąöąĖą░ą│čĆą░ą╝ą╝čŗ čüč湥čéą░ Timer/Counter4]

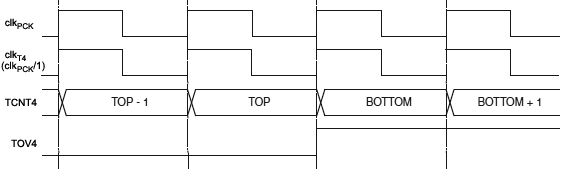

ąóą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ ą┐ąŠ čüąĖąĮčģčĆąŠąĮąĮąŠą╝čā ą┐čĆąĖąĮčåąĖą┐čā, ąĖ ąĮą░ čĆąĖčüčāąĮą║ą░čģ ąĮąĖąČąĄ čéą░ą║čéčŗ čéą░ą╣ą╝ąĄčĆą░ (clkT4) ą┐ąŠą║ą░ąĘą░ąĮčŗ ą║ą░ą║ čüąĖą│ąĮą░ą╗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ąŁčéąĖ čĆąĖčüčāąĮą║ąĖ čüąŠą┤ąĄčƹȹ░čé ąĖąĮč乊čĆą╝ą░čåąĖčÄ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ čäą╗ą░ą│ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ąĀąĖčü. 15-16 čüąŠą┤ąĄčƹȹĖčé ą┤ąĖą░ą│čĆą░ą╝ą╝čā ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ ą▒ą░ąĘąŠą▓ąŠą│ąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░. ą¤ąŠą║ą░ąĘą░ąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čüč湥čéą░ ą▒ą╗ąĖąĘą║ąŠ ą║ ąĘąĮą░č湥ąĮąĖčÄ MAX ą▓ąŠ ą▓čüąĄčģ čĆąĄąČąĖą╝ą░čģ, ą║čĆąŠą╝ąĄ Phase and Frequency Correct PWM.

ąĀąĖčü. 15-16. ąöąĖą░ą│čĆą░ą╝ą╝ą░ čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ ą▒ąĄąĘ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░.

ąĀąĖčü. 15-17 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čéą░ą║čāčÄ ąČąĄ ą┤ąĖą░ą│čĆą░ą╝ą╝čā, ąĮąŠ čü čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╝ ą┐čĆąĄčüą║ą░ą╗ąĄčĆąŠą╝ ą▓ąŠ ą▓čüąĄčģ čĆąĄąČąĖą╝ą░čģ, ą║čĆąŠą╝ąĄ Phase and Frequency Correct PWM Mode.

ąĀąĖčü. 15-17. ąöąĖą░ą│čĆą░ą╝ą╝ą░ čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ čü ą┐čĆąĄčüą║ą░ą╗ąĄčĆąŠą╝ (ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ą┤ąĄą╗ąĖčé čćą░čüč鹊čéčā fclkT4/8).

ąĀąĖčü. 15-18 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čāčüčéą░ąĮąŠą▓ą║čā OCF4A, OCF4B ąĖ OCF4D ą▓ąŠ ą▓čüąĄčģ čĆąĄąČąĖą╝ą░čģ, ąĖ čĆąĖčü. 15-19 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čāčüčéą░ąĮąŠą▓ą║čā TOV4 ą▓ čĆąĄąČąĖą╝ąĄ in Phase and Frequency Correct PWM.

ąĀąĖčü. 15-18. ąöąĖą░ą│čĆą░ą╝ą╝ą░ čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēą░čÅ čāčüčéą░ąĮąŠą▓ą║čā OCF1x, čü ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗ąĄą╝ (fclkT4/8)

ąĀąĖčü. 15-19. ąöąĖą░ą│čĆą░ą╝ą╝ą░ čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ čü ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗ąĄą╝ (fclkT4/8).

[ąæą╗ąŠą║ Fault Protection]

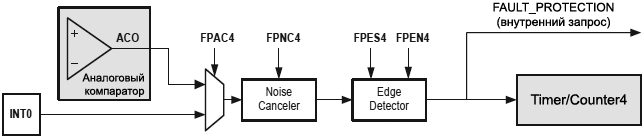

ąÆ Timer/Counter4 čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ąĘą░čēąĖčéą░ ąŠčé čüą▒ąŠąĄą▓ (ą▒ą╗ąŠą║ Fault Protection), ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ąĘą░ą┐čĆąĄčéąĖčéčī ą▓čŗčģąŠą┤čŗ PWM ą┐ąŠ ą▓ąĮąĄčłąĮąĄą╝čā čüąŠą▒čŗčéąĖčÄ. ąÆąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠą▒čŗčéąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĄčé ą┐ąŠčüčéčāą┐ą░čéčī ąĮą░ ą▓čģąŠą┤ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (external interrupt INT0) ąĖą╗ąĖ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ąŠčé ą▒ą╗ąŠą║ą░ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. ąæą╗ąŠą║ ąĘą░čēąĖčéčŗ ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 15-20. ąŁą╗ąĄą╝ąĄąĮčéčŗ čŹč鹊ą╣ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ, ą║ąŠč鹊čĆčŗąĄ ą║ąŠčüą▓ąĄąĮąĮąŠ ąŠčéąĮąŠčüčÅčéčüčÅ ą║ ą▒ą╗ąŠą║čā Fault Protection, ąĘą░ą║čĆą░čłąĄąĮčŗ čüąĄčĆčŗą╝.

ąĀąĖčü. 15-20. ąæą╗ąŠą║-čüčģąĄą╝ą░ čüąĖčüč鹥ą╝čŗ Fault Protection.

ąÜąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮ čĆąĄąČąĖą╝ Fault Protection ą▒ąĖč鹊ą╝ Fault Protection Enable (FPEN4), ąĖ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ (čüąŠą▒čŗčéąĖąĄ) ąĮą░ ąĮąŠąČą║ąĄ external interrupt pin (INT0) ąĖą╗ąĖ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ (Analog Comparator output, ACO), ąĖ čŹč鹊 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąŠ ą┤ąĄč鹥ą║č鹊čĆąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░, č鹊 čüčĆą░ą▒ąŠčéą░ąĄčé čĆąĄąČąĖą╝ ąĘą░čēąĖčéčŗ ąŠčé čüą▒ąŠąĄą▓. ąÜąŠą│ą┤ą░ ąĘą░čēąĖčéą░ čüčĆą░ą▒ąŠčéą░ą╗ą░, ą▒ąĖčéčŗ COM4x ąŠčćąĖčēą░čÄčéčüčÅ ą▓čŗčģąŠą┤ąĮčŗąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆčŗ ąŠčéą║ą╗čÄčćą░čÄčéčüčÅ ąŠčé ą▓čŗčģąŠą┤ąŠą▓ PWM, ąĖ čāčĆąŠą▓ąĮąĖ čĆąĄą│ąĖčüčéčĆą░ PORTB ą┐ąĄčĆąĄčģąŠą┤čÅčé ąĮą░ ą▓čŗčģąŠą┤čŗ ąĮąŠąČąĄą║ PWM. ąæąĖčé Fault Protection Enable (FPEN4) ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ąĮą░ č鹊ą╝ ąČąĄ čüąĖčüč鹥ą╝ąĮąŠą╝ čéą░ą║č鹥, ą║ąŠą│ą┤ą░ ąŠčćąĖčēą░čÄčéčüčÅ ą▒ąĖčéčŗ COM4nx. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé Fault Protection Interrupt Enable (FPIE4), č鹊 čüą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĖ ą▒ąĖčé FPEN4 ąŠčćąĖčüčéąĖčéčüčÅ. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ą▒ąĖčé FPEN4 ą╝ąŠąČąĄčé ąŠą┐čĆą░čłąĖą▓ą░čéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, čćč鹊 čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ ą▓ąŠčłąĄą╗ ą▓ čĆąĄąČąĖą╝ ąĘą░čēąĖčéčŗ Fault Protection.

ąśčüč鹊čćąĮąĖą║ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ Fault Protection. ą×čüąĮąŠą▓ąĮąŠą╣ ąĖčüč鹊čćąĮąĖą║ čŹč鹊 ą▓čŗą▓ąŠą┤ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (external interrupt pin, INT0). ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ą▓ ą║ą░č湥čüčéą▓ąĄ čüąĖą│ąĮą░ą╗ą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ąĘą░čēąĖčéčŗ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓čŗčģąŠą┤ Analog Comparator. ąÆ ą║ą░č湥čüčéą▓ąĄ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ Analog Comparator ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ Fault Protection Analog Comparator (FPAC4) ą▓ čĆąĄą│ąĖčüčéčĆąĄ Timer/Counter4 Control D (TCCR4D). ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░ ąĘą░čēąĖčéčŗ ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī ąĄčæ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąŠčćąĖčüčéąĖčéčī čäą╗ą░ą│ FPF4 ą┐ąŠčüą╗ąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ ąĘą░čēąĖčéčŗ, čāčüčéą░ąĮąŠą▓ą║ąĖ ą┤ąĄč鹥ą║č鹊čĆą░ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ąĖą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ Fault Protection.

ą×ą▒ą░ čüąĖą│ąĮą░ą╗ą░, external interrupt pin (INT0) ąĖ ą▓čŗčģąŠą┤ Analog Comparator (ACO) ą░ąĮą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ ą┐ąŠ čéą░ą║ąŠą╝čā ąČąĄ ą┐čĆąĖąĮčåąĖą┐čā, ą║ą░ą║ ąĖ ą▓čŗą▓ąŠą┤ T0, čüą╝. čĆąĖčü. 12-1. ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĖą┤ąĄąĮčéąĖčćąĮčŗą╣ ą┤ąĄč鹥ą║č鹊čĆ ą┐ąĄčĆąĄą┐ą░ą┤ą░. ą×ą┤ąĮą░ą║ąŠ, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮ ą┐ąŠą┤ą░ą▓ąĖč鹥ą╗čī čłčāą╝ą░ (noise canceler), ą┐ąĄčĆąĄą┤ ą┤ąĄč鹥ą║č鹊čĆąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą▓čüčéą░ą▓ą╗čÅąĄčéčüčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ą╗ąŠą│ąĖą║ą░, ą║ąŠč鹊čĆą░čÅ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé ąĘą░ą┤ąĄčƹȹ║čā ąĮą░ 4 čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║čéą░. ąĪčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ąĘą░čēąĖčéčŗ ą╝ąŠąČąĮąŠ ą▓čŗąĘą▓ą░čéčī ąĖčüą║čāčüčüčéą▓ąĄąĮąĮąŠ ą┐čāč鹥ą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĮąŠąČą║ąŠą╣ ą┐ąŠčĆčéą░ INT0.

ąĀąĖčü. 12-1. ą×čåąĖčäčĆąŠą▓ą║ą░ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ Tn/T0.

Noise Canceler. ąŁčéą░ č鹥čģąĮąĖą║ą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāą╗čāčćčłąĖčéčī ą┐ąŠą╝ąĄčģąŠąĘą░čēąĖčēąĄąĮąĮąŠčüčéčī ąĘą░čēąĖčéčŗ čü ą┐ąŠą╝ąŠčēčīčÄ čüčģąĄą╝čŗ čåąĖčäčĆąŠą▓ąŠą╣ čäąĖą╗čīčéčĆą░čåąĖąĖ. ąÆčģąŠą┤ ą┐ąŠą┤ą░ą▓ąĖč鹥ą╗čÅ čłčāą╝ą░ (noise canceler) ą╝ąŠąĮąĖč鹊čĆąĖčéčüčÅ ą▓ č鹥č湥ąĮąĖąĄ 4 ą▓čŗą▒ąŠčĆąŠą║, ąĖ čćč鹊ą▒čŗ čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐ąŠą┤ą░ą▓ąĖč鹥ą╗čÅ ą┐ąŠą╝ąĄąĮčÅą╗čüčÅ, ą▓čüąĄ 4 ą▓čŗą▒ąŠčĆą║ąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠą┤ąĖąĮą░ą║ąŠą▓čŗąĄ.

ą¤ąŠą┤ą░ą▓ąĖč鹥ą╗čī čłčāą╝ą░ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ Fault Protection Noise Canceler (FPNC4) ą▓ čĆąĄą│ąĖčüčéčĆąĄ Timer/Counter4 Control Register D (TCCR4D). ą¤čĆąĖ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą╝ ą┐ąŠą┤ą░ą▓ąĖč鹥ą╗ąĄ čłčāą╝ą░ ą▓ą▓ąŠą┤ąĖčéčüčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ąĮą░ 4 čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║čéą░. ą¤ąŠą┤ą░ą▓ąĖč鹥ą╗čī čłčāą╝ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüąĖčüč鹥ą╝ąĮčāčÄ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā, ą┐ąŠčŹč鹊ą╝čā ąĮą░čüčéčĆąŠą╣ą║ą░ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĮą░ ąĮąĄą│ąŠ ąĮąĄ ą▓ą╗ąĖčÅąĄčé.

[ąÜą░ą║ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮ ą┤ąŠčüčéčāą┐ ą║ 10-ą▒ąĖčéąĮčŗą╝ čĆąĄą│ąĖčüčéčĆą░ą╝]

ąĢčüą╗ąĖ ą▓ čĆąĄą│ąĖčüčéčĆčŗ TCNT4 ąĖ OCR4A/B/C/D ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ 10-ą▒ąĖčéąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ, č鹊 ą║ čŹčéąĖą╝ 10-ą▒ąĖčéąĮčŗą╝ čĆąĄą│ąĖčüčéčĆą░ą╝ ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ č湥čĆąĄąĘ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ ą┐ąŠ ą▒ą░ą╣čéą░ą╝ č湥čĆąĄąĘ 8-ą▒ąĖčéąĮčāčÄ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ AVR CPU ąĘą░ ą┤ą▓ąĄ ąŠą┐ąĄčĆą░čåąĖąĖ. ąŻ ą▓čüąĄčģ 10-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĄčüčéčī ąŠą▒čēąĖą╣ 2-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čüčéą░čĆčłąĄą│ąŠ ą▒ą░ą╣čéą░ (Timer/Counter4 High Byte, TC4H), ą║ąŠč鹊čĆčŗą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą▓čĆąĄą╝ąĄąĮąĮčŗą╣ ą▒čāč乥čĆ, čģčĆą░ąĮčÅčēąĖą╣ ą┤ą▓ą░ čüčéą░čĆčłąĖčģ ą▒ąĖčéą░ ą┤ą╗čÅ 10-ą▒ąĖčéąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░. ą×ą┤ąĖąĮ ąĖ č鹊čé ąČąĄ čĆąĄą│ąĖčüčéčĆ TC4H ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čüąĄčģ 10-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓. ąöąŠčüčéčāą┐ ą║ ą╝ą╗ą░ą┤čłąĄą╝čā ą▒ą░ą╣čéčā čĆąĄą│ąĖčüčéčĆą░ ą▓čŗąĘčŗą▓ą░ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ 10-ą▒ąĖčéąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ. ąÜąŠą│ą┤ą░ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé 10-ą▒ąĖčéąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čÅą┤čĆąŠą╝ CPU, č鹊 čüčĆą░ąĘčā (ąĮą░ ąŠą┤ąĮąŠą╝ čéą░ą║č鹥 čÅą┤čĆą░) ą▓ 10 ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▒ąĖčé TC4H ąĖ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą▒ą░ą╣čéą░. ąÉąĮą░ą╗ąŠą│ąĖčćąĮąŠ, ą║ąŠą│ą┤ą░ CPU čćąĖčéą░ąĄčé ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé 10-ą▒ąĖčéąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░, č鹊 ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓ TC4H ą┐ąŠą┐ą░ą┤ą░čÄčé čüčéą░čĆčłąĖąĄ ą▒ąĖčéčŗ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░.

ą¦č鹊ą▒čŗ ą▓čŗą┐ąŠą╗ąĮąĖčéčī 10-ą▒ąĖčéąĮčāčÄ ąĘą░ą┐ąĖčüčī, čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ąĘą░ą┐ąĖčüą░ąĮ ą▓ čĆąĄą│ąĖčüčéčĆ TC4H. ąöą╗čÅ 10-ą▒ąĖčéąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ą┐ąĄčĆąĄą┤ čćč鹥ąĮąĖąĄą╝ čüčéą░čĆčłąĄą│ąŠ ą▒ą░ą╣čéą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC4H.

ąØąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░ ą┤ąŠčüčéčāą┐ą░ ą║ 10-ą▒ąĖčéąĮčŗą╝ čĆąĄą│ąĖčüčéčĆą░ą╝ čéą░ą╣ą╝ąĄčĆą░. ą¤ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ ąŠą▒ąĮąŠą▓ą╗čÅčÄčé čĆąĄą│ąĖčüčéčĆ TC4H. ąóąŠčé ąČąĄ čüą░ą╝čŗą╣ ą┐čĆąĖąĮčåąĖą┐ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ OCRnA/B/C/D.

; ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ

...

; ąŻčüčéą░ąĮąŠą▓ą║ą░ TCNT4 ą▓ 0x01FF:

ldi r17,0x01

ldi r16,0xFF

out TC4H,r17

out TCNT4,r16

; ą¦č鹥ąĮąĖąĄ TCNT4 ą▓ r17:r16:

in r16,TCNT4

in r17,TC4H

...

// ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ C

unsigned int i;

...

/* ąŻčüčéą░ąĮąŠą▓ą║ą░ TCNT4 ą▓ 0x01FF */

TC4H = 0x01;

TCNT4 = 0xFF;

/* ą¦č鹥ąĮąĖąĄ TCNT4 ą▓ i */

i = TCNT4;

i |= ((unsigned int)TC4H << 8);

...

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé, čćč鹊 ą┐ąŠą┤ą║ą╗čÄč湥ąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ąĘą░ą│ąŠą╗ąŠą▓ąŠčćąĮčŗą╣ čäą░ą╣ą╗, ąŠą┐ąĖčüčŗą▓ą░čÄčēąĖą╣ čĆąĄą│ąĖčüčéčĆčŗ ąĖ ą▒ąĖčéčŗ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąöą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ I/O, ąĮą░čģąŠą┤čÅčēąĖčģčüčÅ ą▓ čĆą░čüčłąĖčĆąĄąĮąĮąŠą╣ ą║ą░čĆč鹥 ą░ą┤čĆąĄčüąŠą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (extended I/O map), ąĖąĮčüčéčĆčāą║čåąĖąĖ ą░čüčüąĄą╝ą▒ą╗ąĄčĆą░ IN, OUT, SBIS, SBIC, CBI ąĖ SBI ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą╝ąĄąĮąĄąĮčŗ ąĮą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ ą║ extended I/O. ą×ą▒čŗčćąĮąŠ LDS ąĖ STS ą║ąŠą╝ą▒ąĖąĮąĖčĆčāčÄčéčüčÅ čü SBRS, SBRC, SBR ąĖ CBR.

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ ą▓ąŠąĘą▓čĆą░čéąĖčé ąĘąĮą░č湥ąĮąĖąĄ TCNT4 ą▓ čĆąĄą│ąĖčüčéčĆąŠą▓ąŠą╣ ą┐ą░čĆąĄ r17:r16.

ąÆą░ąČąĮąŠ ąŠčéą╝ąĄčéąĖčéčī, čćč鹊 ą┤ąŠčüčéčāą┐ ą║ 10-ą▒ąĖčéąĮčŗą╝ čĆąĄą│ąĖčüčéčĆą░ą╝ ąĮąĄ čÅą▓ą╗čÅąĄčéčüčÅ ą░č鹊ą╝ą░čĆąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĄą╣. ąĢčüą╗ąĖ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ ą╝ąŠą╝ąĄąĮčé, ą║ąŠą│ą┤ą░ ą┤ą▓ąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą┐čŗčéą░čÄčéčüčÅ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ 10-ą▒ąĖčéąĮąŠą╝čā čĆąĄą│ąĖčüčéčĆčā (č鹊ą╝čā ąČąĄ čüą░ą╝ąŠą╝čā ąĖą╗ąĖ ą┤čĆčāą│ąŠą╝čā), č鹊 ą║ąŠą┤ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠą▒ąĮąŠą▓ąĖčé čĆąĄą│ąĖčüčéčĆ TC4H, ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą┤ąŠčüčéčāą┐ ą▓ ą║ąŠą┤ąĄ ą▓ąĮąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▒čāą┤ąĄčé ą┐ąŠą▓čĆąĄąČą┤ąĄąĮ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą║ąŠą│ą┤ą░ ąŠą▒ą░ ą║ąŠą┤ą░, ąĖ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąŠą▒ąĮąŠą▓ą╗čÅčÄčé čĆąĄą│ąĖčüčéčĆ TC4H, ąŠčüąĮąŠą▓ąĮąŠą╣ ą║ąŠą┤ ą┤ąŠą╗ąČąĄąĮ ąĘą░ą┐čĆąĄčéąĖčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ 16-ą▒ąĖčéąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░.

ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą║ąŠą┤ ą┤ą░ąĄčé ą┐čĆąĖą╝ąĄčĆ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą░č鹊ą╝ą░čĆąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ čüąŠą┤ąĄčƹȹĖą╝ąŠą╝čā čĆąĄą│ąĖčüčéčĆą░ TCNT4. ą¦č鹥ąĮąĖąĄ ą╗čÄą▒ąŠą│ąŠ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ OCR4A/B/C/D ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐ąŠ čéą░ą║ąŠą╝čā ąČąĄ ą┐čĆąĖąĮčåąĖą┐čā.

; ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ

TIM1_ReadTCNT4:

; ąĪąŠčģčĆą░ąĮąĄąĮąĖąĄ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čäą╗ą░ą│ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

in r18,SREG

; ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

cli

; ą¦č鹥ąĮąĖąĄ TCNT4 ą▓ r17:r16

in r16,TCNT4

in r17,TC4H

; ąÆąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĄ čäą╗ą░ą│ą░ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

out SREG,r18

ret

// ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ C

unsigned int TIM1_ReadTCNT4 (void)

{

unsigned char sreg;

unsigned int i;

// ąĪąŠčģčĆą░ąĮąĄąĮąĖąĄ čäą╗ą░ą│ą░ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

sreg = SREG;

// ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

_CLI();

// ą¦č鹥ąĮąĖąĄ TCNT4 ą▓ i:

i = TCNT4;

i |= ((unsigned int)TC4H << 8);

// ąÆąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĄ čäą╗ą░ą│ą░ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

SREG = sreg;

return i;

}

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ ą▓ąŠąĘą▓čĆą░čéąĖčé ąĘąĮą░č湥ąĮąĖąĄ TCNT4 ą▓ čĆąĄą│ąĖčüčéčĆąŠą▓ąŠą╣ ą┐ą░čĆąĄ r17:r16.

ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą┐čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą░č鹊ą╝ą░čĆąĮčāčÄ 10-ą▒ąĖčéąĮčāčÄ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ TCNT4. ąŚą░ą┐ąĖčüčī ą▓ ą╗čÄą▒ąŠą╣ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ OCR4A/B/C/D ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐ąŠ čéą░ą║ąŠą╝čā ąČąĄ ą┐čĆąĖąĮčåąĖą┐čā.

; ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ

TIM1_WriteTCNT4:

; ąĪąŠčģčĆą░ąĮąĄąĮąĖąĄ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čäą╗ą░ą│ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

in r18,SREG

; ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

cli

; ąŻčüčéą░ąĮąŠą▓ą║ą░ TCNT4 ą▓ r17:r16

out TC4H,r17

out TCNT4,r16

; ąÆąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĄ čäą╗ą░ą│ą░ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

out SREG,r18

ret

// ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ C:

void TIM1_WriteTCNT4 (unsigned int i)

{

unsigned char sreg;

unsigned int i;

// ąĪąŠčģčĆą░ąĮąĄąĮąĖąĄ čäą╗ą░ą│ą░ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

sreg = SREG;

// ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

_CLI();

// ąŻčüčéą░ąĮąŠą▓ą║ą░ TCNT4 ą▓ i:

TC4H = (i >> 8);

TCNT4 = (unsigned char)i;

// ąÆąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĄ čäą╗ą░ą│ą░ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

SREG = sreg;

}

ąÜąŠą┤ ą░čüčüąĄą╝ą▒ą╗ąĄčĆą░ čéčĆąĄą▒čāąĄčé, čćč鹊ą▒čŗ čĆąĄą│ąĖčüčéčĆąŠą▓ą░čÅ ą┐ą░čĆą░ r17:r16 čüąŠą┤ąĄčƹȹ░ą╗ą░ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ TCNT4.

ą¤ąŠą▓č鹊čĆąĮąŠąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ TC4H. ąĢčüą╗ąĖ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĘą░ą┐ąĖčüčī ą▓ ąĮąĄčüą║ąŠą╗čīą║ąŠ 10-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓, ą║ąŠą│ą┤ą░ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣, č鹊 čĆąĄą│ąĖčüčéčĆ TC4H ąĮčāąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čĆą░ąĘ. ą×ą┤ąĮą░ą║ąŠ ą┤ą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ą░č鹊ą╝ą░čĆąĮąŠčüčéąĖ čüą╗ąĄą┤čāąĄčé čĆą░čüčüą╝ąŠčéčĆąĄčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąŠčéą║ą╗čÄč湥ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ąĄčüą╗ąĖ ąŠąĮąĖ ą╝ąŠą┤ąĖčäąĖčåąĖčĆčāčÄčé čĆąĄą│ąĖčüčéčĆ TC4H.

[ą×ą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ Timer/Counter4]

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé |

COM4A1

|

COM4A0 |

COM4B1 |

COM4B0 |

FOC4A |

FOC4B |

PWM4A |

PWM4B |

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

rw |

rw |

rw |

rw |

w |

w |

rw |

rw |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ŌĆó 7, 6 ŌĆō COM4A1, COM4A0: Comparator A Output Mode

ąŁčéąĖ ą▒ąĖčéčŗ čāą┐čĆą░ą▓ą╗čÅčÄčé ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄą╝ ą▓čŗčģąŠą┤ą░ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čüąĖą│ąĮą░ą╗ąŠą▓ Waveform Output (OCW4A) and the connection of the Output Compare pin (OC4A). ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ąŠą▒ą░ ą▒ąĖčéą░ COM4A1:0, č鹊 ą▓čŗčģąŠą┤ OC4A ąŠčéą╝ąĄąĮčÅąĄčé ąŠą▒čŗčćąĮčŗą╣ čäčāąĮą║čåąĖąŠąĮą░ą╗ ą┐ąŠčĆčéą░ GPIO, ą║ ą║ąŠč鹊čĆąŠą╝čā OC4A ą┐ąŠą┤ą║ą╗čÄč湥ąĮ. ąÜąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗą╣ ą▓čŗčģąŠą┤ ~OC4A ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ą░čģ PWM, ą║ąŠą│ą┤ą░ ą▒ąĖčéčŗ COM4A1:0 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 01. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (DDR), čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čüąĖą│ąĮą░ą╗ą░ą╝ OC4A ąĖ ~OC4A, ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ, čćč鹊ą▒čŗ ąĘą░čĆą░ą▒ąŠčéą░ą╗ ą▓čŗčģąŠą┤ąĮąŠą╣ ą┤čĆą░ą╣ą▓ąĄčĆ čŹčéąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓.

ążčāąĮą║čåąĖčÅ ą▒ąĖčé COM4A1:0 ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĮą░čüčéčĆąŠąĄą║ ą▒ąĖčé PWM4A, WGM40 ąĖ WGM41. ąóą░ą▒ą╗ąĖčåą░ 15-5 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī ą▒ąĖčé COM4A1:0, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé PWM4A, ą▓ ąŠą▒čŗčćąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (Normal Mode, ąĮąĄ PWM).

ąóą░ą▒ą╗ąĖčåą░ 15-5. Compare Output Mode, Normal Mode (ąĮąĄ PWM).

| COM4A1 |

COM4A0 |

ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ OCW4A |

ąÆčŗą▓. OC4A |

ąÆčŗą▓. ~OC4A |

| 0 |

0 |

ą×ą▒čŗčćąĮą░čÅ čĆą░ą▒ąŠčéą░ ą┐ąŠčĆčéą░ |

ą×čéą║ą╗čÄč湥ąĮ |

ą×čéą║ą╗čÄč湥ąĮ |

| 0 |

1 |

ą¤ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą┐čĆąĖ Compare Match |

ą¤ąŠą┤ą║ą╗čÄč湥ąĮ |

ą×čéą║ą╗čÄč湥ąĮ |

| 1 |

0 |

ą×čćąĖčüčéą║ą░ ą┐čĆąĖ Compare Match |

ą¤ąŠą┤ą║ą╗čÄč湥ąĮ |

ą×čéą║ą╗čÄč湥ąĮ |

| 1 |

1 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą┐čĆąĖ Compare Match |

ą¤ąŠą┤ą║ą╗čÄč湥ąĮ |

ą×čéą║ą╗čÄč湥ąĮ |

ąóą░ą▒ą╗ąĖčåą░ 15-6 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī ą▒ąĖčé COM4A1:0, ą║ąŠą│ą┤ą░ ą▒ąĖčéčŗ PWM4A, WGM40 ąĖ WGM41 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ čĆąĄąČąĖą╝ ą▒čŗčüčéčĆąŠą│ąŠ ą©ąśą£.

ąóą░ą▒ą╗ąĖčåą░ 15-6. Compare Output Mode, Fast PWM Mode.

| COM4A1 |

COM4A0 |

ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ OCW4A |

ąÆčŗą▓. OC4A |

ąÆčŗą▓. ~OC4A |

| 0 |

0 |

ą×ą▒čŗčćąĮą░čÅ čĆą░ą▒ąŠčéą░ ą┐ąŠčĆčéą░ |

ą×čéą║ą╗čÄč湥ąĮ |

ą×čéą║ą╗čÄč湥ąĮ |

| 0 |

1 |

ą×čćąĖčüčéą║ą░ ą┐čĆąĖ Compare Match, čāčüčéą░ąĮąŠą▓ą║ą░ ą┐čĆąĖ TCNT4=0x000 |

ą¤ąŠą┤ą║ą╗čÄč湥ąĮ |

ą¤ąŠą┤ą║ą╗čÄč湥ąĮ |

| 1 |

0 |

ą¤ąŠą┤ą║ą╗čÄč湥ąĮ |

ą×čéą║ą╗čÄč湥ąĮ |

| 1 |

1 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą┐čĆąĖ Compare Match, ąŠčćąĖčüčéą║ą░ ą┐čĆąĖ TCNT4=0x000 |

ą¤ąŠą┤ą║ą╗čÄč湥ąĮ |

ą×čéą║ą╗čÄč湥ąĮ |

ąóą░ą▒ą╗ąĖčåą░ 15-7 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī ą▒ąĖčé COM4A1:0, ą║ąŠą│ą┤ą░ ą▒ąĖčéčŗ PWM4A, WGM40 ąĖ WGM41 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ čĆąĄąČąĖą╝ Phase and Frequency Correct PWM.

ąóą░ą▒ą╗ąĖčåą░ 15-7. Compare Output Mode, Phase and Frequency Correct PWM Mode.

| COM4A1 |

COM4A0 |

ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ OCW4A |

ąÆčŗą▓. OC4A |

ąÆčŗą▓. ~OC4A |