|

ąæą░ąĘąŠą▓ąŠąĄ čĆą░čüčłąĖčĆąĄąĮąĮąŠąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ CAN (Basic Extended CAN, ą║ąŠč鹊čĆąŠąĄ čüąŠą║čĆą░čēąĄąĮąĮąŠ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ bxCAN), ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī MCU STM32 čü čüąĄčéąĖ CAN. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ CAN ą┐čĆąŠč鹊ą║ąŠą╗čŗ ą▓ąĄčĆčüąĖą╣ 2.0A ąĖ 2.0B. ąÜąŠąĮčéčĆąŠą╗ąĄčĆ CAN ą▒čŗą╗ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ ą┤ą╗čÅ čŹčäč乥ą║čéąĖą▓ąĮąŠą│ąŠ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖčÅ ą▒ąŠą╗čīčłąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▓čģąŠą┤čÅčēąĖčģ čüąŠąŠą▒čēąĄąĮąĖą╣ čü ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ ąĮą░ą│čĆčāąĘą║ąŠą╣ ąĮą░ ą▓čŗčćąĖčüą╗ąĖč鹥ą╗čīąĮąŠąĄ čÅą┤čĆąŠ CPU. ąóą░ą║ąČąĄ ąŠąĮ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅąĄčé čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąŠąŠą▒čēąĄąĮąĖą╣.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ (ą┐ąĄčĆąĄą▓ąŠą┤ čĆą░ąĘą┤ąĄą╗ą░ "32 Controller area network (bxCAN)" ą┤ą░čéą░čłąĖčéą░ [1]) ąŠčéąĮąŠčüąĖčéčüčÅ ą║ąŠ ą▓čüąĄą╝ ą┐čĆąĄą┤čüčéą░ą▓ąĖč鹥ą╗čÅą╝ MCU čüąĄą╝ąĄą╣čüčéą▓ą░ STM32F4xx, ąĄčüą╗ąĖ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ čćč鹊-č鹊 ąĖąĮąŠąĄ.

ąÆ ą║čĆąĖčéąĖč湥čüą║ąĖ ą▓ą░ąČąĮčŗčģ ą┤ą╗čÅ ą▒ąĄąĘąŠą┐ą░čüąĮąŠčüčéąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą▓čüąĄ ą░ą┐ą┐ą░čĆą░čéąĮčŗąĄ čäčāąĮą║čåąĖąĖ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ąŠą┐čåąĖąĖ ąŠą▒ą╝ąĄąĮą░ CAN Time Triggered Communication.

ą×čüąĮąŠą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ bxCAN:

ŌĆó ąśą╝ąĄąĄčéčüčÅ ą┤ą▓ą░ ąĖąĮč鹥čĆč乥ą╣čüą░ CAN: CAN1 ąĖ CAN2.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą┐čĆąŠč鹊ą║ąŠą╗ CAN ą▓ąĄčĆčüąĖą╣ 2.0A, B Active.

ŌĆó ąĪą║ąŠčĆąŠčüčéąĖ ą┤ąŠ 1 ą╝ąĄą│ą░ą▒ąĖčé/čüąĄą║.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąŠą┐čåąĖčÅ Time Triggered Communication.

ą¤ąĄčĆąĄą┤ą░čćą░:

ŌĆó 3 ą┐ąĄčĆąĄą┤ą░čÄčēąĖčģ mailbox.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗą╣ ą┐čĆąĖąŠčĆąĖč鹥čé ą┐ąĄčĆąĄą┤ą░čćąĖ.

ŌĆó ą£ąĄčéą║ą░ ą▓čĆąĄą╝ąĄąĮąĖ (Time Stamp) ąĮą░ ą┐ąĄčĆąĄą┤ą░č湥 SOF.

ą¤čĆąĖąĄą╝:

ŌĆó 2 ą┐čĆąĖąĮąĖą╝ą░čÄčēąĖčģ FIFO čü čéčĆąĄą╝čÅ čāčĆąŠą▓ąĮčÅą╝ąĖ.

ŌĆó ą£ą░čüčłčéą░ą▒ąĖčĆčāąĄą╝čŗąĄ ą▒ą░ąĮą║ąĖ čäąĖą╗čīčéčĆą░: 28 ą▒ą░ąĮą║ąŠą▓ čäąĖą╗čīčéčĆą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ čüąŠą▓ą╝ąĄčüčéąĮąŠ CAN1 ąĖ CAN2.

ŌĆó ążčāąĮą║čåąĖčÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ čüą┐ąĖčüą║ą░.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗą╣ ą┐ąŠčĆąŠą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ FIFO (FIFO overrun).

ŌĆó ą£ąĄčéą║ą░ ą▓čĆąĄą╝ąĄąĮąĖ (Time Stamp) ąĮą░ ą┐čĆąĖąĄą╝ąĄ SOF.

ą×ą┐čåąĖčÅ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ Time-triggered:

ŌĆó ąŚą░ą┐čĆąĄčé čĆąĄąČąĖą╝ą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ čĆąĄčéčĆą░ąĮčüą╝ąĖčüčüąĖąĖ.

ŌĆó 16-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čüą▓ąŠą▒ąŠą┤ąĮąŠ čüčćąĖčéą░čÄčēąĖą╣ čéą░ą╣ą╝ąĄčĆ.

ŌĆó ą£ąĄčéą║ą░ ą▓čĆąĄą╝ąĄąĮąĖ (Time Stamp) ą▓ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ ą┤ą▓čāčģ ą▒ą░ą╣čéą░čģ ą┤ą░ąĮąĮčŗčģ.

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ:

ŌĆó ą£ą░čüą║ąĖčĆčāąĄą╝čŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó ąŁčäč乥ą║čéąĖą▓ąĮąŠąĄ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ mailbox ąĮą░ čāąĮąĖą║ą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü.

ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮą░čÅ čĆą░ą▒ąŠčéą░ ą┤ą▓čāčģ CAN (Dual CAN):

ŌĆó CAN1: Master bxCAN ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĄą╣ ą╝ąĄąČą┤čā Slave bxCAN ąĖ 512 ą▒ą░ą╣čéą░ą╝ąĖ ą┐ą░ą╝čÅčéąĖ SRAM.

ŌĆó CAN2: Slave bxCAN, ą▒ąĄąĘ ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ SRAM.

ŌĆó ąöą▓ą░ bxCAN ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą▒čēčāčÄ ą┐ą░ą╝čÅčéčī 512 ą▒ą░ą╣čé SRAM (čüą╝. čĆąĖčü. 335).

ąĀąĖčü. 335. ąæą╗ąŠą║-čüčģąĄą╝ą░ Dual CAN.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĮą░čćą░ą╗čīąĮčŗą╣ ą▒ą░ąĮą║ čäąĖą╗čīčéčĆąŠą▓ CAN2 ąĮąŠą╝ąĄčĆ n ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ CAN2SB[5:0] ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_FMR.

[ą×ą▒čēąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ bxCAN]

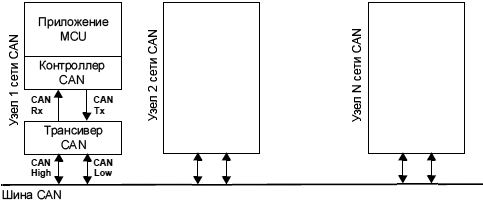

ąÆ čüąŠą▓čĆąĄą╝ąĄąĮąĮčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ CAN ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čāąĘą╗ąŠą▓ čüąĄčéąĖ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ, ąĖ čćą░čüč鹊 čüąĄčéąĖ čüąŠąĄą┤ąĖąĮčÅčÄčéčüčÅ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ č湥čĆąĄąĘ čłą╗čÄąĘčŗ (gateway). ą×ą▒čŗčćąĮąŠ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čüąŠąŠą▒čēąĄąĮąĖą╣ ą▓ čüąĖčüč鹥ą╝ąĄ (ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄą╝čŗčģ ą║ą░ąČą┤čŗą╝ čāąĘą╗ąŠą╝) ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ. ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ čüąŠąŠą▒čēąĄąĮąĖčÅą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą▒čŗą╗ąĖ ą▓ą▓ąĄą┤ąĄąĮčŗ čüąŠąŠą▒čēąĄąĮąĖčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüąĄčéčīčÄ ąĖ ą┤ąĖą░ą│ąĮąŠčüčéąĖą║ąĖ (Network Management and Diagnostic messages).

ŌĆó ąöą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą║ą░ąČą┤ąŠą│ąŠ čéąĖą┐ą░ čüąŠąŠą▒čēąĄąĮąĖčÅ čéčĆąĄą▒čāąĄčéčüčÅ čĆą░čüčłąĖčĆąĄąĮąĮčŗą╣ ą╝ąĄčģą░ąĮąĖąĘą╝ čäąĖą╗čīčéčĆą░čåąĖąĖ.

ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ąĘą░ą┤ą░čćąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ čéčĆąĄą▒čāčÄčé ą▒ąŠą╗čīčłąĄą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ CPU, ą┐ąŠčŹč鹊ą╝čā ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāą╝ąĄąĮčīčłąĄąĮčŗ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ą┐ąŠ čĆąĄą░ą╗čīąĮąŠą╝čā ą▓čĆąĄą╝ąĄąĮąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ, ą▓čŗąĘą▓ą░ąĮąĮčŗąĄ ą┐čĆąĖąĄą╝ąŠą╝ čüąŠąŠą▒čēąĄąĮąĖčÅ.

ŌĆó ąĪčģąĄą╝ą░ FIFO ą┐čĆąĖąĄą╝ą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčī CPU ąĮą░ ąĘą░ą┤ą░čćąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĮą░ ą┤ąŠą╗ą│ąŠąĄ ą▓čĆąĄą╝čÅ ą▒ąĄąĘ ą┐ąŠč鹥čĆąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ čüąŠąŠą▒čēąĄąĮąĖą╣.

ąĪčéą░ąĮą┤ą░čĆčéąĮčŗą╣ ą▓čŗčüąŠą║ąŠčāčĆąŠą▓ąĮąĄą▓čŗą╣ ą┐čĆąŠč鹊ą║ąŠą╗ HLP (ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆą░ ąŠčé Higher Layer Protocol), ąŠčüąĮąŠą▓ą░ąĮąĮčŗą╣ ąĮą░ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ą┤čĆą░ą╣ą▓ąĄčĆą░čģ CAN, čéčĆąĄą▒čāąĄčé čŹčäč乥ą║čéąĖą▓ąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ čü ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ CAN.

ąĀąĖčü. 334. ąóąŠą┐ąŠą╗ąŠą│ąĖčÅ čüąĄčéąĖ CAN.

ąÉą║čéąĖą▓ąĮąŠąĄ čÅą┤čĆąŠ CAN 2.0B. ą£ąŠą┤čāą╗čī bxCAN ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą░ą▓č鹊ąĮąŠą╝ąĮąŠ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ąĖ ą┐čĆąĖąĄą╝ čüąŠąŠą▒čēąĄąĮąĖą╣ CAN. ąĪčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčŗ (11 ą▒ąĖčé) ąĖ čĆą░čüčłąĖčĆąĄąĮąĮčŗąĄ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčŗ (29 ą▒ąĖčé) ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

ąĀąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, čüčéą░čéčāčüą░ ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. ą¤čĆąĖą╗ąŠąČąĄąĮąĖąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčé čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĖčģ čåąĄą╗ąĄą╣:

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ CAN, ąĮą░ą┐čĆąĖą╝ąĄčĆ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ/ą┐čĆąĖąĄą╝ą░ (baud rate).

ŌĆó ąŚą░ą┐čĆąŠčü ą┐ąĄčĆąĄą┤ą░čć.

ŌĆó ą×ą▒čĆą░ą▒ąŠčéą║ą░ ą┐čĆąĖąĄą╝ą░.

ŌĆó ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ.

ŌĆó ą¤ąŠą╗čāč湥ąĮąĖąĄ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┤ąĖą░ą│ąĮąŠčüčéąĖą║ąĖ.

ą¤ąĄčĆąĄą┤ą░čÄčēąĖąĄ čÅčēąĖą║ąĖ (Tx mailboxes). ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮčŗ 3 ą┐ąĄčĆąĄą┤ą░čÄčēąĖčģ mailbox, čćč鹊ą▒čŗ ąĮą░čüčéčĆą░ąĖą▓ą░čéčī ąŠčéą┐čĆą░ą▓ą║čā čüąŠąŠą▒čēąĄąĮąĖą╣. ą¤ą╗ą░ąĮąĖčĆąŠą▓čēąĖą║ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmission Scheduler) ą┐čĆąĖąĮąĖą╝ą░ąĄčé čĆąĄčłąĄąĮąĖąĄ, ą║ą░ą║ąŠą╣ mailbox ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮ ą┐ąĄčĆą▓čŗą╝.

ążąĖą╗čīčéčĆčŗ ą┐čĆąĖąĄą╝ą░ (Acceptance filters). bxCAN ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé 28 ą╝ą░čüčłčéą░ą▒ąĖčĆčāąĄą╝čŗčģ / ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗčģ ą▒ą░ąĮą║ąŠą▓ čäąĖą╗čīčéčĆąŠą▓ ą┐ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā, čćč鹊ą▒čŗ ą▓čŗą┤ąĄą╗čÅčéčī ąĖąĘ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ ąĮčāąČąĮčŗąĄ čüąŠąŠą▒čēąĄąĮąĖčÅ ąĖ ąŠčéą▒čĆą░čüčŗą▓ą░čéčī ą┤čĆčāą│ąĖąĄ.

FIFO ą┐čĆąĖąĄą╝ą░. ąöą╗čÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ ą┐ąŠčüčéčāą┐ą░čÄčēąĖčģ čüąŠąŠą▒čēąĄąĮąĖą╣ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ 2 ą┐čĆąĖąĄą╝ąĮčŗčģ FIFO. ąÆ ą║ą░ąČą┤ąŠą╝ FIFO ą╝ąŠąČąĮąŠ čüąŠčģčĆą░ąĮąĖčéčī 3 ą┐ąŠą╗ąĮčŗčģ čüąŠąŠą▒čēąĄąĮąĖčÅ. FIFO ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąŠą▒čüą╗čāąČąĖą▓ą░čÄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ CAN.

[ąĀą░ą▒ąŠčćąĖąĄ čĆąĄąČąĖą╝čŗ bxCAN]

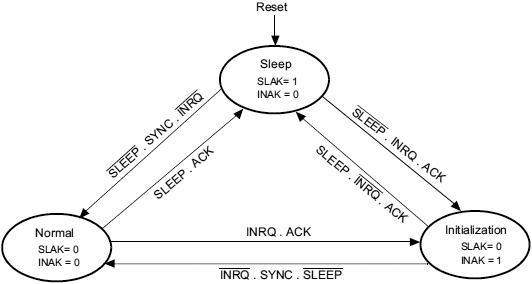

ąŻ bxCAN ąĄčüčéčī 3 ąŠčüąĮąŠą▓ąĮčŗčģ čĆą░ą▒ąŠčćąĖčģ čĆąĄąČąĖą╝ą░: initialization (ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ), normal (ą░ą║čéąĖą▓ąĮą░čÅ čĆą░ą▒ąŠčéą░) ąĖ Sleep (čüąŠąĮ, ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ą░). ą¤ąŠčüą╗ąĄ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čüą▒čĆąŠčüą░ bxCAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Sleep, čćč鹊ą▒čŗ čüąĮąĖąĘąĖčéčī ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ 菹ĮąĄčĆą│ąĖąĖ, ąĖ ąĮą░ CANTX ą░ą║čéąĖą▓ąĄąĮ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ pull-up (ą▓ąĄčĆčģąĮąĖą╣ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖą╣ čĆąĄąĘąĖčüč鹊čĆ). ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄčé bxCAN ąĮą░ ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ initialization ąĖą╗ąĖ Sleep čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé INRQ ąĖą╗ąĖ SLEEP ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCR. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝, bxCAN ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčé čŹč鹊 čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé INAK ąĖą╗ąĖ SLAK ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MSR, ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ pull-up ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ. ąÜąŠą│ą┤ą░ ąĮąĖ ąŠą┤ąĖąĮ ąĖąĘ ą▒ąĖčé INAK ąĖ SLAK ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, bxCAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ normal. ą¤ąĄčĆąĄą┤ ą▓čģąŠą┤ąŠą╝ ą▓ čĆąĄąČąĖą╝ normal bxCAN ą▓čüąĄą│ą┤ą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮ čü čłąĖąĮąŠą╣ CAN. ąöą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ bxCAN ąČą┤ąĄčé, ą┐ąŠą║ą░ čłąĖąĮą░ CAN ąĮąĄ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ (ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ idle), čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąŠčéčüą╗ąĄąČąĖą▓ą░ąĄčéčüčÅ ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄ 11 čüą╗ąĄą┤čāčÄčēąĖčģ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ čĆąĄčåąĄčüčüąĖą▓ąĮčŗčģ ą▒ąĖčéą░ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ CANRX.

ąĀąĄąČąĖą╝ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮą░čÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮą░, ą║ąŠą│ą┤ą░ ąČąĄą╗ąĄąĘąŠ CAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ (Initialization mode). ą¦č鹊ą▒čŗ ą▓ąŠą╣čéąĖ ą▓ čŹč鹊čé čĆąĄąČąĖą╝, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▒ąĖčé INRQ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCR ąĖ ąČą┤ąĄčé, ą┐ąŠą║ą░ ąČąĄą╗ąĄąĘąŠ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčé čŹč鹊čé ąĘą░ą┐čĆąŠčü čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ INAK ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ CAN_MSR.

ą¦č鹊ą▒čŗ ą┐ąŠą║ąĖąĮčāčéčī čĆąĄąČąĖą╝ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąŠčćąĖčēą░ąĄčé ą▒ąĖčé INQR. bxCAN ą┐ąŠą║ąĖąĮąĄčé čĆąĄąČąĖą╝ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ, ą║ąŠą│ą┤ą░ ą▒ąĖčé INAK ąŠčćąĖčüčéąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣.

ąÆąŠ ą▓čĆąĄą╝čÅ čĆąĄąČąĖą╝ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą▓čüąĄ ą▓čģąŠą┤čÅčēąĖąĄ ąĖ ąĖčüčģąŠą┤čÅčēąĖąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ čüąŠąŠą▒čēąĄąĮąĖą╣ CAN, ąĖ čüčéą░čéčāčü čłąĖąĮčŗ CAN ąĮą░ ą▓čŗčģąŠą┤ąĄ CANTX čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ čĆąĄčåąĄčüčüąĖą▓ąĮčŗą╝ (ą╗ąŠą│. 1).

ąÆčģąŠą┤ ą▓ čĆąĄąČąĖą╝ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ąĮąĄ ą╝ąĄąĮčÅąĄčé ąĮąĖ ąŠą┤ąĖąĮ čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

ą¦č鹊ą▒čŗ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ čāčüčéą░ąĮąŠą▓ąĖčéčī ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą▒ąĖčéą░ (Bit Timing, čĆąĄą│ąĖčüčéčĆ CAN_BTR) ąĖ ąŠą┐čåąĖąĖ CAN (čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ CAN_MCR).

ą¦č鹊ą▒čŗ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī čĆąĄą│ąĖčüčéčĆčŗ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ą▒ą░ąĮą║ą░ą╝ąĖ čäąĖą╗čīčéčĆąŠą▓ CAN (mode, scale, FIFO assignment, activation ąĖ ąĘąĮą░č湥ąĮąĖčÅ čäąĖą╗čīčéčĆą░and filter values), ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčé FINIT (ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_FMR). ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ čäąĖą╗čīčéčĆą░ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮą░ ą▓ąĮąĄ čĆąĄąČąĖą╝ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ FINIT=1, ą┐čĆąĖąĄą╝ CAN ą┤ąĄą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ. ąŚąĮą░č湥ąĮąĖčÅ čäąĖą╗čīčéčĆą░ čéą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░čéčī čüą▒čĆąŠčüąŠą╝ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą▒ąĖčé ą░ą║čéąĖą▓ą░čåąĖąĖ (ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_FA1R). ąĢčüą╗ąĖ ą▒ą░ąĮą║ čäąĖą╗čīčéčĆą░ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, č鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąŠčüčéą░ą▓ąĖčéčī ąĄą│ąŠ ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (čé. ąĄ. ąŠčüčéą░ą▓ąĖčéčī ąĄą│ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé FACTx ąŠčćąĖčēąĄąĮąĮčŗą╝).

ąØąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ (normal mode). ąÜą░ą║ č鹊ą╗čīą║ąŠ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ąĘą░ą▓ąĄčĆčłąĄąĮą░, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąĘą░ą┐čĆąŠčüąĖčéčī čā ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ ą▓čģąŠą┤ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝, čćč鹊ą▒čŗ ąŠąĮą░ ą╝ąŠą│ą╗ą░ ąĘą░čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčīčüčÅ čü čłąĖąĮąŠą╣ CAN, ąĖ ąĮą░čćą░čéčī ą┐čĆąĖąĄą╝ ąĖ ą┐ąĄčĆąĄą┤ą░čćčā.

ąŚą░ą┐čĆąŠčü ą▓čģąŠą┤ą░ ą▓ Normal mode ą▓čŗą┤ą░ąĄčéčüčÅ ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ INRQ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ CAN_MCR. ąæą╗ąŠą║ bxCAN ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ Normal ąĖ ą│ąŠč鹊ą▓ ą┐čĆąĖąĮčÅčéčī čāčćą░čüčéąĖąĄ ą▓ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ąĮą░ čłąĖąĮąĄ, ą║ąŠą│ą┤ą░ ąŠąĮ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮ čü ą┐ąĄčĆąĄą┤ą░č湥ą╣ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ čłąĖąĮąĄ CAN. ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąŠąČąĖą┤ą░ąĮąĖąĄą╝ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ ąĮą░ čłąĖąĮąĄ 11 čüą╗ąĄą┤čāčÄčēąĖčģ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ čĆąĄčåąĄčüčüąĖą▓ąĮčŗčģ ą▒ąĖčé (čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ Bus Idle). ą¤ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ Normal mode ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣, ą║ąŠą│ą┤ą░ ąŠąĮą░ čüą▒čĆą░čüčŗą▓ą░ąĄčé ą▒ąĖčé INAK ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ CAN_MSR.

ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ąĘąĮą░č湥ąĮąĖą╣ čäąĖą╗čīčéčĆą░ ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé čĆąĄąČąĖą╝ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ, ąŠą┤ąĮą░ą║ąŠ ą┤ąŠą╗ąČąĮą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčīčüčÅ, ą║ąŠą│ą┤ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄą╝čŗą╣ čäąĖą╗čīčéčĆ ąĮąĄ ą░ą║čéąĖą▓ąĄąĮ (ąĄą│ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé FACTx čüą▒čĆąŠčłąĄąĮ). ą¤ą░čĆą░ą╝ąĄčéčĆčŗ čäąĖą╗čīčéčĆą░ scale ąĖ mode ą┤ąŠą╗ąČąĮčŗ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą┐ąĄčĆąĄą┤ ą▓čģąŠą┤ąŠą╝ ą▓ čĆąĄąČąĖą╝ Normal.

ąĀąĄąČąĖą╝ Sleep (ą╝ą░ą╗ąŠąĄ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą╝ąŠčēąĮąŠčüčéąĖ). ą¦č鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ, čā bxCAN ąĄčüčéčī čĆąĄąČąĖą╝ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą╝ąŠčēąĮąŠčüčéąĖ (low-power mode), ą║ąŠč鹊čĆčŗą╣ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ čĆąĄąČąĖą╝ čüąĮą░ (Sleep mode). ąÆ čŹč鹊čé čĆąĄąČąĖą╝ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą▓čģąŠą┤ ą┐ąŠ ąĘą░ą┐čĆąŠčüčā ą┐čĆąŠą│čĆą░ą╝ą╝čŗ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SLEEP ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCR. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ bxCAN ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ąŠą┤ąĮą░ą║ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą▓čüąĄ ąĄčēąĄ ąĖą╝ąĄąĄčé ą┤ąŠčüčéčāą┐ ą║ čÅčēąĖą║ą░ą╝ (mailboxes) bxCAN.

ąĢčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄčé ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ INRQ, ą║ąŠą│ą┤ą░ bxCAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ Sleep mode, ąŠąĮą░ čéą░ą║ąČąĄ ą┤ąŠą╗ąČąĮą░ ąŠčćąĖčüčéąĖčéčī ą▒ąĖčé SLEEP.

ąæą╗ąŠą║ bxCAN ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘą▒čāąČąĄąĮ (ą▓čŗą▓ąĄą┤ąĄąĮ ąĖąĘ Sleep mode) ą╗ąĖą▒ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ SLEEP, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ą▒čŗą╗ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮą░ ą░ą║čéąĖą▓ąĮąŠčüčéčī čłąĖąĮčŗ CAN.

ąÜąŠą│ą┤ą░ ą▒čŗą╗ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą░ą║čéąĖą▓ąĮąŠčüčéčī ąĮą░ čłąĖąĮąĄ CAN, ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ SLEEP, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé AWUM ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCR. ąĢčüą╗ąĖ ą▒ąĖčé AWUM ąŠčćąĖčēąĄąĮ, č鹊 ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąŠčćąĖčüčéąĖčéčī ą▒ąĖčé SLEEP, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ (wakeup interrupt), čćč鹊ą▒čŗ bxCAN ą▓čŗčłąĄą╗ ąĖąĘ Sleep mode.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ (wakeup interrupt, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé WKUIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_IER), č鹊 ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą▒čŗą╗ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą░ą║čéąĖą▓ąĮąŠčüčéčī čłąĖąĮčŗ CAN, ą┤ą░ąČąĄ ąĄčüą╗ąĖ bxCAN ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒ąĖčé SLEEP ą▒čŗą╗ ąŠčćąĖčēąĄąĮ, ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą▓čŗčģąŠą┤ ąĖąĘ Sleep mode, ą║ąŠą│ą┤ą░ bxCAN ąĘą░čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ą╗čüčÅ čü čłąĖąĮąŠą╣ CAN, čüą╝. čĆąĖčü. 336. ąśąĘ čĆąĄąČąĖą╝ą░ Sleep mode ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą▓čŗčģąŠą┤, ą║ąŠą│ą┤ą░ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ąŠčćąĖčüčéąĖą╗ą░ ą▒ąĖčé SLAK.

ąĀąĖčü. 336. ąĀąĄąČąĖą╝čŗ bxCAN.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ACK = čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ (wait state), ą▓ąŠ ą▓čĆąĄą╝čÅ ą║ąŠč鹊čĆąŠą│ąŠ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčé ąĘą░ą┐čĆąŠčü čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé INAK ąĖą╗ąĖ SLAK ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MSR.

(2) SYNC = čüąŠčüč鹊čÅąĮąĖąĄ, ą▓ąŠ ą▓čĆąĄą╝čÅ ą║ąŠč鹊čĆąŠą│ąŠ bxCAN ąŠąČąĖą┤ą░ąĄčé čüąŠčüč鹊čÅąĮąĖčÅ ąŠąČąĖą┤ą░ąĮąĖčÅ čłąĖąĮčŗ CAN (idle state, ą║ąŠą│ą┤ą░ ą┐čĆąŠčłą╗ąŠ 11 čüą╗ąĄą┤čāčÄčēąĖčģ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ čĆąĄčåąĄčüčüąĖą▓ąĮčŗčģ ą▒ąĖčéą░ ąĮą░ CANRX).

[ąĀąĄąČąĖą╝ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ]

ąĀąĄąČąĖą╝ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ą▒ąĖčéą░ą╝ąĖ SILM ąĖ LBKM ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_BTR. ąŁčéąĖ ą▒ąĖčéčŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ, ą║ąŠą│ą┤ą░ bxCAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ Initialization mode. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▒čŗą╗ ą▓čŗą▒čĆą░ąĮ čĆąĄąČąĖą╝ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ, ą┤ą╗čÅ ą▓čģąŠą┤ą░ ą▓ čĆąĄąČąĖą╝ Normal ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą▒ąĖčé INRQ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCR.

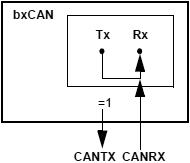

Silent mode. ąæą╗ąŠą║ bxCAN ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ "čéąĖčģąĖą╣ čĆąĄąČąĖą╝" (Silent mode) čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SILM ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_BTR.

ąÆ čéąĖčģąŠą╝ čĆąĄąČąĖą╝ąĄ bxCAN ą╝ąŠąČąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī ą┐čĆą░ą▓ąĖą╗čīąĮčŗąĄ čäčĆąĄą╣ą╝čŗ ą┤ą░ąĮąĮčŗčģ ąĖ ą┐čĆą░ą▓ąĖą╗čīąĮčŗąĄ čäčĆąĄą╣ą╝čŗ remote, ąŠą┤ąĮą░ą║ąŠ bxCAN ą┐ąĄčĆąĄą┤ą░ąĄčé č鹊ą╗čīą║ąŠ čĆąĄčåąĄčüčüąĖą▓ąĮčŗąĄ ą▒ąĖčéčŗ ąĮą░ čłąĖąĮąĄ CAN, ąĖ ąĮąĄ ą╝ąŠąČąĄčé ąĮą░čćą░čéčī ą┐ąĄčĆąĄą┤ą░čćčā. ąĢčüą╗ąĖ bxCAN ą┤ąŠą╗ąČąĄąĮ ąŠčéą┐čĆą░ą▓ąĖčéčī ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╣ ą▒ąĖčé (ą▒ąĖčé ACK, čäą╗ą░ą│ overload, čäą╗ą░ą│ active error), č鹊 ą▒ąĖčé ą┐ąĄčĆąĄą╝ą░čłčĆčāčéąĖąĘąĖčĆčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊 čÅą┤čĆąŠ CAN ą╝ąŠąĮąĖč鹊čĆąĖčé čŹč鹊čé ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╣ ą▒ąĖčé, čģąŠčéčÅ čłąĖąĮą░ CAN ą╝ąŠąČąĄčé ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ čĆąĄčåąĄčüčüąĖą▓ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ. Silent mode ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą░ąĮą░ą╗ąĖąĘą░ čéčĆą░čäąĖą║ą░ ąĮą░ čłąĖąĮąĄ CAN ą▒ąĄąĘ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čłąĖąĮčā ą┐ąĄčĆąĄą┤ą░č湥ą╣ ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗčģ ą▒ąĖčé (ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗąĄ ą▒ąĖčéčŗ Acknowledge, čäčĆąĄą╣ą╝čŗ ąŠčłąĖą▒ą║ąĖ Error Frame čäąĖąĘąĖč湥čüą║ąĖ ąĮąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ).

ąĀąĖčü. 337. ąæą╗ąŠą║ bxCAN ą▓ Silent Mode.

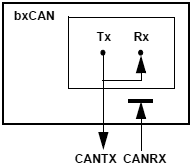

Loop back mode. ąæą╗ąŠą║ bxCAN ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ čĆąĄąČąĖą╝ ąĘą░čåąĖą║ą╗ąĖą▓ą░ąĮąĖčÅ (Loop Back Mode) čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ LBKM ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_BTR. ąÆ Loop Back Mode ą▒ą╗ąŠą║ bxCAN ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé čüą▓ąŠąĖ čüąŠą▒čüčéą▓ąĄąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ čüąŠąŠą▒čēąĄąĮąĖčÅ ą║ą░ą║ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗąĄ, ąĖ čüąŠčģčĆą░ąĮčÅąĄčé ąĖčģ (ąĄčüą╗ąĖ ąŠąĮąĖ ą┐čĆąŠčłą╗ąĖ čäąĖą╗čīčéčĆą░čåąĖčÄ, acceptance filtering) ą▓ čÅčēąĖą║ą░čģ ą┐čĆąĖąĄą╝ą░ (Receive mailbox).

ąĀąĖčü. 338. ąæą╗ąŠą║ bxCAN ą▓ čĆąĄąČąĖą╝ąĄ ąĘą░čåąĖą║ą╗ąĖą▓ą░ąĮąĖčÅ.

ąŁč鹊čé čĆąĄąČąĖą╝ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮ ą┤ą╗čÅ čäčāąĮą║čåąĖą╣ čüą░ą╝ąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ. ą¦č鹊ą▒čŗ ą▒čŗčéčī ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╝ ąŠčé ą▓ąĮąĄčłąĮąĖčģ čüąŠą▒čŗčéąĖą╣, čÅą┤čĆąŠ CAN ąĖą│ąĮąŠčĆąĖčĆčāąĄčé ąŠčłąĖą▒ą║ąĖ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ (acknowledge errors, ąŠčéčüčāčéčüčéą▓ąĖąĄ ą┤ąŠą╝ąĖąĮą░ąĮčéąĮąŠą│ąŠ ą▒ąĖčéą░, ąŠčåąĖčäčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą▓ čüą╗ąŠč鹥 ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ čäčĆąĄą╣ą╝ą░ data / remote), ą▓ čĆąĄąČąĖą╝ąĄ Loop Back. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ bxCAN čüąŠąĄą┤ąĖąĮčÅąĄčé ą▓čŗčģąŠą┤ Tx čüąŠ ą▓čģąŠą┤ąŠą╝ Rx ą▓ąĮčāčéčĆąĖ čćąĖą┐ą░. ąÉą║čéčāą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓čģąŠą┤ą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ CANRX ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ ą▒ą╗ąŠą║ąŠą╝ bxCAN. ą¤ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ čüąŠąŠą▒čēąĄąĮąĖčÅ ą╝ąŠą│čāčé ą╝ąŠąĮąĖč鹊čĆąĖčéčīčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ CANTX.

ąÜąŠą╝ą▒ąĖąĮą░čåąĖčÅ čĆąĄąČąĖą╝ąŠą▓ Loop back ąĖ silent. ą£ąŠąČąĮąŠ čéą░ą║ąČąĄ čüą║ąŠą╝ą▒ąĖąĮąĖčĆąŠą▓ą░čéčī čĆąĄąČąĖą╝čŗ Loop Back ąĖ Silent čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé LBKM ąĖ SILM ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_BTR. ąŁč鹊 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ "ą│ąŠčĆčÅč湥ą│ąŠ čüą░ą╝ąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ", čé. ąĄ. bxCAN ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠą▓ąĄčĆąĄąĮ ą▓ čĆąĄąČąĖą╝ąĄ Loop Back, ąĮąŠ ą▒ąĄąĘ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čĆą░ą▒ąŠčéą░čÄčēčāčÄ čüąĖčüč鹥ą╝čā CAN, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčāčÄ ą║ ą▓čŗą▓ąŠą┤ą░ą╝ CANTX ąĖ CANRX. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą▓čŗą▓ąŠą┤ CANRX ąŠčéą║ą╗čÄč湥ąĮ ąŠčé bxCAN, ąĖ ą▓čŗą▓ąŠą┤ CANTX čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ čĆąĄčåąĄčüčüąĖą▓ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ.

ąĀąĖčü. 339. ąæą╗ąŠą║ bxCAN ą▓ ą║ąŠą╝ą▒ąĖąĮąĖčĆąŠą▓ą░ąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ.

[Debug mode]

ąÜąŠą│ą┤ą░ MCU ą▓ąŠčłąĄą╗ ą▓ ąŠčéą╗ą░ą┤ąŠčćąĮčŗą╣ čĆąĄąČąĖą╝ debug mode (ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ čÅą┤čĆąŠ Cortex┬«-M4 čü FPU), ą▒ą╗ąŠą║ bxCAN ą┐čĆąŠą┤ąŠą╗ąČąĖčé ąĮąŠčĆą╝ą░ą╗čīąĮąŠ čĆą░ą▒ąŠčéą░čéčī ąĖą╗ąĖ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé:

ŌĆó ąæąĖčéą░ DBG_CAN1_STOP ą┤ą╗čÅ CAN1 ąĖą╗ąĖ ą▒ąĖčéą░ DBG_CAN2_STOP ą┤ą╗čÅ CAN2 ą▓ ą╝ąŠą┤čāą╗ąĄ DBG. ąöą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüč鹥ą╣ čüą╝. čüąĄą║čåąĖčÄ "38.16.2 Debug support for timers, watchdog, bxCAN and I2C" ą┤ą░čéą░čłąĖčéą░ [1].

ŌĆó ąæąĖčéą░ DBF ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCR. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. čüąĄą║čåąĖčÄ 32.9.2 ą┤ą░čéą░čłąĖčéą░ [1].

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ bxCAN]

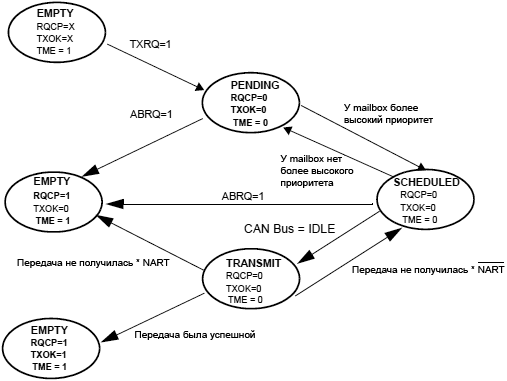

ą×ą▒čĆą░ą▒ąŠčéą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą¦č鹊ą▒čŗ ą┐ąĄčĆąĄą┤ą░čéčī čüąŠąŠą▒čēąĄąĮąĖąĄ, ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą▓čŗą▒čĆą░čéčī ą┐čāčüč鹊ą╣ transmit mailbox, čāčüčéą░ąĮąŠą▓ąĖčéčī ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ, ą║ąŠą┤ ą┤ą╗ąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ (data length code, DLC) ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ąĘą░ą┐čĆąŠčüąĖčéčī ą┐ąĄčĆąĄą┤ą░čćčā čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ TXRQ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TIxR. ąÜą░ą║ č鹊ą╗čīą║ąŠ mailbox ą┐ąŠą║ąĖąĮčāą╗ čüąŠčüč鹊čÅąĮąĖąĄ ąŠą┐čāčüč鹊賹ĄąĮąĮąŠčüčéąĖ (empty state), ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą▒ąŠą╗čīčłąĄ ąĮąĄ ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓ ąĄą│ąŠ čĆąĄą│ąĖčüčéčĆčŗ. ąĪčĆą░ąĘčā ą┐ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ TXRQ mailbox ą▓čģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ ąŠčéą┐čĆą░ą▓ą║ąĖ (enters pending), ąĖ ąČą┤ąĄčé, ą║ąŠą│ą┤ą░ ąŠąĮ čüčéą░ąĮąĄčé čüą░ą╝čŗą╝ ą┐čĆąĖąŠčĆąĖč鹥čéąĮčŗą╝ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, čüą╝. ą▓čĆąĄąĘą║čā "ą¤čĆąĖąŠčĆąĖč鹥čé ą┐ąĄčĆąĄą┤ą░čćąĖ". ąÜą░ą║ č鹊ą╗čīą║ąŠ mailbox ą┐ąŠą╗čāčćąĖą╗ čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé, ąŠąĮ ą▒čāą┤ąĄčé ąĘą░ą┐ą╗ą░ąĮąĖčĆąŠą▓ą░ąĮ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā. ą¤ąĄčĆąĄą┤ą░čćą░ čüąŠąŠą▒čēąĄąĮąĖčÅ ąĘą░ą┐ą╗ą░ąĮąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ mailbox ąĮą░čćąĮąĄčéčüčÅ (ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą▓čģąŠą┤ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ), ą║ąŠą│ą┤ą░ čłąĖąĮą░ CAN ąŠą║ą░ąČąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ (idle). ąÜą░ą║ č鹊ą╗čīą║ąŠ mailbox ą▒čŗą╗ čāčüą┐ąĄčłąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĮ, ąŠąĮ čüąĮąŠą▓ą░ čüčéą░ąĮąĄčé ą┐čāčüčéčŗą╝ (empty). ąÉą┐ą┐ą░čĆą░čéčāčĆą░ ą┐ąŠą║ą░ąČąĄčé čāčüą┐ąĄčłąĮčāčÄ ą┐ąĄčĆąĄą┤ą░čć čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé RQCP ąĖ TXOK ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TSR.

ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ą▒čŗą╗ą░ ąĮąĄčāą┤ą░čćąĮąŠą╣, č鹊 čŹč鹊 čüąŠčüč鹊čÅąĮąĖąĄ ą▒čāą┤ąĄčé ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▒ąĖč鹊ą╝ ALST ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TSR, ą║ąŠą│ą┤ą░ ą▒čŗą╗ ą┐čĆąŠąĖą│čĆčŗčł ą░čĆą▒ąĖčéčĆą░ąČą░ (Arbitration Lost), ąĖ/ąĖą╗ąĖ ą▒ąĖč鹊ą╝ TERR, ą║ąŠą│ą┤ą░ ą▒čŗą╗ą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮą░ ąŠčłąĖą▒ą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ą¤čĆąĖąŠčĆąĖč鹥čé ą┐ąĄčĆąĄą┤ą░čćąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā ąĖ ą┐ąŠ ą┐ąŠčĆčÅą┤ą║čā ąĘą░ą┐čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit request order).

ą¤ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā. ąÜąŠą│ą┤ą░ ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ transmit mailbox ąŠąČąĖą┤ą░čÄčé ą┐ąĄčĆąĄą┤ą░čćąĖ, ą┐ąŠčĆčÅą┤ąŠą║ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąŠąŠą▒čēąĄąĮąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā, čüąŠčģčĆą░ąĮąĄąĮąĮąŠą╝čā ą▓ mailbox. ąĪąŠąŠą▒čēąĄąĮąĖąĄ čü čüą░ą╝čŗą╝ ą╝ą░ą╗čŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ ąĖą╝ąĄąĄčé čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čüąŠ čüčģąĄą╝ąŠą╣ ą░čĆą▒ąĖčéčĆą░ąČą░ ą┐čĆąŠč鹊ą║ąŠą╗ą░ CAN. ąĢčüą╗ąĖ ąČąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗąĄ, č鹊 čüąĮą░čćą░ą╗ą░ ą┐ą╗ą░ąĮąĖčĆčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĖąĘ mailbox čü čüą░ą╝čŗą╝ ą╝ą░ą╗čŗą╝ ąĮąŠą╝ąĄčĆąŠą╝.

ą¤ąŠ ą┐ąŠčĆčÅą┤ą║čā ąĘą░ą┐čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą¤ąĄčĆąĄą┤ą░čÄčēąĖąĄ mailbox ą╝ąŠąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą║ą░ą║ transmit FIFO čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ TXFP ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ CAN_MCR. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąŠčĆąĖč鹥čé ą┤ą╗čÅ ą┐ąŠčĆčÅą┤ą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠ ą┐ąŠčĆčÅą┤ą║čā ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ ąĘą░ą┐čĆąŠčüąŠą▓ ąĮąĄ ą┐ąĄčĆąĄą┤ą░čćčā (č鹊čé čÅčēąĖą║, ą┤ą╗čÅ ą║ąŠč鹊čĆąŠą│ąŠ ąĘą░ą┐čĆąŠčü ą┐ąŠčüčéčāą┐ąĖą╗ čĆą░ąĮčīčłąĄ, ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ ą┐ąĄčĆą▓čŗą╝). ąŁč鹊čé čĆąĄąČąĖą╝ ąŠč湥ąĮčī ą┐ąŠą╗ąĄąĘąĄąĮ ą┤ą╗čÅ čüąĄą│ą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čć.

ą×ą▒čĆčŗą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŚą░ą┐čĆąŠčü ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą▒ąŠčĆą▓ą░ąĮ (abort) ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ ABRQ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TSR. ąÜąŠą│ą┤ą░ mailbox ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ pending ąĖą╗ąĖ scheduled ąŠą▒čĆčŗą▓ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ. ąÜąŠą│ą┤ą░ ąĘą░ą┐čĆąŠčü ąĮą░ abort ą┐ąŠčüčéčāą┐ąĖą╗ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ mailbox, č鹊 čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ąŠąČąĄčé ąĖą╝ąĄčéčī ąŠą┤ąĮąŠ ąĖąĘ 2 čĆąĄąĘčāą╗čīčéą░č鹊ą▓. ąĢčüą╗ąĖ ą▒čŗą╗ą░ čāčüą┐ąĄčłąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░, č鹊 mailbox čüčéą░ąĮąĄčé ą┐čāčüčéčŗą╝ čü čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ TXOK ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TSR. ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ą▒čŗą╗ą░ ąĮąĄčāą┤ą░čćąĮąŠą╣, č鹊 mailbox ą┐ąŠą╗čāčćąĖčé čüąŠčüč鹊čÅąĮąĖąĄ ąĘą░ą┐ą╗ą░ąĮąĖčĆąŠą▓ą░ąĮąĮąŠčüčéąĖ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā (scheduled), ą┐ąĄčĆąĄą┤ą░čćą░ ąŠą▒ąŠčĆą▓ąĄčéčüčÅ ąĖ čÅčēąĖą║ čüčéą░ąĮąĄčé ą┐čāčüčéčŗą╝ čü ąŠčćąĖčēąĄąĮąĮčŗą╝ TXOK. ąÆąŠ ą▓čüąĄčģ čüą╗čāčćą░čÅčģ čÅčēąĖą║ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐čāčüčéčŗą╝, ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą▓ ą║ąŠąĮčåąĄ č鹥ą║čāčēąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąĀąĄąČąĖą╝ ąĮąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ą┐ąŠą▓č鹊čĆąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŁč鹊čé čĆąĄąČąĖą╝ ą▒čŗą╗ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ, čćč鹊ą▒čŗ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĖčéčī čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ ąŠą┐čåąĖąĖ Time Triggered Communication čüčéą░ąĮą┤ą░čĆčéą░ CAN. ą¦č鹊ą▒čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą░ą┐ą┐ą░čĆą░čéčāčĆčā ą▓ čŹč鹊čé čĆąĄąČąĖą╝, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé NART ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCR.

ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą║ą░ąČą┤ą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠ. ąĢčüą╗ąĖ ą┐ąĄčĆą▓ą░čÅ ą┐ąŠą┐čŗčéą║ą░ ą┐ąŠč鹥čĆą┐ąĄą╗ą░ ąĮąĄčāą┤ą░čćčā ąĖąĘ-ąĘą░ ą┐ąŠč鹥čĆąĖ ą░čĆą▒ąĖčéčĆą░ąČą░ ąĖą╗ąĖ ąĖąĘ-ąĘą░ ąŠčłąĖą▒ą║ąĖ, ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ąĮąĄ ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░čéčī ą┐ąĄčĆąĄą┤ą░čćčā čüąŠąŠą▒čēąĄąĮąĖčÅ.

ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆą▓ąŠą╣ ą┐ąŠą┐čŗčéą║ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą░ą┐ą┐ą░čĆą░čéčāčĆą░ čüčćąĖčéą░ąĄčé ąĘą░ą┐čĆąŠčü ąĘą░ą▓ąĄčĆčłąĄąĮąĮčŗą╝, ąĖ čāčüčéą░ąĮąŠą▓ąĖčé ą▒ąĖčé RQCP ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TSR. ąĀąĄąĘčāą╗čīčéą░čé ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TSR ą▒ąĖčéą░ą╝ąĖ TXOK, ALST ąĖ TERR.

ąĀąĖčü. 340. ąĪąŠčüč鹊čÅąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čÄčēąĄą│ąŠ mailbox.

ąĀąĄąČąĖą╝ Time Triggered Communication. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüč湥čéčćąĖą║ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ CAN ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĘąĮą░č湥ąĮąĖčÅ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ (Time Stamp), čüąŠčģčĆą░ąĮčÅąĄą╝ąŠą╣ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ CAN_RDTxR/CAN_TDTxR (čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą┤ą╗čÅ Rx ąĖ Tx mailbox). ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ čüč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą▒ąĖč鹊ą▓ąŠą╝ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ CAN, čüą╝. ą┤ą░ą╗ąĄąĄ čüąĄą║čåąĖčÄ "ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▒ąĖčé (bit timing)". ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ čüč湥čéčćąĖą║ ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčéčüčÅ ą▓ č鹊čćą║ąĄ ąŠčåąĖčäčĆąŠą▓ą║ąĖ (sample point) ą▒ąĖčéą░ ąĮą░čćą░ą╗ą░ čäčĆąĄą╣ą╝ą░ (Start Of Frame, SOF) ąĖ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░, ąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ.

[ą×ą▒čĆą░ą▒ąŠčéą║ą░ ą┐čĆąĖąĄą╝ą░]

ąöą╗čÅ ą┐čĆąĖąĄą╝ą░ čüąŠąŠą▒čēąĄąĮąĖą╣ CAN ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčéčüčÅ čéčĆąĖ mailbox, ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮąĮčŗčģ ą║ą░ą║ FIFO. ą¦č鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī ąĮą░ą│čĆčāąĘą║čā ąĮą░ CPU, čāą┐čĆąŠčüčéąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝čā ąĖ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī čåąĄą╗ąŠčüčéąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ, FIFO ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣. ą¤čĆąĖą╗ąŠąČąĄąĮąĖąĄ ąŠą▒čĆą░čēą░ąĄčéčüčÅ ą║ čüąŠčģčĆą░ąĮąĄąĮąĮčŗą╝ ą▓ FIFO čüąŠąŠą▒čēąĄąĮąĖčÅą╝ č湥čĆąĄąĘ ą▓čŗčģąŠą┤ąĮąŠą╣ mailbox FIFO.

ąÜąŠčĆčĆąĄą║čéąĮąŠ ą┐čĆąĖąĮčÅč鹊ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ. ą¤čĆąĖąĮčÅč鹊ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ čüčćąĖčéą░ąĄčéčüčÅ ą║ąŠčĆčĆąĄą║čéąĮčŗą╝ (valid), ą║ąŠą│ą┤ą░ ąŠąĮąŠ ą▒čŗą╗ąŠ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą┐čĆąĖąĮčÅč鹊 ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┐čĆąŠč鹊ą║ąŠą╗ąŠą╝ CAN (ąĮąĄ ą▒čŗą╗ąŠ ąŠčłąĖą▒ą║ąĖ ą┤ąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ąĖčéą░, ąĮąŠ čü ąŠą┤ąĮąĖą╝ ą▒ąĖč鹊ą╝ ą▓ ą┐ąŠą╗ąĄ EOF), ąĖ ą┐čĆąĖ čŹč鹊ą╝ čāčüą┐ąĄčłąĮąŠ ą┐čĆąŠčłą╗ąŠ čäąĖą╗čīčéčĆą░čåąĖčÄ ą┐ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā (čüą╝. ą┤ą░ą╗ąĄąĄ čüąĄą║čåąĖčÄ "ążąĖą╗čīčéčĆą░čåąĖčÅ ą┐ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā").

ąĀąĖčü. 341. ąĪąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąĖąĄą╝ąĮąŠą│ąŠ FIFO.

ą×ą▒čüą╗čāąČąĖą▓ą░ąĮąĖąĄ FIFO. ąØą░čćąĖąĮą░čÅ čü čüąŠčüč鹊čÅąĮąĖčÅ "ą┐čāčüč鹊" (empty) FIFO, ą┐ąĄčĆą▓ąŠąĄ ą║ąŠčĆčĆąĄą║čéąĮąŠ ą┐čĆąĖąĮčÅč鹊ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ FIFO, ą║ąŠč鹊čĆčŗą╣ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ pending_1 (ąŠąČąĖą┤ą░ąĄčé ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ąŠą┤ąĮąŠ ą┐čĆąĖąĮčÅč鹊ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ). ąÉą┐ą┐ą░čĆą░čéčāčĆą░ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠą▒ čŹč鹊ą╝ čüąŠą▒čŗčéąĖąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé FMP[1:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RFR ą▓ ąĘąĮą░č湥ąĮąĖąĄ 01b. ąĪąŠąŠą▒čēąĄąĮąĖąĄ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┤ąŠčüčéčāą┐ąĮčŗą╝ ą▓ ą▓čŗčģąŠą┤ąĮąŠą╝ mailbox FIFO. ą¤čĆąŠą│čĆą░ą╝ą╝ą░ čüčćąĖčéčŗą▓ą░ąĄčé č鹥ą║čāčēąĖą╣ mailbox ąĖ ąŠčüą▓ąŠą▒ąŠąČą┤ą░ąĄčé ąĄą│ąŠ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ RFOM ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RFR. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ FIFO čüąĮąŠą▓ą░ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐čāčüčéčŗą╝. ąĢčüą╗ąĖ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 ąĮąŠą▓ąŠąĄ ą║ąŠčĆčĆąĄą║čéąĮąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ, č鹊 FIFO ąŠčüčéą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ pending_1, ąĖ ąĮąŠą▓ąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą┤ąŠčüčéčāą┐ąĮąŠ ą▓ ą▓čŗčģąŠą┤ąĮąŠą╝ mailbox FIFO.

ąĢčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮąĄ ąŠčüą▓ąŠą▒ąŠą┤ąĖą╗ą░ mailbox, č鹊 čüą╗ąĄą┤čāčÄčēąĄąĄ ą║ąŠčĆčĆąĄą║čéąĮąŠ ą┐čĆąĖąĮčÅč鹊ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čāą┤ąĄčé čüąŠčģčĆą░ąĮąĄąĮąŠ ą▓ FIFO, ą║ąŠč鹊čĆčŗą╣ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ pending_2 (FMP[1:0] = 10b). ą¤čĆąŠčåąĄčüčü čüąŠčģčĆą░ąĮąĄąĮąĖčÅ čüąŠąŠą▒čēąĄąĮąĖą╣ ą▓ FIFO ą┐čĆąŠą┤ąŠą╗ąČąĖčéčüčÅ ą▓ą┐ą╗ąŠčéčī ą┤ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ FIFO ą▓ čüąŠčüč鹊čÅąĮąĖąĄ pending_3 (FMP[1:0] = 11b). ąÆ čŹč鹊ą╣ č鹊čćą║ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī ą▓čŗčģąŠą┤ąĮąŠą╣ mailbox FIFO čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ RFOM, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī mailbox ą┤ą╗čÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ ąĮąŠą▓ąŠą│ąŠ ą║ąŠčĆčĆąĄą║čéąĮąŠą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ. ąśąĮą░č湥 čüą╗ąĄą┤čāčÄčēąĄąĄ ą║ąŠčĆčĆąĄą║čéąĮąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čāą┤ąĄčé ą┐ąŠč鹥čĆčÅąĮąŠ. ąĪą╝. čéą░ą║ąČąĄ čĆą░ąĘą┤ąĄą╗ "ąźčĆą░ąĮąĖą╗ąĖčēąĄ čüąŠąŠą▒čēąĄąĮąĖą╣".

Overrun. ąÜą░ą║ č鹊ą╗čīą║ąŠ FIFO ą┐ąĄčĆąĄčłąĄą╗ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ pending_3 (čé. ąĄ. ą▓čüąĄ mailbox ąĘą░ą┐ąŠą╗ąĮąĄąĮčŗ), čüą╗ąĄą┤čāčÄčēąĄąĄ ą┐ąŠčüčéčāą┐ąĖą▓čłąĄąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÄ ą┐čĆąĖąĄą╝ą░ (overrun), ąĖ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čāą┤ąĄčé ą┐ąŠč鹥čĆčÅąĮąŠ. ąÉą┐ą┐ą░čĆą░čéčāčĆą░ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠ čüąŠčüč鹊čÅąĮąĖąĖ overrun čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ FOVR ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RFR. ąÜą░ą║ąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą┐ąŠč鹥čĆčÅąĮąŠ, ąĘą░ą▓ąĖčüąĖčé ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ FIFO:

ŌĆó ąĢčüą╗ąĖ čäčāąĮą║čåąĖčÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ FIFO (FIFO lock) ąĘą░ą┐čĆąĄčēąĄąĮą░ (ąŠčćąĖčēąĄąĮ ą▒ąĖčé RFLM ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCR), č鹊 ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ čüąŠčģčĆą░ąĮąĄąĮąĮąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▓ FIFO ą▒čāą┤ąĄčé ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮąŠ ąĮąŠą▓čŗą╝ ą┐ąŠčüčéčāą┐ąĖą▓čłąĖą╝ čüąŠąŠą▒čēąĄąĮąĖąĄą╝. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ ą┐ąŠčüčéčāą┐ąĖą▓čłąĖąĄ (čüą░ą╝čŗąĄ čüą▓ąĄąČąĖąĄ) čüąŠąŠą▒čēąĄąĮąĖčÅ ą▒čāą┤čāčé ą▓čüąĄą│ą┤ą░ ą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ.

ŌĆó ąĢčüą╗ąĖ čäčāąĮą║čåąĖčÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ FIFO čĆą░ąĘčĆąĄčłąĄąĮą░ (čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé RFLM ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCR), č鹊 čüą░ą╝ąŠąĄ čüą▓ąĄąČąĄąĄ ą┐ąŠčüčéčāą┐ąĖą▓čłąĄąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čāą┤ąĄčé ąŠčéą▒čĆąŠčłąĄąĮąŠ, ąĖ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą▒čāą┤čāčé ą▓čüąĄą│ą┤ą░ ą┤ąŠčüčéčāą┐ąĮčŗ 3 čüą░ą╝čŗąĄ čüčéą░čĆčŗąĄ ąĮąĄ ąŠą▒čĆą░ą▒ąŠčéą░ąĮąĮčŗąĄ čüąŠąŠą▒čēąĄąĮąĖčÅ FIFO.

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ą░. ąÜą░ą║ č鹊ą╗čīą║ąŠ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čŗą╗ąŠ čüąŠčģčĆą░ąĮąĄąĮąŠ ą▓ FIFO, ąŠą▒ąĮąŠą▓čÅčéčüčÅ ą▒ąĖčéčŗ FMP[1:0] ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé FMPIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CAN_IER.

ąÜąŠą│ą┤ą░ FIFO čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮčŗą╝ (čé. ąĄ. čüąŠčģčĆą░ąĮąĄąĮąŠ čéčĆąĄčéčīąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ), čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé FULL ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RFR, ąĖ ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé FFIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CAN_IER.

ą¤čĆąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ ą┐čĆąĖąĄą╝ą░ (overrun condition) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé FOVR, ąĖ ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé FOVIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CAN_IER.

[ążąĖą╗čīčéčĆą░čåąĖčÅ ą┐ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā]

ąÆ ą┐čĆąŠč鹊ą║ąŠą╗ąĄ CAN ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ čüąŠąŠą▒čēąĄąĮąĖčÅ ąĮąĄ čüą▓čÅąĘą░ąĮ čü ą░ą┤čĆąĄčüąŠą╝ čāąĘą╗ą░, ąĮąŠ čüą▓čÅąĘą░ąĮ čü čüąŠą┤ąĄčƹȹĖą╝čŗą╝ čüąŠąŠą▒čēąĄąĮąĖčÅ. ąĪą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ą┐ąĄčĆąĄą┤ą░ąĄčé čüą▓ąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▓čüąĄą╝ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ą╝. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĖąĄą╝ą░ čüąŠąŠą▒čēąĄąĮąĖčÅ ą┐čĆąĖąĮąĖą╝ą░čÄčēąĖą╣ čāąĘąĄą╗ čĆąĄčłą░ąĄčé - ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ - ąĮčāąČą┤ą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą▓ čŹč鹊ą╝ čüąŠąŠą▒čēąĄąĮąĖąĖ, ąĖą╗ąĖ ąĮąĄčé. ąĢčüą╗ąĖ čüąŠąŠą▒čēąĄąĮąĖąĄ ąĮčāąČąĮąŠąĄ, č鹊 ąŠąĮąŠ ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ ą▓ SRAM. ąĢčüą╗ąĖ ąĮąĄčé, č鹊 čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čāą┤ąĄčé ąŠčéą▒čĆąŠčłąĄąĮąŠ ą▒ąĄąĘ ą║ą░ą║ąŠą│ąŠ-ą╗ąĖą▒ąŠ ą▓ą╝ąĄčłą░č鹥ą╗čīčüčéą▓ą░ čüąŠ čüč鹊čĆąŠąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ.

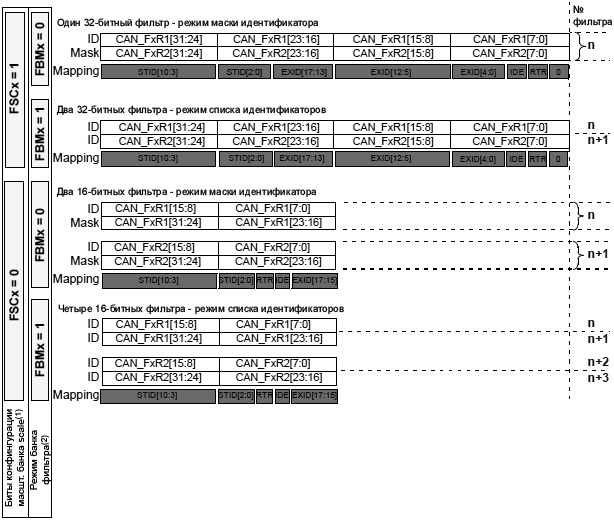

ą¦č鹊ą▒čŗ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĖčéčī čŹč鹊ą╝čā čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÄ, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ bxCAN ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ 28 ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗčģ ąĖ ą╝ą░čüčłčéą░ą▒ąĖčĆčāąĄą╝čŗčģ ą▒ą░ąĮą║ąŠą▓ čäąĖą╗čīčéčĆą░ (27 .. 0). ąŁčéą░ ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ čäąĖą╗čīčéčĆą░čåąĖčÅ čüąŠčģčĆą░ąĮčÅąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠąĄ ą▓čĆąĄą╝čÅ CPU, ą║ąŠč鹊čĆąŠąĄ ąĖąĮą░č湥 čéčĆą░čéąĖą╗ąŠčüčī ą▒čŗ, ąĄčüą╗ąĖ čäąĖą╗čīčéčĆą░čåąĖčÅ ą▒čŗą╗ą░ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ. ąÜą░ąČą┤čŗą╣ ą▒ą░ąĮą║ čäąĖą╗čīčéčĆą░ x čüąŠčüč鹊ąĖčé ąĖąĘ ą┤ą▓čāčģ 32-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░ CAN_FxR0 ąĖ CAN_FxR1.

ą£ą░čüčłčéą░ą▒ąĖčĆčāąĄą╝ą░čÅ čłąĖčĆąĖąĮą░ (scale). ą¦č鹊ą▒čŗ ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ąĖ ą░ą┤ą░ą┐čéąĖčĆąŠą▓ą░čéčī čäąĖą╗čīčéčĆą░čåąĖčÄ ą║ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ą║ą░ąČą┤čŗą╣ ą▒ą░ąĮą║ čäąĖą╗čīčéčĆą░ ą╝ąŠąČąĄčé ą╝ą░čüčłčéą░ą▒ąĖčĆąŠą▓ą░čéčīčüčÅ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą╝ą░čüčłčéą░ą▒ą░ čäąĖą╗čīčéčĆą░ ą▒ą░ąĮą║ čäąĖą╗čīčéčĆą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé (čüą╝. čĆąĖčü. 342):

ŌĆó ą×ą┤ąĖąĮ 32-ą▒ąĖčéąĮčŗą╣ čäąĖą╗čīčéčĆ ą┤ą╗čÅ ą▒ąĖčé STDID[10:0], EXTID[17:0], IDE ąĖ RTR.

ŌĆó ąöą▓ą░ 16-ą▒ąĖčéąĮčŗčģ čäąĖą╗čīčéčĆą░ ą┤ą╗čÅ ą▒ąĖčé STDID[10:0], RTR, IDE ąĖ EXTID[17:15].

ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, čäąĖą╗čīčéčĆčŗ ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą▓ čĆąĄąČąĖą╝ąĄ ą╝ą░čüą║ąĖ (mask mode) ąĖą╗ąĖ ą▓ čĆąĄąČąĖą╝ąĄ čüą┐ąĖčüą║ą░ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓ (identifier list mode).

Mask mode. ąÆ čĆąĄąČąĖą╝ąĄ ą╝ą░čüą║ąĖ čĆąĄą│ąĖčüčéčĆčŗ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ čüą▓čÅąĘą░ąĮčŗ čü čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ ą╝ą░čüą║ąĖ, čāą║ą░ąĘčŗą▓ą░čÄčēąĖą╝ąĖ, ą║ą░ą║ąĖąĄ ą▒ąĖčéčŗ ą▓ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąĄ ą┤ąŠą╗ąČąĮčŗ čüąŠą▓ą┐ą░ą┤ą░čéčī (must match), ą░ ą║ą░ą║ąĖąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą╗čÄą▒čŗą╝ąĖ (donŌĆÖt care).

Identifier list mode. ąÆ čĆąĄąČąĖą╝ąĄ čüą┐ąĖčüą║ą░ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓ čĆąĄą│ąĖčüčéčĆčŗ ą╝ą░čüą║ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ą░ą║ čĆąĄą│ąĖčüčéčĆčŗ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▓ą╝ąĄčüč鹊 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ ąĖ ą╝ą░čüą║ąĖ, čāą║ą░ąĘčŗą▓ą░čÄčéčüčÅ 2 ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░, čāą┤ą▓ą░ąĖą▓ą░čÅ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąŠą┤ąĖąĮąŠčćąĮčŗčģ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓. ąÆčüąĄ ą▒ąĖčéčŗ ą┐čĆąĖčģąŠą┤čÅčēąĄą│ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ ą┤ąŠą╗ąČąĮčŗ čüąŠą▓ą┐ą░ą┤ą░čéčī čü ą▒ąĖčéą░ą╝ąĖ, čāą║ą░ąĘą░ąĮąĮčŗą╝ąĖ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čäąĖą╗čīčéčĆą░.

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ scale ąĖ mode ą▒ą░ąĮą║ą░ čäąĖą╗čīčéčĆą░. ąæą░ąĮą║ąĖ čäąĖą╗čīčéčĆą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ čĆąĄą│ąĖčüčéčĆąŠą╝ CAN_FMR. ąöą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ą░ąĮą║ą░ čäąĖą╗čīčéčĆą░ ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┤ąĄą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ FACT ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_FAR. ą¤ą░čĆą░ą╝ąĄčéčĆ scale čäąĖą╗čīčéčĆą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą▒ąĖč鹊ą╝ FSCx čĆąĄą│ąĖčüčéčĆą░ CAN_FS1R, čüą╝. čĆąĖčü. 342. ąĀąĄąČąĖą╝ ą╝ą░čüą║ąĖ ąĖą╗ąĖ čĆąĄąČąĖą╝ čüą┐ąĖčüą║ą░ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓ ą┤ą╗čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ Mask/Identifier ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ FBMx ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_FMR.

ąöą╗čÅ čäąĖą╗čīčéčĆą░čåąĖąĖ ą│čĆčāą┐ą┐čŗ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 čĆąĄą│ąĖčüčéčĆčŗ Mask/Identifier ą▓ čĆąĄąČąĖą╝ąĄ ą╝ą░čüą║ąĖ.

ąöą╗čÅ ą▓čŗą▒ąŠčĆą░ ąŠą┤ąĖąĮąŠčćąĮčŗčģ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 čĆąĄą│ąĖčüčéčĆčŗ Mask/Identifier ą▓ čĆąĄąČąĖą╝ąĄ čüą┐ąĖčüą║ą░ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓.

ążąĖą╗čīčéčĆčŗ, ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄą╝, ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠčüčéą░ą▓ą╗ąĄąĮčŗ ą┤ąĄą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ.

ąÜą░ąČą┤čŗą╣ čäąĖą╗čīčéčĆ ą▓ ą▒ą░ąĮą║ąĄ čäąĖą╗čīčéčĆą░ ą┐čĆąŠąĮčāą╝ąĄčĆąŠą▓ą░ąĮ (ąĮąŠą╝ąĄčĆ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ Filter Number) ąŠčé 0 ą┤ąŠ ą╝ą░ą║čüąĖą╝čāą╝ą░, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé mode ąĖ scale ą║ą░ąČą┤ąŠą│ąŠ ą▒ą░ąĮą║ą░ čäąĖą╗čīčéčĆą░.

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ čäąĖą╗čīčéčĆą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 342.

ąĀąĖčü. 342. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą╝ą░čüčłčéą░ą▒ąĖčĆąŠą▓ą░ąĮąĖčÅ (scale) ą▒ą░ąĮą║ąŠą▓ čäąĖą╗čīčéčĆą░ - ąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

x = ąĮąŠą╝ąĄčĆčā ą▒ą░ąĮą║ą░ čäąĖą╗čīčéčĆą░.

ID = ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā.

(1) ąŁčéąĖ ą▒ąĖčéčŗ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_FS1R.

(2) ąŁčéąĖ ą▒ąĖčéčŗ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_FM1R.

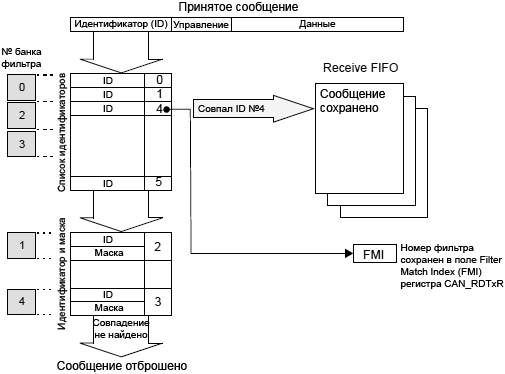

ąśąĮą┤ąĄą║čü čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ čäąĖą╗čīčéčĆą░. ąÜą░ą║ č鹊ą╗čīą║ąŠ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 ą▓ FIFO, ąŠąĮąŠ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┤ąŠčüčéčāą┐ąĮčŗą╝ ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ą×ą▒čŗčćąĮąŠ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą║ąŠą┐ąĖčĆčāčÄčéčüčÅ ą▓ čÅč湥ą╣ą║ąĖ SRAM. ą¦č鹊ą▒čŗ ą║ąŠą┐ąĖčĆąŠą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ ą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ ą╝ąĄčüč鹊, ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą┐ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā. ą¦č鹊ą▒čŗ čāą┐čĆąŠčüąĖčéčī ą┤ąŠčüčéčāą┐ ą║ čÅč湥ą╣ą║ą░ą╝ SRAM ą┐čĆąĖąĮčÅčéčŗčģ čüąŠąŠą▒čēąĄąĮąĖą╣, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĖąĮą┤ąĄą║čü čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ čäąĖą╗čīčéčĆą░ (Filter Match Index).

ąŁč鹊čé ąĖąĮą┤ąĄą║čü čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ mailbox ą▓ą╝ąĄčüč鹥 čü čüąŠąŠą▒čēąĄąĮąĖąĄą╝, ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┐čĆą░ą▓ąĖą╗ą░ą╝ąĖ ą┐čĆąĖąŠčĆąĖč鹥čéą░ čäąĖą╗čīčéčĆą░. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą║ą░ąČą┤ąŠąĄ ą┐čĆąĖąĮčÅč鹊ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ čüą▓čÅąĘčŗą▓ą░ąĄčé čü ąĖąĮą┤ąĄą║čüąŠą╝ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ čäąĖą╗čīčéčĆą░.

ąśąĮą┤ąĄą║čü Filter Match ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮ ą┤ą▓čāą╝čÅ čüą┐ąŠčüąŠą▒ą░ą╝ąĖ:

ŌĆó ąĪčĆą░ą▓ąĮąĄąĮąĖąĄ ąĖąĮą┤ąĄą║čüą░ Filter Match čüąŠ čüą┐ąĖčüą║ąŠą╝ ąŠąČąĖą┤ą░ąĄą╝čŗčģ ąĘąĮą░č湥ąĮąĖą╣.

ŌĆó ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ąĖąĮą┤ąĄą║čüą░ Filter Match ą║ą░ą║ ąĖąĮą┤ąĄą║čüą░ ą▓ ą╝ą░čüčüąĖą▓ąĄ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą╝ąĄčüčéčā ąĮą░čģąŠąČą┤ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ.

ąöą╗čÅ ąĮąĄ ą╝ą░čüą║ąĖčĆčāąĄą╝čŗčģ čäąĖą╗čīčéčĆąŠą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą▒ąŠą╗čīčłąĄ ąĮąĄ ą┤ąŠą╗ąČąĮą░ čüčĆą░ą▓ąĮąĖą▓ą░čéčī ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ.

ąĢčüą╗ąĖ čäąĖą╗čīčéčĆ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮ, č鹊 ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąŠą│čĆą░ąĮąĖčćąĖą▓ą░ąĄčé čüčĆą░ą▓ąĮąĄąĮąĖąĄ č鹊ą╗čīą║ąŠ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ą▒ąĖčéą░ą╝ąĖ.

ąŚąĮą░č湥ąĮąĖąĄ ąĖąĮą┤ąĄą║čüą░ ąĮąŠą╝ąĄčĆą░ čäąĖą╗čīčéčĆą░ ąĮąĄ čāčćąĖčéčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą░ą║čéąĖą▓ą░čåąĖąĖ ą▒ą░ąĮą║ąŠą▓ čäąĖą╗čīčéčĆą░. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą▓ąĄ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗąĄ čüčģąĄą╝čŗ ąĮčāą╝ąĄčĆą░čåąĖąĖ, ą┐ąŠ ąŠą┤ąĮąŠą╣ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ FIFO. ą¤čĆąĖą╝ąĄčĆ čüą╝. ąĮą░ čĆąĖčü. 343.

ąĀąĖčü. 343. ą¤čĆąĖą╝ąĄčĆ ąĮčāą╝ąĄčĆą░čåąĖąĖ čäąĖą╗čīčéčĆąŠą▓. ID ąŠąĘąĮą░čćą░ąĄčé ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ.

ą¤čĆą░ą▓ąĖą╗ą░ ą┐čĆąĖąŠčĆąĖč鹥ąĘą░čåąĖąĖ čäąĖą╗čīčéčĆą░. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ čäąĖą╗čīčéčĆąŠą▓ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ čüąĖčéčāą░čåąĖčÅ, ą║ąŠą│ą┤ą░ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ą┐čĆąŠą╣ą┤ąĄčé č湥čĆąĄąĘ ąĮąĄčüą║ąŠą╗čīą║ąŠ čäąĖą╗čīčéčĆąŠą▓. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čüąŠą▓ą┐ą░ą▓čłąĄą│ąŠ čäąĖą╗čīčéčĆą░ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ mailbox ą┐čĆąĖąĄą╝ą░ ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ ą┐čĆą░ą▓ąĖą╗ą░ą╝ ą┐čĆąĖąŠčĆąĖč鹥čéą░:

ŌĆó 32-ą▒ąĖčéąĮčŗą╣ čäąĖą╗čīčéčĆ ąĖą╝ąĄąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé ąĮą░ą┤ 16-ą▒ąĖčéąĮčŗą╝ čäąĖą╗čīčéčĆąŠą╝.

ŌĆó ąöą╗čÅ čäąĖą╗čīčéčĆąŠą▓ čü ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ scale, ą┐čĆąĖąŠčĆąĖč鹥čé ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ čĆąĄąČąĖą╝čā čüą┐ąĖčüą║ą░ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓ (Identifier List mode) ąĮą░ą┤ čĆąĄąČąĖą╝ąŠą╝ ą╝ą░čüą║ąĖ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓ (Identifier Mask mode).

ŌĆó ąöą╗čÅ čäąĖą╗čīčéčĆąŠą▓ čü ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ scale ąĖ mode, ą┐čĆąĖąŠčĆąĖč鹥čé ą┤ą░ąĄčéčüčÅ ą┐ąŠ ąĮąŠą╝ąĄčĆčā čäąĖą╗čīčéčĆą░ (č湥ą╝ ą╝ąĄąĮčīčłąĄ ąĮąŠą╝ąĄčĆ, č鹥ą╝ ą▓čŗčłąĄ ą┐čĆąĖąŠčĆąĖč鹥čé).

ąĀąĖčü. 344. ą¤čĆąĖą╝ąĄčĆ ą╝ąĄčģą░ąĮąĖąĘą╝ą░ čäąĖą╗čīčéčĆą░čåąĖąĖ. ąóčĆąĖ ą▒ą░ąĮą║ą░ čäąĖą╗čīčéčĆą░ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą▓ 32-ą▒ąĖčéąĮąŠą╝ Unidentified List mode, ąŠčüčéą░ą╗čīąĮčŗąĄ ą▓ 32-ą▒ąĖčéąĮąŠą╝ Identifier Mask mode.

ąØą░ čĆąĖčü. 344 ą▓čŗčłąĄ ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąĖą╝ąĄčĆ ą┐čĆąĖąĮčåąĖą┐ą░ čäąĖą╗čīčéčĆą░čåąĖąĖ bxCAN. ąØą░ ą┐čĆąĖąĄą╝ąĄ čüąŠąŠą▒čēąĄąĮąĖčÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ čüąĮą░čćą░ą╗ą░ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčéčüčÅ čü čäąĖą╗čīčéčĆą░ą╝ąĖ, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ą▓ identifier list mode. ąĢčüą╗ąĖ ą▒čŗą╗ąŠ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ, č鹊 čüąŠąŠą▒čēąĄąĮąĖąĄ čüąŠčģčĆą░ąĮčÅčéčüčÅ ą▓ čüą▓čÅąĘą░ąĮąĮąŠą╝ FIFO ąĖ ąĖąĮą┤ąĄą║čü čüąŠą▓ą┐ą░ą▓čłąĄą│ąŠ čäąĖą╗čīčéčĆą░ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ Filter Match Index (FMI). ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ ą┐čĆąĖą╝ąĄčĆąĄ, ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ čüąŠą▓ą┐ą░ą╗ čü Identifier #2, čéą░ą║ čćč鹊 ą▓ FIFO ą▒čāą┤ąĄčé čüąŠčģčĆą░ąĮąĄąĮąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čüąŠąŠą▒čēąĄąĮąĖčÅ ąĖ FMI 2.

ąĢčüą╗ąĖ ąĮąĄ ą▒čŗą╗ąŠ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ, ą┐čĆąĖčłąĄą┤čłąĖą╣ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčéčüčÅ čü čäąĖą╗čīčéčĆą░ą╝ąĖ, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ą▓ mask mode.

ąĢčüą╗ąĖ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ąĮąĄ čüąŠą▓ą┐ą░ą╗ ąĮąĖ čü ąŠą┤ąĮąĖą╝ ąĖąĘ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą▓ čäąĖą╗čīčéčĆą░čģ, č鹊 čüąŠąŠą▒čēąĄąĮąĖąĄ ąŠčéą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĮąĖą║ą░ą║ ąĮąĄ ą▓ą╗ąĖčÅčÅ ąĮą░ ą┐čĆąŠą│čĆą░ą╝ą╝čā.

[ąźčĆą░ąĮąĖą╗ąĖčēąĄ čüąŠąŠą▒čēąĄąĮąĖą╣]

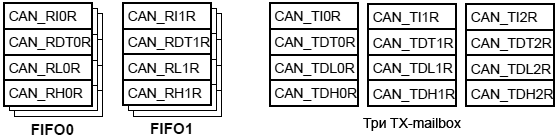

ąśąĮč鹥čĆč乥ą╣čü ą╝ąĄąČą┤čā ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ ą┤ą╗čÅ čüąŠąŠą▒čēąĄąĮąĖą╣ CAN čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ č湥čĆąĄąĘ čÅčēąĖą║ąĖ (mailboxes). Mailbox čüąŠą┤ąĄčƹȹĖčé ą▓čüčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ, ąŠčéąĮąŠčüčÅčēčāčÄčüčÅ ą║ čüąŠąŠą▒čēąĄąĮąĖčÄ: ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ, ą┤ą░ąĮąĮčŗąĄ, čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ, čüčéą░čéčāčü ąĖ ą╝ąĄčéą║čā ą▓čĆąĄą╝ąĄąĮąĖ.

Transmit mailbox. ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčé čüąŠąŠą▒čēąĄąĮąĖąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ ą┐čāčüč鹊ą╝ ą┐ąĄčĆąĄą┤ą░čÄčēąĄą╝ mailbox. ąĪčéą░čéčāčü ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TSR.

ąóą░ą▒ą╗ąĖčåą░ 182. ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ čÅčēąĖą║ąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ (TX mailbox) ą┐ąĄčĆąĄą┤ą░čćąĖ.

| ąĪą╝ąĄčēąĄąĮąĖąĄ ą┤ą╗čÅ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ TX mailbox (ą▓ ą▒ą░ą╣čéą░čģ) |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

| 0 |

CAN_TIxR |

| 4 |

CAN_TDTxR |

| 8 |

CAN_TDLxR |

| 12 |

CAN_TDHxR |

Receive mailbox. ąÜąŠą│ą┤ą░ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 čüąŠąŠą▒čēąĄąĮąĖąĄ, ąŠąĮąŠ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┤ąŠčüčéčāą┐ąĮčŗą╝ ą▓ ą▓čŗčģąŠą┤ąĮąŠą╝ mailbox FIFO. ąÜąŠą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąŠą▒čĆą░ą▒ąŠčéą░ą╗ą░ čüąŠąŠą▒čēąĄąĮąĖąĄ (čé. ąĄ. ą┐čĆąŠčćąĖčéą░ą╗ą░ ąĄą│ąŠ), ąŠąĮą░ ą┤ąŠą╗ąČąĮą░ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī ą▓čŗčģąŠą┤ąĮąŠą╣ mailbox FIFO čü ą┐ąŠą╝ąŠčēčīčÄ ą▒ąĖčéą░ RFOM ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RFR, čćč鹊ą▒čŗ čüčéą░ą╗ąŠ ą┤ąŠčüčéčāą┐ąĮčŗą╝ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĄąĄ ą┐čĆąĖčģąŠą┤čÅčēąĄąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ. ąśąĮą┤ąĄą║čü čüąŠą▓ą┐ą░ą▓čłąĄą│ąŠ čäąĖą╗čīčéčĆą░ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ ą┐ąŠą╗ąĄ MFMI čĆąĄą│ąĖčüčéčĆą░ CAN_RDTxR. 16-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ (time stamp) čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ ą┐ąŠą╗ąĄ TIME[15:0] čĆąĄą│ąĖčüčéčĆą░ CAN_RDTxR.

ąóą░ą▒ą╗ąĖčåą░ 183. ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ čÅčēąĖą║ąŠą▓ (RX mailbox) ą┐čĆąĖąĄą╝ą░.

| ąĪą╝ąĄčēąĄąĮąĖąĄ ą┤ą╗čÅ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ RX mailbox (ą▓ ą▒ą░ą╣čéą░čģ) |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

| 0 |

CAN_RIxR |

| 4 |

CAN_RDTxR |

| 8 |

CAN_RDLxR |

| 12 |

CAN_RDHxR |

[ą×ą▒čĆą░ą▒ąŠčéą║ą░ ąŠčłąĖą▒ąŠą║]

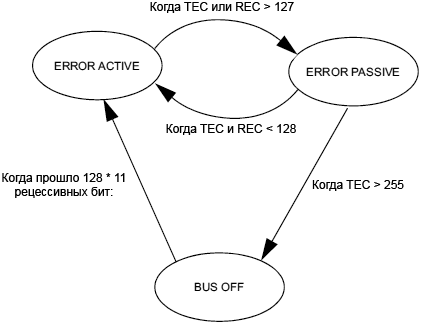

ą×ą▒čĆą░ą▒ąŠčéą║ą░ ąŠčłąĖą▒ąŠą║ (error management), ą║ą░ą║ čŹč鹊 ąŠą┐ąĖčüą░ąĮąŠ ą▓ ą┐čĆąŠč鹊ą║ąŠą╗ąĄ CAN, ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čüč湥čéčćąĖą║ą░ ąŠčłąĖą▒ąŠą║ ą┐ąĄčĆąĄą┤ą░čćąĖ Transmit Error Counter (ąĘąĮą░č湥ąĮąĖąĄ TEC ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_ESR) ąĖ čüč湥čéčćąĖą║ą░ ąŠčłąĖą▒ąŠą║ ą┐čĆąĖąĄą╝ą░ Receive Error Counter (ąĘąĮą░č湥ąĮąĖąĄ REC ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_ESR), ą║ąŠč鹊čĆčŗąĄ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāčÄčéčüčÅ ą┐ąŠ ą╝ąĄčĆąĄ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ čüąŠą▒čŗčéąĖą╣ ąŠčłąĖą▒ą║ąĖ. ąæąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖąĄ TEC ąĖ REC ąŠą┐ąĖčüą░ąĮąŠ ą▓ čüčéą░ąĮą┤ą░čĆč鹥 CAN.

ą×ą▒ą░ čüč湥čéčćąĖą║ą░ TEC ąĖ REC ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī čüčéą░ą▒ąĖą╗čīąĮąŠčüčéčī čüąĄčéąĖ CAN. ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ą░ą┐ą┐ą░čĆą░čéčāčĆą░ CAN ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐ąŠą┤čĆąŠą▒ąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ č鹥ą║čāčēąĄą╝ čüčéą░čéčāčüąĄ ąŠčłąĖą▒ą║ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_ESR. ą¦ąĄčĆąĄąĘ čĆąĄą│ąĖčüčéčĆ CAN_IER (ą▒ąĖčé ERRIE ąĖ čé. ą┐.), ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ąŠč湥ąĮčī ą│ąĖą▒ą║ąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĖ ąŠčłąĖą▒ą║ąĖ.

ąĀąĖčü. 345. ąöąĖą░ą│čĆą░ą╝ą╝ą░ čüąŠčüč鹊čÅąĮąĖą╣ ąŠčłąĖą▒ą║ąĖ CAN.

ąÆąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĄ ąĖąĘ Bus-Off. ąĪąŠčüč鹊čÅąĮąĖąĄ Bus-Off (ąŠčéą║ą╗čÄč湥ąĮąĖąĄ ąŠčé čłąĖąĮčŗ) ą┤ąŠčüčéąĖą│ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ TEC čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąŠą╗čīčłąĄ 255, čŹč鹊 čüąŠčüč鹊čÅąĮąĖąĄ ąĖąĮą┤ąĖčåąĖčĆčāąĄčéčüčÅ ą▒ąĖč鹊ą╝ BOFF čĆąĄą│ąĖčüčéčĆą░ CAN_ESR. ąÆ čüąŠčüč鹊čÅąĮąĖąĖ Bus-Off ą▒ą╗ąŠą║ bxCAN ą▒ąŠą╗čīčłąĄ ąĮąĄ ą╝ąŠąČąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ąĖ ą┐čĆąĖąĮąĖą╝ą░čéčī čüąŠąŠą▒čēąĄąĮąĖčÅ.

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▒ąĖčéą░ ABOM ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCR, ą▒ą╗ąŠą║ bxCAN ą▒čāą┤ąĄčé ą▓ąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčīčüčÅ ąĖąĘ Bus-Off (ą┐ąĄčĆąĄčģąŠą┤ąĖčéčī ą▓ čüąŠčüč鹊čÅąĮąĖąĄ error active) ą╗ąĖą▒ąŠ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą╗ąĖą▒ąŠ ą┐ąŠ ąĘą░ą┐čĆąŠčüčā ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. ą×ą┤ąĮą░ą║ąŠ ą▓ ąŠą▒ąŠąĖčģ čüą╗čāčćą░čÅčģ bxCAN ą▒čāą┤ąĄčé ąČą┤ą░čéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ (recovery sequence), ąŠą┐ąĖčüą░ąĮąĮčāčÄ ą▓ čüčéą░ąĮą┤ą░čĆč鹥 CAN (128 čüą╗čāčćą░ąĄą▓ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ 11 čüą╗ąĄą┤čāčÄčēąĖčģ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ čĆąĄčåąĄčüčüąĖą▓ąĮčŗčģ ą▒ąĖčé, ąŠą▒ąĮą░čĆčāąČąĄąĮąĮčŗčģ ąĮą░ CANRX).

ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ABOM, č鹊 bxCAN ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĮą░čćąĮąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą▓čģąŠą┤ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ Bus-Off. ąĢčüą╗ąĖ ABOM ąŠčćąĖčēąĄąĮ, č鹊 ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░čéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┐čāč鹥ą╝ ąĘą░ą┐čĆąŠčüą░ ą║ bxCAN ąĮą░ ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ąĖ ąĮą░ ą▓čŗčģąŠą┤ ąĖąĘ ąĮąĄą│ąŠ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ bxCAN ąĮąĄ ą╝ąŠąĮąĖč鹊čĆąĖčé čüąĖą│ąĮą░ą╗ CANRX, ą┐ąŠčŹč鹊ą╝čā ąĮąĄ ą╝ąŠąČąĄčé ąĘą░ą▓ąĄčĆčłąĖčéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ. ąöą╗čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ bxCAN ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ normal mode.

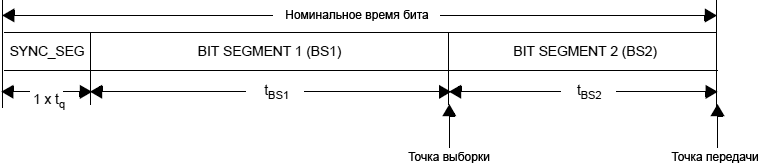

[ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▒ąĖčé (bit timing)]

ąøąŠą│ąĖą║ą░ čéą░ą╣ą╝ąĖąĮą│ą░ ą▒ąĖčéą░ ą╝ąŠąĮąĖč鹊čĆąĖčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčāčÄ ą╗ąĖąĮąĖčÄ čłąĖąĮčŗ ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ąŠčåąĖčäčĆąŠą▓ą║čā čüąĖą│ąĮą░ą╗ą░ čü ą┐ąŠą┤čüčéčĆąŠą╣ą║ąŠą╣ č鹊čćą║ąĖ ą▓čŗą▒ąŠčĆą║ąĖ. ąŁč鹊 ą┤ąĄą╗ą░ąĄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĄą╣ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą▒ąĖčéą░, ąĖ ą┐ąŠą▓č鹊čĆąĮąŠą╣ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĄą╣ ąĮą░ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ ą┐ąĄčĆąĄą┐ą░ą┤ą░čģ.

ąŁčéą░ ąŠą┐ąĄčĆą░čåąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą▒čŖčÅčüąĮąĄąĮą░ ą┐čĆąŠčüčéčŗą╝ čĆą░ąĘą┤ąĄą╗ąĄąĮąĖąĄą╝ ąĮąŠą╝ąĖąĮą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą▒ąĖčéą░ ąĮą░ 3 čüąĄą│ą╝ąĄąĮčéą░ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆó ąĪąĄą│ą╝ąĄąĮčé čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ (SYNC_SEG): ą▓ąŠ ą▓čĆąĄą╝čÅ čŹč鹊ą│ąŠ ąĖąĮč鹥čĆą▓ą░ą╗ą░ ą▓čĆąĄą╝ąĄąĮąĖ ąŠąČąĖą┤ą░ąĄčéčüčÅ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą▒ąĖčé. ąÆąĄą╗ąĖčćąĖąĮą░ čŹč鹊ą│ąŠ čüąĄą│ą╝ąĄąĮčéą░ čäąĖą║čüąĖčĆčāąĄčéčüčÅ ąĮą░ ąŠą┤ąĮąŠą╝ ą║ą▓ą░ąĮč鹥 ą▓čĆąĄą╝ąĄąĮąĖ (time quantum): 1 x tq.

ŌĆó ąĪąĄą│ą╝ąĄąĮčé ą▒ąĖčéą░ 1 (Bit segment 1, BS1): ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąŠą╗ąŠąČąĄąĮąĖąĄ č鹊čćą║ąĖ ą▓čŗą▒ąŠčĆą║ąĖ čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ (sample point). ąĪčéą░ąĮą┤ą░čĆčé ą▓ą║ą╗čÄčćą░ąĄčé čüčÄą┤ą░ ąĖąĮč鹥čĆą▓ą░ą╗čŗ PROP_SEG (čüąĄą│ą╝ąĄąĮčé čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ) ąĖ PHASE_SEG1 (čüąĄą│ą╝ąĄąĮčé čäą░ąĘčŗ 1). ąöą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ čŹčéąĖčģ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ ą╝ąĄąČą┤čā 1 ąĖ 16 time quanta, ąŠą┤ąĮą░ą║ąŠ ąŠąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāą▓ąĄą╗ąĖč湥ąĮčŗ ą┤ą╗čÅ ą║ąŠą╝ą┐ąĄąĮčüą░čåąĖąĖ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą┤čĆąĄą╣čäą░ čäą░ąĘčŗ ąĖąĘ-ąĘą░ čĆą░ąĘąĮąĖčåčŗ čćą░čüč鹊čé čéą░ą║č鹊ą▓ čĆą░ąĘą╗ąĖčćąĮčŗčģ čāąĘą╗ąŠą▓ ą▓ čüąĄčéąĖ.

ŌĆó ąĪąĄą│ą╝ąĄąĮčé ą▒ąĖčéą░ 2 (Bit segment 2, BS2): ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąŠą╗ąŠąČąĄąĮąĖąĄ č鹊čćą║ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit point). ą¤čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮ ą▓ čüčéą░ąĮą┤ą░čĆč鹥 CAN ąĖąĮč鹥čĆą▓ą░ą╗ąŠą╝ PHASE_SEG2 (čüąĄą│ą╝ąĄąĮčé čäą░ąĘčŗ 2). ąĢą│ąŠ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1 ą┤ąŠ 8 time quanta, ąŠą┤ąĮą░ą║ąŠ čŹč鹊čé ąĖąĮč鹥čĆą▓ą░ą╗ ą╝ąŠąČąĄčé ą▒čŗčéčī ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüąŠą║čĆą░čēąĄąĮ ą┤ą╗čÅ ą║ąŠą╝ą┐ąĄąĮčüą░čåąĖąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗčģ čüą╝ąĄčēąĄąĮąĖą╣ čäą░ąĘčŗ.

ą¤ą░čĆą░ą╝ąĄčéčĆ čłąĖčĆąĖąĮčŗ čüą║ą░čćą║ą░ čĆąĄčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ (resynchronization Jump Width, SJW) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą▓ąĄčĆčģąĮčÄčÄ ą│čĆą░ąĮąĖčåčā ą▓ąĄą╗ąĖčćąĖąĮčŗ čāą┤ą╗ąĖąĮąĄąĮąĖčÅ ąĖą╗ąĖ čāą║ąŠčĆąŠč湥ąĮąĖčÅ čüąĄą│ą╝ąĄąĮč鹊ą▓ ą▒ąĖčéą░. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1 ą┤ąŠ 4 time quanta.

ąöąŠčüč鹊ą▓ąĄčĆąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą┤ąĄč鹥ą║čéąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą┐ąĄčĆą▓čŗą╣ ą┐ąĄčĆąĄčģąŠą┤ ą▓ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ ą▒ąĖčéą░ ąŠčé ą┤ąŠą╝ąĖąĮą░ąĮčéąĮąŠą│ąŠ ą║ čĆąĄčåąĄčüčüąĖą▓ąĮąŠą╝čā čāčĆąŠą▓ąĮčÄ čłąĖąĮčŗ ą┐čĆąĖ čāčüą╗ąŠą▓ąĖąĖ, čćč鹊 ą║ąŠąĮčéčĆąŠą╗ąĄčĆ čüą░ą╝ ąĮąĄ ą┐ąĄčĆąĄą┤ą░ąĄčé čĆąĄčåąĄčüčüąĖą▓ąĮčŗą╣ ą▒ąĖčé.

ąĢčüą╗ąĖ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ą▓ BS1 ą▓ą╝ąĄčüč鹊 SYNC_SEG, BS1 čĆą░čüčłąĖčĆčÅąĄčéčüčÅ ąĮą░ ąĖąĮč鹥čĆą▓ą░ą╗ SJW, čćč鹊ą▒čŗ č鹊čćą║ą░ ą▓čŗą▒ąŠčĆą║ąĖ ą▒čŗą╗ą░ ąĘą░ą┤ąĄčƹȹ░ąĮą░. ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ, ąĄčüą╗ąĖ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą▒čŗą╗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą▓ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ BS2 ą▓ą╝ąĄčüč鹊 SYNC_SEG, ąĖąĮč鹥čĆą▓ą░ą╗ BS2 čāą║ąŠčĆą░čćąĖą▓ą░ąĄčéčüčÅ ąĮą░ SJW, čćč鹊ą▒čŗ č鹊čćą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą║ą░ąĘą░ą╗ą░čüčī čĆą░ąĮčīčłąĄ.

ąÆ ą║ą░č湥čüčéą▓ąĄ ąĘą░čēąĖčéčŗ ąŠčé ąŠčłąĖą▒ąŠą║ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ Bit Timing Register (CAN_BTR) ą▓ąŠąĘą╝ąŠąČąĮą░ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Standby.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čéą░ą╣ą╝ąĖąĮą│ą░ ą▒ąĖčé CAN ąĖ ą╝ąĄčģą░ąĮąĖąĘą╝ą░ čĆąĄčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čüą╝. ą▓ čüčéą░ąĮą┤ą░čĆč鹥 ISO 11898.

ąĀąĖčü. 346. ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▒ąĖčé.

1

BaudRate = ----------------

NominalBitTime

NominalBitTime = 1 x tq + tBS1 + tBS2

ąŚą┤ąĄčüčī:

tBS1 = tq x (TS1[3:0] + 1),

tBS2 = tq x (TS2[2:0] + 1),

tq = (BRP[9:0] + 1) x tPCLK

tq ąŠą▒ąŠąĘąĮą░čćą░ąĄčé Time quantum.

tPCLK = ą┐ąĄčĆąĖąŠą┤ čéą░ą║č鹊ą▓ APB, BRP[9:0], TS1[3:0] ąĖ TS2[2:0] ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_BTR.

ąĀąĖčü. 347. ążčĆąĄą╣ą╝čŗ CAN.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

0 Ōēż N Ōēż 8

SOF = Start Of Frame (ąĮą░čćą░ą╗ąŠ čäčĆąĄą╣ą╝ą░).

ID = Identifier (ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ).

RTR = Remote Transmission Request (ąĘą░ą┐čĆąŠčü ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ąŠčé čāą┤ą░ą╗ąĄąĮąĮąŠą│ąŠ čüąĄč鹥ą▓ąŠą│ąŠ čāąĘą╗ą░).

IDE = Identifier Extension Bit (ą▒ąĖčé čĆą░čüčłąĖčĆąĄąĮąĖčÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░).

r0 = Reserved Bit (ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▒ąĖčé).

DLC = Data Length Code (ą║ąŠą┤ ą┤ą╗ąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ).

CRC = Cyclic Redundancy Code (ą║ąŠąĮčéčĆąŠą╗čīąĮą░čÅ čüčāą╝ą╝ą░).

Error flag: čäą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ, 6 ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗčģ ą▒ąĖčé, ąĄčüą╗ąĖ ąĮą░ čāąĘą╗ąĄ ą░ą║čéąĖą▓ąĮą░čÅ ąŠčłąĖą▒ą║ą░, ąĖąĮą░č湥 6 čĆąĄčåąĄčüčüąĖą▓ąĮčŗčģ ą▒ąĖčé.

Suspend transmission: ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą┐čĆąĖą╝ąĄąĮąĖą╝ąŠ č鹊ą╗čīą║ąŠ ą║ čāąĘą╗ą░ą╝ čü ą┐ą░čüčüąĖą▓ąĮąŠą╣ ąŠčłąĖą▒ą║ąŠą╣.

EOF = End of Frame (ą║ąŠąĮąĄčå čäčĆąĄą╣ą╝ą░).

ACK = Acknowledge bit (ą▒ąĖčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ).

Ctrl = Control (čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ).

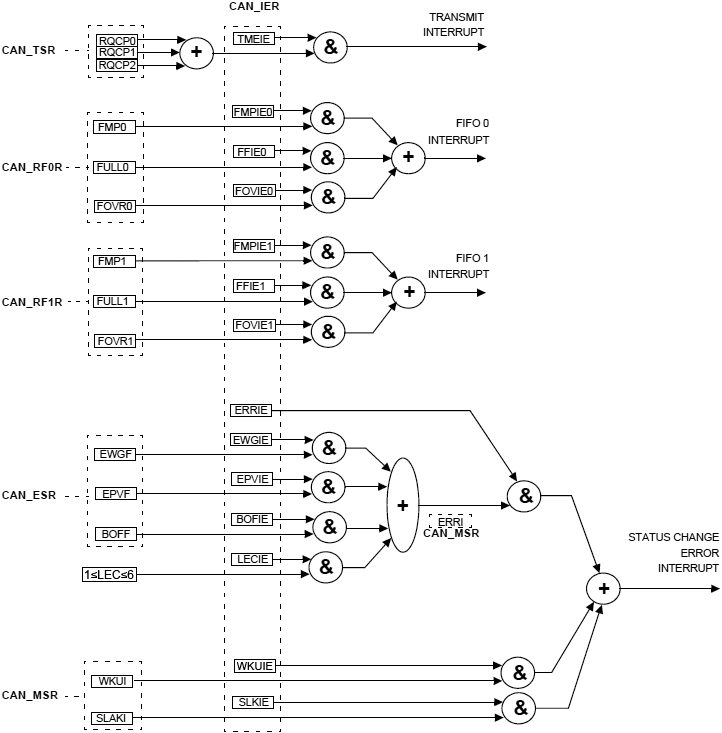

[ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ bxCAN]

ąöą╗čÅ bxCAN ą▓čŗą┤ąĄą╗ąĄąĮąŠ 4 ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąÜą░ąČą┤čŗą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ čĆą░ąĘčĆąĄčłąĄąĮ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CAN (CAN Interrupt Enable Register, CAN_IER).

ąĀąĖčü. 348. ążą╗ą░ą│ąĖ čüąŠą▒čŗčéąĖą╣ ąĖ ą│ąĄąĮąĄčĆą░čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit interrupt) ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ąŠčé čüą╗ąĄą┤čāčÄčēąĖčģ čüąŠą▒čŗčéąĖą╣:

ŌĆō Transmit mailbox 0 čüčéą░ą╗ ą┐čāčüčéčŗą╝, čāčüčéą░ąĮąŠą▓ąĖą╗čüčÅ ą▒ąĖčé RQCP0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TSR.

ŌĆō Transmit mailbox 1 čüčéą░ą╗ ą┐čāčüčéčŗą╝, čāčüčéą░ąĮąŠą▓ąĖą╗čüčÅ ą▒ąĖčé RQCP1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TSR.

ŌĆō Transmit mailbox 2 čüčéą░ą╗ ą┐čāčüčéčŗą╝, čāčüčéą░ąĮąŠą▓ąĖą╗čüčÅ ą▒ąĖčé RQCP2 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TSR.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ FIFO0 ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ąŠčé čüą╗ąĄą┤čāčÄčēąĖčģ čüąŠą▒čŗčéąĖą╣:

ŌĆō ą¤čĆąĖąĄą╝ ąĮąŠą▓ąŠą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ, ą▒ąĖčéčŗ FMP0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RF0R ąĮąĄ čĆą░ą▓ąĮčŗ 00b.

ŌĆō ąĪąŠčüč鹊čÅąĮąĖąĄ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮąŠčüčéąĖ FIFO0, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé FULL0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RF0R.

ŌĆō ąĪąŠčüč鹊čÅąĮąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ FIFO0 (overrun), čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé FOVR0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RF0R.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ FIFO 1 ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ąŠčé čüą╗ąĄą┤čāčÄčēąĖčģ čüąŠą▒čŗčéąĖą╣:

ŌĆō ą¤čĆąĖąĄą╝ ąĮąŠą▓ąŠą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ, ą▒ąĖčéčŗ FMP1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RF1R ąĮąĄ čĆą░ą▓ąĮčŗ 00b.

ŌĆō ąĪąŠčüč鹊čÅąĮąĖąĄ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮąŠčüčéąĖ FIFO1, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé FULL1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RF1R.

ŌĆō ąĪąŠčüč鹊čÅąĮąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ FIFO1 (overrun), čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé FOVR1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RF1R.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ ąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čüčéą░čéčāčüą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ čüąŠą▒čŗčéąĖčÅą╝ąĖ:

ŌĆō ą¤čĆąŠąĖąĘąŠčłą╗ą░ ąŠčłąĖą▒ą║ą░ (Error condition), ą┐ąŠą┤čĆąŠą▒ąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ čģą░čĆą░ą║č鹥čĆąĄ ąŠčłąĖą▒ą║ąĖ ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ ąŠčłąĖą▒ą║ąĖ (CAN Error Status register, CAN_ESR).

ŌĆō ą¤čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ (Wakeup condition), ąĮą░ čüąĖą│ąĮą░ą╗ąĄ ą┐čĆąĖąĄą╝ą░ CAN Rx ąŠą▒ąĮą░čĆčāąČąĄąĮąŠ ąĮą░čćą░ą╗ąŠ čäčĆąĄą╣ą╝ą░ (SOF).

ŌĆō ąÆčģąŠą┤ ą▓ čĆąĄąČąĖą╝ čüąĮą░ (Sleep mode).

[ąĀąĄą│ąĖčüčéčĆčŗ CAN]

ąÜ čĆąĄą│ąĖčüčéčĆą░ą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ CAN ąĮčāąČąĮąŠ ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ą░ą║ ą║ čüą╗ąŠą▓ą░ą╝ (32-ą▒ąĖčéąĮčŗą╣ ą┤ąŠčüčéčāą┐). ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░ čāą║ą░ąĘą░ąĮąŠ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ CAN1_BASE ąĖą╗ąĖ CAN2_BASE (ą╝ąŠąČąĮąŠ čāąĘąĮą░čéčī ą▓ čäą░ą╣ą╗ąĄ stm32f407xx.h). ąöą╗čÅ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ CAN1 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą░ą┤čĆąĄčüą░ 0x40006400 .. 0x400067FF (ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü 0x40006400). ąöą╗čÅ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ CAN2 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą░ą┤čĆąĄčüą░ 0x40006800 .. 0x40006BFF (ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü 0x40006800). ąĀąĄą│ąĖčüčéčĆčŗ čüąŠ čüą╝ąĄčēąĄąĮąĖčÅą╝ąĖ ąŠčé 0x200 ą┤ąŠ 0x31C ąĖą╝ąĄčÄčéčüčÅ č鹊ą╗čīą║ąŠ čā CAN1.

ąÆ ąŠą┐ąĖčüą░ąĮąĖąĖ čäčāąĮą║čåąĖą╣ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ čüąŠą║čĆą░čēąĄąĮąĖčÅ:

read/write (rw) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé čćąĖčéą░čéčī ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī čŹčéąĖ ą▒ąĖčéčŗ.

read-only (r) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé č鹊ą╗čīą║ąŠ čćąĖčéą░čéčī čŹčéąĖ ą▒ąĖčéčŗ.

write-only (w) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą▓ čŹč鹊čé ą▒ąĖčé. ą¦č鹥ąĮąĖąĄ ą▒ąĖčéą░ ą▓ąĄčĆąĮąĄčé ąĘąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░.

read/clear (rc_w1) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī ą▒ąĖčé, ą░ čéą░ą║ąČąĄ čüą▒čĆąŠčüąĖčéčī ąĄą│ąŠ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüčīčÄ 1. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

read/clear (rc_w0) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī ą▒ąĖčé, ą░ čéą░ą║ąČąĄ čüą▒čĆąŠčüąĖčéčī ąĄą│ąŠ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüčīčÄ 0. ąŚą░ą┐ąĖčüčī 1 ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

read/clear by read (rc_r) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī čŹč鹊čé ą▒ąĖčé. ą¦č鹥ąĮąĖąĄ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą▒čĆąŠčüąĖčé ąĄą│ąŠ ą▓ 0. ąŚą░ą┐ąĖčüčī 0 ą▓ ą▒ąĖčé ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

read/set (rs) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī, ą░ čéą░ą║ąČąĄ čāčüčéą░ąĮąŠą▓ąĖčéčī čŹč鹊čé ą▒ąĖčé. ąŚą░ą┐ąĖčüčī 0 ą▓ ą▒ąĖčé ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

read-only write trigger (rt_w) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī čŹč鹊čé ą▒ąĖčé. ąŚą░ą┐ąĖčüčī 0 ąĖą╗ąĖ 1 ą▓čŗąĘąŠą▓ąĄčé ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ (čéčĆąĖą│ą│ąĄčĆ), ąĮąŠ ąĮąĄ ąŠą║ą░ąČąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░.

toggle (t) ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčī čŹč鹊čé ą▒ąĖčé ąĘą░ą┐ąĖčüčīčÄ 1. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

Reserved (Res.) ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▒ąĖčé, ąĄą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ąĮą░ ąĘąĮą░č湥ąĮąĖąĖ čüą▒čĆąŠčüą░.

ąŚą░čēąĖčéą░ ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝. ą×čłąĖą▒ąŠčćąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮčŗą╝ čĆąĄą│ąĖčüčéčĆą░ą╝ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ č鹊ą╝čā, čćč鹊 ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ą▓čĆąĄą╝ąĄąĮąĮąŠ ąĮą░čĆčāčłąĖčé čĆą░ą▒ąŠčéčā ą▓čüąĄą╣ čüąĄčéąĖ CAN. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čĆąĄą│ąĖčüčéčĆ CAN_BTR ą╝ąŠąČąĄčé ą▒čŗčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ CAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ (initialization mode).

ąźąŠčéčÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮąĄą║ąŠčĆčĆąĄą║čéąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐čĆąŠą▒ą╗ąĄą╝ą░ą╝ ąĮą░ čüąĄč鹥ą▓ąŠą╝ čāčĆąŠą▓ąĮąĄ CAN, čŹč鹊 ą╝ąŠąČąĄčé čüąĖą╗čīąĮąŠ ą┐ąŠą╝ąĄčłą░čéčī čĆą░ą▒ąŠč鹥 ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ą¤ąĄčĆąĄą┤ą░čÄčēąĖą╣ mailbox ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ mailbox ą▓ čüąŠčüč鹊čÅąĮąĖąĖ empty, čüą╝. čĆąĖčü. 340.

ąŚąĮą░č湥ąĮąĖčÅ čäąĖą╗čīčéčĆą░ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮčŗ ą╗ąĖą▒ąŠ ą┤ąĄą░ą║čéąĖą▓ą░čåąĖąĄą╣ ą▒ą░ąĮą║ąŠą▓ čäąĖą╗čīčéčĆą░, ą╗ąĖą▒ąŠ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ FINIT. ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čäąĖą╗čīčéčĆą░ (scale, mode ąĖ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ FIFO) ą▓ čĆąĄą│ąĖčüčéčĆą░čģ CAN_FMxR, CAN_FSxR ąĖ CAN_FFAR ą╝ąŠąČąĄčé ą▒čŗčéčī č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čĆąĄąČąĖą╝ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čäąĖą╗čīčéčĆą░ (filter initialization mode, FINIT=1) ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_FMR.

[ąĀąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüąŠčüč鹊čÅąĮąĖčÅ]

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x00

ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░: 0x00010002

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

DBF

rw |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

RESET

rs |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

TTCM

rw |

ABOM

rw |

AWUM

rw |

NART

rw |

RFLM

rw |

TXFP

rw |

SLEEP

rw |

INRQ

rw |

ąæąĖčéčŗ 31:17 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DBF (ą▒ąĖčé 16): DeBug Freeze, ąŠčüčéą░ąĮąŠą▓ą║ą░ CAN ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠčéą╗ą░ą┤ą║ąĖ.

0: ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠčéą╗ą░ą┤ą║ąĖ CAN čĆą░ą▒ąŠčéą░ąĄčé.

1: ą┐čĆąĖąĄą╝/ą┐ąĄčĆąĄą┤ą░čćą░ CAN ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠčéą╗ą░ą┤ą║ąĖ ąĘą░ą╝ąŠčĆą░ąČąĖą▓ą░ąĄčéčüčÅ. ąĪč鹥ą║ąĖ Reception FIFO ą▓čüąĄ ąĄčēąĄ ą╝ąŠą│čāčé ąĮąŠčĆą╝ą░ą╗čīąĮąŠ čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ ąĖ ą║ ąĮąĖą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ ą┤ąŠčüčéčāą┐.

RESET (ą▒ąĖčé 15): ą│ą╗ą░ą▓ąĮčŗą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü (bxCAN software master reset).

0: ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ.

1: ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮčŗą╣ čüą▒čĆąŠčü bxCAN, ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ Sleep mode (ą▒ąĖčéčŗ FMP ąĖ čĆąĄą│ąĖčüčéčĆ CAN_MCR ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ čüą▓ąŠąĖą╝ąĖ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░). ąŁč鹊čé ą▒ąĖčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą▒čĆąŠčüąĖčéčüčÅ ą▓ 0.

ąæąĖčéčŗ 14:8 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

TTCM (ą▒ąĖčé 7): Time Triggered Communication Mode, čĆąĄąČąĖą╝ ąŠą▒ą╝ąĄąĮą░, čüčĆą░ą▒ą░čéčŗą▓ą░čÄčēąĖą╣ ą┐ąŠ ą▓čĆąĄą╝ąĄąĮąĖ.

0: čĆąĄąČąĖą╝ Time Triggered Communication ąĘą░ą┐čĆąĄčēąĄąĮ.

1: čĆąĄąČąĖą╝ Time Triggered Communication čĆą░ąĘčĆąĄčłąĄąĮ.

ABOM (ą▒ąĖčé 6): Automatic Bus-Off Management, ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖąĄą╝ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ ąŠčé čłąĖąĮčŗ. ąŁč鹊čé ą▒ąĖčé čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄą╝ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ CAN ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ Bus-Off.

0: ą▓čŗčģąŠą┤ ąĖąĘ Bus-Off ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐ąŠ ąĘą░ą┐čĆąŠčüčā ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé 128 čüą╗čāčćą░ąĄą▓ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ 11 čĆąĄčåąĄčüčüąĖą▓ąĮčŗčģ ą▒ąĖčé, ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ čüąĮą░čćą░ą╗ą░ ą┤ąŠą╗ąČąĮą░ čāčüčéą░ąĮąŠą▓ąĖčéčī ąĖ ąŠčćąĖčüčéąĖčéčī ą▒ąĖčé INRQ čĆąĄą│ąĖčüčéčĆą░ CAN_MCR.

1: čüąŠčüč鹊čÅąĮąĖąĄ Bus-Off ą▒čāą┤ąĄčé ąŠčüčéą░ą▓ą╗ąĄąĮąŠ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą▒čāą┤ąĄčé ąŠą▒ąĮą░čĆčāąČąĄąĮąŠ 128 čüą╗čāčćą░ąĄą▓ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ 11 čĆąĄčåąĄčüčüąĖą▓ąĮčŗčģ ą▒ąĖčé.

AWUM (ą▒ąĖčé 5): Automatic WakeUp Mode, čĆąĄąČąĖą╝ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ. ąŁč鹊čé ą▒ąĖčé čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄą╝ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ CAN ąĮą░ ą┐čĆąĖąĄą╝ąĄ čüąŠąŠą▒čēąĄąĮąĖčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ Sleep mode.

0: ąĖąĘ čĆąĄąČąĖą╝ą░ čüąĮą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą▓čŗčģąŠą┤ ą┐ąŠ ąĘą░ą┐čĆąŠčüčā ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ SLEEP čĆąĄą│ąĖčüčéčĆą░ CAN_MCR.

1: ąĖąĘ čĆąĄąČąĖą╝ą░ čüąĮą░ ą▓čŗčģąŠą┤ ą▒čāą┤ąĄčé ą┐čĆąŠąĖąĘą▓ąĄą┤ąĄąĮ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ, ą║ąŠą│ą┤ą░ ą▒čāą┤ąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ čüąŠąŠą▒čēąĄąĮąĖąĄ CAN. ąæąĖčé SLEEP čĆąĄą│ąĖčüčéčĆą░ CAN_MCR ąĖ ą▒ąĖčé SLAK čĆąĄą│ąĖčüčéčĆą░ CAN_MSR ąŠčćąĖčüčéčÅčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ.

NART (ą▒ąĖčé 4): No Automatic ReTransmission, ą▒ąĄąĘ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ą┐ąŠą▓č鹊čĆąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

0: ą░ą┐ą┐ą░čĆą░čéčāčĆą░ CAN ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą┐čāčüą║ą░čéčī ą┐ąŠą▓č鹊čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą┐ąŠą║ą░ čüąŠąŠą▒čēąĄąĮąĖąĄ ąĮąĄ ą▒čāą┤ąĄčé čāčüą┐ąĄčłąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čüąŠ čüčéą░ąĮą┤ą░čĆč鹊ą╝ CAN.

1: čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čāą┤ąĄčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąŠ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čĆąĄąĘčāą╗čīčéą░čéą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (čāčüą┐ąĄčłąĮąŠ ąĖą╗ąĖ ąĮąĄčé ąĖąĘ-ąĘą░ ąŠčłąĖą▒ą║ąĖ ąĖą╗ąĖ ą┐ąŠč鹥čĆąĖ ą░čĆą▒ąĖčéčĆą░ąČą░).

RFLM (ą▒ąĖčé 3): Receive FIFO Locked Mode, čĆąĄąČąĖą╝ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą┐čĆąĖąĄą╝ąĮąŠą│ąŠ FIFO.

0: Receive FIFO ąĮąĄ ą▒ą╗ąŠą║ąĖčĆčāąĄčéčüčÅ ą┐čĆąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ (overrun). ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąĖąĄą╝ąĮčŗą╣ FIFO ąĘą░ą┐ąŠą╗ąĮąĖčéčüčÅ, čüą╗ąĄą┤čāčÄčēąĄąĄ ą┐ąŠčüčéčāą┐ąĖą▓čłąĄąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą┐ąĄčĆąĄąĘą░ą┐ąĖčłąĄčé ą┐čĆąĄą┤čŗą┤čāčēąĄąĄ.

1: Receive FIFO ą▒ą╗ąŠą║ąĖčĆčāąĄčéčüčÅ ąĮą░ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčī ą┐čĆąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąĖąĄą╝ąĮčŗą╣ FIFO ąĘą░ą┐ąŠą╗ąĮąĖčéčüčÅ, čüą╗ąĄą┤čāčÄčēąĄąĄ ą┐čĆąĖčłąĄą┤čłąĄąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čāą┤ąĄčé ąŠčéą▒čĆąŠčłąĄąĮąŠ ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą┐ąŠč鹥čĆčÅąĮąŠ.

TXFP (ą▒ąĖčé 2): Transmit FIFO Priority, ą┐čĆąĖąŠčĆąĖč鹥čé FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŁč鹊čé ą▒ąĖčé čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠčĆčÅą┤ą║ąŠą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąŠąŠą▒čēąĄąĮąĖą╣, ą║ąŠą│ą┤ą░ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠąČąĖą┤ą░čÄčé ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ mailbox.

0: ą┐čĆąĖąŠčĆąĖč鹥čé ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ą▒ąĄčĆąĄčéčüčÅ ą┐ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā čüąŠąŠą▒čēąĄąĮąĖčÅ (č湥ą╝ ą╝ąĄąĮčīčłąĄ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ, č鹥ą╝ ą┐čĆąĖąŠčĆąĖč鹥čé ą▓čŗčłąĄ).

1: ą┐čĆąĖąŠčĆąĖč鹥čé ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ą▒ąĄčĆąĄčéčüčÅ ą┐ąŠ ą┐ąŠčĆčÅą┤ą║čā ąĘą░ą┐čĆąŠčüą░ (čģčĆąŠąĮąŠą╗ąŠą│ąĖč湥čüą║ąĖ: č湥ą╝ čĆą░ąĮčīčłąĄ mailbox ą▒čŗą╗ ą┐ąŠčüčéą░ą▓ą╗ąĄąĮ ąĮą░ ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ, č鹥ą╝ čĆą░ąĮčīčłąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąĄą│ąŠ ą┐ąĄčĆąĄą┤ą░čćą░).

SLEEP (ą▒ąĖčé 1): ąĘą░ą┐čĆąŠčü ąĮą░ ą▓čģąŠą┤ čĆąĄąČąĖą╝ čüąĮą░ (Sleep Mode). ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ ąĘą░ą┐čĆąŠčüąĖčéčī čā ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ CAN ąĄčæ ą▓čģąŠą┤ ą▓ Sleep Mode. ąÆ čĆąĄąČąĖą╝ čüąĮą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą▓čģąŠą┤, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą▒čāą┤ąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮą░ č鹥ą║čāčēą░čÅ ą░ą║čéąĖą▓ąĮąŠčüčéčī CAN (ą┐ąĄčĆąĄą┤ą░čćą░ ąĖą╗ąĖ ą┐čĆąĖąĄą╝ čäčĆąĄą╣ą╝ą░ CAN). ąŁč鹊čé ą▒ąĖčé ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ čĆąĄąČąĖą╝ą░ čüąĮą░. ąŁč鹊čé ą▒ąĖčé ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé AWUM ąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ą▒ąĖčé SOF ą▓ čüąĖą│ąĮą░ą╗ąĄ CAN Rx. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ -ą░ą┐ą┐ą░čĆą░čéčāčĆą░ CAN ąĖąĘąĮą░čćą░ą╗čīąĮąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ Sleep mode.

INRQ (ą▒ąĖčé 0): INitialization ReQuest. ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ąŠčćąĖčēą░ąĄčé čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▒čāą┤ąĄčé ąŠą▒ąĮą░čĆčāąČąĄąĮąŠ 11 čüą╗ąĄą┤čāčÄčēąĖčģ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ čĆąĄčåąĄčüčüąĖą▓ąĮčŗčģ ą▒ąĖčé ąĮą░ čüąĖą│ąĮą░ą╗ąĄ RX, ą░ą┐ą┐ą░čĆą░čéčāčĆą░ CAN čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮą░ ąĖ ą│ąŠč鹊ą▓ą░ ą║ ą┐ąĄčĆąĄą┤ą░č湥 ąĖ ą┐čĆąĖąĄą╝ą░. ąÉą┐ą┐ą░čĆą░čéčāčĆą░ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠą▒ čŹč鹊ą╝ čüąŠą▒čŗčéąĖąĖ ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ INAK ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MSR.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ čāčüčéą░ąĮąŠą▓ąĖčé čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ ąĘą░ą┐čĆąŠčüą░ ą░ą┐ą┐ą░čĆą░čéčāčĆąĄ CAN ą▓ąŠą╣čéąĖ ą▓ čĆąĄąČąĖą╝ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ (initialization mode). ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ čāčüčéą░ąĮąŠą▓ąĖčé ą▒ąĖčé INRQ, ą░ą┐ą┐ą░čĆą░čéčāčĆą░ CAN ą┐ąŠą┤ąŠąČą┤ąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ č鹥ą║čāčēąĄą╣ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ CAN (ą┐ąĄčĆąĄą┤ą░čćą░ ąĖą╗ąĖ ą┐čĆąĖąĄą╝) ą┐ąĄčĆąĄą┤ ą▓čģąŠą┤ąŠą╝ ą▓ initialization mode. ąÉą┐ą┐ą░čĆą░čéčāčĆą░ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠą▒ čŹč鹊ą╝ čüąŠą▒čŗčéąĖąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ INAK ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MSR.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x04

ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░: 0x00000C02

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

RX

r |

SAMP

r |

RXM

r |

TXM

r |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

SLAKI

rc_w1 |

WKUI

rc_w1 |

ERRI

rc_w1 |

SLAK

r |

INAK

r |

ąæąĖčéčŗ 31:12 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

RX (ą▒ąĖčé 11): ąĪąĖą│ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ CAN Rx. ą£ąŠąĮąĖč鹊čĆąĖčéčüčÅ ą░ą║čéčāą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗą▓ąŠą┤ą░ CAN_RX (ą║ą░ą║ ąĮą░ ąŠą▒čŗčćąĮąŠą╣ ąĮąŠąČą║ąĄ GPIO).

SAMP (ą▒ąĖčé 10): ą┐ąŠčüą╗ąĄą┤ąĮčÅčÅ č鹊čćą║ą░ ą▓čŗą▒ąŠčĆą║ąĖ (SAMple Point). ąŚąĮą░č湥ąĮąĖąĄ RX ąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ č鹊čćą║ąĄ ą▓čŗą▒ąŠčĆą║ąĖ (č鹥ą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░).

RXM (ą▒ąĖčé 9): Receive mode, čĆąĄąČąĖą╝ ą┐čĆąĖąĄą╝ą░. ąÉą┐ą┐ą░čĆą░čéčāčĆą░ CAN čüąĄą╣čćą░čü čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐čĆąĖąĄą╝ąĮąĖą║.

TXM (ą▒ąĖčé 8): Transmit mode, čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÉą┐ą┐ą░čĆą░čéčāčĆą░ CAN čüąĄą╣čćą░čü čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║.

ąæąĖčéčŗ 7:5 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

SLAKI (ą▒ąĖčé 4): SLeep AcKnowledge Interrupt, ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓čģąŠą┤ą░ ą▓ čĆąĄąČąĖą╝ čüąĮą░. ąÜąŠą│ą┤ą░ SLKIE=1, čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖąĖ, čćč鹊 bxCAN ą▓ąŠčłąĄą╗ ą▓ Sleep Mode. ąÜąŠą│ą┤ą░ ą▒ąĖčé SLAKI čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ (status change interrupt), ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé SLKIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_IER. ąŁč鹊čé ą▒ąĖčé ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĖą╗ąĖ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ąŠčćąĖčēąĄąĮ ą▒ąĖčé SLAK.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ SLKIE=0, ąŠą┐čĆąŠčü SLAKI ąĮąĄą▓ąŠąĘą╝ąŠąČąĄąĮ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą╝ąŠąČąĮąŠ ąŠą┐čĆą░čłąĖą▓ą░čéčī ą▒ąĖčé SLAK.

WKUI (ą▒ąĖčé 3): WaKeUP Interrupt, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖąĖ, ą║ąŠą│ą┤ą░ ą▒čŗą╗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą▒ąĖčé ąĮą░čćą░ą╗ą░ čäčĆąĄą╣ą╝ą░ SOF ąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ CAN ąĮą░čģąŠą┤ąĖą╗ą░čüčī ą▓ Sleep mode. ąŻčüčéą░ąĮąŠą▓ą║ą░ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čüčéą░čéčāčüą░, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé WKUIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_IER. ąŁč鹊čé ą▒ąĖčé ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣.

ERRI (ą▒ąĖčé 2): ERRor Interrupt, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ CAN_ESR ąĮą░ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ, ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ CAN_IER. ąŻčüčéą░ąĮąŠą▓ą║ą░ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čüčéą░čéčāčüą░, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ERRIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_IER.

ąæąĖčé ERRI ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣.

SLAK (ą▒ąĖčé 1): SLeep AcKnowledge, ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ą▓čģąŠą┤ą░ ą▓ čĆąĄąČąĖą╝ čüąĮą░. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą┐ąŠą║ą░ąĘčŗą▓ą░čÅ č鹥ą╝ čüą░ą╝čŗą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ, čćč鹊 ą░ą┐ą┐ą░čĆą░čéčāčĆą░ CAN ąĮą░čģąŠą┤ąĖčéčüčÅ č鹥ą┐ąĄčĆčī ą▓ Sleep mode. ąŁč鹊čé ą▒ąĖčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčé ąĘą░ą┐čĆąŠčü ąĮą░ Sleep mode ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝čŗ (čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ SLEEP ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCR).

ąæąĖčé SLAK ąŠčćąĖčüčéąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ CAN ą▓čŗą╣ą┤ąĄčé ąĖąĘ Sleep mode (čćč鹊ą▒čŗ ąĘą░čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčīčüčÅ ąĮą░ čłąĖąĮąĄ CAN). ąöą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ąŠčéčüą╗ąĄąČąĖą▓ą░ąĄčé 11 čüą╗ąĄą┤čāčÄčēąĖčģ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ čĆąĄčåąĄčüčüąĖą▓ąĮčŗčģ ą▒ąĖčéą░ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ CAN RX.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐čĆąŠčåąĄčüčü ą▓čŗčģąŠą┤ą░ ąĖąĘ Sleep čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ąŠčćąĖčēą░ąĄčéčüčÅ ą▒ąĖčé SLEEP ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCR. ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčéą░ AWUM čĆąĄą│ąĖčüčéčĆą░ CAN_MCR ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ąŠčćąĖčüčéą║ąĄ ą▒ąĖčéą░ SLEEP.

INAK (ą▒ąĖčé 0): INitialization AcKnowledge, ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ čĆąĄąČąĖą╝ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą┐ąŠą║ą░ąĘčŗą▓ą░čÅ č鹥ą╝ čüą░ą╝čŗą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ, čćč鹊 ą░ą┐ą┐ą░čĆą░čéčāčĆą░ CAN ąĮą░čģąŠą┤ąĖčéčüčÅ č鹥ą┐ąĄčĆčī ą▓ initialization mode. ąŁč鹊čé ą▒ąĖčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčé ąĘą░ą┐čĆąŠčü ąĮą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÄ ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝čŗ (čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ INRQ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCR).

ąŁč鹊čé ą▒ąĖčé ąŠčćąĖčüčéąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ CAN ą▓čŗą╣ą┤ąĄčé ąĖąĘ čĆąĄąČąĖą╝ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ (čćč鹊ą▒čŗ ąĘą░čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčīčüčÅ ąĮą░ čłąĖąĮąĄ CAN). ąöą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ąŠčéčüą╗ąĄąČąĖą▓ą░ąĄčé 11 čüą╗ąĄą┤čāčÄčēąĖčģ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ čĆąĄčåąĄčüčüąĖą▓ąĮčŗčģ ą▒ąĖčéą░ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ CAN RX.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x08

ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░: 0x1ąĪ000000

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

LOW2

r |

LOW1

r |

LOW0

r |

TME2

r |

TME1

r |

TME0

r |

CODE[1:0]

r |

ABRQ2

rs |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

TERR2

rc_w1 |

ALST2

rc_w1 |

TXOK2

rc_w1 |

RQCP2

rc_w1 |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ABRQ1

rs |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

TERR1

rc_w1 |

ALST1

rc_w1 |

TXOK1

rc_w1 |

RQCP1

rc_w1 |

ABRQ0

rs |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

TERR0

rc_w1 |

ALST0

rc_w1 |

TXOK0

rc_w1 |

RQCP0

rc_w1 |

LOW2 (ą▒ąĖčé 31): LOWest priority flag for mailbox 2, čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé ą┤ą╗čÅ čÅčēąĖą║ą░ 2. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣, ą║ąŠą│ą┤ą░ ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ mailbox ąŠąČąĖą┤ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ čā mailbox 2 ą▒čŗą╗ čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé.

LOW1 (ą▒ąĖčé 30): LOWest priority flag for mailbox 1, čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé ą┤ą╗čÅ čÅčēąĖą║ą░ 1. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣, ą║ąŠą│ą┤ą░ ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ mailbox ąŠąČąĖą┤ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ čā mailbox 1 ą▒čŗą╗ čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé.

LOW0 (ą▒ąĖčé 29): LOWest priority flag for mailbox 0, čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé ą┤ą╗čÅ čÅčēąĖą║ą░ 0. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣, ą║ąŠą│ą┤ą░ ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ mailbox ąŠąČąĖą┤ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ čā mailbox 0 ą▒čŗą╗ čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖčéčŗ LOW[2:0] čāčüčéą░ąĮąŠą▓čÅčéčüčÅ ą▓ 0, ą║ąŠą│ą┤ą░ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ mailbox ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ąŠąČąĖą┤ą░ąĮąĖąĖ (pending) ą┐ąĄčĆąĄą┤ą░čćąĖ.

TME2 (ą▒ąĖčé 28): Transmit Mailbox 2 Empty, ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╣ čÅčēąĖą║ 2 ą┐čāčüčé. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣, ą║ąŠą│ą┤ą░ ąĮąĄčé ąŠąČąĖą┤ą░čÄčēąĄą│ąŠ ąĘą░ą┐čĆąŠčüą░ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą╗čÅ mailbox 2.

TME1 (ą▒ąĖčé 27): Transmit Mailbox 1 Empty, ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╣ čÅčēąĖą║ 1 ą┐čāčüčé. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣, ą║ąŠą│ą┤ą░ ąĮąĄčé ąŠąČąĖą┤ą░čÄčēąĄą│ąŠ ąĘą░ą┐čĆąŠčüą░ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą╗čÅ mailbox 1.

TME0 (ą▒ąĖčé 26): Transmit Mailbox 0 Empty, ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╣ čÅčēąĖą║ 0 ą┐čāčüčé. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣, ą║ąŠą│ą┤ą░ ąĮąĄčé ąŠąČąĖą┤ą░čÄčēąĄą│ąŠ ąĘą░ą┐čĆąŠčüą░ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą╗čÅ mailbox 0.

CODE[1:0] (ą▒ąĖčéčŗ 25:24): Mailbox code, ą║ąŠą┤ čÅčēąĖą║ą░. ąÆ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╣ mailbox čüą▓ąŠą▒ąŠą┤ąĄąĮ, ąĘąĮą░č湥ąĮąĖąĄ ą║ąŠą┤ą░ čĆą░ą▓ąĮąŠ ąĮąŠą╝ąĄčĆčā čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüą▓ąŠą▒ąŠą┤ąĮąŠą│ąŠ čÅčēąĖą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąÆ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ ą▓čüąĄ ą┐ąĄčĆąĄą┤ą░čÄčēąĖąĄ čÅčēąĖą║ąĖ ąĘą░ąĮčÅčéčŗ ąŠąČąĖą┤ą░ąĮąĖąĄą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĘąĮą░č湥ąĮąĖąĄ ą║ąŠą┤ą░ čĆą░ą▓ąĮąŠ ąĮąŠą╝ąĄčĆčā ą┐ąĄčĆąĄą┤ą░čÄčēąĄą│ąŠ mailbox čü čüą░ą╝čŗą╝ ąĮąĖąĘą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝.

ABRQ2 (ą▒ąĖčé 23): ABort ReQuest for mailbox 2, ąĘą░ą┐čĆąŠčü ąĮą░ ąŠą▒čĆčŗą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ čÅčēąĖą║ą░ 2. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ ąŠą▒ąŠčĆą▓ą░čéčī ąĘą░ą┐čĆąŠčü ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą╗čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ mailbox. ą×čćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ mailbox čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐čāčüčéčŗą╝.

ąŻčüčéą░ąĮąŠą▓ą║ą░ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░, ą║ąŠą│ą┤ą░ mailbox ąĮąĄ ąŠąČąĖą┤ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćąĖ čüą▓ąŠąĄą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ.

ąæąĖčéčŗ 22:20 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

TERR2 (ą▒ąĖčé 19): Transmission ERRor of mailbox 2, ąŠčłąĖą▒ą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ čÅčēąĖą║ą░ 2. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąĄą┤čŗą┤čāčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąŠč鹥čĆą┐ąĄą╗ą░ ąĮąĄčāą┤ą░čćčā ąĖąĘ-ąĘą░ ąŠčłąĖą▒ą║ąĖ.

ALST2 (ą▒ąĖčé 18): Arbitration lost for mailbox 2, ą┐ąŠč鹥čĆčÅ ą░čĆą▒ąĖčéčĆą░ąČą░ ąĮą░ čÅčēąĖą║ąĄ 2. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąĄą┤čŗą┤čāčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąŠč鹥čĆą┐ąĄą╗ą░ ąĮąĄčāą┤ą░čćčā ąĖąĘ-ąĘą░ ą┐ąŠč鹥čĆąĖ ą░čĆą▒ąĖčéčĆą░ąČą░.

TXOK2 (ą▒ąĖčé 17): Transmission OK of mailbox 2, čāčüą┐ąĄčłąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮą░ čÅčēąĖą║ąĄ 2. ąÉą┐ą┐ą░čĆą░čéčāčĆą░ ąŠą▒ąĮąŠą▓ą╗čÅąĄčé čŹč鹊čé ą▒ąĖčé ą┐čĆąĖ ą║ą░ąČą┤ąŠą╣ ą┐ąŠą┐čŗčéą║ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ.

0: ą┐čĆąĄą┤čŗą┤čāčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąŠč鹥čĆą┐ąĄą╗ą░ ąĮąĄčāą┤ą░čćčā.

1: ą┐čĆąĄą┤čŗą┤čāčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą║ąŠąĮčćąĖą╗ą░čüčī čāčüą┐ąĄčłąĮąŠ.

ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ąĘą░ą┐čĆąŠčü ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā čÅčēąĖą║ą░ 2 ą▒čŗą╗ čāčüą┐ąĄčłąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮ. ąĪą╝. čĆąĖčü. 340.

RQCP2 (ą▒ąĖčé 16): Request completed mailbox 2, ąĘą░ą▓ąĄčĆčłąĄąĮ ąĘą░ą┐čĆąŠčü čÅčēąĖą║ą░ 2. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣, ą║ąŠą│ą┤ą░ ą▒čŗą╗ ą▓čŗą┐ąŠą╗ąĮąĄąĮ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąĘą░ą┐čĆąŠčü (transmit ąĖą╗ąĖ abort).

ą×čćąĖčēą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą╗ąŠą│. 1, ąĖą╗ąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ ą┐čĆąĖ ąĘą░ą┐čĆąŠčüąĄ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā (čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ TXRQ2 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TMID2R).

ą×čćąĖčüčéą║ą░ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ąŠčćąĖčüčéąĖčé ą▓čüąĄ ą▒ąĖčéčŗ čüčéą░čéčāčüą░ (TXOK2, ALST2 ąĖ TERR2) ą┤ą╗čÅ Mailbox 2.

ABRQ1 (ą▒ąĖčé 15): ABort ReQuest for mailbox 1, ąĘą░ą┐čĆąŠčü ąĮą░ ąŠą▒čĆčŗą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ čÅčēąĖą║ą░ 1. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣, čćč鹊ą▒čŗ ąŠą▒ąŠčĆą▓ą░čéčī ąĘą░ą┐čĆąŠčü ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą╗čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ mailbox. ą×čćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ mailbox čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐čāčüčéčŗą╝.