|

ąØąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (general purpose input/output, GPIO) ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮčŗ ą║ą░ą║ ąŠą┤ąĖąĮ ą┐ąŠčĆčé, čā ą║ąŠč鹊čĆąŠą│ąŠ ą┤ąŠ 32 čüąĖą│ąĮą░ą╗ąŠą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (ą║ąŠąĮą║čĆąĄčéąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĮąŠąČąĄą║ ą┐ąŠčĆč鹊ą▓ ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą║ąŠčĆą┐čāčüą░). ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čüčćąĖčéčŗą▓ą░čéčī čāčĆąŠą▓ąĮąĖ ą▓čģąŠą┤ąŠą▓ ąĖ čāą┐čĆą░ą▓ą╗čÅčéčī čāčĆąŠą▓ąĮčÅą╝ąĖ ą▓čŗčģąŠą┤ąŠą▓ ą▓ąĮąĄčłąĮąĖčģ ąĮąŠąČąĄą║ ą┐ąŠčĆč鹊ą▓ č湥čĆąĄąĘ ąŠą┤ąĖąĮ 32-ą▒ąĖčéąĮčŗą╣ ą┐ąŠčĆčé. ąÜ ą║ą░ąČą┤ąŠą╣ ąĮąŠąČą║ąĄ GPIO ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćą░čéčī ą┤ąŠčüčéčāą┐ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čĆą░čüčłąĖčäčĆąŠą▓ą║čā č鹥čĆą╝ąĖąĮąŠą▓ ąĖ čüąŠą║čĆą░čēąĄąĮąĖą╣ čüą╝. ą▓ čüą╗ąŠą▓ą░čĆąĖą║ąĄ [5].

ąŻ GPIO ąĖą╝ąĄčÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ čäčāąĮą║čåąĖąĖ:

ŌĆó 8 čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗčģ GPIO, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čģąŠą┤ąĮčŗąĄ ą║ą░ąĮą░ą╗čŗ ą┤ą╗čÅ SAADC, COMP ąĖą╗ąĖ LPCOMP.

ŌĆó ąØą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą▓čŗčģąŠą┤ą░ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ.

ŌĆó ą£ąŠąČąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćą░čéčī ą▓čüčéčĆąŠąĄąĮąĮčŗąĄ ą▓ąĄčĆčģąĮąĖąĄ (pull-up) ąĖ ąĮąĖąČąĮąĖąĄ (pull-down) ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ.

ŌĆó ą¤čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ ąŠčé ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ ą▓čŗčüąŠą║ąŠą│ąŠ ąĖą╗ąĖ ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ ą╗čÄą▒ąŠą╣ ąĖąĘ ąĮąŠąČąĄą║ ą┐ąŠčĆčéą░.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖčÄ čüąŠčüč鹊čÅąĮąĖčÅ ą╗čÄą▒ąŠą╣ ąĖąĘ ąĮąŠąČąĄą║ ą┐ąŠčĆčéą░.

ŌĆó ąÆčüąĄ ąĮąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┐ąŠą┤čüąĖčüč鹥ą╝ąŠą╣ ąĘą░ą┤ą░čć ąĖ čüąŠą▒čŗčéąĖą╣ PPI (PPI task/event system).

ŌĆó ą×ą┤ąĖąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▓čŗčģąŠą┤ąŠą▓ GPIO ą╝ąŠąČąĄčé čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ č湥čĆąĄąĘ PPI ąĖ ą║ą░ąĮą░ą╗čŗ GPIOTE.

ŌĆó ąÆčüąĄ ą▓čŗą▓ąŠą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ ąŠč鹊ą▒čĆą░ąČąĄąĮčŗ ąĮą░ ą▒ą╗ąŠą║ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, čćč鹊 ą┤ą░ąĄčé ą▒ąŠą╗čīčłčāčÄ ą│ąĖą▒ą║ąŠčüčéčī ą▓ čĆą░ąĘą▓ąŠą┤ą║ąĄ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ.

ŌĆó ąśąĘą╝ąĄąĮąĄąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ GPIO ąĘą░čģą▓ą░č湥ąĮąĮčŗąĄ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ SENSE, ą╝ąŠą│čāčé ą▒čŗčéčī čüąŠčģčĆą░ąĮąĄąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ LATCH.

ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠčĆč鹊ą▓ GPIO čĆąĄą░ą╗ąĖąĘčāąĄčé ą┤ąŠ 32 ąĮąŠąČąĄą║ ą▓čŗą▓ąŠą┤ąŠą▓ ą┐ąŠčĆč鹊ą▓, čü ąĖą╝ąĄąĮą░ą╝ąĖ PIN0 .. PIN31. ąÜą░ąČą┤ą░čÅ ąĖąĘ čŹčéąĖčģ ąĮąŠąČąĄą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ PIN_CNF[n] (n = 0 .. 31). ąÆ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆą░čģ ą╝ąŠąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī čüą╗ąĄą┤čāčÄčēąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ:

ŌĆó Direction (ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ - ą▓čģąŠą┤ ąĖą╗ąĖ ą▓čŗčģąŠą┤).

ŌĆó Drive strength (ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą▓čŗčģąŠą┤ą░).

ŌĆó ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ pull-up ąĖ pull-down čĆąĄąĘąĖčüč鹊čĆąŠą▓.

ŌĆó Pin sensing (ąĮą░čüčéčĆąŠą╣ą║ą░ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ čāčĆąŠą▓ąĮčÅ).

ŌĆó Input buffer disconnect (ąŠčéą║ą╗čÄč湥ąĮąĖąĄ ą▓čģąŠą┤ąĮąŠą│ąŠ ą▒čāč乥čĆą░).

ŌĆó Analog input (ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ ą┤ą╗čÅ ą▓čŗą▒čĆą░ąĮąĮčŗčģ ąĮąŠąČąĄą║).

ąĀąĄą│ąĖčüčéčĆčŗ PIN_CNF ąŠčéąĮąŠčüčÅčéčüčÅ ą║ čüąŠčģčĆą░ąĮčÅąĄą╝čŗą╝ (retained) čĆąĄą│ąĖčüčéčĆą░ą╝, čé. ąĄ. ąĖčģ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą┐čĆąĖ ą┐ąĄčĆąĄčģąŠą┤ąĄ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ą┤ą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ retained-čĆąĄą│ąĖčüčéčĆą░ą╝ čüą╝. [2].

[ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ąĮąŠąČą║ąĖ ą▓čŗą▓ąŠą┤ą░ GPIO]

ąØąŠąČą║ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┐ąŠą╗ąĄą╝ SENSE ą▓ čĆąĄą│ąĖčüčéčĆąĄ PIN_CNF[n], čćč鹊ą▒čŗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčī ą╗ąĖą▒ąŠ ą▓čŗčüąŠą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī, ą╗ąĖą▒ąŠ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ čüą▓ąŠąĄą╝ ą▓čģąŠą┤ąĄ.

ąÜąŠą│ą┤ą░ ą║ąŠčĆčĆąĄą║čéąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ąĮą░ ą╗čÄą▒ąŠą╣ ąĖąĘ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąĮąŠąČąĄą║, ą╝ąĄčģą░ąĮąĖąĘą╝ čāčüčéą░ąĮąŠą▓ąĖčé čüąĖą│ąĮą░ą╗ DETECT ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1. ąŻ ą║ą░ąČą┤ąŠą╣ ąĮąŠąČą║ąĖ ąĄčüčéčī ąŠčéą┤ąĄą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ DETECT, ąĖ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, ą║ą░ą║ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ DETECTMODE, čĆą░ą▒ąŠčéą░ąĄčé čéą░ą║, čćč鹊 čüąĖą│ąĮą░ą╗čŗ DETECT ąŠčé ą▓čüąĄčģ ąĮąŠąČąĄą║ ą┐ąŠčĆčéą░ GPIO ą║ąŠą╝ą▒ąĖąĮąĖčĆčāčÄčéčüčÅ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ą▓ ąŠą▒čēąĖą╣ čüąĖą│ąĮą░ą╗ DETECT, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąŠčģąŠą┤ąĖčé ą┐ąŠ ą▓čüąĄą╣ čüąĖčüč鹥ą╝ąĄ. ąŁč鹊čé ąŠą▒čēąĖą╣ čüąĖą│ąĮą░ą╗ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤čĆčāą│ąĖą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, čüą╝. čĆąĖčü. 1. ą£ąĄčģą░ąĮąĖąĘą╝ čüąĖą│ąĮą░ą╗ąŠą▓ DETECT čäčāąĮą║čåąĖąŠąĮą░ą╗ąĄąĮ ą▓ ąŠą▒ąŠąĖčģ čĆąĄąČąĖą╝ą░čģ System ON ąĖ System OFF.

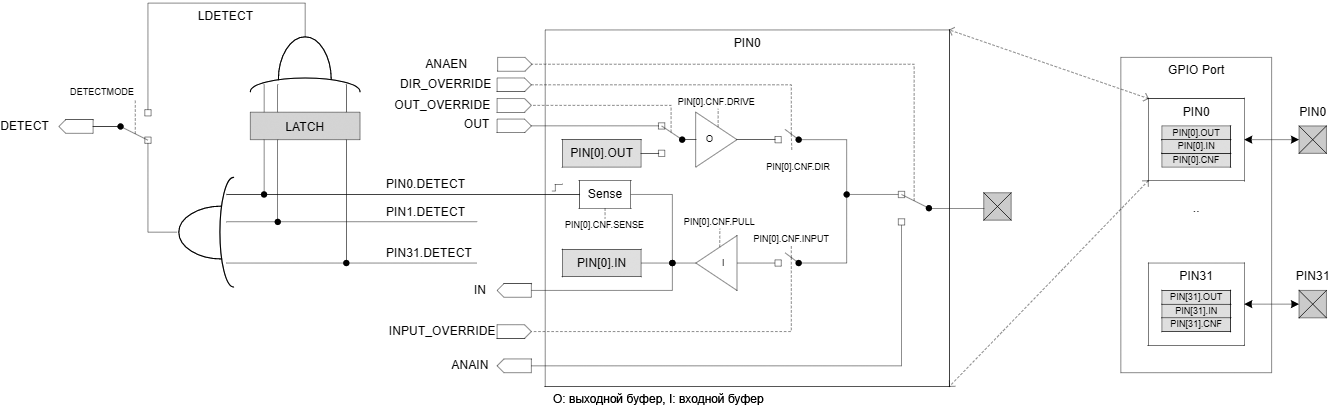

ąĀąĖčü. 1. ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ čüčéčĆčāą║čéčāčĆą░ ą┐ąŠčĆčéą░ GPIO.

ąØą░ čĆąĖčü. 1 ą┐ąŠą║ą░ąĘą░ąĮąŠ, čćč鹊 ą┐ąŠčĆčé GPIO čüąŠą┤ąĄčƹȹĖčé 32 ąŠčéą┤ąĄą╗čīąĮčŗčģ ą▓čŗą▓ąŠą┤ąŠą▓ ąĮąŠąČąĄą║ PIN0 .. PIN31, ą│ą┤ąĄ PIN0 ąĖąĘąŠą▒čĆą░ąČąĄąĮ ą▒ąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ. ąÆčüąĄ čüąĖą│ąĮą░ą╗čŗ ą▓ ą╗ąĄą▓ąŠą╣ čüč鹊čĆąŠąĮąĄ ąĖą╗ą╗čÄčüčéčĆą░čåąĖąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤čĆčāą│ąĖą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ą▓ čüąĖčüč鹥ą╝ąĄ, ąĖ ą┐ąŠčŹč鹊ą╝čā ąŠąĮąĖ ąĮąĄą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ CPU ąĮą░ą┐čĆčÅą╝čāčÄ.

ąŻą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ čéą░ą║ąŠą╣ čāčĆąŠą▓ąĄąĮčī, ą║ąŠč鹊čĆčŗą╣ ąĮąĄ čüą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą╝ąĄčģą░ąĮąĖąĘą╝ą░ sense ą┐ąĄčĆąĄą┤ ąĄą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝. ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüčĆą░ą▒ąŠčéą░ąĄčé ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ, ąĄčüą╗ąĖ čāčüą╗ąŠą▓ąĖąĄ sense, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ PIN_CNF, čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅąĄčé ą┤ąĄą╣čüčéą▓čāčÄčēąĄą╝čā čāčĆąŠą▓ąĮčÄ, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą╝ąĄčģą░ąĮąĖąĘą╝ sense. ąŁč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÄ čüąŠą▒čŗčéąĖčÅ ą┐ąŠčĆčéą░ (PORT event), ąĄčüą╗ąĖ čüąĖą│ąĮą░ą╗ DETECT ą▒čŗą╗ ą▓ ą╗ąŠą│. 0 ą┐ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ ą╝ąĄčģą░ąĮąĖąĘą╝ą░ sense, čüą╝. [3].

ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ čüą╗ąĄą┤čāčÄčēąĖčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą┤ą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ č鹊ą╝, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüąĖą│ąĮą░ą╗ DETECT:

ŌĆó POWER: ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüąĖą│ąĮą░ą╗ DETECT ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ System OFF.

ŌĆó GPIOTE: ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüąĖą│ąĮą░ą╗ DETECT ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ PORT event.

ąÜąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ PINx.DETECT ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1, ą▓ čĆąĄą│ąĖčüčéčĆąĄ LATCH čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čäą╗ą░ą│, ąĮą░ą┐čĆąĖą╝ąĄčĆ ą║ąŠą│ą┤ą░ PIN0.DETECT ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1, ą▓ čĆąĄą│ąĖčüčéčĆąĄ LATCH ą▒ąĖčé 0 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ '1'.

ąæąĖčé LATCH ąŠčćąĖčüčéąĖčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ CPU čÅą▓ąĮąŠ ąŠčćąĖčüčéąĖčé ąĄą│ąŠ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ '1' ą▓ ąĮąĄą│ąŠ. ąØą░ą┐čĆąĖą╝ąĄčĆ, čĆąĄą│ąĖčüčéčĆ LATCH ąĮąĄ ąĖąĘą╝ąĄąĮąĖčéčüčÅ, ą║ąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ PINx.DETECT čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0.

ąĢčüą╗ąĖ CPU ą▓čŗą┐ąŠą╗ąĮąĖčé ąŠą┐ąĄčĆą░čåąĖčÄ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ LATCH, ą║ąŠą│ą┤ą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čüąĖą│ąĮą░ą╗ PINx.DETECT ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1, č鹊 čŹč鹊čé ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ LATCH ąĮąĄ ąŠčćąĖčüčéąĖčéčüčÅ.

ąĪąĖą│ąĮą░ą╗ LDETECT čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ ąŠą┤ąĖąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ LATCH ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ '1'. ąĪąĖą│ąĮą░ą╗ LDETECT čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ 0, ą║ąŠą│ą┤ą░ ą▓čüąĄ ą▒ąĖčéčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ LATCH ą▒čŗą╗ąĖ čāčüą┐ąĄčłąĮąŠ ąŠčćąĖčēąĄąĮčŗ ąĖ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ '0'.

ąĢčüą╗ąĖ ąŠą┤ąĖąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ '1' ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ CPU ą▓čŗą┐ąŠą╗ąĮąĖą╗ ąŠą┐ąĄčĆą░čåąĖčÄ ąŠčćąĖčüčéą║ąĖ ąĮą░ą┤ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ LATCH, čüą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čäčĆąŠąĮčé ąĮą░čĆą░čüčéą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ LDETECT, čćč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 2.

ąÆą░ąČąĮąŠąĄ ąĘą░ą╝ąĄčćą░ąĮąĖąĄ: CPU ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī čĆąĄą│ąĖčüčéčĆ LATCH ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé, čćč鹊ą▒čŗ ą┐čĆąŠą▓ąĄčĆąĖčéčī, čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅąĄčéčüčÅ ą╗ąĖ čāčüą╗ąŠą▓ąĖąĄ SENSE ąĮą░ ąŠą┤ąĮąŠą╣ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąĄ ąĮąŠąČąĄą║ GPIO, ą┤ą░ąČąĄ ąĄčüą╗ąĖ čŹč鹊 čāčüą╗ąŠą▓ąĖąĄ ą▒ąŠą╗čīčłąĄ ąĮąĄ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅąĄčéčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé ąŠą┐čĆąŠčüą░ čĆąĄą│ąĖčüčéčĆą░ LATCH. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čĆąĄą│ąĖčüčéčĆ LATCH čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ąĘą░čēąĄą╗ą║ą░, ąĘą░ą┐ąŠą╝ąĖąĮą░čÅ ą▓ąŠąĘąĮąĖą║ą░čÄčēąĖąĄ čüąŠą▒čŗčéąĖčÅ SENSE. ąŁč鹊čé ą╝ąĄčģą░ąĮąĖąĘą╝ ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī ą┤ą░ąČąĄ ąĄčüą╗ąĖ čüąĖą│ąĮą░ą╗ LDETECT ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ čüąĖą│ąĮą░ą╗ą░ DETECT.

ąĪąĖą│ąĮą░ą╗ LDETECT ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĮąĄ ą┐ąŠą┤čüąŠąĄą┤ąĖąĮąĄąĮ ą║ čüąĖą│ąĮą░ą╗čā DETECT ą┐ąŠčĆčéą░ GPIO. ą×ą┤ąĮą░ą║ąŠ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ DETECTMODE ą╝ąŠąČąĮąŠ ą┐ąŠą╝ąĄąĮčÅčéčī ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čüąĖą│ąĮą░ą╗ą░ DETECT ą┐ąŠčĆčéą░ GPIO, ą║ąŠč鹊čĆąŠąĄ ą▒čŗą╗ąŠ ąŠą┐ąĖčüą░ąĮąŠ ą▓čŗčłąĄ, čćč鹊ą▒čŗ ą▓ą╝ąĄčüč鹊 čŹč鹊ą│ąŠ čüąĖą│ąĮą░ą╗ DETECT č乊čĆą╝ąĖčĆąŠą▓ą░ą╗čüčÅ ąĮą░ą┐čĆčÅą╝čāčÄ ąĖąĘ čüąĖą│ąĮą░ą╗ą░ LDETECT, čüą╝. čĆąĖčü. 1. ąØą░ čĆąĖčü. 2 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ DETECT ą┤ą╗čÅ ą┤ą▓čāčģ čŹčéąĖčģ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓.

ąĀąĖčü. 2. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ DETECT.

ąÆčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ čĆą░ąĘčĆčÅą┤ą░ GPIO ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčéą║ą╗čÄč湥ąĮ ąŠčé ąĮąŠąČą║ąĖ ą▓čŗą▓ąŠą┤ą░, čćč鹊ą▒čŗ ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░čéčī 菹║ąŠąĮąŠą╝ąĖčÄ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝ąŠą╣ 菹ĮąĄčĆą│ąĖąĖ, ą║ąŠą│ą┤ą░ ąĮąŠąČą║ą░ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤, čüą╝. čĆąĖčü. 1. ąÆčģąŠą┤čŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćą░čéčī ą║ąŠčĆčĆąĄą║čéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓čģąŠą┤ą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ IN, ąĖ čćč鹊ą▒čŗ ą┤ą╗čÅ čŹč鹊ą╣ ąĮąŠąČą║ąĖ čĆą░ą▒ąŠčéą░ą╗ ą╝ąĄčģą░ąĮąĖąĘą╝ sense.

ąöčĆčāą│ąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čüąĖčüč鹥ą╝ąĄ ą╝ąŠą│čāčé ą┐ąŠą┤ą║ą╗čÄčćą░čéčīčüčÅ ą║ ąĮąŠąČą║ą░ą╝ GPIO, ą╝ąĄąĮčÅčÅ č鹥ą╝ čüą░ą╝čŗą╝ ą▓čŗčģąŠą┤ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ąĮąŠąČąĄą║ GPIO ąĖ ąĖčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ, ąĖą╗ąĖ čüčćąĖčéčŗą▓ą░čéčī ąĖčģ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ąĖą╗ąĖ čåąĖčäčĆąŠą▓ąŠą╣ čāčĆąŠą▓ąĄąĮčī, čüą╝. čĆąĖčü. 1.

ąÆčŗą▒čĆą░ąĮąĮčŗąĄ ąĮąŠąČą║ąĖ čéą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ą▓ą▓ąŠą┤ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą▓čģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓, čüą╝. ANAIN ąĮą░ čĆąĖčü. 1. ąÉąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čŗą▓ąŠą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ąĮą░ąĘąĮą░č湥ąĮčŗ č鹊ą╗čīą║ąŠ ąĮą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ čĆą░ąĘčĆčÅą┤ą░čģ ą┐ąŠčĆčéą░, čüą╝. čåąŠą║ąŠą╗ąĄą▓ą║čā ą║ąŠčĆą┐čāčüą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ čüą╝. [4]).

ąÆą░ąČąĮąŠąĄ ąĘą░ą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą║ą░ą║ čåąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤, čüą╗ąĄą┤čāąĄčé ą┐ąŠąĘą░ą▒ąŠčéąĖčéčīčüčÅ ą┐čĆąĖ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĄ čüčģąĄą╝čŗ nRF52832, čćč鹊ą▒čŗ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝čŗą╣ č鹊ą║, ą║ąŠą│ą┤ą░ ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą╝ąĄąČą┤čā VIL ąĖ VIH. ą×ą┤ąĮą░ą║ąŠ čģąŠčĆąŠčłąĄą╣ ą┐čĆą░ą║čéąĖą║ąŠą╣ ą▒čāą┤ąĄčé ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ą▓ąĮąĄčłąĮčÅčÅ čüčģąĄą╝ą░ ąĮąĄ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ąĮą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ čāčĆąŠą▓ąĄąĮčī ąĮą░ ąĮąŠąČą║ąĄ ą▓čģąŠą┤ą░ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą╝ąĄąČą┤čā VIL ąĖ VIH.

[GPIO, čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĮčŗąĄ ą▒ą╗ąĖąĘą║ąŠ ą║ RADIO]

ąØą░ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ čĆą░ą┤ąĖąŠčéčĆą░ą║čéą░, čéą░ą║ąĖąĄ ą║ą░ą║ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī, ą╝ąŠą│čāčé ą┐ąŠą▓ą╗ąĖčÅčéčī ą▓čŗčüąŠą║ąŠčćą░čüč鹊čéąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ čåąĖčäčĆąŠą▓čŗčģ ąĮąŠąČąĄą║ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░, č湥čĆąĄąĘ ą║ąŠč鹊čĆčŗąĄ ą▓č鹥ą║ą░ąĄčé/ą▓čŗč鹥ą║ą░ąĄčé ą▒ąŠą╗čīčłąŠą╣ č鹊ą║, ąĖ ą║ąŠą│ą┤ą░ čŹčéąĖ ąĮąŠąČą║ąĖ ąĮą░čģąŠą┤čÅčéčüčÅ ą▒ą╗ąĖąĘą║ąŠ ą║ ą▓čŗą▓ąŠą┤ą░ą╝ ą┐ąĖčéą░ąĮąĖčÅ čĆą░ą┤ąĖąŠčéčĆą░ą║čéą░ ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą░ąĮč鹥ąĮąĮčŗ.

ąöą╗čÅ ąŠą┐čéąĖą╝ą░ą╗čīąĮąŠą╣ čĆą░ąĘą▓ąŠą┤ą║ąĖ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ, ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čÄčēąĄą╣ ą╗čāčćčłąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ čĆą░ą┤ąĖąŠčéčĆą░ą║čéą░, čüą╝. čĆąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ Pin assignments ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ čćąĖą┐ (ąĮą░ą┐čĆąĖą╝ąĄčĆ čüą╝. [4]).

[ąĀąĄą│ąĖčüčéčĆčŗ GPIO]

ąóą░ą▒ą╗ąĖčåą░ 1. ąŁą║ąĘąĄą╝ą┐ą╗čÅčĆčŗ GPIO.

| ąæą░ąĘ. ą░ą┤čĆąĄčü |

ą¤ąĄčĆąĖčä. čāčüčéčĆąŠą╣čüčéą▓ąŠ |

ąŁą║ąĘ. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 0x50000000 |

GPIO |

P0 |

General Purpose Input and Output |

ąóą░ą▒ą╗ąĖčåą░ 2. ą×ą▒ąĘąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓ GPIO.

| ąĀąĄą│ąĖčüčéčĆ |

ąĪą╝ąĄčē. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| OUT |

0x504 |

ąŚą░ą┐ąĖčüčī ą▓ ą┐ąŠčĆčé GPIO. |

| OUTSET |

0x508 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓ ą╗ąŠą│. 1 ąŠčéą┤ąĄą╗čīąĮčŗčģ ą▒ąĖčé ą┐ąŠčĆčéą░ GPIO. |

| OUTCLR |

0x50C |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓ ą╗ąŠą│. 0 ąŠčéą┤ąĄą╗čīąĮčŗčģ ą▒ąĖčé ą┐ąŠčĆčéą░ GPIO. |

| IN |

0x510 |

ą¦č鹥ąĮąĖąĄ ą┐ąŠčĆčéą░ GPIO. |

| DIR |

0x514 |

ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ą▓čŗą▓ąŠą┤ąŠą▓ GPIO (ą▓čģąŠą┤ ąĖą╗ąĖ ą▓čŗčģąŠą┤). |

| DIRSET |

0x518 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ąŠčéą┤ąĄą╗čīąĮčŗčģ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ DIR. |

| DIRCLR |

0x51C |

ąĪą▒čĆąŠčü ąŠčéą┤ąĄą╗čīąĮčŗčģ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ DIR. |

| LATCH |

0x520 |

ąĀąĄą│ąĖčüčéčĆ-ąĘą░čēąĄą╗ą║ą░, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖą╣, ą║ą░ą║ąĖąĄ ąĮąŠąČą║ąĖ GPIO čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĖą╗ąĖ ą║čĆąĖč鹥čĆąĖčÄ, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╝čā ą▓ čĆąĄą│ąĖčüčéčĆą░čģ PIN_CNF[n].SENSE. |

| DETECTMODE |

0x524 |

ąÆčŗą▒ąŠčĆ ą╝ąĄąČą┤čā ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄą╝ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čüąĖą│ąĮą░ą╗ą░ DETECT ąĖ čĆąĄąČąĖą╝ąŠą╝ LDETECT. |

| PIN_CNF[0] |

0x700 |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ąĮąŠąČąĄą║ GPIO. |

| PIN_CNF[1] |

0x704 |

| PIN_CNF[2] |

0x708 |

| PIN_CNF[3] |

0x70C |

| PIN_CNF[4] |

0x710 |

| PIN_CNF[5] |

0x714 |

| PIN_CNF[6] |

0x718 |

| PIN_CNF[7] |

0x71C |

| PIN_CNF[8] |

0x720 |

| PIN_CNF[9] |

0x724 |

| PIN_CNF[10] |

0x728 |

| PIN_CNF[11] |

0x72C |

| PIN_CNF[12] |

0x730 |

| PIN_CNF[13] |

0x734 |

| PIN_CNF[14] |

0x738 |

| PIN_CNF[15] |

0x73C |

| PIN_CNF[16] |

0x740 |

| PIN_CNF[17] |

0x744 |

| PIN_CNF[18] |

0x748 |

| PIN_CNF[19] |

0x74C |

| PIN_CNF[20] |

0x750 |

| PIN_CNF[21] |

0x754 |

| PIN_CNF[22] |

0x758 |

| PIN_CNF[23] |

0x75C |

| PIN_CNF[24] |

0x760 |

| PIN_CNF[25] |

0x764 |

| PIN_CNF[26] |

0x768 |

| PIN_CNF[27] |

0x76C |

| PIN_CNF[28] |

0x770 |

| PIN_CNF[29] |

0x774 |

| PIN_CNF[30] |

0x778 |

| PIN_CNF[31] |

0x77C |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x504. ą¤čĆčÅą╝ą░čÅ ąĘą░ą┐ąĖčüčī ą▓ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ GPIO.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ OUT:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

f |

e |

d |

c |

b |

a |

Z |

Y |

X |

W |

V |

U |

T |

S |

R |

Q |

P |

O |

N |

M |

L |

K |

J |

I |

H |

G |

F |

E |

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PIN0 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ čāčĆąŠą▓ąĮčÅ ą▓čŗčģąŠą┤ą░ ą┐ąŠčĆčéą░ 0.

0: ą▓čŗą▓ąŠą┤ ą╗ąŠą│. 0.

1: ą▓čŗą▓ąŠą┤ ą╗ąŠą│. 1. |

| |

|

|

... |

| f |

RW |

PIN31 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ čāčĆąŠą▓ąĮčÅ ą▓čŗčģąŠą┤ą░ ą┐ąŠčĆčéą░ 31.

0: ą▓čŗą▓ąŠą┤ ą╗ąŠą│. 0.

1: ą▓čŗą▓ąŠą┤ ą╗ąŠą│. 1. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x508.

ąŚą░ą┐ąĖčüčī 1 ą▓ čĆą░ąĘčĆčÅą┤ čĆąĄą│ąĖčüčéčĆą░ čāčüčéą░ąĮąŠą▓ąĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▓čŗčģąŠą┤ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą┐ąŠčĆčéą░ ą▓ ą╗ąŠą│. 1. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąČąĄčé ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ OUT.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ OUTSET:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

f |

e |

d |

c |

b |

a |

Z |

Y |

X |

W |

V |

U |

T |

S |

R |

Q |

P |

O |

N |

M |

L |

K |

J |

I |

H |

G |

F |

E |

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PIN0 |

ąŚą░ą┐ąĖčüčī 1 ą▓ čĆą░ąĘčĆčÅą┤ čāčüčéą░ąĮąŠą▓ąĖčé ąĮą░ ą▓čŗčģąŠą┤ąĄ P0.0 čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąČąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąČąĄčé ąĘąĮą░č湥ąĮąĖąĄ čĆą░ąĘčĆčÅą┤ą░ 0 čĆąĄą│ąĖčüčéčĆą░ OUT. |

| |

|

|

... |

| f |

RW |

PIN31 |

ąŚą░ą┐ąĖčüčī 1 ą▓ čĆą░ąĘčĆčÅą┤ čāčüčéą░ąĮąŠą▓ąĖčé ąĮą░ ą▓čŗčģąŠą┤ąĄ P0.31 čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąČąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąČąĄčé ąĘąĮą░č湥ąĮąĖąĄ čĆą░ąĘčĆčÅą┤ą░ 31 čĆąĄą│ąĖčüčéčĆą░ OUT. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x50C.

ąŚą░ą┐ąĖčüčī 1 ą▓ čĆą░ąĘčĆčÅą┤ čĆąĄą│ąĖčüčéčĆą░ čāčüčéą░ąĮąŠą▓ąĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▓čŗčģąŠą┤ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą┐ąŠčĆčéą░ ą▓ ą╗ąŠą│. 0. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąČąĄčé ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ OUT.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ OUTCLR:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

f |

e |

d |

c |

b |

a |

Z |

Y |

X |

W |

V |

U |

T |

S |

R |

Q |

P |

O |

N |

M |

L |

K |

J |

I |

H |

G |

F |

E |

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PIN0 |

ąŚą░ą┐ąĖčüčī 1 ą▓ čĆą░ąĘčĆčÅą┤ čāčüčéą░ąĮąŠą▓ąĖčé ąĮą░ ą▓čŗčģąŠą┤ąĄ P0.0 čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąČąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąČąĄčé ąĘąĮą░č湥ąĮąĖąĄ čĆą░ąĘčĆčÅą┤ą░ 0 čĆąĄą│ąĖčüčéčĆą░ OUT. |

| |

|

|

... |

| f |

RW |

PIN31 |

ąŚą░ą┐ąĖčüčī 1 ą▓ čĆą░ąĘčĆčÅą┤ čāčüčéą░ąĮąŠą▓ąĖčé ąĮą░ ą▓čŗčģąŠą┤ąĄ P0.31 čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąČąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąČąĄčé ąĘąĮą░č湥ąĮąĖąĄ čĆą░ąĘčĆčÅą┤ą░ 31 čĆąĄą│ąĖčüčéčĆą░ OUT. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x510.

ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąČąĄčé ą╗ąŠą│ąĖč湥čüą║ąĖąĄ čāčĆąŠą▓ąĮąĖ ąĮą░ čåąĖčäčĆąŠą▓čŗčģ ą▓čģąŠą┤ą░čģ.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ IN:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

f |

e |

d |

c |

b |

a |

Z |

Y |

X |

W |

V |

U |

T |

S |

R |

Q |

P |

O |

N |

M |

L |

K |

J |

I |

H |

G |

F |

E |

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

R |

PIN0 |

0: ąĮą░ ą▓čģąŠą┤ąĄ P0.0 ą╗ąŠą│. 0.

1: ąĮą░ ą▓čģąŠą┤ąĄ P0.0 ą╗ąŠą│. 1. |

| |

|

|

... |

| f |

R |

PIN31 |

0: ąĮą░ ą▓čģąŠą┤ąĄ P0.31 ą╗ąŠą│. 0.

1: ąĮą░ ą▓čģąŠą┤ąĄ P0.31 ą╗ąŠą│. 1. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x514.

ąØą░čüčéčĆą░ąĖą▓ą░ąĄčé ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ GPIO ąĮą░ ą▓čģąŠą┤ ąĖą╗ąĖ ąĮą░ ą▓čŗčģąŠą┤.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ DIR:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

f |

e |

d |

c |

b |

a |

Z |

Y |

X |

W |

V |

U |

T |

S |

R |

Q |

P |

O |

N |

M |

L |

K |

J |

I |

H |

G |

F |

E |

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PIN0 |

0: P0.0 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤.

1: P0.0 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗčģąŠą┤. |

| |

|

|

... |

| f |

RW |

PIN31 |

0: P0.31 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤.

1: P0.31 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗčģąŠą┤. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x518.

ą¤ąŠąĘą▓ąŠą╗čÅąĄčé ąĮą░čüčéčĆąŠąĖčéčī ąĮą░ ą▓čŗčģąŠą┤ ą▓čŗą▒čĆą░ąĮąĮčŗąĄ čĆą░ąĘčĆčÅą┤čŗ ą┐ąŠčĆčéą░ GPIO. ąŚą░ą┐ąĖčüčī 1 ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ čĆą░ąĘčĆčÅą┤ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčé ąĄą│ąŠ ąĮą░ ą▓čŗčģąŠą┤, ąĘą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ DIR.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ DIRSET:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

f |

e |

d |

c |

b |

a |

Z |

Y |

X |

W |

V |

U |

T |

S |

R |

Q |

P |

O |

N |

M |

L |

K |

J |

I |

H |

G |

F |

E |

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PIN0 |

ąŚą░ą┐ąĖčüčī 1 ąĮą░čüčéčĆąŠąĖčé P0.0 ąĮą░ ą▓čŗčģąŠą┤, ąĘą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ čĆą░ąĘčĆčÅą┤ą░ 0 čĆąĄą│ąĖčüčéčĆą░ DIR. |

| |

|

|

... |

| f |

RW |

PIN31 |

ąŚą░ą┐ąĖčüčī 1 ąĮą░čüčéčĆąŠąĖčé P0.31 ąĮą░ ą▓čŗčģąŠą┤, ąĘą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ čĆą░ąĘčĆčÅą┤ą░ 31 čĆąĄą│ąĖčüčéčĆą░ DIR. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x51C.

ą¤ąŠąĘą▓ąŠą╗čÅąĄčé ąĮą░čüčéčĆąŠąĖčéčī ąĮą░ ą▓čģąŠą┤ ą▓čŗą▒čĆą░ąĮąĮčŗąĄ čĆą░ąĘčĆčÅą┤čŗ ą┐ąŠčĆčéą░ GPIO. ąŚą░ą┐ąĖčüčī 1 ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ čĆą░ąĘčĆčÅą┤ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčé ąĄą│ąŠ ąĮą░ ą▓čģąŠą┤, ąĘą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ DIR.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ DIRCLR:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

f |

e |

d |

c |

b |

a |

Z |

Y |

X |

W |

V |

U |

T |

S |

R |

Q |

P |

O |

N |

M |

L |

K |

J |

I |

H |

G |

F |

E |

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PIN0 |

ąŚą░ą┐ąĖčüčī 1 ąĮą░čüčéčĆąŠąĖčé P0.0 ąĮą░ ą▓čģąŠą┤, ąĘą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ čĆą░ąĘčĆčÅą┤ą░ 0 čĆąĄą│ąĖčüčéčĆą░ DIR. |

| |

|

|

... |

| f |

RW |

PIN31 |

ąŚą░ą┐ąĖčüčī 1 ąĮą░čüčéčĆąŠąĖčé P0.31 ąĮą░ ą▓čģąŠą┤, ąĘą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ čĆą░ąĘčĆčÅą┤ą░ 31 čĆąĄą│ąĖčüčéčĆą░ DIR. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x520.

ąŁč鹊 čĆąĄą│ąĖčüčéčĆ ąĘą░čēąĄą╗ą║ąĖ, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ąĖąĄ ąĮąŠąČą║ąĖ GPIO čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĖą╗ąĖ ą║čĆąĖč鹥čĆąĖčÄ, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╝čā ą▓ čĆąĄą│ąĖčüčéčĆą░čģ PIN_CNF[n].SENSE. ąĀąĄą│ąĖčüčéčĆ čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā W1C, čé. ąĄ. ą┤ą╗čÅ čüą▒čĆąŠčüą░ čĆą░ąĘčĆčÅą┤ą░ ąĮą░ą┤ąŠ ąĘą░ą┐ąĖčüą░čéčī ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ LATCH:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

f |

e |

d |

c |

b |

a |

Z |

Y |

X |

W |

V |

U |

T |

S |

R |

Q |

P |

O |

N |

M |

L |

K |

J |

I |

H |

G |

F |

E |

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PIN0 |

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüčéą░čéčāčü čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĄąĮąĖčÅ ą║čĆąĖč鹥čĆąĖčÄ, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╝čā ą▓ čĆąĄą│ąĖčüčéčĆąĄ PIN_CNF0.SENSE. ąöą╗čÅ ąŠčćąĖčüčéą║ąĖ ąĘą░ą┐ąĖčłąĖč鹥 ą▓ čŹč鹊čé ą▒ąĖčé 1.

0: NotLatched, ąĮąĄ ą▒čŗą╗ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖčÅ ą║čĆąĖč鹥čĆąĖčÄ.

1: Latched, ą▒čŗą╗ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ ą║čĆąĖč鹥čĆąĖčÄ. |

| |

|

|

... |

| f |

RW |

PIN31 |

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüčéą░čéčāčü čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĄąĮąĖčÅ ą║čĆąĖč鹥čĆąĖčÄ, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╝čā ą▓ čĆąĄą│ąĖčüčéčĆąĄ PIN_CNF31.SENSE. ąöą╗čÅ ąŠčćąĖčüčéą║ąĖ ąĘą░ą┐ąĖčłąĖč鹥 ą▓ čŹč鹊čé ą▒ąĖčé 1.

0: NotLatched, ąĮąĄ ą▒čŗą╗ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖčÅ ą║čĆąĖč鹥čĆąĖčÄ.

1: Latched, ą▒čŗą╗ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ ą║čĆąĖč鹥čĆąĖčÄ. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x524.

ąŁč鹊 čĆąĄą│ąĖčüčéčĆ ą▓čŗą▒ąĖčĆą░ąĄčé ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čüąĖą│ąĮą░ą╗ą░ DETECT ąĖ čĆąĄąČąĖą╝ LDETECT.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ DETECTMODE:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

DETECTMODE |

0: DETECT ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ čüąŠąĄą┤ąĖąĮąĄąĮ čü čüąĖą│ąĮą░ą╗ą░ą╝ąĖ PIN DETECT.

1: ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄą╝ąŠą│ąŠ LDETECT. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x700 + n * 4.

ąŁč鹊 čĆąĄą│ąĖčüčéčĆ ą▓čŗą▒ąĖčĆą░ąĄčé ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čüąĖą│ąĮą░ą╗ą░ DETECT ąĖ čĆąĄąČąĖą╝ LDETECT.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ PIN_CNF[n]:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

E |

|

|

|

|

|

D |

D |

D |

|

|

|

|

C |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

DIR |

ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ą▓čŗą▓ąŠą┤ą░. ąóąŠčé ąČąĄ čäąĖąĘąĖč湥čüą║ąĖą╣ čĆąĄą│ąĖčüčéčĆ, čćč鹊 ąĖ DIR.

0: ąĮąŠąČą║ą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤.

1: ąĮąŠąČą║ą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą▓čŗčģąŠą┤. |

| B |

RW |

INPUT |

ą¤ąŠą┤ą║ą╗čÄčćąĖčéčī ąĖą╗ąĖ ąŠčéą║ą╗čÄčćąĖčéčī ą▓čģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ.

0: ą▓čģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ.

1: ą▓čģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ąŠčéą║ą╗čÄč湥ąĮ. |

| C |

RW |

PULL |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓.

0: Disabled, ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ.

1: Pulldown, ąĮąĖąČąĮąĖąĄ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ.

2: Pullup, ą▓ąĄčĆčģąĮąĖąĄ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ. |

| D |

RW |

DRIVE |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░.

0: S0S1, čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ 0 ąĖ 1.

1: H0S1, ą╝ąŠčēąĮčŗą╣ 0, čüčéą░ąĮą┤ą░čĆčéąĮą░čÅ 1.

2: S0H1, čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ 0 ąĖ ą╝ąŠčēąĮą░čÅ 1.

3: H0H1, ą╝ąŠčēąĮčŗąĄ 0 ąĖ 1.

4: D0S1, ą▓ąĄčĆčģąĮąĖą╣ ą║ą╗čÄčć čüąŠ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╣ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ (ą╝ąŠąĮčéą░ąČąĮąŠąĄ ąśąøąś).

5: D0H1, ą╝ąŠčēąĮčŗą╣ ą▓ąĄčĆčģąĮąĖą╣ ą║ą╗čÄčć (ą╝ąŠąĮčéą░ąČąĮąŠąĄ ąśąøąś).

6: S0D1, ąĮąĖąČąĮąĖą╣ ą║ą╗čÄčć čüąŠ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╣ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ (ą╝ąŠąĮčéą░ąČąĮąŠąĄ ąś).

7: H0D1, ą╝ąŠčēąĮčŗą╣ ąĮąĖąČąĮąĖą╣ ą║ą╗čÄčć (ą╝ąŠąĮčéą░ąČąĮąŠąĄ ąś). |

[ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ GPIO]

| ąĪąĖą╝ą▓ąŠą╗ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

min |

Typ |

MAX |

ąĢą┤. |

| VIH |

ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 1 |

0.7 x VDD |

|

VDD |

V |

| VIL |

ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 0 |

VSS |

|

0.3 x VDD |

| VOH,SD |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 1, čüčéą░ąĮą┤ą░čĆčéąĮą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, č鹊ą║ 0.5 ą╝ąÉ, VDD Ōēź 1.7V |

VDD - 0.4 |

|

VDD |

| VOH,HDH |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 1, ą▓čŗčüąŠą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, č鹊ą║ 5 ą╝ąÉ, VDD Ōēź 2.7V |

|

| VOH,HDL |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 1, ą▓čŗčüąŠą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, č鹊ą║ 3 ą╝ąÉ, VDD Ōēź 1.7V |

|

| VOL,SD |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 0, čüčéą░ąĮą┤ą░čĆčéąĮą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, č鹊ą║ 0.5 ą╝ąÉ, VDD Ōēź 1.7V |

VSS |

|

VSS + 0.4 |

| VOL,HDH |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 0, ą▓čŗčüąŠą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, č鹊ą║ 5 ą╝ąÉ, VDD Ōēź 2.7V |

|

| VOL,HDL |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 0, ą▓čŗčüąŠą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, č鹊ą║ 3 ą╝ąÉ, VDD Ōēź 1.7V |

|

| IOL,SD |

ąóąŠą║ ą┐čĆąĖ VSS + 0.4V ąĮą░ ą▓čŗčģąŠą┤ąĄ, ą▓čŗčģąŠą┤ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 0, čüčéą░ąĮą┤ą░čĆčéąĮą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, VDD Ōēź 1.7V |

1 |

2 |

4 |

ą╝ąÉ |

| IOL,HDH |

ąóąŠą║ ą┐čĆąĖ VSS + 0.4V ąĮą░ ą▓čŗčģąŠą┤ąĄ, ą▓čŗčģąŠą┤ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 0, ą▓čŗčüąŠą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, VDD Ōēź 2.7V |

6 |

10 |

15 |

| IOL,HDL |

ąóąŠą║ ą┐čĆąĖ VSS + 0.4V ąĮą░ ą▓čŗčģąŠą┤ąĄ, ą▓čŗčģąŠą┤ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 0, ą▓čŗčüąŠą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, VDD Ōēź 1.7V |

3 |

|

|

| IOH,SD |

ąóąŠą║ ą┐čĆąĖ VDD - 0.4V ąĮą░ ą▓čŗčģąŠą┤ąĄ, ą▓čŗčģąŠą┤ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1, čüčéą░ąĮą┤ą░čĆčéąĮą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, VDD Ōēź 1.7V |

1 |

2 |

4 |

| IOH,HDH |

ąóąŠą║ ą┐čĆąĖ VDD - 0.4V ąĮą░ ą▓čŗčģąŠą┤ąĄ, ą▓čŗčģąŠą┤ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1, ą▓čŗčüąŠą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, VDD Ōēź 2.7V |

6 |

9 |

14 |

| IOH,HDL |

ąóąŠą║ ą┐čĆąĖ VDD - 0.4V ąĮą░ ą▓čŗčģąŠą┤ąĄ, ą▓čŗčģąŠą┤ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1, ą▓čŗčüąŠą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, VDD Ōēź 1.7V |

3 |

|

|

| tRF,15pF |

ąÆčĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ/čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ, ąĮąĖąĘą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, 10-90%, ąĮą░ą│čĆčāąĘą║ą░ 15 ą┐ąż(1) |

|

9 |

|

ns |

| tRF,25pF |

ąÆčĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ/čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ, ąĮąĖąĘą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, 10-90%, ąĮą░ą│čĆčāąĘą║ą░ 25 ą┐ąż(1) |

|

13 |

|

| tRF,50pF |

ąÆčĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ/čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ, ąĮąĖąĘą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, 10-90%, ąĮą░ą│čĆčāąĘą║ą░ 50 ą┐ąż(1) |

|

25 |

|

| tHRF,15pF |

ąÆčĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ/čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ, ą▓čŗčüąŠą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, 10-90%, ąĮą░ą│čĆčāąĘą║ą░ 15 ą┐ąż(1) |

|

4 |

|

| tHRF,25pF |

ąÆčĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ/čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ, ą▓čŗčüąŠą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, 10-90%, ąĮą░ą│čĆčāąĘą║ą░ 25 ą┐ąż(1) |

|

5 |

|

| tHRF,50pF |

ąÆčĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ/čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ, ą▓čŗčüąŠą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, 10-90%, ąĮą░ą│čĆčāąĘą║ą░ 50 ą┐ąż(1) |

|

8 |

|

| RPU |

ąĪąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą▓ąĄčĆčģąĮąĄą│ąŠ (pull-up) ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĄą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ |

11 |

13 |

16 |

ą║ą×ą╝ |

| RPU |

ąĪąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ąĮąĖąČąĮąĄą│ąŠ (pull-down) ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĄą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ |

11 |

13 |

16 |

| CPAD |

ąĢą╝ą║ąŠčüčéčī ą║ąŠąĮčéą░ą║čéąĮąŠą╣ ą┐ą╗ąŠčēą░ą┤ą║ąĖ ą▓čŗą▓ąŠą┤ąŠą▓ |

|

3 |

|

ą┐ąż |

| CPAD_NFC |

ąĢą╝ą║ąŠčüčéčī ą║ąŠąĮčéą░ą║čéąĮąŠą╣ ą┐ą╗ąŠčēą░ą┤ą║ąĖ ą▓čŗą▓ąŠą┤ąŠą▓ NFC |

|

4 |

|

| INFC_LEAK |

ąóąŠą║ čāč鹥čćą║ąĖ ą╝ąĄąČą┤čā ąĮąŠąČą║ą░ą╝ąĖ NFC, ą║ąŠą│ą┤ą░ ąŠąĮąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮčŗ ą▓ čĆą░ąĘąĮčŗąĄ čüąŠčüč鹊čÅąĮąĖčÅ |

|

2 |

10 |

ą╝ą║ąÉ |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ąĖ čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ ąŠčüąĮąŠą▓ą░ąĮčŗ ąĮą░ čüąĖą╝čāą╗čÅčåąĖčÅčģ.

ą¤ąŠčéčĆąĄą▒ą╗čÅąĄą╝čŗą╣ ąŠčé ą▒ą░čéą░čĆąĄąĖ č鹊ą║, ą║ąŠą│ą┤ą░ ąĮąŠąČą║ąĖ GPIO ą░ą║čéąĖą▓ąĮčŗ ą║ą░ą║ ą▓čŗčģąŠą┤, ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

IGPIO=VDD Cload f

ąŚą┤ąĄčüčī Cload čŹč鹊 ąĄą╝ą║ąŠčüčéčī ąĮą░ą│čĆčāąĘą║ąĖ, f čćą░čüč鹊čéą░ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ.

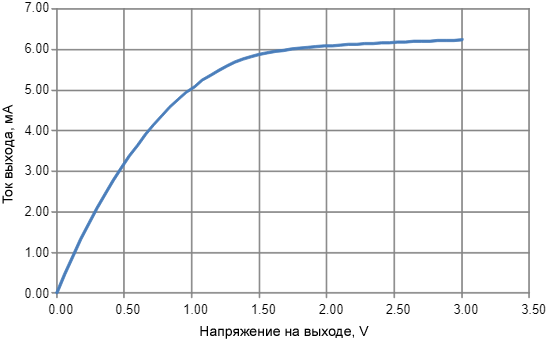

ąĀąĖčü. 3. ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ GPIO ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, čüčéą░ąĮą┤ą░čĆčéąĮą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, VDD = 3.0V.

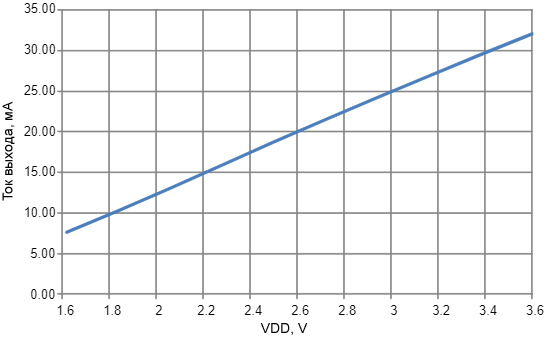

ąĀąĖčü. 4. ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ GPIO ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ą▓čŗčüąŠą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, VDD = 3.0V.

ąĀąĖčü. 5. ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą▓čŗč鹥ą║ą░čÄčēąĄą│ąŠ č鹊ą║ą░ GPIO ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, čüčéą░ąĮą┤ą░čĆčéąĮą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī.

ąĀąĖčü. 6. ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą▓čŗč鹥ą║ą░čÄčēąĄą│ąŠ č鹊ą║ą░ GPIO ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ą▓čŗčüąŠą║ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī.

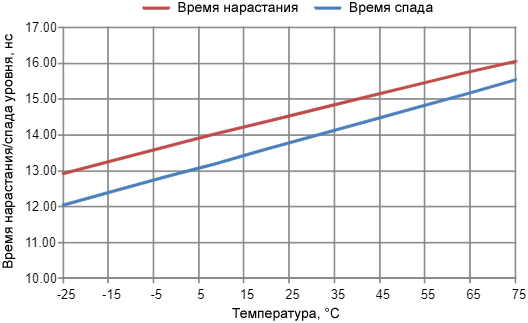

ąĀąĖčü. 7. ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ąĖ čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ ąŠčé č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ, ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 10% - 90%, ąĄą╝ą║ąŠčüčéčī ąĮą░ą│čĆčāąĘą║ąĖ 25 ą┐ąż, VDD = 3.0V.

[ąĪčüčŗą╗ą║ąĖ]

1. GPIO General purpose input/output site:infocenter.nordicsemi.com.

2. nRF52 Series POWER Power supply site:infocenter.nordicsemi.com.

3. nRF5x GPIOTE: čüąŠą▒čŗčéąĖčÅ ąĖ ąĘą░ą┤ą░čćąĖ GPIO.

4. nRF52832 QFN48 pin assignments site:infocenter.nordicsemi.com.

5. Bluetooth: ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆčŗ ąĖ č鹥čĆą╝ąĖąĮčŗ. |