|

SAADC čĆą░čüčłąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ successive approximation ADC, čé. ąĄ. ą░ąĮą░ą╗ąŠą│ąŠ-čåąĖčäčĆąŠą▓ąŠą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī (ąÉą”ą¤), ąĖčüą┐ąŠą╗čīąĘčāčÄčēąĖą╣ ą┤ą╗čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ čĆąĄą│ąĖčüčéčĆ čü ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ ą┐čĆąĖą▒ą╗ąĖąČąĄąĮąĖąĄą╝ (successive approximation register, SAR). ąÆčüąĄ ąĮąĄą┐ąŠąĮčÅčéąĮčŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ ąĪą╗ąŠą▓ą░čĆąĖą║ąĄ [2].

ą×čüąĮąŠą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ SAADC:

ŌĆó ąĀą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī 8/10/12 čĆą░ąĘčĆčÅą┤ąŠą▓, 14 čĆą░ąĘčĆčÅą┤ąŠą▓ čü ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄą╝ č鹥čģąĮąĖą║ąĖ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ (oversampling) [4].

ŌĆó ąöąŠ 8 ą▓čģąŠą┤ąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓, ą┐čĆąĖą▓čÅąĘą░ąĮąĮčŗčģ ą║ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą┐ąŠčĆčéą░ą╝ ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ ą║ąŠčĆą┐čāčüą░:

- ą¤ąŠ ąŠą┤ąĮąŠą╝čā ą║ą░ąĮą░ą╗čā ą┤ą╗čÅ ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░, ąĖ ą┐ąŠ 2 ą║ą░ąĮą░ą╗ą░ ąĮą░ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą▓čģąŠą┤.

- ą£ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ čĆąĄąČąĖą╝ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░ą║ ą┤ą╗čÅ ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ, čéą░ą║ ąĖ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓.

ŌĆó ąöąĖą░ą┐ą░ąĘąŠąĮ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄą╝čŗčģ čāčĆąŠą▓ąĮąĄą╣ ąŠčé 0 ą┤ąŠ VDD.

ŌĆó ąŚą░ą┐čāčüą║ ąŠčåąĖčäčĆąŠą▓ą║ąĖ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ č湥čĆąĄąĘ task, ąĖą╗ąĖ ąŠčé ą║ą░ąĮą░ą╗ą░ PPI.

ŌĆó ąōąĖą▒ą║ą░čÅ ąĮą░čüčéčĆąŠą╣ą║ą░ ą┤ą╗čÅ ą║ąŠą╝ą┐čĆąŠą╝ąĖčüčüą░ ą╝ąĄąČą┤čā 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝ ąĖ č鹊čćąĮąŠčüčéčīčÄ - ą▓čŗą▒ąŠčĆ čćą░čüč鹊čéčŗ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ąŠčé ą╝ą░ą╗ąŠą╝ąŠčēąĮąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ 32.768 ą║ąōčå RTC, ąĖą╗ąĖ čĆą░ą▒ąŠčéą░ čü ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╣ č鹊čćąĮąŠčüčéčīčÄ ąŠčé čéą░ą╣ą╝ąĄčĆąŠą▓ 1/16 ą£ąōčå.

ŌĆó ąĀąĄąČąĖą╝ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (one-shot conversion mode) ą┤ą╗čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ąŠą┤ąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░.

ŌĆó ąĀąĄąČąĖą╝ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą║ą░ąĮą░ą╗ąŠą▓. ąŚą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą║ą░ąĮą░ą╗ą░ą╝ąĖ tACQ + tCONV, ą║ąŠč鹊čĆą░čÅ ą╝ąŠąČąĄčé ą╝ąĄąĮčÅčéčīčüčÅ ą╝ąĄąČą┤čā ą║ą░ąĮą░ą╗ą░ą╝ąĖ čü ą┐ąŠą╝ąŠčēčīčÄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ tack.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ ą┐čĆčÅą╝ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ RAM čü ą┐ąŠą╝ąŠčēčīčÄ EasyDMA.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮą░ čüąŠą▒čŗčéąĖąĖ ąŠą┤ąĖąĮąŠčćąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ąĖ čüąŠą▒čŗčéąĖąĖ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▒čāč乥čĆą░.

ŌĆó ąÆčŗą▒ąŠčĆą║ąĖ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą║ą░ą║ 16-čĆą░ąĘčĆčÅą┤ąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą▓ č乊čĆą╝ą░č鹥 ą┤ą▓ąŠąĖčćąĮąŠą│ąŠ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖčÅ (2ŌĆÖs complement) ą┤ą╗čÅ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╣ ąĖ ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╣ ąŠčåąĖčäčĆąŠą▓ą║ąĖ.

ŌĆó ą¤ąŠą▓č鹊čĆčÅčÄčēąĖąĄčüčÅ ą▓čŗą▒ąŠčĆą║ąĖ ą▒ąĄąĘ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą╣ą╝ąĄčĆą░.

ŌĆó ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ čāą┐čĆą░ą▓ą╗čÅąĄą╝ą░čÅ čåąĄą┐ąŠčćą║ą░ čĆąĄąĘąĖčüč鹊čĆąŠą▓ ą┤ą╗čÅ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ ąĮą░ ą▓čģąŠą┤ą░čģ.

ŌĆó ą£ąŠąĮąĖč鹊čĆąĖąĮą│ ąĮą░ ą╗ąĄčéčā ą▓čŗčģąŠą┤ą░ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čģąŠą┤ąĄ ąĘą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗąĄ ą┐čĆąĄą┤ąĄą╗čŗ.

ą×ą▒čēąĖąĄ čĆąĄčüčāčĆčüčŗ. ADC ą╝ąŠąČąĄčé čüąŠčüčāčēąĄčüčéą▓ąŠą▓ą░čéčī čü COMP ąĖ ą┤čĆčāą│ąĖą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓čŗą▓ąŠą┤ąŠą▓ (ąĮąŠąČąĄą║ ą║ąŠčĆą┐čāčüą░) AIN0 .. AIN7 [5], ą║ąŠą│ą┤ą░ ąŠąĮąĖ ąĮą░ąĘąĮą░č湥ąĮčŗ ąĮą░ čĆą░ąĘąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ. ąØąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą▓čŗą▒ąĖčĆą░čéčī ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ ą╝ąŠą┤čāą╗ąĄą╣ (čģąŠčéčÅ ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ ą┐ąŠąŠč湥čĆąĄą┤ąĮąŠą╣ ą┐ąĄčĆąĄąĮą░čüčéčĆąŠą╣ą║ąĖ).

ąŻ ADC ąĖą╝ąĄąĄčéčüčÅ ą┤ąŠ 8 ą▓ąĮąĄčłąĮąĖčģ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą║ą░ąĮą░ą╗ąŠą▓ ą▓ą▓ąŠą┤ą░, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą║ąŠčĆą┐čāčüą░ čćąĖą┐ą░. ąÜą░ąĮą░ą╗čŗ ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ą▓ čĆąĄąČąĖą╝ąĄ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ąĘą░ą┐čāčüą║ą░ / ąŠą┤ąĮąŠą║čĆą░čéąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ (one-shot mode) ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, ąĖą╗ąĖ ą▓ čĆąĄąČąĖą╝ąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐ąŠą▓č鹊čĆąĄąĮąĖčÅ ą▓čŗą▒ąŠčĆąŠą║ (continuous conversion mode) čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ čćą░čüč鹊č鹊ą╣ ą▓čŗą▒ąŠčĆąŠą║ (sampling rate).

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čģąŠą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ 8 ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą▓čģąŠą┤ąŠą▓ (single-ended inputs), 4 ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą▓čģąŠą┤ą░, ąĖą╗ąĖ ą║ą░ą║ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅ čŹčéąĖčģ ą▓ą░čĆąĖą░ąĮč鹊ą▓. ąÜą░ąČą┤čŗą╣ ą║ą░ąĮą░ą╗ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ąĮąŠąČąĄą║ ąŠčé AIN0 ą┤ąŠ AIN7, ąĖą╗ąĖ ą┤ą╗čÅ ąĮąŠąČą║ąĖ VDD. ąÜą░ąĮą░ą╗čŗ ą╝ąŠą│čāčé ąŠčåąĖčäčĆąŠą▓čŗą▓ą░čéčīčüčÅ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ ą▓ čĆąĄąČąĖą╝ąĄ one-shot ą▓čŗą▒ąŠčĆąŠą║ ąĖą╗ąĖ continuous ą▓čŗą▒ąŠčĆąŠą║, ąĖą╗ąĖ ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ čĆąĄąČąĖą╝ą░ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ (scan mode) ąĮąĄčüą║ąŠą╗čīą║ąŠ ą║ą░ąĮą░ą╗ąŠą▓ ą╝ąŠą│čāčé ąŠčåąĖčäčĆąŠą▓ą░čéčīčüčÅ ą▓ ąĮą░čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ. ąöą╗čÅ ą┐ąŠą▓čŗčłąĄąĮąĖčÅ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ ą▓čŗą▒ąŠčĆąŠą║ ą║ą░ąĮą░ą╗ąŠą▓ ąĖ čāą▓ąĄą╗ąĖč湥ąĮąĖčÅ čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗/čłčāą╝ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą┐čĆąĖą╝ąĄąĮčÅčéčīčüčÅ č鹥čģąĮąĖą║ą░ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ.

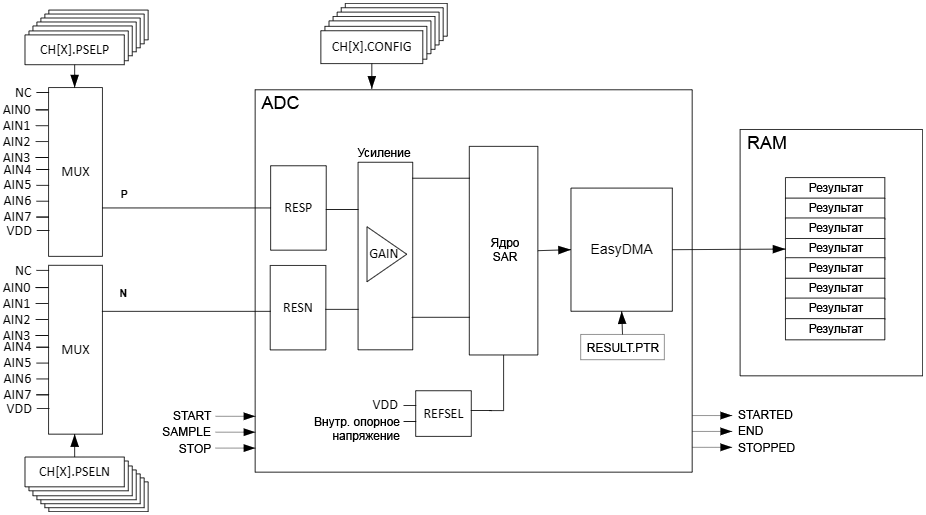

ąĀąĖčü. 1. ąŻą┐čĆąŠčēąĄąĮąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ ąÉą”ą¤.

ąÆąĮčāčéčĆąĄąĮąĮąĄ ADC ą▓čüąĄą│ą┤ą░ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ąÉą”ą¤, ąĮąŠ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ąĮą░ ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗąĄ ą▓čģąŠą┤čŗ (single-ended input) ą▓ ą┐ąŠą╗ąĄ MODE čĆąĄą│ąĖčüčéčĆą░ CH[n].CONFIG. ąÆ čĆąĄąČąĖą╝ąĄ single-ended, ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ą▓čģąŠą┤ ąĘą░ą╝ą║ąĮčāčé ąĮą░ ąĘąĄą╝ą╗čÄ ą▓ąĮčāčéčĆąĖ čćąĖą┐ą░. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąĄą┤ą┐ąŠą╗ą░ą│ą░ąĄčéčüčÅ, čćč鹊 ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ąĮą░ ąĘąĄą╝ą╗čÄ ą▓čģąŠą┤ą░ ąÉą”ą¤ čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü ą┐ąŠč鹥ąĮčåąĖą░ą╗ąŠą╝ ą▓ąĮąĄčłąĮąĄą╣ ąĘąĄą╝ą╗ąĖ, ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą║ąŠč鹊čĆąŠą│ąŠ ąĖąĘą╝ąĄčĆčÅąĄčéčüčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čģąŠą┤ąĄ. ą¤ąŠčŹč鹊ą╝čā ą▓ čĆąĄąČąĖą╝ąĄ single-ended ADC čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠ ą║ ąĖą╝ą┐čāą╗čīčüą░ą╝ ą┐ąŠą╝ąĄčģ ą┐ąŠ ąĘąĄą╝ą╗ąĄ, čāčĆąŠą▓ąĄąĮčī ą║ąŠč鹊čĆčŗčģ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą║ą░č湥čüčéą▓ą░ čĆą░ąĘą▓ąŠą┤ą║ąĖ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ ąĖąĘą╝ąĄčĆąĄąĮąĖą╣.

ąĀąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC ąĘą░ą▓ąĖčüąĖčé ąŠ ąĮą░čüčéčĆąŠąĄą║ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ CH[n].CONFIG ąĖ RESOLUTION:

RESULT = [V(P) ŌĆō V(N) ] * GAIN/REFERENCE * 2(RESOLUTION - m)

ąŚą┤ąĄčüčī:

V(P) ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝ ą▓čģąŠą┤ąĄ P

V(N) ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╝ ą▓čģąŠą┤ąĄ N

GAIN ą▓čŗą▒čĆą░ąĮąĮą░čÅ ąĮą░čüčéčĆąŠą╣ą║ą░ čāčüąĖą╗ąĄąĮąĖčÅ

REFERENCE ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░

m=0, ąĄčüą╗ąĖ CONFIG.MODE=SE (ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝), ąĖą╗ąĖ m=1 ąĄčüą╗ąĖ CONFIG.MODE=Diff (ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝).

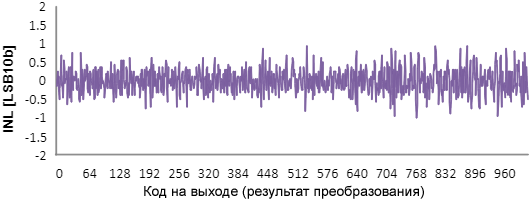

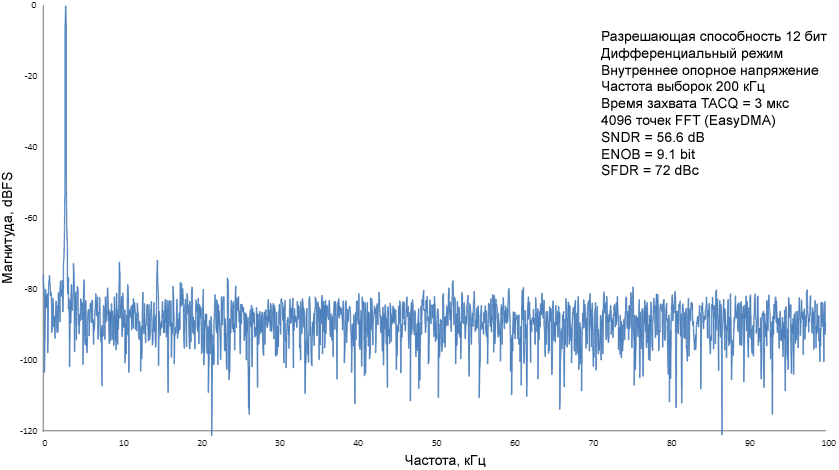

ąĀąĄąĘčāą╗čīčéą░čé, ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗą╣ ADC ą▒čāą┤ąĄčé ąŠčéą╗ąĖčćą░čéčīčüčÅ ąŠčé ąŠąČąĖą┤ą░ąĄą╝ąŠą│ąŠ ąĖąĘ-ąĘą░ ąŠčłąĖą▒ąŠą║ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā (DC errors) čéą░ą║ąĖčģ ą║ą░ą║ čüą╝ąĄčēąĄąĮąĖąĄ (offset), ąŠčłąĖą▒ą║ą░ čāčüąĖą╗ąĄąĮąĖčÅ (gain), ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī (DNL) ąĖ ąĖąĮč鹥ą│čĆą░ą╗čīąĮą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī (INL). ą¤ąŠą┤čĆąŠą▒ąĮąŠ ą┐ąŠ čŹčéąĖą╝ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ čüą╝. ą┤ą░ą╗ąĄąĄ čüąĄą║čåąĖčÄ "ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ADC". ąóą░ą║ąČąĄ čĆąĄąĘčāą╗čīčéą░čé ą╝ąŠąČąĄčé ą▓ą░čĆčīąĖčĆąŠą▓ą░čéčīčüčÅ ąŠčé ąŠčłąĖą▒ąŠą║ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā (AC errors), čéą░ą║ąĖčģ ą║ą░ą║ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī ą▓ ą▒ą╗ąŠą║ąĄ čāčüąĖą╗ąĄąĮąĖčÅ GAIN, ąŠčłąĖą▒ąŠą║ čāčüčéą░ąĮąŠą▓ą║ąĖ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čģąŠą┤ąĄ ąĖąĘ ąĘą░ ą▓čŗčüąŠą║ąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░ ąĖ ą┤ąČąĖčéč鹥čĆą░ ą▓čŗą▒ąŠčĆą║ąĖ. ąöą╗čÅ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▒ą░čéą░čĆąĄąĖ ąĮą░ąĖą▒ąŠą╗ąĄąĄ ą▓ą░ąČąĮčŗ ąŠčłąĖą▒ą║ąĖ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā (DC errors).

ąŻ ADC ąĖą╝ąĄąĄčéčüčÅ čłąĖčĆąŠą║ąĖą╣ ą▓čŗą▒ąŠčĆ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą▓ čāčüąĖą╗ąĄąĮąĖčÅ, čćč鹊 čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ GAIN čĆąĄą│ąĖčüčéčĆą░ CH[n].CONFIG. ąĢčüą╗ąĖ CH[n].CONFIG.REFSEL=0, č鹊 ą▓čģąŠą┤ąĮąŠą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ čÅą┤čĆą░ ADC ąĮąŠą╝ąĖąĮą░ą╗čīąĮąŠ ┬▒0.6V ą┤ą╗čÅ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░, ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą╝ą░čüčłčéą░ą▒ąĖčĆąŠą▓ą░ąĮąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čģąŠą┤ą░čģ.

ą×čłąĖą▒ą║ą░ čüą╝ąĄčēąĄąĮąĖčÅ ADC ąĘą░ą▓ąĖčüąĖčé ąŠčé č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ. ąĢčüą╗ąĖ ADC čĆą░ą▒ąŠčéą░ąĄčé ą▓ čłąĖčĆąŠą║ąŠą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ, č鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĘą░ą┐čāčüą║ą░čéčī CALIBRATEOFFSET čü čĆąĄą│čāą╗čÅčĆąĮčŗą╝ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ąĖ ą▓čĆąĄą╝ąĄąĮąĖ. ą¤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ ą▒čāą┤ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░čéčī čüąŠą▒čŗčéąĖąĄ CALIBRATEDONE.

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čģąŠą┤čŗ ąĖ ą║ą░ąĮą░ą╗čŗ. ą£ąŠąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą┤ąŠ 8 ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą▓čģąŠą┤ąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ CH[n] (n = 0 .. 7). ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī ą▓čŗčłąĄ, čŹčéąĖ ąĮąŠąČą║ąĖ čäąĖą║čüąĖčĆąŠą▓ą░ąĮčŗ ąĮą░ ą║ąŠčĆą┐čāčüąĄ čćąĖą┐ą░, ąĖ čüąŠą▓ą╝ąĄčüčéąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą▓čģąŠą┤ąŠą▓ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆąŠą▓.

ąøčÄą▒ąŠą╣ ąĖąĘ ą┤ąŠčüčéčāą┐ąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┤ą╗čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ADC ą▓ čĆąĄąČąĖą╝ąĄ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ (one-shot mode). ąĢčüą╗ąĖ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ CH[n], č鹊 ADC ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ (scan mode).

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą║ą░ą║ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą▓čģąŠą┤ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ CH[n].PSELP, čāčüčéą░ąĮąŠą▓ą║ą░ CH[n].PSELP čéą░ą║ąČąĄ čĆą░ąĘčĆąĄčłą░ąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ ą║ą░ąĮą░ą╗.

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą║ą░ą║ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ą▓čģąŠą┤ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ CH[n].PSELN. ąŻčüčéą░ąĮąŠą▓ą║ą░ čĆąĄą│ąĖčüčéčĆą░ CH[n].PSELN ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░, ą║čĆąŠą╝ąĄ ą║ą░ą║ ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝, čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą╗čÅ MODE čĆąĄą│ąĖčüčéčĆą░ CH[n].CONFIG.

ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ CH[n].PSELP, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░ąĮą░ą╗ąŠą▓ (scan mode). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą▓čŗą▒čĆą░ąĮąĮčŗąĄ ą▓čģąŠą┤čŗ čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ CH[n].PSELP ąĖ CH[n].PSELN, ą│ą┤ąĄ CH[n].PSELN ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čŹč鹊čé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ čüą║ą░ąĮąĖčĆčāąĄą╝čŗą╣ ą║ą░ąĮą░ą╗ ąĮą░čüčéčĆąŠąĄąĮ ą║ą░ą║ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣, čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą╗čÅ MODE čĆąĄą│ąĖčüčéčĆą░ CH[n].CONFIG.

ąÆą░ąČąĮąŠąĄ ąĘą░ą╝ąĄčćą░ąĮąĖąĄ: ą║ą░ąĮą░ą╗čŗ, ą▓čŗą▒čĆą░ąĮąĮčŗąĄ ą┤ą╗čÅ COMP ąĮąĄ ą╝ąŠą│čā ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┤ą╗čÅ ą▓čģąŠą┤ąŠą▓ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ADC, ąĮąŠ ą║ą░ąĮą░ą╗čŗ, ąĮąĄ ą▓čŗą▒čĆą░ąĮąĮčŗąĄ ą┤ą╗čÅ COMP, ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ADC.

ąóą░ą▒ą╗ąĖčåą░ 1. ąöąŠą┐čāčüčéąĖą╝čŗąĄ ą▓ą░čĆąĖą░ąĮčéčŗ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ CH[n] ą║ą░ą║ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą▓čģąŠą┤ąŠą▓.

| ąÆčģąŠą┤ ą║ą░ąĮą░ą╗ą░ |

ąśčüč鹊čćąĮąĖą║ |

ąÆąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ |

| CH[n].PSELP |

AIN0 .. AIN7 |

ąśą╝ąĄąĄčéčüčÅ (ą║ ą╗čÄą▒ąŠą╝čā ą▓čģąŠą┤čā) |

| VDD |

ąśą╝ąĄąĄčéčüčÅ |

| CH[n].PSELN |

AIN0 .. AIN7 |

ąśą╝ąĄąĄčéčüčÅ (ą║ ą╗čÄą▒ąŠą╝čā ą▓čģąŠą┤čā) |

| VDD |

ąśą╝ąĄąĄčéčüčÅ |

[ąĀą░ą▒ąŠčćąĖąĄ čĆąĄąČąĖą╝čŗ ADC]

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čģąŠą┤ąŠą▓ ADC ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé čĆąĄąČąĖą╝čŗ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠą│ąŠ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ (one-shot mode), ą┐ąŠą▓č鹊čĆčÅčÄčēąĖčģčüčÅ ąĖąĘą╝ąĄčĆąĄąĮąĖą╣ (continuous mode) ąĖ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ (scan mode). ąĀąĄąČąĖą╝ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖčÅ ąĮąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ.

One-shot mode. ą×ą┤ąĮąŠą║čĆą░čéąĮčŗą╣ čĆąĄąČąĖą╝ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą┐čāč鹥ą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą┤ąŠčüčéčāą┐ąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝ąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ CH[n].PSELP, CH[n].PSELN ąĖ CH[n].CONFIG.

ąÆ ąĘą░ą┤ą░č湥 SAMPLE ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī ADC ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┤ą╗čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. CH[n].CONFIG.TACQ čāą┐čĆą░ą▓ą╗čÅąĄčé ą▓čĆąĄą╝ąĄąĮąĄą╝ ąŠčåąĖčäčĆąŠą▓ą║ąĖ (acquisition time, tACQ).

ąĪąŠą▒čŗčéąĖąĄ DONE čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠ č鹊ą╝, čćč鹊 ą┐ąŠą╗čāč湥ąĮ ąŠą┤ąĖąĮ čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (sample).

ąÆ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠą╝ čĆąĄąČąĖą╝ąĄ čüąŠą▒čŗčéąĖąĄ RESULTDONE ąŠąĘąĮą░čćą░ąĄčé č鹊 ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ DONE, ąĄčüą╗ąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖčÅ (oversampling). ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąŠą▒ą░ čŹčéąĖčģ čüąŠą▒čŗčéąĖčÅ ą╝ąŠą│čāčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ čĆąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄąĘčāą╗čīčéą░čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą▓ RAM čü ą┐ąŠą╝ąŠčēčīčÄ EasyDMA. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. ą┤ą░ą╗ąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ EasyDMA.

Continuous mode. ąØąĄą┐čĆąĄčĆčŗą▓ąĮčŗą╣ čĆąĄąČąĖą╝, ą║ąŠą│ą┤ą░ ąĘą░ą┐čāčüą║ ą▓čŗą▒ąŠčĆąŠą║ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ, čĆąĄą░ą╗ąĖąĘčāąĄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čéą░ą╣ą╝ąĄčĆą░ ADC, ąĖą╗ąĖ ąĘą░ą┐čāčüą║ąŠą╝ ąĘą░ą┤ą░čćąĖ SAMPLE ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čéą░ą╣ą╝ąĄčĆąŠą▓ TIMERx čü ą┐ąŠą╝ąŠčēčīčÄ PPI [6].

ąĪą╗ąĄą┤čāąĄčé ą┐ąŠąĘą░ą▒ąŠčéąĖčéčīčüčÅ ąŠ č鹊ą╝, čćč鹊ą▒čŗ čćą░čüč鹊čéą░ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ (sample rate) čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅą╗ą░ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą║čĆąĖč鹥čĆąĖčÄ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹊ą│ąŠ, čüą║ąŠą╗čīą║ąŠ ąĖą╝ąĄąĄčéčüčÅ ą░ą║čéąĖą▓ąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ ADC:

fSAMPLE < 1/[tACQ + tCONV]

ąĀąĄą│ąĖčüčéčĆ SAMPLERATE ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ą╗ąŠą║ą░ą╗čīąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ ą▓ą╝ąĄčüč鹊 čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ čü ą┐ąŠą╝ąŠčēčīčÄ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčŗčģ ąĘą░ą┤ą░čć SAMPLE. ąÜąŠą│ą┤ą░ SAMPLERATE.MODE čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ Timers, ą┤ąŠčüčéą░č鹊čćąĮąŠ ą▓čŗąĘą▓ą░čéčī čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ąĘą░ą┤ą░čćąĖ SAMPLE č鹊ą╗čīą║ąŠ 1 čĆą░ąĘ, čćč鹊ą▒čŗ ąĘą░ą┐čāčüčéąĖčéčī SAADC, ąĖ ą▓čŗąĘą▓ą░čéčī čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ąĘą░ą┤ą░čćąĖ STOP, čćč鹊ą▒čŗ ąŠčüčéą░ąĮąŠą▓ąĖčéčī ąŠčåąĖčäčĆąŠą▓ą║čā. ą¤ąŠą╗ąĄ SAMPLERATE.CC čāą┐čĆą░ą▓ą╗čÅąĄčé čćą░čüč鹊č鹊ą╣ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ (čćą░čüč鹊č鹊ą╣ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▓čŗą▒ąŠčĆąŠą║, sample rate).

ąĀąĄąČąĖą╝ čéą░ą╣ą╝ąĄčĆą░ SAMPLERATE ąĮąĄ ą╝ąŠąČąĄčé ą║ąŠą╝ą▒ąĖąĮąĖčĆąŠą▓ą░čéčīčüčÅ čü čĆąĄąČąĖą╝ąŠą╝ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ (SCAN mode), ąĖ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ č鹊ą╗čīą║ąŠ 1 ą║ą░ąĮą░ą╗.

ąĪąŠą▒čŗčéąĖąĄ DONE čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠ č鹊ą╝, čćč鹊 ą▒čŗą╗ą░ ą┐ąŠą╗čāč湥ąĮą░ ąŠą┤ąĮą░ ą▓čŗą▒ąŠčĆą║ą░ (sample).

ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čüąŠą▒čŗčéąĖąĄ RESULTDONE ąĖą╝ąĄąĄčé č鹊 ąČąĄ čüą░ą╝ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, čćč鹊 ąĖ DONE, ą║ąŠą│ą┤ą░ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖčÅ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąŠą▒ą░ čŹčéąĖčģ čüąŠą▒čŗčéąĖčÅ ą╝ąŠą│čāčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ čĆąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄąĘčāą╗čīčéą░čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą▓ RAM čü ą┐ąŠą╝ąŠčēčīčÄ EasyDMA.

Oversampling. ąÉą║ą║čāą╝čāą╗čÅč鹊čĆ ADC ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čāčüčĆąĄą┤ąĮąĄąĮąĖčÅ čłčāą╝ą░ ąĮą░ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╝ ą▓čģąŠą┤ąĄ. ąÆ ąŠą▒čēąĄą╝, č鹥čģąĮąĖą║ą░ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ (oversampling) čāą╗čāčćčłą░ąĄčé ą┐ą░čĆą░ą╝ąĄčéčĆ čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗/čłčāą╝ (signal-to-noise ratio, SNR). ą×ą┤ąĮą░ą║ąŠ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖčÅ ąĮąĄ čāą╗čāčćčłą░ąĄčé ąĖąĮč鹥ą│čĆą░ą╗čīąĮčāčÄ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī (INL) ąĖą╗ąĖ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčāčÄ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī (DNL).

ą¤ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖčÅ ąĖ čĆąĄąČąĖą╝ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą║ąŠą╝ą▒ąĖąĮąĖčĆąŠą▓ą░čéčīčüčÅ, ą┐ąŠčüą║ąŠą╗čīą║čā ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖčÅ ą┐čĆąĖ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖąĖ ą▒čāą┤ąĄčé čāčüčĆąĄą┤ąĮčÅčéčī ą▓čŗą▒ąŠčĆą║ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓.

ąÉą║ą║čāą╝čāą╗čÅč鹊čĆ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąŠą╝ OVERSAMPLE. ąŚą░ą┤ą░čćą░ SAMPLE ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ą▓ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čāčüčĆąĄą┤ąĮčÅąĄą╝čŗčģ ą▓čŗą▒ąŠčĆąŠą║ 2OVERSAMPLE, ą┐ąŠčüą╗ąĄ ąĮą░ą▒ąŠčĆą░ čŹčéąĖčģ ą▓čŗą▒ąŠčĆąŠą║ čĆąĄąĘčāą╗čīčéą░čé ąĘą░ą┐ąĖčłąĄčéčüčÅ ą▓ RAM. ąŁč鹊ą│ąŠ ą╝ąŠąČąĮąŠ ą┤ąŠčüčéąĖčćčī čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ čćą░čüč鹊čéčŗ ą▓čŗą▒ąŠčĆąŠą║ (sampling rate), ąĖčüą┐ąŠą╗čīąĘčāčÅ ą╗ąŠą║ą░ą╗čīąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ ąĖą╗ąĖ čéą░ą╣ą╝ąĄčĆ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ TIMERx ąĖ PPI, čćč鹊ą▒čŗ ąĘą░ą┐čāčüčéąĖčéčī ąĘą░ą┤ą░čćčā SAMPLE.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ ąĘą░ą┐čāčüą║ąŠą╝ SAMPLE ąĮą░ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ 2OVERSAMPLE čĆą░ąĘ.

ŌĆó ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ čĆąĄąČąĖą╝ą░ BURST.

CH[n].CONFIG.BURST ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮąŠ, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčī ąĘą░ą┤ą░čćčā SAMPLE ą▓ ą║ąŠą╗ąĖč湥čüčéą▓ąĄ 2OVERSAMPLE čĆą░ąĘ. ą¤čĆąĖ BURST = 1 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī ADC ą▒čāą┤ąĄčé ąŠčåąĖčäčĆąŠą▓čŗą▓ą░čéčī ą▓čģąŠą┤ 2OVERSAMPLE čĆą░ąĘ ąĮą░čüč鹊ą╗čīą║ąŠ ą▒čŗčüčéčĆąŠ, ąĮą░čüą║ąŠą╗čīą║ąŠ čüą╝ąŠąČąĄčé (čĆąĄą░ą╗čīąĮčŗą╣ čéą░ą╣ą╝ąĖąĮą│: < (tACQ + tCONV) ├Ś 2OVERSAMPLE). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą┤ą╗čÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ čŹč鹊 ą▒čāą┤ąĄčé ą▓čŗą│ą╗čÅą┤ąĄčéčī ą┐čĆąŠčüč鹊 ą║ą░ą║ ą▒čāą┤č鹊 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ č鹥ą┐ąĄčĆčī ąĘą░ąĮąĖą╝ą░ąĄčé ą▒ąŠą╗čīčłąĄ ą▓čĆąĄą╝ąĄąĮąĖ, ąĮąŠ ą▓ ąŠčüčéą░ą╗čīąĮąŠą╝ č鹊čćąĮąŠ čéą░ą║ ąČąĄ, ą║ą░ą║ ąĖ ą▓ čĆąĄąČąĖą╝ąĄ one-shot. ąĀąĄąČąĖą╝ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą║ąŠą╝ą▒ąĖąĮąĖčĆąŠą▓ą░čéčīčüčÅ čü čāčüčéą░ąĮąŠą▓ą║ąŠą╣ BURST=1, ąĄčüą╗ąĖ burst čĆą░ąĘčĆąĄčłąĄąĮ ąĮą░ ą▓čüąĄčģ ą║ą░ąĮą░ą╗ą░čģ.

ąĪąŠą▒čŗčéąĖąĄ DONE čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠ č鹊ą╝, čćč鹊 ą▒čŗą╗ą░ ą┐ąŠą╗čāč湥ąĮą░ ąŠą┤ąĮą░ ą▓čŗą▒ąŠčĆą║ą░. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čüąŠą▒čŗčéąĖąĄ RESULTDONE ą│ąŠą▓ąŠčĆąĖčé ąŠ č鹊ą╝, čćč鹊 ą▒čŗą╗ąŠ ą┐čĆąŠąĖąĘą▓ąĄą┤ąĄąĮąŠ ą┤ąŠčüčéą░č鹊čćąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ, čćč鹊ą▒čŗ čĆąĄąĘčāą╗čīčéą░čé ą╝ąŠą│ ą▒čŗčéčī ą┐ąĄčĆąĄą╝ąĄčēąĄąĮ ą▓ RAM. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąŠą▒ą░ čŹčéąĖčģ čüąŠą▒čŗčéąĖčÅ ą╝ąŠą│čāčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ čĆąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄąĘčāą╗čīčéą░čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą▓ RAM čü ą┐ąŠą╝ąŠčēčīčÄ EasyDMA.

Scan mode. ąĪčćąĖčéą░čÄčéčüčÅ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╝ąĖ ą║ą░ąĮą░ą╗čŗ, čā ą║ąŠč鹊čĆčŗčģ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ CH[n].PSELP. ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ CH[n], č鹊 ADC ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░ąĮą░ą╗ąŠą▓ (scan mode). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąŠą┤ąĖąĮ ąĘą░ą┐čāčüą║ ąĘą░ą┤ą░čćąĖ SAMPLE ąĘą░ą┐čāčüčéąĖčé ą┐ąŠ ąŠą┤ąĮąŠą╝čā ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÄ ąĮą░ ą║ą░ąČą┤čŗą╣ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╣ ą║ą░ąĮą░ą╗l. ąÆčĆąĄą╝čÅ, ą║ąŠč鹊čĆąŠąĄ ą┐ąŠčéčĆąĄą▒čāąĄčéčüčÅ ąĮą░ ąŠčåąĖčäčĆąŠą▓ą║čā ą▓čüąĄčģ ą║ą░ąĮą░ą╗ąŠą▓, ą╝ąŠąČąĮąŠ čĆą░čüčüčćąĖčéą░čéčī ą┐ąŠ č乊čĆą╝čāą╗ąĄ (x čŹč鹊 ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓):

Total time < Sum(CH[x].tACQ+tCONV)

ąĪąŠą▒čŗčéąĖąĄ DONE čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠ č鹊ą╝, čćč鹊 ą▒čŗą╗ą░ ą┐ąŠą╗čāč湥ąĮą░ ąŠą┤ąĮą░ ą▓čŗą▒ąŠčĆą║ą░.

ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čüąŠą▒čŗčéąĖąĄ RESULTDONE ąŠąĘąĮą░čćą░ąĄčé č鹊 ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ čüąŠą▒čŗčéąĖąĄ DONE, ą║ąŠą│ą┤ą░ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖčÅ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąŠą▒ą░ čŹčéąĖčģ čüąŠą▒čŗčéąĖčÅ ą╝ąŠą│čāčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ čĆąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄąĘčāą╗čīčéą░čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą▓ RAM čü ą┐ąŠą╝ąŠčēčīčÄ EasyDMA.

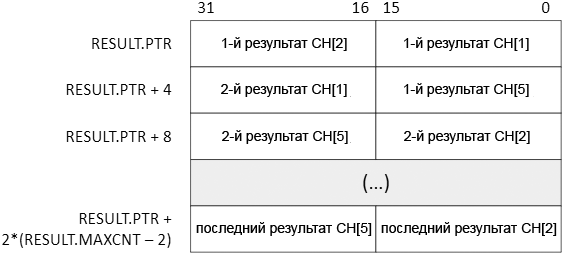

ąĀąĖčü. 2 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆąĖą╝ąĄčĆ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░č鹊ą▓ ą▓ Data RAM, čü č湥čéąĮčŗą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ RESULT.MAXCNT. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą║ą░ąĮą░ą╗čŗ 1, 2 ąĖ 5, ą┤čĆčāą│ąĖąĄ ą║ą░ąĮą░ą╗čŗ ąĘą░ą┐čĆąĄčēąĄąĮčŗ.

ąĀąĖčü. 2. ą¤čĆąĖą╝ąĄčĆ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░č鹊ą▓ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą║ą░ąĮą░ą╗ąŠą▓ ą▓ ą×ąŚąŻ (č湥čéąĮąŠąĄ RESULT.MAXCNT), ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą║ą░ąĮą░ą╗čŗ 1, 2 ąĖ 5.

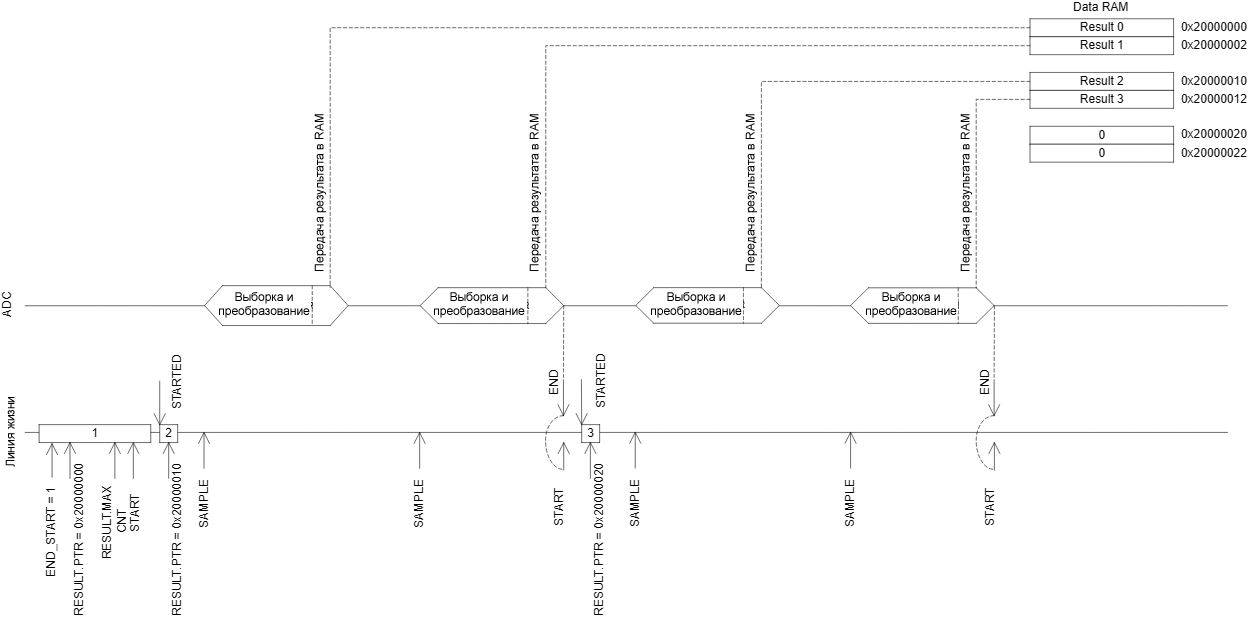

ąĀąĖčü. 3 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆąĖą╝ąĄčĆ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░č鹊ą▓ ą▓ Data RAM, čü ąĮąĄč湥čéąĮčŗą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ RESULT.MAXCNT. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą║ą░ąĮą░ą╗čŗ 1, 2 ąĖ 5, ą┤čĆčāą│ąĖąĄ ą║ą░ąĮą░ą╗čŗ ąĘą░ą┐čĆąĄčēąĄąĮčŗ. ą¤ąŠčüą╗ąĄą┤ąĮąĄąĄ 32-ą▒ąĖčéąĮąŠąĄ čüą╗ąŠą▓ąŠ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ 16-ą▒ąĖčéąĮčŗą╣ čĆąĄąĘčāą╗čīčéą░čé.

ąĀąĖčü. 3. ą¤čĆąĖą╝ąĄčĆ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░č鹊ą▓ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą║ą░ąĮą░ą╗ąŠą▓ ą▓ ą×ąŚąŻ (ąĮąĄč湥čéąĮąŠąĄ RESULT.MAXCNT), ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą║ą░ąĮą░ą╗čŗ 1, 2 ąĖ 5.

[EasyDMA]

ą¤ąŠčüą╗ąĄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ RESULT.PTR ąĖ RESULT.MAXCNT čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄą╝ ąĘą░ą┤ą░čćąĖ START ąĘą░ą┐čāčüą║ą░čÄčéčüčÅ čĆąĄčüčāčĆčüčŗ ADC. ADC ąĖčüą┐ąŠą╗čīąĘčāąĄčé EasyDMA ą┤ą╗čÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░č鹊ą▓ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓ RAM-ą▒čāč乥čĆąĄ Result.

ąæčāč乥čĆ Result ąĮą░čģąŠą┤ąĖčéčüčÅ ą┐ąŠ ą░ą┤čĆąĄčüčā, čāą║ą░ąĘą░ąĮąĮąŠą╝čā ą▓ čĆąĄą│ąĖčüčéčĆąĄ RESULT.PTR. ąĀąĄą│ąĖčüčéčĆ RESULT.PTR čüąĮą░ą▒ąČąĄąĮ ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣, ąĖ ą╝ąŠąČąĄčé ąŠą▒ąĮąŠą▓ą╗čÅčéčīčüčÅ ąĖ ą▒čŗčéčī ą┐ąŠą┤ą│ąŠč鹊ą▓ą╗ąĄąĮąĮčŗą╝ ą║ čüą╗ąĄą┤čāčÄčēąĄą╣ ąĘą░ą┤ą░č湥 START ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąŠčüą╗ąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ STARTED. ąĀą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ Result čāą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ RESULT.MAXCNT, ąĖ ADC ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čüąŠą▒čŗčéąĖąĄ END ą║ąŠą│ą┤ą░ ąĘą░ą┐ąŠą╗ąĮąĖčé ą▒čāč乥čĆ Result, čüą╝. čĆąĖčü. 4. ąĀąĄąĘčāą╗čīčéą░čéčŗ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ little-endian [7] ą┐ąŠčĆčÅą┤ą║ąĄ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ą░ą╣čé Data RAM. ąÜą░ąČą┤ą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ą┐ąĄčĆąĄą┤ čüąŠčģčĆą░ąĮąĄąĮąĖąĄą╝ ą▓ ą▒čāč乥čĆ Result ą┐ąŠą╗čāčćąĖčé ąĘąĮą░ą║ čü čĆą░čüčłąĖčĆąĄąĮąĖąĄą╝ ą┤ąŠ 16 ą▒ąĖčé.

ADC ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĘą░ą┐čāčüą║ąŠą╝ ąĘą░ą┤ą░čćąĖ STOP. ąŚą░ą┤ą░čćą░ STOP ąĘą░ą▓ąĄčĆčłąĖčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčēčāčÄčüčÅ ąŠčåąĖčäčĆąŠą▓ą║čā. ADC čüą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąŠą▒čŗčéąĖąĄ STOPPED, ą║ąŠą│ą┤ą░ ąŠčüčéą░ąĮąŠą▓ąĖčé ąŠčåąĖčäčĆąŠą▓ą║čā. ąĢčüą╗ąĖ ADC čāąČąĄ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ, ą║ąŠą│ą┤ą░ ąĘą░ą┐čāčēąĄąĮą░ ąĘą░ą┤ą░čćą░ STOP, č鹊 čüąŠą▒čŗčéąĖąĄ STOPPED ą▓čüąĄ čĆą░ą▓ąĮąŠ čüą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ.

ąĀąĖčü. 4. ąÉą╗ą│ąŠčĆąĖčéą╝ čĆą░ą▒ąŠčéčŗ ADC.

ąĢčüą╗ąĖ RESULT.PTR ąĮąĄ čāą║ą░ąĘčŗą▓ą░ąĄčé ą▓ ąŠą▒ą╗ą░čüčéčī Data RAM, č鹊 čéčĆą░ąĮąĘą░ą║čåąĖčÅ EasyDMA ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąŠčłąĖą▒ą║ąĄ HardFault ąĖą╗ąĖ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÄ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ RAM. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ čĆąĄą│ąĖąŠąĮą░ą╝ ą┐ą░ą╝čÅčéąĖ čüą╝. [3].

EasyDMA ąĘą░ą▓ąĄčĆčłąĖčé ą┤ąŠčüčéčāą┐ ą║ RAM, ą║ąŠą│ą┤ą░ ą▒čāą┤čāčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮčŗ čüąŠą▒čŗčéąĖčÅ END ąĖą╗ąĖ STOPPED.

ąĀąĄą│ąĖčüčéčĆ RESULT.AMOUNT ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ą┐ąŠčüą╗ąĄ čüąŠą▒čŗčéąĖčÅ END ąĖą╗ąĖ čüąŠą▒čŗčéąĖčÅ STOPPED, čćč鹊ą▒čŗ čāą▓ąĖą┤ąĄčéčī, čüą║ąŠą╗čīą║ąŠ čĆąĄąĘčāą╗čīčéą░č鹊ą▓ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą▓ ą▒čāč乥čĆ Result ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ąĘą░ą┐čāčüą║ą░ ąĘą░ą┤ą░čćąĖ START.

ąÆ čĆąĄąČąĖą╝ąĄ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ Result ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┤ąŠčüčéą░č鹊čćąĮčŗą╝, čćč鹊ą▒čŗ čüąŠčģčĆą░ąĮąĖčéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą┐ąŠ ąŠą┤ąĮąŠą╝čā čĆąĄąĘčāą╗čīčéą░čéčā ąĮą░ ą║ą░ąČą┤čŗą╣ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╣ ą║ą░ąĮą░ą╗. ą¦č鹊ą▒čŗ čŹč鹊 ąŠą▒ąĄčüą┐ąĄčćąĖčéčī, ąĘąĮą░č湥ąĮąĖąĄ RESULT.MAXCNT ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┤ą░ąĮąŠ RESULT.MAXCNT >= "ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓". ąĪą╝. ą▓čŗčłąĄ čüąĄą║čåąĖčÄ "Scan mode" ą┤ą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ čĆąĄąČąĖą╝čā čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ.

[ąĀąĄąĘąĖčüč鹊čĆąĮčŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī]

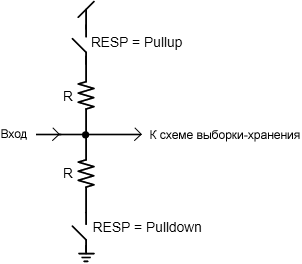

ąÆ ADC ąĄčüčéčī ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čåąĄą┐ąŠčćą║ą░ čĆąĄąĘąĖčüč鹊čĆąŠą▓ ąĮą░ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝ ąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╝ ą▓čģąŠą┤ąĄ, čüą╝. čĆąĖčü. 5. ąŁčéą░ čåąĄą┐ąŠčćą║ą░ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ CH[n].CONFIG.RESP ąĖ CH[n].CONFIG.RESN.

ąĀąĖčü. 5. ą”ąĄą┐ąŠčćą║ą░ čĆąĄąĘąĖčüč鹊čĆąŠą▓ ąĮą░ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝ ą▓čģąŠą┤ąĄ (čåąĄą┐ąŠčćą║ą░ ąĮą░ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╝ ą▓čģąŠą┤ąĄ 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮą░čÅ, ą┐čĆąŠčüč鹊 čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ąŠąĮą░ RESN, ą░ ąĮąĄ RESP).

[ą×ą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ]

ADC ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī 2 čĆą░ąĘąĮčŗčģ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗčģ ą┐ąŠą╗ąĄą╝ REFSEL ą▓ čĆąĄą│ąĖčüčéčĆąĄ CH[n].CONFIG:

ŌĆó ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

ŌĆó VDD ą▓ ą║ą░č湥čüčéą▓ąĄ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ą░ąĄčé čÅą┤čĆčā ADC ąŠčåąĖčäčĆąŠą▓čŗą▓ą░čéčī ą▓čģąŠą┤ąĮčŗąĄ čāčĆąŠą▓ąĮąĖ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ┬▒0.6V. ą×ą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VDD ą┤ą░ąĄčé ą▓čģąŠą┤ąĮąŠą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ┬▒VDD/4. ą£ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▒ą╗ąŠą║ čāčüąĖą╗ąĄąĮąĖčÅ (gain) ą┤ą╗čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čŹčäč乥ą║čéąĖą▓ąĮąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ (input range) ąĖąĘą╝ąĄčĆąĄąĮąĖą╣ ą┤ą╗čÅ ADC.

Input range = (┬▒0.6V ąĖą╗ąĖ ┬▒VDD/4) / Gain

ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ ą▓ ą║ą░č湥čüčéą▓ąĄ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓čŗą▒čĆą░ąĮąŠ VDD, ąĮą░čüčéčĆąŠąĄąĮ ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą▓čģąŠą┤ (ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ą▓čģąŠą┤ ąĘą░ąĘąĄą╝ą╗ąĄąĮ ą▓ąĮčāčéčĆąĖ čćąĖą┐ą░), ąĖ čāčüąĖą╗ąĄąĮąĖčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ 1/4, č鹊 ą▓čģąŠą┤ąĮąŠą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą▒čāą┤ąĄčé čüą╗ąĄą┤čāčÄčēąĖą╣:

Input range = (VDD/4)/(1/4) = VDD

ąĪ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ ąĖčüč鹊čćąĮąĖą║ąŠą╝ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╝ ą▓čģąŠą┤ąŠą╝ ąĖ čāčüąĖą╗ąĄąĮąĖąĄą╝ 1/6 ą▓čģąŠą┤ąĮąŠą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┐ąŠą╗čāčćąĖčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╣:

Input range = (0.6V)/(1/6) = 3.6 V

ąØą░ ą▓čģąŠą┤ą░čģ AIN0 .. AIN7 ąĮąĄą╗čīąĘčÅ ą┐čĆąĄą▓čŗčłą░čéčī čāčĆąŠą▓ąĄąĮčī VDD, ąĖą╗ąĖ ą┤ąĄą╗ą░čéčī ąĄą│ąŠ ąĮąĖąČąĄ ąĘąĄą╝ą╗ąĖ VSS.

[ąÆčĆąĄą╝čÅ ąĘą░čģą▓ą░čéą░ čāčĆąŠą▓ąĮčÅ]

ą¦č鹊ą▒čŗ čüą┤ąĄą╗ą░čéčī ą▓čŗą▒ąŠčĆą║čā ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ADC ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé ą║ąŠ ą▓čģąŠą┤čā ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ. ąŁč鹊 čéčĆą░ą┤ąĖčåąĖąŠąĮąĮą░čÅ č鹥čģąĮąĖą║ą░ ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ, ą┐čĆąĖą╝ąĄąĮčÅąĄą╝ą░čÅ ą┤ą╗čÅ ąĘą░čģą▓ą░čéą░ ąĖąĘą╝ąĄčĆčÅąĄą╝ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

ąĀąĖčü. 6. ąŻą┐čĆąŠčēąĄąĮąĮą░čÅ čüčģąĄą╝ą░ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ ADC.

ąÜą░ą║ čŹč鹊 čĆą░ą▒ąŠčéą░ąĄčé, ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 6. ąÆčĆąĄą╝čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ tACQ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ ą┤ąŠą╗ą│ąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ, čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą╗čÅ TACQ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CH[n].CONFIG. ąóčĆąĄą▒čāąĄą╝ąŠąĄ ą▓čĆąĄą╝čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ąĘą░ą▓ąĖčüąĖčé ąŠčé čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░ (Rsource). ąöą╗čÅ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░ čü ą▓čŗčüąŠą║ąĖą╝ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝ ą▓čĆąĄą╝čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čāą▓ąĄą╗ąĖč湥ąĮąŠ, čüą╝. čéą░ą▒ą╗ąĖčåčā 2.

ąóą░ą▒ą╗ąĖčåą░ 2. ąÆčĆąĄą╝čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ. Rsource čŹč鹊 ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠąĄ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ ą▓čģąŠą┤ąĮąŠą╣ čåąĄą┐ąĖ ADC.

| TACQ (ą╝ą║čü) |

Rsource (ą║ą×ą╝) |

| 3 |

10 |

| 5 |

40 |

| 10 |

100 |

| 15 |

200 |

| 20 |

400 |

| 40 |

800 |

[ą£ąŠąĮąĖč鹊čĆąĖąĮą│ ą▓čŗčģąŠą┤ą░ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čģąŠą┤ąĄ ąĘą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗąĄ ą┐čĆąĄą┤ąĄą╗čŗ]

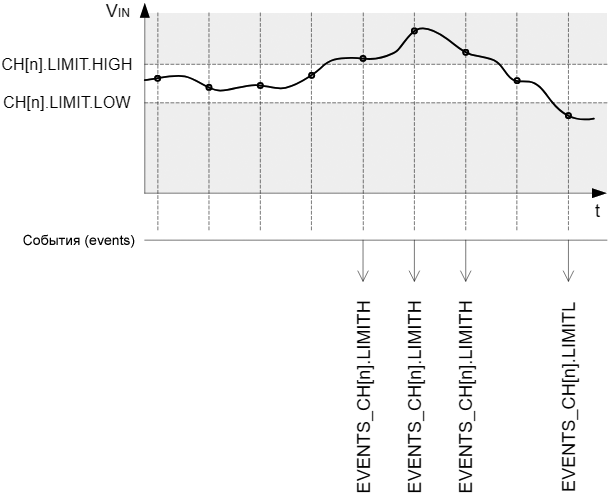

ąÜą░ąĮą░ą╗ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąĮą░ ą│ąĄąĮąĄčĆą░čåąĖčÄ čüąŠą▒čŗčéąĖčÅ ą┐ąŠ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│čā čāčĆąŠą▓ąĮčÅ ą┐čāč鹥ą╝ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ą┐čĆąĄą┤ąĄą╗ąŠą▓ CH[n].LIMIT.

ąĢčüą╗ąĖ čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓čŗčłąĄ, č湥ą╝ ą▒čŗą╗ąŠ ąĘą░ą┤ą░ąĮąŠ ą▓ ą▓ąĄčĆčģąĮąĄą╝ ą┐čĆąĄą┤ąĄą╗ąĄ (high limit), ą╗ąĖą▒ąŠ ąĮąĖąČąĄ, č湥ą╝ ą▒čŗą╗ąŠ ąĘą░ą┤ą░ąĮąŠ ą▓ ąĮąĖąČąĮąĄą╝ ą┐čĆąĄą┤ąĄą╗ąĄ (low limit), č鹊 čüčĆą░ą▒ąŠčéą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ čüąŠą▒čŗčéąĖąĄ.

ąĀąĖčü. 7. ą¤čĆąĖą╝ąĄčĆ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ ą┐čĆąĄą┤ąĄą╗ąŠą▓ ą║ą░ąĮą░ą╗ą░ 'n'.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą║ąŠą│ą┤ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą┐čĆąĄą┤ąĄą╗čŗ, CH[n].LIMIT.HIGH ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čüąĄą│ą┤ą░ ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĄąĮ CH[n].LIMIT.LOW. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, čüąŠą▒čŗčéąĖąĄ ą╝ąŠąČąĄčé čüčĆą░ą▒ąŠčéą░čéčī č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ąŠčåąĖčäčĆąŠą▓ą░ąĮąĮčŗą╣ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą▓čŗčłąĄą╗ ąĘą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗąĄ ą┐čĆąĄą┤ąĄą╗čŗ. ąØąĄą▓ąŠąĘą╝ąŠąČąĮąŠ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░čéčī čüąŠą▒čŗčéąĖąĄ, ą║ąŠą│ą┤ą░ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ąĮąĄ ąĘą░ą┤ą░ąĮąĮąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░, ą┐čāč鹥ą╝ ą┐ąĄčĆąĄčüčéą░ąĮąŠą▓ą║ąĖ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ąŠą▓.

ąÆčüąĄą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čüčĆą░ą▓ąĮąĄąĮąĖąĄ ą┐čĆąĄą┤ąĄą╗ąŠą▓, ąĮąĄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ čŹč鹊 čüą┐ąĄčåąĖą░ą╗čīąĮąŠ čĆą░ąĘčĆąĄčłą░čéčī. ąĢčüą╗ąĖ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ čüčĆą░ą▓ąĮąĄąĮąĖąĄ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ, č鹊 ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąŠčüč鹊 ą┤ąŠą╗ąČąĮą░ ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čüąŠą▒čŗčéąĖčÅ. ąÆ čŹč鹊ą╣ čüąĖčéčāą░čåąĖąĖ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐čĆąĄą┤ąĄą╗ą░ ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ, čéą░ą║ čćč鹊 ąĮąĄ ą▓ą░ąČąĮąŠ, ą╝ąĄąĮčīčłąĄ ą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ CH[n].LIMIT.LOW, č湥ą╝ CH[n].LIMIT.HIGH, ąĖą╗ąĖ ąĮąĄčé.

[ąĀąĄą│ąĖčüčéčĆčŗ ADC]

ąóą░ą▒ą╗ąĖčåą░ 3. ąŁą║ąĘąĄą╝ą┐ą╗čÅčĆ ADC.

| ąæą░ąĘ. ą░ą┤čĆąĄčü |

ą¤ąĄčĆąĖčä. čāčüčéčĆąŠą╣čüčéą▓ąŠ |

ąŁą║ąĘ. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 0x40007000 |

SAADC |

SAADC |

ąÉąĮą░ą╗ąŠą│ąŠ-čåąĖčäčĆąŠą▓ąŠą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī |

ąóą░ą▒ą╗ąĖčåą░ 4. ą×ą▒ąĘąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓ ADC.

| ąĀąĄą│ąĖčüčéčĆ |

ąĪą╝ąĄčē. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| TASKS_START |

0x000 |

ąŚą░ą┐čāčüą║ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC ąĖ ą┐ąŠą┤ą│ąŠč鹊ą▓ą║ą░ ą▒čāč乥čĆą░ čĆąĄąĘčāą╗čīčéą░čéą░ ą▓ RAM. |

| TASKS_SAMPLE |

0x004 |

ą¤ąŠą╗čāčćą░ąĄčé ąŠą┤ąĮčā ą▓čŗą▒ąŠčĆą║čā ADC. ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖąĄ, č鹊 ąŠčåąĖčäčĆąŠą▓čŗą▓ą░čÄčéčüčÅ ą▓čüąĄ ą║ą░ąĮą░ą╗čŗ. |

| TASKS_STOP |

0x008 |

ą×čüčéą░ąĮąŠą▓ą║ą░ ADC, ąŠą▒čĆčŗą▓ ą┐čĆąŠąĖčüčģąŠą┤čÅčēąĄą│ąŠ ą┐čĆąŠčåąĄčüčüą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. |

| TASKS_CALIBRATEOFFSET |

0x00C |

ąŚą░ą┐čāčüą║ ą░ą▓č鹊ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ čüą╝ąĄčēąĄąĮąĖčÅ. |

| EVENTS_STARTED |

0x100 |

ąĪąŠą▒čŗčéąĖąĄ: ADC ąĘą░ą┐čāčüčéąĖą╗čüčÅ. |

| EVENTS_END |

0x104 |

ąĪąŠą▒čŗčéąĖąĄ: ADC ąĘą░ą┐ąŠą╗ąĮąĖą╗ ą▒čāč乥čĆ čĆąĄąĘčāą╗čīčéą░č鹊ą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. |

| EVENTS_DONE |

0x108 |

ąĪąŠą▒čŗčéąĖąĄ: ąĘą░ą┤ą░čćą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłąĄąĮą░. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆąĄąČąĖą╝ą░, ą╝ąŠąČąĄčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣, čćč鹊ą▒čŗ ą║ąŠąĮąĄčćąĮčŗą╣ čĆąĄąĘčāą╗čīčéą░čé ą▒čŗą╗ ą┐ąŠą╝ąĄčēąĄąĮ ą▓ RAM. |

| EVENTS_RESULTDONE |

0x10C |

ąĪąŠą▒čŗčéąĖąĄ: čĆąĄąĘčāą╗čīčéą░čé ą│ąŠč鹊ą▓ ą║ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÄ ą▓ RAM. |

| EVENTS_CALIBRATEDONE |

0x110 |

ąĪąŠą▒čŗčéąĖąĄ: ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░. |

| EVENTS_STOPPED |

0x114 |

ąĪąŠą▒čŗčéąĖąĄ: ADC ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ. |

| EVENTS_CH[0].LIMITH |

0x118 |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄ CH[0].LIMIT.HIGH. |

| EVENTS_CH[0].LIMITL |

0x11C |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ CH[0].LIMIT.LOW. |

| EVENTS_CH[1].LIMITH |

0x120 |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄ CH[1].LIMIT.HIGH. |

| EVENTS_CH[1].LIMITL |

0x124 |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ CH[1].LIMIT.LOW. |

| EVENTS_CH[2].LIMITH |

0x128 |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄ CH[2].LIMIT.HIGH. |

| EVENTS_CH[2].LIMITL |

0x12C |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ CH[2].LIMIT.LOW. |

| EVENTS_CH[3].LIMITH |

0x130 |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄ CH[3].LIMIT.HIGH. |

| EVENTS_CH[3].LIMITL |

0x134 |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ CH[3].LIMIT.LOW. |

| EVENTS_CH[4].LIMITH |

0x138 |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄ CH[4].LIMIT.HIGH. |

| EVENTS_CH[4].LIMITL |

0x13C |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ CH[4].LIMIT.LOW. |

| EVENTS_CH[5].LIMITH |

0x140 |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄ CH[5].LIMIT.HIGH. |

| EVENTS_CH[5].LIMITL |

0x144 |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ CH[5].LIMIT.LOW. |

| EVENTS_CH[6].LIMITH |

0x148 |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄ CH[6].LIMIT.HIGH. |

| EVENTS_CH[6].LIMITL |

0x14C |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ CH[6].LIMIT.LOW. |

| EVENTS_CH[7].LIMITH |

0x150 |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄ CH[7].LIMIT.HIGH. |

| EVENTS_CH[7].LIMITL |

0x154 |

ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ CH[7].LIMIT.LOW. |

| INTEN |

0x300 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ADC. |

| INTENSET |

0x304 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé (čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ) ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ADC. |

| INTENCLR |

0x308 |

ąĪą▒čĆąŠčü ą▒ąĖčé (ąĘą░ą┐čĆąĄčé) ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. |

| STATUS |

0x400 |

ąĪąŠčüč鹊čÅąĮąĖąĄ ADC. |

| ENABLE |

0x500 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ADC. |

| CH[0].PSELP |

0x510 |

ąÆčŗą▒ąŠčĆ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 0. |

| CH[0].PSELN |

0x514 |

ąÆčŗą▒ąŠčĆ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 0. |

| CH[0].CONFIG |

0x518 |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 0. |

| CH[0].LIMIT |

0x51C |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ąŠą▓ ą║ąŠąĮčéčĆąŠą╗čÅ čāčĆąŠą▓ąĮčÅ (ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ čüąŠą▒čŗčéąĖą╣) ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 0. |

| CH[1].PSELP |

0x520 |

ąÆčŗą▒ąŠčĆ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1. |

| CH[1].PSELN |

0x524 |

ąÆčŗą▒ąŠčĆ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1. |

| CH[1].CONFIG |

0x528 |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1. |

| CH[1].LIMIT |

0x52C |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ąŠą▓ ą║ąŠąĮčéčĆąŠą╗čÅ čāčĆąŠą▓ąĮčÅ (ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ čüąŠą▒čŗčéąĖą╣) ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1. |

| CH[2].PSELP |

0x530 |

ąÆčŗą▒ąŠčĆ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2. |

| CH[2].PSELN |

0x534 |

ąÆčŗą▒ąŠčĆ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2. |

| CH[2].CONFIG |

0x538 |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2. |

| CH[2].LIMIT |

0x53C |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ąŠą▓ ą║ąŠąĮčéčĆąŠą╗čÅ čāčĆąŠą▓ąĮčÅ (ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ čüąŠą▒čŗčéąĖą╣) ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2. |

| CH[3].PSELP |

0x540 |

ąÆčŗą▒ąŠčĆ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 3. |

| CH[3].PSELN |

0x544 |

ąÆčŗą▒ąŠčĆ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 3. |

| CH[3].CONFIG |

0x548 |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 3. |

| CH[3].LIMIT |

0x54C |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ąŠą▓ ą║ąŠąĮčéčĆąŠą╗čÅ čāčĆąŠą▓ąĮčÅ (ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ čüąŠą▒čŗčéąĖą╣) ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 3. |

| CH[4].PSELP |

0x550 |

ąÆčŗą▒ąŠčĆ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 4. |

| CH[4].PSELN |

0x554 |

ąÆčŗą▒ąŠčĆ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 4. |

| CH[4].CONFIG |

0x558 |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 4. |

| CH[4].LIMIT |

0x55C |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ąŠą▓ ą║ąŠąĮčéčĆąŠą╗čÅ čāčĆąŠą▓ąĮčÅ (ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ čüąŠą▒čŗčéąĖą╣) ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 4. |

| CH[5].PSELP |

0x560 |

ąÆčŗą▒ąŠčĆ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 5. |

| CH[5].PSELN |

0x564 |

ąÆčŗą▒ąŠčĆ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 5. |

| CH[5].CONFIG |

0x568 |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 5. |

| CH[5].LIMIT |

0x56C |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ąŠą▓ ą║ąŠąĮčéčĆąŠą╗čÅ čāčĆąŠą▓ąĮčÅ (ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ čüąŠą▒čŗčéąĖą╣) ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 5. |

| CH[6].PSELP |

0x570 |

ąÆčŗą▒ąŠčĆ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 6. |

| CH[6].PSELN |

0x574 |

ąÆčŗą▒ąŠčĆ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 6. |

| CH[6].CONFIG |

0x578 |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 6. |

| CH[6].LIMIT |

0x57C |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ąŠą▓ ą║ąŠąĮčéčĆąŠą╗čÅ čāčĆąŠą▓ąĮčÅ (ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ čüąŠą▒čŗčéąĖą╣) ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 6. |

| CH[7].PSELP |

0x580 |

ąÆčŗą▒ąŠčĆ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 7. |

| CH[7].PSELN |

0x584 |

ąÆčŗą▒ąŠčĆ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 7. |

| CH[7].CONFIG |

0x588 |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 7. |

| CH[7].LIMIT |

0x58C |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ąŠą▓ ą║ąŠąĮčéčĆąŠą╗čÅ čāčĆąŠą▓ąĮčÅ (ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ čüąŠą▒čŗčéąĖą╣) ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 7. |

| RESOLUTION |

0x5F0 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ ADC. |

| OVERSAMPLE |

0x5F4 |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ. |

| SAMPLERATE |

0x5F8 |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čćą░čüč鹊č鹊ą╣ ą▓čŗą▒ąŠčĆąŠą║ ąĖ čĆąĄąČąĖą╝ąŠą╝ - ąŠą┤ąĮąŠą║čĆą░čéąĮą░čÅ ąŠčåąĖčäčĆąŠą▓ą║ą░ ąĖą╗ąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąŠą▓č鹊čĆčÅčÄčēąĖąĄčüčÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ. |

| RESULT.PTR |

0x62C |

ąŻą║ą░ąĘą░č鹥ą╗čī ąĮą░ ą▒čāč乥čĆ ą┤ą╗čÅ čĆąĄąĘčāą╗čīčéą░čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC. |

| RESULT.MAXCNT |

0x630 |

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čüą╗ąŠą▓ ą▒čāč乥čĆą░ ą┤ą╗čÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. |

| RESULT.AMOUNT |

0x634 |

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čüą╗ąŠą▓ ą▓ ą▒čāč乥čĆąĄ, ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗčģ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ START. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x300

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ INTEN:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

V |

U |

T |

S |

R |

Q |

P |

O |

N |

M |

L |

K |

J |

I |

H |

G |

F |

E |

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

STARTED |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ STARTED. ąĪą╝. EVENTS_STARTED.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| B |

RW |

END |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ END. ąĪą╝. EVENTS_END.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| C |

RW |

DONE |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ DONE. ąĪą╝. EVENTS_DONE.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| D |

RW |

RESULTDONE |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ RESULTDONE. ąĪą╝. EVENTS_RESULT_DONE.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| E |

RW |

CALIBRATEDONE |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CALIBRATEDONE. ąĪą╝. EVENTS_CALIBRATEDONE.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| F |

RW |

STOPPED |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ STOPPED. ąĪą╝. EVENTS_STOPPED.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| G |

RW |

CH0LIMITH |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[0].LIMITH. ąĪą╝. EVENTS_CH[0].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| H |

RW |

CH0LIMITL |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[0].LIMITL ąĪą╝. EVENTS_CH[0].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| I |

RW |

CH1LIMITH |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[1].LIMITH. ąĪą╝. EVENTS_CH[1].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| J |

RW |

CH1LIMITL |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[1].LIMITL ąĪą╝. EVENTS_CH[1].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| K |

RW |

CH2LIMITH |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[2].LIMITH. ąĪą╝. EVENTS_CH[2].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| L |

RW |

CH2LIMITL |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[2].LIMITL ąĪą╝. EVENTS_CH[2].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| M |

RW |

CH3LIMITH |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[3].LIMITH. ąĪą╝. EVENTS_CH[3].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| N |

RW |

CH3LIMITL |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[3].LIMITL ąĪą╝. EVENTS_CH[3].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| O |

RW |

CH4LIMITH |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[4].LIMITH. ąĪą╝. EVENTS_CH[4].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| P |

RW |

CH4LIMITL |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[4].LIMITL ąĪą╝. EVENTS_CH[4].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| Q |

RW |

CH5LIMITH |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[5].LIMITH. ąĪą╝. EVENTS_CH[5].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| R |

RW |

CH5LIMITL |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[5].LIMITL ąĪą╝. EVENTS_CH[5].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| S |

RW |

CH6LIMITH |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[6].LIMITH. ąĪą╝. EVENTS_CH[6].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| T |

RW |

CH6LIMITL |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[6].LIMITL ąĪą╝. EVENTS_CH[6].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| U |

RW |

CH7LIMITH |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[7].LIMITH. ąĪą╝. EVENTS_CH[7].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| V |

RW |

CH7LIMITL |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[7].LIMITL ąĪą╝. EVENTS_CH[7].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x304. ąŚą░ą┐ąĖčüčī ąĄą┤ąĖąĮąĖčåčŗ ą▓ ą▒ąĖčé čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čĆą░ąĘčĆąĄčłą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, čćč鹥ąĮąĖąĄ ą▓ąĄčĆąĮąĄčé čüąŠčüč鹊čÅąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ INTENSET:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

V |

U |

T |

S |

R |

Q |

P |

O |

N |

M |

L |

K |

J |

I |

H |

G |

F |

E |

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

STARTED |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ STARTED. ąĪą╝. EVENTS_STARTED.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| B |

RW |

END |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ END. ąĪą╝. EVENTS_END.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| C |

RW |

DONE |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ DONE. ąĪą╝. EVENTS_DONE.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| D |

RW |

RESULTDONE |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ RESULTDONE. ąĪą╝. EVENTS_RESULT_DONE.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| E |

RW |

CALIBRATEDONE |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CALIBRATEDONE. ąĪą╝. EVENTS_CALIBRATEDONE.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| F |

RW |

STOPPED |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ STOPPED. ąĪą╝. EVENTS_STOPPED.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| G |

RW |

CH0LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[0].LIMITH. ąĪą╝. EVENTS_CH[0].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| H |

RW |

CH0LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[0].LIMITL ąĪą╝. EVENTS_CH[0].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| I |

RW |

CH1LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[1].LIMITH. ąĪą╝. EVENTS_CH[1].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| J |

RW |

CH1LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[1].LIMITL ąĪą╝. EVENTS_CH[1].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| K |

RW |

CH2LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[2].LIMITH. ąĪą╝. EVENTS_CH[2].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| L |

RW |

CH2LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[2].LIMITL ąĪą╝. EVENTS_CH[2].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| M |

RW |

CH3LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[3].LIMITH. ąĪą╝. EVENTS_CH[3].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| N |

RW |

CH3LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[3].LIMITL ąĪą╝. EVENTS_CH[3].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| O |

RW |

CH4LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[4].LIMITH. ąĪą╝. EVENTS_CH[4].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| P |

RW |

CH4LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[4].LIMITL ąĪą╝. EVENTS_CH[4].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| Q |

RW |

CH5LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[5].LIMITH. ąĪą╝. EVENTS_CH[5].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| R |

RW |

CH5LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[5].LIMITL ąĪą╝. EVENTS_CH[5].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| S |

RW |

CH6LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[6].LIMITH. ąĪą╝. EVENTS_CH[6].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| T |

RW |

CH6LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[6].LIMITL ąĪą╝. EVENTS_CH[6].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| U |

RW |

CH7LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[7].LIMITH. ąĪą╝. EVENTS_CH[7].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| V |

RW |

CH7LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[7].LIMITL ąĪą╝. EVENTS_CH[7].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x308. ąŚą░ą┐ąĖčüčī ąĄą┤ąĖąĮąĖčåčŗ ą▓ ą▒ąĖčé čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ąĘą░ą┐čĆąĄčēą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, čćč鹥ąĮąĖąĄ ą▓ąĄčĆąĮąĄčé čüąŠčüč鹊čÅąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ INTENCLR:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

V |

U |

T |

S |

R |

Q |

P |

O |

N |

M |

L |

K |

J |

I |

H |

G |

F |

E |

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

STARTED |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ STARTED. ąĪą╝. EVENTS_STARTED.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| B |

RW |

END |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ END. ąĪą╝. EVENTS_END.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| C |

RW |

DONE |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ DONE. ąĪą╝. EVENTS_DONE.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| D |

RW |

RESULTDONE |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ RESULTDONE. ąĪą╝. EVENTS_RESULT_DONE.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| E |

RW |

CALIBRATEDONE |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CALIBRATEDONE. ąĪą╝. EVENTS_CALIBRATEDONE.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| F |

RW |

STOPPED |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ STOPPED. ąĪą╝. EVENTS_STOPPED.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| G |

RW |

CH0LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[0].LIMITH. ąĪą╝. EVENTS_CH[0].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| H |

RW |

CH0LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[0].LIMITL ąĪą╝. EVENTS_CH[0].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| I |

RW |

CH1LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[1].LIMITH. ąĪą╝. EVENTS_CH[1].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| J |

RW |

CH1LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[1].LIMITL ąĪą╝. EVENTS_CH[1].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| K |

RW |

CH2LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[2].LIMITH. ąĪą╝. EVENTS_CH[2].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| L |

RW |

CH2LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[2].LIMITL ąĪą╝. EVENTS_CH[2].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| M |

RW |

CH3LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[3].LIMITH. ąĪą╝. EVENTS_CH[3].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| N |

RW |

CH3LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[3].LIMITL ąĪą╝. EVENTS_CH[3].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| O |

RW |

CH4LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[4].LIMITH. ąĪą╝. EVENTS_CH[4].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| P |

RW |

CH4LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[4].LIMITL ąĪą╝. EVENTS_CH[4].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| Q |

RW |

CH5LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[5].LIMITH. ąĪą╝. EVENTS_CH[5].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| R |

RW |

CH5LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[5].LIMITL ąĪą╝. EVENTS_CH[5].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| S |

RW |

CH6LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[6].LIMITH. ąĪą╝. EVENTS_CH[6].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| T |

RW |

CH6LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[6].LIMITL ąĪą╝. EVENTS_CH[6].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| U |

RW |

CH7LIMITH |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[7].LIMITH. ąĪą╝. EVENTS_CH[7].LIMITH.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

| V |

RW |

CH7LIMITL |

ąŚą░ą┐ąĖčüą░ąĮąĮą░čÅ 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ CH[7].LIMITL ąĪą╝. EVENTS_CH[7].LIMITL.

0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x400

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ STATUS:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

R |

STATUS |

ąóąĄą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ ADC.

0: ADC ą│ąŠč鹊ą▓ąŠ ą║ čĆą░ą▒ąŠč鹥, ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĮąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ.

1: ADC ąĘą░ąĮčÅč鹊 ą▓čŗą┐ąŠą╗ąĮčÅčÄčēąĖą╝čüčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄą╝. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x500

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ ENABLE:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

ENABLE |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé čĆą░ą▒ąŠčéčŗ ADC.

0: ADC ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1: ADC čĆą░ąĘčĆąĄčłąĄąĮąŠ.

ąÜąŠą│ą┤ą░ ADC čĆą░ąĘčĆąĄčłąĄąĮ, ąŠąĮ ą▒čāą┤ąĄčé ąĘą░čģą▓ą░čéčŗą▓ą░čéčī ą┤ąŠčüčéčāą┐ ą║ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╝ ą▓čŗą▓ąŠą┤ą░ą╝ ą▓čģąŠą┤ąŠą▓, ąĘą░ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ CH[n].PSELP ąĖ CH[n].PSELN. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x510

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ CH[0].PSELP:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PSELP |

ąÆčŗą▒ąŠčĆ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ ą▓čŗą▓ąŠą┤ą░ ą║ą░ąĮą░ą╗ą░ ADC.

0: NC, Not Connected (ą▓čŗą▓ąŠą┤ ą▓čģąŠą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ).

1: AnalogInput0, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN0.

2: AnalogInput1, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN1.

3: AnalogInput2, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN2.

4: AnalogInput3, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN3.

5: AnalogInput4, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN4.

6: AnalogInput5, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN5.

7: AnalogInput6, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN6.

8: AnalogInput7: ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN7.

9: VDD, ą▓čŗą▒čĆą░ąĮąŠ ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x514

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ CH[0].PSELN:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PSELN |

ąÆčŗą▒ąŠčĆ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ ą▓čŗą▓ąŠą┤ą░ ą║ą░ąĮą░ą╗ą░ ADC, čćč鹊 čĆą░ąĘčĆąĄčłą░ąĄčé ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ ą▓čģąŠą┤ąŠą▓ ADC.

0: NC, Not Connected (ą▓čŗą▓ąŠą┤ ą▓čģąŠą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ).

1: AnalogInput0, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN0.

2: AnalogInput1, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN1.

3: AnalogInput2, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN2.

4: AnalogInput3, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN3.

5: AnalogInput4, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN4.

6: AnalogInput5, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN5.

7: AnalogInput6, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN6.

8: AnalogInput7: ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN7.

9: VDD, ą▓čŗą▒čĆą░ąĮąŠ ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x518

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ CH[0].CONFIG:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

G |

|

|

|

F |

|

E |

E |

E |

|

|

|

D |

|

C |

C |

C |

|

|

B |

B |

|

|

A |

A |

| Reset 0x00020000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

RESP |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆąĄąĘąĖčüč鹊čĆąĮčŗą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╝ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ADC.

0, Bypass: čĆąĄąĘąĖčüč鹊čĆąĮčŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī ą▓čŗą║ą╗čÄč湥ąĮ.

1, Pulldown: ą┐ąŠą┤čéčÅąČą║ą░ ą║ GND.

2, Pullup: ą┐ąŠą┤čéčÅąČą║ą░ ą║ VDD.

3, VDD1_2: čāčüčéą░ąĮąŠą▓ą║ą░ ąĮą░ ą▓čģąŠą┤ąĄ čāčĆąŠą▓ąĮčÅ VDD/2. |

| B |

RW |

RESN |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆąĄąĘąĖčüč鹊čĆąĮčŗą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╝ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ADC.

0, Bypass: čĆąĄąĘąĖčüč鹊čĆąĮčŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī ą▓čŗą║ą╗čÄč湥ąĮ.

1, Pulldown: ą┐ąŠą┤čéčÅąČą║ą░ ą║ GND.

2, Pullup: ą┐ąŠą┤čéčÅąČą║ą░ ą║ VDD.

3, VDD1_2: čāčüčéą░ąĮąŠą▓ą║ą░ ąĮą░ ą▓čģąŠą┤ąĄ čāčĆąŠą▓ąĮčÅ VDD/2. |

| C |

RW |

GAIN |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ (čāčüąĖą╗ąĄąĮąĖąĄą╝) ą┐ąŠ ą▓čģąŠą┤čā.

0, Gain1_6: 1/6 (ąŠčüą╗ą░ą▒ą╗ąĄąĮąĖąĄ ą▓ 6 čĆą░ąĘ).

1, Gain1_5: 1/5 (ąŠčüą╗ą░ą▒ą╗ąĄąĮąĖąĄ ą▓ 5 čĆą░ąĘ).

2, Gain1_4: 1/4 (ąŠčüą╗ą░ą▒ą╗ąĄąĮąĖąĄ ą▓ 4 čĆą░ąĘą░).

3, Gain1_3: 1/3 (ąŠčüą╗ą░ą▒ą╗ąĄąĮąĖąĄ ą▓ 3 čĆą░ąĘą░).

4, Gain1_2: 1/2 (ąŠčüą╗ą░ą▒ą╗ąĄąĮąĖąĄ ą▓ 2 čĆą░ąĘą░).

5, Gain1: 1 (ą▒ąĄąĘ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ).

6, Gain2: 2 (čāčüąĖą╗ąĄąĮąĖąĄ ą▓ 2 čĆą░ąĘą░).

7, Gain4: 4 (čāčüąĖą╗ąĄąĮąĖąĄ ą▓ 4 čĆą░ąĘą░). |

| D |

RW |

REFSEL |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąŠą┐ąŠčĆąĮčŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ADC.

0, Internal: ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ 0.6V.

1, VDD1_4: ą▓ ą║ą░č湥čüčéą▓ąĄ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ VDD/4. |

| E |

RW |

TACQ |

ąÆčĆąĄą╝čÅ ąĘą░čģą▓ą░čéą░ ą┐ąŠ ą▓čģąŠą┤čā, ą▓ č鹥č湥ąĮąĖąĄ ą║ąŠč鹊čĆąŠą│ąŠ čüčģąĄą╝ą░ ą▓čŗą▒ąŠčĆą║ąĖ/čģčĆą░ąĮąĄąĮąĖčÅ ADC ąĮą░ą║ą░ą┐ą╗ąĖą▓ą░ąĄčé čāčĆąŠą▓ąĄąĮčī ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

0, 3us: 3 ą╝ą║čü.

1, 5us: 5 ą╝ą║čü.

2, 10us: 10 ą╝ą║čü.

3, 15us: 15 ą╝ą║čü.

4, 20us: 20 ą╝ą║čü.

5, 40us: 40 ą╝ą║čü. |

| F |

RW |

MODE |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ ADC.

0, SE: Single-Ended. ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ ąĘą░ą┐čĆąĄčēąĄąĮ, čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą▓čģąŠą┤, ąĘąĮą░č湥ąĮąĖąĄ PSELN ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ, ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ą▓čģąŠą┤ ADC ąĘą░ą╝ą║ąĮčāčé ą▓ąĮčāčéčĆąĖ čćąĖą┐ą░ ąĮą░ GND.

1, Diff: ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą▓čģąŠą┤. |

| G |

RW |

BURST |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐ą░ą║ąĄčéąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ ADC.

0: čĆąĄąČąĖą╝ burst ąĘą░ą┐čĆąĄčēąĄąĮ (ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ).

1: čĆąĄąČąĖą╝ burst čĆą░ąĘčĆąĄčłąĄąĮ. ADC ą▒ąĄčĆąĄčé 2SAMPLE ą▓čŗą▒ąŠčĆąŠą║ čéą░ą║ ą▒čŗčüčéčĆąŠ, ą║ą░ą║ čüą╝ąŠąČąĄčé, ąĖ ą┐ąŠčüčŗą╗ą░ąĄčé čāčüčĆąĄą┤ąĮąĄąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓ Data RAM. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x51C

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ CH[0].LIMIT:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

| Reset 0x7FFF8000 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

LOW |

ąØąĖąČąĮąĖą╣ ą┐čĆąĄą┤ąĄą╗ čāčĆąŠą▓ąĮčÅ, čćąĖčüą╗ąŠ ąŠčé -32768 ą┤ąŠ 32767. |

| B |

RW |

HIGH |

ąÆąĄčĆčģąĮąĖą╣ ą┐čĆąĄą┤ąĄą╗ čāčĆąŠą▓ąĮčÅ, čćąĖčüą╗ąŠ ąŠčé -32768 ą┤ąŠ 32767. |

...

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x580

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ CH[7].PSELP:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PSELP |

ąÆčŗą▒ąŠčĆ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ ą▓čŗą▓ąŠą┤ą░ ą║ą░ąĮą░ą╗ą░ ADC.

0: NC, Not Connected (ą▓čŗą▓ąŠą┤ ą▓čģąŠą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ).

1: AnalogInput0, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN0.

2: AnalogInput1, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN1.

3: AnalogInput2, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN2.

4: AnalogInput3, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN3.

5: AnalogInput4, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN4.

6: AnalogInput5, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN5.

7: AnalogInput6, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN6.

8: AnalogInput7: ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN7.

9: VDD, ą▓čŗą▒čĆą░ąĮąŠ ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x584

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ CH[7].PSELN:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PSELP |

ąÆčŗą▒ąŠčĆ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ ą▓čŗą▓ąŠą┤ą░ ą║ą░ąĮą░ą╗ą░ ADC, čćč鹊 čĆą░ąĘčĆąĄčłą░ąĄčé ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ ą▓čģąŠą┤ąŠą▓ ADC.

0: NC, Not Connected (ą▓čŗą▓ąŠą┤ ą▓čģąŠą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ).

1: AnalogInput0, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN0.

2: AnalogInput1, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN1.

3: AnalogInput2, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN2.

4: AnalogInput3, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN3.

5: AnalogInput4, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN4.

6: AnalogInput5, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN5.

7: AnalogInput6, ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN6.

8: AnalogInput7: ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ AIN7.

9: VDD, ą▓čŗą▒čĆą░ąĮąŠ ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x588

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ CH[7].CONFIG:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

G |

|

|

|

F |

|

E |

E |

E |

|

|

|

D |

|

C |

C |

C |

|

|

B |

B |

|

|

A |

A |

| Reset 0x00020000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |