|

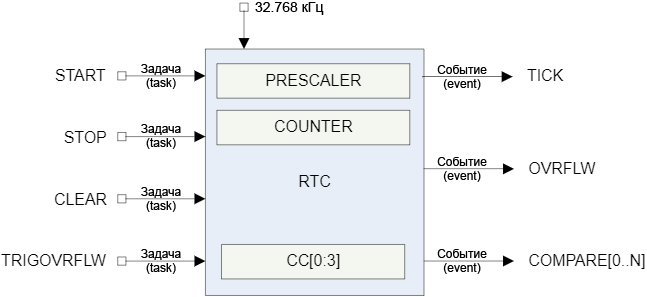

ą£ąŠą┤čāą╗čī čüč湥čéčćąĖą║ą░ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (Real-time counter, RTC) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čéčĆą░ą┤ąĖčåąĖąŠąĮąĮčŗą╣, 菹║ąŠąĮąŠą╝ąĖčćąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ ąĮą░ ąĮąĖąĘą║ąŠą╣ čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓ (LFCLK).

ąĀąĖčü. 1. ąæą╗ąŠą║-čüčģąĄą╝ą░ RTC.

ą£ąŠą┤čāą╗čī RTC čüąŠą┤ąĄčƹȹĖčé 24-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čüč湥čéčćąĖą║ COUNTER, 12-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ (1/X) ą┐čĆąĄčüą║ą░ą╗ąĄčĆ, čĆąĄą│ąĖčüčéčĆčŗ ąĘą░čģą▓ą░čéą░/čüčĆą░ą▓ąĮąĄąĮąĖčÅ (capture/compare) ąĖ ą│ąĄąĮąĄčĆą░č鹊čĆ čüąŠą▒čŗčéąĖą╣ čéąĖą║ą░ ą┤ą╗čÅ čŹąĮąĄčĆą│ąŠčŹčäč乥ą║čéąĖą▓ąĮąŠą╣ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ ą×ąĪąĀąÆ (tickless RTOS).

ą¤ąŠčüą║ąŠą╗čīą║čā RTC čĆą░ą▒ąŠčéą░ąĄčé ąŠčé LFCLK (čé. ąĄ. 32.768 ą║ąōčå), č鹊 čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī COUNTER ą┐ąŠą╗čāčćą░ąĄčéčüčÅ 1/32768 = 30.517 ą╝ą║čü. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĖčüč鹊čćąĮąĖą║ą░, RTC ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī, ą║ąŠą│ą┤ą░ ą│ąĄąĮąĄčĆą░č鹊čĆ HFCLK ą▓čŗą║ą╗čÄč湥ąĮ, ąĖ ąĮąĄą┤ąŠčüčéčāą┐ąĄąĮ PCLK16M. ą¤ąĄčĆąĄą┤ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ RTC ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ čÅą▓ąĮąŠ ąĘą░ą┐čāčüčéąĖčéčī ą│ąĄąĮąĄčĆą░č鹊čĆ LFCLK. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ ąĖčüč鹊čćąĮąĖą║ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüą╝. [2].

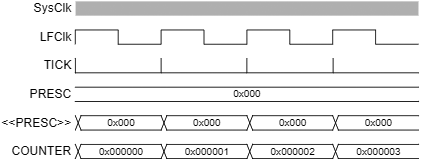

ąĀą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ čüč湥čéčćąĖą║ą░. ą¦ą░čüč鹊čéą░ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ COUNTER čĆą░ą▓ąĮą░:

fRTC [ą║ąōčå] = 32.768 / (PRESCALER + 1 )

ąÜąŠą│ą┤ą░ RTC ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čĆąĄą│ąĖčüčéčĆ PRESCALER ą┤ąŠčüčéčāą┐ąĄąĮ ąĮą░ čćč鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī. ąÜąŠą│ą┤ą░ RTC ąĘą░ą┐čāčēąĄąĮ (ą▒čŗą╗ą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąĘą░ą┤ą░čćą░ START), PRESCALER ą┤ąŠčüčéčāą┐ąĄąĮ č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ. ąŚą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ PRESCALER, ą║ąŠą│ą┤ą░ RTC ąĘą░ą┐čāčēąĄąĮ, ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

PRESCALER ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ąĮą░ ąĘą░ą┤ą░čćą░čģ START, CLEAR ąĖ TRIGOVRFLW, čé. ą║. ąĮą░ čŹčéąĖčģ ąĘą░ą┤ą░čćą░čģ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ čäąĖą║čüąĖčĆčāąĄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ (<< PRESC >>).

ą¤čĆąĖą╝ąĄčĆ 1. ąØčāąČąĮą░ čćą░čüč鹊čéą░ čüč湥čéą░ COUNTER 100 ąōčå (ą┐ąĄčĆąĖąŠą┤ ą╝ąĄąČą┤čā ąŠčéčüč湥čéą░ą╝ąĖ 10 ą╝čü)

PRESCALER = round(32768 / 100) - 1 = 327

fRTC = 99.9 ąōčå, ą┐ąĄčĆąĖąŠą┤ ą╝ąĄąČą┤čā ąŠčéčüč湥čéą░ą╝ąĖ 10009.576 ą╝ą║čü.

ą¤čĆąĖą╝ąĄčĆ 2. ąØčāąČąĮą░ čćą░čüč鹊čéą░ čüč湥čéą░ COUNTER 8 ąōčå (ą┐ąĄčĆąĖąŠą┤ ą╝ąĄąČą┤čā ąŠčéčüč湥čéą░ą╝ąĖ 125 ą╝čü)

PRESCALER = round(32768 / 8 Hz) ŌĆō 1 = 4095

fRTC = 8 ąōčå, ą┐ąĄčĆąĖąŠą┤ ą╝ąĄąČą┤čā ąŠčéčüč湥čéą░ą╝ąĖ 125 ą╝čü.

ąóą░ą▒ą╗ąĖčåą░ 1. ą¤čĆąĖą╝ąĄčĆčŗ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ (ąĖąĮč鹥čĆą▓ą░ą╗ čéąĖą║ą░) ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ RTC.

| ą¤čĆąĄčüą║ą░ą╗ąĄčĆ |

ąśąĮč鹥čĆą▓ą░ą╗ čéąĖą║ą░ |

ą¤ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ |

| 0 |

30.517 ą╝ą║čü |

512 čüąĄą║čāąĮą┤ |

| 28 - 1 |

7812.5 ą╝ą║čü |

131072 čüąĄą║čāąĮą┤ |

| 212 - 1 |

125 ą╝čü |

582.542 čćą░čüą░ |

ąĀąĄą│ąĖčüčéčĆ COUNTER. ąŁč鹊 čüč湥čéčćąĖą║, ą║ąŠč鹊čĆčŗą╣ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ čü čćą░čüč鹊č鹊ą╣ LFCLK, ą║ąŠą│ą┤ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│ąĖčüčéčĆ PRESCALER (<< PRESC >>) čĆą░ą▓ąĄąĮ 0x00. << PRESC >> ą┐ąĄčĆąĄąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ PRESCALER. ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ, č鹊 čüąŠą▒čŗčéąĖąĄ TICK ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĮą░ ą║ą░ąČą┤ąŠą╝ ąĖąĮą║čĆąĄą╝ąĄąĮč鹥 COUNTER. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čüąŠą▒čŗčéąĖąĄ TICK ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

ąĀąĖčü. 2. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ COUNTER_PRESCALER_0.

ąĀąĖčü. 3. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ COUNTER_PRESCALER_1.

ąĪąŠą▒čŗčéąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ (OVRFLW). ąŚą░ą┤ą░čćą░ TRIGOVRFLW čāčüčéą░ąĮąŠą▓ąĖčé ąĘąĮą░č湥ąĮąĖąĄ COUNTER ą▓ 0xFFFFF0, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┐čĆąŠč鹥čüčéąĖčĆąŠą▓ą░čéčī čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ. ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé čüąŠą▒čŗčéąĖąĄ OVRFLW, ą║ąŠą│ą┤ą░ COUNTER ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĖčéčüčÅ, čé. ąĄ. ąĄą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠą╝ąĄąĮčÅąĄčéčüčÅ čü 0xFFFFFF ąĮą░ 0.

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: čüąŠą▒čŗčéąĖąĄ OVRFLW ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

ąĪąŠą▒čŗčéąĖąĄ čéąĖą║ą░ (TICK). TICK event ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī 菹ĮąĄčĆą│ąŠčŹčäč乥ą║čéąĖą▓ąĮčāčÄ "tick-less" čüčģąĄą╝čā ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ RTOS, ą┐ąŠčüą║ąŠą╗čīą║čā ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčéčüčÅ čĆąĄą│čāą╗čÅčĆąĮąŠ čüčĆą░ą▒ą░čéčŗą▓ą░čÄčēąĖą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ RTOS ą▒ąĄąĘ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čäčāąĮą║čåąĖčÄ ARM┬« SysTick.

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ čéąĖą║ą░ RTC ą▓ą╝ąĄčüč鹊 SysTick ą┐ąŠąĘą▓ąŠą╗čÅąĄčé CPU ą▓čŗą║ą╗čÄčćą░čéčīčüčÅ, čüąŠčģčĆą░ąĮčÅčÅ ą┐čĆąĖ ą░ą║čéąĖą▓ąĮąŠčüčéčī ą┐ą╗ą░ąĮąĖčĆąŠą▓čēąĖą║ą░ RTOS.

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: čüąŠą▒čŗčéąĖąĄ TICK ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüąŠą▒čŗčéąĖčÅą╝ąĖ. ąöą╗čÅ ąŠą┐čéąĖą╝ąĖąĘą░čåąĖąĖ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ RTC, čüąŠą▒čŗčéąĖčÅ RTC ą╝ąŠąČąĮąŠ ąĘą░ą┐čĆąĄčēą░čéčī ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī ąĘą░ą┐čĆąŠčüčŗ PCLK16M ąĖ HFCLK, ą║ąŠą│ą┤ą░ čüčĆą░ą▒ą░čéčŗą▓ą░čÄčé čüąŠą▒čŗčéąĖčÅ. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ/ąĘą░ą┐čĆąĄčé čüąŠą▒čŗčéąĖą╣ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ EVTEN.

ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ čüąŠą▒čŗčéąĖąĄ TICK ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ, č鹊 čŹč鹊 čüąŠą▒čŗčéąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮąŠ, ą┐ąŠčüą║ąŠą╗čīą║čā ąŠąĮąŠ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čćą░čüč鹊, ąĖ ą╝ąŠąČąĄčé čāą▓ąĄą╗ąĖčćąĖčéčī ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ 菹ĮąĄčĆą│ąĖąĖ, ąĄčüą╗ąĖ ąĖąĮą░č湥 ą│ąĄąĮąĄčĆą░č鹊čĆ HFCLK ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą║ą╗čÄč湥ąĮ ąĮą░ ą┤ąŠą╗ą│ąĖą╣ ą┐ąĄčĆąĖąŠą┤ ą▓čĆąĄą╝ąĄąĮąĖ.

ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 RTC čĆąĄą░ą╗ąĖąĘčāąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┤čĆčāą│čāčÄ ą┐ąŠą┤čüąĖčüč鹥ą╝čā ąĘą░ą┤ą░čć ąĖ čüąŠą▒čŗčéąĖą╣ (task ąĖ event) ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čüąŠ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╣ čüąĖčüč鹥ą╝ąŠą╣, ąŠą┐ąĖčüą░ąĮąĮąŠą╣ ą┤ą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ [3]. RTC task ąĖ event system ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 4.

ąĀąĖčü. 4. ąĪąĖčüč鹥ą╝ą░ ąĘą░ą┤ą░čć (tasks), čüąŠą▒čŗčéąĖą╣ (events) ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (interrupts) ą▓ RTC.

ążčāąĮą║čåąĖčÅ Compare. ąśą╝ąĄąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆąŠą▓ čüčĆą░ą▓ąĮąĄąĮąĖčÅ CC, čüą╝. ą┤ą░ą╗ąĄąĄ čĆą░ąĘą┤ąĄą╗ "ąĀąĄą│ąĖčüčéčĆčŗ RTC".

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čĆąĄą│ąĖčüčéčĆ čüčĆą░ą▓ąĮąĄąĮąĖčÅ, ąĮą░ą▒ą╗čÄą┤ą░ąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĄąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (compare event) RTC:

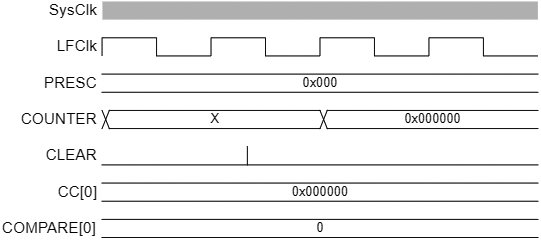

ŌĆó ąĢčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ CC čĆą░ą▓ąĮąŠ 0, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ąĘą░ą┤ą░čćą░ CLEAR, č鹊 čüąŠą▒čŗčéąĖąĄ COMPARE ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé, čüą╝. čĆąĖčü. 5.

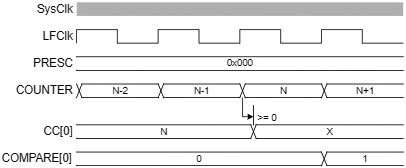

ŌĆó ąĢčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ CC čĆą░ą▓ąĮąŠ N, ąĖ ąĘąĮą░č湥ąĮąĖąĄ COUNTER čĆą░ą▓ąĮąŠ N, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ąĘą░ą┤ą░čćą░ CLEAR, č鹊 čüąŠą▒čŗčéąĖąĄ COMPARE ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé, čüą╝. čĆąĖčü. 6.

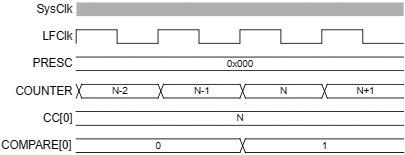

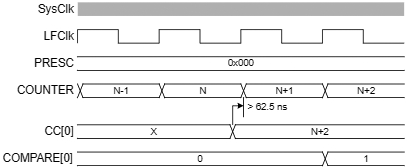

ŌĆó ąĪąŠą▒čŗčéąĖąĄ COMPARE ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé, ą║ąŠą│ą┤ą░ CC = N, ąĖ ąĘąĮą░č湥ąĮąĖąĄ COUNTER ą┐ąĄčĆąĄčłą╗ąŠ ąŠčé N-1 ą║ N (ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ CC ąĖ COUNTER), čüą╝. čĆąĖčü. 7.

ŌĆó ąĢčüą╗ąĖ COUNTER = N, č鹊 ąĘą░ą┐ąĖčüčī N+2 ą▓ čĆąĄą│ąĖčüčéčĆ CC ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░ąĮąĮąŠ ą▓čŗąĘąŠą▓ąĄčé čüąŠą▒čŗčéąĖąĄ COMPARE ą▓ ą╝ąŠą╝ąĄąĮčé COUNTER = N+2, čüą╝. čĆąĖčü. 8.

ŌĆó ąĢčüą╗ąĖ COUNTER = N, č鹊 ąĘą░ą┐ąĖčüčī N ąĖą╗ąĖ N+1 ą▓ čĆąĄą│ąĖčüčéčĆ CC ą╝ąŠąČąĄčé ąĮąĄ ą▓čŗąĘą▓ą░čéčī čüąŠą▒čŗčéąĖąĄ COMPARE, čüą╝. čĆąĖčü. 9.

ŌĆó ąĢčüą╗ąĖ COUNTER = N, ąĖ č鹥ą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ CC čĆą░ą▓ąĮąŠ N+1 ąĖą╗ąĖ N+2, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüą░ąĮąŠ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ CC, ą╝ąŠąČąĄčé čüčĆą░ą▒ąŠčéą░čéčī čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ ąĮą░ ą┐čĆąĄą┤čŗą┤čāčēąĄą╝ ąĘąĮą░č湥ąĮąĖąĖ CC ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ CC ą▓čüčéčāą┐ąĖčé ą▓ ą┤ąĄą╣čüčéą▓ąĖąĄ. ąĢčüą╗ąĖ č鹥ą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ CC ą▒ąŠą╗čīčłąĄ N+2, č鹊 ąĘą░ą┐ąĖčłąĄčéčüčÅ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ąĖ ą┐ąŠ čüčéą░čĆąŠą╝čā ąĘąĮą░č湥ąĮąĖčÄ CC čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé. ąĪą╝. čĆąĖčü. 10.

ąĀąĖčü. 5. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ COMPARE_CLEAR.

ąĀąĖčü. 6. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ COMPARE_START.

ąĀąĖčü. 7. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ COMPARE.

ąĀąĖčü. 8. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ COMPARE_N+2.

ąĀąĖčü. 9. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ COMPARE_N+1.

ąĀąĖčü. 10. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ COMPARE_N-1.

[ąöąČąĖčéč鹥čĆ/ąĘą░ą┤ąĄčƹȹ║ą░ TASK ąĖ EVENT]

ąĪčāčēąĄčüčéą▓čāąĄčé ą┤ąČąĖčéč鹥čĆ ąĖą╗ąĖ ąĘą░ą┤ąĄčƹȹ║ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ąĘą░ą┤ą░čć ąĖ čüąŠą▒čŗčéąĖą╣ RTC čü ą┤čĆčāą│ąĖą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, ą┐ąŠč鹊ą╝čā čćč鹊 ąŠąĮąĖ čĆą░ą▒ąŠčéą░čÄčé ąĮą░ ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╣ čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓ PCLK16M, ąĮąĄ čüąĖąĮčģčĆąŠąĮąĮąŠą╣ čü ąĮąĖąĘą║ąŠą╣ čćą░čüč鹊č鹊ą╣ čéą░ą║č鹊ą▓ (LFCLK).

ąĀąĄą│ąĖčüčéčĆčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ [3], čāčćą░čüčéąĮąĖą║ąĖ ą┤ąŠą╝ąĄąĮą░ čéą░ą║č鹊ą▓ PCLK16M, čüąĮą░ą▒ąČąĄąĮčŗ ąĮą░ą▒ąŠčĆąŠą╝ ąĘąĄčĆą║ą░ą╗čīąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓ ą┤ąŠą╝ąĄąĮąĄ čéą░ą║č鹊ą▓ LFCLK. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĘąĮą░č湥ąĮąĖąĄ COUNTER, ą┤ąŠčüčéčāą┐ąĮąŠąĄ čüąŠ čüč鹊čĆąŠąĮčŗ CPU, ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą┤ąŠą╝ąĄąĮąĄ PCLK16M, ąĖ ą┐čĆąĖ čćč鹥ąĮąĖąĖ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ ąĖąĘ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čü ąĖą╝ąĄąĮąĄą╝ COUNTER, ąĮąŠ ąĮą░čģąŠą┤čÅčēąĄą│ąŠčüčÅ ą▓ ą┤ąŠą╝ąĄąĮąĄ LFCLK. ąŁč鹊čé COUNTER ą║ą░ą║ čĆą░ąĘ č鹊čé čĆąĄą│ąĖčüčéčĆ, ą║ąŠč鹊čĆčŗą╣ ą▓ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą╝ąŠą┤ąĖčäąĖčåąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ čéąĖą║ąĄ RTC. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čŹčéąĖ ą┤ą▓ąĄ ą║ąŠą┐ąĖąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮčŗ ą╝ąĄąČą┤čā ą┤ąŠą╝ąĄąĮą░ą╝ąĖ čéą░ą║č鹊ą▓ (PCLK16M ąĖ LFCLK).

ąóą░ą▒ą╗ąĖčåą░ 2. ąÆąĄą╗ąĖčćąĖąĮą░ ą┤ąČąĖčéč鹥čĆą░ RTC, ą▓ą╗ąĖčÅčÄčēąĄą│ąŠ ąĮą░ ąĘą░ą┐čāčüą║ ąĘą░ą┤ą░čć.

| ąŚą░ą┤ą░čćą░ (task) |

ąŚą░ą┤ąĄčƹȹ║ą░ |

| CLEAR, STOP, START, TRIGOVRFLOW |

+15 .. +45 ą╝ą║čü |

ąóą░ą▒ą╗ąĖčåą░ 3. ąÆąĄą╗ąĖčćąĖąĮą░ ą┤ąČąĖčéč鹥čĆą░ RTC, ą▓ą╗ąĖčÅčÄčēąĄą│ąŠ ąĮą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ čüąŠą▒čŗčéąĖą╣.

| ą×ą┐ąĄčĆą░čåąĖčÅ / čäčāąĮą║čåąĖčÅ |

ąöąČąĖčéč鹥čĆ |

| ą×čé START ą┤ąŠ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ COUNTER |

┬▒15 ą╝ą║čü |

| ą×čé COMPARE ą┤ąŠ COMPARE(1) |

┬▒62.5 ąĮčü |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 RTC ą┐ąŠčüč鹊čÅąĮąĮąŠ čüčćąĖčéą░ąĄčé ą╝ąĄąČą┤čā čŹčéąĖą╝ąĖ čüąŠą▒čŗčéąĖčÅą╝ąĖ. ąÜ ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮčŗą╝ ąĘąĮą░č湥ąĮąĖčÅą╝ ą┤ąŠą▒ą░ą▓ą╗čÅąĄčéčüčÅ ą┤ąČąĖčéč鹥čĆ čéą░ą║č鹊ą▓ 32.768 ą║ąōčå.

ąØąĖąČąĄ ą┐čĆąĖą▓ąŠą┤ąĖčéčüčÅ ą║čĆą░čéą║ąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą┤ąČąĖčéč鹥čĆą░, ą║ąŠč鹊čĆčŗą╣ čüčāčēąĄčüčéą▓čāąĄčé ąĮą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ąĘą░ą┤ą░čć ąĖ čüąŠą▒čŗčéąĖą╣ RTC, čü ą┐ąŠčÅčüąĮčÅčÄčēąĖą╝ąĖ čĆąĖčüčāąĮą║ą░ą╝ąĖ.

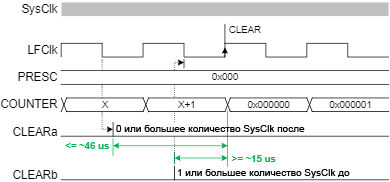

1. ąŚą░ą┤ą░čćąĖ CLEAR ąĖ STOP (ąĖ TRIGOVRFLW, čćč鹊 ąĮą░ čĆąĖčü. 11 ąĮąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ) ą▒čāą┤čāčé ąĘą░ą┤ąĄčƹȹ░ąĮčŗ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░, ą┐ąŠą║ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ąĘą░čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčé čüą▓ąŠą╣ čüą┐ą░ą┤ čéą░ą║č鹊ą▓ čü čäčĆąŠąĮč鹊ą╝ LFCLK. ąŁčéą░ ąĘą░ą┤ąĄčƹȹ║ą░ ą▒čāą┤ąĄčé ą▓ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ ą╝ąĄąČą┤čā 15.2585 ą╝ą║čü ąĖ 45.7755 ą╝ą║čü, čćč鹊 ą▓ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą╝ ąŠą┐ąĖčüą░ąĮąĖąĖ ą▒čāą┤ąĄčé ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ ąŠą║čĆčāą│ą╗ąĄąĮąŠ ą┤ąŠ 15 ą╝ą║čü ąĖ 46 ą╝ą║čü.

ąĀąĖčü. 11. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ DELAY_CLEAR.

ąĀąĖčü. 12. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ DELAY_STOP.

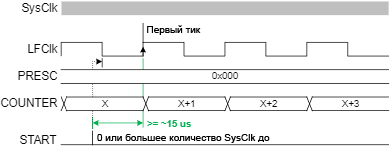

2. ąŚą░ą┤ą░čćą░ START ąĘą░ą┐čāčüčéąĖčé RTC. ąĢčüą╗ąĖ ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĖčéčī, čćč鹊 čéą░ą║čéčŗ LFCLK čāąČąĄ ąĘą░ą┐čāčēąĄąĮčŗ ąĖ čüčéą░ą▒ąĖą╗čīąĮčŗ, č鹊 ą┐ąĄčĆą▓čŗą╣ ąĖąĮą║čĆąĄą╝ąĄąĮčé COUNTER (ąĖ čüąŠą▒čŗčéąĖąĄ TICK) ą┐čĆąŠąĖąĘąŠą╣ą┤čāčé ą┐ąŠčüą╗ąĄ 30.5 +/-15 ą╝ą║čü. ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ čüą╗čāčćą░čÅčģ, ą▓ čćą░čüčéąĮąŠčüčéąĖ ąĄčüą╗ąĖ RTC ąĘą░ą┐čāčēąĄąĮ ąĘą░ą┤ą░č湥ą╣ START ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ąĘą░ą┐čāčüčéąĖą╗ąĖčüčī čéą░ą║čéčŗ LFCLK, čŹč鹊 ą▓čĆąĄą╝čÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠčĆčÅą┤ą║ą░ ~250 ą╝ą║čü. ą¤ąŠčŹč鹊ą╝čā ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ą┐ąŠą┤ąŠąČą┤ą░čéčī ą┐ąĄčĆą▓ąŠą│ąŠ TICK, ąĄčüą╗ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čĆą░ą▒ąŠč湥ąĄ čüąŠčüč鹊čÅąĮąĖąĄ RTC. ą×čéą┐čĆą░ą▓ą║ą░ ąĘą░ą┤ą░čćąĖ TRIGOVRFLW čāčüčéą░ąĮąŠą▓ąĖčé ąĘąĮą░č湥ąĮąĖąĄ COUNTER, ą▒ą╗ąĖąĘą║ąŠąĄ ą║ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÄ. ą×ą┤ąĮą░ą║ąŠ, ą┐ąŠčüą║ąŠą╗čīą║čā ą╝ąŠą╝ąĄąĮčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ COUNTER ąĘą░ą▓ąĖčüąĖčé ąŠčé čüčéą░ą▒ąĖą╗čīąĮąŠčüčéąĖ čćą░čüč鹊čéčŗ LFCLK, ąŠčéą┐čĆą░ą▓ą║ą░ čŹč鹊ą╣ ąĘą░ą┤ą░čćąĖ, ą║ąŠą│ą┤ą░ čéą░ą║čéčŗ LFCLK ąĮąĄ ąĘą░ą┐čāčüčéąĖą╗ąĖčüčī, ąĘą░ą┐čāčüčéąĖčé LFCLK, ąĮąŠ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą▒čāą┤ąĄčé ąĘą░ą┤ąĄčƹȹ░ąĮąŠ ąĮą░ čéčā ąČąĄ ą▓ąĄą╗ąĖčćąĖąĮčā ą▓čĆąĄą╝ąĄąĮąĖ ą┤ąŠ ~250 ą╝ą║čü. ąĀąĖčüčāąĮą║ąĖ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čüą░ą╝čāčÄ ą╝ą░ą╗ąĄąĮčīą║čāčÄ ąĖ čüą░ą╝čāčÄ ą▒ąŠą╗čīčłčāčÄ ąĘą░ą┤ąĄčƹȹ║ąĖ ąĘą░ą┤ą░čćąĖ START, ą║ąŠč鹊čĆą░čÅ ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ čü ą┤ąČąĖčéč鹥čĆąŠą╝ +/-15 ą╝ą║čü ą┤ą╗čÅ ą┐ąĄčĆą▓ąŠą│ąŠ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ COUNTER.

ąĀąĖčü. 13. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ JITTER_START-.

ąĀąĖčü. 14. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ JITTER_START+.

[ą¦č鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ COUNTER]

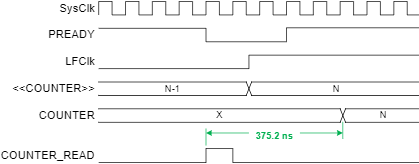

ąöą╗čÅ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ COUNTER ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĘą░čģą▓ą░čé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ << COUNTER >>.

ąöą╗čÅ ą│ą░čĆą░ąĮčéąĖąĖ, čćč鹊 << COUNTER >> ą▒ąĄąĘąŠą┐ą░čüąĮąŠ ąĘą░čģą▓ą░č湥ąĮ (ą┐čĆąĖ čćč鹥ąĮąĖąĖ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┐ąĄčĆąĄą┐ą░ą┤ LFCLK), CPU ąĖ čłąĖąĮą░ čÅą┤čĆą░ ą┐ą░ą╝čÅčéąĖ ą┐čĆąĖąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĮą░ 3 čéą░ą║čéą░ ą┐čāč鹥ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ą░ ą▓ 0 čüąĖą│ąĮą░ą╗ą░ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ čÅą┤čĆą░ (core PREADY). ą¦č鹥ąĮąĖąĄ ąĘą░ą╣ą╝ąĄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ 2 čéą░ą║čéą░ CPU, čéą░ą║ čćč鹊 ą┐ąŠą╗čāčćąĖčéčüčÅ, čćč鹊 čćč鹥ąĮąĖąĄ COUNTER ą┐ąŠ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą╣ą╝ąĄčé čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗąĄ 5 čéą░ą║č鹊ą▓ PCLK16M.

ąĀąĖčü. 15. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ COUNTER_READ.

[ąĀąĄą│ąĖčüčéčĆčŗ RTC]

ąóą░ą▒ą╗ąĖčåą░ 4. ąŁą║ąĘąĄą╝ą┐ą╗čÅčĆčŗ RTC.

| ąæą░ąĘ. ą░ą┤čĆąĄčü |

ą¤ąĄčĆąĖčä. čāčüčéčĆąŠą╣čüčéą▓ąŠ |

ąŁą║ąĘ. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ |

| 0x4000B000 |

RTC |

RTC0 |

ąĪč湥čéčćąĖą║ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ 0 |

CC[0..2] čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ, CC[3] ąĮąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ |

| 0x40011000 |

RTC1 |

ąĪč湥čéčćąĖą║ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ 1 |

ąĀąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ CC[0..3] |

| 0x40024000 |

RTC2 |

ąĪč湥čéčćąĖą║ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ 2 |

ąóą░ą▒ą╗ąĖčåą░ 5. ą×ą▒ąĘąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓ RTC.

| ąĀąĄą│ąĖčüčéčĆ |

ąĪą╝ąĄčē. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| TASKS_START |

0x000 |

ąĪčéą░čĆčé RTC COUNTER. |

| TASKS_STOP |

0x004 |

ąĪč鹊ą┐ RTC COUNTER. |

| TASKS_CLEAR |

0x008 |

ą×čćąĖčüčéą║ą░ RTC COUNTER. |

| TASKS_TRIGOVRFLW |

0x00C |

ąŻčüčéą░ąĮąŠą▓ą║ą░ COUNTER ą▓ ąĘąĮą░č湥ąĮąĖąĄ 0xFFFFF0. |

| EVENTS_TICK |

0x100 |

ąĪąŠą▒čŗčéąĖąĄ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ COUNTER. |

| EVENTS_OVRFLV |

0x104 |

ąĪąŠą▒čŗčéąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ COUNTER. |

| EVENTS_COMPARE[0] |

0x140 |

ąĪąŠą▒čŗčéąĖąĄ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░ ąĖ CC[0]. |

| EVENTS_COMPARE[1] |

0x144 |

ąĪąŠą▒čŗčéąĖąĄ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░ ąĖ CC[1]. |

| EVENTS_COMPARE[2] |

0x148 |

ąĪąŠą▒čŗčéąĖąĄ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░ ąĖ CC[2]. |

| EVENTS_COMPARE[3] |

0x14C |

ąĪąŠą▒čŗčéąĖąĄ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░ ąĖ CC[3]. |

| INTENSET |

0x304 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. |

| INTENCLR |

0x308 |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. |

| EVTEN |

0x340 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖą╣. |

| EVTENSET |

0x344 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖą╣. |

| EVTENCLR |

0x348 |

ąŚą░ą┐čĆąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖą╣. |

| COUNTER |

0x504 |

ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░. |

| PRESCALER |

0x508 |

12-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čī ą┤ą╗čÅ čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ čüč湥čéčćąĖą║ą░ (32768/(PRESCALER+1)). ąöąŠą╗ąČąĄąĮ ąĘą░ą┐ąĖčüčŗą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ą┐čĆąĖ ąŠčüčéą░ąĮąŠą▓ą║ąĄ čüč湥čéčćąĖą║ą░. |

| CC[0] |

0x540 |

ąĀąĄą│ąĖčüčéčĆ čüčĆą░ą▓ąĮąĄąĮąĖčÅ 0. |

| CC[1] |

0x544 |

ąĀąĄą│ąĖčüčéčĆ čüčĆą░ą▓ąĮąĄąĮąĖčÅ 1. |

| CC[2] |

0x548 |

ąĀąĄą│ąĖčüčéčĆ čüčĆą░ą▓ąĮąĄąĮąĖčÅ 2. |

| CC[3] |

0x54C |

ąĀąĄą│ąĖčüčéčĆ čüčĆą░ą▓ąĮąĄąĮąĖčÅ 3. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x304. ąŚą░ą┐ąĖčüčī 1 čĆą░ąĘčĆąĄčłą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ: 0 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ, 1 čĆą░ąĘčĆąĄčłąĄąĮąŠ.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ INTENSET:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

F |

E |

D |

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

TICK |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ TICK. ąĪą╝. EVENTS_TICK. |

| B |

RW |

OVRFLW |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ. ąĪą╝. EVENTS_OVRFLW. |

| C |

RW |

COMPARE0 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[0]. ąĪą╝. EVENTS_COMPARE[0]. |

| D |

RW |

COMPARE1 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[1]. ąĪą╝. EVENTS_COMPARE[1]. |

| E |

RW |

COMPARE2 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[2]. ąĪą╝. EVENTS_COMPARE[2]. |

| F |

RW |

COMPARE3 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[3]. ąĪą╝. EVENTS_COMPARE[3]. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x308. ąŚą░ą┐ąĖčüčī 1 ąĘą░ą┐čĆąĄčēą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ: 0 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ, 1 čĆą░ąĘčĆąĄčłąĄąĮąŠ.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ INTENCLR:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

F |

E |

D |

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

TICK |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ TICK. ąĪą╝. EVENTS_TICK. |

| B |

RW |

OVRFLW |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ. ąĪą╝. EVENTS_OVRFLW. |

| C |

RW |

COMPARE0 |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[0]. ąĪą╝. EVENTS_COMPARE[0]. |

| D |

RW |

COMPARE1 |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[1]. ąĪą╝. EVENTS_COMPARE[1]. |

| E |

RW |

COMPARE2 |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[2]. ąĪą╝. EVENTS_COMPARE[2]. |

| F |

RW |

COMPARE3 |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[3]. ąĪą╝. EVENTS_COMPARE[3]. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x340. ąŚą░ą┐ąĖčüčī 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖčÄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čüąŠą▒čŗčéąĖčÅ, ąĘą░ą┐ąĖčüčī 0 ąĘą░ą┐čĆąĄčēą░ąĄčé. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ: 0 ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖčÅ čüąŠą▒čŗčéąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮą░, 1 čĆą░ąĘčĆąĄčłąĄąĮą░.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ EVTEN:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

F |

E |

D |

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

TICK |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ TICK. ąĪą╝. EVENTS_TICK. |

| B |

RW |

OVRFLW |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ. ąĪą╝. EVENTS_OVRFLW. |

| C |

RW |

COMPARE0 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[0]. ąĪą╝. EVENTS_COMPARE[0]. |

| D |

RW |

COMPARE1 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[1]. ąĪą╝. EVENTS_COMPARE[1]. |

| E |

RW |

COMPARE2 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[2]. ąĪą╝. EVENTS_COMPARE[2]. |

| F |

RW |

COMPARE3 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[3]. ąĪą╝. EVENTS_COMPARE[3]. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x344. ąŚą░ą┐ąĖčüčī 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖčÄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čüąŠą▒čŗčéąĖčÅ. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ: 0 ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖčÅ čüąŠą▒čŗčéąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮą░, 1 čĆą░ąĘčĆąĄčłąĄąĮą░.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ EVTENSET:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

F |

E |

D |

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

TICK |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ TICK. ąĪą╝. EVENTS_TICK. |

| B |

RW |

OVRFLW |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ. ąĪą╝. EVENTS_OVRFLW. |

| C |

RW |

COMPARE0 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[0]. ąĪą╝. EVENTS_COMPARE[0]. |

| D |

RW |

COMPARE1 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[1]. ąĪą╝. EVENTS_COMPARE[1]. |

| E |

RW |

COMPARE2 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[2]. ąĪą╝. EVENTS_COMPARE[2]. |

| F |

RW |

COMPARE3 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[3]. ąĪą╝. EVENTS_COMPARE[3]. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x348. ąŚą░ą┐ąĖčüčī 1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖčÄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čüąŠą▒čŗčéąĖčÅ. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ: 0 ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖčÅ čüąŠą▒čŗčéąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮą░, 1 čĆą░ąĘčĆąĄčłąĄąĮą░.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ EVTENCLR:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

F |

E |

D |

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

TICK |

ąŚą░ą┐čĆąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ TICK. ąĪą╝. EVENTS_TICK. |

| B |

RW |

OVRFLW |

ąŚą░ą┐čĆąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ. ąĪą╝. EVENTS_OVRFLW. |

| C |

RW |

COMPARE0 |

ąŚą░ą┐čĆąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[0]. ąĪą╝. EVENTS_COMPARE[0]. |

| D |

RW |

COMPARE1 |

ąŚą░ą┐čĆąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[1]. ąĪą╝. EVENTS_COMPARE[1]. |

| E |

RW |

COMPARE2 |

ąŚą░ą┐čĆąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[2]. ąĪą╝. EVENTS_COMPARE[2]. |

| F |

RW |

COMPARE3 |

ąŚą░ą┐čĆąĄčé ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ COMPARE[3]. ąĪą╝. EVENTS_COMPARE[3]. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x504. ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ COUNTER:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

R |

COUNTER |

ąŚąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x508. 12-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ą┤ą╗čÅ čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ COUNTER (čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ čĆą░ą▓ąĮą░ 32768 / (PRESCALER+1) ąōčå). ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ą┤ąŠą╗ąČąĄąĮ ąĘą░ą┐ąĖčüčŗą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ PRESCALER:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PRESCALER |

ąŚąĮą░č湥ąĮąĖąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x540 + 4*x, ą│ą┤ąĄ x = 0 .. 3.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ CC[x]:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

COMPARE |

ąŚąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ čüąŠ čüč湥čéčćąĖą║ąŠą╝. |

[ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ RTC]

| ąĪąĖą╝ą▓ąŠą╗ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

min |

Typ |

MAX |

ąĢą┤. |

| IRTC |

ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą▓ čĆą░ą▒ąŠč湥ą╝ čĆąĄąČąĖą╝ąĄ (ąĖčüč鹊čćąĮąĖą║ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ LFCLK) |

|

0.1 |

|

ą╝ą║ąÉ |

[ąĪčüčŗą╗ą║ąĖ]

1. RTC Real-time counter nRF52832 site:nordicsemi.com.

2. CLOCK Clock control nRF52832 site:nordicsemi.com.

3. nRF52: ąĖąĮč鹥čĆč乥ą╣čü ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

4. nRF52 TIMER. |