|

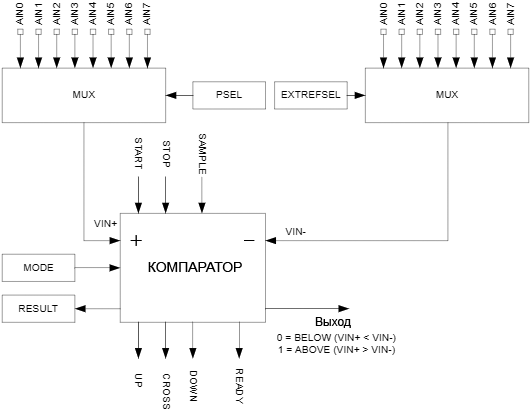

ąÜąŠą╝ą┐ą░čĆą░č鹊čĆ (COMP) čüčĆą░ą▓ąĮąĖą▓ą░ąĄčé ąŠą┤ąĮąŠ ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ (VIN+) čü ą┤čĆčāą│ąĖą╝ ą▓čģąŠą┤ąĮčŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ (VIN-). VIN+ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮąŠ čü ą╗čÄą▒ąŠą│ąŠ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░ (ą▓čŗą▓ąŠą┤čŗ AIN0 .. AIN7). VIN- ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćą░čéčī čāčĆąŠą▓ąĄąĮčī ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆą░ą▒ąŠč湥ą│ąŠ čĆąĄąČąĖą╝ą░ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĮąŠą▓čŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ ąĪą╗ąŠą▓ą░čĆąĖą║ąĄ [2].

ą×čüąĮąŠą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ čüą╗ąĄą┤čāčÄčēąĖąĄ.

ŌĆó ąöąĖą░ą┐ą░ąĘąŠąĮ ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąŠčé 0V ą┤ąŠ VDD.

ŌĆó ąØąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ (Single-ended mode), ą│ąĖą▒ą║ąŠ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄą╝čŗą╣ ą│ąĖčüč鹥čĆąĄąĘąĖčü ąĮą░ ąŠčüąĮąŠą▓ąĄ 64-čāčĆąŠą▓ąĮąĄą▓ąŠą│ąŠ ą┤ąĄą╗ąĖč鹥ą╗čÅ.

ŌĆó ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝, ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗą╣ ą│ąĖčüč鹥čĆąĄąĘąĖčü 50 mV.

ŌĆó ąÆčģąŠą┤čŗ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (VREF):

- VDD.

- ąÆąĮąĄčłąĮąĄąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, ą┐ąŠą┤ą░ąĮąĮąŠąĄ ąĮą░ ąŠą┤ąĖąĮ ąĖąĘ ą▓čŗą▓ąŠą┤ąŠą▓ AIN0 .. AIN7 (čü čāčĆąŠą▓ąĮąĄą╝ ąŠčé 0V ą┤ąŠ VDD).

- ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ čāčĆąŠą▓ąĮąĖ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 1.2V, 1.8V ąĖ 2.4V.

ŌĆó ąóčĆąĖ čĆąĄąČąĖą╝ą░ čü čĆą░ąĘąĮčŗą╝ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄą╝ čüą║ąŠčĆąŠčüčéčī/ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ č鹊ą║ą░: low-power, normal ąĖ high-speed.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ ąŠą┤ąĮąŠą║ąŠąĮčéą░ą║čéąĮąŠą│ąŠ ąĄą╝ą║ąŠčüčéąĮąŠą│ąŠ ą┤ą░čéčćąĖą║ą░.

ŌĆó ąōąĄąĮąĄčĆą░čåąĖčÅ čüąŠą▒čŗčéąĖčÅ ąŠčé ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ:

- ąĪąŠą▒čŗčéąĖąĄ UP, ą║ąŠą│ą┤ą░ VIN- > VIN+.

- ąĪąŠą▒čŗčéąĖąĄ DOWN, ą║ąŠą│ą┤ą░ VIN- < VIN+.

- ąĪąŠą▒čŗčéąĖąĄ CROSS ą┐čĆąĖ ą┐ąĄčĆąĄčüąĄč湥ąĮąĖąĖ čāčĆąŠą▓ąĮąĄą╣ VIN+ ąĖ VIN-.

- ąĪąŠą▒čŗčéąĖąĄ READY ąĮą░ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ čÅą┤čĆą░ ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (ąĄčüą╗ąĖ ąŠąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ).

ąĀąĖčü. 1. ą×ą▒čēą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░.

ąæčāą┤čāčćąĖ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╝ (čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄą│ąĖčüčéčĆą░ ENABLE), ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┐čāč鹥ą╝ ą░ą║čéąĖą▓ą░čåąĖąĖ ąĘą░ą┤ą░čćąĖ START, ąĖ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą║čéąĖą▓ą░čåąĖąĄą╣ ąĘą░ą┤ą░čćąĖ STOP. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąŠą╣ą┤ąĄčé ą▓čĆąĄą╝čÅ ąĘą░ą┐čāčüą║ą░ tCOMP,START, ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ čüą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąŠą▒čŗčéąĖąĄ READY, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī čüą▓ąŠčÄ ą│ąŠč鹊ą▓ąĮąŠčüčéčī ą║ čĆą░ą▒ąŠč鹥, ąĖ čćč鹊 čāčĆąŠą▓ąĄąĮčī ąĮą░ ąĄą│ąŠ ą▓čŗčģąŠą┤ąĄ ą║ąŠčĆčĆąĄą║č鹥ąĮ. ąÜąŠą│ą┤ą░ ą╝ąŠą┤čāą╗čī COMP ąĘą░ą┐čāčēąĄąĮ, čüąŠą▒čŗčéąĖčÅ ą▒čāą┤čāčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄčüąĄą║ą░čÄčéčüčÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čāčĆąŠą▓ąĮąĄą╣ VIN+ ąĖ VIN-.

[ąĀą░ą▒ąŠčćąĖąĄ čĆąĄąČąĖą╝čŗ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░]

ąÜąŠą╝ą┐ą░čĆą░č鹊čĆ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ ą┤ą▓čāčģ ąŠčüąĮąŠą▓ąĮčŗčģ čĆą░ą▒ąŠčćąĖčģ čĆąĄąČąĖą╝ą░čģ, ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ ąĖ ąĮąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ (single-ended) čĆąĄąČąĖą╝. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ MODE. ąÆ čŹčéąĖčģ ąŠą▒ąŠąĖčģ čĆą░ą▒ąŠčćąĖčģ čĆąĄąČąĖą╝ą░čģ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ čéčĆąĄčģ čĆą░ąĘąĮčŗčģ čüą║ąŠčĆąŠčüčéčÅčģ, ąŠčéą╗ąĖčćą░čÄčēąĖčģčüčÅ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄą╝ ą▓čĆąĄą╝ąĄąĮąĖ čĆąĄą░ą║čåąĖąĖ ąĖ č鹊ą║ą░ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (low-power, normal ąĖ high-speed). ąĀąĄąČąĖą╝ high-speed ą┐ąŠčéčĆąĄą▒ą╗čÅąĄčé ą▒ąŠą╗čīčłąĄ č鹊ą║ą░, č湥ą╝ čĆąĄąČąĖą╝ low-power, ąĖ ą▓ čĆąĄąČąĖą╝ąĄ low-power ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ą▒čāą┤ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░čéčī ą╝ąĄą┤ą╗ąĄąĮąĮąĄąĄ, č湥ą╝ ą▓ čĆąĄąČąĖą╝ąĄ high-speed.

ąĀąĄą│ąĖčüčéčĆ PSEL ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą╗čÄą▒ąŠą│ąŠ ąĖąĘ ą▓čŗą▓ąŠą┤ąŠą▓ AIN0 .. AIN7 ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓čģąŠą┤ą░ VIN+, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. ąśčüč鹊čćąĮąĖą║ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ VIN- ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ čĆą░ą▒ąŠč湥ą│ąŠ čĆąĄąČąĖą╝ą░:

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝. ąĪąĖą│ąĮą░ą╗ ąĮą░ VIN- ą┐ąŠčüčéčāą┐ą░ąĄčé ą┐ąŠčüčéčāą┐ą░ąĄčé ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą▓čŗą▓ąŠą┤ąŠą▓ AIN0 .. AIN7.

ąØąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ (single-ended) čĆąĄąČąĖą╝. ąĪąĖą│ąĮą░ą╗ ą┤ą╗čÅ VIN- ą▒ąĄčĆąĄčéčüčÅ ąŠčé VREF. VREF ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮ ąŠčé čāčĆąŠą▓ąĮąĄą╣ VDD, AIN0 .. AIN7, ąĖą╗ąĖ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čāčĆąŠą▓ąĮąĄą╣ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 1.2V, 1.8V ąĖ 2.4V.

ąÆčŗą▒čĆą░ąĮąĮčŗąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čŗą▓ąŠą┤čŗ ą▒čāą┤čāčé ąĘą░čģą▓ą░č湥ąĮčŗ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆąŠą╝, ą║ą░ą║ č鹊ą╗čīą║ąŠ ąŠąĮ čĆą░ąĘčĆąĄčłąĄąĮ.

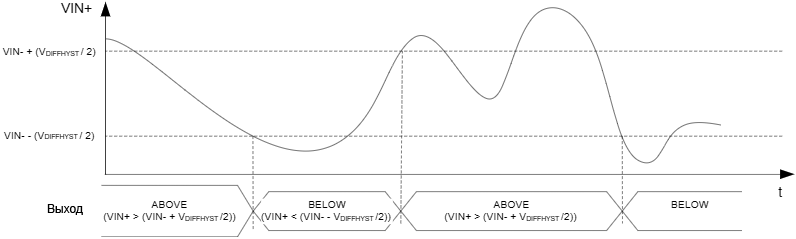

ą×ą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ą│ąĖčüč鹥čĆąĄąĘąĖčü ąĮą░ VIN+ ąĖ VIN-, ą║ąŠą│ą┤ą░ ą╝ąŠą┤čāą╗čī COMP ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ. ąōąĖčüč鹥čĆąĄąĘąĖčü ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ HYST. ąÆ ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┐ąŠčĆąŠą│ąĖ VUP ąĖ VDOWN ą╝ąŠą│čāčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą│ąĖčüč鹥čĆąĄąĘąĖčüą░, ą║ąŠč鹊čĆčŗą╣ ąŠčüąĮąŠą▓ą░ąĮ ąĮą░ čåąĄą┐ąŠčćą║ąĄ čŹčéą░ą╗ąŠąĮąĮčŗčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓ (čüą╝. čĆąĖčü. 4). ąŁč鹊čé ą│ąĖčüč鹥čĆąĄąĘąĖčü ąĖą╝ąĄąĄčé ą▓ąĄą╗ąĖčćąĖąĮčā ą┐ąŠčĆčÅą┤ą║ą░ 50 mV, ąĖ ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░čéčī čłčāą╝ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé čüąŠąĘą┤ą░ą▓ą░čéčī ą╗ąĖčłąĮąĖąĄ ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮčŗąĄ čüąŠą▒čŗčéąĖčÅ. ąĪą╝. čĆąĖčü. 5, ą│ą┤ąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ čĆą░ą▒ąŠčéą░ ą│ąĖčüč鹥čĆąĄąĘąĖčüą░ ąĮą░ ą▓čģąŠą┤ąĮąŠą╝ čüąĖą│ąĮą░ą╗ąĄ, ąĘą░ą│čĆčÅąĘąĮąĄąĮąĮąŠą╝ čłčāą╝ąŠą╝.

ą¤ąĄčĆąĄčüąĄč湥ąĮąĖąĄ ą▓čģąŠą┤ąĮčŗčģ čāčĆąŠą▓ąĮąĄą╣ ą▓ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ (ą║ąŠą│ą┤ą░ VIN+ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąŠą╗čīčłąĄ VIN-) ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąŠą▒čŗčéąĖąĄ UP ąĖ ą┐ąĄčĆąĄčüąĄč湥ąĮąĖąĄ ą▓čģąŠą┤ąĮčŗčģ čāčĆąŠą▓ąĮąĄą╣ ą▓ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ (ą║ąŠą│ą┤ą░ VIN- čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąŠą╗čīčłąĄ VIN+) ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąŠą▒čŗčéąĖąĄ DOWN. ąĪąŠą▒čŗčéąĖąĄ CROSS ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄčüąĄč湥ąĮąĖąĄ ą▓čģąŠą┤ąĮčŗčģ čāčĆąŠą▓ąĮąĄą╣, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ.

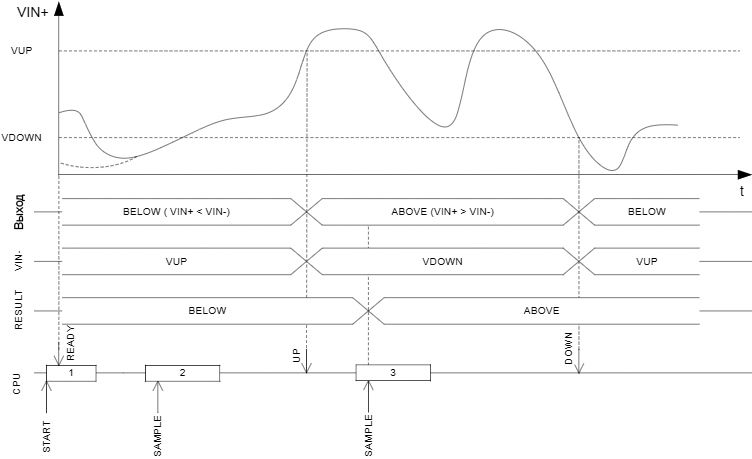

ąØąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ąĘčÅč鹊 čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ RESULT ą┐čāč鹥ą╝ ą░ą║čéąĖą▓ą░čåąĖąĖ ąĘą░ą┤ą░čćąĖ SAMPLE.

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąĮą░ ą▓čģąŠą┤ VIN- (ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ) čüąĖą│ąĮą░ą╗ ą┐ąŠčüčéčāą┐ą░ąĄčé ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ čü ąŠą┤ąĮąŠą╣ ąĖąĘ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ąĮąŠąČąĄą║ AINx.

ą¤ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄą│ąĖčüčéčĆą░ ENABLE ą▓ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ čĆąĄą│ąĖčüčéčĆčŗ PSEL, MODE ąĖ EXTREFSEL.

ąĀąĖčü. 2. ąÜąŠą╝ą┐ą░čĆą░č鹊čĆ ą▓ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ.

ą×ą│čĆą░ąĮąĖč湥ąĮąĖąĄ: ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čāčüčéčĆąŠą╣čüčéą▓ą░, ąĮąĄ ą▓čüąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čģąŠą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ MUX. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą┤ąŠčüčéčāą┐ąĮąŠčüčéąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą▓čŗą▓ąŠą┤ąŠą▓ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čćąĖą┐ą░ čüą╝. ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┤ą╗čÅ PSEL ąĖ EXTREFSEL.

ą¤čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ čĆąĄą│ąĖčüčéčĆą░ HYST ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą▓čŗčģąŠą┤ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ (ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čüąŠą▒čŗčéąĖčÅ) ą▒čāą┤ąĄčé ą╝ąĄąĮčÅčéčī čüą▓ąŠą╣ čāčĆąŠą▓ąĄąĮčī čü ABOVE ("ą▓čŗčłąĄ") ąĮą░ BELOW ("ąĮąĖąČąĄ") ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čāčĆąŠą▓ąĄąĮčī VIN+ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĮąĖąČąĄ čāčĆąŠą▓ąĮčÅ VIN- ąĮą░ ą▓ąĄą╗ąĖčćąĖąĮčā (VDIFFHYST / 2). ąóą░ą║ąČąĄ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐ąŠą╝ąĄąĮčÅąĄčéčüčÅ čü BELOW ąĮą░ ABOVE ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čāčĆąŠą▓ąĄąĮčī ąĮą░ VIN+ čüčéą░ąĮąĄčé ą▒ąŠą╗čīčłąĄ čāčĆąŠą▓ąĮčÅ VIN- ąĮą░ ą▓ąĄą╗ąĖčćąĖąĮčā (VDIFFHYST / 2). ąŁč鹊 ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 3.

ąĀąĖčü. 3. ąĀą░ą▒ąŠčéą░ ą│ąĖčüč鹥čĆąĄąĘąĖčüą░ ą▓ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ.

ąØąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čüąĖą│ąĮą░ą╗ VIN- č乊čĆą╝ąĖčĆčāąĄčéčüčÅ ąŠčé čāčĆąŠą▓ąĮąĄą╣ ąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝ ą╗ąĄčüčéąĮąĖčćąĮąŠą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄ ąĖąĘ ąŠą▒čĆą░ąĘčåąŠą▓čŗčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓.

ą¤ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄą│ąĖčüčéčĆą░ ENABLE ą▓ ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ čĆąĄą│ąĖčüčéčĆčŗ PSEL, MODE, REFSEL, EXTREFSEL, TH.

ąøąĄčüčéąĮąĖčćąĮčŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ (VREF) ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ą▓čāčģ ąĮąŠą▓čŗčģ ąŠą┐ąŠčĆąĮčŗčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣: VUP ąĖ VDOWN. ąØą░ą┐čĆčÅąČąĄąĮąĖčÅ VUP ąĖ VDOWN ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą┐ąŠą╗čÅą╝ąĖ THUP ąĖ THDOWN ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ, ą║ąŠč鹊čĆčŗąĄ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ TH. VREF ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮąŠ ąŠčé ą╗čÄą▒ąŠą│ąŠ ąĖąĘ ą┤ąŠčüčéčāą┐ąĮčŗčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, čćč鹊 ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ EXTREFSEL ąĖ REFSEL, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 4. ąÜąŠą│ą┤ą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ REFSEL ą▓čŗą▒čĆą░ąĮąŠ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ AREF, čĆąĄą│ąĖčüčéčĆ EXTREFSEL ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą▓čŗą▓ąŠą┤ąŠą▓ AIN0 .. AIN7 ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąÆčŗą▒čĆą░ąĮąĮčŗąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čŗą▓ąŠą┤čŗ ą▒čāą┤čāčé ąĘą░čģą▓ą░č湥ąĮčŗ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆąŠą╝, ą║ą░ą║ č鹊ą╗čīą║ąŠ ąŠąĮ čĆą░ąĘčĆąĄčłąĄąĮ.

ąĀąĖčü. 4. ąÜąŠą╝ą┐ą░čĆą░č鹊čĆ ą▓ ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ (single-ended) čĆąĄąČąĖą╝ąĄ.

ą×ą│čĆą░ąĮąĖč湥ąĮąĖąĄ: ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čāčüčéčĆąŠą╣čüčéą▓ą░, ąĮąĄ ą▓čüąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čģąŠą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ MUX. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą┤ąŠčüčéčāą┐ąĮąŠčüčéąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą▓čŗą▓ąŠą┤ąŠą▓ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čćąĖą┐ą░ čüą╝. ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┤ą╗čÅ PSEL ąĖ EXTREFSEL.

ąÜąŠą│ą┤ą░ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ą┤ąĄč鹥ą║čéąĖčĆčāąĄčé, čćč鹊 VIN+ > VIN-, ąĮą░ą┐čĆąĖą╝ąĄčĆ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗčģąŠą┤ąĄ čüčéą░ą╗ ą▓čŗčłąĄ (ABOVE), č湥ą╝ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čĆąĄą│ąĖčüčéčĆ RESULT, VIN- ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčüčÅ ąĮą░ VDOWN. ąÜąŠą│ą┤ą░ čāčĆąŠą▓ąĄąĮčī VIN+ čüąĮąŠą▓ą░ čāą┐ą░ą┤ąĄčé ąĮąĖąČąĄ VIN-, VIN- ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ąĮą░ VUP. ą¤čāč鹥ą╝ čāą║ą░ąĘą░ąĮąĖąĄ VUP ą▒ąŠą╗čīčłąĄ, č湥ą╝ VDOWN, ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮ ą│ąĖčüč鹥čĆąĄąĘąĖčü, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčüčāąĮą║ą░čģ 5 ąĖ 6.

ąÆ ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ HYST ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░, ąĖ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ.

ąĀąĖčü. 5. ą¤čĆąĖą╝ąĄčĆ ą│ąĖčüč鹥čĆąĄąĘąĖčüą░, ą║ąŠą│ą┤ą░ VIN+ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü čāčĆąŠą▓ąĮčÅ ąĮąĖąČąĄ VUP.

ąĀąĖčü. 6. ą¤čĆąĖą╝ąĄčĆ ą│ąĖčüč鹥čĆąĄąĘąĖčüą░, ą║ąŠą│ą┤ą░ VIN+ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü čāčĆąŠą▓ąĮčÅ ą▓čŗčłąĄ VUP.

[ąĀąĄą│ąĖčüčéčĆčŗ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░]

ąóą░ą▒ą╗ąĖčåą░ 1. ąŁą║ąĘąĄą╝ą┐ą╗čÅčĆčŗ COMP.

| ąæą░ąĘ. ą░ą┤čĆąĄčü |

ą¤ąĄčĆąĖčä. čāčüčéčĆąŠą╣čüčéą▓ąŠ |

ąŁą║ąĘ. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ |

| 0x40013000 |

COMP |

COMP |

ąÜąŠą╝ą┐ą░čĆą░č鹊čĆ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ |

|

ąóą░ą▒ą╗ąĖčåą░ 2. ą×ą▒ąĘąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓ COMP.

| ąĀąĄą│ąĖčüčéčĆ |

ąĪą╝ąĄčē. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| TASKS_START |

0x000 |

ąŚą░ą┤ą░čćą░ ąĘą░ą┐čāčüą║ą░ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. |

| TASKS_STOP |

0x004 |

ąŚą░ą┤ą░čćą░ ąŠčüčéą░ąĮąŠą▓ą║ąĖ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. |

| TASKS_SAMPLE |

0x008 |

ąŚą░ą┤ą░čćą░ ą▓čŗą▒ąŠčĆą║ąĖ čüąŠčüč鹊čÅąĮąĖčÅ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. |

| EVENTS_READY |

0x100 |

ąĪąŠą▒čŗčéąĖąĄ, čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāčÄčēąĄąĄ ąŠ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą║ čĆą░ą▒ąŠč鹥, ąĖ čćč鹊 čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╣. |

| EVENTS_DOWN |

0x104 |

ąĪąŠą▒čŗčéąĖąĄ ą┐ąĄčĆąĄčüąĄč湥ąĮąĖčÅ čāčĆąŠą▓ąĮąĄą╣ ąĮą░ ą▓čģąŠą┤ąĄ ą▓ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ (ą▓ąĮąĖąĘ). |

| EVENTS_UP |

0x108 |

ąĪąŠą▒čŗčéąĖąĄ ą┐ąĄčĆąĄčüąĄč湥ąĮąĖčÅ čāčĆąŠą▓ąĮąĄą╣ ąĮą░ ą▓čģąŠą┤ąĄ ą▓ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ (ą▓ą▓ąĄčĆčģ). |

| EVENTS_CROSS |

0x10C |

ąĪąŠą▒čŗčéąĖąĄ ą┐ąĄčĆąĄčüąĄč湥ąĮąĖčÅ čāčĆąŠą▓ąĮąĄą╣ ąĮą░ ą▓čģąŠą┤ąĄ ą▓ ą╗čÄą▒ąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ. |

| SHORTS |

0x200 |

ąĀąĄą│ąĖčüčéčĆ čłąŠčĆčéą║ą░čéą░. |

| INTEN |

0x300 |

ąĀąĄą│ąĖčüčéčĆ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. |

| INTENSET |

0x304 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. |

| INTENCLR |

0x308 |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. |

| RESULT |

0x400 |

ąĀąĄąĘčāą╗čīčéą░čé čüčĆą░ą▓ąĮąĄąĮąĖčÅ. |

| ENABLE |

0x500 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. |

| PSEL |

0x504 |

ąÆčŗą▒ąŠčĆ ąĮąŠąČą║ąĖ. |

| REFSEL |

0x508 |

ąÆčŗą▒ąŠčĆ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓ ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ. |

| EXTREFSEL |

0x50C |

ąÆčŗą▒ąŠčĆ ą▓ąĮąĄčłąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. |

| TH |

0x530 |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ąŠčĆąŠą│ą░ ą▒ą╗ąŠą║ą░ ą│ąĖčüč鹥čĆąĄąĘąĖčüą░. |

| MODE |

0x534 |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čĆąĄąČąĖą╝ą░. |

| HYST |

0x538 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą│ąĖčüč鹥čĆąĄąĘąĖčüą░ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. |

| ISOURCE |

0x53C |

ąÆčŗą▒ąŠčĆ ąĖčüč鹊čćąĮąĖą║ą░ č鹊ą║ą░ ąĮą░ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╝ ą▓čģąŠą┤ąĄ. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x200. ąŚą░ą┐ąĖčüčī 1 čĆą░ąĘčĆąĄčłą░ąĄčé čłąŠčĆčéą║ą░čé, ąĘą░ą┐ąĖčüčī 0 ąĘą░ą┐čĆąĄčēą░ąĄčé. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé č鹥ą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ SHORTS:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

READY_SAMPLE |

ą©ąŠčĆčéą║ą░čé ą╝ąĄąČą┤čā čüąŠą▒čŗčéąĖąĄą╝ READY ąĖ ąĘą░ą┤ą░č湥ą╣ SAMPLE. ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ EVENTS_READY ąĖ TASKS_SAMPLE. |

| B |

RW |

READY_STOP |

ą©ąŠčĆčéą║ą░čé ą╝ąĄąČą┤čā čüąŠą▒čŗčéąĖąĄą╝ READY ąĖ ąĘą░ą┤ą░č湥ą╣ STOP. ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ EVENTS_READY ąĖ TASKS_STOP. |

| C |

RW |

DOWN_STOP |

ą©ąŠčĆčéą║ą░čé ą╝ąĄąČą┤čā čüąŠą▒čŗčéąĖąĄą╝ DOWN ąĖ ąĘą░ą┤ą░č湥ą╣ STOP. ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ EVENTS_DOWN ąĖ TASKS_STOP. |

| D |

RW |

UP_STOP |

ą©ąŠčĆčéą║ą░čé ą╝ąĄąČą┤čā čüąŠą▒čŗčéąĖąĄą╝ UP ąĖ ąĘą░ą┤ą░č湥ą╣ STOP. ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ EVENTS_UP ąĖ TASKS_STOP. |

| E |

RW |

CROSS_STOP |

ą©ąŠčĆčéą║ą░čé ą╝ąĄąČą┤čā čüąŠą▒čŗčéąĖąĄą╝ CROSS ąĖ ąĘą░ą┤ą░č湥ą╣ STOP. ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ EVENTS_CROSS ąĖ TASKS_STOP. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x300. ąŚą░ą┐ąĖčüčī 1 čĆą░ąĘčĆąĄčłą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĘą░ą┐ąĖčüčī 0 ąĘą░ą┐čĆąĄčēą░ąĄčé. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé č鹥ą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ: 0 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ, 1 čĆą░ąĘčĆąĄčłąĄąĮąŠ.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ INTEN:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

READY |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ/ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ READY. ąĪą╝. EVENTS_READY. |

| B |

RW |

DOWN |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ/ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ DOWN. ąĪą╝. EVENTS_DOWN. |

| C |

RW |

UP |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ/ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ UP. ąĪą╝. EVENTS_UP. |

| D |

RW |

CROSS |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ/ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ CROSS. ąĪą╝. EVENTS_CROSS. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x304. ąŚą░ą┐ąĖčüčī 1 čĆą░ąĘčĆąĄčłą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé č鹥ą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ: 0 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ, 1 čĆą░ąĘčĆąĄčłąĄąĮąŠ.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ INTENSET:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

READY |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ READY. ąĪą╝. EVENTS_READY. |

| B |

RW |

DOWN |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ DOWN. ąĪą╝. EVENTS_DOWN. |

| C |

RW |

UP |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ UP. ąĪą╝. EVENTS_UP. |

| D |

RW |

CROSS |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ CROSS. ąĪą╝. EVENTS_CROSS. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x308. ąŚą░ą┐ąĖčüčī 1 ąĘą░ą┐čĆąĄčēą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé č鹥ą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ: 0 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ, 1 čĆą░ąĘčĆąĄčłąĄąĮąŠ.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ INTENCLR:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

READY |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ READY. ąĪą╝. EVENTS_READY. |

| B |

RW |

DOWN |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ DOWN. ąĪą╝. EVENTS_DOWN. |

| C |

RW |

UP |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ UP. ąĪą╝. EVENTS_UP. |

| D |

RW |

CROSS |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ CROSS. ąĪą╝. EVENTS_CROSS. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x400.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ RESULT:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

R |

RESULT |

ąĀąĄąĘčāą╗čīčéą░čé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÅ. ąóąŠčćą║ą░ ą┐čĆąĖąĮčÅčéąĖčÅ čĆąĄčłąĄąĮąĖčÅ ąĘą░ą┤ą░čćąĖ SAMPLE.

0, Below: ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮąĖąČąĄ ą┐ąŠčĆąŠą│ą░ (VIN+ < VIN-).

1, Above: ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓čŗčłąĄ ą┐ąŠčĆąŠą│ą░ (VIN+ > VIN-). |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x500.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ ENABLE:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

ENABLE |

0: COMP ąĘą░ą┐čĆąĄčēąĄąĮ.

2: COMP čĆą░ąĘčĆąĄčłąĄąĮ. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x504.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ PSEL:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PSEL |

ąÆčŗą▒ąŠčĆ ąĮąŠąČą║ąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐ąŠčĆčéą░ ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓čģąŠą┤ą░ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░.

0, AnalogInput0: ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓čģąŠą┤ą░ ą▓čŗą▒čĆą░ąĮą░ ąĮąŠąČą║ą░ AIN0.

..

7, AnalogInput7: ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓čģąŠą┤ą░ ą▓čŗą▒čĆą░ąĮą░ ąĮąŠąČą║ą░ AIN7. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x508.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ REFSEL:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

A |

| Reset 0x00000004 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

REFSEL |

ąÆčŗą▒ąŠčĆ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ single-ended.

0, Int1V2: VREF = 1.2V ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ (VDD ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī Ōēź 1.7V).

1, Int1V8: VREF = 1.8V ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ (VDD ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī Ōēź VREF + 0.2V).

2, Int2V4: VREF = 2.4V ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ (VDD ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī Ōēź VREF + 0.2V).

4, VDD: VREF = VDD.

7, ARef: VREF = AREF (VDD Ōēź VREF Ōēź AREFMIN). |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x50C.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ EXTREFSEL:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

EXTREFSEL |

ąÆčŗą▒ąŠčĆ ąĮąŠąČą║ąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐ąŠčĆčéą░ ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

0, AnalogInput0: ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓čģąŠą┤ą░ ą▓čŗą▒čĆą░ąĮą░ ąĮąŠąČą║ą░ AIN0.

..

7, AnalogInput7: ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓čģąŠą┤ą░ ą▓čŗą▒čĆą░ąĮą░ ąĮąŠąČą║ą░ AIN7. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x530.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ TH:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

B |

B |

B |

B |

B |

|

|

A |

A |

A |

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

THDOWN |

ąŚąĮą░č湥ąĮąĖąĄ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 0 .. 63. ą¤ąŠčĆąŠą│ VDOWN = (THDOWN + 1) / 64 ┬Ę VREF |

| B |

RW |

THUP |

ąŚąĮą░č湥ąĮąĖąĄ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 0 .. 63. ą¤ąŠčĆąŠą│ VUP = (THUP + 1) / 64 ┬Ę VREF |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x534.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ MODE:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

SP |

ąĀąĄąČąĖą╝, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖą╣ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ ąĖ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ.

0, Low: ą┐ąŠąĮąĖąČąĄąĮąĮąŠąĄ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ 菹ĮąĄčĆą│ąĖąĖ, ąĮąĖąĘą║ąŠąĄ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ.

1, Normal: ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝.

2, High: ą┐ąŠą▓čŗčłąĄąĮąĮąŠąĄ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ 菹ĮąĄčĆą│ąĖąĖ, ą▓čŗčüąŠą║ąŠąĄ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ. |

| B |

RW |

MAIN |

ąÆčŗą▒ąĖčĆą░ąĄčé ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ąĖą╗ąĖ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝.

0, SE: ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ (single-ended mode).

1, Diff: ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x538.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ HYST:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

HYST |

0: ą│ąĖčüč鹥čĆąĄąĘąĖčü ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ąĘą░ą┐čĆąĄčēąĄąĮ.

1: ą│ąĖčüč鹥čĆąĄąĘąĖčü ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ čĆą░ąĘčĆąĄčłąĄąĮ. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x53C.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ ISOURCE:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

ISOURCE |

0: ąĖčüč鹊čćąĮąĖą║ č鹊ą║ą░ ąĘą░ą┐čĆąĄčēąĄąĮ.

1: čĆą░ąĘčĆąĄčłąĄąĮ ąĖčüč鹊čćąĮąĖą║ č鹊ą║ą░ (┬▒ 2.5 ą╝ą║ąÉ).

2: čĆą░ąĘčĆąĄčłąĄąĮ ąĖčüč鹊čćąĮąĖą║ č鹊ą║ą░ (┬▒ 5 ą╝ą║ąÉ).

3: čĆą░ąĘčĆąĄčłąĄąĮ ąĖčüč鹊čćąĮąĖą║ č鹊ą║ą░ (┬▒ 10 ą╝ą║ąÉ). |

[ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░]

| ąĪąĖą╝ą▓ąŠą╗ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

min |

Typ |

MAX |

ąĢą┤. |

| ICOMP,LP |

ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą▓ low-power mode |

|

2 |

|

ą╝ą║ąÉ |

| ICOMP,N |

ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ normal mode |

|

5 |

|

| ICOMP,HS |

ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą▓ high-speed mode |

|

10 |

|

| tPROPDLY,LP |

ąŚą░ą┤ąĄčƹȹ║ą░ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ ą▓ low-power mode(1) |

|

0.6 |

|

ą╝ą║čü |

| tPROPDLY,N |

ąŚą░ą┤ąĄčƹȹ║ą░ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ ą▓ normal mode(1) |

|

0.2 |

|

| tPROPDLY,HS |

ąŚą░ą┤ąĄčƹȹ║ą░ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ ą▓ lhigh-speed mode(1) |

|

0.1 |

|

| VDIFFHYST |

ą×ą┐čåąĖąŠąĮą░ą╗čīąĮčŗą╣ ą│ąĖčüč鹥čĆąĄąĘąĖčü, ą┐čĆąĖą╗ąŠąČąĄąĮąĮčŗą╣ ą║ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝čā ą▓čģąŠą┤čā |

|

30 |

|

mV |

| VVDD-VREF |

ąóčĆąĄą▒čāąĄą╝ą░čÅ čĆą░ąĘąĮąĖčåą░ ą╝ąĄąČą┤čā VDD ąĖ ą▓čŗą▒čĆą░ąĮąĮčŗą╝ VREF, VDD ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ VREF |

0.3 |

|

|

V |

| IINT_REF |

ąóąŠą║, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ ąŠą┐ąŠčĆąĮčŗą╝ ą▒ą╗ąŠą║ąŠą╝ ąĘą░ą┐čĆąĄčēąĄąĮąĮąŠą╣ ąĘąŠąĮčŗ, ą║ąŠą│ą┤ą░ ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ ą┤ą╗čÅ VREF |

|

13 |

|

ą╝ą║ąÉ |

| tINT_REF,START |

ąÆčĆąĄą╝čÅ ąĘą░ą┐čāčüą║ą░ ą┤ą╗čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ ąĘą░ą┐čĆąĄčēąĄąĮąĮąŠą╣ ąĘąŠąĮčŗ |

|

50 |

80 |

ą╝ą║čü |

| EINT_REF |

ą×čłąĖą▒ą║ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą▒ą╗ąŠą║ą░ ąĘą░ą┐čĆąĄčēąĄąĮąĮąŠą╣ ąĘąŠąĮčŗ |

-3 |

|

3 |

% |

| RLADDER |

ąĪąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą╗ąĄčüčéąĮąĖčćąĮąŠą│ąŠ ą┤ąĄą╗ąĖč鹥ą╗čÅ, ILADDER = VREF / RLADDER |

|

550 |

|

ą║ą×ą╝ |

| VINPUTOFFSET |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą┐ąŠ ą▓čģąŠą┤čā |

-10 |

|

10 |

mV |

| DNLLADDER |

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī ą╗ąĄčüčéąĮąĖčćąĮąŠą│ąŠ ą┤ąĄą╗ąĖč鹥ą╗čÅ |

|

< 0.1 |

|

LSB |

| tCOMP,START |

ąÆčĆąĄą╝čÅ ąĘą░ą┐čāčüą║ą░ ą▒ą╗ąŠą║ą░ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ |

|

3 |

|

ą╝ą║čü |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ą▓čĆąĄą╝čÅ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĖąĄąĮąĖčÅ čü ą┐ąĄčĆąĄą│čĆčāąĘą║ąŠą╣ 10 mV.

ą×ą▒čēąĖą╣ č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ąŠčé č鹊ą║ąŠą▓ ICOMP, IINT_REF ąĖ ILADDER ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

[ąĪčüčŗą╗ą║ąĖ]

1. nRF52 COMP Comparator site:nordicsemi.com.

2. Bluetooth: ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆčŗ ąĖ č鹥čĆą╝ąĖąĮčŗ. |