|

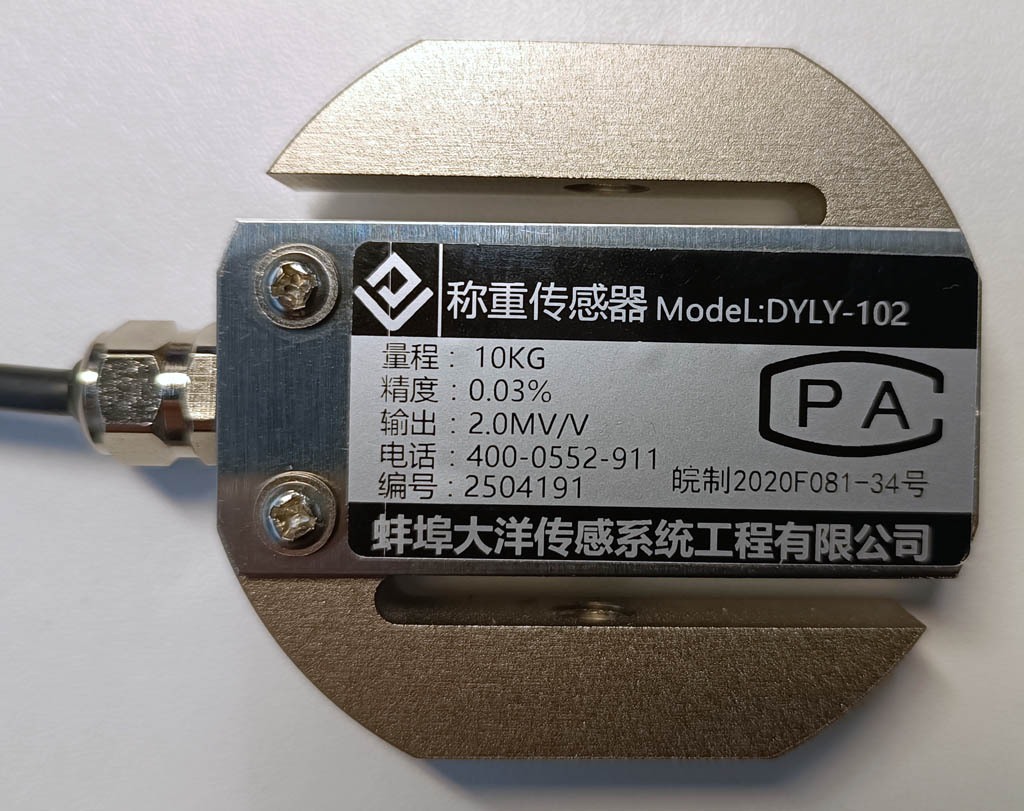

HX711 čŹč鹊 č鹊čćąĮčŗą╣ 24-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ąÉą”ą¤ (ADC), ąŠčüąĮąŠą▓ą░ąĮąĮčŗą╣ ąĮą░ ą┐ą░č鹥ąĮč鹊ą▓ą░ąĮąĮąŠą╣ č鹥čģąĮąŠą╗ąŠą│ąĖąĖ Avia Semiconductor. ą×ąĮ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ ą┤ą╗čÅ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠą│ąŠ čüčćąĖčéčŗą▓ą░ąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čü ą╝ąŠčüčéą░ č鹥ąĮąĘąŠą┤ą░čéčćąĖą║ąŠą▓ ą▓ąĄčüąŠą▓ (čéą░ą║ąĖčģ ą║ą░ą║ DYLY-102 ą║ąŠą╝ą┐ą░ąĮąĖąĖ Daysensor [2]) ąĖ ą┤čĆčāą│ąĖčģ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣.

ąÆčģąŠą┤ąĮąŠą╣ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆ ą▓čŗą▒ąĖčĆą░ąĄčé ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą▓čģąŠą┤ ą║ą░ąĮą░ą╗ą░ A ąĖą╗ąĖ B ą┤ą╗čÅ ą╝ą░ą╗ąŠčłčāą╝čÅčēąĄą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╝ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą╝ čāčüąĖą╗ąĄąĮąĖčÅ (programmable gain amplifier, PGA). ąÜą░ąĮą░ą╗ A ą╝ąŠąČąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĮą░ čāčüąĖą╗ąĄąĮąĖąĄ 128 ąĖą╗ąĖ 64, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą┐ąŠą╗ąĮąŠą╝čā ą┤ąĖą░ą┐ą░ąĘąŠąĮčā (full-scale) ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ┬▒20mV ąĖą╗ąĖ ┬▒40mV čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ, ą║ąŠą│ą┤ą░ ą┐ąĖčéą░ąĮąĖąĄ 5V ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ą║ ą▓čŗą▓ąŠą┤čā ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ AVDD. ąŻ ą║ą░ąĮą░ą╗ą░ B čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠąĄ čāčüąĖą╗ąĄąĮąĖąĄ 32. ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ čĆąĄą│čāą╗čÅč鹊čĆ ą┐ąĖčéą░ąĮąĖčÅ čāčüčéčĆą░ąĮčÅąĄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéčī ą▓ąŠ ą▓ąĮąĄčłąĮąĄą╝ čĆąĄą│čāą╗čÅč鹊čĆąĄ, čćč鹊ą▒čŗ ąĘą░ą┐ąĖčéčŗą▓ą░čéčī ADC ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄą╝čŗą╣ ą║ ąĮąĄą╝čā čüąĄąĮčüąŠčĆ. ą¤čĆąĄą┤čāčüą╝ąŠčéčĆąĄąĮąŠ ą│ąĖą▒ą║ąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ. ąŁč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ą╗ąĖą▒ąŠ ą▓ąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą╗ąĖą▒ąŠ ą║ą▓ą░čĆčåąĄą▓čŗą╣ čĆąĄąĘąŠąĮą░č鹊čĆ, ą╗ąĖą▒ąŠ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ čćąĖą┐ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ RC-ą│ąĄąĮąĄčĆą░č鹊čĆ, ą▓ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝ čüą╗čāčćą░ąĄ ąĮąĖą║ą░ą║ąĖčģ ą▓ąĮąĄčłąĮąĖčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ. ąÆčüčéčĆąŠąĄąĮąĮą░čÅ čüąĖčüč鹥ą╝ą░ čüą▒čĆąŠčüą░ ą┐ąŠ ą▓ą║ą╗čÄč湥ąĮąĖčÄ ą┐ąĖčéą░ąĮąĖčÅ (power-on-reset) čāą┐čĆąŠčēą░ąĄčé ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÄ čåąĖčäčĆąŠą▓ąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░.

ąØąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąĖą║ą░ą║ąĖčģ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓. ąÆčüąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ HX711 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ č湥čĆąĄąĘ ąĄą│ąŠ ą▓čŗą▓ąŠą┤čŗ.

ą×čüąĮąŠą▓ąĮčŗąĄ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗąĄ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéąĖ HX711:

ŌĆó ąöą▓ą░ ą▓čģąŠą┤ąĮčŗčģ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą║ą░ąĮą░ą╗ą░, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ą▓čŗą▒ąĖčĆą░čéčī.

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ ą╝ą░ą╗ąŠčłčāą╝čÅčēąĖą╣ PGA, čā ą║ąŠč鹊čĆąŠą│ąŠ ą╝ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī čāčüąĖą╗ąĄąĮąĖąĄ 32, 64 ąĖ 128.

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ čĆąĄą│čāą╗čÅč鹊čĆ ą┐ąĖčéą░ąĮąĖčÅ ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ ą┤ą░čéčćąĖą║ą░ ąĖ ą┐ąĖčéą░ąĮąĖčÅ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╣ čüčģąĄą╝čŗ ADC.

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ čéą░ą║č鹊ą▓čŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ, ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą║ąŠč鹊čĆąŠą│ąŠ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ąĮąĖą║ą░ą║ąĖčģ ą▓ąĮąĄčłąĮąĖčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓, ąĖą╗ąĖ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ąĮąĄčłąĮąĖą╣ ą║ą▓ą░čĆčå.

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮą░čÅ čüčģąĄą╝ą░ čüą▒čĆąŠčüą░ ą┐ąŠ ą┐ąĖčéą░ąĮąĖčÄ (power-on-reset).

ŌĆó ą¤čĆąŠčüč鹊ąĄ čåąĖčäčĆąŠą▓ąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü: čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤čŗ, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ HX711 ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ.

ŌĆó ąÆčŗą▒ąĖčĆą░ąĄą╝ą░čÅ čćą░čüč鹊čéą░ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ 10SPS ąĖą╗ąĖ 80SPS.

ŌĆó ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠąĄ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠą╝ąĄčģ 50 ąĖ 60 ąōčå.

ŌĆó ą¤ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ č鹊ą║ą░, ą▓ą║ą╗čÄčćą░čÄčēąĄąĄ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čĆąĄą│čāą╗čÅč鹊čĆ ą┐ąĖčéą░ąĮąĖčÅ: ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ < 1.5 mA, power down < 1 uA.

ŌĆó ąöąĖą░ą┐ą░ąĘąŠąĮ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ: 2.6 ~ 5.5V.

ŌĆó ąöąĖą░ą┐ą░ąĘąŠąĮ čĆą░ą▒ąŠčćąĖčģ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ: -40 ~ +85Ōäā.

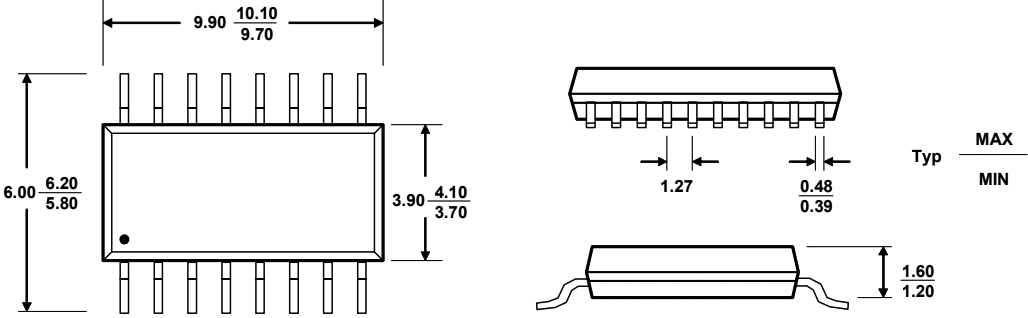

ŌĆó ąÜąŠčĆą┐čāčü SOP-16, 16 ą▓čŗą▓ąŠą┤ąŠą▓.

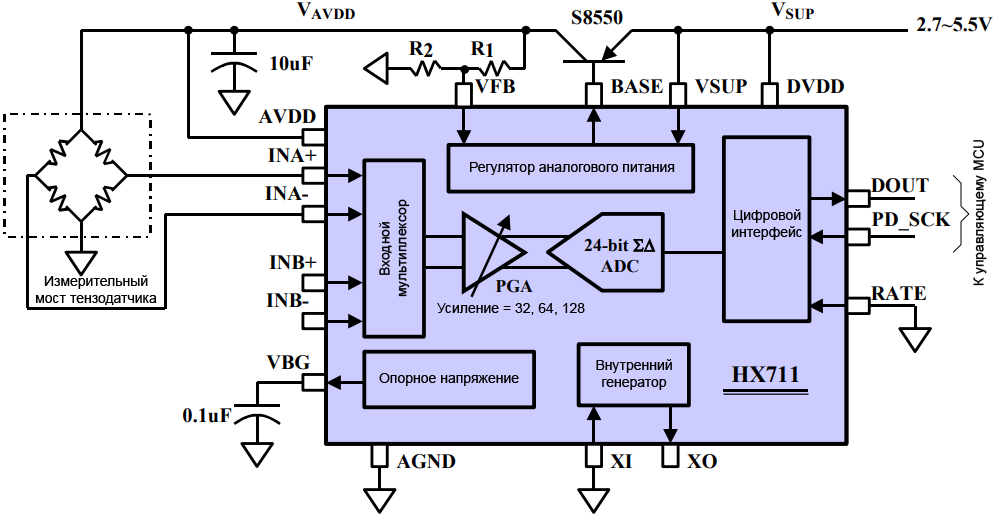

ąĀąĖčü. 1. ąóąĖą┐ąŠą▓ą░čÅ čüčģąĄą╝ą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮąŠą╝čā ą╝ąŠčüčéčā (č鹥ąĮąĘąŠą┤ą░čéčćąĖą║čā) ą▓ąĄčüąŠą▓.

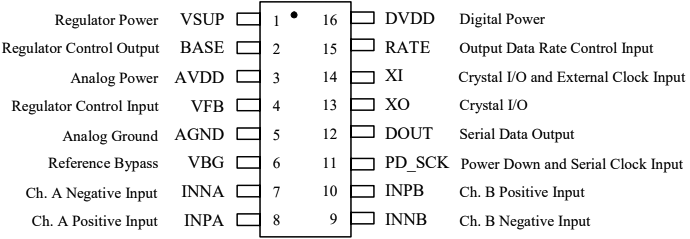

ą”ąŠą║ąŠą╗ąĄą▓ą║ą░ ą▓čŗą▓ąŠą┤ąŠą▓:

ąóą░ą▒ą╗ąĖčåą░ 1. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓.

| Ōä¢ |

ąśą╝čÅ |

ążčāąĮą║čåąĖčÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 1 |

VSUP |

ą¤ąĖčéą░ąĮąĖąĄ |

ą¤ąĖčéą░ąĮąĖąĄ čĆąĄą│čāą╗čÅč鹊čĆą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ: 2.7V .. 5.5V. |

| 2 |

BASE |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ |

ąŻą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą▓čŗčģąŠą┤ čĆąĄą│čāą╗čÅč鹊čĆą░ (NC, ą║ąŠą│ą┤ą░ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ). |

| 3 |

AVDD |

ą¤ąĖčéą░ąĮąĖąĄ |

ąÉąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ą┐ąĖčéą░ąĮąĖąĄ: 2.6V .. 5.5V. |

| 4 |

VFB |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ |

ąŻą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą▓čģąŠą┤ čĆąĄą│čāą╗čÅč鹊čĆą░ (ą┐ąŠą┤ą║ą╗čÄčćąĖč鹥 ą║ AGND, ąĄčüą╗ąĖ ąŠąĮ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ). |

| 5 |

AGND |

ąŚąĄą╝ą╗čÅ, Ground |

ąÉąĮą░ą╗ąŠą│ąŠą▓ą░čÅ ąĘąĄą╝ą╗čÅ, ąŠą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤. |

| 6 |

VBG |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ |

ąÆčŗčģąŠą┤ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. |

| 7 |

INA- |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ |

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą║ą░ąĮą░ą╗ A, ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ą▓čģąŠą┤. |

| 8 |

INA+ |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ |

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą║ą░ąĮą░ą╗ A, ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą▓čģąŠą┤. |

| 9 |

INB- |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ |

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą║ą░ąĮą░ą╗ B, ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ą▓čģąŠą┤. |

| 10 |

INB+ |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ |

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą║ą░ąĮą░ą╗ B, ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą▓čģąŠą┤. |

| 11 |

PD_SCK |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ (ą░ą║čéąĖą▓ąĮčŗą╣ ą▓čŗčüąŠą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī) ąĖ ą▓čģąŠą┤ čéą░ą║č鹊ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░. |

| 12 |

DOUT |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čŗčģąŠą┤ |

ąÆčŗčģąŠą┤ ą┤ą░ąĮąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░. |

| 13 |

XO |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čŗčģąŠą┤ |

ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ čĆąĄąĘąŠąĮą░č鹊čĆą░, ą▓čŗčģąŠą┤ ą│ąĄąĮąĄčĆą░č鹊čĆą░ (NC, ą║ąŠą│ą┤ą░ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ). |

| 14 |

XI |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ |

ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ čĆąĄąĘąŠąĮą░č鹊čĆą░, ą▓čģąŠą┤ ą│ąĄąĮąĄčĆą░č鹊čĆą░. ąóą░ą║ąČąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ą▓čģąŠą┤, ąĮą░ ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą┤ą░ąĄčéčüčÅ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą▓ąĮąĄčłąĮąĄą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░. |

| 15 |

RATE |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čćą░čüč鹊č鹊ą╣ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ, 0: 10 ąōčå, 1: 80 ąōčå. |

| 16 |

DVDD |

ą¤ąĖčéą░ąĮąĖąĄ |

ą”ąĖčäčĆąŠą▓ąŠąĄ ą┐ąĖčéą░ąĮąĖąĄ: 2.6V .. 5.5V. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: NC ąŠąĘąĮą░čćą░ąĄčé Not Connected, ąĮąĖą║čāą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ.

ąóą░ą▒ą╗ąĖčåą░ 2. ą×čüąĮąŠą▓ąĮčŗąĄ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ.

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąŚą░ą╝ąĄčćą░ąĮąĖčÅ |

min |

Typ |

MAX |

ąĢą┤. |

| ąöąĖą░ą┐ą░ąĘąŠąĮ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (full scale) |

V(inp)-V(inn)(1) |

┬▒0.5(AVDD/GAIN) |

V |

| ąØąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠąĄ ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ (common mode input) |

BASE |

AGND+1.2 |

|

AVDD-1.3 |

V |

| ą¦ą░čüč鹊čéą░ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ |

ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ, RATE=0 |

10 |

ąōčå |

| ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ, RATE=DVDD |

80 |

| ąÜą▓ą░čĆčå ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĄąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ, RATE=0 |

fclk/1105920 |

| ąÜą▓ą░čĆčå ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĄąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ, RATE=DVDD |

fclk/138240 |

| ąÜąŠą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ |

ąöąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┤ąŠ 2 |

800000 |

|

7FFFFF |

HEX |

| ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čŗčģąŠą┤ą░(2) |

RATE=0 |

400 |

ą╝čü |

| RATE=DVDD |

50 |

| ąöčĆąĄą╣čä ą▓čģąŠą┤ąĮąŠą│ąŠ čüą╝ąĄčēąĄąĮąĖčÅ |

ąŻčüąĖą╗ąĄąĮąĖąĄ 128 |

0.2 |

mV |

| ąŻčüąĖą╗ąĄąĮąĖąĄ 64 |

0.4 |

ąÆčģąŠą┤ąĮąŠą╣ čłčāą╝

|

ąŻčüąĖą╗ąĄąĮąĖąĄ 128, RATE=0 |

50 |

nV(rms)(3) |

| ąŻčüąĖą╗ąĄąĮąĖąĄ 128, RATE=VDD |

90 |

| ąóąĄą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣ ą┤čĆąĄą╣čä |

ąÆčģąŠą┤ąĮąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ (čāčüąĖą╗ąĄąĮąĖąĄ 128) |

┬▒6 |

nV/Ōäā |

| ąŻčüąĖą╗ąĄąĮąĖąĄ (ą┐čĆąĖ čāčüąĖą╗ąĄąĮąĖąĖ 128) |

┬▒5 |

ppm/Ōäā(4) |

| ą¤ąŠą┤ą░ą▓ą╗ąĄąĮąĖąĄ čüąĖąĮčäą░ąĘąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ |

ąŻčüąĖą╗ąĄąĮąĖąĄ 128’╝īRATE=0 |

100 |

dB |

| ą¤ąŠą┤ą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠą╝ąĄčģ ą┐ąŠ ą┐ąĖčéą░ąĮąĖčÄ |

ąŻčüąĖą╗ąĄąĮąĖąĄ 128, RATE=0 |

100 |

dB |

| ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ (VBG) |

|

1.25 |

V |

| ą¦ą░čüč鹊čéą░ ą║ą▓ą░čĆčåą░ ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ |

|

1 |

11.0592 |

20 |

ą£ąōčå |

| ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ |

DVDD |

2.6 |

|

5.5 |

V |

| AVDD, VSUP |

2.6 |

|

5.5 |

| ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ (ą▓ą║ą╗čÄčćą░čÅ čĆąĄą│čāą╗čÅč鹊čĆ) |

ąØąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ |

|

1400 |

|

┬ĄA |

| ąÆčŗą║ą╗čÄč湥ąĮąŠ (power down) |

|

0.3 |

|

| ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čåąĖčäčĆąŠą▓ąŠą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ |

ąØąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ |

|

100 |

|

┬ĄA |

| ąÆčŗą║ą╗čÄč湥ąĮąŠ (power down) |

|

0.2 |

|

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) V(inp) ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝ ą▓čŗą▓ąŠą┤ąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░, V(inn) ąĮą░ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╝ ą▓čŗą▓ąŠą┤ąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░.

(2) ąÆčĆąĄą╝čÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ (power up), čüą▒čĆąŠčüą░ (reset), ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čģąŠą┤ąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čāčüąĖą╗ąĄąĮąĖčÅ - ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠą╗čāč湥ąĮąĖčÅ čüčéą░ą▒ąĖą╗čīąĮčŗčģ ąĖ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗčģ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ.

(3) nV(rms) - rms ąŠąĘąĮą░čćą░ąĄčé čüčĆąĄą┤ąĮąĄąĄ ą║ą▓ą░ą┤čĆą░čéąĖč湥čüą║ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ (Root Mean Square), ąĮą░ąĮąŠą▓ąŠą╗čīčé.

(4) ppm ąŠąĘąĮą░čćą░ąĄčé čćą░čüč鹥ą╣ ąĮą░ ą╝ąĖą╗ą╗ąĖąŠąĮ (Parts Per Million).

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čģąŠą┤čŗ. ąÜą░ąĮą░ą╗ A ąĖą╝ąĄąĄčé ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą▓čģąŠą┤, ą║ąŠč鹊čĆčŗą╣ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝čā ą▓čŗčģąŠą┤čā ą╝ąŠčüč鹊ą▓ąŠą│ąŠ ą┤ą░čéčćąĖą║ą░ (čéą░ą║ąŠą│ąŠ ą║ą░ą║ ąĮą░ą┐čĆąĖą╝ąĄčĆ č鹥ąĮąĘąŠą┤ą░čéčćąĖą║ DYLY-102 [2]). ąŻčüąĖą╗ąĄąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ A ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮąŠ 128 ąĖą╗ąĖ 64. ąæąŠą╗čīčłąŠąĄ čāčüąĖą╗ąĄąĮąĖąĄ ą┐ąŠą┤ąŠą╣ą┤ąĄčé ą║ ąĮąĄą▒ąŠą╗čīčłąŠą╝čā čāčĆąŠą▓ąĮčÄ čüąĖą│ąĮą░ą╗ą░ ąŠčé čüąĄąĮčüąŠčĆą░. ąÜąŠą│ą┤ą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ AVDD ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ 5V, čŹčéąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ čāčüąĖą╗ąĄąĮąĖčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé ą┐ąŠą╗ąĮąŠą╝čā ą┤ąĖą░ą┐ą░ąĘąŠąĮčā ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ┬▒20 mV ąĖą╗ąĖ ┬▒40 mV čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąŻ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ą░ ą║ą░ąĮą░ą╗ą░ B čāčüąĖą╗ąĄąĮąĖąĄ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠąĄ, ąĖ čĆą░ą▓ąĮąŠąĄ 32. ąÜąŠą│ą┤ą░ ą┤ą╗čÅ AVDD ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąĖčéą░ąĮąĖąĄ 5V, čŹč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą┐ąŠą╗ąĮąŠą╝čā ą┤ąĖą░ą┐ą░ąĘąŠąĮčā ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ┬▒80 mV.

ą¤ąĖčéą░ąĮąĖąĄ. ą”ąĖčäčĆąŠą▓ąŠąĄ ą┐ąĖčéą░ąĮąĖąĄ (DVDD) ą┤ąŠą╗ąČąĮąŠ čüąŠą▓ą┐ą░ą┤ą░čéčī čü ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą│ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ (MCU).

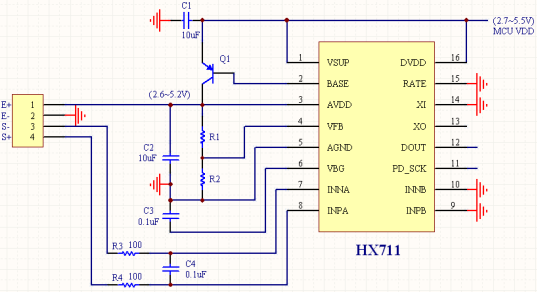

ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čĆąĄą│čāą╗čÅč鹊čĆ ą┐ąĖčéą░ąĮąĖčÅ, ą┐ą░ą┤ąĄąĮąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ čĆąĄą│čāą╗čÅč鹊čĆąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ čéčĆą░ąĮąĘąĖčüč鹊čĆą░. ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čĆą░ą▓ąĮąŠ VAVDD = VBG * (R1+R2) / R1 (čüą╝. čĆąĖčü. 1). ąŁč鹊 ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĮą░ 100 mV ąĮąĖąČąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VSUP.

ąĢčüą╗ąĖ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ čĆąĄą│čāą╗čÅč鹊čĆ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, č鹊 ą▓čŗą▓ąŠą┤ VSUP ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą╗ąĖą▒ąŠ ą║ AVDD, ą╗ąĖą▒ąŠ ą║ DVDD, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹊ą│ąŠ, ą║ą░ą║ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▒ąŠą╗čīčłąĄ. ąÆčŗą▓ąŠą┤ VFB ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ąĘąĄą╝ą╗ąĄ (GND), ąĖ ą▓čŗą▓ąŠą┤ BASE čüčéą░ą▓ąĖčéčüčÅ NC (Not Connected, ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ). ą¤čĆąĖ čŹč鹊ą╝ ąĮąĄ ąĮčāąČąĄąĮ ą▓ąĮąĄčłąĮąĖą╣ ą▒ą╗ąŠą║ąĖčĆąŠą▓ąŠčćąĮčŗą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ VBG, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗą╣ ąĮą░ čĆąĖčü. 1.

ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ. ą¤čĆąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĖ ą▓čŗą▓ąŠą┤ą░ XI ą║ ąĘąĄą╝ą╗ąĄ (GND) ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ. ąØąŠą╝ąĖąĮą░ą╗čīąĮą░čÅ čüą║ąŠčĆąŠčüčéčī ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čĆą░ą▓ąĮąŠ 10SPS (RATE=0) ąĖą╗ąĖ 80SPS (RATE=1).

ąĢčüą╗ąĖ ąĮčāąČąĮą░ č鹊čćąĮą░čÅ čćą░čüč鹊čéą░ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ, č鹊 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą▓ą░čĆčåąĄą▓čŗą╣ čĆąĄąĘąŠąĮą░č鹊čĆ ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĖą╣ ąŠą┐ąŠčĆąĮčŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ. ąÜą▓ą░čĆčå ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą╝ąĄąČą┤čā ą▓čŗą▓ąŠą┤ą░ą╝ąĖ XI ąĖ XO. ąÆąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą▓čŗą▓ąŠą┤čā XI č湥čĆąĄąĘ čĆą░ąĘą▓čÅąĘčŗą▓ą░čÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ 20 ą┐ąż. ąÆąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ąĮąĄąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆčÅą╝ąŠčāą│ąŠą╗čīąĮčŗą╝. ą×ąĮ ą╝ąŠąČąĄčé ą┐ąŠčüčéčāą┐ą░čéčī ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ąŠčé ą▓čŗčģąŠą┤ą░ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čćąĖą┐ą░ MCU, čü ą░ą╝ą┐ą╗ąĖčéčāą┤ąŠą╣ ą┤ąŠ 150 mV.

ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą▓ą░čĆčå ąĖą╗ąĖ ą▓ąĮąĄčłąĮčÅčÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░, ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ.

ąĪą║ąŠčĆąŠčüčéčī ąĖ č乊čĆą╝ą░čé ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ, čüą║ąŠčĆąŠčüčéčī ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąŠą▒čŗčćąĮąŠ 10SPS (RATE=0) ąĖą╗ąĖ 80SPS (RATE=1).

ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ ąĖą╗ąĖ ą║ą▓ą░čĆčå, čüą║ąŠčĆąŠčüčéčī ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┐čĆčÅą╝ąŠ ą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮą░ čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓. ą¤čĆąĖ 11.0592 ą£ąōčå ą┐ąŠą╗čāčćą░ąĄčéčüčÅ č鹊čćąĮą░čÅ čüą║ąŠčĆąŠčüčéčī ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ 10SPS (RATE=0) ąĖą╗ąĖ 80SPS (RATE=1).

ąÆčŗčģąŠą┤ąĮčŗąĄ 24 ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ ąĖą╝ąĄčÄčé č乊čĆą╝ą░čé ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┤ąŠ 2. ąÜąŠą│ą┤ą░ ą▓čģąŠą┤ąĮąŠą╣ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ ą▓čŗčģąŠą┤ąĖčé ąĘą░ ą┤ąĖą░ą┐ą░ąĘąŠąĮ 24 ą▒ąĖčé, ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĮą░čüčŗčēąĄąĮąĖąĄ ą┤ąŠ ąĘąĮą░č湥ąĮąĖąĄ 800000h (MIN) ąĖą╗ąĖ 7FFFFFh (MAX), ą┐ąŠą║ą░ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ąĮąĄ ą▓ąĄčĆąĮąĄčéčüčÅ ą▓ąŠ ą▓čģąŠą┤ąĮąŠą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┐ąŠą╗ąĮąŠą╣ čłą║ą░ą╗čŗ.

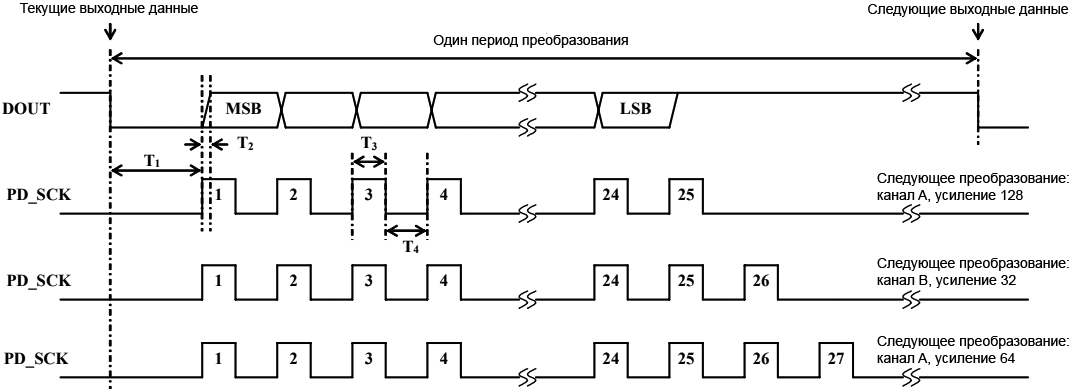

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü. ąÆčŗą▓ąŠą┤čŗ PD_SCK ąĖ DOUT ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čüčćąĖčéčŗą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, ą▓čŗą▒ąŠčĆą░ ą▓čģąŠą┤ą░, ą▓čŗą▒ąŠčĆą░ čāčüąĖą╗ąĄąĮąĖčÅ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖąĄą╝.

ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ čüčģąĄą╝ą░ HX711 čüą░ą╝ą░ ąĘą░ą┐čāčüą║ą░ąĄčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ (ąŠčåąĖčäčĆąŠą▓ą║čā) čāčĆąŠą▓ąĮčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓čģąŠą┤ąŠą▓ ąÉą”ą¤ čü ąĘą░ą┤ą░ąĮąĮąŠą╣ čćą░čüč鹊ą╣, ąĘą░ą▓ąĖčüčÅčēąĄą╣ ąŠčé čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ RATE (10 ąĖą╗ąĖ 80 ąōčå). ąŚą░ą┤ą░čćą░ ą▓ąĮąĄčłąĮąĄą│ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąŠčćąĖčéą░čéčī ą┤ą░ąĮąĮčŗąĄ čĆąĄąĘčāą╗čīčéą░čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąŠąĮąĖ ą▒čāą┤čāčé ą│ąŠč鹊ą▓čŗ. ąōąŠč鹊ą▓ąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ ą╝ąŠąČąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┐ąŠ ą╗ąŠą│ąĖč湥čüą║ąŠą╝čā čāčĆąŠą▓ąĮčÄ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ DOUT.

ąÜąŠą│ą┤ą░ ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą│ąŠč鹊ą▓čŗ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, ąĮą░ čåąĖčäčĆąŠą▓ąŠą╝ ą▓čŗčģąŠą┤ąĄ DOUT ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą╗ąŠą│. 1. ąØą░ ą▓čģąŠą┤ąĄ čéą░ą║č鹊ą▓ PD_SCK ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. ąÜąŠą│ą┤ą░ DOUT ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0, čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé ą│ąŠč鹊ą▓ąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ ą║ čćč鹥ąĮąĖčÄ. ą¤čāč鹥ą╝ ą┐ąŠą┤ą░čćąĖ 25 .. 27 ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĮą░ ą▓čŗą▓ąŠą┤ PD_SCK ą┤ą░ąĮąĮčŗąĄ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĮą░čĆčāąČčā č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ DOUT. ąÜą░ąČą┤čŗą╣ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü PD_SCK ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčé čüą┤ą▓ąĖą│ ąĮą░ 1 ą▒ąĖčé, ąĮą░čćąĖąĮą░čÅ čüąŠ čüčéą░čĆčłąĄą│ąŠ ą▒ąĖčéą░ (MSB), ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤čāčé ą▓čŗą┤ą▓ąĖąĮčāčéčŗ ą▓čüąĄ 24 ą▒ąĖčéą░. 25-ą╣ ąĖą╝ą┐čāą╗čīčü PD_SCK ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąŠą▒čĆą░čéąĮąŠą╝čā ą┐ąĄčĆąĄą▓ąŠą┤čā DOUT ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1 (čüą╝. čĆąĖčü. 2).

ąÆčŗą▒ąŠčĆ ą▓čģąŠą┤ą░ ąĖ čāčüąĖą╗ąĄąĮąĖčÅ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ ą▓čģąŠą┤ąĮčŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ PD_SCK (čéą░ą▒ą╗ąĖčåą░ 3). ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ąĖą╝ą┐čāą╗čīčüąŠą▓ PD_SCK ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą╝ąĄąĮčīčłąĄ 25 ąĖ ą▒ąŠą╗čīčłąĄ 27 ą▓ č鹥č湥ąĮąĖąĄ ą┐ąĄčĆąĖąŠą┤ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, čćč鹊ą▒čŗ ąĮąĄ ą┤ąŠą┐čāčüčéąĖčéčī ąŠčłąĖą▒ą║ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ.

ąóą░ą▒ą╗ąĖčåą░ 3. ąÆčģąŠą┤ąĮąŠą╣ ą║ą░ąĮą░ą╗ ąĖ ą▓čŗą▒ąŠčĆ čāčüąĖą╗ąĄąĮąĖčÅ.

| ąśą╝ą┐čāą╗čīčüąŠą▓ PD_SCK |

ąÆčģąŠą┤ąĮąŠą╣ ą║ą░ąĮą░ą╗ |

ąŻčüąĖą╗ąĄąĮąĖąĄ |

| 25 |

A |

128 |

| 26 |

B |

32 |

| 27 |

A |

64 |

ąĀąĖčü. 2. ąÆčŗčģąŠą┤ ą┤ą░ąĮąĮčŗčģ, čéą░ą╣ą╝ąĖąĮą│ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą▒ąŠčĆąŠą╝ ą▓čģąŠą┤ą░ ąĖ čāčüąĖą╗ąĄąĮąĖčÅ.

| ąĪąĖą╝ą▓. |

ąŚą░ą╝ąĄčćą░ąĮąĖčÅ |

min |

Typ |

MAX |

ąĢą┤. |

| T1 |

DOUT falling edge to PD_SCK rising edge |

0.1 |

|

|

ą╝ą║čü |

| T2 |

PD_SCK rising edge to DOUT data ready |

|

|

0.1 |

| T3 |

ąÆčĆąĄą╝čÅ ą╗ąŠą│. 1 PD_SCK |

0.2 |

1 |

50 |

| T4 |

ąÆčĆąĄą╝čÅ ą╗ąŠą│. 0 PD_SCK |

0.2 |

1 |

|

Reset ąĖ Power-Down. ąÜąŠą│ą┤ą░ ąĮą░ čćąĖą┐ ą┐ąŠą┤ą░ąĄčéčüčÅ ą┐ąĖčéą░ąĮąĖąĄ, ą▓čüčéčĆąŠąĄąĮąĮą░čÅ čüčģąĄą╝ą░ čüą▒čĆą░čüčŗą▓ą░ąĄčé čćąĖą┐ ą▓ ąĖčüčģąŠą┤ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ.

ąÆčŗą▓ąŠą┤ PD_SCK ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ HX711. ąÜąŠą│ą┤ą░ ąĮą░ ą▓čģąŠą┤ąĄ PD_SCK ą╗ąŠą│. 0, čćąĖą┐ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆą░ą▒ąŠč湥ą╝ čĆąĄąČąĖą╝ąĄ.

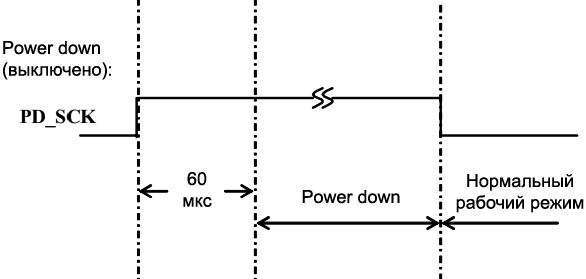

ąĀąĖčü. 3. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ (Power Down).

ąÜąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤ PD_SCK ą╝ąĄąĮčÅąĄčé čāčĆąŠą▓ąĄąĮčī čü ą╗ąŠą│. 0 ąĮą░ ą╗ąŠą│. 1, ąĖ ąŠčüčéą░ąĄčéčüčÅ ą▓ čéą░ą║ąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ąĮą░ ą▓čĆąĄą╝čÅ ą▒ąŠą╗čīčłąĄ 60 ą╝ą║čü, HX711 ą▓čģąŠą┤ąĖčé čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (power down mode, čĆąĖčü. 3). ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čĆąĄą│čāą╗čÅč鹊čĆą░ ą┤ą╗čÅ HX711 ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ, ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ ą║ą░ą║ HX711, čéą░ą║ ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī. ąÜąŠą│ą┤ą░ PD_SCK ą▓ąŠąĘą▓čĆą░čēą░ąĄčéčüčÅ ą║ ąĮąĖąĘą║ąŠą╝čā čāčĆąŠą▓ąĮčÄ, čćąĖą┐ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ąĖ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ.

ą¤ąŠčüą╗ąĄ čüąŠą▒čŗčéąĖčÅ čüą▒čĆąŠčüą░ (reset) ąĖą╗ąĖ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (power-down) ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą║ą░ąĮą░ą╗ A čü čāčüąĖą╗ąĄąĮąĖąĄą╝ 128.

[ą¤čĆąĖą╝ąĄčĆ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ]

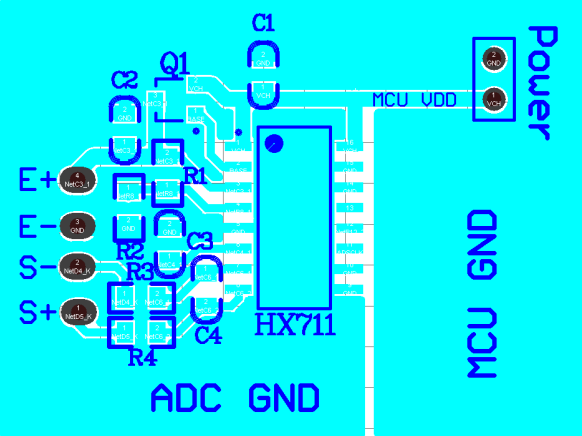

ąØą░ čĆąĖčü. 1 ą┐ąŠą║ą░ąĘą░ąĮą░ čéąĖą┐ąŠą▓ą░čÅ čüčģąĄą╝ą░ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ HX711 ą┤ą╗čÅ ą▓ąĄčüąŠą▓ čü č鹥ąĮąĘąŠą┤ą░čéčćąĖą║ąŠą╝. ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ (XI=0), čüą║ąŠčĆąŠčüčéčī ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ 10 ąōčå (RATE=0). ąĢą┤ąĖąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ (2.7V .. 5.5V’╝ēą┐čĆąĖčģąŠą┤ąĖčé ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ąŠčé čłąĖąĮčŗ ą┐ąĖčéą░ąĮąĖčÅ MCU. ąÜą░ąĮą░ą╗ B ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ąĘą░čĆčÅą┤ą░ ą▒ą░čéą░čĆąĄąĖ, ąĮą░ čĆąĖčü. 1 čüčģąĄą╝ą░ ą┤ą╗čÅ čŹč鹊ą│ąŠ ąĮąĄ ą┐ąŠą║ą░ąĘą░ąĮą░.

ąĀąĖčü. 4. ą×ą▒čĆą░ąĘąĄčå ą┐čĆąĖąĮčåąĖą┐ąĖą░ą╗čīąĮąŠą╣ čüčģąĄą╝čŗ (ą┐ą╗ą░čéą░ čĆąĖčü. 5).

ąĀąĖčü. 5. ą×ą▒čĆą░ąĘąĄčå čĆą░ąĘą▓ąŠą┤ą║ąĖ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ.

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ čÅąĘčŗą║ąĄ ą░čüčüąĄą╝ą▒ą╗ąĄčĆą░:

/*-------------------------------------------------------------------

ąÆčŗąĘąŠą▓ ąĖąĘ ASM: LCALL ReaAD

ąÆčŗąĘąŠą▓ ąĖąĘ C: extern unsigned long ReadAD(void);

.

.

unsigned long data;

data=ReadAD();

.

.

----------------------------------------------------------------------*/

PUBLIC ReadAD

HX711ROM segment code

rseg HX711ROM

sbit ADDO = P1.5;

sbit ADSK = P0.0;

/*--------------------------------------------------

OUT: R4, R5, R6, R7 R7=>LSB

---------------------------------------------------*/

ReadAD:

CLR ADSK //AD čĆą░ąĘčĆąĄčłąĄąĮąŠ’╝łPD_SCK čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 0’╝ē

SETB ADDO //ąĀą░ąĘčĆąĄčłąĄąĮąŠ I/O 51CPU

JB ADDO,$ //AD-ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąŠ?

MOV R4,#24

ShiftOut:

SETB ADSK //PD_SCK čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1’╝łąĮą░čćą░ą╗ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░’╝ē

NOP

CLR ADSK //PD_SCK čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 0 (ą║ąŠąĮąĄčå ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░)

MOV C,ADDO //čćč鹥ąĮąĖąĄ ą▒ąĖčéą░

XCH A,R7 //ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ

RLC A

XCH A,R7

XCH A,R6

RLC A

XCH A,R6

XCH A,R5

RLC A

XCH A,R5

DJNZ R4,ShiftOut //ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąŠ 24 ą▒ąĖčéą░?

SETB ADSK

NOP

CLR ADSK

RET

END

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ čÅąĘčŗą║ąĄ C:

sbit ADDO = P1^5;

sbit ADSK = P0^0;

unsigned long ReadCount(void)

{

unsigned long Count;

unsigned char i;

ADDO=1;

ADSK=0;

Count=0;

while(ADDO);

for (i=0;i<24;i++)

{

ADSK=1;

Count=Count<<1;

ADSK=0;

if(ADDO) Count++;

}

ADSK=1;

Count=Count^0x800000;

ADSK=0;

return Count;

}

ąĀąĖčü. 6. ąĀą░ąĘą╝ąĄčĆčŗ ą║ąŠčĆą┐čāčüą░ SOP-16L, čāą║ą░ąĘą░ąĮąĮčŗąĄ ą▓ ą╝ąĖą╗ą╗ąĖą╝ąĄčéčĆą░čģ.

[ąĪčüčŗą╗ą║ąĖ]

1. HX711 24-Bit Analog-to-Digital Converter (ADC) for Weigh Scales site:sparkfun.com.

2. S Type Load Cells DYLY-102 site:7sensor.com. |