|

ą¤čĆčÅą╝ąŠą╣ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ (Direct Memory Access, DMA) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗčģ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖą╣ ą┤ą░ąĮąĮčŗą╣ ą╝ąĄąČą┤čā ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ąĖ ą┐ą░ą╝čÅčéčīčÄ, ą░ čéą░ą║ąČąĄ ą╝ąĄąČą┤čā ąŠą▒ą╗ą░čüčéčÅą╝ąĖ ą┐ą░ą╝čÅčéąĖ. ąöą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčüčéčĆąŠ ą┐ąĄčĆąĄą╝ąĄčēą░čéčīčüčÅ ą▒ą╗ąŠą║ąŠą╝ DMA ą▒ąĄąĘ čāčćą░čüčéąĖčÅ CPU, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĄą│ąŠ čÅą┤čĆą░ą╝ ą▒ąŠą╗ąĄąĄ čŹčäč乥ą║čéąĖą▓ąĮąŠ ąĘą░ąĮąĖą╝ą░čéčīčüčÅ ąŠą▒čĆą░ą▒ąŠčéą║ąŠą╣ ą┤ą░ąĮąĮčŗčģ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ ą│ą╗ą░ą▓čŗ, ą┐ąŠčüą▓čÅčēąĄąĮąĮąŠą╣ DMA ąĖąĘ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ [1]. ąØąĄąĘąĮą░ą║ąŠą╝čŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ ąĪą╗ąŠą▓ą░čĆąĖą║ąĄ, ą▓ ą║ąŠąĮčåąĄ čüčéą░čéčīąĖ.

ąÆ ESP32 ą┐ąĄčĆąĄčüčŗą╗ą║ąĖ DMA ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░: UART0, UART1, UART2, SPI1, SPI2, SPI3, I2S0, I2S1, SDIO slave, SD/MMC host, EMAC, Bluetooth ąĖ Wi-Fi.

ą×čüąŠą▒ąĄąĮąĮąŠčüčéąĖ ąĖ čäčāąĮą║čåąĖąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ DMA ESP32:

ŌĆó ąÉčĆčģąĖč鹥ą║čéčāčĆą░ čłąĖąĮčŗ AHB

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ full-duplex ąĖ half-duplex ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ ą┤ą╗ąĖąĮą░ ą┐ąĄčĆąĄą┤ą░čć ą▓ ą▒ą░ą╣čéą░čģ

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą┐ą░ą║ąĄčéąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ (4-beat burst transfer)

ŌĆó ąÉą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ 328 KB

ŌĆó ąÆčüąĄ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗąĄ ą╝ąŠą┤čāą╗ąĖ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖą╣ ą┐ąŠą╗čāčćą░čÄčé ą┐ąĖčéą░ąĮąĖąĄ ąŠčé DMA

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ DMA]

ąÆčüąĄ ą╝ąŠą┤čāą╗ąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ, ą║ąŠč鹊čĆčŗąĄ čéčĆąĄą▒čāčÄčé ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗčģ ą┐ą░ą║ąĄčéąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čć, čüąŠą┤ąĄčƹȹ░čé ąĮą░ ą▒ąŠčĆčéčā ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA. ąÉą┤čĆąĄčüą░čåąĖčÅ DMA ąĖčüą┐ąŠą╗čīąĘčāąĄčé čéčā ąČąĄ čüą░ą╝čāčÄ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ, čćč鹊 ąĖ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ CPU, čĆą░ą▒ąŠčéą░čÄčēąĖąĄ čü ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéčīčÄ (IRAM, Internal SRAM 1 ąĖ Internal SRAM 2). ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 DMA ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ 0x3FFE0000 .. 0x3FFFFFFF ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ Internal SRAM 1, ąĖ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ 0x3FFAE000 .. 0x3FFDFFFF ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ Internal SRAM 2.

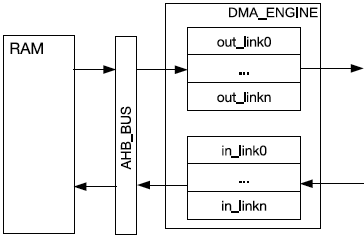

ąÆ ą║ą░ąČą┤ąŠą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ DMA ą┐čĆąĖčüčāčéčüčéą▓čāčÄčé čĆą░ąĘąĮčŗąĄ čäčāąĮą║čåąĖąĖ. ą×ą┤ąĮą░ą║ąŠ ą░čĆčģąĖč鹥ą║čéčāčĆą░ ą┐ąŠą┤čüąĖčüč鹥ą╝čŗ DMA (DMA Engine, DMA_ENGINE) ąŠą┤ąĖąĮą░ą║ąŠą▓ą░čÅ ą┤ą╗čÅ ą▓čüąĄčģ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ DMA.

ąĀąĖčü. 12. ąÉčĆčģąĖč鹥ą║čéčāčĆą░ DMA Engine.

DMA Engine ą┐ąŠą╗čāčćą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ SRAM č湥čĆąĄąĘ čłąĖąĮčā AHB. ąØą░ čĆąĖčüčāąĮą║ąĄ 12 RAM ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ąĖ ą▒ą░ąĮą║ą░ą╝ąĖ SRAM, ą┤ąŠčüčéčāą┐ąĮčŗą╝ąĖ ą▓ ESP32. ąæąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ čüą╝. čĆą░ąĘą┤ąĄą╗ "System and Memory" č鹥čģąĮąĖč湥čüą║ąŠą│ąŠ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ [2].

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī DMA Engine ą┐čāč鹥ą╝ ąĮą░čüčéčĆąŠą╣ą║ąĖ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ (Linked List), ą▓ ą║ąŠč鹊čĆąŠą╝ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ čĆą░ą▒ąŠčćąĖčģ ąŠą┐ąĄčĆą░čåąĖą╣ DMA.

DMA Engine ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ąĖąĘ RAM ą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čüąŠą┤ąĄčƹȹĖą╝čŗą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ out_link. ąóą░ą║ąČąĄ DMA Engine čüąŠčģčĆą░ąĮčÅąĄčé ą┤ą░ąĮąĮčŗąĄ, ą┐čĆąĖąĮčÅčéčŗąĄ ąĖąĘ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ą▓ čāą║ą░ąĘą░ąĮąĮąŠąĄ ą╝ąĄčüč鹊 RAM, ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝ in_link.

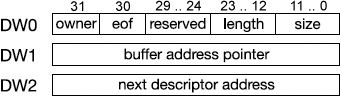

Linked List. ą¤ąŠą┤ čŹčéąĖą╝ č鹥čĆą╝ąĖąĮąŠą╝ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ čüą▓čÅąĘą░ąĮąĮčŗą╣ čüą┐ąĖčüąŠą║ ąŠą┐ąĄčĆą░čåąĖą╣ DMA. ąĪą▓čÅąĘą░ąĮąĮčŗąĄ čüą┐ąĖčüą║ąĖ DMA ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ ąĖ ą▓ą▓ąŠą┤ą░ (out_link ąĖ in_link) ąĖą╝ąĄčÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čāčÄ čüčéčĆčāą║čéčāčĆčā.

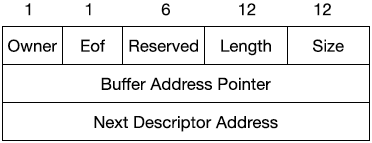

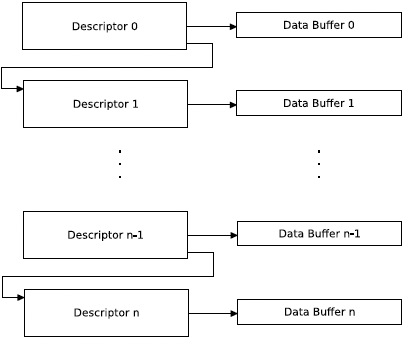

ąĀąĖčü. 13. ąĪčéčĆčāą║čéčāčĆą░ Linked List.

ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 13, ą┤ąĄčüą║čĆąĖą┐č鹊čĆ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ čüąŠčüč鹊ąĖčé ąĖąĘ 3 čüą╗ąŠą▓. ąÜą░ąČą┤ąŠąĄ ą┐ąŠą╗ąĄ ą▓ čüą╗ąŠą▓ąĄ ąŠąĘąĮą░čćą░ąĄčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

owner (DW0) [31]: čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╣ ąŠą┐ąĄčĆą░č鹊čĆ ą▒čāč乥čĆą░, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ č鹥ą║čāčēąĄą╝čā čüą▓čÅąĘą░ąĮąĮąŠą╝čā čüą┐ąĖčüą║čā.

0: čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╣ ąŠą┐ąĄčĆą░č鹊čĆ čŹč鹊 CPU;

1: čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╣ ąŠą┐ąĄčĆą░č鹊čĆ čŹč鹊 ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA.

eof (DW0) [30]: čüąĖą╝ą▓ąŠą╗ ą║ąŠąĮčåą░ čäą░ą╣ą╗ą░ (End-Of-File).

0: 菹╗ąĄą╝ąĄąĮčé čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ ąĮąĄ ą┐ąŠą╝ąĄčćą░ąĄčé ą║ąŠąĮąĄčå čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░;

1: 菹╗ąĄą╝ąĄąĮčé čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ čÅą▓ą╗čÅąĄčéčüčÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄą╝ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░.

reserved (DW0) [29:24]: ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą▒ąĖčéčŗ. ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ąĮąĄ ą┤ąŠą╗ąČąĮą░ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą▓ čŹčéąĖ ą▒ąĖčéčŗ ą╗ąŠą│. 1.

length (DW0) [23:12]: ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ąŠą┐čāčüčéąĖą╝čŗčģ ą▒ą░ą╣čé ą▓ ą▒čāč乥čĆąĄ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ č鹥ą║čāčēąĄą╝čā čüą▓čÅąĘą░ąĮąĮąŠą╝čā čüą┐ąĖčüą║čā. ąŚąĮą░č湥ąĮąĖąĄ čŹč鹊ą│ąŠ ą┐ąŠą╗čÅ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé, ą┐ąĄčĆąĄčüčŗą╗ą░ąĄą╝ąŠąĄ ą▓ ą▒čāč乥čĆ ąĖą╗ąĖ ąĖąĘ ą▒čāč乥čĆą░, ąŠą▒ąŠąĘąĮą░č湥ąĮąĮąŠą│ąŠ čüą╗ąŠą▓ąŠą╝ DW1.

size (DW0) [11:0]: čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ č鹥ą║čāčēąĄą╝čā čüą▓čÅąĘą░ąĮąĮąŠą╝čā čüą┐ąĖčüą║čā. ąÆą░ąČąĮąŠąĄ ąĘą░ą╝ąĄčćą░ąĮąĖąĄ: ąĘąĮą░č湥ąĮąĖąĄ size ą┤ąŠą╗ąČąĮąŠ ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗ąĖčéčīčüčÅ ąĮą░ 4 (word-aligned).

buffer address pointer (DW1): čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ą▒čāč乥čĆ. ąŁč鹊 ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ ą┤ą░ąĮąĮčŗčģ ą▓ ą┐ą░ą╝čÅčéąĖ. ąÆą░ąČąĮąŠąĄ ąĘą░ą╝ąĄčćą░ąĮąĖąĄ: ąĘąĮą░č湥ąĮąĖąĄ ą░ą┤čĆąĄčüą░ ą┤ąŠą╗ąČąĮąŠ ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗ąĖčéčīčüčÅ ąĮą░ 4 (word-aligned).

next descriptor address (DW2): čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ 菹╗ąĄą╝ąĄąĮčé čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░. ąĢą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ čĆą░ą▓ąĮąŠ 0, ąĄčüą╗ąĖ č鹥ą║čāčēąĖą╣ 菹╗ąĄą╝ąĄąĮčé čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▓ čüą┐ąĖčüą║ąĄ (eof=1).

ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, ąĄčüą╗ąĖ length čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą╝ąĄąĮčīčłąĄ, č湥ą╝ čāą║ą░ąĘą░ąĮąĮčŗą╣ čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ size, č鹊 DMA ąĮąĄ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠčüčéą░ą▓čłąĄąĄčüčÅ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ. ąŁčéą░ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéčī ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī DMA Engine ą┤ą╗čÅ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ.

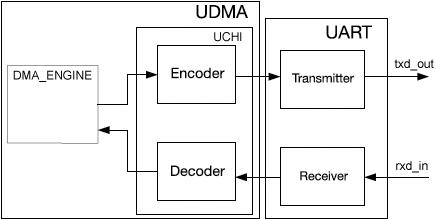

ąŻ ESP32 ąĄčüčéčī 3 ąĖąĮč鹥čĆč乥ą╣čüą░ UART, ą║ąŠč鹊čĆčŗąĄ čüąŠą▓ą╝ąĄčüčéąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčé 2 ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ UART DMA (UDMA). UHCI_UARTx_CE (ąĘą┤ąĄčüčī x ąĘą░ą╝ąĄąĮčÅąĄčéčüčÅ ąĮą░ 0, 1 ąĖą╗ąĖ 2) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ UART, čćč鹊ą▒čŗ ąŠąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗ UDMA.

ąĀąĖčü. 14. ąóčĆą░ąĮąĘą░ą║čåąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ UDMA.

ąĀąĖčüčāąĮąŠą║ 14 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ UDMA. ą¤ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ DMA Engine ą┐čĆąĖą╝ąĄčé ą┤ą░ąĮąĮčŗąĄ, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī čüą▓čÅąĘą░ąĮąĮčŗą╣ čüą┐ąĖčüąŠą║ ą┐čĆąĖąĄą╝ą░ (receive-linked-list). ąĀąĄą│ąĖčüčéčĆ UHCI_INLINK_ADDR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĖčÅ ąĮą░ ą┐ąĄčĆą▓čŗą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ in_link. ąĀąĄą│ąĖčüčéčĆ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą╝ą╗ą░ą┤čłąĖą╝ąĖ 20 ą▒ąĖčéą░ą╝ąĖ ą░ą┤čĆąĄčüą░ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░. ą¤ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ UHCI_INLINK_START ą▒ą╗ąŠą║ Universal Host Controller Interface (UHCI) ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ, ą┐čĆąĖąĮčÅčéčŗąĄ UART, ą▓ Decoder. ą¤ąŠčüą╗ąĄ ą┐ą░čĆčüąĖąĮą│ą░ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé čüąŠčģčĆą░ąĮąĄąĮčŗ ą▓ RAM, ą║ą░ą║ čŹč鹊 čāą║ą░ąĘą░ąĮąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝ receive-linked-list.

ą¤ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ DMA ą┐ąĄčĆąĄą┤ą░čüčé ą┤ą░ąĮąĮčŗąĄ, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī čüą▓čÅąĘą░ąĮąĮčŗą╣ čüą┐ąĖčüąŠą║ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit-linked-list) ąĖ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮčŗ. ąĀąĄą│ąĖčüčéčĆ UHCI_OUTLINK_ADDR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĖčÅ ąĮą░ ą┐ąĄčĆą▓čŗą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ out_link. ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą╝ą╗ą░ą┤čłąĖą╝ąĖ 20 ą▒ąĖčéą░ą╝ąĖ ą░ą┤čĆąĄčüą░ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ transmit-linked-list. ą¤ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ UHCI_OUTLINK_START ą▒ą╗ąŠą║ DMA Engine ą▒čāą┤ąĄčé čüčćąĖčéčŗą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ąŠą▒ą╗ą░čüčéąĖ RAM, čāą║ą░ąĘą░ąĮąĮąŠą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░, ąĖ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī čŹčéąĖ ą┤ą░ąĮąĮčŗąĄ ą▓ Encoder. DMA Engine ąĘą░č鹥ą╝ ą▒čāą┤ąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓čŗą┤ą▓ąĖą│ą░čéčī ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ UART.

UART DMA čüą╗ąĄą┤čāąĄčé č乊čĆą╝ą░čéčā (separator + data + separator). Encoder ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĖčÅ čüąĄą┐ą░čĆą░č鹊čĆąŠą▓ ą┐ąĄčĆąĄą┤ ąĖ ą┐ąŠčüą╗ąĄ ą┤ą░ąĮąĮčŗčģ, ą║ą░ą║ ąĖ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüč鹥ą╣ čüą┐ąĄčåčüąĖą╝ą▓ąŠą╗ąŠą▓ ą┤ą╗čÅ ąĘą░ą╝ąĄąĮčŗ ą┤ą░ąĮąĮčŗčģ, čüąŠą▓ą┐ą░ą┤ą░čÄčēąĖčģ čü čüąĄą┐ą░čĆą░č鹊čĆą░ą╝ąĖ. Decoder ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┤ą░ą╗ąĄąĮąĖčÅ čüąĄą┐ą░čĆą░č鹊čĆąŠą▓ ą┐ąĄčĆąĄą┤ ąĖ ą┐ąŠčüą╗ąĄ ą┤ą░ąĮąĮčŗčģ, ą║ą░ą║ ąĖ ą┤ą╗čÅ ąĘą░ą╝ąĄąĮčŗ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüč鹥ą╣ čüą┐ąĄčåčüąĖą╝ą▓ąŠą╗ąŠą▓ čüąĄą┐ą░čĆą░č鹊čĆą░ą╝ąĖ. ą£ąŠąČąĄčé ą▒čŗčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čüą╗ąĄą┤čāčÄčēąĖčģ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ čüąĄą┐ą░čĆą░č鹊čĆąŠą▓, ą┐ąŠą╝ąĄčćą░čÄčēąĖčģ ąĮą░čćą░ą╗ąŠ ąĖą╗ąĖ ą║ąŠąĮąĄčå ą┤ą░ąĮąĮčŗčģ. ąŁčéąĖ čüąĄą┐ą░čĆą░č鹊čĆčŗ ą╝ąŠą│čāčé ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčīčüčÅ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ UHCI_SEPER_CH, ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0xC0. ąöą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ čüąŠą▓ą┐ą░ą┤ą░čÄčé čü čüąĄą┐ą░čĆą░č鹊čĆą░ą╝ąĖ, ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą╝ąĄąĮąĄąĮčŗ ąĮą░ UHCI_ESC_SEQ0_CHAR0 (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0xDB) ąĖ UHCI_ESC_SEQ0_CHAR1 (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0xDD). ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąŠčåąĄčüčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ UHCI_OUT_TOTAL_EOF_INT. ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą┐čĆąĖąĄą╝ą░ ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ UHCI_IN_SUC_EOF_INT.

ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ UART ąĖ ąĄą│ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA čüą╝. ą▓ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ [1].

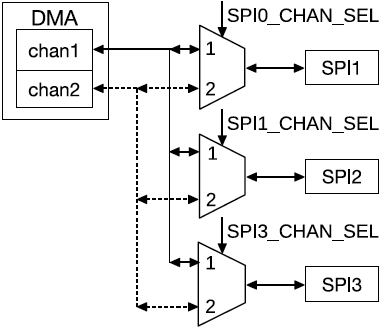

ą£ąŠą┤čāą╗ąĖ ESP32 SPI ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī DMA čéą░ą║ ąČąĄ, ą║ą░ą║ čŹč鹊 ą┤ąĄą╗ą░ąĄčé CPU ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ. ąÜą░ą║ ą╝ąŠąČąĮąŠ čāą▓ąĖą┤ąĄčéčī ąĖąĘ čĆąĖčü. 15, ą┤ą▓ą░ ą║ą░ąĮą░ą╗ą░ DMA čüąŠą▓ą╝ąĄčüčéąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ SPI1, SPI2 ąĖ SPI3. ąÜą░ąČą┤čŗą╣ ą║ą░ąĮą░ą╗ DMA ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą╗čÄą▒čŗą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ SPI ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ.

ąĀąĖčü. 15. SPI DMA.

ESP32 SPI DMA Engine č鹊ąČąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüą▓čÅąĘą░ąĮąĮčŗą╣ čüą┐ąĖčüąŠą║ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░/ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą┐ą░ą║ąĄčéąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą£ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ ą┤ą╗ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ąŠą┤ąĮąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ 1 ą▒ą░ą╣čé. ąóą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ čéčĆą░ąĮąĘą░ą║čåąĖąĖ.

ą¤ąŠą╗čÅ SPI1_DMA_CHAN_SEL[1:0], SPI2_DMA_CHAN_SEL[1:0] ąĖ SPI3_DMA_CHAN_SEL[1:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ DPORT_SPI_DMA_CHAN_SEL_REG ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI DMA ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ SPI. ąÜą░ąČą┤čŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ SPI čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠą┤ąĮąŠą╝čā ą┤ąŠą╝ąĄąĮčā, čā ą║ąŠč鹊čĆąŠą│ąŠ ąĄčüčéčī ą┤ą▓ą░ ą▒ąĖčéą░ čüąŠ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ 0, 1 ąĖ 2. ąŚąĮą░č湥ąĮąĖąĄ 3 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, ąĖ ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣.

ąĢčüą╗ąĖ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čéčī ą┤ą╗čÅ ą┐čĆąĖą╝ąĄčĆą░ SPI1:

ąĢčüą╗ąĖ SPI SPI1_DMA_CHAN_SEL[1:0] = 0, č鹊 SPI1 ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąĮąĖą║ą░ą║ąŠą╣ ą║ą░ąĮą░ą╗ DMA. ąĢčüą╗ąĖ SPI1_DMA_CHAN_SEL[1:0] = 1, č鹊 SPI1 čĆą░ąĘčĆąĄčłą░ąĄčé DMA channel1. ąĢčüą╗ąĖ SPI1_DMA_CHAN_SEL[1:0] = 2, č鹊 SPI1 čĆą░ąĘčĆąĄčłą░ąĄčé DMA channel2.

ąæąĖčé SPI_OUTLINK_START ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_DMA_OUT_LINK_REG, ąĖ ą▒ąĖčé SPI_INLINK_START ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_DMA_IN_LINK_REG ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ DMA Engine. ąŁčéąĖ ą┤ą▓ą░ ą▒ąĖčéą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░čÄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣. ąĢčüą╗ąĖ SPI_OUTLINK_START čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, č鹊 DMA Engine ąĘą░ą┐čāčüą║ą░ąĄčé ąŠą▒čĆą░ą▒ąŠčéą║čā outbound-ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ ąĖ ą┐ąŠą┤ą│ąŠčéą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą║ ą┐ąĄčĆąĄą┤ą░č湥 ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ SPI_INLINK_START čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, č鹊 DMA Engine ąĮą░čćąĖąĮą░ąĄčé ąŠą▒čĆą░ą▒ąŠčéą║čā inbound-ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ ąĖ ą│ąŠč鹊ą▓ąĖčéčüčÅ ą║ ą┐čĆąĖąĄą╝čā ą┤ą░ąĮąĮčŗčģ.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī SPI DMA čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

1. ąĪą▒čĆąŠčü ą╝ą░čłąĖąĮčŗ čüąŠčüč鹊čÅąĮąĖčÅ DMA ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ FIFO.

2. ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓, ąŠčéąĮąŠčüčÅčēąĖčģčüčÅ ą║ DMA.

3. ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ čĆąĄą│ąĖčüčéčĆąŠą▓, ąŠčéąĮąŠčüčÅčēąĖčģčüčÅ ą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā SPI.

4. ąŻčüčéą░ąĮąŠą▓ą║ą░ SPI_USR ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ DMA.

[ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ DMA]

SPI_OUT_TOTAL_EOF_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮčŗ ą▓čüąĄ čüą▓čÅąĘą░ąĮąĮčŗąĄ čüą┐ąĖčüą║ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ.

SPI_OUT_EOF_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ ąŠą┤ąĖąĮ čüą▓čÅąĘą░ąĮąĮčŗą╣ čüą┐ąĖčüąŠą║.

SPI_OUT_DONE_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ 菹╗ąĄą╝ąĄąĮčé čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╝ąĄąĄčé

ąĮčāą╗ąĄą▓čāčÄ ą┤ą╗ąĖąĮčā.

SPI_IN_SUC_EOF_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčéčŗ ą▓čüąĄ ąŠą▒čĆą░ą▒ąŠčéą░ąĮčŗ ą▓čüąĄ čüą▓čÅąĘą░ąĮąĮčŗąĄ čüą┐ąĖčüą║ąĖ ą┐čĆąĖąĄą╝ą░.

SPI_IN_ERR_EOF_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐čĆąĖ ąŠą▒ąĮą░čĆčāąČąĄąĮąĖąĖ ąŠčłąĖą▒ą║ąĖ ą▓ čüą▓čÅąĘą░ąĮąĮčŗčģ čüą┐ąĖčüą║ą░čģ ą┐čĆąĖąĄą╝ą░.

SPI_IN_DONE_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ą┤ą╗ąĖąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ ą┐čĆąĖąĄą╝ą░ čĆą░ą▓ąĮą░ 0.

SPI_INLINK_DSCR_ERROR_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ąŠą▒ąĮą░čĆčāąČąĄąĮ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗą╣ čüą┐ąĖčüąŠą║ ą┐čĆąĖąĄą╝ą░.

SPI_OUTLINK_DSCR_ERROR_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ąŠą▒ąĮą░čĆčāąČąĄąĮ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗą╣ čüą┐ąĖčüąŠą║ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ SPI ąĖ ąĄą│ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA čüą╝. ą▓ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ [1].

ESP32 ąĖą╝ąĄąĄčé ąĮą░ ą▒ąŠčĆčéčā 2 ą╝ąŠą┤čāą╗čÅ I2S, I2S0 ąĖ I2S1, ą║ą░ąČą┤čŗą╣ ąĖąĘ ą║ąŠč鹊čĆčŗčģ čüąĮą░ą▒ąČąĄąĮ ą║ą░ąĮą░ą╗ąŠą╝ DMA. ąæąĖčé REG_I2S_DSCR_EN bit ą▓ čĆąĄą│ąĖčüčéčĆąĄ I2S_FIFO_CONF_REG ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ DMA. ESP32 I2S DMA ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖą╣ ą┤ą░ąĮąĮčŗčģ DMA. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą┐ą░ą║ąĄčéąĮčŗąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ą×ą┤ąĮą░ą║ąŠ, ą▓ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ą║ą░ąĮą░ą╗ąŠą▓ SPI DMA, ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ čĆą░ąĘą╝ąĄčĆ ą┤ą░ąĮąĮčŗčģ čüąŠčüčéą░ą▓ą╗čÅąĄčé 1 čüą╗ąŠą▓ąŠ, ąĖą╗ąĖ 4 ą▒ą░ą╣čéą░. ąæąĖčéčŗ REG_I2S_RX_EOF_NUM[31:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ I2S_RXEOF_NUM_REG ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čĆą░ąĘą╝ąĄčĆą░ ą┤ą░ąĮąĮčŗčģ ąŠą┤ąĖąĮąŠčćąĮąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ, čŹč鹊čé čĆą░ąĘą╝ąĄčĆ ą┤ąŠą╗ąČąĄąĮ ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗ąĖčéčīčüčÅ ąĮą░ 4.

ąæąĖčé I2S_OUTLINK_START ą▓ čĆąĄą│ąĖčüčéčĆąĄ I2S_OUT_LINK_REG ąĖ ą▒ąĖčé I2S_INLINK_START ą▓ čĆąĄą│ąĖčüčéčĆąĄ I2S_IN_LINK_REG ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ DMA Engine ąĖ ąŠąĮąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░čÄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ. ąÜąŠą│ą┤ą░ I2S_OUTLINK_START čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, DMA Engine ąĮą░čćąĖąĮą░ąĄčé ąŠą▒čĆą░ą▒ąŠčéą║čā outbound-ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░, ąĖ ą┐ąŠą┤ą│ąŠčéą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą║ ą┐ąĄčĆąĄą┤ą░č湥 ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ I2S_INLINK_START čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, DMA Engine ąĘą░ą┐čāčüą║ą░ąĄčé ąŠą▒čĆą░ą▒ąŠčéą║čā inbound-ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░, ąĖ ą┐ąŠą┤ą│ąŠčéą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą║ ą┐čĆąĖąĄą╝čā ą┤ą░ąĮąĮčŗčģ.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī I2S DMA čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

1. ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓, ąŠčéąĮąŠčüčÅčēąĖčģčüčÅ ą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā I2S.

2. ąĪą▒čĆąŠčü ą╝ą░čłąĖąĮčŗ čüąŠčüč鹊čÅąĮąĖą╣ DMA ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ FIFO.

3. ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓, ąŠčéąĮąŠčüčÅčēąĖčģčüčÅ ą║ DMA.

4. ąÆ čĆąĄąČąĖą╝ąĄ I2S master čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé I2S_TX_START bit ąĖą╗ąĖ ą▒ąĖčé I2S_RX_START ą┤ą╗čÅ ąĖąĮąĖčåąĖą░čåąĖąĖ ąŠą┐ąĄčĆą░čåąĖąĖ I2S. ąÆ čĆąĄąČąĖą╝ąĄ I2S slave čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé I2S_TX_START bit ąĖą╗ąĖ ą▒ąĖčé I2S_RX_START bit, ąĖ DMA Engine ąŠąČąĖą┤ą░ąĄčé ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą┤ą░ąĮąĮčŗčģ čüąŠ čüč鹊čĆąŠąĮčŗ čāčüčéčĆąŠą╣čüčéą▓ą░ čģąŠčüčéą░.

[ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ DMA]

I2S_OUT_TOTAL_EOF_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮčŗ ą▓čüąĄ čüą▓čÅąĘą░ąĮąĮčŗąĄ čüą┐ąĖčüą║ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ.

I2S_IN_DSCR_EMPTY_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ąĮąĄ ąŠčüčéą░ą╗ąŠčüčī ąĮąĖ ąŠą┤ąĮąŠą│ąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░.

I2S_OUT_DSCR_ERR_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ąŠą▒ąĮą░čĆčāąČąĄąĮ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗą╣ čüą┐ąĖčüąŠą║ ą┐ąĄčĆąĄą┤ą░čćąĖ.

I2S_IN_DSCR_ERR_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ąŠą▒ąĮą░čĆčāąČąĄąĮ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗą╣ čüą┐ąĖčüąŠą║ ą┐čĆąĖąĄą╝ą░.

I2S_OUT_EOF_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ąŠčéą┐čĆą░ą▓ą║ą░ ą┐ą░ą║ąĄčéą░.

I2S_OUT_DONE_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ą▓čüąĄ ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗąĄ ąĖ ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮčŗ.

I2S_IN_SUC_EOF_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą┐čĆąĖąĮčÅčéčŗ.

I2S_IN_DONE_INT: čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ąŠą▒čĆą░ą▒ąŠčéą░ąĮ č鹥ą║čāčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ą┐čĆąĖąĄą╝ą░.

ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ I2S ąĖ ąĄą│ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA čüą╝. ą▓ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ [1].

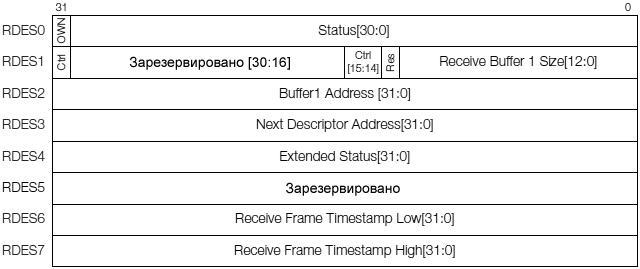

ą£ąŠą┤čāą╗čī SDIO Slave ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ DMA ą║ ą┤ą░ąĮąĮčŗą╝, ąĮą░čģąŠą┤čÅčēąĖą╝čüčÅ ą▓ RAM. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 22, ąŠą▒čĆą░čēąĄąĮąĖąĄ DMA ą║ RAM ą┐čĆąŠąĖčüčģąŠą┤ąĖčé č湥čĆąĄąĘ čłąĖąĮčā AHB, ą┐čĆąĖ ą┐ąŠą╝ąŠčēąĖ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░. ąÜą░ąČą┤čŗą╣ 菹╗ąĄą╝ąĄąĮčé čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ čüąŠčüčéą░ą▓ą╗ąĄąĮ ąĖąĘ 3 čüą╗ąŠą▓, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 25.

ąĀąĖčü. 25. ąĪčéčĆčāą║čéčāčĆą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ (Linked List) SDIO Slave DMA.

Owner: čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╣ ąŠą┐ąĄčĆą░č鹊čĆ ą▒čāč乥čĆą░, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ č鹥ą║čāčēąĄą╝čā čüą▓čÅąĘą░ąĮąĮąŠą╝čā čüą┐ąĖčüą║čā. 0: CPU čÅą▓ą╗čÅąĄčéčüčÅ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╝ ąŠą┐ąĄčĆą░č鹊čĆąŠą╝, 1: DMA čÅą▓ą╗čÅąĄčéčüčÅ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╝ ąŠą┐ąĄčĆą░č鹊čĆąŠą╝.

Eof: ą╝ą░čĆą║ąĄčĆ ąŠą║ąŠąĮčćą░ąĮąĖčÅ, ąŠąĮ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čŹč鹊čé 菹╗ąĄą╝ąĄąĮčé čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▓ ą┐ą░ą║ąĄč鹥 ą┤ą░ąĮąĮčŗčģ.

Length: ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ąŠą┐čāčüčéąĖą╝čŗčģ ą▒ą░ą╣čé ą▓ ą▒čāč乥čĆąĄ, ą║ ą║ąŠč鹊čĆčŗą╝ čĆą░ąĘčĆąĄčłąĄąĮąŠ ąŠą▒čĆą░čēąĄąĮąĖąĄ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ.

Size: ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ąŠčüčéčāą┐ąĮčŗčģ ą▒čāč乥čĆąŠą▓.

Buffer Address Pointer: ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ ą┤ą░ąĮąĮčŗčģ ą▓ ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ RAM.

Next Descriptor Address: ą░ą┤čĆąĄčü čüą╗ąĄą┤čāčÄčēąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ ą▓ ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ RAM. ąĢčüą╗ąĖ č鹥ą║čāčēąĖą╣ čüą▓čÅąĘą░ąĮąĮčŗą╣ čüą┐ąĖčüąŠą║ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣, č鹊 ą▒ąĖčé Eof ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ ą╗ąŠą│. 1, ąĖ ą░ą┤čĆąĄčü ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī 0.

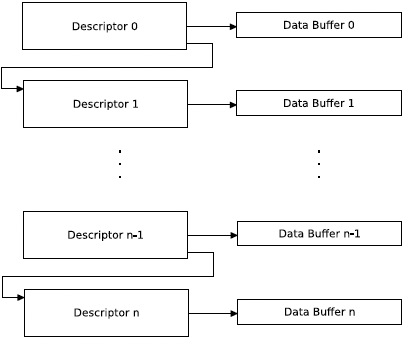

ąÆąŠčé čéą░ą║ ą╝ąŠąČąĄčé ą▓čŗą│ą╗čÅą┤ąĄčéčī čåąĄą┐ąŠčćą║ą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░:

ąĀąĖčü. 26. SDIO Slave Linked List.

ąŻčüčéčĆąŠą╣čüčéą▓ą░ SDIO Host ąĖ SDIO Slave ą┤ąŠą╗ąČąĮčŗ čüą╗ąĄą┤ąŠą▓ą░čéčī čüą╗ąĄą┤čāčÄčēąĖą╝ čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╝ ą┐čĆąŠčåąĄą┤čāčĆą░ą╝ ą┤ą╗čÅ čāčüą┐ąĄčłąĮąŠą│ąŠ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü SDIO.

ą×čéą┐čĆą░ą▓ą║ą░ ą┐ą░ą║ąĄč鹊ą▓ ą▓ SDIO Host. ą¤ąĄčĆąĄą┤ą░čćą░ ą┐ą░ą║ąĄč鹊ą▓ Slave -> Host ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ Slave. Host ą▒čāą┤ąĄčé ąŠą┐ąŠą▓ąĄčēąĄąĮ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ (ą┤ą╗čÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐čĆąŠč鹊ą║ąŠą╗ą░ SDIO). ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ Host ą┐čĆąŠčćąĖčéą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąĖąĘ Slave, ąŠąĮ ąĖąĮąĖčåąĖąĖčĆčāąĄčé ą┐ąŠą┤čģąŠą┤čÅčēčāčÄ čéčĆą░ąĮąĘą░ą║čåąĖčÄ ąĮą░ čłąĖąĮąĄ SDIO. ąÆčüčÅ čŹčéą░ ą┐čĆąŠčåąĄą┤čāčĆą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 27.

ąĀąĖčü. 27: ą¤čĆąŠčåąĄą┤čāčĆą░ ąŠčéą┐čĆą░ą▓ą║ąĖ ą┐ą░ą║ąĄčéą░ (ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ Slave).

ąÜąŠą│ą┤ą░ Host ą┐ąŠą╗čāčćąĖą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąŠčé čüčćąĖčéčŗą▓ą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠčé Slave ą┐čāč鹥ą╝ ąŠą▒čĆą░čēąĄąĮąĖčÅ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ SLC0HOST_INT ąĖ SLCHOST_PKT_LEN.

SLC0HOST_INT: čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąĢčüą╗ąĖ SLC0_RX_NEW_PACKET_INT_ST == 1, č鹊 čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čā Slave ąĄčüčéčī ą┐ą░ą║ąĄčé ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ.

SLCHOST_PKT_LEN: čĆąĄą│ąĖčüčéčĆ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆą░ ą┤ą╗ąĖąĮčŗ ą┐ą░ą║ąĄčéą░. ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ą╝ąĖąĮčāčü ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čĆą░ąĘą░ čĆą░ą▓ąĮąŠ ą┤ą╗ąĖąĮąĄ ą┐ą░ą║ąĄčéą░, ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą│ąŠ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé.

ą¦č鹊ą▒čŗ ąĘą░ą┐čāčüčéąĖčéčī DMA, CPU ą┤ąŠą╗ąČąĄąĮ ąĘą░ą┐ąĖčüą░čéčī ą╝ą╗ą░ą┤čłąĖąĄ 20 ą▒ąĖčé ą░ą┤čĆąĄčüą░ ą┐ąĄčĆą▓ąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ ą▓ ą┐ąŠą╗ąĄ SLC0_RXLINK_ADDR čĆąĄą│ąĖčüčéčĆą░ SLC0RX_LINK, ąĘą░č鹥ą╝ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčé SLC0_RXLINK_START čĆąĄą│ąĖčüčéčĆą░ SLC0RX_LINK. DMA ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą▓ąĄčĆčłąĖčé čéčĆą░ąĮąĘą░ą║čåąĖčÄ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ ąŠą┐ąĄčĆą░čåąĖąĖ DMA ą▓čŗąĘąŠą▓ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ CPU, čćč鹊ą▒čŗ ąŠąĮ ą╝ąŠą│ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī ąĖ/ąĖą╗ąĖ ą┐ąŠą▓č鹊čĆąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą▒čāč乥čĆą░.

ą¤čĆąĖąĄą╝ ą┐ą░ą║ąĄč鹊ą▓ ąŠčé SDIO Host. ą¤ąĄčĆąĄą┤ą░čćą░ ą┐ą░ą║ąĄč鹊ą▓ Host -> Slave ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ Host. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ Slave ą┐čĆąĖąĮąĖą╝ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ DMA ąĖ čüąŠčģčĆą░ąĮčÅąĄčé ąĖčģ ą▓ RAM. ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą┤ą╗čÅ CPU ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, čćč鹊ą▒čŗ ąŠąĮ ąŠą▒čĆą░ą▒ąŠčéą░ą╗ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąÆčüčÅ čŹčéą░ ą┐čĆąŠčåąĄą┤čāčĆą░ ą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆčāąĄčéčüčÅ ąĮą░ čĆąĖčü. 28.

ąĀąĖčü. 28: ą¤čĆąŠčåąĄą┤čāčĆą░ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄčéą░ (ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ Host).

Host ą┐ąŠą╗čāčćą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ąŠčüčéčāą┐ąĮčŗčģ ą▒čāč乥čĆąŠą▓ ą┐čĆąĖąĄą╝ą░ ąŠčé Slave ą┐čāč鹥ą╝ ąŠą▒čĆą░čēąĄąĮąĖčÅ ą║ čĆąĄą│ąĖčüčéčĆčā SLC0HOST_TOKEN_RDATA. CPU ą▓ čāčüčéčĆąŠą╣čüčéą▓ąĄ Slave ą┤ąŠą╗ąČąĄąĮ ąŠą▒ąĮąŠą▓ąĖčéčī čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąŠą┤ą│ąŠč鹊ą▓ą╗ąĄąĮ čüą▓čÅąĘą░ąĮąĮčŗą╣ čüą┐ąĖčüąŠą║ ą┐čĆąĖąĄą╝ą░ ą┤ą╗čÅ DMA. ą¤ąŠą╗ąĄ HOSTREG_SLC0_TOKEN1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ SLC0HOST_TOKEN_RDATA čģčĆą░ąĮąĖčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ąŠčüčéčāą┐ąĮčŗčģ ą▒čāč乥čĆąŠą▓.

Host ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┤ąŠčüčéčāą┐ąĮąŠąĄ ą▒čāč乥čĆąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ, ąĖčüą┐ąŠą╗čīąĘčāčÅ HOSTREG_SLC0_TOKEN1 ą╝ąĖąĮčāčü ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čāąČąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĮčŗčģ ą▒čāč乥čĆąŠą▓. ąĢčüą╗ąĖ ą▒čāč乥čĆąŠą▓ ąĮąĄą┤ąŠčüčéą░č鹊čćąĮąŠ, Host ą┤ąŠą╗ąČąĄąĮ ą┐ąŠčüč鹊čÅąĮąĮąŠ ąŠą┐čĆą░čłąĖą▓ą░čéčī čŹč鹊čé čĆąĄą│ąĖčüčéčĆ, ą┐ąŠą║ą░ ąĮąĄ ą┐ąŠčÅą▓ąĖčéčüčÅ ą┤ąŠčüčéą░č鹊čćąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒čāč乥čĆąŠą▓. ąöą╗čÅ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ąŠčüčéą░č鹊čćąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒čāč乥čĆąŠą▓ ą┐čĆąĖąĄą╝ą░ CPU čāčüčéčĆąŠą╣čüčéą▓ą░ Slave ą┤ąŠą╗ąČąĄąĮ ą┐ąŠčüč鹊čÅąĮąĮąŠ ąĘą░ą│čĆčāąČą░čéčī ą▒čāč乥čĆčŗ ą▓ čüą▓čÅąĘą░ąĮąĮčŗą╣ čüą┐ąĖčüąŠą║ ą┐čĆąĖąĄą╝ą░. ąŁč鹊čé ą┐čĆąŠčåąĄčüčü ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 29.

ąĀąĖčü. 29. ąŚą░ą│čĆčāąĘą║ą░ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░.

ąĪąĮą░čćą░ą╗ą░ CPU ą┤ąŠą╗ąČąĄąĮ ą┐čĆąĖčüąŠąĄą┤ąĖąĮąĖčéčī čüąĄą│ą╝ąĄąĮčéčŗ ąĮąŠą▓ąŠą│ąŠ ą▒čāč乥čĆą░ ą▓ ą║ąŠąĮąĄčå čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░, ą║ąŠč鹊čĆčŗą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ DMA, ąĖ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ.

ąŚą░č鹥ą╝ CPU ą┤ąŠą╗ąČąĄąĮ ąŠą┐ąŠą▓ąĄčüčéąĖčéčī DMA, čćč鹊 čüą▓čÅąĘą░ąĮąĮčŗą╣ čüą┐ąĖčüąŠą║ ą▒čŗą╗ ąŠą▒ąĮąŠą▓ą╗ąĄąĮ. ąŁč鹊 ą╝ąŠąČąĮąŠ čüą┤ąĄą╗ą░čéčī ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ SLC0_TXLINK_RESTART ą▓ čĆąĄą│ąĖčüčéčĆąĄ SLC0TX_LINK. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą║ąŠą│ą┤ą░ CPU ą▓ą┐ąĄčĆą▓čŗąĄ ąĖąĮąĖčåąĖąĖčĆčāąĄčé DMA ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ą┐ą░ą║ąĄč鹊ą▓, ą▒ąĖčé SLC0_TXLINK_RESTART ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1.

ąÆ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ CPU ąŠą▒ąĮąŠą▓ą╗čÅąĄčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ ą╗čÄą▒ąŠą╝ ą┤ąŠčüčéčāą┐ąĮąŠą╝ ą▒čāč乥čĆąĄ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ SLC0TOKEN1.

ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ SDIO Slave ąĖ ąĄą│ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA čüą╝. ą▓ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ [1].

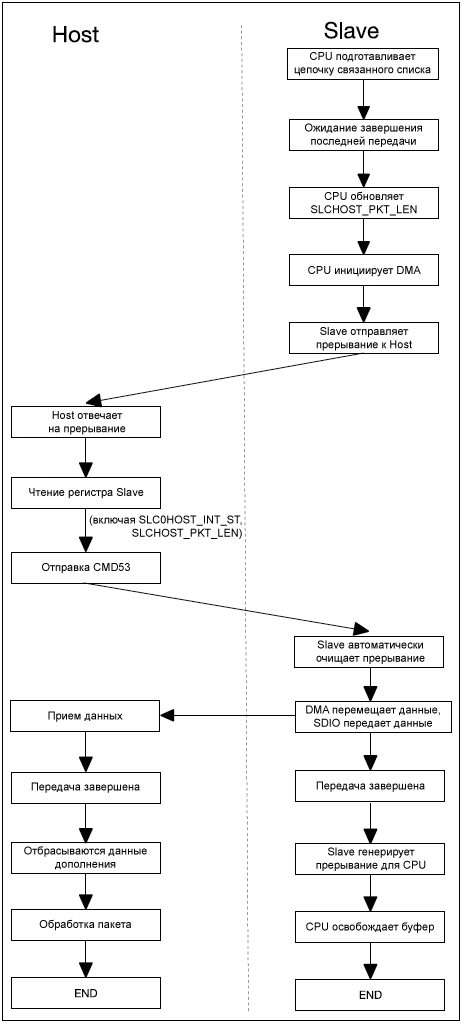

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čģąŠčüčéą░ SD/MMC čüąŠčüč鹊ąĖčé ąĖąĘ ą┤ą▓čāčģ ąŠčüąĮąŠą▓ąĮčŗčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗčģ ą▒ą╗ąŠą║ąŠą▓, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü 34:

Bus Interface Unit (BIU): ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĖąĮč鹥čĆč乥ą╣čüčŗ čłąĖąĮčŗ APB ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ FIFO ąĖ DMA.

Card Interface Unit (CIU): ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐čĆąŠč鹊ą║ąŠą╗čŗ ąĖąĮč鹥čĆč乥ą╣čüą░ ą▓ąĮąĄčłąĮąĄą╣ ą║ą░čĆčéčŗ ą┐ą░ą╝čÅčéąĖ. ąóą░ą║ąČąĄ čŹč鹊čé ą▒ą╗ąŠą║ čāą┐čĆą░ą▓ą╗čÅąĄčé č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čéą░ą║č鹊ą▓.

ąĀąĖčü. 34. ąæą╗ąŠą║-čüčģąĄą╝ą░ SDIO Host.

BIU. ąæą╗ąŠą║ BIU ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ ąĖ FIFO ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ Host Interface Unit (HIU). ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ BIU ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ąŠčüčéčāą┐ FIFO ą║ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╝ ą┤ą░ąĮąĮčŗą╝ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü DMA. ąśąĮč鹥čĆč乥ą╣čü čģąŠčüčéą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ąĖąĮč鹥čĆč乥ą╣čü APB. ąĀąĖčü. 34 ąĖą╗ą╗čÄčüčéčĆąĖčĆčāąĄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ BIU. BIU ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čäčāąĮą║čåąĖąĖ:

ŌĆó ąśąĮč鹥čĆč乥ą╣čü čģąŠčüčéą░

ŌĆó ąśąĮč鹥čĆč乥ą╣čü DMA

ŌĆó ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ

ŌĆó ąöąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝

ŌĆó ąöąŠčüčéčāą┐ ą║ FIFO

ŌĆó ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖąĄą╝ ąĖ ą┐ąŠą┤čéčÅąČą║ąŠą╣ čüąĖą│ąĮą░ą╗ąŠą▓ (power/pull-up control) ąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą║ą░čĆčéčŗ ą┐ą░ą╝čÅčéąĖ.

ąĪčāą▒ą╝ąŠą┤čāą╗čī RAM čŹč鹊 ąŠą▒ą╗ą░čüčéčī ą▒čāč乥čĆą░ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ąĖ ą┐čĆąĖąĄą╝ą░. ąĢą│ąŠ ą╝ąŠąČąĮąŠ čĆą░ąĘą┤ąĄą╗ąĖčéčī ąĮą░ ą┤ą▓ą░ ą▒ą╗ąŠą║ą░: ąŠą┤ąĖąĮ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ (Transmit RAM Module), ą┤čĆčāą│ąŠą╣ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ (Receive RAM Module). ą¤čĆąŠčåąĄčüčü ąŠčéą┐čĆą░ą▓ą║ąĖ ąĖ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčīčüčÅ čćč鹥ąĮąĖąĄą╝ ąĖ ąĘą░ą┐ąĖčüčīčÄ čüąŠ čüč鹊čĆąŠąĮčŗ CPU ąĖ DMA. ąöąŠčüčéčāą┐ čüąŠ čüč鹊čĆąŠąĮčŗ DMA ąŠą┐ąĖčüą░ąĮąŠ ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ ąĮąĖąČąĄ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąĪčéčĆčāą║čéčāčĆą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░".

Transmit RAM Module. ąĢčüčéčī 2 čüą┐ąŠčüąŠą▒ą░ čĆą░ąĘčĆąĄčłąĖčéčī ąŠą┐ąĄčĆą░čåąĖčÄ ąĘą░ą┐ąĖčüąĖ: čćč鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī DMA ąĖ čćč鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī CPU. ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮą░ ąŠčéą┐čĆą░ą▓ą║ą░ SDIO, č鹊 ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą┤ą╗čÅ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą╝ąŠą┤čāą╗ąĄą╝ RAM č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü APB ąĖą╗ąĖ DMA. ąöą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ EMAC_FIFO ąĮą░ą┐čĆčÅą╝čāčÄ ą▓ CPU, č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü APB.

Receive RAM Module. ąĢčüčéčī 2 čüą┐ąŠčüąŠą▒ą░ čĆą░ąĘčĆąĄčłąĖčéčī ąŠą┐ąĄčĆą░čåąĖčÄ čćč鹥ąĮąĖčÅ: čćč鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī DMA ąĖ čćč鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī CPU. ąÜąŠą│ą┤ą░ ą┐ąŠą┤čüąĖčüč鹥ą╝ą░ ą║ą░čĆčéčŗ ą┐čĆąĖąĮąĖą╝ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ, ąŠąĮąĖ ą▒čāą┤čāčé ąĘą░ą┐ąĖčüčŗą▓ą░čéčīčüčÅ ą▓ ą▒čāč乥čĆ RAM. ąŚą░č鹥ą╝ čŹčéąĖ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčēąĄą╣ čüč鹊čĆąŠąĮąŠą╣ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ą╗ąĖą▒ąŠ ą╝ąĄč鹊ą┤ąŠą╝ ąŠą▒čĆą░čēąĄąĮąĖčÅ č湥čĆąĄąĘ APB, ąĖą╗ąĖ ą╝ąĄč鹊ą┤ąŠą╝ DMA. ąĀąĄą│ąĖčüčéčĆ EMAC_FIFO ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░ą┐čĆčÅą╝čāčÄ ą┐čĆąŠčćąĖčéą░ąĮ č湥čĆąĄąĘ APB.

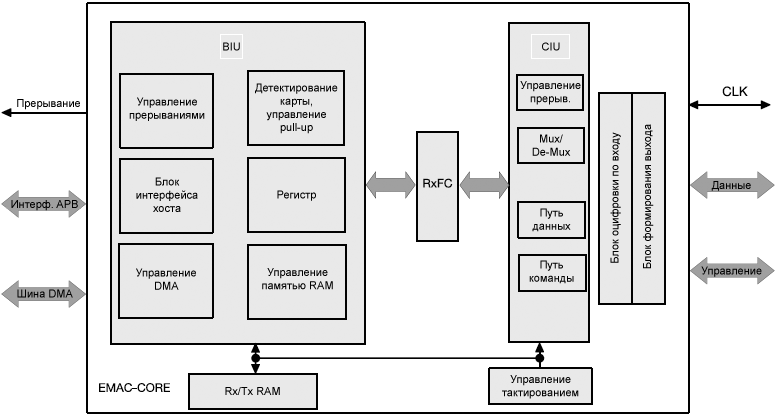

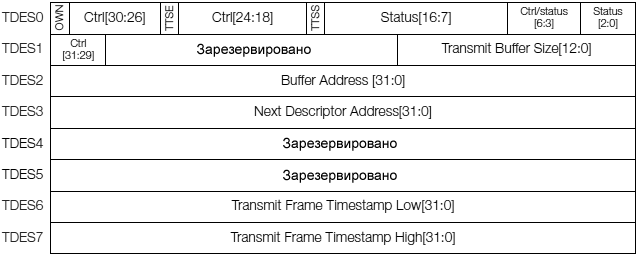

ą”ąĄą┐ąŠčćą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓. ąÜą░ąČą┤čŗą╣ 菹╗ąĄą╝ąĄąĮčé čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░ čüąŠčüč鹊ąĖčé ąĖąĘ ą┤ą▓čāčģ čćą░čüč鹥ą╣: čüą░ą╝ čüą▓čÅąĘą░ąĮąĮčŗą╣ čüą┐ąĖčüąŠą║, ąĖ ą▒čāč乥čĆ ą┤ą░ąĮąĮčŗčģ. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ą║ą░ąČą┤čŗą╣ 菹╗ąĄą╝ąĄąĮčé čüą┐ąĖčüą║ą░ čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ čāąĮąĖą║ą░ą╗čīąĮčŗą╣ ą▒čāč乥čĆ ą┤ą░ąĮąĮčŗčģ ąĖ čüą▓čÅąĘą░ąĮąĮčŗą╣ čüą┐ąĖčüąŠą║, ą║ąŠč鹊čĆčŗą╣ čüą╗ąĄą┤čāąĄčé ąĘą░ čŹčéąĖą╝ 菹╗ąĄą╝ąĄąĮč鹊ą╝. ąĀąĖčü. 38 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čåąĄą┐ąŠčćą║čā ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓.

ąĀąĖčü. 38: Descriptor Chain.

[ąĪčéčĆčāą║čéčāčĆą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░]

ąÜą░ąČą┤čŗą╣ 菹╗ąĄą╝ąĄąĮčé čüą┐ąĖčüą║ą░ čüąŠčüč鹊ąĖčé ąĖąĘ 4 čüą╗ąŠą▓. ąĀąĖčü. 39 ą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆčāąĄčé čüčéčĆčāą║čéčāčĆčā čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░, ąĖ čéą░ą▒ą╗ąĖčåčŗ 34 .. 37 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą╗ąĄą╣ čüą╗ąŠą▓ 菹╗ąĄą╝ąĄąĮčéą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░.

ąĀąĖčü. 39: ąĪčéčĆčāą║čéčāčĆą░ Linked List.

DES0 čüąŠą┤ąĄčƹȹĖčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüąŠčüč鹊čÅąĮąĖčÅ.

ąóą░ą▒ą╗ąĖčåą░ 34. DES0.

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31 |

OWN |

0: ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čŹčéąĖą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝ ą▓ą╗ą░ą┤ąĄąĄčé Host.

1: ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čŹčéąĖą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝ ą▓ą╗ą░ą┤ąĄąĄčé DMAC. DMAC ąŠčćąĖčüčéąĖčé čŹč鹊čé ą▒ąĖčé, ą║ąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłąĖčé ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ. |

| 30 |

CES |

Card Error Summary. ąŁčéąĖ ą▒ąĖčéčŗ ąŠčłąĖą▒ą║ąĖ čāą║ą░ąĘčŗą▓ą░čÄčé ąĮą░ čüąŠčüč鹊čÅąĮąĖąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą▓ ą║ą░čĆčéčā ąĖą╗ąĖ ąĖąĘ ą║ą░čĆčéčŗ. ąĪą╗ąĄą┤čāčÄčēąĖąĄ ą▒ąĖčéčŗ čéą░ą║ąČąĄ ą┐čĆąĖčüčāčéčüčéą▓čāčÄčé ą▓ RINTSTS, ąĖ ą▒ąĖčé CES ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čģąŠčéčÅ ą▒čŗ ąŠą┤ąĖąĮ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ ą▒ąĖčé ąŠčłąĖą▒ą║ąĖ:

ŌĆó EBE: End Bit Error

ŌĆó RTO: Response Time out

ŌĆó RCRC: Response CRC

ŌĆó SBE: Start Bit Error

ŌĆó DRTO: Data Read Timeout

ŌĆó DCRC: Data CRC for Receive

ŌĆó RE: Response Error |

| 29:6 |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 5 |

ER |

End of Ring.

1: ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čüą┐ąĖčüąŠą║ ą┤ąŠčüčéąĖą│ čüą▓ąŠąĄą│ąŠ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░. ąŚą░č鹥ą╝ DMAC ą▓ąŠąĘą▓čĆą░čéąĖčéčüčÅ ą║ ą▒ą░ąĘąŠą▓ąŠą╝čā ą░ą┤čĆąĄčüčā čüą┐ąĖčüą║ą░, čüąŠąĘą┤ą░ą▓ą░čÅ ą║ąŠą╗čīčåąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ (Descriptor Ring). |

| 4 |

CH |

Second Address Chained.

1: ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓č鹊čĆąŠą╣ ą░ą┤čĆąĄčü ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąĄ čŹč鹊 ą░ą┤čĆąĄčü čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ (Next Descriptor Address). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ BS2 (DES1[25:13]) ą▓čüąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĮčāą╗ąĄą▓čŗąĄ. |

| 3 |

FD |

First Descriptor.

1: ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čŹč鹊čé ą┤ąĄčüą║čĆąĖą┐č鹊čĆ čüąŠą┤ąĄčƹȹĖčé ą┐ąĄčĆą▓čŗą╣ ą▒čāč乥čĆ ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ čĆą░ąĘą╝ąĄčĆ ą┐ąĄčĆą▓ąŠą│ąŠ ą▒čāč乥čĆą░ 0, č鹊 čüą╗ąĄą┤čāčÄčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ (Next Descriptor) čüąŠą┤ąĄčƹȹĖčé ąĮą░čćą░ą╗ąŠ ą┤ą░ąĮąĮčŗčģ. |

| 2 |

LD |

Last Descriptor.

ąŁč鹊čé ą▒ąĖčé ą░čüčüąŠčåąĖąĖčĆčāąĄčéčüčÅ čü ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ ą▒ą╗ąŠą║ąŠą╝ čéčĆą░ąĮąĘą░ą║čåąĖąĖ DMA. 1: ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▒čāč乥čĆčŗ ą┤ą░ąĮąĮčŗčģ, ąĮą░ ą║ąŠč鹊čĆčŗąĄ čāą║ą░ąĘčŗą▓ą░ąĄčé čŹč鹊čé ą┤ąĄčüą║čĆąĖą┐č鹊čĆ, ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ. ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čŹč鹊ą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ąŠčüčéą░ą▓čłąĄąĄčüčÅ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ąĮčāą╗ąĄą▓ąŠąĄ. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ čü čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▒ąĖąŠą╝ LD, ąŠčüčéą░ą▓čłąĄąĄčüčÅ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī 0. |

| 1 |

DIC |

Disable Interrupt on Completion.

1: ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčé čāčüčéą░ąĮąŠą▓ą║čā ą▒ąĖčéą░ TI/RI ą▓ čĆąĄą│ąĖčüčéčĆąĄ DMAC Status Register (IDSTS) ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ ąĘą░ą▓ąĄčĆčłą░čÄčéčüčÅ ą▓ ą▒čāč乥čĆąĄ, ąĮą░ ą║ąŠč鹊čĆčŗą╣ čāą║ą░ąĘčŗą▓ą░ąĄčé čŹč鹊čé ą┤ąĄčüą║čĆąĖą┐č鹊čĆ (ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ). |

| 0 |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

DES1 čüąŠą┤ąĄčƹȹĖčé čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░.

ąóą░ą▒ą╗ąĖčåą░ 35. DES1.

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31:26 |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 25:13 |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 12:0 |

BS1 |

Buffer 1 Size.

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗą╣ ą┤ąŠą╗ąČąĄąĮ ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗ąĖčéčīčüčÅ ąĮą░ 4. ąÆ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ ąĮąĄ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░ 4, čĆąĄąĘčāą╗čīčéą░čé ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ. ąŁč鹊 ą┐ąŠą╗ąĄ ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĮčāą╗ąĄą▓čŗą╝. |

DES2 čüąŠą┤ąĄčƹȹĖčé čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ą▒čāč乥čĆ ą┤ą░ąĮąĮčŗčģ.

ąóą░ą▒ą╗ąĖčåą░ 36. DES2.

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31:0 |

Buffer Address Pointer 1 |

ążąĖąĘąĖč湥čüą║ąĖą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ ą┤ą░ąĮąĮčŗčģ. |

DES3 čüąŠą┤ąĄčƹȹĖčé čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ą▓ čåąĄą┐ąŠčćą║ąĄ, ąĄčüą╗ąĖ č鹥ą║čāčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ąĮąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▓ čåąĄą┐ąŠčćą║ąĄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓.

ąóą░ą▒ą╗ąĖčåą░ 37. DES3.

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31:0 |

Next Descriptor Address |

ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé Second Address Chained (DES0[4]), č鹊 čŹč鹊 čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ čäąĖąĘąĖč湥čüą║čāčÄ ą┐ą░ą╝čÅčéčī, ą│ą┤ąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ. ąĢčüą╗ąĖ čŹč鹊 ąĮąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ, č鹊 ąĘąĮą░č湥ąĮąĖąĄ Next Descriptor Address ą┤ąŠą╗ąČąĮąŠ ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗ąĖčéčīčüčÅ ąĮą░ 4 (DES3[1:0] == 0). |

ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ DMAC. ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMAC ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆó ąŚą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ DMAC Bus Mode (BMOD_REG) čāčüčéą░ąĮąŠą▓ąĖčé ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┤ąŠčüčéčāą┐ą░ čłąĖąĮčŗ čģąŠčüčéą░.

ŌĆó ąŚą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ DMAC Interrupt Enable (IDINTEN), čü ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ąĮąĄąĮčāąČąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ ą┤čĆą░ą╣ą▓ąĄčĆ čüąŠąĘą┤ą░ąĄčé čüą▓čÅąĘą░ąĮąĮčŗą╣ čüą┐ąĖčüąŠą║ ą╗ąĖą▒ąŠ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą╗ąĖą▒ąŠ ą┐čĆąĖąĄą╝ą░. ąŚą░č鹥ą╝ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ DMAC Descriptor List Base Address (DBADDR), ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÅ ą┤ą╗čÅ DMAC ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ čüą┐ąĖčüą║ą░.

ŌĆó DMAC engine ą┐čŗčéą░ąĄčéčüčÅ ąĘą░čģą▓ą░čéąĖčéčī ą┤ąĄčüą║čĆąĖą┐č鹊čĆčŗ ąĖąĘ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░.

ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ DMAC. ą¤ąĄčĆąĄą┤ą░čćą░ DMAC ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

1. ąźąŠčüčé ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčé 菹╗ąĄą╝ąĄąĮčéčŗ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ (DES0-DES3) ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ čāčüčéą░ąĮąŠą▓ąĖčé ą▒ąĖčé OWN (DES0[31]). ąóą░ą║ąČąĄ čģąŠčüčé ą┐ąŠą┤ą│ąŠčéą░ą▓ą╗ąĖą▓ą░ąĄčé ą▒čāč乥čĆ ą┤ą░ąĮąĮčŗčģ.

2. ąźąŠčüčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé ą║ąŠą╝ą░ąĮą┤čā write-data ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤ (CMD) ą▒ą╗ąŠą║ą░ BIU.

3. ąóą░ą║ąČąĄ čģąŠčüčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé čéčĆąĄą▒čāąĄą╝čŗą╣ ą┐ąŠčĆąŠą│ ą┐ąĄčĆąĄą┤ą░čćąĖ (ą┐ąŠą╗ąĄ TX_WMARK ą▓ čĆąĄą│ąĖčüčéčĆąĄ FIFOTH).

4. DMAC engine ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčé ą┤ąĄčüą║čĆąĖą┐č鹊čĆ, ąĖ ą┐čĆąŠą▓ąĄčĆčÅąĄčé ąĄą│ąŠ ą▒ąĖčé OWN. ąĢčüą╗ąĖ ą▒ąĖčé OWN ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čģąŠčüčé ą▓ą╗ą░ą┤ąĄąĄčé čŹčéąĖą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ DMAC ą▓čģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ, ąĖ ą▓čŗčüčéą░ą▓ą╗čÅąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Descriptor Unable ą▓ čĆąĄą│ąĖčüčéčĆąĄ IDSTS. ąÆ čéą░ą║ąŠą╣ čüąĖčéčāą░čåąĖąĖ čģąŠčüčéčā ąĮą░ą┤ąŠ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī DMAC ąĘą░ą┐ąĖčüčīčÄ ąĘąĮą░č湥ąĮąĖčÅ ą▓ PLDMND_REG.

5. ąŚą░č鹥ą╝ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąŠąČąĖą┤ą░ąĮąĖąĄ ą▒ąĖčéą░ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤čŗ Command Done (CD) ąĖ ą┐čĆąĖ ąŠčéčüčāčéčüčéą▓ąĖąĖ ąŠčłąĖą▒ąŠą║ ąŠčé BIU, čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čéčĆą░ąĮąĘą░ą║čåąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą▓ąĄčĆčłąĄąĮą░.

6. ąÆą┐ąŠčüą╗ąĄą┤čüčéą▓ąĖąĖ DMAC engine ąČą┤ąĄčé ąĘą░ą┐čĆąŠčüą░ ąĖąĮč鹥čĆč乥ą╣čüą░ DMA (dw_dma_req) ąŠčé BIU. ąŁč鹊čé ąĘą░ą┐čĆąŠčü ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĮą░ ąŠčüąĮąŠą▓ąĄ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠčĆąŠą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąöą╗čÅ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ą║ ą║ąŠč鹊čĆčŗą╝ ąĮąĄą╗čīąĘčÅ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┐ą░ą║ąĄčéąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąŠą┤ąĖąĮąŠčćąĮčŗąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ąĮą░ AHB Master Interface.

7. DMAC ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą▒čāč乥čĆą░ ą▓ ą┐ą░ą╝čÅčéąĖ čģąŠčüčéą░, ąĖ ą┐ąĄčĆąĄą┤ą░ąĄčé ąĖčģ ą▓ FIFO ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ ą║ą░čĆčéčā.

8. ąÜąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą┐ąŠ ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ą╝, DMAC ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ąĖ čĆą░čüčłąĖčĆčÅąĄčé čüą▓ąŠčÄ ąŠą┐ąĄčĆą░čåąĖčÄ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čŹč鹊ą│ąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░. ąæąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čĆą░čüą┐čĆąŠčüčéčĆą░ąĮčÅčÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ ąĮą░ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓, ąĖą╗ąĖ ąĮąĄčé.

9. ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░, ąĖąĮč乊čĆą╝ą░čåąĖčÅ čüčéą░čéčāčüą░ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ IDSTS ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (Transmit Interrupt), ąĄčüą╗ąĖ ąŠąĮąŠ ą▒čŗą╗ąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ. ąóą░ą║ąČąĄ ąŠčćąĖčüčéąĖčéčüčÅ ą▒ąĖčé OWN ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ DMAC ą┐čāč鹥ą╝ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą▓ DES0.

ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ą┐čĆąĖąĄą╝ą░ DMAC. ą¤čĆąĖąĄą╝ DMAC ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

1. ąźąŠčüčé ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčé 菹╗ąĄą╝ąĄąĮčéčŗ (DES0 - DES3) ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░, ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▒ąĖčé OWN (DES0[31]).

2. ąźąŠčüčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé ą║ąŠą╝ą░ąĮą┤čā read-data ą▓ čĆąĄą│ąĖčüčéčĆ CMD ą▒ą╗ąŠą║ą░ BIU.

3. ąźąŠčüčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé čéčĆąĄą▒čāąĄą╝čŗą╣ čāčĆąŠą▓ąĄąĮčī ą┐ąŠčĆąŠą│ą░ ą┐čĆąĖąĄą╝ą░ (ą┐ąŠą╗ąĄ RX_WMARK ą▓ čĆąĄą│ąĖčüčéčĆąĄ FIFOTH).

4. DMAC engine ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčé ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ąĖ ą┐čĆąŠą▓ąĄčĆčÅąĄčé ą▒ąĖčé OWN. ąĢčüą╗ąĖ ą▒ąĖčé OWN ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 čŹč鹊 ąĘąĮą░čćąĖčé, čćč鹊 čģąŠčüčé ą▓ą╗ą░ą┤ąĄąĄčé čŹčéąĖą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ, DMA ą▓čģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ, ąĖ ą▓čŗčüčéą░ą▓ą╗čÅąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Descriptor Unable ą▓ čĆąĄą│ąĖčüčéčĆąĄ IDSTS register. ąöą╗čÅ čéą░ą║ąŠą╣ čüąĖčéčāą░čåąĖąĖ čģąŠčüčéčā ąĮčāąČąĮąŠ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī DMAC ąĘą░ą┐ąĖčüčīčÄ ą╗čÄą▒ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆ PLDMND_REG.

5. ąŚą░č鹥ą╝ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąŠąČąĖą┤ą░ąĮąĖąĄ ą▒ąĖčéą░ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤čŗ Command Done (CD) ąĖ ą┐čĆąĖ ąŠčéčüčāčéčüčéą▓ąĖąĖ ąŠčłąĖą▒ąŠą║ ąŠčé BIU, čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čéčĆą░ąĮąĘą░ą║čåąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą▓ąĄčĆčłąĄąĮą░.

6. ąÆą┐ąŠčüą╗ąĄą┤čüčéą▓ąĖąĖ DMAC engine ąČą┤ąĄčé ąĘą░ą┐čĆąŠčüą░ ąĖąĮč鹥čĆč乥ą╣čüą░ DMA (dw_dma_req) ąŠčé BIU. ąŁč鹊čé ąĘą░ą┐čĆąŠčü ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĮą░ ąŠčüąĮąŠą▓ąĄ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠčĆąŠą│ą░ ą┐čĆąĖąĄą╝ą░. ąöą╗čÅ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ą║ ą║ąŠč鹊čĆčŗą╝ ąĮąĄą╗čīąĘčÅ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┐ą░ą║ąĄčéąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĮą░ AHB Master Interface ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ąŠą┤ąĖąĮąŠčćąĮčŗąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ.

7. DMAC ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ąĖąĘ FIFO, ąĖ ą┐ąĄčĆąĄą┤ą░ąĄčé ąĖčģ ą▓ ą┐ą░ą╝čÅčéčī čģąŠčüčéą░.

8. ąÜąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą┐ąŠ ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ą╝, DMAC ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ąĖ čĆą░čüčłąĖčĆčÅąĄčé čüą▓ąŠčÄ ąŠą┐ąĄčĆą░čåąĖčÄ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čŹč鹊ą│ąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░. ąæąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čĆą░čüą┐čĆąŠčüčéčĆą░ąĮčÅčÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ ąĮą░ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓, ąĖą╗ąĖ ąĮąĄčé.

9. ąÜąŠą│ą┤ą░ ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ ąĘą░ą▓ąĄčĆčłąĄąĮ, ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ čüčéą░čéčāčüą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ IDSTS ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ (Receive Interrupt), ąĄčüą╗ąĖ ąŠąĮąŠ ą▒čŗą╗ąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ. ąóą░ą║ąČąĄ ąŠčćąĖčēą░ąĄčéčüčÅ ą▒ąĖčé OWN ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ DMAC ą┐čāč鹥ą╝ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą▓ DES0.

ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ SD/MMC Host ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čüą╝. ą▓ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ [1].

Ethernet DMA ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╝ąĖ ą┐ąŠą┤čüąĖčüč鹥ą╝ą░ą╝ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░, ąĖ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠą╝ čĆąĄą│ąĖčüčéčĆąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüąŠčüč鹊čÅąĮąĖčÅ CSR (Control and Status Registers). ą¤ąŠą┤čüąĖčüč鹥ą╝ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (Transmit engine) ą┐ąĄčĆąĄą╝ąĄčēą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ąĖąĘ čüąĖčüč鹥ą╝ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą▓ ą┐ąŠčĆčé čāčüčéčĆąŠą╣čüčéą▓ą░ (MTL), ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┐ąŠą┤čüąĖčüč鹥ą╝ą░ ą┐čĆąĖąĄą╝ą░ (Receive engine) ą┐ąĄčĆąĄą╝ąĄčēą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą┐ąŠčĆčéą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ ą┐ą░ą╝čÅčéčī čüąĖčüč鹥ą╝čŗ. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┤ąĄčüą║čĆąĖą┐č鹊čĆčŗ ą┤ą╗čÅ čŹčäč乥ą║čéąĖą▓ąĮąŠą│ąŠ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą╝ąĄčüčéą░ ąĖčüč鹊čćąĮąĖą║ą░ ą▓ ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ čü ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ čéčĆą░č鹊ą╣ ą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ CPU. DMA čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ ą┤ą╗čÅ čéčĆą░ąĮąĘą░ą║čåąĖą╣, ąŠčĆąĖąĄąĮčéąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ą┐ą░ą║ąĄč鹊ą▓, čéą░ą║ąĖčģ ą║ą░ą║ ą║ą░ą┤čĆ (čäčĆąĄą╣ą╝) Ethernet. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ Host CPU ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮčŗčģ čüąĖčéčāą░čåąĖčÅčģ, čéą░ą║ąĖčģ ą║ą░ą║ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ą┐čĆąĖąĄą╝ą░ ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ą░ą┤čĆą░, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ąĖ ąŠčłąĖą▒ą║ąĖ.

ąØąĖąČąĄ ąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čüčéčĆčāą║čéčāčĆą░ čüą▓čÅąĘą░ąĮąĮčŗčģ čüą┐ąĖčüą║ąŠą▓ ąĖ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓. ąÜą░ąČą┤čŗą╣ čüą▓čÅąĘą░ąĮąĮčŗą╣ čüą┐ąĖčüąŠą║ čüąŠčüč鹊ąĖčé ąĖąĘ 8 čüą╗ąŠą▓.

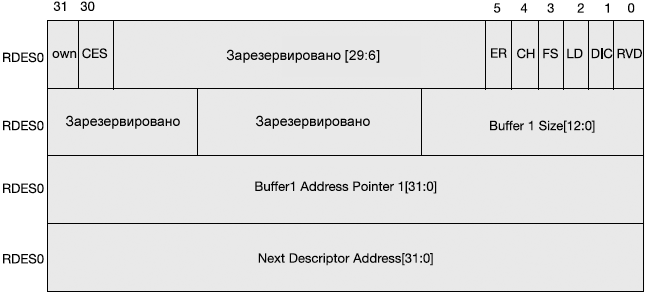

ąöąĄčüą║čĆąĖą┐č鹊čĆčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąĪčéčĆčāą║čéčāčĆą░ čüą▓čÅąĘą░ąĮąĮčŗčģ čüą┐ąĖčüą║ąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. ąÆ čéą░ą▒ą╗ąĖčåą░čģ ąŠčé 43 ą┤ąŠ 48 ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą╗ąĄą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ 菹╗ąĄą╝ąĄąĮčéą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░.

ąĀąĖčü. 49: Transmit Descriptor.

ąóą░ą▒ą╗ąĖčåą░ 43. Transmit Descriptor 0 (TDES0).

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31 |

OWN |

0: ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čŹčéąĖą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝ ą▓ą╗ą░ą┤ąĄąĄčé Host.

1: ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čŹčéąĖą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝ ą▓ą╗ą░ą┤ąĄąĄčé DMA. DMAC ąŠčćąĖčüčéąĖčé čŹč鹊čé ą▒ąĖčé, ą╗ąĖą▒ąŠ ą║ąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłąĖčé ą┐ąĄčĆąĄą┤ą░čćčā čäčĆąĄą╣ą╝ą░, ą╗ąĖą▒ąŠ ą║ąŠą│ą┤ą░ ą┐čāčüčéčŗąĄ ą▒čāč乥čĆčŗ, ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗąĄ ą┤ą╗čÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░. |

| 30 |

IC |

Interrupt on Completion. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ (Transmit Interrupt, Register 5[0]) ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ ą┐ąĄčĆąĄą┤ą░ąĮ č鹥ą║čāčēąĖą╣ čäčĆąĄą╣ą╝. ąŁč鹊čé ą▒ąĖčé ą┤ąŠčüč鹊ą▓ąĄčĆąĄąĮ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čüąĄą│ą╝ąĄąĮčéą░ (TDES0[29]). |

| 29 |

LS |

Last Segment. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▒čāč乥čĆ čüąŠą┤ąĄčƹȹĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ čüąĄą│ą╝ąĄąĮčé čäčĆąĄą╣ą╝ą░. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┐ąŠą╗ąĄ TBS1 ąĖą╗ąĖ TBS2 ą▓ TDES1 ą┤ąŠą╗ąČąĮąŠ ąĖą╝ąĄčéčī ąĮąĄąĮčāą╗ąĄą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ. |

| 28 |

FS |

First Segment. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▒čāč乥čĆ čüąŠą┤ąĄčƹȹĖčé ą┐ąĄčĆą▓čŗą╣ čüąĄą│ą╝ąĄąĮčé čäčĆąĄą╣ą╝ą░. |

| 27 |

DC |

Disable CRC. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, MAC ąĮąĄ ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé ą║ąŠąĮčéčĆąŠą╗čīąĮčāčÄ čüčāą╝ą╝čā (CRC) ą▓ ą║ąŠąĮąĄčå ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čäčĆąĄą╣ą╝ą░. ąŁč鹊 ą┤ąŠą┐čāčüčéąĖą╝ąŠ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ ą┐ąĄčĆą▓ąŠą│ąŠ čüąĄą│ą╝ąĄąĮčéą░ FS (TDES0[28]). |

| 26 |

DP |

Disable Pad.

0: MAC ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┤ąŠą┐ąŠą╗ąĮčÅąĄčé ą┐čāčüčéčŗą╝ąĖ ą▒ą░ą╣čéą░ą╝ąĖ čäčĆąĄą╣ą╝, ą║ąŠč鹊čĆčŗą╣ ą║ąŠčĆąŠč湥 64 ą▒ą░ą╣čé, ąĖ ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé CRC ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčéą░ DC (TDES0[27]). ąŁč鹊 ą┤ąŠą┐čāčüčéąĖą╝ąŠ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ ą┐ąĄčĆą▓ąŠą│ąŠ čüąĄą│ą╝ąĄąĮčéą░ FS (TDES0[28]).

1: MAC ąĮąĄ ą┤ąŠą┐ąŠą╗ąĮčÅąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čäčĆąĄą╣ą╝, ą║ąŠč鹊čĆčŗą╣ ą║ąŠčĆąŠč湥 64 bytes. |

| 25 |

TTSE |

Transmit Timestamp Enable.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé čĆą░ąĘčĆąĄčłą░ąĄčé ą░ą┐ą┐ą░čĆą░čéąĮčāčÄ ą╝ąĄčéą║čā ą▓čĆąĄą╝ąĄąĮąĖ IEEE1588 ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čäčĆąĄą╣ą╝ą░, ąĮą░ ą║ąŠč鹊čĆčŗą╣ čüčüčŗą╗ą░ąĄčéčüčÅ čŹč鹊čé ą┤ąĄčüą║čĆąĖą┐č鹊čĆ. ąŁč鹊 ą┐ąŠą╗ąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ ą┐ąĄčĆą▓ąŠą│ąŠ čüąĄą│ą╝ąĄąĮčéą░ FS (TDES0[28]). |

| 24 |

CRCR |

CRC Replacement Control.

ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, MAC ąĘą░ą╝ąĄąĮąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ 4 ą▒ą░ą╣čéą░ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ą┐ą░ą║ąĄčéą░ ąĮą░ ą┐ąĄčĆąĄčüčćąĖčéą░ąĮąĮčāčÄ CRC. ąźąŠčüčé ą┤ąŠą╗ąČąĄąĮ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ą▒ą░ą╣čéčŗ CRC ą┐čĆąĖčüčāčéčüčéą▓čāčÄčé ą▓ąŠ čäčĆąĄą╣ą╝ąĄ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą╝ ąĖąĘ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŁč鹊čé ą▒ąĖčé ą┤ąŠą┐čāčüčéąĖą╝ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ ą┐ąĄčĆą▓ąŠą│ąŠ čüąĄą│ą╝ąĄąĮčéą░ FS (TDES0[28]). ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ąĘą░ą╝ąĄąĮą░ CRC ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą▒ąĖčé TDES0[27] čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1. |

| 23:22 |

CIC |

Checksum Insertion Control.

ąŁčéąĖ ą▒ąĖčéčŗ čāą┐čĆą░ą▓ą╗čÅčÄčé ą▓čŗčćąĖčüą╗ąĄąĮąĖąĄą╝ ąĖ ą▓čüčéą░ą▓ą║ąŠą╣ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ (CRC). ąĪą╗ąĄą┤čāčÄčēąĖą╣ čüą┐ąĖčüąŠą║ ąŠą┐ąĖčüčŗą▓ą░ąĄčé ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ čŹčéąĖčģ ą▒ąĖčé:

00: ą▓čüčéą░ą▓ą║ą░ CRC ąĘą░ą┐čĆąĄčēąĄąĮą░.

01: čĆą░ąĘčĆąĄčłąĄąĮąŠ ą▓čŗčćąĖčüą╗ąĄąĮąĖąĄ ąĖ ą▓čüčéą░ą▓ą║ą░ CRC č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ IP.

10: čĆą░ąĘčĆąĄčłąĄąĮčŗ ą▓čŗčćąĖčüą╗ąĄąĮąĖąĄ ąĖ ą▓čüčéą░ą▓ą║ą░ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ IP ąĖ ą┐ąŠą╗ąĄąĘąĮąŠą╣ ąĮą░ą│čĆčāąĘą║ąĖ, ąŠą┤ąĮą░ą║ąŠ pseudo-header checksum ą░ą┐ą┐ą░čĆą░čéąĮąŠ ąĮąĄ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ.

11: čĆą░ąĘčĆąĄčłąĄąĮčŗ ą▓čŗčćąĖčüą╗ąĄąĮąĖąĄ ąĖ ą▓čüčéą░ą▓ą║ą░ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ IP ąĖ ą┐ąŠą╗ąĄąĘąĮąŠą╣ ąĮą░ą│čĆčāąĘą║ąĖ, ąĖ pseudo-header checksum ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ.

ąŁč鹊 ą┐ąŠą╗ąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ ą┐ąĄčĆą▓ąŠą│ąŠ čüąĄą│ą╝ąĄąĮčéą░ FS (TDES0[28]) . |

| 21 |

TER |

Transmit End of Ring.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čüą┐ąĖčüąŠą║ ą┤ąŠčüčéąĖą│ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░. DMA ą▓ąĄčĆąĮąĄčéčüčÅ ą║ ą▒ą░ąĘąŠą▓ąŠą╝čā ą░ą┤čĆąĄčüčā čüą┐ąĖčüą║ą░, čüąŠąĘą┤ą░ą▓ą░čÅ ą║ąŠą╗čīčåąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ (Descriptor Ring). |

| 20 |

TCH |

Second Address Chained.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓č鹊čĆąŠą╣ ą░ą┤čĆąĄčü ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąĄ čŹč鹊 ą░ą┤čĆąĄčü čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ (Next Descriptor Address), ą░ ąĮąĄ ą░ą┤čĆąĄčü ą▓č鹊čĆąŠą│ąŠ ą▒čāč乥čĆą░. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ TCH (TDES0[20]), ą┐ąŠą╗ąĄ TBS2 (TDES1[28:16]) ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ. TER (TDES0[21]) ąĖą╝ąĄąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé ąĮą░ą┤ TCH (TDES0[20]). ąŁč鹊čé ą▒ąĖčé ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1. |

| 19:18 |

VLIC |

VLAN Insertion Control.

ąÜąŠą│ą┤ą░ čŹč鹊 ą┐ąŠą╗ąĄ ąĮąĄąĮčāą╗ąĄą▓ąŠąĄ, ąŠąĮąŠ ą┐ąŠą▒čāąČą┤ą░čÄčé MAC ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą▓čüčéą░ą▓ą║čā č鹥ą│ą░/ą╝ąĄčéą║ąĖ VLAN (tagging) ąĖą╗ąĖ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąĖąĘą▓ą╗ąĄč湥ąĮąĖąĄ č鹥ą│ą░ VLAN (untagging) ą┐ąĄčĆąĄą┤ ą┐ąĄčĆąĄą┤ą░č湥ą╣ čäčĆąĄą╣ą╝ą░. ąĢčüą╗ąĖ čäčĆąĄą╣ą╝ ą▒čŗą╗ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮ ą╝ąĄčéą║ą░ą╝ąĖ VLAN, č鹊 MAC ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄčüčćąĖčéą░ąĄčé ąĖ ąĘą░ą╝ąĄąĮąĖčé ą▒ą░ą╣čéčŗ CRC. ąĪą╗ąĄą┤čāčÄčēąĖą╣ čüą┐ąĖčüąŠą║ ąŠą┐ąĖčüčŗą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ čŹčéąĖčģ ą▒ąĖčé:

00: ąĮąĄ ą┤ąŠą▒ą░ą▓ą╗čÅčéčī č鹥ą│ VLAN.

01: čāą┤ą░ą╗ąĖčéčī č鹥ą│ VLAN ąĖąĘ čäčĆąĄą╣ą╝ąŠą▓ ą┐ąĄčĆąĄą┤ ą┐ąĄčĆąĄą┤ą░č湥ą╣. ąŁčéą░ ąŠą┐čåąĖčÅ ą┤ąŠą╗ąČąĮą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ čü čäčĆąĄą╣ą╝ą░ą╝ąĖ VLAN.

10: ą▓čüčéą░ą▓ą║ą░ č鹥ą│ą░ VLAN čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą▓ čĆąĄą│ąĖčüčéčĆ VLAN Tag Inclusion or Replacement.

11: ąĘą░ą╝ąĄąĮą░ č鹥ą│ą░ VLAN ą▓ąŠ čäčĆąĄą╣ą╝ą░čģ ąĮą░ ąĘąĮą░č湥ąĮąĖąĄ č鹥ą│ą░, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą▓ čĆąĄą│ąĖčüčéčĆ VLAN Tag Inclusion or Replacement. ąŁčéą░ ąŠą┐čåąĖčÅ ą┤ąŠą╗ąČąĮą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ čü čäčĆąĄą╣ą╝ą░ą╝ąĖ VLAN. |

| 17 |

TTSS |

Transmit Timestamp Status.

ąŁč鹊 ą┐ąŠą╗ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ ą▒ąĖčéą░ čüčéą░čéčāčüą░, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī, čćč鹊 ą╝ąĄčéą║ą░ ą▓čĆąĄą╝ąĄąĮąĖ ą▒čŗą╗ą░ ąĘą░čģą▓ą░č湥ąĮą░ ą┤ą╗čÅ ąŠą┐ąĖčüčŗą▓ą░ąĄą╝ąŠą│ąŠ čäčĆąĄą╣ą╝ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, TDES2 ąĖ TDES3 čüąŠą┤ąĄčƹȹ░čé ą╝ąĄčéą║čā ą▓čĆąĄą╝ąĄąĮąĖ, ąĘą░čģą▓ą░č湥ąĮąĮčāčÄ ą┤ą╗čÅ čäčĆąĄą╣ą╝ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŁč鹊 ą┐ąŠą╗ąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čüąĄą│ą╝ąĄąĮčéą░ LS (TDES0[29]). |

| 16 |

IHE |

IP Header Error.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ MAC ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗ ąŠčłąĖą▒ą║čā ą┤ą░čéą░ą│čĆą░ą╝ą╝čŗ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ IP. ą¤ąĄčĆąĄą┤ą░čéčćąĖą║ ą┐čĆąŠą▓ąĄčĆčÅąĄčé ą┤ą╗ąĖąĮčā ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ ą▓ ą┐ą░ą║ąĄč鹥 IPv4 ąĮą░ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ąĘą░ą│ąŠą╗ąŠą▓ą║ą░, ą┐ąŠą╗čāč湥ąĮąĮąŠąĄ ąŠčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ąĖ ą▓čŗą┤ą░ąĄčé čüčéą░čéčāčü ąŠčłąĖą▒ą║ąĖ, ąĄčüą╗ąĖ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ąĮąĄčüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ. ąöą╗čÅ čäčĆąĄą╣ą╝ąŠą▓ IPv6 ąŠą▒ ąŠčłąĖą▒ą║ąĄ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ čüąŠąŠą▒čēą░ąĄčéčüčÅ, ąĄčüą╗ąĖ ąŠčüąĮąŠą▓ąĮą░čÅ ą┤ą╗ąĖąĮą░ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ ąĮąĄ čĆą░ą▓ąĮą░ 40 ą▒ą░ą╣čéą░ą╝. ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠą╗čÅ Ethernet Length/Type ą┤ą╗čÅ čäčĆąĄą╣ą╝ą░ IPv4 ąĖą╗ąĖ IPv6 ą┤ąŠą╗ąČąĮąŠ čüąŠą▓ą┐ą░ą┤ą░čéčī čü ą▓ąĄčĆčüąĖąĄą╣ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ IP, ą┐čĆąĖąĮčÅč鹊ą╣ čü ą┐ą░ą║ąĄč鹊ą╝. ąöą╗čÅ čäčĆąĄą╣ą╝ąŠą▓ IPv4 ą▒čāą┤ąĄčé čéą░ą║ąČąĄ ą┐ąŠą║ą░ąĘą░ąĮ čüčéą░čéčāčü ąŠčłąĖą▒ą║ąĖ, ąĄčüą╗ąĖ ą┐ąŠą╗ąĄ ą┤ą╗ąĖąĮčŗ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ ą╝ąĄąĮčīčłąĄ 0x5. |

| 15 |

ES |

Error Summary.

ąŁč鹊čé ą▒ąĖčé ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čģąŠčéčÅ ą▒čŗ ąŠą┤ąĖąĮ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ ą▒ąĖčé ąŠčłąĖą▒ą║ąĖ:

TDES0[14]: Jabber Timeout

TDES0[13]: Frame Flush

TDES0[11]: Loss of Carrier

TDES0[10]: No Carrier

TDES0[9]: Late Collision

TDES0[8]: Excessive Collision

TDES0[2]: Excessive Deferral

TDES0[1]: Underflow Error

TDES0[16]: IP Header Error

TDES0[12]: IP Payload Error |

| 14 |

JT |

Jabber Timeout.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 MAC ąŠą▒ąĮą░čĆčāąČąĖą╗ jabber timeout. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé EMACJABBER čĆąĄą│ąĖčüčéčĆą░ EMACCONFIG_REG. |

| 13 |

FF |

Frame Flushed.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 DMA ąĖą╗ąĖ MTL čüą▒čĆąŠčüąĖą╗ čäčĆąĄą╣ą╝ ąĖąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 CPU ą▓čŗą┤ą░ą╗ ą║ąŠą╝ą░ąĮą┤čā Flush. |

| 12 |

IPE |

IP Payload Error.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ MAC ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗ ąŠčłąĖą▒ą║čā ą▓ ą┐ąŠą╗ąĄąĘąĮąŠą╣ ąĮą░ą│čĆčāąĘą║ąĄ IP-ą┤ą░čéą░ą│čĆą░ą╝ą╝čŗ ą┐ą░ą║ąĄčéą░ TCP, UDP ąĖą╗ąĖ ICMP. ą¤ąĄčĆąĄą┤ą░čéčćąĖą║ ą┐čĆąŠą▓ąĄčĆčÅąĄčé ą┤ą╗ąĖąĮčā ą┐ąŠą╗ąĄąĘąĮąŠą╣ ąĮą░ą│čĆčāąĘą║ąĖ, ą┐čĆąĖąĮčÅč鹊ą╣ ą▓ ąĘą░ą│ąŠą╗ąŠą▓ą║ąĄ IPv4 ąĖą╗ąĖ IPv6 ąĮą░ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ čü čĆąĄą░ą╗čīąĮčŗą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ ą▒ą░ą╣čé ą┐ą░ą║ąĄčéą░ TCP, UDP ąĖą╗ąĖ ICMP, ą┐ąŠą╗čāč湥ąĮąĮčŗą╝ ąŠčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ąĖ ą▓čŗą┤ą░ąĄčé ąŠčłąĖą▒ą║čā, ąĄčüą╗ąĖ ąŠą▒ąĮą░čĆčāąČąĄąĮąŠ ąĮąĄčüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ. |

| 11 |

LOC |

Loss of Carrier.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐čĆąŠąĖąĘąŠčłą╗ą░ ą┐ąŠč鹥čĆčÅ ąĮąĄčüčāčēąĄą╣ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čäčĆąĄą╣ą╝ą░ (čé. ąĄ. čüąĖą│ąĮą░ą╗ MII_CRS ą▒čŗą╗ ąĮąĄą░ą║čéąĖą▓ąĄąĮ ą▓ ą▓čĆąĄą╝čÅ ąŠą┤ąĮąŠą│ąŠ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čäčĆąĄą╣ą╝ą░). ąŁč鹊 ą┤ąŠą┐čāčüčéąĖą╝ąŠ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čäčĆąĄą╣ą╝ąŠą▓, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ą▒ąĄąĘ ą║ąŠą╗ą╗ąĖąĘąĖąĖ, ą║ąŠą│ą┤ą░ MAC čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ half-duplex. |

| 10 |

NC |

No Carrier.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čüąĖą│ąĮą░ą╗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĮąĄčüčāčēąĄą╣ Carrier Sense ąŠčé PHY ąĮąĄ ą▒čŗą╗ ą▓čŗčüčéą░ą▓ą╗ąĄąĮ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. |

| 9 |

LC |

Late Collision.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐ąĄčĆąĄą┤ą░čćą░ čäčĆąĄą╣ą╝ą░ ą▒čŗą╗ą░ ąŠą▒ąŠčĆą▓ą░ąĮą░ ąĖąĘ-ąĘą░ ą║ąŠą╗ą╗ąĖąĘąĖąĖ ą┐ąŠčüą╗ąĄ ąŠą║ąĮą░ ą║ąŠą╗ą╗ąĖąĘąĖąĖ (64 ą▒ą░ą╣čé, ą▓ą║ą╗čÄčćą░čÅ Preamble ą▓ čĆąĄąČąĖą╝ąĄ MII, ąĖ 512 ą▒ą░ą╣čé ą▓ą║ą╗čÄčćą░čÅ Preamble ąĖ Carrier Extension). ąŁč鹊čé ą▒ąĖčé ąĮąĄą┤ąŠą┐čāčüčéąĖą╝, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé Underflow Error. |

| 8 |

EC |

Excessive Collision.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐ąĄčĆąĄą┤ą░čćą░ ą▒čŗą╗ą░ ąŠą▒ąŠčĆą▓ą░ąĮą░ ą┐ąŠčüą╗ąĄ 16 čüą╗ąĄą┤čāčÄčēąĖčģ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ą║ąŠą╗ą╗ąĖąĘąĖą╣ ą┐čĆąĖ ą┐ąŠą┐čŗčéą║ąĄ ą┐ąĄčĆąĄą┤ą░čéčī č鹥ą║čāčēąĖą╣ čäčĆąĄą╣ą╝. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé EMACRETRY ą▓ čĆąĄą│ąĖčüčéčĆąĄ EMACCONFIG_REG, č鹊 čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆą▓ąŠą╣ ą║ąŠą╗ą╗ąĖąĘąĖąĖ, ąĖ ą▒čāą┤ąĄčé ąŠą▒ąŠčĆą▓ą░ąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░ čäčĆąĄą╣ą╝ą░. |

| 7 |

VF |

VLAN Frame.

ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čā ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čäčĆąĄą╣ą╝ą░ čéąĖą┐ VLAN. |

| 6:3 |

Ctrl/status |

ąŁčéąĖ ą▒ąĖčéčŗ čüčéą░čéčāčüą░ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą║ąŠą╗ą╗ąĖąĘąĖą╣, ą║ąŠč鹊čĆąŠąĄ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ čäčĆąĄą╣ą╝ ą▒čŗą╗ ą┐ąĄčĆąĄą┤ą░ąĮ. ąŁč鹊 ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĮąĄą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé EC (TDES0[8]). ą»ą┤čĆąŠ ąŠą▒ąĮąŠą▓ąĖčé čŹč鹊 ą┐ąŠą╗ąĄ čüčéą░čéčāčüą░ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ half-duplex. |

| 2 |

ED |

Excessive Deferral.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐ąĄčĆąĄą┤ą░čćą░ ą▒čŗą╗ą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░ ąĖąĘ-ąĘą░ excessive deferral ą▒ąŠą╗čīčłąĄ č湥ą╝ 24288 ą▒ąĖčé (ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮ Jumbo Frame), ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé EMACDEFERRAL čĆąĄą│ąĖčüčéčĆą░ EMACCONFIG_REG. |

| 1 |

UF |

Underflow Error.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 MAC ąŠą▒ąŠčĆą▓ą░ą╗ čäčĆąĄą╣ą╝ ąĖąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 čüą╗ąĖčłą║ąŠą╝ ą┐ąŠąĘą┤ąĮąŠ ą┐ąŠčüčéčāą┐ąĖą╗ąĖ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą┐ą░ą╝čÅčéąĖ čģąŠčüčéą░ (ąĮąĄą┤ąŠą│čĆčāąĘą║ą░). Underflow Error ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 DMA ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ čäčĆąĄą╣ą╝ą░ ą▓čüčéčĆąĄčéąĖą╗čüčÅ čü ą┐čāčüčéčŗą╝ ą▒čāč乥čĆąŠą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą¤čĆąŠčåąĄčüčü ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓čģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (Suspended state), ąĖ čāčüčéą░ąĮąŠą▓čÅčéčüčÅ ąŠą▒ą░ ą▒ąĖčéą░ Bit[5] ą▓ Transmit Underflow Register (Status Register) ąĖ Bit[0] ą▓ Transmit Interrupt Register (Status Register). |

| 0 |

DB |

Deferred Bit.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 MAC ąŠčéą╗ąŠąČąĖą╗ ą┐ąĄčĆąĄą┤ą░čćčā ąĖąĘ-ąĘą░ ąĮą░ą╗ąĖčćąĖčÅ ąĮąĄčüčāčēąĄą╣. ąŁč鹊čé ą▒ąĖčé ą┤ąŠą┐čāčüčéąĖą╝ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ half-duplex. |

ąóą░ą▒ą╗ąĖčåą░ 44. Transmit Descriptor 1 (TDES1).

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31:29 |

SAIC |

SA Insertion Control.

ąŁčéąĖ ą▒ąĖčéčŗ ą┐ąŠą▒čāąČą┤ą░čÄčé MAC ą┤ąŠą▒ą░ą▓ąĖčéčī ąĖą╗ąĖ ąĘą░ą╝ąĄąĮąĖčéčī ą┐ąŠą╗ąĄ Source Address (ą░ą┤čĆąĄčü ąĖčüč鹊čćąĮąĖą║ą░) ą▓ąŠ čäčĆąĄą╣ą╝ąĄ Ethernet ąĘąĮą░č湥ąĮąĖąĄą╝, ą║ąŠč鹊čĆąŠąĄ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ MAC Address 0. ąĢčüą╗ąĖ ą┐ąŠą╗ąĄ Source Address ą▓ąŠ čäčĆąĄą╣ą╝ąĄ ąĖąĘą╝ąĄąĮąĄąĮąŠ, č鹊 MAC ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄčüčćąĖčéą░ąĄčé ąĖ ąĘą░ą╝ąĄąĮąĖčé ą▒ą░ą╣čéčŗ CRC. ąæąĖčé [31] čāą║ą░ąĘčŗą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ MAC Address Register value (1 ąĖą╗ąĖ 0), ą║ąŠč鹊čĆčŗą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čüčéą░ą▓ą║ąĖ ąĖą╗ąĖ ąĘą░ą╝ąĄąĮčŗ Source Address. ąĪą╗ąĄą┤čāčÄčēąĖą╣ čüą┐ąĖčüąŠą║ ąŠą┐ąĖčüčŗą▓ą░ąĄčé čüą╝čŗčüą╗ ąĘąĮą░č湥ąĮąĖą╣ ą▒ąĖčé [30:29]:

00: ąĮąĄ ą┤ąŠą▒ą░ą▓ą╗čÅčéčī ą░ą┤čĆąĄčü ąĖčüč鹊čćąĮąĖą║ą░.

01: ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ąĖą╗ąĖ ą┤ąŠą▒ą░ą▓ąĖčéčī ą░ą┤čĆąĄčü ąĖčüč鹊čćąĮąĖą║ą░. ąöą╗čÅ ąĮą░ą┤ąĄąČąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī čäčĆąĄą╣ą╝čŗ ą▒ąĄąĘ ą░ą┤čĆąĄčüą░ ąĖčüč鹊čćąĮąĖą║ą░.

10: ąĘą░ą╝ąĄąĮą░ ą░ą┤čĆąĄčüą░ ąĖčüč鹊čćąĮąĖą║ą░. ąöą╗čÅ ąĮą░ą┤ąĄąČąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī čäčĆąĄą╣ą╝čŗ čü ą░ą┤čĆąĄčüąŠą╝ ąĖčüč鹊čćąĮąĖą║ą░.

11: ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ.

ąŁčéąĖ ą▒ąĖčéčŗ ą┤ąŠą┐čāčüčéąĖą╝čŗ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą┐ąĄčĆą▓ąŠą│ąŠ čüąĄą│ą╝ąĄąĮčéą░ FS (TDES0[28]). |

| 28:16 |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15:13 |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 12:0 |

TBS1 |

Transmit Buffer 1 Size.

ąŁčéąĖ ą▒ąĖčéčŗ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒ą░ą╣čéą░čģ. ąĢčüą╗ąĖ čŹč鹊 ą┐ąŠą╗ąĄ čĆą░ą▓ąĮąŠ 0, č鹊 DMA ąĖą│ąĮąŠčĆąĖčĆčāąĄčé čŹč鹊čé ą▒čāč乥čĆ, ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčé Buffer 2 ąĖą╗ąĖ čüą╗ąĄą┤čāčÄčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ. |

ąóą░ą▒ą╗ąĖčåą░ 45. Transmit Descriptor 2 (TDES2).

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31:0 |

Buffer 1 Address Pointer |

ążąĖąĘąĖč湥čüą║ąĖą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ ą┤ą░ąĮąĮčŗčģ 1. |

ąóą░ą▒ą╗ąĖčåą░ 46. Transmit Descriptor 3 (TDES3).

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31:0 |

Next Descriptor Address |

ąŻą║ą░ąĘą░č鹥ą╗čī ąĮą░ čäąĖąĘąĖč湥čüą║čāčÄ ą┐ą░ą╝čÅčéčī, ą│ą┤ąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ. |

ąóą░ą▒ą╗ąĖčåą░ 47. Transmit Descriptor 6 (TDES6).

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31:0 |

TTSL |

Transmit Frame Timestamp Low.

ąŁč鹊 ą┐ąŠą╗ąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ DMA ą╝ą╗ą░ą┤čłąĖą╝ąĖ ąĘąĮą░čćą░čēąĖą╝ąĖ 32 ą▒ąĖčéą░ą╝ąĖ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ, ąĘą░čģą▓ą░č湥ąĮąĮąŠą╣ ą┤ą╗čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čäčĆąĄą╣ą╝ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŁč鹊 ą┐ąŠą╗ąĄ ąĖą╝ąĄąĄčé ą╝ąĄčéą║čā ą▓čĆąĄą╝ąĄąĮąĖ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čüąĄą│ą╝ąĄąĮčéą░ LS, ąĖ čéą░ą║ąČąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé čüčéą░čéčāčüą░ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ (TTSS). |

ąóą░ą▒ą╗ąĖčåą░ 48. Transmit Descriptor 7 (TDES7).

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31:0 |

TTSH |

Transmit Frame Timestamp High.

ąŁč鹊 ą┐ąŠą╗ąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ DMA čüčéą░čĆčłąĖą╝ąĖ ąĘąĮą░čćą░čēąĖą╝ąĖ 32 ą▒ąĖčéą░ą╝ąĖ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ, ąĘą░čģą▓ą░č湥ąĮąĮąŠą╣ ą┤ą╗čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čäčĆąĄą╣ą╝ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŁč鹊 ą┐ąŠą╗ąĄ ąĖą╝ąĄąĄčé ą╝ąĄčéą║čā ą▓čĆąĄą╝ąĄąĮąĖ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čüąĄą│ą╝ąĄąĮčéą░ LS, ąĖ čéą░ą║ąČąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé čüčéą░čéčāčüą░ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ (TTSS). |

ąöąĄčüą║čĆąĖą┐č鹊čĆčŗ ą┐čĆąĖąĄą╝ą░. ąĪčéčĆčāą║čéčāčĆą░ čüą▓čÅąĘą░ąĮąĮčŗčģ čüą┐ąĖčüą║ąŠą▓ ą┐čĆąĖąĄą╝ą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 50. ąóą░ą▒ą╗ąĖčåčŗ ąŠčé 49 ą┤ąŠ 55 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą╗ąĄą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ 菹╗ąĄą╝ąĄąĮčéą░ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░.

ąĀąĖčü. 50. Receive Descriptor.

ąóą░ą▒ą╗ąĖčåą░ 49. Receive Descriptor 0 (RDES0).

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31 |

OWN |

0: ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čŹčéąĖą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝ ą▓ą╗ą░ą┤ąĄąĄčé Host.

1: ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čŹčéąĖą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝ ą▓ą╗ą░ą┤ąĄąĄčé DMA DWC_gmac. DMA ąŠčćąĖčüčéąĖčé čŹč鹊čé ą▒ąĖčé, ą║ąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłąĖčé ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ą▒čāą┤čāčé ąĘą░ą┐ąŠą╗ąĮąĄąĮčŗ ą▒čāč乥čĆčŗ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü čŹčéąĖą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝. |

| 30 |

AFM |

Destination Address Filter Fail.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüą▒ąŠą╣ čäčĆąĄą╣ą╝ą░ ą▓ DA Filter MAC. |

| 29:16 |

FL |

Frame Length.

ąŁčéąĖ ą▒ąĖčéčŗ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ą┤ą╗ąĖąĮčā ą▓ ą▒ą░ą╣čéą░čģ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čäčĆąĄą╣ą╝ą░, ą║ąŠč鹊čĆčŗą╣ ą▒čŗą╗ ą┐ąĄčĆąĄą┤ą░ąĮ ą▓ ą┐ą░ą╝čÅčéčī čģąŠčüčéą░. ąŁčéą░ ą┐ąŠą╗ąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ LS (RDES0[8]), ąĖ čüą▒čĆąŠčłąĄąĮ ą╗ąĖą▒ąŠ ą▒ąĖčé ąŠčłąĖą▒ą║ąĖ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ DE (RDES0[14]), ą╗ąĖą▒ąŠ ą▒ąĖčé ąŠčłąĖą▒ą║ąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ OE (RDES0[11]). ąöą╗ąĖąĮą░ čäčĆąĄą╣ą╝ą░ čéą░ą║ąČąĄ ą▓ą║ą╗čÄčćą░ąĄčé 2 ą▒ą░ą╣čéą░, ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĮčŗčģ ą║ čäčĆąĄą╣ą╝čā Ethernet, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą▓čŗčćąĖčüą╗ąĄąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ IP (Type 1), ąĖ ą┐čĆąĖąĮčÅčéčŗą╣ čäčĆąĄą╣ą╝ ąĮąĄ čÅą▓ą╗čÅąĄčéčüčÅ čäčĆąĄą╣ą╝ąŠą╝ MAC control. |

| 15 |

ES |

Error Summary.

ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ąĄčüą╗ąĖ ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čģąŠčéčÅ ą▒čŗ ąŠą┤ąĖąĮ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ ą▒ąĖčé:

RDES0[1]: CRC Error

RDES0[3]: Receive Error

RDES0[4]: Watchdog Timeout

RDES0[6]: Late Collision

RDES0[7]: Giant Frame

RDES4[4:3]: IP Header or Payload Error

RDES0[11]: Overflow Error

RDES0[14]: Descriptor Error

ąŁč鹊 ą┐ąŠą╗ąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ LS (RDES0[8]). |

| 14 |

DE |

Descriptor Error.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĄ čāčüąĄč湥ąĮąĖąĄ čäčĆąĄą╣ą╝ą░, ą▓čŗąĘą▓ą░ąĮąĮąŠąĄ čäčĆąĄą╣ą╝ąŠą╝, ą║ąŠč鹊čĆčŗą╣ ąĮąĄ ą┐ąŠą╝ąĄčēą░ąĄčéčüčÅ ą▓ ą▒čāč乥čĆčŗ č鹥ą║čāčēąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░, ąĖ DMA ąĮąĄ ą▓ą╗ą░ą┤ąĄąĄčé čüą╗ąĄą┤čāčÄčēąĖą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝. ąŁčéą░ ą┐ąŠą╗ąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠ, č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ LS (RDES0[8]). |

| 13 |

SAF |

Source Address Filter Fail.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓ ą┐ąŠą╗ąĄ SA čäčĆąĄą╣ą╝ą░ ą┐čĆąŠąĖąĘąŠčłąĄą╗ čüą▒ąŠą╣ čäąĖą╗čīčéčĆą░ SA ą▓ MAC. |

| 12 |

LE |

Length Error.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čĆąĄą░ą╗čīąĮą░čÅ ą┤ą╗ąĖąĮą░ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čäčĆąĄą╣ą╝ą░ ąĮąĄ čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü ą┐ąŠą╗ąĄą╝ Length/Type. ąŁč鹊čé ą▒ąĖčé ą┤ąŠčüč鹊ą▓ąĄčĆąĄąĮ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čüą▒čĆąŠčłąĄąĮ ą▒ąĖčé čéąĖą┐ą░ čäčĆąĄą╣ą╝ą░ FT (RDES0[5]). |

| 11 |

OE |

Overflow Error.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐čĆąĖąĮčÅčéčŗą╣ čäčĆąĄą╣ą╝ ą▒čŗą╗ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮ ąĖąĘ-ąĘą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▒čāč乥čĆą░ ą▓ MTL. |

| 10 |

VLAN |

VLAN Tag.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čäčĆąĄą╣ą╝, ąĮą░ ą║ąŠč鹊čĆčŗą╣ čāą║ą░ąĘčŗą▓ą░ąĄčé čŹč鹊čé ą┤ąĄčüą║čĆąĖą┐č鹊čĆ, čÅą▓ą╗čÅąĄčéčüčÅ čäčĆąĄą╣ą╝ąŠą╝ VLAN, ą║ąŠč鹊čĆąŠą╝čā MAC ą┐čĆąĖčüą▓ąŠąĖą╗ ą╝ąĄčéą║čā VLAN (tag). ą¤čĆąĖčüą▓ąŠąĄąĮąĖąĄ ą╝ąĄčéą║ąĖ VLAN ąĘą░ą▓ąĖčüąĖčé ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┐čĆąŠą▓ąĄčĆą║ąĖ ą┐ąŠą╗ąĄą╣ VLAN ą┐čĆąĖąĮčÅč鹊ą│ąŠ čäčĆąĄą╣ą╝ą░ ąĮą░ ąŠčüąĮąŠą▓ąĄ ąĮą░čüčéčĆąŠąĄą║ VLAN Tag Register. |

| 9 |

FS |

First Descriptor.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čŹč鹊čé ą┤ąĄčüą║čĆąĖą┐č鹊čĆ čüąŠą┤ąĄčƹȹĖčé ą┐ąĄčĆą▓čŗą╣ ą▒čāč乥čĆ čäčĆąĄą╣ą╝ą░. ąĢčüą╗ąĖ čĆą░ąĘą╝ąĄčĆ ą┐ąĄčĆą▓ąŠą│ąŠ ą▒čāč乥čĆą░ čĆą░ą▓ąĄąĮ 0, ą▓č鹊čĆąŠą╣ ą▒čāč乥čĆ čüąŠą┤ąĄčƹȹĖčé ąĮą░čćą░ą╗ąŠ čäčĆąĄą╣ą╝ą░. ąĢčüą╗ąĖ čĆą░ąĘą╝ąĄčĆ ą▓č鹊čĆąŠą│ąŠ ą▒čāč乥čĆą░ čéą░ą║ąČąĄ 0, č鹊 čüą╗ąĄą┤čāčÄčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ čüąŠą┤ąĄčƹȹĖčé ąĮą░čćą░ą╗ąŠ čäčĆąĄą╣ą╝ą░. |

| 8 |

LS |

Last Descriptor.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▒čāč乥čĆčŗ, ąĮą░ ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čŹč鹊čé ą┤ąĄčüą║čĆąĖą┐č鹊čĆ, ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ ą▓ čŹč鹊ą╝ čäčĆąĄą╣ą╝ąĄ. |

| 7 |

Timestamp Available, IP Checksum Error (Type1) ąĖą╗ąĖ Giant Frame |

ąÜąŠą│ą┤ą░ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé čäčāąĮą║čåąĖčÅ Advanced Timestamp, ąĖ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čŹč鹊čé ą▒ąĖčé, čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ąĘą░čģą▓ą░čé ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┐ąĖčüą░ąĮ ą▓ čüą╗ąŠą▓ą░ 6 (RDES6) ąĖ 7 (RDES7) ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░. ąŁč鹊 ą┤ąŠą┐čāčüčéąĖą╝ąŠ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ LS (RDES0[8]).

ąÜąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮą░ IP Checksum Engine (Type 1), č鹊 čŹč鹊čé ą▒ąĖčé, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠą┤ąĮąŠ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ:

ŌĆó ąÜąŠąĮčéčĆąŠą╗čīąĮą░čÅ 16-ą▒ąĖčéąĮą░čÅ čüčāą╝ą╝ą░ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ IPv4, ą▓čŗčćąĖčüą╗ąĄąĮąĮą░čÅ čÅą┤čĆąŠą╝, ąĮąĄ čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü ą┐čĆąĖąĮčÅčéčŗą╝ąĖ ą▒ą░ą╣čéą░ą╝ąĖ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ.

ŌĆó ąöą╗čÅ čäčĆąĄą╣ą╝ąŠą▓ non-IPv4 ą┐čĆąŠą▓ąĄčĆą║ą░ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ ą┐čĆąŠą┐čāčēąĄąĮąŠ.

ąśąĮą░č湥, ą║ąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé Giant Frame Status. ążčĆąĄą╣ą╝čŗ Giant, ą║ąŠč鹊čĆčŗąĄ ą▒ąŠą╗čīčłąĄ 1518 ą▒ą░ą╣čé (ąĖą╗ąĖ 1522 ą▒ą░ą╣čé ą┤ą╗čÅ VLAN ąĖą╗ąĖ 2000 ą▒ą░ą╣čé, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé [27] MAC Configuration register), ąĮąŠčĆą╝ą░ą╗čīąĮčŗąĄ čäčĆąĄą╣ą╝čŗ ąĖ čäčĆąĄą╣ą╝čŗ ą▒ąŠą╗čīčłąĄ č湥ą╝ 9018 ą▒ą░ą╣čé (9022 ą▒ą░ą╣čé ą┤ą╗čÅ VLAN), ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮą░ ąŠą▒čĆą░ą▒ąŠčéą║ą░ Jumbo Frame. |

| 6 |

LC |

Late Collision.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐čĆąŠąĖąĘąŠčłą╗ą░ ą┐ąŠąĘą┤ąĮčÅčÅ ą║ąŠą╗ą╗ąĖąĘąĖčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĖąĄą╝ą░ čäčĆąĄą╣ą╝ą░ ą▓ čĆąĄąČąĖą╝ąĄ half-duplex. |

| 5 |

FT |

Frame Type.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐čĆąĖąĮčÅčéčŗą╣ čäčĆąĄą╣ą╝ ąĖą╝ąĄąĄčé čéąĖą┐ Ethernet (ą┐ąŠą╗ąĄ LT ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠ 1536). ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čüą▒čĆąŠčłąĄąĮ, čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐čĆąĖąĮčÅčéčŗą╣ čäčĆąĄą╣ą╝ IEEE 802.3. ąŁč鹊čé ą▒ąĖčé ąĮąĄą┤ąŠą┐čāčüčéąĖą╝ ą┤ą╗čÅ čāčĆąĄąĘą░ąĮąĮčŗčģ čäčĆąĄą╣ą╝ąŠą▓ (Runt frame), ą║ąŠč鹊čĆčŗąĄ ą╝ąĄąĮčīčłąĄ 14 ą▒ą░ą╣čé. |

| 4 |

RWT |

Receive Watchdog Timeout.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĖčüč鹥č湥ąĮąĖąĄ čéą░ą╣ą╝ą░čāčéą░ Receive Watchdog Timer ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĖąĄą╝ą░ č鹥ą║čāčēąĄą│ąŠ čäčĆąĄą╣ą╝ą░, ąĖ čŹč鹊čé čäčĆąĄą╣ą╝ ąŠą▒čĆąĄąĘą░ąĮ ą┐ąŠčüą╗ąĄ Watchdog Timeout. |

| 3 |

RE |

Receive Error.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓čŗčüčéą░ą▓ą╗ąĄąĮ čüąĖą│ąĮą░ą╗ MII_RXER, ą║ąŠą│ą┤ą░ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĖąĄą╝ą░ čäčĆąĄą╣ą╝ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ MII_RXDV. |

| 2 |

DE |

Dribble Bit Error.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐čĆąĖąĮčÅčéčŗą╣ čäčĆąĄą╣ą╝ ąĖą╝ąĄąĄčé ąĮąĄ čåąĄą╗ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé (ąĮąĄč湥čéąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĮąĖą▒ą▒ą╗ąŠą▓). ąŁč鹊čé ą▒ąĖčé ą┤ąŠą┐čāčüčéąĖą╝ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ MII. |

| 1 |

CE |

CRC Error.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąŠčłąĖą▒ą║ą░ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ ąĮą░ ą┐čĆąĖąĮčÅč鹊ą╝ čäčĆąĄą╣ą╝ąĄ. ąŁč鹊 ą┐ąŠą╗ąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ LS (RDES0[8]). |

| 0 |

Extended Status Available / Rx MAC Address |

ąÜąŠą│ą┤ą░ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą╗ąĖą▒ąŠ Advanced Timestamp ąĖą╗ąĖ IP Checksum Offload (Type 2), čŹč鹊čé ą▒ąĖčé, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┤ąŠčüčéčāą┐ąĮąŠčüčéčī čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ čüčéą░čéčāčüą░ ą▓ čüą╗ąŠą▓ąĄ 4 ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ (RDES4). ąŁč鹊 ą┤ąŠą┐čāčüčéąĖą╝ąŠ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ LS (RDES0[8]). ąŁč鹊čé ą▒ąĖčé ąĮąĄą┤ąŠą┐čāčüčéąĖą╝, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé 30.

ąÜąŠą│ą┤ą░ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé IP Checksum Offload (Type 2), čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ ą┐ąŠą┤čüąĖčüč鹥ą╝ą░ IP Checksum Offload ą┐čĆąŠą┐čāčüčéąĖą╗ą░ ąŠą▒čĆą░ą▒ąŠčéą║čā ą┐čĆąĖąĮčÅč鹊ą│ąŠ čäčĆąĄą╣ą╝ą░. ą¤čĆąŠą┐čāčüą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠ ą┐čĆąĖčćąĖąĮąĄ non-IP čäčĆąĄą╣ą╝ą░, ąĖą╗ąĖ IP čäčĆąĄą╣ą╝ą░ čü ą┐ąŠą╗ąĄąĘąĮąŠą╣ ąĮą░ą│čĆčāąĘą║ąŠą╣ non-TCP/UDP/ICMP.

ąÜąŠą│ą┤ą░ ąĮąĄ ą▓čŗą▒čĆą░ąĮą░ čäčāąĮą║čåąĖčÅ Advance Timestamp ąĖą╗ąĖ IPC Full Offload, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüčéą░čéčāčü Rx MAC Address. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ Rx MAC Address (ąŠčé 1 ą┤ąŠ 15) čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü ą┐ąŠą╗ąĄą╝ DA čäčĆąĄą╣ą╝ą░. ąÜąŠą│ą┤ą░ čüą▒čĆąŠčłąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ąĘąĮą░č湥ąĮąĖąĄ Rx MAC Address Register 0 čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü ą┐ąŠą╗ąĄą╝ DA. |

ąóą░ą▒ą╗ąĖčåą░ 50. Receive Descriptor 1 (RDES1).

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31 |

Ctrl |

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčé čāčüčéą░ąĮąŠą▓ą║čā ą▒ąĖčéą░ RI čĆąĄą│ąĖčüčéčĆą░ čüčéą░čéčāčüą░ (CSR5[6]) ą┤ą╗čÅ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čäčĆąĄą╣ą╝ą░, ą║ąŠč鹊čĆčŗą╣ ąĘą░ą║ą░ąĮčćąĖą▓ą░ąĄčéčüčÅ ą▓ ą▒čāč乥čĆąĄ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ čŹč鹊ą╝čā ą┤ąĄčüą║čĆąĖą┐č鹊čĆčā. ąŁč鹊, ą▓ čüą▓ąŠčÄ ąŠč湥čĆąĄą┤čī, ą▒ą╗ąŠą║ąĖčĆčāąĄčé čāčüčéą░ąĮąŠą▓ą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ Host ąĖąĘ-ąĘą░ RI ąĮą░ čŹč鹊ą╝ čäčĆąĄą╣ą╝ąĄ. |

| 30:29 |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 28:16 |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 15 |

RER |

Receive End of Ring.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čüą┐ąĖčüąŠą║ ą┤ąŠčüčéąĖą│ čüą▓ąŠąĄą│ąŠ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░. DMA ą▓ąĄčĆąĮąĄčéčüčÅ ą║ ą▒ą░ąĘąŠą▓ąŠą╝čā ą░ą┤čĆąĄčüčā čüą┐ąĖčüą║ą░, čüąŠąĘą┤ą░ą▓ą░čÅ ą║ąŠą╗čīčåąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ (Descriptor Ring). |

| 14 |

RCH |

Second Address Chained.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓č鹊čĆąŠą╣ ą░ą┤čĆąĄčü ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąĄ čÅą▓ą╗čÅąĄčéčüčÅ ą░ą┤čĆąĄčüąŠą╝ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ (Next Descriptor Address), ą░ ąĮąĄ ą░ą┤čĆąĄčü ą▓č鹊čĆąŠą│ąŠ ą▒čāč乥čĆą░. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĘąĮą░č湥ąĮąĖąĄ RBS2 (RDES1[28:16]) ąĮąĄ ąĖą╝ąĄąĄčé čüą╝čŗčüą╗ą░. RER (RDES1[15]) ąĖą╝ąĄąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé ą┐ąĄčĆąĄą┤ RCH (RDES1[14]). |

| 13 |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 12:0 |

RBS1 |

Receive Buffer 1 Size.

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé čĆą░ąĘą╝ąĄčĆ ą┐ąĄčĆą▓ąŠą│ąŠ ą▒čāč乥čĆą░ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒ą░ą╣čéą░čģ. ąĀą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ ą┤ąŠą╗ąČąĄąĮ ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗ąĖčéčīčüčÅ ąĮą░ 4, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ RDES2 (čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ Buffer 1) ąĮąĄ ą▓čŗčĆąŠą▓ąĮąĄąĮ ąĮą░ čłąĖčĆąĖąĮčā čłąĖąĮčŗ. ąÜąŠą│ą┤ą░ čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ ąĮąĄ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░čåąĄą╗ąŠ ąĮą░ 4, čĆąĄąĘčāą╗čīčéąĖčĆčāčÄčēąĄąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ. ąĢčüą╗ąĖ čŹč鹊 ą┐ąŠą╗ąĄ čĆą░ą▓ąĮąŠ 0, č鹊 DMA ąĖą│ąĮąŠčĆąĖčĆčāąĄčé čŹč鹊čé ą▒čāč乥čĆ, ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčé Buffer 2, ąĖą╗ąĖ čüą╗ąĄą┤čāčÄčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčéą░ RCH (RDES1[14]). |

ąóą░ą▒ą╗ąĖčåą░ 51. Receive Descriptor 2 (RDES2).

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31:0 |

Buffer 1 Address Pointer |

ążąĖąĘąĖč湥čüą║ąĖą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ ą┤ą░ąĮąĮčŗčģ 1. |

ąóą░ą▒ą╗ąĖčåą░ 52. Receive Descriptor 3 (RDES3).

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31:0 |

Next Descriptor Address |

ąŻą║ą░ąĘą░č鹥ą╗čī ąĮą░ čäąĖąĘąĖč湥čüą║čāčÄ ą┐ą░ą╝čÅčéčī, ą│ą┤ąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ. |

ąóą░ą▒ą╗ąĖčåą░ 53. Receive Descriptor 4 (RDES4).

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31:15 |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 14 |

Timestamp Dropped |

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▒čŗą╗ą░ ąĘą░čģą▓ą░č湥ąĮą░ ą╝ąĄčéą║ą░ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ čŹč鹊ą│ąŠ čäčĆąĄą╣ą╝ą░, ąĮąŠ ąŠąĮą░ ą▒čŗą╗ą░ ąŠčéą▒čĆąŠčłąĄąĮą░ ąĖąĘ-ąĘą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▓ MTL Rx FIFO. |

| 13 |

PTP Version |

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐čĆąĖąĮčÅč鹊ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ PTP ąĖą╝ąĄąĄčé č乊čĆą╝ą░čé IEEE 1588 version 2. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čüą▒čĆąŠčłąĄąĮ, č鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č乊čĆą╝ą░čé version 1. |

| 12 |

PTP Frame Type |

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čüąŠąŠą▒čēąĄąĮąĖąĄ PTP ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąŠ ąĮą░ą┐čĆčÅą╝čāčÄ č湥čĆąĄąĘ Ethernet. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čüą▒čĆąŠčłąĄąĮ, ąĖ čéąĖą┐ čüąŠąŠą▒čēąĄąĮąĖčÅ ąĮąĄąĮčāą╗ąĄą▓ąŠą╣, č鹊 čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čüąŠąŠą▒čēąĄąĮąĖąĄ PTP ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąŠ č湥čĆąĄąĘ UDP-IPv4 ąĖą╗ąĖ UDP-IPv6. ąśąĮč乊čĆą╝ą░čåąĖčÅ ąŠ č鹊ą╝, IPv4 ąĖą╗ąĖ IPv6, ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮą░ ąĖąĘ ą▒ąĖčé 6 ąĖ 7. |

| 11:8 |

Message Type |

ąŁčéąĖ ą▒ąĖčéčŗ ą║ąŠą┤ąĖčĆčāčÄčé čéąĖą┐ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ.

0000: ąĮąĄ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 čüąŠąŠą▒čēąĄąĮąĖąĄ PTP

0001: SYNC (ą▓čüąĄ čéąĖą┐čŗ čéą░ą║č鹊ą▓)

0010: Follow_Up (ą▓čüąĄ čéąĖą┐čŗ čéą░ą║č鹊ą▓)

0011: Delay_Req (ą▓čüąĄ čéąĖą┐čŗ čéą░ą║č鹊ą▓)

0100: Delay_Resp (ą▓čüąĄ čéąĖą┐čŗ čéą░ą║č鹊ą▓)

0101: Pdelay_Req (ą▓ ą┐čĆąŠąĘčĆą░čćąĮčŗčģ čéą░ą║čéą░čģ peer-to-peer)

0110: Pdelay_Resp (ą▓ ą┐čĆąŠąĘčĆą░čćąĮčŗčģ čéą░ą║čéą░čģ peer-to-peer)

0111: Pdelay_Resp_Follow_Up (ą▓ ą┐čĆąŠąĘčĆą░čćąĮčŗčģ čéą░ą║čéą░čģ peer-to-peer)

1000: Announce

1001: Management

1010: Signaling

1011-1110: ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

1111: ą┐ą░ą║ąĄčé PTP čü ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ čéąĖą┐ąŠą╝ čüąŠąŠą▒čēąĄąĮąĖčÅ |

| 7 |

IPv6 Packet Received |

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐čĆąĖąĮčÅčéčŗą╣ ą┐ą░ą║ąĄčé IPv6. ąŁč鹊čé ą▒ąĖčé ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé 10 (IPC) čĆąĄą│ąĖčüčéčĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ (MAC Configuration Register). |

| 6 |

IPv4 Packet Received |

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐čĆąĖąĮčÅčéčŗą╣ ą┐ą░ą║ąĄčé IPv4. ąŁč鹊čé ą▒ąĖčé ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé 10 (IPC) čĆąĄą│ąĖčüčéčĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ (MAC Configuration Register). |

| 5 |

IP Checksum Bypassed |

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐ąŠą┤čüąĖčüč鹥ą╝ą░ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ ą┐čĆąŠą┐čāčēąĄąĮą░. |

| 4 |

IP Payload Error |

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓čŗčćąĖčüą╗ąĄąĮąĮą░čÅ čÅą┤čĆąŠą╝ 16-ą▒ąĖčéąĮą░čÅ ą║ąŠąĮčéčĆąŠą╗čīąĮą░čÅ čüčāą╝ą╝ą░ ą┐ąŠą╗ąĄąĘąĮąŠą╣ ąĮą░ą│čĆčāąĘą║ąĖ IP (čé. ąĄ. ą║ąŠąĮčéčĆąŠą╗čīąĮą░čÅ čüčāą╝ą╝ą░ TCP, UDP ąĖą╗ąĖ ICMP) ąĮąĄ čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą┐ąŠą╗ąĄą╝ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čüąĄą│ą╝ąĄąĮčéą░. ąŁč鹊čé ą▒ąĖčé čéą░ą║ąČąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ą┤ą╗ąĖąĮą░ čüąĄą│ą╝ąĄąĮčéą░ TCP, UDP ąĖą╗ąĖ ICMP ąĮąĄ čüąŠą▓ą┐ą░ą┤ą░ąĄčé čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ ą┤ą╗ąĖąĮčŗ ą┐ąŠą╗ąĄąĘąĮąŠą╣ ąĮą░ą│čĆčāąĘą║ąĖ ą▓ ą┐ąŠą╗ąĄ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ IP. ąŁč鹊čé ą▒ąĖčé ą┤ąŠą┐čāčüčéąĖą╝, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé 7 ąĖą╗ąĖ ą▒ąĖčé 6. |

| 3 |

IP Header Error |

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą╗ąĖą▒ąŠ ąĮąĄ čüąŠą▓ą┐ą░ą┤ą░ąĄčé 16-ą▒ąĖčéąĮą░čÅ ą║ąŠąĮčéčĆąŠą╗čīąĮą░čÅ čüčāą╝ą╝ą░ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ IPv4, ą▓čŗčćąĖčüą╗ąĄąĮąĮą░čÅ čÅą┤čĆąŠą╝, ą╗ąĖą▒ąŠ ą▓ąĄčĆčüąĖčÅ ą┤ą░čéą░ą│čĆą░ą╝ą╝čŗ IP ąĮąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąĘąĮą░č湥ąĮąĖčÄ Ethernet Type. ąŁč鹊čé ą▒ąĖčé ą┤ąŠą┐čāčüčéąĖą╝, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé 7 ąĖą╗ąĖ ą▒ąĖčé 6. |

| 2:0 |

IP Payload Type |

ąŁčéąĖ ą▒ąĖčéčŗ ą║ąŠą┤ąĖčĆčāčÄčé čéąĖą┐ ą┐ąŠą╗ąĄąĘąĮąŠą╣ ąĮą░ą│čĆčāąĘą║ąĖ, ąĖąĮą║ą░ą┐čüčāą╗ąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą▓ ą┤ą░čéą░ą│čĆą░ą╝ą╝ąĄ IP, ąŠą▒čĆą░ą▒ąŠčéą░ąĮąĮąŠą╣ ą┐ąŠą┤čüąĖčüč鹥ą╝ąŠą╣ ą┐čĆąŠą▓ąĄčĆą║ąĖ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ (Receive Checksum Offload Engine, COE). COE čéą░ą║ąČąĄ čāčüčéą░ąĮąŠą▓ąĖčé ą▒ąĖčéčŗ 00, ąĄčüą╗ąĖ ąŠąĮą░ ąĮąĄ ąŠą▒čĆą░ą▒ąŠčéą░ą╗ą░ ą┐ąŠą╗ąĄąĘąĮčāčÄ ąĮą░ą│čĆčāąĘą║čā ą┤ą░čéą░ą│čĆą░ą╝ą╝čŗ IP ąĖąĘ-ąĘą░ ąŠčłąĖą▒ą║ąĖ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ IP ąĖą╗ąĖ ąĖąĘ-ąĘą░ čäčĆą░ą│ą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ IP.

000: ąĮąĄąĖąĘą▓ąĄčüčéąĮčŗą╣ čéąĖą┐, ąĖą╗ąĖ ąĮąĄ ą▒čŗą╗ą░ ąŠą▒čĆą░ą▒ąŠčéą░ąĮą░ ą┐ąŠą╗ąĄąĘąĮą░čÅ ąĮą░ą│čĆčāąĘą║ą░ IP

001: UDP

010: TCP

011: ICMP

1xx: ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ąŁč鹊čé ą▒ąĖčé ą┤ąŠą┐čāčüčéąĖą╝, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé 7 ąĖą╗ąĖ ą▒ąĖčé 6. |

ąóą░ą▒ą╗ąĖčåą░ 54. Receive Descriptor 6 (RDES6).

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31:0 |

RTSL |

Receive Frame Timestamp Low.

ąŁč鹊 ą┐ąŠą╗ąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ DMA ą╝ą╗ą░ą┤čłąĖą╝ąĖ ąĘąĮą░čćą░čēąĖą╝ąĖ 32 ą▒ąĖčéą░ą╝ąĖ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ, ąĘą░čģą▓ą░č湥ąĮąĮąŠą╣ ą┤ą╗čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čäčĆąĄą╣ą╝ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŁč鹊 ą┐ąŠą╗ąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ DMA č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čäčĆąĄą╣ą╝ą░ ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą▒ąĖč鹊ą╝ LS (RDES0[8]). |

ąóą░ą▒ą╗ąĖčåą░ 55. Receive Descriptor 7 (RDES7).

| ąæąĖčéčŗ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 31:0 |

RTSH |

Receive Frame Timestamp High.