|

LED PWM Controller (čüąŠą║čĆą░čēąĄąĮąĮąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ LEDC) čŹč鹊 ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮąĮąŠąĄ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą©ąśą£ čüąĖą│ąĮą░ą╗ąŠą▓ (Pulse Width Modulation, PWM), čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ čÅčĆą║ąŠčüčéčīčÄ čüą▓ąĄč鹊ą┤ąĖąŠą┤ąŠą▓ (LED). ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ LEDC čüąĮą░ą▒ąČąĄąĮ čéą░ą║ąČąĄ čäčāąĮą║čåąĖąĄą╣ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ č乥ą╣ą┤ąĖąĮą│ą░ - ą┐ą╗ą░ą▓ąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čÅčĆą║ąŠčüčéčīčÄ. ąÜčĆąŠą╝ąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüą▓ąĄč鹊ą┤ąĖąŠą┤ą░ą╝ąĖ, LEDC ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąĖ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ čåąĄą╗ąĄą╣ - ąĮą░ą┐čĆąĖą╝ąĄčĆ ą┤ą╗čÅ ą”ąÉą¤ ą╗ą░ą▒ąŠčĆą░č鹊čĆąĮčŗčģ ą▒ą╗ąŠą║ąŠą▓ ą┐ąĖčéą░ąĮąĖčÅ, ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĘą▓čāą║ąŠą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖ čé. ą┐.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ ą│ą╗ą░ą▓čŗ 30 ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ [1], ą┐ąŠčüą▓čÅčēąĄąĮąĮąŠą╣ ą░ą┐ą┐ą░čĆą░čéčāčĆąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ LEDC. ą×ą┐ąĖčüą░ąĮąĖąĄ API-čäčāąĮą║čåąĖą╣ ESP-IDF ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ LEDC čüą╝. ą▓ [2].

ąŻ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ LEDC ąĖą╝ąĄčÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ:

ŌĆó 6 ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą│ąĄąĮąĄčĆą░č鹊čĆąŠą▓ PWM (čé. ąĄ. 6 ą║ą░ąĮą░ą╗ąŠą▓).

ŌĆó 4 ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ čéą░ą╣ą╝ąĄčĆą░ čü ą┤ąĄą╗ąĖč鹥ą╗čÅą╝ąĖ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčēąĖą╝ąĖ ą┤čĆąŠą▒ąĮąŠąĄ ą┤ąĄą╗ąĄąĮąĖąĄ.

ŌĆó ąÉą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ą╗ą░ą▓ąĮčŗą╝ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄą╝ čüą║ą▓ą░ąČąĮąŠčüčéąĖ (č乥ą╣ą┤ąĖąĮą│, čé. ąĄ. čāą▓ąĄą╗ąĖč湥ąĮąĖąĄ/čāą╝ąĄąĮčīčłąĄąĮąĖąĄ čüą║ą▓ą░ąČąĮąŠčüčéąĖ ą┐ąĄčĆąĖąŠą┤ą░ ą©ąśą£ čü ąĘą░ą┤ą░ąĮąĮąŠą╣ čüą║ąŠčĆąŠčüčéčīčÄ). ąŁčéą░ čäčāąĮą║čåąĖčÅ čĆą░ą▒ąŠčéą░ąĄčé ą░ą┐ą┐ą░čĆą░čéąĮąŠ (ą▒ąĄąĘ čāčćą░čüčéąĖčÅ CPU), ąĮąĄ ą▓ąĮąŠčüčÅ ą┐ąŠą╝ąĄčģąĖ ą▓ č乊čĆą╝ąĖčĆčāąĄą╝čŗą╣ čüąĖą│ąĮą░ą╗.

ŌĆó ąØą░čüčéčĆą░ąĖą▓ą░ąĄą╝ą░čÅ čäą░ąĘą░ ą▓čŗą▓ąŠą┤ą░ čüąĖą│ąĮą░ą╗ą░ PWM.

ŌĆó ąÆčŗą▓ąŠą┤ čüąĖą│ąĮą░ą╗ą░ PWM ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (Light-sleep mode).

ŌĆó ą£ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī PWM 14 ą▒ąĖčé.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖčÅ, čćč鹊 4 čéą░ą╣ą╝ąĄčĆą░ ąĖą┤ąĄąĮčéąĖčćąĮčŗ ą▓ ą║ąŠąĮč鹥ą║čüč鹥 ąĖčģ čäčāąĮą║čåąĖą╣ ąĖ čĆą░ą▒ąŠč鹊čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ. ąÆ čüą╗ąĄą┤čāčÄčēąĖčģ čüąĄą║čåąĖčÅčģ čéą░ą╣ą╝ąĄčĆčŗ ąŠą▒ąŠąĘąĮą░čćą░čÄčéčüčÅ ą║ą░ą║ Timerx (ą│ą┤ąĄ x čŹč鹊 čćąĖčüą╗ąŠ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 0 ą┤ąŠ 3). ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ čłąĄčüčéčī ą│ąĄąĮąĄčĆą░č鹊čĆąŠą▓ (ą║ą░ąĮą░ą╗ąŠą▓) PWM čéą░ą║ąČąĄ ąĖą┤ąĄąĮčéąĖčćąĮčŗ ą▓ ą║ąŠąĮč鹥ą║čüč鹥 ąĖčģ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ, ąĖ ąŠąĮąĖ ą▓ čŹč鹊ą╝ ąŠą┐ąĖčüą░ąĮąĖąĖ ąŠą▒ąŠąĘąĮą░čćą░čÄčéčüčÅ ą║ą░ą║ PWMn (n ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 0 ą┤ąŠ 5).

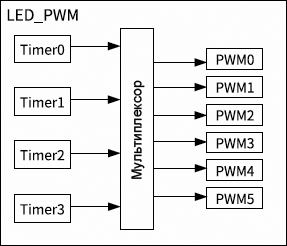

ąĀąĖčü. 30-1. ąÉčĆčģąĖč鹥ą║čéčāčĆą░ LED PWM.

4 čéą░ą╣ą╝ąĄčĆą░ ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ (čé. ąĄ. čā ąĮąĖčģ ą┐ąŠ ąŠčéą┤ąĄą╗čīąĮąŠčüčéąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą┤ąĄą╗ąĖč鹥ą╗čī čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąĖ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░), ąĖ ą▓ ą║ą░ąČą┤ąŠą╝ čéą░ą╣ą╝ąĄčĆąĄ ąĄčüčéčī čüą▓ąŠą╣ ąŠčéą┤ąĄą╗čīąĮčŗą╣ čüč湥čéčćąĖą║ ą▒ą░ąĘčŗ ą▓čĆąĄą╝ąĄąĮąĖ (čé. ąĄ. čüč湥čéčćąĖą║, ą║ąŠč鹊čĆčŗą╣ čüčćąĖčéą░ąĄčé čéą░ą║čéčŗ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ). ąöą╗čÅ ą│ąĄąĮąĄčĆą░č鹊čĆą░ PWM ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąŠą┤ąĖąĮ ąĖąĘ čéą░ą╣ą╝ąĄčĆąŠą▓, čüč湥čéčćąĖą║ ą║ąŠč鹊čĆąŠą│ąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ PWM. ąĀąĖčü. 30-2 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠčüąĮąŠą▓ąĮčŗąĄ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗąĄ ą▒ą╗ąŠą║ąĖ čéą░ą╣ą╝ąĄčĆą░ ąĖ ą│ąĄąĮąĄčĆą░č鹊čĆą░ PWM.

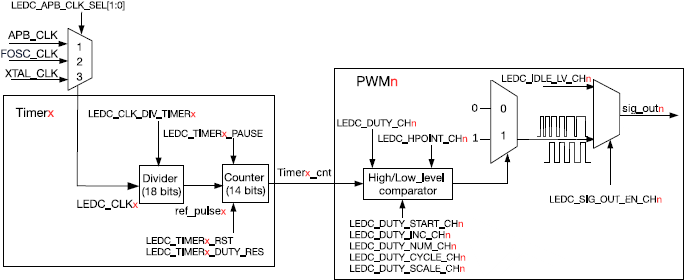

ąĀąĖčü. 30-2. ąæą╗ąŠą║ čüčģąĄą╝ą░ ą│ąĄąĮąĄčĆą░č鹊čĆą░ LED PWM.

[ąóą░ą╣ą╝ąĄčĆčŗ LEDC]

ąÜą░ąČą┤čŗą╣ čéą░ą╣ą╝ąĄčĆ LEDC čüąŠą┤ąĄčƹȹĖčé ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčŗą╣ čüč湥čéčćąĖą║ ą┤ą╗čÅ ąŠčéčüč湥čéą░ ą▒ą░ąĘčŗ ą▓čĆąĄą╝ąĄąĮąĖ. ąóą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ čüč湥čéčćąĖą║ą░ ąŠą▒ąŠąĘąĮą░čćą░ąĄčéčüčÅ ą║ą░ą║ ref_pulsex (čüą╝. čĆąĖčü. 30-2). ąÆčüąĄ čéą░ą╣ą╝ąĄčĆčŗ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ LEDC_CLKx, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąŠčģąŠą┤ąĖčé č湥čĆąĄąĘ ą┤ąĄą╗ąĖč鹥ą╗čī ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čéą░ą║č鹊ą▓ ref_pulsex čüč湥čéčćąĖą║ą░.

ąśčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓. ąöą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ LEDC ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čłąĖąĮčŗ APB_CLK (ą┤ą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ čćą░čüč鹊č鹥 APB_CLK čüą╝. ą│ą╗ą░ą▓čā 6 "Reset and Clock" [1]. ą¦č鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ LED PWM, ą┤ą╗čÅ ąĮąĄą│ąŠ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ čüąĖą│ąĮą░ą╗ APB_CLK. ąĪąĖą│ąĮą░ą╗ APB_CLK ą┤ą╗čÅ LED PWM ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą┐ąŠą╗čÅ SYSTEM_LEDC_CLK_EN ą▓ čĆąĄą│ąĖčüčéčĆąĄ SYSTEM_PERIP_CLK_EN0_REG, ąĖ čüą▒čĆąŠčłąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐ąŠą╗čÅ SYSTEM_LEDC_RST ą▓ čĆąĄą│ąĖčüčéčĆąĄ SYSTEM_PERIP_RST_EN0_REG. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. čéą░ą▒ą╗ąĖčåčā 14-1 ą│ą╗ą░ą▓čŗ 14 "System Registers (SYSREG)" [1].

ąöą╗čÅ čéą░ą╣ą╝ąĄčĆąŠą▓ ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ LEDC ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąŠą▒čēąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ LEDC_CLKx, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┤ąĮąĖą╝ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓: APB_CLK, FOSC_CLK ąĖ XTAL_CLK (ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ ą┐ąŠ ą║ą░ąČą┤ąŠą╝čā ąĖąĘ čŹčéąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓ čéą░ą║č鹊ą▓ čüą╝. ą▓ ą│ą╗ą░ą▓ąĄ 6 "Reset and Clock" [1]). ą¤čĆąŠčåąĄą┤čāčĆą░ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą┤ą╗čÅ LEDC_CLKx čüą╗ąĄą┤čāčÄčēą░čÅ:

APB_CLK: ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ LEDC_APB_CLK_SEL[1:0] ą▓ 1.

FOSC_CLK: ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ LEDC_APB_CLK_SEL[1:0] ą▓ 2.

XTAL_CLK: ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ LEDC_APB_CLK_SEL[1:0] ą▓ 3.

ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ čüąĖą│ąĮą░ą╗ LEDC_CLKx ą┐ąŠčüčéčāą┐ą░ąĄčé ąĮą░ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčŗąĄ ą┤ąĄą╗ąĖč鹥ą╗ąĖ čéą░ą║č鹊ą▓ ą║ą░ąČą┤ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ LEDC.

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┤ąĄą╗ąĖč鹥ą╗čÅ čéą░ą║č鹊ą▓. ąĪąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ LEDC_CLKx, ą┐čĆąŠčģąŠą┤čÅ č湥čĆąĄąĘ ą┤ąĄą╗ąĖč鹥ą╗čī, č乊čĆą╝ąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗ ref_pulsex ą┤ą╗čÅ čüč湥čéčćąĖą║ą░. ą¦ą░čüč鹊čéą░ ref_pulsex čĆą░ą▓ąĮą░ čćą░čüč鹊č鹥 LEDC_CLKx, ą┐ąŠą┤ąĄą╗ąĄąĮąĮąŠą╣ ąĮą░ ąĘąĮą░č湥ąĮąĖąĄ ą┤ąĄą╗ąĖč鹥ą╗čÅ LEDC_CLK_DIV_TIMERx (čüą╝. čĆąĖčü. 30-2).

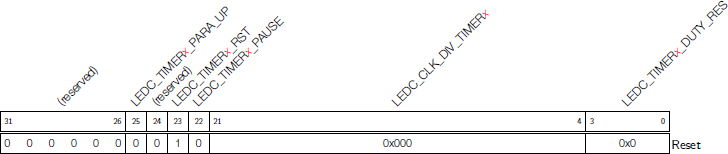

ąŚąĮą░č湥ąĮąĖąĄ ą┤ąĄą╗ąĖč鹥ą╗čÅ LEDC_CLK_DIV_TIMERx ą┤čĆąŠą▒ąĮąŠąĄ, čé. ąĄ. ą┤ąĄą╗ąĖč鹥ą╗čī ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĮąĄ čåąĄą╗čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą▓ ą┤ąĄą╗ąĄąĮąĖčÅ. LEDC_CLK_DIV_TIMERx ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ č湥čĆąĄąĘ ą┐ąŠą╗ąĄ LEDC_CLK_DIV_TIMERx ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čüąŠ čüą╗ąĄą┤čāčÄčēąĄą╣ č乊čĆą╝čāą╗ąŠą╣.

LEDC_CLK_DIV_TIMERx = A + (B/256)

ąŚą┤ąĄčüčī A čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čüčéą░čĆčłąĖą╝ 10 ą▒ąĖčéą░ą╝ LEDC_CLK_DIV_TIMERx (čé. ąĄ. LEDC_TIMERx_CONF_REG[21:12]). ą¦ąĖčüą╗ąĖč鹥ą╗čī ą┤čĆąŠą▒ąĖ B čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé 8 ą╝ą╗ą░ą┤čłąĖą╝ ą▒ąĖčéą░ą╝ LEDC_CLK_DIV_TIMERx (čé. ąĄ. LEDC_TIMERx_CONF_REG[11:4]).

ąÜąŠą│ą┤ą░ ą┤čĆąŠą▒ąĮą░čÅ čćą░čüčéčī B čĆą░ą▓ąĮą░ 0, ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé LEDC_CLK_DIV_TIMERx 菹║ą▓ąĖą▓ą░ą╗ąĄąĮč鹥ąĮ čåąĄą╗ąŠą╝čā ąĘąĮą░č湥ąĮąĖčÄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĖč鹥ą╗čÅ čćą░čüč鹊čéčŗ (čé. ąĄ. ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╣ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ). ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ąĖą╝ą┐čāą╗čīčü čćą░čüč鹊čéčŗ ref_pulsex ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ A-č鹊ą╝ ąĖą╝ą┐čāą╗čīčüąĄ čćą░čüč鹊čéčŗ LEDC_CLKx (čćą░čüč鹊čéą░ ref_pulsex ą▓ A čĆą░ąĘ ą╝ąĄąĮčīčłąĄ čćą░čüč鹊čéčŗ LEDC_CLKx).

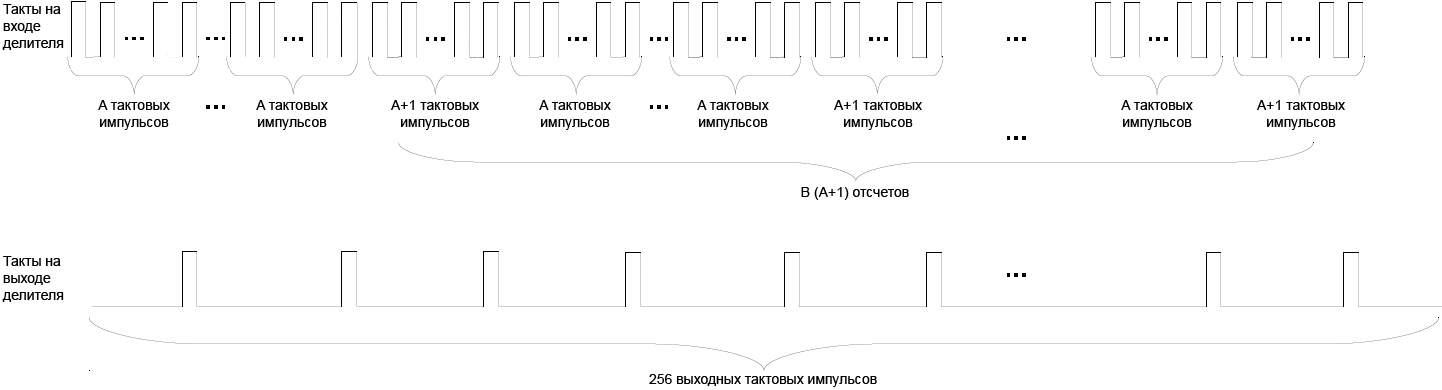

ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ B != 0, č鹊 ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ LEDC_CLK_DIV_TIMERx čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĮąĄ čåąĄą╗čŗą╝. ąöąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čĆąĄą░ą╗ąĖąĘčāąĄčé ą┤čĆąŠą▒ąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ LEDC_CLKx ą┐čāč鹥ą╝ č湥čĆąĄą┤ąŠą▓ą░ąĮąĖčÅ ą╝ąĄąČą┤čā A ąĖ (A+1) čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ LEDC_CLKx ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüą░ ref_pulsex. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▒ąŠą╗ąĄąĄ č鹊čćąĮąŠ ą┐ąŠą┤čüčéčĆąŠąĖčéčī čüčĆąĄą┤ąĮčÄčÄ čćą░čüč鹊čéčā ref_pulsex ąĖą╝ą┐čāą╗čīčüąŠą▓ ą┤ą╗čÅ čüč湥čéčćąĖą║ą░. ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ 256-ą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ ref_pulsex:

ŌĆó ąÜąŠą╗ąĖč湥čüčéą▓ąŠ B ąĖą╝ą┐čāą╗čīčüąŠą▓ ref_pulsex ą▒čāą┤ąĄčé čüąŠą┤ąĄčƹȹ░čéčī (A+1) ąĖą╝ą┐čāą╗čīčüąŠą▓ LEDC_CLKx.

ŌĆó ąÜąŠą╗ąĖč湥čüčéą▓ąŠ (256-B) ąĖą╝ą┐čāą╗čīčüąŠą▓ ref_pulsex ą▒čāą┤ąĄčé čüąŠą┤ąĄčƹȹ░čéčī A ąĖą╝ą┐čāą╗čīčüąŠą▓ LEDC_CLKx.

ŌĆó ąśą╝ą┐čāą╗čīčüčŗ ref_pulsex, čüąŠčüč鹊čÅčēąĖąĄ ąĖąĘ (A+1) ąĖą╝ą┐čāą╗čīčüąŠą▓, čĆą░ą▓ąĮąŠą╝ąĄčĆąĮąŠ čĆą░čüą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ ą╝ąĄąČą┤čā ąĖą╝ą┐čāą╗čīčüą░ą╝ąĖ A.

ąĀąĖčü. 30-3 ąĖą╗ą╗čÄčüčéčĆąĖčĆčāąĄčé ą▓ąĘą░ąĖą╝ąŠčüą▓čÅąĘčī ąĖą╝ą┐čāą╗čīčüąŠą▓ čéą░ą║č鹊ą▓ LEDC_CLKx ąĖ ąĖą╝ą┐čāą╗čīčüąŠą▓ ref_pulsex, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤čĆąŠą▒ąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ LEDC_CLK_DIV_TIMERx (ą║ąŠą│ą┤ą░ B != 0).

ąĀąĖčü. 30-3. ąöąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ LEDC_CLK_DIV_TIMERx ąĮą░ ą┤čĆąŠą▒ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ.

ąöą╗čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ (runtime) čüąĮą░čćą░ą╗ą░ čāčüčéą░ąĮąŠą▓ąĖč鹥 ą┐ąŠą╗ąĄ LEDC_CLK_DIV_TIMERx, ąĖ ąĘą░č鹥ą╝ čāčüčéą░ąĮąŠą▓ąĖč鹥 ą┐ąŠą╗ąĄ LEDC_TIMERx_PARA_UP ą┤ą╗čÅ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ ąĮąŠą▓ąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. ąŁčéąĖ ą┤ąĄą╣čüčéą▓ąĖčÅ ą┐čĆąĖą▓ąĄą┤čāčé ą║ č鹊ą╝čā, čćč鹊 ąĮąŠą▓čŗąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą▓čüčéčāą┐čÅčé ą▓ ą┤ąĄą╣čüčéą▓ąĖąĄ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░. ą¤čĆąĖ čŹč鹊ą╝ ą┐ąŠą╗ąĄ LEDC_TIMERx_PARA_UP ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēąĄąĮąŠ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣.

14-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čüč湥čéčćąĖą║. ąÜą░ąČą┤čŗą╣ čéą░ą╣ą╝ąĄčĆ čüąŠą┤ąĄčƹȹĖčé 14-ą▒ąĖčéąĮčŗą╣ čüč湥čéčćąĖą║ ą▒ą░ąĘčŗ ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠč鹊čĆčŗą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ref_pulsex ą▓ ą║ą░č湥čüčéą▓ąĄ čüą▓ąŠąĄą╣ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ (čüą╝. ą▓čŗčłąĄ čĆąĖčü. 30-2). ą¤ąŠą╗ąĄ LEDC_TIMERx_DUTY_RES ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčé ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┤ą╗čÅ čŹč鹊ą│ąŠ 14-ą▒ąĖčéąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ą░ PWM ą╝ąŠąČąĄčé ą▒čŗčéčī 14 ą▒ąĖčé. ąĪč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą┤ąŠ ąĘąĮą░č湥ąĮąĖčÅ 2^(LEDC_TIM ERx_DUTY_RES - 1), ą┐ąĄčĆąĄą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĖ čüąĮąŠą▓ą░ ąĮą░čćąĖąĮą░ąĄčé čüč湥čé ąŠčé 0. ąŚąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┐čĆąŠčćąĖčéą░ąĮąŠ, čüą▒čĆąŠčłąĄąĮąŠ, ą░ čéą░ą║ąČąĄ čüč湥čéčćąĖą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ.

ąĪč湥čéčćąĖą║ ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ LEDC_TIMERx_OVF_INT (ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ ą▒ąĄąĘ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ) ą║ą░ąČą┤čŗą╣ čĆą░ąĘ ą┐čĆąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ čüč湥čéčćąĖą║ą░. ą£ąŠąČąĮąŠ čéą░ą║ąČąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ LEDC_OVF_CNT_CHn_INT ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░ LEDC_OVF_NUM_CHn + 1 čĆą░ąĘ. ąöą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ LEDC_OVF_CNT_CHn_INT ą▓čŗą┐ąŠą╗ąĮąĖč鹥 čüą╗ąĄą┤čāčÄčēąĄąĄ:

1. ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 LEDC_TIMER_SEL_CHn ą▓ ą║ą░č湥čüčéą▓ąĄ čüč湥čéčćąĖą║ą░ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░č鹊čĆą░ PWM.

2. ąĀą░ąĘčĆąĄčłąĖč鹥 čüč湥čéčćąĖą║ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ LEDC_OVF_CNT_EN_CHn.

3. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 LEDC_OVF_NUM_CHn ą▓ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖą╣ čüč湥čéčćąĖą║ą░ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąĖąĮčāčü 1.

4. ąĀą░ąĘčĆąĄčłąĖč鹥 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ LEDC_OVF_CNT_CHn_INT_ENA.

5. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 LEDC_TIMERx_DUTY_RES ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ ąĖ ąČą┤ąĖč鹥 ąĮą░čüčéčāą┐ą╗ąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ LEDC_OVF_CNT_CHn_INT.

ąÜą░ą║ ą╝ąŠąČąĮąŠ čāą▓ąĖą┤ąĄčéčī ąĮą░ čĆąĖčü. 30-2, čćą░čüč鹊čéą░ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą│ąĄąĮąĄčĆą░č鹊čĆą░ PWM (sig_outn) ąĘą░ą▓ąĖčüąĖčé ąŠčé čćą░čüč鹊čéčŗ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ (LEDC_CLKx), ąĘąĮą░č湥ąĮąĖčÅ ą┤ąĄą╗ąĖč鹥ą╗čÅ čéą░ą║č鹊ą▓ (LEDC_CLK_DIV_TIMERx) ąĖ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ąĘąĮą░č湥ąĮąĖą╣ čüč湥čéčćąĖą║ą░ (LEDC_TIMERx_DUTY_RES):

fLEDC_CLKx

fPWM = ---------------------------------------

LEDC_CLK_DIVx * 2LEDC_TIMERx_DUTY_RES

ąöą╗čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ runtime, čüąĮą░čćą░ą╗ą░ čāčüčéą░ąĮąŠą▓ąĖč鹥 ą┐ąŠą╗ąĄ LEDC_TIMERx_DUTY_RES, ąĖ ąĘą░č鹥ą╝ čāčüčéą░ąĮąŠą▓ąĖč鹥 ą┐ąŠą╗ąĄ LEDC_TIMERx_PARA_UP. ąŁč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓čüčéčāą┐ąĖčé ą▓ čüąĖą╗čā ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ čüč湥čéčćąĖą║ą░. ąĢčüą╗ąĖ ą┐ąŠą╗ąĄ LEDC_OVF_CNT_EN_CHn ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ, ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ LEDC_PARA_UP_CHn ą┤ą╗čÅ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ ąĮąŠą▓ąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čŹčéąĖ ąĘąĮą░č湥ąĮąĖčÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮčŗ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ LEDC_TIMERx_PARA_UP ąĖą╗ąĖ LEDC_PARA_UP_CHn. LEDC_TIMERx_PARA_UP ąĖ LEDC_PARA_UP_CHn ą▒čāą┤čāčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēąĄąĮčŗ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣.

[ąōąĄąĮąĄčĆą░č鹊čĆčŗ PWM]

ąöą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ PWM (PWMn) ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čéą░ą╣ą╝ąĄčĆ (Timerx). ąÜą░ąČą┤čŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ PWM ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąŠčéą┤ąĄą╗čīąĮąŠ ąŠčé ą┤čĆčāą│ąĖčģ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ LEDC_TIMER_SEL_CHn, čćč鹊ą▒čŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠą┤ąĖąĮ ąĖąĘ 4 čéą░ą╣ą╝ąĄčĆąŠą▓ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ PWM-čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ.

ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 30-2, ą║ą░ąČą┤čŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ PWM ąĖą╝ąĄąĄčé ąĮą░ ą▒ąŠčĆčéčā ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ąĖ 2 ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆą░. ąōąĄąĮąĄčĆą░č鹊čĆ PWM čüčĆą░ą▓ąĮąĖą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ 14-ą▒ąĖčéąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ (Timerx_cnt) čü ą┤ą▓čāą╝čÅ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ ą┐ąŠčĆąŠą│ą░ Hpointn ąĖ Lpointn. ąÜąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ čĆą░ą▓ąĮąŠ Hpointn ąĖą╗ąĖ Lpointn, čüąĖą│ąĮą░ą╗ PWM čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ čāčĆąŠą▓ąĮąĖ ą╗ąŠą│. 1 ąĖ ą╗ąŠą│. 0 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ:

ŌĆó ąĢčüą╗ąĖ Timerx_cnt == Hpointn, ąĮą░ ą▓čŗčģąŠą┤ąĄ sig_outn ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ 1.

ŌĆó ąĢčüą╗ąĖ Timerx_cnt == Lpointn, ąĮą░ ą▓čŗčģąŠą┤ąĄ sig_outn ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ 0.

ąĀąĖčü. 30-4 ąĖą╗ą╗čÄčüčéčĆąĖčĆčāąĄčé, ą║ą░ą║ Hpointn ąĖą╗ąĖ Lpointn ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ PWM čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ čüą║ą▓ą░ąČąĮąŠčüčéąĖ.

ąĀąĖčü. 30-4. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ LED_PWM.

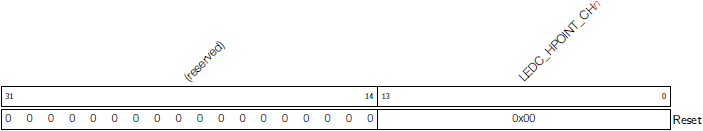

ąöą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ PWMn ąĄą│ąŠ Hpointn ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ą▓ ą┐ąŠą╗ąĄ LEDC_HPOINT_CHn ą║ą░ąČą┤čŗą╣ čĆą░ąĘ ą┐čĆąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ čüč湥čéčćąĖą║ą░. ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ Lpointn čéą░ą║ąČąĄ ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ čüč湥čéčćąĖą║ą░, ąĖ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ąĖąĘ čüčāą╝ą╝čŗ ą┐ąŠą╗ąĄą╣ LEDC_DUTY_CHn[18:4] ąĖ LEDC_HPOINT_CHn. ą¤čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ Hpointn ąĖ Lpointn ą▓ ą┐ąŠą╗čÅčģ LEDC_HPOINT_CHn ąĖ LEDC_DUTY_CHn[18:4], ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮą░čÅ čäą░ąĘą░ ąĖ čüą║ą▓ą░ąČąĮąŠčüčéčī ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ PWM.

ąÆčŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ PWM (sig_outn) čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ LEDC_SIG_OUT_EN_CHn. ąÜąŠą│ą┤ą░ ąŠčćąĖčēąĄąĮ LEDC_SIG_OUT_EN_CHn, ą▓čŗą▓ąŠą┤ čüąĖą│ąĮą░ą╗ą░ PWM ąĘą░ą┐čĆąĄčēąĄąĮ, ąĖ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ (sig_outn) ąŠčüčéą░ąĄčéčüčÅ ąĮą░ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝ čāčĆąŠą▓ąĮąĄ, čāą║ą░ąĘą░ąĮąĮąŠą╝ LEDC_IDLE_LV_CHn.

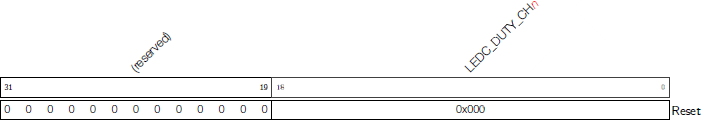

ąæąĖčéčŗ LEDC_DUTY_CHn[3:0] ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą┤ąĖąĘąĄčĆąĖąĮą│ą░ (čüą│ą╗ą░ąČąĖą▓ą░ąĮąĖčÅ) ą┐ąĄčĆąĖąŠą┤ąŠą▓ čüą║ą▓ą░ąČąĮąŠčüčéąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ PWM (sig_outn) ą┐čāč鹥ą╝ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąŠą│ąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čüą║ą▓ą░ąČąĮąŠčüčéąĖ sig_outn. ąÜąŠą│ą┤ą░ LEDC_DUTY_CHn[3:0] čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ ąĮąĄąĮčāą╗ąĄą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, č鹊 ą┤ą╗čÅ ą║ą░ąČą┤čŗčģ 16 ą┐ąĄčĆąĖąŠą┤ąŠą▓ sig_outn ąĘąĮą░č湥ąĮąĖąĄ LEDC_DUTY_CHn[3:0] čŹčéąĖčģ ą┐ąĄčĆąĖąŠą┤ąŠą▓ ą┐ąŠą╗čāčćą░čé ąĖą╝ą┐čāą╗čīčüčŗ PWM ąĮą░ ąŠą┤ąĖąĮ čéąĖą║ čéą░ą╣ą╝ąĄčĆą░ ą┤ą╗ąĖąĮąĮąĄąĄ, č湥ą╝ ą┤čĆčāą│ąĖąĄ (16-LEDC_DUTY_CHn[3:0]) ąĖą╝ą┐čāą╗čīčüčŗ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ LEDC_DUTY_CHn[18:4] čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 10, ąĖ LEDC_DUTY_CHn[3:0] čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 5, č鹊 5 ąĖąĘ 16 ą┐ąĄčĆąĖąŠą┤ąŠą▓ ą▒čāą┤čāčé ąĖą╝ąĄčéčī ąĖą╝ą┐čāą╗čīčüčŗ PWM čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ čüą║ą▓ą░ąČąĮąŠčüčéąĖ 11, ąĖ ąŠčüčéą░ą╗čīąĮčŗąĄ 16 ą┐ąĄčĆąĖąŠą┤ąŠą▓ ą▒čāą┤čāčé ąĖą╝ąĄčéčī ąĖą╝ą┐čāą╗čīčü PWM čüąŠ čüą║ą▓ą░ąČąĮąŠčüčéčīčÄ 10. ąĪčĆąĄą┤ąĮčÅčÅ čüą║ą▓ą░ąČąĮąŠčüčéčī ą┐ąŠčüą╗ąĄ 16 ą┐ąĄčĆąĖąŠą┤ąŠą▓ ą┐ąŠą╗čāčćąĖčéčüčÅ 10.3125.

ąĢčüą╗ąĖ ą┐ąĄčĆąĄą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┐ąŠą╗čÅ LEDC_TIMER_SEL_CHn, LEDC_HPOINT_CHn, LEDC_DUTY_CHn[18:4] ąĖ LEDC_SIG_OUT_EN_CHn, č鹊 ąĮčāąČąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī LEDC_PARA_UP_CHn ą┤ą╗čÅ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ ąĮąŠą▓ąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. ąŁč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 ąĮąŠą▓čŗąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą▓čüčéčāą┐čÅčé ą▓ čüąĖą╗čā ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĖ čüč湥čéčćąĖą║ą░. ą¤ąŠą╗ąĄ LEDC_PARA_UP_CHn ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣.

[Duty Cycle Fading (č乥ą╣ą┤ąĖąĮą│ ą©ąśą£)]

ąÉą┐ą┐ą░čĆą░čéąĮą░čÅ čäčāąĮą║čåąĖčÅ Duty Cycle Fading ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą│ąĄąĮąĄčĆą░č鹊čĆčŗ PWM ą╝ąŠą│čāčé ą┤ąĄą╗ą░čéčī č乥ą╣ą┤ąĖąĮą│ ą┐ąĄčĆąĖąŠą┤ą░ čüą║ą▓ą░ąČąĮąŠčüčéąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ PWM (čé. ąĄ. ą┐ąŠčüč鹥ą┐ąĄąĮąĮąŠ ą╝ąĄąĮčÅčéčī čüą║ą▓ą░ąČąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ą░ ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą┤ąŠ ą┤čĆčāą│ąŠą│ąŠ). ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮą░ Duty Cycle Fading, č鹊 ąĘąĮą░č湥ąĮąĖąĄ Lpointn ą▒čāą┤ąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ/ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ ą┐ąŠčüą╗ąĄ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖą╣ čüč湥čéčćąĖą║ą░. ąĀąĖčü. 30-5 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čĆą░ą▒ąŠčéčā Duty Cycle Fading.

ąĀąĖčü. 30-5. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąĖ č乥ą╣ą┤ąĖąĮą│ąĄ.

Duty Cycle Fading ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ą┐ąŠą╗čÅą╝ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓:

LEDC_DUTY_CHn ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ Lpointn.

LEDC_DUTY_START_CHn čĆą░ąĘčĆąĄčłąĖčé (ąĄčüą╗ąĖ 1) ąĖą╗ąĖ ąĘą░ą┐čĆąĄčéąĖčé (ąĄčüą╗ąĖ 0) č乥ą╣ą┤ąĖąĮą│.

LEDC_DUTY_CYCLE_CHn čāčüčéą░ąĮąŠą▓ąĖčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖą╣ čüč湥čéčćąĖą║ą░ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ ąĖą╗ąĖ ą┤ąĄą║čĆąĄą╝ąĄąĮčéą░ Lpointn. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, Lpointn ą▒čāą┤ąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ/ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ ą┐ąŠčüą╗ąĄ LEDC_DUTY_CYCLE_CHn ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖą╣ čüč湥čéčćąĖą║ą░.

LEDC_DUTY_INC_CHn ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčé, ą▒čāą┤ąĄčé Lpointn ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ (ąĄčüą╗ąĖ 1) ąĖą╗ąĖ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ (ąĄčüą╗ąĖ 0).

LEDC_DUTY_SCALE_CHn čāčüčéą░ąĮąŠą▓ąĖčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ, ąĮą░ ą║ąŠč鹊čĆąŠąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčé/ą┤ąĄą║čĆąĄą╝ąĄąĮčé Lpointn.

LEDC_DUTY_NUM_CHn čāčüčéą░ąĮąŠą▓ąĖčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĖąĮą║čĆąĄą╝ąĄąĮč鹊ą▓ / ą┤ąĄą║čĆąĄą╝ąĄąĮč鹊ą▓ ą┤ąŠ ąŠčüčéą░ąĮąŠą▓ą║ąĖ č乥ą╣ą┤ąĖąĮą│ą░.

ąĢčüą╗ąĖ ą┐ąŠą╗čÅ LEDC_DUTY_CHn, LEDC_DUTY_START_CHn, LEDC_DUTY_CYCLE_CHn, LEDC_DUTY_INC_CHn, LEDC_DUTY_SCALE_CHn ąĖ LEDC_DUTY_NUM_CHn ą▒čŗą╗ąĖ ą┐ąĄčĆąĄą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ, č鹊 ąĮčāąČąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī LEDC_PARA_UP_CHn, čćč鹊ą▒čŗ ąĮąŠą▓ą░čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čüčéčāą┐ąĖą╗ą░ ą▓ čüąĖą╗čā. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čŹč鹊 ą┐ąŠą╗ąĄ ą▒čŗą╗ąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ, ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓čüčéčāą┐čÅčé ą▓ čüąĖą╗čā ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ č乥ą╣ą┤ąĖąĮą│ą░. ą¤ąŠą╗ąĄ LEDC_PARA_UP_CHn ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣.

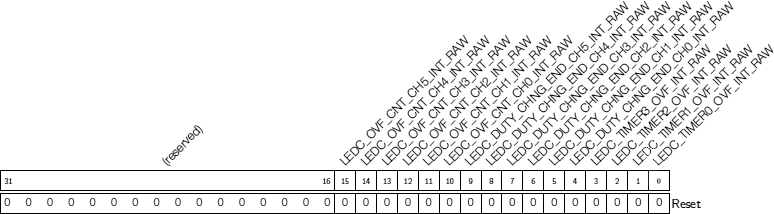

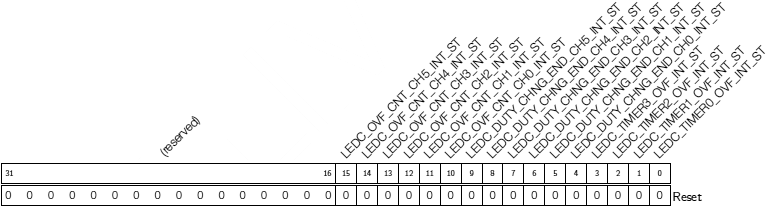

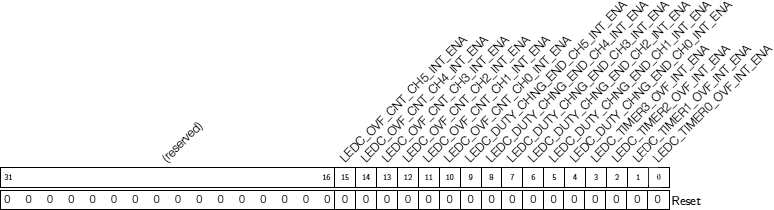

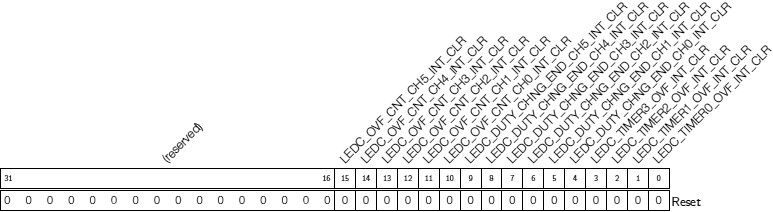

[ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ LEDC]

LEDC_OVF_CNT_CHn_INT: čüčĆą░ą▒ąŠčéą░ąĄčé, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ čéą░ą╣ą╝ąĄčĆą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĖčéčüčÅ (LEDC_OVF_NUM_CHn + 1) čĆą░ąĘ, ąĖ čĆąĄą│ąĖčüčéčĆ LEDC_OVF_CNT_EN_CHn čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1.

LEDC_DUTY_CHNG_END_CHn_INT: čüčĆą░ą▒ąŠčéą░ąĄčé, ą║ąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ č乥ą╣ą┤ąĖąĮą│ ą│ąĄąĮąĄčĆą░č鹊čĆą░ PWM.

LEDC_TIMERx_OVF_INT: čüčĆą░ą▒ąŠčéą░ąĄčé, ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ PWM ą┤ąŠčüčéąĖą│ąĮąĄčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ čüč湥čéčćąĖą║ą░ (ą▓ ą╝ąŠą╝ąĄąĮčé ąĄą│ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ).

[ą×ą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ LEDC]

ąÉą┤čĆąĄčüą░ ą▓ čŹč鹊ą╣ čüąĄą║čåąĖąĖ čāą║ą░ąĘą░ąĮčŗ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ LED PWM Controller, čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 3-4 ą│ą╗ą░ą▓čŗ 3 "System and Memory" [1].

| ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ąÉą┤čĆąĄčü |

ąöąŠčüčéčāą┐(*) |

| Configuration Register (čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ) |

| LEDC_CH0_CONF0_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 0 ą║ą░ąĮą░ą╗ą░ 0 |

0x0000 |

* |

| LEDC_CH0_CONF1_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 1 ą║ą░ąĮą░ą╗ą░ 0 |

0x000C |

* |

| LEDC_CH1_CONF0_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 0 ą║ą░ąĮą░ą╗ą░ 1 |

0x0014 |

* |

| LEDC_CH1_CONF1_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 1 ą║ą░ąĮą░ą╗ą░ 1 |

0x0020 |

* |

| LEDC_CH2_CONF0_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 0 ą║ą░ąĮą░ą╗ą░ 2 |

0x0028 |

* |

| LEDC_CH2_CONF1_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 1 ą║ą░ąĮą░ą╗ą░ 2 |

0x0034 |

* |

| LEDC_CH3_CONF0_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 0 ą║ą░ąĮą░ą╗ą░ 3 |

0x003C |

* |

| LEDC_CH3_CONF1_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 1 ą║ą░ąĮą░ą╗ą░ 3 |

0x0048 |

* |

| LEDC_CH4_CONF0_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 0 ą║ą░ąĮą░ą╗ą░ 4 |

0x0050 |

* |

| LEDC_CH4_CONF1_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 1 ą║ą░ąĮą░ą╗ą░ 4 |

0x005C |

* |

| LEDC_CH5_CONF0_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 0 ą║ą░ąĮą░ą╗ą░ 5 |

0x0064 |

* |

| LEDC_CH5_CONF1_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 1 ą║ą░ąĮą░ą╗ą░ 5 |

0x0070 |

* |

| LEDC_CONF_REG |

ąĀąĄą│ąĖčüčéčĆ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ LEDC |

0x0030 |

R/W |

| Hpoint Register (čĆąĄą│ąĖčüčéčĆ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ą░) |

| LEDC_CH0_HPOINT_REG |

ąĀąĄą│ąĖčüčéčĆ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ą░ ą║ą░ąĮą░ą╗ą░ 0 |

0x0004 |

R/W |

| LEDC_CH1_HPOINT_REG |

ąĀąĄą│ąĖčüčéčĆ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ą░ ą║ą░ąĮą░ą╗ą░ 1 |

0x0018 |

R/W |

| LEDC_CH2_HPOINT_REG |

ąĀąĄą│ąĖčüčéčĆ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ą░ ą║ą░ąĮą░ą╗ą░ 2 |

0x002C |

R/W |

| LEDC_CH3_HPOINT_REG |

ąĀąĄą│ąĖčüčéčĆ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ą░ ą║ą░ąĮą░ą╗ą░ 3 |

0x0040 |

R/W |

| LEDC_CH4_HPOINT_REG |

ąĀąĄą│ąĖčüčéčĆ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ą░ ą║ą░ąĮą░ą╗ą░ 4 |

0x0054 |

R/W |

| LEDC_CH5_HPOINT_REG |

ąĀąĄą│ąĖčüčéčĆ ą▓ąĄčĆčģąĮąĄą│ąŠ ą┐čĆąĄą┤ąĄą╗ą░ ą║ą░ąĮą░ą╗ą░ 5 |

0x0068 |

R/W |

| Duty Cycle Registers (čĆąĄą│ąĖčüčéčĆčŗ čüą║ą▓ą░ąČąĮąŠčüčéąĖ ą┐ąĄčĆąĖąŠą┤ą░ ą©ąśą£) |

| LEDC_CH0_DUTY_REG |

ąØą░čćą░ą╗čīąĮą░čÅ čüą║ą▓ą░ąČąĮąŠčüčéčī ą║ą░ąĮą░ą╗ą░ 0 |

0x0008 |

R/W |

| LEDC_CH0_DUTY_R_REG |

ąóąĄą║čāčēą░čÅ čüą║ą▓ą░ąČąĮąŠčüčéčī ą║ą░ąĮą░ą╗ą░ 0 |

0x0010 |

RO |

| LEDC_CH1_DUTY_REG |

ąØą░čćą░ą╗čīąĮą░čÅ čüą║ą▓ą░ąČąĮąŠčüčéčī ą║ą░ąĮą░ą╗ą░ 1 |

0x001C |

R/W |

| LEDC_CH1_DUTY_R_REG |

ąóąĄą║čāčēą░čÅ čüą║ą▓ą░ąČąĮąŠčüčéčī ą║ą░ąĮą░ą╗ą░ 1 |

0x0024 |

RO |

| LEDC_CH2_DUTY_REG |

ąØą░čćą░ą╗čīąĮą░čÅ čüą║ą▓ą░ąČąĮąŠčüčéčī ą║ą░ąĮą░ą╗ą░ 2 |

0x0030 |

R/W |

| LEDC_CH2_DUTY_R_REG |

ąóąĄą║čāčēą░čÅ čüą║ą▓ą░ąČąĮąŠčüčéčī ą║ą░ąĮą░ą╗ą░ 2 |

0x0038 |

RO |

| LEDC_CH3_DUTY_REG |

ąØą░čćą░ą╗čīąĮą░čÅ čüą║ą▓ą░ąČąĮąŠčüčéčī ą║ą░ąĮą░ą╗ą░ 3 |

0x0044 |

R/W |

| LEDC_CH3_DUTY_R_REG |

ąóąĄą║čāčēą░čÅ čüą║ą▓ą░ąČąĮąŠčüčéčī ą║ą░ąĮą░ą╗ą░ 3 |

0x004C |

RO |

| LEDC_CH4_DUTY_REG |

ąØą░čćą░ą╗čīąĮą░čÅ čüą║ą▓ą░ąČąĮąŠčüčéčī ą║ą░ąĮą░ą╗ą░ 4 |

0x0058 |

R/W |

| LEDC_CH4_DUTY_R_REG |

ąóąĄą║čāčēą░čÅ čüą║ą▓ą░ąČąĮąŠčüčéčī ą║ą░ąĮą░ą╗ą░ 4 |

0x0060 |

RO |

| LEDC_CH5_DUTY_REG |

ąØą░čćą░ą╗čīąĮą░čÅ čüą║ą▓ą░ąČąĮąŠčüčéčī ą║ą░ąĮą░ą╗ą░ 5 |

0x006C |

R/W |

| LEDC_CH5_DUTY_R_REG |

ąóąĄą║čāčēą░čÅ čüą║ą▓ą░ąČąĮąŠčüčéčī ą║ą░ąĮą░ą╗ą░ 5 |

0x0074 |

RO |

| Timer Registers (čĆąĄą│ąĖčüčéčĆčŗ čéą░ą╣ą╝ąĄčĆąŠą▓) |

| LEDC_TIMER0_CONF_REG |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ čéą░ą╣ą╝ąĄčĆą░ 0 |

0x00A0 |

* |

| LEDC_TIMER0_VALUE_REG |

ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ 0 |

0x00A4 |

RO |

| LEDC_TIMER1_CONF_REG |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ čéą░ą╣ą╝ąĄčĆą░ 1 |

0x00A8 |

* |

| LEDC_TIMER1_VALUE_REG |

ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ 1 |

0x00AC |

RO |

| LEDC_TIMER2_CONF_REG |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ čéą░ą╣ą╝ąĄčĆą░ 2 |

0x00B0 |

* |

| LEDC_TIMER2_VALUE_REG |

ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ 2 |

0x00B4 |

RO |

| LEDC_TIMER3_CONF_REG |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ čéą░ą╣ą╝ąĄčĆą░ 3 |

0x00B8 |

* |

| LEDC_TIMER3_VALUE_REG |

ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ 3 |

0x00BC |

RO |

| Interrupt Registers (čĆąĄą│ąĖčüčéčĆčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ) |

| LEDC_INT_RAW_REG |

ąĪčŗčĆąŠą╣ čüčéą░čéčāčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ |

0x00C0 |

R/WTC/SS |

| LEDC_INT_ST_REG |

ą£ą░čüą║ąĖčĆčāąĄą╝čŗą╣ čüčéą░čéčāčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ |

0x00C4 |

RO |

| LEDC_INT_ENA_REG |

ąæąĖčéčŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ |

0x00C8 |

R/W |

| LEDC_INT_CLR_REG |

ąæąĖčéčŗ ąŠčćąĖčüčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ |

0x00CC |

WT |

| Version Register (čĆąĄą│ąĖčüčéčĆ ą▓ąĄčĆčüąĖąĖ) |

| LEDC_DATE_REG |

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ąĄčĆčüąĖąĄą╣ |

0x00FC |

R/W |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (*): * ą┤ąŠčüčéčāą┐ ą╝ąŠąČąĄčé ą╝ąĄąĮčÅčéčīčüčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐ąŠą╗čÅ čĆąĄą│ąĖčüčéčĆą░. R/W ą┤ąŠčüčéčāą┐ ąĖ ąĮą░ čćč鹥ąĮąĖąĄ, ąĖ ąĮą░ ąĘą░ą┐ąĖčüčī. RO ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ.

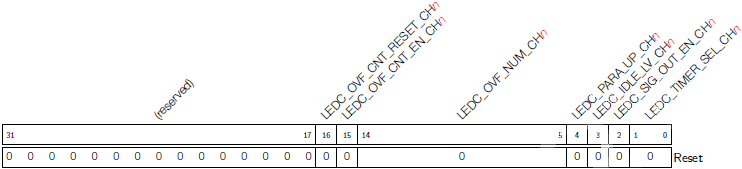

LEDC_TIMER_SEL_CHn ąŁč鹊 ą┐ąŠą╗ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ čéą░ą╣ą╝ąĄčĆąŠą▓ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ n. 0: ą▓čŗą▒čĆą░ąĮ Timer0, 1: ą▓čŗą▒čĆą░ąĮ Timer1, 2: ą▓čŗą▒čĆą░ąĮ Timer2, 3: ą▓čŗą▒čĆą░ąĮ Timer3 (R/W).

LEDC_SIG_OUT_EN_CHn ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī ą▓čŗą▓ąŠą┤ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą║ą░ąĮą░ą╗ąĄ n (R/W).

LEDC_IDLE_LV_CHn ąŁč鹊čé ą▒ąĖčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝, ą║ąŠą│ą┤ą░ ą║ą░ąĮą░ą╗ n ąĮąĄ ą░ą║čéąĖą▓ąĄąĮ (ą║ąŠą│ą┤ą░ LEDC_SIG_OUT_EN_CHn = 0) (R/W).

LEDC_PARA_UP_CHn ąŁč鹊čé ą▒ąĖčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮčŗčģ ąĮąĖąČąĄ ą┐ąŠą╗ąĄą╣ ą║ą░ąĮą░ą╗ą░ n, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą▒ąĖčé LEDC_PARA_UP_CHn ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēąĄąĮ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ (WT).

LEDC_HPOINT_CHn

LEDC_DUTY_START_CHn

LEDC_SIG_OUT_EN_CHn

LEDC_TIMER_SEL_CHn

LEDC_DUTY_NUM_CHn

LEDC_DUTY_CYCLE_CHn

LEDC_DUTY_SCALE_CHn

LEDC_DUTY_INC_CHn

LEDC_OVF_CNT_EN_CHn

LEDC_OVF_NUM_CHn ąŁč鹊 ą┐ąŠą╗ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖą╣ ą╝ąĖąĮčāčü 1. ąĪčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ LEDC_OVF_CNT_CHn_INT, ą║ąŠą│ą┤ą░ ą║ą░ąĮą░ą╗ n ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĖčéčüčÅ (LEDC_OVF_NUM_CHn + 1) čĆą░ąĘ (R/W).

LEDC_OVF_CNT_EN_CHn ąŁč鹊čé ą▒ąĖčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąŠą┤čüč湥čéą░ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖą╣ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ ą║ą░ąĮą░ą╗ą░ n (R/W).

LEDC_OVF_CNT_RESET_CHn ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé, čćč鹊ą▒čŗ čüą▒čĆąŠčüąĖčéčī ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ ą║ą░ąĮą░ą╗ą░ n (WT).

LEDC_DUTY_SCALE_CHn ąŁč鹊 ą┐ąŠą╗ąĄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčé čĆą░ąĘą╝ąĄčĆ čłą░ą│ą░ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čüą║ą▓ą░ąČąĮąŠčüčéąĖ ą┐čĆąĖ č乥ą╣ą┤ąĖąĮą│ąĄ (R/W).

LEDC_DUTY_CYCLE_CHn ąĪą║ą▓ą░ąČąĮąŠčüčéčī ą▒čāą┤ąĄčé ą╝ąĄąĮčÅčéčīčüčÅ ą║ą░ąČą┤čŗąĄ LEDC_DUTY_CYCLE_CHn ą┐ąĄčĆąĖąŠą┤ąŠą▓ ą║ą░ąĮą░ą╗ą░ n (R/W).

LEDC_DUTY_NUM_CHn ąŁč鹊 ą┐ąŠą╗ąĄ čāą┐čĆą░ą▓ą╗čÅąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣ čüą║ą▓ą░ąČąĮąŠčüčéąĖ č乥ą╣ą┤ąĖąĮą│ą░ (R/W).

LEDC_DUTY_INC_CHn ąŁč鹊čé ą▒ąĖčé ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą▒čāą┤ąĄčé ą╗ąĖ čüą║ą▓ą░ąČąĮąŠčüčéčī ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą║ą░ąĮą░ą╗ą░ n čāą▓ąĄą╗ąĖčćąĖą▓ą░čéčīčüčÅ ąĖą╗ąĖ čāą╝ąĄąĮčīčłą░čéčīčüčÅ. 1: čāą▓ąĄą╗ąĖč湥ąĮąĖąĄ čüą║ą▓ą░ąČąĮąŠčüčéąĖ, 0: čāą╝ąĄąĮčīčłąĄąĮąĖąĄ čüą║ą▓ą░ąČąĮąŠčüčéąĖ (R/W).

LEDC_DUTY_START_CHn ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, č鹊 ą┤čĆčāą│ąĖąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą┐ąŠą╗čÅ ą▓ LEDC_CHn_CONF1_REG ą▓čüčéčāą┐čÅčé ą▓ čüąĖą╗čā ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ čéą░ą╣ą╝ąĄčĆą░ (R/W/SC).

LEDC_APB_CLK_SEL ąŁč鹊 ą┐ąŠą╗ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ąŠą▒čēąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ą▓čüąĄčģ 4 čéą░ą╣ą╝ąĄčĆąŠą▓. 1: APB_CLK, 2: FOSC_CLK, 3: XTAL_CLK (R/W).

LEDC_CLK_EN ąŁč鹊čé ą▒ąĖčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čéą░ą║čéą░ą╝ąĖ. 1: čéą░ą║čéčŗ ą┐čĆąĖą╝ąĄąĮąĄąĮčŗ ą┐ąŠčüč鹊čÅąĮąĮąŠ. 0: čéą░ą║čéčŗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ą▓ čĆąĄą│ąĖčüčéčĆčŗ (R/W).

LEDC_HPOINT_CHn ąÆčŗčģąŠą┤ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą╝ąĄąĮčÅąĄčéčüčÅ ą▓ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ ą┤ą╗čÅ čŹč鹊ą│ąŠ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéąĖą│ąĮąĄčé ąĘąĮą░č湥ąĮąĖčÅ, čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ ą▓ čŹč鹊ą╝ ą┐ąŠą╗ąĄ (R/W).

LEDC_DUTY_CHn ąŁč鹊 ą┐ąŠą╗ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą╣ čüą║ą▓ą░ąČąĮąŠčüčéąĖ ą┐čāč鹥ą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ Lpoint. ąÆčŗčģąŠą┤ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą╝ąĄąĮčÅąĄčéčüčÅ ą▓ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ ą┤ą╗čÅ čŹč鹊ą│ąŠ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéąĖą│ąĮąĄčé Lpoint (R/W).

LEDC_DUTY_R_CHn ąŁč鹊 ą┐ąŠą╗ąĄ čģčĆą░ąĮąĖčé č鹥ą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüą║ą▓ą░ąČąĮąŠčüčéąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą║ą░ąĮą░ą╗ą░ n (RO).

LEDC_TIMERx_DUTY_RES ąŁč鹊 ą┐ąŠą╗ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ąĖą░ą┐ą░ąĘąŠąĮąŠą╝ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ x (R/W).

LEDC_CLK_DIV_TIMERx ąŁč鹊 ą┐ąŠą╗ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ąĄą╗ąĖč鹥ą╗čÅ čéą░ą║č鹊ą▓ čéą░ą╣ą╝ąĄčĆą░ x. ą£ą╗ą░ą┤čłąĖąĄ 8 ą▒ąĖč鹊ą▓ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé ą┤čĆąŠą▒ąĮčāčÄ čćą░čüčéčī ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĄąĮąĖčÅ (R/W).

LEDC_TIMERx_PAUSE ąŁč鹊čé ą▒ąĖčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ x (R/W).

LEDC_TIMERx_RST ąŁč鹊čé ą▒ąĖčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čüą▒čĆąŠčüą░ čéą░ą╣ą╝ąĄčĆą░ x. ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ čüč湥čéčćąĖą║ ą┐ąŠą║ą░ąČąĄčé 0 (R/W).

LEDC_TIMERx_PARA_UP ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ LEDC_CLK_DIV_TIMERx ąĖ LEDC_TIMERx_DUTY_RES (WT).

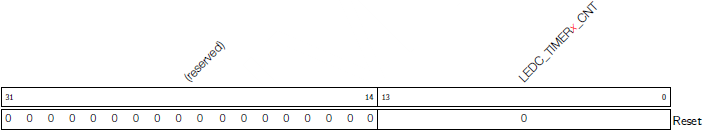

LEDC_TIMERx_CNT ąŁč鹊 ą┐ąŠą╗ąĄ čģčĆą░ąĮąĖčé č鹥ą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ čéą░ą╣ą╝ąĄčĆą░ x (RO).

LEDC_TIMERx_OVF_INT_RAW ąĪčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą║ąŠą│ą┤ą░ čéą░ą╣ą╝ąĄčĆ x ą┤ąŠčüčéąĖą│ąĮąĄčé čüą▓ąŠąĄą│ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ čüč湥čéčćąĖą║ą░ (R/WTC/SS).

LEDC_DUTY_CHNG_END_CHn_INT_RAW ąĪčŗčĆąŠą╣ ą▒ąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ n. ąĪčĆą░ą▒ą░čéčŗą▓ą░ąĄčé, ą║ąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą┐ąŠčüč鹥ą┐ąĄąĮąĮąŠąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čüą║ą▓ą░ąČąĮąŠčüčéąĖ (R/WTC/SS).

LEDC_OVF_CNT_CHn_INT_RAW ąĪčŗčĆąŠą╣ ą▒ąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ n. ąĪčĆą░ą▒ąŠčéą░ąĄčé, ą║ąŠą│ą┤ą░ ovf_cnt ą┤ąŠčüčéąĖą│ąĮąĄčé ąĘąĮą░č湥ąĮąĖčÅ, čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ ą▓ LEDC_OVF_NUM_CHn (R/WTC/SS).

LEDC_TIMERx_OVF_INT_ST ąŁč鹊 ą╝ą░čüą║ąĖčĆčāąĄą╝čŗą╣ ą▒ąĖčé čüčéą░čéčāčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ LEDC_TIMERx_OVF_INT, ą║ąŠą│ą┤ą░ LEDC_TIMERx_OVF_INT_ENA = 1 (RO).

LEDC_DUTY_CHNG_END_CHn_INT_ST ąŁč鹊 ą╝ą░čüą║ąĖčĆčāąĄą╝čŗą╣ ą▒ąĖčé čüčéą░čéčāčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ LEDC_DUTY_CHNG_END_CHn_INT, ą║ąŠą│ą┤ą░ LEDC_DUTY_CHNG_END_CHn_INT_ENA = 1 (RO).

LEDC_OVF_CNT_CHn_INT_ST ąŁč鹊 ą╝ą░čüą║ąĖčĆčāąĄą╝čŗą╣ ą▒ąĖčé čüčéą░čéčāčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ LEDC_OVF_CNT_CHn_INT, ą║ąŠą│ą┤ą░ LEDC_OVF_CNT_CHn_INT_ENA = 1 (RO).

LEDC_TIMERx_OVF_INT_ENA ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ LEDC_TIMERx_OVF_INT interrupt (R/W).

LEDC_DUTY_CHNG_END_CHn_INT_ENA ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ LEDC_DUTY_CHNG_END_CHn_INT (R/W).

LEDC_OVF_CNT_CHn_INT_ENA ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ LEDC_OVF_CNT_CHn_INT (R/W).

LEDC_TIMERx_OVF_INT_CLR ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ LEDC_TIMERx_OVF_INT (WT).

LEDC_DUTY_CHNG_END_CHn_INT_CLR ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ LEDC_DUTY_CHNG_END_CHn_INT (WT).

LEDC_OVF_CNT_CHn_INT_CLR ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ LEDC_OVF_CNT_CHn_INT (WT).

LEDC_LEDC_DATE ąŁč鹊 čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ąĄčĆčüąĖąĄą╣ (R/W).

[ąĪčüčŗą╗ą║ąĖ]

1. ESP32-C3 Technical Reference Manual site:espressif.com.

2. ESP32-C3: API-čäčāąĮą║čåąĖąĖ ESP-IDF čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą©ąśą£-ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ LEDC. |