|

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ESP32-C3 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčī ąĘą░čģą▓ą░čé, ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ ą┤ąĖąĮą░ą╝ąĖč湥čüą║čāčÄ ąĮą░čüčéčĆąŠą╣ą║čā ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ąŠčé čüąĖą│ąĮą░ą╗ąŠą▓ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą┐ąŠčüčéčāą┐ą░čÄčēąĖčģ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ RISC-V CPU. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé:

ŌĆó ąöąŠ 31 ą░čüąĖąĮčģčĆąŠąĮąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čü čāąĮąĖą║ą░ą╗čīąĮčŗą╝ąĖ ID (1-31).

ŌĆó ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÄ č湥čĆąĄąĘ čćč鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī čĆąĄą│ąĖčüčéčĆąŠą▓ MMR (memory mapped register).

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą║ą░ą║ ą┐ąŠ čāčĆąŠą▓ąĮčÄ (level), čéą░ą║ ąĖ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā čüąĖą│ąĮą░ą╗ą░ (edge).

ŌĆó 15 čāčĆąŠą▓ąĮąĄą╣ ą┐čĆąĖąŠčĆąĖč鹥čéą░, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą│ąŠ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗą╣ ą┐ąŠčĆąŠą│ ą┤ą╗čÅ ą╝ą░čüą║ąĖčĆčāąĄą╝čŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čü ą┐ąŠąĮąĖąČąĄąĮąĮčŗą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝.

ŌĆó ID ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠč鹊ą▒čĆą░ąČą░čÄčéčüčÅ ąĮą░ čüą╝ąĄčēąĄąĮąĖčÅ čéą░ą▒ą╗ąĖčåčŗ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (trap-vector address offsets).

ą¤ąŠą╗ąĮčŗą╣ čüą┐ąĖčüąŠą║ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ ąĖčģ ą┐ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čüą╝. ą▓ [1], ą│ą╗ą░ą▓ą░ "Interrupt Matrix (INTMTRX)", čüąĄą║čåąĖčÅ 8.4, ą│čĆčāą┐ą┐ą░ čĆąĄą│ąĖčüčéčĆąŠą▓ "CPU Interrupt Registers".

[ąĪą▓ąŠą╣čüčéą▓ą░ ID ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣]

ąÜą░ąČą┤čŗą╣ ID ąŠą▒ą╗ą░ą┤ą░ąĄčé ą┐čĆąĖą▓čÅąĘą░ąĮąĮčŗą╝ąĖ ą║ ąĮąĄą╝čā 5 čüą▓ąŠą╣čüčéą▓ą░ą╝ąĖ:

1. Enable State (0-1).

ŌĆó ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé, čĆą░ąĘčĆąĄčłąĄąĮąŠ ą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┤ą╗čÅ ąĘą░čģą▓ą░čéą░ ąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čÅą┤čĆąŠą╝ CPU.

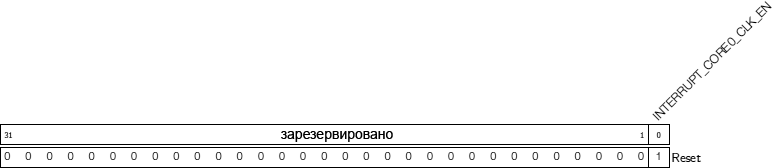

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆ INTERRUPT_CORE0_CPU_INT_ENABLE_REG.

2. Type (0-1).

ŌĆó ą¤ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░čēąĄą╗ą║ąĮčāčéčī čüąŠčüč鹊čÅąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąĄą│ąŠ čäčĆąŠąĮčéčā.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆ INTERRUPT_CORE0_CPU_INT_TYPE_REG.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą┤ą╗čÅ ą║ąŠč鹊čĆąŠą│ąŠ Type čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ čĆą░ą▓ąĮčŗą╝ 0, ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ čéąĖą┐ą░ "level" (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čāčĆąŠą▓ąĮčÄ).

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą┤ą╗čÅ ą║ąŠč鹊čĆąŠą│ąŠ Type čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čĆą░ą▓ąĮčŗą╝ 1, ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ čéąĖą┐ą░ "edge" (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā).

3. Priority (1 .. 15).

ŌĆó ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ą░ą║ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ą╝ąĄčüč鹥 čü ą┤čĆčāą│ąĖą╝ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ, ąŠąČąĖą┤ą░čÄčēąĖą╝ąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ, ą▒čāą┤ąĄčé ąŠą▒čĆą░ą▒ąŠčéą░ąĮąŠ CPU ą▓ ą┐ąĄčĆą▓čāčÄ ąŠč湥čĆąĄą┤čī.

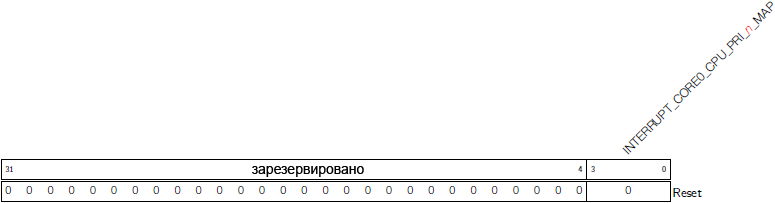

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ INTERRUPT_CORE0_CPU_INT_PRI_n_REG ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ interrupt ID n ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ (1-31).

ŌĆó ąĀą░ąĘčĆąĄčłąĄąĮąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ 0 ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ, č湥ą╝ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčĆąŠą│ą░ ą▓ INTERRUPT_CORE0_CPU_INT_THRESH_REG, ą▒čāą┤čāčé ą╝ą░čüą║ąĖčĆąŠą▓ą░čéčīčüčÅ.

ŌĆó ąŻčĆąŠą▓ąĮąĖ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐ąŠą▓čŗčłą░čÄčéčüčÅ ąŠčé 1 (čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé) ą┤ąŠ 15 (čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé).

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ čüčéą░čéąĖč湥čüą║ąĖ ą┐čĆąĖąŠčĆąĖčéąĖąĘąĖčĆčāčÄčéčüčÅ ą┐ąŠ ąĖčģ ID, ą┐čĆąĖ čŹč鹊ą╝ čüą░ą╝čŗą╣ ą╝ą░ą╗čŗą╣ ID ą┐ąŠą╗čāčćą░ąĄčé čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé.

4. Pending State (0-1).

ŌĆó ą×čéčĆą░ąČą░ąĄčé ąĘą░čģą▓ą░č湥ąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą│ąŠ ąĖ ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ interrupt ID čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé (read-only) ą▓ čĆąĄą│ąĖčüčéčĆąĄ INTERRUPT_CORE0_CPU_INT_EIP_STATUS_REG ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ.

ŌĆó ą×ąČąĖą┤ą░čÄčēąĄąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 CPU ą▓ąŠą╣ą┤ąĄčé ą▓ ą╗ąŠą▓čāčłą║čā (trap), ąĄčüą╗ąĖ ąĮąĄčé ą┤čĆčāą│ąĖčģ ąŠąČąĖą┤ą░čÄčēąĖčģ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝.

ŌĆó ąĪčćąĖčéą░ąĄčéčüčÅ, čćč鹊 ąŠąČąĖą┤ą░čÄčēąĄąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čÅą▓ą╗čÅąĄčéčüčÅ "ąĘą░čÅą▓ą╗ąĄąĮąĮčŗą╝" (claimed) ąĄčüą╗ąĖ ąŠąĮąŠ ą▓čŗč鹥čüąĮčÅąĄčé ąŠą▒čĆą░ą▒ąŠčéą║čā ą┤čĆčāą│ąŠą│ąŠ ą║ąŠą┤ą░ ąĖ ąĘą░čüčéą░ą▓ą╗čÅąĄčé CPU ą┐ąĄčĆąĄą╣čéąĖ ą┐ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝čā ą▓ąĄą║č鹊čĆčā ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (trap vector address).

ŌĆó ąÆčüąĄ ąŠąČąĖą┤ą░čÄčēąĖąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą║ą░ ąĮąĄ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ, ąŠą▒ąŠąĘąĮą░čćą░čÄčéčüčÅ ą║ą░ą║ "ąĮąĄ ąĘą░čÅą▓ą╗ąĄąĮąĮčŗąĄ" (unclaimed).

5. Clear State (0-1).

ŌĆó ą¤ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ąŠčćąĖčüčéąĖčé čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąĘą░čÅą▓ą╗ąĄąĮąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, čĆą░ą▒ąŠčéą░čÄčēąĖčģ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā (edge).

ŌĆó ą¤ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĖ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüą▒čĆąŠčü čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ INTERRUPT_CORE0_CPU_INT_CLEAR_REG.

ŌĆó ąŁč鹊čé ą▒ąĖčé ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, čĆą░ą▒ąŠčéą░čÄčēąĄąĄ ą┐ąŠ čāčĆąŠą▓ąĮčÄ (level), ąĖ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠčćąĖčēąĄąĮąŠ ąĖąĘ ąĖčüč鹊čćąĮąĖą║ą░.

ŌĆó ąĪąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┤ą╗čÅ unclaimed ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéąĖą┐ą░ edge ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ čüą▒čĆąŠčłąĄąĮąŠ (flushed), ą┐čāč鹥ą╝ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ INTERRUPT_CORE0_CPU_INT_ENABLE_REG, ąĖ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ č鹊ą│ąŠ ąČąĄ čüą░ą╝ąŠą│ąŠ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ INTERRUPT_CORE0_CPU_INT_CLEAR_REG.

ąÜąŠą│ą┤ą░ CPU ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé ąŠąČąĖą┤ą░čÄčēąĄąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

ŌĆó CPU čüąŠčģčĆą░ąĮčÅąĄčé ą░ą┤čĆąĄčü č鹥ą║čāčēąĄą╣ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝ąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ mepc, čćč鹊ą▒čŗ ą┐ąŠąĘąČąĄ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖčéčī ąĄčæ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ.

ŌĆó CPU ąŠą▒ąĮąŠą▓ą╗čÅąĄčé ąĘąĮą░č湥ąĮąĖąĄ mcause ąĮą░ ID ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄą╝ąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó CPU ą║ąŠą┐ąĖčĆčāąĄčé čüąŠčüč鹊čÅąĮąĖąĄ MIE ą▓ MPIE, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ąŠčćąĖčēą░ąĄčé MIE, č鹥ą╝ čüą░ą╝čŗą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ ąĘą░ą┐čĆąĄčēą░čÄčéčüčÅ.

ŌĆó CPU ą▓čģąŠą┤ąĖčé ą▓ trap ą┐čāč鹥ą╝ ą┐ąĄčĆąĄčģąŠą┤ą░ ą┐ąŠ ą▓čŗčĆąŠą▓ąĮąĄąĮąĮąŠą╝čā ąĮą░ čĆą░ąĘą╝ąĄčĆ čüą╗ąŠą▓ą░ (word-aligned) čüą╝ąĄčēąĄąĮąĖčÄ ą░ą┤čĆąĄčüą░, čüąŠčģčĆą░ąĮąĄąĮąĮąŠą│ąŠ ą▓ mtvec.

ąóą░ą▒ą╗ąĖčåą░ 1-3 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ą║ą░ąČą┤ąŠą│ąŠ interrupt ID ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▓ąĄą║č鹊čĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (trap-vector address). ąĢčüą╗ąĖ ą║čĆą░čéą║ąŠ, č鹊 word aligned trap address ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ ID = i ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗčćąĖčüą╗ąĄąĮ ą║ą░ą║ (mtvec + 4i).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ID = 0 ąĮąĄą┤ąŠčüčéčāą┐ąĄąĮ, ą┐ąŠčŹč鹊ą╝čā ąĮąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąĘą░čģą▓ą░čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ą¤čĆąĖčćąĖąĮą░ ą▓ č鹊ą╝, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ trap vector address (mtvec + 0x00) ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ąĖčüą║ą╗čÄč湥ąĮąĖą╣ (exceptions).

ąóą░ą▒ą╗ąĖčåą░ 1-3. ąÜą░čĆčéą░ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓ ą┤ą╗čÅ ą░ą┤čĆąĄčüąŠą▓ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

| ID |

ąÉą┤čĆąĄčü |

| 0 |

ąØąĄą┤ąŠčüčéčāą┐ąĮąŠ |

| 1 |

mtvec + 0x04 |

| 2 |

mtvec + 0x08 |

| 3 |

mtvec + 0x0C |

| 4 |

mtvec + 0x10 |

| 5 |

mtvec + 0x14 |

| 6 |

mtvec + 0x18 |

| 7 |

mtvec + 0x1C |

| 8 |

mtvec + 0x20 |

| 9 |

mtvec + 0x24 |

| 10 |

mtvec + 0x28 |

| 11 |

mtvec + 0x2C |

| 12 |

mtvec + 0x30 |

| 13 |

mtvec + 0x34 |

| 14 |

mtvec + 0x38 |

| 15 |

mtvec + 0x3C |

| 16 |

mtvec + 0x40 |

| 17 |

mtvec + 0x44 |

| 18 |

mtvec + 0x48 |

| 19 |

mtvec + 0x4C |

| 20 |

mtvec + 0x50 |

| 21 |

mtvec + 0x54 |

| 22 |

mtvec + 0x58 |

| 23 |

mtvec + 0x5C |

| 24 |

mtvec + 0x60 |

| 25 |

mtvec + 0x64 |

| 26 |

mtvec + 0x68 |

| 27 |

mtvec + 0x6C |

| 28 |

mtvec + 0x70 |

| 29 |

mtvec + 0x74 |

| 30 |

mtvec + 0x78 |

| 31 |

mtvec + 0x7C |

ą¤ąŠčüą╗ąĄ ą┐ąĄčĆąĄčģąŠą┤ą░ ąĮą░ ą░ą┤čĆąĄčü ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠč鹊ą║ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ, čģąŠčéčÅ čüą║ąŠčĆąĄąĄ ą▓čüąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé ąŠą▒čĆą░ą▒ąŠčéą░ąĮąŠ (ąĖ ąŠčćąĖčēąĄąĮąŠ) ą▓ ą║ą░ą║ąŠą╝-č鹊 ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ (interrupt service routine, ISR), ąĖ ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ ą▓ąŠąĘąŠą▒ąĮąŠą▓ąĖčéčüčÅ, ą║ą░ą║ č鹊ą╗čīą║ąŠ CPU ą▓čŗą┐ąŠą╗ąĮąĖčé ąĖąĮčüčéčĆčāą║čåąĖčÄ MRET.

ą¤čĆąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ MRET ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

ŌĆó CPU ą║ąŠą┐ąĖčĆčāąĄčé čüąŠčüč鹊čÅąĮąĖąĄ MPIE ąŠą▒čĆą░čéąĮąŠ ą▓ MIE, ąĖ ąĘą░č鹥ą╝ ąŠčćąĖčēą░ąĄčé MPIE. ąŁč鹊 ąĘąĮą░čćąĖčé, čćč鹊 ąĄčüą╗ąĖ čĆą░ąĮąĄąĄ MPIE ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą┐ąŠčüą╗ąĄ MRET ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ MIE, čćč鹊 ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ čĆą░ąĘčĆąĄčłąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó CPU ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą┐ąŠ ą░ą┤čĆąĄčüčā, čüąŠčģčĆą░ąĮąĄąĮąĮąŠą╝čā ą▓ mepc, ąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ.

ąĢčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ-čāą┐čĆą░ą▓ą╗čÅąĄą╝čāčÄ ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ąĮčāčéčĆąĖ ISR, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą┤ą░ą╗ąĄąĄ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąĀąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ ą┐ąŠ ąŠą▒čĆą░ą▒ąŠčéą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣".

ąØąĖąČąĄ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą╝ąŠą╝ąĄąĮčéčŗ, ąŠą┐ąĖčüčŗą▓ą░čÄčēąĖąĄ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░:

ŌĆó ąóąŠą╗čīą║ąŠ ąĄčüą╗ąĖ čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄąĮčāą╗ąĄą▓ąŠą╣ ą┐čĆąĖąŠčĆąĖč鹥čé, ą║ąŠč鹊čĆčŗą╣ ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĄąĮ ąĘąĮą░č湥ąĮąĖčÄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┐ąŠčĆąŠą│ą░, ąŠąĮąŠ ą▒čāą┤ąĄčé ąŠčéčĆą░ąČąĄąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆąĄ INTERRUPT_CORE0_CPU_INT_EIP_STATUS_REG.

ŌĆó ąĢčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ąĖą┤ąĖą╝ąŠ ą▓ čĆąĄą│ąĖčüčéčĆąĄ INTERRUPT_CORE0_CPU_INT_EIP_STATUS_REG, ąĖ ą┐ąŠą║ą░ ąĮąĄ ąŠą▒čĆą░ą▒ąŠčéą░ąĮąŠ, č鹊 ąĄą│ąŠ ą╝ąŠąČąĮąŠ ą╝ą░čüą║ąĖčĆąŠą▓ą░čéčī (ąĖ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĄą│ąŠ ąŠą▒čĆą░ą▒ąŠčéą║čā) ą┐čāč鹥ą╝ ą╗ąĖą▒ąŠ ą┐ąŠąĮąĖąČąĄąĮąĖčÅ ąĄą│ąŠ ą┐čĆąĖąŠčĆąĖč鹥čéą░, ą╗ąĖą▒ąŠ ą┐čāč鹥ą╝ ą┐ąŠą▓čŗčłąĄąĮąĖčÅ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆąŠą│ą░.

ŌĆó ąĢčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą▓ąĖą┤ąĖą╝ąŠąĄ ą▓ INTERRUPT_CORE0_CPU_INT_EIP_STATUS_REG, ą▒čŗą╗ąŠ čüą▒čĆąŠčłąĄąĮąŠ (ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▒čŗą╗ą░ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮą░ ąĄą│ąŠ ąŠą▒čĆą░ą▒ąŠčéą║ą░), č鹊 ąŠąĮąŠ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮąŠ (ąĖ ąŠčćąĖčēąĄąĮąŠ, ąĄčüą╗ąĖ čā ąĮąĄą│ąŠ čéąĖą┐ edge).

[ąĀąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ ą┐ąŠ ąŠą▒čĆą░ą▒ąŠčéą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣]

ąÉčüą┐ąĄą║čéčŗ ą╗ą░č鹥ąĮčéąĮąŠčüčéąĖ. ą¤čĆąĖ ąĮą░čüčéčĆąŠą╣ą║ąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĘą░ą┤ąĄčƹȹ║ą░. ąÆ čāčüčéą░ąĮąŠą▓ąĖą▓čłąĄą╝čüčÅ čĆą░ą▒ąŠč湥ą╝ čüąŠčüč鹊čÅąĮąĖąĖ (steady state) čā ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĘą░ą┤ąĄčƹȹ║ą░ čäąĖą║čüąĖčĆąŠą▓ą░ąĮą░, ąĖ čĆą░ą▓ąĮą░ 4 čéą░ą║čéą░ą╝. Steady state ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮąĄą┤ą░ą▓ąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĮąĄ ą▒čŗą╗ąŠ ą▓ąĮąĄčüąĄąĮąŠ ąĮąĖą║ą░ą║ąĖčģ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▓čĆąĄą╝čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą╗čÄą▒ąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą│ąŠ ą┤ą╗čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, čüąŠčüčéą░ą▓ąĖčé čĆąŠą▓ąĮąŠ 4 čéą░ą║čéą░ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ CPU ąĮą░čćąĮąĄčé ąŠą▒čĆą░ą▒ąŠčéą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ą¤čĆąĖ čŹč鹊ą╝ čéą░ą║ąČąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 CPU ą╝ąŠąČąĄčé ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┤ąŠ 5 ąĖąĮčüčéčĆčāą║čåąĖą╣ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą▓čŗč鹥čüąĮąĄąĮąĖąĄ č鹥ą║čāčēąĄą│ąŠ ą║ąŠą┤ą░.

ąÆčüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą╝ąŠą┤ąĖčäąĖčåąĖčĆčāčÄčéčüčÅ, ąŠąĮ ą▓čģąŠą┤ąĖčé ą▓ ą┐ąĄčĆąĄčģąŠą┤ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĄčé ąĘą░ąĮąĖą╝ą░čéčī ą┤ąŠ 4 čéą░ą║č鹊ą▓, ą┐ąŠą║ą░ ąĮąĄ čüčéą░ąĮąĄčé čüąĮąŠą▓ą░ ą░ą║čéąĖą▓ąĮčŗą╝ steady state. ąÆąŠ ą▓čĆąĄą╝čÅ čŹč鹊ą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąŠčĆčÅą┤ąŠą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄ ą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝, ąĖ ą┐ąŠčŹč鹊ą╝čā ą┤ą╗čÅ ą▒ąĄąĘąŠą┐ą░čüąĮąŠčüčéąĖ čéčĆąĄą▒čāąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĖąĘą╝ąĄčĆąĄąĮąĖą╣ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐čĆąŠą▒ą╗ąĄą╝ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ.

ąóą░ą║ąČąĄ čüą╗ąĄą┤čāąĄčé ąĘą░ą╝ąĄčéąĖčéčī, čćč鹊 čĆąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą╗ąĄąČą░čé ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą░ą┤čĆąĄčüąŠą▓ APB, čüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą╗čÄą▒ąŠą╣ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī ą▓ čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ą╝ąŠąČąĄčé ąĘą░ąĮčÅčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čéą░ą║č鹊ą▓. ą¤čĆąĖąĮąĖą╝ą░čÅ ą▓ąŠ ą▓ąĮąĖą╝ą░ąĮąĖąĄ ą▓čŗčłąĄčāą┐ąŠą╝čÅąĮčāčéčŗąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅą╝ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čüą╗ąĄą┤ąŠą▓ą░čéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ, ąŠą┐ąĖčüą░ąĮąĮąŠą╣ ąĮąĖąČąĄ, ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ ą╗čÄą▒ąŠą│ąŠ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

1. ąĪąŠčģčĆą░ąĮąĖč鹥 čüąŠčüč鹊čÅąĮąĖąĄ MIE ąĖ ąŠčćąĖčüčéąĖč鹥 ą▓ 0 MIE.

2. ąÆčŗą┐ąŠą╗ąĮąĖč鹥 ąŠą┐ąĄčĆą░čåąĖčÄ read-modify-write ąŠą┤ąĮąŠą│ąŠ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

3. ąÆčŗą┐ąŠą╗ąĮąĖč鹥 ąĖąĮčüčéčĆčāą║čåąĖčÄ FENCE, čćč鹊ą▒čŗ ą┐ąŠą┤ąŠąČą┤ą░čéčī ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą╗čÄą▒ąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ.

4. ąś ąĮą░ą║ąŠąĮąĄčå, ą▓ąŠčüčüčéą░ąĮąŠą▓ąĖč鹥 čüąŠčüč鹊čÅąĮąĖąĄ MIE.

ąśąĘ-ąĘą░ ą║čĆąĖčéąĖč湥čüą║ąĖčģ ąŠą│čĆą░ąĮąĖč湥ąĮąĖą╣ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ąĘą░ą┐čĆąĄčéąĖčéčī ą│ą╗ąŠą▒ą░ą╗čīąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (MIE=0) ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ čĆąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ąĖ ąĘą░č鹥ą╝ ą▓ąŠčüčüčéą░ąĮąŠą▓ąĖčéčī MIE, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▓čŗčłąĄ.

ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąŠą┐ąĖčüą░ąĮąĮąŠą╣ ą▓čŗčłąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ąŠąĘąŠą▒ąĮąŠą▓ąĖčé čĆą░ą▒ąŠčéčā ą▓ čāčüčéą░ąĮąŠą▓ąĖą▓čłąĄą╝čüčÅ čüąŠčüč鹊čÅąĮąĖąĖ (steady state).

ą¤čĆąŠčåąĄą┤čāčĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮčŗ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ, ą┐ąŠčüą║ąŠą╗čīą║čā ą▒ąĖčé MIE ą▓ mstatus čĆą░ą▓ąĄąĮ 0. ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ čāčüčéą░ąĮąŠą▓ąĖčéčī MIE=1 ą┐ąŠčüą╗ąĄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čüč鹥ą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ą▓ą║ą╗čÄčćą░čÅ čāčüčéą░ąĮąŠą▓ą║čā mtvec ą▓ ą░ą┤čĆąĄčü ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ).

ąÆąŠ ą▓čĆąĄą╝čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą┤ą░, ąĄčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ n ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮąŠ, čüą╗ąĄą┤čāąĄčé ą┐čĆąĖą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┤ąĄą╣čüčéą▓ąĖą╣:

1. ąĪąŠčģčĆą░ąĮąĖč鹥 čüąŠčüč鹊čÅąĮąĖąĄ MIE ąĖ ąŠčćąĖčüčéąĖč鹥 MIE ą▓ 0.

2. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čéąĖą┐ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (edge/level) čāčüčéą░ąĮąŠą▓ąĖč鹥 ąĖą╗ąĖ čüą▒čĆąŠčüčīč鹥 n-ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ INTERRUPT_CORE0_CPU_INT_TYPE_REG.

3. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą┐čĆąĖąŠčĆąĖč鹥čé ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ąĘąĮą░č湥ąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆ INTERRUPT_CORE0_CPU_INT_PRI_n_REG ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1 ą┤ąŠ 15.

4. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 n-ą▒ąĖčé ą▓ INTERRUPT_CORE0_CPU_INT_ENABLE_REG.

5. ąÆčŗą┐ąŠą╗ąĮąĖč鹥 ąĖąĮčüčéčĆčāą║čåąĖčÄ FENCE.

6. ąÆąŠčüčüčéą░ąĮąŠą▓ąĖč鹥 čüąŠčüč鹊čÅąĮąĖąĄ MIE.

ąÜąŠą│ą┤ą░ ąŠąČąĖą┤ą░čÄčé ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ąŠą┤ąĮąŠ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, CPU ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčé (claims) ąŠą▒čĆą░ą▒ąŠčéą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü čüą░ą╝čŗą╝ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝, ąĖ ą┐ąĄčĆąĄčüą║ą░ą║ąĖą▓ą░ąĄčé ąĮą░ trap vector address, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ID ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮą░čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖčÅ ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī mcause ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čéąĖą┐ą░ trap (mcause(31) = 1 ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĖ = 0 ą┤ą╗čÅ ąĖčüą║ą╗čÄč湥ąĮąĖą╣), ąĖ ąĘą░č鹥ą╝ ID ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (mcause(4-0) ą┤ą░ąĄčé ID ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖą╗ąĖ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ). ąŁč鹊 ą╝ąŠąČąĄčé ąĮąĄ ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ, ąĄčüą╗ąĖ ą║ą░ąČą┤čŗą╣ ą░ą┤čĆąĄčü ą▓ čéą░ą▒ą╗ąĖčåąĄ ą▓ąĄą║č鹊čĆąŠą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čĆą░ąĘąĮčŗą╝ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ą╝. ąÆ ą║ąŠąĮąĄčćąĮąŠą╝ ąĖč鹊ą│ąĄ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĖ trap ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗čÅčÄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ISR ą┤ą╗čÅ čŹč鹊ą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąØą░ ą▓čģąŠą┤ąĄ ą▓ ISR ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčī n-ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ INTERRUPT_CORE0_CPU_INT_CLEAR_REG, ąĄčüą╗ąĖ čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéąĖą┐ edge, ąĖą╗ąĖ ąŠčćąĖčüčéąĖčéčī ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ čā ąĮąĄą│ąŠ čéąĖą┐ level.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ąŠą▒ąĮąŠą▓ąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ INTERRUPT_CORE0_CPU_INT_THRESH_REG ąĖ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī MIE=1, čćč鹊ą▒čŗ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąŠą┐čĆąĖąŠčĆąĖč鹥čéąĮčŗą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ ą▓čŗč鹥čüąĮąĖčéčī č鹥ą║čāčēąĖą╣ ISR (č鹥ą╝ čüą░ą╝čŗą╝ čĆąĄą░ą╗ąĖąĘčāąĄčéčüčÅ ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣), ąŠą┤ąĮą░ą║ąŠ ą┐ąĄčĆąĄą┤ čŹčéąĖą╝ ą▓čüąĄ čüąŠčüč鹊čÅąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ CSR ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čüąŠčģčĆą░ąĮąĄąĮąŠ (mepc, mstatus, mcause, ąĖ čé. ą┤.), ą┐ąŠčüą║ąŠą╗čīą║čā ąŠąĮąĖ ą▒čāą┤čāčé ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮčŗ ą▓čŗč鹥čüąĮčÅčÄčēąĖą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝. ą¤ąŠąĘąČąĄ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ISR, ąĘąĮą░č湥ąĮąĖčÅ čŹčéąĖčģ CSR ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ.

ąś ąĮą░ą║ąŠąĮąĄčå, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą▓ąĄčĆąĮąĄčéčüčÅ ąĖąĘ ISR ąŠą▒čĆą░čéąĮąŠ ą▓ trap handler, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ MRET ą┤ą╗čÅ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą┤ą░.

ąÆą┐ąŠčüą╗ąĄą┤čüčéą▓ąĖąĖ, ąĄčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ n ą▒ąŠą╗čīčłąĄ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ąĖ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮąŠ, ąĮčāąČąĮąŠ ą┐čĆąĖą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┤ąĄą╣čüčéą▓ąĖą╣:

1. ąĪąŠčģčĆą░ąĮąĖč鹥 čüąŠčüč鹊čÅąĮąĖąĄ MIE ąĖ ąŠčćąĖčüčéąĖč鹥 MIE ą▓ 0.

2. ą¤čĆąŠą▓ąĄčĆčīč鹥 ą▓ čĆąĄą│ąĖčüčéčĆąĄ INTERRUPT_CORE0_CPU_INT_EIP_STATUS_REG, ąĖą╝ąĄąĄčéčüčÅ ą╗ąĖ ąŠąČąĖą┤ą░čÄčēąĄąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

3. ąŻčüčéą░ąĮąŠą▓ąĖč鹥/čüą▒čĆąŠčüčīč鹥 ą▒ąĖčé n čĆąĄą│ąĖčüčéčĆą░ INTERRUPT_CORE0_CPU_INT_ENABLE_REG.

4. ąĢčüą╗ąĖ ąĮą░ čłą░ą│ąĄ 2 ą▒čŗą╗ąŠ ąŠą▒ąĮą░čĆčāąČąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čéąĖą┐ą░ edge, č鹊 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮ n-ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ INTERRUPT_CORE0_CPU_INT_CLEAR_REG, č鹥ą╝ čüą░ą╝čŗą╝ ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ (flush) ąĄą│ąŠ čüčéą░čéčāčü ąŠąČąĖą┤ą░ąĮąĖčÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ.

5. ąÆčŗą┐ąŠą╗ąĮąĖč鹥 ąĖąĮčüčéčĆčāą║čåąĖčÄ FENCE.

6. ąÆąŠčüčüčéą░ąĮąŠą▓ąĖč鹥 čüąŠčüč鹊čÅąĮąĖąĄ MIE.

ą¤ąŠą║ą░ąĘą░ąĮąĮą░čÅ ąĘą┤ąĄčüčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣ ą▓čüąĄą│ąŠ ą╗ąĖčłčī čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝ą░čÅ. ąĀąĄą░ą╗čīąĮą░čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖčÅ ą¤ą× ą╝ąŠąČąĄčé ą╝ąĄąĮčÅčéčīčüčÅ.

[ą×ą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓]

ąÉą┤čĆąĄčü ą╝ą░čéčĆąĖčåčŗ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Interrupt Matrix) čĆą░ą▓ąĄąĮ 0x600C2000, ąĖ ąĘą░ąĮąĖą╝ą░ąĄčé 4 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ (ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąŠčé 0x600C2000 ą┤ąŠ 0x600C2FFF ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ). ąÉą┤čĆąĄčüą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▒ą░ąĘąĖčĆčāčÄčéčüčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą░ą┤čĆąĄčüą░ Interrupt Controller, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮąŠą│ąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 3-4 ą│ą╗ą░ą▓čŗ 3 "System and Memory" [1]. ą¤ąŠą╗ąĮčŗą╣ čüą┐ąĖčüąŠą║ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ ą┐ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čüą╝. ą▓ ą│ą╗ą░ą▓ąĄ 8 "Interrupt Matrix (INTMTRX)", čüąĄą║čåąĖčÅ 8.4, ą│čĆčāą┐ą┐ą░ čĆąĄą│ąĖčüčéčĆąŠą▓ "CPU Interrupt Registers" [1].

ąÆ čéą░ą▒ą╗ąĖčåąĄ 3-4 ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓čüąĄ ą╝ąŠą┤čāą╗ąĖ/ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ąĖčģ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą┤ąĖą░ą┐ą░ąĘąŠąĮčŗ ą░ą┤čĆąĄčüąŠą▓. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ą╝ąŠą┤čāą╗ąĄą╣/ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą▓ čüč鹊ą╗ą▒čåą░čģ "ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓" (ą▓ą║ą╗čÄčćą░čÅ "ąØąĖąČąĮąĖą╣ ą░ą┤čĆąĄčü" ąĖ "ąÆąĄčĆčģąĮąĖą╣ ą░ą┤čĆąĄčü").

ąóą░ą▒ą╗ąĖčåą░ 3-4. ąÜą░čĆčéą░ ą░ą┤čĆąĄčüąŠą▓ ą╝ąŠą┤čāą╗ąĄą╣ / ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ą¤ąĄčĆąĖčä. čāčüčéčĆąŠą╣čüčéą▓ąŠ

|

ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓

|

ąĀą░ąĘą╝ąĄčĆ

(ą▒ą░ą╣čé) |

| ąØąĖąČąĮąĖą╣ ą░ą┤čĆąĄčü |

ąÆąĄčĆčģąĮąĖą╣ ą░ą┤čĆąĄčü |

| UART Controller 0 |

0x60000000 |

0x60000FFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x60001000 |

0x60001FFF |

|

| SPI Controller 1 |

0x60002000 |

0x60002FFF |

4096 |

| SPI Controller 0 |

0x60003000 |

0x60003FFF |

4096 |

| GPIO |

0x60004000 |

0x60004FFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x60005000 |

0x60005FFF |

|

| TIMER |

0x60007000 |

0x60007FFF |

4096 |

| Low-Power Management |

0x60008000 |

0x60008FFF |

4096 |

| IO MUX |

0x60009000 |

0x60009FFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x6000A000 |

0x6000FFFF |

|

| UART Controller 1 |

0x60010000 |

0x60010FFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x60011000 |

0x60012FFF |

|

| I2C Controller |

0x60013000 |

0x60013FFF |

4096 |

| UHCIO |

0x60014000 |

0x60014FFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x60015000 |

0x60015FFF |

|

| Remote Control Peripheral |

0x60016000 |

0x60016FFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x60017000 |

0x60018FFF |

|

| LED PWM Controller |

0x60019000 |

0x60019FFF |

4096 |

| eFuse Controller |

0x6001A000 |

0x6001AFFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x6001B000 |

0x6001EFFF |

|

| Timer Group 0 |

0x6001F000 |

0x6001FFFF |

4096 |

| Timer Group 1 |

0x60020000 |

0x60020FFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x60021000 |

0x60022FFF |

|

| System Timer |

0x60023000 |

0x60023FFF |

4096 |

| SPI Controller 2 |

0x60024000 |

0x60024FFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x60025000 |

0x60025FFF |

|

| APB Controller |

0x60026000 |

0x60026FFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x60027000 |

0x6002AFFF |

|

| Two-wire Automotive Interface |

0x6002B000 |

0x6002BFFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x6002C000 |

0x6002CFFF |

|

| I2S Controller |

0x6002D000 |

0x6002DFFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x6002E000 |

0x60039FFF |

|

| AES Accelerator |

0x6003A000 |

0x6003AFFF |

4096 |

| SHA Accelerator |

0x6003B000 |

0x6003BFFF |

4096 |

| RSA Accelerator |

0x6003C000 |

0x6003CFFF |

4096 |

| Digital Signature |

0x6003D000 |

0x6003DFFF |

4096 |

| HMAC Accelerator |

0x6003E000 |

0x6003EFFF |

4096 |

| GDMA Controller |

0x6003F000 |

0x6003FFFF |

4096 |

| ADC Controller |

0x60040000 |

0x60040FFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x60041000 |

0x6002FFFF |

|

| USB Serial/JTAG Controller |

0x60043000 |

0x60043FFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x60044000 |

0x600BFFFF |

|

| System Registers |

0x600C0000 |

0x600C0FFF |

4096 |

| Sensitive Register |

0x600C1000 |

0x600C1FFF |

4096 |

| Interrupt Matrix |

0x600C2000 |

0x600C2FFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x600C3000 |

0x600C3FFF |

|

| Configure Cache |

0x600C4000 |

0x600CBFFF |

32768 |

| External Memory Encryption and Decryption |

0x600CC000 |

0x600CCFFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x600CD000 |

0x600CDFFF |

|

| Assist Debug |

0x600CE000 |

0x600CEFFF |

4096 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0x600CF000 |

0x600CFFFF |

|

| World Controller |

0x600D0000 |

0x600D0FFF |

4096 |

[Interrupt Matrix (INTMTRX)]

ą£ą░čéčĆąĖčåą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą▓čüčéčĆąŠąĄąĮąĮą░čÅ ą▓ ESP32-C3, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗čÅąĄčé ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą▓ ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ESP-RISC-V CPU, čćč鹊ą▒čŗ čüą▓ąŠąĄą▓čĆąĄą╝ąĄąĮąĮąŠ ąĖąĮč乊čĆą╝ąĖčĆąŠą▓ą░čéčī CPU ąŠ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐ąŠčüčéčāą┐ą░čÄčēąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąŻ ESP32-C3 ąĄčüčéčī 62 ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ąŁčéą░ ą╝ą░čéčĆąĖčåą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░, čćč鹊ą▒čŗ ąŠč鹊ą▒čĆą░ąĘąĖčéčī ąĖčģ ąĮą░ 31 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ CPU.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ čŹč鹊ą╣ ą│ą╗ą░ą▓ąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čüč乊ą║čāčüąĖčĆąŠą▓ą░ąĮąŠ ąĮą░ č鹊ą╝, ą║ą░ą║ ąŠč鹊ą▒čĆą░ąČą░čÄčéčüčÅ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CPU. ąæąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ą┐čĆąŠ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą▓ąĄą║č鹊čĆą░, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝čŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ISA, čüą╝. [2].

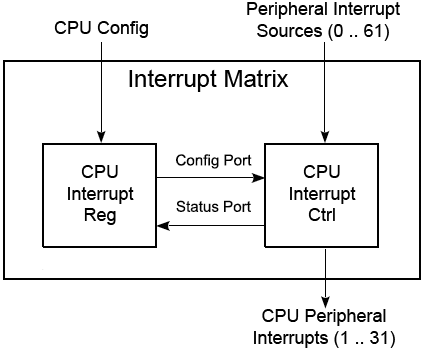

ążčāąĮą║čåąĖąĖ Interrupt Matrix (INTMTRX):

ŌĆó ąØą░ ą▓čģąŠą┤ąĄ ą┐čĆąĖąĮąĖą╝ą░ąĄčé čüąĖą│ąĮą░ą╗čŗ ą┤ąŠ 62 ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ŌĆó ąØą░ ą▓čŗčģąŠą┤ąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┤ą╗čÅ CPU ą┤ąŠ 31 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ŌĆó ą×ą┐čĆąŠčü č鹥ą║čāčēąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐čĆąĖąŠčĆąĖč鹥čéą░, čéąĖą┐ą░, ą┐ąŠčĆąŠą│ą░ ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CPU.

ąØą░ čĆąĖčü. 8-1 ą┐ąŠą║ą░ąĘą░ąĮą░ čüčéčĆčāą║čéčāčĆą░ ą╝ą░čéčĆąĖčåčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ąĀąĖčü. 8-1. ąĪčéčĆčāą║čéčāčĆą░ Interrupt Matrix.

ąśčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąÆčüąĄą│ąŠ čā ESP32-C3 ąĄčüčéčī 62 ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ąÆ čéą░ą▒ą╗ąĖčåąĄ 8-1 ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓čüąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ąĖ ąĖčģ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĖ čüčéą░čéčāčüą░.

ŌĆó ąĪč鹊ą╗ą▒ąĄčå "Ōä¢": ąĮąŠą╝ąĄčĆ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 0 .. 61.

ŌĆó ąĪč鹊ą╗ą▒ąĄčå "ąōą╗ą░ą▓ą░": ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą▓ ą║ą░ą║ąŠą╣ ą│ą╗ą░ą▓ąĄ [1] ą┐ąŠą┤čĆąŠą▒ąĮąŠ ąŠą┐ąĖčüą░ąĮ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó ąĪč鹊ą╗ą▒ąĄčå "ąśčüč鹊čćąĮąĖą║": ąĖą╝čÅ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

ŌĆó ąĪč鹊ą╗ą▒ąĄčå "ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ": čĆąĄą│ąĖčüčéčĆčŗ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ CPU.

ŌĆó ąĪč鹊ą╗ą▒ąĄčå "ąĀąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░": čĆąĄą│ąĖčüčéčĆčŗ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ ąĖąĮą┤ąĖą║ą░čåąĖąĖ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ŌĆō ąĪč鹊ą╗ą▒ąĄčå "ąĀąĄą│ąĖčüčéčĆ čüčéą░čéčāčü - ąæąĖčé": ą┐ąŠąĘąĖčåąĖčÅ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĄą│ąŠ čüčéą░čéčāčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆō ąĪč鹊ą╗ą▒ąĄčå "ąĀąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ - ąśą╝čÅ": ą╝ąĮąĄą╝ąŠąĮąĖč湥čüą║ąŠąĄ ąĖą╝čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ čüčéą░čéčāčüą░.

ąóą░ą▒ą╗ąĖčåą░ 8-1. ąĀąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ/čüčéą░čéčāčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CPU ąĖ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

Ōä¢

|

ąōą╗ą░ą▓ą░

|

ąśčüč鹊čćąĮąĖą║

|

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ

|

ąĀąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ |

| ąæąĖčé |

ąśą╝čÅ |

| 0 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0 |

INTERRUPT_CORE0_

INTR_STATUS_0_REG |

| 1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

1 |

| 2 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

2 |

| 3 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

3 |

| 4 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

4 |

| 5 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

5 |

| 6 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

6 |

| 7 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

7 |

| 8 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

8 |

| 9 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

9 |

| 10 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

10 |

| 11 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

11 |

| 12 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

12 |

| 13 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

13 |

| 14 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

14 |

| 15 |

UART Controller (UART) |

UHCI0_INTR |

INTERRUPT_CORE0_UHCI0_INTR_MAP_REG |

15 |

| 16 |

IO MUX and GPIO Matrix (GPIO, IO MUX) |

GPIO_PROCPU_INTR |

INTERRUPT_CORE0_GPIO_INTERRUPT_PRO_MAP_REG |

16 |

| 17 |

GPIO_PROCPU_NMI_INTR |

INTERRUPT_CORE0_GPIO_INTERRUPT_PRO_NMI_MAP_REG |

17 |

| 18 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

18 |

| 19 |

SPI Controller (SPI) |

GPSPI2_INTR_2 |

INTERRUPT_CORE0_SPI_INTR_2_MAP_REG |

19 |

| 20 |

I2S Controller (I2S) |

I2S_INTR |

INTERRUPT_CORE0_I2S1_INT_MAP_REG |

20 |

| 21 |

UART Controller (UART) |

UART_INTR |

INTERRUPT_CORE0_UART_INTR_MAP_REG |

21 |

| 22 |

UART1_INTR |

INTERRUPT_CORE0_UART1_INTR_MAP_REG |

22 |

| 23 |

LED PWM Controller (LEDC) |

LEDC_INTR |

INTERRUPT_CORE0_LEDC_INT_MAP_REG |

23 |

| 24 |

eFuse Controller (EFUSE) |

EFUSE_INTR |

INTERRUPT_CORE0_EFUSE_INT_MAP_REG |

24 |

| 25 |

Two-wire Automotive Interface (TWAI) |

TWAI_INTR |

INTERRUPT_CORE0_CAN_INT_MAP_REG |

25 |

| 26 |

USB Serial/JTAG Controller (USB_SERIAL_JTAG) |

USB_SERIAL_JTAG_INTR |

INTERRUPT_CORE0_USB_INTR_MAP_REG |

26 |

| 27 |

Low-power Management |

RTC_CNTL_INTR |

INTERRUPT_CORE0_RTC_CORE_INTR_MAP_REG |

27 |

| 28 |

Remote Control Peripheral (RMT) |

RMT_INTR |

INTERRUPT_CORE0_RMT_INTR_MAP_REG |

28 |

| 29 |

I2C Controller (I2C) |

I2C_EXT0_INTR |

INTERRUPT_CORE0_I2C_EXT0_INTR_MAP_REG |

29 |

| 30 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

30 |

| 31 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

31 |

| 32 |

Timer Group (TIMG) |

TG_T0_INTR |

INTERRUPT_CORE0_TG_T0_INT_MAP_REG |

0 |

INTERRUPT_CORE0_

INTR_STATUS_1_REG |

| 33 |

TG_WDT_INTR |

INTERRUPT_CORE0_TG_WDT_INT_MAP_REG |

1 |

| 34 |

TG1_T0_INTR |

INTERRUPT_CORE0_TG1_T0_INT_MAP_REG |

2 |

| 35 |

TG1_WDT_INTR |

INTERRUPT_CORE0_TG1_WDT_INT_MAP_REG |

3 |

| 36 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

4 |

| 37 |

System Timer (SYSTIMER) |

SYSTIMER_TARGET0_INTR |

INTERRUPT_CORE0_SYSTIMER_TARGET0_INT_MAP_REG |

5 |

| 38 |

SYSTIMER_TARGET1_INTR |

INTERRUPT_CORE0_SYSTIMER_TARGET1_INT_MAP_REG |

6 |

| 39 |

SYSTIMER_TARGET2_INTR |

INTERRUPT_CORE0_SYSTIMER_TARGET2_INT_MAP_REG |

7 |

| 40 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

8 |

| 41 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

9 |

| 42 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

10 |

| 43 |

On-Chip Sensor and Analog Signal Processing |

vDIGTAL_ADC_INTR |

INTERRUPT_CORE0_APB_ADC_INT_MAP_REG |

11 |

| 44 |

GDMA Controller (GDMA) |

GDMA_CH0_INTR |

INTERRUPT_CORE0_DMA_CH0_INT_MAP_REG |

12 |

| 45 |

GDMA_CH1_INTR |

INTERRUPT_CORE0_DMA_CH1_INT_MAP_REG |

13 |

| 46 |

GDMA_CH2_INTR |

INTERRUPT_CORE0_DMA_CH2_INT_MAP_REG |

14 |

| 47 |

RSA Accelerator (RSA) |

RSA_INTR |

INTERRUPT_CORE0_RSA_INTR_MAP_REG |

15 |

| 48 |

AES Accelerator (AES) |

AES_INTR |

INTERRUPT_CORE0_AES_INTR_MAP_REG |

16 |

| 49 |

SHA Accelerator (SHA) |

SHA_INTR |

INTERRUPT_CORE0_SHA_INTR_MAP_REG |

17 |

| 50 |

System Registers (SYSREG) |

SW_INTR_0 |

INTERRUPT_CORE0_CPU_INTR_FROM_CPU_0_MAP_REG |

18 |

| 51 |

SW_INTR_1 |

INTERRUPT_CORE0_CPU_INTR_FROM_CPU_1_MAP_REG |

19 |

| 52 |

SW_INTR_2 |

INTERRUPT_CORE0_CPU_INTR_FROM_CPU_2_MAP_REG |

20 |

| 53 |

SW_INTR_3 |

INTERRUPT_CORE0_CPU_INTR_FROM_CPU_3_MAP_REG |

21 |

| 54 |

Debug Assist |

ASSIST_DEBUG_INTR |

INTERRUPT_CORE0_ASSIST_DEBUG_INTR_MAP_REG |

22 |

| 55 |

Permission Control (PMS) [ą▒čāą┤ąĄčé ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąŠ ą┐ąŠąĘąČąĄ] |

PMS_DMA_VIO_INTR |

INTERRUPT_CORE0_DMA_APBPERI_PMS_MONITOR_VIOLATE_INTR_MAP_REG |

23 |

| 56 |

PMS_IBUS_VIO_INTR |

INTERRUPT_CORE0_CORE_0_IRAM0_PMS_MONITOR_VIOLATE_INTR_MAP_REG |

24 |

| 57 |

PMS_DBUS_VIO_INTR |

INTERRUPT_CORE0_CORE_0_DRAM0_PMS_MONITOR_VIOLATE_INTR_MAP_REG |

25 |

| 58 |

PMS_PERI_VIO_INTR |

INTERRUPT_CORE0_CORE_0_PIF_PMS_MONITOR_VIOLATE_INTR_MAP_REG |

26 |

| 59 |

PMS_PERI_VIO_SIZE_INTR |

INTERRUPT_CORE0_CORE_0_PIF_PMS_MONITOR_VIOLATE_SIZE_INTR_MAP_REG |

27 |

| 28 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

28 |

| 29 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

29 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CPU. ESP32-C3 čĆąĄą░ą╗ąĖąĘčāąĄčé čüą▓ąŠą╣ ą╝ąĄčģą░ąĮąĖąĘą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ą╝ąĄčüč鹊 čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ RISC-V Privileged ISA. ąŻ ESP-RISC-V CPU ąĄčüčéčī 31 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą┐čĆąŠąĮčāą╝ąĄčĆąŠą▓ą░ąĮąĮčŗčģ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 1 .. 31. ąÜą░ąČą┤ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ CPU ąĖą╝ąĄąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čüą▓ąŠą╣čüčéą▓ą░.

ŌĆó ąŻčĆąŠą▓ąĮąĖ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ąŠčé 1 (čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé) ą┤ąŠ 15 (čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé).

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗą╣ čéąĖą┐ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ - čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą╗ąĖą▒ąŠ ą┐ąŠ čāčĆąŠą▓ąĮčÄ čüąĖą│ąĮą░ą╗ą░ (level-triggered) ąĖą╗ąĖ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ (edge-triggered).

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü ąĮąĖąĘą║ąĖą╝ čāčĆąŠą▓ąĮąĄą╝ ą╝ąŠąČąĮąŠ ą╝ą░čüą║ąĖčĆąŠą▓ą░čéčī čü ą┐ąŠą╝ąŠčēčīčÄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐ąŠčĆąŠą│ą░ (interrupt threshold).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ą╗čÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ č鹊ą╝, ą║ą░ą║ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CPU, čüą╝. [2].

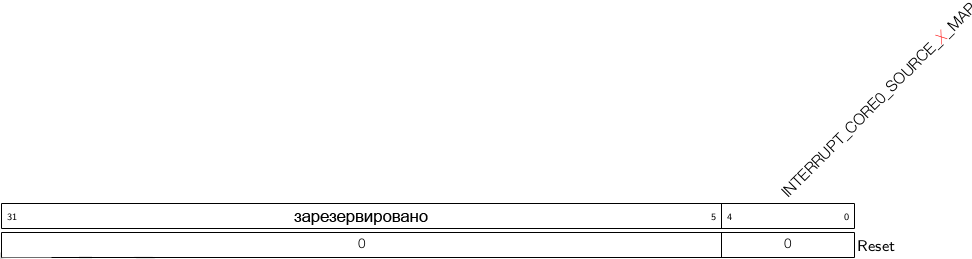

ąÆčŗą┤ąĄą╗ąĄąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ą╗čÅ CPU. ąÆ čŹč鹊ą╣ čüąĄą║čåąĖąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ č鹥čĆą╝ąĖąĮčŗ ą┤ą╗čÅ ąŠą┐ąĖčüą░ąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ą╝ą░čéčĆąĖčåčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ŌĆó Source_X: ąŠąĘąĮą░čćą░ąĄčé ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ą│ą┤ąĄ X ąŠą▒ąŠąĘąĮą░čćą░ąĄčé ąĮąŠą╝ąĄčĆ čŹč鹊ą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ čéą░ą▒ą╗ąĖčåąĄ 8-1.

ŌĆó INTERRUPT_CORE0_SOURCE_X_MAP_REG: ąŠą▒ąŠąĘąĮą░čćą░ąĄčé čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┤ą╗čÅ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (Source_X).

ŌĆó Num_P: ąĖąĮą┤ąĄą║čü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CPU, ą╝ąŠąČąĄčé ą▒čŗčéčī 1 .. 31.

ŌĆó Interrupt_P: ąŠąĘąĮą░čćą░ąĄčé ą┤ą╗čÅ CPU ąĮąŠą╝ąĄčĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ą░ą║ Num_P.

ąÆčŗą┤ąĄą╗ąĄąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (Source_X) ą┤ą╗čÅ CPU. ąŻčüčéą░ąĮąŠą▓ą║ą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ INTERRUPT_CORE0_SOURCE_X_MAP_REG ą┤ą╗čÅ Source_X ą▓ Num_P ą▓čŗą┤ąĄą╗čÅąĄčé čŹč鹊čé ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ Interrupt_P.

ąÆčŗą┤ąĄą╗ąĄąĮąĖąĄ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (Source_Xn) ą┤ą╗čÅ CPU. ąŻčüčéą░ąĮąŠą▓ą║ą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ INTERRUPT_CORE0_SOURCE_Xn_MAP_REG ą║ą░ąČą┤ąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ Num_P ą▓čŗą┤ąĄą╗čÅąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąŠą┤ąĮąŠą│ąŠ ąĖ č鹊ą│ ąČąĄ Interrupt_P. ąøčÄą▒ąŠą╣ ąĖąĘ čŹčéąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī ą░ą║čéąĖą▓ą░čåąĖčÄ CPU Interrupt_P. ąÜąŠą│ą┤ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüąĖą│ąĮą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, CPU ą┤ąŠą╗ąČąĄąĮ ą┐čĆąŠą▓ąĄčĆąĖčéčī čĆąĄą│ąĖčüčéčĆčŗ čüčéą░čéčāčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. [2].

ąŚą░ą┐čĆąĄčé ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ą╗čÅ CPU (Source_X). ą×čćąĖčüčéą║ą░ čĆąĄą│ąĖčüčéčĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ INTERRUPT_CORE0_SOURCE_X_MAP_REG ąĘą░ą┐čĆąĄčéąĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

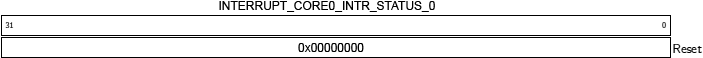

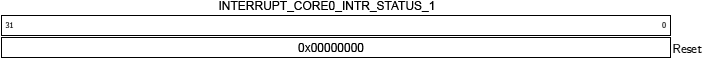

ą×ą┐čĆąŠčü č鹥ą║čāčēąĄą│ąŠ čüčéą░čéčāčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĖ ą╝ąŠą│čāčé ąŠą┐čĆą░čłąĖą▓ą░čéčī čüčéą░čéčāčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ą░ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐čāč鹥ą╝ čćč鹥ąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ INTERRUPT_CORE0_INTR_STATUS_n_REG (čĆąĄą│ąĖčüčéčĆ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ). ąöą╗čÅ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ą╝ąĄąČą┤čā INTERRUPT_CORE0_INTR_STATUS_n_REG ąĖ ąĖčüč鹊čćąĮąĖą║ą░ą╝ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ čüą╝. čéą░ą▒ą╗ąĖčåčā 8-1.

[ą×ą▒čēąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓]

| ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ąÉą┤čĆąĄčü |

ąöąŠčüčéčāą┐ |

| Interrupt Source Mapping Registers (čĆąĄą│ąĖčüčéčĆčŗ ą┐čĆąĖą▓čÅąĘą║ąĖ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ) |

| INTERRUPT_CORE0_PWR_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ PWR_INTR |

0x0008 |

R/W |

| INTERRUPT_CORE0_I2C_MST_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ I2C_MST_INT |

0x002C |

R/W |

| INTERRUPT_CORE0_SLC0_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ SLC0_INTR |

0x0030 |

R/W |

| INTERRUPT_CORE0_SLC1_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ SLC1_INTR |

0x0034 |

R/W |

| INTERRUPT_CORE0_APB_CTRL_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ APB_CTRL_INTR |

0x0038 |

R/W |

| INTERRUPT_CORE0_UHCI0_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ UHCI0_INTR |

0x003C |

R/W |

| INTERRUPT_CORE0_GPIO_INTERRUPT_PRO_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ GPIO_INTERRUPT_PRO |

0x0040 |

R/W |

| INTERRUPT_CORE0_GPIO_INTERRUPT_PRO_NMI_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ GPIO_INTERRUPT_PRO_NMI |

0x0044 |

R/W |

| INTERRUPT_CORE0_SPI_INTR_1_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ SPI_INTR_1 |

0x0048 |

R/W |

| INTERRUPT_CORE0_SPI_INTR_2_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ SPI_INTR_2 |

0x004C |

R/W |

| INTERRUPT_CORE0_I2S1_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ I2S1_INT |

0x0050 |

R/W |

| INTERRUPT_CORE0_UART_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ UART_INTR |

0x0054 |

R/W |

| INTERRUPT_CORE0_UART1_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ UART1_INTR |

0x0058 |

R/W |

| INTERRUPT_CORE0_LEDC_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ LEDC_INT |

0x005C |

R/W |

| INTERRUPT_CORE0_EFUSE_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ EFUSE_INT |

0x0060 |

R/W |

| INTERRUPT_CORE0_CAN_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ CAN_INT |

0x0064 |

R/W |

| INTERRUPT_CORE0_USB_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ USB_INTR |

0x0068 |

R/W |

| INTERRUPT_CORE0_RTC_CORE_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ RTC_CORE_INTR |

0x006C |

R/W |

| INTERRUPT_CORE0_RMT_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ RMT_INTR |

0x0070 |

R/W |

| INTERRUPT_CORE0_I2C_EXT0_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ I2C_EXT0 |

0x0074 |

R/W |

| INTERRUPT_CORE0_TIMER_INT1_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ TIMER_INT1 |

0x0078 |

R/W |

| INTERRUPT_CORE0_TIMER_INT2_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ TIMER_INT2 |

0x007C |

R/W |

| INTERRUPT_CORE0_TG_T0_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ TG_T0_INT |

0x0080 |

R/W |

| INTERRUPT_CORE0_TG_WDT_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ TG_WDT_INT |

0x0084 |

R/W |

| INTERRUPT_CORE0_TG1_T0_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ TG1_T0_INT |

0x0088 |

R/W |

| INTERRUPT_CORE0_TG1_WDT_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ TG1_WDT_INT |

0x008C |

R/W |

| INTERRUPT_CORE0_CACHE_IA_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ CACHE_IA_INT |

0x0090 |

R/W |

| INTERRUPT_CORE0_SYSTIMER_TARGET0_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ SYSTIMER_TARGET0_INT |

0x0094 |

R/W |

| INTERRUPT_CORE0_SYSTIMER_TARGET1_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ SYSTIMER_TARGET1_INT |

0x0098 |

R/W |

| INTERRUPT_CORE0_SYSTIMER_TARGET2_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ SYSTIMER_TARGET2_INT |

0x009C |

R/W |

| INTERRUPT_CORE0_SPI_MEM_REJECT_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ SPI_MEM_REJECT_INTR |

0x00A0 |

R/W |

| INTERRUPT_CORE0_ICACHE_PRELOAD_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ ICACHE_PRELOAD_INT |

0x00A4 |

R/W |

| INTERRUPT_CORE0_ICACHE_SYNC_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ ICACHE_SYNC_INT |

0x00A8 |

R/W |

| INTERRUPT_CORE0_APB_ADC_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ APB_ADC_INT |

0x00AC |

R/W |

| INTERRUPT_CORE0_DMA_CH0_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ DMA_CH0_INT |

0x00B0 |

R/W |

| INTERRUPT_CORE0_DMA_CH1_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ DMA_CH1_INT |

0x00B4 |

R/W |

| INTERRUPT_CORE0_DMA_CH2_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ DMA_CH2_INT |

0x00B8 |

R/W |

| INTERRUPT_CORE0_RSA_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ RSA_INT |

0x00BC |

R/W |

| INTERRUPT_CORE0_AES_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ AES_INT |

0x00C0 |

R/W |

| INTERRUPT_CORE0_SHA_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ SHA_INT |

0x00C4 |

R/W |

| INTERRUPT_CORE0_CPU_INTR_FROM_CPU_0_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ CPU_INTR_FROM_CPU_0 |

0x00C8 |

R/W |

| INTERRUPT_CORE0_CPU_INTR_FROM_CPU_1_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ CPU_INTR_FROM_CPU_1 |

0x00CC |

R/W |

| INTERRUPT_CORE0_CPU_INTR_FROM_CPU_2_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ CPU_INTR_FROM_CPU_2 |

0x00D0 |

R/W |

| INTERRUPT_CORE0_CPU_INTR_FROM_CPU_2_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ CPU_INTR_FROM_CPU_3 |

0x00D4 |

R/W |

| INTERRUPT_CORE0_ASSIST_DEBUG_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ ASSIST_DEBUG_INTR |

0x00D8 |

R/W |

| INTERRUPT_CORE0_DMA_APBPERI_PMS_MONITOR_VIOLATE_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ DMA_APBPERI_PMS_MONITOR_VIOLATE |

0x00DC |

R/W |

| INTERRUPT_CORE0_CORE_0_IRAM0_PMS_MONITOR_VIOLATE_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ IRAM0_PMS_MONITOR_VIOLATE |

0x00E0 |

R/W |

| INTERRUPT_CORE0_CORE_0_DRAM0_PMS_MONITOR_VIOLATE_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ DRAM0_PMS_MONITOR_VIOLATE |

0x00E4 |

R/W |

| INTERRUPT_CORE0_CORE_0_PIF_PMS_MONITOR_VIOLATE_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ PIF_PMS_MONITOR_VIOLATE |

0x00E8 |

R/W |

| INTERRUPT_CORE0_CORE_0_PIF_PMS_MONITOR_VIOLATE_SIZE_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ PIF_PMS_MONITOR_VIOLATE_SIZE |

0x00EC |

R/W |

| INTERRUPT_CORE0_BACKUP_PMS_VIOLATE_INTR_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ BACKUP_PMS_VIOLATE |

0x00F0 |

R/W |

| INTERRUPT_CORE0_CACHE_CORE0_ACS_INT_MAP_REG |

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ CACHE_CORE0_ACS |

0x00F4 |

R/W |

| Interrupt Source Status Registers (čĆąĄą│ąĖčüčéčĆčŗ čüąŠčüč鹊čÅąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ) |

| INTERRUPT_CORE0_INTR_STATUS_0_REG |

ąĀąĄą│ąĖčüčéčĆ ą┤ą╗čÅ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 0 .. 31 |

0x00F8 |

RO |

| INTERRUPT_CORE0_INTR_STATUS_1_REG |

ąĀąĄą│ąĖčüčéčĆ ą┤ą╗čÅ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 32 .. 61 |

0x00FC |

RO |

| Clock Register (čĆąĄą│ąĖčüčéčĆ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ) |

| INTERRUPT_CORE0_CLOCK_GATE_REG |

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝ |

0x0100 |

R/W |

| CPU Interrupt Registers (čĆąĄą│ąĖčüčéčĆčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣) |

| INTERRUPT_CORE0_CPU_INT_ENABLE_REG |

ąĀąĄą│ąĖčüčéčĆ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CPU |

0x0104 |

R/W |

| INTERRUPT_CORE0_CPU_INT_TYPE_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čéąĖą┐ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CPU |

0x0108 |

R/W |

| INTERRUPT_CORE0_CPU_INT_CLEAR_REG |

ąĀąĄą│ąĖčüčéčĆ ąŠčćąĖčüčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CPU |

0x010C |

R/W |

| INTERRUPT_CORE0_CPU_INT_EIP_STATUS_REG |

ąĀąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ ąŠąČąĖą┤ą░čÄčēąĖčģ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CPU |

0x0110 |

RO |

| INTERRUPT_CORE0_CPU_INT_PRI_1_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 1 CPU |

0x0118 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_2_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 2 CPU |

0x011C |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_3_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 3 CPU |

0x0120 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_4_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 4 CPU |

0x0124 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_5_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 5 CPU |

0x0128 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_6_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 6 CPU |

0x012C |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_7_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 7 CPU |

0x0130 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_8_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 8 CPU |

0x0134 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_9_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 9 CPU |

0x0138 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_10_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 10 CPU |

0x013C |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_11_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 11 CPU |

0x0140 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_12_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 12 CPU |

0x0144 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_13_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 13 CPU |

0x0148 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_14_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 14 CPU |

0x014C |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_15_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 15 CPU |

0x0150 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_16_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 16 CPU |

0x0154 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_17_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 17 CPU |

0x0158 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_18_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 18 CPU |

0x015C |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_19_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 19 CPU |

0x0160 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_20_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 20 CPU |

0x0164 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_21_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 21 CPU |

0x0168 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_22_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 22 CPU |

0x016C |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_23_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 23 CPU |

0x0170 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_24_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 24 CPU |

0x0174 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_25_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 25 CPU |

0x0178 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_26_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 26 CPU |

0x017C |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_27_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 27 CPU |

0x0180 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_28_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 28 CPU |

0x0184 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_29_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 29 CPU |

0x0188 |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_30_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 30 CPU |

0x018C |

R/W |

| INTERRUPT_CORE0_CPU_INT_PRI_31_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 31 CPU |

0x0190 |

R/W |

| INTERRUPT_CORE0_CPU_INT_THRESH_REG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠčĆąŠą│ą░ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CPU |

0x0194 |

R/W |

| Version Register (čĆąĄą│ąĖčüčéčĆ ą▓ąĄčĆčüąĖąĖ) |

| INTERRUPT_CORE0_INTERRUPT_DATE_REG |

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ąĄčĆčüąĖąĄą╣ |

0x07FC |

R/W |

ąĪą╗ąĄą┤čāčÄčēąĖąĄ ą░ą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ čāą║ą░ąĘą░ąĮčŗ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ ą╝ą░čéčĆąĖčåčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĖąĘ čéą░ą▒ą╗ąĖčåčŗ 3-4 ą▓ ą│ą╗ą░ą▓ąĄ 3 "System and Memory" [1].

INTERRUPT_CORE0_PWR_INTR_MAP_REG (0x0008)

INTERRUPT_CORE0_I2C_MST_INT_MAP_REG (0x002C)

INTERRUPT_CORE0_SLC0_INTR_MAP_REG (0x0030)

INTERRUPT_CORE0_SLC1_INTR_MAP_REG (0x0034)

INTERRUPT_CORE0_APB_CTRL_INTR_MAP_REG (0x0038)

INTERRUPT_CORE0_UHCI0_INTR_MAP_REG (0x003C)

INTERRUPT_CORE0_GPIO_INTERRUPT_PRO_MAP_REG (0x0040)

INTERRUPT_CORE0_GPIO_INTERRUPT_PRO_NMI_MAP_REG (0x0044)

INTERRUPT_CORE0_SPI_INTR_1_MAP_REG (0x0048)

INTERRUPT_CORE0_SPI_INTR_2_MAP_REG (0x004C)

INTERRUPT_CORE0_I2S1_INT_MAP_REG (0x0050)

INTERRUPT_CORE0_UART_INTR_MAP_REG (0x0054)

INTERRUPT_CORE0_UART1_INTR_MAP_REG (0x0058)

INTERRUPT_CORE0_LEDC_INT_MAP_REG (0x005C)

INTERRUPT_CORE0_EFUSE_INT_MAP_REG (0x0060)

INTERRUPT_CORE0_CAN_INT_MAP_REG (0x0064)

INTERRUPT_CORE0_USB_INTR_MAP_REG (0x0068)

INTERRUPT_CORE0_RTC_CORE_INTR_MAP_REG (0x006C)

INTERRUPT_CORE0_RMT_INTR_MAP_REG (0x0070)

INTERRUPT_CORE0_I2C_EXT0_INTR_MAP_REG (0x0074)

INTERRUPT_CORE0_TIMER_INT1_MAP_REG (0x0078)

INTERRUPT_CORE0_TIMER_INT2_MAP_REG (0x007C)

INTERRUPT_CORE0_TG_T0_INT_MAP_REG (0x0080)

INTERRUPT_CORE0_TG_WDT_INT_MAP_REG (0x0084)

INTERRUPT_CORE0_TG1_T0_INT_MAP_REG (0x0088)

INTERRUPT_CORE0_TG1_WDT_INT_MAP_REG (0x008C)

INTERRUPT_CORE0_CACHE_IA_INT_MAP_REG (0x0090)

INTERRUPT_CORE0_SYSTIMER_TARGET0_INT_MAP_REG (0x0094)

INTERRUPT_CORE0_SYSTIMER_TARGET1_INT_MAP_REG (0x0098)

INTERRUPT_CORE0_SYSTIMER_TARGET2_INT_MAP_REG (0x009C)

INTERRUPT_CORE0_SPI_MEM_REJECT_INTR_MAP_REG (0x00A0)

INTERRUPT_CORE0_ICACHE_PRELOAD_INT_MAP_REG (0x00A4)

INTERRUPT_CORE0_ICACHE_SYNC_INT_MAP_REG (0x00A8)

INTERRUPT_CORE0_APB_ADC_INT_MAP_REG (0x00AC)

INTERRUPT_CORE0_DMA_CH0_INT_MAP_REG (0x00B0)

INTERRUPT_CORE0_DMA_CH1_INT_MAP_REG (0x00B4)

INTERRUPT_CORE0_DMA_CH2_INT_MAP_REG (0x00B8)

INTERRUPT_CORE0_RSA_INT_MAP_REG (0x00BC)

INTERRUPT_CORE0_AES_INT_MAP_REG (0x00C0)

INTERRUPT_CORE0_SHA_INT_MAP_REG (0x00C4)

INTERRUPT_CORE0_CPU_INTR_FROM_CPU_0_MAP_REG (0x00C8)

INTERRUPT_CORE0_CPU_INTR_FROM_CPU_1_MAP_REG (0x00CC)

INTERRUPT_CORE0_CPU_INTR_FROM_CPU_2_MAP_REG (0x00D0)

INTERRUPT_CORE0_CPU_INTR_FROM_CPU_3_MAP_REG (0x00D4)

INTERRUPT_CORE0_ASSIST_DEBUG_INTR_MAP_REG (0x00D8)

INTERRUPT_CORE0_DMA_APBPERI_PMS_MONITOR_VIOLATE_INTR_MAP_REG (0x00DC)

INTERRUPT_CORE0_CORE_0_IRAM0_PMS_MONITOR_VIOLATE_INTR_MAP_REG (0x00E0)

INTERRUPT_CORE0_CORE_0_DRAM0_PMS_MONITOR_VIOLATE_INTR_MAP_REG (0x00E4)

INTERRUPT_CORE0_CORE_0_PIF_PMS_MONITOR_VIOLATE_INTR_MAP_REG (0x00E8)

INTERRUPT_CORE0_CORE_0_PIF_PMS_MONITOR_VIOLATE_SIZE_INTR_MAP_REG (0x00EC)

INTERRUPT_CORE0_BACKUP_PMS_VIOLATE_INTR_MAP_REG (0x00F0)

INTERRUPT_CORE0_CACHE_CORE0_ACS_INT_MAP_REG (0x00F4)

INTERRUPT_CORE0_SOURCE_X_MAP ą×č鹊ą▒čĆą░ąČą░ąĄčé ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (SOURCE_X) ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ CPU. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐čĆąŠ SOURCE_X čüą╝. čéą░ą▒ą╗ąĖčåčā 8-1 (R/W).

INTERRUPT_CORE0_INTR_STATUS_0_REG (0x00F8)

INTERRUPT_CORE0_INTR_STATUS_0 ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ čģčĆą░ąĮąĖčé čüčéą░čéčāčü ą┐ąĄčĆą▓čŗčģ 32 ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ: 0 .. 31. ąĢčüą╗ąĖ ąĘą┤ąĄčüčī ą║ą░ą║ąŠą╣-ą╗ąĖą▒ąŠ ą▒ąĖčé čĆą░ą▓ąĄąĮ 1, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ąĖčüč鹊čćąĮąĖą║ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (RO).

INTERRUPT_CORE0_INTR_STATUS_1_REG (0x00FC)

INTERRUPT_CORE0_INTR_STATUS_1 ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ čģčĆą░ąĮąĖčé čüčéą░čéčāčü čüą╗ąĄą┤čāčÄčēąĖčģ 32 ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ: 32 .. 61. ąĢčüą╗ąĖ ąĘą┤ąĄčüčī ą║ą░ą║ąŠą╣-ą╗ąĖą▒ąŠ ą▒ąĖčé čĆą░ą▓ąĄąĮ 1, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ąĖčüč鹊čćąĮąĖą║ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (RO).

INTERRUPT_CORE0_CLOCK_GATE_REG (0x0100)

INTERRUPT_CORE0_CLK_EN ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▓ 1, čćč鹊ą▒čŗ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą▓ą║ą╗čÄčćąĖčéčī čéą░ą║čéčŗ čĆąĄą│ąĖčüčéčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (R/W).

INTERRUPT_CORE0_CPU_INT_ENABLE_REG (0x0104)

INTERRUPT_CORE0_CPU_INT_ENABLE ąŚą░ą┐ąĖčłąĖč鹥 1 ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ ą▒ąĖčé, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ CPU. ąöą╗čÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ č鹊ą╝, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹč鹊čé čĆąĄą│ąĖčüčéčĆ, čüą╝. [2] (R/W).

INTERRUPT_CORE0_CPU_INT_TYPE_REG (0x0108)

INTERRUPT_CORE0_CPU_INT_TYPE ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčé čéąĖą┐ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CPU. 0: level-triggered, 1: edge-triggered. ąöą╗čÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ č鹊ą╝, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹč鹊čé čĆąĄą│ąĖčüčéčĆ, čüą╝. [2] (R/W).

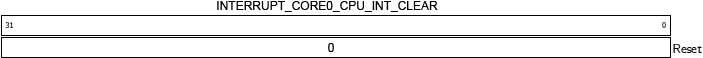

INTERRUPT_CORE0_CPU_INT_CLEAR_REG (0x010C)

INTERRUPT_CORE0_CPU_INT_CLEAR ąŚą░ą┐ąĖčüčī 1 ą▓ čŹč鹊čé ą▒ąĖčé ąŠčćąĖčüčéąĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ CPU. ąöą╗čÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ č鹊ą╝, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹč鹊čé čĆąĄą│ąĖčüčéčĆ, čüą╝. [2] (R/W).

INTERRUPT_CORE0_CPU_INT_EIP_STATUS_REG (0x0110)

INTERRUPT_CORE0_CPU_INT_EIP_STATUS ąźčĆą░ąĮąĖčé čüčéą░čéčāčü ąŠąČąĖą┤ą░ąĮąĖčÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CPU interrupts. ąöą╗čÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ č鹊ą╝, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹč鹊čé čĆąĄą│ąĖčüčéčĆ, čüą╝. [2] (RO).

INTERRUPT_CORE0_CPU_INT_PRI_n_REG (n: 1 .. 31)(0x0118 + 0x4*n)

INTERRUPT_CORE0_CPU_PRI_n_MAP ąŻčüčéą░ąĮąŠą▓ąĖčé ą┐čĆąĖąŠčĆąĖč鹥čé ą┤ą╗čÅ n-ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CPU. ąŚą┤ąĄčüčī ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┐čĆąĖąŠčĆąĖč鹥čé ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1 (čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé) ą┤ąŠ 15 (čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé). ąöą╗čÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ č鹊ą╝, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹč鹊čé čĆąĄą│ąĖčüčéčĆ, čüą╝. [2] (R/W).

INTERRUPT_CORE0_CPU_INT_THRESH_REG (0x0194)

INTERRUPT_CORE0_CPU_INT_THRESH ąŻčüčéą░ąĮąŠą▓ąĖčé ą┐ąŠčĆąŠą│ ą┤ą╗čÅ ą░ą║čéąĖą▓ą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ CPU. ą»ą┤čĆąŠ CPU ąŠčéą▓ąĄčéąĖčé ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ č鹊ą╗čīą║ąŠ ą▓ č鹊ą╝ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ ąĄą│ąŠ ą┐čĆąĖąŠčĆąĖč鹥čé ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĄąĮ čŹč鹊ą╝čā čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╝čā ą┐ąŠčĆąŠą│čā. ąöą╗čÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ č鹊ą╝, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹč鹊čé čĆąĄą│ąĖčüčéčĆ, čüą╝. [2].

INTERRUPT_CORE0_INTERRUPT_DATE_REG (0x07FC).

INTERRUPT_CORE0_INTERRUPT_DATE Version control register (R/W).

[ąĪčüčŗą╗ą║ąĖ]

1. ESP32C3 Technical Reference Manual site:espressif.com.

2. ESP32-C3 ESP-RISC-V CPU. |