|

ą£ąĮąŠą│ąĖąĄ čéčŗčüčÅčćąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ čĆą░ą▒ąŠčéą░čÄčé ą▓ čüčĆąĄą┤ąĄ FreeRTOS ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ čü čÅą┤čĆą░ą╝ąĖ ARM Cortex-M (STM32). ą×čüąĮąŠą▓ąĮčŗąĄ ą┐čĆąŠą▒ą╗ąĄą╝čŗ, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąŠąĖčüčģąŠą┤čÅčé čü čŹčéąĖą╝ ą┐ąŠčĆč鹊ą╝ FreeRTOS, čüą╗čāčćą░čÄčéčüčÅ ąĖąĘ-ąĘą░ ąĮąĄą║ąŠčĆčĆąĄą║čéąĮąŠą╣ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąŁč鹊ą│ąŠ ą▓ąĄčĆąŠčÅčéąĮąŠ čüą╗ąĄą┤ąŠą▓ą░ą╗ąŠ ąŠąČąĖą┤ą░čéčī, ą┐ąŠč鹊ą╝čā čćč鹊 ąĮąĄčüą╝ąŠčéčĆčÅ ąĮą░ č鹊, čćč鹊 ąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ARM Cortex-M ąŠč湥ąĮčī ą╝ąŠčēąĮą░čÅ, ąŠąĮą░ čéą░ą║ąČąĄ ą▓ ąĮąĄą║ąŠč鹊čĆąŠą╝ čĆąŠą┤ąĄ ąĮąĄčāą║ą╗čĹȹ░čÅ, ąĖ ąĮąĄ ąĖąĮčéčāąĖčéąĖą▓ąĮąŠ-ą┐ąŠąĮčÅčéąĮą░čÅ ą┤ą╗čÅ ąĖąĮąČąĄąĮąĄčĆąŠą▓, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĖą▓čŗą║ą╗ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čéčĆą░ą┤ąĖčåąĖąŠąĮąĮčāčÄ čüčģąĄą╝čā ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąØą░ąĘąĮą░č湥ąĮąĖąĄ čŹč鹊ą╣ čüčéą░čéčīąĖ (ą┐ąĄčĆąĄą▓ąŠą┤ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ [1]) - ą┤ą░čéčī ąŠą┐ąĖčüą░ąĮąĖąĄ, ą║ą░ą║ ą╝ąĄčģą░ąĮąĖąĘą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ARM Cortex-M ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ čÅą┤čĆąĄ FreeRTOS.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéąĖ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ FreeRTOS ąĮą░ ą┐ą╗ą░čéč乊čĆą╝ą░čģ Cortex-M3, Cortex-M4, Cortex-M4F ąĖ Cortex-M7. ą×ąĮą░ ąĮąĄ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ čÅą┤čĆą░ą╝ Cortex-M0 ąĖą╗ąĖ Cortex-M0+ cores, ą▓ ą║ąŠč鹊čĆčŗčģ ąĮąĄčé čĆąĄą│ąĖčüčéčĆą░ BASEPRI.

ąĪą╗ąĄą┤čāąĄčé ą┐ąŠą╝ąĮąĖčéčī, čćč鹊 čģąŠčéčÅ čüčģąĄą╝ą░ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓, čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąĮą░čÅ ą▓ ą░ą┐ą┐ą░čĆą░čéčāčĆąĄ čÅą┤čĆą░ ARM Cortex-M3, ą╝ąŠąČąĄčé ą┐ąŠą║ą░ąĘą░čéčīčüčÅ čüą╗ąŠąČąĮąŠą╣, ą║ą░ąČą┤čŗą╣ ąŠčäąĖčåąĖą░ą╗čīąĮčŗą╣ ą┐ąŠčĆčé FreeRTOS ą┐ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ čü ą║ąŠčĆčĆąĄą║čéąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą┤ąĄą╝ąŠąĮčüčéčĆą░čåąĖąŠąĮąĮčŗą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄą╝, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ąŠą▒čĆą░ąĘąĄčå. ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĖ FreeRTOS V7.5.0 ą┤ąŠą▒ą░ą▓ą╗ąĄąĮ ą▓čŗąĘąŠą▓ configASSERT(), čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗą╣ ą┤ą╗čÅ ą┐ąĄčĆąĄčģą▓ą░čéą░ čüąĖčéčāą░čåąĖą╣ čü ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą║ąŠąĮčéčĆąŠą╗ąĄčĆąŠą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (NVIC) ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ARM Cortex-M. ąóą░ą║ čćč鹊 čāą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 configASSERT() ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą▓ąŠ ą▓čĆąĄą╝čÅ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ.

[ąöąŠčüčéčāą┐ąĮčŗąĄ čāčĆąŠą▓ąĮąĖ ą┐čĆąĖąŠčĆąĖč鹥čéą░]

ąÉą┐ą┐ą░čĆą░čéčāčĆą░ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ Cortex-M. ą¤ąĄčĆą▓ąŠąĄ, čćč鹊 ąĮčāąČąĮąŠ ąĘąĮą░čéčī - ąŠą▒čēąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ąŠčüčéčāą┐ąĮčŗčģ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąŠą▒čēąĄą╣ čĆąĄą░ą╗ąĖąĘą░čåąĖąĄą╣, čé. ąĄ. ąŠčé ą▓čüąĄą╣ čüąĖčüč鹥ą╝čŗ čåąĄą╗ąĖą║ąŠą╝, ą▓ą┐ą╗ąŠčéčī ą┤ąŠ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ čüąĖčüč鹥ą╝čŗ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ąĖčüą┐ąŠą╗čīąĘčāčÄčēąĄą│ąŠ čÅą┤čĆąŠ ARM Cortex-M. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ąĮąĄ ą▓čüąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ ARM Cortex-M ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čāąĮąĖą║ą░ą╗čīąĮčŗčģ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ąÉčĆčģąĖč鹥ą║čéčāčĆą░ ARM Cortex-M čüą░ą╝ą░ ą┐ąŠ čüąĄą▒ąĄ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╝ą░ą║čüąĖą╝čāą╝ 256 čĆą░ąĘąĮčŗčģ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ (čüčāčēąĄčüčéą▓čāąĄčé ą╝ą░ą║čüąĖą╝čāą╝ 8 ą▒ąĖč鹊ą▓ ą┐čĆąĖąŠčĆąĖč鹥čéą░, ą┐ąŠčŹč鹊ą╝čā ą▓ąŠąĘą╝ąŠąČąĮčŗ ą┐čĆąĖąŠčĆąĖč鹥čéčŗ ąŠčé 0 ą┤ąŠ 0xff ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ), ąŠą┤ąĮą░ą║ąŠ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ, ąĮąŠ ąĮąĄ ą▓čüąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ, ą▓ ą║ąŠč鹊čĆčŗčģ čÅą┤čĆąŠ ARM Cortex-M, ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č鹊ą╗čīą║ąŠ ą┐ąŠą┤ą╝ąĮąŠąČąĄčüčéą▓ąŠ ąĖąĘ čŹčéąĖčģ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ TI Stellaris Cortex-M3 ąĖ ARM Cortex-M4 čĆąĄą░ą╗ąĖąĘčāčÄčé 3 ą▒ąĖčéą░ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓. ąŁč鹊 ą┤ą░ąĄčé 8 čāąĮąĖą║ą░ą╗čīąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čéą░. ąöčĆčāą│ąŠą╣ ą┐čĆąĖą╝ąĄčĆ - ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ NXP LPC17xx ARM Cortex-M3 čĆąĄą░ą╗ąĖąĘčāčÄčé 5 ą▒ąĖčé čāčĆąŠą▓ąĮčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░, čŹč鹊 ą┤ą░ąĄčé 32 čāąĮąĖą║ą░ą╗čīąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čéą░.

ąĢčüą╗ąĖ ą▓ ąÆą░čłąĄą╝ ą┐čĆąŠąĄą║č鹥 ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ąĘą░ą│ąŠą╗ąŠą▓ąŠčćąĮčŗąĄ čäą░ą╣ą╗čŗ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĖ CMSIS, č鹊 ą┐čĆąŠą▓ąĄčĆčīč鹥 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ __NVIC_PRIO_BITS, čćč鹊ą▒čŗ čāą▓ąĖą┤ąĄčéčī, čüą║ąŠą╗čīą║ąŠ ą▒ąĖčé ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┤ąŠčüčéčāą┐ąĮąŠ.

ąÜą░ą║ čŹč鹊 ąŠčéąĮąŠčüąĖčéčüčÅ ą║ FreeRTOS. ąĪčģąĄą╝ą░ ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ RTOS ą┤ąĄą╗ąĖčé ą▓čüąĄ ą┤ąŠčüčéčāą┐ąĮčŗąĄ ą┐čĆąĖąŠčĆąĖč鹥čéčŗ ąĮą░ 2 ą│čĆčāą┐ą┐čŗ ŌĆō č鹥, ą║ąŠč鹊čĆčŗąĄ ą▒čāą┤čāčé ą╝ą░čüą║ąĖčĆąŠą▓ą░čéčīčüčÅ ą║čĆąĖčéąĖč湥čüą║ąĖą╝ąĖ čüąĄą║čåąĖčÅą╝ąĖ RTOS, ąĖ č鹥, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ ą╝ą░čüą║ąĖčĆčāčÄčéčüčÅ ą║čĆąĖčéąĖč湥čüą║ąĖą╝ąĖ čüąĄą║čåąĖčÅą╝ąĖ, ąĖ ą┐ąŠčŹč鹊ą╝čā ą▓čüąĄą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮčŗ. ąØą░čüčéčĆąŠą╣ą║ą░ configMAX_SYSCALL_INTERRUPT_PRIORITY ą▓ FreeRTOSConfig.h ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą│čĆą░ąĮąĖčåčā ą╝ąĄąČą┤čā čŹčéąĖą╝ąĖ ą┤ą▓čāą╝čÅ ą│čĆčāą┐ą┐ą░ą╝ąĖ. ą×ą┐čéąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čŹč鹊ą╣ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ąĖčé ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓, čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąĮčŗčģ ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ.

[ą¤čĆąĖąŠčĆąĖč鹥čé ą▓čŗč鹥čüąĮąĄąĮąĖčÅ ąĖ čüčāą▒ą┐čĆąĖąŠčĆąĖč鹥čé]

ąÉą┐ą┐ą░čĆą░čéčāčĆą░ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ Cortex-M. 8-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░ 2 čćą░čüčéąĖ: ą┐čĆąĖąŠčĆąĖč鹥čé ą▓čŗč鹥čüąĮąĄąĮąĖčÅ (preempt priority) ąĖ čüčāą▒ą┐čĆąĖąŠčĆąĖč鹥čé (subpriority). ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé, ąĮą░ąĘąĮą░č湥ąĮąĮąŠąĄ ąĮą░ ą║ą░ąČą┤čāčÄ čćą░čüčéčī, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ. ą¤čĆąĖąŠčĆąĖč鹥čé ą▓čŗč鹥čüąĮąĄąĮąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą╝ąŠąČąĄčé ą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆą▓ą░čéčī (ą▓čŗč鹥čüąĮąĖčéčī) čāąČąĄ ą▓čŗą┐ąŠą╗ąĮčÅčÄčēąĄąĄčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. Subpriority ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ą░ą║ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ ą┐ąĄčĆą▓čŗą╝, ą║ąŠą│ą┤ą░ ą┤ą▓ą░ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┤ą▓ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ą▓čŗč鹥čüąĮąĄąĮąĖčÅ.

ąÜą░ą║ čŹč鹊 ąŠčéąĮąŠčüąĖčéčüčÅ ą║ FreeRTOS. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĮą░ąĘąĮą░čćąĖčéčī ą▓čüąĄ ą▒ąĖčéčŗ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą▒ąĖčé ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą▓čŗč鹥čüąĮąĄąĮąĖčÅ, ąĮąĄ ąŠčüčéą░ą▓ą╗čÅčÅ ąĮąĖą║ą░ą║ąĖčģ ą▒ąĖčé ą┐čĆąĖąŠčĆąĖč鹥čéą░ ąĮą░ subpriority. ąøčÄą▒čŗąĄ ą┤čĆčāą│ąĖąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čāčüą╗ąŠąČąĮčÅčÄčé ą┐čĆčÅą╝čāčÄ ą▓ąĘą░ąĖą╝ąŠčüą▓čÅąĘčī ą╝ąĄąČą┤čā čāčüčéą░ąĮąŠą▓ą║ąŠą╣ configMAX_SYSCALL_INTERRUPT_PRIORITY ąĖ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝, ąĮą░ąĘąĮą░č湥ąĮąĮčŗą╝ ąŠčéą┤ąĄą╗čīąĮčŗą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ąæąŠą╗čīčłąĖąĮčüčéą▓ąŠ čüąĖčüč鹥ą╝ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čüą╗ąĄą┤čāąĄčé ąČąĄą╗ą░ąĄą╝ąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĖ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ STM32. ąĢčüą╗ąĖ ąÆčŗ ąĖčüą┐ąŠą╗čīąĘčāąĄč鹥 STM32 ą▓ą╝ąĄčüč鹥 čü STM32 driver library, č鹊 čāą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 ą▓čüąĄ ą▒ąĖčéčŗ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ąĮą░ąĘąĮą░č湥ąĮčŗ ąĮą░ ą▒ąĖčéčŗ preempt priority, ą┐čāč鹥ą╝ ą▓čŗąĘąŠą▓ą░ NVIC_PriorityGroupConfig( NVIC_PriorityGroup_4 ); ą┐ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ RTOS.

[ąśąĮą▓ąĄčĆčüąĮą░čÅ ą▓ąĘą░ąĖą╝ąŠčüą▓čÅąĘčī čćąĖčüą╗ąŠą▓čŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓]

ą£ąĄąČą┤čā ąĮčāą╝ąĄčĆą░čåąĖąĄą╣ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą░ą┐ą┐ą░čĆą░čéčāčĆąĄ Cortex-M ąĖ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ ą╗ąŠą│ąĖč湥čüą║ąŠą╣ ąĮčāą╝ąĄčĆą░čåąĖąĖ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ FreeRTOS čüčāčēąĄčüčéą▓čāąĄčé ąĖąĮą▓ąĄčĆčüąĮą░čÅ ą▓ąĘą░ąĖą╝ąŠčüą▓čÅąĘčī. ąĢčüą╗ąĖ čā Cortex-M č湥ą╝ ą╝ąĄąĮčīčłąĄ čćąĖčüą╗ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, č鹥ą╝ čā ąĮąĄą│ąŠ ą┐čĆąĖąŠčĆąĖč鹥čé ą▓čŗčłąĄ, č鹊 čā FreeRTOS ą▒ąŠą╗čīčłąĄą╝čā čćąĖčüą╗ąŠą▓ąŠą╝čā ą┐čĆąĖąŠčĆąĖč鹥čéčā ąĘą░ą┤ą░čćąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé.

ąÉą┐ą┐ą░čĆą░čéčāčĆą░ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ Cortex-M. ąĪą╗ąĄą┤čāčÄčēąĄąĄ, čćč鹊 ąĮčāąČąĮąŠ ąĘąĮą░čéčī - ą▓ čÅą┤čĆą░čģ ARM Cortex-M ą╝ą░ą╗čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą╗ąŠą│ąĖč湥čüą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥čéą░ą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą╗ąŠą│ąĖč湥čüą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆąŠą╝čā ąĮą░ąĘąĮą░č湥ąĮ čćąĖčüą╗ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĖąŠčĆąĖč鹥čéą░ 2 ą▒čāą┤ąĄčé ą▓čŗčłąĄ, č湥ą╝ čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆąŠą╝čā ąĮą░ąĘąĮą░č湥ąĮ čćąĖčüą╗ąŠą▓ąŠą╣ ą┐čĆąĖąŠčĆąĖč鹥čé 5. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü čćąĖčüą╗ąŠą▓čŗą╝ čāčĆąŠą▓ąĮąĄą╝ ą┐čĆąĖąŠčĆąĖč鹥čéą░ 2 ą▒ąŠą╗ąĄąĄ ą┐čĆąĖąŠčĆąĖč鹥čéąĮąŠąĄ, č湥ą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü čćąĖčüą╗ąŠą▓čŗą╝ čāčĆąŠą▓ąĮąĄą╝ ą┐čĆąĖąŠčĆąĖč鹥čéą░ 5, čģąŠčéčÅ čćąĖčüą╗ąŠ 2 ą╝ąĄąĮčīčłąĄ, č湥ą╝ čćąĖčüą╗ąŠ 5. ąöą╗čÅ ą┐ąŠą╗ąĮąŠą╣ čÅčüąĮąŠčüčéąĖ: čā Cortex-M ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą║ąŠč鹊čĆąŠą╝čā ąĮą░ąĘąĮą░č湥ąĮ čćąĖčüą╗ąŠą▓ąŠą╣ ą┐čĆąĖąŠčĆąĖč鹥čé 2, ą╝ąŠąČąĄčé ą▓čŗč鹥čüąĮąĖčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą║ąŠč鹊čĆąŠą╝čā ąĮą░ąĘąĮą░č湥ąĮ čćąĖčüą╗ąŠą▓ąŠą╣ ą┐čĆąĖąŠčĆąĖč鹥čé 5, ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ 5 ąĮąĄ ą╝ąŠąČąĄčé ą┐čĆąĄčĆą▓ą░čéčī (ą▓čŗč鹥čüąĮąĖčéčī) ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ 2.

ąŁč鹊 ąĮąĄ ąĖąĮčéčāąĖčéąĖą▓ąĮčŗą╣ ą░čüą┐ąĄą║čé ą┐čĆąĖąŠčĆąĖč鹥ąĘą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ARM Cortex-M, ą┐ąŠč鹊ą╝čā čćč鹊 ąĮąĄ čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠą╝ ąĮąĄ ARM Cortex-M3 ą░čĆčģąĖč鹥ą║čéčāčĆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓.

ąÜą░ą║ čŹč鹊 ąŠčéąĮąŠčüąĖčéčüčÅ ą║ FreeRTOS. ążčāąĮą║čåąĖąĖ FreeRTOS, ą║ąŠč鹊čĆčŗąĄ ąĘą░ą║ą░ąĮčćąĖą▓ą░čÄčéčüčÅ ąĮą░ "FromISR", čÅą▓ą╗čÅčÄčéčüčÅ ą▒ąĄąĘąŠą┐ą░čüąĮčŗą╝ąĖ ą┤ą╗čÅ ą▓čŗąĘąŠą▓ą░ ąĖąĘ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (interrupt safe), ąĮąŠ ą┤ą░ąČąĄ čŹčéąĖ čäčāąĮą║čåąĖąĖ ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗąĘą▓ą░ąĮčŗ ąĖąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, čā ą║ąŠč鹊čĆčŗčģ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé (ąĮąĄ čćąĖčüą╗ąŠą▓ąŠą╣!) ą▓čŗčłąĄ, č湥ą╝ ą┐čĆąĖąŠčĆąĖč鹥čé, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ ą╝ą░ą║čĆąŠčüąŠą╝ configMAX_SYSCALL_INTERRUPT_PRIORITY (configMAX_SYSCALL_INTERRUPT_PRIORITY ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą▓ čäą░ą╣ą╗ąĄ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ FreeRTOSConfig.h). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą╗čÄą▒ąŠą╣ ISR, ą║ąŠč鹊čĆčŗą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčé čäčāąĮą║čåąĖčÄ RTOS API, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čü čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▓čĆčāčćąĮčāčÄ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝, ąĮą░ ąĘąĮą░č湥ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą║ą░ą║ čćąĖčüą╗ąŠ čĆą░ą▓ąĮąŠ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄ č湥ą╝ configMAX_SYSCALL_INTERRUPT_PRIORITY. ąŁč鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 ą╗ąŠą│ąĖč湥čüą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé čŹč鹊ą│ąŠ ISR čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ ą╗ąŠą│ąĖč湥čüą║ąŠą╣ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐čĆąĖąŠčĆąĖč鹥čéą░ configMAX_SYSCALL_INTERRUPT_PRIORITY.

ą¤čĆąĖąŠčĆąĖč鹥čé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ Cortex-M ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čĆą░ą▓ąĄąĮ 0. ąŁč鹊 ąĘąĮą░čćąĖčé čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ąŠčüčéą░ą▓ą╗čÅąĄč鹥 ą┐čĆąĖąŠčĆąĖč鹥čé ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ ISR, ą║ąŠč鹊čĆčŗą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓čŗąĘąŠą▓čŗ interrupt safe RTOS API.

[ąÆąĮčāčéčĆąĄąĮąĮąĄąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖąĄ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ Cortex-M]

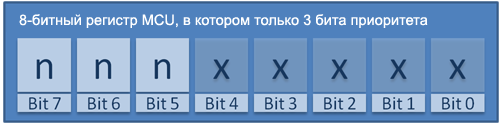

ąÉą┐ą┐ą░čĆą░čéčāčĆą░ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ Cortex-M. ą»ą┤čĆąŠ ARM Cortex-M čüąŠčģčĆą░ąĮčÅąĄčé ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ čüčéą░čĆčłąĖčģ ąĘąĮą░čćą░čēąĖčģ ą▒ąĖčéą░čģ čüą▓ąŠąĖčģ 8-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░čģ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ čĆąĄą░ą╗ąĖąĘą░čåąĖčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ Cortex-M ąĖą╝ąĄąĄčé č鹊ą╗čīą║ąŠ 3 ą▒ąĖčéą░ ą┐čĆąĖąŠčĆąĖč鹥čéą░, č鹊 čŹčéąĖ 3 ą▒ąĖčéą░ čüą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ ą▒ąĖčéčŗ 5, 6 ąĖ 7 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąæąĖčéčŗ ąŠčé 0 ą┤ąŠ 4 ą╝ąŠą│čāčé ąĖą╝ąĄčéčī ą╗čÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, čģąŠčéčÅ ą┤ą╗čÅ ąĮą░ąĖą╗čāčćčłąĄą╣ ą▒čāą┤čāčēąĄą╣ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ ąŠąĮąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 1. ąÆąĮčāčéčĆąĄąĮąĮąĄąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖąĄ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ARM Cortex-M ą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░čĆčéąĖąĮą║ą░čģ ąĮąĖąČąĄ.

ąŻ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐čĆąĖąŠčĆąĖč鹥čéą░ Cortex-M ą▓čüąĄą│ąŠ ąĄčüčéčī ą╝ąĄčüč鹊 ą┤ą╗čÅ ą╝ą░ą║čüąĖą╝čāą╝ 8 ą▒ąĖčé ą┐čĆąĖąŠčĆąĖč鹥čéą░. ąĢčüą╗ąĖ, ą▓ ą║ą░č湥čüčéą▓ąĄ ą┐čĆąĖą╝ąĄčĆą░, ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čĆąĄą░ą╗ąĖąĘčāąĄčé č鹊ą╗čīą║ąŠ 3 ą▒ąĖčéą░ ąĖąĘ čŹčéąĖčģ ą▓ąŠčüčīą╝ąĖ, č鹊 ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ č鹊ą╗čīą║ąŠ 3 čüčéą░čĆčłąĖąĄ ą▒ąĖčéą░:

ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╣ ą║ą░čĆčéąĖąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ąĘąĮą░č湥ąĮąĖąĄ 5 (ą▓ ą┤ą▓ąŠąĖčćąĮąŠą╣ č乊čĆą╝ąĄ 101) čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą▓ ą║ąŠč鹊čĆąŠą╝ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ č鹊ą╗čīą║ąŠ 3 ą▒ąĖčéą░ ą┐čĆąĖąŠčĆąĖč鹥čéą░. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą┐ąŠč湥ą╝čā ąĘąĮą░č湥ąĮąĖąĄ 5 (ą┤ą▓ąŠąĖčćąĮąŠąĄ 00000101) ą╝ąŠąČąĄčé čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čéčīčüčÅ ą║ą░ą║ 191 (ą┤ą▓ąŠąĖčćąĮąŠąĄ 10111111), ą║ąŠą│ą┤ą░ 3 ą▒ąĖčéą░ ą┐čĆąĖąŠčĆąĖč鹥čéą░ čüą┤ą▓ąĖąĮčāčéčŗ ą▓ čéčĆąĄą▒čāąĄą╝čāčÄ ą┐ąŠąĘąĖčåąĖčÄ, ąĖ ąŠčüčéą░ą╗čīąĮčŗąĄ ą▒ąĖčéčŗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 1:

ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╣ ą║ą░čĆčéąĖąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ąĘąĮą░č湥ąĮąĖąĄ 5 (ą┤ą▓ąŠąĖčćąĮąŠąĄ 101) čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą▓ ą║ąŠč鹊čĆąŠą╝ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ 4 ą▒ąĖčéą░ ą┐čĆąĖąŠčĆąĖč鹥čéą░. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą┐ąŠč湥ą╝čā ąĘąĮą░č湥ąĮąĖąĄ 5 (ą┤ą▓ąŠąĖčćąĮąŠąĄ 00000101) ą╝ąŠąČąĄčé čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čéčīčüčÅ ą║ą░ą║ 95 (ą┤ą▓ąŠąĖčćąĮąŠąĄ 01011111), ą║ąŠą│ą┤ą░ 4 ą▒ąĖčéą░ ą┐čĆąĖąŠčĆąĖč鹥čéą░ čüą┤ą▓ąĖąĮčāčéčŗ ą▓ čéčĆąĄą▒čāąĄą╝čāčÄ ą┐ąŠąĘąĖčåąĖčÄ, ąĖ ąŠčüčéą░ą╗čīąĮčŗąĄ ą▒ąĖčéčŗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 1:

ąÜą░ą║ čŹč鹊 ąŠčéąĮąŠčüąĖčéčüčÅ ą║ FreeRTOS. ąÜą░ą║ ą▒čŗą╗ąŠ ąŠą┐ąĖčüą░ąĮąŠ ą▓čŗčłąĄ, ą▓ą░ąČąĮčŗą╝ čÅą▓ą╗čÅąĄčéčüčÅ č鹊čé ą╝ąŠą╝ąĄąĮčé, čćč鹊ą▒čŗ ISR, ą║ąŠč鹊čĆą░čÅ ą┤ąĄą╗ą░ąĄčé ą▓čŗąĘąŠą▓čŗ RTOS API, ąĖą╝ąĄą╗ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé čĆą░ą▓ąĮčŗą╣ ąĖą╗ąĖ ąĮąĖąČąĄ, č湥ą╝ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ configMAX_SYSCALL_INTERRUPT_PRIORITY (č湥ą╝ ą╝ąĄąĮčīčłąĄ ą╗ąŠą│ąĖč湥čüą║ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĖąŠčĆąĖč鹥čéą░ č鹥ą╝ ą▒ąŠą╗čīčłąĄ čćąĖčüą╗ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ Cortex-M).

CMSIS, ąĖ čĆą░ąĘąĮčŗąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą▒ąĖą▒ą╗ąĖąŠč鹥čćąĮčŗąĄ čäčāąĮą║čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąØąĄą║ąŠč鹊čĆčŗąĄ ą▒ąĖą▒ą╗ąĖąŠč鹥čćąĮčŗąĄ čäčāąĮą║čåąĖąĖ ąŠąČąĖą┤ą░čÄčé, čćč鹊ą▒čŗ ą┐čĆąĖąŠčĆąĖč鹥čé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▒čŗą╗ čāą║ą░ąĘą░ąĮ ą▓ ą╝ą╗ą░ą┤čłąĖčģ ąĘąĮą░čćą░čēąĖčģ ą▒ąĖčéą░čģ ą▒ą░ą╣čéą░, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┤čĆčāą│ąĖąĄ ąŠąČąĖą┤ą░čÄčé čāą║ą░ąĘą░ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ čüą░ą╝čŗčģ čüčéą░čĆčłąĖčģ ą▒ąĖčéą░čģ ą▒ą░ą╣čéą░. ą¤čĆąŠą▓ąĄčĆčīč鹥 ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÄ ąĮą░ čäčāąĮą║čåąĖčÄ, ą║ąŠč鹊čĆą░čÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗąĘą▓ą░ąĮą░ ą┤ą╗čÅ ąÆą░čłąĄą│ąŠ čüą╗čāčćą░čÅ, čéą░ą║ ą║ą░ą║ ąŠčłąĖą▒ą║ą░ ąĘą┤ąĄčüčī ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝ąŠą╝čā ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ.

ą£ą░ą║čĆąŠčüčŗ ąĮą░čüčéčĆąŠąĄą║ configMAX_SYSCALL_INTERRUPT_PRIORITY ąĖ configKERNEL_INTERRUPT_PRIORITY ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą▓ čäą░ą╣ą╗ąĄ FreeRTOSConfig.h. ąØąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, čćč鹊ą▒čŗ ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą▓ ąĮąĖčģ ą▒čŗą╗ąĖ čüą┤ą▓ąĖąĮčāčéčŗ čéą░ą║, ą║ą░ą║ č鹊ą│ąŠ čéčĆąĄą▒čāąĄčé čüą░ą╝ą░ ą░čĆčģąĖč鹥ą║čéčāčĆą░ čÅą┤čĆą░ ARM Cortex-M ŌĆō ąŠąĮąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāąČąĄ čüą┤ą▓ąĖąĮčāčéčŗ ą║ čüą░ą╝čŗą╝ čüčéą░čĆčłąĖą╝ ąĘąĮą░čćą░čēąĖą╝ ą▒ąĖčéą░ą╝ ą▒ą░ą╣čéą░. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ configKERNEL_INTERRUPT_PRIORITY, ą║ąŠč鹊čĆąŠąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĖąŠčĆąĖč鹥čéą░, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 255 (ą┤ą▓ąŠąĖčćąĮąŠąĄ 11111111) čģąĄą┤ąĄčĆą░ FreeRTOSConfig.h, ą┐ąŠčüčéą░ą▓ą╗čÅąĄą╝ąŠą│ąŠ čü ą║ą░ąČą┤čŗą╝ ąŠčäąĖčåąĖą░ą╗čīąĮčŗą╝ ą┤ąĄą╝ąŠ FreeRTOS. ąĢčüčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąĖčćąĖąĮ, ą┐ąŠč湥ą╝čā ąĘąĮą░č湥ąĮąĖąĄ čāą║ą░ąĘą░ąĮąĮąŠ čéą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝: čÅą┤čĆąŠ RTOS ąŠą▒čĆą░čēą░ąĄčéčüčÅ ą║ ą░ą┐ą┐ą░čĆą░čéčāčĆąĄ ARM Cortex-M3 ąĮą░ą┐čĆčÅą╝čāčÄ (ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą║ą░ą║ąĖčģ-ą╗ąĖą▒ąŠ ą▒ąĖą▒ą╗ąĖąŠč鹥čćąĮčŗčģ čäčāąĮą║čåąĖą╣ čüč鹊čĆąŠąĮąĮąĖčģ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╣), čĆąĄą░ą╗ąĖąĘą░čåąĖčÅ čÅą┤čĆą░ RTOS ą┐ąŠčÅą▓ąĖą╗ą░čüčī čĆą░ąĮčīčłąĄ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░ ą▒ąĖą▒ą╗ąĖąŠč鹥čćąĮčŗčģ čäčāąĮą║čåąĖą╣, ąĖ čŹčéą░ čüčģąĄą╝ą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗ą░čüčī ą┐ąĄčĆą▓čŗą╝ąĖ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ą░ą╝ąĖ ARM Cortex-M3, ą▓čŗčłąĄą┤čłąĖą╝ąĖ ąĮą░ čĆčŗąĮąŠą║.

[ąÜčĆąĖčéąĖč湥čüą║ąĖąĄ čüąĄą║čåąĖąĖ]

ąÉą┐ą┐ą░čĆą░čéčāčĆą░ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ Cortex-M. ąÆ čÅą┤čĆąĄ RTOS čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ą┐ąŠą┤ą┤ąĄčƹȹ║ą░ ą║čĆąĖčéąĖč湥čüą║ąĖčģ čüąĄą║čåąĖą╣ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ BASEPRI ą░čĆčģąĖč鹥ą║čéčāčĆčŗ čÅą┤čĆą░ ARM Cortex-M. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čÅą┤čĆčā RTOS ą╝ą░čüą║ąĖčĆąŠą▓ą░čéčī č鹊ą╗čīą║ąŠ ą┐ąŠą┤ą╝ąĮąŠąČąĄčüčéą▓ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÅ č鹥ą╝ čüą░ą╝čŗą╝ ą▒ąŠą╗ąĄąĄ ą│ąĖą▒ą║čāčÄ ą╝ąŠą┤ąĄą╗čī ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

BASEPRI čŹč鹊 ą▒ąĖč鹊ą▓ą░čÅ ą╝ą░čüą║ą░. ąŻčüčéą░ąĮąŠą▓ą║ą░ BASEPRI ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą╝ą░čüą║ąĖčĆčāąĄčé ą▓čüąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čā ą║ąŠč鹊čĆčŗčģ ą┐čĆąĖąŠčĆąĖč鹥čé čĆą░ą▓ąĄąĮ čŹč鹊ą╝čā ąĘąĮą░č湥ąĮąĖčÄ ąĖ ąĮąĖąČąĄ (ą╗ąŠą│ąĖč湥čüą║ąĖ). ą¤ąŠčŹč鹊ą╝čā ąĮąĄą╗čīąĘčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī BASEPRI ą┤ą╗čÅ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, čā ą║ąŠč鹊čĆčŗčģ ą┐čĆąĖąŠčĆąĖč鹥čé 0.

ążčāąĮą║čåąĖąĖ FreeRTOS API, ą║ąŠč鹊čĆčŗąĄ ą▒ąĄąĘąŠą┐ą░čüąĮčŗ ą┤ą╗čÅ ą▓čŗąĘąŠą▓ą░ ąĖąĘ ISR, ąĖčüą┐ąŠą╗čīąĘčāčÄčé BASEPRI ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą║čĆąĖčéąĖč湥čüą║ąĖčģ čüąĄą║čåąĖą╣, ą▒ąĄąĘąŠą┐ą░čüąĮčŗčģ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (interrupt safe critical sections). BASEPRI čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ configMAX_SYSCALL_INTERRUPT_PRIORITY, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓čģąŠą┤ ą▓ ą║čĆąĖčéąĖč湥čüą║čāčÄ čüąĄą║čåąĖčÄ, ąĖ ą▓ 0, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓čŗčģąŠą┤ ąĖąĘ ą║čĆąĖčéąĖč湥čüą║ąŠą╣ čüąĄą║čåąĖąĖ. ą¤ąŠą╗čāč湥ąĮąŠ ą╝ąĮąŠąČąĄčüčéą▓ąŠ čüąŠąŠą▒čēąĄąĮąĖą╣ ąŠą▒ ąŠčłąĖą▒ą║ą░čģ (bug report), ą║ąŠč鹊čĆčŗąĄ čāčéą▓ąĄčƹȹ┤ą░čÄčé, čćč鹊 BASEPRI ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓ąŠąĘą▓čĆą░čēąĄąĮąŠ ą▓ čüą▓ąŠąĄ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĖ ą▓čŗčģąŠą┤ąĄ, ąĮąĄ ą┐čĆąŠčüč鹊 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 0, ąĮąŠ Cortex-M NVIC ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą┐čĆąĖą╝ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, čā ą║ąŠč鹊čĆąŠą│ąŠ (ą╗ąŠą│ąĖč湥čüą║ąĖą╣) ą┐čĆąĖąŠčĆąĖč鹥čé ąĮąĖąČąĄ č鹥ą║čāčēąĄą│ąŠ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝ąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ŌĆō ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, čćč鹊 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ BASEPRI. ąĀąĄą░ą╗ąĖąĘą░čåąĖčÅ, ą║ąŠč鹊čĆą░čÅ ą▓čüąĄą│ą┤ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé BASEPRI ą▓ 0, ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą║ąŠą┤ ą▒čŗčüčéčĆąĄąĄ, č湥ą╝ čéą░ čĆąĄą░ą╗ąĖąĘą░čåąĖčÅ, ą║ąŠč鹊čĆą░čÅ čüąŠčģčĆą░ąĮčÅąĄčé ąĖ ąĘą░č鹥ą╝ ą▓ąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ BASEPRI (ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĮąŠą╝ ąŠą┐čéąĖą╝ąĖąĘą░č鹊čĆąĄ ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆą░).

ąÜą░ą║ čŹč鹊 ąŠčéąĮąŠčüąĖčéčüčÅ ą║ FreeRTOS. ą»ą┤čĆąŠ RTOS čüąŠąĘą┤ą░ąĄčé ą║čĆąĖčéąĖč湥čüą║čāčÄ čüąĄą║čåąĖčÄ ąĘą░ą┐ąĖčüčīčÄ ąĘąĮą░č湥ąĮąĖčÅ configMAX_SYSCALL_INTERRUPT_PRIORITY ą▓ čĆąĄą│ąĖčüčéčĆ BASEPRI ą░čĆčģąĖč鹥ą║čéčāčĆčŗ ARM Cortex-M. ą¤ąŠčüą║ąŠą╗čīą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 0 (čü čüą░ą╝čŗą╝ ą▓čŗčüąŠą║ąĖą╝ ą▓ąŠąĘą╝ąŠąČąĮčŗą╝ ą╗ąŠą│ąĖč湥čüą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝) ąĮąĄ ą╝ąŠą│čāčé ą╝ą░čüą║ąĖčĆąŠą▓ą░čéčīčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ BASEPRI, configMAX_SYSCALL_INTERRUPT_PRIORITY ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 0.

ąŚą┤ąĄčüčī ą▓ ą║ą░č湥čüčéą▓ąĄ ą┐čĆąĖą╝ąĄčĆąŠą▓ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▒ą╗ąŠą║ąŠą▓ USART6 ąĖ Ethernet ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ STM32F407xx. ąöą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ ąĘą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮčŗ č鹊ą╗čīą║ąŠ čćą░čüčéąĖ ąĘą░ą│ąŠą╗ąŠą▓ą║ąŠą▓ ąĖ ą╝ąŠą┤čāą╗ąĄą╣, ą║ą░čüą░čÄčēąĖąĄčüčÅ č鹊ą╗čīą║ąŠ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

[FreeRTOSConfig.h]

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮčŗą╣ čäą░ą╣ą╗ FreeRTOS:

...

/* ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ, čüą┐ąĄčåąĖčäąĖčćąĮčŗąĄ ą┤ą╗čÅ Cortex-M. */

#ifdef __NVIC_PRIO_BITS

/* __BVIC_PRIO_BITS ą▒čāą┤ąĄčé ąĘą░ą┤ą░ąĮąŠ, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ CMSIS. */

#define configPRIO_BITS __NVIC_PRIO_BITS

#else

#define configPRIO_BITS 4

#endif

/* ąĪą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą▓čŗąĘąŠą▓ą░

čäčāąĮą║čåąĖąĖ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐čĆąĖąŠčĆąĖč鹥čéą░. */

#define configLIBRARY_LOWEST_INTERRUPT_PRIORITY 15

/* ąĪą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ ą╗čÄą▒ąŠą╝ ISR,

čćč鹊ą▒čŗ ąŠąĮ ą▒čŗą╗ ą▒ąĄąĘąŠą┐ą░čüąĮčŗą╝ ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ čäčāąĮą║čåąĖą╣ FreeRTOS API.

ąØąĢ ąÆą½ąŚą½ąÆąÉąÖąóąĢ ążąŻąØąÜą”ąśąś INTERRUPT SAFE FREERTOS API ąśąŚ ąøą«ąæą×ąōą× ą¤ąĀąĢąĀą½ąÆąÉąØąśą»,

ąŻ ąÜą×ąóą×ąĀą×ąōą× ą¤ąĀąśą×ąĀąśąóąĢąó ąÆą½ą©ąĢ, ą¦ąĢą£ ąŁąóą×ąó! (čā ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖčģ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ FreeRTOS

čćąĖčüą╗ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą╝ąĄąĮčīčłąĄ.) */

#define configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY 5

...

[settings.h]

ą£ąŠąĖ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ USART6 ąĖ Ethernet:

// ąŚą┤ąĄčüčī ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāą║ą░ąĘą░ąĮčŗ ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ

// ąŠčé configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY-1 (čüą░ą╝ąŠąĄ ą▓čŗčüąŠą║ąŠą┐čĆąĖąŠčĆąĖč鹥čéąĮąŠąĄ

// ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ) ą┤ąŠ configLIBRARY_LOWEST_INTERRUPT_PRIORITY (čüą░ą╝ąŠąĄ ąĮąĖąĘą║ąŠą┐čĆąĖąŠčĆąĖč鹥čéąĮąŠąĄ

// ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ).

#define USART6HW_INTERRUPT_PRIORITY (configLIBRARY_LOWEST_INTERRUPT_PRIORITY-4)

// ąŻ Ethernet ą┐čĆąĖąŠčĆąĖč鹥čé ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓čŗčłąĄ, č湥ą╝ čā USART6:

#define ETHERNETHW_INTERRUPT_PRIORITY (configLIBRARY_LOWEST_INTERRUPT_PRIORITY-5)

[stm32f4xx_hal_usart.c]

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐čĆąĖąĄą╝ą░ USART6:

...

__HAL_USART_ENABLE_IT(husart, USART_IT_RXNE);

//__HAL_USART_CLEAR_IT(husart, USART_IT_TXE);

HAL_NVIC_SetPriority(USART6_IRQn, USART6HW_INTERRUPT_PRIORITY, 1);

HAL_NVIC_EnableIRQ(USART6_IRQn);

...

[ethernetif.c]

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ Ethernet:

...

HAL_NVIC_SetPriority(ETH_IRQn, ETHERNETHW_INTERRUPT_PRIORITY, 0);

HAL_NVIC_EnableIRQ(ETH_IRQn);

...

[ąĪčüčŗą╗ą║ąĖ]

1. Running the RTOS on a ARM Cortex-M Core site:freertos.org.

2. STM32: ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆčŗ ąĖ č鹥čĆą╝ąĖąĮčŗ.

3. PM0214 STM32 Cortex®-M4 MCUs and MPUs programming manual site:st.com.

4. FreeRTOS Customisation FreeRTOSConfig.h site:freertos.org. |