|

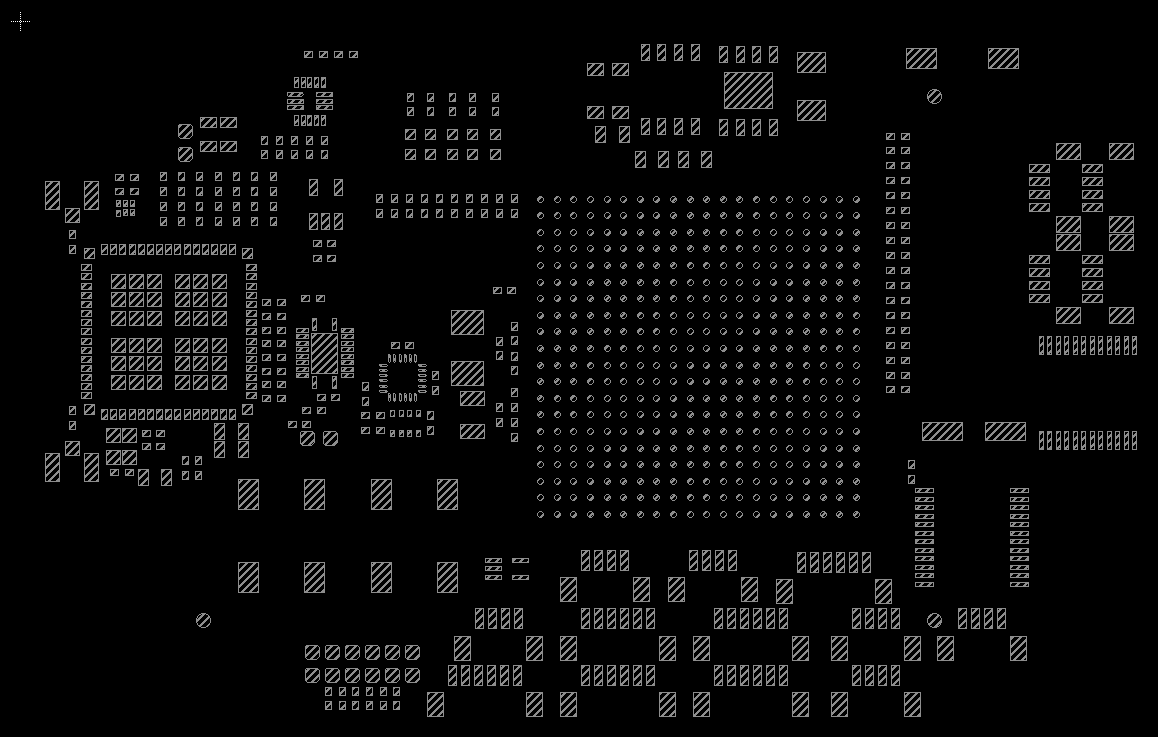

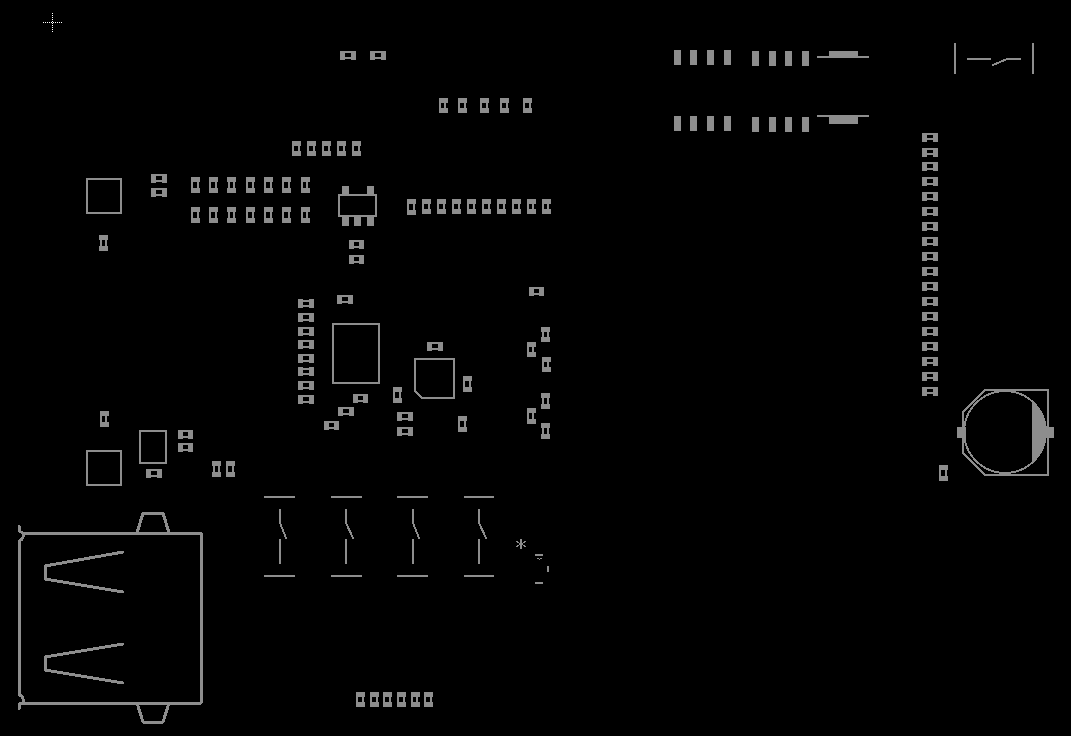

ąĪą╗ąŠąĖ (Layers) ą▓ čüąĖčüč鹥ą╝ąĄ ą┐čĆąŠąĄą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčćą░čéąĮčŗčģ ą┐ą╗ą░čé (PCB) Cadsoft Eagle - ą▓ąĄčüčīą╝ą░ ą║čĆąĖčéąĖč湥čüą║ą░čÅ čćą░čüčéčī ą┐čĆąŠąĄą║čéą░. ąÜąŠą│ą┤ą░ ąÆčŗ ą│ąŠč鹊ą▓čŗ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÄ ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖčÅ ąĮą░ ąĘą░ą▓ąŠą┤-ąĖąĘą│ąŠč鹊ą▓ąĖč鹥ą╗čī, č鹊 čüąŠąĘą┤ą░ą▓ą░ąĄą╝čŗąĄ Gerbers-čäą░ą╣ą╗čŗ ą┐ąŠą╗čāčćą░čé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ čüąŠ čüą╗ąŠąĄą▓ ą┐ą╗ą░čéčŗ, čćč鹊ą▒čŗ č鹊čćąĮąŠ ą┐ąĄčĆąĄą┤ą░čéčī č鹥čģąĮąŠą╗ąŠą│ąĖč湥čüą║čāčÄ ą│čĆą░čäąĖą║čā č鹊ą║ąŠą┐čĆąŠą▓ąŠą┤čÅčēąĖčģ ą┤ąŠčĆąŠąČąĄą║, ąŠčéą▓ąĄčĆčüčéąĖą╣, ą┐ą░čÅą╗čīąĮąŠą╣ ą╝ą░čüą║ąĖ, čłąĄą╗ą║ąŠą│čĆą░čäąĖąĖ ąĖ ą║ąŠąĮčéčāčĆą░ ą┐ą╗ą░čéčŗ. ąöą╗čÅ ąĮą░čćąĖąĮą░čÄčēąĖčģ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╣ ą┐čĆąŠą▒ą╗ąĄą╝ą░ ą▓ č鹊ą╝, čćč鹊 ąĖą╝ąĄąĄčéčüčÅ 38 čüą╗ąŠąĄą▓ (52 čüą╗ąŠčÅ, ąĄčüą╗ąĖ čŹč鹊 EAGLE Premium), ąĖ ąĘą░ą┐ąŠą╝ąĮąĖčéčī, ą┤ą╗čÅ č湥ą│ąŠ ą║ą░ąČą┤čŗą╣ čüą╗ąŠą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ą┤ąŠą▓ąŠą╗čīąĮąŠ čéčĆčāą┤ąĮąŠ. ąØąĄ ą▒ąĄčüą┐ąŠą║ąŠą╣č鹥čüčī, ąĮąĖąČąĄ ąÆčŗ ąĮą░ą╣ą┤ąĄč鹥 ą┐ąŠą╗ąĮčŗą╣ čüą┐ąĖčüąŠą║ čüą╗ąŠąĄą▓ Cadsoft EAGLE, ąĖ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ č鹊ą╝, ą┤ą╗čÅ č湥ą│ąŠ ąŠąĮąĖ ąĮčāąČąĮčŗ.

ąĪąĖčüč鹥ą╝ą░ ą┐čĆąŠąĄą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčćą░čéąĮčŗčģ ą┐ą╗ą░čé Eagle ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąŠčéą┤ąĄą╗čīąĮčŗąĄ ąĖąĘąĮą░čćą░ą╗čīąĮąŠ ąĘą░ą┤ą░ąĮąĮčŗąĄ čüą╗ąŠąĖ (layers) ą┤ą╗čÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ čåąĄą╗ąĄą╣. ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ čüą┤ąĄą╗ą░ąĮą░ ą┐ąŠą┐čŗčéą║ą░ čĆą░ąĘčŖčÅčüąĮąĖčéčī, ą┤ą╗čÅ č湥ą│ąŠ ąĮčāąČąĄąĮ ą║ą░ąČą┤čŗą╣ čüą╗ąŠą╣ čĆąĄą┤ą░ą║č鹊čĆą░ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ (čŹč鹊čé čĆąĄą┤ą░ą║č鹊čĆ ąĄčēąĄ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ Layout). ąĪą╗ąŠąĖ, ą║ąŠč鹊čĆčŗąĄ čĆąĄą┤ą║ąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąĄ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ, čÅ ą┐ąŠą╝ąĄčéąĖą╗ čüąĄčĆčŗą╝ čłčĆąĖčäč鹊ą╝. ąĪą╗ąŠąĖ, ą║ąŠč鹊čĆčŗąĄ ą░ą║čéąĖą▓ąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ - ą▓čŗą┤ąĄą╗ąĖą╗ ąČąĄą╗čéčŗą╝ č乊ąĮąŠą╝.

Ōä¢

|

ą”ą▓ąĄčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 1 |

|

Top |

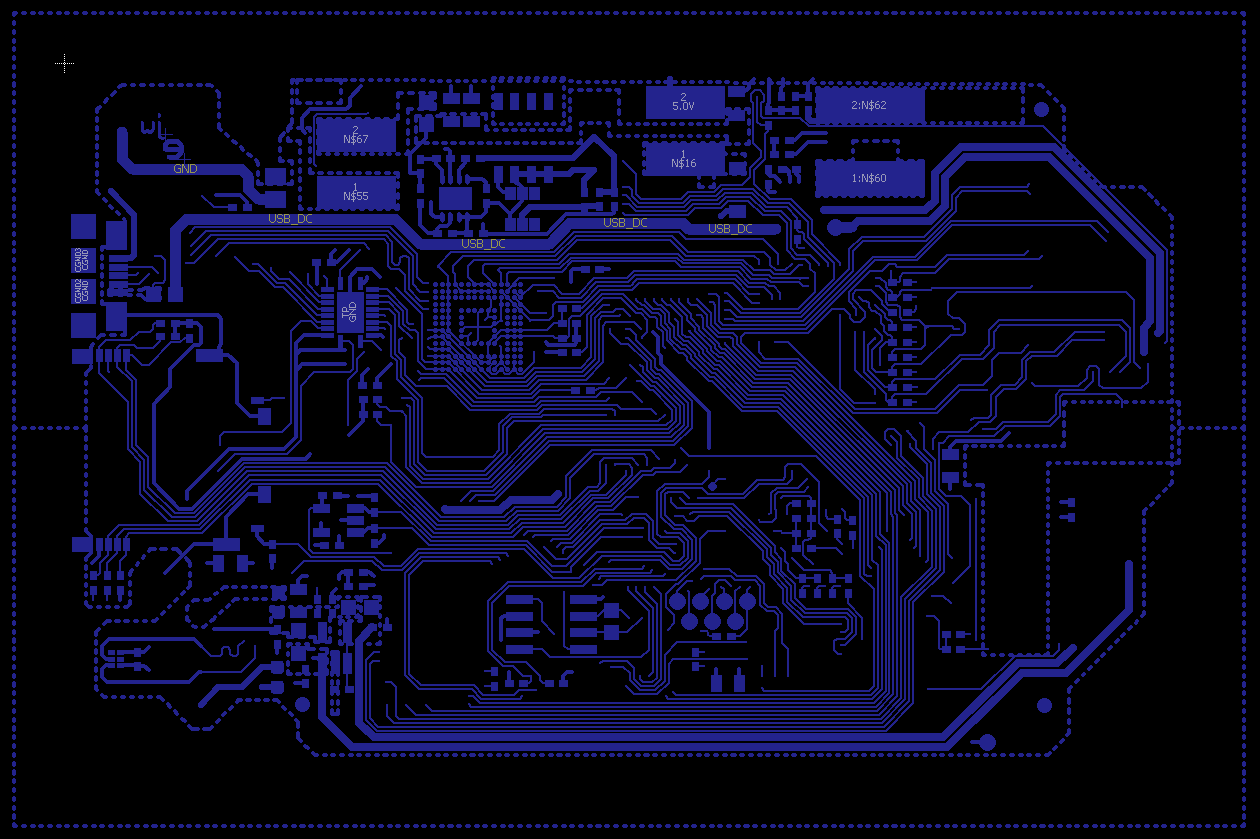

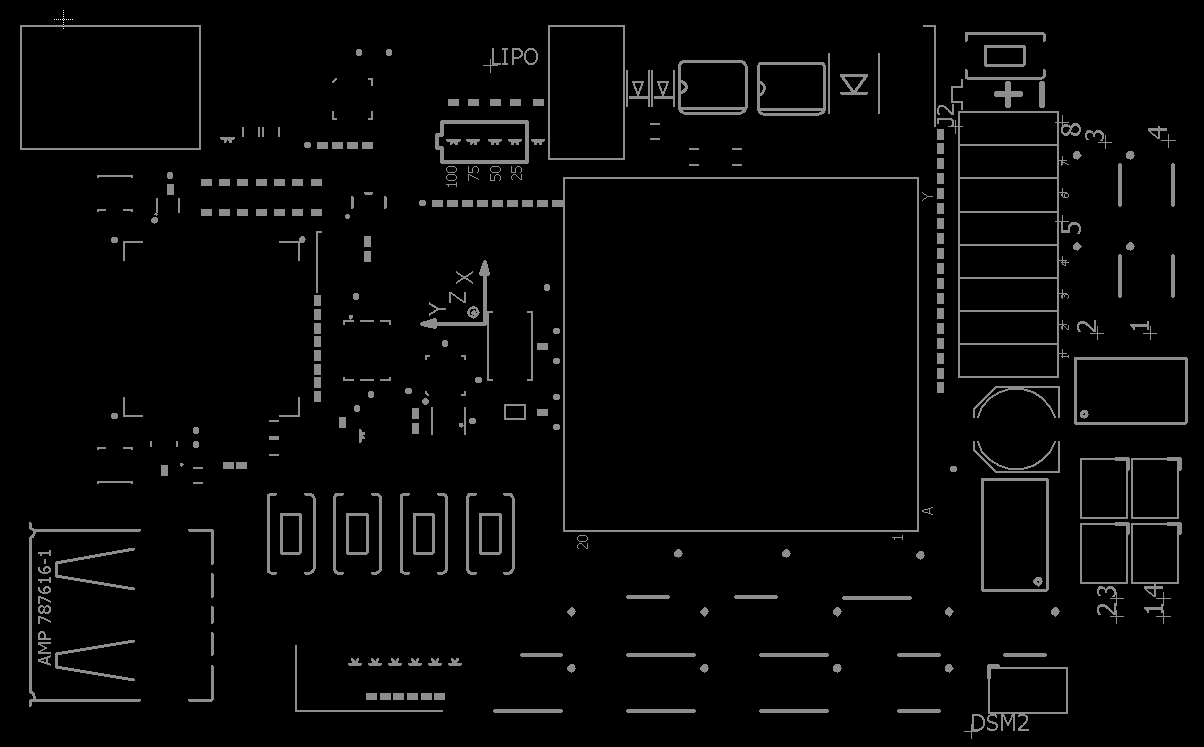

ąÆąĄčĆčģąĮčÅčÅ čüč鹊čĆąŠąĮą░ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ (PCB). ąØą░ čŹčéčā čüč鹊čĆąŠąĮčā čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ ą║čĆčāą┐ąĮąŠą│ą░ą▒ą░čĆąĖčéąĮčŗčģ ą┤ąĄčéą░ą╗ąĄą╣ ąĖ čćą░čēąĄ ą▓čüąĄą│ąŠ ąĮą░ąĮąŠčüąĖčéčüčÅ čłąĄą╗ą║ąŠą│čĆą░čäąĖčÅ. ąĪ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖąĄą╝ ą╝ąŠąĮčéą░ąČą░ SMD čäąĖąĘąĖč湥čüą║ąĖąĄ čĆą░ąĘą╗ąĖčćąĖčÅ čüą╗ąŠąĄą▓ TOP ąĖ BOTTOM ą╝ąŠą│čāčé ą▒čŗčéčī ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗ, ąŠą┤ąĮą░ą║ąŠ č鹥čĆą╝ąĖąĮčŗ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ, čćč鹊ą▒čŗ čĆą░ąĘą╗ąĖčćą░čéčī ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ čüč鹊čĆąŠąĮčŗ ą┐ą╗ą░čé. |

| 2 |

|

Route2 |

ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ čüą╗ąŠą╣ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąŠą║ą╗ą░ą┤ą║ąĖ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖčģ čüąŠąĄą┤ąĖąĮąĄąĮąĖą╣. ą¦ą░čēąĄ ą▓čüąĄą│ąŠ čŹčéąĖ čüą╗ąŠąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ čłąĖąĮčŗ ąĘąĄą╝ą╗ąĖ ąĖ ą┐ąĖčéą░ąĮąĖčÅ, čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čüą┐ą╗ąŠčłąĮąŠą│ąŠ ą┐ąŠą╗ąĖą│ąŠąĮą░ ą┐ąŠ čĆą░ąĘą╝ąĄčĆčā ą┐ą╗ą░čéčŗ. ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ čüą╗ąŠąĖ Route2..Route15 ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čĆąĄą┤ą║ąŠ - č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠč湥ąĮčī čüą╗ąŠąČąĮčŗčģ ą┐ą╗ą░čé, čéą░ą║ ą║ą░ą║ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąŠ čéą░ą║ąĖčģ ą┐ą╗ą░čé ąĮą░ą╝ąĮąŠą│ąŠ čüą╗ąŠąČąĮąĄąĄ ąĖ ą┤ąŠčĆąŠąČąĄ, č湥ą╝ ą┤ą▓čāčģčüč鹊čĆąŠąĮąĮąĖčģ (ą┤ą░ąČąĄ ą┤ą▓čāčģčüč鹊čĆąŠąĮąĮąĖčģ 5-ą│ąŠ, ąĮą░ąĖą▓čŗčüčłąĄą│ąŠ ą║ą╗ą░čüčüą░ č鹊čćąĮąŠčüčéąĖ).

|

| 3 |

|

Route3 |

ąóąŠąČąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüą╗ąŠą╣, čüą╝. Route2 |

| 4 |

|

Route4 |

-- "" --

|

| 5 |

|

Route5 |

-- "" -- |

| 6 |

|

Route6 |

-- "" -- |

| 7 |

|

Route7 |

-- "" -- |

| 8 |

|

Route8 |

-- "" -- |

| 9 |

|

Route9 |

-- "" -- |

| 10 |

|

Route10 |

-- "" -- |

| 11 |

|

Route11 |

-- "" -- |

| 12 |

|

Route12 |

-- "" -- |

| 13 |

|

Route13 |

-- "" -- |

| 14 |

|

Route14 |

-- "" -- |

| 15 |

|

Route15 |

ąóąŠąČąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüą╗ąŠą╣, čüą╝. Route2 |

| 16 |

|

Bottom |

ąØąĖąČąĮčÅčÅ čüč鹊čĆąŠąĮą░ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ (PCB). ąĪą╝. čéą░ą║ąČąĄ čüą╗ąŠą╣ Top. |

| 17 |

|

Pads |

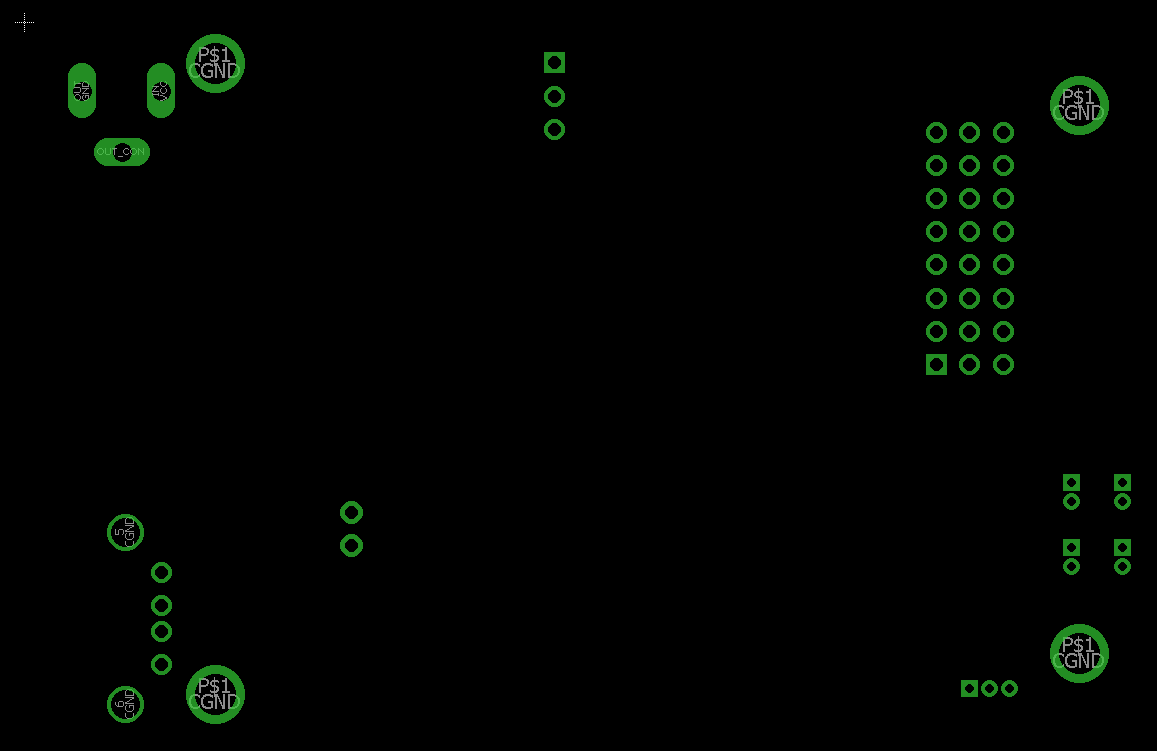

ą×ą▒ąŠąĘąĮą░č湥ąĮąĖąĄ ą┐ą╗ąŠčēą░ą┤ąŠą║ ą┤ą╗čÅ ąĮąŠąČąĄą║ čłčéčŗčĆąĄą▓čŗčģ (ą┤ą╗čÅ ą║ąŠč鹊čĆčŗčģ čüą▓ąĄčĆą╗čÅčéčüčÅ ąŠčéą▓ąĄčĆčüčéąĖčÅ) ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓. |

| 18 |

|

Vias |

ą×ą▒ąŠąĘąĮą░č湥ąĮąĖąĄ čüą║ą▓ąŠąĘąĮčŗčģ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗčģ ąŠčéą▓ąĄčĆčüčéąĖą╣. ą¤ąĄčĆąĄčģąŠą┤ąĮąŠąĄ ąŠčéą▓ąĄčĆčüčéąĖąĄ čüąŠąĘą┤ą░ąĄčé 菹╗ąĄą║čéčĆąĖč湥čüą║ąŠąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą╝ąĄąČą┤čā čüą╗ąŠčÅą╝ąĖ. |

| 19 |

|

Unrouted |

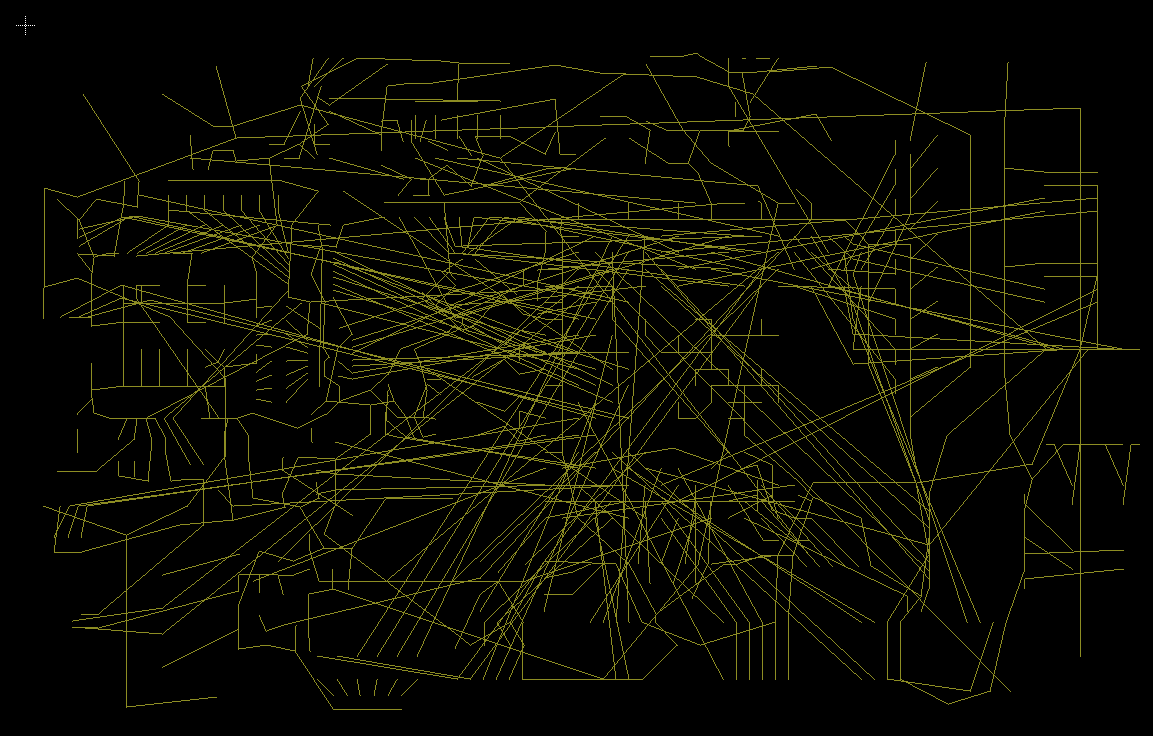

ąÆ čŹč鹊ą╝ čüą╗ąŠąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĄčēąĄ ąĮąĄ čĆą░ąĘą▓ąĄą┤ąĄąĮąĮčŗąĄ ą╝ąĄą┤čīčÄ čŹą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ. ąĪą╗ąŠą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ, ą┤ą╗čÅ ąĘą░ą▓ąŠą┤ą░ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░ ą┐ą╗ą░čé čŹč鹊čé čüą╗ąŠą╣ ąĮąĄ ąĮčāąČąĄąĮ. |

| 20 |

|

Dimension |

ąØą░ čŹč鹊ą╝ čüą╗ąŠąĄ ąĮą░čĆąĖčüąŠą▓ą░ąĮ ą║ąŠąĮčéčāčĆ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ, ą░ čéą░ą║ąČąĄ ą╝ąŠąĮčéą░ąČąĮčŗąĄ čüą║ą▓ąŠąĘąĮčŗąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ. |

| 21 |

|

tPlace |

ąŁč鹊čé čüą╗ąŠą╣ ąĘą░ą┤čāą╝čŗą▓ą░ą╗čüčÅ ą║ą░ą║ čüą╗ąŠą╣ ą┤ą╗čÅ ąĮą░ąĮąĄčüąĄąĮąĖčÅ čłąĄą╗ą║ąŠą│čĆą░čäąĖąĖ ą▓ąĄčĆčģąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ą╗ą░čéčŗ. ą» čŹč鹊čé čüą╗ąŠą╣ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄ, ąĖčüą┐ąŠą╗čīąĘčāčÄ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čüą║čĆąĖą┐č鹊ą╝ čüą╗ąŠą╣ _tsilk. ąĢčüą╗ąĖ čłąĄą╗ą║ąŠą│čĆą░čäąĖąĖ ąĮąĄčé, č鹊 čüą╗ąŠą╣ ą▓ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąĄ ą┐ą╗ą░čéčŗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

ą©ąĄą╗ą║ąŠą│čĆą░čäąĖčÅ čćą░čüč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, čćč鹊ą▒čŗ ąĮą░ąĮąŠčüąĖčéčī ąĮą░ ą┐ą╗ą░čéčā čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą┐ąŠčÅčüąĮčÅčÄčēąĖąĄ č鹥ą║čüč鹊ą▓čŗąĄ ą╝ąĄčéą║ąĖ (ą░ ąĖąĮąŠą│ą┤ą░ ąĖ ą│čĆą░čäąĖą║čā, ąĮą░ą┐čĆąĖą╝ąĄčĆ ą╗ąŠą│ąŠčéąĖą┐). ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 čłąĄą╗ą║ąŠą│čĆą░čäąĖčÅ ąĮąĄą┤ąŠčĆąŠą│ą░, ąĮąŠ ą┐čĆąĖąĮąŠčüąĖčé ąĘąĮą░čćąĖč鹥ą╗čīąĮčŗąĄ čāą┤ąŠą▒čüčéą▓ą░, ą┐ąŠčŹč鹊ą╝čā 菹║ąŠąĮąŠą╝ąĖčéčī ąĮą░ ąĮąĄą╣ ąĮąĄčé čüą╝čŗčüą╗ą░. |

| 22 |

|

bPlace |

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ tPlace, č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čłąĄą╗ą║ąŠą│čĆą░čäąĖąĖ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ą╗ą░čéčŗ. ą» čŹč鹊čé čüą╗ąŠą╣ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄ, ąĖčüą┐ąŠą╗čīąĘčāčÄ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čüą║čĆąĖą┐č鹊ą╝ čüą╗ąŠą╣ _bsilk.

|

| 23 |

|

tOrigins |

ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ ą║čĆąĄčüčéąĖą║ąŠą▓ ą┤ąĄčéą░ą╗ąĄą╣ ąĮą░ čüą╗ąŠąĄ Top. ąÜčĆąĄčüčéąĖą║ąĖ ąĮčāąČąĮčŗ, čćč鹊ą▒čŗ ą▓čŗą▒čĆą░čéčī ą┤ąĄčéą░ą╗čī (ąĖą╗ąĖ č鹥ą║čüč鹊ą▓čāčÄ ą╝ąĄčéą║čā), ąĖ ą┐ąŠč鹊ą╝ čćč鹊-ąĮąĖą▒čāą┤čī čü ąĮąĄą╣ ą┤ąĄą╗ą░čéčī. ąĢčüą╗ąĖ čŹč鹊čé čüą╗ąŠą╣ ą▓čŗą║ą╗čÄč湥ąĮ, č鹊 ąĮąĄą▓ąŠąĘą╝ąŠąČąĮąŠ ą┤ąĄą╗ą░čéčī ąĮąĖą║ą░ą║ąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ čü ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ą╝ąĖ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ. ąöą╗čÅ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░ čüą╗ąŠą╣ tOrigins ąĮąĄ ąĮčāąČąĄąĮ. |

| 24 |

|

bOrigins |

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ tOrigins, č鹊ą╗čīą║ąŠ č鹥ą┐ąĄčĆčī ą┤ą╗čÅ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ą╗ą░čéčŗ. |

| 25 |

|

tNames |

ąÆ čŹč鹊ą╝ čüą╗ąŠąĄ čĆą░ąĘą╝ąĄčēąĄąĮą░ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą┐ąŠ ą┐ąŠąĘąĖčåąĖąŠąĮąĮčŗą╝ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖčÅą╝ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ (ą┤ąĄčéą░ą╗ąĄą╣) ą▓ąĄčĆčģąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ - ąĮą░ą┐čĆąĖą╝ąĄčĆ R1, C3 ąĖ čé. ą┤. ąÆ PCAD čŹč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą░čéčĆąĖą▒čāčéą░ą╝ RefDes. ąśąĮąŠą│ą┤ą░ čüą╗ąŠą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čłąĄą╗ą║ąŠą│čĆą░čäąĖąĖ, ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ ą┐čĆąĖą╝ąĄąĮąĖčéčī ą║ąŠą╝ą░ąĮą┤čā smash (čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą┤ą▓ąĖą│ą░čéčī ąĮą░ą┤ą┐ąĖčüąĖ >NAME ąŠčéą┤ąĄą╗čīąĮąŠ ąŠčé ą║ąŠčĆą┐čāčüą░). ą» čŹč鹊čé čüą╗ąŠą╣ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄ, čéą░ą║ ą║ą░ą║ ą┤ą╗čÅ ą┐ąŠąĘąĖčåąĖąŠąĮąĮčŗčģ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖą╣ ąĮą░ čłąĄą╗ą║ąŠą│čĆą░čäąĖąĖ čā ą╝ąĄąĮčÅ ąĄčüčéčī čüą╗ąŠą╣ _tsilk. |

| 26 |

|

bNames |

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ tNames, č鹊ą╗čīą║ąŠ č鹥ą┐ąĄčĆčī ą┤ą╗čÅ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ą╗ą░čéčŗ. |

| 27 |

|

tValues |

ąÆ čŹč鹊ą╝ čüą╗ąŠąĄ čĆą░ąĘą╝ąĄčēąĄąĮą░ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą┐ąŠ ąĮąŠą╝ąĖąĮą░ą╗ą░ą╝ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ (ą┤ąĄčéą░ą╗ąĄą╣) ą▓ąĄčĆčģąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ. ąÆ PCAD čŹč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą░čéčĆąĖą▒čāčéą░ą╝ Value. ąśąĮąŠą│ą┤ą░ čüą╗ąŠą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čłąĄą╗ą║ąŠą│čĆą░čäąĖąĖ, ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ ą┐čĆąĖą╝ąĄąĮąĖčéčī ą║ąŠą╝ą░ąĮą┤čā smash (čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą┤ą▓ąĖą│ą░čéčī ąĮą░ą┤ą┐ąĖčüąĖ >VALUE ąŠčéą┤ąĄą╗čīąĮąŠ ąŠčé ą║ąŠčĆą┐čāčüą░). ą» čŹč鹊čé čüą╗ąŠą╣ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄ, čéą░ą║ ą║ą░ą║ ą┤ą╗čÅ ą┐ąŠąĘąĖčåąĖąŠąĮąĮčŗčģ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖą╣ ąĮą░ čłąĄą╗ą║ąŠą│čĆą░čäąĖąĖ čā ą╝ąĄąĮčÅ ąĄčüčéčī čüą╗ąŠą╣ _tsilk. |

| 28 |

|

bValues |

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ bValues, č鹊ą╗čīą║ąŠ č鹥ą┐ąĄčĆčī ą┤ą╗čÅ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ą╗ą░čéčŗ. |

| 29 |

|

tStop |

ąĢčüą╗ąĖ ą┤ą╗čÅ ą┐ą╗ą░čéčŗ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ą░čÅą╗čīąĮą░čÅ ą╝ą░čüą║ą░ (ą░ čŹč鹊 ą┤ą╗čÅ čüąŠą▓čĆąĄą╝ąĄąĮąĮčŗčģ ą┐ą╗ą░čé ą┐ąŠčćčéąĖ ą▓čüąĄą│ą┤ą░ čéą░ą║), č鹊 ą▓ čŹč鹊ą╝ čüą╗ąŠąĄ ąĮą░čĆąĖčüąŠą▓ą░ąĮčŗ ąŠą║ąĮą░ ą▓ ą┐ą░čÅą╗čīąĮąŠą╣ ą╝ą░čüą║ąĄ ą┤ą╗čÅ ą▓ąĄčĆčģąĮąĄą│ąŠ čüą╗ąŠčÅ ą┐ą╗ą░čéčŗ. ąóą░ą╝, ą│ą┤ąĄ ąĮą░čĆąĖčüąŠą▓ą░ąĮąŠ ąŠą║ąĮąŠ, ą╝ąĄą┤čī ą▒čāą┤ąĄčé ąŠą▒ą╗čāąČąĄąĮą░. ąóą░ą╝, ą│ą┤ąĄ ąŠą║ąĮą░ ąĮąĄčé, ą▒čāą┤ąĄčé ąĘą░čēąĖčéąĮąŠąĄ ą┐ąŠą║čĆčŗčéąĖąĄ, ąĘą░ą║čĆčŗą▓ą░čÄčēąĄąĄ ą╝ąĄą┤čī (čŹč鹊 ąĖ ąĄčüčéčī ą╝ą░čüą║ą░, ąŠą▒čŗčćąĮąŠ ąŠąĮą░ ąĘąĄą╗ąĄąĮąŠą│ąŠ ąĖą╗ąĖ ą║čĆą░čüąĮąŠą│ąŠ čåą▓ąĄčéą░). ą×ą║ąĮąŠ ą▓ ą╝ą░čüą║ąĄ ąŠą▒čŗčćąĮąŠ ąĮą░ 3..4 mil ą▒ąŠą╗čīčłąĄ čĆą░ąĘą╝ąĄčĆą░ ąŠą▒ą╗čāąČąĖą▓ą░ąĄą╝ąŠą╣ ą║ąŠąĮčéą░ą║čéąĮąŠą╣ ą┐ą╗ąŠčēą░ą┤ą║ąĖ. |

| 30 |

|

bStop |

ą£ą░čüą║ą░ ą┤ą╗čÅ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ą╗ą░čéčŗ. ąĪą╝. čéą░ą║ąČąĄ tStop. |

| 31 |

|

tCream |

ą£ą░čüą║ą░ ą┤ą╗čÅ ąĮą░ąĮąĄčüąĄąĮąĖčÅ ą┐ą░čÅą╗čīąĮąŠą╣ ą┐ą░čüčéčŗ ąĮą░ ą▓ąĄčĆčģąĮąĄą╣ čüč鹊čĆąŠąĮąĄ ą┐ą╗ą░čéčŗ. ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╝ ą╝ąŠąĮčéą░ąČąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓. |

| 32 |

|

bCream |

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 tCream, ąĮąŠ č鹥ą┐ąĄčĆčī ą┤ą╗čÅ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ą╗ą░čéčŗ. |

| 33 |

|

tFinish |

ąĪą╗ąŠą╣ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ ąĮą░ąĮąĄčüąĄąĮąĖčÅ čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗčģ čäąĖąĮąĖčłąĮčŗčģ ą┐ąŠą║čĆčŗčéąĖą╣ ą┤ą╗čÅ ą┐ą╗ą░čéčŗ (ąĘąŠą╗ąŠč鹊, čüąĄčĆąĄą▒čĆąŠ, ą┐ą╗ą░čéąĖąĮą░). ą» čŹč鹊čé čüą╗ąŠą╣ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄ. |

| 34 |

|

bFinish |

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ tFinish, ąĮąŠ ą┤ą╗čÅ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ. |

| 35 |

|

tGlue |

ą£ą░čüą║ą░ ą┤ą╗čÅ ąĮą░ąĮąĄčüąĄąĮąĖčÅ ą║ą╗ąĄčÅ ąĮą░ ą▓ąĄčĆčģąĮąĄą╣ čüč鹊čĆąŠąĮąĄ ą┐ą╗ą░čéčŗ. ąÜą╗ąĄą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĮą░ą┤ąĄąČąĮąŠą╣ čäąĖą║čüą░čåąĖąĖ ąĮą░ ą┐ą╗ą░č鹥 ąĮąĄą║ąŠč鹊čĆčŗčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą╝ąĖą║čĆąŠčüčģąĄą╝). |

| 36 |

|

bGlue |

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 tGlue, ąĮąŠ č鹥ą┐ąĄčĆčī ą┤ą╗čÅ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ą╗ą░čéčŗ. |

| 37 |

|

tTest |

ąÆčŗčĆą░ą▓ąĮąĖą▓ą░čÄčēąĖąĄ ą╝ąĄčéą║ąĖ ąĖ ą┤čĆčāą│ą░čÅ č鹥čģąĮąŠą╗ąŠą│ąĖč湥čüą║ą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ. ąŚą┤ąĄčüčī ąĘą░ą┤ą░čÄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗čīąĮčŗąĄ č鹊čćą║ąĖ ą┤ą╗čÅ čüąĖčüč鹥ą╝ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ą╗ą░čé (ICT, In Circuit Test). ą» čŹč鹊čé čüą╗ąŠą╣ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄ.

|

| 38 |

|

bTest |

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ tTest, ąĮąŠ ą┤ą╗čÅ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ.

|

| 39 |

|

tKeepout |

ąśąĮč乊čĆą╝ą░čåąĖčÅ ą┤ą╗čÅ ą░ą▓č鹊čĆąŠčāč鹥čĆą░, ąŠą│čĆą░ąĮąĖčćąĖą▓ą░čÄčēą░čÅ ąŠą▒ą╗ą░čüčéčī ą┐čĆąŠą║ą╗ą░ą┤ą║ąĖ ą┐čĆąŠą▓ąŠą┤ąĮąĖą║ąŠą▓ ą┐ąŠą┤ ą┤ąĄčéą░ą╗čÅą╝ąĖ ą┤ą╗čÅ ą▓ąĄčĆčģąĮąĄą│ąŠ čüą╗ąŠčÅ. ąØą░ą┐čĆąĖą╝ąĄčĆ, čćč鹊ą▒čŗ ą┐čĆąŠą▓ąŠą┤ąĮąĖą║ąĖ ąĮąĄ ąĘą░ą╝čŗą║ą░ą╗ąĖ ąĮą░ ą╝ąĄčéą░ą╗ą╗ąĖč湥čüą║ąĖąĄ čćą░čüčéąĖ ą║ąŠčĆą┐čāčüą░ ą┤ąĄčéą░ą╗ąĖ. ąÆ PCAD čüą╗ąŠą▓ąĄčćą║ąŠ Keepout ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą▓ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĖąĮąŠą╝ ąĘąĮą░č湥ąĮąĖąĖ (Polygon Keepout ąĮąĄ čüą▓čÅąĘą░ąĮ čü ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ą╝ąĖ ąĖ ą╝ąŠąČąĄčé čĆą░čüą┐čĆąŠčüčéčĆą░ąĮčÅčéčī ą┤ąĄą╣čüčéą▓ąĖąĄ čüčĆą░ąĘčā ąĮą░ ąŠą▒ą░ čüą╗ąŠčÅ). ą£ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖčÅ ą│ą░ą▒ą░čĆąĖč鹊ą▓ ą┤ąĄčéą░ą╗ąĄą╣, čćč鹊ą▒čŗ ą┐čĆąĖ čĆą░ąĘą╝ąĄčēąĄąĮąĖąĖ ąĖčģ ąĮą░ ą┐ą╗ą░č鹥 ą▓čüąĄ ą┤ąĄčéą░ą╗ąĖ ą┐ąŠą╝ąĄčüčéąĖą╗ąĖčüčī. |

| 40 |

|

bKeepout |

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 tKeepout, ąĮąŠ č鹥ą┐ąĄčĆčī ą┤ą╗čÅ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ą╗ą░čéčŗ. |

| 41 |

|

tRestrict |

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ tKeepout, ąĮąŠ ąĘą┤ąĄčüčī ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąŠ ąĘą░ą┐čĆąĄč鹥 ą┐čĆąŠą║ą╗ą░ą┤ą║ąĖ čéčĆą░čüčü ąĮąĄ čüą▓čÅąĘą░ąĮą░ čü ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ą╝ąĖ (ą┤ąĄčéą░ą╗čÅą╝ąĖ). ąÆ ąŠą▒ą╗ą░čüčéąĖ tRestrict ąĘą░ą┐čĆąĄčēąĄąĮą░ ą┐čĆąŠą║ą╗ą░ą┤ą║ą░ čéčĆą░čüčü, čāčüčéą░ąĮąŠą▓ą║ą░ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗčģ ąŠčéą▓ąĄčĆčüčéąĖą╣ (via), ąĖ ąŠčéčüčāčéčüčéą▓čāąĄčé ąĘą░ą╗ąĖą▓ą║ą░ ą╝ąĄą┤čīčÄ. |

| 42 |

|

bRestrict |

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 tRestrict, ąĮąŠ č鹥ą┐ąĄčĆčī ą┤ą╗čÅ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ą╗ą░čéčŗ. |

| 43 |

|

vRestrict |

ąśąĮč乊čĆą╝ą░čåąĖčÅ ą┤ą╗čÅ ą░ą▓č鹊čĆąŠčāč鹥čĆą░ - ąĘą░ą┐čĆąĄčéąĮčŗąĄ ą╝ąĄčüčéą░ ą┤ą╗čÅ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗčģ ąŠčéą▓ąĄčĆčüčéąĖą╣ (via). |

| 44 |

|

Drills |

ą×ą▒ąŠąĘąĮą░č湥ąĮąĖąĄ ąŠčéą▓ąĄčĆčüčéąĖą╣ čü ą╝ąĄčéą░ą╗ą╗ąĖąĘą░čåąĖąĄą╣ (ąŠą▒čŗčćąĮąŠ ą┤ą╗čÅ ą┐ą░ą╣ą║ąĖ ą▓čŗą▓ąŠą┤ąŠą▓ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓, ą┐ąĄčĆąĄčģąŠą┤ąĮčŗčģ ąŠčéą▓ąĄčĆčüčéąĖą╣). ąÆ čéą░ą║ąĖčģ ąŠčéą▓ąĄčĆčüčéąĖčÅčģ ą▓ąĄčĆčģąĮąĖą╣ ąĖ ąĮąĖąČąĮąĖą╣ čüą╗ąŠąĖ ą┐ą╗ą░čéčŗ čüąŠąĄą┤ąĖąĮąĄąĮčŗ ą╝ąĄą┤čīčÄ. |

| 45 |

|

Holes |

ą×ą▒ąŠąĘąĮą░č湥ąĮąĖąĄ ąŠčéą▓ąĄčĆčüčéąĖą╣ ą▒ąĄąĘ ą╝ąĄčéą░ą╗ą╗ąĖąĘą░čåąĖąĖ (ąŠą▒čŗčćąĮąŠ ą┤ą╗čÅ ą┐čĆąŠčüčéčŗčģ ą║čĆąĄą┐ąĄąČąĮčŗčģ ąĖą╗ąĖ ąĮą░ą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ ąŠčéą▓ąĄčĆčüčéąĖą╣). ąóą░ą║ąĖąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ ąĮąĄ ąĖą╝ąĄčÄčé ą╝ąĄą┤ąĖ ą▓ ą║ą░ąĮą░ą╗ąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ, ąĖ čéą░ą║ąČąĄ čćą░čüč鹊 ąĮą░ ą▓ąĄčĆčģąĮąĄą╣ ąĖ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮą░čģ ą┐ą╗ą░čéčŗ ą▓ąŠąĘą╗ąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ ą╝ąĄą┤čī ąŠčéčüčāčéčüčéą▓čāąĄčé. |

| 46 |

|

Milling |

ąŁč鹊čé čüą╗ąŠą╣ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ą▓čŗą┤ąĄą╗ąĄąĮ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░ ą┐ą╗ą░čéčŗ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ ąĮčāąČąĮąŠ čüą┤ąĄą╗ą░čéčī ą┐čĆąŠą┤ąŠą╗ą│ąŠą▓ą░č鹊ąĄ ąŠčéą▓ąĄčĆčüčéąĖąĄ, č鹊 ąĮčāąČąĮąŠ ąĮą░čĆąĖčüąŠą▓ą░čéčī ą│čĆą░čäąĖą║čā ąĮą░ čŹč鹊ą╝ čüą╗ąŠąĄ. ąøčÄą▒čŗąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą▓čŗčĆąĄąĘčŗ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ čĆąĖčüčāčÄčéčüčÅ ą┐ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą▓ąĮąĄčłąĮąĖąĄ ą║čĆą░čÅ ą┐ą╗ą░čéčŗ ą║ čüą╗ąŠčÄ Milling ąĮąĄ ąŠčéąĮąŠčüčÅčéčüčÅ, ąŠąĮąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĮą░čĆąĖčüąŠą▓ą░ąĮčŗ ą▓ čüą╗ąŠąĄ Dimension. ą» čüą╗ąŠą╣ Milling ąŠą▒čŗčćąĮąŠ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄ. |

| 47 |

|

Measures |

ąŁč鹊čé čüą╗ąŠą╣ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą┐čĆąŠčüčéą░ą▓ą╗ąĄąĮąĖčÅ čĆą░ąĘą╝ąĄčĆąŠą▓ ąĮą░ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░č鹥. |

| 48 |

|

Document |

ą» čŹč鹊čé čüą╗ąŠą╣ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄ. ąĪą╗ąŠą╣ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą╗čÅ ą┤ąŠą║čāą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮąĖčÅ č湥čĆč鹥ąČąĄą╣.

|

| 49 |

|

Reference |

ąÆčŗčĆą░ą▓ąĮąĖą▓ą░čÄčēąĖąĄ ą╝ąĄčéą║ąĖ, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗąĄ ą┤ą╗čÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐ąŠąĘąĖčåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ą╗ą░čéčŗ ąĮą░ ą╝ąŠąĮčéą░ąČąĮąŠą╝ ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮąĖąĖ. ą» čŹč鹊čé čüą╗ąŠą╣ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄ. |

| 51 |

|

tDocu |

ą» čŹč鹊čé čüą╗ąŠą╣ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄ. ąĪą╗ąŠą╣ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą╗čÅ ą┤ąŠą║čāą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮą░ ą▓ąĄčĆčģąĮąĄą╣ čüč鹊čĆąŠąĮąĄ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ. |

| 52 |

|

bDocu |

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ tDocu, ąĮąŠ ą┤ą╗čÅ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ. |

| 121 |

|

_tsilk |

ąŁč鹊čé čüą╗ąŠą╣ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüą║čĆąĖą┐č鹊ą╝ silk_gen.ulp. ąÆ ąĮąĄą│ąŠ ą┐ąĄčĆąĄąĮąŠčüąĖčéčüčÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ čüąŠ čüą╗ąŠąĄą▓ tNames ąĖ tValues. |

| 122 |

|

_bsilk |

ąŁč鹊čé čüą╗ąŠą╣ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüą║čĆąĖą┐č鹊ą╝ silk_gen.ulp. ąÆ ąĮąĄą│ąŠ ą┐ąĄčĆąĄąĮąŠčüąĖčéčüčÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ čüąŠ čüą╗ąŠąĄą▓ bNames ąĖ bValues. |

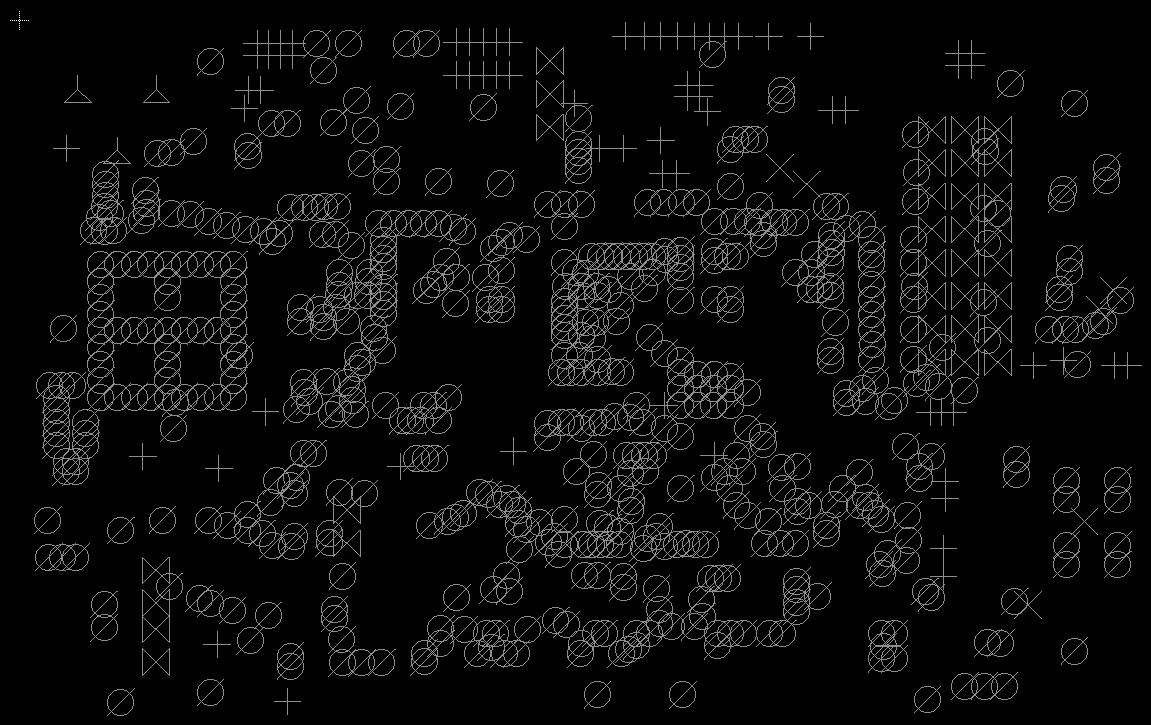

[ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čüą╗ąŠąĄą▓]

Layer 1: Top. ąŁč鹊 ą┐ąĄčĆą▓čŗą╣ čüą╗ąŠą╣, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą╝ąĄą┤ąĖ ąĮą░ ą▓ąĄčĆčģąĮąĄą╣ čüč鹊čĆąŠąĮąĄ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ. ąØą░ ąĮąĄą╝ čüąŠą┤ąĄčƹȹ░čéčüčÅ č鹊ą║ąŠą┐čĆąŠą▓ąŠą┤čÅčēąĖąĄ ą┤ąŠčĆąŠąČą║ąĖ, ą║ąŠąĮčéą░ą║čéąĮčŗąĄ ą┐ą╗ąŠčēą░ą┤ą║ąĖ ąĖ/ąĖą╗ąĖ ą┐ąŠą╗ąĖą│ąŠąĮčŗ ąĘą░ą╗ąĖą▓ą║ąĖ. ąØą░ čŹč鹊ą╝ čüą╗ąŠąĄ čćą░čüč鹊 ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ ąĘą░ą╗ąĖą▓ą║ąĖ ą╝ąĄą┤čīčÄ čü čłąĖąĮąŠą╣ ąĘąĄą╝ą╗ąĖ (GND copper pour) ą▓čüąĄčģ ą╝ąĄčüčé, ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą┤ąŠčĆąŠąČą║ą░ą╝ąĖ, čćč鹊 čāą╗čāčćčłą░ąĄčé 菹║čĆą░ąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ čāčüą╗ąŠą▓ąĖčÅ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖ ą┐ąĖčéą░ąĮąĖčÅ. ąóą░ą║ąČąĄ ą┐čĆąĖ čüąŠąĘą┤ą░ąĮąĖąĖ ą║ąŠąĮčéą░ą║čéąĮčŗčģ ą┐ą╗ąŠčēą░ą┤ąŠą║ (pads) ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ą┐ąŠą▓ąĄčĆčģąĮąŠčüčéąĮąŠą│ąŠ ą╝ąŠąĮčéą░ąČą░ (SMT/SMD) EAGLE ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĖčüą┐ąŠą╗čīąĘčāąĄčé Layer 1 ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą╝ąĄčüčé čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ čŹčéąĖčģ ą┐ą╗ąŠčēą░ą┤ąŠą║.

Layer 2-15: Route. ąŁč鹊 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čüą╗ąŠąĖ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗąĄ ą┤ą╗čÅ ą╝ąĮąŠą│ąŠčüą╗ąŠą╣ąĮčŗčģ (ą╝ąĮąŠą│ąŠčüą╗ąŠą╣ąĮąŠą╣ ąĮą░ąĘčŗą▓ą░čÄčé ą┐ą╗ą░čéčā, čā ą║ąŠč鹊čĆąŠą╣ ą║čĆąŠą╝ąĄ čüą╗ąŠąĄą▓ Top ąĖ Bottom ąĄčüčéčī ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ č鹊ą║ąŠą┐čĆąŠą▓ąŠą┤čÅčēąĖąĄ čüą╗ąŠąĖ) ą┐ąĄčćą░čéąĮčŗčģ ą┐ą╗ą░čé. ąĢčüą╗ąĖ ąÆčŗ ąĮąĄ ą▓ąĖą┤ąĖč鹥 ą▓ ą┤ąĖą░ą╗ąŠą│ąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüą╗ąŠčÅą╝ąĖ čüą╗ąŠąĄą▓ 2..15, č鹊 ą▓ąŠąĘą╝ąŠąČąĮąŠ ą▓ąĄčĆčüąĖčÅ ąĮąĄ Premium EAGLE, ą╗ąĖą▒ąŠ ąĮąĄ ąĮą░čüčéčĆąŠąĄąĮčŗ čüą╗ąŠąĖ ą▓ ą┤ąĖą░ą╗ąŠą│ąĄ DRC -> Layers.

ąĢčüą╗ąĖ ąÆčŗ ą┐ą╗ą░ąĮąĖčĆčāąĄč鹥 čĆą░ąĘčĆą░ą▒ą░čéčŗą▓ą░čéčī ą╝ąĮąŠą│ąŠčüą╗ąŠą╣ąĮčāčÄ ą┐ą╗ą░čéčā, č鹊 ąĖą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą▓ąĄčĆčģąĮąĖąĄ ąĖ ąĮąĖąČąĮąĖąĄ čüą╗ąŠąĖ ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čüą╗ąŠąĖ ą┐ą╗ą░čéčŗ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮčŗ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąŠ-ą┤čĆčāą│ąŠą╝čā, ąĮąĄ čéą░ą║ ą║ą░ą║ ą▓ ą┐čĆąŠąĄą║č鹥 ą┤ą▓čāčģčüą╗ąŠą╣ąĮąŠą╣ ą┐ą╗ą░čéčŗ [2]. ąØą░ą┐čĆąĖą╝ąĄčĆ, čüąŠąĘą┤ą░ąĮąĖąĄ 4-čüą╗ąŠą╣ąĮąŠą╣ ą┐ą╗ą░čéčŗ ąĮąĄ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüą╗ąŠąĖ 1, 2, 3 ąĖ 4. ąÆą╝ąĄčüč鹊 čŹč鹊ą│ąŠ EAGLE ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī Layer 1 (Top), 2, 15 ąĖ 16 (Bottom), čćč鹊ą▒čŗ čüąŠąĄą┤ąĖąĮąĖčéčī ąĖčģ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ą▓ čüč鹥ą║.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠą┤čĆąŠą▒ąĮąŠ ąĮą░čüčéčĆąŠą╣ą║ą░ čüą╗ąŠąĄą▓ ą┤ą▓čāčģčüą╗ąŠą╣ąĮčŗčģ ąĖ ą╝ąĮąŠą│ąŠčüą╗ąŠą╣ąĮčŗčģ ą┐ą╗ą░čé ąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ čüčéą░čéčīąĄ [3].

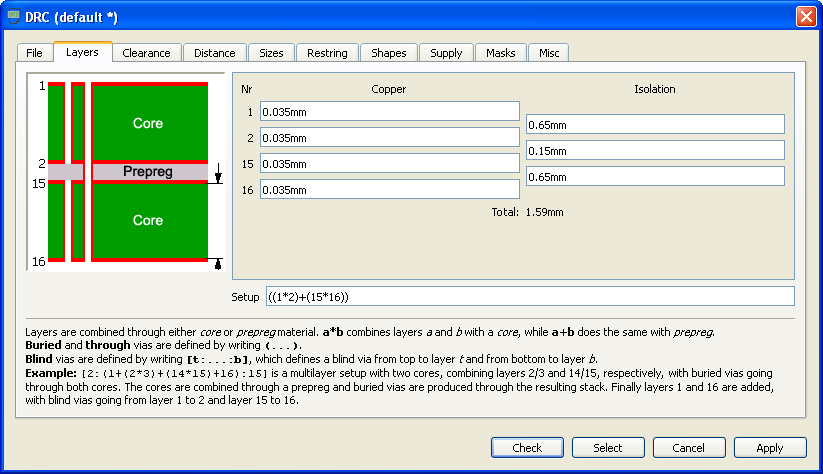

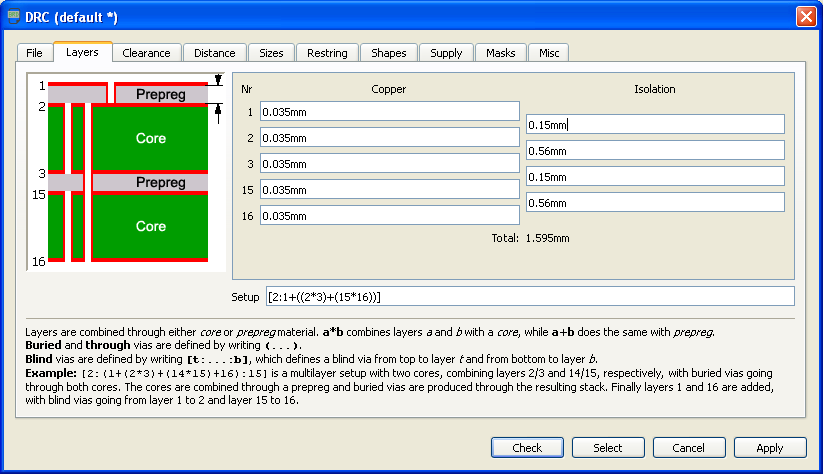

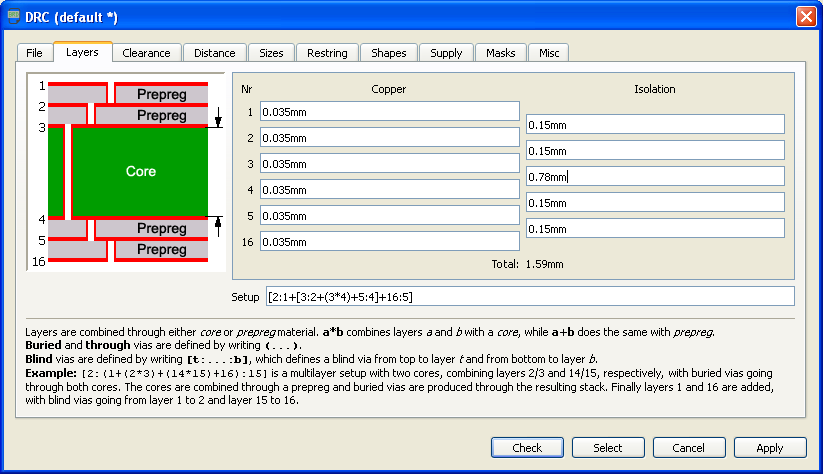

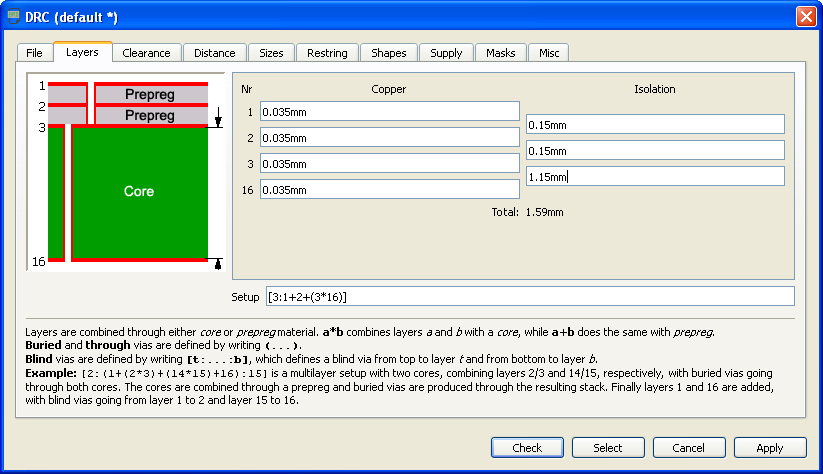

ąŚą░ą║ą╗ą░ą┤ą║ą░ Layers (čüą╗ąŠąĖ) ą┤ąĖą░ą╗ąŠą│ą░ DRC ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčé ąĮą░čüčéčĆąŠą╣ą║čā čüą╗ąŠąĄą▓ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ (layer setup). ąŚą┤ąĄčüčī ą╝ąŠąČąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą║ą░ą║ąĖąĄ čüąĖą│ąĮą░ą╗čīąĮčŗąĄ čüą╗ąŠąĖ ą┐ą╗ą░čéą░ ą▓ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčé, ą║ą░ą║ąŠą╣ č鹊ą╗čēąĖąĮčŗ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą╝ąĄą┤čī ąĮą░ čŹčéąĖčģ čüą╗ąŠčÅčģ, ą║ą░ą║ąŠą▓ą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī č鹊ą╗čēąĖąĮą░ čüą╗ąŠąĄą▓ ąĖąĘąŠą╗čÅčåąĖąĖ ąĖ ą║ą░ą║ąŠą│ąŠ čéąĖą┐ą░ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ (via) ą┤ąŠą╗ąČąĮčŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ. Ečüą╗ąĖ ąĮąĄ ą▒čŗą╗ąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ ąŠčé čüą╗ąŠčÅ 1 ą┤ąŠ čüą╗ąŠčÅ 16 (ą║ą░ą║ ąŠąĮąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ, ą▒čāą┤ąĄčé ą┐ąŠą║ą░ąĘą░ąĮąŠ ą┤ą░ą╗ąĄąĄ), č鹊 ą║ąŠąĮčéą░ą║čéąĮčŗąĄ ą┐ą╗ąŠčēą░ą┤ą║ąĖ (pads) ą▒čāą┤čāčé ą▓čüąĄą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮčŗ.

ąØą░čüčéčĆąŠą╣ą║ą░ čüą╗ąŠąĄą▓ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĘą░ą╝čŗčüą╗ąŠą▓ą░čéčŗą╝ ąĮą░ ą┐ąĄčĆą▓čŗą╣ ą▓ąĘą│ą╗čÅą┤ ą┐ąŠą╗ąĄą╝ "Setup". ąŁč鹊 čüč鹊ą║ą░, čüąŠčüč鹊čÅčēą░čÅ ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĮąŠą╝ąĄčĆąŠą▓ čüą╗ąŠąĄą▓, čĆą░ąĘą┤ąĄą╗ąĄąĮąĮčŗčģ čüąĖą╝ą▓ąŠą╗ą░ą╝ąĖ * ąĖą╗ąĖ +, ą│ą┤ąĄ * ąŠąĘąĮą░čćą░ąĄčé ą╝ą░č鹥čĆąĖą░ą╗ core (čé. ąĄ. ąŠčüąĮąŠą▓ąĮąŠą╣ ąĮąĄčüčāčēąĖą╣ ą╝ą░č鹥čĆąĖą░ą╗ ą┐ą╗ą░čéčŗ, čŹč鹊 ąŠą▒čŗčćąĮąŠ čģąŠčĆąŠčłąŠ ąĖąĘą▓ąĄčüčéąĮčŗą╣ č鹥ą║čüč鹊ą╗ąĖčé FR4 ąĖą╗ąĖ čćč鹊-č鹊 ą┤čĆčāą│ąŠąĄ ą▓ čüą╗čāčćą░ąĄ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą║ ą┐ą╗ą░č鹥) ąĖ + ąŠąĘąĮą░čćą░ąĄčé prepreg (ą▒ąŠą╗ąĄąĄ č鹊ąĮą║ąĖą╣ čüą╗ąŠą╣ ąĖąĘąŠą╗čÅčåąĖąŠąĮąĮąŠą│ąŠ ą╝ą░č鹥čĆąĖą░ą╗ą░). ąĀąĄą░ą╗čīąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĖčÅ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ čüą╗ąŠąĄą▓ core ąĖ prepreg ąĮąĖą║ą░ą║ ąĮąĄ ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ą▓ EAGLE, ą║čĆąŠą╝ąĄ ą║ą░ą║ čåą▓ąĄč鹊ą╝ ąĮą░ ą║ą░čĆčéąĖąĮą║ąĄ čŹč鹊ą╣ ąĘą░ą║ą╗ą░ą┤ą║ąĖ ą┤ąĖą░ą╗ąŠą│ą░ (ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮą░čÅ čüčéčĆčāą║čéčāčĆą░ čüą╗ąŠąĄą▓ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ąŠą│ąŠą▓ąŠčĆąĄąĮą░ čü ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╝ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ). ą¤ąĄčĆąĄčģąŠą┤ąĮčŗąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ ąŠą▒čĆą░ą╝ą╗ąĄąĮąĖąĄą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čüą╗ąŠąĄą▓ ą║čĆčāą│ą╗čŗą╝ąĖ čüą║ąŠą▒ą║ą░ą╝ąĖ (...). ąØą░ą┐čĆąĖą╝ąĄčĆ, čüą╗ąĄą┤čāčÄčēą░čÅ čüčéčĆąŠą║ą░ setup ąŠą▒ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┐ą╗ą░čéą░ ąĖą╝ąĄąĄčé 2 č鹊ą║ąŠą┐čĆąŠą▓ąŠą┤čÅčēąĖčģ čüą╗ąŠčÅ, čĆą░ąĘą┤ąĄą╗ąĄąĮąĮčŗčģ č鹥ą║čüč鹊ą╗ąĖč鹊ą╝ FR4, ą│ą┤ąĄ čüą║ą▓ąŠąĘčŗąĄ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ čüą╗ąŠąĄą▓ 1 ąĖ 16 (čŹč鹊 čüčéčĆąŠą║ą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ čüą╗ąŠąĄą▓ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ).

ąÜąŠą│ą┤ą░ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ą╝ąĮąŠą│ąŠčüą╗ąŠą╣ąĮą░čÅ ą┐ą╗ą░čéą░, čüčéčĆąŠą║ą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┤čĆčāą│ą░čÅ, ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ čüą╗ąĄą┤čāčÄčēąĄą╣:

ąŚą┤ąĄčüčī čā ą┐ą╗ą░čéčŗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ 4 čüą╗ąŠčÅ, ą│ą┤ąĄ ą┐ą░čĆčŗ čüą╗ąŠąĄą▓ 1/2 ąĖ 15/16 čüąŠąĘą┤ą░ąĮčŗ ąĮą░ ą╝ą░č鹥čĆąĖą░ą╗ąĄ core (ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčüčāąĮą║ąĄ ąĘąĄą╗ąĄąĮčŗą╝ čåą▓ąĄč鹊ą╝), ą┐ąĄčĆąĄčģąŠą┤ąĮčŗąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ čüą▓ąĄčĆą╗čÅčéčüčÅ čüą║ą▓ąŠąĘčī čŹčéąĖ ą┐ą░čĆčŗ (ą┐ąŠą╗čāčćą░čÄčéčüčÅ čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗąĄ čüą╗ąĄą┐čŗąĄ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ), ąĖ ąĮą░ą║ąŠąĮąĄčå čŹčéąĖ ą┤ą▓ąĄ ą┐ą░čĆčŗ čüą╗ąŠąĄą▓ čüą┐čĆąĄčüčüąŠą▓čŗą▓ą░čÄčéčüčÅ ą▓ą╝ąĄčüč鹥 č湥čĆąĄąĘ ą┐čĆąĄą┐čĆąĄą│ ą╝ąĄąČą┤čā ąĮąĖą╝ąĖ (ą┐čĆąĄą┐čĆąĄą│ ą┐ąŠą║ą░ąĘą░ąĮ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝), ąĖ čéą░ą║ąČąĄ čüą║ą▓ąŠąĘąĮčŗąĄ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ čüą▓ąĄčĆą╗čÅčéčüčÅ čüą║ąŠąĘčī ą▓čüčÄ čŹčéčā čüčéčĆčāą║čéčāčĆčā.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą╝ąĮąĄ ą▒ąŠą╗čīčłąĄ ąĮčĆą░ą▓ąĖčéčüčÅ čüčéčĆčāą║čéčāčĆą░ ą┤ą╗čÅ 4-čüą╗ąŠą╣ąĮąŠą╣ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ ((1+2)*(15+16)).

ą¤ąŠą╝ąĖą╝ąŠ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗčģ ąŠčéą▓ąĄčĆčüčéąĖą╣, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąŠčģąŠą┤čÅčé č湥čĆąĄąĘ ą▓ąĄčüčī čüč鹥ą║ čüą╗ąŠąĄą▓ (ą║ąŠč鹊čĆčŗąĄ ąŠą▒čŗčćąĮąŠ ąĮą░ąĘčŗą▓ą░čÄčé buried via, ą▓ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ ąŠąĮąĖ ąĮąĄ čüąŠąĘą┤ą░čÄčé čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ čüąŠ čüą╗ąŠąĄą╝ Top ąĖ Bottom), ąĘą┤ąĄčüčī ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąĄčĆąĄčģąŠą┤ąĮčŗąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ čüą▓ąĄčĆą╗čÅčéčüčÅ č湥čĆąĄąĘ ą▓ąĄčüčī čüč鹥ą║, ą▓ą╝ąĄčüč鹊 čŹč鹊ą│ąŠ ąĘą░ą║ą░ąĮčćąĖą▓ą░čÅčüčī ąĮą░ čüą╗ąŠąĄ ą▓ąĮčāčéčĆąĖ čüč鹥ą║ą░. ąóą░ą║ąĖąĄ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ ąĖąĘą▓ąĄčüčéąĮčŗ ą║ą░ą║ blind via, ąĖ ąŠąĮąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ čüčéčĆąŠą║ąŠą╣ Setup ąŠą▒čĆą░ą╝ą╗ąĄąĮąĖąĄą╝ [t:...:b], ą│ą┤ąĄ t ąĖ b čŹč鹊 čüą╗ąŠąĖ, ą║ąŠč鹊čĆčŗąĄ čüąŠąĄą┤ąĖąĮčÅčÄčéčüčÅ ąŠčé ą▓ąĄčĆčģąĮąĄą╣ (top) ąĖą╗ąĖ ąĮąĖąČąĮąĄą╣ (bottom) čüč鹊čĆąŠąĮčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą╝ąŠąČąĄčé ą▒čŗčéčī čüą╗ąĄą┤čāčÄčēą░čÅ ąĮą░čüčéčĆąŠą╣ą║ą░, ąĖčüą┐ąŠą╗čīąĘčāčÄčēą░čÅ blind via:

[2:1+((2*3)+(14*15))+16:15]

ąŁč鹊čé ą┐čĆąĖą╝ąĄčĆ ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé ą┤ą▓ą░ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ čüąĖą│ąĮą░ą╗čīąĮčŗčģ čüą╗ąŠčÅ, ą┤ą╗čÅ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą║ąŠč鹊čĆčŗčģ čüąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ąĖ čüą╗ąŠčÅą╝ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ blind via.

ą£ąŠąČąĮąŠ čéą░ą║ąČąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č鹊ą╗čīą║ąŠ ą┐ą░čĆą░ą╝ąĄčéčĆ t ąĖą╗ąĖ č鹊ą╗čīą║ąŠ b, ąĮą░ą┐čĆąĖą╝ąĄčĆ čüą╗ąĄą┤čāčÄčēą░čÅ čüčéčĆąŠą║ą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ čéą░ą║ąČąĄ ą▒čāą┤ąĄčé ą┐čĆą░ą▓ąĖą╗čīąĮąŠą╣:

ąś ą▓ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ, blind via ąĮąĄ ąŠą│čĆą░ąĮąĖč湥ąĮčŗ č鹥ą╝, čćč鹊 ąĮą░čćąĖąĮą░čÄčéčüčÅ ąĮą░ čüą╗ąŠąĄ Top ąĖą╗ąĖ Bottom, ąŠąĮąĖ čéą░ą║ąČąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąĖ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čüą╗ąŠčÅčģ čüč鹥ą║ą░, ą║ą░ą║ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐čĆąĖą╝ąĄčĆąĄ:

[2:1+[3:2+(3*4)+5:4]+16:5]

Blind via ąŠčé čüą╗ąŠčÅ a ą┤ąŠ čüą╗ąŠčÅ b čéą░ą║ąČąĄ čĆąĄą░ą╗ąĖąĘčāčÄčé ą▓čüąĄ ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ąŠčé čüą╗ąŠčÅ a ą┤ąŠ ą▓čüąĄčģ ą┤čĆčāą│ąĖčģ čüą╗ąŠąĄą▓ ą╝ąĄąČą┤čā čüą╗ąŠčÅą╝ąĖ a ąĖ b. ąØą░ą┐čĆąĖą╝ąĄčĆ, čŹčéą░ čüčéčĆąŠą║ą░ čüąŠąĘą┤ą░ąĄčé blind via ąŠčé čüą╗ąŠčÅ 1 ą┤ąŠ čüą╗ąŠčÅ 2, ą░ čéą░ą║ąČąĄ ąŠčé čüą╗ąŠčÅ 1 ą┤ąŠ čüą╗ąŠčÅ 3:

Layer 16: Bottom. ąóą░ą║ąČąĄ, ą║ą░ą║ Layer 1, čŹč鹊čé čüą╗ąŠą╣ čüąŠą┤ąĄčƹȹĖčé čĆąĖčüčāąĮąŠą║ ą╝ąĄą┤ąĖ, ąĮąŠ ąĮą░ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮąĄ ą┐ą╗ą░čéčŗ. ąØą░ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮąĄ ą┐ą╗ą░čéčŗ čéą░ą║ąČąĄ ą╝ąŠą│čāčé čĆą░ąĘą╝ąĄčēą░čéčīčüčÅ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ SMD, ąŠą┤ąĮą░ą║ąŠ čü čåąĄą╗čīčÄ čāą┤ąĄčłąĄą▓ą╗ąĄąĮąĖčÅ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░ ą┤ą╗čÅ ą╝ąŠąĮčéą░ąČą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąĖčüą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ ą▓ąĄčĆčģąĮąĖą╣ čüą╗ąŠą╣ Top.

Layer 17: Pads. ąŚą┤ąĄčüčī ąÆčŗ ąĮą░ą╣ą┤ąĄč鹥 ą║ąŠąĮčéą░ą║čéąĮčŗąĄ ą┐ą╗ąŠčēą░ą┤ą║ąĖ čüąŠ čüą║ą▓ąŠąĘąĮčŗą╝ąĖ ąŠčéą▓ąĄčĆčüčéąĖčÅą╝ąĖ (through-hole pads), ąĖčģ ąŠčéą▓ąĄčĆčüčéąĖčÅ ąŠą║čĆčāąČą░čÄčé ą║ąŠą╗ąĄčćą║ąĖ ąĖąĘ ą╝ąĄą┤ąĖ (Annular Ring). ąÜąŠą│ą┤ą░ ą║ąŠąĮčéą░ą║čéąĮą░čÅ ą┐ą╗ąŠčēą░ą┤ą║ą░ ą┐ąŠą╝ąĄčēą░ąĄčéčüčÅ ąĮą░ čŹč鹊čé čüą╗ąŠą╣, č鹊 annular ring ą▒čāą┤ąĄčé ąĮą░ ąŠą▒ąŠąĖčģ čüč鹊čĆąŠąĮą░čģ ą┐ą╗ą░čéčŗ, Top ąĖ Bottom. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąÆą░ą╝ čĆąĄą┤ą║ąŠ ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčüčÅ čćč鹊-ą╗ąĖą▒ąŠ ą╝ąĄąĮčÅčéčī ąĮą░ čŹč鹊ą╝ čüą╗ąŠąĄ, ą┐ąŠč鹊ą╝čā čćč鹊 菹╗ąĄą╝ąĄąĮčéčŗ ąĮą░ ąĮąĄą╝ čüąŠąĘą┤ą░čÄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą║ąŠą│ą┤ą░ ąÆčŗ ą┐ąŠą╝ąĄčēą░ąĄč鹥 ąĮą░ ą┐ą╗ą░čéčā ą║ąŠą╝ą┐ąŠąĮąĄąĮčé čüąŠ čłčéčŗčĆąĄą▓čŗą╝ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ.

Layer 18: Vias. ąŁč鹊čé čüą╗ąŠą╣ čüąŠą┤ąĄčƹȹĖčé ą▓čüąĄ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ (via), ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą▒čŗčüčéčĆčŗą╣ ą┐čāčéčī ą┤ą╗čÅ čüąŠąĄą┤ąĖąĮąĄąĮąĖą╣ čüąĖą│ąĮą░ą╗ąŠą▓ ą╝ąĄąČą┤čā čüą╗ąŠčÅą╝ąĖ ą╝ąĄčéą░ą╗ą╗ąĖąĘą░čåąĖąĖ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĖ ą┐ą╗ąŠčēą░ą┤ą║ąĖ via, ąĖ ą┐ą╗ąŠčēą░ą┤ą║ąĖ ą┤ą╗čÅ ą▓ą▓ąŠą┤ąŠą▓ čüąŠ čüą║ą▓ąŠąĘąĮčŗą╝ąĖ ąŠčéą▓ąĄčĆčüčéąĖčÅą╝ąĖ (through-hole pads) ą▓čŗą│ą╗čÅą┤čÅčé ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠ (čģąŠčéčÅ ąĖą╝ąĄčÄčé ąŠą▒čŗčćąĮąŠ čĆą░ąĘąĮčŗąĄ čĆą░ąĘą╝ąĄčĆčŗ), ą┐ąŠčŹč鹊ą╝čā čćą░čüč鹊 ą┐ąŠą╗ąĄąĘąĮąŠ čüą║čĆčŗą▓ą░čéčī/ą┐ąŠą║ą░ąĘčŗą▓ą░čéčī čüą╗ąŠąĖ 18 ąĖą╗ąĖ 17, čćč鹊ą▒čŗ ą┐ąŠąĮčÅčéčī, ą║ą░ą║ąŠą╣ ą║ąŠąĮą║čĆąĄčéąĮąŠ ąŠą▒čŖąĄą║čé ą┐čĆąŠčüą╝ą░čéčĆąĖą▓ą░ąĄč鹥.

Layer 19: Unrouted. ąÜąŠą│ą┤ą░ ąÆčŗ č鹊ą╗čīą║ąŠ čćč鹊 ąĮą░čćą░ą╗ąĖ čĆą░ąĘą▓ąŠą┤ą║čā ą┐ą╗ą░čéčŗ, ą▓čüąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ ą▒čāą┤čāčé čüąŠąĄą┤ąĖąĮčÅčéčīčüčÅ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ č鹊ąĮą║ąĖą╝ąĖ ąČąĄą╗čéčŗą╝ąĖ ą╗ąĖąĮčÅą╝ąĖ, ąŠą▒ąŠąĘąĮą░čćą░čÄčēąĖą╝ąĖ ąĮąĄ čĆą░ąĘą▓ąĄą┤ąĄąĮąĮčŗąĄ čüąĖą│ąĮą░ą╗čīąĮčŗąĄ čåąĄą┐ąĖ. ąŁčéąĖ ą╗ąĖąĮąĖąĖ čéą░ą║ąČąĄ ąĮą░ąĘčŗą▓ą░čÄčéčüčÅ ratsnest (ąĖ ąŠąĮąĖ ąŠą┐čéąĖą╝ąĖąĘąĖčĆčāčÄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ąŠą╣ rat ą▓ ą║ąŠąĮčüąŠą╗ąĖ). ą¤ąŠą║ą░ čåąĄą┐čī ąĮąĄ čĆą░ąĘą▓ąĄą┤ąĄąĮą░ ą┐ąŠą╗ąĮąŠčüčéčīčÄ, ą▓ čüą╗ąŠąĄ Unrouted ą▒čāą┤ąĄčé ą┐čĆąĖčüčāčéčüčéą▓ąŠą▓ą░čéčī ą│čĆą░čäąĖą║ą░ čŹč鹊ą╣ čåąĄą┐ąĖ ą▓ ą▓ąĖą┤ąĄ č鹊ąĮą║ąĖčģ ąČąĄą╗čéčŗčģ ą╗ąĖąĮąĖą╣.

Layer 20: Dimension. ąĪą╗ąŠą╣ Dimension čüą╗čāąČąĖčé ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ čåąĄą╗čÅą╝, ą│ą╗ą░ą▓ąĮą░čÅ ąĖąĘ ą║ąŠč鹊čĆčŗčģ - ąŠą▒ąŠąĘąĮą░čćąĖčéčī ą▓ąĮąĄčłąĮąĖąĄ ą║čĆą░čÅ ą┐ą╗ą░čéčŗ. ąöčĆčāą│ą░čÅ čäčāąĮą║čåąĖčÅ čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊 ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹč鹊čé čüą╗ąŠą╣ ą▓ ą┐čĆą░ą▓ąĖą╗ą░čģ ą┐čĆąŠąĄą║čéą░, čćč鹊ą▒čŗ čāą┤ąĄčƹȹĖą▓ą░čéčī ąĘą░ą╗ąĖą▓ą║čā ą╝ąĄą┤čīčÄ (copper pour) ąĮą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝ čĆą░čüčüč鹊čÅąĮąĖąĖ ąŠčé ą║čĆą░čÅ ą┐ą╗ą░čéčŗ.

ąØąĄą║ąŠč鹊čĆčŗąĄ ąĘą░ą▓ąŠą┤čŗ ąĖčüą┐ąŠą╗čīąĘčāčÄčé čüą╗ąŠą╣ Dimension ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ Gerber-čäą░ą╣ą╗ą░ čü ąĖąĮč乊čĆą╝ą░čåąĖąĄą╣ ąŠ ą║ąŠąĮčéčāčĆąĄ ą┐ą╗ą░čéčŗ. ąŁčéą░ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąĄ ą┤ą╗čÅ ąŠą▒čĆąĄąĘą║ąĖ ą╝ą░č鹥čĆąĖą░ą╗ą░ ąĖ ą┤ą╗čÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąĄąĮąĮąŠą╣ ą┐ą░ąĮąĄą╗ąĖ.

Layer 21-22: tPlace/bPlace. ąŁčéąĖ ą┤ą▓ą░ čüą╗ąŠčÅ čüąŠą┤ąĄčƹȹ░čé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┤ą╗čÅ čłąĄą╗ą║ąŠą│čĆą░čäąĖąĖ ą┤ą╗čÅ ą▓ąĄčĆčģąĮąĄą╣ ąĖ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮčŗ ą┐ą╗ą░čéčŗ, ą│ą┤ąĄ čüąŠą┤ąĄčƹȹ░čéčüčÅ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╝ ą║ąŠąĮčéčāčĆčŗ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄą╝čŗčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓, ąĖ ą┤ą░ąĮąĮčŗąĄ ąŠą▒ ąĖčģ ą┐ąŠąĘąĖčåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĖ. ąæčāą┤čīč鹥 ąŠčüč鹊čĆąŠąČąĮčŗ čü čŹčéąĖą╝ čüą╗ąŠąĄą╝, ąĖ ąĮąĄ ą┐ąŠą╝ąĄčēą░ą╣č鹥 ą│čĆą░čäąĖą║čā čłąĄą╗ą║ąŠą│čĆą░čäąĖąĖ ąĮą░ ą║ą░ą║ąĖąĄ-ąĮąĖą▒čāą┤čī ąŠą▒ą╗ą░čüčéąĖ, ą│ą┤ąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐ą░ą╣ą║ą░. ąśąĮą░č湥 ąĄčüčéčī čĆąĖčüą║ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ ąĮąĄą║ą░č湥čüčéą▓ąĄąĮąĮąŠą╣ ą┐ą░ą╣ą║ąĖ ąĖą╗ąĖ ą┤ą░ąČąĄ ąĘą░ą╝čŗą║ą░ąĮąĖą╣ čłą░čĆąĖą║ą░ą╝ąĖ ąŠą╗ąŠą▓ą░.

ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ čŹčéąĖą╝ čüą╗ąŠčÅą╝ čĆą░čüčüą╝ąŠčéčĆąĖč鹥 čĆą░ąĘą╝ąĄčēąĄąĮąĖąĄ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ čłąĄą╗ą║ąŠą│čĆą░čäąĖąĖ ąĮą░ čüą╗ąŠąĄ Layer 51: tDocu, ą║čāą┤ą░ ą╝ąŠąČąĮąŠ ą▓čüčéą░ą▓ą╗čÅčéčī čüą▓ąŠąĖ ą┐ąĄčĆčüąŠąĮą░ą╗čīąĮčŗąĄ čüčüčŗą╗ą║ąĖ. ąŁč鹊čé čüą╗ąŠą╣ ąĮąĄ ą▒čāą┤ąĄčé ą▓ą║ą╗čÄč湥ąĮ ą▓ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░ ąĖą╗ąĖ ąĮą░ą┐ąĄčćą░čéą░ąĮ ąĮą░ PCB, čéą░ą║ čćč鹊 ąÆčŗ ą╝ąŠąČąĄč鹥 čĆą░ąĘą╝ąĄčēą░čéčī ąĮą░ ąĮąĄą╝ ą╗čÄą▒čāčÄ ą┐ąŠą┤čĆąŠą▒ąĮčāčÄ ąŠą┐ąĖčüą░č鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ąÆčŗ čģąŠčéąĖč鹥 ą┤ąŠą▒ą░ą▓ąĖčéčī ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ą│čĆą░čäąĖą║čā, ąĮąĄ ąŠčéąĮąŠčüčÅčēčāčÄčüčÅ ą║ ąŠą▒čŗčćąĮąŠą╣ čłąĄą╗ą║ąŠą│čĆą░čäąĖąĖ (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ č鹥ą║čüčéą░ ąĖą╗ąĖ ą╗ąŠą│ąŠčéąĖą┐ą░), č鹊 ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 ą┤ą╗čÅ čŹč鹊ą│ąŠ čüą╗ąŠąĖ Layer 21-22.

Layer 23-24: tOrigins/bOrigins. ąØą░ čŹčéąĖčģ ą┤ą▓čāčģ čüą╗ąŠčÅčģ čüąŠą┤ąĄčƹȹ░čéčüčÅ ą│ąĄąŠą╝ąĄčéčĆąĖč湥čüą║ąĖąĄ č鹊čćą║ąĖ ą┐čĆąĖą▓čÅąĘą║ąĖ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ (component origins), ąĘą░ ą║ąŠč鹊čĆčŗąĄ ąĖčģ ą╝ąŠąČąĮąŠ ą┐ąĄčĆąĄčéą░čüą║ąĖą▓ą░čéčī. ąóąŠčćą║ąĖ ą┐čĆąĖą▓čÅąĘą║ąĖ ąŠą▒ąŠąĘąĮą░čćą░čÄčéčüčÅ ą║čĆąĄčüčéąĖą║ą░ą╝ąĖ.

ąĢčüą╗ąĖ ąÆčŗ ąĘą░čģąŠčéąĖč鹥 ąĘą░čäąĖą║čüąĖčĆąŠą▓ą░čéčī ą┐ąŠąĘąĖčåąĖąĖ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓, čćč鹊ą▒čŗ ąĘą░čēąĖčéąĖčéčī ąĖčģ ąŠčé čüą╗čāčćą░ą╣ąĮąŠą│ąŠ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ, č鹊 ąĘą░ą┐čĆąĄčéąĖč鹥 čüą╗ąŠą╣ tOrigins (ą┤ą╗čÅ ą▓ąĄčĆčģąĮąĄą│ąŠ čüą╗ąŠčÅ) ąĖą╗ąĖ bOrigins (ą┤ą╗čÅ ąĮąĖąČąĮąĄą│ąŠ čüą╗ąŠčÅ). ąĢčüą╗ąĖ č鹊čćą║ąĖ ą┐čĆąĖą▓čÅąĘą║ąĖ ąĮąĄ ą▓ąĖą┤ąĮčŗ, č鹊 ąĮąĄą╗čīąĘčÅ ą┐ąĄčĆąĄą╝ąĄčēą░čéčī ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ, čéą░ą║ čćč鹊 ą╝ąŠąČąĮąŠ čüą┐ąŠą║ąŠą╣ąĮąŠ čüč乊ą║čāčüąĖčĆąŠą▓ą░čéčīčüčÅ ąĮą░ ą░čüą┐ąĄą║čéą░čģ čéčĆą░čüčüąĖčĆąŠą▓ą║ąĖ ą┐čĆąŠą▓ąŠą┤ąĮąĖą║ąŠą▓ ą┐ą╗ą░čéčŗ.

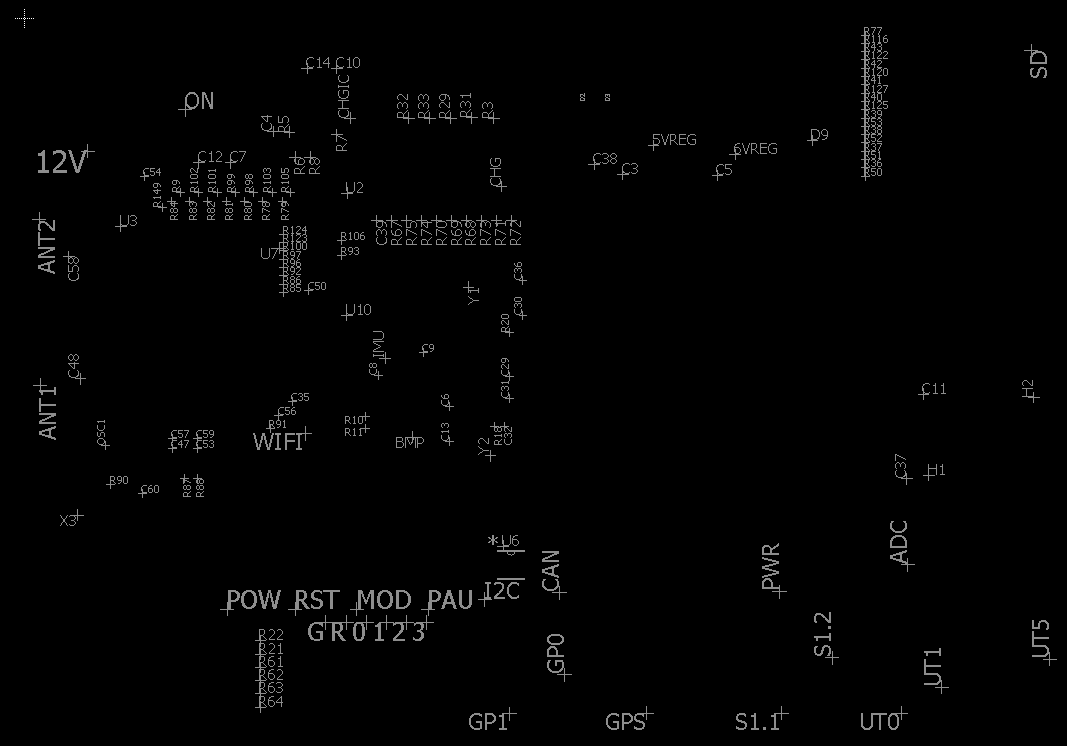

Layer 25-26: tNames/bNames. ąÜą░ą║ ą┐ąŠą┤čüą║ą░ąĘčŗą▓ą░ąĄčé ąĖą╝čÅ čŹčéąĖčģ ą┤ą▓čāčģ čüą╗ąŠąĄą▓, ąĮą░ ąĮąĖčģ čüąŠą┤ąĄčƹȹ░čéčüčÅ ąĖą╝ąĄąĮą░ (čé. ąĄ. ą┐ąŠąĘąĖčåąĖąŠąĮąĮčŗąĄ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖčÅ) ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ą┐ą╗ą░čéčŗ. ąÜą░ąČą┤čŗą╣ ą║ąŠą╝ą┐ąŠąĮąĄąĮčé ąĮą░ ą┐ą╗ą░č鹥 ąĖą╝ąĄąĄčé čāąĮąĖą║ą░ą╗čīąĮąŠąĄ ąĖą╝čÅ (ą║ąŠč鹊čĆąŠąĄ čéą░ą║ąČąĄ ąĮą░ąĘčŗą▓ą░čÄčé reference designator, RefDes), ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ R1, C1, D1 ąĖ čé. ą┐.

ąØąĄ ąĮčāąČąĮąŠ ąŠčüąŠą▒ąĄąĮąĮąŠ ą▒ąĄčüą┐ąŠą║ąŠąĖčéčīčüčÅ ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖąĖ ąĖą╝ąĄąĮ, ą┐ąŠč鹊ą╝čā čćč鹊 ąŠąĮąĖ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐čĆąĖ čĆą░ąĘą╝ąĄčēąĄąĮąĖąĖ ą▓ čüčģąĄą╝ąĄ ąĮąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ (ą┐čĆąĖ čŹč鹊ą╝ ą║ąŠą╝ą┐ąŠąĮąĄąĮčé čéą░ą║ąČąĄ ą┐ąŠą┐ą░ą┤ą░ąĄčé ąĖ ąĮą░ ą┐ą╗ą░čéčā). ą×ą┤ąĮą░ą║ąŠ ą┐ąŠą╗ąĄąĘąĮąŠ čāą┐ąŠčĆčÅą┤ąŠčćąĖčéčī ąĖą╝ąĄąĮą░ (čŹč鹊 ą┤ąĄą╗ą░ąĄčéčüčÅ č湥čĆąĄąĘ ą╝ąĄąĮčÄ Tools -> Renumber parts... čĆąĄą┤ą░ą║č鹊čĆą░ čüčģąĄą╝), ąĖ ą┐čĆąĖą▓ąĄčüčéąĖ č鹥ą║čüčé ąĖą╝ąĄąĮ ąĮą░ ą┐ą╗ą░č鹥 ą▓ ąŠą┤ąĖąĮą░ą║ąŠą▓čāčÄ ąŠčĆąĖąĄąĮčéą░čåąĖčÄ, čćč鹊ą▒čŗ čāą┐čĆąŠčüčéąĖčéčī ąĖčģ čćč鹥ąĮąĖąĄ, ąĖ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą┐čĆąŠčēąĄ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░čéčī ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ.

Layer 27-28: tValues/bValues. ąśą╝ąĄąĮą░ čüą╗ąŠąĄą▓ čüąĮąŠą▓ą░ ąĮą░ą╝ ą┐ąŠą┤čüą║ą░ąĘčŗą▓ą░čÄčé, čćč鹊 ąĮą░ čŹčéąĖčģ ą┤ą▓čāčģ čüą╗ąŠčÅčģ čüąŠą┤ąĄčƹȹĖčéčüčÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąŠ ą┐ą░čĆą░ą╝ąĄčéčĆą░čģ (ąĮąŠą╝ąĖąĮą░ą╗ą░čģ ąĖ čéąĖą┐ą░čģ) ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓. ąØą░ą┐čĆąĖą╝ąĄčĆ, čĆąĄąĘąĖčüč鹊čĆ čģą░čĆą░ą║č鹥čĆąĖąĘčāąĄčéčüčÅ čüą▓ąŠąĖą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝, ąĖ ąĄą╝čā čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠą▒ąŠąĘąĮą░č湥ąĮąĖąĄ ą▓ąĄą╗ąĖčćąĖąĮčŗ ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ 10K. ąÜąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą╝ąŠąČąĄčé ąĖą╝ąĄčéčī ąŠą▒ąŠąĘąĮą░č湥ąĮąĖąĄ ąĄą╝ą║ąŠčüčéąĖ ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ 0.1uF.

ą£ąĮąŠą│ąĖąĄ čĆą░ąĘčĆą░ą▒ąŠčéčćąĖą║ąĖ ąĮąĄ ą┐ąŠą╝ąĄčēą░čÄčé ą▓ čłąĄą╗ą║ąŠą│čĆą░čäąĖčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ čü čŹčéąĖčģ čüą╗ąŠąĄą▓, ąĖ ąŠčéą║čĆčŗą▓ą░čÄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čäą░ą╣ą╗čŗ Bill of Materials (BOM), ą│ą┤ąĄ ą┐ąŠ ąĖą╝ąĄąĮą░ą╝ ąĖčēčāčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ ąĮąŠą╝ąĖąĮą░ą╗ą░čģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ąÆčŗ ą┐ą╗ą░ąĮąĖčĆčāąĄč鹥 čĆą░ąĘčĆą░ą▒ąŠčéą░čéčī ą┐ą╗ą░čéčā ą┤ą╗čÅ ąŠčéą╗ą░ą┤ąŠčćąĮąŠą│ąŠ ą║ąĖčéą░ ąĖą╗ąĖ ą┤ą╗čÅ čüą░ą╝ąŠčüč鹊čÅč鹥ą╗čīąĮąŠą╣ čüą▒ąŠčĆą║ąĖ, č鹊 ą▒čāą┤ąĄčé ąŠč湥ąĮčī ą┐ąŠą╗ąĄąĘąĮąŠ ą┤ąŠą▒ą░ą▓ąĖčéčī ąĮą░ ą┐ą╗ą░čéčā ąĖąĮč乊čĆą╝ą░čåąĖčÄ čłąĄą╗ą║ąŠą│čĆą░čäąĖąĖ čüąŠ čüą╗ąŠąĄą▓ tValues/bValues. ąŁč鹊 ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ čāą┐čĆąŠčēą░ąĄčé ą┐čĆąŠčåąĄčüčü čüą▒ąŠčĆą║ąĖ ąĖ ąŠčéą╗ą░ą┤ą║ąĖ.

Layer 29-30: tStop/bStop. ąŁčéąĖ ą┤ą▓ą░ čüą╗ąŠčÅ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé, ą│ą┤ąĄ ą▓ ą║ą░ą║ąĖčģ ą╝ąĄčüčéą░čģ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĮą░ą╗ąŠąČąĄąĮą░ ą┐ą░čÅą╗čīąĮą░čÅ ą╝ą░čüą║ą░. ąÜąŠą│ą┤ą░ čĆą░ąĘą╝ąĄčēą░čÄčé ąĮą░ ą┐ą╗ą░čéčā ą╗ąĖą▒ąŠ ą║ąŠą╝ą┐ąŠąĮąĄąĮčé čüąŠ čłčéčŗčĆąĄą▓čŗą╝ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ ą╗ąĖą▒ąŠ ą║ąŠą╝ą┐ąŠąĮąĄąĮčé ą┐ąŠą▓ąĄčĆčģąĮąŠčüčéąĮąŠą│ąŠ ą╝ąŠąĮčéą░ąČą░, ą┐ąŠčüą░ą┤ąŠčćąĮčŗąĄ ą╝ąĄčüčéą░ čŹčéąĖčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ čéą░ą║ąČąĄ čüąŠą┤ąĄčƹȹ░čé ą│čĆą░čäąĖą║čā ąŠą║ąŠąĮ ą▓ ą┐ą░čÅą╗čīąĮąŠą╣ ą╝ą░čüą║ąĄ ąĮą░ čŹčéąĖčģ ą┤ą▓čāčģ čüą╗ąŠčÅčģ.

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄą╝čŗąĄ ąŠą▒ą╗ą░čüčéąĖ ąĮą░ čüą╗ąŠčÅčģ tStop/bStop ąĘą░ą┤ą░čÄčé č鹥 ą╝ąĄčüčéą░, ą│ą┤ąĄ ąĮąĄ ą┤ąŠą╗ąČąĮą░ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą┐ą░čÅą╗čīąĮą░čÅ ą╝ą░čüą║ą░, čé. ąĄ. čŹč鹊 č鹥 ą╝ąĄčüčéą░, ą│ą┤ąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐ą░ą╣ą║ą░ ąĖą╗ąĖ ąŠčéą║čāą┤ą░ ąŠčéą▓ąŠą┤ąĖčéčüčÅ č鹥ą┐ą╗ąŠ.

Layer 31-32: tCream/bCream. ąŁčéąĖ čüą╗ąŠąĖ čüąŠą┤ąĄčƹȹ░čé ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ ąŠ ą╝ąĄčüčéą░čģ ąĮą░ąĮąĄčüąĄąĮąĖčÅ ą┐ą░čÅą╗čīąĮąŠą╣ ą┐ą░čüčéčŗ ą┤ą╗čÅ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ą┐ąŠą▓ąĄčĆčģąĮąŠčüčéąĮąŠą│ąŠ ą╝ąŠąĮčéą░ąČą░ (SMD). ąŁč鹊čé čüą╗ąŠą╣ ąŠą▒čŗčćąĮąŠ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ąĘą░ą▓ąŠą┤čā, ą║ąŠč鹊čĆčŗą╣ ąĘą░ąĮąĖą╝ą░ąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ čüą▒ąŠčĆą║ąŠą╣, čćč鹊ą▒čŗ ąŠąĮ čüą╝ąŠą│ čüąŠąĘą┤ą░čéčī čłą░ą▒ą╗ąŠąĮčŗ ą┤ą╗čÅ ąĮą░ąĮąĄčüąĄąĮąĖčÅ ą┐ą░čÅą╗čīąĮąŠą╣ ą┐ą░čüčéčŗ ą┐ąĄčĆąĄą┤ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ąĮą░ ą┐ą╗ą░čéčā.

ąÜąŠą│ą┤ą░ ąĮą░ ą┐ą╗ą░čéčā čĆą░ąĘą╝ąĄčēą░čÄčéčüčÅ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ SMD, ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąŠą▒ ąŠą▒ą╗ą░čüčéąĖ ąĮą░ąĮąĄčüąĄąĮąĖčÅ ą┐ą░čÅą╗čīąĮąŠą╣ ą┐ą░čüčéčŗ. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ąÆčŗ čüą░ą╝ąŠčüč鹊čÅč鹥ą╗čīąĮąŠ čüąŠąĘą┤ą░ąĄč鹥 ą┐ąŠčüą░ą┤ąŠčćąĮąŠąĄ ą╝ąĄčüč鹊 ą┤ą╗čÅ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ ą┐ąŠą▓ąĄčĆčģąĮąŠčüčéąĮąŠą│ąŠ ą╝ąŠąĮčéą░ąČą░ (SMD footprint), č鹊 čāą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 ąŠą▒ą╗ą░čüčéčī ąĮą░ąĮąĄčüąĄąĮąĖčÅ ą┐ą░čÅą╗čīąĮąŠą╣ ą┐ą░čüčéčŗ (cream area) ąĮąĄą╝ąĮąŠą│ąŠ ą╝ąĄąĮčīčłąĄ ąŠą║ąĮą░ ą▓ ą┐ą░čÅą╗čīąĮąŠą╣ ą╝ą░čüą║ąĄ (soldermask), čéą░ą║ čćč鹊 čŹčéąĖ ą┤ą▓ą░ ą╝ą░č鹥čĆąĖą░ą╗ą░ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą┐ąĄčĆąĄčüąĄą║ą░čéčīčüčÅ.

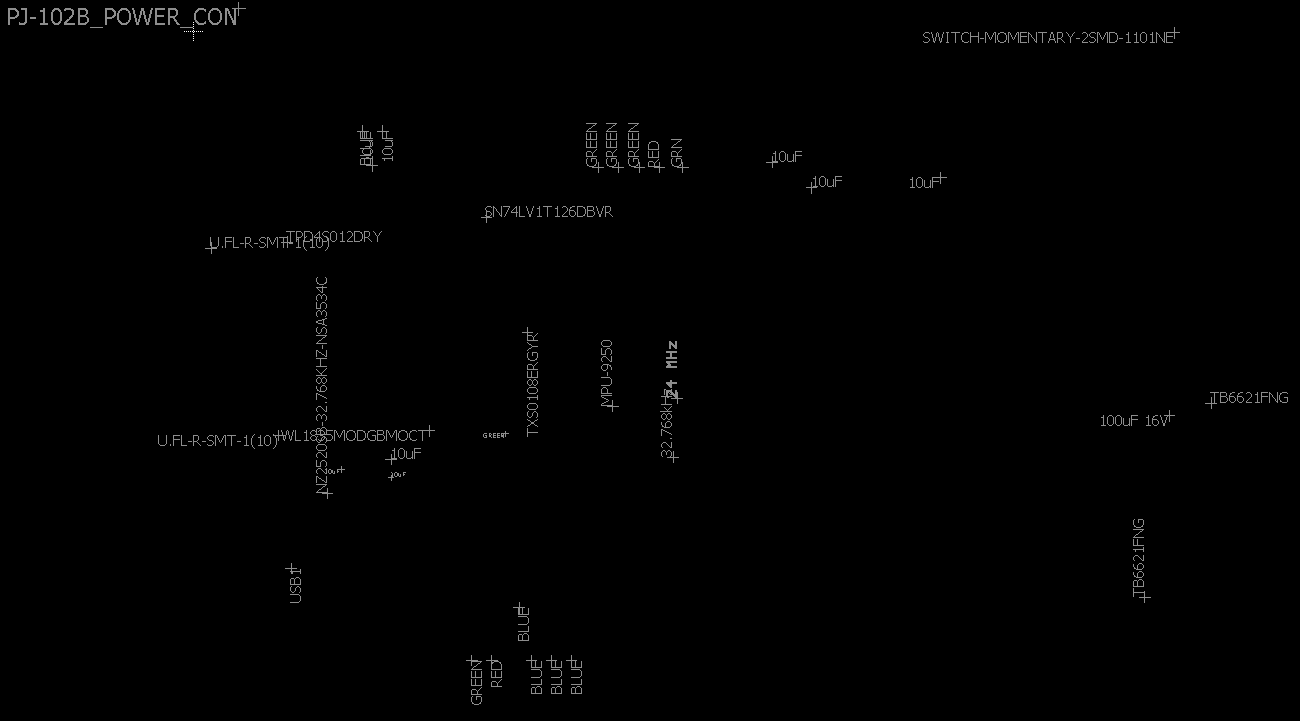

Layer 33-34: tFinish/bFinish. ąŁčéąĖ ą┤ą▓ą░ čüą╗ąŠčÅ čüąŠą┤ąĄčƹȹ░čé ą┤ą░ąĮąĮčŗąĄ ąŠ ą╗čÄą▒ąŠą╝ ą▓ąĖą┤ąĄ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ čäąĖąĮąĖčłąĮąŠą╣ ą┐ąŠą┤ą│ąŠč鹊ą▓ą║ąĖ ą┐ąŠą▓ąĄčĆčģąĮąŠčüčéąĖ ą┐ą╗ą░čéčŗ, ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ ą┐ąŠą║čĆčŗčéąĖčÅ ąĘąŠą╗ąŠč鹊ą╝ (plated gold), čüąĄčĆąĄą▒čĆąĄąĮąĖąĄ ąĖą╗ąĖ čüą╗ąŠą╣ ą║ą░čĆą▒ąŠąĮą░. ąóą░ą║ąČąĄ čŹč鹊čé čüą╗ąŠą╣ ą╝ąŠąČąĄčé čüąŠą┤ąĄčƹȹ░čéčī ą┤ą░ąĮąĮčŗąĄ ąŠ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ ą┐ą╗ąŠčēą░ą┤ą║ą░čģ, čéčĆąĄą▒čāčÄčēąĖčģ ą┐ąŠą║čĆčŗčéąĖčÅ ąĖą╝ą╝ąĄčĆčüąĖąŠąĮąĮčŗą╝ ąĘąŠą╗ąŠč鹊ą╝.

ąĪą╗ąĄą┤čāąĄčé ąĖą╝ąĄčéčī ą▓ ą▓ąĖą┤čā, čćč鹊 čŹč鹊čé čüą╗ąŠą╣ ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą┐ąŠčŹč鹊ą╝čā ą│čĆą░čäąĖą║čā ą▓ ąĮąĄą╝ čéčĆąĄą▒čāąĄčéčüčÅ ąĮą░ąĮąĄčüčéąĖ (ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ) čüą░ą╝ąŠčüč鹊čÅč鹥ą╗čīąĮąŠ. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ąÆčŗ č鹊ą╗čīą║ąŠ ąĮą░čćąĖąĮą░ąĄč鹥 čĆą░ąĘčĆą░ą▒ą░čéčŗą▓ą░čéčī ą┐ą╗ą░čéčŗ, ąĖ ą┤ąĄą╗ą░ąĄč鹥 čŹč鹊 ą┤ą╗čÅ čģąŠą▒ą▒ąĖ, č鹊 čüą║ąŠčĆąĄąĄ ą▓čüąĄą│ąŠ čŹčéąĖ čüą╗ąŠąĖ ąĮąĄ ąĮčāąČąĮčŗ, čéą░ą║ ą║ą░ą║ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ čüą┐ąĄčåąĖą░ą╗čīąĮą░čÅ čäąĖąĮąĖčłąĮą░čÅ ąŠą▒čĆą░ą▒ąŠčéą║ą░ čüą╗ąĖčłą║ąŠą╝ ą┤ąŠčĆąŠą│ąŠąĄ čāą┤ąŠą▓ąŠą╗čīčüčéą▓ąĖąĄ.

ąĪą▓ąŠą╣čüčéą▓ąŠ

|

ąĀą░ąĘąĮąŠą▓ąĖą┤ąĮąŠčüčéąĖ čäąĖąĮąĖčłąĮčŗčģ ą┐ąŠą║čĆčŗčéąĖą╣

|

HASL

(SnPb) |

HASL

Lead-Free |

ENIG |

ImAg |

OSP |

ImSn |

NiAu |

| ąĪąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī čü RoHS |

ąĮąĄčé |

ąöąÉ |

ąöąÉ |

ąöąÉ |

ąöąÉ |

ąöąÉ |

ąöąÉ |

| ą”ąĄąĮą░ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░ |

ąĮąĖąĘą║ą░čÅ |

ąĮąĖąĘą║ą░čÅ |

čüčĆąĄą┤ąĮčÅčÅ |

čüčĆąĄą┤ąĮčÅčÅ |

ąĮąĖąĘą║ą░čÅ |

čüčĆąĄą┤ąĮčÅčÅ |

ą▓čŗčüąŠą║ą░čÅ |

| ąōą░čĆą░ąĮčéąĖą╣ąĮčŗą╣ čüčĆąŠą║ čģčĆą░ąĮąĄąĮąĖčÅ |

1 ą│ąŠą┤ |

1 ą│ąŠą┤ |

1 ą│ąŠą┤ |

9..12 ą╝ąĄčüčÅčåąĄą▓* |

1 ą│ąŠą┤ |

| ąĀąĄą╝ąŠąĮč鹊ą┐čĆąĖą│ąŠą┤ąĮąŠčüčéčī |

ąŠą│čĆą░ąĮąĖč湥ąĮąĮą░čÅ |

ąŠą│čĆą░ąĮąĖč湥ąĮąĮą░čÅ |

ąŠą│čĆą░ąĮąĖč湥ąĮąĮą░čÅ |

čģąŠčĆąŠčłą░čÅ |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

| ąĪą╝ą░čćąĖą▓ą░ąĄą╝ąŠčüčéčī ą┐čĆąĖą┐ąŠąĄą╝ |

ąŠčéą╗ąĖčćąĮą░čÅ |

čģąŠčĆąŠčłą░čÅ |

čģąŠčĆąŠčłą░čÅ |

ąŠč湥ąĮčī čģąŠčĆąŠčłą░čÅ |

čģąŠčĆąŠčłą░čÅ |

čģąŠčĆąŠčłą░čÅ |

čģąŠčĆąŠčłą░čÅ |

| ąÜąŠą╝ą┐ą╗ą░ąĮą░čĆąĮąŠčüčéčī |

ą┐ą╗ąŠčģą░čÅ |

čģąŠčĆąŠčłą░čÅ |

ąŠčéą╗ąĖčćąĮą░čÅ |

ąŠčéą╗ąĖčćąĮą░čÅ |

ąŠčéą╗ąĖčćąĮą░čÅ |

ąŠčéą╗ąĖčćąĮą░čÅ |

čģąŠčĆąŠčłą░čÅ/ą┐ą╗ąŠčģą░čÅ |

| ą”ąĄą╗ąŠčüčéąĮąŠčüčéčī ą┐ą░čÅąĮąŠą│ąŠ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ |

ąŠčéą╗ąĖčćąĮą░čÅ |

čģąŠčĆąŠčłą░čÅ |

čģąŠčĆąŠčłą░čÅ |

ąŠčéą╗ąĖčćąĮą░čÅ |

čģąŠčĆąŠčłą░čÅ |

čģąŠčĆąŠčłą░čÅ |

ą┐ą╗ąŠčģą░čÅ** |

| ąØąĖąĘą║ąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ/ą▓čŗčüąŠą║ą░čÅ čüą║ąŠčĆąŠčüčéčī |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąöąÉ |

ąĮąĄ ą┤ąŠčüčéčāą┐ąĮąŠ |

ąĮąĄčé |

ąĮąĄčé |

| ąĪąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą░ą╗čÄą╝ąĖąĮąĖąĄą▓čŗą╝ąĖ ą┐čĆąŠą▓ąŠą┤ąĮąĖą║ą░ą╝ąĖ |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąĮąĄčé |

ąöąÉ |

ąĮąĄčé |

ąöąÉ |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

* ąóčĆąĄą▒čāąĄčéčüčÅ čāąĮąĖą║ą░ą╗čīąĮą░čÅ č鹥čģąĮąŠą╗ąŠą│ąĖčÅ čģčĆą░ąĮąĄąĮąĖčÅ.

** ą¤čĆąĖą╗ąŠąČąĄąĮąĖčÅ čü čāč鹊ą╗čēąĄąĮąĮčŗą╝ ąĘąŠą╗ąŠč湥ąĮąĖąĄą╝ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą┤ą▓ąĄčƹȹĄąĮčŗ čģčĆčāą┐ą║ąŠčüčéąĖ.

DIG Direct Immersion Gold over copper, ą┐čĆčÅą╝ą░čÅ ąĖą╝ą╝ąĄčĆčüąĖčÅ ąĘąŠą╗ąŠčéą░ ą┐ąŠą▓ąĄčĆčģ ą╝ąĄą┤ąĖ.

ENEPIG 菹╗ąĄą║čéčĆąŠą╗ąĖąĘąĮąŠąĄ ą┐ąŠą║čĆčŗčéąĖąĄ ąĮąĖą║ąĄą╗ąĄą╝ ąĖą╗ąĖ ą┐ą░ą╗ą╗ą░ą┤ąĖąĄą╝, ą┤čĆčāą│ąŠąĄ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ENIG.

ENIG (electroless nickel/immersion gold). ąØą░ąĮąĄčüąĄąĮąĮčŗą╣ 菹╗ąĄą║čéčĆąŠą╗ąĖąĘąŠą╝ ąĮąĖą║ąĄą╗čī ąĖą╗ąĖ ąĖą╝ą╝ąĄčĆčüąĖąŠąĮąĮąŠąĄ ąĘąŠą╗ąŠč鹊.

GOLD ąĘąŠą╗ąŠč湥ąĮąĖąĄ ą╝ąĄą┤ąĮąŠą╣ ą┐ąŠą▓ąĄčĆčģąĮąŠčüčéąĖ.

HASL (hot air solder leveling). ąøčāąČąĄąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĄčé čüąŠą┤ąĄčƹȹ░čéčī čüą▓ąĖąĮąĄčå (Pb), ąĖą╗ąĖ ąĮąĄ čüąŠą┤ąĄčƹȹ░čéčī čéą░ą║ąŠą▓ąŠą│ąŠ (Pb-free). ąĪą░ą╝ąŠąĄ ą┤ąĄčłąĄą▓ąŠąĄ ąĖ ą┐ąŠą┐čāą╗čÅčĆąĮąŠąĄ čäąĖąĮąĖčłąĮąŠąĄ ą┐ąŠą║čĆčŗčéąĖąĄ.

OMN Organic Metal Nano, ą┤čĆčāą│ąŠąĄ ąĮą░ąĘą▓ą░ąĮąĖąĄ ą┤ą╗čÅ OSP.

OSP (organic solderability preservatives). ą¤čĆąŠąĘčĆą░čćąĮčŗą╣ čüą╗ąŠą╣ ąĖąĘ ąŠčĆą│ą░ąĮąĖč湥čüą║ąŠą│ąŠ ą╝ą░č鹥čĆąĖą░ą╗ą░, ąŠą▒čŗčćąĮąŠ čŹč鹊 ą║ą░ąĮąĖč乊ą╗čī ąĖą╗ąĖ ą┤čĆčāą│ąŠą╣ čäą╗čÄčü.

ImAg (immersion silver). ąśą╝ą╝ąĄčĆčüąĖąŠąĮąĮąŠąĄ čüąĄčĆąĄą▒čĆąŠ.

ImSn (immersion tin). ąśą╝ą╝ąĄčĆčüąĖąŠąĮąĮąŠąĄ ąŠą╗ąŠą▓ąŠ.

NiAu 菹╗ąĄą║čéčĆąŠą╗ąĖąĘąĮčŗąĄ ąĮąĖą║ąĄą╗čī ąĖ ąĘąŠą╗ąŠč鹊.

Layer 35-36: tGlue/bGlue. ąŁčéąĖ ą┤ą▓ą░ čüą╗ąŠčÅ čüąŠą┤ąĄčƹȹ░čé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ ą╝ąĄčüčéą░čģ ąĮą░ ą▓ąĄčĆčģąĮąĄą╝ ąĖ ąĮąĖąČąĮąĄą╝ čüą╗ąŠąĄ, ą│ą┤ąĄ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĮą░ą╗ąŠąČąĄąĮ čłą░ą▒ą╗ąŠąĮ ą║ą╗ąĄąĄą▓ąŠą╣ ą╝ą░čüą║ąĖ (glue mask). ąŁčéą░ ą╝ą░čüą║ą░ ą┐ąŠą╗ąĄąĘąĮą░ ą┤ą╗čÅ ąĮą░ą┤ąĄąČąĮąŠą│ąŠ ą║čĆąĄą┐ą╗ąĄąĮąĖčÅ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓, ą║ąŠč鹊čĆčŗąĄ ąĖčüą┐čŗčéčŗą▓ą░čÄčé čüą╗ąĖčłą║ąŠą╝ ą▒ąŠą╗čīčłąĖąĄ ą╝ąĄčģą░ąĮąĖč湥čüą║ąĖąĄ ąĮą░ą│čĆčāąĘą║ąĖ - čéą░ą║ąĖąĄ ą║ą░ą║ ą┐ąĄčĆąĄą║ą╗čÄčćą░č鹥ą╗ąĖ, ą┤ąČąĄą║ąĖ ąĖą╗ąĖ ą║ąŠąĮąĮąĄą║č鹊čĆčŗ.

ąÜą╗ąĄą╣ ąŠą▒čŗčćąĮąŠ ąĮą░ą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╝ ą▓ ąŠą┤ąĮčā č鹊čćą║čā, ąĮą░čģąŠą┤čÅčēčāčÄčüčÅ ą▓ čåąĄąĮčéčĆąĄ ą╝ą░ą╗ąĄąĮčīą║ąŠą│ąŠ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░, ą╗ąĖą▒ąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ č鹊č湥ą║, ąĄčüą╗ąĖ ą║ąŠą╝ą┐ąŠąĮąĄąĮčé ą▒ąŠą╗čīčłąŠą│ąŠ čĆą░ąĘą╝ąĄčĆą░, ąĮą░ą┐čĆąĖą╝ąĄčĆ čüą╗ąŠąČąĮą░čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ (IC). ąóą░ą║ąČąĄ, ą║ą░ą║ ąĖ čüąŠ čüą╗ąŠčÅą╝ąĖ čäąĖąĮąĖčłąĮąŠą│ąŠ ą┐ąŠą║čĆčŗčéąĖčÅ, ą│čĆą░čäąĖą║ą░ čüą╗ąŠąĄą▓ tGlue/bGlue ąĮąĄ čüąŠąĘą┤ą░ąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą┐ąŠčŹč鹊ą╝čā ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ąÆą░ą╝ ąĮčāąČąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą╝ąĄčüčéą░ ąĮą░ąĮąĄčüąĄąĮąĖčÅ ą║ą╗ąĄčÅ ą▓čĆčāčćąĮčāčÄ.

Layer 37-38: tTest/bTest. ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░ (ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą║ąŠč鹊čĆąŠą│ąŠ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą┐čāčüčéą░čÅ ą┐ą╗ą░čéą░) ąĖ čüą▒ąŠčĆą║ąĖ (čāčüčéą░ąĮąŠą▓ą║ąĖ ąĖ ą┐ą░ą╣ą║ąĖ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ąĮą░ ą┐ą╗ą░čéčā), ą┐ą╗ą░čéą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┐čĆąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮą░ ąĮą░ ąŠčéčüčāčéčüčéą▓ąĖąĄ ą║ąŠčĆąŠčéą║ąĖčģ ąĘą░ą╝čŗą║ą░ąĮąĖą╣. ąŁčéąĖ ą┤ą▓ą░ čüą╗ąŠčÅ čüą╗čāąČą░čé ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĖčÅ čŹčéąĖčģ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ č鹥čüč鹊ą▓čŗčģ č鹊č湥ą║ ąĮą░ ą▓ąĄčĆčģąĮąĄą╣ ąĖ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮą░čģ ą┐ą╗ą░čéčŗ. ą¤ą╗ą░čéą░ č鹥čüčéąĖčĆčāąĄčéčüčÅ ąĮą░ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╝ ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮąĖąĖ ICT (In-Circuit Test).

Cadsoft EAGLE ą┐ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ čü ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ą░ą╝ąĖ, ą▓ ą║ąŠč鹊čĆčŗčģ ąĖą╝ąĄčÄčéčüčÅ č鹥čüč鹊ą▓čŗąĄ ą┐ą╗ąŠčēą░ą┤ą║ąĖ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ čüą▓ąŠą▒ąŠą┤ąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą▒čŗčüčéčĆąŠą╣ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĮą░ ą┐ą╗ą░čéčā. ąÆčŗą┐ąŠą╗ąĮąĖč鹥 ą┐ąŠąĖčüą║ čüą╗ąŠą▓ą░ "test" ą▓ ą┤ąĖą░ą╗ąŠą│ąĄ Add EAGLE, ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą╣ą┤ąĖč鹥 ą▓ ą║ą░č鹥ą│ąŠčĆąĖčÄ testpad. ąóą░ą╝ ąĮą░ą╣ą┤ąĄč鹥 čĆą░ąĘą╗ąĖčćąĮčŗąĄ č鹥čüč鹊ą▓čŗąĄ ą┐ą╗ąŠčēą░ą┤ą║ąĖ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ą┤ąŠą▒ą░ą▓ąĖčéčī ą┤ą╗čÅ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ čüąŠ čłčéčŗčĆąĄą▓čŗą╝ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ ąĖą╗ąĖ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ą┐ąŠą▓ąĄčĆčģąĮąŠčüčéąĮąŠą│ąŠ ą╝ąŠąĮčéą░ąČą░.

Layer 39-40: tKeepout/bKeepout. ąŁčéąĖ ą┤ą▓ą░ čüą╗ąŠčÅ ą┐ąŠą╝ąŠą│čāčé čāą┤ąĄčƹȹ░čéčī ą┐ąŠą╗ąŠąČąĄąĮąĖąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ąĖ ą┤ąŠčĆąŠąČąĄą║ ąĮą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝ čĆą░čüčüč鹊čÅąĮąĖąĖ ąŠčé čĆą░ąĘąĮčŗčģ ąŠą▒čŖąĄą║č鹊ą▓. ąĪ ą┐ąŠą╝ąŠčēčīčÄ ą│čĆą░čäąĖą║ąĖ ą▓ čŹčéąĖčģ čüą╗ąŠčÅčģ ąĖąĮčüčéčĆčāą╝ąĄąĮčé Design Rule Check (DRC) ą┐ąŠąĘą▓ąŠą╗ąĖčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐čĆąŠą▓ąĄčĆąĖčéčī, ą▓čüąĄ ą╗ąĖ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ ą┐ą╗ą░čéčŗ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ą│čĆą░ąĮąĖčåą░čģ, ąĖ ąĄčüą╗ąĖ čŹč鹊 ąĮąĄ čéą░ą║, č鹊 ą▒čāą┤čāčé ą▓čŗą┤ą░ąĮčŗ čüąŠąŠą▒čēąĄąĮąĖčÅ ąŠą▒ ąŠčłąĖą▒ą║ąĄ.

Layer 41-43: tRestrict/bRestrict/vRestrict. ąĪą╗ąŠąĖ tRestrict ąĖ bRestrict ąŠą▒ąŠąĘąĮą░čćą░čÄčé ą╝ąĄčüčéą░, ą│ą┤ąĄ ą╝ąĄą┤čī ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čāą┤ą░ą╗ąĄąĮą░ ąĖąĘ čĆą░ąĘą▓ąŠą┤ą║ąĖ ąĮą░ ą┐ą╗ą░č鹥. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, ą║ąŠą│ą┤ą░ ąÆčŗ ąĘą░ą┐ąŠą╗ąĮčÅąĄč鹥 ą┐ąŠą╗ąĖą│ąŠąĮ ąĮą░ ą╝ąĄą┤ąĖ ą▓ čüą╗ąŠčÅčģ restrict, č鹊 ą▓ čŹč鹊ą╣ ąĘą░ą┐čĆąĄčēąĄąĮąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ čāą┤ą░ą╗čÅčÄčéčüčÅ ą╗čÄą▒čŗąĄ čāčćą░čüčéą║ąĖ ą╝ąĄą┤ąĮąŠą╣ č乊ą╗čīą│ąĖ.

ąŁčéąĖ čüą╗ąŠąĖ čéą░ą║ąČąĄ ą┐ąŠą╗ąĄąĘąĮčŗ ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą░ą▓č鹊čĆąŠčāč鹥čĆą░ ą▓ EAGLE, čéą░ą║ ą║ą░ą║ ą│čĆą░čäąĖą║ą░ ą▓ restrict-čüą╗ąŠčÅčģ čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄą╝ ą░ą▓č鹊čĆąŠčāč鹥čĆą░, ą║ąŠą│ą┤ą░ ąŠąĮ ąĮą░čģąŠą┤ąĖčé ą┐čāčéąĖ ą┤ą╗čÅ ą┐čĆąŠą║ą╗ą░ą┤ą║ąĖ čéčĆą░čüčü ą┐čĆąŠą▓ąŠą┤ąĮąĖą║ąŠą▓ (ą▓ ąĘą░ą┤ą░ąĮąĮčŗčģ ąŠą▒ą╗ą░čüčéčÅčģ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ą┐čĆąŠą║ą╗ą░ą┤ą║ą░ čéčĆą░čüčü). ąĪą╗ąŠą╣ vRestrict ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą╝ąĄčüč鹥, ą│ą┤ąĄ ąĮąĄą╗čīąĘčÅ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčī ą┐ąĄčĆąĄčģąŠą┤ąĮčŗąĄ ąŠčéą▓ąĄčĆčüčéąĖčÅ (via), ąĖ čŹč鹊čé čüą╗ąŠą╣ ąĮąĄ ą┤ą░ąĄčé ą░ą▓č鹊čĆąŠčāč鹥čĆčā čĆą░ąĘą╝ąĄčēą░čéčī via ą▓ ąĘą░ą┤ą░ąĮąĮčŗčģ ąŠą▒ą╗ą░čüčéčÅčģ.

Layer 44: Drills. ąŁč鹊čé čüą╗ąŠą╣ čüąŠą┤ąĄčƹȹĖčé ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ čüą▓ąĄčĆą╗ąĄąĮąĖčÅ ąŠčéą▓ąĄčĆčüčéąĖą╣ ą▓ ą┐ą╗ą░č鹥, čéą░ą║ąĖčģ ą║ą░ą║ ąŠčéą▓ąĄčĆčüčéąĖčÅ ą┤ą╗čÅ čłčéčŗčĆąĄą▓čŗčģ ą▓čŗą▓ąŠą┤ąŠą▓ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ (through-hole pad) ąĖ ą┐ąĄčĆąĄčģąŠą┤ąĮčŗčģ ąŠčéą▓ąĄčĆčüčéąĖą╣ (via). ąó. ąĄ. čŹč鹊 ąŠčéą▓ąĄčĆčüčéąĖčÅ, ą║ąŠč鹊čĆčŗąĄ čüąŠą┤ąĄčƹȹ░čé ąĮą░ čüą▓ąŠąĖčģ čüč鹥ąĮą║ą░čģ ą╝ąĄčéą░ą╗ą╗ąĖąĘą░čåąĖčÄ. ąŁč鹊čé čüą╗ąŠą╣ čéą░ą║ąČąĄ ą┐ąŠą╗ąĄąĘąĄąĮ, ą║ąŠą│ą┤ą░ ąĮčāąČąĮąŠ ą┤ąŠą▒ą░ą▓ąĖčéčī ąŠčéą▓ąĄčĆčüčéąĖąĄ ą┤ą╗čÅ ąĘą░ąĘąĄą╝ą╗čÅčÄčēąĄą│ąŠ ą▓ąĖąĮčéą░, čüąŠąĄą┤ąĖąĮčÅčÄčēąĄą│ąŠ čåąĄą┐čī ąĘąĄą╝ą╗ąĖ ą┐ą╗ą░čéčŗ čü ą╝ąĄčéą░ą╗ą╗ąĖč湥čüą║ąĖą╝ čłą░čüčüąĖ.

Layer 45: Holes. ąŁč鹊čé čüą╗ąŠą╣ ą┐ąŠą┤ąŠą▒ąĄąĮ čüą╗ąŠčÄ Drills, ąĮąŠ ąŠąĮ čüąŠą┤ąĄčƹȹĖčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ č鹥čģ ąŠčéą▓ąĄčĆčüčéąĖčÅčģ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ čüą╗čāąČą░čé ą┤ą╗čÅ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ čåąĄą┐ąĄą╣ ąĮą░ čĆą░ąĘąĮčŗčģ čüą╗ąŠčÅčģ (ąĮąĄ čüąŠą┤ąĄčƹȹ░čé ą╝ąĄčéą░ą╗ą╗ąĖąĘą░čåąĖąĖ). ąŁčéąĖ ąŠčéą▓ąĄčĆčüčéąĖčÅ ąŠą▒čŗčćąĮąŠ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ ą┤ą╗čÅ ą╝ąĄčģą░ąĮąĖč湥čüą║ąŠą│ąŠ ą║čĆąĄą┐ą╗ąĄąĮąĖčÅ ą┐ą╗ą░čéčŗ ąĖą╗ąĖ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ąĮą░ ąĮąĄą╣.

Layer 46: Milling. ąŁč鹊čé čüą╗ąŠą╣ ą▓čŗą┤ąĄą╗ąĄąĮ ą┤ą╗čÅ ą┐čĆąŠčĆąĄąĘąĄą╣, ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ą▓čŗčĆąĄąĘąŠą▓ ąĖ ą┤čĆčāą│ąĖčģ ą▓ąĖą┤ąŠą▓ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą║čĆą░čÅ ą┐ą╗ą░čéčŗ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 čŹč鹊čé čüą╗ąŠą╣ ąĮąĄ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĖčÅ čĆą░ąĘą╝ąĄčĆąŠą▓ ą┐ą╗ą░čéčŗ; ą┤ą╗čÅ čĆą░ąĘą╝ąĄčĆąŠą▓ ą┐ą╗ą░čéčŗ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ čüą╗ąŠą╣ Layer 20 Dimension. ąś ą▓ ąŠčéą╗ąĖčćąĖąĄ ąŠčé čüą╗ąŠčÅ Dimension, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĄčé ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąŠą▓ą░čéčī čü ą┐čĆą░ą▓ąĖą╗ą░ą╝ąĖ ą┤ąĖąĘą░ą╣ąĮą░ (design rules, ą┐čĆąŠą▓ąĄčĆą║ą░ DRC), čüą╗ąŠą╣ Milling čĆą░ą▒ąŠčéą░čéčī čü ą┐čĆą░ą▓ąĖą╗ą░ą╝ąĖ ąĮąĄ ą╝ąŠąČąĄčé.

Layer 47: Measures. ąŁč鹊čé čüą╗ąŠą╣ čüąŠą┤ąĄčƹȹĖčé ą▓čüąĄ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖčÅ čĆą░ąĘą╝ąĄčĆąŠą▓, ą║ąŠč鹊čĆčŗąĄ čéčĆąĄą▒čāčÄčéčüčÅ ą┤ą╗čÅ ą┐ą╗ą░čéčŗ, ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ ą┤ą╗ąĖąĮčŗ ąĖ čłąĖčĆąĖąĮčŗ ą┐ą╗ą░čéčŗ, ąĖą╗ąĖ ą┤ą░ąČąĄ čĆą░čüčüč鹊čÅąĮąĖąĄ ą╝ąĄąČą┤čā ą║čĆąĖčéąĖčćąĮčŗą╝ąĖ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ą╝ąĖ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą▓ čŹč鹊ą╝ čüą╗ąŠąĄ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮą░ ą┤ą╗čÅ ąÆą░čłąĄą│ąŠ ą┐ąĄčĆčüąŠąĮą░ą╗čīąĮąŠą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ, ąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÄ ą┐ą╗ą░čé ąŠąĮą░ ąĮąĄ ąĮčāąČąĮą░.

Layer 48: Document. ąŁč鹊čé čüą╗ąŠą╣ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ ą╗čÄą▒ąŠą╣ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ ą┐ąŠ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░č鹥. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┤ąŠą▒ą░ą▓ąĖčéčī ą▓ čŹč鹊čé čüą╗ąŠą╣ ąĘą░ą╝ąĄčćą░ąĮąĖčÅ ą┐ąŠ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓čā ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ:

ŌĆó ąóąŠą╗čēąĖąĮą░ ą┐ą╗ą░čéčŗ.

ŌĆó ąóčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ čüč鹥ą║čā čüą╗ąŠąĄą▓ [2].

ŌĆó ą”ą▓ąĄčéą░ ą┐ą░čÅą╗čīąĮąŠą╣ ą╝ą░čüą║ąĖ ąĖ čłąĄą╗ą║ąŠą│čĆą░čäąĖąĖ.

ŌĆó ą¢ąĄą╗ą░ąĄą╝čŗą╣ čéąĖą┐ ą╝ąĄą┤ąĮąŠą│ąŠ ą┐ąŠą║čĆčŗčéąĖčÅ ąĖ ąĄą│ąŠ č鹊ą╗čēąĖąĮą░.

ŌĆó ąĪą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ą┐ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÄ ąĖą╝ą┐ąĄą┤ą░ąĮčüąŠą╝.

ŌĆó ąĪą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ čäąĖąĮąĖčłąĮąŠą╝čā ą┐ąŠą║čĆčŗčéąĖčÄ, ąĄčüą╗ąĖ čéą░ą║ąŠą▓čŗąĄ ąĄčüčéčī.

Layer 49-50: ReferenceLC/ReferenceLS. ąŁčéąĖ ą┤ą▓ą░ čüą╗ąŠčÅ čüąŠą┤ąĄčƹȹ░čé ą╝ą░čĆą║ąĄčĆčŗ ą┐čĆąĖą▓čÅąĘą║ąĖ (fiducials marks) ą┐ą╗ą░čéčŗ. ąØąĖą║ąŠą│ą┤ą░ ą┐čĆąŠ čŹč鹊 ąĮąĄ čüą╗čŗčłą░ą╗ąĖ? ąŁč鹊 ą┐čĆąŠčüčé ą╝ą░ą╗ąĄąĮčīą║ąĖąĄ ą╝ą░čĆą║ąĄčĆčŗ, ą║ąŠč鹊čĆčŗąĄ ąĮą░ąĮąŠčüčÅčéčüčÅ ąĮą░ ą▓ąĄčĆčģąĮčÄčÄ ąĖ ąĮąĖąČąĮčÄčÄ čüč鹊čĆąŠąĮčā ą┐ą╗ą░čéčŗ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą░ą▓č鹊ą╝ą░čéčā ą┤ą╗čÅ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ (pick and place machine) čĆą░čüą┐ąŠąĘąĮą░čéčī ąŠčĆąĖąĄąĮčéą░čåąĖčÄ ą┐ą╗ą░čéčŗ ąĖ č鹊čćąĮąŠ ąĄčæ ą┐ąŠąĘąĖčåąĖąŠąĮąĖčĆąŠą▓ą░čéčī ą▓ čäąĖąĘąĖč湥čüą║ąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ. ąÜą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą┤ą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī 2 ą╝ą░čĆą║ąĄčĆą░, ąĮąŠ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╣ čģąŠčéčÅčé ą▓ąĖą┤ąĄčéčī ąĄčēąĄ ąĖ čéčĆąĄčéąĖą╣ ą╝ą░čĆą║ąĄčĆ.

Layer 51-52: tDocu/bDocu. ąŁč鹊 ą┤ą▓ą░ čüą╗ąŠčÅ ą┤ą╗čÅ ą┤ąŠą║čāą╝ąĄąĮčéąĖčĆčāčÄčēąĖą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąĮą░ ą▓ąĄčĆčģąĮąĄą╣ ąĖ ąĮąĖąČąĮąĄą╣ čüč鹊čĆąŠąĮą░čģ ą┐ą╗ą░čéčŗ. ąŁčéąĖ čüą╗ąŠąĖ ąĮąĄ ą▓ą║ą╗čÄčćą░čÄčéčüčÅ ą▓ čäą░ą╣ą╗čŗ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░, ąŠą┤ąĮą░ą║ąŠ ąŠąĮąĖ ą┐ąŠą╗ąĄąĘąĮčŗ ą┤ą╗čÅ čģčĆą░ąĮąĄąĮąĖčÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ ą┤ąĖąĘą░ą╣ąĮąĄ. ąŚą┤ąĄčüčī ą╝ąŠąČąĮąŠ čĆą░ąĘą╝ąĄčüčéąĖčéčī čéą░ą║ąĖąĄ ą┤ą░ąĮąĮčŗąĄ, ą║ą░ą║ ą╝ąĄčģą░ąĮąĖč湥čüą║ąĖąĄ čĆą░ąĘą╝ąĄčĆčŗ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ąĖ ąĖčģ ą║ąŠčĆą┐čāčüąŠą▓.

[ąĪčüčŗą╗ą║ąĖ]

1. Every Layer in Autodesk EAGLE and What You Need to Know About Them site:autodesk.com.

2. Eagle: ą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ čüąŠąĘą┤ą░ąĮąĖąĄ čüč鹥ą║ą░ čüą╗ąŠąĄą▓ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ.

3, Eagle: ąĮą░čüčéčĆąŠą╣ą║ą░ ą┐čĆą░ą▓ąĖą╗ Design Rules. |