|

đŚđ┤đÁĐüĐî ĐÇđ░đĚđ╝đÁĐëđÁđŻđż đ║ĐÇđ░Đéđ║đżđÁ đżđ┐đŞĐüđ░đŻđŞđÁ Đüđżđ║ĐÇđ░ĐëđÁđŻđŞđ╣ đŞ ĐéđÁĐÇđ╝đŞđŻđżđ▓, đ║đ░Đüđ░ĐÄĐëđŞĐůĐüĐĆ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝đżđ╣ đ╗đżđ│đŞđ║đŞ Xilinx.

5-Volt Tolerant Đůđ░ĐÇđ░đ║ĐéđÁĐÇđŞĐüĐéđŞđ║đ░ đ▓Đůđżđ┤đ░ đŞđ╗đŞ đŻđżđÂđ║đŞ I/O, đżđĚđŻđ░Đçđ░ĐÄĐëđ░ĐĆ, ĐçĐéđż ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đż Đü đ┐đŞĐéđ░đŻđŞđÁđ╝ 3.3V đ┐đżđĚđ▓đżđ╗ĐĆđÁĐé đ┐đżđ╗ĐâĐçđ░ĐéĐî ĐüđŞđ│đŻđ░đ╗Đő Đü ĐâĐÇđżđ▓đŻĐĆđ╝đŞ đ┤đż 5V đ▒đÁđĚ ĐçĐÇđÁđĚđ╝đÁĐÇđŻđżđ│đż đ▓Đůđżđ┤đŻđżđ│đż Đéđżđ║đ░ đŞ đŻđ░ĐÇĐâĐłđÁđŻđŞĐĆ ĐÇđ░đ▒đżĐéĐő (đ┐đżđ▓ĐÇđÁđÂđ┤đÁđŻđŞĐĆ) ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đ░. đ×ĐçđÁđŻĐî đ┐đżđ╗đÁđĚđŻđ░ĐĆ đ▓đżđĚđ╝đżđÂđŻđżĐüĐéĐî.

ABEL Advanced Boolean Expression Language, đÁĐëđÁ đżđ┤đŞđŻ HDL-ĐĆđĚĐőđ║ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇđżđ▓đ░đŻđŞĐĆ đ╗đżđ│đŞđ║đŞ.

ADC Analog-to-Digital Converter, đ┐ĐÇđÁđżđ▒ĐÇđ░đĚđżđ▓đ░ĐéđÁđ╗Đî ĐüđŞđ│đŻđ░đ╗đ░ đŞđĚ đ░đŻđ░đ╗đżđ│đżđ▓đżđ╣ ĐäđżĐÇđ╝Đő đ▓ ĐćđŞĐäĐÇđżđ▓ĐâĐÄ, đÉđŽđč.

AIM Xilinx Advanced Interconnect Matrix, đ╝đ░ĐéĐÇđŞĐćđ░ đ▓đŻĐâĐéĐÇđÁđŻđŻđŞĐů đ╗đżđ│đŞĐçđÁĐüđ║đŞĐů ĐüđżđÁđ┤đŞđŻđÁđŻđŞđ╣ đ▓ ĐüđÁđ╝đÁđ╣ĐüĐéđ▓đÁ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝ CoolRunner-II CPLD, đżđ▒đÁĐüđ┐đÁĐçđŞđ▓đ░ĐÄĐëđ░ĐĆ đ│đŞđ▒đ║đżđÁ đŻđ░ĐüĐéĐÇđ░đŞđ▓đ░đÁđ╝đżđÁ đ▓đĚđ░đŞđ╝đżđ┤đÁđ╣ĐüĐéđ▓đŞđÁ đ╝đÁđÂđ┤Đâ ĐäĐâđŻđ║ĐćđŞđżđŻđ░đ╗ĐîđŻĐőđ╝đŞ đ▒đ╗đżđ║đ░đ╝đŞ PLA.

Antifuse đ╝đ░đ╗đÁđŻĐîđ║đŞđ╣ ĐŹđ╗đÁđ╝đÁđŻĐé ĐüĐůđÁđ╝Đő, đ║đżĐéđżĐÇĐőđ╣ đ╝đżđÂđŻđż đŻđÁđżđ▒ĐÇđ░ĐéđŞđ╝đż đŞđĚđ╝đÁđŻđŞĐéĐî đŞđĚ ĐüđżĐüĐéđżĐĆđŻđŞĐĆ "đŻđÁ ĐüđżđÁđ┤đŞđŻđÁđŻđż" đ▓ ĐüđżĐüĐéđżĐĆđŻđŞđÁ "ĐüđżđÁđ┤đŞđŻđÁđŻđż" Đü Đüđżđ┐ĐÇđżĐéđŞđ▓đ╗đÁđŻđŞđÁđ╝ ĐüđżđÁđ┤đŞđŻđÁđŻđŞĐĆ ~100 đżđ╝. FPGA, đżĐüđŻđżđ▓đ░đŻđŻĐőđÁ đŻđ░ antifuse, ĐĆđ▓đ╗ĐĆĐÄĐéĐüĐĆ ĐŹđŻđÁĐÇđ│đżđŻđÁđĚđ░đ▓đŞĐüđŞđ╝Đőđ╝đŞ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đ░đ╝đŞ, đŻđÁ ĐéĐÇđÁđ▒ĐâĐÄĐëđŞđ╝đŞ đ▓đŻđÁĐłđŻđÁđ╣ đ┐đ░đ╝ĐĆĐéđŞ đ┤đ╗ĐĆ đĚđ░đ│ĐÇĐâđĚđ║đŞ, đŻđż đżđŻđŞ đ╝đżđ│ĐâĐé đ▒ĐőĐéĐî đĚđ░đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇđżđ▓đ░đŻĐő Đéđżđ╗Đîđ║đż đżđ┤đŞđŻ ĐÇđ░đĚ (Đüđ╝. OTP).

AQL Acceptable Quality Level, đ┤đżđ┐ĐâĐüĐéđŞđ╝Đőđ╣ ĐâĐÇđżđ▓đÁđŻĐî đ║đ░ĐçđÁĐüĐéđ▓đ░. đ×ĐéđŻđżĐüđŞĐéđÁđ╗ĐîđŻđżđÁ đ║đżđ╗đŞĐçđÁĐüĐéđ▓đż ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓, đ▓ĐőĐÇđ░đÂđÁđŻđŻđżđÁ đ▓ đÁđ┤đŞđŻđŞĐćđ░Đů đŻđ░ đ╝đŞđ╗đ╗đŞđżđŻ (parts-per-million, ppm), đ║đżĐéđżĐÇĐőđÁ đ╝đżđ│ĐâĐé đŻđÁ Đâđ┤đżđ▓đ╗đÁĐéđ▓đżĐÇĐĆĐéĐî Đüđ┐đÁĐćđŞĐäđŞđ║đ░ĐćđŞđŞ đŞđ╗đŞ đ▒ĐőĐéĐî đ┤đÁĐäđÁđ║ĐéđŻĐőđ╝đŞ. đóđŞđ┐đŞĐçđŻĐőđÁ đĚđŻđ░ĐçđÁđŻđŞĐĆ đ┤đ╗ĐĆ AQL đżđ║đżđ╗đż 10 ppm.

ARM AMBA Advanced Microcontroller Bus Architecture, đżĐéđ║ĐÇĐőĐéĐőđ╣ ĐüĐéđ░đŻđ┤đ░ĐÇĐé, Đüđ┐đÁĐćđŞĐäđŞđ║đ░ĐćđŞĐĆ ĐüđżđÁđ┤đŞđŻđÁđŻđŞđ╣ đŻđ░ đ║ĐÇđŞĐüĐéđ░đ╗đ╗đÁ đ▒đ╗đżđ║đżđ▓ đ┤đŞđĚđ░đ╣đŻđ░ SoC. đíĐéđ░đŻđ┤đ░ĐÇĐé Đâđ┐ĐÇđżĐëđ░đÁĐé ĐÇđ░đĚĐÇđ░đ▒đżĐéđ║Đâ đ╝đŻđżđ│đżđ┐ĐÇđżĐćđÁĐüĐüđżĐÇđŻĐőĐů ĐüđŞĐüĐéđÁđ╝ Đü đ▒đżđ╗ĐîĐłđŞđ╝ đ║đżđ╗đŞĐçđÁĐüĐéđ▓đżđ╝ đ║đżđŻĐéĐÇđżđ╗đ╗đÁĐÇđżđ▓ đŞ đ┐đÁĐÇđŞĐäđÁĐÇđŞđ╣đŻĐőĐů ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓.

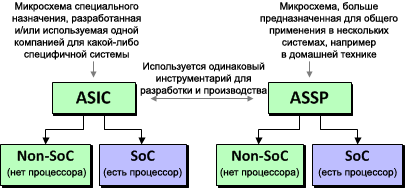

ASIC Application-Specific Integrated Circuit, đŞđŻĐéđÁđ│ĐÇđ░đ╗ĐîđŻđ░ĐĆ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░, đ┐ĐÇđÁđ┤đŻđ░đĚđŻđ░ĐçđÁđŻđŻđ░ĐĆ đ┤đ╗ĐĆ đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđŻđżđ│đż đ┐ĐÇđŞđ╗đżđÂđÁđŻđŞĐĆ. đÜđ░đ║ Đüđ╗đÁđ┤ĐâđÁĐé đŞđĚ đŞđ╝đÁđŻđŞ, ĐŹĐéđż ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đż ĐüđżđĚđ┤đ░đŻđż đ┤đ╗ĐĆ đ▓Đőđ┐đżđ╗đŻđÁđŻđŞĐĆ đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđŻđżđ╣ ĐćđÁđ╗đŞ. đÜđżđ│đ┤đ░ đżđ▒ĐőĐçđŻĐőđ╣ ĐçđÁđ╗đżđ▓đÁđ║ Đüđ╗ĐőĐłđŞĐé ĐéđÁĐÇđ╝đŞđŻ ASIC, Đéđż đ┤đ╗ĐĆ đŻđÁđ│đż ĐŹĐéđż đĚđŻđ░ĐçđŞĐé "đ║đ░đ║đżđÁ-Đéđż đ┐ĐÇđżđ┤đ▓đŞđŻĐâĐéđżđÁ ĐćđŞĐäĐÇđżđ▓đżđÁ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đż". đĺ ĐÇđÁđ░đ╗ĐîđŻđżĐüĐéđŞ đ╗ĐÄđ▒đżđ╣ ĐçđŞđ┐, ĐüđżđĚđ┤đ░đŻđŻĐőđ╣ đ┐đżđ╗ĐîđĚđżđ▓đ░ĐéđÁđ╗đÁđ╝, ĐŹĐéđż ASIC, đ▓ đŻđÁđĚđ░đ▓đŞĐüđŞđ╝đżĐüĐéđŞ đ║đ░đ║đżđ╣ đżđŻ - đ░đŻđ░đ╗đżđ│đżđ▓Đőđ╣, ĐćđŞĐäĐÇđżđ▓đżđ╣, đŞđ╗đŞ đÂđÁ Đüđżđ┤đÁĐÇđÂđŞĐé đ▓ ĐüđÁđ▒đÁ Đüđ╝đÁĐüĐî đŞ Đéđżđ│đż đŞ đ┤ĐÇĐâđ│đżđ│đż. ASIC đ░ĐüđŞđŻĐůĐÇđżđŻđŻĐőđ╝đŞ, đŻđÁ ĐéĐÇđÁđ▒ĐâĐÄĐëđŞđ╝đŞ đ┤đ╗ĐĆ ĐÇđ░đ▒đżĐéĐő Đüđ┐đÁĐćđŞđ░đ╗ĐîđŻđżđ│đż Đéđ░đ║Đéđżđ▓đżđ│đż ĐüđŞđ│đŻđ░đ╗đ░, đŞđ╗đŞ ĐüđŞđŻĐůĐÇđżđŻđŻĐőđ╝đŞ, đ║đżĐéđżĐÇĐőđ╝ đŻĐâđÂđÁđŻ ĐüđŞđŻĐůĐÇđżĐüđŞđ│đŻđ░đ╗. đÉĐüđŞđŻĐůĐÇđżđŻđŻĐőđÁ ĐüĐůđÁđ╝Đő đżđ▒ĐőĐçđŻđż ĐÇđ░đ▒đżĐéđ░ĐÄĐé đ▒ĐőĐüĐéĐÇđÁđÁ ĐüđŞđŻĐůĐÇđżđŻđŻĐőĐů, đżđ┤đŻđ░đ║đż ĐüđŞđŻĐůĐÇđżđŻđŻĐőđÁ đ┐ĐÇđżĐëđÁ ĐüđŞđŻĐéđÁđĚđŞĐÇđżđ▓đ░ĐéĐî, đŞ ĐüđŞđŻĐůĐÇđżđŻđŻĐőđÁ đ╝đÁđŻđÁđÁ ĐçĐâđ▓ĐüĐéđ▓đŞĐéđÁđ╗ĐîđŻĐő đ║ đŞđĚđ╝đÁđŻđÁđŻđŞĐĆđ╝ đ┤đŞđĚđ░đ╣đŻđ░ đŞđ╗đŞ đ▓Đőđ▒đżĐÇĐâ ĐćđÁđ╗đÁđ▓đżđ╣ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝Đő. đíđ╝. Đéđ░đ║đÂđÁ SoC.

ASSP Application-specific standard parts, ĐüĐéđ░đŻđ┤đ░ĐÇĐéđŻĐőđÁ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝Đő, đ┐ĐÇđÁđ┤đŻđ░đĚđŻđ░ĐçđÁđŻđŻĐőđÁ đ┤đ╗ĐĆ đ▓Đőđ┐đżđ╗đŻđÁđŻđŞĐĆ đ║đ░đ║đŞĐů-Đéđż đĚđ░ĐÇđ░đŻđÁđÁ đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđŻĐőĐů ĐäĐâđŻđ║ĐćđŞđ╣. ASSP ĐÇđ░đĚĐÇđ░đ▒đ░ĐéĐőđ▓đ░ĐÄĐéĐüĐĆ đŞ ĐÇđÁđ░đ╗đŞđĚđżđ▓Đőđ▓đ░ĐÄĐéĐüĐĆ ĐéđżĐçđŻđż Đéđ░đ║ đÂđÁ, đ║đ░đ║ đŞ ASIC. đóđ░đ║ ĐçĐéđż đŻđÁ ĐüĐéđżđŞĐé Đâđ┤đŞđ▓đ╗ĐĆĐéĐîĐüĐĆ, ĐçĐéđż ĐŹĐéđż đ▓ ĐüĐâĐëđŻđżĐüĐéđŞ đ┐đżĐçĐéđŞ đżđ┤đŻđż đŞ Đéđż đÂđÁ. đ×Đéđ╗đŞĐçđŞđÁ ASIC đżĐé ASSP Đéđżđ╗Đîđ║đż đ▓ Đéđżđ╝, ĐçĐéđż ASSP đ▒đżđ╗ĐîĐłđÁ đ┐ĐÇđÁđ┤ĐüĐéđ░đ▓đ╗đÁđŻđż đ║đ░đ║ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đż đżđ▒ĐëđÁđ│đż đŻđ░đĚđŻđ░ĐçđÁđŻđŞĐĆ, đ┐ĐÇđÁđ┤đŻđ░đĚđŻđ░ĐçđÁđŻđŻđżđÁ đ┤đ╗ĐĆ đŞĐüđ┐đżđ╗ĐîđĚđżđ▓đ░đŻđŞĐĆ đ▓đż đ╝đŻđżđÂđÁĐüĐéđ▓đÁ ĐÇđ░đĚđŻĐőĐů ĐÇđ░đĚĐÇđ░đ▒đżĐéđżđ║. đŁđ░đ┐ĐÇđŞđ╝đÁĐÇ, đżĐéđ┤đÁđ╗ĐîđŻĐőđ╣ ĐçđŞđ┐ đ┤đ╗ĐĆ đżĐÇđ│đ░đŻđŞđĚđ░ĐćđŞđŞ đŞđŻĐéđÁĐÇĐäđÁđ╣Đüđ░ USB (Đéđ░đ║đŞđÁ ĐçđŞđ┐Đő đ┤đÁđ╗đ░đÁĐé FTDI) đ║đ╗đ░ĐüĐüđŞĐäđŞĐćđŞĐÇĐâđÁĐéĐüĐĆ đ║đ░đ║ ASSP. đíđ╝. Đéđ░đ║đÂđÁ SoC.

ATE automated test equipment, ĐüđŞĐüĐéđÁđ╝Đő đ░đ▓Đéđżđ╝đ░ĐéđŞđĚđŞĐÇđżđ▓đ░đŻđŻđżđ│đż ĐéđÁĐüĐéđŞĐÇđżđ▓đ░đŻđŞĐĆ (đżđ▒ĐőĐçđŻđż ĐçđÁĐÇđÁđĚ đŞđŻĐéđÁĐÇĐäđÁđ╣Đü JTAG).

ATM Asynchronous Transfer Mode, đżĐçđÁđŻĐî Đüđ║đżĐÇđżĐüĐéđŻđżđ╣ (đżĐé đ╝đÁđ│đ░đ│đÁĐÇĐć đ┤đż đ│đŞđ│đ░đ│đÁĐÇĐć) đżĐÇđŞđÁđŻĐéđŞĐÇđżđ▓đ░đŻđŻĐőđ╣ đŻđ░ ĐüđżđÁđ┤đŞđŻđÁđŻđŞđÁ đ┐ĐÇđżĐéđżđ║đżđ╗ đ┤đ╗ĐĆ đ┐đÁĐÇđÁđ┤đ░ĐçđŞ đ┤đ░đŻđŻĐőĐů đ▓ ĐÇđÁđ░đ╗ĐîđŻđżđ╝ đ▓ĐÇđÁđ╝đÁđŻđŞ đ│đżđ╗đżĐüđ░ đŞ đ▓đŞđ┤đÁđż đ┐đ░đ║đÁĐéđ░đ╝đŞ ĐäđŞđ║ĐüđŞĐÇđżđ▓đ░đŻđŻđżđ╣ đ┤đ╗đŞđŻĐő (48 đ▒đ░đ╣Đé đ┐đżđ╗đÁđĚđŻđ░ĐĆ đŻđ░đ│ĐÇĐâđĚđ║đ░, 5-đ▒đ░đ╣ĐéđŻĐőđ╣ đĚđ░đ│đżđ╗đżđ▓đżđ║).

AXI Advanced eXtensible Interface, đ▒đŞđ▒đ╗đŞđżĐéđÁđ║đ░ đ┤đ╗ĐĆ đ┐đżđ┤đ┤đÁĐÇđÂđ║đŞ đ┐ĐÇđżĐéđżđ║đżđ╗đżđ▓ đŞđŻĐéđÁĐÇĐäđÁđ╣Đüđżđ▓, Đçđ░ĐüĐéĐî ĐüĐéđ░đŻđ┤đ░ĐÇĐéđ░ ARM AMBA, Đüđ┐đÁĐćđŞĐäđŞđ║đ░ĐćđŞđŞ ĐüđÁđ╝đÁđ╣ĐüĐéđ▓đ░ ĐłđŞđŻ đ╝đŞđ║ĐÇđżđ║đżđŻĐéĐÇđżđ╗đ╗đÁĐÇđżđ▓, đ┐đżĐĆđ▓đŞđ▓ĐłđÁđ╣ĐüĐĆ đ▓ 1996 đ│đżđ┤Đâ. đčđÁĐÇđ▓đ░ĐĆ đ▓đÁĐÇĐüđŞĐĆ AXI đ▒Đőđ╗đ░ đ▓đ║đ╗ĐÄĐçđÁđŻđ░ đ▓ AMBA 3.0, đ▓ĐőĐłđÁđ┤ĐłđÁđ╣ đ▓ 2003 đ│đżđ┤Đâ. AMBA 4.0, đ▓ĐőĐłđÁđ┤Đłđ░ĐĆ đ▓ 2010 đ│đżđ┤Đâ, đ▓đ║đ╗ĐÄĐçđ░đÁĐé đ▓ĐéđżĐÇĐâĐÄ đ▓đÁĐÇĐüđŞĐÄ AXI, AXI4. đčđżđ┤ĐÇđżđ▒đŻđÁđÁ Đüđ╝. UG761 AXI Reference Guide site:xilinx.com

Back Annotation đ░đ▓Đéđżđ╝đ░ĐéđŞĐçđÁĐüđ║đżđÁ đŻđ░đĚđŻđ░ĐçđÁđŻđŞđÁ đĚđŻđ░ĐçđÁđŻđŞđ╣ đ▓ĐÇđÁđ╝đÁđŻđŞ đ▓đż đ▓đ▓đÁđ┤đÁđŻđŻĐőđ╣ đ┤đŞđĚđ░đ╣đŻ đ┐đżĐüđ╗đÁ Đéđżđ│đż, đ║đ░đ║ đżđŻ đ▒Đőđ╗ ĐÇđ░đĚđ╝đÁĐëđÁđŻ đŞ đ╝đ░ĐÇĐłĐÇĐâĐéđŞđĚđŞĐÇđżđ▓đ░đŻ đ▓ FPGA.

Bare-metal đ┤đżđ▓đżđ╗ĐîđŻđż Đüđ╗đżđÂđŻđ░ĐĆ, đŞđŻĐéđÁđ╗đ╗đÁđ║ĐéĐâđ░đ╗ĐîđŻđ░ĐĆ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đ░, đ║đżĐéđżĐÇđ░ĐĆ đĚđ░đ┐ĐâĐüđ║đ░đÁĐéĐüĐĆ đŻđ░ đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđŻđżđ╣ đ░đ┐đ┐đ░ĐÇđ░ĐéĐâĐÇđÁ đ▒đÁđĚ đ┐ĐÇđŞđ╝đÁđŻđÁđŻđŞĐĆ đ║đ░đ║đżđ╣-đ╗đŞđ▒đż đżđ┐đÁĐÇđ░ĐćđŞđżđŻđŻđżđ╣ ĐüđŞĐüĐéđÁđ╝Đő.

Behavioral Language đŻđŞĐüĐůđżđ┤ĐĆĐëđÁđÁ đżđ┐đŞĐüđ░đŻđŞđÁ đÁĐëđÁ đ▒đżđ╗đÁđÁ đ▓ĐőĐüđżđ║đżđ│đż ĐâĐÇđżđ▓đŻĐĆ, ĐçđÁđ╝ VHDL.

BGA Ball Grid Array, ĐéđŞđ┐ đ║đżĐÇđ┐ĐâĐüđ░ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝. đĽđ│đż đ║đżđŻĐéđ░đ║ĐéĐő ĐÇđ░Đüđ┐đżđ╗đżđÂđÁđŻĐő đŻđ░ đŻđŞđÂđŻđÁđ╣ ĐüĐéđżĐÇđżđŻđÁ đ║đżĐÇđ┐ĐâĐüđ░ đ▓ đ▓đŞđ┤đÁ Đłđ░ĐÇđŞđ║đżđ▓ĐőĐů đ▓Đőđ▓đżđ┤đżđ▓ đŞđĚ Đüđ┐đ╗đ░đ▓đ░ đżđ╗đżđ▓đ░.

Block RAM, BRAM đ▒đ╗đżđ║ đ×đŚđú ĐÇđ░đĚđ╝đÁĐÇđżđ╝ đżĐé 2k đ┤đż 4k đ▒đŞĐé đ▓đŻĐâĐéĐÇđŞ FPGA. đöđ╗ĐĆ Đéđ░đ║đŞĐů đ▒đ╗đżđ║đżđ▓ đÂđÁđ╗đ░ĐéđÁđ╗ĐîđŻđż đŻđ░đ╗đŞĐçđŞđÁ đ┤đ▓đżđ╣đŻđżđ│đż đ┐đżĐÇĐéđ░ đ┤đżĐüĐéĐâđ┐đ░ (đ┤đ▓ĐâĐůđ┐đżĐÇĐéđżđ▓đ░ĐĆ đ┐đ░đ╝ĐĆĐéĐî) đŞ ĐüđŞđŻĐůĐÇđżđŻđŻĐőđ╣ đ┐ĐÇđŞđŻĐćđŞđ┐ ĐÇđ░đ▒đżĐéĐő.

BLVDS Backplane Low Voltage Differential Signaling, đŻđŞđĚđ║đżđ▓đżđ╗ĐîĐéđŻđ░ĐĆ đ┤đŞĐäĐäđÁĐÇđÁđŻĐćđŞđ░đ╗ĐîđŻđ░ĐĆ ĐłđŞđŻđ░ đ┤đ╗ĐĆ đ┐đÁĐÇđÁđ┤đ░ĐçđŞ ĐüđŞđ│đŻđ░đ╗đżđ▓ đ╝đÁđÂđ┤Đâ đżĐéđ┤đÁđ╗ĐîđŻĐőđ╝đŞ đ╝đżđ┤Đâđ╗ĐĆđ╝đŞ.

BSP Board Support Package, đŻđ░đ▒đżĐÇ đ▒đŞđ▒đ╗đŞđżĐéđÁđ║ đŞ/đŞđ╗đŞ đ┐ĐÇđżđÁđ║Đéđżđ▓, đ┐đżđĚđ▓đżđ╗ĐĆĐÄĐëđŞđ╣ đŞĐüđ┐đżđ╗ĐîđĚđżđ▓đ░ĐéĐî ĐäĐâđŻđ║ĐćđŞđżđŻđ░đ╗ĐîđŻĐőđÁ đ▓đżđĚđ╝đżđÂđŻđżĐüĐéđŞ đ║đ░đ║đżđ╣-đ╗đŞđ▒đż đ░đ┐đ┐đ░ĐÇđ░ĐéđŻđżđ╣ ĐüđŞĐüĐéđÁđ╝Đő, đżđ▒ĐőĐçđŻđż ĐŹĐéđż đżĐćđÁđŻđżĐçđŻđ░ĐĆ đ┐đ╗đ░Đéđ░ ĐÇđ░đĚĐÇđ░đ▒đżĐéĐçđŞđ║đ░.

BUFG Global Clock Buffer, đ▒ĐâĐäđÁĐÇ đ┤đ╗ĐĆ đ│đ╗đżđ▒đ░đ╗ĐîđŻđżđ│đż Đéđ░đ║Đéđżđ▓đżđ│đż ĐüđŞđ│đŻđ░đ╗đ░.

CAE Computer Aided Engineering. đíĐéđżĐÇđżđŻđŻđŞđÁ đŻđ░đ▒đżĐÇĐő đŞđŻĐüĐéĐÇĐâđ╝đÁđŻĐéđ░ĐÇđŞĐĆ ĐÇđ░đĚĐÇđ░đ▒đżĐéđ║đŞ đ┤đ╗ĐĆ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝ Xilinx.

CDRST ĐüđŞđŻĐůĐÇđżđŻđŻĐőđ╣ Đüđ▒ĐÇđżĐü đ┤đÁđ╗đŞĐéđÁđ╗ĐĆ Đéđ░đ║Đéđżđ▓ CPLD.

CE Clock Enable, ĐüđŞđ│đŻđ░đ╗ ĐÇđ░đĚĐÇđÁĐłđÁđŻđŞĐĆ Đéđ░đ║ĐéđŞĐÇđżđ▓đ░đŻđŞĐĆ.

Charge Pump đ┐đżđ▓ĐőĐłđ░ĐÄĐëđŞđ╣ đ┐ĐÇđÁđżđ▒ĐÇđ░đĚđżđ▓đ░ĐéđÁđ╗Đî đŻđ░đ┐ĐÇĐĆđÂđÁđŻđŞĐĆ DC-DC, đżĐüđŻđżđ▓đ░đŻđŻĐőđ╣ đŻđ░ ĐÇđ░đĚĐÇĐĆđ┤đÁ đŞ đĚđ░ĐÇĐĆđ┤đÁ đ║đżđŻđ┤đÁđŻĐüđ░ĐéđżĐÇđżđ▓.

CLB Configurable Logic Block, đ║đżđŻĐäđŞđ│ĐâĐÇđŞĐÇĐâđÁđ╝Đőđ╣ đ╗đżđ│đŞĐçđÁĐüđ║đŞđ╣ đ▒đ╗đżđ║. đóđÁĐÇđ╝đŞđŻ Xilinx đ┤đ╗ĐĆ đ▒đ╗đżđ║đ░ đ╗đżđ│đŞđ║đŞ, đżđ║ĐÇĐâđÂđÁđŻđŻđżđ│đż ĐÇđÁĐüĐâĐÇĐüđ░đ╝đŞ đ╝đ░ĐÇĐłĐÇĐâĐéđŞđĚđ░ĐćđŞđŞ. CLB Đüđżđ┤đÁĐÇđÂđŞĐé 2 đŞđ╗đŞ LUT (đ│đÁđŻđÁĐÇđ░ĐéđżĐÇ ĐäĐâđŻđ║ĐćđŞđ╣) đ┐đ╗ĐÄĐü 2 đŞđ╗đŞ 4 ĐéĐÇđŞđ│đ│đÁĐÇđ░.

CLK ĐüđŞđ│đŻđ░đ╗ Đéđ░đ║ĐéđŞĐÇđżđ▓đ░đŻđŞĐĆ, clock.

CMOS Complementary Metal Oxide Semiconductor, đ┐đżđ┐Đâđ╗ĐĆĐÇđŻđ░ĐĆ ĐéđÁĐůđŻđżđ╗đżđ│đŞĐĆ đ┤đ╗ĐĆ ĐüđżđĚđ┤đ░đŻđŞĐĆ đ╗đżđ│đŞĐçđÁĐüđ║đŞĐů ĐüĐůđÁđ╝, đ┤đżđ╝đŞđŻđŞĐÇĐâĐÄĐëđ░ĐĆ đ┤đ╗ĐĆ đ╗đżđ│đŞđ║đŞ đŞ đ┐đ░đ╝ĐĆĐéđŞ. đŚđ░đ╝đÁđŻđŞđ╗đ░ ĐüĐéđ░ĐÇĐâĐÄ đ▒đŞđ┐đżđ╗ĐĆĐÇđŻĐâĐÄ ĐéđÁĐůđŻđżđ╗đżđ│đŞĐÄ TTL đ▓ đ▒đżđ╗ĐîĐłđŞđŻĐüĐéđ▓đÁ đ┐ĐÇđŞđ╗đżđÂđÁđŻđŞđ╣ (đĚđ░ đŞĐüđ║đ╗ĐÄĐçđÁđŻđŞđÁđ╝ Đüđ░đ╝ĐőĐů đ▒ĐőĐüĐéĐÇĐőĐů). CMOS đ┐ĐÇđÁđ┤đżĐüĐéđ░đ▓đ╗ĐĆđÁĐé đ╝đÁđŻĐîĐłđÁđÁ ĐŹđŻđÁĐÇđ│đżđ┐đżĐéĐÇđÁđ▒đ╗đÁđŻđŞđÁ đŞ đ╝đÁđŻĐîĐłđŞđÁ ĐÇđ░đĚđ╝đÁĐÇĐő ĐçđŞđ┐đżđ▓ đ▓ ĐüĐÇđ░đ▓đŻđÁđŻđŞđŞ Đü đ▒đŞđ┐đżđ╗ĐĆĐÇđŻđżđ╣ ĐéđÁĐůđŻđżđ╗đżđ│đŞđÁđ╣, đŞ ĐüđÁđ╣Đçđ░Đü Đâđ┤đżđ▓đ╗đÁĐéđ▓đżĐÇĐĆđÁĐé đ┐đż Đüđ║đżĐÇđżĐüĐéđŞ đŞ đ┤đ░đÂđÁ đ┐đżđ▒đŞđ▓đ░đÁĐé ĐéđÁĐůđŻđżđ╗đżđ│đŞĐÄ TTL.

Configuration đ║đżđŻĐäđŞđ│ĐâĐÇđ░ĐćđŞĐĆ. đĄđ░đ╣đ╗, ĐüđżĐůĐÇđ░đŻĐĆđÁđ╝Đőđ╣ đ▓đŻĐâĐéĐÇđŞ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝Đő đ╗đżđ│đŞđ║đŞ (đ┤đ╗ĐĆ CPLD) đŞđ╗đŞ đĚđ░đ│ĐÇĐâđÂđ░đÁđ╝Đőđ╣ ĐüđŻđ░ĐÇĐâđÂđŞ (đ┤đ╗ĐĆ FPGA), đ║đżĐéđżĐÇĐőđ╣ Đâđ┐ĐÇđ░đ▓đ╗ĐĆđÁĐé đÁĐĹ đ┐đżđ▓đÁđ┤đÁđŻđŞđÁđ╝, Đé. đÁ. đĚđ░đ┤đ░đÁĐé đ╗đżđ│đŞđ║Đâ đÁĐĹ ĐÇđ░đ▒đżĐéĐő.

Constraints đ┤đżđ┐đżđ╗đŻđŞĐéđÁđ╗ĐîđŻĐőđÁ ĐéĐÇđÁđ▒đżđ▓đ░đŻđŞĐĆ đ║ đ┤đŞđĚđ░đ╣đŻĐâ - đżđ▒ĐőĐçđŻđż ĐŹĐéđż đ╝đ░đ║ĐüđŞđ╝đ░đ╗ĐîđŻđż đ┤đżđ┐ĐâĐüĐéđŞđ╝đ░ĐĆ đĚđ░đ┤đÁĐÇđÂđ║đ░ đŞđ╗đŞ ĐéĐÇđÁđ▒ĐâđÁđ╝đ░ĐĆ ĐÇđ░đ▒đżĐçđ░ĐĆ Đçđ░ĐüĐéđżĐéđ░, ĐÇđ░đĚđ▓đżđ┤đ║đ░ đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđŻĐőĐů ĐüđŞđ│đŻđ░đ╗đżđ▓ đŻđ░ đŻĐâđÂđŻĐőđÁ đŻđżđÂđ║đŞ đ║đżĐÇđ┐ĐâĐüđ░ đŞ Đé. đ┐.

CoolCLOCK đ║đżđ╝đ▒đŞđŻđ░ĐćđŞĐĆ ĐäĐâđŻđ║ĐćđŞđ╣ đ┤đÁđ╗đŞĐéđÁđ╗ĐĆ Đçđ░ĐüĐéđżĐéĐő đŞ Đâđ┤đ▓đżđŞĐéđÁđ╗ĐĆ Đéđ░đ║Đéđżđ▓ đ▓ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░Đů CoolRunner-II CPLD. đşĐéđ░ ĐéđÁĐůđŻđżđ╗đżđ│đŞĐĆ đ▓đ▓đÁđ┤đÁđŻđ░ Đü ĐćđÁđ╗ĐîĐÄ Đâđ╝đÁđŻĐîĐłđŞĐéĐî ĐŹđŻđÁĐÇđ│đżđ┐đżĐéĐÇđÁđ▒đ╗đÁđŻđŞđÁ, Đüđ▓ĐĆđĚđ░đŻđŻđżđÁ Đü đ▓ĐőĐüđżđ║đżĐüđ║đżĐÇđżĐüĐéđŻĐőđ╝đŞ ĐćđÁđ┐ĐĆđ╝đŞ Đéđ░đ║ĐéđŞĐÇđżđ▓đ░đŻđŞĐĆ đ▓đŻĐâĐéĐÇđŞ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝Đő. đčđżđ┤ĐÇđżđ▒đŻđÁđÁ Đüđ╝. [3].

CPLD Complex Programmable Logic Device, Đüđ╗đżđÂđŻđżđÁ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝đżđÁ đ╗đżđ│đŞĐçđÁĐüđ║đżđÁ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đż đ▓ ĐéđÁĐÇđ╝đŞđŻđżđ╗đżđ│đŞđŞ Xilinx, ĐüđŞđŻđżđŻđŞđ╝ EPLD. đŁđ░ Đüđ░đ╝đżđ╝ đ┤đÁđ╗đÁ ĐŹĐéđżĐé ĐéđÁĐÇđ╝đŞđŻ đ┐ĐÇđÁđ┤ĐüĐéđ░đ▓đ╗ĐĆđÁĐé đŻđÁ Đüđ░đ╝ĐőđÁ Đüđ╗đżđÂđŻĐőđÁ đ╗đżđ│đŞĐçđÁĐüđ║đŞđÁ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đ░ (đŻđ░đŞđ▒đżđ╗đÁđÁ Đüđ╗đżđÂđŻĐőđÁ ĐÇđÁđ░đ╗đŞđĚĐâĐÄĐéĐüĐĆ đŻđ░ đżĐüđŻđżđ▓đÁ FPGA). đúĐüĐéĐÇđżđ╣ĐüĐéđ▓đ░ CPLD đżđ▒đ╗đ░đ┤đ░ĐÄĐé đ▓ĐüĐéĐÇđżđÁđŻđŻđżđ╣ đ▓ đ║ĐÇđŞĐüĐéđ░đ╗đ╗ ĐŹđŻđÁĐÇđ│đżđŻđÁđĚđ░đ▓đŞĐüđŞđ╝đżđ╣ đ┐đ░đ╝ĐĆĐéĐîĐÄ, đ▒đ╗đ░đ│đżđ┤đ░ĐÇĐĆ ĐçđÁđ╝Đâ đżđŻđŞ đŻđÁ đŻĐâđÂđ┤đ░ĐÄĐéĐüĐĆ đ┐ĐÇđŞ đ▓đ║đ╗ĐÄĐçđÁđŻđŞđŞ đ┐đŞĐéđ░đŻđŞĐĆ đĚđ░đ│ĐÇĐâđĚđ║đÁ đ║đżđŻĐäđŞđ│ĐâĐÇđ░ĐćđŞđŞ đŞđĚ đ▓đŻđÁĐłđŻđÁđ╣ đ┐đ░đ╝ĐĆĐéđŞ (đ▓ đżĐéđ╗đŞĐçđŞđÁ đżĐé ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓ FPGA). đú đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝ CPLD đ╝đÁđŻĐîĐłđÁ đĚđ░đ┤đÁĐÇđÂđ║đŞ đŻđżđÂđ║đ░-đŻđżđÂđ║đ░, đŞ đżđŻđŞ đ╝đżđ│ĐâĐé đŞđ╝đÁĐéĐî đ╝đŻđżđ│đż đ▓Đůđżđ┤đżđ▓, đżđ┤đŻđ░đ║đż Đâ CPLD đżĐéđŻđżĐüđŞĐéđÁđ╗ĐîđŻđż đ▓ĐőĐłđÁ ĐŹđŻđÁĐÇđ│đżđ┐đżĐéĐÇđÁđ▒đ╗đÁđŻđŞđÁ đŞ đ╝đÁđŻĐîĐłđÁ ĐéĐÇđŞđ│đ│đÁĐÇđżđ▓ đ▓ ĐüĐÇđ░đ▓đŻđÁđŻđŞđŞ Đü đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░đ╝đŞ FPGA.

CUPL Compiler Universal for Programmable Logic, đŞđŻĐüĐéĐÇĐâđ╝đÁđŻĐé ĐÇđ░đĚĐÇđ░đ▒đżĐéđ║đŞ CPLD đżĐé đ║đżđ╝đ┐đ░đŻđŞđŞ Logical Devices.

DataGATE ĐäĐâđŻđ║ĐćđŞĐĆ đ▓ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░Đů CoolRunner-II đ┤đ╗ĐĆ đ▒đ╗đżđ║đŞĐÇđżđ▓đ░đŻđŞĐĆ Đüđ▓đżđ▒đżđ┤đŻđż đ┐đÁĐÇđÁđ║đ╗ĐÄĐçđ░ĐÄĐëđŞĐůĐüĐĆ đ▓Đůđżđ┤đŻĐőĐů ĐüđŞđ│đŻđ░đ╗đżđ▓. đ×đŻđ░ ĐŹĐäĐäđÁđ║ĐéđŞđ▓đŻđż đ▒đ╗đżđ║đŞĐÇĐâđÁĐé đ┐đÁĐÇđÁđ║đ╗ĐÄĐçđÁđŻđŞđÁ ĐüđŞđ│đŻđ░đ╗đżđ▓, Đéđ░đ║ ĐçĐéđż đżđŻđŞ đŻđÁ đ┐đÁĐÇđÁđĚđ░ĐÇĐĆđÂđ░ĐÄĐé đ▓đŻĐâĐéĐÇđÁđŻđŻđŞđÁ đÁđ╝đ║đżĐüĐéđŞ ĐçđŞđ┐đ░, ĐçĐéđż đ┤đżđ┐đżđ╗đŻđŞĐéđÁđ╗ĐîđŻđż ĐüđŻđŞđÂđ░đÁĐé đ┐đżĐéĐÇđÁđ▒đ╗đÁđŻđŞđÁ ĐŹđŻđÁĐÇđ│đŞđŞ. đşĐéđ░ ĐäĐâđŻđ║ĐćđŞĐĆ đ╝đżđÂđÁĐé đ▒ĐőĐéĐî đ▓Đőđ▒ĐÇđ░đŻđ░ đ┤đ╗ĐĆ đ▓ĐüđÁĐů đ▓Đůđżđ┤đżđ▓, đ┐đżđ┤ĐÇđżđ▒đŻđÁđÁ Đüđ╝. [3].

DCI Digitally Controlled Impedance, ĐćđŞĐäĐÇđżđ▓đżđÁ Đâđ┐ĐÇđ░đ▓đ╗đÁđŻđŞđÁ Đüđżđ┐ĐÇđżĐéđŞđ▓đ╗đÁđŻđŞđÁđ╝. đóđÁĐůđŻđżđ╗đżđ│đŞĐĆ, đ┐ĐÇđÁđ┤ĐüĐéđ░đ▓đ╗đÁđŻđŻđ░ĐĆ đ▓ Virtex-II, đ┐đżđĚđ▓đżđ╗ĐĆđÁĐé đ┤đŞđŻđ░đ╝đŞĐçđÁĐüđ║đŞ Đâđ┐ĐÇđ░đ▓đ╗ĐĆĐéĐî đŻđ░đ│ĐÇĐâđĚđżĐçđŻđżđ╣ Đüđ┐đżĐüđżđ▒đŻđżĐüĐéĐîĐÄ đ▓ đĚđ░đ▓đŞĐüđŞđ╝đżĐüĐéđŞ đżĐé đŞđĚđ╝đÁđŻđÁđŻđŞĐĆ đŻđ░đ│ĐÇĐâđĚđ║đŞ, ĐéđÁđ╝đ┐đÁĐÇđ░ĐéĐâĐÇĐő đŞ đŻđ░đ┐ĐÇĐĆđÂđÁđŻđŞĐĆ. DCI đŞĐüđ┐đżđ╗ĐîđĚĐâđÁĐé 2 đ▓đŻđÁĐłđŻđŞĐů đ▓ĐőĐüđżđ║đżĐéđżĐçđŻĐőĐů ĐÇđÁđĚđŞĐüĐéđżĐÇđ░, ĐçĐéđżđ▒Đő ĐÇđÁđ░đ╗đŞđĚđżđ▓đ░ĐéĐî ĐŹđ║đ▓đŞđ▓đ░đ╗đÁđŻĐéđŻĐőđ╣ đ▓Đůđżđ┤đŻđżđ╣ đŞ đ▓ĐőĐůđżđ┤đŻđżđ╣ đŞđ╝đ┐đÁđ┤đ░đŻĐü đ┤đ╗ĐĆ ĐüđżĐéđÁđŻ đŻđżđÂđÁđ║ I/O.

DCM Digital Clock Manager, Đüđ┐đÁĐćđŞđ░đ╗ĐîđŻđ░ĐĆ đ┐ĐÇđżđ┤đ▓đŞđŻĐâĐéđ░ĐĆ ĐäĐâđŻđ║ĐćđŞĐĆ ĐäđżĐÇđ╝đŞĐÇđżđ▓đ░đŻđŞĐĆ Đéđ░đ║Đéđżđ▓, ĐÇđÁđ░đ╗đŞđĚđżđ▓đ░đŻđŻđ░ĐĆ Đâ ĐüđÁđ╝đÁđ╣ĐüĐéđ▓đ░ Spartan-3. đčĐÇđÁđ┤đżĐüĐéđ░đ▓đ╗ĐĆđÁĐé đŻĐâđ╗đÁđ▓ĐâĐÄ đĚđ░đ┤đÁĐÇđÂđ║Đâ đ┤đ╗ĐĆ đ▒ĐâĐäđÁĐÇđŞđĚđ░ĐćđŞđŞ Đéđ░đ║Đéđżđ▓, ĐéđżĐçđŻđżđÁ Đâđ┐ĐÇđ░đ▓đ╗đÁđŻđŞđÁ Đäđ░đĚđżđ╣ đŞ ĐéđżĐçđŻĐâĐÄ đ│đÁđŻđÁĐÇđ░ĐćđŞĐÄ Đçđ░ĐüĐéđżĐéĐő đ┤đ╗ĐĆ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝ FPGA Xilinx Virtex-II.

Density đ║đżđ╗đŞĐçđÁĐüĐéđ▓đż đ╗đżđ│đŞđ║đŞ đ▓ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đÁ, Đçđ░ĐüĐéđż đŞĐüđ┐đżđ╗ĐîđĚĐâđÁđ╝đżđÁ đ┤đ╗ĐĆ đżđ▒đżđĚđŻđ░ĐçđÁđŻđŞĐĆ đÁĐĹ đ╗đżđ│đŞđ║đŞ. đ×đ▒ĐőĐçđŻđż đŞđĚđ╝đÁĐÇĐĆđÁĐéĐüĐĆ đ▓ đ▓đÁđŻĐéđŞđ╗ĐĆĐů (gates), đŻđż đ┤đ╗ĐĆ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝ FPGA đ╗ĐâĐçĐłđÁ đ▓ĐőĐÇđ░đÂđ░đÁĐéĐüĐĆ đ▓ đ╗đżđ│đŞĐçđÁĐüđ║đŞĐů ĐĆĐçđÁđ╣đ║đ░Đů (logic cells), đ║đ░đÂđ┤đ░ĐĆ đŞđĚ đ║đżĐéđżĐÇĐőĐů ĐüđżĐüĐéđżđŞĐé đŞđĚ 4-đ▓Đůđżđ┤đżđ▓đżđ╣ LUT đŞ ĐéĐÇđŞđ│đ│đÁĐÇđ░.

DET Dual-Edge Triggering, Đéđ░đ║ĐéđŞĐÇđżđ▓đ░đŻđŞđÁ đ┐đż đżđ▒đżđŞđ╝ đ┐đÁĐÇđÁđ┐đ░đ┤đ░đ╝ Đéđ░đ║Đéđżđ▓đżđ╣ Đçđ░ĐüĐéđżĐéĐő. đíđ╝. Đéđ░đ║đÂđÁ SET.

DES Data Encryption Standard, ĐüĐéđ░đŻđ┤đ░ĐÇĐé ĐłđŞĐäĐÇđżđ▓đ░đŻđŞĐĆ đ┤đ░đŻđŻĐőĐů.

DLL Delay Locked Loop, ĐćđŞĐäĐÇđżđ▓đ░ĐĆ ĐüĐůđÁđ╝đ░, đŞĐüđ┐đżđ╗ĐîđĚĐâđÁđ╝đ░ĐĆ đ┤đ╗ĐĆ Đâđ┐ĐÇđ░đ▓đ╗đÁđŻđŞĐĆ đ│đÁđŻđÁĐÇđ░ĐćđŞđÁđ╣ Đéđ░đ║Đéđżđ▓ đ▓đŻĐâĐéĐÇđŞ đŞ đ▓đŻđÁ ĐçđŞđ┐đ░.

DRAM Dynamic Random Access Memory, đ┤đŞđŻđ░đ╝đŞĐçđÁĐüđ║đżđÁ đ×đŚđú Đü đ┐ĐÇđżđŞđĚđ▓đżđ╗ĐîđŻĐőđ╝ đ┤đżĐüĐéĐâđ┐đżđ╝. đŁđÁđ┤đżĐÇđżđ│đ░ĐĆ đ┐đ░đ╝ĐĆĐéĐî đ┤đ╗ĐĆ ĐçĐéđÁđŻđŞĐĆ đŞ đĚđ░đ┐đŞĐüđŞ, đ│đ┤đÁ đ▒đŞĐéĐő đ┤đ░đŻđŻĐőĐů ĐůĐÇđ░đŻĐĆĐéĐüĐĆ đŻđ░ đ║đżđŻđ┤đÁđŻĐüđ░ĐéđżĐÇđ░Đů, đĚđ░ĐÇĐĆđ┤ đ║đżĐéđżĐÇĐőĐů đ┤đżđ╗đÂđÁđŻ đ┐đÁĐÇđŞđżđ┤đŞĐçđÁĐüđ║đŞ đżđ▒đŻđżđ▓đ╗ĐĆĐéĐîĐüĐĆ. đťđŞđ║ĐÇđżĐüĐůđÁđ╝Đő DRAM đżđ▒ĐőĐçđŻđż đ░đ┤ĐÇđÁĐüĐâĐÄĐéĐüĐĆ đ┐đżĐüđ╗đÁđ┤đżđ▓đ░ĐéđÁđ╗ĐîđŻđżĐüĐéĐîĐÄ đŞđĚ đ┤đ▓ĐâĐů đ░đ┤ĐÇđÁĐüđżđ▓ - đ░đ┤ĐÇđÁĐü ĐüĐéĐÇđżđ║đŞ đŞ đ░đ┤ĐÇđÁĐü ĐüĐéđżđ╗đ▒Đćđ░, ĐçĐéđż đ┤đÁđ╗đ░đÁĐé ĐŹĐéĐâ đ┐đ░đ╝ĐĆĐéĐî đ╝đÁđ┤đ╗đÁđŻđŻđÁđÁ, đŞ đ▒đżđ╗đÁđÁ Đüđ╗đżđÂđŻđżđ╣ đ┤đ╗ĐĆ đŞĐüđ┐đżđ╗ĐîđĚđżđ▓đ░đŻđŞĐĆ (ĐéĐÇđÁđ▒ĐâđÁĐéĐüĐĆ đ┐đżđ┤đ┤đÁĐÇđÂđ║đ░ Đüđ┐đÁĐćđŞđ░đ╗ĐîđŻđżđ│đż đ║đżđŻĐéĐÇđżđ╗đ╗đÁĐÇđ░ DRAM) đ┐đż ĐüĐÇđ░đ▓đŻđÁđŻđŞĐÄ Đü đŞĐüđ┐đżđ╗ĐîđĚđżđ▓đ░đŻđŞđÁđ╝ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝ SRAM.

DRC Design Rule Checker, ĐüđŞĐüĐéđÁđ╝đ░ đ┐ĐÇđżđ▓đÁĐÇđ║đŞ đ┤đŞđĚđ░đ╣đŻđ░ đŻđ░ ĐüđżđżĐéđ▓đÁĐéĐüĐéđ▓đŞđÁ đĚđ░đ┤đ░đŻđŻĐőđ╝ đ┐ĐÇđ░đ▓đŞđ╗đ░đ╝.

DSP Digital Signal Processor, đ┐ĐÇđżĐćđÁĐüĐüđżĐÇ đ┤đ╗ĐĆ ĐćđŞĐäĐÇđżđ▓đżđ╣ đżđ▒ĐÇđ░đ▒đżĐéđ║đŞ ĐüđŞđ│đŻđ░đ╗đżđ▓, ĐćđŞĐäĐÇđżđ▓đ░ĐĆ đżđ▒ĐÇđ░đ▒đżĐéđ║đ░ ĐüđŞđ│đŻđ░đ╗đżđ▓. đťđ░đŻđŞđ┐Đâđ╗ĐĆĐćđŞĐĆ đ┤đ░đŻđŻĐőđ╝đŞ, đżđ▒đżđĚđŻđ░Đçđ░ĐÄĐëđŞđ╝đŞ đ░đŻđ░đ╗đżđ│đżđ▓ĐőđÁ ĐüđŞđ│đŻđ░đ╗Đő, đ║đżĐéđżĐÇĐőđÁ đ▒Đőđ╗đŞ đżĐćđŞĐäĐÇđżđ▓đ░đŻĐő đ▓ đ▓Đőđ▒đżĐÇđ║đŞ (sampled) đŞ đ┐ĐÇđÁđżđ▒ĐÇđ░đĚđżđ▓đ░đŻĐő đ▓ ĐćđŞĐäĐÇđżđ▓đżđÁ đ┐ĐÇđÁđ┤ĐüĐéđ░đ▓đ╗đÁđŻđŞđÁ. đčĐÇđŞđ╝đÁĐÇĐő Đéđ░đ║đŞĐů đ╝đ░đŻđŞđ┐Đâđ╗ĐĆĐćđŞđ╣ - ĐäđŞđ╗ĐîĐéĐÇđ░ĐćđŞĐĆ, Examples are filtering, Đüđ▓đÁĐÇĐéđ║đ░ đŞ đ▒ĐőĐüĐéĐÇđżđÁ đ┐ĐÇđÁđżđ▒ĐÇđ░đĚđżđ▓đ░đŻđŞđÁ đĄĐâĐÇĐîđÁ, đĹđčđĄ (Fast Fourier Transform, FFT).

EAB Embedded Array Block. đóđÁĐÇđ╝đŞđŻ đ║đżđ╝đ┐đ░đŻđŞđŞ Altera, đżđ▒đżđĚđŻđ░Đçđ░ĐÄĐëđŞđ╣ block RAM đ▓ FLEX10K.

ECS Engineering Capture Schematic, ĐÇđÁđ┤đ░đ║ĐéđżĐÇ đ┐ĐÇđŞđŻĐćđŞđ┐đŞđ░đ╗ĐîđŻđżđ╣ ĐüĐůđÁđ╝Đő đ╗đżđ│đŞđ║đŞ đ▓ ĐüĐÇđÁđ┤đÁ ĐÇđ░đĚĐÇđ░đ▒đżĐéđ║đŞ Xilinx (ISE WebPack).

EDIF Electronic Digital Interchange Format, đŞđŻđ┤ĐâĐüĐéĐÇđŞđ░đ╗ĐîđŻĐőđ╣ ĐüĐéđ░đŻđ┤đ░ĐÇĐé đ┤đ╗ĐĆ Đâđ║đ░đĚđ░đŻđŞĐĆ đ┤đŞđĚđ░đ╣đŻđ░ đ╗đżđ│đŞđ║đŞ đ▓ ĐéđÁđ║ĐüĐéđżđ▓đżđ╝ ĐäđżĐÇđ╝đ░ĐéđÁ (ASCII).

Embedded RAM đ┐đ░đ╝ĐĆĐéĐî đ┤đ╗ĐĆ ĐçĐéđÁđŻđŞĐĆ đŞ đĚđ░đ┐đŞĐüđŞ, đ║đżĐéđżĐÇđ░ĐĆ đŻđ░Đůđżđ┤đŞĐéĐüĐĆ đ▓đŻĐâĐéĐÇđŞ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đ░ đ╗đżđ│đŞđ║đŞ (đżđ▒ĐőĐçđŻđż ĐŹĐéđż đżĐéđŻđżĐüđŞĐéĐüĐĆ đ║ FPGA). đčđżđĚđ▓đżđ╗ĐĆđÁĐé ĐâĐüĐéĐÇđ░đŻđŞĐéĐî đ╗đŞĐłđŻđŞđÁ đĚđ░đ┤đÁĐÇđÂđ║đŞ đŞ đ┤đżđ┐đżđ╗đŻđŞĐéđÁđ╗ĐîđŻĐőđÁ ĐüđżđÁđ┤đŞđŻđÁđŻđŞĐĆ, đ║đżĐéđżĐÇĐőđÁ đ▒Đőđ╗đŞ đ▒Đő đ┐ĐÇđŞ đŞĐüđ┐đżđ╗ĐîđĚđżđ▓đ░đŻđŞđŞ đ▓đŻđÁĐłđŻđÁđ╣ RAM.

EMI Electromagnetic Interference, ĐŹđ╗đÁđ║ĐéĐÇđżđ╝đ░đ│đŻđŞĐéđŻĐőđÁ đ┐đżđ╝đÁĐůđŞ, ĐłĐâđ╝Đő.

EPLD Erasable Programmable Logic Devices, ĐüđŞđŻđżđŻđŞđ╝ CPLD. đúĐüĐéĐÇđżđ╣ĐüĐéđ▓đ░ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝đżđ╣ đ╗đżđ│đŞđ║đŞ đŻđ░ đżĐüđŻđżđ▓đÁ PAL, đ│đ┤đÁ đ╗đżđ│đŞđ║đ░ đżđ┐ĐÇđÁđ┤đÁđ╗ĐĆđÁĐéĐüĐĆ đ║đ░đ║ ĐüĐâđ╝đ╝đ░ ĐÇđÁđĚĐâđ╗ĐîĐéđ░Đéđżđ▓ (sum-of-products), đ│đÁđŻđÁĐÇđŞĐÇĐâđÁđ╝ĐőĐů đ╝đ░đ║ĐÇđżĐĆĐçđÁđ╣đ║đ░đ╝đŞ. đóđ░đ║đÂđÁ Đüđ╝. CPLD.

EPROM Erasable Programmable Read Only Memory, đ┐đ░đ╝ĐĆĐéĐî, đ┐ĐÇđÁđ┤đŻđ░đĚđŻđ░ĐçđÁđŻđŻđ░ĐĆ Đéđżđ╗Đîđ║đż đ┤đ╗ĐĆ ĐçĐéđÁđŻđŞĐĆ, Đü đ▓đżđĚđ╝đżđÂđŻđżĐüĐéĐîĐÄ ĐüĐéđŞĐÇđ░đŻđŞĐĆ.

ESD Electro-Static Discharge, đ▓ĐőĐüđżđ║đżđ▓đżđ╗ĐîĐéđŻĐőđ╣ ĐÇđ░đĚĐÇĐĆđ┤, đ║đżĐéđżĐÇĐőđ╣ đ╝đżđÂđÁĐé đ┐đżđ▓ĐÇđÁđ┤đŞĐéĐî đżđ║ĐüđŞđ┤đŻĐőđ╣ đŞđĚđżđ╗ĐĆĐéđżĐÇ đĚđ░Đéđ▓đżĐÇđ░ đ▓Đůđżđ┤đŻđżđ│đż ĐéĐÇđ░đŻđĚđŞĐüĐéđżĐÇđ░. đöđŞđżđ┤Đő đ┤đ╗ĐĆ đĚđ░ĐëđŞĐéĐő đżĐé ESD đĚđ░đ╝Đőđ║đ░ĐÄĐé Đéđżđ║ đżĐé ĐÇđ░đĚĐÇĐĆđ┤đ░ đŻđ░ ĐłđŞđŻĐő đ┐đŞĐéđ░đŻđŞĐĆ.

FB Functional Block, đŻđ░đ▒đżĐÇ đ╗đżđ│đŞĐçđÁĐüđ║đŞĐů ĐäĐâđŻđ║ĐćđŞđ╣, đŞđĚ đ║đżĐéđżĐÇĐőĐů ĐüđżĐüĐéđ░đ▓đ╗ĐĆđÁĐéĐüĐĆ ĐÇđ░đĚđ╗đŞĐçđŻđ░ĐĆ ĐüđŞđŻĐéđÁđĚđŞĐÇĐâđÁđ╝đ░ĐĆ đ╗đżđ│đŞđ║đ░.

FIFO First-In-First-Out, Đüđ┐đÁĐćđŞđ░đ╗ĐîđŻđ░ĐĆ đżĐÇđ│đ░đŻđŞđĚđ░ĐćđŞĐĆ đ▒ĐâĐäđÁĐÇđŻđżđ╣ đ┐đ░đ╝ĐĆĐéđŞ đ┐đż đ┐ĐÇđŞđŻĐćđŞđ┐Đâ "đ┐đÁĐÇđ▓Đőđ╝ đ▓đżĐłđÁđ╗ - đ┐đÁĐÇđ▓Đőđ╝ đ▓ĐőĐłđÁđ╗". đĺĐůđżđ┤ đŞ đ▓ĐőĐůđżđ┤ đ┤đ╗ĐĆ FIFO đ╝đżđ│ĐâĐé ĐÇđ░đ▒đżĐéđ░ĐéĐî đ░ĐüđŞđŻĐůĐÇđżđŻđŻđż đ┤ĐÇĐâđ│ đżĐéđŻđżĐüđŞĐéđÁđ╗ĐîđŻđż đ┤ĐÇĐâđ│đ░. đöđ╗ĐĆ FIFO đŻđÁ ĐéĐÇđÁđ▒ĐâđÁĐéĐüĐĆ đ▓đŻđÁĐłđŻđÁđ│đż đ░đ┤ĐÇđÁĐüđ░, ĐůđżĐéĐĆ đ▓ĐüđÁ Đüđżđ▓ĐÇđÁđ╝đÁđŻđŻĐőđÁ FIFO đ▓đŻĐâĐéĐÇđÁđŻđŻđÁ ĐÇđÁđ░đ╗đŞđĚđżđ▓đ░đŻĐő đŻđ░ đżĐüđŻđżđ▓đ░đŻ RAM, đ║đżĐéđżĐÇđ░ĐĆ Đâđ┐ĐÇđ░đ▓đ╗ĐĆđÁĐéĐüĐĆ đ║đżđ╗ĐîĐćđÁđ▓Đőđ╝đŞ ĐüĐçđÁĐéĐçđŞđ║đ░đ╝đŞ đ░đ┤ĐÇđÁĐüđ░ đ┤đ╗ĐĆ ĐçĐéđÁđŻđŞĐĆ đŞ đĚđ░đ┐đŞĐüđŞ.

FIT Failure In Time, đ║đżđ╗đŞĐçđÁĐüĐéđ▓đż đżĐéđ║đ░đĚđżđ▓ đĚđ░ đÁđ┤đŞđŻđŞĐćĐâ đ▓ĐÇđÁđ╝đÁđŻđŞ. đ×đ┐đŞĐüĐőđ▓đ░đÁĐé đ║đżđ╗đŞĐçđÁĐüĐéđ▓đż đżĐéđ║đ░đĚđżđ▓ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đ░, đżđÂđŞđ┤đ░đÁđ╝ĐőĐů ĐüĐéđ░ĐéđŞĐüĐéđŞĐçđÁĐüđ║đŞ đ┤đ╗ĐĆ đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđŻđżđ│đż đ║đżđ╗đŞĐçđÁĐüĐéđ▓đ░ Đçđ░Đüđżđ▓ ĐÇđ░đ▒đżĐéĐő. đĺĐőĐÇđ░đÂđ░đÁĐéĐüĐĆ đ▓ đżĐéđ║đ░đĚđ░Đů đŻđ░ đ▒đŞđ╗đ╗đŞđżđŻ (đ╝đŞđ╗đ╗đŞđ░ĐÇđ┤) Đçđ░Đüđżđ▓. đöđ╗ĐĆ ĐŹĐéđżđ│đż đ┐đ░ĐÇđ░đ╝đÁĐéĐÇđ░ đ┤đżđ╗đÂđŻđ░ đ▒ĐőĐéĐî Đâđ║đ░đĚđ░đŻđ░ ĐéđÁđ╝đ┐đÁĐÇđ░ĐéĐâĐÇđ░. MTBF đ╝đżđÂđŻđż đ▓ĐőĐçđŞĐüđ╗đŞĐéĐî đŞđĚ FIT.

Fit, fitter Đüđ┐đÁĐćđŞđ░đ╗ĐîđŻđżđÁ đčđ×, đ║đżĐéđżĐÇđżđÁ đ┐đżđ┤đ│đżđŻĐĆđÁĐé ĐüđŞđŻĐéđÁđĚđŞĐÇđżđ▓đ░đŻđŻĐâĐÄ đ╗đżđ│đŞđ║Đâ đ┐đżđ┤ ĐÇđÁĐüĐâĐÇĐüĐő đ▓Đőđ▒ĐÇđ░đŻđŻđżđ│đż ĐçđŞđ┐đ░ CPLD đŞđ╗đŞ FPGA.

Flash ĐŹđŻđÁĐÇđ│đżđŻđÁđĚđ░đ▓đŞĐüđŞđ╝đ░ĐĆ (non-volatile) ĐéđÁĐůđŻđżđ╗đżđ│đŞĐĆ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇđżđ▓đ░đŻđŞĐĆ, đ║đżĐéđżĐÇđ░ĐĆ đŞĐüđ┐đżđ╗ĐîđĚĐâđÁĐéĐüĐĆ đ║đ░đ║ đ░đ╗ĐîĐéđÁĐÇđŻđ░ĐéđŞđ▓đ░ đ┤đ╗ĐĆ ĐéđÁĐůđŻđżđ╗đżđ│đŞđŞ Electrically-Erasable Programmable Read-Only Memory (EEPROM). đíđżđ┤đÁĐÇđÂđŞđ╝đżđÁ đ┐đ░đ╝ĐĆĐéđŞ FLASH đ╝đżđÂđÁĐé đ▒ĐőĐéĐî ĐüĐéđÁĐÇĐéđż ĐŹđ╗đÁđ║ĐéĐÇđŞĐçđÁĐüđ║đŞđ╝ ĐüđŞđ│đŻđ░đ╗đżđ╝, ĐçĐéđż đ┐đżđĚđ▓đżđ╗ĐĆđÁĐé đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇđżđ▓đ░ĐéĐî ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đ░ đ┐ĐÇĐĆđ╝đż đ▓ ĐüđŞĐüĐéđÁđ╝đÁ, ĐâĐüĐéĐÇđ░đŻĐĆĐĆ đŻđÁđżđ▒Đůđżđ┤đŞđ╝đżĐüĐéĐî Đâđ╗ĐîĐéĐÇđ░ĐäđŞđżđ╗đÁĐéđ░ đŞ đ║đ▓đ░ĐÇĐćđÁđ▓ĐőĐů đżđ║đżĐłđÁđ║ đ▓ đ║đżĐÇđ┐ĐâĐüđÁ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝.

FLBGA Flip Chip Ball Grid Array, ĐéđŞđ┐ đ║đżĐÇđ┐ĐâĐüđ░ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝.

Flip-Flop ĐéĐÇđŞđ│đ│đÁĐÇ, đżđ┤đŻđżđ▒đŞĐéđŻđżđÁ ĐůĐÇđ░đŻđŞđ╗đŞĐëđÁ đ┤đ░đŻđŻĐőĐů. đöđ░đŻđŻĐőđÁ đ▒đÁĐÇĐâĐéĐüĐĆ Đüđż đ▓Đůđżđ┤đ░ Data đ┐đż đ░đ║ĐéđŞđ▓đŻđżđ╝Đâ đ┐đÁĐÇđÁđ┐đ░đ┤Đâ (đŻđ░ĐÇđ░ĐüĐéđ░đŻđŞđÁ đŞđ╗đŞ Đüđ┐đ░đ┤) Đéđ░đ║Đéđżđ▓đżđ│đż ĐüđŞđ│đŻđ░đ╗đ░, đŞ đĚđ░ĐéđÁđ╝ đżđŻđŞ đ┐ĐÇđŞĐüĐâĐéĐüĐéđ▓ĐâĐÄĐé đ▓ đ▓đŞđ┤đÁ đŻđżđ▓đżđ│đż ĐüđżĐüĐéđżĐĆđŻđŞĐĆ đŻđ░ đ▓ĐőĐůđżđ┤đÁ Q, Đâđ┤đÁĐÇđÂđŞđ▓đ░ĐĆ Đüđ▓đżđÁ ĐüđżĐüĐéđżĐĆđŻđŞđÁ đ┤đż ĐéđÁĐů đ┐đżĐÇ, đ┐đżđ║đ░ đŻđÁ đ┐đżĐüĐéĐâđ┐đŞĐé đŻđżđ▓Đőđ╣ Đéđ░đ║Đéđżđ▓Đőđ╣ đ┐đÁĐÇđÁđ┐đ░đ┤ đŞ đŻđżđ▓ĐőđÁ đ┤đ░đŻđŻĐőđÁ đŻđ░ đ▓Đůđżđ┤đÁ Data.

Floorplanning đ╝đÁĐéđżđ┤ ĐÇĐâĐçđŻđżđ│đż đŻđ░đĚđŻđ░ĐçđÁđŻđŞĐĆ đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđŻĐőĐů Đçđ░ĐüĐéđÁđ╣ đ┤đŞđĚđ░đ╣đŻđ░ đ▓ Đâđ║đ░đĚđ░đŻđŻĐőĐů đ╝đÁĐüĐéđ░Đů (ĐÇđÁĐüĐâĐÇĐüđ░Đů) đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝Đő đ╗đżđ│đŞđ║đŞ. đčđżđĚđ▓đżđ╗ĐĆđÁĐé ĐâĐüđ║đżĐÇđŞĐéĐî đ║đżđ╝đ┐đŞđ╗ĐĆĐćđŞĐÄ, Đâđ╗ĐâĐçĐłđŞĐéĐî ĐâĐéđŞđ╗đŞđĚđ░ĐćđŞĐÄ ĐÇđÁĐüĐâĐÇĐüđżđ▓ đŞ đ┐đżđ▓ĐőĐüđŞĐéĐî đ┐ĐÇđżđŞđĚđ▓đżđ┤đŞĐéđÁđ╗ĐîđŻđżĐüĐéĐî đ┤đŞđĚđ░đ╣đŻđ░.

Footprint đ┐đżĐüđ░đ┤đżĐçđŻđżđÁ đ╝đÁĐüĐéđż đŻđ░ đ┐đÁĐçđ░ĐéđŻđżđ╣ đ┐đ╗đ░ĐéđÁ, đ║đżĐéđżĐÇđżđÁ đ┐đżđ╗ĐâĐçđ░đÁĐé đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░ đ╗đżđ│đŞđ║đŞ, đŞ ĐüđżđżĐéđ▓đÁĐéĐüĐéđ▓ĐâĐÄĐëđŞđ╝ đżđ▒ĐÇđ░đĚđżđ╝ đ┐đżđ┤đ║đ╗ĐÄĐçđ░đÁĐé đÁĐĹ đ▓Đőđ▓đżđ┤Đő. đťđŞđ║ĐÇđżĐüĐůđÁđ╝Đő, Đüđżđ▓đ╝đÁĐüĐéđŞđ╝ĐőđÁ đ┐đż footprint, đ╝đżđ│ĐâĐé đĚđ░đ╝đÁđŻĐĆĐéĐî đ┤ĐÇĐâđ│ đ┤ĐÇĐâđ│đ░ đ▒đÁđĚ đ╝đżđ┤đŞĐäđŞđ║đ░ĐćđŞđŞ ĐÇđ░đĚđ▓đżđ┤đ║đŞ đ┐đÁĐçđ░ĐéđŻđżđ╣ đ┐đ╗đ░ĐéĐő.

FPGA Field Programmable Gate Array, đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝Đőđ╣ đ╝đ░ĐüĐüđŞđ▓ đ╗đżđ│đŞĐçđÁĐüđ║đŞĐů đ▓đÁđŻĐéđŞđ╗đÁđ╣. đĄĐâđŻđ║ĐćđŞđżđŻđ░đ╗ĐîđŻđż FPGA Đüđ╗đżđÂđŻđÁđÁ CLPD, đŞ đżđ▒đ╗đ░đ┤đ░đÁĐé ĐŹđŻđÁĐÇđ│đżđĚđ░đ▓đŞĐüđŞđ╝đżđ╣ đ┐đ░đ╝ĐĆĐéĐîĐÄ đ┤đ╗ĐĆ ĐůĐÇđ░đŻđÁđŻđŞĐĆ đ║đżđŻĐäđŞđ│ĐâĐÇđ░ĐćđŞđŞ. đčđżĐŹĐéđżđ╝Đâ FPGA, đ▓ đżĐéđ╗đŞĐçđŞđÁ đżĐé CPLD, đŻĐâđÂđ┤đ░ĐÄĐéĐüĐĆ đ┐ĐÇđŞ đ▓đ║đ╗ĐÄĐçđÁđŻđŞđŞ đ┐đŞĐéđ░đŻđŞĐĆ đ▓ đŞĐüĐéđżĐçđŻđŞđ║đÁ đ┤đ░đŻđŻĐőĐů đ┤đ╗ĐĆ đĚđ░đ│ĐÇĐâđĚđ║đŞ đ║đżđŻĐäđŞđ│ĐâĐÇđ░ĐćđŞđŞ. đ×đ▒ĐőĐçđŻđż ĐŹĐéđż đ▓đŻđÁĐłđŻĐĆĐĆ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░ đ┐đżĐüđ╗đÁđ┤đżđ▓đ░ĐéđÁđ╗ĐîđŻđżđ╣ đ┐đ░đ╝ĐĆĐéđŞ FLASH (đŞđŻđżđ│đ┤đ░ ĐŹĐéđż đ╝đżđÂđÁĐé đ▒ĐőĐéĐî đŞ đ╝đŞđ║ĐÇđżđ║đżđŻĐéĐÇđżđ╗đ╗đÁĐÇ [2]).

FSL Fast Simplex Link, đżđ┤đŻđżđŻđ░đ┐ĐÇđ░đ▓đ╗đÁđŻđŻđ░ĐĆ ĐłđŞđŻđ░ Đüđ▓ĐĆđĚđŞ ĐéđŞđ┐đ░ ĐéđżĐçđ║đ░-ĐéđżĐçđ║đ░, đŞĐüđ┐đżđ╗ĐîđĚĐâđÁđ╝đ░ĐĆ đ┤đ╗ĐĆ đ▒ĐőĐüĐéĐÇđżđ│đż đżđ▒đ╝đÁđŻđ░ đ┤đ░đŻđŻĐőđ╝đŞ đ╝đÁđÂđ┤Đâ đ┤đ▓Đâđ╝ĐĆ ĐŹđ╗đÁđ╝đÁđŻĐéđ░đ╝đŞ đ┤đŞđĚđ░đ╣đŻđ░ FPGA.

FSM Finite State Machine, đ░đ▓Đéđżđ╝đ░Đé đ║đżđŻđÁĐçđŻĐőĐů ĐüđżĐüĐéđżĐĆđŻđŞđ╣, đ┐ĐÇđŞđŻĐćđŞđ┐ đżđ┐đŞĐüđ░đŻđŞĐĆ đ░đ╗đ│đżĐÇđŞĐéđ╝đżđ▓.

Function Generator Đéđ░đ║ đŻđ░đĚĐőđ▓đ░đÁđ╝đ░ĐĆ Đéđ░đ▒đ╗đŞĐçđŻđ░ĐĆ ĐÇđÁđ░đ╗đŞđĚđ░ĐćđŞĐĆ đ╗đżđ│đŞđ║đŞ (look-up-table), Đü N-đ▓Đůđżđ┤đ░đ╝đŞ đŞ đżđ┤đŻđŞđ╝ đ▓ĐőĐůđżđ┤đżđ╝. đťđżđÂđÁĐé ĐÇđÁđ░đ╗đŞđĚđżđ▓đ░ĐéĐî đ╗ĐÄđ▒ĐâĐÄ đ╗đżđ│đŞĐçđÁĐüđ║ĐâĐÄ ĐäĐâđŻđ║ĐćđŞĐÄ đ┤đ╗ĐĆ ĐŹĐéđŞĐů N-đ▓Đůđżđ┤đżđ▓. N đ╝đżđÂđÁĐé đ▒ĐőĐéĐî đ▓ đ┤đŞđ░đ┐đ░đĚđżđŻđÁ đ╝đÁđÂđ┤Đâ 2 đŞ 6, đŻđ░đŞđ▒đżđ╗đÁđÁ đ┐đżđ┐Đâđ╗ĐĆĐÇđŻĐő 4-đ▓Đůđżđ┤đżđ▓ĐőđÁ đ│đÁđŻđÁĐÇđ░ĐéđżĐÇĐő ĐäĐâđŻđ║ĐćđŞđ╣.

GAL Generic Array Logic. đóđÁĐÇđ╝đŞđŻ đ║đżđ╝đ┐đ░đŻđŞđŞ Lattice đ┤đ╗ĐĆ đ▓đ░ĐÇđŞđ░ĐćđŞđŞ đ▓đÁđŻĐéđŞđ╗ĐĆ PAL. đíđ░đ╝Đőđ╣ đ╝đ░đ╗đÁđŻĐîđ║đŞđ╣ đ╗đżđ│đŞĐçđÁĐüđ║đŞđ╣ ĐŹđ╗đÁđ╝đÁđŻĐé Đü đŻđÁĐüđ║đżđ╗Đîđ║đŞđ╝đŞ đ▓Đůđżđ┤đ░đ╝đŞ đŞ đżđ┤đŻđŞđ╝ đ▓ĐőĐůđżđ┤đżđ╝. đĺĐőĐůđżđ┤ đ▓đÁđŻĐéđŞđ╗ĐĆ AND đŻđ░Đůđżđ┤đŞĐéĐüĐĆ đ▓ ĐüđżĐüĐéđżĐĆđŻđŞđŞ đ╗đżđ│. 1, đ║đżđ│đ┤đ░ đŻđ░ đ▓ĐüđÁĐů đÁđ│đż đ▓Đůđżđ┤đ░Đů đ╗đżđ│. 1. đĺĐőĐůđżđ┤ đ▓đÁđŻĐéđŞđ╗ĐĆ OR đŻđ░Đůđżđ┤đŞĐéĐüĐĆ đ▓ đ╗đżđ│. 1, đ║đżđ│đ┤đ░ đŻđ░ đ╗ĐÄđ▒đżđ╝ đŞđĚ đÁđ│đż đ▓Đůđżđ┤đÁ đ╗đżđ│. 1. 2-đ▓Đůđżđ┤đżđ▓Đőđ╣ đ▓đÁđŻĐéđŞđ╗Đî NAND đŞĐüđ┐đżđ╗ĐîđĚĐâđÁĐéĐüĐĆ đ║đ░đ║ đÁđ┤đŞđŻđŞĐćđ░ đŞđĚđ╝đÁĐÇđÁđŻđŞĐĆ Đüđ╗đżđÂđŻđżĐüĐéđŞ đ╝đ░ĐüĐüđŞđ▓đ░ đ▓đÁđŻĐéđŞđ╗đÁđ╣.

Gate Array ASIC, đ│đ┤đÁ ĐéĐÇđ░đŻđĚđŞĐüĐéđżĐÇĐő đĚđ░ĐÇđ░đŻđÁđÁ đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻĐő, đŞ đŻđ░ĐüĐéĐÇđ░đŞđ▓đ░đÁĐéĐüĐĆ Đéđżđ╗Đîđ║đż đ╝đ░Đüđ║đ░ đ▓đŻĐâĐéĐÇđÁđŻđŻđŞĐů ĐüđżđÁđ┤đŞđŻđÁđŻđŞđ╣, ĐçĐéđżđ▒Đő đ▒Đőđ╗đż ĐÇđÁđ░đ╗đŞđĚđżđ▓đ░đŻđż đŞđŻđ┤đŞđ▓đŞđ┤Đâđ░đ╗ĐîđŻđżđÁ đ┐ĐÇđŞđ╗đżđÂđÁđŻđŞđÁ.

GCK, GCK2 Global Clock, đżđ▒Đëđ░ĐĆ Đéđ░đ║Đéđżđ▓đ░ĐĆ Đçđ░ĐüĐéđżĐéđ░ đ┤đ╗ĐĆ đ║ĐÇđŞĐüĐéđ░đ╗đ╗đ░ CPLD.

GND ground, đĚđÁđ╝đ╗ĐĆ, đżđ▒ĐëđŞđ╣ đ┐ĐÇđżđ▓đżđ┤ đ┤đ╗ĐĆ đ┐đŞĐéđ░đŻđŞĐĆ đŞ ĐüđŞđ│đŻđ░đ╗đżđ▓.

GTL Gunning Transceiver Logic. đĺĐőĐüđżđ║đżĐüđ║đżĐÇđżĐüĐéđŻđżđ╣, đ╝đ░đ╗đż đ┐đżĐéĐÇđÁđ▒đ╗ĐĆĐÄĐëđŞđ╣ ĐŹđŻđÁĐÇđ│đŞĐÄ ĐüĐéđ░đŻđ┤đ░ĐÇĐé đ▓đŻĐâĐéĐÇđÁđŻđŻđÁđ╣ ĐÇđÁđ░đ╗đŞđĚđ░ĐćđŞđŞ đ║ĐÇđŞĐüĐéđ░đ╗đ╗đ░.

GTLP Gunning Transceiver Logic Plus.

HDL Hardware Description Language, ĐĆđĚĐőđ║ đżđ┐đŞĐüđ░đŻđŞĐĆ đ╗đżđ│đŞđ║đŞ đÂđÁđ╗đÁđĚđ░. đŁđ░đŞđ▒đżđ╗đÁđÁ đ┐đżđ┐Đâđ╗ĐĆĐÇđŻĐő HDL-ĐĆđĚĐőđ║đŞ VHDL đŞ Verilog.

HEX Hexadecimal, ĐäđżĐÇđ╝đ░ đ┐ĐÇđÁđ┤ĐüĐéđ░đ▓đ╗đÁđŻđŞĐĆ đ┤đ░đŻđŻĐőĐů đ▓ ĐłđÁĐüĐéđŻđ░đ┤Đćđ░ĐéđÁĐÇđŞĐçđŻđżđ╝ đ▓đŞđ┤đÁ.

Hierarchical Design đŞđÁĐÇđ░ĐÇĐůđŞĐçđÁĐüđ║đŞđ╣ đ┤đŞđĚđ░đ╣đŻ. đ×đ┐đŞĐüđ░đŻđŞđÁ đ┤đŞđĚđ░đ╣đŻđ░ đŻđ░ đŻđÁĐüđ║đżđ╗Đîđ║đŞĐů Đüđ╗đżĐĆĐů, đ│đ┤đÁ đÁĐüĐéĐî đ┐đÁĐÇđÁĐůđżđ┤ đżĐé Đüđ░đ╝đżđ│đż đ▓đÁĐÇĐůđŻđÁđ│đż Đüđ╗đżĐĆ (đżđ▒đĚđżĐÇ) đ┤đż Đüđ░đ╝đżđ│đż đŻđŞđÂđŻđÁđ│đż (đ┐đżđ┤ĐÇđżđ▒đŻđ░ĐĆ ĐÇđÁđ░đ╗đŞđĚđ░ĐćđŞĐĆ ĐüĐůđÁđ╝Đő). đÉđ╗ĐîĐéđÁĐÇđŻđ░ĐéđŞđ▓đ░: đ┐đ╗đżĐüđ║đŞđ╣ đ┤đŞđĚđ░đ╣đŻ, đ│đ┤đÁ đ▓ĐüđÁ đżđ┐đŞĐüĐőđ▓đ░đÁĐéĐüĐĆ Đü đżđ┤đŞđŻđ░đ║đżđ▓Đőđ╝ ĐâĐÇđżđ▓đŻđÁđ╝ đ┤đÁĐéđ░đ╗đŞđĚđ░ĐćđŞđŞ. đśđŻđ║ĐÇđÁđ╝đÁđŻĐéđ░đ╗ĐîđŻĐőđ╣ đ┤đŞđĚđ░đ╣đŻ đżđĚđŻđ░Đçđ░đÁĐé đ╝đ░đ╗ĐőđÁ đŞđĚđ╝đÁđŻđÁđŻđŞĐĆ đ▓ đ┤đŞđĚđ░đ╣đŻđÁ Đü ĐüđżĐůĐÇđ░đŻđÁđŻđŞđÁđ╝ đżĐüđŻđżđ▓đŻđżđ│đż ĐÇđ░đĚđ╝đÁĐëđÁđŻđŞĐĆ (layout) đŞ đ╝đ░ĐÇĐłĐÇĐâĐéđŞđĚđ░ĐćđŞđŞ (routing).

HSTL High Speed Transceiver Logic.

I/O Inputs/Outputs, đ▓Đůđżđ┤Đő/đ▓ĐőĐůđżđ┤Đő.

IBIS I/O Buffer Information Specification.

IEEE Institute of Electrical and Electronics Engineers, Đüđ┐đÁĐćđŞđ░đ╗ĐîđŻđ░ĐĆ đ│ĐÇĐâđ┐đ┐đ░ ĐÇđ░đĚĐÇđ░đ▒đżĐéđ║đŞ đŞđŻđ┤ĐâĐüĐéĐÇđŞđ░đ╗ĐîđŻĐőĐů ĐüĐéđ░đŻđ┤đ░ĐÇĐéđżđ▓.

Input Hysteresis đ▓Đůđżđ┤đŻđżđ╣ đ│đŞĐüĐéđÁĐÇđÁđĚđŞĐü đ┐đżđĚđ▓đżđ╗ĐĆđÁĐé ĐÇđ░đĚĐÇđ░đ▒đżĐéĐçđŞđ║đ░đ╝ đ╝đŞđŻđŞđ╝đŞđĚđŞĐÇđżđ▓đ░ĐéĐî đ║đżđ╗đŞĐçđÁĐüĐéđ▓đż đ▓đŻđÁĐłđŻđŞĐů đ║đżđ╝đ┐đżđŻđÁđŻĐéđżđ▓ đ╗đŞđ▒đż đ┤đ╗ĐĆ đŞĐüđ┐đżđ╗ĐîđĚđżđ▓đ░đŻđŞĐĆ đ▓Đůđżđ┤đ░ đ┤đ╗ĐĆ ĐüđżđĚđ┤đ░đŻđŞĐĆ đ┐ĐÇđżĐüĐéđżđ│đż đŞĐüĐéđżĐçđŻđŞđ║đ░ Đéđ░đ║Đéđżđ▓, đ╗đŞđ▒đż đ┤đ╗ĐĆ ĐüđŻđŞđÂđÁđŻđŞĐĆ đŻđÁđżđ▒Đůđżđ┤đŞđ╝đżĐüĐéđŞ đ┐ĐÇđŞđ╝đÁđŻđÁđŻđŞĐĆ đ┤đżđ┐đżđ╗đŻđŞĐéđÁđ╗ĐîđŻĐőĐů đ▓Đůđżđ┤đŻĐőĐů đ▒ĐâĐäđÁĐÇđżđ▓ đ┤đ╗ĐĆ đ┐đżđ▓ĐőĐłđÁđŻđŞĐĆ đ║đ░ĐçđÁĐüĐéđ▓đ░ ĐüđŞđ│đŻđ░đ╗đ░ (ĐçĐéđżđ▒Đő Đüđ┤đÁđ╗đ░ĐéĐî đ┐đÁĐÇđÁđ┐đ░đ┤Đő ĐâĐÇđżđ▓đŻđÁđ╣ đ▒đżđ╗đÁđÁ ĐçđÁĐéđ║đŞđ╝đŞ đŞ ĐüđŻđŞđĚđŞĐéĐî ĐłĐâđ╝). đşĐéđ░ ĐäĐâđŻđ║ĐćđŞĐĆ đŞđ╝đÁđÁĐéĐüĐĆ đ▓ CoolRunner-II CPLD (Đéđ░đ║đÂđÁ đżđŻđ░ đ╝đżđÂđÁĐé đŻđ░đĚĐőđ▓đ░ĐéĐîĐüĐĆ ĐéĐÇđŞđ│đ│đÁĐÇđżđ╝ đĘđ╝đŞĐéĐéđ░ đŻđ░ đ▓Đůđżđ┤đÁ).

Interconnect đ╝đÁĐéđ░đ╗đ╗đŞĐçđÁĐüđ║đŞđÁ đ┐ĐÇđżđ▓đżđ┤đŻđŞđ║đŞ đŞ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝ĐőđÁ đ║đ╗ĐÄĐçđŞ, đ║đżĐéđżĐÇĐőđÁ đżĐüĐâĐëđÁĐüĐéđ▓đ╗ĐĆĐÄĐé ĐéĐÇđ░ĐüĐüđŞĐÇđżđ▓đ║Đâ ĐüđŞđ│đŻđ░đ╗đżđ▓ đ╝đÁđÂđ┤Đâ đ╗đżđ│đŞĐçđÁĐüđ║đŞđ╝đŞ đ▒đ╗đżđ║đ░đ╝đŞ đŞ đ╝đÁđÂđ┤Đâ đ╗đżđ│đŞĐçđÁĐüđ║đŞđ╝đŞ đ▒đ╗đżđ║đ░đ╝đŞ đŞ I/O.

IOB Input Output Block, đ▒đ╗đżđ║ đ▓đ▓đżđ┤đ░/đ▓Đőđ▓đżđ┤đ░, Đüđ┐đÁĐćđŞđ░đ╗ĐîđŻĐőđ╣ ĐâđĚđÁđ╗ đ╗đżđ│đŞĐçđÁĐüđ║đŞĐů ĐüĐůđÁđ╝, đ┐đżđĚđ▓đżđ╗ĐĆĐÄĐëđŞđ╣ đŻđ░ĐüĐéĐÇđ░đŞđ▓đ░ĐéĐî ĐÇđÁđÂđŞđ╝ ĐÇđ░đ▒đżĐéĐő đ▓đŻđÁĐłđŻđŞĐů đ▓Đőđ▓đżđ┤đżđ▓ đ║ĐÇđŞĐüĐéđ░đ╗đ╗đ░.

ILA Integrated Logic Analyzer, đ▓ĐüĐéĐÇđżđÁđŻđŻĐőđ╣ đ╗đżđ│đŞĐçđÁĐüđ║đŞđ╣ đ░đŻđ░đ╗đŞđĚđ░ĐéđżĐÇ.

IP, IP core Đüđżđ║ĐÇđ░ĐëđÁđŻđŞđÁ IP đżđĚđŻđ░Đçđ░đÁĐé Intellectual Property. đčđżđ┤ ĐŹĐéđŞđ╝ đ┐đżđ┤ĐÇđ░đĚĐâđ╝đÁđ▓đ░ĐÄĐéĐüĐĆ ĐćđŞĐäĐÇđżđ▓ĐőđÁ đ▒đ╗đżđ║đŞ, đĚđ░ĐëđŞĐëđÁđŻđŻĐőđÁ đ║đżđ┐đŞĐÇđ░đ╣Đéđżđ╝ đ║đ░đ║đżđ│đż-Đéđż đ┐ĐÇđżđŞđĚđ▓đżđ┤đŞĐéđÁđ╗ĐĆ (Đçđ░ĐüĐéđż ĐüĐéđżĐÇđżđŻđŻđÁđ│đż đ┐đż đżĐéđŻđżĐłđÁđŻđŞĐÄ đ║ Xilinx). đşĐéđż đ╝đżđÂđÁĐé đ▒ĐőĐéĐî ĐÇđÁđ░đ╗đŞđĚđżđ▓đ░đŻđŻĐőđ╣ đŻđ░ đ╗đżđ│đŞđ║đÁ đ║ĐÇđŞĐüĐéđ░đ╗đ╗đ░ FPGA đ║đ░đ║đżđ╣-đ╗đŞđ▒đż Đüđ╗đżđÂđŻĐőđ╣ đŞđŻĐéđÁĐÇĐäđÁđ╣ĐüđŻĐőđ╣ đ▒đ╗đżđ║ (đŻđ░đ┐ĐÇđŞđ╝đÁĐÇ đ║đżđŻĐéĐÇđżđ╗đ╗đÁĐÇ USB, đ║đżđŻĐéĐÇđżđ╗đ╗đÁĐÇ CAN đŞ Đé. đ┐.), đŞđ╗đŞ đ║đ░đ║đżđÁ-Đéđż đ┐ĐÇđżĐćđÁĐüĐüđżĐÇđŻđżđÁ ĐĆđ┤ĐÇđż (đ┤đ░đÂđÁ ĐüĐéđ░đŻđ┤đ░ĐÇĐéđŻđżđÁ, đŻđ░đ┐ĐÇđŞđ╝đÁĐÇ MCS-51, 8086, PowerPC đŞđ╗đŞ ARM).

IR-drop đ┐đ░đ┤đÁđŻđŞđÁ đŻđ░đ┐ĐÇĐĆđÂđÁđŻđŞĐĆ đŻđ░ ĐćđÁđ┐đŞ. đśđĚ đĺđŞđ║đŞđ┐đÁđ┤đŞđŞ: "đŽđÁđ┐đŞ đ┐đÁĐÇđÁđ┤đ░ĐçđŞ đ┐đŞĐéđ░đŻđŞĐĆ đ┐đżđ┤đ║đ╗ĐÄĐçđ░ĐÄĐé đŻđ░đ┐ĐÇĐĆđÂđÁđŻđŞđÁ đ┐đŞĐéđ░đŻđŞĐĆ đŞ đĚđÁđ╝đ╗ĐÄ Đü đŻđżđÂđÁđ║ đ║đżĐÇđ┐ĐâĐüđ░ đ║ĐÇđŞĐüĐéđ░đ╗đ╗đ░ đ║đż đ▓ĐüđÁđ╝ đ▓đŻĐâĐéĐÇđÁđŻđŻđŞđ╝ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đ░đ╝. đí Đâđ╝đÁđŻĐîĐłđÁđŻđŞđÁđ╝ ĐÇđ░đĚđ╝đÁĐÇđżđ▓ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đ░, ĐâĐüđ║đżĐÇđÁđŻđŞđÁđ╝ đ┐đÁĐÇđÁđ║đ╗ĐÄĐçđÁđŻđŞđ╣ đŞ Đâđ▓đÁđ╗đŞĐçđÁđŻđŞđÁđ╝ đ┐đżĐéĐÇđÁđ▒đ╗ĐĆđÁđ╝đżđ╣ đ╝đżĐëđŻđżĐüĐéđŞ đ▓ ĐüĐâđ▒đ╝đŞđ║ĐÇđżđŻđŻĐőĐů ĐéđÁĐůđŻđżđ╗đżđ│đŞĐĆĐů đ┐ĐÇđŞđ▓đżđ┤ĐĆĐé đ║ đ▒đżđ╗ĐîĐłđŞđ╝ đ┐Đâđ╗ĐîĐüđŞĐÇĐâĐÄĐëđŞđ╝ Đéđżđ║đ░đ╝ đ┐đÁĐÇđÁđ║đ╗ĐÄĐçđÁđŻđŞĐĆ đ▓ ĐćđÁđ┐ĐĆĐů đ┐đŞĐéđ░đŻđŞĐĆ đŞ đĚđÁđ╝đ╗đŞ, ĐçĐéđż ĐüđŻđŞđÂđ░đÁĐé đ┐ĐÇđżđŞđĚđ▓đżđ┤đŞĐéđÁđ╗ĐîđŻđżĐüĐéĐî đŞ đŻđ░đ┤đÁđÂđŻđżĐüĐéĐî. đŁđ░đ┤đÁđÂđŻđ░ĐĆ ĐćđÁđ┐Đî ĐÇđ░Đüđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđŞĐĆ đ┐đŞĐéđ░đŻđŞĐĆ - đ║ĐÇđŞĐéđŞĐçđÁĐüđ║đŞđ╣ đ╝đżđ╝đÁđŻĐé đ┤đ╗ĐĆ ĐâĐüĐéđżđ╣ĐçđŞđ▓đżđ╣ ĐÇđ░đ▒đżĐéĐő ĐüĐůđÁđ╝ đŻđ░ ĐçđŞđ┐đÁ, đ┐đżĐŹĐéđżđ╝Đâ đ▓đÁĐÇđŞĐäđŞđ║đ░ĐćđŞĐĆ ĐćđÁđ╗đżĐüĐéđŻđżĐüĐéđŞ đ┐đŞĐéđ░đŻđŞĐĆ đżĐçđÁđŻĐî đ▓đ░đÂđŻđż đ┤đ╗ĐĆ đ▓ĐőĐüđżđ║đżđ┐ĐÇđżđŞđĚđ▓đżđ┤đŞĐéđÁđ╗ĐîđŻĐőĐů ĐÇđ░đĚĐÇđ░đ▒đżĐéđżđ║. đśđĚ-đĚđ░ Đüđżđ┐ĐÇđżĐéđŞđ▓đ╗đÁđŻđŞĐĆ đ▓đŻĐâĐéĐÇđÁđŻđŻđŞĐů ĐüđżđÁđ┤đŞđŻđÁđŻđŞđ╣, ĐüđżĐüĐéđ░đ▓đ╗ĐĆĐÄĐëđŞĐů ĐćđÁđ┐Đî, ĐŹĐéđŞ đ┐đ░đ┤đÁđŻđŞĐĆ đŻđ░đ┐ĐÇĐĆđÂđÁđŻđŞđ╣ ĐÇđ░Đüđ┐ĐÇđżĐüĐéĐÇđ░đŻĐĆĐÄĐéĐüĐĆ đ┐đż ĐćđÁđ┐ĐĆđ╝ đ║đ░đ║ ĐüđŞđ│đŻđ░đ╗Đő, đŞ ĐŹĐéđż đŻđ░đĚĐőđ▓đ░ĐÄĐé IR-drop. đąđżĐéĐĆ Đüđżđ┐ĐÇđżĐéđŞđ▓đ╗đÁđŻđŞđÁ đ▓Đőđ▓đżđ┤đżđ▓ đ║đżĐÇđ┐ĐâĐüđ░ đ╝đ░đ╗đÁđŻĐîđ║đżđÁ, đŻđż đ▓đ╝đÁĐüĐéđÁ Đü đ▒đżđ╗ĐîĐłđŞđ╝đŞ Đéđżđ║đ░đ╝đŞ đĚđÁđ╝đ╗đŞ đŞ đŞđŻđ┤Đâđ║ĐéđŞđ▓đŻđżĐüĐéĐîĐÄ đ▓Đőđ▓đżđ┤đżđ▓ ĐŹĐéđż đ┐ĐÇđŞđ▓đżđ┤đŞĐé đ║ đĚđŻđ░ĐçđŞĐéđÁđ╗ĐîđŻĐőđ╝ đ┐đ░đ┤đÁđŻđŞĐĆđ╝ đŻđ░đ┐ĐÇĐĆđÂđÁđŻđŞĐĆ, đŞĐüđ║đ░đÂđ░ĐÄĐëđŞđ╝ đ▓Đůđżđ┤đŻĐőđÁ đŞ đ▓ĐőĐůđżđ┤đŻĐőđÁ ĐüđŞđ│đŻđ░đ╗Đő. đşĐéđż đ┐đ░đ┤đÁđŻđŞđÁ đŻđ░đ┐ĐÇĐĆđÂđÁđŻđŞĐĆ đŻđ░đĚĐőđ▓đ░ĐÄĐé di/dt-drop. đóđ░đ║đŞđ╝ đżđ▒ĐÇđ░đĚđżđ╝ đŻđ░đ┐ĐÇĐĆđÂđÁđŻđŞđÁ, đ║đżĐéđżĐÇđżđÁ đ┐đżđ╗ĐâĐçđŞĐé ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đż, đ▒Đâđ┤đÁĐé ĐÇđ░đ▓đŻđż đŻđ░đ┐ĐÇĐĆđÂđÁđŻđŞĐÄ đ┐đŞĐéđ░đŻđŞĐĆ đ╝đŞđŻĐâĐü IR-drop đŞ di/dt-drop.".

IRL Internet Reconfigurable Logic, ĐéđÁĐůđŻđżđ╗đżđ│đŞĐĆ, đ┐đżđĚđ▓đżđ╗ĐĆĐÄĐëđ░ĐĆ đ┤đŞĐüĐéđ░đŻĐćđŞđżđŻđŻđż (ĐçđÁĐÇđÁđĚ ĐüđÁĐéđÁđ▓đżđÁ ĐüđżđÁđ┤đŞđŻđÁđŻđŞđÁ đśđŻĐéđÁĐÇđŻđÁĐé) đżđ▒đŻđżđ▓đ╗ĐĆĐéĐî đ┐ĐÇđżĐłđŞđ▓đ║Đâ FPGA.

ISE Integrated Software Environment, đżđ▒ĐëđÁđÁ đŻđ░đĚđ▓đ░đŻđŞđÁ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŻđżđ│đż đżđ▒đÁĐüđ┐đÁĐçđÁđŻđŞĐĆ Xilinx đ┤đ╗ĐĆ ĐÇđ░đĚĐÇđ░đ▒đżĐéđ║đŞ đ║đżđŻĐäđŞđ│ĐâĐÇđ░ĐćđŞđżđŻđŻĐőĐů đ┤đ░đŻđŻĐőĐů đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝ đ╗đżđ│đŞđ║đŞ.

ISO9000 đŞđŻĐéđÁĐÇđŻđ░ĐćđŞđżđŻđ░đ╗ĐîđŻĐőđ╣ ĐüĐéđ░đŻđ┤đ░ĐÇĐé đ║đ░ĐçđÁĐüĐéđ▓đ░. đÜđżđ╝đ┐đ░đŻđŞĐĆ Xilinx ĐüđÁĐÇĐéđŞĐäđŞĐćđŞĐÇđżđ▓đ░đŻđ░ đ┐đż ĐüĐéđ░đŻđ┤đ░ĐÇĐéđ░đ╝ ISO9001 đŞ ISO9002.

ISP In-System Programing, ĐäĐâđŻđ║ĐćđŞĐĆ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇđżđ▓đ░đŻđŞĐĆ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝Đő đ╗đżđ│đŞđ║đŞ, đ║đżđ│đ┤đ░ đżđŻđ░ ĐâđÂđÁ ĐâĐüĐéđ░đŻđżđ▓đ╗đÁđŻđ░ đ▓ đ│đżĐéđżđ▓đżđ╝ đŞđĚđ┤đÁđ╗đŞđŞ. đ×đ▒ĐőĐçđŻđż đ▓ đ║đ░ĐçđÁĐüĐéđ▓đÁ đŞđŻĐéđÁĐÇĐäđÁđ╣Đüđ░ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇđżđ▓đ░đŻđŞĐĆ đŞĐüđ┐đżđ╗ĐîđĚĐâđÁĐéĐüĐĆ JTAG.

JEDEC Joint Electron Device Engineering Council.

JTAG Joint Test Advisory Group. đ×đ▒ĐőĐçđŻđż ĐŹĐéđ░ đ░đ▒đ▒ĐÇđÁđ▓đŞđ░ĐéĐâĐÇđ░ đżđ▒đżđĚđŻđ░Đçđ░đÁĐé đ░đ┐đ┐đ░ĐÇđ░ĐéđŻĐőđ╣ đŞđŻĐéđÁĐÇĐäđÁđ╣Đü đ┤đ╗ĐĆ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇđżđ▓đ░đŻđŞĐĆ đŞ ĐéđÁĐüĐéđŞĐÇđżđ▓đ░đŻđŞĐĆ đ╗đżđ│đŞĐçđÁĐüđ║đŞĐů ĐüĐůđÁđ╝. Older name for IEEE 1149.1 Boundary Scan, a method to test PC boards and ICs.

KEEPER, KPR ĐäđżĐÇđ╝đ░đ╗ĐîđŻđżđÁ đżđ┐đŞĐüđ░đŻđŞđÁ (đ░ĐéĐÇđŞđ▒ĐâĐé) đŻđ░ĐüĐéĐÇđżđ╣đ║đŞ đ▓Đőđ▓đżđ┤đ░ đŞđ╗đŞ đ▓đŻĐâĐéĐÇđÁđŻđŻđÁđ│đż ĐüđŞđ│đŻđ░đ╗đ░, đ║đżĐéđżĐÇĐőđ╣ ĐůĐÇđ░đŻđŞĐé Đüđ▓đżđÁ đ┐đÁĐÇđ▓đżđŻđ░Đçđ░đ╗ĐîđŻđżđÁ ĐüđżĐüĐéđżĐĆđŻđŞđÁ.

keeper latch đĚđ░ĐëđÁđ╗đ║đ░ (ĐéĐÇđŞđ│đ│đÁĐÇ), đ┐ĐÇđÁđ┤đŻđ░đĚđŻđ░ĐçđÁđŻđŻđ░ĐĆ đ┤đ╗ĐĆ ĐůĐÇđ░đŻđÁđŻđŞĐĆ đŞđŻĐäđżĐÇđ╝đ░ĐćđŞđŞ đż ĐüđżĐüĐéđżĐĆđŻđŞđŞ ĐüđŞđ│đŻđ░đ╗đ░ (đ▓Đőđ▓đżđ┤đ░).

LC Logic Cell, đ╗đżđ│đŞĐçđÁĐüđ║đ░ĐĆ ĐĆĐçđÁđ╣đ║đ░.

LEC Logic Equivalence Checker, ĐüđŞĐüĐéđÁđ╝đ░ đ┐ĐÇđżđ▓đÁĐÇđ║đŞ đ╗đżđ│đŞđ║đŞ đŻđ░ ĐŹđ║đ▓đŞđ▓đ░đ╗đÁđŻĐéđŻđżĐüĐéĐî.

LHS Left-Hand Side đŻđÁđ║đ░ĐĆ ĐüĐâĐëđŻđżĐüĐéĐî (đżđ▒ĐőĐçđŻđż ĐŹĐéđż đ┐đÁĐÇđÁđ╝đÁđŻđŻđ░ĐĆ, ĐÇđÁđ│đŞĐüĐéĐÇ), đ┐đżĐĆđ▓đ╗ĐĆĐÄĐëđ░ĐĆĐüĐĆ đ▓ đ╗đÁđ▓đżđ╣ Đçđ░ĐüĐéđŞ đ▓ĐőĐÇđ░đÂđÁđŻđŞĐĆ đ┐ĐÇđŞĐüđ▓đ░đŞđ▓đ░đŻđŞĐĆ. đíđ╝. Đéđ░đ║đÂđÁ RHS.

LMG Logic Modeling Group.

LogiBLOX đżđ▒ĐőĐçđŻđż đŻđ░đĚĐőđ▓đ░đÁĐéĐüĐĆ X-Blox. đĹđŞđ▒đ╗đŞđżĐéđÁđ║đ░ đ╗đżđ│đŞĐçđÁĐüđ║đŞĐů đ╝đżđ┤Đâđ╗đÁđ╣, Đçđ░ĐüĐéđż Đü đ┐đ░ĐÇđ░đ╝đÁĐéĐÇđ░đ╝đŞ, đżđ┐ĐÇđÁđ┤đÁđ╗ĐĆđÁđ╝ĐőĐů đ┐đżđ╗ĐîđĚđżđ▓đ░ĐéđÁđ╗đÁđ╝, đŻđ░đ┐đżđ┤đżđ▒đŞđÁ ĐłđŞĐÇđŞđŻĐő đ┤đ░đŻđŻĐőĐů. đ×ĐçđÁđŻĐî đ┐đżđ┤đżđ▒đŻđ░ LPM.

Logic Cell đ╗đżđ│đŞĐçđÁĐüđ║đ░ĐĆ ĐĆĐçđÁđ╣đ║đ░, đÁđ┤đŞđŻđŞĐćđ░ đŞđĚđ╝đÁĐÇđÁđŻđŞĐĆ đ┐đ╗đżĐéđŻđżĐüĐéđŞ FPGA. đ×đ┤đŻđ░ đ╗đżđ│đŞĐçđÁĐüđ║đ░ĐĆ ĐĆĐçđÁđ╣đ║đ░ ĐŹĐéđż đżđ┤đŞđŻ 4-đ▓Đůđżđ┤đżđ▓đ░ĐĆ Đéđ░đ▒đ╗đŞĐćđ░ ĐäĐâđŻđ║ĐćđŞđ╣ (look-up table) đ┐đ╗ĐÄĐü đżđ┤đŞđŻ ĐéĐÇđŞđ│đ│đÁĐÇ.

LPM Library of Parameterized Modules, đ▒đŞđ▒đ╗đŞđżĐéđÁđ║đ░ đ╗đżđ│đŞĐçđÁĐüđ║đŞĐů đ╝đżđ┤Đâđ╗đÁđ╣, Đçđ░ĐüĐéđż Đü đ┐đ░ĐÇđ░đ╝đÁĐéĐÇđ░đ╝đŞ, đżđ┐ĐÇđÁđ┤đÁđ╗ĐĆđÁđ╝ĐőĐů đ┐đżđ╗ĐîđĚđżđ▓đ░ĐéđÁđ╗đÁđ╝, đŻđ░đ┐đżđ┤đżđ▒đŞđÁ ĐłđŞĐÇđŞđŻĐő đ┤đ░đŻđŻĐőĐů. đ×ĐçđÁđŻĐî đ┐đżđ┤đżđ▒đŻđ░ LogiBlox.

LSB Least Significant Bit, Đüđ░đ╝Đőđ╣ đ╝đ╗đ░đ┤ĐłđŞđ╣ đĚđŻđ░Đçđ░ĐëđŞđ╣ đ▒đŞĐé. đśđŻđżđ│đ┤đ░ Đéđ░ đÂđÁ Đüđ░đ╝đ░ĐĆ đ░đ▒đ▒ĐÇđÁđ▓đŞđ░ĐéĐâĐÇđ░ đżđ▒đżđĚđŻđ░Đçđ░đÁĐé Đüđ░đ╝Đőđ╣ đ╝đ╗đ░đ┤ĐłđŞđ╣ đĚđŻđ░Đçđ░ĐëđŞđ╣ đ▒đ░đ╣Đé.

LUT Look Up Table, Đéđ░đ▒đ╗đŞĐçđŻđ░ĐĆ ĐäđżĐÇđ╝đ░ đ┐đÁĐÇđÁđ║đżđ┤đŞĐÇđżđ▓đ║đŞ đ┤đ░đŻđŻĐőĐů. đóđ░đ║đÂđÁ đŻđ░đĚĐőđ▓đ░đÁĐéĐüĐĆ đ│đÁđŻđÁĐÇđ░ĐéđżĐÇđżđ╝ ĐäĐâđŻđ║ĐćđŞđ╣ Đü N đ▓Đůđżđ┤đ░đ╝đŞ đŞ đżđ┤đŻđŞđ╝ đ▓ĐőĐůđżđ┤đżđ╝. N đ╝đżđÂđÁĐé đ▒ĐőĐéĐî đ▓ đ┤đŞđ░đ┐đ░đĚđżđŻđÁ đ╝đÁđÂđ┤Đâ 2 đŞ 6, đŻđ░đŞđ▒đżđ╗đÁđÁ đ┐đżđ┐Đâđ╗ĐĆĐÇđŻĐő 4-đ▓Đůđżđ┤đżđ▓ĐőđÁ đ│đÁđŻđÁĐÇđ░ĐéđżĐÇĐő ĐäĐâđŻđ║ĐćđŞđ╣. LUT đŞđŻđżđ│đ┤đ░ đŻđ░đĚĐőđ▓đ░ĐÄĐé Đéđ░đ▒đ╗đŞĐćđÁđ╣ đ┐ĐÇđÁđżđ▒ĐÇđ░đĚđżđ▓đ░đŻđŞĐĆ, ĐŹĐéđż Đéđ░đ▒đ╗đŞĐçđŻĐőđ╣ Đüđ┐đżĐüđżđ▒ ĐÇđÁđ░đ╗đŞđĚđ░ĐćđŞđŞ đ┐ĐÇđżđŞđĚđ▓đżđ╗ĐîđŻđżđ╣ đ╗đżđ│đŞĐçđÁĐüđ║đżđ╣ ĐäĐâđŻđ║ĐćđŞđŞ đŻđ░ X đ▓Đůđżđ┤đżđ▓ đŞ Y đ▓ĐőĐůđżđ┤đżđ▓. đčĐÇđŞđ╝đÁĐÇ ĐéĐÇđ░đ┤đŞĐćđŞđżđŻđŻđżđ│đż ĐŹđ╗đÁđ╝đÁđŻĐéđ░ LUT - đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░ đżđ┤đŻđżđ║ĐÇđ░ĐéđŻđż đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝đżđ╣ đ╗đżđ│đŞđ║đŞ đÜ155đáđĽ3.

LVCMOS Low Voltage Complementary Metal Oxide Semiconductor.

LVDS Low Voltage Differential Signaling.

LVDSEXT Low Voltage Differential Signaling Extension.

LVPECL Low Voltage Positive Emitter Coupled Logic.

LVTTL Low Voltage Transistor to Transistor Logic.

MAC Multiply and Accumulate, đżđ┐đÁĐÇđ░ĐćđŞĐĆ Đâđ╝đŻđżđÂđÁđŻđŞĐĆ Đü đŻđ░đ║đżđ┐đ╗đÁđŻđŞđÁđ╝, ĐłđŞĐÇđżđ║đż đŞĐüđ┐đżđ╗ĐîđĚĐâđÁđ╝đ░ĐĆ đ▓ ĐćđŞĐäĐÇđżđ▓đżđ╣ đżđ▒ĐÇđ░đ▒đżĐéđ║đÁ ĐüđŞđ│đŻđ░đ╗đżđ▓.

Macrocell đ╗đżđ│đŞĐçđÁĐüđ║đ░ĐĆ ĐĆĐçđÁđ╣đ║đ░ đ▓ ĐüĐâđ╝đ╝đÁ ĐÇđÁđĚĐâđ╗ĐîĐéđ░Đéđżđ▓ ĐĆĐçđÁđÁđ║ (sum-of-products) đ▓ CPLD đŞđ╗đŞ PAL/GAL.

Mapping đ┐ĐÇđżĐćđÁĐüĐü đŻđ░đĚđŻđ░ĐçđÁđŻđŞĐĆ đ┐đżĐÇĐćđŞđ╣ đ┤đŞđĚđ░đ╣đŻđ░ đ╗đżđ│đŞđ║đŞ ĐäđŞđĚđŞĐçđÁĐüđ║đŞđ╝ ĐÇđÁĐüĐâĐÇĐüđ░đ╝ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝Đő đ╗đżđ│đŞđ║đŞ (đ▒đ╗đżđ║đ░đ╝ CLB). đí đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░đ╝đŞ FPGA mapping đ▒đżđ╗ĐîĐłđÁ đżđ┐ĐÇđÁđ┤đÁđ╗ĐĆđÁĐéĐüĐĆ đĚđ░đ┐ĐÇđżĐüđ░đ╝đŞ đŞ đ▒đżđ╗đÁđÁ đ▓đ░đÂđŻĐőđ╣ đ┐ĐÇđżĐćđÁĐüĐü đ┐đż ĐüĐÇđ░đ▓đŻđÁđŻđŞĐÄ Đü đ╝đ░ĐüĐüđŞđ▓đ░đ╝đŞ đ▓đÁđŻĐéđŞđ╗đÁđ╣ đ▓ CPLD đŞđ╗đŞ PAL/GAL.

MCS Manipulate Comment Section.

MOSFET Metal Oxide Semiconductor Field Effect Transistors.

MP3 MPEG Layer III Audio Coding, ĐäđżĐÇđ╝đ░Đé ĐüđÂđ░Đéđżđ│đż đ┐ĐÇđÁđ┤ĐüĐéđ░đ▓đ╗đÁđŻđŞĐĆ đĚđ▓Đâđ║đżđ▓đżđ│đż ĐüđŞđ│đŻđ░đ╗đ░.

MPEG Motion Picture Experts Group, ĐüĐéđ░đŻđ┤đ░ĐÇĐé ĐüđÂđ░ĐéđŞĐĆ đŞđĚđżđ▒ĐÇđ░đÂđÁđŻđŞđ╣ đŞ đ▓đŞđ┤đÁđżĐüđŞđ│đŻđ░đ╗đ░.

MSB Most Significant Bit, Đüđ░đ╝Đőđ╣ ĐüĐéđ░ĐÇĐłđŞđ╣ đĚđŻđ░Đçđ░ĐëđŞđ╣ đ▒đŞĐé. đśđŻđżđ│đ┤đ░ Đéđ░ đÂđÁ Đüđ░đ╝đ░ĐĆ đ░đ▒đ▒ĐÇđÁđ▓đŞđ░ĐéĐâĐÇđ░ đżđ▒đżđĚđŻđ░Đçđ░đÁĐé Đüđ░đ╝Đőđ╣ ĐüĐéđ░ĐÇĐłđŞđ╣ đĚđŻđ░Đçđ░ĐëđŞđ╣ đ▒đ░đ╣Đé.

MTBF Mean Time Between Failure, ĐüĐÇđÁđ┤đŻđÁđÁ đ▓ĐÇđÁđ╝ĐĆ đ╝đÁđÂđ┤Đâ đżĐéđ║đ░đĚđ░đ╝đŞ. đíĐéđ░ĐéđŞĐüĐéđŞĐçđÁĐüđ║đŞ đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđŻđżđÁ đ▓ĐÇđÁđ╝ĐĆ ĐÇđ░đ▒đżĐéđżĐüđ┐đżĐüđżđ▒đŻđżĐüĐéđŞ đżđ▒đżĐÇĐâđ┤đżđ▓đ░đŻđŞĐĆ đ╝đÁđÂđ┤Đâ Đüđ╗ĐâĐçđ░ĐĆđ╝đŞ đżĐéđ║đ░đĚđżđ▓. đóđ░đ║đÂđÁ Đüđ╝. FIT.

MUX Multiplexer, đ╝Đâđ╗ĐîĐéđŞđ┐đ╗đÁđ║ĐüđżĐÇ, đ┐đÁĐÇđÁđ║đ╗ĐÄĐçđ░ĐéđÁđ╗Đî.

NAND Not And, đ╗đżđ│đŞĐçđÁĐüđ║đ░ĐĆ đżđ┐đÁĐÇđ░ĐćđŞĐĆ đś-đŁđĽ.

Netlist ĐéđÁđ║ĐüĐéđżđ▓đżđÁ đżđ┐đŞĐüđ░đŻđŞđÁ đ╗đżđ│đŞđ║đŞ đŞ đ▓đŻĐâĐéĐÇđÁđŻđŻđŞĐů ĐüđżđÁđ┤đŞđŻđÁđŻđŞđ╣ đŻđ░ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đÁ. đóđ░đ║đÂđÁ Đüđ╝. XNF đŞ EDIF.

NGC Native Generic Compiler, ĐüĐéđ░đŻđ┤đ░ĐÇĐéđŻĐőđ╣ đżđ▒ĐőĐçđŻĐőđ╣ đ║đżđ╝đ┐đŞđ╗ĐĆĐéđżĐÇ.

NRE Non-Recurring Engineering, ĐéđÁĐÇđ╝đŞđŻ đżđ▒đżđĚđŻđ░Đçđ░ĐÄĐëđŞđ╣ đŻđÁ đ▓đżđĚđ▓ĐÇđ░Đëđ░đÁđ╝ĐőđÁ đĚđ░ĐéĐÇđ░ĐéĐő. đŁđ░Đçđ░đ╗ĐîđŻđ░ĐĆ ĐüĐéđżđŞđ╝đżĐüĐéĐî đ┤đ╗ĐĆ ĐüđżđĚđ┤đ░đŻđŞĐĆ ASIC, đ╝đ░ĐüĐüđŞđ▓đ░ đ╗đżđ│đŞđ║đŞ đŞđ╗đŞ HardWire. đúĐçđŞĐéĐőđ▓đ░đÁĐé đĚđ░ĐéĐÇđ░ĐéĐő đŻđ░ ĐÇđ░đĚđ▓đżđ┤đ║Đâ, ĐüđżđĚđ┤đ░đŻđŞđÁ đ╝đ░Đüđżđ║ đŞ ĐÇđ░đĚĐÇđ░đ▒đżĐéđ║Đâ ĐéđÁĐüĐéđżđ▓. đťđŞđ║ĐÇđżĐüĐůđÁđ╝Đő FPGA đŞ CPLD đŻđÁ ĐéĐÇđÁđ▒ĐâĐÄĐé đĚđ░ĐéĐÇđ░Đé NRE.

OE Output Enable, ĐüđŞđ│đŻđ░đ╗ ĐÇđ░đĚĐÇđÁĐłđÁđŻđŞĐĆ đ▓ĐőĐůđżđ┤đ░.

Optimization đżđ┐ĐéđŞđ╝đŞđĚđ░ĐćđŞĐĆ, đŞđĚđ╝đÁđŻđÁđŻđŞĐĆ đ┤đŞđĚđ░đ╣đŻđ░ Đü ĐćđÁđ╗ĐîĐÄ đ┐đżđ▓ĐőĐłđÁđŻđŞĐĆ đ┐ĐÇđżđŞđĚđ▓đżđ┤đŞĐéđÁđ╗ĐîđŻđżĐüĐéđŞ. đóđ░đ║đÂđÁ Đüđ╝. Synthesis.

OTF On-The-Fly Reconfiguration, đ┐đÁĐÇđÁđ║đżđŻĐäđŞđ│ĐâĐÇđŞĐÇđżđ▓đ░đŻđŞđÁ "đŻđ░ đ╗đÁĐéĐâ". đĄĐâđŻđ║ĐćđŞĐĆ đĚđ░đ┐đŞĐüđŞ đŻđżđ▓đżđ╣ đ║đżđŻĐäđŞđ│ĐâĐÇđ░ĐćđŞđŞ đ▓ ĐÇđ░đ▒đżĐéđ░ĐÄĐëđÁđ╝ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đÁ.

OTP One Time Programmable, đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░ Đü đżđ┤đŻđżđ║ĐÇđ░ĐéđŻđż đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝đżđ╣ đ┐đ░đ╝ĐĆĐéĐîĐÄ. đŁđÁđżđ▒ĐÇđ░ĐéđŞđ╝Đőđ╣ đ╝đÁĐéđżđ┤ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇđżđ▓đ░đŻđŞĐĆ đ╗đżđ│đŞđ║đŞ đŞđ╗đŞ đ┐đ░đ╝ĐĆĐéđŞ. đóđÁĐÇđ╝đŞđŻĐő ĐäĐîĐÄđĚđżđ▓ đŞ đ░đŻĐéđŞĐäĐîĐÄđĚđżđ▓ (fuses, anti-fuses) đŻđÁđ┐đżĐüĐÇđÁđ┤ĐüĐéđ▓đÁđŻđŻđż Đüđ▓ĐĆđĚđ░đŻĐő Đü OTP. đťđŞđ║ĐÇđżĐüĐůđÁđ╝Đő EEPROM đŞ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝Đő CPLD, đżĐüđŻđżđ▓đ░đŻđŻĐőđÁ đŻđ░ EPROM, ĐĆđ▓đ╗ĐĆĐÄĐéĐüĐĆ OTP, đÁĐüđ╗đŞ đżđŻđŞ đŞđ╝đÁĐÄĐé đ┐đ╗đ░ĐüĐéđŞđ║đżđ▓ĐőđÁ đ║đżĐÇđ┐ĐâĐüđ░ đ▒đÁđĚ đżđ║đżĐłđÁđ║ đ┤đ╗ĐĆ Đâđ╗ĐîĐéĐÇđ░ĐäđŞđżđ╗đÁĐéđ░, đ║đżĐéđżĐÇĐőđ╣ đŻĐâđÂđÁđŻ đ┤đ╗ĐĆ ĐüĐéđŞĐÇđ░đŻđŞĐĆ ĐüđżĐůĐÇđ░đŻđÁđŻđŻĐőĐů đ┤đ░đŻđŻĐőĐů đŞđ╗đŞ đ║đżđŻĐäđŞđ│ĐâĐÇđ░ĐćđŞđŞ.

PACE Pinout and Area Constraints Editor, đ│ĐÇđ░ĐäđŞĐçđÁĐüđ║đŞđ╣ ĐÇđÁđ┤đ░đ║ĐéđżĐÇ đ▓ ĐüđŞĐüĐéđÁđ╝đÁ ISE Xilinx, ĐüđżđĚđ┤đ░ĐÄĐëđŞđ╣ đ║đżđŻĐäđŞđ│ĐâĐÇđ░ĐćđŞđżđŻđŻĐâĐÄ đŞđŻĐäđżĐÇđ╝đ░ĐćđŞĐÄ đ┤đ╗ĐĆ đŻđ░ĐüĐéĐÇđżđ╣đ║đŞ ĐéđÁĐůđŻđżđ╗đżđ│đŞĐçđÁĐüđ║đŞĐů đżđ│ĐÇđ░đŻđŞĐçđÁđŻđŞĐĆ đ┤đ╗ĐĆ ĐüđŞđŻĐéđÁđĚđŞĐÇĐâđÁđ╝đżđ╣ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝Đő đ╗đżđ│đŞđ║đŞ. đÜ đŻđŞđ╝ đżĐéđŻđżĐüđŞĐéĐüĐĆ ĐÇđ░đĚđ▓đżđ┤đ║đ░ đ╗đżđ│đŞĐçđÁĐüđ║đŞĐů ĐüđŞđ│đŻđ░đ╗đżđ▓ đ┐đż đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđŻĐőđ╝ đ▓Đőđ▓đżđ┤đ░đ╝ đ║đżĐÇđ┐ĐâĐüđ░, đŻđ░ĐüĐéĐÇđżđ╣đ║đ░ ĐüĐéđ░đŻđ┤đ░ĐÇĐéđ░ ĐâĐÇđżđ▓đŻđÁđ╣ đ╗đżđ│đŞđ║đŞ đ▓Đőđ▓đżđ┤đ░, đżđ│ĐÇđ░đŻđŞĐçđÁđŻđŞĐĆ đŞđŻĐéđÁĐÇđ▓đ░đ╗đżđ▓ đ▓ĐÇđÁđ╝đÁđŻđŞ.

PAL Programmable Array Logic, đ╝đ░ĐüĐüđŞđ▓ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝đżđ╣ đ╗đżđ│đŞđ║đŞ.

Partitioning ĐÇđ░đĚđ┤đÁđ╗đÁđŻđŞđÁ. đöđ╗ĐĆ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝ FPGA ĐŹĐéđżĐé ĐéđÁĐÇđ╝đŞđŻ đżđ▒đżđĚđŻđ░Đçđ░đÁĐé đ┤đÁđ╗đÁđŻđŞđÁ đ╗đżđ│đŞđ║đŞ đŻđ░ ĐüĐâđ▒-ĐäĐâđŻđ║ĐćđŞđŞ, đ║đżĐéđżĐÇĐőđÁ đ╝đżđÂđŻđż đ┐đżĐéđżđ╝ ĐÇđ░đĚđ╝đÁĐüĐéđŞĐéĐî đ▓ đżĐéđ┤đÁđ╗ĐîđŻĐőĐů CLB. đáđ░đĚđ┤đÁđ╗đÁđŻđŞđÁ đ┐ĐÇđÁđ┤ĐłđÁĐüĐéđ▓ĐâđÁĐé ĐÇđ░đĚđ╝đÁĐëđÁđŻđŞĐÄ (placement).

PCB Printed Circuit Board, đ┐đÁĐçđ░ĐéđŻđ░ĐĆ đ┐đ╗đ░Đéđ░ đ┤đ╗ĐĆ đ╝đżđŻĐéđ░đÂđ░ ĐŹđ╗đÁđ║ĐéĐÇđżđŻđŻĐőĐů ĐüĐůđÁđ╝.

PCI Peripheral Component Interconnect, đ┐đżđ┐Đâđ╗ĐĆĐÇđŻđ░ĐĆ ĐłđŞđŻđ░ ĐÇđ░ĐüĐłđŞĐÇđÁđŻđŞĐĆ, đ┐ĐÇđŞđ╝đÁđŻĐĆđÁđ╝đ░ĐĆ đ▓ đ║đżđ╝đ┐ĐîĐÄĐéđÁĐÇđ░Đů PC. đşĐéđż ĐüđŞđŻĐůĐÇđżđŻđŻđ░ĐĆ ĐłđŞđŻđ░, Đůđ░ĐÇđ░đ║ĐéđÁĐÇđŞđĚĐâđÁđ╝đ░ĐĆ đ║đżĐÇđżĐéđ║đŞđ╝ đ┤đŞđ░đ┐đ░đĚđżđŻđżđ╝, đ╗đÁđ│đ║đżđ╣ đŻđ░đ│ĐÇĐâđĚđ║đżđ╣, đ┤đÁĐłđÁđ▓đŞđĚđŻđżđ╣ đŞ đ▓ĐőĐüđżđ║đżđ╣ đ┐ĐÇđżđŞđĚđ▓đżđ┤đŞĐéđÁđ╗ĐîđŻđżĐüĐéĐîĐÄ. 33 đťđôĐć PCI đ╝đżđÂđÁĐé đ┐đżđ┤đ┤đÁĐÇđÂđŞđ▓đ░ĐéĐî đ┐đÁĐÇđÁđ┤đ░ĐçĐâ đ┤đ░đŻđŻĐőĐů Đüđż Đüđ║đżĐÇđżĐüĐéĐîĐÄ đ┤đż 132 đ╝đÁđ│đ░đ▒đ░đ╣Đé đ▓ ĐüđÁđ║ĐâđŻđ┤Đâ ĐçđÁĐÇđÁđĚ 36 đ┐đ░ĐÇđ░đ╗đ╗đÁđ╗ĐîđŻĐőĐů đ╗đŞđŻđŞđ╣ đ┤đ░đŻđŻĐőĐů (đ▓đ║đ╗ĐÄĐçđ░ĐĆ đ║đżđŻĐéĐÇđżđ╗Đî ĐçđÁĐéđŻđżĐüĐéđŞ) đŞ đżđ▒ĐëđÁđÁ Đéđ░đ║ĐéđŞĐÇđżđ▓đ░đŻđŞđÁ. đóđ░đ║đÂđÁ đÁĐüĐéĐî đŻđżđ▓Đőđ╣ ĐüĐéđ░đŻđ┤đ░ĐÇĐé 66 đťđôĐć PCI.

PCMCIA Personal Computer Memory Card International Association, ĐâĐüĐéđ░ĐÇđÁđ▓Đłđ░ĐĆ ĐłđŞđŻđ░ đ┤đ╗ĐĆ đ┐đżđ┤đ║đ╗ĐÄĐçđÁđŻđŞĐĆ đ║ đ║đżđ╝đ┐ĐîĐÄĐéđÁĐÇĐâ đ▓đŻđÁĐłđŻđŞĐů ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓. đśđŻĐéđÁĐÇđÁĐüđŻđ░ ĐłĐâĐéđżĐçđŻđ░ĐĆ ĐÇđ░ĐüĐłđŞĐäĐÇđżđ▓đ║đ░ ĐŹĐéđżđ╣ đ░đ▒đ▒ĐÇđÁđ▓đŞđ░ĐéĐâĐÇĐő: People's Can't Member Idiotic Computers Abbreviations.

PGA Programmable Gate Array, đ╝đ░ĐüĐüđŞđ▓ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝ĐőĐů đ▓đÁđŻĐéđŞđ╗đÁđ╣ đ╗đżđ│đŞđ║đŞ.

Pin-Locking đ▒đ╗đżđ║đŞĐÇđżđ▓đ║đ░ đ▓Đőđ▓đżđ┤đżđ▓. đľđÁĐüĐéđ║đżđÁ đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđŞđÁ đŞ đ┐đżđ┤đ┤đÁĐÇđÂđ║đ░ ĐäĐâđŻđ║ĐćđŞđżđŻđ░đ╗ĐîđŻđżĐüĐéđŞ đŞ ĐéĐÇđÁđ▒đżđ▓đ░đŻđŞđ╣ đ┐đż đŞđŻĐéđÁĐÇđ▓đ░đ╗đ░đ╝ đ▓ĐÇđÁđ╝đÁđŻđŞ đ┤đ╗ĐĆ đ▓Đőđ▓đżđ┤đżđ▓ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝Đő đ╗đżđ│đŞđ║đŞ, đ│đ┤đÁ đ▓đŻĐâĐéĐÇđÁđŻđŻĐĆĐĆ đ╗đżđ│đŞđ║đ░ đ▓ĐüđÁ đÁĐëđÁ ĐÇđ░đĚĐÇđ░đ▒đ░ĐéĐőđ▓đ░đÁĐéĐüĐĆ đŞđ╗đŞ đ╝đżđ┤đŞĐäđŞĐćđŞĐÇĐâđÁĐéĐüĐĆ. Pin-locking ĐüĐéđ░đŻđżđ▓đŞĐéĐüĐĆ đ▓đ░đÂđŻĐőđ╝ Đäđ░đ║ĐéđżĐÇđżđ╝, đ┐đżĐüđ║đżđ╗Đîđ║Đâ ĐÇđ░đĚĐÇđ░đ▒đżĐéđ║đ░ đ┐đÁĐçđ░ĐéđŻđżđ╣ đ┐đ╗đ░ĐéĐő đżđ▒ĐőĐçđŻđż đĚđ░đŻđŞđ╝đ░đÁĐé đ▒đżđ╗ĐîĐłđÁ đ▓ĐÇđÁđ╝đÁđŻđŞ, ĐçđÁđ╝ đ▓ĐÇđÁđ╝ĐĆ ĐÇđÁđ░đ╗đŞđĚđ░ĐćđŞđŞ đ┤đŞđĚđ░đ╣đŻđ░ PLD.

PIP Programmable Interconnect Point, đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝đ░ĐĆ ĐéđżĐçđ║đ░ đ▓đŻĐâĐéĐÇđÁđŻđŻđÁđ│đż ĐüđżđÁđ┤đŞđŻđÁđŻđŞĐĆ. đĺ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░Đů Xilinx FPGA ĐŹĐéđż ĐéđżĐçđ║đ░, đ│đ┤đÁ đ┤đ▓đÁ ĐüđŞđ│đŻđ░đ╗ĐîđŻĐőĐů đ╗đŞđŻđŞđŞ đ╝đżđ│ĐâĐé đ▒ĐőĐéĐî ĐüđżđÁđ┤đŞđŻđÁđŻĐő đ┤ĐÇĐâđ│ Đü đ┤ĐÇĐâđ│đżđ╝, đ║đ░đ║ ĐŹĐéđż đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđż đ║đżđŻĐäđŞđ│ĐâĐÇđ░ĐćđŞđÁđ╣.

PLA Programmable Logic Array, đ╝đ░ĐüĐüđŞđ▓ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝đżđ╣ đ╗đżđ│đŞđ║đŞ. đčđÁĐÇđ▓đ░ĐĆ đŞ đŻđ░đŞđ▒đżđ╗đÁđÁ đ│đŞđ▒đ║đ░ĐĆ ĐäđżĐÇđ╝đ░ ĐÇđÁđ░đ╗đŞđĚđ░ĐćđŞđŞ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝đżđ╣ đ╗đżđ│đŞđ║đŞ Đü đ┤đ▓Đâđ╝ĐĆ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝Đőđ╝đŞ Đüđ╗đżĐĆđ╝đŞ, đ┐ĐÇđÁđ┤đżĐüĐéđ░đ▓đ╗ĐĆĐÄĐëđ░ĐĆ đ╗ĐÄđ▒ĐâĐÄ đ║đżđ╝đ▒đŞđŻđ░ĐćđŞĐÄ đ▓đÁđŻĐéđŞđ╗đÁđ╣ AND đŞ OR, Đü Đüđżđ▓đ╝đÁĐüĐéđŻĐőđ╝ đŞĐüđ┐đżđ╗ĐîđĚđżđ▓đ░đŻđŞđÁđ╝ ĐéđÁĐÇđ╝đżđ▓ AND ĐçđÁĐÇđÁđĚ đŻđÁĐüđ║đżđ╗Đîđ║đż OR. đşĐéđ░ đ░ĐÇĐůđŞĐéđÁđ║ĐéĐâĐÇđ░ ĐÇđÁđ░đ╗đŞđĚđżđ▓đ░đŻđ░ đ▓ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đ░Đů CoolRunner đŞ CoolRunner-II. đčđżđ┤ĐÇđżđ▒đŻđÁđÁ Đüđ╝. [4].

Placement ĐÇđ░đĚđ╝đÁĐëđÁđŻđŞđÁ. đčĐÇđŞđ╝đÁđŻđŞĐéđÁđ╗ĐîđŻđż đ║ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░đ╝ FPGA ĐŹĐéđżĐé ĐéđÁĐÇđ╝đŞđŻ đżđ▒đżđĚđŻđ░Đçđ░đÁĐé đ┐ĐÇđżĐćđÁĐüĐü đŻđ░đĚđŻđ░ĐçđÁđŻđŞđÁ đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđŻĐőĐů đ║ĐâĐüđ║đżđ▓ đ┤đŞđĚđ░đ╣đŻđ░ đŻđ░ đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđŻĐőđÁ đ╝đÁĐüĐéđ░ (đ▒đ╗đżđ║đŞ CLB) đ║ĐÇđŞĐüĐéđ░đ╗đ╗đ░. đ×đ▒ĐőĐçđŻđż đżĐüĐâĐëđÁĐüĐéđ▓đ╗ĐĆđÁĐéĐüĐĆ đ░đ▓Đéđżđ╝đ░ĐéđŞĐçđÁĐüđ║đŞ.

PLB Processor Local Bus, đ╗đżđ║đ░đ╗ĐîđŻđ░ĐĆ đ┐ĐÇđżĐćđÁĐüĐüđżĐÇđŻđ░ĐĆ ĐłđŞđŻđ░.

PLD Programmable Logic Device, đżđ▒đżđ▒ĐëđÁđŻđŻĐőđ╣ ĐéđÁĐÇđ╝đŞđŻ đ┤đ╗ĐĆ đżđ▒đżđĚđŻđ░ĐçđÁđŻđŞĐĆ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝ CPLD đŞ FPGA.

PLL Phase-Locked Loop, đ┐đÁĐéđ╗ĐĆ Đäđ░đĚđżđ▓đżđ╣ đ░đ▓Đéđżđ┐đżđ┤ĐüĐéĐÇđżđ╣đ║đŞ Đçđ░ĐüĐéđżĐéĐő (đĄđÉđčđž). đčĐÇđŞđ╝đÁđŻĐĆđÁĐéĐüĐĆ đ┤đ╗ĐĆ đ│đÁđŻđÁĐÇđ░ĐćđŞđŞ đ┐đżđ▓ĐőĐłđÁđŻđŻĐőĐů Đéđ░đ║Đéđżđ▓ĐőĐů Đçđ░ĐüĐéđżĐé.

PROM Programmable Read Only Memory, đ┐đ░đ╝ĐĆĐéĐî, đ┐ĐÇđÁđ┤đŻđ░đĚđŻđ░ĐçđÁđŻđŻđ░ĐĆ Đéđżđ╗Đîđ║đż đ┤đ╗ĐĆ ĐçĐéđÁđŻđŞĐĆ.

p-term product term, đ╝đŻđżđÂđŞĐéđÁđ╗Đî. đĺ đ║đżđŻĐéđÁđ║ĐüĐéđÁ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝ĐőĐů đ╗đżđ│đŞĐçđÁĐüđ║đŞĐů đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝ đżđĚđŻđ░Đçđ░đÁĐé ĐŹđ╗đÁđ╝đÁđŻĐéđ░ĐÇđŻĐâĐÄ đÁđ┤đŞđŻđŞĐćĐâ đ╗đżđ│đŞđ║đŞ (đ▒đ░đĚđŞĐü), đŞđĚ đ║đżĐéđżĐÇđżđ╣ ĐüĐéĐÇđżĐĆĐéĐüĐĆ đ╗đżđ│đŞĐçđÁĐüđ║đŞđÁ ĐüĐůđÁđ╝Đő đ╗ĐÄđ▒đżđ╣ Đüđ╗đżđÂđŻđżĐüĐéđŞ.

QFP Quad Flat Pack, ĐéđŞđ┐ đ║đżĐÇđ┐ĐâĐüđ░ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝.

QML Qualified Manufacturers Listing, Đüđ┐đŞĐüđżđ║ đ║đ▓đ░đ╗đŞĐäđŞĐćđŞĐÇđżđ▓đ░đŻđŻĐőĐů đ┐ĐÇđżđŞđĚđ▓đżđ┤đŞĐéđÁđ╗đÁđ╣. đóđ░đ║đÂđÁ đ╝đżđÂđÁĐé đżđĚđŻđ░Đçđ░ĐéĐî Qualified Manufacturing Line. đŁđ░đ┐ĐÇđŞđ╝đÁĐÇ, ISO9000.

QPRO QML Performance Reliability of Supply Off the Shelf ASIC.

RAM Random Access Memory, đ┐đ░đ╝ĐĆĐéĐî Đü đ┐ĐÇđżđŞđĚđ▓đżđ╗ĐîđŻĐőđ╝ đ┤đżĐüĐéĐâđ┐đżđ╝ đ║ Đüđżđ┤đÁĐÇđÂđŞđ╝đżđ╝Đâ (đ×đŚđú).

RC Radio Controlled, ĐÇđ░đ┤đŞđżĐâđ┐ĐÇđ░đ▓đ╗đÁđŻđŞđÁ.

RHS Right-Hand Side, đŻđÁđ║đ░ĐĆ ĐüĐâĐëđŻđżĐüĐéĐî, đ┐đżĐĆđ▓đ╗ĐĆĐÄĐëđ░ĐĆĐüĐĆ đ▓ đ┐ĐÇđ░đ▓đżđ╣ Đçđ░ĐüĐéđŞ đ▓ĐőĐÇđ░đÂđÁđŻđŞĐĆ đ┐ĐÇđŞĐüđ▓đ░đŞđ▓đ░đŻđŞĐĆ. đíđ╝. Đéđ░đ║đÂđÁ LHS.

ROM Read Only Memory, đ┐đ░đ╝ĐĆĐéĐî Đéđżđ╗Đîđ║đż đ┤đ╗ĐĆ ĐçĐéđÁđŻđŞĐĆ.

Routing đ┐ĐÇđżđ║đ╗đ░đ┤đ║đ░ ĐüđżđÁđ┤đŞđŻđÁđŻđŞđ╣, đ╝đ░ĐÇĐłĐÇĐâĐéđŞđĚđ░ĐćđŞĐĆ. đĺ đ║đżđŻĐéđÁđ║ĐüĐéđÁ đ▓đŻĐâĐéĐÇđÁđŻđŻđŞĐů ĐüđżđÁđ┤đŞđŻđÁđŻđŞđ╣ đŻđ░ ĐçđŞđ┐đÁ đ╗đżđ│đŞđ║đŞ đżđ▒đżđĚđŻđ░Đçđ░đÁĐé đ▓đŻĐâĐéĐÇđÁđŻđŻđŞđÁ ĐüđżđÁđ┤đŞđŻđÁđŻđŞĐĆ, đŞđ╗đŞ đ┐ĐÇđżĐćđÁĐüĐü ĐüđżđĚđ┤đ░đŻđŞĐĆ đÂđÁđ╗đ░đÁđ╝ĐőĐů ĐüđżđÁđ┤đŞđŻđÁđŻđŞđ╣ đ╗đżđ│đŞĐçđÁĐüđ║đŞĐů ĐĆĐçđÁđÁđ║, ĐçĐéđżđ▒Đő đżđŻđŞ đ▓Đőđ┐đżđ╗đŻĐĆđ╗đŞ đŻĐâđÂđŻĐâĐÄ ĐäĐâđŻđ║ĐćđŞĐÄ. Routing Đüđ╗đÁđ┤ĐâđÁĐé đĚđ░ đżđ┐đÁĐÇđ░ĐćđŞĐĆđ╝đŞ partitioning đŞ placement.

RTL register-transfer level. đĺ ĐÇđ░đĚĐÇđ░đ▒đżĐéđ║đÁ ĐćđŞĐäĐÇđżđ▓ĐőĐů ĐüĐůđÁđ╝ ĐŹĐéđż đżđĚđŻđ░Đçđ░đÁĐé ĐâĐÇđżđ▓đÁđŻĐî đ░đ▒ĐüĐéĐÇđ░đ║ĐćđŞđŞ, đ║đżĐéđżĐÇđ░ĐĆ đ╝đżđ┤đÁđ╗đŞĐÇĐâđÁĐé ĐüđŞđŻĐůĐÇđżđŻđŻĐâĐÄ ĐćđŞĐäĐÇđżđ▓ĐâĐÄ ĐüĐůđÁđ╝Đâ đ▓ ĐéđÁĐÇđ╝đŞđŻđ░Đů đ┐đżĐéđżđ║đ░ ĐćđŞĐäĐÇđżđ▓ĐőĐů ĐüđŞđ│đŻđ░đ╗đżđ▓ (đ┤đ░đŻđŻĐőĐů) đ╝đÁđÂđ┤Đâ đ░đ┐đ┐đ░ĐÇđ░ĐéđŻĐőđ╝đŞ ĐÇđÁđ│đŞĐüĐéĐÇđ░đ╝đŞ, đŞ đ╗đżđ│đŞĐçđÁĐüđ║đŞĐů đżđ┐đÁĐÇđ░ĐćđŞđ╣, đ▓Đőđ┐đżđ╗đŻĐĆđÁđ╝ĐőĐů đŻđ░đ┤ ĐŹĐéđŞđ╝đŞ ĐüđŞđ│đŻđ░đ╗đ░đ╝đŞ.

đÉđ▒ĐüĐéĐÇđ░đ║ĐćđŞĐĆ RTL đŞĐüđ┐đżđ╗ĐîđĚĐâđÁĐéĐüĐĆ đ▓ ĐĆđĚĐőđ║đ░ đżđ┐đŞĐüđ░đŻđŞĐĆ đ░đ┐đ┐đ░ĐÇđ░ĐéĐâĐÇĐő HDL, đŻđ░đ┐đżđ┤đżđ▒đŞđÁ Verilog đŞ VHDL, ĐçĐéđżđ▒Đő ĐüđżđĚđ┤đ░ĐéĐî đ▓ĐőĐüđżđ║đżĐâĐÇđżđ▓đŻđÁđ▓đżđÁ đ┐ĐÇđÁđ┤ĐüĐéđ░đ▓đ╗đÁđŻđŞđÁ ĐüĐůđÁđ╝Đő, đŞđĚ đ║đżĐéđżĐÇđżđ│đż đ╝đżđÂđÁĐé đ▒ĐőĐéĐî đ▓ĐőĐçđŞĐüđ╗đÁđŻđ░ đŻđŞđĚđ║đżĐâĐÇđżđ▓đŻđÁđ▓đ░ĐĆ đ┐ĐÇđÁđ┤ĐüĐéđ░đ▓đ╗đÁđŻđŞđÁ đ▓ đ▓đŞđ┤đÁ đ║đżđŻđ║ĐÇđÁĐéđŻđżđ╣ đ░đ┐đ┐đ░ĐÇđ░ĐéđŻđżđ╣ ĐÇđÁđ░đ╗đŞđĚđ░ĐćđŞđŞ ĐüĐůđÁđ╝Đő đŻđ░ đ║đ░đ║đżđ╝-đ╗đŞđ▒đż ĐçđŞđ┐đÁ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝đżđ╣ đ╗đżđ│đŞđ║đŞ. đáđ░đĚĐÇđ░đ▒đżĐéđ║đ░ đŻđ░ ĐâĐÇđżđ▓đŻđÁ RTL - ĐéđŞđ┐đŞĐçđŻđ░ĐĆ đ┐ĐÇđ░đ║ĐéđŞđ║đ░ Đüđżđ▓ĐÇđÁđ╝đÁđŻđŻđżđ│đż ĐćđŞĐäĐÇđżđ▓đżđ│đż đ┤đŞđĚđ░đ╣đŻđ░.

Schematic đ│ĐÇđ░ĐäđŞĐçđÁĐüđ║đżđÁ đ┐ĐÇđÁđ┤ĐüĐéđ░đ▓đ╗đÁđŻđŞđÁ đ┤đŞđĚđ░đ╣đŻđ░ đ╗đżđ│đŞđ║đŞ đ▓ ĐäđżĐÇđ╝đÁ ĐüđżđÁđ┤đŞđŻđÁđŻđŻĐőĐů đ┤ĐÇĐâđ│ Đü đ┤ĐÇĐâđ│đżđ╝ đ╗đżđ│đŞĐçđÁĐüđ║đŞĐů ĐŹđ╗đÁđ╝đÁđŻĐéđżđ▓, ĐéĐÇđŞđ│đ│đÁĐÇđżđ▓ đŞ đ▒đżđ╗đÁđÁ đ║ĐÇĐâđ┐đŻĐőĐů đ▒đ╗đżđ║đżđ▓. đíĐéđ░ĐÇđ░ĐĆ đŞ đ▒đżđ╗đÁđÁ đŞđŻĐéĐâđŞĐéđŞđ▓đŻđż đ┐đżđŻĐĆĐéđŻđ░ĐĆ đ░đ╗ĐîĐéđÁĐÇđŻđ░ĐéđŞđ▓đ░ đ┤đ╗ĐĆ ĐüĐéđ░đŻđżđ▓ĐĆĐëđÁđ╣ĐüĐĆ đ▒đżđ╗đÁđÁ đ┐đżđ┐Đâđ╗ĐĆĐÇđŻđżđ╣ ĐüđŞĐüĐéđÁđ╝Đő ĐÇđ░đĚĐÇđ░đ▒đżĐéđ║đŞ đ╗đżđ│đŞđ║đŞ, đżĐüđŻđżđ▓đ░đŻđŻđżđ╣ đŻđ░ đ▓ĐőĐÇđ░đÂđÁđŻđŞĐĆĐů đŞđ╗đŞ đŻđ░ ĐĆđĚĐőđ║đÁ đżđ┐đŞĐüđ░đŻđŞĐĆ đ▓ĐőĐüđżđ║đżđ│đż ĐâĐÇđżđ▓đŻĐĆ.

SelectRAM ĐéđÁĐÇđ╝đŞđŻ Xilinx đ┤đ╗ĐĆ đ╝đ░đ╗đÁđŻĐîđ║đżđ╣ RAM (đżđ▒ĐőĐçđŻđż 16 đ▒đŞĐé), ĐÇđÁđ░đ╗đŞđĚđżđ▓đ░đŻđŻđżđ╣ đ▓ LUT.

SET Single-Edge Triggering, Đéđ░đ║ĐéđŞĐÇđżđ▓đ░đŻđŞđÁ đ┐đż đżđ┤đŻđżđ╝Đâ đ┐đÁĐÇđÁđ┐đ░đ┤Đâ Đéđ░đ║Đéđżđ▓đżđ╣ Đçđ░ĐüĐéđżĐéĐő. đíđ╝. Đéđ░đ║đÂđÁ DET.

Simulation ĐüđŞđ╝Đâđ╗ĐĆĐćđŞĐĆ, đ║đżđ╝đ┐ĐîĐÄĐéđÁĐÇđŻđżđÁ đ╝đżđ┤đÁđ╗đŞĐÇđżđ▓đ░đŻđŞđÁ đ╗đżđ│đŞđ║đŞ đŞ (đŞđŻđżđ│đ┤đ░) đ┐đżđ▓đÁđ┤đÁđŻđŞĐĆ đ▓ đŞđŻĐéđÁĐÇđ▓đ░đ╗đ░Đů đ▓ĐÇđÁđ╝đÁđŻđŞ đ╗đżđ│đŞđ║đŞ đ┐ĐâĐéđÁđ╝ đ┐đżđ┤đ░ĐçđŞ đŻđ░ đÁĐĹ đ▓Đůđżđ┤Đő đĚđ░đ┤đ░đŻđŻĐőĐů ĐüđŞđ│đŻđ░đ╗đżđ▓ (stimuli đŞđ╗đŞ đ▓đÁđ║ĐéđżĐÇĐő).

SoC System on Chip, ĐüđŞĐüĐéđÁđ╝đ░ đŻđ░ đżđ┤đŻđżđ╝ đ║ĐÇđŞĐüĐéđ░đ╗đ╗đÁ. đşĐéđż đ║ĐÇđÁđ╝đŻđŞđÁđ▓Đőđ╣ ĐçđŞđ┐ (đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░), đ▓ đ║đżĐéđżĐÇđżđ╝ Đüđżđ┤đÁĐÇđÂđŞĐéĐüĐĆ đżđ┤đŻđż đŞđ╗đŞ đ▒đżđ╗ĐîĐłđÁđÁ đ║đżđ╗đŞĐçđÁĐüĐéđ▓đż đ┐ĐÇđżĐćđÁĐüĐüđżĐÇđŻĐőĐů ĐĆđ┤đÁĐÇ, đ╝đŞđ║ĐÇđżđ┐ĐÇđżĐćđÁĐüĐüđżĐÇđżđ▓ (MPU), đŞ/đŞđ╗đŞ đ╝đŞđ║ĐÇđżđ║đżđŻĐéĐÇđżđ╗đ╗đÁĐÇđżđ▓ (MCU), đŞ/đŞđ╗đŞ đ┐ĐÇđżĐćđÁĐüĐüđżĐÇđżđ▓ đ┤đ╗ĐĆ ĐćđŞĐäĐÇđżđ▓đżđ╣ đżđ▒ĐÇđ░đ▒đżĐéđ║đŞ ĐüđŞđ│đŻđ░đ╗đżđ▓ (DSP), đ┐đ╗ĐÄĐü ĐÇđ░đĚđ╝đÁĐëđÁđŻđŻđ░ĐĆ đŻđ░ ĐŹĐéđżđ╝ đÂđÁ ĐçđŞđ┐đÁ đ┐đ░đ╝ĐĆĐéĐî, ĐäĐâđŻđ║ĐćđŞđŞ đ░đ┐đ┐đ░ĐÇđ░ĐéđŻđżđ│đż ĐâĐüđ║đżĐÇđÁđŻđŞĐĆ đŞ ĐäĐâđŻđ║ĐćđŞđŞ đ┐đÁĐÇđŞĐäđÁĐÇđŞđ╣đŻĐőĐů ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓. đčđż ĐüĐâĐéđŞ Đéđ░đ║đżđÁ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đż đ╝đżđÂđÁĐé ĐüĐçđŞĐéđ░ĐéĐîĐüĐĆ đ▓ĐőĐüđżđ║đżđŞđŻĐéđÁđ│ĐÇđŞĐÇđżđ▓đ░đŻđŻĐőđ╝ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓đżđ╝, Đüđżđ┤đÁĐÇđÂđ░ĐëđŞđ╝ đ▓ ĐüđÁđ▒đÁ (đ┐đżĐçĐéđŞ) đ▓ĐüđÁ đŻđÁđżđ▒Đůđżđ┤đŞđ╝đżđÁ đ┤đ╗ĐĆ ĐÇđ░đ▒đżĐéĐő. đĽĐüđ╗đŞ ASIC Đüđżđ┤đÁĐÇđÂđŞĐé đżđ┤đŻđż đŞđ╗đŞ đŻđÁĐüđ║đżđ╗Đîđ║đż ĐĆđ┤đÁĐÇ đ┐ĐÇđżĐćđÁĐüĐüđżĐÇđ░, Đéđż ĐŹĐéđż đ╝đżđÂđŻđż ĐüĐçđŞĐéđ░ĐéĐî đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đżđ╣ SoC. đóđż đÂđÁ Đüđ░đ╝đżđÁ đ╝đżđÂđŻđż Đüđ║đ░đĚđ░ĐéĐî đŞ đ┐ĐÇđż ASSP - đÁĐüđ╗đŞ đ▓ đŻđÁđ╝ Đüđżđ┤đÁĐÇđÂđŞĐéĐüĐĆ đżđ┤đŻđż đŞđ╗đŞ đ▒đżđ╗ĐîĐłđÁ đ┐ĐÇđżĐćđÁĐüĐüđżĐÇđŻĐőĐů ĐĆđ┤đÁĐÇ, Đéđż ĐŹĐéđż ĐéđżđÂđÁ SoC.

SOP Sum of Product, ĐüĐâđ╝đ╝đ░ ĐÇđÁđĚĐâđ╗ĐîĐéđ░Đéđżđ▓.

Speed Grade đ║đ╗đ░ĐüĐü Đüđ║đżĐÇđżĐüĐéđŞ. đÜđ╗đ░ĐüĐüđŞĐäđŞđ║đ░ĐćđŞĐĆ ĐâĐüĐéĐÇđżđ╣ĐüĐéđ▓ Xilinx đ┐đż đ▒ĐőĐüĐéĐÇđżđ┤đÁđ╣ĐüĐéđ▓đŞĐÄ.

SPLD Simple Programmable Logic Device.

SPROM Serial Programmable Read-Only Memory. đúĐüĐéĐÇđżđ╣ĐüĐéđ▓đż ĐŹđŻđÁĐÇđ│đżđŻđÁđĚđ░đ▓đŞĐüđŞđ╝đżđ╣ đ┐đ░đ╝ĐĆĐéđŞ, đ▓ đ║đżĐéđżĐÇđżđ╝ đ╝đżđÂđÁĐé đ▒ĐőĐéĐî ĐüđżĐůĐÇđ░đŻđÁđŻ đ┐đżĐéđżđ║ đ▒đŞĐé đ║đżđŻĐäđŞđ│ĐâĐÇđ░ĐćđŞđŞ FPGA. SPROM đŞđ╝đÁđÁĐé đ▓ĐüĐéĐÇđżđÁđŻđŻĐőđ╣ ĐüĐçđÁĐéĐçđŞđ║ đ░đ┤ĐÇđÁĐüđ░, đżđŻđ░ đ┐ĐÇđŞđŻđŞđ╝đ░đÁĐé ĐüđŞđ│đŻđ░đ╗Đő Đéđ░đ║Đéđżđ▓ đŞ đ┐đżĐüđ╗đÁđ┤đżđ▓đ░ĐéđÁđ╗ĐîđŻđż đ▓Đőđ▓đżđ┤đŞĐé đŞđĚ ĐüđÁđ▒ĐĆ đ┐đżĐéđżđ║ đ▒đŞĐé.

SRAM Static Random Access Memory, ĐüĐéđ░ĐéđŞĐçđÁĐüđ║đżđÁ đ×đŚđú. đčđ░đ╝ĐĆĐéĐî đ┤đ╗ĐĆ ĐçĐéđÁđŻđŞĐĆ đŞ đĚđ░đ┐đŞĐüđŞ, đ│đ┤đÁ đ┤đ░đŻđŻĐőđÁ ĐüđżĐůĐÇđ░đŻđÁđŻĐő đ▓ đĚđ░ĐëđÁđ╗đ║đ░Đů (ĐéĐÇđŞđ│đ│đÁĐÇđ░Đů). đşĐéđ░ đ┐đ░đ╝ĐĆĐéĐî đ▒ĐőĐüĐéĐÇđÁđÁ DRAM, đŞ đŞđ╝đÁđÁĐé đ▒đżđ╗đÁđÁ đ┐ĐÇđżĐüĐéĐőđÁ ĐéĐÇđÁđ▒đżđ▓đ░đŻđŞĐĆ đ║ đŞđŻĐéđÁĐÇđ▓đ░đ╗đ░đ╝ đ▓ĐÇđÁđ╝đÁđŻđŞ đ┤đ╗ĐĆ ĐüđŞđ│đŻđ░đ╗đżđ▓, đżđ┤đŻđ░đ║đż đ╝đÁđŻĐîĐłđÁ đ┐đż ĐÇđ░đĚđ╝đÁĐÇĐâ đŞ đ┐ĐÇđŞđ╝đÁĐÇđŻđż đ▓ 4 ĐÇđ░đĚđ░ đ┤đżĐÇđżđÂđÁ, ĐçđÁđ╝ DRAM Đéđżđ╣ đÂđÁ đÁđ╝đ║đżĐüĐéđŞ.

SRL16 Shift Register LUT, đ░đ╗ĐîĐéđÁĐÇđŻđ░ĐéđŞđ▓đŻĐőđ╣ ĐÇđÁđÂđŞđ╝ ĐÇđ░đ▒đżĐéĐő đ┤đ╗ĐĆ đ║đ░đÂđ┤đżđ│đż đ│đÁđŻđÁĐÇđ░ĐéđżĐÇđ░ ĐäĐâđŻđ║ĐćđŞđŞ (LUT), đ║đżĐéđżĐÇĐőđ╣ ĐĆđ▓đ╗ĐĆđÁĐéĐüĐĆ Đçđ░ĐüĐéĐîĐÄ đ║đ░đÂđ┤đżđ│đż CLB đ▓ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░Đů FPGA Virtex đŞ Spartan. đşĐéđżĐé ĐÇđÁđÂđŞđ╝ đ┐đżđ▓ĐőĐłđ░đÁĐé đ║đżđ╗đŞĐçđÁĐüĐéđ▓đż ĐéĐÇđŞđ│đ│đÁĐÇđżđ▓ đŻđ░ 16. đöđżđ▒đ░đ▓đ╗đÁđŻđŞđÁ ĐéĐÇđŞđ│đ│đÁĐÇđżđ▓ đ┐đżđĚđ▓đżđ╗ĐĆđÁĐé ĐüđżđĚđ┤đ░ĐéĐî đ▒ĐőĐüĐéĐÇĐőđ╣ đ║đżđŻđ▓đÁđ╣đÁĐÇ (fast pipelining), ĐçĐéđż đŞđ┤đÁđ░đ╗ĐîđŻđż đ┐đżđ┤Đůđżđ┤đŞĐé đ┤đ╗ĐĆ đ┐ĐÇđŞđ╗đżđÂđÁđŻđŞđ╣ DSP.

SSTL Stub Series Terminated Transceiver Logic.

Static Timing đ┐đżđ┤ĐÇđżđ▒đŻđżđÁ đżđ┐đŞĐüđ░đŻđŞđÁ đ▓ĐüĐéĐÇđżđÁđŻđŻđżđ╣ đ▓ đ║ĐÇđŞĐüĐéđ░đ╗đ╗ đ╗đżđ│đŞđ║đŞ đŞ đĚđ░đ┤đÁĐÇđÂđÁđ║ đŻđ░ đ▓đŻĐâĐéĐÇđÁđŻđŻđŞĐů ĐüđżđÁđ┤đŞđŻđÁđŻđŞĐĆĐů.

Sub-Micron Đüđ░đ╝đ░ĐĆ đ╝đ░đ╗đ░ĐĆ đÁđ┤đŞđŻđŞĐćđ░ đŞđĚđ╝đÁĐÇđÁđŻđŞĐĆ, đ▓ĐőĐÇđ░đÂđÁđŻđŻđ░ĐĆ đ▓ đ╝đŞđ║ĐÇđżđŻđ░Đů (╬╝ = đ╝đŞđ╗đ╗đŞđżđŻđŻđ░ĐĆ đ┤đżđ╗ĐĆ đżĐé đ╝đÁĐéĐÇđ░, đŞđ╗đŞ ĐéĐőĐüĐĆĐçđŻđ░ĐĆ đ┤đżđ╗ĐĆ đ╝đŞđ╗đ╗đŞđ╝đÁĐéĐÇđ░). đíđżđ▓ĐÇđÁđ╝đÁđŻđŻđ░ĐĆ ĐéđÁĐůđŻđżđ╗đżđ│đŞĐĆ đ┐đÁĐÇđÁĐůđżđ┤đŞĐé Đü 0.35╬╝ đŻđ░ 0.25╬╝, đŞ Đüđ║đżĐÇđż đ╝đżđÂđÁĐé đ┐đÁĐÇđÁđ╣ĐéđŞ đŻđ░ 0.18╬╝. đöđ╗đŞđŻđ░ đ▓đżđ╗đŻĐő đ▓đŞđ┤đŞđ╝đżđ│đż Đüđ▓đÁĐéđ░ ĐüđżĐüĐéđ░đ▓đ╗ĐĆđÁĐé đżĐé 0.4 đ┤đż 0.8╬╝. 1 mil = 25.4╬╝.

Synchronous ĐüđŞđŻĐůĐÇđżđŻđŻĐőđ╣. đóđÁĐÇđ╝đŞđŻ đ┐ĐÇđŞđ╝đÁđŻĐĆđÁĐéĐüĐĆ đ║ ĐâđĚđ╗Đâ đ╗đżđ│đŞĐçđÁĐüđ║đżđ╣ ĐüĐůđÁđ╝Đő (đŞđ╗đŞ đ║đż đ▓ĐüđÁđ╣ ĐüĐůđÁđ╝đÁ), đ║đżđ│đ┤đ░ đżđŻ đ╝đÁđŻĐĆđÁĐé Đüđ▓đżđÁ ĐüđżĐüĐéđżĐĆđŻđŞđÁ Đéđżđ╗Đîđ║đż đ▓ đżĐéđ▓đÁĐé đŻđ░ đżđ▒ĐëđŞđ╣ Đéđ░đ║Đéđżđ▓Đőđ╣ ĐüđŞđ│đŻđ░đ╗. đóđ░đ║đżđÁ đ┐đżđ▓đÁđ┤đÁđŻđŞđÁ đżĐéđ╗đŞĐçđ░đÁĐéĐüĐĆ đżĐé đ░ĐüđŞđŻĐůĐÇđżđŻđŻđżđ╣ ĐüĐůđÁđ╝Đő ĐéđÁđ╝, ĐçĐéđż đżđŻđ░ đżĐéđ▓đÁĐçđ░đÁĐé đŻđ░ đ░đ╝đ┐đ╗đŞĐéĐâđ┤Đâ đżđ▒ĐÇđ░đ▒đ░ĐéĐőđ▓đ░đÁđ╝ĐőĐů ĐüđŞđ│đŻđ░đ╗đżđ▓. đíđŞđŻĐůĐÇđżđŻđŻĐőđÁ ĐüĐůđÁđ╝Đő đ┐ĐÇđżĐëđÁ ĐÇđ░đĚĐÇđ░đ▒đ░ĐéĐőđ▓đ░ĐéĐî, đżĐéđ╗đ░đÂđŞđ▓đ░ĐéĐî đŞ đŞđĚđ╝đÁđŻĐĆĐéĐî, đŞ đżđŻđŞ đ┤đżđ┐ĐâĐüđ║đ░ĐÄĐé đŞđĚđ╝đÁđŻđÁđŻđŞĐĆ đ┐đ░ĐÇđ░đ╝đÁĐéĐÇđżđ▓ đŞ đ░đ┐đ│ĐÇđÁđ╣đ┤ đ┐đż Đüđ║đżĐÇđżĐüĐéđŞ đ╗ĐâĐçĐłđÁ, ĐçđÁđ╝ đ░ĐüđŞđŻĐůĐÇđżđŻđŻĐőđÁ ĐüĐůđÁđ╝Đő. đŁđż đ░ĐüđŞđŻĐůĐÇđżđŻđŻĐőđÁ ĐüĐůđÁđ╝Đő đ┐đżđĚđ▓đżđ╗ĐĆĐÄĐé đ┤đżĐüĐéđŞĐçĐî đ▒đżđ╗ĐîĐłđÁđ╣ Đüđ║đżĐÇđżĐüĐéđŞ, ĐçđÁđ╝ ĐüđŞđŻĐůĐÇđżđŻđŻĐőđÁ, đŻđ░ Đéđżđ╣ đÂđÁ Đüđ░đ╝đżđ╣ ĐŹđ╗đÁđ╝đÁđŻĐéđŻđżđ╣ đ▒đ░đĚđÁ.

Synthesis ĐüđŞđŻĐéđÁđĚ. đčĐÇđżĐćđÁĐüĐü đżđ┐ĐéđŞđ╝đŞđĚđ░ĐćđŞđŞ, đ▓đż đ▓ĐÇđÁđ╝ĐĆ đ║đżĐéđżĐÇđżđ│đż đ┤đŞđĚđ░đ╣đŻ đ╗đżđ│đŞđ║đŞ đ░đ┤đ░đ┐ĐéđŞĐÇĐâđÁĐéĐüĐĆ đ║ đ╗đżđ│đŞĐçđÁĐüđ║đŞđ╝ ĐÇđÁĐüĐâĐÇĐüđ░đ╝ ĐçđŞđ┐đ░, đŻđ░đ┐đżđ┤đżđ▒đŞđÁ LUT-Đéđżđ▓, đ┤đ╗đŞđŻđŻĐőĐů đ╗đŞđŻđŞđ╣ đŞ đ▓Đőđ┤đÁđ╗đÁđŻđŻĐőĐů đ▒đ╗đżđ║đżđ▓ đ┐đÁĐÇđÁđŻđżĐüđ░. Synthesis đ┐ĐÇđÁđ┤ĐłđÁĐüĐéđ▓ĐâđÁĐé đżđ┐đÁĐÇđ░ĐćđŞđŞ đżĐéđżđ▒ĐÇđ░đÂđÁđŻđŞĐĆ (mapping).

SystemI/O ĐéđÁĐůđŻđżđ╗đżđ│đŞĐĆ, ĐÇđÁđ░đ╗đŞđĚđżđ▓đ░đŻđŻđ░ĐĆ đ▓ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░Đů Virtex-II FPGA, đ│đ┤đÁ đŞĐüđ┐đżđ╗ĐîđĚĐâĐÄĐéĐüĐĆ đ▒đ╗đżđ║đŞ SelectIO-Ultra, ĐçĐéđżđ▒Đő đ┐ĐÇđÁđ┤đżĐüĐéđ░đ▓đŞĐéĐî Đüđ░đ╝ĐőđÁ đ▒ĐőĐüĐéĐÇĐőđÁ đŞ đ│đŞđ▒đ║đŞđÁ ĐŹđ╗đÁđ║ĐéĐÇđŞĐçđÁĐüđ║đŞđÁ đŞđŻĐéđÁĐÇĐäđÁđ╣ĐüĐő. đÜđ░đÂđ┤đ░ĐĆ đŻđżđÂđ║đ░ I/O đŞđŻđ┤đŞđ▓đŞđ┤Đâđ░đ╗ĐîđŻđż đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁĐéĐüĐĆ đ┤đ╗ĐĆ đ╗ĐÄđ▒đżđ│đż đŞđĚ 19 đŻđÁ đ┤đŞĐäĐäđÁĐÇđÁđŻĐćđŞđ░đ╗ĐîđŻĐőĐů ĐüĐéđ░đŻđ┤đ░ĐÇĐéđ░ đ▓đ▓đżđ┤đ░/đ▓Đőđ▓đżđ┤đ░ (single-ended I/O) đŞđ╗đŞ đ╗ĐÄđ▒đżđ│đż đŞđĚ 6 đ┤đŞĐäĐäđÁĐÇđÁđŻĐćđŞđ░đ╗ĐîđŻĐőĐů (differential I/O) ĐüĐéđ░đŻđ┤đ░ĐÇĐéđ░, đ▓đ║đ╗ĐÄĐçđ░ĐĆ LVDS, SSTL, HSTL II đŞ GTL+. đóđÁĐůđŻđżđ╗đżđ│đŞĐĆ SelectIO-Ultra đ┤đ░đÁĐé Đüđ║đżĐÇđżĐüĐéĐî ĐÇđ░đ▒đżĐéĐő 840 Mbps LVDS Đü đŞĐüđ┐đżđ╗ĐîđĚđżđ▓đ░đŻđŞđÁđ╝ đ▓Đőđ┤đÁđ╗đÁđŻđŻĐőĐů ĐÇđÁđ│đŞĐüĐéĐÇđżđ▓ DDR.

TBUF đ▒ĐâĐäđÁĐÇ Đü đżđ┐ĐćđŞđÁđ╣ ĐéĐÇđÁĐéĐîđÁđ│đż ĐüđżĐüĐéđżĐĆđŻđŞĐĆ, đ║đżđ│đ┤đ░ đ▓ĐőĐůđżđ┤ đ╝đżđÂđŻđż Đüđ┤đÁđ╗đ░ĐéĐî đŻđÁ đ░đ║ĐéđŞđ▓đŻĐőđ╝. đśĐüđ┐đżđ╗ĐîđĚĐâđÁĐéĐüĐĆ đ┤đ╗ĐĆ đ╝Đâđ╗ĐîĐéđŞđ┐đ╗đÁđ║ĐüđŞĐÇđżđ▓đ░đŻđŞĐĆ ĐÇđ░đĚđŻĐőĐů đŞĐüĐéđżĐçđŻđŞđ║đżđ▓ đ┤đ░đŻđŻĐőĐů đ▓ đżđ┤đŻĐâ đżđ▒ĐëĐâĐÄ ĐłđŞđŻĐâ. đ×đ┐ĐćđŞĐĆ pull-down-only (Đéđżđ╗Đîđ║đż đ┐đżđ┤ĐéĐĆđÂđ║đ░ đ║ đ╗đżđ│. 0) đ╝đżđÂđÁĐé đŞĐüđ┐đżđ╗ĐîđĚđżđ▓đ░ĐéĐîĐüĐĆ đ┤đ╗ĐĆ đżĐÇđ│đ░đŻđŞđĚđ░ĐćđŞđŞ ĐäĐâđŻđ║ĐćđŞđŞ "đ╝đżđŻĐéđ░đÂđŻđżđÁ đś" (wired AND).

TCO đŞđŻĐéđÁĐÇđ▓đ░đ╗ đ▓ĐÇđÁđ╝đÁđŻđŞ, đżĐéđŻđżĐüĐĆĐëđŞđ╣ĐüĐĆ đ║ Đéđ░đ║Đéđ░đ╝ đŞ đ┤đÁđ╗đŞĐéđÁđ╗ĐÄ Đéđ░đ║Đéđżđ▓đżđ╣ Đçđ░ĐüĐéđżĐéĐő CPLD.

TDPR timing-driven place and route, ĐÇđ░đĚđ╝đÁĐëđÁđŻđŞđÁ đŞ ĐéĐÇđ░ĐüĐüđŞĐÇđżđ▓đ║đ░ đ╗đżđ│đŞđ║đŞ đŻđ░ đ║ĐÇđŞĐüĐéđ░đ╗đ╗đÁ, ĐâĐçđŞĐéĐőđ▓đ░ĐÄĐëđ░ĐĆ đŞđŻĐéđÁĐÇđ▓đ░đ╗Đő đ▓ĐÇđÁđ╝đÁđŻđŞ.

TIM Time in Market, đ▓ĐÇđÁđ╝ĐĆ đŻđ░ĐůđżđÂđ┤đÁđŻđŞĐĆ đ┐ĐÇđżđ┤Đâđ║ĐćđŞđŞ đŻđ░ ĐÇĐőđŻđ║đÁ.

Timing Đéđ░đ╣đ╝đŞđŻđ│. đóđÁĐÇđ╝đŞđŻ đżĐéđŻđżĐüđŞĐéĐüĐĆ đ║ đĚđ░đ┤đÁĐÇđÂđ║đ░đ╝, đ┐ĐÇđżđŞđĚđ▓đżđ┤đŞĐéđÁđ╗ĐîđŻđżĐüĐéđŞ đŞđ╗đŞ Đüđ║đżĐÇđżĐüĐéđŞ ĐÇđ░đ▒đżĐéĐő.

Timing Driven đ╝đÁĐéđżđ┤ ĐÇđ░đĚđ▓đżđ┤đ║đŞ đ┤đŞđĚđ░đ╣đŻđ░, ĐâĐçđŞĐéĐőđ▓đ░ĐÄĐëđŞđ╣ ĐéĐÇđÁđ▒đżđ▓đ░đŻđŞĐĆ đ┐đż đ┐ĐÇđżđŞđĚđ▓đżđ┤đŞĐéđÁđ╗ĐîđŻđżĐüĐéđŞ.

Tpd Time of Propagation Delay, đ▓ĐÇđÁđ╝ĐĆ đ┐ĐÇđżĐůđżđÂđ┤đÁđŻđŞĐĆ ĐüđŞđ│đŻđ░đ╗đ░ (ĐçđÁĐÇđÁđĚ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝Đâ).

TQFP Thin Quad Flat Pack, ĐéđŞđ┐ đ║đżĐÇđ┐ĐâĐüđ░ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝.

TTM Time to Market, đ▓ĐÇđÁđ╝ĐĆ đ▓ĐőĐůđżđ┤đ░ đ┐ĐÇđżđ┤Đâđ║ĐćđŞđŞ đŻđ░ ĐÇĐőđŻđżđ║.

UCF User Constraints File, Đäđ░đ╣đ╗ đżđ│ĐÇđ░đŻđŞĐçđÁđŻđŞđ╣ đ┐đżđ╗ĐîđĚđżđ▓đ░ĐéđÁđ╗ĐĆ. đíđ┐đÁĐćđŞđ░đ╗ĐîđŻĐőđ╣ Đäđ░đ╣đ╗ Đü đŻđ░ĐüĐéĐÇđżđ╣đ║đ░đ╝đŞ Xilinx ISE, đ│đ┤đÁ đ┐đżđ╗ĐîđĚđżđ▓đ░ĐéđÁđ╗Đî Đâđ┐ĐÇđ░đ▓đ╗ĐĆđÁĐé đ┐ĐÇđŞđ▓ĐĆđĚđ║đżđ╣ đ▓Đőđ▓đżđ┤đżđ▓ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝Đő đ║ đ╗đżđ│đŞĐçđÁĐüđ║đŞđ╝ ĐćđÁđ┐ĐĆđ╝, đżđ│ĐÇđ░đŻđŞĐçđÁđŻđŞĐĆ đ┐đż đ┐đ░ĐÇđ░đ╝đÁĐéĐÇđ░đ╝ đŞđŻĐéđÁĐÇđ▓đ░đ╗đżđ▓ đ▓ĐÇđÁđ╝đÁđŻđŞ, đ▓đ░ĐÇđŞđ░đŻĐé ĐâĐÇđżđ▓đŻđÁđ╣ đ╗đżđ│đŞđ║đŞ đŞ đ┤ĐÇĐâđ│đŞđÁ đ┐đ░ĐÇđ░đ╝đÁĐéĐÇĐő.

UMTS Universal Mobile Telecommunications System.

VCCO Voltage Current Controlled Oscillator, đ│đÁđŻđÁĐÇđ░ĐéđżĐÇ, Đâđ┐ĐÇđ░đ▓đ╗ĐĆđÁđ╝Đőđ╣ đŻđ░đ┐ĐÇĐĆđÂđÁđŻđŞđÁđ╝.

VFM Variable Function Multiplexer, đ╝Đâđ╗ĐîĐéđŞđ┐đ╗đÁđ║ĐüđżĐÇ đ┤đ╗ĐĆ đ┐đÁĐÇđÁđ║đ╗ĐÄĐçđÁđŻđŞĐĆ ĐäĐâđŻđ║ĐćđŞđ╣.

VHDL VHISC High Level Description Language, đ┐đżđ┐Đâđ╗ĐĆĐÇđŻĐőđ╣ HDL-ĐĆđĚĐőđ║ đ┤đ╗ĐĆ ĐüđżđĚđ┤đ░đŻđŞĐĆ đ┐ĐÇđżđ│ĐÇđ░đ╝đ╝đŞĐÇĐâđÁđ╝đżđ╣ đ╗đżđ│đŞđ║đŞ.

VHSIC Very High Speed Integrated Circuit, đżĐçđÁđŻĐî đ▒ĐőĐüĐéĐÇđ░ĐĆ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝đ░.

VME ĐüĐéđ░ĐÇĐőđ╣ ĐüĐéđ░đŻđ┤đ░ĐÇĐé ĐłđŞđŻĐő, đ┐đżđ┐Đâđ╗ĐĆĐÇđŻĐőđ╣ đ▓ đŞđŻđ┤ĐâĐüĐéĐÇđŞđ░đ╗ĐîđŻĐőĐů đ║đżđ╝đ┐ĐîĐÄĐéđÁĐÇđ░Đů đŻđ░ đ▒đ░đĚđÁ đ┐ĐÇđżĐćđÁĐüĐüđżĐÇđ░ MC68000.

VREF Voltage Reference, đżđ┐đżĐÇđŻđżđÁ đŻđ░đ┐ĐÇĐĆđÂđÁđŻđŞđÁ. đ×đ▒ĐőĐçđŻđż đŞĐüđ┐đżđ╗ĐîđĚĐâđÁĐéĐüĐĆ đ┤đ╗ĐĆ đ║đżđ╝đ┐đ░ĐÇđ░ĐéđżĐÇđżđ▓, đÉđŽđč, đŽđÉđč, ĐüđŞĐüĐéđÁđ╝Đő đżđ┐ĐÇđÁđ┤đÁđ╗đÁđŻđŞĐĆ ĐüĐéđ░đŻđ┤đ░ĐÇĐéđ░ ĐâĐÇđżđ▓đŻđÁđ╣ đ╗đżđ│đŞđ║đŞ, ĐüĐéđ░đ▒đŞđ╗đŞđĚđ░ĐéđżĐÇđżđ▓ đŻđ░đ┐ĐÇĐĆđÂđÁđŻđŞĐĆ đ┐đŞĐéđ░đŻđŞĐĆ.

VSS Visual Software Solutions. đžđ░ĐëđÁ ĐŹĐéđ░ đ░đ▒đ▒ĐÇđÁđ▓đŞđ░ĐéĐâĐÇđ░ đżđ▒đżđĚđŻđ░Đçđ░đÁĐé đżĐéĐÇđŞĐćđ░ĐéđÁđ╗ĐîđŻĐőđ╣ đ┐đżđ╗ĐÄĐü đ┐đŞĐéđ░đŻđŞĐĆ ĐüđŞĐüĐéđÁđ╝Đő đŞđ╗đŞ đĚđÁđ╝đ╗ĐÄ (đżđ▒ĐëđŞđ╣ đ┐ĐÇđżđ▓đżđ┤).

WPU Weak Pull Up, Đüđ╗đ░đ▒đ░ĐĆ đ┐đżđ┤ĐéĐĆđÂđ║đ░ ĐâĐÇđżđ▓đŻĐĆ ĐüđŞđ│đŻđ░đ╗đ░ đ║ đ╗đżđ│. 1.

XA ĐüĐâĐäĐäđŞđ║Đü đ┤đ╗ĐĆ đżđ▒đżđĚđŻđ░ĐçđÁđŻđŞĐĆ ĐéđŞđ┐đżđ▓ đ╝đŞđ║ĐÇđżĐüĐůđÁđ╝, đ┐ĐÇđÁđ┤đŻđ░đĚđŻđ░ĐçđÁđŻđŻĐőĐů đ┤đ╗ĐĆ đ░đ▓Đéđżđ╝đżđ▒đŞđ╗ĐîđŻĐőĐů đ┐ĐÇđŞđ╝đÁđŻđÁđŻđŞđ╣.

XCITE Xilinx Controlled Impedance Technology, ĐéđÁĐůđŻđżđ╗đżđ│đŞĐĆ Đâđ┐ĐÇđ░đ▓đ╗đÁđŻđŞĐĆ Đüđżđ┐ĐÇđżĐéđŞđ▓đ╗đÁđŻđŞđÁđ╝ đżĐé Xilinx.

XNF đ┐ĐÇđżđ┐ĐÇđŞđÁĐéđ░ĐÇđŻĐőđ╣ ĐäđżĐÇđ╝đ░Đé Đäđ░đ╣đ╗đ░ Xilinx đ┤đ╗ĐĆ đ┤đŞđĚđ░đ╣đŻđ░ đ╗đżđ│đŞđ║đŞ. đÉđ╗ĐîĐéđÁĐÇđŻđ░ĐéđŞđ▓đ░: ĐäđżĐÇđ╝đ░Đé EDIF.

XOR Exclusive OR, đ╗đżđ│đŞĐçđÁĐüđ║đ░ĐĆ đżđ┐đÁĐÇđ░ĐćđŞĐĆ đŞĐüđ║đ╗ĐÄĐçđ░ĐÄĐëđÁđÁ đśđŤđś.

ZIA Zero Power Interconnect Array, đ╝đ░ĐüĐüđŞđ▓ đ▓đŻĐâĐéĐÇđÁđŻđŻđŞĐů ĐüđżđÁđ┤đŞđŻđÁđŻđŞđ╣ Đü đŻĐâđ╗đÁđ▓Đőđ╝ Đéđżđ║đżđ╝ đ┐đżĐéĐÇđÁđ▒đ╗đÁđŻđŞĐĆ.

XST Xilinx Synthesis Technology, đ┐đ░ĐéđÁđŻĐéđżđ▓đ░đŻđŻđ░ĐĆ ĐéđÁĐůđŻđżđ╗đżđ│đŞĐĆ ĐüđŞđŻĐéđÁđĚđ░ đ╗đżđ│đŞđ║đŞ Xilinx.

[đíĐüĐőđ╗đ║đŞ]

1. đśđĚĐâĐçđ░đÁđ╝ VHDL đŞ đżĐüđ▓đ░đŞđ▓đ░đÁđ╝ đčđŤđśđí ĐäđŞĐÇđ╝Đő Xilinx site:ruecm.forum2x2.ru.

2. đÜđżđŻĐäđŞđ│ĐâĐÇđŞĐÇđżđ▓đ░đŻđŞđÁ Xilinx FPGA Đü đ┐đżđ╝đżĐëĐîĐÄ đ╝đŞđ║ĐÇđżđ║đżđŻĐéĐÇđżđ╗đ╗đÁĐÇđ░.

3. đśĐüđ┐đżđ╗ĐîđĚđżđ▓đ░đŻđŞđÁ đ┐ĐÇđżđ┤đ▓đŞđŻĐâĐéĐőĐů đ▓đżđĚđ╝đżđÂđŻđżĐüĐéđÁđ╣ CPLD Xilinx CoolRunner-II.

4. đíđÁđ╝đÁđ╣ĐüĐéđ▓đż CPLD CoolRunner-II. |