|

–Ь–љ–Њ–≥–Є–µ –Є–љ–ґ–µ–љ–µ—А—Л –Ј–∞–Є–љ—В–µ—А–µ—Б–Њ–≤–∞–љ—Л –≤ —Г–Љ–µ–љ—М—И–µ–љ–Є–Є –Ї–Њ–ї–Є—З–µ—Б—В–≤–∞ –Є—Б–њ–Њ–ї—М–Ј—Г–µ–Љ—Л—Е –Ї–Њ–Љ–њ–Њ–љ–µ–љ—В–Њ–≤, –≤ —Г–≤–µ–ї–Є—З–µ–љ–Є–Є –≥–Є–±–Ї–Њ—Б—В–Є –Є –њ–µ—А–µ–љ–∞—Б—В—А–∞–Є–≤–∞–µ–Љ–Њ—Б—В–Є —Б–≤–Њ–µ–є —А–∞–Ј—А–∞–±–∞—В—Л–≤–∞–µ–Љ–Њ–є —Б–Є—Б—В–µ–Љ—Л. –І—В–Њ–±—Л –і–Њ—Б—В–Є—З—М –Њ–і–љ–Њ–≤—А–µ–Љ–µ–љ–љ–Њ –Є —В–Њ–є –Є –і—А—Г–≥–Њ–є —Ж–µ–ї–Є, –Љ–Њ–ґ–љ–Њ –Ј–∞–і–µ–є—Б—В–≤–Њ–≤–∞—В—М –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А, —З—В–Њ–±—Л –Њ–љ –Љ–Њ–≥ –њ–µ—А–µ–њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞—В—М (—Б–Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞—В—М) FPGA –љ–∞ –љ—Г–ґ–љ—Л–µ —Д—Г–љ–Ї—Ж–Є–Є. –≠—В–Њ—В –∞–њ–љ–Њ—Г—В (–њ–µ—А–µ–≤–Њ–і [1]) —А–∞—Б–Ї—А—Л–≤–∞–µ—В —В–µ–Љ—Г –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П —Б–µ–Љ–µ–є—Б—В–≤ Virtex¬Ѓ –Є Spartan¬Ѓ FPGA —Б –њ–Њ–Љ–Њ—Й—М—О –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞. –Ґ–∞–Ї–ґ–µ —Н—В–Њ—В –∞–њ–љ–Њ—Г—В –њ—А–µ–і—Б—В–∞–≤–ї—П–µ—В –Љ–Њ–і–µ–ї—М —Б–Є—Б—В–µ–Љ–љ–Њ–≥–Њ —Г—А–Њ–≤–љ—П –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є—П Xilinx¬Ѓ Complex Programmable Logic Device (CPLD), —З—В–Њ–±—Л —А–µ–∞–ї–Є–Ј–Њ–≤–∞—В—М –Є–љ—В–µ—А—Д–µ–є—Б –Ї –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–Љ –≤—Л–≤–Њ–і–∞–Љ FPGA. –Я—А–Є–ї–∞–≥–∞–µ—В—Б—П –Ї–Њ–і –љ–∞ —П–Ј—Л–Ї–µ C [4], —З—В–Њ–±—Л –њ–Њ–Ї–∞–Ј–∞—В—М –њ—А–Є–Љ–µ—А –њ—А–Є–ї–Њ–ґ–µ–љ–Є—П, —А–∞–±–Њ—В–∞—О—Й–Є–є –ї–Є–±–Њ –≤ —А–µ–ґ–Є–Љ–µ Slave Serial, –ї–Є–±–Њ SelectMAP. –Ґ–∞–Ї–ґ–µ –Є–Љ–µ–µ—В—Б—П —Д–∞–є–ї—Л –і–Є–Ј–∞–є–љ–∞ CPLD, —З—В–Њ–±—Л –њ–Њ–Ї–∞–Ј–∞—В—М –≤–Њ–Ј–Љ–Њ–ґ–љ—Л–є —Б–Є–љ—Е—А–Њ–љ–љ—Л–є –Є–љ—В–µ—А—Д–µ–є—Б –Љ–µ–ґ–і—Г –њ—А–Њ—Ж–µ—Б—Б–Њ—А–Њ–Љ –Є FPGA.

[–Ю–±–Ј–Њ—А —Б–Є—Б—В–µ–Љ—Л –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П FPGA]

–°–µ–≥–Њ–і–љ—П—И–љ–Є–µ —Б–Є—Б—В–µ–Љ—Л –Є–Љ–µ—О—В —В–µ–љ–і–µ–љ—Ж–Є—О –≤ —А–∞–Ј–≤–Є—В–Є–Є, –Ї–Њ–≥–і–∞ –њ—А–Є —Г–Љ–µ–љ—М—И–∞—О—Й–Є—Е—Б—П —А–∞–Ј–Љ–µ—А–∞—Е –Ї–Њ–љ—Б—В—А—Г–Ї—Ж–Є–Є –Є —Б—Е–µ–Љ—Л –њ—А–µ–і–Њ—Б—В–∞–≤–ї—П–µ—В—Б—П —Г–≤–µ–ї–Є—З–Є–≤–∞—О—Й–Є–є—Б—П —Д—Г–љ–Ї—Ж–Є–Њ–љ–∞–ї –њ—А–Є –Њ–і–љ–Њ–≤—А–µ–Љ–µ–љ–љ–Њ–Љ —Б–љ–Є–ґ–µ–љ–Є–Є —Б—В–Њ–Є–Љ–Њ—Б—В–Є. –Ъ–∞–ґ–і–Њ–µ –љ–Њ–≤–Њ–µ —Б–µ–Љ–µ–є—Б—В–≤–Њ Xilinx FPGA –њ—А–µ–і–Њ—Б—В–∞–≤–ї—П–µ—В —Г–≤–µ–ї–Є—З–µ–љ–Є–µ –±—Л—Б—В—А–Њ–і–µ–є—Б—В–≤–Є—П –Є —А–∞—Б—И–Є—А–µ–љ–љ—Л–µ –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В–Є. –Э–µ—Б–Љ–Њ—В—А—П –љ–∞ —В–Њ, —З—В–Њ —Б–Є—Б—В–µ–Љ–∞ Platform Flash PROM –њ—А–µ–і–Њ—Б—В–∞–≤–ї—П–µ—В –њ—А–Њ—Б—В–Њ–µ, –Ј–∞—А–∞–љ–µ–µ —Б–Њ–Ј–і–∞–љ–љ–Њ–µ —А–µ—И–µ–љ–Є–µ –Ј–∞–ї–Є–≤–Ї–Є –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є –і–ї—П Xilinx FPGA, –і—А—Г–≥–Њ–µ —А–µ—И–µ–љ–Є–µ –і–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П FPGA, –Њ—Б–љ–Њ–≤–∞–љ–љ–Њ–µ –љ–∞ –≤—Б—В—А–Њ–µ–љ–љ–Њ–Љ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–µ, –Љ–Њ–ґ–µ—В —Г–ї—Г—З—И–Є—В—М –≥–Є–±–Ї–Њ—Б—В—М —А–∞–Ј—А–∞–±–Њ—В–Ї–Є –Є —Г–Љ–µ–љ—М—И–Є—В—М —А–µ–∞–ї—М–љ—Л–µ —А–∞–Ј–Љ–µ—А—Л –њ–µ—З–∞—В–љ–Њ–є –њ–ї–∞—В—Л (–µ—Б–ї–Є –њ—А–µ–і–њ–Њ–ї–Њ–ґ–Є—В—М, —З—В–Њ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А —А–∞—Б–њ–Њ–ї–∞–≥–∞–µ—В –і–Њ—Б—В–∞—В–Њ—З–љ—Л–Љ –Ї–Њ–ї–Є—З–µ—Б—В–≤–Њ–Љ –њ–∞–Љ—П—В–Є).

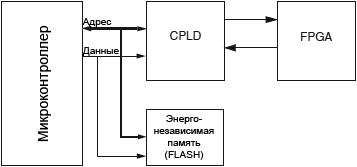

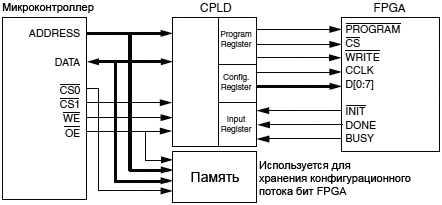

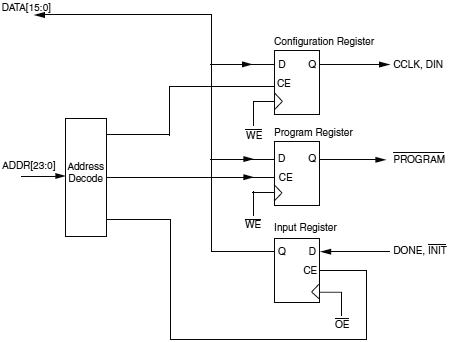

–Ф–ї—П –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П FPGA –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–Њ–Љ —В—А–µ–±—Г–µ—В—Б—П 3 –Ї–Њ–Љ–њ–Њ–љ–µ–љ—В–∞: —Б–Њ–±—Б—В–≤–µ–љ–љ–Њ —Б–∞–Љ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А, –Ї–∞–Ї–∞—П-—В–Њ —Н–љ–µ—А–≥–Њ–љ–µ–Ј–∞–≤–Є—Б–Є–Љ–∞—П –њ–∞–Љ—П—В—М (–Њ–љ–∞ –Љ–Њ–ґ–µ—В –±—Л—В—М –≤–љ—Г—В—А–Є –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –Є–ї–Є –њ–Њ–і–Ї–ї—О—З–µ–љ–∞ –Њ—В–і–µ–ї—М–љ–Њ), –Є CPLD. –°—В–Њ–Є–Љ–Њ—Б—В—М –Є —А–∞–Ј–Љ–µ—А—Л –Ї–Њ–љ—Б—В—А—Г–Ї—Ж–Є–Є –Љ–Њ–≥—Г—В –±—Л—В—М —Г–Љ–µ–љ—М—И–µ–љ—Л, –µ—Б–ї–Є —Д—Г–љ–Ї—Ж–Є—П –≤—Л–і–µ–ї–µ–љ–љ–Њ–≥–Њ —Г—Б—В—А–Њ–є—Б—В–≤–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є, —В–∞–Ї–Њ–≥–Њ –Ї–∞–Ї PROM, –Љ–Њ–ґ–µ—В –±—Л—В—М –Є–љ—В–µ–≥—А–Є—А–Њ–≤–∞–љ–∞ –≤ —Н—В–Є—Е —В—А–µ—Е –Ї–Њ–Љ–њ–Њ–љ–µ–љ—В–∞—Е. –°—Е–µ–Љ–∞ —Б–Є—Б—В–µ–Љ—Л –њ–Њ–Ї–∞–Ј–∞–љ–∞ –љ–∞ —А–Є—Б. 1.

–†–Є—Б. 1. –Ф–Є–∞–≥—А–∞–Љ–Љ–∞ —Б–Є—Б—В–µ–Љ—Л –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П FPGA.

–Я—А–Є–Љ–µ—З–∞–љ–Є–µ: –Є–љ–Њ–≥–і–∞ CPLD –љ–µ –љ—Г–ґ–љ–∞, –µ—Б–ї–Є –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А –Є–Љ–µ–µ—В –≤ –љ–∞–ї–Є—З–Є–Є –і–Њ—Б—В–∞—В–Њ—З–љ–Њ–µ –Ї–Њ–ї–Є—З–µ—Б—В–≤–Њ –≤—Л–≤–Њ–і–Њ–≤ GPIO –і–ї—П –њ–Њ–і–Ї–ї—О—З–µ–љ–Є—П FPGA. –Т —В–∞–Ї–Є—Е —Б–Є—Б—В–µ–Љ–∞—Е Xilinx FPGA –Љ–Њ–ґ–µ—В –±—Л—В—М —Б–Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–∞ –љ–∞–њ—А—П–Љ—Г—О –Њ—В –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞. –Ф–ї—П —В–∞–Ї–Њ–≥–Њ —В–Є–њ–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П —Н—В–Њ—В –∞–њ–љ–Њ—Г—В –≤—Б–µ –µ—Й–µ –њ—А–Є–Љ–µ–љ–Є–Љ. –Ю–±—Й–∞—П –њ—А–Њ—Ж–µ–і—Г—А–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П –Њ—Б—В–∞–µ—В—Б—П –њ—А–µ–ґ–љ–µ–є, –Њ–і–љ–∞–Ї–Њ –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—М –і–Њ–ї–ґ–µ–љ –Є–Ј–Љ–µ–љ–Є—В—М –Є—Б—Е–Њ–і–љ—Л–є –Ї–Њ–і, —З—В–Њ–±—Л –Љ–Є–Ї—А–Њ–њ—А–Њ—Ж–µ—Б—Б–Њ—А —Г–њ—А–∞–≤–ї—П–ї –≤—Л–≤–Њ–і–∞–Љ–Є GPIO –≤–Љ–µ—Б—В–Њ —Г–њ—А–∞–≤–ї–µ–љ–Є—П —И–Є–љ–Њ–є –∞–і—А–µ—Б–∞ –Є –і–∞–љ–љ—Л—Е.

–Т–Љ–µ—Б—В–Њ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є—П –Њ—В–і–µ–ї—М–љ–Њ–є PROM, –њ–Њ—В–Њ–Ї –±–Є—В –і–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П –Љ–Њ–ґ–µ—В –±—Л—В—М –≤–Ј—П—В –Є–Ј –љ–µ–Ј–∞–і–µ–є—Б—В–≤–Њ–≤–∞–љ–љ–Њ–є —Н–љ–µ—А–≥–Њ–љ–µ–Ј–∞–≤–Є—Б–Є–Љ–Њ–є –њ–∞–Љ—П—В–Є —Б–Є—Б—В–µ–Љ—Л. –Ъ—А–Њ–Љ–µ —В–Њ–≥–Њ, –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А (–Њ—Б–љ–Њ–≤–љ–∞—П —Ж–µ–ї—М –Ї–Њ—В–Њ—А–Њ–≥–Њ –≤ –≤—Л–њ–Њ–ї–љ–µ–љ–Є–Є –і—А—Г–≥–Є—Е –Ј–∞–і–∞—З) –Љ–Њ–ґ–µ—В —В–∞–Ї–ґ–µ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М—Б—П, —З—В–Њ–±—Л –Ї–Њ–Њ—А–і–Є–љ–Є—А–Њ–≤–∞—В—М –Ј–∞–≥—А—Г–Ј–Ї—Г –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л—Е –і–∞–љ–љ—Л—Е –≤ —Г—Б—В—А–Њ–є—Б—В–≤–Њ Xilinx FPGA. –Э–µ–Є—Б–њ–Њ–ї—М–Ј—Г–µ–Љ—Л–µ –±–Є—В—Л —А–µ–≥–Є—Б—В—А–Њ–≤ CPLD, –і–Њ—Б—В—Г–њ–љ—Л–µ –і–ї—П –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞, –Љ–Њ–≥—Г—В –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М—Б—П –і–ї—П –Љ–Њ–љ–Є—В–Њ—А–Є–љ–≥–∞ –Є —Г–њ—А–∞–≤–ї–µ–љ–Є—П –±–Є—В–∞–Љ–Є control, data –Є status –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л FPGA. –Ъ–Њ–≥–і–∞ —Г –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –љ–µ–і–Њ—Б—В–∞—В–Њ—З–љ–Њ–µ –Ї–Њ–ї–Є—З–µ—Б—В–≤–Њ –љ–Њ–ґ–µ–Ї –і–ї—П —Г–њ—А–∞–≤–ї–µ–љ–Є—П, –њ—А–Њ—Б—В–∞—П –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ CPLD –Љ–Њ–ґ–µ—В –Њ—В–Њ–±—А–∞–Ј–Є—В—М —З–∞—Б—В—М –∞–і—А–µ—Б–љ–Њ–≥–Њ –њ—А–Њ—Б—В—А–∞–љ—Б—В–≤–∞ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –і–ї—П —Г–њ—А–∞–≤–ї–µ–љ–Є—П –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–µ–є FPGA. –° –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ–Љ —Н—В–Њ–≥–Њ –Љ–µ—В–Њ–і–∞ CPLD —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞–µ—В —Б–Є–љ—Е—А–Њ–љ–љ—Л–є –Є–љ—В–µ—А—Д–µ–є—Б –Љ–µ–ґ–і—Г –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–Њ–Љ –Є Xilinx FPGA. –Ґ–∞–Ї–Њ–є –Є–љ—В–µ—А—Д–µ–є—Б —В–∞–Ї–ґ–µ –Љ–Њ–ґ–µ—В –њ—А–µ–і–Њ—Б—В–∞–≤–Є—В—М –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Г –≤—Л–њ–Њ–ї–љ–Є—В—М –љ–µ—Б–Ї–Њ–ї—М–Ї–Њ —А–∞—Б—И–Є—А–µ–љ–љ—Л—Е —Д—Г–љ–Ї—Ж–Є–є, —В–∞–Ї–Є—Е –Ї–∞–Ї —З–∞—Б—В–Є—З–љ–Њ–µ —А–µ–Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є–µ –Є–ї–Є –Њ–±—А–∞—В–љ–Њ–µ —З—В–µ–љ–Є–µ (–њ—А–Њ–≤–µ—А–Ї–∞) –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є.

[–Ю—Б–љ–Њ–≤–љ–Њ–є –њ—А–Є–љ—Ж–Є–њ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П]

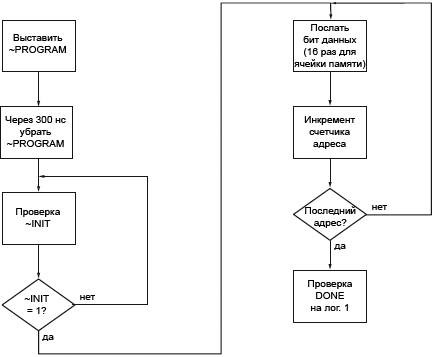

–Я—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є–µ —Б–µ–Љ–µ–є—Б—В–≤ Virtex –Є Spartan FPGA —Б –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ–Љ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –Љ–Њ–ґ–µ—В –њ—А–Њ–Є—Б—Е–Њ–і–Є—В—М –ї–Є–±–Њ –≤ —А–µ–ґ–Є–Љ–µ Slave Serial, –ї–Є–±–Њ –≤ —А–µ–ґ–Є–Љ–µ SelectMAP. –Ь–µ–ґ–і—Г —Н—В–Є–Љ–Є —А–µ–ґ–Є–Љ–∞–Љ–Є –µ—Б—В—М –љ–µ—Б–Ї–Њ–ї—М–Ї–Њ –Њ–±—Й–Є—Е —З–µ—А—В. –°–∞–Љ–Њ–µ –≥–ї–∞–≤–љ–Њ–µ –≤ —В–Њ–Љ, —З—В–Њ –Њ–±—Й–Є–є –њ–Њ—В–Њ–Ї –і–∞–љ–љ—Л—Е –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є –Є–і–µ–љ—В–Є—З–µ–љ –і–ї—П –Њ–±–Њ–Є—Е —А–µ–ґ–Є–Љ–Њ–≤ (—Б–Љ. —А–Є—Б. 2).

–†–Є—Б. 2. –Я—А–Њ—Ж–µ–і—Г—А–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П.

–Я—А–Є–Љ–µ—З–∞–љ–Є–µ: –љ–µ–Ї–Њ—В–Њ—А—Л–µ —Б–µ–Љ–µ–є—Б—В–≤–∞ Spartan FPGA –Ј–∞–і–µ–є—Б—В–≤—Г—О—В —В–µ—А–Љ–Є–љ –њ–∞—А–∞–ї–ї–µ–ї—М–љ–Њ–≥–Њ —А–µ–ґ–Є–Љ–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П (parallel mode). –Я–∞—А–∞–ї–ї–µ–ї—М–љ—Л–є —А–µ–ґ–Є–Љ —Н–Ї–≤–Є–≤–∞–ї–µ–љ—В–µ–љ –њ–Њ —Д—Г–љ–Ї—Ж–Є–Є —А–µ–ґ–Є–Љ—Г SelectMAP (—А–µ–ґ–Є–Љ SelectMap —В–∞–Ї–ґ–µ –љ–∞–Ј—Л–≤–∞—О—В —А–µ–ґ–Є–Љ–Њ–Љ Slave Parallel). –°–Љ. –і–∞—В–∞—И–Є—В—Л Spartan FPGA –і–ї—П –њ–Њ–ї—Г—З–µ–љ–Є—П –њ–Њ–і—А–Њ–±–љ–Њ—Б—В–µ–є. Spartan/XL FPGAs –љ–µ –њ–Њ–і–і–µ—А–ґ–Є–≤–∞—О—В parallel mode.

вАҐ Power-Up (–≤–Ї–ї—О—З–µ–љ–Є–µ –њ–Є—В–∞–љ–Є—П). –≠—В–Њ –Љ–Њ–Љ–µ–љ—В –њ–µ—А–≤–Њ–є –њ–Њ–і–∞—З–Є –њ–Є—В–∞–љ–Є—П –љ–∞ —Г—Б—В—А–Њ–є—Б—В–≤–Њ (–Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Г) FPGA. –Я—А–Є —Н—В–Њ–Љ –≤–љ—Г—В—А–µ–љ–љ—П—П –Љ–∞—И–Є–љ–∞ —Б–Њ—Б—В–Њ—П–љ–Є–є —Б–±—А–∞—Б—Л–≤–∞–µ—В—Б—П, –Є —Г—Б—В—А–Њ–є—Б—В–≤–Њ –љ–∞—З–Є–љ–∞–µ—В –њ—А–Њ–±—Г–ґ–і–µ–љ–Є–µ. –Т —Н—В–Њ—В –Љ–Њ–Љ–µ–љ—В –Њ–±–∞ –≤—Л–≤–Њ–і–∞, –Є ~PROGRAM, –Є ~INIT –њ–µ—А–µ–≤–Њ–і—П—В—Б—П —Б—Е–µ–Љ–Њ–є FPGA –≤ —Б–Њ—Б—В–Њ—П–љ–Є–µ –ї–Њ–≥. 0.

вАҐ Device Initialization (–Є–љ–Є—Ж–Є–∞–ї–Є–Ј–∞—Ж–Є—П —Г—Б—В—А–Њ–є—Б—В–≤–∞ FPGA). –£—Б—В—А–Њ–є—Б—В–≤–Њ –њ—А–∞–≤–Є–ї—М–љ–Њ –Ј–∞–њ–Є—В–∞–љ–Њ, –љ–Њ –≤–љ—Г—В—А–µ–љ–љ—П—П –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ–∞—П –њ–∞–Љ—П—В—М –љ—Г–ґ–і–∞–µ—В—Б—П –≤ —Б–±—А–Њ—Б–µ. –≠—В–Њ—В –Љ–Њ–Љ–µ–љ—В –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П —Б–Є–≥–љ–∞–ї–Є–Ј–Є—А—Г–µ—В—Б—П –њ–µ—А–µ–≤–Њ–і–Њ–Љ –≤—Л–≤–Њ–і–∞ ~PROGRAM –≤ —Б–Њ—Б—В–Њ—П–љ–Є–µ –ї–Њ–≥. 1 –Є ~INIT –љ–µ–Љ–љ–Њ–≥–Њ –њ–Њ–Ј–ґ–µ –≤ –ї–Њ–≥. 1 (—Н—В–∞ –Ј–∞–і–µ—А–ґ–Ї–∞ —Г–Ї–∞–Ј–∞–љ–∞ –≤ –і–∞—В–∞—И–Є—В–µ –љ–∞ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–µ–µ —Г—Б—В—А–Њ–є—Б—В–≤–Њ FPGA). –£—Б—В—А–Њ–є—Б—В–≤–Њ FPGA –Љ–Њ–ґ–µ—В –љ–∞—Е–Њ–і–Є—В—М—Б—П –≤ —Н—В–Њ–Љ —Б–Њ—Б—В–Њ—П–љ–Є–Є —Б–Ї–Њ–ї—М–Ї–Њ —Г–≥–Њ–і–љ–Њ –і–Њ–ї–≥–Њ, –µ—Б–ї–Є –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—М —Г–і–µ—А–ґ–Є–≤–∞–µ—В —Б–љ–∞—А—Г–ґ–Є —Б–Є–≥–љ–∞–ї ~PROGRAM –Є–ї–Є ~INIT –≤ —Б–Њ—Б—В–Њ—П–љ–Є–Є –ї–Њ–≥. 0.

вАҐ Configuration Load (–Ј–∞–≥—А—Г–Ј–Ї–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л—Е –і–∞–љ–љ—Л—Е). –Э–∞—З–∞–ї–Њ —Д–∞–Ј—Л –Ј–∞–≥—А—Г–Ј–Ї–Є –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є —Б–Є–≥–љ–∞–ї–Є–Ј–Є—А—Г–µ—В—Б—П –њ–µ—А–µ—Е–Њ–і–Њ–Љ —Б–Є–≥–љ–∞–ї–∞ ~INIT –≤ —Б–Њ—Б—В–Њ—П–љ–Є–µ –ї–Њ–≥. 1. –Я–Њ—Б–ї–µ —Н—В–Њ–≥–Њ —Б—З–Є—В—Л–≤–∞—О—В—Б—П –≤—Л–≤–Њ–і—Л —А–µ–ґ–Є–Љ–∞ M2:M0 - —Н—В–Є –≤—Л–≤–Њ–і—Л –Њ–њ—А–µ–і–µ–ї—П—О—В, –Ї–∞–Ї–Њ–є –і–Њ–ї–ґ–µ–љ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М—Б—П —А–µ–ґ–Є–Љ –Ј–∞–≥—А—Г–Ј–Ї–Є –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є. –Ю–±—А–∞—В–Є—В–µ—Б—М –Ї –і–∞—В–∞—И–Є—В—Г –љ–∞ —Г—Б—В—А–Њ–є—Б—В–≤–Њ, —З—В–Њ–±—Л –Њ–њ—А–µ–і–µ–ї–Є—В—М, –Ї–∞–Ї –љ—Г–ґ–љ–Њ —Г—Б—В–∞–љ–Њ–≤–Є—В—М —Н—В–Є –≤—Л–≤–Њ–і—Л –і–ї—П —В—А–µ–±—Г–µ–Љ–Њ–≥–Њ —А–µ–ґ–Є–Љ–∞ –Ј–∞–≥—А—Г–Ј–Ї–Є –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є. –Т —Н—В–Њ–є —Д–∞–Ј–µ —Г—Б—В—А–Њ–є—Б—В–≤–Њ –њ—А–Є–љ–Є–Љ–∞–µ—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ –і–∞–љ–љ—Л–µ. –Т—Б–µ —Б–Њ–±—Л—В–Є—П –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П –њ—А–Њ–Є—Б—Е–Њ–і—П—В –њ–Њ –љ–∞—А–∞—Б—В–∞–љ–Є—О (—Д—А–Њ–љ—В—Г) —В–∞–Ї—В–Њ–≤–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ CCLK.

–Я—А–Є–Љ. –њ–µ—А–µ–≤–Њ–і—З–Є–Ї–∞: –≤ Gameduino [5], –≥–і–µ –і–ї—П –Ј–∞–≥—А—Г–Ј–Ї–Є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л Spartan-3A XC3S200A –њ—А–Є–Љ–µ–љ–µ–љ–∞ –≤–љ–µ—И–љ—П—П –њ–∞–Љ—П—В—М AT45DB041D, –≤—Л–≤–Њ–і M0 –Њ—Б—В–∞–≤–ї–µ–љ –љ–µ–њ–Њ–і–Ї–ї—О—З–µ–љ–љ—Л–Љ (—Н—В–Њ –Њ–Ј–љ–∞—З–∞–µ—В –ї–Њ–≥. 1), –∞ –≤—Л–≤–Њ–і—Л M1 –Є M0 –Ј–∞–Љ–Ї–љ—Г—В—Л –љ–∞ GND (–ї–Њ–≥. 0).

вАҐ Start-Up (–Ј–∞–њ—Г—Б–Ї –≤ —А–∞–±–Њ—З–Є–є —А–µ–ґ–Є–Љ). –Я–Њ—Б–ї–µ —В–Њ–≥–Њ, –Ї–∞–Ї —Г—Б—В—А–Њ–є—Б—В–≤–Њ –њ—А–Є–љ—П–ї–Њ –≤—Б–µ –і–∞–љ–љ—Л–µ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є, –Њ–љ–Њ –њ–µ—А–µ—Е–Њ–і–Є—В –Ї –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ—Б—В–Є –Ј–∞–њ—Г—Б–Ї–∞ (start-up sequence). –≠—В–∞ –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ—Б—В—М –Њ–њ—А–µ–і–µ–ї—П–µ—В, –Ї–∞–Ї –±—Г–і—Г—В –њ–µ—А–µ–Ї–ї—О—З–∞—В—М—Б—П –≥–ї–Њ–±–∞–ї—М–љ—Л–µ —Б–Є–≥–љ–∞–ї—Л —Б–±—А–Њ—Б–∞ (GTS, GWE, –Є –і–ї—П Virtex/Virtex-E/Spartan-II/Spartan-IIE FPGAs —Б–Є–≥–љ–∞–ї GSR), –Є –Ї–Њ–≥–і–∞ –≤—Л–≤–Њ–і DONE –њ–µ—А–µ–є–і–µ—В –≤ —Б–Њ—Б—В–Њ—П–љ–Є–µ –ї–Њ–≥. 1. –Я–µ—А–µ—Е–Њ–і DONE –≤ —Б–Њ—Б—В–Њ—П–љ–Є–µ –ї–Њ–≥. 1 –љ–µ –Њ–Ј–љ–∞—З–∞–µ—В –њ–Њ–ї–љ–Њ–≥–Њ –Ј–∞–≤–µ—А—И–µ–љ–Є—П –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П - –љ—Г–ґ–љ–Њ –µ—Й–µ –љ–µ—Б–Ї–Њ–ї—М–Ї–Њ –і–Њ–њ–Њ–ї–љ–Є—В–µ–ї—М–љ—Л—Е —Ж–Є–Ї–ї–Њ–≤ CCLK, —З—В–Њ–±—Л –Ј–∞–≤–µ—А—И–Є—В—М start-up sequence. –Ї–Њ–ї–Є—З–µ—Б—В–≤–Њ —Н—В–Є—Е —Ж–Є–Ї–ї–Њ–≤ CCLK, –Ї–Њ—В–Њ—А—Л–µ –љ—Г–ґ–љ–Њ –≤—Л–і–∞—В—М –њ–Њ—Б–ї–µ –њ–µ—А–µ–і–∞—З–Є –њ–Њ—В–Њ–Ї–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л—Е –±–Є—В, –Ј–∞–≤–Є—Б–Є—В –Њ—В –≤—Л–±—А–∞–љ–љ—Л—Е –Њ–њ—Ж–Є–є BitGen, –≤–ї–Є—П—О—Й–Є—Е –љ–∞ FPGA start-up (–љ–∞–њ—А–Є–Љ–µ—А, DCM_lock –Є–ї–Є DCI_match), –Є—Б–њ–Њ–ї—М–Ј—Г–µ–Љ—Л—Е –і–ї—П –±–Є—В–Њ–≤–Њ–≥–Њ –њ–Њ—В–Њ–Ї–∞ FPGA. –Ъ–Њ–≥–і–∞ –љ–µ –≤—Л–±—А–∞–љ—Л –Њ–њ—Ж–Є–Є —А–∞—Б—И–Є—А–µ–љ–Є—П –Ј–∞–њ—Г—Б–Ї–∞ (start-up extending options), –±–Є—В–Њ–≤—Л–є –њ–Њ—В–Њ–Ї –Њ–±—Л—З–љ–Њ —Б–Њ–і–µ—А–ґ–Є—В –і–Њ—Б—В–∞—В–Њ—З–љ–Њ –і–∞–љ–љ—Л—Е –њ–Њ—Б–ї–µ –Є–љ–Є—Ж–Є–∞–ї–Є–Ј–Є—А–Њ–≤–∞–љ–Є—П start-up sequence, —З—В–Њ–±—Л –Ј–∞–≤–µ—А—И–Є—В—М –µ—С –і–Њ –Њ–Ї–Њ–љ—З–∞–љ–Є—П –њ–Њ—В–Њ–Ї–∞ –і–∞–љ–љ—Л—Е. –Ю–і–љ–∞–Ї–Њ —Б–∞–Љ–Њ–є –ї—Г—З—И–µ–є –њ—А–∞–Ї—В–Є–Ї–Њ–є (–Ї–Њ—В–Њ—А–∞—П –Ј–∞–Ї—А—Л–≤–∞–µ—В –≤—Б–µ –≤–Њ–Ј–Љ–Њ–ґ–љ—Л–µ –Њ–њ—Ж–Є–Є start-up –і–ї—П –±–Є—В–Њ–≤–Њ–≥–Њ –њ–Њ—В–Њ–Ї–∞) –±—Г–і–µ—В –Ј–∞–≥—А—Г–Ј–Є—В—М –≤—Б–µ –і–∞–љ–љ—Л–µ –Є–Ј —Д–∞–є–ї–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є, –Є –Ј–∞—В–µ–Љ –њ—А–Њ–і–Њ–ї–ґ–Є—В—М –≤—Л–і–∞—З—Г —Ж–Є–Ї–ї–Њ–≤ CCLK (–њ—А–Є —Н—В–Њ–Љ –≤—Б–µ –±–Є—В—Л –і–∞–љ–љ—Л—Е —А–∞–≤–љ—Л 1), –њ–Њ–Ї–∞ DONE –љ–µ –њ–µ—А–µ–є–і–µ—В –≤ –ї–Њ–≥. 1, –Є –љ–∞–Ї–Њ–љ–µ—Ж –≤—Л–і–∞—В—М 8 –і–Њ–њ–Њ–ї–љ–Є—В–µ–ї—М–љ—Л—Е —В–∞–Ї—В–Њ–≤ CCLK, –њ–Њ—Б–ї–µ —В–Њ–≥–Њ –Ї–∞–Ї DONE –њ–µ—А–µ–є–і–µ—В –≤ –ї–Њ–≥. 1, —З—В–Њ–±—Л –≥–∞—А–∞–љ—В–Є—А–Њ–≤–∞—В—М –Ј–∞–≤–µ—А—И–µ–љ–Є–µ FPGA

start-up sequence. –Я–Њ–і—А–Њ–±–љ–Њ—Б—В–Є –њ–Њ –Њ—В–і–µ–ї—М–љ—Л–Љ –Њ–њ—Ж–Є—П–Љ BitGen —Б–Љ. –≤ —А—Г–Ї–Њ–≤–Њ–і—Б—В–≤–µ —Б–µ–Љ–µ–є—Б—В–≤–∞ FPGA –Є —Б–µ–Ї—Ж–Є–Є BitGen —А—Г–Ї–Њ–≤–Њ–і—Б—В–≤–∞ Development Systems Reference Guide, –Ї–Њ—В–Њ—А–Њ–µ –Љ–Њ–ґ–љ–Њ –љ–∞–є—В–Є –≤ —А–∞–Ј–і–µ–ї–µ ISE¬Ѓ software manuals [3].

[–Ю—Б–Њ–±–µ–љ–љ–Њ—Б—В–Є —А–µ–ґ–Є–Љ–∞ Slave-Serial]

–Я–Њ—Б–ї–µ —В–Њ–≥–Њ, –Ї–∞–Ї ~INIT –њ–µ—А–µ—И–µ–ї –≤ –ї–Њ–≥. 1, –њ–Њ –Ї–∞–ґ–і–Њ–Љ—Г —Д—А–Њ–љ—В—Г –њ–µ—А–µ–њ–∞–і–∞ —Б–Є–≥–љ–∞–ї–∞ CCLK –±—Г–і–µ—В –Ј–∞–≥—А—Г–ґ–µ–љ 1 –±–Є—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л—Е –і–∞–љ–љ—Л—Е Slave Serial (—Н—В–Њ—В –±–Є—В –њ–Њ–і–∞–µ—В—Б—П –љ–∞ –≤—Л–≤–Њ–і DIN, –њ–∞—А–∞–Љ–µ—В—А—Л –≤—А–µ–Љ–µ–љ–Є –і–ї—П —Г—Б—В–∞–љ–Њ–≤–Ї–Є —Г—А–Њ–≤–љ—П –Є –µ–≥–Њ —Г–і–µ—А–ґ–∞–љ–Є—П —Б–Љ. –≤ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–µ–Љ –і–∞—В–∞—И–Є—В–µ –љ–∞ —Г—Б—В—А–Њ–є—Б—В–≤–Њ FPGA). –Т —В–∞–±–ї–Є—Ж–µ 1 –њ–Њ–Ї–∞–Ј–∞–љ—Л –≤—Л–≤–Њ–і—Л, –Ј–∞–і–µ–є—Б—В–≤–Њ–≤–∞–љ–љ—Л–µ –і–ї—П —А–µ–ґ–Є–Љ–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П Slave Serial.

–Ґ–∞–±–ї–Є—Ж–∞ 1. –Ю–њ–Є—Б–∞–љ–Є–µ –≤—Л–≤–Њ–і–Њ–≤ Slave Serial.

| –Ш–Љ—П —Б–Є–≥–љ–∞–ї–∞ |

–Э–∞–њ—А–∞–≤–ї–µ–љ–Є–µ |

–Ю–њ–Є—Б–∞–љ–Є–µ |

| CCLK |

–Т—Е–Њ–і |

–Ґ–∞–Ї—В–Є—А–Њ–≤–∞–љ–Є–µ –њ—А–Њ—Ж–µ—Б—Б–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П. |

| ~PROGRAM |

–Т—Е–Њ–і |

–Р—Б–Є–љ—Е—А–Њ–љ–љ—Л–є —Б–±—А–Њ—Б –і–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А—Г—О—Й–µ–є –ї–Њ–≥–Є–Ї–Є. |

| ~INIT |

–Т—Е–Њ–і/–Т—Л—Е–Њ–і |

–Т—Е–Њ–і, –Ї–Њ–≥–і–∞ –љ—Г–ґ–љ–Њ –Ј–∞–і–µ—А–ґ–∞—В—М –љ–∞—З–∞–ї–Њ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П. –Т—Л—Е–Њ–і, –Ї–Њ–≥–і–∞ —Г—Б—В—А–Њ–є—Б—В–≤–Њ FPGA –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В, —З—В–Њ –≥–Њ—В–Њ–≤–Њ –њ—А–Є–љ—П—В—М –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ –і–∞–љ–љ—Л–µ. –Ґ–∞–Ї–ґ–µ –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В –ї—О–±—Л–µ –Њ—И–Є–±–Ї–Є –≤ –њ—А–Њ—Ж–µ—Б—Б–µ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П. |

| DONE |

–Т—Е–Њ–і/–Т—Л—Е–Њ–і |

–Т—Е–Њ–і, –Ї–Њ–≥–і–∞ –љ—Г–ґ–љ–Њ –Ј–∞–і–µ—А–ґ–∞—В—М –љ–∞—З–∞–ї–Њ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П. –Т—Л—Е–Њ–і, –Ї–Њ–≥–і–∞ —Г—Б—В—А–Њ–є—Б—В–≤–Њ FPGA –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В, —З—В–Њ –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ—Б—В—М –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П –љ–∞—Е–Њ–і–Є—В—Б—П –≤ —Б–Њ—Б—В–Њ—П–љ–Є–Є start-up (–Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є–µ –Ј–∞–≤–µ—А—И–µ–љ–Њ, FPGA –≤—Е–Њ–і–Є—В –≤ —А–∞–±–Њ—З–Є–є —А–µ–ґ–Є–Љ). |

| M[2:0] |

–Т—Е–Њ–і |

–Т—Л–±–Њ—А —А–µ–ґ–Є–Љ–∞ –Ј–∞–≥—А—Г–Ј–Ї–Є –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є –≤ FPGA. |

| DIN |

–Т—Е–Њ–і |

–Т—Е–Њ–і –і–∞–љ–љ—Л—Е –і–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є. |

| DOUT |

–Т—Л—Е–Њ–і |

–Т—Л—Е–Њ–і –і–∞–љ–љ—Л—Е –і–ї—П –Њ—А–≥–∞–љ–Є–Ј–∞—Ж–Є–Є –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ–є —Ж–µ–њ–Є (daisy chain). |

–Я—А–Є–Љ. –њ–µ—А–µ–≤–Њ–і—З–Є–Ї–∞: –≤ —В–µ—А–Љ–Є–љ–Њ–ї–Њ–≥–Є–Є –Є –≤ –Њ–±–Њ–Ј–љ–∞—З–µ–љ–Є–Є —Б–Є–≥–љ–∞–ї–Њ–≤ Xilinx –ї–µ–≥–Ї–Њ –Ј–∞–њ—Г—В–∞—В—М—Б—П. –Ъ –њ—А–Є–Љ–µ—А—Г, —Б–Є–≥–љ–∞–ї ~PROGRAM –љ—Г–ґ–љ–Њ –њ–Њ–і–Ї–ї—О—З–∞—В—М –Ї–Њ –≤—Е–Њ–і—Г PROG_B –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л FPGA, –∞ —Б–Є–≥–љ–∞–ї ~INIT –Ї –љ–Њ–ґ–Ї–µ INIT_B –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л FPGA. –Ш–Љ–µ–љ–Њ–≤–∞–љ–Є–µ –Њ—Б—В–∞–ї—М–љ—Л—Е —Б–Є–≥–љ–∞–ї–Њ–≤ —В–∞–±–ї–Є—Ж—Л (CCLK, DONE, M[2:0], DIN, DOUT) —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—В –Є–Љ–µ–љ–Њ–≤–∞–љ–Є—О –љ–Њ–ґ–µ–Ї FPGA. –Э–Є–ґ–µ –љ–∞ —А–Є—Б—Г–љ–Ї–µ –њ–Њ–Ї–∞–Ј–∞–љ –њ—А–Є–Љ–µ—А –њ–Њ–і–Ї–ї—О—З–µ–љ–Є—П Xilinx FPGA XC3S200A (—Б–µ–Љ–µ–є—Б—В–≤–Њ Spartan-3A) –≤ –Ї–Њ—А–њ—Г—Б–µ VQFP100 –Ї –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Г –і–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П –≤ —А–µ–ґ–Є–Љ–µ Slave Serial.

[–Ю—Б–Њ–±–µ–љ–љ–Њ—Б—В–Є —А–µ–ґ–Є–Љ–∞ Slave-SelectMAP]

–†–µ–ґ–Є–Љ SelectMAP —В–∞–Ї–ґ–µ –љ–∞–Ј—Л–≤–∞—О—В —А–µ–ґ–Є–Љ–Њ–Љ Slave Parallel. –Ф–∞–љ–љ—Л–µ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є Slave-SelectMAP –Ј–∞–≥—А—Г–ґ–∞—О—В—Б—П –њ–Њ –Њ–і–љ–Њ–Љ—Г –±–∞–є—В—Г, –њ—А–µ–і—Б—В–∞–≤–ї–µ–љ–љ–Њ–Љ—Г –љ–∞ —И–Є–љ–µ D[0:7], —Б –Ї–∞–ґ–і—Л–Љ —Д—А–Њ–љ—В–Њ–Љ —В–∞–Ї—В–Њ–≤–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ CCLK, –њ—А–Є —Н—В–Њ–Љ —Б–∞–Љ—Л–є –Ј–љ–∞—З–∞—Й–Є–є –±–Є—В MSB –≤—Л—Б—В–∞–≤–ї—П–µ—В—Б—П –љ–∞ –≤—Л–≤–Њ–і D0 (—Б–Љ. –і–∞–ї–µ–µ —А–∞–Ј–і–µ–ї "–§–Њ—А–Љ–∞—В–Є—А–Њ–≤–∞–љ–Є–µ –і–∞–љ–љ—Л—Е –Є –њ–µ—А–µ—Б—В–∞–љ–Њ–≤–Ї–∞ –±–∞–є—В"). –Т —В–∞–±–ї–Є—Ж–µ 2 –њ–Њ–Ї–∞–Ј–∞–љ—Л –≤—Л–≤–Њ–і—Л, –Ј–∞–і–µ–є—Б—В–≤–Њ–≤–∞–љ–љ—Л–µ –і–ї—П —А–µ–ґ–Є–Љ–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П SelectMAP.

–Ф–ї—П —А–µ–ґ–Є–Љ–∞ SelectMAP –Є–Љ–µ–µ—В—Б—П 2 –і–Њ–њ–Њ–ї–љ–Є—В–µ–ї—М–љ—Л—Е —Б–Є–≥–љ–∞–ї–∞ ~CS –Є ~WRITE. –Ю–±–∞ —Н—В–Є—Е —Б–Є–≥–љ–∞–ї–∞ –і–Њ–ї–ґ–љ—Л –±—Л—В—М –≤—Л—Б—В–∞–≤–ї–µ–љ—Л –≤ –ї–Њ–≥. 0 –і–ї—П —В–Њ–≥–Њ, —З—В–Њ–±—Л –±–∞–є—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є –±—Л–ї –њ–µ—А–µ–і–∞–љ –≤ FPGA. –Ґ—А–µ—В–Є–є —Б–Є–≥–љ–∞–ї BUSY —П–≤–ї—П–µ—В—Б—П –≤—Л—Е–Њ–і–Њ–Љ FPGA. –Ъ–Њ–≥–і–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є–µ SelectMAP —А–∞–±–Њ—В–∞–µ—В —Б–ї–Є—И–Ї–Њ–Љ –±—Л—Б—В—А–Њ (–љ–∞–њ—А–Є–Љ–µ—А, —Б —З–∞—Б—В–Њ—В–Њ–є –±–Њ–ї—М—И–µ 50 –Ь–У—Ж –і–ї—П —Б–µ–Љ–µ–є—Б—В–≤ Virtex), —В–Њ —Б–Є–≥–љ–∞–ї BUSY –і–Њ–ї–ґ–µ–љ –Њ–њ—А–∞—И–Є–≤–∞—В—М—Б—П, —З—В–Њ–±—Л –≥–∞—А–∞–љ—В–Є—А–Њ–≤–∞—В—М –њ–Њ–ї–љ—Г—О –њ–µ—А–µ–і–∞—З—Г –і–∞–љ–љ—Л—Е. –Я–µ—А–µ—Е–Њ–і BUSY –≤ –ї–Њ–≥. 1 –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В, —З—В–Њ –і–∞–љ–љ—Л–µ –µ—Й–µ –љ–µ –њ–µ—А–µ–і–∞–љ—Л, –Є –і–Њ–ї–ґ–љ—Л —Г–і–µ—А–ґ–Є–≤–∞—В—М—Б—П –љ–∞ —И–Є–љ–µ –і–∞–љ–љ—Л—Е.

–Я—А–Є–Љ–µ—З–∞–љ–Є–µ: –њ—А–Њ–≤–µ—А—М—В–µ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–Є–є –і–∞—В–∞—И–Є—В –Є—Б–њ–Њ–ї—М–Ј—Г–µ–Љ–Њ–≥–Њ —Б–µ–Љ–µ–є—Б—В–≤–∞ FPGA –і–ї—П –љ–∞–ї–Є—З–Є—П –≤—Л–≤–Њ–і–∞ BUSY –Є —З–∞—Б—В–Њ—В—Л CCLK, —Б–≤—Л—И–µ –Ї–Њ—В–Њ—А–Њ–є –≤—Л–≤–Њ–і BUSY —Б—В–∞–љ–Њ–≤–Є—В—Б—П –∞–Ї—В–Є–≤–љ—Л–Љ. –Ґ–∞–Ї–ґ–µ —Б–Љ. —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–Є–є –і–∞—В–∞—И–Є—В –і–ї—П –њ–∞—А–∞–Љ–µ—В—А–Њ–≤ –≤—А–µ–Љ–µ–љ–Є —Г—Б—В–∞–љ–Њ–≤–Ї–Є –Є —Г–і–µ—А–ґ–∞–љ–Є—П –≤—Б–µ—Е —Б–Є–≥–љ–∞–ї–Њ–≤. –≠—В–Њ—В –∞–њ–љ–Њ—Г—В –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В –њ—А–Є–Љ–µ—А –і–Є–Ј–∞–є–љ–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П SelectMAP —В–Њ–ї—М–Ї–Њ –і–ї—П 8-–±–Є—В–љ–Њ–є —И–Є–љ—Л SelectMAP. –Э–µ–Ї–Њ—В–Њ—А—Л–µ —Б–µ–Љ–µ–є—Б—В–≤–∞ FPGA —В–∞–Ї–ґ–µ –њ–Њ–і–і–µ—А–ґ–Є–≤–∞—О—В 16- –Є–ї–Є 32-–±–Є—В–љ—Л–µ —И–Є–љ—Л SelectMAP. –° –њ–Њ–і—Е–Њ–і—П—Й–Є–Љ–Є –Љ–Њ–і–Є—Д–Є–Ї–∞—Ж–Є—П–Љ–Є, —Г—З–Є—В—Л–≤–∞—О—Й–Є–Љ–Є –њ–Њ—А—П–і–Њ–Ї —Б–ї–µ–і–Њ–≤–∞–љ–Є—П –±–Є—В –і–∞–љ–љ—Л—Е, –њ–Њ–Ї–∞–Ј–∞–љ–љ—Л–є –Ј–і–µ—Б—М –њ—А–Є–Љ–µ—А –і–Є–Ј–∞–є–љ–∞ –Љ–Њ–ґ–µ—В –±—Л—В—М —А–∞—Б—И–Є—А–µ–љ –і–ї—П —И–Є–љ –і–∞–љ–љ—Л—Е SelectMAP –љ–∞ 16 –Є–ї–Є 32 –±–Є—В–∞. –°–Љ. —А—Г–Ї–Њ–≤–Њ–і—Б—В–≤–Њ –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П –і–ї—П –Т–∞—И–µ–є —Ж–µ–ї–µ–≤–Њ–є FPGA, —З—В–Њ–±—Л –Њ–њ—А–µ–і–µ–ї–Є—В—М –њ–Њ–і–і–µ—А–ґ–Є–≤–∞–µ–Љ—Л–µ —А–∞–Ј—А—П–і–љ–Њ—Б—В–Є —И–Є–љ—Л –Є –њ–Њ—А—П–і–Њ–Ї —Б–ї–µ–і–Њ–≤–∞–љ–Є—П –±–Є—В –љ–∞ —И–Є–љ–µ.

–Ґ–∞–±–ї–Є—Ж–∞ 2. –Ю–њ–Є—Б–∞–љ–Є–µ –≤—Л–≤–Њ–і–Њ–≤ Slave-SelectMAP.

| –Ш–Љ—П —Б–Є–≥–љ–∞–ї–∞ |

–Э–∞–њ—А–∞–≤–ї–µ–љ–Є–µ |

–Ю–њ–Є—Б–∞–љ–Є–µ |

| CCLK |

–Т—Е–Њ–і |

–Ґ–∞–Ї—В–Є—А–Њ–≤–∞–љ–Є–µ –њ—А–Њ—Ж–µ—Б—Б–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П. |

| ~PROGRAM |

–Т—Е–Њ–і |

–Р—Б–Є–љ—Е—А–Њ–љ–љ—Л–є —Б–±—А–Њ—Б –і–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А—Г—О—Й–µ–є –ї–Њ–≥–Є–Ї–Є. |

| ~INIT |

–Т—Е–Њ–і/–Т—Л—Е–Њ–і |

–Т—Е–Њ–і, –Ї–Њ–≥–і–∞ –љ—Г–ґ–љ–Њ –Ј–∞–і–µ—А–ґ–∞—В—М –љ–∞—З–∞–ї–Њ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П. –Т—Л—Е–Њ–і, –Ї–Њ–≥–і–∞ —Г—Б—В—А–Њ–є—Б—В–≤–Њ FPGA –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В, —З—В–Њ –≥–Њ—В–Њ–≤–Њ –њ—А–Є–љ—П—В—М –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ –і–∞–љ–љ—Л–µ. –Ґ–∞–Ї–ґ–µ –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В –ї—О–±—Л–µ –Њ—И–Є–±–Ї–Є –≤ –њ—А–Њ—Ж–µ—Б—Б–µ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П. |

| DONE |

–Т—Е–Њ–і/–Т—Л—Е–Њ–і |

–Т—Е–Њ–і, –Ї–Њ–≥–і–∞ –љ—Г–ґ–љ–Њ –Ј–∞–і–µ—А–ґ–∞—В—М –љ–∞—З–∞–ї–Њ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П. –Т—Л—Е–Њ–і, –Ї–Њ–≥–і–∞ —Г—Б—В—А–Њ–є—Б—В–≤–Њ FPGA –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В, —З—В–Њ –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ—Б—В—М –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П –љ–∞—Е–Њ–і–Є—В—Б—П –≤ —Б–Њ—Б—В–Њ—П–љ–Є–Є start-up (–Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є–µ –Ј–∞–≤–µ—А—И–µ–љ–Њ, FPGA –≤—Е–Њ–і–Є—В –≤ —А–∞–±–Њ—З–Є–є —А–µ–ґ–Є–Љ). |

| M[2:0] |

–Т—Е–Њ–і |

–Т—Л–±–Њ—А —А–µ–ґ–Є–Љ–∞ –Ј–∞–≥—А—Г–Ј–Ї–Є –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є –≤ FPGA. |

| D[0:7] |

–Т—Е–Њ–і |

–Т—Е–Њ–і –і–∞–љ–љ—Л—Е –і–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є (–±–∞–є—В–Њ–≤–∞—П —И–Є–љ–∞). |

| ~CS |

–Т—Е–Њ–і |

–°–Є–≥–љ–∞–ї –≤—Л–±–Њ—А–Ї–Є (–∞–Ї—В–Є–≤–љ—Л–є –ї–Њ–≥. 0). |

~WRITE –Є–ї–Є

~RDWR_B |

–Т—Е–Њ–і |

–°–Є–≥–љ–∞–ї –Ј–∞–њ–Є—Б–Є –Є–ї–Є —З—В–µ–љ–Є—П (–∞–Ї—В–Є–≤–љ—Л–є –ї–Њ–≥. 0). |

| BUSY |

–Т—Л—Е–Њ–і |

–°–Є–≥–љ–∞–ї —Г–њ—А–∞–≤–ї–µ–љ–Є—П –Њ–±–Љ–µ–љ–Њ–Љ, –њ–Њ–Ї–∞–Ј—Л–≤–∞—О—Й–Є–є —Г—Б–њ–µ—И–љ–Њ–µ –Ј–∞–≤–µ—А—И–µ–љ–Є–µ –њ–µ—А–µ–і–∞—З–Є –њ–Њ—А—Ж–Є–Є –і–∞–љ–љ—Л—Е (—А–∞–±–Њ—В–∞–µ—В —В–∞–Ї –ґ–µ, –Ї–∞–Ї DOUT –≤ —А–µ–ґ–Є–Љ–µ Serial). |

[–§–Њ—А–Љ–∞—В–Є—А–Њ–≤–∞–љ–Є–µ –і–∞–љ–љ—Л—Е –Є –њ–µ—А–µ—Б—В–∞–љ–Њ–≤–Ї–∞ –±–∞–є—В]

–Я–Њ—Б–Ї–Њ–ї—М–Ї—Г –њ–Њ—В–Њ–Ї –±–Є—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є –Ј–∞–≥—А—Г–ґ–∞–µ—В—Б—П –≤ –њ–∞–Љ—П—В—М, –њ–Њ–і–Ї–ї—О—З–µ–љ–љ—Г—О –Ї –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Г (–Є–ї–Є –≤ –µ–≥–Њ –≤–љ—Г—В—А–µ–љ–љ—О—О –њ–∞–Љ—П—В—М), —В–Њ —Н—В–Њ—В –њ–Њ—В–Њ–Ї –±–Є—В –і–Њ–ї–ґ–µ–љ –±—Л—В—М –Њ—В—Д–Њ—А–Љ–∞—В–Є—А–Њ–≤–∞–љ –≤ —В–Њ–Љ –њ–Њ—А—П–і–Ї–µ, –≤ –Ї–Њ—В–Њ—А–Њ–Љ –µ–≥–Њ –Љ–Њ–ґ–µ—В –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М –њ—А–Њ–≥—А–∞–Љ–Љ–∞ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ (–љ–µ–Ј–∞–≤–Є—Б–Є–Љ–Њ –Њ—В —В–Њ–≥–Њ, –Ї–∞–Ї –±—Г–і–µ—В –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞—В—М—Б—П –њ–∞–Љ—П—В—М). –І—В–Њ–±—Л –њ–Њ–і–і–µ—А–ґ–∞—В—М —А–∞–Ј–љ—Л–µ —А–µ—И–µ–љ–Є—П –і–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П, –Є–љ—Б—В—А—Г–Љ–µ–љ—В–∞—А–Є–є Xilinx (–Ї–Њ—В–Њ—А—Л–є –≤—Е–Њ–і–Є—В –≤ —Б–Њ—Б—В–∞–≤ ISE Design Tools) –Љ–Њ–ґ–µ—В —Б–≥–µ–љ–µ—А–Є—А–Њ–≤–∞—В—М –і–∞–љ–љ—Л–µ –≤ —А–∞–Ј–ї–Є—З–љ—Л—Е —Д–Њ—А–Љ–∞—В–∞—Е (—Б–Љ. —В–∞–±–ї–Є—Ж—Г 3).

–Ґ–∞–±–ї–Є—Ж–∞ 3. Xilinx Tool Formats.

| –†–∞—Б—И–Є—А–µ–љ–Є–µ —Д–∞–є–ї–∞ |

–Ю–њ–Є—Б–∞–љ–Є–µ |

| .bit |

–Ф–≤–Њ–Є—З–љ—Л–є —Д–∞–є–ї, –≤ –Ї–Њ—В–Њ—А–Њ–Љ –µ—Б—В—М –Ј–∞–≥–Њ–ї–Њ–≤–Њ–Ї, –љ–µ –њ–µ—А–µ–і–∞–≤–∞–µ–Љ—Л–є –≤ FPGA. |

| .rbt |

–Ґ–µ–Ї—Б—В–Њ–≤—Л–є —Д–∞–є–ї ASCII, —Б–Њ–і–µ—А–ґ–∞—Й–Є–є –Ј–∞–≥–Њ–ї–Њ–≤–Њ–Ї –Є —Б–Є–Љ–≤–Њ–ї—Л ASCII 1 –Є 0. |

| .bin |

–Ф–≤–Њ–Є—З–љ—Л–є —Д–∞–є–ї –±–µ–Ј –Ј–∞–≥–Њ–ї–Њ–≤–Ї–∞. |

| .mcs, .exo, .tek |

–§–Њ—А–Љ–∞—В—Л ASCII PROM, –Ї–Њ—В–Њ—А—Л–µ —Б–Њ–і–µ—А–ґ–∞—В –Є–љ—Д–Њ—А–Љ–∞—Ж–Є—О –Њ–± –∞–і—А–µ—Б–µ –Є –Ї–Њ–љ—В—А–Њ–ї—М–љ—Г—О —Б—Г–Љ–Љ—Г. |

| .hex |

–§–Њ—А–Љ–∞—В ASCII PROM, –Ї–Њ—В–Њ—А—Л–є —Б–Њ–і–µ—А–ґ–Є—В —В–Њ–ї—М–Ї–Њ –і–∞–љ–љ—Л–µ. |

–Я—А–Є–Љ. –њ–µ—А–µ–≤–Њ–і—З–Є–Ї–∞: –µ—Б–ї–Є —Б—А–∞–≤–љ–Є—В—М —Б–Њ–і–µ—А–ґ–Є–Љ–Њ–µ —Д–∞–є–ї–∞ *.bit –Є *.bin, —В–Њ –Є—Е —Б–Њ–і–µ—А–ґ–Є–Љ–Њ–µ –њ–Њ–ї–љ–Њ—Б—В—М—О —Б–Њ–≤–њ–∞–і–∞–µ—В, –Ј–∞ –Є—Б–Ї–ї—О—З–µ–љ–Є–µ–Љ –њ–µ—А–≤—Л—Е 77 –±–∞–є—В, –Ї–Њ—В–Њ—А—Л–µ –і–Њ–±–∞–≤–ї–µ–љ—Л –≤ —Д–∞–є–ї–µ *.bit –Ї–∞–Ї –Ј–∞–≥–Њ–ї–Њ–≤–Њ–Ї.

–Я–Њ —Г–Љ–Њ–ї—З–∞–љ–Є—О —Д–∞–є–ї *.bin –≤ –њ—А–Њ–µ–Ї—В–µ ISE PlanAhead –љ–µ –≥–µ–љ–µ—А–Є—А—Г–µ—В—Б—П. –І—В–Њ–±—Л –љ–∞—Б—В—А–Њ–Є—В—М –µ–≥–Њ –≥–µ–љ–µ—А–∞—Ж–Є—О, –љ—Г–ґ–љ–Њ –і–ї—П bitgen —Г–Ї–∞–Ј–∞—В—М –і–Њ–њ–Њ–ї–љ–Є—В–µ–ї—М–љ—Г—О –Њ–њ—Ж–Є—О. –Ф–ї—П —Н—В–Њ–≥–Њ –Ј–∞–є–і–Є—В–µ –≤ –љ–∞—Б—В—А–Њ–є–Ї–Є –њ—А–Њ–µ–Ї—В–∞ (Bitstream Settings), —А–∞–Ј–і–µ–ї Bitstream –Є–Љ–µ–µ—В –њ–Њ–ї–µ –≤–≤–Њ–і–∞ More Options* (–і–Њ–њ–Њ–ї–љ–Є—В–µ–ї—М–љ—Л–µ –Њ–њ—Ж–Є–Є, –Ї–Њ—В–Њ—А—Л–µ –Љ–Њ–ґ–љ–Њ –і–Њ–±–∞–≤–Є—В—М –≤—А—Г—З–љ—Г—О). –Т–≤–µ–і–Є—В–µ –≤ —Н—В–Њ –њ–Њ–ї–µ¬†-g Binary:Yes –Є –љ–∞–ґ–Љ–Є—В–µ Apply –Є OK.

–Ю–±—Л—З–љ–Њ –і–ї—П –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П —Н–љ–µ—А–≥–Њ–љ–µ–Ј–∞–≤–Є—Б–Є–Љ–Њ–є –њ–∞–Љ—П—В–Є –љ–∞–Є–±–Њ–ї–µ–µ —Г–і–Њ–±–љ—Л —Д–∞–є–ї—Л —Д–Њ—А–Љ–∞—В–∞ .bin –Є–ї–Є .hex. –Т–Љ–µ—Б—В–µ —Б —Н—В–Є–Љ –∞–њ–љ–Њ—Г—В–Њ–Љ –њ–Њ—Б—В–∞–≤–ї—П–µ—В—Б—П —Б–Ї—А–Є–њ—В –љ–∞ —П–Ј—Л–Ї–µ Perl (bitformat.pl) [4], –Ї–Њ—В–Њ—А—Л–є –≤—Л–њ–Њ–ї–љ—П–µ—В —В—А–µ–±—Г–µ–Љ–Њ–µ –і–Њ–њ–Њ–ї–љ–Є—В–µ–ї—М–љ–Њ–µ —Д–Њ—А–Љ–∞—В–Є—А–Њ–≤–∞–љ–Є–µ. –≠—В–Њ—В —Б–Ї—А–Є–њ—В –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В —Д–∞–є–ї—Л .bit –Є–ї–Є .rbt –≤ –Ї–∞—З–µ—Б—В–≤–µ –≤—Е–Њ–і–љ—Л—Е, –Є –≥–µ–љ–µ—А–Є—А—Г–µ—В –љ–∞—Б—В—А–∞–Є–≤–∞–µ–Љ—Л–µ –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—М—Б–Ї–Є–µ —Д–∞–є–ї—Л ASCII, –Ї–Њ—В–Њ—А—Л–µ –Љ–Њ–≥—Г—В –±—Л—В—М –њ–Њ–ї–µ–Ј–љ—Л –і–ї—П –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П –њ–∞–Љ—П—В–Є –≤ —Б–Є—Б—В–µ–Љ–µ. –Э–∞ –Ї–Њ–Љ–њ—М—О—В–µ—А–µ, –≥–і–µ –Ј–∞–њ—Г—Б–Ї–∞–µ—В—Б—П —Н—В–Њ—В —Б–Ї—А–Є–њ—В Perl, –і–Њ–ї–ґ–љ–Њ –±—Л—В—М —Г—Б—В–∞–љ–Њ–≤–ї–µ–љ–Њ Xilinx implementation software, –њ–Њ—В–Њ–Љ—Г —З—В–Њ –њ—А–Њ–≥—А–∞–Љ–Љ–∞ PROMGen –≤—Л–Ј—Л–≤–∞–µ—В—Б—П –Є–Ј —Б–Ї—А–Є–њ—В–∞ (–і–ї—П –њ–Њ–ї—Г—З–µ–љ–Є—П –њ–Њ–і—А–Њ–±–љ–Њ—Б—В–µ–є —Б–Љ. –њ—А–Є–ї–∞–≥–∞–µ–Љ—Л–є —Д–∞–є–ї bitformat.readme).

–° —В–Њ—З–Ї–Є –Ј—А–µ–љ–Є—П –њ–Њ—А—П–і–Ї–∞ —Б–ї–µ–і–Њ–≤–∞–љ–Є—П –±–Є—В —А–µ–ґ–Є–Љ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П Slave Serial –Њ—З–µ–љ—М –њ—А–Њ—Б—В. –Ч–∞–≥—А—Г–Ј–Ї–∞ –љ–∞—З–Є–љ–∞–µ—В—Б—П —Б –њ–µ—А–≤–Њ–≥–Њ –±–Є—В–∞ –Є–Ј –±–Є—В–Њ–≤–Њ–≥–Њ –њ–Њ—В–Њ–Ї–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є –Є –њ—А–Њ–і–Њ–ї–ґ–∞–µ—В—Б—П –±–Є—В –Ј–∞ –±–Є—В–Њ–Љ, –њ–Њ–Ї–∞ –љ–µ –±—Г–і–µ—В –і–Њ—Б—В–Є–≥–љ—Г—В –Ї–Њ–љ–µ—Ж —Д–∞–є–ї–∞.

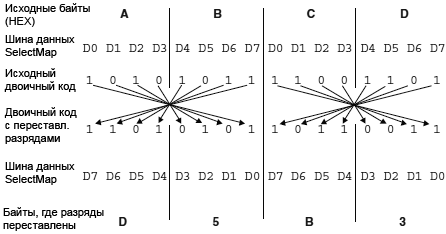

–Т –Њ—В–ї–Є—З–Є–µ –Њ—В Slave Serial —А–µ–ґ–Є–Љ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П SelectMAP –≤—Л–≥–ї—П–і–Є—В –љ–µ—Б–Ї–Њ–ї—М–Ї–Њ —Б–ї–Њ–ґ–љ–µ–µ –Є–Ј-–Ј–∞ –њ–Њ—А—П–і–Ї–∞ —Б–ї–µ–і–Њ–≤–∞–љ–Є—П –і–∞–љ–љ—Л—Е. –Ъ–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ –і–∞–љ–љ—Л–µ –Ј–∞–≥—А—Г–ґ–∞—О—В—Б—П –њ–Њ –Њ–і–љ–Њ–Љ—Г –±–∞–є—В—Г –Ј–∞ —А–∞–Ј —Б –Ї–∞–ґ–і—Л–Љ —Д—А–Њ–љ—В–Њ–Љ —В–∞–Ї—В–Њ–≤–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ CCLK, –Є –Ї–∞–ґ–і—Л–є –±–Є—В MSB –≤ –Ї–∞–ґ–і–Њ–Љ –±–∞–є—В–µ –њ–Њ–і–∞–µ—В—Б—П –љ–∞ –љ–Њ–ґ–Ї—Г D0, –≤–Њ–≤—Б–µ –љ–µ –љ–∞ D7 (–Њ—З–µ–љ—М —Б—В—А–∞–љ–љ–Њ, –њ–Њ—З–µ–Љ—Г —В–∞–Ї —Б–і–µ–ї–∞–ї–∞ Xilinx). –Ш–Ј-–Ј–∞ —Н—В–Њ–≥–Њ –љ–µ—Б—В–∞–љ–і–∞—А—В–љ–Њ–≥–Њ —Г–њ–Њ—А—П–і–Њ—З–Є–≤–∞–љ–Є—П –±–Є—В –њ—А–µ–і—Б—В–∞–≤–ї–µ–љ–Є–µ –і–∞–љ–љ—Л—Е –≤ —Д–∞–є–ї–µ .bin –Њ–±—Л—З–љ–Њ –љ–µ–њ—А–∞–≤–Є–ї—М–љ–Њ–µ. –≠—В–Њ –њ–Њ—В–Њ–Љ—Г —З—В–Њ –±–Њ–ї—М—И–Є–љ—Б—В–≤–Њ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–Њ–≤ –Є–љ—В–µ—А–њ—А–µ—В–Є—А—Г—О—В –±–Є—В D7 (–љ–µ D0) –Ї–∞–Ї —Б–∞–Љ—Л–є –Ј–љ–∞—З–∞—Й–Є–є –±–Є—В (MSB) –≤ –±–∞–є—В–µ. –Я–Њ–і–Ї–ї—О—З–µ–љ–Є–µ D7 –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –љ–∞ D7 —И–Є–љ—Л –і–∞–љ–љ—Л—Е FPGA SelectMAP –≤ —А–µ–∞–ї—М–љ–Њ—Б—В–Є –њ—А–Є–≤–µ–і–µ—В –Ї –Ј–∞–≥—А—Г–Ј–Ї–µ –і–∞–љ–љ—Л—Е "–љ–∞–Њ–±–Њ—А–Њ—В", –≤ —А–µ–Ј—Г–ї—М—В–∞—В–µ –љ–Є—З–µ–≥–Њ —А–∞–±–Њ—В–∞—В—М –љ–µ –±—Г–і–µ—В. –Я–Њ —Н—В–Њ–є –њ—А–Є—З–Є–љ–µ –Є—Б—Е–Њ–і–љ—Л–є –њ–Њ—В–Њ–Ї –і–∞–љ–љ—Л—Е –Љ–Њ–ґ–µ—В –љ—Г–ґ–і–∞—В—М—Б—П –≤ –њ–µ—А–µ—Б—В–∞–љ–Њ–≤–Ї–µ –±–∞–є—В, –њ—А–Є –Ї–Њ—В–Њ—А–Њ–Љ –≤ –Ї–∞–ґ–і–Њ–Љ –±–∞–є—В–µ –њ–Њ—В–Њ–Ї –±–Є—В –і–Њ–ї–ґ–µ–љ –±—Л—В—М –Є–Ј–Љ–µ–љ–µ–љ –љ–∞ –Њ–±—А–∞—В–љ—Л–є. –†–Є—Б. 3 –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В, –Ї–∞–Ї —Н—В–Њ –њ—А–Њ–Є–Ј–Њ–є–і–µ—В —Б –і–≤—Г–Љ—П –±–∞–є—В–∞–Љ–Є (0xABCD).

–†–Є—Б. 3. –Я—А–Є–Љ–µ—А –њ–µ—А–µ–Ї–Њ–і–Є—А–Њ–≤–Ї–Є –±–∞–є—В (Byte-Swapping).

–Э–µ–Ј–∞–≤–Є—Б–Є–Љ–Њ –Њ—В –Њ—А–Є–µ–љ—В–∞—Ж–Є–Є –і–∞–љ–љ—Л—Е, –±–Є—В MSB –Ї–∞–ґ–і–Њ–≥–Њ –±–∞–є—В–∞ –і–Њ–ї–ґ–µ–љ –±—Л—В—М –њ–Њ–і–∞–љ –љ–∞ D0. –Ф–ї—П –≤–µ—А—Б–Є–Є –і–∞–љ–љ—Л—Е, –≤ –Ї–Њ—В–Њ—А–Њ–є –њ–Њ—А—П–і–Њ–Ї –±–Є—В —Г–ґ–µ –Є–Ј–Љ–µ–љ–µ–љ, –љ–∞ D0 –љ–∞–і–Њ –њ–Њ–і–∞–≤–∞—В—М —Б–∞–Љ—Л–є –њ—А–∞–≤—Л–є –±–Є—В –±–∞–є—В–∞ (–Љ–ї–∞–і—И–Є–є –±–Є—В, LSB), –∞ –і–ї—П –≤–µ—А—Б–Є–Є –і–∞–љ–љ—Л—Е, –≤ –Ї–Њ—В–Њ—А–Њ–Љ –њ–Њ—А—П–і–Њ–Ї –±–Є—В –љ–µ –Є–Ј–Љ–µ–љ–µ–љ, –љ–∞ D0 –љ–∞–і–Њ –њ–Њ–і–∞–≤–∞—В—М —Б–∞–Љ—Л–є –ї–µ–≤—Л–є –±–Є—В (—Б—В–∞—А—И–Є–є –±–Є—В, MSB). –Я—А–Є–ї–∞–≥–∞–µ–Љ—Л–є –Ї —Н—В–Њ–Љ—Г –∞–њ–љ–Њ—Г—В—Г —Б–Ї—А–Є–њ—В Perl [4] –Љ–Њ–ґ–µ—В –±—Л—В—М –љ–∞—Б—В—А–Њ–µ–љ –і–ї—П –≥–µ–љ–µ—А–∞—Ж–Є–Є —Д–∞–є–ї–Њ–≤ —Б –Є–Ј–Љ–µ–љ–µ–љ–љ—Л–Љ –њ–Њ—А—П–і–Ї–Њ–Љ –±–Є—В –Є–ї–Є –±–µ–Ј –Є–Ј–Љ–µ–љ–µ–љ–Є—П –њ–Њ—А—П–і–Ї–∞ –±–Є—В (–њ–Њ–і—А–Њ–±–љ–Њ—Б—В–Є —Б–Љ. –≤ —Д–∞–є–ї–µ bitformat.readme). –У–µ–љ–µ—А–Є—А—Г–µ–Љ—Л–µ –њ—А–Њ–≥—А–∞–Љ–Љ–љ—Л–Љ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є–µ–Љ Xilinx —Д–∞–є–ї—Л .mcs, .exo –Є .tek –≤—Б–µ–≥–і–∞ –Є–Љ–µ—О—В –Є–Ј–Љ–µ–љ–µ–љ–љ—Л–є –њ–Њ—А—П–і–Њ–Ї –±–Є—В, –∞ —Д–∞–є–ї—Л .bit, .rbt –Є .bin –Є–Љ–µ—О—В –љ–µ–Є–Ј–Љ–µ–љ–µ–љ–љ—Л–є –њ–Њ—А—П–і–Њ–Ї –±–Є—В. –§–∞–є–ї—Л –≤ —Д–Њ—А–Љ–∞—В–µ HEX –Љ–Њ–≥—Г—В –±—Л—В—М —Б–≥–µ–љ–µ—А–Є—А–Њ–≤–∞–љ—Л —Б –Љ–Њ–і–Є—Д–Є–Ї–∞—Ж–Є–µ–є –њ–Њ—А—П–і–Ї–∞ –±–Є—В –≤ –±–∞–є—В–µ, –≤ –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В –Њ–њ—Ж–Є–є –≤ –Ї–Њ–Љ–∞–љ–і–љ–Њ–є —Б—В—А–Њ–Ї–µ.

–Я—А–Є–Љ–µ—З–∞–љ–Є–µ: –Є–Ј–Љ–µ–љ–µ–љ –ї–Є –њ–Њ—А—П–і–Њ–Ї –±–Є—В –≤ —Д–∞–є–ї–µ –Є–ї–Є –љ–µ—В - –Њ–± —Н—В–Њ–Љ –љ—Г–ґ–љ–Њ –і—Г–Љ–∞—В—М –Њ–±—Л—З–љ–Њ —В–Њ–ї—М–Ї–Њ —В–Њ–≥–і–∞, –Ї–Њ–≥–і–∞ –≤ –њ—А–Є–ї–Њ–ґ–µ–љ–Є–Є –њ—А–Є–Љ–µ–љ–µ–љ —А–µ–ґ–Є–Љ –Ј–∞–≥—А—Г–Ј–Ї–Є SelectMAP. –Ф–∞–љ–љ—Л–µ –±–µ–Ј –Є–Ј–Љ–µ–љ–µ–љ–Є—П –њ–Њ—А—П–і–Ї–∞ –±–Є—В –і–Њ–ї–ґ–љ—Л –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М—Б—П –і–ї—П –Ј–∞–≥—А—Г–Ј–Ї–Є –≤ —А–µ–ґ–Є–Љ–µ Slave Serial.

[–Ю—И–Є–±–Ї–Є –Є –Є—Е —Г—Б—В—А–∞–љ–µ–љ–Є–µ]

–Х—Б–ї–Є –Ј–∞–≥—А—Г–Ј–Ї–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є –њ—А–Њ—И–ї–∞ —Б –Њ—И–Є–±–Ї–Њ–є, –≤—Л–≤–Њ–і DONE –љ–µ –њ–µ—А–µ–є–і–µ—В –≤ —Б–Њ—Б—В–Њ—П–љ–Є–µ –ї–Њ–≥. 1 –њ–Њ—Б–ї–µ —В–Њ–≥–Њ, –Ї–∞–Ї –≤—Б–µ –і–∞–љ–љ—Л–µ –±—Л–ї–Є –Ј–∞–≥—А—Г–ґ–µ–љ—Л. –Ь–Њ–ґ–µ—В –±—Л—В—М –Љ–љ–Њ–ґ–µ—Б—В–≤–Њ –њ—А–Є—З–Є–љ, –Є–Ј-–Ј–∞ —З–µ–≥–Њ —Н—В–Њ –Љ–Њ–ґ–µ—В –њ—А–Њ–Є–Ј–Њ–є—В–Є. –Т–Њ–Ј–Љ–Њ–ґ–љ—Л–µ —Б–ї—Г—З–∞–Є –Є —А–µ—И–µ–љ–Є—П –њ—А–Њ–±–ї–µ–Љ –Љ–Њ–≥—Г—В –±—Л—В—М –љ–∞–є–і–µ–љ—Л –њ–Њ–Є—Б–Ї–Њ–Љ –њ–Њ –±–∞–Ј–µ Xilinx Answers Database –Є–ї–Є —Б –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ–Љ Configuration Problem Solver –љ–∞ —Б–∞–є—В–µ support.xilinx.com.

[–Р–њ–њ–∞—А–∞—В–љ–∞—П —А–µ–∞–ї–Є–Ј–∞—Ж–Є—П —А–µ–ґ–Є–Љ–∞ SelectMAP]

–Я—А–Є–Љ–µ—А –і–Є–Ј–∞–є–љ–∞ –њ—А–Є–ї–Њ–ґ–µ–љ–Є—П –Њ—Б–љ–Њ–≤–∞–љ –љ–∞ –њ—А–Њ—Ж–µ—Б—Б–Њ—А–µ Motorola Dragonball MC68VZ328. –≠—В–Њ—В –і–Є–Ј–∞–є–љ –±—Л–ї –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ –≤ –љ–∞–ї–∞–і–Њ–љ–љ–Є–Ї–µ Handspring Visor –і–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П Virtex FPGA. –Ф–ї—П –њ–Њ–ї–љ–Њ–є —Б–Є—Б—В–µ–Љ—Л –Љ–Њ–ґ–љ–Њ –њ—А–Є–Љ–µ–љ–Є—В—М Insight Springboard Development Kit, –≥–і–µ –љ–∞ –њ–ї–∞—В–µ –њ—А–µ–і–Њ—Б—В–∞–≤–ї–µ–љ–Њ 32 –Љ–µ–≥–∞–±–∞–є—В–∞ –њ–∞–Љ—П—В–Є flash, –Ї–∞–Ї –Є 256-macrocell CoolRunnerвДҐ CPLD.

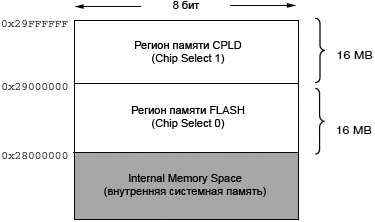

–†–Є—Б—Г–љ–Њ–Ї 4 –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В –Ї–∞—А—В—Г –њ–∞–Љ—П—В–Є –і–ї—П –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ Dragonball, –Є—Б–њ–Њ–ї—М–Ј—Г–µ–Љ—Г—О –і–ї—П —Н—В–Њ–є —А–∞–Ј—А–∞–±–Њ—В–Ї–Є. –°–ї–Њ—В —А–∞—Б—И–Є—А–µ–љ–Є—П Handspring Visor Springboard –њ—А–µ–і–Њ—Б—В–∞–≤–ї—П–µ—В –і–≤–∞ —А–µ–≥–Є–Њ–љ–∞ –∞–і—А–µ—Б–љ–Њ–≥–Њ –њ—А–Њ—Б—В—А–∞–љ—Б—В–≤–∞ —Б –≤—Л–±–Њ—А–Ї–Њ–є –≤–љ–µ—И–љ–µ–є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л (chip select), –і–Њ—Б—В—Г–њ–љ—Л—Е –і–ї—П –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—П, –љ–∞–Ј—Л–≤–∞–µ–Љ—Л–µ Chip Select 0 –Є Chip Select 1. –Я–∞–Љ—П—В—М flash –њ–Њ–і–Ї–ї—О—З–µ–љ–∞ –Ї —А–µ–≥–Є–Њ–љ—Г Chip Select 0, –Њ–њ—А–µ–і–µ–ї–µ–љ–љ–Њ–Љ—Г –Ї–∞–Ї –∞–і—А–µ—Б–љ–Њ–µ –њ—А–Њ—Б—В—А–∞–љ—Б—В–≤–Њ –Љ–µ–ґ–і—Г 0x28000000 –Є 0x28FFFFFF. –Ь–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ CPLD –њ–Њ–і–Ї–ї—О—З–µ–љ–∞ –Ї —А–µ–≥–Є–Њ–љ—Г Chip Select 1, –Њ–њ—А–µ–і–µ–ї–µ–љ–љ–Њ–Љ—Г –Ї–∞–Ї –∞–і—А–µ—Б–љ–Њ–µ –њ—А–Њ—Б—В—А–∞–љ—Б—В–≤–Њ –Љ–µ–ґ–і—Г 0x29000000 –Є 0x29FFFFFF. –Ъ–∞–ґ–і–∞—П —П—З–µ–є–Ї–∞ –њ–∞–Љ—П—В–Є –≤ –∞–і—А–µ—Б–љ–Њ–Љ –њ—А–Њ—Б—В—А–∞–љ—Б—В–≤–µ —Б—Б—Л–ї–∞–µ—В—Б—П –љ–∞ 8 –±–Є—В –і–∞–љ–љ—Л—Е. –Ю–і–љ–∞–Ї–Њ –њ—А–Њ—Ж–µ—Б—Б–Њ—А Dragonball –љ–µ –њ–Њ–і–і–µ—А–ґ–Є–≤–∞–µ—В –њ–Њ–±–∞–є—В–љ—Г—О –∞–і—А–µ—Б–∞—Ж–Є—О. –Ъ–∞–Ї —Б–ї–µ–і—Б—В–≤–Є–µ –ї–Є–љ–Є—П 0 —И–Є–љ—Л –∞–і—А–µ—Б–∞ –љ–µ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П. –Ґ–∞–Ї–Є–Љ –Њ–±—А–∞–Ј–Њ–Љ, –і–∞–љ–љ—Л–µ –Љ–Њ–≥—Г—В –±—Л—В—М –і–Њ—Б—В—Г–њ–љ—Л –≤ —П—З–µ–є–Ї–∞—Е —Б —З–µ—В–љ—Л–Љ –∞–і—А–µ—Б–Њ–Љ (—В. –µ. 0x28000000, 0x28000002, –Є —В. –і.). –Ъ–∞–ґ–і—Л–є –і–Њ—Б—В—Г–њ –љ–∞ —З—В–µ–љ–Є–µ –Є–ї–Є –Ј–∞–њ–Є—Б—М –∞–і—А–µ—Б—Г–µ—В —Б—А–∞–Ј—Г 16 –±–Є—В –і–∞–љ–љ—Л—Е. –Ф–Њ—Б—В—Г–њ –Ї —П—З–µ–є–Ї–∞–Љ, —А–∞—Б–њ–Њ–ї–Њ–ґ–µ–љ–љ—Л–Љ –њ–Њ –љ–µ—З–µ—В–љ—Л–Љ –∞–і—А–µ—Б–∞–Љ, –Ј–∞–њ—А–µ—Й–µ–љ.

–Ч–∞—В–µ–љ–µ–љ–љ–∞—П –Њ–±–ї–∞—Б—В—М –≤ –љ–Є–ґ–љ–µ–є —З–∞—Б—В–Є –Ї–∞—А—В—Л –њ–∞–Љ—П—В–Є, –Ї–∞–Ї —Н—В–Њ –њ–Њ–Ї–∞–Ј–∞–љ–Њ –љ–∞ —А–Є—Б—Г–љ–Ї–µ 4 (Internal Memory Space), –њ—А–µ–і—Б—В–∞–≤–ї—П–µ—В —З–∞—Б—В–Є –њ–∞–Љ—П—В–Є, –Є—Б–њ–Њ–ї—М–Ј—Г–µ–Љ—Л–µ –њ—А–Њ—Ж–µ—Б—Б–Њ—А–Њ–Љ –і–ї—П –≤–љ—Г—В—А–µ–љ–љ–Є—Е —Д—Г–љ–Ї—Ж–Є–є. –≠—В–∞ –Њ–±–ї–∞—Б—В—М –њ–∞–Љ—П—В–Є –љ–µ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –≤ —Н—В–Њ–Љ –њ—А–Є–Љ–µ—А–µ –і–Є–Ј–∞–є–љ–∞.

–†–Є—Б. 4. –Ъ–∞—А—В–∞ –њ–∞–Љ—П—В–Є –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞.

–Я—А–Є–Љ–µ—З–∞–љ–Є–µ: —Е–Њ—В—П –Ј–і–µ—Б—М –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –њ—А–Њ—Ж–µ—Б—Б–Њ—А Motorola Dragonball, –Љ–Њ–ґ–µ—В –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М—Б—П –ї—О–±–Њ–є –і—А—Г–≥–Њ–є –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А. –Ъ—А–Њ–Љ–µ —В–Њ–≥–Њ, –Ї–Њ–і –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ —Н—В–Њ–≥–Њ –њ—А–Є–Љ–µ—А–∞ –і–Є–Ј–∞–є–љ–∞ [4] –Љ–Њ–ґ–µ—В –±—Л—В—М –Њ—З–µ–љ—М –њ—А–Њ—Б—В–Њ –њ–Њ—А—В–Є—А–Њ–≤–∞–љ –љ–∞ –і—А—Г–≥–Є–µ –њ—А–Њ—Ж–µ—Б—Б–Њ—А—Л. –Ю–і–љ–∞–Ї–Њ –њ–µ—А–µ–љ–∞–Ј–љ–∞—З–µ–љ–Є–µ –Њ–±–ї–∞—Б—В–µ–є –њ–∞–Љ—П—В–Є —В—А–µ–±—Г–µ—В –њ–Њ–љ–Є–Љ–∞–љ–Є—П —В–Њ–≥–Њ, –Ї–∞–Ї –±—Л–ї–∞ –Є–Ј–љ–∞—З–∞–ї—М–љ–Њ –Њ—А–≥–∞–љ–Є–Ј–Њ–≤–∞–љ–∞ —Б—В—А—Г–Ї—В—Г—А–∞ –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞ Dragonball, —З—В–Њ–±—Л –Њ–љ–∞ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤–Њ–≤–∞–ї–∞ –Ї–∞—А—В–µ –њ–∞–Љ—П—В–Є –і—А—Г–≥–Њ–≥–Њ –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞.

[–Я–∞–Љ—П—В—М FLASH]

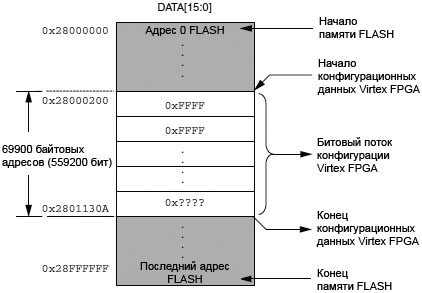

–Т —Н—В–Њ–Љ –њ—А–Є–Љ–µ—А–µ —А–∞–Ј—А–∞–±–Њ—В–Ї–Є 16-–±–Є—В–љ–∞—П –њ–∞–Љ—П—В—М flash –љ–∞—З–Є–љ–∞–µ—В—Б—П —Б –±–∞–є—В–Њ–≤–Њ–≥–Њ –∞–і—А–µ—Б–∞ 0x28000000 –Є –Ј–∞–Ї–∞–љ—З–Є–≤–∞–µ—В—Б—П –∞–і—А–µ—Б–Њ–Љ 0x28FFFFFF. –Ъ–∞–Ї –њ–Њ–Ї–∞–Ј–∞–љ–Њ –љ–∞ —А–Є—Б. 5, –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–є –њ–Њ—В–Њ–Ї –і–∞–љ–љ—Л—Е Virtex XCV50 —Б–Њ—Б—В–Њ–Є—В –Є–Ј 559200 –±–Є—В. –Я–Њ—Б–Ї–Њ–ї—М–Ї—Г –Ї–∞–ґ–і–∞—П —П—З–µ–є–Ї–∞ –њ–∞–Љ—П—В–Є —Б–Њ–і–µ—А–ґ–Є—В 16 –±–Є—В –і–∞–љ–љ—Л—Е, –љ—Г–ґ–љ–Њ –≤—Б–µ–≥–Њ 559200 / 16 = 34950 –∞–і—А–µ—Б–Њ–≤. –Я–µ—А–≤—Л–µ 16 –±–Є—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л—Е –і–∞–љ–љ—Л—Е –љ–∞—Е–Њ–і—П—В—Б—П –њ–Њ –∞–і—А–µ—Б—Г 0x28000200, –Є –њ–Њ—Б–ї–µ–і–љ–Є–µ 16 –±–Є—В –њ–Њ –∞–і—А–µ—Б—Г

0x2801130A (—Н—В–Њ –±–∞–є—В–Њ–≤—Л–µ –∞–і—А–µ—Б–∞). –Т —Н—В–Њ–Љ –њ—А–Њ–µ–Ї—В–µ –∞–і—А–µ—Б 0x28000200 –≤—Л–±—А–∞–љ –њ—А–Њ–Є–Ј–≤–Њ–ї—М–љ–Њ –≤ –Ї–∞—З–µ—Б—В–≤–µ —Б—В–∞—А—В–Њ–≤–Њ–≥–Њ, —З—В–Њ–±—Л –Љ–Њ–і–µ–ї–Є—А–Њ–≤–∞—В—М —А–µ–∞–ї—М–љ—Л–є –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—М—Б–Ї–Є–є —Б—Ж–µ–љ–∞—А–Є–є, –≤ –Ї–Њ—В–Њ—А–Њ–Љ –њ–∞–Љ—П—В—М flash –Љ–Њ–ґ–µ—В —Б–Њ–і–µ—А–ґ–∞—В—М —В–∞–Ї–ґ–µ –Є –і—А—Г–≥–Є–µ —Б–Є—Б—В–µ–Љ–љ—Л–µ –і–∞–љ–љ—Л–µ.

–Ф–∞–љ–љ—Л–µ –≤ –њ–∞–Љ—П—В–Є flash –Љ–Њ–≥—Г—В –љ—Г–ґ–і–∞—В—М—Б—П –≤ –њ–µ—А–µ—Б—В–∞–љ–Њ–≤–Ї–µ, –≤ –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В –њ—А–Є–ї–Њ–ґ–µ–љ–Є—П. –Ф–ї—П —Н—В–Њ–≥–Њ –њ—А–Є–Љ–µ—А–∞ —А–∞–Ј—А–∞–±–Њ—В–Ї–Є –Є—Б–њ–Њ–ї—М–Ј—Г—О—В—Б—П –њ–µ—А–µ—Б—В–∞–≤–ї–µ–љ–љ—Л–µ –і–∞–љ–љ—Л–µ –і–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є –Ј–∞–≥—А—Г–Ј–Ї–Є SelectMAP, –љ–Њ —Н—В–Њ –љ–µ —В—А–µ–±—Г–µ—В—Б—П –і–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є Slave-Serial. –Я–µ—А–µ—Б—В–∞–љ–Њ–≤–Ї–∞ –і–∞–љ–љ—Л—Е –≤ –±–∞–є—В–∞—Е –і–∞–љ–љ—Л—Е –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є FPGA –Ј–∞–Ї–ї—О—З–∞–µ—В—Б—П –≤ —В–Њ–Љ, —З—В–Њ –њ–Њ—А—П–і–Њ–Ї –±–Є—В –≤ –Ї–∞–ґ–і–Њ–Љ –±–∞–є—В–µ –Љ–µ–љ—П–µ—В—Б—П –љ–∞ –Њ–±—А–∞—В–љ—Л–є, –Ї–∞–Ї —Н—В–Њ —Г–ґ–µ –Њ–њ–Є—Б—Л–≤–∞–ї–Њ—Б—М –≤ —А–∞–Ј–і–µ–ї–µ "–§–Њ—А–Љ–∞—В–Є—А–Њ–≤–∞–љ–Є–µ –і–∞–љ–љ—Л—Е –Є –њ–µ—А–µ—Б—В–∞–љ–Њ–≤–Ї–∞ –±–∞–є—В".

–†–Є—Б. 5. –Ъ–∞—А—В–∞ –њ–∞–Љ—П—В–Є FLASH.

[–Р–њ–њ–∞—А–∞—В—Г—А–∞ —А–µ–ґ–Є–Љ–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П Slave-SelectMAP]

–†–µ–ґ–Є–Љ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П FPGA SelectMAP –њ–Њ–Ј–≤–Њ–ї—П–µ—В –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Г –±—Л—Б—В—А–µ–µ —Б–Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞—В—М —З–Є–њ FPGA, –њ–Њ—В–Њ–Љ—Г —З—В–Њ –Ј–∞ –Њ–і–Є–љ —В–∞–Ї—В –Ј–∞–≥—А—Г–ґ–∞–µ—В—Б—П –љ–µ 1, –∞ —Б—А–∞–Ј—Г 8 –±–Є—В, 16 –Є–ї–Є 32 –±–Є—В–∞ (–≤ –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В —И–Є—А–Є–љ—Л —И–Є–љ—Л SelectMAP). –І—В–Њ–±—Л —А–µ–∞–ї–Є–Ј–Њ–≤–∞—В—М –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є–µ SelectMAP, —Н—В–Њ—В –і–Є–Ј–∞–є–љ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В –Ї–Њ–Љ–±–Є–љ–∞—Ж–Є—О –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞, CPLD –Є –њ–∞–Љ—П—В–Є flash (—Б–Љ. —А–Є—Б. 6).

–†–Є—Б. 6. –Ъ–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є—П SelectMAP.

–Ф–ї—П —Е—А–∞–љ–µ–љ–Є—П –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л—Е –і–∞–љ–љ—Л—Е –і–ї—П FPGA –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П 16-–±–Є—В–љ–∞—П –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ –њ–∞–Љ—П—В–Є flash. –Я–Њ—Б–Ї–Њ–ї—М–Ї—Г –Ї–∞–ґ–і—Л–є –∞–і—А–µ—Б flash —Б—Б—Л–ї–∞–µ—В—Б—П –љ–∞ 16 –±–Є—В –і–∞–љ–љ—Л—Е, –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А —З–Є—В–∞–µ—В –Ї–∞–ґ–і—Л–є –∞–і—А–µ—Б —З—В–Њ–±—Л –њ–Њ–ї—Г—З–Є—В—М 16 –±–Є—В –і–∞–љ–љ—Л—Е –Є –њ–µ—А–µ–і–∞–µ—В —Н—В–Є –і–∞–љ–љ—Л–µ –њ–Њ–±–∞–є—В–љ–Њ –≤ FPGA. –Т–Њ –≤—А–µ–Љ—П —Н—В–Њ–≥–Њ –њ—А–Њ—Ж–µ—Б—Б–∞ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А –њ—А–µ–і–Њ—Б—В–∞–≤–ї—П–µ—В –і–ї—П FPGA –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ —В–∞–Ї—В—Л –Є —Б–ї–µ–і–Є—В –Ј–∞ —Б–Њ—Б—В–Њ—П–љ–Є–µ–Љ –≤—Л–≤–Њ–і–Њ–≤ DONE –Є BUSY. –Ь–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ Xilinx CoolRunner CPLD –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –і–ї—П —Д–Њ—А–Љ–Є—А–Њ–≤–∞–љ–Є—П –њ—А–Њ–Љ–µ–ґ—Г—В–Њ—З–љ–Њ–є –ї–Њ–≥–Є–Ї–Є –Љ–µ–ґ–і—Г –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–Њ–Љ –Є —Г—Б—В—А–Њ–є—Б—В–≤–Њ–Љ FPGA.

CoolRunner CPLD

–Т —А–µ–ґ–Є–Љ–µ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П SelectMAP –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ CPLD –Њ—В–≤–µ—З–∞–µ—В –Ј–∞ —Г–њ—А–∞–≤–ї–µ–љ–Є–µ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–Љ–Є –≤—Л–≤–Њ–і–∞–Љ–Є Virtex FPGA, –Ї–Њ—В–Њ—А—Л–µ –љ–Њ—Б—П—В –Є–Љ–µ–љ–∞ ~PROGRAM, ~CS, ~WRITE, CCLK –Є D[0:7]. –Т—Л–≤–Њ–і—Л Virtex FPGA INIT, DONE –Є BUSY —В–∞–Ї–ґ–µ –Ј–∞—Е–Њ–і—П—В –љ–∞ CPLD, —З—В–Њ –њ–Њ–Ј–≤–Њ–ї—П–µ—В –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Г –Ї–Њ–љ—В—А–Њ–ї–Є—А–Њ–≤–∞—В—М —Б–Њ—Б—В–Њ—П–љ–Є–µ —Н—В–Є—Е –≤—Л–≤–Њ–і–Њ–≤.

CoolRunner CPLD –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –і–ї—П –Њ—А–≥–∞–љ–Є–Ј–∞—Ж–Є–Є –Є–љ—В–µ—А—Д–µ–є—Б–∞ –Љ–µ–ґ–і—Г —И–Є–љ–Њ–є –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –Є Xilinx FPGA. –≠—В–Њ—В –Є–љ—В–µ—А—Д–µ–є—Б –њ—А–µ–і—Б—В–∞–≤–ї–µ–љ —В—А–µ–Љ—П —А–µ–≥–Є—Б—В—А–∞–Љ–Є: Configuration Register (—А–µ–≥–Є—Б—В—А –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є), Program Register (—А–µ–≥–Є—Б—В—А –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П) –Є Input Register (–≤—Е–Њ–і–љ–Њ–є —А–µ–≥–Є—Б—В—А). –≠—В–Є —А–µ–≥–Є—Б—В—А—Л —Е—А–∞–љ—П—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ —Б–Є–≥–љ–∞–ї—Л FPGA –Ї–∞–ґ–і—Л–є —А–∞–Ј, –Ї–Њ–≥–і–∞ –њ—А–Њ—Ж–µ—Б—Б–Њ—А –≤—Л–њ–Њ–ї–љ—П–µ—В —З—В–µ–љ–Є–µ –њ–Њ—А—В–∞ –Є–ї–Є –Ј–∞–њ–Є—Б—М –≤ –њ–Њ—А—В, —В–µ–Љ —Б–∞–Љ—Л–Љ –њ–Њ–і–і–µ—А–ґ–Є–≤–∞—П –љ–∞–±–Њ—А —Б–Є–≥–љ–∞–ї–Њ–≤, —В—А–µ–±—Г–µ–Љ—Л—Е –і–ї—П —А–µ–ґ–Є–Љ–∞ SelectMAP (~PROGRAM, CCLK, DATA[0:7], ~INIT, ~CS, ~WRITE, DONE –Є BUSY). Configuration Register –Є Program Register —П–≤–ї—П—О—В—Б—П —А–µ–≥–Є—Б—В—А–∞–Љ–Є —В–Њ–ї—М–Ї–Њ –і–ї—П –Ј–∞–њ–Є—Б–Є (write-only), —В–Њ–≥–і–∞ –Ї–∞–Ї Input Register —П–≤–ї—П–µ—В—Б—П —А–µ–≥–Є—Б—В—А–Њ–Љ —В–Њ–ї—М–Ї–Њ –і–ї—П —З—В–µ–љ–Є—П (read-only).

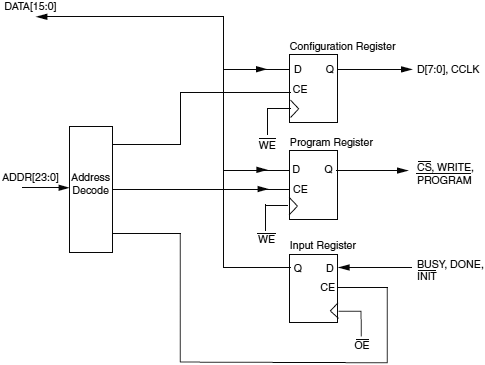

–Ф–µ—В–∞–ї–Є–Ј–Є—А–Њ–≤–∞–љ–љ–∞—П –±–ї–Њ–Ї-—Б—Е–µ–Љ–∞ CPLD –њ–Њ–Ї–∞–Ј–∞–љ–∞ –љ–∞ —А–Є—Б—Г–љ–Ї–µ 7.

–†–Є—Б. 7. –С–ї–Њ–Ї-—Б—Е–µ–Љ–∞ CPLD.

–Ъ–∞—А—В–∞ —А–µ–≥–Є—Б—В—А–Њ–≤ –њ–Њ–Ї–∞–Ј–∞–љ–∞ –≤ —В–∞–±–ї–Є—Ж–µ 4.

–Ґ–∞–±–ї–Є—Ж–∞ 4. –Р–і—А–µ—Б–љ–∞—П –Ї–∞—А—В–∞ —А–µ–≥–Є—Б—В—А–Њ–≤.

–Р–і—А–µ—Б —А–µ–≥–Є—Б—В—А–∞

A[23:0] |

–Ш–Љ—П —А–µ–≥–Є—Б—В—А–∞ |

–Ф–∞–љ–љ—Л–µ –≤ —А–µ–≥–Є—Б—В—А–µ |

| D[15:9] |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

| 0x000000 |

Configuration

Register |

D[7:0] |

- |

- |

- |

- |

- |

- |

- |

- |

CCLK |

| 0x000002 |

Program

Register |

- |

- |

- |

- |

- |

- |

- |

~CS |

~WRITE |

~PROGRAM |

| 0x000004 |

Input

Register |

- |

- |

- |

- |

- |

- |

- |

BUSY |

DONE |

~INIT |

SelectMAP.c

–Т —Н—В–Њ–є —Б–µ–Ї—Ж–Є–Є –Њ–±—Б—Г–ґ–і–∞–µ—В—Б—П –Ї–Њ–і –љ–∞ —П–Ј—Л–Ї–µ C, –Ї–Њ—В–Њ—А—Л–є –њ–Њ–Ј–≤–Њ–ї—П–µ—В –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Г –≤—Л–њ–Њ–ї–љ—П—В—М —Б–ї–µ–і—Г—О—Й–Є–µ –Њ–њ–µ—А–∞—Ж–Є–Є:

вАҐ –І–Є—В–∞—В—М –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ –і–∞–љ–љ—Л–µ FPGA –Є–Ј –њ–∞–Љ—П—В–Є flash.

вАҐ –У–µ–љ–µ—А–Є—А–Њ–≤–∞—В—М —В–∞–Ї—В—Л CCLK.

вАҐ –Я–µ—А–µ–і–∞–≤–∞—В—М –њ–Њ–±–∞–є—В–љ–Њ –і–∞–љ–љ—Л–µ –і–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П FPGA.

вАҐ –Я—А–Њ–≤–µ—А—П—В—М —Б–Њ—Б—В–Њ—П–љ–Є–µ –≤—Л–≤–Њ–і–∞ BUSY (–љ–µ –Њ–±—П–Ј–∞—В–µ–ї—М–љ–∞—П –Њ–њ–µ—А–∞—Ж–Є—П).

–Я—А–Є–Љ–µ—З–∞–љ–Є–µ: —А–∞–Ј–љ—Л–µ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Л –Є–Љ–µ—О—В —А–∞–Ј–ї–Є—З–љ—Л–µ —Б—В—А—Г–Ї—В—Г—А—Л –Њ—А–≥–∞–љ–Є–Ј–∞—Ж–Є–Є –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞ –њ–∞–Љ—П—В–Є, –≤ –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є —Б–Є—Б—В–µ–Љ—Л. –Ґ–∞–Ї–Є–Љ –Њ–±—А–∞–Ј–Њ–Љ, –≤ —В–Њ –≤—А–µ–Љ—П –Ї–∞–Ї –±–Њ–ї—М—И–Є–љ—Б—В–≤–Њ –Ї–Њ–і–∞ C –ї–µ–≥–Ї–Њ –њ–µ—А–µ–љ–Њ—Б–Є—В—Б—П —Б –Њ–і–љ–Њ–є –њ–ї–∞—В—Д–Њ—А–Љ—Л –љ–∞ –і—А—Г–≥—Г—О, –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—М –≤—Б–µ-—В–∞–Ї–Є –і–Њ–ї–ґ–µ–љ –Є–Ј–Љ–µ–љ–Є—В—М —З–∞—Б—В–Є –Ї–Њ–і–∞, —Г–њ—А–∞–≤–ї—П—О—Й–Є–µ —Д–Є–Ј–Є—З–µ—Б–Ї–Є–Љ–Є –Њ–њ–µ—А–∞—Ж–Є—П–Љ–Є —З—В–µ–љ–Є—П –Є –Ј–∞–њ–Є—Б–Є —Б–≤–Њ–µ–є —И–Є–љ—Л –і–∞–љ–љ—Л—Е, —З—В–Њ–±—Л –Њ–љ–Є —Б–Њ–Њ—В–≤–µ—В—Б—В–≤–Њ–≤–∞–ї–Є –Ї–∞—А—В–µ –њ–∞–Љ—П—В–Є —Б–Є—Б—В–µ–Љ—Л –љ–∞ –љ–Њ–≤–Њ–Љ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–µ.

–Ф–ї—П –Љ–∞–Ї—Б–Є–Љ–∞–ї—М–љ–Њ–≥–Њ —Г–і–Њ–±—Б—В–≤–∞ –њ–Њ–љ–Є–Љ–∞–љ–Є—П –Є —З—В–µ–љ–Є—П –≤–µ—Б—М –Ї–Њ–і C, –њ–Њ–Ї–∞–Ј–∞–љ–љ—Л–є –≤ —Н—В–Њ–Љ —А—Г–Ї–Њ–≤–Њ–і—Б—В–≤–µ, –≤—Л–њ–Њ–ї–љ—П–µ—В –і–Њ—Б—В—Г–њ –Ї —И–Є–љ–∞–Љ –∞–і—А–µ—Б–∞ –Є –і–∞–љ–љ—Л—Е –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ —Г–љ–Є—Д–Є—Ж–Є—А–Њ–≤–∞–љ–Њ, —Б –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ–Љ –і–≤—Г—Е –њ—А–Њ—Б—В—Л—Е —Д—Г–љ–Ї—Ж–Є–є: IOWrite() –Є IORead(). IOWrite() –Ј–∞–њ–Є—Б—Л–≤–∞–µ—В 16-–±–Є—В–љ–Њ–µ —Б–ї–Њ–≤–Њ –њ–Њ —Г–Ї–∞–Ј–∞–љ–љ–Њ–Љ—Г –∞–і—А–µ—Б—Г; IORead() –њ–Њ–ї—Г—З–∞–µ—В 16-–±–Є—В–љ—Л–µ –і–∞–љ–љ—Л–µ –Є–Ј —Г–Ї–∞–Ј–∞–љ–љ–Њ–є —П—З–µ–є–Ї–Є –њ–∞–Љ—П—В–Є (–Њ–њ–Є—Б–∞–љ–Є–µ —Б–Є–љ—В–∞–Ї—Б–Є—Б–∞ —Д—Г–љ–Ї—Ж–Є–є —Б–Љ. –≤ –њ—А–Є–ї–Њ–ґ–µ–љ–Є–Є "–Ю–њ–Є—Б–∞–љ–Є–µ —Б–њ–µ—Ж–Є—Д–Є—З–љ—Л—Е –і–ї—П –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ –≤—Л–Ј–Њ–≤–Њ–≤ —Д—Г–љ–Ї—Ж–Є–є –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞").

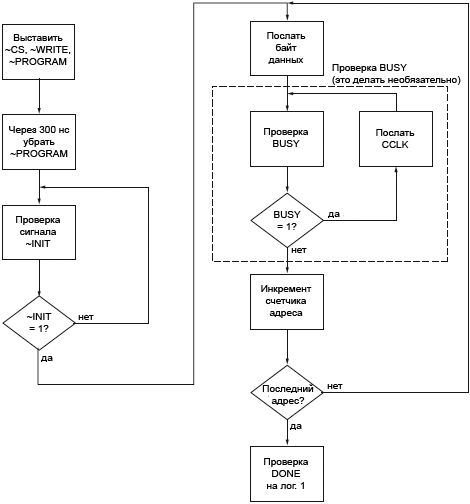

–§–∞–є–ї –Є—Б—Е–Њ–і–љ–Њ–≥–Њ –Ї–Њ–і–∞ SelectMAP.c —Б–Њ–і–µ—А–ґ–Є—В 3 –≤–∞–ґ–љ—Л–µ —Д—Г–љ–Ї—Ж–Є–Є: SelectMAP(), SelectMAP_output() –Є Busy_Check(). –§—Г–љ–Ї—Ж–Є—П SelectMAP() –≤—Л–Ј—Л–≤–∞–µ—В—Б—П, –Є–Ј –≥–ї–∞–≤–љ–Њ–є —Д—Г–љ–Ї—Ж–Є–Є –њ—А–Є–ї–Њ–ґ–µ–љ–Є—П –і–ї—П –љ–∞—З–∞–ї–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є. SelectMAP() –≥–µ–љ–µ—А–Є—А—Г–µ—В –Є–Љ–њ—Г–ї—М—Б—Л –љ–∞ –≤—Л–≤–Њ–і–µ ~PROGRAM –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л FPGA, –Є –њ—А–Њ–≤–µ—А—П–µ—В —Б–Њ—Б—В–Њ—П–љ–Є–µ ~INIT. –Я–Њ—Б–ї–µ —В–Њ–≥–Њ, –Ї–∞–Ї ~INIT –њ–µ—А–µ—И–µ–ї –≤ 1, –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ –≥–Њ—В–Њ–≤–∞ –њ—А–Є–љ—П—В—М –і–∞–љ–љ—Л–µ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є, –Є –≤—Л–Ј—Л–≤–∞–µ—В—Б—П —Д—Г–љ–Ї—Ж–Є—П SelectMAP_output(). –Р–ї–≥–Њ—А–Є—В–Љ —А–∞–±–Њ—В—Л –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–≥–Њ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є—П –њ–Њ–Ї–∞–Ј–∞–љ –љ–∞ —А–Є—Б. 8.

–†–Є—Б. 8. –Ф–Є–∞–≥—А–∞–Љ–Љ–∞ —А–∞–±–Њ—В—Л –Ї–Њ–і–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П FPGA –≤ —А–µ–ґ–Є–Љ–µ SelectMAP.

–°–љ–∞—З–∞–ї–∞ –њ—А–Њ—Ж–µ—Б—Б–Њ—А –Ј–∞–њ–Є—Б—Л–≤–∞–µ—В Program Register, —З—В–Њ–±—Л –≤—Л—Б—В–∞–≤–Є—В—М –≤—Л–≤–Њ–і ~PROGRAM, —З—В–Њ —Б–±—А–∞—Б—Л–≤–∞–µ—В FPGA.

–Я—А–Є–Љ–µ—З–∞–љ–Є–µ: –Љ–Њ–ґ–µ—В –њ–Њ–љ–∞–і–Њ–±–Є—В—М—Б—П —Ж–Є–Ї–ї –Ј–∞–і–µ—А–ґ–Ї–Є –і–ї—П —В–Њ–≥–Њ, —З—В–Њ–±—Л –≤—Л—Б—В–∞–≤–Є—В—М –≤—Л–≤–Њ–і ~PROGRAM –љ–∞ –Љ–Є–љ–Є–Љ–∞–ї—М–љ–Њ —В—А–µ–±—Г–µ–Љ–Њ–µ –≤—А–µ–Љ—П (–Ј–∞ –Ї–Њ–љ–Ї—А–µ—В–љ—Л–Љ –Ј–љ–∞—З–µ–љ–Є–µ–Љ –≤—А–µ–Љ–µ–љ–Є –Њ–±—А–∞—В–Є—В–µ—Б—М –Ї –і–∞—В–∞—И–Є—В—Г –љ–∞ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й—Г—О –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Г FPGA). –Х—Б–ї–Є FPGA —Б—А–∞–Ј—Г –≥–Њ—В–Њ–≤–∞ –Ї –Ј–∞–≥—А—Г–Ј–Ї–µ –њ–Њ—Б–ї–µ –≤–Ї–ї—О—З–µ–љ–Є—П –њ–Є—В–∞–љ–Є—П, –Є–ї–Є —Б–±—А–Њ—Б –њ—А–Њ–Є—Б—Е–Њ–і–Є—В –њ–Њ-–і—А—Г–≥–Њ–Љ—Г, —В–Њ —Н—В–Њ—В —Ж–Є–Ї–ї –Ј–∞–і–µ—А–ґ–Ї–Є –љ–µ –љ—Г–ґ–µ–љ.

–Я–Њ—Б–ї–µ —В–Њ–≥–Њ, –Ї–∞–Ї –≤—Л—Б—В–∞–≤–ї–µ–љ –±–Є—В ~PROGRAM, —Д—Г–љ–Ї—Ж–Є—П SelectMAP() –њ—А–Њ–≤–µ—А—П–µ—В CPLD Input Register, –њ–Њ–Ї–∞ —Б–Њ—Б—В–Њ—П–љ–Є–µ ~INIT –љ–µ –Њ–Ї–∞–ґ–µ—В—Б—П –≤ –ї–Њ–≥. 1. –Ч–∞—В–µ–Љ —Д—Г–љ–Ї—Ж–Є—П –≤—Е–Њ–і–Є—В –≤ —Ж–Є–Ї–ї for, –Ї–Њ—В–Њ—А—Л–є –њ—А–Њ—Е–Њ–і–Є—В –њ–Њ –≤—Б–µ–Љ—Г –і–Є–∞–њ–∞–Ј–Њ–љ—Г –∞–і—А–µ—Б–Њ–≤ –њ–∞–Љ—П—В–Є flash, –Ї–Њ—В–Њ—А—Л–µ —Б–Њ–і–µ—А–ґ–∞—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ –і–∞–љ–љ—Л–µ –і–ї—П FPGA. –Т —Н—В–Њ–Љ –њ—А–Є–Љ–µ—А–µ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П —Г—Б—В—А–Њ–є—Б—В–≤–Њ FPGA XCV50, –Є –і–Є–∞–њ–∞–Ј–Њ–љ –±–∞–є—В–Њ–≤—Л—Е –∞–і—А–µ—Б–Њ–≤ 0x28000200 .. 0x2801130A. –Ф–ї—П –Ї–∞–ґ–і–Њ–є —П—З–µ–є–Ї–Є –њ–∞–Љ—П—В–Є —Б—З–Є—В—Л–≤–∞—О—В—Б—П 16 –±–Є—В –і–∞–љ–љ—Л—Е (–∞–і—А–µ—Б –Є–љ–Ї—А–µ–Љ–µ–љ—В–Є—А—Г–µ—В—Б—П –љ–∞ 2), –Є –≤—Л–Ј—Л–≤–∞–µ—В—Б—П —Д—Г–љ–Ї—Ж–Є—П SelectMAP_output() –і–ї—П –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –њ–Њ–±–∞–є—В–љ–Њ–є –њ–µ—А–µ–і–∞—З–Є –і–∞–љ–љ—Л—Е –≤ FPGA.

–Я—А–Є–Љ–µ—З–∞–љ–Є–µ: –≤ —Д—Г–љ–Ї—Ж–Є–Є SelectMAP_output() –љ—Г–ґ–љ–Њ 2 —Ж–Є–Ї–ї–∞ –і–ї—П –Ї–∞–ґ–і–Њ–≥–Њ –±–∞–є—В–∞ –≤ —Д–∞–є–ї–µ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є. –Ю–і–Є–љ —Ж–Є–Ї–ї –љ—Г–ґ–µ–љ –і–ї—П –њ–µ—А–µ–≤–Њ–і–∞ —В–∞–Ї—В–Њ–≤–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ –≤ —Б–Њ—Б—В–Њ—П–љ–Є–µ –ї–Њ–≥. 0 –Є –і–ї—П –њ—А–µ–і–Њ—Б—В–∞–≤–ї–µ–љ–Є—П —Б–ї–µ–і—Г—О—Й–µ–≥–Њ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ–Њ–≥–Њ –±–∞–є—В–∞. –Т—В–Њ—А–Њ–є —Ж–Є–Ї–ї –љ—Г–ґ–µ–љ –і–ї—П –њ–µ—А–µ–≤–Њ–і–∞ —В–∞–Ї—В–Њ–≤–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ CCLK –≤ —Б–Њ—Б—В–Њ—П–љ–Є–µ High. –°—А–∞–Ј—Г –њ–Њ—Б–ї–µ –њ–µ—А–µ–≤–Њ–і–∞ –≤—Л–≤–Њ–і–∞ CCLK –≤ —Б–Њ—Б—В–Њ—П–љ–Є–µ –ї–Њ–≥. 1 –≤—Л–Ј—Л–≤–∞–µ—В—Б—П —Д—Г–љ–Ї—Ж–Є—П Busy_Check() –і–ї—П —В–Њ–≥–Њ, —З—В–Њ–±—Л –≥–∞—А–∞–љ—В–Є—А–Њ–≤–∞—В—М –њ—А–∞–≤–Є–ї—М–љ—Л–є –њ—А–Є–µ–Љ –і–∞–љ–љ—Л—Е –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–Њ–є FPGA.

–Х—Б–ї–Є —Б–Є–≥–љ–∞–ї BUSY –≤—Л—Б—В–∞–≤–ї–µ–љ –≤ —Б–Њ—Б—В–Њ—П–љ–Є–µ –ї–Њ–≥. 1, —В–Њ —Д—Г–љ–Ї—Ж–Є—П Busy_Check() –њ—А–Њ–і–Њ–ї–ґ–∞–µ—В –њ—А–µ–і–Њ—Б—В–∞–≤–ї—П—В—М –і–Њ–њ–Њ–ї–љ–Є—В–µ–ї—М–љ—Л–µ —Ж–Є–Ї–ї—Л CCLK, –њ–Њ–Ї–∞ BUSY –љ–µ –њ–µ—А–µ–є–і–µ—В –≤ –ї–Њ–≥. 0. –Я—А–Њ–≤–µ—А–Ї–∞ –≤—Л–≤–Њ–і–∞ BUSY –Ј–∞–љ—П—В–Њ—Б—В–Є FPGA —П–≤–ї—П–µ—В—Б—П –љ–µ–Њ–±—П–Ј–∞—В–µ–ї—М–љ–Њ–є —Д—Г–љ–Ї—Ж–Є–µ–є, –µ—Б–ї–Є —З–∞—Б—В–Њ—В–∞ –Ј–∞–њ–Є—Б–Є –і–∞–љ–љ—Л—Е –љ–µ —Б–ї–Є—И–Ї–Њ–Љ –≤—Л—Б–Њ–Ї–∞.

–Я—А–Є–Љ–µ—З–∞–љ–Є–µ: –Љ–∞–Ї—Б–Є–Љ–∞–ї—М–љ–∞—П —Б–Ї–Њ—А–Њ—Б—В—М –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П –≤ —А–µ–ґ–Є–Љ–µ SelectMAP —А–∞–Ј–ї–Є—З–∞–µ—В—Б—П –Љ–µ–ґ–і—Г –Њ—В–і–µ–ї—М–љ—Л–Љ–Є —Б–µ–Љ–µ–є—Б—В–≤–∞–Љ–Є FPGA. –Ф–ї—П –њ–Њ–ї—Г—З–µ–љ–Є—П —В–Њ—З–љ—Л—Е –і–∞–љ–љ—Л—Е –Њ–±—А–∞—В–Є—В–µ—Б—М –Ї —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–µ–Љ—Г –і–∞—В–∞—И–Є—В—Г.

–Я–Њ—Б–ї–µ —В–Њ–≥–Њ, –Ї–∞–Ї –≤—Б–µ –і–∞–љ–љ—Л–µ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є –Ј–∞–≥—А—Г–ґ–µ–љ—Л, —Ж–Є–Ї–ї for –Ј–∞–Ї–∞–љ—З–Є–≤–∞–µ—В—Б—П, –Є —Д—Г–љ–Ї—Ж–Є—П SelectMAP() –њ—А–Њ–≤–µ—А—П–µ—В CPLD Input Register –љ–∞ –њ—А–µ–і–Љ–µ—В –≤—Л—Б—В–∞–≤–ї–µ–љ–Є—П —Б–Є–≥–љ–∞–ї–∞ DONE.

[–Р–њ–њ–∞—А–∞—В–љ–∞—П —А–µ–∞–ї–Є–Ј–∞—Ж–Є—П —А–µ–ґ–Є–Љ–∞ Slave Serial]

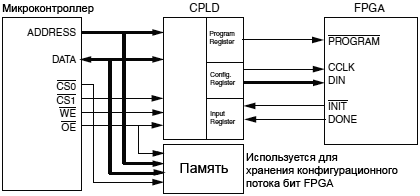

–Т —Н—В–Њ–є —Б–µ–Ї—Ж–Є–Є –Њ–±—Б—Г–ґ–і–∞–µ—В—Б—П –њ—А–Є–Љ–µ—А —А–∞–Ј—А–∞–±–Њ—В–Ї–Є, –Ї–Њ—В–Њ—А—Л–є –њ–Њ–Ј–≤–Њ–ї—П–µ—В –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞—В—М Virtex FPGA –≤ —А–µ–ґ–Є–Љ–µ Slave Serial, –≤ –Ї–Њ–Љ–±–Є–љ–∞—Ж–Є–Є —Б –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–Њ–Љ –Є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–Њ–є CPLD. –Ъ–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є–µ Slave Serial —А–µ–∞–ї–Є–Ј–Њ–≤–∞–љ–Њ –њ—Г—В–µ–Љ –њ—А–µ–і–Њ—Б—В–∞–≤–ї–µ–љ–Є—П –і–ї—П Virtex FPGA —В–∞–Ї—В–Њ–≤–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ –Є –Њ–і–љ–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ –і–∞–љ–љ—Л—Е, –Ї–Њ—В–Њ—А—Л–µ –њ—А–Є–љ–Є–Љ–∞—О—В—Б—П FPGA –њ–Њ –Ї–∞–ґ–і–Њ–Љ—Г –њ–Њ–ї–Њ–ґ–Є—В–µ–ї—М–љ–Њ–Љ—Г –њ–µ—А–µ–њ–∞–і—Г (–љ–∞—А–∞—Б—В–∞—О—Й–µ–Љ—Г —Д—А–Њ–љ—В—Г) —В–∞–Ї—В–Њ–≤–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ - –і–Њ —В–µ—Е –њ–Њ—А, –њ–Њ–Ї–∞ –љ–µ –±—Г–і–µ—В –Њ—В–њ—А–∞–≤–ї–µ–љ –њ–Њ—Б–ї–µ–і–љ–Є–є –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–є –±–Є—В.

–Ю–±—Й–∞—П —Б—Е–µ–Љ–∞ –і–Є–Ј–∞–є–љ–∞ –њ–Њ–Ї–∞–Ј–∞–љ–∞ –љ–∞ —А–Є—Б. 9. –Ф–ї—П —Б–Њ—Е—А–∞–љ–µ–љ–Є—П –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л—Е –і–∞–љ–љ—Л—Е FPGA –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П 16-–±–Є—В–љ–∞—П –њ–∞–Љ—П—В—М flash. –Я–Њ—Б–Ї–Њ–ї—М–Ї—Г –Ї–∞–ґ–і–∞—П —П—З–µ–є–Ї–∞ –њ–∞–Љ—П—В–Є flash —Е—А–∞–љ–Є—В 16 –±–Є—В –і–∞–љ–љ—Л—Е, –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А —З–Є—В–∞–µ—В –Ї–∞–ґ–і—Г—О —П—З–µ–є–Ї—Г, –Є –њ—А–µ–Њ–±—А–∞–Ј—Г–µ—В –µ—С –і–∞–љ–љ—Л–µ –≤ –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ—Л–є –њ–Њ—В–Њ–Ї –±–Є—В. –≠—В–Њ—В –њ—А–Њ—Ж–µ—Б—Б –њ—А–Њ–і–Њ–ї–ґ–∞–µ—В—Б—П, –њ–Њ–Ї–∞ –љ–µ –±—Г–і—Г—В –њ—А–Њ—З–Є—В–∞–љ—Л –Є –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ –Њ—В–њ—А–∞–≤–ї–µ–љ—Л –њ–Њ—Б–ї–µ–і–љ–Є–µ 16 –±–Є—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л—Е –і–∞–љ–љ—Л—Е. –Т–Њ –≤—А–µ–Љ—П —Н—В–Њ–≥–Њ –њ—А–Њ—Ж–µ—Б—Б–∞ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А —В–∞–Ї–ґ–µ –Њ—В–≤–µ—З–∞–µ—В –Ј–∞ —Д–Њ—А–Љ–Є—А–Њ–≤–∞–љ–Є–µ —В–∞–Ї—В–Њ–≤–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П –і–ї—П FPGA. –Ф–Њ–њ–Њ–ї–љ–Є—В–µ–ї—М–љ–∞—П –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ CPLD –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –і–ї—П –і–µ–Ї–Њ–і–Є—А–Њ–≤–∞–љ–Є—П –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ–≥–Њ –±–Є—В–Њ–≤–Њ–≥–Њ –њ–Њ—В–Њ–Ї–∞ –Є —Д–Њ—А–Љ–Є—А–Њ–≤–∞–љ–Є—П —В–∞–Ї—В–Њ–≤–Њ–≥–Њ –Є–Љ–њ—Г–ї—М—Б–∞, –Є –љ–µ–њ–Њ—Б—А–µ–і—Б—В–≤–µ–љ–љ–Њ —Б –љ–µ–µ –њ–Њ–і–∞—О—В—Б—П —Б–Є–≥–љ–∞–ї—Л –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П –љ–∞ Virtex FPGA.

–†–Є—Б. 9. –Ъ–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є—П Slave Serial.

CoolRunner CPLD

–Ь–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ Xilinx CoolRunner CPLD –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –≤ –Ї–∞—З–µ—Б—В–≤–µ —Б–≤—П–Ј—Г—О—Й–µ–є –ї–Њ–≥–Є–Ї–Є –Љ–µ–ґ–і—Г –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–Њ–Љ –Є Xilinx Virtex FPGA. –Т —А–µ–ґ–Є–Љ–µ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П Slave Serial –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ CPLD –Њ—В–≤–µ—З–∞–µ—В –Ј–∞ —Г–њ—А–∞–≤–ї–µ–љ–Є–µ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А—Г—О—Й–Є–Љ–Є —Б–Є–≥–љ–∞–ї–∞–Љ–Є –і–ї—П Virtex FPGA (~PROGRAM, CCLK –Є DIN). –°–Є–≥–љ–∞–ї—Л ~INIT –Є DONE, –њ—А–Є—Е–Њ–і—П—Й–Є–µ –Њ—В —Г—Б—В—А–Њ–є—Б—В–≤–∞ Virtex, —В–∞–Ї–ґ–µ –њ–Њ—Б—В—Г–њ–∞—О—В –љ–∞ CPLD, –±–ї–∞–≥–Њ–і–∞—А—П —З–µ–Љ—Г –Є—Е —Б–Њ—Б—В–Њ—П–љ–Є–µ –Љ–Њ–ґ–µ—В –±—Л—В—М –њ—А–Њ—З–Є—В–∞–љ–Њ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–Њ–Љ.

–Ґ–∞–Ї–Є–Љ –Њ–±—А–∞–Ј–Њ–Љ, CoolRunner CPLD –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –і–ї—П —Г—Б—В–∞–љ–Њ–≤–Ї–Є —Б–Є–љ—Е—А–Њ–љ–љ–Њ–≥–Њ –Є–љ—В–µ—А—Д–µ–є—Б–∞ –Љ–µ–ґ–і—Г –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–Њ–Љ –Є Xilinx FPGA. –Ш–љ—В–µ—А—Д–µ–є—Б –і–Њ—Б—В—Г–њ–∞ —Б–Њ —Б—В–Њ—А–Њ–љ—Л –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –њ—А–µ–і—Б—В–∞–≤–ї–µ–љ —В—А–µ–Љ—П —А–µ–≥–Є—Б—В—А–∞–Љ–Є: Configuration Register, Program Register –Є Input Register. –≠—В–Є —А–µ–≥–Є—Б—В—А—Л —Е—А–∞–љ—П—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ —Б–Є–≥–љ–∞–ї—Л FPGA –≤—Б—П–Ї–Є–є —А–∞–Ј, –Ї–Њ–≥–і–∞ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А –≤—Л–њ–Њ–ї–љ—П–µ—В —З—В–µ–љ–Є–µ –њ–Њ—А—В–∞ –Є–ї–Є –Ј–∞–њ–Є—Б—М –≤ –њ–Њ—А—В, —З—В–Њ –Њ—Б—Г—Й–µ—Б—В–≤–ї—П–µ—В –њ–Њ–і–і–µ—А–ґ–Ї—Г –љ–∞–±–Њ—А–∞ —Б–Є–≥–љ–∞–ї–Њ–≤, —В—А–µ–±—Г–µ–Љ—Л—Е –і–ї—П —А–µ–ґ–Є–Љ–∞ Slave Serial (~PROGRAM, DIN, CCLK, ~INIT –Є DONE). Configuration Register –Є Program Register –њ—А–µ–і–љ–∞–Ј–љ–∞—З–µ–љ—Л —В–Њ–ї—М–Ї–Њ –і–ї—П –Ј–∞–њ–Є—Б–Є (write-only), –≤ —В–Њ –≤—А–µ–Љ—П –Ї–∞–Ї Input Register —В–Њ–ї—М–Ї–Њ –і–ї—П —З—В–µ–љ–Є—П (read-only). –Я–Њ–і—А–Њ–±–љ–∞—П –±–ї–Њ–Ї-—Б—Е–µ–Љ–∞ –і–Є–Ј–∞–є–љ–∞ CPLD –њ–Њ–Ї–∞–Ј–∞–љ–∞ –љ–∞ —А–Є—Б. 10. –Ъ–∞—А—В–∞ –∞–і—А–µ—Б–Њ–≤ —А–µ–≥–Є—Б—В—А–Њ–≤ –њ–Њ–Ї–∞–Ј–∞–љ–∞ –≤ —В–∞–±–ї–Є—Ж–µ 5.

–†–Є—Б. 10. –С–ї–Њ–Ї-—Б—Е–µ–Љ–∞ CPLD.

–Ґ–∞–±–ї–Є—Ж–∞ 5. –Р–і—А–µ—Б–љ–∞—П –Ї–∞—А—В–∞ —А–µ–≥–Є—Б—В—А–Њ–≤.

–Р–і—А–µ—Б —А–µ–≥–Є—Б—В—А–∞

A[23:0] |

–Ш–Љ—П —А–µ–≥–Є—Б—В—А–∞ |

–Ф–∞–љ–љ—Л–µ –≤ —А–µ–≥–Є—Б—В—А–µ |

| D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

| 0x000000 |

Configuration

Register |

- |

- |

- |

- |

- |

- |

CCLK |

DATA |

| 0x000002 |

Program

Register |

- |

- |

- |

- |

- |

- |

- |

~PROGRAM |

| 0x000004 |

Input

Register |

- |

- |

- |

- |

- |

- |

DONE |

~INIT |

SlaveSerial.c

–Т —Н—В–Њ–є —Б–µ–Ї—Ж–Є–Є –Њ–±—Б—Г–ґ–і–∞–µ—В—Б—П –Ї–Њ–і –љ–∞ —П–Ј—Л–Ї–µ C, –Ї–Њ—В–Њ—А—Л–є –њ–Њ–Ј–≤–Њ–ї—П–µ—В –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Г –≤—Л–њ–Њ–ї–љ—П—В—М —Б–ї–µ–і—Г—О—Й–Є–µ –Њ–њ–µ—А–∞—Ж–Є–Є:

вАҐ –І–Є—В–∞—В—М –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ –і–∞–љ–љ—Л–µ FPGA –Є–Ј –њ–∞–Љ—П—В–Є flash.

вАҐ –У–µ–љ–µ—А–Є—А–Њ–≤–∞—В—М —В–∞–Ї—В—Л CCLK.

вАҐ –Я–µ—А–µ–і–∞–≤–∞—В—М –њ–Њ–±–Є—В–љ–Њ –і–∞–љ–љ—Л–µ –і–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П FPGA.

–Я—А–Є–Љ–µ—З–∞–љ–Є–µ: —А–∞–Ј–љ—Л–µ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Л –Є–Љ–µ—О—В —А–∞–Ј–ї–Є—З–љ—Л–µ —Б—В—А—Г–Ї—В—Г—А—Л –Њ—А–≥–∞–љ–Є–Ј–∞—Ж–Є–Є –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞ –њ–∞–Љ—П—В–Є, –≤ –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є —Б–Є—Б—В–µ–Љ—Л. –Ґ–∞–Ї–Є–Љ –Њ–±—А–∞–Ј–Њ–Љ, –≤ —В–Њ –≤—А–µ–Љ—П –Ї–∞–Ї –±–Њ–ї—М—И–Є–љ—Б—В–≤–Њ –Ї–Њ–і–∞ C –ї–µ–≥–Ї–Њ –њ–µ—А–µ–љ–Њ—Б–Є—В—Б—П —Б –Њ–і–љ–Њ–є –њ–ї–∞—В—Д–Њ—А–Љ—Л –љ–∞ –і—А—Г–≥—Г—О, –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—М –≤—Б–µ-—В–∞–Ї–Є –і–Њ–ї–ґ–µ–љ –Є–Ј–Љ–µ–љ–Є—В—М —З–∞—Б—В–Є –Ї–Њ–і–∞, —Г–њ—А–∞–≤–ї—П—О—Й–Є–µ —Д–Є–Ј–Є—З–µ—Б–Ї–Є–Љ–Є –Њ–њ–µ—А–∞—Ж–Є—П–Љ–Є —З—В–µ–љ–Є—П –Є –Ј–∞–њ–Є—Б–Є —Б–≤–Њ–µ–є —И–Є–љ—Л –і–∞–љ–љ—Л—Е, —З—В–Њ–±—Л –Њ–љ–Є —Б–Њ–Њ—В–≤–µ—В—Б—В–≤–Њ–≤–∞–ї–Є –Ї–∞—А—В–µ –њ–∞–Љ—П—В–Є —Б–Є—Б—В–µ–Љ—Л –љ–∞ –љ–Њ–≤–Њ–Љ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–µ.

–Ф–ї—П –Љ–∞–Ї—Б–Є–Љ–∞–ї—М–љ–Њ–≥–Њ —Г–і–Њ–±—Б—В–≤–∞ –њ–Њ–љ–Є–Љ–∞–љ–Є—П –Є —З—В–µ–љ–Є—П –≤–µ—Б—М –Ї–Њ–і C, –њ–Њ–Ї–∞–Ј–∞–љ–љ—Л–є –≤ —Н—В–Њ–Љ —А—Г–Ї–Њ–≤–Њ–і—Б—В–≤–µ, –≤—Л–њ–Њ–ї–љ—П–µ—В –і–Њ—Б—В—Г–њ –Ї —И–Є–љ–∞–Љ –∞–і—А–µ—Б–∞ –Є –і–∞–љ–љ—Л—Е –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ —Г–љ–Є—Д–Є—Ж–Є—А–Њ–≤–∞–љ–Њ, —Б –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ–Љ –і–≤—Г—Е –њ—А–Њ—Б—В—Л—Е —Д—Г–љ–Ї—Ж–Є–є: IOWrite() –Є IORead(). IOWrite() –Ј–∞–њ–Є—Б—Л–≤–∞–µ—В 16-–±–Є—В–љ–Њ–µ —Б–ї–Њ–≤–Њ –њ–Њ —Г–Ї–∞–Ј–∞–љ–љ–Њ–Љ—Г –∞–і—А–µ—Б—Г; IORead() –њ–Њ–ї—Г—З–∞–µ—В 16-–±–Є—В–љ—Л–µ –і–∞–љ–љ—Л–µ –Є–Ј —Г–Ї–∞–Ј–∞–љ–љ–Њ–є —П—З–µ–є–Ї–Є –њ–∞–Љ—П—В–Є (–Њ–њ–Є—Б–∞–љ–Є–µ —Б–Є–љ—В–∞–Ї—Б–Є—Б–∞ —Д—Г–љ–Ї—Ж–Є–є —Б–Љ. –≤ –њ—А–Є–ї–Њ–ґ–µ–љ–Є–Є "–Ю–њ–Є—Б–∞–љ–Є–µ —Б–њ–µ—Ж–Є—Д–Є—З–љ—Л—Е –і–ї—П –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ –≤—Л–Ј–Њ–≤–Њ–≤ —Д—Г–љ–Ї—Ж–Є–є –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞").

–Т —Д–∞–є–ї–µ –Є—Б—Е–Њ–і–љ–Њ–≥–Њ –Ї–Њ–і–∞ SlaveSerial.c –Є–Љ–µ—О—В—Б—П 2 —Д—Г–љ–Ї—Ж–Є–Є SlaveSerial() –Є ShiftDataOut(), –Ї–Њ—В–Њ—А—Л–µ –Њ—Б—Г—Й–µ—Б—В–≤–ї—П—О—В –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є–µ. –І—В–Њ–±—Л –љ–∞—З–∞—В—М –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є–µ, —Д—Г–љ–Ї—Ж–Є—П SlaveSerial() –≤—Л–Ј—Л–≤–∞–µ—В—Б—П –Є–Ј —Д—Г–љ–Ї—Ж–Є–Є main() –њ—А–Є–ї–Њ–ґ–µ–љ–Є—П, –Є –Њ–љ–∞ –Њ—В–≤–µ—З–∞–µ—В –Ј–∞ –≤—Л–і–∞—З—Г –Є–Љ–њ—Г–ї—М—Б–Њ–≤ –љ–∞ –≤—Л–≤–Њ–і–µ –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П, –њ—А–Њ–≤–µ—А–Ї—Г —Б–Є–≥–љ–∞–ї–∞ ~INIT, –Є –Ј–∞—В–µ–Љ –Ј–∞ –≤—Л–Ј–Њ–≤ —Д—Г–љ–Ї—Ж–Є–Є ShiftDataOut(). –Р–ї–≥–Њ—А–Є—В–Љ —А–∞–±–Њ—В—Л –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–≥–Њ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є—П –њ–Њ–Ї–∞–Ј–∞–љ –љ–∞ —А–Є—Б. 11.

–†–Є—Б. 11. –Ф–Є–∞–≥—А–∞–Љ–Љ–∞ —А–∞–±–Њ—В—Л –Ї–Њ–і–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Є—П FPGA –≤ —А–µ–ґ–Є–Љ–µ Slave Serial.

–°–љ–∞—З–∞–ї–∞ –њ—А–Њ—Ж–µ—Б—Б–Њ—А –Ј–∞–њ–Є—Б—Л–≤–∞–µ—В Program Register, —З—В–Њ–±—Л –≤—Л—Б—В–∞–≤–Є—В—М –≤—Л–≤–Њ–і ~PROGRAM, —З—В–Њ —Б–±—А–∞—Б—Л–≤–∞–µ—В FPGA.

–Я—А–Є–Љ–µ—З–∞–љ–Є–µ: –Љ–Њ–ґ–µ—В –њ–Њ–љ–∞–і–Њ–±–Є—В—М—Б—П —Ж–Є–Ї–ї –Ј–∞–і–µ—А–ґ–Ї–Є –і–ї—П —В–Њ–≥–Њ, —З—В–Њ–±—Л –≤—Л—Б—В–∞–≤–Є—В—М –≤—Л–≤–Њ–і ~PROGRAM –љ–∞ –Љ–Є–љ–Є–Љ–∞–ї—М–љ–Њ —В—А–µ–±—Г–µ–Љ–Њ–µ –≤—А–µ–Љ—П (–Ј–∞ –Ї–Њ–љ–Ї—А–µ—В–љ—Л–Љ –Ј–љ–∞—З–µ–љ–Є–µ–Љ –≤—А–µ–Љ–µ–љ–Є –Њ–±—А–∞—В–Є—В–µ—Б—М –Ї –і–∞—В–∞—И–Є—В—Г –љ–∞ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й—Г—О –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Г FPGA). –Х—Б–ї–Є FPGA —Б—А–∞–Ј—Г –≥–Њ—В–Њ–≤–∞ –Ї –Ј–∞–≥—А—Г–Ј–Ї–µ –њ–Њ—Б–ї–µ –≤–Ї–ї—О—З–µ–љ–Є—П –њ–Є—В–∞–љ–Є—П, –Є–ї–Є —Б–±—А–Њ—Б –њ—А–Њ–Є—Б—Е–Њ–і–Є—В –њ–Њ-–і—А—Г–≥–Њ–Љ—Г, —В–Њ —Н—В–Њ—В —Ж–Є–Ї–ї –Ј–∞–і–µ—А–ґ–Ї–Є –љ–µ –љ—Г–ґ–µ–љ.

–Я–Њ—Б–ї–µ —В–Њ–≥–Њ, –Ї–∞–Ї –≤—Л—Б—В–∞–≤–ї–µ–љ –±–Є—В ~PROGRAM, —Д—Г–љ–Ї—Ж–Є—П SlaveSerial() –њ—А–Њ–≤–µ—А—П–µ—В CPLD Input Register, –њ–Њ–Ї–∞ —Б–Є–≥–љ–∞–ї ~INIT –љ–µ –њ–µ—А–µ–є–і–µ—В –≤ –ї–Њ–≥. 1. –Ч–∞—В–µ–Љ —Д—Г–љ–Ї—Ж–Є—П –њ–µ—А–µ—Е–Њ–і–Є—В –≤ —Ж–Є–Ї–ї for, –Ї–Њ—В–Њ—А—Л–є –њ—А–Њ—Е–Њ–і–Є—В –њ–Њ –≤—Б–µ–Љ—Г –і–Є–∞–њ–∞–Ј–Њ–љ—Г –∞–і—А–µ—Б–Њ–≤ flash, –≥–і–µ –Ј–∞–њ–Є—Б–∞–љ—Л –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ –і–∞–љ–љ—Л–µ –і–ї—П FPGA. –Т —Н—В–Њ–Љ –њ—А–Є–Љ–µ—А–µ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П —Г—Б—В—А–Њ–є—Б—В–≤–Њ FPGA XCV50, –Є –і–Є–∞–њ–∞–Ј–Њ–љ –∞–і—А–µ—Б–Њ–≤ flash –љ–∞—Е–Њ–і–Є—В—Б—П –Љ–µ–ґ–і—Г 0x28000200 –Є 0x2801130A. –Ф–ї—П –Ї–∞–ґ–і–Њ–≥–Њ –∞–і—А–µ—Б–∞ —З–Є—В–∞—О—В—Б—П 16 –±–Є—В –і–∞–љ–љ—Л—Е, –Є –≤—Л–Ј—Л–≤–∞–µ—В—Б—П —Д—Г–љ–Ї—Ж–Є—П ShiftDataOut(), —З—В–Њ–±—Л –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ –њ–µ—А–µ–і–∞—В—М –і–∞–љ–љ—Л–µ –≤ FPGA.

–Я—А–Є–Љ–µ—З–∞–љ–Є–µ: —Д—Г–љ–Ї—Ж–Є—П ShiftDataOut() –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В 2 —Ж–Є–Ї–ї–∞ –і–ї—П –Ї–∞–ґ–і–Њ–≥–Њ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ–Њ–≥–Њ –±–Є—В–∞. –Ю–і–Є–љ —Ж–Є–Ї–ї –љ—Г–ґ–µ–љ —З—В–Њ–±—Л –њ–µ—А–µ–≤–µ—Б—В–Є —Б–Є–≥–љ–∞–ї CCLK –≤ —Б–Њ—Б—В–Њ—П–љ–Є–µ –ї–Њ–≥. 0, –Є –≤—Л—Б—В–∞–≤–Є—В—М —Б–ї–µ–і—Г—О—Й–Є–є –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–є –±–Є—В. –Т—В–Њ—А–Њ–є —Ж–Є–Ї–ї –љ—Г–ґ–µ–љ –і–ї—П –њ–µ—А–µ–≤–Њ–і–∞ CCLK –≤ —Б–Њ—Б—В–Њ—П–љ–Є–µ –ї–Њ–≥. 1. –Я–Њ—Б–ї–µ —В–Њ–≥–Њ, –Ї–∞–Ї –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ –і–∞–љ–љ—Л–µ –Ј–∞–≥—А—Г–ґ–µ–љ—Л, —Ж–Є–Ї–ї –Ј–∞–≤–µ—А—И–∞–µ—В—Б—П, –Є —Д—Г–љ–Ї—Ж–Є—П SlaveSerial() –њ—А–Њ–≤–µ—А—П–µ—В CPLD Input Register –љ–∞ –њ—А–µ–і–Љ–µ—В –≤—Л—Б—В–∞–≤–ї–µ–љ–Є—П —Б–Є–≥–љ–∞–ї–∞ DONE.

–Я–Њ—Б–ї–µ–і–љ—О—О –≤–µ—А—Б–Є—О —Н—В–Њ–≥–Њ –∞–њ–љ–Њ—Г—В–∞, —Д–∞–є–ї—Л CPLD –Є –Є—Б—Е–Њ–і–љ–Њ–≥–Њ –Ї–Њ–і–∞ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –Љ–Њ–ґ–љ–Њ —Б–Ї–∞—З–∞—В—М –љ–∞ —Б–∞–є—В–µ Xilinx (—В—А–µ–±—Г–µ—В—Б—П —А–µ–≥–Є—Б—В—А–∞—Ж–Є—П): https://secure.xilinx.com/webreg/clickthrough.do?cid=139211, –Є–ї–Є —Б–Љ. —Б—Б—Л–ї–Ї—Г [4].

[–Ю–њ–Є—Б–∞–љ–Є–µ —Б–њ–µ—Ж–Є—Д–Є—З–љ—Л—Е –і–ї—П –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ –≤—Л–Ј–Њ–≤–Њ–≤ —Д—Г–љ–Ї—Ж–Є–є –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞]

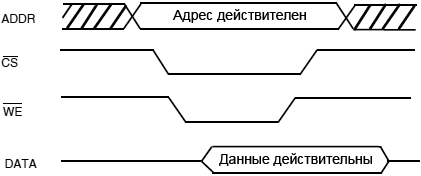

–Я—А–Є –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–Є —Д—Г–љ–Ї—Ж–Є–Є IOWrite() –µ–є –≤ –Ї–∞—З–µ—Б—В–≤–µ –њ–∞—А–∞–Љ–µ—В—А–Њ–≤ –і–Њ–ї–ґ–љ—Л –±—Л—В—М –њ–µ—А–µ–і–∞–љ—Л –∞–і—А–µ—Б –Є –і–∞–љ–љ—Л–µ. –Т –њ—А–Є–Љ–µ—А–µ –і–Є–Ј–∞–є–љ–∞, –Ї–Њ—В–Њ—А—Л–є –Ј–і–µ—Б—М –њ—А–Є–≤–µ–і–µ–љ, –∞–і—А–µ—Б–∞ —А–µ–≥–Є—Б—В—А–Њ–≤ Configuration, Program –Є Input –љ–∞—Е–Њ–і—П—В—Б—П —Б–Њ–Њ—В–≤–µ—В—Б—В–≤–µ–љ–љ–Њ –≤ —П—З–µ–є–Ї–∞—Е 0x29000000, 0x29000002 –Є 0x29000004. –Я–Њ—Н—В–Њ–Љ—Г —Д—Г–љ–Ї—Ж–Є—П –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П —В–Њ–ї—М–Ї–Њ –і–ї—П –Ј–∞–њ–Є—Б–Є –њ–Њ —Н—В–Є–Љ —В—А–µ–Љ –∞–і—А–µ—Б–∞–Љ.

–Ґ–∞–±–ї–Є—Ж–∞ 6. –Я—А–Є–Љ–µ—А—Л –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є—П IOWrite().

| IOWrite(0x29000000, 0x0003) |

–Ч–∞–њ–Є—Б—М –≤ —А–µ–≥–Є—Б—В—А –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є CPLD —А–µ–ґ–Є–Љ–∞ Slave Serial:

1 = CCLK

1 = DATA |

| IOWrite(0x29000000, 0x0001) |

–Ч–∞–њ–Є—Б—М –≤ —А–µ–≥–Є—Б—В—А –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є CPLD —А–µ–ґ–Є–Љ–∞ Slave Serial:

0 = CCLK

1 = DATA |

| IOWrite(0x29000002, 0x0001) |

–Ч–∞–њ–Є—Б—М –≤ —А–µ–≥–Є—Б—В—А –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П CPLD —А–µ–ґ–Є–Љ–∞ Slave Serial:

1 = ~PROGRAM |

–Ф–Є–∞–≥—А–∞–Љ–Љ—Л –≤—А–µ–Љ–µ–љ–Є —Ж–Є–Ї–ї–∞ –Ј–∞–њ–Є—Б–Є –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –њ–Њ–Ї–∞–Ј–∞–љ—Л –љ–∞ —А–Є—Б—Г–љ–Ї–µ 12.

–†–Є—Б. 12. –Ф–Є–∞–≥—А–∞–Љ–Љ—Л —Б–Є–≥–љ–∞–ї–Њ–≤ –њ—А–Њ—Ж–µ—Б—Б–∞ –Ј–∞–њ–Є—Б–Є.

–Ф–ї—П –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є—П —Д—Г–љ–Ї—Ж–Є–Є IORead –≤ –Ї–∞—З–µ—Б—В–≤–µ –њ–∞—А–∞–Љ–µ—В—А–∞ –љ—Г–ґ–љ–Њ –њ–µ—А–µ–і–∞—В—М –∞–і—А–µ—Б. –Я–Њ —Н—В–Њ–Љ—Г –∞–і—А–µ—Б—Г –±—Г–і–µ—В –њ—А–Њ—З–Є—В–∞–љ–∞ –Є –≤–Њ–Ј–≤—А–∞—Й–µ–љ–∞ 16-–±–Є—В–љ–∞—П –≤–µ–ї–Є—З–Є–љ–∞. –Т —Н—В–Њ–Љ –њ—А–Є–Љ–µ—А–µ –і–Є–Ј–∞–є–љ–∞ –і–∞–љ–љ—Л–µ —З–Є—В–∞—О—В—Б—П –њ–Њ –і–Є–∞–њ–∞–Ј–Њ–љ—Г –∞–і—А–µ—Б–Њ–≤ 0x28000200 .. 0x2801130A (–Њ–±–ї–∞—Б—В—М –њ–∞–Љ—П—В–Є, –≥–і–µ —Е—А–∞–љ—П—В—Б—П –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ –і–∞–љ–љ—Л–µ FPGA), –∞ —В–∞–Ї–ґ–µ –њ–Њ –∞–і—А–µ—Б—Г 0x29000004 (–∞–і—А–µ—Б –і–Њ—Б—В—Г–њ–∞ –Ї Input Register).

–Ґ–∞–±–ї–Є—Ж–∞ 7. –Я—А–Є–Љ–µ—А—Л –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є—П IORead().

| IORead(0x28000200) |

–Я—А–Њ—З–Є—В–∞—В—М –њ–µ—А–≤—Л–µ 16 –±–Є—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л—Е –і–∞–љ–љ—Л—Е –Є–Ј –њ–∞–Љ—П—В–Є flash. |

| IORead(0x28000202) |

–Я—А–Њ—З–Є—В–∞—В—М —Б–ї–µ–і—Г—О—Й–Є–µ 16 –±–Є—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л—Е –і–∞–љ–љ—Л—Е –Є–Ј –њ–∞–Љ—П—В–Є flash. |

| IORead(0x2801130A) |

–Я—А–Њ—З–Є—В–∞—В—М –њ–Њ—Б–ї–µ–і–љ–Є–µ 16 –±–Є—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л—Е –і–∞–љ–љ—Л—Е –Є–Ј –њ–∞–Љ—П—В–Є flash. |

| IORead(0x29000004) |

–Я—А–Њ—З–Є—В–∞—В—М —Б–Њ–і–µ—А–ґ–Є–Љ–Њ–µ –≤—Е–Њ–і–љ–Њ–≥–Њ —А–µ–≥–Є—Б—В—А–∞, —З—В–Њ–±—Л –Њ–њ—А–µ–і–µ–ї–Є—В—М –Ј–љ–∞—З–µ–љ–Є—П —Б–Є–≥–љ–∞–ї–Њ–≤ DONE –Є ~INIT (–љ–∞–њ—А–Є–Љ–µ—А, –і–ї—П —А–µ–ґ–Є–Љ–∞ Slave Serial). |

–Ф–Є–∞–≥—А–∞–Љ–Љ—Л –≤—А–µ–Љ–µ–љ–Є —Ж–Є–Ї–ї–∞ —З—В–µ–љ–Є—П –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –њ–Њ–Ї–∞–Ј–∞–љ—Л –љ–∞ —А–Є—Б—Г–љ–Ї–µ 13.

–†–Є—Б. 13. –Ф–Є–∞–≥—А–∞–Љ–Љ—Л —Б–Є–≥–љ–∞–ї–Њ–≤ –њ—А–Њ—Ж–µ—Б—Б–∞ —З—В–µ–љ–Є—П.

[–°–ї–Њ–≤–∞—А–Є–Ї]

BitGen —Г—В–Є–ї–Є—В–∞ –Ї–Њ–Љ–∞–љ–і–љ–Њ–є —Б—В—А–Њ–Ї–Є (–≤—Е–Њ–і–Є—В –≤ –њ–∞–Ї–µ—В Xilinx ISE Design Tools), –Ї–Њ—В–Њ—А–∞—П –њ—А–µ–і–љ–∞–Ј–љ–∞—З–µ–љ–∞ –і–ї—П —Б–Њ–Ј–і–∞–љ–Є—П —Д–∞–є–ї–∞ –њ—А–Њ—И–Є–≤–Ї–Є –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л FPGA (–Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–є —Д–∞–є–ї FPGA).

CPLD Complex Programmable Logic Device, –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ–∞—П –ї–Њ–≥–Є—З–µ—Б–Ї–∞—П –Є–љ—В–µ–≥—А–∞–ї—М–љ–∞—П —Б—Е–µ–Љ–∞ (–Я–Ы–Ш–°) –≤ –і–Є–∞–њ–∞–Ј–Њ–љ–µ —Б–ї–Њ–ґ–љ–Њ—Б—В–Є –Љ–µ–ґ–і—Г –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞–Љ–Є PAL (Programmable Array Logic) –Є FPGA (Field-Programmable Gate Array), —Б–Њ—З–µ—В–∞—О—Й–∞—П –Є—Е –∞—А—Е–Є—В–µ–Ї—В—Г—А–љ—Л–µ —А–µ—И–µ–љ–Є—П (–Є–Ј –Т–Є–Ї–Є–њ–µ–і–Є–Є). –У–Њ–≤–Њ—А—П –њ–Њ-—А—Г—Б—Б–Ї–Є, –љ–µ –Њ—З–µ–љ—М —Б–ї–Њ–ґ–љ–∞—П –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ–Њ–є –ї–Њ–≥–Є–Ї–Є, –≤ –Ї–Њ—В–Њ—А–Њ–є –ї–Њ–≥–Є–Ї–∞ —Г–ґ–µ –Ј–∞–≥—А—Г–ґ–µ–љ–∞ –≤ –Љ–Њ–Љ–µ–љ—В –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П, –Є –Њ–љ–∞ —Б–Њ—Е—А–∞–љ—П–µ—В—Б—П –Љ–µ–ґ–і—Г –≤—Л–Ї–ї—О—З–µ–љ–Є—П–Љ–Є –њ–Є—В–∞–љ–Є—П.

FPGA Field-Programmable Gate Array - –њ–Њ–ї—Г–њ—А–Њ–≤–Њ–і–љ–Є–Ї–Њ–≤–Њ–µ —Г—Б—В—А–Њ–є—Б—В–≤–Њ (–Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞), –Ї–Њ—В–Њ—А–Њ–µ –Љ–Њ–ґ–µ—В –±—Л—В—М —Б–Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞–љ–Њ –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї–µ–Љ –Є–ї–Є —А–∞–Ј—А–∞–±–Њ—В—З–Є–Ї–Њ–Љ –њ–Њ—Б–ї–µ –Є–Ј–≥–Њ—В–Њ–≤–ї–µ–љ–Є—П; –Њ—В—Б—О–і–∞ –љ–∞–Ј–≤–∞–љ–Є–µ: ¬Ђ–њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ–∞—П –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї–µ–Љ¬ї. –Я–Я–Т–Ь –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г—О—В—Б—П –њ—Г—В—С–Љ –Є–Ј–Љ–µ–љ–µ–љ–Є—П –ї–Њ–≥–Є–Ї–Є —А–∞–±–Њ—В—Л –њ—А–Є–љ—Ж–Є–њ–Є–∞–ї—М–љ–Њ–є —Б—Е–µ–Љ—Л, –љ–∞–њ—А–Є–Љ–µ—А, —Б –њ–Њ–Љ–Њ—Й—М—О –Є—Б—Е–Њ–і–љ–Њ–≥–Њ –Ї–Њ–і–∞ –љ–∞ —П–Ј—Л–Ї–µ –њ—А–Њ–µ–Ї—В–Є—А–Њ–≤–∞–љ–Є—П (—В–Є–њ–∞ VHDL), –љ–∞ –Ї–Њ—В–Њ—А–Њ–Љ –Љ–Њ–ґ–љ–Њ –Њ–њ–Є—Б–∞—В—М —Н—В—Г –ї–Њ–≥–Є–Ї—Г —А–∞–±–Њ—В—Л –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л. –Я–Я–Т–Ь —П–≤–ї—П–µ—В—Б—П –Њ–і–љ–Њ–є –Є–Ј –∞—А—Е–Є—В–µ–Ї—В—Г—А–љ—Л—Е —А–∞–Ј–љ–Њ–≤–Є–і–љ–Њ—Б—В–µ–є –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ—Л—Е –ї–Њ–≥–Є—З–µ—Б–Ї–Є—Е –Є–љ—В–µ–≥—А–∞–ї—М–љ—Л—Е —Б—Е–µ–Љ (–Я–Ы–Ш–°) (–Є–Ј –Т–Є–Ї–Є–њ–µ–і–Є–Є). –У–Њ–≤–Њ—А—П –њ–Њ-—А—Г—Б—Б–Ї–Є, —Н—В–Њ –і–Њ–≤–Њ–ї—М–љ–Њ —Б–ї–Њ–ґ–љ–∞—П –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ–∞—П –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ –ї–Њ–≥–Є–Ї–Є, –ї–Њ–≥–Є—З–µ—Б–Ї–∞—П —Б—Е–µ–Љ–∞ —А–∞–±–Њ—В—Л –Ї–Њ—В–Њ—А–Њ–є –Њ–±—Л—З–љ–Њ –Ј–∞–≥—А—Г–ґ–∞–µ—В—Б—П –≤ –Љ–Њ–Љ–µ–љ—В –≤–Ї–ї—О—З–µ–љ–Є—П –њ–Є—В–∞–љ–Є—П –Є–Ј –Ї–∞–Ї–Њ–є-—В–Њ –≤–љ–µ—И–љ–µ–є –њ–∞–Љ—П—В–Є –Є–ї–Є –њ–Њ–і —Г–њ—А–∞–≤–ї–µ–љ–Є–µ–Љ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞.

GPIO General Purpose Input/Output, –њ–Њ—А—В—Л –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞ –Њ–±—Й–µ–≥–Њ –љ–∞–Ј–љ–∞—З–µ–љ–Є—П. –Э–Њ–ґ–Ї–Є –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞, –Ї–Њ—В–Њ—А—Л–Љ–Є –Њ–љ –Љ–Њ–ґ–µ—В —Г–њ—А–∞–≤–ї—П—В—М (–Є —Б–Њ—Б—В–Њ—П–љ–Є–µ –Ї–Њ—В–Њ—А—Л—Е –Њ–љ –Љ–Њ–ґ–µ—В —Б—З–Є—В—Л–≤–∞—В—М) —Б –њ–Њ–Љ–Њ—Й—М—О —Б–≤–Њ–µ–≥–Њ –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–≥–Њ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є—П.

LSB Least Significant Bit, —Б–∞–Љ—Л–є –Љ–ї–∞–і—И–Є–є –Ј–љ–∞—З–∞—Й–Є–є –±–Є—В.

MSB Most Significant Bit, —Б–∞–Љ—Л–є —Б—В–∞—А—И–Є–є –Ј–љ–∞—З–∞—Й–Є–є –±–Є—В.

Platform Flash PROM –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ –њ–∞–Љ—П—В–Є, —Б–њ–µ—Ж–Є–∞–ї—М–љ–Њ –њ—А–µ–і–љ–∞–Ј–љ–∞—З–µ–љ–љ–∞—П –і–ї—П —Е—А–∞–љ–µ–љ–Є—П –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л—Е –і–∞–љ–љ—Л—Е FPGA Xilinx.

PROM Programmable Read-Only Memory, –Ї–ї–∞—Б—Б –њ–Њ–ї—Г–њ—А–Њ–≤–Њ–і–љ–Є–Ї–Њ–≤—Л—Е –Ј–∞–њ–Њ–Љ–Є–љ–∞—О—Й–Є—Е —Г—Б—В—А–Њ–є—Б—В–≤, –њ–Њ—Б—В–Њ—П–љ–љ–∞—П –њ–∞–Љ—П—В—М —Б –њ–µ—А–µ–ґ–Є–≥–∞–µ–Љ—Л–Љ–Є –њ–µ—А–µ–Љ—Л—З–Ї–∞–Љ–Є (–Є–Ј –Т–Є–Ї–Є–њ–µ–і–Є–Є). –Э–∞ —Б–∞–Љ–Њ–Љ –і–µ–ї–µ –≤–Њ–≤—Б–µ –љ–µ –Њ–±—П–Ј–∞—В–µ–ї—М–љ–Њ, —З—В–Њ –≤ —Н—В–Њ–є –њ–∞–Љ—П—В–Є –і–µ–є—Б—В–≤–Є—В–µ–ї—М–љ–Њ –µ—Б—В—М –Ї–∞–Ї–Є–µ-—В–Њ –њ–µ—А–µ–Љ—Л—З–Ї–Є. –Ш–Љ–µ–µ—В—Б—П –≤ –≤–Є–і—Г, —З—В–Њ –њ–∞–Љ—П—В—М –љ–µ –њ–µ—А–µ–њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ—В—Б—П –≤–Њ –≤—А–µ–Љ—П —Б–≤–Њ–µ–≥–Њ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є—П, –Є —Е—А–∞–љ—П—Й–Є–µ—Б—П –≤ –љ–µ–є –і–∞–љ–љ—Л–µ –љ–µ –њ—А–µ–і–љ–∞–Ј–љ–∞—З–µ–љ—Л –і–ї—П –Є–Ј–Љ–µ–љ–µ–љ–Є—П.

PROMGen —Б–њ–µ—Ж–Є–∞–ї—М–љ–∞—П —Г—В–Є–ї–Є—В–∞ Xilinx, –њ—А–µ–і–љ–∞–Ј–љ–∞—З–µ–љ–љ–∞—П –і–ї—П –њ–µ—А–µ—Д–Њ—А–Љ–∞—В–Є—А–Њ–≤–∞–љ–Є—П –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ–Њ–≥–Њ —Д–∞–є–ї–∞ (—Д–∞–є–ї —Б —А–∞—Б—И–Є—А–µ–љ–Є–µ–Љ BIT, –Ї–Њ—В–Њ—А—Л–є —Б–≥–µ–љ–µ—А–Є—А–Њ–≤–∞–љ —Г—В–Є–ї–Є—В–Њ–є BitGen) –≤ —Д–Њ—А–Љ–∞—В PROM (—Д–∞–є–ї –і–ї—П –Ј–∞–ї–Є–≤–Ї–Є –≤ –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Г PROM, –Є–Ј –Ї–Њ—В–Њ—А–Њ–є –±—Г–і–µ—В –Ј–∞–≥—А—Г–ґ–∞—В—М—Б—П FPGA).

SelectMAP —А–µ–ґ–Є–Љ –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П FPGA –њ–Њ–і —Г–њ—А–∞–≤–ї–µ–љ–Є–µ–Љ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞, –њ—А–Є –Ї–Њ—В–Њ—А–Њ–Љ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ –і–∞–љ–љ—Л–µ –њ–Њ–і–∞—О—В—Б—П –њ–∞—А–∞–ї–ї–µ–ї—М–љ–Њ –њ–Њ—А—Ж–Є—П–Љ–Є –њ–Њ 8 –±–Є—В (–Є–ї–Є –њ–Њ 16, –Є–ї–Є –њ–Њ 32 –±–Є—В–∞, –≤ –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В —И–Є—А–Є–љ—Л —И–Є–љ—Л –і–∞–љ–љ—Л—Е SelectMAP). –≠—В–Њ—В —А–µ–ґ–Є–Љ —В–∞–Ї–ґ–µ –љ–∞–Ј—Л–≤–∞—О—В Slave Parallel.

Slave Serial —В–Њ –ґ–µ —Б–∞–Љ–Њ–µ, —З—В–Њ –Є SelectMAP, –љ–Њ –Ј–і–µ—Б—М –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ—Л–µ –і–∞–љ–љ—Л–µ –њ–Њ–і–∞—О—В—Б—П –њ–Њ 1 –±–Є—В—Г.

[–°—Б—Л–ї–Ї–Є]

1. Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode, XAPP502 (v1.6.1) August 24, 2009.

2. Configuration for Spartan-3A/3E FPGAs site:xilinx.com.

3. ISE¬Ѓ software manuals site:xilinx.com.

4. 140922xilinx-FPGA-prog-MCU.zip - –і–Њ–Ї—Г–Љ–µ–љ—В–∞—Ж–Є—П, –њ—А–Є–Љ–µ—А—Л –Ї–Њ–і–∞ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞.

5. Gameduino: —Б–±–Њ—А–Ї–∞, –Ї–Њ–Љ–њ–Є–ї—П—Ж–Є—П –Є—Б—Е–Њ–і–љ–Њ–≥–Њ –Ї–Њ–і–∞ Verilog, —В–µ—Б—В–Є—А–Њ–≤–∞–љ–Є–µ. |