|

ąŚą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ čĆą░ąĘą┤ąĄą╗ą░ "Operating Modes And States" ą┤ąŠą║čāą╝ąĄąĮčéą░ [1], ą│ą┤ąĄ čĆą░čüčüą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ąŠ čĆą░ąĘą╗ąĖčćąĮčŗčģ čĆąĄąČąĖą╝ą░čģ čĆą░ą▒ąŠčéčŗ ąĖ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéčÅčģ čüą▒čĆąŠčüą░ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin ą║ąŠą╝ą┐ą░ąĮąĖąĖ Analog Devices. ąØąĄą┐ąŠąĮčÅčéąĮčŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąĪą╗ąŠą▓ą░čĆąĖą║" čüčéą░čéčīąĖ [6].

ą¤čĆąŠčåąĄčüčüąŠčĆ Blackfin ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čĆąĄąČąĖą╝čŗ:

ŌĆó User mode (čĆąĄąČąĖą╝ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą┤ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ)

ŌĆó Supervisor mode (čĆąĄąČąĖą╝ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░)

ŌĆó Emulation mode (čĆąĄąČąĖą╝ 菹╝čāą╗čÅčåąĖąĖ)

ąÆ čĆąĄąČąĖą╝ą░čģ Emulation ąĖ Supervisor ą┤ąŠčüčéčāą┐ ą║ čĆąĄčüčāčĆčüą░ą╝ čÅą┤čĆą░ ąĮąĖč湥ą╝ ąĮąĄ ąŠą│čĆą░ąĮąĖč湥ąĮ. ąÆ čĆąĄąČąĖą╝ąĄ User ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ čĆąĄčüčāčĆčüą░ą╝ ą┤ąŠčüčéčāą┐ ąŠą│čĆą░ąĮąĖčćąĖą▓ą░ąĄčéčüčÅ, čćč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ąĘą░čēąĖčéčŗ čĆą░ą▒ąŠč湥ą│ąŠ ąŠą║čĆčāąČąĄąĮąĖčÅ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝ąŠą│ąŠ ą║ąŠą┤ą░.

ąĀąĄąČąĖą╝ User čüčćąĖčéą░ąĄčéčüčÅ ą┤ąŠą╝ąĄąĮąŠą╝ (ąŠą▒ą╗ą░čüčéčīčÄ ą┤ąĄą╣čüčéą▓ąĖčÅ) ą┐čĆąŠą│čĆą░ą╝ą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąĀąĄąČąĖą╝čŗ Supervisor ąĖ Emulation ąŠą▒čŗčćąĮąŠ čĆąĄąĘąĄčĆą▓ąĖčĆčāčÄčéčüčÅ ą┤ą╗čÅ ą║ąŠą┤ą░ čÅą┤čĆą░ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čŹč鹊 ąĮąĄ ą▓čüąĄą│ą┤ą░ čéą░ą║, ąĘą░ą▓ąĖčüąĖčé ąŠčé čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ. ąóą░ą║, ą║ ą┐čĆąĖą╝ąĄčĆčā, ą║ąŠą┤ ąĘą░ą┤ą░čć ą┐čĆąŠąĄą║č鹊ą▓ VDK (ą░ čŹč鹊 ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮą░čÅ čüąĖčüč鹥ą╝ą░ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, RTOS) ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą║ąŠą┤ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ VDK ąĮąĖč湥ą╝ ąĮąĄ ąŠą│čĆą░ąĮąĖč湥ąĮ ą▓ ą┤ąŠčüčéčāą┐ąĄ ą║ čĆąĄčüčāčĆčüą░ą╝. VDK ąĖą╝ąĄąĄčé čüą▓ąŠčÄ čüąŠą▒čüčéą▓ąĄąĮąĮčāčÄ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║čā ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čĆąĄčüčāčĆčüą░ą╝ąĖ ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ [2].

ąĀąĄąČąĖą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ čüąŠą▒čŗčéąĖą╣ (Event Controller [3]). ąÜąŠą│ą┤ą░ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ ąŠą▒čŗčćąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĮąĄ ą╝ą░čüą║ąĖčĆčāąĄą╝ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (nonmaskable interrupt, NMI) ąĖą╗ąĖ ąĖčüą║ą╗čÄč湥ąĮąĖąĄ (exception), ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Supervisor. ąÜąŠą│ą┤ą░ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄ 菹╝čāą╗čÅčåąĖąĖ (emulation event, ą░ą║čéąĖą▓ąĖąĘą░čåąĖčÅ ąŠčéą╗ą░ą┤čćąĖą║ą░ JTAG), ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Emulation. ąÜąŠą│ą┤ą░ ąĮąĄ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ čüąŠą▒čŗčéąĖčÅ, ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ User. ąŁč鹊 čüčéą░ąĮą┤ą░čĆčéąĮą░čÅ ą╝ąŠą┤ąĄą╗čī ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ čüąĖčüč鹥ą╝čŗ.

ąóąĄą║čāčēąĖą╣ čĆąĄąČąĖą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░ąĮ čü ą┐ąŠą╝ąŠčēčīčÄ ąŠą┐čĆąŠčüą░ čĆąĄą│ąĖčüčéčĆą░ IPEND, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 3-1.

ąĪą╗ąĄą┤čāąĄčé ąĖą╝ąĄčéčī ą▓ ą▓ąĖą┤čā, čćč鹊 IPEND ąŠčéąĮąŠčüąĖčéčüčÅ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝, ąŠč鹊ą▒čĆą░ąČąĄąĮąĮčŗą╝ ąĮą░ ą┐ą░ą╝čÅčéčī ą┐čĆąŠčåąĄčüčüąŠčĆą░ (memory-mapped register, MMR), ą░ čĆąĄą│ąĖčüčéčĆčŗ MMR ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ą▓ čĆąĄąČąĖą╝ąĄ User.

ąóą░ą▒ą╗ąĖčåą░ 3-1. ąśą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖčÅ č鹥ą║čāčēąĄą│ąŠ čĆąĄąČąĖą╝ą░ (Mode) ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠą▒čŗčéąĖčÅ (Event).

| Event |

Mode |

IPEND |

| Interrupt |

Supervisor |

Ōēź 0x10, ąĮąŠ IPEND[3:0] = b#000. |

| Exception |

Ōēź 0x08

ą»ą┤čĆąŠ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé čüąŠą▒čŗčéąĖąĄ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ, ąĄčüą╗ąĖ IPEND[3:0] = b#1000, ąĖ IPEND[15:4] ąĮčāą╗ąĖ ąĖą╗ąĖ ąĄą┤ąĖąĮąĖčåčŗ. |

| NMI |

Ōēź 0x04

ą»ą┤čĆąŠ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé čüąŠą▒čŗčéąĖąĄ ąĮąĄ ą╝ą░čüą║ąĖčĆčāąĄą╝ąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ IPEND[2:0] = b#100, ąĖ IPEND[15:3] ąĮčāą╗ąĖ ąĖą╗ąĖ ąĄą┤ąĖąĮąĖčåčŗ. |

| Reset |

=0x02

ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą▓čŗčģąŠą┤ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ čüą▒čĆąŠčüą░, IPEND čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 0x02, ąĖ ą║ąŠą┤ ą┐ąŠ ą▓ąĄą║č鹊čĆčā čüą▒čĆąŠčüą░ čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░. |

| Emulation |

ą×čéą╗ą░ą┤ą║ą░ (JTAG) |

=0x01

ą¤čĆąŠčåąĄčüčüąŠčĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ 菹╝čāą╗čÅčåąĖąĖ, ąĄčüą╗ąĖ IPEND[0] = 1, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčé IPEND[15:1]. |

| None (ąĮąĄčé čüąŠą▒čŗčéąĖčÅ) |

User |

=0x00 |

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ 2 čĆąĄąČąĖą╝ą░, ą▓ ą║ąŠč鹊čĆčŗčģ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą║ąŠą┤:

ŌĆó Idle state (čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ)

ŌĆó Reset state (čüąŠčüč鹊čÅąĮąĖąĄ čüą▒čĆąŠčüą░)

ąĀąĖčü. 3-1 ąĖą╗ą╗čÄčüčéčĆąĖčĆčāąĄčé čĆąĄąČąĖą╝čŗ ąĖ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą║ą░ą║ ąĖ čāčüą╗ąŠą▓ąĖčÅ ą┐ąĄčĆąĄčģąŠą┤ą░ ą╝ąĄąČą┤čā ąĮąĖą╝ąĖ.

ąĀąĖčü. 3-1. ąĀąĄąČąĖą╝čŗ ąĖ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ ą▓čŗčģąŠą┤ ąĖąĘ Reset ą▓ čĆąĄąČąĖą╝ Supervisor. ą×ą┤ąĮą░ą║ąŠ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ 菹╝čāą╗čÅčåąĖąĖ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░čéčī čüą▒čĆąŠčü, ąĖ ąĄčüą╗ąĖ čŹč鹊 čéą░ą║, č鹊 ą▓čŗčģąŠą┤ ąĖąĘ čüą▒čĆąŠčüą░ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐ąĄčĆąĄčģąŠą┤čā ą▓ čĆąĄąČąĖą╝ Emulation.

[User Mode]

ą¤čĆąŠčåąĄčüčüąŠčĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (User mode), ą║ąŠą│ą┤ą░ ąŠąĮ ąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (Reset) ąĖą╗ąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ (Idle), ąĖ ą║ąŠą│ą┤ą░ ąŠąĮ ąĮąĄ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé čüąŠą▒čŗčéąĖąĄ ąŠą▒čŗčćąĮąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ NMI, čüąŠą▒čŗčéąĖąĄ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ ąĖą╗ąĖ 菹╝čāą╗čÅčåąĖąĖ. User mode ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą║ąŠą┤ą░ čāčĆąŠą▓ąĮčÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ą║ąŠč鹊čĆčŗą╣ ąĮąĄ čéčĆąĄą▒čāąĄčé ąĖčüą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ čüąĖčüč鹥ą╝ąĮčŗą╝ čĆąĄą│ąĖčüčéčĆą░ą╝. ąøčÄą▒ą░čÅ ą┐ąŠą┐čŗčéą║ą░ ą┤ąŠčüčéčāą┐ą░ ą║ ąŠą│čĆą░ąĮąĖč湥ąĮąĮčŗą╝ čüąĖčüč鹥ą╝ąĮčŗą╝ čĆąĄą│ąĖčüčéčĆą░ą╝ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüąŠą▒čŗčéąĖčÄ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ (exception event). ąóą░ą▒ą╗ąĖčåą░ 3-2 ą┐ąĄčĆąĄčćąĖčüą╗čÅąĄčé čĆąĄą│ąĖčüčéčĆčŗ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ąŠčüčéčāą┐ąĮčŗ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ąóą░ą▒ą╗ąĖčåą░ 3-2. ąĀąĄą│ąĖčüčéčĆčŗ, ą║ ą║ąŠč鹊čĆčŗą╝ ą▓ąŠąĘą╝ąŠąČąĄąĮ ą┤ąŠčüčéčāą┐ ą▓ User Mode.

| ąĀąĄą│ąĖčüčéčĆčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ |

ąśą╝ąĄąĮą░ čĆąĄą│ąĖčüčéčĆąŠą▓ |

| ąĀąĄą│ąĖčüčéčĆčŗ ą┤ą░ąĮąĮčŗčģ |

R[7:0], A[1:0] |

| ąĀąĄą│ąĖčüčéčĆčŗ čāą║ą░ąĘą░č鹥ą╗ąĄą╣ |

P[5:0], SP, FP, I[3:0], M[3:0], L[3:0], B[3:0] |

| ąĀąĄą│ąĖčüčéčĆčŗ čüąĄą║ą▓ąĄąĮčüąŠčĆą░ ąĖ čüąŠčüč鹊čÅąĮąĖčÅ |

RETS, LC[1:0], LT[1:0], LB[1:0], ASTAT, CYCLES, CYCLES2 |

ąŚą░čēąĖčēąĄąĮąĮčŗąĄ čĆąĄčüčāčĆčüčŗ ąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ. ąĪąĖčüč鹥ą╝ąĮčŗąĄ čĆąĄčüčāčĆčüčŗ čüąŠčüč鹊čÅčé ąĖąĘ ą┐ąŠą┤ą╝ąĮąŠąČąĄčüčéą▓ą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą▓čüąĄčģ MMR, ąĖ ąĖąĘ ą┐ąŠą┤ą╝ąĮąŠąČąĄčüčéą▓ą░ ąĘą░čēąĖčēąĄąĮąĮčŗčģ ąĖąĮčüčéčĆčāą║čåąĖą╣. ąŁčéąĖ MMR čüąĖčüč鹥ą╝čŗ ąĖ čÅą┤čĆą░ ąĮą░čćąĖąĮą░čÄčéčüčÅ čü ą░ą┤čĆąĄčüą░ 0xFFC0 0000. ąŁč鹊čé čĆąĄą│ąĖąŠąĮ ą┐ą░ą╝čÅčéąĖ ąĘą░čēąĖčēąĄąĮ ąŠčé ą┤ąŠčüčéčāą┐ą░ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. ąøčÄą▒ą░čÅ ą┐ąŠą┐čŗčéą║ą░ ą┤ąŠčüčéčāą┐ą░ ą║ ąŠą▒ą╗ą░čüčéąĖ MMR ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąĖčüą║ą╗čÄč湥ąĮąĖčÄ (exception).

ąĪą┐ąĖčüąŠą║ ąĘą░čēąĖčēąĄąĮąĮčŗčģ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą▓ čéą░ą▒ą╗ąĖčåąĄ 3-3. ąøčÄą▒ą░čÅ ą┐ąŠą┐čŗčéą║ą░ ą▓čŗąĘą▓ą░čéčī ąĘą░čēąĖčēąĄąĮąĮčāčÄ ąĖąĮčüčéčĆčāą║čåąĖčÄ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüąŠą▒čŗčéąĖčÄ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ (exception event).

ąóą░ą▒ą╗ąĖčåą░ 3-3. ąŚą░čēąĖčēąĄąĮąĮčŗąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ.

| ąśąĮčüčéčĆčāą║čåąĖčÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| RTI |

ąÆąŠąĘą▓čĆą░čé ąĖąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Interrupt). |

| RTX |

ąÆąŠąĘą▓čĆą░čé ąĖąĘ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ (Exception). |

| RTN |

ąÆąŠąĘą▓čĆą░čé ąĖąĘ ąĮąĄ ą╝ą░čüą║ąĖčĆčāąĄą╝ąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (NMI). |

| CLI |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. |

| STI |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. |

| RAISE |

ąōąĄąĮąĄčĆą░čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖą╗ąĖ čüą▒čĆąŠčüą░. |

| RTE |

ąÆąŠąĘą▓čĆą░čé ąĖąĘ 菹╝čāą╗čÅčåąĖąĖ. ą¤čĆąĖą▓ąŠą┤ąĖčé ą║ ąĖčüą║ą╗čÄč湥ąĮąĖčÄ, ąĄčüą╗ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮąĄ ą▓ čĆąĄąČąĖą╝ąĄ Emulation. |

ąŚą░čēąĖčēąĄąĮąĮą░čÅ ą┐ą░ą╝čÅčéčī. ąÆ čĆąĄąČąĖą╝ąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░čēąĖčēąĄąĮčŗ ąŠčé ą┤ąŠčüčéčāą┐ą░ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čÅč湥ą╣ą║ąĖ ą┐ą░ą╝čÅčéąĖ. ąöą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī čüąŠąĘą┤ą░ąĮą░ ąĖ čĆą░ąĘčĆąĄčłąĄąĮą░ ąĘą░ą┐ąĖčüčī Cacheability Protection Lookaside Buffer (CPLB). ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "Memory Management Unit" ą▓ ą┤ąŠą║čāą╝ąĄąĮč鹥 [1] (čéą░ą║ąČąĄ čüą╝. [4, 5]).

ąÆčģąŠą┤ ą▓ User Mode. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓čŗčģąŠą┤ ąĖąĘ čüą▒čĆąŠčüą░, ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Supervisor, ą┐ąŠč鹊ą╝čā čćč鹊 ąŠąĮ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé čüąŠą▒čŗčéąĖąĄ čüą▒čĆąŠčüą░ (reset event). ą¦č鹊ą▒čŗ ą▓ąŠą╣čéąĖ ą▓ čĆąĄąČąĖą╝ User ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ Reset, ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ 2 čłą░ą│ą░. ąÆąŠ-ą┐ąĄčĆą▓čŗčģ, ą░ą┤čĆąĄčü ą▓ąŠąĘą▓čĆą░čéą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮ ą▓ čĆąĄą│ąĖčüčéčĆ RETI. ąÆąŠ ą▓č鹊čĆčŗčģ, ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąĖąĮčüčéčĆčāą║čåąĖčÅ RTI. ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą┐čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ ą▓ąŠą╣čéąĖ ą▓ čĆąĄąČąĖą╝ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░.

//ąøąĖčüčéąĖąĮą│ 3-1. ąÆčģąŠą┤ ą▓ User Mode ąĖąĘ Reset.

P1.L = lo(START); // ąŻą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ ąĮą░čćą░ą╗ąŠ ą║ąŠą┤ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

P1.H = hi(START); //

RETI = P1;

RTI; // ąÆąŠąĘą▓čĆą░čé ąĖąĘ čüąŠą▒čŗčéąĖčÅ čüą▒čĆąŠčüą░ (Reset Event)

START:

// ą¤ąŠą╝ąĄčüčéąĖč鹥 čüčÄą┤ą░ ą║ąŠą┤ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ąśąĮčüčéčĆčāą║čåąĖąĖ ą▓ąŠąĘą▓čĆą░čéą░, ą║ąŠč鹊čĆčŗąĄ ą▓ąŠą▓ą╗ąĄą║ą░čÄčé ą▓čģąŠą┤ ą▓ User Mode. ąÆ čéą░ą▒ą╗ąĖčåąĄ 3-4 čüčāą╝ą╝ą░čĆąĮąŠ ą┐čĆąĖą▓ąĄą┤ąĄąĮčŗ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą▓ąŠąĘą▓čĆą░čéą░, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą▓ąŠą▓ą╗ąĄč湥ąĮąĖčÅ čĆąĄąČąĖą╝ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąĖąĘ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąŠą▓ čüąĖčüč鹥ą╝ąĮčŗčģ čüąŠą▒čŗčéąĖą╣ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąÜąŠą│ą┤ą░ čŹčéąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░čģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ISR), ąĘąĮą░č湥ąĮąĖąĄ ą░ą┤čĆąĄčüą░ ą▓ąŠąĘą▓čĆą░čéą░ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ čüąŠčģčĆą░ąĮąĄąĮąŠ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ čüąŠą▒čŗčéąĖčÅ RETx. ąÆ čüą╗čāčćą░ąĄ ISR, ąĄčüą╗ąĖ čŹč鹊čé ISR ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĄčĆą▓ą░ąĮ ą┤čĆčāą│ąĖą╝ ISR, ą░ą┤čĆąĄčü ą▓ąŠąĘą▓čĆą░čéą░ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ čüč鹥ą║ąĄ. ąöą╗čÅ čŹč鹊ą│ąŠ čüą╗čāčćą░čÅ ą░ą┤čĆąĄčü ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░ą╣ą┤ąĄąĮ ą┐čāč鹥ą╝ ą▓čŗčéą░ą╗ą║ąĖą▓ą░ąĮąĖčÅ ąĖąĘ čüč鹥ą║ą░ (POP) ą▓ čĆąĄą│ąĖčüčéčĆ RETI. ąÜą░ą║ č鹊ą╗čīą║ąŠ RETI ąĘą░ą│čĆčāąČąĄąĮ, ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░ąĮą░ ąĖąĮčüčéčĆčāą║čåąĖčÅ RTI.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▓čŗčéą░ą╗ą║ąĖą▓ą░ąĮąĖąĄ ąĖąĘ čüč鹥ą║ą░ čÅą▓ą╗čÅąĄčéčüčÅ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮčŗą╝ (ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮčŗą╝). ąĢčüą╗ąĖ čĆąĄą│ąĖčüčéčĆ RETI ąĮąĄ čüąŠčģčĆą░ąĮąĄąĮ/ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮ (ą┤ą╗čÅ ąĮąĄą│ąŠ ąĮąĄ ą▒čŗą╗ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ PUSH/POP), č鹊 ISR čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĮąĄ ą┐čĆąĄčĆčŗą▓ą░ąĄą╝čŗą╝, ą┐ąŠč鹊ą╝čā čćč鹊 ą░ą┤čĆąĄčü ą▓ąŠąĘą▓čĆą░čéą░ ąĮąĄ ą▒čŗą╗ čüąŠčģčĆą░ąĮąĄąĮ ą▓ čüč鹥ą║.

ą¤čĆąŠčåąĄčüčüąŠčĆ ąŠčüčéą░ąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ, ą┐ąŠą║ą░ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąŠą┤ąĮąŠ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ čüąŠą▒čŗčéąĖą╣:

ŌĆó ąĪąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, NMI ąĖą╗ąĖ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ ą┐čĆąĖą▓ąĄą┤čāčé ą║ ą▓čģąŠą┤čā ą▓ čĆąĄąČąĖą╝ Supervisor.

ŌĆó ąĪąŠą▒čŗčéąĖąĄ 菹╝čāą╗čÅčåąĖąĖ ą┐ąĄčĆąĄą▓ąĄą┤ąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓ čĆąĄąČąĖą╝ Emulation.

ŌĆó ąĪąŠą▒čŗčéąĖąĄ čüą▒čĆąŠčüą░ ą┐ąĄčĆąĄą▓ąĄą┤ąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ Reset.

ąóą░ą▒ą╗ąĖčåą░ 3-4. ąśąĮčüčéčĆčāą║čåąĖąĖ ą▓ąŠąĘą▓čĆą░čéą░, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▓ąŠą▓ą╗ąĄą║ą░čéčī User Mode.

| ąÉą║čéąĖą▓ąĮąŠčüčéčī č鹥ą║čāčēąĄą│ąŠ ą┐čĆąŠčåąĄčüčüą░ |

ąśąĮčüčéčĆčāą║čåąĖčÅ ą▓ąŠąĘą▓čĆą░čéą░ |

ąÆčŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąŠą┤ąŠą╗ąČąĖčéčüčÅ ą┐ąŠ ą░ą┤čĆąĄčüčā ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ |

| Interrupt Service Routine (ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ISR) |

RTI |

RETI |

| Exception Service Routine (ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ) |

RTX |

RETX |

| ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ąĮąĄ ą╝ą░čüą║ąĖčĆčāąĄą╝ąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (NMI). |

RTN |

RETN |

| Emulation Service Routine (ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ 菹╝čāą╗čÅčåąĖąĖ) |

RTE |

RETE |

[Supervisor Mode]

ą¤čĆąŠčåąĄčüčüąŠčĆ ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé ą▓čüąĄ čüąŠą▒čŗčéąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, NMI ąĖ ąĖčüą║ą╗čÄč湥ąĮąĖą╣ ą▓ čĆąĄąČąĖą╝ąĄ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ (Supervisor).

ąĀąĄąČąĖą╝ Supervisor ąĖą╝ąĄąĄčé ą┐ąŠą╗ąĮčŗą╣, ąĮąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ąŠ ą▓čüąĄą╝ čüąĖčüč鹥ą╝ąĮčŗą╝ čĆąĄčüčāčĆčüą░ą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą▓ą║ą╗čÄčćą░čÅ ą▓čüąĄ čĆąĄčüčāčĆčüčŗ 菹╝čāą╗čÅčåąĖąĖ, ąĄčüą╗ąĖ ąĮąĄ ą▒čŗą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮčŗ ąĖ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ąĘą░ą┐ąĖčüąĖ CPLB [5]. ąóąŠą╗čīą║ąŠ čĆąĄąČąĖą╝ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐čüąĄą▓ą┤ąŠąĮąĖą╝ čĆąĄą│ąĖčüčéčĆą░ USP (User Stack Pointer), ą║ąŠč鹊čĆčŗą╣ čüčüčŗą╗ą░ąĄčéčüčÅ ąĮą░ ą┐ą░ą╝čÅčéčī čüč鹥ą║ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. ąŁč鹊čé ą┐čüąĄą▓ą┤ąŠąĮąĖą╝ čĆąĄą│ąĖčüčéčĆą░ ąĮąĄąŠą▒čģąŠą┤ąĖą╝, ą┐ąŠč鹊ą╝čā čćč鹊 ą▓ čĆąĄąČąĖą╝ąĄ Supervisor ąĖą╝čÅ čĆąĄą│ąĖčüčéčĆą░ SP ąŠčéąĮąŠčüąĖčéčüčÅ ą║ čāą║ą░ąĘą░č鹥ą╗čÄ čüč鹥ą║ą░ čÅą┤čĆą░ (kernel stack pointer) ą▓ą╝ąĄčüč鹊 čāą║ą░ąĘą░č鹥ą╗čÅ čüč鹥ą║ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ą¤čĆąĖ ą▓čŗčģąŠą┤ąĄ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ Reset ąĮąŠčĆą╝ą░ą╗čīąĮą░čÅ ąŠą▒čĆą░ą▒ąŠčéą║ą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Supervisor. ąĪąĮčÅčéąĖąĄ čüąĖą│ąĮą░ą╗ą░ čüą▒čĆąŠčüą░ RESET ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ Reset ą▓ čĆąĄąČąĖą╝ Supervisor, ą│ą┤ąĄ ą┐čĆąŠčåąĄčüčüąŠčĆ ąŠčüčéą░ąĄčéčüčÅ, ą┐ąŠą║ą░ čüąŠą▒čŗčéąĖąĄ 菹╝čāą╗čÅčåąĖąĖ ąĖą╗ąĖ ąĖąĮčüčéčĆčāą║čåąĖčÅ ą▓ąŠąĘą▓čĆą░čéą░ ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüą╝ąĄąĮąĄ čĆąĄąČąĖą╝ą░. ą¤ąĄčĆąĄą┤ ą▓čŗą┤ą░č湥ą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą▓ąŠąĘą▓čĆą░čéą░ ą▓ čĆąĄą│ąĖčüčéčĆ RETI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮ ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü, ą║čāą┤ą░ ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ ą┐ąĄčĆąĄčģąŠą┤ ą┐čĆąĖ ą▓ąŠąĘą▓čĆą░č鹥.

ąĀą░ą▒ąŠč湥ąĄ ąŠą║čĆčāąČąĄąĮąĖąĄ ąŠą▒čŗčćąĮąŠą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąÜąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮąĄ ą▓ čāčüą╗ąŠą▓ąĖčÅčģ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ (Non-OS Environments), č鹊 ą║ąŠą┤ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Supervisor, čćč鹊ą▒čŗ ąŠąĮ ą╝ąŠą│ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ąŠ ą▓čüąĄą╝ čĆąĄčüčāčĆčüą░ą╝ čÅą┤čĆą░ ąĖ čüąĖčüč鹥ą╝čŗ. ąÜąŠą│ą┤ą░ čüąĮčÅčé čüąĖą│ąĮą░ą╗ RESET, ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖąĮąĖčåąĖąĖčĆčāąĄčé čüą▓ąŠčÄ čĆą░ą▒ąŠčéčā ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ čüąŠą▒čŗčéąĖčÅ čüą▒čĆąŠčüą░ (ąŠą▒čŗčćąĮąŠ čŹč鹊 ą░ą┤čĆąĄčü 0xFFA00000). ąóąŠą╗čīą║ąŠ čüąŠą▒čŗčéąĖąĄ 菹╝čāą╗čÅčåąĖąĖ ą╝ąŠąČąĄčé ą┐ąĄčĆąĄčģą▓ą░čéąĖčéčī čŹčéčā ą░ą║čéąĖą▓ąĮąŠčüčéčī ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▒ąŠą╗ąĄąĄ ąĮąĖąĘą║ąŠčāčĆąŠą▓ąĮąĄą▓čŗąĄ čüąŠą▒čŗčéąĖčÅ ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąŠą▒čĆą░ą▒ąŠčéą░ąĮčŗ.

ą×ą┤ąĮąĖą╝ ąĖąĘ čüą┐ąŠčüąŠą▒ąŠą▓, ą║ąŠč鹊čĆčŗą╝ ą╝ąŠąČąĮąŠ čāą┤ąĄčƹȹ░čéčī ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓ čĆąĄąČąĖą╝ąĄ Supervisor, ąĖ čĆą░ąĘčĆąĄčłąĖčéčī ą┐čĆąĖ čŹč鹊ą╝ ąŠą▒čĆą░ą▒ąŠčéą║čā čüąŠą▒čŗčéąĖą╣, čÅą▓ą╗čÅąĄčéčüčÅ čüą┐ąŠčüąŠą▒ ąĮą░čüčéčĆąŠąĖčéčī ąĖ ą▓čŗąĘą▓ą░čéčī čüą░ą╝ąŠąĄ ąĮąĖąĘą║ąŠčāčĆąŠą▓ąĮąĄą▓ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (IVG15). ąĪąŠą▒čŗčéąĖčÅ ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ ąŠą┐ąĖčüą░ąĮčŗ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "Events and Interrupts" ą┤ąŠą║čāą╝ąĄąĮčéą░ [1] (čéą░ą║ąČąĄ čüą╝. [3]). ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ąŠ ą▓čŗąĘą▓ą░ąĮąŠ ąĮąĖąĘą║ąŠčāčĆąŠą▓ąĮąĄą▓ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤ąŠą╣ RAISE 15, ą▓ čĆąĄą│ąĖčüčéčĆ RETI ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮ ą░ą┤čĆąĄčü ą▓ąŠąĘą▓čĆą░čéą░, ą║ąŠč鹊čĆčŗą╣ čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ ą║ąŠą┤ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ, ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗąĘą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ IVG15. ą¤ąŠčüą╗ąĄ ąĘą░ą│čĆčāąĘą║ąĖ RETI ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąĖąĮčüčéčĆčāą║čåąĖčÅ RTI ą┤ą╗čÅ ą▓ąŠąĘą▓čĆą░čéą░ ąĖąĘ čüąŠą▒čŗčéąĖčÅ čüą▒čĆąŠčüą░.

ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ IVG15 ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮ ą┤ą╗čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ ą▓ ą░ą┤čĆąĄčü ąĮą░čćą░ą╗ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ RTI ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐čĆąŠčåąĄčüčüąŠčĆ ąŠčüčéą░ąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Supervisor, ą┐ąŠč鹊ą╝čā čćč鹊 ąŠčüčéą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ IPEND[15]. ąØą░čćąĖąĮą░čÅ čü čŹč鹊ą│ąŠ ą╝ąŠą╝ąĄąĮčéą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüą░ą╝ąŠą│ąŠ ąĮąĖąČąĮąĄą│ąŠ čāčĆąŠą▓ąĮčÅ. ąŁč鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 ą╝ąŠą│čāčé ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčīčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓čüąĄčģ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖčģ čāčĆąŠą▓ąĮąĄą╣.

ąÜą░ą║ ąŠčüčéą░ą▓ąĖčéčī čĆąĄąČąĖą╝ Supervisor ą┐čĆąĖ ą▓čŗčģąŠą┤ąĄ ąĖąĘ čüą▒čĆąŠčüą░. ąØąĖąČąĄ ą┤ą░ąĮ ą║ąŠą┤ ą┐čĆąĖą╝ąĄčĆą░, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą║ąŠą┤ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ Supervisor.

//ąøąĖčüčéąĖąĮą│ 3-2. ąĪąŠčģčĆą░ąĮąĄąĮąĖąĄ Supervisor Mode ą┐čĆąĖ ą▓čŗčģąŠą┤ąĄ ąĖąĘ Reset.

P0.L = lo(EVT15); // ąŻą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ IVG15 ą▓ čéą░ą▒ą╗ąĖčåąĄ ą▓ąĄą║č鹊čĆąŠą▓

P0.H = hi(EVT15); // ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Event Vector Table, EVT)

P1.L = lo(START); // ąŻą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ ąĮą░čćą░ą╗ąŠ ą║ąŠą┤ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ

P1.H = hi(START); //

[P0] = P1; // ąĀą░ąĘą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░ START ą▓ IVG15 EVT

P0.L = lo(IMASK);

R0 = [P0];

R1.L = lo(EVT_IVG15);

// ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ IVG15 (čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ) ą▓ čĆąĄą│ąĖčüčéčĆąĄ IMASK.

R0 = R0 | R1;

[P0] = R0;

RAISE 15; // ąŚą░ą┐čāčüą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ IVG15

P0.L = lo(WAIT_HERE);

P0.H = hi(WAIT_HERE);

RETI = P0; // ąÆ RETI ąĘą░ą│čĆčāąČąĄąĮ ą░ą┤čĆąĄčü ą▓ąŠąĘą▓čĆą░čéą░

RTI; // ąÆąŠąĘą▓čĆą░čé ąĖąĘ Reset Event

// ąæąĄčüą║ąŠąĮąĄčćąĮčŗą╣ čåąĖą║ą╗ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą┐ąŠą║ą░ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ IVG15:

WAIT_HERE:

JUMP WAIT_HERE;

// ąĪčÄą┤ą░ čāą║ą░ąĘčŗą▓ą░ąĄčé ą▓ąĄą║č鹊čĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ IVG15:

START:

// ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ čüąŠčģčĆą░ąĮąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░ ą▓ąŠąĘą▓čĆą░čéą░ ą▓ čüč鹥ą║ąĄ,

// čŹč鹊 čĆą░ąĘčĆąĄčłąĖčéčī ąŠą▒čĆą░ą▒ąŠčéą║čā ą┤čĆčāą│ąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ čüąĖčüč鹥ą╝ąĄ:

[--SP] = RETI;

// ąöą░ą╗ąĄąĄ ąĖą┤ąĄčé ą║ąŠą┤ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ, ą║ąŠč鹊čĆčŗą╣ čĆą░ą▒ąŠčéą░ąĄčé

// ą▓ čĆąĄąČąĖą╝ąĄ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░:

...

[Emulation Mode]

ą¤čĆąŠčåąĄčüčüąŠčĆ ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ 菹╝čāą╗čÅčåąĖąĖ (Emulation), ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮ čĆąĄąČąĖą╝ 菹╝čāą╗čÅčåąĖąĖ, ąĖ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĄąĮąŠ ąŠą┤ąĮąŠ ąĖąĘ čāčüą╗ąŠą▓ąĖą╣:

ŌĆó ą¤čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▒čŗčéąĖąĄ ą▓ąĮąĄčłąĮąĄą╣ 菹╝čāą╗čÅčåąĖąĖ (external emulation event). ą×ąĮąŠ ą▓čŗąĘčŗą▓ą░ąĄčéčüčÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄą╝ ąŠčéą╗ą░ą┤čćąĖą║ą░ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü JTAG.

ŌĆó ąÆčŗą┐ąŠą╗ąĮąĄąĮą░ ąĖąĮčüčéčĆčāą║čåąĖčÅ EMUEXCPT.

ą¤čĆąŠčåąĄčüčüąŠčĆ ąŠčüčéą░ąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Emulation, ą┐ąŠą║ą░ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ čüąŠą▒čŗčéąĖčÅ čŹą╝čāą╗čÅčåąĖąĖ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮąĖčé ąĖąĮčüčéčĆčāą║čåąĖčÄ RTE. ąĢčüą╗ąĖ ąĮąĄčé ąŠąČąĖą┤ą░čÄčēąĖčģ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ RTE, č鹊 ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čĆąĄąČąĖą╝ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (User mode). ąśąĮą░č湥 ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ Supervisor ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąĀąĄąČąĖą╝ Emulation čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐ąŠ ą┐čĆąĖąŠčĆąĖč鹥čéčā, ąĖ ą▓ ąĮąĄą╝ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖą╝ąĄąĄčé ąĮąĄąŠą│čĆą░ąĮąĖč湥ąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ąŠ ą▓čüąĄą╝ čüąĖčüč鹥ą╝ąĮčŗą╝ čĆąĄčüčāčĆčüą░ą╝.

[Idle State]

ąĪąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ (Idle state) ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą░ą║čéąĖą▓ąĮąŠčüčéčī ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐ąŠ čāčüą╝ąŠčéčĆąĄąĮąĖčÄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ, čćč鹊 ąŠą▒čŗčćąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čŹą║ąŠąĮąŠą╝ąĖąĖ 菹ĮąĄčĆą│ąĖąĖ ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĖčéą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĮą░ą▒ą╗čÄą┤ą░ąĄčéčüčÅ ąĘą░čéąĖčłčīąĄ ą▓ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ. ąÆ čŹč鹊ą╝ čüąŠčüč鹊čÅąĮąĖąĖ ąĮąĖą║ą░ą║ąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą║ąŠą┤ą░ ąĮąĄ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ. ąĪąŠčüč鹊čÅąĮąĖąĄ Idle ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖąĄą╣ IDLE, ąŠąĮą░ ąŠą┐ąŠą▓ąĄčēą░ąĄčé ą░ą┐ą┐ą░čĆą░čéčāčĆčā ą┐čĆąŠčåąĄčüčüąŠčĆą░, čćč鹊 ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄčéčüčÅ ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ.

ą¤čĆąŠčåąĄčüčüąŠčĆ ąŠčüčéą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ Idle ą┤ąŠ č鹊ą│ąŠ ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ ą║ą░ą║ąŠąĄ-ą╗ąĖą▒ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, čéą░ą║ąŠąĄ ą║ą░ą║ SPORT ąĖą╗ąĖ čćą░čüčŗ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (Real-Time Clock, RTC), čüą│ąĄąĮąĄčĆąĖčĆčāčÄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, čéčĆąĄą▒čāčÄčēąĄąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čüąĖčüč鹥ą╝ą░ DMA ą▓ čüąŠčüč鹊čÅąĮąĖąĖ Idle ąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé, čćč鹊 ą┤ąŠą▓ąŠą╗čīąĮąŠ ą┐ąĄčćą░ą╗čīąĮąŠ.

ąÆ ą╗ąĖčüčéąĖąĮą│ąĄ 3-3 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čÅą┤čĆą░ ąĘą░ą┐čĆąĄčēą░čÄčéčüčÅ, ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ IDLE. ąÜąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłąĄąĮčŗ ą▓čüąĄ ąŠąČąĖą┤ą░čÄčēąĖąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąŠčåąĄčüčüčŗ, čÅą┤čĆąŠ ąĘą░ą┐čĆąĄčēą░ąĄčé čĆą░ą▒ąŠčéčā čüą▓ąŠąĖčģ čéą░ą║č鹊ą▓. ą¤ąŠčüą║ąŠą╗čīą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮčŗ, čüąŠčüč鹊čÅąĮąĖąĄ Idle ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĄčĆą▓ą░ąĮąŠ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗ą░ WAKEUP. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ SIC_IWR ą▓ ą┤ąŠą║čāą╝ąĄąĮč鹥 [1]. ąĢčüą╗ąĖ čŹč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ, ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ Idle ą║čĆąŠą╝ąĄ čüąĖą│ąĮą░ą╗ą░ WAKEUP čéą░ą║ąČąĄ ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąÜąŠą│ą┤ą░ ą▓čŗčüčéą░ą▓ą╗ąĄąĮ čüąĖą│ąĮą░ą╗ WAKEUP, ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐čĆąŠčüčŗą┐ą░ąĄčéčüčÅ, ąĖ ąĖąĮčüčéčĆčāą║čåąĖčÅ STI čüąĮąŠą▓ą░ čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

//ąøąĖčüčéąĖąĮą│ 3-3. ąöąĄą╝ąŠąĮčüčéčĆą░čåąĖčÅ ą┐ąĄčĆąĄčģąŠą┤ą░ ą▓ Idle State.

CLI R0; // ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

IDLE; // ą×ą┐čāčüč鹊賹ĄąĮąĖąĄ ą║ąŠąĮą▓ąĄą╣ąĄčĆą░ ąĖ ąŠčéą┐čĆą░ą▓ą║ą░ čÅą┤čĆą░ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ IDLE.

STI R0; // ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąŠčüą╗ąĄ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ.

[Reset State]

ąĪąŠčüč鹊čÅąĮąĖąĄ čüą▒čĆąŠčüą░ (Reset State) ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą╗ąŠą│ąĖą║ąŠą╣ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąÆąŠ ą▓čĆąĄą╝čÅ čüąŠčüč鹊čÅąĮąĖčÅ čüą▒čĆąŠčüą░ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĖ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮą░čÅ čüąĖčüč鹥ą╝ą░ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅčÄčé ą║ąŠą┤, ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ.

ą¤čĆąŠčåąĄčüčüąŠčĆ ąŠčüčéą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ Reset, ą┐ąŠą║ą░ ą▓ąĮąĄčłąĮčÅčÅ ą╗ąŠą│ąĖą║ą░ čāą┤ąĄčƹȹĖą▓ą░ąĄčé ą▓ ą░ą║čéąĖą▓ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ RESET. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čŹč鹊čé čüąĖą│ąĮą░ą╗ čüąĮčÅčé, ą┐čĆąŠčåąĄčüčüąŠčĆ ąĘą░ą▓ąĄčĆčłą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čüą▒čĆąŠčüą░ ąĖ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ Supervisor, ą│ą┤ąĄ ąŠąĮ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą║ąŠą┤, ąĮą░čģąŠą┤čÅčēąĖą╣čüčÅ ą┐ąŠ ą▓ąĄą║č鹊čĆčā čüą▒čĆąŠčüą░ (reset event vector).

ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ Supervisor ąĖą╗ąĖ Emulation ą╝ąŠąČąĄčé ąĘą░ą┐čāčüčéąĖčéčī čüąŠčüč鹊čÅąĮąĖąĄ Reset ą▒ąĄąĘ ą▓ąŠą▓ą╗ąĄč湥ąĮąĖčÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ RESET. ąŁč鹊 ą╝ąŠąČąĮąŠ čüą┤ąĄą╗ą░čéčī ą▓čŗą┤ą░č湥ą╣ ą▓ąĄčĆčüąĖąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ RAISE, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮąŠą╣ ą┤ą╗čÅ čüą▒čĆąŠčüą░.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (User mode) ąĮąĄ ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī čüąŠčüč鹊čÅąĮąĖąĄ Reset, ą║čĆąŠą╝ąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ čÅą┤čĆąŠą╝ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ą┤ą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ. ąÆ čéą░ą▒ą╗ąĖčåąĄ 3-5 čüčāą╝ą╝ą░čĆąĮąŠ ą┐ąŠą║ą░ąĘą░ąĮąŠ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐čĆąĖ čüą▒čĆąŠčüąĄ.

ąóą░ą▒ą╗ąĖčåą░ 3-5. ąĪąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐čĆąĖ čüą▒čĆąŠčüąĄ.

| ąŁą╗ąĄą╝ąĄąĮčé |

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ čüą▒čĆąŠčüą░ |

| ą»ą┤čĆąŠ |

| ąĀą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ |

Supervisor ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ čüąŠą▒čŗčéąĖčÅ čüą▒čĆąŠčüą░, čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ. |

| ąĀąĄąČąĖą╝ ąŠą║čĆčāą│ą╗ąĄąĮąĖčÅ |

ąØąĄ čüą╝ąĄčēąĄąĮąĮąŠąĄ ąŠą║čĆčāą│ą╗ąĄąĮąĖąĄ (Unbiased Rounding). |

| Cycle Counters (čüč湥čéčćąĖą║ąĖ čéą░ą║č鹊ą▓) |

ąŚą░ą┐čĆąĄčēąĄąĮčŗ ąĖ ąŠą▒ąĮčāą╗ąĄąĮčŗ. |

| ąĀąĄą│ąĖčüčéčĆčŗ DAG (ą│ąĄąĮąĄčĆą░č鹊čĆčŗ ą░ą┤čĆąĄčüą░ I, L, B, M) |

ąĪą╗čāčćą░ą╣ąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠčćąĖčēąĄąĮčŗ ą┐čĆąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ). |

| ąĀąĄą│ąĖčüčéčĆčŗ ą┤ą░ąĮąĮčŗčģ ąĖ ą░ą┤čĆąĄčüą░ |

| IPEND, IMASK, ILAT |

ą×čćąĖčēąĄąĮčŗ, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ ąĘą░ą┐čĆąĄčēąĄąĮčŗ ą▒ąĖč鹊ą╝ 4 čĆąĄą│ąĖčüčéčĆą░ IPEND. |

| CPLB |

ąŚą░ą┐čĆąĄčēąĄąĮčŗ. |

| L1 Instruction Memory |

SRAM (čĆą░ą▒ąŠčéą░ ą║čŹčłą░ ąĘą░ą┐čĆąĄčēąĄąĮą░). |

| L1 Data Memory |

| Cache Validity Bits (ą▒ąĖčéčŗ ą░ą║čéčāą░ą╗čīąĮąŠčüčéąĖ ą║čŹčłą░) |

Invalid (ą║čŹčł ąĮąĄ ą┤ąŠčüč鹊ą▓ąĄčĆąĮą░). |

| ąĪąĖčüč鹥ą╝ą░ |

| ąĀąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ |

ą×ą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ čāčĆąŠą▓ąĮčÅą╝ąĖ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ BMODE ą▓ ą╝ąŠą╝ąĄąĮčé čüą▒čĆąŠčüą░. |

| ąÆčŗą▒ąŠčĆ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ MSEL |

ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą╗čÅ MSEL čĆąĄą│ąĖčüčéčĆą░ PLL_CTL čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ ą┐ąŠ ąÆą░čłąĄą╝čā ą┐čĆąŠčåąĄčüčüąŠčĆčā, ą│ą┤ąĄ ąŠą┐ąĖčüą░ąĮąŠ čüąŠčüč鹊čÅąĮąĖąĄ čŹčéąĖčģ ą▒ąĖčé ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ. |

| PLL Bypass Mode (ą┐čĆąŠą┐čāčüą║ čüąĖčüč鹥ą╝čŗ ążąÉą¤ą¦ ą┐čĆąĖ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĖ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé) |

ąŚą░ą┐čĆąĄčēąĄąĮąŠ. |

| ąĪąŠąŠčéąĮąŠčłąĄąĮąĖąĄ čćą░čüč鹊čé VCO/čÅą┤čĆą░ |

ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą╗čÅ CSEL čĆąĄą│ąĖčüčéčĆą░ PLL_DIV čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ ą┐ąŠ ąÆą░čłąĄą╝čā ą┐čĆąŠčåąĄčüčüąŠčĆčā, ą│ą┤ąĄ ąŠą┐ąĖčüą░ąĮąŠ čüąŠčüč鹊čÅąĮąĖąĄ čŹčéąĖčģ ą▒ąĖčé ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ. |

| ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ |

ąŚą░ą┐čĆąĄčēąĄąĮąŠ. |

[ąĪąĖčüč鹥ą╝ąĮčŗą╣ čüą▒čĆąŠčü ąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ]

ąÆ čéą░ą▒ą╗ąĖčåąĄ 3-6 ą┐ąŠą║ą░ąĘą░ąĮąŠ 5 čéąĖą┐ąŠą▓ čüą▒čĆąŠčüą░. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▓čüąĄ čüą▒čĆąŠčüčŗ, ą║čĆąŠą╝ąĄ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ (System Software), čüą▒čĆą░čüčŗą▓ą░čÄčé čÅą┤čĆąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ąóą░ą▒ą╗ąĖčåą░ 3-6. ąÆąĖą┤čŗ čüą▒čĆąŠčüą░.

| ąóąĖą┐ čüą▒čĆąŠčüą░ |

ąśčüč鹊čćąĮąĖą║ |

ąĀąĄąĘčāą╗čīčéą░čé |

| Hardware Reset |

ąÉą║čéąĖą▓ąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü ąĮą░ ą▓čŗą▓ąŠą┤ąĄ RESET ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╝čā čüą▒čĆąŠčüčā. |

ąĪą▒čĆąŠčü čÅą┤čĆą░ ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą▓ą║ą╗čÄčćą░čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖąĄą╝ Dynamic Power Management Controller (DPMC). ąĪą▒čĆą░čüčŗą▓ą░ąĄčé No Boot ą▒ąĖčéą░ Software Reset čĆąĄą│ąĖčüčéčĆą░ SYSCR (čüą╝. ąĮąĖąČąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░). |

| System Software Reset |

ąŚą░ą┐ąĖčüčī b#111 ą▓ ą▒ąĖčéčŗ [2:0] čüąĖčüč鹥ą╝ąĮąŠą│ąŠ MMR-čĆąĄą│ąĖčüčéčĆą░ SWRST ą┐ąŠ ą░ą┤čĆąĄčüčā 0xFC00 0100 ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝čā čüą▒čĆąŠčüčā. |

ąĪą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, ą║čĆąŠą╝ąĄ RTC (čćą░čüčŗ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ) ąĖ DPMC (ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖąĄą╝). DPMC čüą▒čĆą░čüčŗą▓ą░ąĄčé č鹊ą╗čīą║ąŠ No Boot ą▓ ą▒ąĖč鹥 Software Reset čĆąĄą│ąĖčüčéčĆą░ SYSCR. ą»ą┤čĆąŠ ąĮąĄ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ. ą¤čĆąŠčåąĄčüčü ąĘą░ą│čĆčāąĘą║ąĖ ąĮąĄ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ. |

| Watchdog Timer Reset |

ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ |

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čüą▒čĆąŠčü, ąĮąŠ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé, ąĄčüą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ čüąĮą░ (Sleep mode). ą£ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ čĆąĄą│ąĖčüčéčĆ SWRST, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, č湥ą╝ ą▒čŗą╗ ą▓čŗąĘą▓ą░ąĮ čüą▒čĆąŠčü. |

| Core Double-Fault Reset |

ąĢčüą╗ąĖ čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ ą▒ąĖč鹊ą╝ DOUBLE_FAULT čĆąĄą│ąĖčüčéčĆą░ SWRST, čŹč鹊čé čüą▒čĆąŠčü ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ čÅą┤čĆąŠ ą▓čģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ double-fault. |

ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čüą▒čĆąŠčü. ą£ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ čĆąĄą│ąĖčüčéčĆ SWRST, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, č湥ą╝ ą▒čŗą╗ ą▓čŗąĘą▓ą░ąĮ čüą▒čĆąŠčü. |

| Core-Only Software Reset |

ąŁč鹊čé čüą▒čĆąŠčü ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ąĖąĮčüčéčĆčāą║čåąĖąĖ RAISE 1 ąĖą╗ąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ Software Reset (SYSRST) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąŠčéą╗ą░ą┤ą║ąŠą╣ (DBGCTL). ąĀąĄą│ąĖčüčéčĆ DBGCTL čÅą┤čĆąŠ ąĮąĄ ą▓ąĖą┤ąĖčé, ąŠąĮ ą┤ąŠčüčéčāą┐ąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ čŹą╝čāą╗čÅč鹊čĆą░ č湥čĆąĄąĘ ą┐ąŠčĆčé JTAG. |

ąĪą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ čÅą┤čĆąŠ. ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čŹč鹊čé čüą▒čĆąŠčü ąĮąĄ čĆą░čüą┐ąŠąĘąĮą░čÄčé. |

Hardware Reset. ąÉą┐ą┐ą░čĆą░čéąĮčŗą╣ čüą▒čĆąŠčü ą║čĆąĖčüčéą░ą╗ą╗ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (Hardware Reset) čÅą▓ą╗čÅąĄčéčüčÅ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╝ čüąŠą▒čŗčéąĖąĄą╝. ą¦č鹊ą▒čŗ čüą▒čĆąŠčü čāčüą┐ąĄčłąĮąŠ ąĘą░ą▓ąĄčĆčłąĖą╗čüčÅ, ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ RESET ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ąĖąĘ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. ą┤ą░čéą░čłąĖčé ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ.

ąÉą┐ą┐ą░čĆą░čéąĮąŠ-ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čüą▒čĆąŠčü ą▓ą╗ąĖčÅąĄčé ąĮą░ ą▓čüčÄ čüąĖčüč鹥ą╝čā ą┐čĆąŠčåąĄčüčüąŠčĆą░ čåąĄą╗ąĖą║ąŠą╝, ą▓ą║ą╗čÄčćą░čÅ čÅą┤čĆąŠ ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čüąĮčÅčé čüąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░ čü ą▓čŗą▓ąŠą┤ą░ RESET, ą┐čĆąŠčåąĄčüčüąŠčĆ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 ą▓čüąĄ ą░čüąĖąĮčģčĆąŠąĮąĮčŗąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čĆą░čüą┐ąŠąĘąĮą░ą╗ąĖ ąĖ ąĘą░ą▓ąĄčĆčłąĖą╗ąĖ čüą▓ąŠą╣ čüą▒čĆąŠčü. ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą║ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą│čĆčāąĘą║ąĖ ą║ąŠą┤ą░ (Boot mode sequence), ą║ąŠč鹊čĆą░čÅ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ čüąŠčüč鹊čÅąĮąĖąĄą╝ ą▓čŗą▓ąŠą┤ąŠą▓ BMODE [7].

ąÆčŗą▓ąŠą┤čŗ ą║ąŠčĆą┐čāčüą░ BMODE čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ą×ąĮąĖ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅčÄčé ąĮąĖą║ą░ą║ąĖčģ ą┤čĆčāą│ąĖčģ čäčāąĮą║čåąĖą╣, ą║čĆąŠą╝ąĄ ą║ą░ą║ čŹčéąĖ ą▓čŗą▓ąŠą┤čŗ ą┤ąŠą╗ąČąĮčŗ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą┐ąŠą┤čéčÅąĮčāčéčŗ ą║ čāčĆąŠą▓ąĮčÅą╝ VDD ąĖą╗ąĖ VSS. ąŁčéąĖ ą▓čŗą▓ąŠą┤čŗ ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ SYSCR ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčé čĆąĄąČąĖą╝ ąĘą░ą│čĆčāąĘą║ąĖ, ą║ąŠč鹊čĆčŗą╣ čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠčüą╗ąĄ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čüą▒čĆąŠčüą░ (hardware reset) ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ čüąĖčüč鹥ą╝čŗ (System Software). ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ "Reset Interrupt" ąĖ čéą░ą▒ą╗ąĖčåčā 4-12 ą┤ąŠą║čāą╝ąĄąĮčéą░ [1].

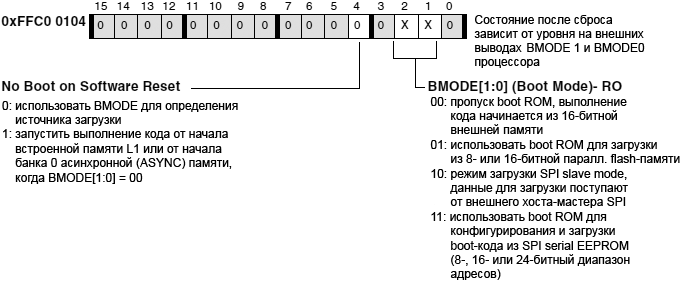

ąĀąĄą│ąĖčüčéčĆ SYSCR. ąŚąĮą░č湥ąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ą▒čŗą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮčŗ čü ą▓čŗą▓ąŠą┤ąŠą▓ BMODE ą┐čĆąĖ čüą▒čĆąŠčüąĄ, ąĘąĄčĆą║ą░ą╗čīąĮąŠ ąŠč鹊ą▒čĆą░ąČą░čÄčéčüčÅ ą▓ ą▒ąĖčéą░čģ čĆąĄą│ąĖčüčéčĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ (System Reset Configuration register, čüąŠą║čĆą░čēąĄąĮąĮąŠ SYSCR). ąŁčéąĖ ąĘąĮą░č湥ąĮąĖčÅ ą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ąĖ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ ą┐ąŠčüą╗ąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čüą▒čĆąŠčüą░. ąśąĘ SYSCR čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮčŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐ąĄčĆąĄąĮąŠčüčÅčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą╝ąĄčüčéą░. ąöą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠą▒čĆą░čéąĖč鹥čüčī ą║ ą│ą╗ą░ą▓ąĄ čü ąŠą┐ąĖčüą░ąĮąĖąĄą╝ čüą▒čĆąŠčüą░ ąĖ ąĘą░ą│čĆčāąĘą║ąĖ (Reset and Booting) čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (čéą░ą║ąČąĄ čüą╝. [7]).

ąĀąĖčü. 3-2. ąĀąĄą│ąĖčüčéčĆ System Reset Configuration (SYSCR). ąŚąĮą░č湥ąĮąĖčÅ ą▒ąĖčé, ą┐ąŠą╝ąĄč湥ąĮąĮčŗčģ ą║čĆąĄčüčéąĖą║ą░ą╝ąĖ X, ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ąŠčé ą▓ąĮąĄčłąĮąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ BMODE1 ąĖ BMODE0 ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▓ ą╝ąŠą╝ąĄąĮčé ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čüą▒čĆąŠčüą░ (čüą╝. [7]).

ąÆąĖą┤čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ąĖ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü (Software Reset) ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮ čéčĆąĄą╝čÅ čüą┐ąŠčüąŠą▒ą░ą╝ąĖ:

ŌĆó ąĪ ą┐ąŠą╝ąŠčēčīčÄ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (Watchdog Timer), ąĄčüą╗ąĖ ąŠąĮ ą▒čŗą╗ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ.

ŌĆó ąŻčüčéą░ąĮąŠą▓ą║ąŠą╣ ą┐ąŠą╗čÅ čüą▒čĆąŠčüą░ čüąĖčüč鹥ą╝čŗ (ą▒ąĖčéčŗ System Reset) ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ (čüą╝. čĆąĖčü. 3-3).

ŌĆó ąśąĮčüčéčĆčāą║čåąĖąĄą╣ RAISE 1.

ąĪč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ čüą▒čĆą░čüčŗą▓ą░ąĄčé ą║ą░ą║ čÅą┤čĆąŠ, čéą░ą║ ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░. ąĪąĖčüč鹥ą╝ąĮčŗą╣ čüą▒čĆąŠčü (System Reset) ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ čüą▒čĆąŠčüčā ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą▒ąĄąĘ čüą▒čĆąŠčüą░ čÅą┤čĆą░ ąĖ ą▒ąĄąĘ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą│čĆčāąĘą║ąĖ (booting sequence).

System Reset ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮ, ą║ąŠą│ą┤ą░ ą║ąŠą┤ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĖąĘ ą┐ą░ą╝čÅčéąĖ L1 (ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╣ ą╗ąĖą▒ąŠ ą║ą░ą║ ą║čŹčł, ą╗ąĖą▒ąŠ ą║ą░ą║ SRAM). ąÜąŠą│ą┤ą░ ą┐ą░ą╝čÅčéčī ąĖąĮčüčéčĆčāą║čåąĖą╣ L1 čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą║ą░ą║ ą║čŹčł, ą│ą░čĆą░ąĮčéąĖčĆčāą╣č鹥, čćč鹊 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą║ąŠą┤ą░ System Reset ą┐čĆąŠčćąĖčéą░ąĮą░ ą▓ ą║čŹčł.

ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░, ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą╗ąĖą▒ąŠ čüč鹊čĆąŠąČąĄą▓čŗą╝ čéą░ą╣ą╝ąĄčĆąŠą╝ Watchdog Timer, ą╗ąĖą▒ąŠ System Reset, ą┐čĆąŠčåąĄčüčüąŠčĆ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 ą▓čüąĄ ą░čüąĖąĮčģčĆąŠąĮąĮčŗąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čĆą░čüą┐ąŠąĘąĮą░ą╗ąĖ ąĖ ąĘą░ą▓ąĄčĆčłąĖą╗ąĖ čüą▒čĆąŠčü.

ąöą╗čÅ čüą▒čĆąŠčüą░, ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čüč鹊čĆąŠąČąĄą▓čŗą╝ čéą░ą╣ą╝ąĄčĆąŠą╝, ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą║ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÄ Boot mode sequence, ąĖ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą┐ąŠą╗ąĮąŠą│ąŠ ą▓ą║ą╗čÄč湥ąĮąĖčÅ (Full-On) ąĖą╗ąĖ čĆąĄąČąĖą╝ąĄ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ (Active mode). ąĀąĄąČąĖą╝ ąĘą░ą│čĆčāąĘą║ąĖ (Boot mode) ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ čüąŠčüč鹊čÅąĮąĖąĄą╝ ą▒ąĖč鹊ą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ BMODE ąĖ NOBOOT (no boot ą┐čĆąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝ čüą▒čĆąŠčüąĄ).

ąĢčüą╗ąĖ ąŠčćąĖčēąĄąĮ ą▒ąĖčé NOBOOT ą▓ čĆąĄą│ąĖčüčéčĆąĄ SYSCR, ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čüą▒čĆąŠčüą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ BMODE. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ čĆąĄą│ąĖčüčéčĆą░ SYSCR ą╝ąŠąČąĄčé ą╝ąĄąĮčÅčéčīčüčÅ ą╝ąĄąČą┤čā čüąĄą╝ąĄą╣čüčéą▓ą░ą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓. ąĪą┐ąĄčåąĖčäąĖą║čā čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ čüą╝. ą▓ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ ą┐ąŠ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā (hardware reference manual) ąÆą░čłąĄą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

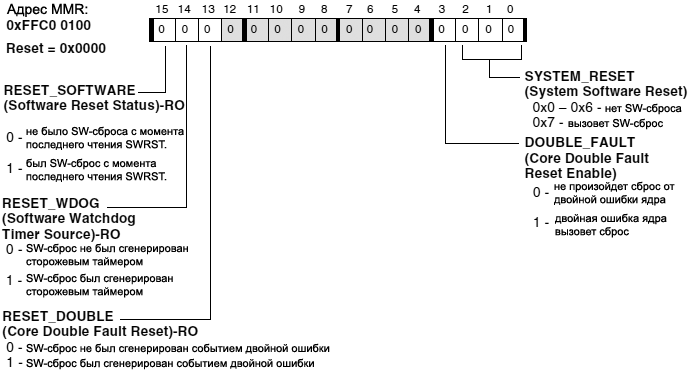

ąĀąĄą│ąĖčüčéčĆ SWRST. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü (software reset) ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą┐ąŠą╗čÅ System Reset ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ (Software Reset register, SWRST, čüą╝. čĆąĖčü. 3-3). ąæąĖčé 15 čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą▒čŗą╗ ą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ SWRST. ąæąĖčéčŗ 14 ąĖ 13 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé, ą▒čŗą╗ ą╗ąĖ čüą▒čĆąŠčü ą▓čŗąĘą▓ą░ąĮ Watchdog Timer ąĖą╗ąĖ ąŠčłąĖą▒ą║ąŠą╣ Core Double Fault. ąæąĖčéčŗ [15:13] ą┤ąŠčüčéčāą┐ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, ąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░čÄčéčüčÅ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąŠčćąĖčéą░ąĮ čĆąĄą│ąĖčüčéčĆ SWRST. ąæąĖčéčŗ [3:0] ą┤ąŠčüčéčāą┐ąĮčŗ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī.

ąÜąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤čŗ BMODE ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ b#00, ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé No Boot ą▓ čĆąĄą│ąĖčüčéčĆąĄ SYSCR, ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮą░čćąĖąĮą░ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ ąŠčé ąĮą░čćą░ą╗ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ L1 (čĆą░ą▒ąŠčéą░ ąĘą░ą│čĆčāąĘčćąĖą║ą░ boot ROM ąŠčéą╝ąĄąĮčÅąĄčéčüčÅ). ąÆ čŹč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čÅą┤čĆąŠ ąĮą░čćąĖąĮą░ąĄčé ą▓čŗą▒ąŠčĆą║čā ąĖąĮčüčéčĆčāą║čåąĖą╣ ąŠčé ąĮą░čćą░ą╗ą░ ą┐ą░ą╝čÅčéąĖ L1, ąĮą░čģąŠą┤čÅčēąĄą╣čüčÅ ąĮą░ ą║čĆąĖčüčéą░ą╗ą╗ąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ąÜąŠą│ą┤ą░ ą▒ąĖčéčŗ BMODE čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ b#00, ą┐čĆąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╝ ą▒ąĖč鹥 No Boot ą▓ čĆąĄą│ąĖčüčéčĆąĄ SYSCR čÅą┤čĆąŠ ąĮą░čćąĖąĮą░ąĄčé ą▓čŗą▒ąŠčĆą║čā ąĖąĮčüčéčĆčāą║čåąĖą╣ čü ą░ą┤čĆąĄčüą░ 0x2000 0000 (ąĮą░čćą░ą╗ąŠ ą▒ą░ąĮą║ą░ 0 ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ASYNC Bank 0, ąŠą▒čŗčćąĮąŠ čŹč鹊 ą┐ą░ą╝čÅčéčī FLASH).

ąĀąĖčü. 3-3. ąĀąĄą│ąĖčüčéčĆ Software Reset (SWRST).

Software Reset. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü (Software Reset) ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ąĖąĮčüčéčĆčāą║čåąĖąĖ RAISE 1 ąĖą╗ąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ Software Reset (SYSRST) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąŠčéą╗ą░ą┤ą║ąŠą╣ (Debug Control register, DBGCTL) ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄą╝ 菹╝čāą╗čÅč鹊čĆą░ č湥čĆąĄąĘ ą┐ąŠčĆčé JTAG (čĆąĄą│ąĖčüčéčĆ DBGCTL ąĮąĄ ą▓ąĖą┤ąĄąĮ ąĮą░ ą║ą░čĆč鹥 ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░).

ąØą░ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąŠčåąĄčüčüąŠčĆą░čģ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü ą▓ą╗ąĖčÅąĄčé č鹊ą╗čīą║ąŠ ąĮą░ čüąŠčüč鹊čÅąĮąĖąĄ čÅą┤čĆą░. ąØą░ ą┤čĆčāą│ąĖčģ ą┐čĆąŠčåąĄčüčüąŠčĆą░čģ ą║ąŠą┤ ąĘą░ą│čĆčāąĘą║ąĖ (boot ROM) ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ čüą▒čĆą░čüčŗą▓ą░ąĄčé čüąĖčüč鹥ą╝čā, ą║ąŠą│ą┤ą░ ąŠąĮ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĖąĘ-ąĘą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čüąŠčüč鹊čÅąĮąĖąĄ čüąĖčüč鹥ą╝ąĮčŗčģ čĆąĄčüčāčĆčüąŠą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝, ą╗ąĖą▒ąŠ ąŠąĮąĖ ą╝ąŠą│čāčé ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ ąĮąĄąĮą░ą┤ąĄąČąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ, čŹč鹊 ą╝ąŠąČąĄčé ąĘą░ą▓ąĖčüąĄčéčī ąŠčé ą░ą║čéąĖą▓ąĮąŠčüčéąĖ čüąĖčüč鹥ą╝čŗ ą▓ ą╝ąŠą╝ąĄąĮčé čüą▒čĆąŠčüą░.

ą»ą┤čĆąŠ ąĖ čüąĖčüč鹥ą╝ąĮčŗą╣ čüą▒čĆąŠčü (Core and System Reset). ąöą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čüą▒čĆąŠčüą░ čüąĖčüč鹥ą╝čŗ ąĖ čÅą┤čĆą░ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą║ąŠą┤ą░, ą┐ąŠą║ą░ąĘą░ąĮąĮčāčÄ ą▓ ąøąĖčüčéąĖąĮą│ąĄ 3-4. ąÜą░ą║ ąŠą┐ąĖčüą░ąĮąŠ ą▓ ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖčÅčģ, system soft reset ąĘą░ąĮąĖą╝ą░ąĄčé ą┐ąŠ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ 5 čéą░ą║č鹊ą▓ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ, ą┐ąŠčŹč鹊ą╝čā ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čüą▒čĆąŠčüą░ čéčĆąĄą▒čāąĄčéčüčÅ ąĮąĄą║ą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░, ą▓čŗą┐ąŠą╗ąĮąĄąĮąĮą░čÅ ą▓ ą▓ąĖą┤ąĄ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ čåąĖą║ą╗ą░. ąŁč鹊čé ą║ąŠą┤ ą┤ąŠą╗ąČąĄąĮ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą┐ą░ą╝čÅčéąĖ L1, čćč鹊ą▒čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü čüąĖčüč鹥ą╝čŗ čüą╝ąŠą│ čüčĆą░ą▒ąŠčéą░čéčī ą┐čĆą░ą▓ąĖą╗čīąĮąŠ.

//ąøąĖčüčéąĖąĮą│ 3-4. ąĪą▒čĆąŠčü čÅą┤čĆą░ ąĖ čüąĖčüč鹥ą╝čŗ (Core and System Reset).

// ąÆčŗą┤ą░čćą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ čüąĖčüč鹥ą╝čŗ (system soft reset).

P0.L = LO(SWRST);

P0.H = HI(SWRST);

R0.L = 0x0007;

W[P0] = R0;

SSYNC;

// ą×ąČąĖą┤ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ System reset (čéčĆąĄą▒čāąĄčé 5 ą┐ąĄčĆąĖąŠą┤ąŠą▓ SCLK)

// ąĢčüą╗ąĖ ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĖčéčī čüą░ą╝čŗą╣ ą║čĆą░ą╣ąĮąĖą╣ čüą╗čāčćą░ą╣ čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ CCLK:SCLK (15:1),

// ą┤ą╗čÅ čüč湥čéčćąĖą║ą░ čåąĖą║ą╗ąŠą▓ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čćąĖčüą╗ąŠ 5*15 = 75.

P1 = 75;

LSETUP(start, end) LCO = P1;

start:

end:

NOP;

// ą×čćąĖčüčéą║ą░ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░

R0.L = 0x0000;

W[P0] = R0;

SSYNC;

RAISE 1;

ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 č鹊čćąĮąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐čĆąĖ čüą▒čĆąŠčüąĄ ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ čŹč鹊ą│ąŠ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą╝ąŠą│čāčé ą╝ąĄąĮčÅčéčīčüčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čéąĖą┐ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą║ąŠą┤ą░ ą▓ ąøąĖčüčéąĖąĮą│ąĄ 3-4 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓, ą▓ ą║ąŠč鹊čĆčŗčģ ąĮąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ API-čäčāąĮą║čåąĖčÅ bfrom_SysControl() ą▓ ą¤ąŚąŻ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (ROM).

ŌĆó ąÆčŗą┐ąŠą╗ąĮąĄąĮąĖąĄ RAISE 1 ąĮąĄ ą▓čŗčüčéą░ą▓ą╗čÅąĄčé ąĮą░ą┐čĆčÅą╝čāčÄ čüą▒čĆąŠčü čÅą┤čĆą░. ąŁčéą░ ąĖąĮčüčéčĆčāą║čåąĖčÅ ą┐čĆąŠčüč鹊 čüąŠąĘą┤ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ 1 (interrupt level 1).

ŌĆó ąśčüą┐ąŠą╗čīąĘčāą╣č鹥 EVT1 ą┤ą╗čÅ ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ RAISE 1, čćč鹊 čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ 15 čĆąĄą│ąĖčüčéčĆą░ EVT_OVERRIDE.

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ 1 ą▒čāą┤čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▒ąĖčé 15 čĆąĄą│ąĖčüčéčĆą░ EVT_OVERRIDE, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī EVT1 ąĖą╗ąĖ čüą▒čĆąŠčü čłąĖąĮčŗ ą░ą┤čĆąĄčüą░ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ čÅą┤čĆą░ ą▒čāą┤čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ą╝ąĄčüč鹊 čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ ą▓ąĄą║č鹊čĆą░.

ąĢčüą╗ąĖ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ ąĮčāąČąĄąĮ čäčāąĮą║čåąĖąŠąĮą░ą╗ RAISE 1, č鹊 ą┤ą╗čÅ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╣ čĆą░ą▒ąŠčéčŗ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĄąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ:

ŌĆó ą¤ąŠčüą╗ąĄ ąĘą░ą│čĆčāąĘą║ąĖ EVT1 ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ąĮą░ ą╝ąĄčüč鹊 čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ ISR ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ interrupt level 1.

ŌĆó ą×čćąĖčēąĄąĮ ą▒ąĖčé 15 ą▓ čĆąĄą│ąĖčüčéčĆąĄ EVT_OVERRIDE.

ŌĆó ąÜąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ RAISE 1:

- ąÜąŠą┤ ISR ą┐čĆąŠčģąŠą┤ąĖčé č湥čĆąĄąĘ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą╝ąĄčģą░ąĮąĖąĘą╝čŗ č湥čĆąĄąĘ RCU (Reset Core Unit), čćč鹊ą▒čŗ ą▓čŗą║ą╗čÄčćąĖčéčī ą▓čüąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ čÅą┤čĆą░.

- ąŚą░č鹥ą╝ RCU čüą▒čĆą░čüčŗą▓ą░ąĄčé čÅą┤čĆąŠ. ą»ą┤čĆąŠ čŹč鹊 čāą▓ąĖą┤ąĖčé ą║ą░ą║ ą▓ąĮąĄčłąĮąĖą╣ čüą▒čĆąŠčü.

[ą£ąĄč鹊ą┤čŗ ąĘą░ą│čĆčāąĘą║ąĖ Blackfin]

ąÆąĮčāčéčĆąĄąĮąĮąĄąĄ ą¤ąŚąŻ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (boot ROM) čüąŠą┤ąĄčƹȹĖčé ą╝ą░ą╗ąĄąĮčīą║ąŠąĄ ąĘą░ą│čĆčāąĘąŠčćąĮąŠąĄ čÅą┤čĆąŠ, ąĘą░ą│čĆčāąĘčćąĖą║ (boot kernel), ąĘą░ą┐čāčüą║ ą║ąŠč鹊čĆąŠą│ąŠ ą╝ąŠąČąĮąŠ ą╗ąĖą▒ąŠ ą┐čĆąŠą┐čāčüčéąĖčéčī, ą╗ąĖą▒ąŠ ąĄą│ąŠ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ą║ąŠą┤ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, čüą╝. čéą░ą▒ą╗ąĖčåčā 4-10.

ąóą░ą▒ą╗ąĖčåą░ 4-10. ąÉą┤čĆąĄčüą░ ą▓ąĄą║č鹊čĆąŠą▓ čüą▒čĆąŠčüą░.

| ąśčüč鹊čćąĮąĖą║ ąĘą░ą│čĆčāąĘą║ąĖ |

BMODE[1:0] |

ąĪčéą░čĆč鹊ą▓čŗą╣ ą░ą┤čĆąĄčü |

| ąÆčŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ 16-ą▒ąĖčéąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ |

00 |

0x20000000 |

| ąŚą░ą│čĆčāąĘą║ą░ ąĖąĘ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą╣ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ FLASH čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčīčÄ 8 ąĖą╗ąĖ 16 ą▒ąĖčé. |

01 |

0xEF000000 |

| ąŚą░ą│čĆčāąĘą║ą░ čü ą┐ąŠą╗čāč湥ąĮąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ ąŠčé čģąŠčüčéą░, čĆąĄąČąĖą╝ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (SPI slave mode) |

10 |

| ąŚą░ą│čĆčāąĘą║ą░ ąĖąĘ 8-, 16- ąĖą╗ąĖ 24-ą▒ąĖčéąĮąŠą╣ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ SPI EEPROM (SPI master mode) |

11 |

Boot kernel čćąĖčéą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą▓ąĮąĄčłąĮąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ ą┐čĆąŠčåąĄčüčüąŠčĆą░ BMODE[1:0] ą▓ ą╝ąŠą╝ąĄąĮčé čüą▒čĆąŠčüą░, čćč鹊ą▒čŗ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░čéčī ąĖčüč鹊čćąĮąĖą║ ąĘą░ą│čĆčāąĘą║ąĖ (čüą╝. čéą░ą▒ą╗ąĖčåčā 4-7 ą▓ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖą╗ąĖ ą▓ čüčéą░čéčīąĄ [3]). ąÆ čĆąĄąČąĖą╝ąĄ ąĘą░ą│čĆčāąĘą║ąĖ boot mode 0 ą┐čĆąŠčåąĄčüčüąŠčĆ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĮą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ ąĖąĘ 16-ą▒ąĖčéąĮąŠą╣ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ąĮą░čģąŠą┤čÅčēąĄą╣čüčÅ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x20000000 (ASYNC bank 0).

ąöąŠčüčéčāą┐ąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą╝ąĄč鹊ą┤ąŠą▓ ąĘą░ą│čĆčāąĘą║ąĖ, čü ą┐ąŠą╝ąŠčēčīčÄ ą║ąŠč鹊čĆčŗčģ ą║ąŠą┤ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮ ą▓ ąŠą┐ąĄčĆą░čéąĖą▓ąĮčāčÄ ą┐ą░ą╝čÅčéčī ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ąĖą╗ąĖ ąĖąĘ ą┤ą░ąĮąĮčŗčģ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ čģąŠčüč鹊ą╝ (ą▓ čŹč鹊ą╝ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝ čüą╗čāčćą░ąĄ ą░ą║čéąĖą▓ąĄąĮ čĆąĄąČąĖą╝ ąĘą░ą│čĆčāąĘą║ąĖ SPI slave mode, ą▓ ą║ąŠč鹊čĆąŠą╝ ą┐čĆąŠčåąĄčüčüąŠčĆ Blackfin ą▓ąĄą┤ąĄčé čüąĄą▒čÅ ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI, ą┐čĆąĖąĮąĖą╝ą░čÅ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą│čĆčāąĘą║ąĖ ąŠčé ą┤čĆčāą│ąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░). ąÆ čŹčéąĖčģ čĆąĄąČąĖą╝ą░čģ ąĘą░ą│čĆčāąĘą║ąĖ boot kernel ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčé ą▓čŗą▒čĆą░ąĮąĮąŠąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ąŠčéą║čāą┤ą░ ą▒čāą┤ąĄčé ąĖą┤čéąĖ ąĘą░ą│čĆčāąĘą║ą░, ą▒ą░ąĘąĖčĆčāčÅčüčī ąĮą░ ą╗ąŠą│ąĖč湥čüą║ąĖčģ čāčĆąŠą▓ąĮčÅčģ ą▓ąĮąĄčłąĮąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ BMODE[1:0] ą┐čĆąŠčåąĄčüčüąŠčĆą░ (čüą╝. čéą░ą▒ą╗ąĖčåčā 1 ąĖąĘ čüčéą░čéčīąĖ [7]).

ąÆ ą║ą░ąČą┤ąŠą╝ ąĖąĘ čĆąĄąČąĖą╝ąŠą▓ ąĘą░ą│čĆčāąĘą║ąĖ ą║ąŠą┤ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ ą┐ąŠą╝ąĄčēą░ąĄčéčüčÅ ą▓ ąĮą░čćą░ą╗čīąĮčāčÄ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ L1, čéą░ą║ąČąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮčŗ ąĖ ą┤čĆčāą│ąĖąĄ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ, ąĮą░ą┐čĆąĖą╝ąĄčĆ SDRAM. ąśąĮč乊čĆą╝ą░čåąĖčÅ, ą║ą░ą║ąĖąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮčŗ ą┐ąŠ ą║ą░ą║ąŠą╝čā ą░ą┤čĆąĄčüčā, ą▒ąĄčĆąĄčéčüčÅ ąĖąĘ ą┤ą░ąĮąĮčŗčģ ąĘą░ą│čĆčāąĘą║ąĖ (loader file). Boot kernel ąĘą░ą▓ąĄčĆčłą░ąĄčé ą┐čĆąŠčåąĄčüčü ąĘą░ą│čĆčāąĘą║ąĖ ą┐ąĄčĆąĄčģąŠą┤ąŠą╝ ą▓ ąĮą░čćą░ą╗ąŠ ą┐ą░ą╝čÅčéąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣ L1. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮą░čćąĖąĮą░ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ čü čŹč鹊ą│ąŠ ą░ą┤čĆąĄčüą░.

ąĢčüą╗ąĖ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĘą░ą│čĆčāąĘą║ą░ č湥čĆąĄąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü (SPI0), č鹊 ą▓čŗą▓ąŠą┤ ą┐ąŠčĆčéą░ GPIO PF2 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ (SPI-chip select), čŹč鹊čé ą▓čŗą▓ąŠą┤ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą┐ąŠą┤čüąŠąĄą┤ąĖąĮąĄąĮ.

Core-only software reset čéą░ą║ąČąĄ ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗čÅąĄčé čÅą┤čĆąŠ ąĮą░ boot ROM. ąóą░ą║ąŠą╣ čüą▒čĆąŠčü čüą▒čĆą░čüčŗą▓ą░ąĄčé č鹊ą╗čīą║ąŠ čÅą┤čĆąŠ, ąĮąĄ ą▓ą╗ąĖčÅčÅ ąĮą░ ąŠčüčéą░ą╗čīąĮčāčÄ čćą░čüčéčī čüąĖčüč鹥ą╝čŗ. Boot ROM kernel ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą▓ ą╝ąŠą╝ąĄąĮčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ą┐ąŠ ą▒ąĖčéą░ą╝ SYSCR, čćč鹊 ą┐čĆąŠąĖąĘąŠčłąĄą╗ software reset, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąĖąĮąĖčåąĖą░čåąĖąĖ. ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┐čĆąĖ software reset, č鹊 ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ ą┐čĆąŠčåąĄčüčü ąĘą░ą│čĆčāąĘą║ąĖ, ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ąĮą░čćą░ą╗ąŠ ą┐ą░ą╝čÅčéąĖ L1 ąĖ ąĮą░čćąĖąĮą░ąĄčé ąŠčéčéčāą┤ą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░.

ąÆ čĆąĄąČąĖą╝ąĄ ąĘą░ą│čĆčāąĘą║ąĖ ąĖąĘ FLASH (flash boot mode, BMODE = 01) boot kernel ąŠąČąĖą┤ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čĆą░ą▒ąŠčćąĖąĄ čāčüą╗ąŠą▓ąĖčÅ:

ŌĆó ąĀą░ąĘčĆąĄčłąĄąĮ ą▒ą░ąĮą║ 0 ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (AMB0).

ŌĆó ąöą╗čÅ ą▒ą░ąĮą║ą░ AMB0 čĆą░ąĘčĆąĄčłąĄąĮą░ 16-ą▒ąĖčéąĮą░čÅ čāą┐ą░ą║ąŠą▓ą║ą░ ą┤ą░ąĮąĮčŗčģ.

ŌĆó ąĪąĖą│ąĮą░ą╗ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ą▒ą░ąĮą║ą░ (bank 0 RDY) čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą░ą║čéąĖą▓ąĮčāčÄ ą╗ąŠą│. 1.

ŌĆó ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą▒ą░ąĮą║ą░ (bank 0 hold time, čüąĖą│ąĮą░ą╗ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ čüąĮąĖą╝ą░ąĄčéčüčÅ ą┤ą╗čÅ čüąĮčÅčéąĖčÅ AOE) = 3 čåąĖą║ą╗ą░.

ŌĆó ąÆčĆąĄą╝ąĄąĮą░ ą┤ąŠčüčéčāą┐ą░ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ą▒ą░ąĮą║ą░ (bank 0 read/write access times) = 15 čåąĖą║ą╗ąŠą▓.

ąöą╗čÅ čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ SPI master (BMODE = 11) boot kernel ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé, čćč鹊 čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ SPI0 čüąŠčüčéą░ą▓ą╗čÅąĄčé 500 ą║ąōčå. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ SPI serial EEPROM čü čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčīčÄ 8, 16 ąĖ 24 ą▒ąĖčéą░. SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąĮąŠąČą║čā ą▓čŗčģąŠą┤ą░ PF2, čćč鹊ą▒čŗ ą▓čŗą▒čĆą░čéčī ąŠą┤ąĮčā ą╝ąĖą║čĆąŠčüčģąĄą╝čā SPI EEPROM. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ SPI0 ąŠčéą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ čćč鹥ąĮąĖčÅ ą┐ąŠ ą░ą┤čĆąĄčüą░ą╝ 0x00, 0x0000 ąĖ 0x000000, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ EEPROM čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčīčÄ 8, 16 ąĖą╗ąĖ 24 ą▒ąĖčéą░. ąŚą░č鹥ą╝ ąŠąĮ ąĮą░čćąĮąĄčé ą▓čŗčćąĖčéčŗą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĖ ą┐ąŠą╝ąĄčēą░čéčī ąĖčģ ą▓ ąĮą░čćą░ą╗ąŠ ą┐ą░ą╝čÅčéąĖ L1.

ąÆčŗą▓ąŠą┤ MISOx ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčé ą║ ą╗ąŠą│. 1 ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ SPI master (BMODE = 11).

ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĖąĘ čĆąĄąČąĖą╝ąŠą▓ ąĘą░ą│čĆčāąĘą║ąĖ čüąĮą░čćą░ą╗ą░ ąĖąĘ ą▓ąĮąĄčłąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ ą▓čŗčćąĖčéčŗą▓ą░ąĄčéčüčÅ 10-ą▒ą░ą╣čéąĮčŗą╣ ąĘą░ą│ąŠą╗ąŠą▓ąŠą║. ąŁč鹊čé ąĘą░ą│ąŠą╗ąŠą▓ąŠą║ ąĘą░ą┤ą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ą▒ą░ą╣čé ąĖ ą░ą┤čĆąĄčü ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (ą║čāą┤ą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ąĘą░ą│čĆčāąČą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ). ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▓čüąĄ ą▒ą╗ąŠą║ąĖ ąĘą░ą│čĆčāąČąĄąĮčŗ, ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąŠčé ąĮą░čćą░ą╗ą░ ą┐ą░ą╝čÅčéąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣ L1 SRAM.

ąöą╗čÅ čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ SPI slave (BMODE = 10) ą┐čĆąĄą┤ą┐ąŠą╗ą░ą│ą░ąĄčéčüčÅ, čćč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ, ą┐ąŠą║ą░ąĘą░ąĮąĮą░čÅ ąĮą░ čĆąĖčü. 3-4.

ąĀąĖčü. 3-4. SPI Slave Boot Mode.

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄą╝ą░čÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ GPIO PFx čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗčģąŠą┤ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin ąĖ ą▓čģąŠą┤ ą┐čĆąŠčåąĄčüčüąŠčĆą░ čģąŠčüčéą░. ąŁč鹊čé ą▓čŗą▓ąŠą┤ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāą┤ąĄčƹȹĖą▓ą░čéčī ą┐čĆąŠčåąĄčüčüąŠčĆ čģąŠčüčéą░ ąŠčé ąŠčéą┐čĆą░ą▓ą║ąĖ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠą╝ąĄčēą░čÄčéčüčÅ ą▓ ąĮčāąČąĮčŗąĄ čüąĄą║čåąĖąĖ ą┐ą░ą╝čÅčéąĖ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ąĘą░ą│čĆčāąĘą║ąĖ. ąÜąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ ąĮą░ čŹč鹊ą╝ ą▓čŗą▓ąŠą┤ąĄ čüąĮąĖą╝ą░ąĄčéčüčÅ, čģąŠčüčé ą╝ąŠąČąĄčé ą┐čĆąŠą┤ąŠą╗ąČąĖčéčī ąŠčéą┐čĆą░ą▓ą╗čÅčéčī ą┤ą░ąĮąĮčŗąĄ ąĘą░ą│čĆčāąĘčćąĖą║čā Blackfin.

ą¤ąŠą┤čĆąŠą▒ąĮąŠ čĆąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ ąŠą┐ąĖčüą░ąĮčŗ ą▓ čüčéą░čéčīąĄ [7].

[ąĪčüčŗą╗ą║ąĖ]

1. Blackfin® Processor Programming Reference site:analog.com.

2. VDK: ą╝ąĄąĮąĄą┤ąČąĄčĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

3. ADSP-BF538: ąŠą▒čĆą░ą▒ąŠčéą║ą░ čüąŠą▒čŗčéąĖą╣ (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĖčüą║ą╗čÄč湥ąĮąĖčÅ).

4. ą¤ą░ą╝čÅčéčī Blackfin.

5. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą║čŹčłą░ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆą░čģ Blackfin.

6. Blackfin FAQ.

7. ąÜą░ą║ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĘą░ą│čĆčāąĘą║ą░ ADSP-BF533 Blackfin. |